## S1C31 マニュアル 正誤表

| 項目 RDWAIT 設定変更時の制限      |           |            |      |

|-------------------------|-----------|------------|------|

| 対象マニュアル                 | 発行 No.    | 項目         | ページ  |

| S1C31W65 テクニカルマニュアル     | 414063200 | 4.8 制御レジスタ | 4-10 |

| S1C31W73 テクニカルマニュアル     | 414076200 | 4.9 制御レジスタ | 4-11 |

| S1C31W74 テクニカルマニュアル     | 413374400 | 4.9 制御レジスタ | 4-10 |

| S1C31D01 テクニカルマニュアル     | 413520300 | 4.8 制御レジスタ | 4-12 |

| S1C31D50/D51 テクニカルマニュアル | 413699302 | 4.8 制御レジスタ | 4-10 |

### (誤) 制御レジスタ

#### FLASHC Flash Read Cycle Register

Bits1-0 RDWAIT[1:0]

これらのビットは、Flash メモリリード時のバスアクセスサイクル数を設定します。

注：FLASHWAIT.RDWAIT[1:0]ビットの設定は、システムクロックを変更する前に行ってください。

### (正) 制御レジスタ

#### FLASHC Flash Read Cycle Register

Bits1-0 RDWAIT[1:0]

これらのビットは、Flash メモリリード時のバスアクセスサイクル数を設定します。

注：・FLASHWAIT.RDWAIT[1:0]ビットの設定は、システムクロックを変更する前に行ってください。

・FLASHCWAIT.RDWAIT[1:0]ビットを 0x2 から 0x1 に設定変更する場合、その直後に NOP を

2 命令入れてください。

(プログラム例)

```

FLASHC->WAIT_b.RDWAIT = 1;

asm("NOP");

asm("NOP");

CLG->OSC_b.IOSCEN = 0;

```

## S1C31 マニュアル 正誤表

| 項目 リアルタイムクロックの有効範囲外の値をセットした場合の補正動作 |           |                          |      |

|------------------------------------|-----------|--------------------------|------|

| 対象マニュアル                            | 発行 No.    | 項目                       | ページ  |

| S1C31W65 テクニカルマニュアル                | 414063200 | 10.4.2 リアルタイムクロックカウンタの動作 | 10-4 |

| S1C31W73 テクニカルマニュアル                | 414076200 | 10.4.2 リアルタイムクロックカウンタの動作 | 10-4 |

| S1C31W74 テクニカルマニュアル                | 413374400 | 10.4.2 リアルタイムクロックカウンタの動作 | 10-4 |

| S1C31D01 テクニカルマニュアル                | 413520300 | 10.4.2 リアルタイムクロックカウンタの動作 | 10-4 |

| S1C31D50/D51 テクニカルマニュアル            | 413699302 | 10.4.2 リアルタイムクロックカウンタの動作 | 10-4 |

|                                    |           |                          |      |

|                                    |           |                          |      |

(誤)

### 有効範囲外の値をセットした場合の補正動作

年、曜日、時(24H モード時)カウンタに、有効範囲外の値をセットすると、次のカウントアップで 0 にクリアされます。月、日、時(12H モード時)カウンタに、有効範囲外の値をセットすると、次のカウントアップタイミングで 1 にセットされます。

(正)

### 有効範囲外の値をセットした場合の補正動作

年、曜日、時(24H モード時)カウンタに、有効範囲外の値をセットすると、次のカウンタのカウントアップで 0 にクリアされます。月、日、時(12H モード時)カウンタに、有効範囲外の値をセットすると、次のカウンタのカウントアップタイミングで 1 にセットされます。

注：RTCMON.RTCMOH ビット=0 & RTCMON.RTCMOL[3:0]ビット=0x0 の設定を禁止します。

## S1C31 マニュアル 正誤表

| 項目 リアルタイムクロック(RTCA) 論理緩急機能 |           |               |      |

|----------------------------|-----------|---------------|------|

| 対象マニュアル                    | 発行 No.    | 項目            | ページ  |

| S1C31W74 テクニカルマニュアル        | 413374400 | 10.3.2 論理緩急機能 | 10-2 |

| S1C31D01 テクニカルマニュアル        | 413520300 | 10.3.2 論理緩急機能 | 10-2 |

|                            |           |               |      |

|                            |           |               |      |

|                            |           |               |      |

(誤)

### 10.3.2 論理緩急機能

OSC1周波数fOSC1が、32.768 kHzに対して発振周波数偏差を持つ場合、時計は誤差を生じます。

RTCAは、この誤差を外付け部品の変更なしに補正する論理緩急機能を搭載しています。論理緩急は、以下の手順で行います。

1. fOSC1の発振周波数偏差 m [ppm]を測定する。

2. 論理緩急実行間隔 n秒を決める。

3. 1と2からRTCCTL.RTCTRM[6:0]ビットへ書き込む値を決定する。

4. RTCAのアラーム割り込みや秒割り込みを利用し、n秒間隔でRTCCTL.RTCTRM[6:0]ビットへ3で決めた値を書き込む。

5. RTC1S信号をモニタし、n秒の周期が、誤差のない周期になっているかを確認する。

論理緩急の調整値は-64～+63の範囲で設定可能で、RTCCTL.RTCTRM[6:0]ビットには2の補数として書き込みます。調整値は式9.1で計算できます。

n: 論理緩急実行間隔 [秒](ソフトウェアで定期的にRTCCTL.RTCTRM[6:0]ビットに書き込む間隔)

m: OSC1の発振周波数偏差 [ppm]

(正)

### 10.3.2 論理緩急機能

OSC1周波数fOSC1が、32.768 kHzに対して発振周波数偏差を持つ場合、時計は誤差を生じます。

RTCAは、この誤差を外付け部品の変更なしに補正する論理緩急機能を搭載しています。論理緩急は、以下の手順で行います。

1. fOSC1を測定し、発振周波数偏差の補正值 m [ppm] = -{(fOSC1-32768[Hz]) / 32768[Hz]} × 10<sup>6</sup>を求める。

2. 論理緩急実行間隔 n秒を決める。

3. 1と2からRTCCTL.RTCTRM[6:0]ビットへ書き込む値を決定する。

4. RTCAのアラーム割り込みや秒割り込みを利用し、n秒間隔でRTCCTL.RTCTRM[6:0]ビットへ3で決めた値を書き込む。

5. RTC1S信号をモニタし、n秒の周期が、誤差のない周期になっているかを確認する。

論理緩急の調整値は-64～+63の範囲で設定可能で、RTCCTL.RTCTRM[6:0]ビットには2の補数として書き込みます。調整値は式9.1で計算できます。

n: 論理緩急実行間隔 [秒](ソフトウェアで定期的にRTCCTL.RTCTRM[6:0]ビットに書き込む間隔)

m: OSC1の発振周波数偏差の補正值 [ppm]

## S1C31 ファミリテクニカルマニュアル正誤表

| 項目 LCD ドライバ動作                                                                                                                                                                                                         |           |                   |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|------|

| 対象マニュアル                                                                                                                                                                                                               | 発行 No.    | 項目                | ページ  |

| S1C31W74 テクニカルマニュアル                                                                                                                                                                                                   | 413374400 | 20.5.2 表示の ON/OFF | 20-8 |

| S1C31W74                                                                                                                                                                                                              |           |                   |      |

| (誤)<br>表示OFFを選択した場合、LCD駆動電圧の供給が停止し、LCD ドライバ端子の出力はすべてVSSレベルとなります。<br>全点灯および全消灯はLCDドライバが出力する駆動波形を直接制御するもので、表示データRAMのデータは変更されません。また、コモン端子は全点灯ではダイナミック駆動、全消灯ではスタティック駆動となります。この機能を使用することにより、表示データメモリを変更せずに表示を点滅させることができます。 |           |                   |      |

| (正)<br>表示OFFを選択した場合、LCD駆動電圧の供給が停止し、LCD ドライバ端子の出力はすべてVSSレベルとなります。<br>全点灯および全消灯はLCDドライバが出力する駆動波形を直接制御するもので、表示データRAMのデータは変更されません。また、コモン端子は全点灯ではダイナミック駆動、全消灯ではスタティック駆動となります。この機能を使用することにより、表示データメモリを変更せずに表示を点滅させることができます。 |           |                   |      |

| <u>注：全点灯表示では、高温時にパネル負荷の変動により、表示が薄くなることがあります。回避策としては、VC2 端子-VC1 端子間に抵抗を挿入する手段があります。LCD パネルの負荷容量、使用温度を考慮し、抵抗値を決めてください。但し、VC2 端子-VC1 端子間に抵抗を挿入すると、LCD 回路電流が上昇します。</u>                                                    |           |                   |      |

## S1C31 マニュアル 正誤表

| 項目 Flash メモリ端子      |           |                   |      |

|---------------------|-----------|-------------------|------|

| 対象マニュアル             | 発行 No.    | 項目                | ページ  |

| S1C31W74 テクニカルマニュアル | 413374400 | 1.3.3 端子説明        | 1-8  |

|                     |           | 4.3.1 Flash メモリ端子 | 4-2  |

|                     |           | 24 基本外部結線図        | 24-1 |

(誤)

### 1.3.3 端子説明

表1.3.3.1 端子説明

|       |     |     |      |   |                     |

|-------|-----|-----|------|---|---------------------|

| P26   | P26 | I/O | Hi-Z | - | 出力兼用ポート<br>入出力兼用ポート |

| EXOSC |     | I   |      | / | クロックジェネレータ外部クロック入力  |

### 4.3.1 Flash メモリ端子

表4.3.1.1 Flashメモリ端子

| 端子名 | I/O | イニシャル状態 | 機能             |

|-----|-----|---------|----------------|

| VPP | P   | -       | Flashプログラミング電源 |

VPP電圧に関しては“電気的特性”の章の“推奨動作条件、Flashプログラミング電圧VPP”を参照してください。

注: Flashプログラミング時以外は、VPP端子をオープンにしてください。

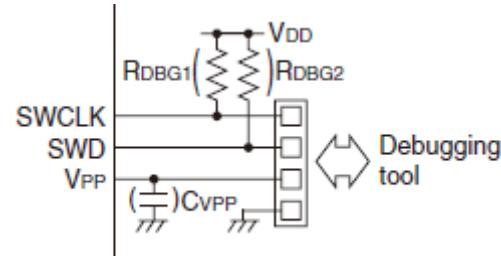

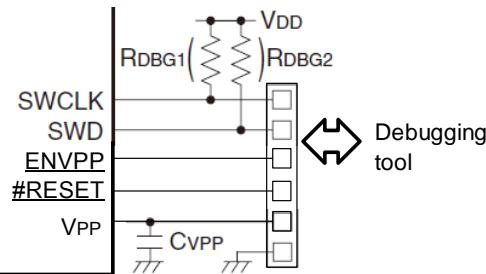

### 25 基本外部結線図

(正)

### 1.3.3 端子説明

表1.3.3.1 端子説明

|       |             |     |      |   |                                                                 |

|-------|-------------|-----|------|---|-----------------------------------------------------------------|

| P26   | P26 (ENVPP) | I/O | Hi-Z | - | 出力兼用ポート (Flash プログラミング制御信号出力)<br>入出力兼用ポート (Flash プログラミング制御信号出力) |

| EXOSC |             | I   |      | / | クロックジェネレータ外部クロック入力                                              |

### 4.3.1 Flash メモリ端子

表4.3.1.1 Flashメモリ端子

| 端子名                  | I/O                    | イニシャル状態           | 機能                              |

|----------------------|------------------------|-------------------|---------------------------------|

| V <sub>PP</sub>      | P                      | –                 | Flashプログラミング電源                  |

| (ENVPP) <sup>↓</sup> | O or Hi-Z <sup>↓</sup> | Hi-Z <sup>↓</sup> | Flashプログラミング制御信号出力 <sup>↓</sup> |

V<sub>PP</sub>電圧に関しては“電気的特性”の章の“推奨動作条件、Flashプログラミング電圧V<sub>PP</sub>”を参照してください。

注: Flashプログラミング時以外は、V<sub>PP</sub>端子をオープンにしてください。

ENVPP 端子は、Flash プログラミング時に、Bridge Board(S5U1C31001L)への制御信号を出力します。

通常の端子としてご利用いただけますが、この信号の外部回路への影響を考慮してください。

### 25 基本外部結線図

## S1C31 マニュアル 正誤表

| 項目 Flash プログラミング    |           |                     |        |

|---------------------|-----------|---------------------|--------|

| 対象マニュアル             | 発行 No.    | 項目                  | ページ    |

| S1C31W74 テクニカルマニュアル | 413374400 | 1.1 特長              | 1-2    |

|                     |           | 4.3.3 Flash プログラミング | 4-3    |

|                     |           | 23.2 推奨動作条件         | 23-1   |

|                     |           | 24 基本外部結線図          | 24-1   |

|                     |           | Appendix C 実装上の注意事項 | AP-C-1 |

(誤)

1.1 特長

| 電源電圧                 |                     |

|----------------------|---------------------|

| VDD 動作電圧             | 1.8~3.6V            |

| Flash 書き換え時 VDD 動作電圧 | 2.7~3.6V(内部昇圧回路使用時) |

| LCD ドライバ使用時 VDD 動作電圧 | 2.5~3.6V            |

4.3.3 Flash プログラミング

Flash メモリはオンボードプログラミングに対応しており、フラッシュローダを使用して ROM データをプログラミングすることができます。VPP 電圧は外部電源または内蔵昇圧回路から供給可能です。それぞれに対応したフラッシュローダを使用してください。

注: 内蔵昇圧回路使用時は、VDD を 2.7V 以上にする必要があります。

23.2 推奨動作条件

| 項目             | 記号   | 条件             | Min. | Typ. | Max. | 単位      |

|----------------|------|----------------|------|------|------|---------|

| 電源電圧           | VDD  | 通常動作時          | 1.8  | -    | 3.6  | V       |

|                |      | Flash プログラミング時 | 2.7  | -    | 3.6  | V       |

|                |      | LCD ドライバ使用時    | 2.5  | -    | 3.6  | V       |

| VSS~VPP 間キャパシタ | CVPP | *5             | -    | 0.1  | -    | $\mu F$ |

\*5 VPP 電圧が安定しない場合に接続してください。

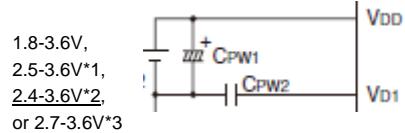

24 基本外部結線図

1.8-3.6 V,

2.5-3.6 V \*1,

or 2.7-3.6 V \*2

\*1: LCD ドライバ使用時

\*2: Flash プログラミング時(VPP 内部生成時)

## Appendix C 実装上の注意事項

### VPP 端子

Flash プログラミング電圧 VPP が大きく変動する場合、Vss～VPP 間キャパシタ CVPP を接続して、VPP ± 1 V 以下の変動に抑えてください。

このとき、CVPP は可能な限り VPP 端子の近くに配置し、数十 mA が流れるように十分な太さを持つパターンを用いて配線してください。

(正)

#### 1.1 特長

##### 電源電圧

|                      |                                                              |

|----------------------|--------------------------------------------------------------|

| VDD 動作電圧             | 1.8～3.6V                                                     |

| Flash 書き換え時 VDD 動作電圧 | <u>2.4～3.6V(VPP 電圧外部印加時)</u><br><u>2.7～3.6V(VPP 電圧内部生成時)</u> |

| LCD ドライバ使用時 VDD 動作電圧 | 2.5～3.6V                                                     |

#### 4.3.3 Flash プログラミング

Flash メモリはオンボードプログラミングに対応しており、フラッシュローダを使用して ROM データをプログラミングすることができます。VPP 電圧は外部電源または内蔵昇圧回路から供給可能です。

VPP 外部供給時は電圧安定用に、内蔵昇圧回路使用時は電圧生成用に、VPP 端子に VSS～VPP 間キャパシタ CVPP を必ず接続してください。

Flash プログラミング時以外は、VPP 端子をオープンにする必要があります。ただし、Bridge Board(S5U1C31001L) から VPP 電圧を供給する場合、Flash プログラミング時のみ供給するように制御されているため、接続したままでも問題ありません。

- 注:

- VPP 電圧を外部印加する場合は、VDD を 2.4 V 以上にする必要があります。

- VPP 電圧を内部生成する場合は、VDD を 2.7 V 以上にする必要があります。

- VPP 電圧を内部生成する場合は、VPP 端子の出力を外部回路の駆動には絶対に使用しないでください。

#### 23.2 推奨動作条件

| 項目             | 記号   | 条件             |           | Min.       | Typ. | Max.       | 単位 |

|----------------|------|----------------|-----------|------------|------|------------|----|

| 電源電圧           | VDD  | 通常動作時          |           | 1.8        | -    | 3.6        | V  |

|                |      | Flash プログラミング時 | VPP 外部印加時 | <u>2.4</u> | -    | <u>3.6</u> | V  |

|                |      |                | VPP 内部生成時 | 2.7        | -    | 3.6        | V  |

|                |      | LCD ドライバ使用時    |           | 2.5        | -    | 3.6        | V  |

| VSS～VPP 間キャパシタ | Cvpp | *5             |           | -          | 0.1  | -          | μF |

\*5 VPP 電圧が安定しない場合に接続してください。

**24 基本外部結線図**

\*1: LCD ドライバ使用時

\*2: Flash プログラミング時(VPP 外部印加時)

\*3: Flash プログラミング時(VPP 内部生成時)

**Appendix C 実装上の注意事項****VPP 端子**

Flash プログラミング電圧 VPP が大きく変動する場合、Vss～VPP 間キャパシタ CVPP を接続して、VPP ± 1 V 以下の変動に抑えてください。

このとき、CVPP は可能な限り VPP 端子の近くに配置し、数十 mA が流れるように十分な太さを持つパターンを用いて配線してください。