## S1C17 シリーズテクニカルマニュアル正誤表

| 項目 出荷形態 VFBGA5H-81 追加                                            |           |                                                          |                            |

|------------------------------------------------------------------|-----------|----------------------------------------------------------|----------------------------|

| 対象マニュアル                                                          | 発行 No.    | 項目                                                       | ページ                        |

| S1C17554/564 テクニカルマニュアル                                          | 411914303 | 1.1 特長<br>1.3.2 S1C17564 端子配置図<br>1.3.3 端子説明<br>26 パッケージ | 1-2<br>1-9<br>1-12<br>26-1 |

| <b>1.1 特長 (P.1-2)</b>                                            |           |                                                          |                            |

| (誤)<br>出荷形態<br>-                                                 |           |                                                          |                            |

| (正)<br>出荷形態<br>VFBGA5H-81 (5mm x 5mm x 1.0mm, ball pitch: 0.5mm) |           |                                                          |                            |

| <b>1.3.2 S1C17564 端子配置図 (P.1-9)</b>                              |           |                                                          |                            |

| (誤)<br>-                                                         |           |                                                          |                            |

| (正)<br>次頁追加                                                      |           |                                                          |                            |

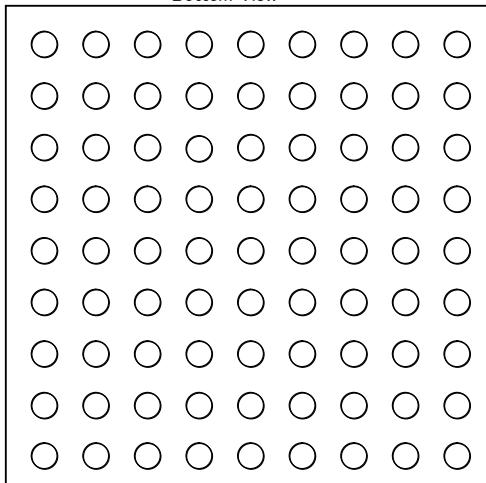

## S1C17564 端子配置図(VFBGA5H-81)

TOP View

Bottom View

TOP View

|   | 1                       | 2                               | 3                      | 4                             | 5                    | 6                             | 7                            | 8                    | 9                      |

|---|-------------------------|---------------------------------|------------------------|-------------------------------|----------------------|-------------------------------|------------------------------|----------------------|------------------------|

| A | NC                      | P00<br>AIN0                     | P02<br>AIN2<br>US_SSI0 | AVDD                          | VSS                  | P42<br>SCLK0<br>TOUT1<br>CAP1 | P40<br>SIN0<br>TOUT6<br>CAP6 | #RESET               | NC                     |

| B | P10<br>SDIO             | P01<br>AIN1                     | P03<br>AIN3<br>US_SSI1 | P32<br>TOUT4<br>CAP4<br>FOUTA | HVDD                 | P41<br>SOUT0<br>TOUT7<br>CAP7 | LVDD                         | REGEN                | VSS                    |

| C | P12<br>SPICLK0          | P50<br>US_SDIO                  | P11<br>SDO0            | VSS                           | P17<br>SCL0          | P45<br>(EXCL0)<br>SDAO        | VIN                          | VOUT                 | P23<br>(EXCL2)<br>SDI2 |

| D | LVDD                    | P13<br>#SPISS0<br>TOUT5<br>CAP5 | HVDD                   | VSS                           | VSS                  | VSS                           | P22<br>(EXCL1)<br>FOUTB      | P21<br>TOUT3<br>CAP3 | P20<br>TOUT2<br>CAP2   |

| E | P51<br>US_SDO0          | P14<br>SIN1<br>SDI1             | P15<br>SOUT1<br>SDO1   | VSS                           | VSS                  | VSS                           | HVDD                         | VSS                  | OSC4                   |

| F | P16<br>SCLK1<br>SPICLK1 | P43<br>SDA1<br>REMI             | P44<br>SCL1<br>REMO    | VSS                           | VSS                  | VSS                           | P54<br>US_SDO1               | VSS                  | OSC3                   |

| G | HVDD                    | P24<br>(EXCL3)<br>SDO2          | VSS                    | LVDD                          | DST2<br>P37          | TEST                          | P34<br>REMO<br>#SPISS1       | VPP                  | OSC2                   |

| H | VSS                     | P25<br>#BFR<br>#SPISS2          | P26<br>SDA1            | HVDD                          | P53<br>US_SDI1       | LVDD                          | P33<br>REMI<br>SPICLK2       | VSS                  | OSC1                   |

| J | NC                      | P52<br>US_SCK0                  | P27<br>SCL1            | P30<br>TOUT0<br>CAP0          | P31<br>#BFR<br>ADTRG | DSIO<br>P36                   | DCLK<br>P35                  | P55<br>US_SCK1       | NC                     |

## 1.3.3 端子説明 (P.1-12)

(誤)

-

(正)

| 名称                 | I/O | 初期状態         | 機能                                      | S1C17564<br>VFBGA                                                  |

|--------------------|-----|--------------|-----------------------------------------|--------------------------------------------------------------------|

| <b>HVDD</b>        | -   | -            | I/O電源端子(1.85~5.5V)                      | B5, D3, E7, G1, H4                                                 |

| <b>LVDD</b>        | -   | -            | コア電源端子(1.85~1.95V)                      | D1, G4, H6, B7                                                     |

| <b>VSS</b>         | -   | -            | GND端子                                   | A5, B9, C4, D4, D5, D6, E4, E5, E6, E8, F4, F5, F6, F8, G3, H1, H8 |

| <b>VPP</b>         | -   | -            | Flashプログラミング/消去電源端子(7/7.5V)(通常動作時はオープン) | G8                                                                 |

| <b>AVDD</b>        | -   | -            | アナログ電源端子(2.7~5.5V)                      | A4                                                                 |

| <b>VIN</b>         | -   | -            | レギュレータ入力端子(2.0~5.5V)                    | C7                                                                 |

| <b>VOUT</b>        | -   | -            | レギュレータ出力端子(1.8V)                        | C8                                                                 |

| <b>REGEN</b>       | I   | I            | レギュレータイネーブル入力端子                         | B8                                                                 |

| <b>OSC3</b>        | I   | I            | OSC3発振入力端子/外部クロック(LVDDレベル)入力端子          | F9                                                                 |

| <b>OSC4</b>        | O   | O            | OSC3発振出力端子                              | E9                                                                 |

| <b>OSC1</b>        | I   | I            | OSC1発振入力端子/外部クロック(LVDDレベル)入力端子          | H9                                                                 |

| <b>OSC2</b>        | O   | O            | OSC1発振出力端子                              | G9                                                                 |

| <b>#RESET</b>      | I   | I(Pull-up)   | イニシャルリセット入力端子                           | A8                                                                 |

| <b>TEST</b>        | I   | I(Pull-down) | テスト用入力端子(通常動作時はVSSに接続)                  | G6                                                                 |

| <b>P00</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | A2                                                                 |

| <b>AIN0</b>        | I   |              | A/D変換器 Ch.0アナログ信号入力端子                   |                                                                    |

| <b>P01</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | B2                                                                 |

| <b>AIN1</b>        | I   |              | A/D変換器 Ch.1アナログ信号入力端子                   |                                                                    |

| <b>P02</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | A3                                                                 |

| <b>AIN2</b>        | I   |              | A/D変換器 Ch.2アナログ信号入力端子                   |                                                                    |

| <b>US_SSI0</b>     | I/O |              | USI Ch.0データ入出力端子(S1C17564)              |                                                                    |

| <b>P03</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | B3                                                                 |

| <b>AIN3</b>        | I   |              | A/D変換器 Ch.3アナログ信号入力端子                   |                                                                    |

| <b>US_SSI1</b>     | I/O |              | USI Ch.1データ入出力端子(S1C17564)              |                                                                    |

| <b>P10</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | B1                                                                 |

| <b>SDI0</b>        | I   |              | SPI Ch.0データ入力端子                         |                                                                    |

| <b>P11</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | C3                                                                 |

| <b>SDO0</b>        | O   |              | SPI Ch.0データ出力端子                         |                                                                    |

| <b>P12</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | C1                                                                 |

| <b>SPICLK0</b>     | I/O |              | SPI Ch.0クロック入出力端子                       |                                                                    |

| <b>P13</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | D2                                                                 |

| <b>#SPISS0</b>     | I   |              | SPI Ch.0スレーブセレクト信号入力端子                  |                                                                    |

| <b>TOUT5</b>       | O   |              | T16A Ch.2 TOUT B信号出力端子                  |                                                                    |

| <b>CAP5</b>        | I   |              | T16A Ch.2キャプチャBトリガ信号入力端子                |                                                                    |

| <b>P14</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | E2                                                                 |

| <b>SIN1</b>        | I   |              | UART Ch.1データ入力端子                        |                                                                    |

| <b>SDI1</b>        | I   |              | SPI Ch.1データ入力端子                         |                                                                    |

| <b>P15</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | E3                                                                 |

| <b>SOUT1</b>       | O   |              | UART Ch.1データ出力端子                        |                                                                    |

| <b>SDO1</b>        | O   |              | SPI Ch.1データ出力端子                         |                                                                    |

| <b>P16</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | F1                                                                 |

| <b>SCLK1</b>       | I   |              | UART Ch.1外部クロック入力端子                     |                                                                    |

| <b>SPICLK1</b>     | I/O |              | SPI Ch.1クロック入出力端子                       |                                                                    |

| <b>P17</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | C5                                                                 |

| <b>SCL0</b>        | I/O |              | I2CマスタSCL入出力端子                          |                                                                    |

| <b>P20</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | D9                                                                 |

| <b>TOUT2</b>       | O   |              | T16A Ch.1 TOUT A信号出力端子                  |                                                                    |

| <b>CAP2</b>        | I   |              | T16A Ch.1キャプチャAトリガ信号入力端子                |                                                                    |

| <b>P21</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | D8                                                                 |

| <b>TOUT3</b>       | O   |              | T16A Ch.1 TOUT B信号出力端子                  |                                                                    |

| <b>CAP3</b>        | I   |              | T16A Ch.1キャプチャBトリガ信号入力端子                |                                                                    |

| <b>P22 (EXCL1)</b> | I/O | I(Pull-up)   | 入出力ポート端子(T16A Ch.1外部クロック入力端子)           | D7                                                                 |

| <b>FOUTB</b>       | O   |              | クロック出力端子                                |                                                                    |

| <b>P23 (EXCL2)</b> | I/O | I(Pull-up)   | 入出力ポート端子(T16A Ch.2外部クロック入力端子)           | C9                                                                 |

| <b>SDI2</b>        | I   |              | SPI Ch.2データ入力端子                         |                                                                    |

| <b>P24 (EXCL3)</b> | I/O | I(Pull-up)   | 入出力ポート端子(T16A Ch.3外部クロック入力端子)           | G2                                                                 |

| <b>SDO2</b>        | O   |              | SPI Ch.2データ出力端子                         |                                                                    |

| <b>P25</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | H2                                                                 |

| <b>#BFR</b>        | I   |              | I2Cスレーブバス解放要求入力端子                       |                                                                    |

| <b>#SPISS2</b>     | I   |              | SPI Ch.2スレーブセレクト信号入力端子                  |                                                                    |

| <b>P26</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | H3                                                                 |

| <b>SDA1</b>        | I/O |              | I2Cスレーブデータ入出力端子                         |                                                                    |

| <b>P27</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | J3                                                                 |

| <b>SCL1</b>        | I/O |              | I2CスレーブSCL入出力端子                         |                                                                    |

| <b>P30</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | J4                                                                 |

| <b>TOUT0</b>       | O   |              | T16A Ch.0 TOUT A信号出力端子                  |                                                                    |

| <b>CAP0</b>        | I   |              | T16A Ch.0キャプチャAトリガ信号入力端子                |                                                                    |

| <b>P31</b>         | I/O | I(Pull-up)   | 入出力ポート端子                                | J5                                                                 |

|             |         |                                      |                                    |                |

|-------------|---------|--------------------------------------|------------------------------------|----------------|

| #BFR        | I       | I2Cスレーブバス解放要求入力端子<br>A/D変換器外部トリガ入力端子 |                                    |                |

| P32         | I/O     | I(Pull-up)                           | 入出力ポート端子<br>T16A Ch.2 TOUT A信号出力端子 | B4             |

|             | O       |                                      | T16A Ch.2キャプチャAトリガ信号入力端子           |                |

|             | I       |                                      | クロック出力端子                           |                |

|             | O       |                                      |                                    |                |

| P33         | I/O     | I(Pull-up)                           | 入出力ポート端子<br>REMC入力端子               | H7             |

|             | I       |                                      | SPI CLK2入出力端子                      |                |

|             | I/O     |                                      | 入出力ポート端子<br>REMC出力端子               |                |

| P34         | I/O     | I(Pull-up)                           | SPI Ch.1スレーブセレクト信号入力端子             | G7             |

|             | O       |                                      | O(H) オンチップデバッグクロック出力端子             |                |

|             | I       |                                      | 入出力ポート端子                           |                |

| P35         | O       | I(Pull-up)                           | オンチップデバッグデータ入出力端子                  | J6             |

|             | I/O     |                                      | 入出力ポート端子                           |                |

|             | I/O     |                                      | O(L) オンチップデバッグステータス出力端子            |                |

| P36         | O       | I(Pull-up)                           | 入出力ポート端子                           | G5             |

|             | I/O     |                                      | UART Ch.0データ入力端子                   |                |

|             | I       |                                      | T16A Ch.3 TOUT A信号出力端子             |                |

| P37         | O       | I(Pull-up)                           | T16A Ch.3キャプチャAトリガ信号入力端子           | A7             |

|             | I/O     |                                      | 入出力ポート端子                           |                |

|             | I       |                                      | UART Ch.0データ出力端子                   |                |

| P38         | I       | I(Pull-up)                           | T16A Ch.3 TOUT B信号出力端子             | B6             |

|             | O       |                                      | T16A Ch.3キャプチャBトリガ信号入力端子           |                |

|             | I       |                                      | 入出力ポート端子                           |                |

| P39         | I/O     | I(Pull-up)                           | UART Ch.0外部クロック入力端子                | A6             |

|             | I       |                                      | T16A Ch.0 TOUT B信号出力端子             |                |

|             | I       |                                      | T16A Ch.0キャプチャBトリガ信号入力端子           |                |

| P40         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | F2             |

|             | O       |                                      | UART Ch.0データ入出力端子                  |                |

|             | I       |                                      | REMC入力端子                           |                |

| P41         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | F3             |

|             | O       |                                      | UART Ch.0データ出力端子                   |                |

|             | O       |                                      | T16A Ch.3 TOUT B信号入力端子             |                |

| P42         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | C6             |

|             | I       |                                      | T16A Ch.0外部クロック入力端子                |                |

|             | O       |                                      | T16A Ch.0 TOUT B信号入力端子             |                |

| P43         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | C2             |

|             | I/O     |                                      | I2Cスレーブデータ入出力端子                    |                |

|             | I       |                                      | REMC出力端子                           |                |

| P44         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | E1             |

|             | I/O     |                                      | I2CスレーブSCL入出力端子                    |                |

|             | O       |                                      | REMC出力端子                           |                |

| P45 (EXCLO) | I/O     | I(Pull-up)                           | 入出力ポート端子 (T16A Ch.0外部クロック入力端子)     | J2             |

|             | I/O     |                                      | I2Cマスターデータ入出力端子                    |                |

| P50         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | H5             |

|             | US SDIO |                                      | USI Ch.0データ入出力端子 (S1C17564)        |                |

|             | O       |                                      | USI Ch.0データ出力端子 (S1C17564)         |                |

| P51         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | F7             |

|             | US SDO0 |                                      | USI Ch.0クロック入出力端子 (S1C17564)       |                |

|             | O       |                                      | USI Ch.1データ入出力端子 (S1C17564)        |                |

| P52         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | J8             |

|             | US SCK0 |                                      | USI Ch.0クロック入出力端子 (S1C17564)       |                |

|             | O       |                                      | USI Ch.1データ出力端子 (S1C17564)         |                |

| P53         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | A1, A9, J1, J9 |

|             | US SDH  |                                      | USI Ch.1データ入出力端子 (S1C17564)        |                |

|             | O       |                                      | USI Ch.1データ出力端子 (S1C17564)         |                |

| P54         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | F1             |

|             | US SDO1 |                                      | USI Ch.1クロック入出力端子 (S1C17564)       |                |

| P55         | I/O     | I(Pull-up)                           | 入出力ポート端子                           | J8             |

|             | US SCK1 |                                      | USI Ch.1データ出力端子 (S1C17564)         |                |

| N.C.        |         |                                      | 未使用端子*                             |                |

\* 未使用端子についても基板上にランドパターンを設け実装してください。

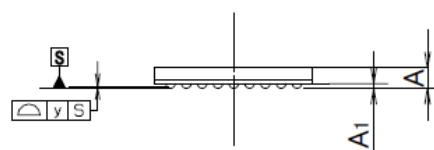

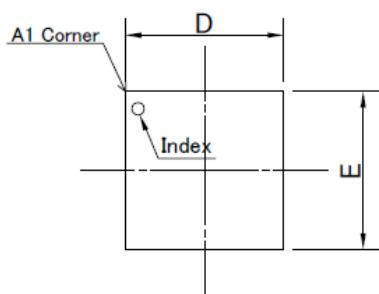

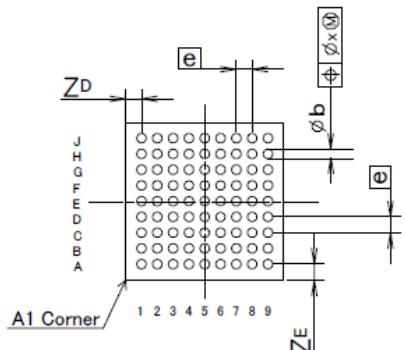

## 26 パッケージ (P.26-1)

(誤)

-

(正)

追加

Top ViewBottom View

| Symbol         | Dimension in Millimeters |      |      |

|----------------|--------------------------|------|------|

|                | Min                      | Nom  | Max  |

| D              | -                        | 5    | -    |

| E              | -                        | 5    | -    |

| A              | -                        | -    | 1.0  |

| A <sub>1</sub> | -                        | 0.23 | -    |

| [e]            | -                        | 0.5  | -    |

| b              | 0.26                     | -    | 0.36 |

| x              | -                        | -    | 0.08 |

| y              | -                        | -    | 0.1  |

| Z <sub>D</sub> | -                        | 0.5  | -    |

| Z <sub>E</sub> | -                        | 0.5  | -    |

1 = 1mm

## S1C17 マニュアル正誤表

| 項目 USI/USIL AC 特性       |           |                        |      |  |  |

|-------------------------|-----------|------------------------|------|--|--|

| 対象マニュアル                 | 発行 No.    | 項目                     | ページ  |  |  |

| S1C17554/564 テクニカルマニュアル | 411914303 | 24.11 USI 特性(S1C17564) | 24-8 |  |  |

24-8

(誤)

### SPI マスタモード(8 または 9 ビット, ノーマルモード)

特記なき場合: HVDD = 1.65~5.5V, VSS = 0V, Ta = -40~85° C

| 項目               | 記号    | Min.       | Typ. | Max. | 単位 |

|------------------|-------|------------|------|------|----|

| spi_sck サイクル時間   | tSPCK | 85 + tPCLK | -    | -    | ns |

| spi_sdi セットアップ時間 | tSDS  | 85 + tPCLK | -    | -    | ns |

### SPI マスタモード(8 または 9 ビット, ファストモード)

特記なき場合: HVDD = 1.65~5.5V, VSS = 0V, Ta = -40~85° C

| 項目               | 記号    | Min. | Typ. | Max. | 単位 |

|------------------|-------|------|------|------|----|

| spi_sck サイクル時間   | tSPCK | 85   | -    | -    | ns |

| spi_sdi セットアップ時間 | tSDS  | 85   | -    | -    | ns |

(正)

### SPI マスタモード(8 または 9 ビット, ノーマルモード)

特記なき場合: HVDD = 1.65~5.5V, VSS = 0V, Ta = -40~85° C

| 項目               | 記号    | Min.                    | Typ. | Max. | 単位 |

|------------------|-------|-------------------------|------|------|----|

| spi_sck サイクル時間   | tSPCK | <b>(85 + tPCLK) x 2</b> | -    | -    | ns |

| spi_sdi セットアップ時間 | tSDS  | 85 + tPCLK              | -    | -    | ns |

### SPI マスタモード(8 または 9 ビット, ファストモード)

特記なき場合: HVDD = 1.65~5.5V, VSS = 0V, Ta = -40~85° C

| 項目               | 記号    | Min.          | Typ. | Max. | 単位 |

|------------------|-------|---------------|------|------|----|

| spi_sck サイクル時間   | tSPCK | <b>85 x 2</b> | -    | -    | ns |

| spi_sdi セットアップ時間 | tSDS  | 85            | -    | -    | ns |

## S1C17 シリーズテクニカルマニュアル正誤表

| 項目 T16A/T16A2 の CBUFEN レジスタについて                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-------|

| 対象マニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 発行 No.    | 項目            | ページ   |

| S1C17624/604/622/602/621 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                          | 411914802 | 13.8 制御レジスタ詳細 | 13-15 |

| S1C17705/703 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                      | 411706502 | 10.8 制御レジスタ詳細 | 10-18 |

| S1C17706 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                          | 412026301 | 10.8 制御レジスタ詳細 | 10-17 |

| S1C17711 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                          | 411905502 | 10.8 制御レジスタ詳細 | 10-14 |

| S1C17554/564 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                      | 411914302 | 11.8 制御レジスタ詳細 | 11-14 |

| S1C17651 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                          | 412120500 | 12.8 制御レジスタ詳細 | 12-13 |

| <b>13-15 ページ</b> S1C17624/604/622/602/621 テクニカルマニュアル<br><b>10-17 ページ</b> S1C17706 テクニカルマニュアル<br><b>12-13 ページ</b> S1C17651 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                         |           |               |       |

| (誤)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |               |       |

| <b>D3 CBUFEN: Compare Buffer Enable Bit</b><br>コンペアバッファを有効/無効に設定します。<br>1(R/W): 有効<br>0(R/W): 無効(デフォルト)<br>CBUFEN を 1 に設定するとコンペアバッファが有効になり、コンパレータはコンペア A、コンペア B レジスタの代わりにコンペア A、コンペア B バッファとカウンタ値を比較してコンペア A、コンペア B 信号を生成します。ソフトウェアでコンペア A、コンペア B レジスタに書き込んだ比較値は、コンペア B 信号が発生した時点でコンペア A、コンペア B バッファにロードされます。<br>CBUFEN を 0 に設定するとコンペアバッファが無効となり、コンパレータはコンペア A、コンペア B レジスタとカウンタ値を比較してコンペア A、コンペア B 信号を生成します。<br>注: CBUFEN の設定は、カウンタが停止中 (PRUN = 0) に行ってください。 |           |               |       |

| (正)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |               |       |

| <b>D3 CBUFEN: Compare Buffer Enable Bit</b><br>コンペアバッファを有効/無効に設定します。                                                                                                                                                                                                                                                                                                                                                                                         |           |               |       |

1(R/W): 有効

0(R/W): 無効(デフォルト)

CBUFENを1に設定するとコンペアバッファが有効になり、コンパレータはコンペアA、コンペアBレジスタの代わりにコンペアA、コンペアBバッファとカウンタ値を比較してコンペアA、コンペアB信号を生成します。ソフトウェアでコンペアA、コンペアBレジスタに書き込んだ比較値は、コンペアB信号が発生した時点でコンペアA、コンペアBバッファにロードされます。

CBUFENを0に設定するとコンペアバッファが無効となり、コンパレータはコンペアA、コンペアBレジスタとカウンタ値を比較してコンペアA、コンペアB信号を生成します。

注: CBUFENの設定は、カウンタが停止中(**CLKEN** = 0)に行ってください。

10-18 ページ S1C17705/703 テクニカルマニュアル

10-14 ページ S1C17711 テクニカルマニュアル

11-14 ページ S1C17554/564 テクニカルマニュアル

(誤)

### D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファへの書き込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

CBUFENが1に設定されていると、コンペアデータの書き込みがコンペアデータバッファに対して行われます。

バッファの内容は、コンペアB信号が発生した時点でコンペアAおよびコンペアBレジスタにロードされます。

CBUFENが0に設定されている場合は、コンペアデータの書き込みがコンペアAおよびコンペアBレジスタに対して直接行われます。

注: CBUFENの設定は、カウンタが停止中(**PRUN** = 0)に行ってください。

(正)

### D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファへの書き込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

CBUFENが1に設定されていると、コンペアデータの書き込みがコンペアデータバッファに対して行われます。

バッファの内容は、コンペアB信号が発生した時点でコンペアAおよびコンペアBレジスタにロードされます。

CBUFENが0に設定されている場合は、コンペアデータの書き込みがコンペアAおよびコンペアBレジスタに対して直接行われます。

注: CBUFENの設定は、カウンタが停止中(**CLKEN** = 0)に行ってください。