## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 I2CM 入出力端子       |           |                    |        |

|---------------------|-----------|--------------------|--------|

| 対象マニュアル             | 発行 No.    | 項目                 | ページ    |

| S1C17601 テクニカルマニュアル | 411806001 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17611 テクニカルマニュアル | 411882201 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17701 テクニカルマニュアル | 411089703 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17704 テクニカルマニュアル | 411511803 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17706 テクニカルマニュアル | 412026301 | 17.2 I2CM 入出力端子    | 17-1   |

| S1C17001 テクニカルマニュアル | 411412002 | 20.2 I2C 入出力端子     | 252    |

| S1C17002 テクニカルマニュアル | 411554302 | V.2.2 I2C マスタ入出力端子 | V-2-2  |

| S1C17003 テクニカルマニュアル | 411635002 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17501 テクニカルマニュアル | 411525502 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17801 テクニカルマニュアル | 411390602 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17803 テクニカルマニュアル | 411820701 | 20.2 I2CM 入出力端子    | 20-1   |

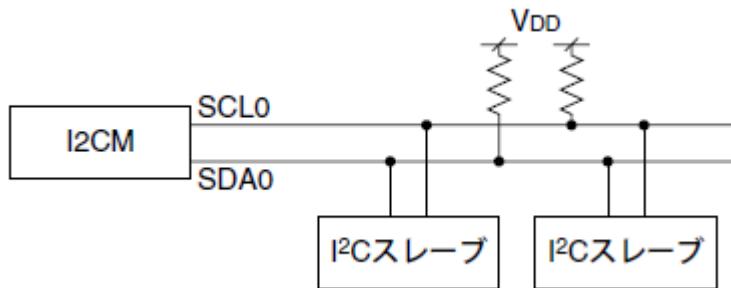

(追加)

注: ポート機能切り換え時は、端子がハイインピーダンスになります。High レベルは出力しませんので、SCL と SDA ラインは外部で VDD レベルにプルアップしてください。なお、VDD を超える電圧値にはプルアップしないでください。

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 ポート入力割り込みについて                                                                                                                                                                   |           |                                           |                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------|-------------------|

| 対象マニュアル                                                                                                                                                                            | 発行 No.    | 項目                                        | ページ               |

| S1C17501 テクニカルマニュアル                                                                                                                                                                | 411525502 | IV.1 割り込みコントローラ(ITC)<br>VII.1.5 ポート入力割り込み | IV-1-1<br>VII-1-3 |

| S1C17801 テクニカルマニュアル                                                                                                                                                                | 411390603 | IV.1 割り込みコントローラ(ITC)<br>VII.1.5 ポート入力割り込み | IV-1-1<br>VII-1-3 |

|                                                                                                                                                                                    |           |                                           |                   |

| <b>VII-1-3 ページ S1C17501 テクニカルマニュアル</b>                                                                                                                                             |           |                                           |                   |

| <b>VII-1-3 ページ S1C17801 テクニカルマニュアル</b>                                                                                                                                             |           |                                           |                   |

| (誤)                                                                                                                                                                                |           |                                           |                   |

| <b>VII.1.5 ポート入力割り込み</b>                                                                                                                                                           |           |                                           |                   |

| GPIOモジュールは8本の割り込み系列(ポート入力割り込み0～7)を持ち、それぞれの割り込み要因を発生するポートを選択することができます。割り込み条件についても、入力信号のエッジ(立ち上がりエッジまたは立ち下がりエッジ)で割り込みを発生させるか、レベル(HighレベルまたはLowレベル)によって発生させるか、割り込みコントローラ(ITC)で選択可能です。 |           |                                           |                   |

| 図 VII.1.5.1 にポート入力割り込み回路の構成を示します。                                                                                                                                                  |           |                                           |                   |

| (正)                                                                                                                                                                                |           |                                           |                   |

| <b>VII.1.5 ポート入力割り込み</b>                                                                                                                                                           |           |                                           |                   |

| GPIOモジュールは8本の割り込み系列(ポート入力割り込み0～7)を持ち、それぞれの割り込み要因を発生するポートを選択することができます。割り込みは、レベル(HighレベルまたはLowレベル)によって発生させることができ、設定は割り込みコントローラ(ITC)で行います。                                            |           |                                           |                   |

| 図 VII.1.5.1 にポート入力割り込み回路の構成を示します。                                                                                                                                                  |           |                                           |                   |

VII-1-4 ページ S1C17501 テクニカルマニュアル

VII-1-4 ページ S1C17801 テクニカルマニュアル

(誤)

### VII.1.5.2 割り込みコントローラの制御レジスタ

#### トリガモードと極性の選択

割り込みコントローラ(ITC)は、ポート割り込み要求をパルス信号とレベル信号のどちらでも受け付けられるように、パルストリガモードとレベルトリガモードの2つの割り込みモードを持っています。

トリガモードは、ITC\_ELVxレジスタ(0x4306～0x430c)のEITG<sub>x</sub>ビットで選択できます。EITG<sub>x</sub>を1に設定するとレベルトリガモードが選択され、0(デフォルト)に設定するとパルストリガモードが選択されます。

また、ITCに入力するポート入力割り込み要求信号の極性もITC\_ELVxレジスタ(0x4306～0x430c)内のEITPxビットで選択できます。EITPxを1に設定すると正極性パルス/立ち上がりエッジ(パルストリガモード時)またはアクティブHigh(レベルトリガモード時)が選択され、0(デフォルト)に設定すると負極性パルス/立ち下がりエッジ(パルストリガモード時)またはアクティブLow(レベルトリガモード時)が選択されます。

.....

これらのレジスタにより、ポート入力割り込み条件は表VII.1.5.2.2のようになります。

表VII.1.5.2.2 ポート入力割り込み条件

| EITG <sub>x</sub> | EITPx | ポート入力割り込み条件 |

|-------------------|-------|-------------|

| 1                 | 1     | Highレベル     |

| 1                 | 0     | Lowレベル      |

| 0                 | 1     | 立ち上がりエッジ    |

| 0                 | 0     | 立ち下がりエッジ    |

(正)

### VII.1.5.2 割り込みコントローラの制御レジスタ

#### トリガモードと極性の選択

割り込みコントローラ(ITC)は、ポート割り込み要求をレベル信号を受け付けられるように、レベルトリガモードの割り込みモードを持っています。

トリガモードは、ITC\_ELVxレジスタ(0x4306～0x430c)のEITG<sub>x</sub>ビットで選択できます。EITG<sub>x</sub>を1に設定することでレベルトリガモードが選択されます。EITG<sub>x</sub>のデフォルトは0になっていますので、割り込みを使用する場合は1に変更して使用します。

また、ITCに入力するポート入力割り込み要求信号の極性もITC\_ELVxレジスタ(0x4306～0x430c)内のEITPxビットで選択できます。EITPxを1に設定するとアクティブHigh(レベルトリガモード時)が選択され、0(デフォルト)に設定するとアクティブLow(レベルトリガモード時)が選択されます。

.....

これらのレジスタにより、ポート入力割り込み条件は表VII.1.5.2.2のようになります。

表VII.1.5.2.2 ポート入力割り込み条件

| EITG <sub>x</sub> | EITPx | ポート入力割り込み条件 |

|-------------------|-------|-------------|

| 1                 | 1     | Highレベル     |

| 1                 | 0     | Lowレベル      |

| 0                 | 1     | 未サポート       |

| 0                 | 0     | 未サポート       |

VII-1-11 ページ S1C17501 テクニカルマニュアル

VII-1-11 ページ S1C17801 テクニカルマニュアル

(誤)

### **VII.1.7 注意事項**

.....

- パルストリガ割り込みモードを選択した場合、割り込みを確実に発生させるには、システムクロックの 1 サイクル以上のパルス幅を持つ信号を入力する必要があります。

(正)

### **VII.1.7 注意事項**

.....

- ~~パルストリガ割り込みモードを選択した場合、割り込みを確実に発生させるには、システムクロックの 1 サイクル以上のパルス幅を持つ信号を入力する必要があります。~~

- レベル割り込みは、割り込みを発生させる機器とハンドシェイクが必要です。S1C17 コアが割り込みを受け付けるまで外部機器はレベルを保持し、受付後、外部機器に対して ack を返すようにしてください。

## IV-1-2 ページ S1C17501 テクニカルマニュアル

## IV-1-2 ページ S1C17801 テクニカルマニュアル

(誤)

(正)の取消部分のないもの。

(正)

表 IV.1.2.1 ベクターテーブル

| ベクタNo.        | ベクタアドレス     | ハードウェア割り込み名          | ハードウェア割り込み要因                                                      | 優先順位         |

|---------------|-------------|----------------------|-------------------------------------------------------------------|--------------|

| 0 (0x00)      | TTBR + 0x00 | リセット                 | · #RESET 端子へのLow 入力・ウォッチドッグタイマオーバーフロー*2                           | 1            |

| 1 (0x01)      | TTBR + 0x04 | アドレス不整割り込み           | メモリアクセス命令                                                         | 2            |

| - (0xffffc00) |             | デバッグ割り込み             | brk命令等                                                            | 3            |

| 2 (0x02)      | TTBR + 0x08 | NMI                  | · #NMI 端子へのLow 入力・ウォッチドッグタイマオーバーフロー*2                             | 4            |

| 3 (0x03)      | TTBR + 0x0c | Cコンバイラ(reserved)     | Cコンバイラのエミュレーションライブラリが使用                                           | 5            |

| 4 (0x04)      | TTBR + 0x10 | ポート入力割り込み0           | Px0入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      | High *1<br>↑ |

| 5 (0x05)      | TTBR + 0x14 | ポート入力割り込み1           | Px1入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

| 6 (0x06)      | TTBR + 0x18 | ポート入力割り込み2           | Px2入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

| 7 (0x07)      | TTBR + 0x1c | ポート入力割り込み3           | Px3入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

| 8 (0x08)      | TTBR + 0x20 | MFT 割り込み             | · コンペアマッチ・ピリオドマッチ<br>· ADC プロテクション入力<br>· ポートプロテクション入力            |              |

| 9 (0x09)      | TTBR + 0x24 | reserved             | -                                                                 |              |

| 10 (0x0a)     | TTBR + 0x28 | A/D変換器割り込み           | 範囲外(上限/下限)                                                        |              |

| 11 (0x0b)     | TTBR + 0x2c |                      | 変換完了                                                              |              |

| 12 (0x0c)     | TTBR + 0x30 | CLG_T16U0 タイマ割り込み    | タイマアンダーフロー                                                        | Low *1<br>↓  |

|               |             |                      | ポート入力割り込み4                                                        |              |

| 13 (0x0d)     | TTBR + 0x34 | CLG_T8S タイマ割り込み      | Px4入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

| 14 (0x0e)     | TTBR + 0x38 |                      | ポート入力割り込み5                                                        |              |

| 15 (0x0f)     | TTBR + 0x3c | CLG_T8I タイマ割り込み      | Px5入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

|               |             |                      | ポート入力割り込み6                                                        |              |

| 16 (0x10)     | TTBR + 0x40 | UART(+I2DA)CH.0 割り込み | Px6入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

|               |             |                      | · 送信バッファエンプティ<br>· 受信バッファフル<br>· 受信エラー                            |              |

| 17 (0x11)     | TTBR + 0x44 | ポート入力割り込み4           | Px4入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

| 18 (0x12)     | TTBR + 0x48 | SPI CH.0 割り込み        | Px5入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

|               |             |                      | · 送信バッファエンプティ・受信バッファフル                                            |              |

| 19 (0x13)     | TTBR + 0x4c | I2C割り込み              | Px6入力(立ち上がり/下がりエッジまたはH/Lレベル)                                      |              |

|               |             |                      | · 送信バッファエンプティ・受信バッファフル                                            |              |

| 20 (0x14)     | TTBR + 0x50 | RTC 割り込み             | 1/64 秒、1秒、1分、または1時間カウントアップ                                        |              |

| 21 (0x15)     | TTBR + 0x54 | PT8 CH.0 割り込み        | タイマ0アンダーフロー                                                       |              |

| 22 (0x16)     | TTBR + 0x58 | PT8 CH.1 割り込み        | タイマ1アンダーフロー                                                       |              |

| 23 (0x17)     | TTBR + 0x5c | PT8 CH.2 割り込み        | タイマ2アンダーフロー                                                       |              |

| 24 (0x18)     | TTBR + 0x60 | PT8 CH.3 割り込み        | タイマ3アンダーフロー                                                       |              |

| 25 (0x19)     | TTBR + 0x64 | LCDC 割り込み            | · フレームエンド<br>· SPI 転送終了<br>· DMA 転送終了                             |              |

| 26 (0x1a)     | TTBR + 0x68 | SPI CH.1 割り込み        | · 送信バッファエンプティ・受信バッファフル                                            |              |

| 27 (0x1b)     | TTBR + 0x6c | USB 割り込み             | USB 割り込み                                                          |              |

| 28 (0x1c)     | TTBR + 0x70 | I2S割り込み              | · I2S FIFO エンプティ                                                  |              |

| 29 (0x1d)     | TTBR + 0x74 |                      | · I2S FIFO フル                                                     |              |

| 30 (0x1e)     | TTBR + 0x78 | REMC 割り込み            | · エンベロープカウンタアンダーフロー<br>· REMC_IN立ち上がりエッジ検出<br>· REMC_IN立ち下がりエッジ検出 |              |

| 31 (0x1f)     | TTBR + 0x7c | reserved             | -                                                                 |              |

IV-1-2 ページ S1C17501 テクニカルマニュアル

IV-1-2 ページ S1C17801 テクニカルマニュアル

(誤)

(正)の取消部分のないもの。

(正)

表 IV.1.3.2.1 ハードウェア割り込み要因と割り込みフラグ

| ハードウェア割り込み要求                                       | 割り込みフラグ                    |

|----------------------------------------------------|----------------------------|

| I2C割り込み: 送信バッファエンプティ/受信バッファフル                      | IIFT7(D15/ITC_IFLG レジスタ)   |

| SPI CH.0 割り込み: 送信バッファエンプティ/受信バッファフル                | IIFT6(D14/ITC_IFLG レジスタ)   |

| UART 割り込み: 送信バッファエンプティ/受信バッファフル/受信エラー              | IIFT4(D12/ITC_IFLG レジスタ)   |

| CLG_T8I タイマ割り込み: タイマアンダーフロー                        | IIFT3(D11/ITC_IFLG レジスタ)   |

| CLG_T8S タイマ割り込み: タイマアンダーフロー                        | IIFT2(D10/ITC_IFLG レジスタ)   |

| CLG_T16U0 タイマ割り込み: タイマアンダーフロー                      | IIFT0(D8/ITC_IFLG レジスタ)    |

| ポート入力割り込み7: Px7立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT7(D7/ITC_IFLG レジスタ)    |

| ポート入力割り込み6: Px6立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT6(D6/ITC_IFLG レジスタ)    |

| ポート入力割り込み5: Px5立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT5(D5/ITC_IFLG レジスタ)    |

| ポート入力割り込み4: Px4立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT4(D4/ITC_IFLG レジスタ)    |

| ポート入力割り込み3: Px3立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT3(D3/ITC_IFLG レジスタ)    |

| ポート入力割り込み2: Px2立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT2(D2/ITC_IFLG レジスタ)    |

| ポート入力割り込み1: Px1立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT1(D1/ITC_IFLG レジスタ)    |

| ポート入力割り込み0: Px0立ち上がり/立ち下がりエッジまたはH/Lレベル入力           | EIFT0(D0/ITC_IFLG レジスタ)    |

| REMC 割り込み: エンベロープカウンタアンダーフロー/入力立ち上がりエッジ/入力立ち下がりエッジ | AIFT14(D14/ITC_AIFLG レジスタ) |

| I2S割り込み: I2S FIFO フル                               | AIFT13(D13/ITC_AIFLG レジスタ) |

| I2S割り込み: I2S FIFO エンプティ                            | AIFT12(D12/ITC_AIFLG レジスタ) |

| USB 割り込み: USB 割り込み                                 | AIFT11(D11/ITC_AIFLG レジスタ) |

| SPI CH.1 割り込み: 送信バッファエンプティ/受信バッファフル                | AIFT10(D10/ITC_AIFLG レジスタ) |

| LCDC 割り込み: フレームエンド/SPI 転送終了/DMA 転送終了               | AIFT9(D9/ITC_AIFLG レジスタ)   |

| PT8 CH.3 割り込み: タイマアンダーフロー                          | AIFT8(D8/ITC_AIFLG レジスタ)   |

| PT8 CH.2 割り込み: タイマアンダーフロー                          | AIFT7(D7/ITC_AIFLG レジスタ)   |

| PT8 CH.1 割り込み: タイマアンダーフロー                          | AIFT6(D6/ITC_AIFLG レジスタ)   |

| PT8 CH.0 割り込み: タイマアンダーフロー                          | AIFT5(D5/ITC_AIFLG レジスタ)   |

| RTC 割り込み: 1/64 秒、1秒、1分、または1時間カウントアップ               | AIFT4(D4/ITC_AIFLG レジスタ)   |

| ADC 割り込み: 変換終了                                     | AIFT3(D3/ITC_AIFLG レジスタ)   |

| ADC 割り込み: 範囲外                                      | AIFT2(D2/ITC_AIFLG レジスタ)   |

| MFT 割り込み: コンペアマッチ/ピリオドマッチ/保護入力                     | AIFT0(D0/ITC_AIFLG レジスタ)   |

IV-1-7 ページ S1C17501 テクニカルマニュアル

IV-1-7 ページ S1C17801 テクニカルマニュアル

(誤)

#### IV.1.3.5 割り込みのトリガモード

ポート入力割り込みにはパルストリガモードおよびレベルトリガモードの2つのトリガモードが用意され

ており、ITCはポート入力割り込み要求をパルス信号またはレベル信号として受け付けることができます。

トリガモードはITC\_ELV $x$ レジスタ(0x4306～0x430c)内のEITG $x$ ビットで選択できます。EITG $x$ を1に設定

するとレベルトリガモードが選択され、0(デフォルト)に設定するとパルストリガモードが選択されます。

また、ITCに入力するこれらの割り込み要求信号の極性もITC\_ELV $x$ レジスタ(0x4306～0x430c)内のEITP $x$

ビットで選択できます。EITP $x$ を1に設定すると正極性パルス/立ち上がりエッジ(パルストリガモード時)

またはアクティブHigh(レベルトリガモード時)が選択され、0(デフォルト)に設定すると負極性パルス/立

ち下がりエッジ(パルストリガモード時)またはアクティブLow(レベルトリガモード時)が選択されます。

(正)

#### IV.1.3.5 割り込みのトリガモード

ポート入力割り込みにはパルストリガモードおよびレベルトリガモードの2つのトリガモードが用意され

ており、ITCはポート入力割り込み要求をパルス信号またはレベル信号として受け付けることができます。

トリガモードはITC\_ELV $x$ レジスタ(0x4306～0x430c)内のEITG $x$ ビットで選択できます。EITG $x$ を1に設定

するとレベルトリガモードが選択されます。

また、ITCに入力するこれらの割り込み要求信号の極性もITC\_ELV $x$ レジスタ(0x4306～0x430c)内のEITP $x$

ビットで選択できます。EITP $x$ を1に設定すると正極性パルス/立ち上がりエッジ(パルストリガモード時)

またはアクティブHigh(レベルトリガモード時)が選択され、0(デフォルト)に設定すると負極性パルス/立

ち下がりエッジ(パルストリガモード時)またはアクティブLow(レベルトリガモード時)が選択されます。

IV-1-27、28 ページ S1C17501 テクニカルマニュアル

IV-1-27、28 ページ S1C17801 テクニカルマニュアル

(誤)

**0x4306: External Interrupt Level Setup Register 0 (ITC\_ELVO)**

| Register name                                                | Address             | Bit    | Name       | Function                          | Setting |          | Init. | R/W      | Remarks            |

|--------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|----------|-------|----------|--------------------|

| External<br>Interrupt Level<br>Setup Register0<br>(ITC_ELVO) | 0x4306<br>(16 bits) | D15–14 | –          | reserved                          | –       | –        | –     | –        | 0 when being read. |

|                                                              |                     | D13    | EITP1      | Port interrupt 1 trigger polarity | 1       | Positive | 0     | Negative | 0 R/W              |

|                                                              |                     | D12    | EITG1      | Port interrupt 1 trigger mode     | 1       | Level    | 0     | Pulse    | 0 R/W              |

|                                                              |                     | D11    | –          | reserved                          | –       | –        | –     | –        | 0 when being read. |

|                                                              |                     | D10–8  | EILV1[2:0] | Port interrupt 1 level            | 0 to 7  |          |       | 0x0 R/W  |                    |

|                                                              |                     | D7–6   | –          | reserved                          | –       | –        | –     | –        | 0 when being read. |

|                                                              |                     | D5     | EITP0      | Port interrupt 0 trigger polarity | 1       | Positive | 0     | Negative | 0 R/W              |

|                                                              |                     | D4     | EITG0      | Port interrupt 0 trigger mode     | 1       | Level    | 0     | Pulse    | 0 R/W              |

|                                                              |                     | D3     | –          | reserved                          | –       | –        | –     | –        | 0 when being read. |

|                                                              |                     | D2–0   | EILV0[2:0] | Port interrupt 0 level            | 0 to 7  |          |       | 0x0 R/W  |                    |

**D13 EITP1: Port Interrupt 1 Trigger Polarity Bit**

ポート割り込み1信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

パルストリガモードの場合にこのビットが1に設定されると、ポートはITCへの割り込み要求として正極性パルスを出力します。0に設定されている場合は負極性パルスを出力します。

レベルトリガモードの場合にこのビットが1に設定されると、ポートはITCへの割り込み要求としてアクティブHighの信号を出力します。0に設定されている場合はアクティブLowの信号を出力します。

**D12 EITG1: Port Interrupt 1 Trigger Mode Bit**

ポート割り込み1のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

パルストリガモードの場合、ITCは割り込み信号をシステムクロックの立ち上がりエッジでサンプリングします。指定極性のパルスが検出されると、ITCは割り込みフラグ(EIFT<sub>x</sub>)を1にセットし、その割り込み信号のサンプリングを停止します。アプリケーションプログラム(割り込み処理ルーチン)が割り込みフラグ(EIFT<sub>x</sub>)を0にリセット後、ITCはこの割り込み信号のサンプリングを再開します。

レベルトリガモードの場合、ITCは割り込み信号をシステムクロックの立ち上がりエッジで連続的にサンプリングします。割り込みフラグ(EIFT<sub>x</sub>)はHighレベルが検出されると1に設定され、その後Lowレベルが検出されると0にリセットされます。このモードでは1の書き込みで割り込みフラグ(EIFT<sub>x</sub>)をリセットすることはできません。したがって、割り込み発生源モジュールが、S1C17コアに受け付けられるまで割り込み信号をHighに保持し、その後割り込み信号をクリアする必要があります。

**D5 EITP0: Port Interrupt 0 Trigger Polarity Bit**

ポート割り込み0信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

EITP1(D13)の説明を参照してください。

**D4 EITG0: Port Interrupt 0 Trigger Mode Bit**

ポート割り込み0のトリガモードを選択します。

1(R/W): レベルトリガモード

0(R/W): パルストリガモード(デフォルト)

EITG1(D12)の説明を参照してください。

(正)

**0x4306: External Interrupt Level Setup Register 0 (ITC\_ELV0)**

| Register name                                       | Address          | Bit    | Name       | Function                          | Setting |             |   | Init.      | R/W | Remarks            |

|-----------------------------------------------------|------------------|--------|------------|-----------------------------------|---------|-------------|---|------------|-----|--------------------|

| External Interrupt Level Setup Register0 (ITC_ELV0) | 0x4306 (16 bits) | D15~14 | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                     |                  | D13    | EITP1      | Port interrupt 1 trigger polarity | 1       | Active high | 0 | Active low | 0   | R/W                |

|                                                     |                  | D12    | EITG1      | Port interrupt 1 trigger mode     | 1       | Level       | 0 | No support | 0   | R/W                |

|                                                     |                  | D11    | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                     |                  | D10~8  | EILV1[2:0] | Port interrupt 1 level            | 0 to 7  |             |   | 0x0        | R/W |                    |

|                                                     |                  | D7~6   | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                     |                  | D5     | EITP0      | Port interrupt 0 trigger polarity | 1       | Active high | 0 | Active low | 0   | R/W                |

|                                                     |                  | D4     | EITG0      | Port interrupt 0 trigger mode     | 1       | Level       | 0 | No support | 0   | R/W                |

|                                                     |                  | D3     | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                     |                  | D2~0   | EILV0[2:0] | Port interrupt 0 level            | 0 to 7  |             |   | 0x0        | R/W |                    |

.....

**D13 EITP1: Port Interrupt 1 Trigger Polarity Bit**

ポート割り込み1信号の極性を選択します。

1(R/W): 正極性/アクティブHigh

0(R/W): 負極性/アクティブLow(デフォルト)

パルストリガモードの場合にこのビットが1に設定されていると、ポートはITCへの割り込み要求として正極性パルスを出力します。0に設定されている場合は負極性パルスを出力します。

レベルトリガモードの場合にこのビットが1に設定されていると、ポートはITCへの割り込み要求としてアクティブHighの信号を出力します。0に設定されている場合はアクティブLowの信号を出力します。

**D12 EITG1: Port Interrupt 1 Trigger Mode Bit**

ポート割り込み1のトリガモードを選択します。

1(R/W): レベルトリガモード

0(R/W): 未サポート(デフォルト)

パルストリガモードの場合、ITCは割り込み信号をシステムクロックの立ち上がりエッジでサンプリングします。指定極性のパルスが検出されると、ITCは割り込みフラグ(EIFT<sub>x</sub>)を1にセットし、その割り込み信号のサンプリングを停止します。アプリケーションプログラム(割り込み処理ルーチン)が割り込みフラグ(EIFT<sub>x</sub>)を0にリセット後、ITCはこの割り込み信号のサンプリングを再開します。

レベルトリガモードの場合、ITCは割り込み信号をシステムクロックの立ち上がりエッジで連続的にサンプリングします。割り込みフラグ(EIFT<sub>x</sub>)はHighレベルが検出されると1に設定され、その後Lowレベルが検出されると0にリセットされます。このモードでは1の書き込みで割り込みフラグ(EIFT<sub>x</sub>)をリセットすることはできません。したがって、割り込み発生源モジュールが、S1C17コアに受け付けられるまで割り込み信号をHighに保持し、その後割り込み信号をクリアする必要があります。

.....

**D5 EITP0: Port Interrupt 0 Trigger Polarity Bit**

ポート割り込み0信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

EITP1 (D13) の説明を参照してください。

**D4 EITG0: Port Interrupt 0 Trigger Mode Bit**

ポート割り込み0のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

EITG1 (D12) の説明を参照してください。

IV-1-29 ページ S1C17501 テクニカルマニュアル

IV-1-29 ページ S1C17801 テクニカルマニュアル

(誤)

### 0x4308: External Interrupt Level Setup Register 1 (ITC\_ELV1)

| Register name                                                | Address             | Bit    | Name       | Function                          | Setting |          |   | Init.    | R/W | Remarks            |

|--------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|----------|---|----------|-----|--------------------|

| External<br>Interrupt Level<br>Setup Register1<br>(ITC_ELV1) | 0x4308<br>(16 bits) | D15–14 | –          | reserved                          | –       |          |   | –        | –   | 0 when being read. |

|                                                              |                     | D13    | EITP3      | Port interrupt 3 trigger polarity | 1       | Positive | 0 | Negative | 0   | R/W                |

|                                                              |                     | D12    | EITG3      | Port interrupt 3 trigger mode     | 1       | Level    | 0 | Pulse    | 0   | R/W                |

|                                                              |                     | D11    | –          | reserved                          | –       |          |   | –        | –   | 0 when being read. |

|                                                              |                     | D10–8  | EILV3[2:0] | Port interrupt 3 level            | 0 to 7  |          |   | 0x0      | R/W |                    |

|                                                              |                     | D7–6   | –          | reserved                          | –       |          |   | –        | –   | 0 when being read. |

|                                                              |                     | D5     | EITP2      | Port interrupt 2 trigger polarity | 1       | Positive | 0 | Negative | 0   | R/W                |

|                                                              |                     | D4     | EITG2      | Port interrupt 2 trigger mode     | 1       | Level    | 0 | Pulse    | 0   | R/W                |

|                                                              |                     | D3     | –          | reserved                          | –       |          |   | –        | –   | 0 when being read. |

|                                                              |                     | D2–0   | EILV2[2:0] | Port interrupt 2 level            | 0 to 7  |          |   | 0x0      | R/W |                    |

.....

#### D13 EITP3: Port Interrupt 3 Trigger Polarity Bit

ポート割り込み3信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

#### D12 EITG3: Port Interrupt 3 Trigger Mode Bit

ポート割り込み3のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

.....

#### D5 EITP2: Port Interrupt 2 Trigger Polarity Bit

ポート割り込み2信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

#### D4 EITG2: Port Interrupt 2 Trigger Mode Bit

ポート割り込み2のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

(正)

**0x4308: External Interrupt Level Setup Register 1 (ITC\_ELV1)**

| Register name                                                | Address             | Bit    | Name       | Function                          | Setting |             |   | Init.      | R/W | Remarks            |

|--------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|-------------|---|------------|-----|--------------------|

| External<br>Interrupt Level<br>Setup Register1<br>(ITC_ELV1) | 0x4308<br>(16 bits) | D15–14 | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                              |                     | D13    | EITP3      | Port interrupt 3 trigger polarity | 1       | Active high | 0 | Active low | 0   | R/W                |

|                                                              |                     | D12    | EITG3      | Port interrupt 3 trigger mode     | 1       | Level       | 0 | No support | 0   | R/W                |

|                                                              |                     | D11    | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                              |                     | D10–8  | EILV3[2:0] | Port interrupt 3 level            | 0 to 7  |             |   | 0x0        | R/W |                    |

|                                                              |                     | D7–6   | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                              |                     | D5     | EITP2      | Port interrupt 2 trigger polarity | 1       | Active high | 0 | Active low | 0   | R/W                |

|                                                              |                     | D4     | EITG2      | Port interrupt 2 trigger mode     | 1       | Level       | 0 | No support | 0   | R/W                |

|                                                              |                     | D3     | –          | reserved                          | –       | –           | – | –          | –   | 0 when being read. |

|                                                              |                     | D2–0   | EILV2[2:0] | Port interrupt 2 level            | 0 to 7  |             |   | 0x0        | R/W |                    |

.....

**D13 EITP3: Port Interrupt 3 Trigger Polarity Bit**

ポート割り込み3信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1 (D13)の説明を参照してください。

**D12 EITG3: Port Interrupt 3 Trigger Mode Bit**

ポート割り込み3のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1 (D12)の説明を参照してください。

.....

**D5 EITP2: Port Interrupt 2 Trigger Polarity Bit**

ポート割り込み2信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1 (D13)の説明を参照してください。

**D4 EITG2: Port Interrupt 2 Trigger Mode Bit**

ポート割り込み2のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1 (D12)の説明を参照してください。

IV-1-30 ページ S1C17501 テクニカルマニュアル

IV-1-30 ページ S1C17801 テクニカルマニュアル

(誤)

**0x430a: External Interrupt Level Setup Register 2 (ITC\_ELV2)**

| Register name                                                 | Address             | Bit    | Name       | Function                          | Setting |          |   |          | Init. | R/W | Remarks            |

|---------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|----------|---|----------|-------|-----|--------------------|

| External<br>Interrupt Level<br>Setup Register 2<br>(ITC_ELV2) | 0x430a<br>(16 bits) | D15-14 | —          | reserved                          | —       | —        | — | —        | —     | —   | 0 when being read. |

|                                                               |                     | D13    | EITP5      | Port interrupt 5 trigger polarity | 1       | Positive | 0 | Negative | 0     | R/W |                    |

|                                                               |                     | D12    | EITG5      | Port interrupt 5 trigger mode     | 1       | Level    | 0 | Pulse    | 0     | R/W |                    |

|                                                               |                     | D11    | —          | reserved                          | —       | —        | — | —        | —     | —   | 0 when being read. |

|                                                               |                     | D10-8  | EILV5[2:0] | Port interrupt 5 level            | 0 to 7  |          |   | 0x0      | R/W   |     |                    |

|                                                               |                     | D7-6   | —          | reserved                          | —       | —        | — | —        | —     | —   | 0 when being read. |

|                                                               |                     | D5     | EITP4      | Port interrupt 4 trigger polarity | 1       | Positive | 0 | Negative | 0     | R/W |                    |

|                                                               |                     | D4     | EITG4      | Port interrupt 4 trigger mode     | 1       | Level    | 0 | Pulse    | 0     | R/W |                    |

|                                                               |                     | D3     | —          | reserved                          | —       | —        | — | —        | —     | —   | 0 when being read. |

|                                                               |                     | D2-0   | EILV4[2:0] | Port interrupt 4 level            | 0 to 7  |          |   | 0x0      | R/W   |     |                    |

**D13 EITP5: Port Interrupt 5 Trigger Polarity Bit**

ポート割り込み5信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D12 EITG5: Port Interrupt 5 Trigger Mode Bit**

ポート割り込み5のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

**D5 EITP4: Port Interrupt 4 Trigger Polarity Bit**

ポート割り込み4信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D4 EITG4: Port Interrupt 4 Trigger Mode Bit**

ポート割り込み4のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

(正)

**0x430a: External Interrupt Level Setup Register 2 (ITC\_ELV2)**

| Register name                                                 | Address             | Bit    | Name       | Function                          | Setting |             |        | Init.      | R/W | Remarks            |

|---------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|-------------|--------|------------|-----|--------------------|

| External<br>Interrupt Level<br>Setup Register 2<br>(ITC_ELV2) | 0x430a<br>(16 bits) | D15-14 | –          | reserved                          | –       | –           | –      | –          | –   | 0 when being read. |

|                                                               |                     | D13    | EITP5      | Port interrupt 5 trigger polarity | 1       | Active high | 0      | Active low | 0   | R/W                |

|                                                               |                     | D12    | EITG5      | Port interrupt 5 trigger mode     | 1       | Level       | 0      | No support | 0   | R/W                |

|                                                               |                     | D11    | –          | reserved                          | –       | –           | –      | –          | –   | 0 when being read. |

|                                                               |                     | D10-8  | EILV5[2:0] | Port interrupt 5 level            | –       | –           | 0 to 7 | –          | 0x0 | R/W                |

|                                                               |                     | D7-6   | –          | reserved                          | –       | –           | –      | –          | –   | 0 when being read. |

|                                                               |                     | D5     | EITP4      | Port interrupt 4 trigger polarity | 1       | Active high | 0      | Active low | 0   | R/W                |

|                                                               |                     | D4     | EITG4      | Port interrupt 4 trigger mode     | 1       | Level       | 0      | No support | 0   | R/W                |

|                                                               |                     | D3     | –          | reserved                          | –       | –           | –      | –          | –   | 0 when being read. |

|                                                               |                     | D2-0   | EILV4[2:0] | Port interrupt 4 level            | –       | –           | 0 to 7 | –          | 0x0 | R/W                |

**D13 EITP5: Port Interrupt 5 Trigger Polarity Bit**

ポート割り込み5信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D12 EITG5: Port Interrupt 5 Trigger Mode Bit**

ポート割り込み5のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

**D5 EITP4: Port Interrupt 4 Trigger Polarity Bit**

ポート割り込み4信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D4 EITG4: Port Interrupt 4 Trigger Mode Bit**

ポート割り込み4のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

IV-1-31 ページ S1C17501 テクニカルマニュアル

IV-1-31 ページ S1C17801 テクニカルマニュアル

(誤)

**0x430c: External Interrupt Level Setup Register 3 (ITC\_ELV3)**

| Register name                                                | Address             | Bit    | Name       | Function                          | Setting |          | Init. | R/W      | Remarks            |

|--------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|----------|-------|----------|--------------------|

| External<br>Interrupt Level<br>Setup Register3<br>(ITC_ELV3) | 0x430c<br>(16 bits) | D15-14 | —          | reserved                          | —       | —        | —     | —        | 0 when being read. |

|                                                              |                     | D13    | EITP7      | Port interrupt 7 trigger polarity | 1       | Positive | 0     | Negative | 0 R/W              |

|                                                              |                     | D12    | EITG7      | Port interrupt 7 trigger mode     | 1       | Level    | 0     | Pulse    | 0 R/W              |

|                                                              |                     | D11    | —          | reserved                          | —       | —        | —     | —        | 0 when being read. |

|                                                              |                     | D10-8  | EILV7[2:0] | Port interrupt 7 level            | 0 to 7  |          |       | 0x0 R/W  |                    |

|                                                              |                     | D7-6   | —          | reserved                          | —       | —        | —     | —        | 0 when being read. |

|                                                              |                     | D5     | EITP6      | Port interrupt 6 trigger polarity | 1       | Positive | 0     | Negative | 0 R/W              |

|                                                              |                     | D4     | EITG6      | Port interrupt 6 trigger mode     | 1       | Level    | 0     | Pulse    | 0 R/W              |

|                                                              |                     | D3     | —          | reserved                          | —       | —        | —     | —        | 0 when being read. |

|                                                              |                     | D2-0   | EILV6[2:0] | Port interrupt 6 level            | 0 to 7  |          |       | 0x0 R/W  |                    |

.....

**D13 EITP7: Port Interrupt 7 Trigger Polarity Bit**

ポート割り込み7信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D12 EITG7: Port Interrupt 7 Trigger Mode Bit**

ポート割り込み7のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

.....

**D5 EITP6: Port Interrupt 6 Trigger Polarity Bit**

ポート割り込み6信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D4 EITG6: Port Interrupt 6 Trigger Mode Bit**

ポート割り込み6のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): パルストリガモード(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

(正)

**0x430c: External Interrupt Level Setup Register 3 (ITC\_ELV3)**

| Register name                                                | Address             | Bit    | Name       | Function                          | Setting |             | Init. | R/W        | Remarks            |

|--------------------------------------------------------------|---------------------|--------|------------|-----------------------------------|---------|-------------|-------|------------|--------------------|

| External<br>Interrupt Level<br>Setup Register3<br>(ITC_ELV3) | 0x430c<br>(16 bits) | D15–14 | –          | reserved                          | –       | –           | –     | –          | 0 when being read. |

|                                                              |                     | D13    | EITP7      | Port interrupt 7 trigger polarity | 1       | Active high | 0     | Active low | 0 R/W              |

|                                                              |                     | D12    | EITG7      | Port interrupt 7 trigger mode     | 1       | Level       | 0     | No support | 0 R/W              |

|                                                              |                     | D11    | –          | reserved                          | –       | –           | –     | –          | 0 when being read. |

|                                                              |                     | D10–8  | EILV7[2:0] | Port interrupt 7 level            | 0 to 7  |             | 0x0   | R/W        |                    |

|                                                              |                     | D7–6   | –          | reserved                          | –       | –           | –     | –          | 0 when being read. |

|                                                              |                     | D5     | EITP6      | Port interrupt 6 trigger polarity | 1       | Active high | 0     | Active low | 0 R/W              |

|                                                              |                     | D4     | EITG6      | Port interrupt 6 trigger mode     | 1       | Level       | 0     | No support | 0 R/W              |

|                                                              |                     | D3     | –          | reserved                          | –       | –           | –     | –          | 0 when being read. |

|                                                              |                     | D2–0   | EILV6[2:0] | Port interrupt 6 level            | 0 to 7  |             | 0x0   | R/W        |                    |

.....

**D13 EITP7: Port Interrupt 7 Trigger Polarity Bit**

ポート割り込み7信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D12 EITG7: Port Interrupt 7 Trigger Mode Bit**

ポート割り込み7のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

.....

**D5 EITP6: Port Interrupt 6 Trigger Polarity Bit**

ポート割り込み6信号の極性を選択します。

1 (R/W): 正極性/アクティブHigh

0 (R/W): 負極性/アクティブLow(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITP1(D13)の説明を参照してください。

**D4 EITG6: Port Interrupt 6 Trigger Mode Bit**

ポート割り込み6のトリガモードを選択します。

1 (R/W): レベルトリガモード

0 (R/W): 未サポート(デフォルト)

ITC\_ELV0レジスタ(0x4306)のEITG1(D12)の説明を参照してください。

|                                                              |                                                                     |                      |                |                                   |             |                 |                |            |              |            |                    |

|--------------------------------------------------------------|---------------------------------------------------------------------|----------------------|----------------|-----------------------------------|-------------|-----------------|----------------|------------|--------------|------------|--------------------|

| (正)                                                          | <b>0x430c: External Interrupt Level Setup Register 3 (ITC_ELV3)</b> | <b>Register name</b> | <b>Address</b> | <b>Bit</b>                        | <b>Name</b> | <b>Function</b> | <b>Setting</b> |            | <b>Init.</b> | <b>R/W</b> | <b>Remarks</b>     |

| External<br>Interrupt Level<br>Setup Register3<br>(ITC_ELV3) | 0x430c<br>(16 bits)                                                 | D15–14               | –              | reserved                          | –           | –               | –              | –          | –            | –          | 0 when being read. |

|                                                              |                                                                     | D13                  | EITP7          | Port interrupt 7 trigger polarity | 1           | Active high     | 0              | Active low | 0            | R/W        |                    |

|                                                              |                                                                     | D12                  | EITG7          | Port interrupt 7 trigger mode     | 1           | Level           | 0              | No support | 0            | R/W        |                    |

|                                                              |                                                                     | D11                  | –              | reserved                          | –           | –               | –              | –          | –            | –          | 0 when being read. |

|                                                              |                                                                     | D10–8                | EILV7[2:0]     | Port interrupt 7 level            | 0 to 7      |                 | 0x0            | R/W        |              |            |                    |

|                                                              |                                                                     | D7–6                 | –              | reserved                          | –           | –               | –              | –          | –            | –          | 0 when being read. |

|                                                              |                                                                     | D5                   | EITP6          | Port interrupt 6 trigger polarity | 1           | Active high     | 0              | Active low | 0            | R/W        |                    |

|                                                              |                                                                     | D4                   | EITG6          | Port interrupt 6 trigger mode     | 1           | Level           | 0              | No support | 0            | R/W        |                    |

|                                                              |                                                                     | D3                   | –              | reserved                          | –           | –               | –              | –          | –            | –          | 0 when being read. |

|                                                              |                                                                     | D2–0                 | EILV6[2:0]     | Port interrupt 6 level            | 0 to 7      |                 | 0x0            | R/W        |              |            |                    |

## IV-1-37 ページ S1C17801 テクニカルマニュアル

(誤)

(正)の取消部分のないもの。

(正)

表IV.1.8.1 割り込みに必要なクロック設定

| クロック系統        | CMUレジスタ<br>設定有效範囲 | クロック供給状態 |       | 割り込み発生に必要なクロック設定                |                                                 |

|---------------|-------------------|----------|-------|---------------------------------|-------------------------------------------------|

|               |                   | 通常動作時    | HALT時 | 通常HALT時                         | SLEEP時                                          |

| PCLK          | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| LCDC_SAPB_CLK | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| LCDC_HIF      | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| USB_CLK       | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| USB_SAPB_CLK  | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| FLASHC        | HALT              | 停止不可     | REG   | 停止                              |                                                 |

| MFT_CLK       | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| PT8_CLK       | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| SRAMC_CLK     | HALT              | 停止不可     | REG   | 停止                              |                                                 |

| RTC_SAPB_CLK  | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| PORT_CLK      | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| WDT_CLK       | 通常HALT            | REG      | REG   | 停止                              | *3                                              |

| ADC_CLK       | 通常HALT            | REG      | REG   | 停止                              | ○                                               |

| FEMC_CLK      | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| SPI_CLK       | 通常HALT            | REG      | REG   | 停止                              |                                                 |

| CPU           | -                 | 停止不可     | 停止    | / / / / / / / / / / / / / / / / |                                                 |

| RTC           | -                 | 停止不可     | *1    | 停止不可                            | *1                                              |

| OSC1発振回路      | -                 | 停止不可     | *2    | 停止不可                            | *2                                              |

| OSC3発振回路      | 通常HALT            | REG      | REG   | REG                             | *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 *7 |

REG: レジスタにより設定可能

○: 割り込みを発生させるために供給必須クロック

AMI: アドレス不整 例外

AMI: 隅辺モジュールにて機能をディセーブルに設定する場合は差し配しません。

\*1: 外部入力を固定した場合は差し配しません。

\*2: WDTよりNMIを発生させる場合はクロック供給が必要です。

\*3: WDTよりNMIを発生させる場合はクロック供給が必要です。

\*4: レジスタ設定後は不要です。(レベルトリガ割り込みのみ)

\*5: レジスタ設定後は不要です。(レベルトリガ割り込みのみ)

\*6: スヌーズ状態からのVBU5\_ChangedおよびNMIによる割り込みにクロックは不要です。他は必要です。

\*7: システムのクロックとして使用されるOSC1またはOSC3発振回路が、SLEEP時以外に動作する必要があります。

## IV-1-37 ページ S1C17501 テクニカルマニュアル

(誤)

(正)の取消部分のないもの。

(正)

表IV.8.1 割り込みに必要なクロック設定

| クロック系統       | CMUレジスタ<br>設定有効範囲 | クロック供給状態 |         |         | 割り込み発生に必要なクロック設定 |

|--------------|-------------------|----------|---------|---------|------------------|

|              |                   | 通常動作時    | HALT時   | SLEEP時  |                  |

| PLLK         | 通常HALT            | REG      | REG     | 停止      |                  |

| USB_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| USB_SAPB_CLK | 通常HALT            | REG      | REG     | 停止      |                  |

| FLASHC       | HALT              | 停止不可     | REG     | 停止      |                  |

| MFT_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| PT8_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| SRAMC_CLK    | HALT              | 停止不可     | REG     | 停止      |                  |

| RTC_SAPB_CLK | 通常HALT            | REG      | REG     | 停止      |                  |

| PORT_CLK     | 通常HALT            | REG      | REG     | 停止      |                  |

| WDT_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| ADC_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| REMC_CLK     | 通常HALT            | REG      | REG     | 停止      |                  |

| SPI_CLK      | 通常HALT            | REG      | REG     | 停止      |                  |

| CPU          | —                 | 停止不可     | 停止      | 停止      |                  |

| RTC          | —                 | 停止不可 *1  | 停止不可 *1 | 停止不可 *1 |                  |

| OSC1発振回路     | —                 | 停止不可 *2  | 停止不可 *2 | 停止不可 *2 |                  |

| OSC3発振回路     | 通常HALT            | REG      | REG     | REG     |                  |

REG: レジスタにより設定可能

○: 割り込みを発生するために供給必須クロック

AM: アドレス不整例外

\*1: 周辺モジュールにて機能をディセーブルにて設定することで停止します。

\*2: 外部入力を固定した場合は発振しません。

\*3: WDTによりNMIを発生させる場合はクロック供給が必要です。

\*4: レジスタ設定後は不要です。(レベルトリガ割り込みのみ)

\*5: レジスタ設定後は不要です。(OSC1またはOSC3発振回路が、SLEEP時以外に動作する必要があります。

\*6: スヌーズ状態からのVBUS\_ChangedおよびNMIによる割り込みにクロックは不要です。他の必要です。

\*7: システムのクロックとして使用されるOSC1またはOSC3発振回路が、SLEEP時以外に動作する必要があります。