## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 出荷形態の一部新規受付終了                           |           |      |     |

|--------------------------------------------|-----------|------|-----|

| 対象マニュアル                                    | 発行 No.    | 項目   | ページ |

| S1C17121 テクニカルマニュアル                        | 411790502 | 出荷形態 | 1-2 |

| (誤)                                        |           |      |     |

| ●出荷形態                                      |           |      |     |

| • TQFP14-100      12mm × 12mmボディー、0.4mmピッチ |           |      |     |

| • VFBGA7H-144    7mm × 7mmボディー、0.5mmピッチ    |           |      |     |

| • ベアチップ 100μmピッチ                           |           |      |     |

| (正)                                        |           |      |     |

| ●出荷形態                                      |           |      |     |

| • TQFP14-100      12mm × 12mmボディー、0.4mmピッチ |           |      |     |

| • VFBGA7H-144    7mm × 7mmボディー、0.5mmピッチ #1 |           |      |     |

| • ベアチップ 100μmピッチ                           |           |      |     |

| #1 : VFBGA7H-144 は新規受付終了                   |           |      |     |

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 重負荷保護機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |             |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-----|

| 対象マニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 発行 No.    | 項目          | ページ |

| S1C17121 テクニカルマニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 411790502 | 4.4 重負荷保護機能 | 4-4 |

| (誤)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |             |     |

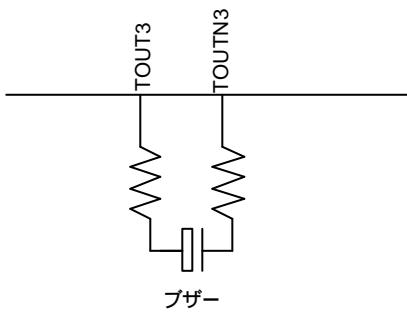

| 内部定電圧回路は HVLD(D5/VD1_CTL レジスタ)に 1 を書き込むと重負荷保護モードとなり、VD1 出力の安定化を図ります。ポート出力によりランプやブザーなどの重負荷を駆動する前に設定してください。<br>* HVLD: VD1 Heavy Load Protection Mode Bit in the VD1 Control (VD1_CTL) Register (D5/0x5120)<br>LCD 系定電圧回路は LHVLD(D4/LCD_VREG レジスタ)に 1 を書き込むと重負荷保護モードとなり、VC1～VC3 出力の安定化を図ります。液晶表示に濃淡が現れる場合などに設定してください。<br>* LHVLD: LCD Heavy Load Protection Mode Bit in the LCD Voltage Regulator Control (LCD_VREG) Register<br>(D4/0x50a3)<br>注: 重負荷保護モードでは、通常動作時より消費電流が多くなります。したがって、必要なとき以外はソフトウェアで重負荷保護モードに設定しないでください。                              |           |             |     |

| (正)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |             |     |

| 内部定電圧回路は HVLD(D5/VD1_CTL レジスタ)に 1 を書き込むと重負荷保護モードとなり、VD1 出力の安定化を図ります。ポート出力によりランプやブザーなどの重負荷を駆動する前に設定してください。<br>* HVLD: VD1 Heavy Load Protection Mode Bit in the VD1 Control (VD1_CTL) Register (D5/0x5120)<br>LCD 系定電圧回路は LHVLD(D4/LCD_VREG レジスタ)に 1 を書き込むと重負荷保護モードとなり、VC1～VC3 出力の安定化を図ります。液晶表示に濃淡が現れる場合などに設定してください。<br>* LHVLD: LCD Heavy Load Protection Mode Bit in the LCD Voltage Regulator Control (LCD_VREG) Register<br>(D4/0x50a3)<br>注: 重負荷保護モードでは、通常動作時より消費電流が多くなります。したがって、必要なとき以外はソフトウェアで重負荷保護モードに設定しないでください。S1C17121 では、HVLDレジスタは使用できません。 |           |             |     |

## S1C17 マニュアル 正誤表

| 項目 基本外部結線図                                                                          |           |       |

|-------------------------------------------------------------------------------------|-----------|-------|

| 対象マニュアル                                                                             | 発行 No.    | 項目番号  |

| S1C17705                                                                            | 411706500 | P26-1 |

| S1C17711                                                                            | 411905500 | P26-1 |

| S1C17121                                                                            | 411790500 | P29-1 |

| S1C17601                                                                            | 411806000 | P29-1 |

| S1C17611                                                                            | 411882200 | P29-1 |

| S1C17621/602/622/604/624                                                            | 411914800 | P30-1 |

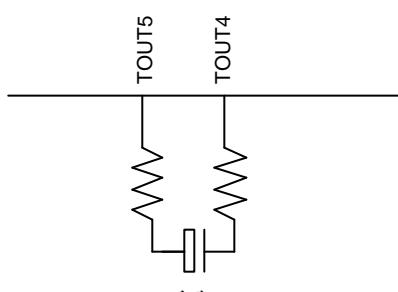

| <b>P26-1(S1C17705)</b>                                                              |           |       |

| (誤)                                                                                 |           |       |

|   |           |       |

| (正)                                                                                 |           |       |

|  |           |       |

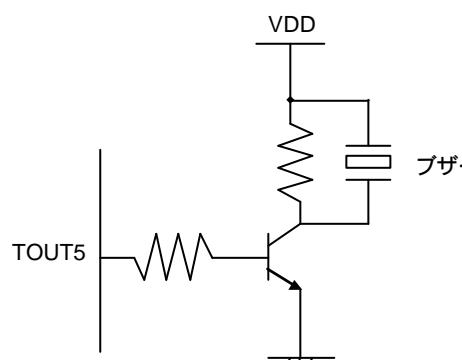

**P26-1(S1C17711)**

(誤)

(正)

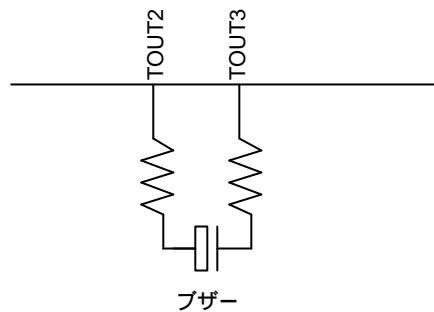

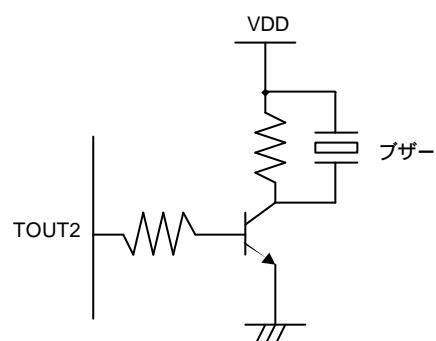

**P29-1(S1C17121, S1C17601, S1C17611)**

**P30-1(S1C17621/602/622/604/624)**

(誤)

(正)

## S1C17121 マニュアル 正誤表

| 項目 テストサンプル用セラミックパッケージ                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|

| 対象マニュアル                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 発行 No.    | 項目番号  |

| S1C17121                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 411790500 | P30-1 |

| (追加)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |       |

| <p>QFP8-128pin</p> <p>The top view diagram shows a rectangular package with a grid of pins. Key dimensions are: total width 32<sup>+0.4</sup>, total height 32<sup>+0.4</sup>, center distance 28<sup>+0.28</sup>, side wall height 64, side wall thickness 33, lead thickness 0.8, lead pitch 0.35, and pin height 97. The bottom view diagram shows the lead profile with a maximum height of 3.05mm, lead thicknesses of 0.2 and 0.15, and a lead pitch of 0.8<sup>+0.2</sup>.</p> |           |       |

| 端子No. | 名称                    | 端子No. | 名称                            |

|-------|-----------------------|-------|-------------------------------|

| 1     | N.C.                  | 65    | <b>V<sub>DD</sub></b>         |

| 2     | <b>SEG1</b>           | 66    | <b>OSC4</b>                   |

| 3     | N.C.                  | 67    | <b>OSC3</b>                   |

| 4     | <b>SEG2</b>           | 68    | <b>V<sub>ss</sub></b>         |

| 5     | <b>SEG3</b>           | 69    | <b>V<sub>D1</sub></b>         |

| 6     | <b>SEG4</b>           | 70    | <b>OSC2</b>                   |

| 7     | <b>SEG5</b>           | 71    | <b>OSC1</b>                   |

| 8     | <b>SEG6</b>           | 72    | #TEST                         |

| 9     | <b>SEG7</b>           | 73    | #RESET                        |

| 10    | <b>SEG8</b>           | 74    | N.C.                          |

| 11    | <b>SEG9</b>           | 75    | <b>P00</b> /REMO              |

| 12    | N.C.                  | 76    | N.C.                          |

| 13    | <b>SEG10</b>          | 77    | <b>P01</b> /REMI              |

| 14    | N.C.                  | 78    | <b>P02</b> /EXCL0             |

| 15    | <b>SEG11</b>          | 79    | N.C.                          |

| 16    | <b>SEG12</b>          | 80    | <b>P03</b> /#ADTRG            |

| 17    | N.C.                  | 81    | N.C.                          |

| 18    | <b>SEG13</b>          | 82    | <b>P04</b> /SPICLK            |

| 19    | <b>SEG14</b>          | 83    | <b>P05</b> /SDO               |

| 20    | <b>SEG15</b>          | 84    | N.C.                          |

| 21    | <b>SEG16</b>          | 85    | <b>P06</b> /SDI               |

| 22    | <b>SEG17</b>          | 86    | <b>P07</b> /#SPISS            |

| 23    | <b>SEG18</b>          | 87    | <b>P10</b> /SCLK0             |

| 24    | <b>SEG19</b>          | 88    | <b>P11</b> /SOUT0             |

| 25    | <b>SEG20</b>          | 89    | N.C.                          |

| 26    | <b>SEG21</b>          | 90    | <b>P12</b> /SIN0              |

| 27    | <b>SEG22</b>          | 91    | N.C.                          |

| 28    | <b>SEG23</b>          | 92    | <b>P13</b> /EXCL1/AIN7        |

| 29    | <b>SEG24</b>          | 93    | <b>P14</b> /EXCL2/AIN6        |

| 30    | N.C.                  | 94    | <b>P15</b> /EXCL3/AIN5        |

| 31    | <b>SEG25</b>          | 95    | <b>V<sub>ss</sub></b>         |

| 32    | N.C.                  | 96    | <b>A<sub>VDD</sub></b>        |

| 33    | N.C.                  | 97    | <b>P16</b> /SCLK1/AIN4        |

| 34    | <b>SEG26</b>          | 98    | <b>P17</b> /AIN3              |

| 35    | N.C.                  | 99    | <b>P20</b> /AIN2              |

| 36    | <b>SEG27</b>          | 100   | <b>P21</b> /AIN1              |

| 37    | N.C.                  | 101   | <b>P22</b> /AIN0              |

| 38    | <b>SEG28</b>          | 102   | <b>V<sub>DD</sub></b>         |

| 39    | <b>SEG29</b>          | 103   | <b>P23</b> /SENBO             |

| 40    | <b>SEG30</b>          | 104   | <b>P24</b> /SENA0             |

| 41    | <b>SEG31</b>          | 105   | <b>P25</b> /REF0              |

| 42    | <b>SEG32</b>          | 106   | <b>P26</b> /RFIN0             |

| 43    | <b>SEG33</b>          | 107   | <b>V<sub>ss</sub></b>         |

| 44    | <b>SEG34</b>          | 108   | N.C.                          |

| 45    | <b>SEG35</b>          | 109   | <b>P27</b> /SOUT1/RFIN1       |

| 46    | N.C.                  | 110   | <b>P30</b> /SIN1/REF1         |

| 47    | <b>COM7</b> /SEG36    | 111   | N.C.                          |

| 48    | <b>COM6</b> /SEG37    | 112   | <b>P31</b> /SCL0/SENA1        |

| 49    | <b>COM5</b> /SEG38    | 113   | <b>P32</b> /SDA0/SENBO1       |

| 50    | <b>COM4</b> /SEG39    | 114   | <b>P33</b> /SCL1/SCL0         |

| 51    | N.C.                  | 115   | N.C.                          |

| 52    | <b>COM3</b>           | 116   | <b>P34</b> /SDA1/SDA0         |

| 53    | <b>COM2</b>           | 117   | <b>P35</b> /FOUT1/#BFR        |

| 54    | <b>COM1</b>           | 118   | <b>P36</b> /TOUT3/RFCLK0      |

| 55    | <b>COM0</b>           | 119   | <b>P37</b> /TOUTN3/LFRO/TOUT4 |

| 56    | N.C.                  | 120   | N.C.                          |

| 57    | <b>TEST2</b>          | 121   | <b>P40</b> /FOUTH             |

| 58    | N.C.                  | 122   | <b>P41</b>                    |

| 59    | <b>CB</b>             | 123   | <b>P42</b>                    |

| 60    | <b>CA</b>             | 124   | N.C.                          |

| 61    | <b>V<sub>c3</sub></b> | 125   | <b>P43</b>                    |

| 62    | <b>V<sub>c2</sub></b> | 126   | N.C.                          |

| 63    | <b>V<sub>c1</sub></b> | 127   | <b>SEG0</b>                   |

| 64    | <b>V<sub>ss</sub></b> | 128   | N.C.                          |

## S1C17 マニュアル 正誤表

| 項目 SPI クロックについて                                                                                                                                        |           |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|

| 対象マニュアル                                                                                                                                                | 発行 No.    | 項目番号  |

| S1C17121                                                                                                                                               | 411790500 | P19-3 |

| S1C17702                                                                                                                                               | 411602400 | P19-3 |

| S1C17003                                                                                                                                               | 411635001 | P19-3 |

| S1C17601                                                                                                                                               | 411806000 | P19-3 |

| S1C17705                                                                                                                                               | 411706500 | P15-2 |

| S1C17621/S1C17602/S1C17622/<br>S1C17604/S1C17624                                                                                                       | 411914800 | P19-3 |

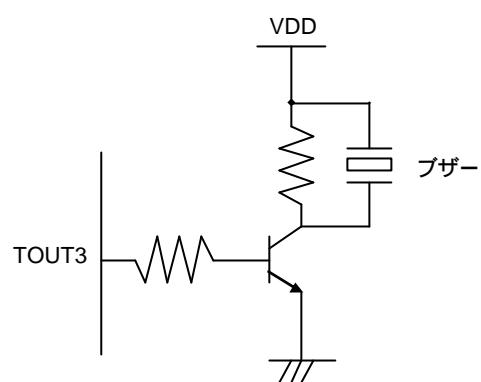

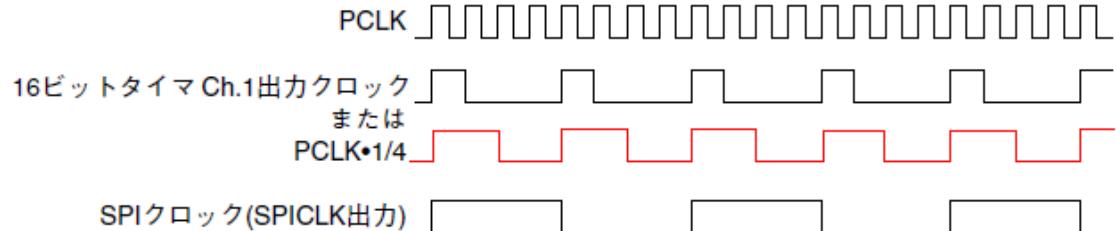

| <b>P19-3(S1C17121,S1C17702,S1C17003,S1C17601)</b>                                                                                                      |           |       |

| (誤)                                                                                                                                                    |           |       |

| マスター mode の SPI は、16 ビットタイマ Ch.1 が出力するクロックまたは PCLK・1/4 のクロックを SPI クロックとして使用します。このクロックはシフトレジスタを駆動すると共に、SPICLK 端子からスレーブデバイスへ出力されます。                      |           |       |

| 16 ビットタイマ Ch.1 出力クロックと PCLK・1/4 クロックのどちらを使用するかについては MCLK (D9/SPI_CTL レジスタ) で選択します。MCLK を 1 に設定すると 16 ビットタイマ Ch.1 出力クロック、0 に設定すると PCLK・1/4 クロックが選択されます。 |           |       |

| *MCLK: SPI Clock Source Select Bit in the SPI Control (SPI_CTL) Register (D9/0x4326)                                                                   |           |       |

| 16 ビットタイマ Ch.1 を使用すると、転送レートをプログラマブルに設定できます。16 ビットタイマの制御については、"11 16 ビットタイマ(T16)"を参照してください。                                                             |           |       |

|                                                                                                                                                        |           |       |

(正)

マスター モードの SPI は、16 ビットタイマ Ch.1 が出力するクロックまたは PCLK・1/4 のクロックを SPI クロックとして使用します。このクロックはシフトレジスタを駆動すると共に、SPICLK 端子からスレーブデバイスへ出力されます。

16 ビットタイマ Ch.1 出力クロックと PCLK・1/4 クロックのどちらを使用するかについては MCLK (D9/SPI\_CTL レジスタ) で選択します。MCLK を 1 に設定すると 16 ビットタイマ Ch.1 出力クロック、0 に設定すると PCLK・1/4 クロックが選択されます。

\*MCLK: SPI Clock Source Select Bit in the SPI Control (SPI\_CTL) Register (D9/0x4326)

16 ビットタイマ Ch.1 を使用すると、転送レートをプログラマブルに設定できます。16 ビットタイマの制御については、"11 16 ビットタイマ(T16)" を参照してください。

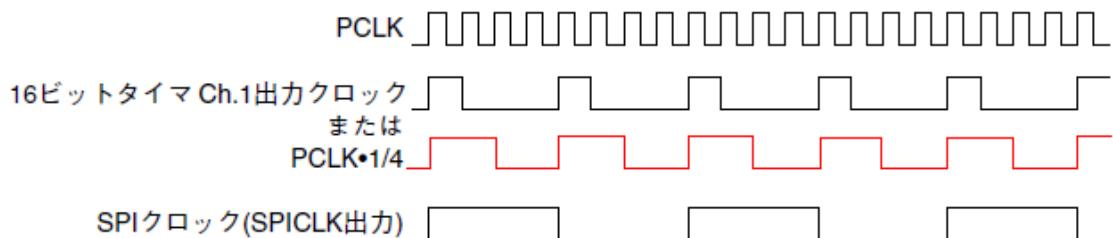

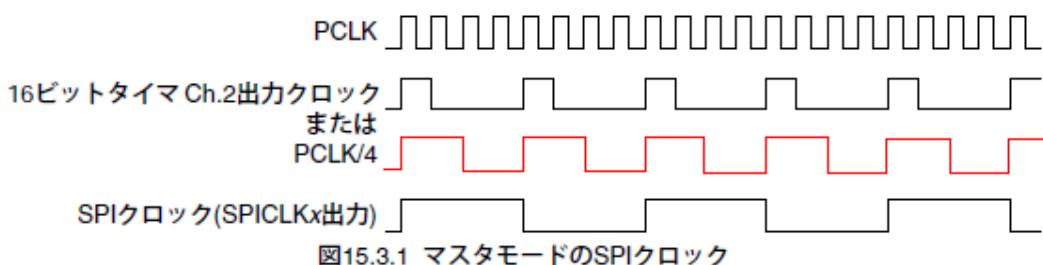

## P15-2(S1C17705)

(誤)

マスター モードの SPI は、16 ビットタイマ Ch.2 が出力するクロックまたは PCLK/4 のクロックを SPI クロックとして使用します。このクロックはシフトレジスタを駆動すると共に、SPICLK 端子からスレーブデバイスへ出力されます。

16 ビットタイマ Ch.2 出力クロックと PCLK/4 クロックのどちらを使用するかについては MCLK (D9/SPI\_CTLx レジスタ) で選択します。MCLK を 1 に設定すると 16 ビットタイマ Ch.2 出力クロック、0 に設定すると PCLK/4 クロックが選択されます。

16 ビットタイマ Ch.2 を使用すると、転送レートをプログラマブルに設定できます。16 ビットタイマの制御については、"16 ビットタイマ(T16)" の章を参照してください。

図15.3.1 マスター モードの SPI クロック

(正)

マスター モードの SPI は、16 ビットタイマ Ch.2 が出力するクロックまたは PCLK/4 のクロックを SPI クロックとして使用します。このクロックはシフトレジスタを駆動すると共に、SPICLK 端子からスレーブ デバイスへ出力されます。

16 ビットタイマ Ch.2 出力クロックと PCLK/4 クロックのどちらを使用するかについては MCLK (D9/SPI\_CTLx レジスタ) で選択します。MCLK を 1 に設定すると 16 ビットタイマ Ch.2 出力クロック、0 に設定すると PCLK/4 クロックが選択されます。

16 ビットタイマ Ch.2 を使用すると、転送レートをプログラマブルに設定できます。16 ビットタイマの制御については、"16 ビットタイマ(T16)" の章を参照してください。

図15.3.1 マスタモードのSPIクロック

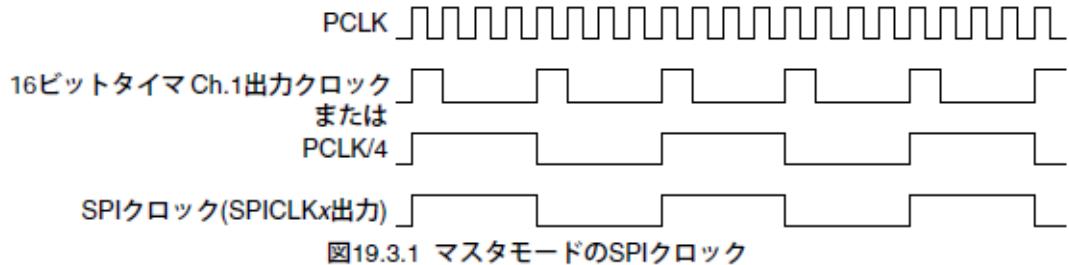

#### P19-3(S1C17621/S1C17602/S1C17622/S1C17604/S1C17624)

(誤)

図19.3.1 マスタモードのSPIクロック

(正)

図19.3.1 マスタモードのSPIクロック

## S1C17 マニュアル 正誤表

| 項目 入出力ポートのチャタリング除去機能 (P) |           |                                                         |                        |

|--------------------------|-----------|---------------------------------------------------------|------------------------|

| 対象マニュアル                  | 発行 No.    | 項目                                                      | ページ                    |

| S1C17121                 | 411790501 | 10.6 P0/P1 ポートのチャタリング除去機能<br>10.8 制御レジスタ詳細<br>10.9 注意事項 | 10-7<br>10-20<br>10-32 |

| S1C17554/564             | 411914300 | 8.5 チャタリング除去機能<br>8.8 制御レジスタ詳細                          | 8-4<br>8-10            |

| S1C17601                 | 411806000 | 10.6 P0/P1 ポートのチャタリング除去機能<br>10.8 制御レジスタ詳細<br>10.9 注意事項 | 10-7<br>10-19<br>10-28 |

| S1C17611                 | 411882200 | 10.6 P0/P1 ポートのチャタリング除去機能<br>10.8 制御レジスタ詳細<br>10.9 注意事項 | 10-7<br>10-19<br>10-28 |

| S1C17624/604/622/602/621 | 411914800 | 9.6 P0 と P1 ポートのチャタリング除去機能<br>9.9 制御レジスタ詳細              | 9-5<br>9-11            |

| S1C17705                 | 411706500 | 8.6 P0～P3 ポートのチャタリング除去機能<br>8.9 制御レジスタ詳細                | 8-4<br>8-10            |

| S1C17711                 | 411905500 | 8.6 P0～P3 ポートのチャタリング除去機能<br>8.9 制御レジスタ詳細                | 8-4<br>8-10            |

(正)

- (1)チャタリング除去機能の注記に追加

- (2)制御レジスタ詳細の“Px\_CHATレジスタ”的注記に追加

- (3)注意事項のP0、P1ポートチャタリング除去回路に追加 (S1C17121/601/611)

・チャタリング除去機能を有効にしている状態でslp命令を実行した場合は、SLEEP状態からの復帰後に予期せぬ割り込みが発生する可能性があります。SLEEPモード移行前にチャタリング除去機能を無効にしてください。

## S1C17 マニュアル 正誤表

| 項目 I2CS データ送信時の制御        |           |                 |       |

|--------------------------|-----------|-----------------|-------|

| 対象マニュアル                  | 発行 No.    | 項目              | ページ   |

| S1C17002                 | 411554301 | V.3.5 データ送受信の制御 | V-3-7 |

| S1C17003                 | 411635001 | 21.5 データ送受信の制御  | 21-7  |

| S1C17121                 | 411790501 | 21.5 データ送受信の制御  | 21-7  |

| S1C17554/564             | 411914300 | 18.5 データ送受信の制御  | 18-4  |

| S1C17601                 | 411806000 | 21.5 データ送受信の制御  | 21-7  |

| S1C17611                 | 411882200 | 21.5 データ送受信の制御  | 21-7  |

| S1C17624/604/622/602/621 | 411914800 | 21.5 データ送受信の制御  | 21-4  |

| S1C17705                 | 411706500 | 17.5 データ送受信の制御  | 17-4  |

| S1C17711                 | 411905500 | 17.5 データ送受信の制御  | 17-4  |

|                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (誤)                                                                                                                                                                                                                                                     |

| <b>データ送信</b>                                                                                                                                                                                                                                            |

| <b>クロックストレッチ機能が無効(デフォルト)の場合</b>                                                                                                                                                                                                                         |

| TXEMPが1にセットされてからI2Cクロック(SCL*入力クロック)の1サイクル以内に送信データをSDATA[7:0]に書き込む必要があります。この時間が短いため、TXEMPがセットされる前に先行して送信データの書き込みを行っておきます。SDATA[7:0]に前回の送信データが残っていた場合も今回のデータにより上書きされますので、TBUF_CLRによるクリア操作(下記参照)は不要です。                                                     |

| <b>クロックストレッチ機能が有効の場合</b>                                                                                                                                                                                                                                |

| クロックストレッチによるウェイト機能が働くため、TXEMPがセットされた後でも送信データの書き込みが可能です。ただし、SDATA[7:0]に前回の送信データが残っているとTXEMPがセットされた時点でそのデータが送信されてしまいますので、I2CSがスレーブデバイスとして選択される前にTBUF_CLR/I2CS_CTLレジスタを使用してI2CS_TRNSレジスタをクリアしておきます。TBUF_CLRに1を書き込んだ後、もう一度0を書き込むことによりI2CS_TRNSレジスタがクリアされます。 |

| TXEMPがセットされる前に最初の送信データを書き込んでおく場合は、I2CS_TRNSレジスタをクリアする必要はありません。                                                                                                                                                                                          |

(正)

## データ送信

### クロックストレッチ機能が無効(デフォルト)の場合

TXEMPが1にセットされてからI2Cクロック(SCL\*入力クロック)の1サイクル以内に送信データをSDATA[7:0]に書き込む必要があります。この時間が短いため、TXEMPがセットされる前に先行して送信データの書き込みを行っておきます。SDATA[7:0]に前回の送信データが残っていた場合も今回のデータにより上書きされますので、TBUF\_CLRによるクリア操作(下記参照)は不要です。

**非同期アドレス検出機能を使用する場合には、ASDET\_ENを0にリセットする前に書き込みを行ったデータは無効となる為、TXEMPが1にセットされてから送信データを書き込む必要があります。**

### クロックストレッチ機能が有効の場合

クロックストレッチによるウェイト機能が働くため、TXEMPがセットされた後でも送信データの書き込みが可能です。ただし、SDATA[7:0]に前回の送信データが残っているとTXEMPがセットされた時点でそのデータが送信されてしましますので、I2CSがスレーブデバイスとして選択される前にTBUF\_CLR/I2CS\_CTLレジスタを使用してI2CS\_TRNSレジスタをクリアしておきます。TBUF\_CLRに1を書き込んだ後、もう一度0を書き込むことによりI2CS\_TRNSレジスタがクリアされます。

TXEMPがセットされる前に最初の送信データを書き込んでおく場合は、I2CS\_TRNSレジスタをクリアする必要はありません。

**非同期アドレス検出機能を使用する場合には、ASDET\_ENを0にリセットする前に書き込みを行ったデータは無効となる為、TXEMPが1にセットされてから送信データを書き込む必要があります。**

## S1C17 マニュアル 正誤表

| 項目 UART 割り込み信号の注釈について                                         |           |               |       |

|---------------------------------------------------------------|-----------|---------------|-------|

| 対象マニュアル                                                       | 発行 No.    | 項目            | ページ   |

| S1C17704 テクニカルマニュアル                                           | 411511802 | 18.10 注意事項    | 18-21 |

| S1C17702 テクニカルマニュアル                                           | 411602401 | 18.10 注意事項    | 18-21 |

| S1C17705 テクニカルマニュアル                                           | 411706500 | 14.9 制御レジスタ詳細 | 14-11 |

| S1C17601 テクニカルマニュアル                                           | 411806000 | 18.10 注意事項    | 18-21 |

| S1C17602 テクニカルマニュアル                                           | 411620000 | 18.10 注意事項    | 18-21 |

| S1C17611 テクニカルマニュアル                                           | 411882200 | 18.10 注意事項    | 18-21 |

| S1C17121 テクニカルマニュアル                                           | 411790501 | 18.10 注意事項    | 18-21 |

| S1C17003 テクニカルマニュアル                                           | 411790501 | 18.10 注意事項    | 18-21 |

| (誤)                                                           |           |               |       |

| S1C17705                                                      |           |               |       |

| · UARTの以下のビットは、送受信禁止の状態(RXEN = 0)で設定してください。                   |           |               |       |

| .....                                                         |           |               |       |

| - UART_CTLレジスタの RXEN以外のビットすべて(RBFI, TIEN, RIEN, REIEN, TEIEN) |           |               |       |

| .....                                                         |           |               |       |

| S1C17704/702/601/602/611/121/003                              |           |               |       |

| · UARTの以下のビットは、送受信禁止の状態(RXEN = 0)で設定してください。                   |           |               |       |

| .....                                                         |           |               |       |

| - UART_CTLレジスタの RXEN以外のビットすべて(RBFI, TIEN, RIEN, REIEN)        |           |               |       |

| .....                                                         |           |               |       |

| (正)                                                           |           |               |       |

| · UARTの以下のビットは、送受信禁止の状態(RXEN = 0)で設定してください。                   |           |               |       |

| .....                                                         |           |               |       |

| - UART_CTLxレジスタのRBFIビット                                       |           |               |       |

| .....                                                         |           |               |       |

## S1C17 マニュアル 正誤表

| 項目 I2CM 割り込み        |           |              |       |

|---------------------|-----------|--------------|-------|

| 対象マニュアル             | 発行 No.    | 項目           | ページ   |

| S1C17701 テクニカルマニュアル | 411089702 | I2C 割り込み     | 20-11 |

| S1C17704 テクニカルマニュアル | 411511802 | I2C 割り込み     | 20-11 |

| S1C17702 テクニカルマニュアル | 411602401 | I2C 割り込み     | 20-10 |

| S1C17705 テクニカルマニュアル | 411706500 | I2CM 割り込み    | 16-6  |

| S1C17601 テクニカルマニュアル | 411806000 | I2C マスター割り込み | 20-10 |

| S1C17602 テクニカルマニュアル | 411620000 | I2C マスター割り込み | 20-10 |

| S1C17611 テクニカルマニュアル | 411882200 | I2C マスター割り込み | 20-10 |

| S1C17121 テクニカルマニュアル | 411790501 | I2C マスター割り込み | 20-10 |

| S1C17001 テクニカルマニュアル | 411412001 | I2C 割り込み     | 259   |

| S1C17003 テクニカルマニュアル | 411635001 | I2C マスター割り込み | 20-10 |

( 誤 )

### 送信バッファエンプティ割り込み

この割り込みを使用するには、TINTE/I2CM\_ICTL レジスタを 1 に設定します。TINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

送信バッファエンプティ割り込みが許可されていれば(TINTE=1)、RTDT[7:0]/I2CM\_DAT レジスタに設定された送信データがシフトレジスタに転送された時点で割り込み要求が ITC に出力されます。

### 受信バッファフル割り込み

この割り込みを使用するには、RINTE/I2CM\_ICTL レジスタを 1 に設定します。RINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

受信バッファフル割り込みが許可されていれば(RINTE=1)、シフトレジスタに受信したデータが RTDT[7:0]にロードされた時点で割り込み要求が ITC に出力されます。

ITC については、“割り込みコントローラ(ITC)”の章を参照してください

( 正 )

### 送信バッファエンプティ割り込み

この割り込みを使用するには、TINTE/I2CM\_ICTL レジスタを 1 に設定します。TINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

送信バッファエンプティ割り込みが許可されていれば(TINTE=1)、RTDT[7:0]/I2CM\_DAT

レジスタに設定された送信データがシフトレジスタに転送された時点で割り込み要求が ITC に出力されます。

送信バッファエンプティ割り込みは、データ送信時にのみ、発生します。

・送信バッファエンプティ割り込みのクリア方法

RTDT/I2CM\_DAT にデータをライトします。

TXE/I2CM\_DAT=0 とした場合、データは送信されず、割り込みクリアのみ行います。

### 受信バッファフル割り込み

この割り込みを使用するには、RINTE/I2CM\_IOCTL レジスタを 1 に設定します。RINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

受信バッファフル割り込みが許可されていれば(RINTE=1)、シフトレジスタに受信したデータが RTDT[7:0]にロードされた時点で割り込み要求が ITC に出力されます。

受信バッファフル割り込みは、データ受信時にのみ、発生します。

・受信バッファフル割り込みのクリア方法

RTDT/I2CM\_DAT からデータをリードします。

**注:I2CM の割り込み発生時、I2C マスターのシーケンス処理に応じて送信バッファエンプティ 割り込みと受信バッファフル割り込みを判断して下さい。送信バッファエンプティ割り込み、 または、受信バッファフル割り込みのどちらが発生したかを確認できるレジスタはありません。**

ITC については、“割り込みコントローラ(ITC)”の章を参照してください。

## S1C17 マニュアル 正誤表

| 項目 UART RXEN=0 時の受信バッファの状態                                                                                                                                                                                                                               |           |         |                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----------------------|

| 対象マニュアル                                                                                                                                                                                                                                                  | 発行 No.    | 項目      | ページ                   |

| S1C17121 テクニカルマニュアル                                                                                                                                                                                                                                      | 411790500 | 18 UART | 18-7, 18-19,<br>18-21 |

| <b>P18-7(S1C17121)</b>                                                                                                                                                                                                                                   |           |         |                       |

| (誤)<br>RXEN ビットを 0 に設定すると、送信および受信データバッファは空の状態になります(データが残っていればクリアされます)。また、データの送受信中に RXEN を 0 に設定した場合、転送中のデータは保証されません。                                                                                                                                     |           |         |                       |

| (正)<br>RXEN ビットを 0 に設定すると、送信および受信データバッファは空の状態になります(データが残っていればクリアされます)。また、データの送受信中に RXEN を 0 に設定した場合、転送中のデータは保証されません。                                                                                                                                     |           |         |                       |

| <b>P 18-19(S1C17121)</b>                                                                                                                                                                                                                                 |           |         |                       |

| (誤)<br><b>D0 RXEN: UART Enable Bit</b><br>UART によるデータ送受信を許可します。<br>1(R/W): 許可<br>0(R/W): 禁止(デフォルト)<br><br>UART で送受信を始める前に RXEN を 1 に設定してください。RXEN を 0 に設定するとデータ送受信が禁止されます。転送条件の設定は、RXEN が 0 の状態で行ってください。<br>RXEN に 0 を書き込んで送受信を禁止すると、送受信データバッファもクリアされます。 |           |         |                       |

| (正)<br><b>D0 RXEN: UART Enable Bit</b><br>UART によるデータ送受信を許可します。<br>1(R/W): 許可<br>0(R/W): 禁止(デフォルト)<br><br>UART で送受信を始める前に RXEN を 1 に設定してください。RXEN を 0 に設定するとデータ送受信が禁止されます。転送条件の設定は、RXEN が 0 の状態で行ってください。<br>RXEN に 0 を書き込んで送受信を禁止すると、送受信データバッファもクリアされます。 |           |         |                       |

| <b>P 18-21(S1C17121)</b>                                                                                                                                                                                                                                 |           |         |                       |

(誤)

- RXEN を 0 に設定して送受信を禁止すると、送受信データバッファがクリア(初期化)されます。RXEN に 0 を書き込む前に、バッファ内に送信待ちまたは読み出し前のデータが残っていないことを確認してください。

(正)

- RXEN を 0 に設定して送受信を禁止すると、送受信データバッファがクリア(初期化)されます。RXEN に 0 を書き込む前に、バッファ内に送信待ち **または読み出し前** のデータが残っていないことを確認してください。

## S1C17 マニュアル 正誤表

| 項目 UART 受信エラーフラグのリセット方法                                                                                                 |           |         |       |

|-------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|

| 対象マニュアル                                                                                                                 | 発行 No.    | 項目      | ページ   |

| S1C17121 テクニカルマニュアル                                                                                                     | 411790500 | 18 UART | 18-14 |

| <b>P 18-14(S1C17121)</b>                                                                                                |           |         |       |

| (誤)                                                                                                                     |           |         |       |

| <b>D6 FER: Framing Error Flag Bit</b>                                                                                   |           |         |       |

| フレーミングエラーが発生しているか否かを示します。                                                                                               |           |         |       |

| 1(R): エラー発生                                                                                                             |           |         |       |

| 0(R): エラーなし(デフォルト)                                                                                                      |           |         |       |

| 1(W): 0 にリセット                                                                                                           |           |         |       |

| 0(W): 無効                                                                                                                |           |         |       |

| FER はフレーミングエラーが発生すると 1 にセットされます。フレーミングエラーは、ストップビットを 0 としてデータを受信した場合に発生します。                                              |           |         |       |

| FER は 1 を書き込むか、あるいは RXEN/UART_CTLx レジスタを 0 に設定することによりリセットされます。                                                          |           |         |       |

| <b>D5 PER: Parity Error Flag Bit</b>                                                                                    |           |         |       |

| パリティエラーが発生しているか否かを示します。                                                                                                 |           |         |       |

| 1(R): エラー発生                                                                                                             |           |         |       |

| 0(R): エラーなし(デフォルト)                                                                                                      |           |         |       |

| 1(W): 0 にリセット                                                                                                           |           |         |       |

| 0(W): 無効                                                                                                                |           |         |       |

| PER はパリティエラーが発生すると 1 にセットされます。パリティチェックは PREN/UART_MODx レジスタが 1 に設定されている場合にのみ有効で、受信データがシフトレジスタから受信データバッファに転送される際に実行されます。 |           |         |       |

| PER は 1 を書き込むか、あるいは RXEN/UART_CTLx レジスタを 0 に設定することによりリセットされます。                                                          |           |         |       |

| <b>D4 OER: Overrun Error Flag Bit</b>                                                                                   |           |         |       |

| オーバーランエラーが発生しているか否かを示します。                                                                                               |           |         |       |

| 1(R): エラー発生                                                                                                             |           |         |       |

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

OER はオーバーランエラーが発生すると 1 にセットされます。オーバーランエラーは、受信データバッファが満杯の状態で、次のデータをシフトレジスタに受信し、さらに続くデータが送られてきた場合に発生します。このエラーが発生した場合、受信データバッファは上書きされず、エラーが発生した時点のシフトレジスタが上書きされます。

OER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

(正)

#### D6 FER: Framing Error Flag Bit

フレーミングエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

FER はフレーミングエラーが発生すると 1 にセットされます。フレーミングエラーは、ストップビットを 0 としてデータを受信した場合に発生します。

FER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

#### D5 PER: Parity Error Flag Bit

パリティエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

PER はパリティエラーが発生すると 1 にセットされます。パリティチェックは PREN/UART\_MODx レジスタが 1 に設定されている場合にのみ有効で、受信データがシフトレジスタから受信データバッファに転送される際に実行されます。

PER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

#### D4 OER: Overrun Error Flag Bit

オーバーランエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

OER はオーバーランエラーが発生すると 1 にセットされます。オーバーランエラーは、受信データバッファが満杯の状態で、次のデータをシフトレジスタに受信し、さらに続くデータが送られてきた場合に発生します。このエラーが発生した場合、受信データバッファは上書きされず、エラーが発生した時点のシフトレジスタが上書きされます。

OER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

## S1C17 シリーズ マニュアル 正誤表

| 項目: HSCLK 切替時の注意点の追加 |                                                                                                                                                                                                                |       |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 対象マニュアル              | 発行 No.                                                                                                                                                                                                         | 対象ページ |

| S1C17702 テクニカルマニュアル  | 411602400                                                                                                                                                                                                      | 7-5   |

| S1C17602 テクニカルマニュアル  | 411620000                                                                                                                                                                                                      | 7-5   |

| S1C17121 テクニカルマニュアル  | 411790500                                                                                                                                                                                                      | 7-5   |

|                      |                                                                                                                                                                                                                |       |

|                      |                                                                                                                                                                                                                |       |

|                      |                                                                                                                                                                                                                |       |

|                      |                                                                                                                                                                                                                |       |

|                      |                                                                                                                                                                                                                |       |

| <b>7-5</b>           |                                                                                                                                                                                                                |       |

| (誤)                  | 注: HSCLKの選択を行なう場合は、IOSCおよびOSC3の両方がOnしている必要があります。両方がOnでない状態でHSCLKSELへの書き込みを行なってもHSCLKの切替は行なわれず、HSCLKSELの値も変化しません。                                                                                               |       |

| (正)                  | 注: HSCLKの選択を行なう場合は、IOSCおよびOSC3の両方がOnしている必要があります。両方がOnでない状態でHSCLKSELへの書き込みを行なってもHSCLKの切替は行なわれず、HSCLKSELの値も変化しません。 <b>また、HSCLKの切り替えを行なう場合は PCLKEN ビット (D[1:0]/0x5080)を 0x3 に設定してからHSCLKSELビットへの書き込みを行ってください。</b> |       |