## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 I2CM 入出力端子       |           |                    |        |

|---------------------|-----------|--------------------|--------|

| 対象マニュアル             | 発行 No.    | 項目                 | ページ    |

| S1C17601 テクニカルマニュアル | 411806001 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17611 テクニカルマニュアル | 411882201 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17701 テクニカルマニュアル | 411089703 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17704 テクニカルマニュアル | 411511803 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17706 テクニカルマニュアル | 412026301 | 17.2 I2CM 入出力端子    | 17-1   |

| S1C17001 テクニカルマニュアル | 411412003 | 20.2 I2C 入出力端子     | 252    |

| S1C17002 テクニカルマニュアル | 411554302 | V.2.2 I2C マスタ入出力端子 | V-2-2  |

| S1C17003 テクニカルマニュアル | 411635002 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17501 テクニカルマニュアル | 411525502 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17801 テクニカルマニュアル | 411390602 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17803 テクニカルマニュアル | 411820701 | 20.2 I2CM 入出力端子    | 20-1   |

(追加)

注: ポート機能切り換え時は、端子がハイインピーダンスになります。High レベルは出力しませんので、SCL と SDA ラインは外部で VDD レベルにプルアップしてください。なお、VDD を超える電圧値にはプルアップしないでください。

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 T16E フайнモードについて                                                                                                                                                                            |           |                |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|------|

| 対象マニュアル                                                                                                                                                                                        | 発行 No.    | 項目             | ページ  |

| S1C17001 テクニカルマニュアル                                                                                                                                                                            | 411412003 | 13.6 クロック出力の制御 | 13-8 |

| S1C17003 テクニカルマニュアル                                                                                                                                                                            | 411635002 | 13.6 クロック出力の制御 | 13-8 |

| S1C17624/604/622/602/621 テクニカルマニュアル                                                                                                                                                            | 411014802 | 12.7 クロック出力の制御 | 12-6 |

| S1C17701 テクニカルマニュアル                                                                                                                                                                            | 411089704 | 13.6 クロック出力の制御 | 13-8 |

| S1C17702 テクニカルマニュアル                                                                                                                                                                            | 411602402 | 13.6 クロック出力の制御 | 13-8 |

| S1C17704 テクニカルマニュアル                                                                                                                                                                            | 411511804 | 13.6 クロック出力の制御 | 13-8 |

| <b>150 ページ S1C17001 テクニカルマニュアル</b><br><b>13-8 ページ S1C17003 テクニカルマニュアル</b><br><b>13-8 ページ S1C17701 テクニカルマニュアル</b><br><b>13-8 ページ S1C17702 テクニカルマニュアル</b><br><b>13-8 ページ S1C17704 テクニカルマニュアル</b> |           |                |      |

| <b>「クロック出力ファインモードの設定」の注意事項に、以下の記載を追加</b><br>(3) フайнモードは、T16EDF = 0x0 (PCLK 1/1)のみで使用してください。                                                                                                   |           |                |      |

| <b>12-6 ページ S1C17624/604/622/602/621 テクニカルマニュアル</b>                                                                                                                                            |           |                |      |

| <b>「クロック出力ファインモードの設定」の注意事項に、以下の記載を追加</b><br>(4) フайнモードは、T16EDF = 0x0 (PCLK 1/1)のみで使用してください。                                                                                                   |           |                |      |

## S1C17 マニュアル 正誤表

| 項目 I2CM 割り込み        |           |              |       |

|---------------------|-----------|--------------|-------|

| 対象マニュアル             | 発行 No.    | 項目           | ページ   |

| S1C17701 テクニカルマニュアル | 411089702 | I2C 割り込み     | 20-11 |

| S1C17704 テクニカルマニュアル | 411511802 | I2C 割り込み     | 20-11 |

| S1C17702 テクニカルマニュアル | 411602401 | I2C 割り込み     | 20-10 |

| S1C17705 テクニカルマニュアル | 411706500 | I2CM 割り込み    | 16-6  |

| S1C17601 テクニカルマニュアル | 411806000 | I2C マスター割り込み | 20-10 |

| S1C17602 テクニカルマニュアル | 411620000 | I2C マスター割り込み | 20-10 |

| S1C17611 テクニカルマニュアル | 411882200 | I2C マスター割り込み | 20-10 |

| S1C17121 テクニカルマニュアル | 411790501 | I2C マスター割り込み | 20-10 |

| S1C17001 テクニカルマニュアル | 411412001 | I2C 割り込み     | 259   |

| S1C17003 テクニカルマニュアル | 411635001 | I2C マスター割り込み | 20-10 |

( 誤 )

### 送信バッファエンプティ割り込み

この割り込みを使用するには、TINTE/I2CM\_ICTL レジスタを 1 に設定します。TINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

送信バッファエンプティ割り込みが許可されていれば(TINTE=1)、RTDT[7:0]/I2CM\_DAT レジスタに設定された送信データがシフトレジスタに転送された時点で割り込み要求が ITC に出力されます。

### 受信バッファフル割り込み

この割り込みを使用するには、RINTE/I2CM\_ICTL レジスタを 1 に設定します。RINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

受信バッファフル割り込みが許可されていれば(RINTE=1)、シフトレジスタに受信したデータが RTDT[7:0]にロードされた時点で割り込み要求が ITC に出力されます。

ITC については、“割り込みコントローラ(ITC)”の章を参照してください

( 正 )

### 送信バッファエンプティ割り込み

この割り込みを使用するには、TINTE/I2CM\_ICTL レジスタを 1 に設定します。TINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

送信バッファエンプティ割り込みが許可されていれば(TINTE=1)、RTDT[7:0]/I2CM\_DAT

レジスタに設定された送信データがシフトレジスタに転送された時点で割り込み要求が ITC に出力されます。

送信バッファエンプティ割り込みは、データ送信時にのみ、発生します。

・送信バッファエンプティ割り込みのクリア方法

RTDT/I2CM\_DAT にデータをライトします。

TXE/I2CM\_DAT=0 とした場合、データは送信されず、割り込みクリアのみ行います。

### 受信バッファフル割り込み

この割り込みを使用するには、RINTE/I2CM\_IOCTL レジスタを 1 に設定します。RINTE が 0(デフォルト)に設定されていると、この要因による割り込み要求は ITC に送られません。

受信バッファフル割り込みが許可されていれば(RINTE=1)、シフトレジスタに受信したデータが RTDT[7:0]にロードされた時点で割り込み要求が ITC に出力されます。

受信バッファフル割り込みは、データ受信時にのみ、発生します。

・受信バッファフル割り込みのクリア方法

RTDT/I2CM\_DAT からデータをリードします。

**注:I2CM の割り込み発生時、I2C マスターのシーケンス処理に応じて送信バッファエンプティ 割り込みと受信バッファフル割り込みを判断して下さい。送信バッファエンプティ割り込み、 または、受信バッファフル割り込みのどちらが発生したかを確認できるレジスタはありません。**

ITC については、“割り込みコントローラ(ITC)”の章を参照してください。

## S1C17001 マニュアル 正誤表

| 項目                                     |           |       |     |

|----------------------------------------|-----------|-------|-----|

| 対象マニュアル                                | 発行 No.    | 項目    | ページ |

| S1C17001                               | 411412000 | 1.3.1 | 12  |

| ( 誤 )                                  |           |       |     |

| 1.3.1 端子配置図(WCSP)の後に、チップ、PKG 情報無し。     |           |       |     |

| ( 正 )                                  |           |       |     |

| 1.3.1 端子配置図(WCSP)の後に、チップ、PKG 情報を追加します。 |           |       |     |

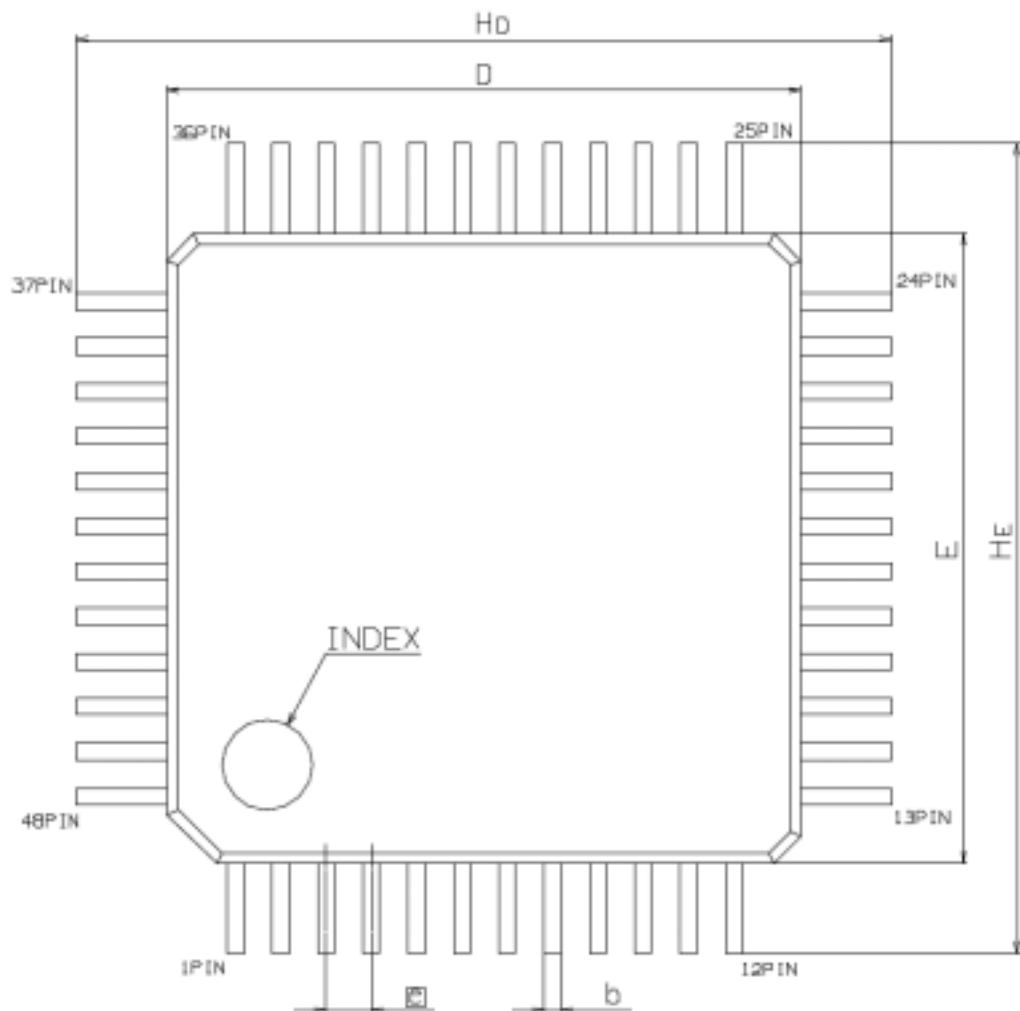

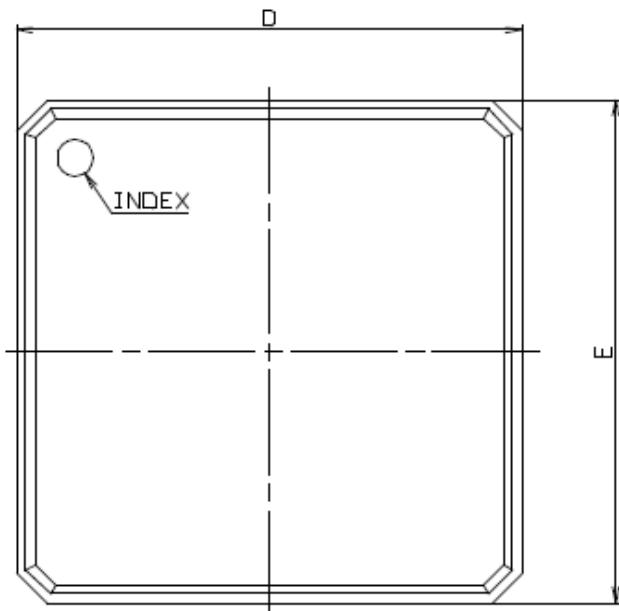

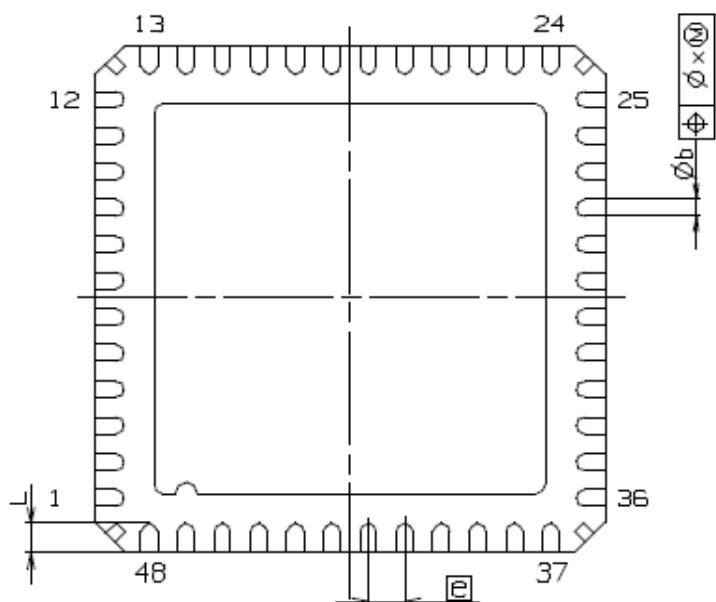

## QFP12-48

## QFN7-48

Top View

Bottom View

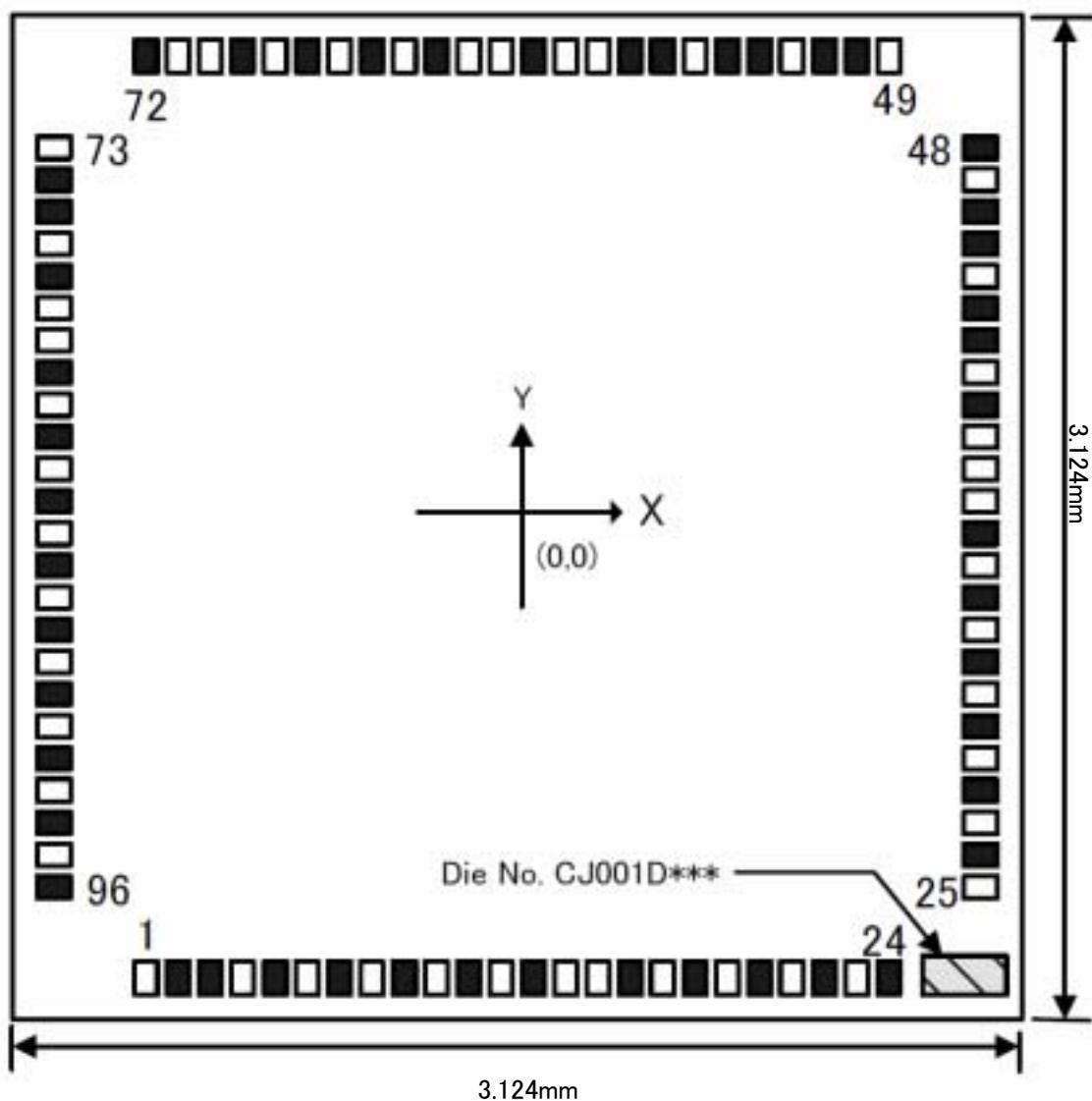

## CHIP

注:\*\*\*は任意の3文字

■は NC パッド

■は DieNo.

チップ厚 400um

パッド開口部

No.1~24 , 49~72 90um × 86um

# PAD 座標

| PAD No. | X(mm) | Y(mm)  | 名称        | PAD No. | X(mm)  | Y(mm) | 名称         |

|---------|-------|--------|-----------|---------|--------|-------|------------|

| 1       | -1.15 | -1.434 | #TEST2    | 49      | 1.15   | 1.434 | #TEST5     |

| 2       | -1.05 | -1.434 | NC        | 50      | 1.05   | 1.434 | NC         |

| 3       | -0.95 | -1.434 | NC        | 51      | 0.95   | 1.434 | NC         |

| 4       | -0.85 | -1.434 | P05/REMO  | 52      | 0.85   | 1.434 | OSC3       |

| 5       | -0.75 | -1.434 | NC        | 53      | 0.75   | 1.434 | NC         |

| 6       | -0.65 | -1.434 | P04/REMI  | 54      | 0.65   | 1.434 | NC         |

| 7       | -0.55 | -1.434 | NC        | 55      | 0.55   | 1.434 | OSC4       |

| 8       | -0.45 | -1.434 | VSS       | 56      | 0.45   | 1.434 | NC         |

| 9       | -0.35 | -1.434 | NC        | 57      | 0.35   | 1.434 | NC         |

| 10      | -0.25 | -1.434 | P03       | 58      | 0.25   | 1.434 | VSS        |

| 11      | -0.15 | -1.434 | NC        | 59      | 0.15   | 1.434 | P25/SCLK   |

| 12      | -0.05 | -1.434 | P02       | 60      | 0.05   | 1.434 | NC         |

| 13      | 0.05  | -1.434 | NC        | 61      | -0.05  | 1.434 | P24/SOUT   |

| 14      | 0.15  | -1.434 | P01       | 62      | -0.15  | 1.434 | P23/SIN    |

| 15      | 0.25  | -1.434 | P00       | 63      | -0.25  | 1.434 | NC         |

| 16      | 0.35  | -1.434 | NC        | 64      | -0.35  | 1.434 | HVDD       |

| 17      | 0.45  | -1.434 | HVDD      | 65      | -0.45  | 1.434 | NC         |

| 18      | 0.55  | -1.434 | NC        | 66      | -0.55  | 1.434 | P22/SPICLK |

| 19      | 0.65  | -1.434 | P12       | 67      | -0.65  | 1.434 | NC         |

| 20      | 0.75  | -1.434 | NC        | 68      | -0.75  | 1.434 | P21/SDO    |

| 21      | 0.85  | -1.434 | P11       | 69      | -0.85  | 1.434 | NC         |

| 22      | 0.95  | -1.434 | NC        | 70      | -0.95  | 1.434 | P20/SDI    |

| 23      | 1.05  | -1.434 | P10       | 71      | -1.05  | 1.434 | P17/#SPISS |

| 24      | 1.15  | -1.434 | NC        | 72      | -1.15  | 1.434 | NC         |

| 25      | 1.434 | -1.15  | #TEST3    | 73      | -1.434 | 1.15  | #TEST1     |

| 26      | 1.434 | -1.05  | NC        | 74      | -1.434 | 1.05  | NC         |

| 27      | 1.434 | -0.95  | #RESET    | 75      | -1.434 | 0.95  | NC         |

| 28      | 1.434 | -0.85  | NC        | 76      | -1.434 | 0.85  | TEST0      |

| 29      | 1.434 | -0.75  | VSS       | 77      | -1.434 | 0.75  | NC         |

| 30      | 1.434 | -0.65  | NC        | 78      | -1.434 | 0.65  | DCLK/P31   |

| 31      | 1.434 | -0.55  | P27/EXCL3 | 79      | -1.434 | 0.55  | DST2/P32   |

| 32      | 1.434 | -0.45  | NC        | 80      | -1.434 | 0.45  | NC         |

| 33      | 1.434 | -0.35  | P26/TOUT  | 81      | -1.434 | 0.35  | DSI0/P33   |

| 34      | 1.434 | -0.25  | NC        | 82      | -1.434 | 0.25  | NC         |

| 35      | 1.434 | -0.15  | P13/FOUT1 | 83      | -1.434 | 0.15  | VSS        |

| 36      | 1.434 | -0.05  | NC        | 84      | -1.434 | 0.05  | NC         |

| 37      | 1.434 | 0.05   | P30/FOUT3 | 85      | -1.434 | -0.05 | LVDD       |

| 38      | 1.434 | 0.15   | LVDD      | 86      | -1.434 | -0.15 | NC         |

| 39      | 1.434 | 0.25   | VSS       | 87      | -1.434 | -0.25 | P14/SDA    |

| 40      | 1.434 | 0.35   | NC        | 88      | -1.434 | -0.35 | NC         |

| 41      | 1.434 | 0.45   | OSC1      | 89      | -1.434 | -0.45 | P15/SCL    |

| 42      | 1.434 | 0.55   | NC        | 90      | -1.434 | -0.55 | NC         |

| 43      | 1.434 | 0.65   | NC        | 91      | -1.434 | -0.65 | P16/EXCL0  |

| 44      | 1.434 | 0.75   | OSC2      | 92      | -1.434 | -0.75 | NC         |

| 45      | 1.434 | 0.85   | NC        | 93      | -1.434 | -0.85 | P07/EXCL1  |

| 46      | 1.434 | 0.95   | NC        | 94      | -1.434 | -0.95 | NC         |

| 47      | 1.434 | 1.05   | #TEST4    | 95      | -1.434 | -1.05 | P06/EXCL2  |

| 48      | 1.434 | 1.15   | NC        | 96      | -1.434 | -1.15 | NC         |

| PAD/端子/ボール No. |                |                 |      | 名称        | I/O | 初期状態       | 機能                              |

|----------------|----------------|-----------------|------|-----------|-----|------------|---------------------------------|

| CHIP           | QFN7<br>-48PIN | QFP12<br>-48PIN | WCSP |           |     |            |                                 |

| 1              | 37             | 37              | A1   | #TEST2    | I   | I(Pull-Up) | テスト端子(通常動作時は High に固定)          |

| 4              | 38             | 38              | A2   | P05/REMO  | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/リモート出力端子      |

| 6              | 39             | 39              | B3   | P04/REMI  | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/リモート入力端子      |

| 8              | 40             | 40              | A3   | VSS       | -   | -          | 電源端子(GND)                       |

| 10             | 41             | 41              | B4   | P03       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 12             | 42             | 42              | A4   | P02       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 14             | 43             | 43              | C4   | P01       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 15             | 44             | 44              | D4   | P00       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 17             | 45             | 45              | A5   | HVDD      | -   | -          | 電源端子(HVDD+)                     |

| 19             | 46             | 46              | B5   | P12       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 21             | 47             | 47              | A6   | P11       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 23             | 48             | 48              | C5   | P10       | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)                |

| 25             | 1              | 1               | A7   | #TEST3    | I   | I(Pull-Up) | テスト端子(通常動作時は High に固定)          |

| 27             | 2              | 2               | B6   | #RESET    | I   | I(Pull-Up) | イニシャルセット入力端子                    |

| 29             | 3              | 3               | B7   | VSS       | -   | -          | 電源端子(GND)                       |

| 31             | 4              | 4               | C6   | P27/EXCL3 | I/O | I(Pull-Up) | 入出力ポート端子*/T16E 外部クロック入力端子       |

| 33             | 5              | 5               | C7   | P26/TOUT  | I/O | I(Pull-Up) | 入出力ポート端子*/T16E PWM 信号出力端子       |

| 35             | 6              | 6               | D5   | P13/FOUT1 | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/OSC1 クロック出力端子 |

| 37             | 7              | 7               | D7   | P30/FOUT3 | I/O | I(Pull-Up) | 入出力ポート端子*/OSC3 分周クロック出力端子       |

|    |    |    |    |                   |     |              |                                    |

|----|----|----|----|-------------------|-----|--------------|------------------------------------|

| 38 | 8  | 8  | D6 | <b>LVDD</b>       | -   | -            | 電源端子(LVDD+)                        |

| 39 | 9  | 9  | E6 | <b>VSS</b>        | -   | -            | 電源端子(GND)                          |

| 41 | 10 | 10 | E7 | <b>OSC1</b>       | I   | I            | OSC1 発振入力端子(外部クロック入力可能)            |

| 44 | 11 | 11 | F7 | <b>OSC2</b>       | O   | O            | OSC1 発振出力端子                        |

| 47 | 12 | 12 | F6 | <b>#TEST4</b>     | I   | I(Pull-Up)   | テスト端子(通常動作時は High に固定)             |

| 49 | 13 | 13 | G7 | <b>#TEST5</b>     | I   | I(Pull-Up)   | テスト端子(通常動作時は High に固定)             |

| 52 | 14 | 14 | G6 | <b>OSC3</b>       | I   | I            | OSC3 発振入力端子(外部クロック入力可能)            |

| 55 | 15 | 15 | G5 | <b>OSC4</b>       | O   | O            | OSC3 発振出力端子                        |

| 58 | 16 | 16 | F5 | <b>VSS</b>        | -   | -            | 電源端子(GND)                          |

| 59 | 17 | 17 | E5 | <b>P25/SCLK</b>   | I/O | I(Pull-Up)   | 入出力ポート端子*/UART クロック入力端子            |

| 61 | 18 | 18 | G4 | <b>P24/SOUT</b>   | I/O | I(Pull-Up)   | 入出力ポート端子*/UART データ出力端子             |

| 62 | 19 | 19 | F4 | <b>P23/SIN</b>    | I/O | I(Pull-Up)   | 入出力ポート端子*/UART データ入力端子             |

| 64 | 20 | 20 | G3 | <b>HVDD</b>       | -   | -            | 電源端子(HVDD+)                        |

| 66 | 21 | 21 | E4 | <b>P22/SPICLK</b> | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI クロック入出力端子            |

| 68 | 22 | 22 | G2 | <b>P21/SDO</b>    | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI データ出力端子              |

| 70 | 23 | 23 | F3 | <b>P20/SDI</b>    | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI データ入力端子              |

| 71 | 24 | 24 | F2 | <b>P17/#SPISS</b> | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/SPI スレーブセレクト入力端子 |

| 73 | 25 | 25 | G1 | <b>#TEST1</b>     | I   | I(Pull-Up)   | テスト端子(通常動作時は High に固定)             |

| 76 | 26 | 26 | F1 | <b>TEST0</b>      | I   | I(Pull-Down) | テスト端子(通常動作時は Low に固定)              |

| 78 | 27 | 27 | E3 | <b>DCLK/P31</b>   | I/O | O(H)         | オンチップデバッガクロック出力端子*/入出力ポート端子        |

| 79 | 28 | 28 | E2 | <b>DST2/P32</b>   | I/O | O(L)         | オンチップデバッガステータス出力端子*/入出力ポート端子       |

| 81 | 29 | 29 | E1 | <b>DSIO/P33</b>   | I/O | I(Pull-Up)   | オンチップデバッガデータ入出力端子*/入出力ポート端子        |

|    |    |    |    |                  |     |            |                                       |

|----|----|----|----|------------------|-----|------------|---------------------------------------|

| 83 | 30 | 30 | D2 | <b>VSS</b>       | -   | -          | 電源端子(GND)                             |

| 85 | 31 | 31 | D1 | <b>LVDD</b>      | -   | -          | 電源端子(LVDD+)                           |

| 87 | 32 | 32 | D3 | <b>P14/SDA</b>   | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/I2C データ入出力端子        |

| 89 | 33 | 33 | C1 | <b>P15/SCL</b>   | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/I2C クロック出力端子        |

| 91 | 34 | 34 | C2 | <b>P16/EXCL0</b> | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/T16 Ch.0 外部クロック入力端子 |

| 93 | 35 | 35 | B1 | <b>P07/EXCL1</b> | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/T16 Ch.1 外部クロック入力端子 |

| 95 | 36 | 36 | B2 | <b>P06/EXCL2</b> | I/O | I(Pull-Up) | 入出力ポート端子(割り込み付き)*/T16 Ch.2 外部クロック入力端子 |

注: 太字の端子名、および“\*”の付いた機能がデフォルト設定の内容です。

## S1C17 マニュアル 正誤表

| 項目 UART RXEN=0 時の受信バッファの状態                                                                                                                                                                                                                |           |         |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|---------------|

| 対象マニュアル                                                                                                                                                                                                                                   | 発行 No.    | 項目      | ページ           |

| S1C17001 テクニカルマニュアル                                                                                                                                                                                                                       | 411412000 | 18 UART | 217, 229, 231 |

| <b>P217 (S1C17001)</b>                                                                                                                                                                                                                    |           |         |               |

| (誤)<br>RXENビットを0に設定すると、送信および受信データバッファは空の状態になります(データが残っていればクリアされます)。また、データの送受信中にRXENを0に設定した場合、転送中のデータは保証されません。                                                                                                                             |           |         |               |

| (正)<br>RXENビットを0に設定すると、送信および受信データバッファは空の状態になります(データが残っていればクリアされます)。また、データの送受信中にRXENを0に設定した場合、転送中のデータは保証されません。                                                                                                                             |           |         |               |

| <b>P229 (S1C17001)</b>                                                                                                                                                                                                                    |           |         |               |

| (誤)<br><b>D0 RXEN: UART Enable Bit</b><br>UARTによるデータ送受信を許可します。<br>1(R/W): 許可<br>0(R/W): 禁止(デフォルト)<br><br>UARTで送受信を始める前にRXENを1に設定してください。RXENを0に設定するとデータ送受信が禁止されます。転送条件の設定は、RXENが0の状態で行ってください。<br>RXENに0を書き込んで送受信を禁止すると、送受信データバッファもクリアされます。 |           |         |               |

| (正)<br><b>D0 RXEN: UART Enable Bit</b><br>UARTによるデータ送受信を許可します。<br>1(R/W): 許可<br>0(R/W): 禁止(デフォルト)<br><br>UARTで送受信を始める前にRXENを1に設定してください。RXENを0に設定するとデータ送受信が禁止されます。転送条件の設定は、RXENが0の状態で行ってください。<br>RXENに0を書き込んで送受信を禁止すると、送受信データバッファもクリアされます。 |           |         |               |

| <b>P 231(S1C17001)</b>                                                                                                                                                                                                                    |           |         |               |

(誤)

- RXEN を 0 に設定して送受信を禁止すると、送受信データバッファがクリア(初期化)されます。RXEN に 0 を書き込む前に、バッファ内に送信待ちまたは読み出し前のデータが残っていないことを確認してください。

(正)

- RXEN を 0 に設定して送受信を禁止すると、送受信データバッファがクリア(初期化)されます。RXEN に 0 を書き込む前に、バッファ内に送信待ち **または読み出し前** のデータが残っていないことを確認してください。

## S1C17 マニュアル 正誤表

| 項目 UART 受信エラーフラグのリセット方法                                                                                                 |           |         |     |

|-------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----|

| 対象マニュアル                                                                                                                 | 発行 No.    | 項目      | ページ |

| S1C17001 テクニカルマニュアル                                                                                                     | 411412000 | 18 UART | 224 |

| <b>P.224 (S1C17001)</b>                                                                                                 |           |         |     |

| (誤)                                                                                                                     |           |         |     |

| <b>D6 FER: Framing Error Flag Bit</b>                                                                                   |           |         |     |

| フレーミングエラーが発生しているか否かを示します。                                                                                               |           |         |     |

| 1(R): エラー発生                                                                                                             |           |         |     |

| 0(R): エラーなし(デフォルト)                                                                                                      |           |         |     |

| 1(W): 0 にリセット                                                                                                           |           |         |     |

| 0(W): 無効                                                                                                                |           |         |     |

| FER はフレーミングエラーが発生すると 1 にセットされます。フレーミングエラーは、ストップビットを 0 としてデータを受信した場合に発生します。                                              |           |         |     |

| FER は 1 を書き込むか、あるいは RXEN/UART_CTLx レジスタを 0 に設定することによりリセットされます。                                                          |           |         |     |

| <b>D5 PER: Parity Error Flag Bit</b>                                                                                    |           |         |     |

| パリティエラーが発生しているか否かを示します。                                                                                                 |           |         |     |

| 1(R): エラー発生                                                                                                             |           |         |     |

| 0(R): エラーなし(デフォルト)                                                                                                      |           |         |     |

| 1(W): 0 にリセット                                                                                                           |           |         |     |

| 0(W): 無効                                                                                                                |           |         |     |

| PER はパリティエラーが発生すると 1 にセットされます。パリティチェックは PREN/UART_MODx レジスタが 1 に設定されている場合にのみ有効で、受信データがシフトレジスタから受信データバッファに転送される際に実行されます。 |           |         |     |

| PER は 1 を書き込むか、あるいは RXEN/UART_CTLx レジスタを 0 に設定することによりリセットされます。                                                          |           |         |     |

| <b>D4 OER: Overrun Error Flag Bit</b>                                                                                   |           |         |     |

| オーバーランエラーが発生しているか否かを示します。                                                                                               |           |         |     |

| 1(R): エラー発生                                                                                                             |           |         |     |

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

OER はオーバーランエラーが発生すると 1 にセットされます。オーバーランエラーは、受信データバッファが満杯の状態で、次のデータをシフトレジスタに受信し、さらに続くデータが送られてきた場合に発生します。このエラーが発生した場合、受信データバッファは上書きされず、エラーが発生した時点のシフトレジスタが上書きされます。

OER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

(正)

#### D6 FER: Framing Error Flag Bit

フレーミングエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

FER はフレーミングエラーが発生すると 1 にセットされます。フレーミングエラーは、ストップビットを 0 としてデータを受信した場合に発生します。

FER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

#### D5 PER: Parity Error Flag Bit

パリティエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

PER はパリティエラーが発生すると 1 にセットされます。パリティチェックは PREN/UART\_MODx レジスタが 1 に設定されている場合にのみ有効で、受信データがシフトレジスタから受信データバッファに転送される際に実行されます。

PER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

#### D4 OER: Overrun Error Flag Bit

オーバーランエラーが発生しているか否かを示します。

1(R): エラー発生

0(R): エラーなし(デフォルト)

1(W): 0 にリセット

0(W): 無効

OER はオーバーランエラーが発生すると 1 にセットされます。オーバーランエラーは、受信データバッファが満杯の状態で、次のデータをシフトレジスタに受信し、さらに続くデータが送られてきた場合に発生します。このエラーが発生した場合、受信データバッファは上書きされず、エラーが発生した時点のシフトレジスタが上書きされます。

OER は 1 を書き込むか、あるいは RXEN/UART\_CTLx レジスタを 0 に設定することによりリセットされます。

## S1C17 シリーズ マニュアル 正誤表

| 項目: CPU 命令一覧の誤記                                                                                                    |                     |             |                    |

|--------------------------------------------------------------------------------------------------------------------|---------------------|-------------|--------------------|

| 対象マニュアル                                                                                                            | 発行 No.              | 対象ページ       |                    |

| S1C17701 テクニカルマニュアル                                                                                                | 411089701           | 2-5         |                    |

| S1C17704 テクニカルマニュアル                                                                                                | 411511801           | 2-5         |                    |

| S1C17702 テクニカルマニュアル                                                                                                | 411602400           | 2-5         |                    |

| S1C17602 テクニカルマニュアル                                                                                                | 411620000           | 2-5         |                    |

| S1C17001 テクニカルマニュアル                                                                                                | 411412000           | 2-5         |                    |

| S1C17003 テクニカルマニュアル                                                                                                | 411635000           | 2-5         |                    |

| S1C17002 テクニカルマニュアル                                                                                                | 411554301           | I-5-5       |                    |

| S1C17501 テクニカルマニュアル                                                                                                | 411525501           | I-5-5       |                    |

| S1C17801 テクニカルマニュアル                                                                                                | 411390601           | I-5-5       |                    |

| <b>2-5 (S1C17701, S1C17704, S1C17702, S1C17602, S1C17001, S1C17003) /<br/>I-5-5 (S1C17501, S1C17801, S1C17002)</b> |                     |             |                    |

| (誤)                                                                                                                |                     |             |                    |

| 分岐                                                                                                                 | jpa<br>ipa.d        | imm7<br>%rb | 絶対ジャンプ<br>ディレイド分岐可 |

| (正)                                                                                                                |                     |             |                    |

| 分岐                                                                                                                 | jpa<br><b>ipa.d</b> | imm7<br>%rb | 絶対ジャンプ<br>ディレイド分岐可 |

## S1C17 シリーズ マニュアル 正誤表

| 項目: SPI スレーブモード時の SPICLK 周波数制限 |           |                |

|--------------------------------|-----------|----------------|

| 対象マニュアル                        | 発行 No.    | 対象ページ          |

| S1C17001 テクニカルマニュアル            | 411412000 | 235            |

| S1C17701 テクニカルマニュアル            | 411089701 | 19-3           |

| S1C17602 テクニカルマニュアル            | 411620000 | 19-3           |

| S1C17702 テクニカルマニュアル            | 411602400 | 19-3           |

| S1C17002 テクニカルマニュアル            | 411554301 | V-4-3, V-5-3   |

| S1C17501 テクニカルマニュアル            | 411525501 | VI-3-3, VI-4-3 |

| S1C17801 テクニカルマニュアル            | 411390601 | VI-3-3, VI-4-3 |

(誤)

注: SPICLK 端子から入力するクロックの周波数は PCLK の 1/3 以下で、クロックのデューティ比は 50%である必要があります。

図 19.3.2 スレーブモードの SPI クロック

(正)

注: SPICLK端子から入力するクロックの周波数はPCLKの1/3以下で、クロックのデューティ比は50%である必要があります。

図 19.3.2 スレーブモードの SPI クロック

## S1C17001 マニュアル 正誤表

| 項目: 外部クロック入力 AC 特性                                             |           |       |

|----------------------------------------------------------------|-----------|-------|

| 対象マニュアル                                                        | 発行 No.    | 対象ページ |

| S1C17001 テクニカルマニュアル                                            | 411412000 | 301   |

|                                                                |           |       |

|                                                                |           |       |

|                                                                |           |       |

|                                                                |           |       |

|                                                                |           |       |

|                                                                |           |       |

| (誤)<br>EXCLx入力Highパルス幅 Min=1/fSYS<br>EXCLx入力Lowパルス幅 Min=1/fSYS |           |       |

| (正)<br>EXCLx入力Highパルス幅 Min=2/fSYS<br>EXCLx入力Lowパルス幅 Min=2/fSYS |           |       |