# **S1R72U01**

## **Data Sheet**

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

# 目 次

|                             |    |

|-----------------------------|----|

| 1. 概要 .....                 | 1  |

| 2. 特長 .....                 | 2  |

| 3. ブロック図 .....              | 3  |

| 4. 機能説明 .....               | 4  |

| 4.1 Serial I/F (UART) ..... | 4  |

| 4.2 USB Host SIE .....      | 4  |

| 4.3 USB Device SIE .....    | 4  |

| 4.4 Transceiver Macro ..... | 4  |

| 4.5 FIFO .....              | 4  |

| 4.6 Bridge Sequencer .....  | 4  |

| 4.7 SIO .....               | 4  |

| 4.8 debug i/f .....         | 5  |

| 4.9 1.8V Regulator .....    | 5  |

| 4.10 3.3V Regulator .....   | 5  |

| 4.11 VBUS SW .....          | 5  |

| 4.12 test circuit .....     | 5  |

| 5. 端子配置図 .....              | 6  |

| 6. 端子機能説明 .....             | 7  |

| 7. コマンド .....               | 11 |

| 8. 電気的特性 .....              | 12 |

| 8.1 絶対最大定格 .....            | 12 |

| 8.2 推奨動作条件 .....            | 12 |

| 8.3 DC特性 .....              | 13 |

| 8.3.1 消費電流 .....            | 13 |

| 8.3.2 入力特性 .....            | 14 |

| 8.3.3 出力特性 .....            | 15 |

| 8.3.4 端子容量 .....            | 17 |

| 8.3.5 VBUS供給機能特性 .....      | 18 |

| 8.3.6 Fail-Safeセル .....     | 19 |

| 8.4 AC特性 .....              | 20 |

| 8.4.1 電源投入／切断タイミング .....    | 20 |

| 8.4.2 RESETタイミング .....      | 21 |

| 8.4.3 クロックタイミング .....       | 21 |

| 8.4.4 USB I/Fタイミング .....    | 21 |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| 8.4.5 Serial I/F (Main CPU) タイミング (S1R72U01 はSPIをサポートしていません) ..... | 22        |

| 8.4.6 Serial I/F (History Display) タイミング .....                     | 22        |

| <b>9. 接続例.....</b>                                                 | <b>23</b> |

| <b>10. 外形寸法図 .....</b>                                             | <b>24</b> |

| 10.1 QFP12-48 .....                                                | 24        |

| 10.2 QFN7-48.....                                                  | 25        |

| <b>11. 製品型番 .....</b>                                              | <b>26</b> |

| <b>改訂履歴表 .....</b>                                                 | <b>27</b> |

### 1. 概要

S1R72U01 は USB2.0 FS/LS に対応したシリアル (UART) –USB2.0 Host/Device ブリッジ LSI です。Main CPU は、本 LSI の USB 機能を、簡易化されたコマンドにより制御できます。USB ドライバは必要ありません。サポートする USB クラスは Human Interface Device Class です。

## 2. 特長

---

### 2. 特長

#### ■ Easy-to-use & Easy-to-connect (シリアル接続)

##### 簡易化されたコマンドで USB を制御可能

Main CPU は、本 LSI の USB 機能を、簡易化されたコマンドを用いて制御できます。Main CPU は USB ドライバを実装する必要はありません。

UART (2 線調歩同期) のシリアルインターフェイスで様々な CPU と容易に接続できます。

#### ■ レギュレータ内蔵

##### USB 用レギュレータ

##### コア電圧用レギュレータ

USB 用 3.3V を生成するレギュレータ (3.3~5.0V の入力範囲) および、内部コア電圧 1.8V を生成するレギュレータ (3.3~5.0V の入力範囲) を内蔵します。したがって、3.3V 以上の電圧であれば、単一電源での動作が可能です。

#### ■ VBUS 供給機能内蔵

##### 外付け VBUS パワーSW 不要

USB ホスト動作時の VBUS 供給機能を内蔵します。従来の USB ホストコントローラで必要とされている VBUS パワーSW を外付けする必要がありません。内蔵の VBUS 供給機能では電流容量が不足する場合に備え、外付け VBUS パワーSW を制御するためのインターフェイスを設けております。バスパワーデバイスのサポート等で電流能力が必要とされる場合は、VBUS パワーSW を外付けしてください。

#### ■ 製品（システム）開発サポート機能

##### 履歴表示

シリアルインターフェイス（調歩同期式）を使用して、本 LSI 内部の実行履歴を表示します。この機能により、製品（システム）開発をサポートします。

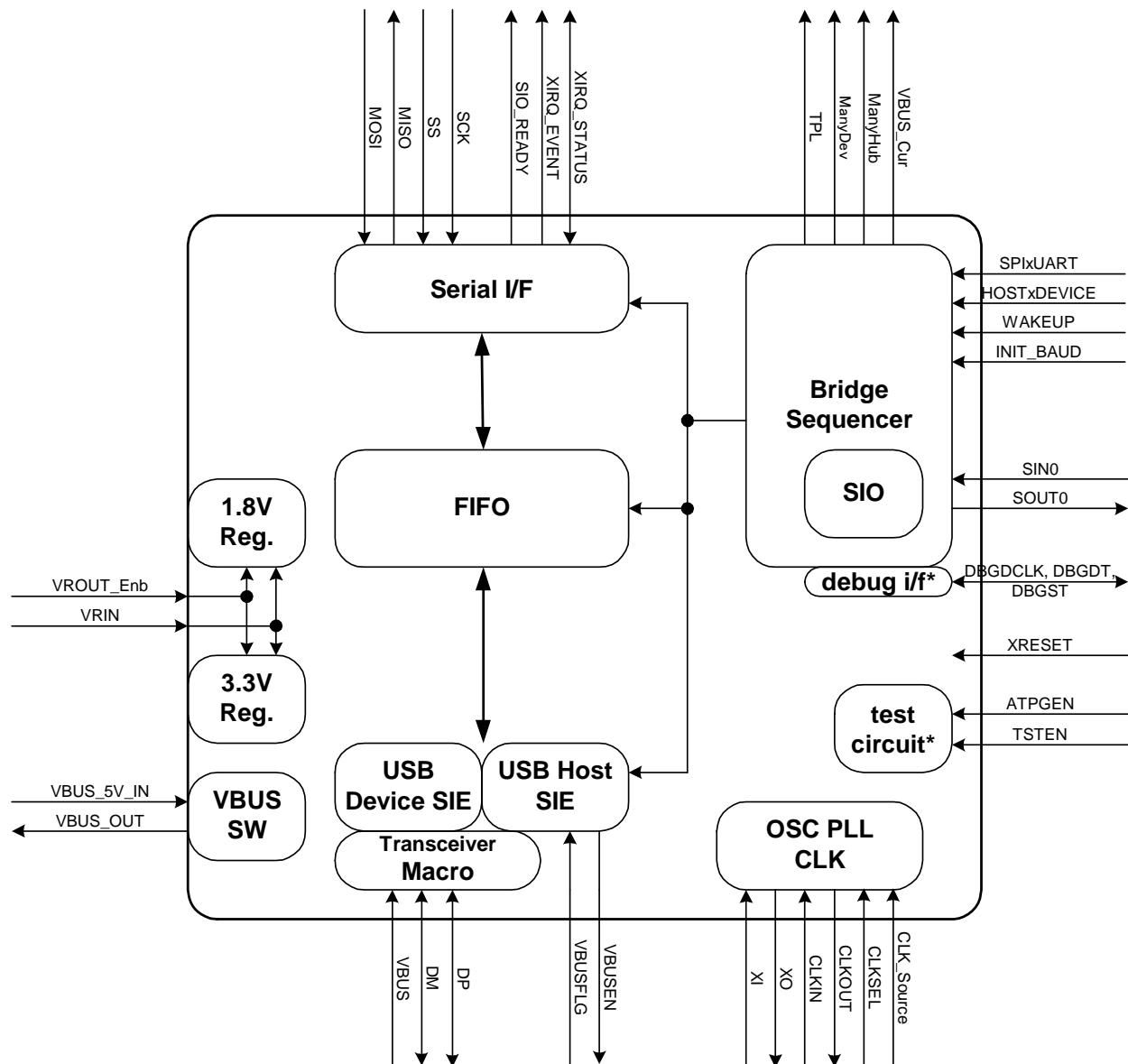

## 3. ブロック図

図 3.1 ブロック図

## 4. 機能説明

---

### 4. 機能説明

#### 4.1 Serial I/F (UART)

Main CPUとの接続はUART(2線調歩同期)です。モード設定端子SPIxUARTをLowにしてください。

インターフェイス電圧(CVDD)は1.8~5.0Vのワイドレンジで使用可能です。

- UART接続(調歩同期シリアルI/F)

初期ボーレート: 300/9600bps (モード設定端子INIT\_BAUDにて設定)

転送ボーレート: 設定可 (~3Mbps)

lsbファースト

8bit Data

1/2 stop bit

Odd/Even/No Parity

#### 4.2 USB Host SIE

USB2.0(Universal Serial Bus Specification Revision 2.0)規格に準拠したUSBホスト機能です。FS(12Mbps)、LS(1.5Mbps)のスピードモードをサポートします。USBの制御は、LSI内部のBridge Sequencerブロックが行います。サポートするUSBのクラスはHuman Interface Device Classです。

#### 4.3 USB Device SIE

USB2.0(Universal Serial Bus Specification Revision 2.0)規格に準拠したUSBデバイス機能です。FS(12Mbps)、LS(1.5Mbps)のスピードモードをサポートします。USBの制御は、LSI内部のBridge Sequencerブロックが行います。サポートするUSBのクラスはHuman Interface Device Classです。

#### 4.4 Transceiver Macro

USBのアナログマクロブロックです。ホスト/デバイス共通で動作します。

#### 4.5 FIFO

シリアル-USB間でデータのバッファリングを行うためのFIFOブロックです。

#### 4.6 Bridge Sequencer

シリアルからのコマンドに応じてUSBの制御を行います。

#### 4.7 SIO

本ブロックは製品(システム)開発サポート機能の履歴表示およびアナログテストに使用します。

### 4.8 debug i/f

内蔵 Bridge Sequencer のデバッグ用端子です。ユーザーは使用しません。

### 4.9 1.8V Regulator

内部コア用 1.8V 電圧を生成するためのレギュレータです。入力電圧は 3.3～5.0V の範囲で可能です。

### 4.10 3.3V Regulator

USB 用 3.3V 電圧を生成するためのレギュレータです。入力電圧は 3.3～5.0V の範囲で可能です。

### 4.11 VBUS SW

LSI 内蔵の VBUS 出力ブロックです。

### 4.12 test circuit

IC テスト用の回路です。ユーザーは使用しません。

## 5. 端子配置図

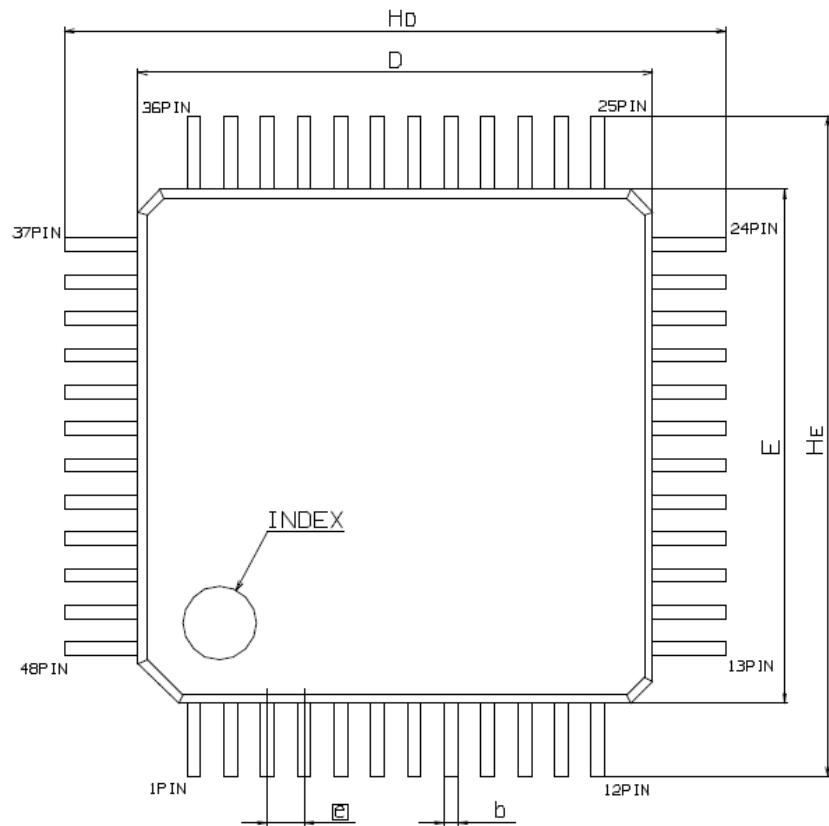

### 5. 端子配置図

|    |            |             |            |    |

|----|------------|-------------|------------|----|

| 36 | ATPGEN     | SIO_READY   | TPL        | 24 |

| 37 | INIT_BAUD  | XIRQ_EVENT  | ManyDev    | 23 |

| 38 | CLKSEL     | XIRQ_STATUS | ManyHub    | 22 |

| 39 | CLKIN      | XRESET      | VBUS_Cur   | 21 |

| 40 | CLK_Source | MISO        | <b>VSS</b> | 20 |

| 41 | CLKOUT     | SS          | (NC)       | 19 |

| 42 | <b>VSS</b> | CVDD        | DBGDT      | 18 |

| 43 | TSTEN      | SCK         | DBGST      | 17 |

| 44 | VROUT_Enb  | SPIUART     | DBGDCLK    | 16 |

| 45 | LVDD       | HOSTXDEV    | SIN0       | 15 |

| 46 | VRIN       | WAKEUP      | SOUT0      | 14 |

| 47 | <b>VSS</b> |             | VBUSEN     | 13 |

| 48 |            |             | VBUSFLG    |    |

図 5.1 パッケージ端子配置図 (QFP/QFN 共通)

## 6. 端子機能説明

| GENERAL (CVDD 系統) |     |            |     |       |                                                                                             |

|-------------------|-----|------------|-----|-------|---------------------------------------------------------------------------------------------|

| BGA               | QFP | 名称         | I/O | RESET | 端子説明                                                                                        |

| -                 | 29  | XRESET     | IN  | -     | リセット信号                                                                                      |

| -                 | 39  | CLKSEL     | IN  | -     | クロック周波数選択<br>クロックソース (CLKIN 端子または XI 端子) から入力する周波数を設定してください。<br>1 : 24MHz 0 : 12MHz         |

| -                 | 41  | CLK_Source | IN  | -     | クロックソース選択<br>クロックソースを CLKIN 端子と XI 端子のどちらから入力するかを設定してください。<br>1 : CLKIN 0 : XI              |

| -                 | 40  | CLKIN      | IN  | -     | クロック入力<br>12MHz/24MHz<br>XI 端子からクロックを入力する場合は、Low 固定してください。                                  |

| -                 | 42  | CLKOUT     | OUT | Low   | クロック出力<br>出力するクロックの切り替え方法は『S1R72U01 テクニカルマニュアル』を参照してください。<br>48MHz/24MHz/12MHz/6MHz/3MHz/停止 |

| OSC (LVDD 系統) |     |    |     |       |                                                                  |

|---------------|-----|----|-----|-------|------------------------------------------------------------------|

| BGA           | QFP | 名称 | I/O | RESET | 端子説明                                                             |

| -             | 10  | XI | IN  | -     | 内部発振回路用入力<br>12MHz/24MHz<br>CLKIN 端子からクロックを入力する場合は、Low 固定してください。 |

| -             | 11  | XO | OUT | -     | 内部発振回路用出力<br>CLKIN 端子からクロックを入力する場合は、Open にしてください。                |

| TEST (LVDD, CVDD 系統) |     |        |        |       |                    |

|----------------------|-----|--------|--------|-------|--------------------|

| BGA                  | QFP | 名称     | I/O    | RESET | 端子説明               |

| -                    | 44  | TSTEN  | IN(PD) | -     | テスト端子 (※1) ユーザー未使用 |

| -                    | 37  | ATPGEN | IN(PD) | -     | テスト端子 (※1) ユーザー未使用 |

PD: Pull Down I/O 使用

※1 LSI 内部で Pull Down されていますが、基板上での Low 固定を推奨します。

| USB (UVDD3 系統) |     |      |     |       |                                                                                    |

|----------------|-----|------|-----|-------|------------------------------------------------------------------------------------|

| BGA            | QFP | 名称   | I/O | RESET | 端子説明                                                                               |

| -              | 9   | VBUS | IN  | -     | VBUS 入力端子<br>USB デバイスとして本 LSI を使用する場合の VBUS 入力端子です。USB ホストとして使用する場合は Open にしてください。 |

| -              | 8   | DP   | BI  | Hi-Z  | USB データライン Data+                                                                   |

| -              | 7   | DM   | BI  | Hi-Z  | USB データライン Data-                                                                   |

## 6. 端子機能説明

| VBUS (UVDD3 系統) |     |         |        |       |                                                                                                              |

|-----------------|-----|---------|--------|-------|--------------------------------------------------------------------------------------------------------------|

| BGA             | QFP | 名称      | I/O    | RESET | 端子説明                                                                                                         |

| -               | 12  | VBUSFLG | IN(PU) | -     | USB パワースイッチ・フォールト検出信号<br>1 : 正常 0 : 異常<br>CMOS シュミット入力<br>USB パワースイッチを外付けする場合にご使用ください。使用しない場合は Open にしてください。 |

| -               | 13  | VBUSEN  | OUT    | Low   | USB パワースイッチ制御信号<br>USB パワースイッチを外付けする場合にご使用ください。使用しない場合は Open にしてください。                                        |

PU: Pull Up I/O 使用

| Serial I/F (CVDD 系統) : Main CPU |     |             |     |       |                                                                                   |

|---------------------------------|-----|-------------|-----|-------|-----------------------------------------------------------------------------------|

| BGA                             | QFP | 名称          | I/O | RESET | 端子説明                                                                              |

| -                               | 30  | MISO        | Tri | High  | シリアルデータ出力<br>(SS 端子を High にすると Hi-z 出力になります)                                      |

| -                               | 28  | MOSI        | IN  | -     | シリアルデータ入力                                                                         |

| -                               | 31  | SS          | IN  | -     | スレーブセレクト<br>(MISO 端子の出力制御に使用できます。<br>Hi-z 出力が不要の場合は Low 固定してください)                 |

| -                               | 33  | SCK         | IN  | -     | シリアルクロック (未使用 : Low 固定してください)                                                     |

| -                               | 25  | SIO_READY   | OUT | Low   | 通信開始可能通知端子<br>この端子の使用方法の詳細は『S1R72U01 テクニカルマニュアル』を参照ください。<br>未使用の場合は Open にしてください。 |

| -                               | 27  | XIRQ_STATUS | OUT | High  | ステータス通知<br>この端子の使用方法の詳細は『S1R72U01 テクニカルマニュアル』を参照ください。<br>未使用の場合は Open にしてください。    |

| -                               | 26  | XIRQ_EVENT  | OUT | High  | イベントリード要求<br>この端子の使用方法の詳細は『S1R72U01 テクニカルマニュアル』を参照ください。<br>未使用の場合は Open にしてください。  |

| Serial I/F (UVDD3 系統) : History Display |     |       |     |       |                                                                                                      |

|-----------------------------------------|-----|-------|-----|-------|------------------------------------------------------------------------------------------------------|

| BGA                                     | QFP | 名称    | I/O | RESET | 端子説明                                                                                                 |

| -                                       | 15  | SIN0  | IN  | -     | 調歩同期式シリアルデータイン<br>履歴表示用のシリアル端子です。履歴表示に関する詳細は『S1R72U01 開発サポートマニュアル』を参照ください。<br>未使用の場合は High にしてください。  |

| -                                       | 14  | SOUT0 | OUT | High  | 調歩同期式シリアルデータアウト<br>履歴表示用のシリアル端子です。履歴表示に関する詳細は『S1R72U01 開発サポートマニュアル』を参照ください。<br>未使用の場合は Open にしてください。 |

| DEBUG I/F (UVDD3 系統) |     |         |        |       |          |

|----------------------|-----|---------|--------|-------|----------|

| BGA                  | QFP | 名称      | I/O    | RESET | 端子説明     |

| -                    | 16  | DBGDCLK | OUT    | High  | 未使用 (※1) |

| -                    | 18  | DBGDT   | BI(PU) | -     | 未使用 (※2) |

| -                    | 17  | DBGST   | OUT    | Low   | 未使用 (※1) |

PU: Pull Up I/O 使用

※1 Openにしてください。

※2 LSI 内部で Pull up されていますが、10kΩ程度の外付け Pull Up を推奨します。

| GPI (CVDD 系統) |     |             |     |       |                                                                                                                                        |

|---------------|-----|-------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| BGA           | QFP | 名称          | I/O | RESET | 端子説明                                                                                                                                   |

| -             | 34  | SPIxUART    | IN  | -     | 設定端子 (Low 固定してください)<br>0 : UART モード                                                                                                    |

| -             | 35  | HOSTxDEVICE | IN  | -     | 設定端子<br>1 : HOST モード 0 : DEVICE モード<br>設定切り替え時には本 LSI にリセットがかかります。                                                                     |

| -             | 36  | WAKEUP      | IN  | -     | ウェイクアップ端子<br>SLEEP 状態からの復帰に使用します。<br>立ち上がりリエッジでウェイクアップトリガがかかります。                                                                       |

| -             | 38  | INIT_BAUD   | IN  | -     | 初期ボーレート設定端子<br>1 : 9600bps 0 : 300bps<br>シリアルポート設定により UART のボーレートは 300~3Mbps まで設定できます。<br>シリアルポート設定方法の詳細は『S1R72U01 テクニカルマニュアル』を参照ください。 |

| GPO (CVDD 系統) |     |          |     |       |                                                                             |

|---------------|-----|----------|-----|-------|-----------------------------------------------------------------------------|

| BGA           | QFP | 名称       | I/O | RESET | 端子説明                                                                        |

| -             | 24  | TPL      | OUT | Low   | Unsupported Device<br>1 : エラー 0 : -<br>USB ロゴ認証に使用します。未使用の場合は Open にしてください。 |

| -             | 23  | ManyDev  | OUT | Low   | Too Many Devices<br>1 : エラー 0 : -<br>USB ロゴ認証に使用します。未使用の場合は Open にしてください。   |

| -             | 22  | ManyHub  | OUT | Low   | Too Many Hubs<br>1 : エラー 0 : -<br>USB ロゴ認証に使用します。未使用の場合は Open にしてください。      |

| -             | 21  | VBUS_Cur | OUT | Low   | VBUS Over Current<br>1 : エラー 0 : -<br>USB ロゴ認証に使用します。未使用の場合は Open にしてください。  |

## 6. 端子機能説明

| Regulator (VRIN 系統) |       |           |       |       |                                                                                            |

|---------------------|-------|-----------|-------|-------|--------------------------------------------------------------------------------------------|

| BGA                 | QFP   | 名称        | I/O   | RESET | 端子説明                                                                                       |

| -                   | 4, 47 | VRIN      | Power | -     | レギュレータ入力<br>それぞれの端子に $C_{in}=1.0\mu F$ を接続してください。<br><u>レギュレータ未使用時は必ずオーブンにしてください。</u>      |

| -                   | 45    | VROUT_Enb | IN    | -     | Regulator イネーブル<br>レギュレータ使用時には VRIN と同レベルに固定してください。<br><u>レギュレータ未使用時には必ず Low 固定してください。</u> |

| VBUS SW (VBUS_5V_IN 系統) |     |            |       |       |                                                                                 |

|-------------------------|-----|------------|-------|-------|---------------------------------------------------------------------------------|

| BGA                     | QFP | 名称         | I/O   | RESET | 端子説明                                                                            |

| -                       | 2   | VBUS_5V_IN | Power | -     | VBUS 生成入力<br>内蔵 VBUS 供給機能用、電圧入力端子です。<br>同機能を未使用の場合も電源 (8.3.5 の VSWIN) を与えてください。 |

| -                       | 1   | VBUS_OUT   | Power | -     | VBUS 出力<br>内蔵 VBUS 供給機能用、VBUS 出力端子です。<br>同機能を未使用の場合は Open にしてください。              |

| POWER |                  |       |          |  |                                                                                                   |

|-------|------------------|-------|----------|--|---------------------------------------------------------------------------------------------------|

| BGA   | QFP              | 名称    | 電圧       |  | 端子説明                                                                                              |

| -     | 5                | UVDD3 | 3.3V     |  | USB 用電源<br>レギュレータ使用時 : $C_{out}=1.0\mu F$ を接続してください。<br>レギュレータ未使用時 : 左記電圧を印加してください。               |

| -     | 46               | LVDD  | 1.8V     |  | 内部電源, TEST 電源, OSC 電源<br>レギュレータ使用時 : $C_{out}=1.0\mu F$ を接続してください。<br>レギュレータ未使用時 : 左記電圧を印加してください。 |

| -     | 32               | CVDD  | 1.8~5.0V |  | Main CPU I/F 用電源                                                                                  |

| -     | 3, 6, 20, 43, 48 | VSS   | 0V       |  | GND                                                                                               |

### 7. コマンド

MainCPUとの通信はコマンドで行います。コマンドの詳細は『S1R72U01 テクニカルマニュアル』をご参照ください。

## 8. 電気的特性

### 8. 電気的特性

#### 8.1 絶対最大定格

| 項目      | 記号                | 定格値                                              | 単位 |

|---------|-------------------|--------------------------------------------------|----|

| 電源電圧    | CVDD<br>VRIN (※1) | -0.3~7.0                                         | V  |

|         | UVDD3             | -0.3~4.0                                         | V  |

|         | LVDD (※2)         | -0.3~2.5                                         | V  |

| 入力電圧    | VI (※3)           | -0.3~CVDD+0.5<br>-0.3~UVDD3+0.5<br>-0.3~LVDD+0.5 | V  |

|         | VBUS_5V_IN        | -0.3~7.0                                         | V  |

| 出力電圧    | VO (※3)           | -0.3~CVDD+0.5<br>-0.3~UVDD3+0.5<br>-0.3~LVDD+0.5 | V  |

|         | VBUS_OUT          | VBUS_5V_IN+0.3                                   | V  |

| 出力電流／端子 | Iout              | ±10                                              | mA |

| 保存温度    | Tstg              | -65~150                                          | °C |

※1 VRIN $\geq$ UVDD3、VRIN $\geq$ LVDD

※2 CVDD、UVDD3 $\geq$ LVDD

※3 各電源の印加電圧

#### 8.2 推奨動作条件

| 項目   | 記号             | MIN  | TYP       | MAX                               | 単位 |

|------|----------------|------|-----------|-----------------------------------|----|

| 電源電圧 | CVDD           | 1.65 | 1.80~5.00 | 5.50                              | V  |

|      | VRIN           | 3.00 | 3.30~5.00 | 5.50                              | V  |

|      | UVDD3          | 3.00 | 3.30      | 3.60                              | V  |

|      | LVDD           | 1.65 | 1.80      | 1.95                              | V  |

| 入力電圧 | VI (※)         | -0.3 | -         | CVDD+0.3<br>UVDD3+0.3<br>LVDD+0.3 | V  |

| 周囲温度 | T <sub>a</sub> | -40  | 25        | 85                                | °C |

※各端子の電源電圧

#### [電源投入順序の注意事項]

内蔵レギュレータを使用せずに外部から電源を供給する場合、電源印加タイミングにご注意ください。詳細は「8.4.1 電源投入／切断タイミング」を参照ください。

### 8.3 DC特性

#### 8.3.1 消費電流

| 項目               | 記号    | 条件                            | MIN | TYP   | MAX | 単位 |

|------------------|-------|-------------------------------|-----|-------|-----|----|

| 電源供給電流（※1）       |       |                               |     |       |     |    |

| 電源電流             | IDDH0 | CVDD = 5.5V                   | -   | 5     | -   | mA |

|                  | IDDH1 | UVDD3 = 3.6V                  | -   | 5 ※2  | -   | mA |

|                  | IDDL  | LVDD = 1.95V                  | -   | 25 ※2 | -   | mA |

|                  | IDDR  | VRIN = 5.5V                   | -   | 30 ※3 | -   | mA |

| 電源供給電流（静止電流）（※4） |       |                               |     |       |     |    |

| 電源電流             | IDDS  | 各電源の MAX 条件<br>電源もしくは GND に固定 | -   | 50    | -   | μA |

| 入力リーク            |       |                               |     |       |     |    |

| 入力リーク電流          | IL    | 各電源の MAX 条件                   | -5  | -     | 5   | μA |

※1 推奨動作条件 ( $T_a = 25^{\circ}\text{C}$ ) による。弊社評価ボード環境における動作時電流です。

※2 内蔵レギュレータ未使用、外部電源印加時の弊社評価ボード環境における動作時電流です。

※3 内蔵レギュレータ使用時の弊社評価ボード環境における動作時電流です。

※4  $T_a=25^{\circ}\text{C}$ 、レギュレータ使用時の静止電流です。

## 8. 電気的特性

### 8.3.2 入力特性

| 項目                    | 記号    | 条件                                                                             | MIN                          | TYP               | MAX                          | 単位 |

|-----------------------|-------|--------------------------------------------------------------------------------|------------------------------|-------------------|------------------------------|----|

| 入力特性                  | 端子 :  | LVDD 系統の端子                                                                     |                              |                   |                              |    |

| “H”レベル入力電圧            | VIH1  | LVDD = 1.95V                                                                   | 1.27                         | -                 | -                            | V  |

| “L”レベル入力電圧            | VIL1  | LVDD = 1.65V                                                                   | -                            | -                 | 0.57                         | V  |

| 入力特性 (シュミット)          | 端子 :  | CVDD, UVDD3 系統の端子                                                              |                              |                   |                              |    |

| “H”レベルトリガ電圧           | VT1+  | CVDD = 5.5V<br>CVDD = 3.6V<br>CVDD = 1.95V<br>UVDD3 = 3.6V                     | -                            | -                 | 4.00<br>2.52<br>1.36<br>2.52 | V  |

| “L”レベルトリガ電圧           | VT1-  | CVDD = 4.5V<br>CVDD = 3.0V<br>CVDD = 1.65V<br>UVDD3 = 3.0V                     | 0.80<br>0.75<br>0.42<br>0.75 | -                 | -                            | V  |

| ヒステリシス電圧              | ΔV1   | CVDD = 4.5V<br>CVDD = 3.0V<br>CVDD = 1.65V<br>UVDD3 = 3.0V                     | 0.30<br>0.30<br>0.17<br>0.30 | -                 | -                            | V  |

| シュミット入力特性<br>(USB:FS) | 端子 :  | DP, DM                                                                         |                              |                   |                              |    |

| “H”レベルトリガ電圧           | VTU+  | UVDD3 = 3.6V                                                                   | -                            | -                 | 2.0                          | V  |

| “L”レベルトリガ電圧           | VTU-  | UVDD3 = 3.0V                                                                   | 0.8                          | -                 | -                            | V  |

| 入力特性(USB:FS 差動入力)     | 端子 :  | DP, DM のペア                                                                     |                              |                   |                              |    |

| 差動入力の感度               | VDSU  | UVDD3 = 3.0V<br>差動入力電圧 0.8V~2.5V                                               | 0.2                          | -                 | -                            | V  |

| 入力特性                  | 端子 :  | VBUSFLG, DBGDT                                                                 |                              |                   |                              |    |

| プルアップ抵抗               | RPLU  | VI = 0V (UVDD3 = 3.0V)                                                         | 52                           | 160               | 384                          | kΩ |

| 入力特性                  | 端子 :  | ATPGEN                                                                         |                              |                   |                              |    |

| プルダウン抵抗               | RPLD  | VI = CVDD (CVDD = 4.5V)<br>VI = CVDD (CVDD = 3.0V)<br>VI = CVDD (CVDD = 1.65V) | 32<br>52<br>200              | 100<br>160<br>600 | 240<br>384<br>1440           | kΩ |

| 入力特性                  | 端子 :  | TSTEN                                                                          |                              |                   |                              |    |

| プルダウン抵抗               | RPLDL | VI = LVDD (LVDD=1.65V)                                                         | 40                           | 120               | 288                          | kΩ |

| 入力特性                  | 端子名 : | VBUS                                                                           |                              |                   |                              |    |

| プルダウン抵抗               | RPLDB | VI = 5.0V                                                                      | 100                          | 125               | 165                          | kΩ |

## 8.3.3 出力特性

(V<sub>SS</sub>=0V)

| 項目                 | 記号   | 条件                                                                                                                     | MIN                                                   | TYP | MAX                      | 単位 |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|--------------------------|----|

| 出力特性               | 端子 : | SIO_READY, XIRQ_EVENT, XIRQ_STATUS, TPL, ManyDev, ManyHUB, VBUS_Cur, VBUSEN                                            |                                                       |     |                          |    |

| "H"レベル出力電圧         | VOH1 | CVDD = 4.5V (IOH = -2.0mA)<br>CVDD = 3.0V (IOH = -1.4mA)<br>CVDD = 1.65V (IOH = -0.6mA)<br>UVDD3 = 3.0V (IOH = -1.4mA) | CVDD – 0.4<br>CVDD – 0.4<br>CVDD – 0.4<br>UVDD3 – 0.4 | -   | -                        | V  |

| "L"レベル出力電圧         | VOL1 | CVDD = 4.5V (IOH = 2.0mA)<br>CVDD = 3.0V (IOH = 1.4mA)<br>CVDD = 1.65V (IOH = 0.6mA)<br>UVDD3 = 3.0V (IOH = 1.4mA)     | -                                                     | -   | 0.4<br>0.4<br>0.4<br>0.4 | V  |

| 出力特性               | 端子 : | MISO, SOUT0, CLKOUT                                                                                                    |                                                       |     |                          |    |

| "H"レベル出力電圧         | VOH2 | CVDD = 4.5V (IOH = -4.0mA)<br>CVDD = 3.0V (IOH = -2.8mA)<br>CVDD = 1.65V (IOH = -1.2mA)<br>UVDD3 = 3.0V (IOH = -2.8mA) | CVDD – 0.4<br>CVDD – 0.4<br>CVDD – 0.4<br>UVDD3 – 0.4 | -   | -                        | V  |

| "L"レベル出力電圧         | VOL2 | CVDD = 4.5V (IOH = 4.0mA)<br>CVDD = 3.0V (IOH = 2.8mA)<br>CVDD = 1.65V (IOH = 1.2mA)<br>UVDD3 = 3.0V (IOH = 2.8mA)     | -                                                     | -   | 0.4<br>0.4<br>0.4<br>0.4 | V  |

| 出力特性 (USB:FS)      | 端子 : | DP, DM                                                                                                                 |                                                       |     |                          |    |

| "H"レベル出力電圧         | VOHF | UVDD3 = 3.0V                                                                                                           | 2.8                                                   | -   | -                        | V  |

| "L"レベル出力電圧         | VOLF | UVDD3 = 3.6V                                                                                                           | -                                                     | -   | 0.3                      | V  |

| 出力特性               | 端子 : | CVDD 系統の端子の端子                                                                                                          |                                                       |     |                          |    |

| OFF-STATE<br>リーク電流 | IOZ  | CVDD = 5.5V<br>VOH = CVDD<br>VOL = VSS                                                                                 | -5                                                    | -   | 5                        | μA |

## 8. 電気的特性

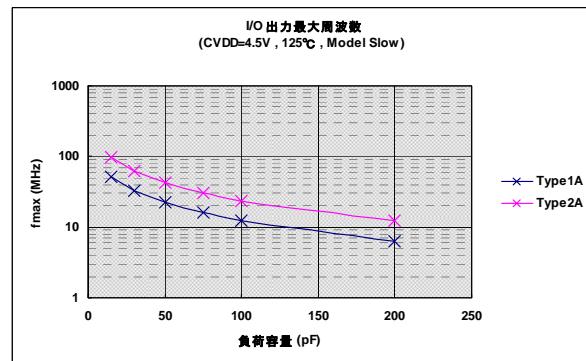

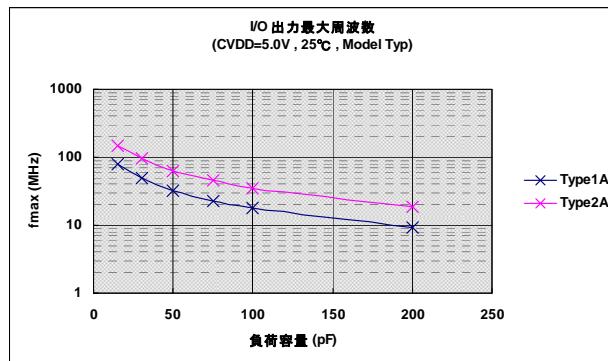

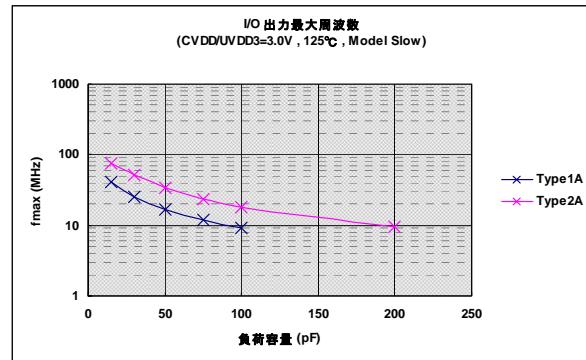

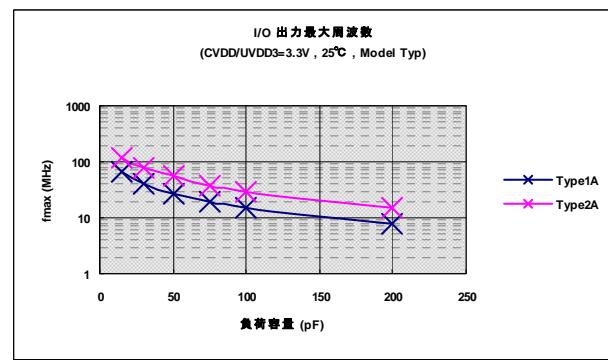

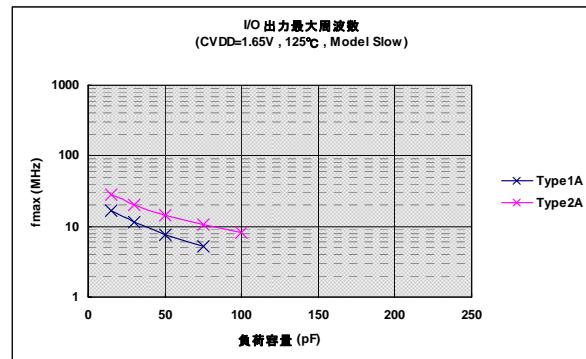

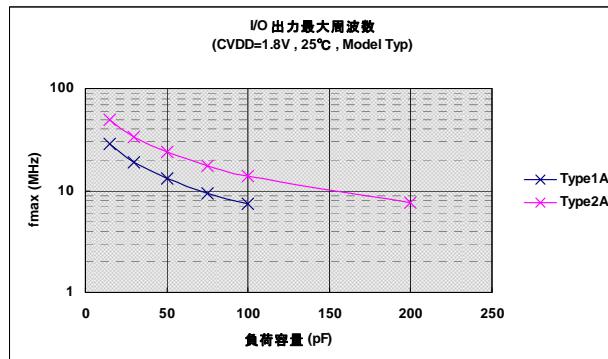

○Fmax-Cl

<出力バッファ分類>

Type1A: SIO\_READY, XIRQ\_EVENT, XIRQ\_STATUS, TPL, ManyDev, ManyHUB, VBUS\_Cur, VBUSEN

Type2A: MISO, SOUT0, CLKOUT

■IO 電圧 5.0V 使用時

■IO 電圧 3.3V 使用時

■IO 電圧 1.8V 使用時

## 8.3.4 端子容量

| 項目                                        | 記号  | 条件                    | MIN | TYP | MAX | 単位 |

|-------------------------------------------|-----|-----------------------|-----|-----|-----|----|

| 端子容量                                      |     | 端子名 : 全入力端子           |     |     |     |    |

| <input type="checkbox"/> 入力端子容量           | Cl  | f = 1MHz              | -   | -   | 8   | pF |

| 端子容量                                      |     | 端子名 : 全出力端子           |     |     |     |    |

| <input type="checkbox"/> 出力端子容量           | CO  | f = 1MHz              | -   | -   | 8   | pF |

| 端子容量                                      |     | 端子名 : DP, DM を除く入出力端子 |     |     |     |    |

| <input type="checkbox"/> 入出力端子容量          | CB  | f = 1MHz              | -   | -   | 8   | pF |

| 端子容量                                      |     | 端子名 : DP, DM          |     |     |     |    |

| <input type="checkbox"/> 入出力端子容量<br>(USB) | CBU | f = 1MHz              | -   | -   | 15  | pF |

## 8. 電氣的特性

---

### 8.3.5 VBUS供給機能特性

| 項目      | 記号     | 条件                                     | MIN | TYP        | MAX        | 単位 |

|---------|--------|----------------------------------------|-----|------------|------------|----|

| 入力電圧    | VSWIN  |                                        | 3.0 | 5.0        | 5.5        | V  |

| オン抵抗    | RSWON  | VBUS_5V_IN = 5.0V<br>VBUS_5V_IN = 3.0V | -   | 2.4<br>3.5 | 4.0        | Ω  |

| オフリーケ電流 | ISWOFF | VBUS_5V_IN = 5.0V<br>VBUS_5V_IN = 3.0V | -   | 10<br>10   | 100<br>100 | nA |

| 過電流検出   | ISWLMT | VBUS_5V_IN = 5.0V<br>VBUS_5V_IN = 3.0V | 21  | 26<br>17   | 35         | mA |

| 過電流応答時間 | TSWOFF | 過電流状態->VBUS OFF                        | 300 |            |            | μs |

### 8.3.6 Fail-Safeセル

本LSIの一部の端子にはFail-Safeセルを採用しています。Fail-Safeセルの特長は以下の通りです。

- 入力端子、または入出力端子の入力状態においては、電源が印加された状態で、電源電圧以上の信号が入力されても、入力リーコンデンサーは発生しません。(ただし、プルアップ抵抗付きの端子は30uA程度のリーコンデンサーが発生します。)

- 電源がCut-offされた状態で、外部から入力信号が印加されても、入力リーコンデンサーは発生しません。

動作電圧以上の電圧レベルの信号を受けることができますが、Fail-Safeセルに印加可能な信号電圧は、絶対最大定格を超えることはできませんのでご注意ください。

<Fail-Safe 対象端子>

MISO, MOSI, SCK, SS, SIO\_READY, XIRQ\_EVENT, XIRQ\_STATUS, SPIxUART, HOSTxDEVICE, WAKEUP, INIT\_BAUD, TPL, ManyDev, ManyHUB, VBUS\_Cur, SIN0, SOUT0, VBUSFLG, VBUSEN, CLKOUT, CLKIN, CLK\_Source, CLKSEL, DBGCLK, DBGDT, DBGST, XRESET, ATPGEN

## 8. 電気的特性

### 8.4 AC特性

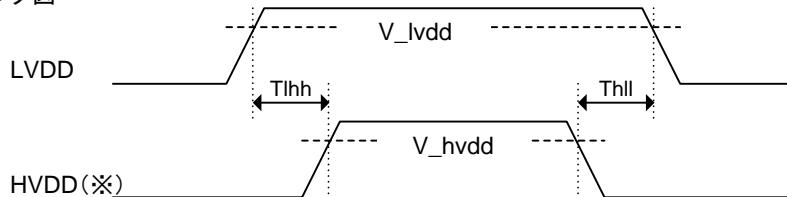

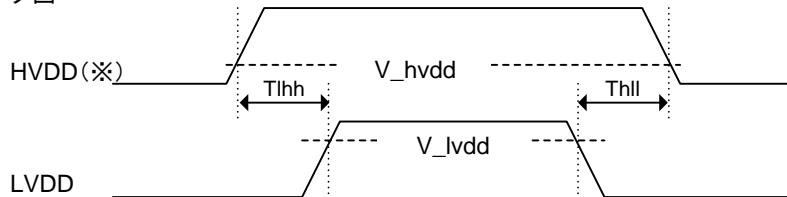

#### 8.4.1 電源投入／切斷タイミング

##### A. 電源投入／切斷タイミング(LVDD⇒HVDD／HVDD⇒LVDDの場合:推奨条件)

タイミングパラメータ

| 項目            | 記号   | min | typ | max | 単位  |

|---------------|------|-----|-----|-----|-----|

| HVDD電源投入タイミング | Tlhh | 0   | -   | 10  | sec |

| HVDD切斷タイミング   | Thll | 0   | -   | 10  | sec |

電圧パラメータ

| 項目       | 記号     | 電圧条件     |          | 単位 |

|----------|--------|----------|----------|----|

|          |        | 投入時      | 遮断時      |    |

| LVDD起点電圧 | V_lvdd | LVDD_min | LVDD_min | V  |

| HVDD起点電圧 | V_hvdd | HVDD_min | HVDD_min | V  |

タイミング図

##### B. 電源投入・切斷タイミング(HVDD⇒LVDD／LVDD⇒HVDDの場合)

タイミングパラメータ

| 項目            | 記号   | min | typ | max | 単位  |

|---------------|------|-----|-----|-----|-----|

| LVDD電源投入タイミング | Tlhh | 0   | -   | 1   | sec |

| LVDD切斷タイミング   | Thll | 0   | -   | 1   | sec |

電圧パラメータ

| 項目       | 記号     | 電圧条件     |          | 単位 |

|----------|--------|----------|----------|----|

|          |        | 投入時      | 遮断時      |    |

| LVDD起点電圧 | V_lvdd | LVDD_min | LVDD_min | V  |

| HVDD起点電圧 | V_hvdd | 0.1      | 0.1      | V  |

タイミング図

※HVDDとはUSB用のUVDD3及びインターフェース用のCVDDを示します。

※電源投入／切斷ともにLVDD⇒HVDDのタイミングの場合、投入はA.、切斷はB.を参照ください。

同様に、電源投入／切斷ともにHVDD⇒LVDDのタイミングの場合、投入はB.、切斷はA.を参照ください。

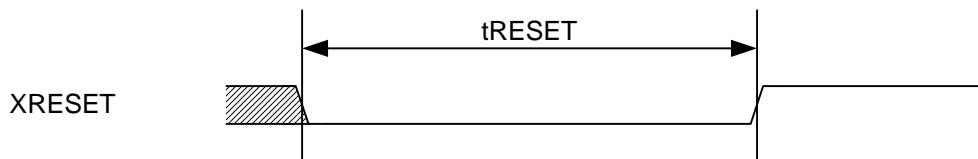

## 8.4.2 RESETタイミング

| 記号          | 説明       | min | typ | max | 単位 |

|-------------|----------|-----|-----|-----|----|

| $t_{RESET}$ | リセットパルス幅 | 40  | -   | -   | ns |

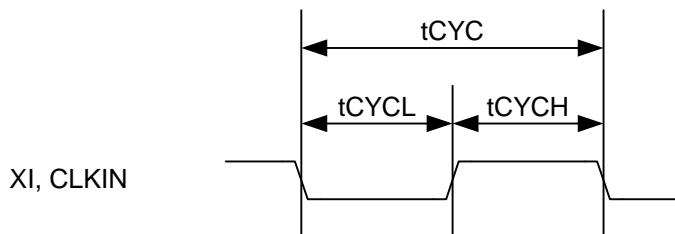

## 8.4.3 クロックタイミング

| 記号                       | 説明                         | min | typ    | max | 単位  |

|--------------------------|----------------------------|-----|--------|-----|-----|

| $t_{CYC}$                | クロックサイクル( $CLKSEL = "L"$ ) | -   | 12.000 | -   | MHz |

| $t_{CYC}$                | クロックサイクル( $CLKSEL = "H"$ ) | -   | 24.000 | -   | MHz |

| $t_{CYCL}$<br>$t_{CYCH}$ | クロックデューティ                  | 45  | 50     | 55  | %   |

※USB 規格に要求される精度を満足できるよう、クロックソースを選定すること。FS: 2,500ppm LS: 15,000ppm

## 8.4.4 USB I/Fタイミング

USB2.0 『Universal Serial Bus Specification Revision 2.0』 規格に準拠します。

## 8. 電気的特性

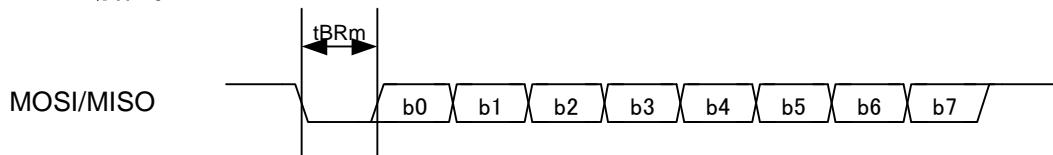

### 8.4.5 Serial I/F (Main CPU) タイミング (S1R72U01 はSPIをサポートしていません)

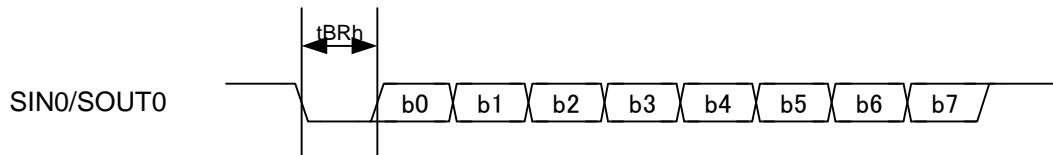

UART動作時

| 記号   | 説明    | min | typ | max | 単位  |

|------|-------|-----|-----|-----|-----|

| tBRm | ボーレート | 300 | -   | 3M  | bps |

### 8.4.6 Serial I/F (History Display) タイミング

| 記号   | 説明    | min | typ   | max | 単位  |

|------|-------|-----|-------|-----|-----|

| tBRh | ボーレート | -   | 38400 | -   | bps |

## 9. 接続例

『S1R72U01 評価ボードマニュアル』を参照してください。

## 10. 外形寸法図

### 10. 外形寸法図

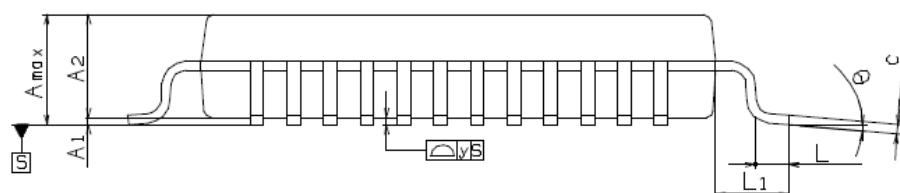

#### 10.1 QFP12-48

| Symbol           | Dimension in Millimeters |     |      |

|------------------|--------------------------|-----|------|

|                  | Min                      | Nom | Max  |

| E                | -                        | 7   | -    |

| D                | -                        | 7   | -    |

| A <sub>max</sub> | -                        | -   | 1.7  |

| A <sub>1</sub>   | -                        | 0.1 | -    |

| A <sub>2</sub>   | -                        | 1.4 | -    |

| ■                | -                        | 0.5 | -    |

| b                | 0.13                     | -   | 0.27 |

| c                | 0.09                     | -   | 0.2  |

| θ                | 0°                       | -   | 10°  |

| L                | 0.3                      | -   | 0.7  |

| L <sub>1</sub>   | -                        | 1   | -    |

| H <sub>E</sub>   | -                        | 9   | -    |

| H <sub>B</sub>   | -                        | 9   | -    |

| y                | -                        | -   | 0.08 |

1 = 1mm

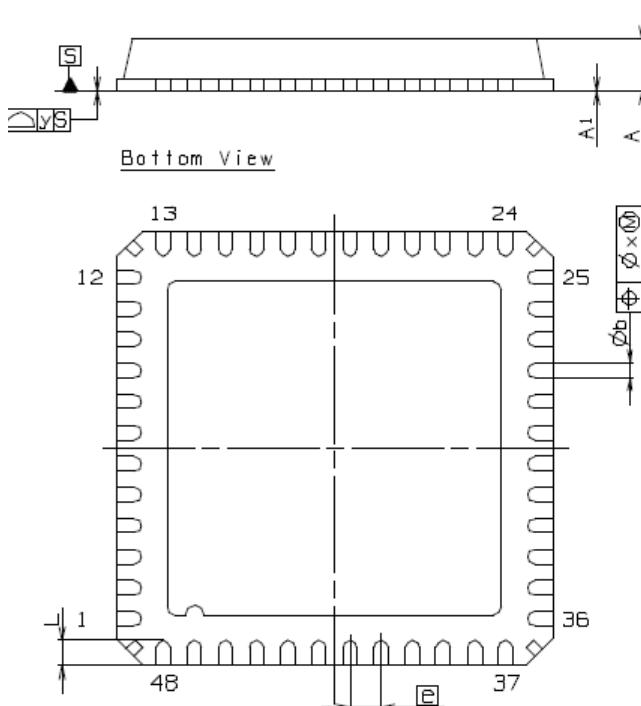

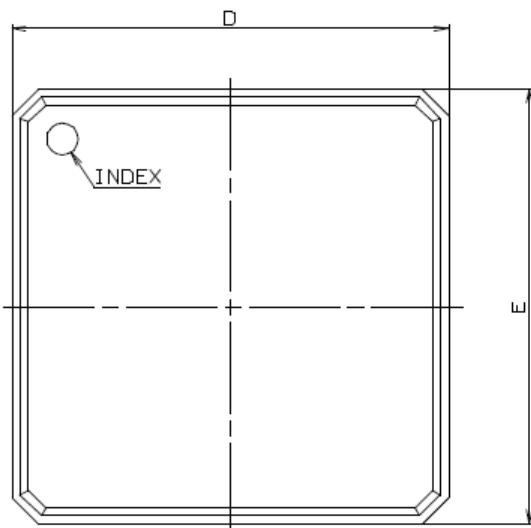

## 10.2 QFN7-48

Top View

| Symbol | Dimension in Millimeters |     |      |

|--------|--------------------------|-----|------|

|        | Min                      | Nom | Max  |

| D      | -                        | 7   | -    |

| E      | -                        | 7   | -    |

| A      | -                        | -   | 1    |

| A1     | 0                        | -   | -    |

| b      | 0.17                     | -   | 0.3  |

|        | -                        | 0.5 | -    |

| L      | 0.3                      | -   | 0.5  |

| X      | -                        | -   | 0.1  |

| Y      | -                        | -   | 0.08 |

1 = 1mm

## 11. 製品型番

---

### 11. 製品型番

| 製品型番            | 説明              |

|-----------------|-----------------|

| S1R72U01F12E300 | QFP12-48 パッケージ品 |

| S1R72U01F07E300 | QFN7-48 パッケージ品  |

## 改訂履歴表

付-1

| Rev. No. | 日付         | ページ  | 種別 | 改訂内容（旧内容を含む）<br>および改訂理由                                                                     |

|----------|------------|------|----|---------------------------------------------------------------------------------------------|

| Rev.1.00 | 2009/02/25 | 全ページ | 新規 | 新規制定                                                                                        |

| Rev.1.10 | 2009/06/06 | P10  | 訂正 | 機能未使用時の処理方法訂正<br>改訂前：Open 改訂後：電源を与える                                                        |

|          |            | P13  | 追記 | 電源供給電流（静止電流）の条件記載<br>改訂後：※4 条件記載                                                            |

|          |            | P14  | 改訂 | VTU+ Min 特性削除                                                                               |

|          |            |      | 改訂 | VTU- Min 特性改訂、Max 特性削除<br>改訂前：0.9[V] (min) 改訂後：0.8[V] (min)                                 |

|          |            |      | 削除 | △V 項目削除                                                                                     |

|          |            |      | 改訂 | RPLU Min 特性改訂、条件訂正<br>改訂前：64[kΩ] (min) 改訂後：52[kΩ] (min)                                     |

|          |            |      | 改訂 | RPLD Min 特性改訂、条件訂正<br>改訂前：40/64/240[kΩ] (min)<br>改訂後：32/52/200[kΩ] (min)                    |

|          |            |      | 改訂 | RPLDL Min 特性改訂、条件訂正<br>改訂前：48[kΩ] (min) 改訂後：40[kΩ] (min)                                    |

|          |            |      | 改訂 | RPLDB Min/Max 特性改訂<br>改訂前：105[kΩ] (min) 155[kΩ] (max)<br>改訂前：100[kΩ] (min) 165[kΩ] (max)    |

|          |            | P15  | 訂正 | IOZ 条件訂正                                                                                    |

|          |            | P18  | 改訂 | RSWON Max 特性改訂<br>改訂前：3.0/4.5[Ω] (max)<br>改訂後：4.0[Ω] (max)                                  |

|          |            |      | 改訂 | ISWOFF Max 特性改訂<br>改訂前：10[nA] (max) 改訂後：100[nA] (max)                                       |

|          |            |      | 改訂 | ISWLMT Min/Max 特性改訂<br>改訂前：21/14[mA] (min) 30/20[mA] (max)<br>改訂後：21[mA] (min) 35[mA] (max) |

|          |            | P19  | 追記 | <Fail-Safe 対象端子>追加<br>改訂後：XRESET, ATPGEN 追加                                                 |

| Rev.1.20 | 2009/09/07 | P8   | 訂正 | I/O 種および機能未使用時の処理方法訂正<br>改訂前：IN(PU) 未使用時 Open<br>改訂後：IN 未使用時 High                           |

|          |            | P14  | 削除 | RPLU 対象端子から S1N0 を削除                                                                        |

|          |            |      |    |                                                                                             |

|          |            |      |    |                                                                                             |

|          |            |      |    |                                                                                             |

|          |            |      |    |                                                                                             |

## **セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード: 411565304

2008 年 9 月 作成

2009 年 9 月 改訂①