# S1R72C05\*\*\*

## データシート

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## **適用範囲**

本ドキュメントは、USB2.0 デバイス・ホストコントローラ LSI 「S1R72C05」 に適用されます。

# 目 次

|                               |    |

|-------------------------------|----|

| 1. 概要.....                    | 1  |

| 2. 特長.....                    | 2  |

| 3. ブロック図 .....                | 3  |

| 4. 機能説明.....                  | 4  |

| 4.1 電源.....                   | 4  |

| 4.2 バウンダリスキャン.....            | 4  |

| 4.2.1 対応インストラクション .....       | 4  |

| 4.2.2 DEVICE_CODE について .....  | 5  |

| 4.2.3 バウンダリスキャン除外端子 .....     | 5  |

| 4.3 リセット.....                 | 5  |

| 4.3.1 ハードリセット .....           | 5  |

| 4.3.2 ソフトリセット .....           | 5  |

| 4.4 クロック .....                | 6  |

| 4.5 パワーマネージメント .....          | 6  |

| 4.6 CPU-I/F .....             | 7  |

| 4.7 IDE-I/F .....             | 8  |

| 4.8 USB デバイス I/F .....        | 8  |

| 4.8.1 スピードモードと転送タイプ .....     | 8  |

| 4.8.2 リソース .....              | 8  |

| 4.8.2.1 エンドポイント .....         | 8  |

| 4.8.2.2 FIFO .....            | 8  |

| 4.8.3 データフロー .....            | 8  |

| 4.8.4 USB デバイスポートの外付け回路 ..... | 10 |

| 4.9 USB ホスト I/F .....         | 10 |

| 4.9.1 スピードモードと転送タイプ .....     | 10 |

| 4.9.2 リソース .....              | 10 |

| 4.9.2.1 チャネル .....            | 10 |

| 4.9.2.2 FIFO .....            | 10 |

| 4.9.3 データフロー .....            | 10 |

| 4.9.4 USB ホストポートの外付け回路 .....  | 12 |

| 4.10 FIFO.....                | 12 |

| 4.10.1 USB FIFO .....         | 12 |

| 4.10.2 Media FIFO .....       | 12 |

| 5. 端子配置図 .....                | 13 |

| 6. 端子機能説明 .....               | 15 |

| 7. 電気的特性 .....                | 19 |

| 7.1 絶対最大定格 .....              | 19 |

| 7.2 推奨動作条件 .....              | 19 |

| 7.3 DC 特性 .....               | 20 |

| 7.3.1 消費電流 .....              | 20 |

| 7.3.2 入力特性 .....              | 22 |

| 7.3.3 出力特性 .....              | 23 |

| 7.3.4 端子容量 .....              | 24 |

| 7.4 AC 特性.....                | 25 |

| 7.4.1 RESET タイミング .....       | 25 |

|                                                   |           |

|---------------------------------------------------|-----------|

| 7.4.2 クロックタイミング .....                             | 25        |

| 7.4.3 CPU/DMA I/F アクセスタイミング .....                 | 26        |

| 7.4.3.1 CVDD=1.65V～3.6V での規定 .....                | 26        |

| 7.4.3.2 CVDD=3.0～3.6V に制限した場合の規定 .....            | 27        |

| 7.4.4 IDE I/F タイミング .....                         | 28        |

| 7.4.4.1 PIO Read Timing .....                     | 28        |

| 7.4.4.2 PIO Write Timing .....                    | 29        |

| 7.4.4.3 DMA Read Timing .....                     | 30        |

| 7.4.4.4 DMA Write Timing .....                    | 31        |

| 7.4.4.5 Ultra DMA Read Timing .....               | 32        |

| 7.4.4.6 Ultra DMA Write Timing .....              | 34        |

| 7.4.5 USB I/F タイミング .....                         | 35        |

| <b>8. 接続例 .....</b>                               | <b>36</b> |

| <b>8.1 CPU I/F 接続例 .....</b>                      | <b>36</b> |

| <b>8.2 USB I/F 接続例 .....</b>                      | <b>37</b> |

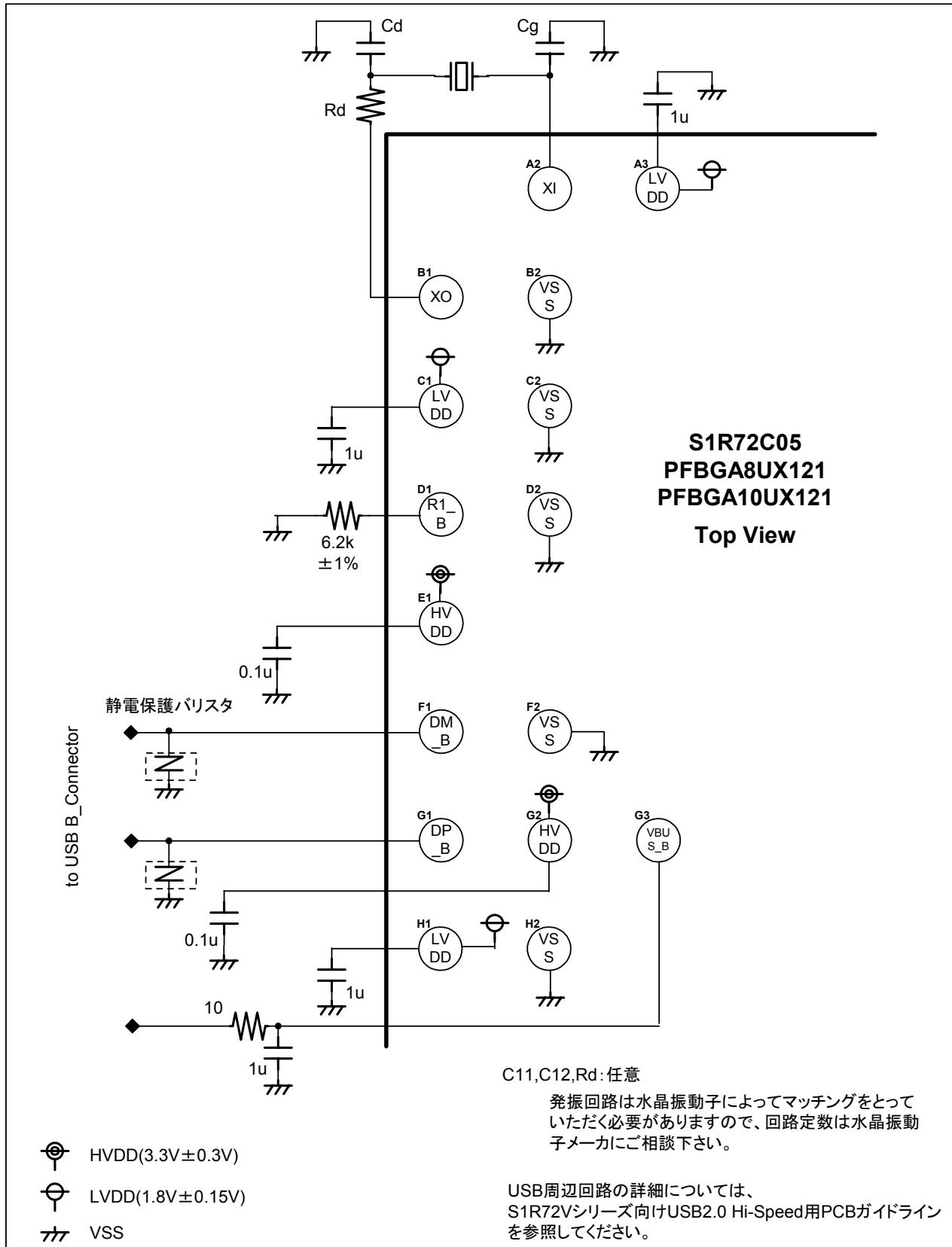

| 8.2.1 QFP15-128 の場合（デバイス部周辺） .....                | 37        |

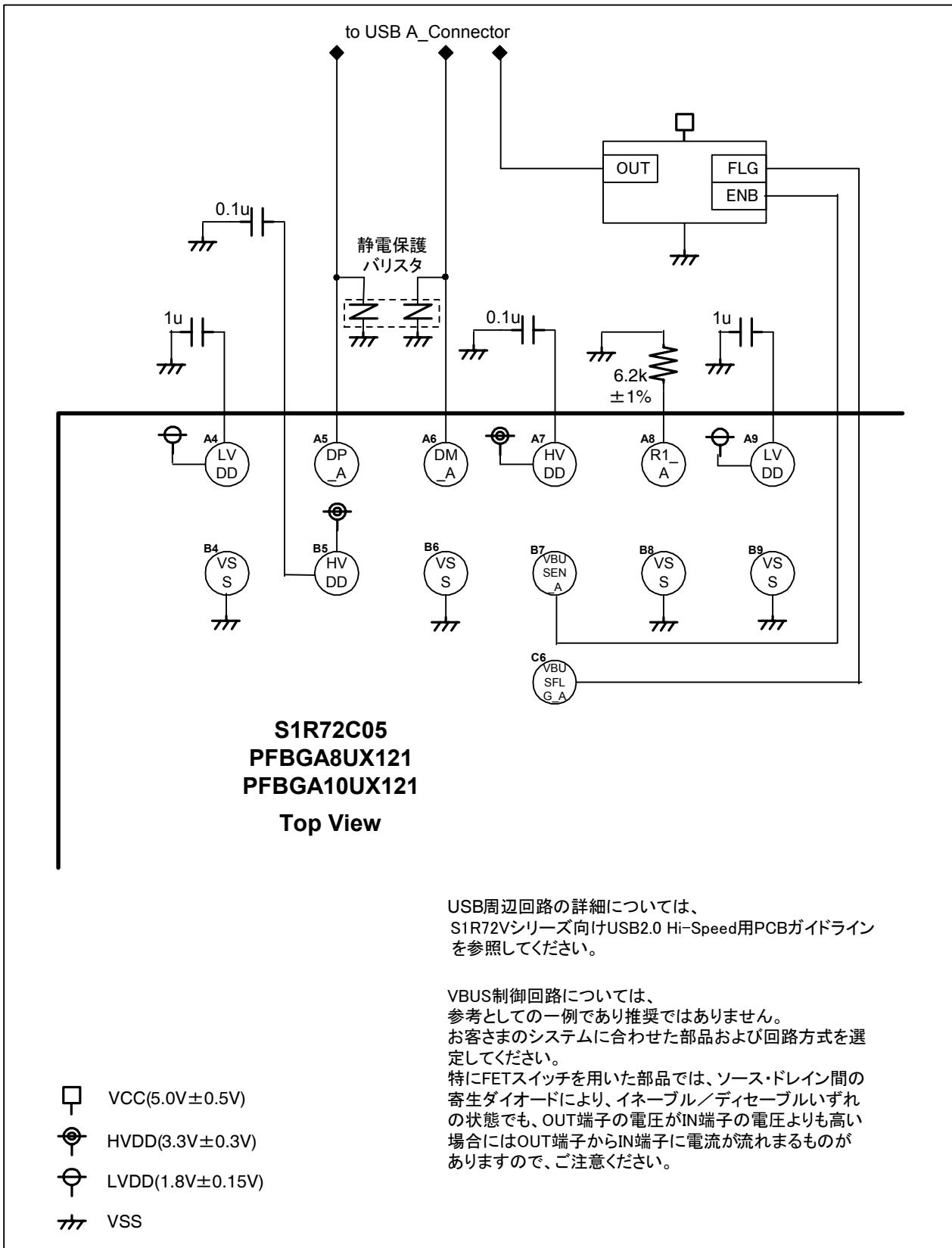

| 8.2.2 QFP15-128 の場合（ホスト部周辺） .....                 | 38        |

| 8.2.3 PFBGA8UX121/PFBGA10UX121 の場合（デバイス部周辺） ..... | 39        |

| 8.2.4 PFBGA8UX121/PFBGA10UX121 の場合（ホスト部周辺） .....  | 40        |

| <b>9. 製品型番 .....</b>                              | <b>41</b> |

| <b>10. 外形寸法図 .....</b>                            | <b>42</b> |

| <b>改訂履歴 .....</b>                                 | <b>43</b> |

### 1. 概要

S1R72C05\*\*はUSB2.0準拠のハイスピードモードに対応するUSBホスト / デバイスコントローラLSIです。ホストポートとデバイスポートを独立に備え、制御を切り替えることによりUSBホストまたはUSBデバイスとして動作することができます。

また、IDE I/Fを備え、HDDを内蔵する携帯機器や車載機器に適した特長を持ちます。

## 2. 特長

---

### 2. 特長

#### 《 USB2.0 デバイス機能 》

- HS (480Mbps) および FS (12Mbps) 転送サポート

- FS/HS ターミネーション内蔵 (外付け回路不要)

- VBUS 5V I/F (外付け保護回路要)

- コントロール、バルク、インターラプトおよびアイソクロナス転送をサポート

- Bulk, Interrupt, Isochronous 転送用 5 本、および、Endpoint 0 をサポート

#### 《 USB2.0 ホスト機能 》

- HS (480Mbps), FS (12Mbps) および LS (1.5Mbps) 転送サポート

- ダウンストリームポート用プルダウン抵抗内蔵 (外付け回路不要)

- HS ターミネーション内蔵 (外付け回路不要)

- コントロール、バルク、インターラプトおよびアイソクロナス転送をサポート

Channel 方式

- Control 転送専用 Channel 1 本

- Bulk 転送専用 Channel 1 本

- Bulk、Interrupt および Isochronous 転送用 Channel 4 本

- USB パワースイッチインターフェース

#### 《 Media データ転送機能 》

- USB 用 FIFO とは独立した FIFO により、IDE $\leftrightarrow$ CPU データ転送が可能

#### 《 CPU I/F 》

- 16bit 幅の、汎用 CPU I/F に対応

- DMA 2ch. 搭載 (Multi-word 手順)

- Big Endian (Little Endian の CPU に対応するためのバススワップ機能を搭載)

- I/F 電圧変更可能 (3.3V ~ 1.8V)

#### 《 IDE I/F 》

- ATA/ATAPI6 に対応

- PIO モード 0~4, Multi word DMA, UDMA モード 0~5

#### 《 その他 》

- クロック入力 : 12MHz, 24MHz の水晶発振子対応。(発振回路および帰還抵抗 1 MΩ 内蔵)

- 電源電圧 : 3.3V と 1.8V および CPU I/F 電源 (3.3V~1.8V) の 3 電圧系統

- バウンダリスキャン対応

- パッケージタイプ QFP15-128, PFBGA8UX121, PFBGA10UX121

- 動作保証温度範囲 -40°C~85°C

## 3. ブロック図

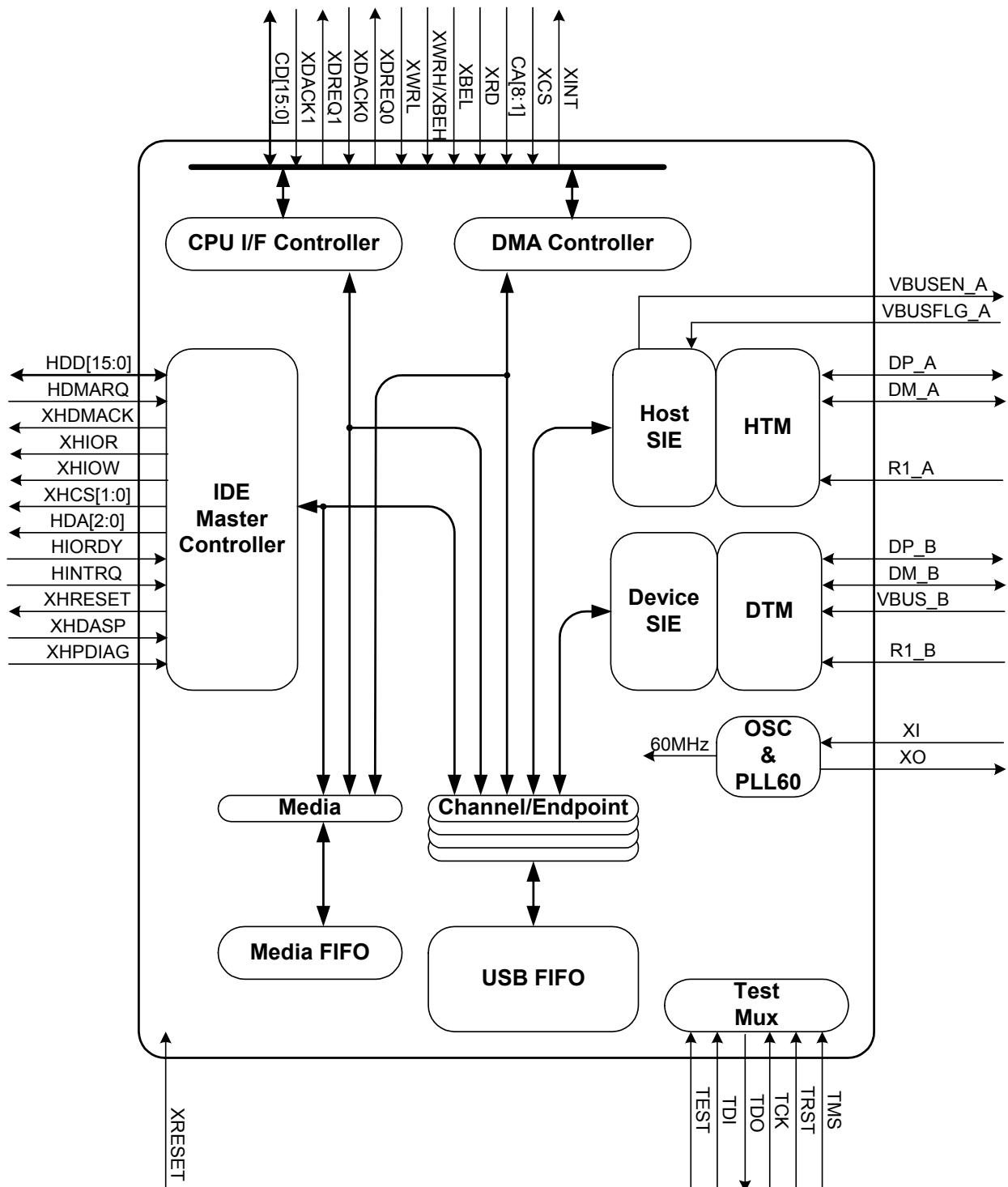

図 3.1 全体ブロック図

## 4. 機能説明

### 4. 機能説明

#### 4.1 電源

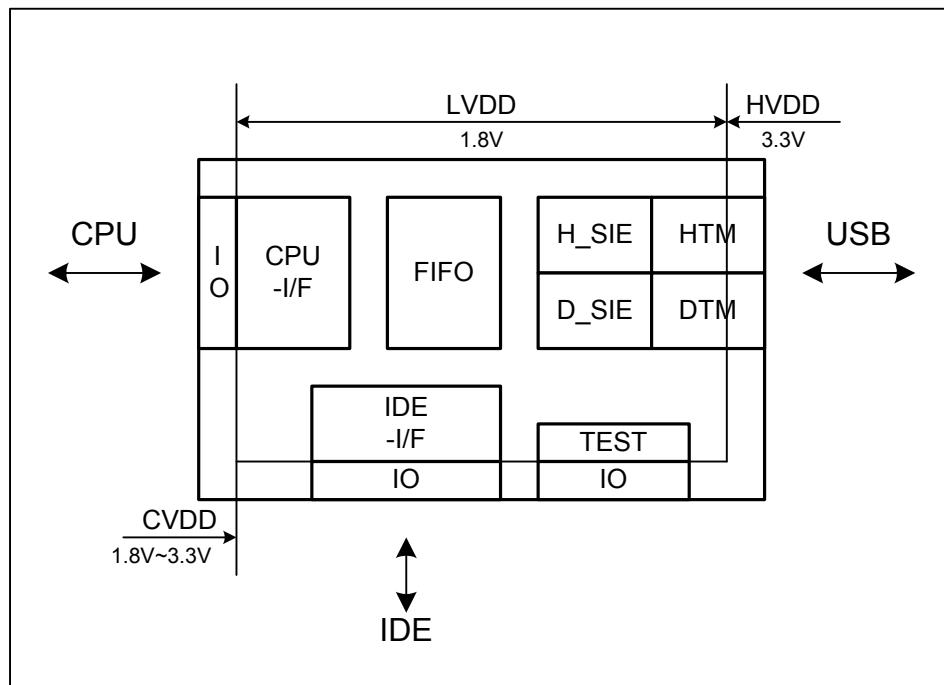

本 LSI には 3 系統の電源と、共通の GND があります。USB I/O、IDE I/O、および、TEST I/O 用の電源である HVDD (3.3V)、CPU I/F I/O 用の電源である CVDD (3.3V~1.8V) と、内部回路用の電源である LVDD (1.8V) を電源としています。(図 4.1 参照)

図 4.1 S1R72C05 電源

以下に電源投入順ならびに電源オフ順を説明します。

本 LSI は、定常的に一部の電源のみを ON または OFF することはできません。また、CVDD および HVDD の I/O 電源と、LVDD の内部電源との間で、電源投入順および遮断順に、下記の制限があります。CVDD と HVDD の投入順および遮断順には制限がありません。

- ・LVDD を先に ON にした後、CVDD および HVDD を ON にするように、電源を投入してください。

- ・CVDD および HVDD を OFF にした後、LVDD を OFF にするように、電源を遮断してください。

なお、電源回路の特性や、電源負荷の関係などによって前記の順序を厳密に守れない場合は、LVDD が OFF であり、かつ、CVDD または HVDD が ON となるような状態が 1sec 以下となるようにしてください。

#### 4.2 バウンダリスキャン

バウンダリスキャン (JTAG) は、TEST 端子が Low (デフォルト) である時に使用可能です。バウンダリスキャンは、JTAG (IEEE 1149.1) 仕様に準拠した、BSR (Boundary Scan Register)、それを繋ぐスキャンパスおよび TAP コントローラで構成されます。バウンダリスキャンの接続情報は、BSLD フォーマットにて提供可能です。

##### 4.2.1 対応インストラクション

本 LSI の JTAG インストラクションビット幅は 4 ビットとなっており、以下の JTAG インストラクションに対応致します。

表 4.1 JTAG インストラクションコード

| インストラクション      | 説明                            | コード  |

|----------------|-------------------------------|------|

| SAMPLE/PRELOAD | LSI 内部状態の BSR への取り込みおよびデータ設定。 | 0010 |

| BYPASS         | BSR によるスキャンパスをバイパスする。         | 1111 |

| EXTEST         | デバイスの物理的な接続チェック。              | 0000 |

| CLAMP          | 出力値を保持しながら、スキャンパスをバイパスする。     | 0011 |

| HIGHZ          | 出力を全て Hi-Z に固定する。             | 0100 |

| IDCODE         | 定められた DEVICE_CODE の出力。        | 0001 |

#### 4.2.2 DEVICE\_CODE について

IDCODE インストラクションに対する DEVICE\_CODE の構成要素は以下のとおりとなります。

表 4.2 DEVICE\_CODE

|              |        |

|--------------|--------|

| Version      | 1      |

| Part Number  | 0x0015 |

| Manufacturer | 0x0BE  |

したがって、IDCODE インストラクションに対する DEVICE\_CODE 応答は、

0001\_0000000000010101\_00010111110\_1

となります。

#### 4.2.3 バウンダリスキャン除外端子

本 LSI の端子のうち、DP\_A、DM\_A、DP\_B、DM\_B、R1\_A、R1\_B、XI、XO、VBUS\_B、および、TEST にはバウンダリスキャンセルが挿入されていないため、スキャン対象外となります。

### 4.3 リセット

本 LSI は外部 XRESET 端子によるハードリセットと、レジスタ設定によるソフトリセットの機能を持ちます。

#### 4.3.1 ハードリセット

電源投入時はリセット状態から立ち上げ、電源確定後にリセットを解除してください。

#### 4.3.2 ソフトリセット

ソフトウェア的に LSI 全回路のリセット、または、内蔵の USB アナログマクロを個別にリセットすることができます。ChipReset.AllReset ビットにより、本 LSI の全回路をリセットします。また、D\_Reset.ResetDTM ビット、または、H\_Reset.ResetHTM ビットにより、それぞれ、デバイスアナログマクロ、または、ホストアナログマクロをリセットします。ただし、スリープステート以外では、アナログマクロをリセットしないでください。

## 4. 機能説明

### 4.4 クロック

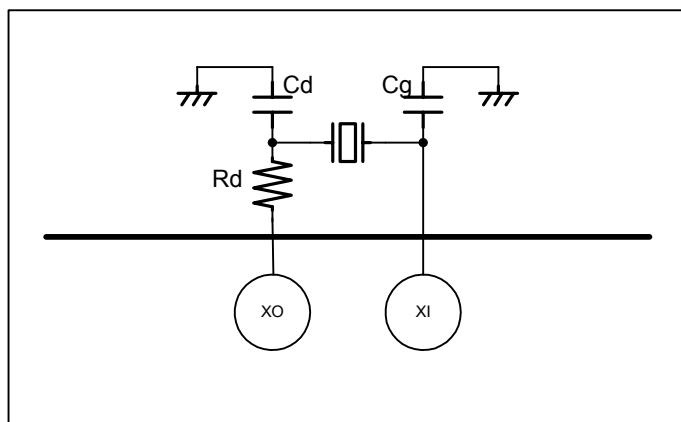

本 LSI は、オシレータと帰還抵抗（ $1M\Omega$ ）を内蔵し、外付けの振動子によるクロック生成に対応しています。またレジスタ設定により、発振周波数を 12MHz または 24MHz に設定できます。

図 4.2 に発振回路の接続例を示します。図中の発振回路の  $C_d, C_g, R_d$  は、振動子によってマッチングをとっていただく必要がありますので、これらの回路定数は振動子メーカーにご相談ください。

図 4.2 内蔵オシレータと外付け振動子によるクロック生成

### 4.5 パワーマネージメント

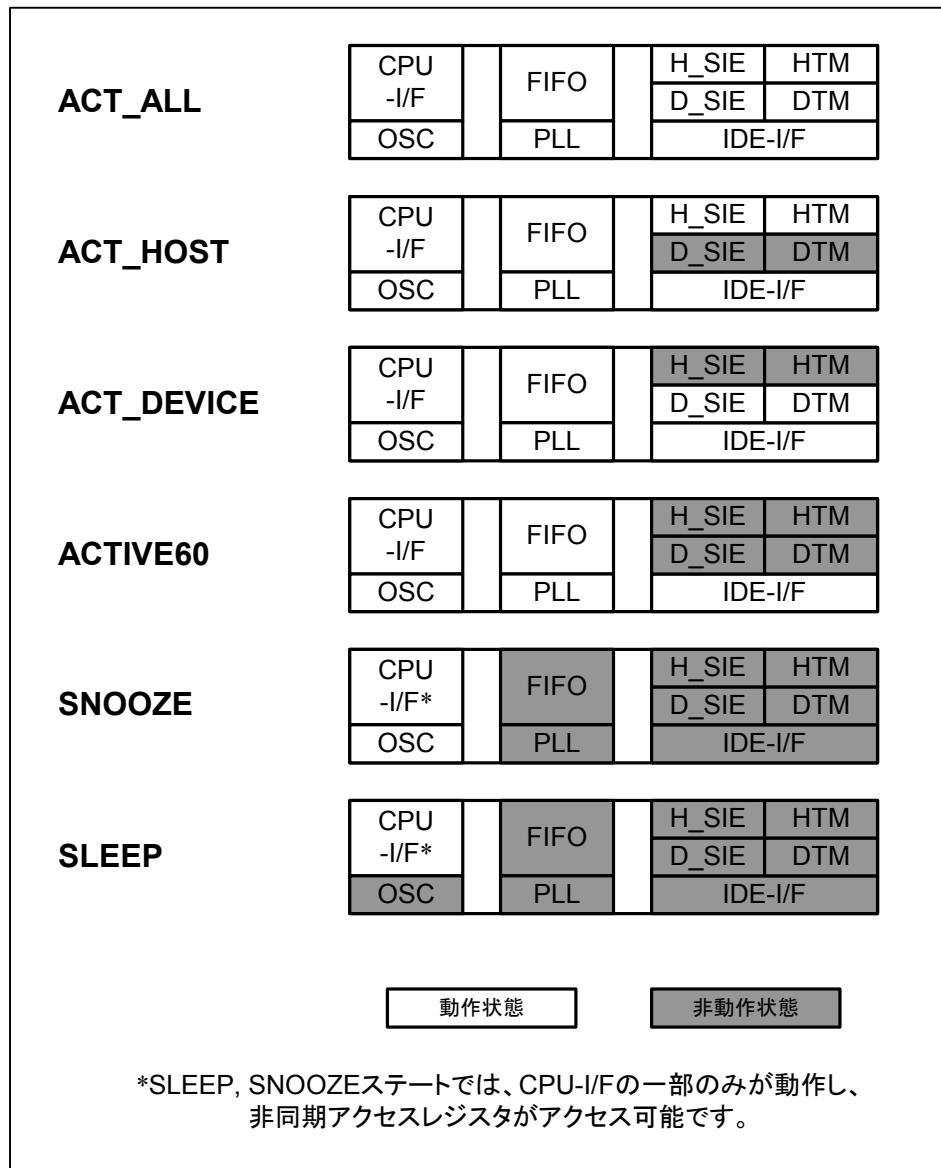

本 LSI はパワーマネジメント機能を装備し、SLEEP / SNOOZE / ACTIVE60 / ACT\_DEVICE / ACT\_HOST / ACT\_ALL の 6 通りのパワーマネジメントステートを持ちます。（図 4.3 参照）

ACT\_ALL ステートでは全ての機能ブロックが動作状態となります（ただし、USB ホスト機能、および、USB デバイス機能を同時に使用できません）。一方、SLEEP ステートでは待機状態からの復帰するために必要な最低限の回路のみが動作します。ACT\_ALL と SLEEP の間には、動作状態に応じた段階的なパワーマネジメントステートが存在します。

図 4.3 パワーマネージメントステート

## 4.6 CPU-I/F

本 LSI は 16 ビットインターフェースで CPU と接続します。16bit 単位での Big Endian または Little Endian のEndianを設定できます。Big Endian では、偶数アドレスのレジスタがバスの上位 (CD[15:8]) で、奇数アドレスのレジスタがバスの下位 (CD[7:0]) でアクセスできます。Little Endian では、偶数アドレスのレジスタがバスの下位 (CD[7:0]) で、奇数アドレスのレジスタがバスの上位 (CD[15:8]) でアクセスできます。

また、8bit での書き込みに対し、High/Low のストローブ (XWRH/XWRL) でアクセスするストローブモードか、または、High/Low のバイトイネーブル (XBEP/XBEL) でアクセスするバイトイネーブルモードかのバスモードを設定することができます。Endian およびバスモードは、リセット解除直後にCPUIF\_MODE レジスタで設定します。

また、本 LSI の CPU-I/F は、2ch の DMA (スレーブ) を装備しています。

パワーマネジメントステートにより、アクセス可能なレジスタが異なります。詳しくは、本 LSI のテクニカルマニュアルをご参照ください。

## 4. 機能説明

---

### 4.7 IDE-I/F

本LSIは、ATA/ATAPI6に対応するIDEホスト機能を装備し、PIOモード0~4、Multi Word DMAおよびUDMAモード0~5の転送モードをサポートします。

### 4.8 USB デバイス I/F

本LSIは、USB2.0（Universal Serial Bus Specification Revision 2.0）規格に準拠した、High-Speed仕様のUSBデバイス機能をサポートします。

#### 4.8.1 スピードモードと転送タイプ

本LSIは、USBデバイス動作時にHS（480Mbps）およびFS（12Mbps）のスピードモードをサポートします。バスリセット時に行われるスピードネゴシエーションにより、スピードモードは自動的に決定されます。たとえばHSスピードモードに対応するUSBホストと接続した場合は、スピードネゴシエーションにより自動的にHS転送モードが選択されます。（ただし、レジスタ設定により、意図的にFSスピードモードに設定することが可能です。）

転送タイプは、コントロール転送（エンドポイント0）、バルク転送、インタラプト転送、および、アイソクロナス転送の、USB2.0規格が定める全ての転送タイプをサポートします。

#### 4.8.2 リソース

##### 4.8.2.1 エンドポイント

本LSIは、エンドポイント0と、5本の汎用エンドポイントを備えています。エンドポイント0はコントロール転送をサポートします。汎用エンドポイントはバルク転送、インタラプト転送、および、アイソクロナス転送をサポートします。汎用エンドポイントのエンドポイントナンバー、マックスパケットサイズ、および、転送方向（IN/OUT）は任意に設定できます。

##### 4.8.2.2 FIFO

本LSIは、USBのデータ転送で使用可能なFIFOを4.5kB備え、USBとのデータ転送路を形成します。各エンドポイントへのFIFO容量の割り当て量を、ソフトウェアから任意に設定できます。たとえば、バルク転送を行うエンドポイントに、十分大きなサイズのFIFOエリアを割り当てるにより、パフォーマンスの向上を図ることができます。

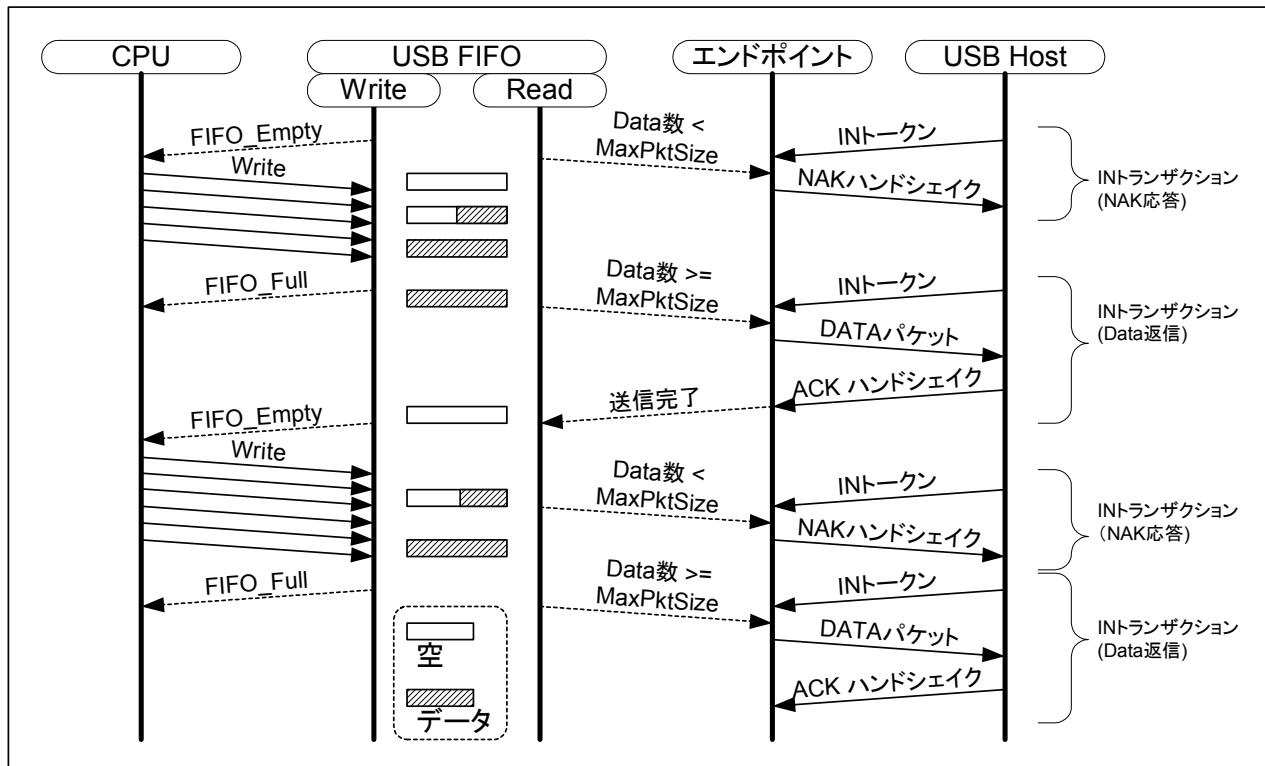

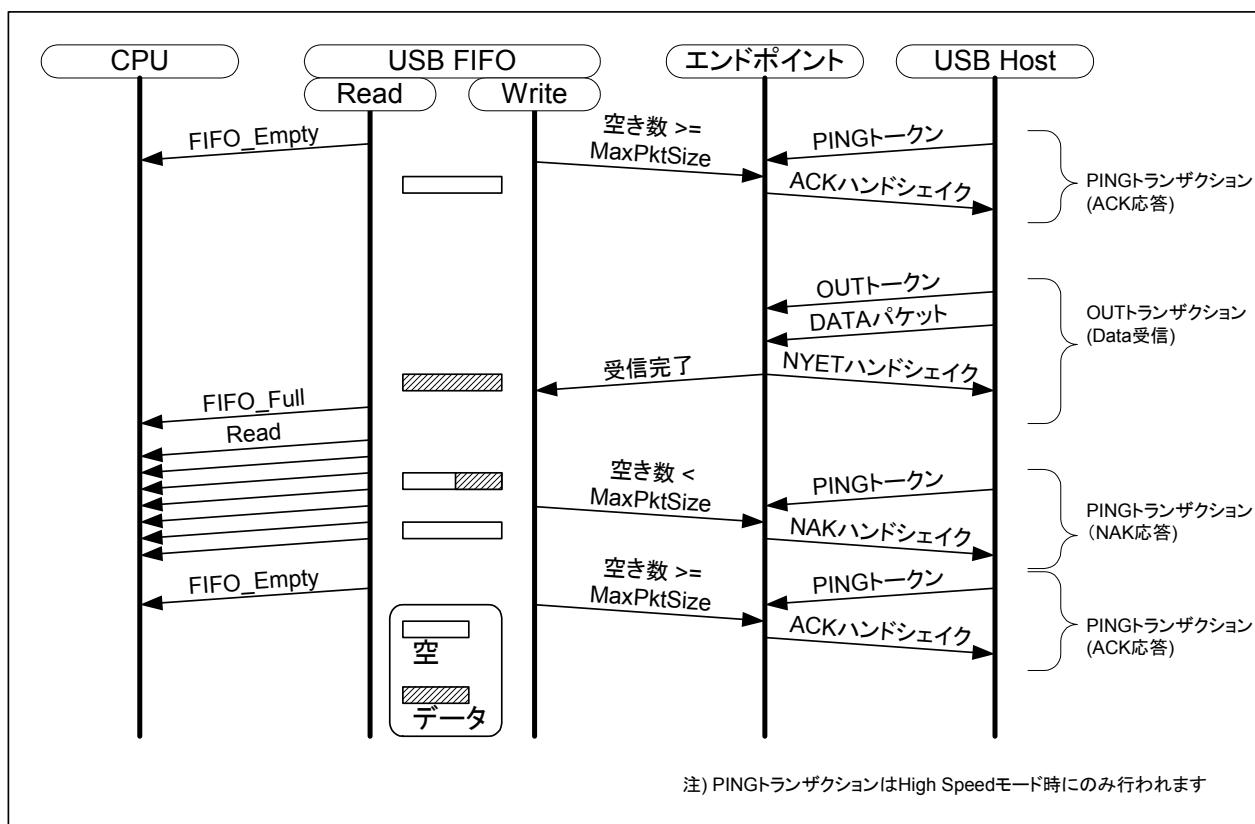

##### 4.8.3 データフロー

エンドポイントは、USB FIFOエリアと一对一に割り当られ、USB FIFOの有効空き容量（OUT転送の場合）、または、有効データ数（IN転送の場合）によって、自動的にUSB上のトランザクションへの応答を行います。したがって、ソフトウェアは個々のトランザクションの実行に関与する必要がなく、USB FIFO上のデータフローとしてUSBのデータ転送を制御することができます。

図 4.4 データフローの例（IN 転送で MaxPktSize 分の FIFO を割り当てた場合）

図 4.5 データフローの例（OUT 転送で MaxPktSize 分の FIFO を割り当てた場合）

## 4. 機能説明

---

### 4.8.4 USB デバイスポートの外付け回路

本 LSI は FS および HS のデバイス終端抵抗を内蔵しており、一般的に用いられているインピーダンス調整のための外付け部品が不要です。そのため、DP/DM ラインは、本 LSI の端子とコネクタとを直結することができます。ただし、静電保護や EMI 対策につきましては、必要に応じて適切な部品をご使用ください。

VBUS 端子は 5V 入力となっており、外部での電圧変換を必要としません。ただし市場の USB ホスト製品や HUB 製品によっては、VBUS に定格を超えるサージを印加するものがありますので、そのための保護回路を推奨しています。

別途、「S1R72V シリーズ向け USB2.0 Hi-Speed 用 PCB 設計ガイドライン」を用意しておりますので、ご参照ください。

## 4.9 USB ホスト I/F

本 LSI は、USB2.0 (Universal Serial Bus Specification Revision 2.0) 規格に準拠した、High-Speed 仕様の USB ホスト機能をサポートします。

### 4.9.1 スピードモードと転送タイプ

本 LSI は、USB ホスト動作時に HS (480Mbps)、FS (12Mbps) および LS (1.5Mbps) のスピードモードをサポートします。バスリセット時に行われるスピードネゴシエーションにより、スピードモードは自動的に決定されます。

転送タイプは、コントロール転送、バルク転送、インターラプト転送、および、アイソクロナス転送の、USB2.0 規格が定める全ての転送タイプをサポートします。

### 4.9.2 リソース

#### 4.9.2.1 チャネル

本 LSI では、デバイスのエンドポイントと 1 対 1 で対応し、そのエンドポイントと行う転送の為の設定レジスタセットをチャネルと呼びます。本 LSI は、コントロール転送専用チャネルを 1 本と、バルク転送専用チャネルを 1 本と、バルク転送、インターラプト転送、および、アイソクロナス転送をサポートする汎用チャネルを 4 本備えています。全てのチャネルのエンドポイントナンバー、マックスパケットサイズ、および、転送方向 (IN/OUT) は任意に設定できます。また、チャネルをソフトウェアで時分割で使用することにより、チャネル数を越える数のエンドポイントと転送を行うことができます。

#### 4.9.2.2 FIFO

本 LSI は、USB のデータ転送を行う FIFO を 4.5kB 備え、USB とのデータ転送路を形成します。各チャネルへの FIFO 容量の割り当て量を、ソフトウェアから任意に設定できます。たとえば、バルク転送を行うチャネルに、十分大きなサイズの FIFO エリアを割り当てる事により、パフォーマンスの向上を図ることができます。

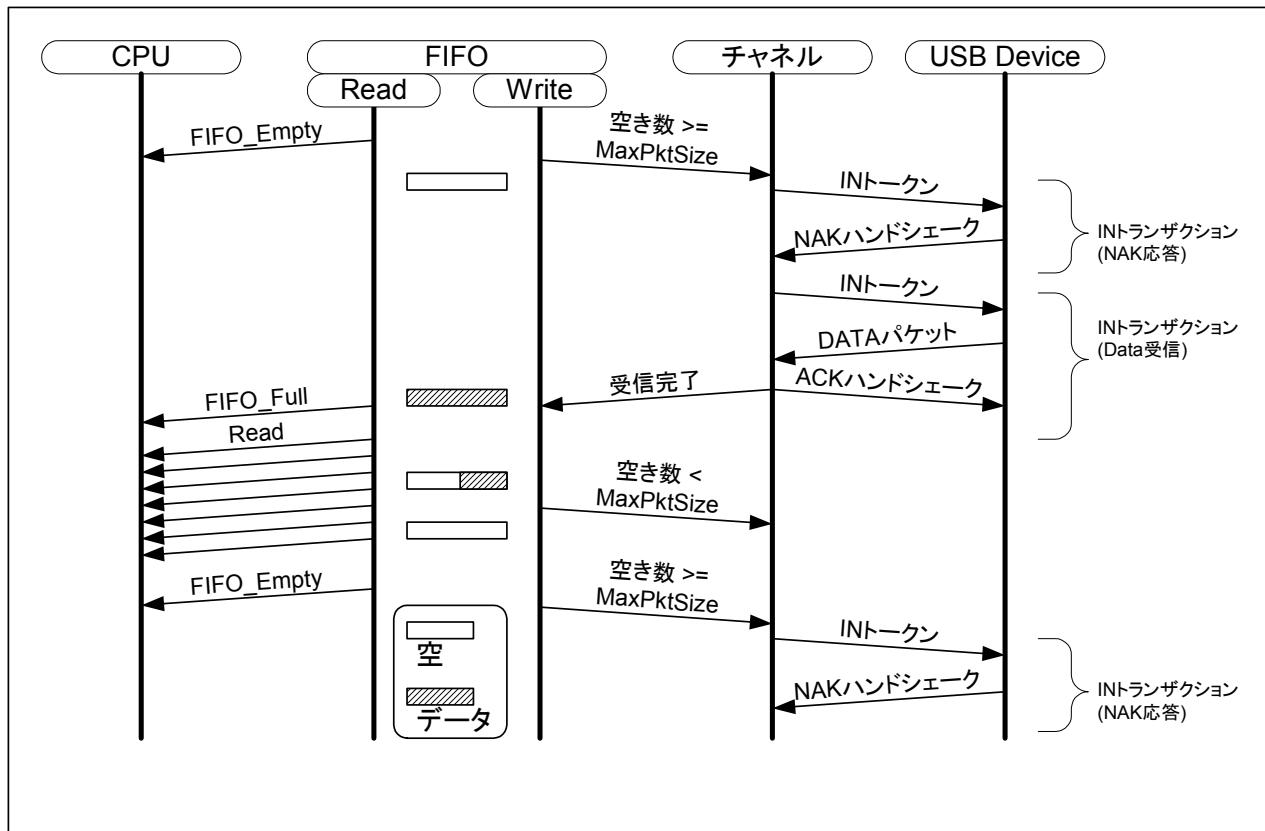

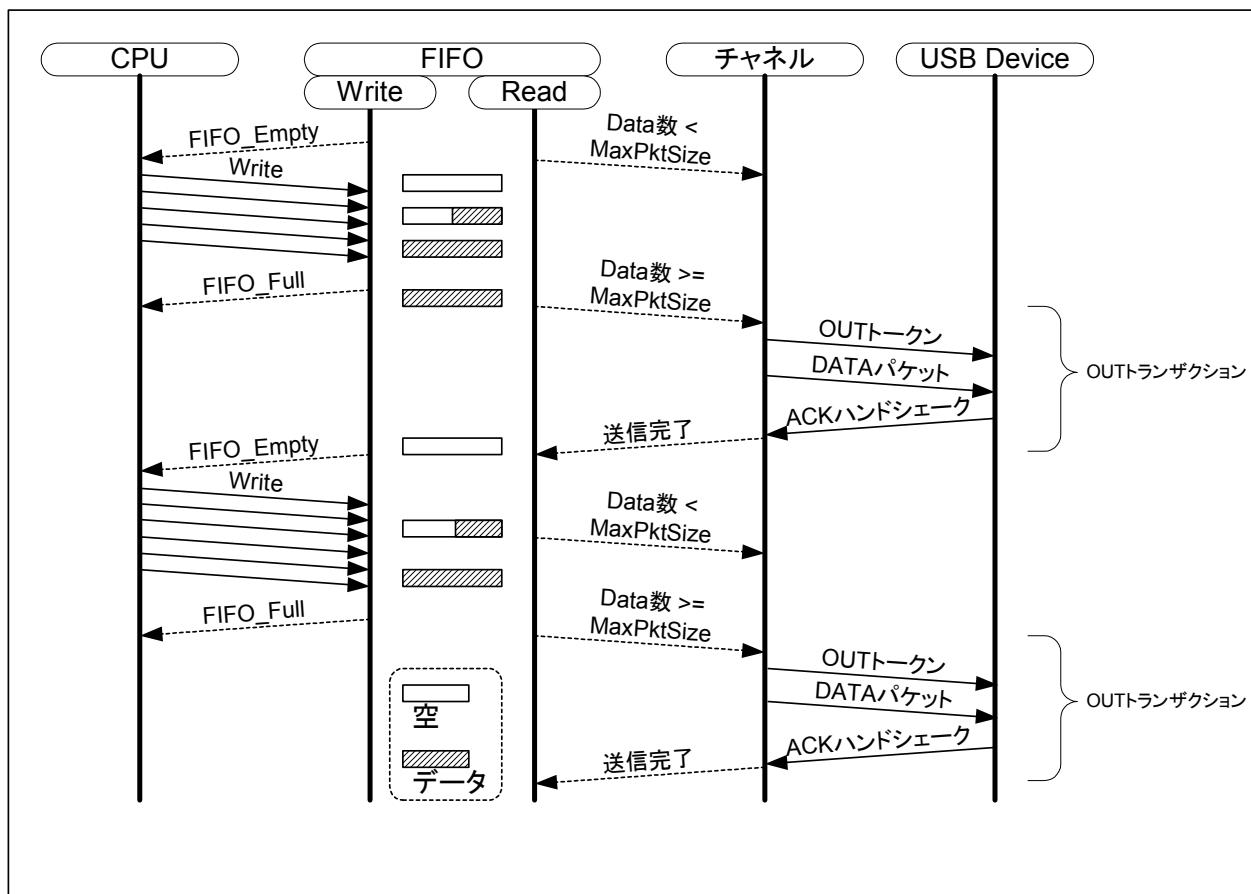

#### 4.9.3 データフロー

チャネルは、FIFO エリアと一対一に割り当てられ、FIFO の有効空き容量 (IN 転送の場合)、または、有効データ数 (OUT 転送の場合) によって、自動的に USB 上へトランザクションの発行を行います。したがって、ソフトウェアは個々のトランザクションの実行に関与する必要がなく、FIFO 上のデータフローとして USB のデータ転送を制御することができます。

図 4.6 データフローの例 (IN 転送で MaxPktSize 分の FIFO を割り当てた場合)

## 4. 機能説明

図 4.7 データフローの例（OUT 転送で MaxPktSize 分の FIFO を割り当てた場合）

### 4.9.4 USB ホストポートの外付け回路

本 LSI は HS 終端抵抗を含めた USB ホストの終端抵抗を内蔵しているので、一般的に用いられているインピーダンス調整のための外付け部品が不要です。そのため、DP/DM ラインは、本 LSI の端子とコネクタとを直結することができます。ただし、静電保護や EMI 対策につきましては、必要に応じて適切な部品をご使用ください。

VBUS に関しては外付けの VBUS 制御部品が必要となります。

## 4.10 FIFO

### 4.10.1 USB FIFO

本 LSI は、USB のデータ転送を行う USB FIFO を 4.5kB 備え、USB デバイス I/F と USB ホスト I/F とで共有します。各エンドポイントまたはチャネルへの USB FIFO 容量の割り当て量を、ソフトウェアから任意に設定できます。

USB FIFO を介して、USB-I/F と CPU-I/F との間の転送や、USB-I/F と IDE-I/F との間のダイレクト転送を行うことができます。

### 4.10.2 Media FIFO

本 LSI は、IDE のデータ転送を行う Media FIFO を 64B 備え、IDE-I/F と CPU-I/F とのデータ転送路を形成します。Media FIFO では USB-I/F とのデータ転送を行うことはできません。

## 5. 端子配置図

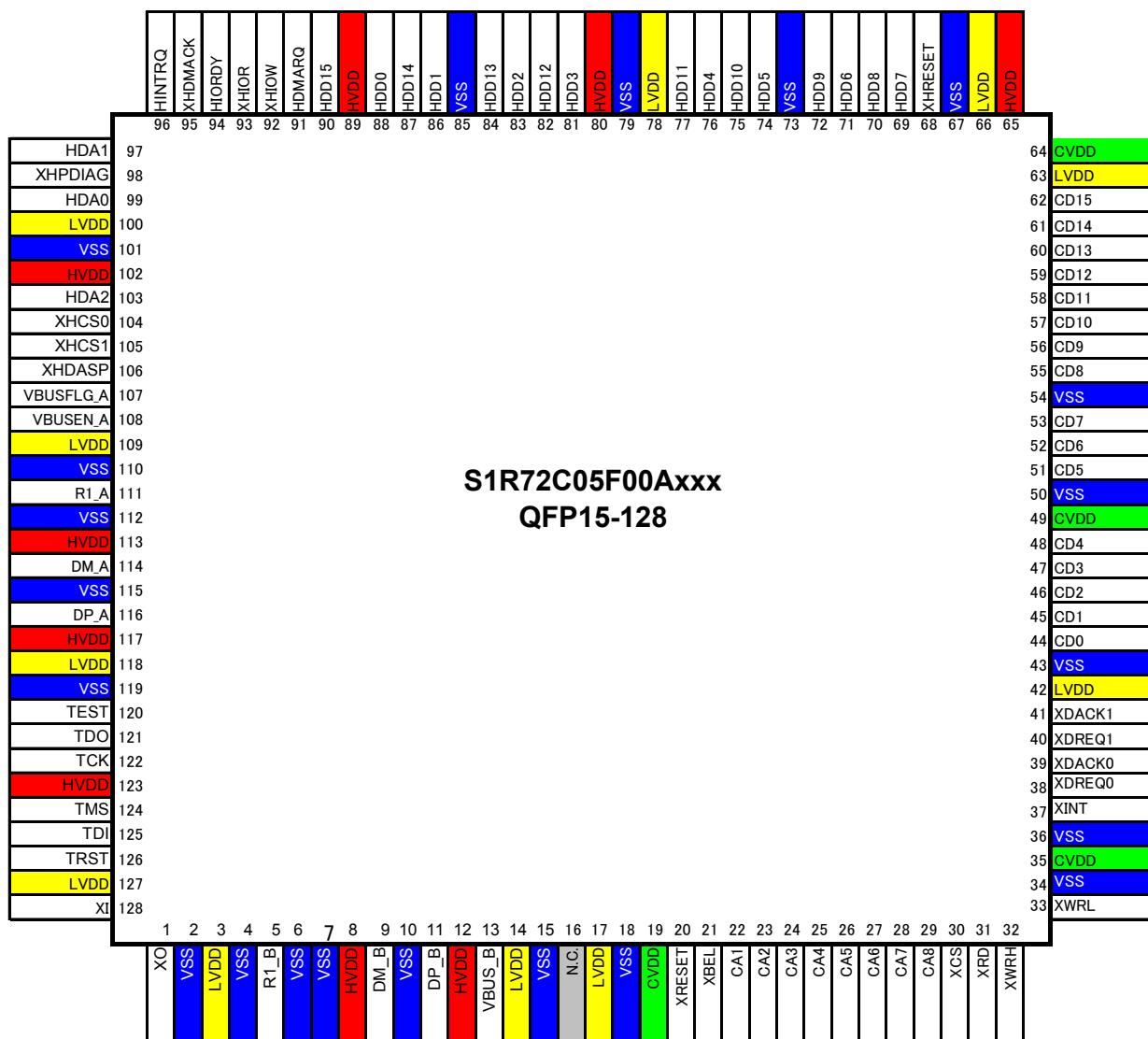

図 5.1 QFP パッケージ端子配置図

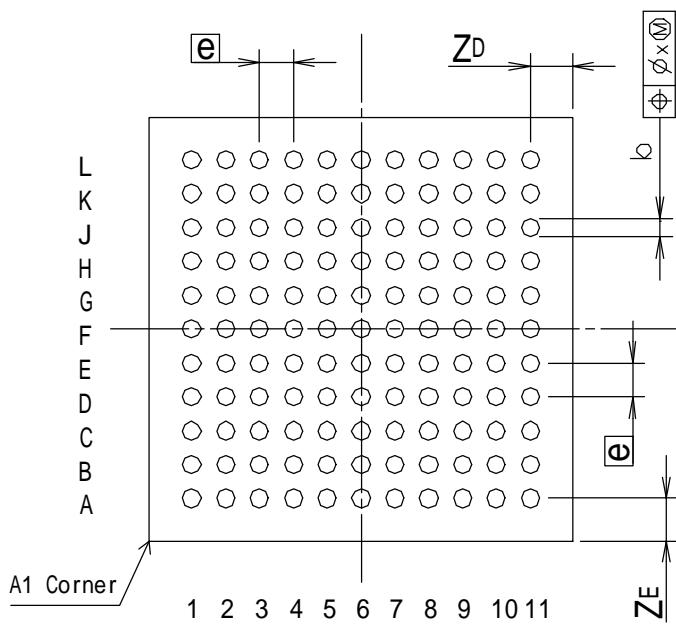

## 5. 端子配置図

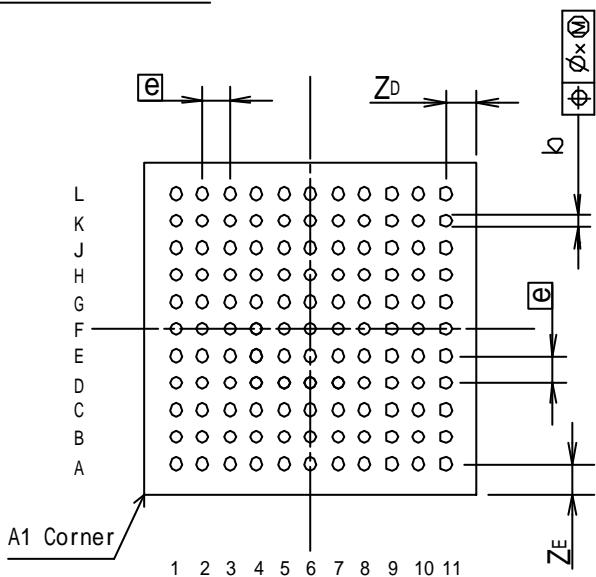

| S1R72C05/PFBGA8UX121,PFBGA10UX121<br>TOP View |        |        |        |        |         |           |       |       |       |         |

|-----------------------------------------------|--------|--------|--------|--------|---------|-----------|-------|-------|-------|---------|

| 1                                             | 2      | 3      | 4      | 5      | 6       | 7         | 8     | 9     | 10    | 11      |

| NC                                            | XI     | LVDD   | LVDD   | DP_A   | DM_A    | HVDD      | R1_A  | LVDD  | HDA0  | NC      |

| XO                                            | VSS    | TRST   | VSS    | HVDD   | VSS     | VBUSEN_A  | VSS   | VSS   | HDA2  | XHPDIAG |

| LVDD                                          | VSS    | TDI    | TCK    | TEST   | XHCS0   | VBUSFLG_A | VSS   | XHCS1 | HDA1  | HINTRQ  |

| R1_B                                          | VSS    | TDO    | XHDASP | HVDD   | XHDMACK | XIORDY    | XHIOW | XHIOR | HDD0  | HDMARQ  |

| HVDD                                          | TMS    | VSS    | LVDD   | VSS    | HDD14   | HDD15     | HDD12 | VSS   | HDD2  | HDD13   |

| DM_B                                          | VSS    | VSS    | CA2    | VSS    | LVDD    | HDD3      | VSS   | HDD1  | VSS   | HVDD    |

| DP_B                                          | HVDD   | VBUS_B | CA3    | XINT   | XDACK1  | HVDD      | HDD11 | HDD5  | HDD10 | HDD4    |

| LVDD                                          | VSS    | CVDD   | CA4    | XDACK0 | CD3     | CD6       | CVDD  | CD13  | HDD8  | HDD9    |

| LVDD                                          | XRESET | CA1    | XBEL   | XDREQ1 | CD0     | CD4       | CD7   | CD10  | HDD6  | HDD7    |

| CA8                                           | XCS    | CA5    | CA6    | CA7    | CD1     | CD5       | CD9   | CD12  | CD14  | XHRESET |

| NC                                            | XRD    | XWRH   | XWRL   | XDREQ0 | CD2     | CVDD      | CD8   | CD11  | CD15  | NC      |

図 5.2 BGA パッケージ端子配置図

## 6. 端子機能説明

| OSC |      |    |     |       |        |                          |

|-----|------|----|-----|-------|--------|--------------------------|

| Pin | Ball | 名称 | I/O | RESET | 端子タイプ  | 端子説明                     |

| 128 | A2   | XI | IN  | —     | Analog | 内部発振回路用入力<br>12MHz/24MHz |

| 1   | B1   | XO | OUT | —     | Analog | 内部発振回路用出力                |

| TEST |      |      |     |       |       |                   |

|------|------|------|-----|-------|-------|-------------------|

| Pin  | Ball | 名称   | I/O | RESET | 端子タイプ | 端子説明              |

| 120  | C5   | TEST | IN  | —     | —     | テスト端子 (Low 固定)    |

| 121  | D3   | TDO  | OUT | Hi-Z  | 2mA   | バウンダリスキャン TDO 端子  |

| 122  | C4   | TCK  | IN  | —     | —     | バウンダリスキャン TCK 端子  |

| 124  | E2   | TMS  | IN  | —     | —     | バウンダリスキャン TMS 端子  |

| 125  | C3   | TDI  | IN  | —     | —     | バウンダリスキャン TDI 端子  |

| 126  | B3   | TRST | IN  | —     | —     | バウンダリスキャン TRST 端子 |

バウンダリスキャン機能を使用しない場合は、TEST, TCK, TMS, TDI, TRST の各端子は Low 固定、TDO 端子はオープンとして処理してください。

PD: Pull Down

PU: Pull Up

| USB |      |           |     |       |              |                                        |

|-----|------|-----------|-----|-------|--------------|----------------------------------------|

| Pin | Ball | 名称        | I/O | RESET | 端子タイプ        | 端子説明                                   |

| 111 | A8   | R1_A      | IN  | —     | Analog       | 内部動作基準電流設定端子<br>6.2kΩ ±1%の抵抗を Vss 間に接続 |

| 116 | A5   | DP_A      | BI  | Hi-Z  | Analog       | USB ホスト・データライン Data+                   |

| 114 | A6   | DM_A      | BI  | Hi-Z  | Analog       | USB ホスト・データライン Data-                   |

| 107 | C7   | VBUSFLG_A | IN  | (PU)  | Schmitt (PU) | USB パワースイッチ・フォールト検出信号<br>1:正常 0:異常     |

| 108 | B7   | VBUSEN_A  | OUT | Lo    | 2mA          | USB パワースイッチ制御信号                        |

| 5   | D1   | R1_B      | IN  | —     | Analog       | 内部動作基準電流設定端子<br>6.2kΩ ±1%の抵抗を Vss 間に接続 |

| 11  | G1   | DP_B      | BI  | Hi-Z  | Analog       | USB デバイス・データライン Data+                  |

| 9   | F1   | DM_B      | BI  | Hi-Z  | Analog       | USB デバイス・データライン Data-                  |

| 13  | G3   | VBUS_B    | IN  | (PD)  | (PD)         | USB デバイス・バス検出信号                        |

PD: Pull Down

PU: Pull Up

## 6. 端子機能説明

CPU I/F

| Pin | Ball | 名称          | I/O | RESET | 端子タイプ              | 端子説明            |                   |                 |  |  |

|-----|------|-------------|-----|-------|--------------------|-----------------|-------------------|-----------------|--|--|

|     |      |             |     |       |                    | Bus Mode ⇒      | 16bit Strobe mode | 16bit BE mode   |  |  |

| 20  | J2   | XRESET      | IN  | —     | —                  | リセット信号          |                   |                 |  |  |

| 31  | L2   | XRD         | IN  | —     | —                  | リード・ストローブ       |                   |                 |  |  |

| 33  | L4   | XWRL (XWR)  | IN  | —     | —                  | ライト・ストローブ<br>下位 | ライト・ストローブ         | ハイ・バイト<br>イネーブル |  |  |

| 32  | L3   | XWRH (XBEP) | IN  | —     | —                  | ライト・ストローブ<br>上位 | ハイ・バイト<br>イネーブル   |                 |  |  |

| 30  | K2   | XCS         | IN  | —     | —                  | チップセレクト信号       |                   |                 |  |  |

| 37  | G5   | XINT        | OUT | High  | 2mA<br>(Tri-state) | 割り込み出力信号        |                   |                 |  |  |

| 38  | L5   | XDREQ0      | OUT | High  | 2mA                | DMA0 リクエスト      |                   |                 |  |  |

| 39  | H5   | XDACK0      | IN  | —     | —                  | DMA0 アクノリッジ     |                   |                 |  |  |

| 40  | J5   | XDREQ1      | OUT | High  | 2mA                | DMA1 リクエスト      |                   |                 |  |  |

| 41  | G6   | XDACK1      | IN  | —     | —                  | DMA1 アクノリッジ     |                   |                 |  |  |

| 21  | J4   | XBEL        | IN  | —     | —                  | High or Low 固定  | ロー・バイト<br>イネーブル   |                 |  |  |

| 22  | J3   | CA1         | IN  | —     | —                  | CPU バスアドレス      |                   |                 |  |  |

| 23  | F4   | CA2         | IN  | —     | —                  |                 |                   |                 |  |  |

| 24  | G4   | CA3         | IN  | —     | —                  |                 |                   |                 |  |  |

| 25  | H4   | CA4         | IN  | —     | —                  |                 |                   |                 |  |  |

| 26  | K3   | CA5         | IN  | —     | —                  |                 |                   |                 |  |  |

| 27  | K4   | CA6         | IN  | —     | —                  |                 |                   |                 |  |  |

| 28  | K5   | CA7         | IN  | —     | —                  |                 |                   |                 |  |  |

| 29  | K1   | CA8         | IN  | —     | —                  |                 |                   |                 |  |  |

| 44  | J6   | CD0         | BI  | Hi-Z  | 2mA                | CPU データバス       |                   |                 |  |  |

| 45  | K6   | CD1         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 46  | L6   | CD2         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 47  | H6   | CD3         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 48  | J7   | CD4         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 51  | K7   | CD5         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 52  | H7   | CD6         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 53  | J8   | CD7         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 55  | L8   | CD8         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 56  | K8   | CD9         | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 57  | J9   | CD10        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 58  | L9   | CD11        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 59  | K9   | CD12        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 60  | H9   | CD13        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 61  | K10  | CD14        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

| 62  | L10  | CD15        | BI  | Hi-Z  | 2mA                |                 |                   |                 |  |  |

XINT 端子は、レジスタ設定により、I/O モードと Hi-Z/0 モードを選択できます。

PD: Pull Down

PU: Pull Up

IDE I/F

| Pin | Ball | 名称             | I/O       | RESET       | 端子タイプ       | 端子説明                     |

|-----|------|----------------|-----------|-------------|-------------|--------------------------|

| 103 | B10  | HDA2           | OUT       | Hi-Z        | 4mA         | IDE レジスタ・アドレス            |

| 97  | C10  | HDA1           | OUT       | Hi-Z        | 4mA         |                          |

| 99  | A10  | HDA0           | OUT       | Hi-Z        | 4mA         |                          |

| 105 | C9   | XHCS1          | OUT       | Hi-Z        | 4mA         | コントロールレジスタアクセス用チップセレクト   |

| 104 | C6   | XHCS0          | OUT       | Hi-Z        | 4mA         | コマンドブロックレジスタアクセス用チップセレクト |

| 93  | D9   | XHIOR          | OUT       | Hi-Z        | 4mA         | IDE リードストローブ             |

| 92  | D8   | XHIOW          | OUT       | Hi-Z        | 4mA         | IDE ライトストローブ             |

| 91  | D11  | HDMARQ         | IN        | (PD)        | (PD)        | DMA 転送要求                 |

| 95  | D6   | XHDMACK        | OUT       | Hi-Z        | 4mA         | DMA 転送許可                 |

| 94  | D7   | HIORDY         | IN        | (PU)        | (PU)        | IDE レジスタレディ信号            |

| 96  | C11  | HINTRQ         | IN        | (PD)        | (PD)        | IDE 割り込み要求               |

| 68  | K11  | XHRESET        | OUT       | Hi-Z        | 4mA         | IDE バスリセット               |

| 106 | D4   | XHDASP         | IN        | (PU)        | (PU)        | ドライブ有効／スレーブドライブ有り        |

| 98  | B11  | <b>XHPDIAG</b> | <b>IN</b> | <b>(PU)</b> | <b>(PU)</b> | 診断シーケンス終了信号              |

| 90  | E7   | HDD15          | BI        | Hi-Z        | 4mA(PU)     | IDE データ・バス               |

| 87  | E6   | HDD14          | BI        | Hi-Z        | 4mA(PU)     |                          |

| 84  | E11  | HDD13          | BI        | Hi-Z        | 4mA(PU)     |                          |

| 82  | E8   | HDD12          | BI        | Hi-Z        | 4mA(PU)     |                          |

| 77  | G8   | HDD11          | BI        | Hi-Z        | 4mA(PU)     |                          |

| 75  | G10  | HDD10          | BI        | Hi-Z        | 4mA(PU)     |                          |

| 72  | H11  | HDD9           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 70  | H10  | HDD8           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 69  | J11  | HDD7           | BI        | (PD)        | 4mA(PD)     |                          |

| 71  | J10  | HDD6           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 74  | G9   | HDD5           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 76  | G11  | HDD4           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 81  | F7   | HDD3           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 83  | E10  | HDD2           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 86  | F9   | HDD1           | BI        | Hi-Z        | 4mA(PU)     |                          |

| 88  | D10  | HDD0           | BI        | Hi-Z        | 4mA(PU)     |                          |

PU および PD はレジスタ設定により ON/OFF できます。

PD: Pull Down

PU: Pull Up

(注) IDE I/F 端子は全て 5V トレンジトになっております。

## 6. 端子機能説明

| POWER                                                                                           |                                                                                |      |           |                                    |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|-----------|------------------------------------|

| Pin                                                                                             | Ball                                                                           | 名称   | 電圧        | 端子説明                               |

| 8, 12, 65, 80, 89,<br>102, 113, 117, 123                                                        | G7, D5, F11,<br>E1, G2, B5, A7                                                 | HVDD | 3.3V      | IDE I/F I/O, USB I/O, TEST I/O 用電源 |

| 19, 35, 49, 64                                                                                  | H3, L7, H8                                                                     | CVDD | 1.8~3.3 V | CPU I/F I/O 用電源                    |

| 3, 14, 17, 42, 63,<br>66, 78, 100, 109,<br>118, 127                                             | J1, E4, F6, H1,<br>A3, A4 , C1, A9                                             | LVDD | 1.8V      | OSC I/O, 内部電源                      |

| 2, 4, 6, 7, 10, 15,<br>18, 34, 36, 43, 50,<br>54, 67, 73, 79, 85,<br>101, 110, 112, 115,<br>119 | F3, E3, E5, F5,<br>C8,F8, E9, F10,<br>H2, F2, B2, B4,<br>B6, B8, D2, C2,<br>B9 | Vss  | 0V        | GND                                |

| 16                                                                                              | A1, L1, A11, L11                                                               | N.C. | 0V        | N.C.端子 (GND に接続してください)             |

## 7. 電気的特性

### 7.1 絶対最大定格

| 項目      | 記号    | 定格値                    | 単位 |

|---------|-------|------------------------|----|

| 電源電圧    | HVDD  | Vss - 0.3 ~ 4.0        | V  |

|         | CVDD  | Vss - 0.3 ~ 4.0        | V  |

|         | LVDD  | Vss - 0.3 ~ 2.5        | V  |

| 入力電圧    | HVI   | Vss - 0.3 ~ HVDD + 0.5 | V  |

|         | CVI*1 | Vss - 0.3 ~ CVDD + 0.5 | V  |

|         | IVI*2 | Vss - 0.3 ~ 5.5        | V  |

|         | VVI*3 | Vss - 0.3 ~ 6.0        | V  |

|         | LVI*4 | Vss - 0.3 ~ LVDD + 0.5 | V  |

| 出力電圧    | HVO   | Vss - 0.3 ~ HVDD + 0.5 | V  |

|         | CVO*1 | Vss - 0.3 ~ CVDD + 0.5 | V  |

| 出力電流／端子 | IOUT  | ±10                    | mA |

| 保存温度    | Tstg  | -65 ~ +150             | °C |

\*1 CPU-I/F

\*2 IDE-I/F

\*3 VBUS\_B

\*4 XI

### 7.2 推奨動作条件

| 項目   | 記号    | Min. | Typ. | Max.     | 単位 |

|------|-------|------|------|----------|----|

| 電源電圧 | HVDD  | 3.00 | 3.30 | 3.60     | V  |

|      | CVDD  | 1.65 | —    | 3.60     | V  |

|      | LVDD  | 1.65 | 1.80 | 1.95     | V  |

| 入力電圧 | HVI   | -0.3 | —    | HVDD+0.3 | V  |

|      | CVI*1 | -0.3 | —    | CVDD+0.3 | V  |

|      | IVI*2 | -0.3 | —    | 5.5      | V  |

|      | VVI*3 | -0.3 | —    | 6.0      | V  |

|      | LVI*4 | -0.3 | —    | LVDD+0.3 | V  |

| 周囲温度 | Ta    | -40  | 25   | 85       | °C |

\*1 CPU-I/F

\*2 IDE-I/F

\*3 VBUS\_B

\*4 XI

本 IC は下記順序で電源投入を行ってください。

**LVDD (内部) →HVDD, CVDD (IO 部)**

また、本 IC は下記順序で電源遮断を行ってください。

**HVDD, CVDD (IO 部) →LVDD (内部)**

注)

LVDD が切断されている状態で HVDD, CVDD のみを継続的（1Sec 以上）に印可することは Chip の信頼性上問題がありますので避けてください。

## 7. 電気的特性

### 7.3 DC 特性

#### 7.3.1 消費電流

| 項目                   | 記号    | 条件                                                                                                   | Min. | Typ. | Max. | 単位 |

|----------------------|-------|------------------------------------------------------------------------------------------------------|------|------|------|----|

| 電源供給電流 ※1            |       |                                                                                                      |      |      |      |    |

| 電源電流                 | IDDH  | HVDD = 3.3V(Typ.),<br>HVDD = 3.6V(Max.)                                                              | —    | 41   | 65   | mA |

|                      | IDDCH | CVDD = 3.3V(Typ.),<br>CVDD = 3.6V(Max.)                                                              | —    | 1    | 4    | mA |

|                      | IDDCL | CVDD = 1.8V(Typ.),<br>CVDD = 1.95V(Max.)                                                             | —    | 0.7  | 2    | mA |

|                      | IDDL  | LVDD = 1.8V(Typ.),<br>LVDD = 1.95V(Max.)                                                             | —    | 75   | 120  | mA |

| 静止電流 ※2              |       |                                                                                                      |      |      |      |    |

| 電源電流                 | IDDS  | VIN = HVDD,CVDD,LVDD or Vss<br>HVDD = 3.6V<br>CVDD = 3.6V<br>LVDD = 1.95V                            | —    | —    | 80   | μA |

| 入力リーク                |       |                                                                                                      |      |      |      |    |

| 入力リーク電流              | IL    | HVDD = 3.6V<br>CVDD = 3.6V<br>LVDD = 1.95V<br>HVIH = HVDD<br>CVIH = CVDD<br>LVIH = LVDD<br>VIL = VSS | -5   | —    | 5    | μA |

| 入力リーク                |       |                                                                                                      |      |      |      |    |

| 入力リーク電流<br>(5V トレント) | ILIF  | HVDD = 3.0V<br>CVDD = 1.65V<br>LVDD = 1.65V<br>HVOH = 5.5V                                           | -10  | —    | 10   | μA |

※1： Typ.は USB ホストとして USB-HDD を接続し、IDE-HDD と USB-HDD 間でデータを送受信している状態（実転送レート 30MB/s）での測定値。Max.は同値からの見積値。

※2： Ta = 25°C、双方向端子が入力状態である場合の静止電流値。

弊社動作環境下における、各パワーマネジメントステートでの消費電力測定値 (Ta = 25°C)

| 項目                              | 条件                                        | Min. | Typ. | Max. | 単位 |

|---------------------------------|-------------------------------------------|------|------|------|----|

| SLEEP                           | CPU バス動作※1※2                              |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 0.23 | —    | mW |

| SNOOZE                          | CPU バス動作※1※2                              |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 1.8  | —    | mW |

| ACTIVE60(IDE↔CPU)               | ※3                                        |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 41   | —    | mW |

| ACT_DEVICE/ACT_ALL<br>(IDE↔USB) | ※4                                        |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 131  | —    | mW |

| ACT_HOST/ACT_ALL<br>(IDE↔USB)   | Copy※5                                    |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 134  | —    | mW |

| ACT_HOST/ACT_ALL<br>(IDE↔USB)   | Direct Copy※6                             |      |      |      |    |

| 電源電力                            | HVDD = 3.3V<br>CVDD = 3.3V<br>LVDD = 1.8V | —    | 273  | —    | mW |

※1: CPU が CPU バス上に接続されているメモリ (SRAM や ROM 等) にアクセスしている状態。

※2: S1R72C05 が内蔵している DP プルアップ抵抗による消費電流値 (約 200 μA) を除く。

※3: IDE-HDD と CPU 間でデータを送受信している状態 (実転送レート 4MB/s)。

※4: USB デバイスとして PC に接続し、IDE-HDD と USB 間でデータを送受信している状態 (実転送レート 25MB/s)。

※5: USB ホストとして USB-HDD を接続し、IDE-HDD と USB-HDD 間でデータを送受信している状態 (実転送レート 5.3MB/s)。

※6: USB ホストとして USB-HDD を接続し、IDE-HDD と USB-HDD 間でデータを送受信している状態 (実転送レート 30MB/s)。

## 7. 電気的特性

### 7.3.2 入力特性

| 項目                    | 記号                                                                          | 条件                                | Min. | Typ. | Max. | 単位 |

|-----------------------|-----------------------------------------------------------------------------|-----------------------------------|------|------|------|----|

| 入力特性(LVC MOS)         | 端子名 : TEST, TDI, TCK, TRST, TMS                                             |                                   |      |      |      |    |

| "H"レベル入力電圧            | VIH1                                                                        | HVDD = 3.6V                       | 2.2  | —    | —    | V  |

| "L"レベル入力電圧            | VIL1                                                                        | HVDD = 3.0V                       | —    | —    | 0.8  | V  |

| 入力特性(LVC MOS)         | 端子名 : CA[8:1], CD[15:0], XCS, XRD, XWRL, XWRH, XBEL, XDACK0, XDACK1, XRESET |                                   |      |      |      |    |

| "H"レベル入力電圧            | VIH2                                                                        | CVDD = 3.6V                       | 2.2  | —    | —    | V  |

| "L"レベル入力電圧            | VIL2                                                                        | CVDD = 3.0V                       | —    | —    | 0.8  | V  |

| "H"レベル入力電圧            | VIH3                                                                        | CVDD = 1.95V                      | 1.27 | —    | —    | V  |

| "L"レベル入力電圧            | VIL3                                                                        | CVDD = 1.65V                      | —    | —    | 0.57 | V  |

| 入力特性(LVC MOS)         | 端子名 : HDD[15:0], HDMARQ, HIORDY, HINTRQ, XHDASP, XHPDIAG                    |                                   |      |      |      |    |

| "H"レベル入力電圧            | VIH4                                                                        | HVDD = 3.6V                       | 2.2  | —    | —    | V  |

| "L"レベル入力電圧            | VIL4                                                                        | HVDD = 3.0V                       | —    | —    | 0.8  | V  |

| シユミット入力特性             | 端子名 : VBUSFLG_A                                                             |                                   |      |      |      |    |

| "H"レベルトリガ電圧           | VT+                                                                         | HVDD = 3.6V                       | 1.4  | —    | 2.7  | V  |

| "L"レベルトリガ電圧           | VT-                                                                         | HVDD = 3.0V                       | 0.6  | —    | 1.8  | V  |

| ヒステリシス電圧              | ΔV                                                                          | HVDD = 3.0V                       | 0.3  | —    | —    | V  |

| シユミット入力特性<br>(USB FS) | 端子名 : DP_A, DM_A, DP_B, DM_B                                                |                                   |      |      |      |    |

| "H"レベルトリガ電圧           | VT+(USB)                                                                    | HVDD = 3.6V                       | 1.1  | —    | 1.8  | V  |

| "L"レベルトリガ電圧           | VT-(USB)                                                                    | HVDD = 3.0V                       | 1.0  | —    | 1.5  | V  |

| ヒステリシス電圧              | ΔV(USB)                                                                     | HVDD = 3.0V                       | 0.1  | —    | —    | V  |

| 入力特性(USB FS 差動)       | 端子名 : DP_A, DM_A のペア、 DP_B, DM_B のペア                                        |                                   |      |      |      |    |

| 差動入力感度                | VDS(USB)                                                                    | HVDD = 3.0V<br>差動入力電圧 = 0.8V~2.5V | —    | —    | 0.2V | V  |

| 入力特性(VBUS)            | 端子名 : VBUS_B                                                                |                                   |      |      |      |    |

| "H"レベルトリガ電圧           | VT+(VBUS)                                                                   | HVDD = 3.6V                       | 1.86 | —    | 2.85 | V  |

| "L"レベルトリガ電圧           | VT-(VBUS)                                                                   | HVDD = 3.0V                       | 1.48 | —    | 2.23 | V  |

| ヒステリシス電圧              | ΔV(VBUS)                                                                    | HVDD = 3.0V                       | 0.31 | —    | 0.64 | V  |

| 入力特性                  | 端子名 : HDD[15:8], HDD[6:0], HIORDY, XHDASP, XHPDIAG, VBUSFLG_A               |                                   |      |      |      |    |

| プルアップ抵抗               | RPLU                                                                        | VIL = Vss                         | 50   | 100  | 240  | kΩ |

| 入力特性                  | 端子名 : HDD[7], HDMARQ, HINTRQ                                                |                                   |      |      |      |    |

| プルダウン抵抗               | RPLD                                                                        | VIH = HVDD                        | 50   | 100  | 240  | kΩ |

| 入力特性                  | 端子名 : VBUS_B                                                                |                                   |      |      |      |    |

| プルダウン抵抗               | RPLDV                                                                       | VIH = 5.0V                        | 110  | 125  | 150  | kΩ |

## 7.3.3 出力特性

| 項目                           | 記号                                                                      | 条件                                                      | Min.     | Typ. | Max.    | 単位      |

|------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|----------|------|---------|---------|

| 出力特性                         | 端子名 : CD[15:0], XDREQ0, XDREQ1, XINT                                    |                                                         |          |      |         |         |

| "H"レベル出力電圧                   | VOH1                                                                    | CVDD = 3.0V<br>IOH = -2mA                               | CVDD-0.4 | —    | —       | V       |

| "L"レベル出力電圧                   | VOL1                                                                    | CVDD = 3.0V<br>IOL = 2mA                                | —        | —    | Vss+0.4 | V       |

| "H"レベル出力電圧                   | VOH2                                                                    | CVDD = 1.65V<br>IOH = -1mA                              | CVDD-0.4 | —    | —       | V       |

| "L"レベル出力電圧                   | VOL2                                                                    | CVDD = 1.65V<br>IOL = 1mA                               | —        | —    | Vss+0.4 | V       |

| 出力特性                         | 端子名 : HDD[15:0], HDA[2:0], XHCS1, XHCS0, XHIOR, XHIOW, XHDMACK, XHRESET |                                                         |          |      |         |         |

| "H"レベル出力電圧                   | VOH3                                                                    | HVDD = 3.0V<br>IOH = -4mA                               | HVDD-1.0 | —    | —       | V       |

| "L"レベル出力電圧                   | VOL3                                                                    | HVDD = 3.0V<br>IOL = 4mA                                | —        | —    | Vss+0.4 | V       |

| 出力特性                         | 端子名 : TDO, VBUSEN_A                                                     |                                                         |          |      |         |         |

| "H"レベル出力電圧                   | VOH4                                                                    | HVDD = 3.0V<br>IOH = -2mA                               | HVDD-0.4 | —    | —       | V       |

| "L"レベル出力電圧                   | VOL4                                                                    | HVDD = 3.0V<br>IOL = 2mA                                | —        | —    | Vss+0.4 | V       |

| 出力特性(USB FS)                 | 端子名 : DP_A, DM_A, DP_B, DM_B                                            |                                                         |          |      |         |         |

| "H"レベル出力電圧                   | VOH(USB)                                                                | HVDD=3.0V                                               | 2.8      | —    | —       | V       |

| "L"レベル出力電圧                   | VOL(USB)                                                                | HVDD=3.6V                                               | —        | —    | 0.3     | V       |

| 出力特性(USB HS)                 | 端子名 : DP_A, DM_A, DP_B, DM_B                                            |                                                         |          |      |         |         |

| "H"レベル出力電圧                   | VHSOH<br>(USB)                                                          | HVDD = 3.0V                                             | 360      | —    | —       | mV      |

| "L"レベル出力電圧                   | VHSOL<br>(USB)                                                          | HVDD = 3.6V                                             | —        | —    | 10.0    | mV      |

| 出力特性                         | 端子名 : CD[15:0], XINT                                                    |                                                         |          |      |         |         |

| OFF-STATE リーク電流              | IOZ                                                                     | HVDD = 3.6V<br>CVDD = 1.95V<br>CVOH = CVDD<br>VOL = VSS | -5       | —    | 5       | $\mu$ A |

| 出力特性                         | 端子名 : HDD[15:0], HDA[2:0], XHCS1, XHCS0, XHIOR, XHIOW, XHDMACK, XHRESET |                                                         |          |      |         |         |

| OFF-STATE リーク電流<br>(5V トレント) | IOZHF                                                                   | HVDD = 3.0V<br>HVOH = 5.5V                              | -10      | —    | 10      | $\mu$ A |

## 7. 電気的特性

### 7.3.4 端子容量

| 項目        | 記号                                     | 条件                                    | Min. | Typ. | Max. | 単位 |

|-----------|----------------------------------------|---------------------------------------|------|------|------|----|

| 端子容量      | 端子名：全入力端子                              |                                       |      |      |      |    |

| 入力端子容量    | Cl                                     | f = 10MHz<br>HVDD = CVDD = LVDD = Vss | —    | —    | 10   | pF |

| 端子容量      | 端子名：全出力端子                              |                                       |      |      |      |    |

| 出力端子容量    | CO                                     | f = 10MHz<br>HVDD = CVDD = LVDD = Vss | —    | —    | 10   | pF |

| 端子容量      | 端子名：全入出力端子(DP_A, DM_A, DP_B, DM_B を除く) |                                       |      |      |      |    |

| 入出力端子容量 1 | CIO1                                   | f = 10MHz<br>HVDD = CVDD = LVDD = Vss | —    | —    | 10   | pF |

| 端子容量      | 端子名：DP_A, DM_A, DP_B, DM_B             |                                       |      |      |      |    |

| 入出力端子容量 2 | CIO2                                   | f = 10MHz<br>HVDD = CVDD = LVDD = Vss | —    | —    | 10   | pF |

## 7.4 AC 特性

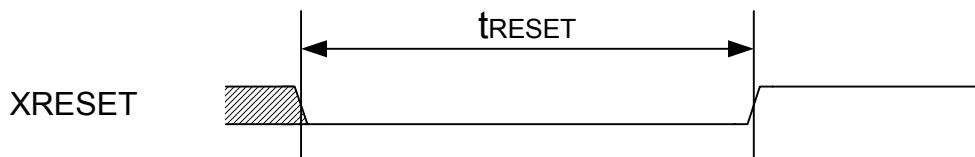

### 7.4.1 RESET タイミング

| 記号          | 説明       | Min. | Typ. | Max. | 単位 |

|-------------|----------|------|------|------|----|

| $t_{RESET}$ | リセットパルス幅 | 40   | —    | —    | ns |

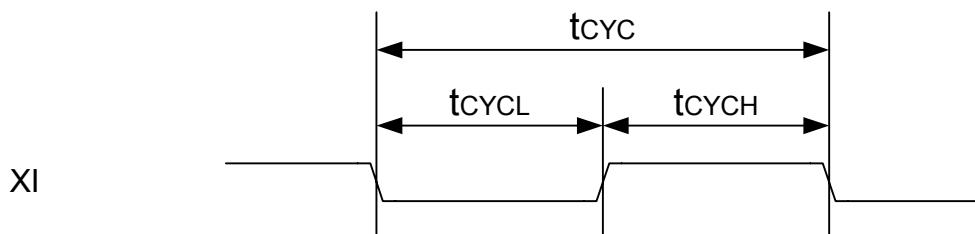

### 7.4.2 クロックタイミング

| 記号                       | 説明                    | Min.   | Typ. | Max.   | 単位  |

|--------------------------|-----------------------|--------|------|--------|-----|

| $t_{CYC}$                | クロックサイクル(ClkSelect=0) | 11.999 | 12   | 12.001 | MHz |

| $t_{CYC}$                | クロックサイクル(ClkSelect=1) | 23.998 | 24   | 24.002 | MHz |

| $t_{CYCH}$<br>$t_{CYCL}$ | クロックデューティ             | 45     | —    | 55     | %   |

## 7. 電気的特性

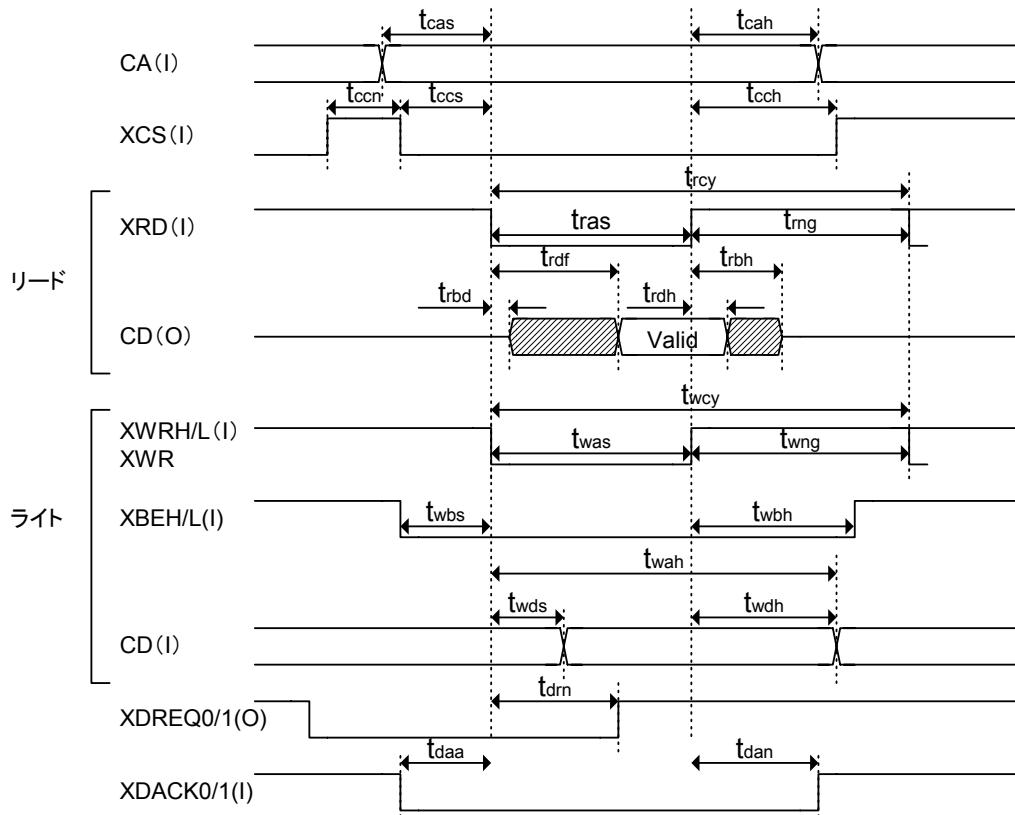

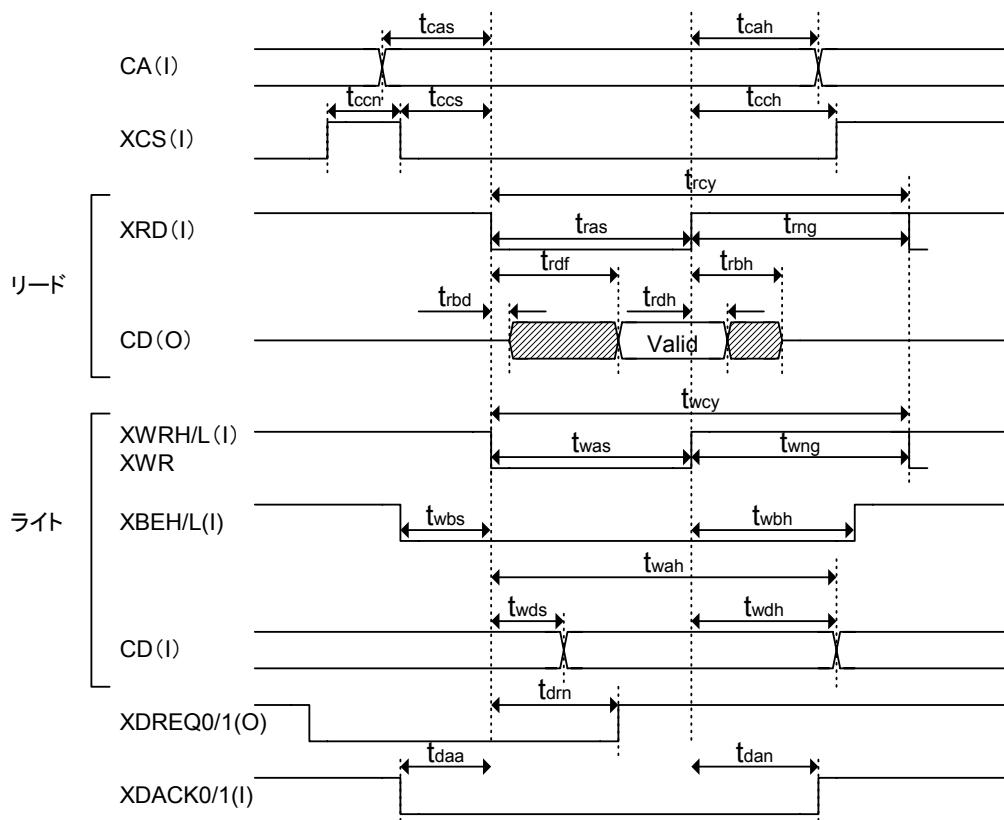

### 7.4.3 CPU/DMA I/F アクセスタイミング

#### 7.4.3.1 CVDD=1.65V~3.6V での規定

( $C_L=30\text{pF}$ )

| 記号               | 項目                          | Min. | Typ. | Max. | unit |

|------------------|-----------------------------|------|------|------|------|

| t <sub>cas</sub> | アドレスセットアップ時間                | 6    | —    | —    | ns   |

| t <sub>cah</sub> | アドレスホールド時間                  | 6    | —    | —    | ns   |

| t <sub>ccs</sub> | XCSセットアップ時間                 | 6    | —    | —    | ns   |

| t <sub>ch</sub>  | XCSホールド時間                   | 6    | —    | —    | ns   |

| t <sub>ccn</sub> | XCSネゲート時間(CPUIFモード設定時のみ※)   | 15   | —    | —    | ns   |

| t <sub>rcy</sub> | リードサイクル                     | 80   | —    | —    | ns   |

| t <sub>ras</sub> | リードストローブアサート時間              | 40   | —    | —    | ns   |

| t <sub>rng</sub> | リードストローブネゲート時間              | 25   | —    | —    | ns   |

| t <sub>rbd</sub> | リードデータ出力開始時間                | 1    | —    | —    | ns   |

| t <sub>rdt</sub> | リードデータ確定時間                  | —    | —    | 35   | ns   |

| t <sub>rdh</sub> | リードデータホールド時間                | 3    | —    | —    | ns   |

| t <sub>rbh</sub> | リードデータ出力遅延時間                | —    | —    | 10   | ns   |

| t <sub>wcy</sub> | ライトサイクル                     | 80   | —    | —    | ns   |

| t <sub>was</sub> | ライトストローブアサート時間              | 40   | —    | —    | ns   |

| t <sub>wng</sub> | ライトストローブネゲート時間              | 25   | —    | —    | ns   |

| t <sub>wbs</sub> | ライトバイトイネーブルセットアップ時間         | 6    | —    | —    | ns   |

| t <sub>wbh</sub> | ライトバイトイネーブルホールド時間           | 6    | —    | —    | ns   |

| t <sub>wdt</sub> | ライトデータ遅延許容時間                | —    | —    | 10   | ns   |

| t <sub>wdh</sub> | ライトデータホールド時間(ストローブネゲーションから) | 6    | —    | —    | ns   |

| t <sub>wah</sub> | ライトデータホールド時間(ストローブアサーションから) | 50   | —    | —    | ns   |

| t <sub>drn</sub> | XDREQ0/1ネゲート遅延時間            | —    | —    | 35   | ns   |

| t <sub>daa</sub> | XDACK0/1セットアップ時間            | 6    | —    | —    | ns   |

| t <sub>dan</sub> | XDACK0/1ホールド時間              | 6    | —    | —    | ns   |

※CPUIFモードの設定に関しては『テクニカルマニュアル』を参照してください。

## 7.4.3.2 CVDD=3.0~3.6Vに制限した場合の規定

(CL=30pF)

| 記号               | 項目                          | Min. | Typ. | Max. | unit |

|------------------|-----------------------------|------|------|------|------|

| t <sub>cas</sub> | アドレスセットアップ時間                | 6    | —    | —    | ns   |

| t <sub>cah</sub> | アドレスホールド時間                  | 6    | —    | —    | ns   |

| t <sub>ccs</sub> | XCSセットアップ時間                 | 6    | —    | —    | ns   |

| t <sub>cch</sub> | XCSホールド時間                   | 6    | —    | —    | ns   |

| t <sub>cnn</sub> | XCSネゲート時間(CPUIFモード設定時のみ※)   | 15   | —    | —    | ns   |

| t <sub>rcy</sub> | リードサイクル                     | 75   | —    | —    | ns   |

| t <sub>ras</sub> | リードストローブアサート時間              | 37   | —    | —    | ns   |

| t <sub>rng</sub> | リードストローブネゲート時間              | 25   | —    | —    | ns   |

| t <sub>rbd</sub> | リードデータ出力開始時間                | 1    | —    | —    | ns   |

| t <sub>rdt</sub> | リードデータ確定時間                  | —    | —    | 30   | ns   |

| t <sub>rdh</sub> | リードデータホールド時間                | 3    | —    | —    | ns   |

| t <sub>rbh</sub> | リードデータ出力遅延時間                | —    | —    | 10   | ns   |

| t <sub>wcy</sub> | ライトサイクル                     | 75   | —    | —    | ns   |

| t <sub>was</sub> | ライトストローブアサート時間              | 37   | —    | —    | ns   |

| t <sub>wng</sub> | ライトストローブネゲート時間              | 25   | —    | —    | ns   |

| t <sub>wbs</sub> | ライトバイトイネーブルセットアップ時間         | 6    | —    | —    | ns   |

| t <sub>wbh</sub> | ライトバイトイネーブルホールド時間           | 6    | —    | —    | ns   |

| t <sub>wds</sub> | ライトデータ遅延許容時間                | —    | —    | 10   | ns   |

| t <sub>wdh</sub> | ライトデータホールド時間(ストローブネゲーションから) | 6    | —    | —    | ns   |

| t <sub>wah</sub> | ライトデータホールド時間(ストローブアサーションから) | 50   | —    | —    | ns   |

| t <sub>drn</sub> | XDREQ0/1ネゲート遅延時間            | —    | —    | 30   | ns   |

| t <sub>daa</sub> | XDACK0/1セットアップ時間            | 6    | —    | —    | ns   |

| t <sub>dan</sub> | XDACK0/1ホールド時間              | 6    | —    | —    | ns   |

※CPUIFモードの設定に関しては『テクニカルマニュアル』を参照してください。

## 7. 電気的特性

### 7.4.4 IDE I/F タイミング

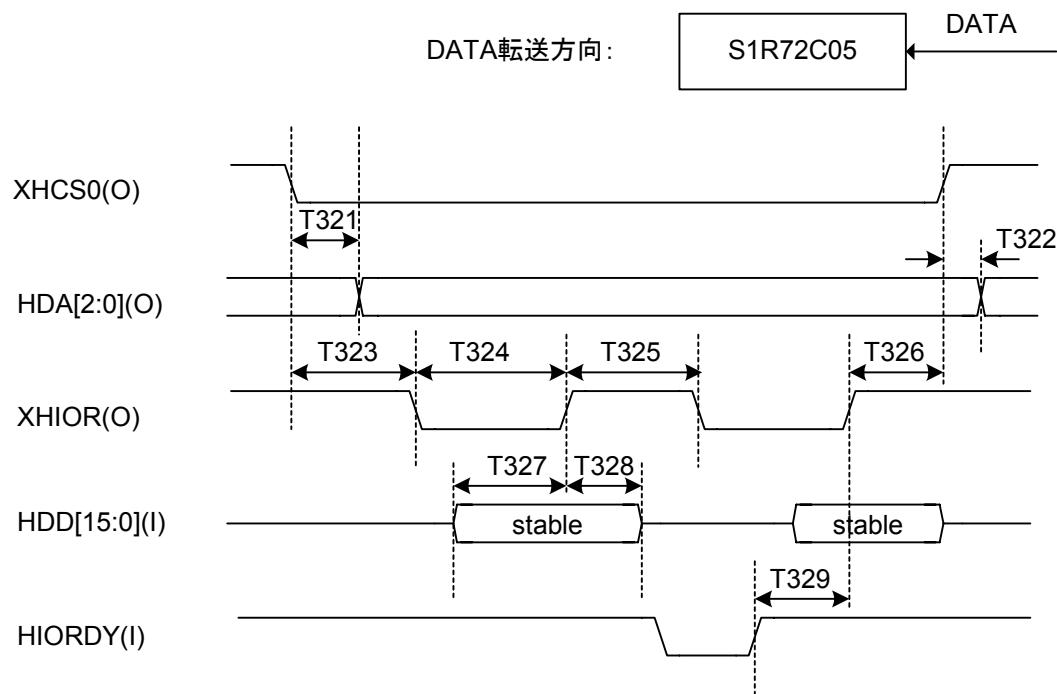

#### 7.4.4.1 PIO Read Timing

| 記号   | 説明                                 | Min. | Typ.                 | Max. | 単位 |

|------|------------------------------------|------|----------------------|------|----|

| T321 | XHCS0 ↓ → HDA<br>HDA出力遅延時間         | —    | 0                    | —    | ns |

| T322 | XHCS0 ↑ → HDA<br>HDAホールド時間         | —    | 0                    | —    | ns |

| T323 | XHCS0 ↓ → XHIOR ↓<br>XHCS0セットアップ時間 | 80   | —                    | —    | ns |

| T324 | XHIOR ↓ → XHIOR ↑<br>XHIORアサートパルス幅 | —    | (AP+4) *<br>16.7 - 3 | —    | ns |

| T325 | XHIOR ↑ → XHIOR ↓<br>XHIORネガートパルス幅 | —    | (NP+4) *<br>16.7 + 3 | —    | ns |

| T326 | XHIOR ↑ → XHCS0 ↑<br>XHCS0ホールド時間   | 50   | —                    | —    | ns |

| T327 | HDD → XHIOR ↑<br>データセットアップ時間       | 10   | —                    | —    | ns |

| T328 | XHIOR ↑ → HDD<br>データホールド時間         | 0    | —                    | —    | ns |

| T329 | HIORDYアサート→ XHIOR ↑<br>XHIOR出力遅延時間 | —    | —                    | 25   | ns |

\*1: AP=IDE\_Tmod.AssertPulseWidth, NP=IDE\_Tmod.NegatePulseWidth

詳細はレジスタ説明、“IDE Transfer Mode”を参照のこと

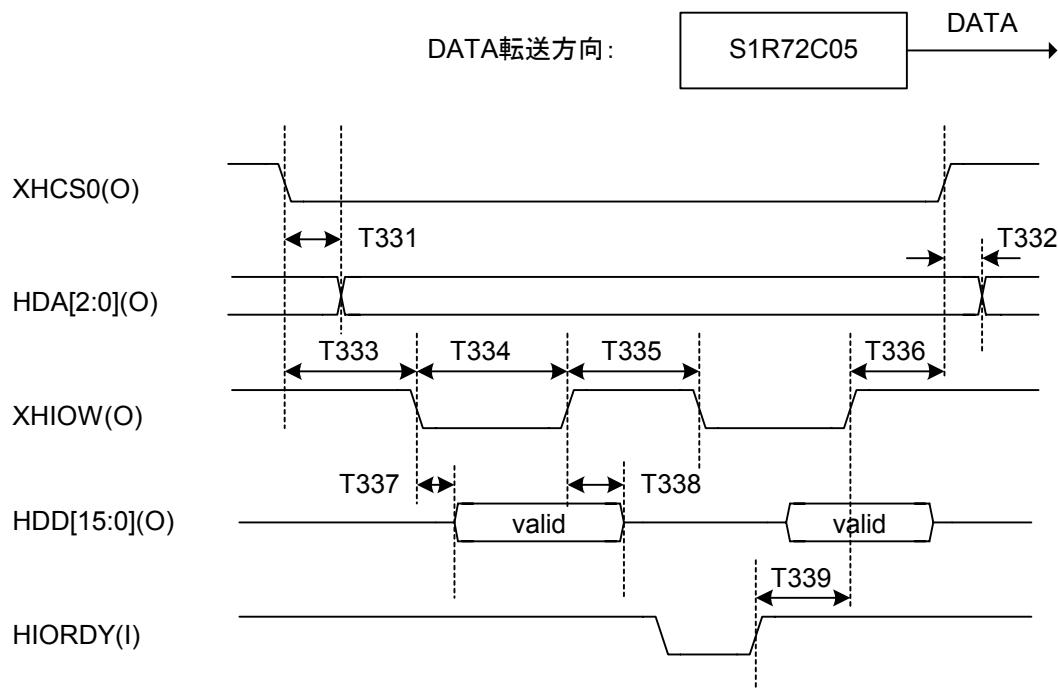

## 7.4.4.2 PIO Write Timing

| 記号   | 説明                                 | Min. | Typ.                 | Max. | 単位 |

|------|------------------------------------|------|----------------------|------|----|

| T331 | XHCS0 ↓ → HDA<br>HDA出力遅延時間         | —    | 0                    | —    | ns |

| T332 | XHCS0 ↑ → HDA<br>HDAホールド時間         | —    | 0                    | —    | ns |

| T333 | XHCS0 ↓ → XHIOW ↓<br>XHCS0セットアップ時間 | 80   | —                    | —    | ns |

| T334 | XHIOW ↓ → XHIOW ↑<br>XHIOWアサートパルス幅 | —    | (AP+4) *<br>16.7 - 3 | —    | ns |

| T335 | XHIOW ↑ → XHIOW ↓<br>XHIOWネゲートパルス幅 | —    | (NP+4) *<br>16.7 + 3 | —    | ns |

| T336 | XHIOW ↑ → XHCS0 ↑<br>XHCS0ホールド時間   | 50   | —                    | —    | ns |

| T337 | XHIOW ↓ → HDD<br>データ出力遅延時間         | 0    | —                    | 10   | ns |

| T338 | XHIOW ↑ → HDD<br>データバスネゲート時間       | 33   | —                    | 45   | ns |

| T339 | HIORDYアサート→ XHIOW ↑<br>XHIOW出力遅延時間 | —    | —                    | 25   | ns |

\*1: AP=IDE\_Tmod.AssertPulseWidth, NP=IDE\_Tmod.NegatePulseWidth

詳細はレジスタ説明、“IDE Transfer Mode”を参照のこと

## 7. 電気的特性

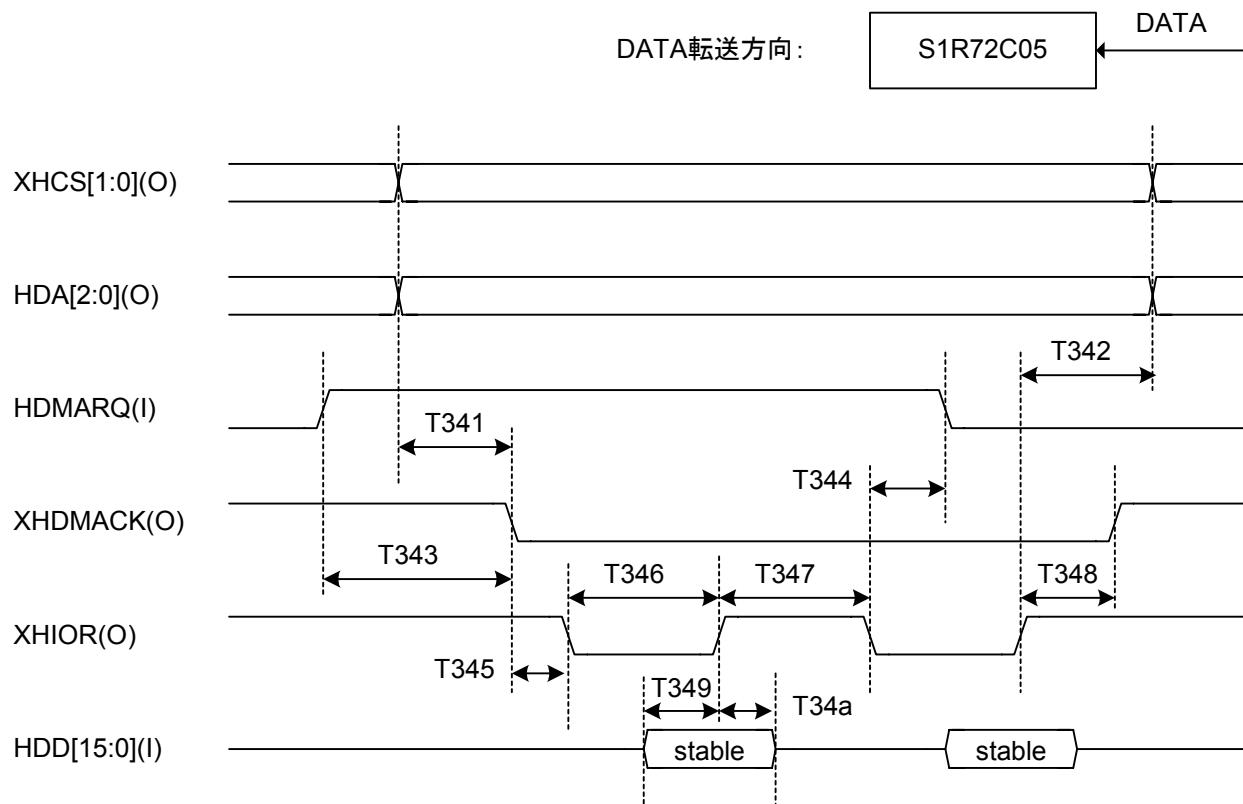

### 7.4.4.3 DMA Read Timing

| 記号   | 説明                                       | Min. | Typ.                 | Max. | 単位 |

|------|------------------------------------------|------|----------------------|------|----|

| T341 | XHCS ↑, HDA → XHDMAACK ↓<br>アドレスセットアップ時間 | 70   | —                    | —    | ns |

| T342 | XHIOR ↑ → XHCS ↑, HDA<br>アドレスホールド時間      | 50   | —                    | —    | ns |

| T343 | HDMARQ ↑ → XHDMAACK ↓<br>XHDMAACK応答時間    | 17   | —                    | —    | ns |

| T344 | XHIOR ↓ → HDMARQネゲート<br>HDMARQホールド時間     | 0    | —                    | —    | ns |

| T345 | XHDMAACK ↓ → XHIOR ↓<br>XHDMAACKセットアップ時間 | 0    | —                    | —    | ns |

| T346 | XHIOR ↓ → XHIOR ↑<br>XHIORアサートパルス幅       | —    | (AP+4) *<br>16.7 - 3 | —    | ns |

| T347 | XHIOR ↑ → XHIOR ↓<br>XHIORネゲートパルス幅       | —    | (NP+4) *<br>16.7 + 3 | —    | ns |

| T348 | XHIOR ↑ → XHDMAACK ↑<br>XHDMAACKホールド時間   | 30   | —                    | 90   | ns |

| T349 | HDD → XHIOR ↑<br>データセットアップ時間             | 10   | —                    | —    | ns |

| T34a | XHIOR ↑ → HDD<br>データバスホールド時間             | 0    | —                    | —    | ns |

\*1: AP=IDE\_Tmod.AssertPulseWidth, NP=IDE\_Tmod.NegatePulseWidth

詳細はレジスタ説明、“IDE Transfer Mode”を参照のこと

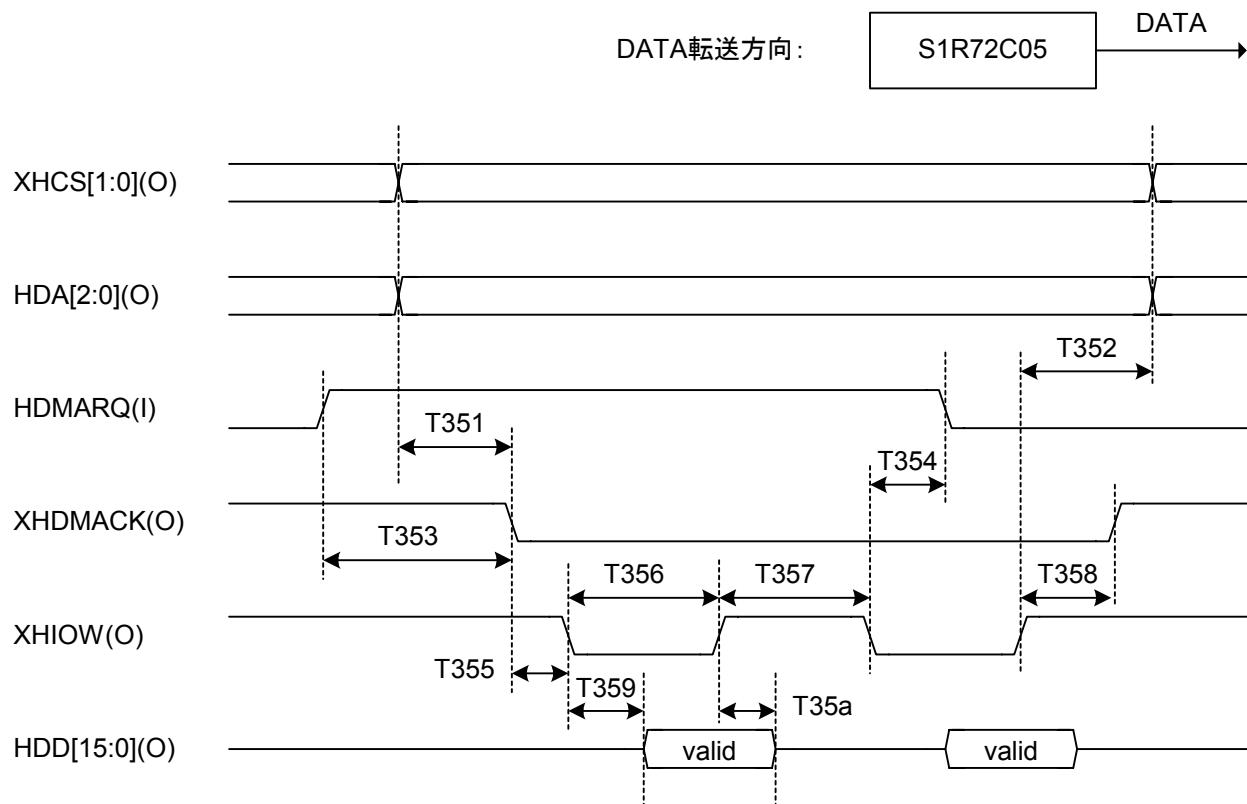

## 7.4.4.4 DMA Write Timing

| 記号   | 説明                                    | Min. | Typ.                 | Max. | 単位 |

|------|---------------------------------------|------|----------------------|------|----|

| T351 | XHCS ↑、HDA → XHDMAK ↓<br>アドレスセットアップ時間 | 70   | —                    | —    | ns |

| T352 | XHIOW ↑ → XHCS ↑、HDA<br>アドレスホールド時間    | 50   | —                    | —    | ns |

| T353 | HDMARQ ↑ → XHDMAK ↓<br>XHDMAK応答時間     | 17   | —                    | —    | ns |

| T354 | XHIOW ↓ → HDMARQネゲート<br>HDMARQホールド時間  | 0    | —                    | —    | ns |

| T355 | XHDMAK ↓ → XHIOW ↓<br>XHDMAKセットアップ時間  | 0    | —                    | —    | ns |

| T356 | XHIOW ↓ → XHIOW ↑<br>XHIOWアサートパルス幅    | —    | (AP+4) *<br>16.7 - 3 | —    | ns |

| T357 | XHIOW ↑ → XHIOW ↓<br>XHIOWネゲートパルス幅    | —    | (NP+4) *<br>16.7 + 3 | —    | ns |

| T358 | XHIOW ↑ → XHDMAK ↑<br>XHDMAKホールド時間    | 30   | —                    | 90   | ns |

| T359 | XHIOW ↓ → HDD<br>データ出力遅延時間            | 0    | —                    | 10   | ns |

| T35a | XHIOW ↑ → HDD<br>データバスネゲート時間          | 33   | —                    | 45   | ns |

\*1: AP=IDE\_Tmod.AssertPulseWidth, NP=IDE\_Tmod.NegatePulseWidth

詳細はレジスタ説明、“IDE Transfer Mode”を参照のこと

## 7. 電気的特性

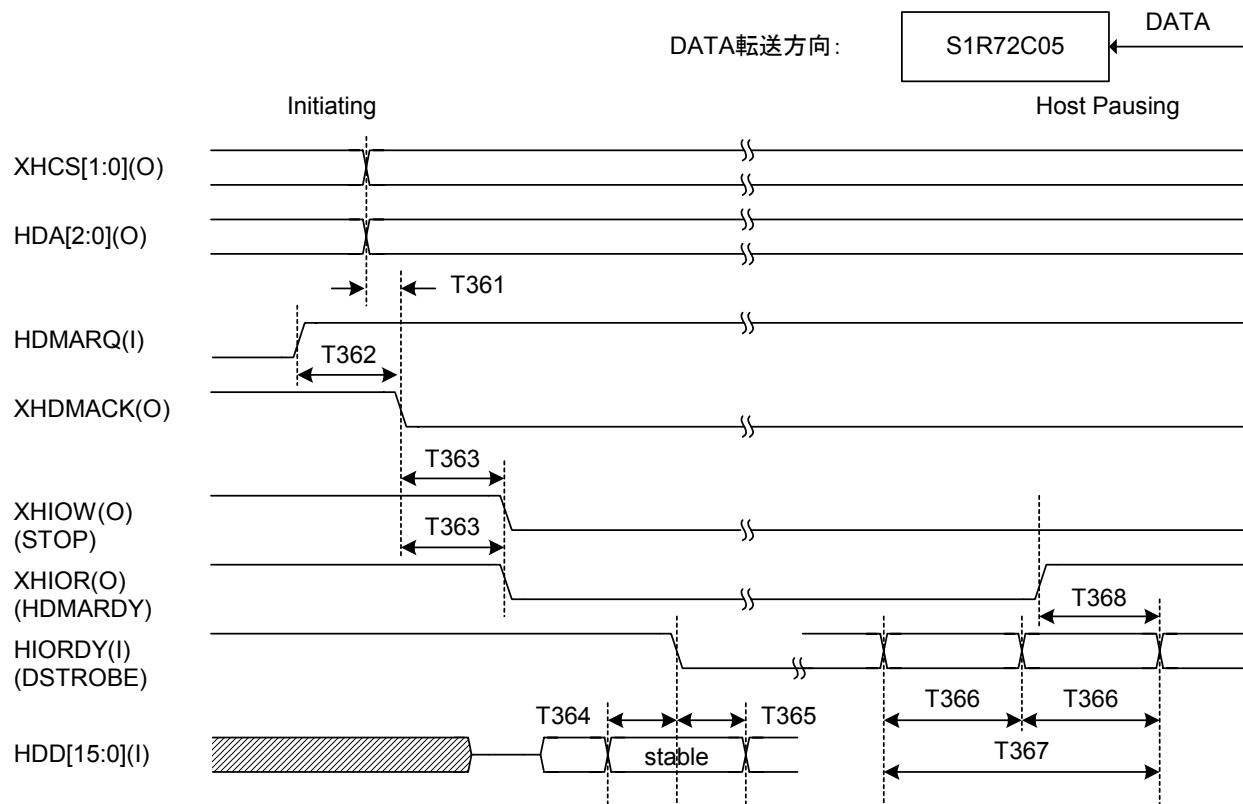

### 7.4.4.5 Ultra DMA Read Timing

| 記号   | 説明                                   | Min. | Typ. | Max.               | 単位 |

|------|--------------------------------------|------|------|--------------------|----|

| T361 | XHCS↑、HDA → XHDMACK↓<br>アドレスセットアップ時間 | 80   | —    | —                  | ns |

| T362 | HDMARQ↑ → XHDMACK↓<br>XHDMACK応答時間    | 65   | —    | —                  | ns |

| T363 | XHDMACK↓ → XHIOR(W)↓<br>エンベロープ時間     | 28   | —    | 40                 | ns |

| T364 | HDD → HIORDY<br>データセットアップ時間          | 4    | —    | —                  | ns |

| T365 | HIORDY → HDD<br>データホールド時間            | 4    | —    | —                  | ns |

| T366 | HIORDY → HIORDY<br>HIORDYサイクル時間      | 15   | —    | —                  | ns |

| T367 | HIORDY → HIORDY<br>HIORDYサイクル時間 × 2  | 30   | —    | —                  | ns |

| T368 | XHIOR↑ → HIORDY<br>最終のSTROBE時間       | —    | —    | IDE規格<br>$t_{RFS}$ | ns |

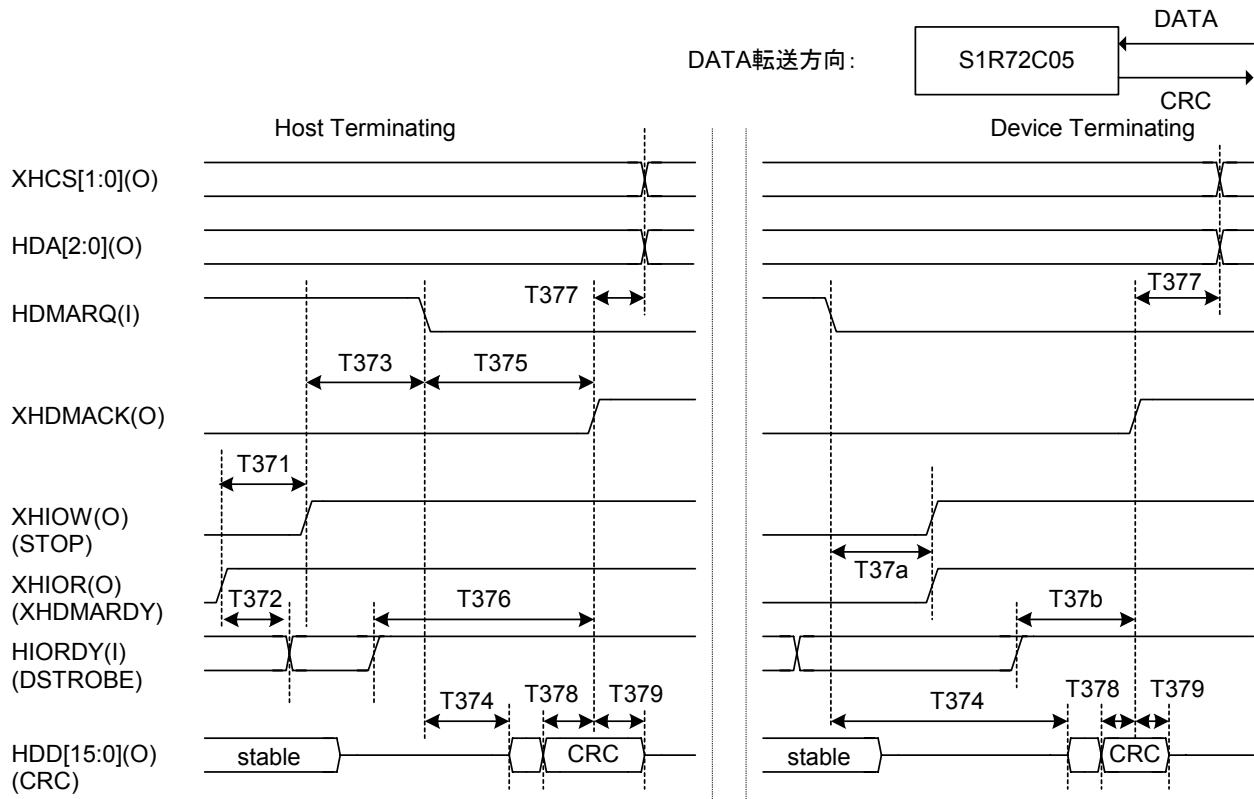

## Ultra DMA Read Timing (つづき)

| 記号   | 説明                                    | Min. | Typ. | Max.               | 単位 |

|------|---------------------------------------|------|------|--------------------|----|

| T371 | XHIOR ↑ → XHIOW ↑<br>STOPアサートまでの時間    | 180  | —    | —                  | ns |

| T372 | XHIOR ↑ → HIORDY<br>最終のSTROBE時間       | —    | —    | IDE規格<br>$t_{RFS}$ | ns |

| T373 | XHIOW ↑ → HDMARQ ↓<br>制限付きインターロック時間   | —    | —    | IDE規格<br>$t_{LI}$  | ns |

| T374 | HDMARQ ↓ → HDD<br>出力ディレイ時間            | 70   | —    | —                  | ns |

| T375 | HDMARQ ↓ → XHDMAK ↑<br>最小インターロック時間    | 160  | —    | —                  | ns |

| T376 | HIORDY → XHDMAK ↑<br>最小インターロック時間      | 110  | —    | —                  | ns |

| T377 | XHDMAK ↑ → XHCS0,1<br>XHCS0,1ホールド時間   | 35   | —    | —                  | ns |

| T378 | HDD(CRC) → XHDMAK ↑<br>CRCデータセットアップ時間 | 75   | —    | —                  | ns |

| T379 | XHDMAK ↑ → HDD(CRC)<br>CRCデータホールド時間   | 12   | —    | —                  | ns |

| T37a | HDMARQ ↓ → XHIOR ↑<br>制限付きインターロック時間   | 20   | —    | 38                 | ns |

| T37b | HIORDY → XHDMAK ↑<br>最小インターロック時間      | 110  | —    | —                  | ns |

## 7. 電気的特性

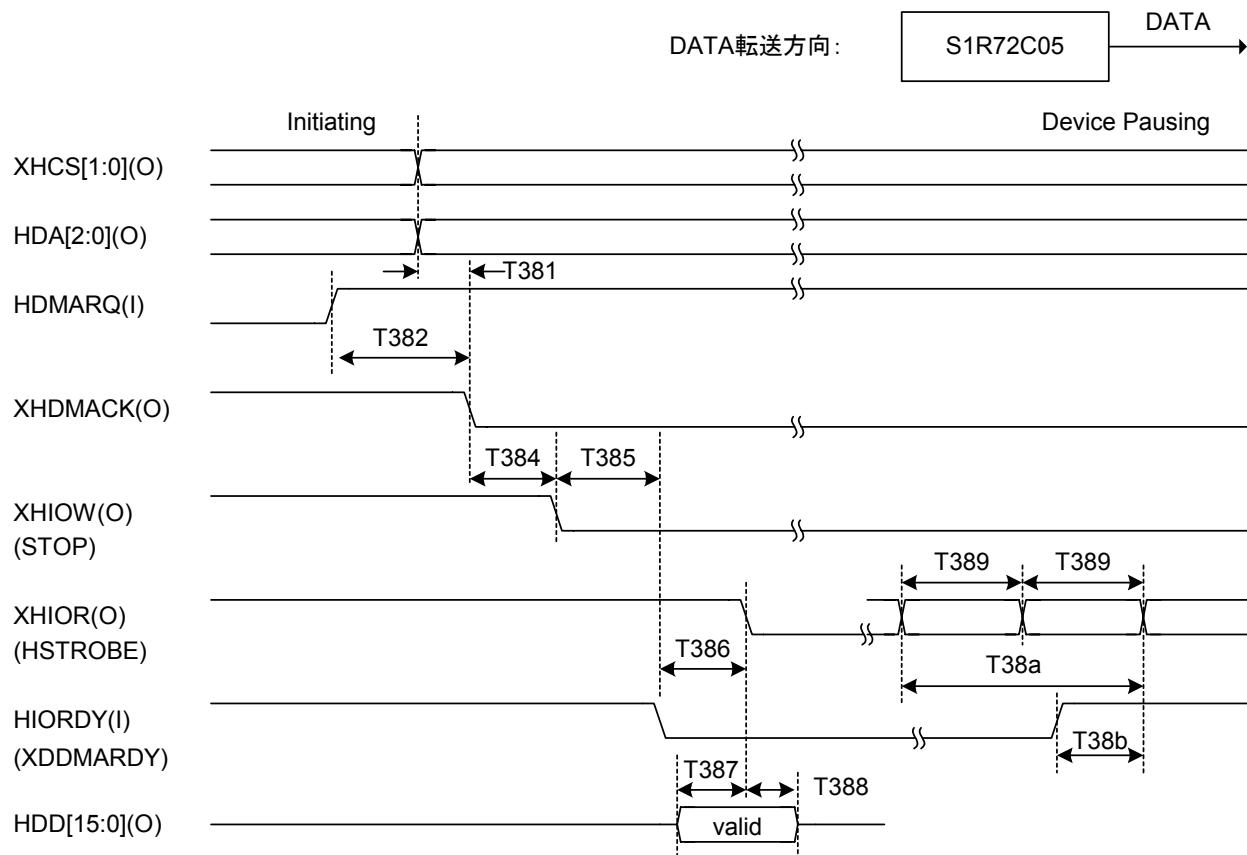

### 7.4.4.6 Ultra DMA Write Timing

| 記号   | 説明                                   | Min.              | Typ.             | Max.              | 単位 |

|------|--------------------------------------|-------------------|------------------|-------------------|----|

| T381 | XHCS↑、HDA → XHDMACK↓<br>アドレスセットアップ時間 | 80                | —                | —                 | ns |

| T382 | HDMARQ↑ → XHDMACK↓<br>XHDMACK応答時間    | 65                | —                | —                 | ns |

| T384 | XHDMACK↓ → XHIOW↓<br>エンベロープ時間        | 28                | —                | 40                | ns |

| T385 | XHIOW↓ → HIORDY↓<br>制限付きインターロック時間    | IDE規格<br>$t_{LI}$ | —                | IDE規格<br>$t_{LI}$ | ns |

| T386 | HIORDY↓ → XHIOR↓<br>制限無しインターロック時間    | 20                | —                | —                 | ns |

| T387 | HDD → XHIOR↓<br>データセットアップ時間          | —                 | $(cyc+1) * 16.7$ | —                 | ns |

| T388 | XHIOR↓ → HDD<br>データホールド時間            | —                 | $(cyc+1) * 16.7$ | —                 | ns |

| T389 | XHIOR → XHIOR<br>XHIORサイクル時間         | —                 | $(cyc+2) * 16.7$ | —                 | ns |

| T38a | XHIOR → XHIOR<br>XHIORサイクル時間 × 2     | —                 | $T389 * 2$       | —                 | ns |

| T38b | HIORDY↑ → XHIOR<br>最終のSTROBE時間       | 20                | —                | 38                | ns |

\*1:cyc=UltraDMAcycle

詳細はレジスタ説明、“IDE Ultra-DMA Transfer Mode”を参照のこと

### 7.4.5 USB I/F タイミング

USB2.0 規格に準拠します。

<Universal Serial Bus Specification Revision 2.0 Released on April 27, 2000 >

## 8. 接続例

### 8. 接続例

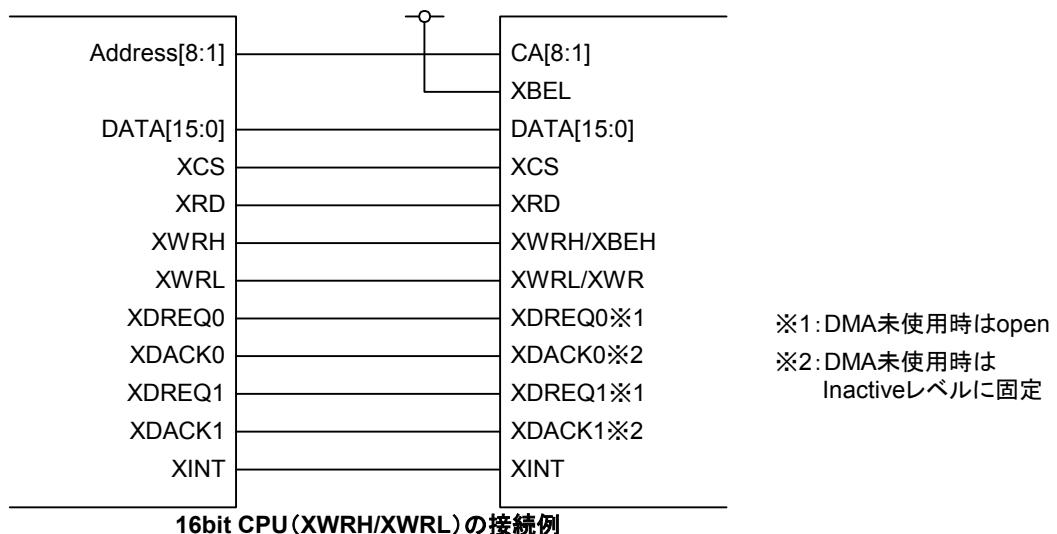

#### 8.1 CPU I/F 接続例

16bit CPU (XWRH/XWRL) の接続例

16bit CPU (XBEH/XBEL) の接続例

## 8.2 USB I/F 接続例

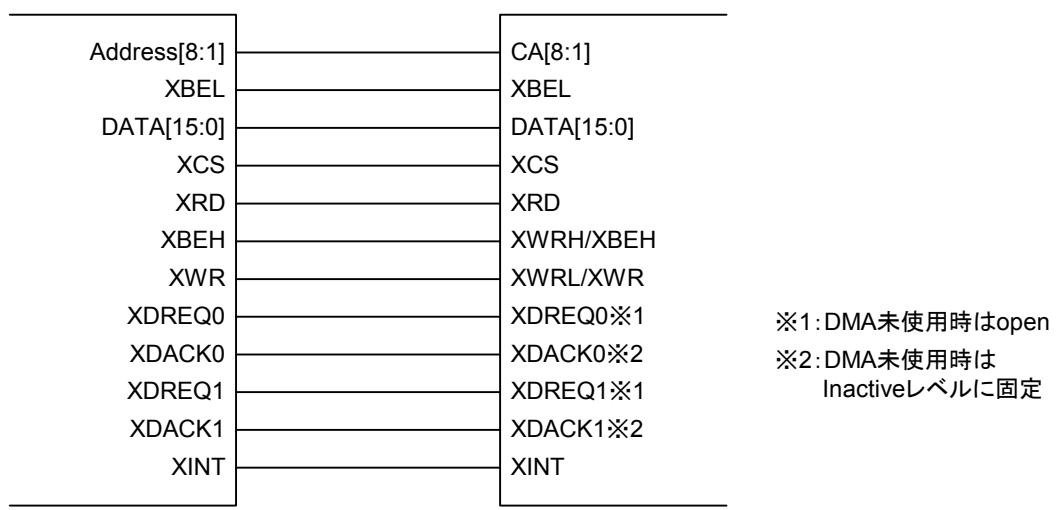

### 8.2.1 QFP15-128 の場合（デバイス部周辺）

電源素子の性能はUSB信号波形品質影響を与えるため、その選定には注意してください。

## 8. 接続例

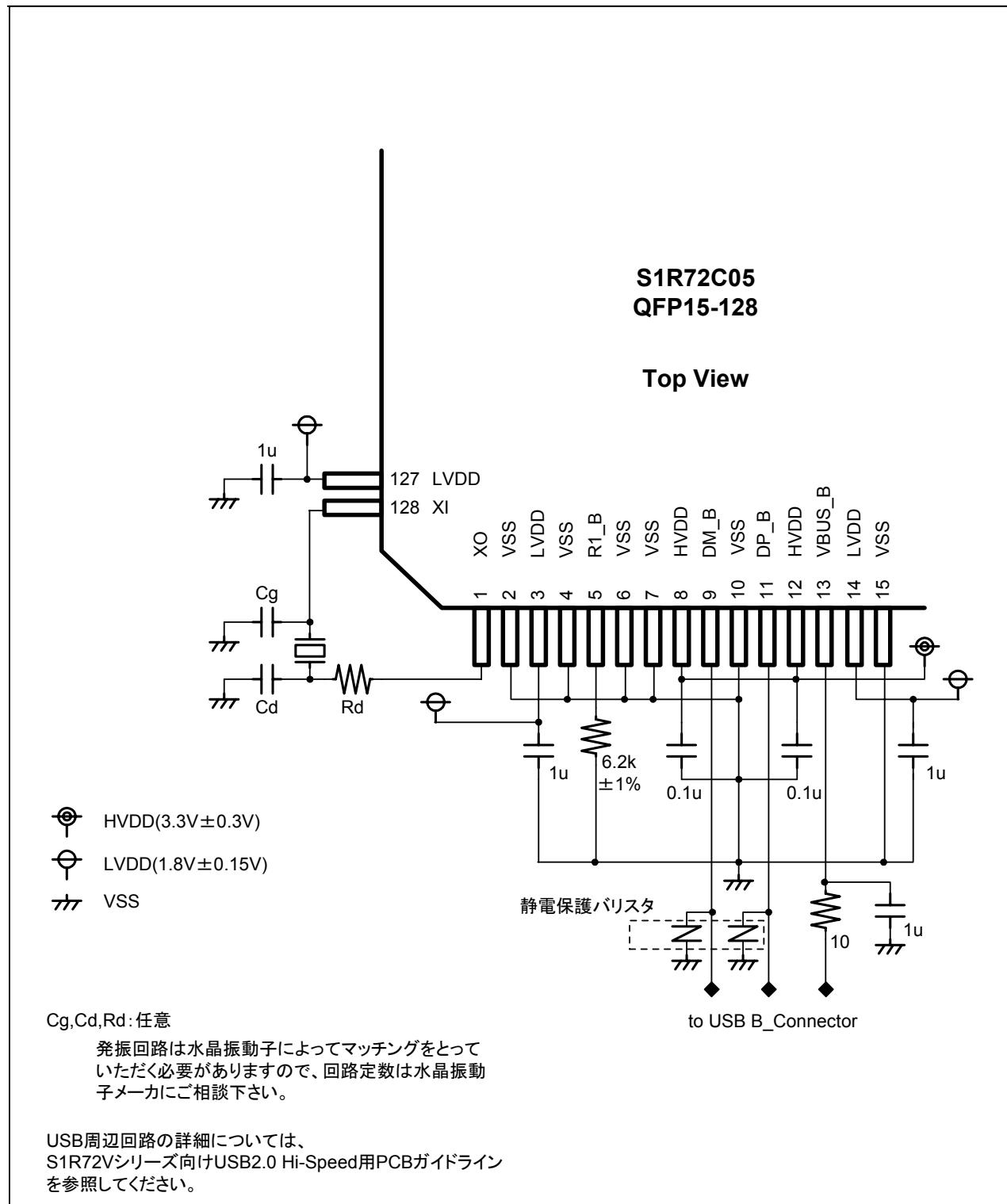

### 8.2.2 QFP15-128 の場合（ホスト部周辺）

電源素子の性能はUSB信号波形品質影響を与えるため、その選定には注意してください。

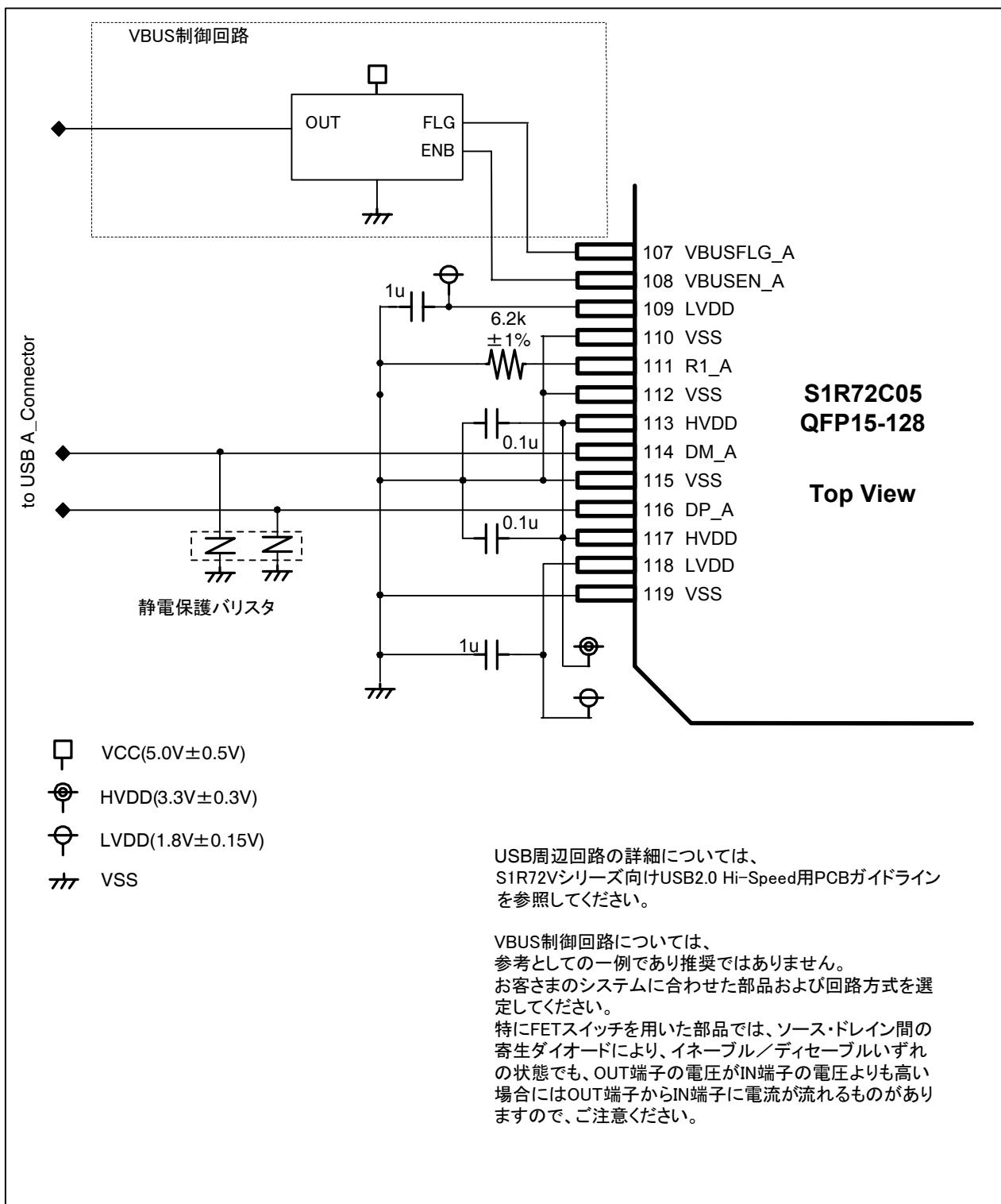

## 8.2.3 PFBGA8UX121/PFBGA10UX121 の場合（デバイス部周辺）

電源素子の性能はUSB信号波形品質影響を与えるため、その選定には注意してください。

## 8. 接続例

### 8.2.4 PFBGA8UX121/PFBGA10UX121 の場合（ホスト部周辺）

電源素子の性能はUSB信号波形品質影響を与えるため、その選定には注意してください。

## 9. 製品型番

表 9.1 製品型番

| 製品型番            | 製品種別                |

|-----------------|---------------------|

| S1R72C05B08**** | PFBGA8UX121 パッケージ品  |

| S1R72C05B10**** | PFBGA10UX121 パッケージ品 |

| S1R72C05F15**** | QFP15-128 パッケージ品    |

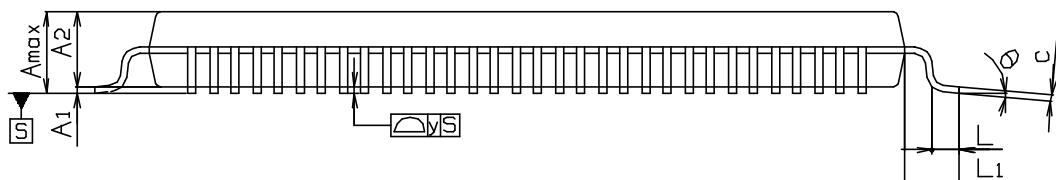

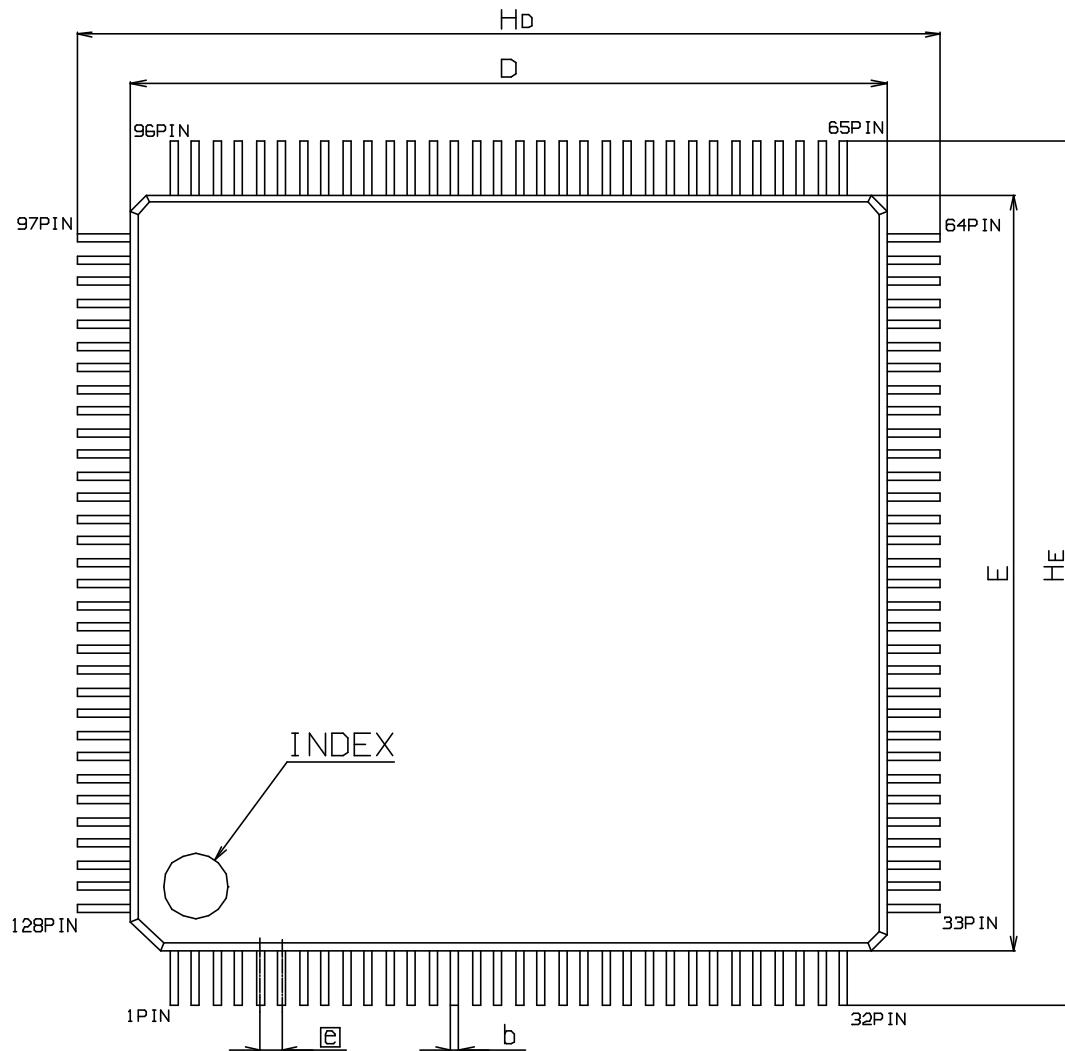

## 10. 外形寸法図

---

### 10. 外形寸法図

下記の各パッケージにつき、巻末の外形寸法図を参照してください。

- QFP パッケージ (QFP15-128)

- BGA パッケージ (PFBGA8UX121)

- BGA パッケージ (PFBGA10UX121)

## 改訂履歴

| 年月日      | 改訂内容 |       |    |      |

|----------|------|-------|----|------|

|          | Rev. | 項（旧版） | 種別 | 内 容  |

| 07/08/21 | 1.00 | 全項    | 新規 | 新規制定 |

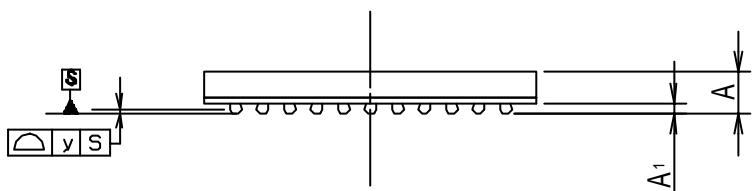

| Symbol           | Dimension in Millimeters |     |      |

|------------------|--------------------------|-----|------|

|                  | Min                      | Nom | Max  |

| E                | -                        | 14  | -    |

| D                | -                        | 14  | -    |

| A <sub>max</sub> | -                        | -   | 1.7  |

| A <sub>1</sub>   | -                        | 0.1 | -    |

| A <sub>2</sub>   | -                        | 1.4 | -    |

|                  | -                        | 0.4 | -    |

| b                | 0.13                     | -   | 0.23 |

| c                | 0.09                     | -   | 0.2  |

| θ                | 0°                       | -   | 10°  |

| L                | 0.3                      | -   | 0.75 |

| L <sub>1</sub>   | -                        | 1   | -    |

| H <sub>E</sub>   | -                        | 16  | -    |

| H <sub>D</sub>   | -                        | 16  | -    |

| y                | -                        | -   | 0.08 |

1 = 1mm

|                   |                                   |         |         |          |                         |

|-------------------|-----------------------------------|---------|---------|----------|-------------------------|

| 5.0               | 2004.08.11                        | C.SAITO | M.SONE  | T.OTSUKI | -                       |

| REV.              | DATE                              | DRAW    | CHECKED | APPROVED | CORRECTION ARTICLE      |

| TITLE             | P-LQFP128-1414-0.40(QFP15-128PIN) |         |         |          |                         |

| SEIKO EPSON CORP. |                                   |         |         |          | DWG No. 4900-0057       |

|                   |                                   |         |         |          | SCALE Free SHEET 1 of 1 |

## Top View

## Bottom View

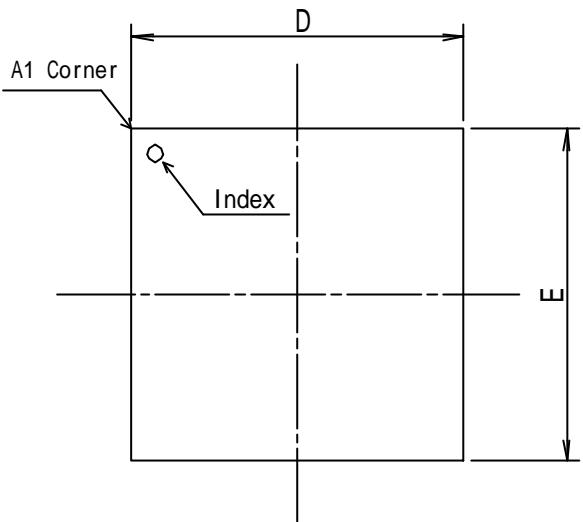

| Symbol         | Dimension in Millimeters |      |      |

|----------------|--------------------------|------|------|

|                | Min                      | Nom  | Max  |

| D              | -                        | 8    | -    |

| E              | -                        | 8    | -    |

| A              | -                        | -    | 1.2  |

| A <sub>1</sub> | -                        | 0.22 | -    |

| [e]            | -                        | 0.65 | -    |

| b              | 0.27                     | -    | 0.37 |

| x              | -                        | -    | 0.08 |

| y              | -                        | -    | 0.1  |

| Z <sub>D</sub> | -                        | 0.75 | -    |

| Z <sub>E</sub> | -                        | 0.75 | -    |

1 = 1mm

|       |                                    |          |            |              |                    |

|-------|------------------------------------|----------|------------|--------------|--------------------|

| 1.0   | 2005.03.25                         | O. SHOJI | M. SONE    | T. OTSUKI    | -                  |

| REV.  | DATE                               | DRAW     | CHECKED    | APPROVED     | CORRECTION ARTICLE |

| TITLE | P-TFBGA-121-0808-0.65(PFBGA8U-121) |          |            |              |                    |

|       |                                    |          |            |              | CAD FILE -         |

|       |                                    |          |            |              | DWG No. 4900-0395  |

|       |                                    |          | SCALE Free | SHEET 1 of 1 |                    |

## Top View

## Bottom View

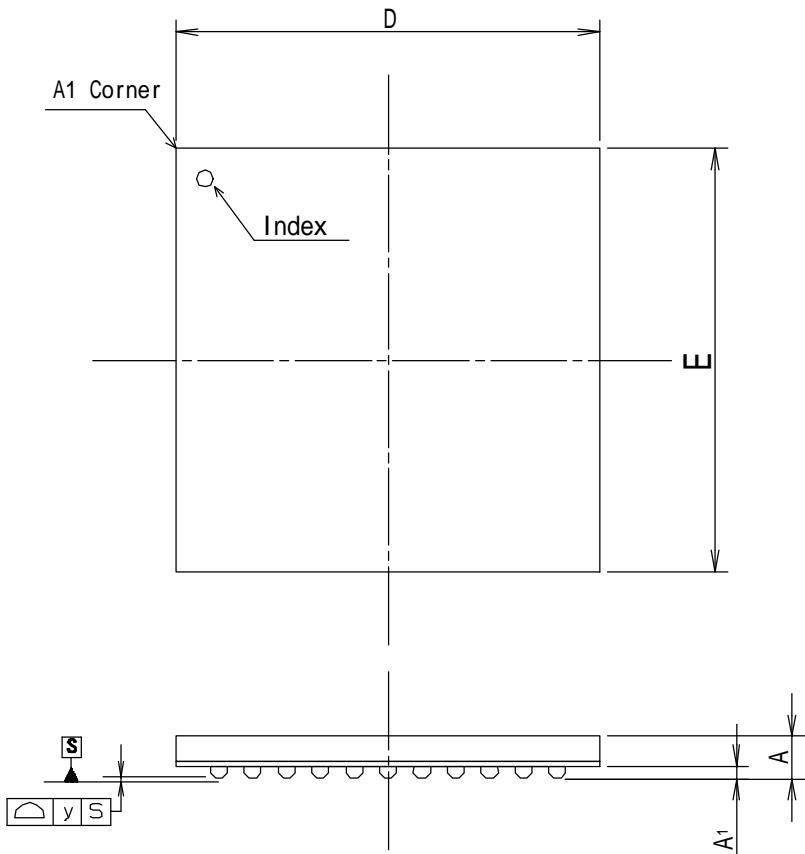

| Symbol         | Dimension in Millimeters |     |      |

|----------------|--------------------------|-----|------|

|                | Min                      | Nom | Max  |

| D              | -                        | 10  | -    |

| E              | -                        | 10  | -    |

| A              | -                        | -   | 1.2  |

| A <sub>1</sub> | -                        | 0.3 | -    |

| e              | -                        | 0.8 | -    |

| b              | 0.38                     | -   | 0.48 |

| x              | -                        | -   | 0.08 |

| y              | -                        | -   | 0.1  |

| Z <sub>D</sub> | -                        | 1   | -    |

| Z <sub>E</sub> | -                        | 1   | -    |

1 = 1mm

|                                     |            |          |         |           |                         |

|-------------------------------------|------------|----------|---------|-----------|-------------------------|

| 2.0                                 | 2004.10.18 | C. SHOJI | M. SONE | T. OTSUKI | —                       |

| REV.                                | DATE       | DRAW     | CHECKED | APPROVED  | CORRECTION ARTICLE      |

| TITLE                               |            |          |         |           | —                       |

| P-TFBGA-121-1010-0.80(PFBGA10U-121) |            |          |         |           | CAD FILE                |

| SEIKO EPSON CORP.                   |            |          |         |           | DWG No. 4900-0350       |

|                                     |            |          |         |           | SCALE Free SHEET 1 of 1 |

**セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 411234500

2007 年 9 月 作成