# 高耐圧・大電流対応 DMOS-ASICのご紹介

セイコーエプソン株式会社

MD営業部

本資料の内容は2022年3月時点の情報であり、予告なく変更される場合があります。

© Seiko Epson Corporation 2022. All rights reserved.

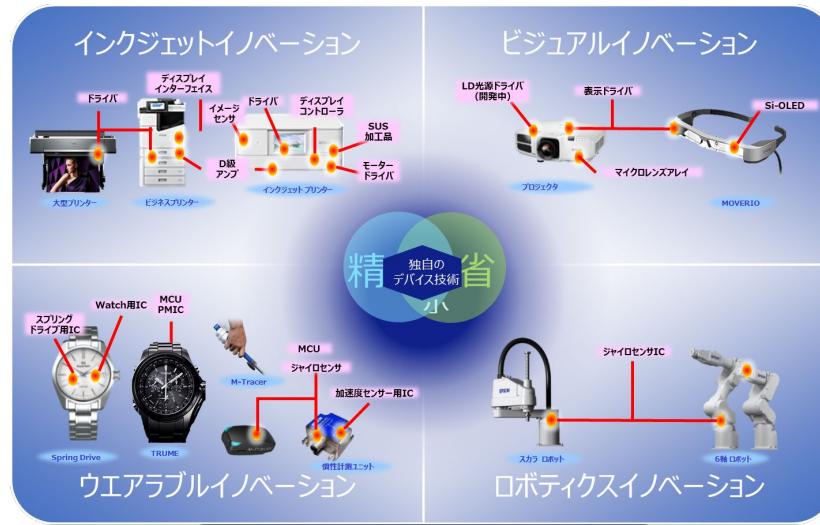

## ◆エプソンの半導体領域

- エプソン製品での半導体採用事例

- お客様製品での半導体採用事例

## ◆高耐圧/大電流対応製品をASICでラインアップ

- DMOS-ASICの概要

- IPロードマップ

- DMOS-ASICの仕様

- DMOS-ASICシステム構成の例

## ◆エプソンの半導体領域

- エプソン製品での半導体採用事例

- お客様製品での半導体採用事例

## ◆高耐圧/大電流対応製品をASICでラインアップ

- DMOS-ASICの概要

- IPロードマップ

- DMOS-ASICの仕様

- DMOS-ASICシステム構成の例

# エプソンの半導体領域と採用事例

EPSON

EXCEED YOUR VISION

- 【長期供給】 内製時計用CMOS ICをルーツとして40年以上にわたり幅広い製品群を展開

- 【国内製造】 ウエハ製造は国内の自社工場(山形県)で製造

- 【信頼の実績】 自社完成品に多数のICを供給し事業継続計画を策定

# お客様製品での半導体採用事例

EPSON

EXCEED YOUR VISION

## マイクロコントローラ

- バッテリー駆動に最適 低消費電流

- 幅広い液晶表示もサポート

エプソン

半導体

## LCDドライバ / LCDコントローラ

- 実績ある車載対応

- 特徴ある機能を搭載

## ◆エプソンの半導体領域

- エプソン製品での半導体採用事例

- お客様製品での半導体採用事例

## ◆高耐圧/大電流対応製品をASICでラインアップ

- DMOS-ASICの概要

- IPロードマップ

- DMOS-ASICの仕様

- DMOS-ASICシステム構成の例

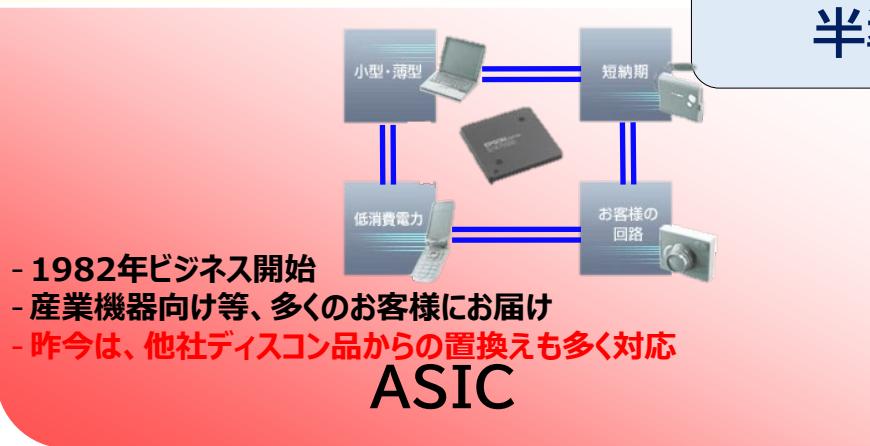

## 高耐圧/大電流対応製品をASICでラインアップ

エプソン内製品で実績のあるDMOSプロセスにてASIC製品を展開します

当社従来のCMOS製品に加えて 高耐圧/大電流を実現するDMOS製品を

ASIC開発手法でご提供 お客様のニーズにお応えします

### DMOS-ASIC

エプソン製品向けに開発したプロセスとIP

- 高耐圧/大電流(DMOS)

- アナログ混載技術

- エプソン製品向けに開発したIPをラインアップ

DMOSとアナログの混載対応

周辺機能IPラインアップ強化

ASIC

システム設計

ロジック部の仕様決定

搭載するマクロセル決定

長年培ったカスタム

製品開発手法

- 長期安定供給

- 柔軟な設計対応

- 産業系を中心とした多くの採用実績

RTL設計

論理合成

物理シミュレーション

レイアウト検証

サインオフ

マクロセル搭載

ベースパリック製造

配線行程

サンプル完成

サンプル評価

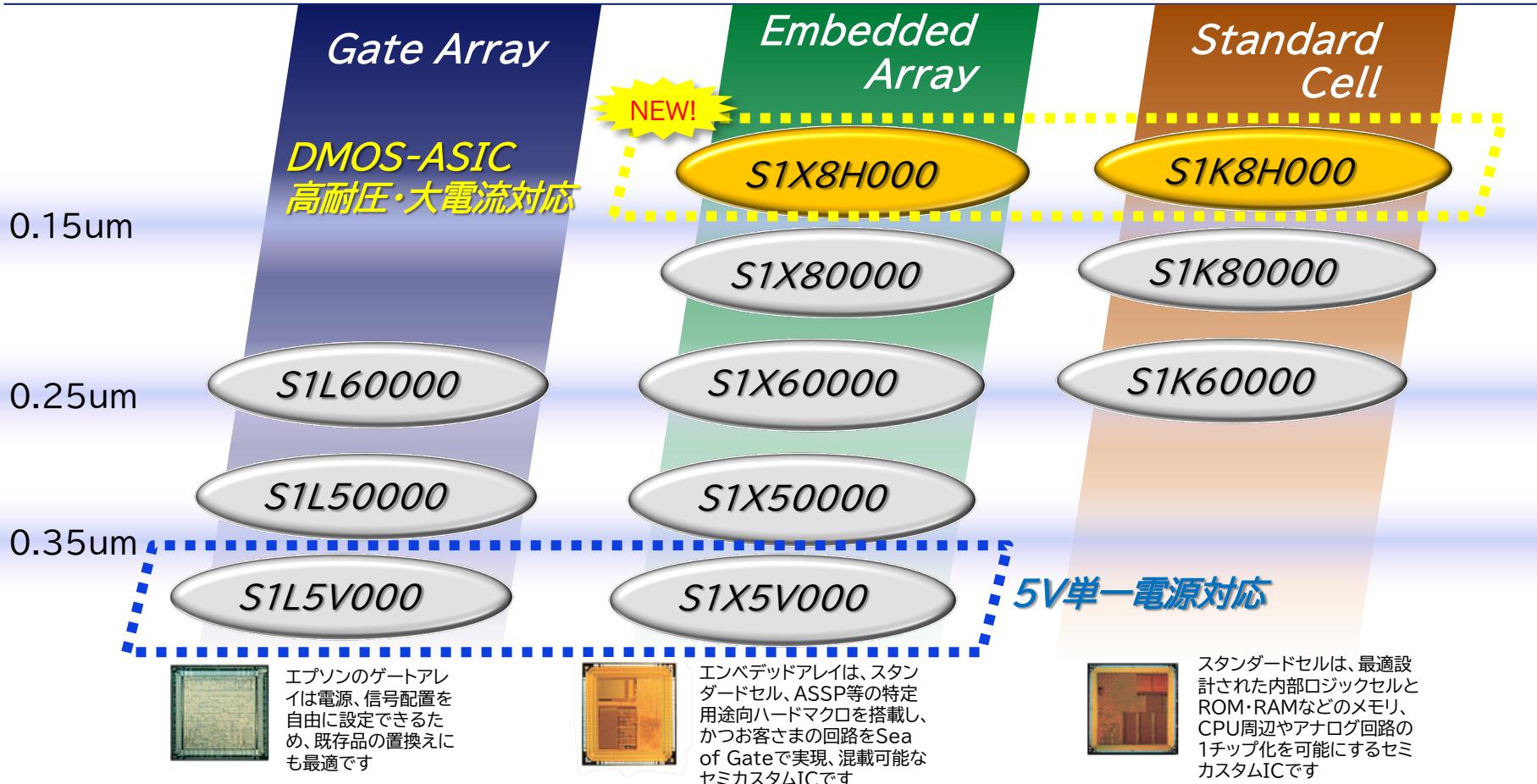

# ASICシリーズラインアップ

# 提供する価値

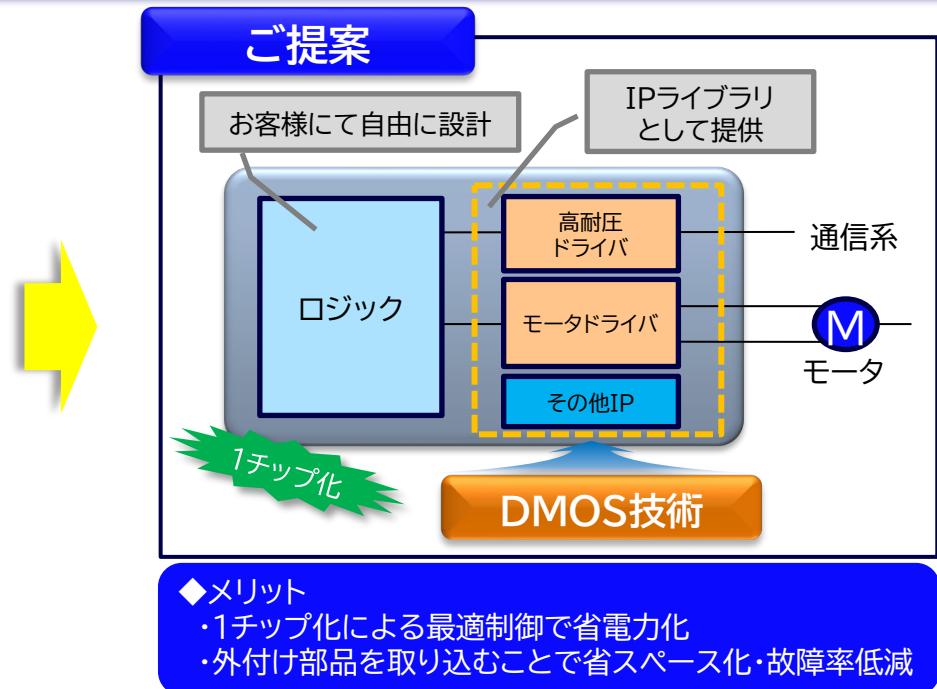

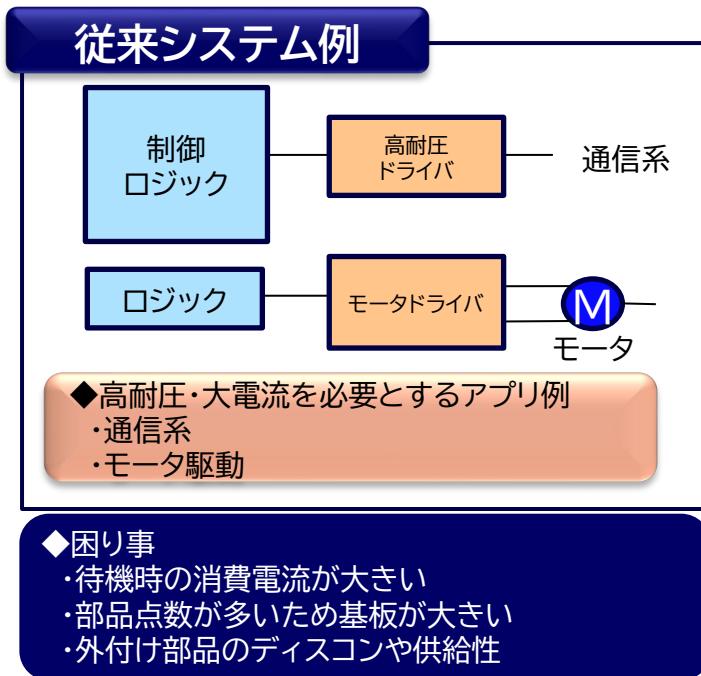

- ・従来、外付け部品や専用ICで実現していた、高耐圧・大電流部分を1チップ化することで、部品点数削減・省電力化・故障率低減を実現します

- ・ASIC開発手法を用いて、用意されたIPを組み合わせることにより、開発費の削減が可能です

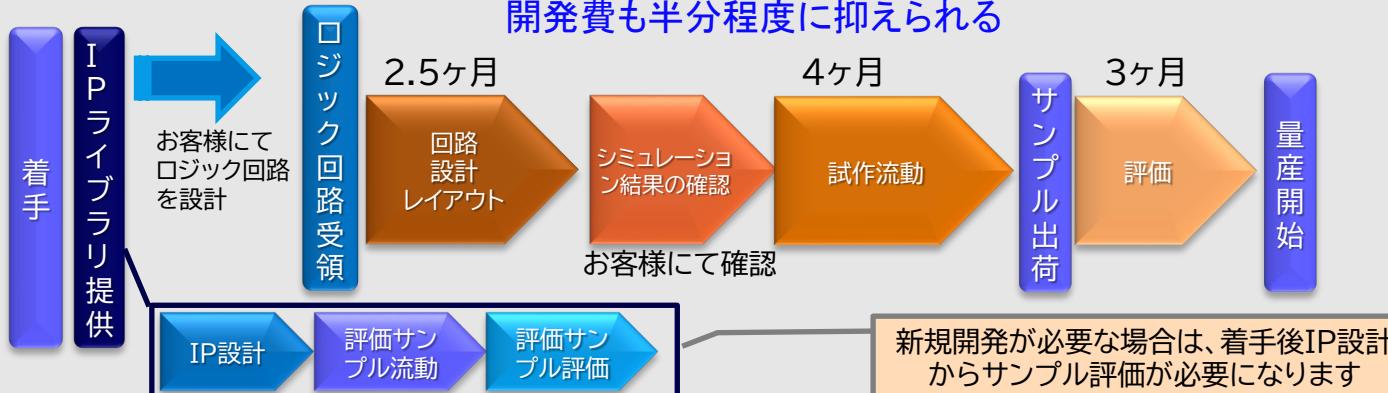

# 製品開発のイメージ

- 下記はエンベデッドアレイによる開発を前提とした、基本的な日程イメージです

- お客様のご要望に合わせて都度見積させて頂きますのでご相談ください

<フルカスタム日程イメージ>：新規IPの修正が必要になり、約2年の開発期間が必要

<DMOS-ASIC日程イメージ>：開発済みIPを搭載することで、フルカスタムの半分の期間で量産が可能になり

開発費も半分程度に抑えられる

IPは順次開発していきます。ラインアップにないIPについてはご相談ください

| 開発中                   | 検討中                 |

|-----------------------|---------------------|

| POR                   | H-Bridge            |

| TSD<br>(サーマルシャットダウン)  | EEPROM              |

| LDO                   | SRAM                |

| 過電圧保護                 | SW-REG              |

| UVLO<br>(電圧下限検知)      | 電流検知                |

| HV PMOS ドライバ<br>(40V) | AMP                 |

| HV NMOS ドライバ<br>(60V) | 内蔵発振回路<br>(4, 8MHz) |

|                       | モータ制御 (FOC)         |

|                       | コンパレータ              |

|                       | DAC                 |

|                       | Pre-Driver          |

|                       | Flash               |

|                       | FAMOS               |

|                       | IO-Link             |

# DMOS-ASICの仕様

| 項目      | 仕様                                                                                  |

|---------|-------------------------------------------------------------------------------------|

| 電源電圧    | I/O : $5.0V \pm 0.5V$<br>$3.3V \pm 0.3V$<br>$3.0V \pm 0.3V$<br>内部: $1.8V \pm 0.15V$ |

| DMOS耐圧  | PMOS 40V<br>NMOS 60V                                                                |

| DMOS電流  | 2A (参考値)                                                                            |

| 温度範囲    | Ta=-40~105°C(Tjmax=150°C)                                                           |

| プロセス    | 0.15um CMOS+不揮発性メモリ+DMOS                                                            |

| 内部ゲート遅延 | 41.5ps/1.8V (2入力NAND typ)                                                           |

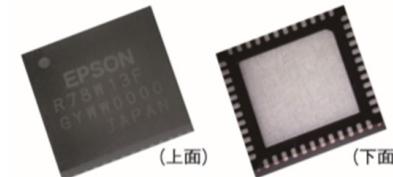

| パッケージ   | QFP、QFN                                                                             |

| I/Oセル   | 入力:CMOS、CMOSシュミット (プルアップ、プルダウン抵抗内蔵可)<br>出力:IOL=2/4/8/12mA @3.3V<br>その他:双方向、オープンドレイン |

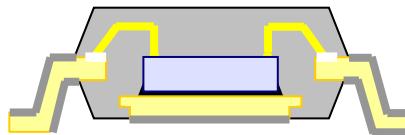

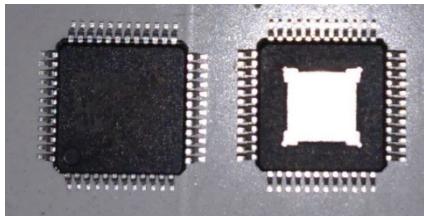

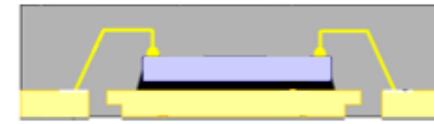

# 放熱板付パッケージラインアップ

QFP (Quad Flat Package)

|           | Pkg Size (mm) | Lead Count | Pitch (mm) |

|-----------|---------------|------------|------------|

| TQFP12 EP | 7x7           | 32/48      | 0.8/0.5    |

| TQFP13 EP | 10x10         | 64         | 0.5        |

| TQFP14 EP | 12x12         | 80         | 0.5        |

| TQFP15 EP | 14x14         | 100/128    | 0.5/0.4    |

| QFP12 EP  | 7x7           | 48         | 0.5        |

| QFP13 EP  | 10x10         | 64         | 0.5        |

| QFP15 EP  | 14x14         | 100/128    | 0.5/0.4    |

QFN (Quad Flat Non-leaded Package)

|       | Pkg Size (mm) | Lead Count | Pitch (mm)   |

|-------|---------------|------------|--------------|

| SQFN4 | 4x4           | 16/24/32   | 0.65/0.5/0.4 |

| SQFN5 | 5x5           | 32         | 0.5          |

| SQFN6 | 6x6           | 36         | 0.5          |

| SQFN7 | 7x7           | 48         | 0.5          |

| SQFN9 | 9x9           | 64/80      | 0.5/0.4      |

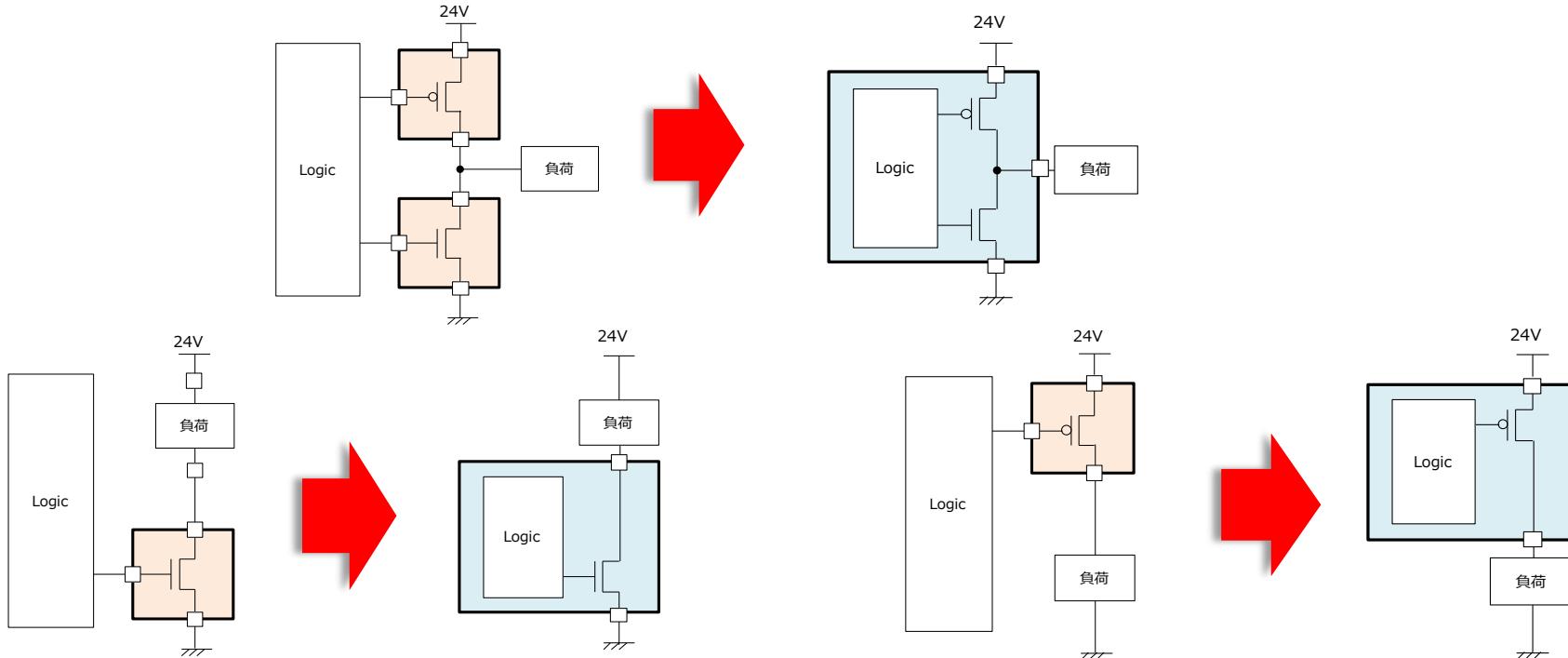

# DMOS-ASIC システム構成の例

# 外付けディスクリートを取り込む例①

## PMOS、NMOSドライバを取り込むケース

ロジックにてPMOSとNMOSを個別に制御可能

# 外付けディスクリートを取り込む例②

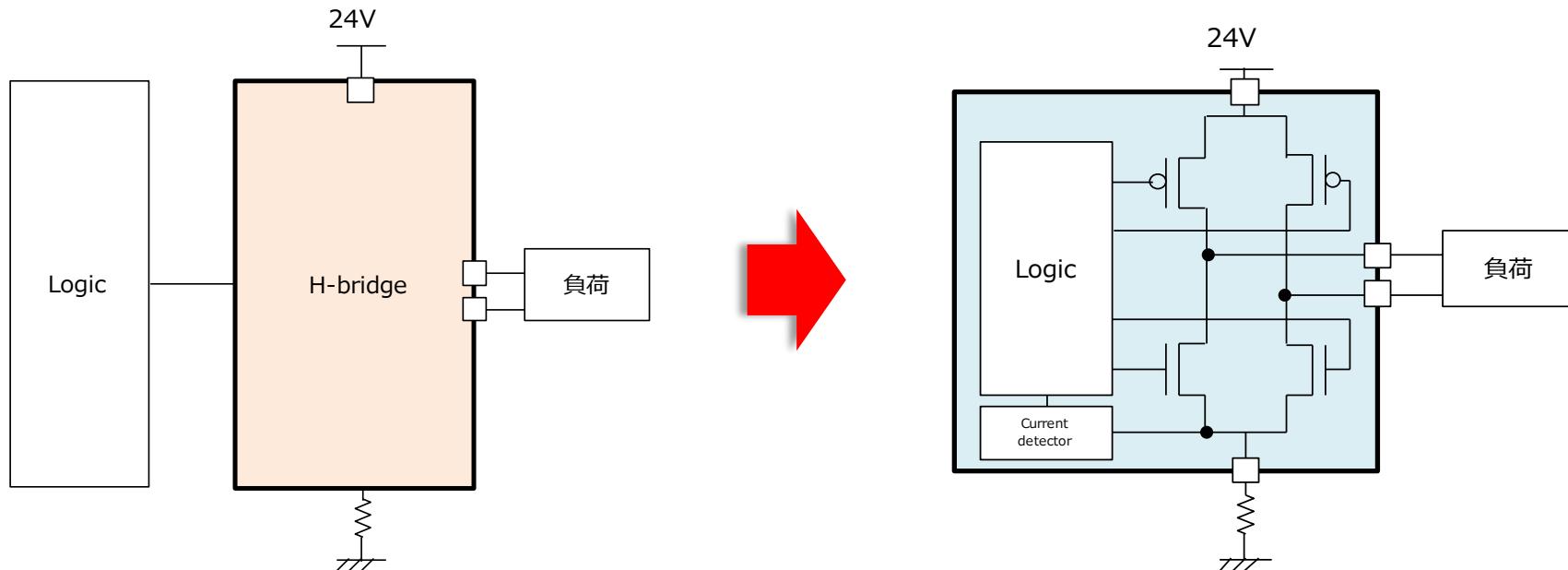

## Hブリッジを取り込むケース

HVインバーターを2つ組み合わせてHブリッジとして使用可能

電流検知回路により電流値をモニターしHブリッジをコントロール可能

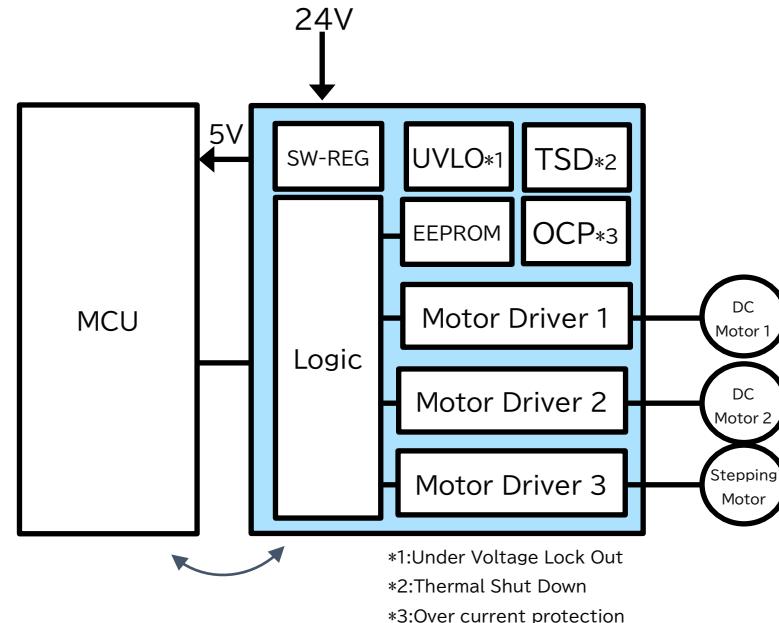

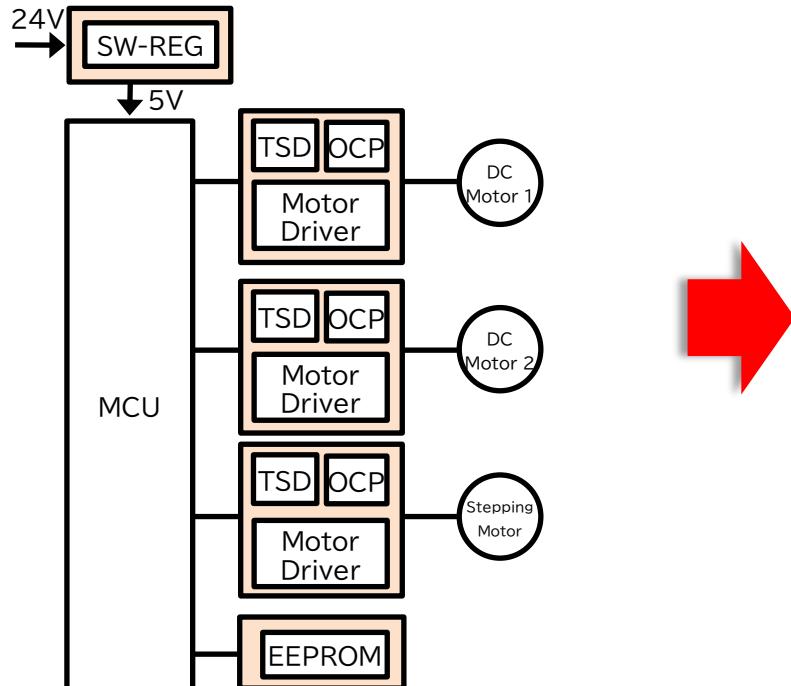

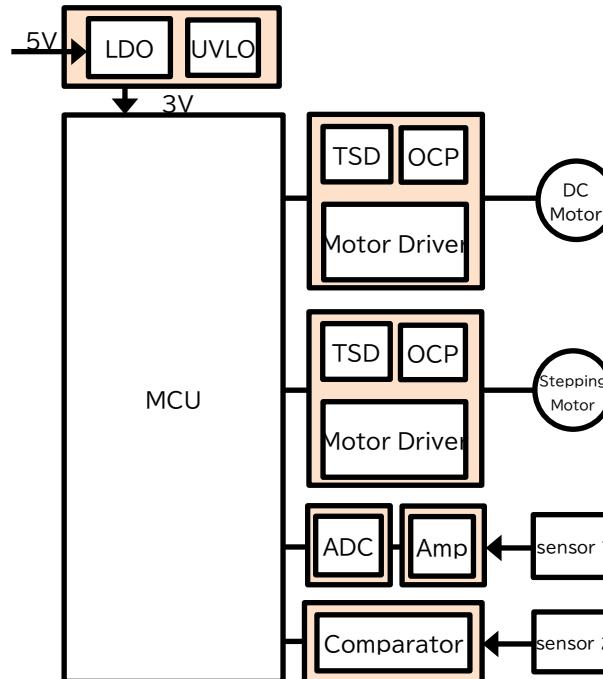

# 小型化を必要とする製品構成の例

## <課題>

- ✓ 基板面積大

- ✓ MCUの制御ピンが多い

- ✓ MCUが誤動作した時の安全性が担保できない

- ✓ 小型化

- ✓ MCUの制御ピン削減

- ✓ 相互監視による安全性の強化

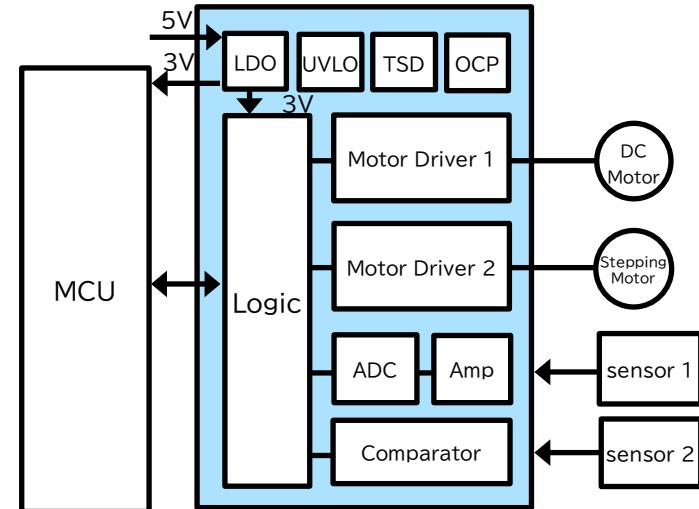

# バッテリー駆動を有する製品構成の例

## <課題>

- ✓ 基板面積大

- ✓ 省エネ基準を満たせない、バッテリーの駆動時間を延ばしたい

- ✓ モータドライバにAFEを取り込むことで小型化、トータルコスト削減

- ✓ 待機時の低パワーモードにより、バッテリー駆動時間向上

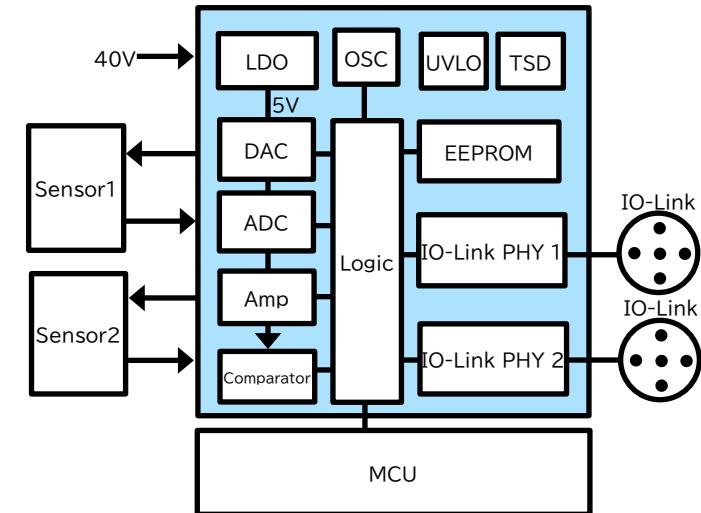

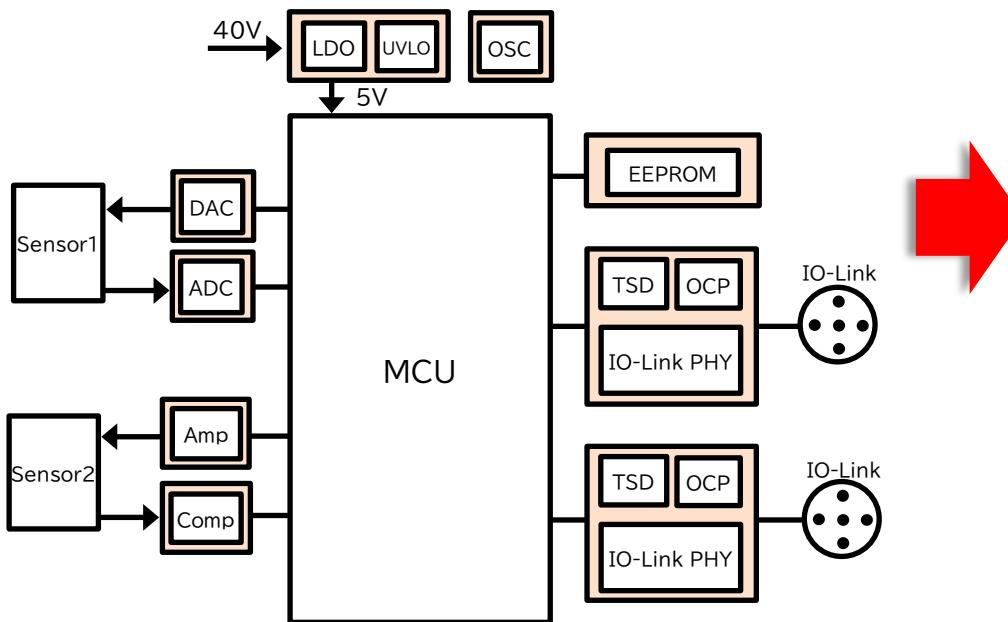

# IO-Linkシステム構成例

## <課題>

- ✓ 基板面積大

- ✓ MCUの制御ピンが多い

- ✓ 小型化

- ✓ MCUの制御ピン削減

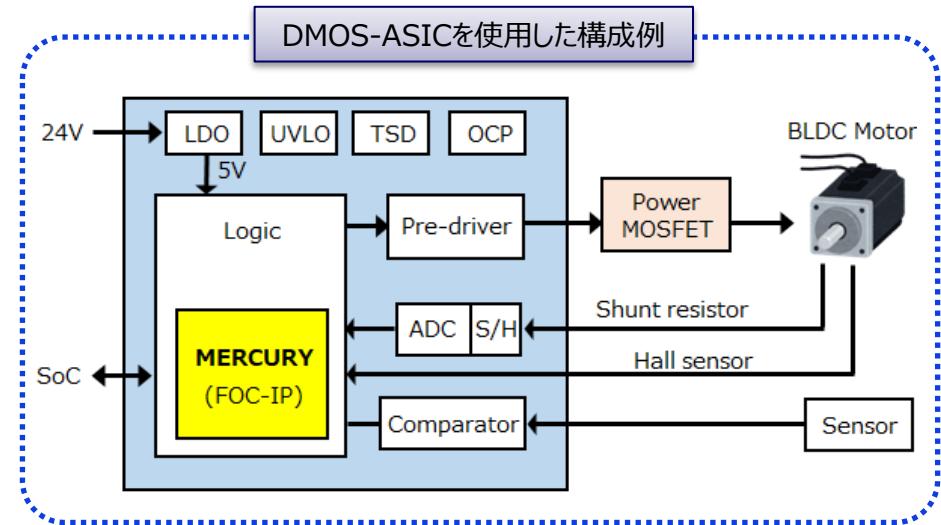

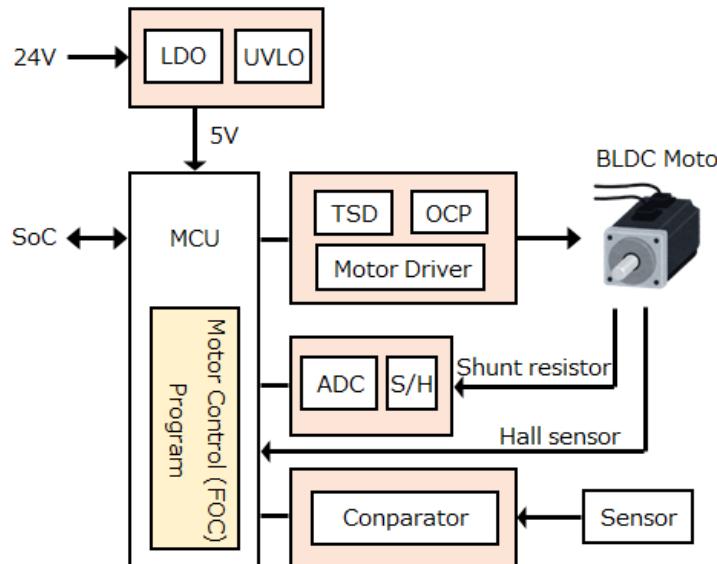

# BLDCモータ制御システム構成例

## <課題>

- ✓ モータ制御用のマイコンが必要

- ✓ プログラム開発が必要

- ✓ モータ制御のためのマイコンが不要

- ✓ 高効率なモータ制御(FOC)をソフトウェア開発不要で実現可能

エプソン半導体ホームページ

# エプソン半導体ホームページご紹介

EPSON

EXCEED YOUR VISION

<https://www.epson.jp/prod/semicon/>

製品ラインアップ

ドキュメントダウンロード

マクロセル

電源インターフェース

パッケージ

開発フロー

ゲートアレイ便利ツール

- マスター選択ツール

- G/A 速度の目安表示ツール

- G/A 消費電力見積りツール

- G/A RAM ライブラリ作成ツール

カスタムICにつきましても対応しております

カスタムICのご要望がございましたらお気軽にご連絡ください

**EPSON**

EXCEED YOUR VISION