# QFN 実装マニュアル

本マニュアルは、当社製品をご利用するにあたっての注意事項を記したものですが、お客様の使用方法に対する保証をするものではありません。 実装条件につきましては、お客様にて十分な評価を行ったうえ、設定いただきますようお願いいたします。

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、および、全部を当社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

2. 当社製品のご購入、および、ご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される最新情報を常にご注意ください。

3. 本資料によって、第三者、または、当社の知的財産権、および、その他の権利の実施権の許諾を行うものではありません。

4. 当社製品をご使用の際は、十分な実装評価確認を行い、必ず、保証範囲内でご使用ください。当社の保証範囲を超えてご使用された場合の故障、誤動作の発生、人身事故、火災事故、社会的損害の発生につきましては、当社は、一切その責任を負いかねます。

5. 当社は、正確さを期すために慎重に本資料を作成しておりますが、本資料に掲載されている情報に誤りがないことを保証するものではありません。万一、本資料に掲載されている情報の誤りによってお客様に損害が生じた場合においても、当社は一切その責任を負いかねます。

また、本資料に掲載されている内容は、保証するものではなく、あくまでも参考情報となります。

6. 本資料に掲載されている当社製品、および、当該技術を国内外の法令および規則により、製造・使用・販売が禁止されている機器・システムに使用することはできません。また、弊社製品、および、当該技術を大量破壊兵器の開発などの目的、軍事利用の目的、その他軍事用途に使用しないでください。

当社製品、または、当該技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、係る法令の定めるところにより必要な手続きを行ってください。

7. 本資料に掲載されている諸条件に反して当社製品が使用され、その使用から損害が発生した場合、当社は一切その責任を負いかねます。

8. 当社製品の環境適合性等の詳細につきましては、当社 HP を確認ください。

9. 製品取扱い時、実装、および、お客様の工程内での外的要因（静電気破壊 ESD、過電圧／過電流 EOS、熱的ストレス、機械的ストレス、環境雰囲気）により、故障や特性変動が生じた場合、当社は、一切その責任を負いかねます。

また、防湿包装を必要とする製品は、保存期間、開封後の放置時間など、個々の仕様書の条件をお守りください。

©SEIKO EPSON CORPORATION 2018, All rights reserved.

# 目 次

|                                  |    |

|----------------------------------|----|

| 1. QFN の概要                       | 5  |

| 1.1 QFN の構造                      | 5  |

| 1.2 外観写真                         | 5  |

| 1.3 QFN パッケージラインナップ              | 6  |

| 1.4 ウェッタブル QFN (オプション)           | 7  |

| 2. QFN の実装技術                     | 8  |

| 2.1 一般的なはんだ実装技術                  | 8  |

| 2.2 実装フロー (リフロー方式)               | 9  |

| 3. 実装基板の設計                       | 10 |

| 3.1 実装基板設計の注意点                   | 10 |

| 3.2 実装基板ランド構造 NSMD 方式／SMD 方式     | 10 |

| 3.3 実装基板ランドデザイン                  | 11 |

| 3.4 Exposed Die Pad のランド設計       | 12 |

| 3.5 実装基板ランドの表面処理                 | 13 |

| 3.6 実装基板の反り                      | 13 |

| 4. はんだ印刷                         | 14 |

| 4.1 はんだペースト                      | 14 |

| 4.2 印刷マスクの設計                     | 15 |

| 4.2.1 Exposed Die Pad 部の印刷マスクの設計 | 16 |

| 4.3 はんだペースト供給                    | 17 |

| 4.4 スキージ                         | 17 |

| 4.4.1 ウレタンスキージ                   | 17 |

| 4.4.2 メタルスキージ                    | 17 |

| 4.4.3 プラスチックスキージ                 | 17 |

| 4.5 はんだ印刷                        | 18 |

| 5. 部品搭載                          | 19 |

| 5.1 部品搭載の注意事項                    | 19 |

| 5.1.1 キャリアテープ、トレイからの取出し          | 19 |

| 5.1.2 実装基板への部品搭載                 | 19 |

| 6. リフロー                          | 20 |

| 6.1 リフロー装置                       | 20 |

| 6.1.1 予備加熱 (プリヒート) ゾーン           | 20 |

| 6.1.2 本加熱ゾーン                     | 20 |

| 6.1.3 冷却ゾーン                      | 20 |

| 6.2 リフロー条件                       | 21 |

| 6.3 本製品のはんだ付けにおける注意事項            | 22 |

| 7. 洗浄                            | 23 |

| 7.1 QFN の洗浄                      | 23 |

|                      |    |

|----------------------|----|

| 7.2 一般的な基板洗浄方法 ..... | 23 |

| 7.2.1 実装基板の洗浄方法..... | 23 |

| 7.2.2 標準的な洗浄フロー..... | 23 |

| 7.2.3 水洗浄.....       | 23 |

| 7.2.4 無洗浄.....       | 23 |

| 7.3 その他 .....        | 23 |

| 8. リワーク .....        | 24 |

| 9. 半導体の取扱注意事項.....   | 25 |

| 9.1 はじめに .....       | 25 |

| 9.2 保管時 .....        | 25 |

| 9.3 ご使用時 .....       | 25 |

| 改定履歴 .....           | 27 |

## 1. QFN の概要

QFN(Quad Flat Non-leaded package)は、パッケージ4辺にそれぞれ1列の外部接続端子を有しているペリフェラルパッケージ(Peripheral package)の一つです。このQFNは、同じペリフェラルパッケージのQFP(Quad Flat Package)と異なりパッケージ外側に接続端子が突出していない構造を特徴としているため、部品搭載エリアがQFPと比較して小さくなり、パッケージ厚も薄いことからも高密度実装に適した小型パッケージとなります。

当社のQFNは、一括プラスチック樹脂封止をしたリードフレームをダイシング技術で切り分けパッケージ化したSQFN(Saw singulation QFN)をラインナップしています。

また、実装後外観検査の視認性向上や、よりいっそうの高信頼性を求める場合は、オプションになりますが1.4項のウェッタブル(Wettable Flank)構造のQFNタイプも準備していますのでご相談ください。

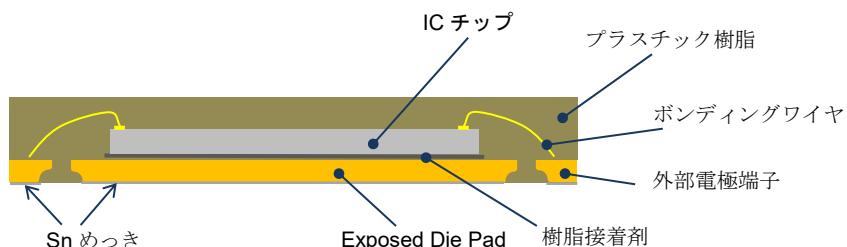

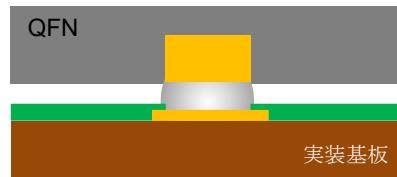

### 1.1 QFN の構造

QFNは、銅リードフレームのダイパッド(Die Pad)の一方の面が外部にそのまま露出する構造となります。この露出部分はExposed Die Pad(Ex-DP)と呼ばれ、ICチップの基板面電位がEx-DP介して外部に露出される構造となります。

このEx-DPを実装基板とはんだ付けすることにより、ICチップの電位安定性、パッケージの放熱特性、取り付け強度特性を高めることができます。

QFNのEx-DPを実装基板と接続する場合は、実装基板ランド電位への配慮が必要です。また、非接続の場合にも、Ex-DP下の実装基板配線に注意が必要となりますので、3.4項「Exposed Die Padのランド設計」をご参考ください。

図 1.1 QFN パッケージ構造図

### 1.2 外観写真

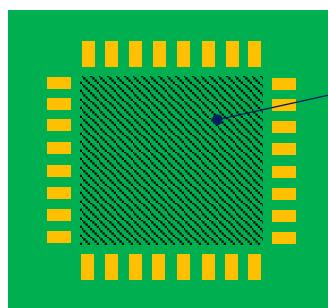

SQFN6-36

図 1.2 パッケージ表面

SQFN5-32

図 1.3 パッケージ裏面

## 1. QFN の概要

---

### 1.3 QFN パッケージラインナップ

当社 QFN の標準的なパッケージラインナップです。詳細な仕様、寸法、および、パッケージ図面につきましては、当社 HP、または、納入仕様書、パッケージ外形図をご確認ください。

表 1.1 QFN パッケージラインナップ<sup>注1</sup>

| QFN タイプ | ボディサイズ     | 端子数   | 端子ピッチ <sup>注2</sup> | 名称       |

|---------|------------|-------|---------------------|----------|

| SQFN4   | 4mm□ t=1mm | 16pin | 0.65mm              | SQFN4-16 |

|         |            | 24pin | 0.50mm              | SQFN4-24 |

|         |            | 32pin | 0.40mm              | SQFN4-32 |

| SQFN5   | 5mm□ t=1mm | 32pin | 0.50mm              | SQFN5-32 |

| SQFN6   | 6mm□ t=1mm | 36pin | 0.50mm              | SQFN6-36 |

| SQFN7   | 7mm□ t=1mm | 48pin | 0.50mm              | SQFN7-48 |

| SQFN9   | 9mm□ t=1mm | 64pin | 0.50mm              | SQFN9-64 |

|         |            | 76pin | 0.40mm              | SQFN9-76 |

|         |            | 80pin | 0.40mm              | SQFN9-80 |

注 1: ウェッタブル構造のカスタム対応をしている QFN もございます。必要時は、当社までお尋ねください。

注 2 : 端子間の繰り返しピッチとなります。

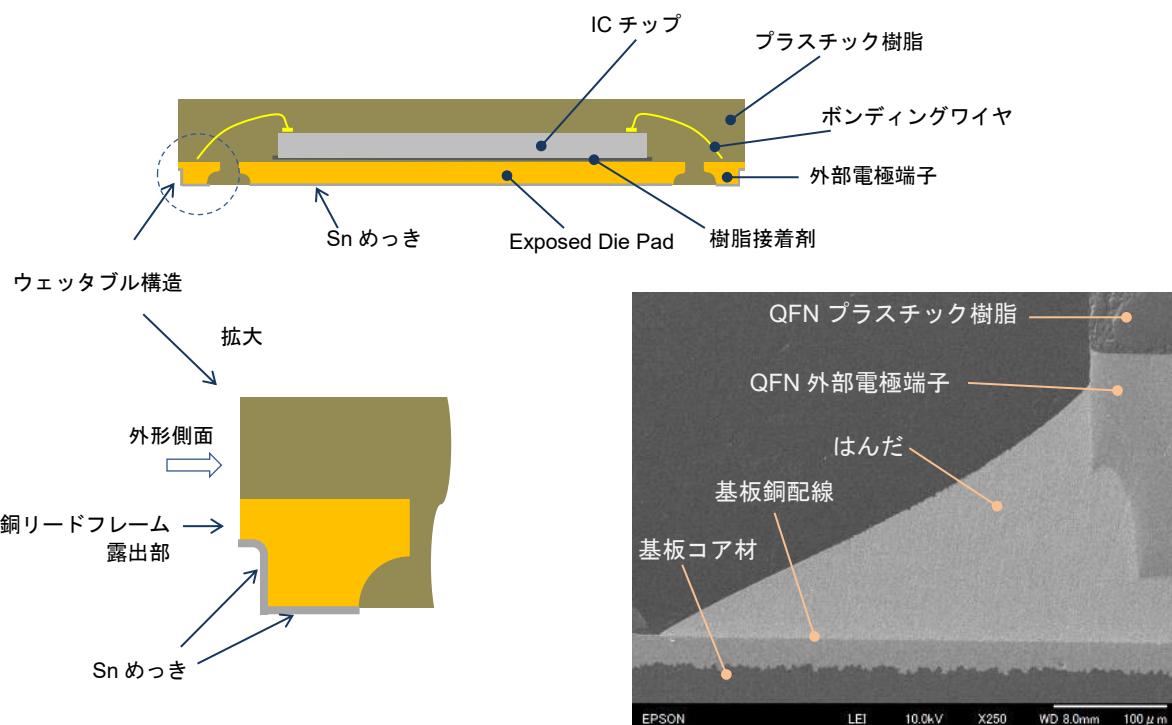

## 1.4 ウエッタブル QFN (オプション)

当社の QFN は、パッケージ個片化のためにソーダイシング(Saw Dicing)が行われるため、パッケージ側面のリード部は、銅(Cu)剥き出しの構造となります。このため、保管環境や実装基板はんだ付け時の条件によって、この側面部の銅酸化被膜に阻害され、パッケージ側面電極端子にはんだフィレットが形成されない場合があります。この影響を受け難くするため、当社では、オプション仕様として Wettable Flank 構造 QFN (ウェッタブル QFN) のラインナップを揃えています。

当社のウェッタブル QFN は、パッケージ側面電極端子部にスズ(Sn)めっき被膜を施しており、実装時のはんだフィレット形成を容易にし、下記のメリットを得ることが可能となります。<sup>注1</sup>

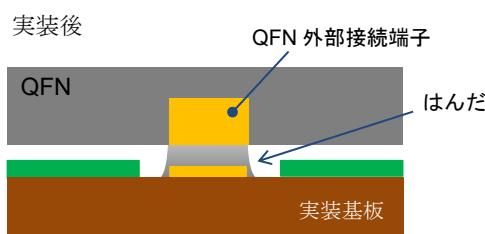

図 1.4 ウエッタブル構造説明図

図 1.5 はんだ実装後断面 SEM 写真

- (1) パッケージ側面のはんだ濡れを促し、底面、側面での立体的なはんだ接続構造を得ることが容易となります。

- (2) 実装後の外観検査において、側面よりのはんだフィレットの観察が容易となり、自動外観検査装置の適用が容易となります。

<sup>注1</sup> ウエッタブル QFN によって得られるはんだフィレットの形成は、保管条件、実装条件により完全な形状を得られない場合があるため、これを保証するものではありません。お客様で十分な実装評価を行い、適切な条件の設定を行ってください。

### 2. QFN の実装技術

#### 2.1 一般的なはんだ実装技術

表面実装型の部品：SMD（Surface Mount Device）の QFN の実装方式としては、一般的にリフロー方式が用いられます。リフロー方式は、実装基板上にはんだペースト（はんだ粒子にフラックス等を加えて適切な粘度にしたもの）を印刷し、その上に部品を搭載したのち、加熱を行いはんだ溶融し部品を基板に実装する方式です。この実装技術は、SMT（Surface mount technology：表面実装）と呼ばれ、SMD に広く用いられます。加熱方法には、赤外線式、熱風式（対流式）、赤外線熱風併用式、および、ホットプレート式などがあります。

リフロー方式の場合、部品接合の位置精度は部品搭載時の精度ではなく、はんだ溶融時の表面張力によるセルフアライメント<sup>注1</sup>機能で決定されます。したがいまして、実装基板の設計には、このセルフアライメント機能の特性に配慮したラント設計、実装基板設計が必要となります。

また QFN は、熱源が赤外線加熱等の直射加熱のみの場合、一部実装接合面がパッケージモールド面で熱が遮られるため、熱風を利用（併用）したリフロー加熱方式を採用することをお奨めします。特に大きなサイズのパッケージでは注意が必要となります。

**注 1 セルフアライメント機能とは**、実装基板に印刷されたはんだペーストに対して若干の位置ズレが発生し搭載された場合、リフロー時のはんだ溶融の表面張力で自動的に正しい搭載位置に補正される現象を言います。セルフアライメント機能は、はんだ表面張力とパッケージ自重の相対関係にあるため、比較的軽量のパッケージで有効となります。なお、搭載部品と実装基板の接続する電極端子が離れた場合や大きくズレが生じた場合は、セルフアライメント効果は期待できません。

## 2.2 実装フロー（リフロー方式）

QFN の実装方式として最も多く用いられるリフロー方式の一般的な手順を下表に示します。

表 2.2 リフロー方式工程フロー

|     | 工程                                                                          | 原材料                                      | 装置、治具、補材、他                               |

|-----|-----------------------------------------------------------------------------|------------------------------------------|------------------------------------------|

| 1   | 印刷工程 [4.5 項]<br>（はんだ印刷検査）                                                   | 実装基板 [3 項]<br>はんだペースト [4.1 項]<br>[4.3 項] | 印刷装置<br>・印刷マスク [4.2 項]<br>・スキージ [4.4 項]  |

| (2) |                                                                             | ——                                       | 外観検査機器<br>自動検査装置 (SPI)                   |

| 3   | 部品搭載工程 [5 項]                                                                | 実装部品 QFN<br>・チップ部品等<br>・コネクタ等            | 部品搭載装置                                   |

| 4   | リフロー工程 [6 項]<br>・予備加熱ゾーン [6.1.1 項]<br>・本加熱ゾーン [6.1.2 項]<br>・冷却ゾーン [6.1.3 項] | 部品搭載済み実装基板                               | リフロー装置<br>・リフロー条件 [6.2 項]<br>・窒素 (N2) ガス |

| 5   | 洗浄 [7 項]                                                                    | リフロー済み実装基板                               | 洗浄装置<br>・洗浄剤                             |

| (6) | （機能検査）                                                                      | ——                                       | インサーキットテスター                              |

| (7) | （外観検査）                                                                      | ——                                       | 外観検査機器<br>自動検査装置 (AVI)                   |

注 各工程の詳細につきましては、解説ページをご参照ください。

(2),(6),(7)は、検査確認工程のため、説明は省略します。

### 3. 実装基板の設計

## 3. 実装基板の設計

### 3.1 実装基板設計の注意点

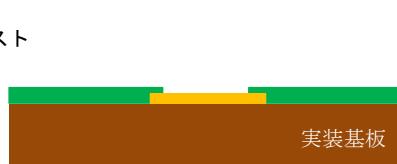

電子部品を搭載する実装基板ランドには、その構造から NSMD(Non Solder Mask Defined)と SMD (Solder Mask Defined) の 2 種類のタイプがあります。

一般的に、NSMD 方式はランド側面にもはんだを接合させることができるために、接合強度が向上すると言われています。しかし、はんだペーストを印刷するときの印刷条件やマスクの仕様（開口サイズ、厚みなど）によっては、SMD 方式の印刷性が優れていることがありますので、お客様での使用用途に応じて NSMD 方式と SMD 方式の選択を行ってください。

### 3.2 実装基板ランド構造 NSMD 方式／SMD 方式

NSMD 方式は、実装基板上のランドと間隔を空けてソルダーレジストを配置する構造で、SMD 方式は、ランドの一部にソルダーレジストをオーバーラップさせる構造となります。

図 3.1 NSMD 断面構造図

図 3.2 SMD 断面構造図

表 3.1 【参考】 NSMD 方式と SMD 方式のはんだ強度の相対比較

|                               |             |

|-------------------------------|-------------|

| ランドと実装基板の接合面の強度 <sup>注1</sup> | NSMD <= SMD |

| ランドとはんだ接合面の接合強度 <sup>注2</sup> | NSMD >= SMD |

注 1 ランドがソルダーレジストで覆われているため、ランドパターンの接合強度が高くなります。

注 2 ランドを覆うようにはんだが包み込むため、搭載部品との接合強度が上がります。

### 3.3 実装基板ランドデザイン

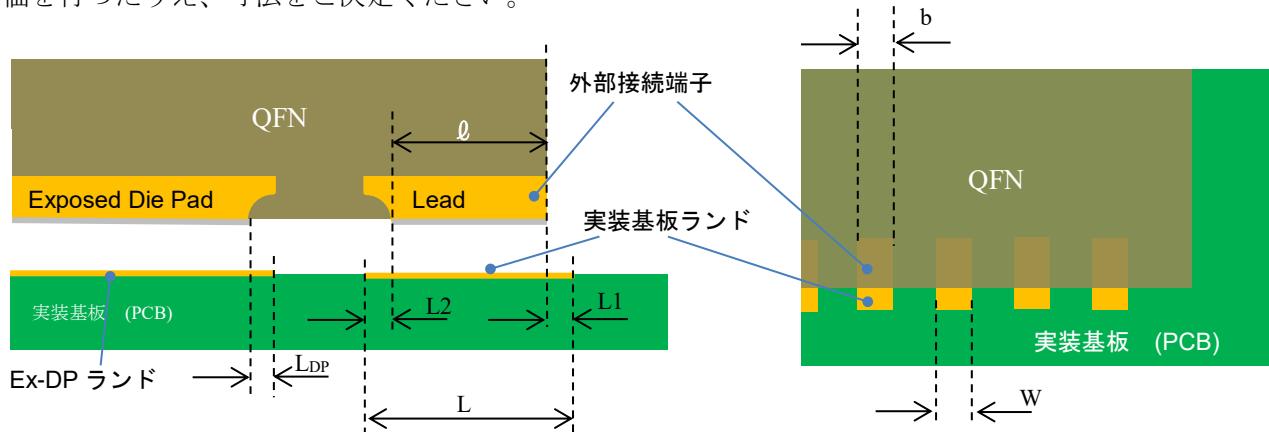

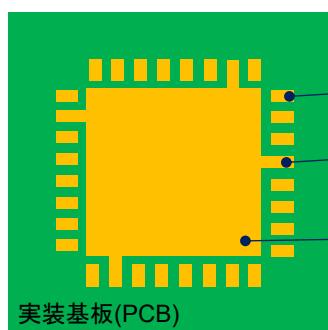

実装基板へのQFN取り付けランドデザインは、下図に提示のQFNのランドパターンを参考に設計してください。(JEITA ED-4702C 準拠)

しかしながら、当社QFNは、Exposed Die Pad(Ex-DP)を有しているため、このEx-DPと実装基板電極ランド部とのはんだブリッジ、および、電気的短絡(含むマイグレーション)を防止するために、L2寸法、および、 $L_{DP}$ 寸法は0.00mmを推奨します。

これらの問題は、はんだペーストの量、印刷エリアにも影響を受けるため、お客様にて総合的な実装評価を行ったうえ、寸法をご決定ください。

図 3.3 実装基板ランドデザイン

表 3.2 実装基板ランドデザイン

| 記号       | 項目                 | 参考寸法 <sup>注1</sup> |

|----------|--------------------|--------------------|

| $\ell$   | パッケージ外部電極端子長(リード長) | パッケージ外形図参照         |

| $b$      | パッケージ外部電極端子幅(リード幅) | パッケージ外形図参照         |

| $L$      | 実装基板ランド長           | $\ell+L_1+L_2$     |

| $L_1$    | ——                 | $0.30\pm0.05$      |

| $L_2$    | ——                 | 0.00               |

| $W$      | 実装基板ランド幅           | $b\pm0.05$         |

| $L_{DP}$ | ——                 | 0.00               |

注 1 寸法は、参考値であり保証するものではありません。

### 3. 実装基板の設計

#### 3.4 Exposed Die Pad のランド設計

当社 QFN は、内蔵された IC チップの基板電位が Exposed Die Pad (Ex-DP) を介してパッケージ外部に露出する構造となっています。このため、実装基板の Ex-DP ランド部の回路基板設計によっては、本来の製品機能を果たさない場合や製品仕様を満足しないことが発生します。したがいまして、当該製品の Ex-DP の電位仕様を確認していただいたのち、適切な Ex-DP のランド設計を行ってください。

なお、Ex-DP の電位仕様につきましては、テクニカルマニュアル、納入仕様書等をご確認いただくか、当社営業までお尋ねください。

適正な設計による実装基板への Ex-DP 接続は、IC チップの電位安定やノイズ(EMI/EMC)の軽減、および、放熱特性の改善が期待されます。

表 3.3 Exposed Die Pad ランド設計注意事項

| Exposed Die Pad 実装基板接続                     | 注意事項                                                                                                                       |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 実装基板に、<br>はんだ付けを行う場合<br><br>図 3.4、図 3.5 参照 | IC チップの基板電位(Ex-DP)と同電位になるように、実装基板設計を行ってください。<br>もしくは、電気的オープンになるよう設計してください。<br>異電位接続となった場合は、電気的ショート、リーク電流等の不具合が発生することがあります。 |

| 実装基板に、<br>はんだ付けを行わない場合<br><br>図 3.6 参照     | QFN の Ex-DP の下には、電気的配線を行わない設計にしてください。<br>不測の異物挟み込みや、長期の使用環境による影響等で、稀に、実装基板ランドとのリーク電流の発生やマイグレーションを引き起こすことがあります。             |

図 3.4 Ex-DP 電気接続ランド設計例

図 3.5 Ex-DP オープンランド設計例

図 3.6 Ex-DP をはんだ付けしない場合のランドデザイン

#### 3.5 実装基板ランドの表面処理

実装基板をそのまま大気雰囲気中に放置すると、ランド表面が酸化してしまい部品実装時はなんだ濡れ性に影響をおよぼす可能性があります。これを防ぐため、実装基板のランドを保護する表面処理として、保護被膜形成やめっき被膜形成を施すことが良いとされています。一般的には、OSP(Organic Solder-ability Preservatives)処理や Ni/Au めっき処理が用いられていますので、これらの採用をお奨めします。

#### 3.6 実装基板の反り

リフロー時、および、リフロー後の実装基板の反りが大きい場合、部品と実装基板とのはんだ接続が得られなかつたり、接合信頼性に悪影響を与えたりすることがあります。実装基板設計の際には、反りを抑制する実装基板材料の選定、回路設計の配慮を行ってください。

また、実装加熱中や基板使用時に応力が集中しやすい部分、例えば、スイッチやコネクタ部の近傍や裏面、ヒンジ等摺動部周辺に、QFN をはじめとする SMD 部品の配置ができるだけ避けた実装基板設計を行うことをお奨めします。

## 4. はんだ印刷

### 4. はんだ印刷

#### 4.1 はんだペースト

はんだペーストは、はんだ（合金）粒子とフラックス、界面活性剤、および、チキソ剤等で構成されています。はんだペーストには、多くの種類が存在するため、その種類毎にはんだペースト仕様に合わせたりフロー温度プロファイルを決定する必要があります。

はんだペーストに含まれるはんだ粒子の組成と粒度は、使用用途、および、実装ピッチ等によって決定され、はんだ粒子の粒度は分布が狭いものが、はんだ接合安定性に有利となります。

はんだ粒子の粒度が小さい場合は、保管環境、はんだ印刷、リフロー時の表面酸化の影響を受け易く、実装条件によっては、はんだ表面の酸化影響によるはんだ濡れ性が低下する不具合が発生する場合がありますので、はんだ粒子の粒度選定には注意が必要となります。

なお、はんだペーストの選定は、上記を参考にしていただき、はんだ濡れ性、金属間化合物の生成状態等、十分な実装性確認を行ったうえ、ご判断ください。

表4.1 【参考】 はんだペースト構成

| 構成              | 役割                                                          |

|-----------------|-------------------------------------------------------------|

| はんだ粒子           | はんだ粒子が溶融し濡れることで、QFN電極端子の電気的接続、機械的接合強度を得ます。                  |

| フラックス剤<br>(活性剤) | それぞれの端子表面の酸化膜を還元し、また、実装加熱時のはんだ表面の再酸化を防ぐと共に、溶融したはんだ流動性を促します。 |

| 表面活性剤           | フラックス成分やはんだペースト有効成分を行き渡らるために微量用いられます。                       |

| チキソ剤            | はんだ粒子のバインダーとして機能し、印刷後の形状、および、搭載実装部品を保持するために用いられます。          |

表4.2 【参考】 はんだ溶融温度

| はんだ組成               | 溶融温度(℃) |                     |     |

|---------------------|---------|---------------------|-----|

|                     | 固相線     | ピーク温度 <sup>注1</sup> | 液相線 |

| Sn - 3.5Ag - 0.75Cu | 218     | 219                 | 219 |

| Sn - 3.0Ag - 0.5Cu  | 217     | 219                 | 220 |

| Sn - 1.0Ag - 0.5Cu  | 217     | 219                 | 227 |

注1 ピーク温度とは、DSC曲線での最大吸熱量点の温度

## 4.2 印刷マスクの設計

印刷マスクの設計は、実装歩留り（はんだ接合性、スタンドオフ、はんだブリッジ等）に大きく影響するため、適切な設計を行う必要があります。印刷マスクの主な仕様項目は、板厚、開口径（はんだペーストを充填する穴）サイズ、平面形状、および、断面形状であり、これらで実装基板側に転写されるはんだペースト量や安定性が決定されます。

はんだ印刷工程では、安定したはんだペースト転写量を確保する必要があり、寸法変化の少ないマスク材を選定するのが一般的です。印刷マスクは、はんだペースト印刷時の版離れ（はんだペーストを印刷、充填後、マスクと実装基板を離す作業）性に優れたものを選定する必要があります。また、複数の実装部品を搭載する場合、それぞれの部品で最適なはんだペースト量（はんだ厚み）が異なる場合もあるため、印刷マスクの設計には注意が必要となります。

なお、印刷マスクの選定、設計を誤ると、転写されたはんだペースト量の不均一やはんだペースト量の過不足となり、はんだ接合不良の原因となりますので、お客様で十分な実装評価、接合評価のうえ、印刷マスクの選定、および、設計を行ってください。

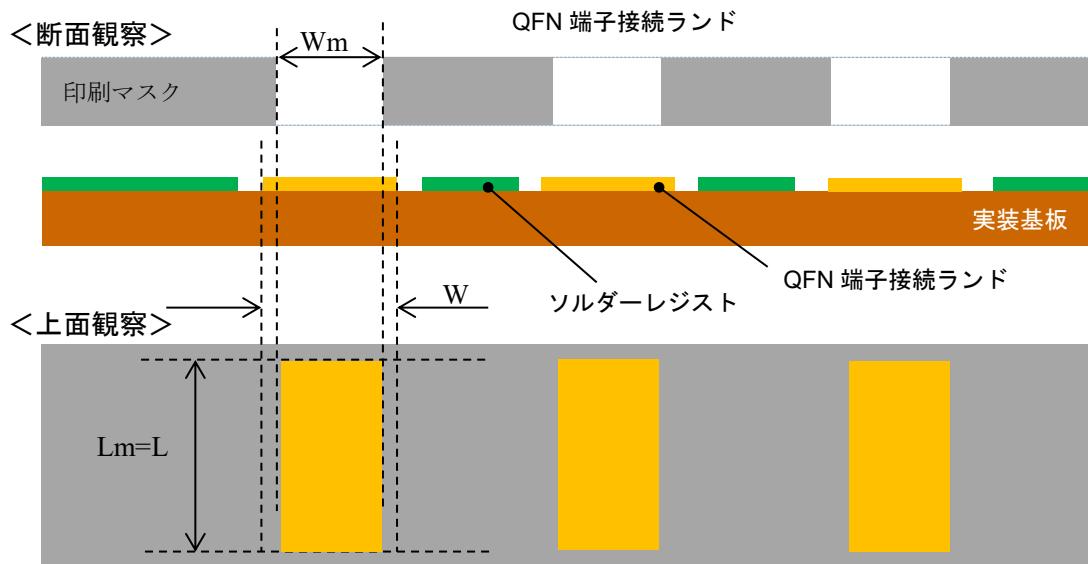

図4.1 印刷マスク、および実装基板の断面、上面観察模式図

表4.3 【参考】 はんだ印刷マスク設計

| 実装基板ランドサイズ  | 長さ方向のマスク開口 Lm | 幅方向のマスク開口 Wm  | マスク厚        |

|-------------|---------------|---------------|-------------|

| L,W（表3.2参照） | Lm=L          | Wm=W・100%～90% | 100um～150um |

注 隣接端子間ははんだブリッジを防ぐため、幅方向印刷は 100%～90%で適正值を検討してください。

表4.4 【参考】 はんだペースト印刷起因の不良モード

| はんだペースト印刷状態 | 主な不良モード                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------|

| はんだペースト過多   | <ul style="list-style-type: none"> <li>・はんだブリッジ</li> <li>・はんだボール飛散</li> <li>・部品偏傾き、浮き上がり</li> </ul> |

| はんだペースト不足   | <ul style="list-style-type: none"> <li>・はんだ不着</li> <li>・はんだ濡れ不足</li> </ul>                          |

## 4. はんだ印刷

### 4.2.1 Exposed Die Pad 部の印刷マスクの設計

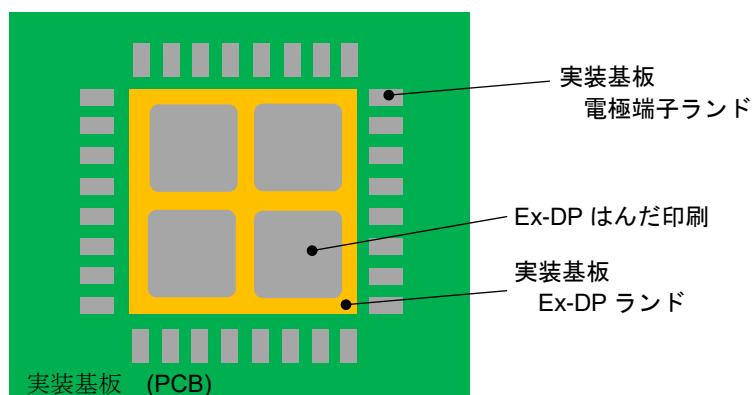

比較的大きな面積を有する Exposed Die Pad(Ex-DP)を接続する実装基板ランドに、過剰なはんだペーストが印刷された場合、電極端子とのはんだブリッジやパッケージの浮き上がり（マウンテンはんだ）が発生し、正常なはんだ付けがされない場合がありますので、はんだペーストの印刷エリア、はんだ量を適正に管理する必要があります。

一般的には、下図に示すような形状のはんだ印刷が良いとされています。これは、はんだペースト印刷後に行われる QFN 搭載の押し込みによる、はんだペースト広がりを起点としたはんだブリッジを防止する効果と、リフロー実装時のはんだ溶融で発生する表面張力による QFN の浮き上がり防止の効果があります。

はんだペースト印刷マスクの厚みにもよりますが、QFN の Ex-DP の 60%程度の面積を目安として、お客様にて、最適なはんだ印刷マスクの設計を行ってください。

図 4.2 Exposed Die Pad 部のはんだ印刷参考図

### 4.3 はんだペースト供給

はんだペーストは、メーカーの保証条件（製造からの定められた期限）を守り、推奨条件下で保管してください。また、開封後の取扱いも、メーカーの保証条件、使用条件、および、推奨条件等を守りご使用ください。

以下に、一般的なはんだペーストの使用条件を示しますので、参考としてください。

- ・はんだペーストは、室温近くの温度になってから開封してください。

- ・容器の蓋を開けてヘラ等ではんだペーストを10~20回程度攪拌するか、適量のペーストを印刷マスク上に取り出し、スキージで数回慣らし印刷をしてください。

- ・一度、印刷マスク上に取り出し使用したはんだペーストは、元の容器に戻さず廃棄してください。

### 4.4 スキージ

スキージには、様々な種類が有りますので、実装基板、はんだペーストの仕様、および、印刷装置の仕様に応じて最適なものを選定いただくようお願いします。

表 4.5 【参考】 スキージ素材の特徴

| スキージ種類     | 凹凸追従性 | はんだ転写量 | 印刷マスク寿命 | スキージ寿命 |

|------------|-------|--------|---------|--------|

| ウレタンスキージ   | ◎     | △      | ◎       | △      |

| メタルスキージ    | △     | ◎      | △       | ◎      |

| プラスチックスキージ | △     | ◎      | ○       | ○      |

注 評価は、一般的な相対比較を示します。 ( ◎ ; 優 ○ ; 良 △ ; 可 )

#### 4.4.1 ウレタンスキージ

スキージの材料にウレタンゴムを使用したもので、印刷マスクの寿命を長くすることができますが、はんだ転写量が低下する傾向があります。

凹凸の大きい実装基板に用いることにより、凹凸への追従性があり良好なはんだ印刷を得ることができます。

#### 4.4.2 メタルスキージ

スキージの材料に金属を使用したもので、マスク開口部でのはんだ転写量に優れていますが、印刷マスクの寿命を短くしてしまう傾向があります。

凹凸の小さい実装基板に対して用いることにより、良好なはんだ印刷を得ることができます。

#### 4.4.3 プラスチックスキージ

スキージの材料にプラスチック材料を使用したもので、メタルスキージと同等のはんだ転写量を確保し、かつ、印刷マスクの寿命を長くすることができますが、スキージ自体の寿命はメタルスキージに劣ります。

## 4. はんだ印刷

---

### 4.5 はんだ印刷

QFN を含む搭載部品をはんだ接続する部分に、はんだペーストを印刷します。一般的には、印刷マスクの孔にスキージュ用いてはんだペーストを充填し、版離れ工程を経る事で必要箇所に一定の厚さではんだペーストを転写します。

はんだペーストの印刷性は、マスククリアランス、印圧、スキージスピード等の印刷装置条件や、装置状態の管理、および、はんだペーストの状態管理も重要になります。特に、はんだペーストは、環境（温度、湿度、大気の対流等）によっても変化しますので、これら環境への留意も必要となります。

なお、はんだ印刷後の実装基板は、はんだペーストメーカーの推奨条件に従い、できるだけ早く部品搭載を終え、はんだ付け加熱処理（リフロー処理）を行ってください。

### 5. 部品搭載

はんだペーストが印刷された部分に QFN を搭載します。QFN の搭載は、一般的な部品搭載装置（表面実装機、部品装着機）を使用してください。

リフロー方式の場合、接合の位置精度は部品搭載時の精度ではなく、セルフアライメントにより若干の位置ズレに対しては位置補正機能が働きますので、このセルフアライメント許容範囲内での部品搭載を行ってください。

一般的には、微小チップ部品（チップコンデンサー等）から搭載を行い、QFP 等の大型部品は、最後に搭載します。搭載部品、および、QFN のサイズを考慮して搭載する順番を決定してください。

#### 5.1 部品搭載の注意事項

##### 5.1.1 キャリアテープ、トレイからの取出し

QFN を吸着する際、過度な荷重や衝撃を加えないように注意してください。

##### 5.1.2 実装基板への部品搭載

QFN を実装基板へ部品搭載（搭載）する際、適正なはんだペースト塗布部への押し込みが必要となります。この際、過度な荷重や押し込みは、QFN／実装基板端子間のはんだペーストつぶれによるはんだブリッジの発生やはんだボール（はんだ跳ね）の発生の可能性があります。

また、限界を超えた衝撃や押し込みは、QFN のパッケージ破損が発生することがありますので、十分に評価のうえ、実装条件の設定を行ってください。

## 6. リフロー

### 6. リフロー

#### 6.1 リフロー装置

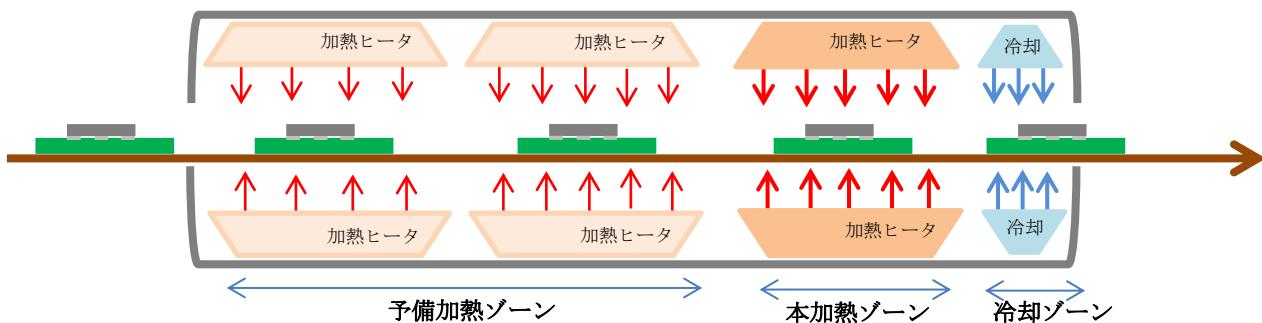

表面実装型部品（SMD; Surface Mount Device）の実装に一般的に用いられるリフロー装置について解説を行います。リフロー装置は以下のような温度ゾーン構成となっており、それぞれで最適な温度プロファイルの設定、および、環境の設定が必要となります。

図 6.1 リフロー炉概念図

##### 6.1.1 予備加熱（プリヒート）ゾーン

リフロー炉の中で、実装基板と部品を予熱します。（一般的には 140°Cから 200°C程度）

予熱の目的は、部品への急激な熱衝撃の緩和、フラックスの活性化促進、有機溶剤の気化、および、実装基板上に搭載されている様々な熱容量の部品の温度を均一化し、本加熱ゾーンで安定したはんだ接合性を得ることを目的としています。

##### 6.1.2 本加熱ゾーン

はんだが溶融する温度まで、短時間高温にします。（一般的には 220°Cから 260°C）

はんだ組成によってはんだ溶融温度が異なりますが、鉛フリーはんだの場合には、従来の鉛はんだより高温にする必要があります。ただし、リフロー炉加熱温度が、より高温になると金属表面の酸化が促進され濡れ性が悪くなる傾向にあり、高温下での酸化防止のため、炉内の酸素濃度を低く抑えることがはんだ実装の安定性に有効です。

また、同時に実装される搭載部品のなかには、耐熱保証温度が低く鉛フリー工法には適さない可能性もありますので、事前にそれぞれの部品の耐熱温度の確認が必要となります。

##### 6.1.3 冷却ゾーン

自然冷却が一般的ですが、搭載部品への熱ストレス時間をいち早く解放するためと、はんだ接合部の薄く均一な金属間化合物を生成するために、急激に冷却することが推奨されています。

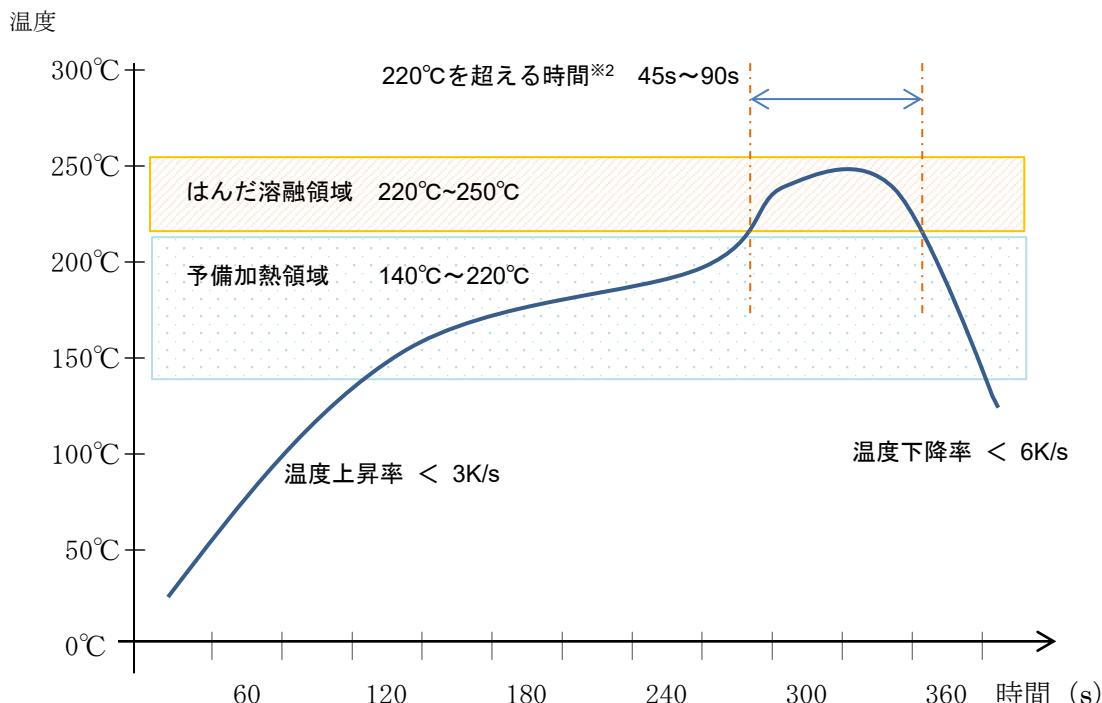

## 6.2 リフロー条件

下図に、代表的な鉛フリーはんだ (Sn, Ag, Cu 合金はんだ) のリフロー温度プロファイルを示します。搭載部品のはんだ接合部の温度は、搭載部品の構造（エリアアレイやペリフェラルパッケージ）、周囲の部品、実装基板上での位置、および、部品の搭載密度や熱容量によって影響を受けますので、実装基板上の複数の位置（はんだ接合部）での温度プロファイル確認を行うようしてください。

お客様で設定いただく際は、はんだペーストメーカーの推奨温度プロファイルを参考に、実際に使用されるリフロー装置、実装基板の温度プロファイルを確認し、最適な温度条件の設定を行ってください。

また、一般的に、大気環境下より窒素雰囲気下でリフロー加熱を行うと部品実装性、はんだ濡れ性において有利ですので窒素雰囲気下でのリフロー実施をお奨めします。

なお、当社 QFN については、6.3 項の「本製品のはんだ付けにおける注意事項」の当社保証範囲内の条件を、お守りいただくようお願いいたします。

図 6.2 【参考】 代表的なリフロー温度プロファイル<sup>注1</sup>

注 1 JEITA ET-7407B 図-3 Sn-3.0Ag-0.5Cuを参考に記載しています。詳細は、JEITA規格をご参照ください。

注 2 搭載される部品、パッケージにより許容される温度、時間は、それぞれで異なりますので許容仕様をご確認ください。

## 6. リフロー

### 6.3 本製品のはんだ付けにおける注意事項

本製品は表面実装型パッケージ(SMD)です。

はんだ付け時のストレスに対するICパッケージの耐熱性は、製品の保管条件(環境)及び、はんだ付け方式・条件によって影響されます。

従いまして本製品に関しては、次に示すはんだ付け推奨条件の範囲内にてご使用されることをお願い申し上げます。

| 実装前保管条件                                           |                                   |                                                            |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------|

| 防湿梱包開封前                                           | 保管条件<br>30°C 85%RH 以下             | 期間<br>1年間                                                  |

| 防湿梱包開封後                                           | 保管条件<br>30°C 70%RH 以下             | 期間<br>1ヶ月(720時間)                                           |

| 許容温度プロファイル条件                                      |                                   |                                                            |

| (パッケージボディ表面温度)                                    | 予備加熱<br>140~200°C<br>60~120秒      | 最大ピーク温度 260°C<br>255°C 10sec以内<br>本加熱部<br>220°C以上<br>60秒以内 |

| 推奨乾燥条件                                            |                                   |                                                            |

| 梱包(防湿袋)開封後の許容保管期間を超えた場合は、実装前に下記条件にて乾燥処理を実施してください。 | ベーキング実施後から実装までの保管条件は、上記保管条件と同一です。 |                                                            |

| ※出荷形態がテープ&リールの場合、耐熱性のトレイ等に移して乾燥処理を実施してください。       |                                   | (保管ランク: MSL2a)                                             |

図 6.3 本製品のはんだ付けにおける注意事項

## 7. 洗浄

### 7.1 QFN の洗浄

はんだ実装されたQFNは、スタンドオフ<sup>注1</sup>が狭いため、QFNと実装基板の間に残っているはんだペースト残渣（フラックス残渣）を除去することは困難なため、洗浄を必要としないはんだペーストの選定をお奨めします。

また、洗浄を必要とするはんだペーストを選定する場合には、はんだペーストメーカーに十分にご相談のうえ、決定してください。

注1 スタンドオフ： 部品取り付け面とパッケージ本体の下端との距離

### 7.2 一般的な基板洗浄方法

#### 7.2.1 実装基板の洗浄方法

搭載部品を実装基板に実装する際に生じるフラックス残渣は、端子間リークやマイグレーションを引き起こす要因となり、製品の信頼性に影響を与える可能性があります。また、搭載部品の特性上フラックス洗浄を必要とする部品や接続端子はもとより、リフロー実装中に発生したはんだボール、フラックス固着を取り除くためにも洗浄は有効です。特に、ご使用のはんだペーストが無洗浄対応ではない場合には、フラックスの除去洗浄を確実に行うことをお奨めします。

#### 7.2.2 標準的な洗浄フロー

実装基板の標準的な洗浄方法として、浸漬洗浄、超音波洗浄、スプレー洗浄、蒸気洗浄等がありますが、一般的には、温浴浸漬、超音波洗浄が広く行われています。詳細な洗浄条件に関しては、はんだペーストメーカー、および、洗浄剤メーカーの推奨条件を参照してください。

#### 7.2.3 水洗浄

水洗浄対応のはんだペーストを使用した場合は、吸湿を抑えるため、はんだペースト印刷後速やかに部品搭載を行い、はんだ付けリフロー加熱処理を行う必要があります。この際の時間管理については、はんだペーストメーカーの推奨条件を参照してください。

#### 7.2.4 無洗浄

無洗浄化のためには、フラックス中のハロゲン含有量（特に塩素含有量）の影響確認やフラックス残渣の少ないはんだペーストを使用する必要があります。この際、ご使用のはんだペーストが無洗浄対応であることをご確認のうえ、事前に使用される基板を用いた実装評価、信頼性評価を行ってください。

## 7.3 その他

- (1) 洗浄温度は可能な限り低温で、短時間に行ってください。

- (2) 洗浄後の品質確認（端子への影響）を必ず実施してください。

- (3) 洗浄後にQFNの端子部分に水分が付着、残留していると、湿気による不具合を生じる危険性がありますので乾燥処理を十分に行ってください。

- (4) 洗浄中の洗浄剤、希釈剤、および、水（純水）がおよぼす、実装基板や搭載部品への影響を十分に評価してください。（酸、アルカリ、有機溶剤、水分による影響があります。）

## 8. リワーク

### 8. リワーク

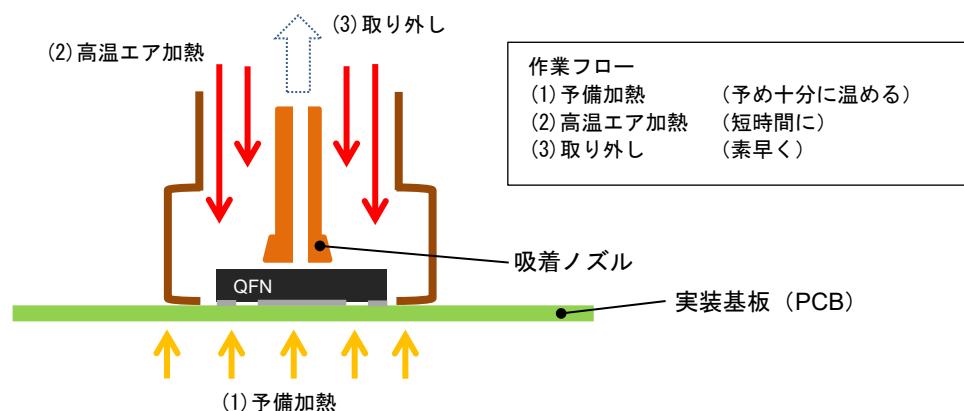

はんだ実装が終った QFN を取り外す実装基板リワークを行う場合、取り外した QFN の再利用（再実装）は当社の品質保証外となりますので避けてください。

また、QFN を取り外した実装基板に、新たな QFN を再実装する場合は、基板表面を洗浄し、新たなはんだペーストを印刷した後に QFN をはんだ実装してください。

実装済みの QFN を取り外す方法としては、部品取り外し用の専用治具等を用いて、高温の空気で局所的に加熱しながら、はんだ接続を溶かして取り外します。QFN を加熱する前に実装基板周辺部全体に予備加熱を行ってください。予備加熱を行うことにより、取り外しに必要な高温加熱時間を短縮でき、実装基板の歪、変形を最小限に留めます。

なお、実装基板のリワーク、再利用を行う場合は、お客様にて実装基板の破損や変形、実装性、信頼性等への影響について、十分に確認を行ってください。

図8.1 【参考】 QFN取り外し概図

### 9. 半導体の取扱注意事項

当社、半導体製品の一般注意事項につきましては、以下をお守りください。なお、QFNに関する個別の内容は、前項までの各章に記載しました注意事項も併せてお守りください。

#### 9.1 はじめに

当社、半導体製品は、通常の使用時に予想されるある程度のストレスに対しては故障のないよう設計・製造され、また、各種の信頼性試験などの実施により品質を保証しています。しかし、半導体製品をいかに高い技術管理のもとで設計・製造しても、適切に使用されなければ、期待する信頼性は得られません。当社、半導体製品をより高信頼の状態でご使用いただくために、システム設計時や取扱い時、また、保管時には以下の事項について十分な注意をお願いいたします。

#### 9.2 保管時

- (1) 梱包箱に衝撃・振動・被水(水濡れ)を及ぼさないよう注意してください。

- (2) 急激な温度変化により、水分の結露が起きないような環境で保管し、使用するようにしてください。また、保管中は製品に荷重がかからないようにしてください。

- (3) 腐食性ガスのある環境や、ほこりの多い環境での保管は避けてください。

- (4) 使用時に防湿袋の破れ・傷のないことを確認し、開封直後にシリカゲルが吸湿した状態ではないことを確認してください。

- (5) 保管が長期間に及んだ場合は、端子の変色、はんだ付け性の低下等がないことをご確認のうえでご使用ください。

#### 9.3 ご使用時

- (1) 使用電圧や使用温度、入出力電圧・電流などについては、定格の範囲内でご使用ください。定格外で使用した場合、短期的には正常に動作しても、故障率を高める可能性があります。また定格の範囲内であっても、故障率は動作時の温度や電圧により変化しますので、装置の設計の際にはこの点も考慮してください。

- (2) 入出力端子からスパーク、静電気放電などの雑音が入った場合は誤動作する可能性があります。また、電磁波により誤動作する可能性もありますので、必要に応じて機器のシールドを行う等、機器設計時に十分に注意してください。

- (3) 半導体製品は、電源あるいは入出力端子に過大な外来雑音が印加されるとラッチアップ現象を引き起こし、回路の誤動作や破壊の原因となることがあります。この現象が生じた場合は、すぐに電源を切り、原因を取り除いた後、再通電してください。

- (4) 端子には静電気保護回路を内蔵していますが、その能力を超える静電気が加わった場合には破壊されることがありますので、製品を取り扱う場合には充分な静電気対策を実施してください。

- (5) 包装・運搬容器はプラスチック製を極力避け、導電性容器をご使用ください。また製品のハンドリングについても充分に考慮してください。(リストストラップの使用等)

- (6) はんだゴテや測定回路などは高電圧リークのないものを、必ずアースを取ってご使用ください。

- (7) 防湿袋開封後の保管条件、実装方法及び実装温度条件は、製品ごとに規定される当社指定条件の範囲内にて管理してください。

- (8) 実装基板への実装工程中あるいは実装後に受ける機械的ストレスは、できる限り小さくしてください。

## 9. 半導体の取扱注意事項

---

- (9) 面実装パッケージは、実装基板のパターンとパッケージの外部電極端子とが面接触ではんだ付けされます。そこで当社では、はんだ付けに十分な外部電極端子の平坦度を保証し出荷していますが、取扱いに際しては、外部電極端子当社の変形を招くような力が加わらないように細心の注意をお払いください。

- (10) 適切な温度・湿度の環境下でご使用ください。湿度に関しては 85%以内（結露なきこと）としてください。また、万が一、半導体製品がちり・ほこり・塩気・SO<sub>2</sub> ガスのような酸性ガスなどに直接さらされる環境の場合は、素子のリード間のリーク、サビなどの原因となります。その場合は回路基板、半導体製品等をコーティングするなどの対策を施して使用してください。

- (11) 機械的な振動や衝撃、継続的な応力、急激な温度変化などはパッケージのクラックやワイヤの断線を引き起こす可能性があるため、なるべく避けてください。

- (12) 一部のパッケージには表面に信号線の一部が露出する構造を持つものがあります。このような製品についてはご使用の際にパッケージが汚染等を受けないよう十分にご注意ください。また素手による製品の取り扱いは避けてください。

- (13) 光に対する注意事項

半導体素子は、光が照射されると特性が変化します。特性の変化による誤動作を防ぐため、半導体製品が実装される実装基板及び製品について以下の考慮をしてください。

- 実使用時に半導体製品 (IC チップ) の遮光が考慮された構造となるように設計及び実装を行ってください。

- 検査工程では、半導体製品 (IC チップ) の遮光が考慮された環境設計を行ってください。

- 半導体製品の遮光は、IC チップの表面、裏面、及び側面について考慮してください。

## 改定履歴

付-1

| Rev. No. | 日付         | ページ  | 種別 | 改訂内容（旧内容を含む）<br>および改訂理由 |

|----------|------------|------|----|-------------------------|

| Rev 1.0  | 2018/05/10 | 全ページ | 新規 | 新規制定                    |

|          |            |      |    |                         |

|          |            |      |    |                         |

|          |            |      |    |                         |

## **セイコーエプソン株式会社**

### **営業本部 デバイス営業部**

---

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 御堂筋グランタワー15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 3990-0003

2018 年 5 月 作成