# S1D13513 Display Controller

# Hardware Functional Specification

Document Number: X78C-A-001-02.3

#### NOTICE: PLEASE READ THE FOLLOWING NOTICE CAREFULLY BEFORE USING THIS DOCUMENT

The contents of this document are subject to change without notice.

- 1. This document may not be copied, reproduced, or used for any other purpose, in whole or in part, without the consent of the Seiko Epson Corporation ("Epson").

- 2. Before purchasing or using Epson products, please contact our sales representative for the latest information and always be sure to check the latest information published on Epson's official web sites and other sources.

- Information provided in this document such as application circuits, programs, usage, etc., are for reference purposes only. Using the application circuits, programs, usage, etc. in the design of your equipment or systems is your own responsibility. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- Epson is committed to constantly improving quality and reliability, but semiconductor products in general are subject to malfunction and failure. By using Epson products, you shall be responsible for your hardware. Software and systems must be designed well enough to prevent death or injury as well as any property damage even if any of the malfunctions or failures might be caused by Epson products. When designing your products using Epson products, please be sure to check and comply with the latest information regarding Epson products (this document, specifications, data sheets, manuals, Epson's web site, etc.). When using the information included above materials such as product data, charts, technical contents, programs, algorithms and application circuit examples, you shall evaluate your products both on a stand-alone basis as well as within your overall systems. You shall be solely responsible for deciding whether or not to adopt and use Epson

- Epson has prepared this document and programs provided in this document carefully to be accurate and dependable, but Epson does not guarantee that the information and the programs are always accurate and complete. Epson assumes no responsibility for any damages which you incur due to misinformation in this document and the programs.

- No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

- Epson products have been designed, developed and manufactured to be used in general electronic applications (office equipment, communications equipment, measuring instruments, home electronics, etc.) ("General Purpose") and applications which is individually listed in this document or designated by Epson ("Designated by Epson ( nated Purpose"). Epson products are NOT intended for any use beyond the General Purpose and Designated Purpose uses that requires particular/higher quality or reliability in order to refrain from causing any malfunction or failure leading to death, injury, serious property damage or severe impact on society, including, but not limited to those listed below ("Particular Purpose"). Therefore, you are advised to use Epson products only for General Purpose and Designated Purpose uses. Should you desire to buy and use Epson products for a Particular Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any Particular Purpose. Please be sure to contact our sales representative and obtain approval in advance.

[Examples of Particular Purpose]

Space equipment (artificial satellites, rockets, etc.) /

Transportation vehicles and their control equipment (automobiles, aircraft, trains, ships, etc.) /

Medical equipment / Relay equipment to be placed on ocean floor /

Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment

Other applications requiring similar levels of reliability as those listed above. Please be sure to contact our sales representative for details of the other applications.

- Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for developing weapons of mass destruction, or any other military purposes or applications. If exporting Epson products or our associated technologies, you shall comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A. (EAR) and other export-related laws and regulations in Japan and any other countries and follow the required procedures as provided by the relevant laws and regulations.

- Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document.

- Epson assumes no responsibility for any damages (whether direct or indirect) incurred by any third party that you assign, transfer, loan, etc., Epson products to.

- 11. For more details or other concerns about this document, please contact our sales representative.

- Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

#### Evaluation board/kit and Development tool important notice

- 1. Epson evaluation board/kit or development tool is designed for use for engineering evaluation, demonstration, or development purposes only. Do not use it for other purposes. It is not intended to meet the requirements of design for finished products.

- 2. Epson evaluation board/kit or development tool is intended for use by an electronic engineer and is not a consumer product. The user should use it properly and in a safe manner. Epson does not assume any responsibility or liability of any kind of damage and/or fire caused by the use of it. The user should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. The part used for Epson evaluation board/kit or development tool may be changed without any notice.

Rev. e1.5, 2025. 7

© Seiko Epson Corporation 2006-2025, All rights reserved.

# **Table Of Contents**

| 1 | Intro | oduction                                 | . 9 |

|---|-------|------------------------------------------|-----|

|   | 1.1   | Scope                                    | .9  |

|   | 1.2   | Overview Description                     | .9  |

|   | 1.3   | Package Limitations                      | 10  |

| 2 | Feat  | tures                                    | 11  |

|   | 2.1   | Memory                                   | 11  |

|   | 2.2   | CPU Interfaces                           | 11  |

|   | 2.3   | Panel Interface Support                  | 12  |

|   | 2.4   | Display Features                         | 13  |

|   | 2.5   | Clock Source                             | 14  |

|   | 2.6   | 2D Acceleration                          | 15  |

|   | 2.7   | Sprite Engine                            | 15  |

|   | 2.8   | Command FIFO                             | 16  |

|   | 2.9   | Camera Interface                         | 16  |

|   | 2.10  | Miscellaneous                            | 17  |

| 3 | Syst  | tem Diagram                              | 18  |

| 4 | _     | ck Diagram                               |     |

| 5 |       | )                                        |     |

| 5 | 5.1   |                                          |     |

|   | •     | 5.1.1 QFP22 208-pin Pinout               |     |

|   | _     | 5.1.2 PBGA 256-pin Pinout                |     |

|   | _     | Pin Description                          |     |

|   |       | 5.2.1 Host Interface                     |     |

|   | _     | 5.2.2 LCD Interface                      |     |

|   | _     | 5.2.3 SDRAM Interface                    |     |

|   | _     | 5.2.4 GPIO / Multi Function Interface    |     |

|   | _     | 5.2.5 Miscellaneous                      |     |

|   | _     | 5.2.6 Power And Ground                   |     |

|   | 5.3   | Summary of Configuration Options         |     |

|   | 5.4   | Host Bus Interface Pin Mapping           |     |

|   | 5.5   | LCD Interface Pin Mapping                |     |

|   | 5.6   | GPIO Pin Mapping                         |     |

|   | 5.7   | YUV Digital Output Interface Pin Mapping |     |

|   | 5.8   | Camera Interface Pin Mapping             |     |

|   | 5.8   | I2C Interface Pin Mapping                |     |

|   |       | PWM Interface Pin Mapping                |     |

|   | J.10  | _ 1                                      | ~~  |

|   | 5.11 Keyp | pad Interface Pin Mapping                  |

|---|-----------|--------------------------------------------|

| 6 | D.C. Char | acteristics                                |

| 7 | A.C. Char | racteristics                               |

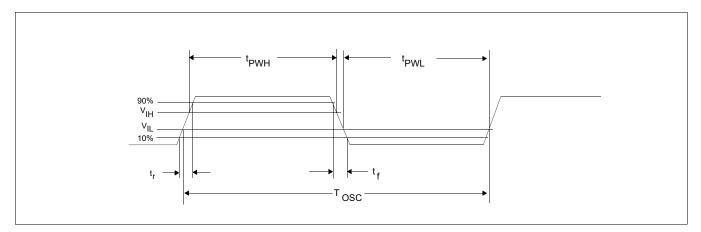

|   | 7.1 Clock | k Timing                                   |

|   | 7.1.1     | Input Clocks                               |

|   | 7.1.2     | Internal Clocks                            |

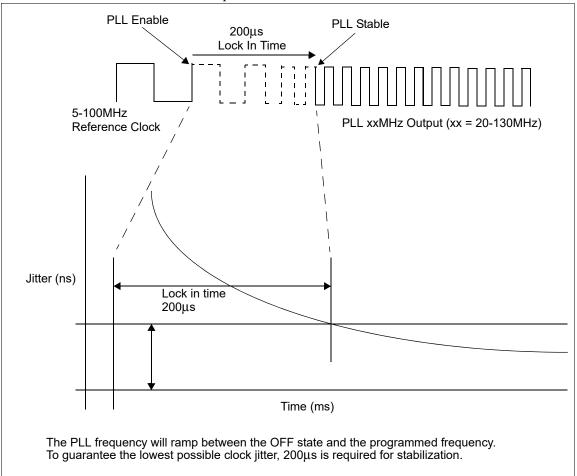

|   | 7.1.3     | PLL Clock                                  |

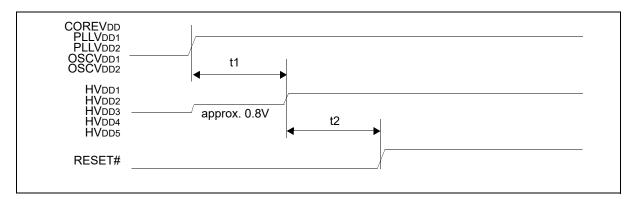

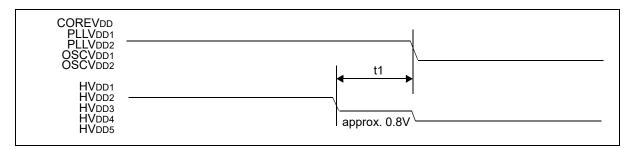

|   | 7.2 Power | er Supply Sequence                         |

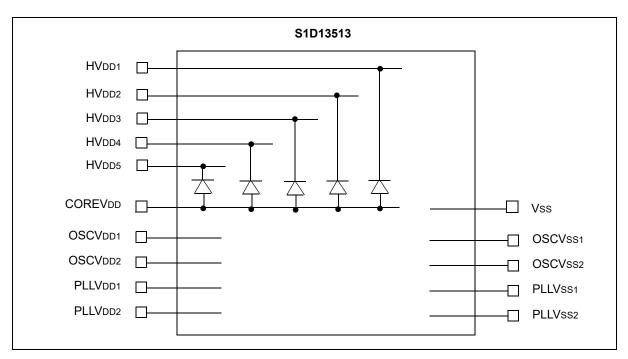

|   | 7.2.1     | Power Supply Structure                     |

|   | 7.2.2     | Power-On Sequence                          |

|   | 7.2.3     | Power-Off Sequence                         |

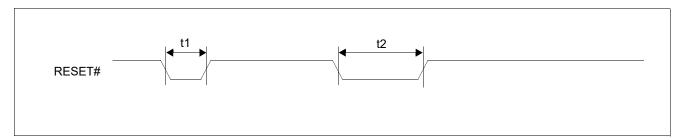

|   | 7.3 RES   | ET# Timing                                 |

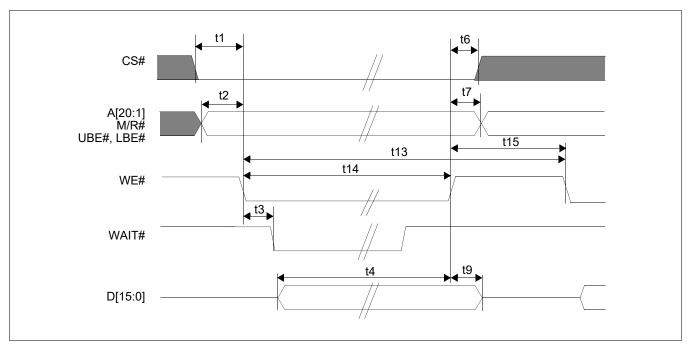

|   | 7.4 Host  | Bus Interface Timing                       |

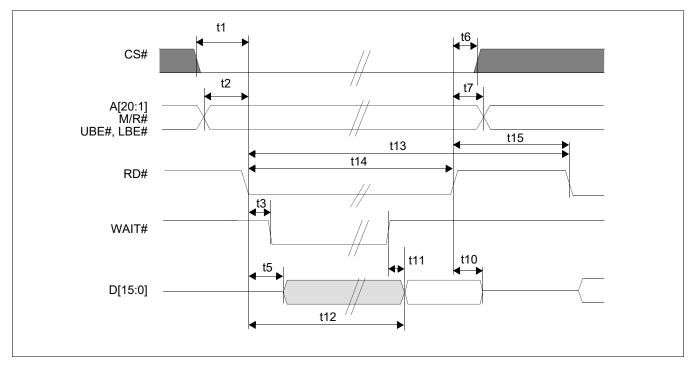

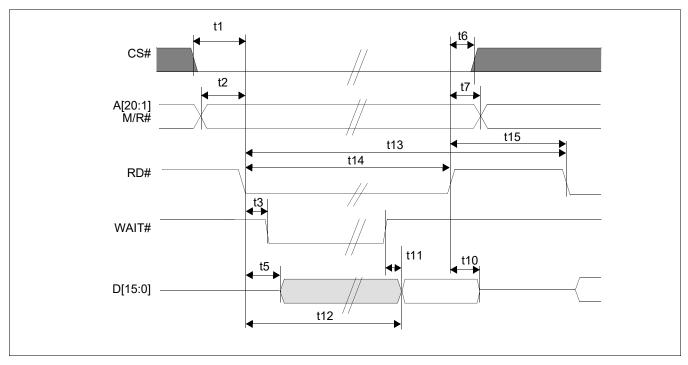

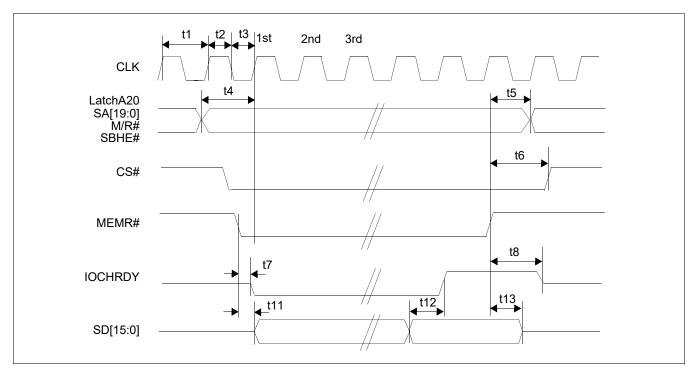

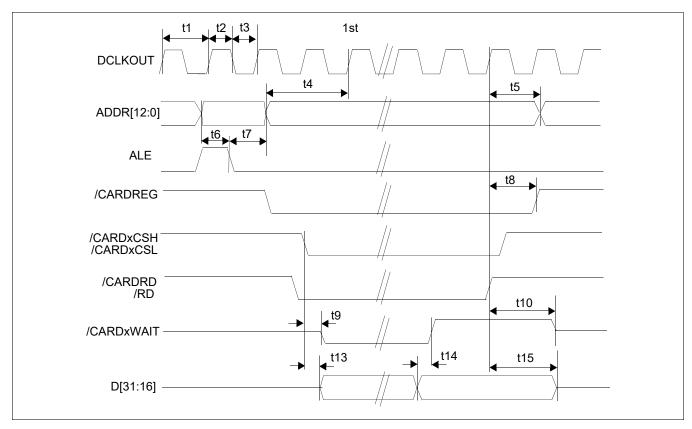

|   | 7.4.1     | Direct/Indirect 80 Type 1                  |

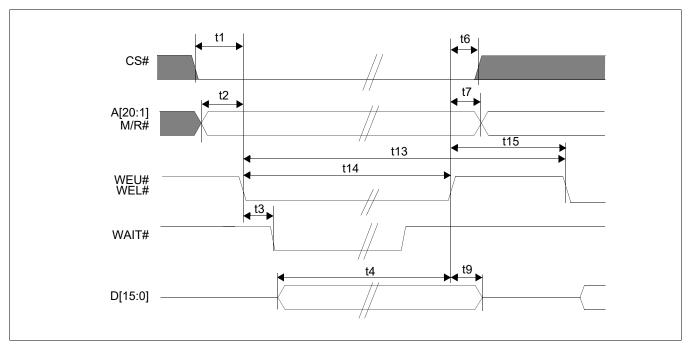

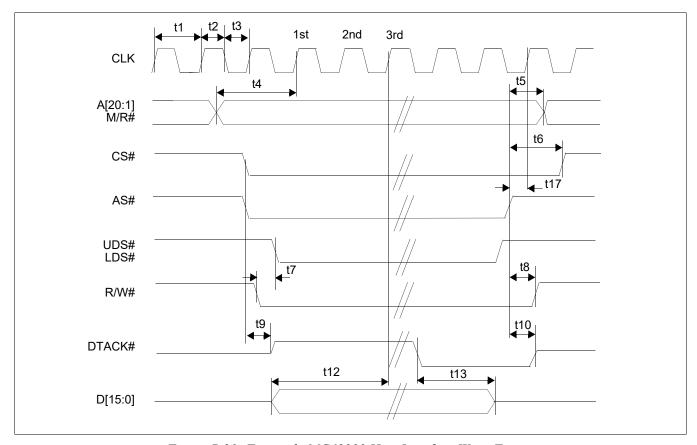

|   | 7.4.2     | Direct/Indirect 80 Type 2                  |

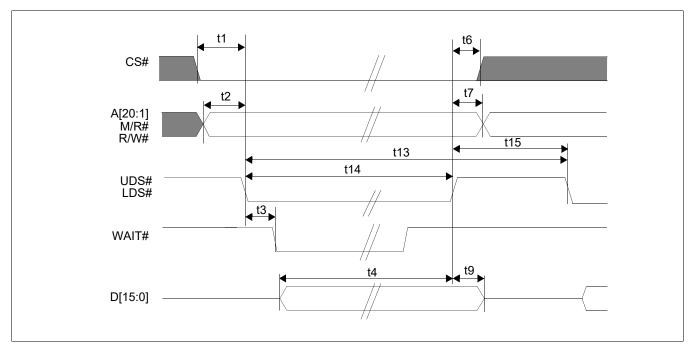

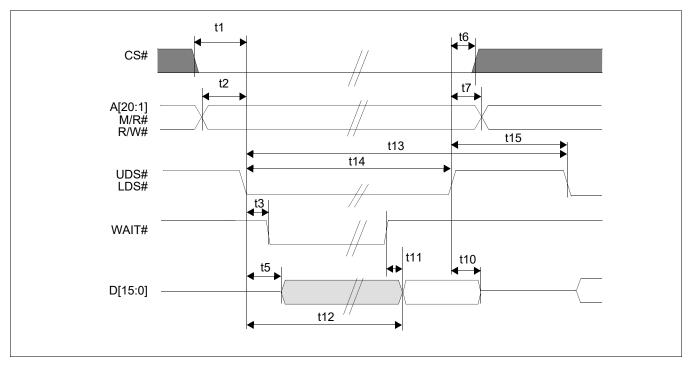

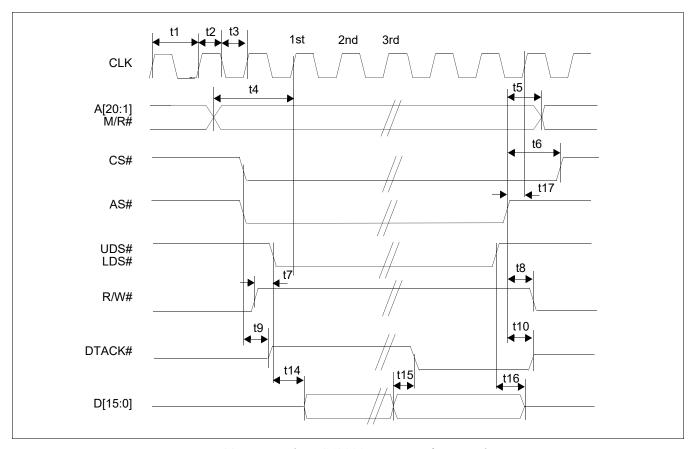

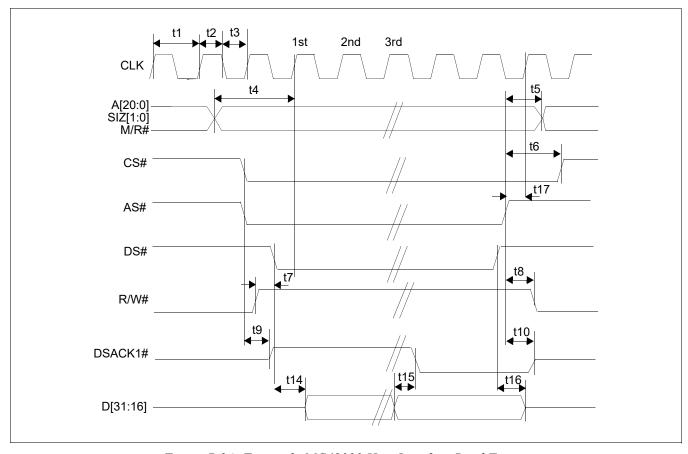

|   | 7.4.3     | Direct/Indirect 68                         |

|   | 7.4.4     | Generic (i.e. C33)                         |

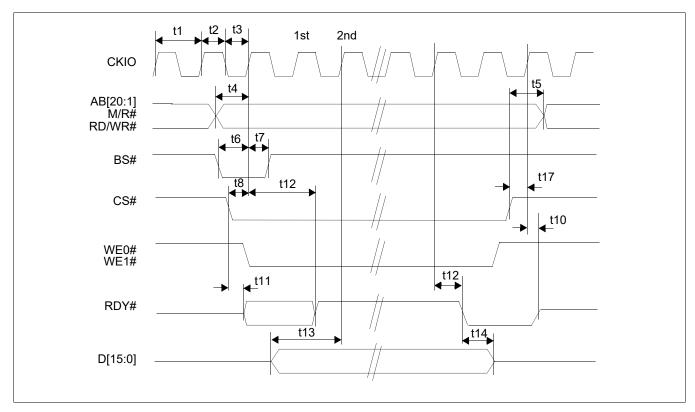

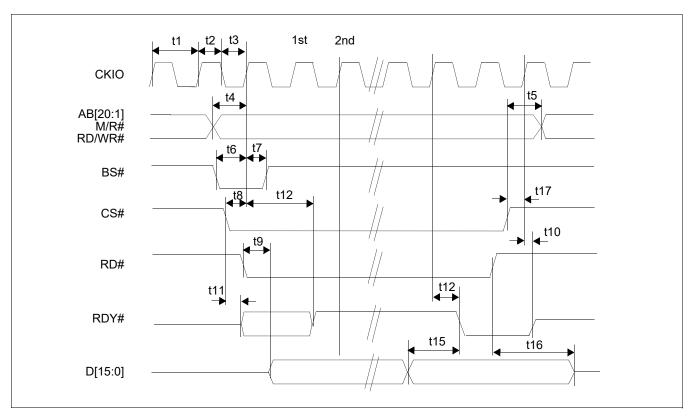

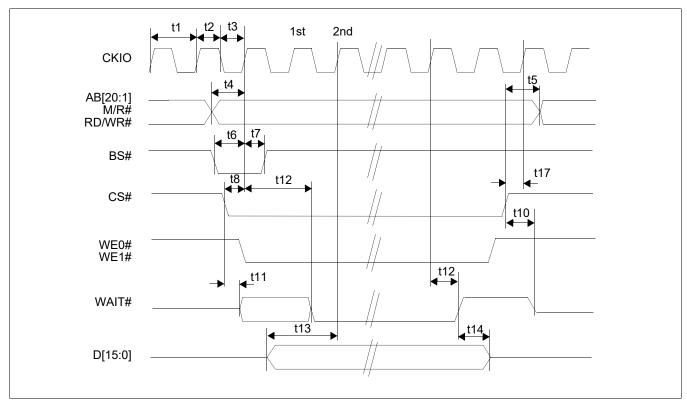

|   | 7.4.5     | Renesas SH4                                |

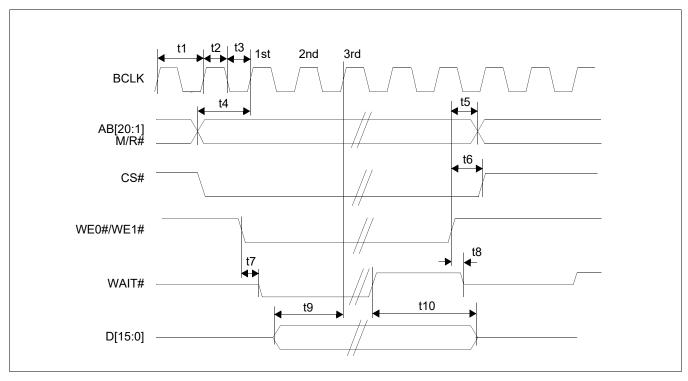

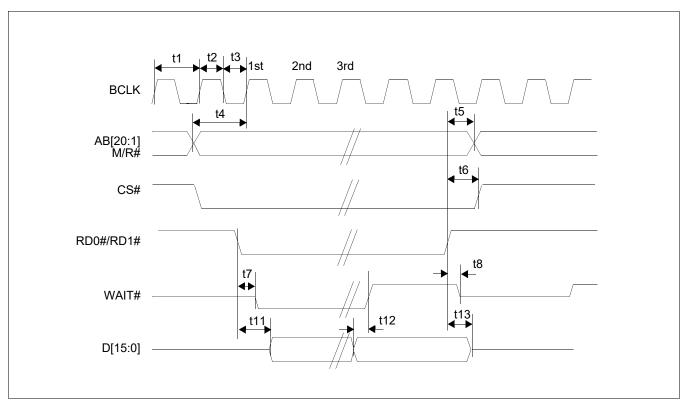

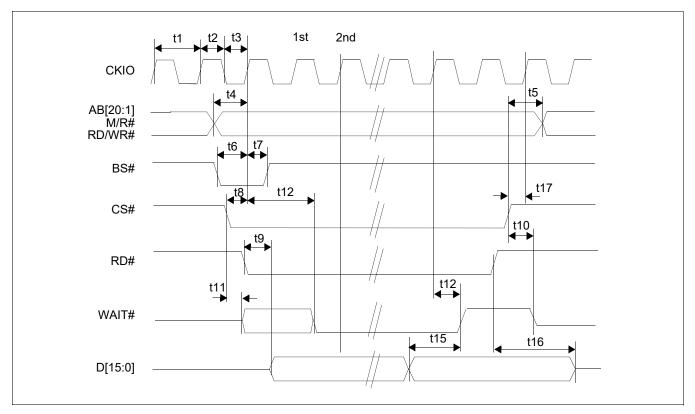

|   | 7.4.6     | Renesas SH3                                |

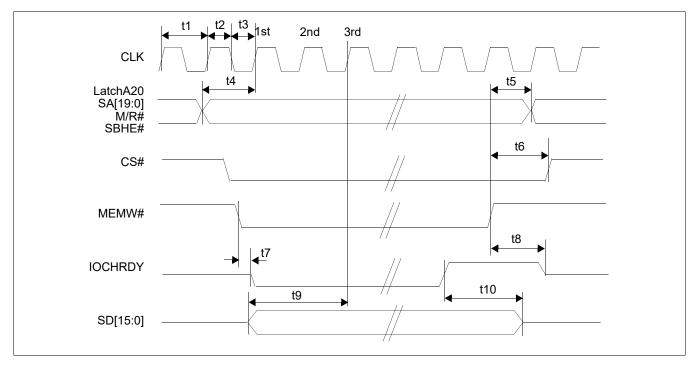

|   | 7.4.7     | MIPS/ISA (i.e. NEC VR41xx)                 |

|   | 7.4.8     | Freescale MC68000                          |

|   | 7.4.9     | Freescale MC68030                          |

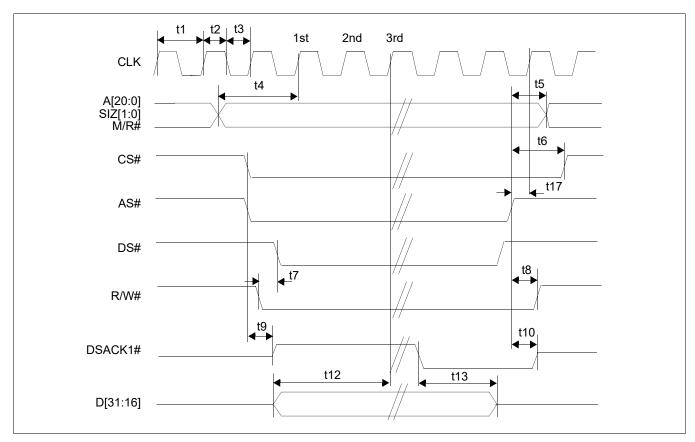

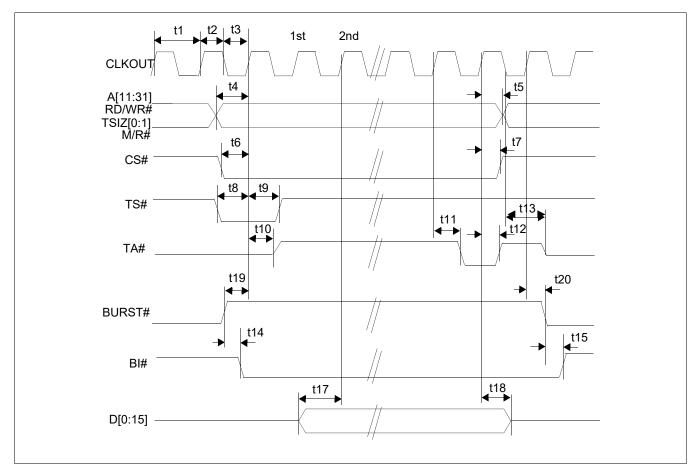

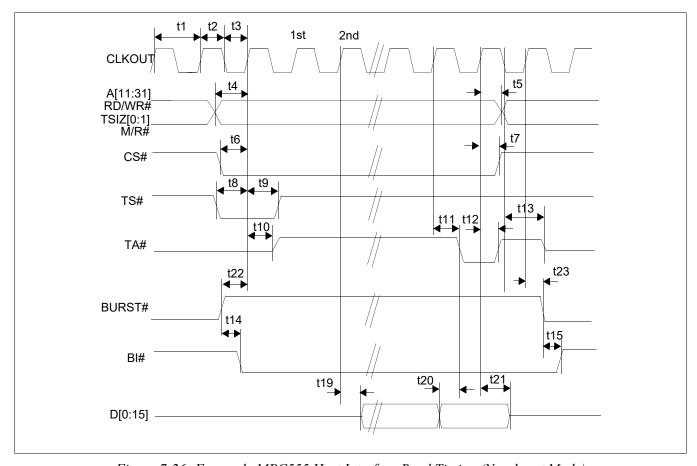

|   | 7.4.10    | Freescale MPC555 (Non-burst Mode)          |

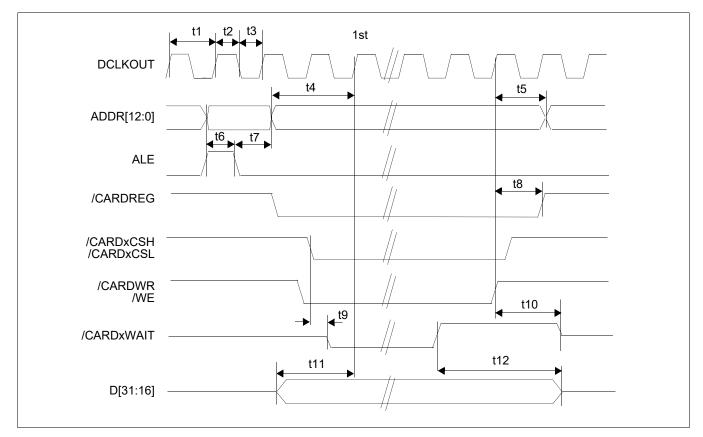

|   | 7.4.11    | Philips PR31500/PR31700 / Toshiba TX3912   |

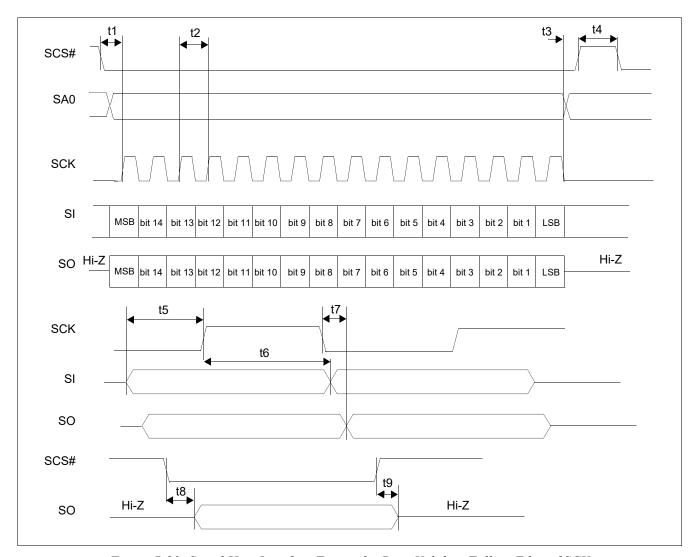

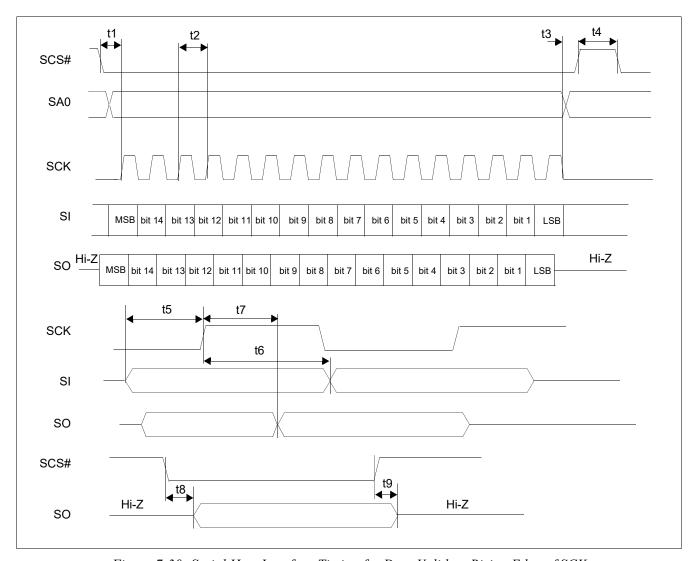

|   | 7.4.12    | Serial Host                                |

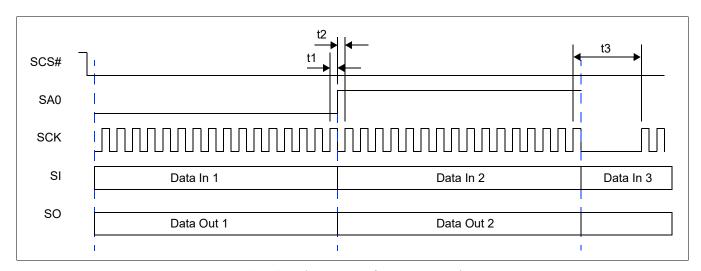

|   | 7.4.13    | Serial Host Interface Burst Mode           |

|   | 7.5 Power | er Sequencing                              |

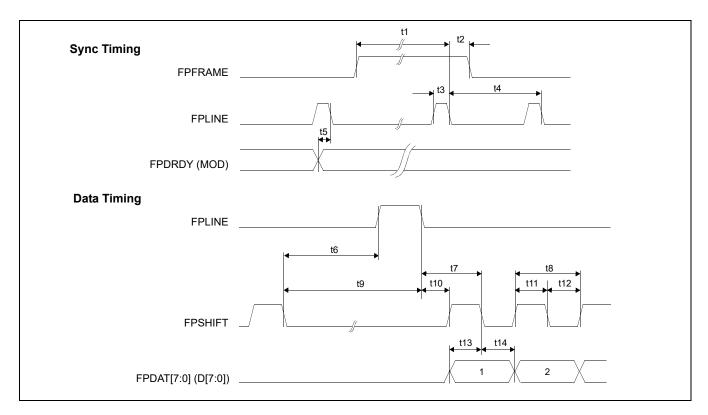

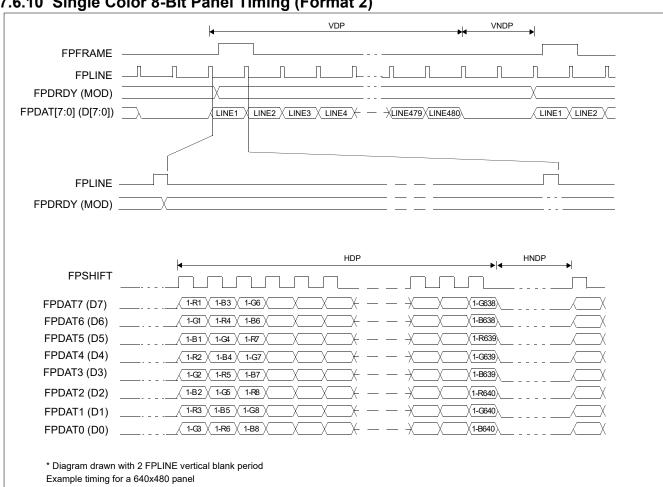

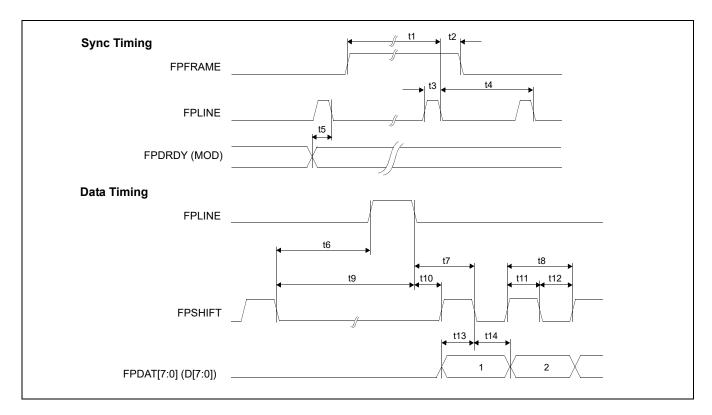

|   | 7.6 Pane  | 1 Interface Timing                         |

|   | 7.6.1     | Generic TFT Panel Timing                   |

|   | 7.6.2     | HR-TFT Panel Timing                        |

|   | 7.6.3     | ND-TFD 8-Bit Serial Interface Timing       |

|   | 7.6.4     | ND-TFD 9-Bit Serial Interface Timing       |

|   | 7.6.5     | a-Si TFT Serial Interface Timing           |

|   | 7.6.6     | uWIRE Serial Interface Timing              |

|   | 7.6.7     | 24-bit Serial Interface Timing             |

|   | 7.6.8     | YUV Digital Output                         |

|   | 7.6.9     | Single Monochrome 8-Bit Panel Timing       |

|   | 7.6.10    | Single Color 8-Bit Panel Timing (Format 2) |

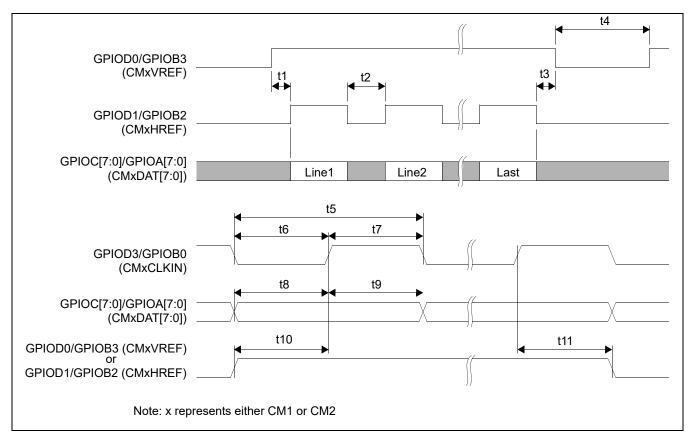

|   | 7.7 Came  | era Interface Timing                       |

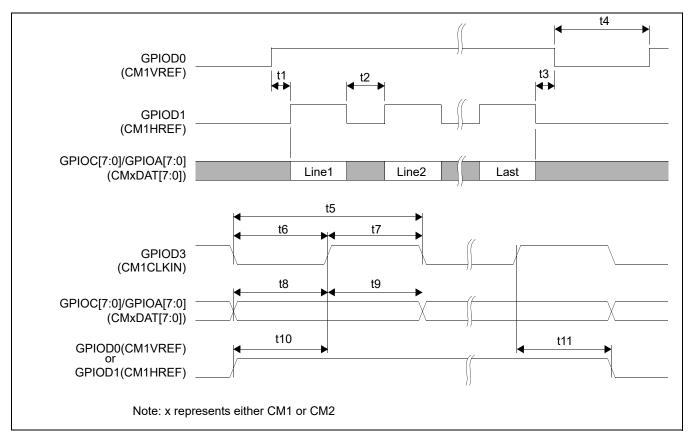

|    | 7.7   | .1 Camera Interface YUV Timing (8-bit Data Bus Mode)  |

|----|-------|-------------------------------------------------------|

|    | 7.7   | .2 Camera Interface YUV Timing (16-bit data bus mode) |

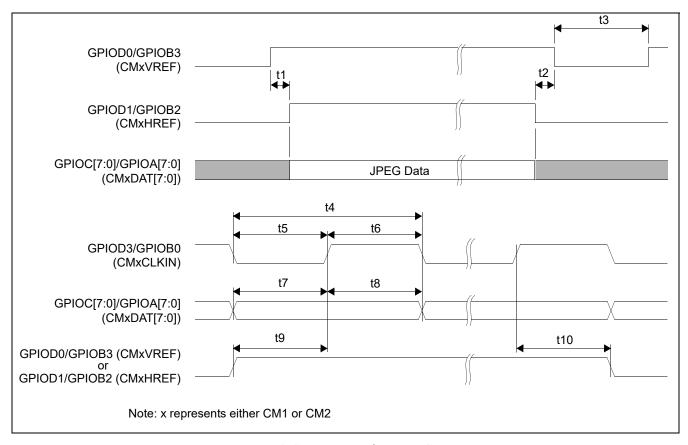

|    | 7.7   | .3 Camera Interface JPEG Timing                       |

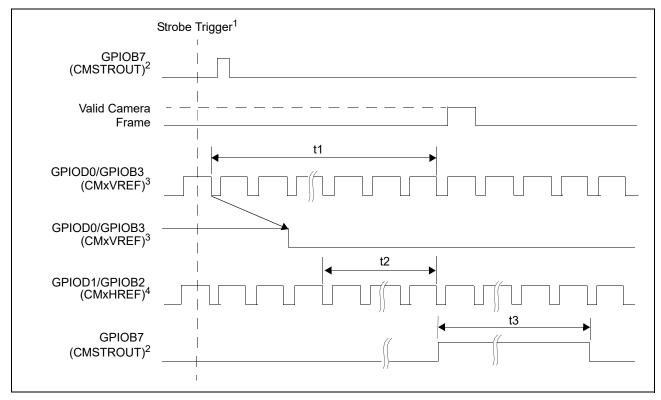

|    | 7.7   | .4 Strobe Control Output Timing                       |

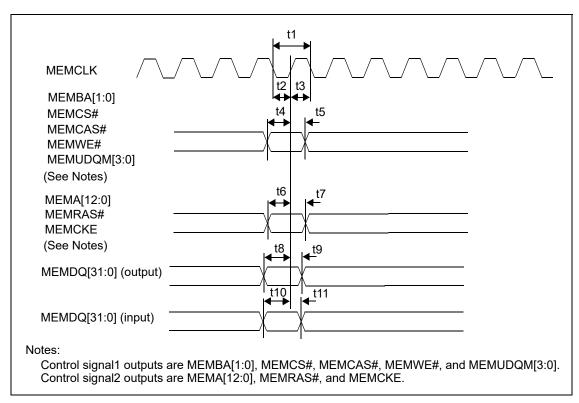

|    | 7.8   | DRAM Interface Timing                                 |

|    | 7.9   | 2C Interface Timing                                   |

|    | 7.10  | Keypad Interface Timing                               |

| 8  | Memo  | ry Map                                                |

|    | 8.1   | Accessing Memory using Direct Addressing              |

|    | 8.2   | Accessing Memory using Indirect Addressing            |

|    | 8.3   | O Map                                                 |

| 9  | Clock | s                                                     |

|    | 9.1   | Clock Overview                                        |

|    | 9.2   | PLL Programming Examples                              |

| 10 | Regis | ters                                                  |

|    | •     | Register Mapping                                      |

|    | 10.2  | Register Set                                          |

|    | 10.3  | Register Restrictions                                 |

|    | 10.4  | Register Descriptions                                 |

|    | 10    | 4.1 Host Interface Registers                          |

|    | 10    | 4.2 System Control Registers                          |

|    | 10    | 4.3 LCD Panel Configuration Registers                 |

|    | 10    | 4.4 HR-TFT Configuration Registers                    |

|    | 10    | 4.5 LCD Display Mode Registers                        |

|    | 10    | 4.6 GPIO Registers                                    |

|    | 10    | 4.7 Sprite Registers                                  |

|    | 10    | 4.8 Sprite Engine Registers                           |

|    | 10    | 4.9 2D BitBLT Registers                               |

|    | 10    | 4.10 Memory Controller Registers                      |

|    | 10    | 4.11 Camera Interface Registers                       |

|    |       | 4.12 Resizer Operation Registers                      |

|    |       | 4.13 YUV Capture Module Registers                     |

|    |       | 4.14 YUV Capture FIFO Registers                       |

|    |       | 4.15 YRC Registers                                    |

|    | 10    | 4.16 PWM Registers                                    |

|    |       | 4.17 I2C Registers                                    |

|    |       | 4.18 DMA Control Registers                            |

|    |       | 4.19 Command FIFO (For BitBLT and Sprite) Registers   |

|    | 10    | 4.20 Keypad Interface Register                        |

| 11 | Power Save Modes                                      |

|----|-------------------------------------------------------|

|    | 11.1 Power-On/Power-Off Sequence                      |

|    | 11.2 Operational Modes                                |

|    | 11.2.1 Power-On                                       |

|    | 11.2.2 Reset                                          |

|    | 11.2.3 Standby Mode                                   |

|    | 11.2.4 Power Save Mode                                |

|    | 11.2.5 Normal Mode                                    |

|    | 11.2.6 Power-Off                                      |

|    | 11.3 Power Save Mode Functions                        |

| 12 | Data Formats                                          |

|    | 12.1 Memory Data Formats                              |

| 13 | Display Functions                                     |

|    | 13.1 SwivelView <sup>TM</sup>                         |

|    | 13.1.1 0° SwivelView                                  |

|    | 13.1.2 180° SwivelView                                |

|    | 13.2 Mirror Display                                   |

|    | 13.2.1 Mirror Display for 0° SwivelView               |

|    | 13.2.2 Mirror Display Combined with SwivelView Modes  |

|    | 13.3 Gamma Correction                                 |

|    | 13.3.1 Gamma LUT Bank Selection                       |

|    | 13.3.2 Programming the Gamma LUTs                     |

|    | 13.4 Pseudo Color Mode                                |

| 14 | Resizers                                              |

|    | 14.1 Resizer Descriptions                             |

|    | 14.2 Trimming Function                                |

|    | 14.3 Scaling Function                                 |

|    | 14.3.1 Odd Number Scaling                             |

|    | 14.3.2 Even Number Scaling                            |

|    | 14.3.3 Averaging Method                               |

|    | 14.3.4 Calculating the Number of Pixels After Scaling |

| 15 | 2D BitBLT Engine                                      |

|    | 15.1 Overview                                         |

|    | 15.2 BitBLT Terms and Definition                      |

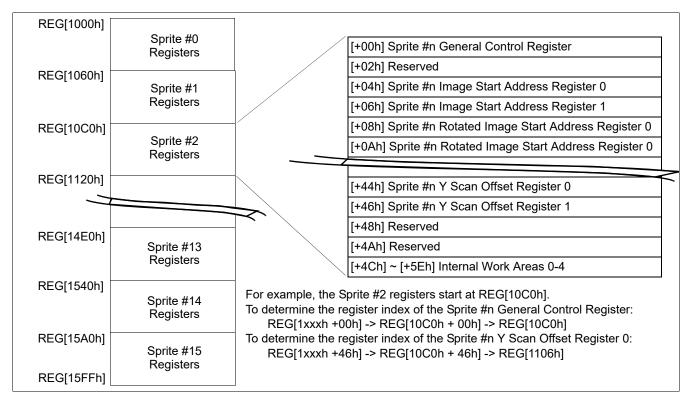

| 16 | Sprite Engine                                         |

|    | 16.1 Sprite Data Path                                 |

|    | 16.2 16 Sprite Support with Z-ordering Transparency   |

|    | 16.3 16 Sprite Support with Z-ordering Alpha-Blending |

|    | 16.4 16 Sequences for Each Sprite                     |

|    | 16.5 Reference Point Based 90°, 180° and 270° Rotation + Mirror | 400 |

|----|-----------------------------------------------------------------|-----|

|    | 16.6 Sprite Display Orientation and Positioning                 | 401 |

|    | 16.7 Arbitrary Angle Rotation                                   | 406 |

|    | 16.7.1 Sprite Example with Arbitrary Rotation Disabled          | 406 |

|    | 16.7.2 Sprite Example with Arbitrary Rotation Enabled           | 408 |

|    | 16.8 Programming Flow                                           | 411 |

|    | 16.9 Image Format Conversion                                    | 415 |

| 17 | Command FIFO                                                    | 416 |

| 18 | SDRAM Interface                                                 | 418 |

|    | 18.1 SDRAM Initialization                                       | 418 |

|    | 18.1.1 Initializing Normal SDRAM                                | 418 |

|    | 18.1.2 Initializing Mobile SDRAM                                | 419 |

|    | 18.2 Memory Bandwidth                                           | 420 |

| 19 | Pulse Width Modulation (PWM)                                    | 421 |

|    | 19.1 PWM Circuit Overview                                       | 421 |

|    | 19.2 Other Notes                                                | 425 |

| 20 | Host Interface                                                  | 426 |

|    | 20.1 Hardware Configuration                                     | 426 |

|    | 20.1.1 Bus Type (CNF6)                                          |     |

|    | 20.1.2 Chip Select (1 CS# vs. 2 CS#)                            |     |

|    | 20.1.3 Endian Mode                                              | 427 |

|    | 20.1.4 CNF[4:0]- Host Bus Interface Type                        | 427 |

|    | 20.1.5 Serial Host Interface Clock Polarity                     | 427 |

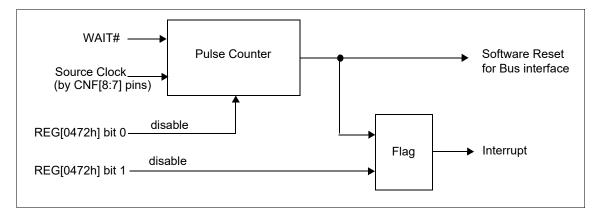

|    | 20.2 Host Bus Time-out Function                                 | 428 |

|    | 20.2.1 Host Read/Write Cycle Time-out                           | 428 |

|    | 20.2.2 Host WAIT# Length Time-out                               | 429 |

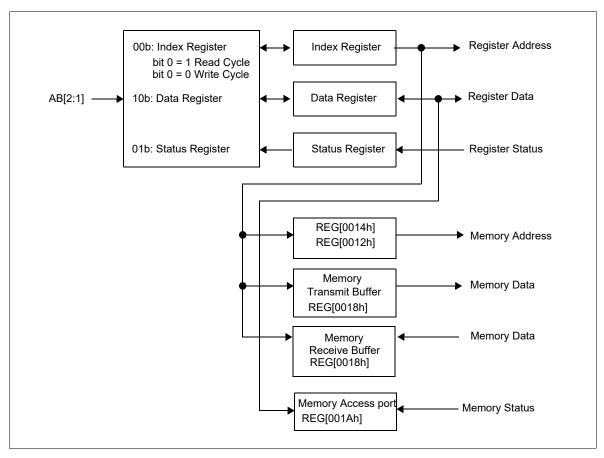

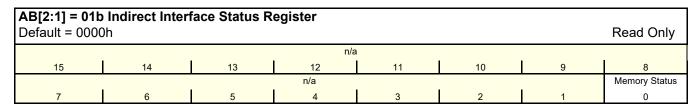

|    | 20.3 Indirect Interface                                         | 430 |

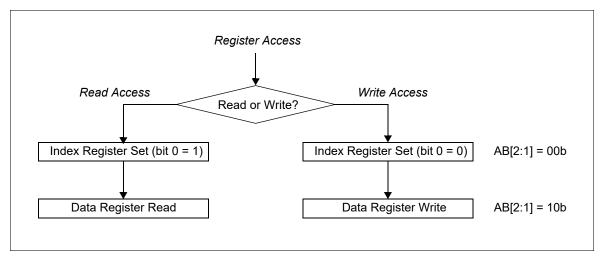

|    | 20.3.1 Indirect Addressing for Register Access                  | 431 |

|    | 20.3.2 Register Access                                          |     |

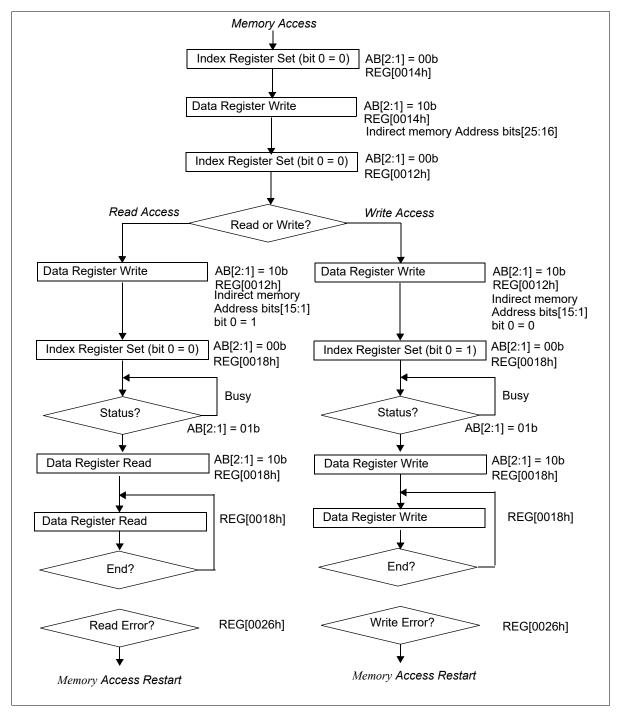

|    | 20.3.3 Memory Access                                            | 433 |

|    | 20.4 Read Ahead Feature                                         | 434 |

|    | 20.5 Serial Interface                                           |     |

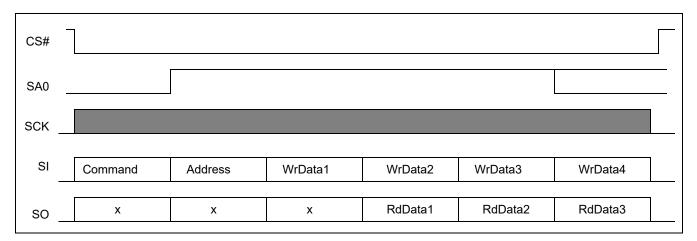

|    | 20.5.1 Description                                              |     |

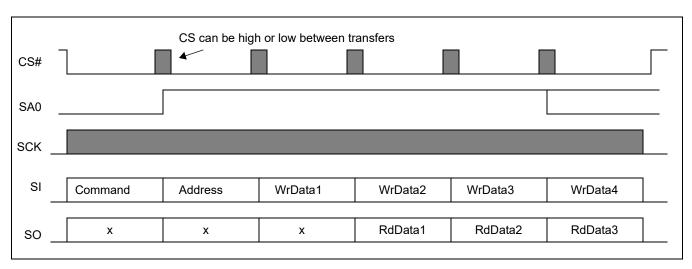

|    | 20.5.2 Burst Mode Operation                                     |     |

|    | 20.5.3 Data Transfer Examples                                   |     |

|    | 20.5.4 Indirect Register Address Auto Increment Serial Examples |     |

|    | 20.5.5 Serial Host Voltage Selection                            |     |

|    | 20.6 Register Accesses for Big Endian Host Interfaces           | 444 |

| 21 | LCD Panel Interface                                             | 445 |

|    | 21.1 TFT/ND-TFD Panels                     |

|----|--------------------------------------------|

|    | 21.1.1 TFT/ND-TFD Data Output Formats      |

|    | 21.1.2 RGB Serial Command Interfaces       |

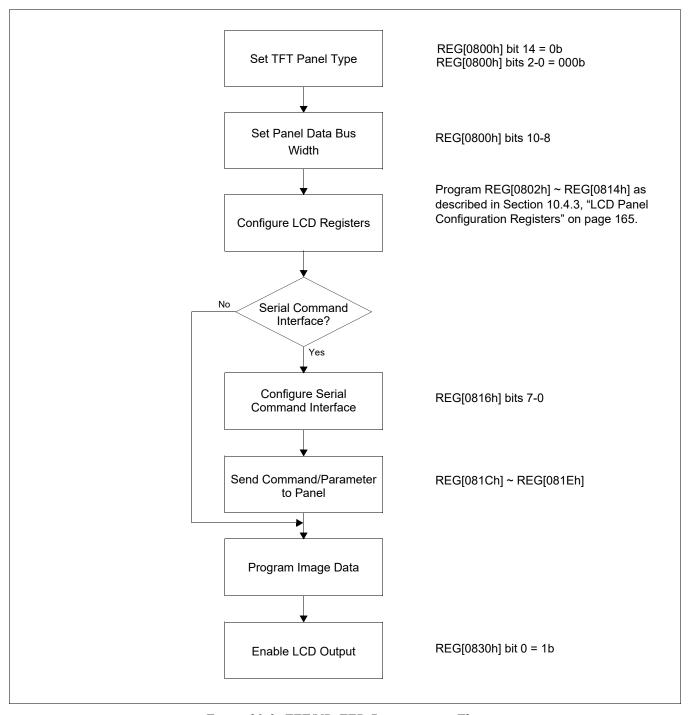

|    | 21.1.3 TFT/ND-TFD Programming Flow         |

|    | 21.2 HR-TFT Panels                         |

|    | 21.2.1 HR-TFT Data Output Formats          |

|    | 21.2.2 HR-TFT Interface Pins               |

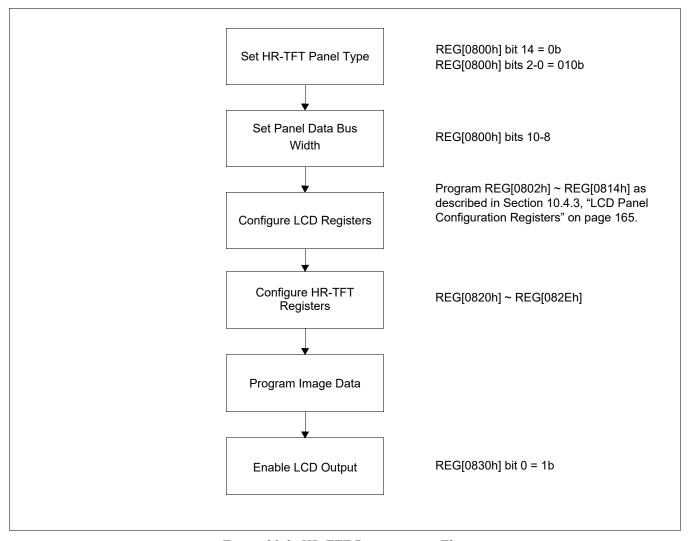

|    | 21.2.3 HR-TFT Programming Flow             |

|    | 21.3 Passive Panels                        |

|    | 21.3.1 Passive Panel Data Output Format    |

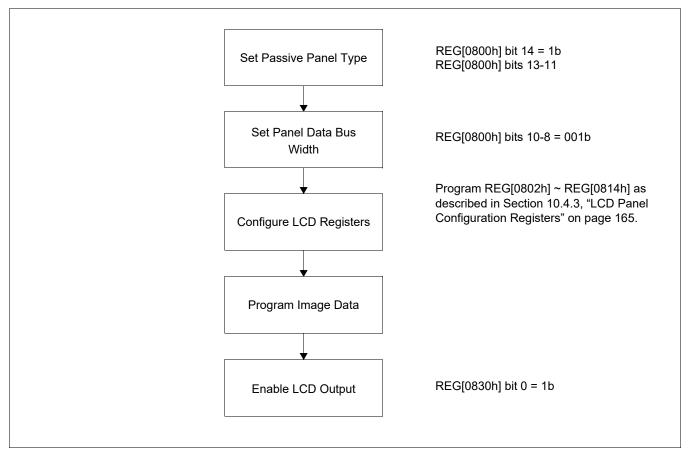

|    | 21.3.2 Passive Panel Programming Flow      |

|    | 21.4 YUV Digital Output                    |

|    | 21.4.1 YUV Digital Data Output Format      |

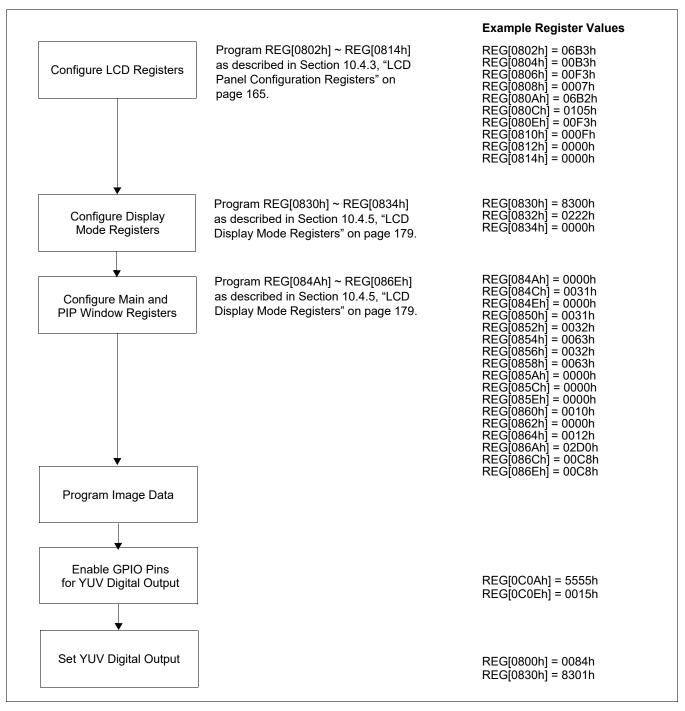

|    | 21.4.2 YUV Digital Output Programming Flow |

| 22 | Camera Interface                           |

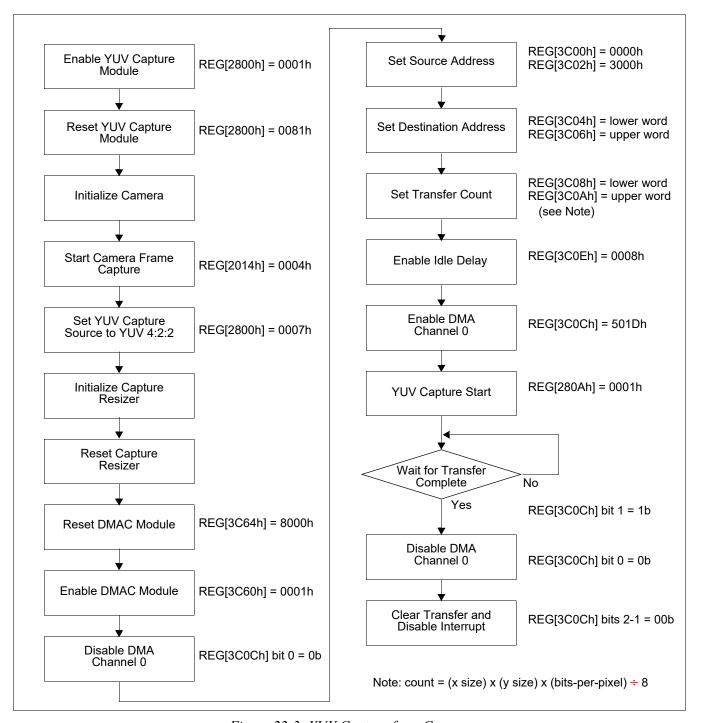

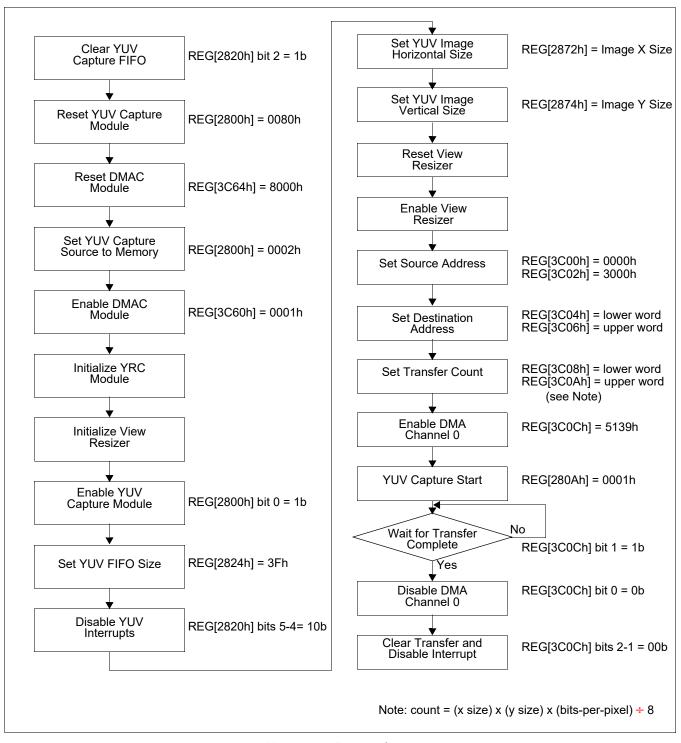

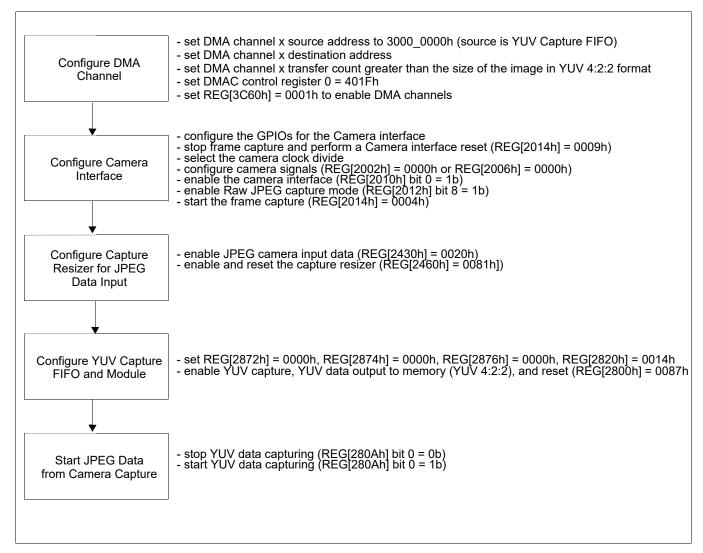

|    | 22.1 Programming Flows                     |

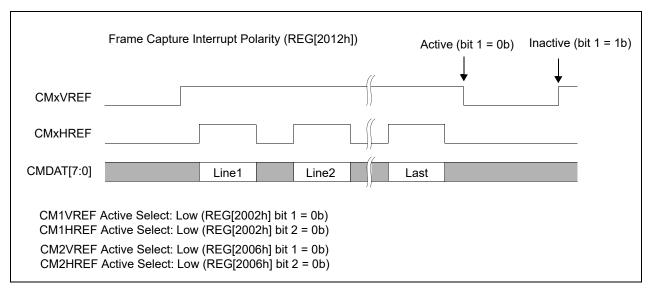

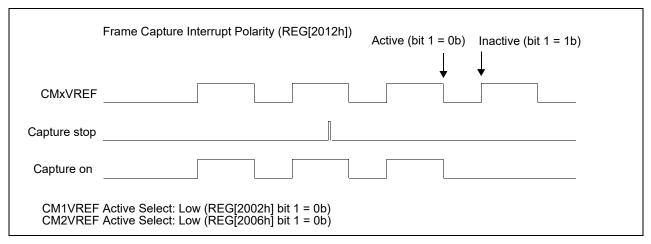

|    | 22.2 Frame Capture Interrupt               |

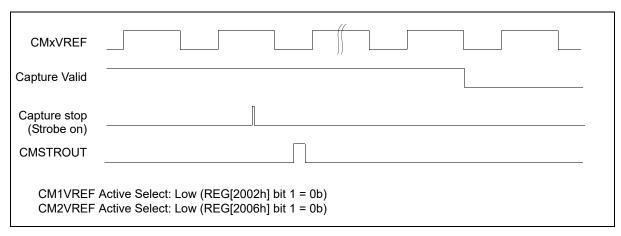

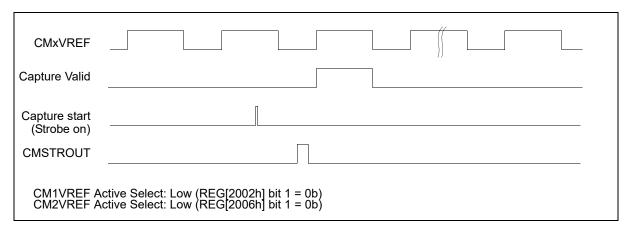

|    | 22.3 Strobe Control Signal                 |

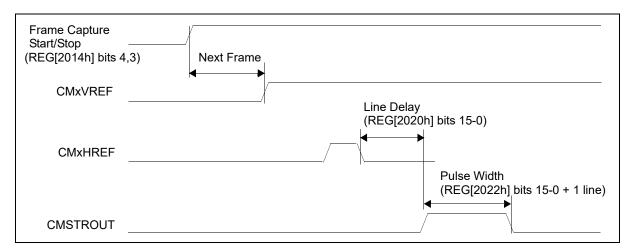

|    | 22.3.1 Generating a Strobe Pulse           |

|    | 22.3.2 Strobe Timing                       |

| 23 | I2C Interface                              |

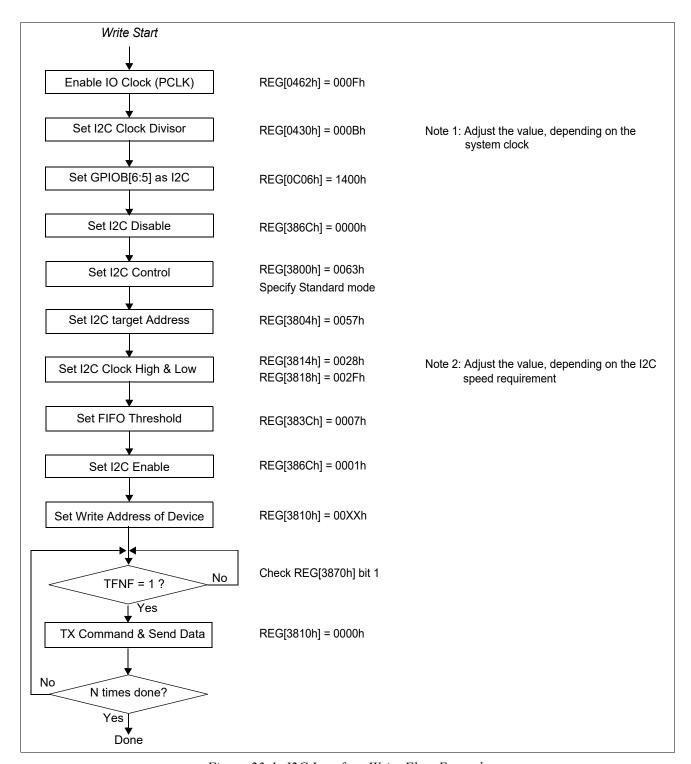

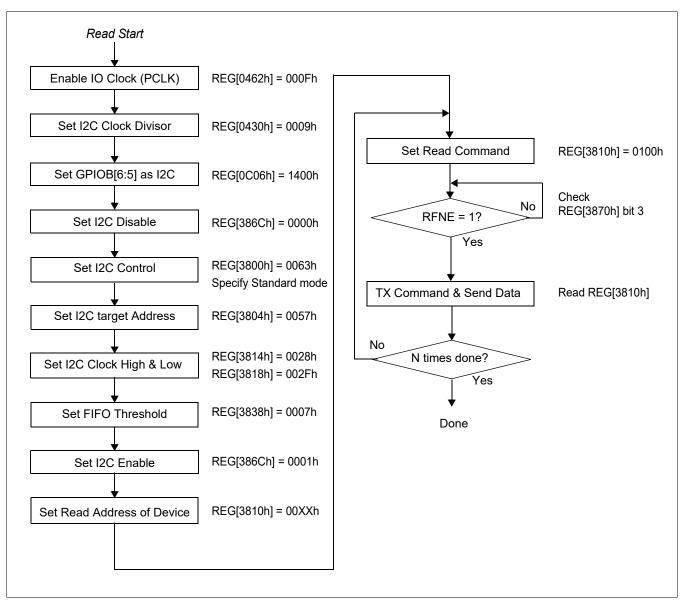

|    | 23.1 Programming Flows                     |

| 24 | Keypad Interface                           |

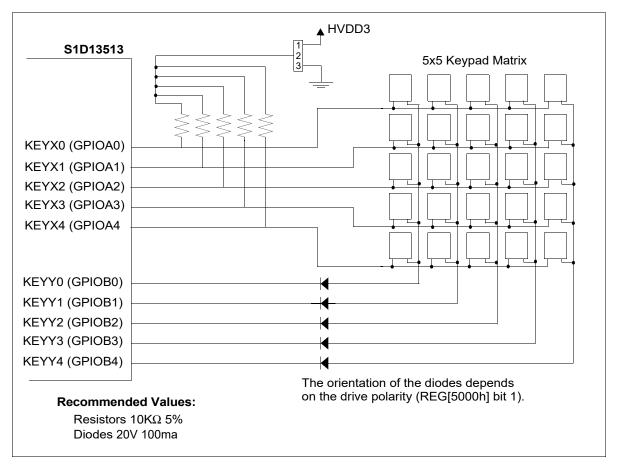

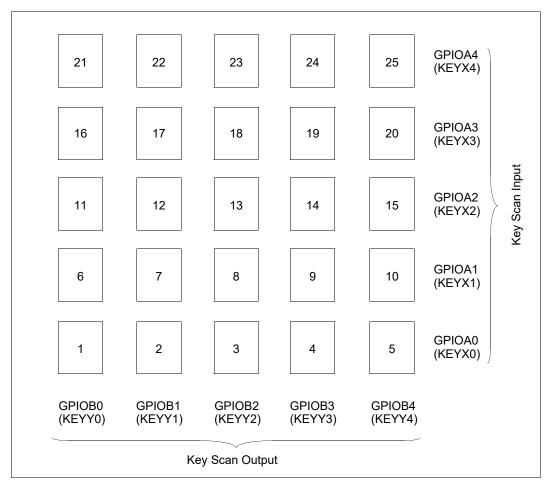

|    | 24.1 Keypad Interface Example Connection   |

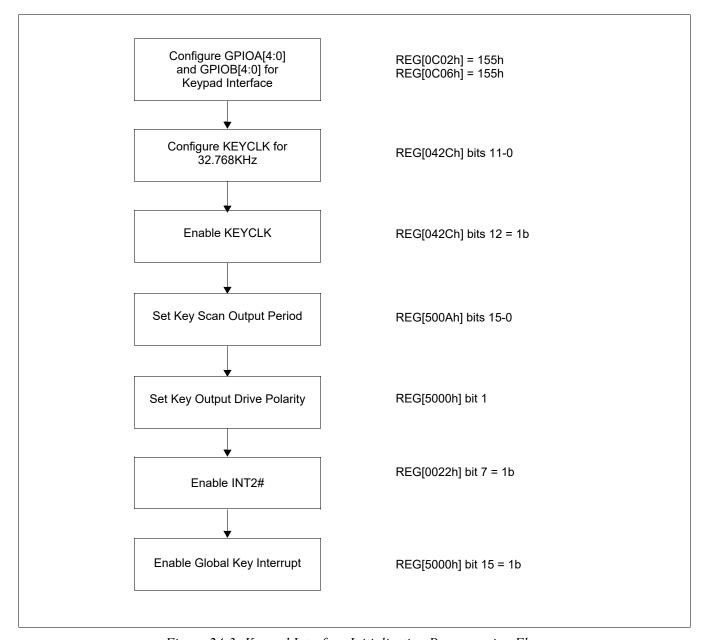

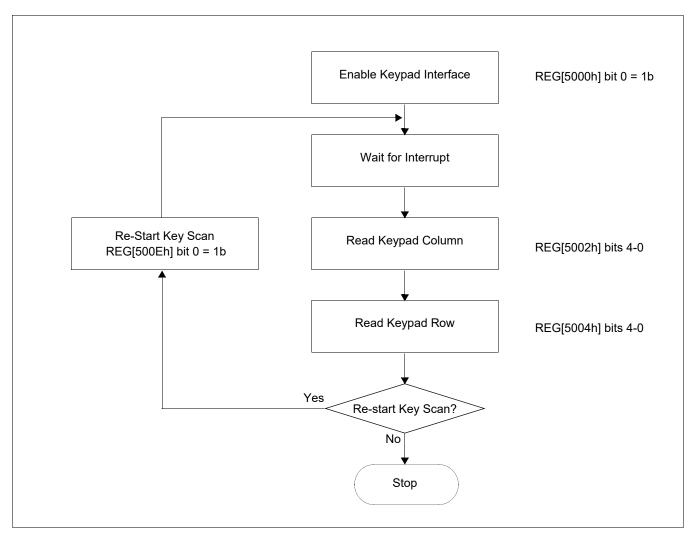

|    | 24.2 Key Scanning                          |

|    | 24.3 Example Programming Flows             |

| 25 | Crystal Oscillator Circuit                 |

|    | Design Considerations                      |

|    | 26.1 Guidelines for PLL Power Layout       |

| 27 | Mechanical Data                            |

|    |                                            |

| 28 | Change Record                              |

# 1 Introduction

# 1.1 Scope

This is the Hardware Functional Specification for the S1D13513 LCD Display Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at vdc-documentation@ea.epson.com.

# 1.2 Overview Description

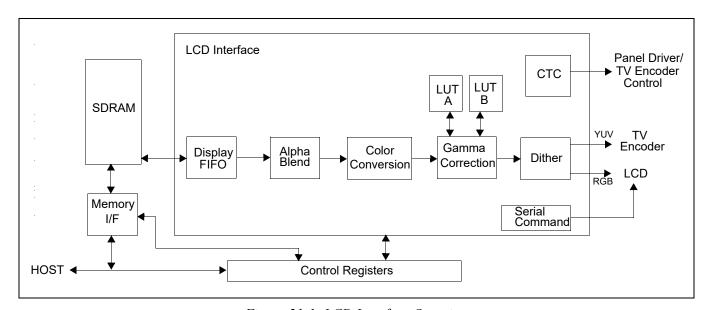

The S1D13513 is a highly integrated Display Controller capable of outputting to LCD or TV. With the flexibility of an external SDRAM memory interface, this low cost, low power, device supports a wide range of CPUs, panels, and a camera port that can be configured as 2x 8-bit ports. The S1D13513 feature set and architecture are designed to meet the requirements of embedded systems such as Mobile Communications, Hand-Held PC's, Office Automation, and Automotive applications.

The S1D13513 features both Sprite and 2D BitBLT engines designed to reduce the load on the Host, while increasing the performance of graphics intensive operations. Additionally, the S1D13513 offers such features as multiple windows, alpha blending, gamma correction, and mirror/rotation function which allow user configurability of various images on the Main/PIP1/PIP2 displays. While focusing on devices targeted by the Microsoft Windows CE Operating System, the S1D13513's impartiality to CPU type or operating system makes it an ideal display solution for a wide variety of applications.

# 1.3 Package Limitations

The S1D13513 is available in two package formats: PBGA 256-pin and QFP22 208-pin. However, the QFP package has less pins and does not support the full feature set of the S1D13513. The following features are not available on the QFP package of the S1D13513.

- x32 SDRAM is not supported (x16 SDRAM only)

- 256Mbit (32M byte) and 512Mbit (64M byte) SDRAM sizes are not supported

- 24-bit TFT is not supported (18-bit TFT maximum)

- Camera2 interface is not available (only Camera1 interface multiplexed with YUV Digital Out)

- Keypad Interface is not available

- INT2# is not supported (INT1# only)

# 2 Features

# 2.1 Memory

- Uses external SDRAM or mobile SDRAM as the display buffer (no embedded memory)

- External memory can be used for certain 2D BitBLT and Sprite functions

- Memory is addressable using direct or indirect access modes

- Linear access to the first 1M bytes of memory and four configurable 256K byte windows into the remaining area

- SDRAM Interface

- Supports up to 100MHz SDRAM bus clock

- Supports x16 and x32 SDRAM interfaces (x32 only available for PBGA package)

- Supports 8/16/32/64M bytes of 4 bank SDRAM (32/64M bytes only supported for PBGA package)

- Supports 8/16/32/64M bytes of 4 bank Mobile SDRAM (32/64M bytes only supported for PBGA package)

- Low power design

- Automatic re-entry into self refresh mode

#### Note

For memory usage guidelines, see Section 18.2, "Memory Bandwidth" on page 420.

#### 2.2 CPU Interfaces

- Direct and indirect interface support of the following 16-bit CPU interfaces:

- Generic MPU bus interface

- Renesas SH-4 / SH-3

- MIPS/ISA bus interface

- FreeScale MC68K Bus1 type interface

- FreeScale MC68K Bus2 type interface

- FreeScale PowerPC bus interface

- Philips PR31500/PR31700 (16-bit memory accesses only)

- Toshiba TX3912 (16-bit memory accesses only)

- FreeScale MPC555 with Burst Transfer

- · Serial Host Interface

- Registers are memory-mapped M/R# input selects between memory and register address space

# 2.3 Panel Interface Support

- RGB interface single-panels

- Color TFT Panels

- 16/18/24-bit interface (24-bit panels are not supported for QFP package)

- Generic TFT/TFD interface

- HR-TFT interface

- Passive Panels

- 8-bit Monochrome (PIP2 window is not supported for passive panels)

- 8-bit Color Type 2 (PIP2 window is not supported for passive panels)

- Passive panels have additional maximum display size limitations. Please contact your EPSON representative for details.

- Optional serial command interface supports:

- TFT w/µ-Wire interface (16-bit)

- EPSON ND-TFD 4 pin interface (8-bit)

- EPSON ND-TFD 3 pin interface (9-bit)

- 8/24-bit command interface

- Panel Resolution Examples

- For memory usage guidelines, see Section 18.2, "Memory Bandwidth" on page 420.

- YUV Digital Output (YUV 4:2:2) which supports NTSC/PAL format TV via an external video encoder (i.e. ADV7170)

## 2.4 Display Features

- Multiple window (layer) support

- Main window and PIP1 window (if enabled) form the View Port (bottom layer)

- 8/16/32 bit-per-pixel (bpp) color depths

- alpha blending is not supported for the View Port

- mirror and 180° rotation functions

- Main or PIP1 window can be double-buffered

- · optional gamma correction

- PIP2 window (if enabled) is the top layer (PIP2 is not supported for passive panels)

- 8/16/32 bit-per-pixel (bpp) color depths

- optional alpha blending function (ARGB 1:5:5:5 / ARGB 4:4:4:4 / ARGB 8:8:8:8 formats including alpha map)

- optional transparency function

- mirror and 180° rotation functions

- PIP2 window can be double-buffered

- · optional gamma correction

- Mirror and Rotation

- Mirror function performs a horizontal flip of the display image

- independent controls for View Port (Main/PIP window) and PIP2 window

- Rotation function performs a 180° counter-clockwise rotation of the display image

- independent controls for View Port (Main/PIP window) and PIP2 window

- Double-Buffering Support

- Double-buffered window is selectable from Main/PIP1/PIP2 window (only one window can be double-buffered at a time)

- · Automatically switches between front and back buffer

- Image data source can be from the Camera interface or the Sprite Engine

- · Alpha Blending

- Supports alpha blending between the View Port (Main + PIP1) and the PIP2 window

- 8-bit constant alpha value

- Dynamic alpha with alpha map

- Combined with transparency

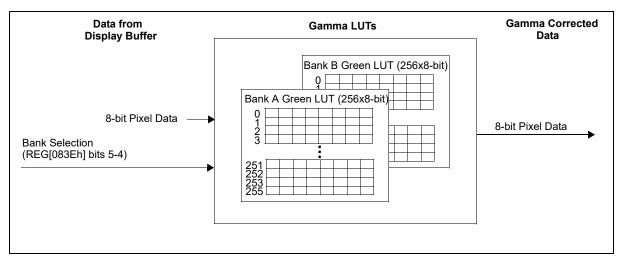

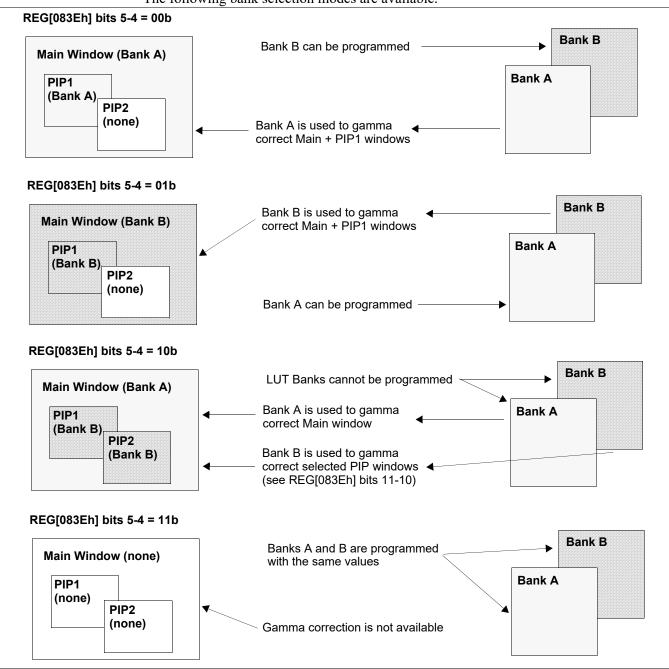

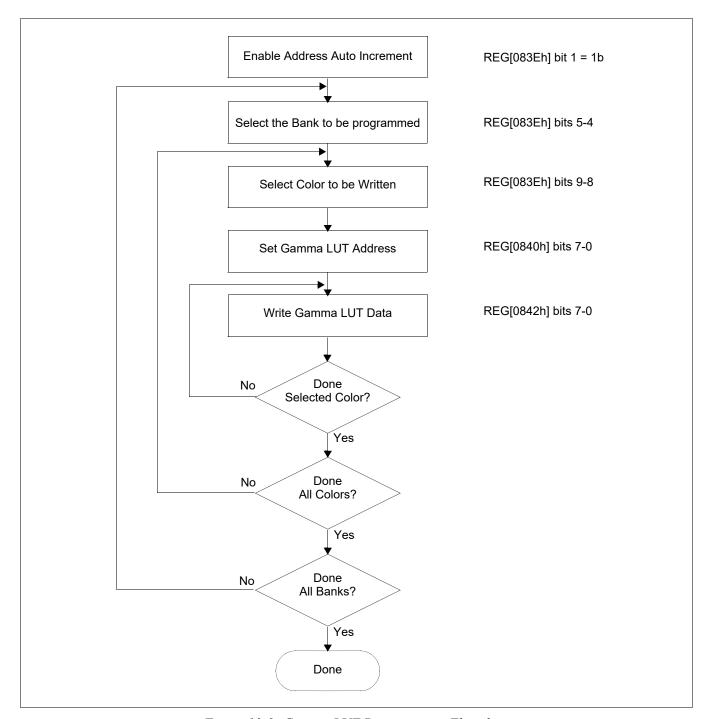

- Gamma Correction

- Selectable gamma correction for Main/PIP1/PIP2 windows

- 2 Gamma Correction Look-up Tables (Bank A and Bank B) using Single Port SRAM

- Independent color correction for each of RGB components

- View Port (Main+PIP1 window) can be dynamically switched between LUT banks

- · Async table access

- Pseudo Color Expansion

- · Async table access

- 2x2 Dither matrix

- 2x2 FRM

- Error Diffusion

- 2-bit color reduction

- Hardware cursor is available using the Sprite Engine

- Camera 1 or Camera 2 YUV image can be displayed in the PIP1 or PIP2 window

- · Interrupt support

- Maskable Non-Display (Vsync) interrupt

- Vsync interrupt assertion can be delayed a configurable number of lines

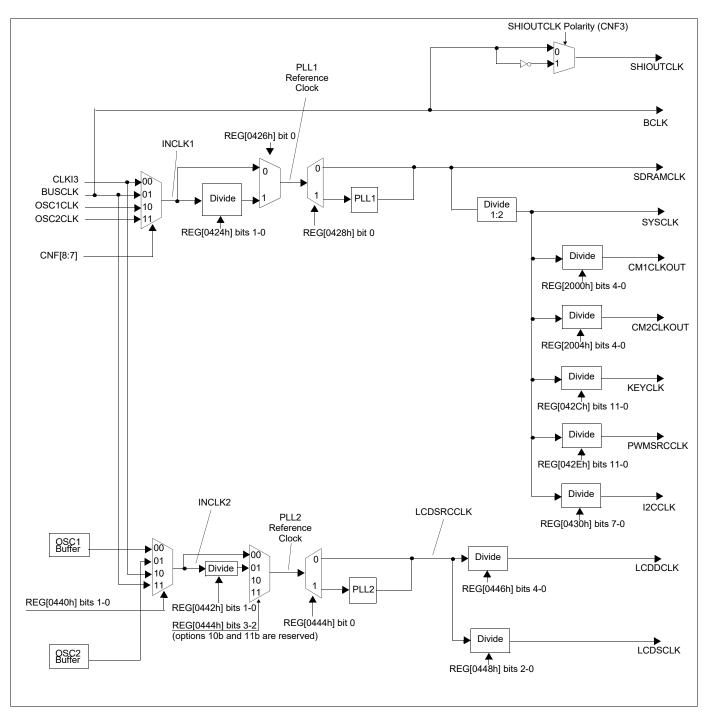

#### 2.5 Clock Source

- 2 embedded PLLs

- PLL1 source: BUSCLK, CLKI3, OSCI1/OSCO1, or OSCI2/OSCO2

- PLL2 source: BUSCLK, CLKI3, OSCI1/OSCO1, or OSCI2/OSCO2

- Two crystal inputs: OSCI1/OSCO1 and OSCI2/OSCO2

- Four digital inputs: BUSCLK, CLKI3, CMCLKIN1, CMCLKIN2

- Clock Outputs: MEMCLK, CMCLKOUT1, CMCLKOUT2

#### 2.6 2D Acceleration

- Supports 8/16/32 bit-per-pixel (bpp) color depths

- Linear or Rectangular data transfers for the Source or Destination

- 64-bit 2D BitBLT engine including:

Write BitBLT w/Color Expansion

Write BitBLT w/Transparency

Read BitBLT

Move BitBLT w/Reverse Direction

Move BitBLT w/Color Expansion

Move BitBLT w/Clipping

Move BitBLT w/Alpha Blending

Move BitBLT w/ROP

Move BitBLT w/Transparency

Solid Fill BitBLT

Pattern Fill BitBLT w/Transparency

# 2.7 Sprite Engine

- The Sprite Engine is a 2D animation accelerator which supports:

- up to 16 sprites, each with up to 16 frames to be displayed in a sequence

- Z-order value for each sprite which is used for alpha blending and transparency

- Image rotation and mirror settings specific for each sprite

- Optional arbitrary rotation settings for each sprite

- Sprite Source format: RGB 5:6:5, ARGB 1:5:5:5, ARGB 4:4:4:4, ARGB 8:8:8:8

- Sprite Output formats: RGB 3:3:2, RGB 5:6:5, RGB 8:8:8

- Sprite display size up to 1280 x 1280

- Sprite virtual image size up to 8192 x 8192

- Alpha Blending

- Up to 256 pattern sequential animation function

#### 2.8 Command FIFO

- Command FIFO is designed to reduce CPU load when issuing BitBLT and Sprite commands

- Allows up to a maximum of 64 entries

- BitBLT and Sprite commands can be mixed within the Command FIFO. However, the BitBLT and Sprite Engines cannot be performing operations simultaneously.

- Command FIFO automatically sends the next command to the BitBLT/Sprite engine as soon as it is available

- Commands are sent to the FIFO by writing to register space

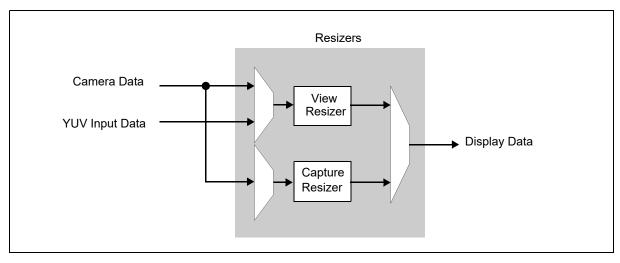

#### 2.9 Camera Interface

- Dual Port Camera Interface

- Configurable as two 8-bit camera interfaces or one 16-bit camera interface

- YUV 4:2:2 input format (8 or 16-bit)

- Optionally capture raw JPEG data from a JPEG capable camera

- Supports ITU-R BT656 (CCIR-656) YUV format

- Camera strobe function

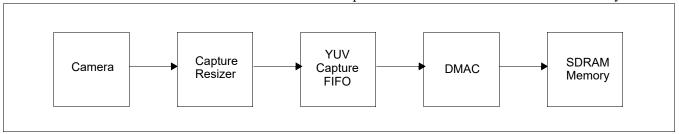

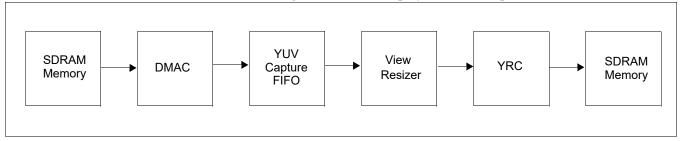

- Dual resizers allow resizing of YUV data for both the Capture and View path

- YUV image data can be "Captured" and stored into SDRAM as YUV 4:2:2 format

- YUV image data can be "Viewed" (or displayed) on the LCD or TV

#### Note

Camera2 8-bit input and Camera1 16-bit input are not available for QFP package.

#### 2.10 Miscellaneous

- Supports 20-50MHz Host bus clock

- Supports maximum 50MHz Internal System Clock

- Two IRQ output pins (INT2# pin is only available on PBGA package)

- IRQ Source (VSYNC, Delayed VSYNC, BitBLT done, Sprite Done, Etc.)

- I2C interface (typically used to program the Camera)

- PWM: 4 channel for backlight control

- Keypad Interface (only available on PBGA package)

- 5 x 5 matrix support

- Software initiated power save mode

- Clocks are dynamically turned off when modules are not needed

- General Purpose Input/Output pins are available

- Operating system independent

- Power Supplies:

- IO operates at 3.3 volts  $\pm$  0.3V

- Core operates at 1.8 volts  $\pm 0.15$ V

- Package Types:

- PBGA 256-pin package (17 x 17 x 1.7 mm, Ball pitch: 1.0 mm)

- QFP22 208-pin package (28 x 28 x 1.4 mm, Pin pitch: 0.5 mm)

#### Note

The QFP package does not support all S1D13513 features. For further information, refer to Section 1.3, "Package Limitations" on page 10.

# 3 System Diagram

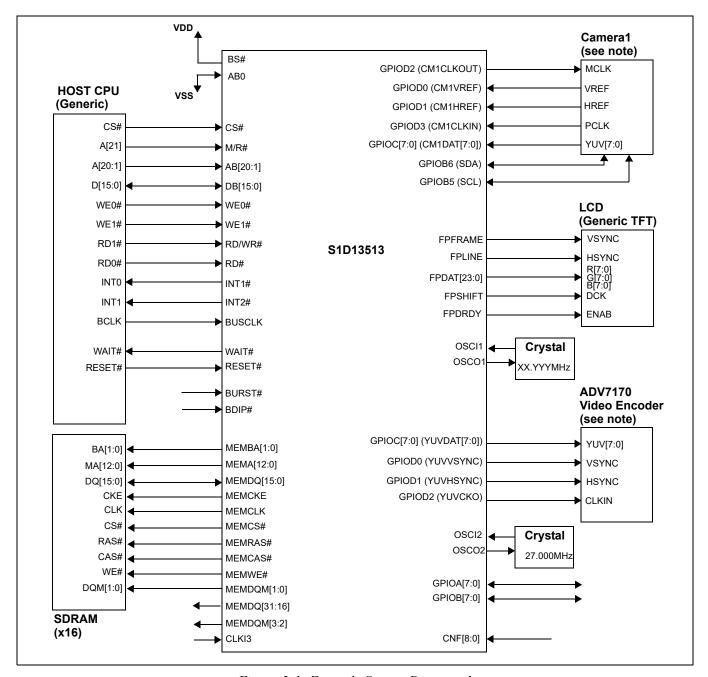

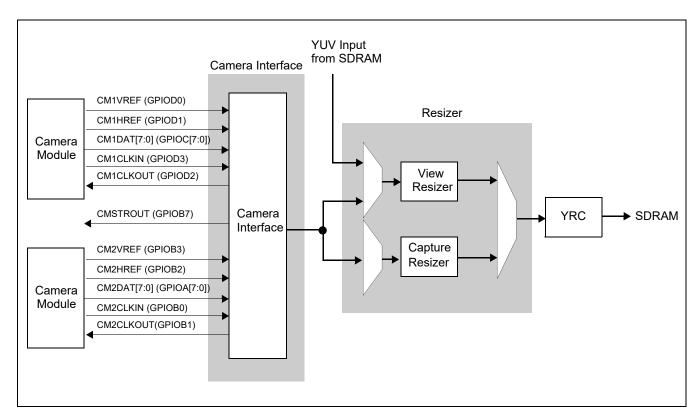

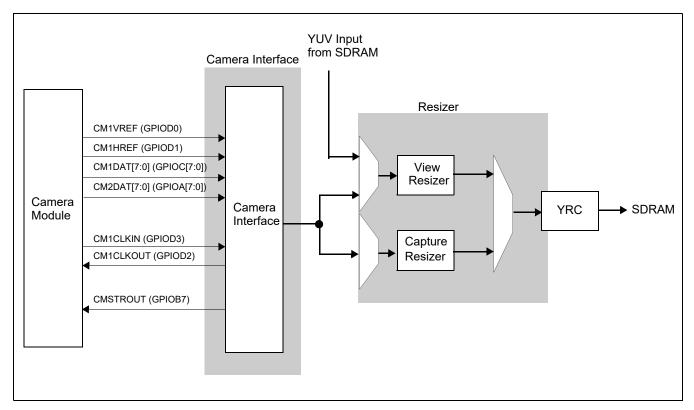

The following diagrams are examples of a typical system implementation. For detailed pin descriptions and pin mapping, refer to Section 5, "Pins" on page 21.

Figure 3-1: Example System Diagram 1

#### Note

For the above example system diagram, Camera1 and the ADV7170 Video Encoder cannot be active at the same time.

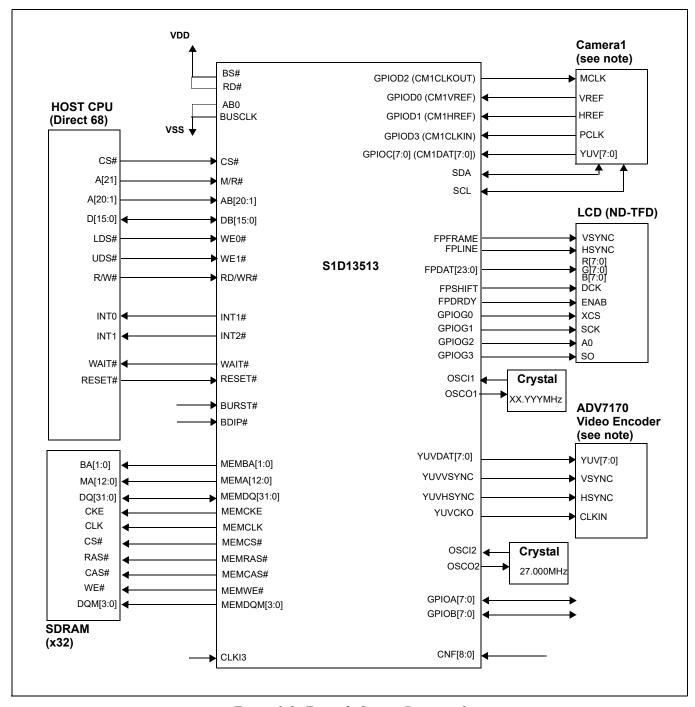

Figure 3-2: Example System Diagram 2

#### Note

For the above example system diagram, Camera1 and the ADV7170 Video Encoder cannot be active at the same time.

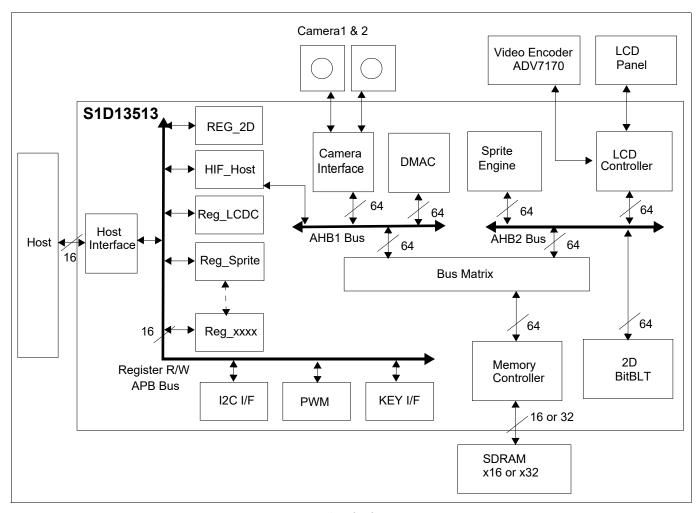

# 4 Block Diagram

Figure 4-1: Block Diagram

# 5 Pins

The S1D13513 is available in two package formats:

- PFBGA 256-pin

- QFP22 208-pin

However, the QFP package has less pins and does not support the full feature set of the S1D13513. For a summary of the QFP limitations, see Section 1.3, "Package Limitations" on page 10.

# 5.1 S1D13513 Pinout Diagrams

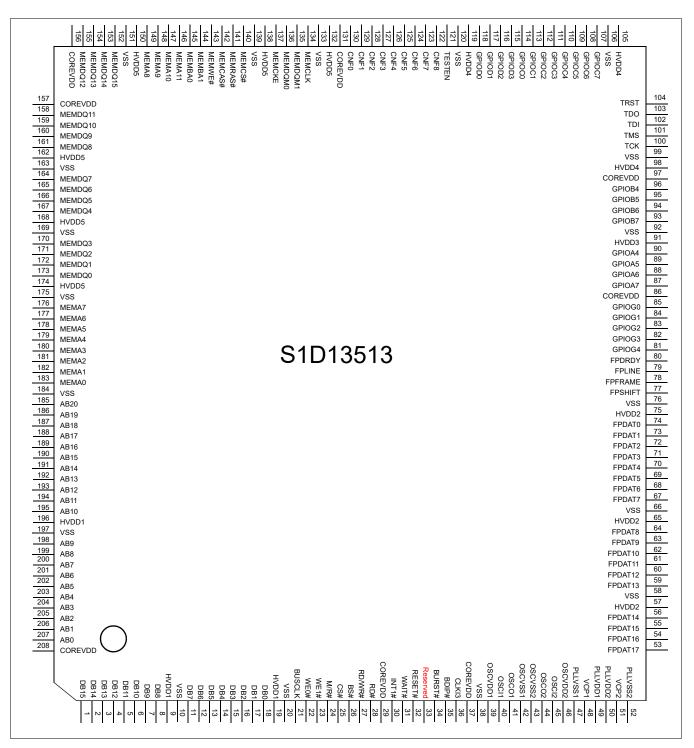

#### 5.1.1 QFP22 208-pin Pinout

Figure 5-1: OFP22-208 Pinout

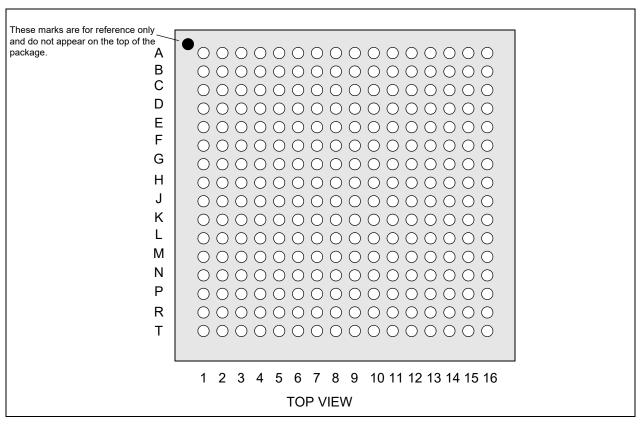

### 5.1.2 PBGA 256-pin Pinout

Figure 5-2: PBGA 256-pin Pinout

Table 5-1: PBGA 256-pin Pinout

|   | 1       | 2       | 3       | 4       | 5        | 6       | 7      | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15      | 16      |   |

|---|---------|---------|---------|---------|----------|---------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---|

| Α | VSS     | AB1     | AB3     | AB7     | AB8      | AB14    | AB15   | MEMA4   | MEMA7   | MEMDQ1  | MEMDQ22 | MEMDQ7  | MEMDQ24 | MEMDQ10 | MEMDQ27 | VSS     | Α |

| В | AB0     | AB2     | AB4     | AB6     | AB9      | AB13    | AB19   | МЕМА3   | HVDD5   | MEMDQ2  | MEMDQ4  | MEMDQ23 | MEMDQ25 | MEMDQ26 | MEMDQ11 | MEMDQ12 | В |

| С | DB15    | DB14    | COREVDD | AB5     | AB10     | AB11    | AB16   | MEMA2   | MEMDQ0  | MEMDQ3  | MEMDQ21 | HVDD5   | MEMDQ9  | COREVDD | MEMDQ28 | MEMDQ29 | С |

| D | DB13    | DB11    | DB12    | VSS     | HVDD1    | AB12    | AB18   | VSS     | MEMDQ16 | MEMDQ19 | MEMDQ5  | MEMDQ8  | VSS     | MEMDQ13 | MEMDQ14 | MEMDQ31 | D |

| Е | DB7     | HVDD1   | DB9     | DB10    | DB8      | AB17    | AB20   | MEMA1   | MEMA6   | MEMDQ18 | MEMDQ20 | MEMDQ6  | MEMDQ30 | MEMDQ15 | HVDD5   | MEMA8   | Е |

| F | DB1     | DB3     | DB5     | DB6     | DB4      | COREVDD | DB2    | MEMA0   | MEMA5   | MEMDQ17 | COREVDD | MEMA9   | MEMA10  | MEMA11  | MEMA12  | MEMBA0  | F |

| G | M/R#    | BUSCLK  | DB0     | HVDD1   | WE1#     | CS#     | VSS    | VSS     | VSS     | VSS     | HVDD5   | MEMBA1  | VSS     | MEMCAS# | MEMRAS# | MEMWE#  | G |

| Н | WE0#    | RD/WR#  | BS#     | RD#     | INT1#    | INT2#   | VSS    | VSS     | VSS     | VSS     | MEMCS#  | HVDD5   | MEMDQM0 | MEMDQM1 | MEMDQM2 | MEMCKE  | н |

| J | VSS     | WAIT#   | RESET#  | BURST#  | Reserved | BDIP#   | VSS    | VSS     | VSS     | VSS     | MEMDQM3 | HVDD5   | CNF1    | CNF3    | CNF0    | MEMCLK  | J |

| K | CLKI3   | VSS     | COREVDD | FPDAT23 | FPDAT19  | FPDAT7  | VSS    | VSS     | VSS     | VSS     | CNF2    | CNF5    | VSS     | CNF8    | CNF6    | CNF4    | ĸ |

| L | OSCI1   | OSCO1   | OSCVSS1 | OSCVDD1 | HVDD2    | COREVDD | FPDAT5 | HVDD2   | GPIOG0  | GPIOA6  | COREVDD | HVDD4   | GPIOD1  | GPIOD2  | TESTEN  | CNF7    | L |

| М | OSCI2   | OSCO2   | OSCVDD2 | OSCVSS2 | FPDAT10  | FPDAT6  | FPDAT0 | FPDRDY  | GPIOA7  | GPIOA5  | GPIOB7  | GPIOC1  | HVDD4   | GPIOC4  | GPIOD3  | GPIOD0  | М |

| Ν | VCP1    | PLLVSS1 | VSS     | FPDAT17 | FPDAT11  | VSS     | FPDAT1 | GPIOG4  | VSS     | GPIOA1  | GPIOB6  | TDI     | VSS     | GPIOC5  | GPIOC3  | GPIOC0  | N |

| Р | PLLVDD1 | PLLVDD2 | COREVDD | FPDAT16 | FPDAT20  | FPDAT9  | FPDAT4 | FPSHIFT | GPIOG1  | GPIOA0  | GPIOB1  | TCK     | TRST    | COREVDD | GPIOC6  | GPIOC2  | Р |

| R | VCP2    | PLLVSS2 | FPDAT22 | FPDAT14 | FPDAT18  | FPDAT8  | FPDAT3 | FPFRAME | GPIOG2  | GPIOA2  | HVDD3   | GPIOB2  | GPIOB0  | TMS     | TDO     | GPIOC7  | R |

| Т | VSS     | FPDAT15 | FPDAT21 | FPDAT13 | FPDAT12  | HVDD2   | FPDAT2 | FPLINE  | GPIOG3  | GPIOA3  | GPIOA4  | GPIOB3  | GPIOB5  | GPIOB4  | HVDD4   | VSS     | Т |

|   | 1       | 2       | 3       | 4       | 5        | 6       | 7      | 8       | 9       | 10      | 11      | 12      | 13      | 14      | 15      | 16      |   |

# 5.2 Pin Description

#### Key:

#### Pin Types

I = Input O = Output

IO = Bi-Directional (Input/Output)

P = Power pin

#### **RESET# States**

H = High level output

L = Low level output

Z = High Impedance (Hi-Z)

1 = Pull-up resistor on input

0 = Pull-down resistor on input

# = Active low level

Table 5-2: Cell Descriptions

| Cell     | Description                                                                       |

|----------|-----------------------------------------------------------------------------------|

| ILTR     | Low voltage transparent input                                                     |

| OLTR     | Low voltage transparent output                                                    |

| IC       | LVCMOS input                                                                      |

| ICD1     | LVCMOS input with pull-down resistor (50kΩ@3.3V)                                  |

| ICD2     | LVCMOS input with pull-down resistor (100kΩ@3.3V)                                 |

| ICU1     | LVCMOS input with pull-up resistor (50kΩ@3.3V)                                    |

| ICS      | LVCMOS schmitt input                                                              |

| ICSD1    | LVCMOS schmitt input with pull-down resistor (50kΩ@3.3V)                          |

| ICSP1    | LVCMOS schmitt input with pull-up resistor (50kΩ@3.3V)                            |

| ICSP2    | LVCMOS schmitt input with pull-up resistor (100kΩ@3.3V)                           |

| OTLN4    | Low noise output buffer (4mA@3.3V, deltaV = 0.4V)                                 |

| OTLN8    | Low noise output buffer (8mA@3.3V, deltaV = 0.4V)                                 |

| BLNC4D1  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-down resistor (50kΩ@3.3V)         |

| BLNC4D2  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-down resistor (100kΩ@3.3V)        |

| BLNC4P1  | Low noise LVCMOS IO buffer (4mA@3.3V) with pull-up resistor (50kΩ@3.3V)           |

| BLNCS4D1 | Low noise LVCMOS schmitt IO buffer (4mA@3.3V) with pull-down resistor (50kΩ@3.3V) |

| Р        | Power                                                                             |

#### 5.2.1 Host Interface

Many of the host interface pins have different functions depending on the host bus interface that is selected using the CNF[6:0] pins (see Section 5.3, "Summary of Configuration Options" on page 41). To determine the pin mapping and pin functions for each host bus interface, refer to Table 5-11:, "Host Bus Interface Pin Mapping 1 (Direct Interfaces)," on page 44, Table 5-12:, "Host Bus Interface Pin Mapping 2 (Indirect Interfaces)," on page 45, Table 5-13:, "Host Bus Interface Pin Mapping 3 (Direct Interfaces)," on page 46, and Table 5-14:, "Host Bus Interface Pin Mapping 4 (Indirect Interfaces)," on page 47.

Table 5-3: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin#         | PBGA<br>Ball #                                                                         | Cell    | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|---------------------|----------------------------------------------------------------------------------------|---------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB[20:0] | ı    | 185-195,<br>198-207 | E7,B7,D7,<br>E6,C7,A7,<br>A6,B6,D6,<br>C6,C5.B5.<br>A5.A4,B4,<br>C4,B3,A3,<br>B2,A2,B1 | ICD1    | HVDD1 | Z               | These input pins are System Address pins 20-0.  For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                                                                                                                                          |

| DB[15:0] | Ю    | 1-8,11-18           | C1,C2,D1,<br>D3,D2,E4,<br>E3,E5,E1,<br>F4,F3,F5,<br>F2,F7,F1,G3                        | BLNC4D1 | HVDD1 | Z               | These input/output pins are System Data Bus pins 15-0.  For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                                                                                                                                  |

| CS#      | ı    | 25                  | G6                                                                                     | ICU1    | HVDD1 | Z               | <ul> <li>This input pin is Chip Select and has multiple functions configured according to the Host Bus Interface selected using CNF[4:0].</li> <li>For 1 CS# mode, this pin inputs the chip select signal (CS#).</li> <li>For 2 CS# mode, this pin inputs the memory chip select signal (CSM#).</li> <li>When the Serial Host Interface is selected, this pin is the Serial Host Chip Select (SCS#).</li> <li>For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.</li> </ul> |

Table 5-3: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | PBGA<br>Ball # | Cell   | Power  | RESET#<br>State | Description                                                                                                                                                                                                                             |

|----------|------|-------------|----------------|--------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |             |                |        |        |                 | This input pin has multiple functions.                                                                                                                                                                                                  |

|          |      |             |                |        |        |                 | <ul> <li>For 1 CS# mode, this pin selects between the<br/>display buffer and register address spaces.<br/>When M/R# is set high, the display buffer is<br/>accessed and when M/R# is set low the<br/>registers are accessed.</li> </ul> |

|          |      |             |                |        |        |                 | <ul> <li>For 2 CS# mode, this pin inputs the register<br/>chip select (CSR#).</li> </ul>                                                                                                                                                |

| M/R#     | I    | 24          | G1             | ICU1   | HVDD1  | Z               | For Indirect Host Bus Interfaces and Serial<br>Host Bus Interfaces, the internal pull-down<br>resistor is enabled and this pin must be left<br>unconnected.                                                                             |

|          |      |             |                |        |        |                 | For Serial Host Bus Interfaces, the internal<br>pull-down resistor is enabled and this pin must<br>be left unconnected.                                                                                                                 |

|          |      |             |                |        |        |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                   |

|          |      |             |                | ICU1   | HVDD1  |                 | This input pin has multiple functions.                                                                                                                                                                                                  |

|          |      |             | H4             |        |        |                 | <ul> <li>For the Generic interface, this pin is the lower<br/>byte read command (RD0#).</li> </ul>                                                                                                                                      |

|          |      |             |                |        |        |                 | For the Direct/Indirect 68 interface, this pin must<br>be connected to VDD.                                                                                                                                                             |

| RD#      | ı    | 28          |                |        |        | Z               | For the Direct/Indirect 80 Type 1 and Type 2 interfaces, this pin is the read enable signal (RD#).                                                                                                                                      |

|          |      |             |                |        |        |                 | For detailed pin functions for all other interfaces, refer to the Specification for each Host.                                                                                                                                          |

|          |      |             |                |        |        |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                   |

|          |      |             |                |        |        |                 | This input pin has multiple functions.                                                                                                                                                                                                  |

|          |      |             |                |        |        |                 | <ul> <li>For the Generic interface, this pin is the upper<br/>byte read command (RD1#).</li> </ul>                                                                                                                                      |

|          |      |             |                |        |        |                 | <ul> <li>For the Direct/Indirect 68 interface, this pin is<br/>the read/write signal (R/W#).</li> </ul>                                                                                                                                 |

| RD/WR#   |      | 27          | UЭ             | ICI I4 | HVDD1  | z               | <ul> <li>For the Direct/Indirect 80 Type 1 interface, this<br/>pin is the write enable signal (WE#).</li> </ul>                                                                                                                         |

| ND/WN#   | '    | 27          | H2             | ICU1   | TIVDDT |                 | <ul> <li>For the Direct/Indirect 80 Type 2 interface, this<br/>pin must be connected to VDD.</li> </ul>                                                                                                                                 |

|          |      |             |                |        |        |                 | For detailed pin functions for all other interfaces, refer to the Specification for each Host.                                                                                                                                          |

|          |      |             |                |        |        |                 | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                   |

Table 5-3: Host Interface Pin Descriptions

| Din Nama | Type | QFP  | PBGA   | Cell    | Power | RESET# | Pagarintian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|------|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Туре | Pin# | Ball # | Cell    | Power | State  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WE0#     | ı    | 22   | H1     | ICU1    | HVDD1 | Z      | <ul> <li>This input pin has multiple functions.</li> <li>For the Generic interface, this pin is the lower byte write enable signal (WE0#).</li> <li>For the Direct/Indirect 68 interface, this pin is the lower data strobe (LDS#).</li> <li>For the Direct/Indirect 80 Type 1 interface, this pin is the lower byte enable signal (LBE#).</li> <li>For the Direct/Indirect 80 Type 2 interface, this pin is the lower byte write enable signal (WEL#).</li> <li>For detailed pin functions for all other interfaces, refer to the Specification for each Host.</li> <li>For detailed pin functions for each host bus</li> </ul> |

|          |      |      |        |         |       |        | interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |      |      |        |         |       |        | This input/output pin has multiple functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |      |      |        | BLNC4P1 | HVDD1 |        | <ul> <li>For the Generic interface, this pin is the upper<br/>byte write enable signal (WE1#).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |      |      |        |         |       |        | For the Direct/Indirect 68 interface, this pin is<br>the upper data strobe (UDS#).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |      | 23   |        |         |       |        | <ul> <li>For the Direct/Indirect 80 Type 1 interface, this<br/>pin is the upper byte enable signal (UBE#).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WE1#     | Ю    |      | G5     |         |       | Z      | <ul> <li>For the Direct/Indirect 80 Type 2 interface, this<br/>pin is the upper byte write enable signal<br/>(WEU#).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |      |      |        |         |       |        | For detailed pin functions for all other interfaces,<br>refer to the Specification for each Host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |      |      |        |         |       |        | For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |      |      |        |         |       |        | Note: For the MPC555 host interface, this pin is the burst inhibit output (BI#).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BS#      | I    | 26   | НЗ     | ICU1    | HVDD1 | Z      | This input pin has multiple functions. For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BURST#   | I    | 34   | J4     | ICU1    | HVDD1 | Z      | For the MPC555 interface, the internal pull-up on this pin is disabled. If this pin is not used, it must be connected to HVDD1. For all other interfaces, the internal pull-up is enabled and this pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                 |

| BDIP#    | ı    | 35   | J6     | ICU1    | HVDD1 | Z      | For the MPC555 interface, the internal pull-up on this pin is disabled. If this pin is not used, it must be connected to HVDD1. For all other interfaces, the internal pull-up is enabled and this pin must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 5-3: Host Interface Pin Descriptions

| Pin Name | Туре     | QFP<br>Pin# | PBGA<br>Ball # | Cell  | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|----------|-------------|----------------|-------|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT#    | 0        | 31          | J2             | OTLN4 | HVDD1 | Z               | During a data transfer, this output pin is driven active to force the system to insert wait states. It is driven inactive to indicate the completion of a data transfer. WAIT# is released to the high impedance state after the data transfer is complete. The active polarity is configured according to the Host Bus Interface selected using CNF[4:0]. For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44. |

| RESET#   |          | 32          | J3             | ICS   | HVDD1 | 1               | This active low input sets all internal registers to their default state and to force all signals to their inactive states.                                                                                                                                                                                                                                                                                                                                                      |

| RESET#   | <b>'</b> | 32          | 33             | 103   | нурот | '               | <b>Note:</b> For details on RESET# timing, refer to Section 7.3, "RESET# Timing" on page 62 and Section 7.2, "Power Supply Sequence" on page 60.                                                                                                                                                                                                                                                                                                                                 |

| BUSCLK   | ı        | 21          | G2             | ICU1  | HVDD1 | Z               | This input clock is typically used as an external clock source for the Host CPU Bus interface. For detailed pin functions for each host bus interface, see Section 5.4, "Host Bus Interface Pin Mapping" on page 44.                                                                                                                                                                                                                                                             |

|          |          |             |                |       |       |                 | For details on the S1D13513 clock structure, refer to Section 9, "Clocks" on page 124.                                                                                                                                                                                                                                                                                                                                                                                           |

| INT1#    | 0        | 30          | H5             | OTLN4 | HVDD1 | Z               | This output pin is the primary IRQ output from the S1D13513. When enabled (REG[002Ah] bit 15 = 1b), it can output all internal IRQ requests to the Host. The output and polarity is configurable using REG[002Ah].                                                                                                                                                                                                                                                               |

| INT2#    | 0        | _           | Н6             | OTLN4 | HVDD1 | Z               | This output pin is the secondary IRQ output from the S1D13513 and can output all internal IRQ requests to the Host. Additionally, it can be configured to serve as a dedicated output for a specific Interrupt (see REG[0022h). The output and polarity is configurable using REG[002Ah].                                                                                                                                                                                        |

|          |          |             |                |       |       |                 | Note: The QFP package does not support INT2#.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 5.2.2 LCD Interface

For a pin mapping summary for each panel type, refer to Table 5-15:, "LCD Interface Pin Mapping for TFT Panels," on page 48.

## Note

The QFP package does not support 24-bit panels.

Table 5-4: LCD Interface Pin Descriptions

| Table 5-4: LCD Interjace Pin Descriptions |      |                       |                                                                           |          |       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------------|------|-----------------------|---------------------------------------------------------------------------|----------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                  | Type | QFP<br>Pin#           | PBGA<br>Ball #                                                            | Cell     | Power | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| FPDAT[23:18]                              | Ю    | _                     | K4,R3,T3,<br>P5,K5,R5                                                     | BLNCS4D1 | HVDD2 | 0               | <ul> <li>These input/output pins have multiple functions.</li> <li>For 24-bit panels (REG[0800h] bits 10-8 = 011b), these bits are Panel Data bits 23-18. Note that GPIOH[5:0] must also be configured for 24-bit panels by setting REG[0C1Eh] bits 11-0 to 555h.</li> <li>For 18-bit panels (REG[0800h] bits 10-8 = 001b or 010b), these pins can be used as general purpose IO pins (GPIOH[5:0]). For details on configuring these pins as GPIOs, refer to Section 5.6, "GPIO Pin Mapping" on page 50.</li> <li>For passive panels, these pins can be used as general purpose IO pins (GPIOH[5:0]). For details on configuring these pins as GPIOs, refer to Section 5.6, "GPIO Pin Mapping" on page 50.</li> <li>Note: These pins have internal pull-down resistors that are controlled using REG[0468h] bits 13-8.</li> <li>Note: The QFP package does not support 24-bit TFT panels.</li> </ul> |  |

| FPDAT[17:0]                               | 0    | 53-56,<br>59-64,67-74 | N4,P4,T2,<br>R4,T4,T5,<br>N5,M5,P6,<br>R6,K6,M6,<br>L7,P7,R7,<br>T7,N7,M7 | OTLN4    | HVDD2 | L               | These output pins are Panel Data bits 17-0.  For a summary of pin usage for each panel type, see Section 5.5, "LCD Interface Pin Mapping" on page 48.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| FPFRAME                                   | 0    | 78                    | R8                                                                        | OTLN4    | HVDD2 | L               | This output pin is Frame Pulse for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| FPLINE                                    | 0    | 79                    | T8                                                                        | OTLN4    | HVDD2 | L               | This output pin is Line Pulse for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| FPSHIFT                                   | 0    | 77                    | P8                                                                        | OTLN4    | HVDD2 | L               | This output pin is Shift Clock for the LCD panel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

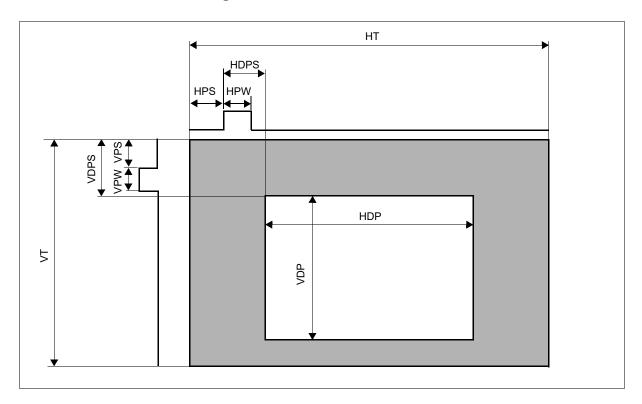

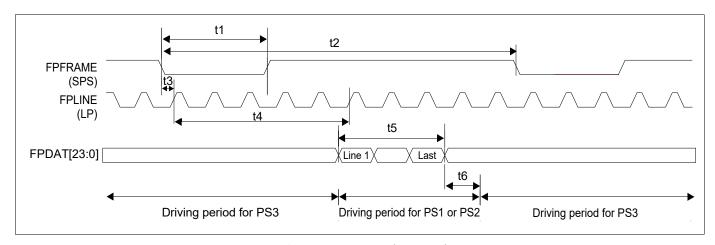

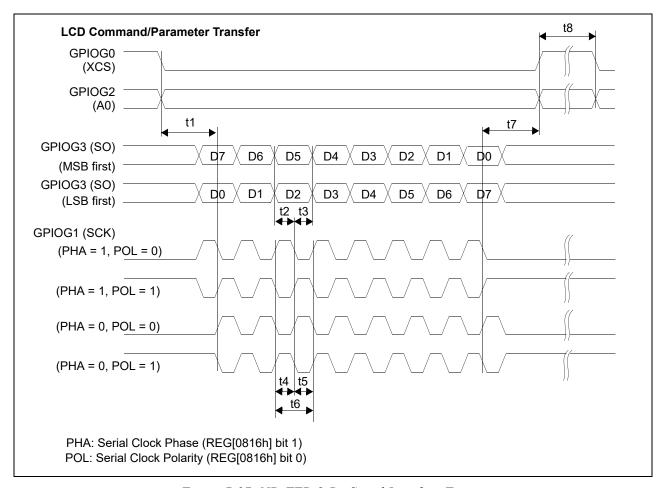

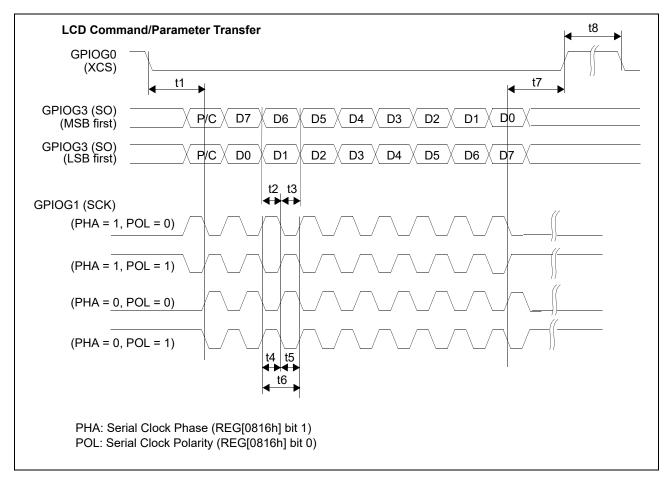

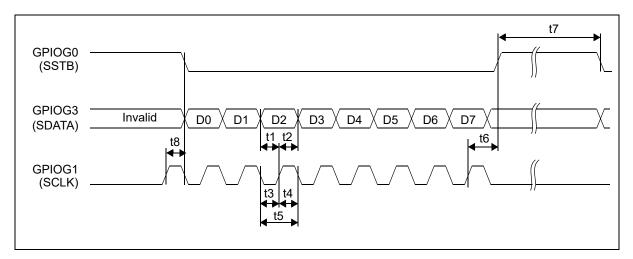

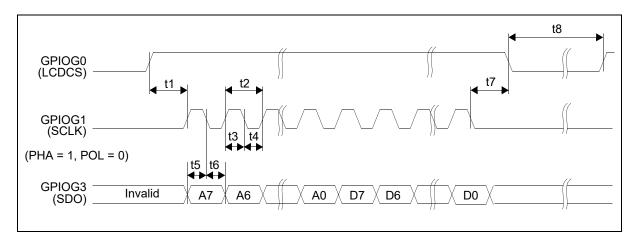

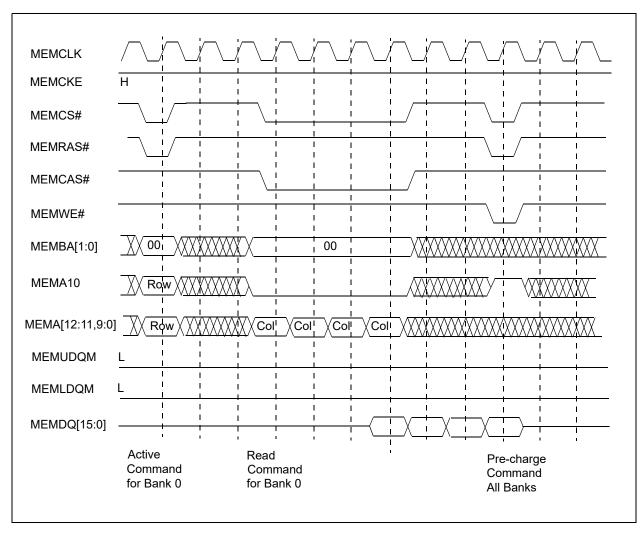

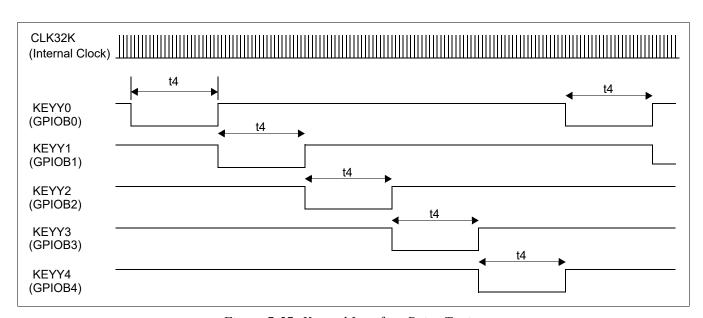

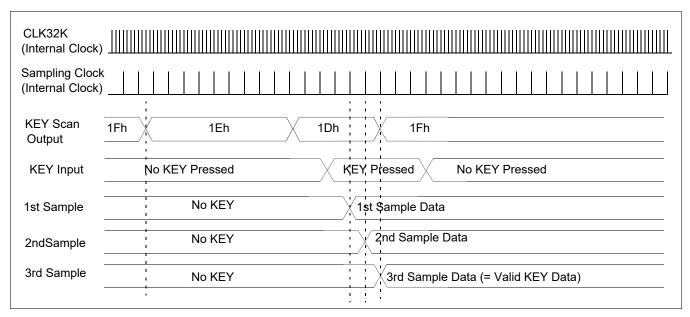

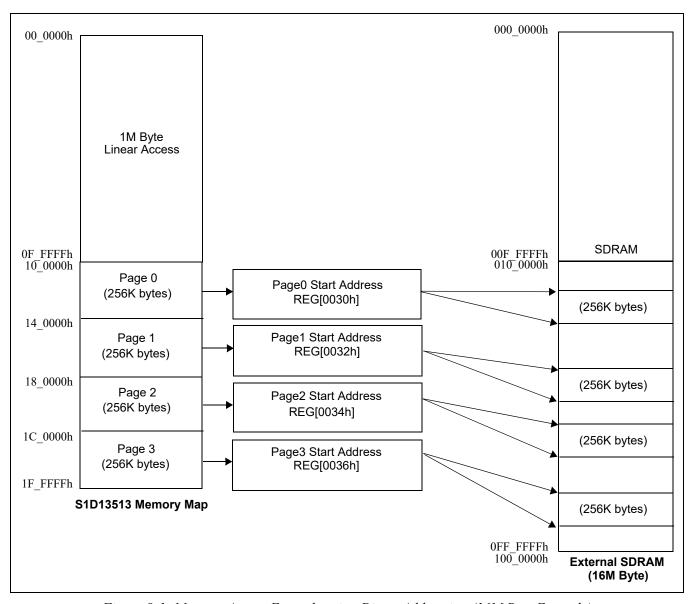

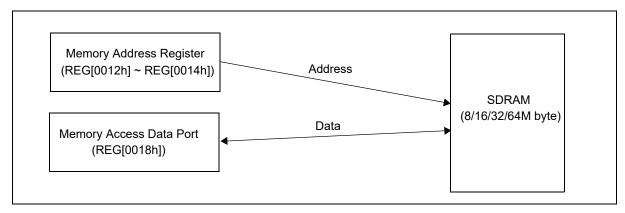

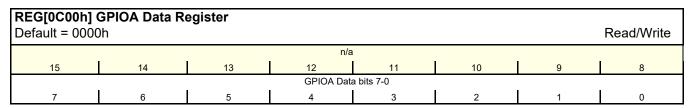

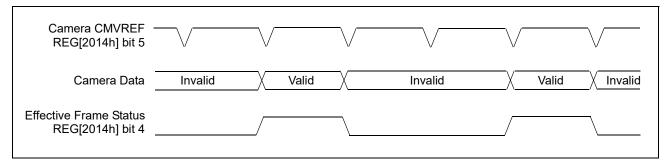

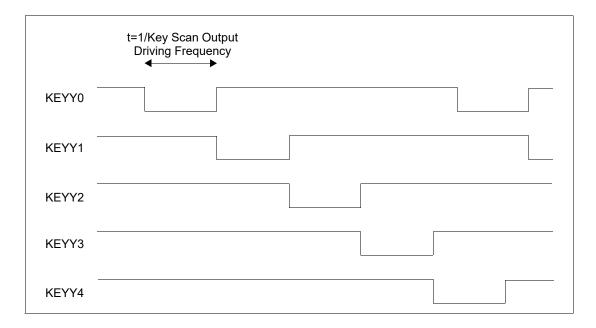

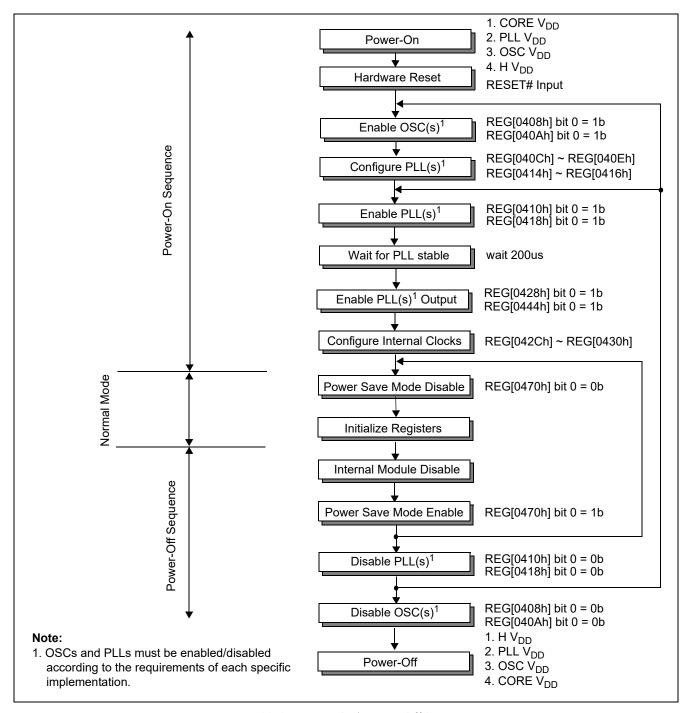

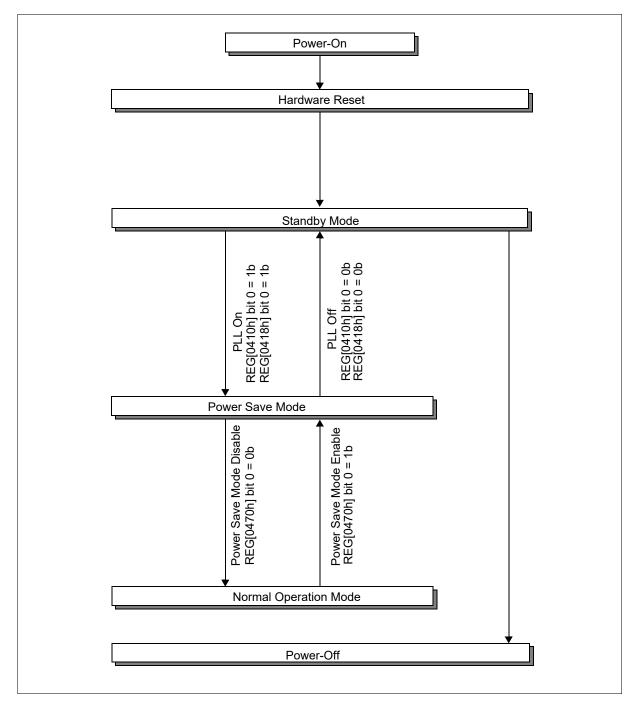

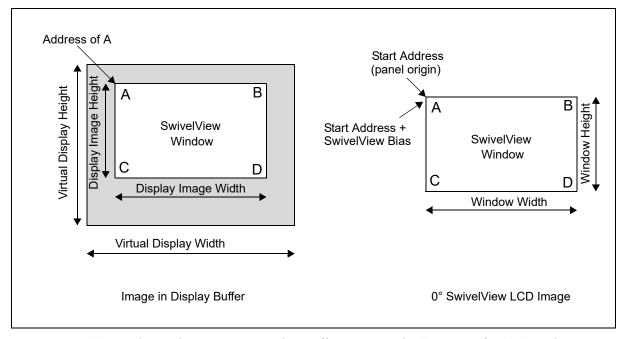

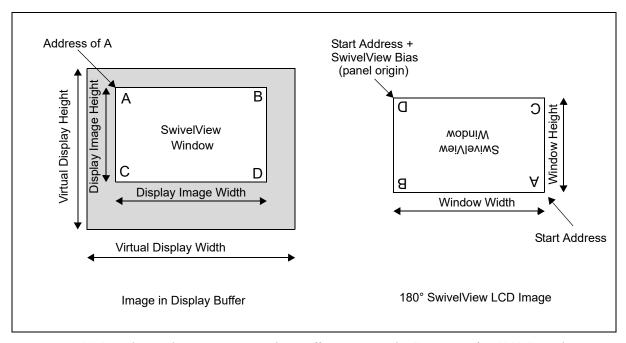

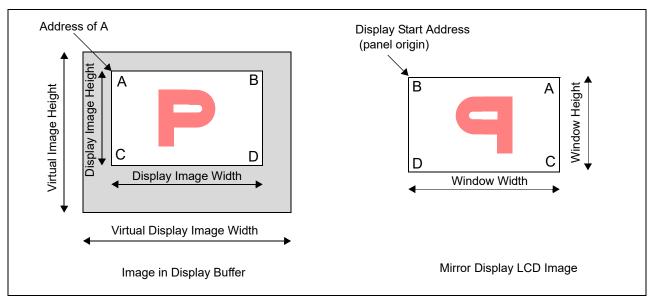

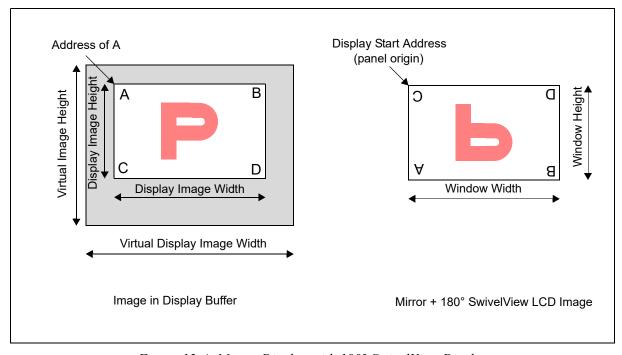

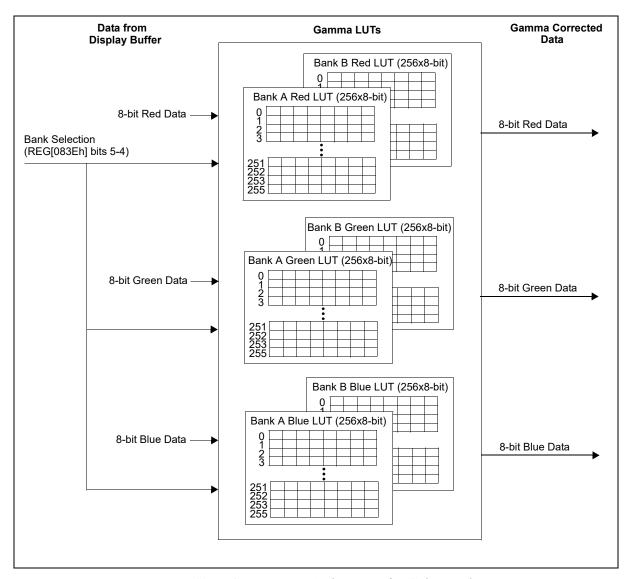

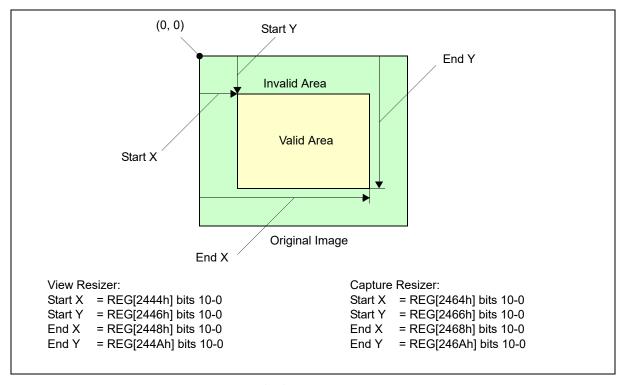

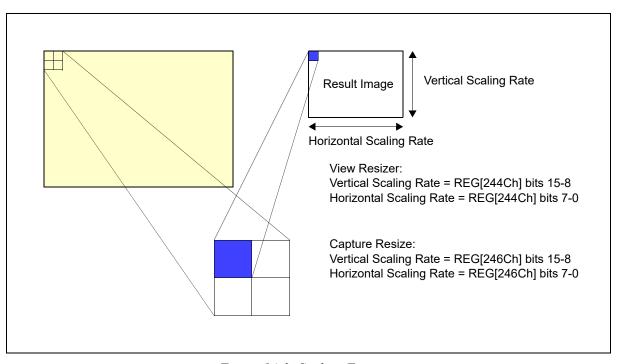

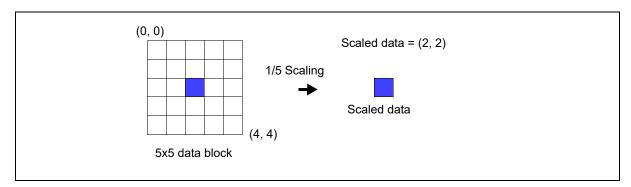

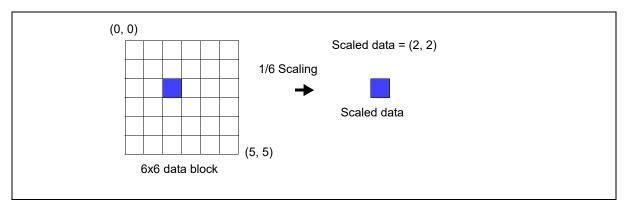

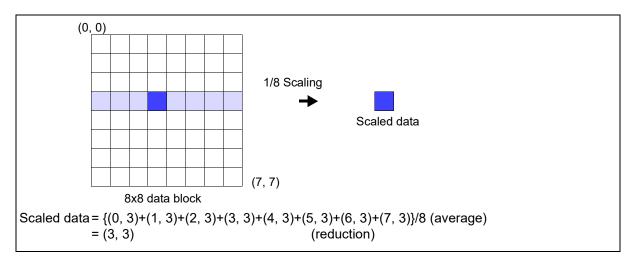

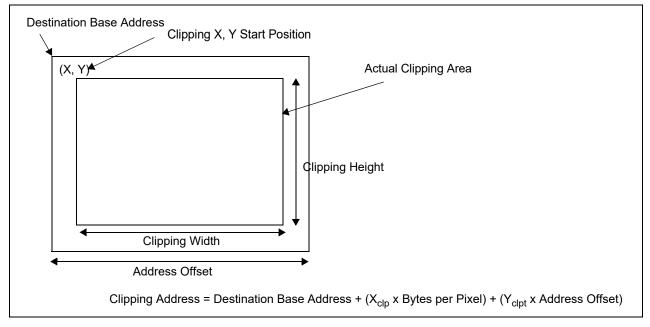

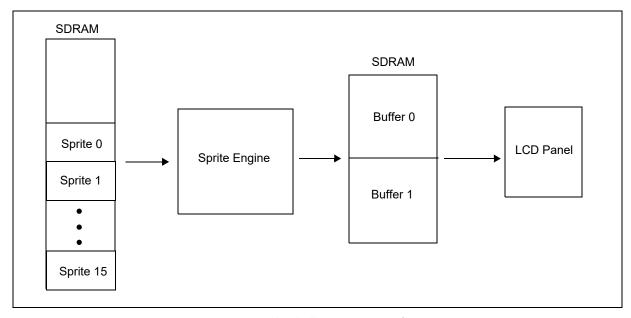

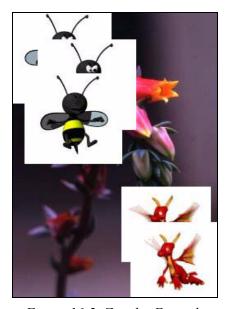

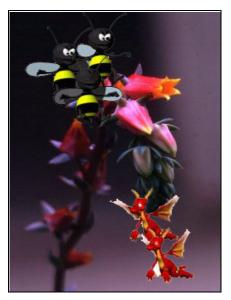

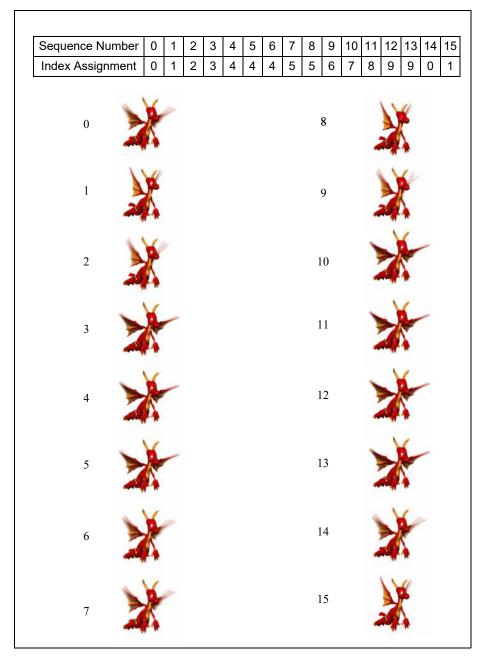

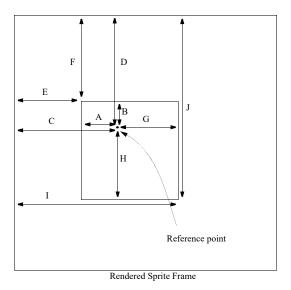

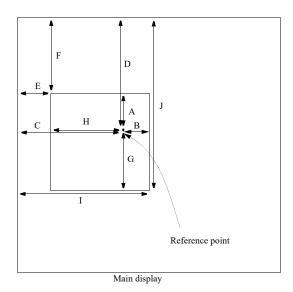

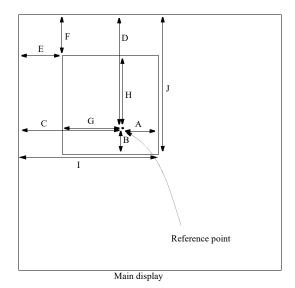

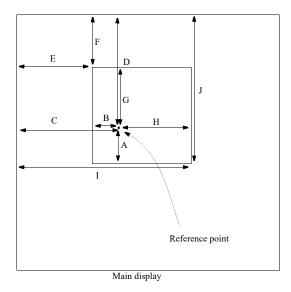

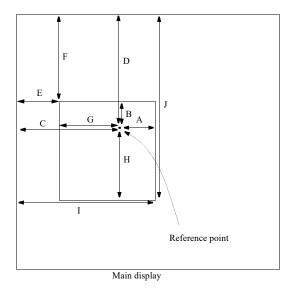

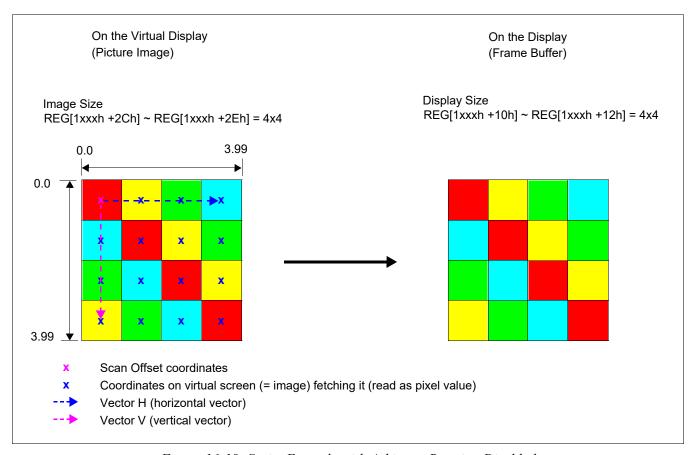

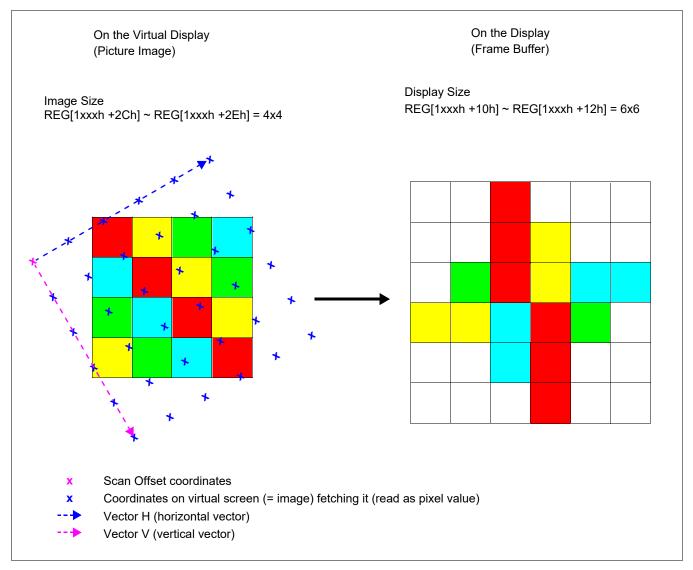

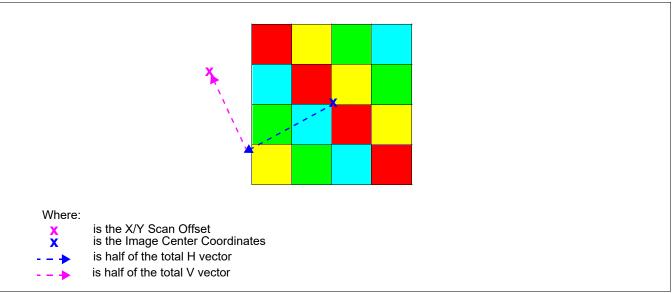

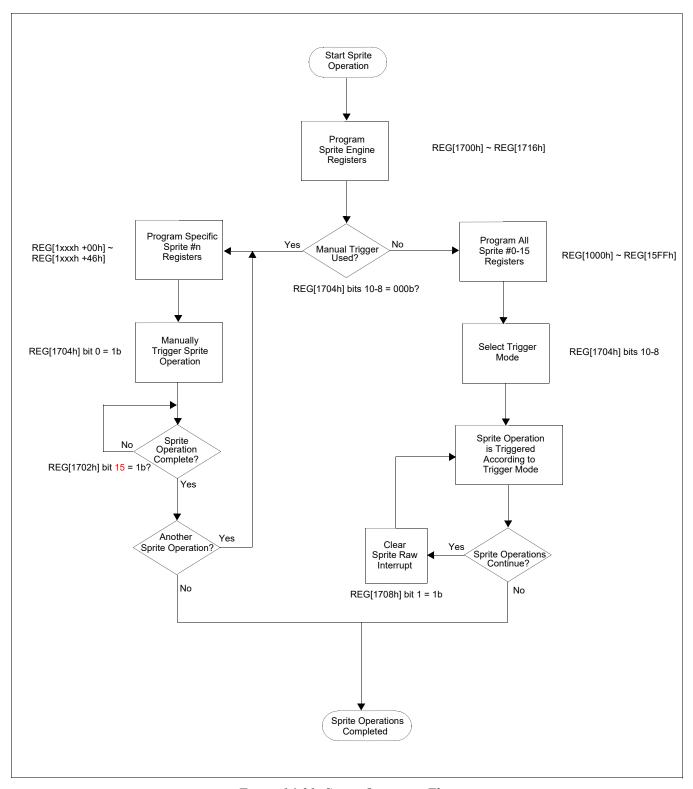

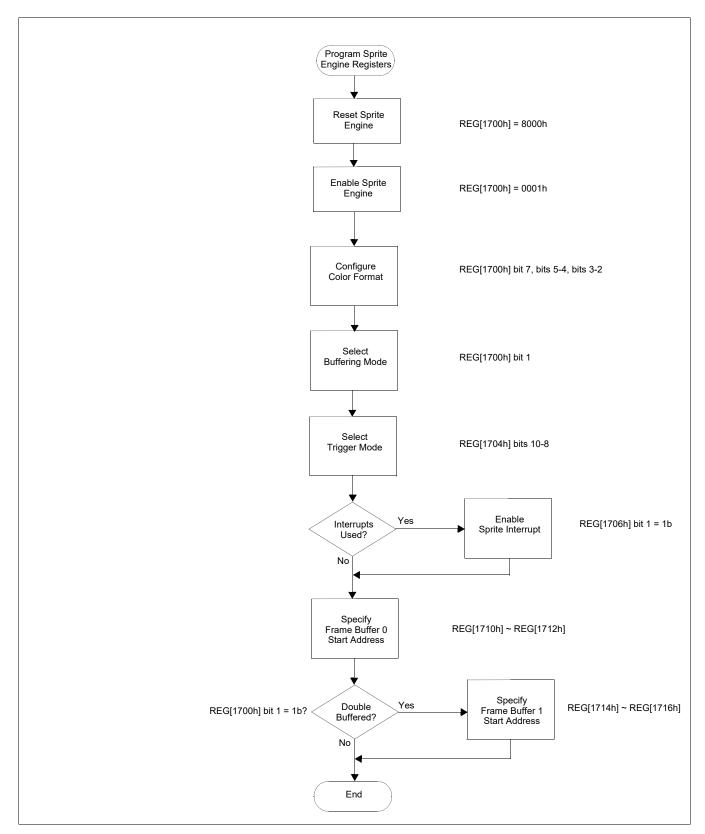

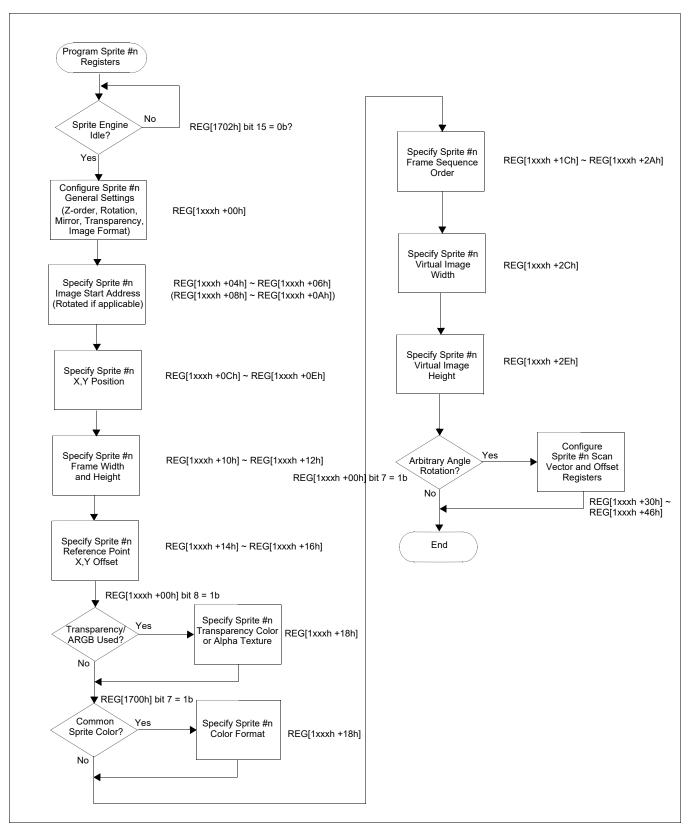

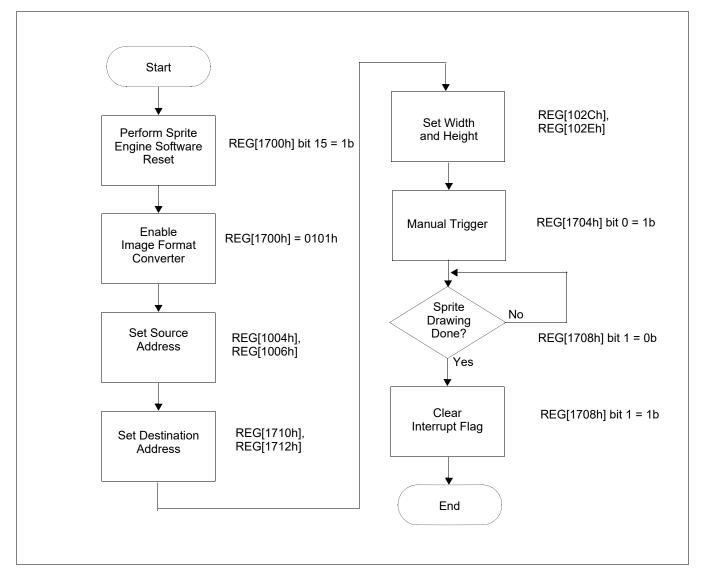

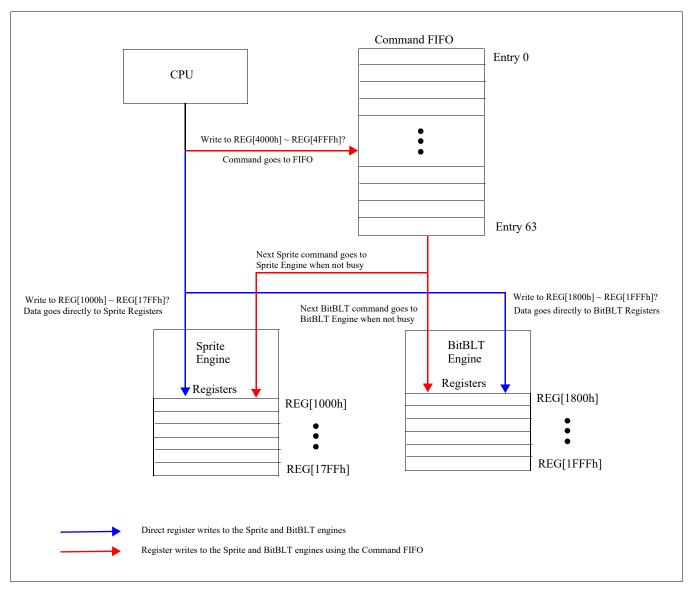

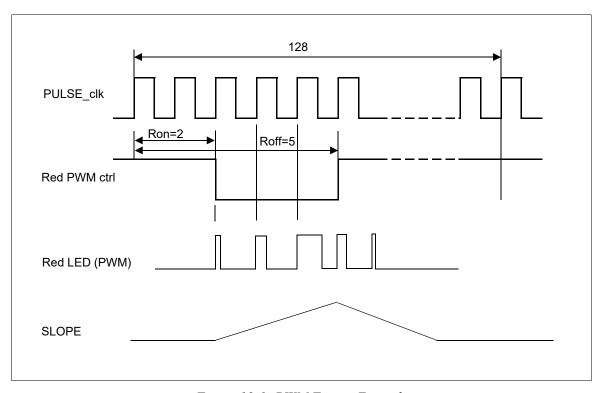

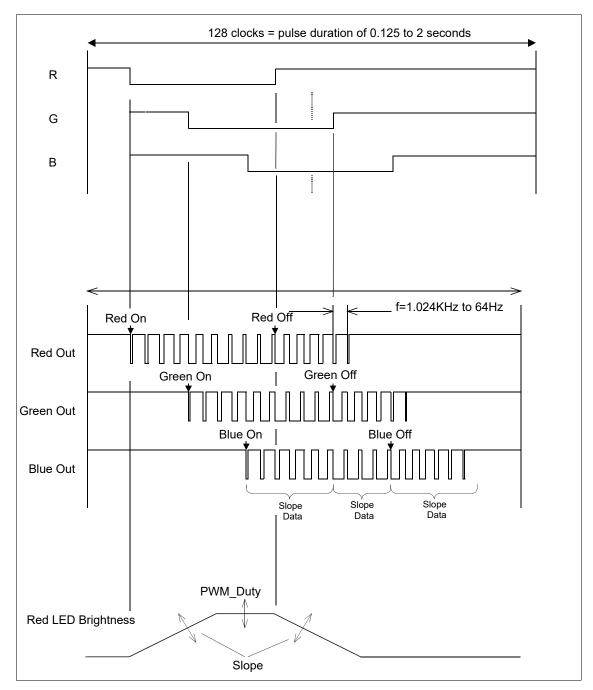

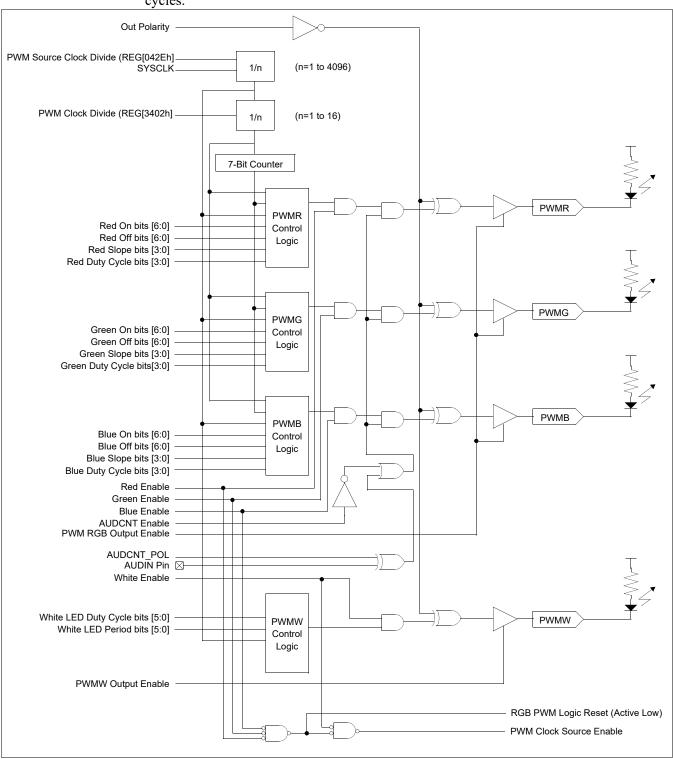

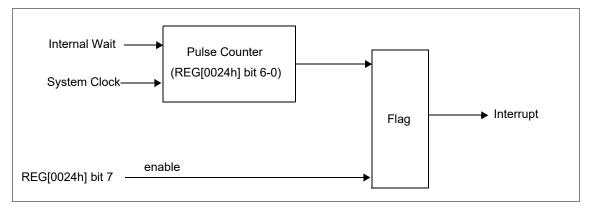

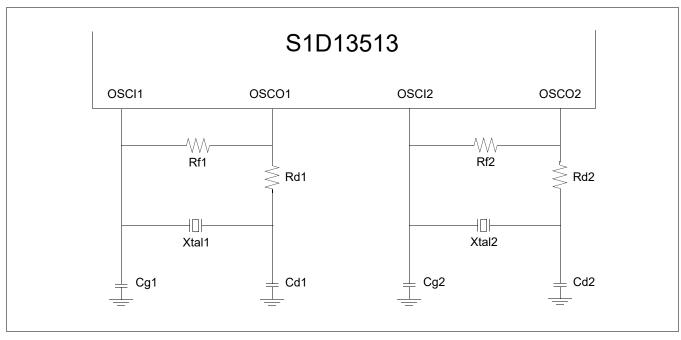

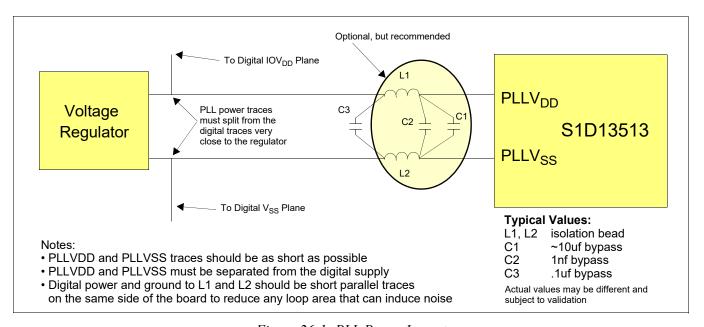

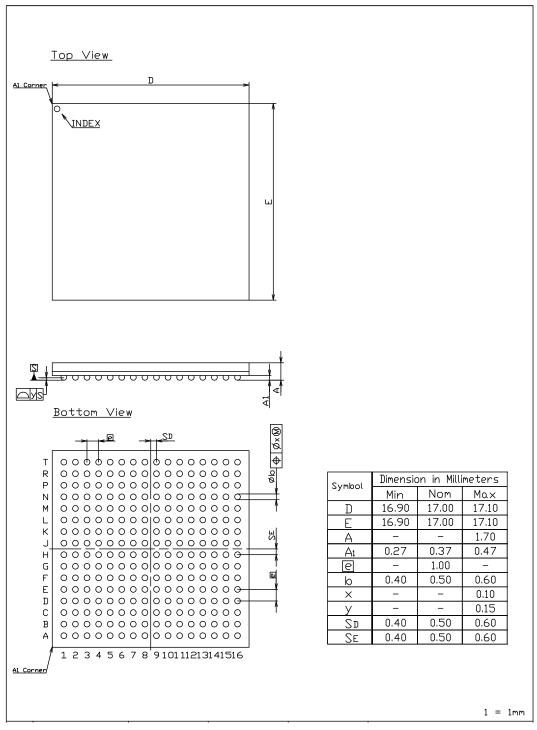

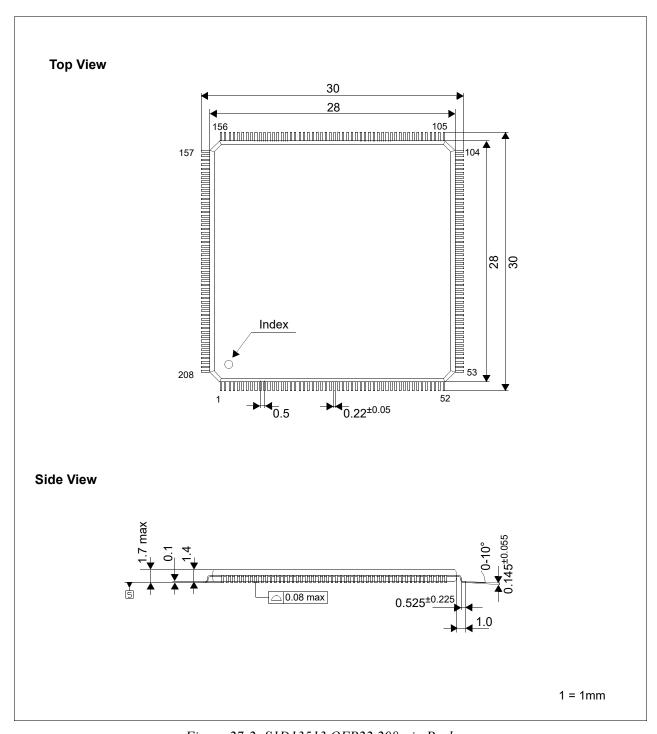

| FPDRDY                                    | 0    | 80                    | M8                                                                        | OTLN4    | HVDD2 | L               | This output pin has multiple functions.  • Display Enable (DRDY) for TFT panels  • LCD backplane bias signal (MOD) for passive LCD panels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |