CMOS 32-BIT SINGLE CHIP MICROCONTROLLER

**S1C31W74**

テクニカルマニュアル

## 評価ボード・キット、開発ツールご使用上の注意事項

1. 本評価ボード・キット、開発ツールは、お客様での技術的評価、動作の確認および開発のみに用いられる想定し設計されています。それらの技術評価・開発等の目的以外には使用しないでください。本品は、完成品に対する設計品質に適合していません。

2. 本評価ボード・キット、開発ツールは、電子エンジニア向けであり、消費者向け製品ではありません。お客様において、適切な使用と安全に配慮願います。弊社は、本品を用いることで発生する損害や火災に対し、いかなる責も負いかねます。通常の使用においても、異常がある場合は使用を中止してください。

3. 本評価ボード・キット、開発ツールに用いられる部品は、予告なく変更されることがあります。

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

2. 弊社製品のご購入およびご使用にあたりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページなどを通じて公開される最新情報に常にご注意ください。

3. 本資料に掲載されている応用回路、プログラム、使用方法などはあくまでも参考情報です。お客様の機器・システムの設計において、応用回路、プログラム、使用方法などを使用する場合には、お客様の責任において行ってください。これらに起因する第三者の知的財産権およびその他の権利侵害ならびに損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

4. 弊社は常に品質、信頼性の向上に努めていますが、一般的に半導体製品は誤作動または故障する場合があります。弊社製品のご使用にあたりましては、弊社製品の誤作動や故障により生命・身体に危害を及ぼすこと又は財産が侵害されることのないように、お客様の責任において、お客様のハードウェア、ソフトウェア、システムに必要な安全設計を行うようお願いします。なお、設計および使用に際しては、弊社製品に関する最新の情報(本資料、仕様書、データシート、マニュアル、弊社ホームページなど)をご確認いただき、それに従ってください。また、上記資料などに掲載されている製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価を行い、お客様の責任において適用可否の判断をお願いします。

5. 弊社は、正確さを期すために慎重に本資料およびプログラムを作成しておりますが、本資料およびプログラムに掲載されている情報に誤りがないことを保証するものではありません。万一、本資料およびプログラムに掲載されている情報の誤りによってお客様に損害が生じた場合においても、弊社は一切その責任を負いかねます。

6. 弊社製品の分解、解析、リバースエンジニアリング、改造、改変、翻案、複製などは堅くお断りします。

7. 弊社製品は、一般的な電子機器(事務機器、通信機器、計測機器、家電製品など)および本資料に個別に掲載されている用途に使用されることを意図して設計、開発、製造されています(一般用途)。特別な品質、信頼性が要求され、その誤動作や故障により生命・身体に危害を及ぼす恐れ、膨大な財産侵害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある以下の特定用途に使用されることを意図していません。お客様に置かれましては、弊社製品を一般用途に使用されることを推奨いたします。もし一般用途以外の用途で弊社製品のご使用およびご購入を希望される場合、弊社はお客様の特定用途に弊社製品を使用されることへの商品性、適合性、安全性について、明示的・黙示的に関わらずいかなる保証を行うものではありません。お客様が特定用途での弊社製品の使用を希望される場合は、弊社営業窓口まで事前にご連絡の上、承諾を得てください。

### 【特定用途】

宇宙機器(人工衛星・ロケットなど) / 輸送車両並びにその制御機器(自動車・航空機・列車・船舶など)

医療機器(本資料に個別に掲載されている用途を除く) / 海底中継機器 / 発電所制御機器 / 防災・防犯装置

交通用機器 / 金融関連機器

上記と同等の信頼性を必要とする用途

8. 本資料に掲載されている弊社製品および当該技術を国内外の法令および規制により製造・使用・販売が禁止されている機器・システムに使用することはできません。また、弊社製品および当該技術を大量破壊兵器等の開発および軍事利用の目的その他軍事用途等に使用しないでください。弊社製品または当該技術を輸出または海外に提供する場合は、「外国為替及び外国為替法」、「米国輸出管理規則(EAR)」、その他輸出関連法令を遵守し、係る法令の定めるところにより必要な手続きを行ってください。

9. お客様が本資料に掲載されている諸条件に反したことに起因して生じいかなる損害(直接・間接を問わず)に関して、弊社は一切その責任を負いかねます。

10. お客様が弊社製品を第三者に譲渡、貸与などをしたことにより、損害が発生した場合、弊社は一切その責任を負いかねます。

11. 本資料についての詳細に関するお問合せ、その他お気付きの点などがありましたら、弊社営業窓口までご連絡ください。

12. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

(Rev. J1.0, 2021.9)

## はじめに

本書はS1C31W74を使用する製品を開発される設計者、プログラマを対象とした技術マニュアルで、ICの機能、内蔵周辺回路の動作、およびその制御方法を説明します。

## 本書内の表記や記号について

### レジスタのアドレス

各周辺回路の説明には制御レジスタのアドレスは記載されておりません。レジスタのアドレスは“メモリ、バス”の章の“周辺回路エリア”、またはAppendixの“周辺回路制御レジスター一覧”を参照してください。

### レジスタと制御ビットの表記

説明の中では、レジスタや制御ビットを信号名や端子名と区別するため、次のように記載します。

XXXレジスタ: 1つのレジスタの全体を示します。

XXX.YYYビット: XXXレジスタ内にある1ビットの制御ビットYYYを示します。

XXX.ZZZ[1:0]ビット: XXXレジスタ内にある2ビットの制御ビットZZZ1とZZZ0を示します。

### レジスタ表の内容と記号

Initial: 初期化時の値

Reset: 初期化条件。初期化条件はリセットグループ(H0、H1、S0)により決まります。リセットグループについては、“電源、リセット、クロック”の章の“初期化条件(リセットグループ)”を参照してください。

R/W: R = 読み出し可能

W = 書き込み可能

WP = 書き込み可能(SYSPROT.PROT[15:0]ビットによる書き込み保護あり)

R/W = 読み書き可能

R/WP = 読み書き可能(SYSPROT.PROT[15:0]ビットによる書き込み保護あり)

### 制御ビットの読み出し/書き込み値

本書では1ビット値を除き、制御ビットの値を16進数で記載します(説明上、10進数や2進数が必要な場合を除く)。制御ビットのビット幅により次のように記載します。

1ビット: 0または1

2~4ビット: 0x0~0xf

5~8ビット: 0x00~0xff

9~12ビット: 0x000~0xffff

13~16ビット: 0x0000~0xffff

10進数: 0~9999...

2進数: 0b0000...~0b1111...

### チャネル番号

周辺回路によっては複数チャネルの機能を搭載可能な場合があります(例: 16ビットタイマなど)。これらの周辺回路の章は実装されているチャネル数にかかわらず、レジスタ名や端子名などに付いているチャネル番号を表す数値を‘n’と記述しています。基本的に、説明は全チャネルに適用されます。機能が異なるチャネルについてはチャネル番号を明記しています。

例) 16ビットタイマのT16\_nCTLレジスタ

1チャネル搭載機種(Ch.0のみ): T16\_nCTL = T16\_0CTLのみ

2チャネル搭載機種(Ch.0とCh.1): T16\_nCTL = T16\_0CTLとT16\_1CTL

本ICの周辺回路の搭載チャネル数は、“概要”の章の“特長”を参照してください。

### 低電力モード

本マニュアルでは、低電力モードをHALTモード、SLEEPモードと記述しています。それぞれ、Cortex®-M0+プロセッサのスリープモード、ディープスリープモードに相当します。

## - 目 次 -

|                                          |            |

|------------------------------------------|------------|

| はじめに .....                               | i          |

| 本書内の表記や記号について .....                      | i          |

| <b>1 概要 .....</b>                        | <b>1-1</b> |

| 1.1 特長 .....                             | 1-1        |

| 1.2 ブロック図 .....                          | 1-3        |

| 1.3 端子 .....                             | 1-4        |

| 1.3.1 端子配置図 .....                        | 1-4        |

| 1.3.2 パッド配置図 .....                       | 1-5        |

| 1.3.3 端子説明 .....                         | 1-7        |

| <b>2 電源, リセット, クロック .....</b>            | <b>2-1</b> |

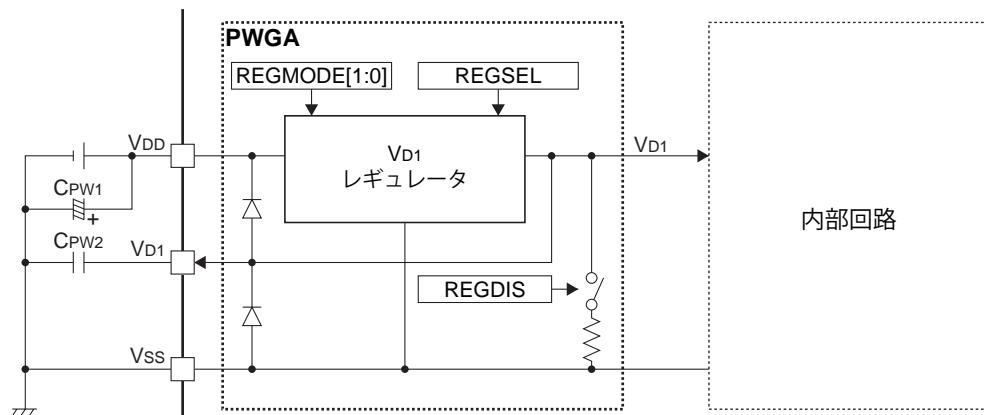

| 2.1 パワージェネレータ(PWGA) .....                | 2-1        |

| 2.1.1 概要 .....                           | 2-1        |

| 2.1.2 端子 .....                           | 2-1        |

| 2.1.3 V <sub>D1</sub> レギュレータの動作モード ..... | 2-2        |

| 2.1.4 V <sub>D1</sub> レギュレータの電圧モード ..... | 2-2        |

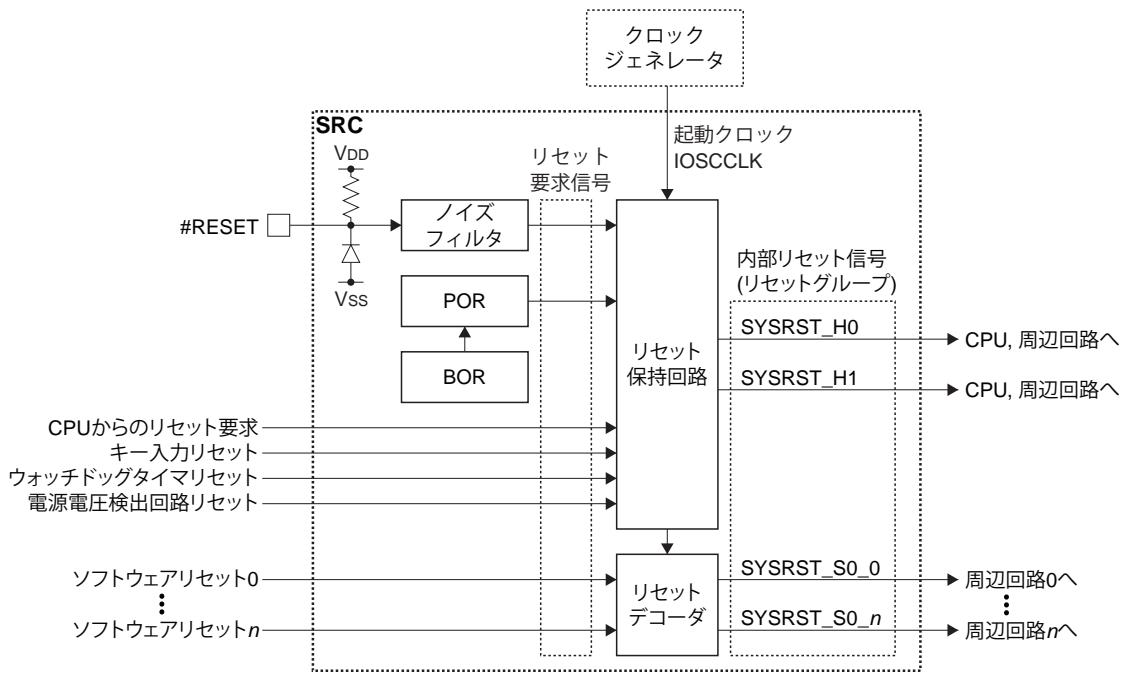

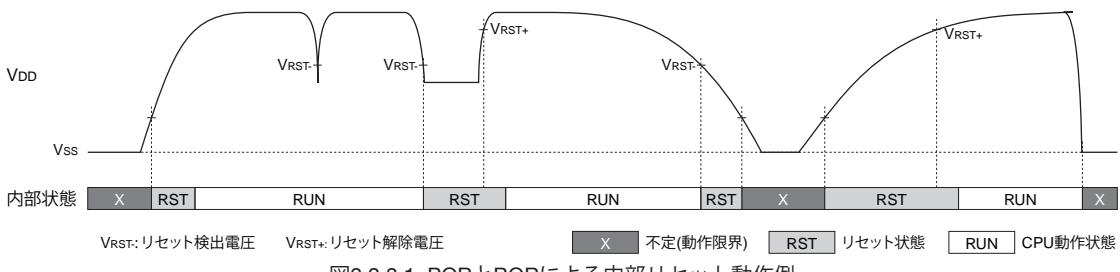

| 2.2 システムリセットコントローラ(SRC) .....            | 2-3        |

| 2.2.1 概要 .....                           | 2-3        |

| 2.2.2 入力端子 .....                         | 2-3        |

| 2.2.3 リセットソース .....                      | 2-4        |

| 2.2.4 初期化条件(リセットグループ) .....              | 2-4        |

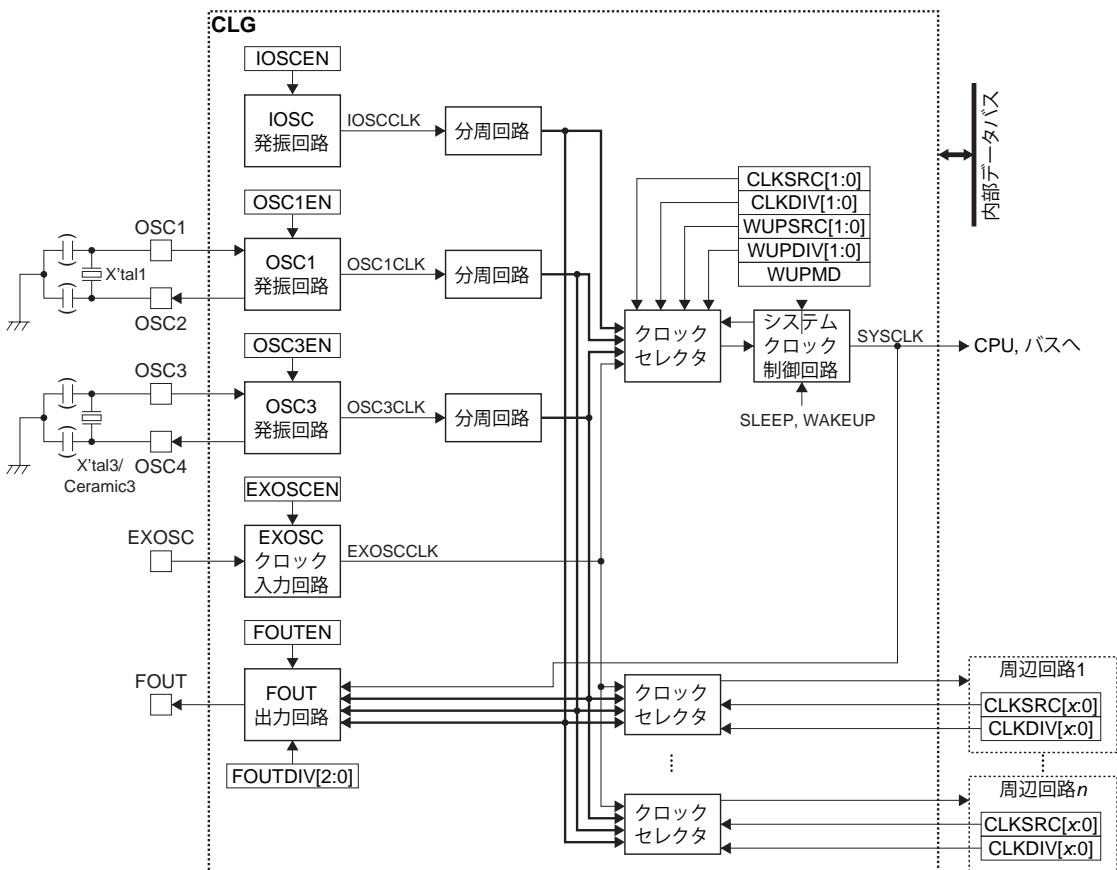

| 2.3 クロックジェネレータ(CLG) .....                | 2-5        |

| 2.3.1 概要 .....                           | 2-5        |

| 2.3.2 入出力端子 .....                        | 2-6        |

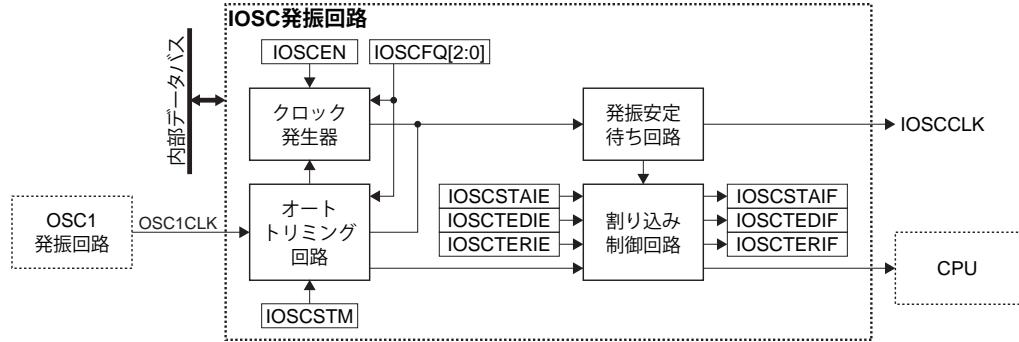

| 2.3.3 クロックソース .....                      | 2-7        |

| 2.3.4 動作 .....                           | 2-8        |

| 2.4 動作モード .....                          | 2-13       |

| 2.4.1 イニシャル起動シーケンス .....                 | 2-13       |

| 2.4.2 動作モードの遷移 .....                     | 2-13       |

| 2.5 割り込み .....                           | 2-15       |

| 2.6 制御レジスタ .....                         | 2-15       |

| PWGA Control Register .....              | 2-15       |

| CLG System Clock Control Register .....  | 2-16       |

| CLG Oscillation Control Register .....   | 2-17       |

| CLG IOSC Control Register .....          | 2-18       |

| CLG OSC1 Control Register .....          | 2-18       |

| CLG OSC3 Control Register .....          | 2-20       |

| CLG Interrupt Flag Register .....        | 2-20       |

| CLG Interrupt Enable Register .....      | 2-21       |

| CLG FOUT Control Register .....          | 2-22       |

| <b>3 CPU, デバッガ .....</b>                 | <b>3-1</b> |

| 3.1 概要 .....                             | 3-1        |

| 3.2 CPU .....                            | 3-1        |

| 3.3 デバッガ .....                           | 3-1        |

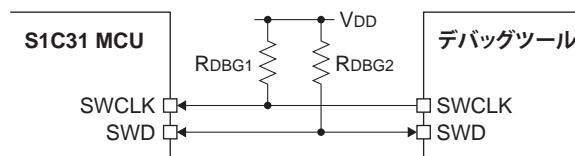

| 3.3.1 デバッガ入出力端子一覧 .....                  | 3-1        |

| 3.3.2 外部接続 .....                         | 3-1        |

| 3.4 参照ドキュメント .....                       | 3-2        |

| <b>4 メモリ, バス .....</b>                   | <b>4-1</b> |

| 4.1 概要 .....                             | 4-1        |

|                                                         |            |

|---------------------------------------------------------|------------|

| 4.2 バスアクセスサイクル .....                                    | 4-2        |

| 4.3 Flashメモリ .....                                      | 4-2        |

| 4.3.1 Flashメモリ端子 .....                                  | 4-2        |

| 4.3.2 Flash/バスアクセスサイクルの設定.....                          | 4-2        |

| 4.3.3 Flashプログラミング .....                                | 4-3        |

| 4.4 RAM .....                                           | 4-3        |

| 4.5 表示データRAM .....                                      | 4-3        |

| 4.6 周辺回路制御レジスタ .....                                    | 4-3        |

| 4.6.1 システムプロテクト機能 .....                                 | 4-9        |

| 4.7 命令キャッシュ .....                                       | 4-9        |

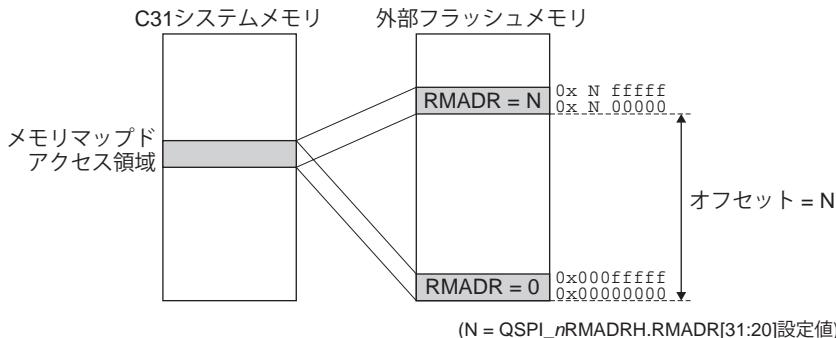

| 4.8 外部Flashメモリ用メモリマップドアクセスエリア .....                     | 4-9        |

| 4.9 制御レジスタ .....                                        | 4-10       |

| System Protect Register .....                           | 4-10       |

| CACHE Control Register .....                            | 4-10       |

| FLASHC Flash Read Cycle Register .....                  | 4-10       |

| <b>5 割り込み .....</b>                                     | <b>5-1</b> |

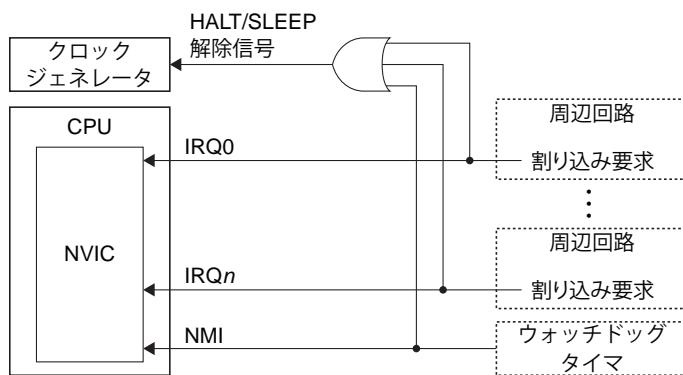

| 5.1 概要 .....                                            | 5-1        |

| 5.2 ベクターテーブル .....                                      | 5-1        |

| 5.2.1 ベクターテーブルオフセットアドレス(VTOR) .....                     | 5-3        |

| 5.2.2 割り込みの優先順位.....                                    | 5-3        |

| 5.3 周辺回路の割り込み制御.....                                    | 5-3        |

| 5.4 NMI.....                                            | 5-4        |

| <b>6 DMAコントローラ(DMAC) .....</b>                          | <b>6-1</b> |

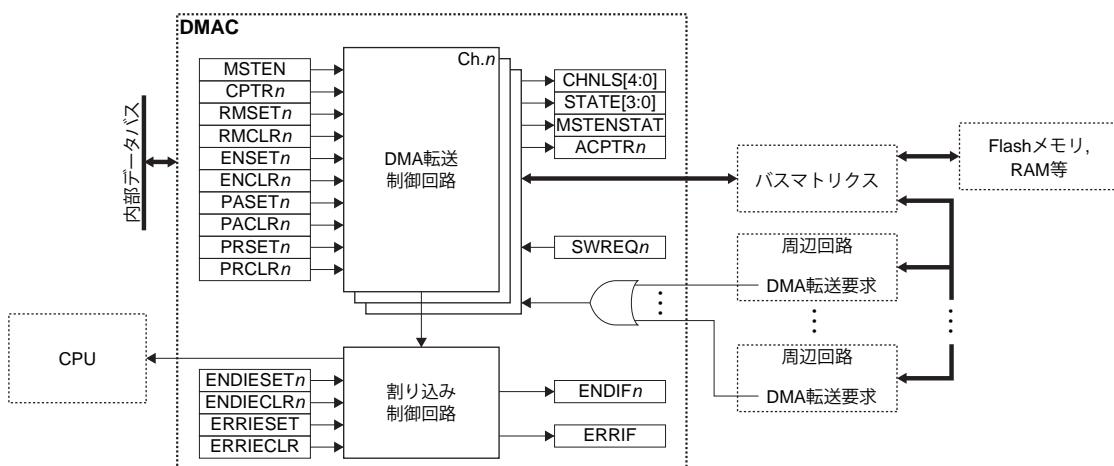

| 6.1 概要 .....                                            | 6-1        |

| 6.2 動作 .....                                            | 6-2        |

| 6.2.1 初期設定 .....                                        | 6-2        |

| 6.3 優先度 .....                                           | 6-2        |

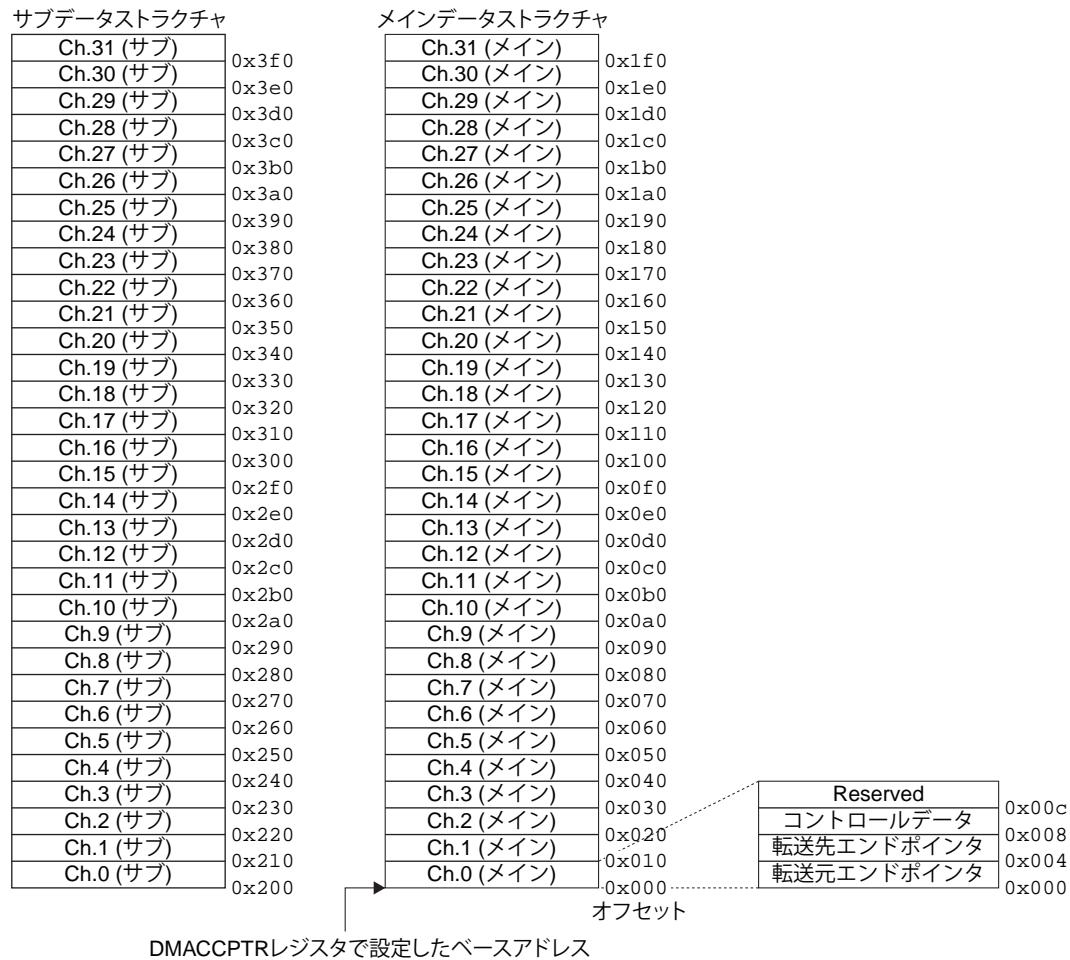

| 6.4 データストラクチャ .....                                     | 6-2        |

| 6.4.1 転送元エンドポインタ .....                                  | 6-3        |

| 6.4.2 転送先エンドポインタ .....                                  | 6-3        |

| 6.4.3 コントロールデータ .....                                   | 6-4        |

| 6.5 DMA転送モード .....                                      | 6-5        |

| 6.5.1 通常転送 .....                                        | 6-5        |

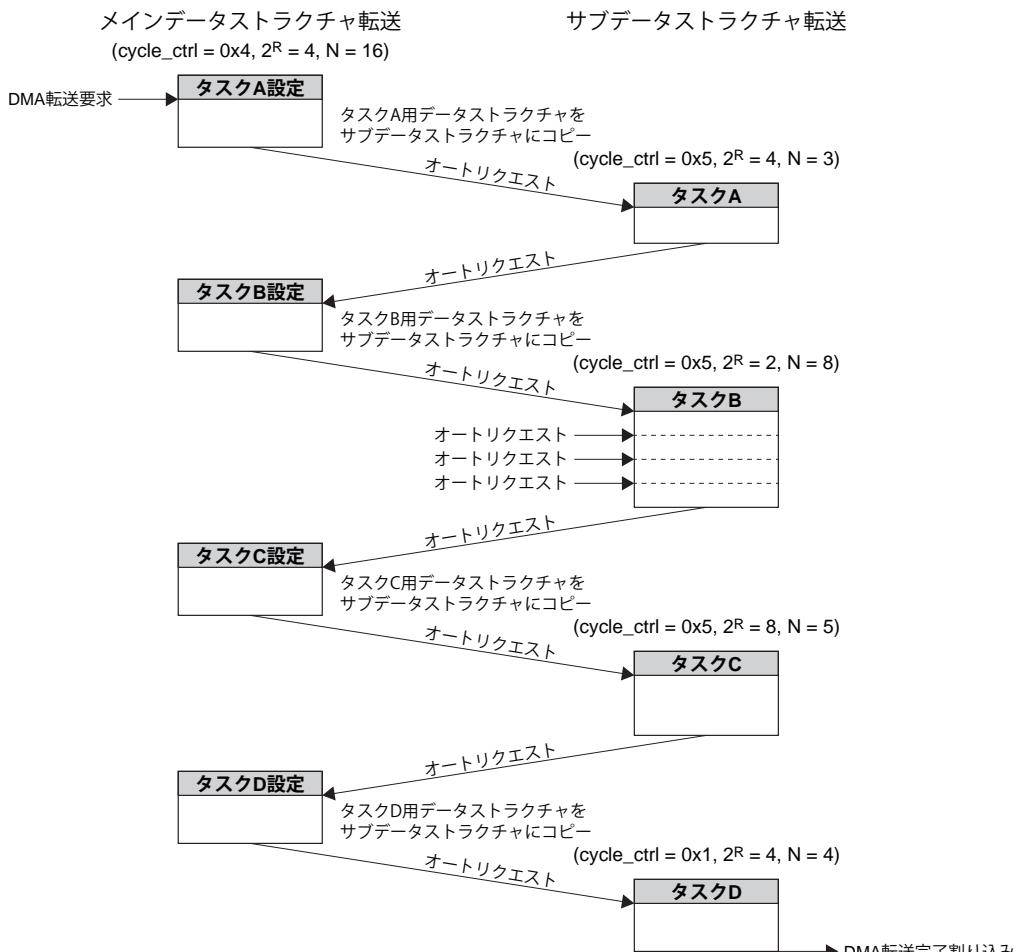

| 6.5.2 オートリクエスト転送.....                                   | 6-5        |

| 6.5.3 ピンポン転送 .....                                      | 6-6        |

| 6.5.4 メモリスキッタ/ギャザー転送 .....                              | 6-7        |

| 6.5.5 周辺回路スキッタ/ギャザー転送.....                              | 6-8        |

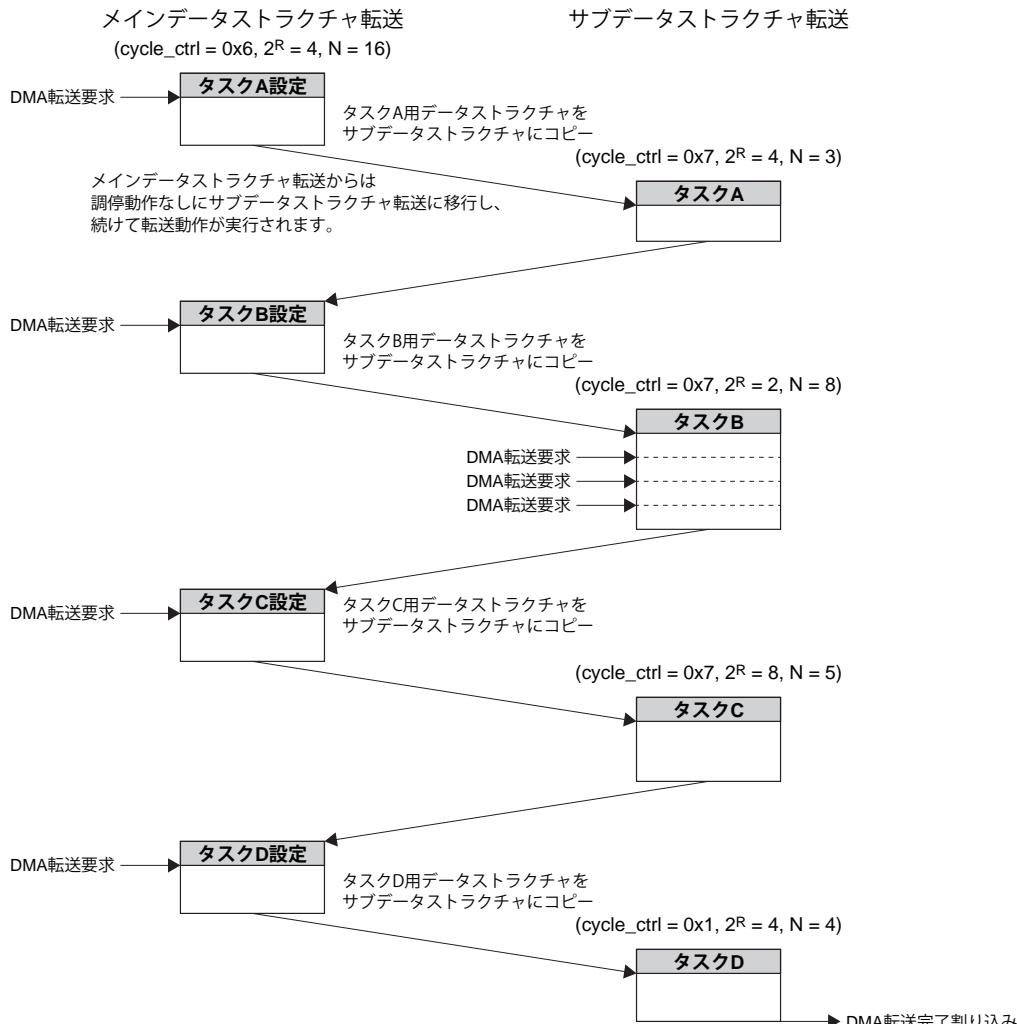

| 6.6 DMA転送サイクル.....                                      | 6-9        |

| 6.7 割り込み .....                                          | 6-9        |

| 6.8 制御レジスタ .....                                        | 6-10       |

| DMAC Status Register .....                              | 6-10       |

| DMAC Configuration Register .....                       | 6-10       |

| DMAC Control Data Base Pointer Register.....            | 6-11       |

| DMAC Alternate Control Data Base Pointer Register ..... | 6-11       |

| DMAC Software Request Register .....                    | 6-11       |

| DMAC Request Mask Set Register .....                    | 6-11       |

| DMAC Request Mask Clear Register .....                  | 6-12       |

| DMAC Enable Set Register .....                          | 6-12       |

| DMAC Enable Clear Register .....                        | 6-12       |

| DMAC Primary-Alternate Set Register .....               | 6-12       |

| DMAC Primary-Alternate Clear Register .....             | 6-13       |

| DMAC Priority Set Register .....                        | 6-13       |

|                                                               |            |

|---------------------------------------------------------------|------------|

| DMAC Priority Clear Register.....                             | 6-13       |

| DMAC Error Interrupt Flag Register .....                      | 6-13       |

| DMAC Transfer Completion Interrupt Flag Register.....         | 6-14       |

| DMAC Transfer Completion Interrupt Enable Set Register.....   | 6-14       |

| DMAC Transfer Completion Interrupt Enable Clear Register..... | 6-14       |

| DMAC Error Interrupt Enable Set Register.....                 | 6-14       |

| DMAC Error Interrupt Enable Clear Register.....               | 6-15       |

| <b>7 入出力ポート(PPORT) .....</b>                                  | <b>7-1</b> |

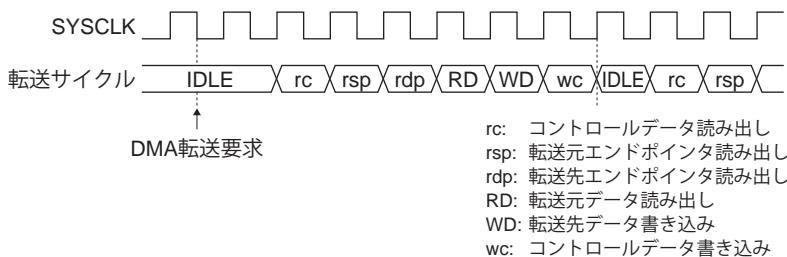

| 7.1 概要 .....                                                  | 7-1        |

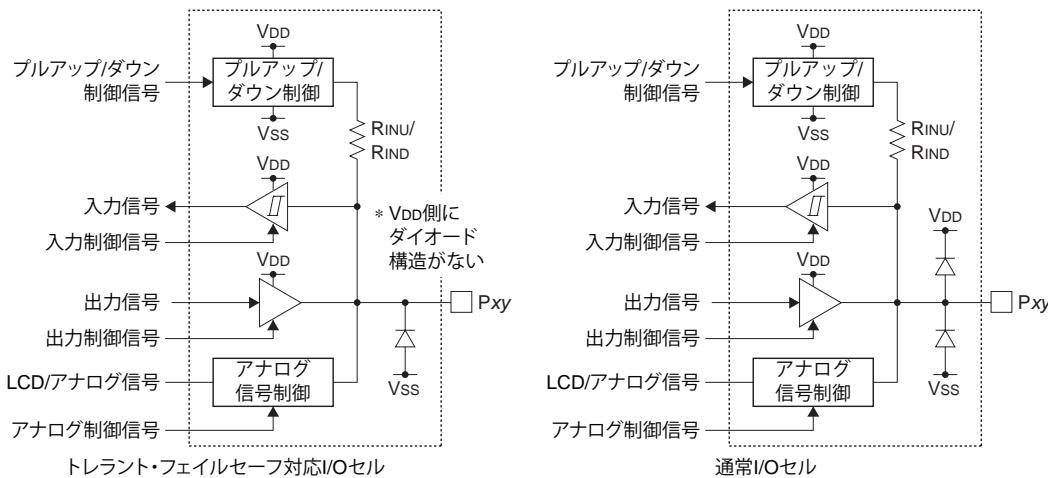

| 7.2 I/Oセルの構造と機能.....                                          | 7-2        |

| 7.2.1 シュミット入力.....                                            | 7-2        |

| 7.2.2 トレラント・フェイルセーフ .....                                     | 7-2        |

| 7.2.3 プルアップ/プルダウン .....                                       | 7-2        |

| 7.2.4 CMOS出力とハイインピーダンス状態.....                                 | 7-3        |

| 7.3 クロック設定.....                                               | 7-3        |

| 7.3.1 PPORTの動作クロック .....                                      | 7-3        |

| 7.3.2 SLEEPモード時のクロック供給 .....                                  | 7-3        |

| 7.3.3 デバッグ時のクロック供給.....                                       | 7-3        |

| 7.4 動作 .....                                                  | 7-3        |

| 7.4.1 初期設定 .....                                              | 7-3        |

| 7.4.2 ポートの入出力制御.....                                          | 7-5        |

| 7.5 割り込み .....                                                | 7-6        |

| 7.6 制御レジスタ .....                                              | 7-6        |

| Px Port Data Register.....                                    | 7-6        |

| Px Port Enable Register .....                                 | 7-7        |

| Px Port Pull-up/down Control Register .....                   | 7-7        |

| Px Port Interrupt Flag Register.....                          | 7-8        |

| Px Port Interrupt Control Register .....                      | 7-8        |

| Px Port Chattering Filter Enable Register.....                | 7-8        |

| Px Port Mode Select Register .....                            | 7-9        |

| Px Port Function Select Register .....                        | 7-9        |

| P Port Clock Control Register .....                           | 7-9        |

| P Port Interrupt Flag Group Register.....                     | 7-10       |

| 7.7 本ICの制御レジスタ/ポート機能の構成 .....                                 | 7-11       |

| 7.7.1 P0ポートグループ .....                                         | 7-11       |

| 7.7.2 P1ポートグループ .....                                         | 7-12       |

| 7.7.3 P2ポートグループ .....                                         | 7-13       |

| 7.7.4 P3ポートグループ .....                                         | 7-14       |

| 7.7.5 P4ポートグループ .....                                         | 7-15       |

| 7.7.6 P5ポートグループ .....                                         | 7-16       |

| 7.7.7 P6ポートグループ .....                                         | 7-17       |

| 7.7.8 P7ポートグループ .....                                         | 7-18       |

| 7.7.9 P8ポートグループ .....                                         | 7-19       |

| 7.7.10 P9ポートグループ .....                                        | 7-20       |

| 7.7.11 Pdポートグループ .....                                        | 7-21       |

| 7.7.12 ポートグループ共通 .....                                        | 7-22       |

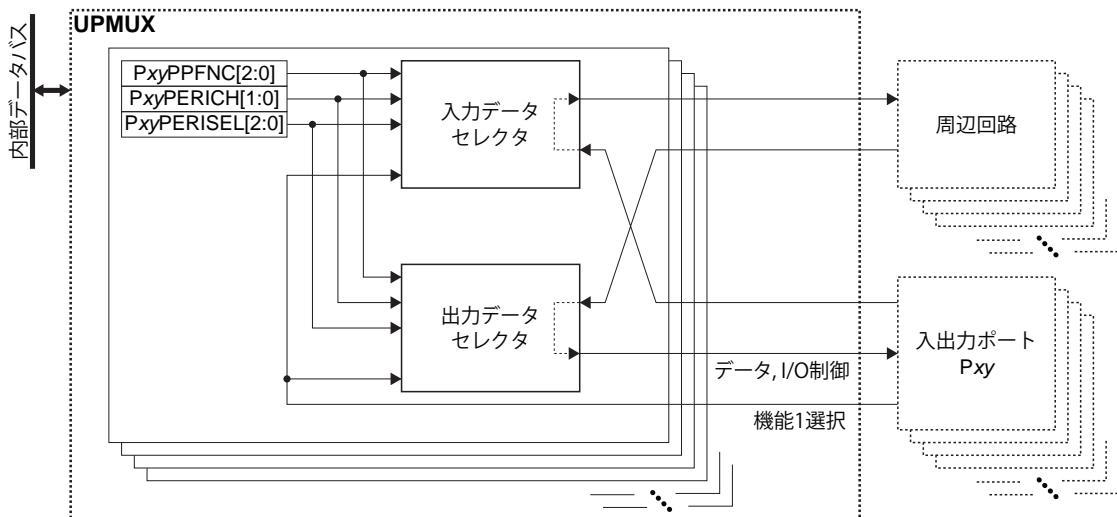

| <b>8 ユニバーサルポートマルチプレクサ(UPMUX) .....</b>                        | <b>8-1</b> |

| 8.1 概要 .....                                                  | 8-1        |

| 8.2 周辺入出力機能の割り当て .....                                        | 8-1        |

| 8.3 制御レジスタ .....                                              | 8-2        |

| Pxy-xz Universal Port Multiplexer Setting Register.....       | 8-2        |

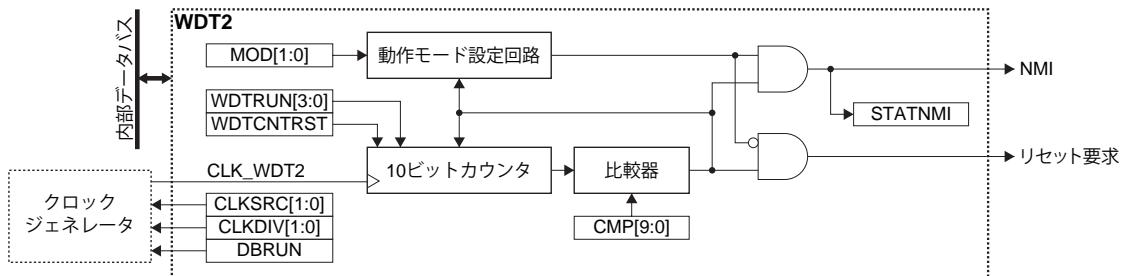

| <b>9 ウオッチドッグタイマ(WDT2) .....</b>                               | <b>9-1</b> |

| 9.1 概要 .....                                                  | 9-1        |

|                                           |             |

|-------------------------------------------|-------------|

| 9.2 クロック設定.....                           | 9-1         |

| 9.2.1 WDT2の動作クロック .....                   | 9-1         |

| 9.2.2 DEBUGモード時のクロック供給.....               | 9-1         |

| 9.3 動作 .....                              | 9-2         |

| 9.3.1 WDT2の制御 .....                       | 9-2         |

| 9.3.2 HALT, SLEEPモード時の動作 .....            | 9-3         |

| 9.4 制御レジスタ .....                          | 9-3         |

| WDT2 Clock Control Register .....         | 9-3         |

| WDT2 Control Register .....               | 9-4         |

| WDT2 Counter Compare Match Register ..... | 9-5         |

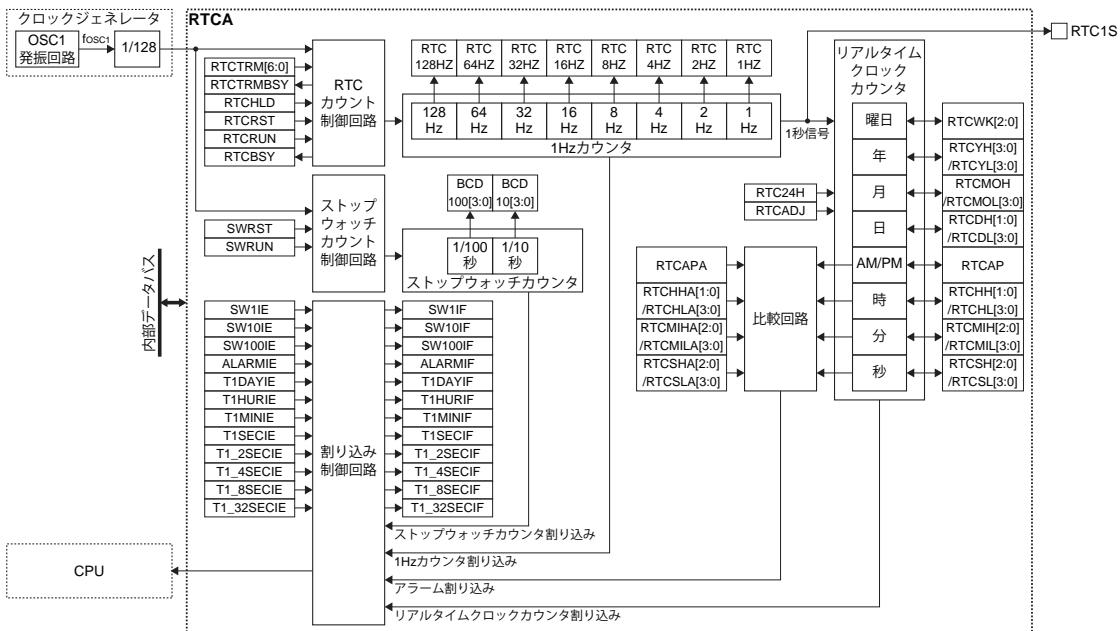

| <b>10 リアルタイムクロック(RTCA).....</b>           | <b>10-1</b> |

| 10.1 概要 .....                             | 10-1        |

| 10.2 出力端子と外部接続.....                       | 10-1        |

| 10.2.1 出力端子 .....                         | 10-1        |

| 10.3 クロック設定.....                          | 10-2        |

| 10.3.1 RTCAの動作クロック .....                  | 10-2        |

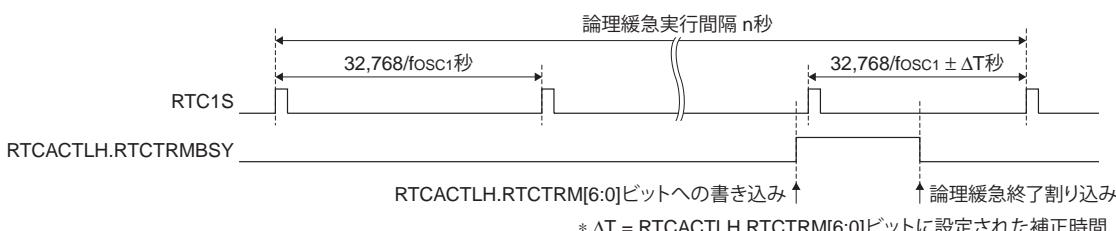

| 10.3.2 論理緩急機能 .....                       | 10-2        |

| 10.4 動作 .....                             | 10-3        |

| 10.4.1 RTCAの制御.....                       | 10-3        |

| 10.4.2 リアルタイムクロックカウンタの動作.....             | 10-4        |

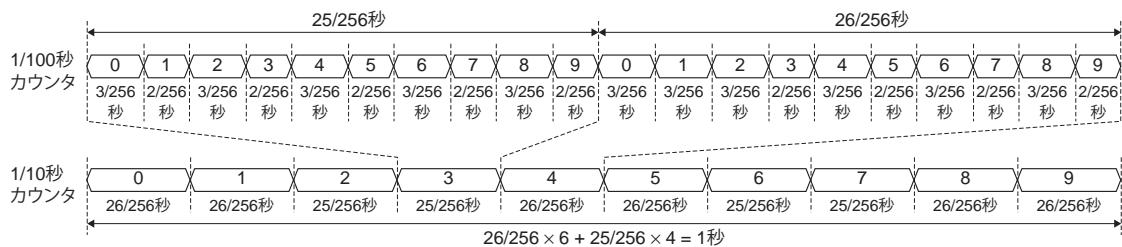

| 10.4.3 ストップウォッチの制御 .....                  | 10-4        |

| 10.4.4 ストップウォッチのカウントアップ/パターン .....        | 10-4        |

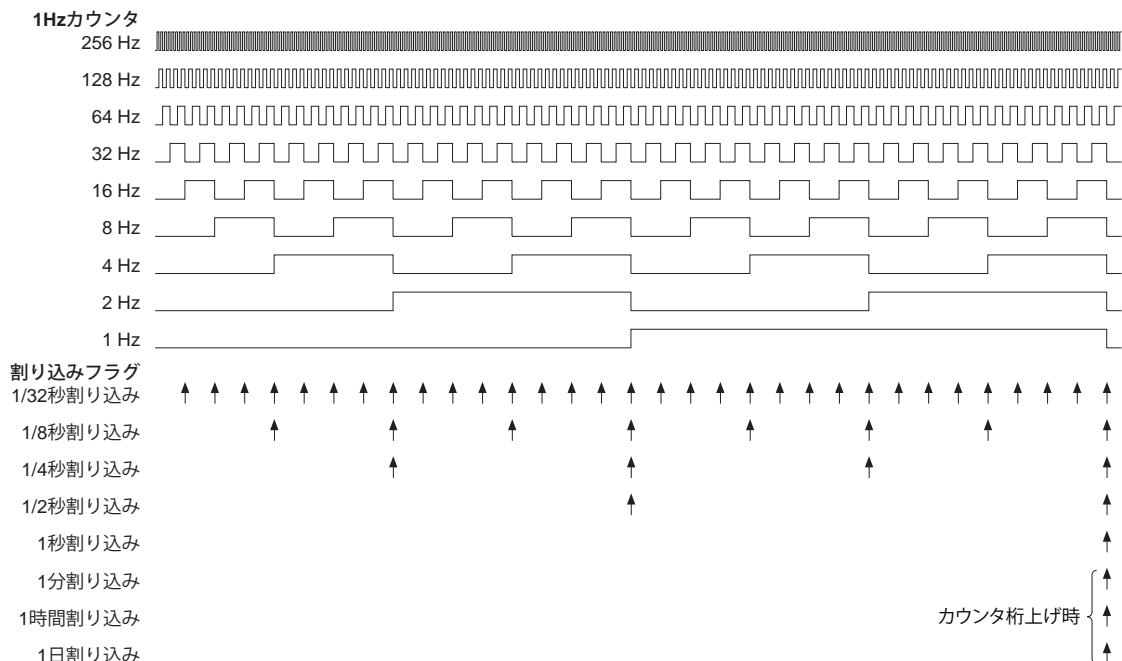

| 10.5 割り込み .....                           | 10-5        |

| 10.6 制御レジスタ .....                         | 10-6        |

| RTCA Control Register (Low Byte) .....    | 10-6        |

| RTCA Control Register (High Byte) .....   | 10-7        |

| RTCA Second Alarm Register .....          | 10-8        |

| RTCA Hour/Minute Alarm Register .....     | 10-8        |

| RTCA Stopwatch Control Register.....      | 10-9        |

| RTCA Second/1Hz Register.....             | 10-9        |

| RTCA Hour/Minute Register.....            | 10-10       |

| RTCA Month/Day Register .....             | 10-11       |

| RTCA Year/Week Register.....              | 10-11       |

| RTCA Interrupt Flag Register .....        | 10-12       |

| RTCA Interrupt Enable Register .....      | 10-13       |

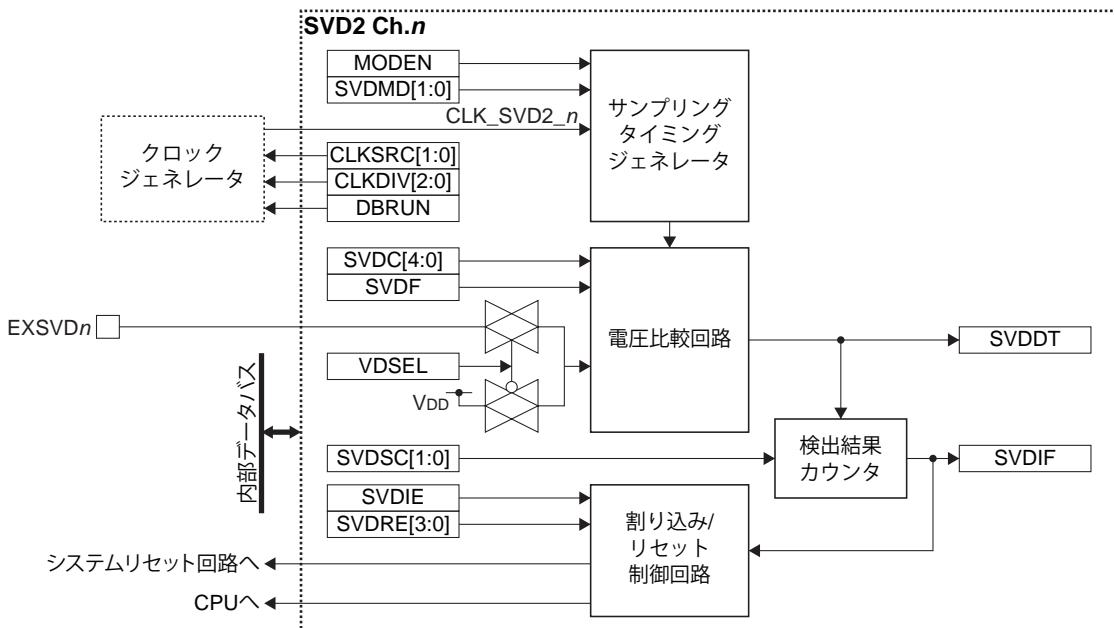

| <b>11 電源電圧検出回路(SVD2) .....</b>            | <b>11-1</b> |

| 11.1 概要 .....                             | 11-1        |

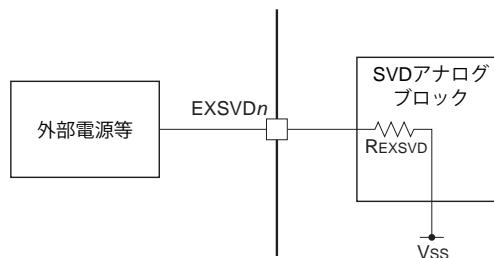

| 11.2 入力端子と外部接続.....                       | 11-2        |

| 11.2.1 入力端子 .....                         | 11-2        |

| 11.2.2 外部との接続 .....                       | 11-2        |

| 11.3 クロック設定.....                          | 11-2        |

| 11.3.1 SVD2の動作クロック .....                  | 11-2        |

| 11.3.2 SLEEPモード時のクロック供給 .....             | 11-2        |

| 11.3.3 デバッグ時のクロック供給 .....                 | 11-3        |

| 11.4 動作 .....                             | 11-3        |

| 11.4.1 SVD2の制御 .....                      | 11-3        |

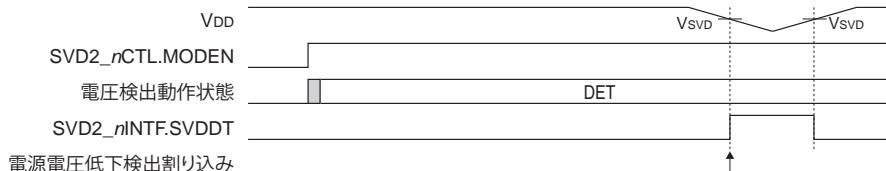

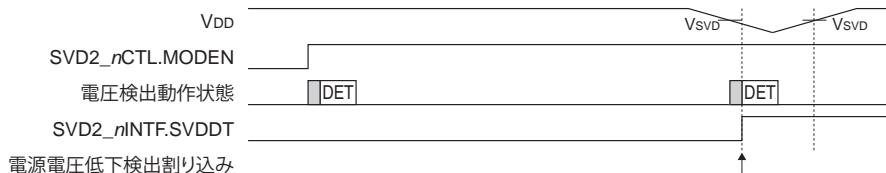

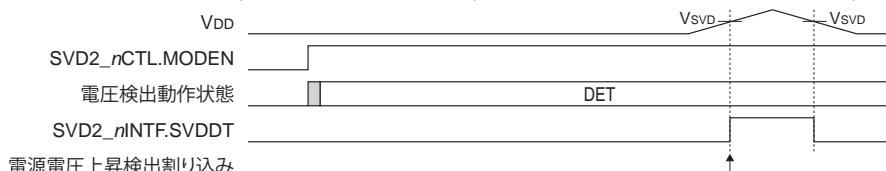

| 11.4.2 SVD2の動作 .....                      | 11-4        |

| 11.5 SVD2割り込みとリセット .....                  | 11-5        |

| 11.5.1 SVD2割り込み .....                     | 11-5        |

| 11.5.2 SVD2リセット .....                     | 11-5        |

| 11.6 制御レジスタ .....                         | 11-6        |

| SVD2 Ch.n Clock Control Register .....    | 11-6        |

|                                                           |             |

|-----------------------------------------------------------|-------------|

| SVD2 Ch. <i>n</i> Control Register.....                   | 11-6        |

| SVD2 Ch. <i>n</i> Status and Interrupt Flag Register..... | 11-8        |

| SVD2 Ch. <i>n</i> Interrupt Enable Register.....          | 11-8        |

| <b>12 16ビットタイマ(T16).....</b>                              | <b>12-1</b> |

| 12.1 概要 .....                                             | 12-1        |

| 12.2 入力端子 .....                                           | 12-1        |

| 12.3 クロック設定 .....                                         | 12-2        |

| 12.3.1 T16の動作クロック .....                                   | 12-2        |

| 12.3.2 SLEEPモード時のクロック供給 .....                             | 12-2        |

| 12.3.3 デバッグ時のクロック供給 .....                                 | 12-2        |

| 12.3.4 イベントカウンタクロック .....                                 | 12-2        |

| 12.4 動作 .....                                             | 12-2        |

| 12.4.1 初期設定 .....                                         | 12-2        |

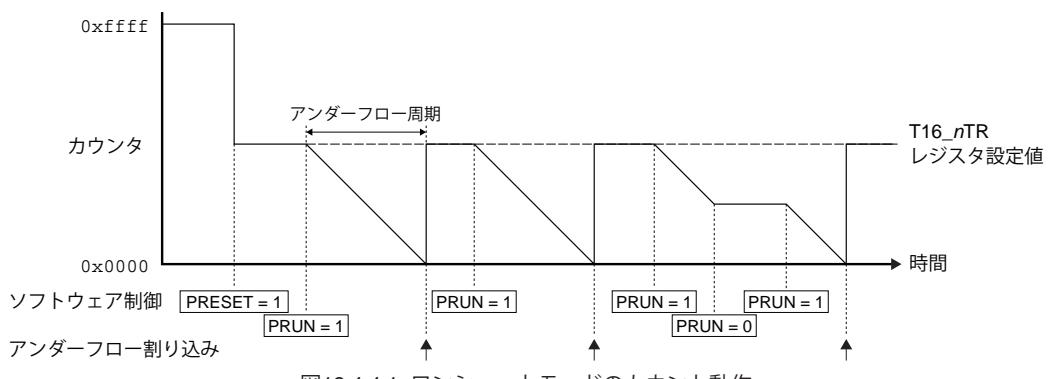

| 12.4.2 カウンタのアンダーフロー .....                                 | 12-3        |

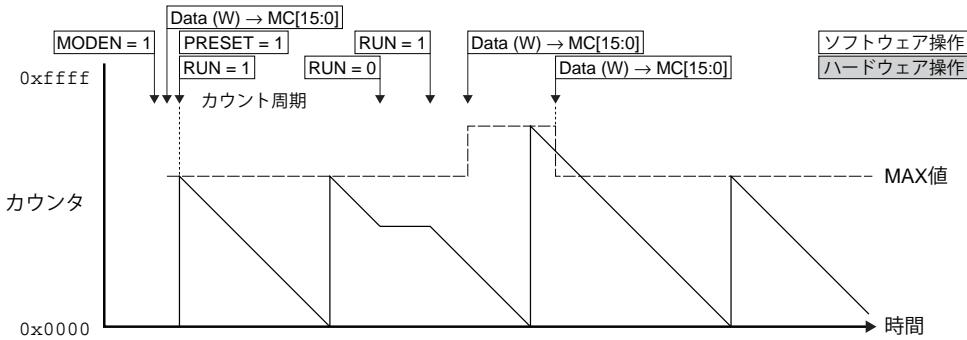

| 12.4.3 リピートモードの動作 .....                                   | 12-3        |

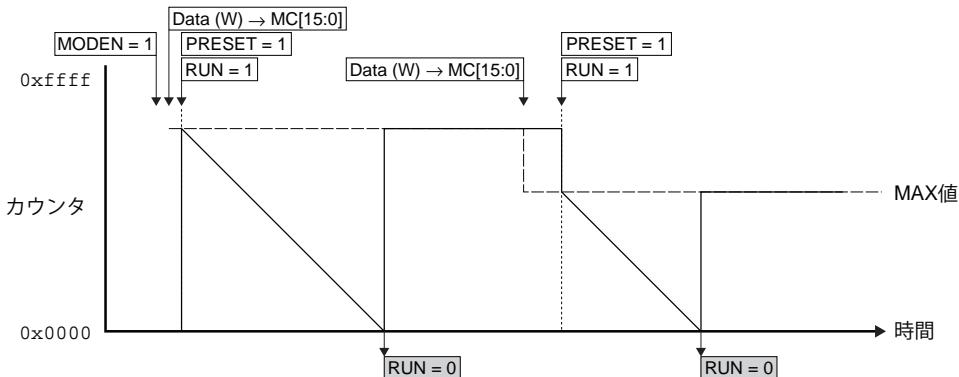

| 12.4.4 ワンショットモードの動作 .....                                 | 12-3        |

| 12.4.5 カウンタ値のリード .....                                    | 12-4        |

| 12.5 割り込み .....                                           | 12-4        |

| 12.6 制御レジスタ .....                                         | 12-4        |

| T16 Ch. <i>n</i> Clock Control Register .....             | 12-4        |

| T16 Ch. <i>n</i> Mode Register .....                      | 12-5        |

| T16 Ch. <i>n</i> Control Register .....                   | 12-5        |

| T16 Ch. <i>n</i> Reload Data Register .....               | 12-6        |

| T16 Ch. <i>n</i> Counter Data Register .....              | 12-6        |

| T16 Ch. <i>n</i> Interrupt Flag Register .....            | 12-6        |

| T16 Ch. <i>n</i> Interrupt Enable Register .....          | 12-7        |

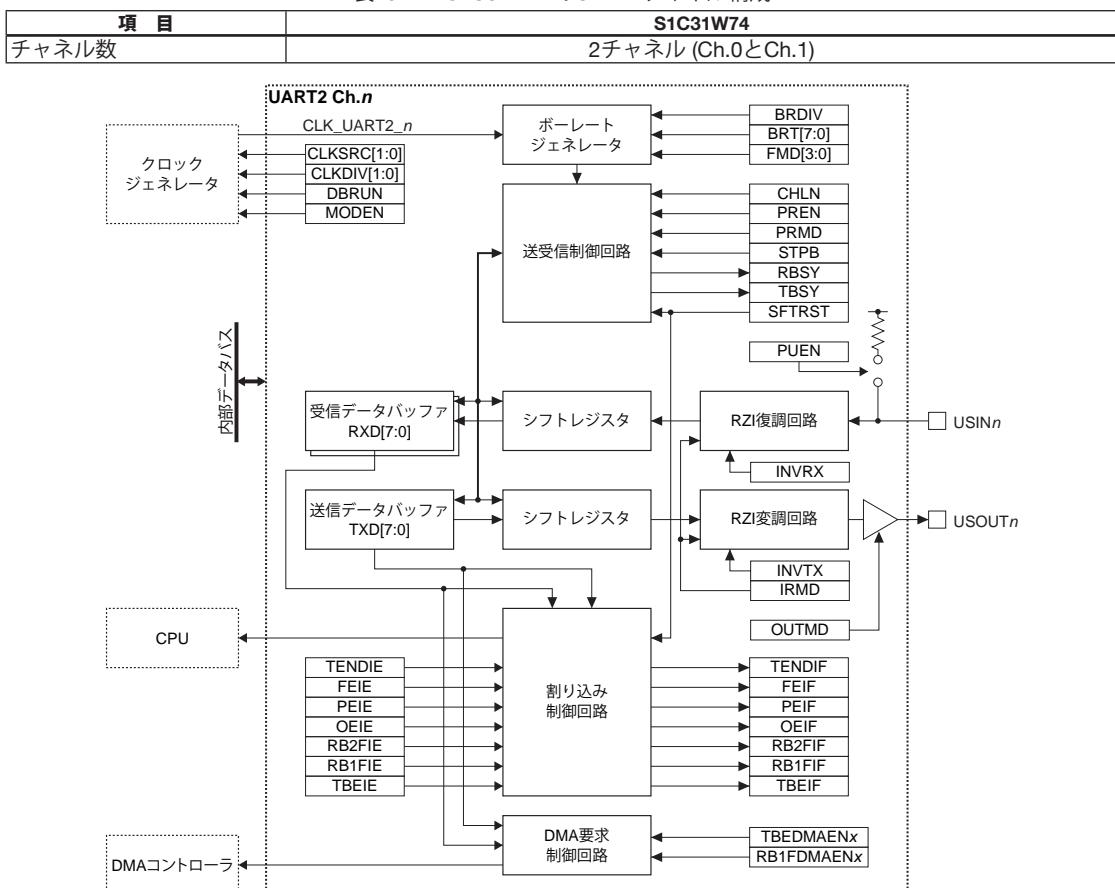

| <b>13 UART(UART2).....</b>                                | <b>13-1</b> |

| 13.1 概要 .....                                             | 13-1        |

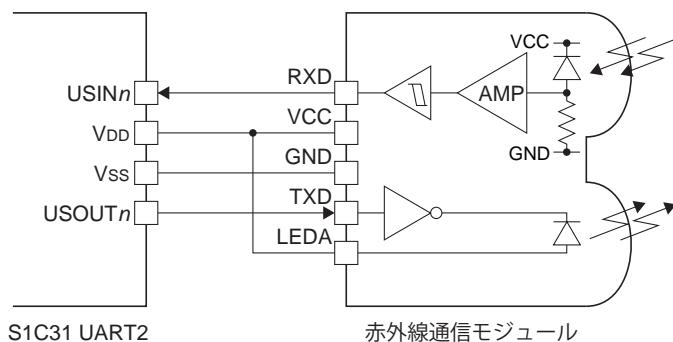

| 13.2 入出力端子と外部接続 .....                                     | 13-2        |

| 13.2.1 入出力端子一覧 .....                                      | 13-2        |

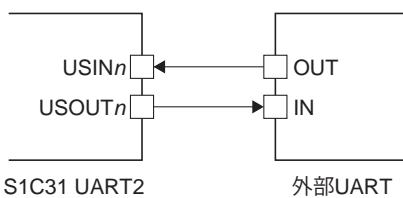

| 13.2.2 外部との接続 .....                                       | 13-2        |

| 13.2.3 入力端子のプルアップ機能 .....                                 | 13-2        |

| 13.2.4 出力端子のオーブンドレイン出力機能 .....                            | 13-2        |

| 13.2.5 入出力信号の反転機能 .....                                   | 13-2        |

| 13.3 クロック設定 .....                                         | 13-2        |

| 13.3.1 UART2の動作クロック .....                                 | 13-2        |

| 13.3.2 SLEEPモード時のクロック供給 .....                             | 13-3        |

| 13.3.3 DEBUGモード時のクロック供給 .....                             | 13-3        |

| 13.3.4 ボーレートジェネレータ .....                                  | 13-3        |

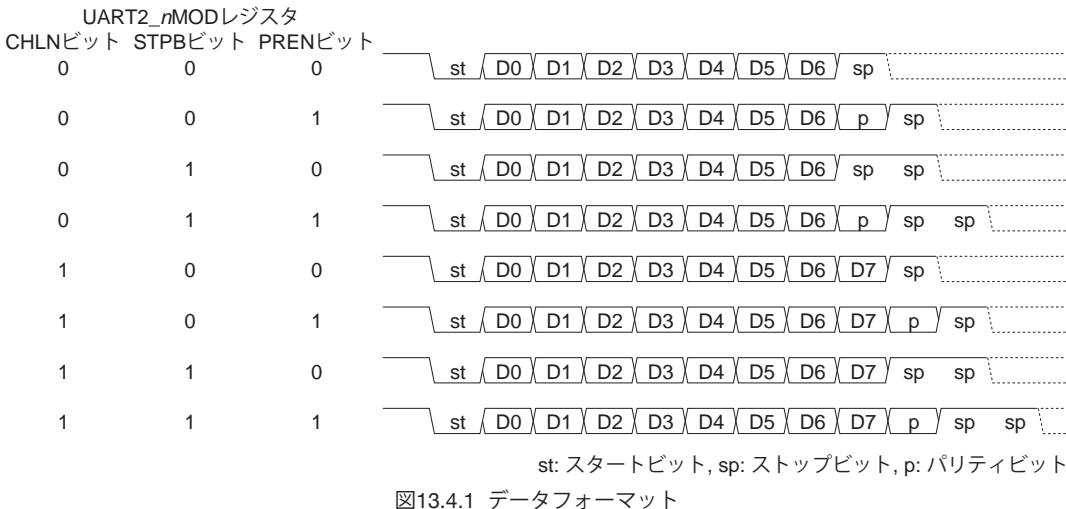

| 13.4 データフォーマット .....                                      | 13-3        |

| 13.5 動作 .....                                             | 13-4        |

| 13.5.1 初期設定 .....                                         | 13-4        |

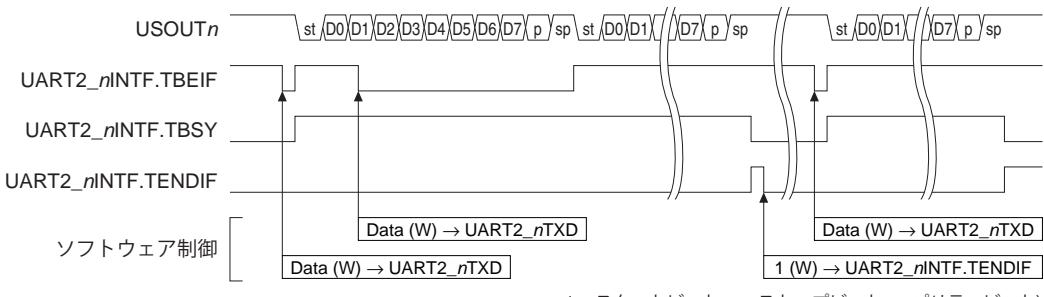

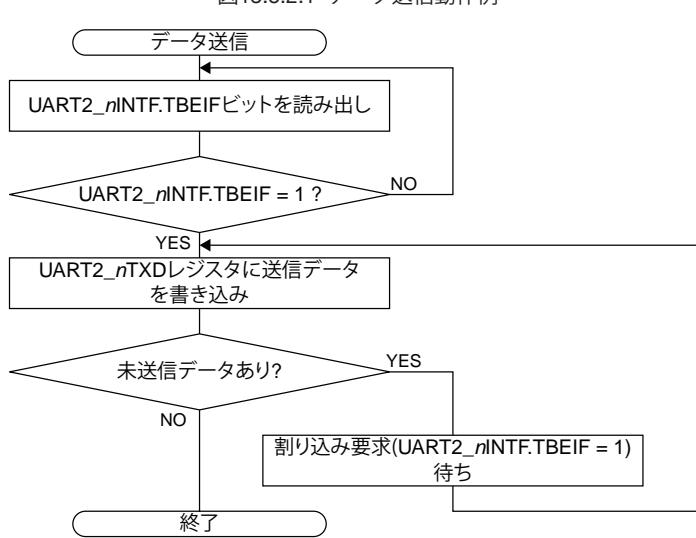

| 13.5.2 データ送信 .....                                        | 13-5        |

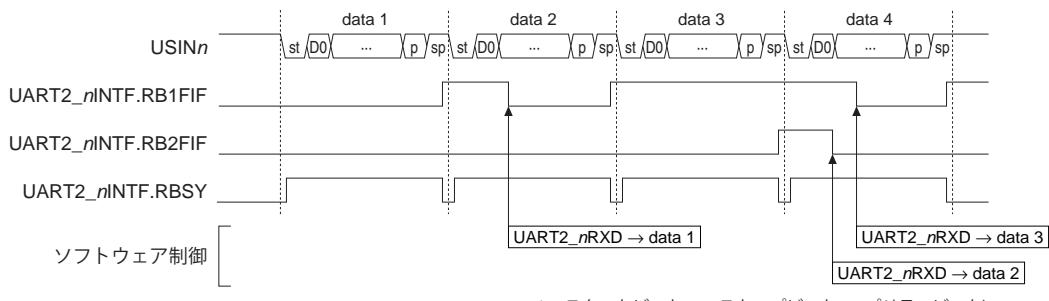

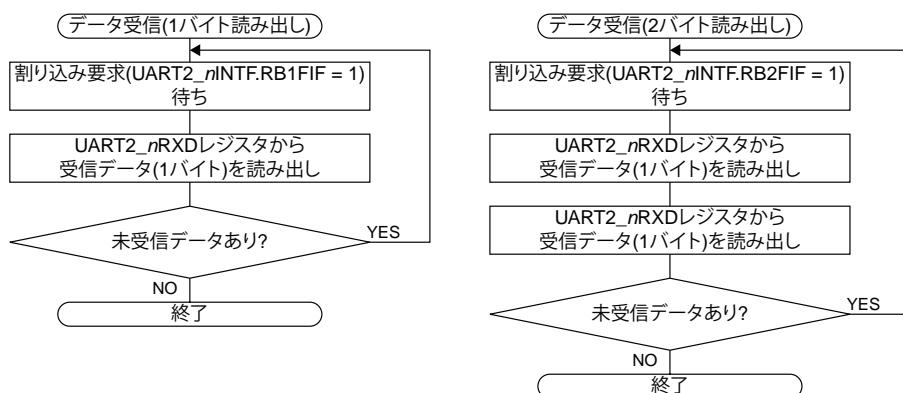

| 13.5.3 データ受信 .....                                        | 13-6        |

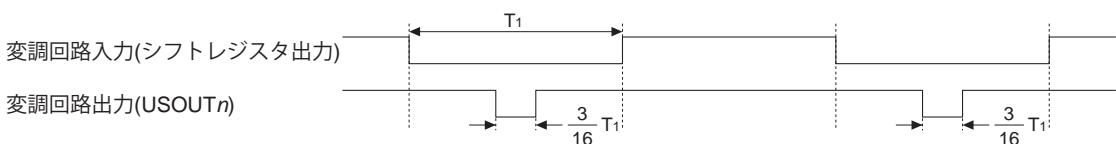

| 13.5.4 IrDAインターフェース .....                                 | 13-7        |

| 13.6 受信エラー .....                                          | 13-8        |

| 13.6.1 フレーミングエラー .....                                    | 13-8        |

| 13.6.2 パリティエラー .....                                      | 13-9        |

| 13.6.3 オーバーランエラー .....                                    | 13-9        |

| 13.7 割り込み .....                                           | 13-9        |

| 13.8 DMA転送要求 .....                                        | 13-9        |

| 13.9 制御レジスタ .....                                         | 13-10       |

|                                                                                   |             |

|-----------------------------------------------------------------------------------|-------------|

| UART2 Ch. <i>n</i> Clock Control Register .....                                   | 13-10       |

| UART2 Ch. <i>n</i> Mode Register .....                                            | 13-11       |

| UART2 Ch. <i>n</i> Baud-Rate Register .....                                       | 13-12       |

| UART2 Ch. <i>n</i> Control Register .....                                         | 13-12       |

| UART2 Ch. <i>n</i> Transmit Data Register .....                                   | 13-13       |

| UART2 Ch. <i>n</i> Receive Data Register .....                                    | 13-13       |

| UART2 Ch. <i>n</i> Status and Interrupt Flag Register .....                       | 13-13       |

| UART2 Ch. <i>n</i> Interrupt Enable Register .....                                | 13-14       |

| UART2 Ch. <i>n</i> Transmit Buffer Empty DMA Request Enable Register .....        | 13-15       |

| UART2 Ch. <i>n</i> Receive Buffer One Byte Full DMA Request Enable Register ..... | 13-15       |

| <b>14 同期式シリアルインターフェース(SPIA).....</b>                                              | <b>14-1</b> |

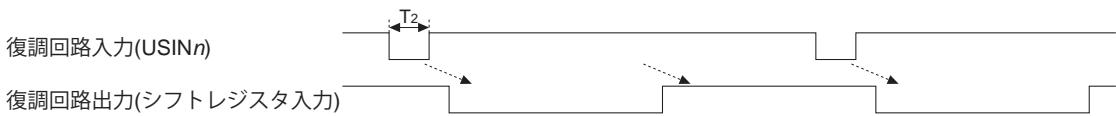

| 14.1 概要 .....                                                                     | 14-1        |

| 14.2 入出力端子と外部接続 .....                                                             | 14-2        |

| 14.2.1 入出力端子一覧.....                                                               | 14-2        |

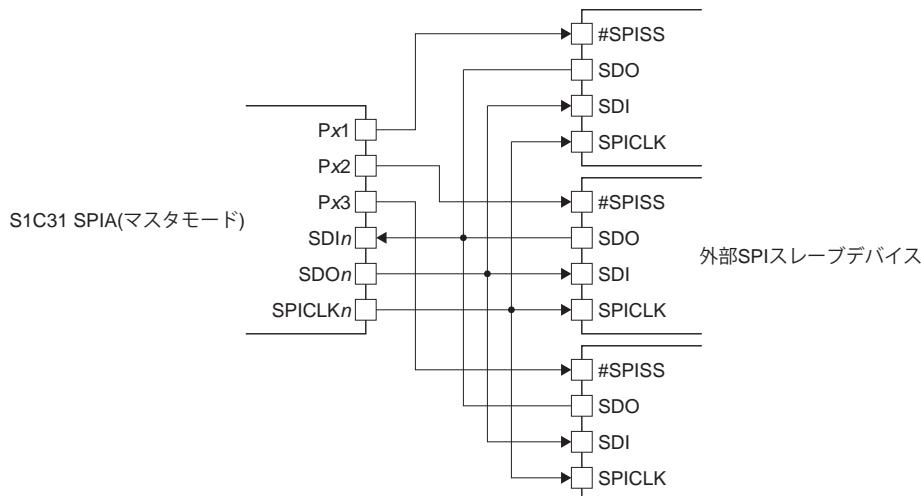

| 14.2.2 外部との接続 .....                                                               | 14-2        |

| 14.2.3 マスタモードとスレーブモードの端子機能.....                                                   | 14-3        |

| 14.2.4 入力端子のプルアップ/プルダウン機能.....                                                    | 14-3        |

| 14.3 クロック設定.....                                                                  | 14-3        |

| 14.3.1 SPIAの動作クロック .....                                                          | 14-3        |

| 14.3.2 デバッグ時のクロック供給 .....                                                         | 14-4        |

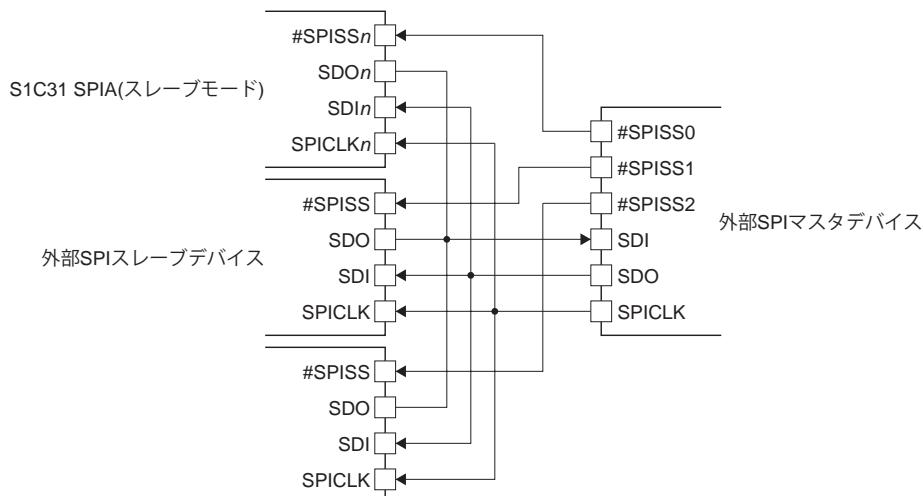

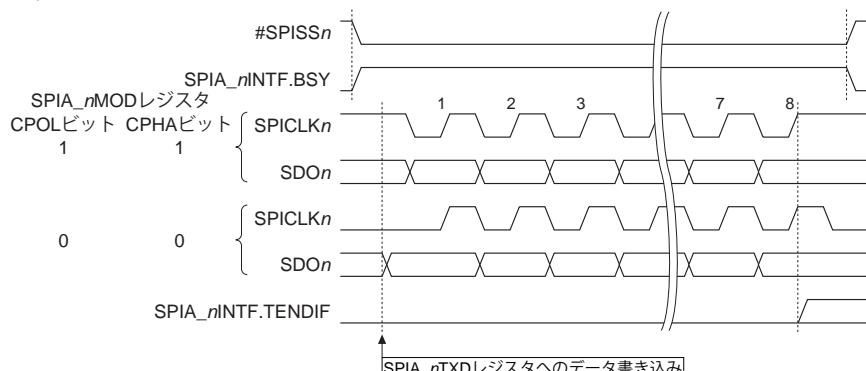

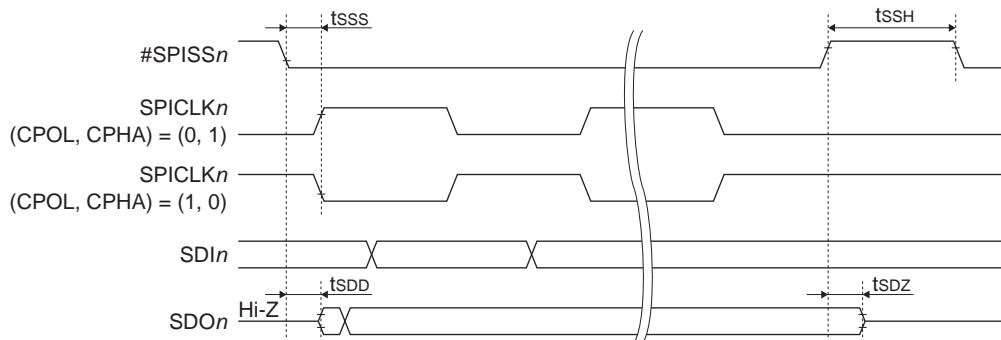

| 14.3.3 SPIクロック(SPICLK <i>n</i> )の位相と極性 .....                                      | 14-4        |

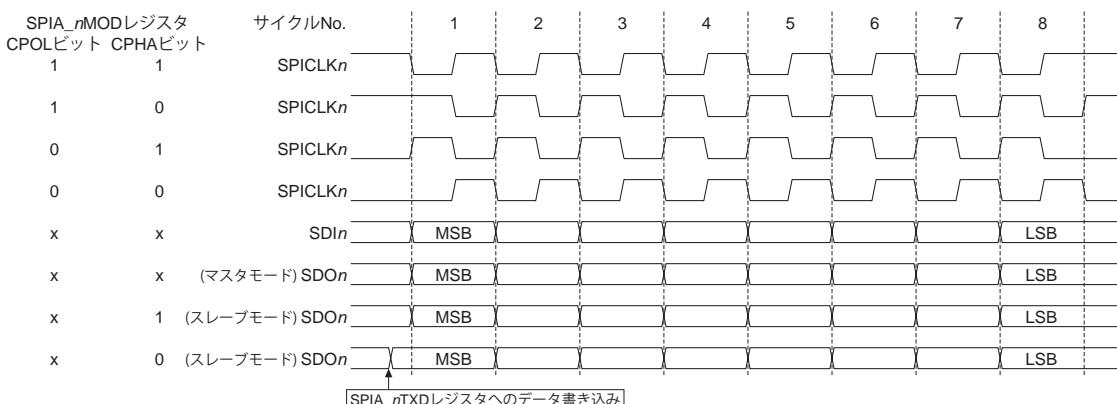

| 14.4 データフォーマット .....                                                              | 14-5        |

| 14.5 動作 .....                                                                     | 14-5        |

| 14.5.1 初期設定 .....                                                                 | 14-5        |

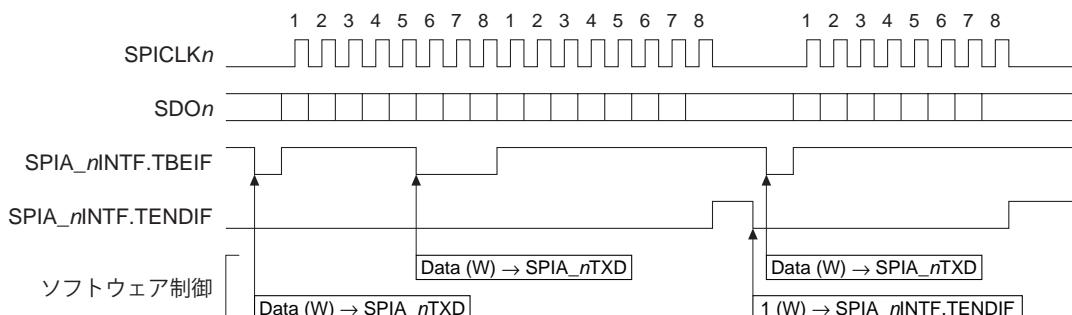

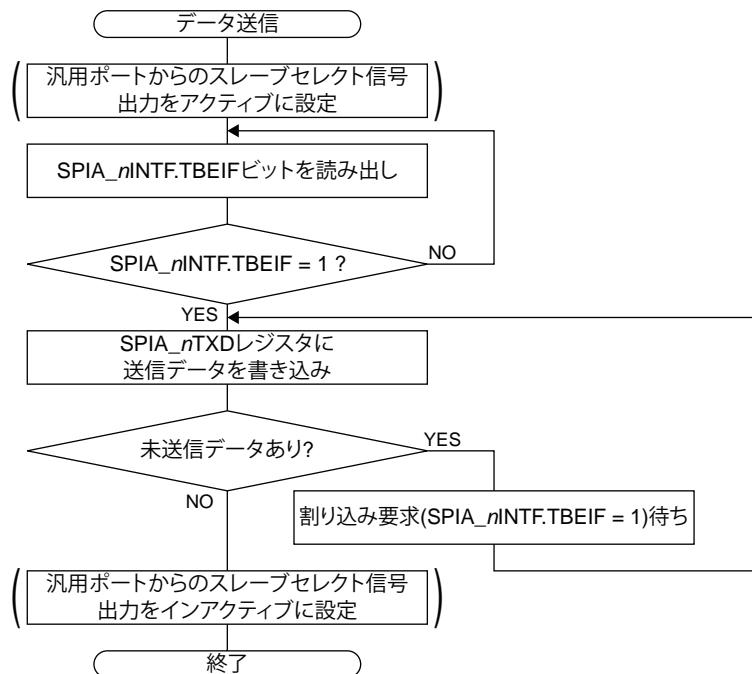

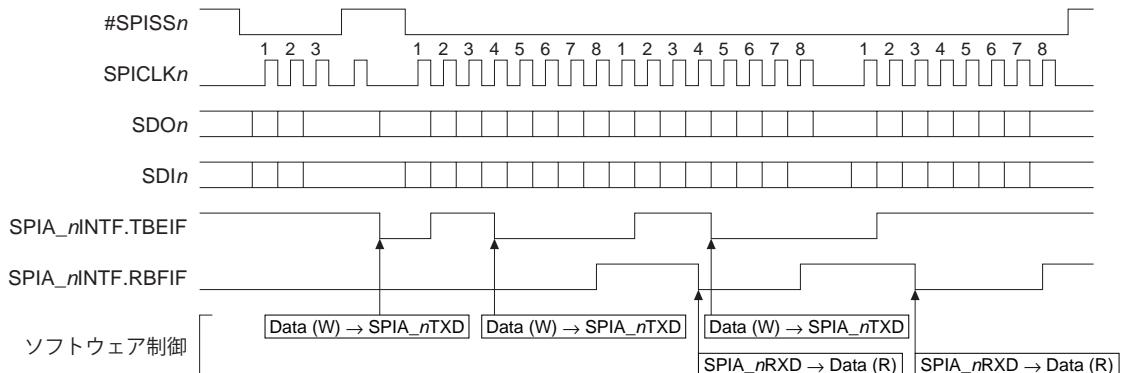

| 14.5.2 マスタモードのデータ送信 .....                                                         | 14-6        |

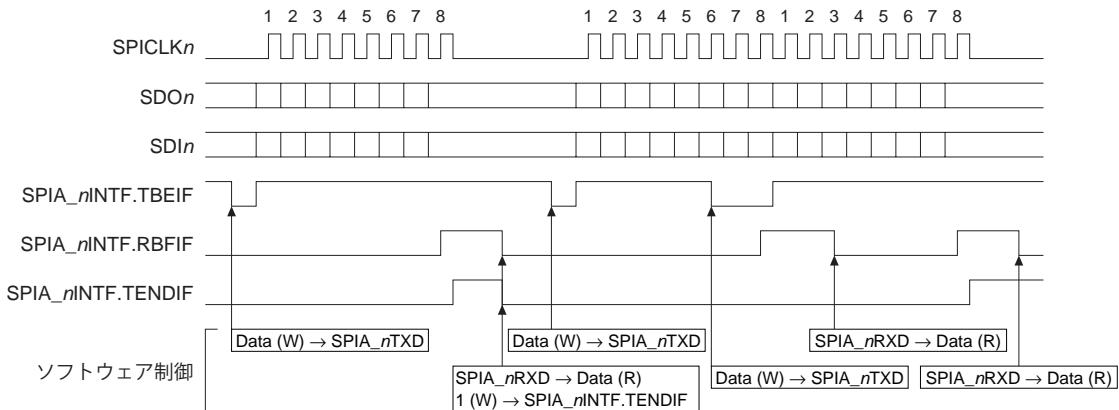

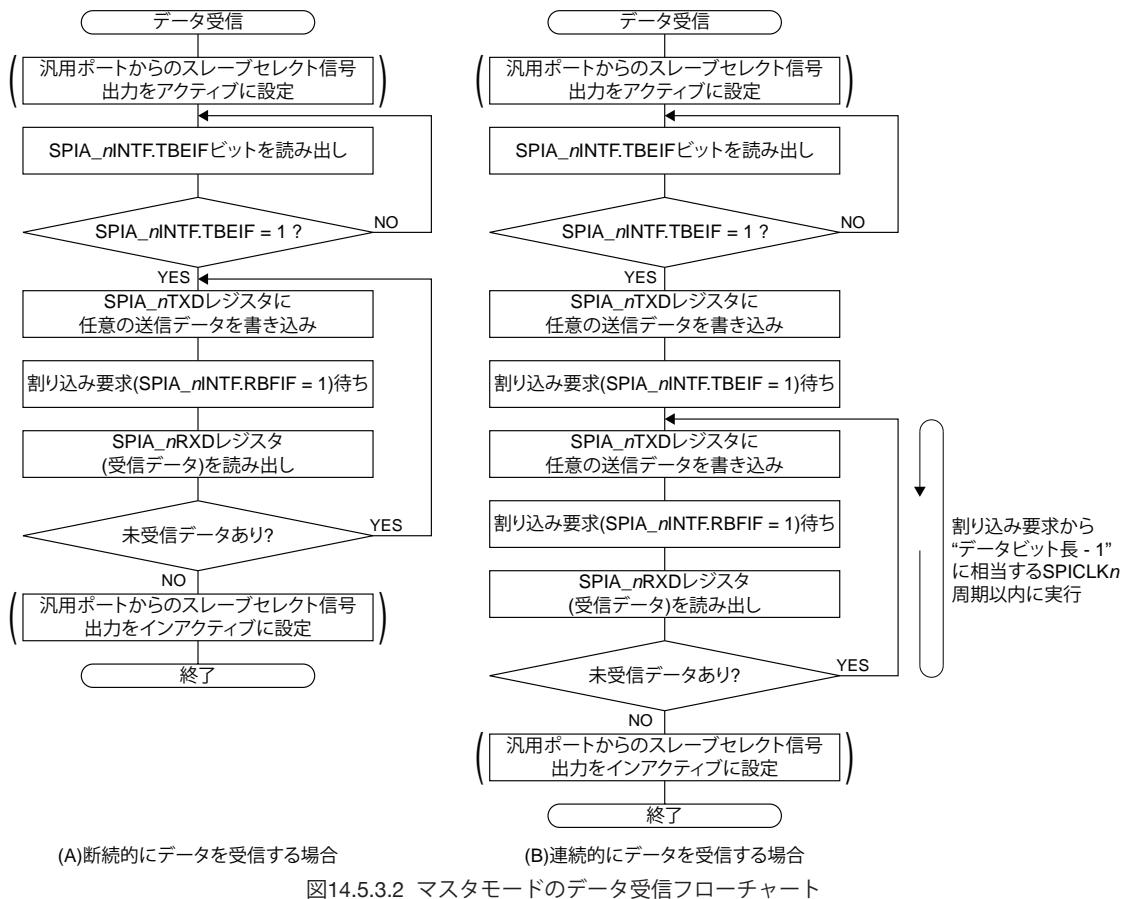

| 14.5.3 マスタモードのデータ受信 .....                                                         | 14-8        |

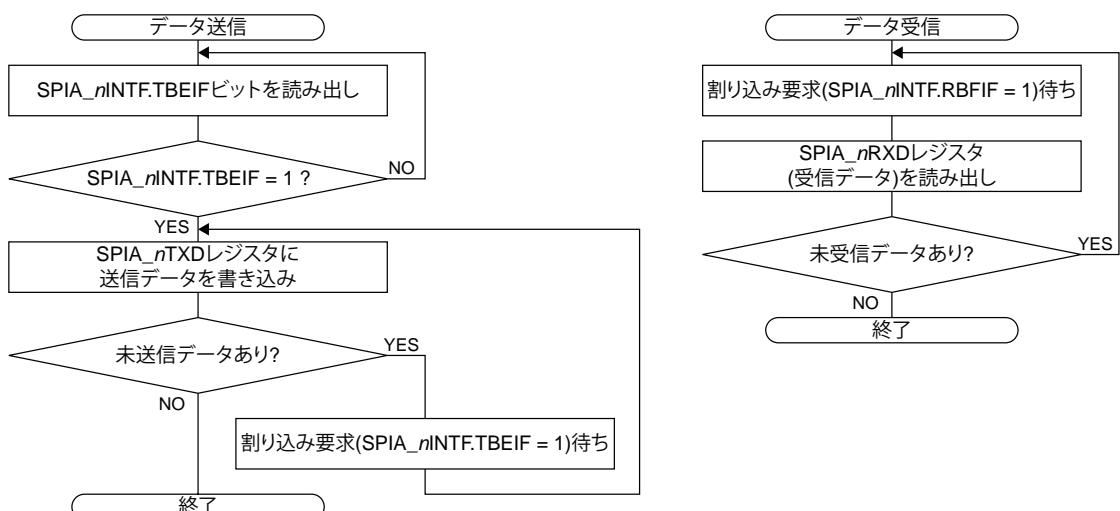

| 14.5.4 マスタモードのデータ送受信終了 .....                                                      | 14-10       |

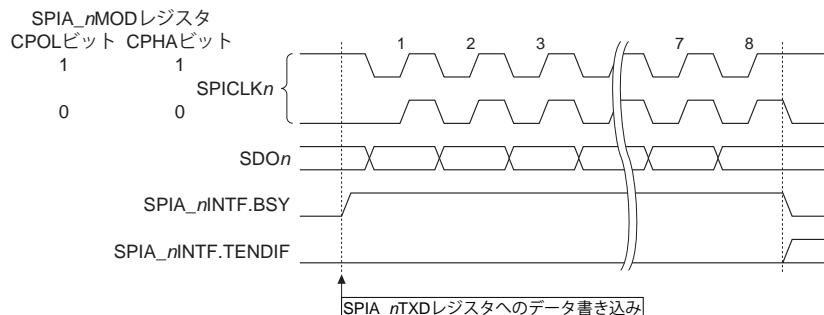

| 14.5.5 スレーブモードのデータ送受信 .....                                                       | 14-10       |

| 14.5.6 スレーブモードのデータ送受信終了 .....                                                     | 14-12       |

| 14.6 割り込み .....                                                                   | 14-12       |

| 14.7 DMA転送要求 .....                                                                | 14-13       |

| 14.8 制御レジスター .....                                                                | 14-13       |

| SPIA Ch. <i>n</i> Mode Register .....                                             | 14-13       |

| SPIA Ch. <i>n</i> Control Register .....                                          | 14-14       |

| SPIA Ch. <i>n</i> Transmit Data Register .....                                    | 14-15       |

| SPIA Ch. <i>n</i> Receive Data Register .....                                     | 14-15       |

| SPIA Ch. <i>n</i> Interrupt Flag Register .....                                   | 14-15       |

| SPIA Ch. <i>n</i> Interrupt Enable Register .....                                 | 14-16       |

| SPIA Ch. <i>n</i> Transmit Buffer Empty DMA Request Enable Register .....         | 14-16       |

| SPIA Ch. <i>n</i> Receive Buffer Full DMA Request Enable Register .....           | 14-16       |

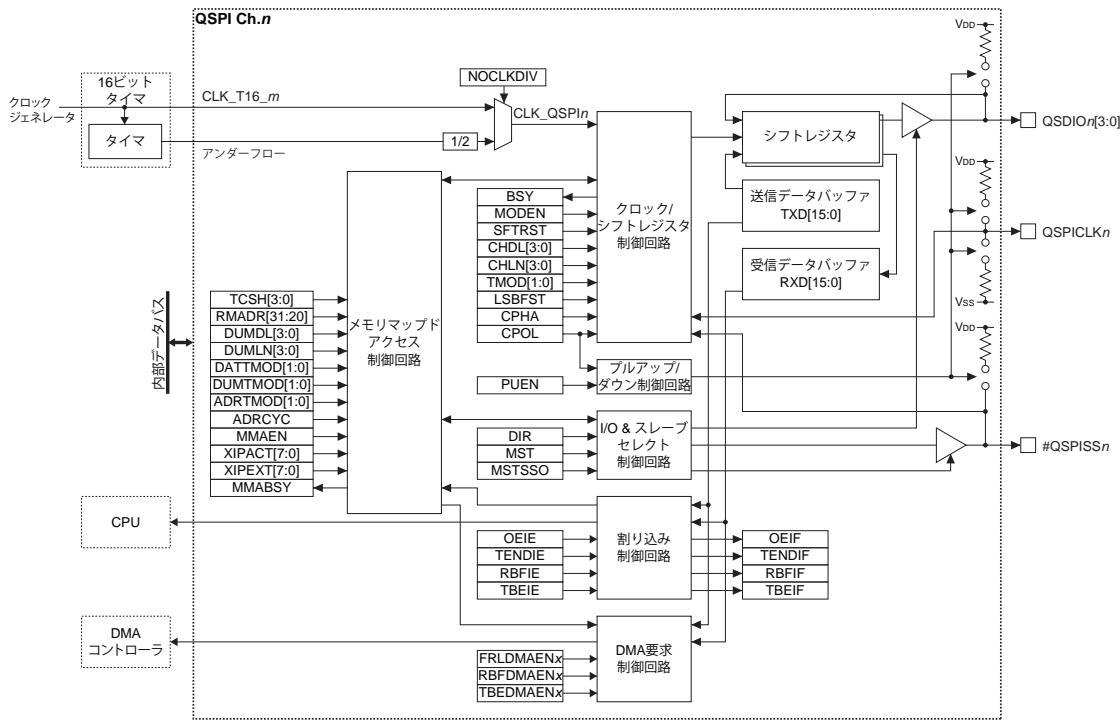

| <b>15 同期式クワッドシリアルインターフェース(QSPI).....</b>                                          | <b>15-1</b> |

| 15.1 概要 .....                                                                     | 15-1        |

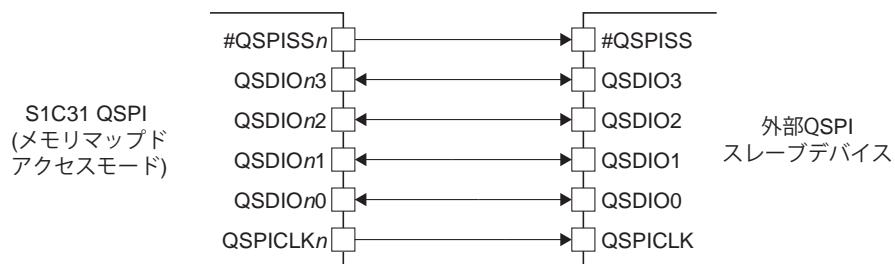

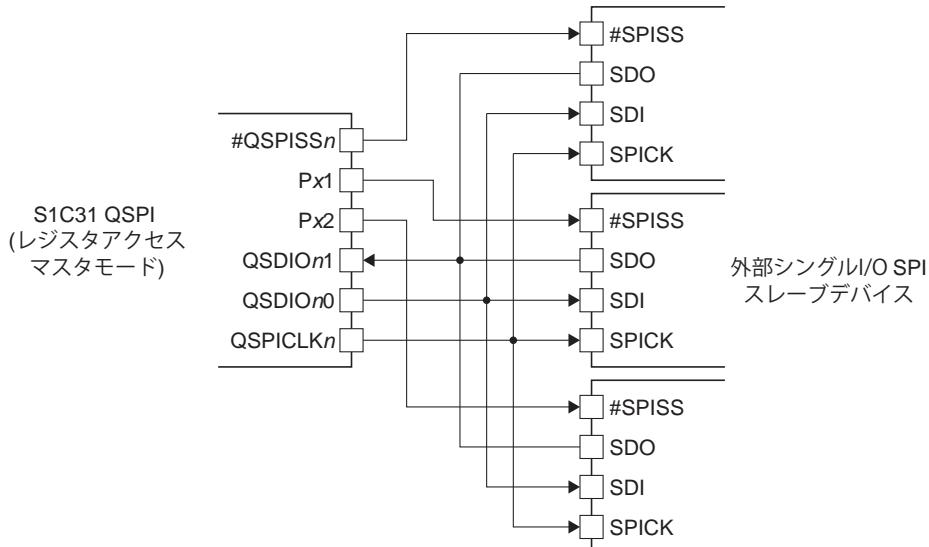

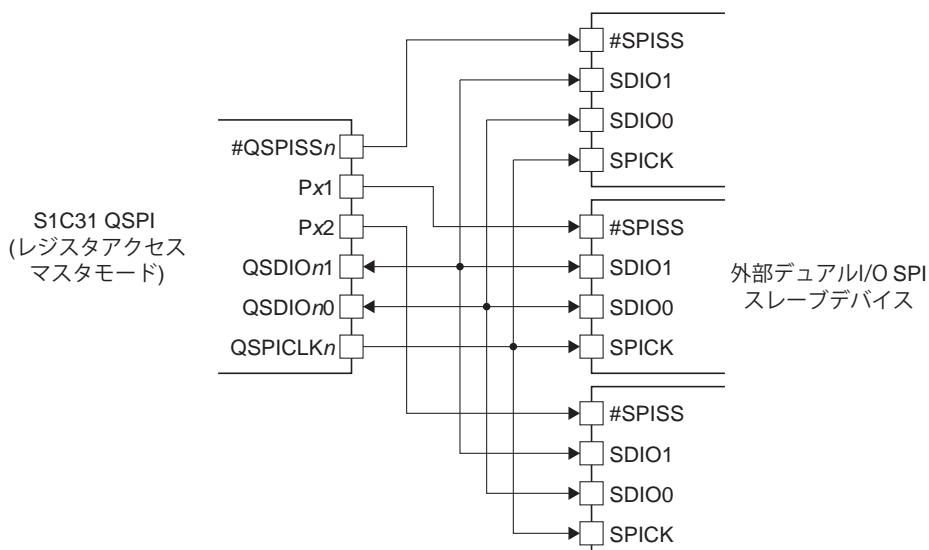

| 15.2 入出力端子と外部接続 .....                                                             | 15-2        |

| 15.2.1 入出力端子一覧.....                                                               | 15-2        |

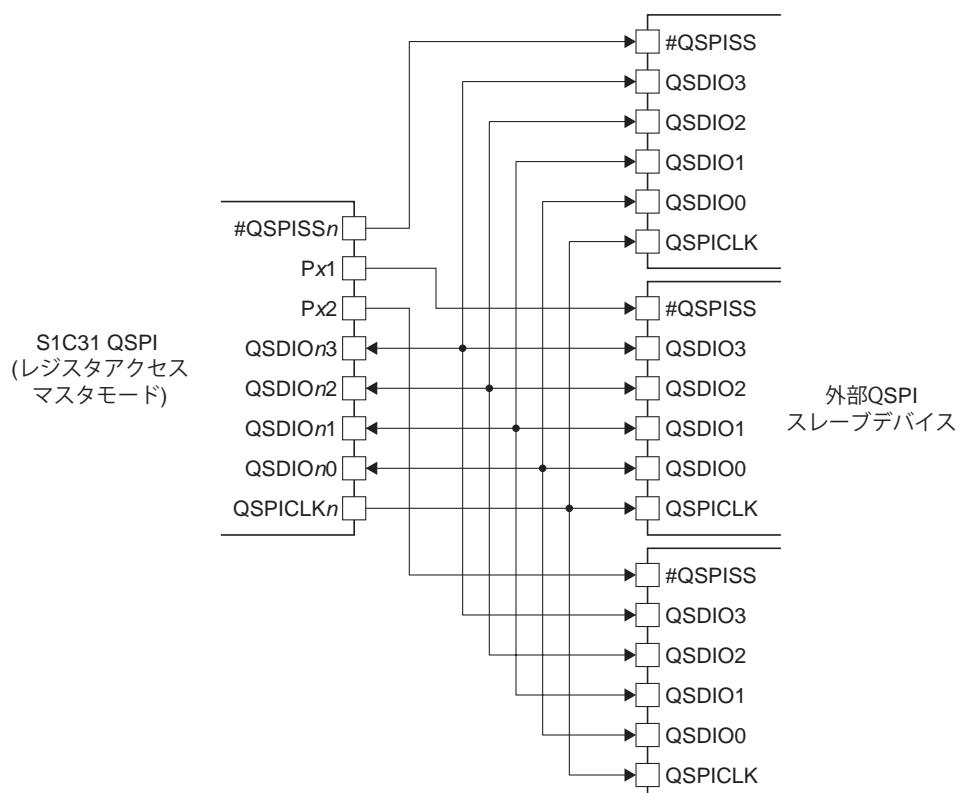

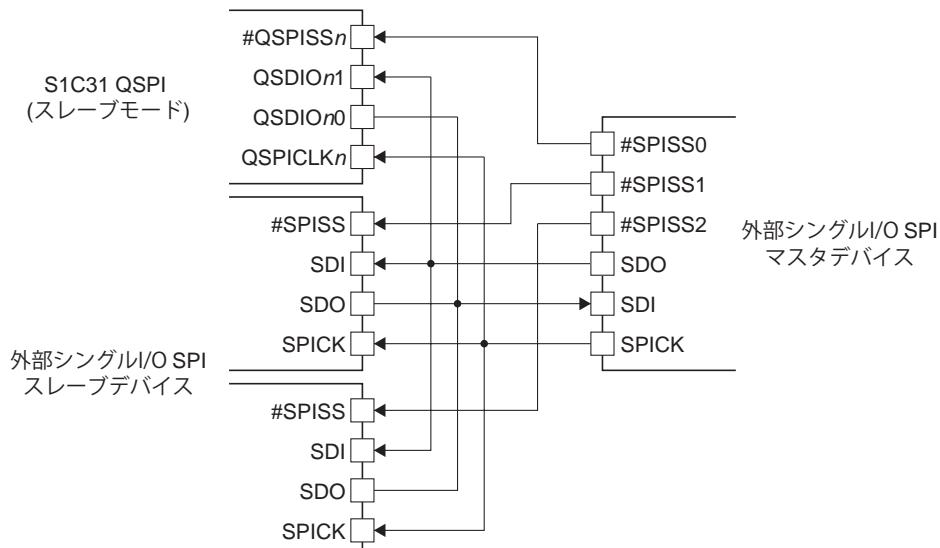

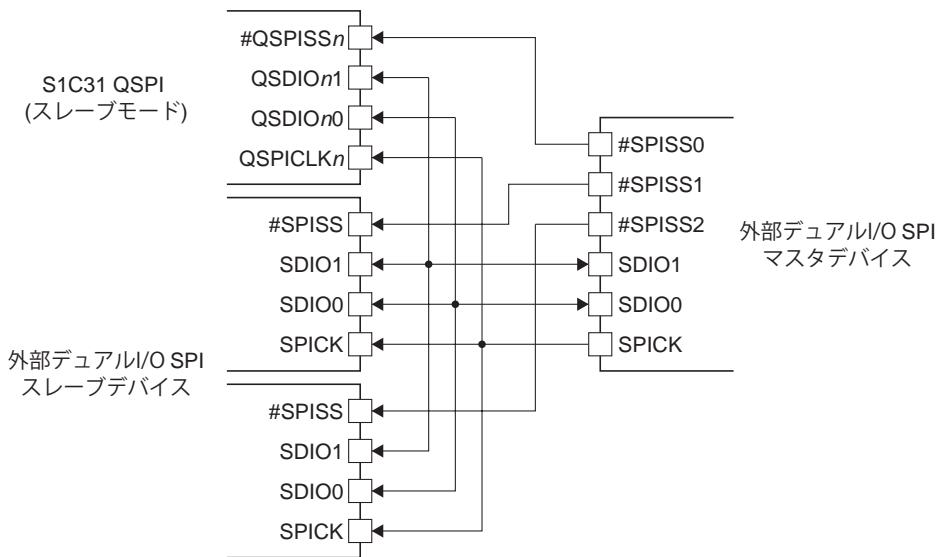

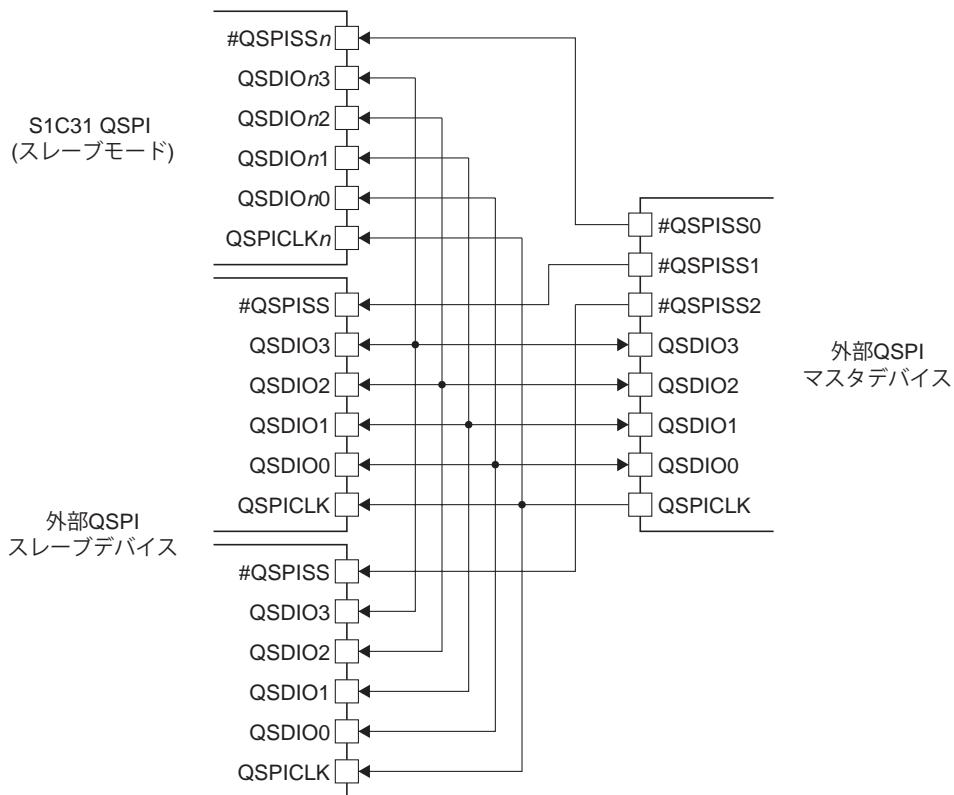

| 15.2.2 外部との接続 .....                                                               | 15-2        |

| 15.2.3 マスタモードとスレーブモードの端子機能.....                                                   | 15-6        |

| 15.2.4 入力端子のプルアップ/プルダウン機能.....                                                    | 15-6        |

| 15.3 クロック設定 .....                                                                 | 15-6        |

| 15.3.1 QSPIの動作クロック .....                                                          | 15-6        |

| 15.3.2 デバッグ時のクロック供給 .....                                                         | 15-7        |

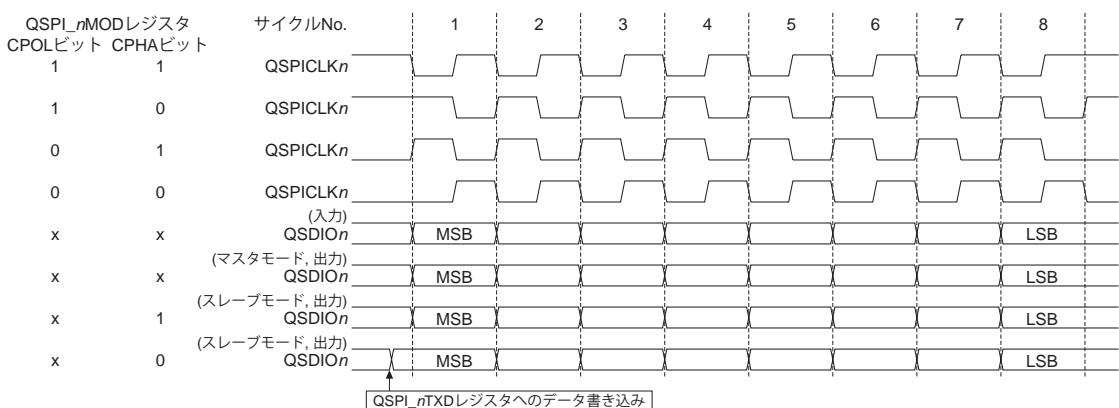

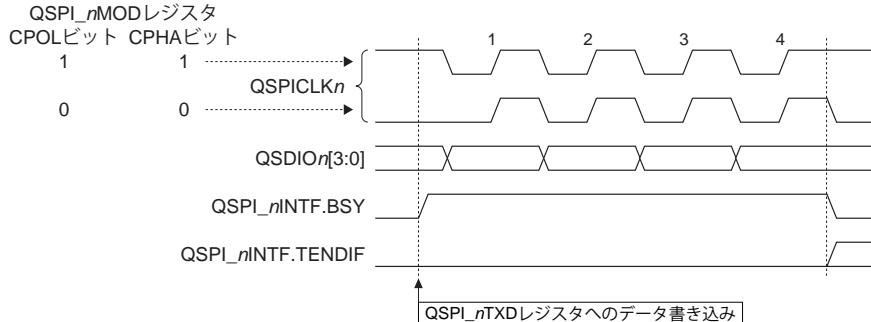

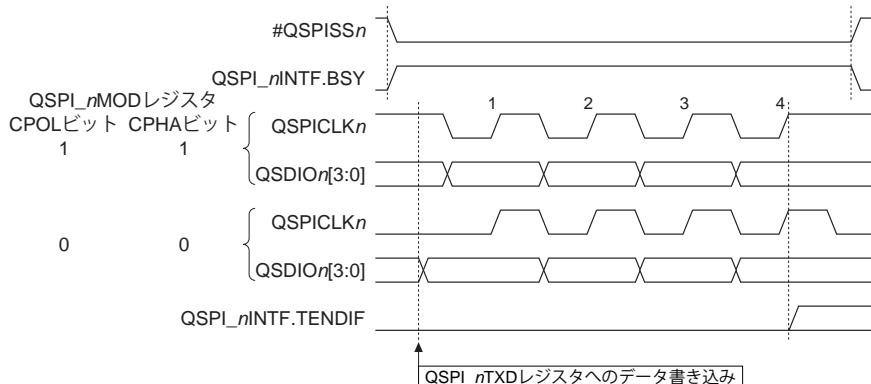

| 15.3.3 QSPIクロック(QSPICLK <i>n</i> )の位相と極性 .....                                    | 15-7        |

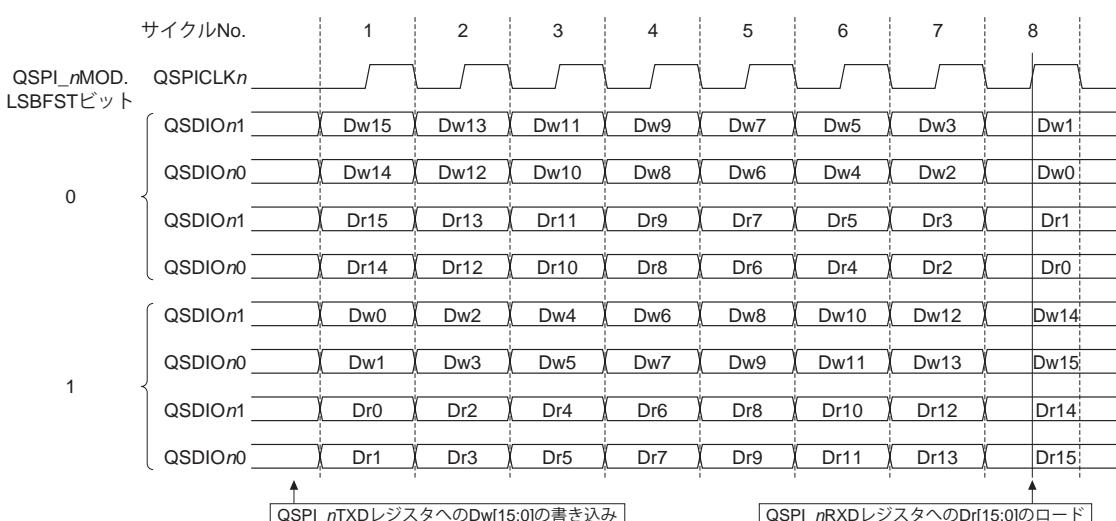

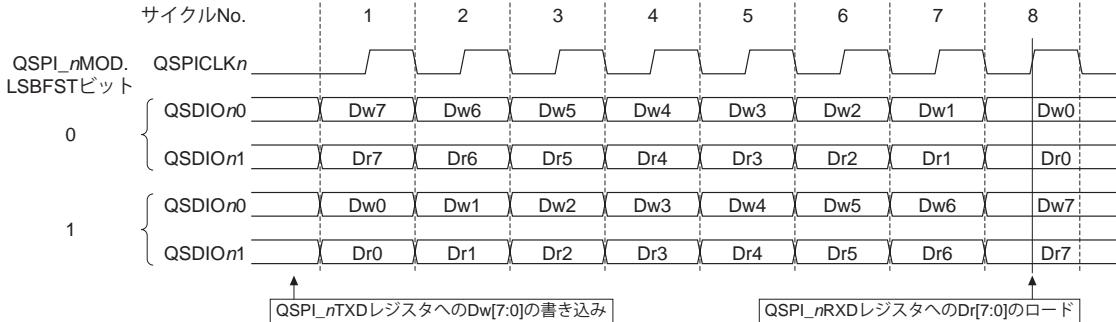

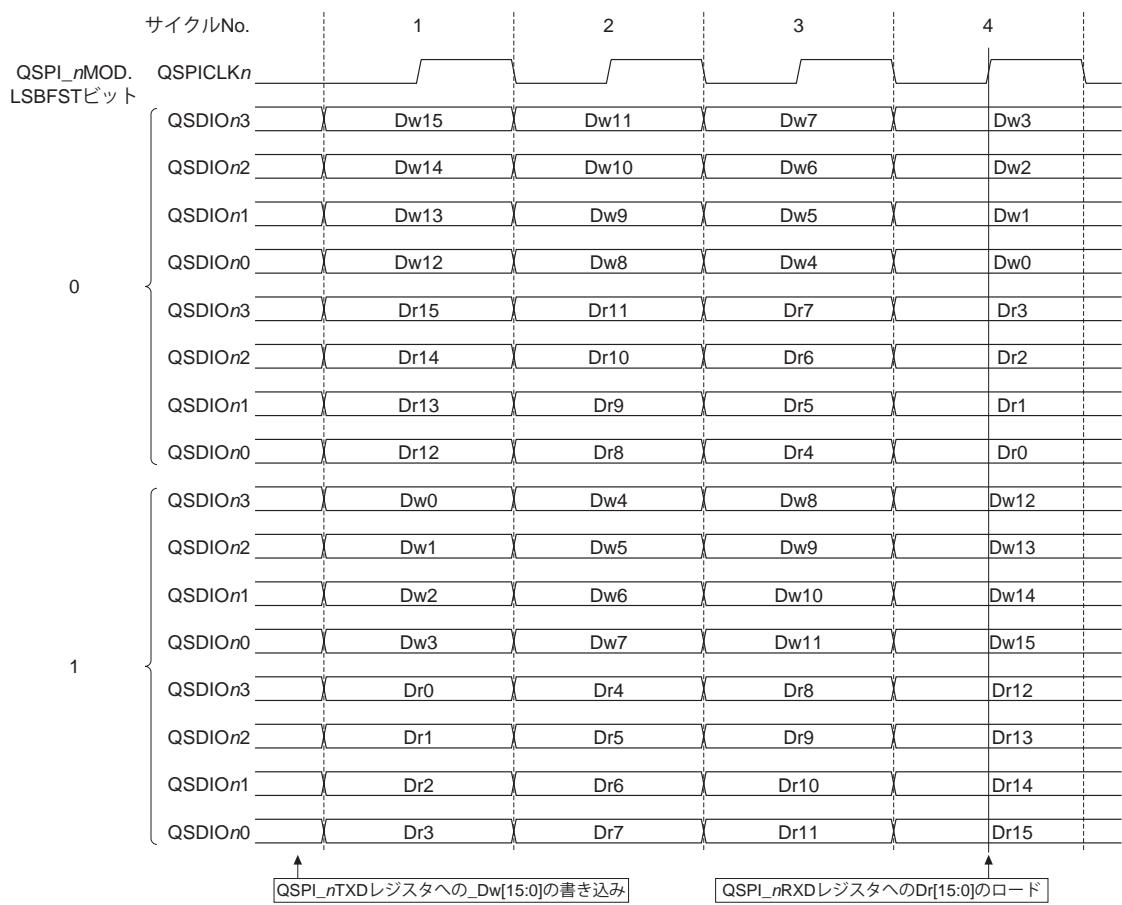

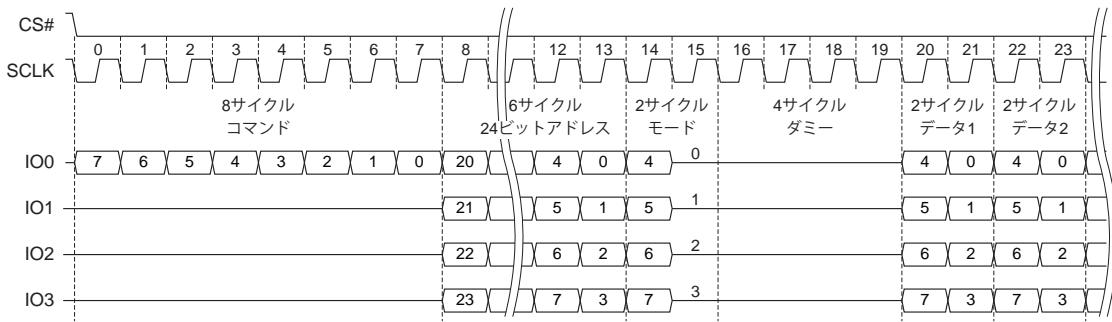

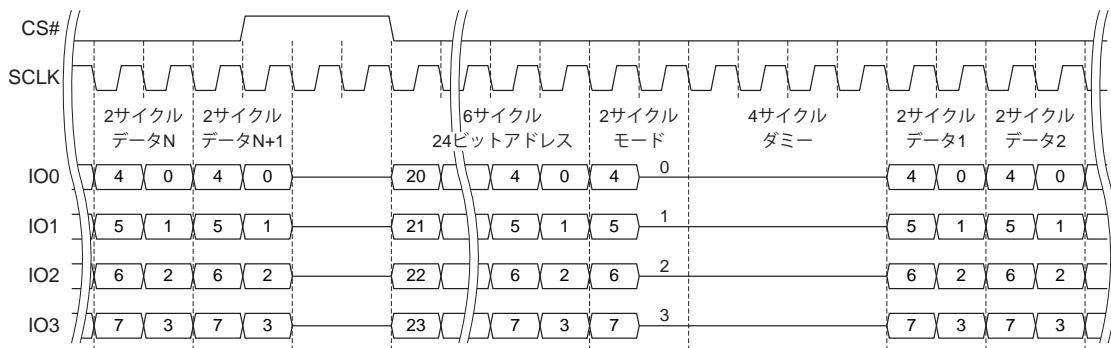

| 15.4 データフォーマット .....                                                              | 15-8        |

| 15.5 動作 .....                                                                     | 15-9        |

|                                                                   |             |

|-------------------------------------------------------------------|-------------|

| 15.5.1 レジスタアクセスモード .....                                          | 15-9        |

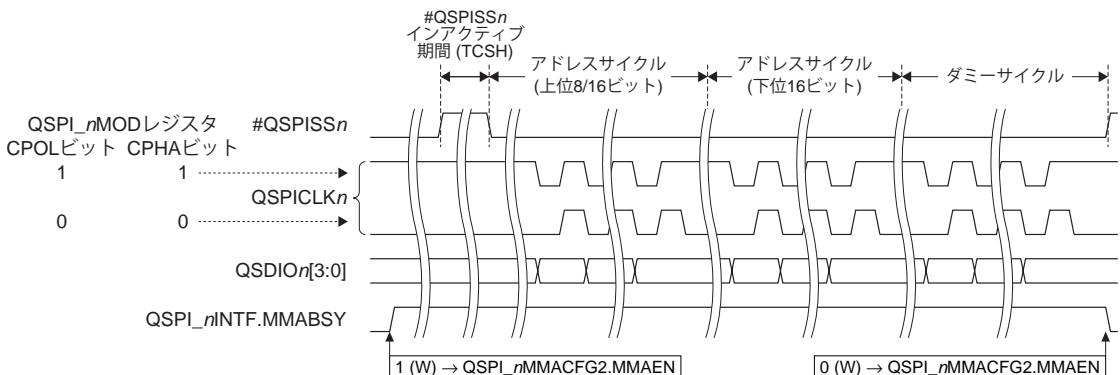

| 15.5.2 メモリマップドアクセスモード.....                                        | 15-10       |

| 15.5.3 初期設定 .....                                                 | 15-11       |

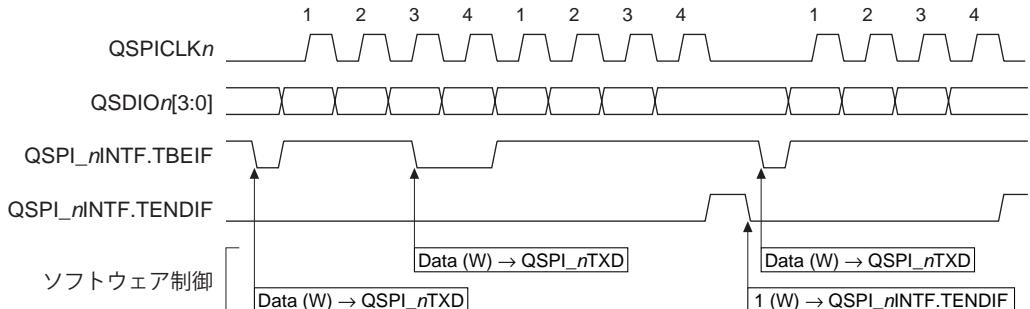

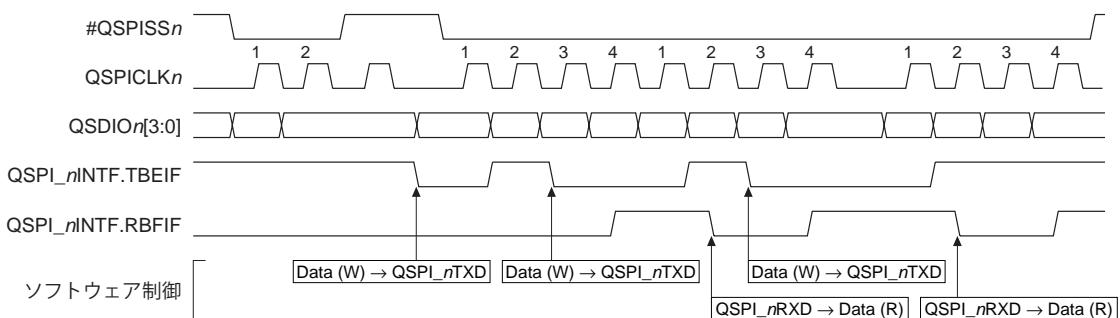

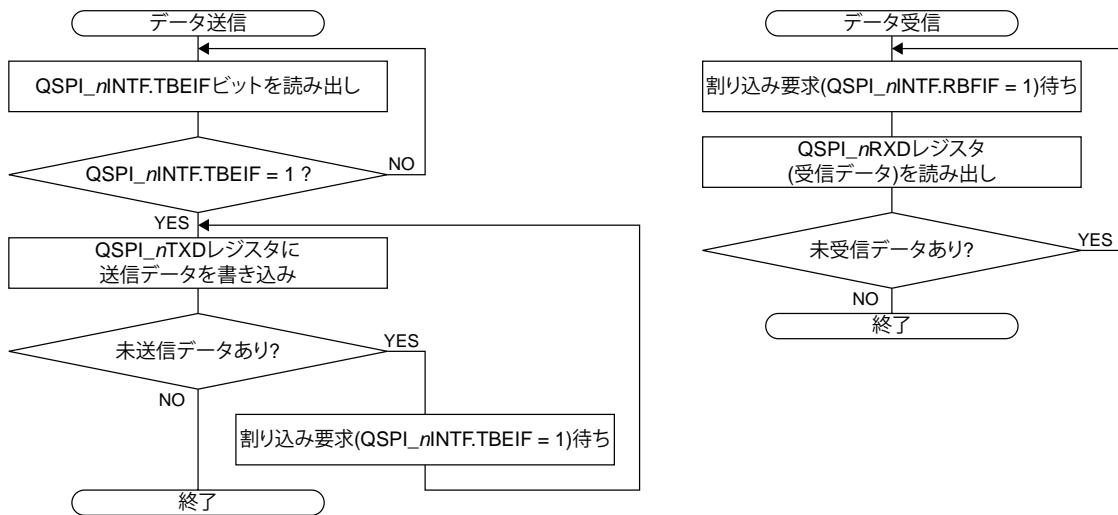

| 15.5.4 マスターモードのデータ送信.....                                         | 15-12       |

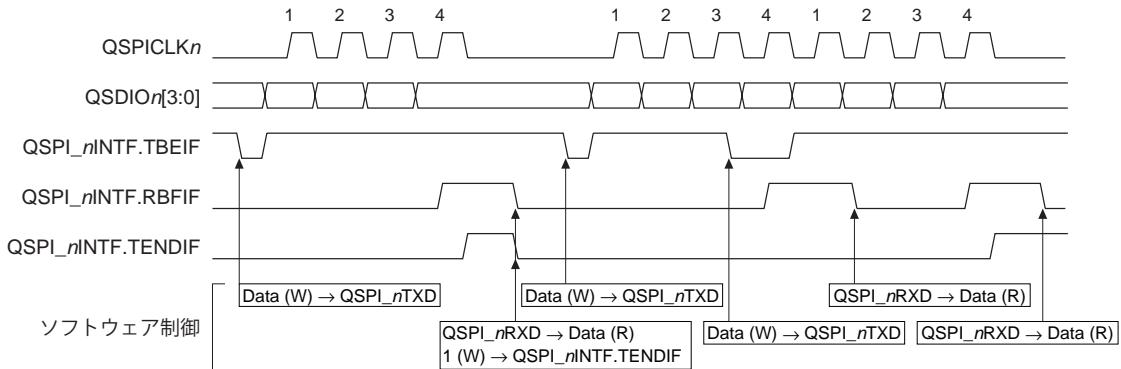

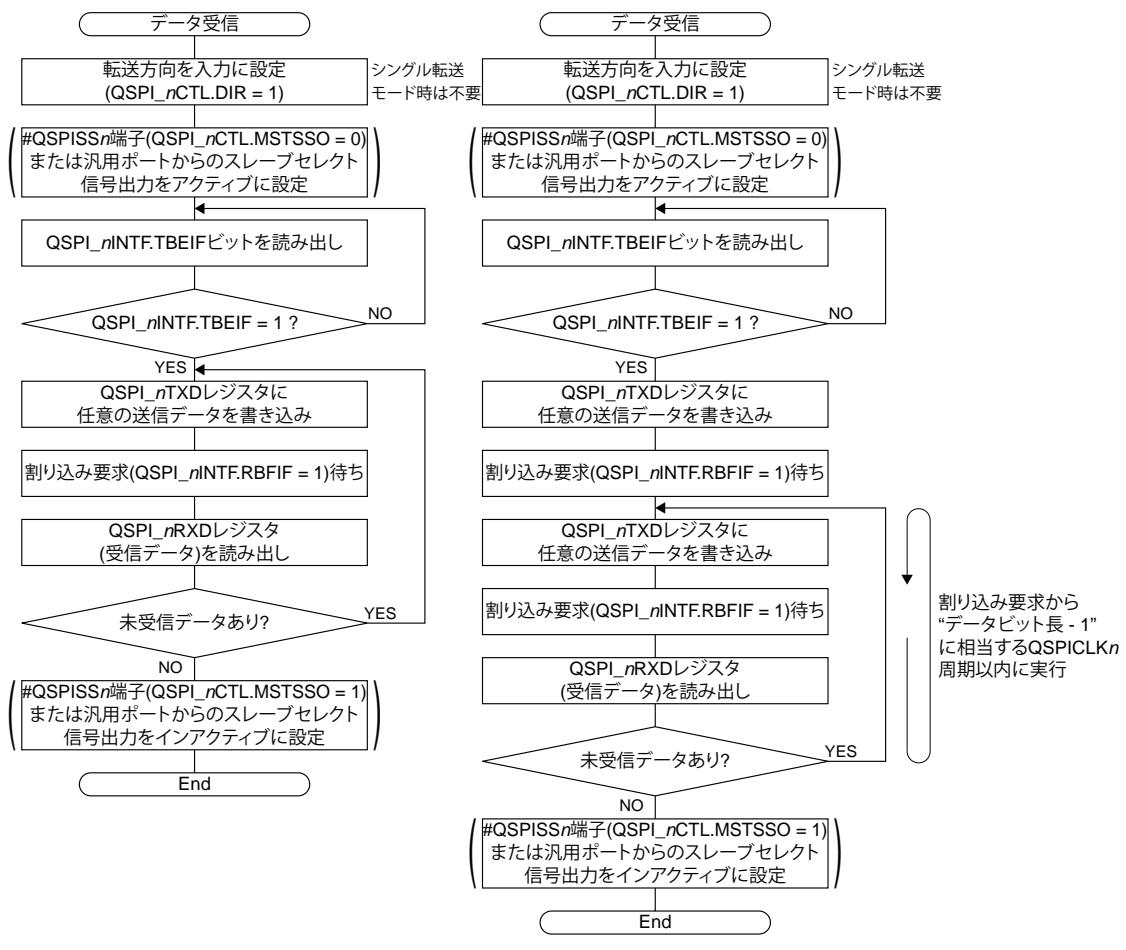

| 15.5.5 レジスタアクセスマスタモードのデータ受信 .....                                 | 15-14       |

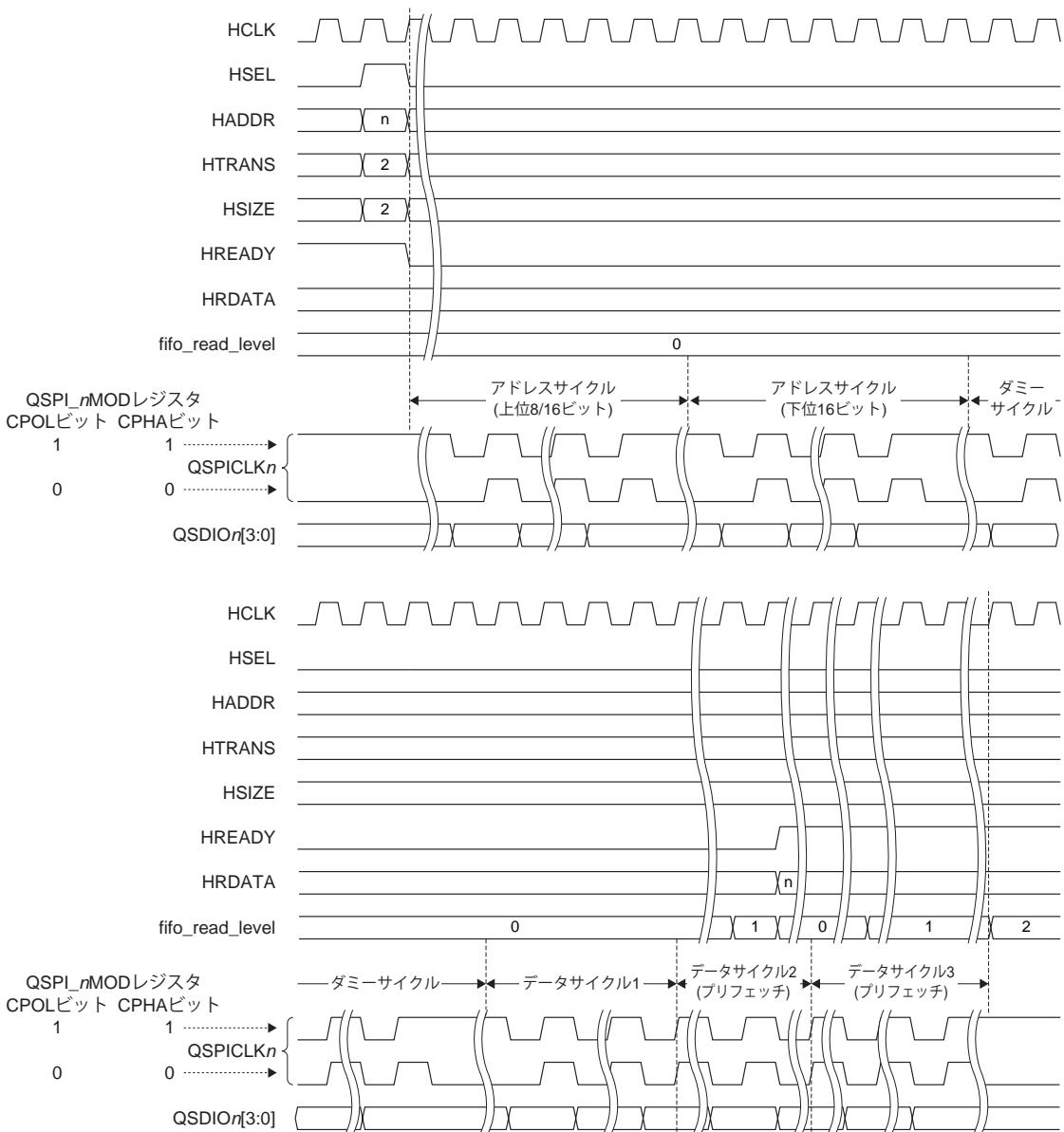

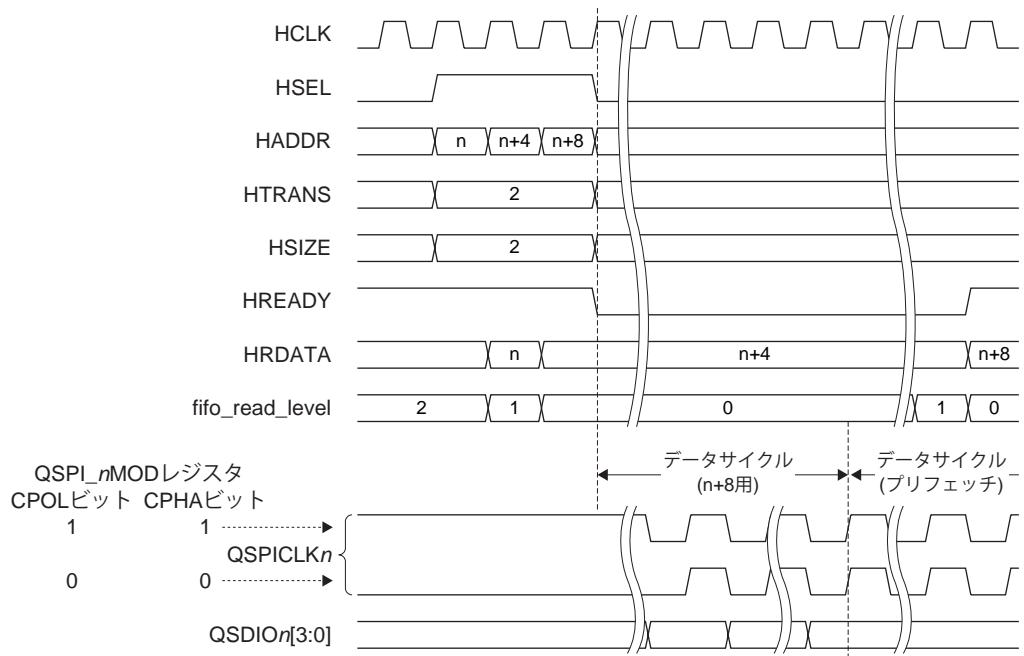

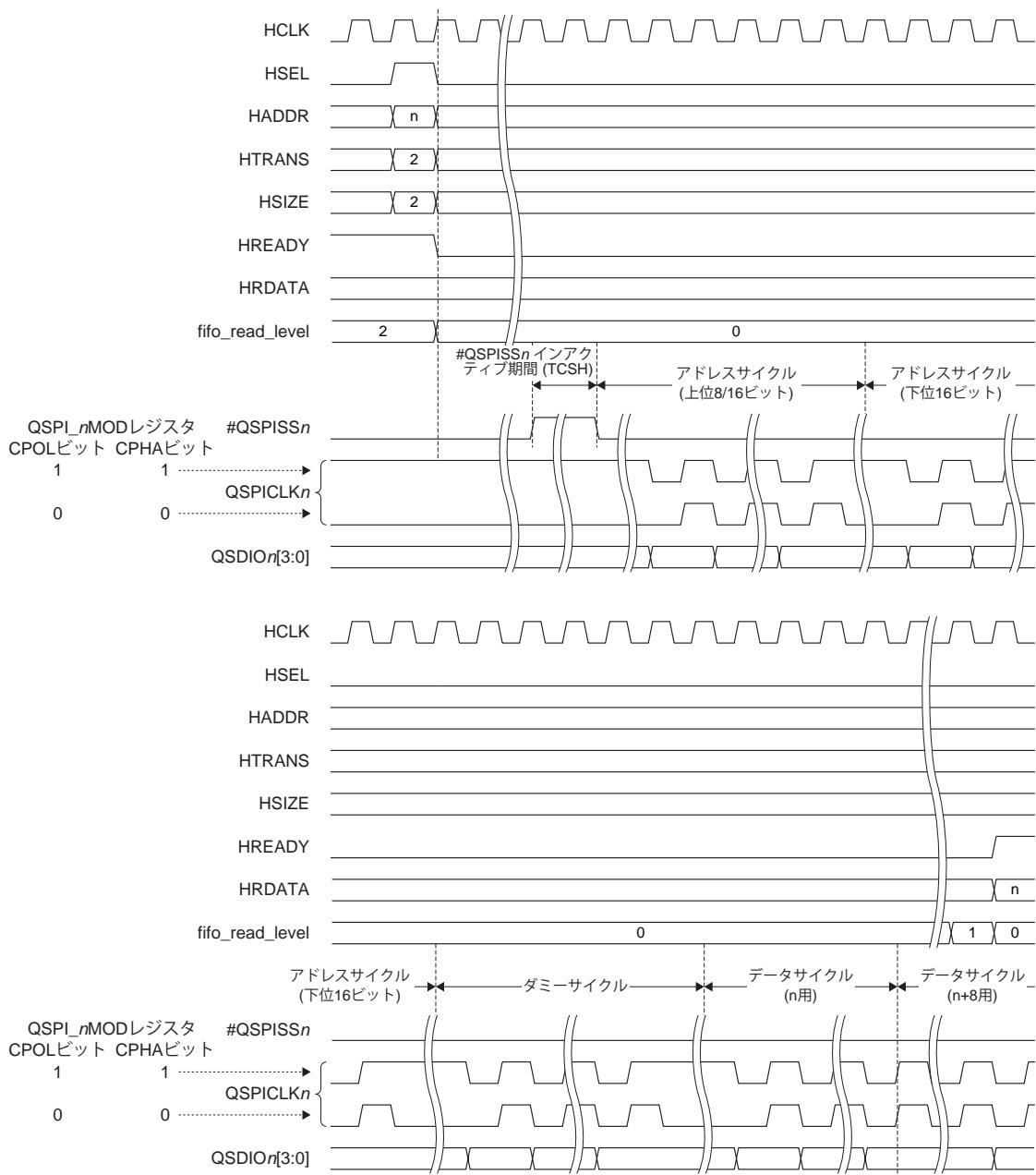

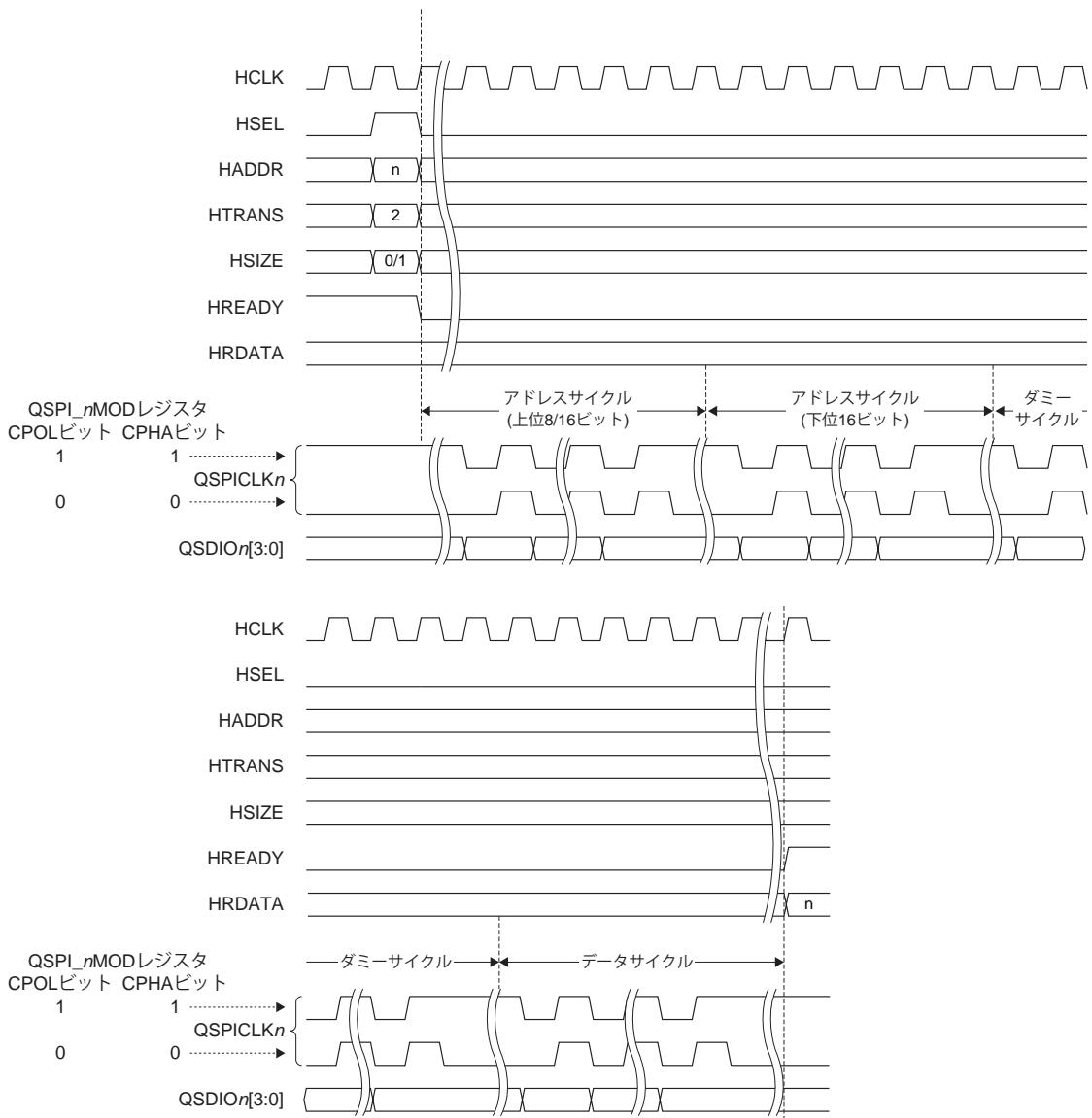

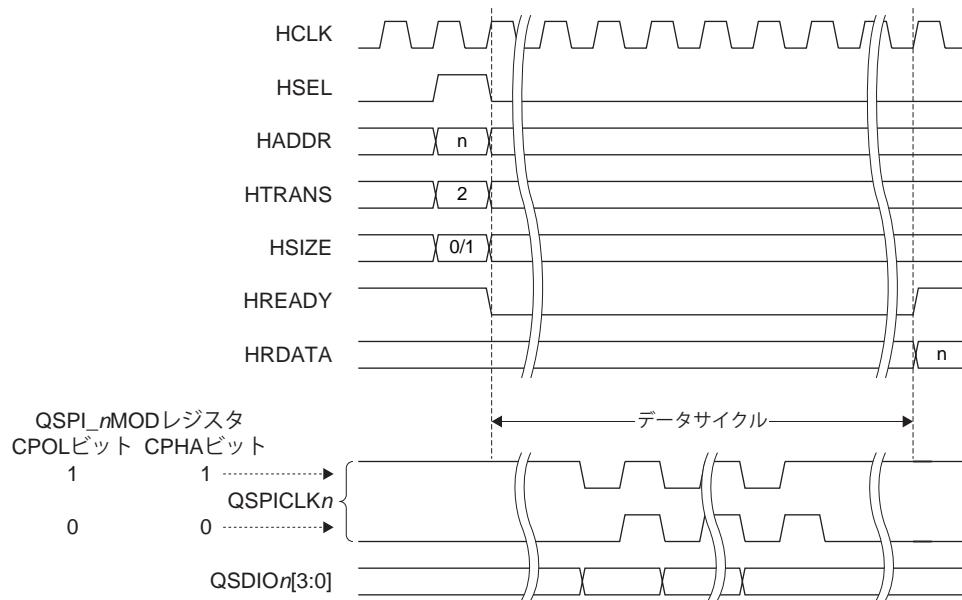

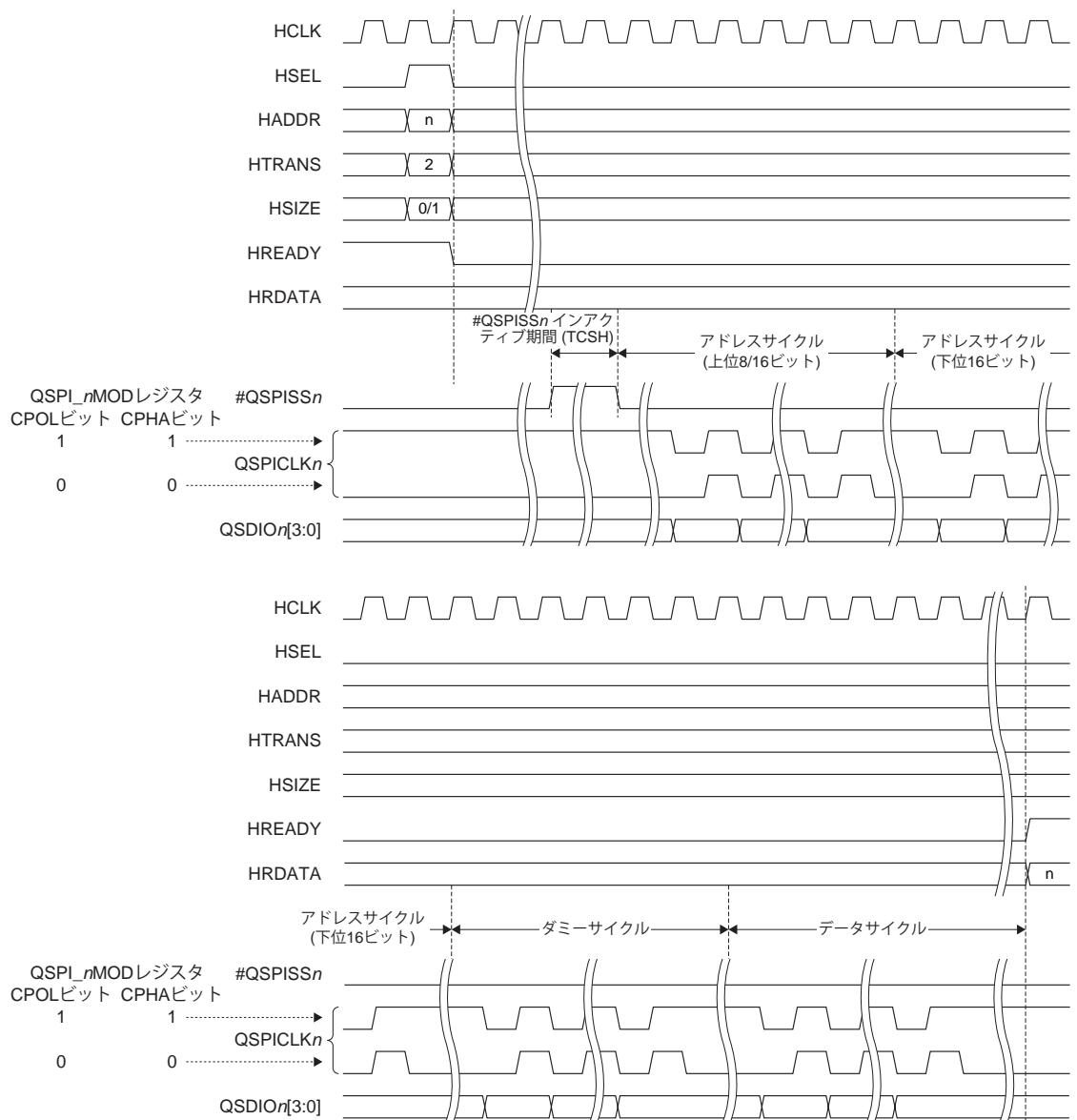

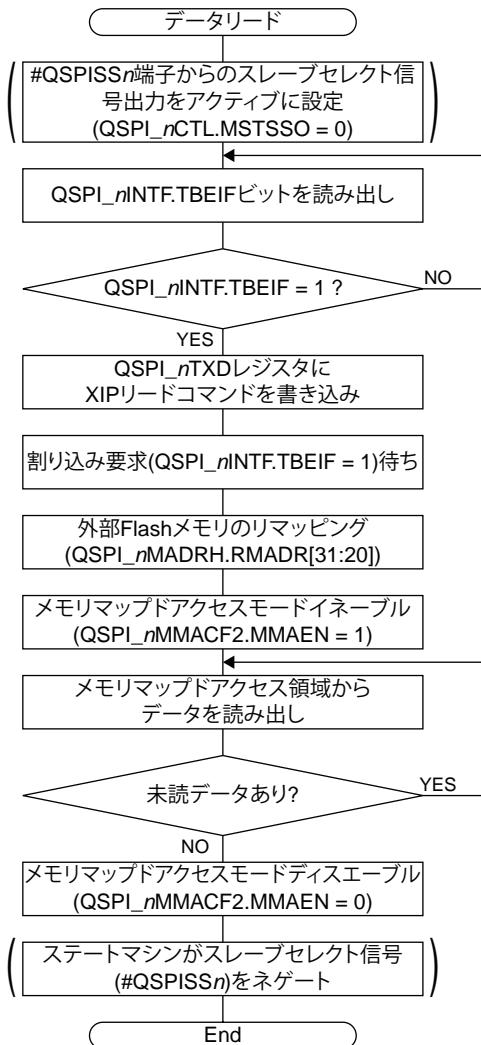

| 15.5.6 メモリマップドアクセスモードのデータ受信 .....                                 | 15-17       |

| 15.5.7 メモリマップドアクセス操作の終了 .....                                     | 15-25       |

| 15.5.8 マスターモードのデータ送受信終了 .....                                     | 15-25       |

| 15.5.9 スレーブモードのデータ送受信.....                                        | 15-25       |

| 15.5.10 スレーブモードのデータ送受信終了 .....                                    | 15-27       |

| 15.6 割り込み .....                                                   | 15-27       |

| 15.7 DMA転送要求 .....                                                | 15-28       |

| 15.8 制御レジスタ .....                                                 | 15-29       |

| QSPI Ch.n Mode Register .....                                     | 15-29       |

| QSPI Ch.n Control Register .....                                  | 15-31       |

| QSPI Ch.n Transmit Data Register .....                            | 15-31       |

| QSPI Ch.n Receive Data Register .....                             | 15-32       |

| QSPI Ch.n Interrupt Flag Register .....                           | 15-32       |

| QSPI Ch.n Interrupt Enable Register .....                         | 15-33       |

| QSPI Ch.n Transmit Buffer Empty DMA Request Enable Register ..... | 15-33       |

| QSPI Ch.n Receive Buffer Full DMA Request Enable Register .....   | 15-33       |

| QSPI Ch.n FIFO Data Ready DMA Request Enable Register .....       | 15-34       |

| QSPI Ch.n Memory Mapped Access Configuration Register 1 .....     | 15-34       |

| QSPI Ch.n Remapping Start Address High Register .....             | 15-34       |

| QSPI Ch.n Memory Mapped Access Configuration Register 2 .....     | 15-35       |

| QSPI Ch.n Mode Byte Register .....                                | 15-37       |

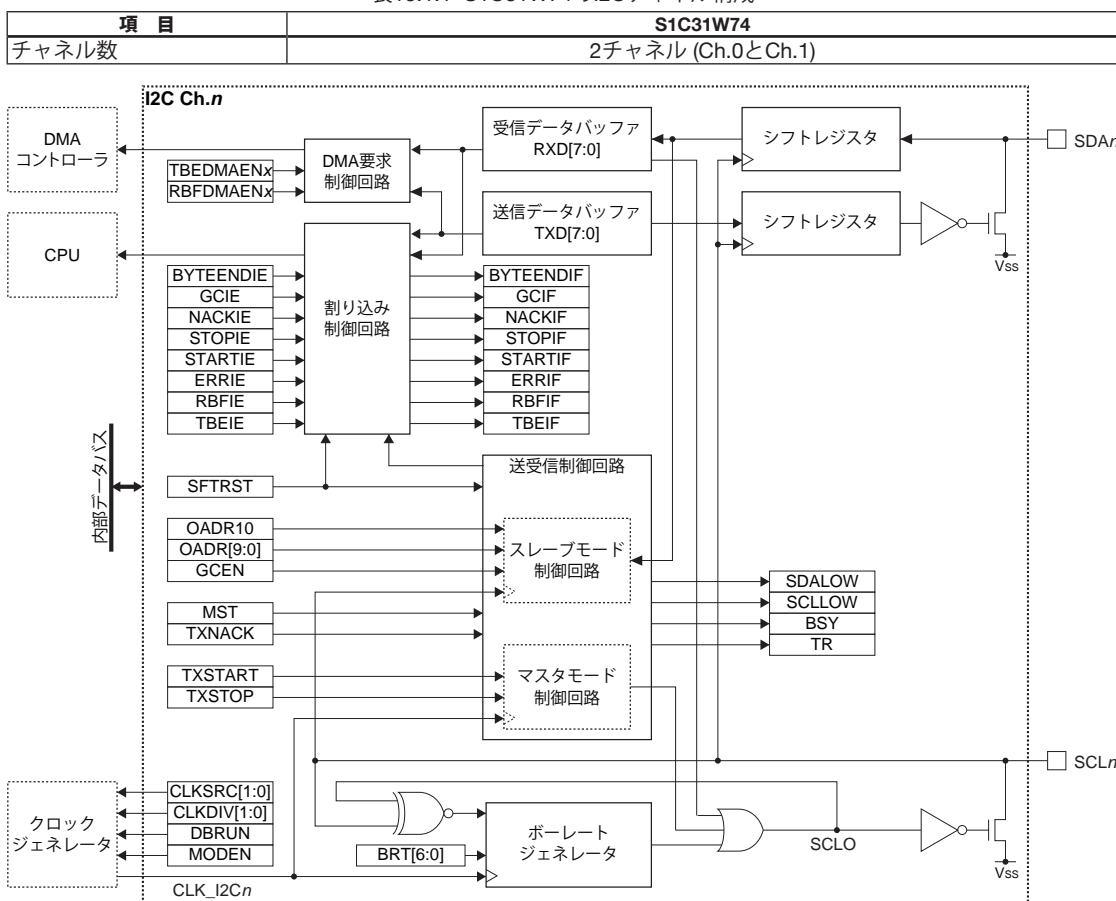

| <b>16 I<sup>2</sup>C(I2C).....</b>                                | <b>16-1</b> |

| 16.1 概要 .....                                                     | 16-1        |

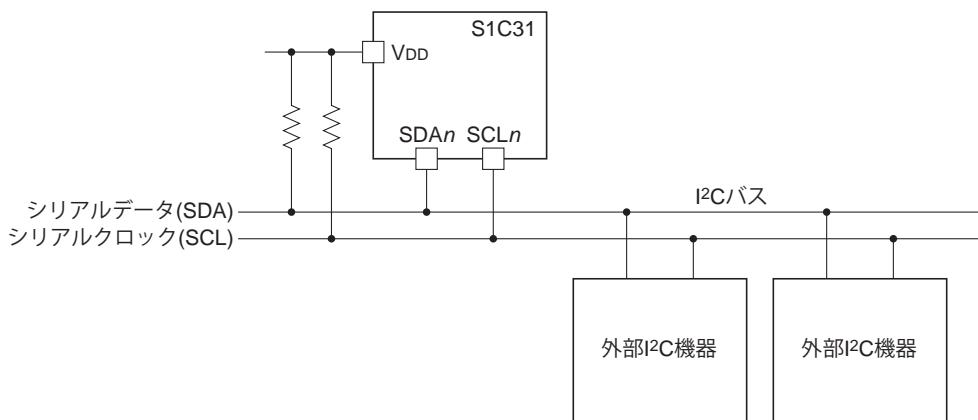

| 16.2 入出力端子と外部接続 .....                                             | 16-2        |

| 16.2.1 入出力端子一覧 .....                                              | 16-2        |

| 16.2.2 外部との接続 .....                                               | 16-2        |

| 16.3 クロック設定 .....                                                 | 16-3        |

| 16.3.1 I <sup>2</sup> Cの動作クロック .....                              | 16-3        |

| 16.3.2 デバッグ時のクロック供給 .....                                         | 16-3        |

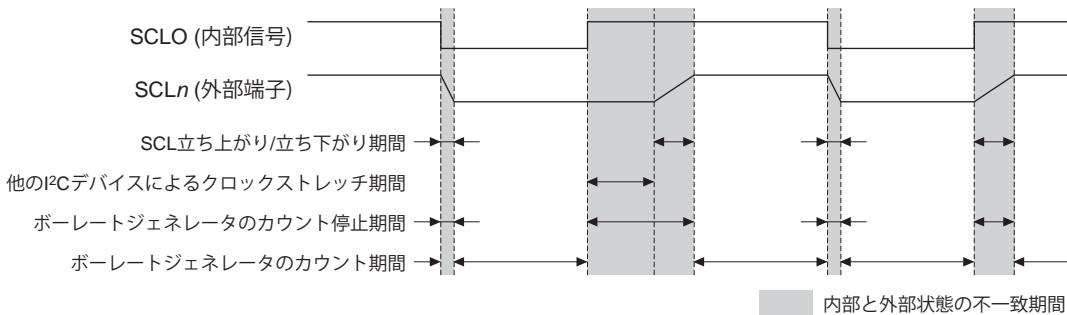

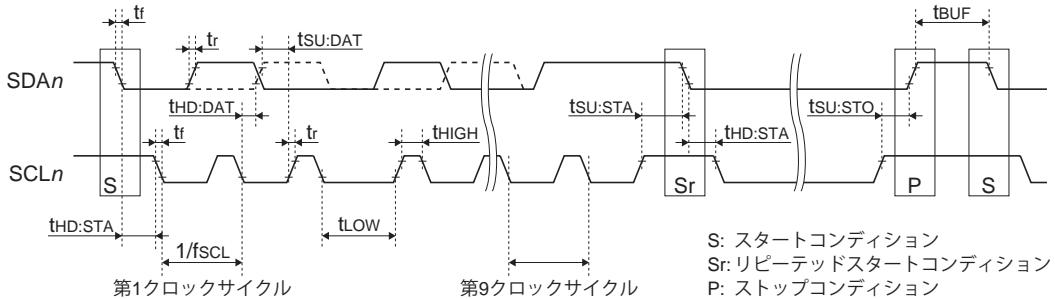

| 16.3.3 ポーレートジェネレータ .....                                          | 16-3        |

| 16.4 動作 .....                                                     | 16-4        |

| 16.4.1 初期設定 .....                                                 | 16-4        |

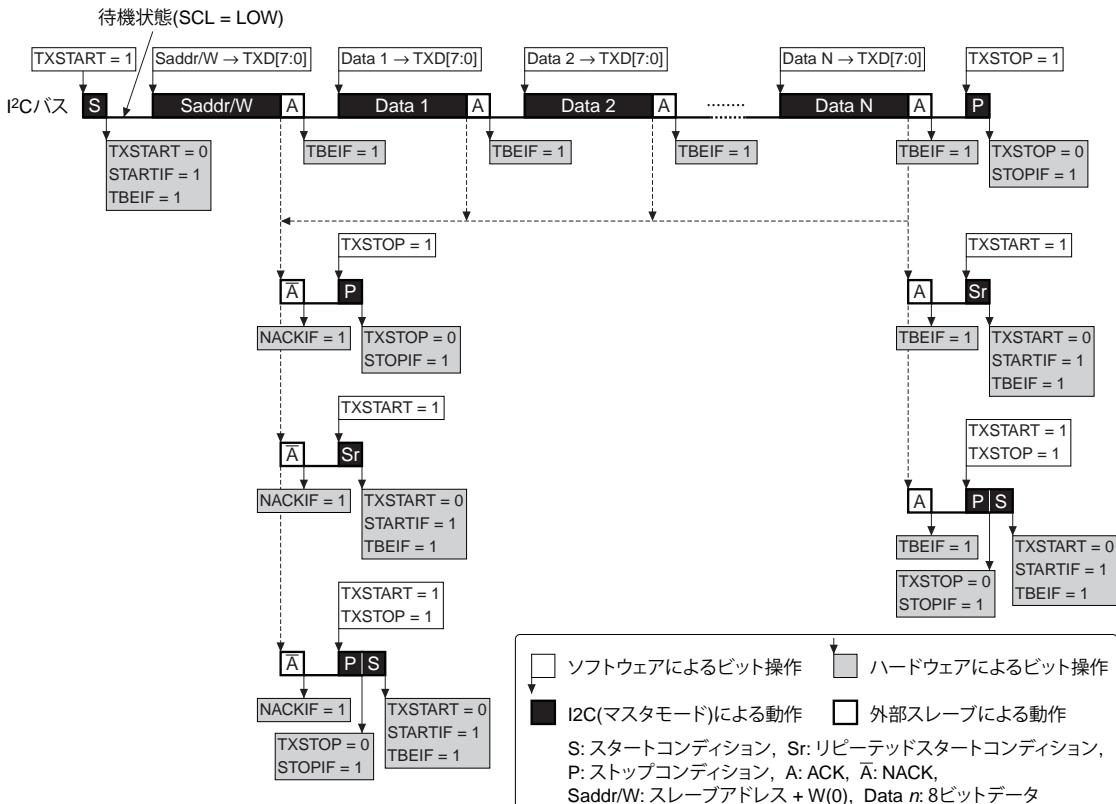

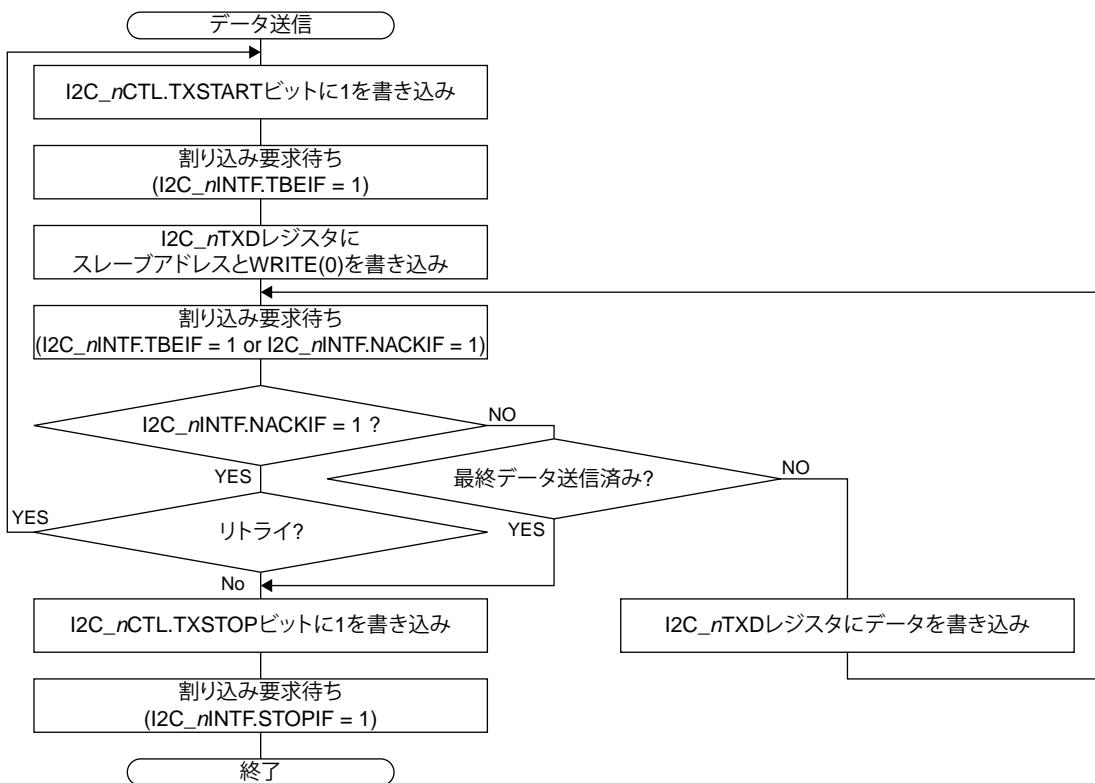

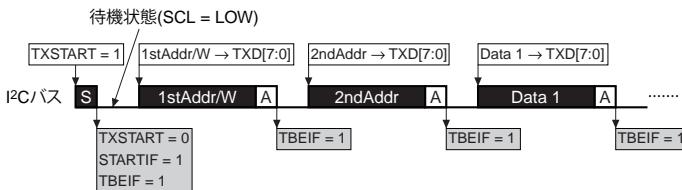

| 16.4.2 マスターモードのデータ送信 .....                                        | 16-5        |

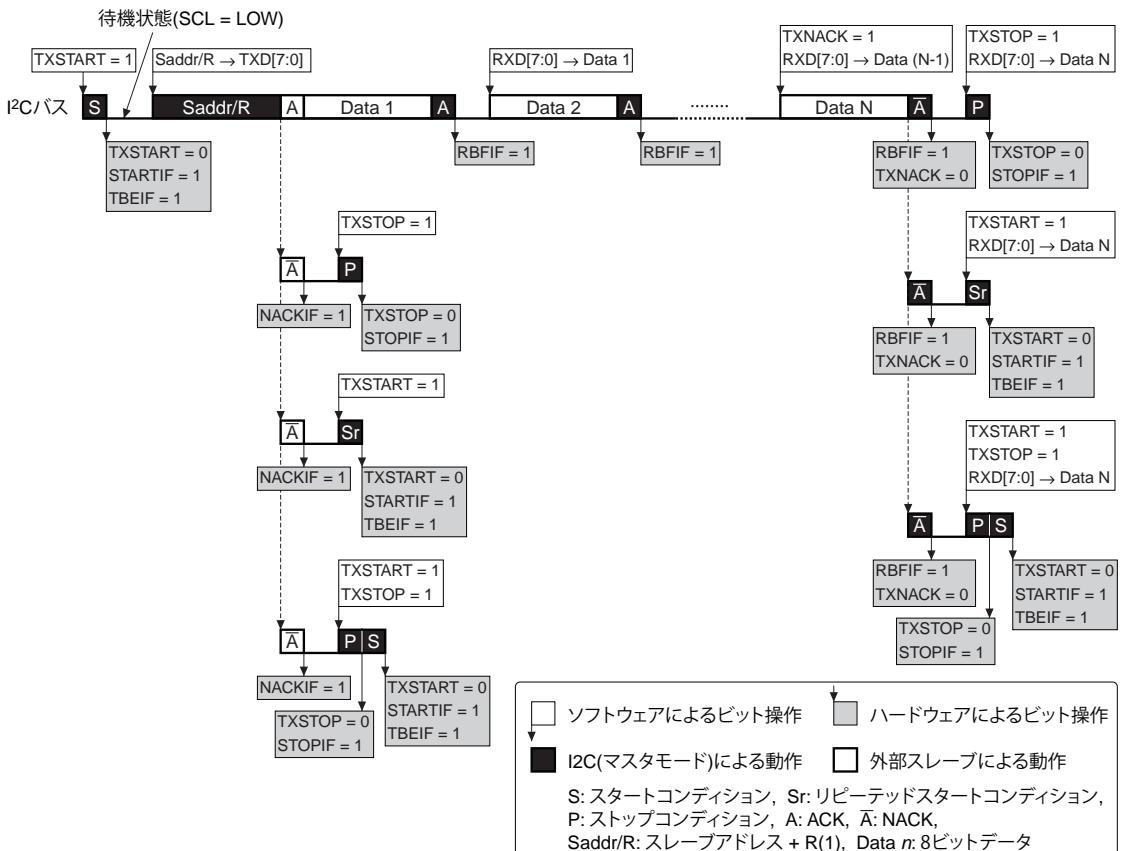

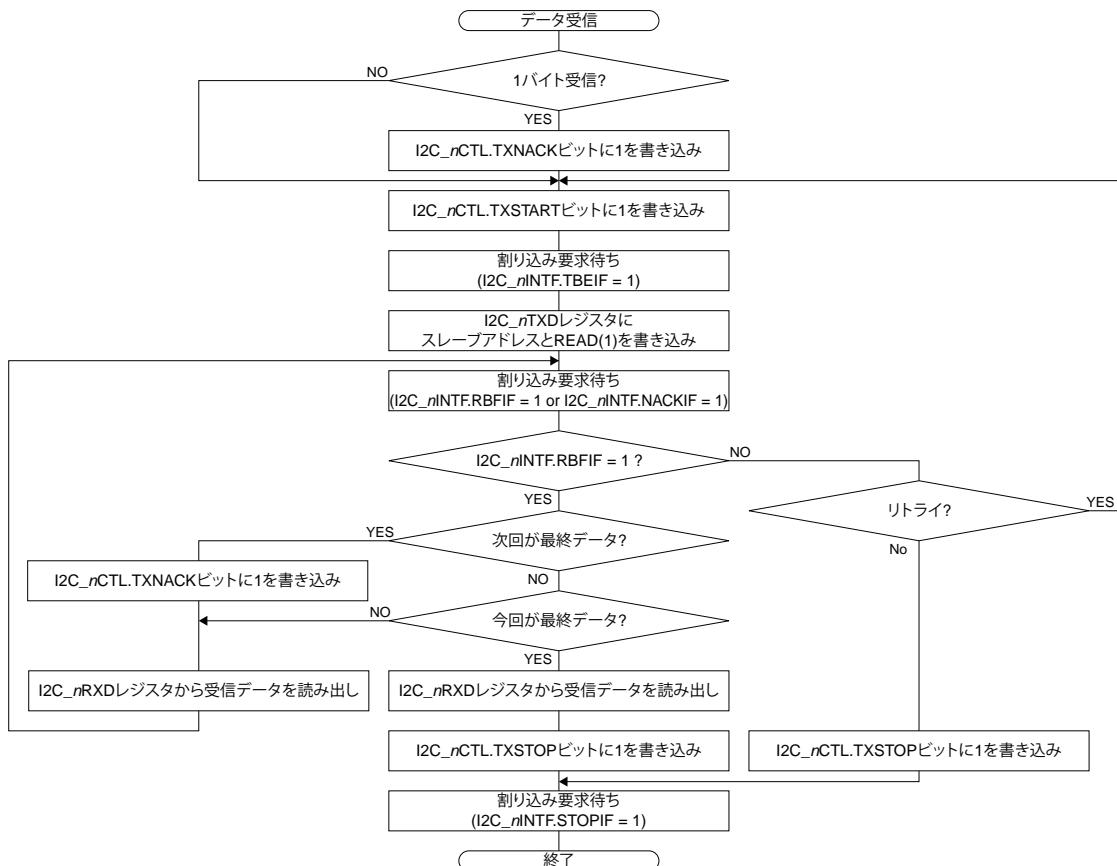

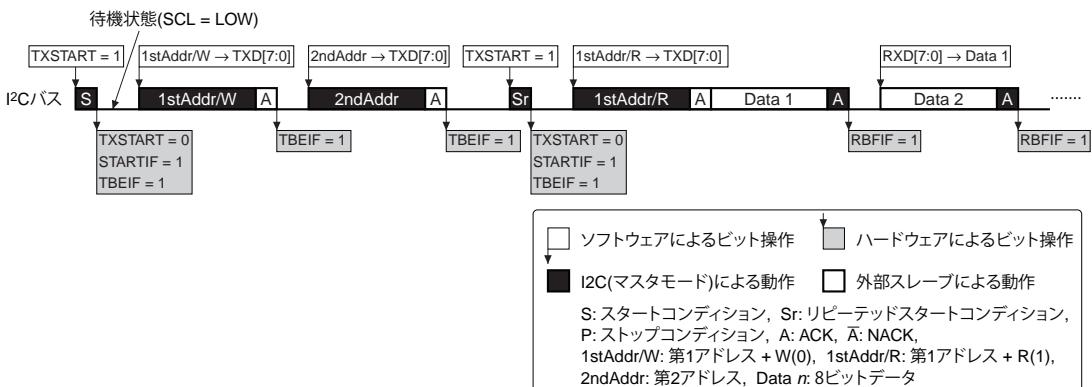

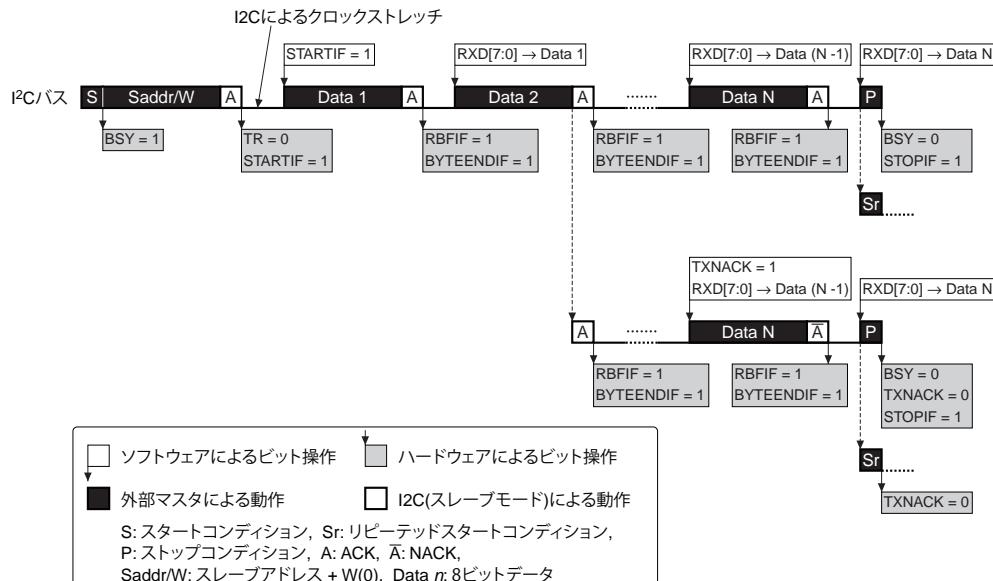

| 16.4.3 マスターモードのデータ受信 .....                                        | 16-7        |

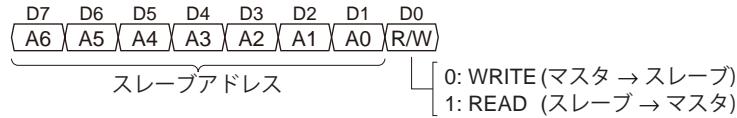

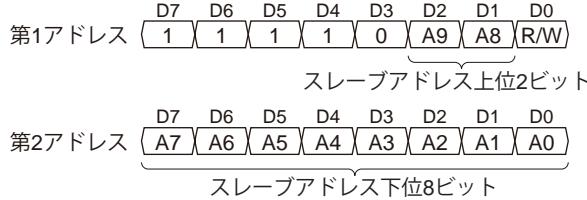

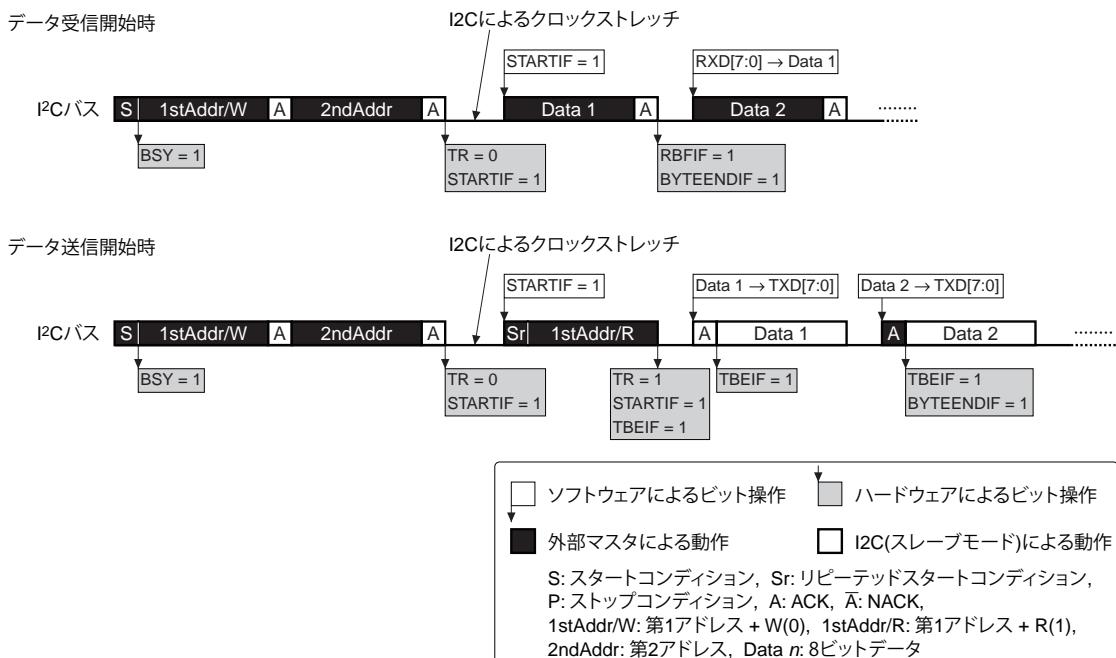

| 16.4.4 マスターモードでの10ビットアドレス指定 .....                                 | 16-10       |

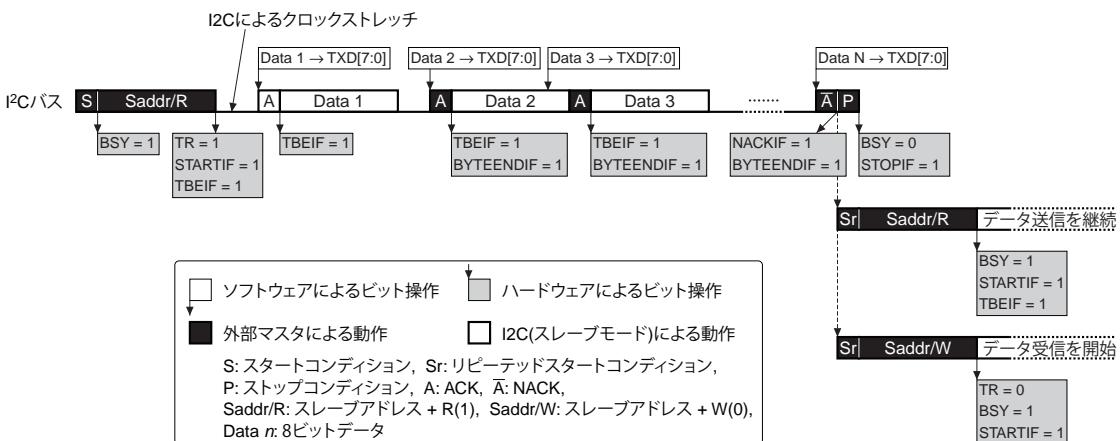

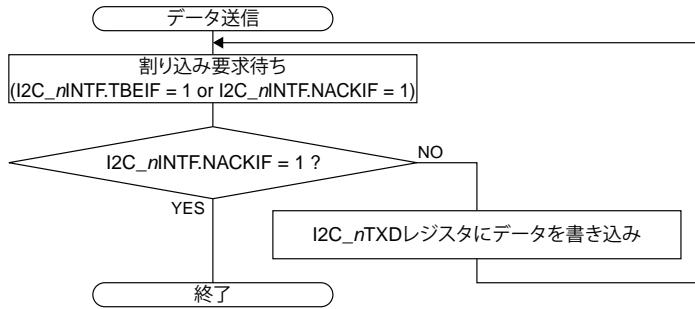

| 16.4.5 スレーブモードのデータ送信 .....                                        | 16-11       |

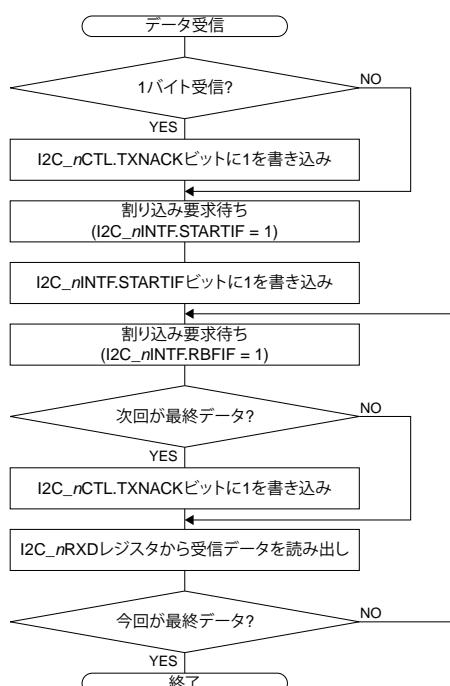

| 16.4.6 スレーブモードのデータ受信 .....                                        | 16-13       |

| 16.4.7 10ビットアドレスモードのスレーブ動作 .....                                  | 16-15       |

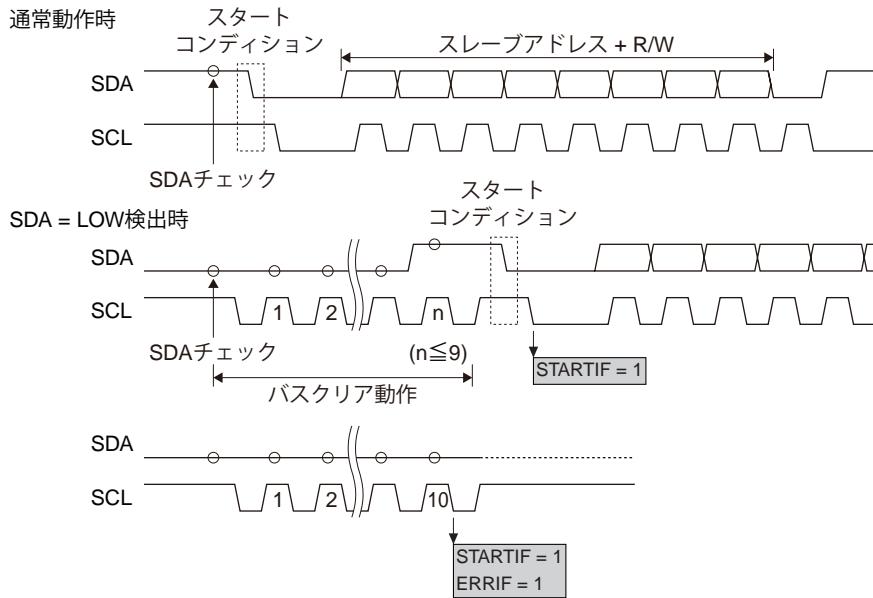

| 16.4.8 自動バスクリア動作 .....                                            | 16-15       |

| 16.4.9 エラー検出 .....                                                | 16-16       |

| 16.5 割り込み .....                                                   | 16-17       |

| 16.6 DMA転送要求 .....                                                | 16-18       |

| 16.7 制御レジスタ .....                                                 | 16-18       |

| I2C Ch.n Clock Control Register .....                             | 16-18       |

| I2C Ch.n Mode Register .....                                      | 16-19       |

| I2C Ch.n Baud-Rate Register .....                                 | 16-19       |

| I2C Ch.n Own Address Register .....                               | 16-20       |

| I2C Ch.n Control Register .....                                   | 16-20       |

| I2C Ch.n Transmit Data Register .....                             | 16-21       |

|                                                                             |             |

|-----------------------------------------------------------------------------|-------------|

| I2C Ch. <i>n</i> Receive Data Register.....                                 | 16-21       |

| I2C Ch. <i>n</i> Status and Interrupt Flag Register .....                   | 16-22       |

| I2C Ch. <i>n</i> Interrupt Enable Register .....                            | 16-23       |

| I2C Ch. <i>n</i> Transmit Buffer Empty DMA Request Enable Register.....     | 16-24       |

| I2C Ch. <i>n</i> Receive Buffer Full DMA Request Enable Register.....       | 16-24       |

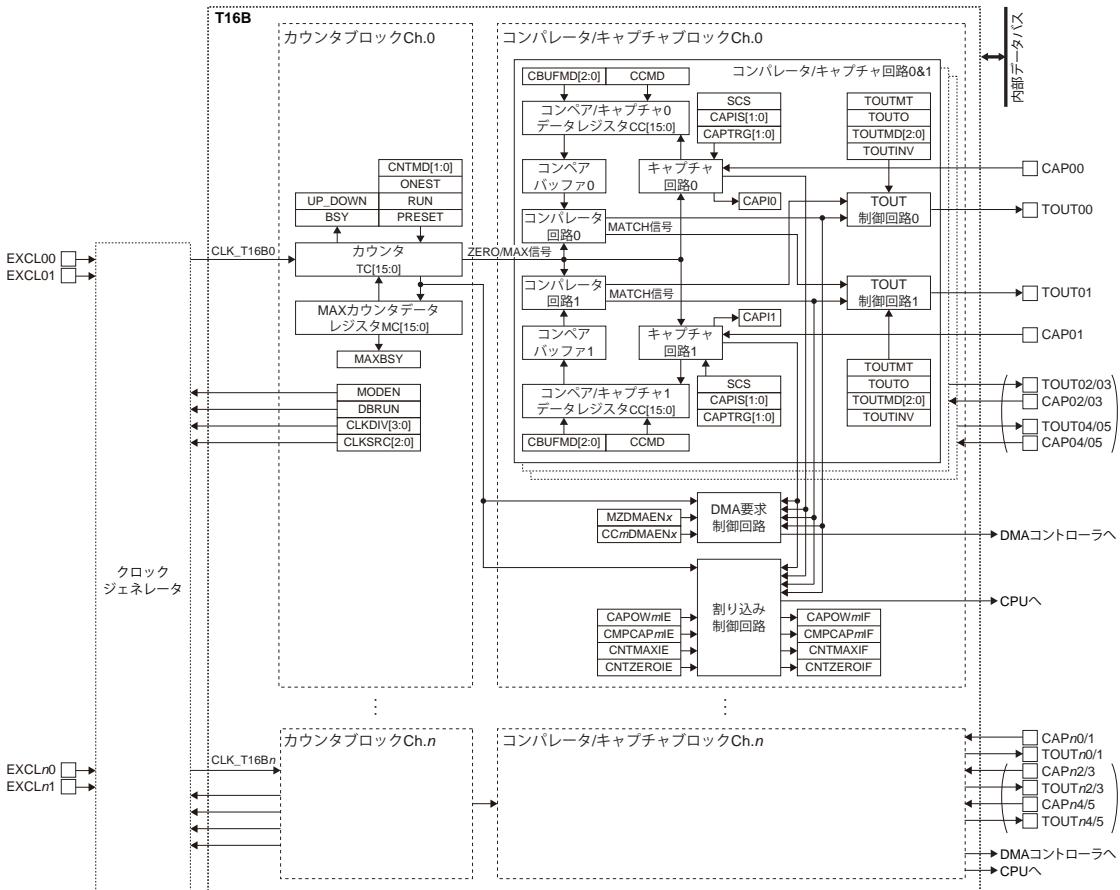

| <b>17 16ビットPWMタイマ(T16B).....</b>                                            | <b>17-1</b> |

| 17.1 概要 .....                                                               | 17-1        |

| 17.2 入出力端子 .....                                                            | 17-2        |

| 17.3 クロック設定.....                                                            | 17-3        |

| 17.3.1 T16Bの動作クロック .....                                                    | 17-3        |

| 17.3.2 SLEEPモード時のクロック供給 .....                                               | 17-3        |

| 17.3.3 デバッグ時のクロック供給.....                                                    | 17-3        |

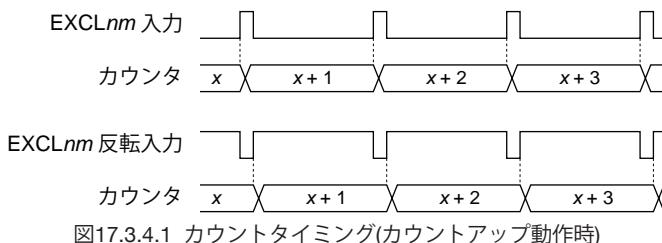

| 17.3.4 イベントカウンタクロック .....                                                   | 17-3        |

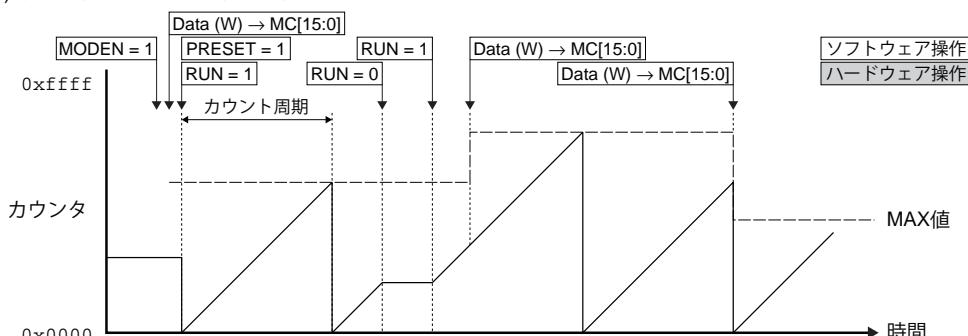

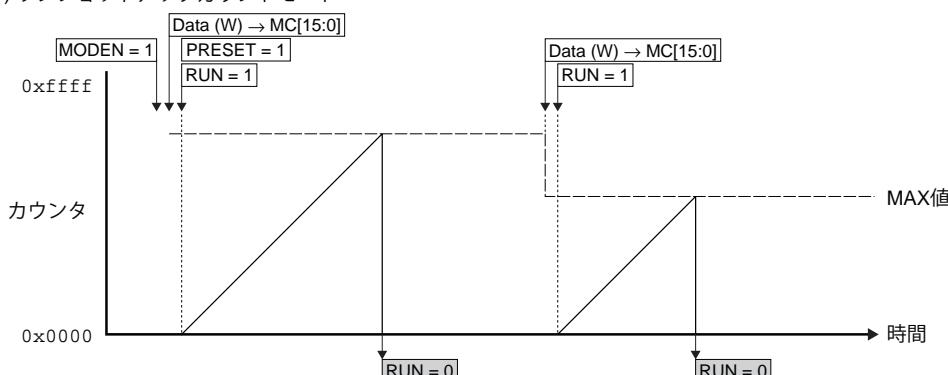

| 17.4 動作 .....                                                               | 17-4        |

| 17.4.1 初期設定 .....                                                           | 17-4        |

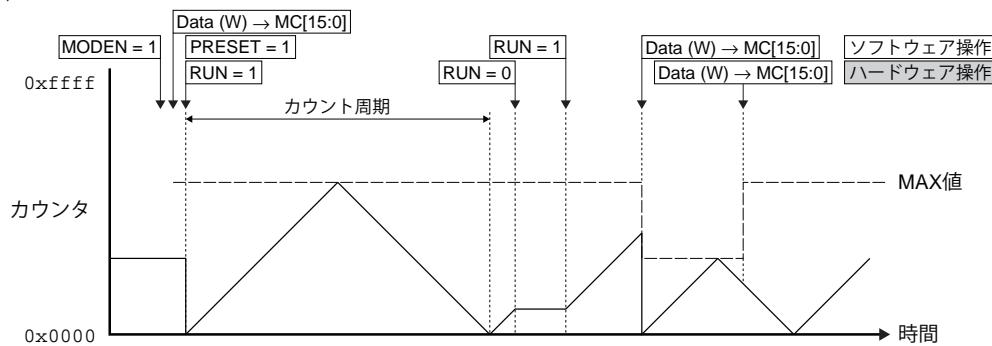

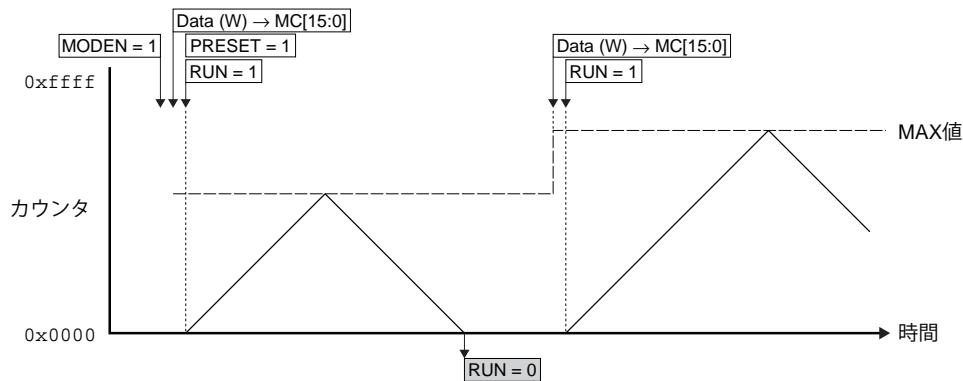

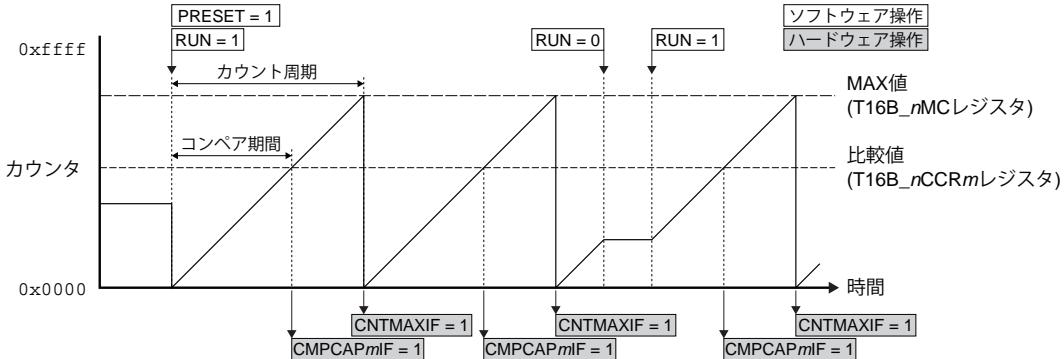

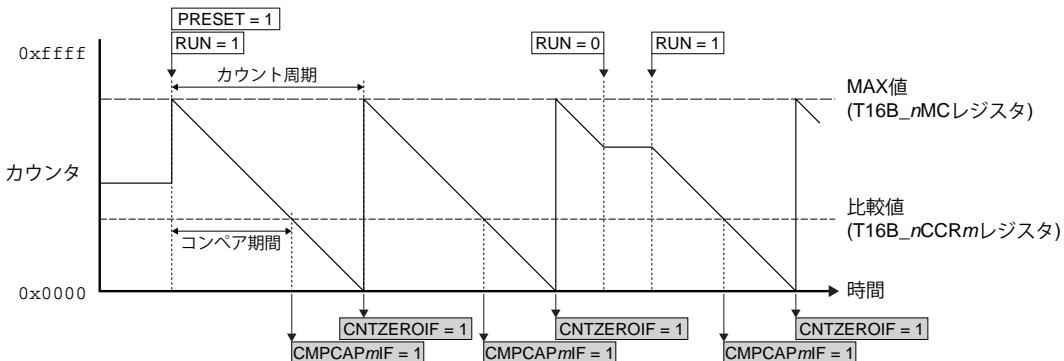

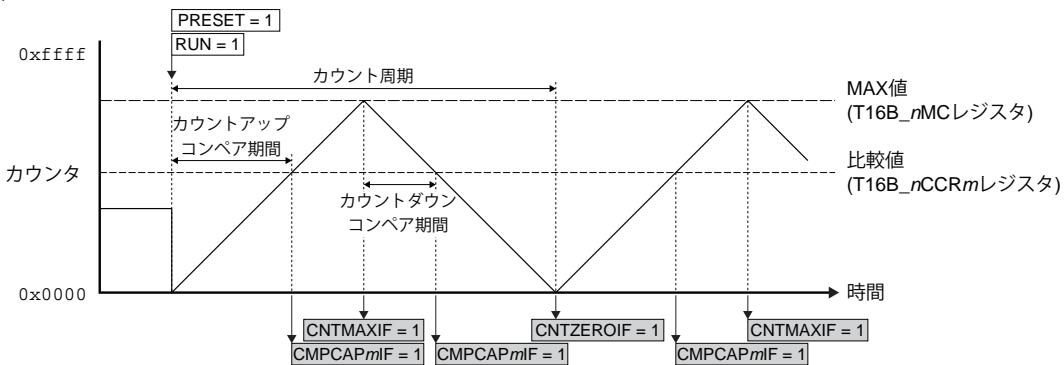

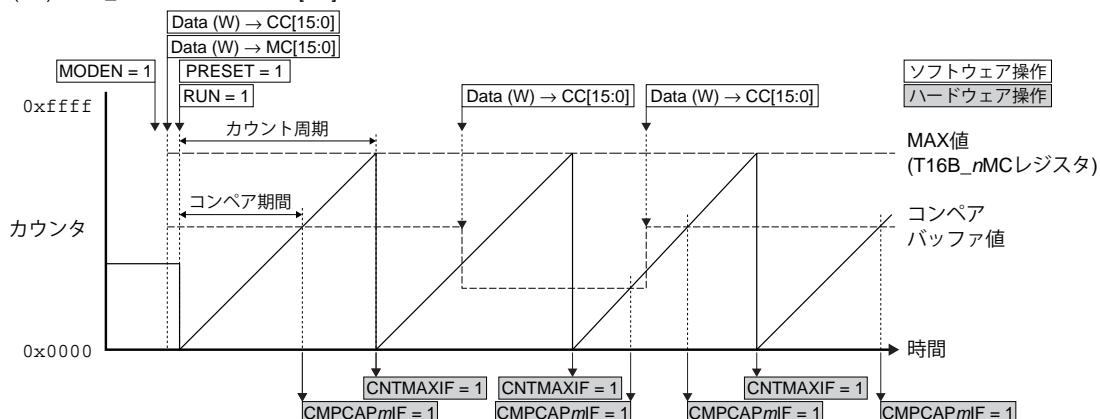

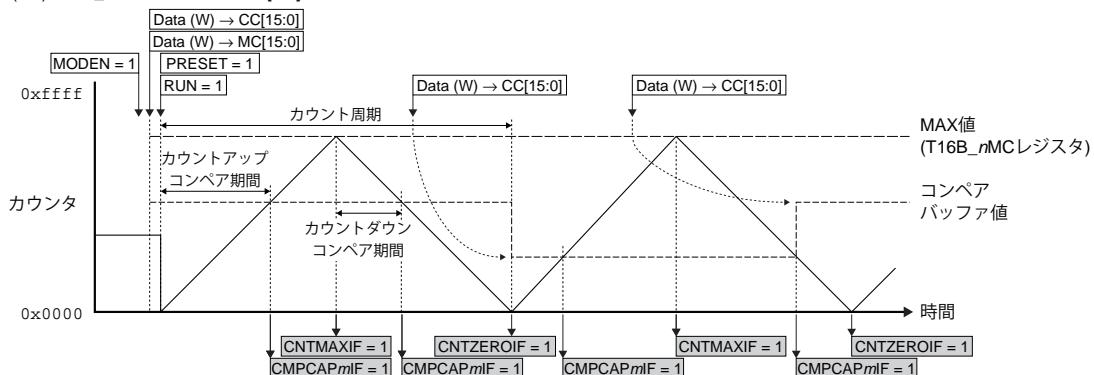

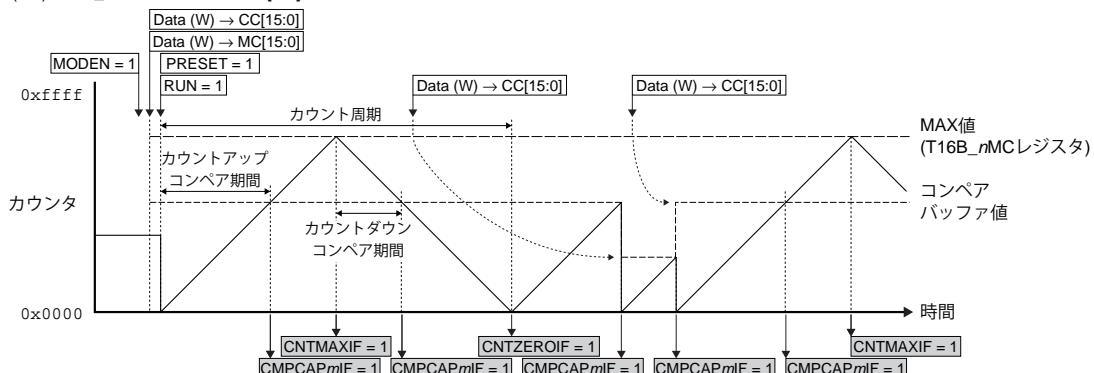

| 17.4.2 カウンタブロックの動作 .....                                                    | 17-5        |

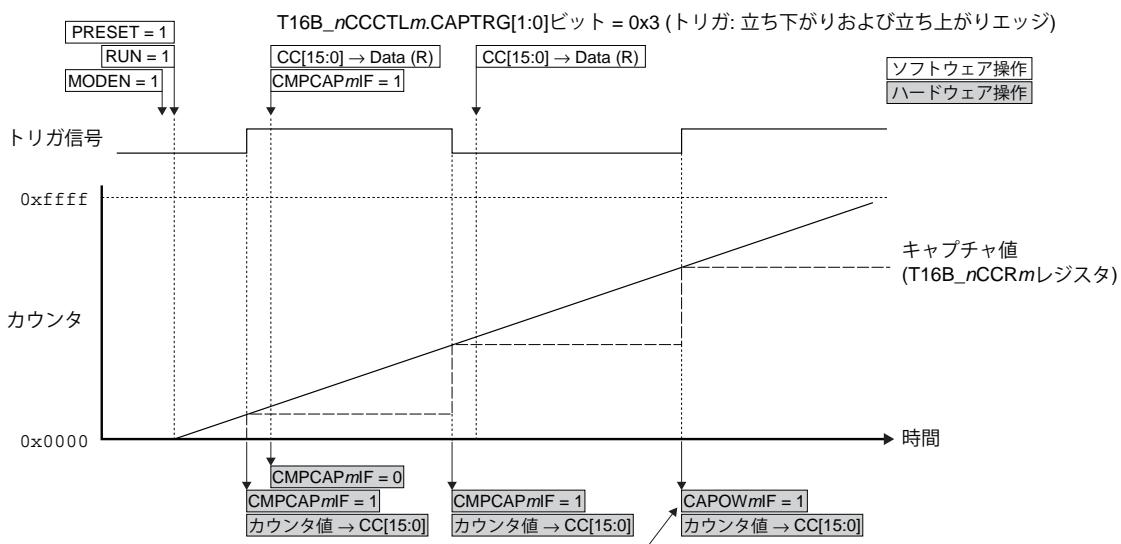

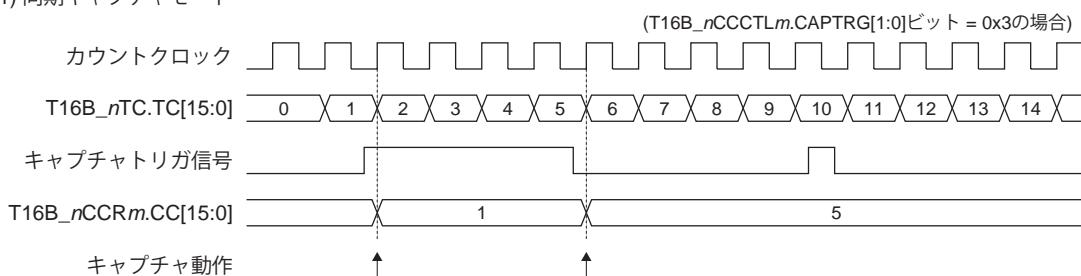

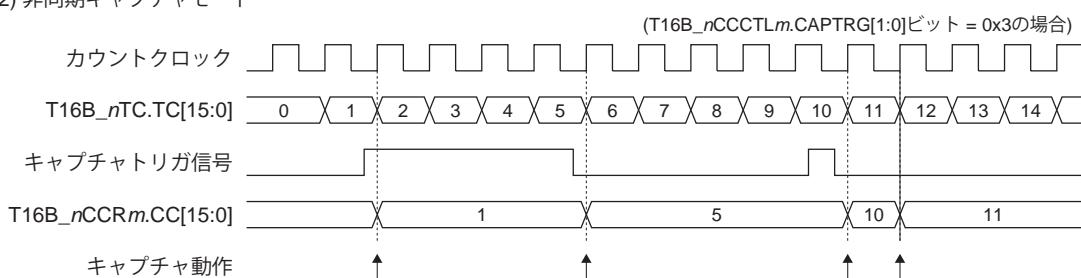

| 17.4.3 コンパレータ/キャプチャブロックの動作.....                                             | 17-8        |

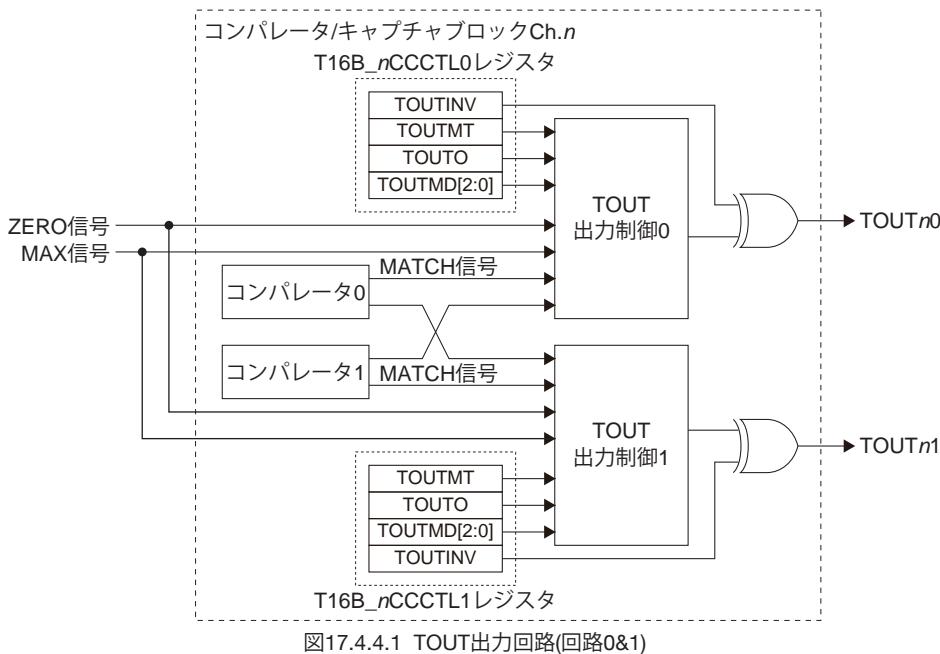

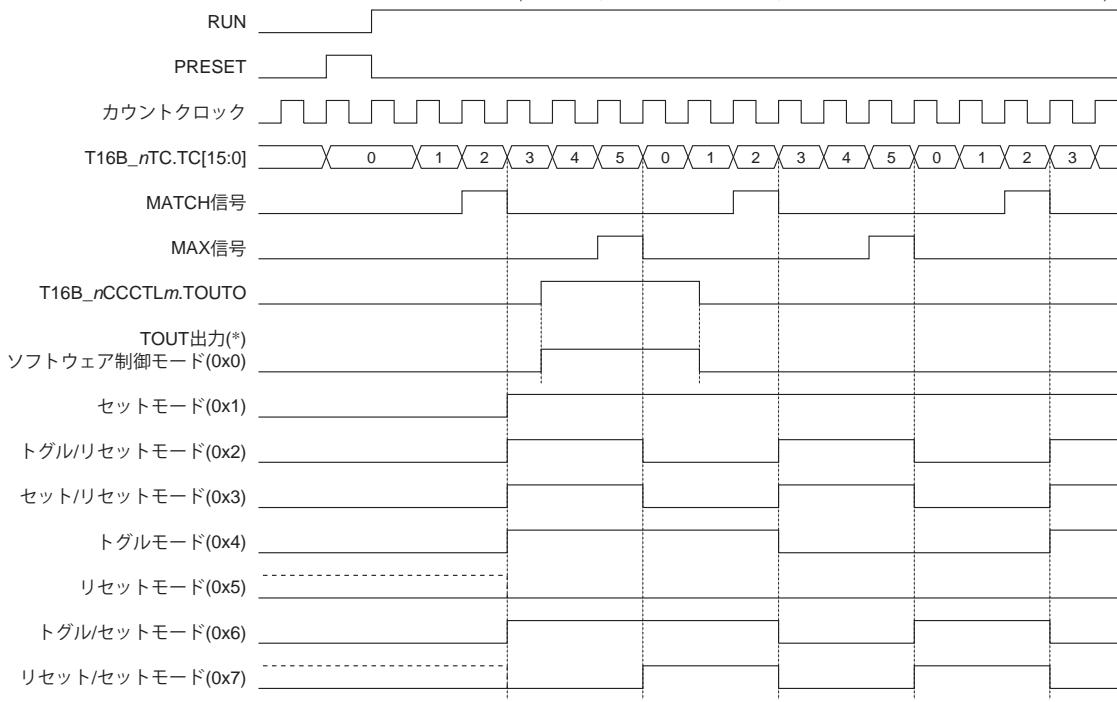

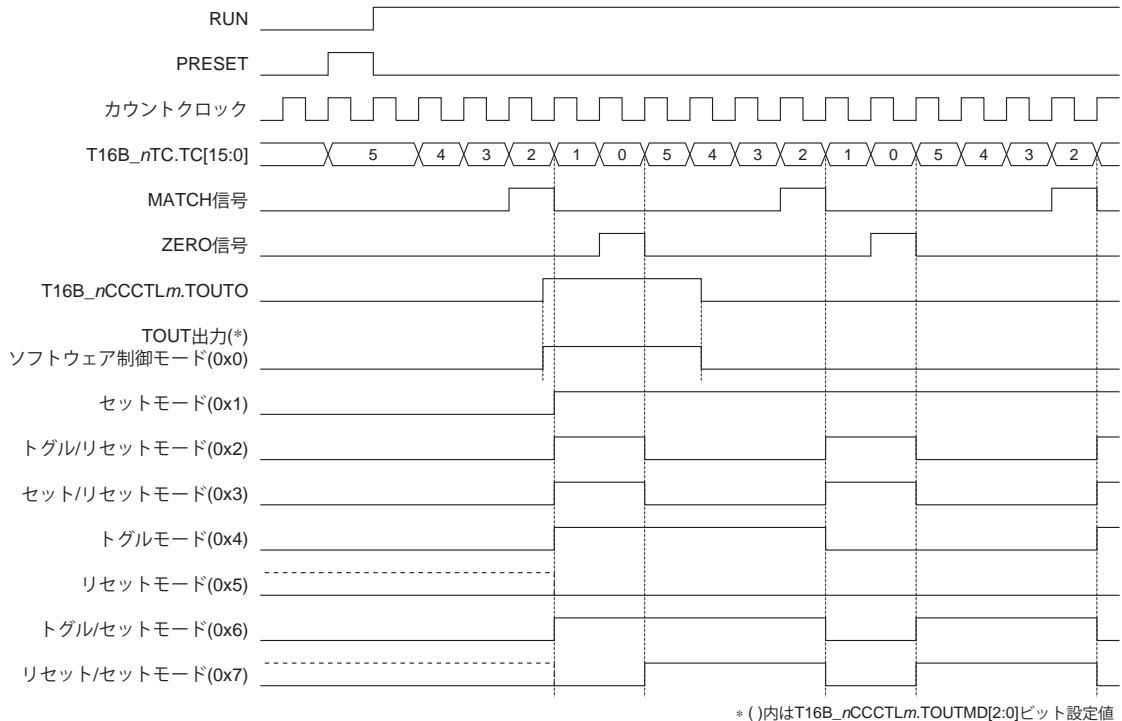

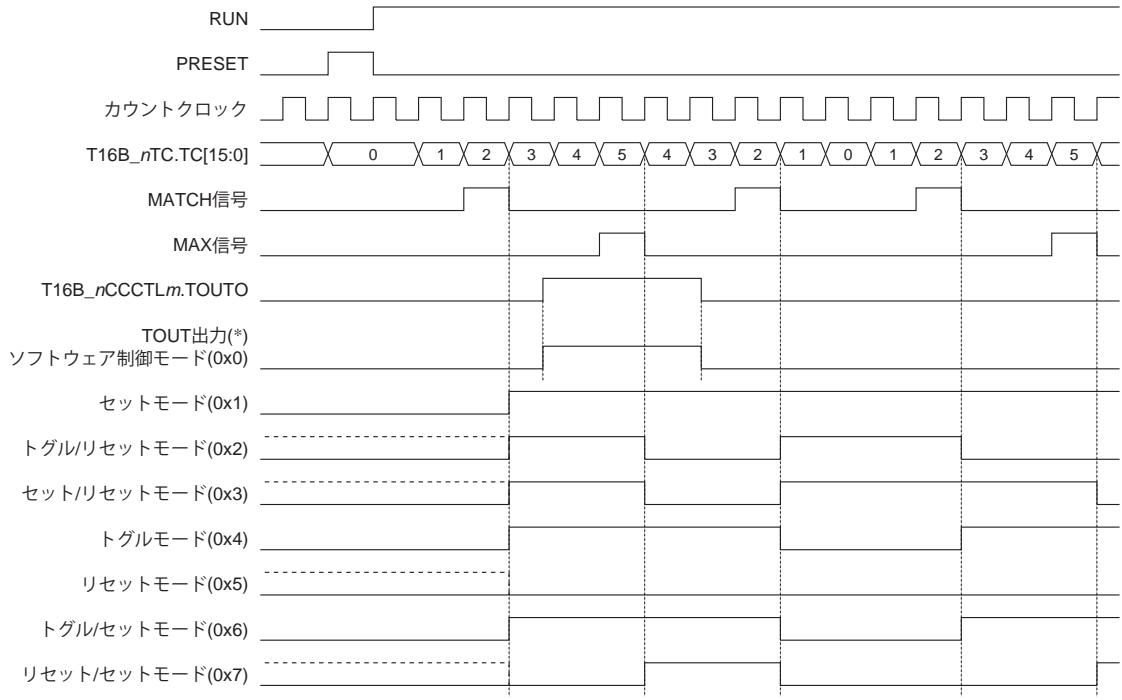

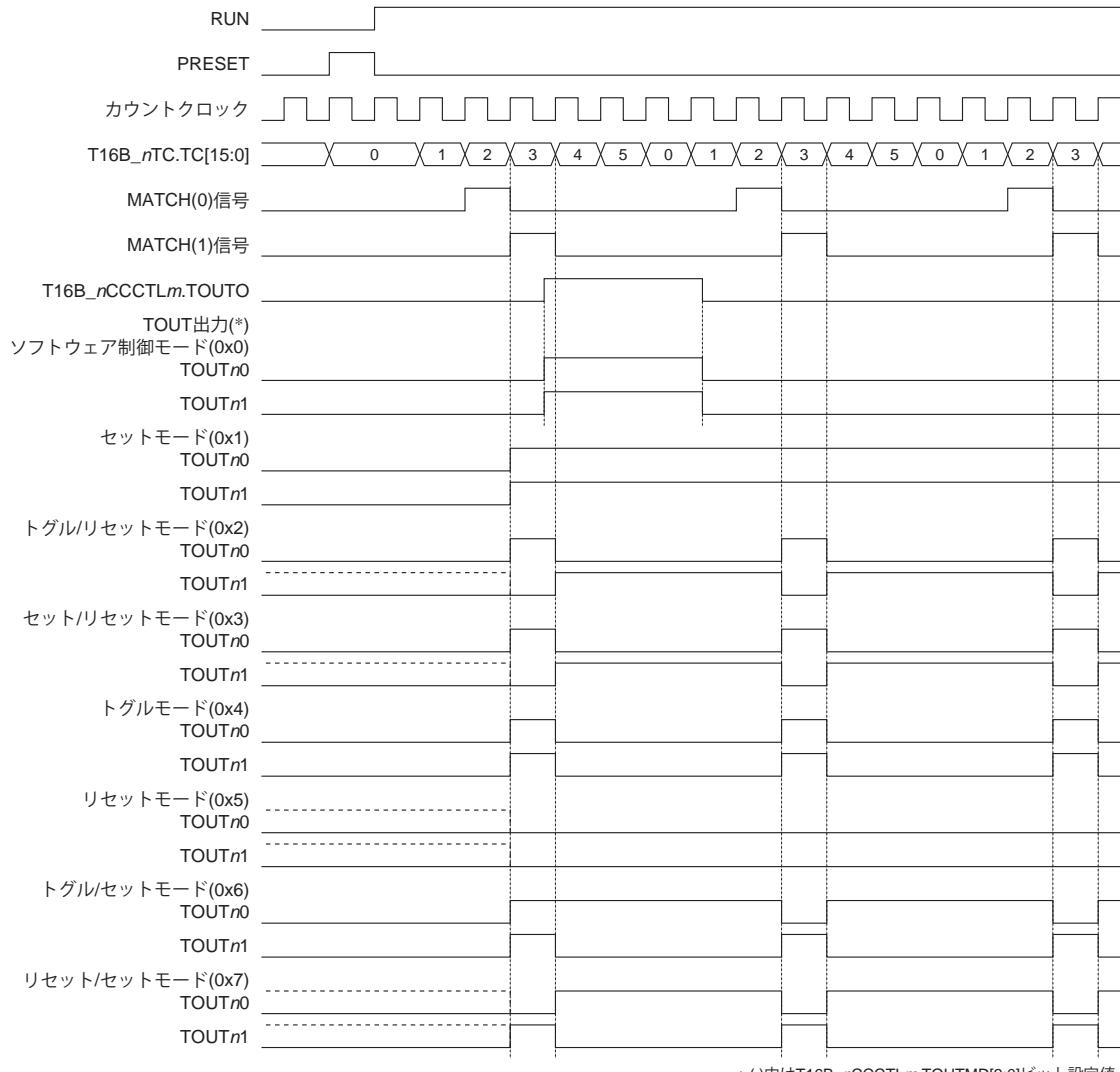

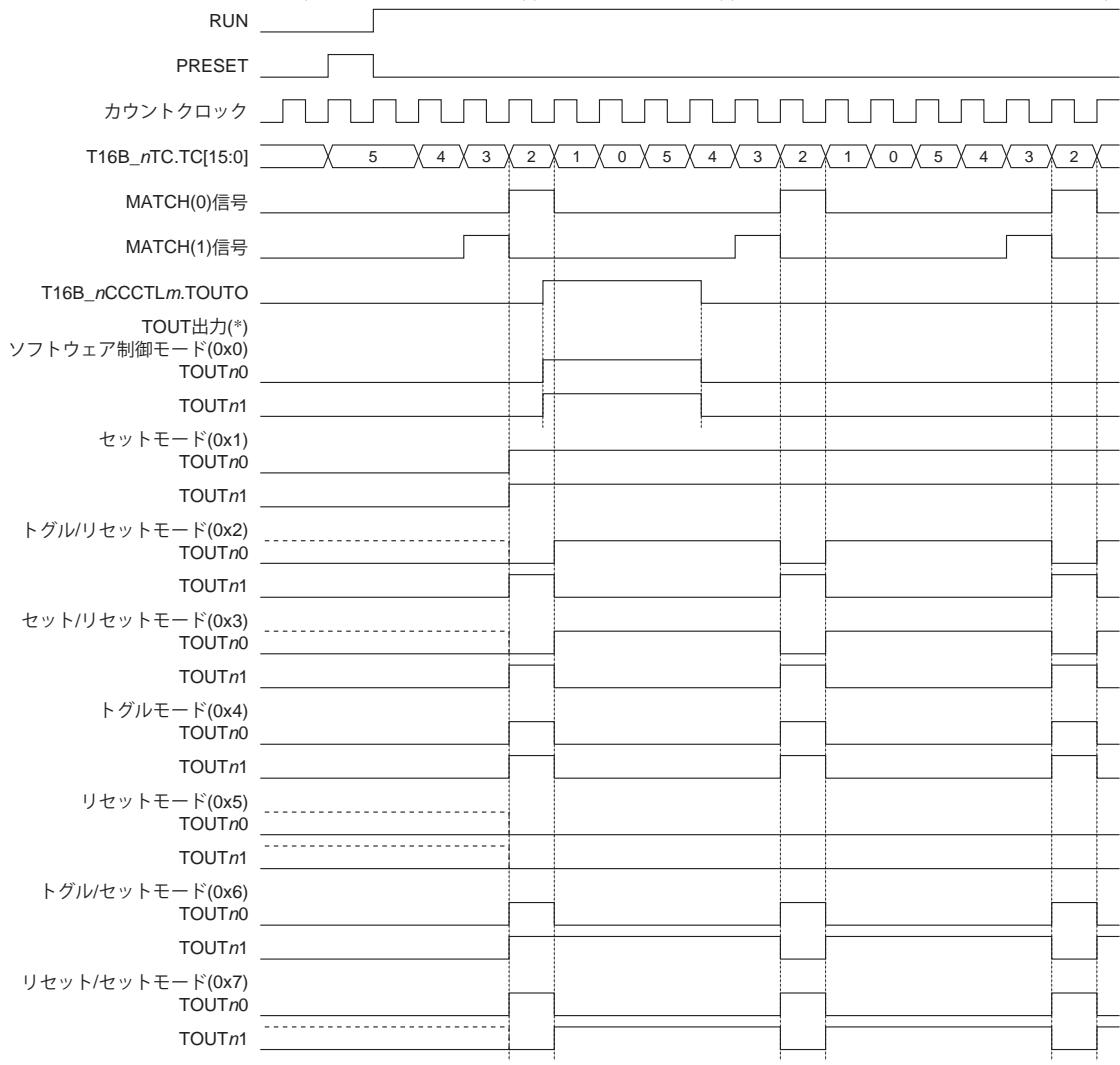

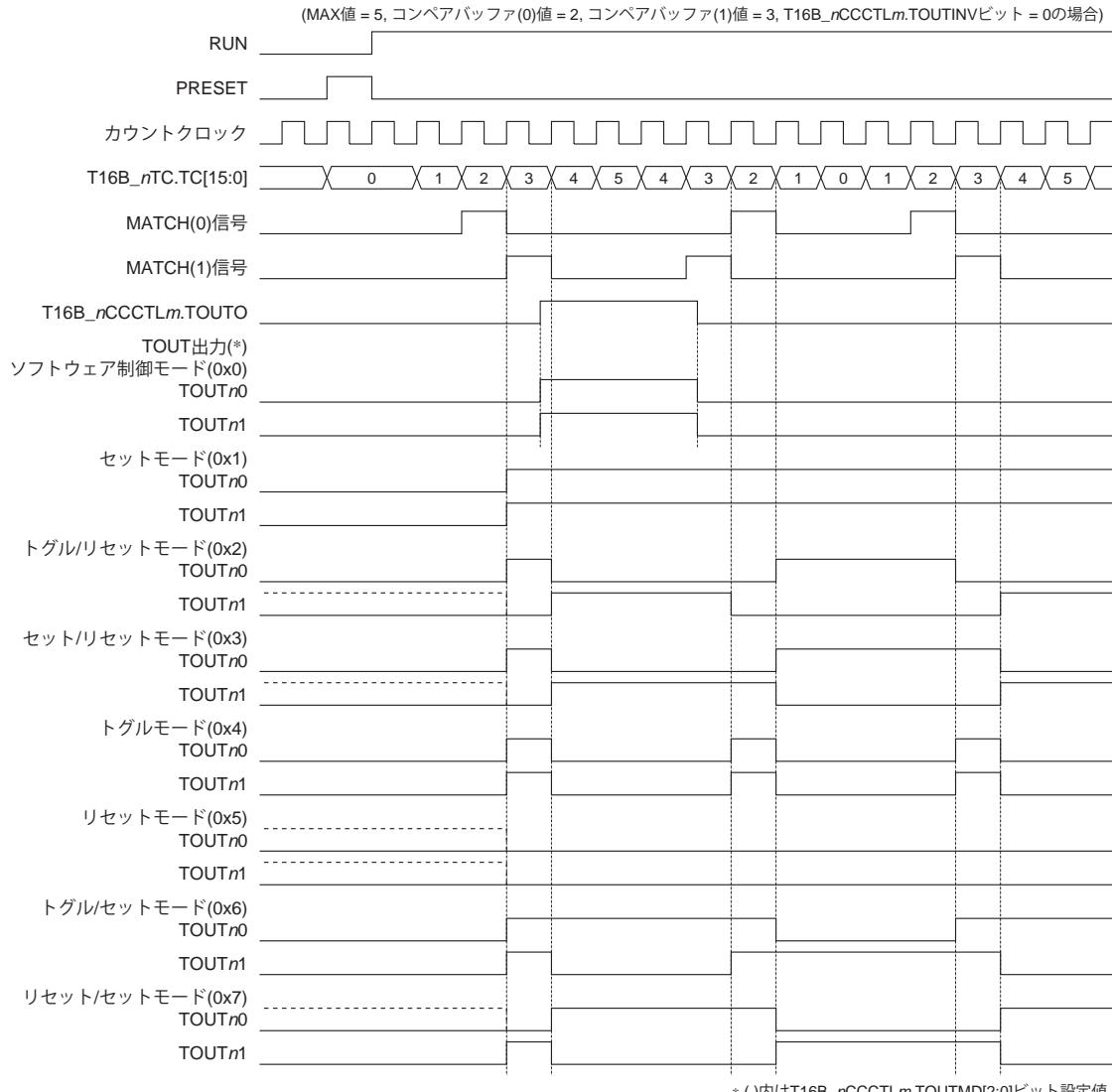

| 17.4.4 TOUT出力の制御 .....                                                      | 17-17       |

| 17.5 割り込み.....                                                              | 17-23       |

| 17.6 DMA転送要求.....                                                           | 17-23       |

| 17.7 制御レジスタ .....                                                           | 17-23       |

| T16B Ch. <i>n</i> Clock Control Register .....                              | 17-23       |

| T16B Ch. <i>n</i> Counter Control Register .....                            | 17-24       |

| T16B Ch. <i>n</i> Max Counter Data Register.....                            | 17-25       |

| T16B Ch. <i>n</i> Timer Counter Data Register.....                          | 17-26       |

| T16B Ch. <i>n</i> Counter Status Register.....                              | 17-26       |

| T16B Ch. <i>n</i> Interrupt Flag Register.....                              | 17-27       |

| T16B Ch. <i>n</i> Interrupt Enable Register .....                           | 17-28       |

| T16B Ch. <i>n</i> Comparator/Capture <i>m</i> Control Register.....         | 17-29       |

| T16B Ch. <i>n</i> Compare/Capture <i>m</i> Data Register.....               | 17-31       |

| T16B Ch. <i>n</i> Counter Max/Zero DMA Request Enable Register .....        | 17-32       |

| T16B Ch. <i>n</i> Compare/Capture <i>m</i> DMA Request Enable Register..... | 17-32       |

| <b>18 サウンドジェネレータ(SNDA).....</b>                                             | <b>18-1</b> |

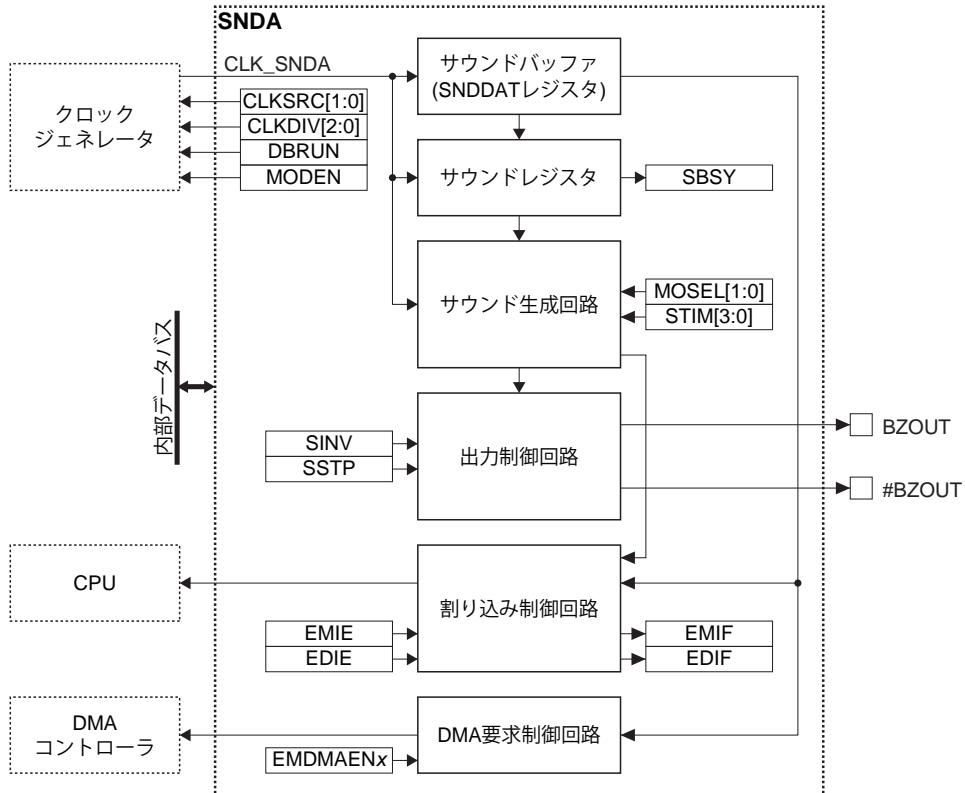

| 18.1 概要 .....                                                               | 18-1        |

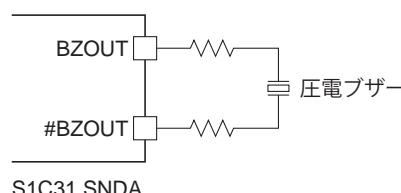

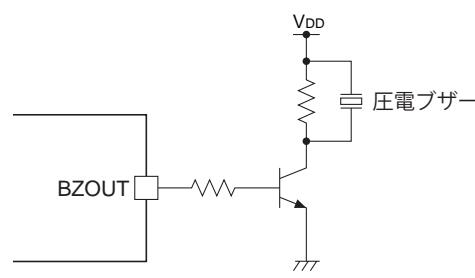

| 18.2 出力端子と外部接続.....                                                         | 18-2        |

| 18.2.1 出力端子一覧 .....                                                         | 18-2        |

| 18.2.2 出力端子の駆動モード .....                                                     | 18-2        |

| 18.2.3 外部との接続 .....                                                         | 18-2        |

| 18.3 クロック設定.....                                                            | 18-3        |

| 18.3.1 SNDAの動作クロック .....                                                    | 18-3        |

| 18.3.2 SLEEPモード時のクロック供給 .....                                               | 18-3        |

| 18.3.3 DEBUGモード時のクロック供給.....                                                | 18-3        |

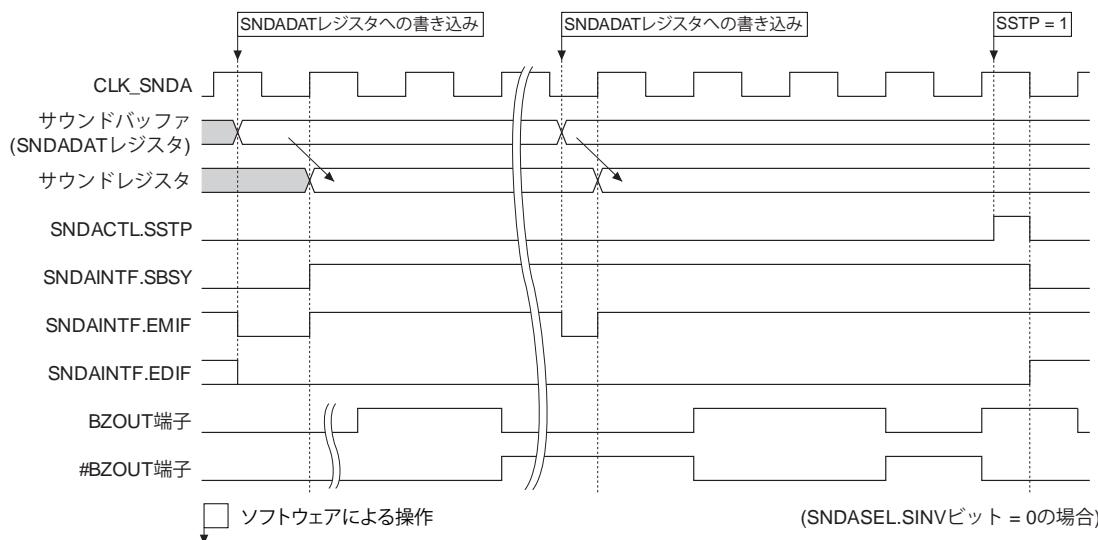

| 18.4 動作 .....                                                               | 18-3        |

| 18.4.1 初期設定 .....                                                           | 18-3        |

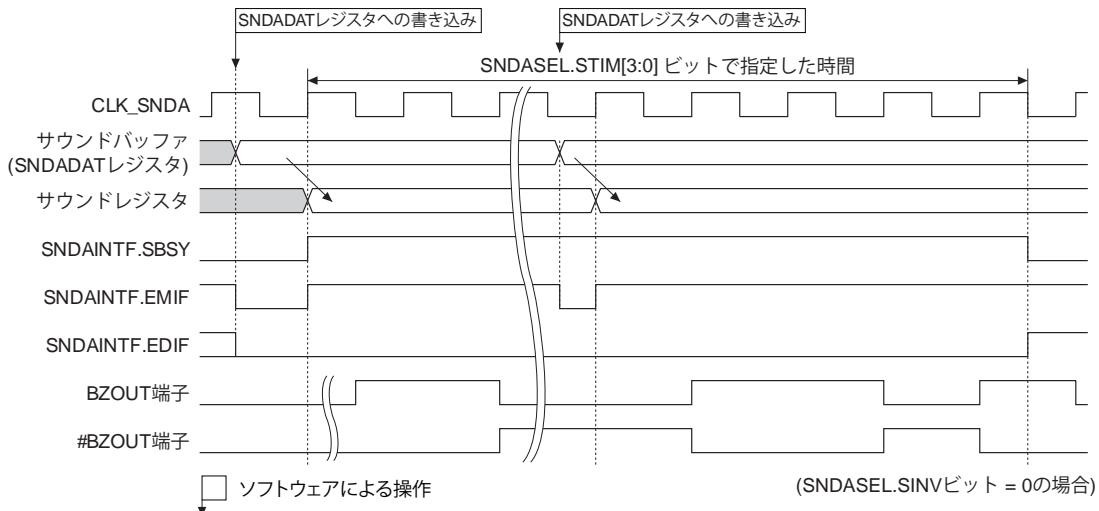

| 18.4.2 ノーマルブザーモードのブザー出力 .....                                               | 18-3        |

| 18.4.3 ワンショットブザーモードのブザー出力 .....                                             | 18-6        |

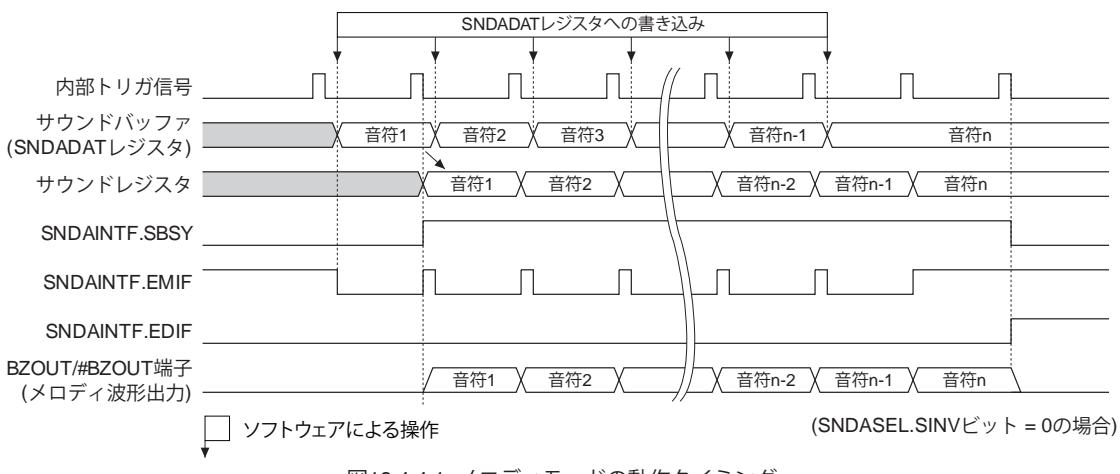

| 18.4.4 メロディモードの出力 .....                                                     | 18-7        |

| 18.5 割り込み .....                                                             | 18-9        |

| 18.6 DMA転送要求 .....                                                          | 18-10       |

| 18.7 制御レジスタ .....                                                           | 18-10       |

| SNDA Clock Control Register .....                                           | 18-10       |

| SNDA Select Register .....                                                  | 18-11       |

| SNDA Control Register.....                                                  | 18-12       |

|                                                           |             |

|-----------------------------------------------------------|-------------|

| SNDA Data Register .....                                  | 18-12       |

| SNDA Interrupt Flag Register .....                        | 18-13       |

| SNDA Interrupt Enable Register .....                      | 18-13       |

| SNDA Sound Buffer Empty DMA Request Enable Register ..... | 18-14       |

| <b>19 IRリモートコントローラ(REMC2).....</b>                        | <b>19-1</b> |

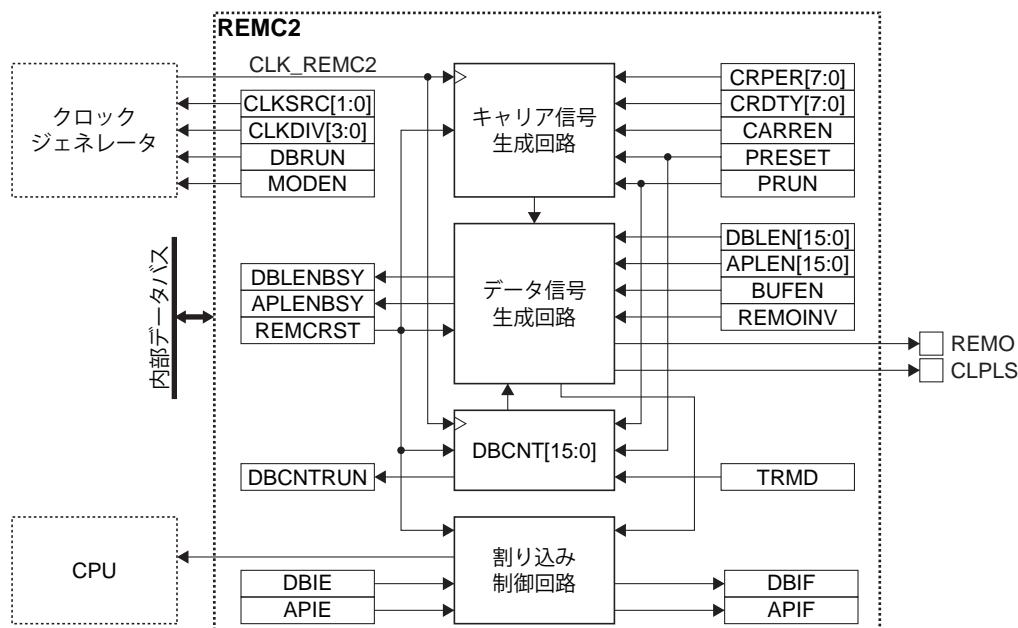

| 19.1 概要 .....                                             | 19-1        |

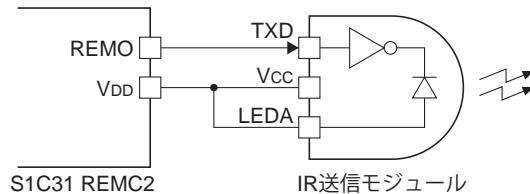

| 19.2 入出力端子と外部接続 .....                                     | 19-1        |

| 19.2.1 出力端子 .....                                         | 19-1        |

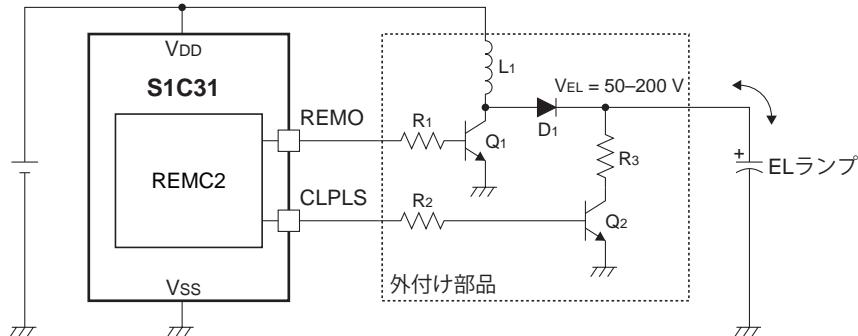

| 19.2.2 外部との接続 .....                                       | 19-2        |

| 19.3 クロック設定 .....                                         | 19-2        |

| 19.3.1 REMC2の動作クロック .....                                 | 19-2        |

| 19.3.2 SLEEPモード時のクロック供給 .....                             | 19-2        |

| 19.3.3 デバッグ時のクロック供給 .....                                 | 19-2        |

| 19.4 動作 .....                                             | 19-2        |

| 19.4.1 初期設定 .....                                         | 19-2        |

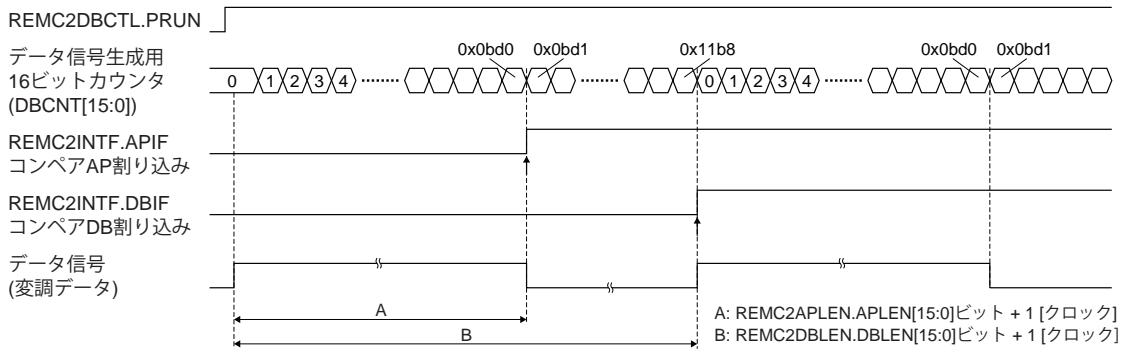

| 19.4.2 送信手順 .....                                         | 19-3        |

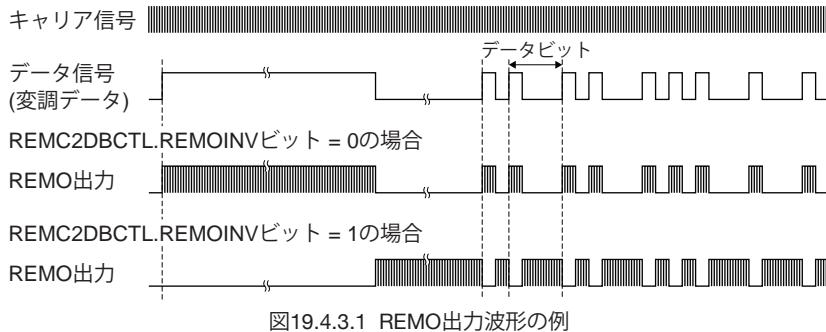

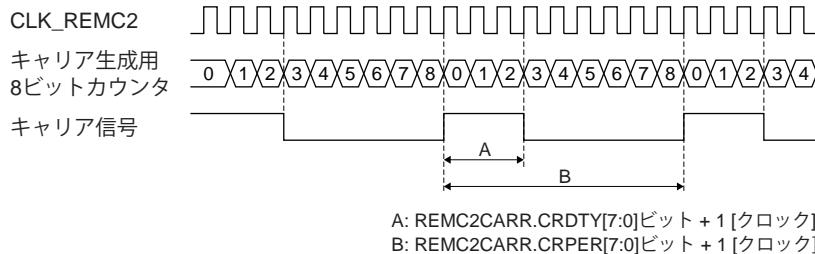

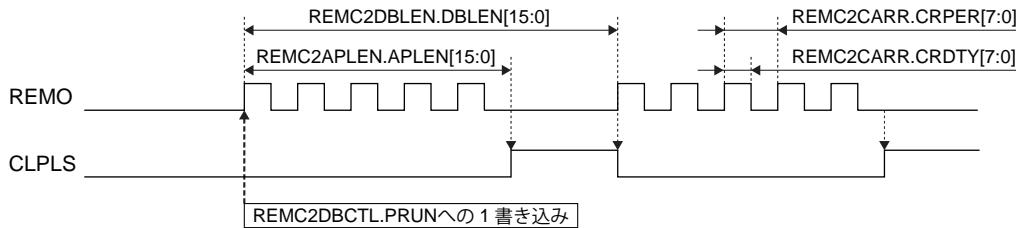

| 19.4.3 REMO出力波形 .....                                     | 19-3        |

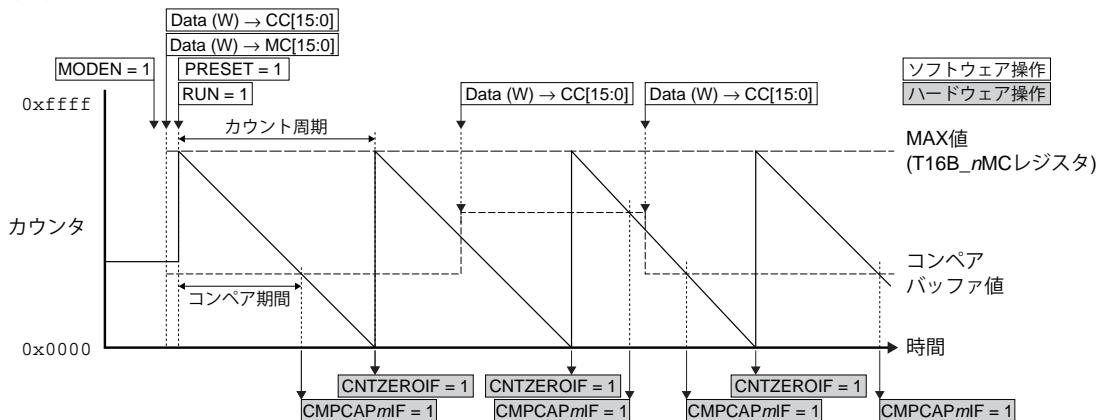

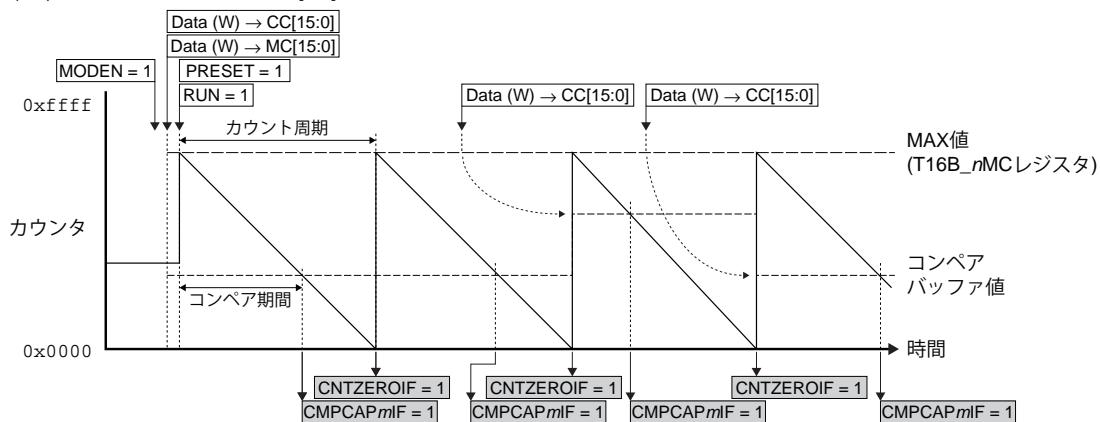

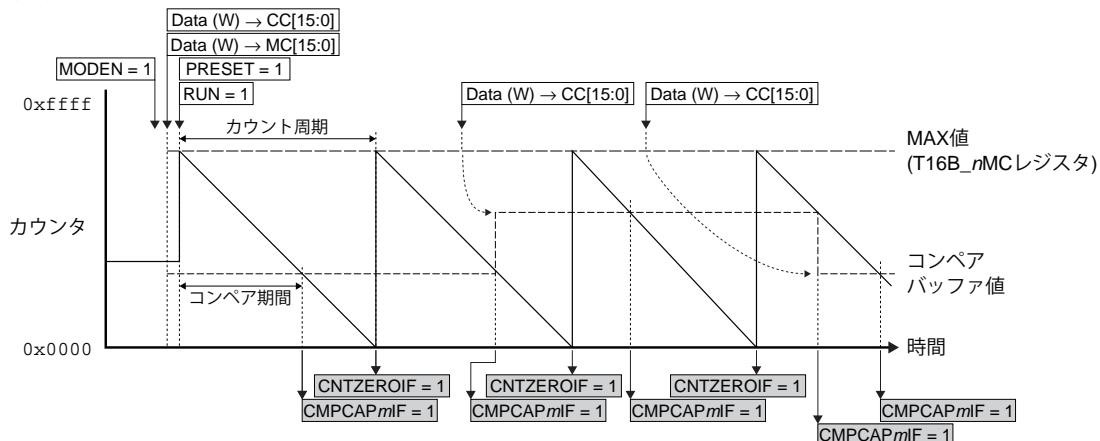

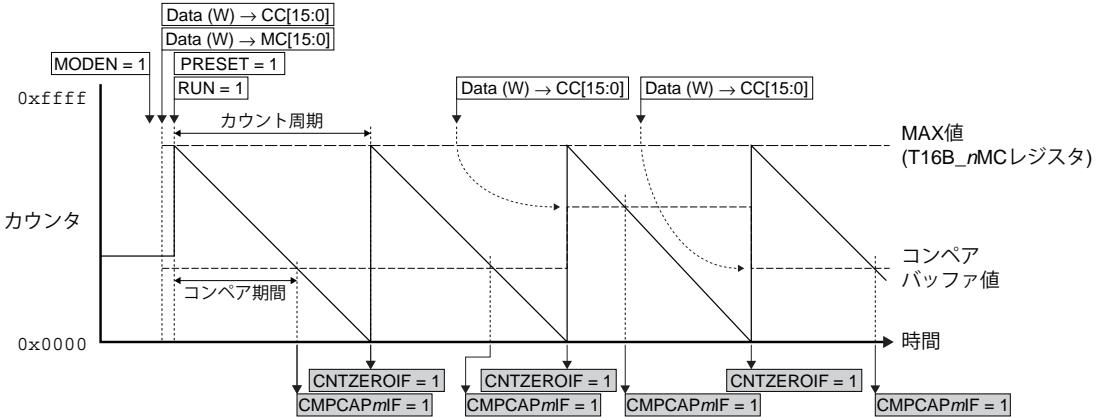

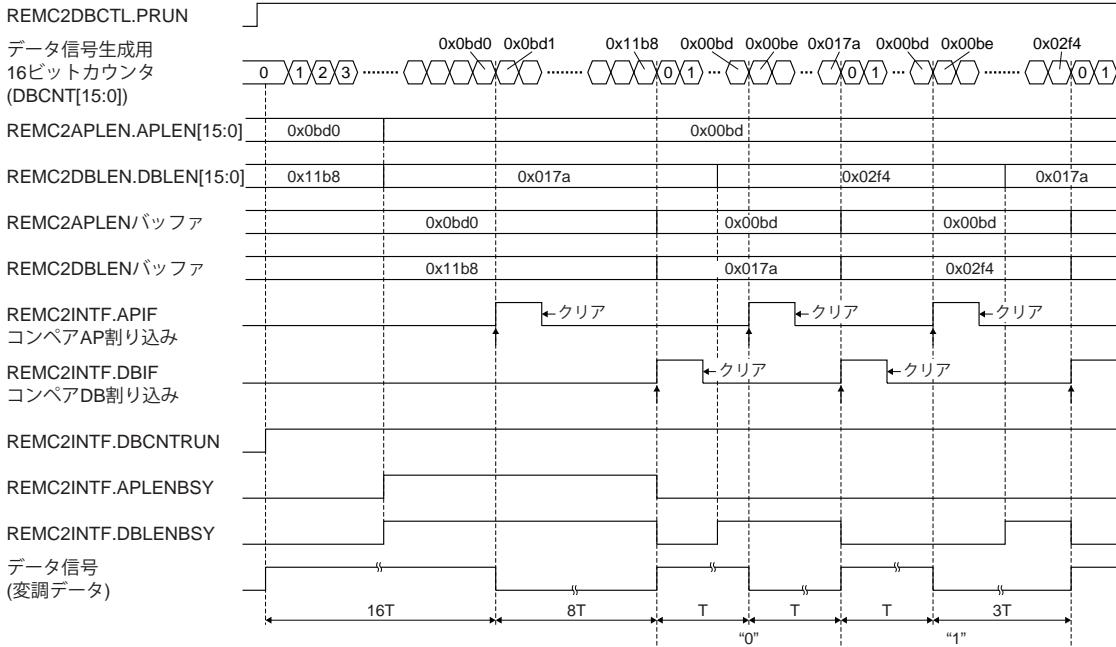

| 19.4.4 連続送信とコンペアバッファ .....                                | 19-5        |

| 19.5 割り込み .....                                           | 19-6        |

| 19.6 応用例: ELランプの駆動 .....                                  | 19-7        |

| 19.7 制御レジスタ .....                                         | 19-7        |

| REMC2 Clock Control Register .....                        | 19-7        |

| REMC2 Data Bit Counter Control Register .....             | 19-8        |

| REMC2 Data Bit Counter Register .....                     | 19-10       |

| REMC2 Data Bit Active Pulse Length Register .....         | 19-10       |

| REMC2 Data Bit Length Register .....                      | 19-10       |

| REMC2 Status and Interrupt Flag Register .....            | 19-10       |

| REMC2 Interrupt Enable Register .....                     | 19-11       |

| REMC2 Carrier Waveform Register .....                     | 19-11       |

| REMC2 Carrier Modulation Control Register .....           | 19-12       |

| <b>20 LCDドライバ(LCD32B).....</b>                            | <b>20-1</b> |

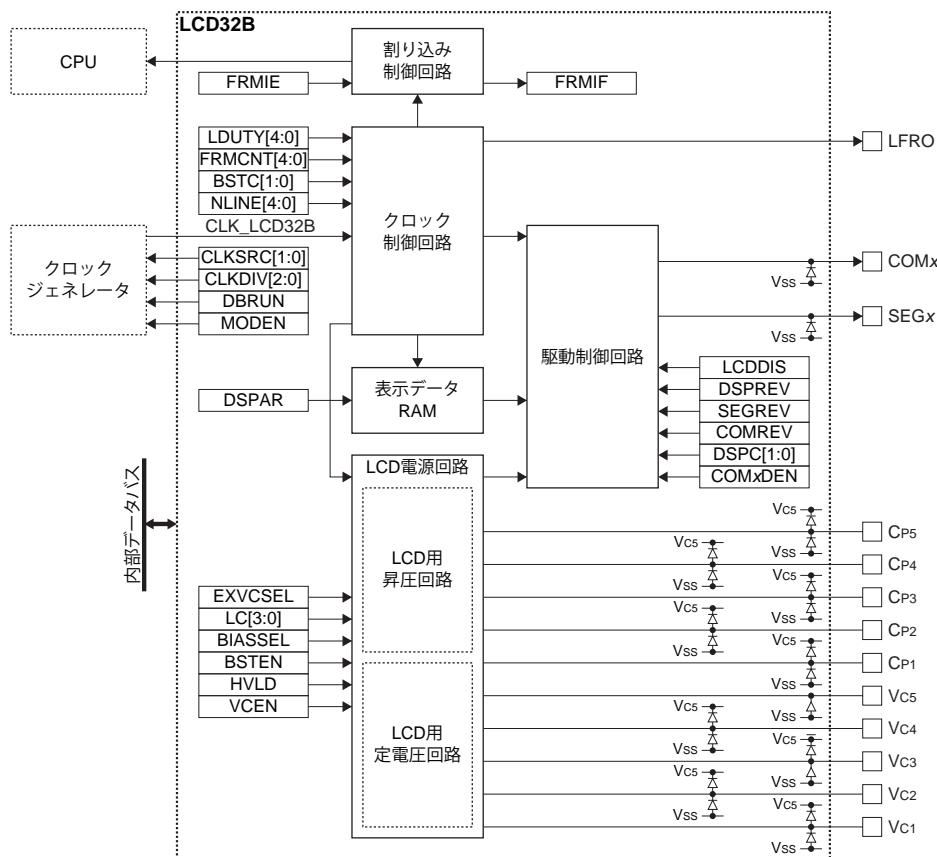

| 20.1 概要 .....                                             | 20-1        |

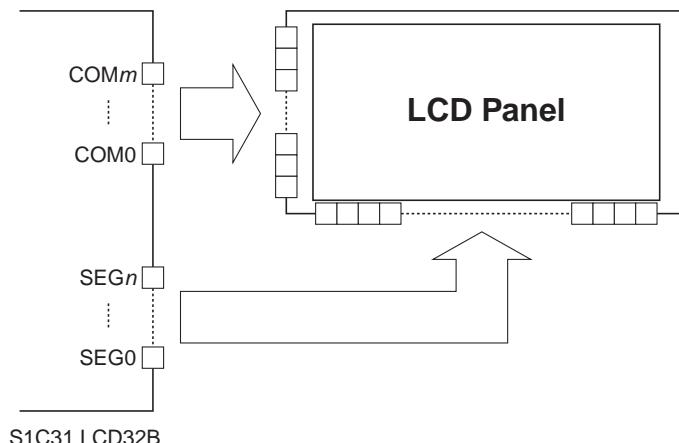

| 20.2 出力端子と外部接続 .....                                      | 20-2        |

| 20.2.1 出力端子一覧 .....                                       | 20-2        |

| 20.2.2 外部との接続 .....                                       | 20-2        |

| 20.3 クロック設定 .....                                         | 20-3        |

| 20.3.1 LCD32Bの動作クロック .....                                | 20-3        |

| 20.3.2 SLEEPモード時のクロック供給 .....                             | 20-3        |

| 20.3.3 デバッグ時のクロック供給 .....                                 | 20-3        |

| 20.3.4 フレーム周波数 .....                                      | 20-3        |

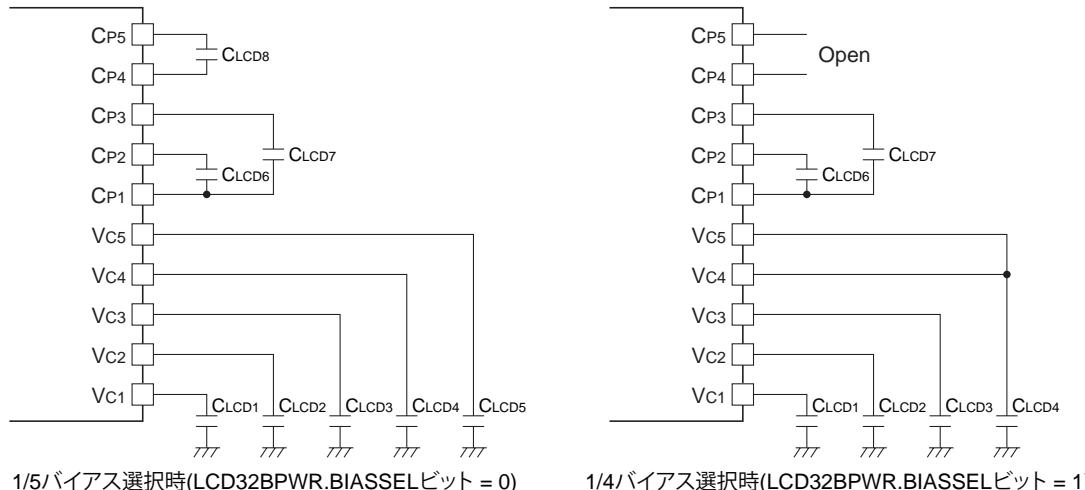

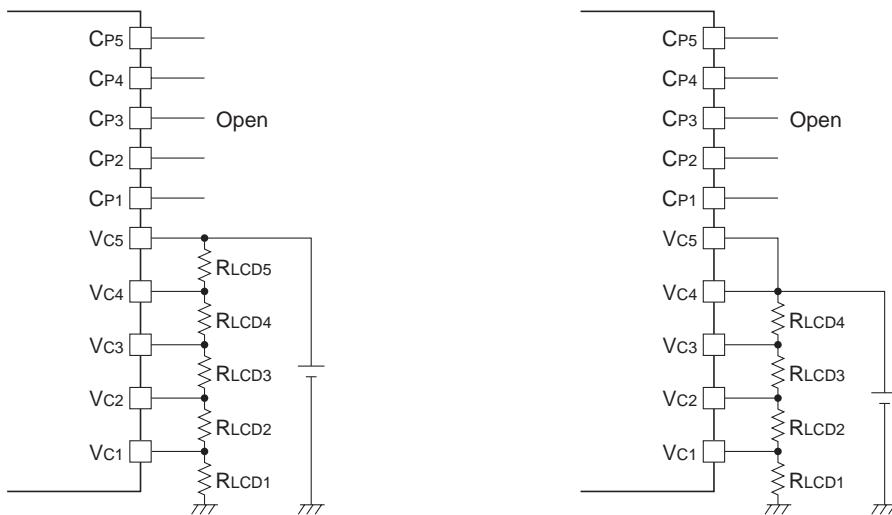

| 20.4 LCD電源 .....                                          | 20-6        |

| 20.4.1 内部生成モード .....                                      | 20-6        |

| 20.4.2 外部印加モード .....                                      | 20-6        |

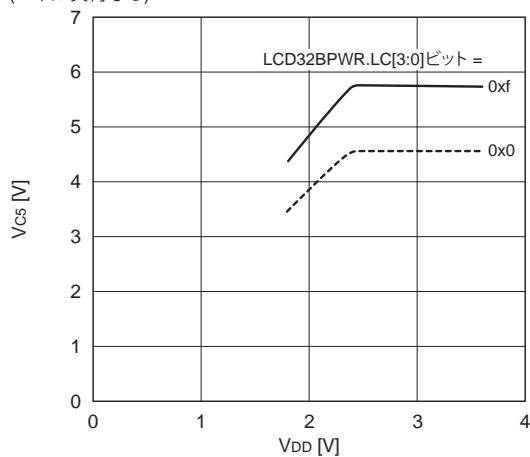

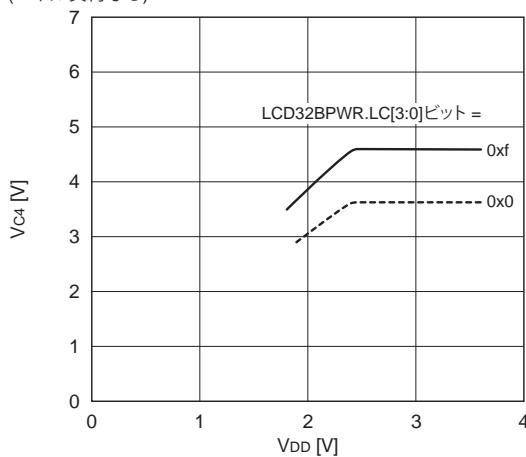

| 20.4.3 LCD用定電圧回路の設定 .....                                 | 20-7        |

| 20.4.4 LCD用昇圧回路の設定 .....                                  | 20-7        |

| 20.4.5 LCDコントラスト調整 .....                                  | 20-7        |

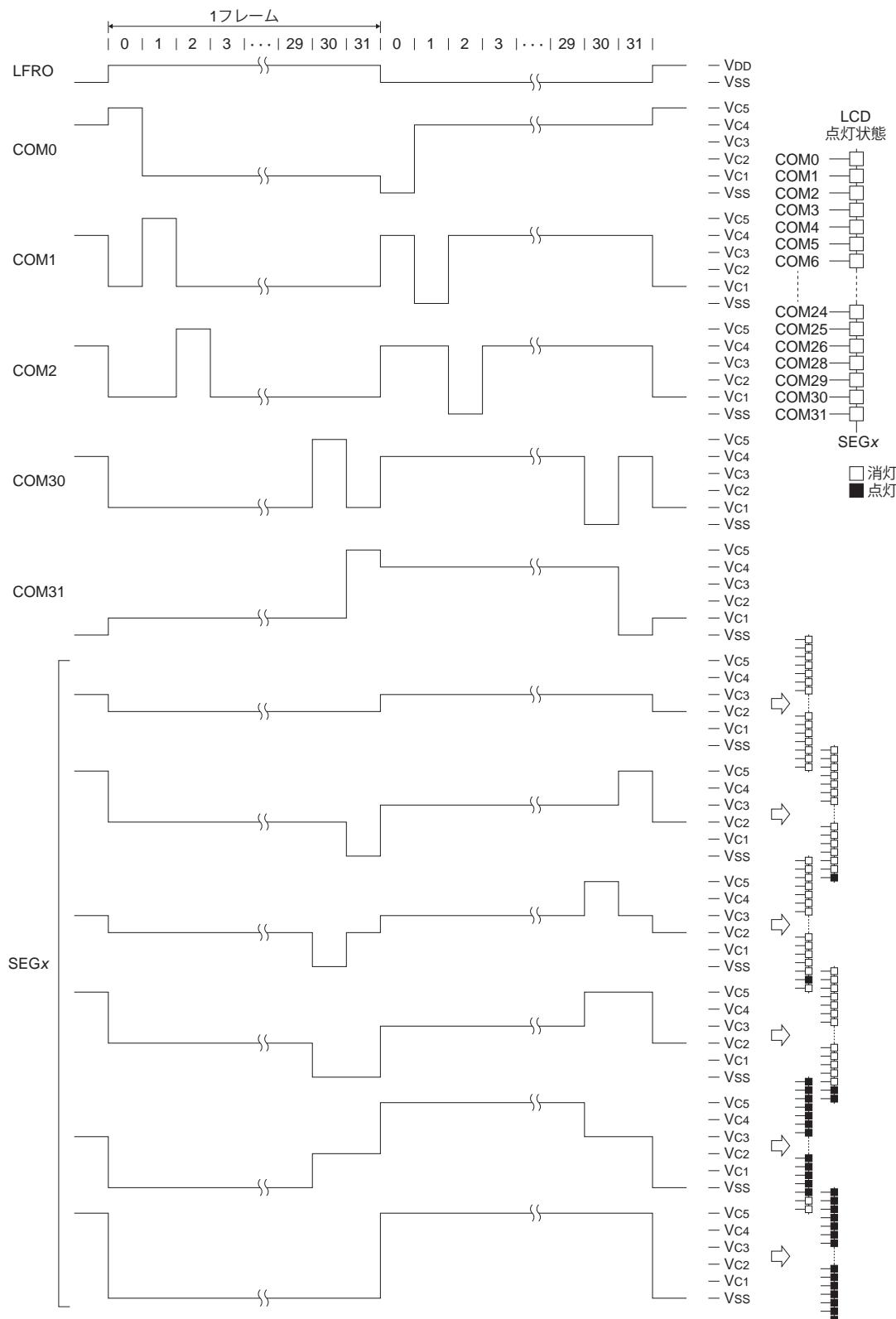

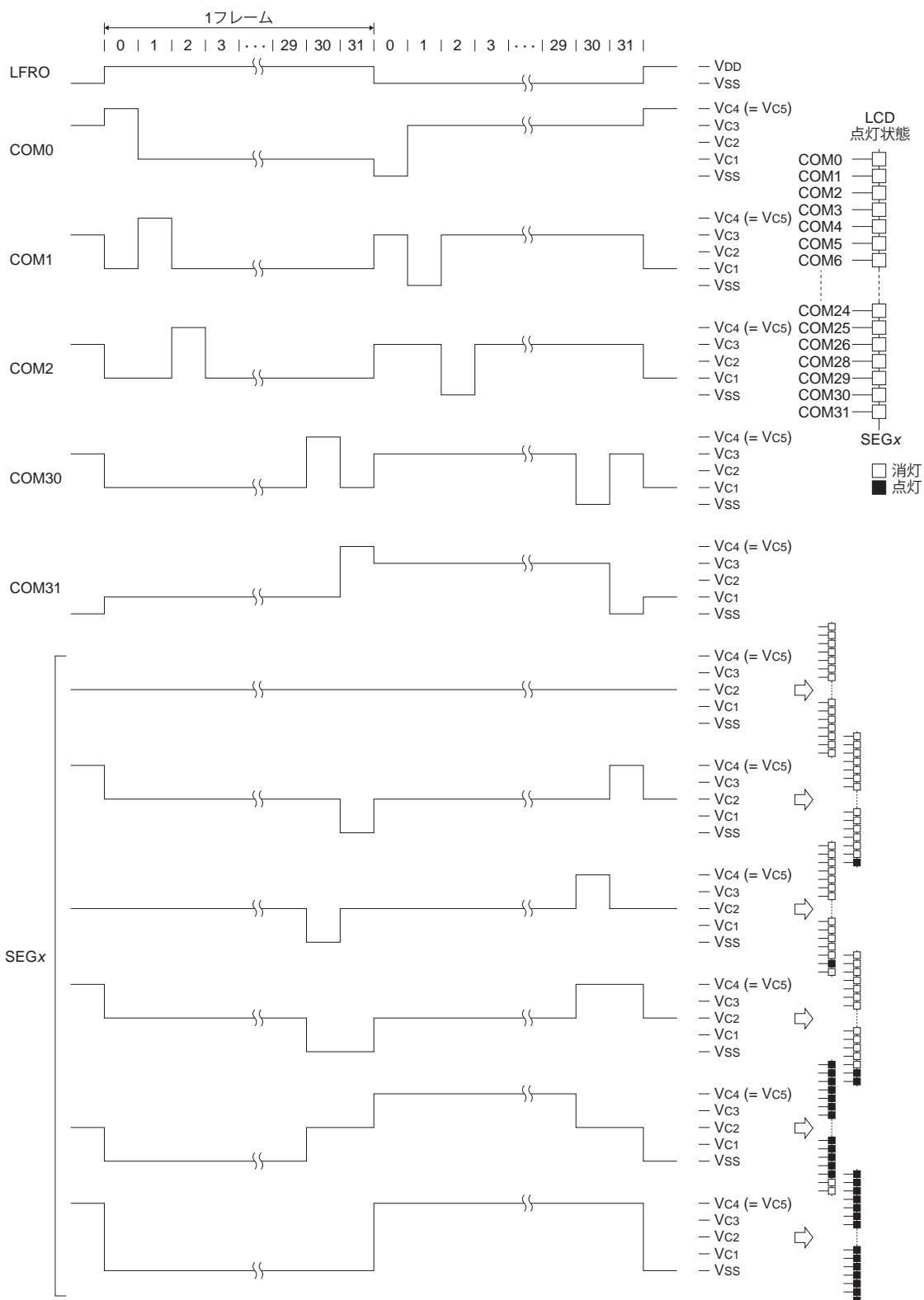

| 20.5 動作 .....                                             | 20-7        |

| 20.5.1 初期設定 .....                                         | 20-7        |

| 20.5.2 表示のON/OFF .....                                    | 20-8        |

| 20.5.3 反転表示 .....                                         | 20-8        |

| 20.5.4 駆動デューティの切り換え .....                                 | 20-8        |

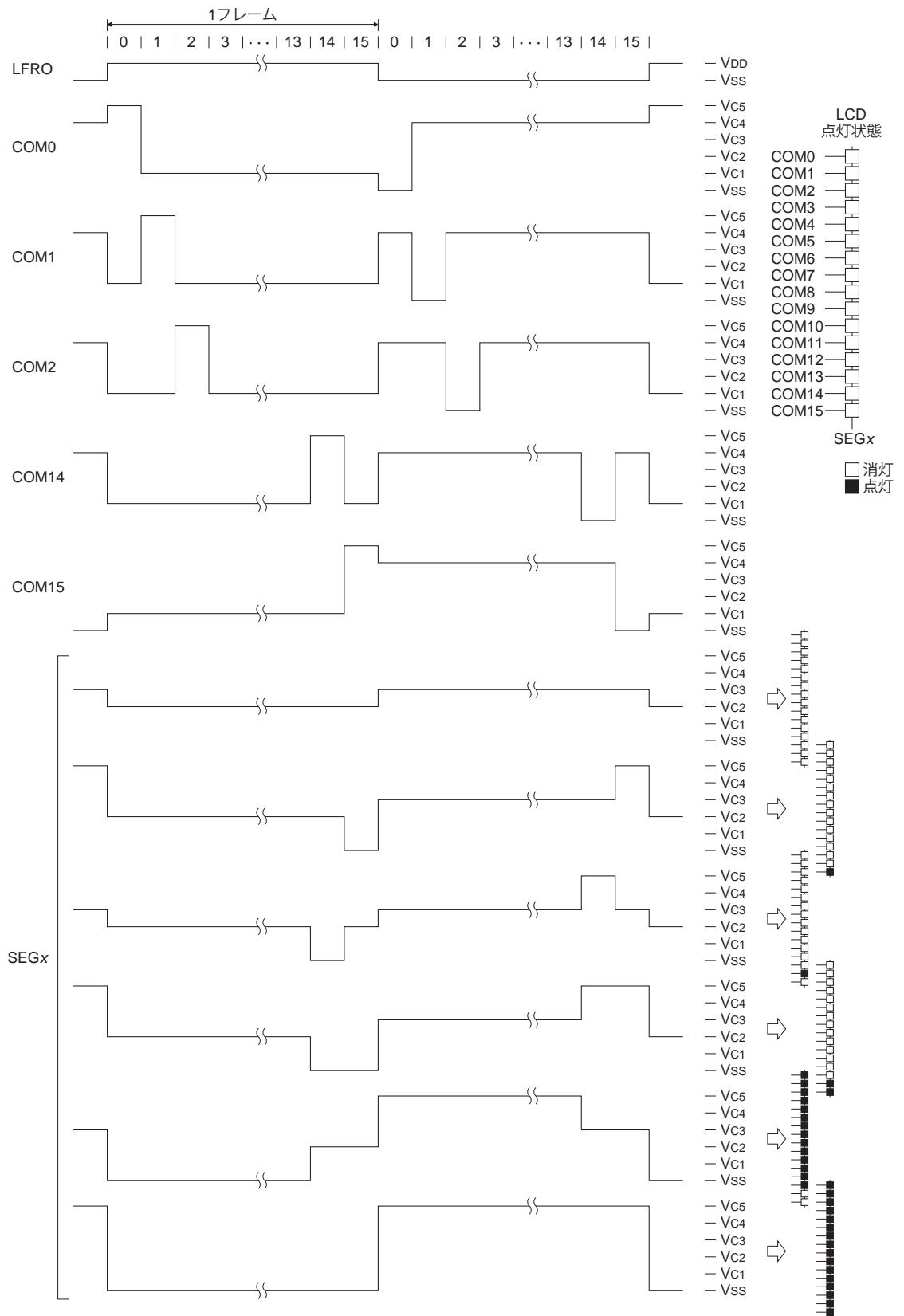

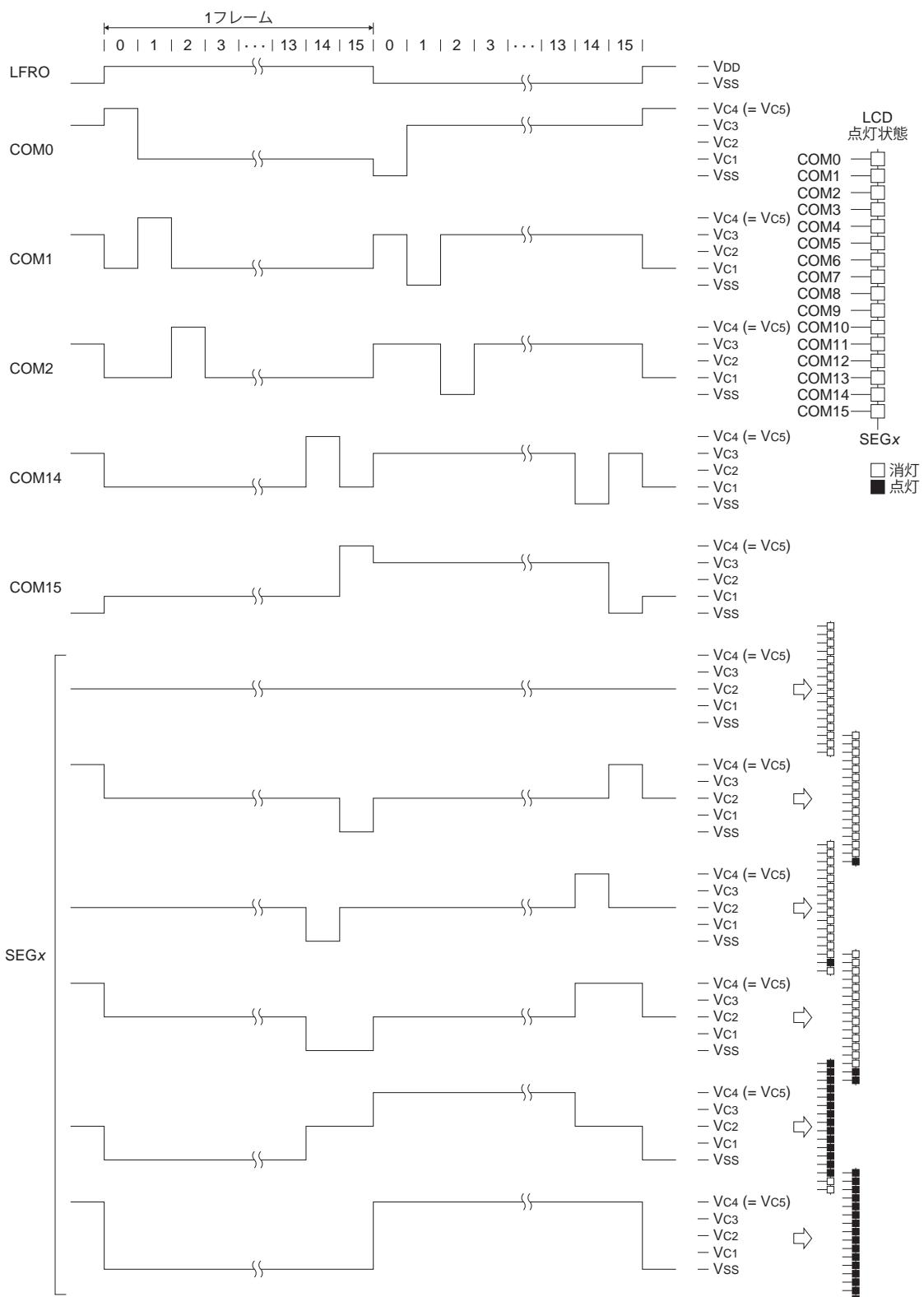

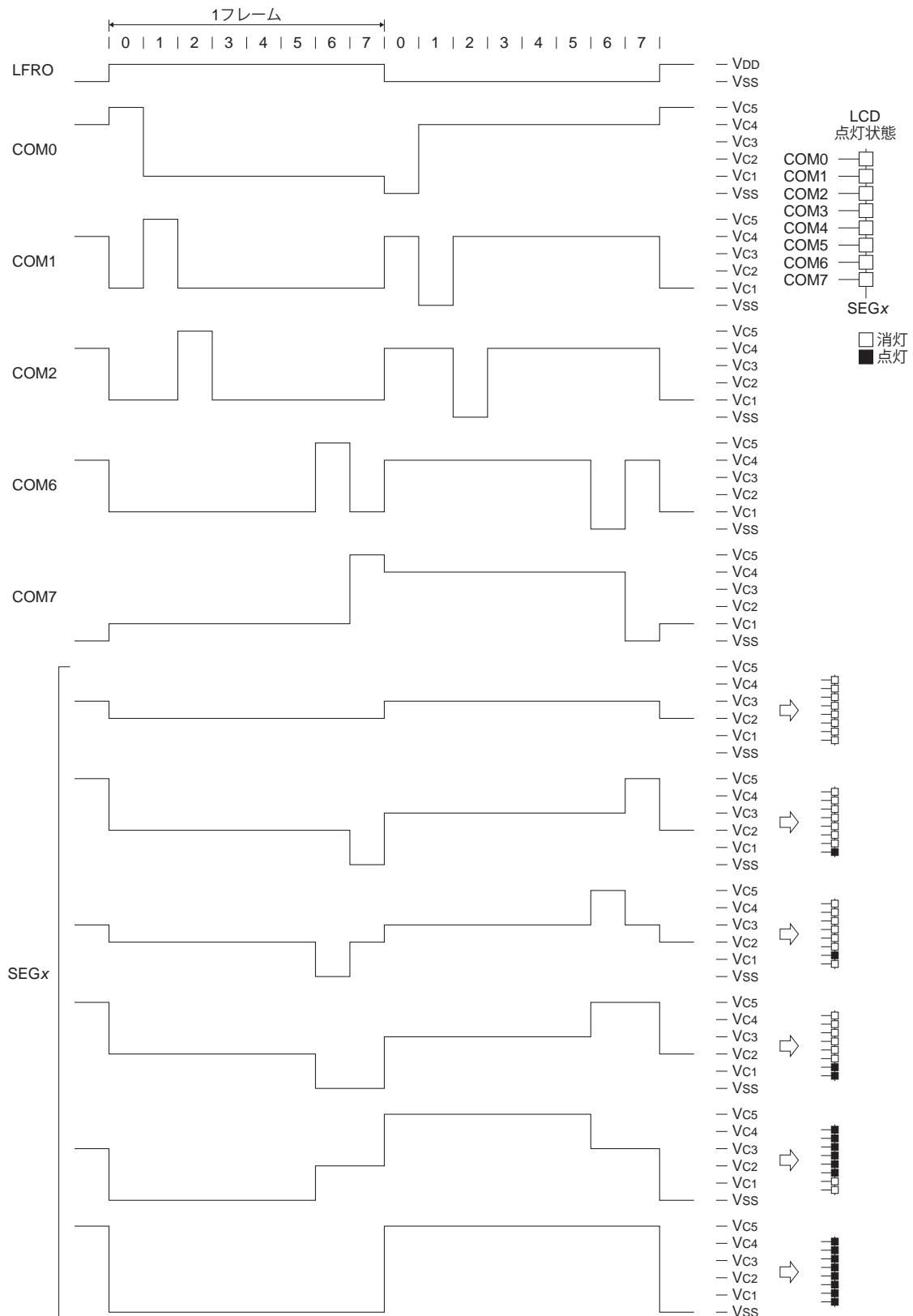

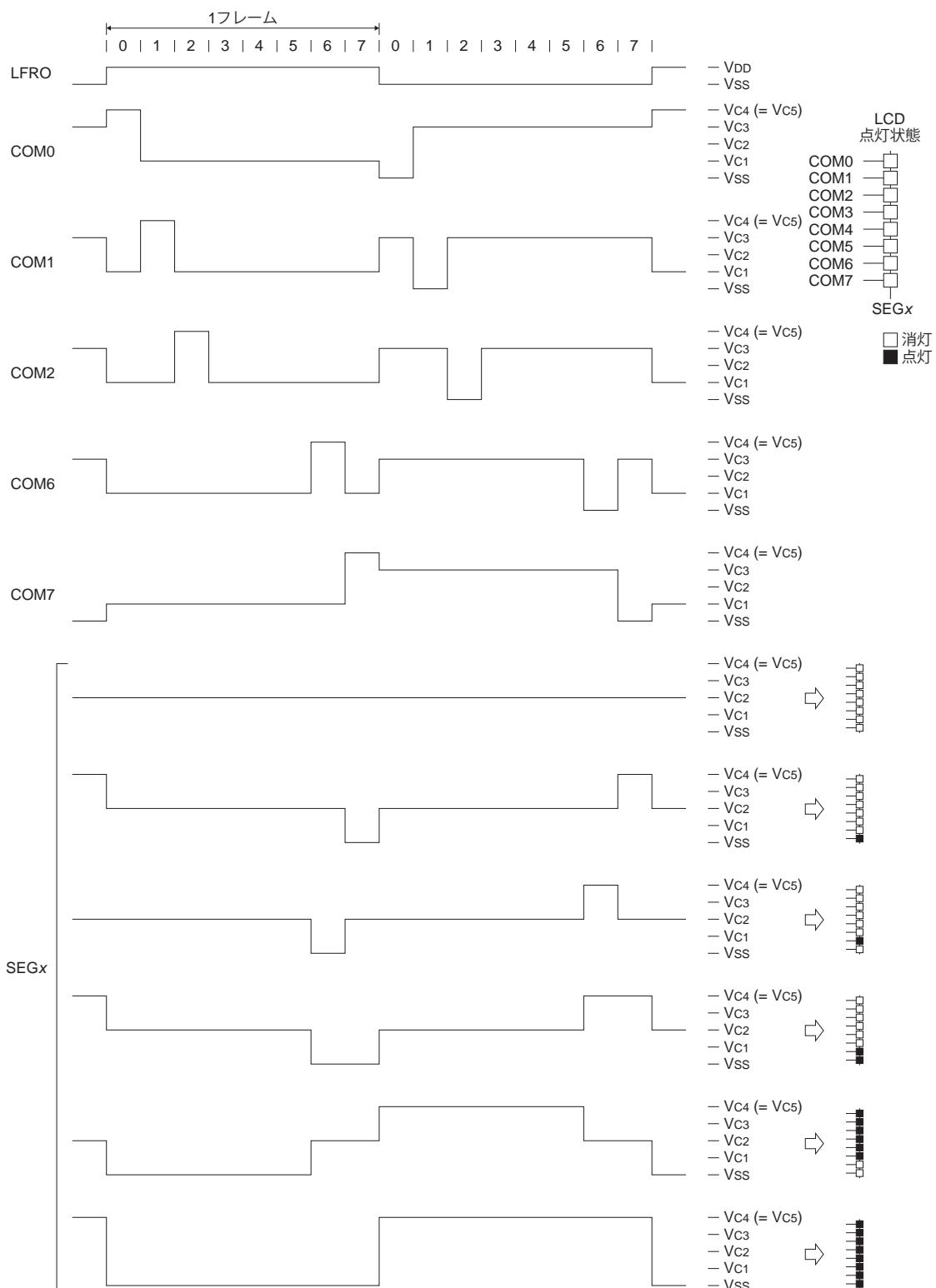

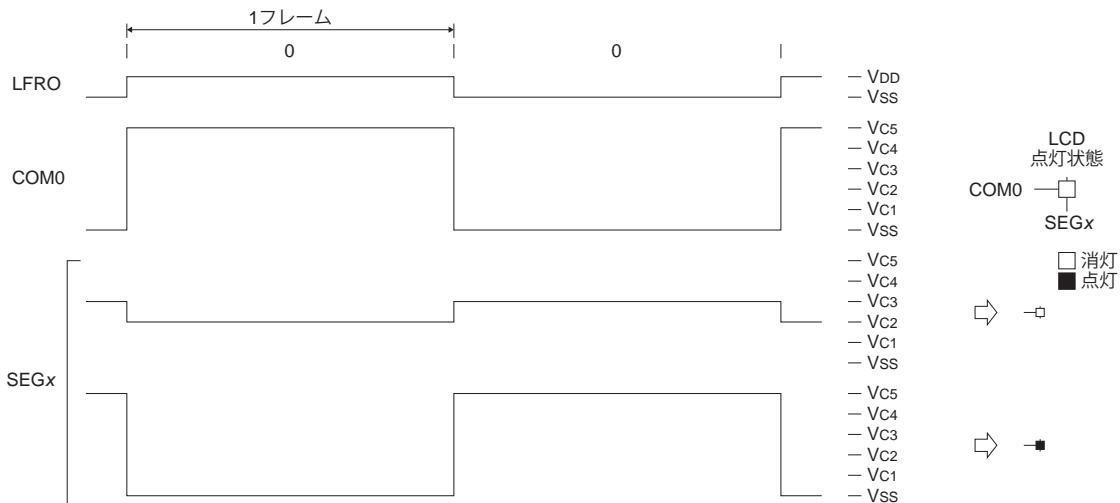

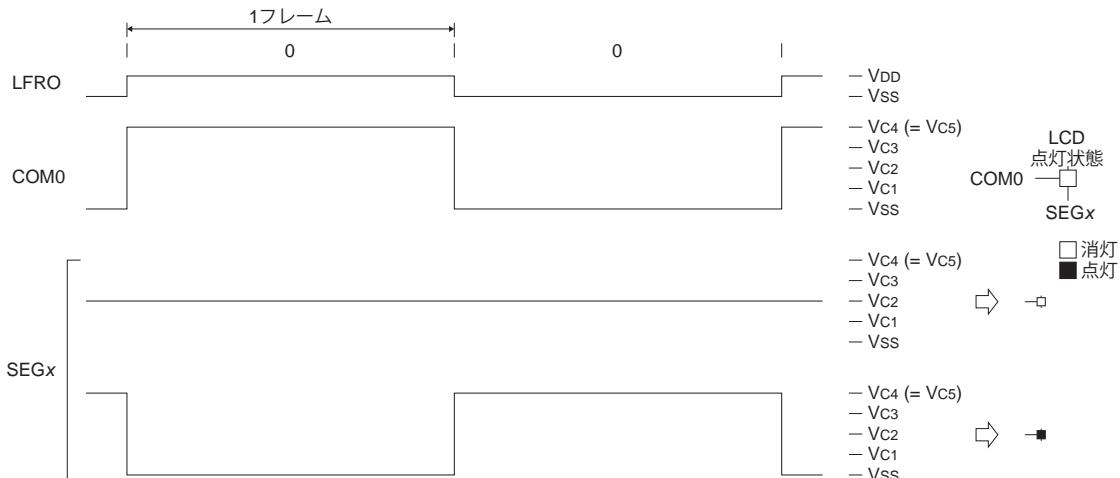

| 20.5.5 駆動波形 .....                                         | 20-10       |

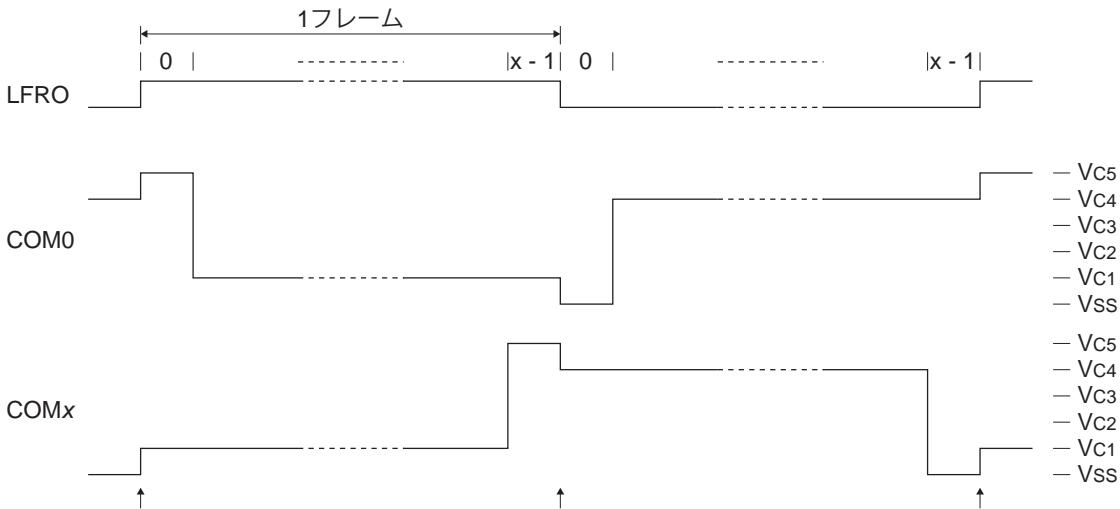

| 20.5.6 コモン出力パーシャル駆動 .....                                 | 20-16       |

|                                                           |             |

|-----------------------------------------------------------|-------------|

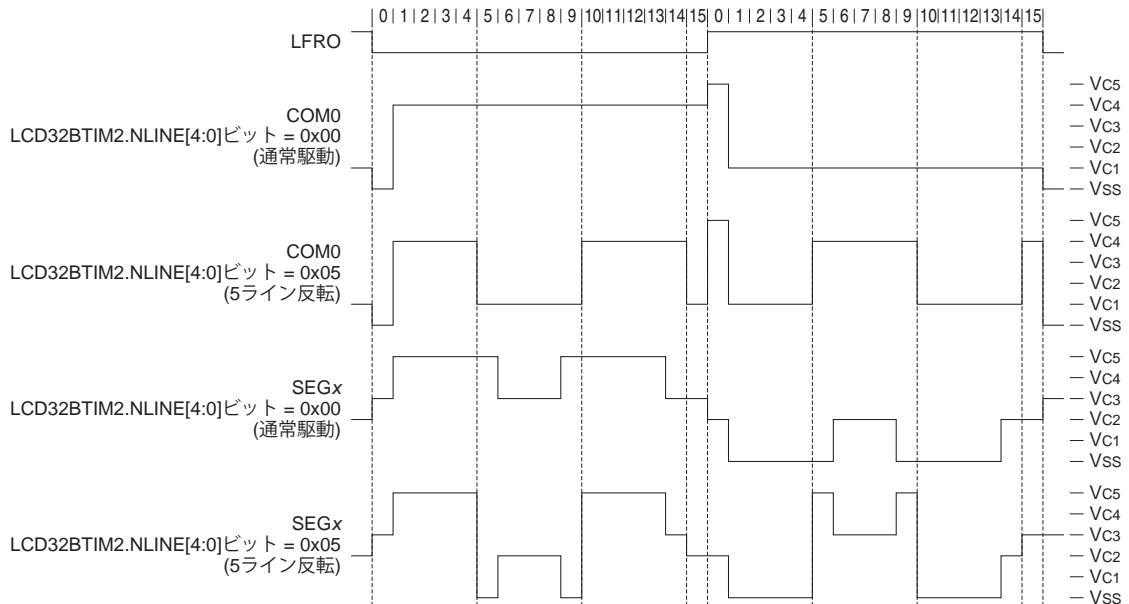

| 20.5.7 セグメント出力nライン反転交流駆動 .....                            | 20-16       |

| 20.6 表示データRAM .....                                       | 20-17       |

| 20.6.1 表示領域の選択.....                                       | 20-17       |

| 20.6.2 セグメント端子割り付け .....                                  | 20-17       |

| 20.6.3 コモン端子割り付け.....                                     | 20-17       |

| 20.7 割り込み .....                                           | 20-26       |

| 20.8 制御レジスタ .....                                         | 20-26       |

| LCD32B Clock Control Register.....                        | 20-26       |

| LCD32B Control Register.....                              | 20-27       |

| LCD32B Timing Control Register 1 .....                    | 20-27       |

| LCD32B Timing Control Register 2 .....                    | 20-28       |

| LCD32B Power Control Register.....                        | 20-28       |

| LCD32B Display Control Register.....                      | 20-29       |

| LCD32B COM Pin Control Registers 0 and 1 .....            | 20-30       |

| LCD32B Interrupt Flag Register .....                      | 20-31       |

| LCD32B Interrupt Enable Register.....                     | 20-31       |

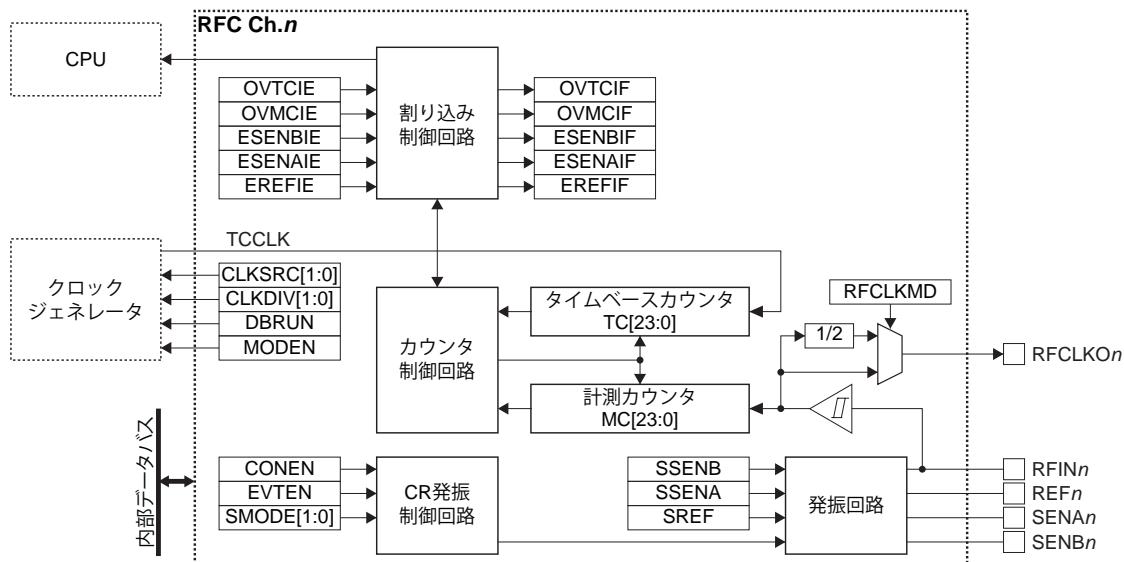

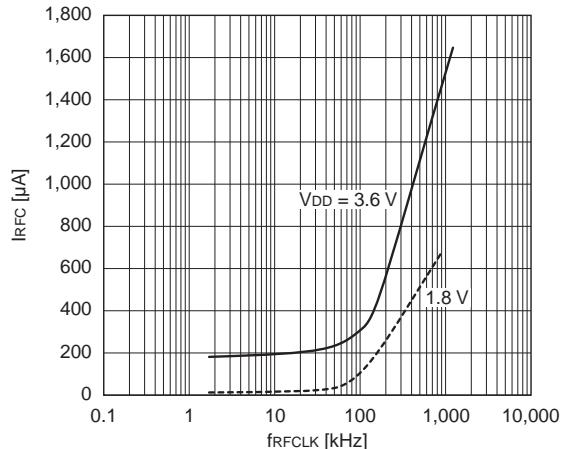

| <b>21 R/F変換器(RFC) .....</b>                               | <b>21-1</b> |

| 21.1 概要 .....                                             | 21-1        |

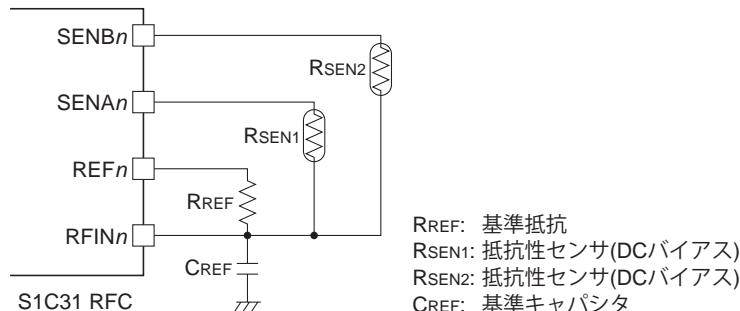

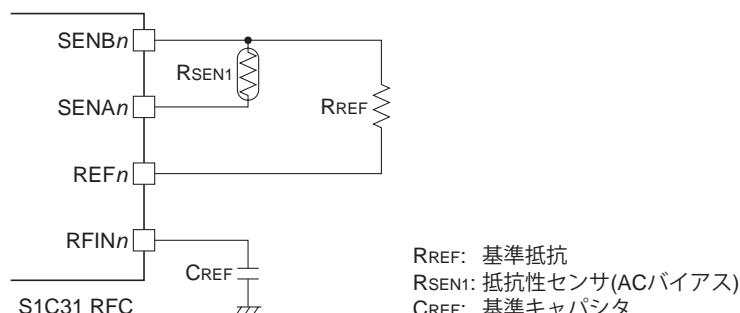

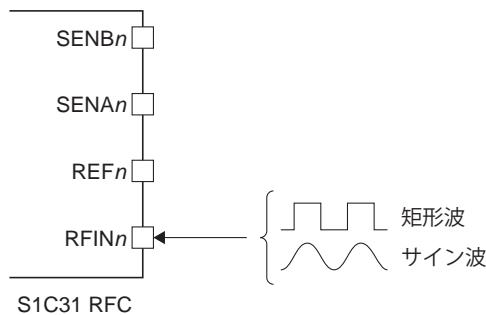

| 21.2 入出力端子と外部接続 .....                                     | 21-2        |

| 21.2.1 入出力端子一覧.....                                       | 21-2        |

| 21.2.2 外部との接続 .....                                       | 21-2        |

| 21.3 クロック設定.....                                          | 21-3        |

| 21.3.1 RFCの動作クロック .....                                   | 21-3        |

| 21.3.2 SLEEPモード時のクロック供給 .....                             | 21-3        |

| 21.3.3 DEBUGモード時のクロック供給 .....                             | 21-3        |

| 21.4 動作 .....                                             | 21-3        |

| 21.4.1 初期設定 .....                                         | 21-3        |

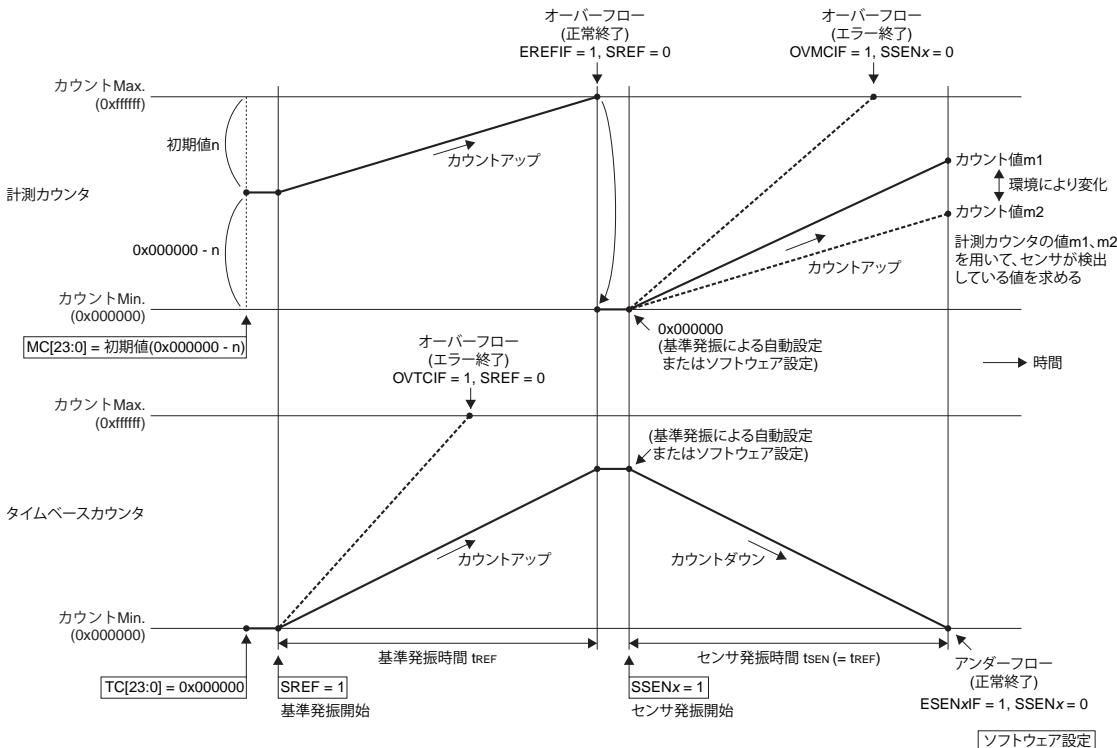

| 21.4.2 動作モード .....                                        | 21-4        |

| 21.4.3 RFCカウンタ .....                                      | 21-4        |

| 21.4.4 変換動作と制御手順.....                                     | 21-5        |

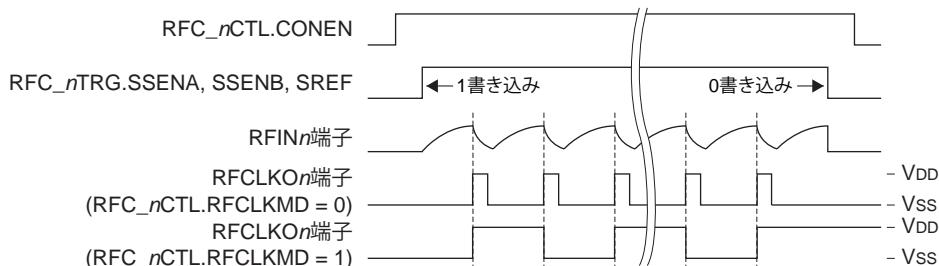

| 21.4.5 CR発振周波数モニタ機能 .....                                 | 21-7        |

| 21.5 割り込み .....                                           | 21-7        |

| 21.6 制御レジスタ .....                                         | 21-8        |

| RFC Ch.n Clock Control Register .....                     | 21-8        |

| RFC Ch.n Control Register.....                            | 21-8        |

| RFC Ch.n Oscillation Trigger Register .....               | 21-9        |

| RFC Ch.n Measurement Counter Low and High Registers ..... | 21-10       |

| RFC Ch.n Time Base Counter Low and High Registers .....   | 21-10       |

| RFC Ch.n Interrupt Flag Register .....                    | 21-11       |

| RFC Ch.n Interrupt Enable Register .....                  | 21-11       |

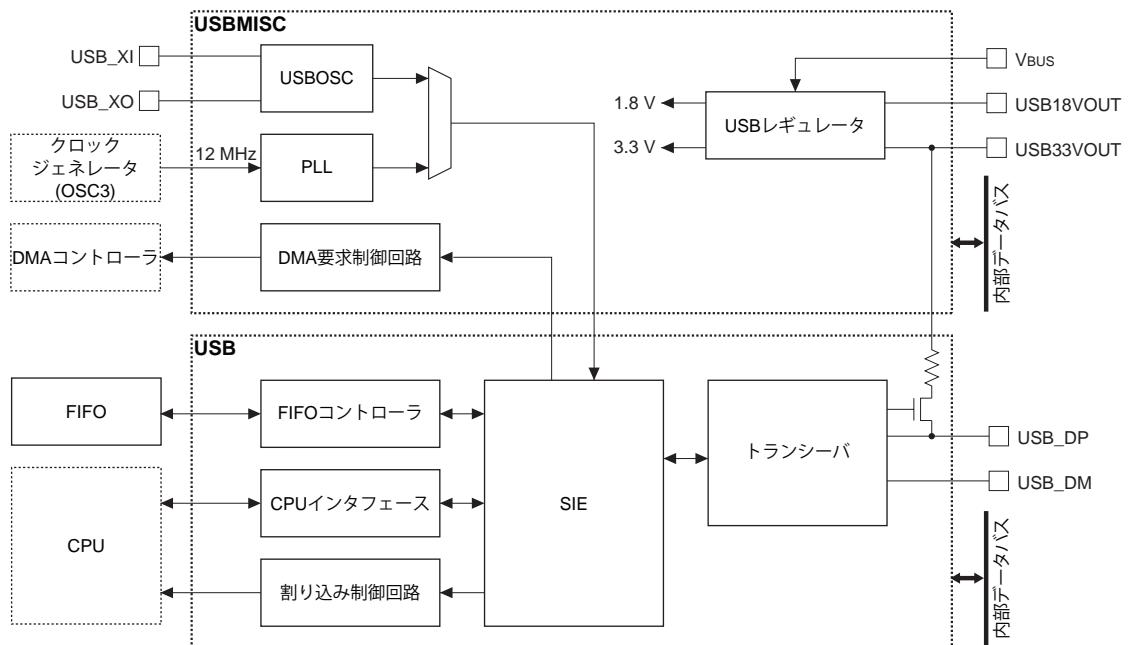

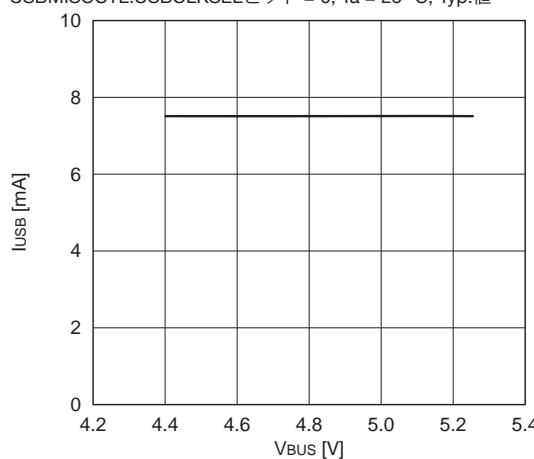

| <b>22 USB 2.0 FSデバイスコントローラ(USB, USBMISC) .....</b>        | <b>22-1</b> |

| 22.1 概要 .....                                             | 22-1        |

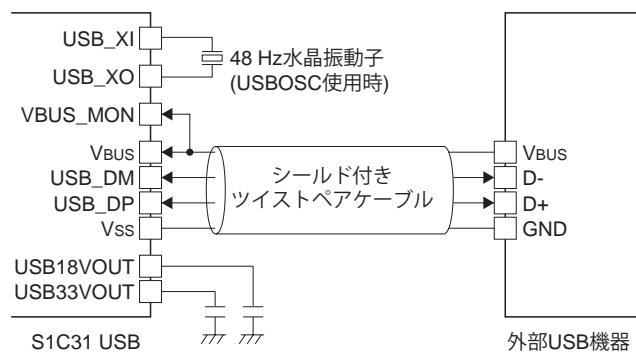

| 22.2 入出力端子と外部接続 .....                                     | 22-2        |

| 22.2.1 入出力端子一覧.....                                       | 22-2        |

| 22.2.2 外部との接続 .....                                       | 22-2        |

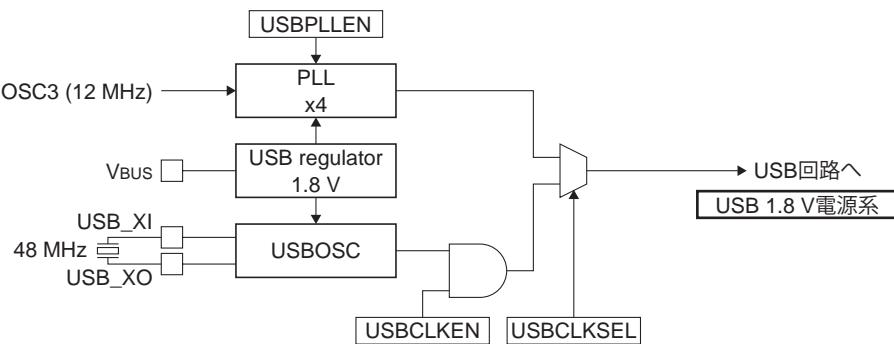

| 22.3 クロック設定 .....                                         | 22-3        |

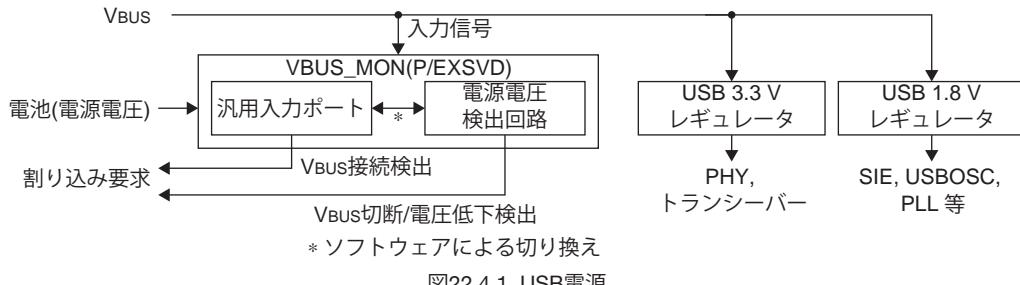

| 22.4 USB電源 .....                                          | 22-4        |

| 22.5 動作 .....                                             | 22-4        |

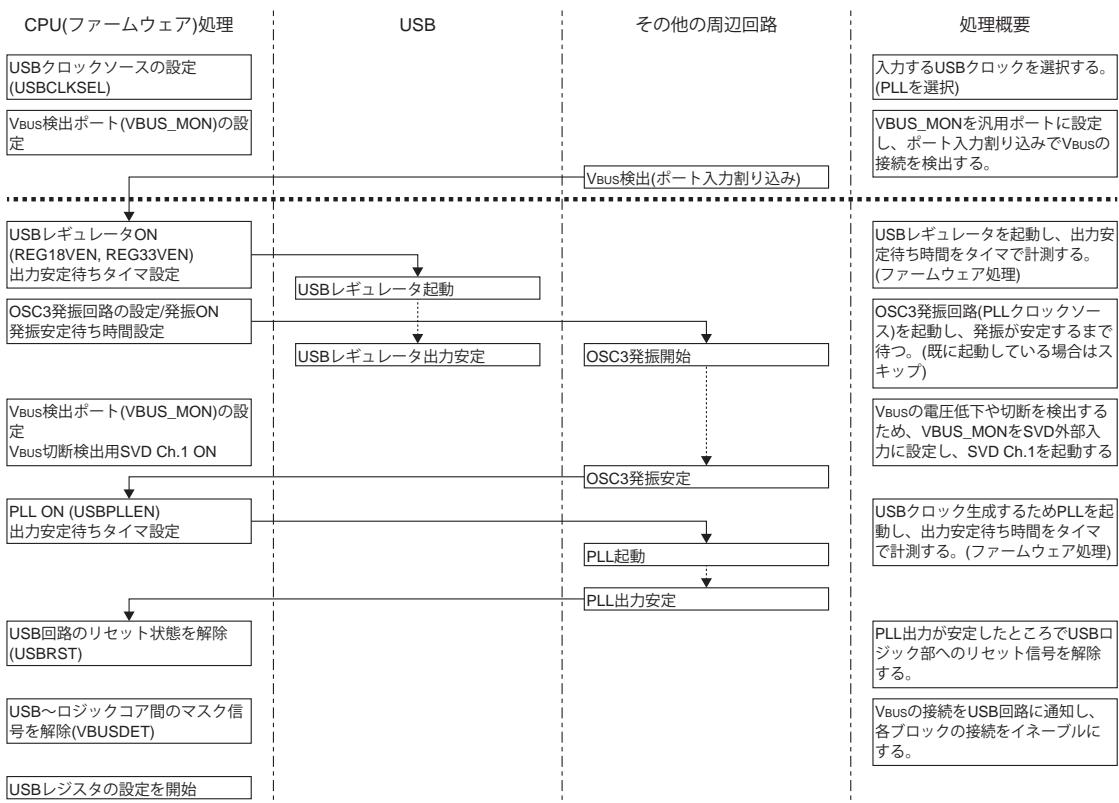

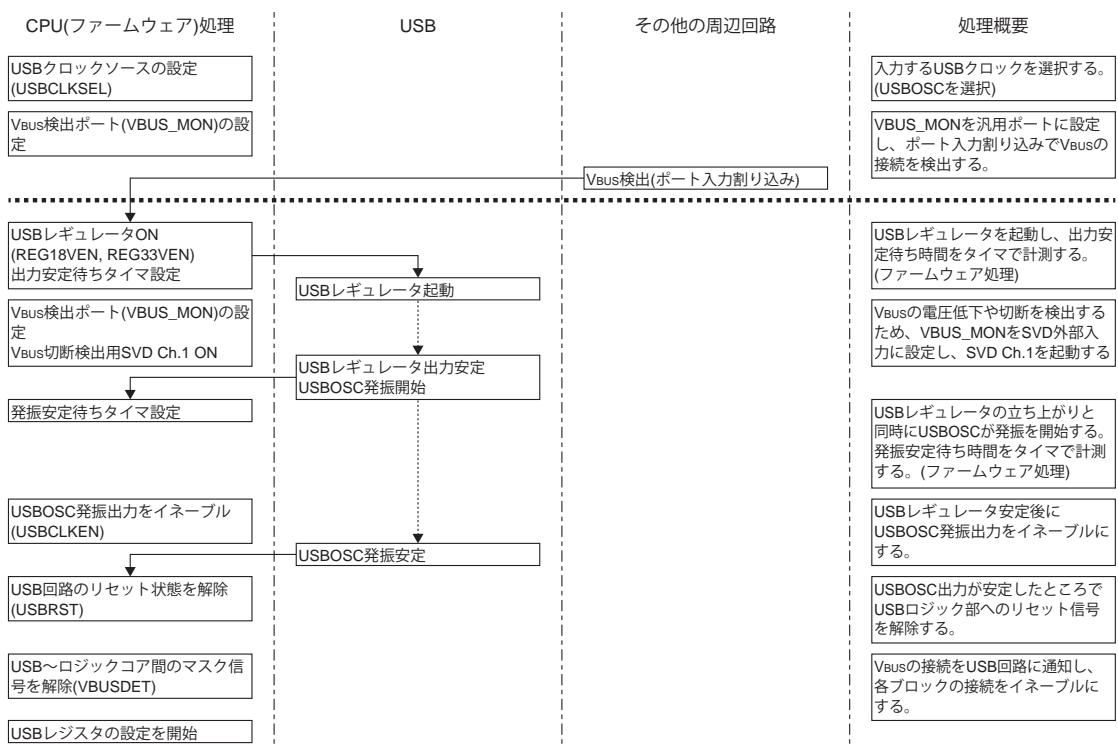

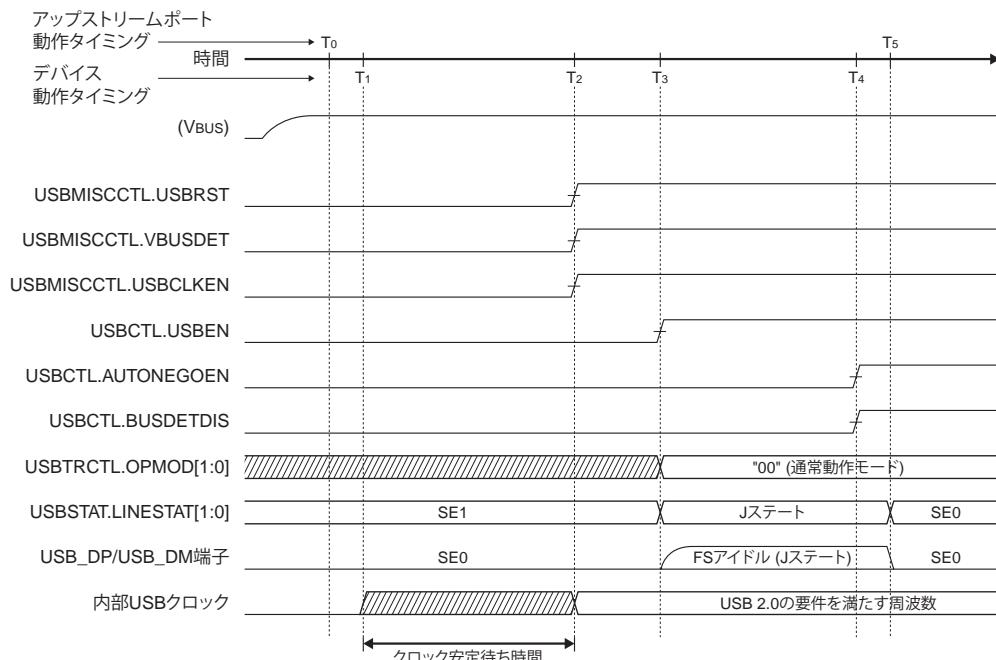

| 22.5.1 初期設定 .....                                         | 22-4        |

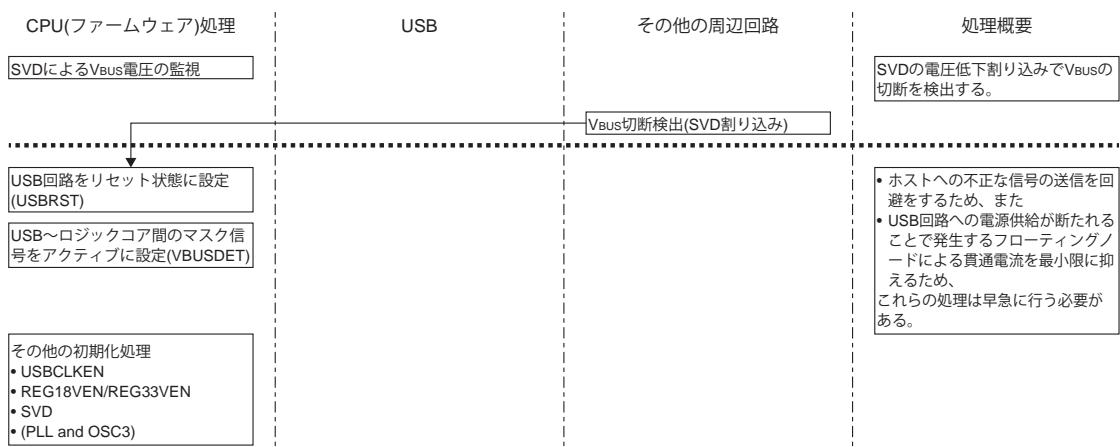

| 22.5.2 VBUS切断時の設定 .....                                   | 22-6        |

| 22.5.3 トランザクションの制御 .....                                  | 22-7        |

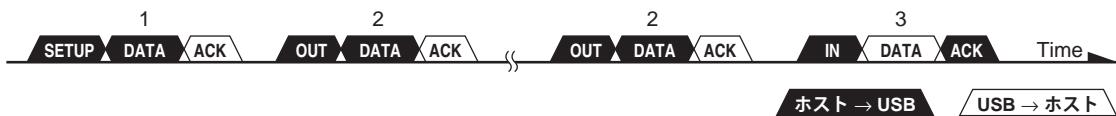

| 22.5.4 コントロール転送 .....                                     | 22-9        |

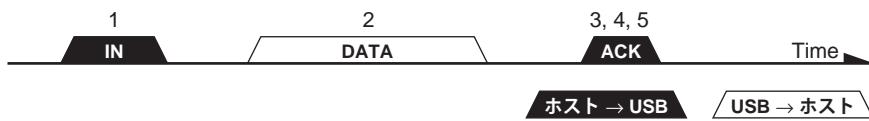

| 22.5.5 バルク転送/インターラプト転送 .....                              | 22-11       |

|                                                              |             |

|--------------------------------------------------------------|-------------|

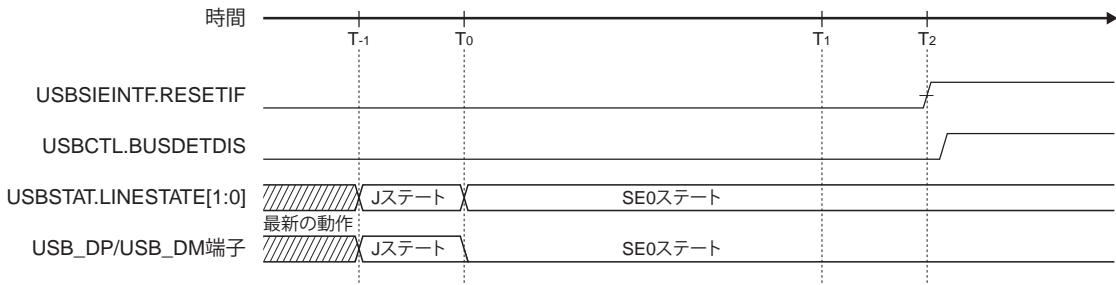

| 22.5.6 データフローの制御.....                                        | 22-12       |

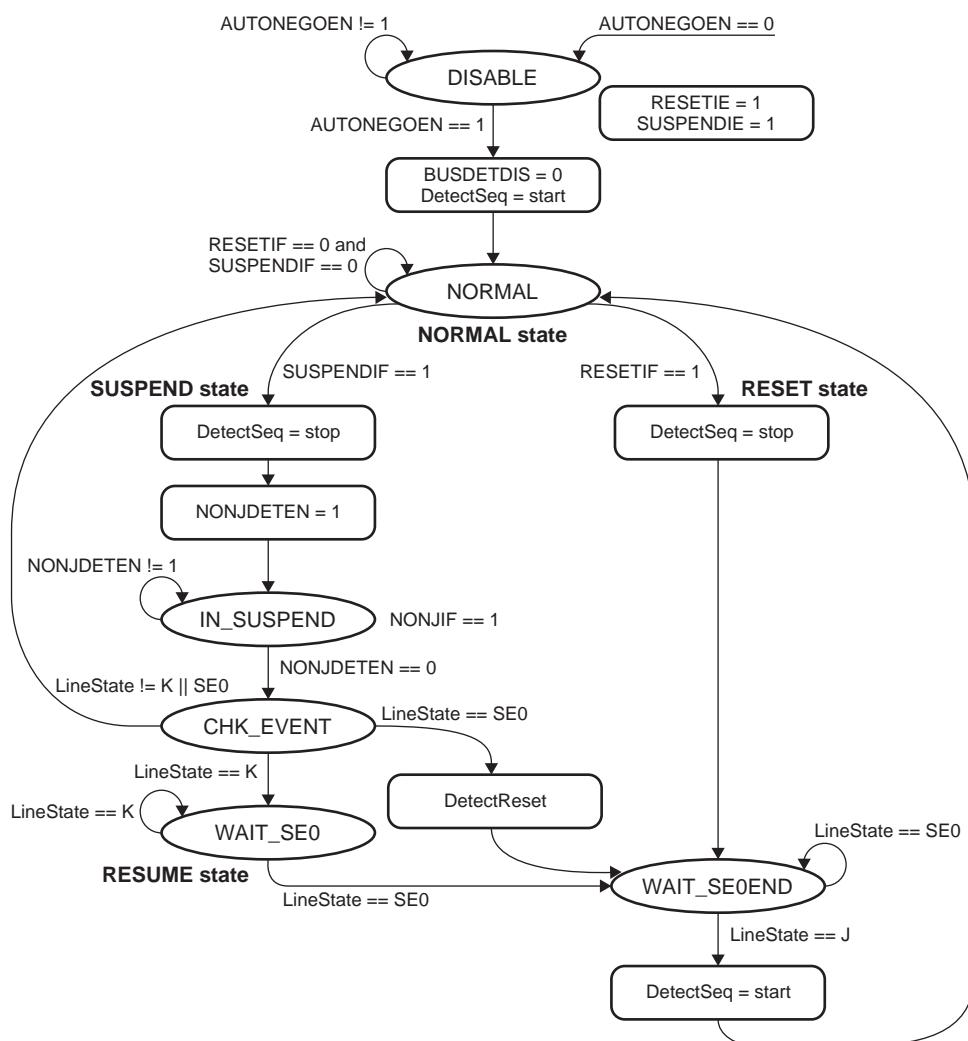

| 22.5.7 オートネゴシエーション機能.....                                    | 22-13       |

| 22.5.8 ネゴシエーション機能説明.....                                     | 22-15       |

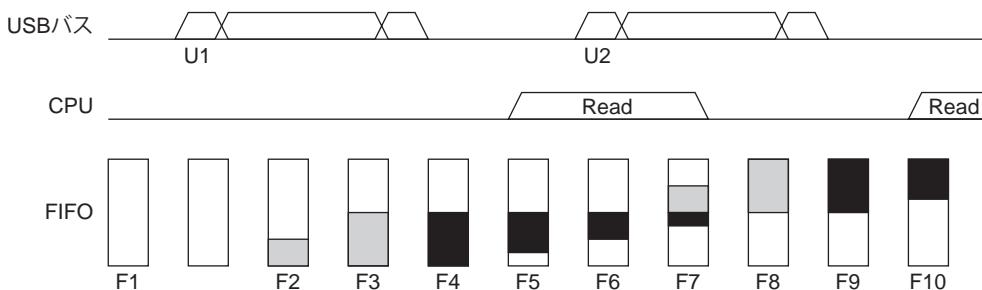

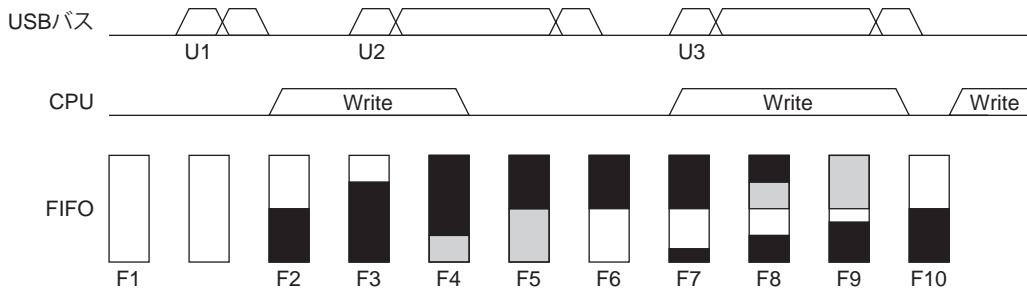

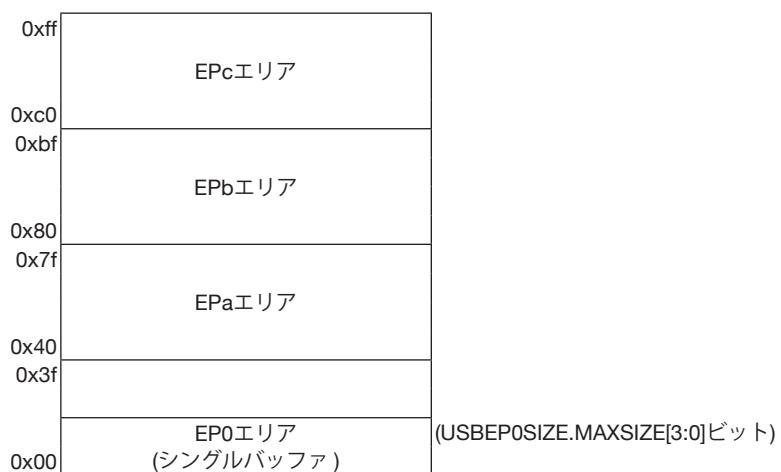

| 22.5.9 FIFO管理.....                                           | 22-18       |

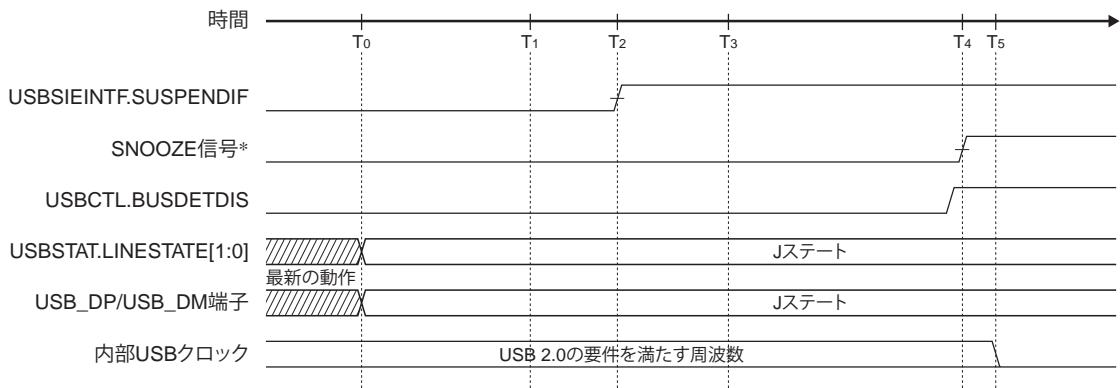

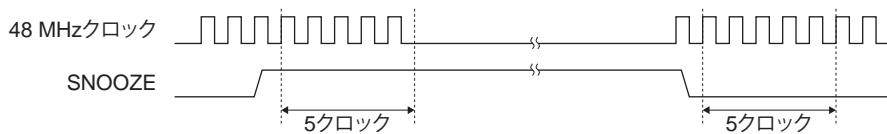

| 22.5.10 スヌーズ.....                                            | 22-20       |

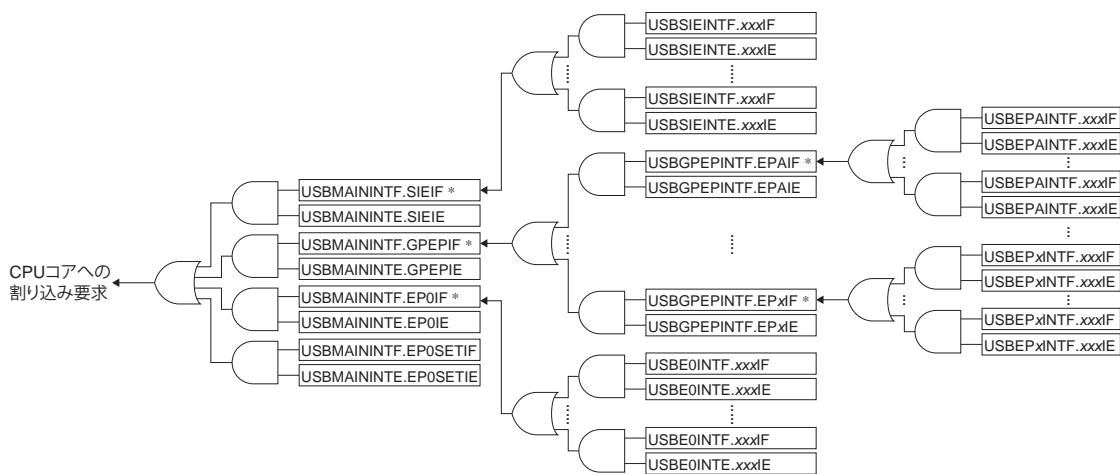

| 22.6 割り込み.....                                               | 22-21       |

| 22.7 DMA転送要求.....                                            | 22-22       |

| 22.8 制御レジスタ .....                                            | 22-22       |

| USB Control Register .....                                   | 22-22       |

| USB Transceiver Control Register.....                        | 22-24       |

| USB Status Register .....                                    | 22-24       |

| USB Endpoint Control Register.....                           | 22-25       |

| USB General-Purpose Endpoint FIFO Clear Register.....        | 22-25       |

| USB FIFO Read Cycle Setup Register .....                     | 22-26       |

| USB Revision Number Register .....                           | 22-26       |

| USB EP0 Setup Data Registers 0~7.....                        | 22-26       |

| USB Address Register.....                                    | 22-27       |

| USB EP0 Configuration Register.....                          | 22-27       |

| USB EP0 Maximum Packet Size Register .....                   | 22-27       |

| USB EP0 IN Transaction Control Register .....                | 22-28       |

| USB EP0 OUT Transaction Control Register.....                | 22-29       |

| USB EP <sub>m</sub> Control Registers.....                   | 22-30       |

| USB EP <sub>m</sub> Configuration Registers.....             | 22-31       |

| USB EP <sub>m</sub> Maximum Packet Size Registers.....       | 22-32       |

| USB Read FIFO Select Register .....                          | 22-32       |

| USB Write FIFO Select Register.....                          | 22-33       |

| USB FIFO Read/Write Enable Register .....                    | 22-33       |

| USB Remaining FIFO Data Count Register .....                 | 22-34       |

| USB Remaining FIFO Space Count Register .....                | 22-34       |

| USB Debug RAM Address Register .....                         | 22-34       |

| USB Main Interrupt Flag Register .....                       | 22-35       |

| USB SIE Interrupt Flag Register .....                        | 22-35       |

| USB General-Purpose Endpoint Interrupt Flag Register .....   | 22-36       |

| USB EP0 Interrupt Flag Register.....                         | 22-37       |

| USB EP <sub>m</sub> Interrupt Flag Registers.....            | 22-37       |

| USB Main Interrupt Enable Register .....                     | 22-38       |

| USB SIE Interrupt Enable Register .....                      | 22-39       |

| USB General-Purpose Endpoint Interrupt Enable Register ..... | 22-39       |

| USB EP0 Interrupt Enable Register.....                       | 22-40       |

| USB EP <sub>m</sub> Interrupt Enable Registers.....          | 22-40       |

| USB FIFO Data Register .....                                 | 22-41       |

| USB Debug RAM Data Register.....                             | 22-41       |

| USB Misc Control Register .....                              | 22-42       |

| USB FIFO Write DMA Request Enable Register .....             | 22-43       |

| USB FIFO Read DMA Request Enable Register .....              | 22-43       |

| <b>23 電気的特性.....</b>                                         | <b>23-1</b> |

| 23.1 絶対最大定格 .....                                            | 23-1        |

| 23.2 推奨動作条件 .....                                            | 23-1        |

| 23.3 消費電流 .....                                              | 23-2        |

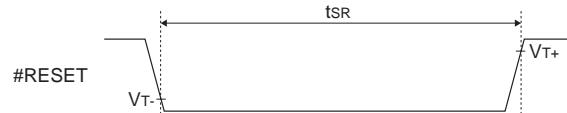

| 23.4 システムリセットコントローラ(SRC)特性 .....                             | 23-4        |

| 23.5 クロックジェネレータ(CLG)特性 .....                                 | 23-5        |

| 23.6 Flashメモリ特性 .....                                        | 23-6        |

| 23.7 入出力ポート(PPORT)特性 .....                                   | 23-7        |

| 23.8 電源電圧検出回路(SVD2)特性 .....                                  | 23-7        |

| 23.9 UART(UART2)特性 .....                                     | 23-9        |

|                                                                           |               |

|---------------------------------------------------------------------------|---------------|

| 23.10 同期式シリアルインターフェース(SPIA)特性.....                                        | 23-9          |

| 23.11 同期式クワッドシリアルインターフェース(QSPI)特性 .....                                   | 23-11         |

| 23.12 I <sup>2</sup> C(I2C)特性.....                                        | 23-12         |

| 23.13 LCD ドライバ(LCD32B)特性 .....                                            | 23-12         |

| 23.14 R/F変換器(RFC)特性.....                                                  | 23-15         |

| 23.15 USB 2.0 FSデバイスコントローラ(USB)特性 .....                                   | 23-16         |

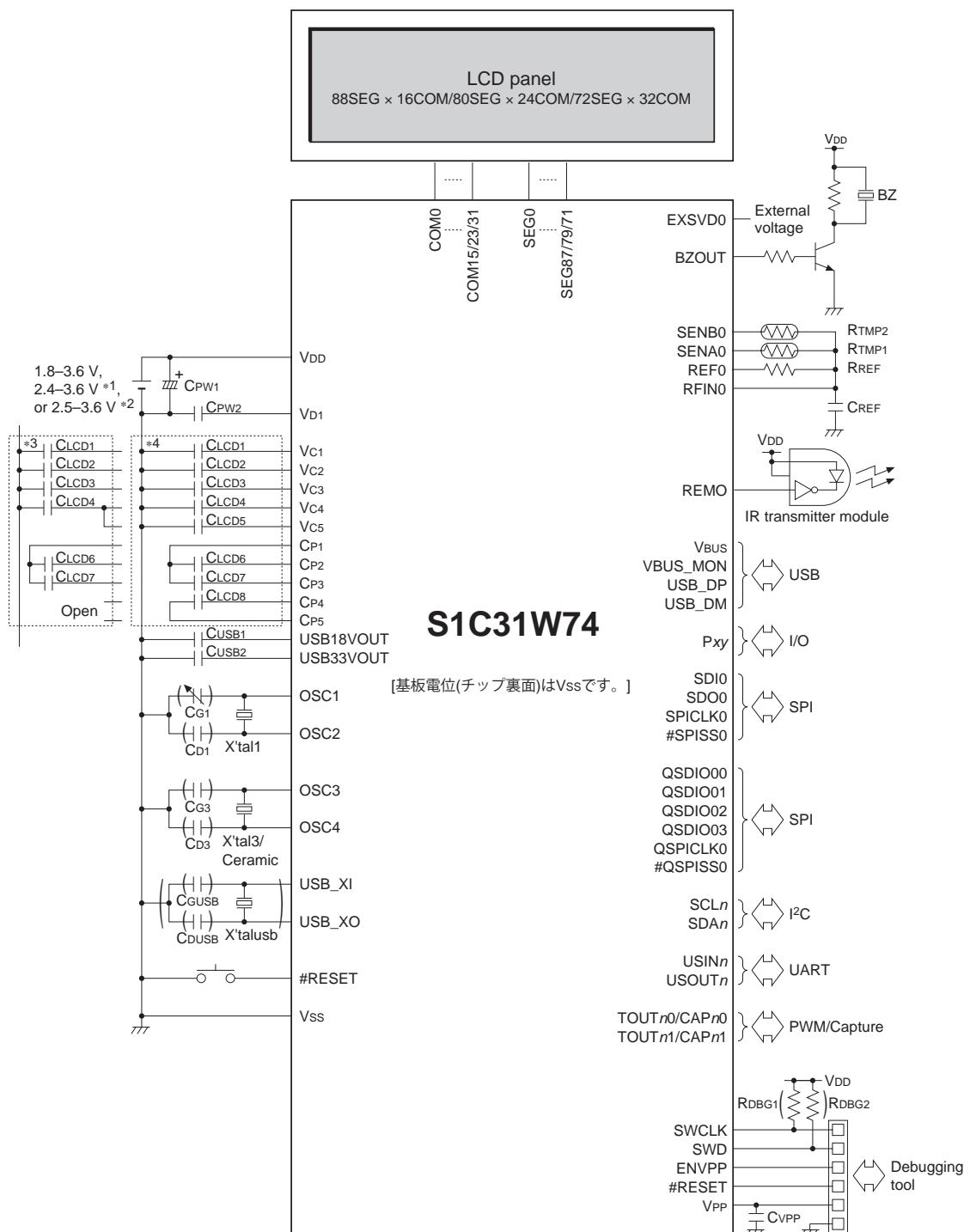

| <b>24 基本外部結線図 .....</b>                                                   | <b>24-1</b>   |

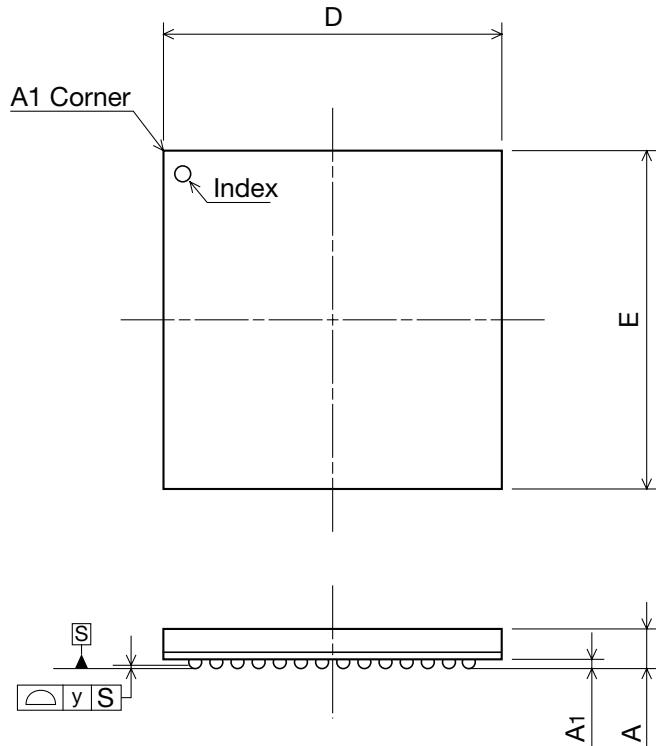

| <b>25 パッケージ.....</b>                                                      | <b>25-1</b>   |

| <b>Appendix A 周回回路制御レジスター覧.....</b>                                       | <b>AP-A-1</b> |

| 0x4000 0000 System Register (SYS).....                                    | AP-A-1        |

| 0x4000 0020 Power Generator (PWGA) .....                                  | AP-A-1        |

| 0x4000 0040–0x4000 0050 Clock Generator (CLG).....                        | AP-A-1        |

| 0x4000 0080 Cache Controller (CACHE).....                                 | AP-A-2        |

| 0x4000 00a0–0x4000 00a4 Watchdog Timer (WDT2).....                        | AP-A-2        |

| 0x4000 00c0–0x4000 00d2 Real-time Clock (RTCA) .....                      | AP-A-3        |

| 0x4000 0100–0x4000 0106 Supply Voltage Detector (SVD2) Ch.0.....          | AP-A-4        |

| 0x4000 0160–0x4000 016c 16-bit Timer (T16) Ch.0 .....                     | AP-A-5        |

| 0x4000 01b0 Flash Controller (FLASHC) .....                               | AP-A-5        |

| 0x4000 0200–0x4000 02e2 I/O Ports (PPORT) .....                           | AP-A-5        |

| 0x4000 0300–0x4000 031e Universal Port Multiplexer (UPMUX) .....          | AP-A-11       |

| 0x4000 0380–0x4000 0392 UART (UART2) Ch.0 .....                           | AP-A-12       |

| 0x4000 03a0–0x4000 03ac 16-bit Timer (T16) Ch.1 .....                     | AP-A-13       |

| 0x4000 03b0–0x4000 03be Synchronous Serial Interface (SPIA) Ch.0.....     | AP-A-14       |

| 0x4000 03c0–0x4000 03d6 I <sup>2</sup> C (I2C) Ch.0 .....                 | AP-A-15       |

| 0x4000 0400–0x4000 041c 16-bit PWM Timer (T16B) Ch.0 .....                | AP-A-16       |

| 0x4000 0440–0x4000 045c 16-bit PWM Timer (T16B) Ch.1 .....                | AP-A-17       |

| 0x4000 0480–0x4000 048c 16-bit Timer (T16) Ch.3 .....                     | AP-A-19       |

| 0x4000 0600–0x4000 0612 UART (UART2) Ch.1 .....                           | AP-A-19       |

| 0x4000 0680–0x4000 068c 16-bit Timer (T16) Ch.2 .....                     | AP-A-21       |

| 0x4000 0690–0x4000 06a8 Quad Synchronous Serial Interface (QSPI) Ch.0.... | AP-A-21       |

| 0x4000 06c0–0x4000 06d6 I <sup>2</sup> C (I2C) Ch.1 .....                 | AP-A-22       |

| 0x4000 0700–0x4000 070c Sound Generator (SNDA) .....                      | AP-A-24       |

| 0x4000 0720–0x4000 0732 IR Remote Controller (REMC2) .....                | AP-A-24       |

| 0x4000 0800–0x4000 0812 LCD Driver (LCD32B) .....                         | AP-A-25       |

| 0x4000 0840–0x4000 0850 R/F Converter (RFC) Ch.0 .....                    | AP-A-26       |

| 0x2040 0000–0x2040 0104, USB 2.0 FS Device Controller (USB, USBMISC) .... | AP-A-27       |

| 0x4000 0970–0x4000 0976 Supply Voltage Detector (SVD2) Ch.1 .....         | AP-A-32       |

| 0x4000 0980–0x4000 0986 DMA Controller (DMAC) .....                       | AP-A-33       |

| <b>Appendix B パワーセーブ .....</b>                                            | <b>AP-B-1</b> |

| B.1 パワーセーブを考慮した動作状態の設定例 .....                                             | AP-B-1        |

| B.2 その他のパワーセーブ方法.....                                                     | AP-B-2        |

| <b>Appendix C 実装上の注意事項 .....</b>                                          | <b>AP-C-1</b> |

| <b>Appendix D ノイズ対策 .....</b>                                             | <b>AP-D-1</b> |

| <b>改訂履歴表</b>                                                              |               |

# 1 概要

S1C31W74は、Arm® Cortex®-M0+プロセッサを搭載した低電力動作を特長とする32ビットMCUです。豊富なシリアルインターフェースを搭載しており、電池駆動のコントローラ機器などへの応用に適しています。

## 1.1 特長

表1.1.1 特長

| S1C31W74                      |                                                                                                                                                                                         |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>機種</b>                     |                                                                                                                                                                                         |

| <b>CPU</b>                    |                                                                                                                                                                                         |

| CPU                           | Arm® 32ビットRISCプロセッサCortex®-M0+                                                                                                                                                          |

| その他                           | シリアルワイヤデバッグポート(SW-DP), マイクロトレースバッファ(MTB)を内蔵                                                                                                                                             |

| <b>内蔵Flashメモリ</b>             |                                                                                                                                                                                         |

| 容量                            | 512Kバイト(命令/データ共用)                                                                                                                                                                       |

| 書き換え回数                        | 1,000回(min.) *専用フラッシュユーローダからの書き換え時                                                                                                                                                      |

| その他                           | オンボード書き換えが可能<br>Flashプログラミング電圧を内部生成可能                                                                                                                                                   |

| <b>内蔵RAM</b>                  |                                                                                                                                                                                         |

| 汎用RAM                         | 128Kバイト(MTBと共に)                                                                                                                                                                         |

| 表示RAM                         | 704バイト                                                                                                                                                                                  |

| 命令キャッシュ                       | 512バイト                                                                                                                                                                                  |

| <b>DMAコントローラ(DMAC)</b>        |                                                                                                                                                                                         |

| チャネル数                         | 4チャネル                                                                                                                                                                                   |

| データ転送バス                       | メモリ→メモリ, メモリ→周辺回路, 周辺回路→メモリ                                                                                                                                                             |

| 転送モード                         | 通常転送モード, ピンポン転送モード, スキッタ/ギャザ転送モード                                                                                                                                                       |

| DMAトリガソース                     | UART2, SPIA, QSPI, I2C, USB, T16B, SNDA, ソフトウェア                                                                                                                                         |

| <b>クロックジェネレータ(CLG)</b>        |                                                                                                                                                                                         |

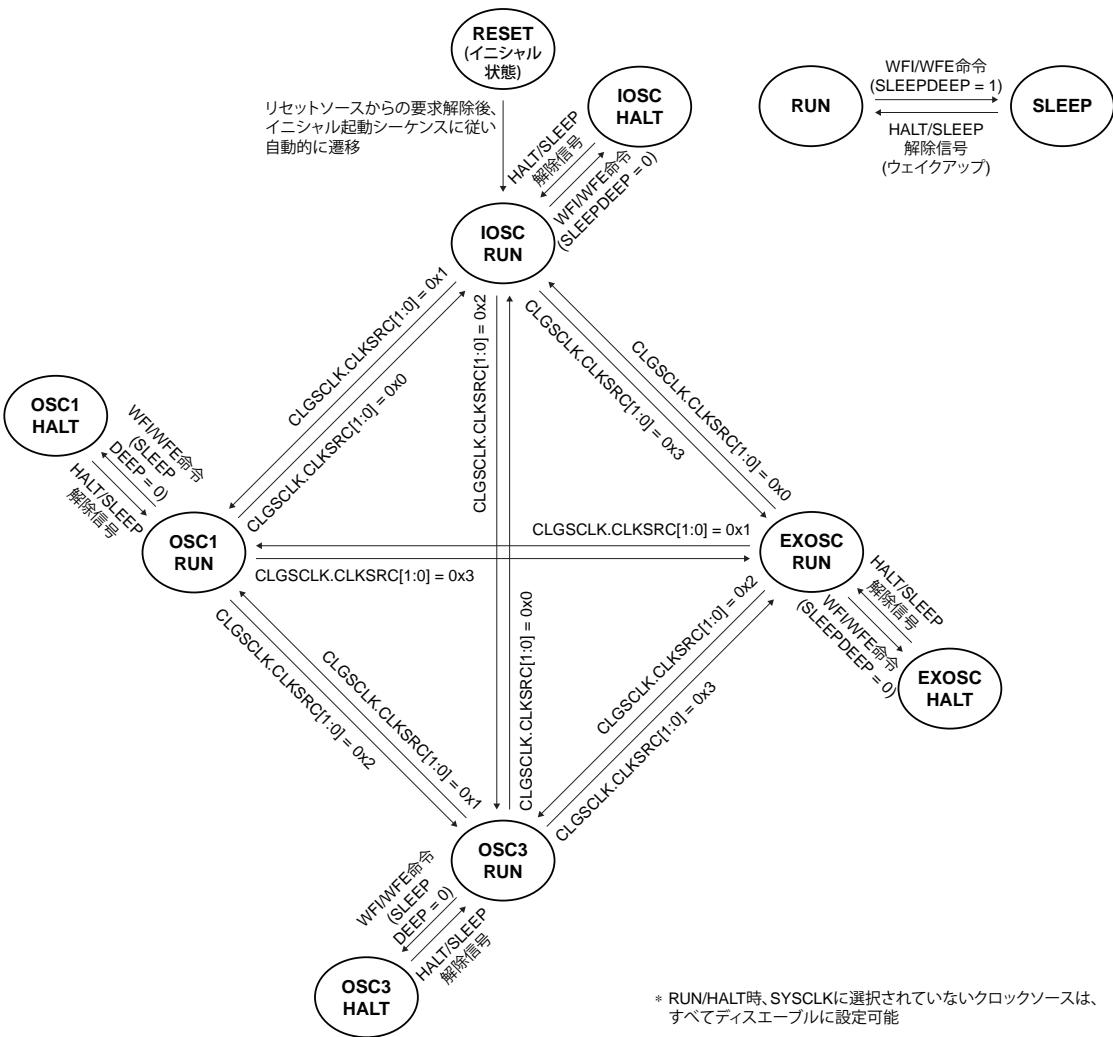

| システムクロックソース                   | 4種類(OSC1/OSC2/OSC3/EXOSC)                                                                                                                                                               |

| システムクロック周波数(動作周波数)            | V <sub>DD</sub> 電圧モード = mode0: 21 MHz(max.)<br>V <sub>DD</sub> 電圧モード = mode1: 2.1 MHz(max.)                                                                                             |

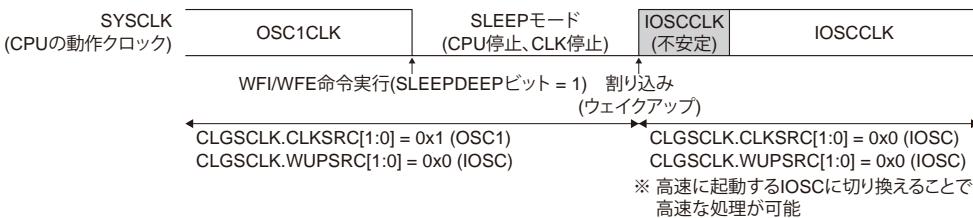

| IOSC発振回路(起動クロックソース)           | V <sub>DD</sub> 電圧モード = mode0: 20/16/12/8/2/1 MHz(typ.)からソフトウェアにて選択可能<br>V <sub>DD</sub> 電圧モード = mode1: 2/1 MHz(typ.)からソフトウェアにて選択可能<br>10 µs(max.)の起動時間(SLEEP状態からCPUがベクタテーブルを読み出すまでの時間) |

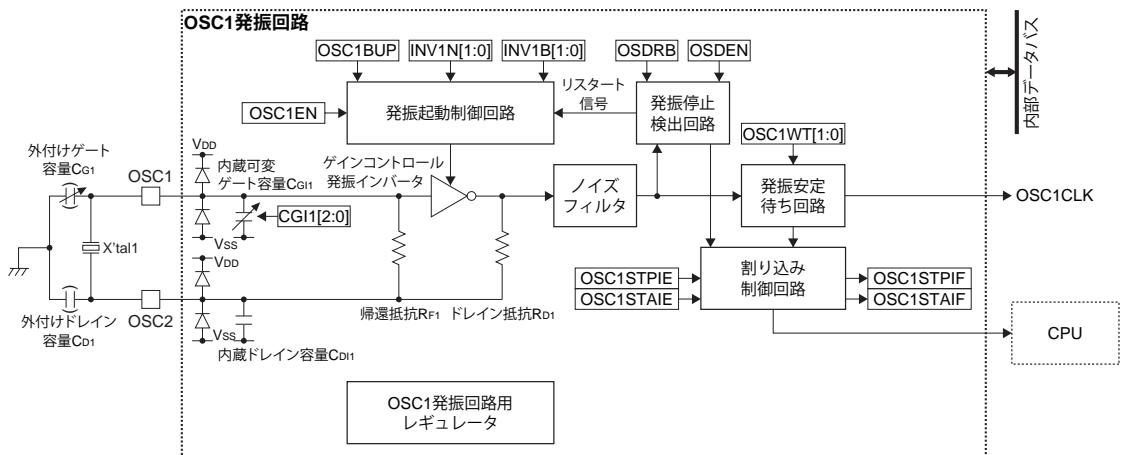

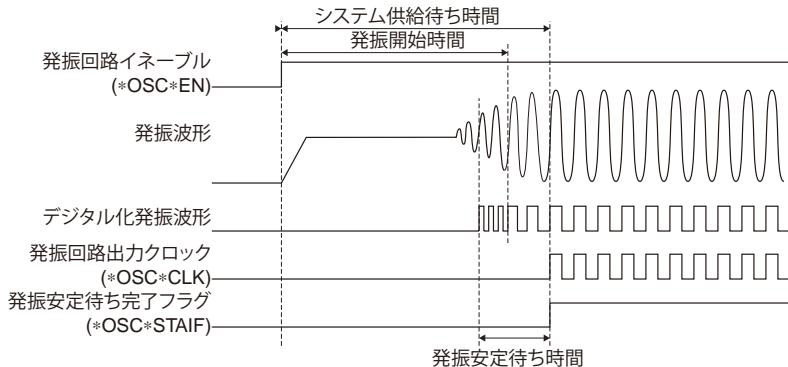

| OSC1発振回路                      | 32.768 kHz(typ.)水晶発振回路<br>発振停止検出回路内蔵                                                                                                                                                    |

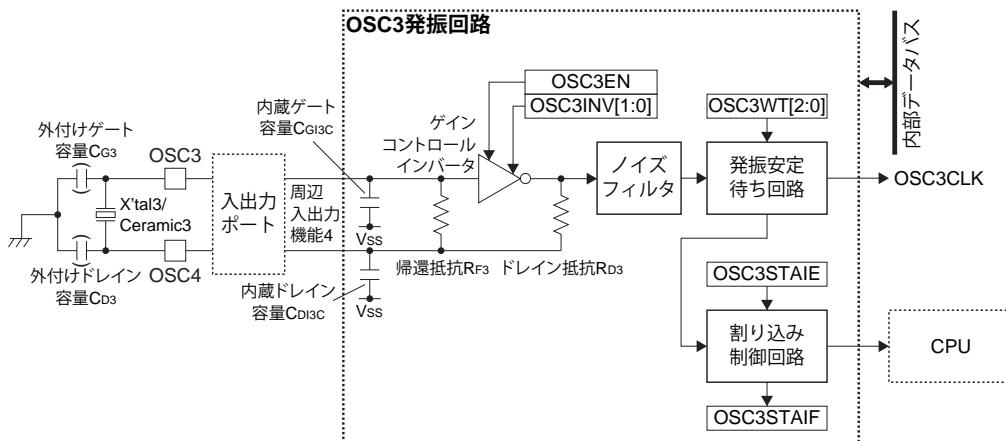

| OSC3発振回路                      | 20.5 MHz(max.)水晶/セラミック発振回路                                                                                                                                                              |

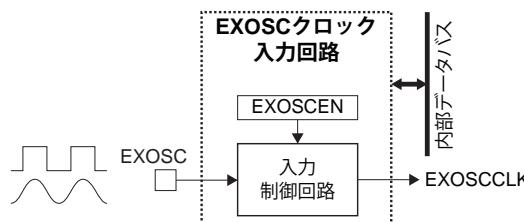

| EXOSCクロック入力                   | 21 MHz(max.)矩形波または正弦波入力                                                                                                                                                                 |

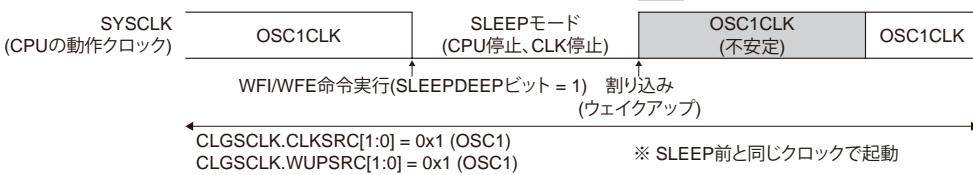

| その他                           | システムクロックの分周比を設定可能<br>SLEEP復帰時のシステムクロックを任意に設定可能<br>CPUとすべての周辺回路が、任意に選択されたクロック周波数で動作可能                                                                                                    |

| <b>入出力ポート(PPORT)</b>          |                                                                                                                                                                                         |

| 汎用入出力ポート数                     | 71ビット(max.)<br>周辺回路の入出力端子と共に                                                                                                                                                            |

| 入力割り込み対応ポート数                  | 67ビット(max.)                                                                                                                                                                             |

| ユニバーサルポートマルチブレクサ(UPMUX)対応ポート数 | 24ビット<br>ソフトウェアで選択した周辺回路入出力機能を各ポートに割り付け可能                                                                                                                                               |

| <b>タイマ</b>                    |                                                                                                                                                                                         |

| ウォッチドッグタイマ(WDT2)              | NMI, またはウォッチドッグタイマリセットを生成<br>NMI/リセット発生周期を設定可能                                                                                                                                          |

| リアルタイムクロック(RTCA)              | 128~1 Hzカウント, 秒/分/時/日/曜日/月/年カウント<br>1秒補正のための論理緩急機能<br>アラーム機能, ストップウォッチ機能                                                                                                                |

| 16ビットタイマ(T16)                 | 4チャネル<br>SPIAとQSPIのマスタクロックを生成                                                                                                                                                           |

| 16ビットPWMタイマ(T16B)             | 2チャネル<br>イベントカウンタ/キャプチャ機能<br>PWM波形生成機能<br>PWM出力またはキャプチャ入力ポート数: 2ポート/チャネル                                                                                                                |

| <b>電源電圧検出回路(SVD2)</b>         |                                                                                                                                                                                         |

| チャネル数                         | 2チャネル                                                                                                                                                                                   |

| 検出レベル                         | 32値(1.7~4.3 V)                                                                                                                                                                          |

| その他                           | 間欠動作モード<br>検出レベル判定で割り込み、またはリセット(Ch.0)を発生                                                                                                                                                |

## 1 概要

| シリアルインターフェース                                     |                                                                                                                    |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| UART(UART2)                                      | 2チャネル<br>ボーレート生成回路内蔵, IrDA1.0対応<br>オープンドレイン出力, 信号極性, ボーレート分周比を選択可能                                                 |

| 同期式シリアルインターフェース(SPI)                             | 1チャネル<br>転送データ長を2~16ビットに設定可能<br>マスター mode のボーレート生成回路として16ビットタイマ(T16)を使用可能                                          |

| 同期式クワッドシリアルインターフェース(QSPI)                        | 1チャネル<br>シングル、デュアル、クワッド転送モードに対応<br>XIP(eXecute-In-Place)モードを持つ外部フラッシュメモリを直接リード可能な、CPUのオーバーヘッドが低いメモリマップドアクセス機能      |

| I <sup>2</sup> C(I <sup>2</sup> C) <sup>*1</sup> | 2チャネル<br>ボーレート生成回路内蔵                                                                                               |

| USB 2.0 FSデバイスコントローラ(USB)                        |                                                                                                                    |

| 送受信チャネル数                                         | 1チャネル                                                                                                              |

| 転送レート                                            | FS (12 Mbps)                                                                                                       |

| クロックソース                                          | 48 MHz水晶発振回路またはOSC3(12 MHz) + PLLから選択可能                                                                            |

| エンドポイント数                                         | 4本(3本の汎用エンドポイントとエンドポイント0を搭載)                                                                                       |

| 電源                                               | USB専用レギュレータを内蔵                                                                                                     |

| サウンドジェネレータ(SNDA)                                 |                                                                                                                    |

| ブザー出力機能                                          | 出力周波数: 512 Hz~16 kHz<br>1ショット出力機能                                                                                  |

| メロディ生成機能                                         | 音高: 128 Hz~16 kHz ≈ C3~C6<br>音長: 7種類(2分音符/休符~32分音符/休符)<br>テンポ: 16種類(30~480)<br>タイマー指定可能                            |

| IRリモートコントローラ(REMC2)                              |                                                                                                                    |

| 送信チャネル数                                          | 1チャネル                                                                                                              |

| その他                                              | 応用としてELランプ駆動波形を生成可能(ハードウェア)                                                                                        |

| LCD ドライバ(LCD32B)                                 |                                                                                                                    |

| LCD出力                                            | 88SEG × 1~16COM(max.), 80SEG × 17~24COM(max.), 72SEG × 25~32COM(max.)                                              |

| LCDコントラスト                                        | 16値                                                                                                                |

| その他                                              | 1/5または1/4バイアス電源内蔵、外部電圧を印加可能                                                                                        |

| R/F変換器(RFC)                                      |                                                                                                                    |

| 変換方式                                             | CR発振型、24ビットカウンタ                                                                                                    |

| 変換チャネル数                                          | 1チャネル(最大2個のセンサを接続可能)                                                                                               |

| 対応センサ                                            | DCバイアス抵抗性センサ、ACバイアス抵抗性センサ                                                                                          |

| リセット                                             |                                                                                                                    |

| #RESET端子                                         | リセット端子Lowレベル検出時                                                                                                    |

| パワーオンリセット                                        | 電源投入時                                                                                                              |

| ブラウンアウトリセット                                      | 電源電圧低下時(V <sub>DD</sub> ≤ 1.45 V (typ.)検出時)                                                                        |

| キー入力リセット                                         | P00~P01/P02/P03キーの同時入力時(レジスタでON/OFF設定可能)                                                                           |

| ウォッチドッグタイマリセット                                   | ウォッチドッグタイマオーバーフロー時(レジスタでON/OFF設定可能)                                                                                |

| 電源電圧検出回路リセット                                     | 電源電圧検出回路による設定電圧検出時(レジスタでON/OFF設定可能)                                                                                |

| 割り込み                                             |                                                                                                                    |

| ノンマスクブル割り込み                                      | 6本(リセット、NMI、ハードフォルト、SVCALL、PENDSV、SYSTICK)                                                                         |

| プログラマブル割り込み                                      | 外部割り込み: 1本<br>内部割り込み: 23本                                                                                          |

| 電源電圧                                             |                                                                                                                    |

| V <sub>DD</sub> 動作電圧                             | 1.8~3.6 V                                                                                                          |

| Flash書き換え時V <sub>DD</sub> 動作電圧                   | 2.4~3.6 V (V <sub>PP</sub> 電圧外部印加時)<br>2.4~3.6 V (V <sub>PP</sub> 電圧内部生成時)                                         |

| LCD ドライバ使用時V <sub>DD</sub> 動作電圧                  | 2.5~3.6 V                                                                                                          |

| 動作温度                                             |                                                                                                                    |

| 動作温度範囲                                           | -40~85 °C                                                                                                          |

| 消費電流 (Typ. 値)                                    |                                                                                                                    |

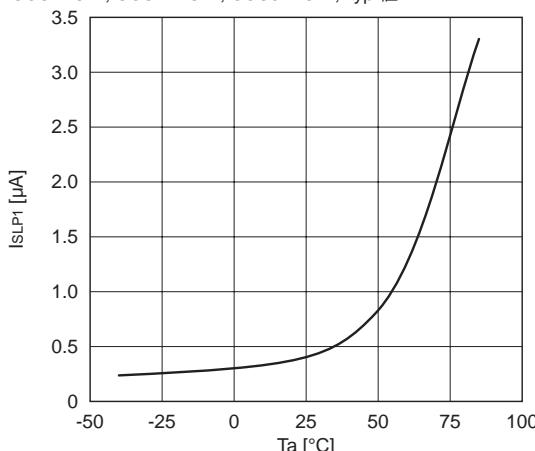

| SLEEPモード <sup>*2</sup>                           | 0.4 μA<br>IOSC = OFF, OSC1 = OFF, OSC3 = OFF<br>0.9 μA<br>IOSC = OFF, OSC1 = ON, OSC3 = OFF, RTC = ON              |

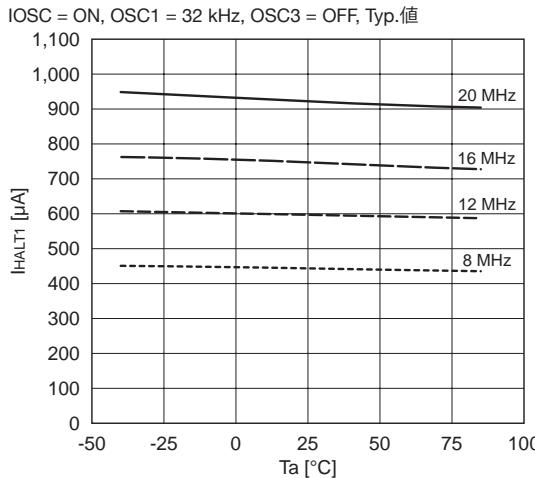

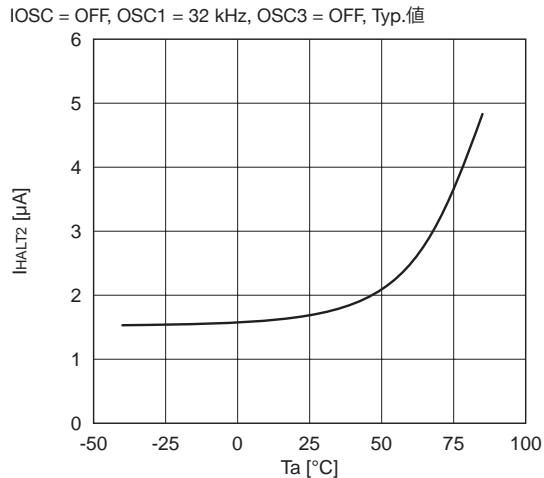

| HALTモード <sup>*3</sup>                            | 1.7 μA<br>OSC1 = 32 kHz<br>7.7 μA<br>OSC1 = 32 kHz, LCD = ON(パネル負荷なし)                                              |

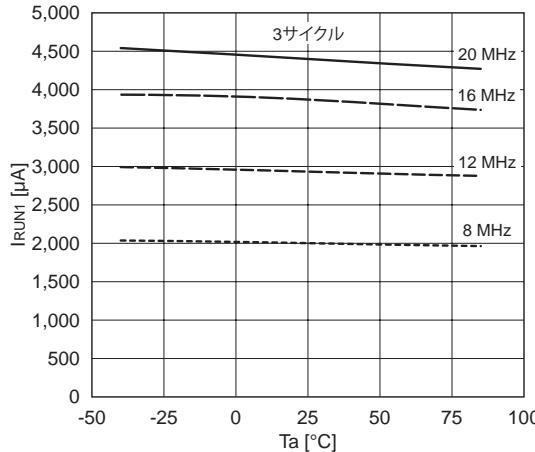

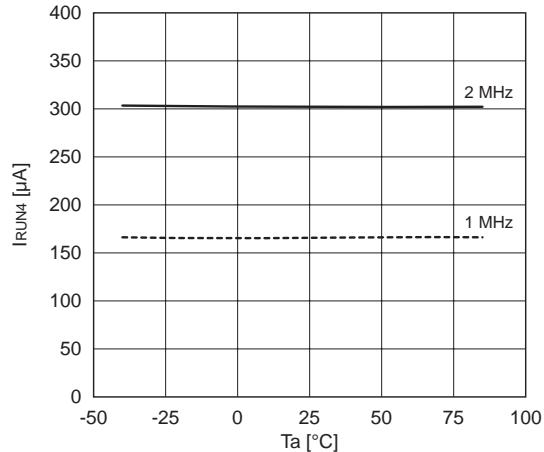

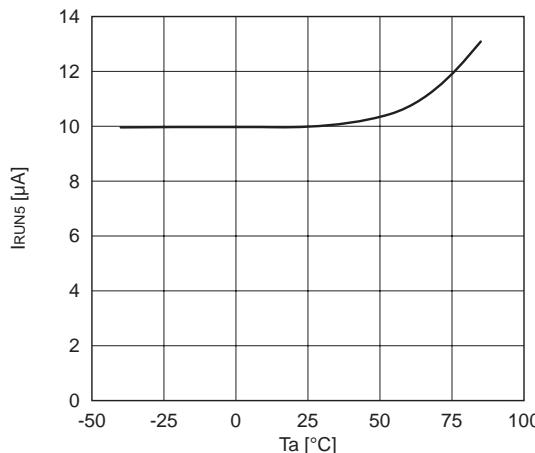

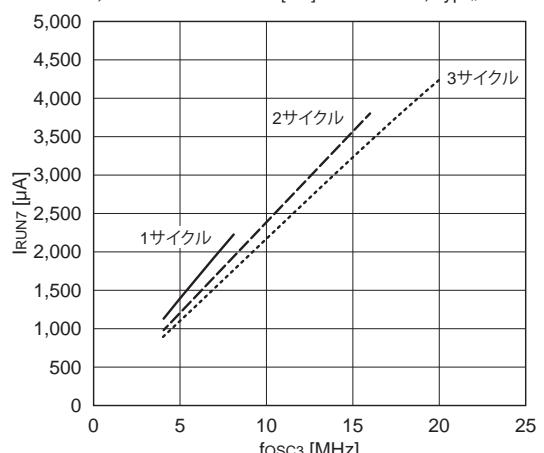

| RUNモード                                           | 250 μA/MHz<br>V <sub>b1</sub> 電圧モード = mode0, CPU = IOSC<br>150 μA/MHz<br>V <sub>b1</sub> 電圧モード = mode1, CPU = IOSC |

## 出荷形態

|                 |                                                                         |

|-----------------|-------------------------------------------------------------------------|

| 1 <sup>*4</sup> | VFBGA8H-181 (P-VFBGA-181-0808-0.50, 8 × 8 mm, t = 1.0 mm, 0.5 mm pitch) |

| 2               | チップ(パッドピッチ: 80 µm(min.))                                                |

\*1 I2C(SDAおよびSCL入力)の入力フィルタは、50 ns未満のノイズスパイク除去の規格に準拠していません。

\*2 Cortex®-M0+プロセッサのディープスリーブモードに相当します。SLEEP中もRAMのデータは保持されます。

\*3 Cortex®-M0+プロセッサのスリーブモードに相当します。

\*4 ()内はJEITAのパッケージ名称です。

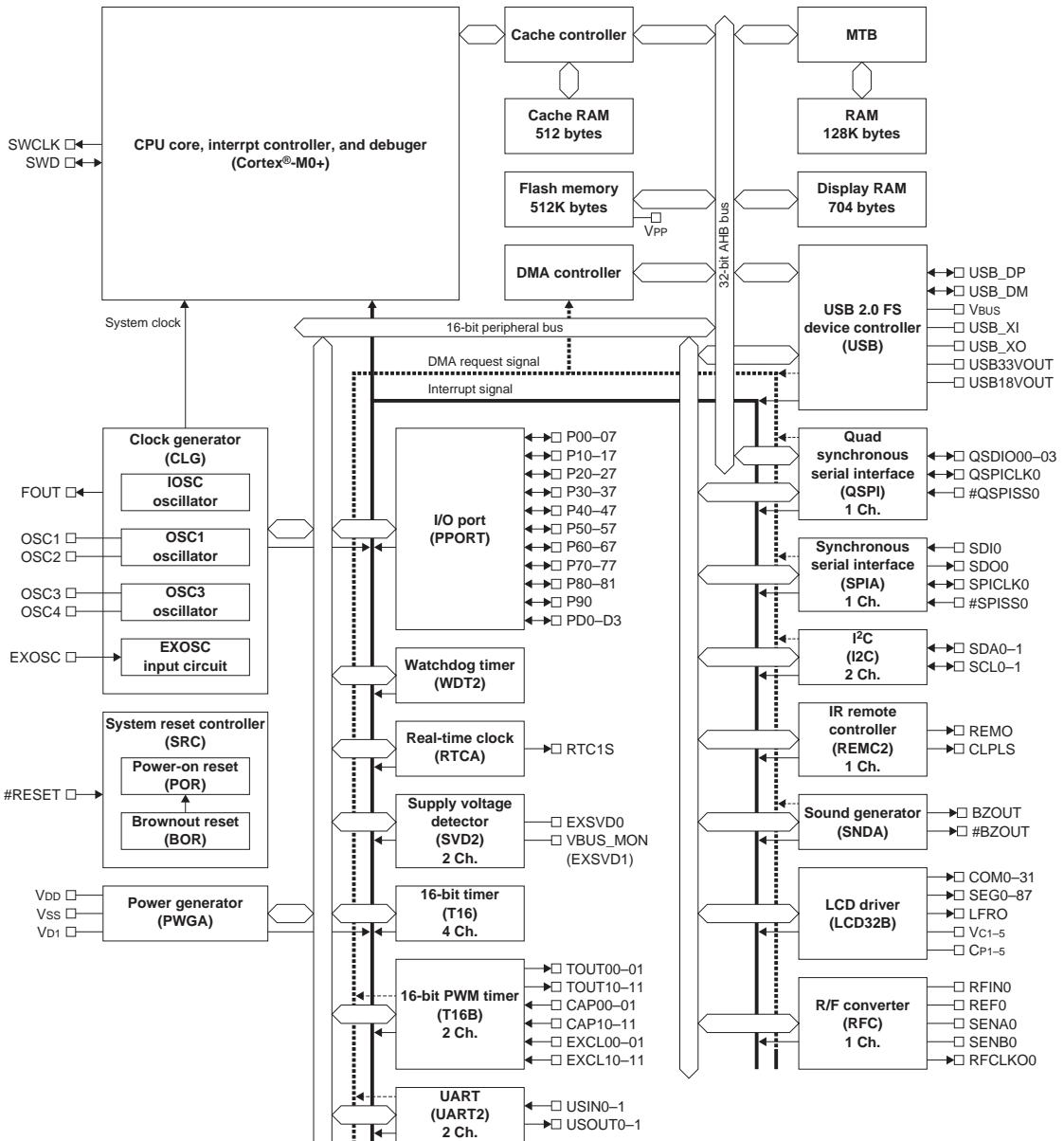

## 1.2 ブロック図

図1.2.1 S1C31W74ブロック図

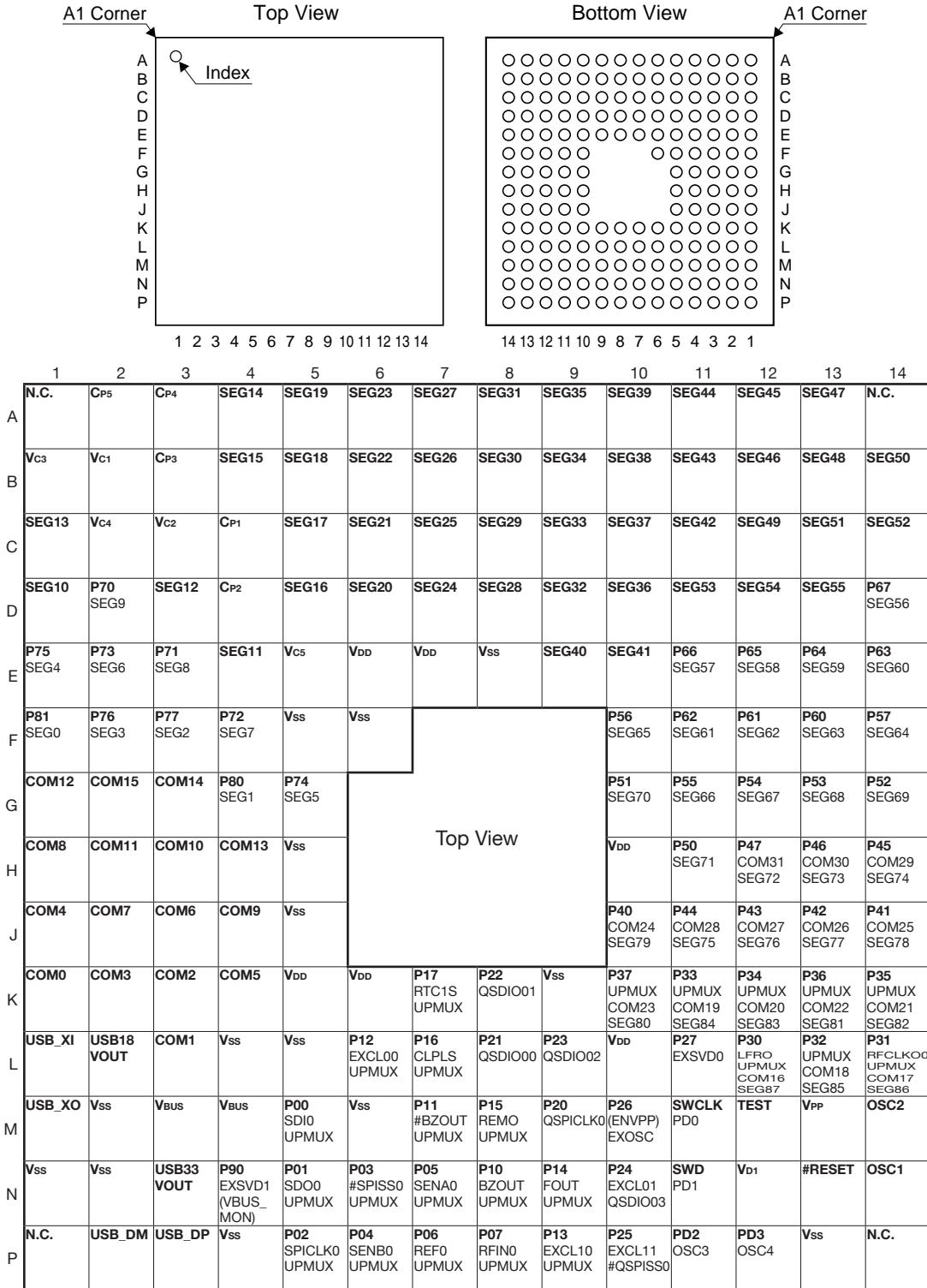

## 1.3 端子

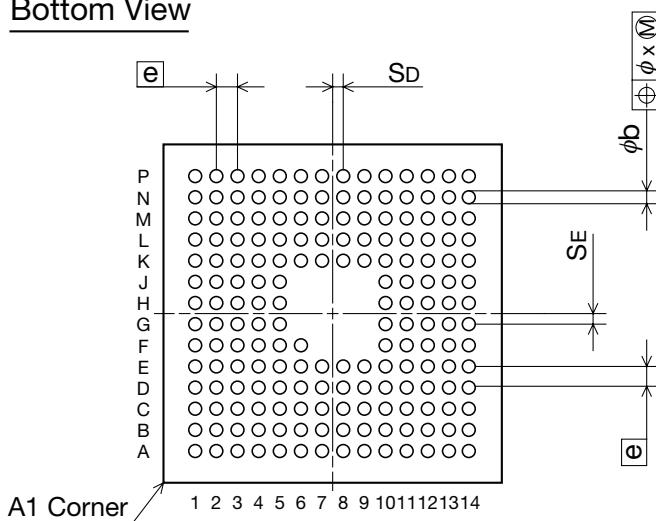

### 1.3.1 端子配置図

VFBGA8H-181

図1.3.1.1 S1C31W74端子配置図 (VFBGA8H-181)

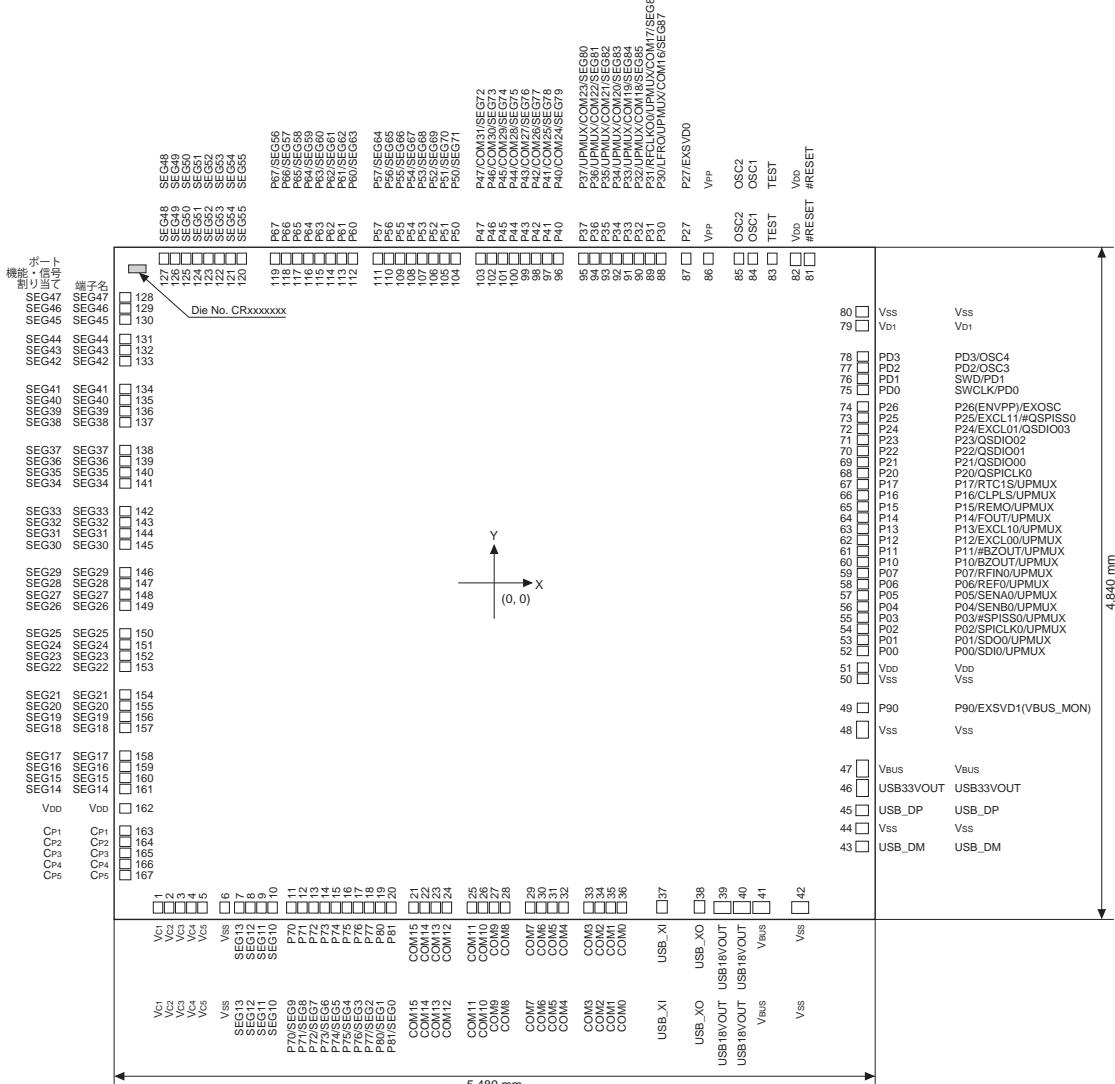

### 1.3.2 パッド配置図

図1.3.2.1 S1C31W74/パッド配置図

パッド開口部: Pad No. 1~36, 83~127

Pad No. 49~78, 128~167

Pad No. 37, 38, 81, 82

Pad No. 43~45, 79, 80

Pad No. 46~48

Pad No. 39~42

X = 68 μm, Y = 80 μm

X = 80 μm, Y = 68 μm

X = 76 μm, Y = 90 μm

X = 90 μm, Y = 76 μm

X = 85 μm, Y = 122 μm

X = 122 μm, Y = 85 μm

チップ厚: 400 μm

表1.3.2.1 S1C31W74/パッド座標

| No. | X μm     | Y μm     | No. | X μm    | Y μm     | No. | X μm     | Y μm    | No. | X μm     | Y μm     |

|-----|----------|----------|-----|---------|----------|-----|----------|---------|-----|----------|----------|

| 1   | -2,424.0 | -2,334.5 | 43  | 2,649.5 | -1,898.0 | 81  | 2,272.2  | 2,329.5 | 128 | -2,654.5 | 2,056.0  |

| 2   | -2,344.0 | -2,334.5 | 44  | 2,649.5 | -1,768.0 | 82  | 2,172.2  | 2,329.5 | 129 | -2,654.5 | 1,976.0  |

| 3   | -2,264.0 | -2,334.5 | 45  | 2,649.5 | -1,638.0 | 83  | 2,004.0  | 2,334.5 | 130 | -2,654.5 | 1,896.0  |

| 4   | -2,184.0 | -2,334.5 | 46  | 2,652.0 | -1,477.0 | 84  | 1,864.0  | 2,334.5 | 131 | -2,654.5 | 1,756.0  |

| 5   | -2,104.0 | -2,334.5 | 47  | 2,652.0 | -1,337.0 | 85  | 1,764.0  | 2,334.5 | 132 | -2,654.5 | 1,676.0  |

| 6   | -1,944.0 | -2,334.5 | 48  | 2,652.0 | -1,057.0 | 86  | 1,544.0  | 2,334.5 | 133 | -2,654.5 | 1,596.0  |

| 7   | -1,839.0 | -2,334.5 | 49  | 2,654.5 | -900.0   | 87  | 1,384.0  | 2,334.5 | 134 | -2,654.5 | 1,396.0  |

| 8   | -1,759.0 | -2,334.5 | 50  | 2,654.5 | -690.0   | 88  | 1,204.0  | 2,334.5 | 135 | -2,654.5 | 1,316.0  |

| 9   | -1,679.0 | -2,334.5 | 51  | 2,654.5 | -610.0   | 89  | 1,124.0  | 2,334.5 | 136 | -2,654.5 | 1,236.0  |

| 10  | -1,599.0 | -2,334.5 | 52  | 2,654.5 | -490.0   | 90  | 1,044.0  | 2,334.5 | 137 | -2,654.5 | 1,156.0  |

| 11  | -1,464.0 | -2,334.5 | 53  | 2,654.5 | -410.0   | 91  | 964.0    | 2,334.5 | 138 | -2,654.5 | 956.0    |

| 12  | -1,384.0 | -2,334.5 | 54  | 2,654.5 | -330.0   | 92  | 884.0    | 2,334.5 | 139 | -2,654.5 | 876.0    |

| 13  | -1,304.0 | -2,334.5 | 55  | 2,654.5 | -250.0   | 93  | 804.0    | 2,334.5 | 140 | -2,654.5 | 796.0    |

| 14  | -1,224.0 | -2,334.5 | 56  | 2,654.5 | -170.0   | 94  | 724.0    | 2,334.5 | 141 | -2,654.5 | 716.0    |

| 15  | -1,144.0 | -2,334.5 | 57  | 2,654.5 | -90.0    | 95  | 644.0    | 2,334.5 | 142 | -2,654.5 | 516.0    |

| 16  | -1,064.0 | -2,334.5 | 58  | 2,654.5 | -10.0    | 96  | 464.0    | 2,334.5 | 143 | -2,654.5 | 436.0    |

| 17  | -984.0   | -2,334.5 | 59  | 2,654.5 | 70.0     | 97  | 384.0    | 2,334.5 | 144 | -2,654.5 | 356.0    |

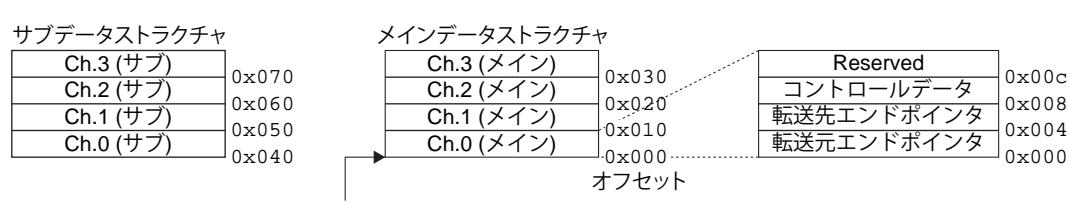

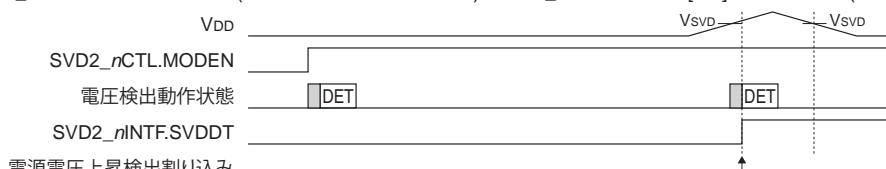

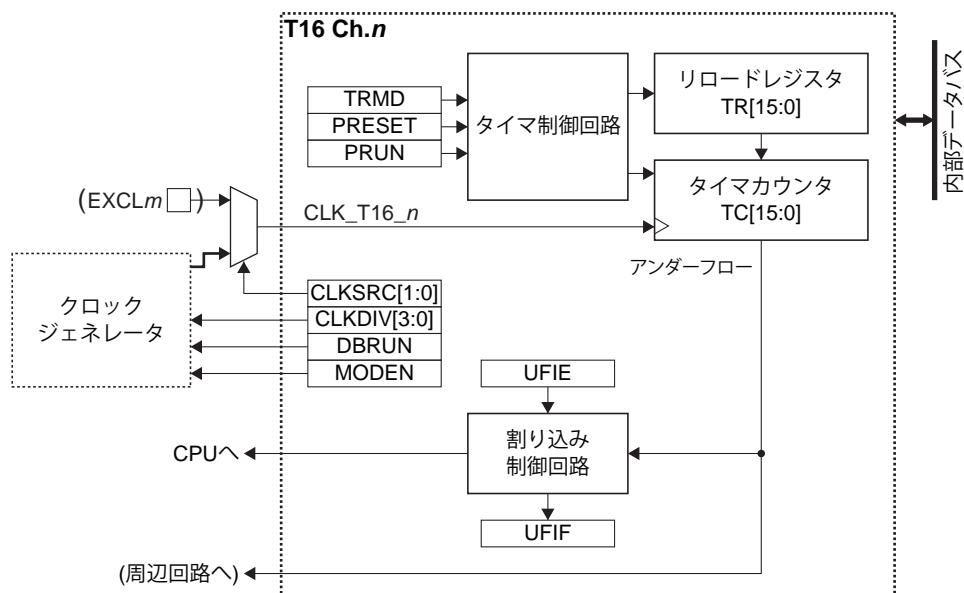

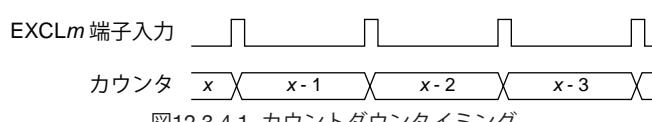

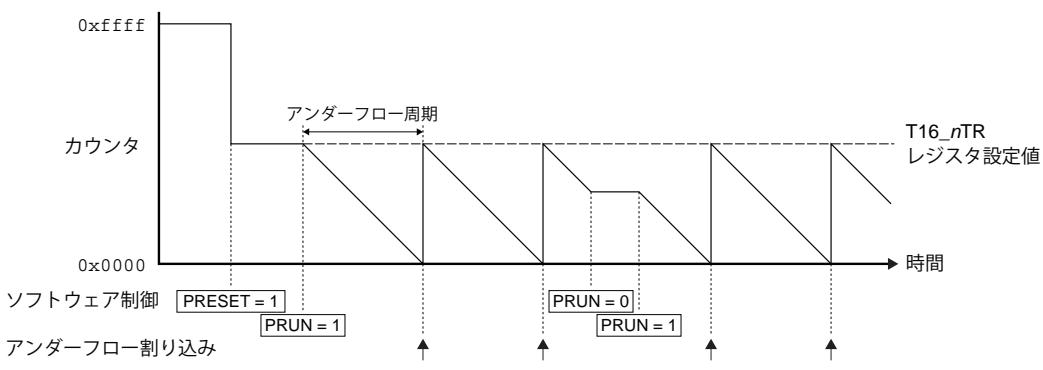

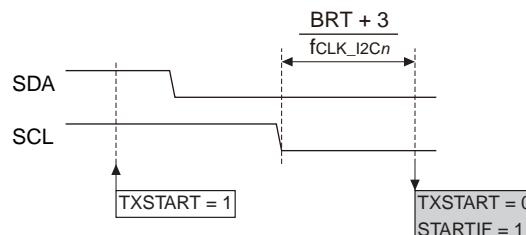

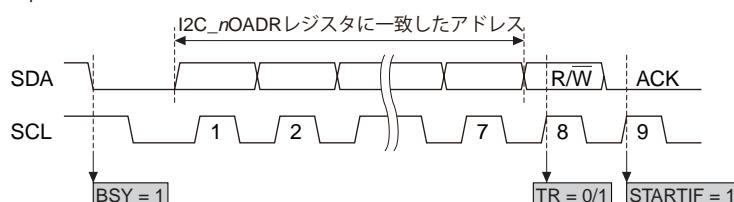

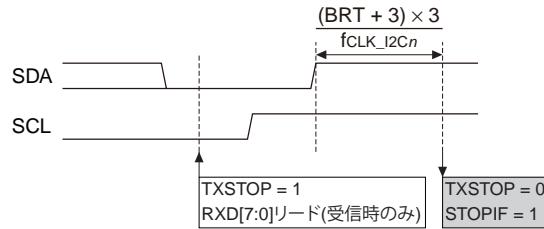

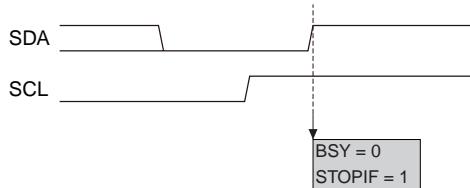

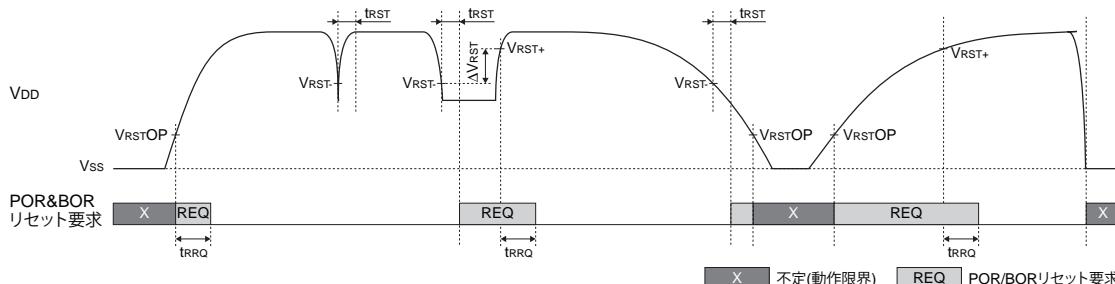

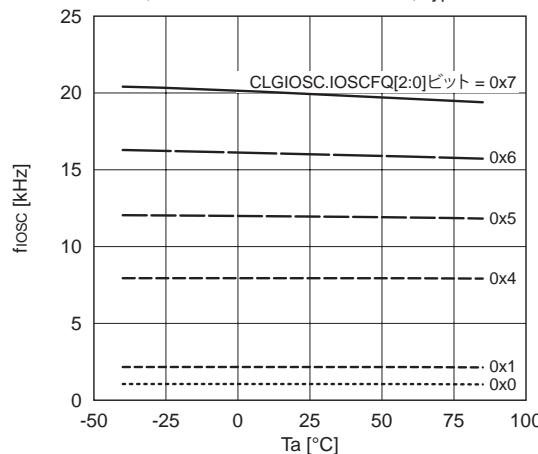

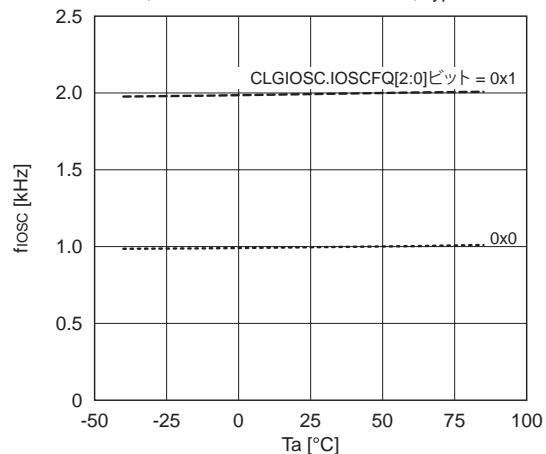

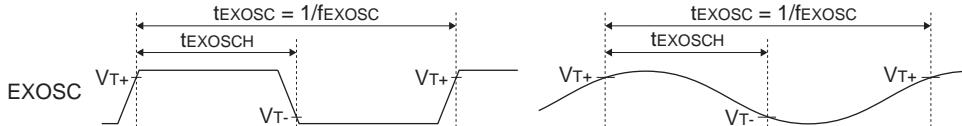

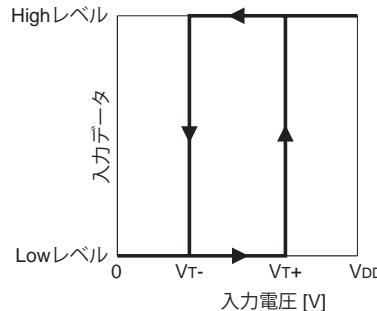

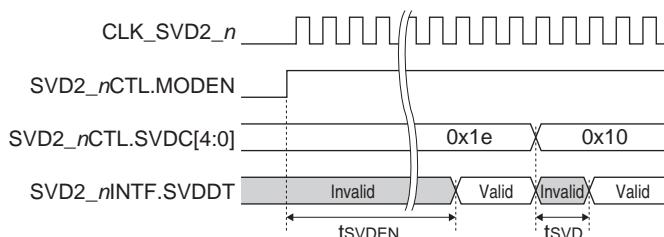

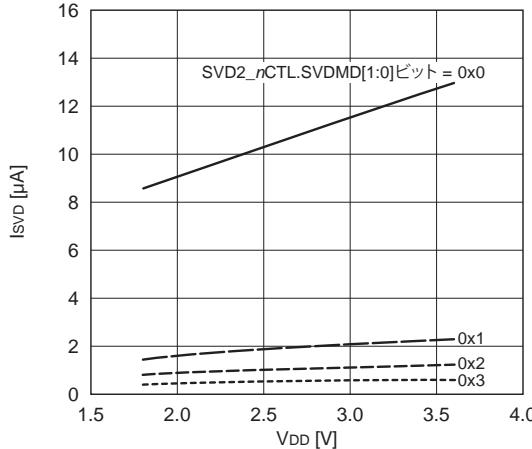

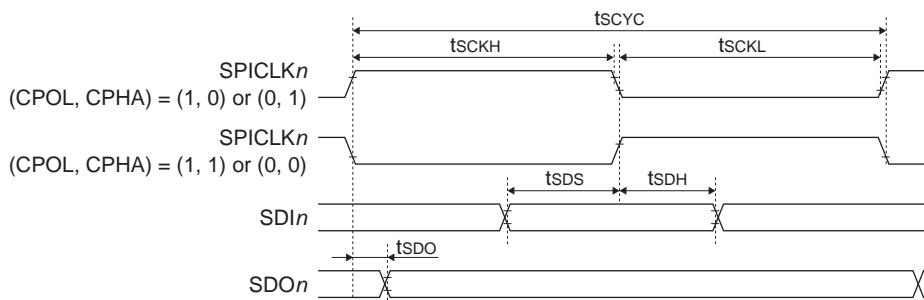

| 18  | -904.0   | -2,334.5 | 60  | 2,654.5 | 150.0    | 98  | 304.0    | 2,334.5 | 145 | -2,654.5 | 276.0    |