**EPSON**

GATE ARRAY

**S1L5V000 シリーズ

デザインガイド**

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

2. 弊社製品のご購入およびご使用にあたりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページなどを通じて公開される最新情報に常にご注意ください。

3. 本資料に掲載されている応用回路、プログラム、使用方法などはあくまでも参考情報です。お客様の機器・システムの設計において、応用回路、プログラム、使用方法などを使用する場合には、お客様の責任において行ってください。これらに起因する第三者の知的財産権およびその他の権利侵害ならびに損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

4. 弊社は常に品質、信頼性の向上に努めていますが、一般的に半導体製品は誤作動または故障する場合があります。弊社製品のご使用にあたりましては、弊社製品の誤作動や故障により生命・身体に危害を及ぼすこと又は財産が侵害されることのないように、お客様の責任において、お客様のハードウエア、ソフトウエア、システムに必要な安全設計を行うようお願いします。なお、設計および使用に際しては、弊社製品に関する最新の情報（本資料、仕様書、データシート、マニュアル、弊社ホームページなど）をご確認いただき、それに従ってください。また、上記資料などに掲載されている製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価を行い、お客様の責任において適用可否の判断をお願いします。

5. 弊社は、正確さを期すために慎重に本資料およびプログラムを作成しておりますが、本資料およびプログラムに掲載されている情報に誤りがないことを保証するものではありません。万一、本資料およびプログラムに掲載されている情報の誤りによってお客様に損害が生じた場合においても、弊社は一切その責任を負いかねます。

6. 弊社製品の分解、解析、リバースエンジニアリング、改造、改変、翻案、複製などは堅くお断りします。

7. 弊社製品は、一般的な電子機器（事務機器、通信機器、計測機器、家電製品など）に使用されること（一般用途）、および本資料に個別に掲載または弊社が個別に指定する用途に使用されること（指定用途）を意図して設計、開発、製造されています。これら一般用途および指定用途以外の用途（特別な品質、信頼性が要求され、その誤動作や故障により生命・身体に危害を及ぼす恐れ、膨大な財産侵害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある用途。以下、特定用途といいます）に使用されることを意図していません。お客様に置かれましては、弊社製品を一般用途および指定用途に使用されることを推奨いたします。もし特定用途で弊社製品のご使用およびご購入を希望される場合、弊社はお客様が弊社製品を使用されることへの商品性、適合性、安全性について、明示的・黙示的に関わらずいかなる保証を行うものではありません。お客様が特定用途での弊社製品の使用を希望される場合は、弊社営業窓口まで事前にご連絡の上、承諾を得てください。

- 【特定用途（例）】

- 宇宙機器（人工衛星・ロケットなど）/ 輸送車両並びにその制御機器（自動車・航空機・列車・船舶など）

- 医療機器 / 海底中継機器 / 発電所制御機器 / 防災・防犯装置 / 交通用機器 / 金融関連機器

- 上記と同等の信頼性を必要とする用途。詳細は、弊社営業窓口までお問い合わせください。

8. 本資料に掲載されている弊社製品および当該技術を国内外の法令および規制により製造・使用・販売が禁止されている機器・システムに使用することはできません。また、弊社製品および当該技術を大量破壊兵器等の開発および軍事利用の目的その他軍事用途等に使用しないでください。弊社製品または当該技術を輸出または海外に提供する場合は、「外国為替及び外国為替法」、「米国輸出管理規則（EAR）」、その他輸出関連法令を遵守し、係る法令の定めるところにより必要な手続きを行ってください。

9. お客様が本資料に掲載されている諸条件に反したことによる起因して生じたいかなる損害（直接・間接を問わず）に関して、弊社は一切その責任を負いかねます。

10. お客様が弊社製品を第三者に譲渡、貸与などをしたことにより、損害が発生した場合、弊社は一切その責任を負いかねます。

11. 本資料についての詳細に関するお問合せ、その他お気付きの点などがありましたら、弊社営業窓口までご連絡ください。

12. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

Rev. j1.2, 2023. 4

©2013 Seiko Epson Corporation All rights reserved.

## 目 次

|                                    |    |

|------------------------------------|----|

| <b>第1章 概要</b>                      | 1  |

| 1.1 特長                             | 1  |

| 1.2 マスタ構成                          | 2  |

| 1.2.1 標準マスタ構成                      | 2  |

| 1.2.2 PLL搭載マスタ構成                   | 3  |

| 1.3 電気的特性・規格                       | 3  |

| 1.3.1 絶対最大定格                       | 3  |

| 1.3.2 推奨動作条件                       | 4  |

| 1.3.3 電気的特性                        | 5  |

| 1.3.4 オーバーシュート／アンダーシュート            | 7  |

| 1.4 静的消費電流                         | 8  |

| 1.5 開発フロー                          | 9  |

| 1.5.1 サインオフまでの開発フロー                | 9  |

| 1.5.2 論理合成・配置配線作業フロー（セイコーエプソン作業）   | 9  |

| 1.5.3 仮データ（トライアル用）の提出              | 13 |

| 1.5.4 試作から量産制定、製造フロー               | 14 |

| <b>第2章 RTL設計上の注意 (Verilog-HDL)</b> | 15 |

| 2.1 基本構成                           | 15 |

| 2.1.1 論理合成可能なRTLデータの提出             | 15 |

| 2.1.2 ライブラリセルの使用                   | 15 |

| 2.1.3 ifdefとparameter              | 15 |

| 2.2 端子名の制約                         | 15 |

| 2.2.1 外部端子名制約                      | 15 |

| 2.2.2 内部端子名制約                      | 15 |

| 2.2.3 Verilog予約語                   | 16 |

| 2.3 タイミング制約情報の提出                   | 17 |

| 2.3.1 クロック情報                       | 17 |

| 2.3.2 外部端子のタイミング制約                 | 20 |

| 2.4 入出力バッファの挿入                     | 25 |

| 2.5 RAMの記述                         | 25 |

| 2.6 発振セルの記述                        | 25 |

| <b>第3章 テスト回路設計上の注意</b>             | 26 |

| 3.1 推奨DC・ACテスト回路の挿入                | 26 |

| 3.1.1 推奨テスト回路 テスト回路付き入出力バッファを使用    | 26 |

| 3.1.2 テスト回路付き出力バッファおよび双方向バッファのセル名  | 26 |

| 3.1.3 お客様設計によりテスト回路挿入される場合         | 26 |

| 3.2 スキャン(SCAN)回路の挿入                | 27 |

| 3.2.1 スキャン(SCAN)回路                 | 27 |

# 目次

---

|                                                    |           |

|----------------------------------------------------|-----------|

| 3.3 バウンダリスキャン (JTAG) 回路の挿入.....                    | 28        |

| 3.3.1 インストラクション.....                               | 28        |

| 3.3.2 ゲート数の見積り .....                               | 28        |

| 3.3.3 お客さま設計にてバウンダリスキャン (JTAG) 回路挿入される場合 .....     | 28        |

| 3.4 RAM のテスト回路：メモリ BIST (Built in Self Test) ..... | 31        |

| <b>第4章 テストパターン作成上の注意 .....</b>                     | <b>32</b> |

| 4.1 サインオフシミュレーション向けテストパターンの作成 .....                | 32        |

| 4.1.1 テストパターンの形式 .....                             | 32        |

| 4.1.2 テストパターンの制限 .....                             | 34        |

| 4.1.3 外部双方向端子のイネーブル信号 .....                        | 35        |

| 4.2 製品出荷テスト向けのテストパターン作成 .....                      | 36        |

| 4.2.1 使用可能な入力波形 .....                              | 36        |

| 4.2.2 テストパターンの制限 .....                             | 36        |

| 4.2.3 DC・AC テストパターンの作成について .....                   | 38        |

| 4.2.4 ハイインピーダンス状態の扱いに関する注意点 .....                  | 39        |

| <b>第5章 回路設計上の注意 .....</b>                          | <b>40</b> |

| 5.1 発振回路 .....                                     | 40        |

| 5.1.1 発振回路の構成 .....                                | 40        |

| 5.1.2 発振回路を使用する場合の注意 .....                         | 42        |

| 5.1.3 発振セルの RTL 記述について .....                       | 42        |

| 5.2 メタステーブル (Metastable) .....                     | 43        |

| <b>第6章 入出力バッファの種類と使用上の注意 .....</b>                 | <b>44</b> |

| 6.1 入出力バッファの種類及び選択 .....                           | 44        |

| 6.1.1 入出力バッファの選択 .....                             | 44        |

| 6.1.2 バスホールド機能つき入出力バッファ .....                      | 44        |

| 6.2 入出力バッファの構成 .....                               | 45        |

| 6.2.1 入力バッファ .....                                 | 45        |

| 6.2.2 出力バッファ .....                                 | 47        |

| 6.2.3 双方向バッファ .....                                | 51        |

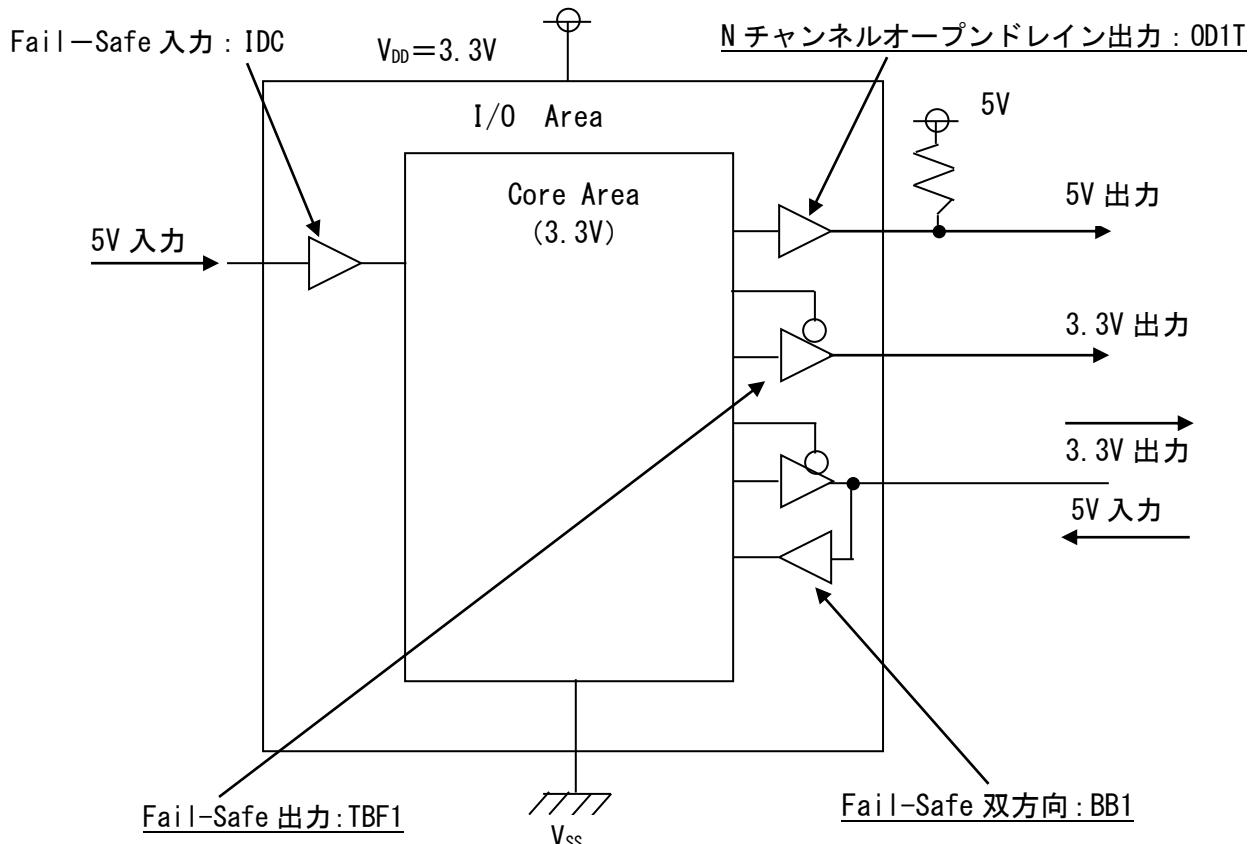

| 6.3 Fail-Safe 入出力バッファ .....                        | 56        |

| 6.3.1 概要 .....                                     | 56        |

| 6.3.2 特長 .....                                     | 56        |

| 6.3.3 使用上の注意点 .....                                | 56        |

| 6.3.4 セル一覧 .....                                   | 57        |

| 6.4 Gated 入出力バッファ .....                            | 59        |

| 6.4.1 概要 .....                                     | 59        |

| 6.4.2 特長 .....                                     | 59        |

| 6.4.3 使用上の注意点 .....                                | 59        |

| 6.4.4 セル一覧 .....                                   | 60        |

---

|                                                                              |            |

|------------------------------------------------------------------------------|------------|

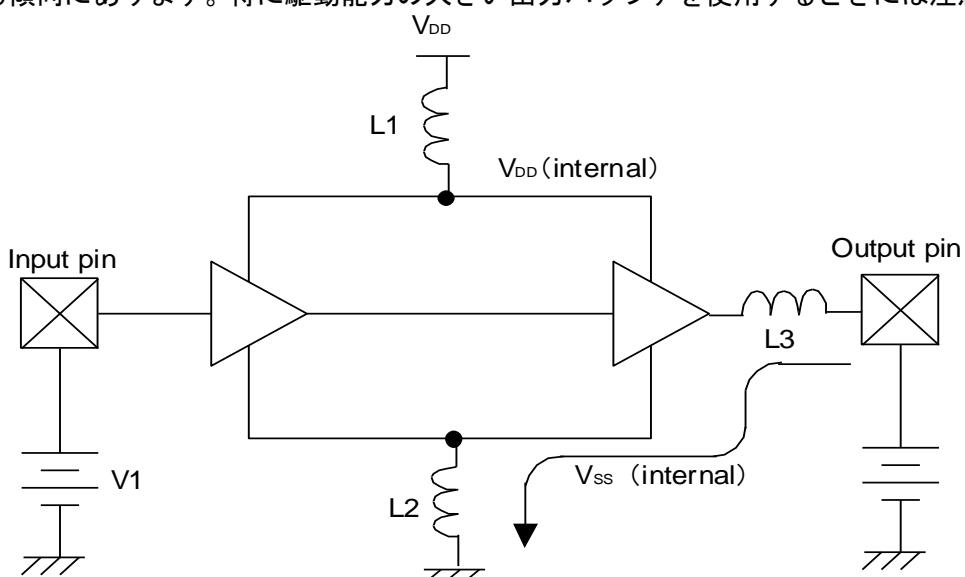

| <b>第 7 章 端子配置の注意 .....</b>                                                   | <b>62</b>  |

| <b>7.1 電源端子数の見積り .....</b>                                                   | <b>62</b>  |

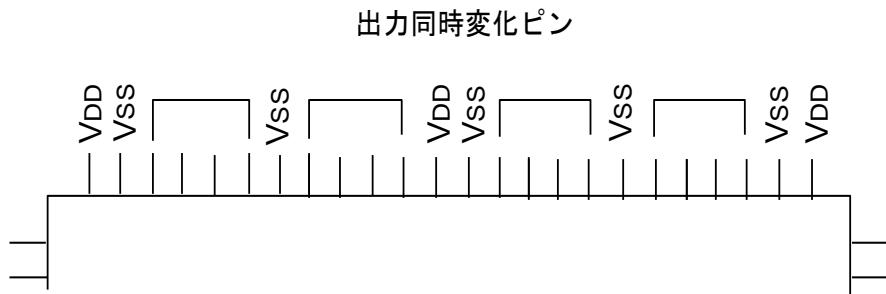

| <b>7.2 同時動作と電源追加 .....</b>                                                   | <b>62</b>  |

| <b>7.3 端子配置上の注意点 .....</b>                                                   | <b>65</b>  |

| 7.3.1 固定電源端子 .....                                                           | 65         |

| 7.3.2 端子配列上の注意事項 .....                                                       | 65         |

| 7.3.3 推奨端子配列例 .....                                                          | 72         |

| <b>第 8 章 RAM 仕様 .....</b>                                                    | <b>74</b>  |

| <b>8.1 非同期 1 ポート RAM .....</b>                                               | <b>74</b>  |

| 8.1.1 特長 .....                                                               | 74         |

| 8.1.2 ワードビット構成と RAM セル名との対応 .....                                            | 74         |

| 8.1.3 RAM サイズ .....                                                          | 74         |

| 8.1.4 機能説明 .....                                                             | 75         |

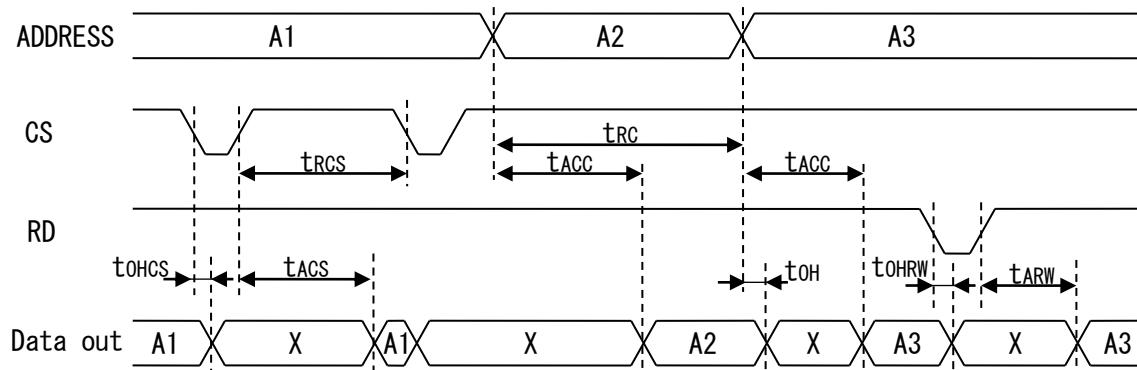

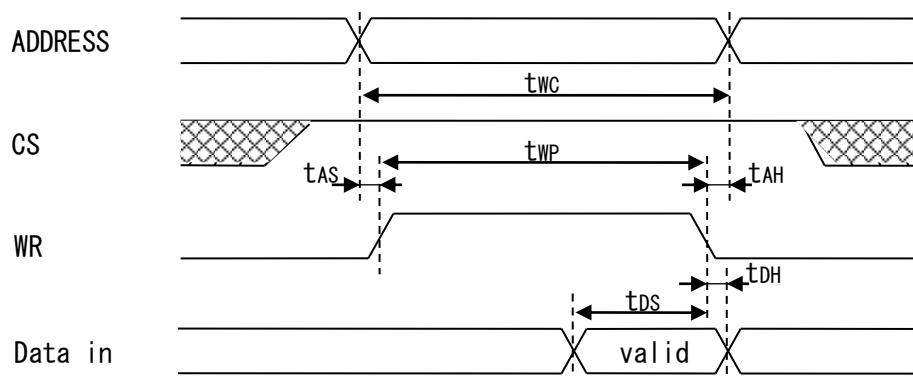

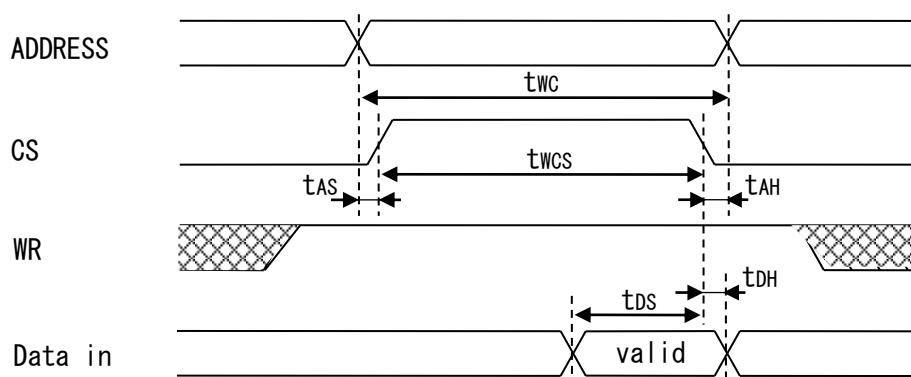

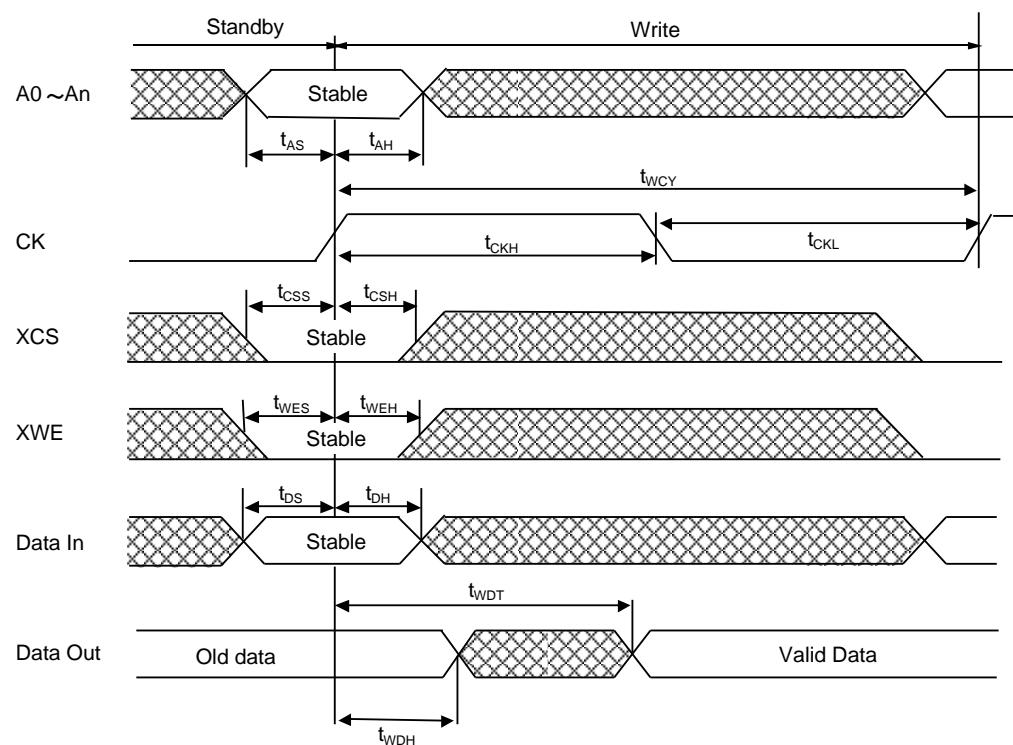

| 8.1.5 タイミングチャート（非同期 1 ポート RAM） .....                                         | 76         |

| <b>8.2 非同期 2 ポート RAM .....</b>                                               | <b>77</b>  |

| 8.2.1 特長 .....                                                               | 77         |

| 8.2.2 ワードビット構成と RAM セル名との対応 .....                                            | 77         |

| 8.2.3 RAM サイズ .....                                                          | 77         |

| 8.2.4 機能説明 .....                                                             | 78         |

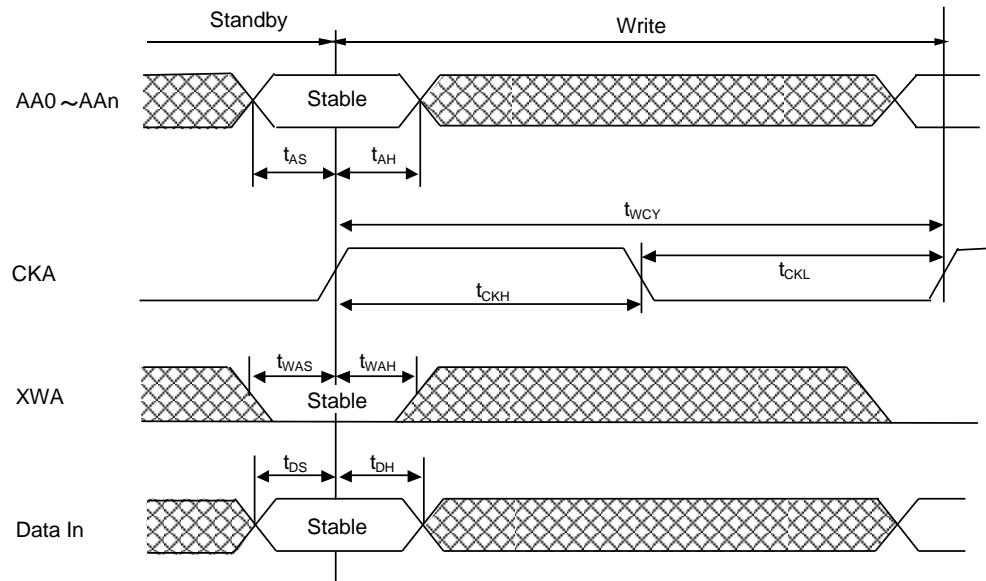

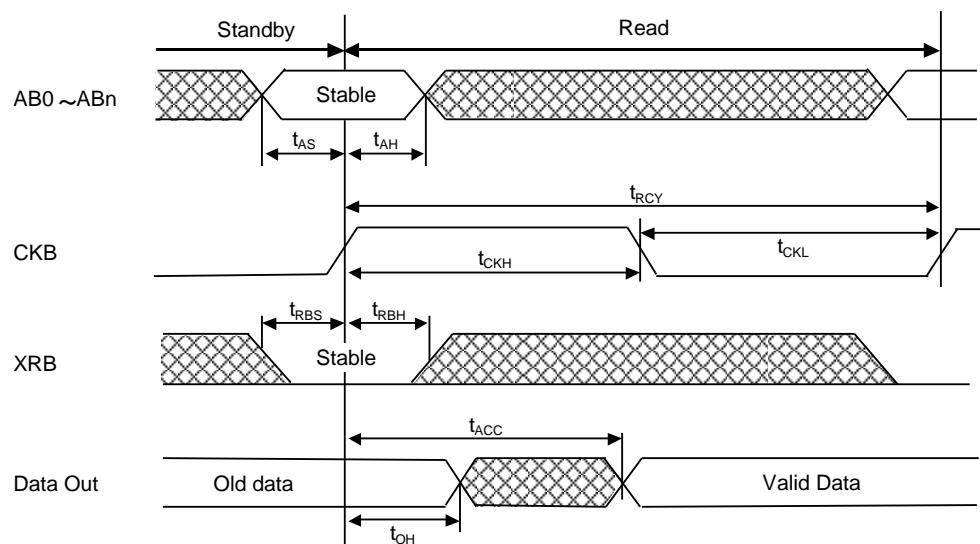

| 8.2.5 タイミングチャート（非同期 2 ポート RAM） .....                                         | 79         |

| <b>8.3 非同期 RAM 遅延パラメータ .....</b>                                             | <b>80</b>  |

| 8.3.1 5.0V 仕様 ( $V_{DD}=4.5 \sim 5.5V$ , $T_a=-40 \sim 110^{\circ}C$ ) ..... | 80         |

| 8.3.2 3.3V 仕様 ( $V_{DD}=3.0 \sim 3.6V$ , $T_a=-40 \sim 110^{\circ}C$ ) ..... | 82         |

| <b>8.4 同期 1 ポート RAM .....</b>                                                | <b>84</b>  |

| 8.4.1 特長 .....                                                               | 84         |

| 8.4.2 ワードビット構成と RAM セル名との対応 .....                                            | 85         |

| 8.4.3 RAM サイズ .....                                                          | 85         |

| 8.4.4 機能説明 .....                                                             | 86         |

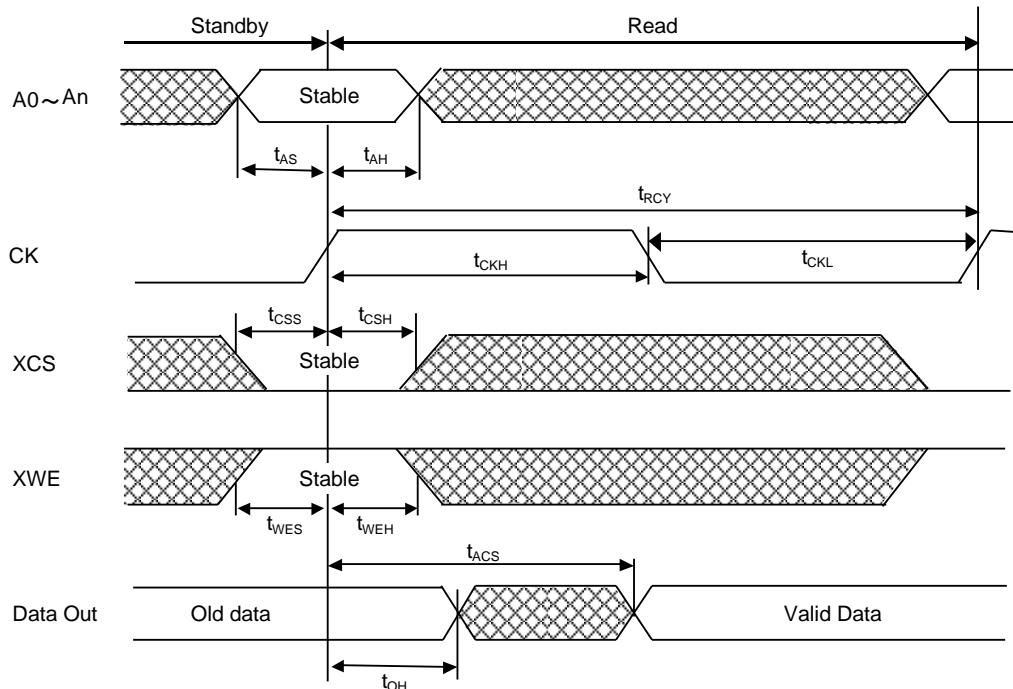

| 8.4.5 タイミングチャート（同期 1 ポート RAM） .....                                          | 87         |

| <b>8.5 同期 2 ポート RAM .....</b>                                                | <b>88</b>  |

| 8.5.1 特長 .....                                                               | 88         |

| 8.5.2 ワードビット構成と RAM セル名との対応 .....                                            | 88         |

| 8.5.3 RAM サイズ .....                                                          | 88         |

| 8.5.4 機能説明 .....                                                             | 89         |

| 8.5.5 タイミングチャート（同期 2 ポート RAM） .....                                          | 91         |

| <b>8.6 同期 RAM 遅延パラメータ .....</b>                                              | <b>92</b>  |

| 8.6.1 5.0V 仕様 ( $V_{DD}=4.5 \sim 5.5V$ , $T_a=-40 \sim 110^{\circ}C$ ) ..... | 92         |

| 8.6.2 3.3V 仕様 ( $V_{DD}=3.0 \sim 3.6V$ , $T_a=-40 \sim 110^{\circ}C$ ) ..... | 96         |

| <b>8.7 非存在アドレスへのアクセス禁止 .....</b>                                             | <b>100</b> |

| <b>8.8 RAM の搭載可否判断 .....</b>                                                 | <b>100</b> |

# 目次

---

|                                |     |

|--------------------------------|-----|

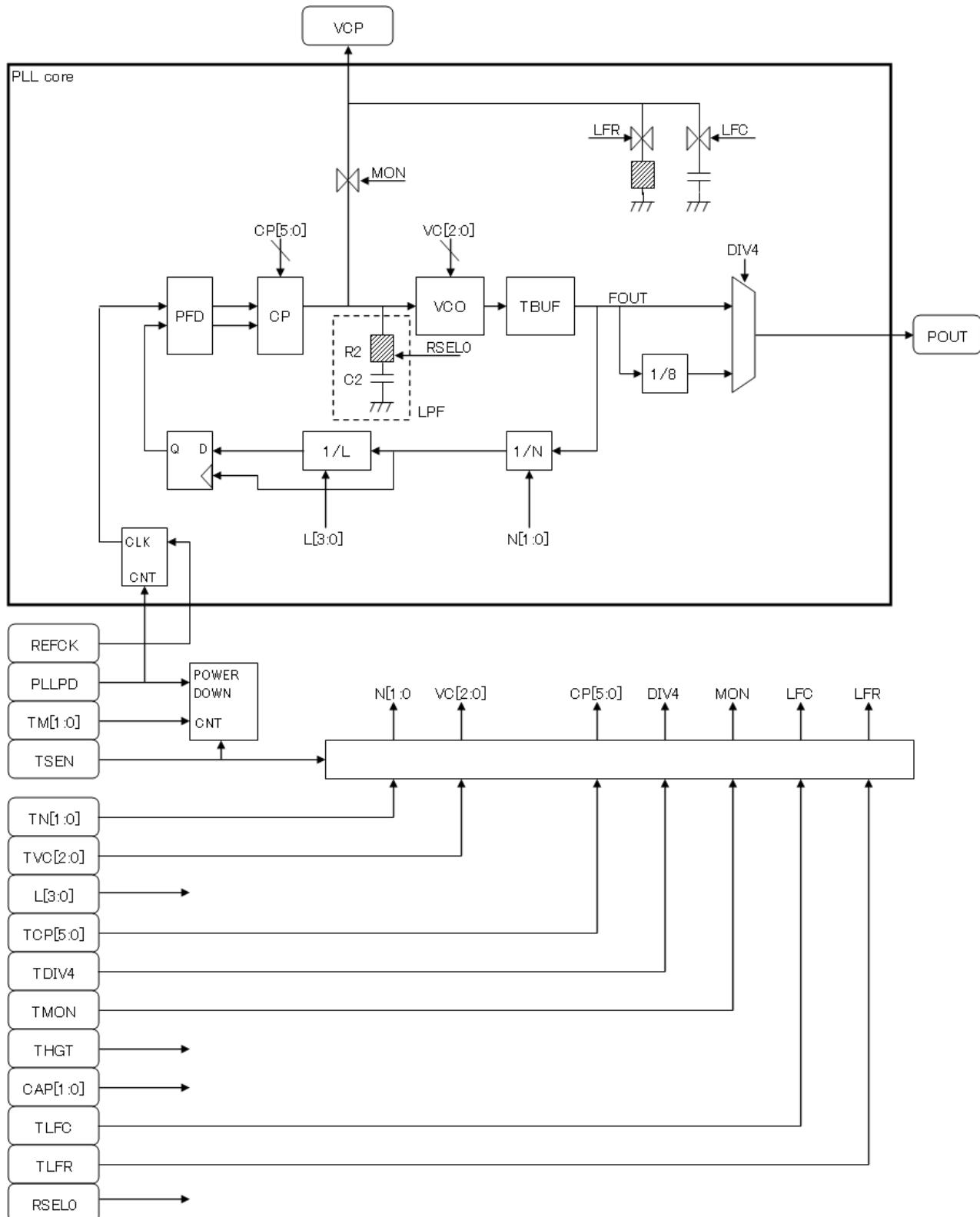

| <b>第 9 章 PLL 仕様</b>            | 101 |

| 9.1 特長                         | 101 |

| 9.2 ブロック 図                     | 102 |

| 9.3 端子機能                       | 103 |

| 9.4 電気的特性                      | 104 |

| 9.4.1 動作条件                     | 104 |

| 9.4.2 DC 特性                    | 104 |

| 9.4.3 AC 特性                    | 105 |

| 9.4.4 通倍率の設定方法                 | 106 |

| <b>第 10 章 消費電力の見積り</b>         | 107 |

| 10.1 消費電力計算                    | 107 |

| 10.1.1 内部セル ( $P_{int}$ )      | 107 |

| 10.1.2 入力バッファ ( $P_i$ )        | 108 |

| 10.1.3 出力バッファ ( $P_o$ )        | 108 |

| 10.2 消費電力制限                    | 109 |

| <b>付録</b>                      | 110 |

| A1. シミュレーション結果例                | 110 |

| A1.1 シミュレーション結果と期待値とのコンペアファイル例 | 110 |

| A1.2 タイミングエラーリスト               | 112 |

| A2. RTL 設計上の注意 (VHDL)          | 115 |

| A2.1 論理合成可能な RTL の提出           | 115 |

| A2.2 階層設計図の提出                  | 115 |

| A2.3 RAM の記述                   | 115 |

| A2.4 入力ポートへの定数割り当て             | 115 |

| A2.5 端子名の制約                    | 116 |

| A2.6 ポートのデータ型                  | 117 |

| A2.7 integer の使用について           | 117 |

| A2.8 入出力バッファ                   | 118 |

| A2.9 プリミティブセルの使用               | 119 |

| A3. DC・AC テストパターン              | 120 |

| A3.1 DC テストパターン                | 120 |

| A3.2 AC テストパターン                | 121 |

| A4. 入出力バッファ特性                  | 123 |

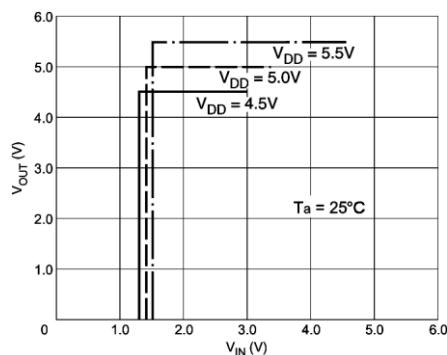

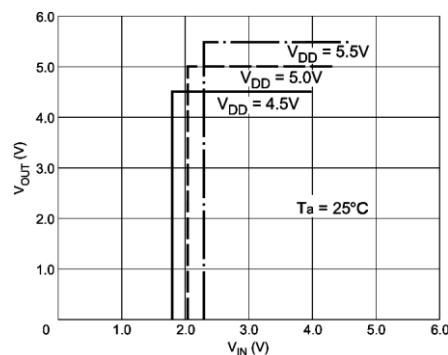

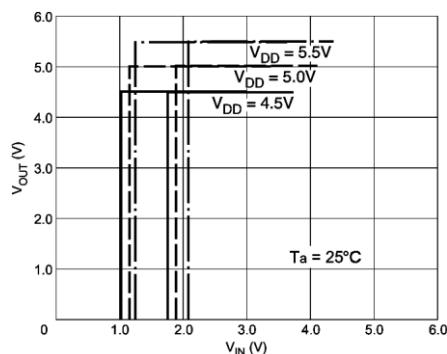

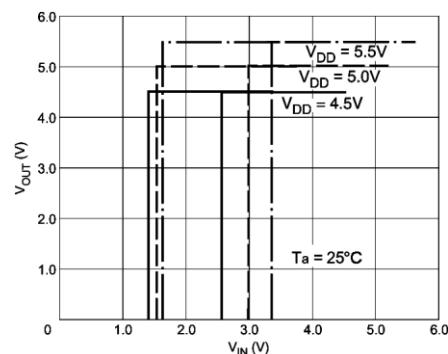

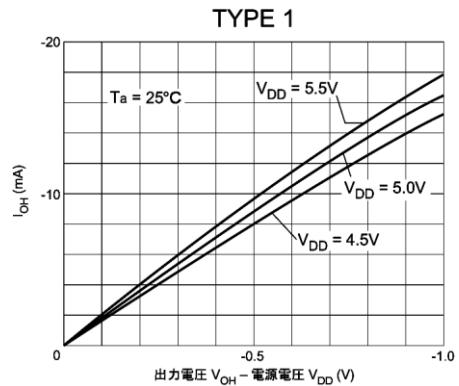

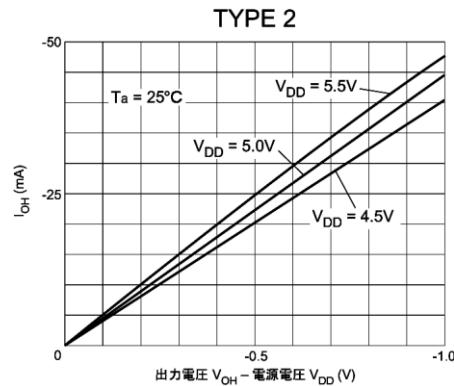

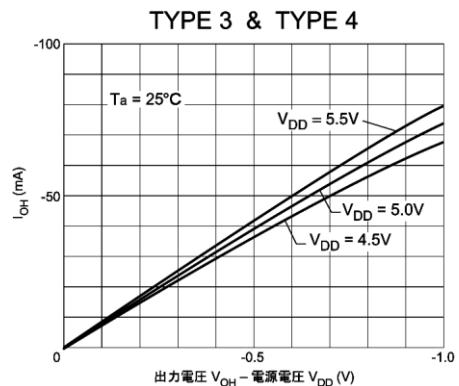

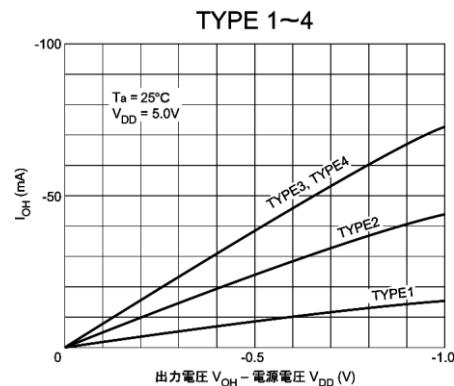

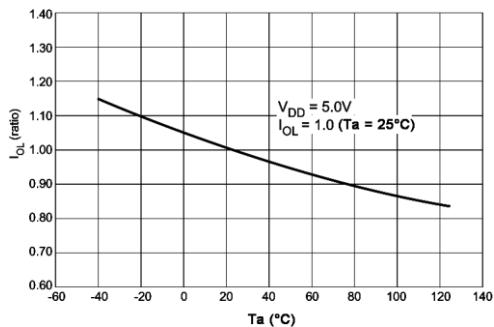

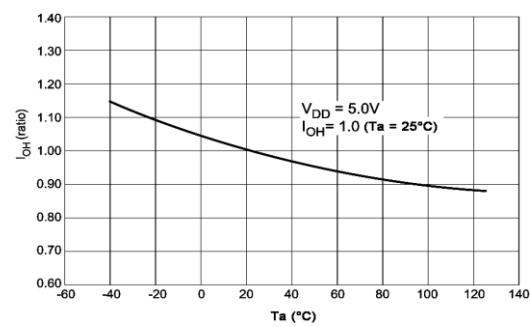

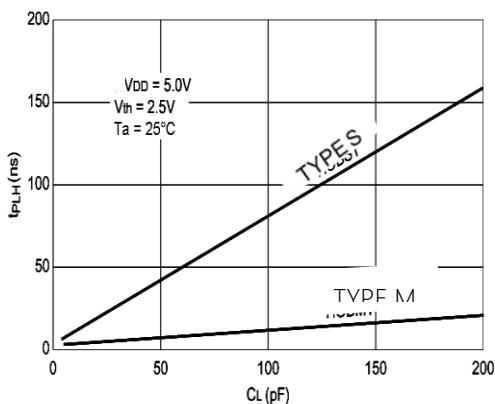

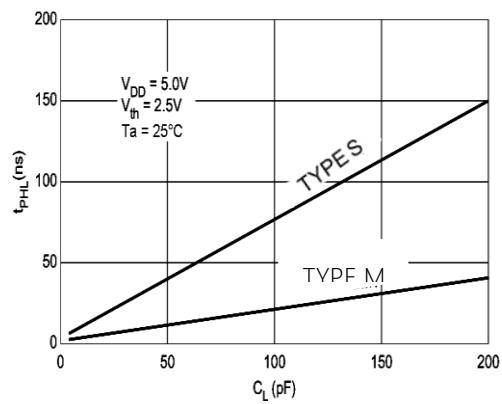

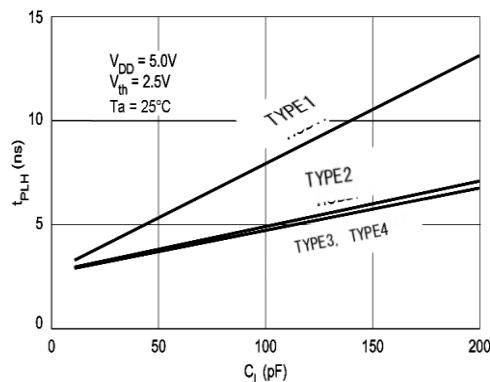

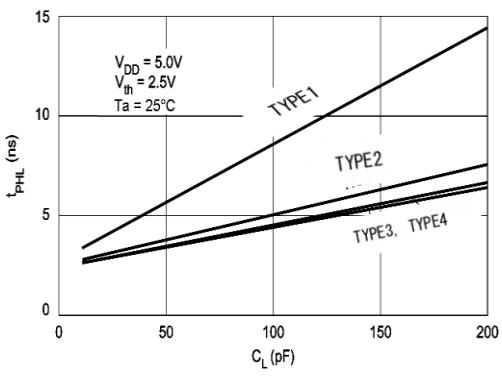

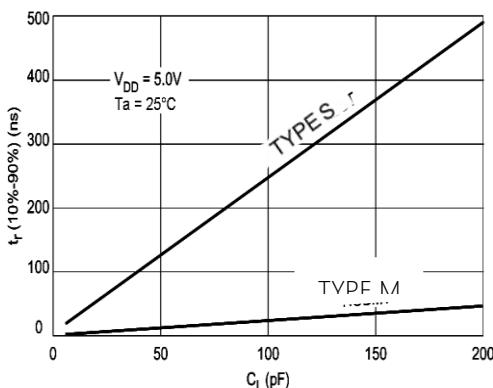

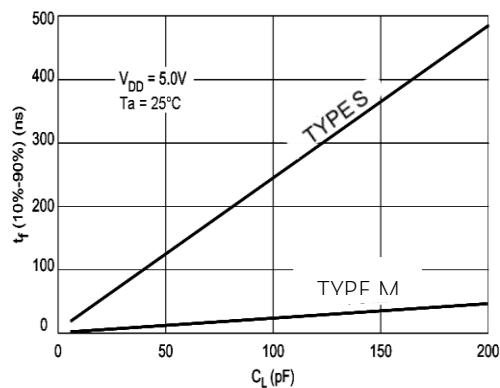

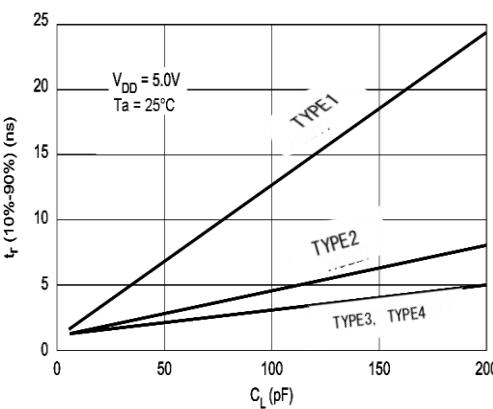

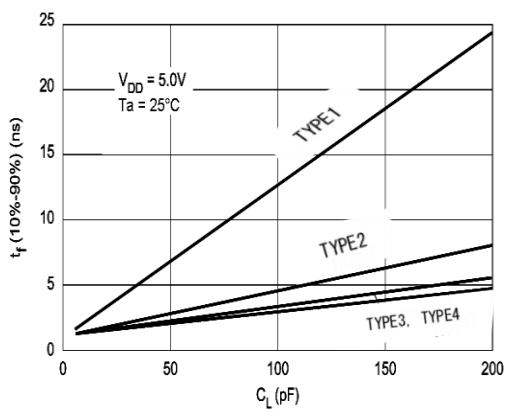

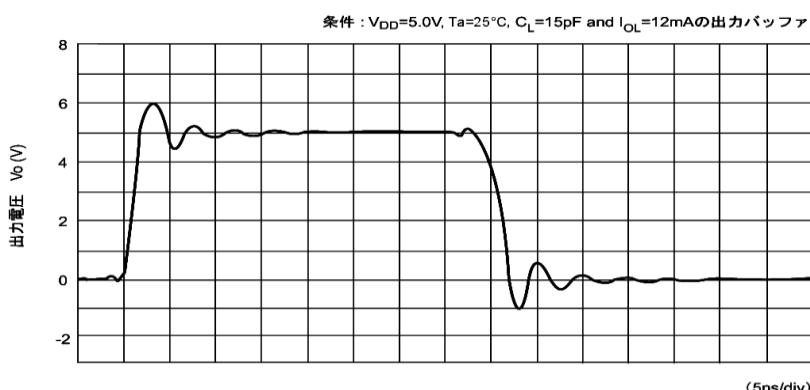

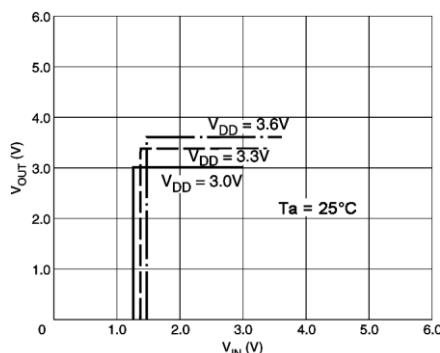

| A4.1 5.0V 動作時                  | 123 |

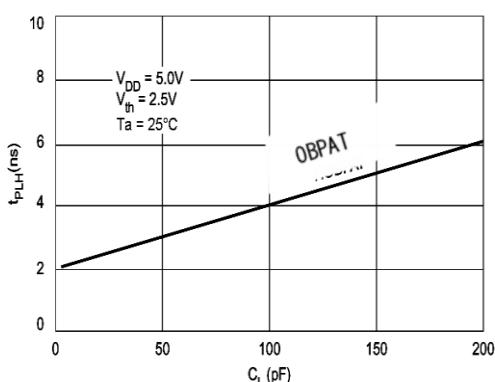

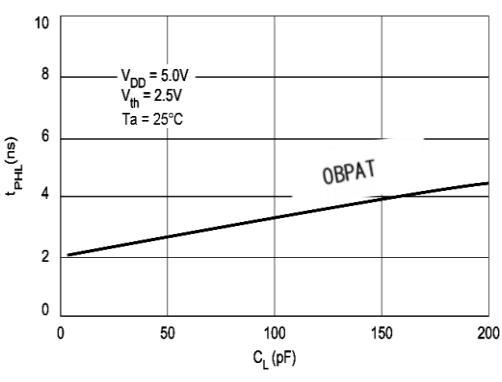

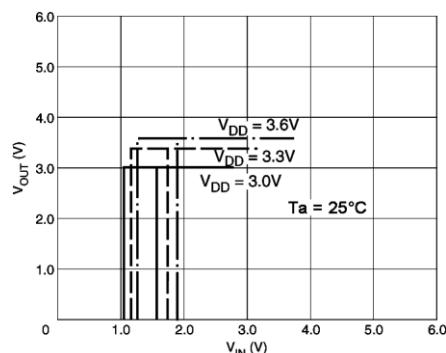

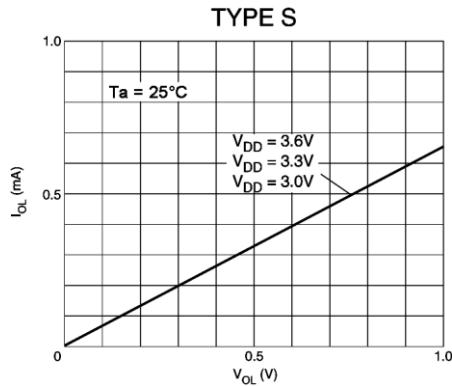

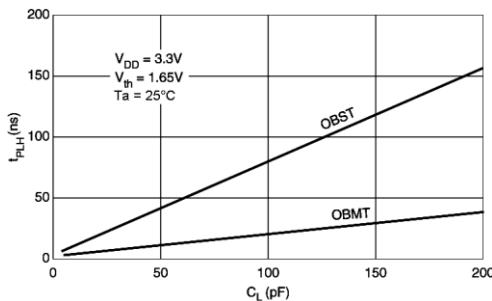

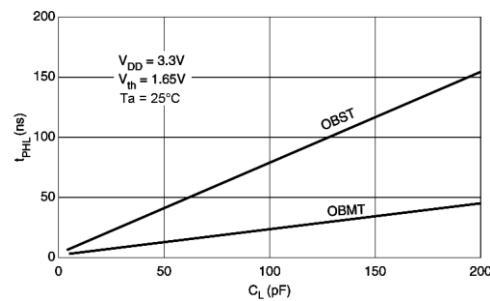

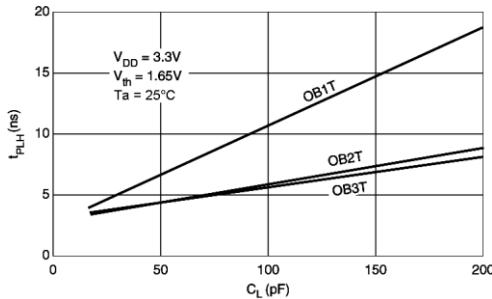

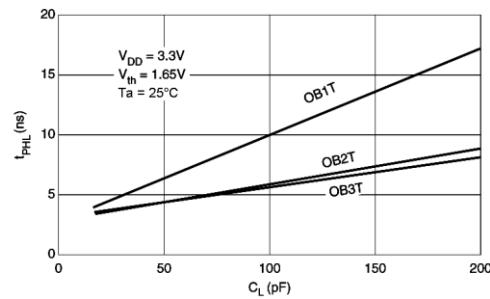

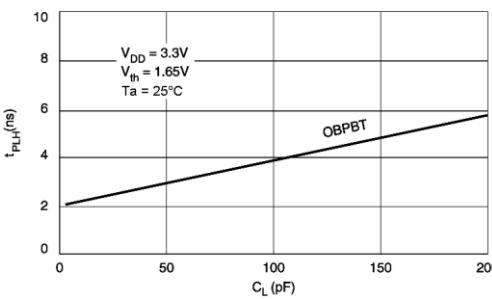

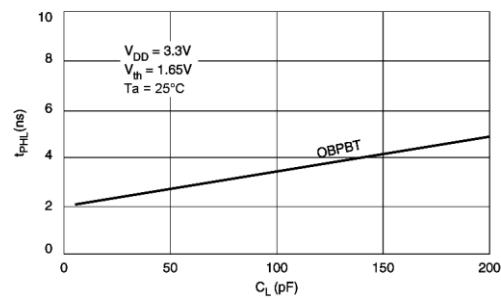

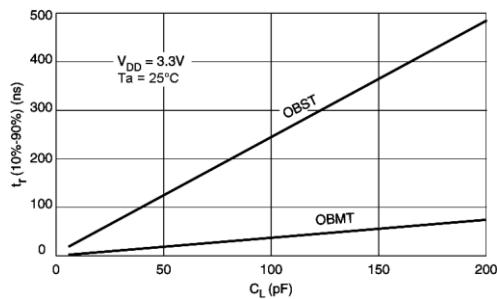

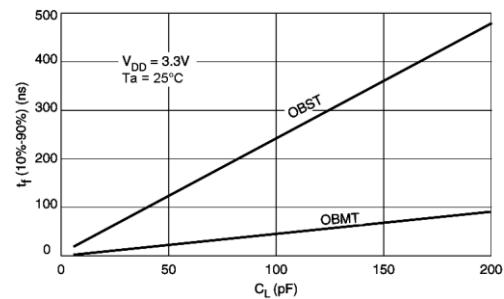

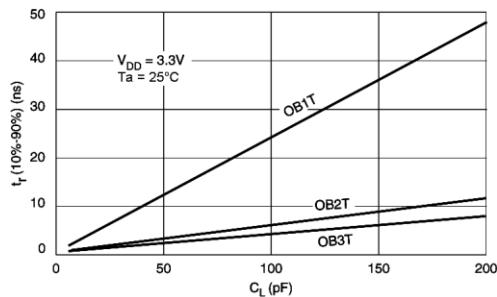

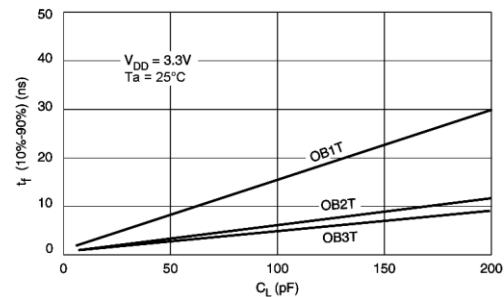

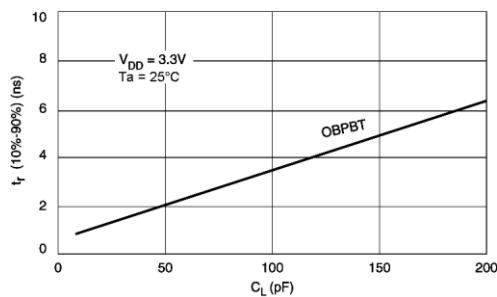

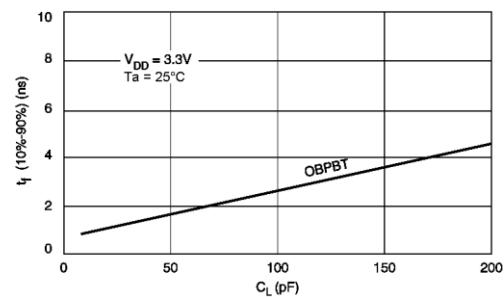

| A4.2 3.3V 動作時                  | 132 |

| A4.3 シュミット入力バッファの電気的特性について     | 140 |

| <b>改訂履歴表</b>                   | 141 |

## 第1章 概要

S1L5V000 シリーズは、 $0.35\mu\text{m}$  プロセスを採用した Sea of Gates タイプのゲートアレイシリーズです。

### 1.1 特長

- プロセス  $0.35\mu\text{m}$  CMOS 2/3/4 層 配線

- 最大搭載ゲート数 479,988 ゲート (2 入力 NAND ゲート換算)

- 動作速度 内部ゲート : 190ps (5.0V Typ.)

290ps (3.3V Typ.)

(2 入力 Power NAND、F/0=2、標準配線負荷)

- 入力バッファ : 450ps (5.0V Typ.)

550ps (3.3V Typ.)

(F/0=2、標準配線負荷)

- 出力バッファ : 2.07ns (5.0V Typ.)

2.95ns (3.3V Typ.)

( $C_L=15\text{pF}$ )

- I/F レベル TTL 入力、CMOS 入出力、LVTTL コンパチブル

- 入力モード TTL、CMOS、LVTTL、TTL シュミット、CMOS シュミット、LVTTL シュミット、Fail-Safe 入力 (出力ディスエーブル時)

プルアップ、プルダウン抵抗内蔵可能 (抵抗値各 2 種)

- 出力モード ノーマル、3-ステート、双方向、Fail-Safe 出力

- 駆動出力  $I_{OL}=0.1, 1, 3, 8, 12\text{mA}$  選択可能 ( $V_{DD}=5.0\text{V}$  時)

$I_{OL}=0.1, 1, 2, 6, 10\text{mA}$  選択可能 ( $V_{DD}=3.3\text{V}$  時)

- RAM 非同期 1 ポート、非同期 2 ポート : 最大構成 8Kbits/Module

同期 1 ポート、同期 2 ポート : 最大構成 8Kbits/Module

- PLL 入力周波数 : 5MHz ~ 40MHz、出力周波数 : 20MHz ~ 135MHz

遙倍率 : 2, 3, 4, 6, 8, 9, 10, 12, 14, 16, 18, 20, 22, 24, 26

- 電源/入出力電圧  $5.0V \pm 0.5V$  単一電源動作対応

$3.3V \pm 0.3V$  単一電源動作対応

### 1.2 マスタ構成

#### 1.2.1 標準マスタ構成

S1L5V000 シリーズは、5 種類のマスタを用意しています。ゲート規模、入出力端子数（電源端子を含む）および使用するパッケージにより、表 1-1-1 のマスター一覧より選択下さい。

なお、表 1-1-1 は RAM セル等を搭載しない場合の値です。RAM を回路に含む場合の見積りは「[第8章 RAM 仕様](#)」を参照して下さい。RAM セルの形状は固定されており、BC 数からの概算式が適用できなくなる場合がありますのでご注意下さい。

表 1-1-1 S1L5V000 シリーズ マスター一覧

| マスタ                  | BC 総数<br>BC <sub>G</sub> *1 | PAD 数 | BC 配列数 |      | セル使用率 U(%) *2 |     |     |

|----------------------|-----------------------------|-------|--------|------|---------------|-----|-----|

|                      |                             |       | X 方向   | Y 方向 | 2 層           | 3 層 | 4 层 |

| S1L5V012/5V013/5V014 | 8,856                       | 48    | 164    | 54   | 30            | 60  | 70  |

| S1L5V042/5V043/5V044 | 42,008                      | 104   | 356    | 118  | 30            | 60  | 70  |

| S1L5V112/5V113/5V114 | 109,250                     | 168   | 575    | 190  | 30            | 60  | 70  |

| S1L5V252/5V253/5V254 | 254,330                     | 256   | 877    | 290  | 25            | 55  | 65  |

| S1L5V482/5V483/5V484 | 479,988                     | 308   | 1206   | 398  | 25            | 50  | 60  |

注) \*1 : 使用可能な BC (ベーシックセル : G/A 基本セル) 数は、各マスタごとの BC 数総数 (BC<sub>G</sub>) とセル使用効率 (U) を用い次の式で計算します。

$$\text{BC}_A = \text{BC}_G \times U$$

BC 数見積りの際、弊社推奨テスト回路用として 550BC 程度、見積りに加えて下さい。

\*2 : セル使用効率は、回路規模だけでなく信号線数、1 信号当たりの分岐数等によっても変わりますので、表中の値は目安としてご参考ください。

### 1.2.2 PLL 搭載マスタ構成

S1L5V000 シリーズでは、PLL を搭載したマスタを 3 種類用意しています。PLL を搭載したシリーズ名は S1X5V000 シリーズです。ゲート規模、入出力端子数（電源端子を含む）および使用するパッケージにより、表 1-1-2 のマスター一覧より選択下さい。

なお、表 1-1-2 は RAM セル等を搭載しない場合の値です。RAM を回路に含む場合の見積りは「[第8章 RAM仕様](#)」を参照して下さい。RAM セルの形状は固定されており、BC 数からの概算式が適用できなくなる場合がありますのでご注意下さい。

表 1-1-2 PLL 内蔵 S1X5V000 シリーズ マスター一覧 (5V 単一)

| マスタ            | BC 総数 BC <sub>G</sub> | PAD 数 | 使用可能数 BC <sub>A</sub> (セル使用効率 U% <sup>*1</sup> ) |             |

|----------------|-----------------------|-------|--------------------------------------------------|-------------|

|                |                       |       | 3 層                                              | 4 層         |

| S1X5V513/5V514 | 25,960                | 104   | 14,267(55)                                       | 16,861(65)  |

| S1X5V523/5V524 | 90,276                | 168   | 49,652(55)                                       | 58,679(65)  |

| S1X5V533/5V534 | 235,000               | 256   | 117,500(50)                                      | 141,000(60) |

\*1 : セル使用効率 (U) は、回路規模だけでなく信号線数、1 信号当たりの分岐数等によっても変わりますので、表中の値は目安としてご参照して下さい。

PLL より発生するノイズがお客様回路に影響する場合があります。そのため、PLL 専用の電源を用意し、お客様回路と電源分離することを推奨します。

## 1.3 電気的特性・規格

### 1.3.1 絶対最大定格

表 1-2 絶対最大定格

(V<sub>SS</sub>=0V)

| 項目      | 記号               | 定格値                                     | 単位 |

|---------|------------------|-----------------------------------------|----|

| 電源電圧    | V <sub>DD</sub>  | -0.3~7.0                                | V  |

| 入力電圧    | V <sub>I</sub>   | -0.3~V <sub>DD</sub> +0.5 <sup>*1</sup> | V  |

| 出力電圧    | V <sub>O</sub>   | -0.3~V <sub>DD</sub> +0.5 <sup>*1</sup> | V  |

| 出力電流／端子 | I <sub>OUT</sub> | ±30                                     | mA |

| 保存温度    | T <sub>stg</sub> | -65~150                                 | °C |

注) \*1 : N チャンネルオープンドレイン、双方向バッファ、セル名が “ID” で始まる入力バッファと、Fail-Safe バッファについては、7.0V までです。

## 第1章 概要

### 1.3.2 推奨動作条件

表 1-3 推奨動作条件 ( $V_{DD}=5.0V$ )

( $V_{SS}=0V$ )

| 項目                                | 記号       | Min. | Typ. | Max.              | 単位 |

|-----------------------------------|----------|------|------|-------------------|----|

| 電源電圧                              | $V_{DD}$ | 4.5  | 5.0  | 5.5               | V  |

| 入力電圧                              | $V_I$    | -0.3 | —    | $V_{DD}+0.3^{*1}$ | V  |

| 周囲温度                              | $T_a$    | -40  | 25   | 110 <sup>*2</sup> | °C |

| 入力立ち上がり時間 (ノーマル入力) <sup>*3</sup>  | $t_{r1}$ | —    | —    | 50                | ns |

| 入力立ち下がり時間 (ノーマル入力) <sup>*3</sup>  | $t_{f1}$ | —    | —    | 50                | ns |

| 入力立ち上がり時間 (シュミット入力) <sup>*3</sup> | $t_{r2}$ | —    | —    | 5                 | ms |

| 入力立ち下がり時間 (シュミット入力) <sup>*3</sup> | $t_{f2}$ | —    | —    | 5                 | ms |

注) \*1 : N チャンネルオープンドレイン双方向バッファと、セル名が“ID”で始まる入力バッファについては、5.8Vまで入力可能です。Fail-Safe セルについては、5.8Vまで入力可能です。

ただし、“HIGH”レベル出力時に、外部より出力電圧以上の電圧を印加しないでください。

\*2 : この温度範囲は、 $T_j=-40\sim135$  [°C] を想定した推奨周囲温度です。

\*3 : この時間は、電源電圧の 10%~90% の変化時間です。

表 1-4 推奨動作条件 ( $V_{DD}=3.3V$ )

( $V_{SS}=0V$ )

| 項目                                | 記号       | Min. | Typ. | Max.              | 単位 |

|-----------------------------------|----------|------|------|-------------------|----|

| 電源電圧 <sup>*4</sup>                | $V_{DD}$ | 3.0  | 3.3  | 3.6               | V  |

| 入力電圧                              | $V_I$    | -0.3 | —    | $V_{DD}+0.3^{*1}$ | V  |

| 周囲温度                              | $T_a$    | -40  | 25   | 110 <sup>*2</sup> | °C |

| 入力立ち上がり時間 (ノーマル入力) <sup>*3</sup>  | $t_{r1}$ | —    | —    | 50                | ns |

| 入力立ち下がり時間 (ノーマル入力) <sup>*3</sup>  | $t_{f1}$ | —    | —    | 50                | ns |

| 入力立ち上がり時間 (シュミット入力) <sup>*3</sup> | $t_{r2}$ | —    | —    | 5                 | ms |

| 入力立ち下がり時間 (シュミット入力) <sup>*3</sup> | $t_{f2}$ | —    | —    | 5                 | ms |

注) \*1 : N チャンネルオープンドレイン双方向バッファと、セル名が“ID”で始まる入力バッファについては、5.8Vまで入力可能です。Fail-Safe セルについては、5.8Vまで入力可能です。

ただし、“HIGH”レベル出力時に、外部より出力電圧以上の電圧を印加しないでください。

\*2 : この温度範囲は、 $T_j=-40\sim135$  [°C] を想定した推奨周囲温度です。

\*3 : この時間は、電源電圧の 10%~90% の変化時間です。

\*4 : PLL 搭載マスタは、 $V_{DD}=3.3V$  は非対応です。

## 1.3.3 電気的特性

表 1-5 電気的特性

$(V_{DD}=5.0V \pm 0.5V, V_{SS}=0V, T_a=-40 \sim 110^{\circ}C)$

| 項目          | 記号         | 条件                                                                                                                   |                  | Min. | Typ. | Max.             | 単位        |

|-------------|------------|----------------------------------------------------------------------------------------------------------------------|------------------|------|------|------------------|-----------|

| 入力リーク電流     | $I_{LI}$   | —                                                                                                                    |                  | -5   | —    | 5                | $\mu A$   |

| オフステートリーク電流 | $I_{OZ}$   | —                                                                                                                    |                  | -5   | —    | 5                | $\mu A$   |

| 高レベル出力電圧    | $V_{OH}$   | $I_{OH}=-0.1mA$ (Type S) , $-1mA$ (Type M)<br>$-3mA$ (Type 1) , $-8mA$ (Type 2)<br>$-12mA$ (Type 3)<br>$V_{DD}=Min.$ | $V_{DD}$<br>-0.4 | —    | —    | —                | V         |

| 低レベル出力電圧    | $V_{OL}$   | $I_{OL}=0.1mA$ (Type S) , $1mA$ (Type M)<br>$3mA$ (Type 1) , $8mA$ (Type 2)<br>$12mA$ (Type 3)<br>$V_{DD}=Min.$      | —                | —    | —    | 0.4              | V         |

| 高レベル入力電圧    | $V_{IH1}$  | CMOS レベル、 $V_{DD}=Max.$                                                                                              |                  | 3.5  | —    | $V_{DD}$<br>+0.3 | V         |

| 低レベル入力電圧    | $V_{IL1}$  | CMOS レベル、 $V_{DD}=Min.$                                                                                              |                  | -0.3 | —    | 1.0              | V         |

| 高レベル入力電圧    | $V_{T1+}$  | CMOS シュミット                                                                                                           |                  | 2.0  | —    | 4.0              | V         |

| 低レベル入力電圧    | $V_{T1-}$  | CMOS シュミット                                                                                                           |                  | 0.8  | —    | 3.1              | V         |

| ヒステリシス電圧    | $\Delta V$ | CMOS シュミット                                                                                                           |                  | 0.3  | —    | —                | V         |

| 高レベル入力電圧    | $V_{IH2}$  | TTL レベル、 $V_{DD}=Max.$                                                                                               |                  | 2.0  | —    | $V_{DD}$<br>+0.3 | V         |

| 低レベル入力電圧    | $V_{IL2}$  | TTL レベル、 $V_{DD}=Min.$                                                                                               |                  | -0.3 | —    | 0.8              | V         |

| 高レベル入力電圧    | $V_{T2+}$  | TTL シュミット                                                                                                            |                  | 1.2  | —    | 2.4              | V         |

| 低レベル入力電圧    | $V_{T2-}$  | TTL シュミット                                                                                                            |                  | 0.6  | —    | 1.8              | V         |

| ヒステリシス電圧    | $V_{H2}$   | TTL シュミット                                                                                                            |                  | 0.1  | —    | —                | V         |

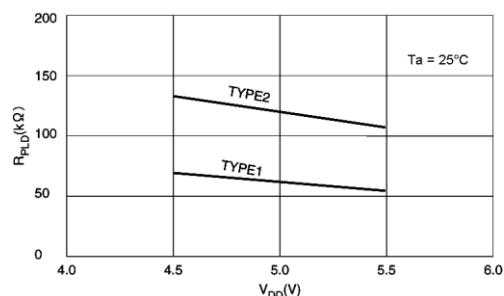

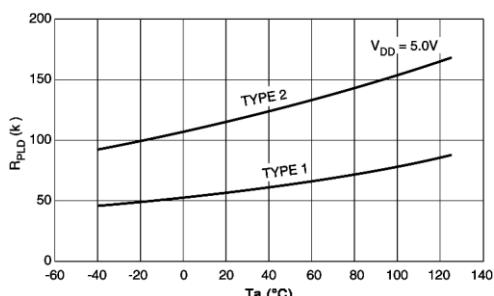

| プルアップ抵抗     | $P_{PU}$   | $V_I=0V$                                                                                                             | Type 1           | 30   | 60   | 150              | $k\Omega$ |

|             |            |                                                                                                                      | Type 2           | 60   | 120  | 300              | $k\Omega$ |

| プルダウン抵抗     | $P_{PD}$   | $V_I=V_{DD}$                                                                                                         | Type 1           | 30   | 60   | 150              | $k\Omega$ |

|             |            |                                                                                                                      | Type 2           | 60   | 120  | 300              | $k\Omega$ |

| 高レベル保持電流    | $I_{BHH}$  | バスホールド対応、 $V_{IN}=2.0V$<br>$V_{DD}=Min.$                                                                             |                  | —    | —    | -75              | $\mu A$   |

| 低レベル保持電流    | $I_{BHL}$  | バスホールド対応、 $V_{IN}=0.8V$<br>$V_{DD}=Min.$                                                                             |                  | —    | —    | 30               | $\mu A$   |

| 高レベル反転電流    | $I_{BHHO}$ | バスホールド対応、 $V_{IN}=0.8V$<br>$V_{DD}=Max.$                                                                             |                  | -550 | —    | —                | $\mu A$   |

| 低レベル反転電流    | $I_{BHLO}$ | バスホールド対応、 $V_{IN}=2.0V$<br>$V_{DD}=Max.$                                                                             |                  | 330  | —    | —                | $\mu A$   |

| 入力端子容量      | $C_1$      | $f=1MHz, V_{DD}=0V$                                                                                                  |                  | —    | —    | 10               | $pF$      |

| 出力端子容量      | $C_0$      | $f=1MHz, V_{DD}=0V$                                                                                                  |                  | —    | —    | 10               | $pF$      |

| 入出力端子容量     | $C_{IO}$   | $f=1MHz, V_{DD}=0V$                                                                                                  |                  | —    | —    | 10               | $pF$      |

表 1-6 電気的特性

( $V_{DD}=3.3V \pm 0.3V$ 、 $V_{SS}=0V$ 、 $T_a=-40 \sim 110^{\circ}C$ )

| 項目          | 記号         | 条件                                                                                                                 | Min.             | Typ.     | Max.         | 単位      |

|-------------|------------|--------------------------------------------------------------------------------------------------------------------|------------------|----------|--------------|---------|

| 入力リーク電流     | $I_{LI}$   | —                                                                                                                  | -5               | —        | 5            | $\mu A$ |

| オフステートリーク電流 | $I_{OZ}$   | —                                                                                                                  | -5               | —        | 5            | $\mu A$ |

| 高レベル出力電圧    | $V_{OH}$   | $I_{OH}=-0.1mA$ (Type S)、 $-1mA$ (Type M)<br>$-2mA$ (Type 1)、 $-6mA$ (Type 2)<br>$-10mA$ (Type 3)<br>$V_{DD}=Min.$ | $V_{DD}-0.4$     | —        | —            | V       |

| 低レベル出力電圧    | $V_{OL}$   | $I_{OL}=0.1mA$ (Type S)、 $1mA$ (Type M)<br>$2mA$ (Type 1)、 $6mA$ (Type 2)<br>$10mA$ (Type 3)<br>$V_{DD}=Min.$      | —                | —        | 0.4          | V       |

| 高レベル入力電圧    | $V_{IH1}$  | LVTTL レベル、 $V_{DD}=Max.$                                                                                           | 2.0              | —        | $V_{DD}+0.3$ | V       |

| 低レベル入力電圧    | $V_{IL1}$  | LVTTL レベル、 $V_{DD}=Min.$                                                                                           | -0.3             | —        | 0.8          | V       |

| 高レベル入力電圧    | $V_{T1+}$  | LVTTL シュミット                                                                                                        | 1.1              | —        | 2.4          | V       |

| 低レベル入力電圧    | $V_{T1-}$  | LVTTL シュミット                                                                                                        | 0.6              | —        | 1.8          | V       |

| ヒステリシス電圧    | $\Delta V$ | LVTTL シュミット                                                                                                        | 0.1              | —        | —            | V       |

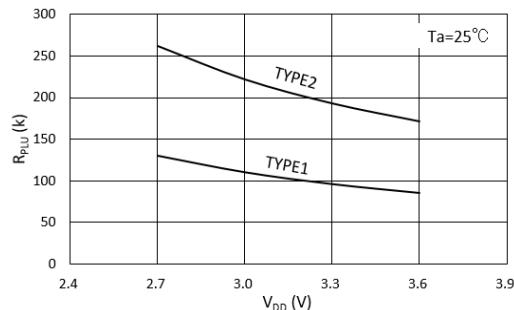

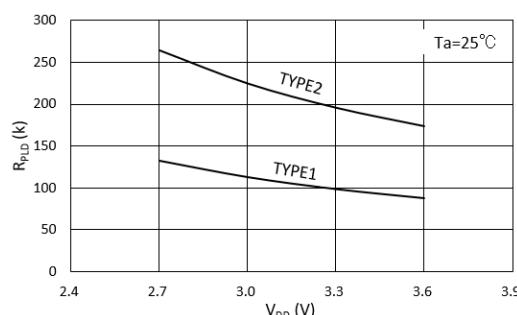

| プルアップ抵抗     | $R_{PU}$   | $V_I=0V$                                                                                                           | Type 1<br>Type 2 | 40<br>80 | 100<br>200   | kΩ      |

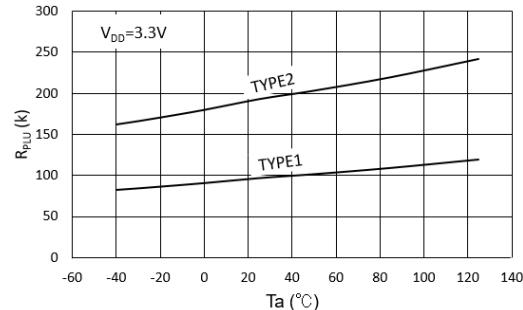

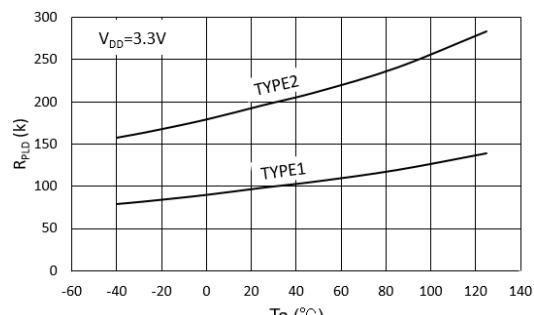

| プルダウン抵抗     | $R_{PD}$   | $V_I=V_{DD}$                                                                                                       | Type 1<br>Type 2 | 40<br>80 | 100<br>200   | kΩ      |

| 高レベル保持電流    | $I_{BHH}$  | バスホールド対応、 $V_{IN}=2.0V$<br>$V_{DD}=Min.$                                                                           | —                | —        | -18          | $\mu A$ |

| 低レベル保持電流    | $I_{BHL}$  | バスホールド対応、 $V_{IN}=0.8V$<br>$V_{DD}=Min.$                                                                           | —                | —        | 15           | $\mu A$ |

| 高レベル反転電流    | $I_{BHHO}$ | バスホールド対応、 $V_{IN}=0.8V$<br>$V_{DD}=Max.$                                                                           | -350             | —        | —            | $\mu A$ |

| 低レベル反転電流    | $I_{BHLO}$ | バスホールド対応、 $V_{IN}=2.0V$<br>$V_{DD}=Max.$                                                                           | 210              | —        | —            | $\mu A$ |

| 入力端子容量      | $C_1$      | $f=1MHz$ 、 $V_{DD}=0V$                                                                                             | —                | —        | 10           | pF      |

| 出力端子容量      | $C_0$      | $f=1MHz$ 、 $V_{DD}=0V$                                                                                             | —                | —        | 10           | pF      |

| 出入力端子容量     | $C_{10}$   | $f=1MHz$ 、 $V_{DD}=0V$                                                                                             | —                | —        | 10           | pF      |

### 1.3.4 オーバーシュート／アンダーシュート

入力バッファ、双方向バッファへの入力波形に関して、用途によってオーバーシュート、アンダーシュートが 表1-3、表1-4 の推奨動作条件の最大入力電圧を超える場合、下記のような時間内でのオーバーシュート／アンダーシュートを規定しています。

- (1)  $V_{DD} = 5.0V \pm 0.5V$  条件でオーバーシュート／アンダーシュートを許容できる電圧と時間

オーバーシュート 最大ピーク電圧 :  $V_{DD} + 1.5V$  (\*1)

オーバーシュート 最大時間(\*2) : 50 ns

アンダーシュート 最小ピーク電圧 :  $V_{SS} - 1.5V$

アンダーシュート 最大時間(\*2) : 50 ns

注)\*1:Nチャンネルオープンドレインの双方向バッファと、セル名が “ID” で始まる入力バッファと、Fail-Safeセルについては、7.0Vまで許容できます。

\*2：時間とは、入力電圧が $V_{DD}$ より上回っている時間、または、 $V_{SS}$ より下回っている時間を指します。ただし、上記 (\*1) の場合は、5.8Vより上回っている時間になります。

- (2)  $V_{DD} = 3.3V \pm 0.3V$  条件でオーバーシュート／アンダーシュートを許容できる電圧と時間

オーバーシュート 最大ピーク電圧 :  $V_{DD} + 1.0V$  (\*1)

オーバーシュート 最大時間(\*2) : 50 ns

アンダーシュート 最小ピーク電圧 :  $V_{SS} - 1.0V$

アンダーシュート 最大時間(\*2) : 50 ns

注) \*1 : Nチャンネルオープンドレインの双方向バッファと、セル名が “ID” で始まる入力バッファと、Fail-Safeセルについては、7.0Vまで許容できます。

\*2：時間とは、入力電圧が $V_{DD}$ より上回っている時間、または、 $V_{SS}$ より下回っている時間を指します。ただし、上記\*1の場合は、5.8Vより上回っている時間になります。

(補足) オーバーシュート、アンダーシュートの大きな波形では、反射波が入力の $V_{IH}/V_{IL}$ の規格を満足しているかどうかを確認して下さい。たとえ上記規格を満足していても、反射波が $V_{IH}/V_{IL}$ の規格を満足しない範囲まで到達していた場合は、誤動作を起こす危険性があります。(オシロスコープ等で、入力波形を直接確認することをお奨めします。)

### 1.4 静的消費電流

表 1-7 静的消費電流

( $T_j = 110^{\circ}\text{C}$ )

| マスタ                                          | $5.0\text{V} \pm 0.5\text{V}$<br>$I_{DDS}^{*1} \text{ Max.}$ | $3.3\text{V} \pm 0.3\text{V}$<br>$I_{DDS}^{*1} \text{ Max.}$ | 単位            |

|----------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|---------------|

| S1L5V012/5V013/5V014                         | 64                                                           | 48                                                           | $\mu\text{A}$ |

| S1L5V042/5V043/5V044<br>S1L5V112/5V113/5V114 | 240                                                          | 200                                                          | $\mu\text{A}$ |

| S1L5V252/5V253/5V254                         | 360                                                          | 280                                                          | $\mu\text{A}$ |

| S1L5V482/5V483/5V484                         | 520                                                          | 400                                                          | $\mu\text{A}$ |

注) \*1 :  $I_{DDS} : V_{DD} \sim V_{SS}$  間の静的消費電流

\*)  $T_j=110^{\circ}\text{C}$ 以外での静的消費電流に関しては、以下の式を用いることで概算値を求めることができます。

(ただし、 $T_j=-40\sim 110^{\circ}\text{C}$ の間のみとなります。 $T_j=110^{\circ}\text{C}\sim 135^{\circ}\text{C}$ の場合は、弊社営業担当までお問合せください。)

$$I_{DDS}(T_j) = I_{DDS}(T_j=110^{\circ}\text{C}) \times \text{温度係数}$$

$$= I_{DDS}(T_j=110^{\circ}\text{C}) \times 10^{\frac{T_j-110}{60}}$$

(例) S1L5V112 で、 $V_{DD}=5.0\text{V}$ 、 $T_j=60^{\circ}\text{C}$ での  $I_{DDS}$  の概算値は以下のとおりです。

$$I_{DDS}(T_j=60^{\circ}\text{C}) = I_{DDS}(T_j=110^{\circ}\text{C}) \times 10^{\frac{60-110}{60}}$$

$$= 240 \times 0.147$$

$$= 35 (\mu\text{A})$$

## 1.5 開発フロー

開発手順でのお客様からの開発着手依頼およびデータ提出、セイコーエプソンでの論理合成・配置配線作業フロー、試作から量産制定までのフローを示します。

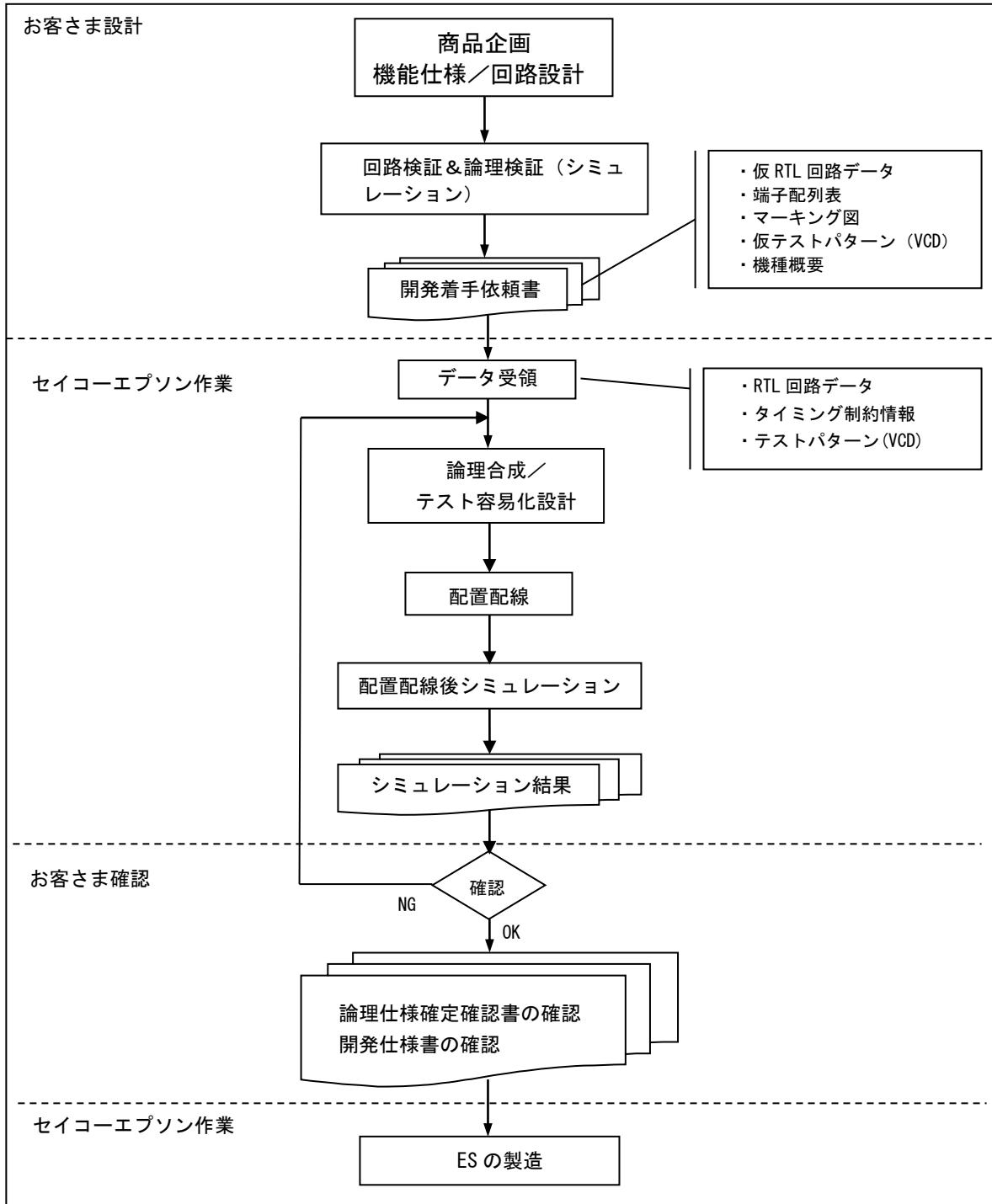

### 1.5.1 サインオフまでの開発フロー

図1-1は、サインオフまでの開発フローです。RTLインターフェースが前提となっています。

図1-1：サインオフまでの開発フロー

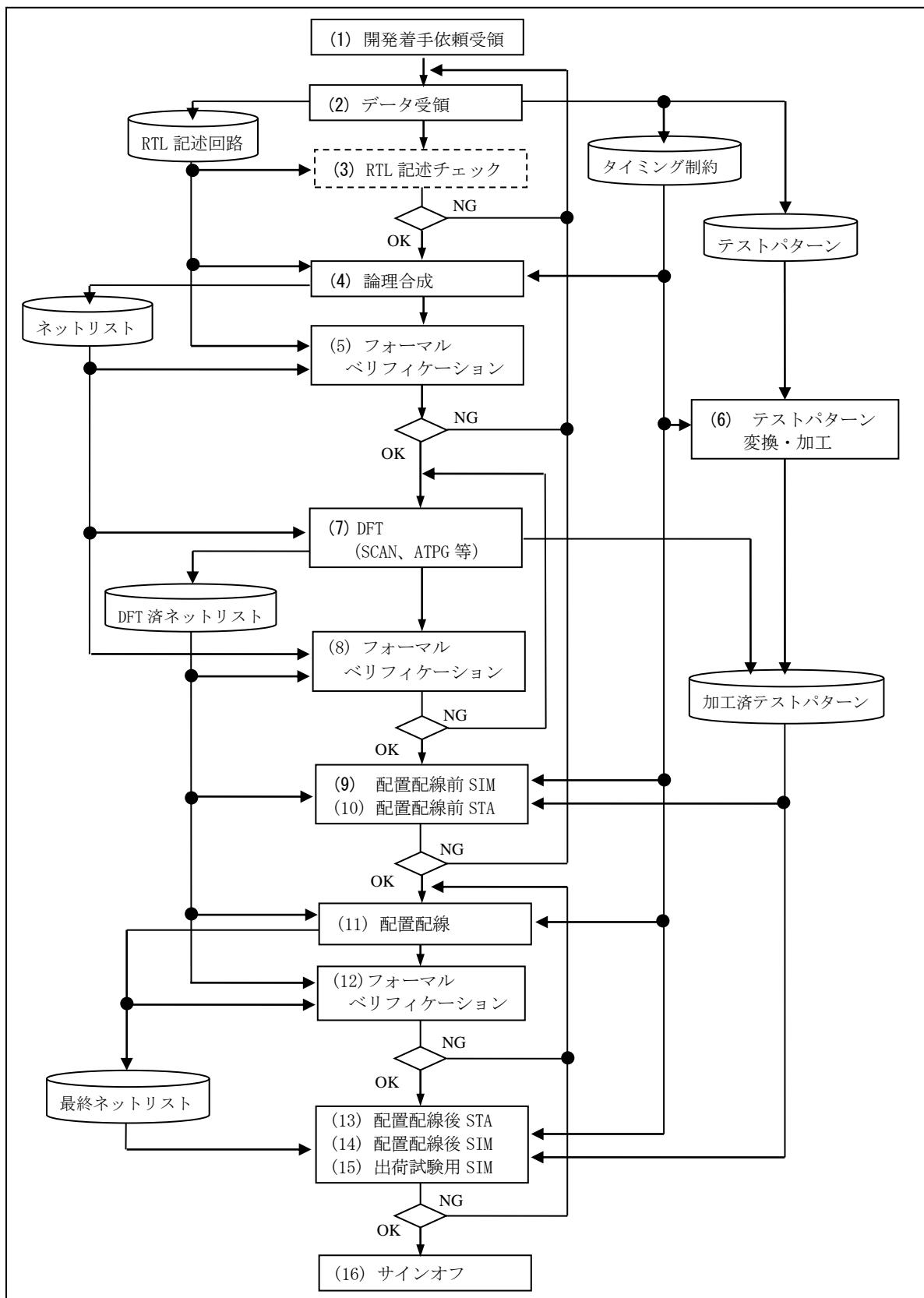

## 1.5.2 論理合成・配置配線作業フロー（セイコーエプソン作業）

図 1-2：論理合成・配置配線作業 工程フロー（セイコーエプソン作業）

図1-2は、データ受領から、サインオフまでの論理合成・配置配線作業フローを記述しています。各作業の概要を以下に説明します。

## (1) 開発着手依頼受領

お客さまからセイコーエプソン帳票「開発着手依頼書」を代理店またはセイコーエプソンに送付いただきます。受領後、セイコーエプソン内で設計作業の着手を行います。開発着手依頼書と一緒に、お客さまより送付いただくデータは以下の通りです。

- ① 仮 RTL 回路データ。「[1.5.3 仮データ\(トライアル用\)の提出](#)」を参照して下さい。

- ② 端子配列表

- ③ マーキング図（セイコーエプソン作成フォーマット帳票）

- ④ 仮テストパターン（VCD 形式）

- ⑤ 機種概要

## (2) データ受領

お客さまより送付いただくデータとしては以下の通りです。

- ① 正式 RTL 回路データ

- ② タイミング制約情報

- ③ テストパターン（VCD 形式）

## (3) RTL 記述チェック

必要に応じて、RTL チェッカーを使用して、文法エラーなどの確認を行います。

## (4) 論理合成

初期段階で、ゲート数の確認やクロックの解析などのために、最小限の制約による仮の論理合成を行います。問題がなければ、タイミング制約などを付けて、実際の論理合成を行います。

## (5) フォーマルベリフィケーション（等価性チェック）

お客さまの RTL 記述と、論理合成後のネットリストとの、フォーマルベリフィケーション（等価性チェック）を行います。

## (6) テストパターンの変換

お客さまから受領したテストパターン：VCD（Value Change Dump）ファイルを、セイコーエプソン独自フォーマット APF（Advanced Press Format）ファイル（サイクルベース、テーブル形式のテストパターン）に変換します。

## (7) DFT（スキャン挿入、ATPG など）

DFT（Design For Test：故障検出率を上げるためのテスト専用回路の追加）を実施し、スキャンテスト回路などを挿入します。また、ATPG（Automatic Test Pattern Generation）によるテストパターン生成を行います。故障検出率の要望については、開発着手時に連絡下さい。

## (8) フォーマルベリフィケーション（等価性チェック）

DFT 前と DFT 後でのネットリストに対するフォーマルベリフィケーションを行います。

## 第1章 概要

---

### (9) 配置配線前シミュレーション

ゲートレベルのネットリストにおいて、必要なファンクションが得られていることを確認するために、上記(6)(7)のテストパターンと、仮想遅延データによるシミュレーションを行います。結果に問題などがあった場合は、解析を実施します。

### (10) 配置配線前 STA

お客さまより受領したタイミング制約を基に、STA（静的タイミング解析）によるタイミング確認を行います。明らかに問題となるタイミングエラーを発見した場合は、お客さまに連絡すると共に、再度の論理合成などの対応を行います。

### (11) 配置配線

上記(10)のデータを使い配置配線を実施します。その結果から、実配線後の遅延時間データを算出します。

### (12) フォーマルベリフィケーション（等価性チェック）

配置配線前と後でのネットリストに対するフォーマルベリフィケーションを行います。

### (13) 配置配線後 STA

配置配線後のデータについて、実配線後の遅延時間データを用いて、タイミングを確認します。明らかに問題となるタイミングエラーを発見した場合は、ECO（局所レイアウト変更）などで、調整を行います。

### (14) 配置配線後シミュレーション（リアルレート）

配置配線後のデータについて、ICを実際に使用する条件で、シミュレーションを行います。結果をお客さまに送付し内容をご確認いただきます。

### (15) 出荷試験用シミュレーション（テストレート）

テストパターンのタイミング条件を、出荷試験向けに変更させていただき、配置配線後データのシミュレーションを行います。結果をお客さまに送付し内容をご確認いただきます。また、出荷試験の条件を満たしていることを確認いただきます。

#### <シミュレーション結果の送付>

シミュレーションの結果は APF (Advanced Press Format セイコーエプソン独自フォーマット : \*.sammax, \*.sammin) 形式で送付します。要望に応じて VCD (Value Change Dump) の波形ファイルを添付します。

#### <シミュレーション結果とのコンペアの送付>

シミュレーション結果と期待値とのコンペアを行い、コンペアファイル (\*.exp\_max, \*.exp\_min) が output されます。同様に、min 結果と max 結果のコンペアファイル (\*.min\_max) の出力を送付します。

出力例について、「[付録 A1.1 シミュレーション結果と期待値とのコンペアファイル例](#)」を参照下さい。

## <タイミングエラーリストの送付>

シミュレーション中にタイミングエラーが発生した場合、リスト(\*.errmax, \*.errmin)出力を送付します。

タイミングエラーリストの見方については、「[付録A1.2 タイミングエラーリスト](#)」を参照下さい。

## (16) サインオフ

セイコーエプソン作成帳票（論理仕様確定確認書）を送付します。内容をご確認いただき、問題なければ帳票への確認結果の記載および署名・捺印いただきセイコーエプソンに送付下さい。帳票受領後、ES（エンジニアリングサンプル）の製造を開始します。

### 1.5.3 仮データ（トライアル用）の提出

正式な RTL 回路データ提出前にあらかじめ、仮（トライアル用）データを提出していただくよう、お願いします。

仮データを用いて、正式なデータ受領後の作業をスムーズにするための準備を行います。

なお、タイミング条件が厳しい場合、仮 RTL 回路データ提出時にご連絡下さい。

#### (1) ゲート規模の見積り

お客様から受領した仮 RTL 回路データから、概略のゲート規模を見積もることが可能です。

#### (2) 仮 RTL データのチェック

お客様から受領した仮 RTL 回路データに対して、論理合成を行います。文法上の問題や、合成後の問題を事前に知ることができます。チェックで問題のあった箇所を、お客様に報告いたします。

また、仮 RTL データと、論理合成後のネットリストとの、フォーマルベリフィケーション（等価性チェック）を行います。論理の不一致が現われた場合は、お客様に報告いたします。

#### (3) 論理合成における制約条件設定

最低限の制約条件を用いて、論理合成を行います。その際、タイミング制約情報を提出していただくことで、論理合成の制約条件をあらかじめ調整します。また、STA（静的タイミング検証）の制約条件を作成することも可能です。

#### (4) ファンクションの確認

仮のテストパターンを提出していただくことで、APP パターンへの変換チェック、テストパターンの整合性チェック、及びゲートレベルシミュレーションによるファンクションの確認が可能です。

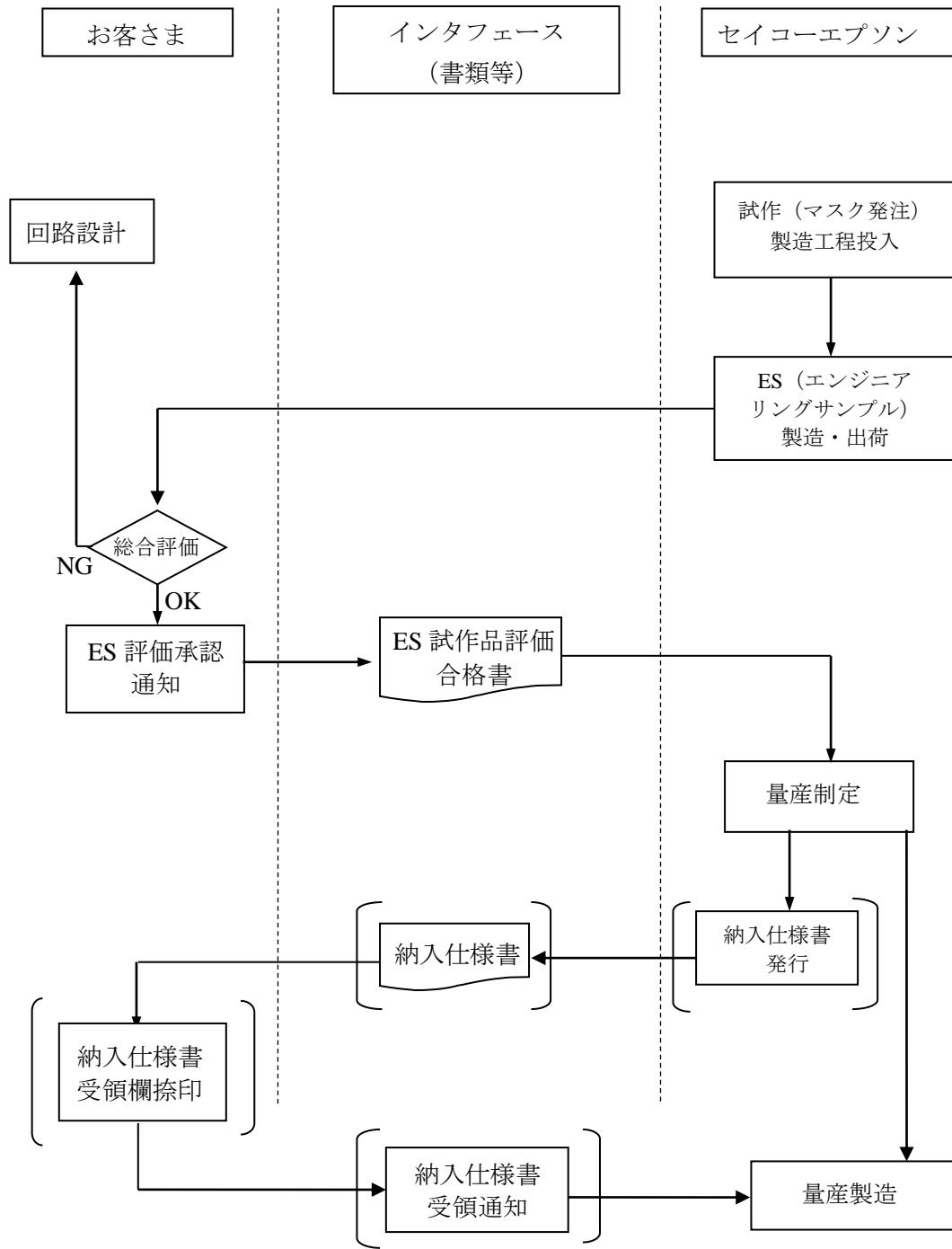

### 1.5.4 試作から量産制定、製造フロー

図1-3は、セイコーエプソンにての試作から量産制定までのフローです。

( ) 内はお客様からの要望がある場合行います。

図1-3：試作から量産制定までのフロー

## 第2章 RTL 設計上の注意 (Verilog-HDL)

セイコーエプソンにて論理合成を行うにあたり、お客さままでの RTL 設計における留意点について説明します。本章では言語を Verilog-HDL として説明しています。VHDL を使用されるお客さまは、「[付録 A2 RTL 設計上の注意 VHDL](#)」を参照下さい。また、開発着手依頼時に VHDL で設計を行うことをご連絡下さい。

### 2.1 基本構成

#### 2.1.1 論理合成可能な RTL データの提出

提出する RTL データは、論理合成可能な記述のみにして下さい。ビヘイビアレベルの記述が含まれていると、論理合成ができません。論理合成可能であれば、複数個のファイルにわかれても問題ありません。

#### 2.1.2 ライブラリセルの使用

RTL 内で、セイコーエプソンのライブラリセルを呼び出しているモジュール名と、ライブラリセル名を連絡下さい。ライブラリセルが論理合成時に消されないための設定を行います。

#### 2.1.3 ifdef と parameter

ifdef 文や parameter 文で、RTL の外部や別ファイルから値を設定する必要がある場合は、その旨を連絡下さい。

### 2.2 端子名の制約

外部端子、および内部端子の名前に制限・制約があります。制限・制約に沿っていただくことを推奨します。制限・制約に沿っていない名前が使われている場合は、論理合成時にお客様の意図しない名前に付け替えられることがありますことをご了承下さい。

#### 2.2.1 外部端子名制約

- (1) 全て大文字にて記述して下さい。

- (2) 使用可能文字は、英数字とアンダーバー' \_ 'のみです。

ただし、先頭文字は英字のみ使用可能です。

- (3) '[' と ']' は使用できませんので、バスの記述もできないことに注意下さい。

- (4) ' \_ ' が2つ連続してはいけません。

- (5) 文字数は、2~32 文字の範囲です。

#### 2.2.2 内部端子名制約

- (1) 大文字・小文字の混合は可能です。ただし、大文字小文字混在の同一名は使用できません。

例：“ABC”と“Abc”の混在は禁止。

- (2) 使用可能文字は、英数字、アンダーバー' \_ '、バス記述用のかっこ' [ '、' ]' です。

- (3) 文字数は、2~32 文字の範囲です。

### 2.2.3 Verilog 予約語

以下の文字列は、Verilog の予約語ですので、ユーザー定義名として使用できません。

|              |            |          |         |           |           |             |

|--------------|------------|----------|---------|-----------|-----------|-------------|

| always       | and        | assign   | begin   | buf       | bufif0    | bufif1      |

| case         | casex      | casez    | cmos    | deassign  | default   | defparam    |

| disable      | edge       | else     | end     | endcase   | endmodule | endfunction |

| endprimitive | endspecify | endtable | endtask | event     | for       | force       |

| forever      | fork       | function | highz0  | highz1    | if        | ifnone      |

| initial      | inout      | input    | integer | join      | large     | macromodule |

| medium       | module     | nand     | negedge | nmos      | nor       | not         |

| notif0       | notif1     | or       | output  | parameter | pmos      | posedge     |

| primitive    | pull0      | pull1    | pullup  | pulldown  | rcmos     | real        |

| realtime     | reg        | release  | repeat  | rnmos     | rpmos     | rtranif0    |

| rtranif1     | scalared   | small    | specify | specparam | strong0   | strong1     |

| supply0      | supply1    | table    | task    | time      | tran      | tranif0     |

| tranif1      | tri        | tri0     | triand  | trior     | trireg    | vectored    |

| wait         | wand       | weak0    | weak1   | while     | wire      | wor         |

| xnor         | xor        |          |         |           |           |             |

## 2.3 タイミング制約情報の提出

お客様から、クロックや入力遅延、外部遅延に関するタイミング制約情報を RTL データ送付時に一緒に送付していただきます。この情報をもとに、論理合成や STA におけるタイミング制約の作成などの挿入を行います。

### 2.3.1 クロック情報

#### (1) 外部クロック

すべての外部クロックについて、以下の事項を指定して下さい。

- ① 端子名

- ② クロックの基準周期

- ③ 基準周期の開始から、クロックの立上りエッジ・立下りエッジまでの遅延

- ④ Duty およびその変動量

- ⑤ クロックジッタの有無

- ⑥ スキュー調整必要の有無

- ⑦ 用途（メイン、テスト用など）

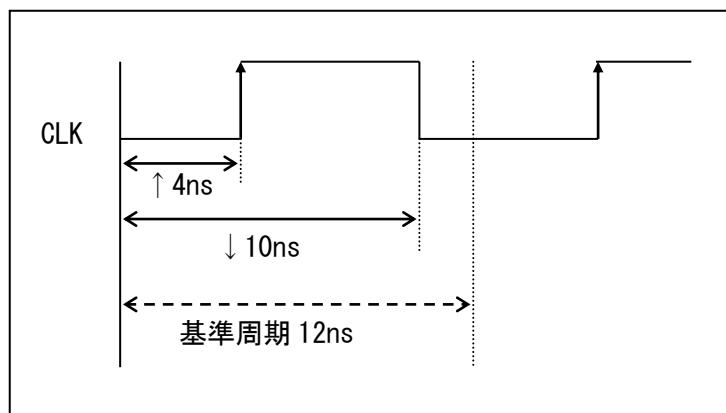

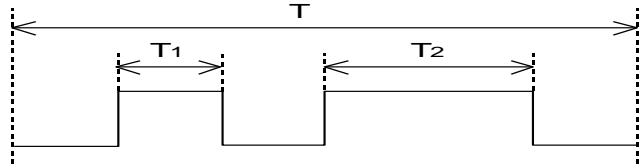

図 2-1：外部クロック波形図

例えば図 2-1 の場合、外部クロック端子名は CLK、クロック基準周期 12ns、立上りエッジ遅延 4ns、立下りエッジ遅延 10ns、Duty50±0%になります。

### (2) 内部生成クロック

PLL、分周などによって回路内部で生成されるクロックを指します。すべての内部生成クロックについて、以下の事項を指定して下さい。

- ① 内部生成クロックの信号名、及び生成されるモジュール名

- ② マスタクロックの信号名（外部クロックなら、端子名）

- ③ マスタクロックとの関係（分周数、または倍数）

- ④ スキュー調整必要の有無

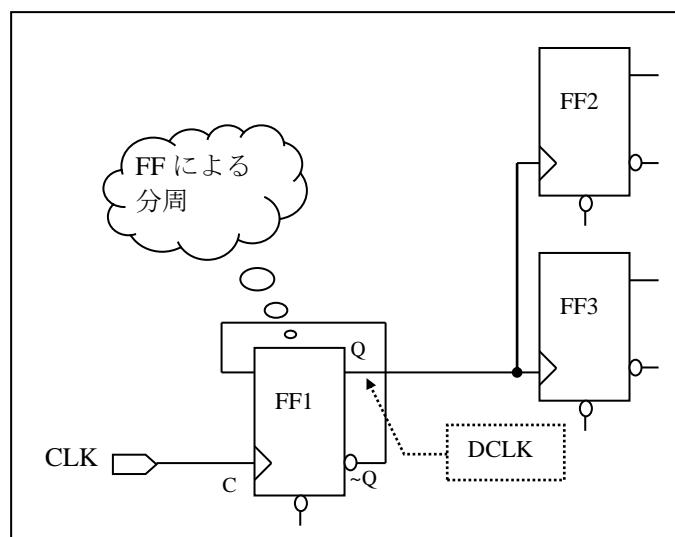

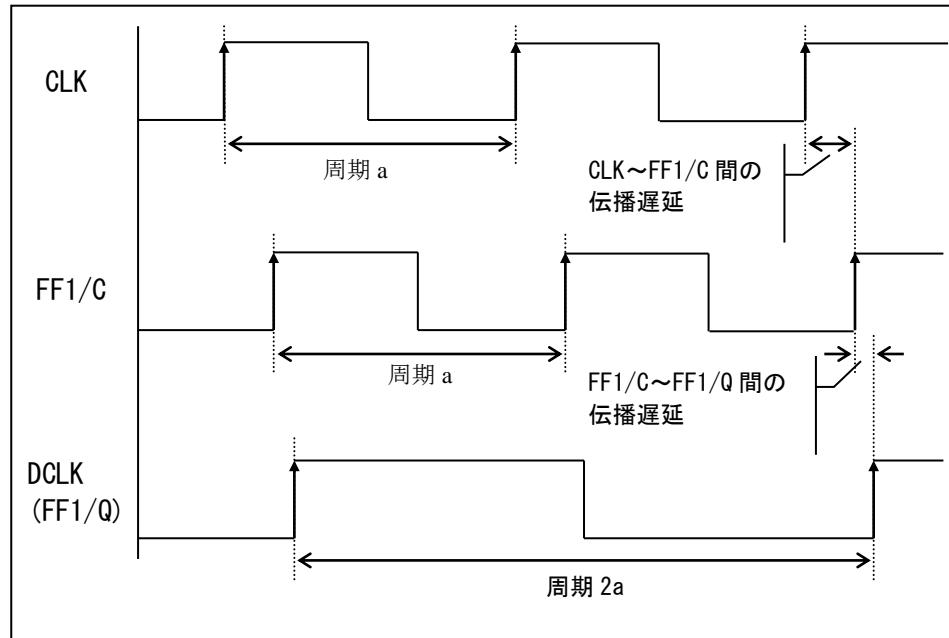

図2-2は、マスタクロック CLK を D-FF で 2 分周して、内部クロック DCLK を生成する RTL 記述の例です。これを論理合成すると、図2-3のような回路となります。ここで、CLK と DCLK は、タイミングの異なるクロックとなることにご注意して下さい。これは、CLK から FF の出力端子までの伝播遅延分のスキューが生じるためです。図2-4を参照して下さい。

```

always @(posedge CLK or negedge RST)

begin

if(!RST)

Q <= 1' b0;

else

Q <= ~Q;

end

assign DCLK = Q;

always @(posedge DCLK or negedge RST)

.

.

.

```

図2-2：分周による内部クロック生成の記述例

図2-3：図2-2より合成される回路例

図 2-4：図 2-3 の回路の波形図

## (3) 複数クロックの組み合わせ

複数のクロックと組み合わせ回路から、パルスを作ることは避けて下さい。各クロックのスキーにより意図しないパルスとなる可能性があります。

## (4) 異なるクロックで動作するレジスタ間のデータパスについて

異なるクロックで動作するレジスタ間にデータパスがある場合、そのタイミングを保証することは困難ですので、非同期でデータの受け渡しができるような設計を行って下さい。また、同クロックであってもエッジが異なる場合は、異なるクロックとして扱ってよいかをご指示下さい。

### 2.3.2 外部端子のタイミング制約

#### (1) 外部入力タイミング

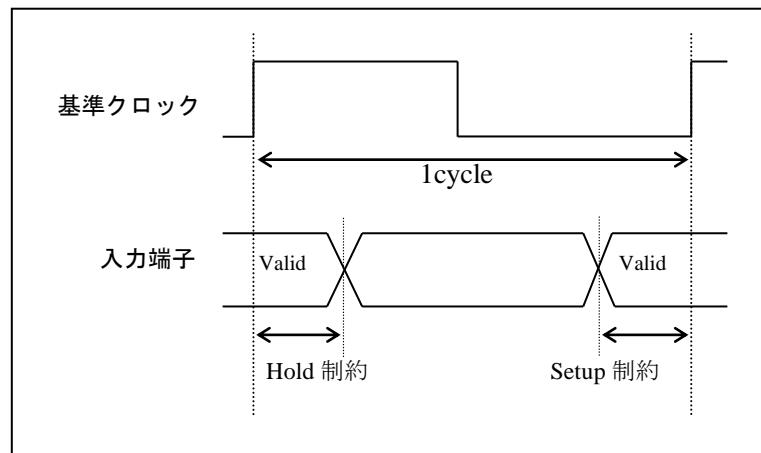

外部入力端子に、基準クロックに対するセットアップタイム、ホールドタイムを指定して下さい。

図 2-5：外部入力タイミング

#### (2) 外部出力タイミング

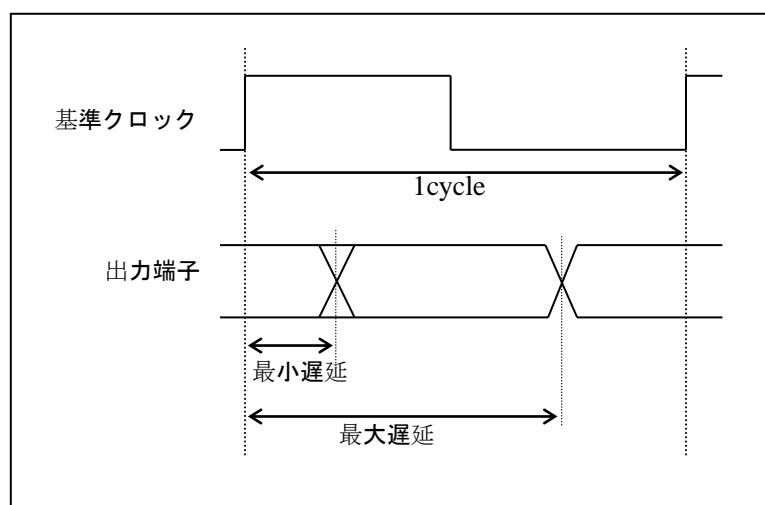

外部出力端子に、定義したクロックに対する出力遅延を設定します。基準クロックに対する遅延の最小値と最大値を指定して下さい。基準クロックが回路内に存在しないときは、仮想クロックの制約を指定して下さい。

図 2-6：外部出力タイミング

## (3) マルチサイクルパス

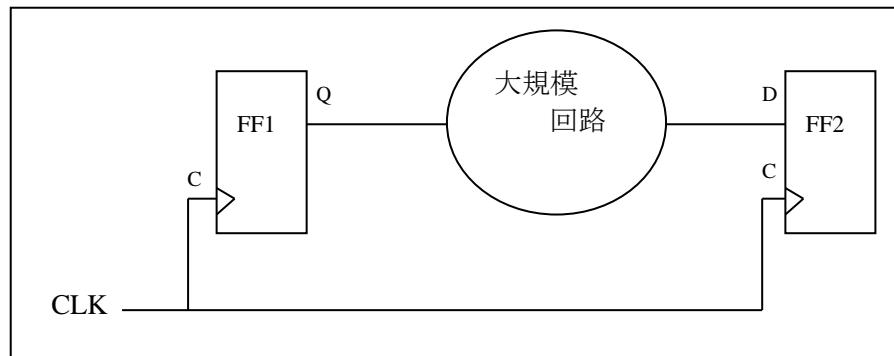

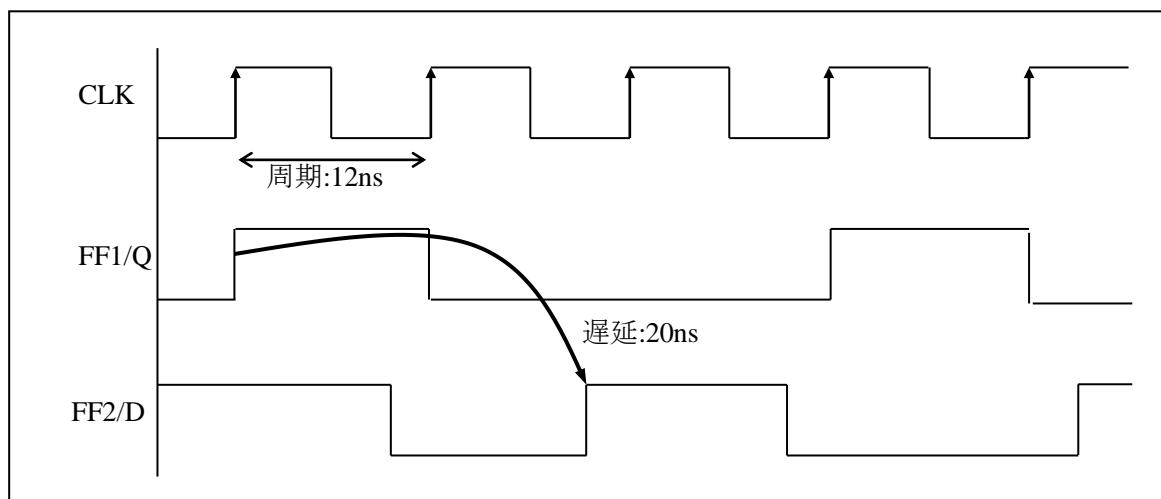

図2-7は、乗算器などの大規模回路を通るパスの例です。FF1/Q～FF2/D間のタイミングに複数サイクルを必要とする（もしくは、必要としても構わない）場合は、FF1/Q～FF2/D間のパスに対して、マルチサイクルパスを指定します。

データの受け渡しに複数サイクルが必要なパスと、サイクル数を指定して下さい。

例えば、FF1/Q～FF2/D間のパスのデータ伝播に2サイクルを必要とする場合は、図2-8のようにFF1/Q～FF2/D間に2サイクルのマルチサイクルパスを指定して下さい。

図2-7：大規模回路を通るパスの例

図2-8 マルチサイクルパス

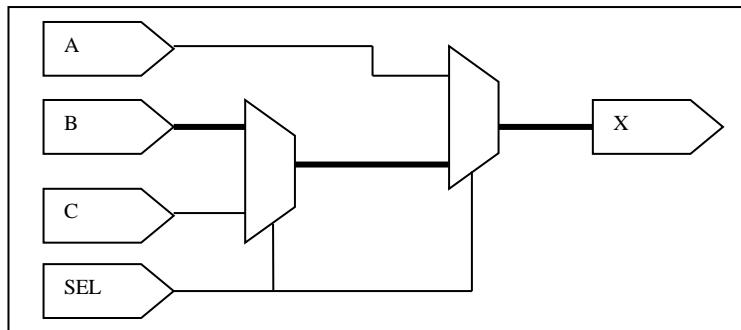

### (4) フォルスパス

論理的、仕様的にありえないパスを、わかるかぎり指定して下さい。フォルスパスは、最適化の対象外となります。例えば、図 2-9において、B～X 間のパスは論理的にありませんので、フォルスパスになります。

図 2-9 フォルスパス

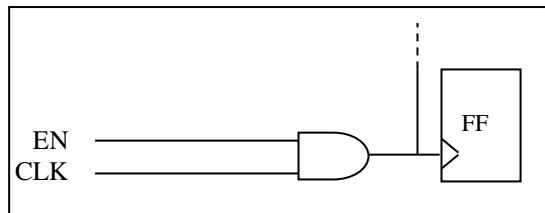

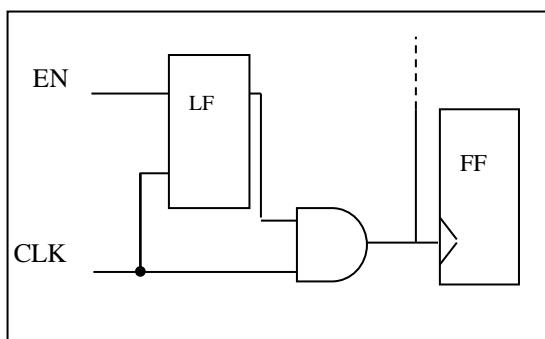

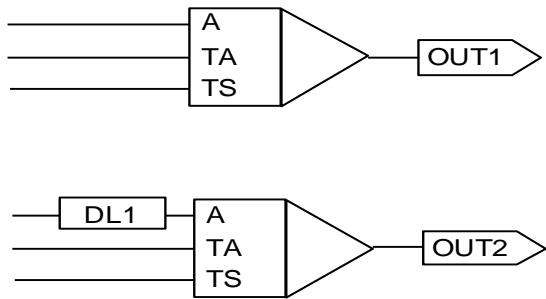

### (5) クロックゲーティング

消費電力削減などのため、クロックゲーティングを行う場合は、できるだけ上位階層で行うようにして下さい。

クロックツリー構築時にスキュート調整が必要となる場合がありますので、クロックゲーティングを行った箇所を指定して下さい。また、ラッチベース方式のクロックゲーティングセルを使用する場合は、あわせて指定して下さい。

図 2-10 : クロックゲーティングの例

図 2-11 : ラッチベース方式のクロックゲーティングの例

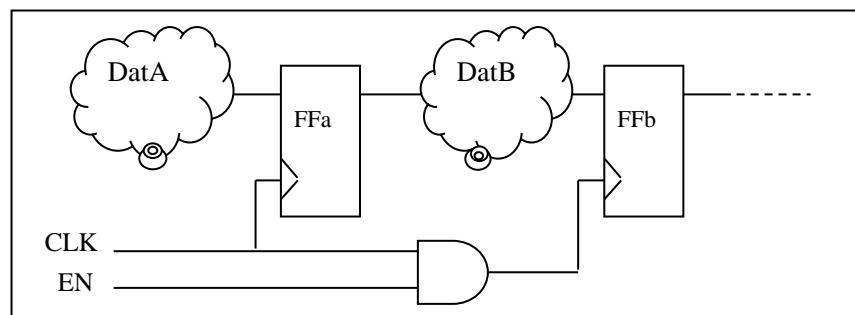

## (6) クロックゲーティングしたRTLでのシミュレーション実施時の注意点

RTLシミュレーションにおいて、図2-12のようにゲーティングされたクロックは、ゲーティングされる前のクロックとは非同期の扱いとなります。2段の非同期FF両方にゼロ遅延でクロックが入った場合は、どちらが先に処理されるかは、シミュレータ依存となります。これを回避するには、RTL中に遅延の記述を付加して、意図通りの順番で処理が行われるようにして下さい。RTL中の遅延記述は、論理合成時には無視されます。

図2-12：ゲーティングされたクロックとの接続例

```

parameter DELAY = 10;

.....

always @(posedge CLK) begin

FFa <= #(DELAY) DatA;

end

assign ENCLK = CLK & EN;

always @(posedge ENCLK) begin

FFb <= DatB;

end

```

図2-13：遅延記述の付加

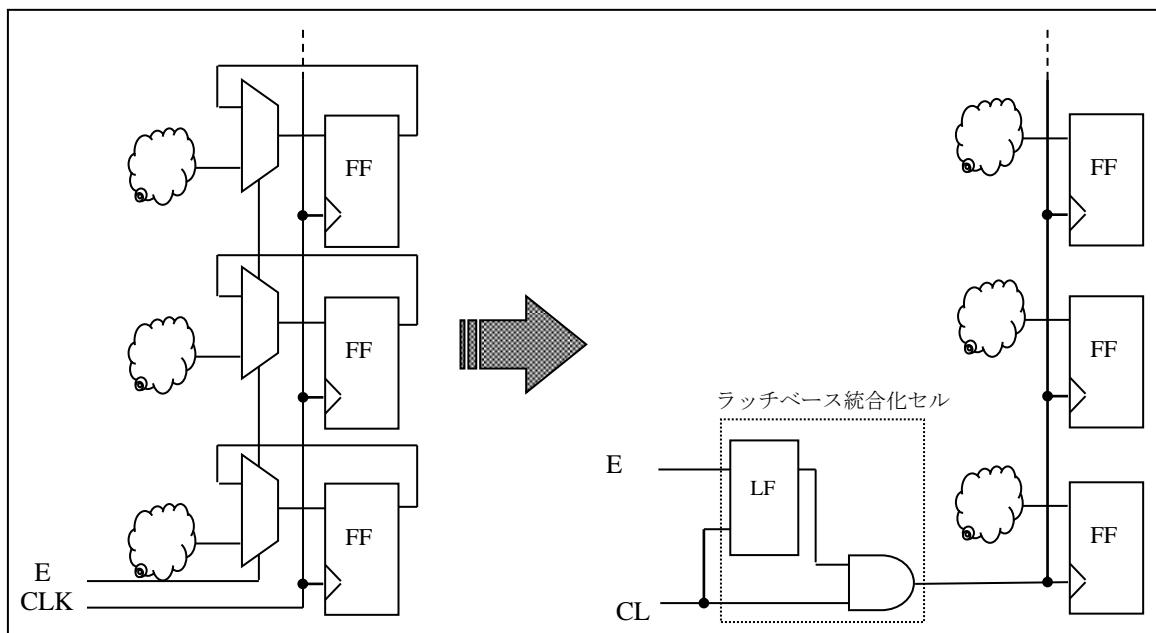

### (7) 論理合成時のクロックゲーティングセル自動挿入

セイコーエプソンでの論理合成時に、消費電力とゲートサイズの削減のため、ラッチベース方式のクロックゲーティングセルを自動挿入することが可能です。

しかし、これによりクロックスキューが増大するため、タイミング制約が厳しい場合は、調整に数日の日数を必要と致しますことをご了解下さい。

図2-14：クロックゲーティングセル自動挿入の例

### (8) セット／リセット信号について

図2-15のような、非同期セットとリセットの両端子を持つフリップフロップの有無をお知らせ下さい。非同期セット／リセット両端子を持つフリップフロップのセット／リセット間のリカバリータイムやリムーバルタイムは解析できません。また、クロック端子を持たないセルのセット／リセットは解析できません。

```

always @(posedge CLK or negedge SET or negedge RST) begin

if (!SET)

Q <= 1' b1;

else if (!RST)

Q <= 1' b0;

else

Q <= D;

end

```

図2-15：セット／リセット両端子を持つフリップフロップの記述例

## 2.4 入出力バッファの挿入

- (1) 送付いただいた「端子配列表」でのバッファの種類にしたがって、セイコーエプソンにて、入出力バッファを挿入いたします。

バッファの種類および構成については、「[第6章 入出力バッファの種類と使用上の注意](#)」を参照して下さい。

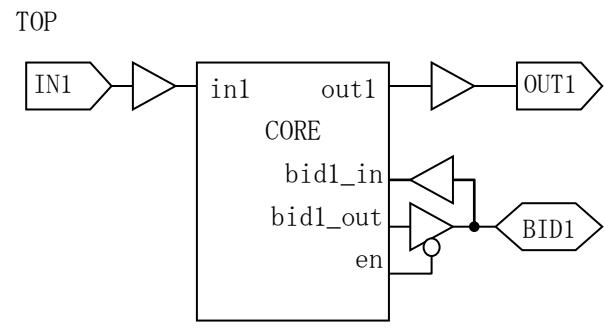

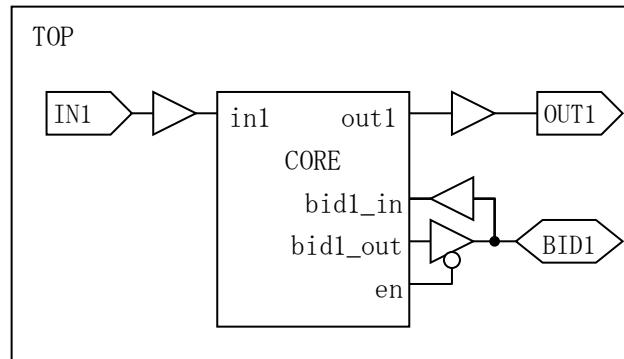

- (2) 入出力バッファは、トップモジュールを RTL 用からゲート用に置き換える方法が安全で簡単です。セイコーエプソンでゲート用のトップ モジュールを作成いたしますので、RTL 用のトップ モジュールには、入出力に関する記述のみとして下さい。具体的には、単方向ポートは、下位モジュールと 1 対 1 に接続するだけにして下さい。そして、双方向ポートの記述は、下位階層から入力信号ポートと出力信号ポートとイネーブル信号ポートを引き出して、トップ モジュール内で双方向信号を記述して下さい。

```

module TOP ( IN1, OUT1, BID1);

input IN1 ;

output OUT1 ;

inout BID1 ;

assign BID1 = (en) ? 1'b1 : bid1_out ;

CORE U_CORE( .in1(IN1),

.out1(OUT1), .bid1_in(BID1),

.bid1_out(bid1_out), .en(en) );

endmodule

```

図 2-16：トップモジュールの RTL 例

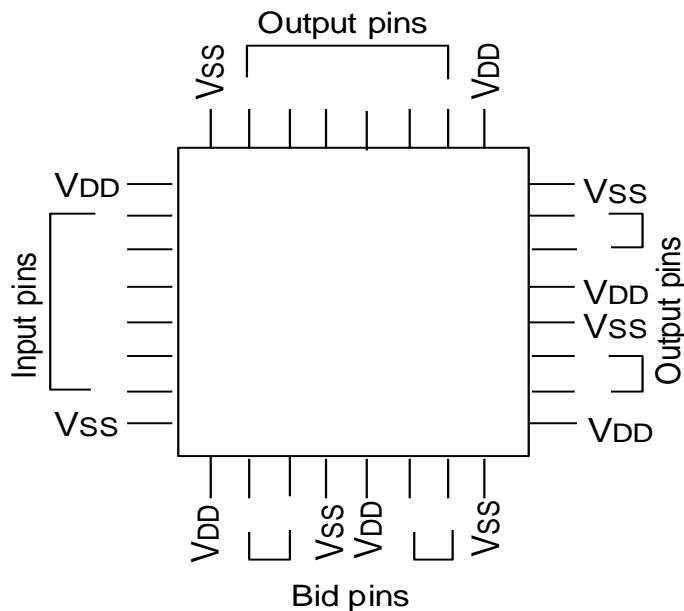

図 2-17：トップモジュール イメージ

## 2.5 RAM の記述

- (1) RAM を搭載される場合、RAM の仕様の確認をして下さい。仕様の詳細は「[第8章 RAM 仕様](#)」を参照して下さい。

- (2) RAM のライブラリはセイコーエプソンにて提供いたします。必要な RAM のサイズおよび個数を開発着手依頼書へ記入して下さい。なお、RAM の（モデル）ライブラリ提供には日数が掛る場合がございます。ご了承下さい。

- (3) お客様にて RAM を記述する場合は、そのモデルのモジュール名を連絡して下さい。

## 2.6 発振セルの記述

- (1) 発振セルを搭載される場合、発振セルの詳細、「[第5章 5.1 発振回路](#)」を参照して下さい。

- (2) RTL 記述時には、発振セルはインスタンス化して記述して下さい。

- (3) お客様が論理合成をする場合、発振セルの外部端子接続ネットにバッファが挿入されないように、入力および出力ネットに対して、set\_dont\_touch コマンドで dont\_touch 属性を付けて下さい。

### 第3章 テスト回路設計上の注意

テスト回路設計については、セイコーエプソンにてテスト容易化設計、テスト回路挿入することを推奨いたします。挿入手順については「[第1章 1.5 開発フロー](#)」を参照して下さい。

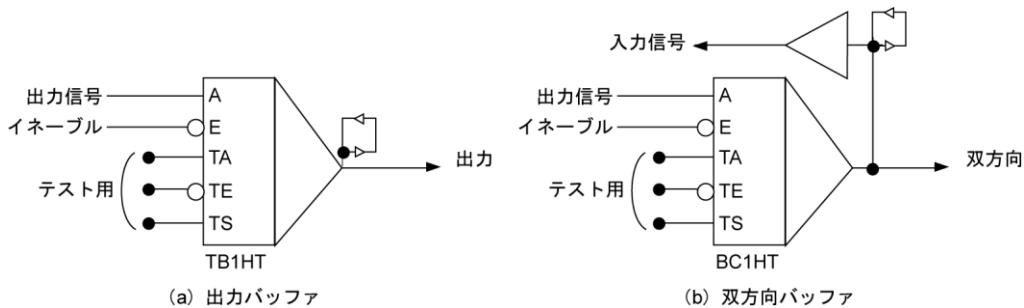

#### 3.1 推奨 DC・AC テスト回路の挿入

セイコーエプソンで、DC および AC テスト等の出荷時の試験を効率良く行えるように、推奨のテスト回路を用意し、お客様の回路に挿入させていただきます。

##### 3.1.1 推奨テスト回路 テスト回路付き入出力バッファを使用

セイコーエプソン推奨 DC および AC テスト回路については、送付いただいたお客様回路にセイコーエプソンにて挿入させていただきます。推奨テスト回路を構成する為に、テスト回路付き入出力バッファを選択いたします。

DC・AC テスト専用端子として入力端子を最低 1 本用意をお願いします。

##### 3.1.2 テスト回路付き出力バッファおよび双方向バッファのセル名

推奨テスト回路を構成する為に選択したテスト回路付き出力バッファおよび双方方向バッファのセル名は、出力バッファでは「0\*\*\*T」または「TB\*\*\*T」、双方方向バッファでは「B\*\*\*T」とセル名の末尾が「T」となります。

##### 3.1.3 お客様設計によりテスト回路挿入される場合

お客様にて、テスト回路を設計される場合、またお客様の回路設計の構成上の理由で、セイコーエプソン推奨のテスト回路をご使用いただけない場合、または、テスト機能付き出力バッファをご使用いただけない場合には、開発着手依頼時に連絡をして下さい。

## 3.2 スキャン (SCAN) 回路の挿入

スキャン回路の挿入の要否については、開発着手依頼時に連絡をお願いします。スキャン回路の挿入は、セイコーエプソンにて行ないます。

その際、スキャンテスト専用端子2本を回路の入出力端子として用意していただくことになります。

### 3.2.1 スキャン (SCAN) 回路

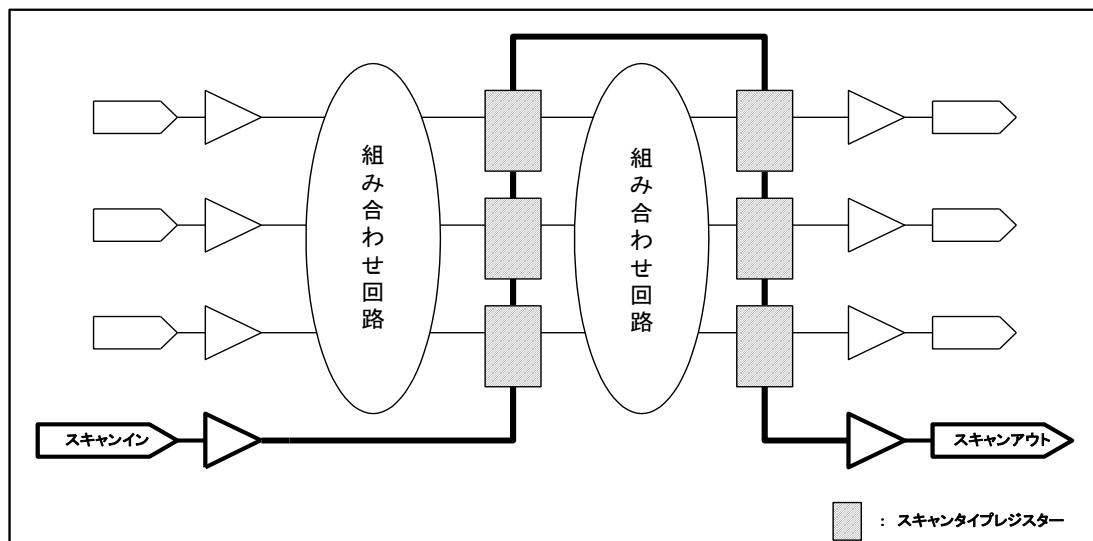

セイコーエプソンでのスキャン挿入は、設計されたデザインに存在するすべてのレジスタ (D-FF, JK-FF) をスキャンタイプレジスタに置換し、スキャンパスを構築します（フルスキャン設計）。このデザインを用いて ATPG (Auto Test Pattern Generation) を実施することにより高故障検出率のテストパターンを生成します。

図3-1 スキャン回路の例

[注意] ATPG (Auto Test Pattern Generation) が生成するテストパターンは仕様を確認するものではありません。

トランスペアレントラッチはスキャンタイプレジスタに置換されません。

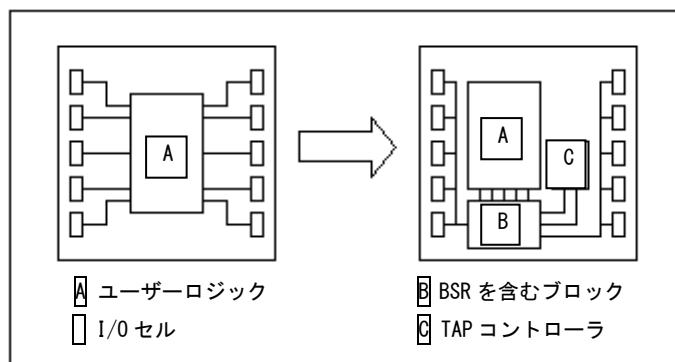

### 3.3 バウンダリスキャン (JTAG) 回路の挿入

バウンダリスキャン (JTAG) 回路の挿入の要否については、開発着手依頼時に連絡をお願いします。バウンダリスキャン (JTAG) 回路挿入は、セイコーエプソンにて行ないます。

バウンダリスキャン (JTAG) 回路挿入に際しては、論理回路の外周に、IEEE 1149.1 に準拠したバウンダリスキャン回路、および、その制御回路 (TAP コントローラ) の挿入を実施します。同時にその回路の情報を記した BSDL ファイルを提供します。

また、挿入したバウンダリスキャン用ファンクションパターンはセイコーエプソンにて作成しますので、お客さま側でのバウンダリスキャンに関するパターン作成は必要はありません。

#### 3.3.1 インストラクション

以下のバウンダリスキャンインストラクションに対応します。

表 3-1 対応可能なインストラクションコード一覧

| インストラクション      | コード                  |

|----------------|----------------------|

| SAMPLE/PRELOAD | 0...10               |

| BYPASS         | 1...11               |

| EXTEST         | 0...00               |

| CLAMP          | 任意選択可能 <sup>*1</sup> |

| HIGHZ          | 任意選択可能 <sup>*1</sup> |

| IDCODE         | 0...01               |

注) \*1: 特に要求のない場合はセイコーエプソンでアサインします。また他コードとの重複はできません。

また、インストラクションのビット幅は 2~32 ビットの範囲で選択可能です。

特に要求のない場合は、セイコーエプソンにて決定します。

#### 3.3.2 ゲート数の見積り

バウンダリスキャン回路挿入によるゲート数の増加に関しては、対応するインストラクションやビット幅などにより前後します。ゲート数の見積りには以下の情報を用いて概算して下さい。

表 3-2 ゲート数見積り (BC : ベーシックセル換算)

| バウンダリスキャンブロック   | ゲート数                                                |

|-----------------|-----------------------------------------------------|

| TAP コントローラ+雑ゲート | 約 1000 (BC)                                         |

| 入力端子            | ノーマルセル使用時：約 30 (BC／端子)<br>オブザーブ専用セル使用時：約 15 (BC／端子) |

| 2-ステート出力端子      | 約 35 (BC／端子)                                        |

| 3-ステート出力端子      | 約 65 (BC／端子)                                        |

| 双方向端子           | 約 95 (BC／端子)                                        |

#### 3.3.3 お客さま設計にてバウンダリスキャン (JTAG) 回路挿入される場合

お客さまにて JTAG 回路挿入する場合、以下の設計ルールを考慮いただくようお願いします。

### (1) DC テスト・AC テスト容易回路との共存禁止

セイコーエプソン推奨のテスト容易回路との共存はできません。バウンダリスキャンに対応する場合には、推奨 DC テスト・AC テスト回路の挿入はできません。

#### 外部端子に使用できる文字列

外部端子名は、BSDL フォーマットのルールにより、以下の制約があります。

- ① 使用可能なキャラクタは、英数字 (a~z, A~Z, 0~9) と “\_” (アンダスコア) のみ。

- ② 大文字と小文字の区別はされない。(CLK と clk は同一と見なされます)

- ③ 先頭文字は英字にする。(悪い例 OCLK, \_CLK)

- ④ アンダスコアは続けて使用しない。(悪い例 SYS\_CLK)

- ⑤ 文字列がアンダスコアで終了しない。(悪い例 CLK\_)

### (2) 専用外部端子の準備

バウンダリスキャン回路には、必ず 5 本の専用外部端子が必須です。以下のルールに基づいた外部端子挿入を行ってください。

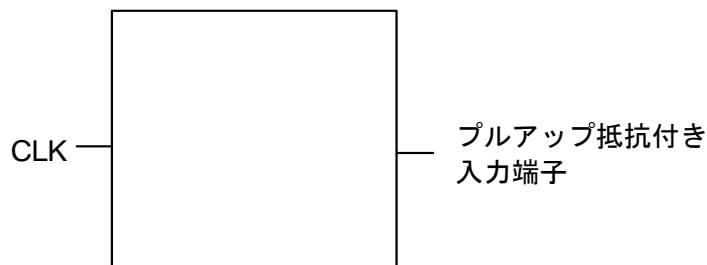

#### ① クロック (TCK)

バウンダリスキャン回路用のクロック用端子。入力セルを用意し、その出力ポートは、どこにも接続しない。

#### ② モードセレクト (TMS)

バウンダリスキャン回路用のモードセレクト用端子。入力セルを使用し、その出力ポートは、どこにも接続しない。また、この時使用する入力セルは、プルアップ付き入力セルを使用する。

#### ③ データ入力 (TDI)

バウンダリスキャン回路用のスキャンデータ入力端子。入力セルを使用し、その出力ポートは、どこにも接続しない。また、この時使用する入力セルは、プルアップ付き入力セルを使用する。

#### ④ データ出力 (TDO)

バウンダリスキャン回路用のスキャンデータ出力端子。3-ステート出力セルを使用し、その入力ポートは、プルダウンしておく。

#### ⑤ リセット (TRST)

バウンダリスキャン回路用の非同期リセット用端子。入力セルを使用し、その出力ポートは、どこにも接続しない。また、この時使用する入力セルは、プルアップ付き入力セルを使用する。

## 第3章 テスト回路設計上の注意

```

IBC U1 (.PAD(TCK)); // IBC: ノーマル入力セル

IBCP1 U2 (.PAD(TMS)); // IBCP1: プルアップ付き入力セル

IBCP1 U3 (.PAD(TDI));

IBCP1 U4 (.PAD(TRST));

TB1 U5 (.PAD(TDO), .A(1'b0), .E(1'b0)); // TB1: 3-state 出力セル

```

図3-2 専用端子記述の例 (verilog 記述)

### (3) 階層ブロックについて

ネットリストの階層ブロックは、以下のような構成としてください。また、バウンダリスキャン挿入後はTAPコントローラ等の階層ブロックが追加されます。

- I/Oセルはトップブロックに配置してください。

- その他の論理は、できるだけ一階層下のサブブロックに納めてください。

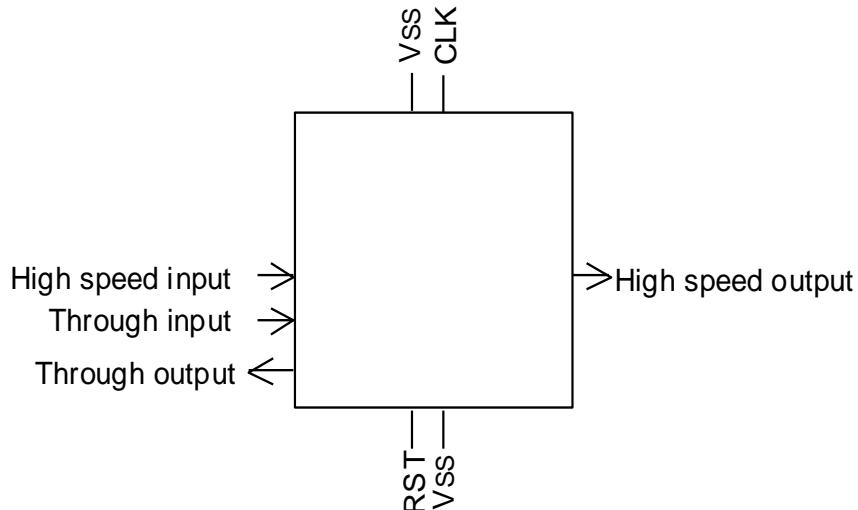

図3-3 階層ブロック構成イメージ

### (4) I/Oセル種について

下記I/Oセル種を使用している場合、対応できません。

- テストモード付きI/Oセル

- Gated入力セル

- オープンドレイン出力セル

### (5) アナログ信号を扱う外部端子

発振回路用入出力端子やアナログ信号を扱う外部端子にはバウンダリスキャンセルを挿入しません。

### (6) パッケージのピンとパッドの制約

パッケージのピンとチップ上のパッドが一対一に接続されている必要があります。

パッケージの一つのピンとチップ上の複数個のパッドを接続した場合（マルチボンディング）や複数個のパッド同士を接続した場合（マルチパッド）は対応できません。

### 3.4 RAM のテスト回路：メモリ BIST (Built in Self Test)

セイコーエプソンでは内蔵メモリのテスト回路として自己診断回路であるメモリ BIST (Built In Self Test) を用意しています。

セイコーエプソンでは、お客様より提出していただいた RTL またはゲートレベルのネットリストに対してメモリ BIST を挿入します。

### 第4章 テストパターン作成上の注意

テストパターン作成における留意点について説明します。

#### 4.1 サインオフシミュレーション向けテストパターンの作成

##### 4.1.1 テストパターンの形式

RTL シミュレーションにて、結果が得られましたら、その ASIC のプライマリ入出力信号の波形を VCD (Value Change Dump) フォーマットで提出していただきます。なお、VCD の形式につきまして、Extended VCD などの拡張された VCD は扱えません。外部双方向端子を使用する場合は、イネーブル信号の波形も出力して下さい。なお、セイコーエプソンのサインオフシミュレーションでは、HDL で記述されたテストベンチを使うことはできません。

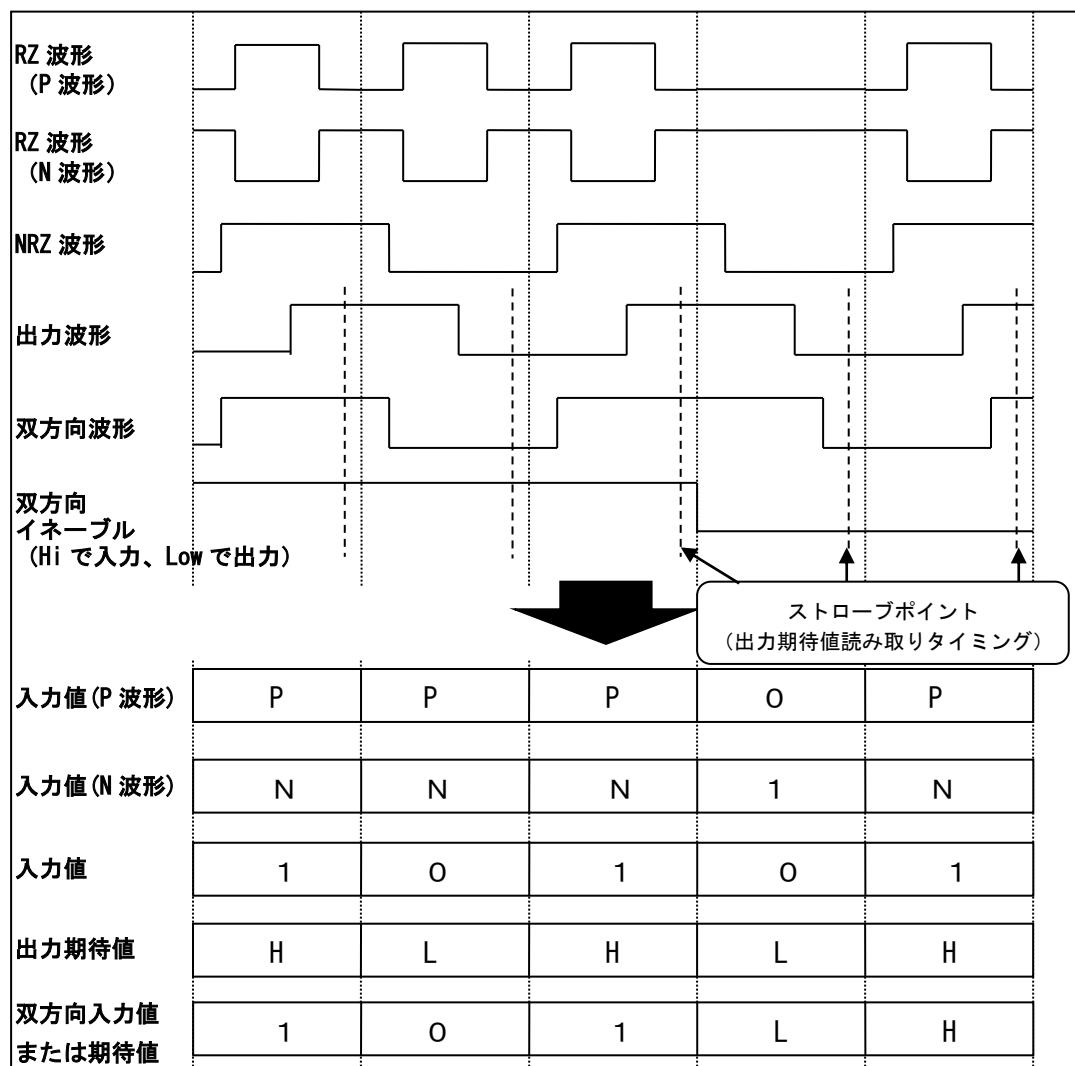

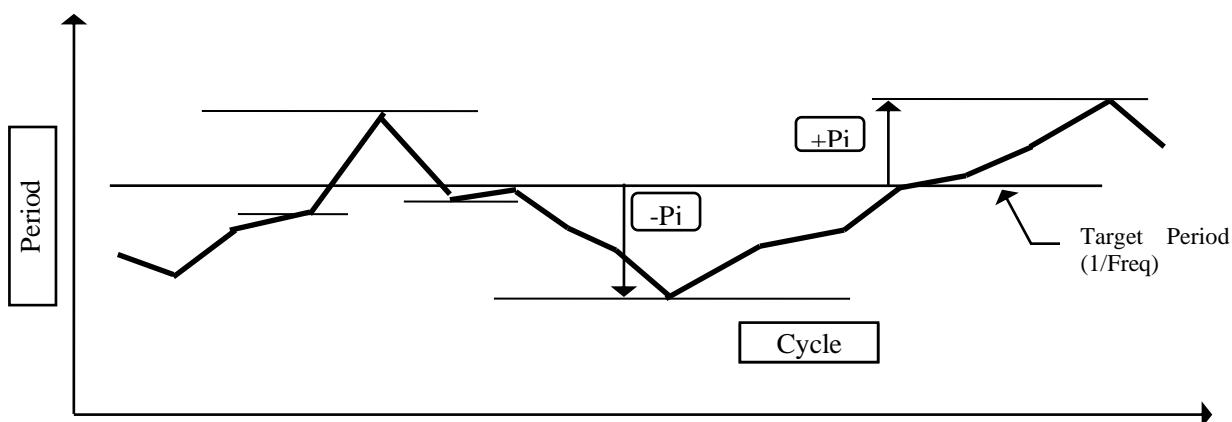

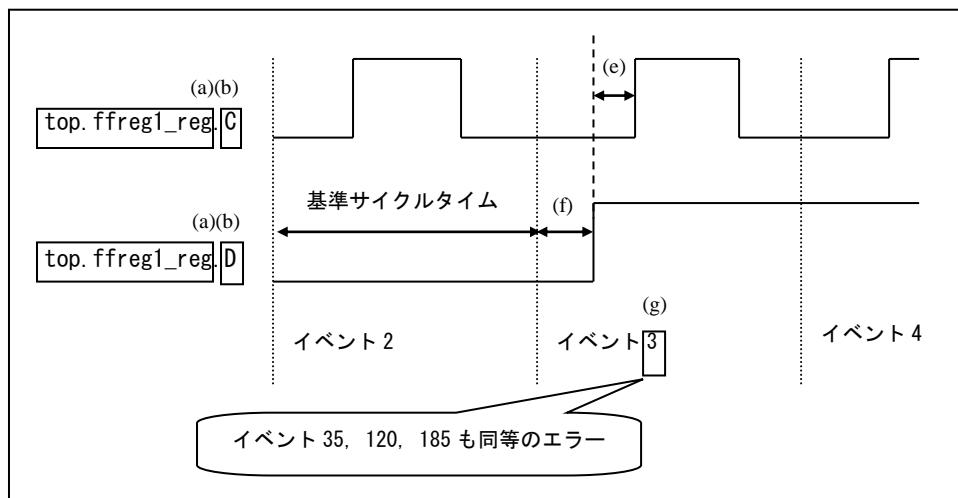

セイコーエプソンでは、VCD を APF (Advanced Press Format : セイコーエプソン独自テストパターン形式) に変換して、シミュレーションを行います。図 4-1 は、VCD から APF への変換イメージです。各波形を基準となるサイクルタイム毎にサンプリングした信号値に置き換えます。APF のサンプルを図 4-2 に示します。

図 4-1：波形から APF への変換イメージ

```

# Create by Netlist Rule Check Utility at Fri Oct 6 11:42:55

$DESIGN SAMPLE

$RATE      100000 ← レート（サイクル） 100ns

$RESOLUTION 0.001ns

$STROBE    85000 ← ストローブポイント 85ns

##HEX

##ENDHEX

$IOCONT

inst01.Z0   E0     BID1

inst02.Z0   E0     BID2 ← 双方向信号をコントロールしている内部ノード

$ENDIOCONT

$NODE

RST        I 10000 ← 入力遅延 10ns の入力端子

CLK        P 50000 90000 ← 入力遅延 50ns、幅 40ns の RZ 波形 (P 波形) 入力端子

XCLK       N 50000 90000 ← 入力遅延 50ns、幅 40ns の RZ 波形 (N 波形) 入力端子

INPUTB     IU 0

INPUTC     IU 0 ← 入力遅延 0ns のプルアップ付き入力端子

#

OUTA      0 ← 出力端子

OUTB      0

#

BID1      B 0 ← 入力遅延 0ns の双方向端子

BID2      B 30000

#

$ENDNODE

$PATTERN

#          RCXIIOBB

#          SLCNNUUII

#          TKLPPTDD ← 入力／出力信号名 (コメント行)

#          KUKAB12

#          TT

#          BC

#

#          IPNIIIOBB

#          1PN11XZ1L ← イベント番号 (パターンの周期番号)

#          1PN01XZ0L

#          1PN11XH1L

#          10101LHL1

#          1PN11LHH0

$ENDPATTERN

```

注：信号中に使える文字

O : 入力 Low    1 : 入力 High    P : P型 RZ 波形入力    N : N型 RZ 波形入力

L : 出力 Low    H : 出力 High    Z : 出力ハイインピーダンス    X : Unknown

図 4-2 : APF のサンプル

### 4.1.2 テストパターンの制限

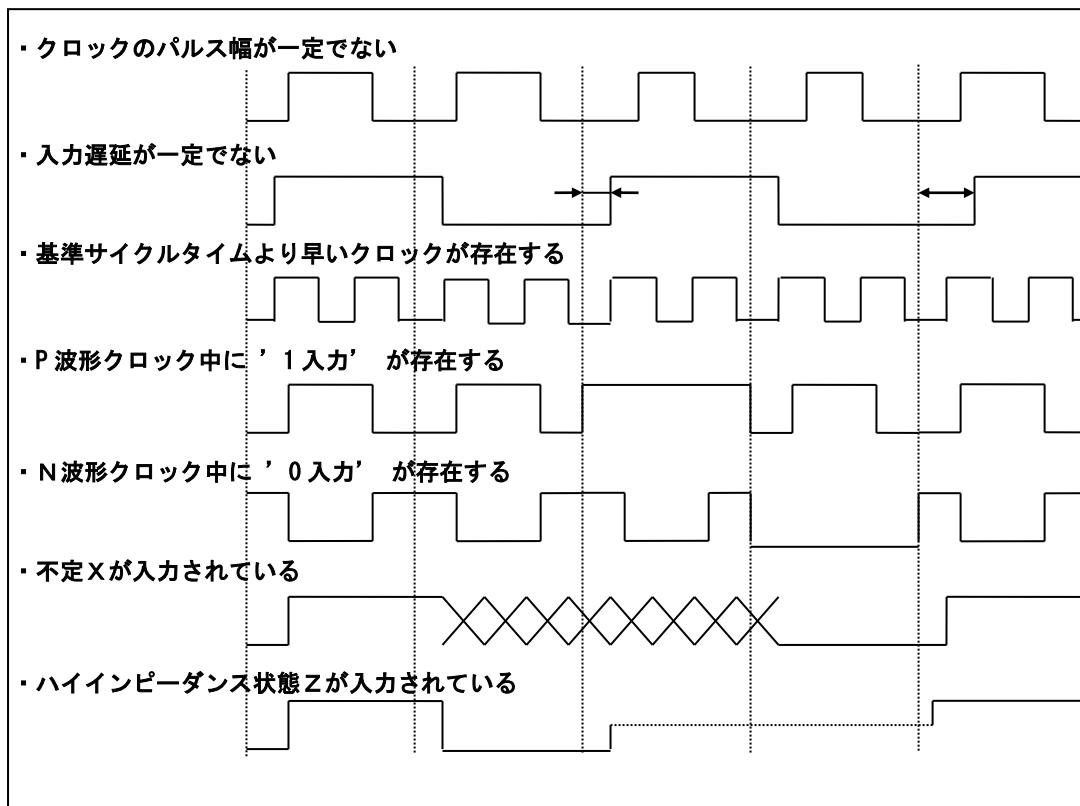

セイコーエプソンでは、サイクルベースでのシミュレーションを行っています。つきましては、以下の制限を満足するようにして下さい。入力信号および出力信号のタイミングを厳密にチェックしたいときは、STAによる解析が必要となります。

- (1) 同一 VCD 内では、クロックの周期やパルス幅を変化させないで下さい。

- (2) 同一 VCD 内では、クロック間のスキュー、クロックと入力信号の関係を変化させないで下さい。サイクル単位における入力遅延を一定にして下さい。

- (3) 同一 VCD 内に、周期の異なるクロックが存在する場合、もっとも早いクロックの周期を基準サイクルタイムとし、他クロックの周期は基準サイクルタイムの倍数となるようにして下さい。

- (4) P 波形クロックを止めるときは 0 入力状態にして下さい。

- (5) N 波形クロックを止めるときは 1 入力状態にして下さい。

- (6) 不定(X)や、ハイインピーダンス状態(Z)を入力することはできません。

図 4-3 に使用できない入力波形の例を示します。

図 4-3： 使用できない入力波形の例

#### 4.1.3 外部双方向端子のイネーブル信号

外部双方向端子を使用する場合は、イネーブル信号の波形を合わせて出力して下さい。その際、一つの外部双方向端子は、必ず一つのイネーブル信号で動作するようにして下さい。RTL 内の双方向イネーブル信号が複数信号の論理で構成されている場合（図 4-4）は、一つの信号に置き換えて下さい（図 4-5）。

```

inout data;

wire data, cs, rd;

.....

assign data = (cs & rd) ? outdata : 1'bz;

```

図 4-4：複数信号の論理で構成された双方向イネーブルの例

```

inout data;

wire data, cs, rd, dataen;

.....

assign dataen = cs & rd;

assign data = dataen ? outdata : 1'bz;

```

図 4-5：一つの信号に置き換えた例

### 4.2 製品出荷テスト向けのテストパターン作成

お客様より受領したテストパターンを基に、セイコーエプソンにて製品の出荷テスト用のテストパターンを作成します。IC テスターの能力などによって制限があり、IC の仕様確認用のテストパターンを以下の制限に合うよう、変更して作成いたします。この際、テストパターンが非常に長い場合や、テストパターンの本数が非常に多い場合など、IC テスターへの適用が困難な場合には、テストパターンの調整を行うことがありますのでご了承下さい。

製品出荷テスト向けに変換する必要が無いテストパターンや、製品出荷テスト専用のテストパターンがある場合は、弊社営業担当までご連絡下さい。

#### 4.2.1 使用可能な入力波形

テストパターンは、通常 0/1 の集まりですが、シミュレーション実行時や IC テスターでのテスト時においては、入力波形に遅延を与えたいたり、パルスを作成したりすることができます。テストパターン作成時に使用できる波形には次の 2 つがあります。

##### (1) NRZ (Non Return to Zero)

通常はクロック以外の信号に使用します。1 レート内で 1 回変化することができ、遅延を与えることができます。

##### (2) RZ (Return to Zero)

クロック信号などに使用します。1 レート内で正または負のパルスを発生することができる所以、効率よくクロック信号を作ることができます。NRZ 同様、遅延を与えることができます。

#### 4.2.2 テストパターンの制限

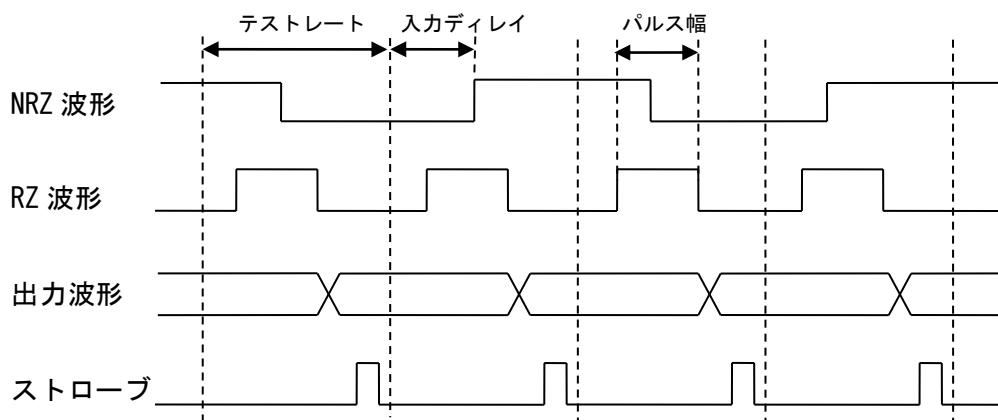

テストパターン作成の制限を説明するため、図 4-6 にテストレート、入力ディレイ、パルス幅について示します。

図 4-6 テストパターンにおけるタイミング

テストパターン作成での各種制限を、以下の(1)～(5)に示します。

(1) テストレートおよびイベント数の制限

|                      |                                   |

|----------------------|-----------------------------------|

| テストレート :             | 100nsec 以上、1nsec 単位（標準 : 200nsec） |

| テストパターン1本あたりのイベント数 : | 256K イベント以内                       |

| テストパターンの本数 :         | 30 本以内                            |

| テストパターンの総イベント数 :     | 1M イベント以内                         |

(2) 入力ディレイの制限

(a) 入力ディレイの範囲

入力ディレイの値は、以下の範囲で与えて下さい。また、ストローブポイントの制限については「[4.2.2. \(5\) ストローブの制限](#)」を参照して下さい。

$$0\text{nsec} \leq \text{入力ディレイ値} < \text{ストローブポイント}$$

(b) 入力ディレイの位相差

入力ディレイに位相差を設ける場合は、3nsec 以上の差をつけて下さい。

(c) 入力ディレイの種類

入力ディレイの値は、ひとつのテストパターンで、8 種類以内にして下さい。ここで、0nsec 遅延も 1 種類と數えます。また、ディレイ値が同じでも、波形 (RZ と NRZ) やパルス幅が異なれば、異なる種類として数えます。

(3) パルス幅の制限

RZ 波形のパルス幅は、15nsec 以上として下さい。

(4) 入力波形フォーマットの制限

入力波形は、0、1、P、N の値を取ることができます。ここで、P と N は、RZ 波形におけるパルスの入力を表しています。また、P と N の値はひとつのテストパターン内で、同一の端子に対して 0 と P または、1 と N の組み合わせ以外を扱うことができません。

さらに、双方向端子におきましては、ひとつのテストパターン内で、出力状態が存在しない場合のみ、RZ 波形を入力することができます。

(5) ストローブの制限

- (a) ストローブはテストパターンごとに 1 種類のみ定義可能です。

- (b) ストローブの最小値は、すべてのイベントにおいて、与えられた入力信号によってすべての出力信号が変化し終わってから、30nsec 以上後にして下さい。

- (c) ストローブの最大値は、(テストレート-15nsec) よりも小さくして下さい。

- (d) ストローブは、1nsec 単位で設定して下さい。

## 第4章 テストパターン作成上の注意

---

### 4.2.3 DC・AC テストパターンの作成について

DC および AC テストについては、挿入させていただいたセイコーエプソン推奨テスト回路に対して DC および AC テストパターン作成を、セイコーエプソンにて行います。

お客様にて DC・AC テスト回路挿入される場合は、「[付録 A3. DC・AC テストパターン](#)」を参照いただき、テストパターン作成をお願いします。

#### 4.2.4 ハイインピーダンス状態の扱いに関する注意点

入力端子のハイインピーダンス状態は、動作を保証できないため、シミュレーション時に禁止事項としています。

また、ハイインピーダンスに関する対策としまして、プルアップ／プルダウン抵抗付きの I/O セルを用意しています。ただし、下記の理由からシミュレーションにおいてプルアップ／プルダウン抵抗については伝播遅延を考慮していません。したがって、正確な動作をシミュレーションできないことから、プルアップ／プルダウン抵抗付きの双方向端子の入力モードにおける未入力状態も、シミュレーション時に禁止事項としています。

<プルアップ／プルダウン抵抗の伝播遅延を考慮していない理由について>

- (1) 外部負荷容量により遅延が大きく変動するため

- (2) プルアップ／プルダウン抵抗は、ハイインピーダンス状態によるフローティングゲートを回避することのみを目的としているため

上記内容を、シミュレーション前にツールによりテストパターンのチェックを行います。ハイインピーダンス状態を表す “Z” が検出された場合には、テストパターンの修正が必要です。

この時、前記理由からプルアップ／プルダウン抵抗付きの双方向端子での “Z” も警告しています。また、オープンドレインの双方向端子も同様です。

<対策>

テストパターンのチェックで双方向端子のすべての “Z” をエラーで警告します。(3-ステート、オープンドレイン等の出力端子で表現される “Z” は除きます)

このエラーを回避する手段として、前記双方向端子の “Z” はプルアップ抵抗付きであれば “1” を、プルダウン抵抗付きであれば “0” に置き換えるユーティリティプログラムをご用意しています。

双方向端子において、“X” が表現されている時間に入力モードとなった場合は、プルアップ／プルダウン抵抗の有無に関わらず、シミュレーションでは “X” を入力信号として伝播し、シミュレーション結果には “?” を表示します。この “?” は修正いただき、改めてシミュレーションを行います。

表 4-1 シミュレーションにおける双方向端子の信号の扱いについて

| 入力パターン   | 入出力モード | シミュレーション | シミュレーション結果<br>(出力パターン) |

|----------|--------|----------|------------------------|

| “X”      | 入力モード  | “X”      | “?”                    |

| “1”、 “H” | 入力モード  | “1”      | “1”                    |

| “0”、 “L” | 入力モード  | “0”      | “0”                    |

### 第5章 回路設計上の注意

発振回路、外部バスとの競合防止、メタステーブル対策での留意点について説明します。

#### 5.1 発振回路

##### 5.1.1 発振回路の構成

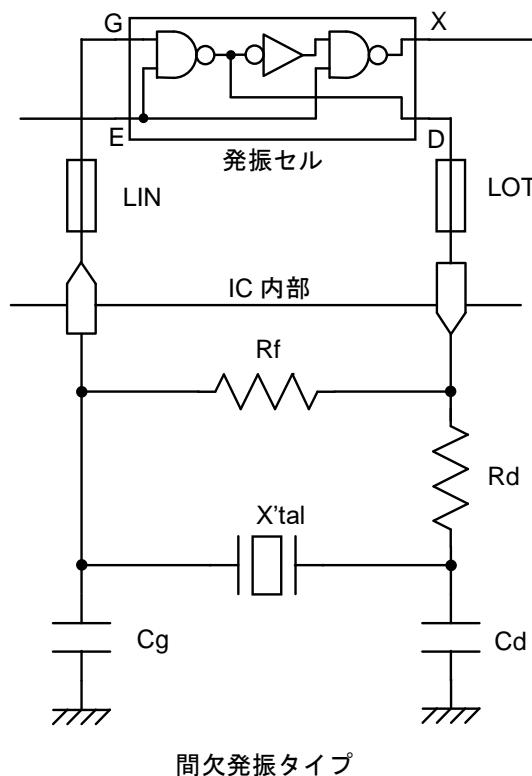

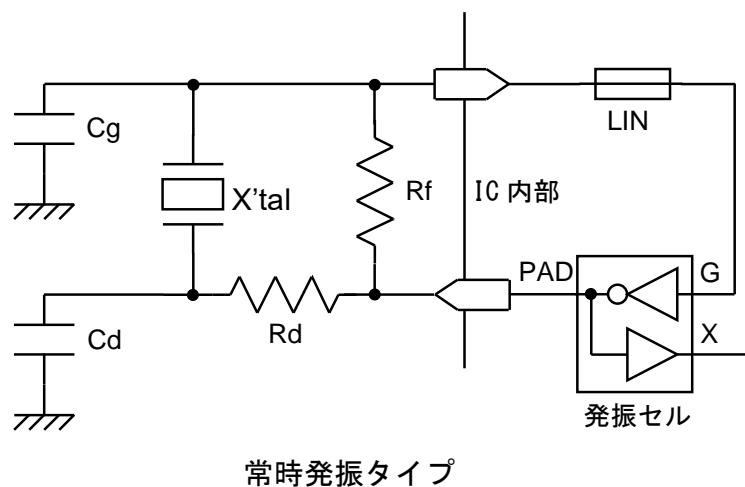

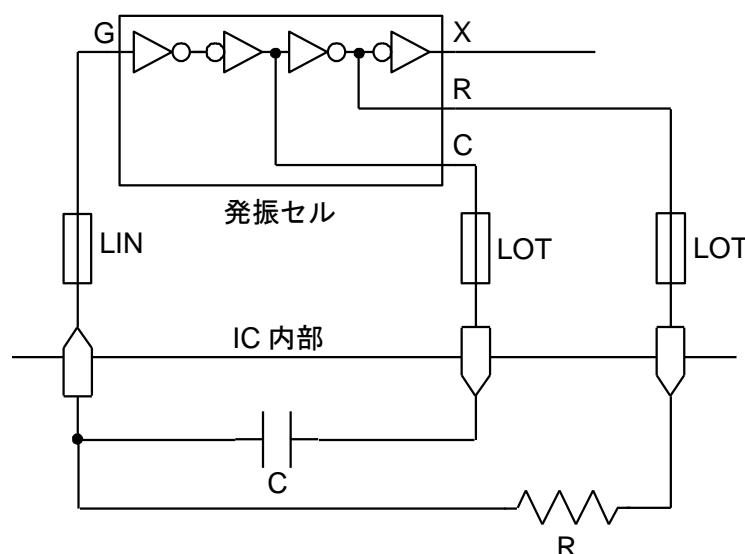

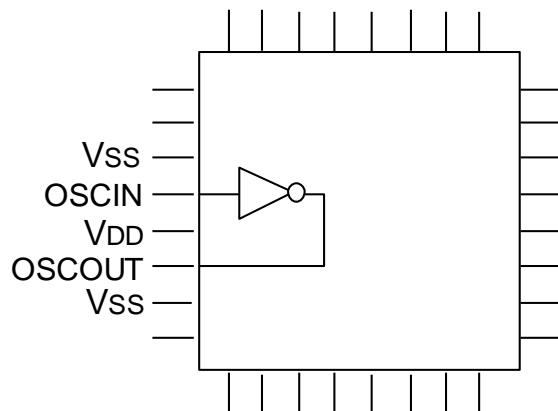

S1L5V000 シリーズでは、発振回路を構成するための発振専用セルに、水晶発振用と CR 発振用を用意しています。

水晶発振用には IC 内部セル領域に配置される間欠発振タイプ（図 5-1）と、I/O セル領域に配置される常時発振タイプ（図 5-2）があります。間欠発振タイプを常時発振タイプとして使用する場合は、発振セルの端子 E を ‘H’ として使用ください。

CR 発振回路は図 5-3 となります。

発振回路構成例は以下のようになります。

図 5-1 水晶発振回路（内部セル領域に配置）

図5-2 水晶発振回路 (I/Oセル領域に配置)

図5-3 CR発振回路

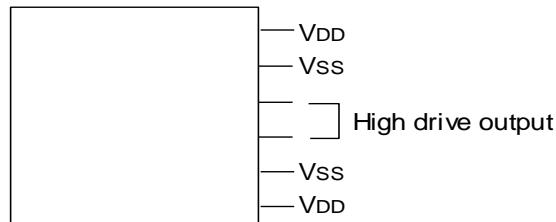

### 5.1.2 発振回路を使用する場合の注意

#### (1) 端子配列

- ① 発振回路の入出力端子は隣接させて配置し、その両側を電源端子 ( $V_{DD}$ 、 $V_{SS}$ ) を挟んで下さい。

- ② 発振回路の入出力端子は、他の出力端子から離して配置して下さい。特に、発振波形と同相あるいは逆相の出力からは離して配置して下さい。このような出力はパッケージの対辺に配置するようにして下さい。

- ③ 発振回路の入出力端子は、クロックなど高速で動作する入力端子から離して配置して下さい。

- ④ 発振回路の入出力端子はできるだけパッケージの辺の中心に配置して下さい。

- ⑤ 発振回路を複数搭載する場合は、干渉を避けるために発振回路は離して配置して下さい。

- ⑥ BGA 等エリアアレイパッケージを使用する場合の端子配列は弊社営業担当までお問い合わせ下さい。

#### (2) 発振セル選択の目安

発振可能周波数は、およそ数十 kHz～数十 MHz 程度です。詳細は弊社営業担当までお問い合わせ下さい。

#### (3) 外付け抵抗、コンデンサ値の設定

発振特性は、その回路の構成要素 (IC、X' tal、Rf、Rd、Cg、Cd、基板) に依存します。したがって、外付けの Rf、Rd や Cg、Cd の値は、実際の基盤上に各部品を実装させた状態で十分な評価を行い最適なものを選んで下さい。

#### (4) 保証のレベル

発振特性は、その回路の構成要素 (IC、X' tal、Rf、Rd、Cg、Cd、基板) に依存します。したがって、発振動作・特性についてはセイコーエプソンでは保証できません。発振特性についてはお客様において ES サンプルで十分な評価を行って確認していただく必要があります。

#### (5) IC 内部回路へのクロック信号について

生成されるクロック信号(発振セル X の信号)の波形を予め特定することは困難であるため、クロックの周波数以外は論理シミュレータで正確に扱うことができません。例えば、実際の IC でのクロックデューティーはシミュレーション結果と異なります。

よって、生成されたクロック信号の立上りと立下りの両方を利用した回路を使用することは避けて下さい。シミュレータでの検証結果と一致しないような不具合を持った回路ができる可能性があります。生成されたクロック信号の立上りあるいは立下りのいずれか一方を利用した回路を使用して下さい。

### 5.1.3 発振セルの RTL 記述について

発振セルの RTL 記述については、「[第2章 2.6 発振セルの記述](#)」を参照をして下さい。

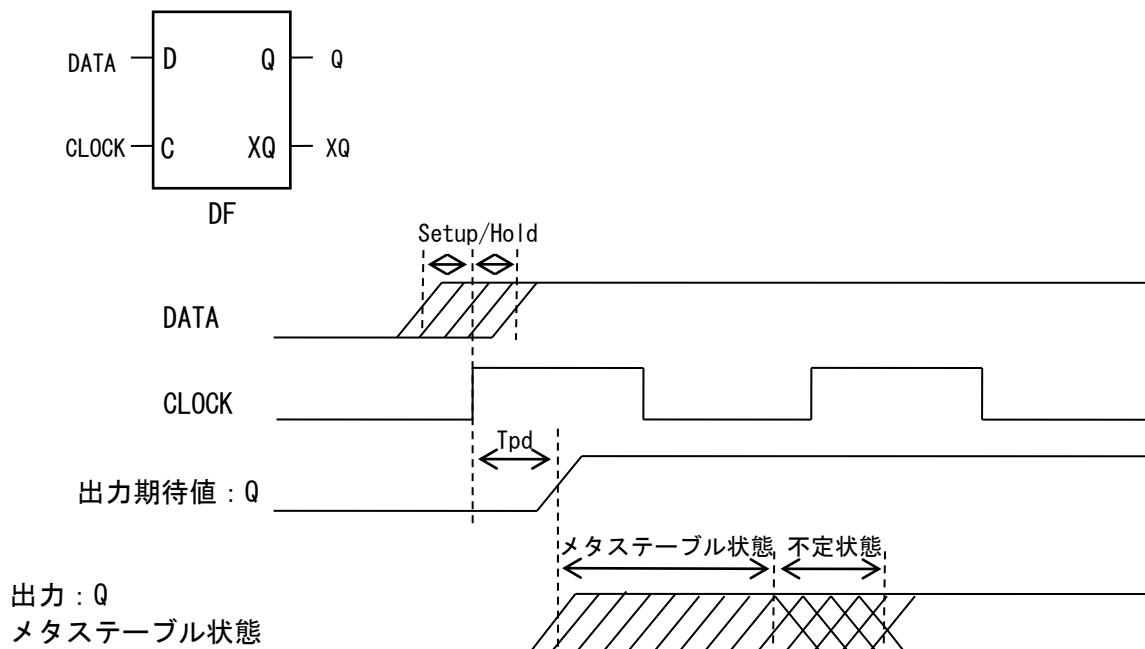

## 5.2 メタステーブル (Metastable)

FF やラッチセルの入力信号において、クロックとデータのセットアップ、ホールド時間、クロックとセットあるいはリセットのリリース、リムーバル時間のタイミング規格に違反している場合、FF やラッチセルの出力信号は、ある一定の時間、発振または、“HIGH” レベルでも “LOW” レベルでもない中間電位になる可能性があります。このような出力信号の不安定な状態をメタステーブル (Metastable) と呼びます。

メタステーブル状態は、ある時間経過後に終了し、出力は “HIGH” あるいは “LOW” レベルの状態に確定します。しかし、確定したレベルはデータの入力のレベルには依存しませんので、出力は不定状態となります。

セットアップ／ホールド、リリース／リムーバルのタイミングの規格が満足できない場合は、回路全体にこのような不安定な状態が伝播しないような回路上の対策をとって下さい。

セットアップ／ホールド、リリース／リムーバル時間の規格値を満足できなかった場合のメタステーブル時間の目安値を、次のように定義しています。

$$\text{メタステーブル時間} = T_{pd} \times 6$$

$T_{pd}$  : FF、ラッチセルのクロック、セット、リセット信号のアクティブエッジから出力変化までの遅延時間

なお、論理シミュレーションではこのようなメタステーブル状態での遅延値は考慮されませんので、必ずタイミング規格を満足した設計をして下さい。

図 5-4 DF のメタステーブル状態

### 第6章 入出力バッファの種類と使用上の注意

#### 6.1 入出力バッファの種類及び選択

S1L5V000 シリーズでは入力インターフェースレベル、シュミットトリガ入力の有無、プルアップ／プルダウン抵抗の有無、出力駆動能力、ノイズ対策対応の有無等に対応した、入出力バッファを用意しています。以下の項目を考慮して、所望の入出力バッファを選択して下さい。

出力駆動能力およびプルアップ／プルダウン抵抗については 「[1.3.3 電気的特性 表 1-5、表 1-6](#)」 及び 「[付録 A4 入出力バッファ特性](#)」 を参照して下さい。

##### 6.1.1 入出力バッファの選択

入出力バッファ選択の為のツールを用意しています。以下 URL を参照して下さい。

デザインガイド補足資料：S1L5V000 シリーズ入出力バッファの一覧表

[www.epson.jp/prod/semicon/products/asic/gatearray/s1l5v\\_io.htm](http://www.epson.jp/prod/semicon/products/asic/gatearray/s1l5v_io.htm)

##### 6.1.2 バスホールド機能つき入出力バッファ

出力端子あるいは双方向端子がハイインピーダンス状態にならないよう、出力端子のデータを保持するバスホールド機能付きの入出力バッファを用意しています。

ただし、通常の動作に影響を与えないようにバスホールド回路の保持能力は抑えてありますので、保持されているデータ出力を有効なデータとして使用しないで下さい。外部から何らかのデータが供給された場合には容易にデータは変化します。

バスホールド回路の出力保持電流につきましては、「[1.3.3 電気的特性 表 1-5、表 1-6](#)」 を参照して下さい。

図 6-1 バスホールド回路シンボルの一例

## 6.2 入出力バッファの構成

S1L5V000シリーズは、電源電圧  $V_{DD}=5.0V$  または  $V_{DD}=3.3V$  の単一電源で使用することができます。

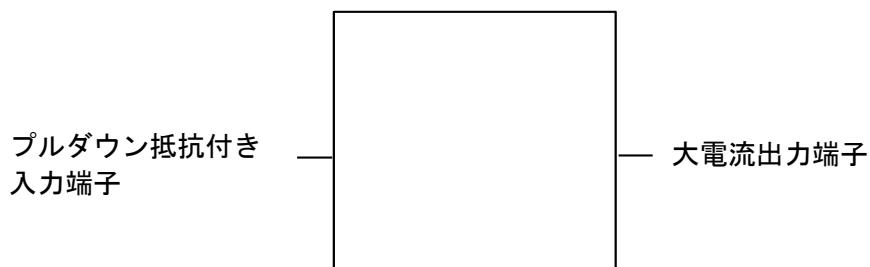

### 6.2.1 入力バッファ

入力バッファは 5.0V および 3.3V で使用することができます。

$V_{DD}=5.0V$  の場合および  $V_{DD}=3.3V$  の場合の入力バッファについて以下説明をします。

入力バッファは、入力回路のみで構成されています。

表 6-1 に入力バッファのプルアップ／プルダウン抵抗値を示します。

表 6-1 プルアップ／プルダウン抵抗の各電圧における規格値

| プルアップ／プルダウン抵抗の種類 | 抵抗値           |               | 単位 |

|------------------|---------------|---------------|----|

|                  | $V_{DD}=5.0V$ | $V_{DD}=3.3V$ |    |

| Type 1           | 60            | 100           | kΩ |

| Type 2           | 120           | 200           | kΩ |

表 6-2、表 6-3 に  $V_{DD}=5.0V$  の場合の入力バッファの一覧を示します。

表 6-2 入力バッファ一覧 ( $V_{DD}=5.0V$ )

| セル名 <sup>*1</sup> | 入力レベル      | プルアップ／プルダウン抵抗 <sup>*2*3</sup> の有無 |

|-------------------|------------|-----------------------------------|

| IBT               | TTL        | なし                                |

| IBTP#             | TTL        | プルアップ抵抗 (60kΩ、120kΩ)              |

| IBTD#             | TTL        | プルダウン抵抗 (60kΩ、120kΩ)              |

| IBC               | CMOS       | なし                                |

| IBCP#             | CMOS       | プルアップ抵抗 (60kΩ、120kΩ)              |

| IBCD#             | CMOS       | プルダウン抵抗 (60kΩ、120kΩ)              |

| IBS               | TTL シュミット  | なし                                |

| IBSP#             | TTL シュミット  | プルアップ抵抗 (60kΩ、120kΩ)              |

| IBSD#             | TTL シュミット  | プルダウン抵抗 (60kΩ、120kΩ)              |

| IBH               | CMOS シュミット | なし                                |

| IBHP#             | CMOS シュミット | プルアップ抵抗 (60kΩ、120kΩ)              |

| IBHD#             | CMOS シュミット | プルダウン抵抗 (60kΩ、120kΩ)              |

注) \*1 : 「#」は 1 または 2 で、1 は Type 1、2 は Type 2 の抵抗値に対応しています。

\*2 : プルダウン／プルアップの抵抗値の詳細は「[表 1-5](#)」および「[付録 A4.1.6](#)」を参照下さい。

\*3 : 入力バッファ特性のグラフは付録 A4.1.2 を参照下さい。

## 第6章 入出力バッファの種類と使用上の注意

---

表 6-3 入力レベルシフター一覧 ( $V_{DD}=5.0V$ )

| セル名 <sup>*1</sup> | 入力レベル                    | プルアップ／プルダウン抵抗 <sup>*2*3</sup> の有無 |

|-------------------|--------------------------|-----------------------------------|

| IDC<br>IDCD#      | CMOS<br>CMOS             | なし<br>プルダウン抵抗 (60kΩ、120kΩ)        |

| IDH<br>IDHD#      | CMOS シュミット<br>CMOS シュミット | なし<br>プルダウン抵抗 (60kΩ、120kΩ)        |

注) \*1 : 「#」は1または2で、1はType 1、2はType 2の抵抗値に対応しています。

\*2 : プルダウンの抵抗値の詳細は「[表 1-5](#)」および「[付録 A4. 1. 6](#)」を参照下さい。

\*3 : 入力バッファ特性のグラフは付録 A4. 1. 2 を参照下さい。

表 6-4、表 6-5 に  $V_{DD}=3.3V$  の場合の入力バッファの一覧を示します。

表 6-4 入力バッファ一覧 ( $V_{DD}=3.3V$ )

| セル名 <sup>*1</sup>     | 入力レベル                                     | プルアップ／プルダウン抵抗 <sup>*2*3</sup> の有無                    |

|-----------------------|-------------------------------------------|------------------------------------------------------|

| IBC<br>IBCP#<br>IBCD# | LVTTL<br>LVTTL<br>LVTTL                   | なし<br>プルアップ抵抗 (100kΩ、200kΩ)<br>プルダウン抵抗 (100kΩ、200kΩ) |

| IBH<br>IBHP#<br>IBHD# | LVTTL シュミット<br>LVTTL シュミット<br>LVTTL シュミット | なし<br>プルアップ抵抗 (100kΩ、200kΩ)<br>プルダウン抵抗 (100kΩ、200kΩ) |

注) \*1 : 「#」は1または2で、1はType 1、2はType 2の抵抗値に対応しています。

\*2 : プルダウン／プルアップの抵抗値の詳細は「[表 1-6](#)」を参照下さい。

\*3 : 入力バッファ特性のグラフは「[付録 A4. 2. 2](#)」を参照下さい。

表 6-5 入力レベルシフター一覧 ( $V_{DD}=3.3V$ ) (5V を入力可能です)

| セル名 <sup>*1</sup> | 入力レベル                      | プルアップ／プルダウン抵抗 <sup>*2*3</sup> の有無 |

|-------------------|----------------------------|-----------------------------------|

| IDC<br>IDCD#      | LVTTL<br>LVTTL             | なし<br>プルダウン抵抗 (100kΩ、200kΩ)       |

| IDH<br>IDHD#      | LVTTL シュミット<br>LVTTL シュミット | なし<br>プルダウン抵抗 (100kΩ、200kΩ)       |

注) \*1 : 「#」は1または2で、1はType 1、2はType 2の抵抗値に対応しています。

\*2 : プルダウンの抵抗値の詳細は「[表 1-6](#)」を参照下さい。

\*3 : 入力バッファ特性のグラフは「[付録 A4. 2. 2](#)」を参照下さい。

### 6.2.2 出力バッファ

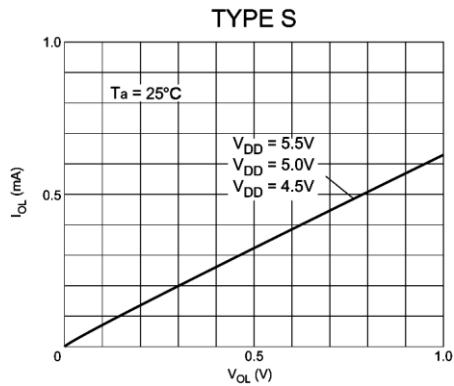

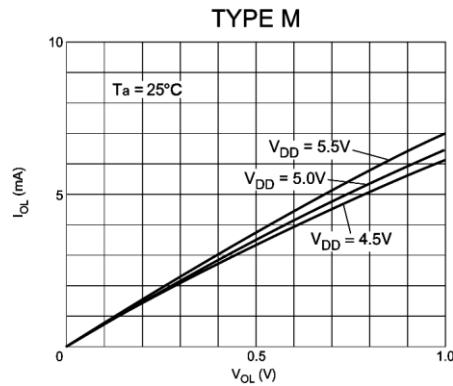

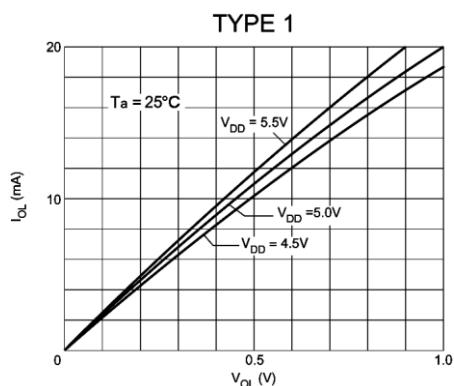

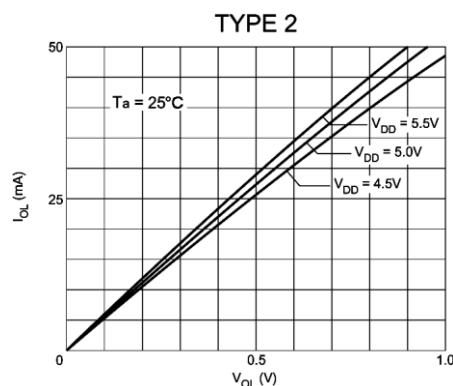

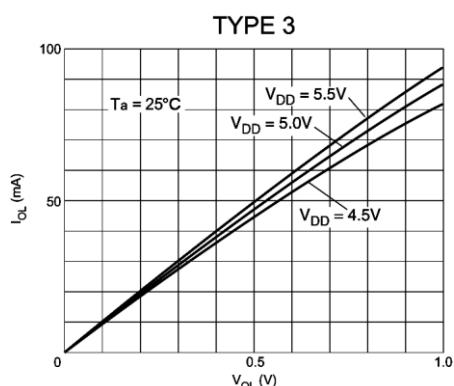

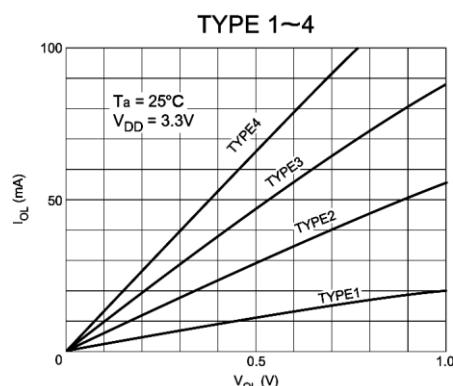

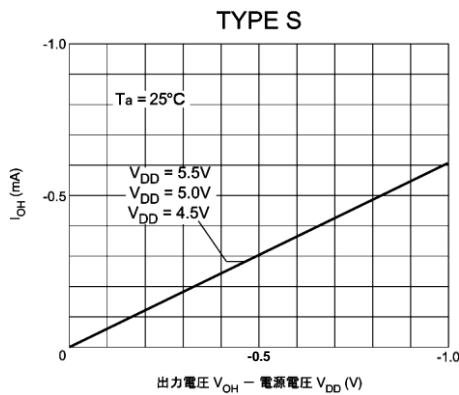

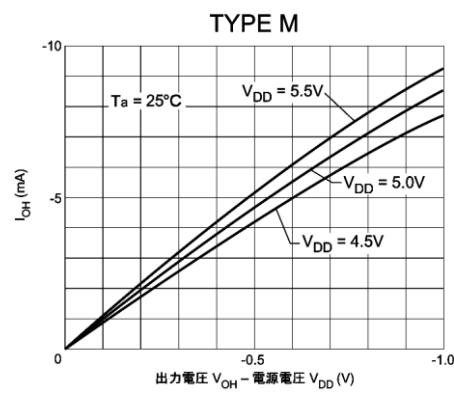

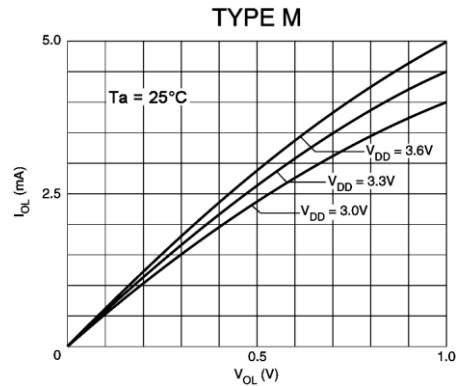

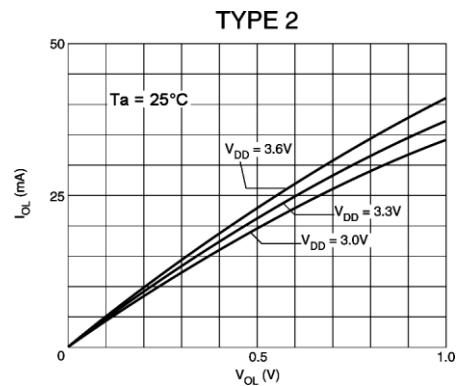

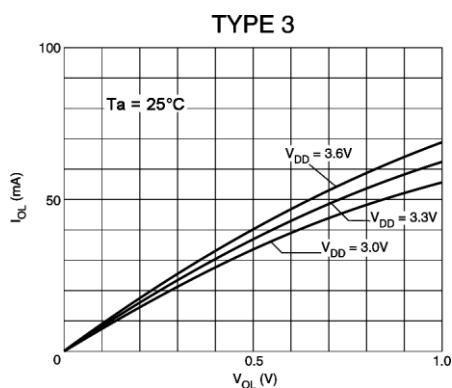

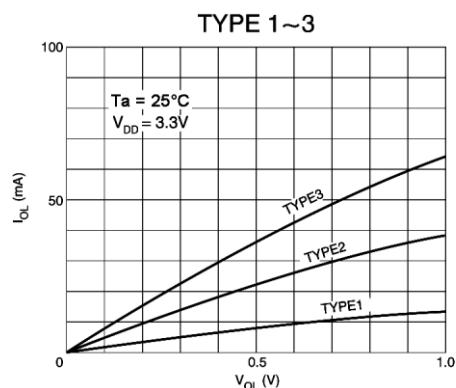

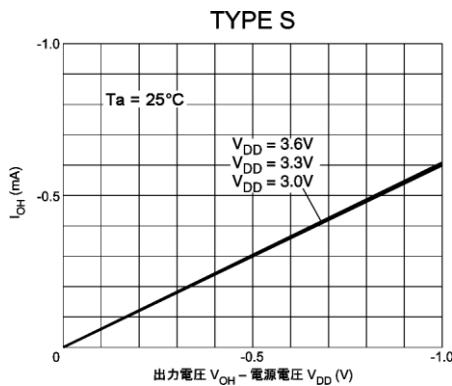

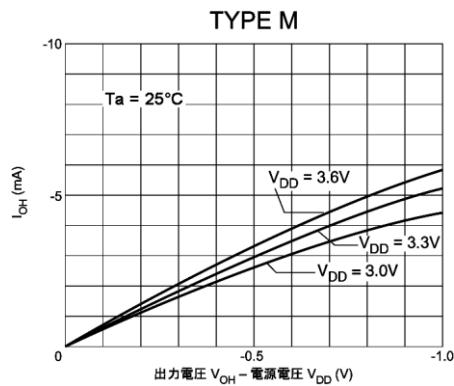

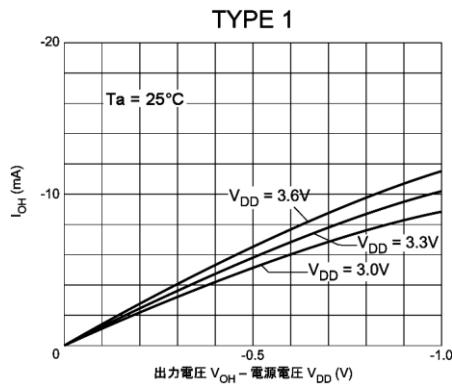

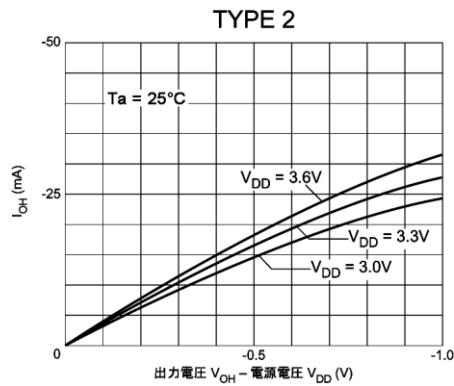

表6-6に出力バッファにおける $I_{OL}$ 、 $I_{OH}$ の規格値を示します。

表6-6  $I_{OL}$ 、 $I_{OH}$ の各電圧における規格値

| 出力電流の種類 | $I_{OL}^{*1}/I_{OH}^{*2}$ |               | 単位 |

|---------|---------------------------|---------------|----|

|         | $V_{DD}=5.0V$             | $V_{DD}=3.3V$ |    |

| Type S  | 0.1/-0.1                  | 0.1/-0.1      | mA |

| Type M  | 1/-1                      | 1/-1          | mA |

| Type 1  | 3/-3                      | 2/-2          | mA |

| Type 2  | 8/-8                      | 6/-6          | mA |

| Type 3  | 12/-12                    | 10/-10        | mA |

注) \*1 :  $V_{OL}=0.4V$  です。

\*2 :  $V_{OH}=V_{DD}-0.4V$  です。

## 第6章 入出力バッファの種類と使用上の注意

表6-7に $V_{DD}=5.0V$ の場合の出力バッファの一覧を示します。

セル名の末尾「T」はテスト回路付き出力バッファを示しています。

表6-7 出力バッファ一覧 ( $V_{DD}=5.0V$ )

| Function                                     | $I_{OL}/I_{OH}^{*1} {^*2}$ | セル名    |

|----------------------------------------------|----------------------------|--------|

| Normal output                                | 0.1mA/-0.1mA               | OBST   |

|                                              | 1mA/-1mA                   | OBMT   |

|                                              | 3mA/-3mA                   | OB1T   |

|                                              | 8mA/-8mA                   | OB2T   |

|                                              | 12mA/-12mA                 | OB3T   |

| Normal output for high speed                 | 3mA/-3mA                   | OB1CT  |

|                                              | 8mA/-8mA                   | OB2CT  |

|                                              | 12mA/-12mA                 | OB3AT  |

| Normal output for low noise                  | 12mA/-12mA                 | OB3BT  |

| 3-ステート output                                | 0.1mA/-0.1mA               | TBST   |

|                                              | 1mA/-1mA                   | TBMT   |

|                                              | 3mA/-3mA                   | TB1T   |

|                                              | 8mA/-8mA                   | TB2T   |

|                                              | 12mA/-12mA                 | TB3T   |

| 3-ステート output for high speed                 | 3mA/-3mA                   | TB1CT  |

|                                              | 8mA/-8mA                   | TB2CT  |

|                                              | 12mA/-12mA                 | TB3AT  |

| 3-ステート output for low noise                  | 12mA/-12mA                 | TB3BT  |

| 3-ステート output<br>(バスホールド機能付き)                | 1mA/-1mA                   | TBMHT  |

|                                              | 3mA/-3mA                   | TB1HT  |

|                                              | 8mA/-8mA                   | TB2HT  |

|                                              | 12mA/-12mA                 | TB3HT  |

| 3-ステート output for high speed<br>(バスホールド機能付き) | 3mA/-3mA                   | TB1CHT |

|                                              | 8mA/-8mA                   | TB2CHT |

|                                              | 12mA/-12mA                 | TB3AHT |

| 3-ステート output for low noise<br>(バスホールド機能付き)  | 12mA/-12mA                 | TB3BHT |

注) \*1 :  $V_{OL}=0.4V$  、  $V_{OH}=V_{DD}-0.4V$  です。

\*2 : 出力電流の詳細は、「[A4.1.3 出力ドライバ特性](#)」を参照下さい。

表6-8に $V_{DD}=3.3V$ の場合の出力バッファの一覧を示します。

セル名の末尾「T」はテスト回路付き出力バッファを示しています。

表6-8 出力バッファ一覧 ( $V_{DD}=3.3V$ )

| Function                                     | $I_{OL}/I_{OH}^{*1} *2$ | セル名    |

|----------------------------------------------|-------------------------|--------|

| Normal output                                | 0.1mA/-0.1mA            | OBST   |

|                                              | 1mA/-1mA                | OBMT   |

|                                              | 2mA/-2mA                | OB1T   |

|                                              | 6mA/-6mA                | OB2T   |

|                                              | 10mA/-10mA              | OB3T   |

| Normal output for high speed                 | 2mA/-2mA                | OB1CT  |

|                                              | 6mA/-6mA                | OB2CT  |

|                                              | 10mA/-10mA              | OB3AT  |

| Normal output for low noise                  | 10mA/-10mA              | OB3BT  |

| 3-ステート output                                | 0.1mA/-0.1mA            | TBST   |

|                                              | 1mA/-1mA                | TBMT   |

|                                              | 2mA/-2mA                | TB1T   |

|                                              | 6mA/-6mA                | TB2T   |

|                                              | 10mA/-10mA              | TB3T   |

| 3-ステート output for high speed                 | 2mA/-2mA                | TB1CT  |

|                                              | 6mA/-6mA                | TB2CT  |

|                                              | 10mA/-10mA              | TB3AT  |

| 3-ステート output for low noise                  | 10mA/-10mA              | TB3BT  |

| 3-ステート output<br>(バスホールド機能付き)                | 1mA/-1mA                | TBMHT  |

|                                              | 2mA/-2mA                | TB1HT  |

|                                              | 6mA/-6mA                | TB2HT  |

|                                              | 10mA/-10mA              | TB3HT  |

| 3-ステート output for high speed<br>(バスホールド機能付き) | 2mA/-2mA                | TB1CHT |

|                                              | 6mA/-6mA                | TB2CHT |

|                                              | 10mA/-10mA              | TB3AHT |

| 3-ステート output for low noise<br>(バスホールド機能付き)  | 10mA/-10mA              | TB3BHT |

注) \*1 :  $V_{OL}=0.4V$  、  $V_{OH}=V_{DD}-0.4V$  です。

\*2 : 出力電流の詳細は、「[A4.2.3 出力ドライバ特性](#)」を参照下さい。

## 第6章 入出力バッファの種類と使用上の注意

表6-9にNチャンネルオープンドレイン出力バッファにおける $I_{OL}$ の規格値を示します。

表6-9 Nチャンネルオープンドレイン出力バッファ  $I_{OL}$  の各電圧における規格値

| 出力電流の種類 | $I_{OL}^{*1}$ |               | 単位 |

|---------|---------------|---------------|----|

|         | $V_{DD}=5.0V$ | $V_{DD}=3.3V$ |    |

| Type 1  | 3             | 2             | mA |

| Type 2  | 8             | 6             | mA |

| Type 3  | 12            | 10            | mA |

注) \*1 :  $V_{OL}=0.4V$  です。

表6-10、表6-11にNチャンネルオープンドレイン出力バッファの一覧を示します。

表6-10 Nチャンネルオープンドレイン出力バッファ一覧 ( $V_{DD}=5.0V$ )

| Function          | $I_{OL}^{*1} *2$ | セル名   |

|-------------------|------------------|-------|

| Normal output     | 3mA              | OD1T  |

|                   | 8mA              | OD2T  |

|                   | 12mA             | OD3T  |

| High speed output | 3mA              | OD1CT |

|                   | 8mA              | OD2CT |

注) \*1 :  $V_{OL}=0.4V$  です。

\*2 : 出力電流の詳細は、「[A4.1.3 出力ドライバ特性](#)」を参照下さい。

表6-11 Nチャンネルオープンドレイン出力バッファ一覧 ( $V_{DD}=3.3V$ )

| Function          | $I_{OL}^{*1} *2$ | セル名   |

|-------------------|------------------|-------|

| Normal output     | 2mA              | OD1T  |

|                   | 6mA              | OD2T  |

|                   | 10mA             | OD3T  |

| High speed output | 2mA              | OD1CT |

|                   | 6mA              | OD2CT |

注) \*1 :  $V_{OL}=0.4V$  です。

\*2 : 出力電流の詳細は、「[A4.2.3 出力ドライバ特性](#)」を参照下さい。

### 6.2.3 双方向バッファ

表6-12-1、6-12-2、6-13に $V_{DD}=5.0V$ 時、表6-14、6-15に $V_{DD}=3.3V$ 時の双方向バッファ一覧を示します。セル名の末尾「T」はテスト回路付き出力バッファを示しています。

表6-12-1 双方向バッファ一覧 (1/2) ( $V_{DD}=5.0V$ )

| 入力レベル         | Function                             | $I_{OL}/I_{OH}^{*1} *2$                                        | 抵抗なし                                 | プルダウン抵抗付 <sup>*3</sup>                         | プルアップ抵抗付 <sup>*3</sup>                         |

|---------------|--------------------------------------|----------------------------------------------------------------|--------------------------------------|------------------------------------------------|------------------------------------------------|

| TTL           | Bi-directional output                | 0.1mA/-0.1mA<br>1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BTST<br>BTMT<br>BT1T<br>BT2T<br>BT3T | BTSD*T<br>BTMD*T<br>BT1D*T<br>BT2D*T<br>BT3D*T | BTSP*T<br>BTMP*T<br>BT1P*T<br>BT2P*T<br>BT3P*T |

|               | Bi-directional output for high speed | 12mA/-12mA                                                     | BT3AT                                | BT3AD*T                                        | BT3AP*T                                        |

|               | Bi-directional output for low noise  | 12mA/-12mA                                                     | BT3BT                                | BT3BD*T                                        | BT3BP*T                                        |

| TTL<br>シミュット  | Bi-directional output                | 0.1mA/-0.1mA<br>1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BSST<br>BSMT<br>BS1T<br>BS2T<br>BS3T | BSSD*T<br>BSMD*T<br>BS1D*T<br>BS2D*T<br>BS3D*T | BSSP*T<br>BSMP*T<br>BS1P*T<br>BS2P*T<br>BS3P*T |

|               | Bi-directional output for high speed | 12mA/-12mA                                                     | BS3AT                                | BS3AD*T                                        | BS3AP*T                                        |

|               | Bi-directional output for low noise  | 12mA/-12mA                                                     | BS3BT                                | BS3BD*T                                        | BS3BP*T                                        |

| CMOS          | Bi-directional output                | 0.1mA/-0.1mA<br>1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BCST<br>BCMT<br>BC1T<br>BC2T<br>BC3T | BCSD*T<br>BCMD*T<br>BC1D*T<br>BC2D*T<br>BC3D*T | BCSP*T<br>BCMP*T<br>BC1P*T<br>BC2P*T<br>BC3P*T |

|               | Bi-directional output for high speed | 3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA                             | BC1CT<br>BC2CT<br>BC3AT              | BC1CD*T<br>BC2CD*T<br>BC3AD*T                  | BC1CP*T<br>BC2CP*T<br>BC3AP*T                  |

|               | Bi-directional output for low noise  | 12mA/-12mA                                                     | BC3BT                                | BC3BD*T                                        | BC3BP*T                                        |

| CMOS<br>シミュット | Bi-directional output                | 0.1mA/-0.1mA<br>1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BHST<br>BHMT<br>BH1T<br>BH2T<br>BH3T | BHSD*T<br>BHMD*T<br>BH1D*T<br>BH2D*T<br>BH3D*T | BHSP*T<br>BHMP*T<br>BH1P*T<br>BH2P*T<br>BH3P*T |

|               | Bi-directional output for high speed | 3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA                             | BH1CT<br>BH2CT<br>BH3AT              | BH1CD*T<br>BH2CD*T<br>BH3AD*T                  | BH1CP*T<br>BH2CP*T<br>BH3AP*T                  |

|               | Bi-directional output for low noise  | 12mA/-12mA                                                     | BH3BT                                | BH3BD*T                                        | BH3BP*T                                        |

注) \*1 :  $V_{OL}=0.4V$ 、 $V_{OH}=V_{DD}-0.4V$ です。

\*2 : 出力電流の詳細は、「[A4.1.3 出力ドライバ特性](#)」を参照下さい。

\*3 : \*は1または2で、抵抗値1:60kΩ、2:120kΩに対応しています。

## 第6章 入出力バッファの種類と使用上の注意

表 6-12-2 双方向バッファ一覧 (2/2) ( $V_{DD}=5.0V$ )

| 入力レベル         | Function                                             | $I_{OL}/I_{OH}$ *1 *2                          | 抵抗なし                             | プルダウン抵抗付 | プルアップ抵抗付 |

|---------------|------------------------------------------------------|------------------------------------------------|----------------------------------|----------|----------|

| TTL           | Bi-directional output<br>(バスホールド機能付き)                | 1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BTMHT<br>BT1HT<br>BT2HT<br>BT3HT | なし       | なし       |

|               | Bi-directional output for high speed<br>(バスホールド機能付き) | 12mA/-12mA                                     | BT3AHT                           | なし       | なし       |

|               | Bi-directional output for low noise<br>(バスホールド機能付き)  | 12mA/-12mA                                     | BT3BHT                           | なし       | なし       |

| TTL<br>シュミット  | Bi-directional output<br>(バスホールド機能付き)                | 1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BSMHT<br>BS1HT<br>BS2HT<br>BS3HT | なし       | なし       |

|               | Bi-directional output for high speed<br>(バスホールド機能付き) | 12mA/-12mA                                     | BS3AHT                           | なし       | なし       |

|               | Bi-directional output for low noise<br>(バスホールド機能付き)  | 12mA/-12mA                                     | BS3BHT                           | なし       | なし       |

| CMOS          | Bi-directional output<br>(バスホールド機能付き)                | 1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BCMHT<br>BC1HT<br>BC2HT<br>BC3HT | なし       | なし       |

|               | Bi-directional output for high speed<br>(バスホールド機能付き) | 3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA             | BC1CHT<br>BC2CHT<br>BC3AHT       | なし       | なし       |

|               | Bi-directional output for low noise<br>(バスホールド機能付き)  | 12mA/-12mA                                     | BC3BHT                           | なし       | なし       |

| CMOS<br>シュミット | Bi-directional output<br>(バスホールド機能付き)                | 1mA/-1mA<br>3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA | BHMHT<br>BH1HT<br>BH2HT<br>BH3HT | なし       | なし       |

|               | Bi-directional output for high speed<br>(バスホールド機能付き) | 3mA/-3mA<br>8mA/-8mA<br>12mA/-12mA             | BH1CHT<br>BH2CHT<br>BH3AHT       | なし       | なし       |

|               | Bi-directional output for low noise<br>(バスホールド機能付き)  | Type<br>3(12mA/-12mA)                          | BH3BHT                           | なし       | なし       |

注) \*1 :  $V_{OL}=0.4V$ 、 $V_{OH}=V_{DD}-0.4V$  です。

\*2 : 出力電流の詳細は、「[A4.1.3 出力ドライバ特性](#)」を参照下さい。

表 6-13 N チャンネルオープンドレイン双方向バッファ一覧 ( $V_{DD}=5.0V$ )

| 入力レベル         | Function                             | $I_{OL}^{*1 *2}$ | セル名    |

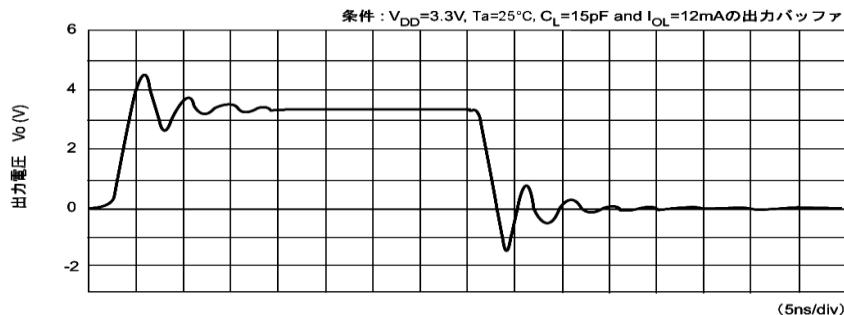

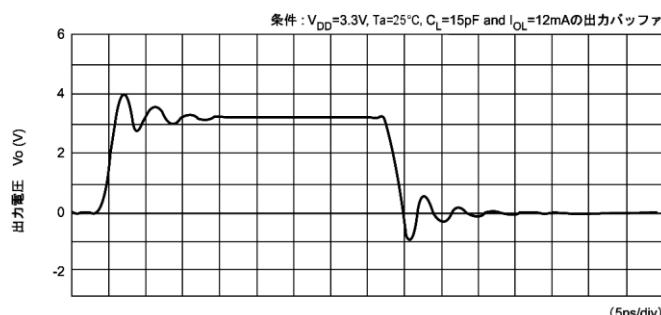

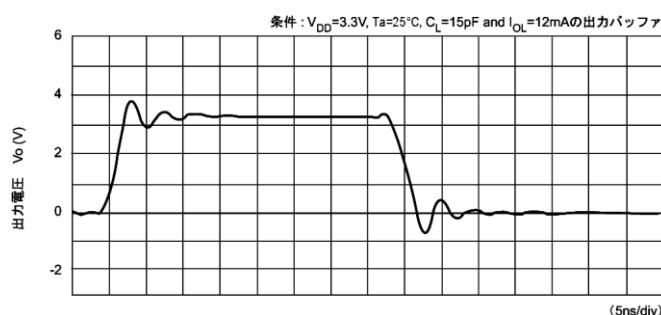

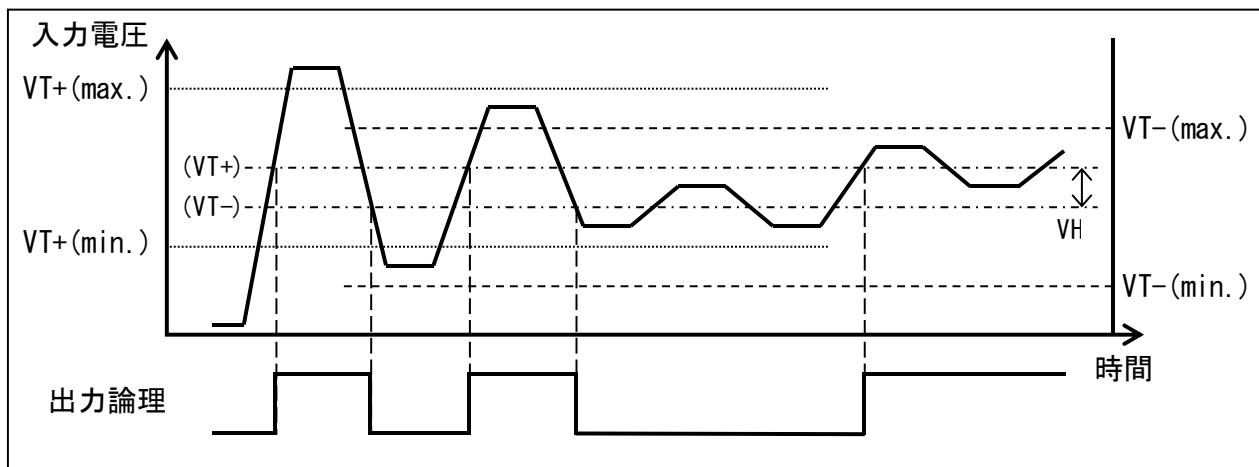

|---------------|--------------------------------------|------------------|--------|