# **S2S65A30**

## **USB2.0 Device**

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

ARM は、ARM 社の登録商標です。

CompactFlash は Sandisk 社の登録商標です。

その他記載の会社名、製品名は、それぞれの会社の商標もしくは登録商標です。

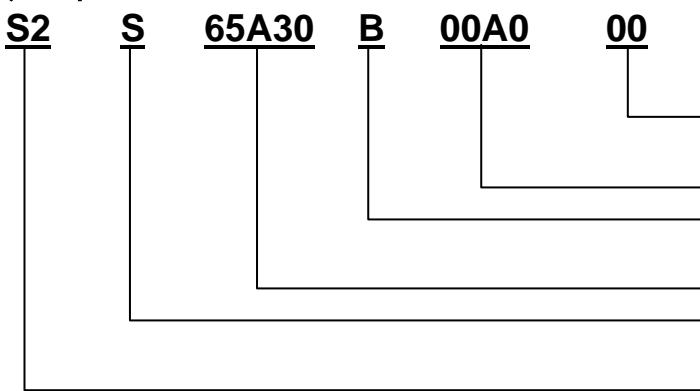

## 製品型番体系

### ●デバイス

梱包仕様

[00: テープ & リール以外]

仕様

形状

[B : BGAP]

機種番号

製品中分類

[S : 通信用]

製品分類

[S2: 半導体 IC]

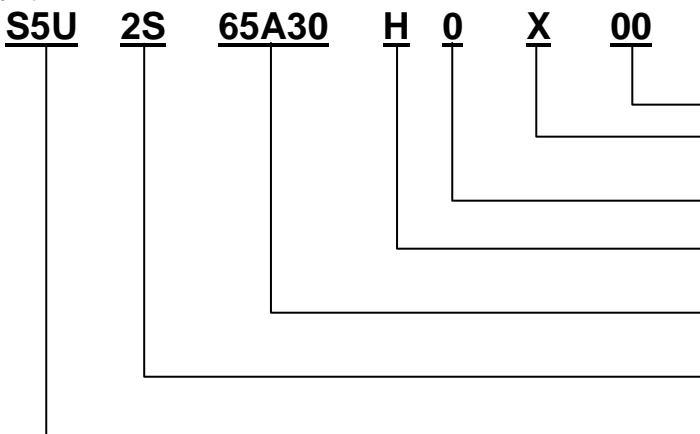

### ●開発ツール

梱包仕様

ボード仕様

[1: ITRON 版、2: Linux 版]

ボードコード

区分

[H: ハードウェア、S: ソフトウェア]

仕様 (対応半導体 IC)

[65A30: S2S65A30]

製品中分類

[1S: 半導体 IC 通信用]

製品分類

[S5U: 半導体用開発ツール]

## 使用上の注意事項

本書のレジスタの記述に関しては、以下のことにご注意ください。

本書のレジスタに関する記述については、以下のような省略を用いることがあります。

|       |                                         |

|-------|-----------------------------------------|

| R/W : | リードおよびライト                               |

| RO :  | リードオンリ                                  |

| WO :  | ライトオンリ                                  |

| RSV : | 予約ビット／レジスタ（特に指定のない場合は“0”を書き込んでください。）    |

| n/a : | not available（特に指定のない場合は“0”を書き込んでください。） |

特に指定のない場合、レジスタの予約ビットには“0”をセットしてください。予約ビットに書き込みを行うと予想できない結果になることがあります。“n/a”と記載してあるビットはハードウェアに影響をあたえません。

あるレジスタは特定の条件のときのみアクセスできるようになっています。アクセス不可のレジスタへのリード／ライトは無効です。

## *< Table of Contents >*

|                                            |           |

|--------------------------------------------|-----------|

| <b>A2.1 Scope .....</b>                    | <b>1</b>  |

| <b>A2.2 Overview .....</b>                 | <b>1</b>  |

| <b>A2.3 Block Diagram .....</b>            | <b>1</b>  |

| <b>A2.4 Pin List .....</b>                 | <b>2</b>  |

| <b>A2.5 Register .....</b>                 | <b>3</b>  |

| <b>A2.5.1 Register一覧 .....</b>             | <b>3</b>  |

| <b>A2.5.2 Register詳細説明 .....</b>           | <b>7</b>  |

| A2.5.2.1 Register Access上の注意事項 .....       | 7         |

| A2.5.2.2 割込み制御レジスタ .....                   | 7         |

| A2.5.2.3 Power Management制御レジスタ .....      | 10        |

| A2.5.2.4 MISCレジスタ .....                    | 12        |

| A2.5.2.5 DMA制御レジスタ .....                   | 15        |

| A2.5.2.6 USB制御レジスタ .....                   | 19        |

| A2.5.2.7 USB FIFO設定レジスタ .....              | 48        |

| <b>A2.6 機能説明 .....</b>                     | <b>57</b> |

| <b>A2.6.1 初期設定 .....</b>                   | <b>57</b> |

| A2.6.1.1 USBコントローラへのアクセス設定 .....           | 57        |

| A2.6.1.2 割り込みの設定 .....                     | 57        |

| A2.6.1.3 Macro Config1[0x37]に関する注意事項 ..... | 57        |

| <b>A2.6.2 USBデバイス制御 .....</b>              | <b>58</b> |

| A2.6.2.1 エンドポイント .....                     | 58        |

| A2.6.2.2 トランザクション .....                    | 59        |

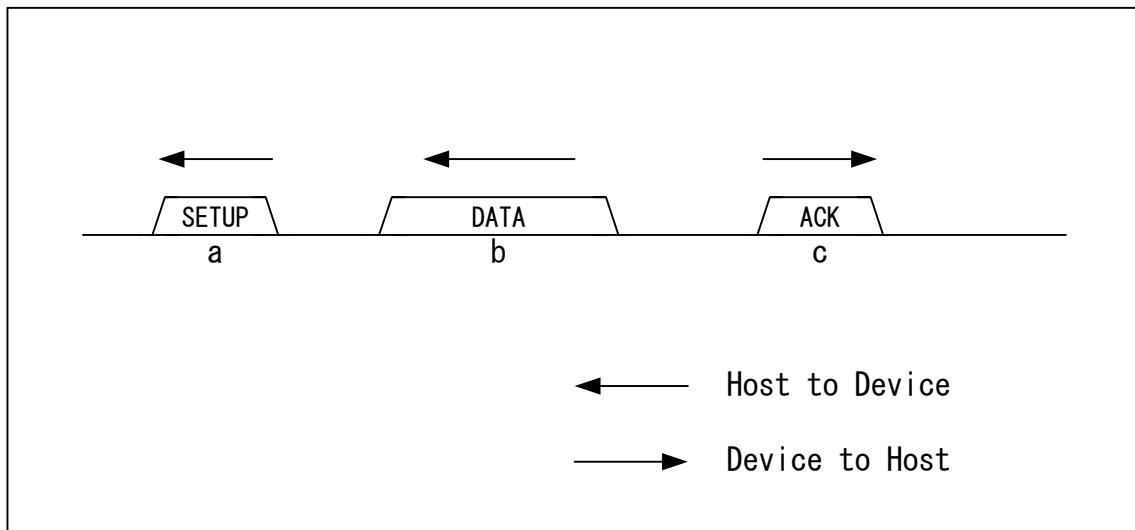

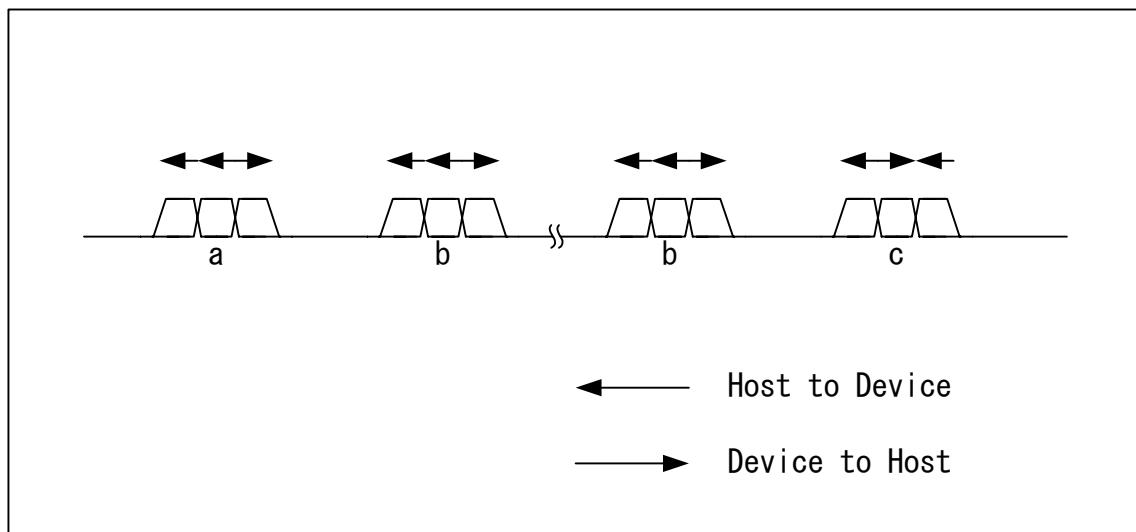

| A2.6.2.2.1 SETUPトランザクション .....             | 61        |

| A2.6.2.2.2 バルク/インタラプトOUTトランザクション .....     | 62        |

| A2.6.2.2.3 バルク/インタラプトINトランザクション .....      | 63        |

| A2.6.2.2.4 PINGトランザクション .....              | 64        |

| A2.6.2.3 コントロール転送 .....                    | 65        |

| A2.6.2.3.1 セットアップステージ .....                | 66        |

| A2.6.2.3.2 データステージ/ステータスステージ .....         | 66        |

| A2.6.2.3.3 自動アドレス設定機能 .....                | 66        |

| A2.6.2.3.4 デスクリプタ返信機能 .....                | 67        |

| A2.6.2.4 バルク転送/インタラプト転送 .....              | 67        |

| A2.6.2.5 データフロー .....                      | 67        |

| A2.6.2.5.1 OUT転送 .....                     | 67        |

| A2.6.2.5.2 IN転送 .....                      | 68        |

| A2.6.2.6 バルクオンリーサポート .....                 | 68        |

| A2.6.2.6.1 CBWサポート .....                   | 68        |

| A2.6.2.6.2 CSWサポート .....                   | 69        |

| A2.6.2.7 オート・ネゴシエーション機能 .....              | 70        |

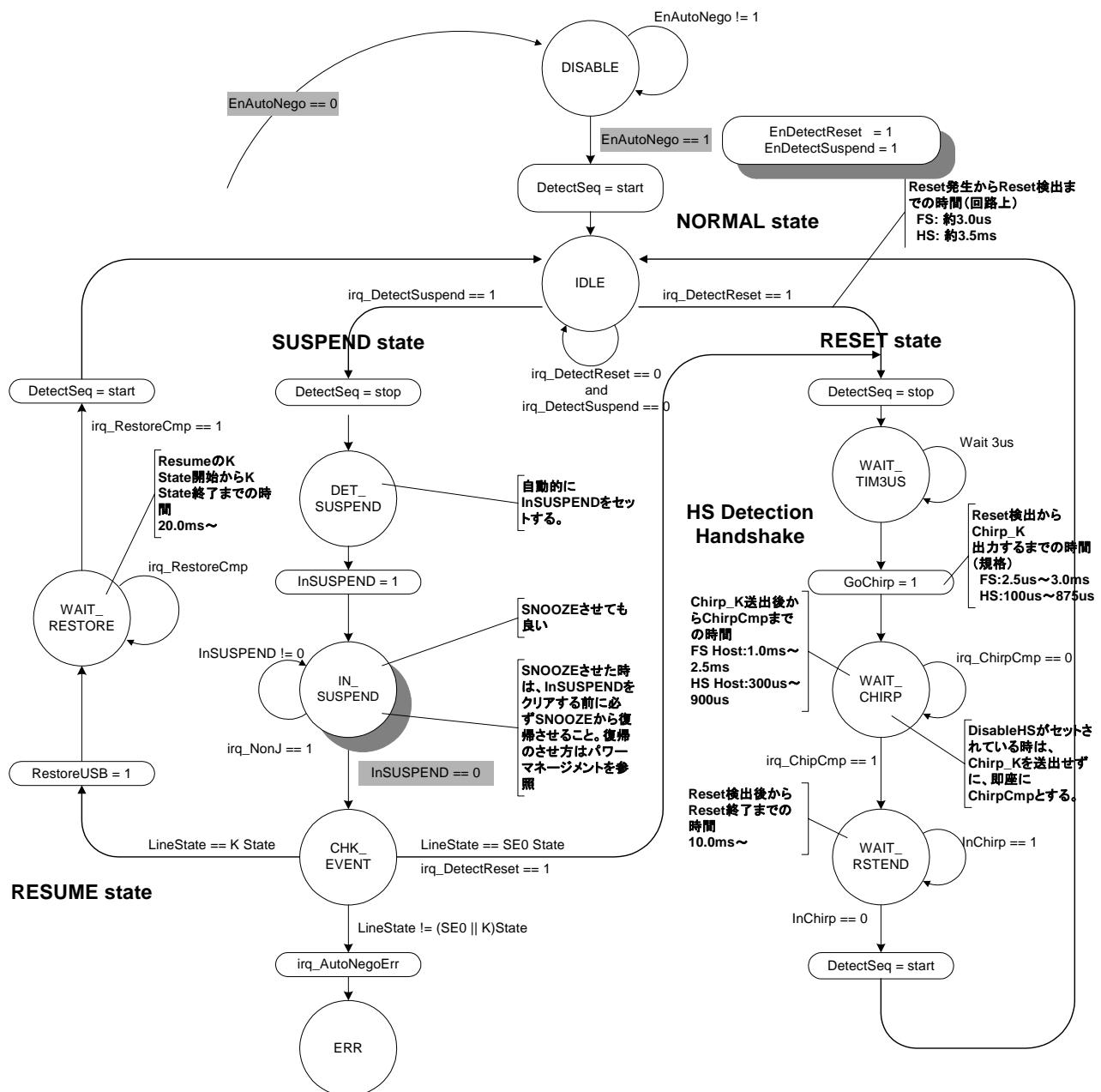

| A2.6.2.7.1 DISABLE .....                   | 70        |

| A2.6.2.7.2 IDLE .....                      | 71        |

| A2.6.2.7.3 WAIT_TIM3US .....               | 71        |

| A2.6.2.7.4 WAIT_CHIRP .....                | 71        |

| A2.6.2.7.5 WAIT_RSTEND .....               | 71        |

| A2.6.2.7.6 DET_SUSPEND .....               | 71        |

| A2.6.2.7.7 IN_SUSPEND .....                | 72        |

| A2.6.2.7.8 CHK_EVENT .....                 | 72        |

| A2.6.2.7.9 WAIT_RESTORE .....              | 72        |

| A2.6.2.7.10 ERR .....                      | 72        |

|                                             |            |

|---------------------------------------------|------------|

| A2.6.2.7.11 各ネゴシエーション機能の単体説明.....           | 72         |

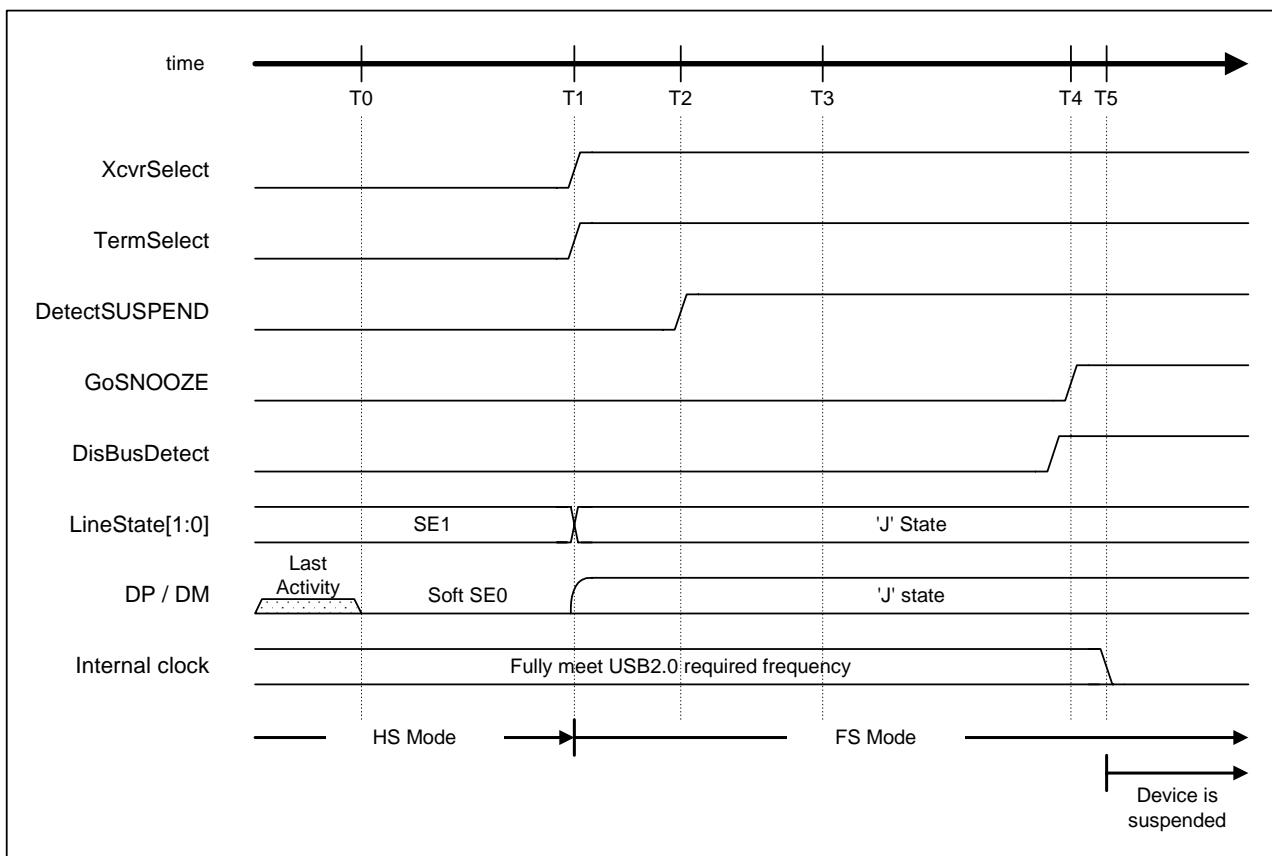

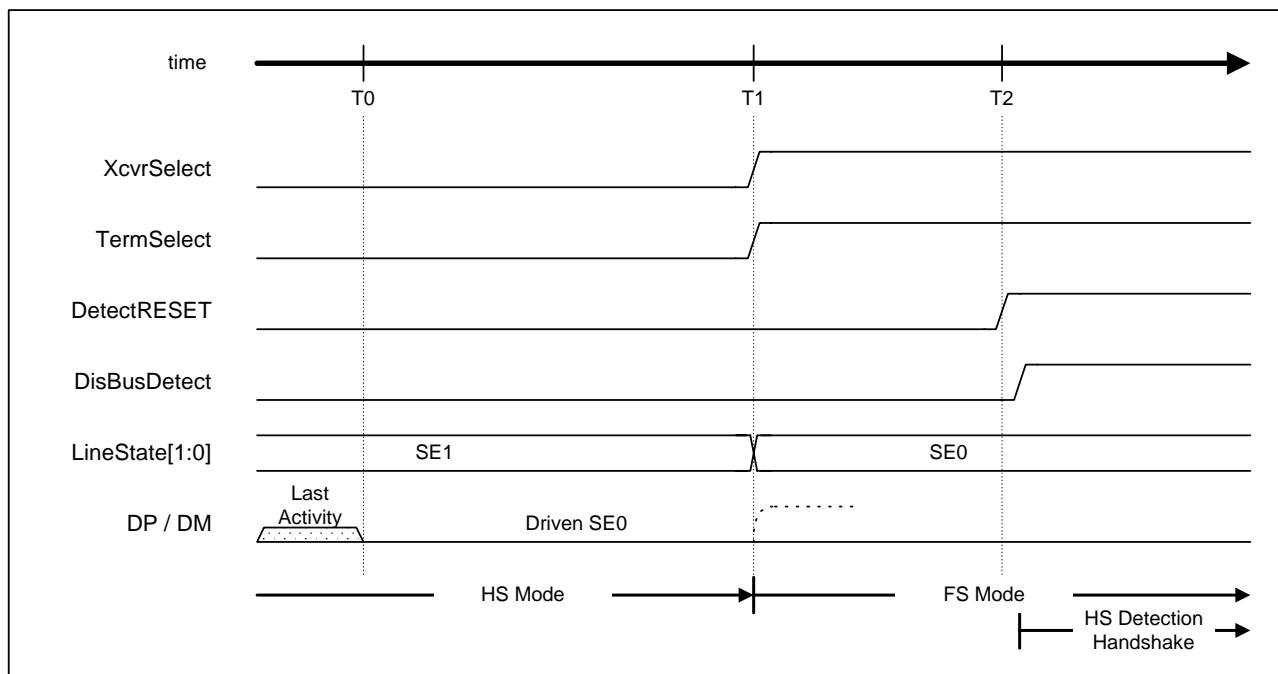

| A2.6.2.7.11.1 サスPEND検出 (HSモード) .....        | 72         |

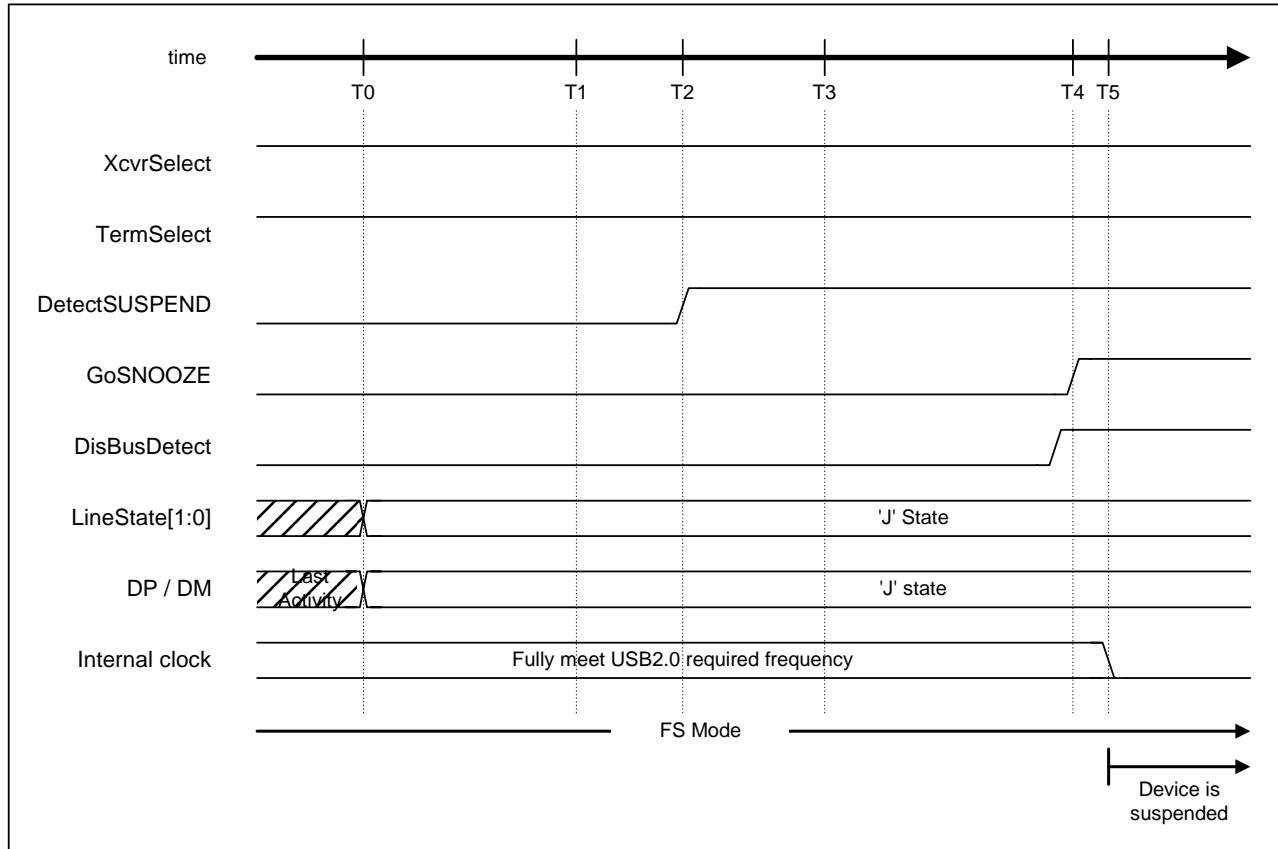

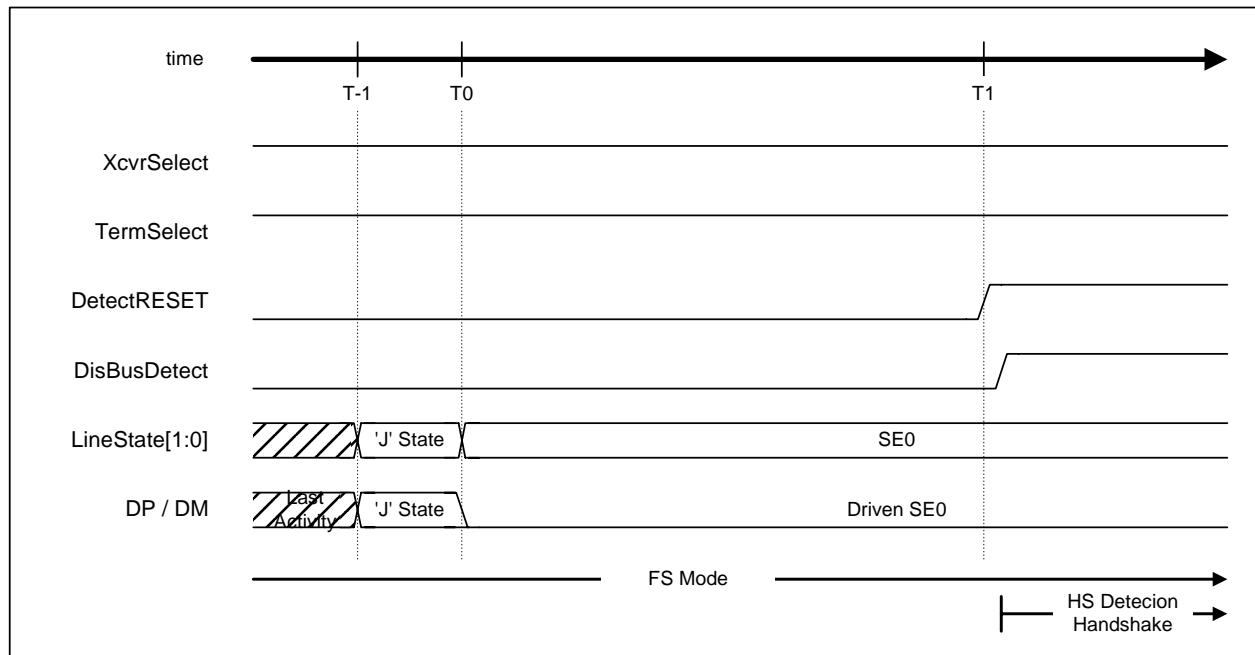

| A2.6.2.7.11.2 サスPEND検出 (FSモード) .....        | 74         |

| A2.6.2.7.11.3 リセット検出 (HSモード) .....          | 75         |

| A2.6.2.7.11.4 HS Detection Handshake .....  | 77         |

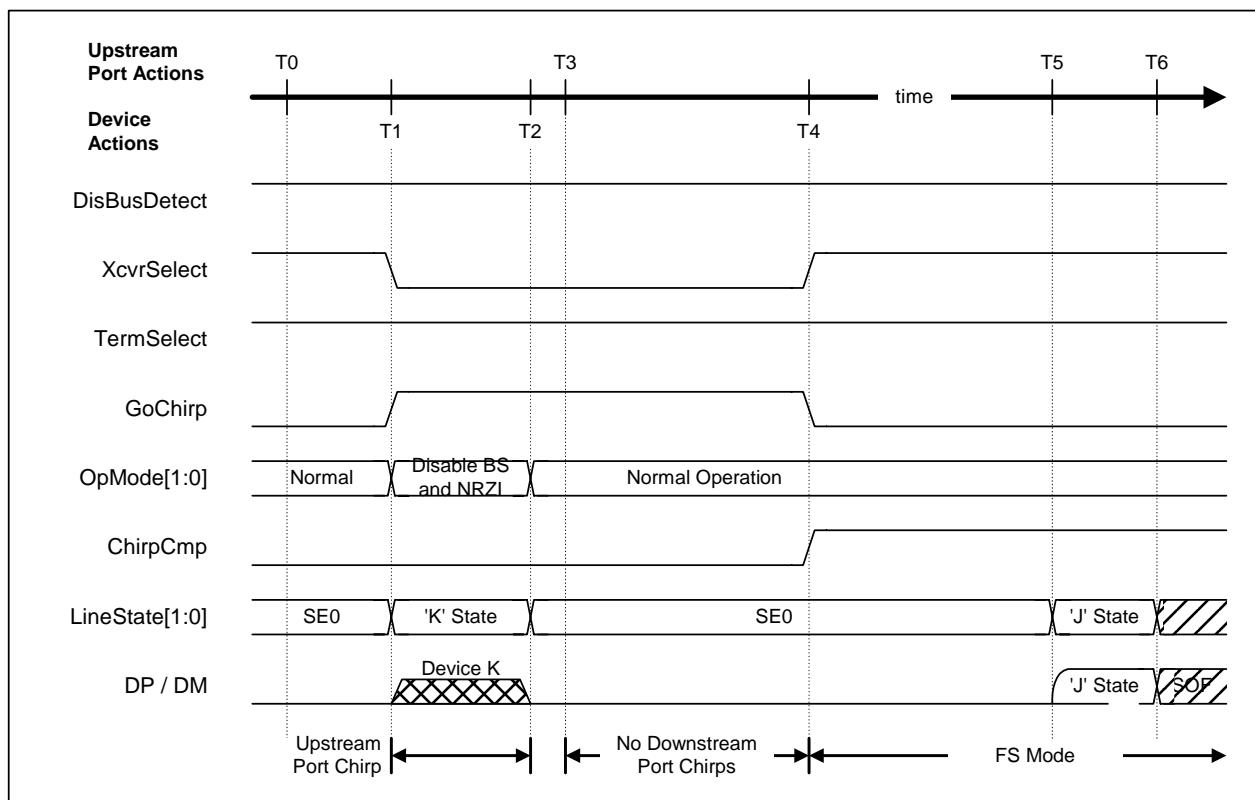

| A2.6.2.7.11.5 FSのダウンストリームポートに繋がれた場合 .....   | 77         |

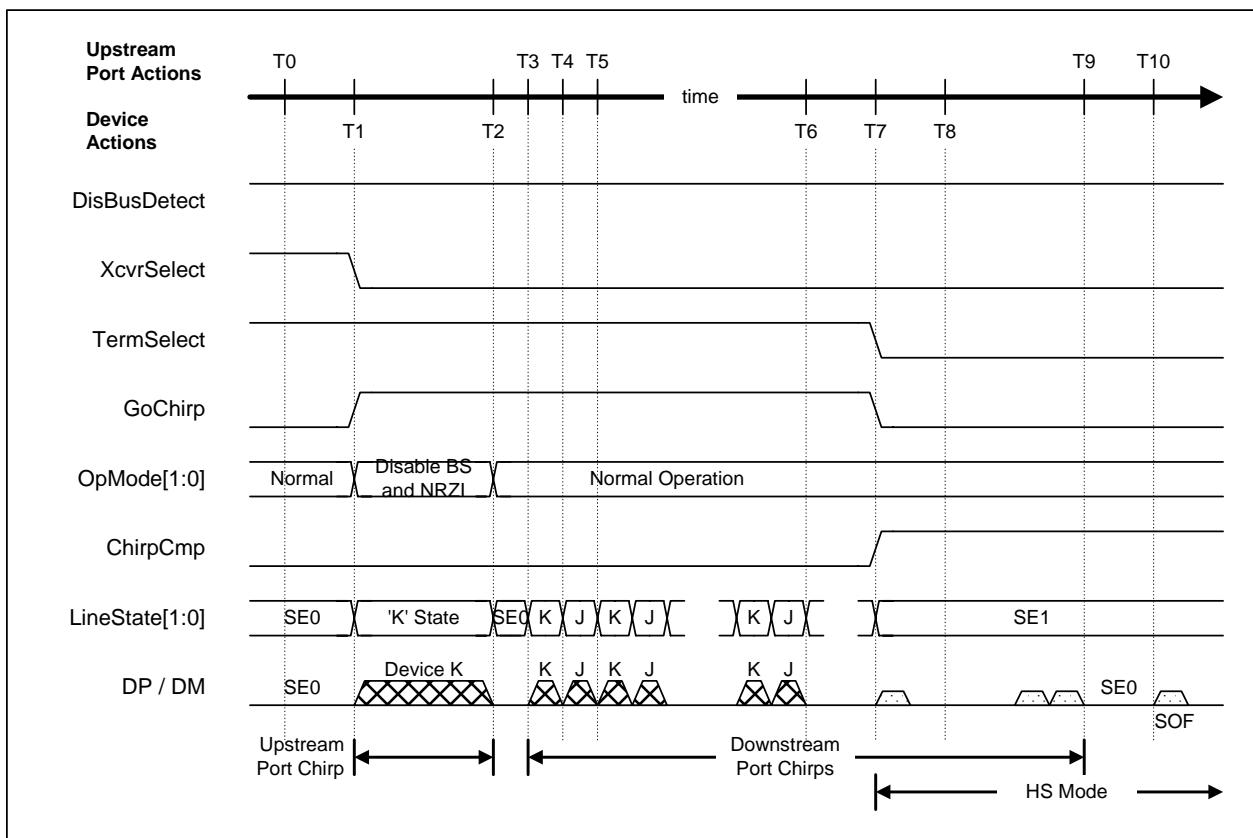

| A2.6.2.7.11.6 HSのダウンストリームポートに繋がれた場合 .....   | 79         |

| A2.6.2.7.11.7 スヌーズ中にリセットされた場合 .....         | 81         |

| A2.6.2.7.11.8 レジュームの発行 .....                | 82         |

| A2.6.2.7.11.9 レジュームの検出 .....                | 84         |

| A2.6.2.7.11.10 ケーブル挿入 .....                 | 85         |

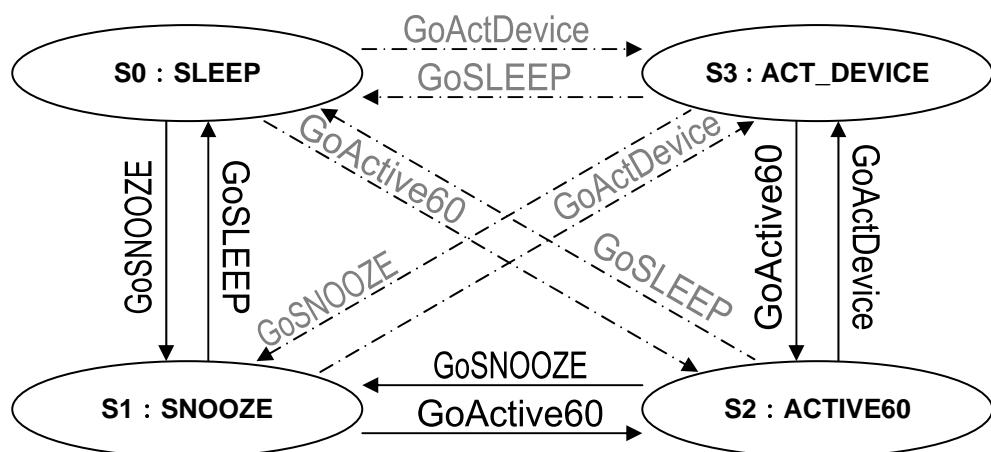

| <b>A2.6.3 パワーマネジメント機能.....</b>              | <b>87</b>  |

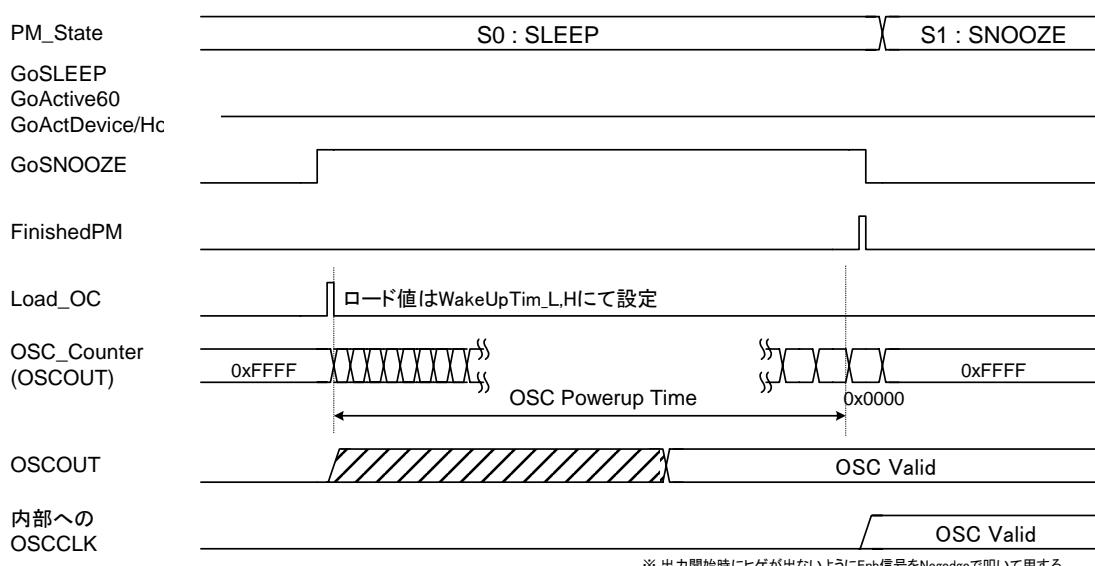

| A2.6.3.1SLEEP (スリープ) .....                  | 88         |

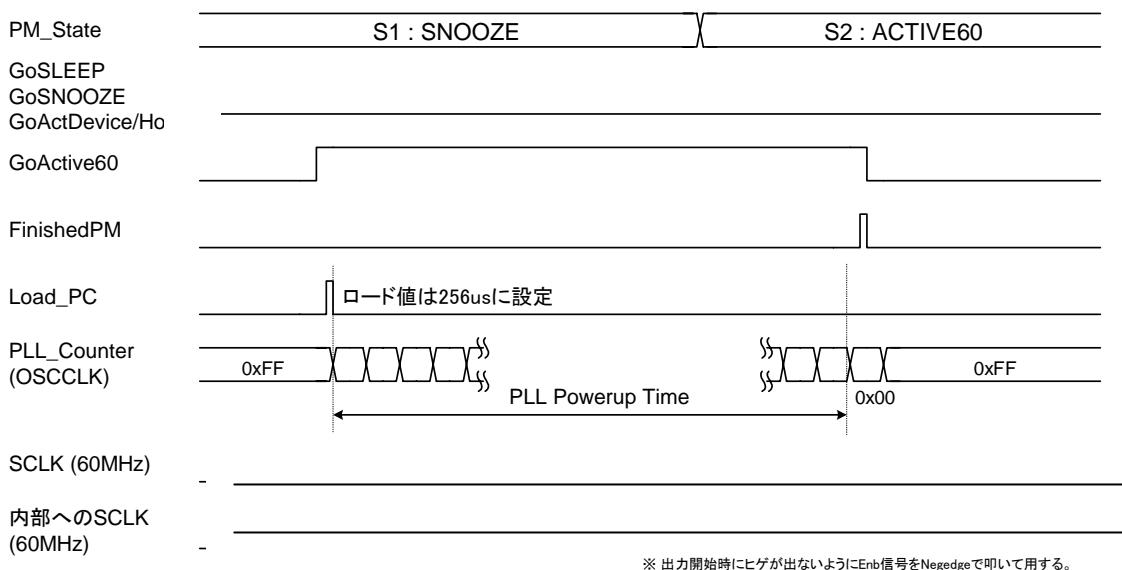

| A2.6.3.2SNOOZE (スヌーズ) .....                 | 89         |

| A2.6.3.3ACTIVE60 (アクティブ 60) .....           | 89         |

| A2.6.3.4ACT_DEVICE (アクトデバイス) .....          | 89         |

| <b>A2.6.4 FIFO管理.....</b>                   | <b>90</b>  |

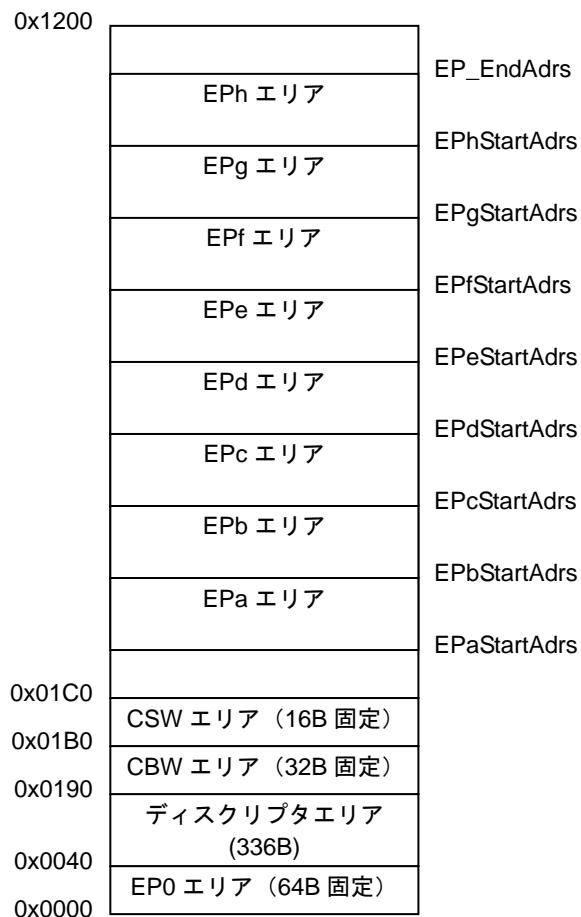

| A2.6.4.1FIFOメモリマップ .....                    | 90         |

| A2.6.4.2デスクリプタエリアの使用方法 .....                | 91         |

| A2.6.4.2.1 デスクリプタエリアへのデータの書き込み .....        | 91         |

| A2.6.4.2.2 デスクリプタエリアでのデータステージ (IN) の実行..... | 91         |

| A2.6.4.3CBWエリアの使用方法 .....                   | 91         |

| A2.6.4.3.1 CBWエリアへの受信 .....                 | 92         |

| A2.6.4.3.2 CBWエリアからのデータの読み出し .....          | 92         |

| A2.6.4.4CSWエリアの使用方法 .....                   | 92         |

| A2.6.4.4.1 CSWエリアからの送信 .....                | 92         |

| A2.6.4.4.2 CSWエリアへのデータの書き込み.....            | 92         |

| A2.6.4.5FIFOへのアクセス方法 .....                  | 92         |

| A2.6.4.5.1 FIFOへのアクセス方法 (RAM_Rd) .....      | 92         |

| A2.6.4.5.2 FIFOへのアクセス方法 (RAM_WrDoor) .....  | 93         |

| A2.6.4.5.3 FIFOへのアクセス方法 (レジスタアクセス) .....    | 93         |

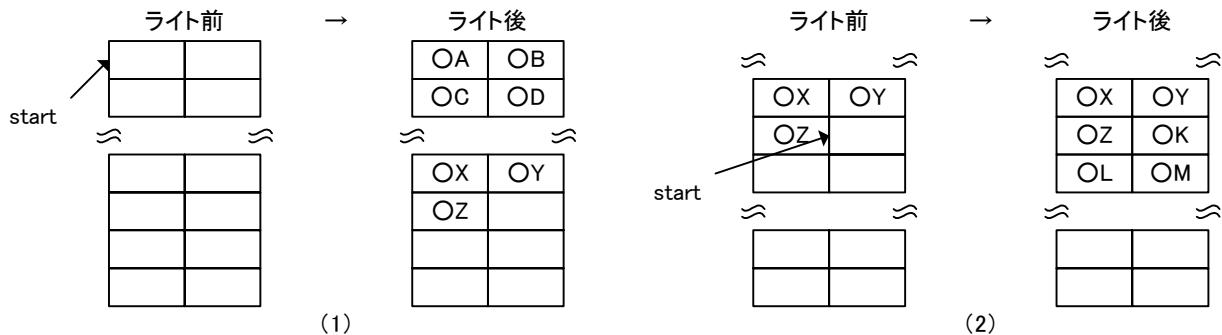

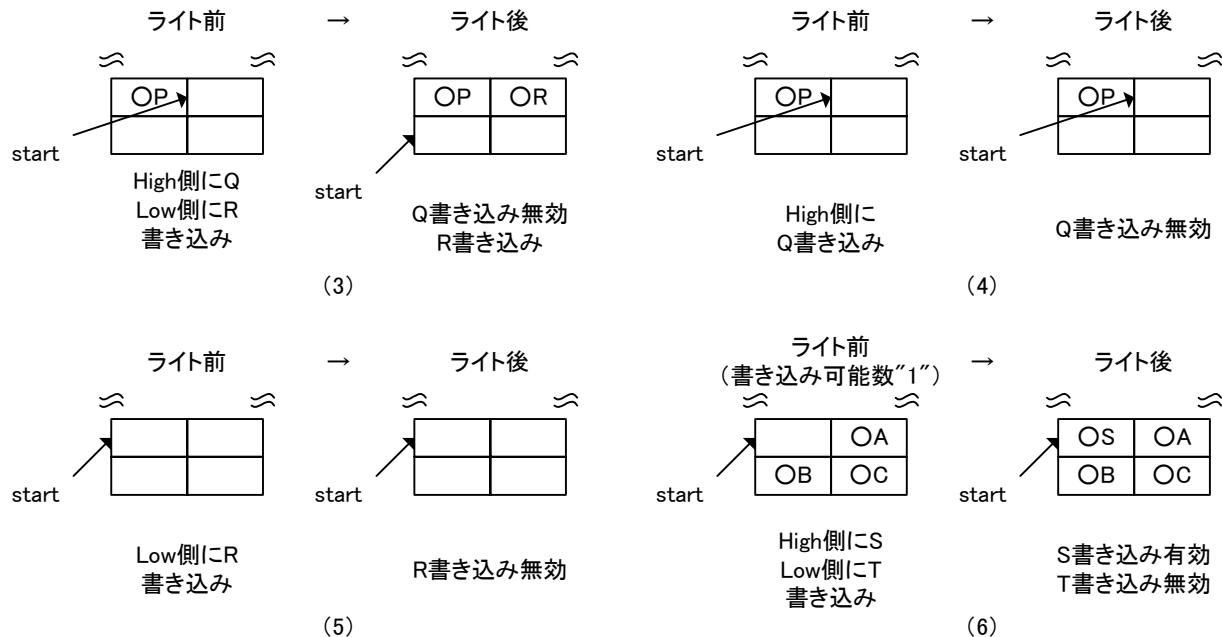

| A2.6.4.5.3.1 FIFOアクセス (ライト) .....           | 93         |

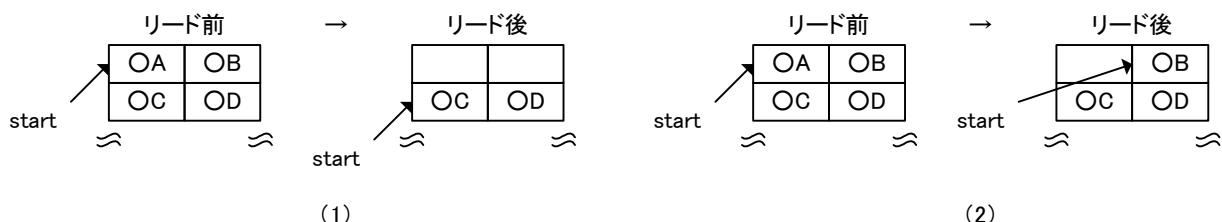

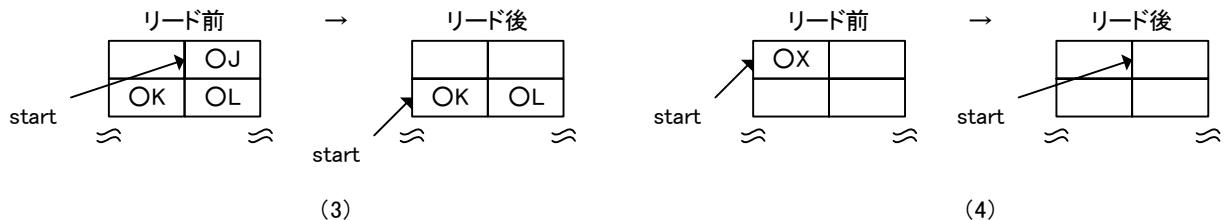

| A2.6.4.5.3.2 FIFOアクセス (リード) .....           | 93         |

| A2.6.4.5.3.3 FIFOアクセスの端数処理.....             | 94         |

| A2.6.4.5.4 FIFOへのアクセス方法 (DMA) .....         | 96         |

| A2.6.4.5.5 FIFOへのアクセス制限.....                | 96         |

| <b>A2.6.5 DMA.....</b>                      | <b>97</b>  |

| A2.6.5.1概要 .....                            | 97         |

| A2.6.5.2基本機能 .....                          | 97         |

| A2.6.5.2.1 カウントモード .....                    | 97         |

| A2.6.5.2.2 フリーランモード .....                   | 98         |

| A2.6.5.3強制終了 .....                          | 98         |

| <b>改訂履歴 .....</b>                           | <b>100</b> |

## **<List of Figures>**

|                |                                                  |    |

|----------------|--------------------------------------------------|----|

| Figure A2.3.1  | S2S65A30 USB Controller Block Diagram .....      | 1  |

| Figure A2.4.2  | USB 外部端子 .....                                   | 2  |

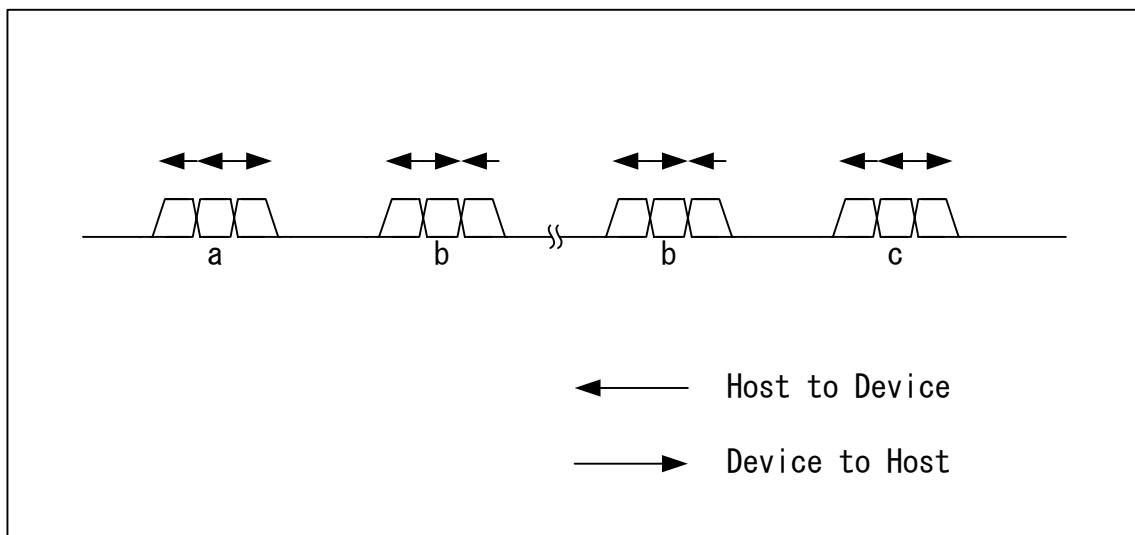

| Figure A2.6.1  | SETUP トランザクション .....                             | 62 |

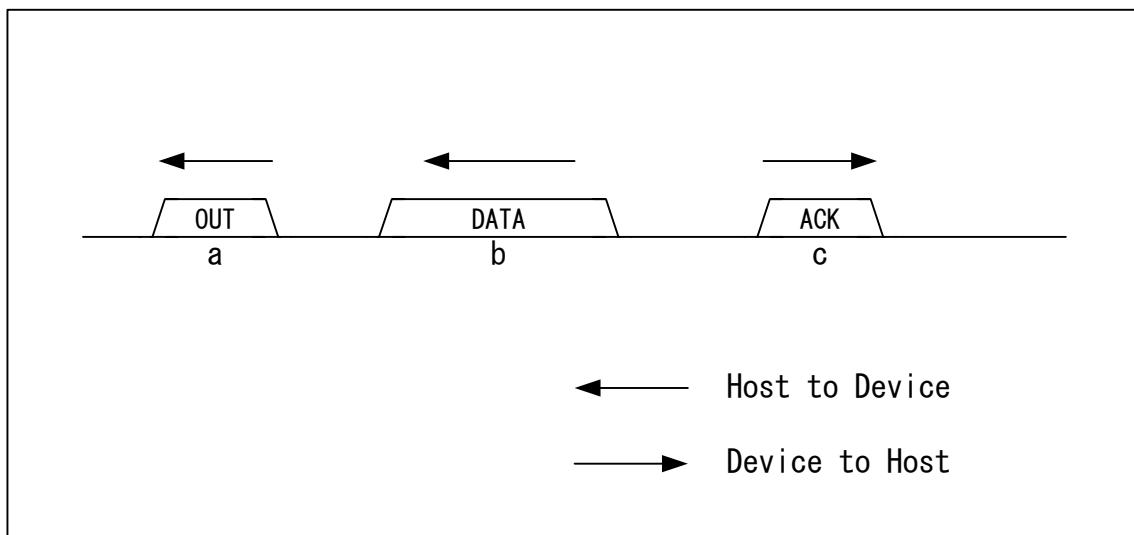

| Figure A2.6.2  | OUT トランザクション .....                               | 63 |

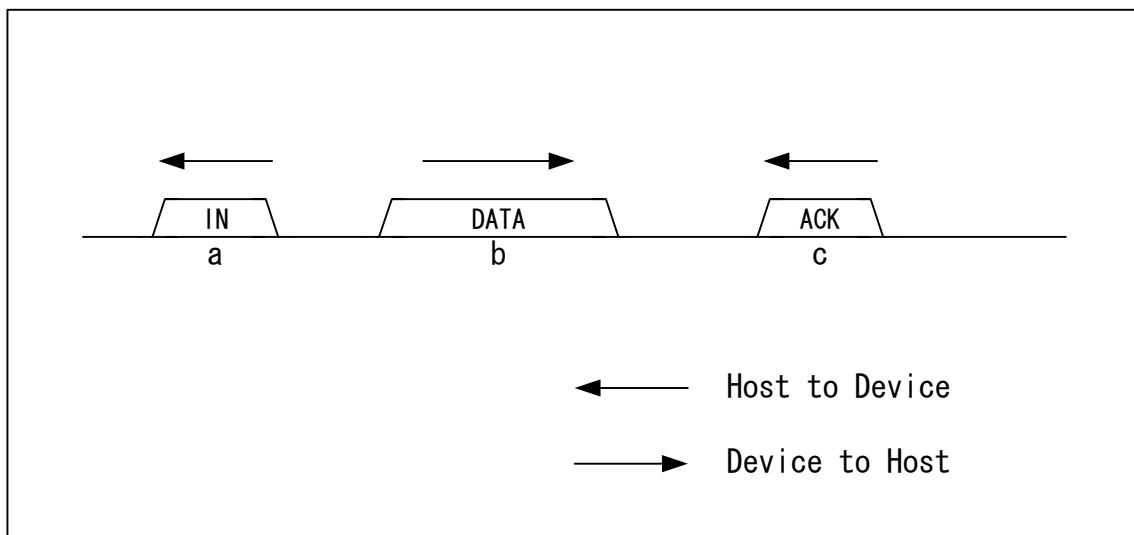

| Figure A2.6.3  | IN トランザクション .....                                | 64 |

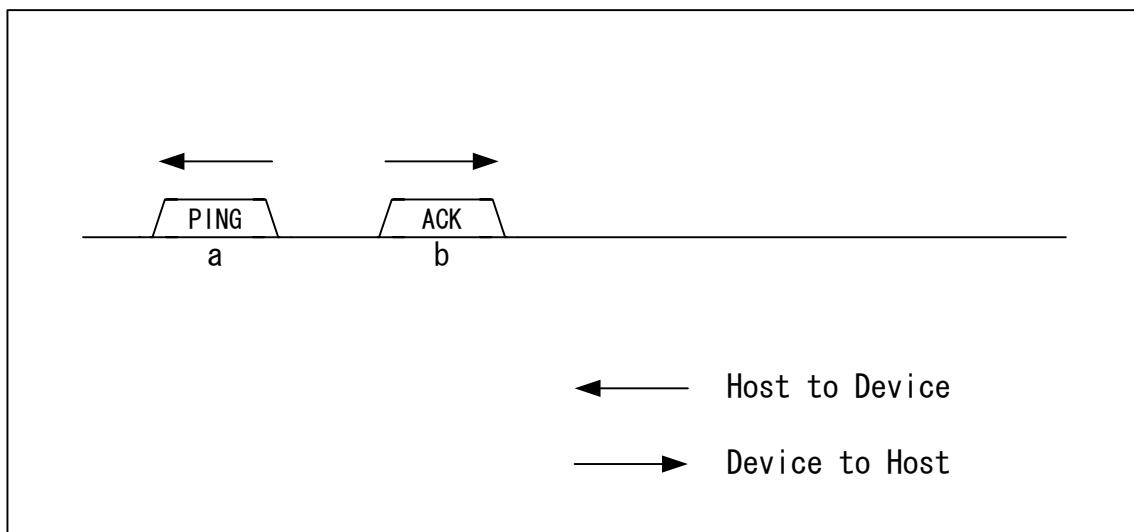

| Figure A2.6.4  | PING トランザクション .....                              | 64 |

| Figure A2.6.5  | データステージが OUT 方向のコントロール転送 .....                   | 65 |

| Figure A2.6.6  | データステージが IN 方向のコントロール転送 .....                    | 66 |

| Figure A2.6.7  | オート・ネゴシエータ .....                                 | 70 |

| Figure A2.6.8  | Suspend Timing (HS mode) .....                   | 73 |

| Figure A2.6.9  | Suspend Timing (FS mode) .....                   | 74 |

| Figure A2.6.10 | Reset Timing (HS mode) .....                     | 75 |

| Figure A2.6.11 | Reset Timing (FS mode) .....                     | 76 |

| Figure A2.6.12 | HS Detection Handshake (FS mode) .....           | 78 |

| Figure A2.6.13 | HS Detection Handshake Timing (HS mode) .....    | 80 |

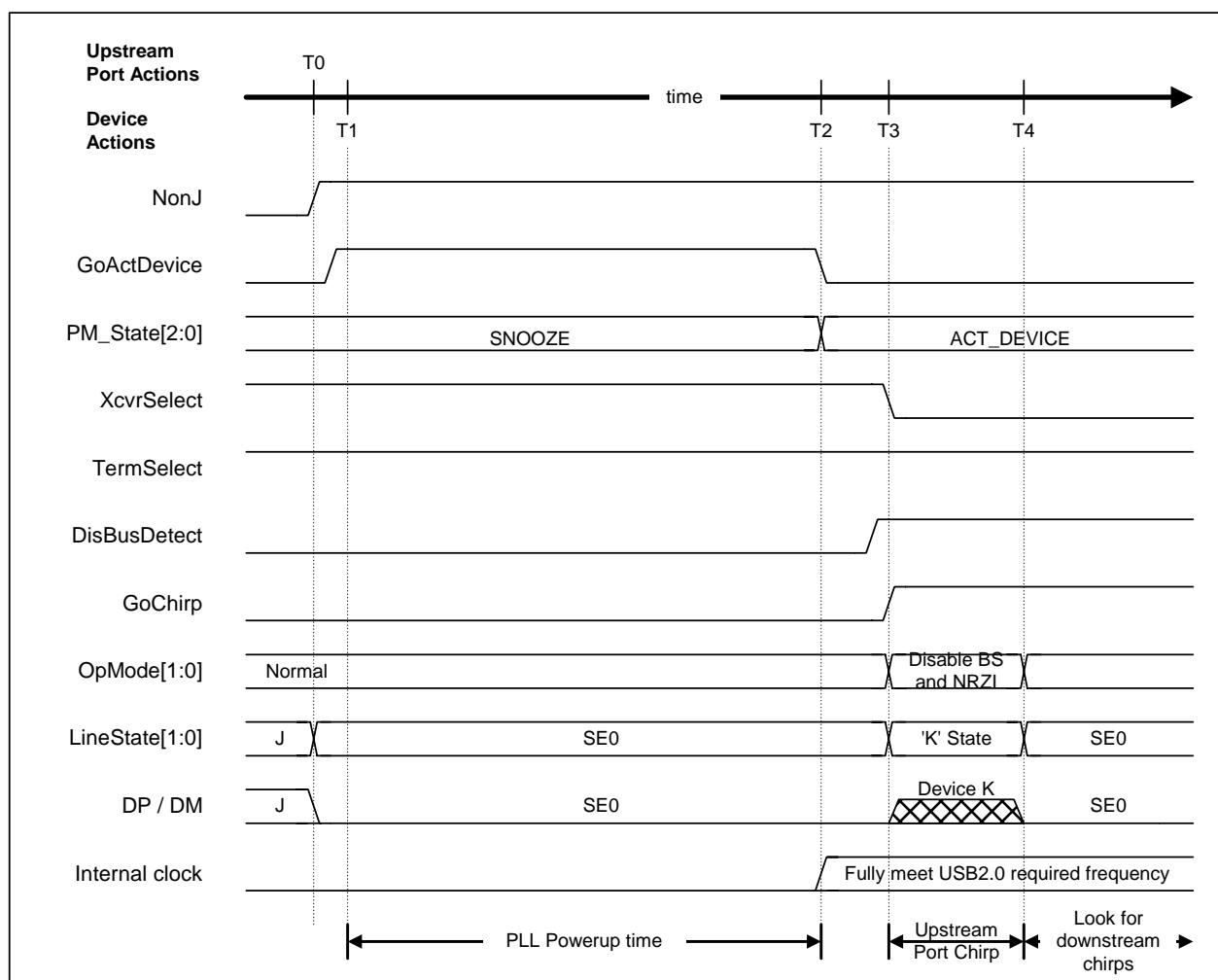

| Figure A2.6.14 | HS Detection Handshake Timing from Suspend ..... | 81 |

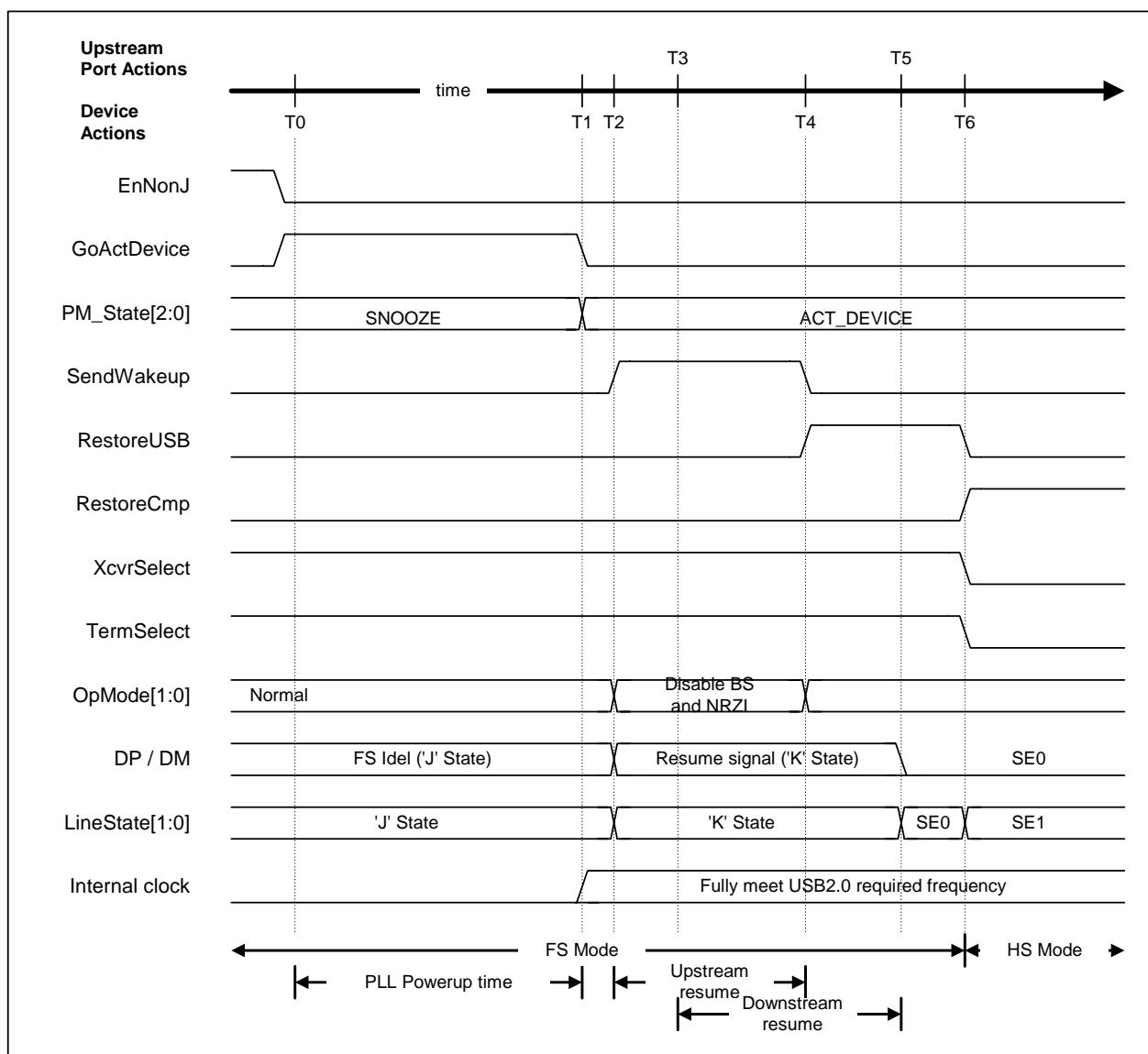

| Figure A2.6.15 | Assert Resume Timing (HS mode) .....             | 83 |

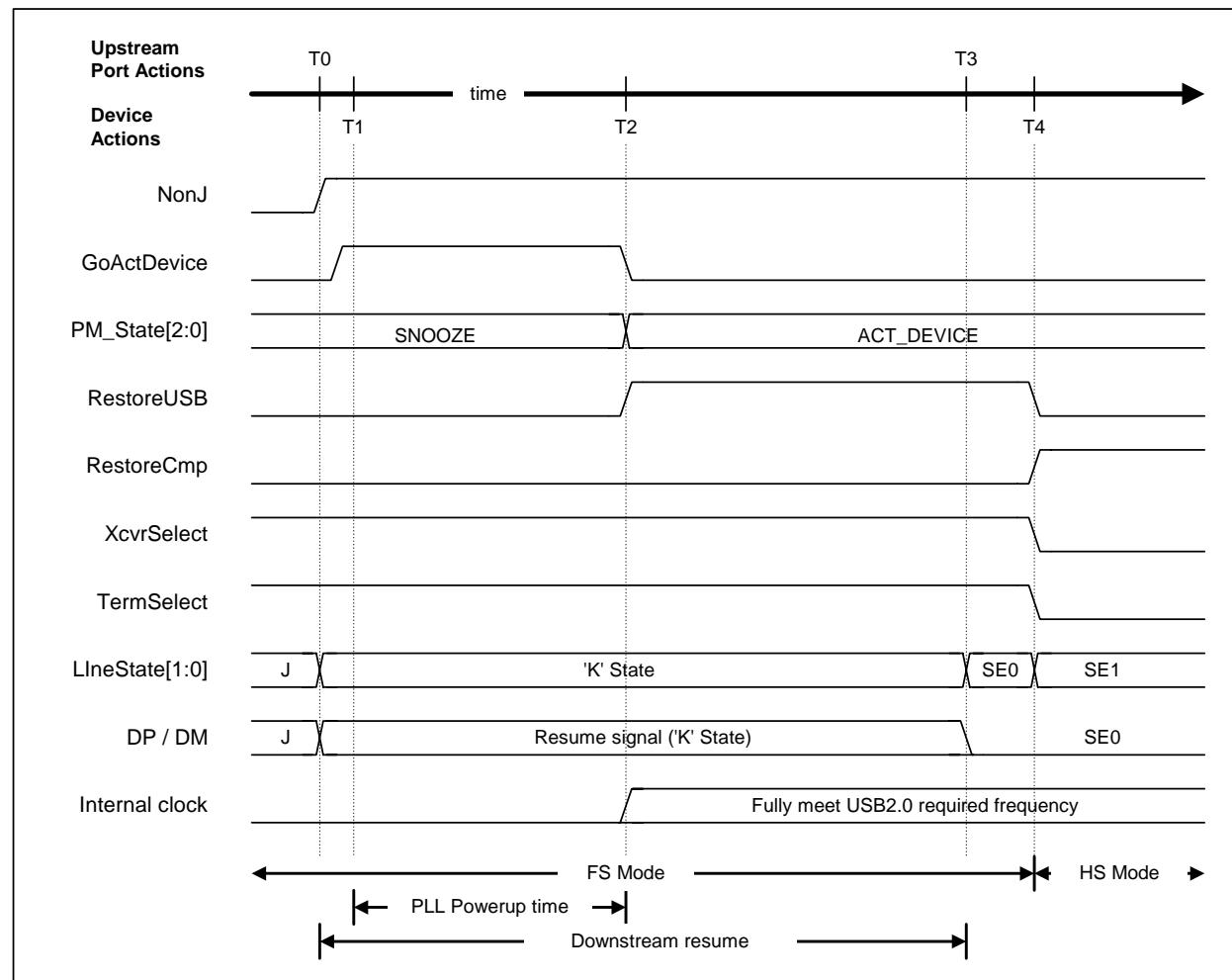

| Figure A2.6.16 | Detect Resume Timing (HS mode) .....             | 84 |

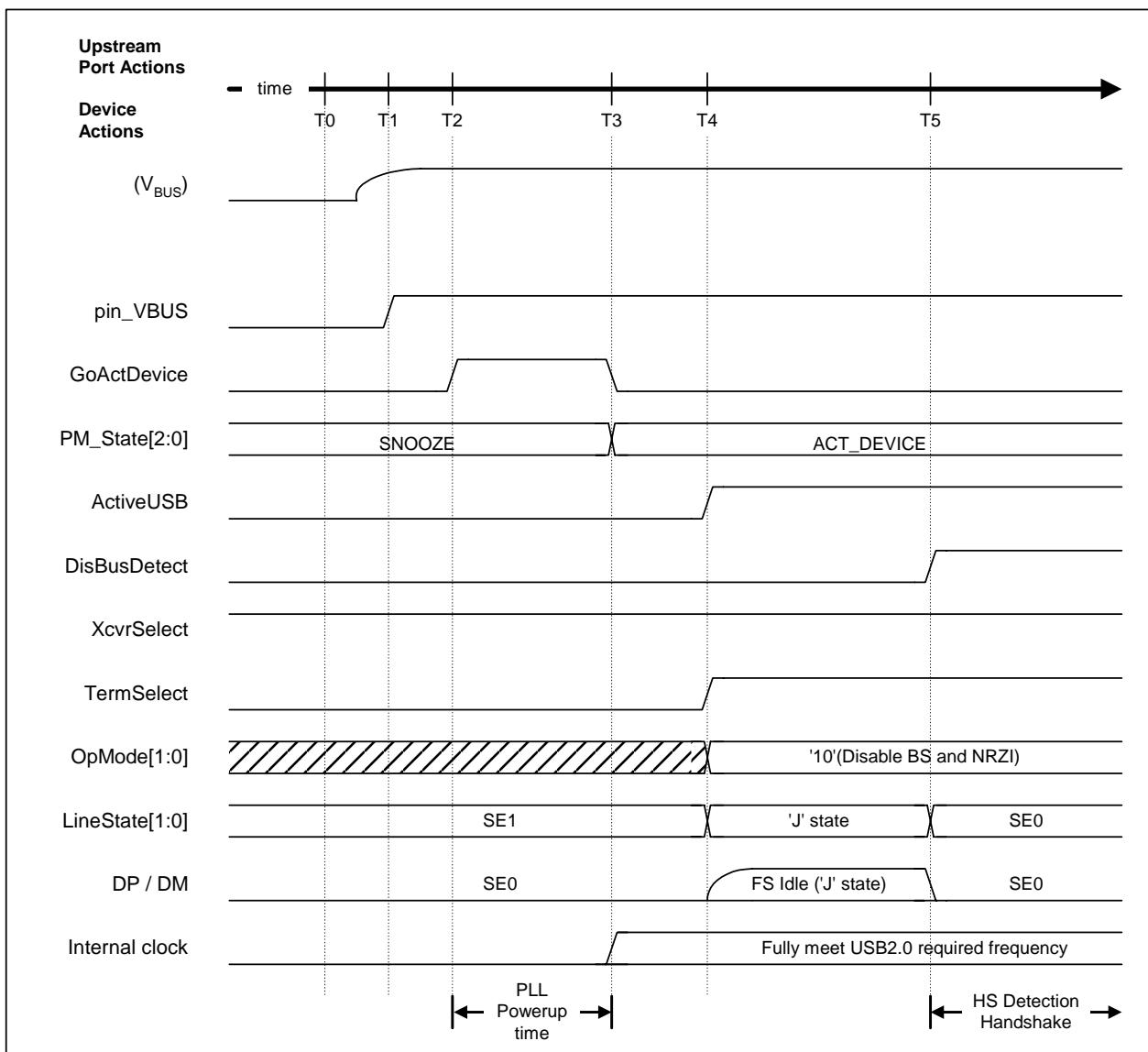

| Figure A2.6.17 | Device Attach Timing .....                       | 86 |

| Figure A2.6.18 | パワーマネージメント .....                                 | 87 |

| Figure A2.6.19 | SLEEP ステートからの離脱 (GoSNOOZE 時) .....               | 88 |

| Figure A2.6.20 | SNOOZE ステートからの離脱 (GoActive60 時) .....            | 89 |

| Figure A2.6.21 | FIFO メモリマップ例 .....                               | 90 |

| Figure A2.6.22 | FIFO ライト処理 (正常動作) .....                          | 94 |

| Figure A2.6.23 | FIFO ライト処理 (注意が必要な動作) .....                      | 95 |

| Figure A2.6.24 | FIFO リード処理 (正常動作) .....                          | 95 |

| Figure A2.6.25 | FIFO リード処理 (注意が必要な動作) .....                      | 96 |

| Figure A2.6.26 | DMA 転送手順例 .....                                  | 99 |

## **<List of Tables>**

|               |                                                         |    |

|---------------|---------------------------------------------------------|----|

| Table A2.5.1  | USB レジスター一覧 (1/4) .....                                 | 3  |

| Table A2.5.2  | USB レジスター一覧 (2/4) .....                                 | 4  |

| Table A2.5.3  | USB レジスター一覧 (3/4) .....                                 | 5  |

| Table A2.5.4  | USB レジスター一覧 (4/4) .....                                 | 6  |

| Table A2.6.1  | エンドポイント EP0 の基本設定項目 .....                               | 58 |

| Table A2.6.2  | 汎用エンドポイントの基本設定項目 .....                                  | 59 |

| Table A2.6.3  | エンドポイント EP0 の制御項目及びステータス .....                          | 60 |

| Table A2.6.4  | 汎用エンドポイントの制御項目とステータス .....                              | 61 |

| Table A2.6.5  | Suspend Timing Values (HS mode) .....                   | 73 |

| Table A2.6.6  | Suspend Timing Values (FS mode) .....                   | 74 |

| Table A2.6.7  | Reset Timing Values (HS mode) .....                     | 75 |

| Table A2.6.8  | Reset Timing Values (FS mode) .....                     | 76 |

| Table A2.6.9  | HS Detection Handshake Timing Values (FS mode) .....    | 78 |

| Table A2.6.10 | HS Detection Handshake Timing Values (HS mode) .....    | 80 |

| Table A2.6.11 | HS Detection Handshake Timing Values from Suspend ..... | 82 |

| Table A2.6.12 | Assert Resume Timing Values (HS mode) .....             | 83 |

| Table A2.6.13 | Detect Resume Timing Values (HS mode) .....             | 85 |

| Table A2.6.14 | Device Attach Timing Values .....                       | 86 |

## Appendix 2 USB Device コントローラ

### A2.1 Scope

本仕様書は、セイコーエプソン(株)製 S2S65A30\*に内蔵されている USB HS Device Controller の機能仕様について説明します。

### A2.2 Overview

S2S65A30\*には、セイコーエプソン製の USB コントローラ「S1R72V05\*」のデバイス機能と互換性のある USB コントローラを搭載しています。

- HS (High Speed=480Mbps) 及び FS (Full Speed=12Mbps) 転送サポート

- FS/HS ターミネーション内蔵 (外付け回路不要)

- VBUS 5V I/F (外付け保護回路は必要)

- コントロール/バルク/インターラプト転送をサポート

- コントロール転送用 (EP0)、Bulk 転送専用 1 本、Bulk/Interrupt 転送用 4 本の Endpoint をサポート S2S65A30 では、EPa-e を使用します。マニュアル中の f-h は使用できません。

- 4.5KB の Endpoint 用 FIFO

- DMA I/F (DMAC3 と組み合わせて使用することが可能)

- 12MHz / 24MHz の水晶発振子によるクロック入力 (帰還抵抗 1MΩ 内蔵)

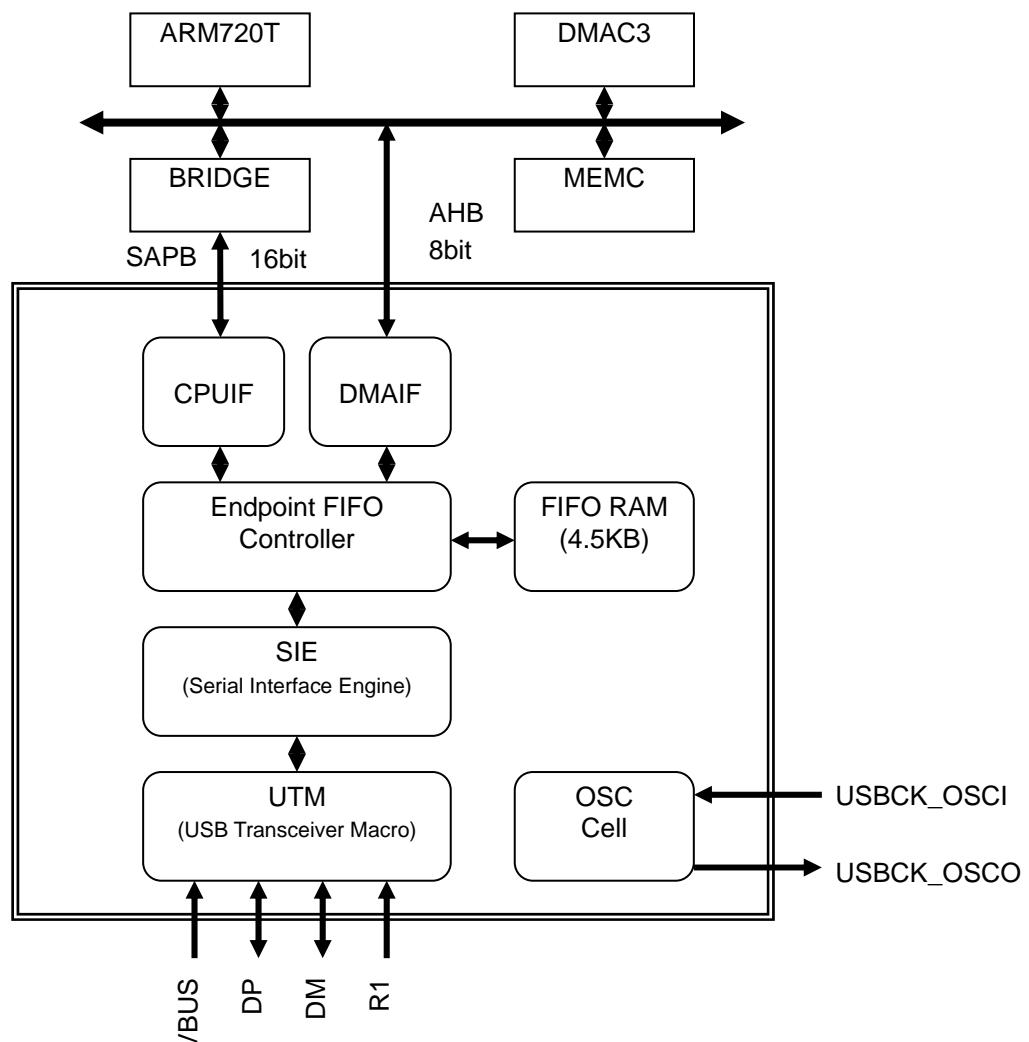

### A2.3 Block Diagram

Figure A2.3.1 S2S65A30 USB Controller Block Diagram

### A2.4 Pin List

USB インタフェース関連の外部端子は以下のようになっています。

Figure A2.4.2 USB 外部端子

| 端子名        | 入出力 | 端子機能                            |

|------------|-----|---------------------------------|

| VBUS       | I   | USB バス検出信号                      |

| DP         | I/O | USB データライン Data+                |

| DM         | I/O | USB データライン Data-                |

| R1         | I   | 内部動作設定<br>6.2KΩ±1%の抵抗を VSS 間に接続 |

| USBCK_OSCI | I   | USB 内部発振回路入力 (12/24MHz)         |

| USBCK_OSCO | O   | USB 内部発振回路出力                    |

## A2.5 Register

### A2.5.1 Register 一覧

本ブロック内にあるコントロール・レジスタのレジスタ・マップをTable A2.5.1～Table A2.5.4 に示します。表中のアドレスはAPBバスにおけるアドレスとなります。これらのベースアドレスは、**0xFFFF\_F000**です。

Table A2.5.1 USB レジスター一覧 (1/4)

| アドレス<br>オフセット                | レジスタ名称         | 説明                         | R/W   | 初期値  |

|------------------------------|----------------|----------------------------|-------|------|

| <b>割込み制御レジスタ</b>             |                |                            |       |      |

| 0x000                        | MainIntStat    | 割込みステータスレジスタ               | R/(W) | 0x00 |

| 0x003                        | CPU_IntStat    | CPUIF 関連割込みステータスレジスタ       | R/(W) | 0x00 |

| 0x007                        | DMA_IntStat    | DMA 関連割込みステータスレジスタ         | R/(W) | 0x00 |

| 0x010                        | MainIntEnb     | 割込みイネーブルレジスタ               | R/W   | 0x00 |

| 0x013                        | CPU_IntEnb     | CPUIF 関連割込みイネーブルレジスタ       | R/W   | 0x00 |

| 0x017                        | DMA_IntEnb     | DMA 関連割込みイネーブルレジスタ         | R/W   | 0x00 |

| <b>Power Management レジスタ</b> |                |                            |       |      |

| 0x020                        | PM_Control0    | Power Management 制御レジスタ    | R/W   | 0x00 |

| 0x021                        | PM_Control1    | Power Management ステータスレジスタ | R     | 0x00 |

| 0x022                        | WakeupTim_L    | Wakeup Time 設定レジスタ         | R/W   | 0x00 |

| 0x023                        | WakeupTim_H    |                            | R/W   | 0x00 |

| <b>MISC レジスタ</b>             |                |                            |       |      |

| 0x031                        | MacroReset     | ソフトウェアリセットレジスタ             | R/W   | 0x00 |

| 0x033                        | ModeProtect    | 設定プロテクトレジスタ                | R/W   | 0x56 |

| 0x035                        | MacroConfig0   | クロック設定レジスタ                 | R/W   | 0x41 |

| 0x037                        | MacroConfig1   | マクロ動作モード設定レジスタ             | R/W   | 0x06 |

| 0x039                        | (fix_CPU_Swap) |                            | R     |      |

| 0x03A                        | MacroType0     | マクロタイプレジスタ 0               | R     | 0x44 |

| 0x03B                        | MacroType1     | マクロタイプレジスタ 1               | R     | 0x08 |

| 0x03C                        | MacroType2     | マクロタイプレジスタ 2               | R     | 0x01 |

| 0x03D                        | MacroType3     | マクロタイプレジスタ 3               | R     | 0x10 |

| 0x03E                        | FIFO_CapacityL | FIFO RAM 容量レジスタ            | R     | 0x00 |

| 0x03F                        | FIFO_CapacityH |                            | R     | 0x12 |

| <b>DMA 制御レジスタ</b>            |                |                            |       |      |

| 0x041                        | DMA0_Config    | DMA0 設定レジスタ                | R/W   | 0x00 |

| 0x042                        | DMA0_Control   | DMA0 制御レジスタ                | R/W   | 0x00 |

| 0x044                        | DMA0_Remain_L  | DMA0 FIFO 残量レジスタ           | R     | 0x00 |

| 0x045                        | DMA0_Remain_H  |                            | R     | 0x00 |

| 0x048                        | DMA0_Count_HL  | DMA0 転送カウンタレジスタ            | R/W   | 0x00 |

| 0x049                        | DMA0_Count_HH  |                            | R/W   | 0x00 |

| 0x04A                        | DMA0_Count_LL  |                            | R/W   | 0x00 |

| 0x04B                        | DMA0_Count_LH  |                            | R/W   | 0x00 |

## Appendix 2 USB Device コントローラ

Table A2.5.2 USB レジスター一覧 (2/4)

| アドレス<br>オフセット     | レジスタ名称          | 説明                      | R/W   | 初期値  |

|-------------------|-----------------|-------------------------|-------|------|

| <b>USB 制御レジスタ</b> |                 |                         |       |      |

| 0x080             | DeviceIntStat   | USB 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x081             | EPrIntStat      | Endpoint 割込みステータスレジスタ   | R     | 0x00 |

| 0x082             | SIE_IntStat     | SIE 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x084             | FIFO_IntStat    | FIFO 割込みステータスレジスタ       | R/(W) | 0x00 |

| 0x085             | BulkIntStat     | Bulk 転送サポート割込みステータスレジスタ | R/(W) | 0x00 |

| 0x087             | EP0IntStat      | EP0 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x088             | EPaIntStat      | EPa 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x089             | EPbIntStat      | EPb 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x08A             | EPcIntStat      | EPc 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x08B             | EPdIntStat      | EPd 割込みステータスレジスタ        | R/(W) | 0x00 |

| 0x08C             | EPeIntStat      | EPe 割込みステータスレジスタ        | R/(W) | 0x00 |

|                   |                 |                         |       |      |

|                   |                 |                         |       |      |

|                   |                 |                         |       |      |

| 0x090             | DeviceIntEnb    | USB 割込み制御レジスタ           | R/W   | 0x00 |

| 0x091             | EPrIntEnb       | Endpoint 割込み制御レジスタ      | R/W   | 0x00 |

| 0x092             | SIE_IntEnb      | SIE 割込み制御レジスタ           | R/W   | 0x00 |

| 0x094             | FIFO_IntEnb     | FIFO 割込み制御レジスタ          | R/W   | 0x00 |

| 0x095             | BulkIntEnb      | Bulk 転送サポート割込み制御レジスタ    | R/W   | 0x00 |

| 0x097             | EP0IntEnb       | EP0 割込み制御レジスタ           | R/W   | 0x00 |

| 0x098             | EPaIntEnb       | EPa 割込み制御レジスタ           | R/W   | 0x00 |

| 0x099             | EPbIntEnb       | EPb 割込み制御レジスタ           | R/W   | 0x00 |

| 0x09A             | EPcIntEnb       | EPc 割込み制御レジスタ           | R/W   | 0x00 |

| 0x09B             | EPdIntEnb       | EPd 割込み制御レジスタ           | R/W   | 0x00 |

| 0x09C             | EPeIntEnb       | EPe 割込み制御レジスタ           | R/W   | 0x00 |

|                   |                 |                         |       |      |

|                   |                 |                         |       |      |

|                   |                 |                         |       |      |

| 0x0A0             | ResetDTM        | トランシーバマクロリセットレジスタ       | R/W   | 0x01 |

| 0x0A2             | NegoControl     | ネゴシエーション制御レジスタ          | R/W   | 0x00 |

| 0x0A4             | USB_Status      | USB バスステータスレジスタ         | R/W   | 0XX  |

| 0x0A5             | XcvrControl     | トランシーバマクロ制御レジスタ         | R/W   | 0x41 |

| 0x0A6             | USB_Test        | USB テストレジスタ             | R/W   | 0x00 |

| 0x0A8             | EPnControl      | EP 共通制御レジスタ             | W     | 0XX  |

| 0x0A9             | EPrFIFO_Clr     | FIFO クリアレジスタ            | W     | 0XX  |

| 0x0AA             | ClrAllEPnJoin   | EP ジョインクリアレジスタ          | W     | 0XX  |

| 0x0AC             | BulkOnlyControl | Bulk 転送サポート制御レジスタ       | R/W   | 0x00 |

| 0x0AD             | BulkOnlyConfig  | Bulk 転送サポート設定レジスタ       | R/W   | 0x00 |

| 0x0B0             | EP0SETUP_0      | EP0 セットアップデータレジスタ       | R     | 0x00 |

| 0x0B1             | EP0SETUP_1      |                         | R     | 0x00 |

| 0x0B2             | EP0SETUP_2      |                         | R     | 0x00 |

| 0x0B3             | EP0SETUP_3      |                         | R     | 0x00 |

| 0x0B4             | EP0SETUP_4      |                         | R     | 0x00 |

| 0x0B5             | EP0SETUP_5      |                         | R     | 0x00 |

| 0x0B6             | EP0SETUP_6      |                         | R     | 0x00 |

| 0x0B7             | EP0SETUP_7      |                         | R     | 0x00 |

| 0x0B8             | USB_Address     | USB アドレスレジスタ            | R/(W) | 0x00 |

| 0x0BA             | SETUP_Control   | セットアップステージ制御レジスタ        | R/W   | 0x00 |

| 0x0BE             | FrameNumber_L   | フレーム番号レジスタ              | R     | 0x00 |

| 0x0BF             | FrameNumber_H   |                         | R     | 0x80 |

Table A2.5.3 USB レジスター一覧 (3/4)

| アドレス<br>オフセット     | レジスタ名称        | 説明                    | R/W | 初期値  |

|-------------------|---------------|-----------------------|-----|------|

| <b>USB 制御レジスタ</b> |               |                       |     |      |

| 0x0C0             | EP0MaxSize    | EP0 マックスパケットサイズ設定レジスタ | R/W | 0x40 |

| 0x0C1             | EP0Control    | EP0 制御レジスタ            | R/W | 0x00 |

| 0x0C2             | EP0ControlIN  | EP0 IN 転送制御レジスタ       | R/W | 0x00 |

| 0x0C3             | EP0ControlOUT | EP0 OUT 転送制御レジスタ      | R/W | 0x00 |

| 0x0C5             | EP0Join       | EP0 ジョイン設定レジスタ        | R/W | 0x00 |

| 0x0D0             | EPaMaxSize_L  | EPa マックスパケットサイズ設定レジスタ | R/W | 0x00 |

| 0x0D1             | EPaMaxSize_H  |                       | R/W | 0x00 |

| 0x0D2             | EPaConfig     | EPa 設定レジスタ            | R/W | 0x00 |

| 0x0D4             | EPaControl    | EPa 制御レジスタ            | R/W | 0x00 |

| 0x0D5             | EPaJoin       | EPa ジョイン設定レジスタ        | R/W | 0x00 |

| 0x0D8             | EPbMaxSize_L  | EPb マックスパケットサイズ設定レジスタ | R/W | 0x00 |

| 0x0D9             | EPbMaxSize_H  |                       | R/W | 0x00 |

| 0x0DA             | EPbConfig     | EPb 設定レジスタ            | R/W | 0x00 |

| 0x0DC             | EPbControl    | EPb 制御レジスタ            | R/W | 0x00 |

| 0x0DD             | EPbJoin       | EPb ジョイン設定レジスタ        | R/W | 0x00 |

| 0x0E0             | EPcMaxSize_L  | EPc マックスパケットサイズ設定レジスタ | R/W | 0x00 |

| 0x0E1             | EPcMaxSize_H  |                       | R/W | 0x00 |

| 0x0E2             | EPcConfig     | EPc 設定レジスタ            | R/W | 0x00 |

| 0x0E4             | EPcControl    | EPc 制御レジスタ            | R/W | 0x00 |

| 0x0E5             | EPcJoin       | EPc ジョイン設定レジスタ        | R/W | 0x00 |

| 0x0E8             | EPdMaxSize_L  | EPd マックスパケットサイズ設定レジスタ | R/W | 0x00 |

| 0x0E9             | EPdMaxSize_H  |                       | R/W | 0x00 |

| 0x0EA             | EPdConfig     | EPd 設定レジスタ            | R/W | 0x00 |

| 0x0EC             | EPdControl    | EPd 制御レジスタ            | R/W | 0x00 |

| 0x0ED             | EPdJoin       | EPd ジョイン設定レジスタ        | R/W | 0x00 |

| 0x0F0             | EPeMaxSize_L  | EPe マックスパケットサイズ設定レジスタ | R/W | 0x00 |

| 0x0F1             | EPeMaxSize_H  |                       | R/W | 0x00 |

| 0x0F2             | EPeConfig     | EPe 設定レジスタ            | R/W | 0x00 |

| 0x0F4             | EPeControl    | EPe 制御レジスタ            | R/W | 0x00 |

| 0x0F5             | EPeJoin       | EPe ジョイン設定レジスタ        | R/W | 0x00 |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

|                   |               |                       |     |      |

## Appendix 2 USB Device コントローラ

Table A2.5.4 USB レジスター一覧 (4/4)

| アドレス<br>オフセット       | レジスタ名称                      | 説明                      | R/W | 初期値  |

|---------------------|-----------------------------|-------------------------|-----|------|

| USB FIFO 設定レジスタ     |                             |                         |     |      |

| 0x110               | EPaStartAdrs_L              | EPa FIFO スタートアドレス設定レジスタ | R/W | 0x00 |

| 0x111               | EPaStartAdrs_H              |                         | R/W | 0x00 |

| 0x112               | EPbStartAdrs_L              | EPb FIFO スタートアドレス設定レジスタ | R/W | 0x00 |

| 0x113               | EPbStartAdrs_H              |                         | R/W | 0x00 |

| 0x114               | EPcStartAdrs_L              | EPc FIFO スタートアドレス設定レジスタ | R/W | 0x00 |

| 0x115               | EPcStartAdrs_H              |                         | R/W | 0x00 |

| 0x116               | EPdStartAdrs_L              | EPd FIFO スタートアドレス設定レジスタ | R/W | 0x00 |

| 0x117               | EPdStartAdrs_H              |                         | R/W | 0x00 |

| 0x118               | EPeStartAdrs_L              | EPe FIFO スタートアドレス設定レジスタ | R/W | 0x00 |

| 0x119               | EPeStartAdrs_H              |                         | R/W | 0x00 |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

|                     |                             |                         |     |      |

| 0x128               | DMA0_FIFO_Control           | DMA0-FIFO 制御レジスタ        | R/W | 0x00 |

| 0x12A               |                             |                         |     |      |

| 0x130               | FIFO_Rd_0                   | FIFO リードレジスタ            | R   | 0xXX |

| 0x131               | FIFO_Rd_1                   |                         | R   | 0xXX |

| 0x132               | FIFO_Wr_0                   | FIFO ライトレジスタ            | W   | 0xXX |

| 0x133               | FIFO_Wr_1                   |                         | W   | 0xXX |

| 0x134               | FIFO_RdRemain_L             | FIFO リード残量レジスタ          | R   | 0x00 |

| 0x135               | FIFO_RdRemain_H             |                         | R   | 0x00 |

| 0x136               | FIFO_WrRemain_L             | FIFO ライト残量レジスタ          | R   | 0x00 |

| 0x137               | FIFO_WrRemain_H             |                         | R   | 0x00 |

| 0x138               | FIFO_BytRd                  | FIFO バイトリードレジスタ         | R   | 0xXX |

| 0x140               | RAM_RdAdrs_L                | RAM リードアドレス設定レジスタ       | R/W | 0x00 |

| 0x141               | RAM_RdAdrs_H                |                         | R/W | 0x00 |

| 0x142               | RAM_RdControl               | RAM リード制御レジスタ           | R/W | 0x00 |

| 0x143               | RAM_RdCount                 | RAM リードカウント設定レジスタ       | R/W | 0x00 |

| 0x144               | RAM_WrAdrs_L                | RAM ライトアドレス設定レジスタ       | R/W | 0x00 |

| 0x145               | RAM_WrAdrs_H                |                         | R/W | 0x00 |

| 0x146               | RAM_WrDoor_0                | RAM ライトレジスタ             | W   | 0xXX |

| 0x147               | RAM_WrDoor_1                |                         | W   | 0xXX |

| 0x150<br>~<br>0x16F | RAM_Rd_00<br>~<br>RAM_Rd_1F | RAM リードデータレジスタ          | R   | 0XX  |

| テストレジスタ (Reserved)  |                             |                         |     |      |

| 0x170<br>~<br>0x17F | Reserved                    | テスト用レジスタ                | —   |      |

### A2.5.2 Register 詳細説明

#### A2.5.2.1 Register Access 上の注意事項

- (1) Register が割り付けられていない Address に対しては書き込みを行わないでください。

- (2) Register が割り付けられていない bit に対しては“0x0”的書き込みのみとしてください。

- (3) SLEEP / SNOOZE 時にでも読み書きできる Register は**太字斜体**で示しています。

- (4) それ以外の Register は、ACTIVE60 / ACT\_DEVICE 時に読み書きができます。

#### A2.5.2.2 割込み制御レジスタ

| Main Interrupt Status |        |                         |        |        |                         |        |                     |

|-----------------------|--------|-------------------------|--------|--------|-------------------------|--------|---------------------|

| USB[0x000] 初期値 = 0x00 |        |                         |        |        |                         |        |                     |

| Device<br>IntStat(R)  | —<br>7 | CPU_<br>IntStat(R)<br>5 | —<br>4 | —<br>3 | DMA_<br>IntStat(R)<br>2 | —<br>1 | Finished<br>PM<br>0 |

USB マクロの割り込み要因を示します。

このレジスタには割り込み要因を間接指示するビットと直接指示するビットがあります。割り込み要因を間接指示するビットは、それぞれに対応する割り込みステータスレジスタをリードすることにより、割り込み要因を直接指示するビットまで辿ることができます。割り込み要因を間接指示するビットは、リードオンリーであり、大元の割り込み要因を直接指示するビットをクリアすることにより、自動的にクリアされます。割り込み要因を直接指示しているビットは、書き込み可能であり、該当ビットに“1”を書き込むことにより、割り込み要因をクリアすることができます。MainInterruptEnb レジスタにより、対応するビットの割り込みがイネーブルにされているときに、割り込み要因が“1”にセットされると INTC に対して割り込みが発生します。

- Bit 7 : **DeviceIntStat**

割り込み要因を間接指示します。

Device\_IntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する SIE\_DeviceIntEnb レジスタのビットがイネーブルにされているときに“1”にセットされます。このビットは、SLEEP / SNOOZE 中もリード有効です。

- Bit 6 : **Reserved**

- Bit 5 : **CPU\_IntStat**

割り込み要因を間接指示します。

CPU\_IntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する CPU\_IntEnb レジスタのビットがイネーブルにされているときに“1”にセットされます。

- Bit [4:3] : **Reserved**

- Bit 2 : **DMAIntStat**

割り込み要因を間接指示します。

DMAIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する DMAIntEnb レジスタのビットがイネーブルにされているときに“1”にセットされます。

- Bit 1 : **Reserved**

- Bit 0 : **FinishedPM**

割り込み要因を直接指示します。

PM\_Control レジスタで、GoSLEEP, GoSNOOZE, GoActive60, GoActDevice を設定した場合、指示したそれぞれの状態に達したら、このビットは“1”にセットされます。このビットは SLEEP / SNOOZE 中も有効です。

## Appendix 2 USB Device コントローラ

| CPU Interrupt Status  |   |   |   |   |   |   |   |   |

|-----------------------|---|---|---|---|---|---|---|---|

| USB[0x003] 初期値 = 0x00 |   |   |   |   |   |   |   |   |

| RAM_RdCmp             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

CPU インタフェース関連の割り込みを表示します。

全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit 7 : **RAM\_RdCmp**

割り込み要因を直接指示します。

RAM\_Rd 機能において、RAM からデータを読み出し、RAM\_Rd\_XX のデータが有効になったところで、“1”にセットされます。

Bit [6:0] : **Reserved**

| DMA Interrupt Status  |   |   |   |   |   |   |              |          |

|-----------------------|---|---|---|---|---|---|--------------|----------|

| USB[0x007] 初期値 = 0x00 |   |   |   |   |   |   |              |          |

| —                     | — | — | — | — | — | — | DMA0_CountUp | DMA0_Cmp |

DMA 関連の割り込みを表示します。

全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit [7:2] : **Reserved**

Bit 1 : **DMA0\_CountUp**

割り込み要因を直接指示します。

転送モードがフリーランモードで動作しているときに、DMA0\_Count\_HH,HL,LH,LL の値がオーバーフローしたときに、“1”にセットされます。DMA0\_Count\_HH,HL,LH,LL の値は 0 に戻り、DMA 動作は継続します。

Bit 0 : **DMA0\_Cmp**

割り込み要因を直接指示します。

DMA 転送が停止されるか、或いは、指定された転送数が終了し、終了処理が完了したときに“1”にセットされます。

| Main Interrupt Enable    |        |                       |        |        |                        |        |                       |

|--------------------------|--------|-----------------------|--------|--------|------------------------|--------|-----------------------|

| USB[0x010] 初期値 = 0x00    |        |                       |        |        |                        |        |                       |

| EnDevice<br>IntStat<br>7 | —<br>6 | EnCPU<br>IntStat<br>5 | —<br>4 | —<br>3 | EnDMA_<br>IntStat<br>2 | —<br>1 | EnFinished<br>PM<br>0 |

MainIntStat レジスタの割り込み要因による INTC モジュールに対する割り込み信号のアサートを許可／禁止するレジスタです。対応するビットを“1”にセットすることで割り込みを許可します。

EnDeviceIntStat, EnFinishedPM ビットは SLEEP / SNOOZE 中も有効です。

| CPU Interrupt Enable  |        |        |        |        |        |        |        |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|

| USB[0x013] 初期値 = 0x00 |        |        |        |        |        |        |        |

| EnRAM_<br>RdCmp<br>7  | —<br>6 | —<br>5 | —<br>4 | —<br>3 | —<br>2 | —<br>1 | —<br>0 |

CPU\_IntStat レジスタの割り込み要因による、MainIntStat レジスタの CPU\_IntStat ビットのアサートを許可／禁止します。

| DMA Interrupt Enable  |        |        |        |        |        |                         |                     |

|-----------------------|--------|--------|--------|--------|--------|-------------------------|---------------------|

| USB[0x017] 初期値 = 0x00 |        |        |        |        |        |                         |                     |

| —<br>7                | —<br>6 | —<br>5 | —<br>4 | —<br>3 | —<br>2 | EnDMA0_<br>CountUp<br>1 | EnDMA0_<br>Cmp<br>0 |

DMAIntStat レジスタの割り込み要因による、MainIntStat レジスタの DMAIntStat ビットのアサートを許可／禁止します。

## Appendix 2 USB Device コントローラ

### A2.5.2.3 Power Management 制御レジスタ

| Power Management Control 0 |                   |                     |                      |        |        |        |        |

|----------------------------|-------------------|---------------------|----------------------|--------|--------|--------|--------|

| USB[0x020]                 |                   | 初期値 = 0x00          |                      |        |        |        |        |

| Go<br>SLEEP<br>7           | Go<br>SNOOZE<br>6 | Go<br>Active60<br>5 | Go<br>ActDevice<br>4 | -<br>3 | -<br>2 | -<br>1 | -<br>0 |

本 LSI のパワーマネージメント関連の動作設定を行います。

このレジスタは SLEEP / SNOOZE 中も有効です。

Bit 7 :

#### GoSLEEP

SLEEP ステート以外のステートから、SLEEP ステートへの移行を開始します。

SNOOZE ステート時に本ビットを“1”にセットすると、オシレータの発振を停止し SLEEP ステートに移行します。

ACTIVE60 ステート時に本ビットを“1”にセットすると、まず PLL60 の発振を停止し、その後オシレータの発振を停止し SLEEP ステートに移行します。

ACT\_DEVICE ステート時に本ビットを“1”にセットすると、最初に DevicePLL480 の発振を停止し、次に PLL60 の発振を停止し、その後オシレータの発振を停止し SLEEP ステートに移行します。

どのステートからの移行であっても、移行が完了し次第、本ビットは自動的にクリアされ、同時に MainIntStat.FinishedPM ビットがセットされます。

Bit 6 :

#### GoSNOOZE

SNOOZE ステート以外のステートから、SNOOZE ステートへの移行を開始します。

SLEEP ステート時に本ビットを“1”にセットすると、オシレータの発振を開始し、オシレータ発振安定時間 (WakeupTim\_H, L に設定された時間) 経過後、SNOOZE ステートに移行します。

ACTIVE60 ステート時に本ビットを“1”にセットすると、PLL60 の発振を停止し、SNOOZE ステートに移行します。

ACT\_DEVICE ステート時に本ビットを“1”にセットすると、最初に DevicePLL480 の発振を停止し、次に PLL60 の発振を停止し、SNOOZE ステートに移行します。

どのステートからの移行であっても、移行が完了し次第、本ビットは自動的にクリアされ、同時に MainIntStat.FinishedPM ビットがセットされます。

Bit 5 :

#### GoActive60

ACTIVE60 ステート以外のステートから、ACTIVE60 ステートへの移行を開始します。

SLEEP ステート時に本ビットを“1”にセットすると、オシレータの発振を開始し、オシレータ発振安定時間 (WakeupTim\_H, L に設定された時間) 経過後、PLL60 の発振を開始し、PLL60 発振安定時間 (約 250μs) 経過後、ACTIVE60 ステートに移行します。

SNOOZE ステート時に本ビットを“1”にセットすると、PLL60 の発振を開始し、PLL 発振安定時間 (約 250μs) 経過後、ACTIVE60 ステートに移行します。

ACT\_DEVICE ステート時に本ビットを“1”にセットすると、DevicePLL480 の発振を停止し、ACTIVE60 ステートに移行します。

どのステートからの移行であっても、移行が完了し次第、本ビットは自動的にクリアされ、同時に MainIntStat.FinishedPM ビットがセットされます。

Bit 4 :

**GoActDevice**

ACT\_DEVICE ステート以外のステートから、ACT\_DEVICE ステートへの移行を開始します。

SLEEP・ステート時に本ビットを“1”にセットすると、オシレータの発振を開始し、オシレータ発振安定時間 (WakeupTim\_H, L に設定された時間) 経過後、PLL60 の発振を開始し、PLL60 発振安定時間 (約 250μs) 経過後、DevicePLL480 の発振を開始し、PLL480 発振安定時間 (約 250μs) 経過後、ACT\_DEVICE ステートに移行します。

SNOOZE ステート時に本ビットを“1”にセットすると、PLL60 の発振を開始し、PLL 発振安定時間 (約 250μs) 経過後、DevicePLL480 の発振を開始し、PLL480 発振安定時間 (約 250μs) 経過後、ACT\_DEVICE・ステートに移行します。

ACTIVE60 ステート時に本ビットを“1”にセットすると、DevicePLL480 の発振を開始し、PLL480 発振安定時間 (約 250μs) 経過後、ACT\_DEVICE ステートに移行します。

どのステートからの移行であっても、移行が完了し次第、本ビットは自動的にクリアされ、同時に MainIntStat.FinishedPM ビットがセットされます。

※本 LSI は SLEEP / SNOOZE 中にアクセスできない割り込みステータス（以下、同期ステータス）により、SNOOZE 中に XINT 信号がアサートされないようマスクしておりますが、SNOOZE 解除と同時に XINT 端子がアサートされるのを回避するため、F/W により以下の処理を行って下さい。

&lt;SLEEP / SNOOZE 開始前&gt;

- 同期ステータスを処理し、クリアする。 (~IntStat)

- 同期ステータスをディスエーブルにする。 (~IntEnb)

&lt;SLEEP / SNOOZE 解除後&gt;

- 同期ステータスをクリアする。 (~IntStat)

- 同期ステータスをイネーブルにする。 (~IntEnb)

Bit [3:0] :

**Reserved**

| Power Management Control 1 |   |   |   |   |   |   |   |

|----------------------------|---|---|---|---|---|---|---|

| USB[0x021] 初期値 = 0x00      |   |   |   |   |   |   |   |

| PM_State[3:0](R)           |   |   |   |   |   |   |   |

| —                          | — | — | — | 3 | 2 | 1 | 0 |

| 7                          | 6 | 5 | 4 |   |   |   |   |

本 LSI のパワーマネージメント関連の動作状態をモニタできます。

このレジスタは SLEEP / SNOOZE 中も有効です。

Bit [7:4] :

**Reserved**

Bit [3:0] :

**PM\_State[3:0]**

電力モードのステートを表します。

|                       |                                  |

|-----------------------|----------------------------------|

| 0000 : SLEEPステート      | (OSCオフ、PLL60 オフ、DevicePLL480 オフ) |

| 0001 : SNOOZEステート     | (OSCオン、PLL60 オフ、DevicePLL480 オフ) |

| 0011 : ACTIVE60 ステート  | (OSCオン、PLL60 オン、DevicePLL480 オフ) |

| 0111 : ACT_DEVICEステート | (OSCオン、PLL60 オン、DevicePLL480 オン) |

その他 : 未使用

なお本ステートは、PM\_Control0.GoXXXX をセットしてから MainIntStat.FinishedPM 割り込みステータスがセットされ、PM\_Control0.GoXXXX ビットがクリアされるまでは、該当ステートに向かい逐次変化致しますので、参照しないでください。

## Appendix 2 USB Device コントローラ

| Wakeup Time[7:0]      |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x022] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| WakeupTim[7:0]        |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Wakeup Time[15:8]     |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x023] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| WakeupTim[15:8]       |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

SLEEP ステートから SNOOZE ステートへ復帰する際のオシレータ発振安定時間を設定します。本レジスタは SLEEP 時にもアクセスが可能です。

SLEEP ステート時に、PM\_Control0.GoActDevice、PM\_Control0.GoActive60、PM\_Control0.GoSNOOZE ビットに“1”が書き込まれた際に、発振セルをイネーブルにし、オシレータの発振を開始します。この時、カウンタにこの Wakeup\_Tim の設定値をロードし、OSC の立ち上がりにてカウントダウンを始めます。カウントダウン終了後、内部 OSCCLK のゲートを開き、PLL 等の回路に CLK を送出開始します。このオシレータ発振安定時間は、発振子、発振セル、基板、負荷容量等により変化します。もし、デバイス動作時において、USB の SUSPEND 時に SLEEP ステートまで落とす場合は、USB の RESET 検出から 5.1ms 以内に 60MHz±10% に内部 SCLK が安定していなければなりません。

したがって、オシレータ発振安定時間 + PLL60 安定時間 (250μs 未満) + PLL480 安定時間 (250μs 未満) の合計が 5.1ms 以下とならなければなりません。

### A2.5.2.4 MISC レジスタ

| Macro Reset           |   |   |   |   |   |   |   |              |

|-----------------------|---|---|---|---|---|---|---|--------------|

| USB[0x031] 初期値 = 0xXX |   |   |   |   |   |   |   |              |

|                       |   |   |   |   |   |   |   | AllReset (W) |

| —                     | — | — | — | — | — | — | — | 0            |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |              |

本 LSI をリセットします。

SLEEP / SNOOZE 時でもアクセス有効です。

Bit [7:1] : **Reserved**

Bit 0 : **AllReset**

本 LSI の全回路をリセットします。外部リセット端子(XRST)と同義です。

なお、このレジスタにリセット用途以外で、書き込みしないで下さい。

AC スペックに違反してこのレジスタにリセット用途以外の書き込みを行った場合、誤動作の原因となりますのでご注意下さい。

| Mode Protect          |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x033] 初期値 = 0x56 |   |   |   |   |   |   |   |  |

| ModeProtect[7:0]      |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

Bit [7:0] : **ModeProtect[7:0]**

MacroConfig0 レジスタ及び ClkSelect.ClkSelect ビットの値を保護します。このレジスタに 56h を書き込むと MacroConfig0 レジスタ及び ClkSelect.ClkSelect ビットへのライトアクセスが有効になります。

通常使用においては、MacroConfig0 レジスタ及び ClkSelect.ClkSelect ビットを任意に設定した後、このレジスタに 56h 以外の値（例えば 00h）を設定して、MacroConfig0 レジスタ及び ClkSelect.ClkSelect ビットの設定を保護して下さい。

このビットは、SLEEP / SNOOZE 中もアクセス有効です。

| <b>Macro Configuration 0</b> |        |        |        |        |        |        |                       |

|------------------------------|--------|--------|--------|--------|--------|--------|-----------------------|

| USB[0x035] 初期値 = 0x41        |        |        |        |        |        |        |                       |

| —<br>7                       | —<br>6 | —<br>5 | —<br>4 | —<br>3 | —<br>2 | —<br>1 | <b>ClkSelect</b><br>0 |

Bit [7:1] : **Reserved**Bit 0 : **ClkSelect**

本LSIで使用するクロックを選択します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : 12MHz

- 1 : 24MHz

| <b>Macro Configuration 1</b> |                     |                        |                        |                     |                      |                     |                     |

|------------------------------|---------------------|------------------------|------------------------|---------------------|----------------------|---------------------|---------------------|

| USB[0x037] 初期値 = 0x06        |                     |                        |                        |                     |                      |                     |                     |

| <b>IntLevel</b><br>7         | <b>IntMode</b><br>6 | <b>DREQ_Level</b><br>5 | <b>DACK_Level</b><br>4 | <b>CS_Mode</b><br>3 | <b>CPU_Swap</b><br>2 | <b>BusMode</b><br>1 | <b>Bus8x16</b><br>0 |

本LSIの動作モードを設定します。本レジスタの初期値はS2S65A30用に最適化されていますので、特に必要のない限り設定を変更しないでください。

Bit 7 : **IntLevel**

XINTの論理レベルを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : 負論理

- 1 : 正論理

Bit 6 : **IntMode**

XINTの出力モードを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : 1/0モード

- 1 : Hi-z/0モード

Bit 5 : **DREQ\_Level**

XDREQ0,1の論理レベルを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : 負論理

- 1 : 正論理

Bit 4 : **DACK\_Level**

XDACK0,1の論理レベルを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : 負論理

- 1 : 正論理

Bit 3 : **CS\_Mode**

DMA0の動作モードを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

- 0 : XDACK0,1がアサートされているとき有効なDMAアクセスとして動作します。

- 1 : XCS且つXDACK0,1がアサートされているとき有効なDMAアクセスとして動作します。

Bit 2 : **CPU\_Swap**

16bit mode 時のCPUバスを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

8bit mode 時はこのビットをセットしないで下さい。

- 0 : 偶数アドレスを上位側、奇数アドレスを下位側とします。

- 1 : 偶数アドレスを下位側、奇数アドレスを上位側とします。

このビットの設定は、レジスタ書き込み後、039h番地をリードすることにより有効になります。

ChipReset.ResetAllビットにて、回路のリセットを行った場合、レジスタの値は初期化されますが、その設定が有効になるのは、上述同様に039h番地をリードした後になります。

## Appendix 2 USB Device コントローラ

Bit [1:0] :

### BusMode, Bus8x16

CPU の動作モードを設定します。このビットは、SLEEP / SNOOZE 中もアクセス有効です。

| 動作モード             | bit1.BusMode | bit0.Bus8x16 |

|-------------------|--------------|--------------|

| 16bit Strobe mode | 0            | 0            |

| 16bit BE mode     | 1            | *            |

| 8bit mode         | 0            | 1            |

### Macro Type 0

USB[0x03A] 初期値 = 0x44

#### Device\_Host[7:0](R)

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

本マクロのマクロタイプを表します。

Bit [7:0] :

### Device/Host[7:0]

Device か Host かを表します。

Device : 0x44

Host : 0x48

### Macro Type 1

USB[0x03B] 初期値 = 0x05

#### Exist\_IDE(R)

#### EP\_Num[3:0] (R)

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| — | — | — | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

本マクロのマクロタイプを表します。

Bit [7:5] :

### Reserved

Bit 4 :

### Exist\_IDE

IDE が実装されているかを表します。

Not mount : 0x0

Mount : 0x1

Bit [3:0] :

### EP\_Num[3:0]

End Point 数を表します。

16 進数で表します。

### Macro Type 2

USB[0x03C] 初期値 = 0x01

#### DM Ach\_Count[3:0] (R)

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| — | — | — | — | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

本マクロのマクロタイプを表します。

Bit [7:4] :

### Reserved

Bit [3:0] :

### DM Ach\_Count[3:0]

DMA チャンネル数の総数を表します。

16 進数でチャンネル数を表します

| Macro Type 3           |   |   |   |   |   |   |   |  |

|------------------------|---|---|---|---|---|---|---|--|

| USB[0x03D] 初期値 = 0x10  |   |   |   |   |   |   |   |  |

| PortDMA_Mount[3:0] (R) |   |   |   |   |   |   |   |  |

| 7                      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

本マクロのマクロタイプを表します。

Bit [7:4] : **PortDMA\_Mount[3:0]**

実装されている Sync DMA のチャンネルを表します。

2 進数で実装されているチャンネルを表します。

Bit [3:0] : **CPUDMA\_Mount[3:0]**

実装されている CPU DMA のチャンネルを表します。

2 進数で実装されているチャンネルを表します。

| FIFO Capacity[7:0]    |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x03E] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| FIFO_Capacity[7:0]    |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| FIFO Capacity[15:8]   |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x03F] 初期値 = 0x12 |   |   |   |   |   |   |   |  |

| FIFO_Capacity[15:8]   |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

実装されている FIFO RAM の容量を表します。

#### A2.5.2.5 DMA 制御レジスタ

| DMA0 Configuration    |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x041] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| FreeRun               |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

DMA0 の動作モードを設定します。

Bit 7 : **FreeRun**

DMA0 の動作モードを設定します。

0 : カウントモード

1 : フリーランモード

Bit [6:4] : **Reserved**

## Appendix 2 USB Device コントローラ

Bit 3 :

### ActiveDMA

PortDMA0 を有効にします。転送中にこの bit をクリアすると即座に転送を中止します。再転送する際は USB FIFO、PortDMA の初期化を行ってください。通常の停止では DMA\_Stop を使用してください。

なおこの bit は USBFIFO が Clear されたり、Join が切り替えられた場合、自動的に Clear されます。

1 : PortDMA0 有効

0 : PortDMA0 無効

Bit [2:0] :

### Reserved

| DMA0 Control          |        |        |                         |          |        |                  |                |

|-----------------------|--------|--------|-------------------------|----------|--------|------------------|----------------|

| USB[0x042] 初期値 = 0x00 |        |        |                         |          |        |                  |                |

| Running<br>(R)<br>7   | —<br>6 | —<br>5 | Counter<br>Clr (W)<br>4 | Dir<br>3 | —<br>2 | Stop<br>(W)<br>1 | Go<br>(W)<br>0 |

DMA0 の制御、及び状態を表示します。

Bit 7 :

### Running

DMA0 の転送中、このビットが“1”にセットされます。このビットが“1”である間は、EPx{x=0,a~h}Join.JoinDMA0 を書き換えることはできません。

Bit [6:5] :

### Reserved

Bit 4 :

### CounterClr

このビットに“1”をセットすると、Count\_HH,HL,LH,LL レジスタが 0x00 にクリアされます。Running ビットが“1”であるときは、このビットへの書き込みは無視されます。

Bit 3 :

### Dir

DMA0 の転送方向を設定します。

0 : Port → FIFO RAM (DMA ライト)

1 : Port ← FIFO RAM (DMA リード)

Bit 2 :

### Reserved

Bit 1 :

### Stop

このビットに“1”をセットすると、DMA0 の転送を終了します。DMA0 の転送を停止すると、DMA\_Running ビットを“0”にクリアします。また、CPU\_IntStat レジスタの DMA0\_Cmp ビットに“1”をセットします。DMA の転送を再開する場合、Running ビットまたは DMA0\_Cmp ビットを確認し、DMA が終了するのを待って行って下さい。

Bit 0 :

### Go

このビットを“1”にセットすると、DMA0 の転送を開始します。

**DMA0 Remain[7:0]**

USB[0x044] 初期値 = 0x00

| Remain[7:0](R) |   |   |   |   |   |   |   |

|----------------|---|---|---|---|---|---|---|

| 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

**DMA0 Remain[12:8]**

USB[0x045] 初期値 = 0x00

| Remain[12:8](R) |   |   |   |   |   |   |   |

|-----------------|---|---|---|---|---|---|---|

| —               | — | — | 4 | 3 | 2 | 1 | 0 |

Bit [7:0] : **Remain[7:0]**Bit [7:5] : **Reserved**Bit [4:0] : **Remain[12:8]**

読み出しの場合、EPx{x=0,a~h}Join.JoinDMA0 ビットによって DMA に接続しているエンドポイントの FIFO 内の残りデータ数を示します。

書き込みの場合、EPx{x=0,a~h}Join.JoinDMA0 ビットによって DMA に接続しているエンドポイントの FIFO の空き容量を示します。DMA 書き込みを行った直後にはこのレジスタで正しい FIFO の空き容量を参照することが出来ません。1CPU サイクル以上の間隔を空けて FIFO の空き容量を確認してください。

このレジスタを読み出す場合は上位バイト、下位バイトの順に読み出してください。

**DMA0 Count[23:16]**

USB[0x048] 初期値 = 0x00

| Count[23:16] |   |   |   |   |   |   |   |

|--------------|---|---|---|---|---|---|---|

| 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

## Appendix 2 USB Device コントローラ

| DMA0 Count[31:24]     |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x049] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| Count[31:24]          |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| DMA0 Count[7:0]       |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x04A] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| Count[7:0]            |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| DMA0 Count[15:8]      |   |   |   |   |   |   |   |  |

|-----------------------|---|---|---|---|---|---|---|--|

| USB[0x04B] 初期値 = 0x00 |   |   |   |   |   |   |   |  |

| Count[15:8]           |   |   |   |   |   |   |   |  |

| 7                     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

Bit [7:0] : **Count[23:16]**

Bit [7:0] : **Count[31:24]**

Bit [7:0] : **Count[7:0]**

Bit [7:0] : **Count[15:8]**

カウントモード時に DMA0 の、転送データ長をバイト単位で設定します。最大 0xFFFF\_FFFF バイトまで設定可能です。設定された値からダウンカウントします。本レジスタに転送数を設定した後、DMA0\_Control.Go ビットに“1”をセットして DMA 転送を起動してください。本レジスタに設定された転送 Byte 数の転送が終了すると、DMA 転送は終了します。

フリーランモードの場合、設定された値からカウントアップします。DMA0\_Count レジスタの値がオーバーフローすると、DMAIntStat レジスタの DMA0\_CountUp ビットに“1”をセットします。オーバーフロー後もカウントは継続されます。このモードでは、DMA の転送数が参照できます。

DMA 書き込みを行った直後は、このレジスタで正確なカウント数を確認することは出来ません。1CPU サイクル以上の間隔をあけて、カウント数を確認してください。このレジスタをリードする場合は上位バイトから順に読み出してください。

## A2.5.2.6 USB 制御レジスタ

| Device Interrupt Status |                |                |                 |              |                 |                |                |

|-------------------------|----------------|----------------|-----------------|--------------|-----------------|----------------|----------------|

| USB[0x080] 初期値 = 0x00   |                |                |                 |              |                 |                |                |

| VBUS_Changed            | Descriptor Cmp | SIE_IntStat(R) | Bulk_IntStat(R) | RcvEP0 SETUP | FIFO_IntStat(R) | EP0_IntStat(R) | EPr_IntStat(R) |

| 7                       | 6              | 5              | 4               | 3            | 2               | 1              | 0              |

USB デバイス関連の割り込みを表示します。

このレジスタには割り込み要因を間接指示するビットと直接指示するビットがあります。割り込み要因を間接指示するビットは、それぞれに対応する割り込みステータスレジスタをリードすることにより、割り込み要因を直接指示するビットまで辿ることができます。割り込み要因を間接指示するビットは、リードオンリーであり、大元の割り込み要因を直接指示するビットをクリアすることにより、自動的にクリアされます。割り込み要因を直接指示しているビットは、書き込み可能であり、該当ビットに“1”を書き込むことにより、割り込み要因をクリアすることができます。

Bit 7 :

#### **VBUS\_Changed**

割り込み要因を直接指示します。

VBUS 端子の状態が変化したときに “1” にセットされます。

USB\_Status レジスタの VBUS ビットによって VBUS の状態を確認して下さい。VBUS が“0”であれば、ケーブルが抜かれたことを示します。このビットは SLEEP / SNOOZE 中も有効です。

Bit 6 :

#### **DescriptorCmp**

割り込み要因を直接指示します。

Descriptor 返信機能において、DescriptorSize レジスタの設定数のデータを返信し終えると、“1”にセットされます。

また、DescriptorSize レジスタの設定数まで送信する前にステータスステージへ移行 (OUT トーカンを受信) した場合には EP0IntStat レジスタの OUT\_TranNAK ビットと共に、“1”にセットされます。

Bit 5 :

#### **SIE\_IntStat**

割り込み要因を間接指示します。

SIE\_IntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する SIE\_IntEnb レジスタのビットがイネーブルにされているときに“1”にセットされます。このビットは、SLEEP / SNOOZE 中もリード有効です。

Bit 4 :

#### **BulkIntStat**

割り込み要因を間接指示します。

BulkIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する BulkIntEnb レジスタのビットがイネーブルにされているときに “1” にセットされます。

Bit 3 :

#### **RcvEP0SETUP**

割り込み要因を直接指示します。

コントロール転送のセットアップステージが終了し、受信したデータがEP0SETUP\_0～EP0SETUP\_7 レジスタに格納されると“1”にセットされます。同時にEP0ControlIN, EP0ControlOUT レジスタのForceSTALLビットが“0”にEP0ControlIN, EP0ControlOUT レジスタのForceNAKビット、ToggleStatビット、SETUP\_Control レジスタのProtectEP0 ビットが“1”に、自動的に設定されます。SetAddress()リクエストに対しては、AutoSetAddress機能が自動応答し、このステータスはセットされません。

Bit 2 :

#### **FIFO\_IntStat**

割り込み要因を間接指示します。

FIFO\_IntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する FIFO\_IntEnb レジスタのビットがイネーブルにされているときに “1” にセットされます。

## Appendix 2 USB Device コントローラ

Bit 1 :

### EP0IntStat

割り込み要因を間接指示します。

EP0IntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EP0IntEnb レジスタのビットがイネーブルにされているときに “1” にセットされます。

Bit 0 :

### EPriIntStat

割り込み要因を間接指示します。

EPriIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPaIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

| <b>EPr Interrupt Status</b> |                 |                 |                 |                 |                 |                 |                 |

|-----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| USB[0x081] 初期値 = 0x00       |                 |                 |                 |                 |                 |                 |                 |

| EP h                        | EPg             | EPf             | EPe             | EPd             | EPc             | EPb             | EPa             |

| IntStat(R)<br>7             | IntStat(R)<br>6 | IntStat(R)<br>5 | IntStat(R)<br>4 | IntStat(R)<br>3 | IntStat(R)<br>2 | IntStat(R)<br>1 | IntStat(R)<br>0 |

エンドポイント EPr の割り込みを表示します。

Bit 7 :

### EPhIntStat

割り込み要因を間接指示します。

EPhIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPhIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 6 :

### EPgIntStat

割り込み要因を間接指示します。

EPgIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPgIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 5 :

### EPfIntStat

割り込み要因を間接指示します。

EPfIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPfIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 4 :

### EPeIntStat

割り込み要因を間接指示します。

EPeIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPeIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 3 :

### EPdIntStat

割り込み要因を間接指示します。

EPdIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPdIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 2 :

### EPcIntStat

割り込み要因を間接指示します。

EPcIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPcIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 1 :

### EPbIntStat

割り込み要因を間接指示します。

EPbIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPbIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

Bit 0 :

### EPaIntStat

割り込み要因を間接指示します。

EPaIntStat レジスタに割り込み要因があり、かつその割り込み要因に対応する EPaIntEnb レジスタのビットがイネーブルにされているとき、 “1” にセットされます。

| SIE Interrupt Status  |      |        |                 |                   |              |                |                   |

|-----------------------|------|--------|-----------------|-------------------|--------------|----------------|-------------------|

| USB[0x082] 初期値 = 0x00 |      |        |                 |                   |              |                |                   |

| —                     | NonJ | RcvSOF | Detect<br>Reset | Detect<br>Suspend | Chirp<br>Cmp | Restore<br>Cmp | SetAddress<br>Cmp |

| 7                     | 6    | 5      | 4               | 3                 | 2            | 1              | 0                 |

デバイス SIE 関連の割り込みを表示します。

全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit 7 : **Reserved**

Bit 6 : **NonJ**

割り込み要因を直接指示します。

USB バス上で J ステート以外の状態を検出すると“1”にセットされます。このビットは、本 LSI が SNOOZE 状態 (PM\_Control レジスタの InSnooze ビットが“1”) のとき、及び AutoNegotiation 機能使用時に USB\_Control レジスタの InSUSPEND ビットが“1”にセットされているときに有効です。

Bit 5 : **RcvSOF**

割り込み要因を直接指示します。

SOF トークンを受信すると“1”にセットされます。

Bit 4 : **DetectReset**

割り込み要因を直接指示します。

USB のリセットステートを検出すると“1”にセットされます。このビットがセットされている間は USB のサスPENDステートの検出ができません (DetectSUSPEND がセットされません)。

このリセット検出は、NegoControl レジスタの ActiveUSB ビットが “1” にセットされているときに有効です。

“HS”動作モードの場合は、バス・アクティビティが一定時間無くなると、USB のリセット／サスPEND検出のために FS ターミネーションを自動的に設定し、SEO が検出されるとリセットと判断して、このビットが“1”にセットされます。

AutoNegotiation 機能を使用しない場合には、このビットが“1”にセットされた場合、継続するリセットを誤検出しないよう、NegoControl レジスタの DisBusDetect ビットを“1”にセットして USB のリセット／サスPENDステートの検出を無効にして下さい。リセットに対する処理終了後に DisBusDetect ビットを“0”にクリアして USB のリセット／サスPENDステートの検出を有効にして下さい。

リセット検出時、NegoControl レジスタの GoChirp ビットにより、“HS Detection Handshake” を開始することができます。

AutoNegotiation 機能については、NegoControl レジスタの EnAutoNego ビットの項を参照して下さい。

Bit 3 : **DetectSuspend**

割り込み要因を直接指示します。

USB のサスPENDステートを検出すると “1” にセットされます。このビットがセットされている間は USB のリセットステートの検出ができません (DetectRESET がセットされません)。

“HS” 動作モード の場合は、バス・アクティビティが一定時間無くなると、USB のリセット／サスPEND検出のために“FS”動作モードに自動的に設定されます。USB のサスPENDステートの検出後は、PM\_Control0 レジスタの GoSnooze ビットを “1” にセットすることにより、本 LSI をスヌーズモード(内蔵 PLL の発振を停止)にすることが出来ます。

Bit 2 : **ChirpCmp**

割り込み要因を直接指示します。

NegoControl レジスタの GoChirp ビットにより開始された“HS Detection Handshake”が完了すると “1” にセットされます。

割り込み発生後に USB\_Status レジスタの FSxHS ビットをリードすることで、現在の動作モード (FS or HS)の判定をすることができます。

## Appendix 2 USB Device コントローラ

Bit 1 :

### RestoreCmp

割り込み要因を直接指示します。

NegoControl レジスタの RestoreUSB ビットにより開始された Restore 処理が終了すると“1”にセットされます。このビットが“1”にセットされると動作モード (FS or HS) が Suspend する前の状態に戻ります。

Bit 0 :

### SetAddressCmp

割り込み要因を直接指示します。

SetAddress()リクエストを受信すると、AutoSetAddress 機能(USB\_Address レジスタ参照)が、そのコントロール転送の処理を自動的に行います。ステータスステージを行って SetAddress()リクエストに関わるコントロール転送が完了したときに、このステータスが“1”にセットされます。また、同時に USB\_Address レジスタにアドレスがセットされます。

同期ビット (Bit5~0) は ACTIVE60 ステートのとき、読み出しができますが、書き込み (割り込み要因クリア) できません。

ACT\_DEVICE ステートを出る際には、これらの割り込みステータスにより割り込み信号 XINT がアサートされないよう、F/W にて以下の処理を行って下さい。

<ACT\_DEVICE ステートを出るとき>

- 1) 割り込みステータスを処理し、クリアする (SIE\_IntStat.Bit5~0)

- 2) 割り込みステータスをディスエーブルにする (SIE\_IntEnb.Bit5~0)

<ACT\_DEVICE ステートに入るとき>

- 1) 割り込みステータスをクリアする (SIE\_IntStat.Bit5~0)

- 2) 割り込みステータスをイネーブルにする (SIE\_IntEnb.Bit5~0)

| FIFO Interrupt Status |   |   |               |   |               |           |            |

|-----------------------|---|---|---------------|---|---------------|-----------|------------|

| USB[0x084] 初期値 = 0x00 |   |   |               |   |               |           |            |

|                       |   |   |               |   |               |           |            |

| —                     | — | — | FIFO_DMA0_Cmp | — | FIFO_NotEmpty | FIFO_Full | FIFO_Empty |

| 7                     | 6 | 5 | 4             | 3 | 2             | 1         | 0          |

デバイス FIFO 関連の割り込みステータスを表示します。

全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit [7:5] :

### Reserved

Bit 4 :

### FIFO\_DMA0\_Cmp

割り込み要因を直接指示します。

DMA0にジョインされているエンドポイントがIN方向の場合、DMA0の転送が終了した後にFIFOが空になると、“1”にセットされます。DMA0にジョインされているエンドポイントがOUT方向の場合、DMA0の転送が終了すると、“1”にセットされます。

Bit 3 :

### Reserved

Bit 2 :

### FIFO\_NotEmpty

割り込み要因を直接指示します。

EPx{x=0,a~h}Join.JoinFIFO\_Stat ビットが“1”にセットされているときに、該当するエンドポイントの FIFO 領域が Empty でないときに、“1”にセットされます。

Bit 1 :

**FIFO\_Full**

割り込み要因を直接指示します。

EPx{x=0,a~h}Join.JoinFIFO\_Stat ビットが“1”にセットされているときに、該当するエンドポイントの FIFO 領域が Full になると、“1”にセットされます。

Bit 0 :

**FIFO\_Empty**

割り込み要因を直接指示します。

EPx{x=0,a~h}Join.JoinFIFO\_Stat ビットが“1”にセットされているときに、該当するエンドポイントの FIFO 領域が Empty になると、“1”にセットされます。

| <b>Bulk Interrupt Status</b> |                    |              |        |              |              |        |        |

|------------------------------|--------------------|--------------|--------|--------------|--------------|--------|--------|

| USB[0x085] 初期値 = 0x00        |                    |              |        |              |              |        |        |

| CBW_Cmp<br>7                 | CBW_LengthErr<br>6 | CBW_Err<br>5 | —<br>4 | CSW_Cmp<br>3 | CSW_Err<br>2 | —<br>1 | —<br>0 |

Bulk 転送機能関連の割り込みステータスを表示します。全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit 7 :

**CBW\_Comp**

割り込み要因を直接指示します。

CBW の 31 バイトを正常に受信できたときに“1”にセットされます。

Bit 6 :

**CBW\_LengthErr**

割り込み要因を直接指示します。

受信した CBW のパケット長が 31 バイト以外であったときに“1”にセットされます。

Bit 5 :

**CBW\_Err**

割り込み要因を直接指示します。

受信した CBW に CRC エラー等のトランザクションエラーを検出したときに“1”にセットされます。

Bit 4 :

**Reserved**

Bit 3 :

**CSW\_Cmp**

割り込み要因を直接指示します。

CSW の 13 バイトを正常に送信できたときに“1”にセットされます。

Bit 2 :

**CSW\_Err**

割り込み要因を直接指示します。

CSW の送信にエラーがあったとき (ACK が返ってこなかったとき) に“1”にセットされます。

Bit [1:0] :

**Reserved**

## Appendix 2 USB Device コントローラ

| <b>EP0 Interrupt Status</b> |              |            |             |            |             |            |             |

|-----------------------------|--------------|------------|-------------|------------|-------------|------------|-------------|

| USB[0x087] 初期値 = 0x00       |              |            |             |            |             |            |             |

| —                           | OUT_ShortACK | IN_TranACK | OUT_TranACK | IN_TranNAK | OUT_TranNAK | IN_TranErr | OUT_TranErr |

| 7                           | 6            | 5          | 4           | 3          | 2           | 1          | 0           |

エンドポイント EP0 の割り込みステータスを表示します。全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

Bit 7 : **Reserved**

Bit 6 : **OUT\_ShortACK**

割り込み要因を直接指示します。

OUT トランザクションでショートパケットを受信し、ACK を返信したとき、OUT\_TranACK と同時に“1”にセットされます。

Bit 5 : **IN\_TranACK**

割り込み要因を直接指示します。

IN トランザクションで ACK を受信したとき、“1”にセットされます。

Bit 4 : **OUT\_TranACK**

割り込み要因を直接指示します。

OUT トランザクションで ACK を返信したとき、“1”にセットされます。

Bit 3 : **IN\_TranNAK**

割り込み要因を直接指示します。

IN トランザクションで NAK を返信したとき、“1”にセットされます。

Bit 2 : **OUT\_TranNAK**

割り込み要因を直接指示します。

OUT トランザクション及び PING トランザクションに対して NAK を返信したとき、“1”にセットされます。

Bit 1 : **IN\_TranErr**

割り込み要因を直接指示します。

IN トランザクションにおいて STALL を返した場合、パケットにエラーがあった場合、及びハンドシェイクがタイムアウトになった場合に、“1”にセットされます。

Bit 0 : **OUT\_TranErr**

割り込み要因を直接指示します。

OUT トランザクションにおいて STALL を返信した場合、及び、パケットにエラーがあった場合に、“1”にセットされます。

| EPa Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x088] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPb Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x089] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPc Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08A] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPd Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08B] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPe Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08C] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPf Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08D] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPg Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08E] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

| EPh Interrupt Status  |                       |                     |                      |                     |                      |                     |                      |

|-----------------------|-----------------------|---------------------|----------------------|---------------------|----------------------|---------------------|----------------------|

| USB[0x08F] 初期値 = 0x00 |                       |                     |                      |                     |                      |                     |                      |

| —                     | OUT_<br>ShortACK<br>6 | IN_<br>TranACK<br>5 | OUT_<br>TranACK<br>4 | IN_<br>TranNAK<br>3 | OUT_<br>TranNAK<br>2 | IN_<br>TranErr<br>1 | OUT_<br>TranErr<br>0 |

| 7                     |                       |                     |                      |                     |                      |                     |                      |

エンドポイント EPx {a~h} の割り込みステータスを表示します。全てのビットは“1”を書き込むことで割り込み要因をクリアできます。

## Appendix 2 USB Device コントローラ

|         |                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------|

| Bit 7 : | <b>Reserved</b>                                                                                                          |

| Bit 6 : | <b>OUT_ShortACK</b><br>割り込み要因を直接指示します。<br>OUT トランザクションでショートパケットを受信し、ACK を返信したとき、OUT_TranACK と同時に“1”にセットされます。             |

| Bit 5 : | <b>IN_TranACK</b><br>割り込み要因を直接指示します。<br>IN トランザクションで ACK を受信したとき、“1”にセットされます。                                            |

| Bit 4 : | <b>OUT_TranACK</b><br>割り込み要因を直接指示します。<br>OUT トランザクションで ACK を返信したとき、“1”にセットされます。                                          |

| Bit 3 : | <b>IN_TranNAK</b><br>割り込み要因を直接指示します。<br>IN トランザクションで NAK を返信したとき、“1”にセットされます。                                            |

| Bit 2 : | <b>OUT_TranNAK</b><br>割り込み要因を直接指示します。<br>OUT トランザクション及び PING トランザクションに対して NAK を返信したとき、“1”にセットされます。                       |

| Bit 1 : | <b>IN_TranErr</b><br>割り込み要因を直接指示します。<br>IN トランザクションにおいて STALL を返した場合、パケットにエラーがあった場合、及びハンドシェイクがタイムアウトになった場合に、“1”にセットされます。 |

| Bit 0 : | <b>OUT_TranErr</b><br>割り込み要因を直接指示します。<br>OUT トランザクションにおいて STALL を返信した場合、及び、パケットにエラーがあった場合に、“1”にセットされます。                  |

| Device Interrupt Enable    |                       |                           |                     |                     |                     |                    |                    |

|----------------------------|-----------------------|---------------------------|---------------------|---------------------|---------------------|--------------------|--------------------|

| USB[0x090] 初期値 = 0x00      |                       |                           |                     |                     |                     |                    |                    |

| <b>EnVBus_Changed</b><br>7 | EnDescriptor Cmp<br>6 | <b>EnSIE_IntStat</b><br>5 | EnBulk IntStat<br>4 | EnRcvEP0 SETUP<br>3 | EnFIFO_IntStat<br>2 | EnEP0 IntStat<br>1 | EnEPr IntStat<br>0 |

DeviceIntStat レジスタの割り込み要因による、MainIntStat レジスタの DeviceIntStat ビットのアサートを許可／禁止します。

EnVBus\_Changed, EnSIE\_IntStat ビットは SLEEP / SNOOZE 中も有効です。

| EPr Interrupt Enable  |                    |                    |                    |                    |                    |                    |                    |

|-----------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| USB[0x091] 初期値 = 0x00 |                    |                    |                    |                    |                    |                    |                    |

| EnEPh IntStat<br>7    | EnEPg IntStat<br>6 | EnEPf IntStat<br>5 | EnEPe IntStat<br>4 | EnEPd IntStat<br>3 | EnEPc IntStat<br>2 | EnEPb IntStat<br>1 | EnEPa IntStat<br>0 |

EPrIntStat レジスタの割り込み要因による、DeviceIntStat レジスタの EPrIntStat ビットのアサートを許可／禁止します。

| <b>SIE Interrupt Enable</b> |               |          |                   |                     |                |                  |                     |

|-----------------------------|---------------|----------|-------------------|---------------------|----------------|------------------|---------------------|

| USB[0x092] 初期値 = 0x00       |               |          |                   |                     |                |                  |                     |

| —                           | <b>EnNonJ</b> | EnRcvSOF | EnDetect<br>RESET | EnDetect<br>SUSPEND | EnChirp<br>Cmp | EnRestore<br>Cmp | EnSet<br>AddressCmp |

| —                           | 6             | 5        | 4                 | 3                   | 2              | 1                | 0                   |

SIE\_IntStat レジスタの割り込み要因による、DeviceIntStat レジスタの SIE\_IntStat ビットのアサートを許可／禁止します。

EnNonJ ビットは SLEEP / SNOOZE 中も有効です。

同期ビット (Bit5~0) は ACTIVE60 ステートのとき、読み出しができますが、書き込みできません。これら同期ビットの ACT\_DEVICE ステートを出る際の処理に関しては、SIE\_IntStat レジスタの説明をご参照下さい。

| <b>FIFO Interrupt Enable</b> |   |   |                     |   |                     |                 |                  |

|------------------------------|---|---|---------------------|---|---------------------|-----------------|------------------|

| USB[0x094] 初期値 = 0x00        |   |   |                     |   |                     |                 |                  |

| —                            | — | — | EnFIFO_<br>DMA0_Cmp | — | EnFIFO_<br>NotEmpty | EnFIFO_<br>Full | EnFIFO_<br>Empty |

| —                            | 6 | 5 | 4                   | 3 | 2                   | 1               | 0                |

FIFO\_IntStat レジスタの割り込み要因による、DeviceIntStat レジスタの FIFO\_IntStat ビットのアサートを許可／禁止します。

| <b>Bulk Interrupt Enable</b> |                     |               |   |               |           |   |   |

|------------------------------|---------------------|---------------|---|---------------|-----------|---|---|

| USB[0x095] 初期値 = 0x00        |                     |               |   |               |           |   |   |

| EnCBW_<br>Cmp                | EnCBW_<br>LengthErr | EnCBW_<br>Err | — | EnCSW_<br>Cmp | EnCSW_Err | — | — |

| —                            | 6                   | 5             | 4 | 3             | 2         | 1 | 0 |

BulkIntStat レジスタの割り込み要因による、DeviceIntStat レジスタの BulkIntStat ビットのアサートを許可／禁止します。

| <b>EP0 Interrupt Enable</b> |                    |                  |                   |                  |                   |                  |                   |

|-----------------------------|--------------------|------------------|-------------------|------------------|-------------------|------------------|-------------------|

| USB[0x097] 初期値 = 0x00       |                    |                  |                   |                  |                   |                  |                   |

| —                           | EnOUT_<br>ShortACK | EnIN_<br>TranACK | EnOUT_<br>TranACK | EnIN_<br>TranNAK | EnOUT_<br>TranNAK | EnIN_<br>TranErr | EnOUT_<br>TranErr |