# **S1R77022F00B000**

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

# 目 次

|                                                |    |

|------------------------------------------------|----|

| 1. 概要                                          | 1  |

| 2. 特長                                          | 1  |

| 3. ブロック図                                       | 2  |

| 4. 端子配置図                                       | 3  |

| 5. 端子説明                                        | 4  |

| 6. 機能説明                                        | 6  |

| 6.1 ホストインターフェース部                               | 6  |

| 6.1.1 シリアルインターフェース                             | 6  |

| 6.1.2 画像データ出力                                  | 8  |

| 6.1.3 テストモード                                   | 10 |

| 6.2 LVDS 部                                     | 11 |

| 6.3 RSDS 部                                     | 15 |

| 6.4 入力クロック波形整形機能部                              | 16 |

| 6.5 アナログ部                                      | 18 |

| 6.5.1 概要                                       | 18 |

| 6.5.2 仕様                                       | 19 |

| 6.5.3 内部ブロック構成                                 | 21 |

| 6.5.4 パワーダウン機能                                 | 22 |

| 6.5.5 基準電圧発生回路 (Reference Voltage Generator)   | 22 |

| 6.5.6 クランプ回路                                   | 22 |

| 6.5.7 CDS/PGA                                  | 22 |

| 6.5.8 A/D コンバータ                                | 26 |

| 6.5.9 オフセット調整                                  | 26 |

| 6.5.10 プログラマブル・ゲイン・アンプ(PGA)                    | 27 |

| 6.5.11 自動オフセット・ゲイン調整機能                         | 29 |

| 6.5.12 自動黒レベル補正機能                              | 31 |

| 6.5.13 レジスタ設定シーケンス例                            | 35 |

| 7. レジスタ                                        | 36 |

| 7.1 レジスタマップ                                    | 36 |

| 7.2 ビットマップ                                     | 37 |

| 7.3 レジスタ詳細説明                                   | 38 |

| 7.3.1 0x00 パワーダウンレジスタ (POWERDOWN)              | 38 |

| 7.3.2 0x01 画素解析機能制御レジスタ(CALCTL)                | 39 |

| 7.3.3 0x02 AFE 動作モード設定レジスタ(AFEMD)              | 40 |

| 7.3.4 0x03 データ出力制御レジスタ(DATACTL)                | 41 |

| 7.3.5 0x04 黒ダミー画素・白基準画素開始位置設定レジスタ(BKWHST)      | 42 |

| 7.3.6 0x05 黒ダミー画素数設定レジスタ(BKNUM)                | 42 |

| 7.3.7 0x06~7 白基準画素数設定レジスタ(WHNUM)               | 43 |

| 7.3.8 0x08 白画素出力レベル設定レジスタ(WHLEVEL)             | 44 |

| 7.3.9 0x09 黒画素出力レベル設定レジスタ(BKLEVEL)             | 44 |

| 7.3.10 0x0A 自動オフセット・ゲイン調整機能設定レジスタ(AUTOOFSGAIN) | 45 |

| 7.3.11 0x0B AFE 制御レジスタ(AFECTL)                 | 46 |

| 7.3.12 0x0C サンプリング信号制御レジスタ (CKGENMD)           | 47 |

| 7.3.13 0x0D 入力制御レジスタ (INCTL)                   | 47 |

| 7.3.14 0x0F A/D コンバータ動作モード設定レジスタ(ADCMD)        | 48 |

| 7.3.15 0x10 R チャネル (ODD) オフセットレジスタ (RD1OFS)    | 49 |

| 7.3.16 0x11 R チャネル (EVEN) オフセットレジスタ (RD2OFS)   | 49 |

|                                                  |           |

|--------------------------------------------------|-----------|

| 7.3.17 0x12 G チャネル(ODD)オフセットレジスタ (GR1OFS).....   | 49        |

| 7.3.18 0x13 G チャネル(EVEN)オフセットレジスタ(GR2OFS).....   | 50        |

| 7.3.19 0x14 B チャネル(ODD)オフセットレジスタ(BL1OFS).....    | 50        |

| 7.3.20 0x15 B チャネル(EVEN)オフセットレジスタ(BL2OFS).....   | 50        |

| 7.3.21 0x16 LVDS 設定レジスタ(LVDSCTL) .....           | 51        |

| 7.3.22 0x18 R チャネル I (ODD)ゲインレジスタ(RD1GAIN).....  | 52        |

| 7.3.23 0x19 R チャネル(EVEN) ゲインレジスタ (RD2GAIN) ..... | 52        |

| 7.3.24 0x1A G チャネル (ODD) ゲインレジスタ (GR1GAIN).....  | 53        |

| 7.3.25 0x1B G チャネル(EVEN)ゲインレジスタ(GR2GAIN) .....   | 53        |

| 7.3.26 0x1C B チャネル(ODD)ゲインレジスタ(BL1GAIN) .....    | 54        |

| 7.3.27 0x1D B チャネル(EVEN)ゲインレジスタ (BL2GAIN).....   | 54        |

| <b>8. 電気的特性 .....</b>                            | <b>55</b> |

| <b>8.1 絶対最大定格 .....</b>                          | <b>55</b> |

| <b>8.2 推奨動作条件 .....</b>                          | <b>55</b> |

| <b>8.3 DC 特性 .....</b>                           | <b>56</b> |

| <b>8.4 AC 特性 .....</b>                           | <b>57</b> |

| 8.4.1 システムリセット .....                             | 57        |

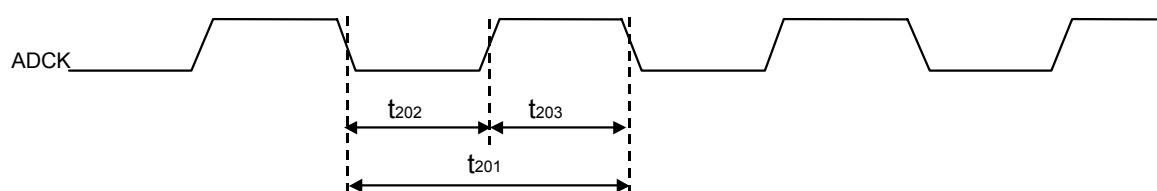

| 8.4.2 クロックタイミング .....                            | 57        |

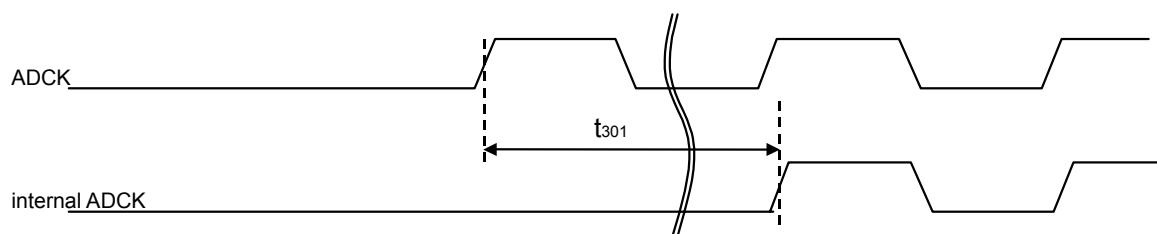

| 8.4.3 入力クロック波形整形機能動作タイミング .....                  | 57        |

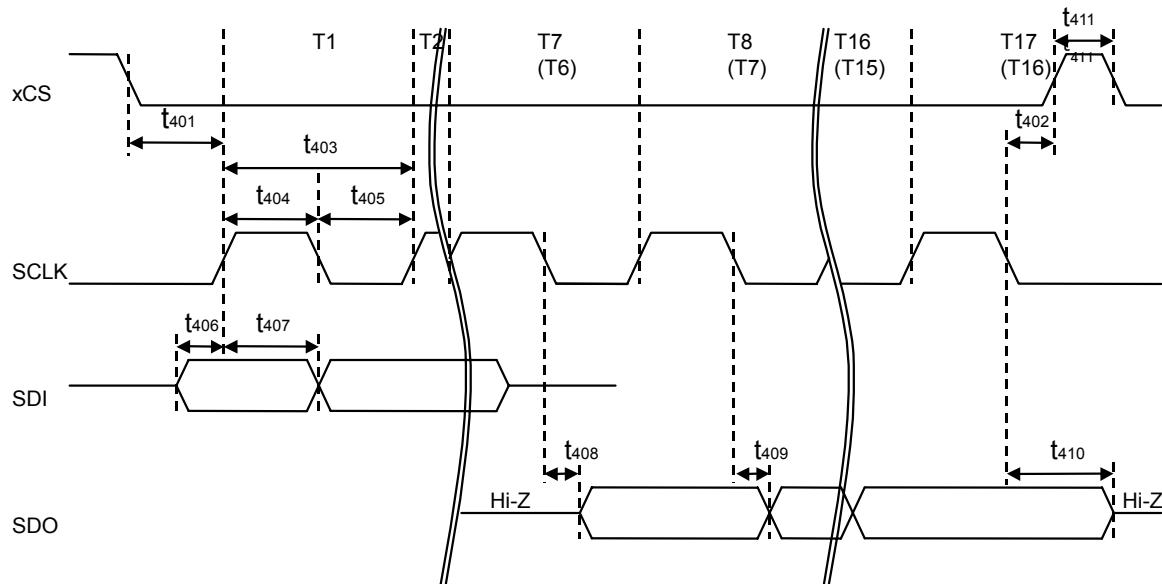

| 8.4.4 シリアルインタフェースタイミング .....                     | 58        |

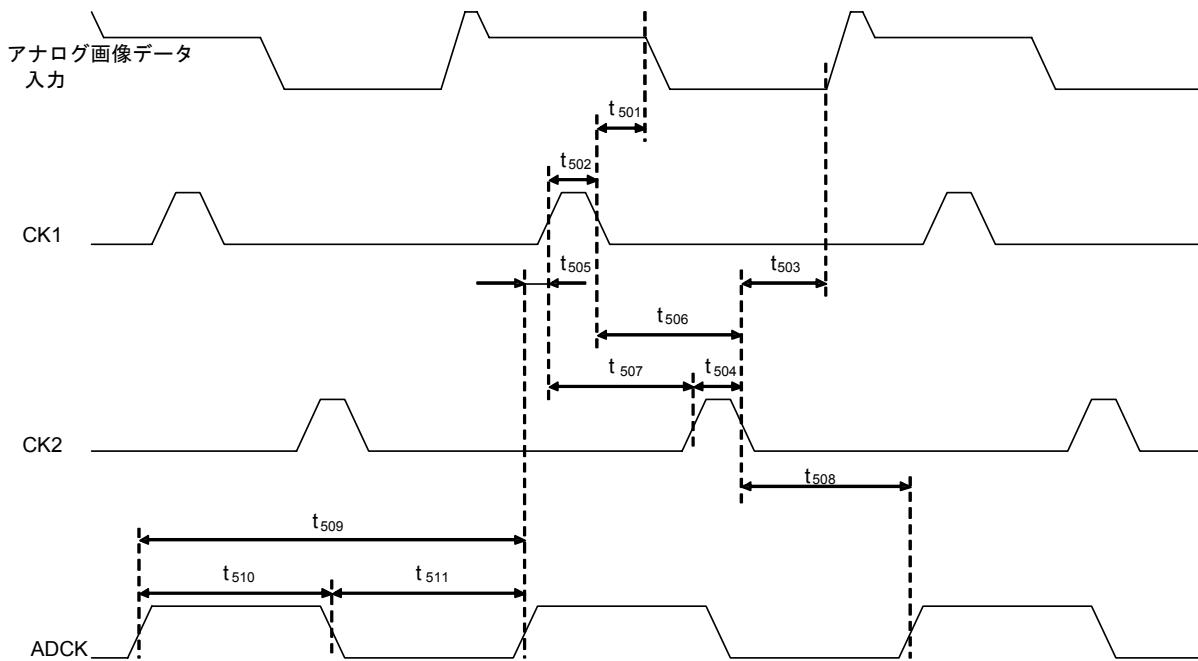

| 8.4.5 CDS モード サンプリングタイミング .....                  | 59        |

| 8.4.6 S/H モード (差電圧入力) サンプリングタイミング .....          | 60        |

| 8.4.7 S/H モード (ライン・クランプ) サンプリングタイミング .....       | 61        |

| 8.4.8 S/H モードサンプリングタイミング (サンプリングクロック自動生成時) ..... | 62        |

| 8.4.9 画素入力指示タイミング .....                          | 62        |

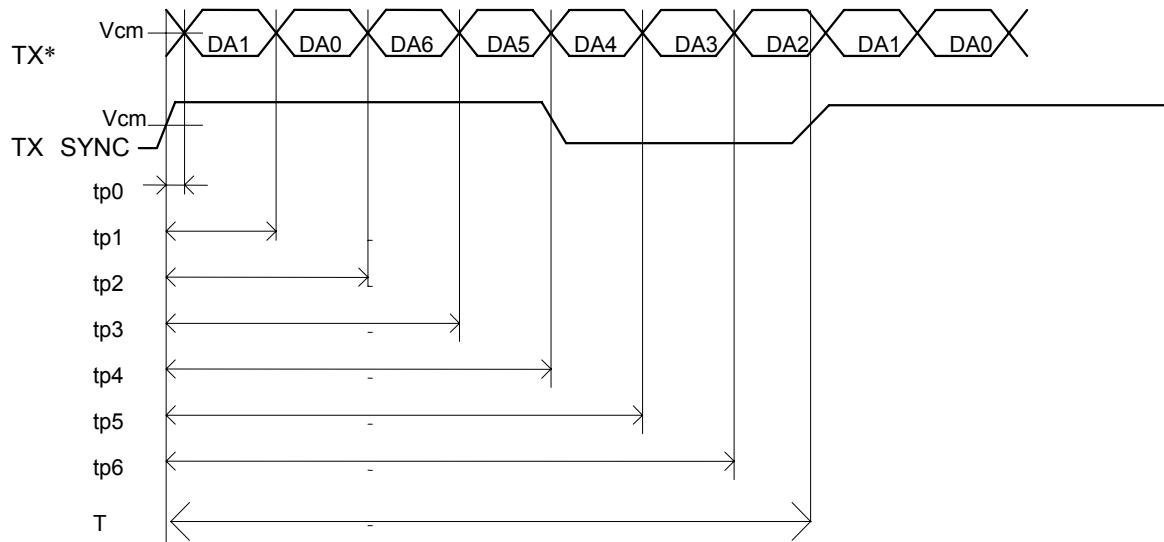

| 8.4.10 LVDS 出力タイミング .....                        | 63        |

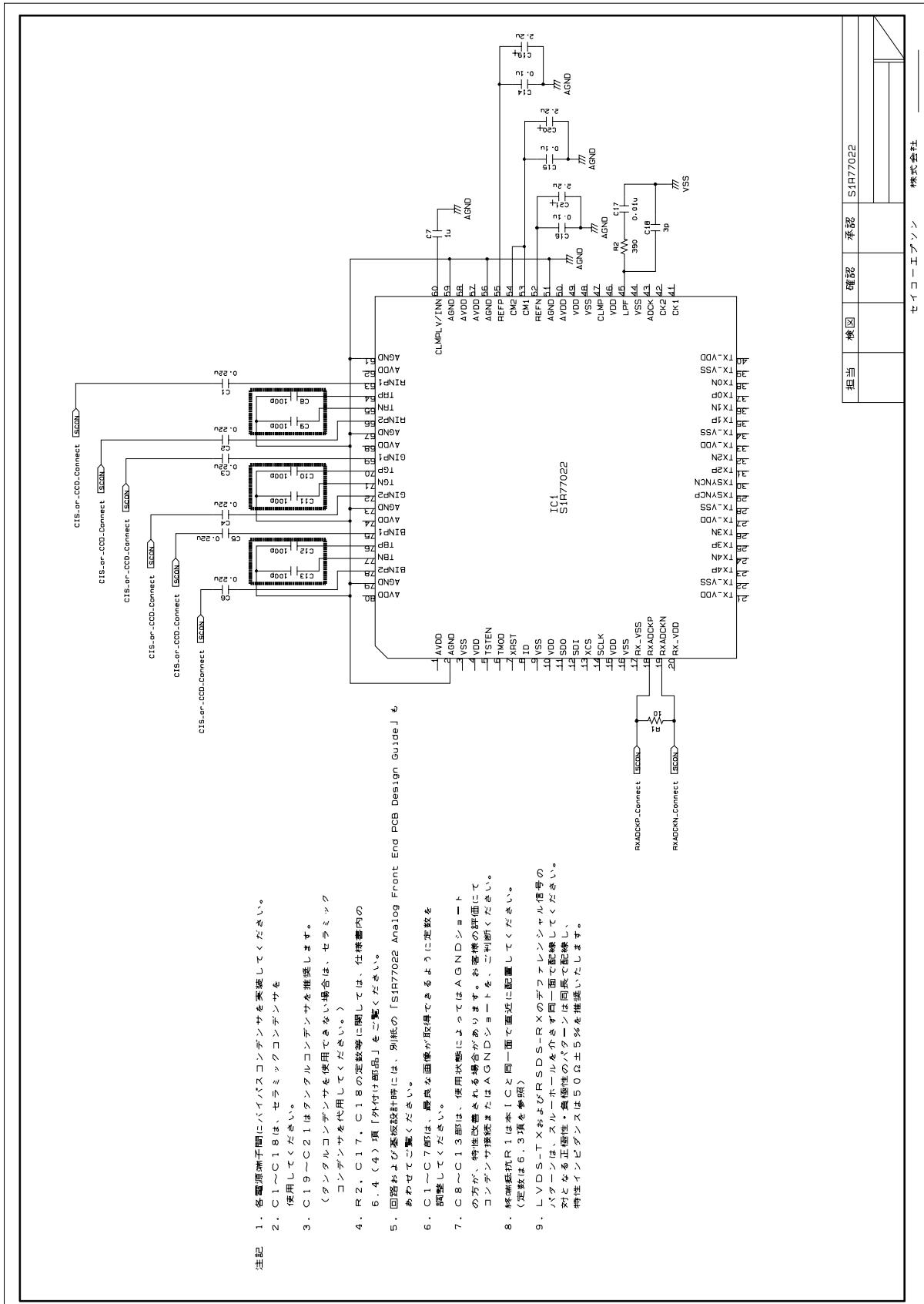

| <b>9. 応用接続例 .....</b>                            | <b>64</b> |

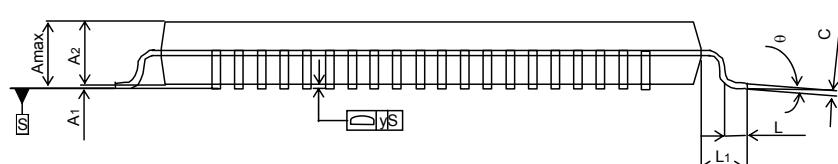

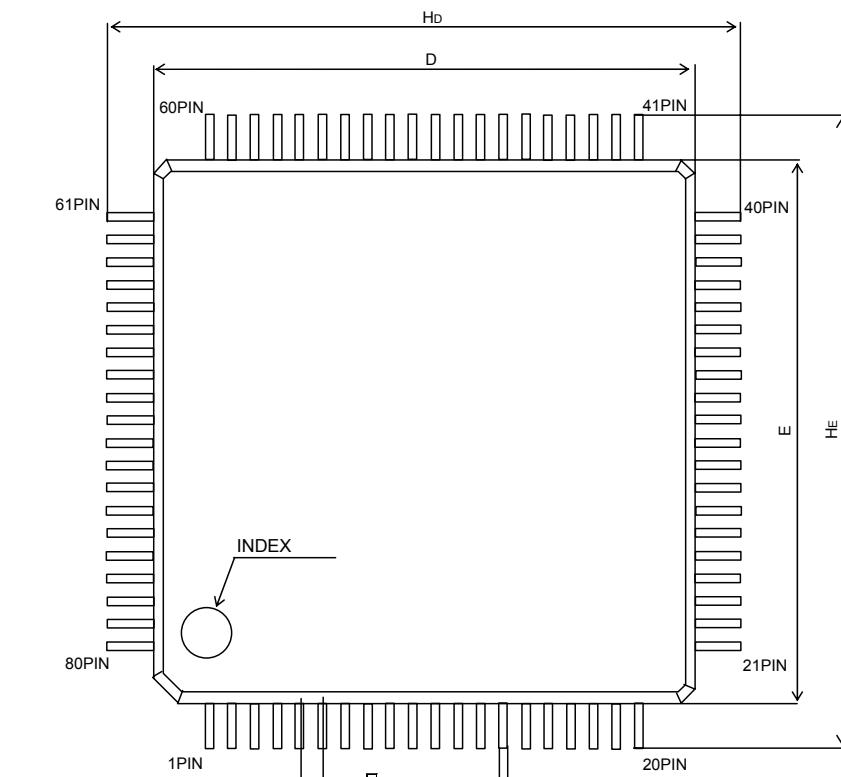

| <b>10. 外形寸法図 .....</b>                           | <b>65</b> |

## 1. 概要

本 IC は、高速読取動作を実現するアナログフロントエンド IC です。また、本 IC は解像度 10 ビット A/D コンバータを 6 個内蔵しており、高速スキャナシステムを容易に実現することができます。

## 2. 特長

### 共通部

- パッケージ 0.5 mm ピッチ QFP80 ピン

- 3.3V 単一電源

- 入力クロック波形整形機能内蔵

### ホストインターフェース部

- シリアルインターフェース

- 画像データ出力は LVDS 出力 (転送速度 : 10~80MHz)

- マルチプレクス出力時において画像出力シーケンスを選択可能

ODD → EVEN または EVEN → ODD

- 点順次出力モード (LVDS 出力 2 チャネルを用いて画像データを出力)

3 チャネルモード転送速度 : 4~20MHz

6 チャネルモード転送速度 : 2~13MHz

### AFE (Analog Front End) 部

- 10 ビット A/D コンバータ 6 個内蔵

- 1 チャネルあたりの最大変換速度 (AFE 転送クロック) : 40MHz

- 動作モード : CDS または S/H モード

- 動作チャネル数 : 1、2、3、4 または 6 チャネル選択可

- アナログ信号入力レンジ : 2.6Vp-p

- A/D コンバータへのフルスケール入力レンジ : 1.2Vp-p

- プログラマブル・ゲイン・アンプ (PGA) 調整レンジ : ゲイン特性をレジスタで選択

-6.9dB (0.45 倍) ~+12.0dB (4.0 倍) (分解能 128 ステップ)、

-0.9dB (0.9 倍) ~+18.0dB (8.0 倍) (分解能 128 ステップ)、

+5.1dB (1.8 倍) ~+24.1dB (16.0 倍) (分解能 128 ステップ)

- オフセット調整レンジ : ±300mV (分解能 1024 ステップ)

- 自動オフセット・ゲイン調整機能内蔵

- 自動オフセット・ゲイン調整完了結果時画素レベルモニタ機能内蔵

- 自動黒レベル補正機能内蔵

- サンプリング信号自動生成機能内蔵 (S/H モードのみ)

- 2 画素平均機能内蔵 (ODD、EVEN チャネル同時使用時)

※ 耐放射性設計はされておりません。

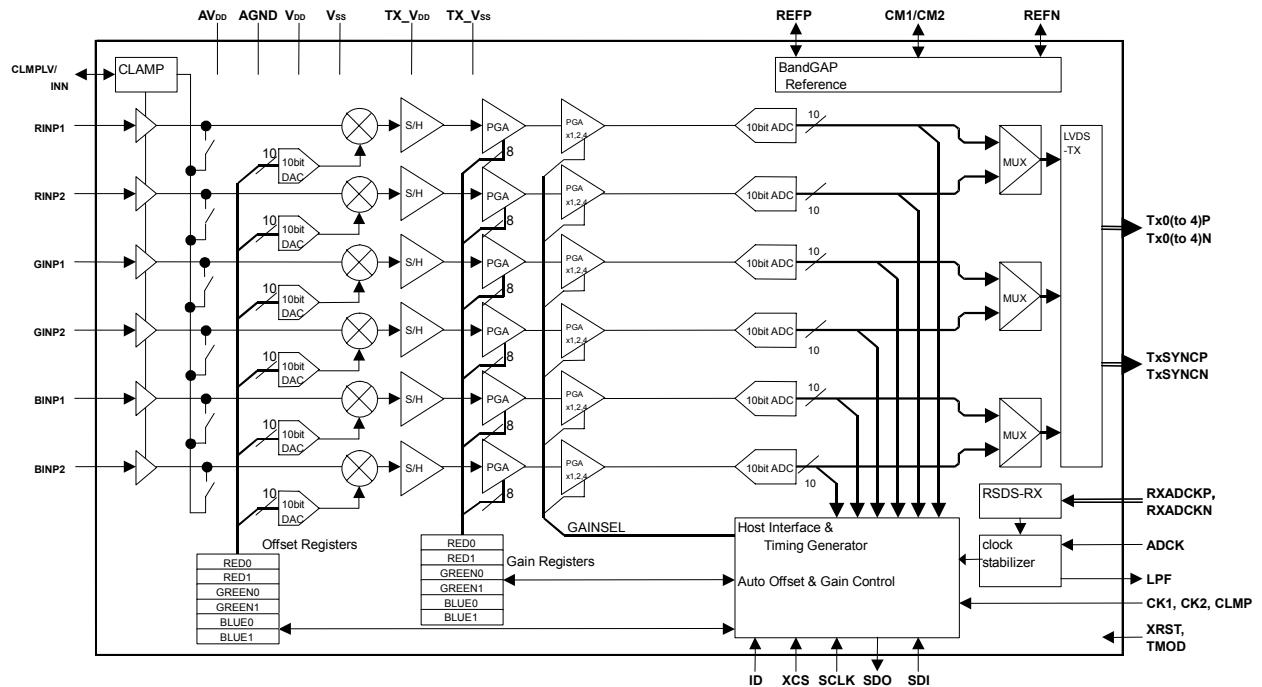

### 3. ブロック図

### 3. ブロック図

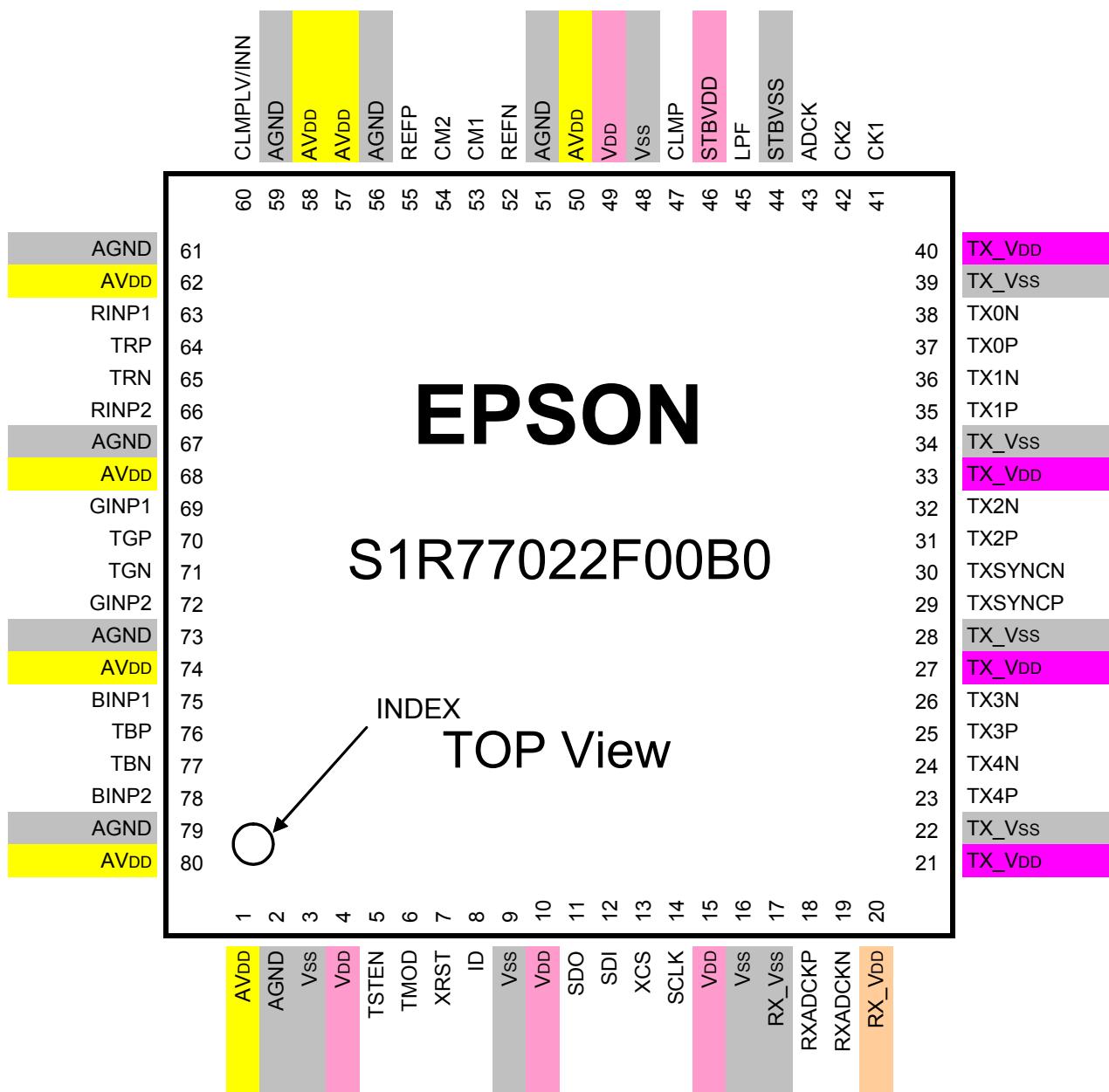

## 4. 端子配置図

## 「注意事項」

電源系の分離は、各電源系を分離することを推奨します。但し、実装基板上の制限から電源系を共通にする場合は、少なくとも AVDD-AGND 系とその他の電源系を分離してください。その場合はノイズの回りこみ等により最良な特性が得られない場合があります。

## 5. 端子説明

### 5. 端子説明

| No.    | Pin | 端子名        | I/O | Reset | 端子機能                         | 備考      | 駆動能力 |

|--------|-----|------------|-----|-------|------------------------------|---------|------|

| アナログ端子 |     |            |     |       |                              |         |      |

| 1      | 55  | REFP       | A   | —     | 高電位リファレンス                    |         | アナログ |

| 2      | 53  | CM1        | A   | —     | 同相モード電圧 1                    |         | アナログ |

| 3      | 54  | CM2        | A   | —     | 同相モード電圧 2                    |         | アナログ |

| 4      | 52  | REFN       | A   | —     | 低電位リファレンス                    |         | アナログ |

| 5      | 63  | RINP1      | A   | —     | R チャネルアナログ入力 (ODD)           |         | アナログ |

| 6      | 66  | RINP2      | A   | —     | R チャネルアナログ入力 (EVEN)          |         | アナログ |

| 7      | 69  | GINP1      | A   | —     | G チャネルアナログ入力 (ODD)           |         | アナログ |

| 8      | 72  | GINP2      | A   | —     | G チャネルアナログ入力 (EVEN)          |         | アナログ |

| 9      | 75  | BINP1      | A   | —     | B チャネルアナログ入力 (ODD)           |         | アナログ |

| 10     | 78  | BINP2      | A   | —     | B チャネルアナログ入力 (EVEN)          |         | アナログ |

| 11     | 60  | CLMPLV/INN | A   | —     | クランプレベルモニタ／リファレンスレベル入力       |         | アナログ |

| 12     | 64  | TRP        | A   | —     | R チャネル A/D コンバータ高電位入力 (テスト用) |         | アナログ |

| 13     | 65  | TRN        | A   | —     | R チャネル A/D コンバータ低電位入力 (テスト用) |         | アナログ |

| 14     | 70  | TGP        | A   | —     | G チャネル A/D コンバータ高電位入力 (テスト用) |         | アナログ |

| 15     | 71  | TGN        | A   | —     | G チャネル A/D コンバータ低電位入力 (テスト用) |         | アナログ |

| 16     | 76  | TBP        | A   | —     | G チャネル A/D コンバータ高電位入力 (テスト用) |         | アナログ |

| 17     | 77  | TBN        | A   | —     | G チャネル A/D コンバータ低電位入力 (テスト用) |         | アナログ |

| 18     | 1   | AVDD       | P   | —     | アナログ電源+3.3V                  |         | —    |

| 19     | 50  | AVDD       | P   | —     |                              |         |      |

| 20     | 57  | AVDD       | P   | —     |                              |         |      |

| 21     | 58  | AVDD       | P   | —     |                              |         |      |

| 22     | 62  | AVDD       | P   | —     |                              |         |      |

| 23     | 68  | AVDD       | P   | —     |                              |         |      |

| 24     | 74  | AVDD       | P   | —     |                              |         |      |

| 25     | 80  | AVDD       | P   | —     |                              |         |      |

| 26     | 2   | AGND       | P   | —     | アナロググランド                     |         | —    |

| 27     | 51  | AGND       | P   | —     |                              |         |      |

| 28     | 56  | AGND       | P   | —     |                              |         |      |

| 29     | 59  | AGND       | P   | —     |                              |         |      |

| 30     | 61  | AGND       | P   | —     |                              |         |      |

| 31     | 67  | AGND       | P   | —     |                              |         |      |

| 32     | 73  | AGND       | P   | —     |                              |         |      |

| 33     | 79  | AGND       | P   | —     |                              |         |      |

| 制御信号   |     |            |     |       |                              |         |      |

| 34     | 7   | XRST       | I   | —     | リセット信号                       | SMT, PD | —    |

| 35     | 43  | ADCK       | I5  | —     | A/D 変換クロック                   |         | —    |

| 36     | 18  | RXADCKP    | A   | —     | A/D 変換クロック(RSDS 入力)          |         | アナログ |

| 37     | 19  | RXADCKN    | A   | —     | A/D 変換クロック(RSDS 入力)          |         | アナログ |

| 38     | 41  | CK1        | I5  | —     | サンプリングクロック 1                 | PD      | —    |

| 39     | 42  | CK2        | I5  | —     | サンプリングクロック 2                 | PD      | —    |

| 40     | 47  | CLMP       | I5  | —     | クランプタイミング                    | PD      | —    |

| 41     | 45  | LPF        | A   | —     | 入力クロック波形整形用フィルタ接続端子          |         | アナログ |

I/O 欄の記号

A: アナログ端子

I: 入力端子

I5: 入力端子 (5V トレント入力)

O: 出力端子

B: 双方向端子

P: 電源端子

Reset (初期状態時) 欄の記号

HI-Z: ハイ・インピーダンス状態

備考欄の記号

PU: プルアップ

PD: プルダウン

SMT: シュミット入力

| No.            | Pin               | 端子名     | I/O | Reset              | 端子機能                  | 備考           | 駆動能力 |  |  |

|----------------|-------------------|---------|-----|--------------------|-----------------------|--------------|------|--|--|

| シリアルインターフェース   |                   |         |     |                    |                       |              |      |  |  |

| 42             | 8                 | ID      | I   | —                  | チップアップ ID 選択設定        | PD           | —    |  |  |

| 43             | 6                 | TMOD    | I   | —                  | シリアル I/F アクセスサイクル選択設定 | PD           | —    |  |  |

| 44             | 13                | XCS     | I5  | —                  | チップセレクト               | SMT          | —    |  |  |

| 45             | 14                | SCLK    | I5  | —                  | シリアルデータ入出力同期クロック      | SMT, PD      | —    |  |  |

| 46             | 12                | SDI     | I5  | —                  | シリアルデータ入力             | SMT, PD      | —    |  |  |

| 47             | 11                | SDO     | O   | Hi-Z               | シリアルデータ出力             |              | 2mA  |  |  |

| 画像データ出力 (LVDS) |                   |         |     |                    |                       |              |      |  |  |

| 48             | 37                | TX0P    | A   | —                  | 画像データ出力               |              | アナログ |  |  |

| 49             | 38                | TX0N    | A   | —                  |                       |              |      |  |  |

| 50             | 35                | TX1P    | A   | —                  |                       |              |      |  |  |

| 51             | 36                | TX1N    | A   | —                  |                       |              |      |  |  |

| 52             | 31                | TX2P    | A   | —                  |                       |              |      |  |  |

| 53             | 32                | TX2N    | A   | —                  |                       |              |      |  |  |

| 54             | 25                | TX3P    | A   | —                  |                       |              |      |  |  |

| 55             | 26                | TX3N    | A   | —                  |                       |              |      |  |  |

| 56             | 23                | TX4P    | A   | —                  |                       |              |      |  |  |

| 57             | 24                | TX4N    | A   | —                  |                       |              |      |  |  |

| 58             | 29                | TXSYNCP | A   | —                  |                       |              |      |  |  |

| 59             | 30                | TXSYNCN | A   | —                  |                       |              |      |  |  |

| テスト端子          |                   |         |     |                    |                       |              |      |  |  |

| 60             | 5                 | TSTEN   | I   | —                  | テスト端子                 | PD           | —    |  |  |

| 電源端子           |                   |         |     |                    |                       |              |      |  |  |

| 61             | 4                 | VDD     | P   | —                  | 3.3V ロジック系電源供給端子      |              | —    |  |  |

| 62             | 10                | VDD     | P   | —                  |                       |              |      |  |  |

| 63             | 15                | VDD     | P   | —                  |                       |              |      |  |  |

| 64             | 49                | VDD     | P   | —                  |                       |              |      |  |  |

| 65             | 21                | TX_VDD  | P   | —                  | LVDS-TX 電源供給端子 (3.3V) |              | —    |  |  |

| 66             | 27                | TX_VDD  | P   | —                  |                       |              |      |  |  |

| 67             | 33                | TX_VDD  | P   | —                  |                       |              |      |  |  |

| 68             | 40                | TX_VDD  | P   | —                  |                       |              |      |  |  |

| 69             | 20                | RX_VDD  | P   | —                  | RSDS-RX 電源供給端子 (3.3V) |              | —    |  |  |

| 70             | 46                | STBVDD  | P   | —                  |                       |              |      |  |  |

| 71             | 3                 | Vss     | P   | —                  |                       |              |      |  |  |

| 72             | 9                 | Vss     | P   | —                  |                       |              |      |  |  |

| 73             | 16                | Vss     | P   | —                  | ロジックランド               |              | —    |  |  |

| 74             | 48                | Vss     | P   | —                  |                       |              |      |  |  |

| 75             | 22                | TX_Vss  | P   | —                  |                       |              |      |  |  |

| 76             | 28                | TX_Vss  | P   | —                  |                       |              |      |  |  |

| 77             | 34                | TX_Vss  | P   | —                  | LVDS-TX グランド          |              | —    |  |  |

| 78             | 39                | TX_Vss  | P   | —                  |                       |              |      |  |  |

| 79             | 17                | RX_Vss  | P   | —                  |                       |              |      |  |  |

| 80             | 44                | STBVss  | P   | —                  |                       |              |      |  |  |

| I/O 欄の記号       |                   |         |     | Reset (初期状態時) 欄の記号 |                       | 備考欄の記号       |      |  |  |

| A:             | アナログ端子            |         |     | HI-Z: ハイ・インピーダンス状態 |                       | PU: プルアップ    |      |  |  |

| I:             | 入力端子              |         |     | PD: プルダウン          |                       | SMT: シュミット入力 |      |  |  |

| I5:            | 入力端子 (5V トレラント入力) |         |     |                    |                       |              |      |  |  |

| O:             | 出力端子              |         |     |                    |                       |              |      |  |  |

| B:             | 双方向端子             |         |     |                    |                       |              |      |  |  |

| P:             | 電源端子              |         |     |                    |                       |              |      |  |  |

## 6. 機能説明

### 6. 機能説明

各ブロックの機能を以下に説明します。

#### 6.1 ホストインターフェース部

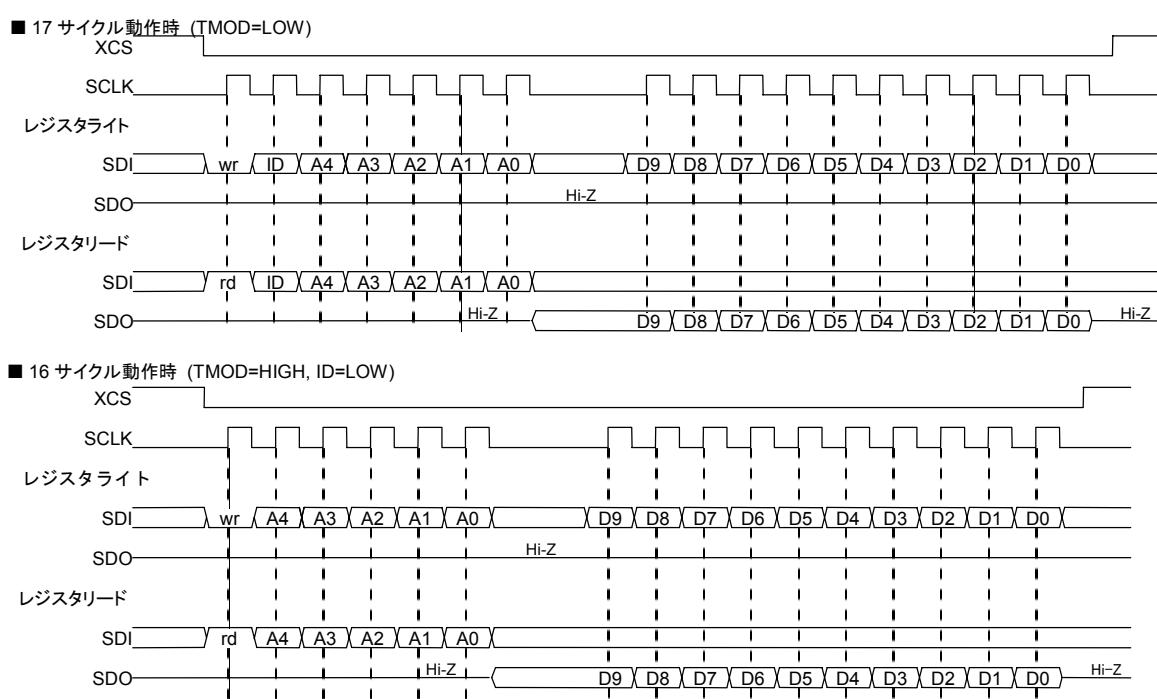

##### 6.1.1 シリアルインターフェース

シリアルインターフェースは、XCS 信号（チップセレクト）、SCLK 信号（シリアルデータ入出力同期クロック）、SDI 信号（シリアルデータ入力）および SDO 信号（シリアルデータ出力）の 4 信号で構成されます。本 IC がアクティブ状態（XCS 信号が LOW）の時、SCLK 信号に同期してデータ送受信を行います。アクセスサイクルはチップ ID 選択ビットの有無により 17 サイクルまたは 16 サイクルで行います。サイクル数の設定は TMOD 信号と ID 信号の状態によって表 6.1 のとおりとなります。

表 6.1 アクセスサイクル設定

| アクセスサイクル | TMOD | ID          |

|----------|------|-------------|

| 17 サイクル  | LOW  | チップ ID 選択設定 |

| 16 サイクル  | HIGH | LOW         |

レジスタアクセスはまずライトまたはリードアクセスを示す識別ビットをライトします。識別ビットは、LOW のときにライトアクセス、HIGH のときにリードアクセスを行います。識別ビットに引き続きチップ ID 選択ビット（17 サイクル動作時のみ）および 5 ビットのレジスタ識別番号をライトし、その後データのライトまたはリードを行います。なお、17 サイクル動作時はチップ ID 選択ビットの入力レベルが ID 信号（チップ ID 選択設定）と同論理の場合に本 IC へのアクセスが有効となります。

チップ ID 選択ビット、レジスタ識別番号およびデータ転送はいずれもクロックの立ち上がりに同期し MSB から順に転送します。

本 IC 内部にはシリアル-パラレル変換（またはパラレル-シリアル変換）のためカウンタがあり、XCS 信号を HIGH にすることによりリセットされます。従って、レジスタライトまたはレジスタリードの各アクセスサイクル終了後、必ず XCS 信号をネガート（XCS 信号を HIGH）してください。

図 6.1 に各アクセス時のタイミングを示します。

図 6.1 シリアルインターフェースアクセスタイミング

### 「注意事項」

レジスタライト時、各アクセスサイクル動作時における SCLK 信号のパルス数に過不足がある場合、誤書き込みとなることがあります。

SCLK 信号のパルス数が少ない場合は、下記のパルス数以下のとき、XCS 信号を HIGH によりレジスタライト動作はキャンセルされます。

17 サイクル動作時 : 15 パルス以下

16 サイクル動作時 : 14 パルス以下

また、SCLK 信号のパルス数が多い場合は、レジスタライト動作後、下記のパルス数の範囲のとき、XCS 信号を HIGH によりレジスタライト動作を正常終了します。

17 サイクル動作時 : 18~25 パルス (+1~+8 パルス)

16 サイクル動作時 : 17~24 パルス (+1~+8 パルス)

上記のパルス数を超えた場合 (17 サイクル動作時で 26 パルス目 (+9 パルス目)) 、誤書き込みします。

一方、レジスタリード時は SCLK 信号のパルス数に過不足が生じても、レジスタの内容は書き換わりません。

## 6. 機能説明

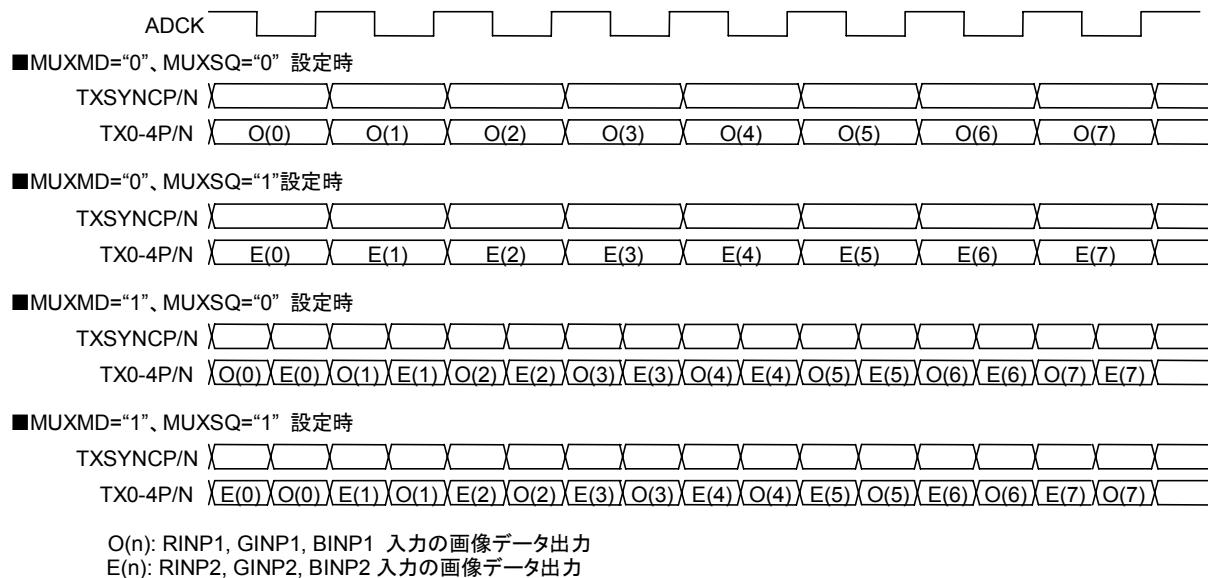

### 6.1.2 画像データ出力

#### (1) 出力シーケンス

画像データ出力は、外部から入力される ADCK 信号 (A/D 変換クロック) に同期して出力されます。画像データ出力は、チャネル毎に 10 ビットの画像データとして出力します。DATACTL レジスタ (No.0x03) の MUXMD ビットに“1”を設定した場合、ODD および EVEN のアナログ入力信号は、A/D 変換され画像データとしてマルチプレクスされて出力されます。一方、“0”に設定した場合は、ODD または EVEN のアナログ入力のどちらかが A/D 変換され画像データとして出力されます。また、DATACTL レジスタ (No.0x03) の XOER ビット、XOEG ビットおよび XOEB ビットは、“1”を設定した場合、対応するチャネルの出力は null コード (0x000) となります。

マルチプレクス出力時において、DATACTL レジスタ (No.0x03) の MUXSQ ビットにより、そのシーケンスを設定することができます。“0”設定時において出力シーケンスは ODD→EVEN となり、“1”を設定することによって EVEN→ODD となります。

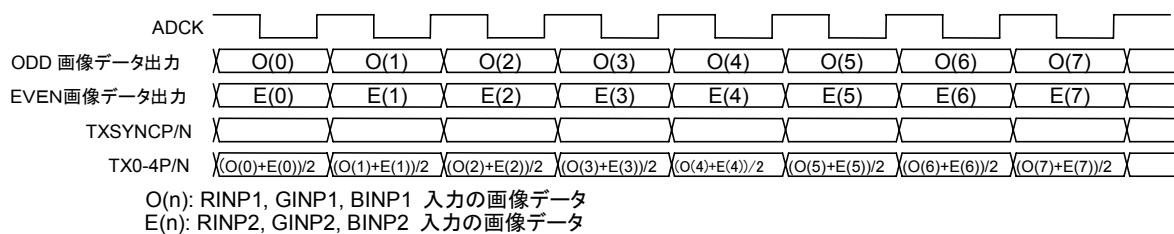

#### (2) 2 画素平均機能

DATACTL レジスタ (No.0x03) の AVEMD ビットに“1”を設定した場合、ODD および EVEN の A/D 変換された画像データを各色ごとに平均して出力することができます。

レジスタ設定それぞれの場合における画像データ出力の関係を表 6.2 に示し、図 6.2 にその動作例を示します。また、図 6.3 に 2 画素平均機能動作時におけるタイミング例を示します。

表 6.2 画像データ出力

| レジスタ設定 |      |      |       |       |       |             | 入力               | 出力データ出力          |                  |  |

|--------|------|------|-------|-------|-------|-------------|------------------|------------------|------------------|--|

| XOEB   | XOEG | XOER | MUXSQ | AVEMD | MUXMD | ADCK        | B チャネル           | G チャネル           | R チャネル           |  |

| “1”    | “1”  | “1”  | X     | X     | X     | X           | null             | null             | null             |  |

| “0”    | “0”  | “1”  | “0”   | “0”   | “0”   | X           | BINP1            | GINP1            | null             |  |

| “0”    | “1”  | “0”  | “0”   | “0”   | “0”   | X           | BINP1            | null             | RINP1            |  |

| “1”    | “0”  | “0”  | “0”   | “0”   | “0”   | X           | null             | GINP1            | RINP1            |  |

| “0”    | “0”  | “0”  | “0”   | “0”   | “0”   | X           | BINP1            | GINP1            | RINP1            |  |

| “0”    | “0”  | “0”  | X     | “1”   | “0”   | X           | BINP1+BINP2<br>2 | GINP1+GINP2<br>2 | RINP1+RINP2<br>2 |  |

| “0”    | “0”  | “0”  | “1”   | “0”   | “0”   | X           |                  |                  |                  |  |

| “0”    | “0”  | “0”  | “0”   | “0”   | “1”   | HIGH<br>LOW | BINP1            | GINP1            | RINP1            |  |

| “0”    | “0”  | “0”  | “1”   | “1”   | “1”   |             | BINP2            | GINP2            | RINP2            |  |

| “0”    | “0”  | “0”  | “1”   | “0”   | “0”   | HIGH<br>LOW | BINP2            | GINP2            | RINP2            |  |

| “0”    | “0”  | “0”  | “0”   | “1”   | “1”   |             | BINP1            | GINP1            | RINP1            |  |

0: レジスタ“0”設定

1: レジスタ“1”設定

X: don't care.

L: LOW レベル端子入力

H: HIGH レベル端子入力

#### 「制限注意事項」

MUXMD, AVEMD ビットを設定する際は、POWERDOWN レジスタ (No.0x00) の PDLVDS ビットおよび PDSTB ビットを“1”に設定してから行ってください。

図 6.2 画像データ出力動作例

図 6.3 2 画素平均機能動作タイミング

### (3) ライン監視機能

画像データの画素数をカウントし、それぞれの画素位置における画像データの属性を監視する機能です。その属性は下記のとおりです。また、それぞれの属性は画像データと共に出力されます。

wh : 白基準画素（または有効画素データ）

dm : 黒ダミ一画素

ob : 墨基準画素 (OB 画素)

本機能は、BKWST レジスタ (No.0x04)、BKNUM レジスタ (No.0x05) および WHNUM レジスタ (No.0x06~0x07) にそれぞれの画素数を適宜設定し DATACTL レジスタ (No.0x03) の INSTGO ビットに“1”を設定することにより有効となります。なお、ライン監視のために外部信号入力が必要となります。詳細は 6.5.11 自動オフセット・ゲイン調整機能を参照してください。

## 6. 機能説明

### 6.1.3 テストモード

DATACTL レジスタ(No.03)の TSTMD[1:0]ビットを設定することによって、画像データ出力テストモードとなります。出力されるデータは、固定値またはインクリメントデータを、出力データとしてテストを行うことができます。インクリメントデータは、BKHST レジスタ (No.0x04)、BKNUM レジスタ (No.0x05) および WHNUM レジスタ (No.0x06~0x07) にそれぞれの画素数を適宜設定し、DATACTL レジスタ (No.0x03) の INSTGO ビットに“1”を設定することにより出力可能となります。インクリメントデータ出力には 2 種類あり、色チャネル識別コードの有無を選択することができます。色チャネル識別コード無し設定時の R チャネルのマルチプレクス出力時における出力例を以下に示します。

|       |       |       |       |     |       |       |       |       |       |     |

|-------|-------|-------|-------|-----|-------|-------|-------|-------|-------|-----|

| Rodd  | Reven | Rodd  | Reven | ... | Rodd  | Reven | Rodd  | Reven | Rodd  | ... |

| 0xXXX | 0xXXX | 0x002 | 0x003 | ... | 0x0FE | 0x0FF | 0x000 | 0x001 | 0x002 | ... |

なお、データフォーマットは表 6.3 に示すとおりです。

表 6.3 インクリメントデータ出力時データフォーマット

■TSTMD [1:0]=“10” 設定時

|          |   |   |   |   |   |   |   |   |    |

|----------|---|---|---|---|---|---|---|---|----|

| 9        | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| CNT[8:0] |   |   |   |   |   |   |   |   | ch |

CNT[8:0] 画素カウンタ

ch: ODD/EVEN 識別子

0: ODD(xINP1)チャネル

1: EVEN(xINP2)チャネル

■TSTMD [1:0]=“01”設定時

|         |   |   |   |   |   |   |   |   |    |

|---------|---|---|---|---|---|---|---|---|----|

| 9       | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

| CL[1:0] |   |   |   |   |   |   |   |   | ch |

CL[1:0] 色チャネル識別子

00: 赤チャネル

01: 緑チャネル

10: 青チャネル

CNT[8:0] 画素カウンタ

ch: ODD/EVEN 識別子

0: ODD(xINP1)チャネル

1: EVEN(xINP2)チャネル

一方、TSTMD[1:0]ビットを“11”に設定することによって固定出力となります。なお、固定データは、各チャネルのオフセットレジスタ設定値となります。表 6.4 にそのフォーマットを示します。

表 6.4 固定値出力時データフォーマット

■If TSTMD [1:0]=“11”設定時

|          |   |   |   |   |   |   |   |   |   |

|----------|---|---|---|---|---|---|---|---|---|

| 9        | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OFS[9:0] |   |   |   |   |   |   |   |   |   |

「注意事項」

インクリメントデータ出力時において先頭画素はゴミデータが出力されます。

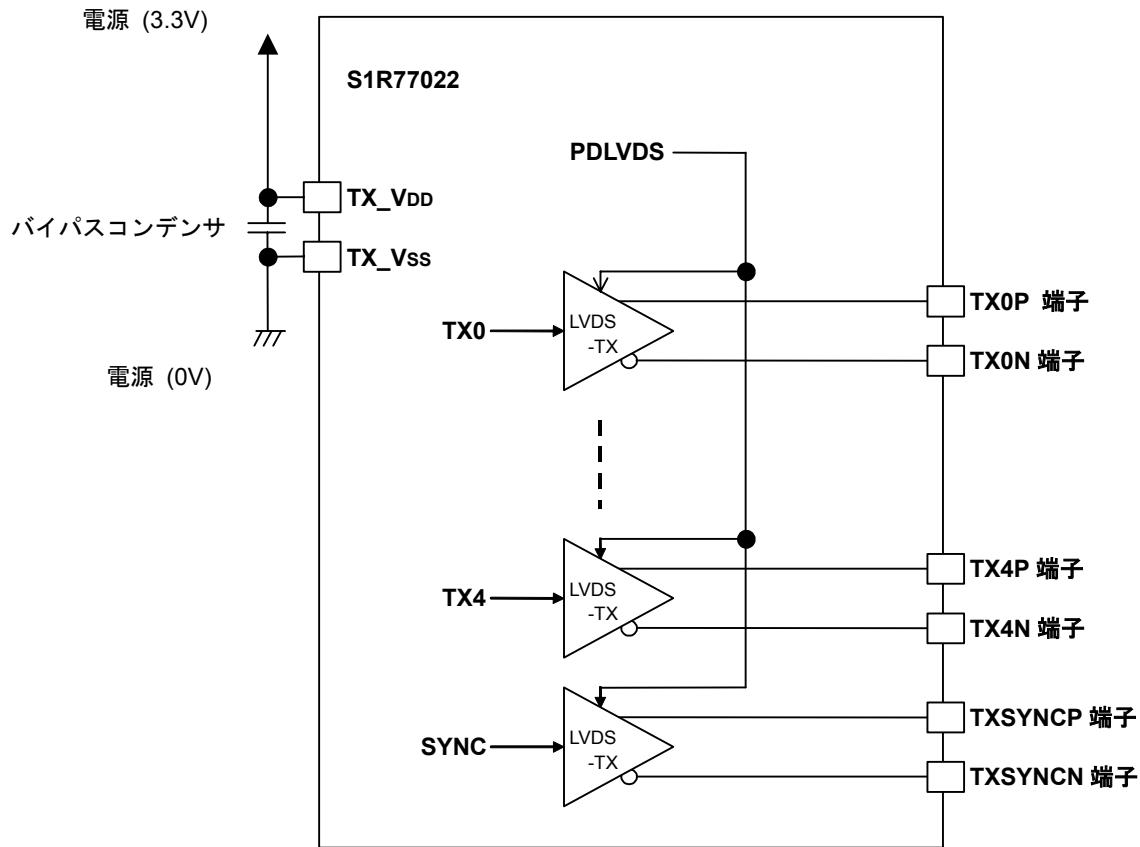

## 6.2 LVDS 部

画像データの出力は LVDS にて出力します。LVDS 部は画像データ出力用に 5 チャネル、同期クロック出力用に 1 チャネルで構成されています。図 6.4 に LVDS 部周辺の接続関係を示します。

図 6.4 LVDS 接続図

### (1) パワーダウン機能

LVDS 部は、パワーダウン機能を有しており、POWERDOWN レジスタ (No.0x00) の PDLVDS ビットによって制御することができます。PDLVDS ビットを“1”に設定することにより、LVDS 部はパワーダウンモードとなり画像データ送信を停止します。また、“0”に設定することにより、パワーダウンモードが解除され画像データ送信を開始します。なお、パワーダウンモード解除後、安定した画像データ送信を行うまで最大で 10ms 必要です。

#### 「制限注意事項」

AFFECTL レジスタ (No.0x0B) の VCOSEL[1:0]ビットおよび DATACTL レジスタ (No.0x03) の MUXMD、AVEMD、PIXSQMD ビットを設定を設定する際は、POWERDOWN レジスタ (No.0x00) の PDLVDS ビットおよび PDSTB ビットを“1”に設定してから行ってください。

### (2) 終端抵抗

LVDS 出力は受信デバイスの入力端子直近にて  $100\Omega$  で終端してください。

#### 「制限注意事項」

外付け抵抗は公差  $\pm 1.0\%$  以下を推奨します。また、基板実装において本 IC とコネクタ間は、スルーホール等を介さず同一面に実装してください。

## 6. 機能説明

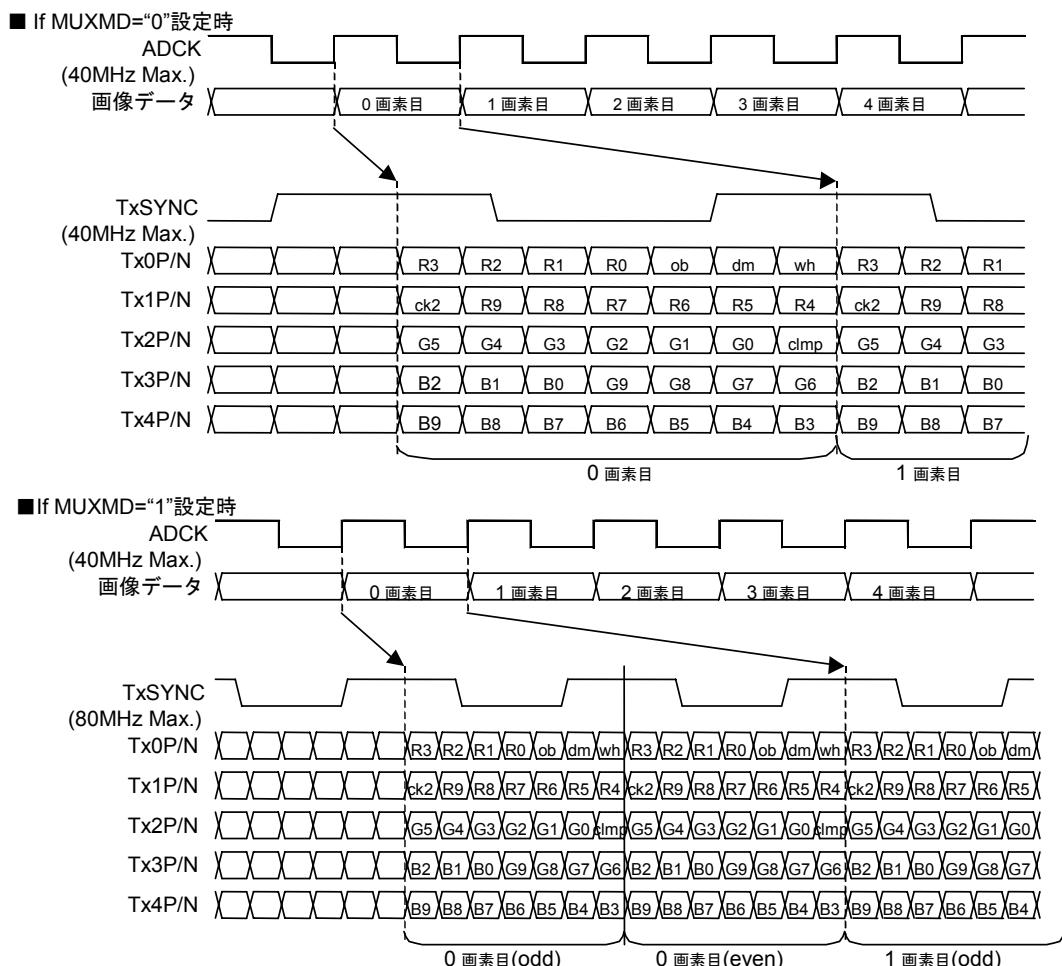

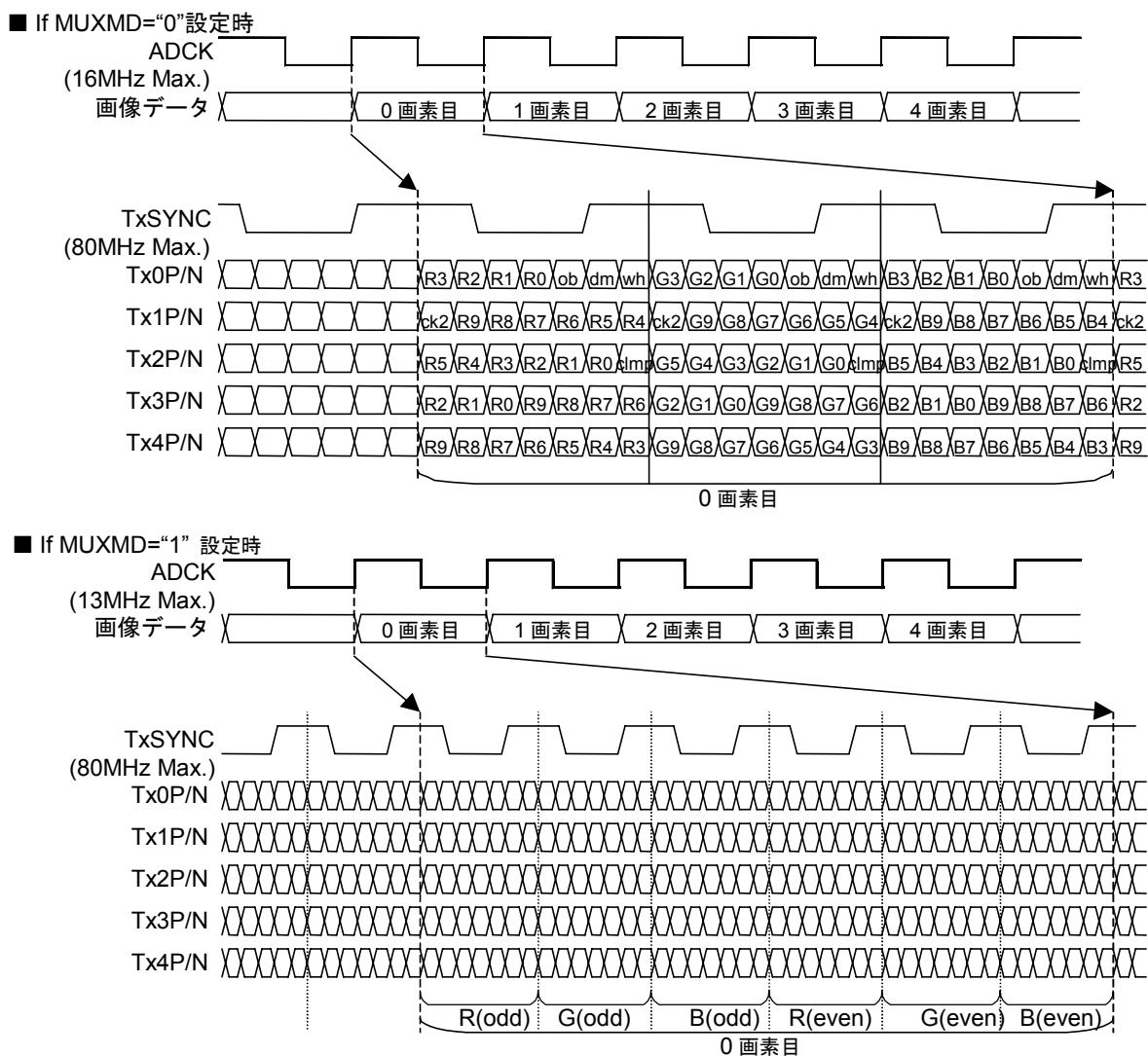

### (3) 画像データ出力フォーマット

LVDS にて出力される画像データのフォーマットは、図 6.5 に示すとおりです。画像データの空きビットには、それぞれ内部動作状態を示す符号がアサインされています。図 6.5 に示されている各ビットの意味は次のとおりです。

R9~0 : R チャネル画像データ出力

G9~0 : G チャネル画像データ出力

B9~0 : B チャネル画像データ出力

wh : 白基準画素（または有効画素データ）

dm : 黒ダミ一画素

ob : 黒基準画素（OB 画素）

ck2 : CK2 端子モニタ

clmp : CLMP 端子モニタ

図 6.5 LVDS 画像データ出力

#### 「制限注意事項」

通常出力モードの ADCK 信号周波数範囲は下記のとおりとなります。

##### ■ MUXMD=“0”設定時

$10\text{MHz} \leq \text{ADCK 信号周波数} \leq 40\text{MHz}$

##### ■ MUXMD=“1”設定時

$5\text{MHz} \leq \text{ADCK 信号周波数} \leq 40\text{MHz}$

DATACTL レジスタ (No.0x03) の PIXSQMD ビットに“1”を設定することにより、点順次出力モードとなります。点順次出力モードで動作することにより、画像データの出力を LVDS 出力 2 対で送信することが可能です。

図 6.6 にその動作例を示します。

図 6.6 点順次出力モード時の LVDS 画像データ出力

### 「制限注意事項 1」

点順次出力モードは ADCK 信号周波数が下記の範囲の場合のみ使用可能です。

### ■MUXMD="0"設定時

3.33MHz ≤ ADCK 信号周波数 ≤ 16.6MHz

### ■MUXMD="1"設定時

1.66MHz ≤ ADCK 信号周波数 ≤ 13.3MHz

## 「制限注意事項 2」

PIXSQMD ビットを設定を設定する際は、POWERDOWN レジスタ (No.0x00) の PDLVDS ビットおよび PDSTB ビットを“1”に設定してから行ってください。

## 6. 機能説明

---

### (4) プリエンファシス機能

プリエンファシス機能は、LVDS 転送周波数が高い等のデータ送信が確実に行えない場合において、内部回路のスイッチング電流を多く流すことにより安定したデータ送信を可能とします。プリエンファシス機能によりスイッチング電流を多く流すためには LVDSCTL レジスタ (No.0x16) の PE ビットに“1”を設定してください。なお、通常時は“0”設定で使用します。

### (5) チャネル出力有効機能

チャネル毎に LVDS 出力の有効／禁止の制御が可能です。LVDSCTL レジスタ (No.0x16) の TX0EN ～TX4EN ビットで設定してください。出力禁止設定のときはゼロが出力されます。

### (6) テストコード出力機能

LVDS の送信テストを行う場合に使用します。LVDSCTL レジスタ (No.0x16) の LVDSDT ビットに“1”を設定することにより各チャネルの出力データは表 6.5 に示すデータを出力します。

表 6.5 テストコード出力機能データフォーマット

| 出力チャネル | 6 | 5 | 4 | 3 | 2 | 1 | 0           |

|--------|---|---|---|---|---|---|-------------|

| Tx0P/N |   |   |   |   |   |   | RD1OFS[6:0] |

| Tx1P/N |   |   |   |   |   |   | RD2OFS[6:0] |

| Tx2P/N |   |   |   |   |   |   | GR1OFS[6:0] |

| Tx3P/N |   |   |   |   |   |   | GR2OFS[6:0] |

| Tx4P/N |   |   |   |   |   |   | BL1OFS[6:0] |

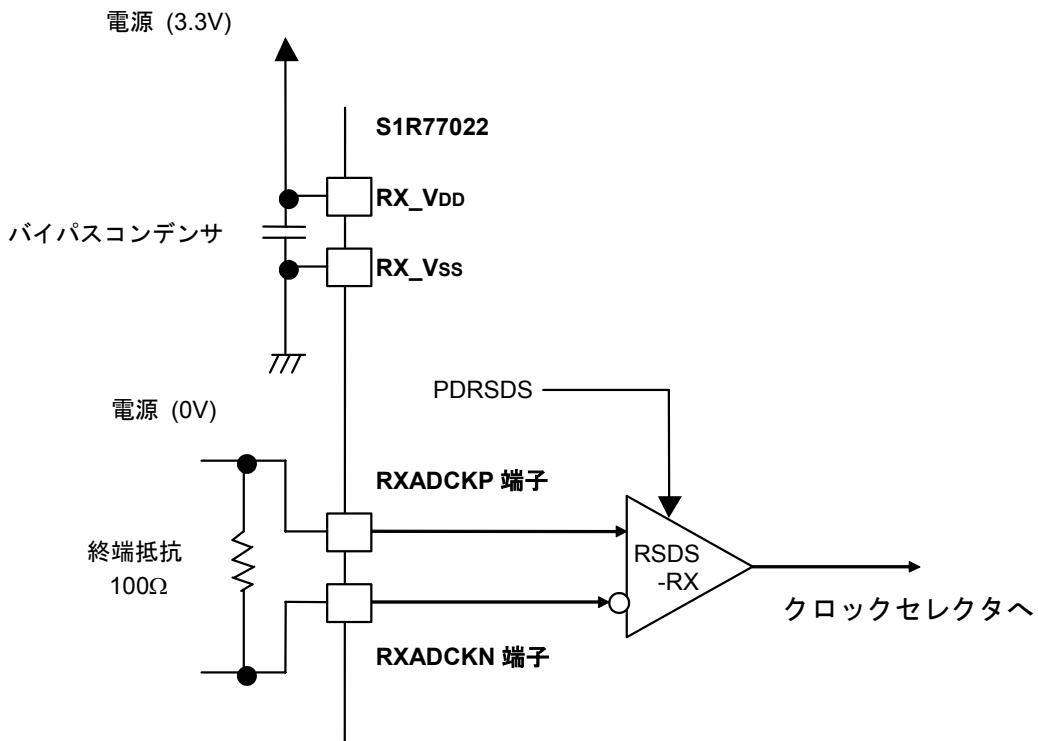

### 6.3 RSDS 部

ADCK 信号を RSDS にて入力することができます。図 6.7 に RSDS 部周辺の接続関係を示します。

図 6.7 RSDS 接続図

#### (1) パワーダウン機能

RSDS 部は、パワーダウン機能を有しており、POWERDOWN レジスタ (No.0x00) の PDRSDS ビットによって制御することができます。PDRSDS ビットを“1”に設定することにより、RSDS 部はパワーダウンモードとなり ADCK 信号入力を停止します。また、“0”に設定することにより、パワーダウンモードが解除され ADCK 信号入力を開始します。なお、パワーダウンモード解除後、安定動作を開始するまで最大で 10ms 必要です。

#### (2) 終端抵抗

RSDS 入力端子の直近に  $100\Omega$  の終端抵抗を接続してください。

#### 「制限注意事項」

外付け抵抗は公差 $\pm 1.0\%$ 以下を推奨します。また、基板実装において本 IC とコネクタ間は、スルーホール等を介さず同一面に実装してください。

#### (3) 空き端子処理

ADCK 信号を RSDS 入力しない場合は、RXCLKP を Low レベルに、RXCLKN を High レベルに固定してください。

## 6. 機能説明

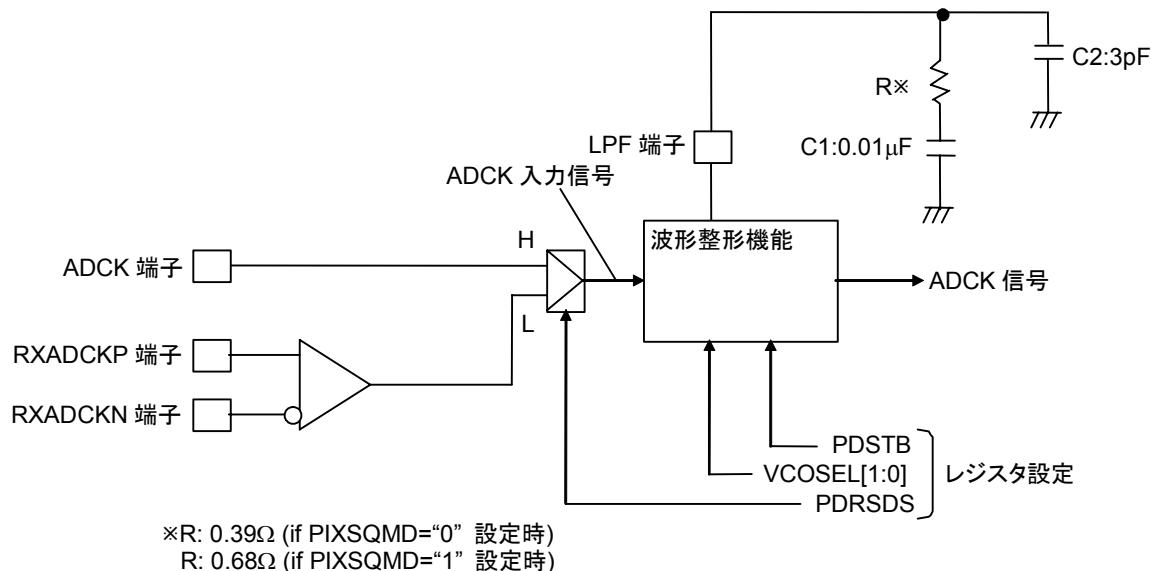

### 6.4 入力クロック波形整形機能部

ADCK 信号を波形整形（デューティを 50%化）するために波形整形機能を内蔵しております。図 6.8 に入力クロック波形整形機能周辺の接続関係を示します。

図 6.8 入力クロック波形整形機能

#### 「制限注意事項」

本 IC を安定動作させるために、入力クロック波形整形機能は必ず有効（動作状態）にしてご使用ください。

#### (1) パワーダウン機能

入力クロック波形整形機能のパワーダウン機能は、POWERDOWN レジスタ (No.0x00) の PDSTB ビットによって制御することができます。PDSTB ビットを“1”に設定することにより、入力クロック波形整形機能はパワーダウンモードとなり機能を停止します。また、“0”に設定することにより、パワーダウンモードが解除され動作を開始します。なお、パワーダウンモード解除後、安定動作を行うまで最大で 10ms 必要とします。

#### (2) ADCK 信号入力方式選択

ADCK 信号の外部端子からの入力は、表 6.6 に示すとおりクロックパルス入力または RSRS 入力のどちらかを選択して入力することができます。

表 6.6 ADCK 入力信号選択設定

| 入力方式      | レジスタ設定 |        | 端子処理   |        |  |

|-----------|--------|--------|--------|--------|--|

|           | PDRSDS | CLKIN  | RXCLKP | RXCLKN |  |

| クロックパルス入力 | “1”    | クロック入力 | LOW    | HIGH   |  |

| RSRS 入力   | “0”    | LOW    | クロック入力 |        |  |

0: レジスタ“0”設定

1: レジスタ“1”設定

L: LOW レベル端子入力

H: HIGH レベル端子入力

## (3) ADCK 信号入力周波数設定

ADCK 信号の周波数により AFECTL レジスタ (No.0x0B) の VCOSEL[1:0] ビットを表 6.7 に従い設定する必要があります。

表 6.7 VCOSEL [1:0] ビット設定

| ADCK 信号周波数     |               | VCOSEL [1:0] ビット設定 |

|----------------|---------------|--------------------|

| PIXSQMD="0"    | PIXSQMD="1"   |                    |

| 25.0 ~ 40.0MHz | 8.3 ~ 13.3MHz | "11"               |

| 20.0 ~ 25.0MHz | 6.6 ~ 8.3MHz  | "10"               |

| 12.5 ~ 20.0MHz | 4.1 ~ 6.6MHz  | "01"               |

| 10.0 ~ 12.5MHz | 3.3 ~ 4.1MHz  | "00"               |

## 「制限注意事項」

AFECTL レジスタ (No.0x0B) の VCOSEL[1:0] ビットおよび DATACTL レジスタ (No.0x03) の MUXMD、AVEMD、PIXSQMD ビットを設定を設定する際は、POWERDOWN レジスタ (No.0x00) の PDLVDS ビットおよび PDSTB ビットを“1”に設定してから行ってください。

## (4) 外付け部品

入力クロック波形整形機能は安定した動作を行うため LPF 端子に外付けの抵抗とコンデンサを接続する必要があります。外付け抵抗およびコンデンサは下記の定数の部品を接続してください。但し、DATACTL レジスタ (No.0x03) の PIXSQMD ビット設定の設定により R の定数が異なります。

R:0.39KΩ(PIXSQMD="0"設定時)

0.68KΩ(PIXSQMD="1"設定時)

C1:0.01μF

C2:3pF

## 6. 機能説明

---

### 6.5 アナログ部

#### 6.5.1 概要

アナログ部は CCD (電荷結合素子) から出力されるアナログ画像データをデジタルに変換するブロックです。本ブロックは主に CDS 部 (相関二重サンプリング)、オフセット調整、プログラマブル・ゲイン・アンプ (PGA) および 10 ビット A/D コンバータから構成されています。

- 10 ビット A/D コンバータ 6 個内蔵

- 最大変換レート : 1 チャネルあたり 40Msps

- 動作モード : CDS モードまたは S/H (サンプル／ホールド) モード

- 動作チャネル数 : 1、2、3、4 または 6 チャネル

- A/D コンバータへのフルスケール入力レンジ: 1.2Vp-p

- プログラマブル・ゲイン・アンプ (PGA) 調整レンジ : ゲイン調整特性をレジスタで選択

-6.9dB(0.45 倍)～+12.0dB(4.0 倍),

-0.9dB(0.9 倍)～+18.0dB(8.0 倍),

+5.1dB(1.8 倍)～+24.1dB(16.0 倍)

- オフセット調整レンジ : ±300mV

- 自動オフセット・ゲイン調整機能内蔵

- 自動黒レベル補正機能内蔵

- サンプリング信号自動生成機能内蔵 (S/H モードのみ)

## 6.5.2 仕様

表 6.8 アナログ部仕様

| 項目                                  | 仕様            |                                                             |                  |

|-------------------------------------|---------------|-------------------------------------------------------------|------------------|

|                                     | Min.          | Typ.                                                        | Max.             |

| <b>内部基準電圧レベル</b>                    |               |                                                             |                  |

| 低電位リファレンス (REFN)                    | 1.10V         | 1.20V                                                       | 1.30V            |

| 同相モード電圧 (CM1)                       | 1.40V         | 1.50V                                                       | 1.60V            |

| 高電位リファレンス (REFP)                    | 1.70V         | 1.80V                                                       | 1.90V            |

| <b>変換特性</b>                         |               |                                                             |                  |

| 最大変換レート (1 チャネルあたり)                 |               |                                                             | 40Msps           |

| 解像度                                 |               | 10bits                                                      |                  |

| <b>アナログ入力</b>                       |               |                                                             |                  |

| 外部差動入力レンジ                           |               |                                                             | 2.6Vp-p          |

| A/D コンバータ入力レンジ                      |               |                                                             | 1.2Vp-p          |

| 入力電圧範囲                              | AGND          |                                                             | AV <sub>DD</sub> |

| 有効アナログ入力範囲 ※1                       | 0V            |                                                             | 1.5V             |

| 最小ゲイン調整 ※2                          |               | -6.9 dB (0.45 倍)、<br>-0.9 dB (0.9 倍)、<br>+5.1 dB (1.8 倍)    |                  |

| 最大ゲイン調整 ※2                          |               | +12.0 dB (4.0 倍)、<br>+18.0 dB (8.0 倍)、<br>+24.1 dB (16.0 倍) |                  |

| ゲイン分解能                              |               | 128 ステップ                                                    |                  |

| ゲイン誤差                               |               | ±1dB                                                        |                  |

| オフセット調整レンジ                          |               | ±300mV                                                      |                  |

| オフセット分解能                            |               | 1024 ステップ                                                   |                  |

| オフセット誤差                             |               | ±20mV                                                       |                  |

| クランプレベル                             |               | レジスタ選択(16 ステップ)                                             |                  |

| ライン・クランプ機能                          |               | バッファアンプ能力 (バイアス電流) レジスタ選択<br>(0.5 倍～1.7 倍)                  |                  |

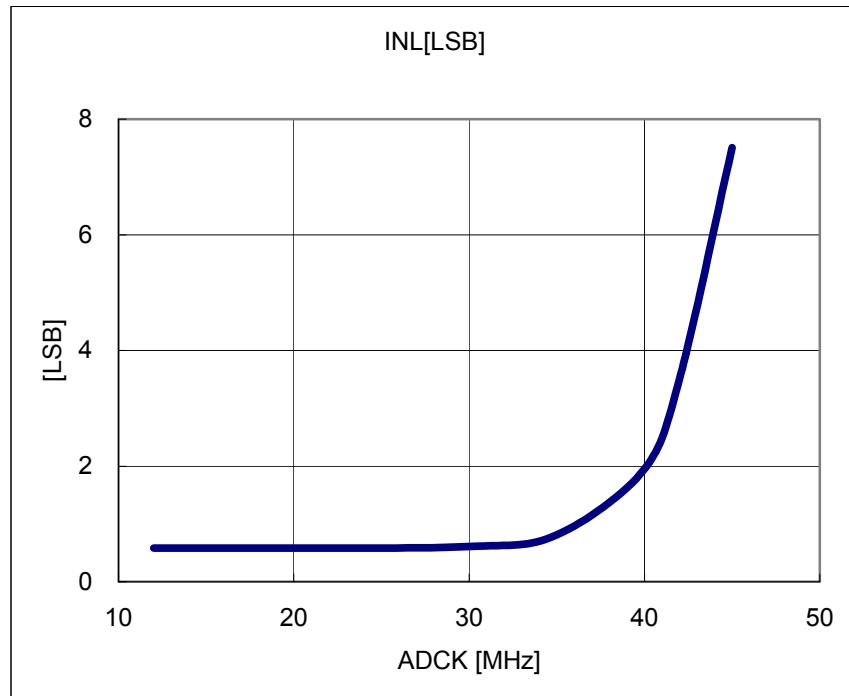

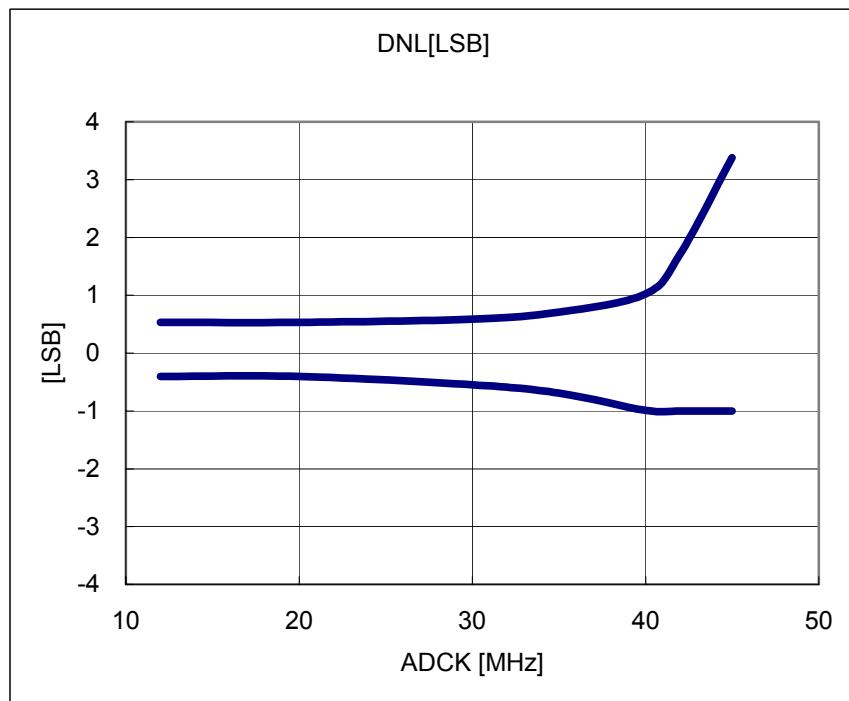

| <b>A/D コンバータ ダイナミック特性(ADCK 周波数)</b> |               |                                                             |                  |

| 積分非直線性<br>(INL)                     | 30[MHz] 以下    |                                                             | ±1.0             |

|                                     | 30～35[MHz] 以下 |                                                             | ±1.1             |

|                                     | 35～40[MHz]    |                                                             | ±4.7             |

| 微分非直線性<br>(DNL)                     | 30[MHz] 以下    |                                                             | ±0.6             |

|                                     | 30～35[MHz] 以下 |                                                             | ±0.9             |

|                                     | 35～40[MHz]    |                                                             | +4.5/-1.0        |

| ノーミッシングコード                          |               | 保証                                                          | ※3               |

| <b>電源条件</b>                         |               |                                                             |                  |

| 電源電圧(AV <sub>DD</sub> )             | +3.135V       | +3.3V                                                       | +3.465V          |

※1 S/H モード (ライン・クランプ) 時のみ、A/D 変換可能な入力範囲

(CCD のリセットノイズ等の無効なアナログ成分は含まない)

※2 レジスタ設定により切り換え

※3 35MHz 以下の場合

## 6. 機能説明

図 6.9 A/D コンバータ積分非直線性 (INL)

図 6.10 A/D コンバータ微分非直線性 (DNL)

## 6.5.3 内部ブロック構成

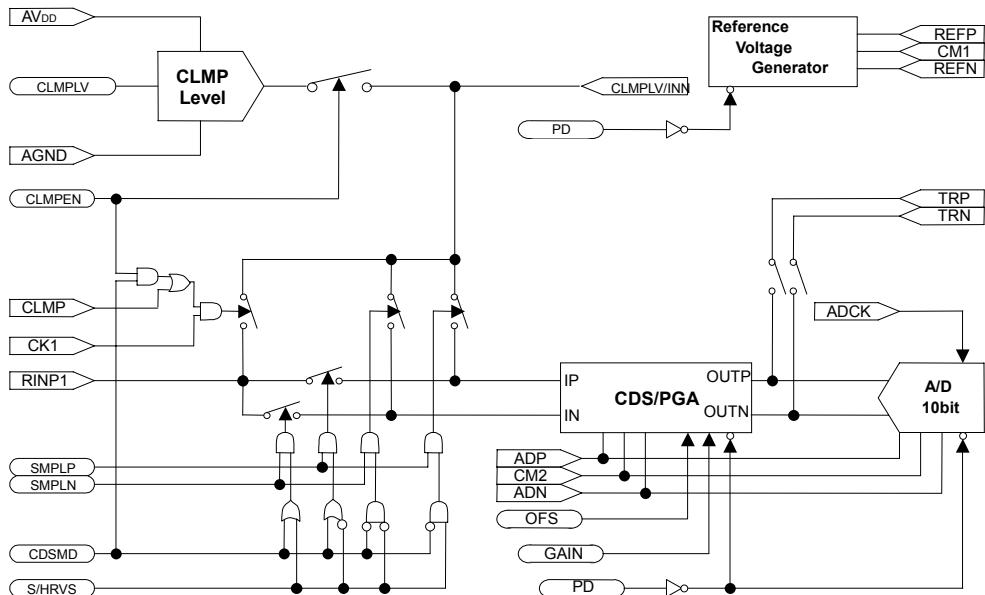

図 6.11 アナログ部ブロック図 (R チャネル[ODD])

表 6.9 アナログ部端子説明

| 端子名称       | 端子説明                       | 接続先                           |

|------------|----------------------------|-------------------------------|

| 外部接続       |                            |                               |

| AVDD       | アナログ電源+3.3V                | 外部接続                          |

| AGND       | アナロググランド                   | 外部接続                          |

| REFN       | 低電位リファレンス 1 (1.2V)         | 外部接続                          |

| ADN        | 低電位リファレンス 2 (1.2V)         | 外部接続                          |

| CM1        | 同相モード電圧 1 (1.5V)           | 外部接続                          |

| CM2        | 同相モード電圧 2 (1.5V)           | 外部接続                          |

| REFP       | 高電位リファレンス 1 (1.8V)         | 外部接続                          |

| ADP        | 高電位リファレンス 2 (1.8V)         | 外部接続                          |

| RINP1      | アナログ入力                     | 外部接続                          |

| CLMPLV/INN | クランプレベルモニタ/<br>リファレンスレベル入力 | 外部接続                          |

| TRP1       | A/D コンバータ高電位入力 (ODD)       | 外部接続                          |

| TRN1       | A/D コンバータ低電位入力 (ODD)       | 外部接続                          |

| ADCK       | A/D 変換クロック                 | 外部入力                          |

| CK1        | クロック信号 1                   | 外部入力                          |

| CLMP       | クランプ信号                     | 外部入力                          |

| 内部接続       |                            |                               |

| PD         | パワーダウン                     | レジスタ出力                        |

| SMPLP      | 高電位入力レベルサンプリング信号           | 内部生成 (動作モードによって CK1 から生成)     |

| SMPLN      | 低電位入力レベルサンプリング信号           | 内部生成 (動作モードによって CK1、CK2 から生成) |

| CDSMD      | サンプリングモード設定                | レジスタ出力                        |

| S/HRVs     | S/H モード差電圧極性設定             | レジスタ出力                        |

| OFS        | オフセット設定値                   | レジスタ出力                        |

| GAIN       | ゲイン設定値                     | レジスタ出力                        |

| CLMPEN     | クランプ許可設定                   | レジスタ出力                        |

| CLMPLV     | クランプレベル設定                  | レジスタ出力                        |

## 6. 機能説明

### 6.5.4 パワーダウン機能

アナログ部のパワーダウン機能は、POWERDOWN レジスタ (No.0x00) の PD ビットによって制御することができます。“1”に設定することにより、パワーダウンモードとなります。また、“0”に設定することにより、パワーダウンモードが解除され動作を開始します。なお、動作しないチャネルのアナログ部については、自動的にパワーダウンモードとなります。

### 6.5.5 基準電圧発生回路 (Reference Voltage Generator)

アナログ部は基準電圧発生回路にて生成した基準電圧レベルを基準に動作を行います。また、内部基準電圧は REF0 端子、CM1 端子および REFN 端子にてモニタすることができます。

### 6.5.6 クランプ回路

クランプ回路は、CCD のアナログ出力の DC 成分を除去するために、アナログ入力を AC カップリングコンデンサを介して入力し、内部バイアス回路で適正な電圧にクランプします。

クランプ動作は、CLMP 信号（クランプタイミング）の入力タイミングにより、各画素単位に動作する「ビット・クランプ」、または指定された範囲の画像について動作する「ライン・クランプ」で動作することができます。クランプタイミングは CLMP 信号（クランプタイミング）と CK1 信号（サンプリングクロック 1）が共に HIGH 入力時のタイミングで動作します。なお、CLMP 信号は AFEMD レジスタ (No.0x02) の CLMPPOL ビットによって、その論理極性を反転させることができます。

クランプレベルは内部生成または外部入力することができます。外部入力する場合は、AFEMD レジスタ (No.0x02) の CLMPEN ビットを“0”設定にし、CLMPLV/INN 端子から限界範囲内の電圧レベルを入力してください。一方、内部生成する場合は、CLMPEN ビットを“1”設定にしてください。内部生成されるクランプレベルは下記に示すとおり AFEMD レジスタ (No.0x02) の CLMPLV[3:0] ビットの設定によって、その電圧レベルを選択させることができます。また、CLMPLV/INN 端子によってその電圧レベルをモニタすることができます。

$$\text{クランプ電圧 (V)} \doteq \text{AVDD} \times \frac{\text{レジスタ設定値 (0~15)}}{16}$$

### 6.5.7 CDS/PGA

本 IC は、CCD から出力されるアナログ画像データに対し、アナログ-デジタル変換をします。アナログ画像データのサンプリング方式には、CDS モードまたは S/H モードがあります。その切り換えは、AFEMD レジスタ (No.0x02) の CDSMD ビットで行います。“1”設定時において CDS モードとなり、“0”では S/H モードに切り換わります。

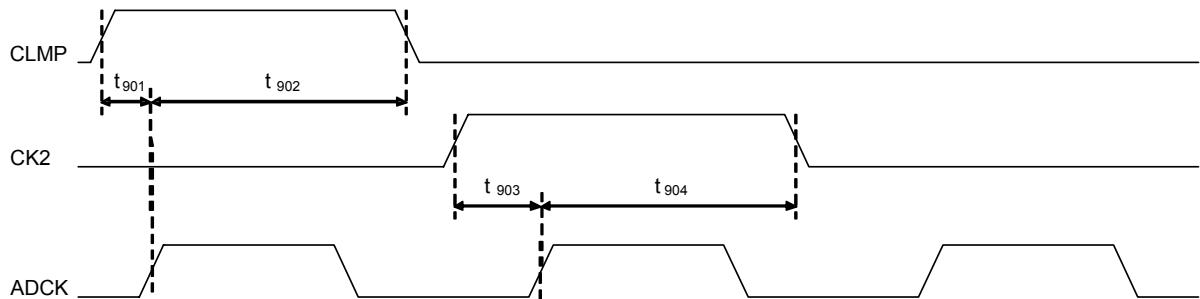

また、S/H モード動作時のみ AFECTL レジスタ (No.0x0B) の CKGEN ビットに“1”を設定することによって、CK1 信号（サンプリングクロック 1）を外部入力せずともサンプリング信号を自動生成します。外部入力の ADCK 信号を元にサンプリング信号を生成し、サンプリングポイントは外部入力の ADCK 信号の立ち上がりとなります。なお、CKGENMD レジスタ (No.0x0C) の CKGENMD ビットに“1”を設定することにより、そのパルス幅（立ち上がりを遅延（約 2~7ns）させる）を短くすることができます。

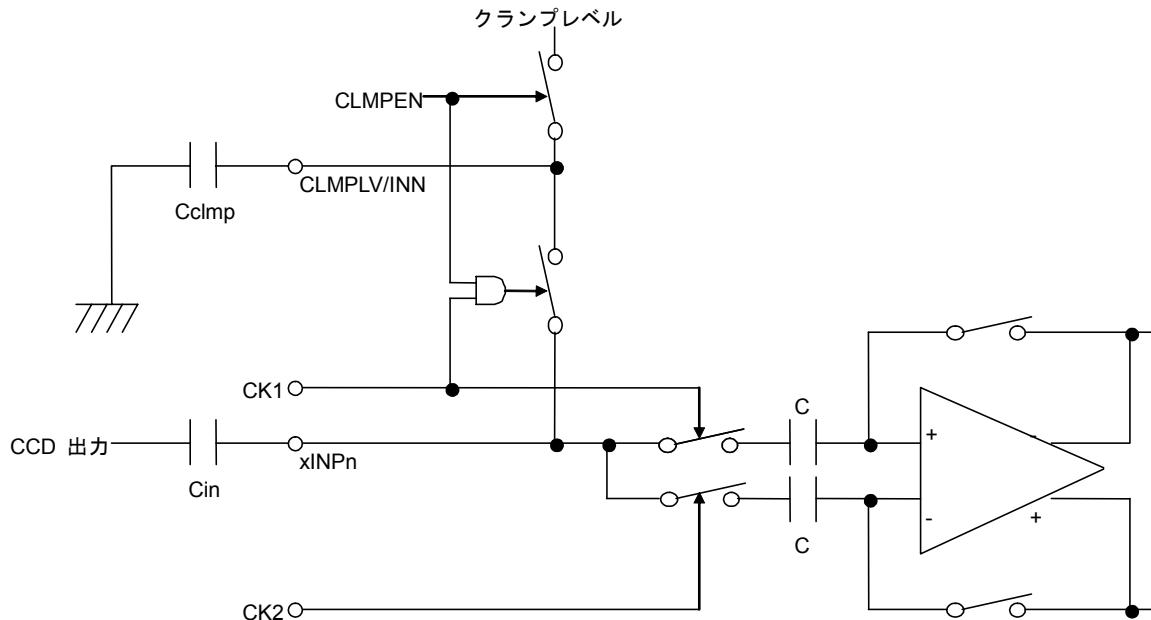

## (1) CDS モード機能

図 6.12 CDS モード内部構成図

AFEMD レジスタ (No.0x02) の CDSMD ビットに “1” を設定することにより CDS モードとなります。また、AFEMD レジスタ (No.0x02) の CLMPEN ビットに “1” を設定することにより、画素毎にクランプするビット・クランプを行うことができます。

CDS モードは CK1 信号 (サンプリングクロック 1) でクランプレベルを、CK2 信号 (サンプリングクロック 2) が HIGH 入力時に CCD 出力レベルをサンプリングします。なお、CK1 信号および CK2 信号は AFEMD レジスタ (No.0x02) の CKPOL ビットにより、その論理極性を反転させることができます。

図 6.12 に CDS モード時における内部構成図を示します。

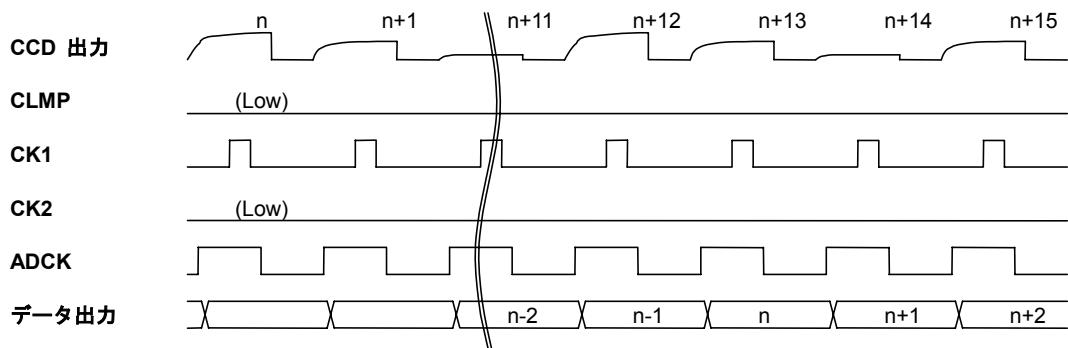

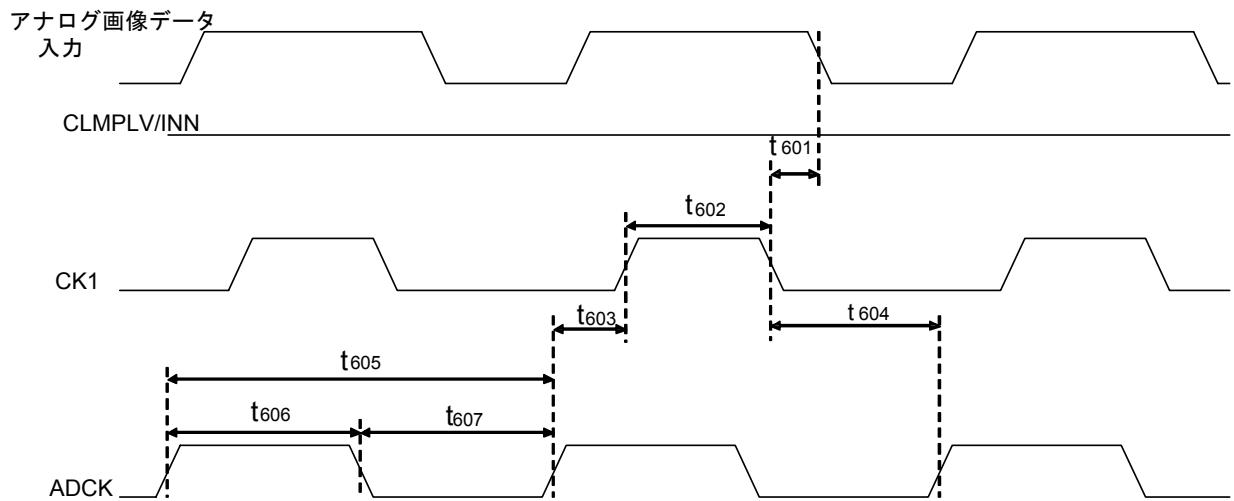

図 6.13 CDS モード動作タイミング例

図 6.13 に CDS モード時の動作タイミング例を示します。また、下記にその設定例を示します。

AFEMD レジスタ (No.0x02) : XX XX01 0001(2) 注) X は基準電圧レベルにより任意に設定

## 6. 機能説明

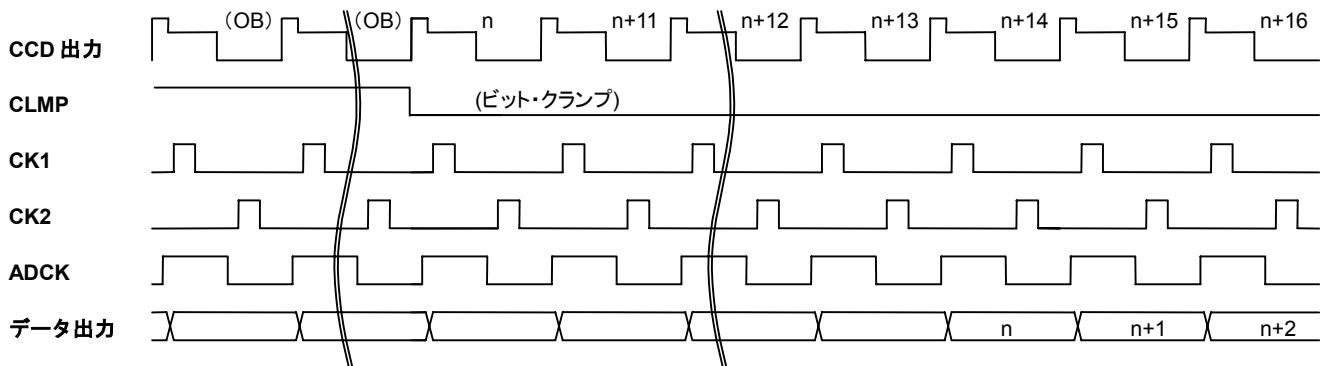

### (2) S/H モード機能 (差電圧入力)

図 6.14 S/H モード (差電圧入力) 内部構成図

AFEMD レジスタ (No.0x02) の CDSMD ビットを“0”に設定することによって S/H モードとなり、CLMPLV/INN 端子に基準電圧レベル入力し、画像データ信号レベルとの差電圧入力を行うことができます。サンプリングは、CK1 信号 (サンプリングクロック 1) で基準電圧レベルと CCD 出力レベルを同時に行います。CLMPLV/INN 端子から基準電圧レベルを入力する場合は、AFEMD レジスタ (No.0x02) の CLMPEN ビットに“0”を設定してください。

一方、CLMPEN ビットに“1”を設定することにより、クランプレベルを基準電圧レベルとして内部生成させることができ、その電圧レベルを CLMPLV/INN 端子でモニタすることができます。その際は外部から電圧レベルを供給しないでください。

図 6.14 に S/H モード (差電圧入力) 時における内部構成図を示します。

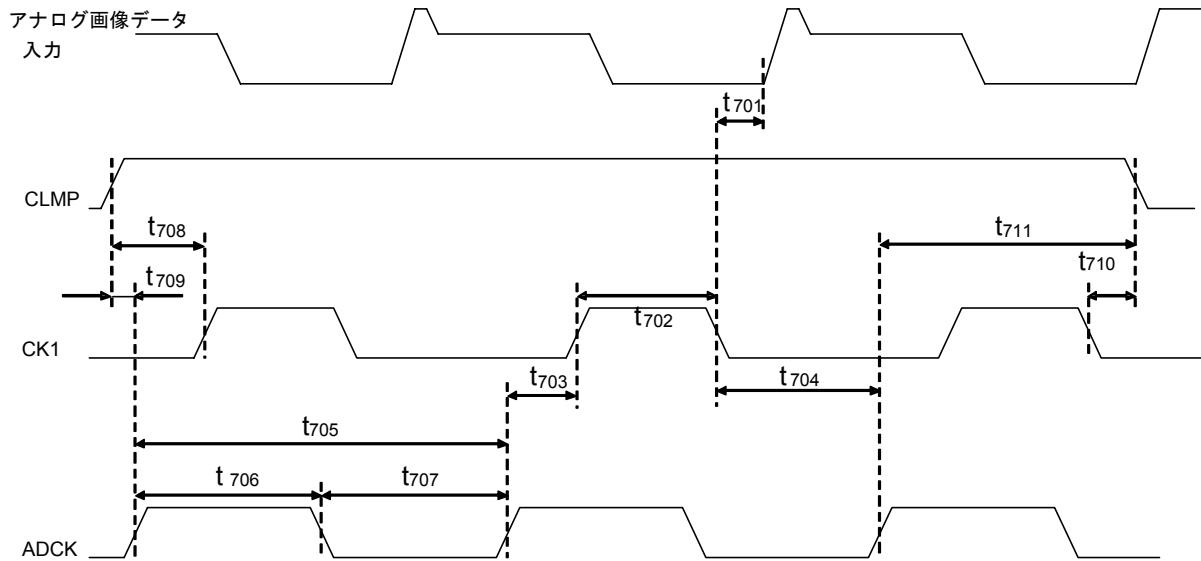

図 6.15 S/H モード (差電圧入力) 動作タイミング例

図 6.15 に S/H モード (差電圧入力) 時で基準電圧を外部入力の場合の動作タイミング例を示します。また、下記にその設定例を示します。

AFEMD レジスタ (No.0x02) : 00 0000 0000(2)

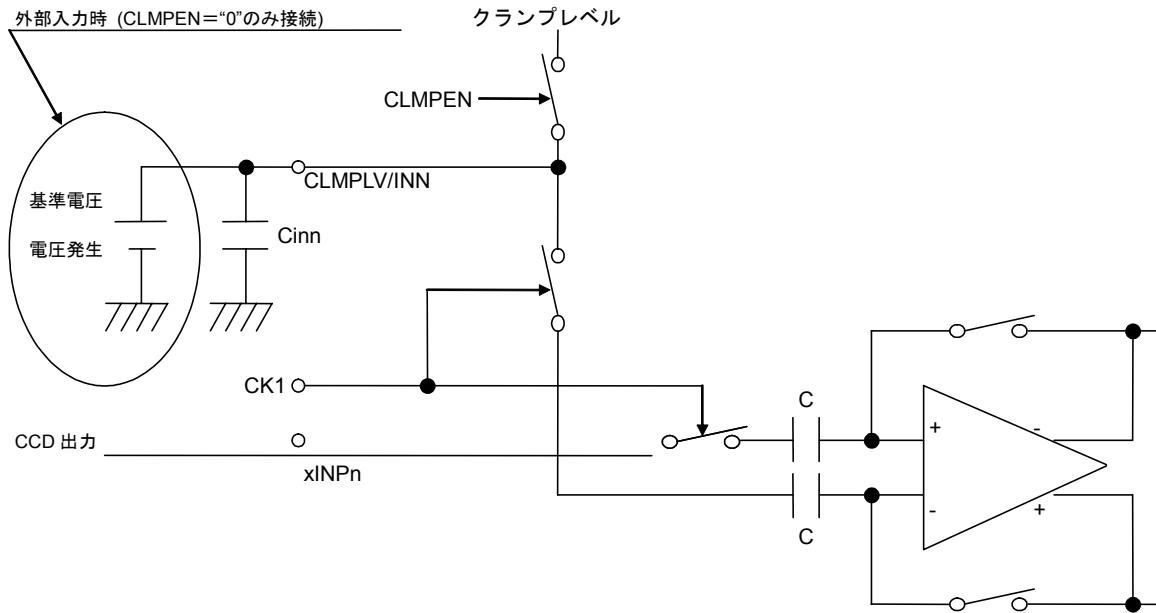

## (3) S/H モード機能 (ライン・クランプ)

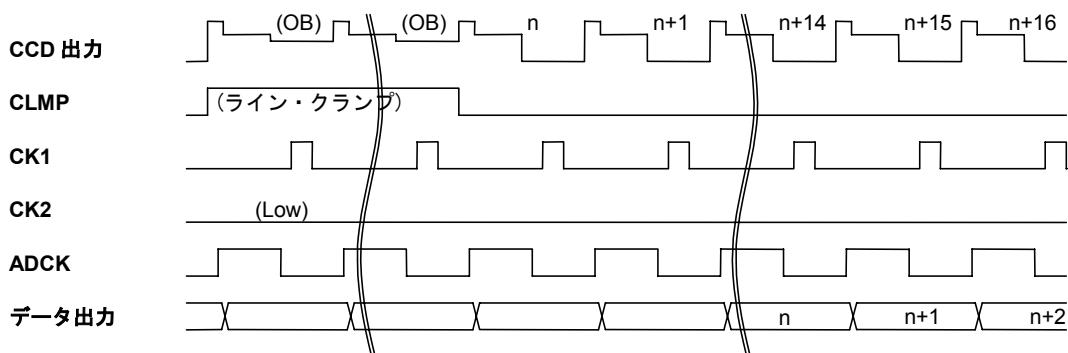

図 6.16 S/H モード (ライン・クランプ) 内部構成図

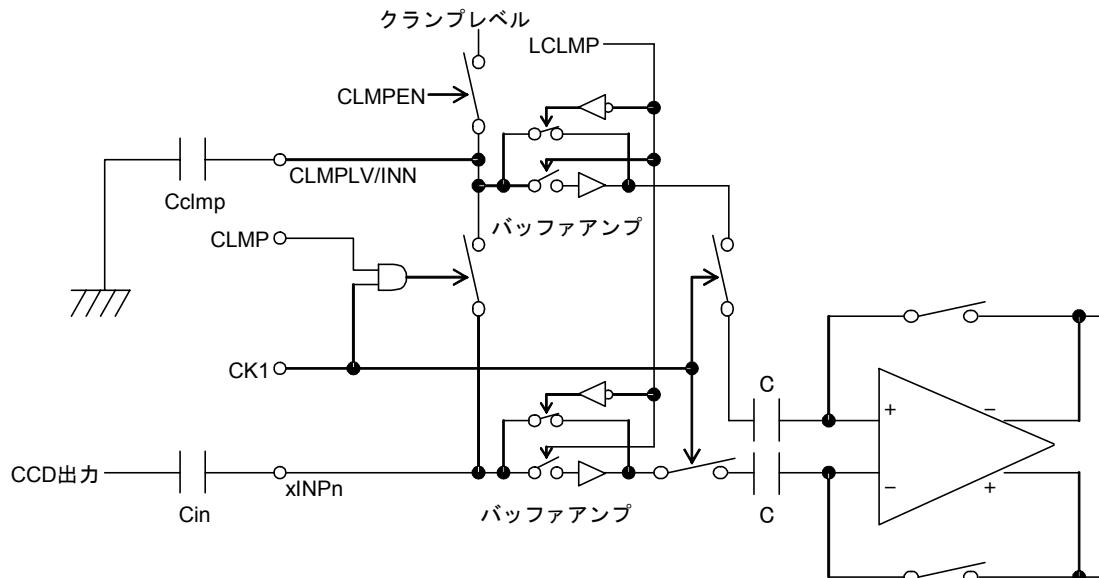

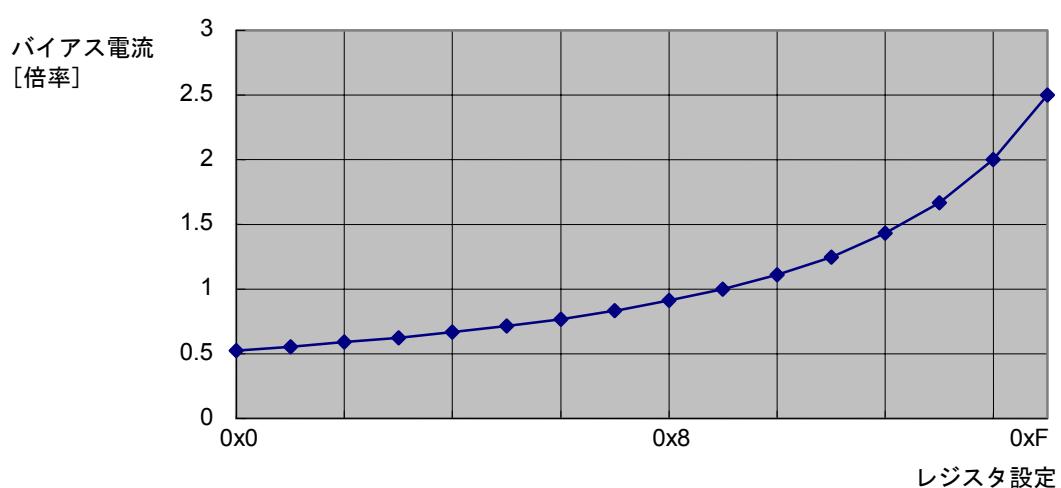

S/H モード設定時において、AFEMD レジスタ (No.0x02) の S/HRVS ビットと CLMPEN ビットとともに“1”に設定することにより、基準電圧レベルと画像データ信号レベルの入力極性が正負逆となり、ライン・クランプすることができます。ライン・クランプは CCD 出力の OB (Optical Black) 画素のタイミングで CLMP 信号に HIGH にし、有効画素データ入力時は LOW にすることにより、クランプレベルと CCD 出力レベルの差電圧がサンプリングされます。なお、サンプリングは、CK1 信号 (サンプリングクロック 1) でクランプレベルと CCD 出力レベルを同時に行います。INCLT レジスタ (No.0x0D) の LCLMP ビットに“1”を設定することにより、バッファアンプ機能が有効となり、クランプレベルに引き込まれたアナログ入力レベル (xINPn 端子) が安定します。ADCMD レジスタ (No.0x0F) の BL[1:0]ビットによりバッファアンプの能力を設定することができます。

図 6.16 に S/H モード (ライン・クランプ) 時における内部構成図を示します。

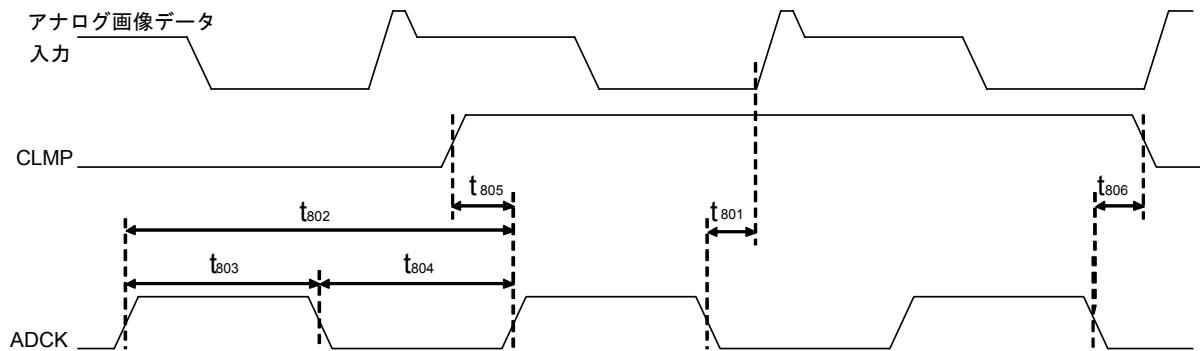

図 6.17 S/H モード (ライン・クランプ) 動作タイミング例

図 6.17 に S/H モード (ライン・クランプ) 時で基準電圧を外部入力の場合の動作タイミング例を示します。また、下記にその設定例を示します。

AFEMD レジスタ (No.0x02) : XX XX01 0010(2)      注) X は基準電圧レベルにより任意に設定

## 6. 機能説明

### 6.5.8 A/D コンバータ

高速タイプ 10 ビット A/D コンバータです。ADCK 信号 1 サイクルで 1 画素分を A/D 変換します。なお、ADCK 信号は AFEMD レジスタ (No.0x02) の ADCKPOL ビットにより、その論理極性を反転させることができます。

### 6.5.9 オフセット調整

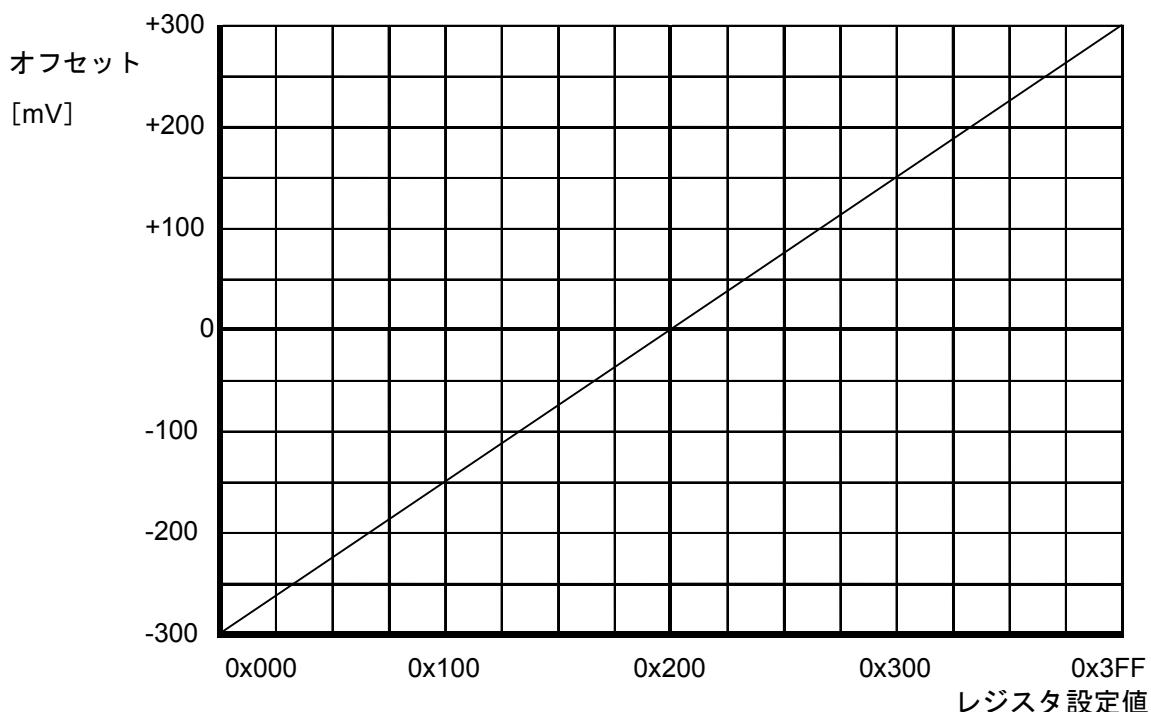

本 IC は入力信号レベルに対してオフセットを調整することができます。

オフセット調整には 1024 ステップのオフセット調整レジスタを持ち、このレジスタを設定することによってオフセット値を調整します。また、オフセット調整は各チャネルそれぞれレジスタが用意されており独立して設定することができます。

オフセット調整レンジは  $-300\text{mV}$  から  $+300\text{mV}$  まで設定することができ “0x000” を設定すると  $-300\text{mV}$  となり、“0x3FF” を設定すると  $+300\text{mV}$  となります。

図 6.18 はオフセット調整レジスタと得られるオフセット値を示しています。

図 6.18 オフセット特性

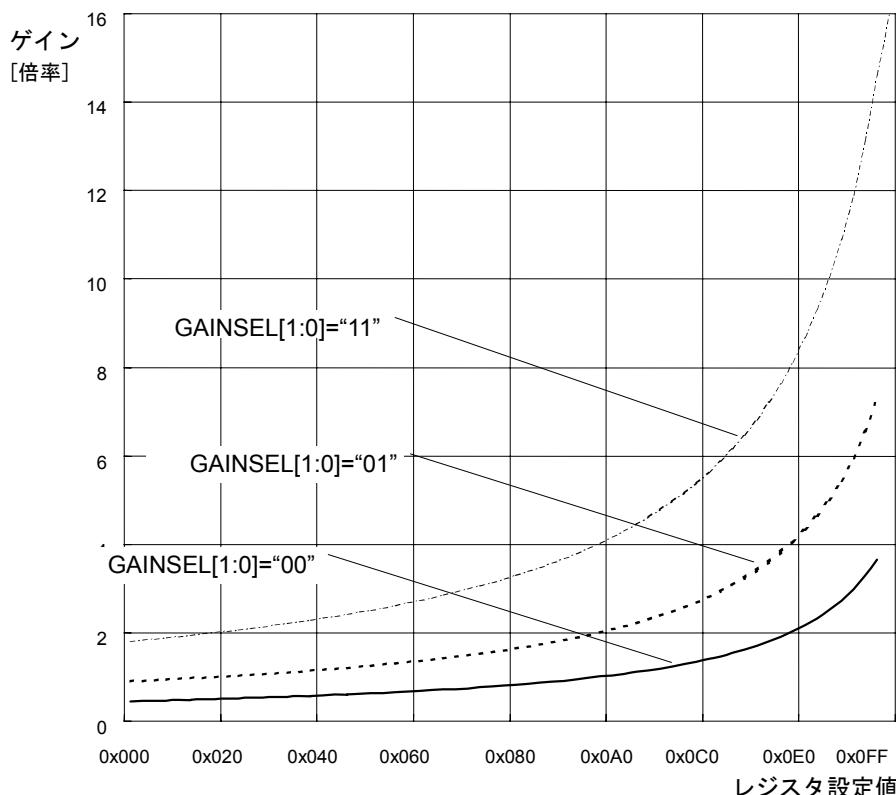

## 6.5.10 プログラマブル・ゲイン・アンプ(PGA)

本ICにはプログラマブル・ゲイン・アンプが内蔵されております。

プログラマブル・ゲイン・アンプには128ステップのゲイン調整レジスタを持ち、このレジスタを設定することによってゲイン値を調整します。また、ゲイン調整は各チャネルそれぞれレジスタが用意されており独立して設定することができます。

ゲイン調整レンジは-6.9dB(0.45倍)から+12.0dB(4倍)まで設定することができ、“0x00”を設定すると最小ゲインとなり、“0xFE”を設定すると最大ゲインとなります。また、それぞれのGAINSEL[1:0]ビットに“01”を設定することによって-0.9dB(0.9倍)から+18.0dB(8.0倍)の範囲で設定することができ、“11”を設定することによって-5.1dB(1.8倍)から+24.1dB(16.0倍)の範囲で設定することができます。これらのゲイン調整を行い10ビットA/Dコンバータの入力レンジ(1.2V)とマッチングさせるように値を設定します。

図6.19はゲイン調整レジスタと得られるゲイン値を示しています。また、レジスタ設定値と得られるゲインは下記の計算式により近似することができます。

$$\text{ゲイン (倍率)} \doteq \frac{128}{32 + (255 - \text{レジスタ設定値})}$$

注) GAINSEL[1:0]ビット“00”設定時は上記ゲイン (倍率) の1倍

GAINSEL[1:0]ビット“01”設定時は上記ゲイン (倍率) の2倍

GAINSEL[1:0]ビット“11”設定時は上記ゲイン (倍率) の4倍

図6.19 ゲイン特性 (倍率)

## 6. 機能説明

### 【制限注意事項】

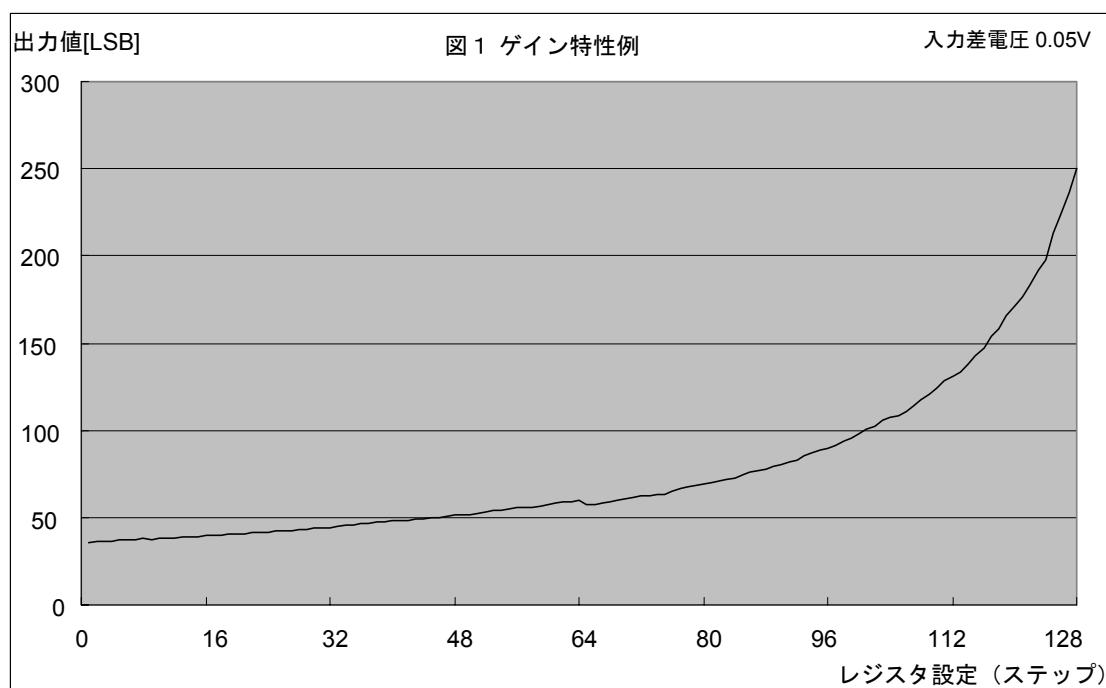

#### ・PGA 特性

本 IC のプログラマブル・ゲイン・アンプ (PGA) の設定階調は 128 ステップとなります。

レジスタへの設定は、上位 7 ビットについて行い、最下位ビットへは必ずゼロを設定してください。

レジスタ設定値 - 取得ゲイン特性は図 6.19 を参照してください。

図 6.20 は入力差電圧として 0.05V を入力した場合におけるレジスタ設定値と出力値 [LSB] の関係を示したものです。また、図 6.20 は下記の計算式により近似することができます。

$$\text{出力値[LSB]} \doteq \{\text{入力差電圧} \times (\text{ゲイン [倍率]}) + \text{err}\}$$

err はレジスタ設定 (ステップ) が 0~64 の範囲で 0[LSB]

レジスタ設定 (ステップ) が 65~127 の範囲で -2.2[LSB]

但し、レジスタ設定が固定の場合、入力差電圧に対する出力値のリニアリティは確保されます。

図 6.20 ゲイン特性例 (出力値[LSB])

## 6.5.11 自動オフセット・ゲイン調整機能

自動オフセット・ゲイン調整機能は、画像読み取り動作前に行うオフセット設定およびゲイン設定を自動的に行う機能です。本機能を使用することにより、高速かつ容易に本画像の読み取りを行うことができます。それぞれの機能は、黒基準画素または黒ダミー画素を A/D 変換後の黒レベル、および白基準画素の A/D 変換後の白レベルが、レジスタに設定した値が得られるようオフセット・ゲインレジスタを自動的に調整します。

自動オフセット調整機能または自動ゲイン調整機能は、AUTOOFSGAIN レジスタ(No.0x0A)の AOEN ビットまたは AGEN ビットを“1”に設定することにより有効となり、それぞれ独立して動作させることができます。なお、両ビットを同時に“1”設定することにより両機能が同時に有効となります。

自動オフセット調整機能および自動ゲイン調整機能は、それぞれ基準となる画素のレベルを解析することによって動作します。従って、それぞれの画素の入力タイミングを指定する必要があります。自動オフセット調整機能は調整完了までに 11 ライン分のデータ取得を必要とし、自動ゲイン調整機能は 9 ライン分のデータ取得を必要とします。また、自動オフセット調整機能と同時に有効とした場合、自動オフセット調整完了後に自動ゲイン調整機能が働きます。この場合、45 ライン分のデータを必要とします。なお、本機能動作完了後、AUTOOFSGAIN レジスタ(No.0x0A)の AOEN ビットおよび AGEN ビットは、自動的に“0”となります。また、CALCTL レジスタ(No.0x01)の AOGCMPOUT ビットを“1”に設定することにより、その動作状態を SDO 端子に出力することができ、調整機能動作完了後“H”を出力します。自動オフセット調整機能および自動ゲイン調整機能を同時に有効とした場合は、両機能の動作が完了した際にその状態を出力します。

自動オフセット調整機能は、黒レベルを BKLEVEL レジスタ(No.0x09)設定値を下限とし、その設定値に近づくように、オフセットを自動的に調整します。また、自動ゲイン調整機能は、白レベルが WHLEVEL レジスタ(No.0x08)レジスタ設定値を上限とし、その設定値に近づくように、ゲインを自動的に調整します。なお、それぞれ画素のレベル解析は、それぞれの指定範囲の画素を CALCTL レジスタ(No.0x01)の WHAVE[2:0]ビットまたは BKAVE[2:0]で設定された画素数毎に平均化した値について解析します。

各調整機能動作完了後、CALCTL レジスタ(No.0x01)の AOGMON ビットに“1”を設定することにより、調整後の出力画素レベルをモニタすることができます。なお、モニタレジスタは表 6.10 に示すとおり他レジスタと兼用となっています。

表 6.10 モニタレジスター一覧

| 入力チャネル        | 黒レベルモニタ               | 白レベルモニタ                |

|---------------|-----------------------|------------------------|

| R チャネル (odd)  | RD1OFS レジスタ (No.0x10) | RD1GAIN レジスタ (No.0x18) |

| R チャネル (even) | RD2OFS レジスタ (No.0x11) | RD2GAIN レジスタ (No.0x19) |

| G チャネル (odd)  | GR1OFS レジスタ (No.0x12) | GR1GAIN レジスタ (No.0x1A) |

| G チャネル (even) | GR2OFS レジスタ (No.0x13) | GR2GAIN レジスタ (No.0x1B) |

| B チャネル (odd)  | BL1OFS レジスタ (No.0x14) | BL1GAIN レジスタ (No.0x1C) |

| B チャネル (even) | BL2OFS レジスタ (No.0x15) | BL2GAIN レジスタ (No.0x1D) |

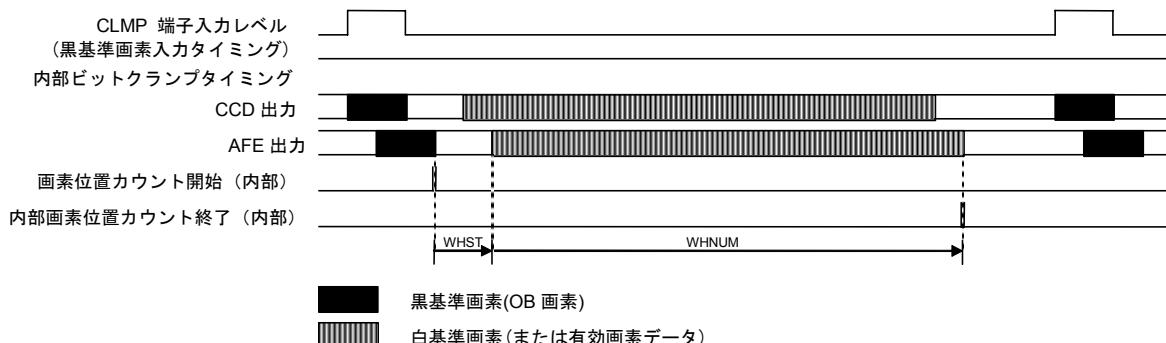

## (1) CDS モード時

自動オフセット調整機能は、CCD の黒基準画素 (OB 画素) の A/D 変換結果を黒レベルとしオフセットを自動的に調整します。また、自動ゲイン調整機能は、BKHST レジスタ (No.0x04) の WHST[3:0] ビットおよび WHNUM レジスタ (No.0x06~7) で指定された範囲の画素の A/D 変換結果を白レベルとしゲインを自動的に調整します。黒基準画素位置の指定は、黒基準画素入力タイミング時において CLMP 端子に HIGH を入力してください。図 6.21 にその動作タイミング例を示します。

## 6. 機能説明

■ BKPIXCNTEN="0", AOEN="1", AGEN="0" または "1"

図 6.21 CDS モード時自動オフセット・ゲイン調整機能タイミング例

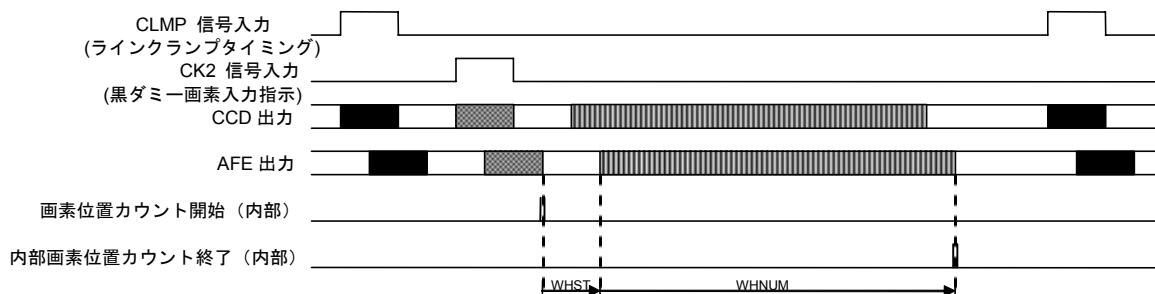

### (2) S/H モード時

自動オフセット調整機能は、CCD の黒ダミー画素の A/D 変換結果を黒レベルとしオフセットを自動的に調整します。また、自動ゲイン調整機能は、CDS モード時と同様に、BKWHST レジスタ(No.0x04)の WHST[3:0]ビットおよび WHNUM レジスタ(No.0x06~7)で指定された範囲の画素の A/D 変換結果を白レベルとしゲインを自動的に調整します。

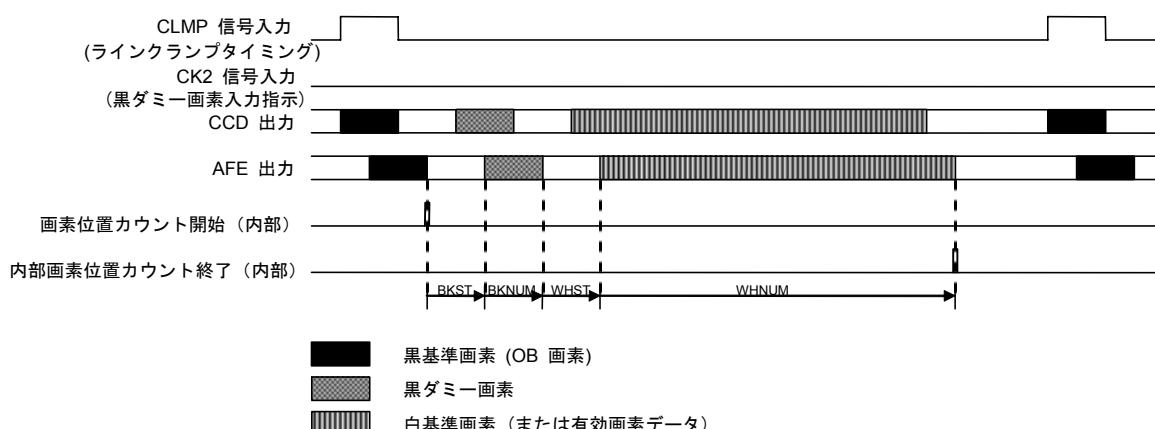

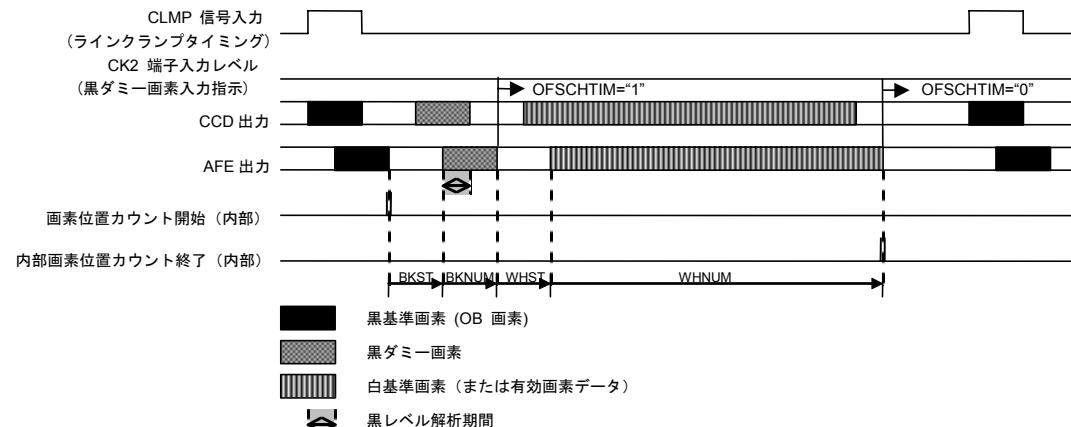

黒ダミー画素位置の指示は、外部から信号入力する方法と、内部画素位置カウンタを利用する方法の 2 とあります。外部から信号入力する場合は、BKMNUM レジスタ(No.0x05)の BKPIXCNTEN ビットを“0”に設定し、黒ダミー画素入力タイミング時において CK2 端子に HIGH を入力してください。一方、内部画素位置カウンタ利用時は、BKMNUM レジスタ(No.0x05)の BKPIXCNTEN ビットを“1”設定し、BKWHST レジスタ(No.0x04)の BKST[5:0]ビットに黒ダミー画素開始位置を設定し、BKNUM レジスタ(No.0x05)に黒ダミー画素数を設定してください。図 6.22 にその動作タイミング例を示します。

■ BKPIXCNTEN="0", AOEN="1", AGEN="0" または "1"

■ BKPIXCNTEN="1", AOEN="1" または "0", AGEN="1"

図 6.22 S/H モード時自動オフセット・ゲイン調整機能タイミング

## 6.5.12 自動黒レベル補正機能

AUTOOFSGAIN レジスタ(No.0x0A)の ABKADJ ビットを“1”に設定することにより、自動黒レベル補正機能が有効となります。本機能はスキャナシステムが原稿を取り込み時に、オフセット設定を自動調整することにより、CCD の黒レベル変動またはライン・クランプ時におけるクランプレベルへの引き込み電圧レベル変動を吸収します。

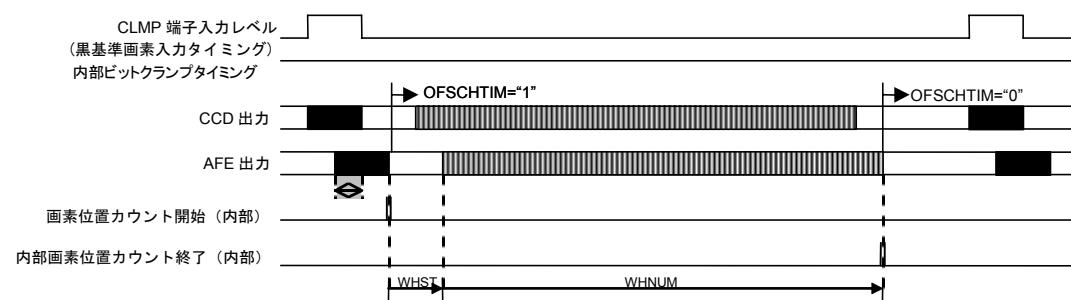

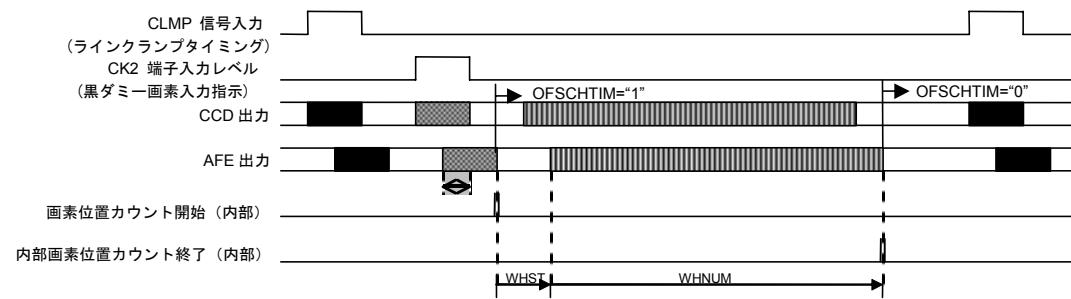

自動黒レベル補正機能は、ラインごとに黒レベルの解析を行い、オフセット設定を自動的に更新し、黒レベルを補正します。また、黒レベルの解析は自動オフセット調整機能と同様に、CALCTL レジスタ(No.0x01)の BKAVE[2:0] ビットで設定された画素数毎に平均化した値について解析します。黒レベル解析後のオフセット設定の更新タイミングは、CALCTL レジスタ(No.0x01)の OFSCHTIM ビット設定によって、図 6.23 に示すとおり切り換えることが可能です。また、解析および調整方法は、AUTOOFSGAIN レジスタ(No.0x0A)の ABKMD0～5 ビットの設定によりその動作モードを選択することができます。

なお、CDS モードにおける黒基準画素または S/H モード時における黒ダミー画素の位置指定方法は、自動オフセット・ゲイン調整機能と同様です。その際、BKHST レジスタ(No.0x04)の WHST[3:0] ビットおよび WHNUM レジスタ(No.0x06～7)は最適な値を設定してください。にその動作タイミング例を示します。

## ■CDS モード時(BKPIXCNTEN="0", AOEN="1", AGEN="0" または "1")

## ■S/H モード時 1 (BKPIXCNTEN="0", AOEN="1", AGEN="0" または "1")

## ■S/H モード時 2 (BKPIXCNTEN="1", AOEN="1" または "0", AGEN="1")

図 6.23 自動黒レベル補正機能動作タイミング例

## 6. 機能説明

### (1) 黒レベル変動検出

黒レベルの変動の検出は、図 6.23 中の黒レベル解析期間内の画素について、CALCTL レジスタ (No.0x01) の BKAVE[2:0] ビットで設定された画素数を平均化した値について検出します。その平均化された値について BKLEVEL レジスタ (No.0x09) 設定を基準に解析を行います。

黒レベル変動の検出は、AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD4, ABKMD1 または ABKMD0 ビットの設定により、その検出方法を選択することができます。使用されるアプリケーションの環境によって最適な検出方法は異なりますので、最適な画像が取得できるよう設定してください。

#### - 検出ライン数設定(ABKMD4 ビット)

AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD4 ビットを“0”に設定した場合、連続して 2 ライン同一方向に黒レベル変動を検出したときにオフセット設定を更新し補正します。一方、“1”に設定した場合、毎ライン黒レベルの変動を検出したときにオフセット設定を更新し補正します。CDS モード時や S/H モード（差電圧入力）時のように、黒レベルの変動が小さい場合には ABKMD4 ビットを“0”に設定し、補正量を抑えることが可能です。

#### - 検出設定(ABKMD1 ビット)

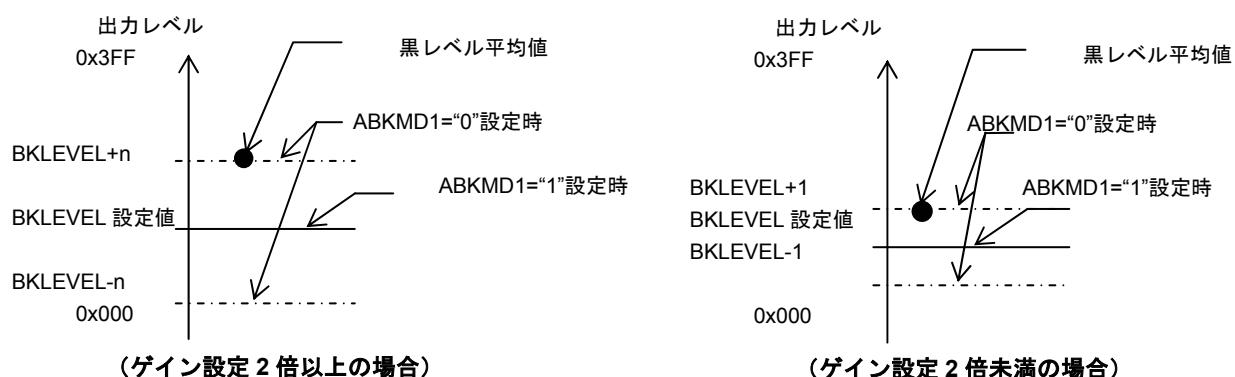

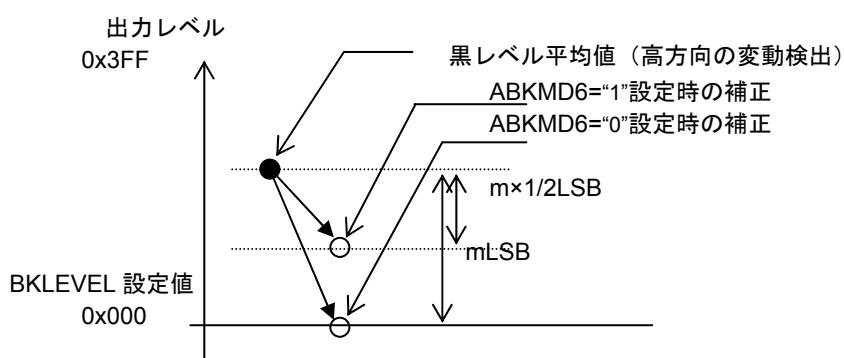

黒レベル変動検出範囲は、AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD1 ビットの設定によって設定することができます。黒レベル変動の検出範囲は図 6.24 に示すとおりです。図 6.24 中の黒レベル平均値が図に示すレベルの場合、ABKMD1 ビット設定が“1”的とき BKLEVEL レジスタ (No.0x09) 設定値から黒レベルが外れているので、変動を検出しオフセット設定を更新します。一方、ABKMD1 ビット設定が“0”的場合、BKLEVEL レジスタ (No.0x09)  $\pm n$  範囲内の変動は不感となります。よって、変動検出せずオフセット更新を行いません。なお、変換範囲の  $n$  値は、A/D 変換結果のオフセット設定 1LSB 変動相当分となり、ゲイン設定によって異なります。一方、ゲイン設定が 2 倍未満の場合は  $n=1$  として動作します。

例：ゲイン設定が 4 倍の場合の  $n$  値

$$\text{検出範囲 } n = \frac{0.586\text{mv} \text{ (オフセット設定 1LSB 変動分)} \times 4 \text{ (ゲイン設定)} \times 1023}{1.2\text{Vp-p} \text{ (A/D 変換範囲)}} = 2$$

注) 小数点以下は切り捨て

図 6.24 黒レベル変動検出範囲

## - 不感帯 2 倍設定 (ABKMD0 ビット)

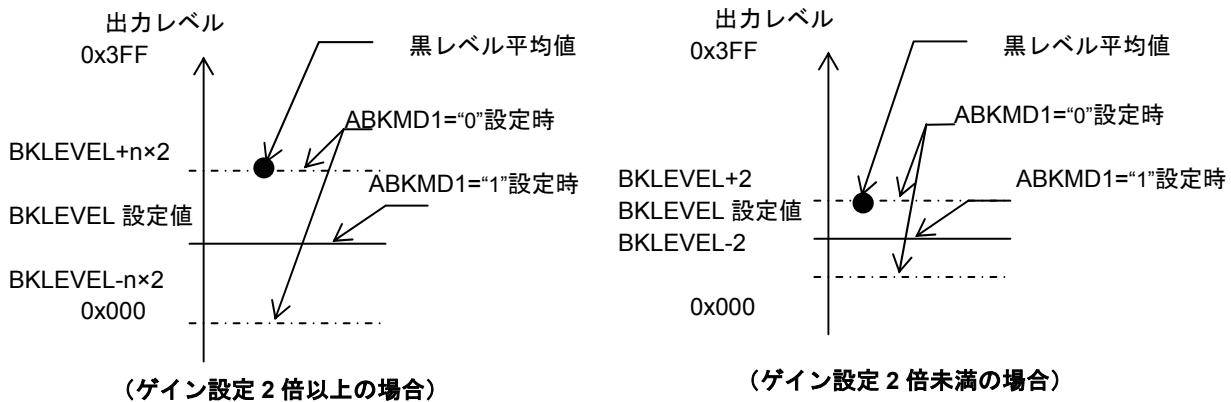

黒レベル変動検出範囲は、AUTOOFSGAIN レジスタ(No.0x0A)の ABKMD0 ビット設定により ABKMD1 ビット設定よりも更に不感帯を 2 倍に広げることができます。黒レベル変動の検出範囲は図 6.25 に示すとおりです。図 6.25 中の黒レベル平均値が図に示すレベルの場合、ABKMD0 ビット設定が“0”的とき BKLEVEL レジスタ(No.0x09)設定値から黒レベルが外れているので、変動を検出しオフセット設定を更新します。一方、ABKMD0 ビット設定が“1”的場合、BKLEVEL レジスタ(No.0x09) $\pm n \times 2$ 範囲内の変動は不感となります。よって、変動検出せずオフセット更新を行いません。なお、変換範囲の  $n$  値は、A/D 変換結果のオフセット設定 1LSB 変動相当分となり、ゲイン設定によって異なります。一方、ゲイン設定が 2 倍未満の場合は  $n=1$  として動作します。

図 6.25 黒レベル変動検出範囲 (不感帯 2 倍)

## (2) 黒レベル補正

黒レベルの変動を検出後、その補正方法を AUTOOFSGAIN レジスタ(No.0x0A)の ABKMD2, ABKMD3 または ABKMD5 ビットの設定により、その補正方法を選択することができます。使用されるアプリケーションの環境によって最適な補正方法は異なりますので、最適な画像が取得できるよう設定してください。

## - 補正目標設定(ABKMD2 ビット)

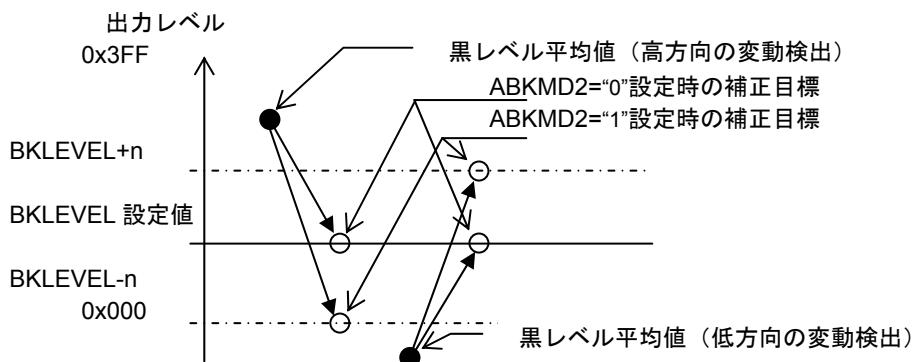

AUTOOFSGAIN レジスタ(No.0x0A)の ABKMD2 ビット設定により、黒レベルの変動を検出し、補正後の目標となるレベルを設定します。“0”に設定することにより BKLEVEL レジスタ(No.0x09)設定値を目標に補正します。一方、“1”に設定した場合、BKLEVEL レジスタ(No.0x09) $\pm n$  を目標に補正します。

その動作例を図 6.26 に示します。

図 6.26 補正目標動作例

## 6. 機能説明

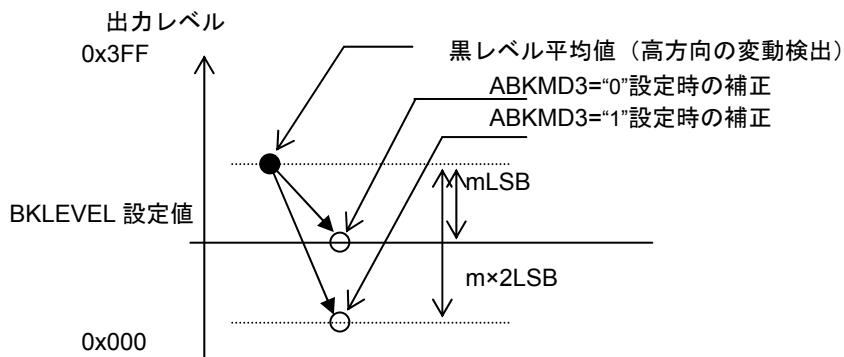

### - 過補正設定 (ABKMD3 ビット)

AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD3 ビットを“1”に設定することにより、補正量を 2 倍にし補正します。“0”に設定した場合は最適値の補正を行います。

その動作例を図 6.27 に示します。

図 6.27 過補正動作例

### - 補正量設定(ABKMD5 ビット)

AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD5 ビットを“1”に設定することにより、黒レベル変動を検出した際、補正目標まで補正します。“0”設定の場合は、ゲイン設定 2 倍以上のときオフセット 1LSB の補正を行います。一方、ゲイン設定 2 倍未満の場合は、A/D 変換で 1LSB 相当の補正を行います。

### - 過小補正設定(ABKMD6 ビット)

AUTOOFSGAIN レジスタ (No.0x0A) の ABKMD6 ビットを“1”に設定することにより、補正量を 1/2 倍にし補正します。“0”に設定した場合は最適値の補正を行います。

その動作例を図 6.28 に示します。

図 6.28 過小補正動作例

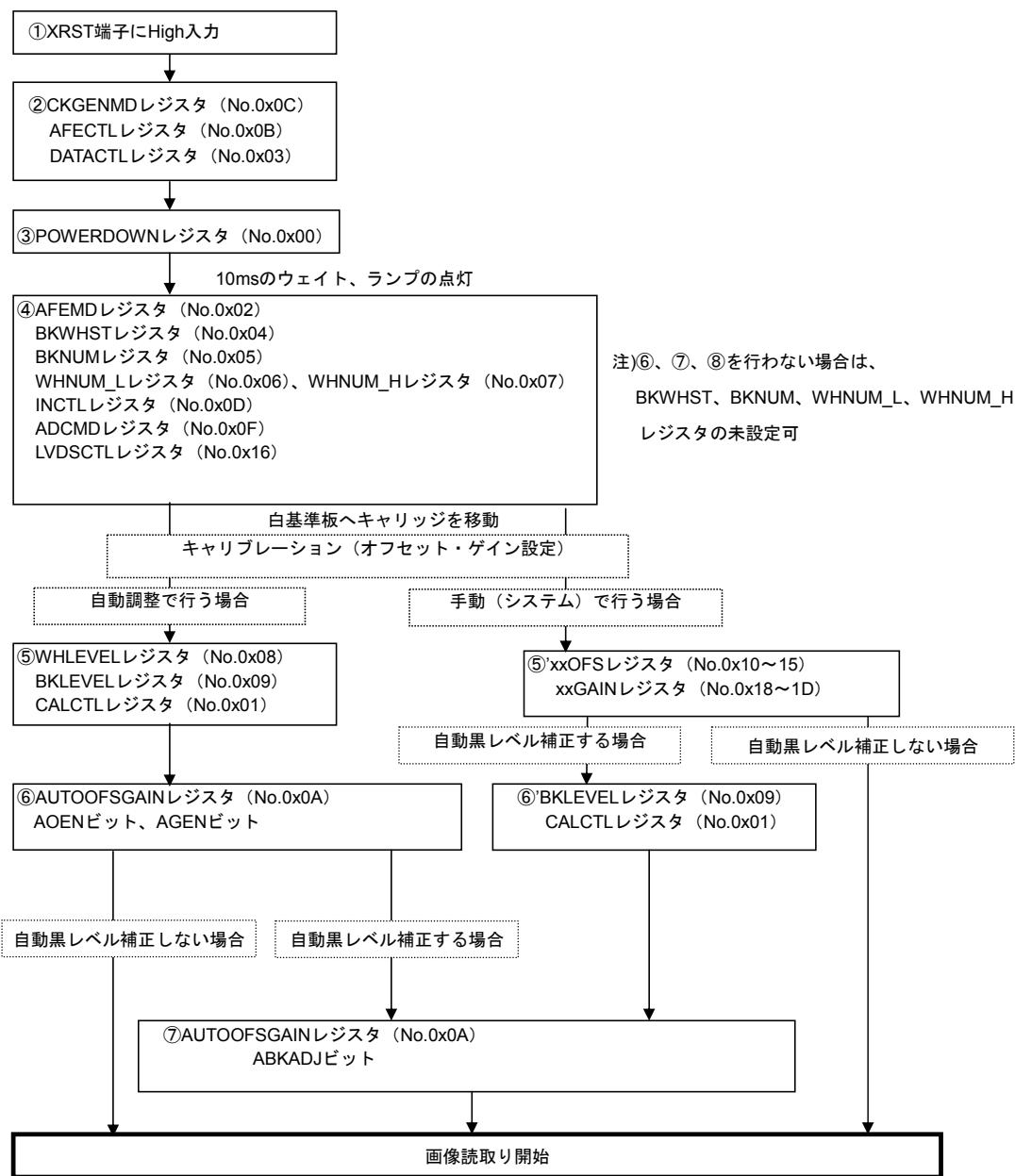

## 6.5.13 レジスタ設定シーケンス例

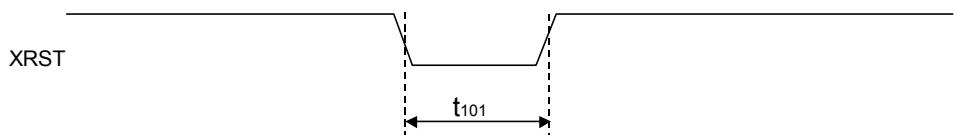

電源投入時または待機状態からの復帰～画像取得までのレジスタ設定シーケンス例を図6.29に示します。なお、図6.29のシーケンス例は、電源投入時から電源電圧が安定するまでの期間または待機状態において、XRST端子にLowが入力されている場合を示します。なお、各ステージ（四角で囲まれた部分）内のレジスタ設定は順不同でもかまいません。

図 6.29 レジスタ設定シーケンス例

## 7. レジスタ

### 7. レジスタ

#### 7.1 レジスタマップ

| No.  | Register Name | R/W | Function               |

|------|---------------|-----|------------------------|

| 0x00 | POWERDOWN     | R/W | パワーダウンレジスタ             |

| 0x01 | CALCTL        | R/W | 画素解析機能制御レジスタ           |

| 0x02 | AFEMD         | R/W | AFE 動作モード設定レジスタ        |

| 0x03 | DATACTL       | R/W | データ出力制御レジスタ            |

| 0x04 | BKWHST        | R/W | 黒ダミー画素・白基準画素開始位置設定レジスタ |

| 0x05 | BKNUM         | R/W | 黒ダミー画素数設定レジスタ          |

| 0x06 | WHNUM_L       | R/W | 白基準画素数設定レジスタ（下位）       |

| 0x07 | WHNUM_H       | R/W | 白基準画素数設定レジスタ（上位）       |

| 0x08 | WHLEVEL       | R/W | 白画素出力レベル設定レジスタ         |

| 0x09 | BKLEVEL       | R/W | 黒画素出力レベル設定レジスタ         |

| 0x0A | AUTOOFSGAIN   | R/W | 自動オフセット・ゲイン調整機能設定レジスタ  |

| 0x0B | AFECTL        | R/W | AFE 制御レジスタ             |

| 0x0C | CKGENMD       | R/W | サンプリング信号制御レジスタ         |

| 0x0D | INCTL         | R/W | 入力制御レジスタ               |

| 0x0E | (Reserved)    |     |                        |

| 0x0F | ADCMD         | R/W | A/D コンバータ動作モード設定レジスタ   |

| 0x10 | RD1OFS        | R/W | R チャネル(ODD)オフセットレジスタ   |

| 0x11 | RD2OFS        | R/W | R チャネル(EVEN)オフセットレジスタ  |

| 0x12 | GR1OFS        | R/W | G チャネル(ODD)オフセットレジスタ   |

| 0x13 | GR2OFS        | R/W | G チャネル(EVEN)オフセットレジスタ  |

| 0x14 | BL1OFS        | R/W | B チャネル(ODD)オフセットレジスタ   |

| 0x15 | BL2OFS        | R/W | B チャネル(EVEN)オフセットレジスタ  |

| 0x16 | LVDSCTL       | R/W | LVDS 設定レジスタ            |

| 0x17 | (Reserved)    |     |                        |

| 0x18 | RD1GAIN       | R/W | R チャネル(ODD)ゲインレジスタ     |

| 0x19 | RD2GAIN       | R/W | R チャネル(EVEN)ゲインレジスタ    |

| 0x1A | GR1GAIN       | R/W | G チャネル(ODD)ゲインレジスタ     |

| 0x1B | GR2GAIN       | R/W | G チャネル(EVEN)ゲインレジスタ    |

| 0x1C | BL1GAIN       | R/W | B チャネル(ODD)ゲインレジスタ     |

| 0x1D | BL2GAIN       | R/W | B チャネル(EVEN)ゲインレジスタ    |

| 0x1E | (Reserved)    |     |                        |

| 0x1F | (Reserved)    |     |                        |

## 7.2 ビットマップ

| No.  | Register Name | bit9       | bit8            | bit7        | bit6   | bit5       | bit4         | bit3         | bit2         | bit1       | bit0   |

|------|---------------|------------|-----------------|-------------|--------|------------|--------------|--------------|--------------|------------|--------|

| 0x00 | POWERDOWN     |            |                 |             |        |            |              | PDLVDS       | PDRSDS       | PDSTB      | PD     |

| 0x01 | CALCTL        | AOGMON     | OFSCHTIM        |             |        | WHAVE[2:0] |              | AOGCMPOUT    |              | BKAVE[2:0] |        |

| 0x02 | AFEMD         |            |                 | CLMPLV[3:0] |        | CLMPOL     | CLMPEN       | ADCKPOL      | CKPOL        | S/HRVS     | CDSMD  |

| 0x03 | DATACTL       |            | TSTMD[1:0]      |             | INSTGO | XOEB       | XOEG         | XOER         | PIXSQMD      | MUXSQ      | AVEMD  |

| 0x04 | BKWHST        |            |                 | WHST[3:0]   |        |            |              |              | BKST[5:0]    |            |        |

| 0x05 | BKNUM         | BKPIXCNTEN |                 |             |        |            |              | BKNUM[7:0]   |              |            |        |

| 0x06 | WHNUM_L       |            |                 |             |        |            | WHNUM[9:0]   |              |              |            |        |

| 0x07 | WHNUM_H       |            |                 |             |        |            |              |              | WHNUM[15:10] |            |        |

| 0x08 | WHLEVEL       |            |                 |             |        |            | WHLEVEL[9:0] |              |              |            |        |

| 0x09 | BKLEVEL       |            |                 |             |        |            |              | BKLEVEL[9:0] |              |            |        |

| 0x0A | AUTOOFSGAIN   | ABKMD5     | ABKMD4          | ABKMD3      | ABKMD2 | ABKMD1     | ABKMD0       | AOEN         | AGEN         | ABKMD6     | ABKADJ |

| 0x0B | AFECTL        | CKGEN      |                 | VCOSEL[1:0] |        |            |              |              |              |            |        |

| 0x0C | CKGENMD       | CKGENMD    |                 |             |        |            |              |              |              |            |        |

| 0x0D | INCTL         |            | LCLMP           |             |        |            |              |              |              |            |        |

| 0x0E | (Reserved)    |            |                 |             |        |            |              |              |              |            |        |

| 0x0F | ADCMD         |            |                 | BL[1:0]     |        |            |              |              | BIAS[3:0]    |            |        |

| 0x10 | RD1OFS        |            |                 |             |        |            | RD1OFS[9:0]  |              |              |            |        |

| 0x11 | RD2OFS        |            |                 |             |        |            | RD2OFS[9:0]  |              |              |            |        |

| 0x12 | GR1OFS        |            |                 |             |        |            | GR1OFS[9:0]  |              |              |            |        |

| 0x13 | GR2OFS        |            |                 |             |        |            | GR2OFS[9:0]  |              |              |            |        |

| 0x14 | BL1OFS        |            |                 |             |        |            | BL1OFS[9:0]  |              |              |            |        |

| 0x15 | BL2OFS        |            |                 |             |        |            | BL2OFS[9:0]  |              |              |            |        |

| 0x16 | LVDSCTL       |            | TX4EN           | TX3EN       | TX2EN  | TX1EN      | TX0EN        |              | LVDSDT       |            | PE     |

| 0x17 | (Reserved)    |            |                 |             |        |            |              |              |              |            |        |

| 0x18 | RD1GAIN       |            | RD1GAINSEL[1:0] |             |        |            |              | RD1GAIN[7:0] |              |            |        |

| 0x19 | RD2GAIN       |            | RD2GAINSEL[1:0] |             |        |            |              | RD2GAIN[7:0] |              |            |        |

| 0x1A | GR1GAIN       |            | GR1GAINSEL[1:0] |             |        |            |              | GR1GAIN[7:0] |              |            |        |

| 0x1B | GR2GAIN       |            | GR1GAINSEL[1:0] |             |        |            |              | GR2GAIN[7:0] |              |            |        |

| 0x1C | BL1GAIN       |            | BL1GAINSEL[1:0] |             |        |            |              | BL1GAIN[7:0] |              |            |        |

| 0x1D | BL2GAIN       |            | BL1GAINSEL[1:0] |             |        |            |              | BL2GAIN[7:0] |              |            |        |

| 0x1E | (Reserved)    |            |                 |             |        |            |              |              |              |            |        |

| 0x1F | (Reserved)    |            |                 |             |        |            |              |              |              |            |        |

## 7. レジスタ

### 7.3 レジスタ詳細説明

#### 7.3.1 0x00 パワーダウンレジスタ (POWERDOWN)

| No.  | Register Name | R/W | Bit Symbol | Description |               |  | Reset |

|------|---------------|-----|------------|-------------|---------------|--|-------|

| 0x00 | POWERDOWN     |     | 9:         |             |               |  | 0x00F |

|      |               |     | 8:         |             |               |  |       |

|      |               |     | 7:         |             |               |  |       |

|      |               |     | 6:         |             |               |  |       |

|      |               |     | 5:         |             |               |  |       |

|      |               |     | 4:         |             |               |  |       |

|      |               | R/W | 3: PDLVDS  | 0: normal   | 1: power down |  |       |

|      |               |     | 2: PDRSDS  | 0: normal   | 1: power down |  |       |

|      |               |     | 1: PDSTB   | 0: normal   | 1: power down |  |       |

|      |               |     | 0: PD      | 0: normal   | 1: power down |  |       |

Bit9～4 Reserved

Bit3 PDLVDS

LVDS 部のパワーダウンレジスタです。

Bit2 PDRSDS

RSDS 部のパワーダウンレジスタです。

Bit1 PDSTB

入力クロック波形整形機能のパワーダウンレジスタです。

Bit0 PD

アナログ部のパワーダウンレジスタです。

## 7.3.2 0x01 画素解析機能制御レジスタ(CALCTL)

| No.  | Register Name | R/W | Bit Symbol   | Description    |                | Reset |  |

|------|---------------|-----|--------------|----------------|----------------|-------|--|

| 0x01 | CALCTL        | R/W | 9: AOGMON    | 0: disable     | 1: enable      | 0x000 |  |

|      |               |     | 8: OFSCHTIM  | 0: after WHNUM | 1: after BKNUM |       |  |

|      |               |     | 7:           |                |                |       |  |

|      |               |     | 6: WHAVE[2]  | 白基準画素数設定レジスタ   |                |       |  |

|      |               |     | 5: WHAVE[1]  |                |                |       |  |

|      |               |     | 4: WHAVE[0]  |                |                |       |  |

|      |               |     | 3: AOGCMPOUT | 0: disable     | 1: enable      |       |  |

|      |               |     | 2: BKAVE[2]  | 黒基準画素数設定レジスタ   |                |       |  |

|      |               |     | 1: BKAVE[1]  |                |                |       |  |

|      |               |     | 0: BKAVE[0]  |                |                |       |  |

Bit9

**AOGMON**

本ビットに“1”を設定することにより、自動オフセット・ゲイン調整機能動作完了後の出力画素レベルをモニタすることができます。

Bit8

**OFSCHTIM**

自動黒レベル補正機能有効時において、オフセットレジスタ更新タイミングを設定します。

Bit7

**Reserved**

Bit6~4

**WHAVE[2:0]**

自動ゲイン調整機能動作時において、白基準画素を検出するための平均化を行う画素数を設定します。

WHAVE[2:0] : 平均化画素数

000:1 画素

001:2 画素

010:4 画素

011:8 画素

100:16 画素

101:32 画素

110:64 画素

111:128 画素

Bit3

**AOGCMPOUT**

自動オフセット調整機能、自動ゲイン調整機能または補正量検出機能動作時において、その動作状態を SDO 端子に出力します。

Bit2~0

**BKAVE[2:0]**

自動オフセット調整機能および自動黒レベル補正機能有効時において、黒基準画素または黒ダミー画素を検出するための平均化を行う画素数を設定します。

BKAVE[2:0] : 検出画素数

000:1 画素

001:2 画素

010:4 画素

011:8 画素

100:16 画素

101:32 画素

110:64 画素

111:128 画素

## 7. レジスタ

### 7.3.3 0x02 AFE 動作モード設定レジスタ(AFEMD)

| No.  | Register Name | R/W | Bit Symbol   | Description |             | Reset |

|------|---------------|-----|--------------|-------------|-------------|-------|

| 0x02 | AFEMD         | R/W | 9: CLMPLV[3] | クランプレベル設定   |             | 0x000 |

|      |               |     | 8: CLMPLV[2] |             |             |       |

|      |               |     | 7: CLMPLV[1] |             |             |       |

|      |               |     | 6: CLMPLV[0] |             |             |       |

|      |               |     | 5: CLMPPOL   | 0: normal   | 1: invert   |       |

|      |               |     | 4: CLMPEN    | 0: disable  | 1: enable   |       |

|      |               |     | 3: ADCKPOL   | 0: normal   | 1: invert   |       |

|      |               |     | 2: CKPOL     | 0: normal   | 1: invert   |       |

|      |               |     | 1: S/HRVS    | 0: normal   | 1: reverse  |       |

|      |               |     | 0: CDSMD     | 0: S/H mode | 1: CDS mode |       |

Bit9~6

CLMPLV[3:0]

クランプレベルの設定を行います。

Bit5

CLMPPOL

本ビットに“1”を設定すると CLMP 信号の論理を反転します。

Bit4

CLMPEN

本ビットに“1”を設定するとクランプレベルを内部生成します。また、CDS モード時は、本ビットに“1”を設定すると自動的にビット・クランプとなります。

Bit3

ADCKPOL

本ビットに“1”を設定すると ADCK 信号の論理を反転します。

Bit2

CKPOL

本ビットに“1”を設定すると CK1 信号および CK2 信号の論理を反転します。

Bit1

S/HRVS

S/H モードのとき、CLMPLV/INN 端子レベルとアナログ入力 (RINP, GINP, BINP) レベルとの差電圧の極性に応じて設定します。

“0”:CLMPLV/INN < RINP(GINP, BINP)

“1”:CLMPLV/INN > RINP(GINP, BINP)

なお、CDS モード時、本レジスタは無効となります。

Bit0

CDSMD

AFE のサンプリング方式を設定します。

“0”:S/H モード

“1”:CDS モード

## 7.3.4 0x03 データ出力制御レジスタ(DATACTL)

| No.  | Register Name | R/W | Bit Symbol   | Description  |                   | Reset |

|------|---------------|-----|--------------|--------------|-------------------|-------|

| 0x03 | DATACTL       | R/W | 9: TSTMID[1] | テストモード設定レジスタ |                   | 0x070 |

|      |               |     | 8: TSTMID[0] |              |                   |       |

|      |               |     | 7: INSTGO    | 0: disable   | 1: enable         |       |

|      |               |     | 6: XOEB      | 0: enable    | 1: disable        |       |

|      |               |     | 5: XOEG      | 0: enable    | 1: disable        |       |

|      |               |     | 4: XOER      | 0: enable    | 1: disable        |       |

|      |               |     | 3: PIXSQMD   | 0: normal    | 1: pixel sequence |       |

|      |               |     | 2: MUXSQ     | 0: normal    | 1: reverse        |       |

|      |               |     | 1: AVEMD     | 0: normal    | 1: average mode   |       |

|      |               |     | 0: MUXMD     | 0: normal    | 1: multiplex mode |       |

Bit9~8

TSTMID[1:0]

テストモードを設定します。

Bit7

INSTGO

本ビットに“1”を設定すると監視機能が有効になります。

Bit6

XOEB

“0”:B チャネルの出力が有効

“1”:B チャネルの出力を禁止（ゼロ出力）

Bit5

XOEG

“0”:G チャネルの出力が有効

“1”:G チャネルの出力を禁止（ゼロ出力）

Bit4

XOER

“0”:R チャネルの出力が有効

“1”:R チャネルの出力を禁止（ゼロ出力）

Bit3

PIXSQMD

“0”:通常出力モード

“1”:点順次出力モード

Bit2

MUXSQ

マルチプレクス出力時において、そのシーケンスを設定することができます。

“0”:ODD → EVEN

“1”:EVEN → ODD

また、通常出力時（非マルチプレクス出力）は、その出力チャネルを設定します。

“0”:ODD

“1”:EVEN

Bit1

AVEMD

本ビットに“1”を設定すると 2 画素平均機能が有効になります。

Bit0

MUXMD

画像データ出力の出力モードを設定します。

“0”:通常モード ODD または EVEN

“1”:ODD、EVEN マルチプレクスモード

## 「制限注意事項」

MUXMD、AVEMD、PIXSQMD ビットの設定を設定する際は、POWERDOWN レジスタ (No.0x00) のPDLVDS ビットおよびPDSTB ビットを“1”に設定してから行ってください。

## 7. レジスタ

### 7.3.5 0x04 黒ダミー画素・白基準画素開始位置設定レジスタ(BKWHST)

| No.  | Register Name | R/W | Bit Symbol                                                                                                                               | Description                         | Reset |

|------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|

| 0x04 | BKWHST        | R/W | 9: WHST[3]<br>8: WHST[2]<br>7: WHST[1]<br>6: WHST[0]<br>5: BKST[5]<br>4: BKST[4]<br>3: BKST[3]<br>2: BKST[2]<br>1: BKST[1]<br>0: BKST[0] | 白基準画素開始位置設定レジスタ<br>黒ダミー画素開始位置設定レジスタ | 0x000 |

黒ダミー画素および白基準画素開始位置を設定するレジスタです。なお、本レジスタは1画素単位で設定してください。

#### 「制限注意事項」

本レジスタを変更するときは、DATACTL レジスタ(No.0x03)の INSTGO ビット、AUTOOGAIN レジスタ(No.0x0A)の AOEN ビット、AGEN ビット、ABKST ビットおよび ABKADJ ビットを“0”に設定してから行ってください。

### 7.3.6 0x05 黒ダミー画素数設定レジスタ(BKNUM)

| No.  | Register Name | R/W | Bit Symbol                                                                                                                                      | Description                             | Reset |

|------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|

| 0x05 | BKNUM         | R/W | 9: BKPIXCNTEN<br>8:<br>R/W 7: BKNUM[7]<br>6: BKNUM[6]<br>5: BKNUM[5]<br>4: BKNUM[4]<br>3: BKNUM[3]<br>2: BKNUM[2]<br>1: BKNUM[1]<br>0: BKNUM[0] | 0: disable<br>1: enable<br>黒基準画素数設定レジスタ | 0x000 |

- Bit9                   BKPIXCNTEN

黒ダミー画素位置を検出する際、画素位置カウント機能を有効にします。

- Bit8                   Reserved

- Bit7～0               BKNUM[7:0]

黒ダミー画素数を設定するレジスタです。なお、本レジスタは1画素単位で設定してください。

#### 「制限注意事項」

本レジスタを変更するときは、DATACTL レジスタ(No.0x03)の INSTGO ビット、AUTOOGAIN レジスタ(No.0x0A)の AOEN ビット、AGEN ビット、ABKST ビットおよび ABKADJ ビットを“0”に設定してから行ってください。

また、CDS モード使用時には本レジスタを 0x000 に設定してください。

## 7.3.7 0x06~7 白基準画素数設定レジスタ(WHNUM)

| No.  | Register Name | R/W | Bit Symbol                                                                                                                                         | Description  | Reset |

|------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|

| 0x07 | WHNUM_H       |     | 9:<br>8:<br>7:<br>6:                                                                                                                               |              | 0x000 |

|      |               | R/W | 5: WHNUM[15]<br>4: WHNUM[14]<br>3: WHNUM[13]<br>2: WHNUM[12]<br>1: WHNUM[11]<br>0: WHNUM[10]                                                       | 白基準画素数設定レジスタ |       |

| 0x06 | WHNUM_L       |     | 9: WHNUM[9]<br>8: WHNUM[8]<br>7: WHNUM[7]<br>6: WHNUM[6]<br>5: WHNUM[5]<br>4: WHNUM[4]<br>3: WHNUM[3]<br>2: WHNUM[2]<br>1: WHNUM[1]<br>0: WHNUM[0] |              | 0x001 |

白基準画素数を設定するレジスタです。なお、本レジスタは1画素単位で設定してください。

「制限注意事項 1」

本レジスタを変更するときは、DATACTL レジスタ(No.0x03)の INSTGO ビット、AUTOFGAIN レジスタ(No.0x0A)の AOEN ビット、AGEN ビット、ABKST ビットおよび ABKADJ ビットを“0”に設定してから行ってください。

「制限注意事項 2」

WHNUM  $\geq$  1 の範囲で設定してください。

## 7. レジスタ

### 7.3.8 0x08 白画素出力レベル設定レジスタ(WHLEVEL)

| No.  | Register Name | R/W | Bit Symbol                                                                                                                                                             | Description | Reset |

|------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| 0x08 | WHLEVEL       | R/W | 9: WHLEVEL[9]<br>8: WHLEVEL[8]<br>7: WHLEVEL[7]<br>6: WHLEVEL[6]<br>5: WHLEVEL[5]<br>4: WHLEVEL[4]<br>3: WHLEVEL[3]<br>2: WHLEVEL[2]<br>1: WHLEVEL[1]<br>0: WHLEVEL[0] | 白画素出力レベル設定  | 0x000 |

自動ゲイン調整機能動作時において、白レベルの上限値を設定します。

### 7.3.9 0x09 黒画素出力レベル設定レジスタ(BKLEVEL)

| No.  | Register Name | R/W | Bit Symbol                                                                                                                                                             | Description | Reset |

|------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| 0x09 | BKLEVEL       | R/W | 9: BKLEVEL[9]<br>8: BKLEVEL[8]<br>7: BKLEVEL[7]<br>6: BKLEVEL[6]<br>5: BKLEVEL[5]<br>4: BKLEVEL[4]<br>3: BKLEVEL[3]<br>2: BKLEVEL[2]<br>1: BKLEVEL[1]<br>0: BKLEVEL[0] | 黒画素出力レベル設定  | 0x000 |

自動オフセット調整機能または自動黒レベル補正機能動作時において、黒レベルの出力値を設定します。

## 7.3.10 0x0A 自動オフセット・ゲイン調整機能設定レジスタ(AUTOOFSGAIN)

| No.  | Register Name | R/W | Bit Symbol | Description            |                         | Reset |

|------|---------------|-----|------------|------------------------|-------------------------|-------|

| 0x0A | AUTOOFSGAIN   | R/W | 9: ABKMD5  | 0: static adjustment   | 1: dynamic adjustment   | 0x000 |

|      |               |     | 8: ABKMD4  | 0: 1 line filter       | 1: filter disable       |       |

|      |               |     | 7: ABKMD3  | 0: moderate adjustment | 1: extreme adjustment   |       |

|      |               |     | 6: ABKMD2  | 0: normal correction   | 1: over correction      |       |

|      |               |     | 5: ABKMD1  | 0: low sensitivity     | 1: high sensitivity     |       |

|      |               |     | 4: ABKMD0  | 0: low sensitivity     | 1: very low sensitivity |       |

|      |               |     | 3: AOEN    | 0: disable             | 1: enable               |       |

|      |               |     | 2: AGEN    | 0: disable             | 1: enable               |       |

|      |               |     | 1: ABKMD6  | 0: disable             | 1: enable               |       |

|      |               |     | 0: ABKADJ  | 0: disable             | 1: enable               |       |

Bit9

## ABKMD5

オフセットレジスタを更新する補正量を設定します。

“0”:1 ラインあたり 1 単位の補正量

“1”:黒レベル変動分相当の補正量

Bit8

## ABKMD4

黒レベル変動の検出ライン数を設定します。

“0”:2 ライン連続して黒レベルの変動を検出したとき補正

“1”:毎ライン黒レベルの変動を検出したとき補正

Bit7

## ABKMD3

オフセットレジスタを更新する補正量を設定します。

“0”:黒レベル変動分相当の補正量

“1”:補正量 2 倍

Bit6

## ABKMD2

黒レベル変動検出後の目標となる補正量を設定します。

“0”:BKLEVEL[9:0]設定を目標に補正

“1”:BKLEVEL[9:0]を超えるオフセット設定±1LSB 相当を目標に補正

Bit5

## ABKMD1

黒レベル変動検出のしきい値を設定します。

“0”:オフセット設定±1LSB 相当を超える変動を検出したとき補正

“1”:黒レベルが BKLEVEL[9:0]設定を外れたとき補正

Bit4

## ABKMD0

ABKMD1 ビットが“0”設定時に不感帯を 2 倍に設定します。

“0”:BKLEVEL[9:0]±1LSB 範囲を超える変動を検出したとき補正

“1”:BKLEVEL[9:0]±2LSB 範囲を超える変動を検出したとき補正

Bit3

## AOEN

自動オフセット調整機能動作を開始するとき、“1”を設定します。なお、本ビットは動作完了後、自動的に“0”となります。

Bit2

## AGEN

自動ゲイン調整機能動作を開始するとき、“1”を設定します。なお、本ビットは動作完了後、自動的に“0”となります。

Bit1

## ABKMD6

オフセットレジスタを更新する補正量を設定します。

“0”:黒レベル変動分相当の補正量

“1”:補正量 1/2 倍

## 7. レジスタ

Bit0 ABKADJ

自動黒レベル補正機能動作を有効にする場合、“1”を設定します。

「制限注意事項 1」

本レジスタは ADCK 信号入力時（定常動作時）のみアクセス可能です。

「制限注意事項 2」

自動オフセット調整機能、自動ゲイン調整機能または補正量検出機能有効（AOEN ビットまたは AGEN ビットに“1”設定時）にした後、動作完了まで他レジスタへのアクセスを禁止します。

「制限注意事項 3」

自動オフセット調整機能、自動ゲイン調整機能または補正量検出機能有効（AOEN ビットまたは AGEN ビットに“1”設定時）時、動作完了前に動作をキャンセルする場合は、AOEN ビットおよび AGEN ビットへ同時に“0”を設定してください。

### 7.3.11 0x0B AFE 制御レジスタ(AFECTL)

| No.  | Register Name | R/W | Bit Symbol   | Description      |           | Reset |  |

|------|---------------|-----|--------------|------------------|-----------|-------|--|

| 0x0B | AFECTL        | R/W | 9: CKGEN     | 0: disable       | 1: enable | 0x000 |  |

|      |               |     | 8: VCOSEL[1] | ADCK 信号周波数設定レジスタ |           |       |  |

|      |               |     | 7: VCOSEL[0] |                  |           |       |  |

|      |               |     | 6:           |                  |           |       |  |

|      |               |     | 5:           |                  |           |       |  |

|      |               |     | 4:           |                  |           |       |  |

|      |               |     | 3:           |                  |           |       |  |

|      |               |     | 2:           |                  |           |       |  |

|      |               |     | 1:           |                  |           |       |  |

|      |               |     | 0:           |                  |           |       |  |

Bit9 CKGEN

本ビットに“1”を設定すると S/H モードにおいて外部入力のサンプリング信号を自動的に内部生成します。

Bit8～7 VCOSEL[1:0]

入力クロック波形整形機能へ入力される ADCK 信号の周波数に応じて下記に従い本ビットを設定します。

| VCOSEL[1:0] : ADCK 信号周波数設定 |                |

|----------------------------|----------------|

| PIXSQMD=“0”設定時             | PIXSQMD=“1”設定時 |

| 11 : 25～40MHz              | 8.3～13.3MHz    |

| 10 : 20～25MHz              | 6.6～8.3MHz     |

| 01 : 12.5～20MHz            | 4.1～6.6MHz     |

| 00 : 5.0～12.5MHz           | 1.66～4.1MHz    |

Bit6～0 Reserved

「制限注意事項」

VCOSEL[1:0]ビットを設定する際は、POWERDOWN レジスタ（No.0x00）のPDLVDS ビットおよびPDSTB ビットを“1”に設定してから行ってください。

## 7.3.12 0x0C サンプリング信号制御レジスタ (CKGENMD)

| No.  | Register Name | R/W | Bit Symbol | Description |                      | Reset |

|------|---------------|-----|------------|-------------|----------------------|-------|

| 0x0C | CKGENMD       | R/W | 9: CKGENMD | 0: normal   | 1: delay rising edge | 0x000 |

|      |               |     | 8:         |             |                      |       |

|      |               |     | 7:         |             |                      |       |

|      |               |     | 6:         |             |                      |       |

|      |               |     | 5:         |             |                      |       |

|      |               |     | 4:         |             |                      |       |

|      |               |     | 3:         |             |                      |       |

|      |               |     | 2:         |             |                      |       |

|      |               |     | 1:         |             |                      |       |

|      |               |     | 0:         |             |                      |       |

Bit9 Reserved

Bit8 CKGENMD

サンプリング信号を自動生成時において、内部生成されたタイミング信号の立ち上がりを遅延(約2~7ns)させ、パルス幅を短くすることができます。

Bit7~0 Reserved

## 7.3.13 0x0D 入力制御レジスタ (INCTL)

| No.  | Register Name | R/W | Bit Symbol | Description |                    | Reset |

|------|---------------|-----|------------|-------------|--------------------|-------|

| 0x0D | INCTL         | R/W | 9:         |             |                    | 0x000 |

|      |               |     | 8: LCLMP   | 0: normal   | 1: line clamp mode |       |

|      |               |     | 7:         |             |                    |       |

|      |               |     | 6:         |             |                    |       |

|      |               |     | 5:         |             |                    |       |

|      |               |     | 4:         |             |                    |       |

|      |               |     | 3:         |             |                    |       |

|      |               |     | 2:         |             |                    |       |

|      |               |     | 1:         |             |                    |       |

|      |               |     | 0:         |             |                    |       |

Bit9 Reserved

Bit8 LCLMP

アナログ入力部におけるバッファアンプ機能の制御をします。通常、S/H モード (ライン・クランプ) 機能動作時において“1”に設定してください。

Bit7~0 Reserved

## 7. レジスタ

### 7.3.14 0x0F A/D コンバータ動作モード設定レジスタ(ADCMD)

| No.  | Register Name | R/W | Bit Symbol | Description       | Reset |  |

|------|---------------|-----|------------|-------------------|-------|--|

| 0x0F | ADCMD         |     | 9:         |                   | 0x049 |  |

|      |               |     | 8:         |                   |       |  |

|      |               | R/W | 7: BL[1]   | バッファアンプ能力設定       |       |  |

|      |               |     | 6: BL[0]   |                   |       |  |

|      |               |     | 5:         |                   |       |  |

|      |               |     | 4:         |                   |       |  |