# **S7R77021B/77021F**

## **テクニカルマニュアル**

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告無く変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性値の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## - 総 則 -

### 【適用範囲】

本仕様書は、セイコーエプソン株式会社 半導体事業部製 C C D 駆動クロック生成機能搭載アナログフロントエンド (AFE : Analog Front End) 「S7R77021B00A100/S7R77021F00A100」（以降、本 I C とする）に適用する。

### 【品名説明】

S 7 R 7 7 0 2 1 0 0 A 1 0 0

パッケージ選択

B : 0.8 mmピッチ BGA 121 ピン

F : 0.5 mmピッチ QFP 100 ピン

## - 目 次 -

|                                             |    |

|---------------------------------------------|----|

| 1. 概要                                       | 9  |

| 2. 特長                                       | 10 |

| 3. ブロック図                                    | 11 |

| 4. 端子配置図                                    | 12 |

| 5. 端子説明                                     | 14 |

| 6. 機能説明                                     | 16 |

| 6.1 ホストインターフェース部                            | 16 |

| 6.1.1 ホストインターフェース                           | 16 |

| 6.1.2 シリアルインターフェース                          | 17 |

| 6.1.3 画像データ出力                               | 18 |

| 6.2 内蔵PLL部                                  | 20 |

| 6.3 RSDS部                                   | 22 |

| 6.4 アナログフロントエンド(AFE)部                       | 24 |

| 6.4.1 概要                                    | 24 |

| 6.4.2 仕様                                    | 25 |

| 6.4.3 内部ブロック構成                              | 26 |

| 6.4.4 パワーダウン機能                              | 27 |

| 6.4.5 動作チャネル                                | 27 |

| 6.4.6 基準電圧発生回路(Reference Voltage Generator) | 27 |

| 6.4.7 クランプ回路                                | 27 |

| 6.4.8 CDSブロック                               | 28 |

| 6.4.9 オフセット調整                               | 31 |

| 6.4.10 プログラマブル・ゲイン・アンプ(PGA)                 | 32 |

| 6.4.11 タイミング                                | 33 |

| 6.5 タイミング生成部                                | 34 |

| 6.5.1 概要                                    | 34 |

| 6.5.2 画像取り込み動作                              | 35 |

| 6.5.3 内部動作                                  | 36 |

| 6.5.4 制御信号出力                                | 39 |

| 6.5.5 画像データ出力                               | 50 |

| 6.5.6 兼用汎用ポート                               | 50 |

| 6.5.7 テストモード                                | 52 |

| 7. レジスタ                                     | 53 |

| 7.1 メモリマップ                                  | 53 |

|                                                           |    |

|-----------------------------------------------------------|----|

| 7.2 レジスタマップ .....                                         | 54 |

| 7.3 ビットマップ .....                                          | 56 |

| 7.4 レジスタ詳細説明 .....                                        | 58 |

| 7.4.1 0x00~1F クロックパルスパターン設定レジスタ 0 0 ~ 1 F (SNCK_PAT00~1F) | 58 |

| 7.4.2 0x20~1 ライン周期設定レジスタ (TGPERIOD) .....                 | 59 |

| 7.4.3 0x22 TGCK パルス幅設定レジスタ (TGCKWDTH) .....               | 60 |

| 7.4.4 0x24 クロックパルススタートタイミング設定レジスタ (CKSTART) .....         | 61 |

| 7.4.5 0x26 シフトパルス立ち上がりタイミング設定レジスタ (SH_RISE) .....         | 62 |

| 7.4.6 0x27 シフトパルス立ち下がりタイミング設定レジスタ (SH_FALL) .....         | 63 |

| 7.4.7 0x28~9 クロックオフ時間設定レジスタ (STCKOFF) .....               | 64 |

| 7.4.8 0x2A~B クロックパルススタートタイミング設定レジスタ 2 (CKSTART2) .....    | 65 |

| 7.4.9 0x30~1 シフトパルス立ち上がり時間設定レジスタ (赤) (SHR2_RISE) .....    | 66 |

| 7.4.10 0x32~3 シフトパルス立ち下がり時間設定レジスタ (赤) (SHR2_FALL) .....   | 67 |

| 7.4.11 0x34~5 シフトパルス立ち上がり時間設定レジスタ (緑) (SHG2_RISE) .....   | 68 |

| 7.4.12 0x36~7 シフトパルス立ち下がり時間設定レジスタ (緑) (SHG2_FALL) .....   | 69 |

| 7.4.13 0x38~9 シフトパルス立ち上がり時間設定レジスタ (青) (SHB2_RISE) .....   | 70 |

| 7.4.14 0x3A~B シフトパルス立ち下がり時間設定レジスタ (青) (SHB2_FALL) .....   | 71 |

| 7.4.15 0x40 クロックパルス信号出力遅延設定レジスタ 1 (SNCK_ADJ1) .....       | 72 |

| 7.4.16 0x41 クロックパルス信号出力遅延設定レジスタ 2 (SNCK_ADJ2) .....       | 73 |

| 7.4.17 0x42 クロックパルス信号出力遅延設定レジスタ 3 (SNCK_ADJ3) .....       | 74 |

| 7.4.18 0x43 クロックパルス信号出力遅延設定レジスタ 4 (SNCK_ADJ4) .....       | 75 |

| 7.4.19 0x44 クロックパルス信号出力遅延設定レジスタ 5 (SNCK_ADJ5) .....       | 76 |

| 7.4.20 0x48 シフトパルス駆動パターンスタートタイミング設定レジスタ (TG2START) ..     | 77 |

| 7.4.21 0x49 シフトパルス駆動パターンエンドタイミング設定レジスタ (TG2END) .....     | 78 |

| 7.4.22 0x4A シフトパルス駆動パターン動作許可レジスタ (TG2EN) .....            | 79 |

| 7.4.23 0x50 タイミング生成機能設定レジスタ (TGCTL) .....                 | 80 |

| 7.4.24 0x51 内部ステート設定レジスタ (STCTL) .....                    | 81 |

| 7.4.25 0x52 画像データ設定レジスタ (ADCTL) .....                     | 82 |

| 7.4.26 0x53 クロックパルス設定レジスタ (SNCKCTL) .....                 | 83 |

| 7.4.27 0x54 C C D / A F E モード設定レジスタ (CCAEMODE) .....      | 84 |

| 7.4.28 0x5F テストモード設定レジスタ (TESTMODE) .....                 | 86 |

| 7.4.29 0x60 汎用ポート制御レジスタ (GPIOEN) .....                    | 87 |

| 7.4.30 0x61 汎用ポート入出力切り替えレジスタ (GPIODIR) .....              | 88 |

| 7.4.31 0x62 汎用ポートレジスタ (GPIOST) .....                      | 89 |

| 7.4.32 0x64 汎用ポート2制御レジスタ (GPIO2EN) .....                  | 90 |

| 7.4.33 0x65 汎用ポート2入出力切り替えレジスタ (GPIO2DIR) .....            | 91 |

| 7.4.34 0x66 汎用ポート2レジスタ (GPIO2ST) .....                    | 92 |

| 7.4.35 0x70 アナログモジュールリセットレジスタ (ANA_RESET) .....           | 93 |

| 7.4.36 0x78 A F E ゲイン・オフセットレジスタ (赤) (RDGAINOFS) .....     | 94 |

| 7.4.37 0x79 A F E ゲイン・オフセットレジスタ (緑) (RGAINOFS) .....      | 95 |

|                                                    |     |

|----------------------------------------------------|-----|

| 7.4.3 8 0x7A AFEゲイン・オフセットレジスタ(青)(BLGAINOFS).....   | 96  |

| 7.4.3 9 0x7E AFEモード設定レジスタ(AFEMODE).....            | 97  |

| 7.4.4 0 0x7F PLL・画像出力信号制御レジスタ(PLL_IMGSIG_CTL)..... | 98  |

| 7.5 レジスタ設定制限事項.....                                | 99  |

| 7.5.1 信号出力タイミング .....                              | 99  |

| 7.5.2 レジスタ設定制限 .....                               | 100 |

| 8. 電気的特性 .....                                     | 101 |

| 8.1 絶対最大定格 .....                                   | 101 |

| 8.2 推奨動作条件 .....                                   | 101 |

| 8.3 DC特性 .....                                     | 102 |

| 8.4 AC特性 .....                                     | 103 |

| 8.4.1 システムリセット .....                               | 103 |

| 8.4.2 クロックタイミング .....                              | 103 |

| 8.4.3 PLLロックタイミング .....                            | 103 |

| 8.4.4 シリアルインターフェースタイミング .....                      | 104 |

| 8.4.5 CDSモード サンプリングタイミング .....                     | 105 |

| 8.4.6 S/Hモード(差電圧入力)サンプリングタイミング .....               | 106 |

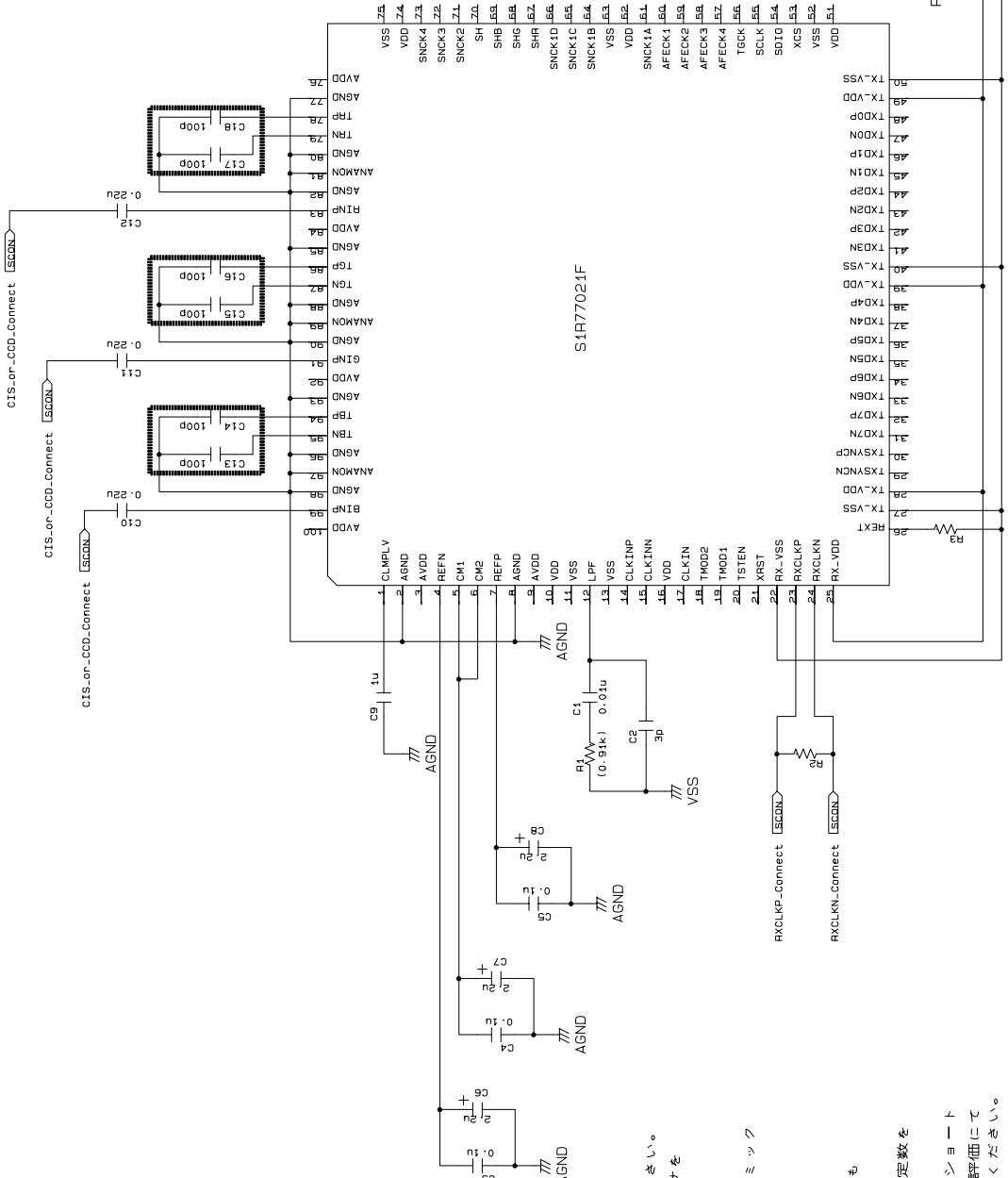

| 9. 応用接続例 .....                                     | 107 |

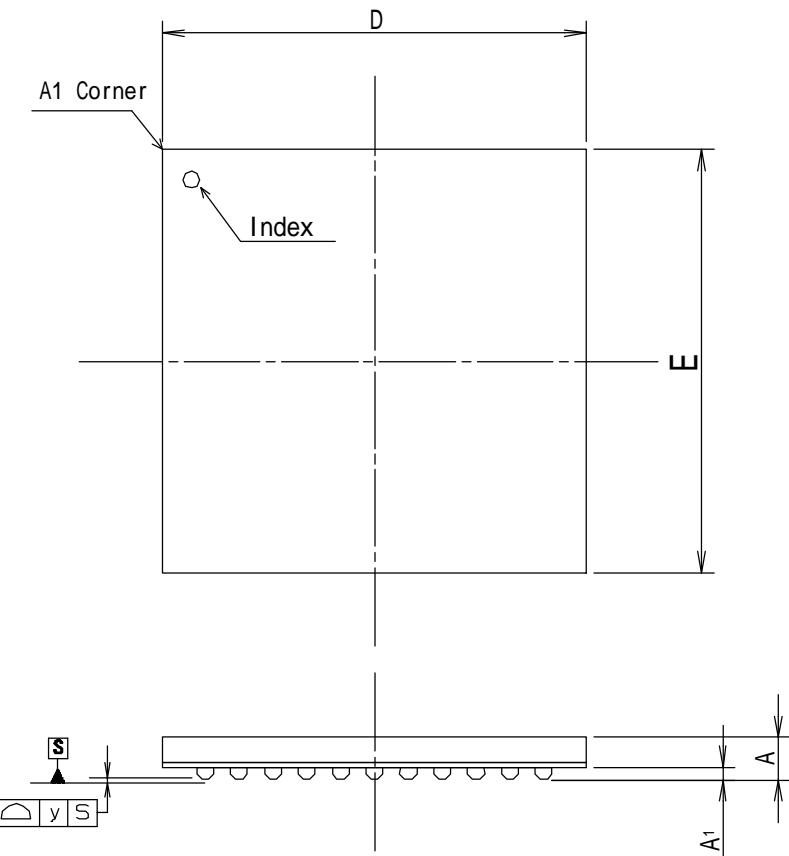

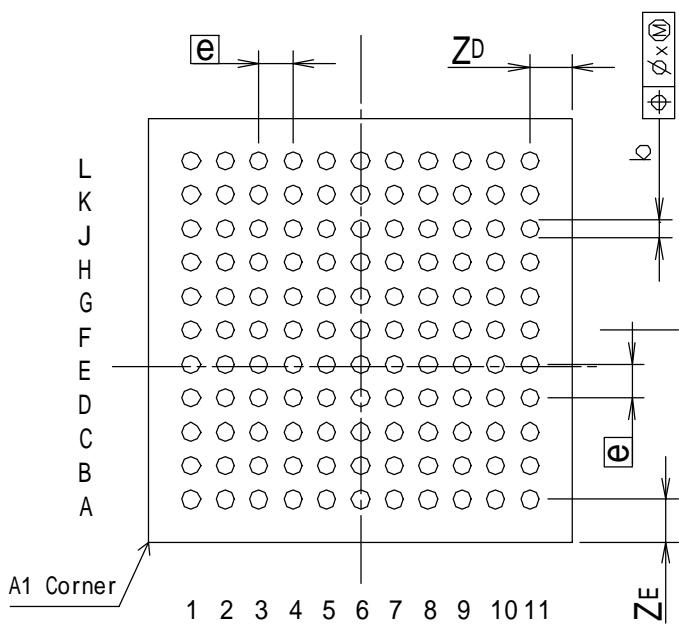

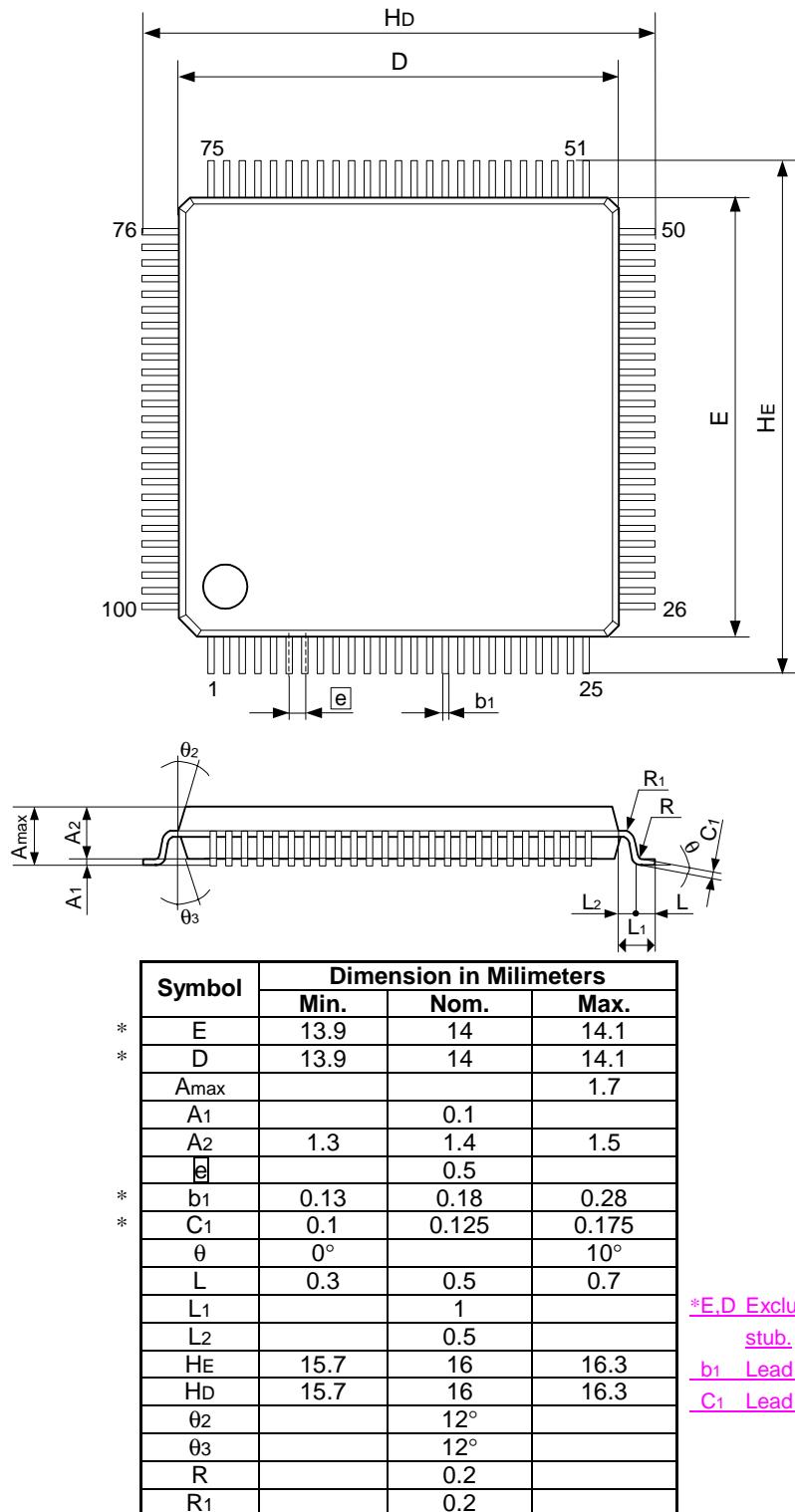

| 10. 外形寸法図 .....                                    | 108 |

## 1.概要

本 I C は、高速読取動作を実現する C C D 駆動クロック生成機能搭載アナログフロントエンド I C です。また、本 I C は高解像度 16 ビット A / D コンバータを 3 個内蔵、および画像センサを駆動する制御機能を有しており、高速スキャナシステムを容易に実現することができます。

## 2. 特長

### 共通部

- 2種類のパッケージを選択可能

- BGAパッケージ : 0.8mmピッチ BGA 121ピン

- QFPパッケージ : 0.5mmピッチ QFP 100ピン

- 3.3V 単一電源

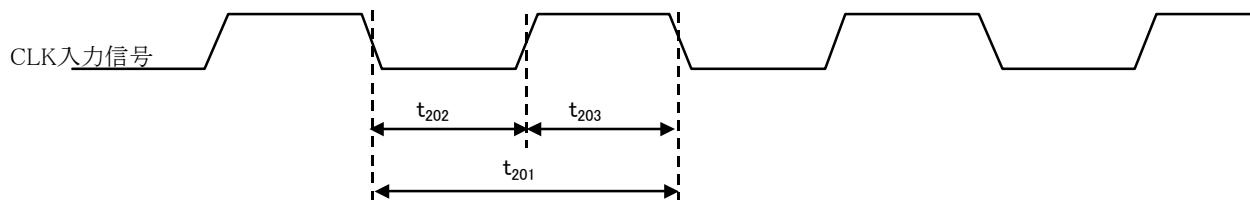

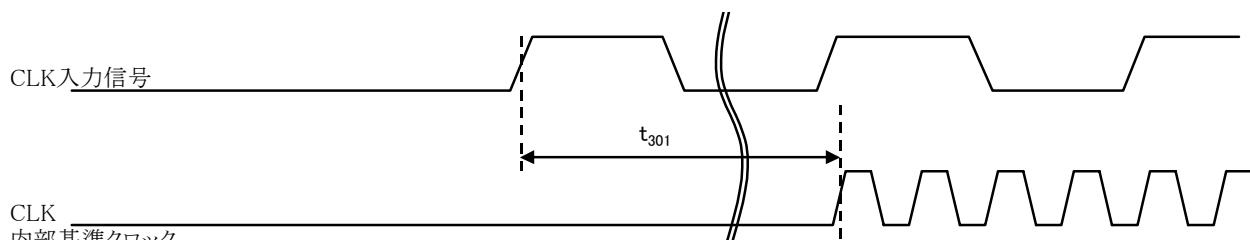

- PLLを内蔵し CLK入力信号入力を4~16倍することにより内部基準クロックを生成

- 内部基準クロック周波数 : 75MHz 内部基準クロック周波数 120MHz

### ホストインターフェース部

- シリアルインターフェース

- 画像データ出力方式

- デファレンシャル出力 (BGAパッケージ、QFPパッケージ)

- シングルエンド出力 (BGAパッケージ)

- 画像データ出力に8ビット×2マルチプレクサ出力、4ビット×4マルチプレクサ出力を選択可能

- 3チャネル画像データ出力シーケンスを赤 緑 青または青 緑 赤に選択可能

### AFE (Analog Front End) 部

- 16ビットA/Dコンバータ3個内蔵

- 画像データ最大転送レート : 30MHz

- 1チャネルあたりの最大変換速度(AFE転送クロック) : 10MHz

- 動作モード : CDSまたはS/Hモード

- 動作チャネル数 : 1、2または3チャネル選択可

- アナログ信号入力レンジ : 2Vp-p

- A/Dコンバータへのフルスケール入力レンジ : 1Vp-p

- プログラマブル・ゲイン・アンプ(PGA)調整レンジ :

- 6.9 (約0.45倍) ~ +12.0dB(約4.0倍) (分解能6ビット)

- オフセット調整レンジ : ±250mV (分解能8ビット)

### 駆動クロック生成部

- 画像センサおよびAFE駆動に必要な下記シフト信号・LED制御信号・クロック信号を生成

- ADCK, SH, SHR(LEDR), SHG(LEDG), SHB(LEDB), SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK2, SNCK3, SNCK4, CK1, CK2, CLMP

- (但し、ADCK, CK1, CK2, CLMP信号はAFEモジュールへ内部接続)

- クロック信号駆動パターン生成用メモリ内蔵

- ダミー画素転送数をプログラマブルに設定可能

- 画像読み取り時およびダミー画素出力時のクロック信号駆動パターンを自由にプログラム可能

- ADCK信号1サイクルあたりの駆動パターン分解能は設定により8、10、12、14、16から選択

- シャッタレスCCDに対応

- 駆動クロック3.3V出力

耐放射性設計はされておりません。

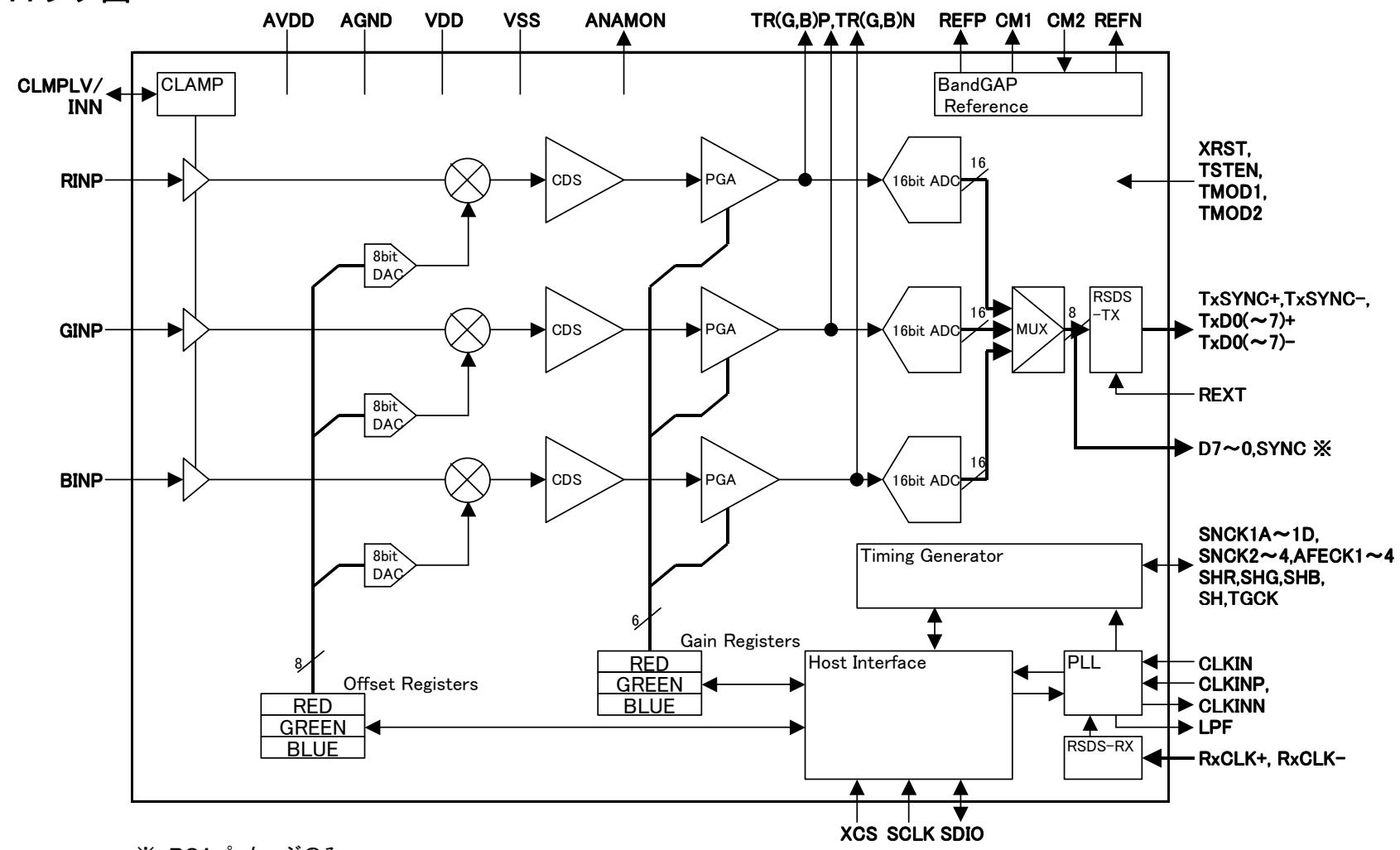

## 3. ブロック図

※ BGAパッケージのみ

## 4. 端子配置図

### (1) BGAパッケージ

S7R77021B00A100/PFBGA10UX121

TOP VIEW

|   | 1         | 2              | 3      | 4        | 5     | 6        | 7      | 8        | 9      | 10       | 11     |   |

|---|-----------|----------------|--------|----------|-------|----------|--------|----------|--------|----------|--------|---|

| A | NC        | CLMPLV/<br>INN | AVDD   | AGND     | BINP  | AGND     | GINP   | AGND     | RINP   | AGND     | NC     | A |

| B | REFN      | AGND           | AVDD   | (ANAMON) | TBN   | (ANAMON) | TGN    | (ANAMON) | TRN    | AVDD     | SNCK4  | B |

| C | CM1       | CM2            | AGND   | AVDD     | TBP   | AVDD     | TGP    | AVDD     | TRP    | VSS      | SNCK3  | C |

| D | REFP      | AGND           | AVDD   | AGND     | AVDD  | AGND     | AVDD   | AGND     | VDD    | SHB/LEDB | SNCK2  | D |

| E | Vref_AGND | Vref_AVDD      | AVDD   | D7       | D6    | D5       | D4     | VSS      | SH     | SHG/LEDG | SNCK1D | E |

| F | LPF       | PLL_VDD        | VSS    | D3       | D2    | D1       | D0     | SYNC     | VDD    | SHR/LEDR | SNCK1C | F |

| G | PLL_VSS   | CLKINN         | VDD    | TMOD2    | TMOD1 | AFECK4   | AFECK3 | AFECK2   | AFECK1 | VSS      | SNCK1B | G |

| H | CLKIN     | CLKINP         | TSTEN  | XRST     | VSS   | VDD      | XCS    | SDIO     | SCLK   | TGCK     | SNCK1A | H |

| J | RXCLKP    | RX_VSS         | TXD7N  | TXD7P    | TXD5N | TXD5P    | TXD3N  | TXD3P    | TXD1N  | TXD1P    | VSS    | J |

| K | RXCLKN    | RX_VDD         | TX_VDD | TXSYNCN  | TXD6N | TXD4N    | TX_VDD | TXD2N    | TXD0N  | TX_VDD   | VDD    | K |

| L | NC        | REXT           | TX_VSS | TXSYNCN  | TXD6P | TXD4P    | TX_VSS | TXD2P    | TXD0P  | TX_VSS   | NC     | L |

注) TX\_VDD と RXVDD、TX\_VSS と RX\_VSS は内部接続されていますので同一電源から供給してください。

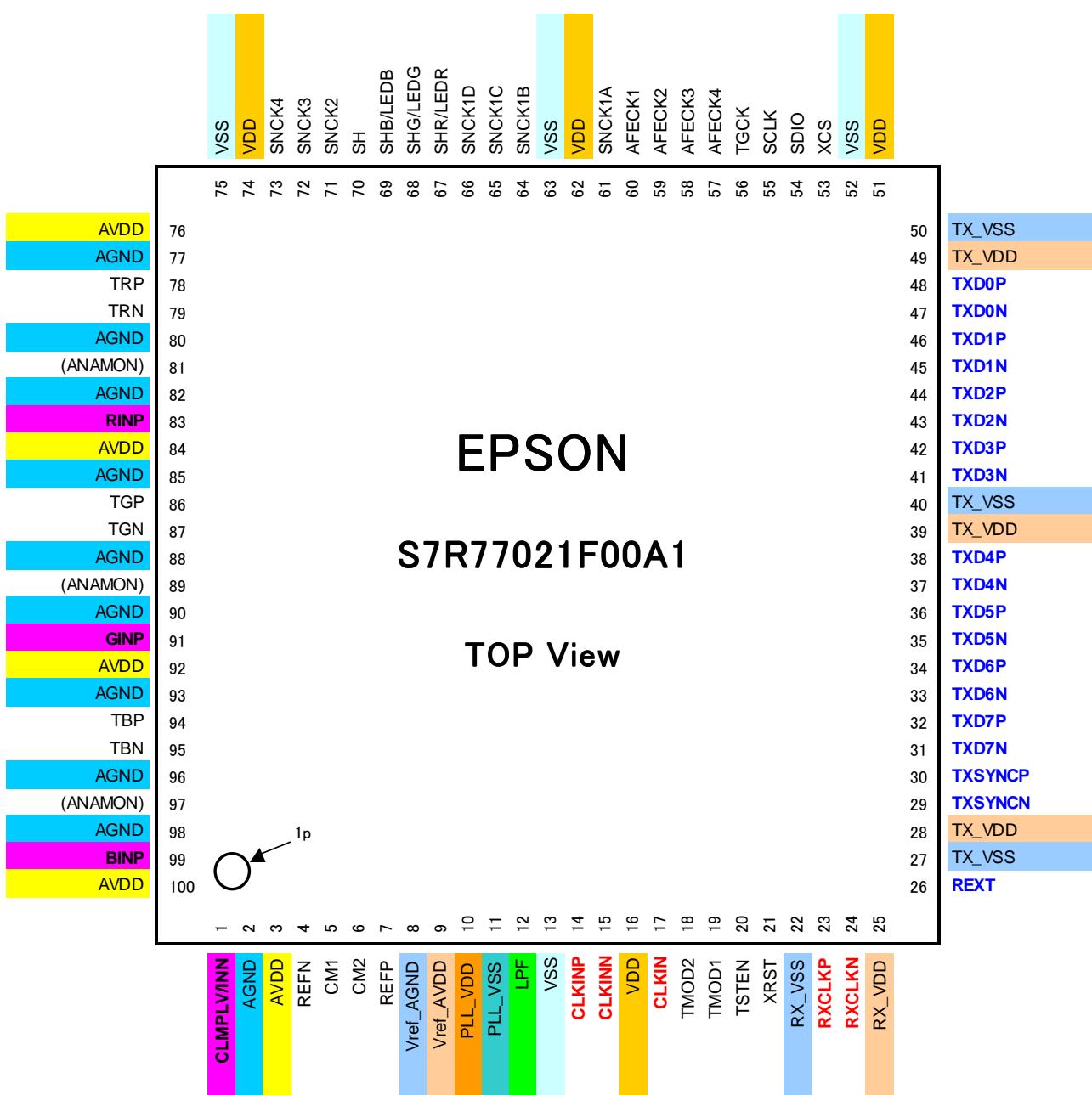

( 2 ) Q F P パッケージ

**S7R77021F00A100/QFP15-100**

## 5. 端子説明

|               | BGA | QFP | 端子名        | I/O | Reset | 端子機能                   | 備考     | 駆動能力 |

|---------------|-----|-----|------------|-----|-------|------------------------|--------|------|

| AFE           |     |     |            |     |       |                        |        |      |

| 1             | B1  | 4   | REFN       | A   | -     | 低電位リファレンス              |        | アナログ |

| 2             | C1  | 5   | CM1        | A   | -     | 同相モード電圧1               |        | アナログ |

| 3             | C2  | 6   | CM2        | A   | -     | 同相モード電圧2               |        | アナログ |

| 4             | D1  | 7   | REFP       | A   | -     | 高電位リファレンス              |        | アナログ |

| 5             | A9  | 83  | R1NP       | A   | -     | Rチャネルアナログ入力            |        | アナログ |

| 6             | A7  | 91  | G1NP       | A   | -     | Gチャネルアナログ入力            |        | アナログ |

| 7             | A5  | 99  | B1NP       | A   | -     | Bチャネルアナログ入力            |        | アナログ |

| 8             | A2  | 1   | CLMPLV/INN | A   | -     | クランプレベルモニタ/リファレンスレベル入力 |        | アナログ |

| 9             | C9  | 78  | TRP        | A   | -     | ADC高電位入力モニタ(赤)         |        | アナログ |

| 10            | B9  | 79  | TRN        | A   | -     | ADC低電位入力モニタ(赤)         |        | アナログ |

| 11            | C7  | 86  | TGP        | A   | -     | ADC高電位入力モニタ(緑)         |        | アナログ |

| 12            | B7  | 87  | TGN        | A   | -     | ADC低電位入力モニタ(緑)         |        | アナログ |

| 13            | C5  | 94  | TBP        | A   | -     | ADC高電位入力モニタ(青)         |        | アナログ |

| 14            | B5  | 95  | TBN        | A   | -     | ADC低電位入力モニタ(青)         |        | アナログ |

| 15            | B8  | 81  | (ANAMON)   | A   | -     | アナログモニタ端子              |        | アナログ |

| 16            | B6  | 89  | (ANAMON)   | A   | -     |                        |        |      |

| 17            | B4  | 97  | (ANAMON)   | A   | -     |                        |        |      |

| 18            | A3  | 3   | AVDD       | P   | -     | アナログ電源 +3.3V           |        | -    |

| 19            | B3  | 76  | AVDD       | P   | -     |                        |        |      |

| 20            | B10 | 84  | AVDD       | P   | -     | 基準電圧発生回路用アナログ電源 +3.3V  |        | -    |

| 21            | C4  | 92  | AVDD       | P   | -     |                        |        |      |

| 22            | C6  | 100 | AVDD       | P   | -     | アナロググランド               |        | -    |

| 23            | C8  | -   | AVDD       | P   | -     |                        |        |      |

| 24            | D3  | -   | AVDD       | P   | -     | 基準電圧発生回路用アナログ電源 +3.3V  |        | -    |

| 25            | D5  | -   | AVDD       | P   | -     |                        |        |      |

| 26            | D7  | -   | AVDD       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 27            | E3  | -   | AVDD       | P   | -     |                        |        |      |

| 28            | E2  | 9   | Vref_AVDD  | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 29            | A4  | 2   | AGND       | P   | -     |                        |        |      |

| 30            | A6  | 77  | AGND       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 31            | A8  | 80  | AGND       | P   | -     |                        |        |      |

| 32            | A10 | 82  | AGND       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 33            | B2  | 85  | AGND       | P   | -     |                        |        |      |

| 34            | C3  | 88  | AGND       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 35            | D2  | 90  | AGND       | P   | -     |                        |        |      |

| 36            | D4  | 93  | AGND       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 37            | D6  | 96  | AGND       | P   | -     |                        |        |      |

| 38            | D8  | 98  | AGND       | P   | -     | 基準電圧発生回路用アナロググランド      |        | -    |

| 39            | E1  | 8   | Vref_AGND  | P   | -     |                        |        |      |

| CDC駆動クロック     |     |     |            |     |       |                        |        |      |

| 40            | E9  | 70  | SH         | B   | PD    | CISシフト信号               | PD     | 2mA  |

| 41            | F10 | 67  | SHR/LEDR   | B   | PD    | CDCシフト/CIS LED点灯(赤)    | PD     | 2mA  |

| 42            | E10 | 68  | SHG/LEDG   | B   | PD    | CDCシフト/CIS LED点灯(緑)    | PD     | 2mA  |

| 43            | D10 | 69  | SHB/LEDB   | B   | PD    | CDCシフト/CIS LED点灯(青)    | PD     | 2mA  |

| 44            | H11 | 61  | SNCK1A     | B   | PD    | クロックA                  | PD     | 2mA  |

| 45            | G11 | 64  | SNCK1B     | B   | PD    | クロックB                  | PD     | 2mA  |

| 46            | F11 | 65  | SNCK1C     | B   | PD    | クロックC                  | PD     | 2mA  |

| 47            | E11 | 66  | SNCK1D     | B   | PD    | クロックD                  | PD     | 2mA  |

| 48            | D11 | 71  | SNCK2      | B   | PD    | クロック2                  | PD     | 2mA  |

| 49            | C11 | 72  | SNCK3      | B   | PD    | クロック3                  | PD     | 2mA  |

| 50            | B11 | 73  | SNCK4      | B   | PD    | クロック4                  | PD     | 2mA  |

| 51            | G9  | 60  | AFECK1     | B   | PD    | A FEクロックモニタ1           | PD     | 2mA  |

| 52            | G8  | 59  | AFECK2     | B   | PD    | A FEクロックモニタ2           | PD     | 2mA  |

| 53            | G7  | 58  | AFECK3     | B   | PD    | A FEクロックモニタ3           | PD     | 2mA  |

| 54            | G6  | 57  | AFECK4     | B   | PD    | A FEクロックモニタ4           | PD     | 2mA  |

| 画像取り込みタイミング信号 |     |     |            |     |       |                        |        |      |

| 55            | H10 | 56  | TGCK       | B   | Hi-Z  | CDCシフト信号トリガ            | SMT    | 2mA  |

| システム信号        |     |     |            |     |       |                        |        |      |

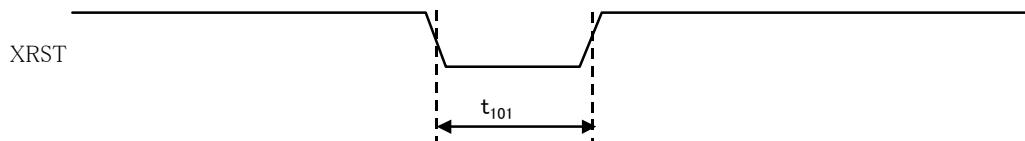

| 56            | H4  | 21  | XRST       | I   | -     | リセット信号                 | SMT、PD | -    |

| 57            | H2  | 14  | CLKINP     | A   | -     | 基準クロック(正) [OSC入力]      |        | アナログ |

| 58            | G2  | 15  | CLKINN     | A   | -     | 基準クロック(負) [OSC入力]      |        | アナログ |

| 59            | J1  | 23  | RXCLKP     | A   | -     | 基準クロック(正) [デファレンシャル入力] |        | アナログ |

| 60            | K1  | 24  | RXCLKN     | A   | -     | 基準クロック(負) [デファレンシャル入力] |        | アナログ |

| 61            | H1  | 17  | CLKIN      | I   | -     | 基準クロック [CLK入力]         |        | -    |

| 62            | F1  | 12  | LPF        | A   | -     | 内部PLL用ローパスフィルタ接続端子     |        | アナログ |

|                        | BGA | QFP | 端子名            | I/O | Reset | 端子機能             | 備考     | 駆動能力 |

|------------------------|-----|-----|----------------|-----|-------|------------------|--------|------|

| システム信号                 |     |     |                |     |       |                  |        |      |

| 63                     | H7  | 53  | XCS            | I   | -     | チップセレクト          | SMT、PU | -    |

| 64                     | H9  | 55  | SCLK           | I   | -     | シリアルデータ入出力同期クロック | SMT、PD | -    |

| 65                     | H8  | 54  | SDIO           | B   | PD    | シリアルデータ入出力2      | SMT、PD | 2mA  |

| 画像データ出力 [ デファレンシャル出力 ] |     |     |                |     |       |                  |        |      |

| 66                     | L9  | 48  | <b>TXD0P</b>   | A   | -     | 画像データ出力          |        | アナログ |

| 67                     | K9  | 47  | <b>TXD0N</b>   | A   | -     |                  |        |      |

| 68                     | J10 | 46  | <b>TXD1P</b>   | A   | -     |                  |        |      |

| 69                     | J9  | 45  | <b>TXD1N</b>   | A   | -     |                  |        |      |

| 70                     | L8  | 44  | <b>TXD2P</b>   | A   | -     |                  |        |      |

| 71                     | K8  | 43  | <b>TXD2N</b>   | A   | -     |                  |        |      |

| 72                     | J8  | 42  | <b>TXD3P</b>   | A   | -     |                  |        |      |

| 73                     | J7  | 41  | <b>TXD3N</b>   | A   | -     |                  |        |      |

| 74                     | L6  | 38  | <b>TXD4P</b>   | A   | -     |                  |        |      |

| 75                     | K6  | 37  | <b>TXD4N</b>   | A   | -     |                  |        |      |

| 76                     | J6  | 36  | <b>TXD5P</b>   | A   | -     |                  |        |      |

| 77                     | J5  | 35  | <b>TXD5N</b>   | A   | -     |                  |        |      |

| 78                     | L5  | 34  | <b>TXD6P</b>   | A   | -     |                  |        |      |

| 79                     | K5  | 33  | <b>TXD6N</b>   | A   | -     |                  |        |      |

| 80                     | J4  | 32  | <b>TXD7P</b>   | A   | -     |                  |        |      |

| 81                     | J3  | 31  | <b>TXD7N</b>   | A   | -     |                  |        |      |

| 82                     | L4  | 30  | <b>TXSYNCP</b> | A   | -     | 画像データ同期          |        | アナログ |

| 83                     | K4  | 29  | <b>TXSYNCN</b> | A   | -     |                  |        |      |

| 84                     | L2  | 26  | <b>REXT</b>    | A   | -     | 出力電流調整用外付け抵抗接続端子 |        | アナログ |

| 画像データ出力 [ シングルエンド出力 ]  |     |     |                |     |       |                  |        |      |

| 85                     | F7  | -   | D0             | 0   | L0    | 画像データ出力          |        | 2mA  |

| 86                     | F6  | -   | D1             | 0   | L0    |                  |        |      |

| 87                     | F5  | -   | D2             | 0   | L0    |                  |        |      |

| 88                     | F4  | -   | D3             | 0   | L0    |                  |        |      |

| 89                     | E7  | -   | D4             | B   | PD    |                  |        |      |

| 90                     | E6  | -   | D5             | B   | PD    |                  |        |      |

| 91                     | E5  | -   | D6             | B   | PD    |                  |        |      |

| 92                     | E4  | -   | D7             | B   | PD    |                  |        |      |

| 93                     | F8  | -   | SYNC           | B   | PD    | 画像データ同期          |        | 2mA  |

| テスト端子                  |     |     |                |     |       |                  |        |      |

| 94                     | H3  | 20  | TSTEN          | I   | -     | テスト端子            | PD     | -    |

| 95                     | G5  | 19  | TMOD1          | I   | -     | テストモード設定端子1      | PD     | -    |

| 96                     | G4  | 18  | TMOD2          | I   | -     | テストモード設定端子2      | PD     | -    |

| 電源端子                   |     |     |                |     |       |                  |        |      |

| 97                     | D9  | 16  | <b>VDD</b>     | P   | -     | 3.3V ロジック系電源供給端子 |        | -    |

| 98                     | F9  | 51  | <b>VDD</b>     | P   | -     |                  |        |      |

| 99                     | G3  | 62  | <b>VDD</b>     | P   | -     |                  |        |      |

| 100                    | H6  | 74  | <b>VDD</b>     | P   | -     |                  |        |      |

| 101                    | K11 | -   | <b>VDD</b>     | P   | -     |                  |        |      |

| 102                    | F2  | 10  | <b>PLL_VDD</b> | P   | -     |                  |        |      |

| 103                    | K3  | 28  | <b>TX_VDD</b>  | P   | -     |                  |        |      |

| 104                    | K7  | 39  | <b>TX_VDD</b>  | P   | -     |                  |        |      |

| 105                    | K10 | 49  | <b>TX_VDD</b>  | P   | -     |                  |        |      |

| 106                    | K2  | 25  | <b>RX_VDD</b>  | P   | -     |                  |        |      |

| 107                    | C10 | 13  | <b>VSS</b>     | P   | -     |                  |        |      |

| 108                    | E8  | 52  | <b>VSS</b>     | P   | -     |                  |        |      |

| 109                    | F3  | 63  | <b>VSS</b>     | P   | -     |                  |        |      |

| 110                    | G10 | 75  | <b>VSS</b>     | P   | -     |                  |        |      |

| 111                    | H5  | -   | <b>VSS</b>     | P   | -     |                  |        |      |

| 112                    | J11 | -   | <b>VSS</b>     | P   | -     |                  |        |      |

| 113                    | G1  | 11  | <b>PLL_VSS</b> | P   | -     | PLL グランド         |        | -    |

| 114                    | L3  | 27  | <b>TX_VSS</b>  | P   | -     | RSDS-TX グランド     |        | -    |

| 115                    | L7  | 40  | <b>TX_VSS</b>  | P   | -     |                  |        |      |

| 116                    | L10 | 50  | <b>TX_VSS</b>  | P   | -     |                  |        |      |

| 117                    | J2  | 22  | <b>RX_VSS</b>  | P   | -     |                  |        |      |

| 118                    | A1  | -   | <b>NC</b>      | -   | -     | RSDS-RX グランド     |        | -    |

| 119                    | A11 | -   | <b>NC</b>      | -   | -     |                  |        |      |

| 120                    | L1  | -   | <b>NC</b>      | -   | -     |                  |        |      |

| 121                    | L11 | -   | <b>NC</b>      | -   | -     |                  |        |      |

## I/O 欄の記号

A: アナログ端子

I: 入力端子

O: 出力端子

B: 双方向端子

P: 電源端子

## Reset(初期状態時)欄の記号

Lo: 'L' 出力

HI-Z: ハイ・インピーダンス状態

PD: 入力状態で電位は I/O 内のブルダウントラップにより Low 状態

## QFP 欄の記号

- : QFP パッケージではアサインされていない端子

## 備考欄の記号

PD: ブルダウン

SMT: シュミット入力

注) TX\_VDD と RXVDD、TX\_VSS と RX\_VSS は内部接続されていますので同一電源から供給してください。

## 6. 機能説明

各ブロックの機能を以下に説明します。

なお、本章の中で特に指示がない項目については、PLL 遅倍設定を 16 遅倍設定および駆動パターン分解能設定を 16 分周設定にした際の仕様となります。

### 6.1 ホストインターフェース部

#### 6.1.1 ホストインターフェース

ホストインターフェースは、レジスタアクセスおよび画像データ出力に使用されます。但し、画像データは、TGCTL レジスタ ( 0x50 ) の TGSTART ビットに ‘ 1 ’ を設定した際に出力します。

その動作を表 6.1 に示します。

表 6.1 ホストインターフェース

| アクセス対象                          | パラレル /<br>シリアル | 信号  |      |      |                          |

|---------------------------------|----------------|-----|------|------|--------------------------|

|                                 |                | XCS | SCLK | SDIO | D0 ~ 7<br>or<br>TXDO ~ 7 |

| レジスタアクセス                        | シリアル           | XCS | SCLK | SDIO | -                        |

| 画像データ出力<br>( TGSTART= ‘ 1 ’ 時 ) | パラレル           | -   | -    | -    | D0 ~ 7<br>TXDO ~ 7       |

注 ) D0 ~ 7 信号は QFP パッケージではアサインされていません

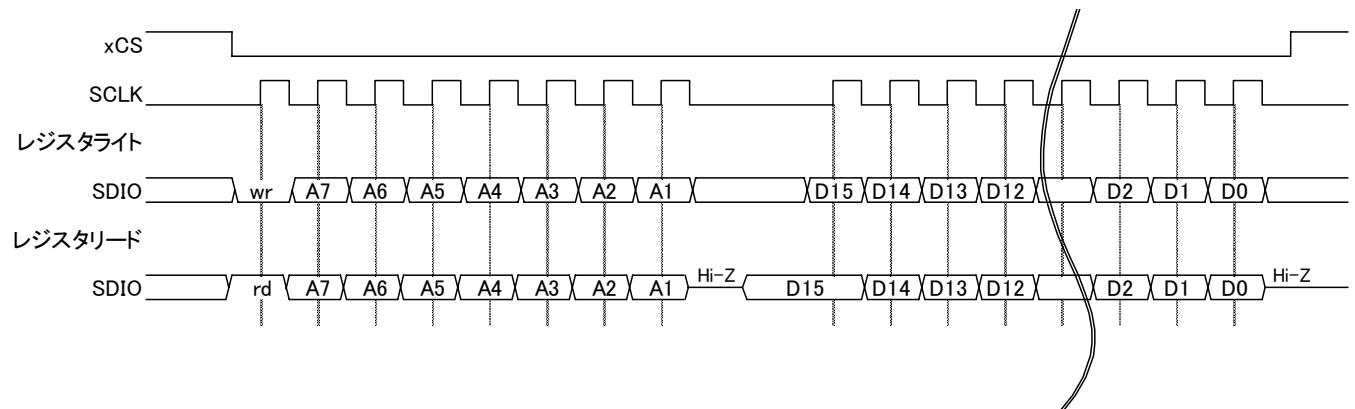

### 6.1.2 シリアルインタフェース

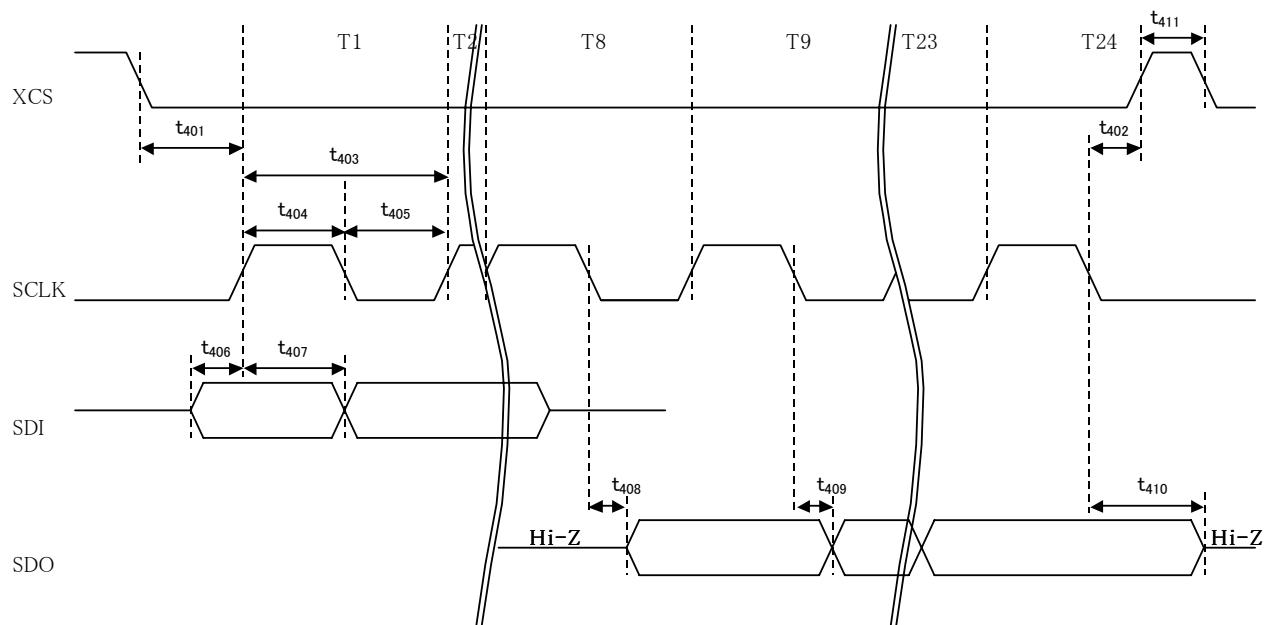

シリアルインタフェースは、チップセレクト(XCS)、シリアルクロック(SCLK)およびシリアルデータ入出力(SDIO)の3信号で構成されます。本ICがアクティブ状態(XCS信号が‘L’)の時、SCLKに同期してデータ送受信を行います。

レジスタアクセスはまずライトまたはリードアクセスを示す識別ビットをライトします。識別ビットは、‘L’のときにライトアクセス、‘H’のときにリードアクセスを行います。識別ビットに引き続き7ビットのレジスタ識別番号をライトし、その後データのライトまたはリードを行います。

レジスタ識別番号およびデータ転送はいずれもクロックの立ち上がりに同期し MSB から順に転送します。

本IC内部にはシリアル - パラレル変換(またはパラレル - シリアル変換)のためカウンタがあり、XCS信号を‘H’にすることによりリセットされます。従って、レジスタライトまたはレジスタリードの各アクセスサイクル終了後、必ずXCS信号をネゲート(XCS信号を‘H’)してください。

図6.1に各アクセス時のタイミングを示します。

図6.1 シリアルインタフェースアクセスタイミング

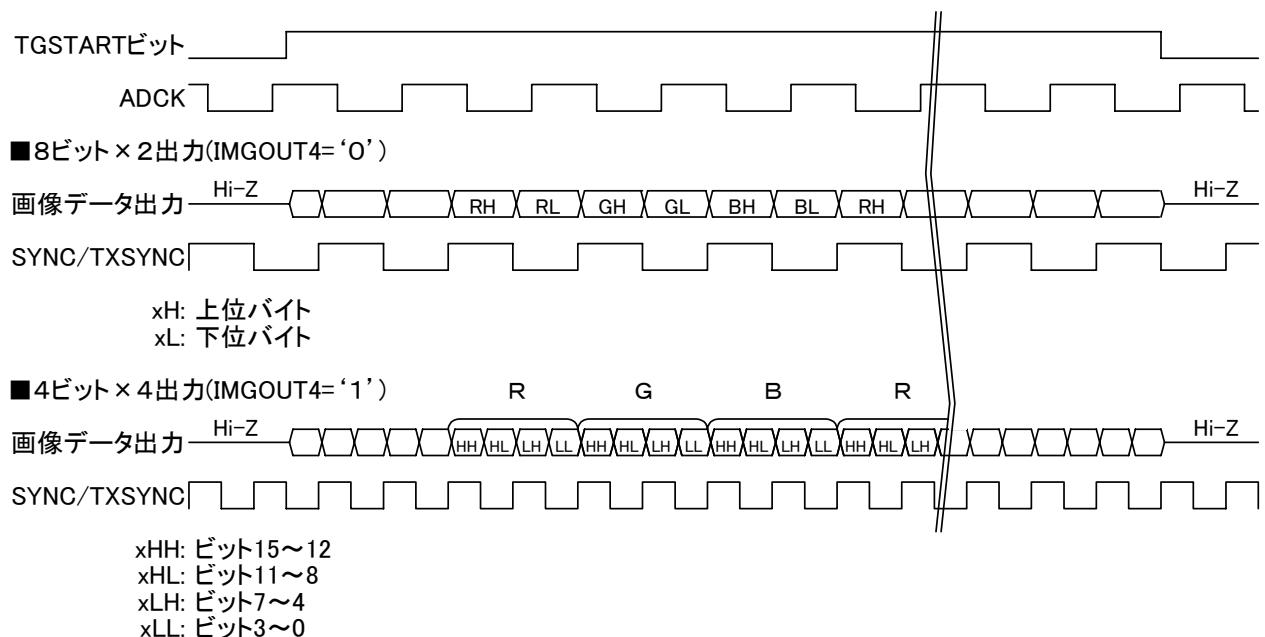

### 6.1.3 画像データ出力

#### (1) 画像データ出力動作

TGCTL レジスタ ( 0x50 ) の TGSTART ビットに ‘ 1 ’ を設定することにより、画像取り込み状態となり画像データを出力します。

画像データ出力は、画像データ同期信号に同期し、デファレンシャルまたはシングルエンドのどちらかの方式にて出力します。但し、QFP パッケージはデファレンシャル出力にのみ対応します。画像データをデファレンシャル出力する場合は、ANA\_RESET レジスタの ( 0x70 ) の xPD\_RSRS ビットに ‘ 1 ’ を設定してください。一方、シングルエンド出力する場合は、GPIO2EN レジスタ ( 0x64 ) の PSYNCEN, PD7EN ~ PDOEN ビットを ‘ 0 ’ に設定してください。

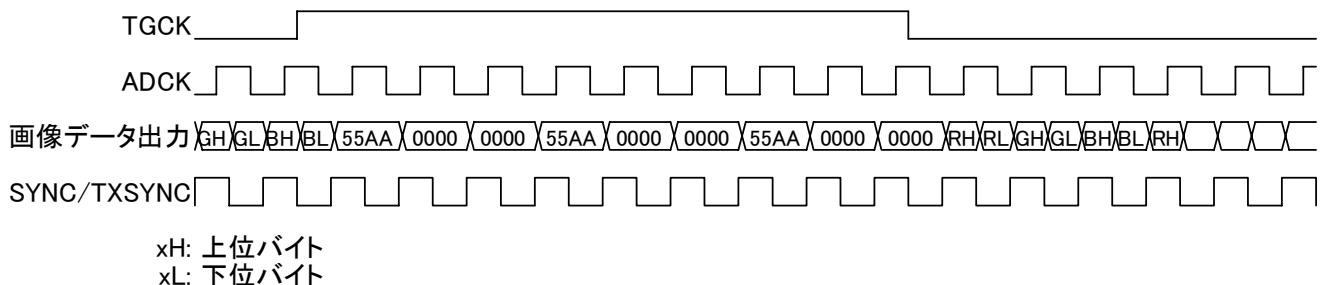

画像データ出力単位は、通常 16 ビットの画像データを上位バイト・下位バイト出力をそれぞれ出力するマルチプレクス出力します。また、PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の IMGOUT4 ビットに ‘ 1 ’ を設定することにより、画像データを MSB から 4 ビット単位で出力します。レジスタ設定それぞれの場合における外部端子と画像データの関係を表 6.2 に示し、図 6.2 にそのタイミングを示します。

表 6.2 画像データ出力

| レジスタ設定   |                        |         | デファレンシャル出力端子 |         |      |         |      |         |      |         |        |    | シングルエンド出力端子 ( BGA パッケージのみ ) |         |     |         |     |         |    |         |   |

|----------|------------------------|---------|--------------|---------|------|---------|------|---------|------|---------|--------|----|-----------------------------|---------|-----|---------|-----|---------|----|---------|---|

| xPD_RSRS | PSYNCEN, PD7EN ~ PDOEN | IMGOUT4 | TXD7         | TXD6    | TXD5 | TXD4    | TXD3 | TXD2    | TXD1 | TXD0    | TXSYNC | D7 | D6                          | D5      | D4  | D3      | D2  | D1      | D0 | SYNC    |   |

| 1        | 1                      | 0       | D15          | D14     | D13  | D12     | D11  | D10     | D9   | D8      | H      | L  |                             |         |     |         |     |         |    |         |   |

|          |                        |         | D7           | D6      | D5   | D4      | D3   | D2      | D1   | D0      | L      |    |                             |         |     |         |     |         |    |         |   |

| 0        | 0                      | 0       | Hi-Z         |         |      |         |      |         |      |         |        |    | D15                         | D14     | D13 | D12     | D11 | D10     | D9 | D8      | H |

| 1        | 1                      | 1       | L            | D15 /D7 | L    | D14 /D6 | L    | D13 /D5 | L    | D12 /D4 | H      | L  |                             |         |     |         |     |         |    |         |   |

|          |                        |         |              | D11 /D3 |      | D10 /D2 |      | D9 /D1  |      | D8 /D0  | L      |    |                             |         |     |         |     |         |    |         |   |

| 0        | 0                      | 1       | Hi-Z         |         |      |         |      |         |      |         |        |    | L                           | D15 /D7 | L   | D14 /D6 | L   | D13 /D5 | L  | D12 /D4 | H |

|          |                        |         |              | D11 /D3 |      | D10 /D2 |      | D9 /D1  |      | D8 /D0  |        |    |                             |         |     |         |     |         |    |         |   |

図 6.2 画像データ出力タイミング

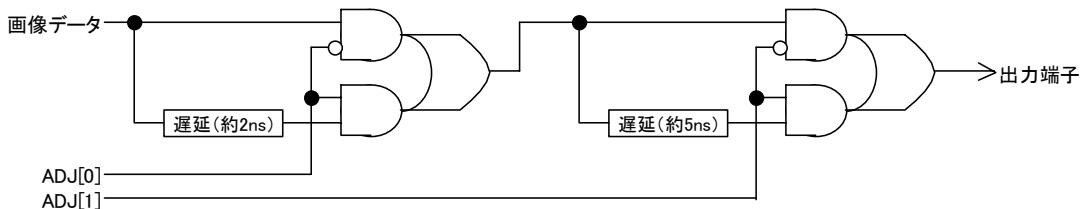

また、画像データの全てのビットは遅延を加えて出力することができます。出力遅延回路は図 6.3 の回路で構成されており、PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の IMGOUTADJ[1:0] ビットの設定により約 2 ~ 7 ns の範囲で遅延出力することができます。

図 6.3 出力遅延回路

表 6.3 遅延特性

| 素子            | MIN.      | TYP.      | MAX.      |

|---------------|-----------|-----------|-----------|

| 遅延 ( 約 2 ns ) | 1 . 2 n s | 2 . 3 n s | 4 . 0 n s |

| 遅延 ( 約 5 ns ) | 3 . 1 n s | 5 . 6 n s | 9 . 7 n s |

画像データ同期信号は、TGCTL レジスタ ( 0x50 ) の ADCKEN ビットを ‘ 1 ’ に設定することにより、内部的に動作を開始します。そして、PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の SYNC\_EN ビットの設定により出力を制御します。また、PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の SYNC\_POL ビットを ‘ 1 ’ に設定することにより、その論理を反転して出力することができます。

## ( 2 ) 画像データ固定値出力設定

CCAEMODE レジスタ ( 0x54 ) の INDEX ビットに ‘ 1 ’ を設定することによって、TGCK 信号が ‘ H ’ 期間、固定値を画像データとして出力します。本機能を用いることによって本 I C とメインコントローラ間の画素位置調整が容易に行えます。

固定値出力は CCAEMODE レジスタ ( 0x54 ) の INDEXMODE[1:0] ビットで設定したチャネルの上位バイト出力に TESTMODE レジスタ ( 0x5F ) の ADTD\_DT[7:0] ビット設定値を出力し、下位バイトはそのビット反転を出力します。また、他チャネル出力には “ 0x0000 ” を出力します。

図 6.4 に ADTD\_DT[7:0] に “ 0x55 ” 、 INDEXMODE[1:0] に “ 00 ” を設定した際の動作例を示します。

図 6.4 固定値出力動作例

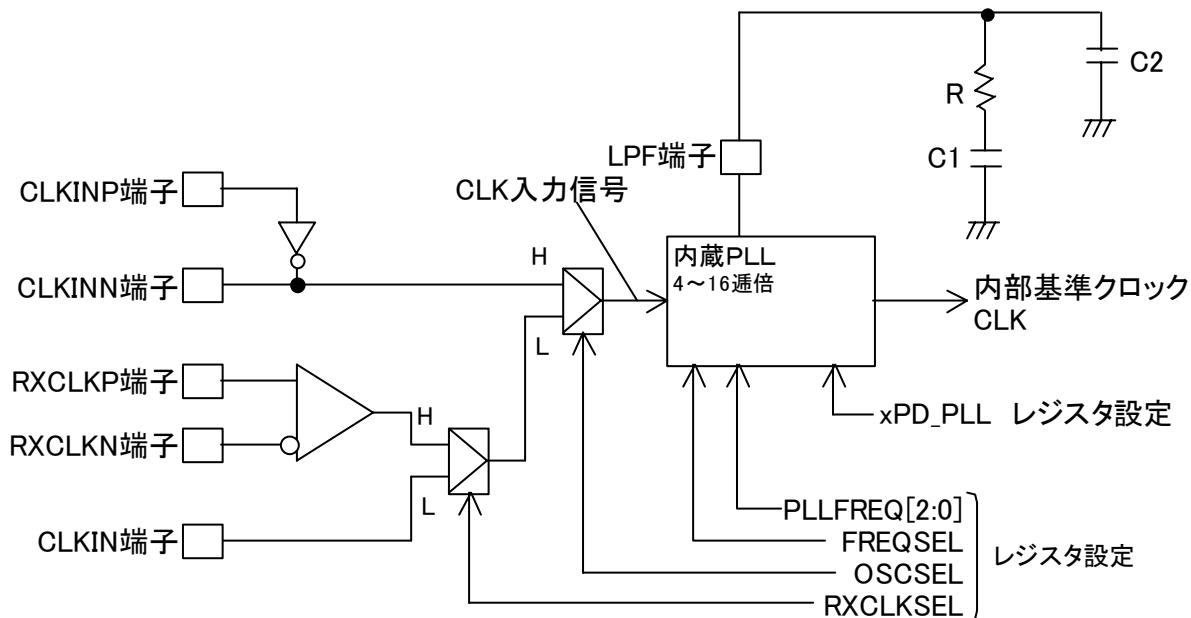

## 6.2 内蔵PLL部

本 I C は外部入力クロックである CLK 入力信号を内蔵 PLL によって 4 ~ 16 適倍し、基準となる内部基準クロックを生成します。また、内部基準クロックは 1 画素あたりの処理を行うために必要な内部ステートを生成します。

図6.5に内蔵PLL周辺の接続関係を示します。

図 6.5 内蔵PLL

## 「制限注意事項」

PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の下記ビットの設定を変更する際は、ANA\_RESET レジスタ ( 0x70 ) の xPD\_PLL ビットを必ず ‘ 0 ’ にして、内蔵 PLL の発振を停止してから行ってください。

FREQSEL, OSCSEL, RXCLKSEL, PLLFREQ[2:0]

### ( 1 ) パワーダウン機能

内蔵PLLのパワーダウン機能は、ANA\_RESETレジスタ(0x70)のxPD\_PLLビットによって制御することができます。xPD\_PLLビットを‘0’に設定することにより、内蔵PLLはパワーダウンモードとなり発振を停止します。また、‘1’に設定することにより、パワーダウンモードが解除され発振を開始します。なお、PLLパワーダウンモード解除後、安定した発振出力を行うまで最大で10ms必要とします。

## (2) 外部クロック選択

本 I C は外部クロックを表 6.4 に示すとおり、クロックパルス入力、デファレンシャルクロック入力または発振回路入力の何れかを選択して入力することができます。また、入力方式にあわせて、PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の RXCLKSEL ビットおよび OSCSEL ビットを設定する必要があります。

表 6.4 OSESEL 設定

| 外部クロック入力         | レジスタ設定 |            | 端子処理   |        |        |          |        |

|------------------|--------|------------|--------|--------|--------|----------|--------|

|                  | OSCSEL | RXCLKSEL   | CLKIN  | RXCLKP | RXCLKN | CLKINP   | CLKINN |

| クロックパルス          | 0      | 0          | クロック入力 | ‘L’ 固定 | ‘H’ 固定 | ‘L’ 固定   | 未接続    |

| デファレンシャル<br>クロック | 0      | 1          | ‘L’ 固定 | クロック入力 |        | ‘L’ 固定   | 未接続    |

| 発振回路             | 1      | don't care | ‘L’ 固定 | ‘L’ 固定 | ‘H’ 固定 | X’tal 接続 |        |

## (3) 内部基準クロック周波数設定

内部基準クロック ( CLK ) 周波数 ( fclk ) 設定は、CLK 入力信号の周波数および遅倍数に応じて表 6.5 に従い PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の FREQSEL ビットを設定します。

表 6.5 FREQSEL 設定

| 内部基準クロック ( CLK 入力信号周波数 ( fclkin MHz ) × 遅倍数 ) | FREQSEL ビット設定 |

|-----------------------------------------------|---------------|

| 75MHz fclkin × ( 遅倍設定 ) 100MHz                | 0             |

| 100MHz fclkin × ( 遅倍設定 ) 120MHz               | 1             |

### 「制限注意事項」

内部基準クロック周波数 ( fclk ) は下記のことに注意して設定してください。

75MHz 内部基準クロック周波数 ( fclk ) 120MHz

## (4) 遅倍設定

内部 PLL の遅倍設定は PLL\_IMGSIG\_CTL レジスタ ( 0x7F ) の PLLFREQ[2:0] ビットにより設定します。PLLFREQ[2:0] ビット設定にて基準となる遅倍数を 4 ~ 16 遅倍の範囲で設定します。以下にその例を示します。また、内蔵 PLL には設定した遅倍数に応じた、LPF 端子に外付けの抵抗とコンデンサを接続する必要があります。外付け抵抗およびコンデンサは表 6.6 の定数の部品を接続してください。

表 6.6 LPF 定数

| PLL 遅倍数 | LPF 定数 |        |     |

|---------|--------|--------|-----|

|         | R      | C 1    | C 2 |

| 4 遅倍    | 0.56K  | 0.01μF | 3pF |

| 6 遅倍    | 0.68K  |        |     |

| 8 遅倍    | 0.75K  |        |     |

| 10 遅倍   | 0.82K  |        |     |

| 12 遅倍   | 0.91K  |        |     |

| 14 遅倍   | 1.0K   |        |     |

| 16 遅倍   | 1.1K   |        |     |

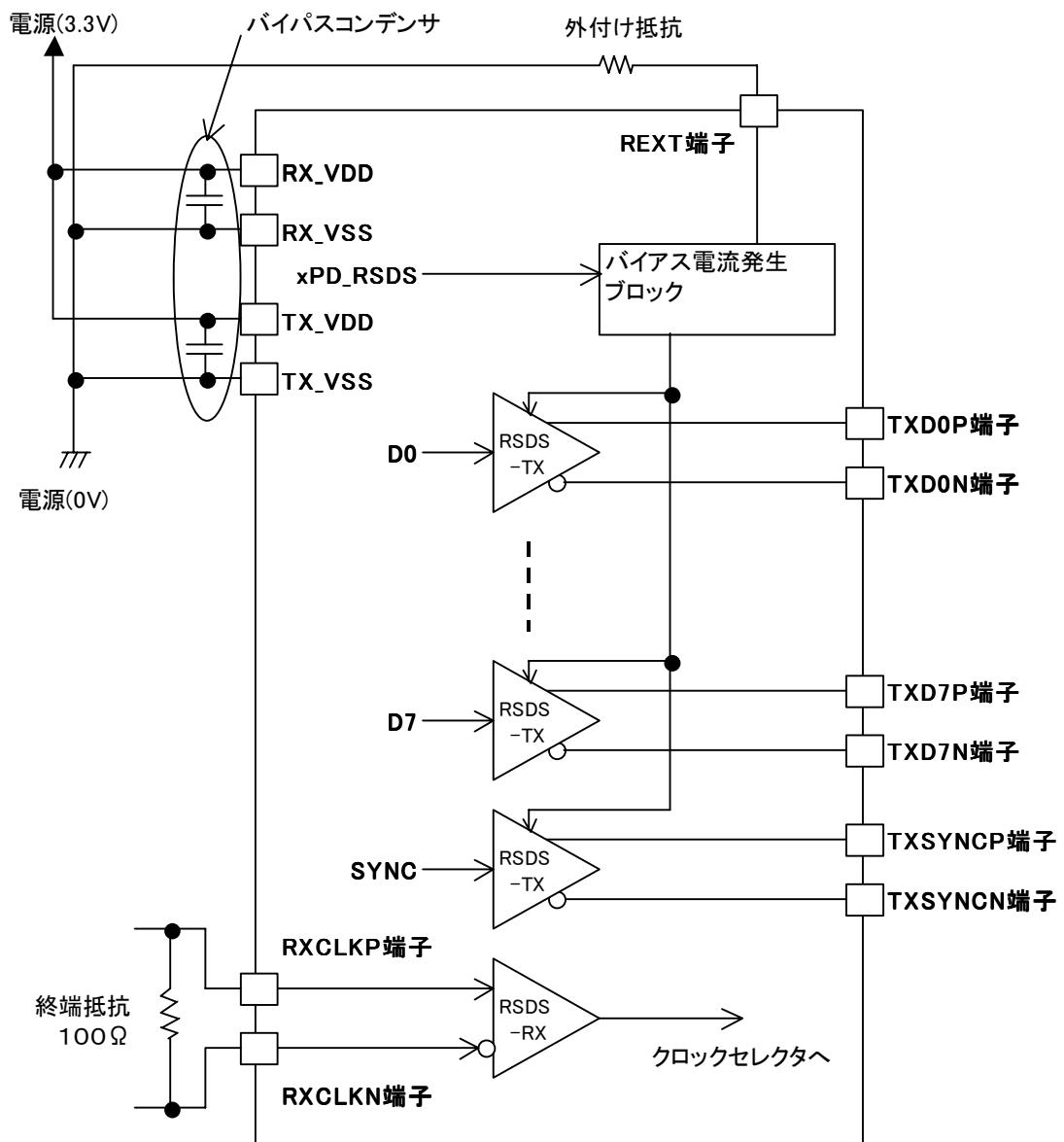

### 6.3 R S D S部

本 I C は画像データのデファレンシャル出力および外部入力クロックに R S D S にて外部とインターフェースすることができます。R S D S 部は送信 9 チャネル、受信 1 チャネルで構成されています。

図 6.6 に R S D S 部周辺の接続関係を示します。

注) TX\_VDD と RXVDD、TX\_VSS と RX\_VSS は内部接続されていますので同一電源から供給してください。

図 6.6 R S D S 接続図

#### (1) パワーダウン機能

R S D S 部送信チャネルは、パワーダウン機能を有しており、ANA\_RESET レジスタ ( 0x70 ) の xPD\_RSDS ビットによって制御することができます。xPD\_RSDS ビットを ‘ 0 ’ に設定することにより、R S D S はパワーダウンモードとなりデータ送信を停止します。また、‘ 1 ’ に設定することにより、パワーダウンモードが解除されデータ送信を開始します。なお、パワーダウンモード解除後、安定したデータ送信を行うまで最大で 10ms 必要です。

## ( 2 ) バイアス電流発生機能

R S D S 部送信チャネルの出力電流は、内蔵されるバイアス電流発生機能によって制御されます。外付け抵抗を REXT 端子に接続することによってその出力電流を調整することが可能です。

表 6.7 R S D S 出力電流特性

| 外付け抵抗定数 | MIN.   | TYP.   | MAX.   |

|---------|--------|--------|--------|

| 26 K    | 0.7 mA | 1.0 mA | 1.4 mA |

| 13 K    | 1.4 mA | 2.0 mA | 2.8 mA |

| 6.5 K   | 2.8 mA | 4.0 mA | 5.6 mA |

| 4.3 K   | 4.0 mA | 6.0 mA | 8.0 mA |

「制限注意事項」

外付け抵抗は公差  $\pm 1.0\%$  以下を推奨します。

## ( 3 ) 終端抵抗

R S D S 部受信端子の直近に 100 の終端抵抗を接続してください。また、R S D S 部送信チャネルにおいても受信デバイスの入力端子直近にて 100 で終端してください。

「制限注意事項」

外付け抵抗は公差  $\pm 1.0\%$  以下を推奨します。

また、基板実装は本 I C とスルーホール等を介さず同一面に実装してください。

## ( 4 ) 空き端子処理

送信チャネル ( TX0 ~ 7P/N, TXSYNCP/N ) において使用しないチャネルはオープンにしてください。

一方、受信チャネル ( RXCLKP/N ) は、RXCLKP を Low レベルに、RXCLKN を High レベルに固定してください。

## 6.4 アナログフロントエンド ( A F E ) 部

### 6.4.1 概要

アナログフロントエンド部はアナログ画像データをデジタルに変換するブロックです。本ブロックは主に C D S 部 ( 相関二重サンプリング ) 、プログラマブル・ゲイン・アンプ ( P G A ) および 16 ビット A / D コンバータから構成されています。

- 16 ビット A / D コンバータ 3 個内蔵

- 最大変換レート : 1 チャネルあたり 10Msps

- 動作モード : C D S モードまたは S / H ( サンプル / ホールド ) モード

- 動作チャネル数 : 1 、 2 または 3 チャネル

- A / D コンバータへのフルスケール入力レンジ : 1 Vp-p

- プログラマブル・ゲイン・アンプ ( P G A ) 調整レンジ : -6.9(0.45 倍 ) ~ +12.0dB(4.0 倍 )

- オフセット調整レンジ : ± 250mV

## 6.4.2 仕様

表6.8 アナログフロントエンド部仕様

| 項目                | 仕様                          |                 |           |

|-------------------|-----------------------------|-----------------|-----------|

|                   | Min.                        | Type            | Max.      |

| 内部基準電圧レベル         |                             |                 |           |

| 低電位リファレンス (REFN)  | 1.10V                       | 1.15V           | 1.20V     |

| 同相モード電圧 (CM1)     | 1.38V                       | 1.40V           | 1.42V     |

| 高電位リファレンス (REFP)  | 1.60V                       | 1.65V           | 1.70V     |

| 変換特性              |                             |                 |           |

| 最大変換レート(1チャネルあたり) |                             |                 | 10Msps    |

| 解像度               |                             | 16 bits         |           |

| アナログ入力            |                             |                 |           |

| 外部入力レンジ           |                             |                 | 2Vp-p     |

| A/Dコンバータ入力レンジ     |                             |                 | 1Vp-p     |

| 入力限界              | -0.3V                       |                 | AVDD+0.5V |

| 最小ゲイン調整           |                             | -6.9dB(約0.45倍)  |           |

| 最大ゲイン調整           |                             | +12dB(約4.0倍)    |           |

| ゲイン分解能            |                             | 6 bits(64ステップ)  |           |

| ゲイン誤差             |                             | ±1dB            |           |

| オフセット調整レンジ        |                             | ±250mV          |           |

| オフセット分解能          |                             | 8 bits(256ステップ) |           |

| オフセット誤差           |                             | ±10mV           |           |

| クランプレベル           | AVDD×1.0、×0.8、×0.6、×0.4から選択 |                 |           |

| 電源条件              |                             |                 |           |

| 電源電圧 (AVDD)       | +3.135V                     | +3.3V           | +3.465V   |

### 6.4.3 内部ブロック構成

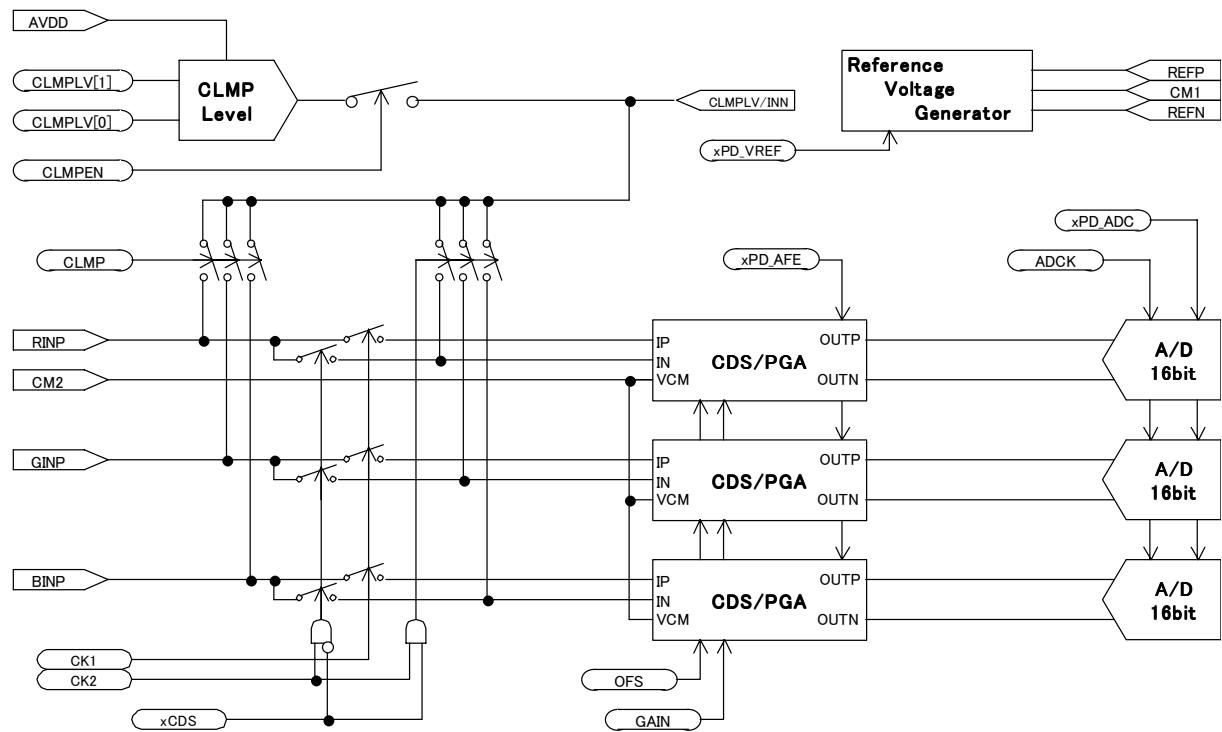

図6.7 AFE内部ブロック図

表6.9 AFE端子説明

| 端子名称             | 端子説明                     | 接続先           |

|------------------|--------------------------|---------------|

| 外部接続             |                          |               |

| AVDD             | アナログ電源                   | 外部接続          |

| REFN             | 低電位リファレンス (1.15V)        | 外部接続          |

| CM1              | 同相モード電圧 (1.4V)           | 外部接続          |

| CM2              | 同相モード電圧 (1.4V)           | 外部接続          |

| REFP             | 高電位リファレンス (1.65V)        | 外部接続          |

| RINP, GINP, BINP | アナログ入力(赤, 緑, 青)          | 外部接続          |

| CLMPLV/INN       | クランプレベルモニタ / リファレンスレベル入力 | 外部接続          |

| 内部接続             |                          |               |

| xPD_VREF         | 基準電圧生成回路パワーダウン           | レジスタ出力        |

| xPD_AFE          | CDS / PGAパワーダウン          | レジスタ出力        |

| xPD_ADC          | A / Dパワーダウン              | レジスタ出力        |

| xCDS             | サンプリングモード設定              | レジスタ出力        |

| OFS              | オフセット設定値                 | レジスタ出力        |

| GAIN             | ゲイン設定値                   | レジスタ出力        |

| CLMPLV[1:0]      | クランプレベル設定                | レジスタ出力        |

| ADCK             | A / D変換クロック              | クロックパターン出力    |

| CK1              | クロック信号1                  | クロックパターン出力    |

| CK2              | クロック信号2                  | クロックパターン出力    |

| CLMP             | クランプ信号                   | クランプ信号 (内部生成) |

#### 6.4.4 パワーダウン機能

アナログフロントエンド部のパワーダウン機能は、ANA\_RESET レジスタ ( 0x70 ) の xPD\_VREF ビット、xPD\_AFE ビットおよび xPD\_ADC ビットによって制御することができます。xPD\_VREF は基準電圧発生回路、xPD\_AFE ビットは内蔵する CDS / PGA ブロックを、xPD\_ADC ビットは内蔵する A / D コンバータのパワーダウン機能を制御します。‘ 0 ’に設定することにより、パワーダウンモードとなります。また、‘ 1 ’に設定することにより、パワーダウンモードが解除され動作を開始します。

#### 6.4.5 動作チャネル

入力チャネル数は 1 チャネルモード、2 チャネルモードおよび 3 チャネルモードを選択することができます。入力チャネル数の切り替えは CCAEMODE レジスタ ( 0x54 ) の CHMODE[1:0] ビットで行います。1 チャネルモードおよび 2 チャネルモード設定時は、CCAEMODE レジスタ ( 0x54 ) の MONOMODE[1:0] ビットによって赤、青または緑の何れかのチャネル入力を選択します。また、3 チャネルモード設定時は画像データの赤、緑および青の出力シーケンスを CCAEMODE レジスタ ( 0x54 ) の MUXSEQ ビットで選択することができます。‘ 0 ’設定時において出力シーケンスは赤 緑 青となり、‘ 1 ’を設定することによって青 緑 赤となります。なお、2 チャネルモードおよび 3 チャネルモード設定時においてその RGB シーケンスの先頭を CCAEMODE レジスタ ( 0x54 ) の RGBMODE[1:0] ビットで選択することができます。

#### 6.4.6 基準電圧発生回路 (Reference Voltage Generator)

アナログフロントエンド部は基準電圧発生回路にて生成した基準電圧レベルを基準に動作を行います。また、内部基準電圧は REFP 端子、CM1 端子および REFN 端子にてモニタすることができます。

#### 6.4.7 クランプ回路

クランプ回路は入力信号を A C カップリングで印加する場合、内部バイアス回路で適正な電圧にクランプします。AFEMODE レジスタ ( 0x7E ) の CLMPEN ビットに ‘ 1 ’を設定した際に有効となります。クランプは CK1 が‘ H ’のタイミングで動作します。なお、クランプは各画素単位に動作する「ビット・クランプ方式」となります。

なお、クランプレベルは表 6.10 に示すとおり、AFEMODE レジスタ ( 0x7E ) の CLMPLV[1:0] ビットの設定によって、その電圧レベルを選択させることができます。CLMPLV / INN 端子によってその電圧レベルをモニタすることができます。

表 6.10 クランプレベル設定

| CLMPLV[1:0] ビット設定 | クランプレベル [V] |

|-------------------|-------------|

| “ 0 0 ”           | AVDD × 0.4  |

| “ 0 1 ”           | AVDD × 0.6  |

| “ 1 0 ”           | AVDD × 0.8  |

| “ 1 1 ”           | AVDD × 1.0  |

### 6.4.8 CDS ブロック

CDS ブロックは、制御部からの制御信号により、アナログ入力信号をサンプリングします。また、CDS ブロックは、全差動アンプで電荷移動にて動作します。

サンプリング方式には、CDS モードまたは S / H モードがあります。その切り替えは、AFEMODE レジスタ ( 0x7E ) の xCDS ビットで行います。レジスタ設定は、‘ 0 ’ 設定時において CDS モードとなり、‘ 1 ’ 設定時は S / H モードに切り替わります。

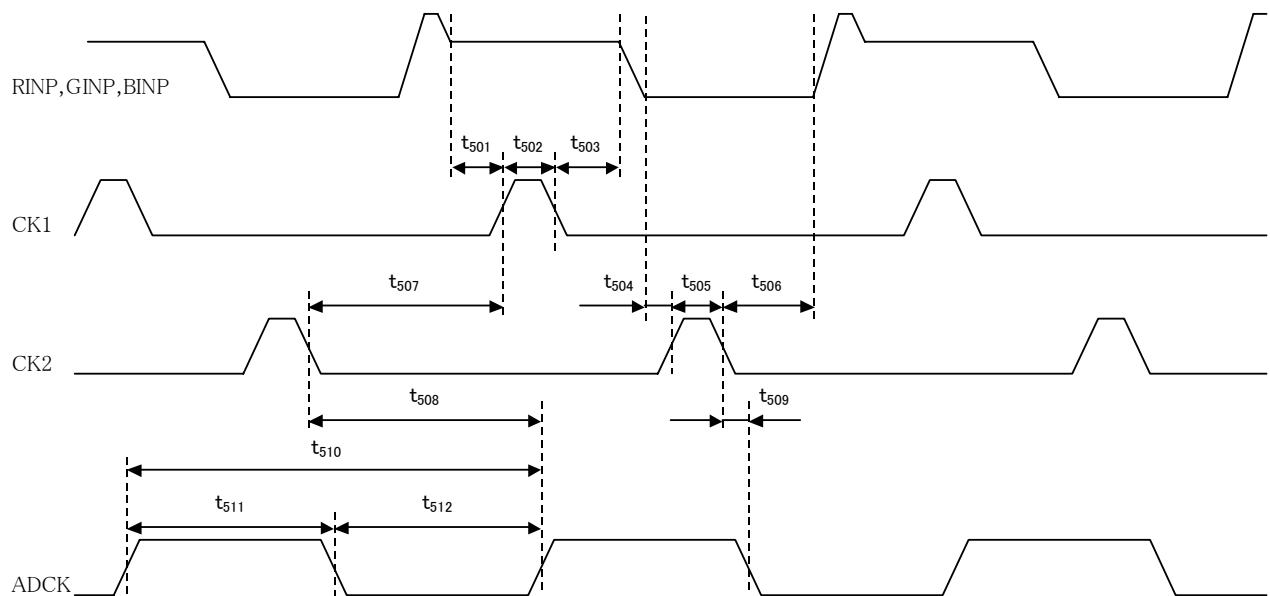

CDS モードは、RINP ( GINP, BINP ) 端子にそれぞれ入力されたアナログ入力信号を、黒基準レベルおよび画像データレベルをサンプリングし、その差電圧成分を A / D 変換します。

S / H モードは、差電圧入力が可能です。差電圧入力は、CLMPLV / INN 端子に基準電圧レベルを入力し、RINP ( GINP, BINP ) 端子へ入力されるアナログ入力信号との差電圧入力を行います。

表 6.11 に各動作モードにおけるレジスタ設定例を示します。

表 6.11 動作モード設定例

| 動作モード |          | AFEMODE レジスタ ( 0x7E ) |        |

|-------|----------|-----------------------|--------|

|       |          | xCDS                  | CLMPEN |

| CDS   | DC 入力    | ‘ 0 ’                 | ‘ 0 ’  |

|       | ビット・クランプ | ‘ 0 ’                 | ‘ 1 ’  |

| S / H | 差電圧入力    | ‘ 1 ’                 | ‘ 0 ’  |

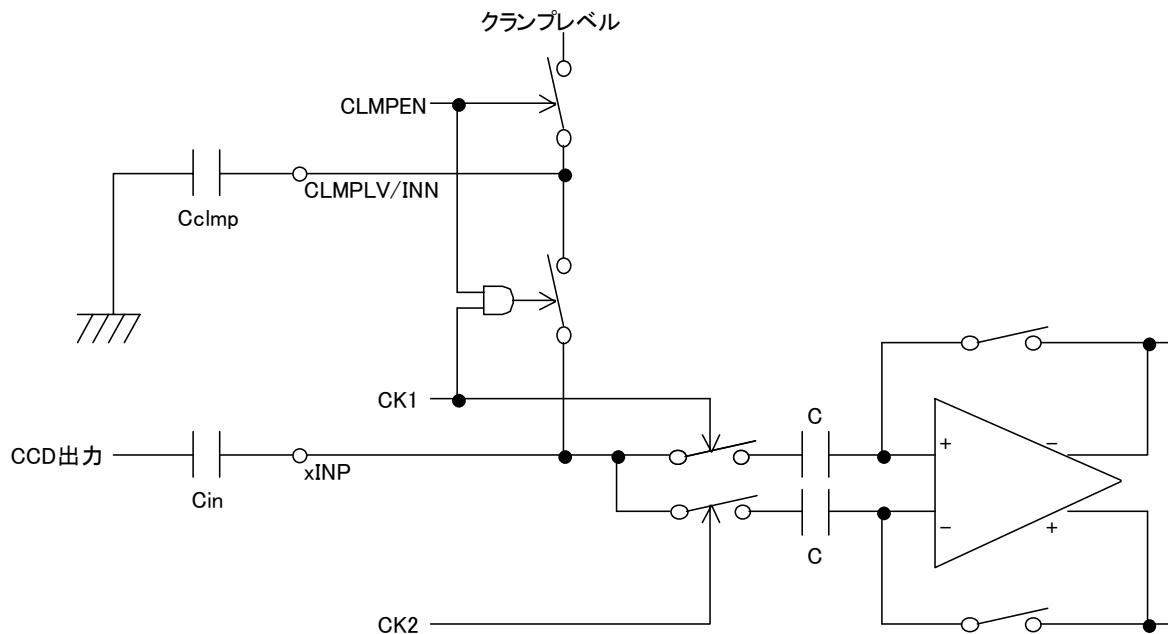

## ( 1 ) C D S モード機能

図 6.8 C D S モード内部構成図

AFEMODE レジスタ ( 0x7E ) の xCDS ビットに ‘ 0 ’ を設定することにより C D S モードとなります。また、AFEMODE レジスタ ( 0x7E ) の CLMPEN ビットに ‘ 1 ’ を設定することにより、画素毎にクランプするビット・クランプを行います。

C D S モードは CK1 信号でクランプレベルに引き込んだ黒基準レベルを、CK2 信号が ‘ H ’ 入力時に画像データレベルをサンプリングします。図 6.8 に C D S モード時における内部構成図を示します。

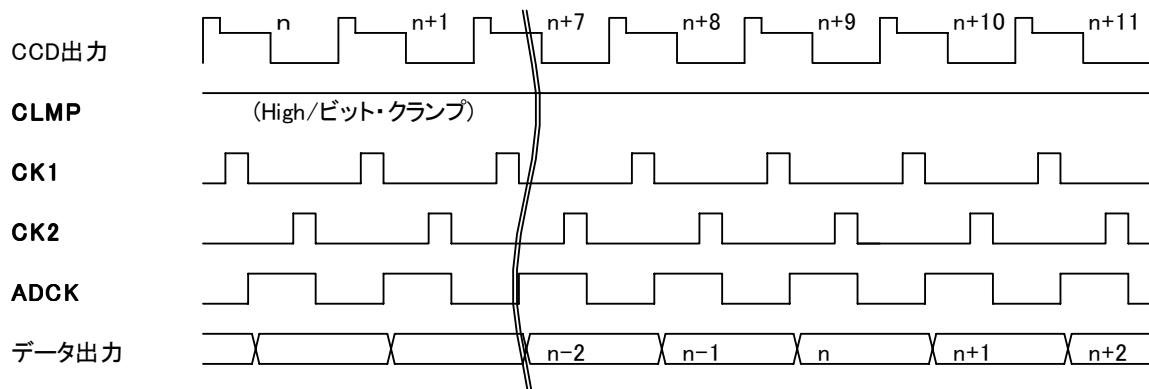

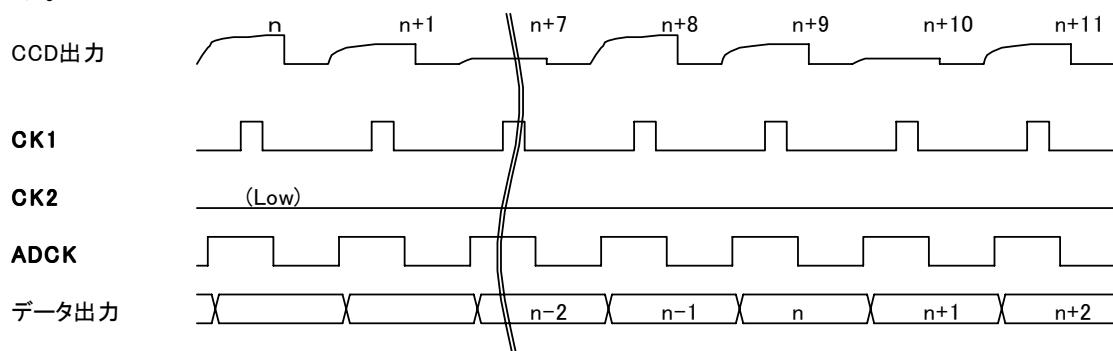

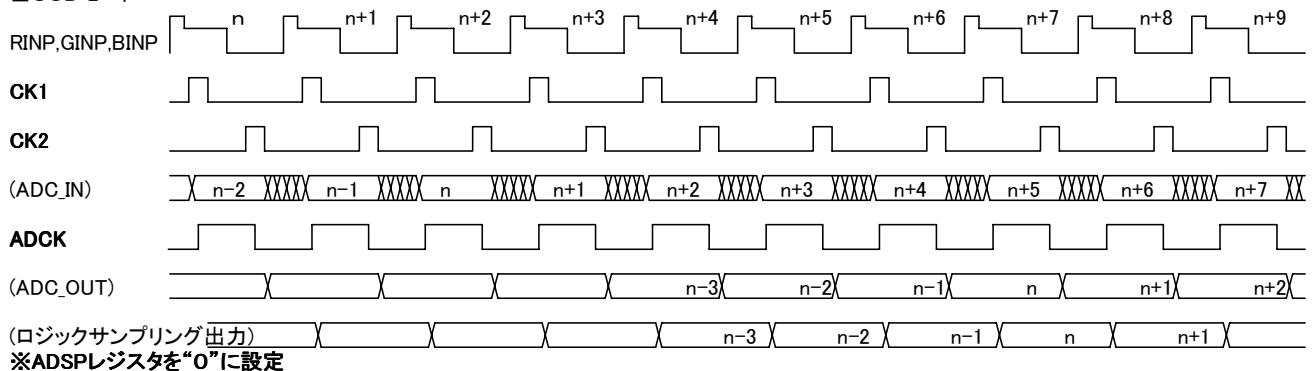

図 6.9 C D S モード動作タイミング例

図 6.9 に C D S モード時の動作タイミング例を示します。

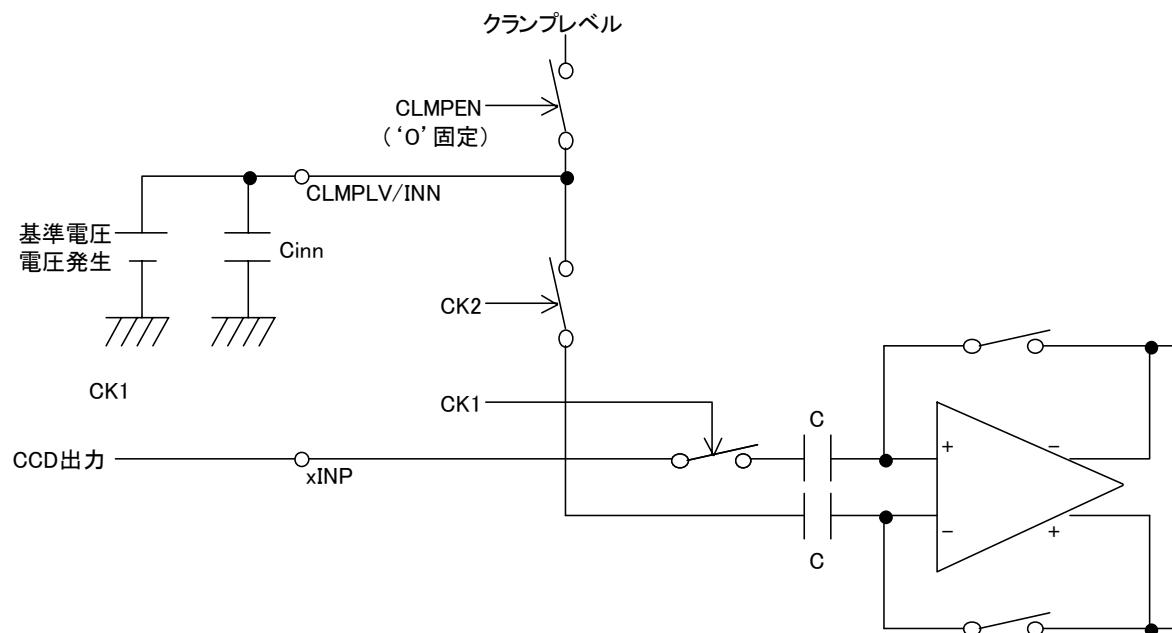

## (2) S / H モード機能 (差電圧入力)

図 6.10 S / H モード (差電圧入力) 内部構成図

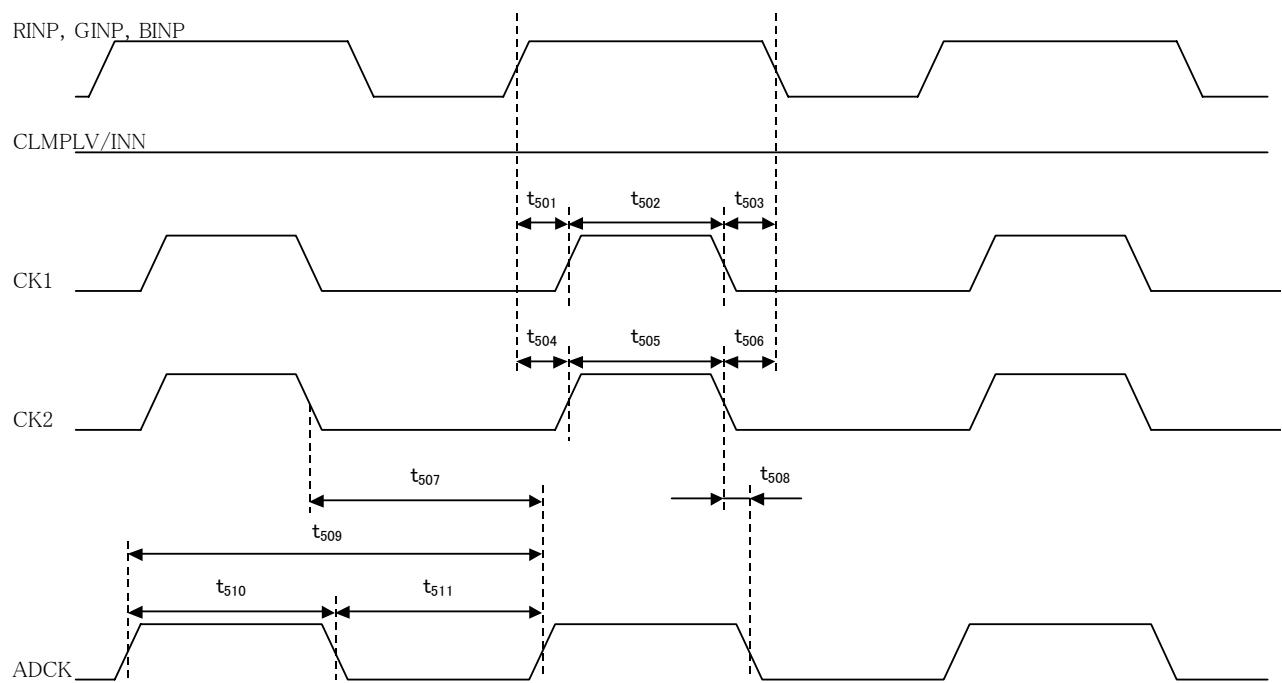

AFEMODE レジスタ (0x7E) の xCDS ビットに ‘1’ を設定することにより S / H モード (差電圧入力) となります。S / H モード (差電圧入力) は、CLMPLV / INN 端子に基準電圧レベルを入力し、アナログ入力信号との差電圧入力を行います。

サンプリングは、CK1 信号および CK2 信号を同タイミングで入力することにより、基準電圧レベルと CCD 出力レベルを同時にいます。図 6.10 に S / H モード (差電圧入力) 時における内部構成図を示します。

図 6.11 S / H モード (差電圧入力) 動作タイミング例

図 6.11 に S / H モード (差電圧入力) 時で基準電圧を外部入力の場合の動作タイミング例を示します。

#### 6.4.9 オフセット調整

本 I C は入力信号レベルに対してオフセットを調整することが可能です。

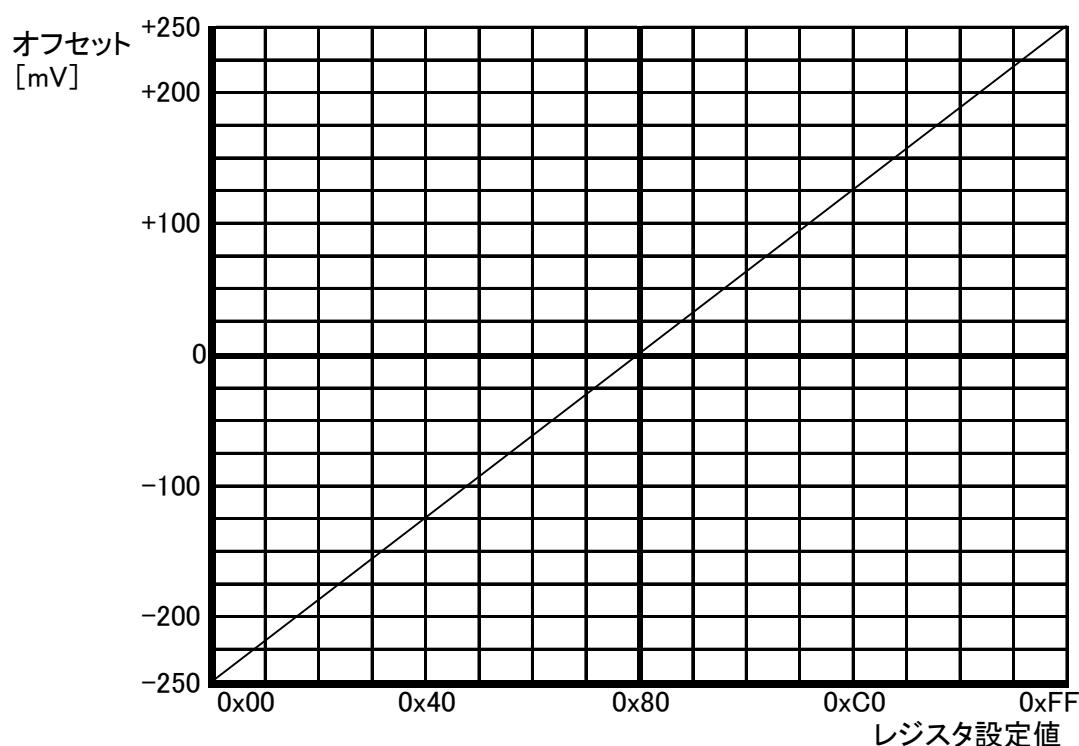

オフセット調整には 8 ビットのオフセット調整レジスタを持ち、このレジスタを設定することによってオフセット値を調整します。また、オフセット調整は赤チャネル、緑チャネルおよび青チャネルをそれぞれ独立して設定することができるよう、RDGAINOFS レジスタ ( 0x78 ) 、GRGAINOFS レジスタ ( 0x79 ) および BLGAINOFS レジスタ ( 0x7A ) のそれぞれ RD0FS[7:0] 、 GROFS[7:0] および BLOFS[7:0] ビットが用意されています。

オフセット調整レンジは - 250mV から + 250mV まで設定することができ “ 0x00 ” を設定すると - 250mV となり、“ 0xFF ” を設定すると + 250mV となります。

図 6.1.2 はオフセット調整レジスタと得られるオフセット値を示しています。

図 6.1.2 オフセット調整特性

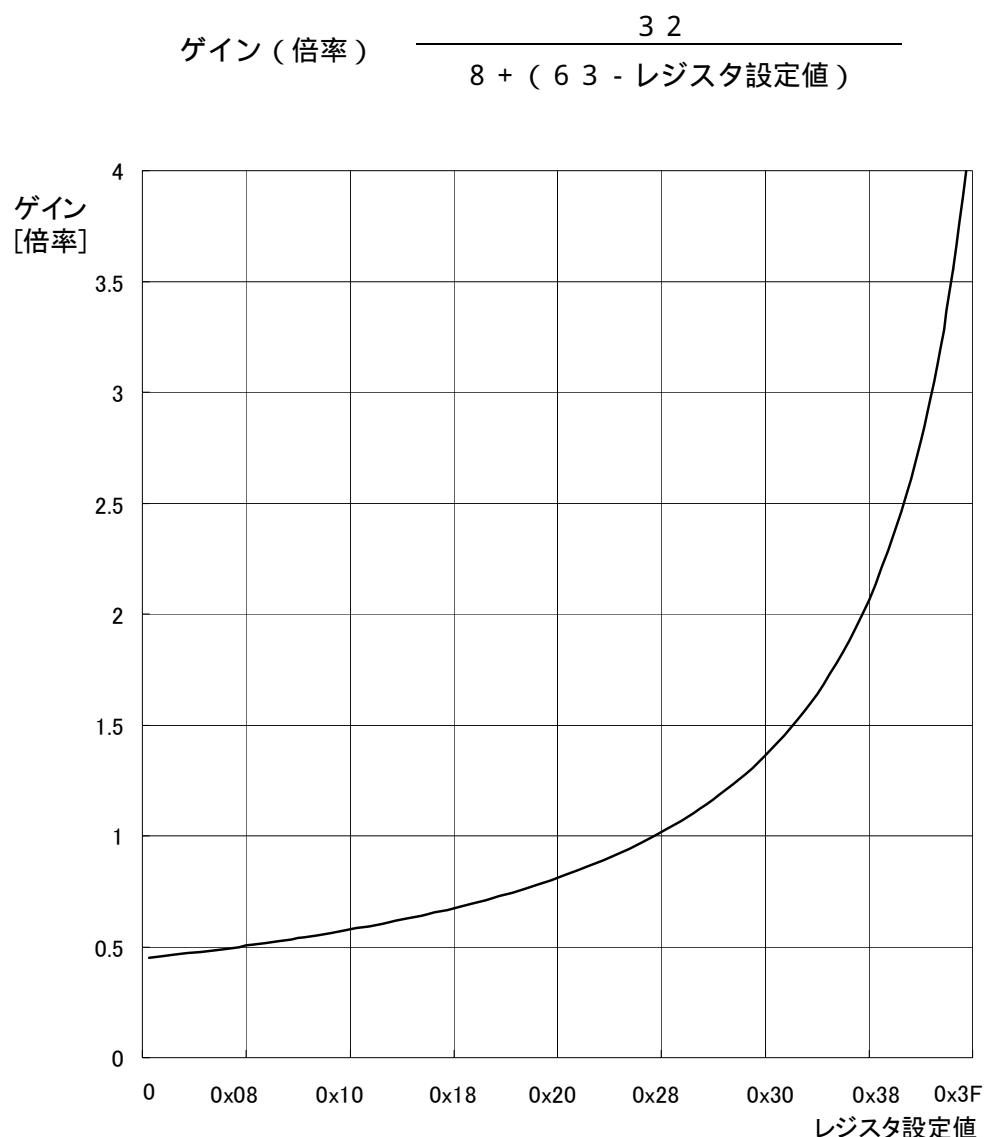

#### 6.4.1.0 プログラマブル・ゲイン・アンプ (PGA)

本ICにはプログラマブル・ゲイン・アンプが内蔵されてあります。

プログラマブル・ゲイン・アンプには6ビットのゲイン調整レジスタを持ち、このレジスタを設定することによってゲイン値を調整します。また、ゲイン調整は赤チャネル、緑チャネルおよび青チャネルをそれぞれ独立して設定することができるよう、RDGAIN0FSレジスタ(0x78)、GRGAIN0FSレジスタ(0x79)およびBLGAIN0FSレジスタ(0x7A)のそれぞれRDGAIN[7:0]、GRGAIN[7:0]およびBLGAIN[7:0]ビットが用意されています。

ゲイン調整レンジは-6.9dB(0.45倍)から+12.0dB(4倍)まで設定することができ、“0x00”を設定すると最小ゲイン(-6.9dB)となり、“0x3F”を設定すると最大ゲイン(+12.0dB)となります。16ビットA/Dコンバータの入力レンジ(1V)とマッチングさせるように値を設定します。

図6.1.3はゲイン調整レジスタと得られるゲイン値を示しています。また、レジスタ設定値と得られるゲインは下記の計算式により近似することができます。

図6.1.3 ゲイン調整特性

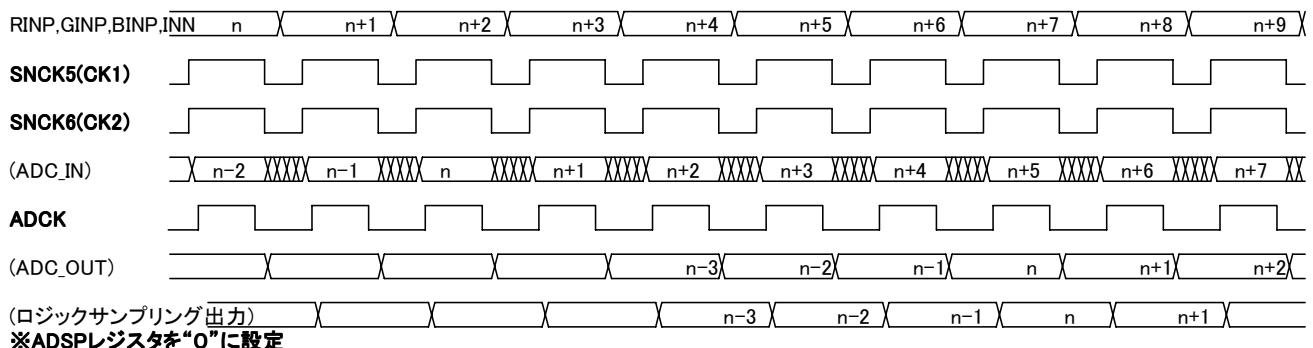

### 6.4.1.1 タイミング

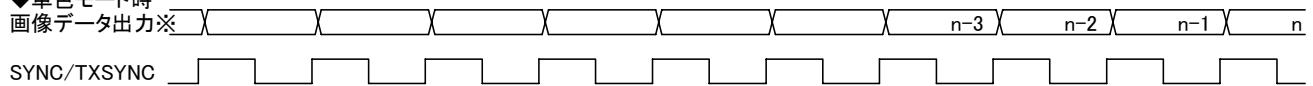

#### ■CCDモード

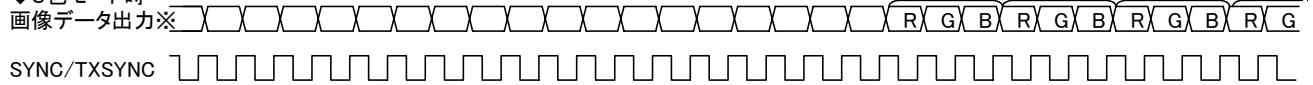

#### ◆単色モード時

#### ◆3色モード時

※ 画像データ出力はD7～D0端子またはTXD7～0端子から設定により8ビット×2出力または4ビット4出力を行います。

注1) ADCKとSYNC/TXSYNCは基準クロックの同一タイミングにて出力されます。

従って、素子遅延によるスキューが挿入されるが同位相での出力になります(3色モード時は画素の先頭に同期)。

注2) 3色モード時のD15～0出力は出力シーケンスがR→G→B設定時を示します。

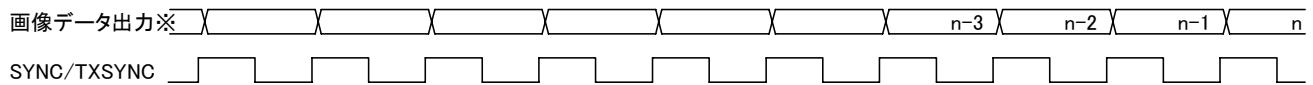

#### ■CISモード

※ 画像データ出力はD7～D0端子またはTXD7～0端子から設定により8ビット×2出力または4ビット4出力を行います。

注1) ADCKとSYNC/TXSYNCは基準クロックの同一タイミングにて出力されます。

従って、素子遅延によるスキューが挿入されるが同位相での出力になります。

図 6.1.4 タイミング例

## 6.5 タイミング生成部

### 6.5.1 概要

制御部は画像センサおよび内部AFEの制御信号を生成します。

- シャッタレスCCDおよびCISに対応

- 画像センサおよび内部AFEの制御信号をプログラマブルに対応

- 画像データ出力は8ビット×2出力または4ビット×4出力に対応

- 画像センサの有効画素転送時およびダミー画素転送時のクロックパルスパターン出力をプログラマブルに対応

- 各クロック、制御信号の出力制御対応

- 画像データ取り込みサンプルポイントの制御対応

- 外部LED点灯制御機能搭載 ( CIS制御モード動作時 )

### 6.5.2 画像取り込み動作

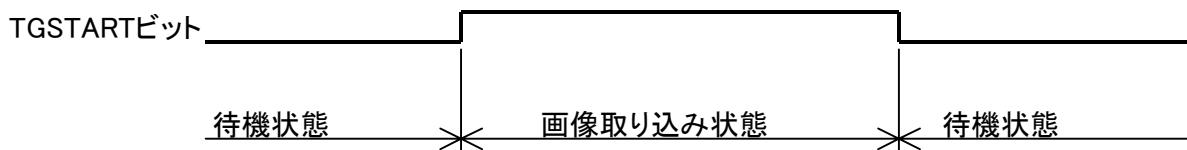

本 I C の動作には、待機状態と画像取り込み状態の二つの状態があります。待機状態にするためには TGCTL レジスタ ( 0x50 ) の TGSTART ビットに ‘ 0 ’ を設定する必要があります。一方、画像取り込み状態にするためには同じく TGSTART ビットに ‘ 1 ’ を設定します。 TGSTART ビットに ‘ 1 ’ が設定されると画像取り込み動作を開始します。

図 6.15 待機状態と画像取り込み状態

#### 「制限注意事項」

画像取り込み状態のとき TGSTART ビット以外のレジスタ設定変更は禁止です。変更した場合正常動作を行わない場合があります。

## 6.5.3 内部動作

### 6.5.3.1 1画素処理

#### (1) 内部ステートおよび駆動パターン分解能設定

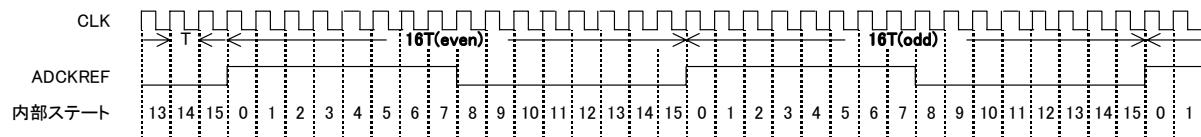

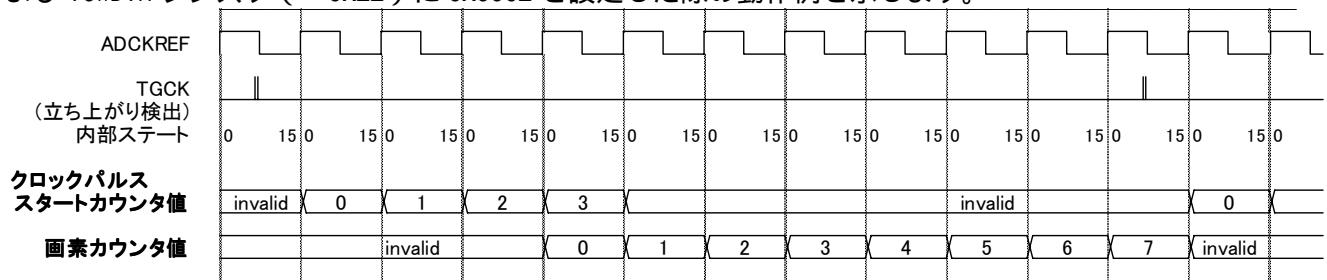

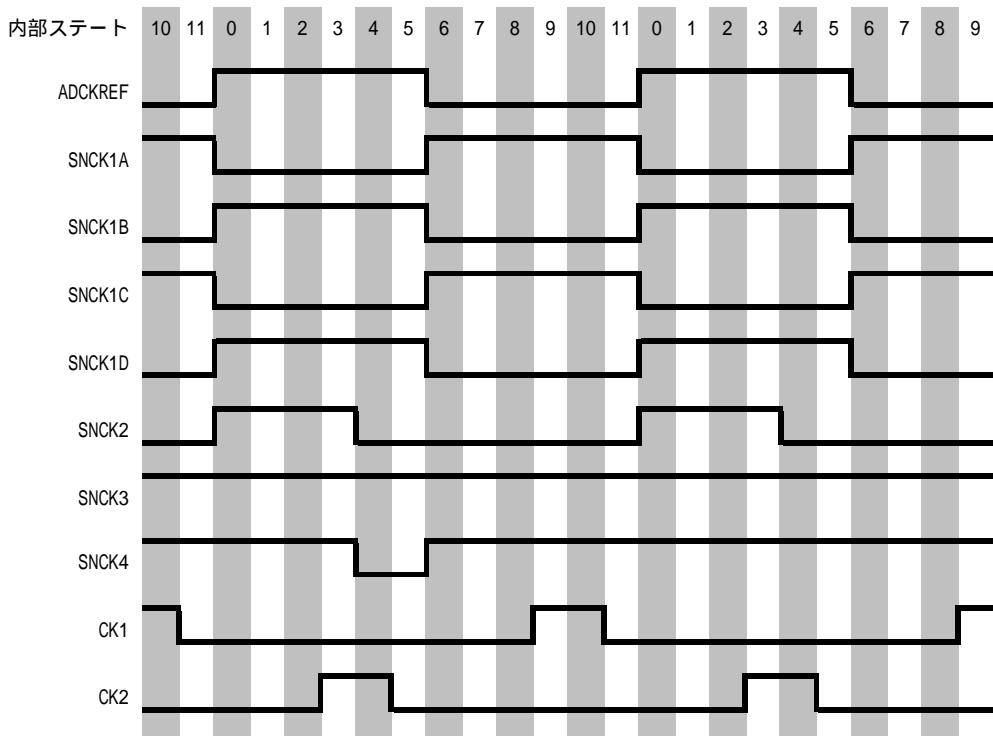

本 I C の 1 画素あたりの処理動作は全て内部ステートを基準に動作を行います。また、内部信号「ADCKREF」は内部ステートの基点となる信号でその周期は駆動パターン分解能設定に依存されます。ADCKREF 1 サイクルで 1 画素の処理を行います。

また、内部ステートのステート数は駆動パターン分解能設定に依存し、STCTL レジスタ ( 0x51 ) の STNUM[2:0] ビットで設定します。例えば 16 分周設定時において分解能は 16 となり、ADCKREF は 16 ステートで 1 サイクルとなります。

図 6.1.6 に駆動パターン分解能設定を 16 分周に設定した際の内部ステートと ADCKREF 信号の関係を示します。なお、図中は「T」は内部ステートの 1 ステート時間を示し、1 画素を 0 ~ 15 ステート ( 全 16T ) で処理します。

図 6.1.6 内部ステートと ADCKREF 信号の関係 (16 分周設定時)

1 画素の処理単位 ( 1 チャネル / 2 チャネル / 3 チャネル ) は CCAEMODE レジスタ ( 0x54 ) の CHMODE[1:0] ビットで設定します。C I S 制御モード時は線順次出力に対応するため、自動的に 1 画素の処理単位を 1 チャネル設定となります。

表 6.1.2 に 8 ビット × 2 出力時における駆動パターン分解能設定、全ステート数および設定可能な 1 画素の処理単位の関係を示します。また、カッコ内に 4 ビット × 4 出力時における設定可否を示します。

表 6.1.2 内部ステート数

| 駆動パターン分解能設定<br>設定値(STNUM[2:0]) | 分周 | ステート範囲   | 全ステート数 | 1 画素処理単位 |         |         |

|--------------------------------|----|----------|--------|----------|---------|---------|

|                                |    |          |        | 1 チャネル   | 2 チャネル  | 3 チャネル  |

| “ 111 ” ~ “ 101 ”              |    | ( 禁止設定 ) |        |          |         |         |

| “ 100 ”                        | 8  | 0 ~ 7    | 8T     | ( )      | ( )     | × ( × ) |

| “ 011 ”                        | 10 | 0 ~ 9    | 10T    | ( × )    | × ( × ) | × ( × ) |

| “ 010 ”                        | 12 | 0 ~ 11   | 12T    | ( )      | ( × )   | ( )     |

| “ 001 ”                        | 14 | 0 ~ 13   | 14T    | ( × )    | × ( × ) | × ( × ) |

| “ 000 ”                        | 16 | 0 ~ 15   | 16T    | ( )      | ( )     | × ( × ) |

：設定可

× : 設定不可

## ( 2 ) 同期モード

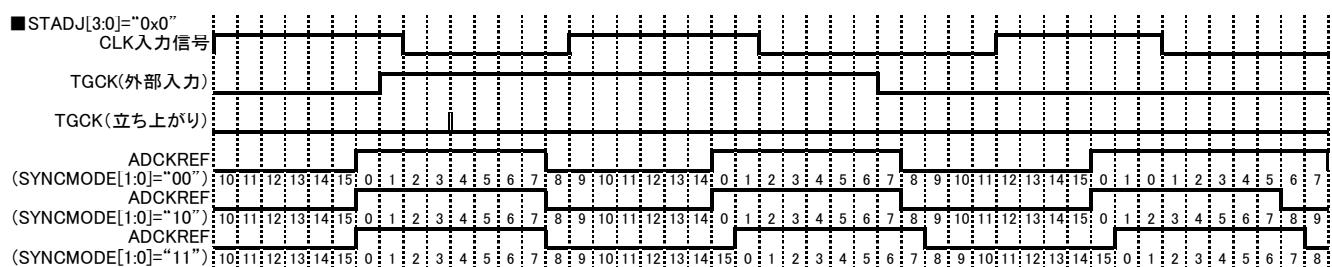

本 I C は内部ステートを CLK 入力信号に対する位相を調整( 同期化 )する機能を有しています。STCTL レジスタ ( 0x51 ) の SYNCODE[1:0] ビットの設定によりその同期方法を選択することができます。

SYNCODE[1:0] ビットが “ 00 ” 設定の場合、常に CLK 入力信号の立ち上がりに同期して内部ステートを初期化します。 “ 10 ” 設定の場合は、TGCK 信号 ( シフトパルレストリガ信号 ) の立ち上がりを検出後、次の CLK 入力信号の立ち上がりでのみ内部ステートの同期化を行います。そして、 “ 11 ” 設定の場合は同期化動作を行わず、内部カウンタフル検出でのみ内部ステートの初期化を行います。図 6.17 にそれぞれの設定時における動作例を示します。

図 6.17 同期モード設定例 (16 遅倍・16 分周設定時)

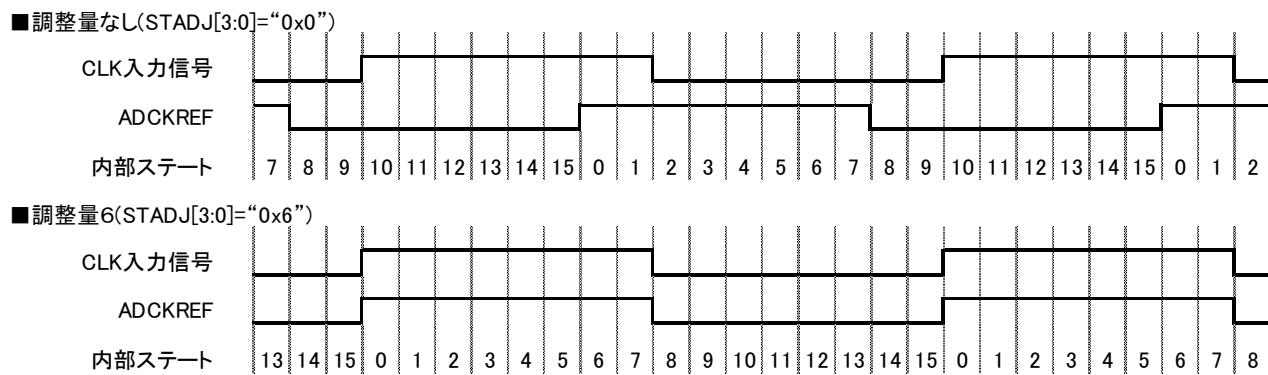

また、内部ステートを CLK 入力信号と同期する際、STCTL レジスタ ( 0x51 ) の STADJ[3:0] ビットにより、その位相差を設定することができます。図 6.18 にそのおける動作例を示します。

図 6.18 内部ステート同期化調整例

### 「制限注意事項 2 」

遅倍設定と分周設定が異なる場合、同期モードは TGCK の立ち上がり検出時のみ同期化設定 ( SYNCODE[1:0] = “ 10 ” ) または同期化禁止設定 ( SYNCODE[1:0] = “ 11 ” ) にしてください。

### 6.5.3.2 1ライン処理

1ライン処理はTGSK 信号を基準に行います。TGCK 信号は1ライン処理の開始を示す信号であり、本 I C は TGCK 信号のアクティブ検出後、1ライン分の処理を開始します。また、TGCK 信号の周期をライン周期といいます。

TGCK 信号は、CCAEMODE レジスタ ( 0x54 ) の INTGCK ビットにより、外部入力または内部生成を選択することができます。TGCK 信号を内部生成した場合、その周期( ライン周期 )は TGPERIOD レジスタ ( 0x20~1 )と CKSTART レジスタ( 0x24 )で設定することができ、パルス幅を TGCKWDTH レジスタ( 0x22 )で設定することができます。また、ライン周期は1画素単位で設定することができます。なお、具体的なライン周期は次に示す計算式で求められます。

$$\text{ライン周期} = 1 / \text{ADCKREF 周波数} \times (\text{TGPERIOD}[20:0] + \text{CKSTART}[11:0] + 1)$$

設定例： ADCKREF 周波数 5MHz、TGPERIOD = 0x10000、CKSTART=0x010 のとき

$$\text{ライン周期} = 1 / 5 \text{MHz} \times (0x10000 + 0x010 + 1) \quad 13.1\text{ms}$$

なお、TGCK 信号を内部生成した場合、TGCK 端子にその状態を出力します。

図 6.19 は TGPERIOD レジスタ ( 0x20~1 ) に 0x00007、CKSTART レジスタ ( 0x24 ) に 0x0003 および TGWDTH レジスタ ( 0x22 ) に 0x0002 を設定した際の動作例を示します。

図 6.19 1ライン処理動作例

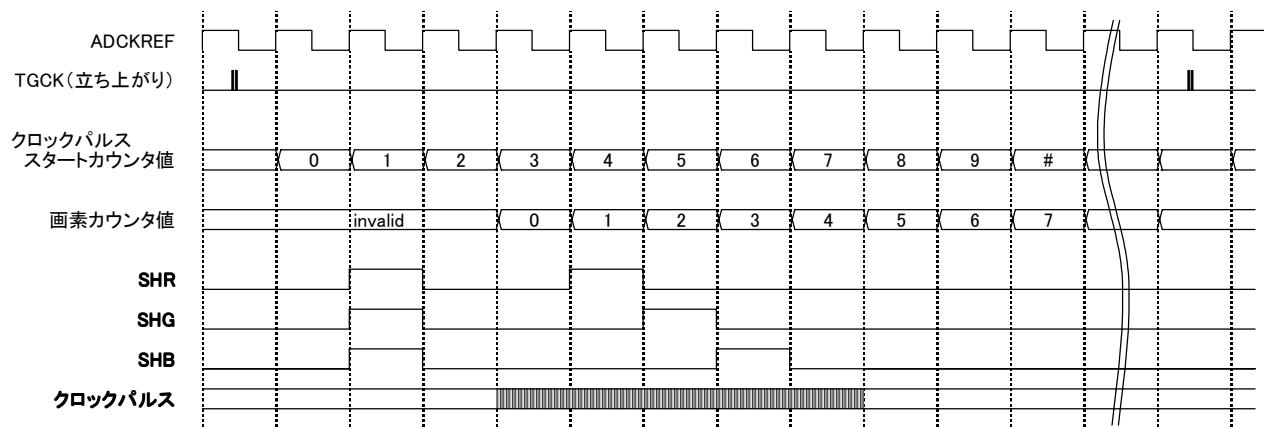

本 I C は1ライン分の取り込み処理を行うために次の2カウンタによって各タイミングを生成します。

#### ■ クロックパルススタートカウンタ

SNCK1A、SNCK1B、SNCK1C、SNCK1D、SNCK2~4、CK1、CK2、SH、SHR、SHG、SHB 信号の

出力開始タイミングを生成

TGCK 信号アクティブを受信後の内部ステート先頭 “ 0 ステート ” からカウント開始

#### ■ 画素カウンタ

A F E から転送されてきた画像データの画素数をカウント

クロックパルススタートカウンタ値が CKSTART レジスタ ( 0x24 )の設定値に達した時点でカウント開始

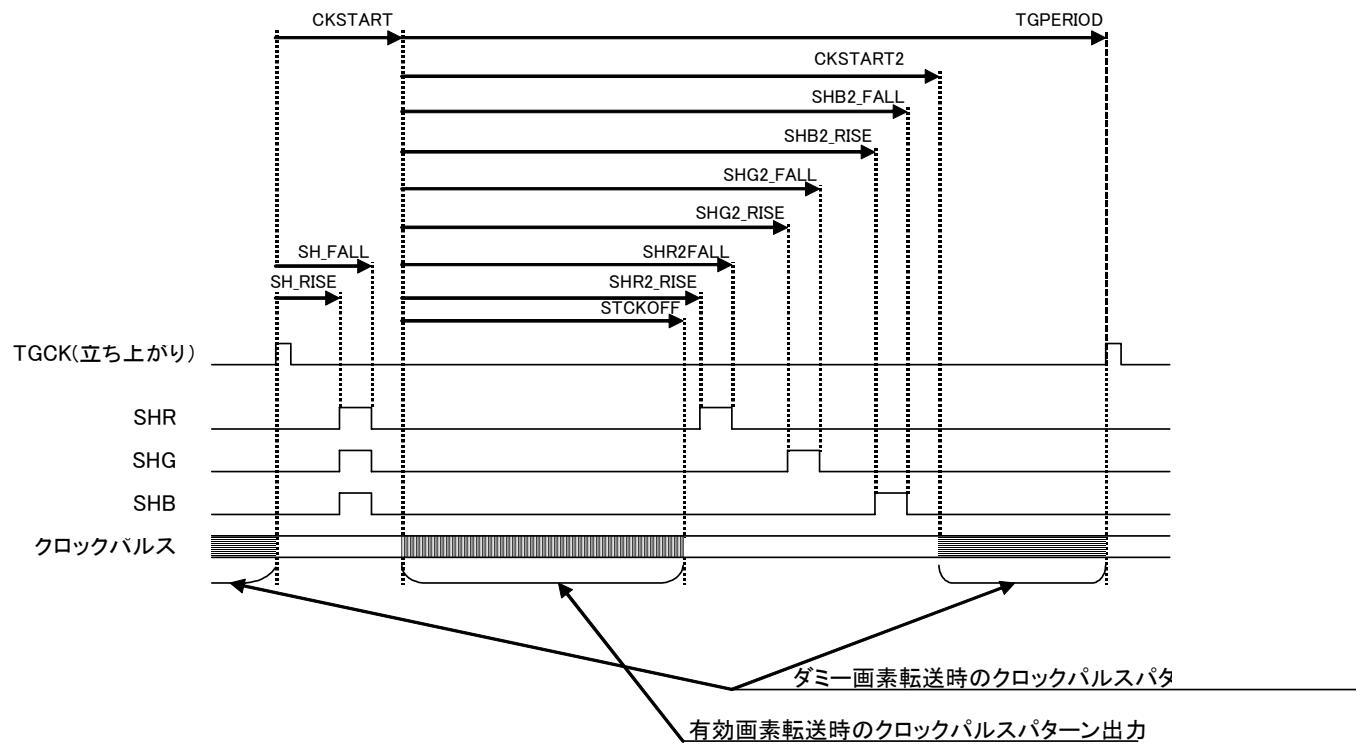

## 6.5.4 制御信号出力

### 6.5.4.1 シフト信号、クロックパルス、出力タイミング

#### (1) タイミング設定

制御信号は動作させる画像センサによって、その出力モードを設定する必要があります。CCEAMODE レジスタ ( 0x54 ) の CIS ビットの設定により出力モードを設定することができます。‘ 0 ’に設定することによって C C D 制御モードとなり、‘ 1 ’に設定することによって C I S 制御モードとなります。

また、各制御信号の出力タイミングはそれぞれ対応したレジスタで設定します。表 6.1.3 に各信号の出力タイミングに関連したレジスタを示します。

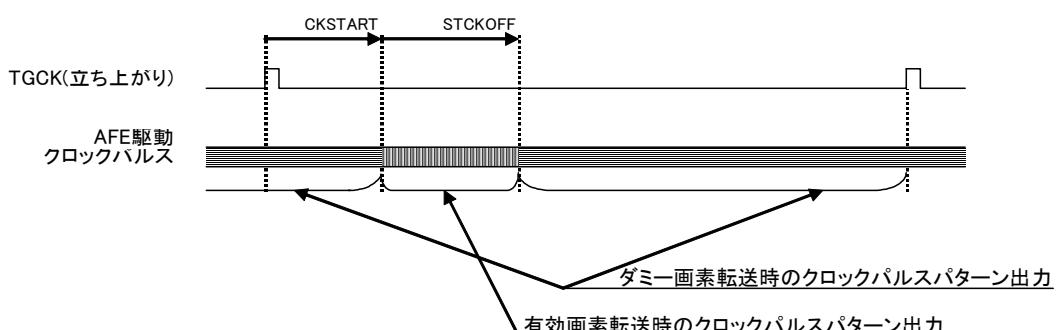

A F E 駆動クロックである下記クロックパルスは、TGSTART ビットに関わらず TGCTL レジスタ ( 0x50 ) の ADCKEN ビットにより出力制御を行います。ADCKEN ビットが‘ 1 ’のとき常に出力を行います。

CK1, CK2

また、出力パターンは CKSTART レジスタ ( 0x24 ) から STCKOFF レジスタ ( 0x28 ~ 9 ) 範囲内において有効画素転送時のクロックパターンを出力し、それ以外の期間はダミー画素転送時のクロックパルスパターン出力を行います。但し、TGSTART ビットを‘ 1 ’設定後の最初の TGCK 信号 1 パルス目では有効画素転送時のクロックパルスパターンを出力します。

図 6.2.0 A F E 駆動クロックのクロックパルス出力タイミング

表6.13 各信号出力タイミング設定レジスタ

| 制御モード | 信号名                  | 信号端子名                                                        | タイミング設定レジスタ                                                  |                                                                          |

|-------|----------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|

|       |                      |                                                              | アクティブ設定                                                      | インアクティブ設定<br>またはパルス幅設定                                                   |

| C C D | シフト信号                | SH                                                           |                                                              |                                                                          |

|       |                      | SHR                                                          | SH_RISE( 0x26)<br>SHR2_RISE( 0x30 ~ 1)                       | SH_FALL( 0x27)<br>SHR2_FALL( 0x32 ~ 3)                                   |

|       |                      | SHG                                                          | SH_RISE( 0x26)<br>SHG2_RISE( 0x34 ~ 5)                       | SH_FALL( 0x27)<br>SHG2_FALL( 0x36 ~ 7)                                   |

|       |                      | SHB                                                          | SH_RISE( 0x26)<br>SHB2_RISE( 0x38 ~ 9)                       | SH_FALL( 0x27)<br>SHB2_FALL( 0x3A ~ B)                                   |

|       | クロックパルス<br>( C C D ) | SNCK1A, SNCK1B,<br>SNCK1C, SNCK1D,<br>SNCK2, SNCK3,<br>SNCK4 | 有効画素転送時：<br>CKSTART( 0x24)<br>ダミー画素転送時：<br>CKSTART2( 2A ~ B) | 有効画素転送時：<br>STCKOFF( 28 ~ 9)<br>ダミー画素転送時：<br>次 TGCK 信号アクティブ<br>を検出するまで出力 |

|       |                      | CK1, CK2                                                     | TGCTL( 0x50)<br>ADCKEN ビット                                   | TGCTL( 0x50)<br>ADCKEN ビット                                               |

|       | シフト信号                | SH                                                           | SH_RISE( 0x26)                                               | SH_FALL( 0x27)                                                           |

|       | L E D制御信号            | LEDR                                                         | SHR2_RISE( 0x30 ~ 1)                                         | SHR2_FALL( 0x32 ~ 3)                                                     |

|       |                      | LEDG                                                         | SHG2_RISE( 0x34 ~ 5)                                         | SHG2_FALL( 0x36 ~ 7)                                                     |

|       |                      | LEDB                                                         | SHB2_RISE( 0x38 ~ 9)                                         | SHB2_FALL( 0x3A ~ B)                                                     |

|       | クロックパルス<br>( C I S ) | SNCK1A, SNCK1B,<br>SNCK1C, SNCK1D                            | 有効画素転送時：<br>CKSTART( 0x24)<br>ダミー画素転送時：<br>CKSTART2( 2A ~ B) | 有効画素転送時：<br>STCKOFF( 28 ~ 9)<br>ダミー画素転送時：<br>次 TGCK 信号アクティブ<br>を検出するまで出力 |

|       |                      | SNCK2, SNCK3,<br>SNCK4                                       | TGCTL( 0x50)<br>ADCKEN ビット                                   | TGCTL( 0x50)<br>ADCKEN ビット                                               |

|       | クロックパルス<br>( A F E ) | CK1, CK2                                                     | TGCTL( 0x50)<br>ADCKEN ビット                                   | TGCTL( 0x50)<br>ADCKEN ビット                                               |

注) レジスタ値と比較するカウンタ

クロックパルススタートカウンタ : CKSTART, SH\_RISE, SH\_FALL

画素カウンタ : STCKOFF, SHR2\_RISE, SHR2\_FALL, SHG2\_RISE, SHG2\_FALL,

SHB2\_RISE, SHB2\_FALL, CKSTART2

#### 「制限注意事項」

シフト信号はそれぞれ  $SHR(G,B)2\_RISE < SHR(G,B)2\_FALL$  の関係を守り設定してください。

各設定は TGCK 信号の周期を考慮して、設定値 < TGCK 周期の関係を守り設定してください。

入力する TGCK 信号の周期は CLK 入力信号周期の 64 倍より大きい周期としてください。

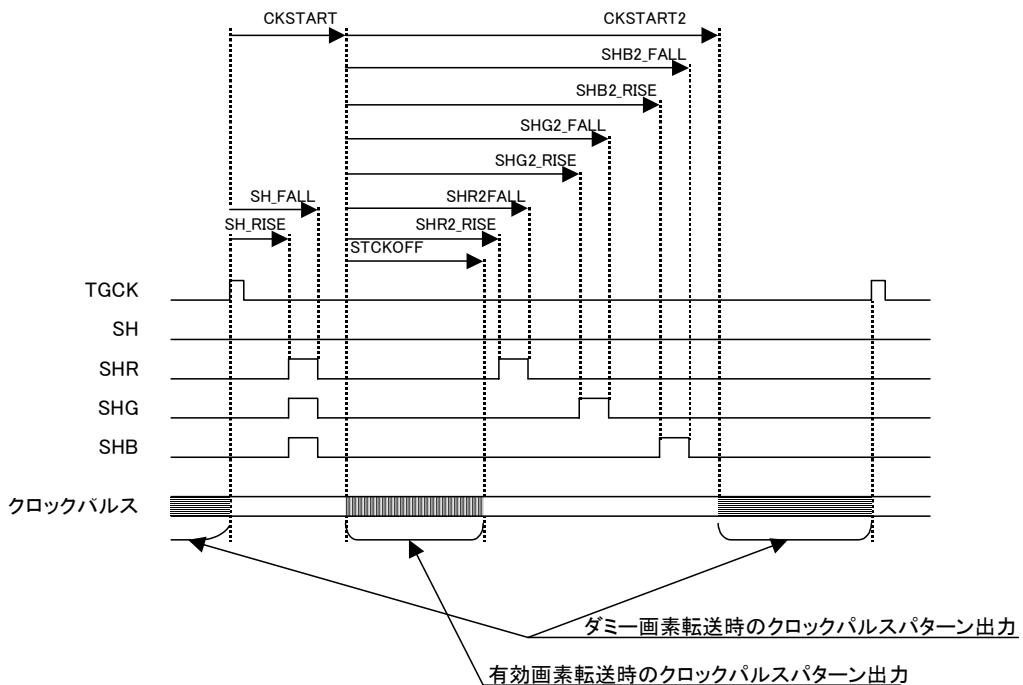

## ( 2 ) C C D 制御モード

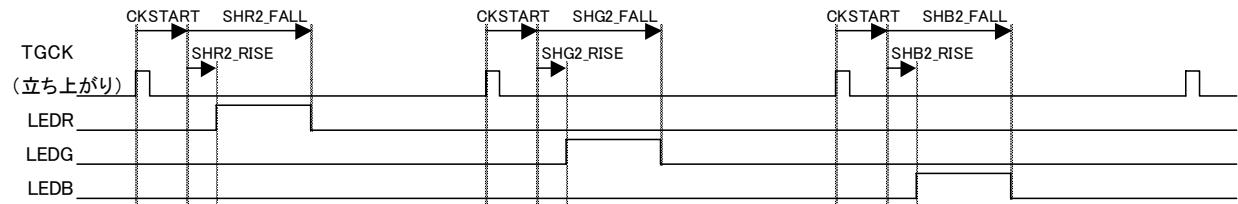

図6.2.1に各信号出力タイミングを設定するレジスタと出力信号の関係を示します。なお、SHR、SHG および SHB 信号は1ラインにつき2回のシフトパルスを出力することができます。

図6.2.1 CCD用シフト信号出力タイミング

2回目のシフトパルスを出力させない場合は、ライン周期よりも出力タイミング長くなるように設定してください。

設定例： TGCK 内部生成のとき 2回目の SHR シフトパルスを出力させない場合

SHR2\_RISE > TGPERIOD

SHR2\_FALL > SHR2\_RISE

SHG, SHB も同様です。

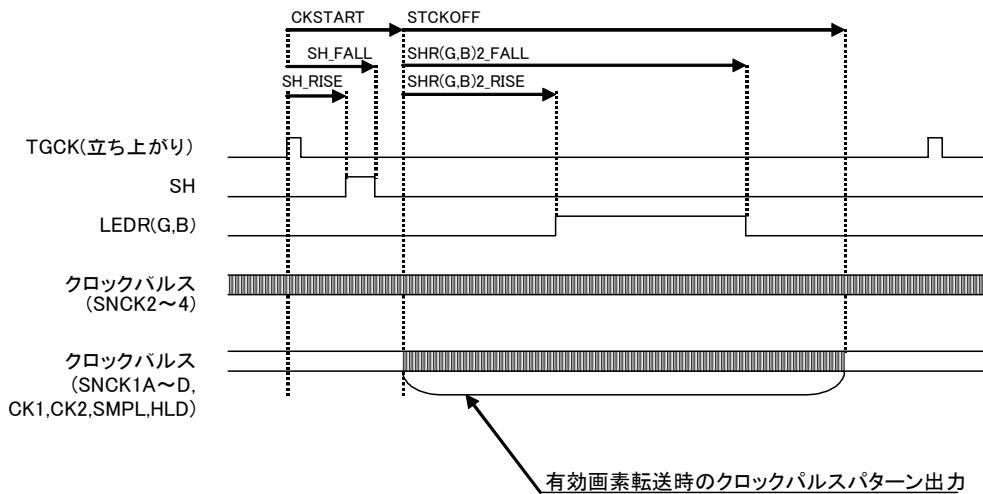

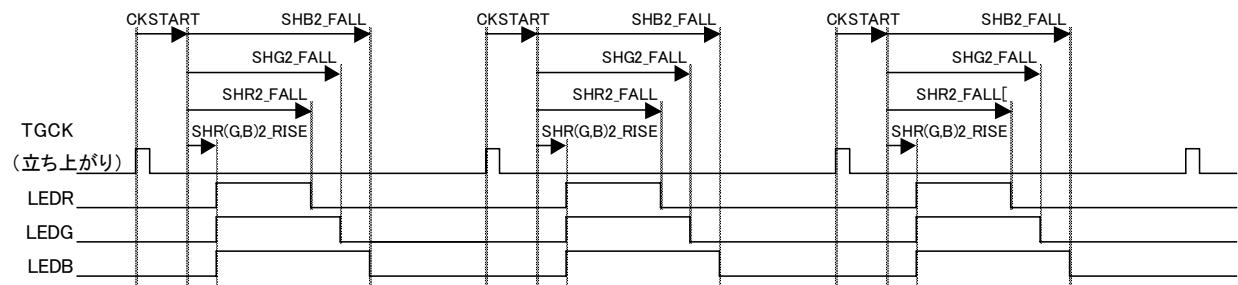

## (3) CIS制御モード

図6.22に各信号出力タイミング設定レジスタと信号出力のタイミングを示します。なお、SH信号は1ラインにつき1回だけ出力します。

図6.22 CCD用シフト信号出力タイミング

LEDR、LEDG および LEDB 信号の出力シーケンスを図6.23に示します。

3チャネルモード時においてLED制御信号出力シーケンスは、CCAEMODE レジスタ (0x54) の MUXSEQ ビットで出力シーケンスの正転または逆転に設定することができます。また、LED制御信号出力シーケンスの先頭を同レジスタのRGBMODE ビットで選択することができます。なお、1チャネルモード時は図6.23に示すとおり1ライン中に LEDR, LEDG および LEDB 信号が同時に出力されます。

## ■3色モード時(R→G→Bシーケンス設定時)

## ■単色モード時(緑チャネル選択時)

図6.23 LED制御信号出力シーケンス

## ( 4 ) 動作例

図6.24はCCD制御モード(1チャネルモード)時における各レジスタの設定値が下記に示す場合の動作例を示します。

```

SH_RISE    = 0x001,      SH_FALL    = 0x002

CKSTART    = 0x003

SHR2_RISE = 0x000001,    SHR2_FALL = 0x000002

SHG2_RISE = 0x000002,    SHG2_FALL = 0x000003

SHB2_RISE = 0x000003,    SHB2_FALL = 0x000004

STCKOFF   = 0x000005

```

図6.24 1チャネル設定時動作例

#### 6.5.4.2 クロックパルス信号のパターン出力

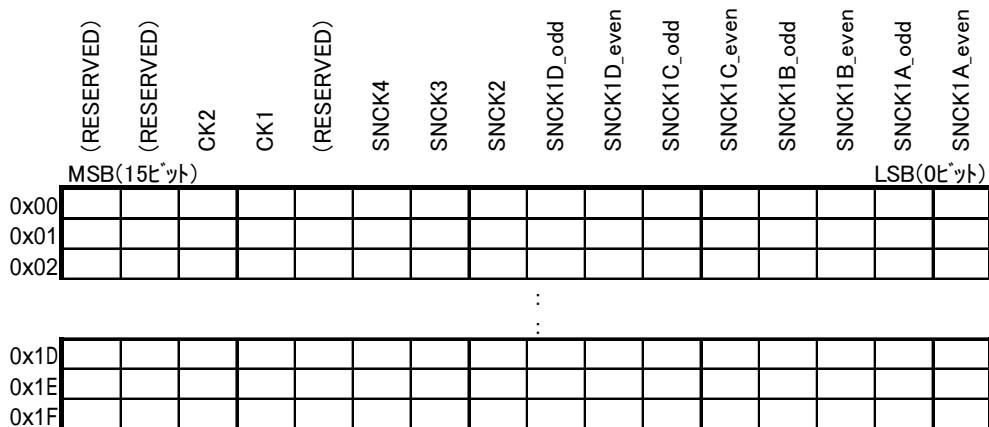

クロックパルス信号 ( SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK2, SNCK3, SCNK4, CK1, CK2 ) のパターン出力は、有効画素転送時において対応する内部ステート番号のクロックパルスパターン設定レジスタ ( 0x00 ~ 1F ) に設定されたパターンを出力します。

なお、次の各信号は 1 画素単位で even、odd の別々のパターン出力をすることが可能です。また、出力信号は 1 画素単位で even、odd の順に対応したパターンを交互に出力します。

SNCK1A, SNCK1B, SNCK1C, SNCK1D

クロックパルス信号のパターン出力は分周設定によります。

クロックパルスパターン設定レジスタを読み書きする際には、必ず TGCTL レジスタ ( 0x50 ) の MEMEN ビットを ‘ 1 ’ に設定し、ADCKEN ビットを ‘ 0 ’ に設定してから行ってください。また、クロックパルスパターン設定レジスタの読み書き終了後は、MEMEN ビットを ‘ 0 ’ に設定してください。また、使用されないステートのクロックパルスパターン設定レジスタには 0x0000 を設定してください。

##### ( 1 ) クロックパルス出力設定

クロックパルス出力設定はクロックパルス信号について設定することができます。

SNCKCTL レジスタ ( 0x53 ) の SNCK1AMD ~ SNCK4MD の各ビットを設定することにより、対応するクロックパルス信号の出力モードをクロックパルスパターン出力または固定出力に設定することができます。また、固定出力設定時には SNCK1ALV ~ SNCK4LV ビットの設定に応じて、対応するクロックパルス信号が固定出力されます。また、クロックパルスパターン出力設定の場合においてもクロックパルスがパターン出力時以外は、SNCK1ALV ~ SNCK4LV ビットで設定した出力をします。

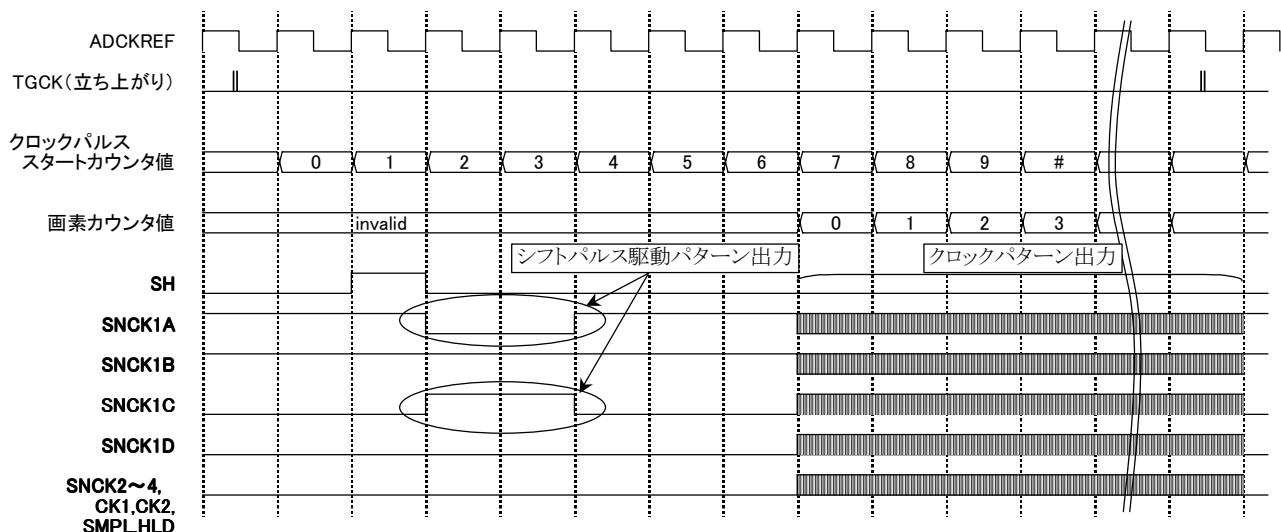

## ( 2 ) シフトパルス駆動パターン設定

C C D 制御モード時、次の信号はシフトパルス駆動パターン出力をすることが可能です。本機能は、C C D シフト動作時においてクロックパルス信号を反転出力を必要とするような、特殊な C C D を制御する際に使用する機能です。

SNCK1A, SNCK1B, SNCK1C, SNCK1D

シフトパルス駆動パターン出力は TGCK 立ち上がりから CKSTART レジスタ ( 0x24 ) 設定タイミング ( 有効画素転送時のクロックパルスパターン出力開始 ) 間の固定出力期間中において、1 パルスのみ信号出力を行います。TG2EN レジスタ ( 0x4A ) にてその動作を有効にし、TG2START レジスタ ( 0x48 ) にパルス出力開始タイミング、TG2END レジスタ ( 0x49 ) に出力終了タイミングを設定します。また、パルス出力は SNCKCTL レジスタ ( 0x53 ) の SNCKLV ビットの設定により、その対応する信号の反転のパターンが出力されます

図 6.2.5 にそのシフトパルス駆動パターン出力の動作例を示します。

```

SH_RISE = 0x001,           SH_FALL = 0x002

CKSTART = 0x007

STCKOFF = 0x1FFFFE

SNCKCTL = 0x0300

TG2EN   = 0x0005

TG2START = 0x002,          TG2END   = 0x004

```

図 6.2.5 シフトパルス駆動パターン出力動作例

### 「制限注意事項」

0 < TG2START < TG2END < CKSTART の関係を守って設定してください。

## (3) 有効画素転送時のクロックパルスパターン出力

クロックパルスパターン設定レジスタの設定例と出力される波形の例を示します。ここでは駆動パターン分解能設定を12分周にした場合の動作例を示します。

表6.14 有効画素転送時のクロックパルスパターン設定例

|      | 内部ステート     |    |            |    |     |    |            |   |       |   |       |   |       |   |            | bit |             |   |            |   |             |   |            |   |             |   |            |   |

|------|------------|----|------------|----|-----|----|------------|---|-------|---|-------|---|-------|---|------------|-----|-------------|---|------------|---|-------------|---|------------|---|-------------|---|------------|---|

|      | (RESERVED) |    | (RESERVED) |    | CK1 |    | (RESERVED) |   | SNCK4 |   | SNCK3 |   | SNCK2 |   | SNCK1D_odd |     | SNCK1D_even |   | SNCK1C_odd |   | SNCK1C_even |   | SNCK1B_odd |   | SNCK1B_even |   | SNCK1A_odd |   |

|      | 15         | 14 | 13         | 12 | 11  | 10 | 9          | 8 | 7     | 6 | 5     | 4 | 3     | 2 | 1          | 0   | 5           | 4 | 3          | 2 | 1           | 0 | 5          | 4 | 3           | 2 | 1          | 0 |

| 0x00 | -          | -  | 0          | 0  | -   | 1  | 1          | 1 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x01 | -          | -  | 0          | 0  | -   | 1  | 1          | 1 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x02 | -          | -  | 0          | 0  | -   | 1  | 1          | 1 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x03 | -          | -  | 1          | 0  | -   | 1  | 1          | 1 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x04 | -          | -  | 1          | 0  | -   | 0  | 1          | 0 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x05 | -          | -  | 0          | 0  | -   | 0  | 1          | 0 | 1     | 1 | 0     | 0 | 1     | 1 | 0          | 0   | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 | 0           | 0 | 0          | 0 |

| 0x06 | -          | -  | 0          | 0  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x07 | -          | -  | 0          | 0  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x08 | -          | -  | 0          | 0  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x09 | -          | -  | 0          | 1  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x0A | -          | -  | 0          | 1  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x0B | -          | -  | 0          | 0  | -   | 1  | 1          | 0 | 0     | 0 | 0     | 1 | 1     | 0 | 0          | 0   | 1           | 1 | 0          | 0 | 0           | 1 | 1          | 0 | 0           | 0 | 0          | 0 |

| 0x0C | -          | -  | x          | x  | -   | x  | x          | x | x     | x | x     | x | x     | x | x          | x   | x           | x | x          | x | x           | x | x          | x | x           | x | x          |   |

| 0x0D | -          | -  | x          | x  | -   | x  | x          | x | x     | x | x     | x | x     | x | x          | x   | x           | x | x          | x | x           | x | x          | x | x           | x | x          |   |

| 0x0E | -          | -  | x          | x  | -   | x  | x          | x | x     | x | x     | x | x     | x | x          | x   | x           | x | x          | x | x           | x | x          | x | x           | x | x          |   |

| 0x0F | -          | -  | x          | x  | -   | x  | x          | x | x     | x | x     | x | x     | x | x          | x   | x           | x | x          | x | x           | x | x          | x | x           | x | x          |   |

- : 使用しないビット

x : don't care

図6.26 有効画素転送時のクロックパルスパターン出力動作例

## (4) ダミー画素転送時のクロックパルスパターン出力

ダミー画素転送時は有効画素転送時の内部ステート番号とは別のステート番号を用います。また、対応する番号のクロックパルスパターン設定レジスタに書き込まれたパターンで出力します。なお、CIS制御モード時は全て0x0000を設定してください。

出力されるパターンは、駆動パターン分解能設定を16分周にした場合、0x10レジスタを先頭に内部ステートの「T」時間単位に最終レジスタ（0x1F）までを出力します。また、同様に駆動パターン分解能設定を12分周にした場合は、0x10レジスタを先頭に0x1Bレジスタまでを出力します。

表6.15はダミー画素転送時のクロックパルスパターン設定レジスタを示します。

表6.15 ダミー画素転送時のクロックパルスパターン設定例

|      | (RESERVED) | (RESERVED) | CK2 | CK1 | (RESERVED) | SNCK4 | SNCK3 | SNCK2 | SNCK1D_odd | SNCK1D_even | SNCK1C_odd | SNCK1C_even | SNCK1B_odd | SNCK1B_even | SNCK1A_odd | SNCK1A_even | bit | 内部ステート |

|------|------------|------------|-----|-----|------------|-------|-------|-------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|-----|--------|

| 0x00 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 0   |        |

| 0x01 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 1   |        |

| 0x02 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 2   |        |

| 0x03 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 3   |        |

| 0x04 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 4   |        |

| 0x05 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 5   |        |

| 0x06 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 6   |        |

| 0x07 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 7   |        |

| 0x08 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 8   |        |

| 0x09 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 9   |        |

| 0x0A | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 10  |        |

| 0x0B | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 11  |        |

| 0x0C | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           |     |        |

| 0x0D | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           |     |        |

| 0x0E | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           |     |        |

| 0x0F | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           |     |        |

| 0x10 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 0   |        |

| 0x11 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 1   |        |

| 0x12 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 2   |        |

| 0x13 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 3   |        |

| 0x14 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 4   |        |

| 0x15 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 5   |        |

| 0x16 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 6   |        |

| 0x17 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 7   |        |

| 0x18 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 8   |        |

| 0x19 | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 9   |        |

| 0x1A | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 10  |        |

| 0x1B | -          | -          | -   | -   | -          | -     | -     | -     | -          | -           | -          | -           | -          | -           | -          | -           | 11  |        |

| 0x1C | -          | -          | x   | x   | -          | x     | x     | x     | x          | x           | x          | x           | x          | x           | x          | x           |     |        |

| 0x1D | -          | -          | x   | x   | -          | x     | x     | x     | x          | x           | x          | x           | x          | x           | x          | x           |     |        |

| 0x1E | -          | -          | x   | x   | -          | x     | x     | x     | x          | x           | x          | x           | x          | x           | x          | x           |     |        |

| 0x1F | -          | -          | x   | x   | -          | x     | x     | x     | x          | x           | x          | x           | x          | x           | x          | x           |     |        |

- : 使用しないビット

x : don't care

### 6.5.4.3 制御信号出力遅延設定

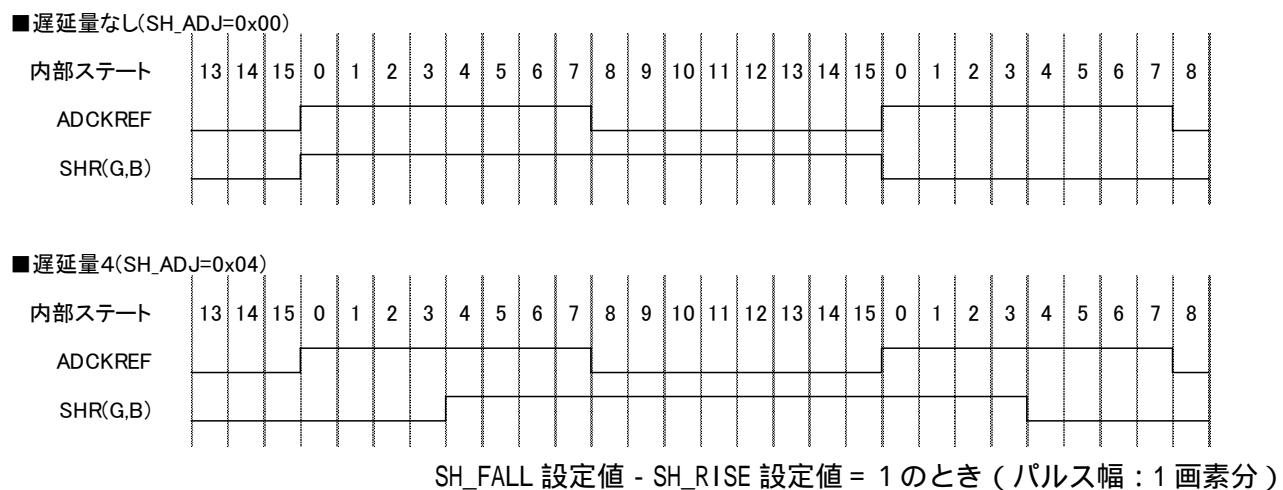

#### (1) シフト信号出力遅延

SH\_RISE レジスタ ( 0x26 ) の SH\_ADJ[3:0] ビットにより、C C D 制御モード時は 1 パルス目の SHR(G,B) 信号変化タイミング、C I S 制御モード時は SH 信号変化タイミングの遅延量を設定することができます。設定により、各信号の立ち上がり、立ち下がりタイミングを ADCKREF 1 サイクル内で設定値  $\times$  T 時間分遅延します。

図 6.2.7 は遅延設定時の動作例です。

図 6.2.7 SHR(G,B)信号出力遅延量設定動作例

また、上記の出力遅延量設定と同様に C C D 制御モード時の 2 パルス目の SHR(G,B) 信号出力遅延量または C I S 制御モード時の LEDR(G,B) 信号出力遅延量を設定することができます。表 6.1.6 に対象端子と対応するレジスタを示します。

表 6.1.6 遅延量設定レジスタ (その1)

| 制御モード | 信号名   | 信号端子名 | 遅延量設定              |               |

|-------|-------|-------|--------------------|---------------|

|       |       |       | レジスタ               | ビット           |

| C C D | シフト信号 | SHR   | SH_RISE( 0x26)     | SH_ADJ[3:0]   |

|       |       |       | SHR2_RISE_H( 0x31) | SHR2_ADJ[3:0] |

|       |       | SHG   | SH_RISE( 0x26)     | SH_ADJ[3:0]   |

|       |       |       | SHG2_RISE_H( 0x35) | SHG2_ADJ[3:0] |

|       |       | SHB   | SH_RISE( 0x26)     | SH_ADJ[3:0]   |

|       |       |       | SHB2_RISE_H( 0x39) | SHB2_ADJ[3:0] |

| C I S | シフト信号 | SH    | SH_RISE( 0x26)     | SH_ADJ[3:0]   |

|       |       | LEDR  | SHR2_RISE_H( 0x31) | SHR2_ADJ[3:0] |

|       |       | LEDG  | SHG2_RISE_H( 0x35) | SHG2_ADJ[3:0] |

|       |       | LEDB  | SHB2_RISE_H( 0x39) | SHB2_ADJ[3:0] |

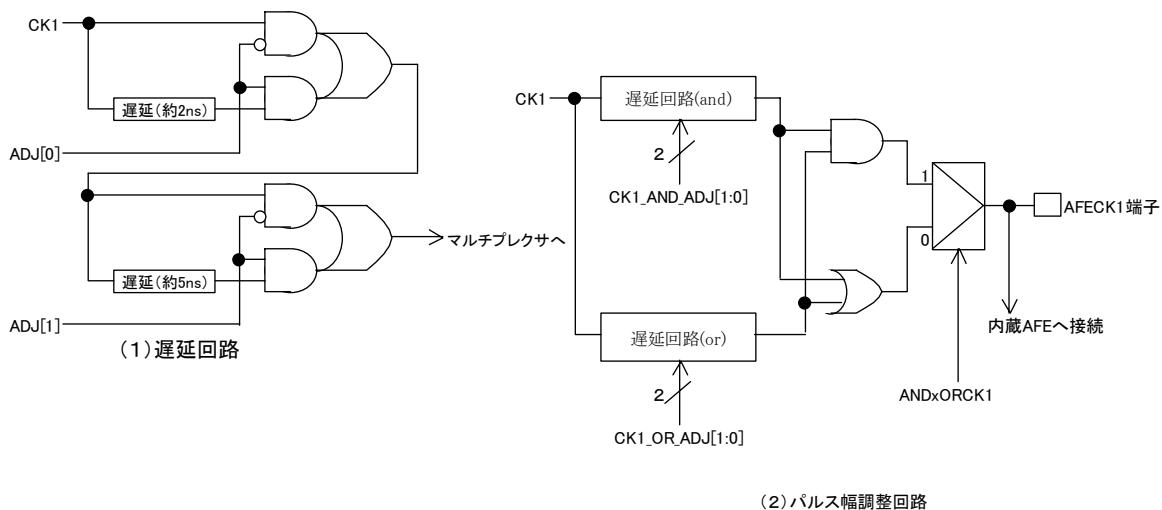

## (2) クロックパルス信号出力遅延設定

クロックパルス信号に遅延を加えて出力することができます。出力遅延は図6.2.8の回路で構成されており、レジスタの設定によって組み合わせにより約2~7nsの範囲で設定することができます。また、内部AFE接続信号は遅延回路を経た信号が接続されています。

図6.2.8 出力遅延回路

表6.1.7 遅延特性

| 素子       | MIN.  | TYP.  | MAX.  |

|----------|-------|-------|-------|

| 遅延(約2ns) | 1.2ns | 2.3ns | 4.0ns |

| 遅延(約5ns) | 3.1ns | 5.6ns | 9.7ns |

表6.1.8に各信号の遅延量設定レジスタを示します。

表6.1.8 遅延量設定レジスタ(その2)

| 信号名     | 信号端子名  | 遅延量設定                |                     |                    |           |

|---------|--------|----------------------|---------------------|--------------------|-----------|

|         |        | レジスタ                 | 遅延設定(and)           | 遅延設定(or)           | and/or 切替 |

| クロックパルス | SNCK1A | SNCK_ADJ1<br>( 0x40) | SNCK1A_AND_ADJ[1:0] | SNCK1A_OR_ADJ[1:0] | ANDxOR1A  |

|         | SNCK1B |                      | SNCK1B_AND_ADJ[1:0] | SNCK1B_OR_ADJ[1:0] | ANDxOR1B  |

|         | SNCK1C | SNCK_ADJ2<br>( 0x41) | SNCK1C_AND_ADJ[1:0] | SNCK1C_OR_ADJ[1:0] | ANDxOR1C  |

|         | SNCK1D |                      | SNCK1D_AND_ADJ[1:0] | SNCK1D_OR_ADJ[1:0] | ANDxOR1D  |

|         | SNCK2  | SNCK_ADJ3<br>( 0x42) | SNCK2_AND_ADJ[1:0]  | SNCK2_OR_ADJ[1:0]  | ANDxOR2   |

|         | SNCK3  |                      | SNCK3_AND_ADJ[1:0]  | SNCK3_OR_ADJ[1:0]  | ANDxOR3   |

|         | SNCK4  | SNCK_ADJ4<br>( 0x43) | SNCK4_AND_ADJ[1:0]  | SNCK4_OR_ADJ[1:0]  | ANDxOR4   |

|         | CK1    | SNCK_ADJ5<br>( 0x44) | CK1_AND_ADJ[1:0]    | CK1_OR_ADJ[1:0]    | ANDxORCK1 |

|         | CK2    |                      | CK2_AND_ADJ[1:0]    | CK2_OR_ADJ[1:0]    | ANDxORCK2 |

#### 6.5.4.4 制御信号出力極性設定

表6.19はA F E転送クロック信号、シフト信号およびL E D制御信号の極性を設定するレジスタを示します。

表6.19 制御信号出力極性設定レジスタ

| 制御モード  | 信号名           | 信号端子名 | 遅延量設定           |          |

|--------|---------------|-------|-----------------|----------|

|        |               |       | レジスタ            | ビット      |

| 各モード共通 | A F E転送クロック信号 | ADCK  | CCAEMODE( 0x54) | ADCK_POL |

|        |               | SHR   |                 | SH_POL   |

|        |               | SHG   |                 |          |

|        |               | SHB   |                 |          |

| C I S  | シフト信号         | SH    |                 | SH_POL   |

|        |               | LEDR  |                 | LED_POL  |

|        |               | LEDG  |                 |          |

|        |               | LEDB  |                 |          |

#### 6.5.5 画像データ出力

動作モードが1チャネル、2チャネルまたは3チャネルモードに関わらず、画像データ出力を禁止することができます。ADCTLレジスタ( 0x52 )のxADREN、xADGENまたはxADBENビットを‘H’にすることにより、対応するチャネルの画像データ出力を禁止します。なお、禁止設定にした場合、対応するチャネルの出力画像データは全てゼロとなります。

#### 6.5.6 兼用汎用ポート

表6.20に各制御信号と兼用の汎用ポートを示します。

汎用ポート機能有効設定はGPIOENレジスタ( 0x60 )またはGPIO2ENレジスタ( 0x64 )で制御します。‘0’を設定するとそのレジスタに対応した端子は、該当端子の機能信号を出力します。また、‘1’を設定すると対応端子の汎用I/Oポート機能を有効にします。各信号とも初期化時は汎用ポート設定(‘1’設定)となっているため、該当端子の機能信号を出力する際は、GPIOENレジスタ( 0x60 )またはGPIO2ENレジスタ( 0x64 )を設定してください。

汎用ポート入出力の切り替えはGPIODIRレジスタ( 0x61 )またはGPIO2DIRレジスタ( 0x65 )で制御します。‘0’を設定するとそのレジスタに対応した端子は、入力ポートとなります。また、‘1’を設定すると出力ポートとなります。

該当端子が出力設定となっている場合、汎用ポートへの信号出力は、GPIOSTレジスタ( 0x62 )またはGPIO2STレジスタ( 0x66 )をライトするとレジスタに設定された値を出力します。一方、GPIOSTレジスタ( 0x62 )またはGPIO2STレジスタ( 0x66 )をリードすると汎用ポートの設定に関わらず、対応する端子の状態が読み出せます。

表6.20 汎用ポート

| 信号端子名                                                                                                  | 汎用ポート制御レジスタ    |                 |                |                |

|--------------------------------------------------------------------------------------------------------|----------------|-----------------|----------------|----------------|

|                                                                                                        | 汎用ポート機能有効設定    | 汎用ポート入出力切り替え    | 汎用ポート出力        | 汎用ポート入力        |

| SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK2, SNCK3, SNCK4, AFECK1, AFECK2, AFECK3, AFECK4, SHR, SHG, SHB, SH | GPIOEN( 0x60)  | GPIODIR( 0x61)  | GPIOST( 0x62)  | GPIOST( 0x62)  |

| D0, D1, D2, D3                                                                                         | GPIO2EN( 0x64) | (出力のみ)          | GPIO2ST( 0x66) | (出力のみ)         |

| D4, D5, D6, D7, SYNC                                                                                   |                | GPIO2DIR( 0x65) |                | GPIO2ST( 0x66) |

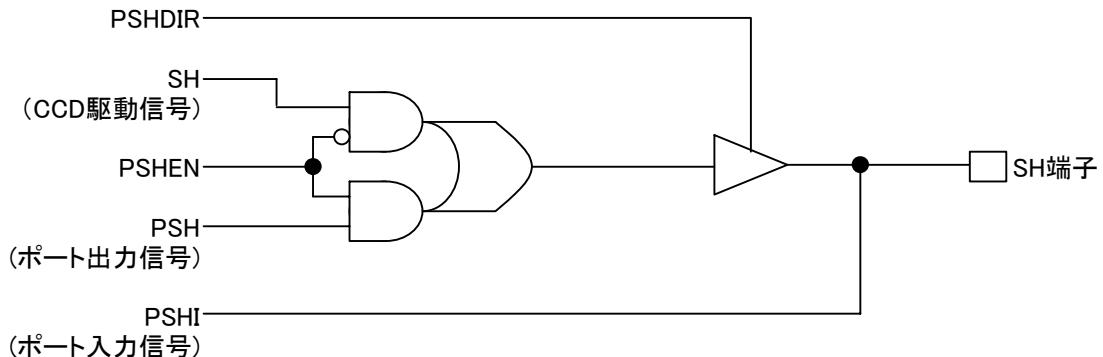

図6.29はSH信号の汎用ポート部分の内部接続を示しています。また、SNCK1A、SNCK1B、SNCK1C、SNCK1D、SNCK2～4、SHR、SHG、SHB、D0～7およびSYNCの各端子も同様の接続となっています。但し、D0～3端子は出力のみとなっているため入出力切り替え機能はありません。

図6.29 汎用ポート内部接続

#### 「制限注意事項」

QFP選択時は、汎用ポート2機能はありません。従って、次に示すレジスタは必ず下記のとおり設定してください。

GPIO2EN レジスタ ( 0x64 ) : 0x01FF

GPIO2DIR レジスタ ( 0x65 ) : 0x01F0

GPIO2ST レジスタ ( 0x66 ) : 0x0000

## 6.5.7 テストモード

### (1) 画像データ出力テストモード

TESTMODE レジスタ( 0x5F)の ADTD\_TST ビットを設定することによって、画像データ出力テストモードとなります。ADTD\_DT[7:0]の設定値またはインクリメントデータを、画像データ出力としてテストを行うことができます。ADTD\_MD ビットを‘0’に設定することによってインクリメントデータ出力となります。なお、インクリメントデータは出力データの0～7ビットにて出力され、8～15ビットは0～7ビットの反転値が出力されます。また、インクリメントデータは、TGCK 信号入力を検出するとカウンタがリセットされます。

3チャネルモード設定時における出力例を以下に示します。

|        |        |        |        |        |        |     |

|--------|--------|--------|--------|--------|--------|-----|

| R      | G      | B      | R      | G      | B      | ... |

| 0x00FF | 0x40BF | 0x807F | 0x01FE | 0x41BE | 0x817E | ... |

なお、データフォーマットは表6.2.1に示すとおりです。

表6.2.1 テストモードデータフォーマット

| 出力データ | 上位バイト   |          |    |    |    |    |   |   | 下位バイト      |   |   |   |   |   |   |   |

|-------|---------|----------|----|----|----|----|---|---|------------|---|---|---|---|---|---|---|

|       | 15      | 14       | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|       | CL[1:0] | CNT[5:0] |    |    |    |    |   |   | (上位バイトの反転) |   |   |   |   |   |   |   |

CL[1:0]: カラーコード

00: 赤チャネル

01: 緑チャネル

10: 青チャネル

11: (予約)

一方、ADTD\_MD ビットを‘1’に設定することによって固定出力となります。なお、固定データは、ADTD\_DT 設定値の0～7ビットおよび8～15ビットにそれぞれ出力されます。

### (2) AFEクロックモニタ

AFECK1～4端子にてAFEクロック信号をモニタすることができます。

表6.2.2 AFEクロックモニタ

| TESTMODE レジスタ<br>( 0x5F)<br>MONMD ビット設定 | AFECK1 | AFECK2 | AFECK3 | AFECK4 |

|-----------------------------------------|--------|--------|--------|--------|

| ‘0’                                     | CK1    | CK2    | (不定)   | ADCK   |

| ‘1’                                     | CK1    | CK2    | (不定)   | (不定)   |

## 7. レジスタ

### 7.1 メモリマップ

|      | Address | Description                        | Size | Access Size |

|------|---------|------------------------------------|------|-------------|

| 0x00 | 0x00    | SNCK Pattern Registers             | 64B  | 16bit       |

| 0x1F | 0x3F    |                                    |      |             |

| 0x20 | 0x40    | Timing Parameter Registers         | 96B  |             |

| 0x4F | 0x9F    |                                    |      |             |

| 0x50 | 0xA0    | Control Registers                  | 32B  |             |

| 0x5F | 0xBF    |                                    |      |             |

| 0x60 | 0xC0    | GPIO Registers                     | 32B  |             |

| 0x6F | 0xDF    |                                    |      |             |

| 0x70 | 0xE0    | AFE & External Interface Registers | 32B  |             |

| 0x7F | 0xFF    |                                    |      |             |

## 7.2 レジスタマップ

|                                   | Address | Register Name | R/W | Function                    | Relation |

|-----------------------------------|---------|---------------|-----|-----------------------------|----------|

| <b>SNCK Pattern Registers</b>     |         |               |     |                             |          |

| 0x00                              | 0x00    | SNCK_PAT00    | R/W | クロックパルスパターン設定レジスタ 0 0       |          |

| :                                 | :       | :             | R/W | :                           |          |

| 0x1F                              | 0x3E    | SNCK_PAT1F    | R/W | クロックパルスパターン設定レジスタ 1 F       |          |

| <b>Timing Parameter Registers</b> |         |               |     |                             |          |

| 0x20                              | 0x40    | TGPERIOD_L    | R/W | ライン周期設定レジスタ                 | 下位       |

| 0x21                              | 0x42    | TGPERIOD_H    | R/W | ライン周期設定レジスタ                 | 上位       |

| 0x22                              | 0x44    | TGCKWDTH      | R/W | TGCKパルス幅設定レジスタ              |          |

| 0x23                              | 0x46    | (Reserved)    |     |                             |          |

| 0x24                              | 0x48    | CKSTART       | R/W | クロックパルススタートタイミング設定レジスタ      |          |