# ディスプレイコントローラ アプリケーションマニュアル

(京セラディスプレイ株式会社

(旧オプトレックス株式会社)製

LCD パネルインターフェース)

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 製品および弊社が提供する技術を輸出等するにあたっては「外国為替および外国貿易法」を遵守し、当該法令の定める手続きが必要です。大量破壊兵器の開発等およびその他の軍事用途に使用する目的をもって製品および弊社が提供する技術を費消、再販売または輸出等しないでください。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

# 目次

|                                               |    |

|-----------------------------------------------|----|

| 1. 概要 .....                                   | 1  |

| 2. ディスプレイコントローラの接続性について .....                 | 1  |

| 3. T-55343GD035JU-LW とディスプレイコントローラとの接続 .....  | 2  |

| 3.1 T-55343GD035JU-LW の端子配列 .....             | 2  |

| 3.2 T-55343GD035JU-LW 接続例 .....               | 3  |

| 3.2.1 T-55343GD035JU-LW と S1D13513 との接続 ..... | 4  |

| 3.2.2 T-55343GD035JU-LW と S1D13517 との接続 ..... | 7  |

| 3.2.3 T-55343GD035JU-LW と S1D13743 との接続 ..... | 10 |

| 3.2.4 T-55343GD035JU-LW と S1D13781 との接続 ..... | 13 |

| 3.3 T-55343GD035JU-LW レジスタ設定例 .....           | 16 |

| 4. T-55265GD057J-LW とディスプレイコントローラとの接続 .....   | 22 |

| 4.1 T-55265GD057J-LW の端子配列 .....              | 22 |

| 4.2 T-55265GD057J-LW 接続例 .....                | 23 |

| 4.2.1 T-55265GD057J-LW と S1D13513 との接続 .....  | 24 |

| 4.2.2 T-55265GD057J-LW と S1D13517 との接続 .....  | 26 |

| 4.2.3 T-55265GD057J-LW と S1D13743 との接続 .....  | 28 |

| 4.2.4 T-55265GD057J-LW と S1D13781 との接続 .....  | 30 |

| 4.3 T-55265GD057J-LW レジスタ設定例 .....            | 32 |

| 5. T-51750GD065J-LW とディスプレイコントローラとの接続 .....   | 36 |

| 5.1 T-51750GD065J-LW の端子配列 .....              | 36 |

| 5.2 T-51750GD065J-LW 接続例 .....                | 37 |

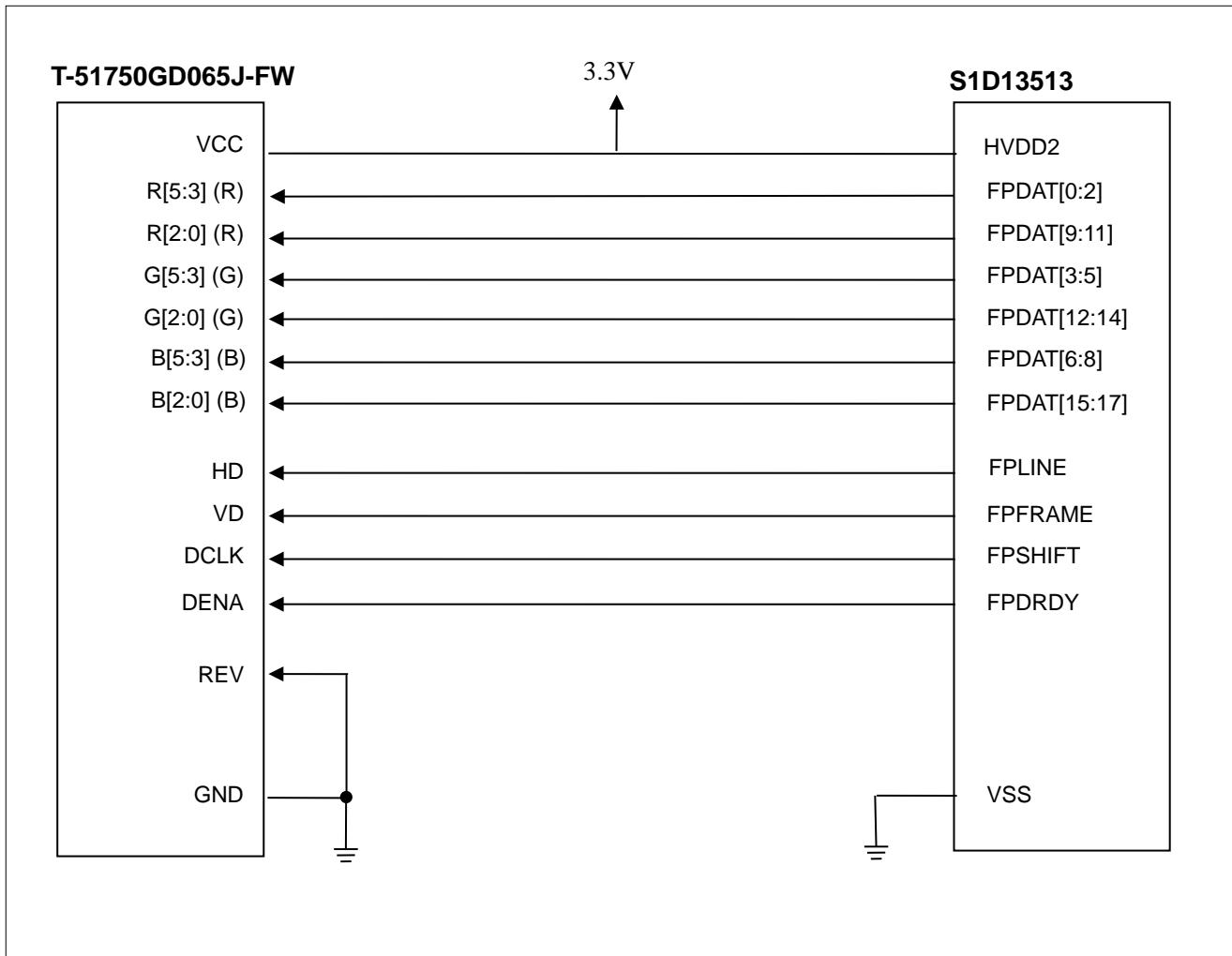

| 5.2.1 T-51750GD065J-LW と S1D13513 との接続 .....  | 37 |

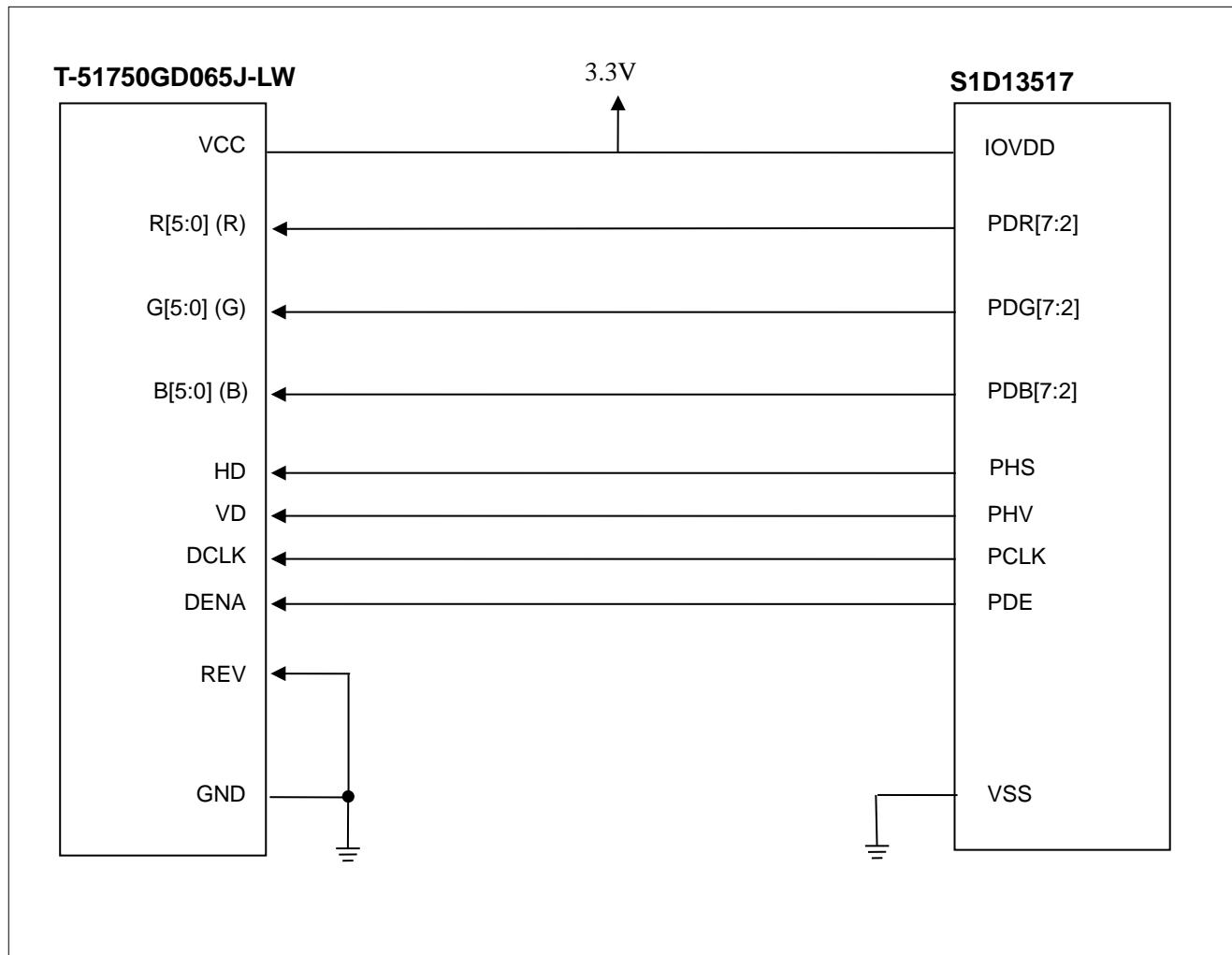

| 5.2.2 T-51750GD065J-LW と S1D13517 との接続 .....  | 39 |

| 5.3 T-51750GD065J-LW レジスタ設定例 .....            | 42 |

| 改訂履歴 .....                                    | 44 |

## 1. 概要

本書では、京セラディスプレイ株式会社（旧オプトレックス株式会社、以下京セラ）製 LCD パネルと当社ディスプレイコントローラとの端子接続、および LCD パネルインターフェースに関する主なレジスタの設定例について説明します。

端子、レジスタの詳細仕様については各製品のテクニカルマニュアルを参照してください。

なお、本書は適宜改訂されています。最新版は、

[http://www.epson.jp/prod/semicon/products/lcd\\_controllers/](http://www.epson.jp/prod/semicon/products/lcd_controllers/)

<http://vdc.epson.com/>

からダウンロードできます。

## 2. ディスプレイコントローラの接続性について

本書では、下記京セラ製 LCD パネルと当社ディスプレイコントローラの接続例について説明します。

京セラ製 LCD パネル

- ・ T-55343GD035JU-LW (TFT 3.5inch, QVGA)

- ・ T-55265GD057J-LW (TFT 5.7inch, QVGA)

- ・ T-51750GD065J-LW (TFT 6.5inch, VGA)

当社ディスプレイコントローラ

- ・ S1D13513 (QFP 208-pin or PBGA 256-pin)

- ・ S1D13517 (QFP 128-pin)

- ・ S1D13743 (QFP 144-pin or FCBGA 128-pin)

- ・ S1D13781 (QFP 100-pin)

下表は、各 LCD パネルに接続可能なディスプレイコントローラの対応表です。

表 2-1 各 LCD パネルに接続可能なディスプレイコントローラの対応表

| 京セラ LCD パネル       | S1D13513 | S1D13517 | S1D13743 | S1D13781 |

|-------------------|----------|----------|----------|----------|

| T-55343GD035JU-LW | √        | √        | √        | √        |

| T-55265GD057J-LW  | √        | √        | √        | √        |

| T-51750GD065J-LW  | √        | √        |          |          |

京セラディスプレイ株式会社 LCD 製品ページへのリンク

<http://www.kyocera-display.co.jp/products/tft.html>

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

## 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

本章では、T-55343GD035JU-LW と下記ディスプレイコントローラとの接続例について説明します。

- S1D13513

- S1D13517

- S1D13743

- S1D13781

### 3.1 T-55343GD035JU-LW の端子配列

以下に、T-55343GD035JU-LW のコネクタの端子配列を示します。

実装コネクタ：ELCO 製 6240 シリーズ 40 ピン FPC コネクタ(0.3mm 厚、0.5mm ピッチ)

表 3-1 T-55343GD035JU-LW コネクタの端子配列

| コネクタ端子 No. | 端子名    | 端子説明                                              |

|------------|--------|---------------------------------------------------|

| 1          | RL     | Input to select Source driver Datashift direction |

| 2          | TB     | Input to select Gate driver Datashift direction   |

| 3          | DOTCLK | Clock Signal                                      |

| 4          | VSYNC  | Vertical Sync Input                               |

| 5          | HSYNC  | Horizontal Sync Input                             |

| 6          | ENABLE | Input Data Enable Control                         |

| 7          | DB23   | Data Signal Graphic Display Data Red-data (MSB)   |

| 8          | DB22   | Data Signal Graphic Display Data Red-data         |

| 9          | DB21   | Data Signal Graphic Display Data Red-data         |

| 10         | DB20   | Data Signal Graphic Display Data Red-data         |

| 11         | DB19   | Data Signal Graphic Display Data Red-data         |

| 12         | DB18   | Data Signal Graphic Display Data Red-data         |

| 13         | DB17   | Data Signal Graphic Display Data Red-data         |

| 14         | DB16   | Data Signal Graphic Display Data Red-data (LSB)   |

| 15         | GND    | Power Supply (0V, GND)                            |

| 16         | DB15   | Data Signal Graphic Display Data Green-data (MSB) |

| 17         | DB14   | Data Signal Graphic Display Data Green-data       |

| 18         | DB13   | Data Signal Graphic Display Data Green-data       |

| 19         | DB12   | Data Signal Graphic Display Data Green-data       |

| 20         | DB11   | Data Signal Graphic Display Data Green-data       |

| 21         | DB10   | Data Signal Graphic Display Data Green-data       |

| 22         | DB9    | Data Signal Graphic Display Data Green-data       |

| 23         | DB8    | Data Signal Graphic Display Data Green-data (LSB) |

| 24         | GND    | Power Supply (0V, GND)                            |

| 25         | DB7    | Data Signal Graphic Display Data Blue-data (MSB)  |

| 26         | DB6    | Data Signal Graphic Display Data Blue-data        |

| 27         | DB5    | Data Signal Graphic Display Data Blue-data        |

| 28         | DB4    | Data Signal Graphic Display Data Blue-data        |

| 29         | DB3    | Data Signal Graphic Display Data Blue-data        |

| 30         | DB2    | Data Signal Graphic Display Data Blue-data        |

| 31         | DB1    | Data Signal Graphic Display Data Blue-data        |

| 32         | DB0    | Data Signal Graphic Display Data Blue-data (LSB)  |

| 33         | SDI    | Serial Interface Data                             |

| 34         | SCL    | Serial Interface Clock                            |

| 35         | CS     | Serial Interface Chip Select L:Active             |

| 36         | RESET  | System RESET L:Reset                              |

| 37         | SDO    | Serial Interface Data                             |

| 38         | GND    | Power Supply (0V, GND)                            |

| 39         | VCC    | Power Supply for System                           |

| 40         | VCC    | Power Supply for System                           |

#### 3.2 T-55343GD035JU-LW 接続例

本項では、T-55343GD035JU-LW と各ディスプレイコントローラとの信号接続について説明します。

(QFP、BGA など複数のパッケージをサポートする製品については、各々のピン/ポール No.を表記します。)

T-55343GD035JU-LW は以下の電源を必要とします。

- VDD            +3.3V (±0.3V)

- V<sub>F</sub>            +19.2V

上記電圧の範囲内で、コントローラ側の LCD 用 VDD に適合した電圧を選択してください。

消費電力、絶対最大定格等の詳細仕様については、京セラの営業担当にお問い合わせください。

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

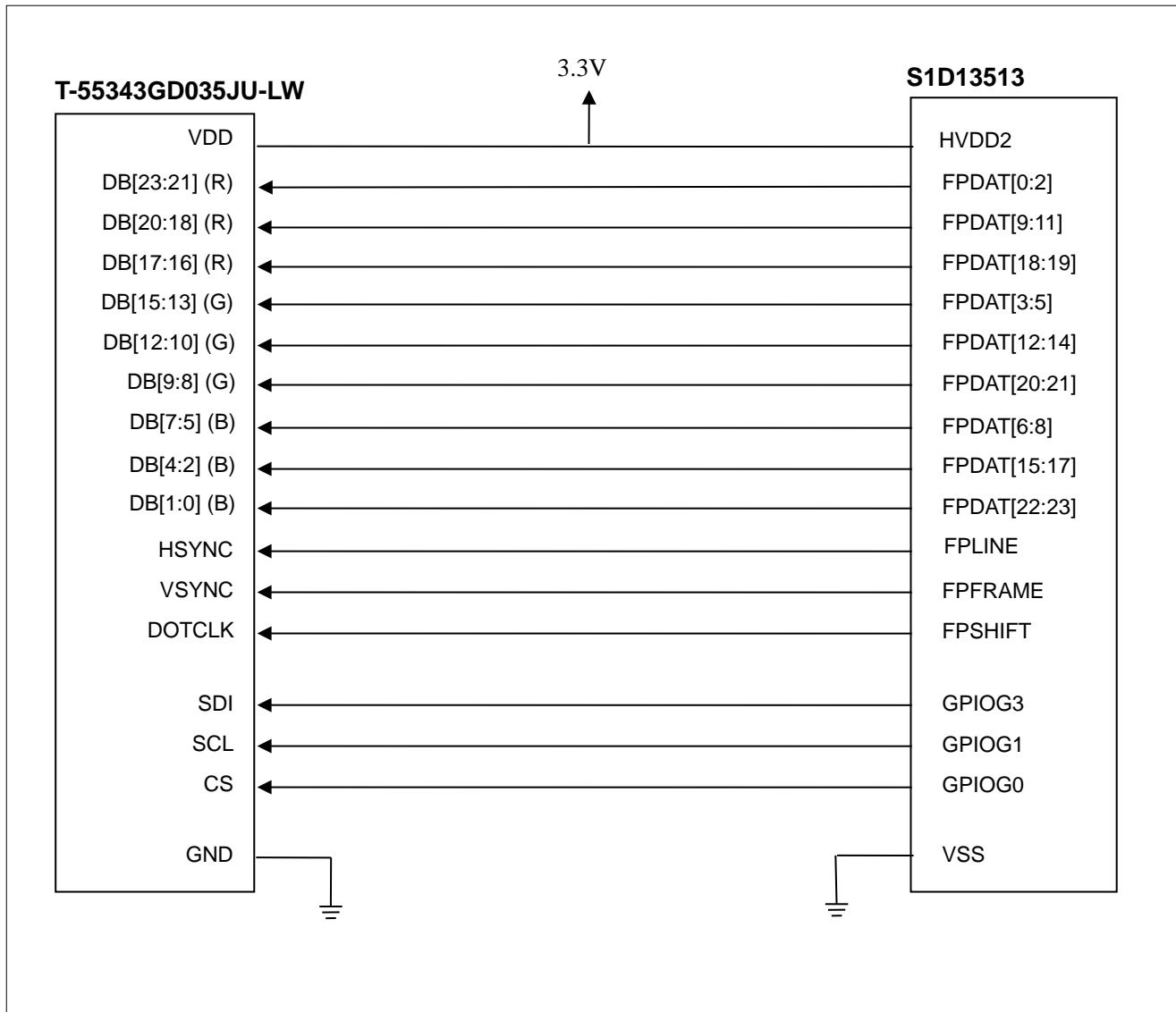

#### 3.2.1 T-55343GD035JU-LW と S1D13513 との接続

下図は、T-55343GD035JU-LW と S1D13513 の接続例です。

図 3-1 T-55343GD035JU-LW と S1D13513 の接続

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

表 3-2 T-55343GD035JU-LW と S1D13513 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD パネル<br>端子名 | LCD パネル端子説明                                          | S1D13513<br>QFP<br>ピン No. | S1D13513<br>PBGA<br>ポール No. | S1D13513<br>端子名 |

|------------------------------|----------------|------------------------------------------------------|---------------------------|-----------------------------|-----------------|

| 1                            | RL             | Input to select Source driver<br>Datashift direction | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 2                            | TB             | Input to select Gate driver<br>Datashift direction   | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 3                            | DOTCLK         | Clock Signal                                         | 77                        | P8                          | FPSHIFT         |

| 4                            | VSYNC          | Vertical Sync Input                                  | 78                        | R8                          | FPPFRAME        |

| 5                            | HSYNC          | Horizontal Sync Input                                | 79                        | T8                          | FPLINE          |

| 6                            | ENABLE         | Input Data Enable Control                            | —                         | —                           | —               |

| 7                            | DB23           | Data Signal Graphic Display Data<br>Red-data (MSB)   | 74                        | M7                          | FPDAT0          |

| 8                            | DB22           | Data Signal Graphic Display Data<br>Red-data         | 73                        | N7                          | FPDAT1          |

| 9                            | DB21           | Data Signal Graphic Display Data<br>Red-data         | 72                        | T7                          | FPDAT2          |

| 10                           | DB20           | Data Signal Graphic Display Data<br>Red-data         | 63                        | P6                          | FPDAT9          |

| 11                           | DB19           | Data Signal Graphic Display Data<br>Red-data         | 62                        | M5                          | FPDAT10         |

| 12                           | DB18           | Data Signal Graphic Display Data<br>Red-data         | 61                        | N5                          | FPDAT11         |

| 13                           | DB17           | Data Signal Graphic Display Data<br>Red-data         | 注 2                       | R5                          | FPDAT18         |

| 14                           | DB16           | Data Signal Graphic Display Data<br>Red-data (LSB)   | 注 2                       | K5                          | FPDAT19         |

| 15                           | GND            | Power Supply (0V, GND)                               | 注 1                       | 注 1                         | VSS             |

| 16                           | DB15           | Data Signal Graphic Display Data<br>Green-data (MSB) | 71                        | R7                          | FPDAT3          |

| 17                           | DB14           | Data Signal Graphic Display Data<br>Green-data       | 70                        | P7                          | FPDAT4          |

| 18                           | DB13           | Data Signal Graphic Display Data<br>Green-data       | 69                        | L7                          | FPDAT5          |

| 19                           | DB12           | Data Signal Graphic Display Data<br>Green-data       | 60                        | T5                          | FPDAT12         |

| 20                           | DB11           | Data Signal Graphic Display Data<br>Green-data       | 59                        | T4                          | FPDAT13         |

| 21                           | DB10           | Data Signal Graphic Display Data<br>Green-data       | 56                        | R4                          | FPDAT14         |

| 22                           | DB9            | Data Signal Graphic Display Data<br>Green-data       | 注 2                       | P5                          | FPDAT20         |

| 23                           | DB8            | Data Signal Graphic Display Data<br>Green-data (LSB) | 注 2                       | T3                          | FPDAT21         |

| 24                           | GND            | Power Supply (0V, GND)                               | 注 1                       | 注 1                         | VSS             |

| 25                           | DB7            | Data Signal Graphic Display Data<br>Blue-data (MSB)  | 68                        | M6                          | FPDAT6          |

| 26                           | DB6            | Data Signal Graphic Display Data<br>Blue-data        | 67                        | K6                          | FPDAT7          |

| 27                           | DB5            | Data Signal Graphic Display Data<br>Blue-data        | 64                        | R6                          | FPDAT8          |

| 28                           | DB4            | Data Signal Graphic Display Data<br>Blue-data        | 55                        | T2                          | FPDAT15         |

| 29                           | DB3            | Data Signal Graphic Display Data<br>Blue-data        | 54                        | P4                          | FPDAT16         |

| 30                           | DB2            | Data Signal Graphic Display Data<br>Blue-data        | 53                        | N4                          | FPDAT17         |

| 31                           | DB1            | Data Signal Graphic Display Data<br>Blue-data        | 注 2                       | R3                          | FPDAT22         |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD パネル<br>端子名 | LCD パネル端子説明                                         | S1D13513<br>QFP<br>ピン No. | S1D13513<br>PBGA<br>ボール No. | S1D13513<br>端子名 |

|------------------------------|----------------|-----------------------------------------------------|---------------------------|-----------------------------|-----------------|

| 32                           | DB0            | Data Signal Graphic Display Data<br>Blue-data (LSB) | 注 2                       | K4                          | FPDAT23         |

| 33                           | SDI            | Serial Interface Data                               | 82                        | T9                          | GPIOG3          |

| 34                           | SCL            | Serial Interface Clock                              | 84                        | P9                          | GPIOG1          |

| 35                           | CS             | Serial Interface Chip Select L:Active               | 85                        | L9                          | GPIOG0          |

| 36                           | RESET          | System RESET L:Reset                                | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 37                           | SDO            | Serial Interface Data                               | —                         | —                           | —               |

| 38                           | GND            | Power Supply (0V, GND)                              | 注 1                       | 注 1                         | VSS             |

| 39                           | VCC            | Power Supply for System                             | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 40                           | VCC            | Power Supply for System                             | 57,65,75                  | L5,L8,T6                    | HVDD2           |

注 1) S1D13513 の VSS ピン No.は以下のとおりです。

QFP: 10,20,38,58,66,76,92,99,106,120,133,139,151,163,169,175,184,197

BGA: A1,A16,D4,D8,D13,G7-G10,G13,H7-H10,J1,J7-J10,K2,K7-K10,K13,N3,N6,N9,N13,T1,T16

注 2) QFP パッケージでは、S1D13513 の VSS ピンに接続してください。

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

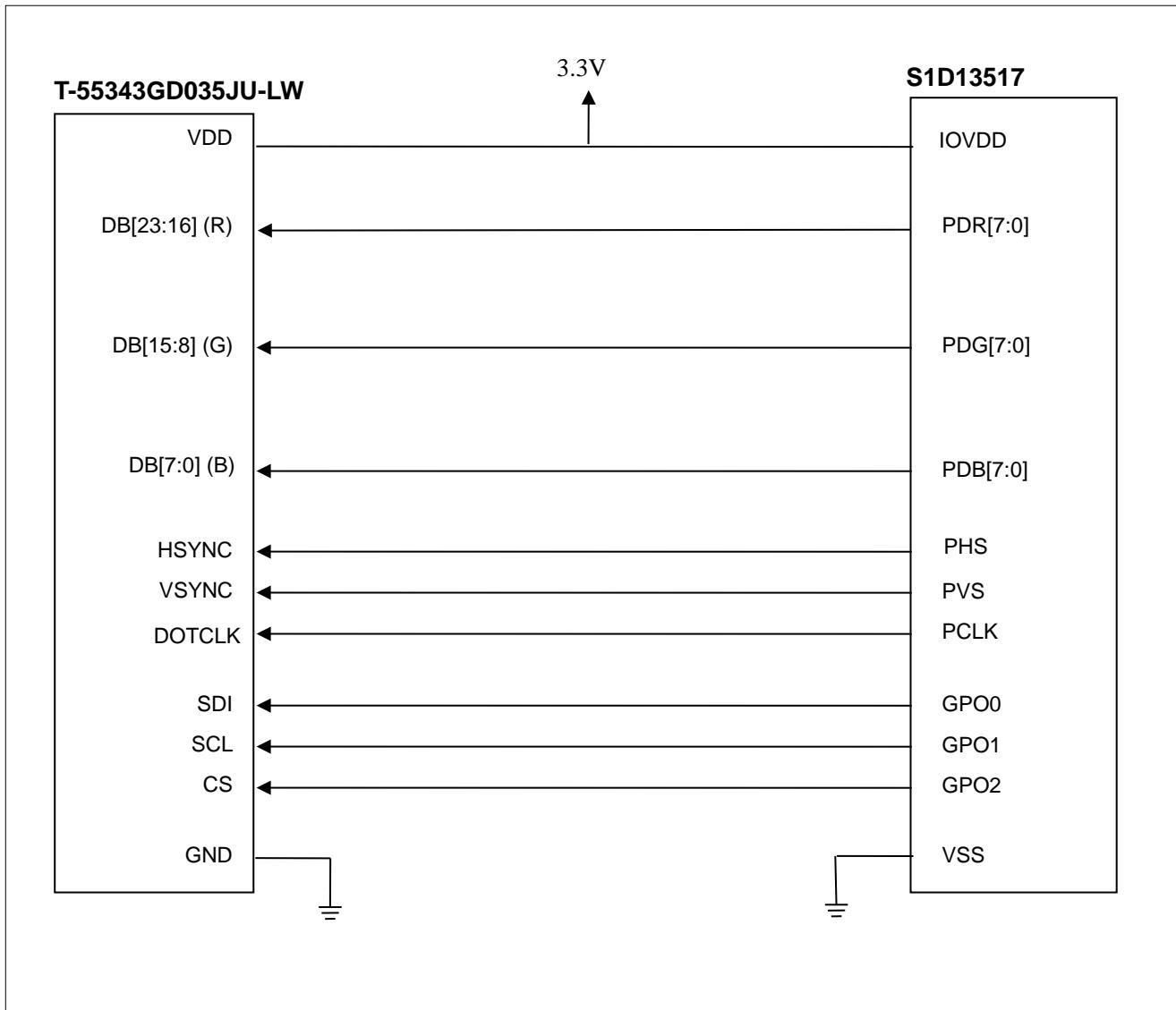

#### 3.2.2 T-55343GD035JU-LW と S1D13517 との接続

下図は、T-55343GD035JU-LW と S1D13517 の接続例です。

図 3-2 T-55343GD035JU-LW と S1D13517 の接続

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

表 3-3 T-55343GD035JU-LW と S1D13517 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                          | S1D13517<br>QFP<br>ピン No. | S1D13517<br>端子名 |

|-----------------------------|----------------|------------------------------------------------------|---------------------------|-----------------|

| 1                           | RL             | Input to select Source driver<br>Datashift direction | 注 2                       | IOVDD           |

| 2                           | TB             | Input to select Gate driver<br>Datashift direction   | 注 2                       | IOVDD           |

| 3                           | DOTCLK         | Clock Signal                                         | 110                       | PCLK            |

| 4                           | VSYNC          | Vertical Sync Input                                  | 82                        | PVS             |

| 5                           | H SYNC         | Horizontal Sync Input                                | 83                        | PHS             |

| 6                           | ENABLE         | Input Data Enable Control                            | —                         | —               |

| 7                           | DB23           | Data Signal Graphic Display Data<br>Red-data (MSB)   | 102                       | PDR7            |

| 8                           | DB22           | Data Signal Graphic Display Data<br>Red-data         | 103                       | PDR6            |

| 9                           | DB21           | Data Signal Graphic Display Data<br>Red-data         | 104                       | PDR5            |

| 10                          | DB20           | Data Signal Graphic Display Data<br>Red-data         | 105                       | PDR4            |

| 11                          | DB19           | Data Signal Graphic Display Data<br>Red-data         | 106                       | PDR3            |

| 12                          | DB18           | Data Signal Graphic Display Data<br>Red-data         | 107                       | PDR2            |

| 13                          | DB17           | Data Signal Graphic Display Data<br>Red-data         | 108                       | PDR1            |

| 14                          | DB16           | Data Signal Graphic Display Data<br>Red-data (LSB)   | 109                       | PDR0            |

| 15                          | GND            | Power Supply (0V, GND)                               | 注 1                       | VSS             |

| 16                          | DB15           | Data Signal Graphic Display Data<br>Green-data (MSB) | 92                        | PDG7            |

| 17                          | DB14           | Data Signal Graphic Display Data<br>Green-data       | 93                        | PDG6            |

| 18                          | DB13           | Data Signal Graphic Display Data<br>Green-data       | 94                        | PDG5            |

| 19                          | DB12           | Data Signal Graphic Display Data<br>Green-data       | 95                        | PDG4            |

| 20                          | DB11           | Data Signal Graphic Display Data<br>Green-data       | 98                        | PDG3            |

| 21                          | DB10           | Data Signal Graphic Display Data<br>Green-data       | 99                        | PDG2            |

| 22                          | DB9            | Data Signal Graphic Display Data<br>Green-data       | 100                       | PDG1            |

| 23                          | DB8            | Data Signal Graphic Display Data<br>Green-data (LSB) | 101                       | PDG0            |

| 24                          | GND            | Power Supply (0V, GND)                               | 注 1                       | VSS             |

| 25                          | DB7            | Data Signal Graphic Display Data<br>Blue-data (MSB)  | 84                        | PDB7            |

| 26                          | DB6            | Data Signal Graphic Display Data<br>Blue-data        | 85                        | PDB6            |

| 27                          | DB5            | Data Signal Graphic Display Data<br>Blue-data        | 86                        | PDB5            |

| 28                          | DB4            | Data Signal Graphic Display Data<br>Blue-data        | 87                        | PDB4            |

| 29                          | DB3            | Data Signal Graphic Display Data<br>Blue-data        | 88                        | PDB3            |

| 30                          | DB2            | Data Signal Graphic Display Data<br>Blue-data        | 89                        | PDB2            |

| 31                          | DB1            | Data Signal Graphic Display Data                     | 90                        | PDB1            |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                         | S1D13517<br>QFP<br>ピン No. | S1D13517<br>端子名 |

|-----------------------------|----------------|-----------------------------------------------------|---------------------------|-----------------|

|                             |                | Blue-data                                           |                           |                 |

| 32                          | DB0            | Data Signal Graphic Display Data<br>Blue-data (LSB) | 91                        | PDB0            |

| 33                          | SDI            | Serial Interface Data                               | 117                       | GPO0            |

| 34                          | SCL            | Serial Interface Clock                              | 116                       | GPO1            |

| 35                          | CS             | Serial Interface Chip Select L:Active               | 115                       | GPO2            |

| 36                          | RESET          | System RESET L:Reset                                | 注 2                       | IOVDD           |

| 37                          | SDO            | Serial Interface Data                               | —                         | —               |

| 38                          | GND            | Power Supply (0V, GND)                              | 注 1                       | VSS             |

| 39                          | VCC            | Power Supply for System                             | 注 2                       | IOVDD           |

| 40                          | VCC            | Power Supply for System                             | 注 2                       | IOVDD           |

注 1) S1D13517 の VSS ピン No.は以下のとおりです。

QFP: 1, 17, 24, 32, 48, 54, 65, 80, 97, 114

注 2) S1D13517 の IOVDD ピン No.は以下のとおりです。

QFP: 16, 31, 47, 64, 79, 96, 113, 128

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

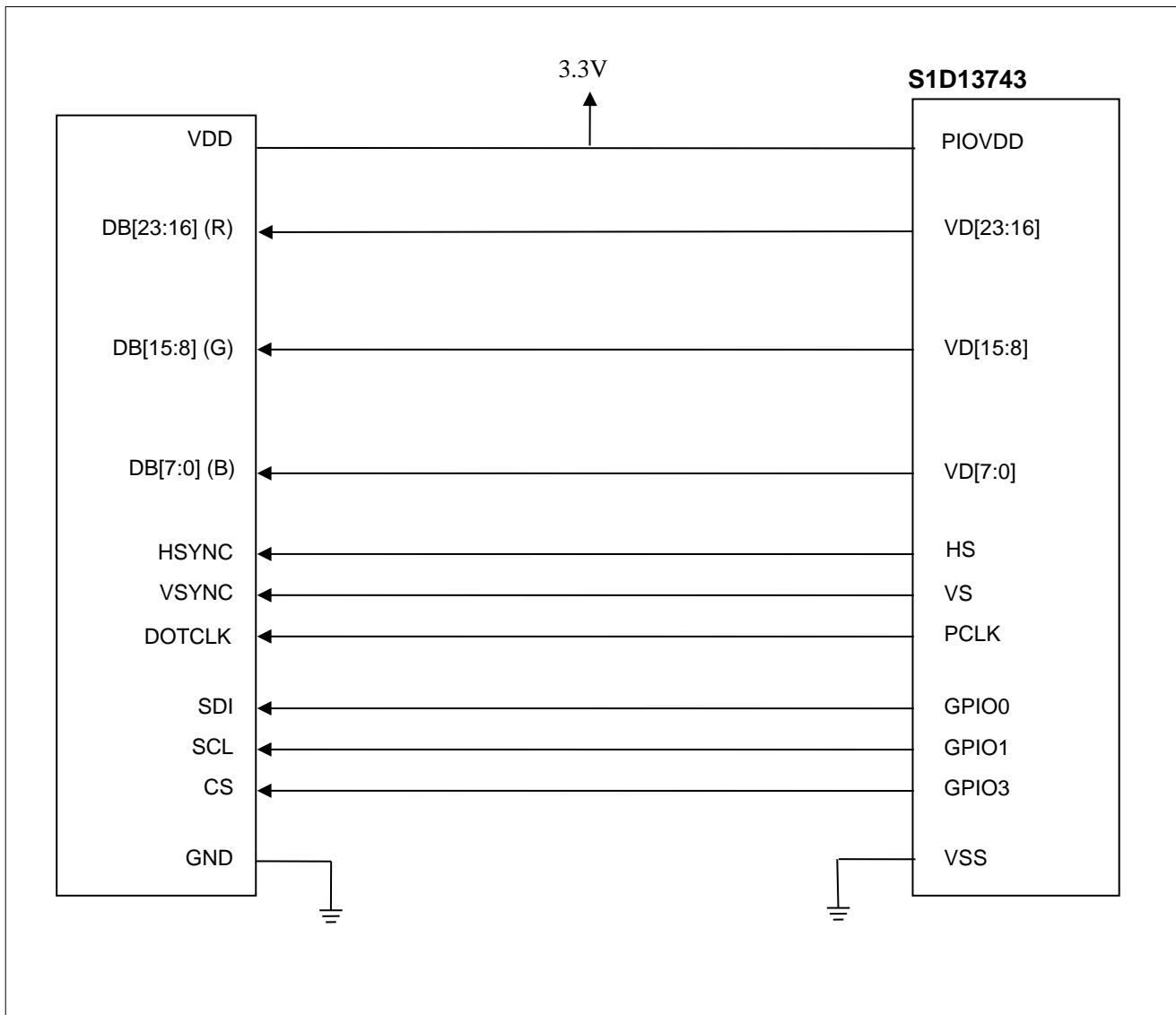

#### 3.2.3 T-55343GD035JU-LW と S1D13743 との接続

下図は、T-55343GD035JU-LW と S1D13743 の接続例です。

図 3-3 T-55343GD035JU-LW と S1D13743 の接続

表 3-4 T-55343GD035JU-LW と S1D13743 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                          | S1D13743<br>QFP<br>ピン No. | S1D13743<br>FCBGA<br>ボール No. | S1D13743<br>端子名 |

|-----------------------------|----------------|------------------------------------------------------|---------------------------|------------------------------|-----------------|

| 1                           | RL             | Input to select Source driver<br>Datashift direction | 1,9,18,<br>28,46,<br>58   | E8,G4,<br>H5,H7              | PIOVDD          |

| 2                           | TB             | Input to select Gate driver<br>Datashift direction   | 1,9,18,<br>28,46,<br>58   | E8,G4,<br>H5,H7              | PIOVDD          |

| 3                           | DOTCLK         | Clock Signal                                         | 8                         | D11                          | PCLK            |

| 4                           | VSYNC          | Vertical Sync Input                                  | 5                         | D10                          | VS              |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                          | S1D13743<br>QFP<br>ピン No. | S1D13743<br>FCBGA<br>ボール No. | S1D13743<br>端子名 |

|-----------------------------|----------------|------------------------------------------------------|---------------------------|------------------------------|-----------------|

| 5                           | H SYNC         | Horizontal Sync Input                                | 4                         | D9                           | HS              |

| 6                           | ENABLE         | Input Data Enable Control                            | —                         | —                            | —               |

| 7                           | DB23           | Data Signal Graphic Display Data<br>Red-data (MSB)   | 12                        | H10                          | VD23            |

| 8                           | DB22           | Data Signal Graphic Display Data<br>Red-data         | 13                        | H11                          | VD22            |

| 9                           | DB21           | Data Signal Graphic Display Data<br>Red-data         | 60                        | J4                           | VD21            |

| 10                          | DB20           | Data Signal Graphic Display Data<br>Red-data         | 55                        | J5                           | VD20            |

| 11                          | DB19           | Data Signal Graphic Display Data<br>Red-data         | 50                        | J6                           | VD19            |

| 12                          | DB18           | Data Signal Graphic Display Data<br>Red-data         | 45                        | J7                           | VD18            |

| 13                          | DB17           | Data Signal Graphic Display Data<br>Red-data         | 40                        | J8                           | VD17            |

| 14                          | DB16           | Data Signal Graphic Display Data<br>Red-data (LSB)   | 20                        | J9                           | VD16            |

| 15                          | GND            | Power Supply (0V, GND)                               | Note                      | Note                         | VSS             |

| 16                          | DB15           | Data Signal Graphic Display Data<br>Green-data (MSB) | 14                        | J10                          | VD15            |

| 17                          | DB14           | Data Signal Graphic Display Data<br>Green-data       | 15                        | J11                          | VD14            |

| 18                          | DB13           | Data Signal Graphic Display Data<br>Green-data       | 61                        | K4                           | VD13            |

| 19                          | DB12           | Data Signal Graphic Display Data<br>Green-data       | 56                        | K5                           | VD12            |

| 20                          | DB11           | Data Signal Graphic Display Data<br>Green-data       | 51                        | K6                           | VD11            |

| 21                          | DB10           | Data Signal Graphic Display Data<br>Green-data       | 48                        | K7                           | VD10            |

| 22                          | DB9            | Data Signal Graphic Display Data<br>Green-data       | 44                        | K8                           | VD9             |

| 23                          | DB8            | Data Signal Graphic Display Data<br>Green-data (LSB) | 38                        | K9                           | VD8             |

| 24                          | GND            | Power Supply (0V, GND)                               | Note                      | Note                         | VSS             |

| 25                          | DB7            | Data Signal Graphic Display Data<br>Blue-data (MSB)  | 21                        | K10                          | VD7             |

| 26                          | DB6            | Data Signal Graphic Display Data<br>Blue-data        | 63                        | L3                           | VD6             |

| 27                          | DB5            | Data Signal Graphic Display Data<br>Blue-data        | 62                        | L4                           | VD5             |

| 28                          | DB4            | Data Signal Graphic Display Data<br>Blue-data        | 57                        | L5                           | VD4             |

| 29                          | DB3            | Data Signal Graphic Display Data<br>Blue-data        | 54                        | L6                           | VD3             |

| 30                          | DB2            | Data Signal Graphic Display Data<br>Blue-data        | 49                        | L7                           | VD2             |

| 31                          | DB1            | Data Signal Graphic Display Data<br>Blue-data        | 43                        | L8                           | VD1             |

| 32                          | DB0            | Data Signal Graphic Display Data<br>Blue-data (LSB)  | 39                        | L9                           | VD0             |

| 33                          | SDI            | Serial Interface Data                                | 81                        | H2                           | GPIO3           |

| 34                          | SCL            | Serial Interface Clock                               | 83                        | G2                           | GPIO1           |

| 35                          | CS             | Serial Interface Chip Select L:Active                | 84                        | G1                           | GPIO0           |

| 36                          | RESET          | System RESET L:Reset                                 | 1,9,18,<br>28,46,         | E8,G4,<br>H5,H7              | PIOVDD          |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明             | S1D13743<br>QFP<br>ピン No. | S1D13743<br>FCBGA<br>ボール No. | S1D13743<br>端子名 |

|-----------------------------|----------------|-------------------------|---------------------------|------------------------------|-----------------|

|                             |                |                         | 58                        |                              |                 |

| 37                          | SDO            | Serial Interface Data   | —                         | —                            | —               |

| 38                          | GND            | Power Supply (0V, GND)  | Note                      | Note                         | VSS             |

| 39                          | VCC            | Power Supply for System | 1,9,18,<br>28,46,<br>58   | E8,G4,<br>H5,H7              | PIOVDD          |

| 40                          | VCC            | Power Supply for System | 1,9,18,<br>28,46,<br>58   | E8,G4,<br>H5,H7              | PIOVDD          |

注)S1D13743 の VSS ピン No.は以下のとおりです。

QFP: 2,7,10,19,27,42, 47,53,59,65,69, 75,80,86,92,96,99,104,113,116, 129,134,140

BGA: C5, C6, E5,E6, E7, F4, F5,F6, F7, G5, G6

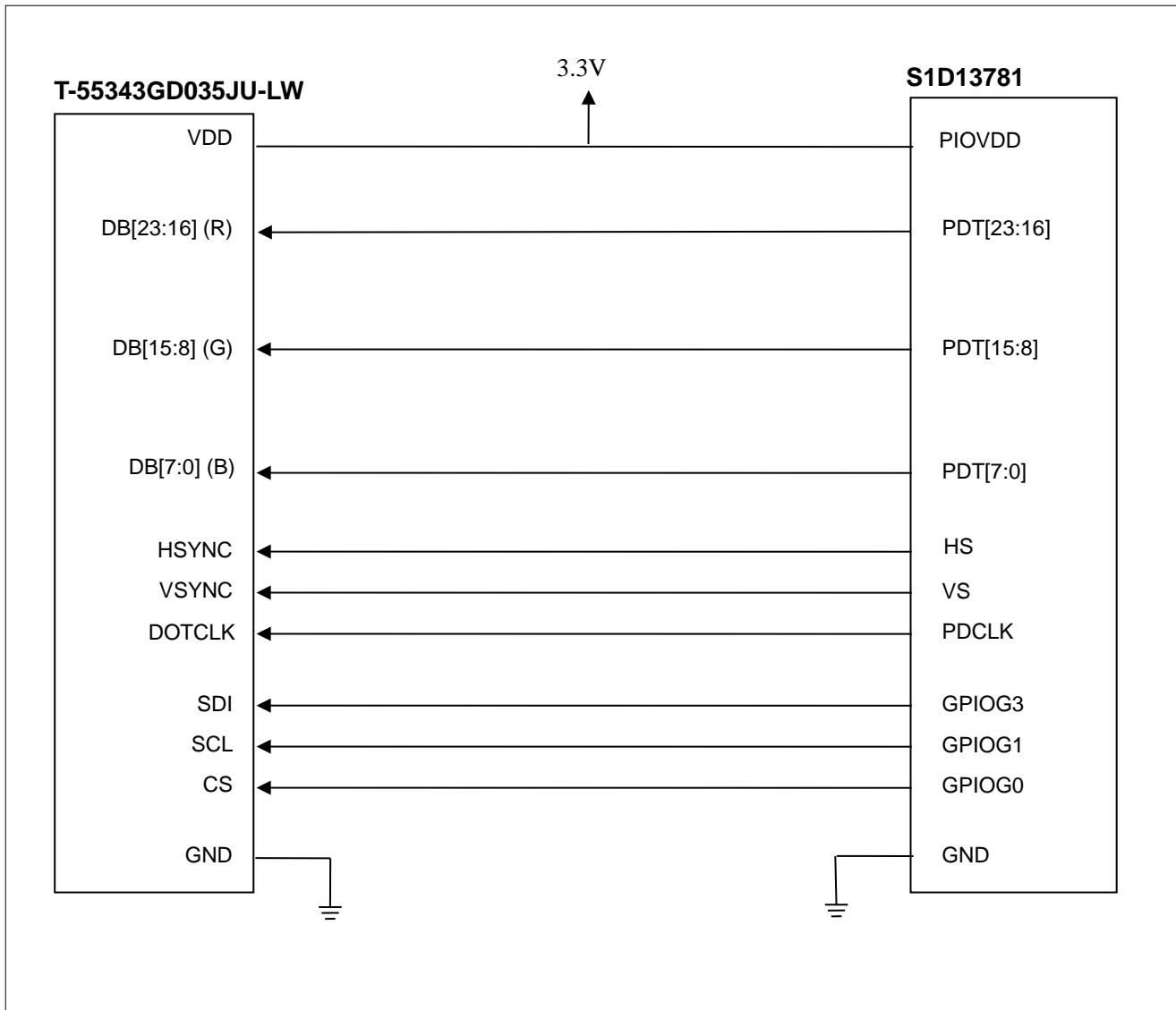

#### 3.2.4 T-55343GD035JU-LW と S1D13781 との接続

下図は、T-55343GD035JU-LW と S1D13781 の接続例です。

図 3-4 T-55343GD035JU-LW と S1D13781 の接続

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

表 3-5 T-55343GD035JU-LW と S1D13781 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD パネル<br>端子名 | LCD パネル端子説明                                          | S1D13781<br>QFP<br>ピン No. | S1D13781<br>端子名 |

|------------------------------|----------------|------------------------------------------------------|---------------------------|-----------------|

| 1                            | RL             | Input to select Source driver<br>Datashift direction | 注 2                       | PIOVDD          |

| 2                            | TB             | Input to select Gate driver<br>Datashift direction   | 注 2                       | PIOVDD          |

| 3                            | DOTCLK         | Clock Signal                                         | 59                        | PDCLK           |

| 4                            | VSYNC          | Vertical Sync Input                                  | 54                        | VS              |

| 5                            | HSYNC          | Horizontal Sync Input                                | 55                        | HS              |

| 6                            | ENABLE         | Input Data Enable Control                            | —                         | —               |

| 7                            | DB23           | Data Signal Graphic Display Data<br>Red-data (MSB)   | 88                        | PDT23           |

| 8                            | DB22           | Data Signal Graphic Display Data<br>Red-data         | 87                        | PDT22           |

| 9                            | DB21           | Data Signal Graphic Display Data<br>Red-data         | 86                        | PDT21           |

| 10                           | DB20           | Data Signal Graphic Display Data<br>Red-data         | 85                        | PDT20           |

| 11                           | DB19           | Data Signal Graphic Display Data<br>Red-data         | 84                        | PDT19           |

| 12                           | DB18           | Data Signal Graphic Display Data<br>Red-data         | 83                        | PDT18           |

| 13                           | DB17           | Data Signal Graphic Display Data<br>Red-data         | 82                        | PDT17           |

| 14                           | DB16           | Data Signal Graphic Display Data<br>Red-data (LSB)   | 81                        | PDT16           |

| 15                           | GND            | Power Supply (0V, GND)                               | 注 1                       | GND             |

| 16                           | DB15           | Data Signal Graphic Display Data<br>Green-data (MSB) | 78                        | PDT15           |

| 17                           | DB14           | Data Signal Graphic Display Data<br>Green-data       | 77                        | PDT14           |

| 18                           | DB13           | Data Signal Graphic Display Data<br>Green-data       | 76                        | PDT13           |

| 19                           | DB12           | Data Signal Graphic Display Data<br>Green-data       | 75                        | PDT12           |

| 20                           | DB11           | Data Signal Graphic Display Data<br>Green-data       | 74                        | PDT11           |

| 21                           | DB10           | Data Signal Graphic Display Data<br>Green-data       | 72                        | PDT10           |

| 22                           | DB9            | Data Signal Graphic Display Data<br>Green-data       | 71                        | PDT9            |

| 23                           | DB8            | Data Signal Graphic Display Data<br>Green-data (LSB) | 70                        | PDT8            |

| 24                           | GND            | Power Supply (0V, GND)                               | 注 1                       | GND             |

| 25                           | DB7            | Data Signal Graphic Display Data<br>Blue-data (MSB)  | 69                        | PDT7            |

| 26                           | DB6            | Data Signal Graphic Display Data<br>Blue-data        | 68                        | PDT6            |

| 27                           | DB5            | Data Signal Graphic Display Data<br>Blue-data        | 66                        | PDT5            |

| 28                           | DB4            | Data Signal Graphic Display Data<br>Blue-data        | 65                        | PDT4            |

| 29                           | DB3            | Data Signal Graphic Display Data<br>Blue-data        | 64                        | PDT3            |

| 30                           | DB2            | Data Signal Graphic Display Data<br>Blue-data        | 63                        | PDT2            |

| 31                           | DB1            | Data Signal Graphic Display Data                     | 62                        | PDT1            |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD パネル<br>端子名 | LCD パネル端子説明                                         | S1D13781<br>QFP<br>ピン No. | S1D13781<br>端子名 |

|------------------------------|----------------|-----------------------------------------------------|---------------------------|-----------------|

|                              |                | Blue-data                                           |                           |                 |

| 32                           | DB0            | Data Signal Graphic Display Data<br>Blue-data (LSB) | 61                        | PDT0            |

| 33                           | SDI            | Serial Interface Data                               | 94                        | GPIO3           |

| 34                           | SCL            | Serial Interface Clock                              | 92                        | GPIO1           |

| 35                           | CS             | Serial Interface Chip Select L:Active               | 91                        | GPIO0           |

| 36                           | RESET          | System RESET L:Reset                                | 注 2                       | PIOVDD          |

| 37                           | SDO            | Serial Interface Data                               | —                         | —               |

| 38                           | GND            | Power Supply (0V, GND)                              | 注 1                       | GND             |

| 39                           | VCC            | Power Supply for System                             | 注 2                       | PIOVDD          |

| 40                           | VCC            | Power Supply for System                             | 注 2                       | PIOVDD          |

注 1) S1D13781 の VSS ピン No.は以下のとおりです。

QFP: 12, 23, 38, 48, 57, 67, 80, 90

注 2) S1D13781 の PIOVDD ピン No.は以下のとおりです。

QFP: 60, 73, 89

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

#### 3.3 T-55343GD035JU-LW レジスタ設定例

本項では、T-55343GD035JU-LW を表示動作させるための各ディスプレイコントローラの主なレジスタの設定例について説明します。

本項で示す設定例は参考値です。ユーザの仕様・用途に応じて変更してください。

また、LCD パネルの代表的なフレーム周波数を実現するためのクロック設定についても以下に示します。各ディスプレイコントローラのレジスタ設定値の詳細については、テクニカルマニュアルを参照してください。

表 3-6 S1D13513 レジスタ設定

| 設定項目、レジスタ名                                                       | レジスタ設定 | 設定値  |

|------------------------------------------------------------------|--------|------|

| REG[0800h] LCD Panel Type Select Register                        | 0380h  | —    |

| REG[0802h] LCD Horizontal Total Register                         | 407    | 408  |

| REG[0804h] LCD Horizontal Display Period Register                | 159    | 320  |

| REG[0806h] LCD Horizontal Display Period Start Position Register | 50     | 51   |

| REG[0808h] LCD Horizontal Pulse Width Register                   | 29     | 30   |

| REG[080Ah] LCD Horizontal Pulse Start Position Register          | 0      | 0    |

| REG[080Ch] LCD Vertical Total Register                           | 261    | 262  |

| REG[080Eh] LCD Vertical Display Period Register                  | 239    | 240  |

| REG[0810h] LCD Vertical Display Period Start Position Register   | 18     | 18   |

| REG[0812h] LCD Vertical Pulse Width Register                     | 2      | 3    |

| REG[0814h] LCD Vertical Pulse Start Position Register            | 0      | 0    |

| REG[0C1Eh] GPIOH Pin Function Register                           | 0555h  | —    |

| PLL2 output frequency in MHz                                     | —      | 90   |

| REG[0446h] LCD Clock Control Register 0                          | 13     | 14   |

| FPSHIFT in MHz                                                   | —      | 6.4  |

| LCD Refresh in Hz                                                | —      | 60.1 |

パネルのインデックスレジスタへの書き込みはS1D13513を通して行うことが可能です。

S1D13513のシリアルコマンドインターフェースを有効にするためには、

REG[0C1Ah] GPIOG Pin Function Register = 03FFh

とし、GPIOG[4:0]の機能を Non-GPIO Function #2 に設定してください。

表 3-7 S1D13513 シリアル出力シーケンス例

| シーケンス | レジスタ  | データ   | 内容                                   |

|-------|-------|-------|--------------------------------------|

| 1     | 081Eh | 7000h | Set Index                            |

| 2     | 081Ch | 0001h | Index: Driver Output                 |

| 3     | 081Eh | 7200h | Write Instruction Value              |

| 4     | 081Ch | 6300h | Value: Driver Output                 |

| 5     | 081Eh | 7000h | Set Index                            |

| 6     | 081Ch | 0002h | Index: LCD Driver AC Control         |

| 7     | 081Eh | 7200h | Write Instruction Value              |

| 8     | 081Ch | 0200h | Value: LCD Driver AC Control         |

| 9     | 081Eh | 7000h | Set Index                            |

| 10    | 081Ch | 0003h | Index: Power Control (1)             |

| 11    | 081Eh | 7200h | Write Instruction Value              |

| 12    | 081Ch | 6064h | Value: Power Control (1)             |

| 13    | 081Eh | 7000h | Set Index                            |

| 14    | 081Ch | 0004h | Index: Data and Color Filter Control |

| 15    | 081Eh | 7200h | Write Instruction Value              |

| 16    | 081Ch | 0447h | Value: Data and Color Filter Control |

| 17    | 081Eh | 7000h | Set Index                            |

| 18    | 081Ch | 0005h | Index: Function Control              |

| 19    | 081Eh | 7200h | Write Instruction Value              |

| 20    | 081Ch | B084h | Value: Function Control              |

| 21    | 081Eh | 7000h | Set Index                            |

| 22    | 081Ch | 000Ah | Index: Contrast / Brightness Control |

| 23    | 081Eh | 7200h | Write Instruction Value              |

| 24    | 081Ch | 4008h | Value: Contrast / Brightness Control |

| 25    | 081Eh | 7000h | Set Index                            |

| 26    | 081Ch | 000Bh | Index: Frame Cycle Control           |

| 27    | 081Eh | 7200h | Write Instruction Value              |

| 28    | 081Ch | D400h | Value: Frame Cycle Control           |

| 29    | 081Eh | 7000h | Set Index                            |

| 30    | 081Ch | 000Dh | Index: Power Control (2)             |

| 31    | 081Eh | 7200h | Write Instruction Value              |

| 32    | 081Ch | 0423h | Value: Power Control (2)             |

| 33    | 081Eh | 7000h | Set Index                            |

| 34    | 081Ch | 000Eh | Index: Power Control (3)             |

| 35    | 081Eh | 7200h | Write Instruction Value              |

| 36    | 081Ch | 3140h | Value: Power Control (3)             |

| 37    | 081Eh | 7000h | Set Index                            |

| 38    | 081Ch | 000Fh | Index: Gate Scan Starting Position   |

| 39    | 081Eh | 7200h | Write Instruction Value              |

| 40    | 081Ch | 0000h | Value: Gate Scan Starting Position   |

| 41    | 081Eh | 7000h | Set Index                            |

| 42    | 081Ch | 0016h | Index: Horizontal Porch              |

| 43    | 081Eh | 7200h | Write Instruction Value              |

| 44    | 081Ch | 9F80h | Value: Horizontal Porch              |

| 45    | 081Eh | 7000h | Set Index                            |

| 46    | 081Ch | 0017h | Index: Vertical Porch                |

### 3. T-55343GD035JU-LW とディスプレイコントローラとの接続

| シーケンス | レジスタ  | データ   | 内容                       |

|-------|-------|-------|--------------------------|

| 47    | 081Eh | 7200h | Write Instruction Value  |

| 48    | 081Ch | 2212h | Value: Vertical Porch    |

| 49    | 081Eh | 7000h | Set Index                |

| 50    | 081Ch | 001Eh | Index: Power Control (4) |

| 51    | 081Eh | 7200h | Write Instruction Value  |

| 52    | 081Ch | 00DBh | Value: Power Control (4) |

| 53    | 081Eh | 7000h | Set Index                |

| 54    | 081Ch | 0030h | Index: Gamma Control 1   |

| 55    | 081Eh | 7200h | Write Instruction Value  |

| 56    | 081Ch | 0000h | Value: Gamma Control 1   |

| 57    | 081Eh | 7000h | Set Index                |

| 58    | 081Ch | 0031h | Index: Gamma Control 2   |

| 59    | 081Eh | 7200h | Write Instruction Value  |

| 60    | 081Ch | 0607h | Value: Gamma Control 2   |

| 61    | 081Eh | 7000h | Set Index                |

| 62    | 081Ch | 0032h | Index: Gamma Control 3   |

| 63    | 081Eh | 7200h | Write Instruction Value  |

| 64    | 081Ch | 0006h | Value: Gamma Control 3   |

| 65    | 081Eh | 7000h | Set Index                |

| 66    | 081Ch | 0033h | Index: Gamma Control 4   |

| 67    | 081Eh | 7200h | Write Instruction Value  |

| 68    | 081Ch | 0307h | Value: Gamma Control 4   |

| 69    | 081Eh | 7000h | Set Index                |

| 70    | 081Ch | 0034h | Index: Gamma Control 5   |

| 71    | 081Eh | 7200h | Write Instruction Value  |

| 72    | 081Ch | 0107h | Value: Gamma Control 5   |

| 73    | 081Eh | 7000h | Set Index                |

| 74    | 081Ch | 0035h | Index: Gamma Control 6   |

| 75    | 081Eh | 7200h | Write Instruction Value  |

| 76    | 081Ch | 0001h | Value: Gamma Control 6   |

| 77    | 081Eh | 7000h | Set Index                |

| 78    | 081Ch | 0036h | Index: Gamma Control 7   |

| 79    | 081Eh | 7200h | Write Instruction Value  |

| 80    | 081Ch | 0707h | Value: Gamma Control 7   |

| 81    | 081Eh | 7000h | Set Index                |

| 82    | 081Ch | 0037h | Index: Gamma Control 8   |

| 83    | 081Eh | 7200h | Write Instruction Value  |

| 84    | 081Ch | 0703h | Value: Gamma Control 8   |

| 85    | 081Eh | 7000h | Set Index                |

| 86    | 081Ch | 003Ah | Index: Gamma Control 9   |

| 87    | 081Eh | 7200h | Write Instruction Value  |

| 88    | 081Ch | 0C00h | Value: Gamma Control 9   |

| 89    | 081Eh | 7000h | Set Index                |

| 90    | 081Ch | 003Bh | Index: Gamma Control 10  |

| 91    | 081Eh | 7200h | Write Instruction Value  |

| 92    | 081Ch | 0006h | Value: Gamma Control 10  |

表 3-8 S1D13517 レジスタ設定

| 設定項目、レジスタ名                                             | レジスタ設定 | 設定値                                                    |

|--------------------------------------------------------|--------|--------------------------------------------------------|

| REG[14h] LCD Panel Type Register                       | 00h    | 24bpp<br>mode1, 24-bit                                 |

| REG[16h] Horizontal Display Width Register (H DISP)    | 27h    | 320                                                    |

| REG[18h] Horizontal Non-Display Period Register (HNDP) | 2Bh    | 88                                                     |

| REG[1Ah] Vertical Display Height Register 0 (V DISP)   | EFh    | 240                                                    |

| REG[1Ch] Vertical Display Height Register 1 (V DISP)   | 00h    | —                                                      |

| REG[1Eh] Vertical Non-Display Period Register (VNDP)   | 0Ah    | 22                                                     |

| REG[20h] PHS Pulse Width Register (HSW)                | 01h    | 2                                                      |

| REG[22h] PHS Pulse Start Position Register (HPS)       | 14h    | 20                                                     |

| REG[24h] PVS Pulse Width Register (VSW)                | 0Bh    | 12                                                     |

| REG[26h] PVS Pulse Start Position Register (VPS)       | 04h    | 4                                                      |

| REG[28h] PCLK Polarity Register                        | 80h    | PCLK polarity<br>is falling edge.                      |

| REG[04h] PLL D-Divider Register                        | 17h    | PLL D-div is<br>1:24.<br>Input 24MHz<br>-> Output 1MHz |

| REG[06h] PLL Setting Register 0                        | 01h    | PLL output =<br>50MHz                                  |

| REG[08h] PLL Setting Register 1                        | 01h    | PLL clock<br>Divide ratio =<br>1/2.<br>(50MHz /2)      |

| REG[0Ch] PLL N-Divider Register                        | 18h    | PLL<br>N-counter<br>50MHz                              |

| REG[0Eh] SS Control Register 0                         | 3Fh    | SS disabled                                            |

| REG[12h] Clock Source Select Register                  | 80h    | SYCLK =<br>1/3<br>((50MHz/2)/3 =<br>8.33MHz)           |

| REG[8Ch] SDRAM Refresh Counter Register 0              | 80h    | Refresh<br>counter<br>1/25MHz x 384<br>= 15.36us       |

| REG[8Eh] SDARM Refresh Counter Register 1              | 01h    | —                                                      |

| FPSHIFT in MHz                                         | —      | 8.33                                                   |

| LCD Refresh in Hz                                      | —      | 78                                                     |

注) パネルのインデックスレジスタへの書き込みは S1D13517 の GPIO ピン GPO[2:0]を通して行うことが可能です。GPIO ピンの詳細は S1D13517 のテクニカルマニュアルを参照ください。

表 3-9 S1D13743 レジスタ設定

| 設定項目、レジスタ名                                             | レジスタ設定 | 設定値                                                  |

|--------------------------------------------------------|--------|------------------------------------------------------|

| REG[14h] Panel Type Register                           | 01h    | 24bpp                                                |

| REG[16h] Horizontal Display Width Register (HDISP)     | 28h    | 320                                                  |

| REG[18h] Horizontal Non-Display Period Register (HNDP) | 58h    | 88                                                   |

| REG[1Ah] Vertical Display Height Register 0 (VDISP)    | F0h    | 240                                                  |

| REG[1Ch] Vertical Display Height Register 1 (VDISP)    | 00h    | —                                                    |

| REG[1Eh] Vertical Non-Display Period Register (VNDP)   | 16h    | 22                                                   |

| REG[20h] HS Pulse Width Register (HSW)                 | 1Eh    | 30                                                   |

| REG[22h] HS Pulse Start Position Register (HPS)        | 14h    | 20                                                   |

| REG[24h] VS Pulse Width Register (VSW)                 | 03h    | 3                                                    |

| REG[26h] VS Pulse Start Position Register (VPS)        | 04h    | 4                                                    |

| REG[28h] PCLK Polarity Register                        | 80h    | PCLK polarity<br>is falling edge                     |

| REG[04h] PLL M-Divider Register                        | 03h    | PLL M-div is<br>1:4.<br>Input 4MHz<br>-> Output 1MHz |

| REG[06h] PLL Setting Register 0                        | F8h    | Default                                              |

| REG[08h] PLL Setting Register 1                        | 80h    | Default                                              |

| REG[0Ah] PLL Setting Register 2                        | 28h    | Default                                              |

| REG[0Ch] PLL Setting Register 3                        | 00h    | Default                                              |

| REG[0Eh] PLL Setting Register 4                        | 3Eh    | PLL LL is 63.<br>Input 1MHz -><br>Output 63MHz       |

| REG[12h] Clock Source Select Register                  | 49h    | Input 63MHz<br>->Output<br>6.3MHz                    |

| REG[0Eh] SS Control Register 0                         | 3Fh    | SS disabled                                          |

| REG[12h] Clock Source Select Register                  | 80h    | SYSCLK =<br>1/3<br>((50MHz/2)/3 =<br>8.33MHz)        |

| PCLK in MHz                                            | —      | 6.3                                                  |

| LCD Refresh in Hz                                      | —      | 58.93Hz                                              |

注) パネルのインデックスレジスタへの書き込みは S1D13743 の GPIO ピン GPIO[7:0]を通して行うことが可能です。GPIO ピンの詳細は S1D13743 のテクニカルマニュアルを参照ください。

表 3-10 S1D13781 レジスタ設定

| 設定項目、レジスタ名                                      | レジスタ設定 | 設定値                                                                               |

|-------------------------------------------------|--------|-----------------------------------------------------------------------------------|

| REG[20h] Panel Setting Register                 | 002Fh  | DE:Low active<br>PCLK Polarity:<br>Falling edge<br>PanelType:<br>Color TFT 24-bit |

| REG[24h] Horizontal Display Width Register      | 0028h  | 320                                                                               |

| REG[26h] Horizontal Non-Display Period Register | 0058h  | 88                                                                                |

| REG[28h] Vertical Display Height Register       | 00F0h  | 240                                                                               |

| REG[2Ah] Vertical Non-Display Period Register   | 0016h  | 22                                                                                |

| REG[2Ch] HS Pulse Width Register                | 001Eh  | 30                                                                                |

| REG[2Eh] HS Pulse Start Position Register       | 0014h  | 20                                                                                |

| REG[30h] VS Pulse Width Register                | 0003h  | 3                                                                                 |

| REG[32h] VS Pulse Start Position Register       | 0004h  | 4                                                                                 |

| REG[12h] PLL Setting Register 1                 | 0011h  | MM=18                                                                             |

| REG[14h] PLL Setting Register 2                 | 002Ch  | LL=45                                                                             |

| REG[16h] Internal Clock Configuration Register  | 0008h  | fPLL_REF_CLK<br>= fCLKI /9                                                        |

| CLKI in MHz                                     | —      | 24                                                                                |

| PCLK in MHz                                     | —      | 6.66                                                                              |

| LCD refresh in Hz                               | —      | 62.3                                                                              |

注) パネルのインデックスレジスタへの書き込みは S1D13781 の GPIO ピン GPO[3:0]を通して行うことが可能です。GPIO ピンの詳細は S1D13781 のテクニカルマニュアルを参照ください。

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

### 4. T-55265GD057J-LW とディスプレイコントローラとの接続

本章では、T-55265GD057J-LW と下記ディスプレイコントローラとの接続例について説明します。

- S1D13513

- S1D13517

- S1D13743

- S1D13781

#### 4.1 T-55265GD057J-LW の端子配列

以下に、T-55265GD057J-LW のコネクタの端子配列を示します。

実装コネクタ：ELCO 製 08-6210-033 22 ピン FPC コネクタ(0.3mm 厚、0.5mm ピッチ)

表 4-1 T-55265GD057J-LW コネクタの端子配列

| コネクタ端子 No. | 端子名  | 端子説明                                                          |

|------------|------|---------------------------------------------------------------|

| 1          | GND  | Power Supply (0V, GND)                                        |

| 2          | CK   | Clock Signal                                                  |

| 3          | HSYC | Horizontal Sync Input                                         |

| 4          | VSYC | Vertical Sync Input                                           |

| 5          | GND  | Power Supply (0V, GND)                                        |

| 6          | R0   | Data Signal Graphic Display Data Red-data (LSB)               |

| 7          | R1   | Data Signal Graphic Display Data Red-data                     |

| 8          | R2   | Data Signal Graphic Display Data Red-data                     |

| 9          | R3   | Data Signal Graphic Display Data Red-data                     |

| 10         | R4   | Data Signal Graphic Display Data Red-data                     |

| 11         | R5   | Data Signal Graphic Display Data Red-data (MSB)               |

| 12         | GND  | Power Supply (0V, GND)                                        |

| 13         | G0   | Data Signal Graphic Display Data Green-data (LSB)             |

| 14         | G1   | Data Signal Graphic Display Data Green-data                   |

| 15         | G2   | Data Signal Graphic Display Data Green-data                   |

| 16         | G3   | Data Signal Graphic Display Data Green-data                   |

| 17         | G4   | Data Signal Graphic Display Data Green-data                   |

| 18         | G5   | Data Signal Graphic Display Data Green-data (MSB)             |

| 19         | GND  | Power Supply (0V, GND)                                        |

| 20         | B0   | Data Signal Graphic Display Data Blue-data (LSB)              |

| 21         | B1   | Data Signal Graphic Display Data Blue-data                    |

| 22         | B2   | Data Signal Graphic Display Data Blue-data                    |

| 23         | B3   | Data Signal Graphic Display Data Blue-data                    |

| 24         | B4   | Data Signal Graphic Display Data Blue-data                    |

| 25         | B5   | Data Signal Graphic Display Data Blue-data (MSB)              |

| 26         | GND  | Power Supply (0V, GND)                                        |

| 27         | ENAB | Input Data Enable Control                                     |

| 28         | VCC  | Power Supply for Logic (3.3V)                                 |

| 29         | VCC  | Power Supply for Logic (3.3V)                                 |

| 30         | R/L  | Control the shift direction of device internal shift register |

| 31         | U/D  | Set the Up/Down scan direction                                |

| 32         | NC   | Non Connection                                                |

| 33         | GND  | Power Supply (0V, GND)                                        |

### 4.2 T-55265GD057J-LW 接続例

本項では、T-55265GD057J-LW と各ディスプレイコントローラとの信号接続について説明します。

(QFP、BGA など複数のパッケージをサポートする製品については、各々のピン/ポール No.を表記します。)

T-55265GD057J-LW は以下の電源を必要とします。

- VDD            +3.3V (±0.3V)

- V<sub>F</sub>            +13.2V

上記電圧の範囲内で、コントローラ側の LCD 用 VDD に適合した電圧を選択してください。

消費電力、絶対最大定格等の詳細仕様については、京セラの営業担当にお問い合わせください。

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

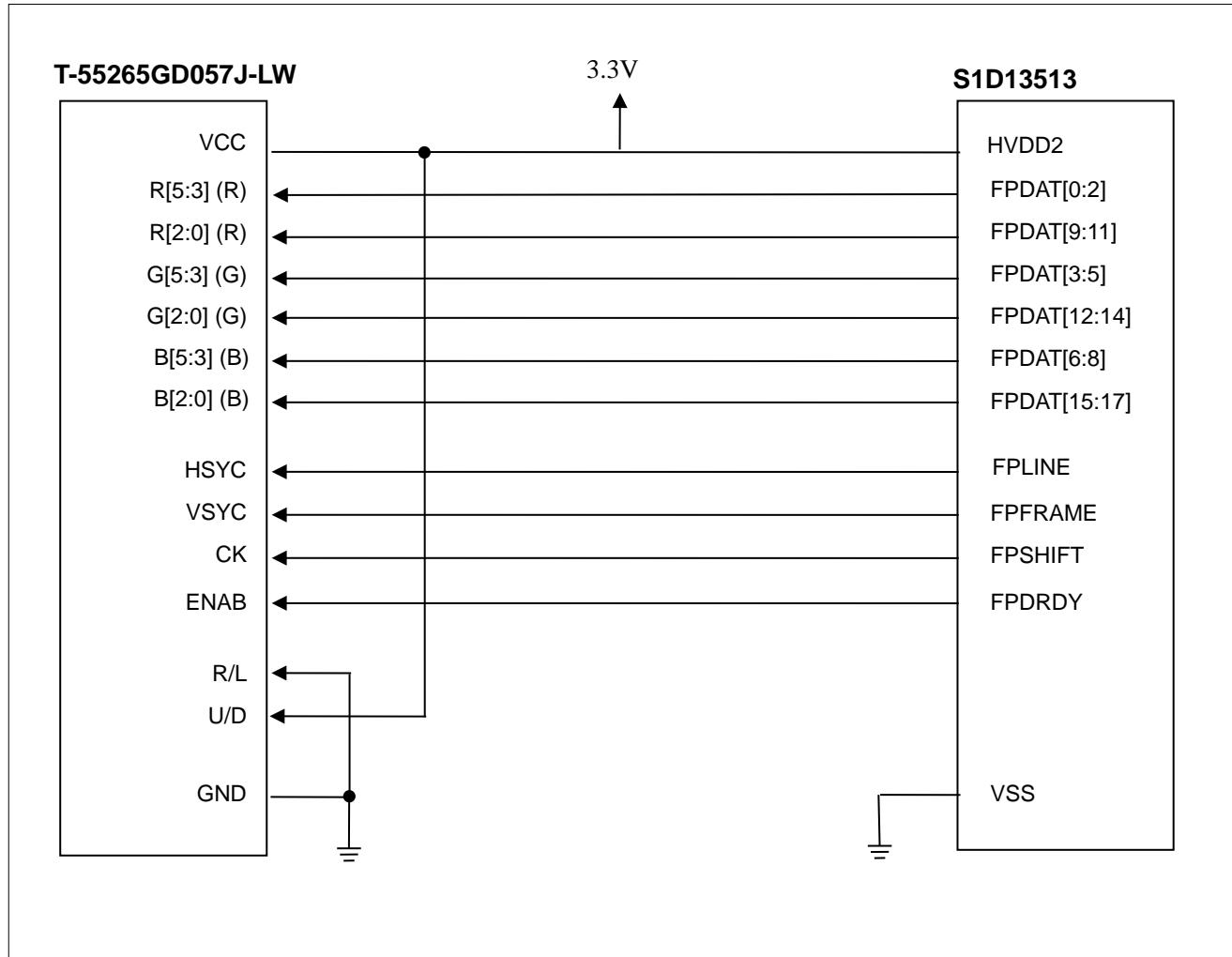

### 4.2.1 T-55265GD057J-LW と S1D13513 との接続

下図は、T-55265GD057J-LW と S1D13513 の接続例です。

図 4-1 T-55265GD057J-LW と S1D13513 の接続

表 4-2 T-55265GD057J-LW と S1D13513 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD<br>パネル<br>端子名 | LCD パネル端子説明                                        | S1D13513<br>QFP<br>ピン No. | S1D13513<br>PBGA<br>ポール No. | S1D13513<br>端子名 |

|------------------------------|-------------------|----------------------------------------------------|---------------------------|-----------------------------|-----------------|

| 1                            | GN<br>D           | Power Supply (0V, GND)                             | 注                         | 注                           | VSS             |

| 2                            | CK                | Clock Signal                                       | 77                        | P8                          | FPSHIFT         |

| 3                            | HSY<br>C          | Horizontal Sync Input                              | 79                        | T8                          | FPLINE          |

| 4                            | VSY<br>C          | Vertical Sync Input                                | 78                        | R8                          | FPFRAME         |

| 5                            | GN<br>D           | Power Supply (0V, GND)                             | 注                         | 注                           | VSS             |

| 6                            | R0                | Data Signal Graphic Display Data<br>Red-data (LSB) | 61                        | N5                          | FPDAT11         |

| 7                            | R1                | Data Signal Graphic Display Data<br>Red-data       | 62                        | M5                          | FPDAT10         |

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No. | LCD<br>パネル<br>端子名 | LCD パネル端子説明                                                      | S1D13513<br>QFP<br>ピン No. | S1D13513<br>PBGA<br>ポール No. | S1D13513<br>端子名 |

|------------------------------|-------------------|------------------------------------------------------------------|---------------------------|-----------------------------|-----------------|

| 8                            | R2                | Data Signal Graphic Display Data<br>Red-data                     | 63                        | P6                          | FPDAT9          |

| 9                            | R3                | Data Signal Graphic Display Data<br>Red-data                     | 72                        | T7                          | FPDAT2          |

| 10                           | R4                | Data Signal Graphic Display Data<br>Red-data                     | 73                        | N7                          | FPDAT1          |

| 11                           | R5                | Data Signal Graphic Display Data<br>Red-data (MSB)               | 74                        | M7                          | FPDAT0          |

| 12                           | GN<br>D           | Power Supply (0V, GND)                                           | 注                         | 注                           | VSS             |

| 13                           | G0                | Data Signal Graphic Display Data<br>Green-data (LSB)             | 56                        | R4                          | FPDAT14         |

| 14                           | G1                | Data Signal Graphic Display Data<br>Green-data                   | 59                        | T4                          | FPDAT13         |

| 15                           | G2                | Data Signal Graphic Display Data<br>Green-data                   | 60                        | T5                          | FPDAT12         |

| 16                           | G3                | Data Signal Graphic Display Data<br>Green-data                   | 69                        | L7                          | FPDAT5          |

| 17                           | G4                | Data Signal Graphic Display Data<br>Green-data                   | 70                        | P7                          | FPDAT4          |

| 18                           | G5                | Data Signal Graphic Display Data<br>Green-data (MSB)             | 71                        | R7                          | FPDAT3          |

| 19                           | GN<br>D           | Power Supply (0V, GND)                                           | 注                         | 注                           | VSS             |

| 20                           | B0                | Data Signal Graphic Display Data<br>Blue-data (LSB)              | 53                        | N4                          | FPDAT17         |

| 21                           | B1                | Data Signal Graphic Display Data<br>Blue-data                    | 54                        | P4                          | FPDAT16         |

| 22                           | B2                | Data Signal Graphic Display Data<br>Blue-data                    | 55                        | T2                          | FPDAT15         |

| 23                           | B3                | Data Signal Graphic Display Data<br>Blue-data                    | 64                        | R6                          | FPDAT8          |

| 24                           | B4                | Data Signal Graphic Display Data<br>Blue-data                    | 67                        | K6                          | FPDAT7          |

| 25                           | B5                | Data Signal Graphic Display Data<br>Blue-data (MSB)              | 68                        | M6                          | FPDAT6          |

| 26                           | GN<br>D           | Power Supply (0V, GND)                                           | 注                         | 注                           | VSS             |

| 27                           | ENA<br>B          | Input Data Enable Control                                        | 80                        | M8                          | FPDRDY          |

| 28                           | VC<br>C           | Power Supply for Logic (3.3V)                                    | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 29                           | VC<br>C           | Power Supply for Logic (3.3V)                                    | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 30                           | R/L               | Control the shift direction of device<br>internal shift register | 注                         | 注                           | VSS             |

| 31                           | U/D               | Set the Up/Down scan direction                                   | 57,65,75                  | L5,L8,T6                    | HVDD2           |

| 32                           | NC                | Non Connection                                                   | —                         | —                           | —               |

| 33                           | GN<br>D           | Power Supply (0V, GND)                                           | 注                         | 注                           | VSS             |

注) S1D13513 の VSS ピン No.は以下のとおりです。

QFP: 10,20,38,58,66,76,92,99,106,120,133,139,151,163,169,175,184,197

BGA: A1,A16,D4,D8,D13,G7-G10,G13,H7-H10,J1,J7-J10,K2,K7-K10,K13,N3,N6,N9,N13,T1,T16

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

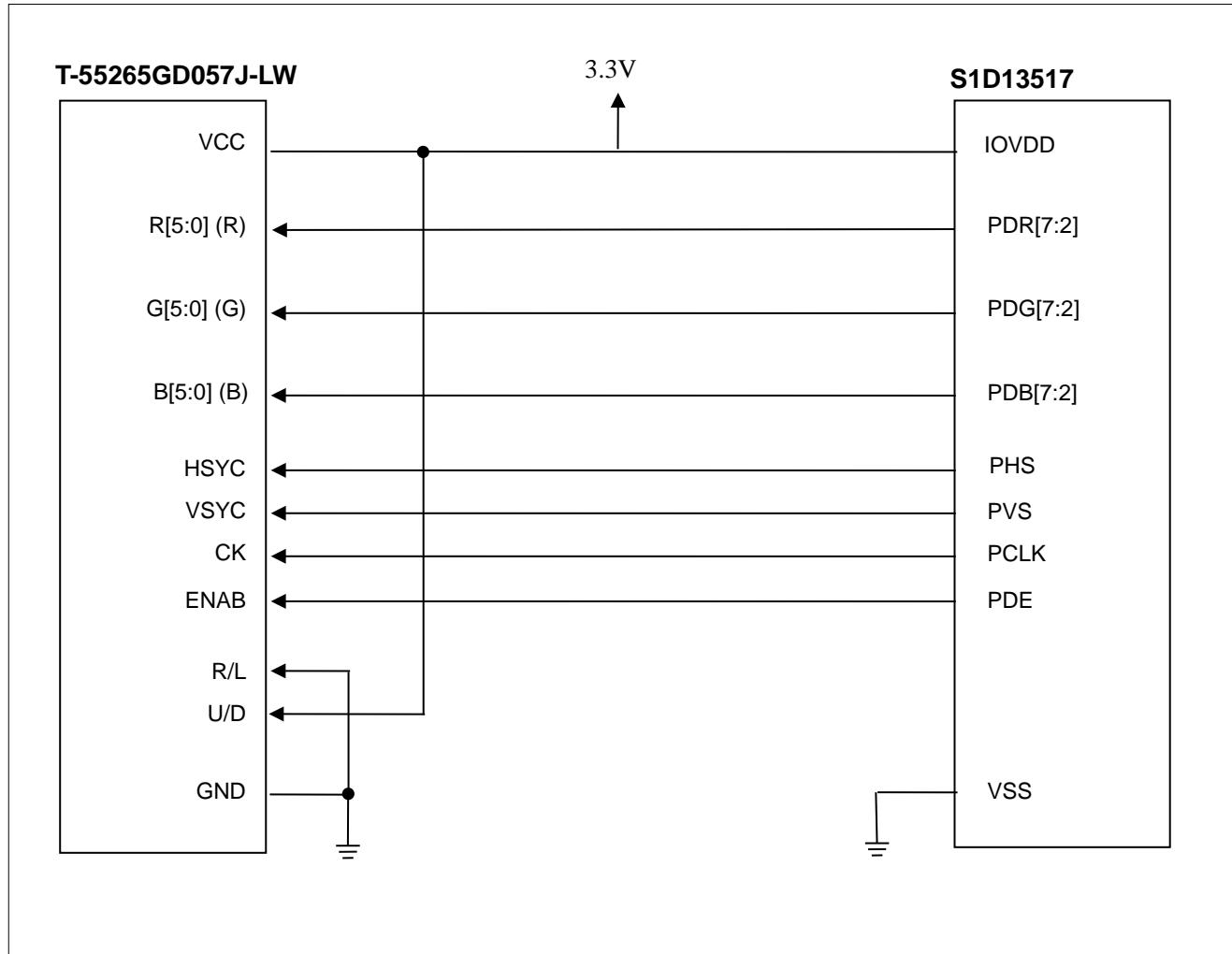

### 4.2.2 T-55265GD057J-LW と S1D13517 との接続

下図は、T-55265GD057J-LW と S1D13517 の接続例です。

図 4-2 T-55343GD035JU-LW と S1D13517 の接続

表 4-3 T-55265GD057J-LW と S1D13517 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                        | S1D13517<br>QFP<br>ピン No. | S1D13517<br>端子名 |

|-----------------------------|----------------|----------------------------------------------------|---------------------------|-----------------|

| 1                           | GND            | Power Supply (0V, GND)                             | 注 1                       | VSS             |

| 2                           | CK             | Clock Signal                                       | 110                       | PCLK            |

| 3                           | HSYC           | Horizontal Sync Input                              | 83                        | PHS             |

| 4                           | VSYC           | Vertical Sync Input                                | 82                        | PVS             |

| 5                           | GND            | Power Supply (0V, GND)                             | 注 1                       | VSS             |

| 6                           | R0             | Data Signal Graphic Display Data<br>Red-data (LSB) | 107                       | PDR2            |

| 7                           | R1             | Data Signal Graphic Display Data<br>Red-data       | 106                       | PDR3            |

| 8                           | R2             | Data Signal Graphic Display Data<br>Red-data       | 105                       | PDR4            |

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD パネル<br>端子名 | LCD パネル端子説明                                                      | S1D13517<br>QFP<br>ピン No. | S1D13517<br>端子名 |

|-----------------------------|----------------|------------------------------------------------------------------|---------------------------|-----------------|

| 9                           | R3             | Data Signal Graphic Display Data<br>Red-data                     | 104                       | PDR5            |

| 10                          | R4             | Data Signal Graphic Display Data<br>Red-data                     | 103                       | PDR6            |

| 11                          | R5             | Data Signal Graphic Display Data<br>Red-data (MSB)               | 102                       | PDR7            |

| 12                          | GND            | Power Supply (0V, GND)                                           | 注 1                       | VSS             |

| 13                          | G0             | Data Signal Graphic Display Data<br>Green-data (LSB)             | 99                        | PDG2            |

| 14                          | G1             | Data Signal Graphic Display Data<br>Green-data                   | 98                        | PDG3            |

| 15                          | G2             | Data Signal Graphic Display Data<br>Green-data                   | 95                        | PDG4            |

| 16                          | G3             | Data Signal Graphic Display Data<br>Green-data                   | 94                        | PDG5            |

| 17                          | G4             | Data Signal Graphic Display Data<br>Green-data                   | 93                        | PDG6            |

| 18                          | G5             | Data Signal Graphic Display Data<br>Green-data (MSB)             | 92                        | PDG7            |

| 19                          | GND            | Power Supply (0V, GND)                                           | 注 1                       | VSS             |

| 20                          | B0             | Data Signal Graphic Display Data<br>Blue-data (LSB)              | 89                        | PDB2            |

| 21                          | B1             | Data Signal Graphic Display Data<br>Blue-data                    | 88                        | PDB3            |

| 22                          | B2             | Data Signal Graphic Display Data<br>Blue-data                    | 87                        | PDB4            |

| 23                          | B3             | Data Signal Graphic Display Data<br>Blue-data                    | 86                        | PDB5            |

| 24                          | B4             | Data Signal Graphic Display Data<br>Blue-data                    | 85                        | PDB6            |

| 25                          | B5             | Data Signal Graphic Display Data<br>Blue-data (MSB)              | 84                        | PDB7            |

| 26                          | GND            | Power Supply (0V, GND)                                           | 注 1                       | VSS             |

| 27                          | ENAB           | Input Data Enable Control                                        | 81                        | PDE             |

| 28                          | VCC            | Power Supply for Logic (3.3V)                                    | 注 2                       | IOVDD           |

| 29                          | VCC            | Power Supply for Logic (3.3V)                                    | 注 2                       | IOVDD           |

| 30                          | R/L            | Control the shift direction of device<br>internal shift register | 注 1                       | VSS             |

| 31                          | U/D            | Set the Up/Down scan direction                                   | 注 2                       | IOVDD           |

| 32                          | NC             | Non Connection                                                   | —                         | —               |

| 33                          | GND            | Power Supply (0V, GND)                                           | 注 1                       | VSS             |

注 1) S1D13517 の VSS ピン No.は以下のとおりです。

QFP: 1, 17, 24, 32, 48, 54, 65, 80, 97, 114

注 2) S1D13517 の IOVDD ピン No.は以下のとおりです。

QFP: 16, 31, 47, 64, 79, 96, 113, 128

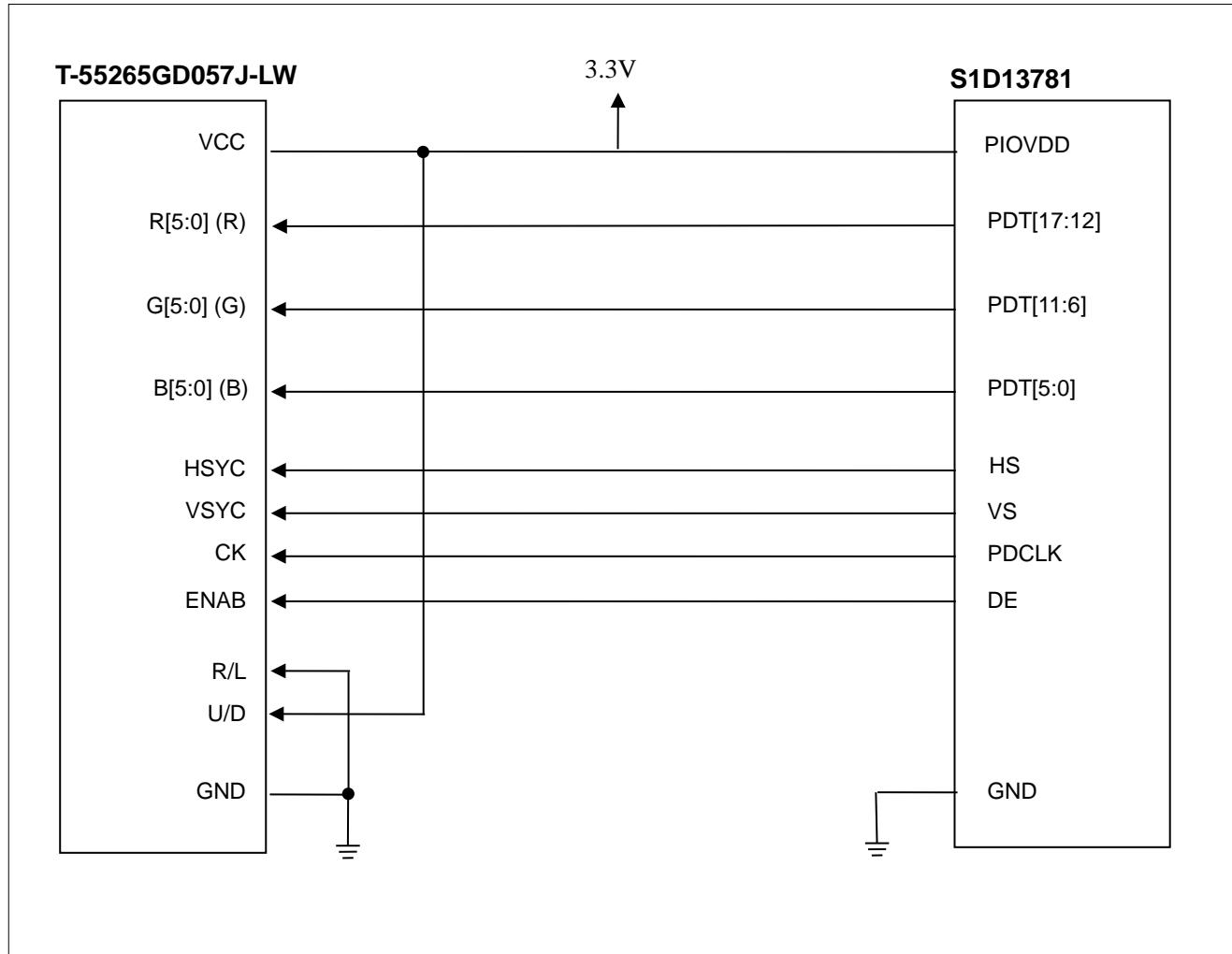

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

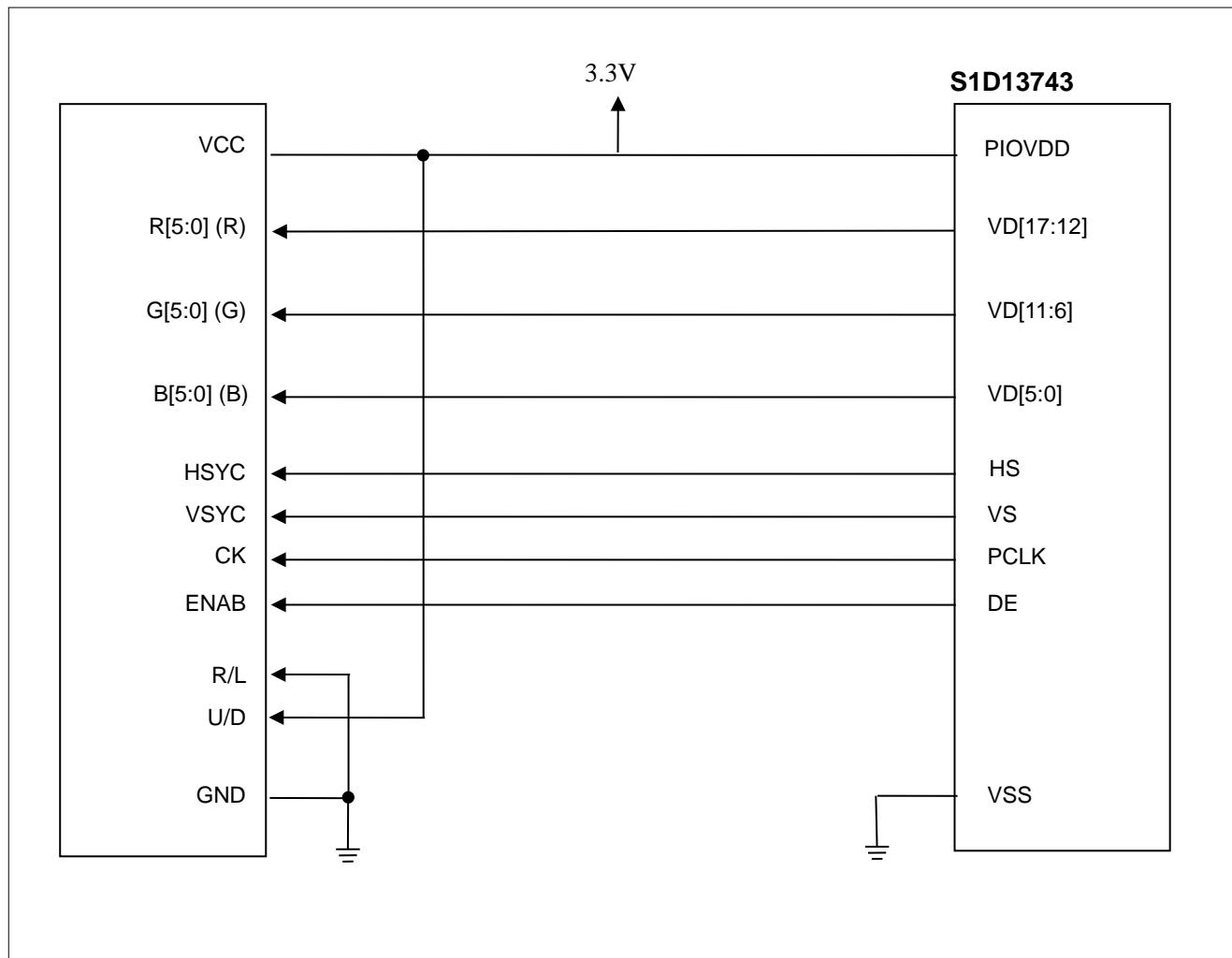

### 4.2.3 T-55265GD057J-LW と S1D13743 との接続

下図は、T-55265GD057J-LW と S1D13743 の接続例です。

図 4-3 T-55265GD057J-LW と S1D13743 の接続

表 4-4 T-55265GD057J-LW と S1D13743 との接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD<br>パネル<br>端子名 | LCD パネル端子説明                                        | S1D1374<br>3<br>QFP<br>ピン No. | S1D1374<br>3<br>FCBGA<br>ボール No. | S1D1374<br>3<br>端子名 |

|-----------------------------|-------------------|----------------------------------------------------|-------------------------------|----------------------------------|---------------------|

| 1                           | GND               | Power Supply (0V, GND)                             | Note                          | Note                             | VSS                 |

| 2                           | CK                | Clock Signal                                       | 8                             | D11                              | PCLK                |

| 3                           | HSY<br>C          | Horizontal Sync Input                              | 4                             | D9                               | HS                  |

| 4                           | VSY<br>C          | Vertical Sync Input                                | 5                             | D10                              | VS                  |

| 5                           | GND               | Power Supply (0V, GND)                             | Note                          | Note                             | VSS                 |

| 6                           | R0                | Data Signal Graphic Display Data<br>Red-data (LSB) | 56                            | K5                               | VD12                |

| 7                           | R1                | Data Signal Graphic Display Data<br>Red-data       | 61                            | K4                               | VD13                |

| 8                           | R2                | Data Signal Graphic Display Data                   | 15                            | J11                              | VD14                |

## 4. T-55265GD057J-LW とディスプレイコントローラとの接続

| LCD<br>パネル<br>コネクタ<br>端子 No | LCD<br>パネル<br>端子名 | LCD パネル端子説明                                                      | S1D1374<br>3<br>QFP<br>ピン No. | S1D1374<br>3<br>FCBGA<br>ボール No. | S1D1374<br>3<br>端子名 |

|-----------------------------|-------------------|------------------------------------------------------------------|-------------------------------|----------------------------------|---------------------|

|                             |                   | Red-data                                                         |                               |                                  |                     |

| 9                           | R3                | Data Signal Graphic Display Data<br>Red-data                     | 14                            | J10                              | VD15                |