# S2S65A30

## データーシート

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

ARM<sup>®</sup> は、ARM 社の登録商標です。

CompactFlash は Sandisk 社の登録商標です。

その他記載の会社名、製品名は、それぞれの会社の商標もしくは登録商標です。

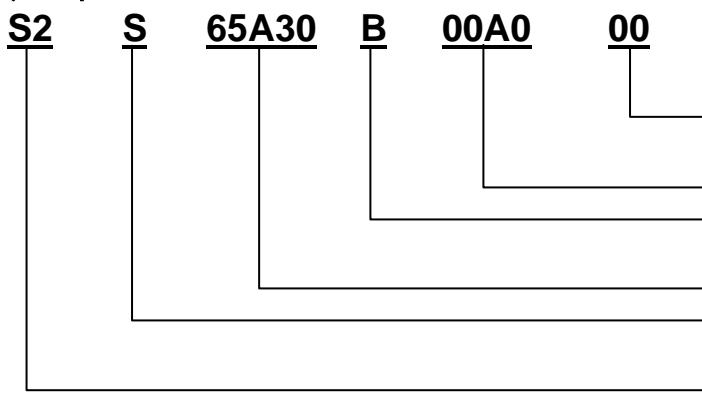

## 製品型番体系

### ●デバイス

梱包仕様

[00: テープ & リール以外]

仕様

形状

[B : BGAP]

機種番号

製品中分類

[S : 通信用]

製品分類

[S2: 半導体 IC]

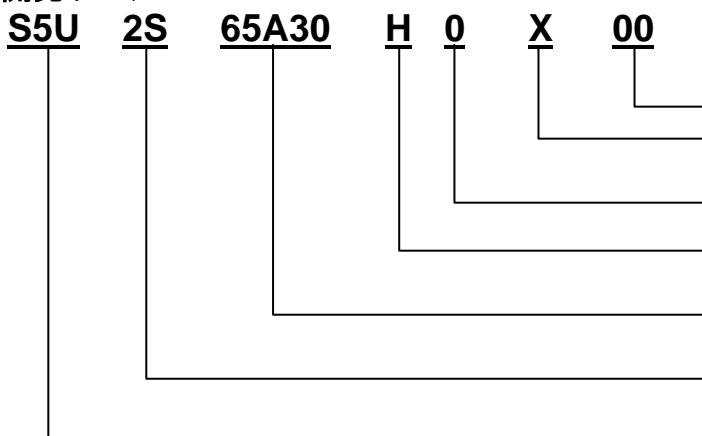

### ●開発ツール

梱包仕様

ボード仕様

[1: ITRON 版、2: Linux 版]

ボードコード

区分

[H: ハードウェア、S: ソフトウェア]

仕様 (対応半導体 IC)

[65A30: S2S65A30]

製品中分類

[1S : 半導体 IC 通信用]

製品分類

[S5U: 半導体用開発ツール]

# 目 次

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 1. 概要 .....                                                         | 1  |

| 1.1 特長 .....                                                        | 1  |

| 1.2 内蔵機能 .....                                                      | 1  |

| 2. ブロック図 .....                                                      | 4  |

| 3. 端子 .....                                                         | 5  |

| 3.1 端子配置図 .....                                                     | 5  |

| 3.2 端子の説明 .....                                                     | 7  |

| 3.3 GPIO端子のマルチプレクス端子機能、リセット直後の端子機能 .....                            | 19 |

| 3.4 リセット中の端子の状態 .....                                               | 21 |

| 4. 絶対最大定格 .....                                                     | 22 |

| 4.1 絶対最大定格 .....                                                    | 22 |

| 4.2 推奨動作条件（2電源、3.3V対応入出力バッファ） .....                                 | 22 |

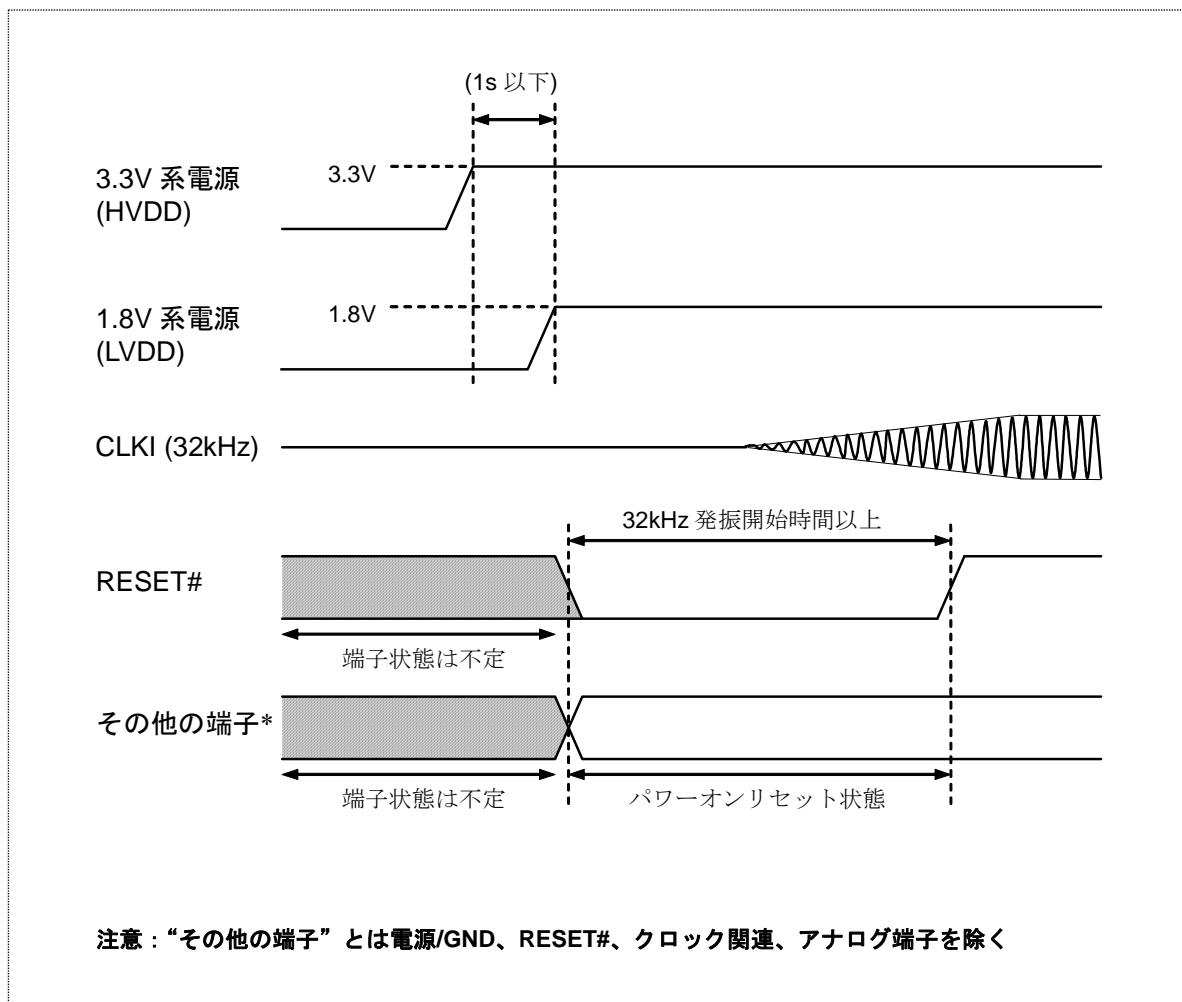

| 4.3 電源投入タイミング .....                                                 | 24 |

| 4.4 電源切断タイミング .....                                                 | 24 |

| 5. 電気的特性 .....                                                      | 25 |

| 5.1 DC特性 .....                                                      | 25 |

| 6. 参考外部接続例 .....                                                    | 27 |

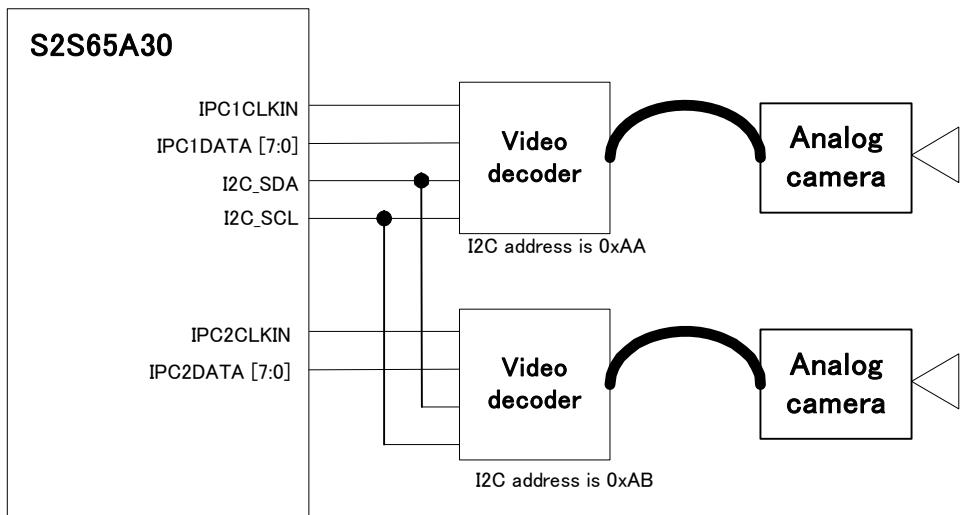

| 6.1 analog camera接続例(Bt.656 mode) .....                             | 27 |

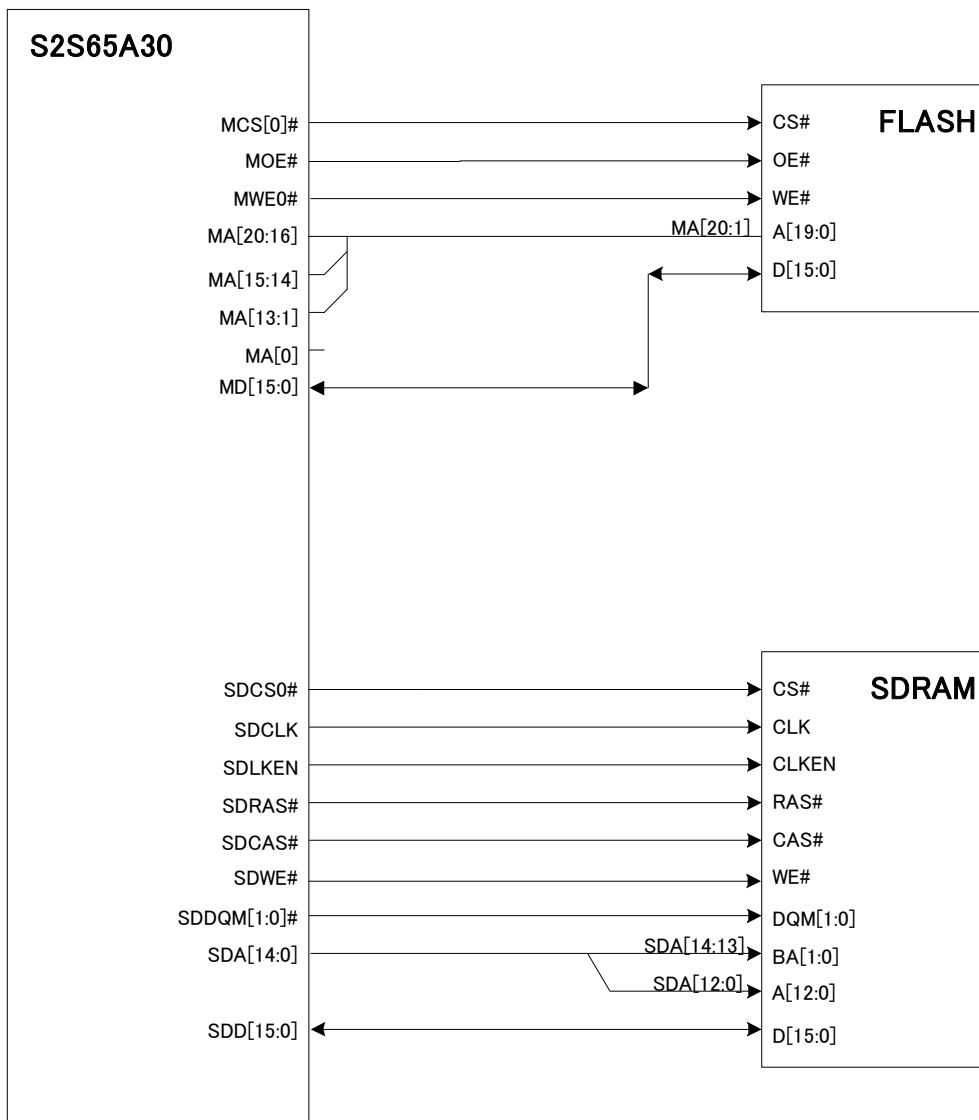

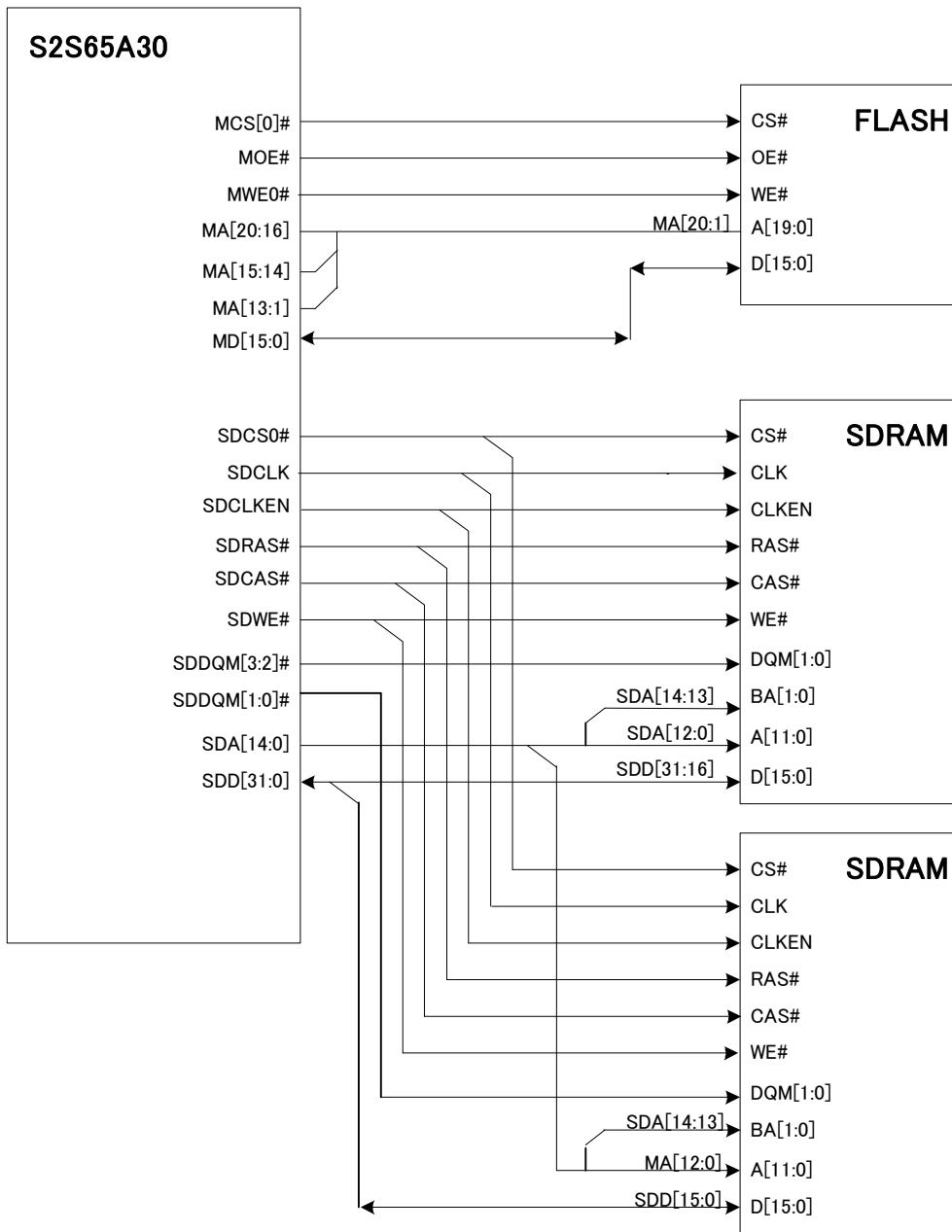

| 6.2 メモリ接続例 .....                                                    | 28 |

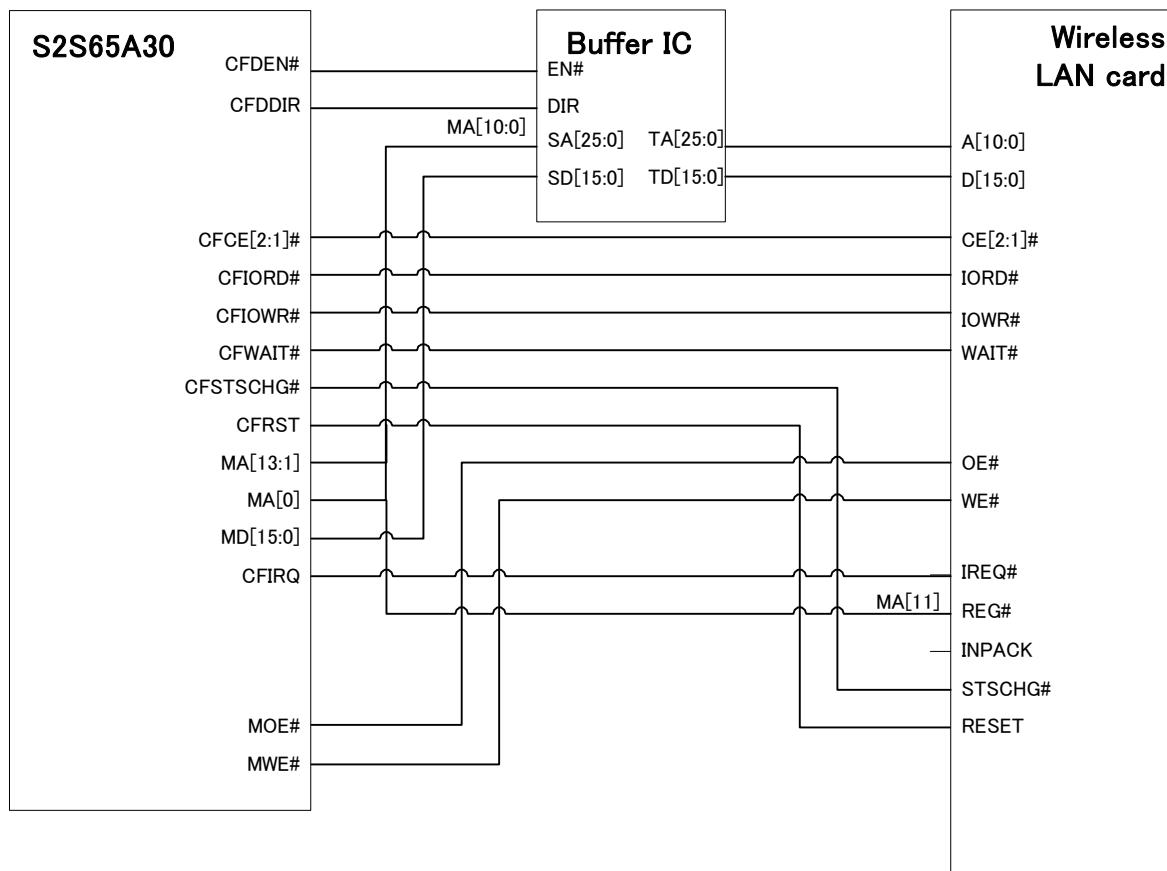

| 6.3 コンパクトフラッシュ接続例（16ビットバス対応） .....                                  | 30 |

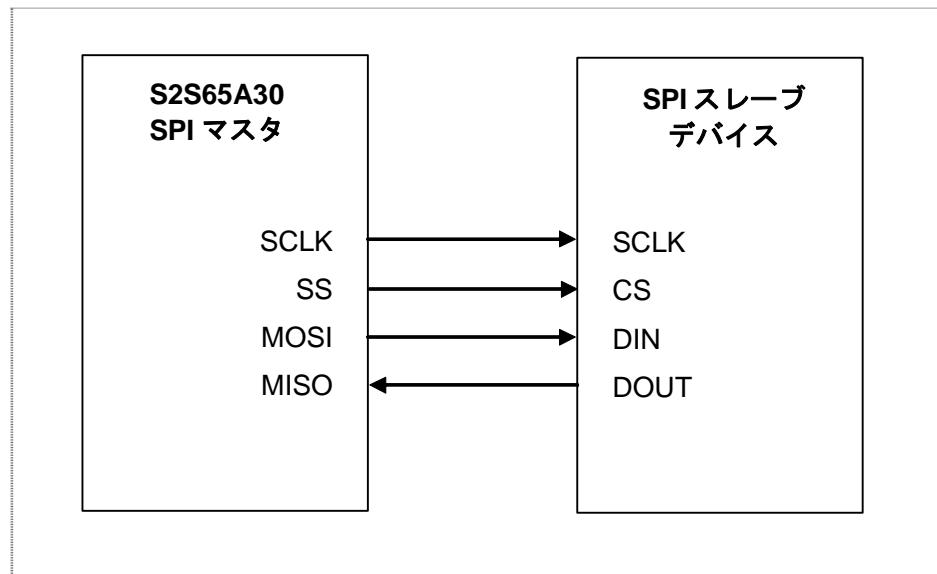

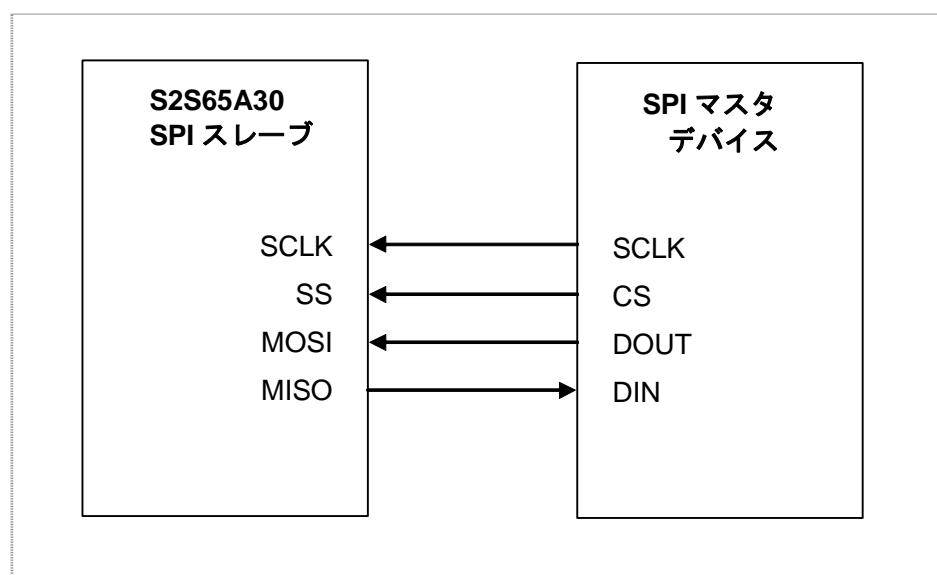

| 6.4 シリアル周辺機器インターフェース（SPI）接続例 .....                                  | 31 |

| 6.4.1 マスタ時 .....                                                    | 31 |

| 6.4.2 スレーブ時 .....                                                   | 31 |

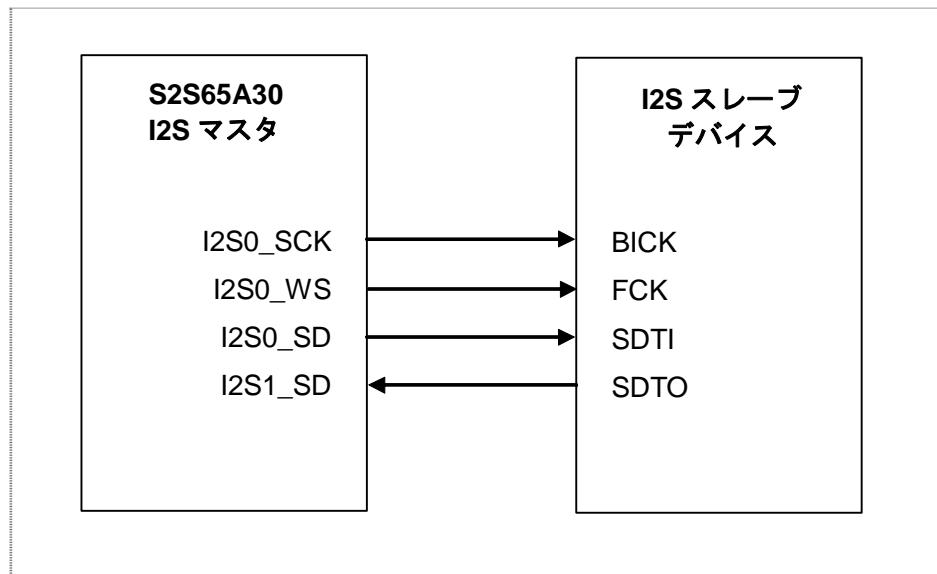

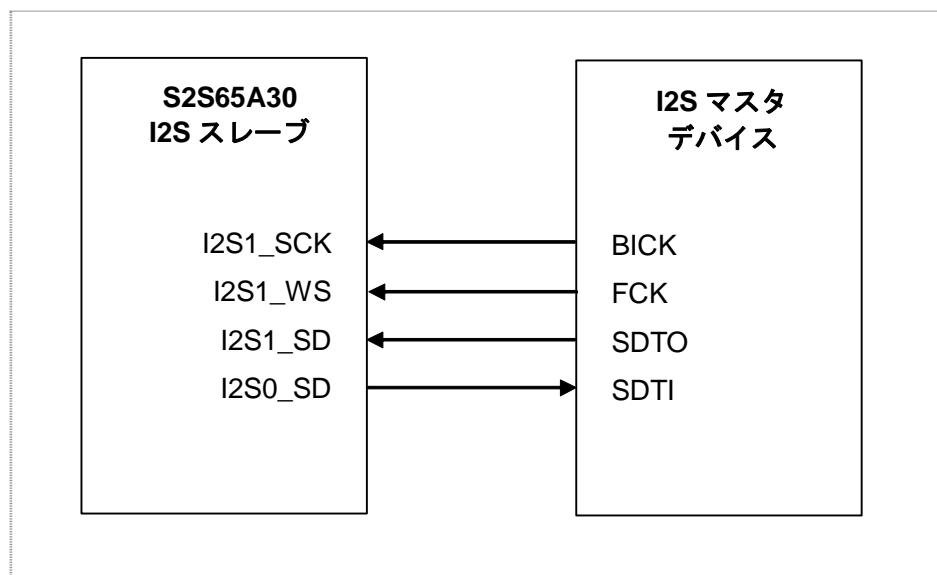

| 6.5 I <sup>2</sup> S接続例 .....                                       | 32 |

| 6.5.1 マスタ時 .....                                                    | 32 |

| 6.5.2 スレーブ時 .....                                                   | 32 |

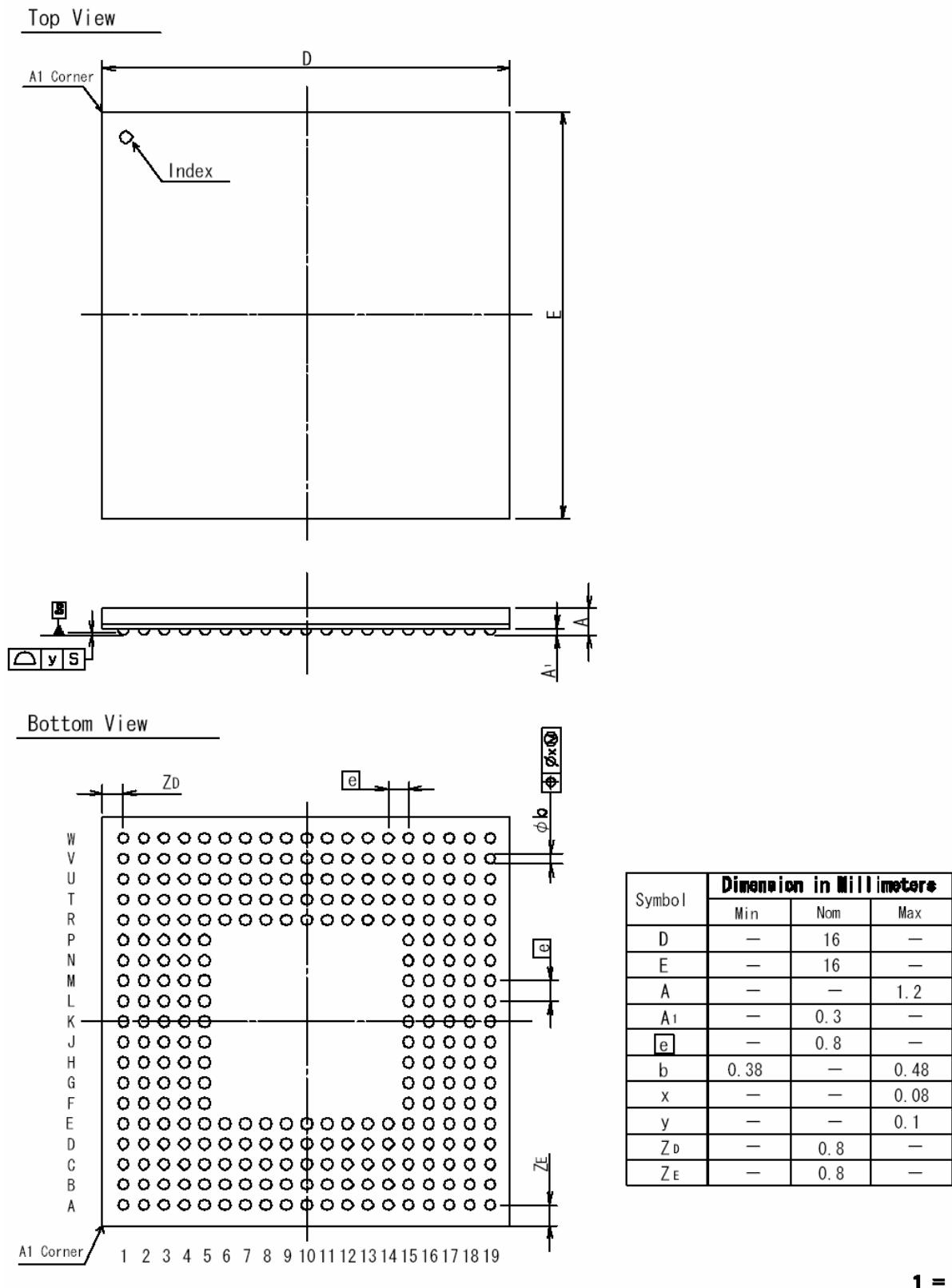

| 7. 外形寸法図 .....                                                      | 33 |

| 7.1 Plastic TFBGA 280pin Body size 16x16x1.2mm (PFBGA16U-280) ..... | 33 |

| 改訂履歴 .....                                                          | 34 |

## 1. 概要

本製品 S2S65A30 はドライブレコーダ専用 IC です。カーラインインターフェース機能、JPEG エンコーダ/デコーダ機能に加え、Interlace/progressive 変換、画像補正、CF、SD Memory、USB2.0 Device(High-Speed 対応) 各種インターフェース及び 8ch の ADC を内蔵しています。S2S65A30 にカメラモジュール、SDRAM、外付けのストレージ(CF Memory Card または SD Memory Card)とファームウェアを格納した Flash ROM を接続することにより、ドライブレコーダが簡単に構成できます。一例として、内蔵エンコーダで生成した JPEG データを SDRAM に常時蓄積しておきます。加速度センサ IC による急な速度変化の検出など外部トリガを受けて、蓄積した画像データを外付けのストレージ (CF Memory Card または SD Memory Card) に転送、保存することができます。また、S2S65A30 は GPIO および I<sup>2</sup>C バスを搭載していますので、カメラの設定や外部機器の制御を行うことも可能です。

### 1.1 特長

- 1 Chip ソリューション：低システムコストを実現可能

- 30 fps @VGA のハードウェアによる JPEG エンコードを実現 (ISO 10918 準拠)

- 2 台までカメラモジュール接続対応

- カメラモジュールごとにハードウェア JPEG エンコーダを 2 個搭載

- 動体検知機能による動き検出をサポート

- I<sup>2</sup>S による音声データのサポート

- CompactFlash インタフェースによる CF Memory Card 又は無線 LAN インタフェース (802.11b/g) 対応可能

- SD Memory インタフェースによる SD Memory Card の接続対応

- ARM720T 50MHz 動作

- USB 2.0 Device(High-Speed) 機能サポートとによる PC との接続が可能

- 8ch の ADC サポートによる各種アナログセンサとの接続が可能

- イベントカウンタ用のタイマを搭載

- メモリバス：2 ポート (16bit-Bus: FROM/SRAM, 16/32bit-Bus: SDRAM)

- Interlace/Progressive 変換機能

- JPEG デコード機能

- 画像の明暗補正機能

### 1.2 内蔵機能

#### CPU :

- ・ 32 ビット RISC ARM720T (最大 50MHz)

- ・ 32 ビット長命令と効率の良い Thumb コードと呼ばれる 16 ビット長命令コードを切り替えて利用可能

- ・ 32 ビット汎用レジスタ (31 本)

- ・ 乗算器を内蔵

#### RAM :

- ・ 56 KB の CPU/JPEG Work 用内蔵 RAM (CPU Work: 32KB max.)

#### スタンバイ機能

- ・ CPU の動作が必要ない場合には CPU のクロックをとめることができる HALT 機能

- ・ 主要な I/O ブロックごとにクロックをとめられる I/O クロックストップ機能

#### カメラ入力/Interlace/Progressive 変換 :

- ・ 8 ビット パラレルインターフェース × 2 ポート

- ・ 2 台のカメラモジュールを接続可能

- ・ 解像度 640×480 程度まで (VGA, QVGA, CIF, QCIF)

- ・ YUV4-2-2 プログレッシブ (2 ポート共)

- ・ Interlace/Progressive 変換機能によりインターレース信号 (2 ポート共)

- ・ カメラデータ入力用ピクセルクロック周波数は CPU クロック周波数の 2/3 未満

## 1. 概要

---

### 画像補正 :

- ・カメラ 2ch の明暗部の補正機能

### JPEG :

- ・ハードウェア JPEG エンコーダ×2

- ・Max 30 fps @VGA 以上の処理能力 (カメラモジュール 1 台接続時)

- ・Resize 機能 (画面切り取り可)

- ・専用の Line Buffer

- ・JPEG エンコーダ出力に容量可変 FIFO 内蔵

- ・Enhanced DMA 内蔵

- ・ハードウェア JPEG デコーダ

### USB2.0 Device:

- ・HS(480Mbps)および FS(12Mbps)の転送をサポート

- ・FS/HS Termination 機能内蔵 (外付け回路不要)

- ・VBUS 5V Interface (ただし、外付け保護回路が必要です)

- ・Control Bulk および Interrupt 転送をサポート

- ・Control(End Point 0)および Bulk/Interrupt 共用 End Point (5 本) をサポート

- ・16-bit または 8-bit 幅の汎用 CPU Interface 搭載

- ・Little Endian 対応

- ・Register Table については S1R72V05 の HS-Device 部を基本として追加／削除

- ・USB 用 Clock 入力として 12MHz または 24MHz 水晶発振子入力に対応

- ・内部 Clock 用途としては入力 USB 用 Clock を元にして、以下の周波数が使用可能

- ・入力 USB 用 Clock : 12MHz または 24MHz

- ・内部 USB 用 Clock : 60MHz (内蔵 USB 用 PLL 経由)

### メモリコントローラ :

- ・AHB バスインターフェースのメモリコントローラ

- ・SRAM タイミングデバイスを最大 4つまでサポート可能

- ・SDRAM を最大 8 つまでサポート可能

- ・SDRAM オートリフレッシュのリフレッシュ間隔をデバイスにあわせて調整可能

- ・SDRAM バーストリフレッシュサポート

- ・SDRAM のセルフリフレッシュをサポート

### CF カードインターフェース :

- ・CF+ 仕様 Rev1.4 準拠

- ・無線 LAN および PHS カードなどの interface として利用可能

- ・True IDE モードのサポート

### SD メモリインターフェース :

- ・SD Memory Card Physical Layer Spec. ver.2.0 準拠

- ・1bit/4bits インタフェースサポート

### 割り込みコントローラ :

- ・32 本の IRQ と 2 本の FIQ のサポート

### シリアルインターフェース :

- ・UART : 16550 ソフトウェア互換 × 3 チャンネル

- ・SPI : クロック同期式 ×1 チャンネル

- ・I<sup>2</sup>C マスタインターフェース (カメラ I/F および汎用用途)

- ・I<sup>2</sup>S インタフェース (音声／オーディオデータ対応、I<sup>2</sup>S 規格に準拠)

### タイマ A :

- ・16 ビットタイマ ×3 チャンネルのタイマ

- ・リロード/Cyclic または One Shot 動作モード

- ・アンダーフロー出力によるトグル出力、または Port 出力をサポート

### タイマ B : イベントカウンタ用

- 16 ビット・アップ・カウント・タイマ

- COMMON レジスタを 4 つ実装し、それぞれアウトプット・レジスタ、インプットキャプチャレジスタとして設定可能

### ウォッチドッグタイマ

- 割り込み出力またはリセット可能なウォッチドッグタイマ

### リアルタイムクロック

- 年、月、日、時間、分、秒、うるう年のサポート

- 1/128 – 1/2<sup>31</sup>までの内部タイマタップを割り込みソースとしても利用可

- アラーム機能および割り込みをサポート

### GPIO :

- 汎用 I/O Port (最大 82 本)

- すべてのポートに対して方向がプログラマブル設定可能

- 一部は他の I/O 機能と選択

### A/D コンバータ :

- 8-Channel Input (コントローラによるセレクト)

- 10-bit 分解能

- 1 回あたりの変換処理時間は 20μs 以下

### 電源 :

- 3.3V (I/O 電源)

- 3.3V (USB)

- 1.8V (コア電源)

- 2.4~3.6V (カメラ 1/2 I/O 電源)

- 2.7~3.6V (SDRAM I/O 電源)

- 3.3V (A/D 電源)

- 1.8V (USB/PLL/RTC)

### パッケージ :

- PFBGA 280 Pin (PFBGA16UX280) 16 x 16 x 1.2 mm, 0.8mm ボールピッチ

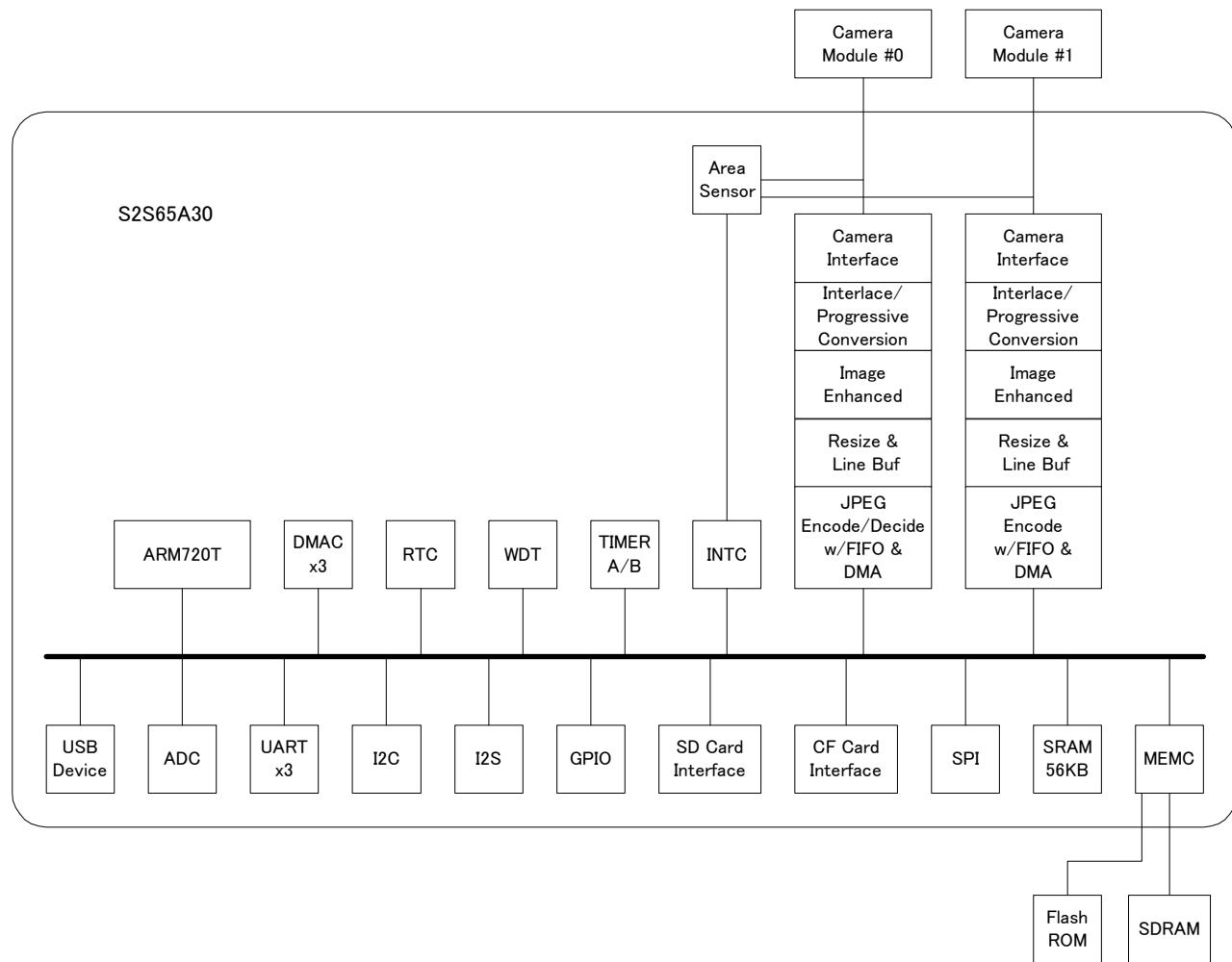

## 2. ブロック図

### 2. ブロック図

\*1 : 内蔵 SRAM は JPG[2:1]のラインバッファと共有しています。JPG[2:1]を使用する場合は CPU-Work として使用することは出来ません。

図 2.1 S2S65A30 内部ブロック図

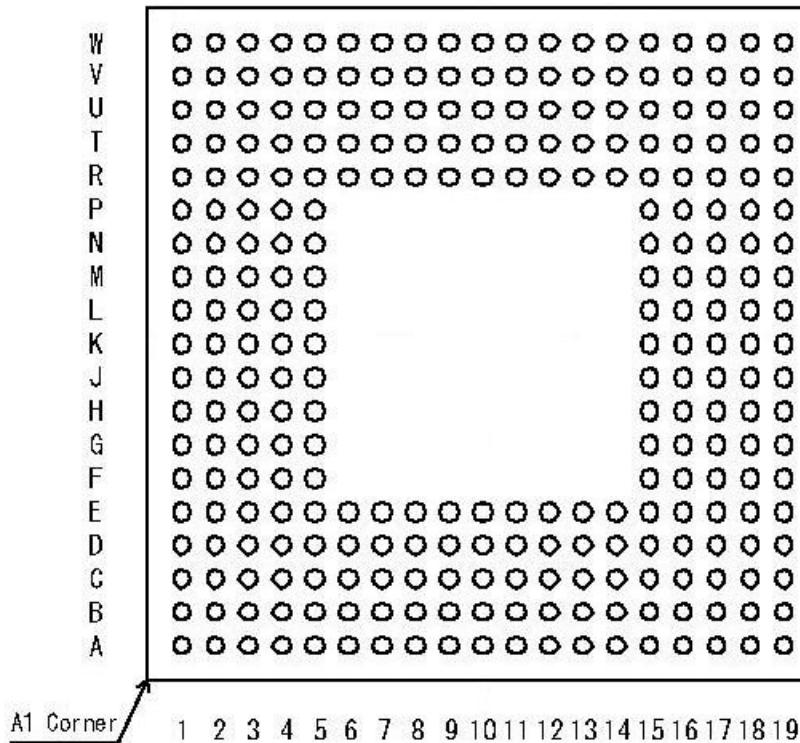

### 3. 端子

#### 3.1 端子配置図

図 3.1 端子配置図 (BOTTOM VIEW)

| ピン No. | 端子名称      | ピン No. | 端子名称     | ピン No. | 端子名称      | ピン No. | 端子名称     |

|--------|-----------|--------|----------|--------|-----------|--------|----------|

| A1     | NC        | D14    | HVDD     | K15    | LVDD      | T7     | CM2DATA2 |

| A2     | CM1CLKIN  | D15    | GPIOA2   | K16    | CFDEN#    | T8     | GPIOD2   |

| A3     | CM1CLKOUT | D16    | GPIOA4   | K17    | CFDDIR    | T9     | GPIOD1   |

| A4     | C1VDD     | D17    | GPIOA0   | K18    | LVDD      | T10    | MA17     |

| A5     | SYS_OSCO  | D18    | LVDD     | K19    | CFSTSCHG# | T11    | MA15     |

| A6     | SYS_OSCI  | D19    | GPIOA1   | L1     | VSS       | T12    | MA11     |

| A7     | RTCVDD    | E1     | LVDD     | L2     | GPIOJ6    | T13    | MA7      |

| A8     | PLLVSS    | E2     | VSS      | L3     | GPIOJ3    | T14    | VSS      |

| A9     | SYSVCP    | E3     | SDA6     | L4     | GPIOJ5    | T15    | MA2      |

| A10    | SYSCLKI   | E4     | VSS      | L5     | LVDD      | T16    | MCS1#    |

| A11    | LVDD      | E5     | SDA0     | L15    | HVDD      | T17    | MD13     |

| A12    | VSS       | E6     | GPIOK5   | L16    | CFWAIT#   | T18    | MD12     |

| A13    | UXVDD     | E7     | GPIOK4   | L17    | CFRST     | T19    | MD10     |

| A14    | DP        | E8     | VSS      | L18    | VSS       | U1     | SDD0     |

| A15    | DM        | E9     | CM1DATA0 | L19    | CFIRQ     | U2     | SDDQM1#  |

| A16    | UVDD3     | E10    | TESTEN1  | M1     | GPIOJ0    | U3     | CM2HREF  |

| A17    | R1        | E11    | VSS      | M2     | GPIOJ2    | U4     | VSS      |

| A18    | UPVDD     | E12    | LVDD     | M3     | GPIOJ1    | U5     | CM2DATA4 |

| A19    | NC        | E13    | TDI      | M4     | SDD15     | U6     | AVSS     |

| B1     | SDA13     | E14    | GPIOB3   | M5     | VSS       | U7     | CM2DATA5 |

| B2     | SDA14     | E15    | GPIOB1   | M15    | CFCE2#    | U8     | CM2DATA7 |

| B3     | CM1HREF   | E16    | GPIOB0   | M16    | MD3       | U9     | GPIOD3   |

### 3. 端子

| ピン No. | 端子名称       | ピン No. | 端子名称    | ピン No. | 端子名称     | ピン No. | 端子名称      |

|--------|------------|--------|---------|--------|----------|--------|-----------|

| B4     | VSS        | E17    | GPIOA3  | M17    | CFCE1#   | U10    | GPIOD0    |

| B5     | CM1DATA3   | E18    | HVDD    | M18    | CFIORD#  | U11    | MA16      |

| B6     | CM1DATA6   | E19    | GPIOA5  | M19    | CFIOWR#  | U12    | MA12      |

| B7     | VSS        | F1     | SDA1    | N1     | SDD11    | U13    | MA8       |

| B8     | BUP#       | F2     | SDVDD   | N2     | VSS      | U14    | MA4       |

| B9     | PLLVDD     | F3     | SDA5    | N3     | SDD13    | U15    | MA1       |

| B10    | SYSCKSEL   | F4     | SDA2    | N4     | SDD14    | U16    | VSS       |

| B11    | TRST#      | F5     | GPIOK1  | N5     | SDD12    | U17    | MBEL#     |

| B12    | TESTCK     | F15    | LVDD    | N15    | MD5      | U18    | MD14      |

| B13    | XVSS       | F16    | GPIOB2  | N16    | MD1      | U19    | MD15      |

| B14    | UVDD3      | F17    | GPIOA6  | N17    | VSS      | V1     | GPIOD6    |

| B15    | UVSS       | F18    | LVDD    | N18    | MD2      | V2     | VSS       |

| B16    | VSS        | F19    | GPIOA7  | N19    | MD0      | V3     | CM2VREF   |

| B17    | UVSS       | G1     | GPIOK7  | P1     | SDVDD    | V4     | CM2DATA0  |

| B18    | PVSS       | G2     | GPIOK6  | P2     | SDD10    | V5     | AVDD      |

| B19    | USBCK_OSCO | G3     | GPIOK3  | P3     | SDD9     | V6     | ADIN7     |

| C1     | SDA11      | G4     | GPIOK0  | P4     | SDD8     | V7     | ADIN5     |

| C2     | VSS        | G5     | VSS     | P5     | VSS      | V8     | ADIN3     |

| C3     | SDVDD      | G15    | GPIOC1  | P15    | MD9      | V9     | ADIN1     |

| C4     | SDA12      | G16    | HVDD    | P16    | MD8      | V10    | AVSS      |

| C5     | CM1VREF    | G17    | GPIOB5  | P17    | MD6      | V11    | MA19      |

| C6     | CM1DATA5   | G18    | VSS     | P18    | MD4      | V12    | MA14      |

| C7     | CM1DATA7   | G19    | GPIOB4  | P19    | LVDD     | V13    | VSS       |

| C8     | VSS        | H1     | LVDD    | R1     | SDD6     | V14    | MA3       |

| C9     | HVDD       | H2     | VSS     | R2     | SDD5     | V15    | GPIOD5    |

| C10    | VSS        | H3     | GPIOK2  | R3     | SDD4     | V16    | MCS0#     |

| C11    | TESTEN0    | H4     | SDWE#   | R4     | SDD7     | V17    | MWE#      |

| C12    | TDO        | H5     | SDCAS#  | R5     | SDD3     | V18    | LVDD      |

| C13    | VSS        | H15    | GPIOC6  | R6     | SDD2     | V19    | VSS       |

| C14    | VBUS       | H16    | GPIOC0  | R7     | CM2DATA1 | W1     | NC        |

| C15    | VSS        | H17    | GPIOB6  | R8     | CM2DATA6 | W2     | CM2CLKIN  |

| C16    | HVDD       | H18    | HVDD    | R9     | VSS      | W3     | CM2CLKOUT |

| C17    | VSS        | H19    | GPIOB7  | R10    | HVDD     | W4     | C2VDD     |

| C18    | VSS        | J1     | SDCS1#  | R11    | MA13     | W5     | AVDD      |

| C19    | USBCK_OSCI | J2     | SDCS0#  | R12    | MA9      | W6     | ADIN6     |

| D1     | SDA8       | J3     | SDRAS#  | R13    | MA6      | W7     | ADIN4     |

| D2     | SDA9       | J4     | GPIOJ7  | R14    | MA5      | W8     | ADIN2     |

| D3     | SDA7       | J5     | GPIOJ4  | R15    | HVDD     | W9     | ADIN0     |

| D4     | SDA10      | J15    | GPIOC7  | R16    | GPIOD4   | W10    | AVDD      |

| D5     | SDA4       | J16    | GPIOC5  | R17    | MD11     | W11    | MA18      |

| D6     | SDA3       | J17    | GPIOC4  | R18    | VSS      | W12    | HVDD      |

| D7     | CM1DATA1   | J18    | GPIOC3  | R19    | MD7      | W13    | MA10      |

| D8     | CM1DATA2   | J19    | GPIOC2  | T1     | VSS      | W14    | LVDD      |

| D9     | CM1DATA4   | K1     | SDCLK   | T2     | LVDD     | W15    | HVDD      |

| D10    | LVDD       | K2     | SDCLKEN | T3     | SDD1     | W16    | MA0       |

| D11    | TCK        | K3     | SDVDD   | T4     | GPIOD7   | W17    | MOE#      |

| D12    | TMS        | K4     | SDVDD   | T5     | SDDQM0#  | W18    | MBEH#     |

| D13    | RESET#     | K5     | VSS     | T6     | CM2DATA3 | W19    | NC        |

注意：端子名称右端の#は、ローакティブ信号であることを示しています。

### 3.2 端子の説明

# : 端子名称右端の#は、そのローアクティブ信号であることを示しています。

I : 入力ピン

O : 出力ピン

IO : 双方向ピン

P : 電源

表 3.1 Cell Type の説明

| Cell Type | 説明                                                                             | 使用端子例                               |              |

|-----------|--------------------------------------------------------------------------------|-------------------------------------|--------------|

|           |                                                                                | 端子名                                 | 使用電源電圧       |

| ILS       | Low Voltage LVC MOS Schmitt input                                              | BUP#                                | RTCVDD       |

| ICD1      | LVC MOS input with pull-down resistor (50kΩ@3.3V)                              | TESTEN[1:0], TESTCK                 | HVDD         |

| ICU1      | LVC MOS input with pull-up resistor (50kΩ@3.3V)                                | TMS, TDI                            | HVDD         |

| ICSU1     | LVC MOS Schmitt input with pull-up resistor (50kΩ@3.3V)                        | TRST#, TCK, RESET#                  | HVDD         |

| ICSD1     | LVC MOS Schmitt input with pull-down resistor (50kΩ@3.3V)                      | SYSCKSEL                            | HVDD         |

| ILTR      | Low Voltage Transparent Input                                                  | SYS_OSCI                            | RTCVDD       |

|           |                                                                                | USBCK_OSCI                          | UPVDD        |

|           |                                                                                | R1                                  | UVDD3        |

| IHTR      | High Voltage Transparent Input                                                 | ADIN[7:0]                           | ADVDD        |

| OLTR      | Low Voltage Transpatent Output                                                 | SYS_OSCO, SYSVCP                    | PLLVDD       |

|           |                                                                                | USBCK_OSCO                          | UPVDD        |

| BLNC4U1   | Low noise LVC MOS IO buffer with pull-up resistor (50kΩ@3.3V) (±4mA)           | CF I/F                              | HVDD         |

| BLNC4D2   | Low noise LVC MOS IO buffer with pull-down resistor (100kΩ@3.3V) (±4mA)        | MD [15:0]                           | HVDD         |

|           |                                                                                | SDD[15:0], GPIOJ, GPIOK             | SDVDD        |

| BLNS4     | Low noise LVC MOS Schmitt IO buffer (±4mA)                                     | GPIOA, GPIOB, GPIOC, GPIOD, SYSCLKI | HVDD         |

| BLNS4D1   | Low noise LVC MOS Schmitt IO buffer with pull-down resistor (50kΩ@3.3V) (±4mA) | Camera I/F                          | C1VDD, C2VDD |

| OLN4      | Low noise output buffer (±4mA)                                                 | SRAM デバイス I/F (MD を除く)              | HVDD         |

|           |                                                                                | SDRAM I/F(SDD[15:0]を除く)             | SDVDD        |

| OTLN4     | Low noise Tri-state output buffer (±4mA)                                       | TDO                                 | HVDD         |

| USBDM     | USB DM buffer                                                                  | DM                                  | UVDD3        |

| USBDP     | USB DP buffer                                                                  | DP                                  | UVDD3        |

| USBVBUS   | USB VBUS output buffer                                                         | VBUS                                | UVDD3        |

### 3. 端子

表 3.2 端子の説明

| 端子名称         | Type  | Cell Type | ピン No.                                                                              | 説明                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------|-----------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (MA [23:20]) | (I/O) | (BLNS4)   |                                                                                     | これらの端子については GPIOD[3:0]の説明を参照してください。                                                                                                                                                                                                                                                                                                                               |

| MA [19:12]   | O     | OLN4      | V11,W11,T10,<br>U11,T11,V12,<br>R11,U12                                             | <b>Flash-ROM/SRAM 用アドレス出力信号[19:12]</b>                                                                                                                                                                                                                                                                                                                            |

| MA 11        | O     | OLN4      | T12                                                                                 | この端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li>・MA11 : Flash-ROM/SRAM 用アドレス出力信号 11<br/>(リセット直後の端子機能)</li> <li>・CFREG#出力信号<br/>コンパクトフラッシュ(CF)インタフェース動作時は、CF インタフェースのアトリビュートおよび I/O 空間を選択する REG 信号として動作します。</li> </ul>                                                                                                                                |

| MA [10:0]    | O     | OLN4      | W13,R12,U13,<br>T13,R13,R14,<br>U14,V14,T15,<br>U15,W16                             | これらの端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li>・MA[10:0] : Flash-ROM/SRAM 用アドレス出力信号 [10:0] (リセット直後の端子機能)</li> <li>・CFADDR[10:0]出力信号<br/>CF インタフェース動作時は、CF インタフェースのアドレス信号[10:0]となります。</li> </ul>                                                                                                                                                   |

| MBEL#        | I/O   | OLN4      | U17                                                                                 | <b>Flash-ROM/SRAM 用データバス下位バイト・イネーブル出力</b>                                                                                                                                                                                                                                                                                                                         |

| MBEH#        | I/O   | OLN4      | W18                                                                                 | <b>Flash-ROM/SRAM 用データバス上位バイト・イネーブル出力</b>                                                                                                                                                                                                                                                                                                                         |

| MD [15:0]    | I/O   | BLNC4D2   | U19,U18,T17,<br>T18,R17,T19,<br>P15,P16,R19,<br>P17,N15,P18,<br>M16,N18,N16,<br>N19 | これらの端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li>・16Bit の Flash-ROM/SRAM 用 Data Bus (リセット直後の端子機能)</li> <li>・CF インタフェース動作時は 16Bit データとなります。</li> <li>・MODESEL[15:0]<br/>パワーオンリセット時 (RESET#の Low から High への遷移時) に内部の動作モードを決めるためにサンプリングされます。“4.1 システムコンフィギュレーション” の項を参照してください。<br/>このとき、動作モードを決めるために外部でプルアップ抵抗が必要になる場合があります。(4.7~10kΩ程度の抵抗)</li> </ul> |

| MCS [3:2]#   | O     | (BLNS4)   | V15,R16                                                                             | これらの端子については GPIOD[5:4]の説明を参照してください。                                                                                                                                                                                                                                                                                                                               |

| MCS [1:0]#   | O     | OLN4      | T16,V16                                                                             | <b>Flash-ROM/SRAM 用チップセレクト信号[1:0]</b><br>(ローアクティブ信号)                                                                                                                                                                                                                                                                                                              |

| MOE#         | O     | OLN4      | W17                                                                                 | この端子は以下の機能を持っています。<br>(ローアクティブ信号)<br><ul style="list-style-type: none"> <li>・MOE# : Flash-ROM/SRAM 用ストローブ信号 (リセット直後の端子機能)</li> <li>・CFOE#出力信号<br/>CF インタフェース動作時は、CF インタフェースのメモリおよびアトリビュート空間の出力イネーブル信号となります。</li> </ul>                                                                                                                                            |

| 端子名称         | Type  | Cell Type | ピン No.                                                              | 説明                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|-------|-----------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MWE#         | O     | OLN4      | V17                                                                 | <p>この端子は以下の機能を持っています。<br/>(ローアクティブ信号)</p> <ul style="list-style-type: none"> <li>• MWE# : Flash-ROM/SRAM 用 Write Enable 信号 (スタティックメモリ用) (リセット直後の端子機能)</li> <li>• CFWE#出力信号<br/>CF インタフェース動作時は、CF インタフェースのメモリおよびアトリビュート空間のライトイネーブル信号となります。</li> </ul>                                                                                                                                                                 |

| SDA [14:0]   | O     | OLN4      | B2,B1,C4,<br>C1,D4,D2,<br>D1,D3,E3,<br>F3,D5,D6,<br>F4,F1,E5        | <b>SDRAM 用アドレス出力[14:0]</b>                                                                                                                                                                                                                                                                                                                                                                                           |

| SDD[31:16]   | (I/O) | (BLNC4D2) |                                                                     | これらの端子については <b>GPIOK[7:0],GPIOJ[7:0]</b> の説明を参照してください。                                                                                                                                                                                                                                                                                                                                                               |

| SDD [15:0]   | I/O   | BLNC4D2   | M4,N4,N3,<br>N5,N1,P2,<br>P3,P4,R4,<br>R1,R2,R3,<br>R5,R6,T3,<br>U1 | <b>SDRAM 用データ入出力[15:0]</b>                                                                                                                                                                                                                                                                                                                                                                                           |

| SDWE#        | O     | OLN4      | H4                                                                  | <b>SDRAM 用 Write Enable 信号</b>                                                                                                                                                                                                                                                                                                                                                                                       |

| SDCLK        | O     | OLN4      | K1                                                                  | <b>SDRAM 用クロック出力</b><br>内部動作周波数 (CPUCLK) と同じ周波数が出力されます。                                                                                                                                                                                                                                                                                                                                                              |

| SDCLKEN      | O     | OLN4      | K2                                                                  | <b>SDRAM 用クロック・イネーブル信号</b>                                                                                                                                                                                                                                                                                                                                                                                           |

| SDRAS#       | O     | OLN4      | J3                                                                  | <b>SDRAM 用 RAS 信号</b> (ローアクティブ信号)                                                                                                                                                                                                                                                                                                                                                                                    |

| SDCAS#       | O     | OLN4      | H5                                                                  | <b>SDRAM 用 CAS 信号</b> (ローアクティブ信号)                                                                                                                                                                                                                                                                                                                                                                                    |

| SDCS[1:0]#   | O     | OLN4      | J1,J2                                                               | <b>SDRAM 用チップセレクト信号</b> (ローアクティブ信号)                                                                                                                                                                                                                                                                                                                                                                                  |

| SDDQM[3:2]#  | (I/O) | (BLNS4)   |                                                                     | これらの端子については <b>GPIOD[7:6]</b> の説明を参照してください。                                                                                                                                                                                                                                                                                                                                                                          |

| SDDQM[1:0]#  | O     | OLN4      | U2,T5                                                               | <b>SDRAM 用 DQM 信号</b> (ローアクティブ信号)<br>SDDQM0#が下位バイトに対応し、SDDQM1#が上位バイトに対応します。                                                                                                                                                                                                                                                                                                                                          |

| CM1DATA[7:0] | I/O   | BLNS4D1   | C7,B6,C6,<br>D9,B5,D8,<br>D7,E9                                     | <p>これらの端子は以下の機能を持っています。リセット時は GPIOE[7:0]入力になっています。</p> <ul style="list-style-type: none"> <li>• CM1DATA[7:0] : Progressive カメラ 1YUV データ入力<br/>CM1DATA[7:0]端子として使用するためには GPIOE 端子機能レジスタのビット[15:0]を “GPIO 以外の機能 1” に設定してください。</li> <li>• IPC1DATA[7:0] : Interlace カメラ 1YUV データ入力<br/>IPC1DATA[7:0]端子として使用するためには GPIOE 端子機能レジスタのビット[15:0]を “GPIO 以外の機能 2” に設定してください。</li> <li>• GPIOE[7:0]入出力 (リセット直後の端子機能)</li> </ul> |

### 3. 端子

| 端子名称      | Type | Cell Type | ピン No. | 説明                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM1VREF   | I/O  | BLNS4D1   | C5     | <p>この端子は以下の機能を持っています。リセット時は GPIOF0 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM1VREF : Progressive カメラ 1 データ入力時の垂直同期入力<br/>CM1VREF 端子として使用するためには GPIOF 端子機能レジスタのビット[1:0]を “GPIO 以外の機能 1” に設定してください。</li> <li>・IPC1VREF : Interlace カメラ 1 データ入力時の垂直同期入力<br/>IPC1VREF 端子として使用するためには GPIOF 端子機能レジスタのビット[1:0]を “GPIO 以外の機能 2” に設定してください。</li> <li>・GPIOF0 入出力 (リセット直後の端子機能)</li> </ul>     |

| CM1HREF   | I/O  | BLNS4D1   | B3     | <p>この端子は以下の機能を持っています。リセット時は GPIOF1 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM1HREF : Progressive カメラ 1 データ入力時の水平同期入力<br/>CM1HREF 端子として使用するためには GPIOF 端子機能レジスタのビット[3:2]を “GPIO 以外の機能 1” に設定してください。</li> <li>・IPC1HREF : Interlace カメラ 1 データ入力時の水平同期入力<br/>IPC1HREF 端子として使用するためには GPIOF 端子機能レジスタのビット[3:2]を “GPIO 以外の機能 2” に設定してください。</li> <li>・GPIOF1 入出力 (リセット直後の端子機能)</li> </ul>     |

| CM1CLKOUT | I/O  | BLNS4D1   | A3     | <p>この端子は以下の機能を持っています。リセット時は GPIOF2 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM1CLKOUT : Progressive カメラ 1 用基本クロック出力<br/>CM1CLKOUT 端子として使用するためには GPIOF 端子機能レジスタのビット[5:4]を “GPIO 以外の機能 1” に設定してください。</li> <li>・IPC1FIELD : Interlace カメラ 1 用フィールド識別信号入力<br/>IPC1FIELD 端子として使用するためには GPIOF 端子機能レジスタのビット[5:4]を “GPIO 以外の機能 2” に設定してください。</li> <li>・GPIOF2 入出力 (リセット直後の端子機能)</li> </ul>    |

| CM1CLKIN  | I/O  | BLNS4D1   | A2     | <p>この端子は以下の機能を持っています。リセット時は GPIOF3 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM1CLKIN : Progressive カメラ 1 データ入力用ピクセルロック<br/>CM1CLKIN 端子として使用するためには GPIOF 端子機能レジスタのビット[7:6]を “GPIO 以外の機能 1” に設定してください。</li> <li>・IPC1CLKIN : Interlace カメラ 1 データ入力用ピクセルロック<br/>IPC1CLKIN 端子として使用するためには GPIOF 端子機能レジスタのビット[7:6]を “GPIO 以外の機能 2” に設定してください。</li> <li>・GPIOF3 入出力 (リセット直後の端子機能)</li> </ul> |

| 端子名称         | Type | Cell Type | ピン No.                          | 説明                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------|-----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM2DATA[7:0] | I/O  | BLNS4D1   | U8,R8,U7,<br>U5,T6,T7,<br>R7,V4 | <p>これらの端子は以下の機能を持っています。リセット時は GPIOG[7:0]入力になっています。</p> <ul style="list-style-type: none"> <li>・CM2DATA[7:0] : Progressive カメラ 2YUV データ入力<br/>CM2DATA[7:0]端子として使用するためには GPIOG 端子機能レジスタのビット[15:0]を“GPIO 以外の機能 1”に設定してください。</li> <li>・IPC2DATA[7:0] : Interlace カメラ 2YUV データ入力<br/>IPC2DATA[7:0]端子として使用するためには GPIOG 端子機能レジスタのビット[15:0]を“GPIO 以外の機能 2”に設定してください。</li> <li>・GPIOG[7:0]入出力 (リセット直後の端子機能)</li> </ul> |

| CM2VREF      | I/O  | BLNS4D1   | V3                              | <p>この端子は以下の機能を持っています。リセット時は GPIOF4 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM2VREF : Progressive カメラ 2 データ入力時の垂直同期入力<br/>CM2VREF 端子として使用するためには GPIOF 端子機能レジスタのビット[9:8]を“GPIO 以外の機能 1”に設定してください。</li> <li>・IPC2VREF : Interlace カメラ 2 データ入力時の垂直同期入力<br/>IPC2VREF 端子として使用するためには GPIOF 端子機能レジスタのビット[9:8]を“GPIO 以外の機能 2”に設定してください。</li> <li>・GPIOF4 入出力 (リセット直後の端子機能)</li> </ul>                   |

| CM2HREF      | I/O  | BLNS4D1   | U3                              | <p>この端子は以下の機能を持っています。リセット時は GPIOF5 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM2HREF : Progressive カメラ 2 データ入力時の水平同期入力<br/>CM2HREF 端子として使用するためには GPIOF 端子機能レジスタのビット[11:10]を“GPIO 以外の機能 1”に設定してください。</li> <li>・IPC2HREF : Interlace カメラ 2 データ入力時の水平同期入力<br/>IPC2HREF 端子として使用するためには GPIOF 端子機能レジスタのビット[11:10]を“GPIO 以外の機能 2”に設定してください。</li> <li>・GPIOF5 入出力 (リセット直後の端子機能)</li> </ul>               |

| CM2CLKOUT    | I/O  | BLNS4D1   | W3                              | <p>この端子は以下の機能を持っています。リセット時は GPIOF6 入力になっています。</p> <ul style="list-style-type: none"> <li>・CM2CLKOUT : Progressive カメラ 2 用基本クロック出力<br/>CM2CLKOUT 端子として使用するためには GPIOF 端子機能レジスタのビット[13:12]を“GPIO 以外の機能 1”に設定してください。</li> <li>・IPC2FIELD : Interlace カメラ 2 用フィールド識別信号入力<br/>IPC2FIELD 端子として使用するためには GPIOF 端子機能レジスタのビット[13:12]を“GPIO 以外の機能 2”に設定してください。</li> <li>・GPIOF6 入出力 (リセット直後の端子機能)</li> </ul>              |

### 3. 端子

| 端子名称     | Type | Cell Type | ピン No. | 説明                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM2CLKIN | I/O  | BLNS4D1   | W2     | <p>この端子は以下の機能を持っています。リセット時は GPIOF7 入力になっています。</p> <ul style="list-style-type: none"> <li>・ CM2CLKIN : Progressive カメラ 2 データ入力用ピクセルクロック<br/>CM2CLKIN 端子として使用するためには GPIOF 端子機能レジスタのビット[15:14]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ IPC2CLKIN : Interlace カメラ 2 データ入力用ピクセルクロック<br/>IPC2CLKIN 端子として使用するためには GPIOF 端子機能レジスタのビット[15:14]を“GPIO 以外の機能 2”に設定してください。</li> <li>・ GPIOF7 入出力 (リセット直後の端子機能)</li> </ul> |

| CFCE2#   | I/O  | BLNC4U1   | M15    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ CFCE2# : Compact Flash Memory Interface 用 (以下 CF 用) カードイネーブル 2(CE2#)出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOH0 入力になっています。CFCE2#端子として使用するためには GPIOH 端子機能レジスタのビット[1:0]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ GPIOH0 入出力 (リセット直後の端子機能)</li> <li>・ SDMDATA0 : SD カード用データ入出力 0 (GPIO 以外の端子機能 2)</li> </ul>                                      |

| CFCE1#   | I/O  | BLNC4U1   | M17    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ CFCE1# : CF 用カードイネーブル 1 (CE1#) 出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOH1 入力になっています。CFCE1#端子として使用するためには GPIOH 端子機能レジスタのビット[3:2]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ GPIOH1 入出力 (リセット直後の端子機能)</li> <li>・ SDMDATA1 : SD カード用データ入出力 1 (GPIO 以外の端子機能 2)</li> </ul>                                                                           |

| CFIORD#  | I/O  | BLNC4U1   | M18    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ CFIORD# : CF 用 IO Read ストローブ出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOH2 入力になっています。CFIORD#端子として使用するためには GPIOH 端子機能レジスタのビット[5:4]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ GPIOH2 入出力 (リセット直後の端子機能)</li> <li>・ SDMDATA2 : SD カード用データ入出力 2 (GPIO 以外の端子機能 2)</li> </ul>                                                                             |

| CFIOWR#  | I/O  | BLNC4U1   | M19    | <p>この端子は以下の機能を持っています。<br/>(ロー/アクティブ信号)</p> <ul style="list-style-type: none"> <li>・ CFIOWR# : CF 用 IO Write ストローブ出力<br/>この端子は、リセット時は GPIOH3 入力になっています。CFIOWR#端子として使用するためには GPIOH 端子機能レジスタのビット[7:6]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ GPIOH3 入出力 (リセット直後の端子機能)</li> <li>・ SDMDATA3 : SD カード用データ入出力 3 (GPIO 以外の端子機能 2)</li> </ul>                                                                        |

| 端子名称      | Type | Cell Type | ピン No. | 説明                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFWAIT#   | I/O  | BLNC4U1   | L16    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・CFWAIT# : CF 用ウエイト要求力 (ローアクティブ信号)</li> </ul> <p>この端子は、リセット時は GPIOH4 入力になっています。CFWAIT#端子として使用するためには GPIOH 端子機能レジスタのビット[9:8]を “GPIO 以外の機能 1” に設定してください。</p> <ul style="list-style-type: none"> <li>・GPIOH4 入出力 (リセット直後の端子機能)</li> <li>・SDMCMD : SD カード用コマンド入出力 (GPIO 以外の機能 2)</li> </ul>                                  |

| CFRST     | I/O  | BLNC4U1   | L17    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・CFRST : CF カードへのリセット信号</li> </ul> <p>カードリセット時に HIGH、カードの通常動作時に LOW となります。</p> <p>この端子は、リセット時は GPIOH5 入力になっています。CFRST 端子として使用するためには GPIOH 端子機能レジスタのビット[11:10]を “GPIO 以外の機能 1” に設定してください。</p> <ul style="list-style-type: none"> <li>・GPIOH5 入出力 (リセット直後の端子機能)</li> <li>・SDMCLK : SD カード用クロック出力 (GPIO 以外の機能 2)</li> </ul> |

| CFIRQ     | I/O  | BLNC4U1   | L19    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・CFIRQ : CF カードからの割り込み要求信号</li> </ul> <p>この端子は、リセット時は GPIOH6 入力になっています。CFIRQ 端子として使用するためには GPIOH 端子機能レジスタのビット[13:12]を “GPIO 以外の機能 1” に設定してください。</p> <ul style="list-style-type: none"> <li>・GPIOH6 入出力 (リセット直後の端子機能)</li> <li>・SDMCD# : SD カード用カードディテクト入力 (GPIO 以外の機能 2)</li> </ul>                                      |

| CFSTSCHG# | I/O  | BLNC4U1   | K19    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・CFSTSCHG# : CF カードからのステータスチェンジ信号 (ローアクティブ信号)</li> </ul> <p>この端子は、リセット時は GPIOH7 入力になっています。CFSTSCHG#端子として使用するためには GPIOH 端子機能レジスタのビット[15:14]を “GPIO 以外の機能 1” に設定してください。</p> <ul style="list-style-type: none"> <li>・GPIOH7 入出力 (リセット直後の端子機能)</li> <li>・SDMWP : SD カード用ライトプロテクト入力 (GPIO 以外の機能 2)</li> </ul>                 |

| CFDEN#    | I/O  | BLNC4U1   | K16    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・CFDEN# : CF カードの外部バッファ用データバスインターフェース信号 (ローアクティブ信号)</li> </ul> <p>この端子は、リセット時は GPIOI0 入力になっています。CFDEN#端子として使用するためには GPIOI 端子機能レジスタのビット[1:0]を “GPIO 以外の機能 1” に設定してください。</p> <ul style="list-style-type: none"> <li>・GPIOI0 入出力端子 (リセット直後の端子機能)</li> <li>・SDMGPO : SD カード用汎用出力 (GPIO 以外の機能 2)</li> </ul>                   |

### 3. 端子

| 端子名称             | Type | Cell Type | ピン No.                              | 説明                                                                                                                                                                                                                                                                                                |

|------------------|------|-----------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CFDDIR</b>    | I/O  | BLNC4U1   | K17                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CFDDIR : CF 用データバス方向指示出力</b><br/>この端子は、CF 用データのリード時に LOW となります。また、この端子はリセット時には GPIOI1 入力になっています。CFDDIR 端子として使用するためには GPIOI 端子機能レジスタのビット[3:2]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOI1 入出力 (リセット直後の端子機能)</b></li> </ul> |

| <b>R1</b>        | I    | ILTR      | A17                                 | USB Device 内部動作設定端子                                                                                                                                                                                                                                                                               |

| <b>DM</b>        | I/O  | USBDM     | A15                                 | USB Device D- 入出力                                                                                                                                                                                                                                                                                 |

| <b>DP</b>        | I/O  | USBDP     | A14                                 | USB Device D+ 入出力                                                                                                                                                                                                                                                                                 |

| <b>VBUS</b>      | I    | USBVBUS   | C14                                 | USB Device VBUS 入力                                                                                                                                                                                                                                                                                |

| <b>ADIN[7:0]</b> | I    | IHTR      | V6,W6,<br>V7,W7,<br>V8,W8,<br>V9,W9 | アナログ信号入力                                                                                                                                                                                                                                                                                          |

| <b>GPIOA0</b>    | I/O  | BLNS4     | D17                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA0 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>TXD1 : UART1 送信データ出力 (GPIO 以外の機能 1)</b></li> </ul>                                                                                                                               |

| <b>GPIOA1</b>    | I/O  | BLNS4     | D19                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA1 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>RXD1 : UART1 受信データ入力 (GPIO 以外の機能 1)</b></li> </ul>                                                                                                                               |

| <b>GPIOA2</b>    | I/O  | BLNS4     | D15                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA2 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>RTS1 : UART1 送信要求出力 (GPIO 以外の機能 1)</b></li> <li>・ <b>I2S1_WS : I2S1 用ワードセレクト (GPIO 以外の機能 2)</b></li> </ul>                                                                       |

| <b>GPIOA3</b>    | I/O  | BLNS4     | E17                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA3 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>CTS1 : UART1 送信可能入力 (GPIO 以外の機能 1)</b></li> <li>・ <b>I2S1_SCK : I2S1 用シリアルクロック (GPIO 以外の機能 2)</b></li> </ul>                                                                     |

| <b>GPIOA4</b>    | I/O  | BLNS4     | D16                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA4 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>TXD2 : UART2 送信データ出力 (GPIO 以外の機能 1)</b></li> </ul>                                                                                                                               |

| <b>GPIOA5</b>    | I/O  | BLNS4     | E19                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA5 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>RXD2 : UART2 受信データ入力 (GPIO 以外の機能 1)</b></li> </ul>                                                                                                                               |

| <b>GPIOA6</b>    | I/O  | BLNS4     | F17                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA6 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>RTS2 : UART2 送信要求出力 (GPIO 以外の機能 1)</b></li> <li>・ <b>SCL : I2C クロック入出力 (GPIO 以外の機能 2)</b></li> </ul>                                                                             |

| <b>GPIOA7</b>    | I/O  | BLNS4     | F19                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOA7 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>CTS2 : UART2 受信可能入力 (GPIO 以外の機能 1)</b></li> <li>・ <b>SDA : I2C データ入出力 (GPIO 以外の機能 2)</b></li> </ul>                                                                              |

| <b>GPIOB0</b>    | I/O  | BLNS4     | E16                                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>GPIOB0 入出力 (リセット直後の端子機能)</b></li> <li>・ <b>INT0 入力</b></li> <li>・ <b>I2S0_WS : I2S0 用ワードセレクト (GPIO 以外の機能 1)</b></li> </ul>                                                                                                  |

| 端子名称          | Type | Cell Type | ピン No. | 説明                                                                                                                                        |

|---------------|------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>GPIOB1</b> | I/O  | BLNS4     | E15    | この端子は以下の機能を持っています。<br>- <b>GPIOB1</b> 入出力（リセット直後の端子機能）<br>- INT1 入力<br>- I2S0_SCK : I2S0 用シリアルクロック（GPIO 以外の機能 1）                          |

| <b>GPIOB2</b> | I/O  | BLNS4     | F16    | この端子は以下の機能を持っています。<br>- <b>GPIOB2</b> 入出力（リセット直後の端子機能）<br>- INT2 入力<br>- I2S0_SD : I2S0 用シリアルデータ（GPIO 以外の機能 1）                            |

| <b>GPIOB3</b> | I/O  | BLNS4     | E14    | この端子は以下の機能を持っています。<br>- <b>GPIOB3</b> 入出力（リセット直後の端子機能）<br>- INT3 入力<br>- I2S1_SD : I2S1 用シリアルデータ（GPIO 以外の機能 1）                            |

| <b>GPIOB4</b> | I/O  | BLNS4     | G19    | この端子は以下の機能を持っています。<br>- <b>GPIOB4</b> 入出力（リセット直後の端子機能）<br>- INT4 入力<br>- TimerA0Out (GPIO 以外の機能 1)                                        |

| <b>GPIOB5</b> | I/O  | BLNS4     | G17    | この端子は以下の機能を持っています。<br>- <b>GPIOB5</b> 入出力（リセット直後の端子機能）<br>- INT5 入力<br>- TimerA1Out (GPIO 以外の機能 1)<br>- DREQ# (GPIO 以外の機能 2)              |

| <b>GPIOB6</b> | I/O  | BLNS4     | H17    | この端子は以下の機能を持っています。<br>- <b>GPIOB6</b> 入出力（リセット直後の端子機能）<br>- INT6 入力<br>- TimerA2Out (GPIO 以外の機能 1)                                        |

| <b>GPIOB7</b> | I/O  | BLNS4     | H19    | この端子は以下の機能を持っています。<br>- <b>GPIOB7</b> 入出力（リセット直後の端子機能）<br>- INT7 入力<br>- TimerB1In (GPIO 以外の機能 1)                                         |

| <b>GPIOC0</b> | I/O  | BLNS4     | H16    | この端子は以下の機能を持っています。<br>- <b>GPIOC0</b> 入出力（リセット直後の端子機能）<br>- TimerB0IO (GPIO 以外の機能 1)                                                      |

| <b>GPIOC1</b> | I/O  | BLNS4     | G15    | この端子は以下の機能を持っています。<br>- <b>GPIOC1</b> 入出力（リセット直後の端子機能）<br>- TimerB1IO (GPIO 以外の機能 1)<br>- DACK# (GPIO 以外の機能 2)                            |

| <b>GPIOC2</b> | I/O  | BLNS4     | J19    | この端子は以下の機能を持っています。<br>- <b>GPIOC2</b> 入出力（リセット直後の端子機能）<br>- TimerB2IO (GPIO 以外の機能 1)<br>- CFRST# (GPIO 以外の機能 2)                           |

| <b>GPIOC3</b> | I/O  | BLNS4     | J18    | この端子は以下の機能を持っています。<br>- <b>GPIOC3</b> 入出力（リセット直後の端子機能）<br>- TimerB3IO (GPIO 以外の機能 1)<br>- UART3_CLK (GPIO 以外の機能 2)                        |

| <b>GPIOC4</b> | I/O  | BLNS4     | J17    | この端子は以下の機能を持っています。<br>- <b>GPIOC4</b> 入出力（リセット直後の端子機能）<br>- SPI_SS : SPI 用チップセレクト (GPIO 以外の機能 1)<br>- TXD3 : UART3 送信データ出力 (GPIO 以外の機能 2) |

### 3. 端子

| 端子名称              | Type | Cell Type | ピン No.                              | 説明                                                                                                                                                                         |

|-------------------|------|-----------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>GPIOC5</b>     | I/O  | BLNS4     | J16                                 | この端子は以下の機能を持っています。<br>- <b>GPIOC5 入出力</b> (リセット直後の端子機能)<br>- <b>SPI_SCLK : SPI 用シリアルクロック</b> (GPIO 以外の機能 1)<br>- <b>RXD3 : UART3 受信データ入力</b> (GPIO 以外の機能 2)                |

| <b>GPIOC6</b>     | I/O  | BLNS4     | H15                                 | この端子は以下の機能を持っています。<br>- <b>GPIOC6 入出力</b> (リセット直後の端子機能)<br>- <b>SPI_MISO : SPI 用シリアルデータマスタ入力／スレーブ出力</b> (GPIO 以外の機能 1)<br>- <b>RTS3 : UART3 送信要求出力</b> (GPIO 以外の機能 2)      |

| <b>GPIOC7</b>     | I/O  | BLNS4     | J15                                 | この端子は以下の機能を持っています。<br>- <b>GPIOC6 入出力</b> (リセット直後の端子機能)<br>- <b>SPI_MOSI : SPI 用シリアルデータマスタ出力／スレーブ入力</b> (GPIO 以外の機能 1)<br>- <b>CTS3 : UART3 受信可能入力</b> (GPIO 以外の機能 2)      |

| <b>GPIOD[3:0]</b> | I/O  | BLNS4     | U9,T8,<br>T9,U10                    | この端子は以下の機能を持っています。<br>- <b>GPIOD [3:0]入出力</b> (リセット直後の端子機能)<br>- <b>MA [23:20] : アドレス出力信号 [23:20]</b> (GPIO 以外の機能 1)                                                       |

| <b>GPIOD[5:4]</b> | I/O  | BLNS4     | V15,R16                             | この端子は以下の機能を持っています。<br>- <b>GPIOD[5:4]入出力</b> (リセット直後の端子機能)<br>- <b>MCS[3:2]# : メモリ用チップセレクト出力信号</b> (GPIO 以外の機能 1)                                                          |

| <b>GPIOD6</b>     | I/O  | BLNS4     | V1                                  | この端子は以下の機能を持っています。<br>- <b>GPIOD6 入出力</b> (リセット直後の端子機能)<br>- <b>SDRAM 用 DQM2#信号</b> (ロー・アクティブ・サイン)                                                                         |

| <b>GPIOD7</b>     | I/O  | BLNS4     | T4                                  | この端子は以下の機能を持っています。<br>- <b>GPIOD7 入出力</b> (リセット直後の端子機能)<br>- <b>SDRAM 用 DQM3#信号</b> (ロー・アクティブ・サイン)<br>- <b>SDDQM3# : SDRAM32 ビットデータ幅の上位 16 ビットの下位バイトに対応</b> (GPIO 以外の機能 1) |

| <b>GPIOJ[7:0]</b> | I/O  | BLNC4D2   | J4,L2,<br>L4,J5,<br>L3,M2,<br>M3,M1 | この端子は以下の機能を持っています。<br>- <b>GPIOJ[7:0]入出力</b> (リセット直後の端子機能)<br>- <b>SDD[23:16] : SDRAM 用データ入出力</b> (GPIO 以外の機能 1)                                                           |

| <b>GPIOK[7:0]</b> | I/O  | BLNC4D2   | G1,G2,<br>E6,E7,<br>G3,H3,<br>F5,G4 | この端子は以下の機能を持っています。<br>- <b>GPIOK[7:0]入出力</b> (リセット直後の端子機能)<br>- <b>SDD[31:24] : SDRAM 用データ入出力</b> (GPIO 以外の機能 1)                                                           |

| <b>SYSCLKI</b>    | I/O  | BLNS4     | A10                                 | <b>32KHz システムクロック入力</b><br>SYSCKSEL="High" の時、基本クロック入力。<br>SYSCKSEL="Low" の時、設定により 32KHz またはシステムクロックの 1/4 が出力。                                                             |

| <b>SYS_OSCI</b>   | I    | ILTR      | A6                                  | <b>水晶振動子用接続端子</b><br>動作クロック発振端子です。32KHz の水晶振動子を接続します。                                                                                                                      |

| <b>SYS_OSCO</b>   | O    | OLTR      | A5                                  | <b>水晶振動子用接続端子</b><br>動作クロック発振端子です。32KHz の水晶振動子を接続します。                                                                                                                      |

| <b>SYSVCP</b>     | O    | OLTR      | A9                                  | <b>内蔵 PLL 用システムテスト端子</b><br>システムのテスト時に PLL の出力をモニタするため使用します。<br>通常使用時はオープンにしてください。                                                                                         |

| 端子名称       | Type | Cell Type | ピン No.                                                 | 説明                                                                                           |

|------------|------|-----------|--------------------------------------------------------|----------------------------------------------------------------------------------------------|

| SYSCKSEL   | I    | ICSD1     | B10                                                    | 32KHz システムクロック入力の水晶振動子/発振器の選択信号<br>SYSCKSEL="High"の時、水晶発振器を使用。<br>SYSCKSEL="Low"の時、水晶振動子を使用。 |

| USBCK_OSCI | I    | ILTR      | C19                                                    | 水晶振動子用接続端子<br>USB 専用の動作クロック発振端子です。12/24MHz の水晶振動子を接続します。                                     |

| USBCK_OSCO | O    | OLTR      | B19                                                    | 水晶振動子用接続端子<br>USB 専用の動作クロック発振端子です。12/24MHz の水晶振動子を接続します。                                     |

| TRST#      | I    | ICSU1     | B11                                                    | JTAG Interface 用リセット (ローアクティブ信号)<br>プルアップ抵抗付シミットトリガ入力になっています。                                |

| TCK        | I    | ICSU1     | D11                                                    | JTAG Interface 用クロック入力ピン<br>シミットトリガ入力になっています。                                                |

| TMS        | I    | ICU1      | D12                                                    | JTAG Interface 用 TMS ピン<br>この端子はプルアップ抵抗を内蔵しています。                                             |

| TDI        | I    | ICU1      | E13                                                    | JTAG Interface 用シリアルデータ入力ピン<br>この端子はプルアップ抵抗を内蔵しています。                                         |

| TDO        | O    | OTLN4     | C12                                                    | JTAG Interface 用シリアルデータ出力ピン                                                                  |

| TESTEN0    | I    | ICD1      | C11                                                    | テストイネーブル 0 (ハイアクティブ信号)<br>この端子はプルダウン抵抗を内蔵しています。<br>通常使用時は VSS へ接続するか、またはオープンにしてください。         |

| TESTEN1    | I    | ICD1      | E10                                                    | テストイネーブル 1 (ハイアクティブ信号)<br>この端子はプルダウン抵抗を内蔵しています。<br>通常使用時は VSS へ接続するか、またはオープンにしてください。         |

| TESTCK     | I    | ICD1      | B12                                                    | テストロック端子<br>この端子はプルダウン抵抗を内蔵しています。<br>通常使用時は VSS へ接続するか、またはオープンにしてください。                       |

| RESET#     | I    | ICSU1     | D13                                                    | システムリセット信号 (ローアクティブ信号)<br>HVDD1 および LVDD が安定した後も 100ms の間 Reset#をアクティブ(Low) に保ってください。        |

| BUP#       | I    | ILS       | B8                                                     | スタンバイ信号 (ローアクティブ信号) 1.8V 信号                                                                  |

| HVDD       | P    | P         | C9,C16,D14,<br>E18,G16,H18,<br>L15,R10,R15,<br>W12,W15 | I/O セル用電源 : 3.3V(Typical)<br>3.0V (Min) – 3.6V (Max)                                         |

| C1VDD      | P    | P         | A4                                                     | カメラ 1 インタフェース用電源 : 3.0 (Typical)<br>2.4V (Min) – 3.6V (Max)                                  |

| C2VDD      | P    | P         | W4                                                     | カメラ 2 インタフェース用電源 : 3.0 (Typical)<br>2.4V (Min) – 3.6V (Max)                                  |

| SDVDD      | P    | P         | C3,F2,<br>K3,K4,<br>P1                                 | SDRAM 用電源 3.3V(Typical)<br>2.7V (Min) – 3.6V (Max)                                           |

| AVDD       | P    | P         | V5,W5,<br>W10                                          | A/D C 用電源 : 3.3V(Typical)<br>3.0V (Min) – 3.6V (Max)                                         |

| UVDD3      | P    | P         | A16,B14                                                | USB 用電源 : 3.3V(Typical)<br>3.0V (Min) – 3.6V (Max)                                           |

### 3. 端子

| 端子名称   | Type | Cell Type | ピン No.                                                                                                                                                            | 説明                                                                                                       |

|--------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| LVDD   | P    | P         | A11,D10,D18,<br>E1,E12,F15,<br>F18,H1,K15,<br>K18,L5,P19,<br>T2,V18,W14                                                                                           | コア（内部）用電源 : 1.8V(Typical)<br>1.65V (Min) – 1.95V (Max)                                                   |

| UPVDD  | P    | P         | A18                                                                                                                                                               | USB 用電源 : 1.8V(Typical)<br>1.65V (Min) – 1.95V (Max)                                                     |

| UXVDD  | P    | P         | A13                                                                                                                                                               | USB 用電源 : 1.8V(Typical)<br>1.65V (Min) – 1.95V (Max)                                                     |

| PLLVDD | P    | P         | B9                                                                                                                                                                | アナログ(PLL)用電源 : 1.8V(Typical)<br>1.65V (Min) – 1.95V (Max)<br>アナログ電源としての取り扱いが必要です。ノイズの少ない安定した電源を供給してください。 |

| RTCVDD | P    | P         | A7                                                                                                                                                                | RTC 用電源 : 1.8V(Typical)<br>1.65V (Min) – 1.95V (Max)                                                     |

| UVSS   | P    | P         | B15,B17                                                                                                                                                           | USB 用グラウンド                                                                                               |

| PVSS   | P    | P         | B18                                                                                                                                                               | USB 用グラウンド                                                                                               |

| XVSS   | P    | P         | B13                                                                                                                                                               | USB 用グラウンド                                                                                               |

| AVSS   | P    | P         | U6,V10                                                                                                                                                            | A/D C 用グラウンド                                                                                             |

| PLLVSS | P    | P         | A8                                                                                                                                                                | アナログ(PLL)用グラウンド<br>アナログ電源としての取り扱いが必要です。ノイズの少ない安定したグラウンドを供給してください。                                        |

| VSS    | P    | P         | A12,B4,B7,<br>B16,C2,C8,<br>C10,C13,C15,<br>C17,C18,E2,<br>E4,E8,E11,<br>G5,G18,H2,<br>K5,L1,L18,<br>M5,N2,N17,<br>P5,R9,R18,<br>T1,T14,U4,<br>U16,V2,V13,<br>V19 | I/O セル、カメラインターフェースおよびコア電源共通グラウンド                                                                         |

### 3.3 GPIO端子のマルチプレクス端子機能、リセット直後の端子機能

| S2S65A30<br>端子名称 | リセット<br>直後の<br>端子機能 | FlashROM/<br>SAM<br>拡張 | SDRAM<br>拡張 | UART     | I2C/<br>I2S/<br>SPI | タイマ        | Progressive<br>カメラ<br>I/F | Interlace<br>カメラ<br>I/F | CF<br>カード | SD<br>カード |

|------------------|---------------------|------------------------|-------------|----------|---------------------|------------|---------------------------|-------------------------|-----------|-----------|

| GPIOA0           | GPIOA0              |                        |             | TXD1     |                     |            |                           |                         |           |           |

| GPIOA1           | GPIOA1              |                        |             | RXD1     |                     |            |                           |                         |           |           |

| GPIOA2           | GPIOA2              |                        |             | RTS1     | I2S1_WS             |            |                           |                         |           |           |

| GPIOA3           | GPIOA3              |                        |             | CTS1     | I2S1_SCK            |            |                           |                         |           |           |

| GPIOA4           | GPIOA4              |                        |             | TXD2     |                     |            |                           |                         |           |           |

| GPIOA5           | GPIOA5              |                        |             | RXD2     |                     |            |                           |                         |           |           |

| GPIOA6           | GPIOA6              |                        |             | RTS2     | SCL                 |            |                           |                         |           |           |

| GPIOA7           | GPIOA7              |                        |             | CTS2     | SDA                 |            |                           |                         |           |           |

| GPIOB0           | GPIOB0              |                        |             |          | I2S0_WS             |            |                           |                         |           |           |

| GPIOB1           | GPIOB1              |                        |             |          | I2S0_SCK            |            |                           |                         |           |           |

| GPIOB2           | GPIOB2              |                        |             |          | I2S0_SD             |            |                           |                         |           |           |

| GPIOB3           | GPIOB3              |                        |             |          | I2S1_SD             |            |                           |                         |           |           |

| GPIOB4           | GPIOB4              |                        |             |          |                     | TimerA0out |                           |                         |           |           |

| GPIOB5           | GPIOB5              | DREQ#                  |             |          |                     | TimerA1out |                           |                         |           |           |

| GPIOB6           | GPIOB6              |                        |             |          |                     | TimerA2out |                           |                         |           |           |

| GPIOB7           | GPIOB7              |                        |             |          |                     | TimerBIN   |                           |                         |           |           |

| GPIOC0           | GPIOC0              |                        |             |          |                     | TimerB0IO  |                           |                         |           |           |

| GPIOC1           | GPIOC1              | DACK#                  |             |          |                     | TimerB1IO  |                           |                         |           |           |

| GPIOC2           | GPIOC2              |                        |             |          |                     | TimerB2IO  |                           |                         | CFRST     |           |

| GPIOC3           | GPIOC3              |                        | UART3_CLK   |          |                     | TimerB3IO  |                           |                         |           |           |

| GPIOC4           | GPIOC4              |                        | TXD3        | SPI_SS   |                     |            |                           |                         |           |           |

| GPIOC5           | GPIOC5              |                        | RXD3        | SPI_SCLK |                     |            |                           |                         |           |           |

| GPIOC6           | GPIOC6              |                        | RTS3        | SPI_MISO |                     |            |                           |                         |           |           |

| GPIOC7           | GPIOC7              |                        | CTS3        | SPI莫斯    |                     |            |                           |                         |           |           |

| GPIOD0           | GPIOD0              | MA20                   |             |          |                     |            |                           |                         |           |           |

| GPIOD1           | GPIOD1              | MA21                   |             |          |                     |            |                           |                         |           |           |

| GPIOD2           | GPIOD2              | MA22                   |             |          |                     |            |                           |                         |           |           |

| GPIOD3           | GPIOD3              | MA23                   |             |          |                     |            |                           |                         |           |           |

| GPIOD4           | GPIOD4              | MCS2#                  |             |          |                     |            |                           |                         |           |           |

| GPIOD5           | GPIOD5              | MCS3#                  |             |          |                     |            |                           |                         |           |           |

| GPIOD6           | GPIOD6              | SDDQM2#                |             |          |                     |            |                           |                         |           |           |

| GPIOD7           | GPIOD7              | SDDQM3#                |             |          |                     |            |                           |                         |           |           |

| CM1DATA0         | GPIOE0              |                        |             |          |                     | CM1DATA0   | IPC1DATA0                 |                         |           |           |

| CM1DATA1         | GPIOE1              |                        |             |          |                     | CM1DATA1   | CM1DATA1                  |                         |           |           |

| CM1DATA2         | GPIOE2              |                        |             |          |                     | CM1DATA2   | IPC1DATA2                 |                         |           |           |

| CM1DATA3         | GPIOE3              |                        |             |          |                     | CM1DATA3   | IPC1DATA3                 |                         |           |           |

| CM1DATA4         | GPIOE4              |                        |             |          |                     | CM1DATA4   | IPC1DATA4                 |                         |           |           |

| CM1DATA5         | GPIOE5              |                        |             |          |                     | CM1DATA5   | IPC1DATA5                 |                         |           |           |

| CM1DATA6         | GPIOE6              |                        |             |          |                     | CM1DATA6   | IPC1DATA6                 |                         |           |           |

| CM1DATA7         | GPIOE7              |                        |             |          |                     | CM1DATA7   | IPC1DATA7                 |                         |           |           |

| CM1VREF          | GPIOF0              |                        |             |          |                     | CM1VREF    | IPC1VREF                  |                         |           |           |

| CM1HREF          | GPIOF1              |                        |             |          |                     | CM1HREF    | IPC1HREF                  |                         |           |           |

| CM1CLKOUT        | GPIOF2              |                        |             |          |                     | CM1CLKOUT  | IPC1FIELD                 |                         |           |           |

| CM1CLKIN         | GPIOF3              |                        |             |          |                     | CM1CLKIN   | IPC1CLKIN                 |                         |           |           |

| CM2VREF          | GPIOF4              |                        |             |          |                     | CM2VREF    | IPC2VREF                  |                         |           |           |

| CM2HREF          | GPIOF5              |                        |             |          |                     | CM2HREF    | IPC2HREF                  |                         |           |           |

| CM2CLKOUT        | GPIOF6              |                        |             |          |                     | CM2CLKOUT  | IPC2FIELD                 |                         |           |           |

| CM2CLKIN         | GPIOF7              |                        |             |          |                     | CM2CLKIN   | IPC2CLKIN                 |                         |           |           |

| CM2DATA0         | GPIOG0              |                        |             |          |                     | CM2DATA0   | IPC2DATA0                 |                         |           |           |

| CM2DATA1         | GPIOG1              |                        |             |          |                     | CM2DATA1   | IPC2DATA1                 |                         |           |           |

| CM2DATA2         | GPIOG2              |                        |             |          |                     | CM2DATA2   | IPC2DATA2                 |                         |           |           |

| CM2DATA3         | GPIOG3              |                        |             |          |                     | CM2DATA3   | IPC2DATA3                 |                         |           |           |

| CM2DATA4         | GPIOG4              |                        |             |          |                     | CM2DATA4   | IPC2DATA4                 |                         |           |           |

| CM2DATA5         | GPIOG5              |                        |             |          |                     | CM2DATA5   | IPC2DATA5                 |                         |           |           |

| CM2DATA6         | GPIOG6              |                        |             |          |                     | CM2DATA6   | IPC2DATA6                 |                         |           |           |

| CM2DATA7         | GPIOG7              |                        |             |          |                     | CM2DATA7   | IPC2DATA7                 |                         |           |           |

### 3. 端子

---

| S2S65A30<br>端子名称 | リセット<br>直後の<br>端子機能 | FlashROM/<br>SAM<br>拡張 | SDRAM<br>拡張 | UART/<br>SPI | I2C/<br>I2S | タイマ | Progressive<br>カメラ<br>I/F | Interlace<br>カメラ<br>I/F | CF<br>カード | SD<br>カード |

|------------------|---------------------|------------------------|-------------|--------------|-------------|-----|---------------------------|-------------------------|-----------|-----------|

| CFCE2#           | GPIOH0              |                        |             |              |             |     |                           |                         | CFCE2#    | SDMDATA0  |

| CFCE1#           | GPIOH1              |                        |             |              |             |     |                           |                         | CFCE1#    | SDMDATA1  |

| CFIORD#          | GPIOH2              |                        |             |              |             |     |                           |                         | CFIORD#   | SDMDATA2  |

| CFIOWR#          | GPIOH3              |                        |             |              |             |     |                           |                         | CFIOWR#   | SDMDATA3  |

| CFWAIT#          | GPIOH4              |                        |             |              |             |     |                           |                         | CFWAIT#   | SDMCMD    |

| CFRST            | GPIOH5              |                        |             |              |             |     |                           |                         | CFRST     | SDMCLK    |

| CFIRQ            | GPIOH6              |                        |             |              |             |     |                           |                         | CFIRQ     | SDMCD#    |

| CFSTSCHG#        | GPIOH7              |                        |             |              |             |     |                           |                         | CFSTSCHG# | SDMWP     |

| CFDEN#           | GPIOI0              |                        |             |              |             |     |                           |                         | CFDEN#    | SDMGPO    |