# S1R72E11

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

7. 本資料に含まれているSDホスト機能に関する情報は、SD Associationのwebsiteで公開されているSimplified Specificationに基づいています。（SD Association website: <http://www.sdcards.org/>）

## **適用範囲**

本ドキュメントは、SD/MMC ホストコントローラ LSI 「S1R72E11」 に適用されます。

# 目 次

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>1. レジスタマップ .....</b>                                  | <b>1</b>  |

| <b>2. 機能説明.....</b>                                      | <b>3</b>  |

| <b>2.1 ICの初期化.....</b>                                   | <b>3</b>  |

| <b>2.2 パワーマネージメント .....</b>                              | <b>5</b>  |

| 2.2.1 SLEEPモード設定 .....                                   | 5         |

| 2.2.2 SLEEPモード解除 .....                                   | 5         |

| <b>2.3 SD/MMCホスト共通基本機能 .....</b>                         | <b>6</b>  |

| 2.3.1 CMDラインのみ使用するコマンドの送信 .....                          | 6         |

| 2.3.1.1 コマンド送信時に設定するレジスタ .....                           | 6         |

| 2.3.1.2 レスポンスを伴わないコマンドの動作説明 .....                        | 7         |

| 2.3.1.3 レスポンスを伴うコマンドの動作説明 .....                          | 7         |

| 2.3.2 RespBusyを伴うコマンドの送信 .....                           | 8         |

| 2.3.2.1 コマンド送信時に設定するレジスタ .....                           | 8         |

| 2.3.2.2 RespBusyの動作説明 .....                              | 9         |

| 2.3.3 データ転送を伴うコマンドの送信 .....                              | 10        |

| 2.3.3.1 コマンド送信時に設定するレジスタ .....                           | 10        |

| 2.3.3.2 リード転送の動作説明 .....                                 | 12        |

| 2.3.3.3 ライト転送の動作説明 .....                                 | 14        |

| 2.3.3.4 RespBusyを伴うライト転送の動作説明 .....                      | 16        |

| 2.3.4 Auto系コマンド .....                                    | 18        |

| 2.3.4.1 AutoCMD55 機能 .....                               | 18        |

| 2.3.4.1.1 AutoCMD55 使用時に設定するレジスタ .....                   | 18        |

| 2.3.4.1.2 AutoCMD55 の動作説明概要 .....                        | 18        |

| 2.3.4.1.3 AutoCMD55 の動作説明詳細 .....                        | 18        |

| 2.3.4.2 AutoCMD12 機能 .....                               | 20        |

| 2.3.4.2.1 AutoCMD12 使用時に設定するレジスタ .....                   | 20        |

| 2.3.4.2.2 AutoCMD12 の動作説明概要 .....                        | 20        |

| 2.3.4.2.3 AutoCMD12 の動作説明詳細 .....                        | 20        |

| <b>2.4 個別特殊機能 .....</b>                                  | <b>22</b> |

| 2.4.1 Abortコマンド発行による、データ転送の終了方法 .....                    | 22        |

| 2.4.2 WaitCCS機能の使用方法 (CE-ATA ドライブ専用) .....               | 23        |

| 2.4.2.1 コマンド送信時に設定するレジスタ .....                           | 23        |

| 2.4.2.2 WaitCCSモードでの動作説明詳細 .....                         | 23        |

| 2.4.2.3 WaitCCSモード中のAbortコマンド発行 .....                    | 23        |

| <b>2.5 PIO転送方法 .....</b>                                 | <b>24</b> |

| 2.5.1 リード転送時のFIFOアクセス .....                              | 24        |

| 2.5.2 ライト転送時のFIFOアクセス .....                              | 25        |

| <b>2.6 DMA転送方法 .....</b>                                 | <b>26</b> |

| 2.6.1 DMA基本機能 .....                                      | 26        |

| 2.6.1.1 DMA転送アクセス方法 .....                                | 26        |

| 2.6.1.2 バーストモード設定 .....                                  | 27        |

| 2.6.2 DMA動作フロー .....                                     | 28        |

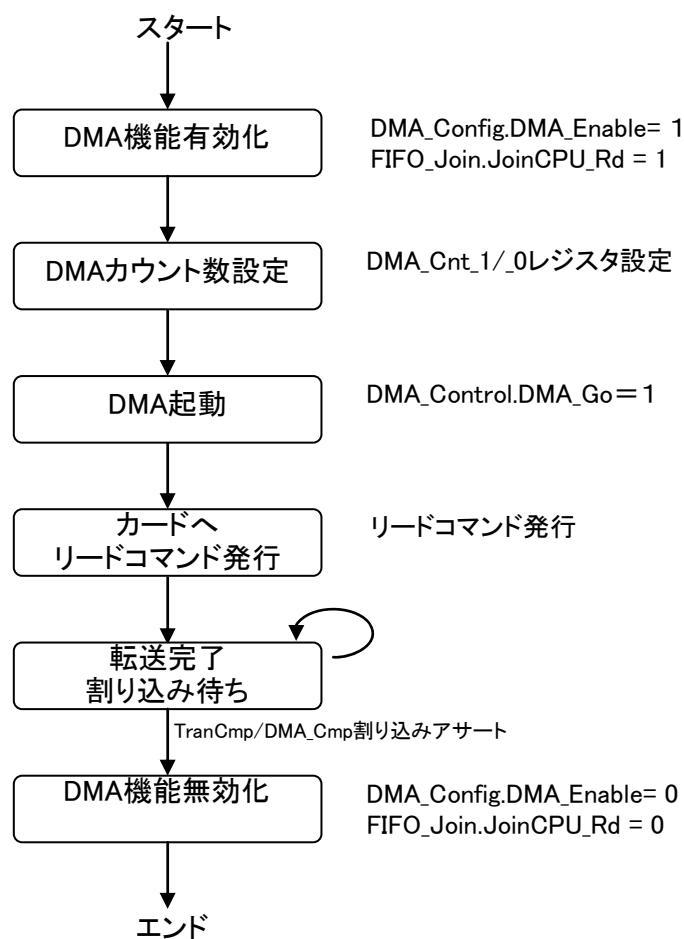

| 2.6.2.1 DMAリード .....                                     | 28        |

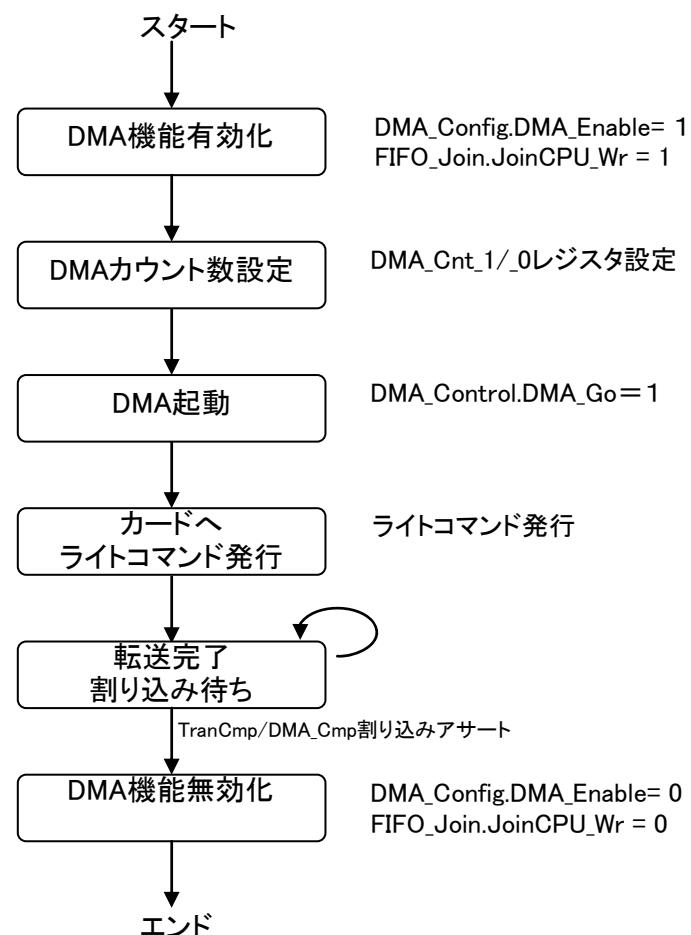

| 2.6.2.2 カウントモード (DMAライト) .....                           | 29        |

| <b>3. レジスタ詳細説明 .....</b>                                 | <b>30</b> |

| <b>3.1 00h BlkSize ( Transfer Block Size ) .....</b>     | <b>30</b> |

| <b>3.2 04h BlkCnt_0 ( Transfer Block Count 0 ) .....</b> | <b>31</b> |

| <b>3.3 06h BlkCnt_1 ( Transfer Block Count 1 ) .....</b> | <b>31</b> |

| <b>3.4 08h Argument_0 ( Command Argument 0 ) .....</b>   | <b>33</b> |

|                                                                  |    |

|------------------------------------------------------------------|----|

| 3.5 0Ah Argument_1 ( Command Argument 1 ).....                   | 33 |

| 3.6 0Ch TransferMode ( Transfer Mode ).....                      | 34 |

| 3.7 0Eh Command ( Command ).....                                 | 35 |

| 3.8 10h Response_0 ( Command Response 0 ).....                   | 38 |

| 3.9 12h Response_1 ( Command Response 1 ).....                   | 38 |

| 3.10 14h Response_2 ( Command Response 2 ).....                  | 38 |

| 3.11 16h Response_3 ( Command Response 3 ).....                  | 38 |

| 3.12 18h Response_4 ( Command Response 4 ).....                  | 38 |

| 3.13 1Ah Response_5 ( Command Response 5 ).....                  | 38 |

| 3.14 1Ch Response_6 ( Command Response 6 ).....                  | 38 |

| 3.15 1Eh Response_7 ( Command Response 7 ) .....                 | 38 |

| 3.16 28h PresentStateCard ( Present State Card ).....            | 40 |

| 3.17 2Ah PresentStateBus ( Present State Bus ).....              | 42 |

| 3.18 2Ch HostConfig ( Host Config ) .....                        | 43 |

| 3.19 2Eh HostOperation ( Host Operation ) .....                  | 44 |

| 3.20 30h ClockControl ( Clock Control ) .....                    | 46 |

| 3.21 32h TimeoutControl ( Timeout Control ) .....                | 47 |

| 3.22 34h SoftwareReset ( Software Reset ).....                   | 49 |

| 3.23 36h TEST_Mode ( TEST Mode ) .....                           | 50 |

| 3.24 38h TimeoutCnt_0 ( Timeout Count 0 ) .....                  | 51 |

| 3.25 3Ah TimeoutCnt_1 ( Timeout Count 1 ).....                   | 51 |

| 3.26 3Ch GPIO_Config ( GPIO Configuration ) .....                | 52 |

| 3.27 3Eh GPIO_RdWr ( GPIO Read/Write ) .....                     | 53 |

| 3.28 40h NormIntStat ( Normal Interrupt Status ) .....           | 54 |

| 3.29 42h ErrIntStat ( Error Interrupt Status ) .....             | 57 |

| 3.30 44h NormIntFactEnb ( Normal Interrupt Factor Enable ) ..... | 59 |

| 3.31 48h NormIntEnb ( Normal Interrupt Enable ) .....            | 60 |

| 3.32 4Ah ErrIntEnb ( Error Interrupt Enable ) .....              | 61 |

| 3.33 4Ch AutoCMD12ErrStat ( AutoCM12 Error Status ) .....        | 62 |

| 3.34 4Eh AutoCMD55ErrStat ( AutoCMD55 Error Status ) .....       | 63 |

| 3.35 50h ExArgument_0 ( External Command Argument 0 ).....       | 64 |

| 3.36 52h ExArgument_1 ( External Command Argument 1 ).....       | 64 |

| 3.37 58h CPU_Endian ( CPU Endian ) .....                         | 65 |

| 3.38 5Ah CPU_Config ( CPUIF Configuration ).....                 | 66 |

| 3.39 5Ch PM_Control ( Power Manegement Control ) .....           | 67 |

| 3.40 60h FIFO_Rd ( FIFO Read Data Word ).....                    | 68 |

| 3.41 62h FIFO_Wr ( FIFO Write Data ).....                        | 69 |

| 3.42 64h FIFO_RdRemain ( FIFO Read Remain ).....                 | 70 |

| 3.43 66h FIFO_WrRemain ( FIFO Write Remain ).....                | 71 |

| 3.44 68h FIFO_BytRd ( FIFO Read Data Byte ) .....                | 72 |

| 3.45 6Ah FIFO_BytWr ( FIFO Wite Data Byte ) .....                | 73 |

| 3.46 6Ch FIFO_Join ( FIFO Join ).....                            | 74 |

| 3.47 70h DMA_Config ( DMA Configuration ).....                   | 75 |

| 3.48 72h DMA_Control ( DMA Control ) .....                       | 76 |

| 3.49 74h DMA_Cnt_0 ( DMA Counter 0 ) .....                       | 77 |

| 3.50 76h DNA_Cnt_1 ( DMA Counter 1 ) .....                       | 77 |

| 改訂履歴 .....                                                       | 78 |

## 1. レジスタマップ

| Address | Register Name    | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0              |

|---------|------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|-------------------|

| 00h     | BlkSize          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | BlkSize [15:0]    |

| 02h     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

| 04h     | BlkCnt_0         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | BlkCnt [15:0]     |

| 06h     | BlkCnt_1         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | BlkCnt [31:16]    |

| 08h     | Argument_0       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdArg [15:0]     |

| 0Ah     | Argument_1       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdArg [31:16]    |

| 0Ch     | TransferMode     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

| 0Eh     | Command          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | AutoCMD12         |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | AutoCMD55         |

| 0Fh     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | TranType          |

| 10h     | Response_0       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [15:0]    |

| 12h     | Response_1       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [31:16]   |

| 14h     | Response_2       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [47:32]   |

| 16h     | Response_3       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [63:48]   |

| 18h     | Response_4       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [79:64]   |

| 1Ah     | Response_5       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [95:80]   |

| 1Ch     | Response_6       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [1111:96] |

| 1Eh     | Response_7       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CmdResp [127:112] |

| 20h     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |                   |

| 22h     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |                   |

| 24h     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |                   |

| 26h     |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |                   |

| 28h     | PresentStateCard |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

| 2Ah     | PresentStateBus  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | WP_Sig            |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CD_Sig            |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CardStateStable   |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CardInserted      |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | DAT_TrnAct        |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | CMD_TrnAct        |

| 2Ch     | HostConfig       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

| 2Eh     | HostOperation    |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | HighSpeed         |

| 30h     | ClockControl     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | DataTranWidth     |

| 32h     | TimeoutControl   |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsrd              |

| 34h     | SoftwareReset    |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsrd              |

| 36h     | TEST_Mode        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsrd              |

| 38h     | TimeoutCnt_0     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | TO_Cnt [18:3]     |

| 3Ah     | TimeoutCnt_1     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | TO_Cnt [34:19]    |

| 3Ch     | GPIO_Config      |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | ActiveGPIO        |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO3_Dir         |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO2_Dir         |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO1_Dir         |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO0_Dir         |

| 3Eh     | GPIO_RdWr        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | Rsvd              |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO3             |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO2             |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO1             |

|         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      | GPIO0             |

# 1. レジスタマップ

| Address | Register Name      | bit15                 | bit14               | bit13             | bit12                | bit11               | bit10                | bit9                  | bit8             |

|---------|--------------------|-----------------------|---------------------|-------------------|----------------------|---------------------|----------------------|-----------------------|------------------|

| 40h     | NormIntStat        | CardStateStabilized   | <b>AsyncCardChg</b> | SyncSDIO Int      | <b>AsyncSDIO Int</b> | Rsvd                | DMA_Cmp              | CCS                   | bit0             |

|         |                    | ErrInt                | Rsvd                | FIFO_RcvdBlk      | FIFO_Empty           | AutoCMD12Cmp        | BlkGapEvent          | TranCmp               | CmdCmp           |

| 42h     | ErrIntStat         | Rsvd                  | DataEndBitErr       | DataCRC Err       | DataTimeoutErr       | RespIndexErr        | RespEndBitErr        | RespCRC Err           | RespTimeoutErr   |

|         |                    |                       |                     | Rsvd              |                      |                     |                      | AutoCMD55Err          | AutoCMD12Err     |

| 44h     | NormIntFactEnb     | Rsvd                  |                     | SyncSDIO_IntEnb   | AsyncSDIO_IntEnb     |                     | Rsvd                 |                       |                  |

| 46h     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 48h     | NormIntEnb         | EnCardStateStabilized | EnAsyncCardChg      | EnSyncSDIO_Int    | EnAsyncSDIO_Int      | Rsvd                | EnDMA_Cmp            | EnCCS                 |                  |

|         |                    | EnErrInt              | Rsvd                | EnFIFO_RcvdBlk    | EnFIFO_Empty         | EnAutoCMD12Cmp      | EnBlkGapEvent        | EnTranCmp             | EnCmdCmp         |

| 4Ah     | ErrIntEnb          | Rsvd                  | EnDataEndBitErr     | EnDataCRC_Err     | EnDataTimeoutErr     | EnRespIndexErr      | EnRespEndBitErr      | EnRespCRC_Err         | EnRespTimeoutErr |

|         |                    |                       |                     | Rsvd              |                      |                     |                      | EnAutoCMD55Err        | EnAutoCMD12Err   |

| 4Ch     | AutoCMD12ErrStat   | NoCmdByAutoCMD12Err   | Rsvd                |                   | AutoCMD12Index_Err   | AutoCMD12EndBit_Err | AutoCMD12CRC_Err     | AutoCMD12TltimeoutErr | AutoCMD12NotExec |

| 4Eh     | AutoCMD55ErrStat   | Rsvd                  |                     |                   | AutoCMD55Index_Err   | AutoCMD55EndBit_Err | AutoCMD55CRC_Err     | AutoCMD55TltimeoutErr | Rsvd             |

| 50h     | ExArgument_0       |                       |                     |                   | ExCmdArg [15:0]      |                     |                      |                       |                  |

| 52h     | ExArgument_1       |                       |                     |                   | ExCmdArg [31:16]     |                     |                      |                       |                  |

| 54h     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 56h     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 58h     | <b>CPU_Endian</b>  | <b>CPU_Endian</b>     |                     |                   | Rsvd                 |                     | <b>FIFO_BReqSwap</b> | <b>FIFO_BReqSwap</b>  |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     | <b>FIFO_BReqSwap</b> | <b>FIFO_BReqSwap</b>  |                  |

| 5Ah     | <b>CPU_Config</b>  | <b>IntLevel</b>       | <b>IntMode</b>      | <b>DREQ_Level</b> | <b>DACK_Level</b>    |                     | Rsvd                 |                       | <b>CkSource</b>  |

| 5Ch     | <b>PML_Control</b> | <b>INT_Dis</b>        | <b>GoSLEEP</b>      | <b>GoACTIVE</b>   |                      |                     | Rsvd                 |                       | <b>SLEEP</b>     |

| 5Eh     |                    |                       |                     |                   |                      | Rsvd                |                      |                       |                  |

| 60h     | FIFO_Rd            |                       |                     |                   | FIFO_Rd_1[7:0]       |                     |                      |                       |                  |

|         |                    |                       |                     |                   | FIFO_Rd_0[7:0]       |                     |                      |                       |                  |

| 62h     | FIFO_Wr            |                       |                     |                   | FIFO_Wr_1[7:0]       |                     |                      |                       |                  |

|         |                    |                       |                     |                   | FIFO_Wr_0[7:0]       |                     |                      |                       |                  |

| 64h     | FIFO_RdRemain      | RdRemainValid         |                     |                   | Rsvd                 | RdRemain[7:0]       |                      | RdRemain[9:8]         |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 66h     | FIFO_WrRemain      |                       |                     |                   | Rsvd                 | WrRemain[7:0]       |                      | WrRemain[9:8]         |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 68h     | FIFO_BytRd         |                       |                     |                   | FIFO_BytRd[7:0]      |                     |                      |                       |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 6Ah     | FIFO_BytWr         |                       |                     |                   | FIFO_BytWr[7:0]      |                     |                      |                       |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 6Ch     | FIFO_Join          |                       |                     |                   | Rsvd                 |                     |                      | JoinCPU_Rd            | JoinCPU_Wr       |

| 6Eh     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 70h     | DMA_Config         |                       | NgtCnt[3:0]         |                   | Rsvd                 |                     |                      | DMA_Mode              |                  |

|         |                    |                       |                     |                   | Rsvd                 |                     | BurstCnt[1:0]        |                       |                  |

| 72h     | DMA_Control        | DMA_Running           |                     |                   | Rsvd                 | Rsvd                |                      | DMA_Enable            |                  |

|         |                    |                       |                     |                   | DMA_Stop             |                     |                      | DMA_Go                |                  |

| 74h     | DMA_Cnt_0          |                       |                     | DMA_Cnt[7:2]      |                      |                     |                      | Rsvd                  |                  |

|         |                    |                       |                     |                   | DMA_Cnt[31:16]       |                     |                      |                       |                  |

| 76h     | DMA_Cnt_1          |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 78h     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 7Ah     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 7Ch     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

| 7Eh     |                    |                       |                     |                   | Rsvd                 |                     |                      |                       |                  |

## 2. 機能説明

### 2.1 IC の初期化

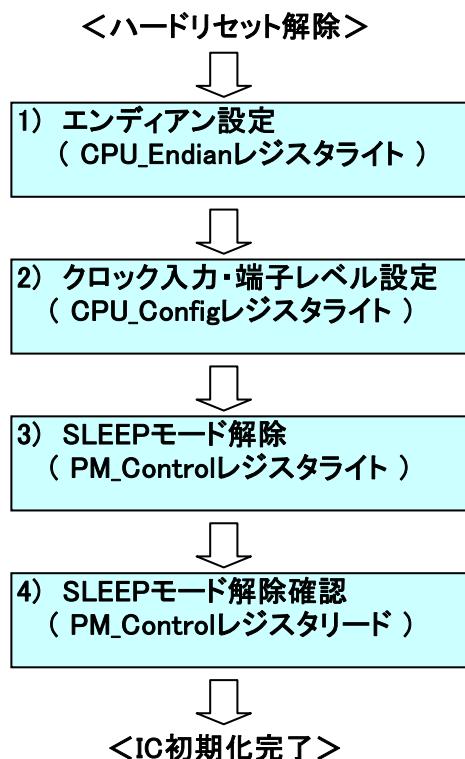

本 IC は、ハードリセット後、パワーマネージメントは SLEEP 状態から始まります。本 IC を動作可能な状態にするために、下記の手順を実行してください。

初期化時に使用するレジスタは、下記の通りです。

下記にあげるレジスタは、ハードリセットで初期化されますが、SoftwareReset.SoftReset\_for\_All レジスタによるソフトリセットでは初期化されません。

| Address | Register Name     | bit15<br>bit7     | bit14<br>bit6  | bit13<br>bit5     | bit12<br>bit4     | bit11<br>bit3 | bit10<br>bit2 | bit9<br>bit1         | bit8<br>bit0        |

|---------|-------------------|-------------------|----------------|-------------------|-------------------|---------------|---------------|----------------------|---------------------|

| 58h     | <i>CPU_Endian</i> | <i>CPU_Endian</i> |                |                   | Rsvd              |               |               | <i>FIFO_BRegSwap</i> | <i>FIFO_RegSwap</i> |

| 5Ah     | <i>CPU_Config</i> | <i>IntLevel</i>   | <i>IntMode</i> | <i>DREQ_Level</i> | <i>DACK_Level</i> | Rsvd          | Rsvd          | <i>FIFO_BRegSwap</i> | <i>FIFO_RegSwap</i> |

| 5Ch     | <i>PM_Control</i> | <i>INT_Dis</i>    | <i>GoSLEEP</i> | <i>GoACTIVE</i>   |                   | Rsvd          | Rsvd          |                      | <i>ClkSource</i>    |

図 2.1 IC の初期化で設定が必要なレジスタ

図 2.2 に、ハードリセット後の初期化手順を示します。次ページで、各フェーズの詳細な説明をします。

図 2.2 IC の初期化手順

## 2. 機能説明

### 1) CPU エンディアン設定

CPU\_Endian レジスタに、ご使用のモード設定値をライトしてください。

PIO 転送／DMA 転送において内蔵 FIFO にアクセスする際のエンディアンを個別に切り替える事が可能です。

個別にエンディアン切り替え可能な FIFO アクセスレジスタは、

FIFO\_Rd／FIFO\_Wr／FIFO\_BytRd／FIFO\_BytWr レジスタです。

CPU\_Endian レジスタは、上位/下位両方に同じレジスタを配置しています。本レジスタに書き込む場合は、上位と下位両方に同じ値を書き込んでください。

表 2.3 CPU エンディアン設定

| AccessMode レジスタ | 設定値 | エンディアンモード | CD[15:8]   | CD[7:0]    | 対応するレジスタ          |

|-----------------|-----|-----------|------------|------------|-------------------|

| CPU_Endian      | 0   | リトルエンディアン | レジスタの上位バイト | レジスタの下位バイト | FIFO アクセスレジスタ以外全て |

|                 | 1   | ビックエンディアン | レジスタの下位バイト | レジスタの上位バイト |                   |

| FIFO_BRegSwap   | 0   | リトルエンディアン | レジスタの上位バイト | レジスタの下位バイト | FIFO_BytRd        |

|                 | 1   | ビックエンディアン | レジスタの下位バイト | レジスタの上位バイト | FIFO_BytWr        |

| FIFO_RegSwap    | 0   | リトルエンディアン | レジスタの上位バイト | レジスタの下位バイト | FIFO_Rd           |

|                 | 1   | ビックエンディアン | レジスタの下位バイト | レジスタの上位バイト | FIFO_Wr           |

### 2) クロック入力・端子レベル設定

CPU\_Config レジスタの、IntLevel、IntMode、DREQ\_Level、DACK\_Level、ClkSource ビットに、ご使用の設定値をライトして下さい。これらのビットは、初期化時に全て “0b” となっていて下記の設定になっています。必要に合わせて設定を変更して下さい。

表 2.4 CPU\_Config レジスタ初期設定値

| CPU_Config レジスタ | 初期値 | 内容                        |

|-----------------|-----|---------------------------|

| IntLevel        | 0b  | XINT 割り込み出力レベル（負論理）       |

| IntMode         | 0b  | XINT 割り込み出力モード（1／0 出力モード） |

| DREQ_Level      | 0b  | XDREQ 端子アサート論理レベル（負論理）    |

| DACK_Level      | 0b  | XDACK 端子アサート論理レベル（負論理）    |

| ClkSource       | 0b  | 水晶振動子使用                   |

レジスタの詳細内容は、レジスタ説明を参照して下さい。

### 3) SLEEP モード解除

PM\_Control レジスタに、“0040h” をライトしてください。

GoACTIVE ビットに “1” をセットすることで、内部システムクロックの動作が開始されます。

### 4) SLEEP モード解除確認

PM\_Control レジスタをリードして、SLEEP ビットが “0” にクリアされている事を確認して下さい。

GoACTIVE ビットにセットしてから、SLEEP ビットが “0” にクリアされるまで、約 5ms 程度（内部システムクロック周波数 50MHz 時）の時間がかかります。

## 2.2 パワーマネジメント

本 IC は、SLEEP 状態（内部システムクロック停止中）と ACTIVE 状態（内部システムクロック動作中）の 2 つの状態があります。

それぞれのモードへの遷移させる手順を下記に示します。

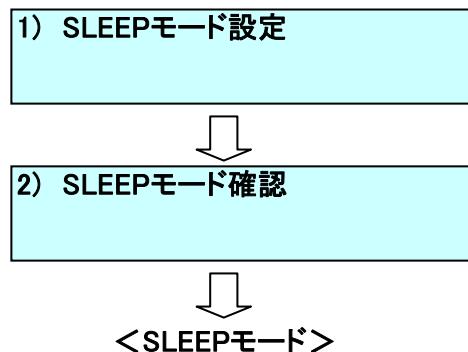

### 2.2.1 SLEEP モード設定

図 2.5 SLEEP モード設定手順

#### 1) SLEEP モード設定

PM\_Control レジスタの GoSLEEP ビットに “1” をセットして下さい。

GoSLEEP ビットに “1” をセットすることで、内部システムクロックが停止します。

#### 2) SLEEP モード確認

PM\_Control レジスタをリードして、SLEEP ビットに “1” がセットされている事を確認して下さい。

本 LSI は、GoSLEEP ビットに “1” をセットすると、即時に SLEEP モードに入り、SLEEP ビットに “1” がセットされます。

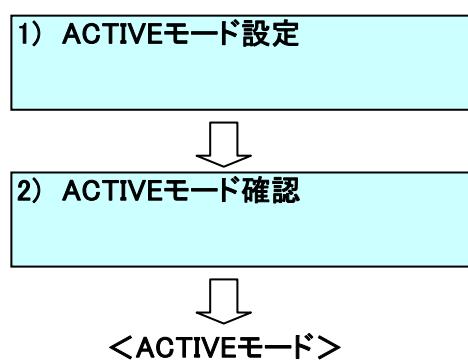

### 2.2.2 SLEEP モード解除

図 2.6 ACTIVE モード設定手順

#### 1) ACTIVE モード設定

PM\_Control レジスタの GoACTIVE ビットに “1” をセットして下さい。

GoACTIVE ビットに “1” をセットすることで、ACTIVE モードへの遷移が開始されます。

#### 2) ACTIVE モード確認

PM\_Control レジスタをリードして、SLEEP ビットに “0” がセットされている事を確認して下さい。

本 LSI は、GoACTIVE ビットに “1” をセットされてから、SLEEP ビットが “0” にクリアされるまで、5ms 程度（内部システムクロック 50MHz 時）の時間がかかります。

## 2. 機能説明

### 2.3 SD/MMC ホスト共通基本機能

#### 2.3.1 CMD ラインのみ使用するコマンドの送信

##### 2.3.1.1 コマンド送信時に設定するレジスタ

カードへコマンドを送信する場合は、表 2.1 に示すレジスタにカード規格書に記載されているコマンドフォーマットを元に値をセットしてください。SDMMC ホストコントローラは、Command レジスタの上位 Byte に書き込みが発生すると、カードへのコマンド送信が開始されます。したがって、Command レジスタへの書き込みは、一番最後に行ってください。コマンド送信中は、PresentStateBus.CMD\_TranAct ビットに“1”がセットされます。PresentStateBus.CMD\_TranAct ビットに“1”がセットされている間は、表 2.1 に示すレジスタを変更しないで下さい。

表 2.1 コマンド送信時に必要な設定レジスタ

| レジスタ                     | ビット                                           | 説明                                                                                                                                   |

|--------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Argument_0<br>Argument_1 | CmdArg[31:0]                                  | コマンドの Argument を指定します。<br>カード規格書記載のコマンド定義を参照し、設定して下さい。                                                                               |

| TransferMode             | AutoCMD55                                     | カード規格書記載の APP_CMD を自動で送信する機能です。<br>本機能を使用しない場合は、“0”を設定して下さい。<br><b>AutoCMD55 の使用方法は、2.3.4.1 章を参照してください。</b>                          |

| Command                  | CmdType                                       | コマンドのタイプを設定します。<br>00b : Normal コマンド、 01b : Reserved<br>10b : Reserved、 11b : Abort コマンド<br>送信するコマンドが、Normal コマンドの場合は、“00b”を設定して下さい。 |

|                          | UseDAT_Line                                   | データ転送を伴うコマンドかどうかを設定します。<br>データ転送を伴わないコマンドの場合は、“0”を設定して下さい。                                                                           |

|                          | RespIndexChk<br>RespCRC_Chk<br>RespTimeoutChk | レスポンスのチェックの有無を設定します。<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。                                                                                |

|                          | ResponseType                                  | レスポンスのタイプを設定します。<br>00b : レスpons無し、 01b : 136bit レスpons<br>10b : 48bit レスpons、 11b : RespBusy<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。       |

|                          | WaitCCS                                       | CE-ATA ドライブ用のモードです。<br>CE-ATA ドライブを使用しない場合は、“0”を設定して下さい。                                                                             |

|                          | Resp                                          | MMC カードの Interrupt Mode 用の機能です。<br>Interrupt Mode を使用しない場合は、“0”を設定して下さい。                                                             |

|                          | CmdIndex                                      | コマンドのコマンド Index を設定します。<br>カード規格書記載のコマンド定義を参照し、設定して下さい。                                                                              |

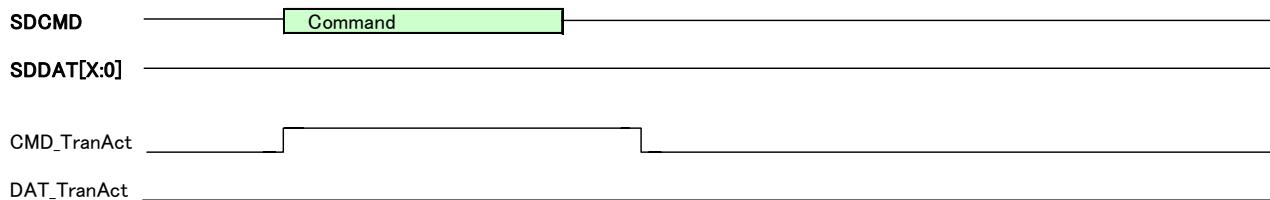

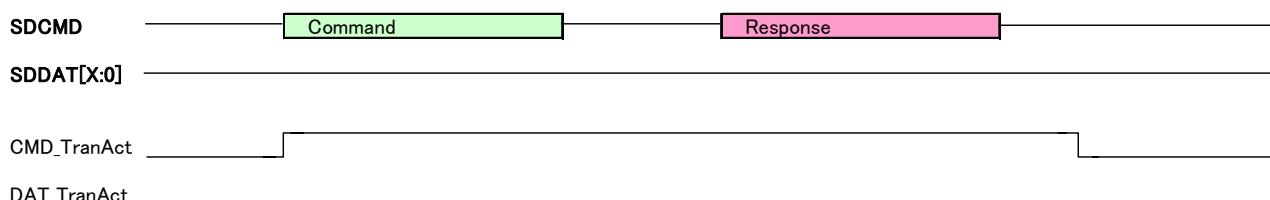

### 2.3.1.2 レスポンスを伴わないコマンドの動作説明

レスポンスを伴わないコマンドを送信する場合は、Command.RespType レジスタに “00b” を設定してください（他のレジスタ設定は、表 2.1 を参照）。コマンドの送信中は、PresentStateBus.CMD\_TranAct ビットに “1” がセットされます。PresentStateBus.CMD\_TranAct ビットが、“1” から “0” に変化するのと同時に、NormIntStat.CmdCmp 割り込み要因ビットに “1” がセットされます。

図 2.7 レスポンスを伴わないコマンド送信

### 2.3.1.3 レスポンスを伴うコマンドの動作説明

レスポンスを伴うコマンドを送信する場合は、対応するレスポンスの長さによって Command.RespType レジスタに “01” もしくは “10” を設定してください（他のレジスタ設定は、表 2.1 を参照）。コマンド送信からレスポンス受信完了までの間、PresentStateBus.CMD\_TranAct ビットに “1” がセットされます。レスポンス受信時にエラーが発生しなければ、PresentStateBus.CMD\_TranAct ビットが、“1” から “0” に変化するのと同時に、NormIntStat.CmdCmp 割り込み要因ビットに “1” がセットされます。

下記にエラー終了する場合の条件を説明します。エラー終了の場合は、NormIntStat.CmdCmp ビットはセットされず、ErrIntStat レジスタの対応するビットがセットされます。

#### 1) レスポンスタイムアウトエラー

コマンドの送信が完了した後、規定クロックサイクル以内にレスポンスの StartBit を検出しなかつた場合は、エラー終了となり ErrIntStat.RespTimeoutErr ビットに “1” がセットされます。

(Command.RespTimeoutChk= “1” の時のみ)

#### 2) レスポンス Index エラー

Command.CmdIndex フィールドの内容と、受信したレスポンス中の Index フィールドの内容が異なっていた場合、エラー終了となり ErrIntStat.RespIndexErr ビットに “1” がセットされます。

(Command.RespIndexChk= “1” の時のみ)

#### 3) レスポンス CRC エラー

レスポンス受信時に、CRC エラーが検出された場合は、ErrIntStat.RespCRC\_ErrBitErr に “1” がセットされます。

(Command.RespCRC\_Chk= “1” の時のみ)

#### 4) レスポンス EndBit エラー

レスポンス受信時に、EndBit が検出されなかった場合は、ErrIntStat.RespEndBitErr に “1” がセットされます。

図 2.8 レスポンスを伴うコマンド送信

## 2. 機能説明

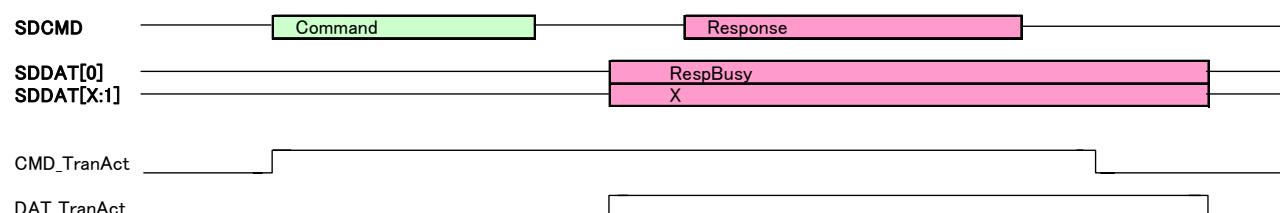

### 2.3.2 RespBusy を伴うコマンドの送信

#### 2.3.2.1 コマンド送信時に設定するレジスタ

RespBusy を伴うコマンドを送信する場合は、表 2.2 に示すレジスタにカード規格書に記載されているコマンドフォーマットを元に値をセットしてください。SDMMC ホストコントローラは、Command レジスタの上位 Byte に書き込みが発生すると、コマンドの送信が開始されます。したがって、Command レジスタへの書き込みは、一番最後に行ってください。コマンド送信中は、PresentStateBus.CMD\_TranAct ビットに “1” がセットされます。またコマンド送信後、DAT[0] ライン上に RespBusy がアサートされている間は、PresentStatBus.DAT\_TranAct ビットが “1” にセットされます。

下記のように、PresentStateBus レジスタの内容によって、書き換え可能なレジスタが異なりますので注意してください。

- PresentStateBus.CMD\_TranAct ビット = “1”、 PresentStatBus.DAT\_TranAct ビット = “1”

全てのコマンド送信が出来ません。この期間、表 2.2 に示すレジスタは、全て書き換え禁止です。

- PresentStateBus.CMD\_TranAct ビット = “0”、 PresentStatBus.DAT\_TranAct ビット = “1”

CMD ラインのみ使用するコマンドだけが送信可能です。この期間、表 2.2 に示すレジスタは、全て書き換え可能です。

表 2.2 コマンド送信時に必要な設定レジスタ

| レジスタ                     | ビット                                           | 説明                                                                                                                                   |

|--------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Argument_0<br>Argument_1 | CmdArg[31:0]                                  | コマンドのアーギュメントを指定します。<br>カード規格書記載のコマンド定義を参照し、設定して下さい。                                                                                  |

| TransferMode             | AutoCMD55                                     | カード規格書記載の APP_CMD を自動で送信する機能です。<br>本機能を使用しない場合は、“0”を設定して下さい。<br><b>AutoCMD55 の使用方法は、2.3.4.1 章を参照してください。</b>                          |

| Command                  | CmdType                                       | コマンドのタイプを設定します。<br>00b : Normal コマンド、 01b : Reserved<br>10b : Reserved、 11b : Abort コマンド<br>送信するコマンドが、Normal コマンドの場合は、“00b”を設定して下さい。 |

|                          | UseDAT_Line                                   | データ転送を伴うコマンドかどうかを設定します。<br>データ転送を伴わないコマンドの場合は、“0”を設定して下さい。                                                                           |

|                          | RespIndexChk<br>RespCRC_Chk<br>RespTimeoutChk | レスポンスのチェックの有無を設定します。<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。                                                                                |

|                          | ResponseType                                  | レスポンスのタイプを設定します。<br>00b : レスポンス無し、 01b : 136bit レスポンス<br>10b : 48bit レスポンス、 11b : RespBusy<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。          |

|                          | WaitCCS                                       | CE-ATA ドライブ用のモードです。<br>CE-ATA ドライブを使用しない場合は、“0”を設定して下さい。                                                                             |

|                          | Resp                                          | MMC カードの Interrupt Mode 用の機能です。<br>Interrupt Mode を使用しない場合は、“0”を設定してください。                                                            |

|                          | CmdIndex                                      | コマンドのコマンドインデックスを設定します。<br>カード規格書記載のコマンド定義を参照し、設定してください。                                                                              |

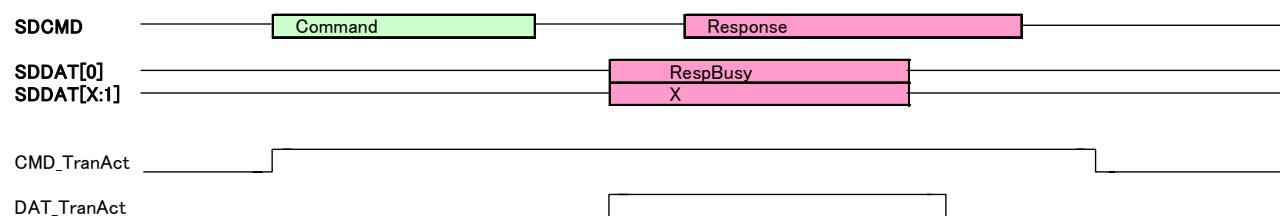

### 2.3.2.2 RespBusy の動作説明

RespBusy を伴うコマンドを送信する場合は、Command.RespType レジスタに “11b” を設定して、コマンドの送信を実行して下さい（他のレジスタ設定は、表 2.2 を参照）。コマンド送信中の動作は、CMD ラインのみ使用するコマンドと同様です（2.3.1 章を参照）。

コマンドの送信完了後、DAT[0] ライン上の RespBusy がアサートされている期間、PresentStateBus.DAT\_TranAct ビットに “1” がセットされます。RespBusy がネゲートされると、PresentStateBus.DAT\_TranAct ビットが “0” になり、同時に NromIntStat.TranCmp 割り込み要因ビットに “1” がセットされます。

もし、RespBusy が TimeoutControl.WrTimeoutCnt レジスタの内容によって決定されるクロックサイクル時間が経過しても、ネゲートされない場合はタイムアウトエラーとなり、ErrIntStat.DataTimeoutErr ビットに “1” がセットされます。

図 2.9 RespBusy 動作（RespBusy 期間>レスポンス期間）

図 2.10 RespBusy 動作（RespBusy 期間<レスポンス期間）

## 2. 機能説明

---

### 2.3.3 データ転送を伴うコマンドの送信

#### 2.3.3.1 コマンド送信時に設定するレジスタ

データ転送を伴うコマンドを送信する場合は、表 2.3 に示すレジスタにカード規格書に記載されているコマンドフォーマットを元に値をセットしてください。SDMMC ホストコントローラは、Command レジスタの上位 Byte に書き込みが発生すると、コマンドの送信が開始されます。したがって、Command レジスタへの書き込みは、一番最後に行ってください。コマンド送信中は、PresentStateBus.CMD\_TranAct ビットに “1” がセットされます。また、コマンド送信後の、データ転送中は PresentStatBus.DAT\_TranAct ビットに “1” がセットされます。

下記のように、PresentStateBus レジスタの内容によって、書き換え可能なレジスタが異なりますので注意してください。

- PresentStateBus.CMD\_TranAct ビット = “1”、PresentStatBus.DAT\_TranAct ビット = “1”

全てのコマンド送信が出来ません。この期間、表 2.3 に示すレジスタは、全て書き換え禁止です。

- PresentStateBus.CMD\_TranAct ビット = “0”、PresentStatBus.DAT\_TranAct ビット = “1”

CMD ラインのみ使用するコマンドだけが送信可能です。この期間、表 2.3 中の、※1 がついているレジスタは書き換え禁止です。

データ転送を伴うコマンドを送信する時は、TranBlkSize[15:0] レジスタに “0000h” を設定しないで下さい。また、Multi 転送と Stream 転送設定時 (TransferMode.TranType= “10b”、“11” b) は、BlkCnt[31:0] レジスタに “0000\_0000h” を設定しないで下さい。この場合、データ転送が開始されません。

表 2.3 データ転送を伴うコマンド送信時に必要な設定レジスタ

| レジスタ                     | ビット                                           | 説明                                                                                                                                   |

|--------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| BlkSize                  | TranBlkSize[15:0] ※1                          | データ転送時の転送ブロックサイズを設定して下さい。                                                                                                            |

| BlkCnt_0<br>BlkCnt_1     | BlkCnt[31:0] ※1                               | データ転送時の転送ブロック数を設定して下さい。                                                                                                              |

| Argument_0<br>Argument_1 | CmdArg[31:0]                                  | コマンドのアーギュメントを指定します。<br>カード規格書記載のコマンド定義を参照し、設定して下さい。                                                                                  |

| TransferMode             | DataDir ※1                                    | データ転送の方向を設定して下さい。<br>“0” : Write (SDMMC ホストコントローラ→カード)<br>“1” : Read (カード→SDMMC コントローラ)                                              |

|                          | TranType[1:0] ※1                              | データ転送のタイプを設定して下さい。<br>“00” : Single 転送 “01” : Infinite 転送<br>“10” : Multiple 転送 “11” : Stream 転送                                     |

|                          | AutoCMD12 ※1                                  | Abort コマンドを自動で送信する機能です。<br>本機能を使用しない場合は、“0”を設定して下さい。<br><i>AutoCMD12 の使用方法は、2.3.4.2 章を参照してください。</i>                                  |

|                          | AutoCMD55                                     | カード規格書記載の APP_CMD を自動で送信する機能です。<br>本機能を使用しない場合は、“0”を設定して下さい。<br><i>AutoCMD55 の使用方法は、2.3.4.1 章を参照してください。</i>                          |

| Command                  | CmdType                                       | コマンドのタイプを設定します。<br>00b : Normal コマンド、 01b : Reserved<br>10b : Reserved、 11b : Abort コマンド<br>送信するコマンドが、Normal コマンドの場合は、“00b”を設定して下さい。 |

|                          | UseDAT_Line                                   | データ転送を伴うコマンドかどうかを設定します。<br>データ転送を伴わなうコマンドの場合は、“1”を設定して下さい。                                                                           |

|                          | RespIndexChk<br>RespCRC_Chk<br>RespTimeoutChk | レスポンスのチェックの有無を設定します。<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。                                                                                |

|                          | ResponseType                                  | レスポンスのタイプを設定します。<br>00b : レスポンス無し、 01b : 136bit レスポンス<br>10b : 48bit レスpons、 11b : RespBusy<br>カード規格書記載のレスポンス定義を参照し、設定して下さい。         |

|                          | WaitCCS                                       | CE-ATA ドライブ用のモードです。<br>CE-ATA ドライブを使用しない場合は、“0”を設定して下さい。                                                                             |

|                          | Resp                                          | MMC カードの Interrupt Mode 用の機能です。<br>Interrupt Mode を使用しない場合は、“0”を設定してください。                                                            |

|                          | CmdIndex                                      | コマンドの Index を設定します。<br>カード規格書記載のコマンド定義を参照し、設定してください。                                                                                 |

※1 : PresentStateBus.CMD\_TranAct ビット = “0”、PresentStatBus.DAT\_TranAct ビット = “1” の時、書き換え禁止レジスタ

## 2. 機能説明

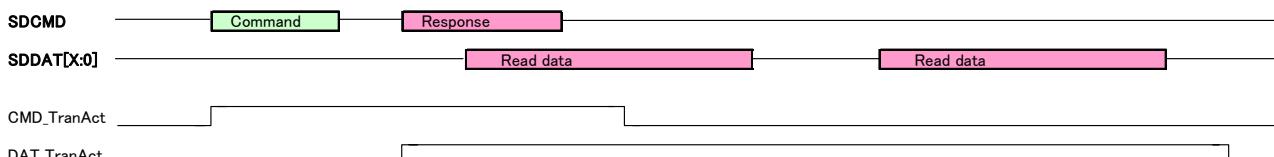

### 2.3.3.2 リード転送の動作説明

リード転送を行う場合は、TransferMode.DataDir=“1”を設定して、コマンドの送信を実行して下さい。

(他のレジスタ設定は、表 2.3 を参照)。コマンド送信中の動作は、CMD ラインのみ使用するコマンドと同様です (2.3.1 章を参照)。

下記に、Multi 転送を例にとって説明します (TransferMode.TranType= “10b”)。

コマンドの送信が完了した後、データブロック単位でデータを受信します。最後のデータブロックの受信が完了すると、データ転送終了となり、NorimIntStat.TranCmp ビットに “1” がセットされます。

下記にエラー終了する場合の動作を説明します。エラー終了の場合は、NormIntStat.TranCmp ビットはセットされません。

- 1) データタイムアウトエラー

リード転送コマンド送信後、及びデータブロックの受信完了後 (次のデータブロックがある場合)、TimeoutControl.RdTimeoutCnt レジスタに設定された時間以内に、データブロックの StartBit を検出しなかった場合は、エラー終了となり ErrIntStat.DataTimeoutErr ビットに “1” がセットされます。

- 2) データ CRC エラー

データブロック受信時に CRC エラーが発生した場合は、エラー終了となり、ErrIntStat.DataCRC\_Err ビットに “1” がセットされます。

- 3) データ EndBit エラー

データブロック受信時に、EndBit が検出されなかった場合は、エラー終了となり、ErrIntStat.DataEndBitErr ビットに “1” がセットされます。

BlkCnt[31:0] レジスタがデクリメントされるタイミングは、データブロックの EndBit を受信するタイミングです。データブロック受信時に CRC エラーが発生した場合は、BlkCnt[31:0] レジスタは、デクリメントされません。データブロック受信時に EndBit が検出されなかった場合には、受信したデータは有効とみなし、BlkCnt[31:0] レジスタは、デクリメントされます。

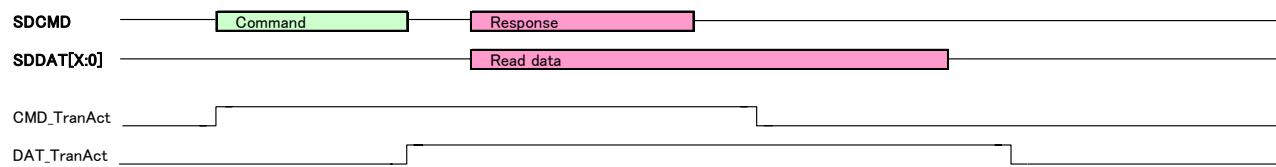

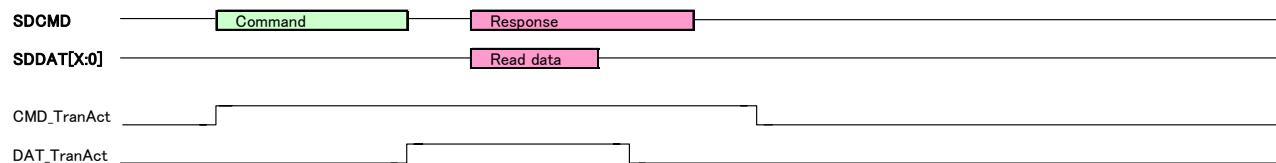

図 2.11 リード転送動作波形 (Multi 転送)

Single 転送 (TransferMode.TranType= “00”) の場合は、BlkCnt[31:0] レジスタの設定に関わらず、1つデータブロックのリード転送が完了した時点で転送終了となり、NorimIntStat.TranCmp ビットに “1” がセットされます。(図 2.12 参照)

図 2.12 リード転送動作波形 (Single 転送 : リードデータ期間>レスポンス期間)

図 2.13 リード転送動作波形 (Single 転送 : リードデータ期間<レスポンス期間)

Infinite 転送 (TransferMode.TranType= “01”) は、データブロックのリード転送完了後 BlkCnt[31:0] レジスタの値は更新されず、リード転送が無限に続く事になります。その他の動作は、Multi 転送動作と同様です。転送を止める場合は、Abort コマンドを送信します (2.4.1 章参照)。

Stream 転送 (TransferMode.TranType= “11”) は、データブロックという概念がありません。BlkSize レジスタ x BlkCnt レジスタ分のデータの受信が完了した時点で、転送終了となり NorimIntStat.TranCmp ビットに “1” がセットされます。

## 2. 機能説明

### 2.3.3.3 ライト転送の動作説明

ライト転送を行う場合は、TransferMode.DataDir=“0”を設定して、コマンドの送信を実行して下さい（他のレジスタ設定は、表 2.3 を参照）。コマンド送信中の動作は、CMD ラインのみ使用するコマンドと同様です（2.3.1 章を参照）。

下記に、Multi 転送を例にとって説明します。（TransferMode.TranType=“10”）

コマンドに対するレスポンス受信が完了し、受信したレスポンスにエラーが無ければ、データブロックの送信が開始されます。最後のデータブロックに対する WriteBusy がネゲートされると、データ転送終了となり、NromIntStat.TranCmp ビットに“1”がセットされます。

コマンドに対するレスポンス受信が完了し、受信したレスポンスにエラーがあった場合は、ライト転送は開始されません。このとき NromIntStat.TranCmp ビットは“1”にセットされません。

下記にエラー終了する場合の動作を説明します。エラー終了の場合は、NormIntStat.TranCmp ビットはセットされません。

#### 1) CRC ステータスタイムアウトエラー

データブロック送信後、TimeoutControl.WrTimeoutCnt レジスタに設定された時間以内に、CRC ステータスの StartBit を検出しなかった場合は、エラー終了となり ErrIntStat.DataTimeoutErr ビットに“1”がセットされます。

#### 2) CRC ステータスエラー

CRC ステータスの内容がエラーだった場合は、エラー終了となり ErrIntStat.DataCRCErr ビットに“1”がセットされます。

#### 3) CRC ステータス EndBit エラー

CRC ステータス受信時に、EndBit が検出されなかった場合は、エラー終了となり ErrIntStat.DataEndBitErr ビットに“1”がセットされます。

#### 4) WriteBusy タイムアウトエラー

CRC ステータス受信後、TimeoutControl.WrTimeoutCnt レジスタに設定された時間以内に、WriteBusy がネゲートされなかった場合は、エラー終了となり ErrIntStat.DataTimeoutErr ビットに“1”がセットされます。

BlkCnt[31:0] レジスタがデクリメントされるタイミングは、データブロックに対する CRC ステータスの EndBit を受信するタイミングです。CRC ステータスの内容がエラーだった場合は、BlkCnt[31:0] レジスタは、デクリメントされません。CRC ステータス受信時に EndBit が検出されなかった場合は、ライトデータは有効とみなし、BlkCnt[31:0] レジスタは、デクリメントされます。

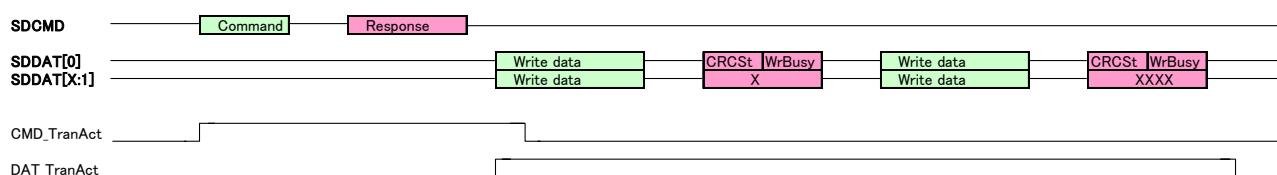

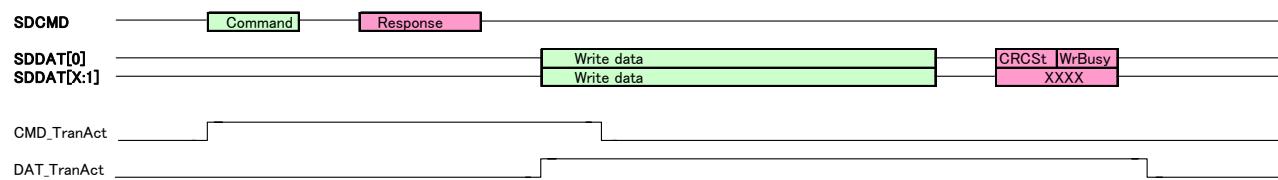

図 2.14 ライト転送動作波形（Multi 転送）

Single 転送 (TransferMode.TranType= “00”) の場合は、BlkCnt[31:0] レジスタの設定に関わらず、1つデータブロックのライト転送が完了した時点で転送終了となり、NorimIntStat.TranCmp ビットに “1” がセットされます。(図 2.15 参照)

図 2.15 ライト転送動作波形 (Single 転送)

Infinite 転送 (TransferMode.TranType= “01”) は、データブロックの転送完了後 BlkCnt[31:0] レジスタの値は更新されずに、ライト転送が無限に続く事になります。転送を止める場合は、Abort コマンドを送信します (2.4.1 章参照)。

Stream 転送 (TransferMode.TranType= “11”) は、データブロックという概念がありません。BlkSize レジスタ x BlkCnt レジスタ分のデータの送信が完了した時点で、転送終了となり NorimIntStat.TranCmp ビットに “1” がセットされます。

## 2. 機能説明

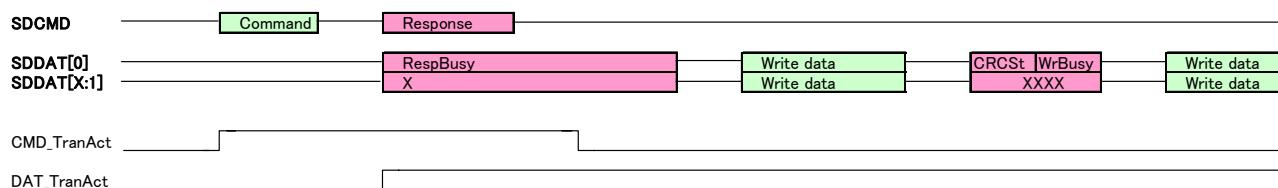

### 2.3.3.4 RespBusy を伴うライト転送の動作説明

ライト転送を行う場合は、Command.RespType=“11”、TransferMode.DataDir=“0”を設定して、コマンドの送信を実行して下さい（他のレジスタ設定は、表2.3を参照）。コマンド送信中の動作は、CMDラインのみ使用するコマンドと同様です（2.3.1章を参照）。

下記のように、Multi転送を例にとって説明します。（TransferMode.TranType=“10”）

コマンドの送信が完了すると、DAT[0]ライン上のRespBusyの監視を開始します。その後、レスポンスを正常に受信した後、RespBusyがネゲートされるのを待って、データブロックの送信を開始します。最後のデータブロックのWriteBusyがネゲートされると、データ転送終了となり、NromIntStat.TranCmpビットに“1”がセットされます。

エラー終了する場合の動作は、RespBusyを伴う転送及び、ライト転送と同様です。

BlkCnt[31:0]レジスタがデクリメントされるタイミングは、データブロックに対するCRCステータスのEndBitを受信するタイミングです。CRCステータスの内容がエラーだった場合は、BlkCnt[31:0]レジスタは、デクリメントされません。CRCステータス受信時にEndBitが検出されなかった場合は、ライトデータは有効とみなし、BlkCnt[31:0]レジスタは、デクリメントされます。

図2.16 RespBusyを伴うライト転送動作波形（Multi転送）

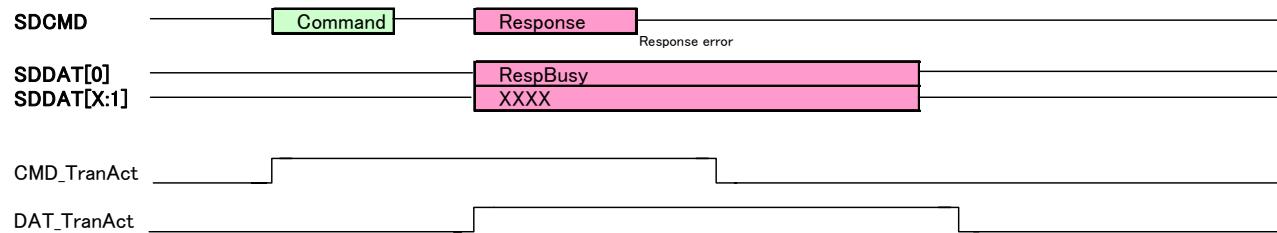

レスポンスにエラーが発生した場合には、DAT[0]ライン上の RespBusy がネゲートされた時点で、転送完了となり NormIntStat.TranCmp ビットに“1”がセットされます。データ転送は開始されません。

図 2.17 RespBusy を伴うライト転送動作波形（レスポンスエラー時）

Single 転送 (TransferMode.TranType= “00”) の場合は、BlkCnt[31:0]レジスタの設定に関わらず、1つのデータブロックのライト転送が完了した時点で転送終了となり、NormIntStat.TranCmp ビットに“1”がセットされます。

Infinite 転送 (TransferMode.TranType= “01”) は、1 ブロックの転送完了後 BlkCnt[31:0]レジスタの値は更新されずに、ライト転送が無限に続く事になります。転送を止める場合は、Abort コマンドを送信します（2.4.1 章参照）。

RespBusy を伴う転送で、Stream 転送 (TransferMode.TranType= “11”) は禁止です。

## 2. 機能説明

### 2.3.4 Auto 系コマンド

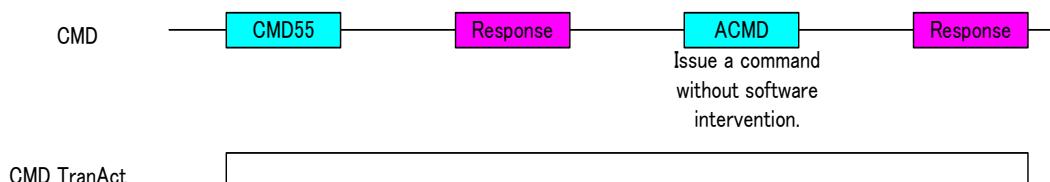

本ホストコントローラには、コマンド発行に関する一連のシーケンスを、ソフトウェアを介すことなくハードウェアのみで行う機能を具備しています。例えば、ACMD を発行する際にはそれに先立ち CMD55 を発行する必要があります。また、データ転送を発行した後にはこれを止めるために CMD12 を発行する必要があります。これらのようにある決まったコマンド（CMD55 や CMD12）を、発行したコマンドの前後に自動的に挿入する機能です。

#### 2.3.4.1 AutoCMD55 機能

カード規格書記載の APP\_CMD (CMD55) を自動で送信する機能です。CMD55 — ACMD の順でコマンドが発行されます。コマンド発行のための各種パラメータはそれぞれのコマンド発行時に切り替わります。

##### 2.3.4.1.1 AutoCMD55 使用時に設定するレジスタ

本機能を使用する際には、TransferMode.AutoCMD55 ビットに “1” をセットして、コマンドの送信を実行して下さい。その他の設定は、2.3.1.1 章、2.3.2.1 章、2.3.3.1 章に示されているレジスタに ACMD の設定をして、さらに、ExArgument\_0, \_1 レジスタに CMD55 のアーギュメントをカード規格書記載のコマンド定義を参照し設定して下さい。PresentStateBus.CMD\_TranAct ビットに “1” がセットされている間は、上記レジスタを変更しないで下さい。

##### 2.3.4.1.2 AutoCMD55 の動作説明概要

AutoCMD55 機能は、CMD55 を発行した後、そのコマンドの完了を待ちます。コマンドが正常に完了（レスポンスを正常に受信）した後、即座に ACMD の発行を行います。その後は通常のデータ転送として処理されます。

##### 2.3.4.1.3 AutoCMD55 の動作説明詳細

AutoCMD55 機能は、TransferMode.AutoCMD55 ビットに “1” をセットした状態で Command レジスタにライトを行うことで起動されます。コマンド発行のためのレジスタ設定は、2.3.1.1 章、2.3.2.1 章、2.3.3.1 章に示すレジスタに ACMD のための設定を行います。加えて、ExArgument\_0, \_1 レジスタに CMD55 のアーギュメントを設定します。

CMD55 発行時は ExArgument\_0, \_1 に設定された値をコマンドの Argument として出力し、続く ACMD 発行時は Argument\_0, \_1 に設定された値をコマンドの Argument として出力します。また、レスポンスは CMD55 の時は Response\_6, \_7 レジスタに格納され、ACMD の時は Response\_0, \_1 レジスタに格納されます。等々、詳細は下表を参照してください。

表 2.4 コマンド毎のパラメータ

| パラメータ    | CMD55                            | ACMD                         |

|----------|----------------------------------|------------------------------|

| Argument | ExArgument_0 / ExArgument_1 レジスタ | Argument_0 / Argument_1 レジスタ |

| Response | Response_6 / Response_7 レジスタ     | Response_0 / Response_1 レジスタ |

| TranType | 右記ビットそのまま                        | TransferMode.TranType ビット    |

| CmdIndex | 55h 固定                           | Command.CmdIndex ビット         |

| RespType | R1 固定                            | Command.RespType ビット         |

| CmdType  | Normal 固定                        | Command.CmdType ビット          |

| DAT Line | “0” 固定 (DAT Line 未使用)            | Command.UseDAT_Line ビット      |

| Dir      | 右記ビットそのまま                        | TransferMode.DataDir ビット     |

| RespChk  | Command.RespxxxChk 全て “1” *      | Command.RespxxxChk           |

\*CMD55 時の Response のチェック機能は、Command.RespxxxChk ビットによらず全て有効となります。

本 AutoCMD55 機能の完了は、CMD55 に続いて ACMD が発行されそのコマンド発行（レスポンス受信）が完了した時になります。よって、NormIntStat.CmdCmp ビットは ACMD のコマンド発行が完了した時に“1”にセットされます。

CMD55 にて何らかのレスポンスエラーが発生した場合には続く ACMD は発行されません。また、NormIntStat.CmdCmp ビットは“1”にセットされず、ErrIntStat .AutoCMD55Err が“1”にセットされます。その詳細は AtuoCMD55ErrStat レジスタをチェックすることでわかります。CMD55, ACMD の終了状態によるレジスタの状態は下表のようになります。

表 2.5 CMD55, ACMD 終了状態によるレジスタの状態

| レジスタ                    | CMD55 正常<br>→ACMD 正常 | CMD55 正常<br>→ACMD 異常 | CMD55 異常<br>→ACMD 未発行 |

|-------------------------|----------------------|----------------------|-----------------------|

| NormIntStat.CmdCmp      | 1                    | 0                    | 0                     |

| ErrIntStat.AutoCMD55Err | 0                    | 0                    | 1                     |

| ErrIntStat              | 0                    | 1                    | 0                     |

本機能を使用すれば、CMD55 完了後、ACMD を発行するために、再度 Command レジスタにライトする必要はありません。下図のように CMD55 終了後、ハードウェアにて自動で ACMD を発行します。CMD\_TranAct はこの一連のシーケンスが完了するまで“1”的状態を保ちます。また、NormIntStat.CmdCmp ビットも一連のシーケンスが完了（ACMD のレスポンス受信後）時に“1”になります。CMD55 終了時には“1”なりません。

図 2.18 AutoCMD55 動作波形

## 2. 機能説明

### 2.3.4.2 AutoCMD12 機能

データ転送の後に CMD12 を自動で送信する機能です。データ転送 – CMD12 の順でコマンドが発行されます。コマンド発行のための各種パラメータはそれぞれのコマンド発行時に切り替わります。

#### 2.3.4.2.1 AutoCMD12 使用時に設定するレジスタ

本機能を使用する際には、TransferMode.AutoCMD12 ビットに “1” をセットして、コマンドの送信を実行して下さい。その他の設定は、2.3.1.1 章、2.3.2.1 章、2.3.3.1 章に示されているレジスタにデータ転送コマンドの設定をして下さい。PresentStateBus.CMD\_TranAct ビットに “1” がセットされている間は、上記レジスタを変更しないで下さい。尚、TransferMode.AutoCMD12 ビットを “1” にセットして、Command.WaitCCS ビットを “1” にセットすることは禁止です。

#### 2.3.4.2.2 AutoCMD12 の動作説明概要

AutoCMD12 機能は、データ転送コマンドを発行した後、そのコマンドの完了とデータ転送の完了を待ちます。それぞれが正常に完了した後、即座に CMD12 の発行を行います。CMD12 は RespBusy を伴うコマンドであるため、CMD12 の完了は RespBusy がネゲートされてからになります。

#### 2.3.4.2.3 AutoCMD12 の動作説明詳細

AutoCMD12 機能は、TransferMode.AutoCMD12 ビットに “1” をセットした状態で Command レジスタにライトを行うことで起動されます。コマンド発行のためのレジスタ設定は、2.3.3.1 章に示すレジスタにデータ転送コマンドのための設定を行います。

CMD12 発行時の各パラメータは下表のようになります。レスポンスは CMD12 の時は Response\_6, \_7 レジスタに格納され、データ転送コマンドの時は Response\_0, \_1 レジスタに格納されます。等々、詳細は下表を参照してください。

表 2.6 コマンド毎のパラメータ

| パラメータ        | Ex. CMD18 /CMD25             | CMD12                        |

|--------------|------------------------------|------------------------------|

| Argument     | Argument_0 / Argument_1 レジスタ | “0” 固定                       |

| Response     | Response_0 / Response_1 レジスタ | Response_6 / Response_7 レジスタ |

| TranType     | TransferMode.TranType ビット    | 左記ビットそのまま                    |

| CmdIndex     | Command.CmdIndex ビット         | 12h 固定                       |

| ResponseType | Command.RespType ビット         | R1b 固定                       |

| CmdType      | Command.CmdType ビット          | Abort 固定                     |

| DAT Line     | Command.UseDAT_Line ビット      | “0” 固定 (DAT Line 未使用)        |

| Dir          | TransferMode.DataDir ビット     | 左記ビットそのまま                    |

| RespChk      | Command.RespxxxChk           | Command.RespxxxChk 全て “1” *  |

\*CMD12 時の Response のチェック機能は、Command.RespxxxChk ビットによらず全て有効となります。

本 AutoCMD12 機能は以下の条件でデータ転送が行われる時に起動されます。尚、Infinite 転送時は、BlkSize, BlkCnt レジスタの値にかかわらず AutoCMD12 機能は起動されません。

- Multiple or Stream 転送時 – BlkSize レジスタ及び BlkCnt レジスタが “0” でない。且つ Command.UseDAT\_Line = 1

- Single 転送時 – BlkSize レジスタが “0” でない。且つ Command.UseDAT\_Line = 1

本 AutoCMD12 機能を実行時の、それぞれのコマンドの完了状態は下表のようになります。

- CMD12 が正常に終了したとき：NormIntStat. AutoCMD12Cmp と NormIntStat. TranCmp が “1” にセット。

NormIntStat. CmdCmp は “1” にセットされません。

- CMD12 より前のコマンドにてエラー発生時：CMD12 未実行。AutoCMD12ErrStat. AutoCMD12NotExec が “1” にセット。

- CMD12 でエラー発生：その後に CMD\_wo\_DAT がある場合は未実行。AutoCMD12ErrStat. NoCmdByAutoCMD12Err が “1” にセット。

表 2.7 データ転送, CMD12 終了状態によるレジスタの状態

| 時系列<br>早い _____ 遅い |            |           |            |                  |                         |                      |           |                     |

|--------------------|------------|-----------|------------|------------------|-------------------------|----------------------|-----------|---------------------|

| データ転送              | CMD_wo_DAT | AutoCMD12 | CMD_wo_DAT | AutoCMD12<br>Cmp | NoCmdBy<br>AutoCMD12Err | AutoCMD12<br>NotExec | TranCmp   | CmdCmp              |

| 正常                 | なし         | 正常        | なし         | ○                | —                       | —                    | AutoCMD12 | データ転送               |

| 正常                 | 正常         | 正常        | なし         | ○                | —                       | —                    | AutoCMD12 | データ転送<br>CMD_wo_DAT |

| 正常                 | なし         | 正常        | 正常         | ○                | —                       | —                    | AutoCMD12 | データ転送<br>CMD_wo_DAT |

| 正常                 | なし         | 正常        | エラー        | ○                | —                       | —                    | AutoCMD12 | データ転送               |

| 正常                 | なし         | エラー       | なし         | —                | —                       | —                    | —         | データ転送               |

| 正常                 | なし         | エラー       | 未実行        | —                | ○                       | —                    | —         | データ転送               |

| 正常                 | 正常         | エラー       | なし         | —                | —                       | —                    | —         | データ転送<br>CMD_wo_DAT |

| 正常                 | 正常         | エラー       | 未実行        | —                | ○                       | —                    | —         | データ転送<br>CMD_wo_DAT |

| 正常                 | エラー        | 未実行       | なし         | —                | —                       | ○                    | —         | データ転送               |

| エラー                | なし         | 未実行       | なし         | —                | —                       | ○                    | —         | —                   |

\*CMD\_wo\_DAT：データ転送を伴わないコマンドを指します。

\*未実行：AutoCMD12 のエラーにより実行されないことを指します。

\*AutoCMD12Cmp, TranCmp, CmdCmp : NormIntStat レジスタ内のビットです。

\*AutoCMD12NotExec, NoCmdByAutoCMD12Err : AutoCMD12ErrStat レジスタ内のビットです。

データ転送に続いてホストドライバより Abort コマンドが発行された場合、AutoCMD12 機能による CMD12 は発行しません。正常に Abort (データ転送が終了) したかは CmdCmp と TranCmp で確認をしてください。

## 2. 機能説明

### 2.4 個別特殊機能

#### 2.4.1 Abort コマンド発行による、データ転送の終了方法

現在実行中のデータ転送を終了する場合は、Abort コマンドを発行します。

カードへ Abort コマンドを送信する場合は、表 2.1 に示すレジスタにカード規格書に記載されているコマンドフォーマットを元に値をセットしてください。

この際、Command.CmdType レジスタに “11b” (Abort コマンド) )をセットしてください。

Multi 転送中 (TransferMode.TranType=10h) に、Abort コマンドを発行して転送を停止した場合、BlkCnt\_0 / \_1 レジスタを読み出すことで、転送が完了したブロック数を知ることができます。

Abort コマンド発行によって、データ転送を終了した場合、次のデータ転送を開始する場合は、必ず FIFO\_Join レジスタに 00h を書き込んで内蔵 FIFO をクリアした後、新たな転送を開始するための適切な値を FIFO\_Join レジスタに設定してください。

リード転送中に Abort コマンドを発行した場合、Abort コマンドに対するレスポンスを受信した時点で、データ転送終了となり、NromIntStat.TranCmp ビットに “1” がセットされます。

図 2.19 リード転送中の Abort コマンドの発行

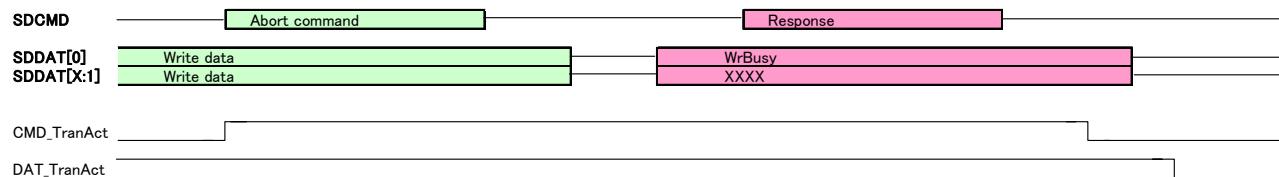

ライト転送中に Abort コマンドを発行した場合、DAT[0]ライン上の WriteBusy がネゲートされた時点で、データ転送終了となり、NromIntStat.TranCmp ビットに “1” がセットされます。

図 2.20 ライト転送中の Abort コマンドの発行

#### 2.4.2 WatiCCS 機能の使用方法（CE-ATA ドライブ専用）

CE-ATA ドライブからの、CCS 割り込みを使った転送を行う場合、Command.WaitCCS ビットを使用します。

##### 2.4.2.1 コマンド送信時に設定するレジスタ

カードへコマンドを送信する場合は、表 2.1 に示すレジスタにカード規格書に記載されているコマンドフォーマットを元に値をセットしてください。

この際、Command.WaitCCS ビットに “1” をセットしてください。

##### 2.4.2.2 WaitCCS モードでの動作説明詳細

コマンドの送信中からレスポンスを受信するまでの間は、PresentStateBus.CMD\_TranAct ビットに “1” がセットされます。

レスポンスの受信完了後、CE-ATA ドライブからの CCS 割り込みを受信すると、NormIntStat.CCS 割り込みビットに “1” がセットされます。

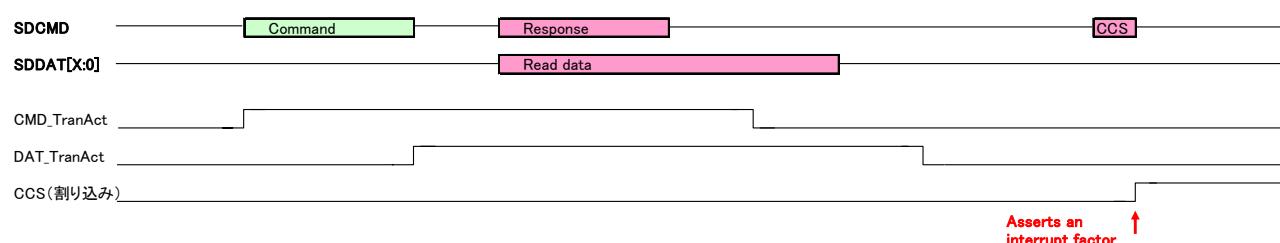

図 2.21 WaitCCS 動作波形

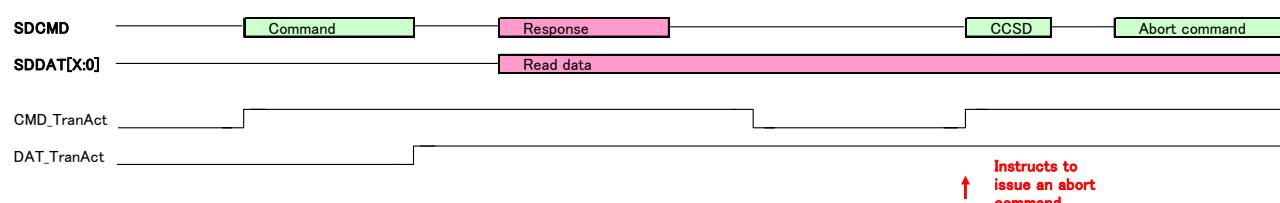

##### 2.4.2.3 WaitCCS モード中の Abort コマンド発行

WaitCCS モードでデータ転送中に、Abort コマンドを発行した場合、HW は CCSD を CE-ATA ドライブに送信した後、Abort コマンドを発行します。

図 2.22 WaitCCS モード中の Abort コマンド発行

## 2. 機能説明

### 2.5 PIO 転送方法

SDMMC ホストコントローラは、512Byte の FIFO を搭載しています。データ転送を伴うコマンドを送信し、FIFO\_Rd/FIFO\_Wr/FIFO\_BytRd/FIFO\_BytWr レジスタにアクセスする事で、カードからのデータ読み出しもしくは、カードへの書き込みを行うことができます。

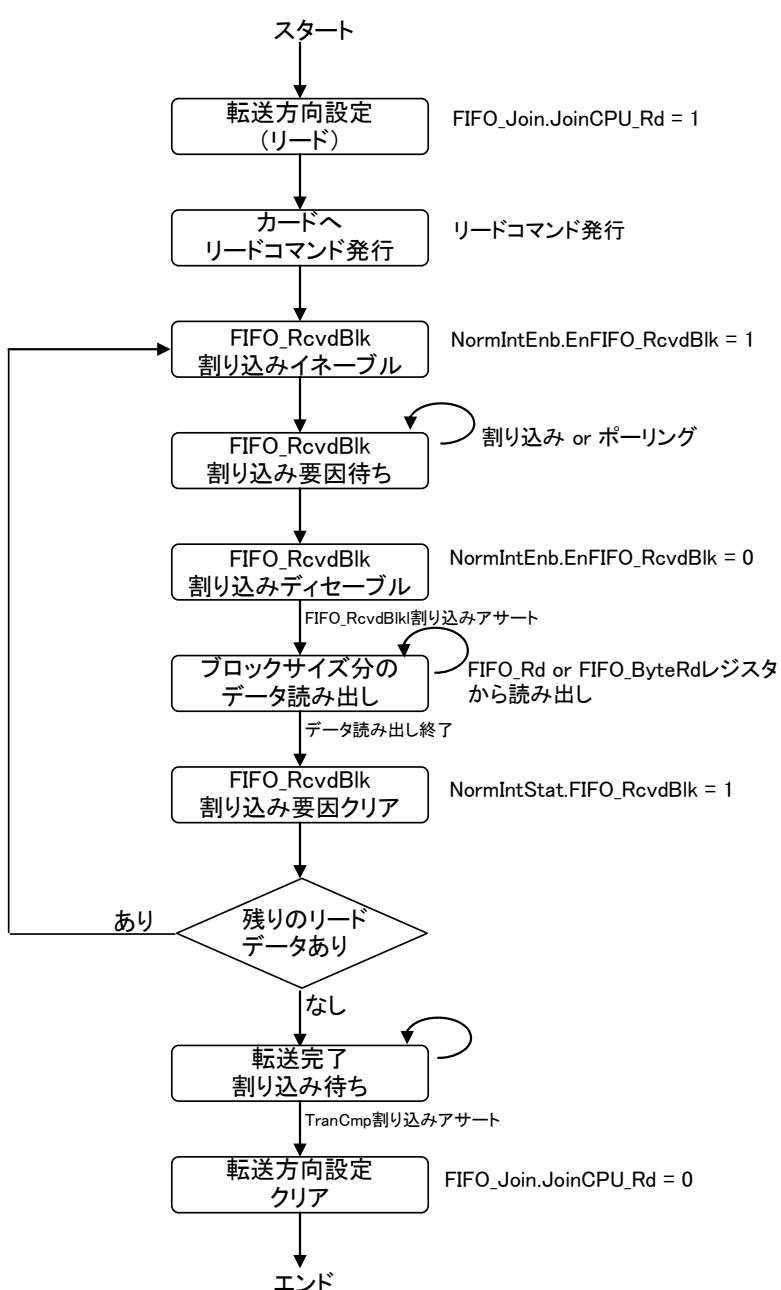

#### 2.5.1 リード転送時の FIFO アクセス

下記に、リード転送時の FIFO へのアクセス手順を示します。

必ず、リードコマンド発行前に、FIFO\_Join.JoinCPU\_Rd ビットに “1” をセットしてください。

FIFO からのリードは、ブロックサイズ単位でアクセスします。但し、ブロックサイズが 1Kbyte 以上の場合には、512Byte 単位でリードしてください。この場合、FIFO\_RcvdBlk 割り込みは、512Byte 受信する毎にアサートされます。

図 2.23 リード転送時の FIFO アクセス手順

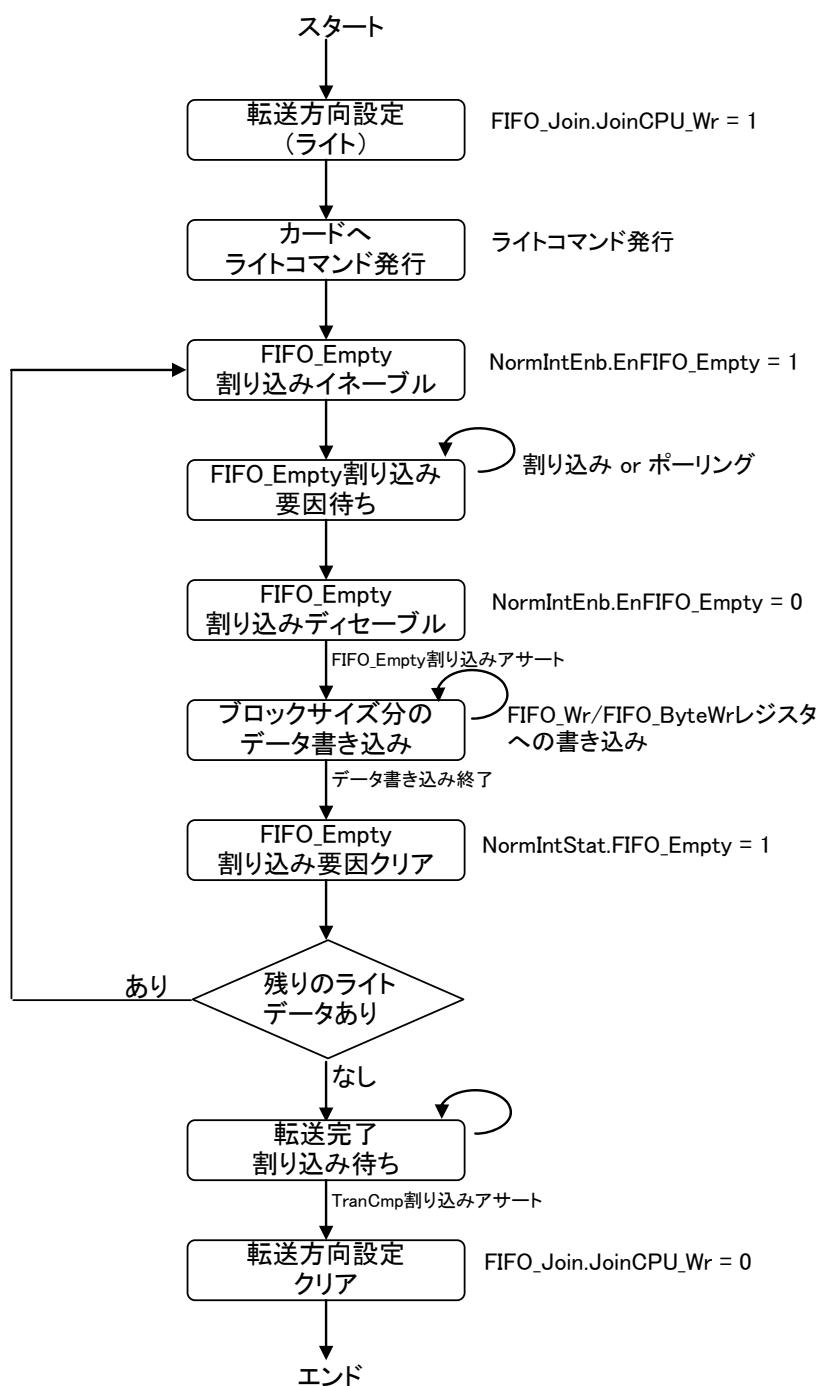

## 2.5.2 ライト転送時の FIFO アクセス

下記に、ライト転送時の FIFO へのアクセス手順を示します。

必ず、ライトコマンド発行前に、FIFO\_Join.JoinCPU\_Wr ビットに “1” をセットしてください。

FIFO へのライトは、ブロックサイズ単位でアクセスします。但し、ブロックサイズが 1Kbyte 以上の場合には、512Byte 毎に書き込んでください。

図 2.24 ライト転送時の FIFO アクセス手順

## 2. 機能説明

### 2.6 DMA 転送方法

本 LSI は、DMA 転送をサポートしています。DMA 転送機能を使って、カードからのデータ読み出しもしくはカードへの書き込みを行うことができます。

DMA 転送は、4Byte 未満の端数のある転送はサポートしていません。4Byte 未満の端数のあるデータをリード/ライトする場合は、PIO 転送を使用してください。

#### 2.6.1 DMA 基本機能

CPU\_Config レジスタの DREQ\_Level/DACK\_Level ビットの設定により、XDREQ/XDACK 端子の論理レベルを設定する事が出来ます。

以降の説明では特に断りの無い限り、XDREQ,XDACK 共に負論理で説明します。

DMA 機能を有効にするには、下記の設定を行ってください。

- DMA\_Config.DMA\_Enable ビットに “1” をセットして下さい。

DMA の基本動作は、以下の通りです。

ライト動作：内蔵 FIFO に DMA\_Config.BurstCnt[1:0] レジスタで設定したバーストサイズ分の空き領域がある場合に XDREQ 端子をアサートします。

リード動作：内蔵 FIFO に DMA\_Config.BurstCnt[1:0] レジスタで設定したバーストサイズ分のデータがある場合に XDREQ 端子をアサートします。

#### 2.6.1.1 DMA 転送アクセス方法

DMA 転送時のアクセス方法は、下記の 2 通りあります。各モードの設定は、DMA\_Config.DMA\_Mode レジスタで設定できます。

表 2.8 DMA 転送アクセスモード設定

| DMA_Mode 設定   | アクセス方法                                                                                          |

|---------------|-------------------------------------------------------------------------------------------------|

| 0b (CS_Mode)  | XCS 入力端子がアサートされている時の、FIFO_Rd/FIFO_Wr レジスタへのリードアクセス／ライトアクセス <sup>(注)</sup> を DMA アクセスと見なして動作します。 |

| 1b (ACK_Mode) | XDACK 入力端子がアサートされている時の、リードアクセス／ライトアクセス <sup>(注)</sup> を DMA アクセスと見なして動作します。                     |

注：

リードアクセス：XRD 端子のアサート

ライトアクセス：XWR 端子のアサート

## 2.6.1.2 バーストモード設定

DMA 転送時のバーストサイズは、DMA\_Config.BurstCnt[1:0]レジスタで設定できます。

表 2.9 DMA バーストサイズ設定

| BurstCnt 設定 | アクセス方法                                                                                                                                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 00b         | 内蔵 FIFO に 2Byte 以上のデータが存在する時（リード時）もしくは内蔵 FIFO に 2Byte 以上の空き領域がある時（ライト時）に、XDREQ 端子をアサートし、2Byte 転送される毎に一旦 XDREQ をネゲートします。（DMA アクセス 1 回）     |

| 01b         | 内蔵 FIFO に 16Byte 以上のデータが存在する時（リード時）もしくは内蔵 FIFO に 16Byte 以上の空き領域がある時（ライト時）に、XDREQ 端子をアサートし、16Byte 転送される毎に一旦 XDREQ をネゲートします。（DMA アクセス 8 回）  |

| 10b         | 内蔵 FIFO に 32Byte 以上のデータが存在する時（リード時）もしくは内蔵 FIFO に 32Byte 以上の空き領域がある時（ライト時）に、XDREQ 端子をアサートし、32Byte 転送される毎に一旦 XDREQ をネゲートします。（DMA アクセス 16 回） |

| 11b         | 内蔵 FIFO に 64Byte 以上のデータが存在する時（リード時）もしくは内蔵 FIFO に 64Byte 以上の空き領域がある時（ライト時）に、XDREQ 端子をアサートし、64Byte 転送される毎に一旦 XDREQ をネゲートします。（DMA アクセス 32 回） |

ネゲートされた XDREQ 端子が、再度アサートされるまでの最小ネゲート期間は、NgtCnt レジスタの設定によって決定します。

最小ネゲート期間計算式：(NgtCnt の値 + 1) × クロックサイクル幅

## 2. 機能説明

### 2.6.2 DMA 動作フロー

#### 2.6.2.1 DMA リード

設定されたカウント数分の DMA 転送を行います。

内部 FIFO に読み出し可能なデータがあり、且つ DMA\_Cnt\_1/\_0 レジスタに残りカウントがある場合に XDREQ をアサートし DMA 転送が可能になります。

図 2.25 カウントモード（DMA リード）手順

## 2.6.2.2 カウントモード（DMA ライト）

設定されたカウント数分の DMA 転送を行います。

内部 FIFO に書き込み可能な空き領域があり、且つ DMA\_Cnt\_1/\_0 レジスタに残りカウントがある場合に XDREQ をアサートし DMA 転送が可能になります。

図 2.26 カウントモード（DMA ライト）手順

### 3. レジスタ詳細説明

## 3. レジスタ詳細説明

### 3.1 00h BlkSize ( Transfer Block Size )

| Address | Register Name | Bit | R / W | Bit Symbol   | Description                | Reset |

|---------|---------------|-----|-------|--------------|----------------------------|-------|

| 00h     | BlkSize       | 15  | R / W | BlkSize [15] | Transfer Block Size [15:0] | 0     |

|         |               | 14  | R / W | BlkSize [14] |                            | 0     |

|         |               | 13  | R / W | BlkSize [13] |                            | 0     |

|         |               | 12  | R / W | BlkSize [12] |                            | 0     |

|         |               | 11  | R / W | BlkSize [11] |                            | 0     |

|         |               | 10  | R / W | BlkSize [10] |                            | 0     |

|         |               | 9   | R / W | BlkSize [9]  |                            | 0     |

|         |               | 8   | R / W | BlkSize [8]  |                            | 0     |

|         |               | 7   | R / W | BlkSize [7]  |                            | 0     |

|         |               | 6   | R / W | BlkSize [6]  |                            | 0     |

|         |               | 5   | R / W | BlkSize [5]  |                            | 0     |

|         |               | 4   | R / W | BlkSize [4]  |                            | 0     |

|         |               | 3   | R / W | BlkSize [3]  |                            | 0     |

|         |               | 2   | R / W | BlkSize [2]  |                            | 0     |

|         |               | 1   | R / W | BlkSize [1]  |                            | 0     |

|         |               | 0   | R / W | BlkSize [0]  |                            | 0     |

データ転送時のブロックサイズを指定します。本レジスタは、“0001h”～“8000h”の範囲で設定可能です（表 3.1 参照）。

本レジスタは、HW によって更新されません。

PresentStateBus.DAT\_TranAct ビットに“1”がセットされている間は、本レジスタの内容を変更しないで下さい。

表 3.1 BlkSize レジスタの設定可能範囲

| レジスタ設定値     | データ転送時のブロックサイズ       |

|-------------|----------------------|

| FFFFh～8001h | 設定禁止（動作を保証できません。）    |

| 8000h       | 32768 Bytes          |

| ...         | ...                  |

| 0400h       | 1024Bytes            |

| ...         | ...                  |

| 0200h       | 512 Bytes            |

| ...         | ...                  |

| 0001h       | 1 Byte               |

| 0000h       | 設定禁止（データ転送は開始されません。） |

### 3.2 04h BlkCnt\_0 ( Transfer Block Count 0 )

### 3.3 06h BlkCnt\_1 ( Transfer Block Count 1 )

| Address | Register Name | Bit | R / W | Bit Symbol    | Description                  | Reset |

|---------|---------------|-----|-------|---------------|------------------------------|-------|

| 04h     | BlkCnt_0      | 15  | R / W | BlkCnt_0 [15] | Transfer Block Count [15:0]  | 0     |

|         |               | 14  | R / W | BlkCnt_0 [14] |                              | 0     |

|         |               | 13  | R / W | BlkCnt_0 [13] |                              | 0     |

|         |               | 12  | R / W | BlkCnt_0 [12] |                              | 0     |

|         |               | 11  | R / W | BlkCnt_0 [11] |                              | 0     |

|         |               | 10  | R / W | BlkCnt_0 [10] |                              | 0     |

|         |               | 9   | R / W | BlkCnt_0 [9]  |                              | 0     |

|         |               | 8   | R / W | BlkCnt_0 [8]  |                              | 0     |

|         |               | 7   | R / W | BlkCnt_0 [7]  |                              | 0     |

|         |               | 6   | R / W | BlkCnt_0 [6]  |                              | 0     |

|         |               | 5   | R / W | BlkCnt_0 [5]  |                              | 0     |

|         |               | 4   | R / W | BlkCnt_0 [4]  |                              | 0     |

|         |               | 3   | R / W | BlkCnt_0 [3]  |                              | 0     |

|         |               | 2   | R / W | BlkCnt_0 [2]  |                              | 0     |

|         |               | 1   | R / W | BlkCnt_0 [1]  |                              | 0     |

|         |               | 0   | R / W | BlkCnt_0 [0]  |                              | 0     |

| 06h     | BlkCnt_1      | 15  | R / W | BlkCnt_1 [15] | Transfer Block Count [31:16] | 0     |

|         |               | 14  | R / W | BlkCnt_1 [14] |                              | 0     |

|         |               | 13  | R / W | BlkCnt_1 [13] |                              | 0     |

|         |               | 12  | R / W | BlkCnt_1 [12] |                              | 0     |

|         |               | 11  | R / W | BlkCnt_1 [11] |                              | 0     |

|         |               | 10  | R / W | BlkCnt_1 [10] |                              | 0     |

|         |               | 9   | R / W | BlkCnt_1 [9]  |                              | 0     |

|         |               | 8   | R / W | BlkCnt_1 [8]  |                              | 0     |

|         |               | 7   | R / W | BlkCnt_1 [7]  |                              | 0     |

|         |               | 6   | R / W | BlkCnt_1 [6]  |                              | 0     |

|         |               | 5   | R / W | BlkCnt_1 [5]  |                              | 0     |

|         |               | 4   | R / W | BlkCnt_1 [4]  |                              | 0     |

|         |               | 3   | R / W | BlkCnt_1 [3]  |                              | 0     |

|         |               | 2   | R / W | BlkCnt_1 [2]  |                              | 0     |

|         |               | 1   | R / W | BlkCnt_1 [1]  |                              | 0     |

|         |               | 0   | R / W | BlkCnt_1 [0]  |                              | 0     |

データ転送時のブロック数を設定します。

本レジスタは Multiple 転送と Stream 転送時 (TransferMode.TranType レジスタで設定) に有効となります。本レジスタは、“0000\_0001h”～“FFFF\_FFFFh” の範囲で設定可能です (表 3.2 参照)。

本レジスタをリードする事で、正常に転送が完了したブロック数を知ることができます。本レジスタは、1 データブロックの転送が完了した時点で CRC エラーが発生していないければ、デクリメントされます。詳細な更新タイミングは、2.3.3 章を参照してください。

本レジスタをリードするときは、BlkCnt\_1、BlkCnt\_0 レジスタの順にリードしてください。

PresentStateBus.DAT\_TranAct ビットに “1” がセットされている間は、本レジスタの内容を変更しないで下さい。

### 3. レジスタ詳細説明

---

表 3.2 BlkCnt レジスタの設定可能範囲

| レジスタ設定値    | データ転送時のブロック数         |

|------------|----------------------|

| FFFF_FFFFh | 4G – 1 blocks        |

| ...        | ...                  |

| 0400_0000h | 64M blocks           |

| ...        | ...                  |

| 0040_0000h | 4M blocks            |

| ...        | ...                  |

| 0001_0000h | 64K blocks           |

| ...        | ...                  |

| 0000_0001h | 1 block              |

| 0000_0000h | 設定禁止(データ転送は開始されません。) |

### 3.4 08h Argument\_0 ( Command Argument 0 )

### 3.5 0Ah Argument\_1 ( Command Argument 1 )

| Address | Register Name | Bit | R / W | Bit Symbol    | Description              | Reset |

|---------|---------------|-----|-------|---------------|--------------------------|-------|

| 08h     | Argument_0    | 15  | R / W | CmdArg_0 [15] | Command Argument [15:0]  | 0     |

|         |               | 14  | R / W | CmdArg_0 [14] |                          | 0     |

|         |               | 13  | R / W | CmdArg_0 [13] |                          | 0     |

|         |               | 12  | R / W | CmdArg_0 [12] |                          | 0     |

|         |               | 11  | R / W | CmdArg_0 [11] |                          | 0     |

|         |               | 10  | R / W | CmdArg_0 [10] |                          | 0     |

|         |               | 9   | R / W | CmdArg_0 [9]  |                          | 0     |

|         |               | 8   | R / W | CmdArg_0 [8]  |                          | 0     |

|         |               | 7   | R / W | CmdArg_0 [7]  |                          | 0     |

|         |               | 6   | R / W | CmdArg_0 [6]  |                          | 0     |

|         |               | 5   | R / W | CmdArg_0 [5]  |                          | 0     |

|         |               | 4   | R / W | CmdArg_0 [4]  |                          | 0     |

|         |               | 3   | R / W | CmdArg_0 [3]  |                          | 0     |

|         |               | 2   | R / W | CmdArg_0 [2]  |                          | 0     |

|         |               | 1   | R / W | CmdArg_0 [1]  |                          | 0     |

|         |               | 0   | R / W | CmdArg_0 [0]  |                          | 0     |

| 0Ah     | Argument_1    | 15  | R / W | CmdArg_1 [15] | Command Argument [31:16] | 0     |

|         |               | 14  | R / W | CmdArg_1 [14] |                          | 0     |

|         |               | 13  | R / W | CmdArg_1 [13] |                          | 0     |

|         |               | 12  | R / W | CmdArg_1 [12] |                          | 0     |

|         |               | 11  | R / W | CmdArg_1 [11] |                          | 0     |

|         |               | 10  | R / W | CmdArg_1 [10] |                          | 0     |

|         |               | 9   | R / W | CmdArg_1 [9]  |                          | 0     |

|         |               | 8   | R / W | CmdArg_1 [8]  |                          | 0     |

|         |               | 7   | R / W | CmdArg_1 [7]  |                          | 0     |

|         |               | 6   | R / W | CmdArg_1 [6]  |                          | 0     |

|         |               | 5   | R / W | CmdArg_1 [5]  |                          | 0     |

|         |               | 4   | R / W | CmdArg_1 [4]  |                          | 0     |

|         |               | 3   | R / W | CmdArg_1 [3]  |                          | 0     |

|         |               | 2   | R / W | CmdArg_1 [2]  |                          | 0     |

|         |               | 1   | R / W | CmdArg_1 [1]  |                          | 0     |

|         |               | 0   | R / W | CmdArg_1 [0]  |                          | 0     |

コマンド送信時の Argument を設定します。本レジスタは、コマンド送信時に使用されます。本レジスタに設定された値は、カード規格書記載のコマンドフォーマット中の Argument (bit[39 : 8]) としてカードへ送信されます（表 3.3 参照）。本レジスタは、HW によって更新されません。

PresentStateBus.CMD\_TranAct ビットに “1” がセットされている間は、本レジスタの内容を変更しないで下さい。

表 3.3 コマンドフォーマット (Argument フィールド)

| Bit Position | [47]      | [46]             | [45:40] | [39:8]   | [7:1] | [0]     |

|--------------|-----------|------------------|---------|----------|-------|---------|

| Width (bits) | 1         | 1                | 6       | 32       | 7     | 1       |

| Value        | “0”       | “1”              | “X”     | “X”      | “X”   | “1”     |

| Description  | Start Bit | Transmission Bit | Index   | Argument | CRC7  | End Bit |

TransferMode.AutoCMD55 ビットに “1” を設定してコマンドの送信を行った場合は、HW が自動的に送信する CMD55 の後に送信されるコマンドの Argument となります。

### 3. レジスタ詳細説明

---

#### 3.6 0Ch TransferMode ( Transfer Mode )

| Address | Register Name | Bit | R / W | Bit Symbol   | Description                                           | Reset |

|---------|---------------|-----|-------|--------------|-------------------------------------------------------|-------|

| 0Ch     | TransferMode  | 15  |       |              |                                                       | 0     |

|         |               | 14  |       |              |                                                       | 0     |

|         |               | 13  |       |              |                                                       | 0     |

|         |               | 12  |       |              |                                                       | 0     |

|         |               | 11  |       |              |                                                       | 0     |

|         |               | 10  |       |              |                                                       | 0     |

|         |               | 9   | R / W | AutoCMD12    | 0: Disable<br>1: Enable                               | 0     |

|         |               | 8   | R / W | AutoCMD55    | 0: Disable<br>1: Enable                               | 0     |

|         |               | 7   |       |              |                                                       | 0     |

|         |               | 6   |       |              |                                                       | 0     |

|         |               | 5   |       |              |                                                       | 0     |

|         |               | 4   | R / W | DataDir      | 0: Write ( Host -> Card )<br>1: Read ( Host <- Card ) | 0     |

|         |               | 3   |       |              |                                                       | 0     |

|         |               | 2   |       |              |                                                       | 0     |

|         |               | 1   | R / W | TranType [1] | Transfer Type [1:0]                                   |       |

|         |               | 0   | R / W | TranType [0] | 0                                                     |       |

データ転送時の動作を設定します。本レジスタは、HWによって更新されません。

AutoCMD12 機能と AutoCMD55 機能は、同時に使用できません。したがって、AutoCMD12 と AutoCMD55 ビットの両方に“1”をセットしないで下さい。

- Bit15-10      Reserved

- Bit9            AutoCMD12

AutoCMD12 機能の使用有無を設定します。

本ビットに“1”をセットして、データ転送を伴うコマンドを送信した場合、データ転送が正常に完了した後、自動的に CMD12 が送信されます。本機能の詳細な使用方法は、2.3.4.2 章を参照して下さい。

PresentStateBus.DAT\_TranAct ビットに“1”がセットされている間は、本レジスタの内容を変更しないで下さい。

- Bit8            AutoCMD55

AutoCMD55 機能の使用有無を設定します。

本ビットに“1”をセットしてコマンドを発行した場合、最初に CMD55 が自動的に発行され CMD55 の送信が正常に完了した後、コマンドが送信されます。本機能の詳細な使用方法は、2.3.4.1 章を参照して下さい。

PresentStateBus.CMD\_TranAct ビットに“1”がセットされている間は、本レジスタの内容を変更しないで下さい。

- Bit7-5          Reserved

- Bit4            DataDir

本ビットは、データ転送の方向を設定します。

0 : Write ( SDMMC ホストコントローラ → カード )

1 : Read ( SDMMC ホストコントローラ ← カード )

PresentStateBus.DAT\_TranAct ビットに“1”がセットされている間は、本レジスタの内容を変更しないで下さい。

- Bit3-2          Reserved

- Bit1-0          TranType [1:0]

本ビットは、データ転送のタイプを設定します。

00b : Single 転送

BlkSize[15:0] レジスタに設定されたサイズのブロックの転送が、1 回だけ行なわれます。

01b : Infinite 転送

BlkSize[15:0] レジスタに設定されたサイズのブロックの転送が、無限に繰りかえされます。

10b : Multiple 転送

BlkSize[15:0] レジスタに設定されたサイズのブロックの転送が、BlkCnt[31:0] レジスタに設定された回数分繰り返されます。

11b : Stream 転送

BlkSize[15:0] レジスタに設定されたサイズのデータ転送が、BlkCnt[31:0] レジスタに設定された回数分繰り返されます。

本モードでは、データブロックに CRC/EndBit は挿入されません。

PresentStateBus.DAT\_TranAct ビットに“1”がセットされている間は、本レジスタの内容を変更しないで下さい。

### 3.7 0Eh Command ( Command )

| Address | Register Name | Bit | R / W | Bit Symbol       | Description         |                  | Reset |

|---------|---------------|-----|-------|------------------|---------------------|------------------|-------|

| 0Eh     | Command       | 15  | R / W | WaitCCS          | 0: Disable          | 1: Enable        | 0     |

|         |               | 14  | R / W | Resp             | 0: Disable          | 1: Enable        | 0     |

|         |               | 13  | R / W | CmdIndex [5]     | Command Index [5:0] |                  | 0     |

|         |               | 12  | R / W | CmdIndex [4]     |                     |                  | 0     |

|         |               | 11  | R / W | CmdIndex [3]     |                     |                  | 0     |