# S1R72E11 データシート

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

7. 本資料に含まれているSDホスト機能に関する情報は、SD Associationのwebsiteで公開されているSimplified Specificationに基づいています。（SD Association website: <http://www.sdcard.org/>）

## **適用範囲**

本ドキュメントは、SD/MMC ホストコントローラ LSI 「S1R72E11」 に適用されます。

## 目 次

|                                       |    |

|---------------------------------------|----|

| 1. 概要 .....                           | 1  |

| 2. 特長 .....                           | 1  |

| 3. ブロック図 .....                        | 2  |

| 4. 端子配置図 .....                        | 3  |

| 5. 端子機能説明 .....                       | 4  |

| 6. 機能説明 .....                         | 7  |

| 6.1 リセット .....                        | 7  |

| 6.2 クロック .....                        | 7  |

| 6.3 CPU-IF .....                      | 7  |

| 6.4 パワーマネージメント .....                  | 8  |

| 7. 電気的特性 .....                        | 9  |

| 7.1 絶対最大定格 .....                      | 9  |

| 7.2 推奨動作条件 .....                      | 9  |

| 7.3 DC特性 .....                        | 10 |

| 7.3.1 消費電流 .....                      | 10 |

| 7.3.2 入力特性 .....                      | 10 |

| 7.3.3 出力特性 .....                      | 11 |

| 7.3.4 出力特性 .....                      | 11 |

| 7.4 AC特性 .....                        | 12 |

| 7.4.1 RESETタイミング .....                | 12 |

| 7.4.2 クロックタイミング .....                 | 12 |

| 7.4.3 CPU/DMA IF Writeアクセスタイミング ..... | 13 |

| 7.4.4 CPU/DMA IF Readアクセスタイミング .....  | 14 |

| 7.4.5 SDMMC IFタイミング .....             | 15 |

| 8. 接続例 .....                          | 16 |

| 8.1 CPU I/F接続例 .....                  | 16 |

| 9. 型番 .....                           | 17 |

| 10. 外形寸法図 .....                       | 18 |

| 10.1 TQFP13-64pin .....               | 18 |

| 改訂履歴 .....                            | 19 |

### 1. 概要

S1R72E11 は、メイン CPU の 16bit 汎用メモリバスに接続可能な、SD/MMC ホストコントローラ LSI です。

### 2. 特長

#### 《 SD ホスト機能 》

- SD 規格 Ver2.0 準拠

- 転送クロック 最大 50MHz

- SDHC カード対応

- バス幅 4bit/1bit

#### 《 MMC ホスト機能 》

- MMC 規格 Ver4.2 準拠 (CE-ATA Ver1.1 準拠)

- 転送クロック 最大 50MHz

- High Capacity カード対応

- バス幅 8bit/4bit/1bit

#### 《 CPU-IF 機能 》

- 16bit 汎用 CPU バス IF

- DMA 1ch

- Little Endian／Big Endian 対応

#### 《 その他 》

- クロック：外部クロック入力もしくは、水晶振動子に対応 最大 50MHz

- パワーマネージメント：SLEEP 機能搭載 (発振回路停止モード)

- 電源電圧：3.3V±0.3V 単一

- パッケージ：TQFP13-64pin

- 動作保証温度：-40°C~85°C

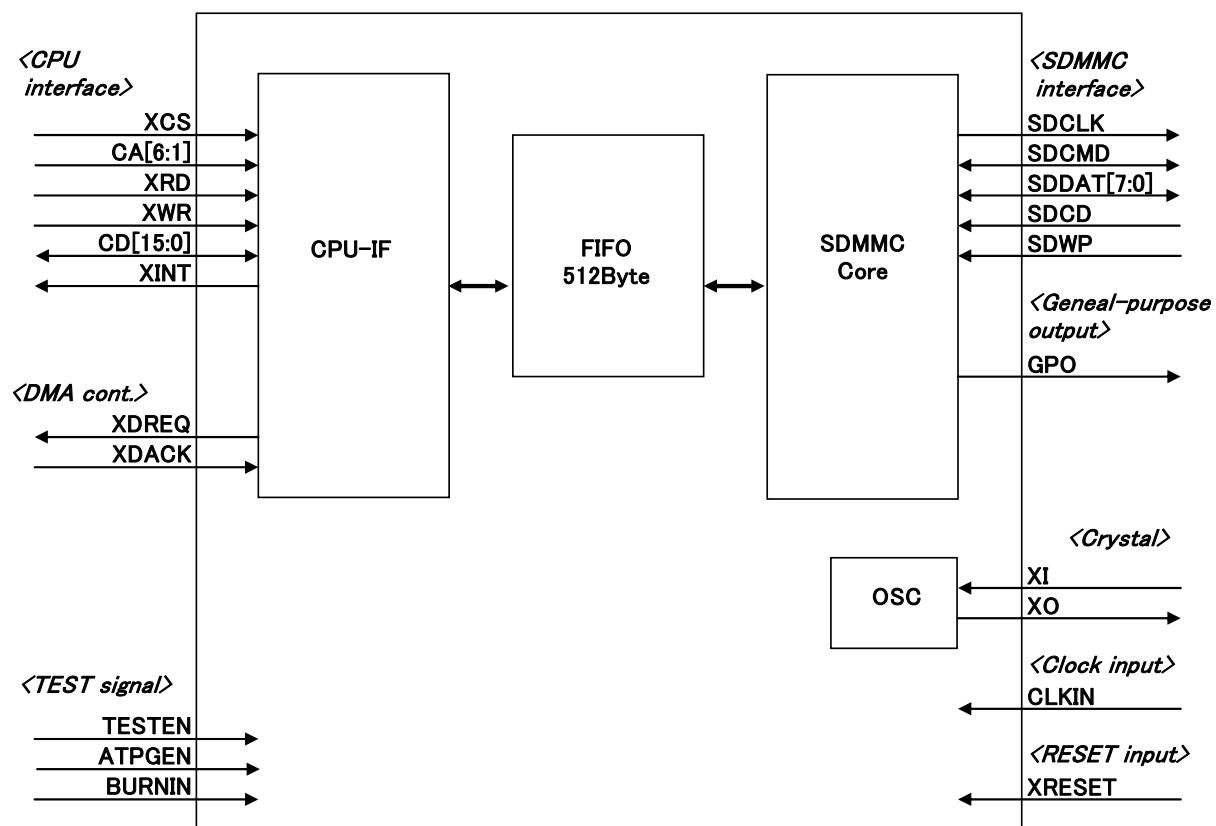

### 3. ブロック図

#### 3. ブロック図

図 3.1 全体ブロック図

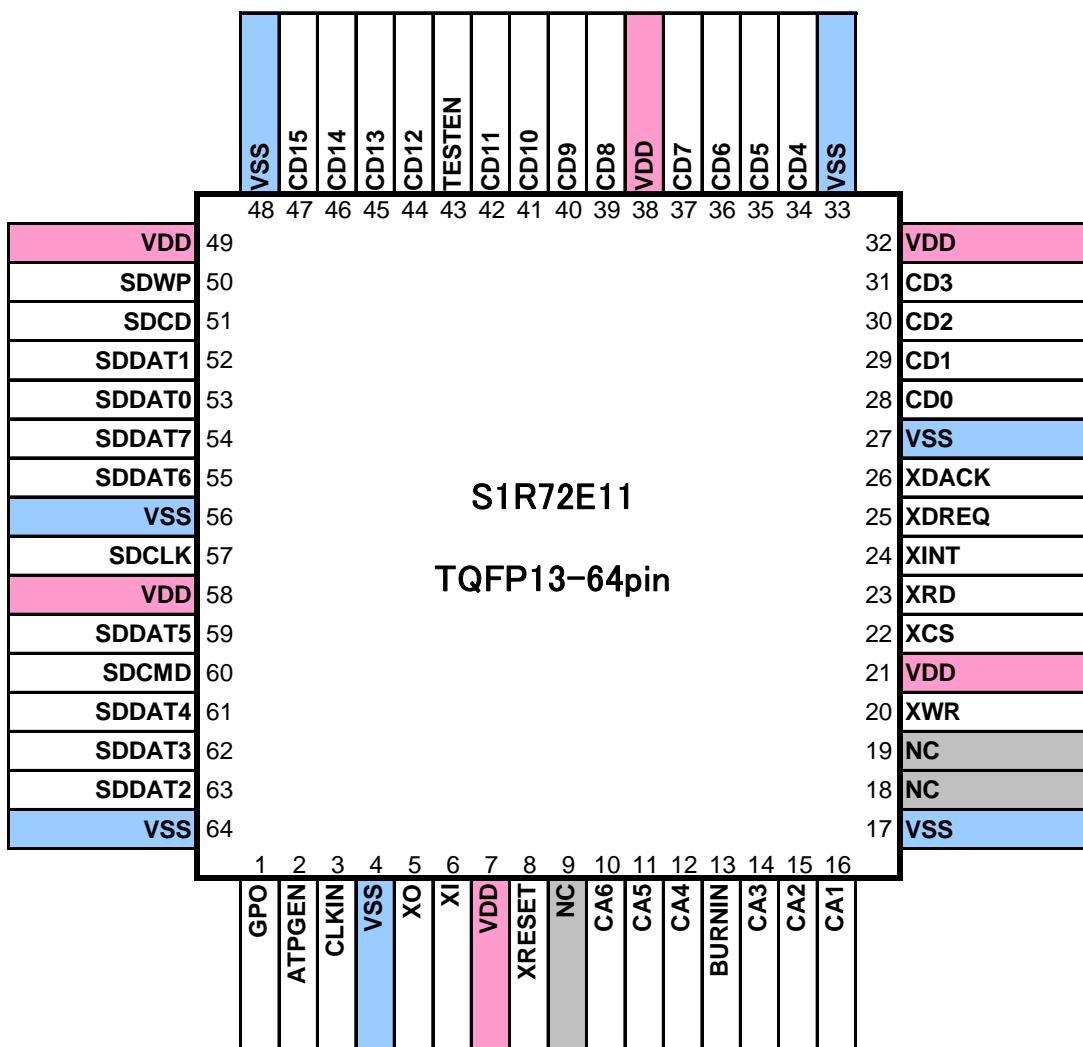

## 4. 端子配置図

図 4.1 端子配置図

## 5. 端子機能説明

### 5. 端子機能説明

| CPU-I/F |      |     |       |                    |                       |

|---------|------|-----|-------|--------------------|-----------------------|

| QFP-Pin | 名称   | I/O | RESET | 端子<br>タイプ          | 端子説明                  |

| 22      | XCS  | IN  | —     | (PU)               | チップセレクト<br>CPU バスアドレス |

| 10      | CA6  | IN  | —     | —                  |                       |

| 11      | CA5  | IN  | —     | —                  |                       |

| 12      | CA4  | IN  | —     | —                  |                       |

| 14      | CA3  | IN  | —     | —                  |                       |

| 15      | CA2  | IN  | —     | —                  |                       |

| 16      | CA1  | IN  | —     | —                  |                       |

| 23      | XRD  | IN  | —     | —                  | リード・ストローブ             |

| 20      | XWR  | IN  | —     | —                  | ライト・ストローブ             |

| 47      | CD15 | BI  | Hi-Z  | 2mA                | CPU バスデータ上位           |

| 46      | CD14 | BI  | Hi-Z  | 2mA                |                       |

| 45      | CD13 | BI  | Hi-Z  | 2mA                |                       |

| 44      | CD12 | BI  | Hi-Z  | 2mA                |                       |

| 42      | CD11 | BI  | Hi-Z  | 2mA                |                       |

| 41      | CD10 | BI  | Hi-Z  | 2mA                |                       |

| 40      | CD9  | BI  | Hi-Z  | 2mA                |                       |

| 39      | CD8  | BI  | Hi-Z  | 2mA                | CPU バスデータ下位           |

| 37      | CD7  | BI  | Hi-Z  | 2mA                |                       |

| 36      | CD6  | BI  | Hi-Z  | 2mA                |                       |

| 35      | CD5  | BI  | Hi-Z  | 2mA                |                       |

| 34      | CD4  | BI  | Hi-Z  | 2mA                |                       |

| 31      | CD3  | BI  | Hi-Z  | 2mA                |                       |

| 30      | CD2  | BI  | Hi-Z  | 2mA                |                       |

| 29      | CD1  | BI  | Hi-Z  | 2mA                | 割り込み出力                |

| 28      | CD0  | BI  | Hi-Z  | 2mA                |                       |

| 24      | XINT | OUT | High  | 2mA<br>(Tri-State) |                       |

PU: Pull Up

| DMA 制御  |       |     |       |           |            |

|---------|-------|-----|-------|-----------|------------|

| QFP-Pin | 名称    | I/O | RESET | 端子<br>タイプ | 端子説明       |

| 25      | XDREQ | OUT | High  | 2mA       | DMA リクエスト  |

| 26      | XDACK | IN  | —     | —         | DMA アクノリッジ |

DMA 未使用時 : XDREQ=Open。XDACK= High or Low 固定

## SDMMC-IF

| QFP-Pin | 名称            | I/O | RESET | 端子<br>タイプ | 端子説明                                 |

|---------|---------------|-----|-------|-----------|--------------------------------------|

| 57      | SDCLK         | OUT | Low   | 6mA       | SD/MMC バスクロック                        |

| 60      | SDCMD         | BI  | Hi-Z  | 6mA       | SD/MMC コマンドライン                       |

| 54      | SDDAT7(GPIO3) | BI  | Hi-Z  | 6mA       | SD/MMC データバス<br>GPIO 設定時<br>汎用入出力ポート |

| 55      | SDDAT6(GPIO2) | BI  | Hi-Z  | 6mA       |                                      |

| 59      | SDDAT5(GPIO1) | BI  | Hi-Z  | 6mA       |                                      |

| 61      | SDDAT4(GPIO0) | BI  | Hi-Z  | 6mA       |                                      |

| 62      | SDDAT3        | BI  | Hi-Z  | 6mA       |                                      |

| 63      | SDDAT2        | BI  | Hi-Z  | 6mA       | SD/MMC データバス                         |

| 52      | SDDAT1        | BI  | Hi-Z  | 6mA       |                                      |

| 53      | SDDAT0        | BI  | Hi-Z  | 6mA       |                                      |

| 51      | SDCD          | IN  | —     | —         | SD/MMC カードディテクト                      |

| 50      | SDWP          | IN  | —     | —         | SD/MMC ライトプロテクト                      |

SDDAT[7:4]未使用時：SDDAT[7:4]= High or Low 固定。

## 汎用出力

| QFP-Pin | 名称  | I/O | RESET | 端子<br>タイプ | 端子説明             |

|---------|-----|-----|-------|-----------|------------------|

| 1       | GPO | OUT | Low   | 6mA       | 汎用出力ポート (LED 制御) |

汎用出力未使用時：GPO=Open。

## 水晶振動子 (CLKIN 未使用時)

| QFP-Pin | 名称 | I/O | RESET | 端子<br>タイプ | 端子説明      |

|---------|----|-----|-------|-----------|-----------|

| 6       | XI | IN  | —     | Analog    | 内部発振回路用入力 |

| 5       | XO | OUT | —     | Analog    | 内部発振回路用出力 |

水晶振動子未使用時：XI 端子=High or Low 固定。 XO 端子=Open。

## クロック入力 (水晶振動子未使用時)

| QFP-Pin | 名称    | I/O | RESET | 端子<br>タイプ | 端子説明     |

|---------|-------|-----|-------|-----------|----------|

| 3       | CLKIN | IN  | —     | —         | 外部クロック入力 |

CLKIN 端子未使用時：CLKIN=High or Low 固定。

## リセット入力

| QFP-Pin | 名称     | I/O | RESET | 端子<br>タイプ | 端子説明   |

|---------|--------|-----|-------|-----------|--------|

| 8       | XRESET | IN  | —     | Schmitt   | リセット入力 |

## 5. 端子機能説明

TEST 信号

| QFP-Pin | 名称     | I/O | RESET | 端子<br>タイプ | 端子説明           |

|---------|--------|-----|-------|-----------|----------------|

| 43      | TESTEN | IN  | (PD)  | (PD)      | テスト端子 (Low 固定) |

| 2       | ATPGEN | IN  | (PD)  | (PD)      | テスト端子 (Low 固定) |

| 13      | BURNIN | IN  | (PD)  | (PD)      | テスト端子 (Low 固定) |

PD: Pull Down

NC

| QFP-Pin | 名称 | I/O | RESET | 端子<br>タイプ | 端子説明  |

|---------|----|-----|-------|-----------|-------|

| 9,18,19 | NC | —   | —     | —         | 未使用端子 |

POWER

| QFP-Pin                 | 名称  | I/O | 電圧   | 端子説明 |

|-------------------------|-----|-----|------|------|

| 7,21,32,38,<br>49,58    | VDD | IN  | 3.3V | 電源   |

| 4,17,27,33,<br>48,56,64 | Vss | IN  | 0V   | GND  |

## 6. 機能説明

### 6.1 リセット

本 LSI は外部 XRESET 端子によるハードリセットと、レジスタ設定によるソフトリセットの機能を持ちます。

電源投入時は、XRESET 端子によるハードリセット状態から立ち上げ、電源確定後にハードリセットを解除してください。

ハードリセット後の初期化手順は、テクニカルマニュアルを参照してください。

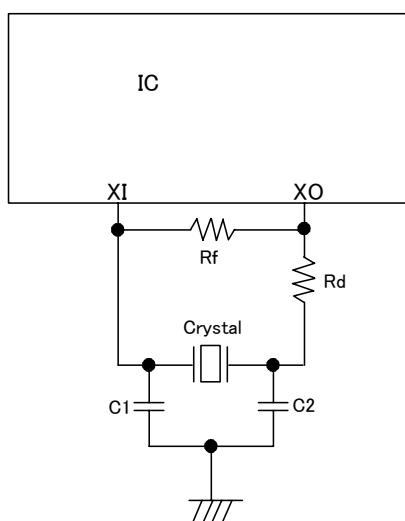

### 6.2 クロック

本 LSI は、オシレータを内蔵し、外付けの振動子によるクロック生成に対応しています。

また、CLKIN 端子からのクロックの外部入力に対応しています。

下記に発振回路の接続例を示します。図中の発振回路の Rf、Rd、C1、C2 は、振動子によってマッチングをとっていただく必要があります。これらの回路定数は振動子メーカーにご相談ください。

図 6.1 発振回路接続例

### 6.3 CPU-IF

本 LSI は、メイン CPU の 16bit 汎用メモリバスに接続が可能です。下記に CPU-IF のモード毎の真理値表を記します。

表 6.1 CPU-IF 真理値表

| XCS | XRD | XWR | CD[15:0] |

|-----|-----|-----|----------|

| H   | X   | X   | Hi-Z     |

| L   | L   | H   | Read     |

| L   | H   | L   | Write    |

## 6. 機能説明

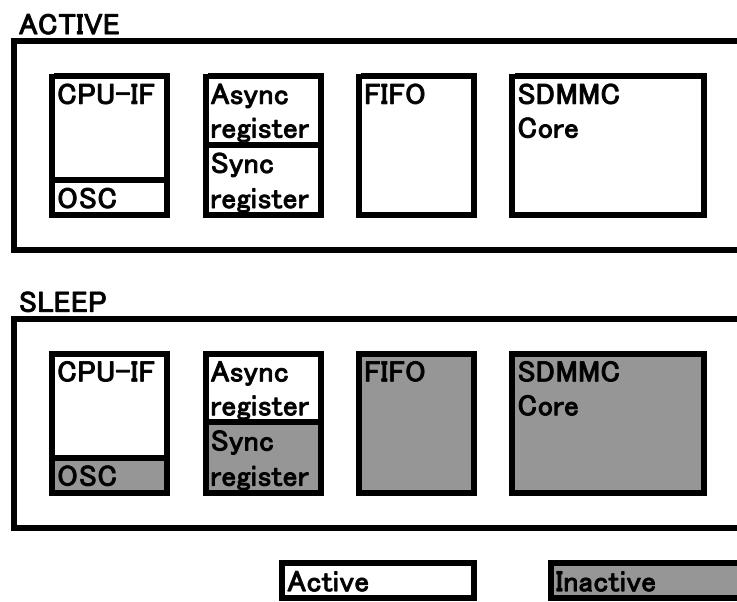

### 6.4 パワーマネージメント

本LSIは、パワーマネージメント機能を装備し、SLEEP / ACTIVE の2通りのパワーマネージメントステートを持ちます。

ACTIVEステートでは、全ての機能ブロックが動作状態となります。

SLEEPステートでは、待機状態から復帰する為に必要な最低限の回路のみが動作し、非同期レジスタのみアクセスが可能です。

図 6.2 パワーマネージメントステート

## 7. 電気的特性

### 7.1 絶対最大定格

| (Vss=0V) |      |                       |     |

|----------|------|-----------------------|-----|

| 項目       | 記号   | 定 格                   | 単 位 |

| 電 源 電 圧  | VDD  | Vss - 0.3 ~ 4.0       | V   |

| 入 力 電 圧  | VI   | Vss - 0.3 ~ VDD + 0.5 | V   |

| 出 力 電 圧  | VO   | Vss - 0.3 ~ VDD + 0.5 | V   |

| 出力電流／端子  | IOUT | ±30                   | mA  |

| 保 存 温 度  | Tstg | -65 ~ 150             | °C  |

### 7.2 推奨動作条件

| 項目      | 記 号 | Min. | Typ. | Max.  | 単 位 |

|---------|-----|------|------|-------|-----|

| 電 源 電 圧 | VDD | 3.0  | 3.3  | 3.6   | V   |

| 入 力 電 圧 | VI  | -0.3 | —    | VDD   | V   |

| 周 囲 温 度 | Ta  | -40  | 25   | 85 *1 | °C  |

(注) \*1: この温度範囲は、Tj=-40~125°Cを想定した推奨周囲温度です。

## 7. 電気的特性

### 7.3 DC 特性

#### 7.3.1 消費電流

| 項目                                  | 記号   | 条件                                                        | Min. | Typ. | Max. | 単位      |

|-------------------------------------|------|-----------------------------------------------------------|------|------|------|---------|

| 電源供給電 ACTIVE モード SD カードリード/ライト時 (※) |      |                                                           |      |      |      |         |

| 電源電流                                | IDD1 | $V_{DD} = 3.3V$                                           | —    | 45   | —    | mA      |

| 静止電流                                |      |                                                           |      |      |      |         |

| 電源電流                                | IDDS | $V_I = V_{DD}$ or $V_{SS}$<br>$V_{DD} = 3.6V$             | —    | —    | 35   | $\mu A$ |

| 入力リーク                               |      |                                                           |      |      |      |         |

| 入力リーク電流                             | IL   | $V_{DD} = 3.6V$<br>$V_{IH} = V_{DD}$<br>$V_{IL} = V_{SS}$ | -1   | —    | 1    | $\mu A$ |

※推奨動作条件 ( $T_a = 25^{\circ}\text{C}$ ) による平均電流値。

#### 7.3.2 入力特性

| 項目                                                                            | 記号           | 条件                     | Min. | Typ. | Max. | 単位        |

|-------------------------------------------------------------------------------|--------------|------------------------|------|------|------|-----------|

| CA[6:1], XRD, XWR, CD[15:0], XDACK,<br>SDCMD, SDDAT[7:0], SDCLD, SDWP, CLKIN, |              |                        |      |      |      |           |

| 入力特性                                                                          | 端子名 :        | TESTEN, ATPGEN, BURNIN |      |      |      |           |

| "H"レベル入力電圧                                                                    | VIH1         | $V_{DD} = 3.6V$        | 2.0  | —    | 3.6- | V         |

| "L"レベル入力電圧                                                                    | VIL1         | $V_{DD} = 3.0V$        | -0.3 | —    | 0.8  | V         |

| 入力特性 (ショットキ) 端子名 : XRESET, XCS                                                |              |                        |      |      |      |           |

| "H"レベルトリガ電圧                                                                   | VT1+         | —                      | 1.1  | —    | 2.4  | V         |

| "L"レベルトリガ電圧                                                                   | VT1-         | —                      | 0.6  | —    | 1.8  | V         |

| ヒステリシス電圧                                                                      | $\Delta V_1$ | —                      | 0.1  | —    | —    | V         |

| 入力特性                                                                          | 端子名 :        | XCS                    |      |      |      |           |

| プルアップ抵抗                                                                       | RPU2         | $V_I = V_{SS}$         | 40   | 100  | 240  | $k\Omega$ |

| 入力特性                                                                          | 端子名 :        | TSTEN                  |      |      |      |           |

| プルダウン抵抗                                                                       | RPD1         | $V_I = V_{DD}$         | 20   | 50   | 120  | $k\Omega$ |

| 入力特性                                                                          | 端子名 :        | ATPGEN, BURNIN         |      |      |      |           |

| プルダウン抵抗                                                                       | RPD2         | $V_I = V_{DD}$         | 40   | 100  | 240  | $k\Omega$ |

## 7.3.3 出力特性

| 項目              | 記号    | 条件                                   | Min.      | Typ. | Max. | 単位 |

|-----------------|-------|--------------------------------------|-----------|------|------|----|

| 出力特性            | 端子名 : | CD[15:0], XDREQ                      |           |      |      |    |

| "H" レベル出力電圧     | VOH1  | VDD = 3.0V<br>IOH = -2.0mA           | VDD - 0.4 | —    | —    | V  |

| "L" レベル出力電圧     | VOL1  | VDD = 3.0V<br>IOL = 2.0mA            | —         | —    | 0.4  | V  |

| 出力特性            | 端子名 : | SDCLK, SDCMD, SDDAT[7:0], GPO        |           |      |      |    |

| "H" レベル出力電圧     | VOH2  | VDD = 3.0V<br>IOH = -6.0mA           | VDD - 0.4 | —    | —    | V  |

| "L" レベル出力電圧     | VOL2  | VDD = 3.0V<br>IOL = 6.0mA            | —         | —    | 0.4  | V  |

| 出力特性            | 端子名 : | XINT                                 |           |      |      |    |

| OFF-STATE リーク電流 | IOZ   | VDD = 3.6V<br>VOH = VDD<br>VOL = VSS | -1        | —    | 1    | uA |

## 7.3.4 出力特性

| 項目      | 記号    | 条件                    | Min. | Typ. | Max. | 単位 |

|---------|-------|-----------------------|------|------|------|----|

| 端子容量    | 端子名 : | 全入力端子                 |      |      |      |    |

| 入力端子容量  | CI    | f = 1MHz<br>VDD = VSS | —    | —    | 10   | pF |

| 端子容量    | 端子名 : | 全出力端子                 |      |      |      |    |

| 出力端子容量  | CO    | f = 1MHz<br>VDD = VSS | —    | —    | 10   | pF |

| 端子容量    | 端子名 : | 全入出力端子                |      |      |      |    |

| 入出力端子容量 | CB    | f = 1MHz<br>VDD = VSS | —    | —    | 10   | pF |

## 7. 電気的特性

### 7.4 AC 特性

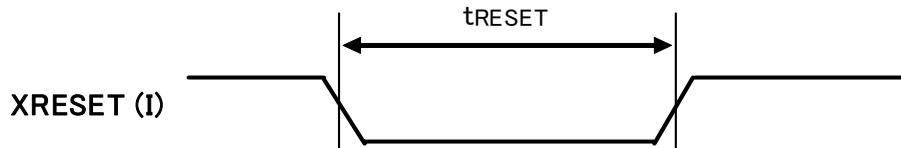

#### 7.4.1 RESET タイミング

| Symbol      | Parameter         | Min. | Typ. | Max. | Unit |

|-------------|-------------------|------|------|------|------|

| $t_{RESET}$ | RESET pulse width | 40   | —    | —    | ns   |

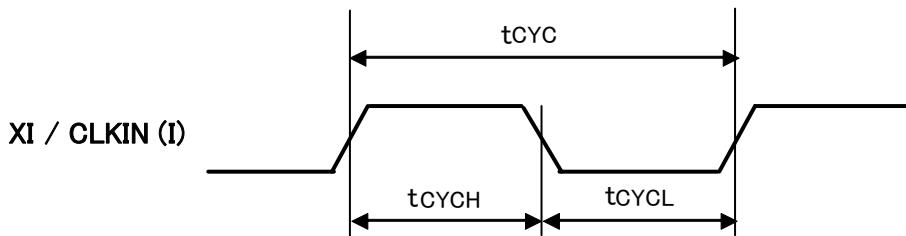

#### 7.4.2 クロックタイミング

| Symbol                   | Parameter              | Min. | Typ. | Max. | Unit |

|--------------------------|------------------------|------|------|------|------|

| $t_{CYC}$                | Clock cycle            | —    | —    | 50   | MHz  |

| $t_{CYCH}$<br>$t_{CYCL}$ | Clock High / Low width | 9.0  | —    | —    | ns   |

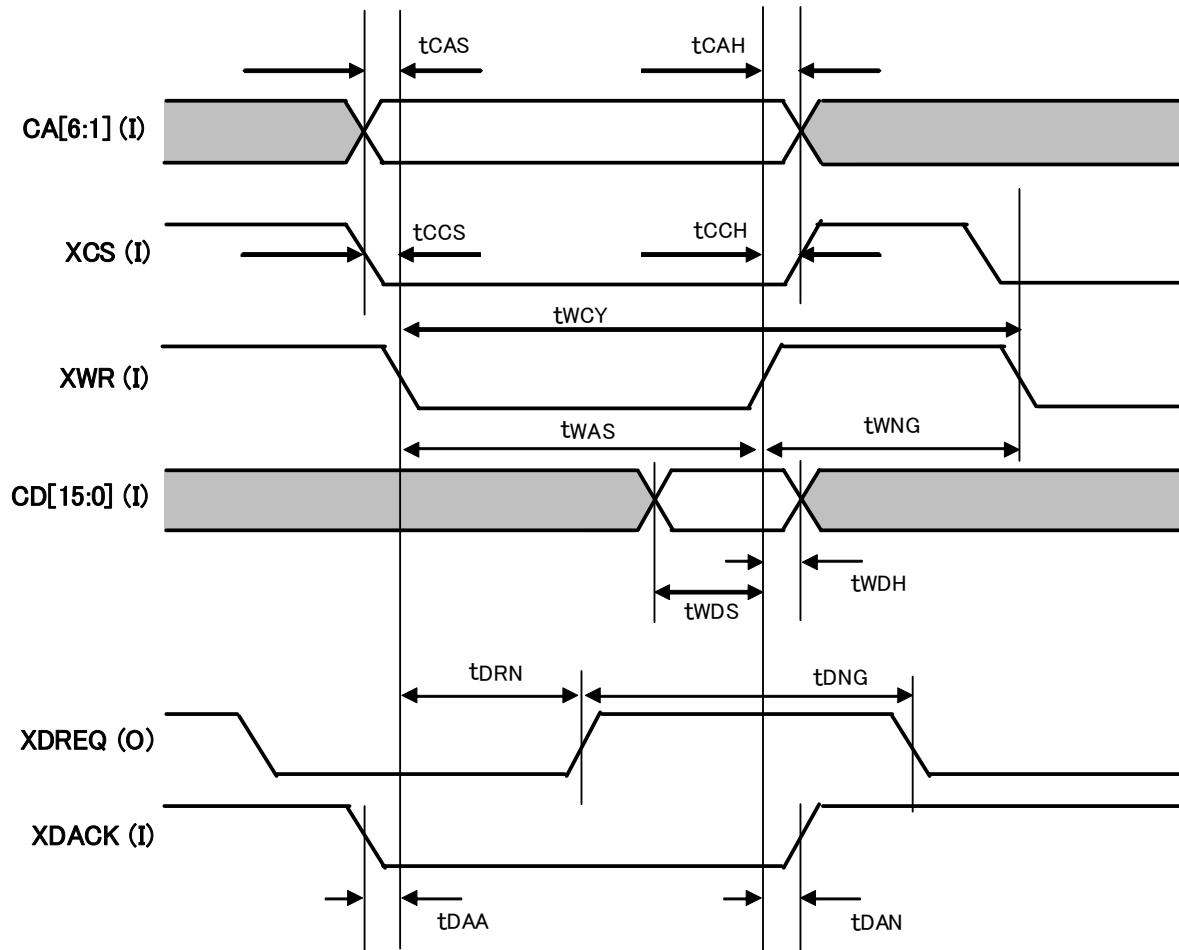

## 7.4.3 CPU/DMA IF Write アクセスタイミング

条件 : C1 = 30pf

| Symbol | Parameter                                     | Min.        | Typ. | Max.        | Unit |

|--------|-----------------------------------------------|-------------|------|-------------|------|

| tcAS   | CA[6:1] setup time to negative edge of XWR    | 2           | —    | —           | ns   |

| tCAH   | CA[6:1] hold time from positive edge of XWR   | 6           | —    | —           | ns   |

| tCCS   | XCS setup time to negative edge of XWR        | 0           | —    | —           | ns   |

| tCCH   | XCS hold time from positive edge of XWR       | 0           | —    | —           | ns   |

| twCY   | XWR access time                               | (3 x TC)+10 | —    | —           | ns   |

| twAS   | XWR assert pulse width                        | (2 x TC)+10 | —    | —           | ns   |

| twNG   | XWR negate pulse width                        | TC          | —    | —           | ns   |

| twDS   | CD[15:0] setup time to negative edge of XWR   | 10          | —    | —           | ns   |

| tWDH   | CD[15:0] hold time from positive edge of XWR  | 8           | —    | —           | ns   |

| tDRN   | XDREQ negate delay from negative edge of XWR  | —           | —    | (2 x TC)+15 | ns   |

| tDNG   | XDREQ negate time from positive edge of XDREQ | RN x TC     | —    | —           | ns   |

| tDAA   | XDACK setup time to negative edge of XWR      | 0           | —    | —           | ns   |

| TDAN   | XDACK hold time from positive edge of XWR     | 0           | —    | —           | ns   |

TC = 入力クロックサイクル (例 : 50MHz クロック入力の場合、20ns)

RN = DMA\_Config.NgtCnt[3:0] レジスタの設定値 + 1

## 7. 電気的特性

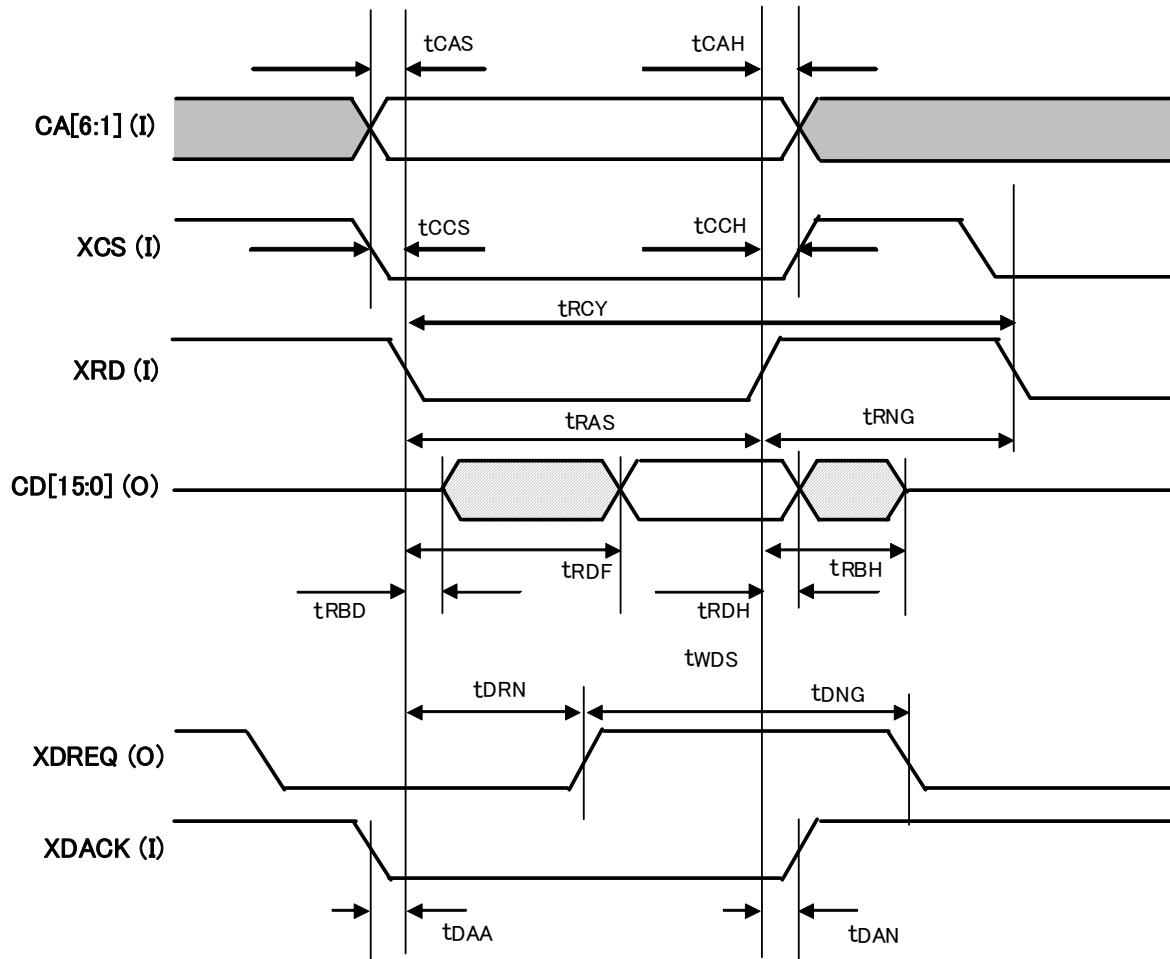

### 7.4.4 CPU/DMA IF Read アクセスタイミング

C1 = 30pf

| Symbol | Parameter                                           | Min.        | Typ. | Max.        | Unit |

|--------|-----------------------------------------------------|-------------|------|-------------|------|

| tcAS   | CA[6:1] setup time to negative edge of XRD          | 2           | —    | —           | ns   |

| tCAH   | CA[6:1] hold time from positive edge of XRD         | 6           | —    | —           | ns   |

| tCCS   | XCS setup time to negative edge of XRD              | 0           | —    | —           | ns   |

| tCCH   | XCS hold time from positive edge of XRD             | 0           | —    | —           | ns   |

| tRCY   | XRD access time                                     | (3 x TC)+30 | —    | —           | ns   |

| tRAS   | XRD assert pulse width                              | (2 x TC)+30 | —    | —           | ns   |

| tRNG   | XRD negate pulse width                              | TC          | —    | —           | ns   |

| tRBD   | CD[15:0] driven delay from negative edge of XRD     | 2           | —    | —           | ns   |

| tRDF   | CD[15:0] Valid Data delay from negative edge of XRD | —           | —    | (2 x TC)+30 | ns   |

| tRDH   | CD[15:0] hold time from positive edge of XRD        | 2           | —    | —           | ns   |

| tRBH   | CD[15:0] release delay from positive edge of XRD    | —           | —    | 15          | ns   |

| tDRN   | XDREQ negate delay from negative edge of XRD        | —           | —    | (2 x TC)+15 | ns   |

| tdNG   | XDREQ negate time from positive edge of XDREQ       | RN x TC     | —    | —           | ns   |

| tdAA   | XDACK setup time to negative edge of XRD            | 0           | —    | —           | ns   |

| tdAN   | XDACK hold time from positive edge of XDACK         | 0           | —    | —           | ns   |

TC = 入力クロックサイクル (例 : 50MHz クロック入力の場合、20ns)

RN = DMA\_Config.NgtCnt[3:0] レジスタの設定値 + 1

### 7.4.5 SDMMC IF タイミング

SD 規格 Ver2.0 に準拠します。

“SD Specifications Part1 Physical Layer Specification Version 2.00” を参照して下さい。

## 8. 接続例

---

### 8. 接続例

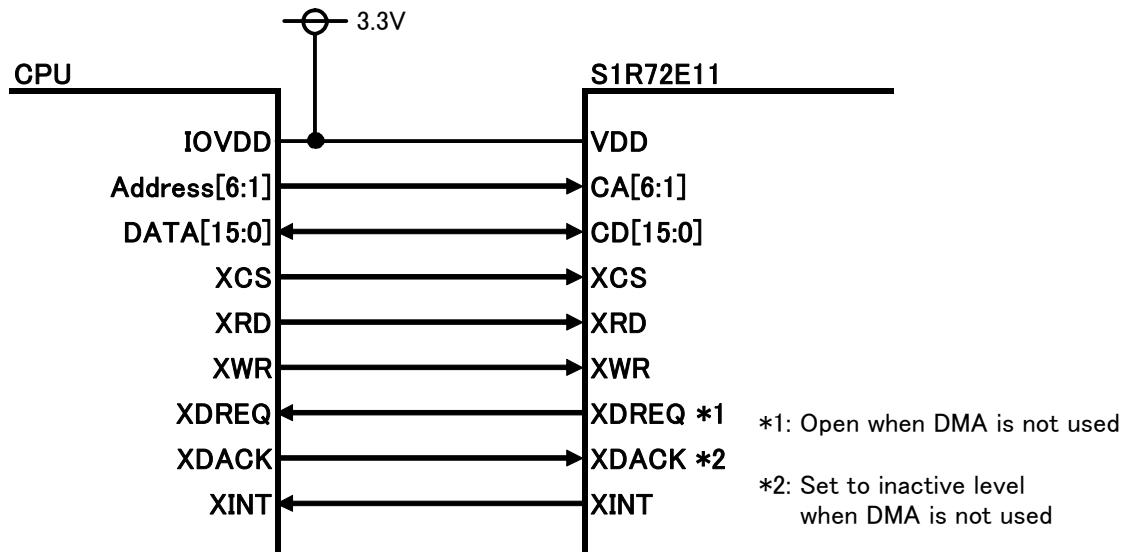

#### 8.1 CPU I/F 接続例

図 8.1 CPU-IF 接続例

## 9. 型番

表 9.1 製品型番

| 製品型番               | 製品種別             |

|--------------------|------------------|

| S1R72E11F13E10**** | TQFP13-64 パッケージ品 |

## 10. 外形寸法図

### 10. 外形寸法図

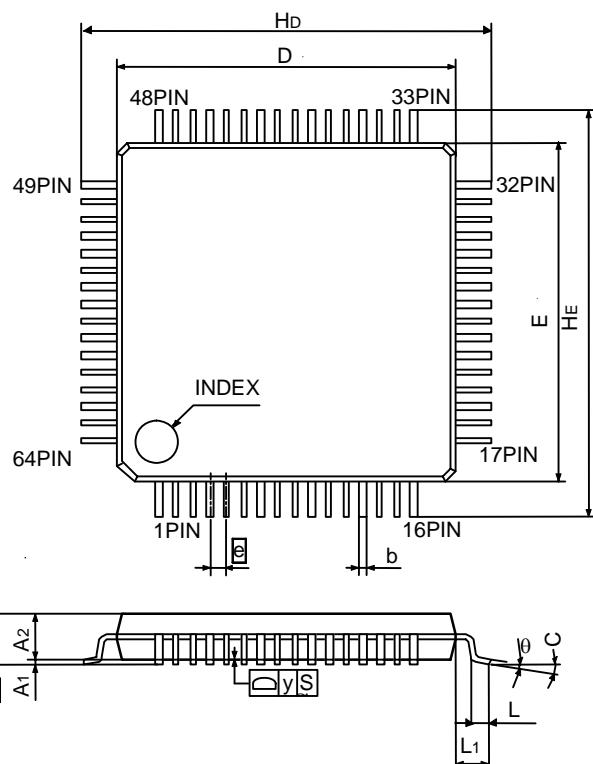

#### 10.1 TQFP13-64pin

| Symbol           | Dimension in Millimeters |      |      |

|------------------|--------------------------|------|------|

|                  | Min.                     | Nom. | Max. |

| E                | —                        | 10   | —    |

| D                | —                        | 10   | —    |

| A <sub>max</sub> | —                        | —    | 1.2  |

| A <sub>1</sub>   | —                        | 0.1  | —    |

| A <sub>2</sub>   | —                        | 1    | —    |

| e                | —                        | 0.5  | —    |

| b                | 0.17                     | —    | 0.27 |

| c                | 0.09                     | —    | 0.2  |

| θ                | 0°                       | —    | 10°  |

| L                | 0.3                      | —    | 0.75 |

| L <sub>1</sub>   | —                        | 1    | —    |

| H <sub>E</sub>   | —                        | 12   | —    |

| H <sub>D</sub>   | —                        | 12   | —    |

| y                | —                        | —    | 0.08 |

1 = 1mm

## 改訂履歴

|         | Rev. | 頁  | 種別 | 内 容    |

|---------|------|----|----|--------|

| 09/3/31 | 1.00 | 全頁 | 新規 | 新規制定   |

| 09/7/17 | 1.10 | -  | 改訂 | 留意事項改訂 |

**セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 411691501

2009 年 4 月 作成 (H)

2009 年 7 月 改訂