# S1R77009

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

# 目 次

|                                                          |    |

|----------------------------------------------------------|----|

| 1. 概要.....                                               | 1  |

| 2. 特長.....                                               | 1  |

| 3. ブロック図 .....                                           | 2  |

| 4. 端子配置図 .....                                           | 3  |

| 5. 端子説明.....                                             | 4  |

| 6. 機能説明.....                                             | 6  |

| 6.1 ホストインターフェース部 .....                                   | 6  |

| 6.1.1 シリアルインターフェース .....                                 | 6  |

| 6.2 RSDS(LVDS)部.....                                     | 9  |

| 6.3 内蔵 PLL 部.....                                        | 10 |

| 6.4 制御部 .....                                            | 12 |

| 6.4.1 概要 .....                                           | 12 |

| 6.4.2 画像取り込み動作 .....                                     | 12 |

| 6.4.3 画素処理 .....                                         | 12 |

| 6.4.4 ライン処理.....                                         | 14 |

| 6.4.5 シフト信号、クロックパルス等出力タイミング.....                         | 15 |

| 6.4.6 クロックパルスのパターン出力.....                                | 18 |

| 6.4.7 SLINE 出力処理 .....                                   | 21 |

| 6.4.8 制御信号出力遅延設定 .....                                   | 23 |

| 6.4.9 制御信号出力極性設定 .....                                   | 27 |

| 6.4.10 兼用汎用ポート .....                                     | 28 |

| 7. レジスタ.....                                             | 30 |

| 7.1 メモリマップ .....                                         | 30 |

| 7.2 レジスタマップ .....                                        | 31 |

| 7.3 ビットマップ .....                                         | 32 |

| 7.4 レジスタ詳細説明 .....                                       | 33 |

| 7.4.1 0x00～0x3F パターン設定レジスタ No.00～No.3F (PAT00～3F).....   | 33 |

| 7.4.2 0x40 SLINE 開始ライン設定レジスタ (SLINEST).....              | 35 |

| 7.4.3 0x41 SLINE 終了ライン設定レジスタ(SLINEEND) .....             | 35 |

| 7.4.4 0x42 シフトパルス信号出力遅延設定レジスタ 1 (SH_ADJ1).....           | 36 |

| 7.4.5 0x43 シフトパルス信号出力遅延設定レジスタ 2 (SH_ADJ2).....           | 37 |

| 7.4.6 0x44 シフトパルス信号出力遅延設定レジスタ 3 (SH_ADJ3).....           | 38 |

| 7.4.7 0x45 シフトパルス信号出力遅延設定レジスタ 4 (SH_ADJ4).....           | 39 |

| 7.4.8 0x48 クロックパルス遅延設定ページ選択レジスタ (SNCK_ADJ_PAGESEL) ..... | 40 |

| 7.4.9 0x49 クロックパルス出力遅延設定レジスタ 1 (SNCK_ADJ1) .....         | 41 |

| 7.4.10 0x4A クロックパルス出力遅延設定レジスタ 2 (SNCK_ADJ2) .....        | 42 |

| 7.4.11 0x4B クロックパルス出力遅延設定レジスタ 3 (SNCK_ADJ3) .....        | 43 |

| 7.4.12 0x4C クロックパルス反転出力遅延設定レジスタ 1 (SNCK_INV1) .....      | 44 |

| 7.4.13 0x4D クロックパルス反転出力遅延設定レジスタ 2 (SNCK_INV2) .....      | 45 |

| 7.4.14 0x4E クロックパルス反転出力遅延設定レジスタ 3 (SNCK_INV3) .....      | 46 |

| 7.4.15 0x50 タイミング生成機能制御レジスタ (TGCTL).....                 | 47 |

| 7.4.16 0x51 タイミング生成機能設定レジスタ (TGMD).....                  | 48 |

| 7.4.17 0x52 内部ステート制御レジスタ (STCTL).....                    | 49 |

| 7.4.18 0x53 パターン設定制御レジスタ (PATEN).....                    | 50 |

| 7.4.19 0x54 ラインセンサ駆動クロックパルス極性設定レジスタ(SNCKINV).....        | 51 |

| 7.4.20 0x55 ラインセンサ駆動クロックパルスパターン設定レジスタ 1 (SNCK1CTL) ..... | 51 |

| 7.4.21 0x56 ラインセンサ駆動クロックパルスパターン設定レジスタ 2 (SNCK2CTL) ..... | 52 |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 7.4.22 0x57 ラインセンサ駆動クロックパルス出力設定レジスタ (SNCKxSHCTL) ..... | 52        |

| 7.4.23 0x58 極性制御レジスタ(POLCTL) .....                     | 54        |

| 7.4.24 0x59 汎用ポート制御レジスタ (GPIOEN1) .....                | 55        |

| 7.4.25 0x5A 汎用ポート制御レジスタ (GPIOEN2) .....                | 55        |

| 7.4.26 0x5B 汎用ポート入出力切り替えレジスタ 1 (GPIODIR1) .....        | 56        |

| 7.4.27 0x5C 汎用ポート入出力切り替えレジスタ 2 (GPIODIR2) .....        | 56        |

| 7.4.28 0x5D 汎用ポート入出力切り替えレジスタ 3 (GPIODIR3) .....        | 57        |

| 7.4.29 0x5E 汎用ポートレジスタ 1 (GPIOST1) .....                | 58        |

| 7.4.30 0x5F 汎用ポートレジスタ 2 (GPIOST2) .....                | 58        |

| 7.4.31 0x70 アナログモジュールリセットレジスタ (ANA_RESET) .....        | 59        |

| 7.4.32 0x7F PLL・画像出力制御レジスタ (PLL_IMGSIG_CTL) .....      | 60        |

| <b>8. 電気的特性 .....</b>                                  | <b>61</b> |

| <b>8.1 絶対最大定格 .....</b>                                | <b>61</b> |

| <b>8.2 推奨動作条件 .....</b>                                | <b>61</b> |

| <b>8.3 電源シーケンス .....</b>                               | <b>62</b> |

| 8.3.1 Power ON 時 .....                                 | 62        |

| 8.3.2 Power OFF 時 .....                                | 62        |

| 8.3.3 DC 特性 .....                                      | 63        |

| <b>8.4 AC 特性 .....</b>                                 | <b>64</b> |

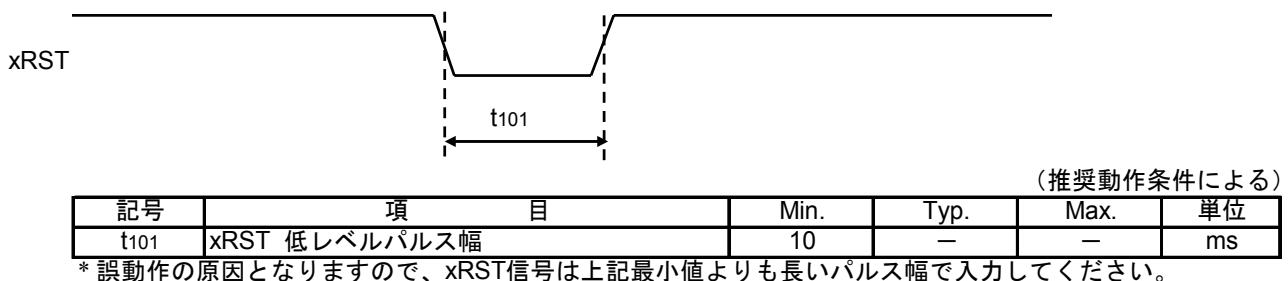

| 8.4.1 システムリセット .....                                   | 64        |

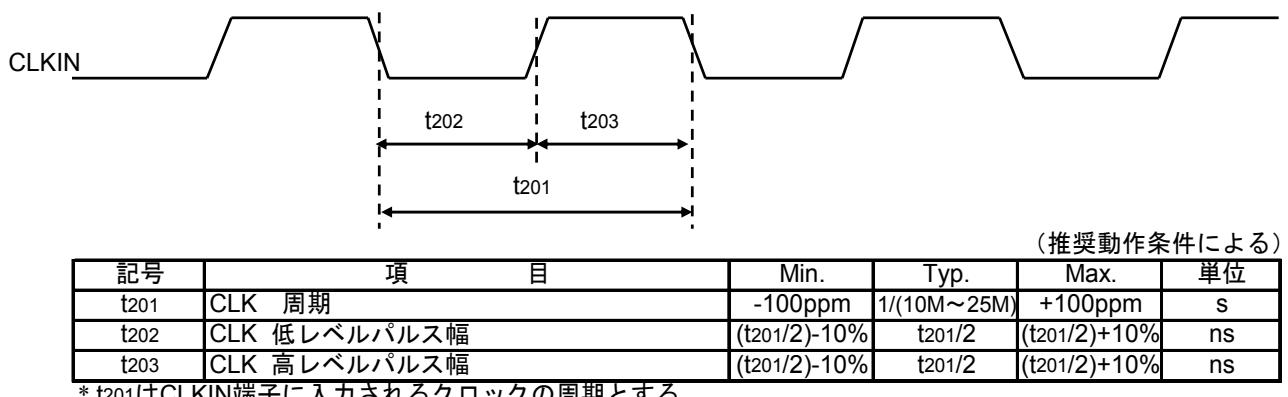

| 8.4.2 クロックタイミング .....                                  | 64        |

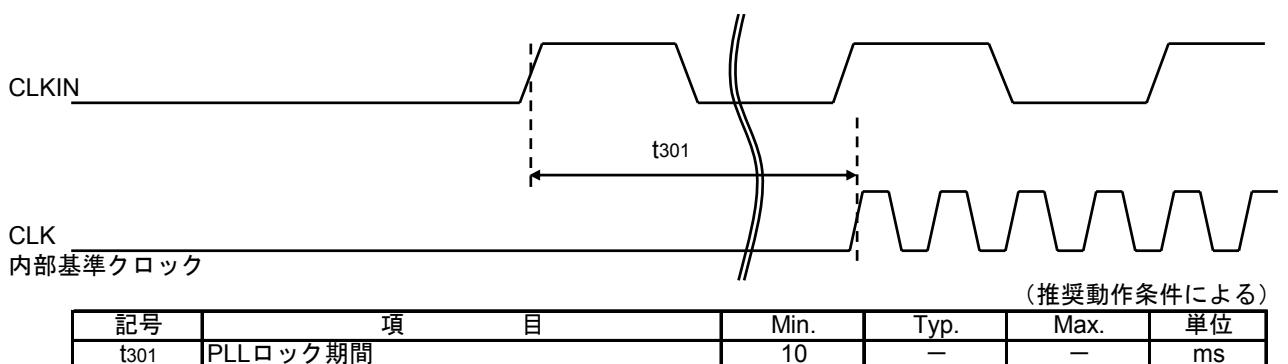

| 8.4.3 PLL ロックタイミング .....                               | 64        |

| 8.4.4 シリアルインターフェースタイミング .....                          | 65        |

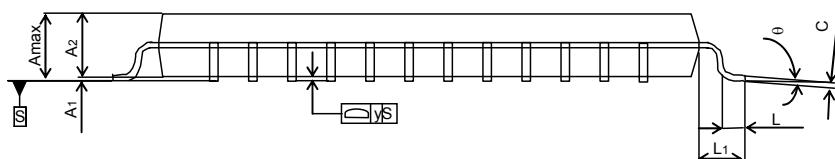

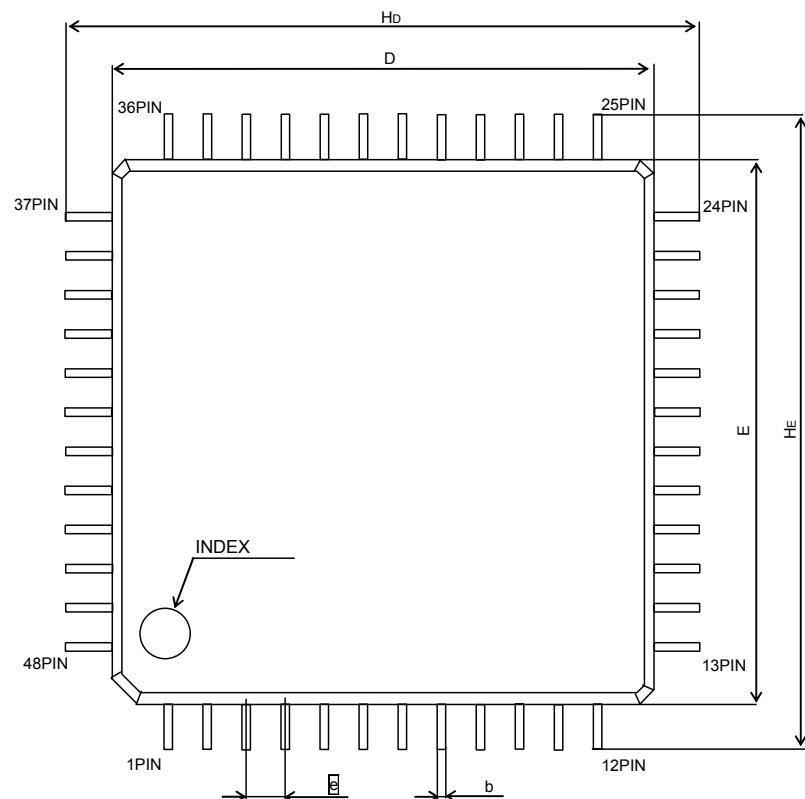

| <b>9. 外形寸法図 .....</b>                                  | <b>66</b> |

### 1. 概要

本 IC は、高速読取動作を実現するラインセンサ用駆動クロック生成 IC です。

### 2. 特長

#### 共通部

- パッケージ 0.5 mm ピッチ QFP48 ピン

- 3.3V、5V 二電源

- PLL を内蔵し CLK 入力信号入力を 3、6 適倍することにより内部基準クロックを生成

- 内部基準クロック周波数 :  $60\text{MHz} \leq \text{内部基準クロック周波数} \leq 150\text{MHz}$

#### ホストインターフェース部

- シリアルインターフェース

#### 駆動クロック生成部

- ラインセンサおよび AFE 駆動に必要な下記シフト信号・クロック信号を生成

ADCK, SH1, SH2, SH3, SH4, SH5, SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK1E,

SNCK2, SNCK3, SNCK4, SNCK5, SNCK6, CK1, CK2, CLMP

- クロック信号駆動パターン生成用メモリ内蔵

- 画像読み取り時およびダミー画素出力時のクロック信号駆動パターンを自由にプログラム可能

- ADCK 信号 1 サイクルあたりの駆動パターン分解能は設定により 3、6 から選択

- ラインセンサに対応

- 駆動クロック 5.0V 出力

※ 耐放射性設計はされておりません。

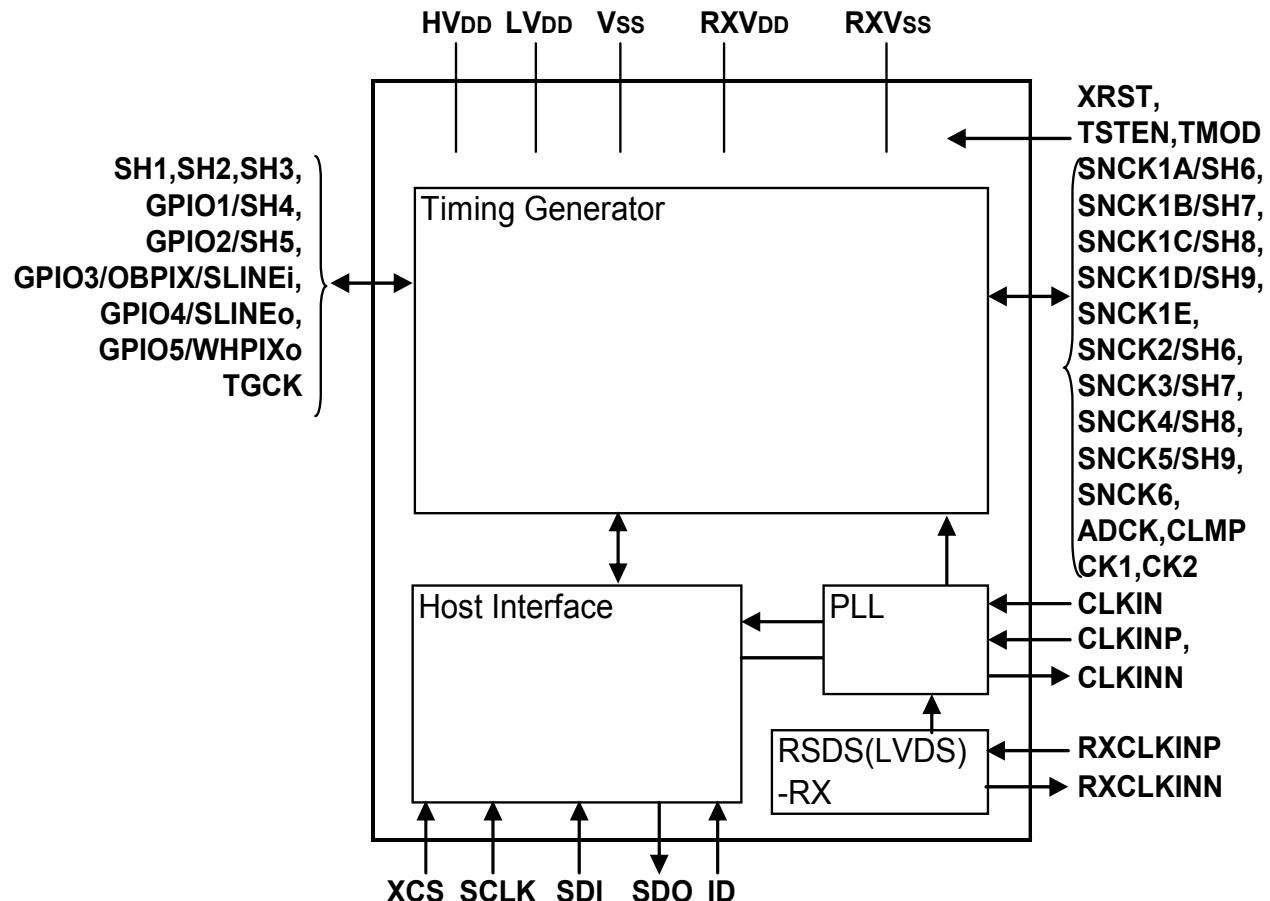

### 3. ブロック図

#### 3. ブロック図

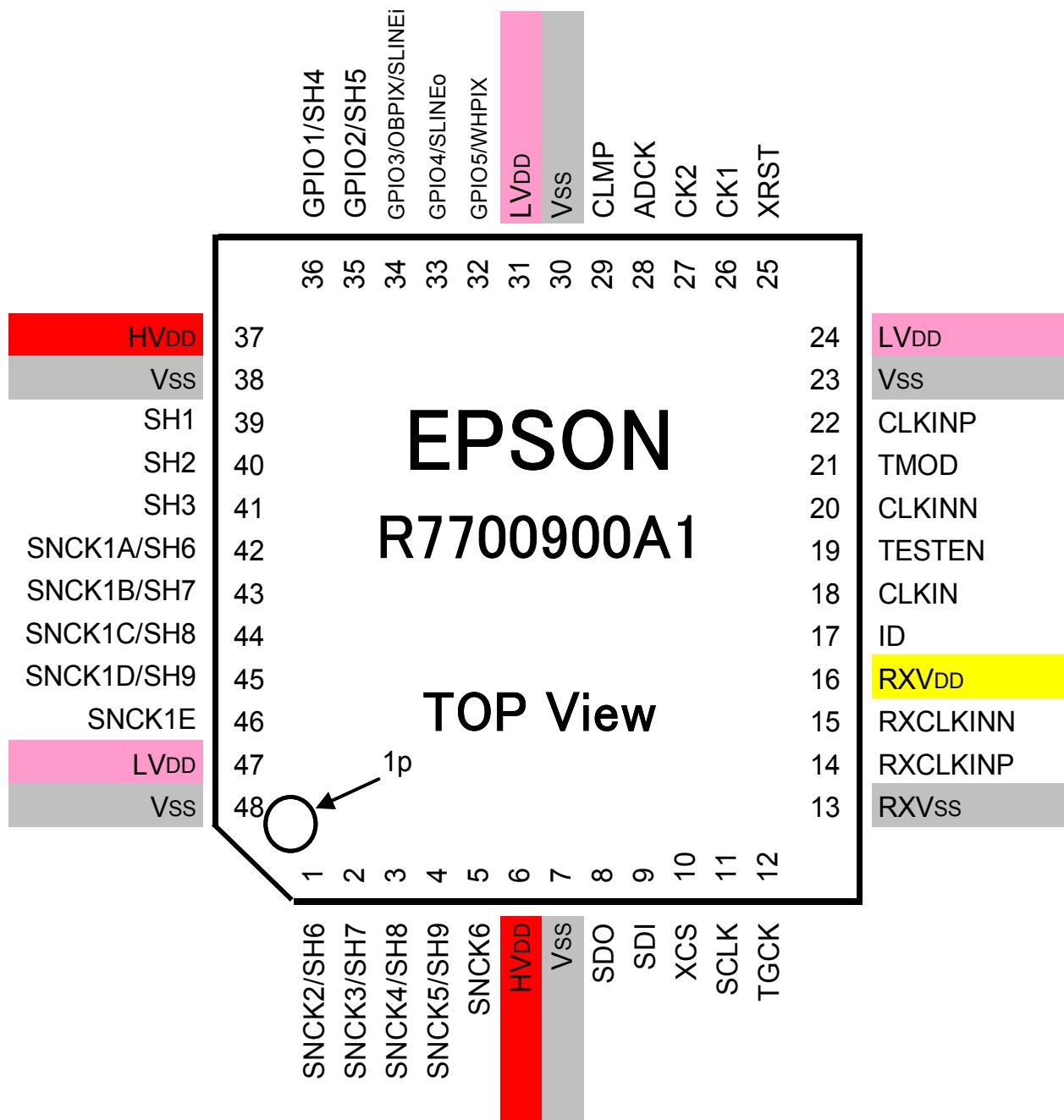

## 4. 端子配置図

## 5. 端子説明

### 5. 端子説明

| No.                      | Pin | Pin Name           | I/O | Reset | Pin Function                     | Remarks | Drive Capacity |

|--------------------------|-----|--------------------|-----|-------|----------------------------------|---------|----------------|

| Line Sensor Drive Clocks |     |                    |     |       |                                  |         |                |

| 1                        | 39  | SH1                | B5  | PD    | Line Sensor shift 1              | PD      | 12mA*          |

| 2                        | 40  | SH2                | B5  | PD    | Line Sensor shift 2              | PD      | 12mA*          |

| 3                        | 41  | SH3                | B5  | PD    | Line Sensor shift 3              | PD      | 12mA*          |

| 4                        | 42  | SNCK1A/SH6         | B5  | PD    | Line Sensor clock 1A/SH6         | PD      | 12mA*/24mA*    |

| 5                        | 43  | SNCK1B/SH7         | B5  | PD    | Line Sensor clock 1B/SH7         | PD      | 12mA*/24mA*    |

| 6                        | 44  | SNCK1C/SH8         | B5  | PD    | Line Sensor clock 1C/SH8         | PD      | 12mA*/24mA*    |

| 7                        | 45  | SNCK1D/SH9         | B5  | PD    | Line Sensor clock 1D/SH9         | PD      | 12mA*/24mA*    |

| 8                        | 46  | SNCK1E             | B5  | PD    | Line Sensor clock 1E             | PD      | 12mA*/24mA*    |

| 9                        | 1   | SNCK2/SH6          | B5  | PD    | Line Sensor clock 2/SH6          | PD      | 12mA*/24mA*    |

| 10                       | 2   | SNCK3/SH7          | B5  | PD    | Line Sensor clock 3/SH7          | PD      | 12mA*/24mA*    |

| 11                       | 3   | SNCK4/SH8          | B5  | PD    | Line Sensor clock 4/SH8          | PD      | 12mA*/24mA*    |

| 12                       | 4   | SNCK5/SH9          | B5  | PD    | Line Sensor clock 5/SH9          | PD      | 12mA*/24mA*    |

| 13                       | 5   | SNCK6              | B5  | PD    | Line Sensor clock 6              | PD      | 12mA*/24mA*    |

| Host Interface           |     |                    |     |       |                                  |         |                |

| 14                       | 36  | GPIO1/SH4          | B   | PD    | General Purpose1/SH4             | PD      | 12mA*          |

| 15                       | 35  | GPIO2/SH5          | B   | PD    | General Purpose2/SH5             | PD      | 12mA*          |

| 16                       | 34  | GPIO3/SLINEi/OBPIX | B   | PD    | General Purpose3/SLINEi/OBPIX    | PD      | 12mA*          |

| 17                       | 33  | GPIO4/SLINEo       | O   | Hi-Z  | General Purpose4/SLINEo          |         | 12mA*          |

| 18                       | 32  | GPIO5/WHPIX        | O   | Hi-Z  | General Purpose5/WHPIX           |         | 12mA*          |

| 19                       | 12  | TGCK               | B5T | Hi-Z  | Line Sensor shift signal trigger | SMT     | 12mA*          |

| 20                       | 10  | XCS                | I5T | —     | Chip select                      | SMT     | —              |

| 21                       | 11  | SCLK               | I5T | —     | Serial clock                     | SMT     |                |

| 22                       | 9   | SDI                | I5T | —     | Serial data input                | SMT     |                |

| 23                       | 8   | SDO                | O   | Hi-Z  | Serial data output               |         | 2mA            |

| 24                       | 17  | ID                 | I   | —     | Chip ID select                   | PD      | —              |

Symbols in the I/O section

A: Analog pin

I: Input pin (3.3V input)

I5T: Input pin (5.0V tolerant input)

O: Output pin (3.3V output)

B: Bi-directional pin (3.3V input/output)

B5: Bi-directional pin (5.0V input/output)

B5T: Bi-directional pin (5.0V tolerant input/output)

P: Power supply pin

Symbols in the Reset (in the initial state) section

HI-Z: High impedance state

PD: In the input state, potential is Low due to pull-down register

Symbols in the Remarks section

PU: Pull-up

PD: Pull-down

SMT: Schmitt input

\* Low Noise type output

| No.                  | Pin | Pin Name | I/O | Reset | Pin Function                                     | Remarks | Drive Capacity |

|----------------------|-----|----------|-----|-------|--------------------------------------------------|---------|----------------|

| <b>AFE Interface</b> |     |          |     |       |                                                  |         |                |

| 25                   | 28  | ADCK     | B   | PD    | A/D Converter clock                              | PD      | 12mA*          |

| 26                   | 26  | CK1      | B   | PD    | Sampling clock 1                                 | PD      | 12mA*          |

| 27                   | 27  | CK2      | B   | PD    | Sampling clock 2                                 | PD      | 12mA*          |

| 28                   | 29  | CLMP     | B   | PD    | Clamp timing                                     | PD      | 12mA*          |

| <b>System Signal</b> |     |          |     |       |                                                  |         |                |

| 29                   | 25  | XRST     | I   | —     | Reset signal                                     | SMT     | —              |

| 30                   | 18  | CLKIN    | I   | —     | Reference clock                                  | PD      | —              |

| 31                   | 22  | CLKINP   | A   | —     | Reference clock (Positive) [OSC input]           |         | Analog         |

| 32                   | 20  | CLKINN   | A   | —     | Reference clock (Negative) [OSC input]           |         | Analog         |

| 33                   | 14  | RXCLKINP | A   | —     | Differential clock (Positive) [RSDS(LVDS) input] |         | Analog         |

| 34                   | 15  | RXCLKINN | A   | —     | Differential clock (Negative) [RSDS(LVDS) input] |         | Analog         |

| 35                   | 19  | TESTEN   | I   | —     | Test pin                                         | PD      | —              |

| 36                   | 21  | TMOD     | I   | —     | Test pin                                         | PD      | —              |

| <b>Power Supply</b>  |     |          |     |       |                                                  |         |                |

| 37                   | 6   | HVDD     | P   | —     | 5.0V logic power supply                          |         | —              |

| 38                   | 37  | HVDD     |     |       |                                                  |         |                |

| 39                   | 24  | LVDD     | P   | —     | 3.3V logic power supply                          |         | —              |

| 40                   | 31  | LVDD     | P   | —     |                                                  |         |                |

| 41                   | 47  | LVDD     | P   | —     |                                                  |         |                |

| 42                   | 16  | RXVDD    | P   | —     | RSDS(LVDS)-RX power supply +3.3V                 |         | —              |

| 43                   | 7   | Vss      | P   | —     | Logic ground                                     |         | —              |

| 44                   | 23  | Vss      | P   | —     |                                                  |         |                |

| 45                   | 30  | Vss      | P   | —     |                                                  |         |                |

| 46                   | 38  | Vss      | P   | —     |                                                  |         |                |

| 47                   | 48  | Vss      | P   | —     |                                                  |         |                |

| 48                   | 13  | RXVss    | P   | —     | RSDS(LVDS)-RX ground                             |         | —              |

## Symbols in the I/O section

A: Analog pin

I: Input pin (3.3V input)

I5T: Input pin (5.0V tolerant input)

O: Output pin (3.3V output)

B: Bi-directional pin (3.3V input/output)

B5: Bi-directional pin (5.0V input/output)

B5T: Bi-directional pin (5.0V tolerant input/output)

P: Power supply pin

## Symbols in the Reset (in the initial state) section

HI-Z: High impedance state

PD: In the input state, potential is Low due to pull-down register

## Symbols in the Remarks section

PU: Pull-up

PD: Pull-down

SMT: Schmitt input

\*: Low Noise type output

## 6. 機能説明

---

### 6. 機能説明

各ブロックの機能を以下に説明します。

#### 6.1 ホストインターフェース部

##### 6.1.1 シリアルインターフェース

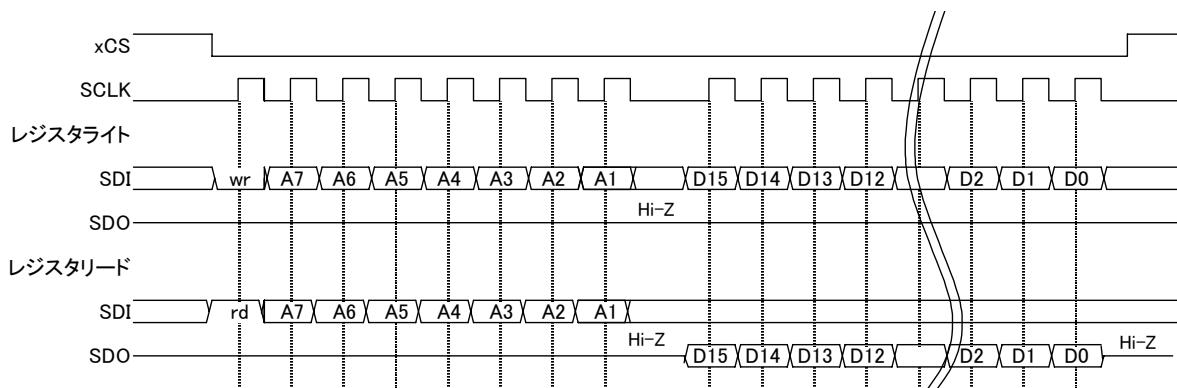

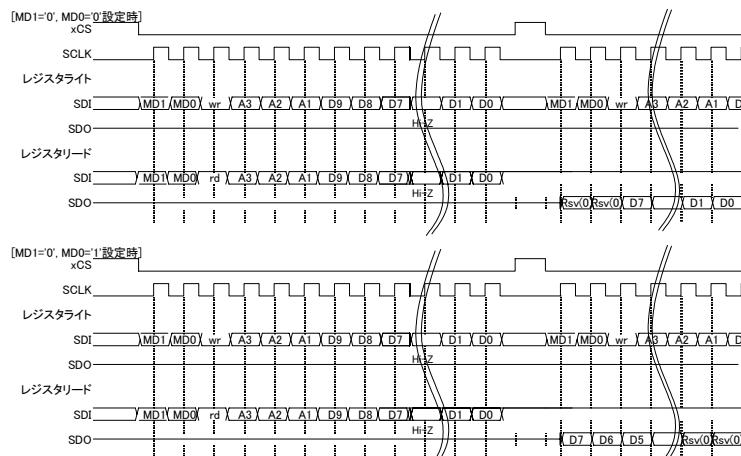

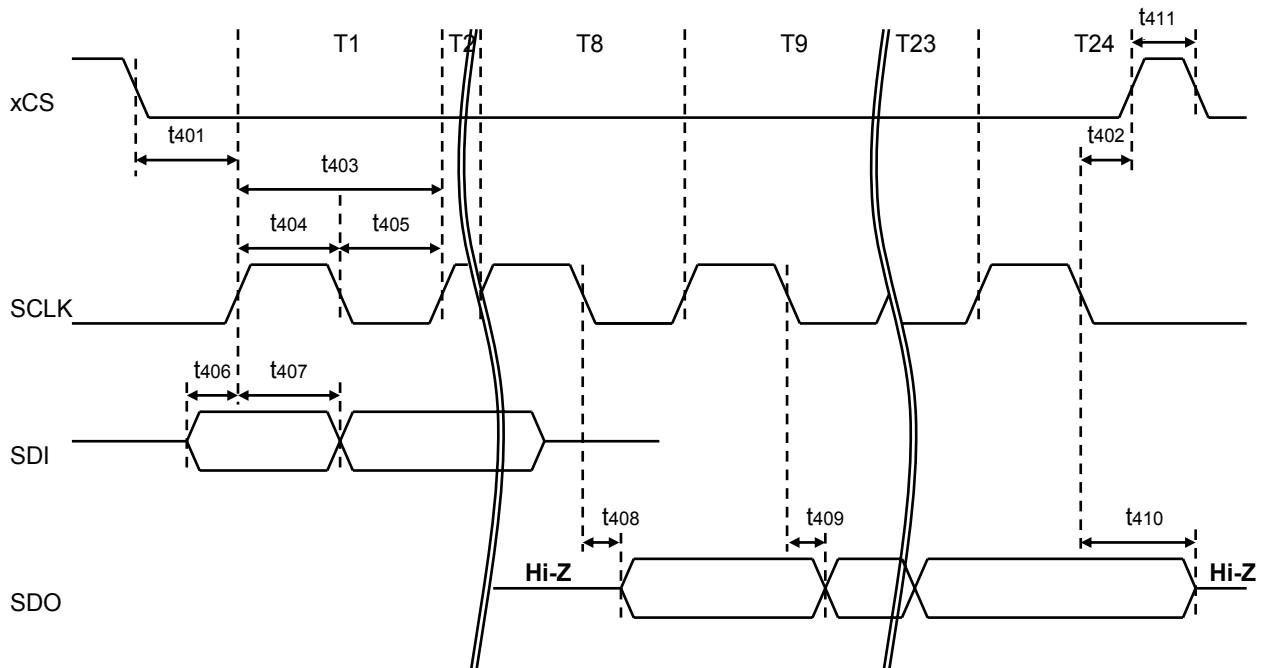

シリアルインターフェースは、XCS 信号（チップセレクト）、SCLK 信号（シリアルデータ入出力同期クロック）、SDI 信号（シリアルデータ入力）および SDO 信号（シリアルデータ出力）の 4 信号で構成されます。本 IC がアクティブ状態（XCS 信号が LOW）の時、SCLK 信号に同期してデータ送受信を行います。アクセスサイクルは TMOD 信号および ID 信号の組み合わせにより 16 ビットレジスタアクセスモード（25 サイクルまたは 24 サイクル）、8 ビットレジスタアクセスモード（16 サイクル）で行います。サイクル数の設定は TMOD 信号と ID 信号の状態によって表 6.1 のとおりとなります。

表 6.1 アクセスサイクル設定

| アクセスサイクル | TMOD | ID          |

|----------|------|-------------|

| 25 サイクル  | LOW  | チップ ID 選択設定 |

| 24 サイクル  | HIGH | LOW         |

| 16 サイクル  | HIGH | HIGH        |

本 IC 内部にはシリアルパラレル変換（またはパラレルシリアル変換）のためのカウンタがあり、XCS 信号を HIGH にすることによりリセットされます。従って、レジスタライトまたはレジスタリードの各サイクル終了後は、必ず XCS 信号をネゲート（XCS 信号を HIGH）してください。

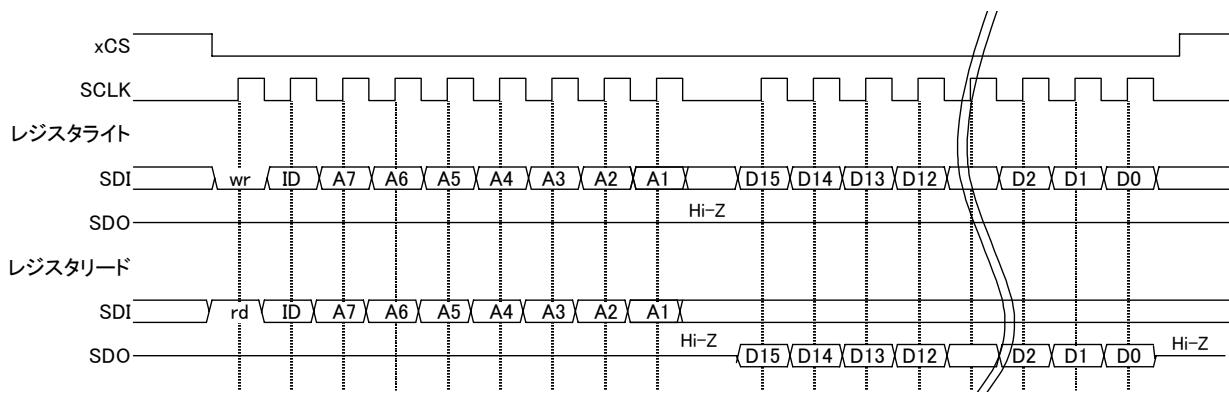

16 ビットレジスタアクセスモード時は、まずライトまたはリードアクセスを示す識別ビットをライトします。識別ビットは、LOW のときにライトアクセス、HIGH のときにリードアクセスを行います。識別ビットに引き続きチップ ID 選択ビット（25 サイクル動作時のみ）および 7 ビットのレジスタ識別番号をライトし、その後データのライトまたはリードを行います。なお、25 サイクル動作時はチップ ID 選択ビットの入力レベルが ID 信号（チップ ID 選択設定）と同論理の場合に本 IC へのアクセスが有効となります。

チップ ID 選択ビット、レジスタ識別番号およびデータ転送はいずれもクロックの立ち上がりに同期し MSB から順に転送します。図 6.1、図 6.2 に各アクセス時のタイミングを示します。

図 6.1 16 ビット ID なしレジスタアクセスモード シリアルインタフェースアクセスタイミング

図 6.2 16 ビット ID 付レジスタアクセスモード シリアルインタフェースアクセスタイミング

8 ビットレジスタアクセスモード時は、まずリード動作時のデータフォーマット指定ビットをライトします。MD[1:0] = “00”的場合、上位 2 ビットが“00”となり 8 ビットのデータを出力します。MD[1:0] = “01”的場合、下位 2 ビットが“00”となり 8 ビットのデータを出力します。データフォーマット指定ビットに引き続きライトまたはリードアクセスを示す識別ビットをライトします。識別ビットは、LOW のときにライトアクセス、HIGH のときにリードアクセスを行います。その後、識別ビットに引き続き 3 ビットのレジスタ識別番号をライトし、その後データのライトまたはリードを行います。なお、本レジスタアクセス時においては、1 アドレスにおいて 8 ビットの L データおよび H データをアクセスする必要があります。さらに、レジスタアドレスを直接指定することはできません。

アクセス方法としては、アドレスレジスタにアクセス先のアドレスを設定後、データ L レジスタへライトデータをセット、データ H レジスタへライトデータをセットすることによりレジスタアクセスが完了します。アドレス、データ L、データ H のレジスタアドレスを表 6.2 のとおりとなります。

表 6.2 アクセスサイクル設定

| アドレス A[3:1] | レジスタ名        |

|-------------|--------------|

| 001         | アドレス設定レジスタ   |

| 010         | データ L 設定レジスタ |

| 100         | データ H 設定レジスタ |

レジスタ識別番号およびデータ転送はいずれもクロックの立ち上がりに同期し MSB から順に転送します。図 6.3 に各アクセス時のタイミングおよび図 6.4 にてアクセスシーケンスを示します。

## 6. 機能說明

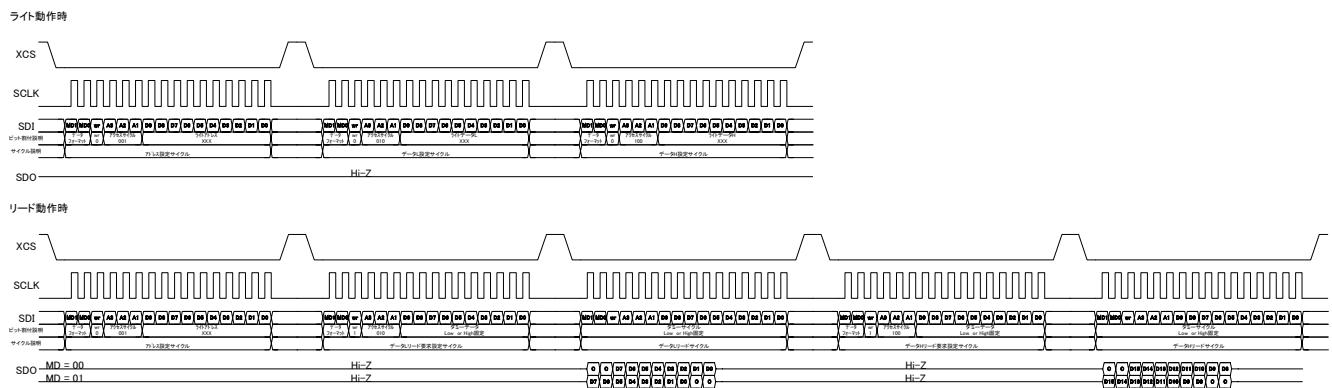

図 6.3 8 ビットレジスタアクセスモード シリアルインターフェースアクセスタイル

図 6.4 8 ビットレジスタアクセスモード シリアルインターフェースアクセスシーケンス

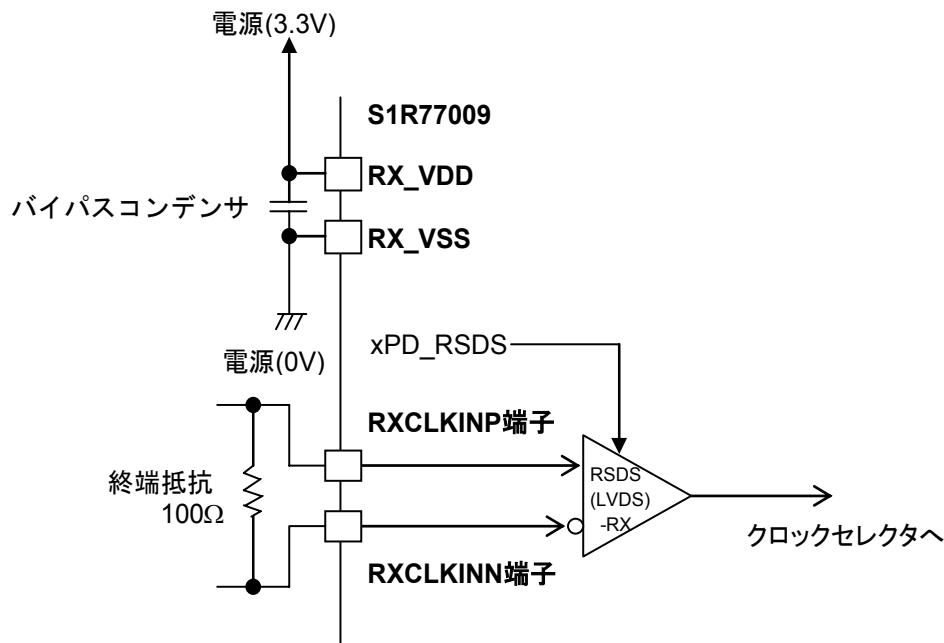

## 6.2 RSDS(LVDS)部

入力クロック信号を RSDS(LVDS)にて入力することができます。図 6.5 に RSDS(LVDS)部周辺の接続関係を示します。

図 6.5 RSDS(LVDS)接続図

### (1) パワーダウン機能

RSDS(LVDS)部は、パワーダウン機能を有しており、ANA\_RESET レジスタ (No.0x70) の xPD\_RSDS ビットによって制御することができます。xPD\_RSDS ビットを“0”に設定することにより、RSDS(LVDS)部はパワーダウンモードとなり入力信号の出力を停止します。また、“1”に設定することにより、パワーダウンモードが解除され入力信号の出力を開始します。なお、パワーダウンモード解除後、安定動作を開始するまで最大で 10ms 必要です。

### (2) 終端抵抗

RSDS(LVDS)入力端子の直近に  $100\Omega$  の終端抵抗を接続してください。

#### 「制限注意事項」

外付け抵抗は公差 $\pm 1.0\%$ 以下を推奨します。また、基板実装において本 IC とコネクタ間は、スルーホール等を介さず同一面に実装してください。

### (3) 空き端子処理

クロック入力を RSDS(LVDS)にて入力しない場合は、RX\_CLKINP を Low レベルに、RX\_CLKINN を High レベルに固定してください。

## 6. 機能説明

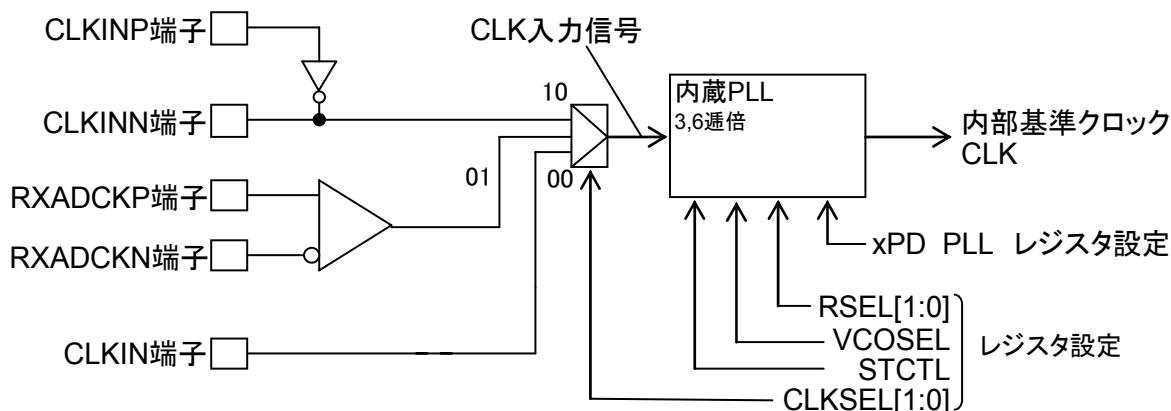

### 6.3 内蔵 PLL 部

外部入力クロックである CLK 入力信号を内蔵 PLL によって 3, 6 遅倍し、基準となる内部基準クロックを生成します。内部基準クロックは 1 画素あたりの処理を行うために必要な内部ステートを生成します。なお、内部基準クロック 1 サイクルは、1 ステート(T)に相当します。

図 6.6 に内蔵 PLL 周辺の接続関係を示します。

図 6.6 内蔵 PLL

#### 「制限注意事項」

PLL\_IMGSIG\_CTL レジスタ (No.0x7F) の下記ビットの設定を変更する際は、ANA\_RESET レジスタ (No.0x70) の xPD\_PLL ビットを必ず“0”にして、内蔵 PLL の発振を停止してから行ってください。

VCOSEL、CLKSEL[1:0]、RSEL[1:0]

#### (1) パワーダウン機能

内蔵 PLL のパワーダウン機能は、ANA\_RESET レジスタ (No.0x70) の xPD\_PLL ビットによって制御することができます。xPD\_PLL ビットを“0”に設定することにより、内蔵 PLL はパワーダウンモードとなり発振を停止します。また、“1”に設定することにより、パワーダウンモードが解除され発振を開始します。なお、PLL パワーダウンモード解除後、安定した発振出力を行うまで最大で 10ms 必要とします。

#### (2) 外部クロック選択

本 IC は外部クロックを表 6.3 に示すとおり、クロックパルス入力、RSDS(LVDS)差動入力、または発振回路入力の選択することができます。入力方式にあわせて、PLL\_IMGSIG\_CTL レジスタ (No.0x7F) の CLKSEL ビットを設定する必要があります。

表 6.3 CLKSEL 設定

| 外部クロック入力     | レジスタ設定<br>CLKSEL[1:0] | 端子処理   |          |          |          |        |

|--------------|-----------------------|--------|----------|----------|----------|--------|

|              |                       | CLKIN  | RXCLKINP | RXCLKINN | CLKINP   | CLKINN |

| クロックパルス      | 00                    | クロック入力 | LOW 固定   | HIGH 固定  | LOW 固定   | 未接続    |

| RSDS(LVDS)差動 | 01                    | LOW 固定 | クロック入力   |          | LOW 固定   | 未接続    |

| 発振回路         | 10                    | LOW 固定 | LOW 固定   | HIGH 固定  | X'tal 接続 |        |

## (3) 内部基準クロック周波数設定

内部基準クロック周波数設定は、CLK 入力信号の周波数および遡倍数に応じて表 6.4 に従い PLL\_IMGSIG\_CTL レジスタ (No.0x7F) の VCOSEL ビットを設定します。

表 6.4 VCOSEL 設定

| 内部基準クロック (入力クロック周波数(fCLKIN MHz)×遡倍数)                                        | VCOSEL ビット設定 |

|-----------------------------------------------------------------------------|--------------|

| $60\text{MHz} \leq f_{\text{CLKIN}} \times (\text{倍数}) \leq 100\text{MHz}$  | 0            |

| $100\text{MHz} \leq f_{\text{CLKIN}} \times (\text{倍数}) \leq 150\text{MHz}$ | 1            |

## 「制限注意事項」

内部基準クロック周波数(fclk)は下記のこととに注意して設定してください。

$$60\text{MHz} \leq \text{内部基準クロック周波数 (f}_{\text{CLKIN}} \text{)} \leq 150\text{MHz}$$

## (5) 遡倍設定

内蔵 PLL の遡倍設定は STCTL レジスタ (No.0x52) の STNUM ビットにより設定します。STNUM ビット設定にて基準となる遡倍数を 3, 6 遡倍の何れかを選択します。

## 6. 機能説明

### 6.4 制御部

#### 6.4.1 概要

制御部は内部 AFE およびラインセンサに対応した、制御信号を生成します。

- ラインセンサに対応

- ラインセンサおよび AFE の制御信号をプログラマブルに対応

- ラインセンサの駆動クロックパルスパターン出力をプログラマブルに対応

- AFE クロックパルスパターン出力をプログラマブルに対応

#### 6.4.2 画像取り込み動作

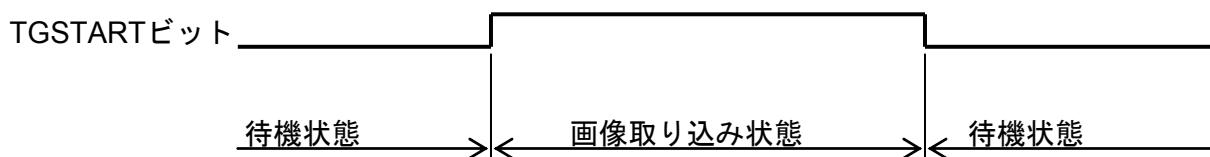

待機状態と画像取り込み状態の二つの状態があります。待機状態にするためには TGCTL レジスタ (No.0x50) の TGSTART ビットに“0”を設定する必要があります。一方、画像取り込み状態にするためには同じく TGSTART ビットに“1”を設定します。また、TGSTART ビットに“1”が設定されると画像取り込み動作を開始します。

図 6.7 待機状態と画像取り込み状態

#### 「制限注意事項」

画像取り込み状態のとき TGSTART ビット以外のレジスタ設定変更は禁止です。従って、画像データ取得状態のときに TGSTART ビット以外を変更した場合、正常動作を行わない場合があります。

#### 「制限注意事項 2」

ADCKEN ビットが“0”的とき TGSTART ビットを“1”に設定することは禁止です。ADCKEN ビットが“0”的とき TGSTART ビットを“1”にした場合、正常動作を行わない場合があります。

#### 6.4.3 画素処理

##### (1) 内部ステートおよび駆動パターン分解能設定

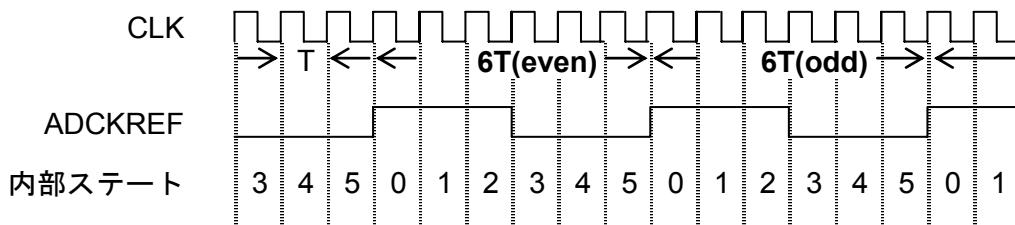

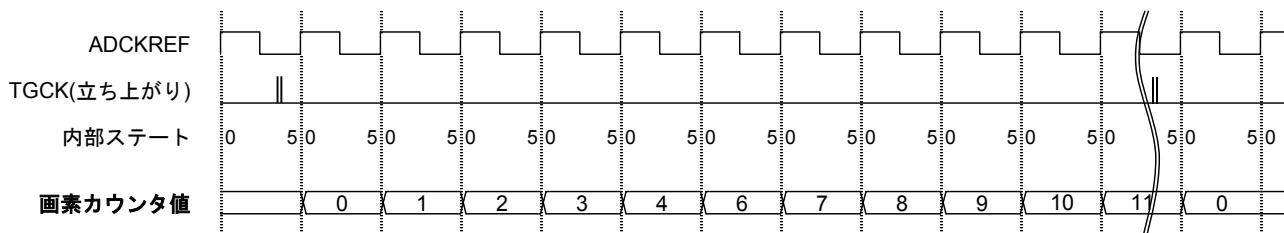

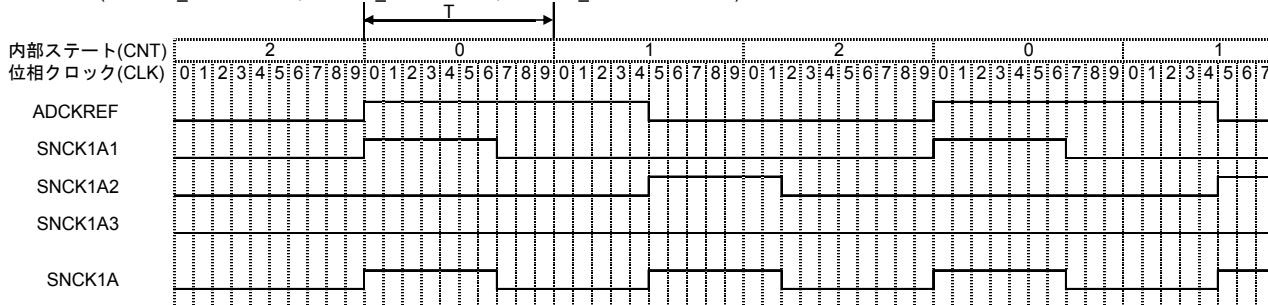

本 IC の 1 画素あたりの処理動作は全て内部ステートを基準に動作を行います。また、内部信号「ADCKREF」は内部ステートの基点となる信号でその周期は駆動パターン分解能設定に依存されます。ADCKREF 1 サイクルで 1 画素の処理時間となります。また、内部ステートのステート数は駆動パターン分解能設定に依存し、STCTL レジスタ (No.0x52) の STNUM ビットで設定します。例えば 6 分周設定時において分解能は 6 となり、ADCKREF は 6 ステートで 1 サイクルとなります。表 6.5 に駆動パターン分解能設定、全ステート数の関係を示します。

表 6.5 内部ステート数

| 駆動パターン分解能設定 |    | ステート範囲 | 全ステート数 |

|-------------|----|--------|--------|

| 設定値(STNUM)  | 分周 |        |        |

| “1”         | 6  | 0~5    | 6T     |

| “0”         | 3  | 0~2    | 3T     |

図 6.8 に駆動パターン分解能設定を 6 分周に設定した際の内部ステートと ADCKREF 信号の関係を示します。なお、図中は「T」は内部ステートの 1 ステート時間を示し、1 画素を 0~5 ステート（全 6T）で処理します。図中、ADCKREF 信号はパターン RAM にて 0~2 までが High、3~5 までが Low の設

定とした場合の例となります。

図 6.8 内部ステートと ADCKREF 信号の関係 (6 分周設定時)

## (2) 同期モード

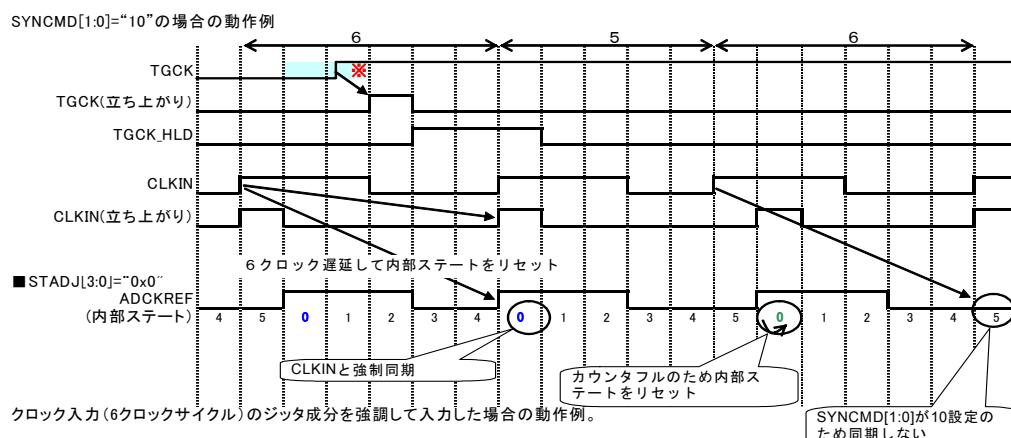

本 IC は内部ステートを CLK 入力信号に対する位相調整(同期化)する機能を有しています。STCTL レジスタ (No.0x52) の SYNCMD[1:0]ビットの設定によりその同期方法を選択することができます。

SYNCMD[1:0]ビットが“00”設定の場合、常に CLK 入力信号の立ち上がりに同期して内部ステートを初期化します。“10”設定の場合は、1 ライン分の処理開始を示すシフトパルストリガ信号(TGCK)の立ち上がりを検出後、次の CLK 入力信号の立ち上がりでのみ内部ステートの同期化を行います。そして、“11”設定の場合は同期化動作を行わず、内部カウンタフル検出でのみ内部ステートの初期化を行います。図 6.9 にそれぞれの設定時における動作例を示します。

外部から入力された TGCK 信号は、本 IC 内部でフィルタ処理を行うため、図 6.9 に示すとおり内部基準クロックで約 2 クロック遅延します。この遅延した信号 [図中 TGCK (立ち上がり)] の立ち上がりを基準に内部ステートの同期化を行います。また、TGCK 信号外部入力時において、TGMD レジスタ (No.0x51) の TGCKINV ビットを“1”に設定することにより、TGCK 信号を負論理で入力することができます。

なお、1 ライン処理についての詳細は 6.4.4 を参照してください。

図 6.9 同期モード設定例 (その 1)

図 6.10 同期モード内部動作例

## 6. 機能説明

### 「制限注意事項」

TGCK 立ち上がりが ADCKREF 1 サイクル遅れて検出することを防ぐために、ADCKREF 信号に対し TGCK(内部 TGCK 立ち上がり)の変化点が同時になることを避ける必要があります。そのため、CLKIN 信号の立ち上がり後 1 ステートを避けて TGCK を入力してください。

図 6.10 に内部動作例を示します。

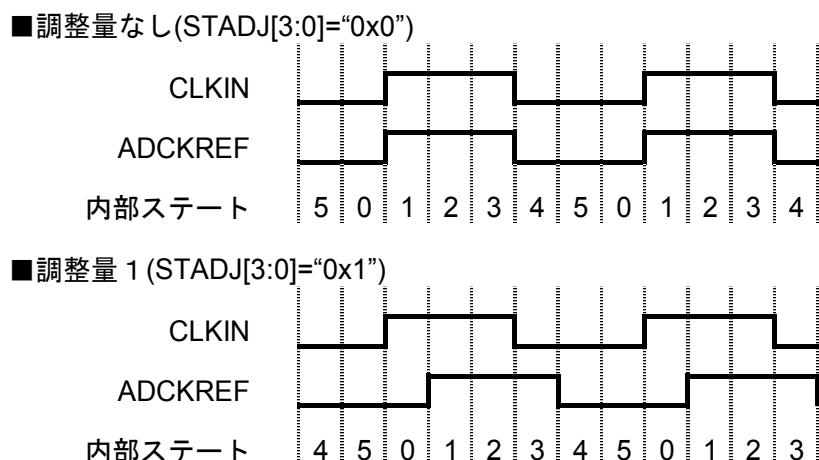

内部ステートを CLK 入力信号と同期する際、STCTL レジスタ (No.0x52) の STADJ[3:0] ビットにより、その位相差を設定することができます。図 6.11 に動作例を示します。なお、図 6.11 に示すとおり位相差設定の調整量なし (STADJ[3:0] = "0x0") の場合、CLK 入力信号と内部ステートの位相差は、内部基準クロックで 0 となります。

図 6.11 内部ステート同期化調整例

### 「制限注意事項 1」

6 遍倍動作時、STADJ[3:0] 遍倍数 (0x5) を越える設定は禁止となります。同様に 3 遍倍設定時は 0x02 を超える値の設定は禁止となります。

6 遍倍動作時、基準クロックの設定をあわせるためには、0x0 を設定してください。

3 遍倍動作時、基準クロックの設定をあわせるためには、0x0 を設定してください。

### 6.4.4 ライン処理

#### 1 ライン動作

1 ライン処理は TGCK 信号（トリガ信号）を基準に行います。TGCK 信号は 1 ライン処理の開始を示す信号であり、TGCK 信号のアクティブ検出後、1 ライン分の処理を開始します。なお、TGCK 信号の周期をライン周期といいます。

図 6.12 に 1 ライン処理の動作例を示します。

図 6.12 1 ライン処理動作例

1 ライン分の取り込み処理を行うために次のカウンタによって各タイミングを生成します。

- 画素カウンタ

- AFE から転送してきた画像データの画素数をカウント

- TGCK 信号立ち上がりを検出後、内部ステート先頭“0 ステート”からカウント開始

#### 6.4.5 シフト信号、クロックパルス等出力タイミング

(1) タイミング設定

シフト信号、クロックパルスの各出力タイミングおよび黒基準画素、白画素位置指定は、それぞれの状態変化をイベントとして扱い、イベントパターン設定レジスタ (PAT00~7F レジスタ) にて設定します。

イベントパターン設定は表 6.6 に示すとおりで、それぞれのイベントは 2 ワード単位で設定します。従って、全イベント数は 64 イベント (0x40 イベント) まで設定することができます。各イベントは画素単位に設定することができ、画素カウンタと PIXNUM[15:0] ビットが等しいとき、設定されているビットのイベントを発生させます。イベントの発生は所望のビットに“1”を設定することによって、対応するタイミングの状態が変化します。イベントの状態を変化させない場合は、“0”を設定してください。

また、TGMD レジスタ (No.0x51) の INTGCK ビットに“1”を設定し、TGCK 内部生成モードとして動作させる場合は、イベント設定の最終ラインに、SH1 から WHPIX の全ビットに“1”を設定し、かつ TGCK を生成させたいタイミングの画素カウンタ値を設定したパターンを設定してください。なお、PAT00~PAT7F レジスタ (No.0x00~3F) は 2 バンク構成となっています。0 バンク目である PAT00~PAT3F レジスタ (No.0x00~3F) をアクセスする場合には、必ず PATEN レジスタ (No.0x53) の EVENTPAT0EN ビットを“1”に設定してから行ってください。そして、アクセス終了後は、EVENTPAT0EN ビットを“0”に設定してください。同様に 1 バンク目である PAT40~7F レジスタ (No.0x00~3F) をアクセスする場合は、PATEN レジスタ (No.0x53) の EVENTPAT1EN ビットを設定してください。使用されないイベントパターン設定レジスタには 0xFFFF を設定してください。

表 6.6 各信号出力タイミング設定レジスタ

| レジスタ           | ビット   | 記号           | 意味                                                                                            |

|----------------|-------|--------------|-----------------------------------------------------------------------------------------------|

| PAT00、PAT02... | 0~15  | PIXNUM[15:0] | イベントを発生させる画素位置を設定 (画素カウンタとの比較)                                                                |

| PAT01、PAT03... | 0     | SH1          | SH1 信号タイミング                                                                                   |

|                | 1     | SH2          | SH2 信号タイミング                                                                                   |

|                | 2     | SH3          | SH3 信号タイミング                                                                                   |

|                | 3     | SH4          | GPIO1/SH4 信号タイミング                                                                             |

|                | 4     | SH5          | GPIO2/SH5 信号タイミング                                                                             |

|                | 5     | SH6          | SNCK1A/SNCK2/SH6 信号タイミング                                                                      |

|                | 6     | SH7          | SNCK1B/SNCK3/SH7 信号タイミング                                                                      |

|                | 7     | SH8          | SNCK1C/SNCK4/SH8 信号タイミング                                                                      |

|                | 8     | SH9          | SNCK1D/SNCK5/SH9 信号タイミング                                                                      |

|                | 9     | SLINE_RISE   | GPIO4/SLINEo 信号タイミング                                                                          |

|                | 10    | SLINE_FALL   | GPIO4/SLINEo 信号タイミング                                                                          |

|                | 11    | CLMP         | クランプタイミング                                                                                     |

|                | 12~13 | SNCKCTL[1:0] | クロックパターン出力タイミング<br>00 : (状態変化なし)<br>01 : パターン 1 出力<br>10 : パターン 2 出力<br>11 : 固定値出力、固定値出力切り替え※ |

|                | 14    | OBPIX        | 黒基準画素位置指定                                                                                     |

|                | 15    | WHPIX        | 白画素位置指定                                                                                       |

※固定値出力時において“11”設定のイベントが発生すると固定値出力を切り替えます

(SNCKxxLV1 設定レベル出力 ←→ SNCKxxLV2 設定レベル出力)

## 6. 機能說明

## 「制限注意事項 1」

PIXNUM のイベント発生、最大設定値は 0xFFFF までとなります。

また、最小値は 0x0001 からとなります。

0xFFFF はイベント設定を行わない箇所に設定してください。

## 「制限注意事項 2」

1 ライン周期の最後のクロックパターン出力タイミングは固定値出力に設定することを推奨します。

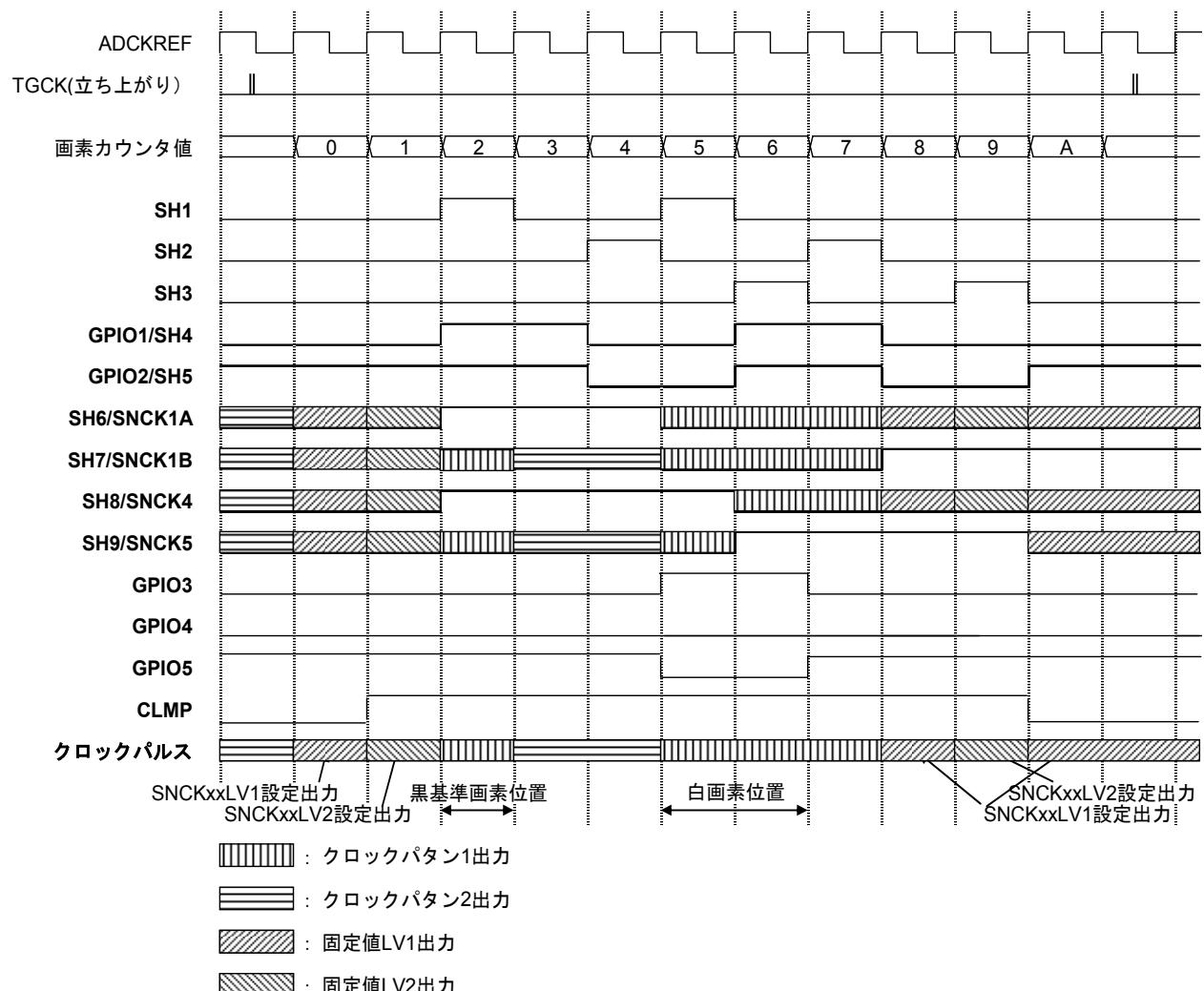

## (2) 動作例

1 チャネルモード動作時において、イベントパターン設定を表 6.7 のとおり設定した場合の動作例を図 6.13 に示します。

表 6.7 タイミング設定例

TGCK 入力モード時は、イベント信号のフィールドは 0xFFFF を設定、PIXNUM フィールドは TGCK を生成したいタイミングの画素カウンタ値を設定してください。

図 6.13 1 チャネルモード時動作例

## 6. 機能説明

### 6.4.6 クロックパルスのパターン出力

クロックパルス (SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK1E, SNCK2, SNCK3, SNCK4, SNCK5, SNCK6, CK1, CK2, ADCK) のパターン出力は、レジスタで設定された任意のパターンを出力します。クロックパルスには次のとおりラインセンサ駆動クロックパルスと AFE クロックパルスがあります。なお、CK1, CK2, ADCK はパターン周期出力数をレジスタにより、切り替えることができます。

- ラインセンサ駆動クロックパルス

- SNCK1A, SNCK1B, SNCK1C, SNCK1D, SNCK1E, SNCK2, SNCK3, SNCK4, SNCK5, SNCK6

- AFE クロックパルス

- CK1, CK2, ADCK

表 6.8 に示すとおりパターン周期は、各クロックパルスによって異なります。

表 6.8 パターン周期

| クロックパルス                                      | パターン周期  |          |

|----------------------------------------------|---------|----------|

|                                              | 3 分周    | 6 分周     |

| SNCK1A, SNCK1B,<br>SNCK1C, SNCK1D,<br>SNCK1E | 6T      | 12T      |

| SNCK2, SNCK3,<br>SNCK4, SNCK5,<br>SNCK6      | 3T      | 6T       |

| CK1, CK2, ADCK                               | 6T (3T) | 12T (6T) |

#### (1) クロックパルスパターン出力設定

各クロックパルスのパターン設定レジスタを表 6.9 に示します。

表 6.9 パターン設定レジスタ

| クロックパルス                                                   | パターン設定レジスタ                                    |                                               |

|-----------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

|                                                           | パターン1 出力時                                     | パターン2 出力時                                     |

| SNCK1A, SNCK1B, SNCK1C, SNCK1D,<br>SNCK1E, CK1, CK2, ADCK | SNCK1PAT00 (No.0x00)<br>~ADCKPAT00 (No.0x07)  | SNCK1PAT10 (No.0x08)<br>~ADCKPAT10 (No.0xF)   |

| SNCK2, SNCK3, SNCK4, SNCK5,<br>SNCK6,                     | SNCK2PAT00 (No.0x10)<br>~SNCK6PAT00 (No.0x14) | SNCK2PAT00 (No.0x18)<br>~SNCK6PAT00 (No.0x1C) |

PAT00～PAT1F レジスタ (No.0x00～1F) を読み書きする際には、必ず PATEN レジスタ (No.0x53) の SNCKPATEN ビットを“1”に設定してから行ってください。そして、読み書き終了後は、SNCKPATEN ビットを“0”に設定してください。使用されないステートのラインセンサ駆動クロックパルスパターン設定レジスタには null コード (0x0000) を設定してください。

また、SNCKCTL レジスタ (No.0x55～56) の SNCK1ALV1～SNCK6LV1 ビットおよび SNCK1ALV2～SNCK6LV2 ビットで、固定値出力期間の出力レベルを設定します。固定値出力設定は、信号ごとに SNCK1ALV1～SNCK6LV1 ビットおよび SNCK1ALV2～SNCK6LV2 ビットの 2 つの設定が用意されており、イベントが発生するたびにそれぞれ設定されている値に応じて出力を切り替えます。

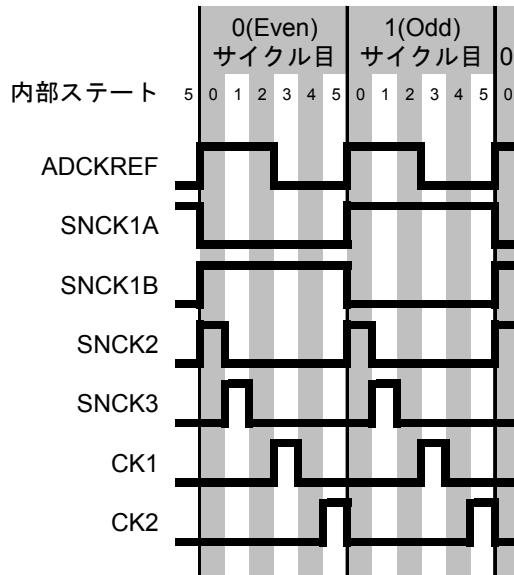

(2) パターン1出力時のラインセンサ駆動クロックパルスパターン出力

1チャネルモード、12分周設定時、ラインセンサ駆動クロックパルスパターン設定レジスタの設定例と出力される波形の例を示します。

表 6.10 1チャネルモードにおけるパターン1設定例

| Bit<br>レジスタ No   | Even サイクル |   |   |   |   |   | Odd サイクル |   |   |   |    |    | Reserved |    |    |    |

|------------------|-----------|---|---|---|---|---|----------|---|---|---|----|----|----------|----|----|----|

|                  | 0         | 1 | 2 | 3 | 4 | 5 | 6        | 7 | 8 | 9 | 10 | 11 | 12       | 13 | 14 | 15 |

| 0x00 SNCK1APAT00 | 0         | 0 | 0 | 0 | 0 | 0 | 1        | 1 | 1 | 1 | 1  | 1  | x        | x  | x  | x  |

| 0x01 SNCK1BPAT00 | 1         | 1 | 1 | 1 | 1 | 1 | 0        | 0 | 0 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x05 CK1PAT00    | 0         | 0 | 0 | 1 | 0 | 0 | 0        | 0 | 0 | 1 | 0  | 0  | x        | x  | x  | x  |

| 0x06 CK2PAT00    | 0         | 0 | 0 | 0 | 0 | 1 | 0        | 0 | 0 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x07 ADCKPAT00   | 1         | 1 | 1 | 0 | 0 | 0 | 1        | 1 | 1 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x10 SNCK2PAT00  | 1         | 0 | 0 | 0 | 0 | 0 | 0        | 0 | x | x | x  | x  | x        | x  | x  | x  |

| 0x11 SNCK3PAT00  | 0         | 1 | 0 | 0 | 0 | 0 | 0        | 0 | x | x | x  | x  | x        | x  | x  | x  |

x : don't care

図 6.14 1チャネルモード時のパターン1出力波形の例

## 6. 機能説明

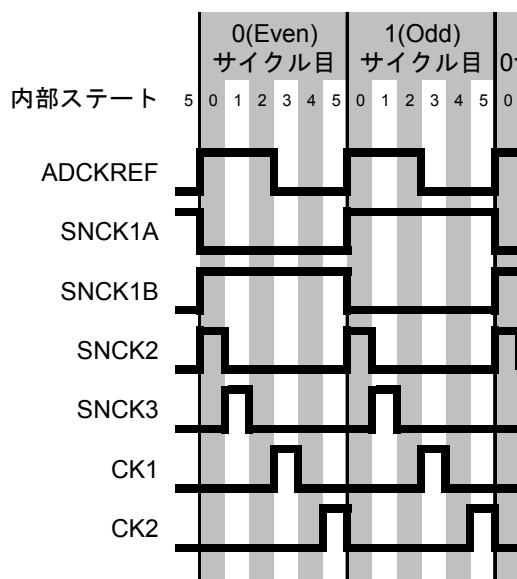

### (3) パターン2出力時のラインセンサ駆動クロックパルスパターン出力

パターン2出力時はパターン1出力時の内部ステート番号とは別のステート番号を用います。出力されるパターンは、表6.11に示すとおりパターン1と同様の出力方法にて出力されます。

表6.11 パターン2出力時の出力パターン

| Bit<br>レジスタ No   | Even サイクル |   |   |   |   |   | Odd サイクル |   |   |   |    |    | Reserved |    |    |    |

|------------------|-----------|---|---|---|---|---|----------|---|---|---|----|----|----------|----|----|----|

|                  | 0         | 1 | 2 | 3 | 4 | 5 | 6        | 7 | 8 | 9 | 10 | 11 | 12       | 13 | 14 | 15 |

| 0x08 SNCK1PAT10  | 0         | 0 | 0 | 0 | 0 | 0 | 1        | 1 | 1 | 1 | 1  | 1  | x        | x  | x  | x  |

| 0x09 SNCK1BPAT10 | 1         | 1 | 1 | 1 | 1 | 1 | 0        | 0 | 0 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x0D CK1PAT10    | 0         | 0 | 0 | 1 | 0 | 0 | 0        | 0 | 0 | 1 | 0  | 0  | x        | x  | x  | x  |

| 0x0E CK2PAT10    | 0         | 0 | 0 | 0 | 0 | 1 | 0        | 0 | 0 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x0F ADCKPAT10   | 1         | 1 | 1 | 0 | 0 | 0 | 1        | 1 | 1 | 0 | 0  | 0  | x        | x  | x  | x  |

| 0x18 SNCK2PAT10  | 1         | 0 | 0 | 0 | 0 | 0 | 0        | 0 | x | x | x  | x  | x        | x  | x  | x  |

| 0x19 SNCK3PAT10  | 0         | 1 | 0 | 0 | 0 | 0 | 0        | 0 | x | x | x  | x  | x        | x  | x  | x  |

図6.15 1チャネルモード時のパターン2出力波形の例

### (4) AFEクロックパルスのクロックパルスパターン出力切り替え機能

AFEクロックパルスのADCK, CK1, CK2信号は、パターン周期を切り替えて出力することができます。通常は、EVEN/ODDサイクル(6T/12T)出力ですが、TGCTLレジスタ(No.0x50)のAFEDISOEビットを“1”に設定することにより、EVENサイクルのみ(3T/6T)出力に設定可能です。

また、AFEクロックパルスはSNCK信号と同様イベントパターンレジスタのLV出力時は、クロックが停止してしまいますが、TGCTLレジスタ(No.0x50)のAFECKOUTビットを“1”に設定することにより、ADCKENビットが“1”的間パターン1を出力し続けることができます。AFE ICにてPLL等を搭載していてクロックを停止することが出来ない場合等に使用ください。

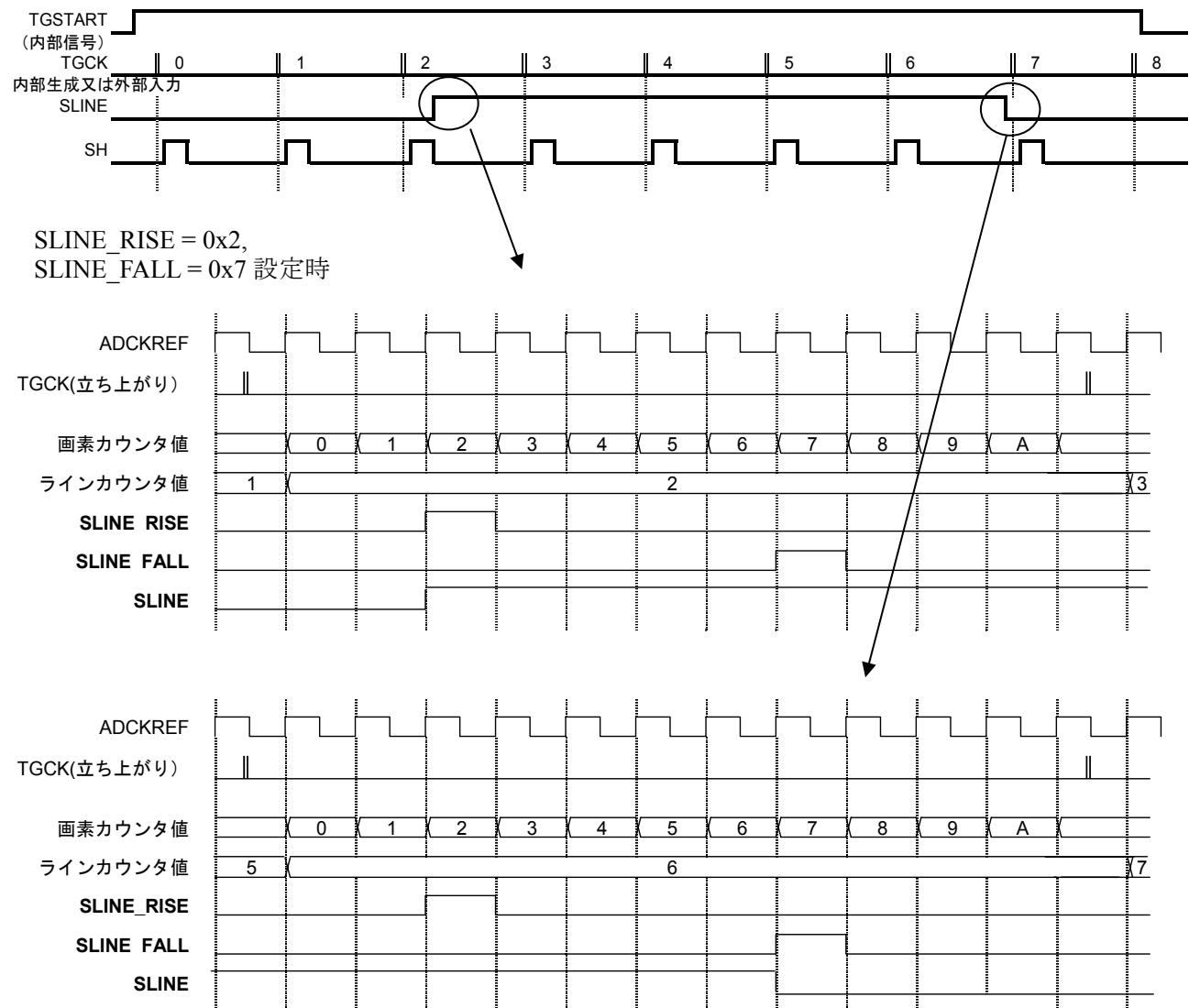

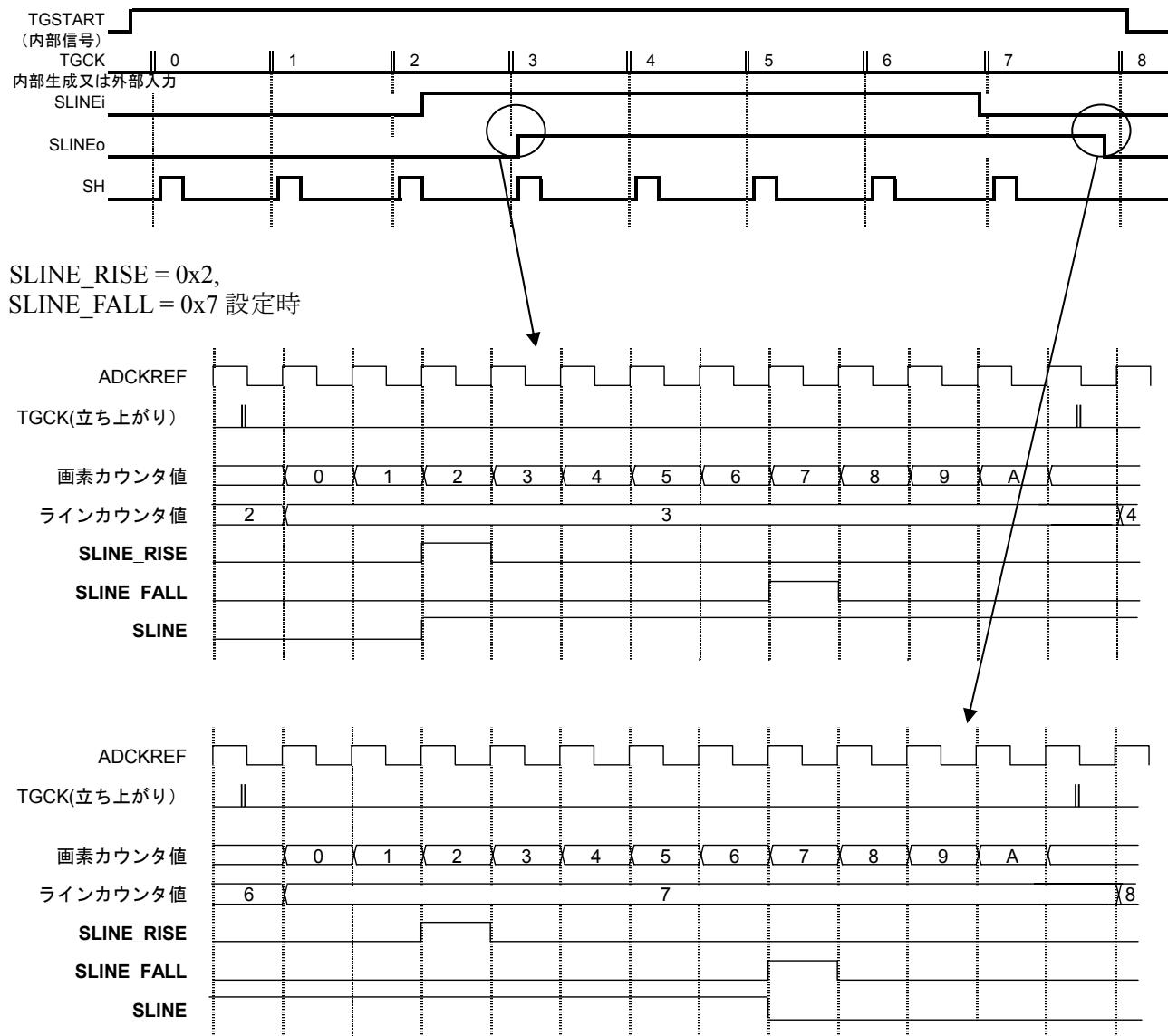

## 6.4.7 SLINE 出力処理

画像取り込み許可信号 (TGSTART ビット) のアクティブ後、SLINE の外部入力又は、レジスタ設定により出力を行います。

SLINE 信号は、TGMD レジスタ(No.0x51)の INSLINE、MUXSLINE ビットにより外部入力または内部生成を選択することができます。INSLINE ビットに“0”設定時、SLINE 信号を内部生成します。INSLINE ビットに“1”、MUXSLINE ビットに“1”を設定する事により立上りを外部入力、立下りを内部生成することができます。INSLINE ビットに “1”、MUXSLINE ビットに “0”を設定した場合は SLINEi にて外部入力したタイミングにて生成します。表 6.12 にて INSLINE、MUXSLINE ビット組み合わせ動作を示します。

SLINE 信号を内部生成、または立上り外部・立下り内部生成した場合、TGSTART ビットのアクティブ後、TGCK 信号を基準に副操作方向ライン数をカウントします。SLINEST レジスタ(No.0x40)設定値とイベントパターン設定レジスタ (No.0x00~0x3F) SLINE\_RISE ビットの設定箇所から SLINE 出力を開始し、SLINEEND レジスタ(No.0x41)設定値とイベントパターン設定レジスタ (No.0x00~0x3F) SLINE\_FALL ビットの設定箇所で SLINE 信号出力を終了します。

なお、SLINE 信号を外部生成時は、TGSTART ビットのアクティブ後 TGCK 立上り時に、入力される SLINE を同期化し出力します。

図 6.16 は SLINE 信号内部生成とし、SLINEST=2、SLINEEND=6 に設定した場合の動作例を示します。図 6.17 は SLINE 信号外部入力とした場合の動作例を示します。

図 6.16 SLINE 信号内部生成動作例

## 6. 機能説明

図 6.17 SLINE 信号外部入力動作例

表 6.12 INSLINE、MUXSLINE ビット組み合わせ動作表

|                        | INSLINE/MUXSLINE 組み合わせ                    |       |                                           |                                           |

|------------------------|-------------------------------------------|-------|-------------------------------------------|-------------------------------------------|

|                        | “0/0”                                     | “0/1” | “1/0”                                     | “1/1”                                     |

| <b>SLINE_RISE 生成方法</b> | ラインカウンタ設定<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 | 設定禁止  | SLINEi 入力<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 | SLINEi 入力<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 |

| <b>SLINE_FALL 生成方法</b> | ラインカウンタ設定<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 | 設定禁止  | SLINEi 入力<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 | ラインカウンタ設定<br>タイミング<br>+<br>画素カウンタ<br>遅延出力 |

## 6.4.8 制御信号出力遅延設定

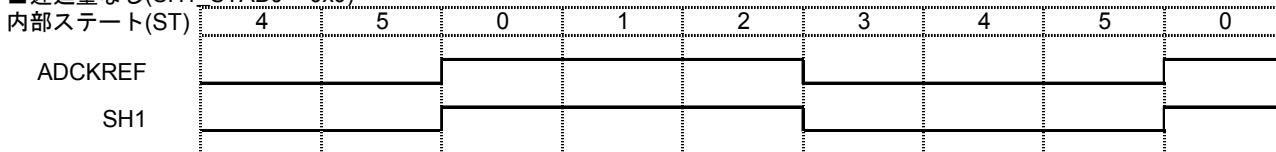

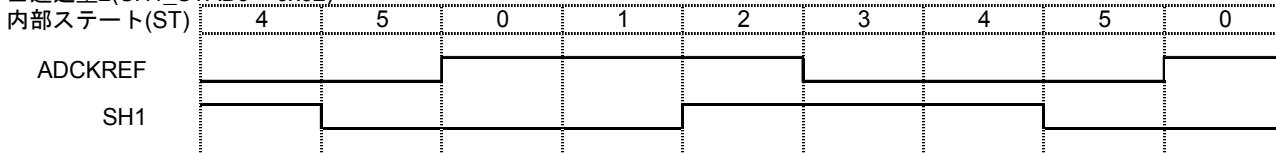

## (1) シフト信号出力遅延

SH<sub>1</sub>～SH<sub>9</sub> および CLMP～WHPIX 信号の変化タイミングの遅延量を設定します。設定値により、SH<sub>1</sub>～SH<sub>9</sub> および CLMP～WHPIX 信号の立ち上がり、立ち下がりタイミングは設定値×T 時間、遅延します。

図 6.18 は SH<sub>1</sub> 信号の出力遅延の動作例です。なお、SH<sub>2</sub>～9 および CLMP～WHPIX 信号も同様の動作を行います。

## ■遅延量なし(SH1\_STADJ = 0x0)

## ■遅延量2(SH1\_STADJ = 0x02)

パルス幅：1画素分

図 6.18 SH<sub>1</sub> 信号出力遅延量設定動作例

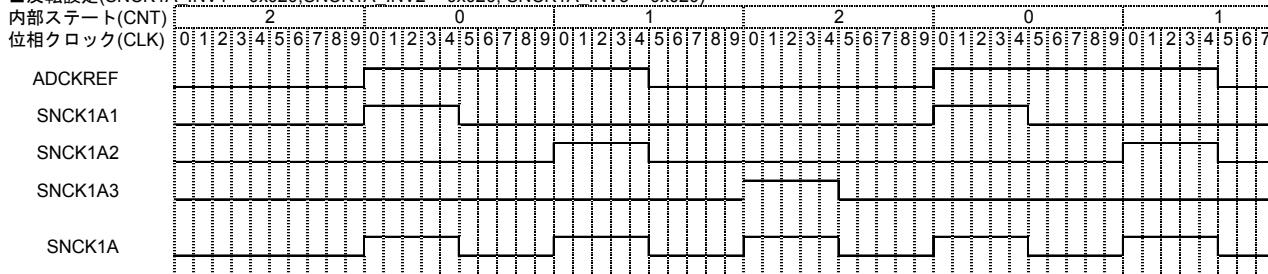

## (2) クロックパルス出力遅延設定

クロックパルスに遅延を加えて出力することができます。遅延設定についてはステート 0～ステート 5 ごとに個別に 3 種類の遅延を組み合わせて設定することができます。また、レジスタ設定の組み合わせにより、パルス幅を変更することができます。出力遅延は T/10 の位相クロックにより遅延を個別に設定することができ、かつ正転出力、反転出力を個別に選択して出力することができます。設定する際は、表 6.13 にしたがって有効とする出力クロックのビットに“1”を設定してください。

表 6.13 SNCK クロック該当表

| SNCK クロック該当            |               |                        |                   |                        |             |

|------------------------|---------------|------------------------|-------------------|------------------------|-------------|

| ビット名<br>(No.0x49～0x4B) | 該当クロック        | ビット名<br>(No.0x4C～0x4E) | 該当クロック            | ビット名<br>(No.0x4C～0x4E) | 該当ステート      |

| SNCK_CLKADJ*[9]        | 位相クロック 9 出力許可 | SNCK_INV*[9]           | 反転出力位相クロック 9 出力許可 | ADJ*_STATE[5]          | ステート 5 出力許可 |

| SNCK_CLKADJ*[8]        | 位相クロック 8 出力許可 | SNCK_INV*[8]           | 反転出力位相クロック 8 出力許可 | ADJ*_STATE[4]          | ステート 4 出力許可 |

| SNCK_CLKADJ*[7]        | 位相クロック 7 出力許可 | SNCK_INV*[7]           | 反転出力位相クロック 7 出力許可 | ADJ*_STATE[3]          | ステート 3 出力許可 |

| SNCK_CLKADJ*[6]        | 位相クロック 6 出力許可 | SNCK_INV*[6]           | 反転出力位相クロック 6 出力許可 | ADJ*_STATE[2]          | ステート 2 出力許可 |

| SNCK_CLKADJ*[5]        | 位相クロック 5 出力許可 | SNCK_INV*[5]           | 反転出力位相クロック 5 出力許可 | ADJ*_STATE[1]          | ステート 1 出力許可 |

| SNCK_CLKADJ*[4]        | 位相クロック 4 出力許可 | SNCK_INV*[4]           | 反転出力位相クロック 4 出力許可 | ADJ*_STATE[0]          | ステート 0 出力許可 |

| SNCK_CLKADJ*[3]        | 位相クロック 3 出力許可 | SNCK_INV*[3]           | 反転出力位相クロック 3 出力許可 |                        |             |

| SNCK_CLKADJ*[2]        | 位相クロック 2 出力許可 | SNCK_INV*[2]           | 反転出力位相クロック 2 出力許可 |                        |             |

| SNCK_CLKADJ*[1]        | 位相クロック 1 出力許可 | SNCK_INV*[1]           | 反転出力位相クロック 1 出力許可 |                        |             |

| SNCK_CLKADJ*[0]        | 位相クロック 0 出力許可 |                        |                   |                        |             |

## 6. 機能説明

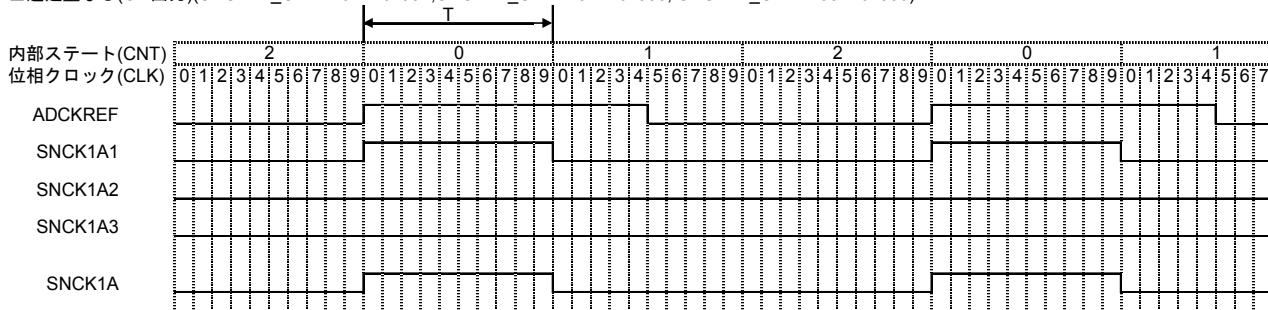

■遅延量なし(OR出力)(SNCK1A\_CLKADJ1 = 0x001, SNCK1A\_CLKADJ2 = 0x000, SNCK1A\_CLKADJ3 = 0x000)

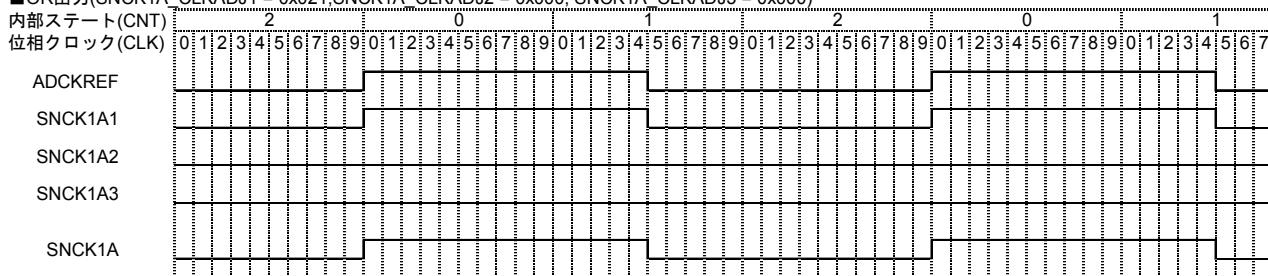

■OR出力(SNCK1A\_CLKADJ1 = 0x021, SNCK1A\_CLKADJ2 = 0x000, SNCK1A\_CLKADJ3 = 0x000)

図 6.19 SNCK1A 信号 OR 出力遅延量設定動作例

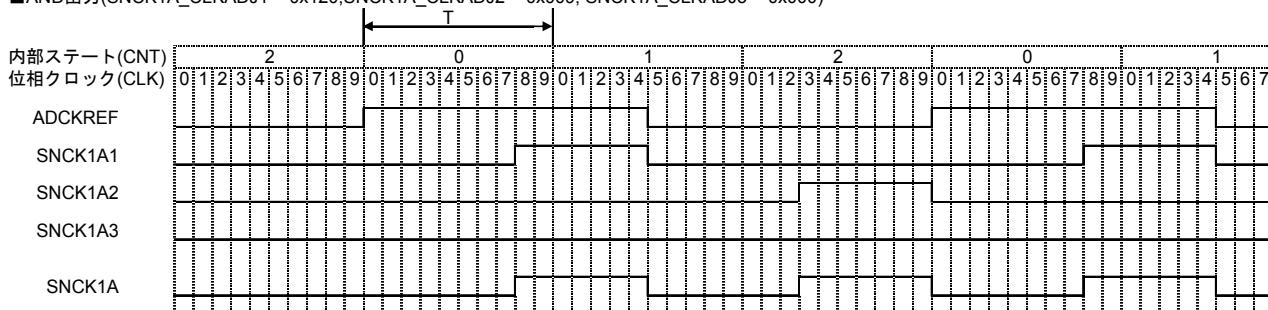

■AND出力(SNCK1A\_CLKADJ1 = 0x120, SNCK1A\_CLKADJ2 = 0x009, SNCK1A\_CLKADJ3 = 0x000)

■AND出力(SNCK1A\_CLKADJ1 = 0x021, SNCK1A\_CLKADJ2 = 0x021, SNCK1A\_CLKADJ3 = 0x021)

図 6.20 SNCK1A 信号 AND 出力遅延量設定動作例

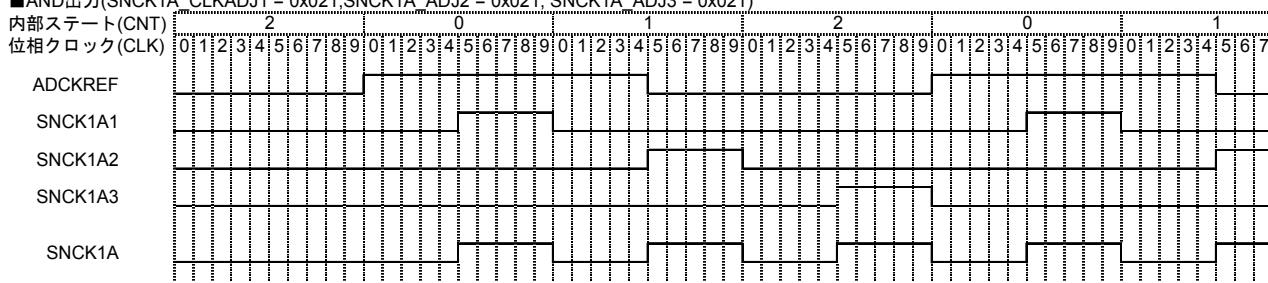

- AND出力(SNCK1A\_CLKADJ1 = 0x081, SNCK1A\_CLKADJ2 = 0x00A, SNCK1A\_CLKADJ3 = 0x000)

■反転設定(SNCK1A\_INV1 = 0x081, SNCK1A\_INV2 = 0x000, SNCK1A\_CLKINV3 = 0x000)

- AND出力(SNCK1A\_CLKADJ1 = 0x021, SNCK1A\_CLKADJ2 = 0x021, SNCK1A\_CLKADJ3 = 0x021)

■反転設定(SNCK1A\_INV1 = 0x020, SNCK1A\_INV2 = 0x020, SNCK1A\_CLKINV3 = 0x020)

図 6.21 SNCK1A 信号 AND 反転出力遅延量設定動作例

遅延設定レジスタを設定する際には、SNCK\_ADJ\_PAGESEL レジスタ (No.0x48) を設定してレジスタ設定ページを切り替えてから行ってください。

表 6.14 に各信号の遅延量設定レジスタおよびページ設定レジスタを示します。

表 6.14 クロックパルス遅延量設定レジスタ

| 信号名                                                | 遅延量設定 |                              |                    |           |                 |

|----------------------------------------------------|-------|------------------------------|--------------------|-----------|-----------------|

|                                                    | ページ設定 | レジスタ                         | 遅延設定               | AND/OR 切替 | 出力論理反転切替        |

| SNCK1A、<br>SNCK1B、<br>SNCK1C、<br>SNCK1D、<br>SNCK1E | 0x0   | SNCK1A_CLKADJ/<br>SNCK1A_INV | SNCK1A_CLKADJ[9:0] | ANDxOR1A  | SNCK1A_INV[9:1] |

|                                                    | 0x1   | SNCK1B_CLKADJ/<br>SNCK1B_INV | SNCK1B_CLKADJ[9:0] | ANDxOR1B  | SNCK1B_INV[9:1] |

|                                                    | 0x2   | SNCK1C_CLKADJ/<br>SNCK1C_INV | SNCK1C_CLKADJ[9:0] | ANDxOR1C  | SNCK1C_INV[9:1] |

|                                                    | 0x3   | SNCK1D_CLKADJ/<br>SNCK1D_INV | SNCK1D_CLKADJ[9:0] | ANDxOR1D  | SNCK1D_INV[9:1] |

|                                                    | 0x4   | SNCK1E_CLKADJ/<br>SNCK1E_INV | SNCK1E_CLKADJ[9:0] | ANDxOR1E  | SNCK1E_INV[9:1] |

| SNCK2、<br>SNCK3、<br>SNCK4、<br>SNCK5、<br>SNCK6      | 0x5   | SNCK2_CLKADJ/<br>SNCK2_INV   | SNCK2_CLKADJ[9:0]  | ANDxOR2   | SNCK2_INV[9:1]  |

|                                                    | 0x6   | SNCK3_CLKADJ/<br>SNCK3_INV   | SNCK3_CLKADJ[9:0]  | ANDxOR3   | SNCK3_INV[9:1]  |

|                                                    | 0x7   | SNCK4_CLKADJ/<br>SNCK4_INV   | SNCK4_CLKADJ[9:0]  | ANDxOR4   | SNCK4_INV[9:1]  |

|                                                    | 0x8   | SNCK5_CLKADJ/<br>SNCK5_INV   | SNCK5_CLKADJ[9:0]  | ANDxOR5   | SNCK5_INV[9:1]  |

|                                                    | 0x9   | SNCK6_CLKADJ/<br>SNCK6_INV   | SNCK6_CLKADJ[9:0]  | ANDxOR6   | SNCK6_INV[9:1]  |

| CK1                                                | 0xA   | CK1_CLKADJ/<br>CK1_INV       | CK1_CLKADJ[9:0]    | ANDxORCK1 | CK1_INV[9:1]    |

| CK2                                                | 0xB   | CK2_CLKADJ/<br>CK2_INV       | CK2_CLKADJ[9:0]    | ANDxORCK2 | CK2_INV[9:1]    |

| ADCK                                               | 0xC   | ADCK_CLKADJ/<br>ADCK_INV     | ADCK_CLKADJ[9:0]   | ANDxORA   | ADCK_INV[9:1]   |

## 6. 機能説明

SNCKXSHCTL レジスタ (No.0x57) の SNCKXXxSHX に“1”を設定することにより SNCK 信号に SH 信号との論理和を出力することができます。

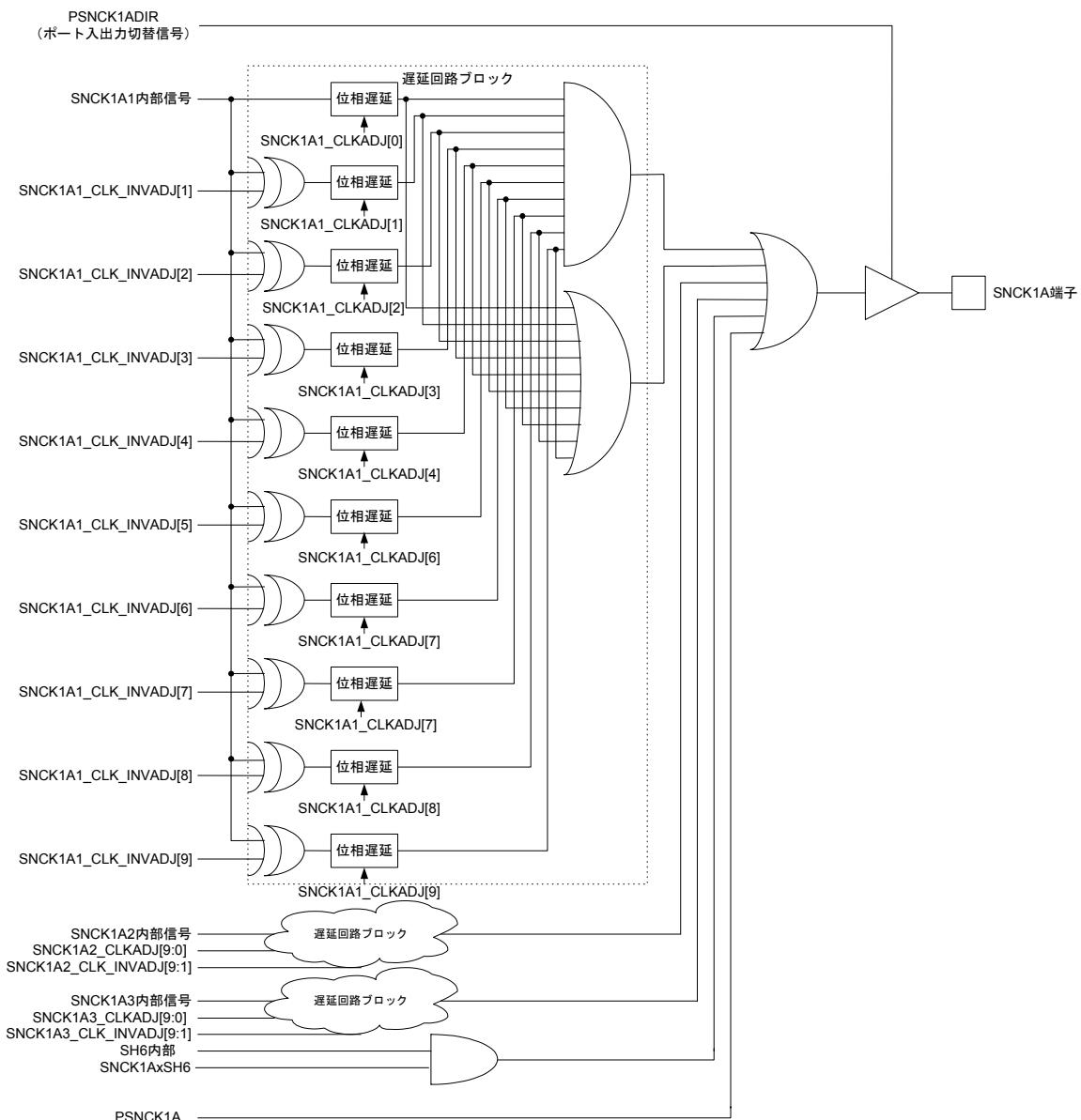

図 6.22 に出力遅延回路構成図を示します。

図 6.22 出力遅延回路

## 6.4.9 制御信号出力極性設定

表 6.15 は AFE 転送クロック信号、ラインセンサ駆動クロックパルスおよびシフト信号の極性を設定するレジスタを示します。本ビットに“1”を設定することにより該当信号の出力論理を反転することができます。

表 6.15 制御信号出力極性設定レジスタ

| 信号             | 信号名       | 極性設定             |           |

|----------------|-----------|------------------|-----------|

|                |           | レジスタ             | ビット       |

| AFE タイミング信号    | CLMP      | POLCTL(No.0x58)  | CLMPPOL   |

| シフト信号          | SH1       |                  | SH1POL    |

|                | SH2       |                  | SH2POL    |

|                | SH3       |                  | SH3POL    |

|                | SH4       |                  | GPIO1POL  |

|                | SH5       |                  | GPIO2POL  |

|                | SH6       |                  | SH6POL    |

|                | SH7       |                  | SH7POL    |

|                | SH8       |                  | SH8POL    |

|                | SH9       |                  | SH9POL    |

|                | OBPIX     |                  | GPIO3POL  |

|                | SLINE     |                  | GPIO4POL  |

|                | WHPIX     |                  | GPIO5POL  |

| ラインセンサ駆動クロック信号 | SNCK1A    | SNCKINV(No.0x54) | SNCK1AINV |

| SNCK1B         | SNCK1BINV |                  |           |

| SNCK1C         | SNCK1CINV |                  |           |

| SNCK1D         | SNCK1DINV |                  |           |

| SNCK1E         | SNCK1EINV |                  |           |

| SNCK2          | SNCK2INV  |                  |           |

| SNCK3          | SNCK3INV  |                  |           |

| SNCK4          | SNCK4INV  |                  |           |

| SNCK5          | SNCK5INV  |                  |           |

| SNCK6          | SNCK6INV  |                  |           |

## 「制限注意事項」

SH6～SH9 信号を SNCK 信号として使用する際、SNCK 信号と SH 信号の論理和の出力を行っていますので、それぞれの信号の出力論理が排他的になるよう SH6POL～SH9POL を設定してください。

## 6. 機能説明

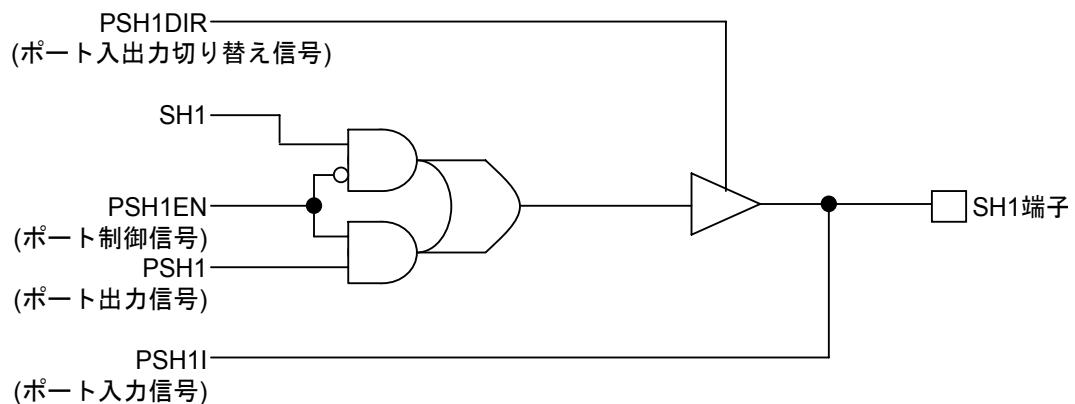

### 6.4.10 兼用汎用ポート

表 6.16 に各制御信号と兼用の汎用ポートを示します。

汎用ポート機能有効設定は GPIOEN1/GPIOEN2 レジスタ(No.0x59～5A)で制御します。“0”を設定するとそのレジスタビットに対応した端子は、該当端子の機能信号を出力します。また、“1”を設定すると対応端子の汎用 I/O ポート機能を有効にします。各信号とも初期化時は汎用ポート設定 (“1”設定) となっているため、機能信号を出力する際は、GPIOEN1/GPIOEN2 レジスタ(No.0x59～5A)の該当端子のビットに“0”を設定してください。

なお、SNCK 端子と SH1～3/GPIO1～4 端子において汎用ポートの構成が異なります。そのため、SNCK 端子を汎用ポートとして使用する場合には、SNCK\_CLKADJ1～3/SNCK\_INV1～3 レジスタ(No.0x48～4E)の出力クロック選択ビットを全て“0”に設定、ANDxOR ビットも“0”に設定してください。

汎用ポート入出力切り替えは GPIODIR1/GPIODIR2/GPIODIR3 レジスタ(No.0x5B～5D)で制御します。GPIODIR1/GPIODIR2 は、“00”を設定するとそのレジスタに対応した端子は、入力ポートとなります。また、“01”/“10”を設定すると出力ポートとなります。なお、機能信号を出力する場合は、“01”/“10”に設定し出力状態にする必要があります。

“01”設定時は、出力電流が 12mA 駆動となり、“10”設定時は、出力電流が 24mA 駆動となります。出力負荷に応じて設定を変更することが可能です。

GPIODIR3 は、“0”を設定するとそのレジスタに対応した端子は、入力ポートとなります。また、“1”を設定すると出力ポートとなります。なお、機能信号を出力する場合は、“1”に設定し出力状態にする必要があります。

該当端子が出力設定となっている場合、汎用ポートへの信号出力は、GPIOST1/GPIOST2 レジスタ(No.0x5E～5F)をライトするとレジスタに設定された値を出力します。一方、GPIOST1/GPIOST2 レジスタ(No.0x5E～5F)をリードすると汎用ポートの設定に関わらず、対応する端子の状態が読み出せます。

表 6.16 汎用ポート

| 信号端子名      | 汎用ポート制御レジスタ      |                                   |                  |                  |

|------------|------------------|-----------------------------------|------------------|------------------|

|            | 汎用ポート機能有効設定      | 汎用ポート入出力切替                        | 汎用ポート出力          | 汎用ポート入力          |

| SNCK1A/SH6 | GPIOEN1(No.0x59) | GPIODIR1/GPIODIR2<br>(No.0x5B～5C) | GPIOST1(No.0x5E) | GPIOST1(No.0x5E) |

| SNCK1B/SH7 |                  |                                   |                  |                  |

| SNCK1C/SH8 |                  |                                   |                  |                  |

| SNCK1D/SH9 |                  |                                   |                  |                  |

| SNCK1E     |                  |                                   |                  |                  |

| SNCK2/SH6  |                  |                                   |                  |                  |

| SNCK3/SH7  |                  |                                   |                  |                  |

| SNCK4/SH8  |                  |                                   |                  |                  |

| SNCK5/SH9  |                  |                                   |                  |                  |

| SNCK6      |                  |                                   |                  |                  |

| SH1        | GPIOEN2(No.0x5A) | GPIODIR3(No.0x5D)                 | GPIOST2(No.0x5F) | GPIOST2(No.0x5F) |

| SH2        |                  |                                   |                  |                  |

| SH3        |                  |                                   |                  |                  |

| GPIO1/SH4  |                  |                                   |                  |                  |

| GPIO2/SH5  |                  |                                   |                  |                  |

| GPIO3      |                  |                                   |                  |                  |

| GPIO4      |                  |                                   |                  |                  |

| GPIO5      |                  |                                   |                  |                  |

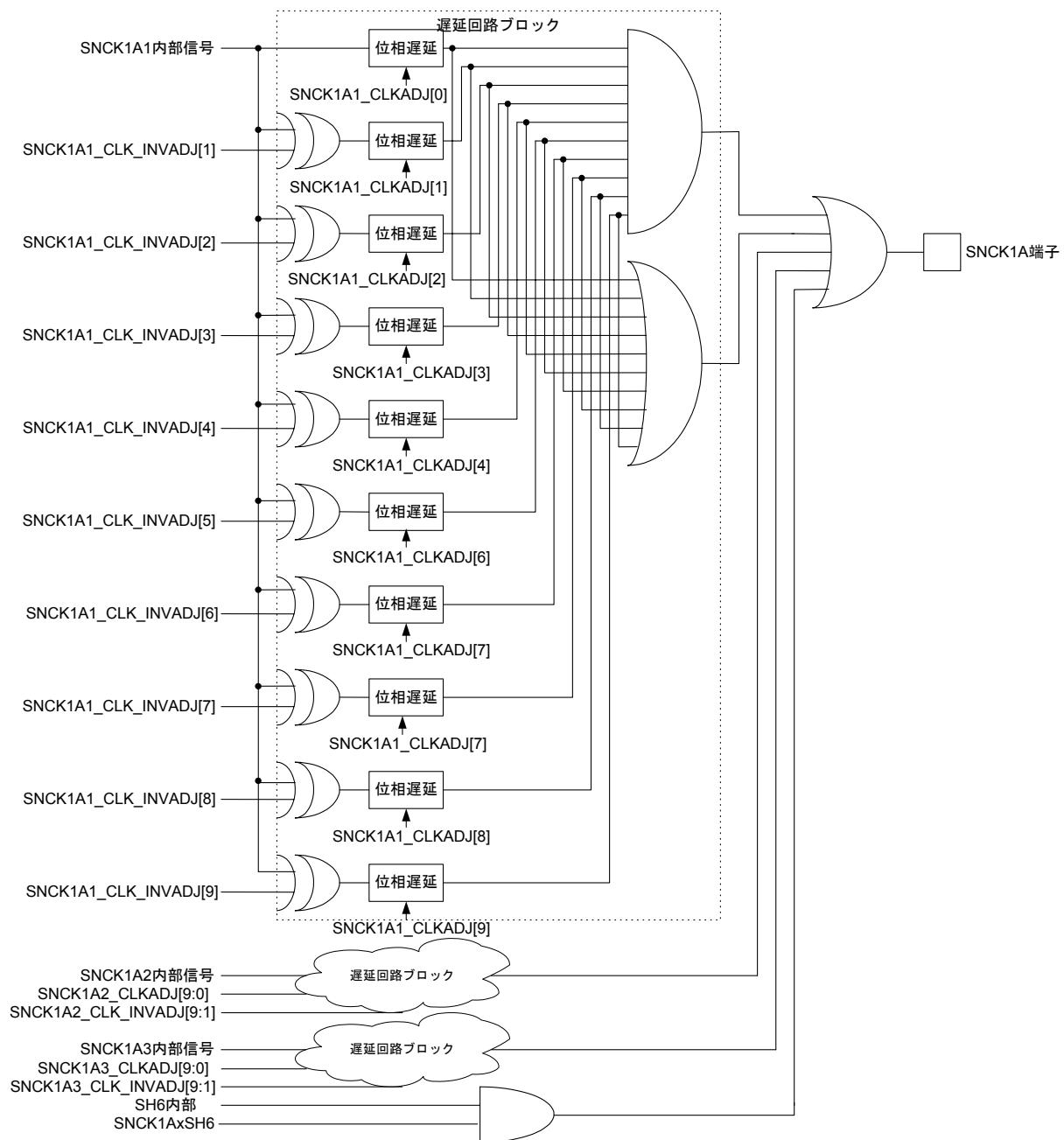

図 6.23 は SH1 信号の汎用ポート部分の内部接続を示しています。また、SH2、SH3、GPIO1、GPIO2、GPIO3、GPIO4 の各端子も同様の接続となっています。

図 6.24 は SNCK1A 信号の汎用ポート部分の内部接続を示しています。

SNCK1B、SNCK1C、SNCK1D、SNCK1E、SNCK2、SNCK3、SNCK4、SNCK5、SNCK6 の端子も同様の接続となっています。

図 6.23 SH/GPIO 汎用ポート内部接続

図 6.24 SNCK1A 汎用ポート内部接続

## 7. レジスタ

### 7. レジスタ

#### 7.1 メモリマップ

| No.  | Address | Description                            |                                          |                                          | Size | Access Size |

|------|---------|----------------------------------------|------------------------------------------|------------------------------------------|------|-------------|

| 0x00 | 0x00    | SNCK Pattern Registers (No.0x00 ~0x1F) | EVENT Pattern1 Registers (No.0x00 ~0x3F) | EVENT Pattern2 Registers (No.0x40 ~0x7F) | 128B | 16-bit      |

| 0x3F | 0x7F    | Reserved                               |                                          |                                          |      |             |

| 0x40 | 0x80    | Timing Parameter Registers             |                                          |                                          | 32B  |             |

| 0x4F | 0x9F    |                                        |                                          |                                          |      |             |

| 0x50 | 0xA0    | Control Registers                      |                                          |                                          | 32B  |             |

| 0x5F | 0xBF    |                                        |                                          |                                          |      |             |

| 0x60 | 0xC0    | Reserved                               |                                          |                                          | 32B  |             |

| 0x6F | 0xDF    |                                        |                                          |                                          |      |             |

| 0x70 | 0xE0    | AFE & External Interface Registers     |                                          |                                          | 32B  |             |

| 0x7F | 0xFF    |                                        |                                          |                                          |      |             |

## 7.2 レジスタマップ

| No.                                | Address | Register Name   | R/W | Function                  |

|------------------------------------|---------|-----------------|-----|---------------------------|

| SNCK/Event Pattern Registers       |         |                 |     |                           |

| 0x00                               | 0x00    | PAT00           | R/W | パタン設定レジスタNo.00            |

| :                                  | :       | :               | R/W | :                         |

| 0x3F                               | 0x7E    | PAT3F           | R/W | パタン設定レジスタNo.3F            |

| Timing Parameter Registers         |         |                 |     |                           |

| 0x40                               | 0x80    | SLINEST         | R/W | SLINE開始ライン設定レジスタ          |

| 0x41                               | 0x82    | SLINEEND        | R/W | SLINE終了ライン設定レジスタ          |

| 0x42                               | 0x84    | SH_ADJ1         | R/W | シフトパルス信号出力遅延設定レジスタ1       |

| 0x43                               | 0x86    | SH_ADJ2         | R/W | シフトパルス信号出力遅延設定レジスタ2       |

| 0x44                               | 0x88    | SH_ADJ3         | R/W | クロックパルス信号出力遅延設定レジスタ1      |

| 0x45                               | 0x8A    | SH_ADJ4         | R/W | クロックパルス信号出力遅延設定レジスタ2      |

| 0x46                               | 0x8C    | (Reserved)      |     |                           |

| 0x47                               | 0x8E    | (Reserved)      |     |                           |

| 0x48                               | 0x90    | SNCK_ADJ_PAGESE | R/W | クロックパルス遅延設定ページ選択レジスタ      |

| 0x49                               | 0x92    | SNCK_CLKADJ1    | R/W | クロックパルス信号出力遅延設定レジスタ1      |

| 0x4A                               | 0x94    | SNCK_CLKADJ2    | R/W | クロックパルス信号出力遅延設定レジスタ2      |

| 0x4B                               | 0x96    | SNCK_CLKADJ3    | R/W | クロックパルス信号出力遅延設定レジスタ3      |

| 0x4C                               | 0x98    | SNCK_INV1       | R/W | クロックパルス反転出力遅延設定レジスタ1      |

| 0x4D                               | 0x9A    | SNCK_INV2       | R/W | クロックパルス反転出力遅延設定レジスタ2      |

| 0x4E                               | 0x9C    | SNCK_INV3       | R/W | クロックパルス反転出力遅延設定レジスタ3      |

| 0x4F                               | 0x9E    | (Reserved)      |     |                           |

| Control Registers                  |         |                 |     |                           |

| 0x50                               | 0xA0    | TGCTL           | R/W | タイミング生成機能制御レジスタ           |

| 0x51                               | 0xA2    | TGMD            | R/W | タイミング生成機能設定レジスタ           |

| 0x52                               | 0xA4    | STCTL           | R/W | 内部ステート制御レジスタ              |

| 0x53                               | 0xA6    | PATEN           | R/W | パタン設定制御レジスタ               |

| 0x54                               | 0xA8    | SNCKINV         | R/W | ラインセンサ駆動クロックパルス極性設定レジスタ   |

| 0x55                               | 0xAA    | SNCK1CTL        | R/W | ラインセンサ駆動クロックパルスバタン設定レジスタ1 |

| 0x56                               | 0xAC    | SNCK2CTL        | R/W | ラインセンサ駆動クロックパルスバタン設定レジスタ2 |

| 0x57                               | 0xAE    | SNCKXSHCTL      | R/W | ラインセンサ駆動クロックパルス出力設定レジスタ   |

| 0x58                               | 0xB0    | POLCTL          | R/W | 極性制御レジスタ                  |

| 0x59                               | 0xB2    | GPIOEN1         | R/W | 汎用ポート制御レジスタ1              |

| 0x5A                               | 0xB4    | GPIOEN2         | R/W | 汎用ポート制御レジスタ2              |

| 0x5B                               | 0xB6    | GPIODIR1        | R/W | 汎用ポート入出力切り替えレジスタ1         |

| 0x5C                               | 0xB8    | GPIODIR2        | R/W | 汎用ポート入出力切り替えレジスタ2         |

| 0x5D                               | 0xBA    | GPIODIR3        | R/W | 汎用ポート入出力切り替えレジスタ3         |

| 0x5E                               | 0xBC    | GPIOST1         | R/W | 汎用ポートレジスタ1                |

| 0x5F                               | 0xBE    | GPIOST2         | R/W | 汎用ポートレジスタ2                |

| 0x60                               | 0xC0    | (Reserved)      |     |                           |

| 0x61                               | 0xC2    | (Reserved)      |     |                           |

| 0x62                               | 0xC4    | (Reserved)      |     |                           |

| 0x63                               | 0xC6    | (Reserved)      |     |                           |

| 0x64                               | 0xC8    | (Reserved)      |     |                           |

| 0x65                               | 0xCA    | (Reserved)      |     |                           |

| 0x66                               | 0xCC    | (Reserved)      |     |                           |

| 0x67                               | 0xCE    | (Reserved)      |     |                           |

| 0x68                               | 0xD0    | (Reserved)      |     |                           |

| 0x69                               | 0xD2    | (Reserved)      |     |                           |

| 0x6A                               | 0xD4    | (Reserved)      |     |                           |

| 0x6B                               | 0xD6    | (Reserved)      |     |                           |

| 0x6C                               | 0xD8    | (Reserved)      |     |                           |

| 0x6D                               | 0xDA    | (Reserved)      |     |                           |

| 0x6E                               | 0xDC    | (Reserved)      |     |                           |

| 0x6F                               | 0xDE    | (Reserved)      |     |                           |

| AFE & External Interface Registers |         |                 |     |                           |

| 0x70                               | 0xE0    | ANA_RESET       | R/W | アナログモジュールリセットレジスタ         |

| 0x71                               | 0xE2    | (Reserved)      |     |                           |

| 0x72                               | 0xE4    | (Reserved)      |     |                           |

| 0x73                               | 0xE6    | (Reserved)      |     |                           |

| 0x76                               | 0xE8    | (Reserved)      |     |                           |

| 0x77                               | 0xEA    | (Reserved)      |     |                           |

| 0x76                               | 0xEC    | (Reserved)      |     |                           |

| 0x77                               | 0xEE    | (Reserved)      |     |                           |

| 0x78                               | 0xF0    | (Reserved)      |     |                           |

| 0x79                               | 0xF2    | (Reserved)      |     |                           |

| 0x7A                               | 0xF4    | (Reserved)      |     |                           |

| 0x7B                               | 0xF6    | (Reserved)      |     |                           |

| 0x7C                               | 0xF8    | (Reserved)      |     |                           |

| 0x7D                               | 0xFA    | (Reserved)      |     |                           |

| 0x7E                               | 0xFC    | (Reserved)      |     |                           |

| 0x7F                               | 0xFE    | PLL_IMGSIG_CTL  | R/W | PLL・画像出力信号制御レジスタ          |

## 7. レジスタ

### 7.3 ビットマップ

| No.                          | Address | Register Name    | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------------------------------|---------|------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| SNCKEevent_Pattern Registers |         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x00                         | 0x00    | SNCK1PAT00       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x01                         | 0x00    | SNCK1PAT00       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x02                         | 0x00    | SNCK1PAT00       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x03                         | 0x00    | SNCK1PAT00       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x04                         | 0x00    | SNCK1PAT00       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x05                         | 0x00    | CK1PAT00         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x06                         | 0x00    | CK2PAT00         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x07                         | 0x00    | CK3PAT00         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x08                         | 0x00    | ADCKPAT00        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x09                         | 0x10    | SNCK1PAT10       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0A                         | 0x14    | SNCK1PAT10       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0B                         | 0x10    | SNCK1PAT10       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0C                         | 0x10    | SNCK1PAT10       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0D                         | 0x10    | CK1PAT10         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0E                         | 0x10    | CK2PAT10         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x0F                         | 0x10    | ADCKPAT10        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x10                         | 0x20    | SNCK2PAT0        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x11                         | 0x22    | SNCK3PAT0        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x12                         | 0x22    | SNCK4PAT0        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x13                         | 0x28    | SNCK5PAT0        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x14                         | 0x28    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x15                         | 0x28    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x16                         | 0x28    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x17                         | 0x28    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x18                         | 0x30    | SNCK2PAT1        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x19                         | 0x32    | SNCK3PAT1        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1A                         | 0x34    | SNCK4PAT1        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1B                         | 0x36    | SNCK5PAT1        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1C                         | 0x38    | SNCK6PAT1        |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1D                         | 0x3A    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1E                         | 0x3C    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x1F                         | 0x3E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x20                         | 0x3E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x21                         | 0x42    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x22                         | 0x44    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x23                         | 0x46    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x24                         | 0x48    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x25                         | 0x4A    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x26                         | 0x4C    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x27                         | 0x4E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x28                         | 0x50    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x29                         | 0x52    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2A                         | 0x54    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2B                         | 0x56    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2C                         | 0x58    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2D                         | 0x5A    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2E                         | 0x5C    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x2F                         | 0x5E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x30                         | 0x70    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x31                         | 0x72    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x32                         | 0x74    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x33                         | 0x76    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x34                         | 0x78    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x35                         | 0x7A    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x36                         | 0x7C    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x37                         | 0x7E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x38                         | 0x7F    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x39                         | 0x7F    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3A                         | 0x7A    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3B                         | 0x7B    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3C                         | 0x7C    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3D                         | 0x7D    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3E                         | 0x7E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x3F                         | 0x7F    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| Timing Parameter Registers   |         |                  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x40                         | 0x00    | SLINEST          |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x41                         | 0x00    | SLINEEND         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x42                         | 0x04    | SH_ADJ           |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x43                         | 0x04    | SH_STADJ         |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x44                         | 0x04    | ADJ1             |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x45                         | 0x04    | ADJ2             |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x46                         | 0x04    | ADJ3             |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x47                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x48                         | 0x0E    | SNCK ADJ PAGESEL |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x49                         | 0x02    | SNCK CLKADJ1     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4A                         | 0x04    | SNCK CLKADJ2     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4B                         | 0x06    | SNCK CLKADJ3     |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4C                         | 0x06    | SNCK INV1V1      |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4D                         | 0x06    | SNCK INV1V2      |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4E                         | 0x06    | ADJ1 STATE[5:0]  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x4F                         | 0x06    | ADJ2 STATE[5:0]  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x50                         | 0x06    | ADJ3 STATE[5:0]  |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x51                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x52                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x53                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x54                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x55                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x56                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x57                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x58                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x59                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5A                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5B                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5C                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5D                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5E                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x5F                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x60                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x61                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x62                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x63                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x64                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x65                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x66                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x67                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x68                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x69                         | 0x0E    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x6A                         | 0x0D    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x6B                         | 0x0D    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x6C                         | 0x0D    | (Reserved)       |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

| 0x6D                         | 0x0D    | (Reserved)       |       |       |       |       | </    |       |      |      |      |      |      |      |      |      |      |      |

## 7.4 レジスタ詳細説明

### 7.4.1 0x00～0x3F パターン設定レジスタ No.00～No.3F (PAT00～3F)

| No.  | Register Name | R/W | Bit Symbol  | Description  | Reset  |

|------|---------------|-----|-------------|--------------|--------|

| 0x00 | PAT00         | R/W | PAT00[15:0] | パターン設定 No.00 | 0xFFFF |

| 0x01 | PAT01         |     | PAT01[15:0] | パターン設定 No.01 | 0xFFFF |

| :    | :             |     | :           | :            | :      |

| 0x3E | PAT3E         |     | PAT3E[15:0] | パターン設定 No.3E | 0xFFFF |

| 0x3F | PAT3F         |     | PAT3F[15:0] | パターン設定 No.3F | 0xFFFF |

本レジスタはラインセンサ駆動クロックパルスパターン設定またはイベントパターン設定を行います。それぞれの設定は PATEN レジスタ(No.0x53)にて SNCKPATEN ビット、EVENTPAT0EN ビットまたは EVENTPAT1EN に“1”を設定することによって行います。SNCKPATEN ビットに“1”設定時はラインセンサ駆動クロックパルスパターン設定が有効になります。EVENTPAT0PAT ビットに“1”設定時はイベントパターン設定（バンク 0）が有効となり、EVENTPAT1EN ビットに“1”設定時はイベントパターン設定（バンク 1）が有効となります。

#### (1) ラインセンサ駆動クロックパルスパターン設定時

(SNCKPATEN=“1”, EVENTPAT0EN=“0”, EVENTPAT1EN=“0”)