## **CMOS 32-bit Application Specific Controller**

- 32 ビット RISC CPU コア (EPSON S1C33PE core) Max.90MHz 動作

- 命令キャッシュ 1KB / データキャッシュ 1KB

- 100KB の RAM を内蔵 (キャッシュ、バッテリーバックアップ RAM を含む)

- PLL による動作クロック制御 (分周比: 1/1 ~ 1/16、遅倍率: ×1 ~ ×16)

- ハードウェアマルチメディアアクセラレータ内蔵 (内部 64 ビット演算)

- 高機能演算モジュール内蔵 (積和演算、行列演算、ベクトル演算)

- 入力 1ch./出力 1ch. の I<sup>2</sup>S オーディオインターフェース

(24 ビットフォーマット対応)

- 16ch. の DMA コントローラ内蔵 (周辺回路と連動可能)

- バースト制御付き SDRAM コントローラ

- 多彩なシリアルインターフェース (UART × 2ch, FSIO × 2ch, EFSIO(ISO7816 モード/IrDA1.0 対応 FIFO 付シリアル I/F) × 2ch, SPI × 4ch, DCSIO(I<sup>2</sup>C バスマスター I/F エミュレーション) × 4ch.)

- 4ch. の IGBT 制御機能付き 16 ビット PWM コントロールタイマ

- 4ch. の 8 ビットプログラマブルタイマ

- NAND Flash インターフェース

- 赤外線リモートコントローラ

- 16M/64K カラーTFT、64K カラーSTN、モノクロ STN LCD コントローラ

内蔵 VRAM(80KB)による最大表示: 320 × 240, 8bpp(256 色)

外部メモリによる最大表示: 640 × 480, 24bpp(フルカラー)

Picture in Picture(PIP)による 2 画面重ね合わせ表示

- ホストプロセッサインターフェース (HIF)

### ■ 概要

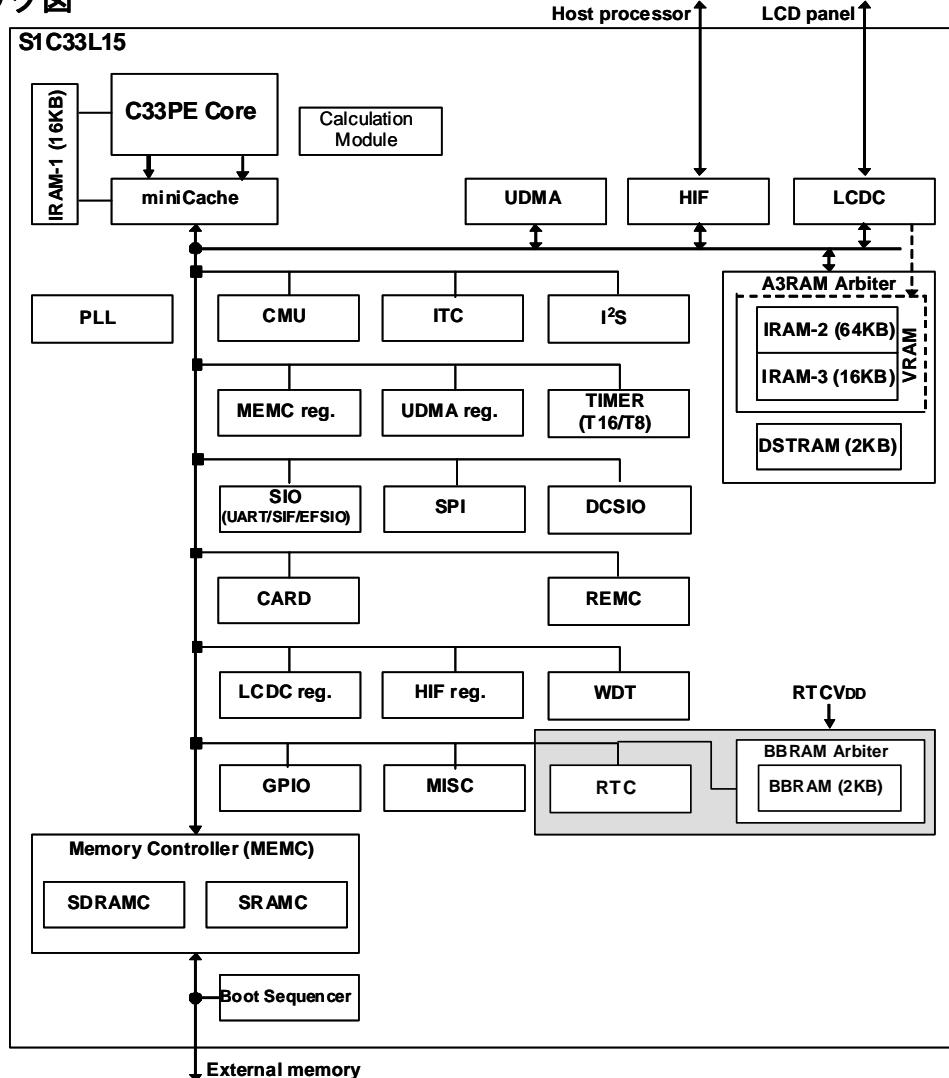

S1C33L15 は 16M/64K TFT/64K CSTN 対応 LCD コントローラとハードウェア演算アクセラレータを内蔵した、マルチメディアアプリケーション向けのハイパフォーマンス 32 ビットコントローラです。特に、電子辞書、オーディオプレイヤー、画像ビューア、モバイル端末など、LCD パネルを備えたオーディオ機能を持つアプリケーションへの組み込みに適しています。

S1C33L15 は 100KB の内蔵メモリを活用することで QVGA 256 色表示を 1 チップで実現できるだけでなく、大容量外部メモリを利用して VGA フルカラーまで対応可能と、中・小型 LCD パネルに幅広く対応することができます。また、ハードウェア PIP 機能による 2 画面重ね合わせ制御ができるなど、アプリケーションの描画処理の負荷軽減をサポートし、容易に LCD パネルへの表示処理を行えます。ハードウェア演算アクセラレータと入出力 I<sup>2</sup>S インターフェースを組み合わせることで、各種オーディオデコード処理を実現可能です。外部インターフェースとして、NAND Flash コントローラ、SPI を内蔵していますので、メディアカードを利用した画像表示、オーディオ再生アプリケーションも実現可能です。

さらに各種シリアルインターフェースや赤外線リモートコントローラを利用して、多彩なユーザインターフェースを持った電子機器も実現できます。

また、S1C33L15 は単体で LCD コントロールプロセッサとして動作するだけでなく、ホストプロセッサインターフェース (HIF) を介して外部ホストプロセッサに接続することで、LCD コントローラとして動作させることも可能です。

S1C33L15 は基本機能として、C33 PE 32 ビット RISC CPU コア、2KB の命令/データキャッシュ、100KB 内蔵 RAM、DMA コントローラ、メモリコントローラ (SRAM/SDRAM)、各種タイマ、リアルタイムクロック、汎用入出力ポートなどを備えており、汎用 CPU としても高いパフォーマンスを有します。S1C33L15 はこれらの機能を、0.18μm 混在 Vt. CMOS プロセスを使用した EPSON SoC (System on Chip) テクノロジにより実装しています。

# S1C33L15

## ■ 特長

### ● テクノロジ

- 0.18μm AL-4 層 Vth. 混在 CMOS プロセス技術

### ● CPU

- SoC に最適化された、AMBA バス付き EPSON オリジナル 32 ビット RISC CPU コア C33 PE

- 最大動作周波数: 90MHz

- 内部 2 段パイプライン

- 命令セット: 125 命令(16 ビット固定長)

- キャッシュ: 命令キャッシュ 1KB+データキャッシュ 1KB

- メモリ空間

- 最大 4GB の空間をアクセス可能(32 ビットアドレス)

### ● 内蔵メモリ(RAM)

- 16KB IRAM1

2KB のキャッシュを含む高速汎用 RAM。UDMA からはアクセス不可

- 64KB IRAM2

汎用 RAM または VRAM。CPU、LCDC、HIF、UDMA からアクセス可能

- 16KB IRAM3

汎用 RAM または VRAM。CPU、LCDC、HIF、UDMA からアクセス可能

- 2KB DSTRAM

256 バイトのデバッグ領域を含む汎用 RAM。CPU、UDMA からアクセス可能

- 2KB BBRAM

システムとは別電源でデータを保持可能

### ● 入力クロック

- 高速クロック(OSC3)

- 90MHz (max.)

- 発振クロック入力(水晶またはセラミック発振)

- PLL: 整数倍 PLL 回路

- 低速クロック(OSC1)

- 32.768kHz(typ.) RTC および低速(省電力)動作用

- 発振クロック入力(水晶発振)

### ● ミニキャッシュコントローラ(miniCache)

- 4Way セットアソシエイティブ方式の 1KB 命令キャッシュと 1KB データキャッシュ

- LRU 置き換えアルゴリズム

- デバッグモード時や指定優先度の割り込み処理中の自動ロック機能

- 1 ワードバッファ付きのライトスルー機能

- \*キャッシュメモリとして IRAM1 の一部を使用します。

## ● LCD コントローラ(LCDC)

- 最大 24 ビットのカラーTFT、最大 16 ビットのカラー/モノクロ STN LCD パネルに対応

- 640 x 480(VGA)、320 x 240(QVGA)等、VGA クラス以下の主要な解像度に対応(パネルに合わせ任意に設定可能)

- 最大 16M 色(TFT)、最大 64K 色(カラーSTN)、16~2 階調(モノクロ STN)の表示モードをサポート

- 内蔵 VRAM(80KB)を使用した表示設定例: 320 x 240、8bpp(256 色)

- 外部メモリを使用した表示設定例: 640 x 480、24bpp(フルカラー)

- Picture in Picture(PIP)による 2 画面重ね合わせ表示制御が可能(8/16bpp モード)

- Picture in Picture(PIP)による 2 画面重ね合わせ表示制御が可能(32bpp モード)

- ルックアップテーブル(LUT)による輝度/階調制御が可能

## ● ユニバーサル DMA コントローラ(UDMA)

- 2 チャネルの高速 DMA と最大 14 チャネルのテーブル DMA

- デュアルアドレス転送(転送元と転送先アドレスを指定)

- シングル転送または連続転送を指定可能

- SDRAM コントローラ運動高性能バースト転送機能

- 転送単位を 1 または 4 バイト、1 または 4 ハーフワード、1 または 4 ワードにプログラム可能

- リンク機能付き内蔵 DMA トリガシステム

- ソフトウェアトリガまたは各種周辺回路ハードウェアトリガを選択可能

## ● SRAM コントローラ(SRAMC)

- 外部デバイスの接続に最大 8 本のチップイネーブル信号を使用可能

- Flash ROM、SRAM、その他外部デバイス(LCD ドライバなど)を接続可能

- 24 ビットアドレスバスと 8/16 ビット選択可能なデータバス

- バスアクセスウェイトサイクル数をプログラマブルに設定可能(1~15 サイクル)

- リトルエンディアンアクセスに対応

- メモリマップド I/O

- メモリ領域の一部(エリア 6)をチップ内蔵周辺モジュールに予約

- A0 または BS(バストローブ)のいずれかのアクセス方式に対応

- #WAIT 端子による外部ウェイト要求に対応

## ● SDRAM コントローラ(SDRAMC)

- 最大 90MHz の 16 ビット SDRAM インターフェース

- 16M ビット(2MB)から 512M ビット(64MB)の SDRAM に対応

- DQB(データキューバッファ)を搭載

- 最適化されたマルチマスタアクセス要求で平均リードレイテンシを低減

- CAS レイテンシを 1、2 または 3 に設定可能

- バースト転送に対応

- 同期クロックを CPU クロックと同一または 2 倍の周波数に設定可能

- 12 ビットオートリフレッシュカウンタを内蔵

- 省電力動作のためのインテリジェントなセルフリフレッシュ機能

# S1C33L15

## ● 高機能演算モジュール(Calculation Module)

- ベクトル演算(加算/減算/乗算)

- 積和演算(MAC)

- 行列演算( $2 \times 2$ 、 $3 \times 3$ 、 $4 \times 4$ )

- アフィン変換( $3 \times 3 + 3$ )

- バタフライ演算

- 演算モードとして符号付き 32 ビット整数、符号なし 32 ビット整数、飽和処理付き 32 ビット固定小数点をサポート

## ● I<sup>2</sup>S オーディオインターフェース(I<sup>2</sup>S)

- ユニバーサルオーディオ I<sup>2</sup>S バスインターフェースに対応

- 入力 1 チャネル、出力 1 チャネルの I<sup>2</sup>S インターフェースを内蔵

- 最大 24 ビットのデータフォーマットに対応

- 出力チャネルでは DAC デバイスクロック、ワードクロック、ビットクロックをそれぞれ制御可能

(外部クロック利用可能)

- 入力/出力それぞれに 24 ビット  $\times$  2 チャネル  $\times$  4 の FIFO を内蔵

- DMA 転送に対応

- \*スピーカ/イヤホンへの出力やマイクからの入力を行うには外部 DAC/ADC デバイスを接続する必要があります。

## ● ホストプロセッサインターフェース(HIF)

- 8 ビット非同期制御による外部ホストプロセッサから S1C33L15 周辺回路の制御が可能

- ハードウェアセマフォによる排他処理が可能

## ● クロックマネージメントユニット(CMU)

- システムクロックソース(OSC3、PLL、OSC1)を選択可能

- OSC3、OSC1 発振回路の On/Off を制御可能

- システムクロック分周比( $1/1 \sim 1/32$ )と PLL 周波数倍率( $x1 \sim x16$ )を制御可能

- スタンバイモード(SLEEP、HALT)時のクロック制御

- 内部コアクロックと周辺回路クロックの分周比、外部バスクロックを制御可能

## ● 割り込みコントローラ(ITC)

- 16 チャネルの S1C33 PE コアに予約された割り込みの制御

- 48 チャネルの割り込みに対応(一部はシステム予約)

## ● ウオッチドッグタイマ(WDT)

- NMI(ノンマスカブル割り込み)またはリセットを発生可能な 30 ビットウォッチドッグタイマ

- ウォッチドッグタイマのオーバーフロー周期(NMI/リセット発生周期)をプログラマブルに設定可能

- ウォッチドッグタイマのオーバーフロー信号を外部にも出力可能

## ● 16 ビットタイマ(T16)

- 4 チャネルの PWM 制御機能付き 16 ビットタイマ/カウンタ

- PWM 出力と外部 RC フィルタによりデジタル DAC 機能を実現可能

- IGBT 制御を可能とする 4 チャネルの出力比較器を内蔵

- **8 ビットタイマ(T8)**

- ・ 4 チャネルのプログラム可能な 8 ビットタイマ/カウンタ

- \*最大 2 チャネルはシリアルインターフェース(UART)用のボーレートカウンタとして使用されます。

- **シリアルインターフェース(UART、SIF、EFSIO)**

- UART**

- ・ 2 チャネルの UART

- ・ 2 バイトの受信バッファと 1 バイトの送信バッファを内蔵し、全二重通信をサポート

- ・ 転送レート: 150~115200bps、データ長: 7 または 8 ビット、パリティモード: 偶数、奇数、または

パリティなし、ストップビット: 1 または 2 ビット

- ・ パリティエラー、フレーミングエラー、オーバーランエラーを検出可能

- SIF(シリアルインターフェース)**

- ・ 2 チャネルのクロック同期式/調歩同期式シリアルインターフェース

- ・ 各チャネルに 4 バイトの受信データバッファと 2 バイトの送信データバッファを搭載

- ・ ボーレートジェネレータ(12 ビットプログラマブルタイマ)を内蔵

- EFSIO(FIFO 付き拡張シリアルインターフェース)**

- ・ 2 チャネルのクロック同期式/調歩同期式シリアルインターフェース

- ・ FIFO 内蔵(各チャネルに 4 バイトの受信データバッファと 2 バイトの送信データバッファを搭載)

- ・ ボーレートジェネレータ(12 ビットタイマ)を内蔵

- ・ ISO7816 モードに対応

- データの並び(MSB 先頭、LSB 先頭)を変更可能

- ISO7816-3 T=0 & T=1 プロトコル互換のメモリカードインターフェースに対応

- ボーレートとガードタイムをプログラマブルに設定可能

- ISO7816 アクノリッジとオートリピート転送に対応

- **SPI(シリアルペリフェラルインターフェース)**

- ・ 4 チャネルの SPI

- ・ マスタおよびスレーブモードに対応

- ・ データ長: 8 ビット固定(MSB 先頭)

- ・ データ転送タイミング(クロック極性と位相の組み合わせ)を 4 種類から選択可能

- ・ 受信データビットマスク機能および DMA 転送に対応

- **DCSIO(I<sup>2</sup>C マスタエミュレータ)**

- ・ 4 チャネルのシリアルシフタ付き入出力ポート

- ・ I<sup>2</sup>C マスタをエミュレート可能

- ・ ステートマシンを駆動するための入出力レベル検出

- ・ 汎用の単線式または 2 線式通信プロトコルをソフトウェアによりエミュレート

- ・ DMA 転送に対応

- **リアルタイムクロック(RTC)**

- ・ 時刻(秒、分、時)カウンタとカレンダ(日、曜日、月、年)カウンタを内蔵

- ・ カウンタは BCD データでリード/ライト可能

- ・ システム電源(LVDD)とは別の独立電源(RTCVDD = 1.8V(typ.))で動作可能

- ・ WAKEUP 信号出力および#STBY 入力によりウェイクアップおよびスタンバイ制御が可能

# S1C33L15

- **汎用入出力ポート制御(GPIO)**

- ・ 最大 96 本の入出力ポートを制御可能

- ・ レジスタにより内蔵プルアップ抵抗を制御可能(一部のポートを除く)

- \*入出力ポートは周辺回路(インターフェースやタイマなど)と端子を兼用しています。したがって、使用可能な入出力ポート数は周辺回路の使用状況により変わります。

- **リードソロモン EDC 対応 SLC/MLC NAND Flash インターフェース(CARD)**

- ・ 8 ビット SLC/MLC NAND Flash を制御可能

- ・ SLC/MLC NAND Flash 用ハードウェアリードソロモン-EDC 演算機能を搭載

- ハードウェアリードソロモン-EDC 演算機能はエラー検出のみ行うことができます。

- ・ スマートメディアを制御可能(#SMRD、#SMWR を生成可能)

- ・ NAND Flash ブートに対応

- **赤外線リモートコントローラ(REMC)**

- ・ 入力 1 チャネル、出力 1 チャネルの赤外線リモコンインターフェースを内蔵

- ・ 1 ビットごとのデューティ比、パルス幅を任意に設定可能

- (ソフト制御により各種の論理フォーマットに対応可能)

- \*赤外線リモコンからの受信には赤外線受光モジュールを接続する必要があります。

- **動作電圧**

- ・ コア電圧(LVDD): 1.65~1.95V(1.8V typ.)

- ・ I/O 電圧(HVDD): 2.70~3.60V(3.3V typ.)

- ・ SDRAM 電圧(BUSVDD): 2.30~3.60V(3.3V typ.)

- ・ RTC 電圧(RTCVDD): 1.65~1.95V(1.8V typ.)

- ・ PLL 電圧(PLLVDD): 1.65~1.95V(1.8V typ.)

- **動作温度**

- ・ -40°C~85°C

- **消費電力**

- ・ SLEEP 時: 1.0µA \*1

- ・ HALT 時: 3.5mA \*2

- ・ 実行時: 103.5mA \*3

- \*1 RTC のみ動作時(RTCVDD のみ電源を供給し、RTCVDD を除く電源供給を停止)

- \*2 PLL = Off、全クロックを 48MHz に設定時

- \*3 PCLK = 45MHz、MCLK = SDCLK = 90MHz、全周辺回路へクロック供給時

- \*クロックマネージメントユニットでクロック制御を行うことにより、消費電力を低減できます。

- **出荷形態**

- ・ PFBGA12U-180(12mm × 12mm × 1.2mm, 0.8mm ポール間ピッチ)

- ・ QFP20-184pin (20mm × 20mm × 1.4mm, 0.4mm 端子間ピッチ)

- ・ チップ

# S1C33L15

## ■ ブロック図

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

©SEIKO EPSON CORPORATION 2009

**セイコーエプソン株式会社**

エプソン半導体のご紹介

<http://www.epson.jp/device/semicon/>

**半導体事業部 IC 営業部**

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042)587-5313(直通) FAX (042)587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06)6120-6000(代表) FAX (06)6120-6100

ドキュメントコード : 411214101

2008 年 4 月作成

2009 年 12 月改訂