CMOS 16-BIT SINGLE CHIP MICROCONTROLLER

**S1C17001**

**テクニカルマニュアル**

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち、「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

本製品はSilicon Storage Technology, Inc.よりライセンスされたSuperFlash®テクノロジを使用しています。

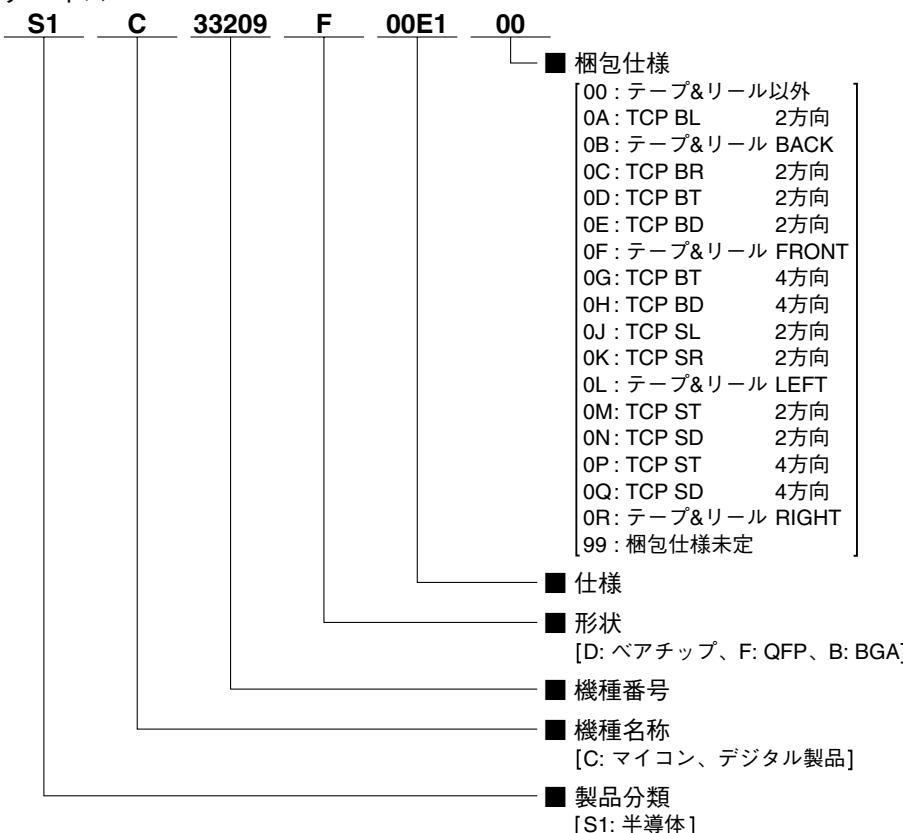

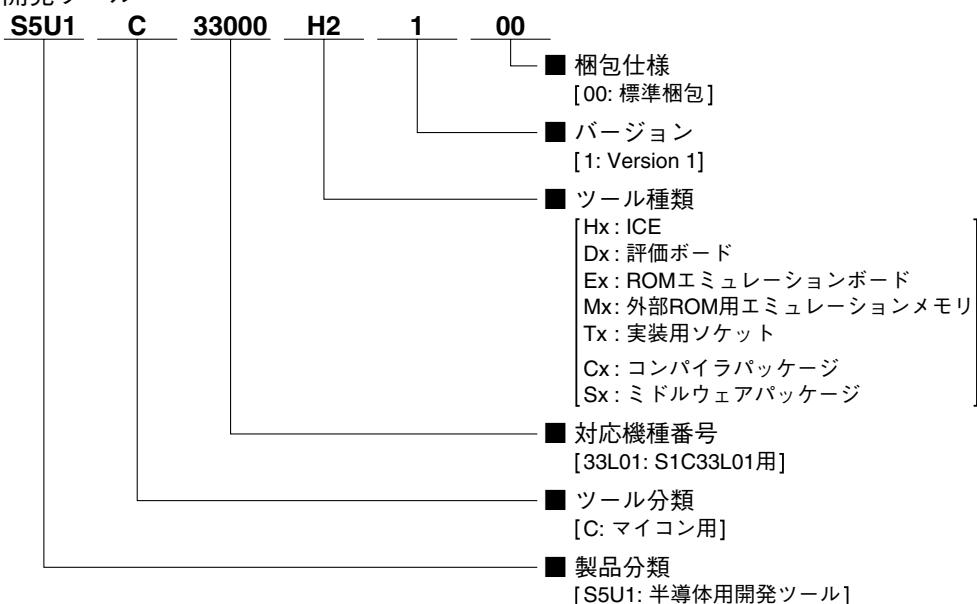

## 製品型番体系

### ●デバイス

### ●開発ツール

## - 目 次 -

|                                        |    |

|----------------------------------------|----|

| <b>1 概要</b>                            | 1  |

| 1.1 特長                                 | 1  |

| 1.2 ブロック図                              | 2  |

| 1.3 端子                                 | 3  |

| 1.3.1 端子配置図                            | 3  |

| 1.3.2 パッケージ(QFP12-48pin)               | 4  |

| 1.3.3 端子説明                             | 6  |

| <b>2 CPU</b>                           | 7  |

| 2.1 S1C17コアの特長                         | 7  |

| 2.2 CPUレジスタ                            | 8  |

| 2.3 命令セット                              | 9  |

| 2.4 ベクタテーブル                            | 13 |

| 2.5 プロセッサ情報                            | 14 |

| <b>3 メモリマップ, バス制御</b>                  | 15 |

| 3.1 バスサイクル                             | 16 |

| 3.1.1 アクセスサイズ制限                        | 16 |

| 3.1.2 命令実行サイクルの制限                      | 16 |

| 3.2 内蔵ROMエリア                           | 17 |

| 3.2.1 内蔵ROM                            | 17 |

| 3.2.2 ROMのリードアクセスサイクルの設定               | 17 |

| 0x5320: ROM Control Register (MISC_FL) | 17 |

| 3.3 内蔵RAMエリア                           | 18 |

| 3.3.1 内蔵RAM                            | 18 |

| 3.4 内蔵周辺回路エリア                          | 19 |

| 3.4.1 内蔵周辺回路エリア1(0x4000~)              | 19 |

| 3.4.2 内蔵周辺回路エリア2(0x5000~)              | 19 |

| 3.4.3 I/Oマップ                           | 20 |

| 3.5 コアI/O予約エリア                         | 23 |

| <b>4 電源電圧</b>                          | 25 |

| <b>5 イニシャルリセット</b>                     | 27 |

| 5.1 イニシャルリセット要因                        | 27 |

| 5.1.1 #RESET端子                         | 27 |

| 5.1.2 P0ポートキー入力リセット                    | 28 |

| 5.1.3 ウォッチドッグタイマによるリセット                | 28 |

| 5.2 イニシャルリセットシーケンス                     | 29 |

| 5.3 イニシャルリセット時の初期設定                    | 30 |

| <b>6 割り込みコントローラ(ITC)</b>               | 31 |

| 6.1 ITCの構成                             | 31 |

| 6.2 ベクタテーブル                            | 32 |

| 6.3 マスク可能割り込みの制御                       | 33 |

| 6.3.1 ITCイネーブル                         | 33 |

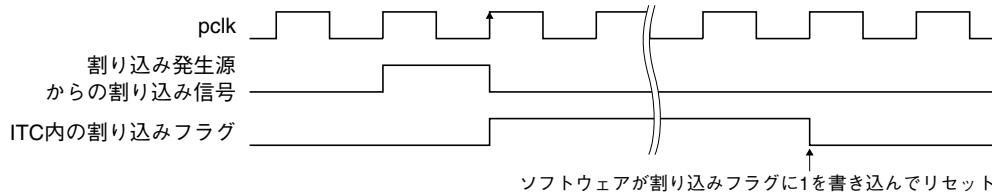

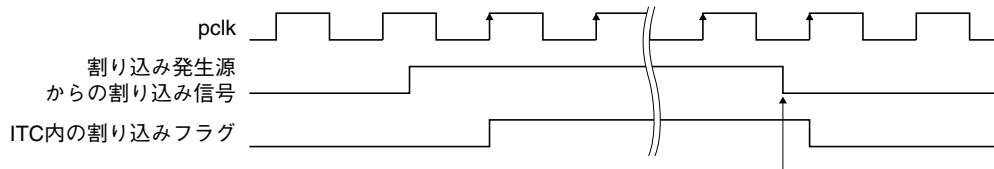

| 6.3.2 周辺モジュールからの割り込み要求と割り込みフラグ         | 33 |

| 6.3.3 割り込みの許可/禁止                       | 34 |

| 6.3.4 複数の割り込み発生時の処理                    | 35 |

| 6.3.5 割り込みのトリガモード                      | 36 |

| 6.3.6 S1C17コアの割り込み処理                   | 38 |

| 6.4 NMI                                | 39 |

---

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| 6.5 ソフトウェア割り込み .....                                               | 40        |

| 6.6 割り込み要因によるHALT, SLEEPモードの解除 .....                               | 41        |

| 6.7 制御レジスタ詳細 .....                                                 | 42        |

| 0x4300: Interrupt Flag Register (ITC_IFLG) .....                   | 43        |

| 0x4302: Interrupt Enable Register (ITC_EN) .....                   | 45        |

| 0x4304: ITC Control Register (ITC_CTL) .....                       | 46        |

| 0x4306: External Interrupt Level Setup Register 0 (ITC_ELV0) ..... | 47        |

| 0x4308: External Interrupt Level Setup Register 1 (ITC_ELV1) ..... | 48        |

| 0x430a: External Interrupt Level Setup Register 2 (ITC_ELV2) ..... | 49        |

| 0x430c: External Interrupt Level Setup Register 3 (ITC_ELV3) ..... | 50        |

| 0x430e: Internal Interrupt Level Setup Register 0 (ITC_ILV0) ..... | 51        |

| 0x4310: Internal Interrupt Level Setup Register 1 (ITC_ILV1) ..... | 52        |

| 0x4312: Internal Interrupt Level Setup Register 2 (ITC_ILV2) ..... | 53        |

| 0x4314: Internal Interrupt Level Setup Register 3 (ITC_ILV3) ..... | 54        |

| 6.8 注意事項 .....                                                     | 55        |

| <b>7 発振回路(OSC) .....</b>                                           | <b>57</b> |

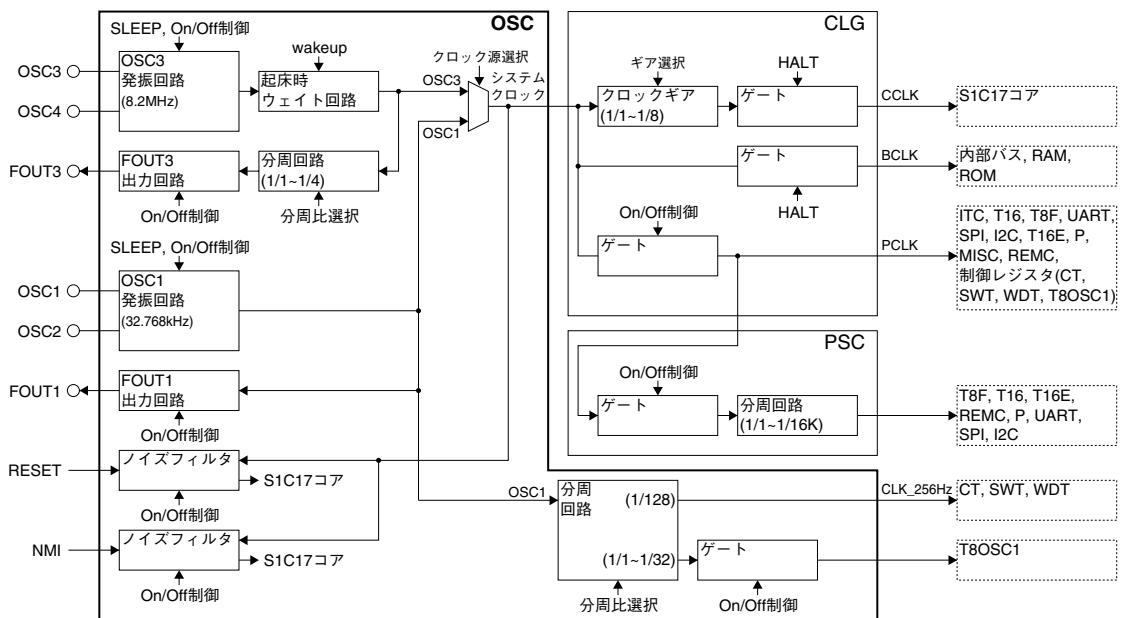

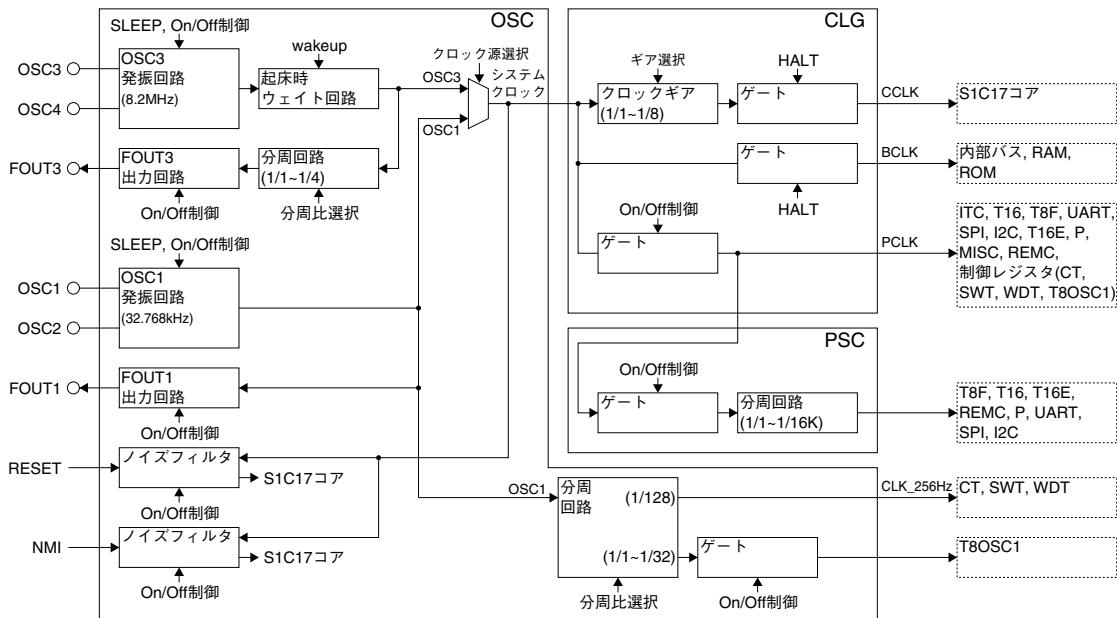

| 7.1 OSCモジュールの構成 .....                                              | 57        |

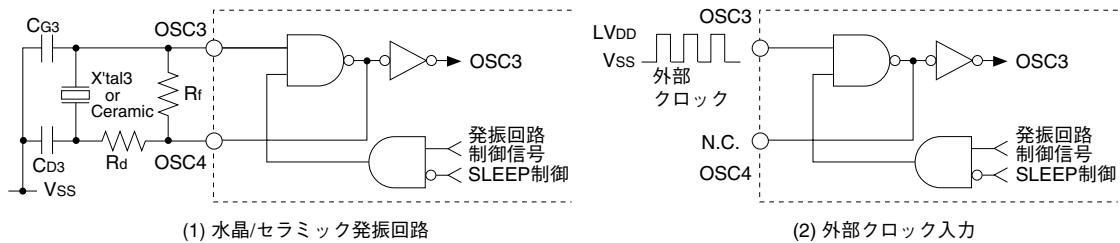

| 7.2 OSC3発振回路 .....                                                 | 58        |

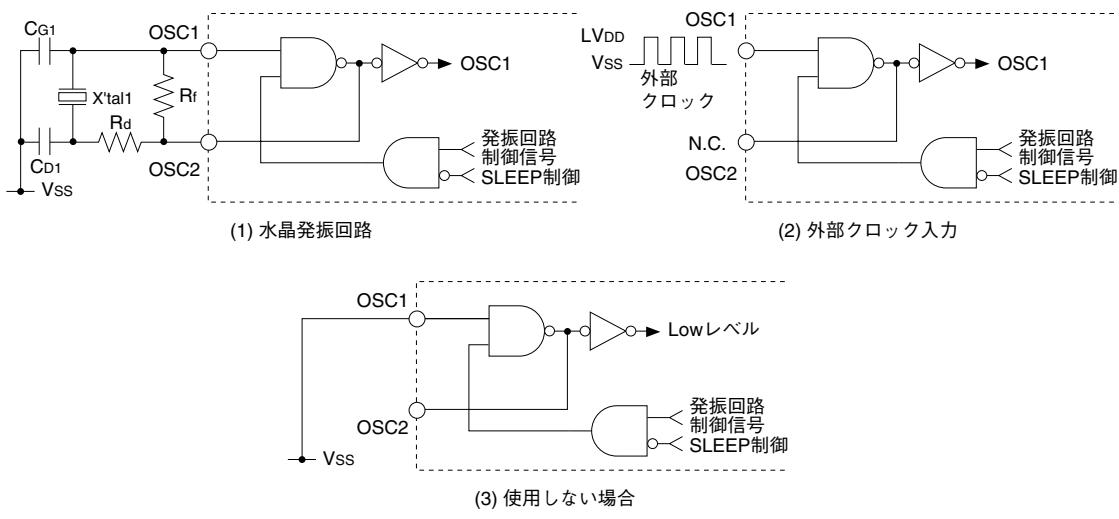

| 7.3 OSC1発振回路 .....                                                 | 60        |

| 7.4 システムクロックの切り換え .....                                            | 61        |

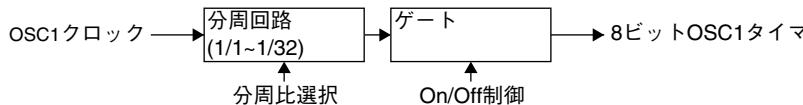

| 7.5 8ビットOSC1タイマクロックの制御 .....                                       | 62        |

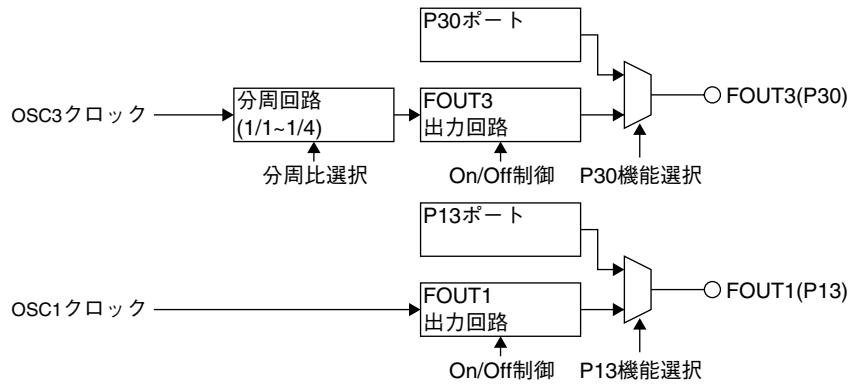

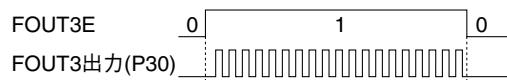

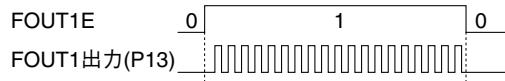

| 7.6 クロック外部出力(FOUT3, FOUT1) .....                                   | 63        |

| 7.7 RESET, NMI入力ノイズフィルタ .....                                      | 65        |

| 7.8 制御レジスタ詳細 .....                                                 | 66        |

| 0x5060: Clock Source Select Register (OSC_SRC) .....               | 67        |

| 0x5061: Oscillation Control Register (OSC_CTL) .....               | 68        |

| 0x5062: Noise Filter Enable Register (OSC_NFEN) .....              | 69        |

| 0x5064: FOUT Control Register (OSC_FOUT) .....                     | 70        |

| 0x5065: T8OSC1 Clock Control Register (OSC_T8OSC1) .....           | 71        |

| 7.9 注意事項 .....                                                     | 72        |

| <b>8 クロックジェネレータ(CLG) .....</b>                                     | <b>73</b> |

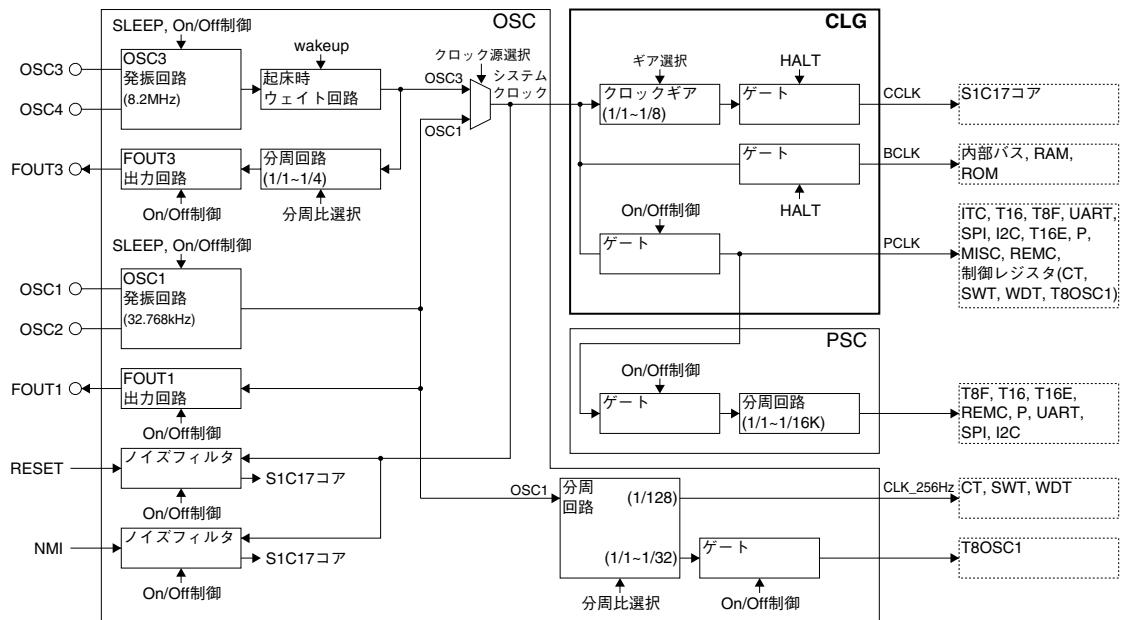

| 8.1 クロックジェネレータの構成 .....                                            | 73        |

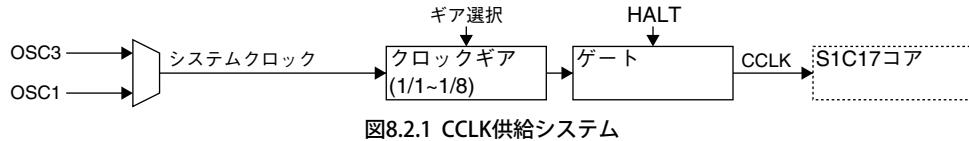

| 8.2 CPUコアクロック(CCLK)の制御 .....                                       | 74        |

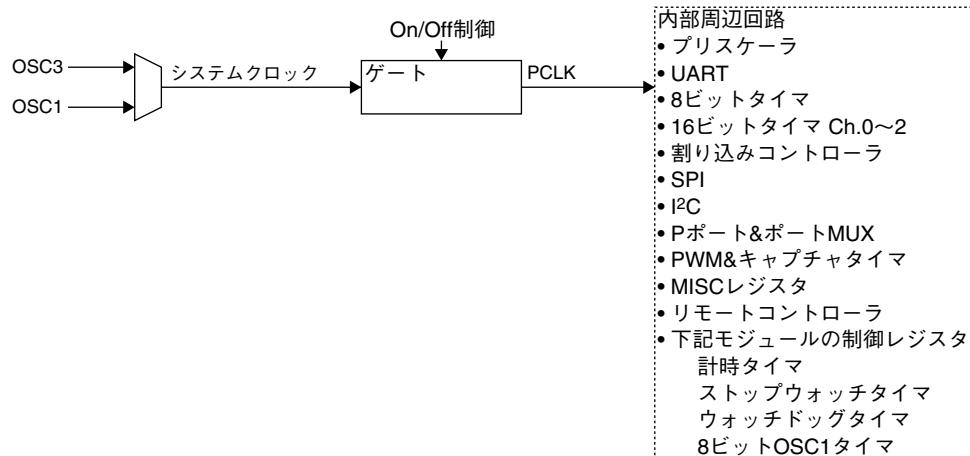

| 8.3 周辺モジュールクロック(PCLK)の制御 .....                                     | 75        |

| 8.4 制御レジスタ詳細 .....                                                 | 76        |

| 0x5080: PCLK Control Register (CLG_PCLK) .....                     | 77        |

| 0x5081: CCLK Control Register (CLG_CCLK) .....                     | 78        |

| 8.5 注意事項 .....                                                     | 79        |

| <b>9 プリスケーラ(PSC) .....</b>                                         | <b>81</b> |

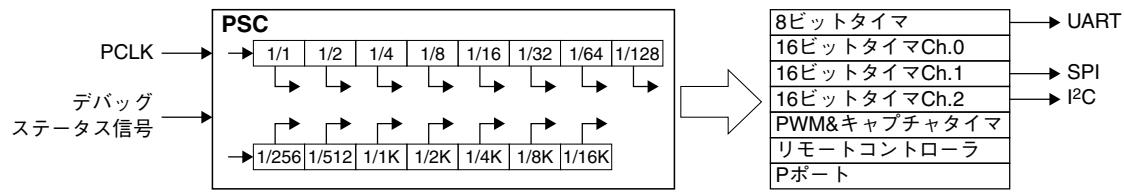

| 9.1 プリスケーラの構成 .....                                                | 81        |

| 9.2 制御レジスタ詳細 .....                                                 | 82        |

| 0x4020: Prescaler Control Register (PSC_CTL) .....                 | 82        |

| 9.3 注意事項 .....                                                     | 83        |

| <b>10 入出力ポート(P) .....</b>                                          | <b>85</b> |

| 10.1 入出力ポートの構成 .....                                               | 85        |

| 10.2 入出力端子機能の選択(ポートMUX) .....                                      | 86        |

| 10.3 データの入出力 .....                                                 | 87        |

| 10.4 プルアップ制御 .....                                                 | 88        |

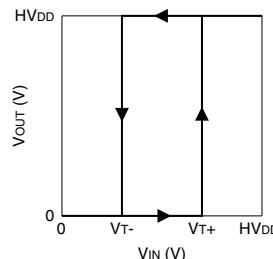

| 10.5 入力インタフェースレベル .....                                            | 89        |

| 10.6 P0ポートのチャタリング除去機能 .....                                        | 90        |

|                                                                                 |            |

|---------------------------------------------------------------------------------|------------|

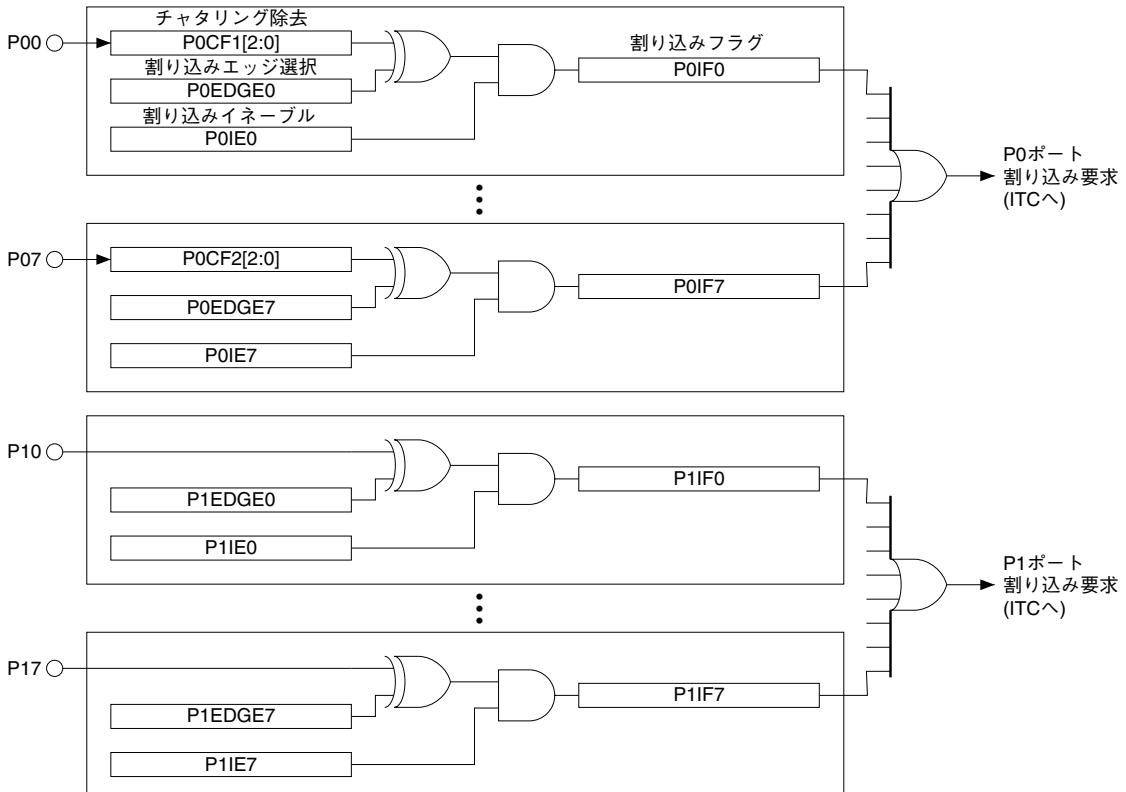

| 10.7 ポート入力割り込み                                                                  | 91         |

| 10.8 制御レジスタ詳細                                                                   | 94         |

| 0x5200/0x5210/0x5220/0x5230: Px Port Input Data Registers (Px_IN)               | 95         |

| 0x5201/0x5211/0x5221/0x5231: Px Port Output Data Registers (Px_OUT)             | 96         |

| 0x5202/0x5212/0x5222/0x5232: Px Port I/O Direction Control Registers (Px_IO)    | 97         |

| 0x5203/0x5213/0x5223/0x5233: Px Port Pull-up Control Registers (Px_PU)          | 98         |

| 0x5205/5215: Px Port Interrupt Mask Registers (Px_IMSK)                         | 99         |

| 0x5206/5216: Px Port Interrupt Edge Select Registers (Px_EDGE)                  | 100        |

| 0x5207/5217: Px Port Interrupt Flag Registers (Px_IFLG)                         | 101        |

| 0x5208: P0 Port Chattering Filter Control Register (P0_CHAT)                    | 102        |

| 0x5209: P0 Port Key-Entry Reset Configuration Register (P0_KRST)                | 103        |

| 0x52a0: P0 Port Function Select Register (P0_PMUX)                              | 104        |

| 0x52a1: P1 Port Function Select Register (P1_PMUX)                              | 105        |

| 0x52a2: P2 Port Function Select Register (P2_PMUX)                              | 106        |

| 0x52a3: P3 Port Function Select Register (P3_PMUX)                              | 107        |

| 10.9 注意事項                                                                       | 108        |

| <b>11 16ビットタイマ(T16)</b>                                                         | <b>109</b> |

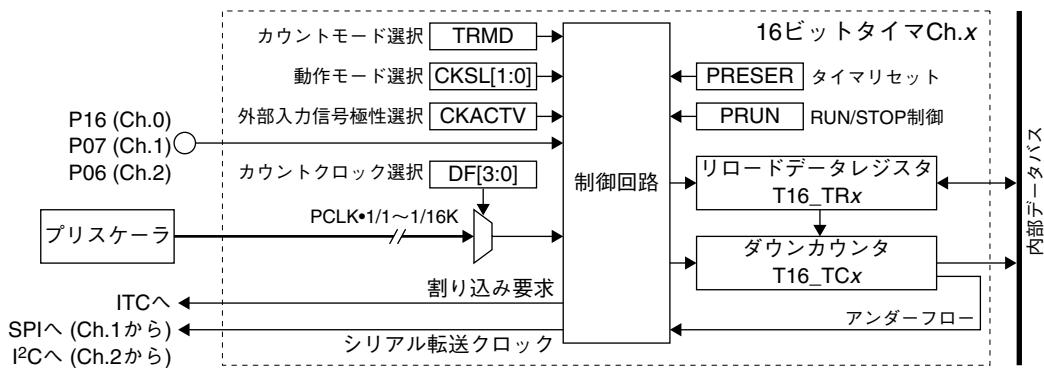

| 11.1 16ビットタイマの概要                                                                | 109        |

| 11.2 16ビットタイマの動作モード                                                             | 110        |

| 11.2.1 内部クロックモード                                                                | 110        |

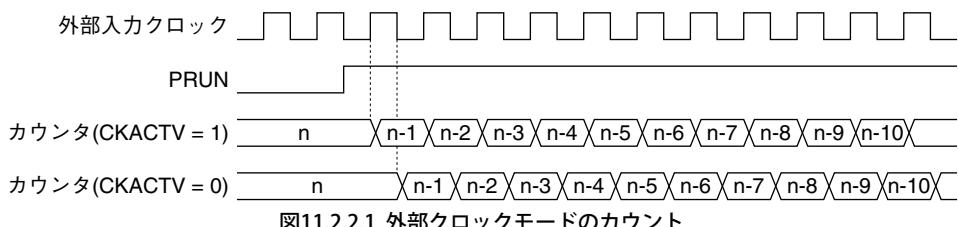

| 11.2.2 外部クロックモード                                                                | 111        |

| 11.2.3 パルス幅測定モード                                                                | 112        |

| 11.3 カウントモード                                                                    | 113        |

| 11.4 16ビットタイマリロードレジスタとアンダーフロー周期                                                 | 114        |

| 11.5 16ビットタイマのリセット                                                              | 115        |

| 11.6 16ビットタイマRUN/STOP制御                                                         | 116        |

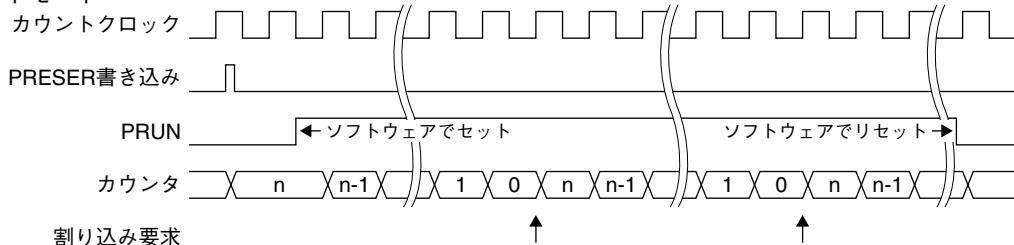

| 11.7 16ビットタイマ出力信号                                                               | 117        |

| 11.8 16ビットタイマ割り込み                                                               | 118        |

| 11.9 制御レジスタ詳細                                                                   | 119        |

| 0x4220/0x4240/0x4260: 16-bit Timer Ch.x Input Clock Select Registers (T16_CLKx) | 120        |

| 0x4222/0x4242/0x4262: 16-bit Timer Ch.x Reload Data Registers (T16_TRx)         | 121        |

| 0x4224/0x4244/0x4264: 16-bit Timer Ch.x Counter Data Registers (T16_TCx)        | 122        |

| 0x4226/0x4246/0x4266: 16-bit Timer Ch.x Control Registers (T16_CTLx)            | 123        |

| 11.10 注意事項                                                                      | 125        |

| <b>12 8ビットタイマ(T8F)</b>                                                          | <b>127</b> |

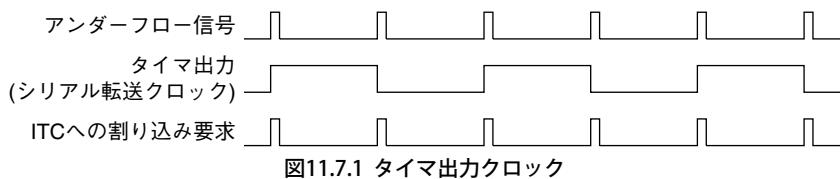

| 12.1 8ビットタイマの概要                                                                 | 127        |

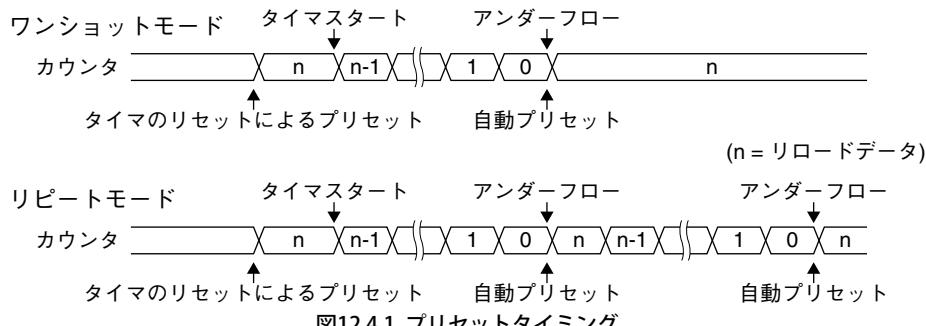

| 12.2 8ビットタイマのカウントモード                                                            | 128        |

| 12.3 カウントクロック                                                                   | 129        |

| 12.4 8ビットタイマリロードレジスタとアンダーフロー周期                                                  | 130        |

| 12.5 8ビットタイマのリセット                                                               | 131        |

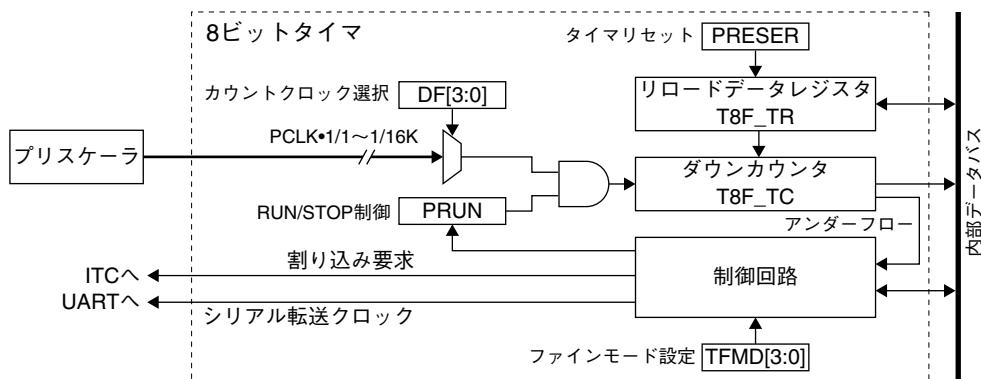

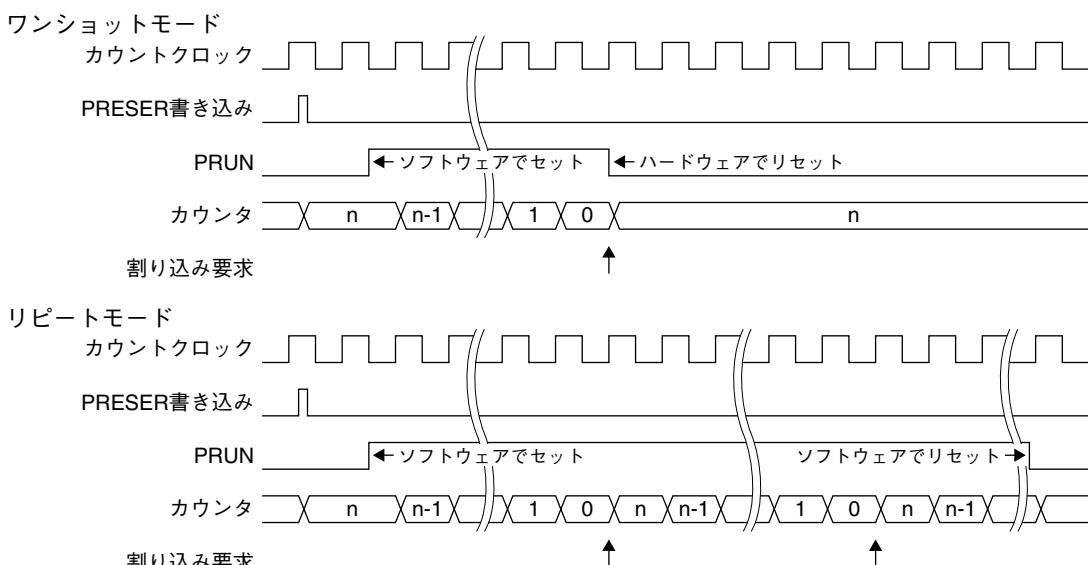

| 12.6 8ビットタイマRUN/STOP制御                                                          | 132        |

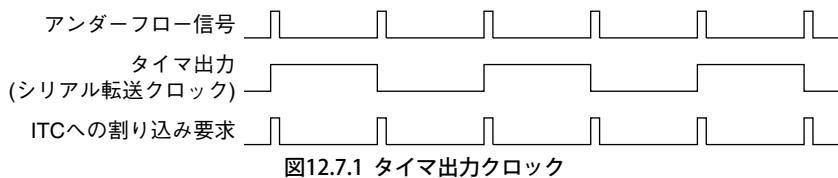

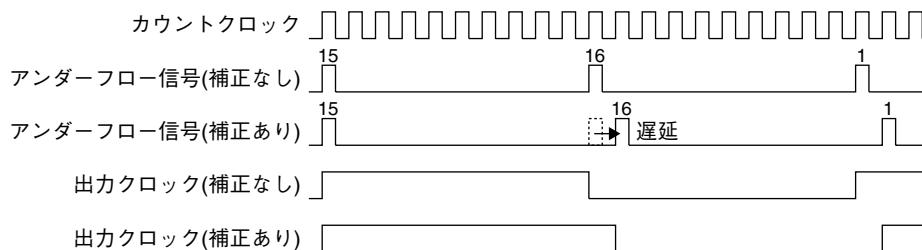

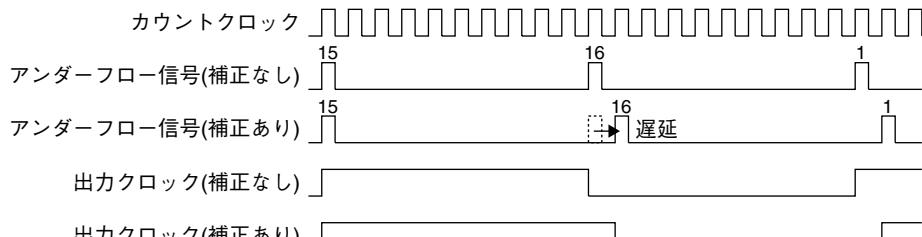

| 12.7 8ビットタイマ出力信号                                                                | 133        |

| 12.8 フайнモード                                                                    | 134        |

| 12.9 8ビットタイマ割り込み                                                                | 135        |

| 12.10 制御レジスタ詳細                                                                  | 136        |

| 0x4200: 8-bit Timer Input Clock Select Register (T8F_CLK)                       | 137        |

| 0x4202: 8-bit Timer Reload Data Register (T8F_TR)                               | 138        |

| 0x4204: 8-bit Timer Counter Data Register (T8F_TC)                              | 139        |

| 0x4206: 8-bit Timer Control Register (T8F_CTL)                                  | 140        |

| 12.11 注意事項                                                                      | 142        |

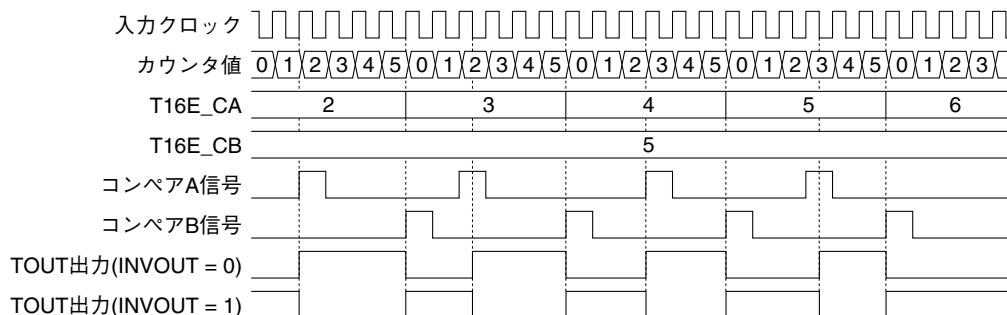

| <b>13 PWM&amp;キャプチャタイマ(T16E)</b>                                                | <b>143</b> |

---

|                                                                      |            |

|----------------------------------------------------------------------|------------|

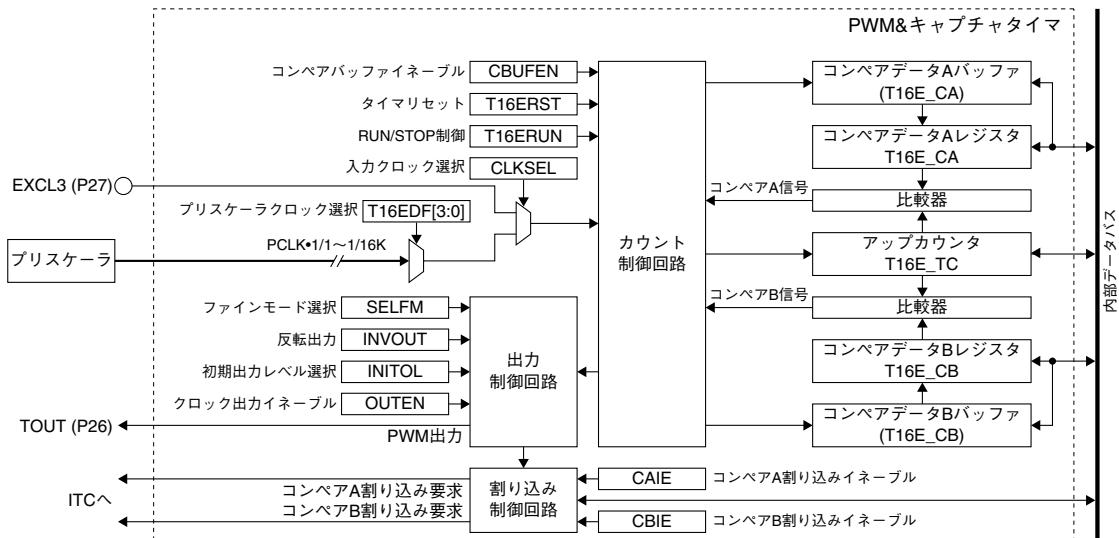

| 13.1 PWM&キャプチャタイマの概要 .....                                           | 143        |

| 13.2 PWM&キャプチャタイマの動作モード .....                                        | 144        |

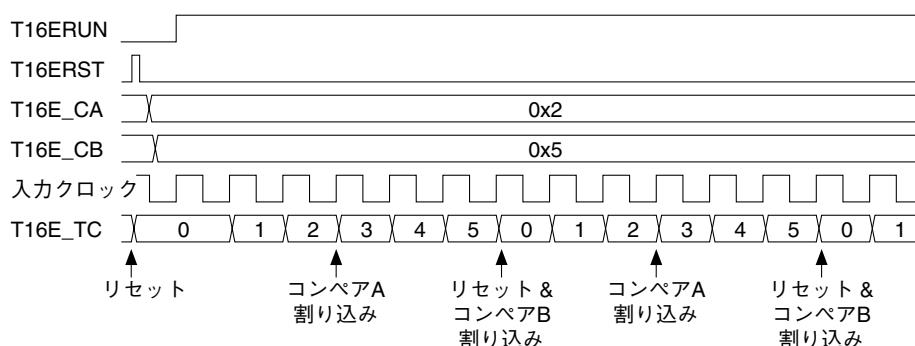

| 13.3 カウンタ値のセット/リセット .....                                            | 145        |

| 13.4 コンペアデータの設定 .....                                                | 146        |

| 13.5 PWM&キャプチャタイマRUN/STOP制御 .....                                    | 147        |

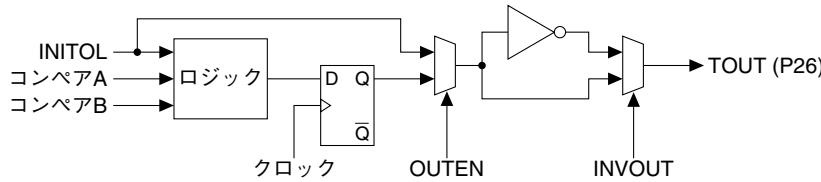

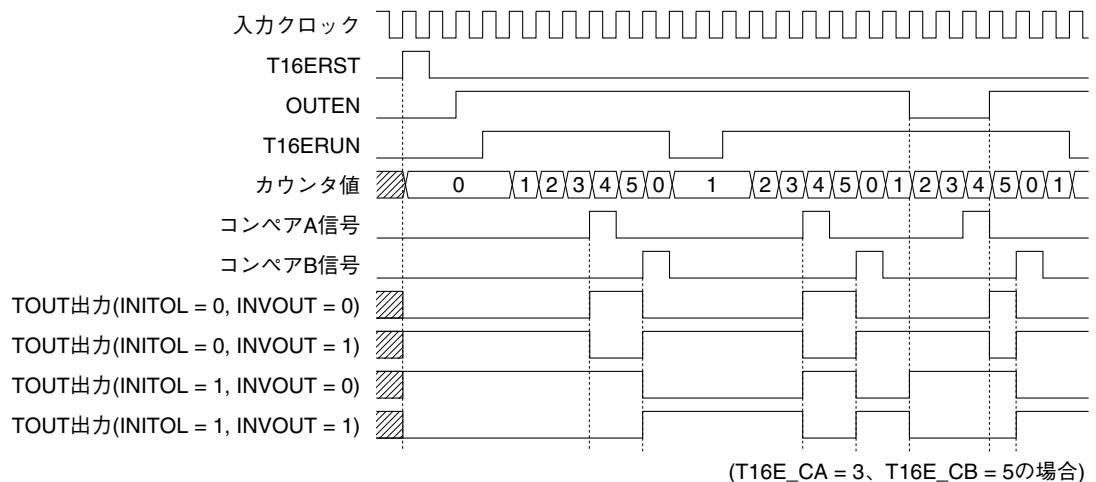

| 13.6 クロック出力の制御 .....                                                 | 148        |

| 13.7 PWM&キャプチャタイマ割り込み .....                                          | 151        |

| 13.8 制御レジスタ詳細 .....                                                  | 153        |

| 0x5300: PWM Timer Compare Data A Register (T16E_CA) .....            | 154        |

| 0x5302: PWM Timer Compare Data B Register (T16E_CB) .....            | 155        |

| 0x5304: PWM Timer Counter Data Register (T16E_TC) .....              | 156        |

| 0x5306: PWM Timer Control Register (T16E_CTL) .....                  | 157        |

| 0x5308: PWM Timer Input Clock Select Register (T16E_CLK) .....       | 159        |

| 0x530a: PWM Timer Interrupt Mask Register (T16E_IMSK) .....          | 160        |

| 0x530c: PWM Timer Interrupt Flag Register (T16E_IFLG) .....          | 161        |

| 13.9 注意事項 .....                                                      | 162        |

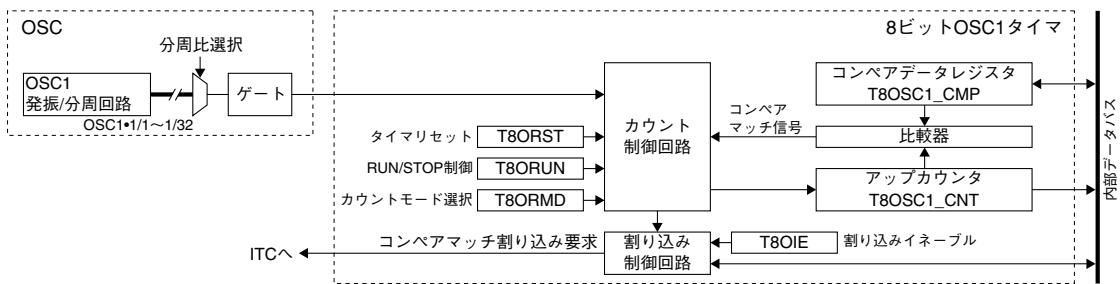

| <b>14 8ビットOSC1タイマ(T8OSC1) .....</b>                                  | <b>163</b> |

| 14.1 8ビットOSC1タイマの概要 .....                                            | 163        |

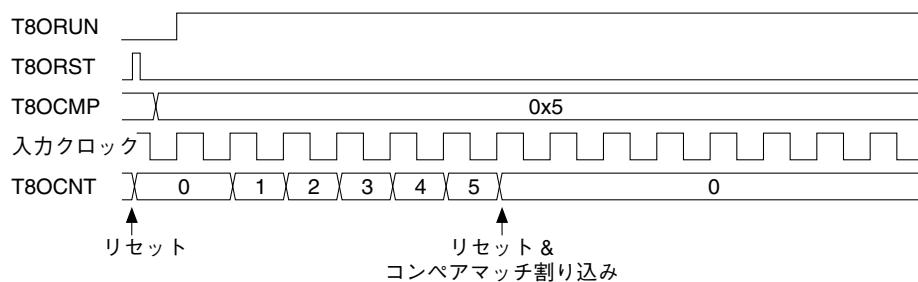

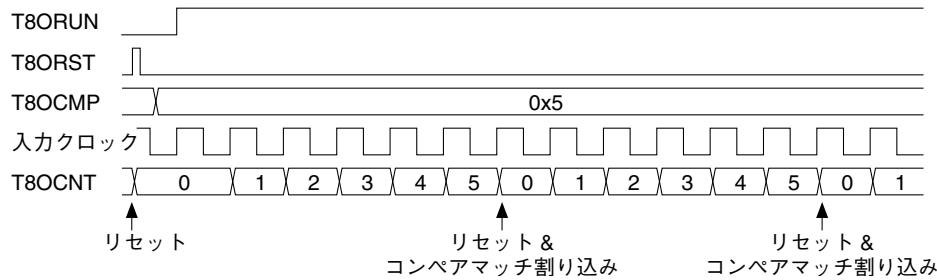

| 14.2 8ビットOSC1タイマのカウントモード .....                                       | 164        |

| 14.3 カウントクロック .....                                                  | 165        |

| 14.4 8ビットOSC1タイマのリセット .....                                          | 166        |

| 14.5 コンペアデータの設定 .....                                                | 167        |

| 14.6 8ビットOSC1タイマRUN/STOP制御 .....                                     | 168        |

| 14.7 8ビットOSC1タイマ割り込み .....                                           | 169        |

| 14.8 制御レジスタ詳細 .....                                                  | 171        |

| 0x50c0: 8-bit OSC1 Timer Control Register (T8OSC1_CTL) .....         | 172        |

| 0x50c1: 8-bit OSC1 Timer Counter Data Register (T8OSC1_CNT) .....    | 173        |

| 0x50c2: 8-bit OSC1 Timer Compare Data Register (T8OSC1_CMP) .....    | 174        |

| 0x50c3: 8-bit OSC1 Timer Interrupt Mask Register (T8OSC1_IMSK) ..... | 175        |

| 0x50c4: 8-bit OSC1 Timer Interrupt Flag Register (T8OSC1_IFLG) ..... | 176        |

| 14.9 注意事項 .....                                                      | 177        |

| <b>15 計時タイマ(CT) .....</b>                                            | <b>179</b> |

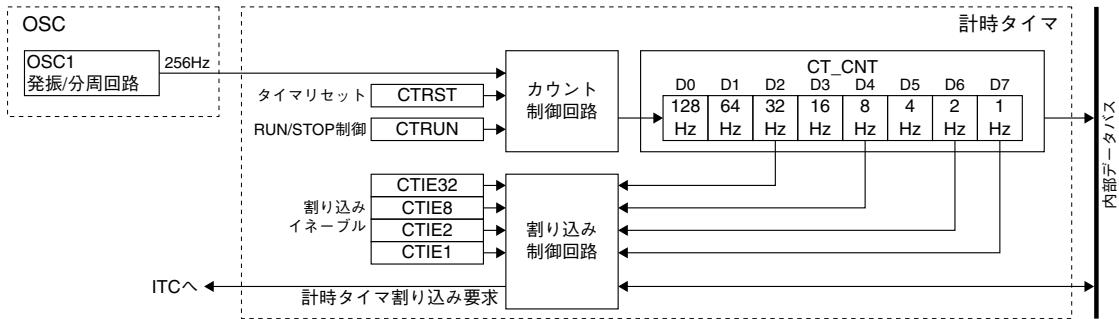

| 15.1 計時タイマの概要 .....                                                  | 179        |

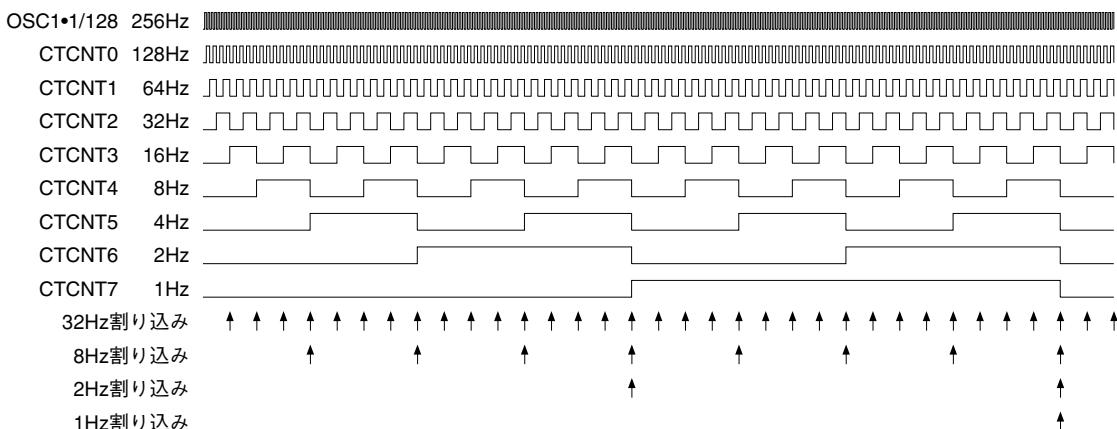

| 15.2 動作クロック .....                                                    | 180        |

| 15.3 計時タイマのリセット .....                                                | 181        |

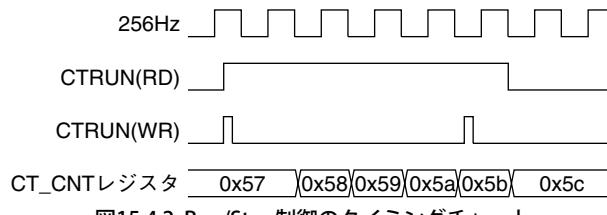

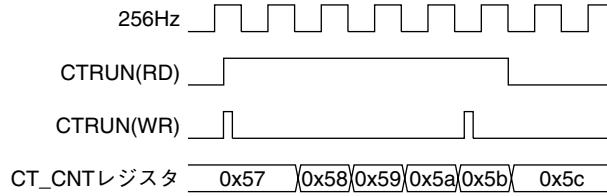

| 15.4 計時タイマRUN/STOP制御 .....                                           | 182        |

| 15.5 計時タイマ割り込み .....                                                 | 183        |

| 15.6 制御レジスタ詳細 .....                                                  | 185        |

| 0x5000: Clock Timer Control Register (CT_CTL) .....                  | 186        |

| 0x5001: Clock Timer Counter Register (CT_CNT) .....                  | 187        |

| 0x5002: Clock Timer Interrupt Mask Register (CT_IMSK) .....          | 188        |

| 0x5003: Clock Timer Interrupt Flag Register (CT_IFLG) .....          | 189        |

| 15.7 注意事項 .....                                                      | 190        |

| <b>16 ストップウォッチタイマ(SWT) .....</b>                                     | <b>191</b> |

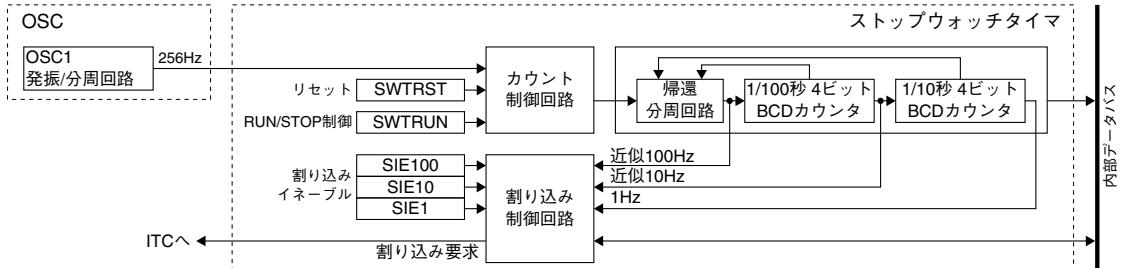

| 16.1 ストップウォッチタイマの概要 .....                                            | 191        |

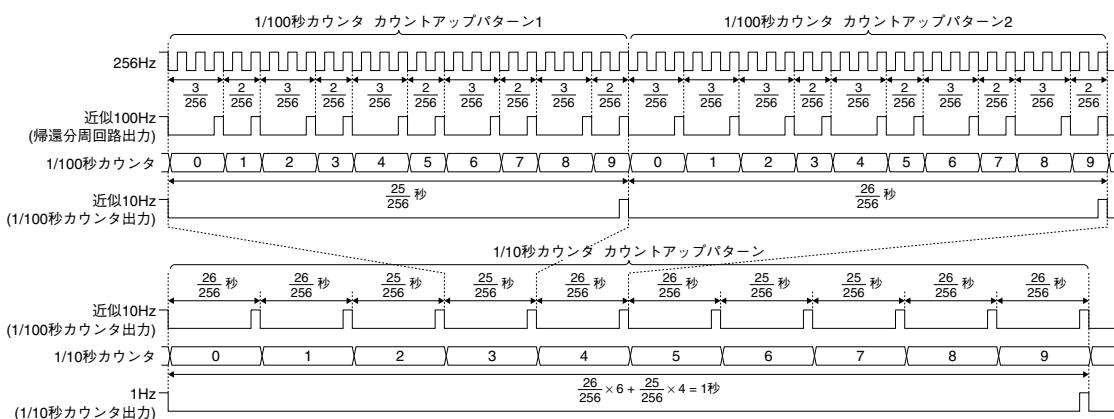

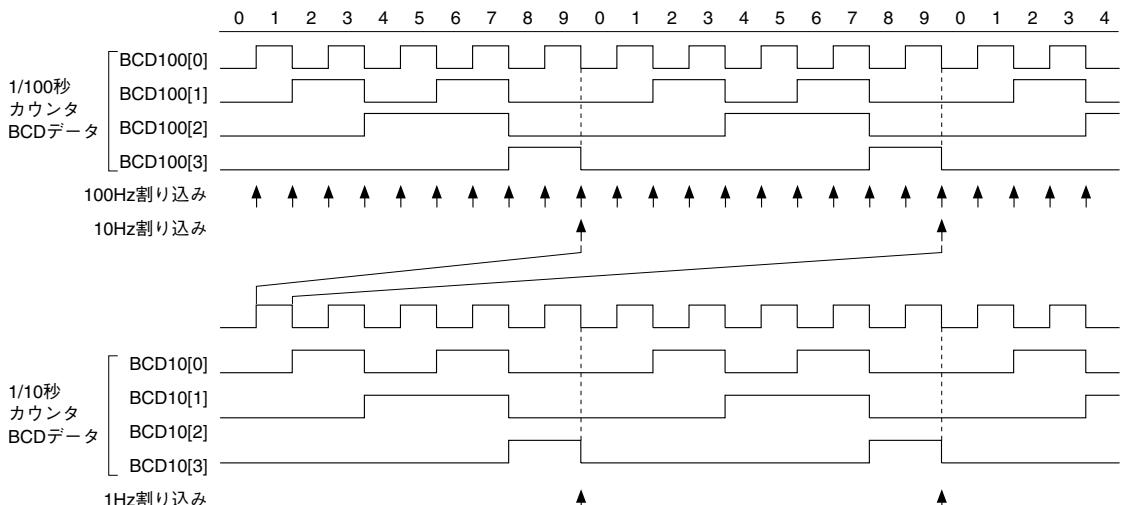

| 16.2 BCDカウンタ .....                                                   | 192        |

| 16.3 動作クロック .....                                                    | 193        |

| 16.4 ストップウォッチタイマのリセット .....                                          | 194        |

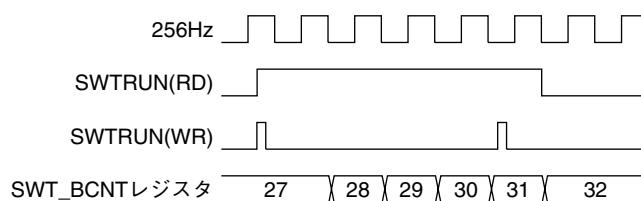

| 16.5 ストップウォッチタイマRUN/STOP制御 .....                                     | 195        |

| 16.6 ストップウォッチタイマ割り込み .....                                           | 196        |

|                                                                  |            |

|------------------------------------------------------------------|------------|

| 16.7 制御レジスタ詳細 .....                                              | 198        |

| 0x5020: Stopwatch Timer Control Register (SWT_CTL) .....         | 199        |

| 0x5021: Stopwatch Timer BCD Counter Register (SWT_BCNT) .....    | 200        |

| 0x5022: Stopwatch Timer Interrupt Mask Register (SWT_IMSK) ..... | 201        |

| 0x5023: Stopwatch Timer Interrupt Flag Register (SWT_IFLG) ..... | 202        |

| 16.8 注意事項 .....                                                  | 203        |

| <b>17 ウオッチドッグタイマ(WDT) .....</b>                                  | <b>205</b> |

| 17.1 ウオッチドッグタイマの概要 .....                                         | 205        |

| 17.2 動作クロック .....                                                | 206        |

| 17.3 ウオッチドッグタイマの制御 .....                                         | 207        |

| 17.3.1 NMI/リセットモードの選択 .....                                      | 207        |

| 17.3.2 ウオッチドッグタイマのRUN/STOP制御 .....                               | 207        |

| 17.3.3 ウオッチドッグタイマのリセット .....                                     | 207        |

| 17.3.4 スタンバイモード時の動作 .....                                        | 207        |

| 17.4 制御レジスタ詳細 .....                                              | 209        |

| 0x5040: Watchdog Timer Control Register (WDT_CTL) .....          | 210        |

| 0x5041: Watchdog Timer Status Register (WDT_ST) .....            | 211        |

| <b>18 UART .....</b>                                             | <b>213</b> |

| 18.1 UARTの構成 .....                                               | 213        |

| 18.2 UART端子 .....                                                | 214        |

| 18.3 転送クロック .....                                                | 215        |

| 18.4 転送データの設定 .....                                              | 216        |

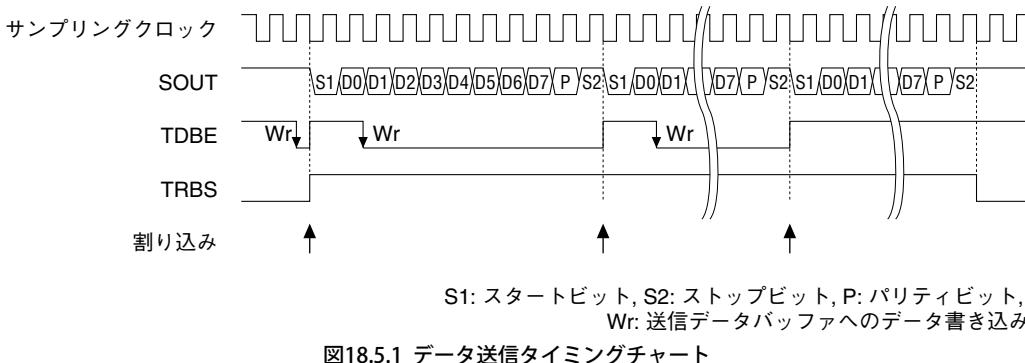

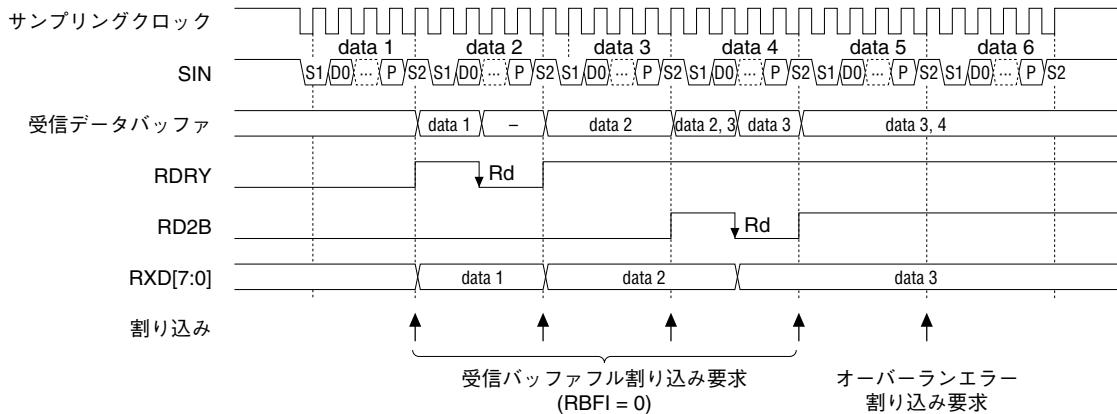

| 18.5 データ送受信の制御 .....                                             | 217        |

| 18.6 受信エラー .....                                                 | 220        |

| 18.7 UART割り込み .....                                              | 221        |

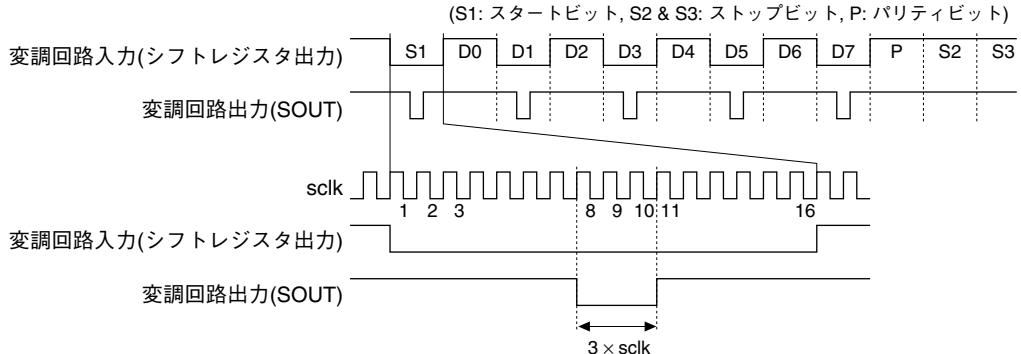

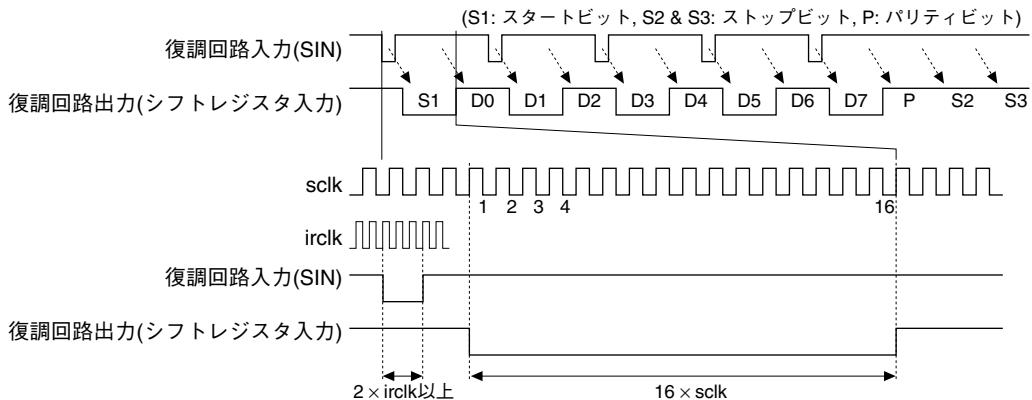

| 18.8 IrDAインターフェース .....                                          | 223        |

| 18.9 制御レジスタ詳細 .....                                              | 225        |

| 0x4100: UART Status Register (UART_ST) .....                     | 226        |

| 0x4101: UART Transmit Data Register (UART_TXD) .....             | 228        |

| 0x4102: UART Receive Data Register (UART_RXD) .....              | 229        |

| 0x4103: UART Mode Register (UART_MOD) .....                      | 230        |

| 0x4104: UART Control Register (UART_CTL) .....                   | 231        |

| 0x4105: UART Expansion Register (UART_EXP) .....                 | 232        |

| 18.10 注意事項 .....                                                 | 233        |

| <b>19 SPI .....</b>                                              | <b>235</b> |

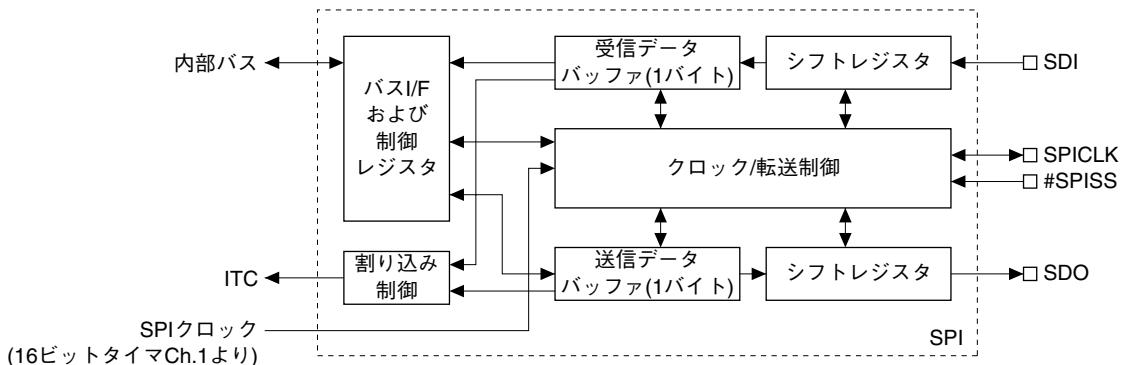

| 19.1 SPIの構成 .....                                                | 235        |

| 19.2 SPI入出力端子 .....                                              | 236        |

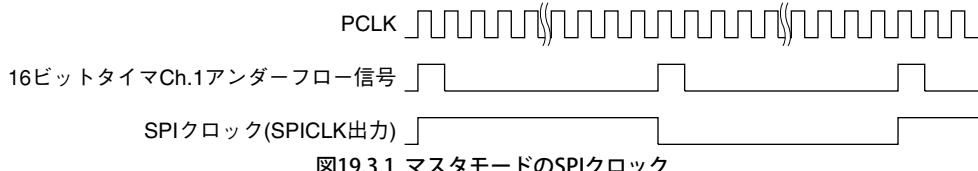

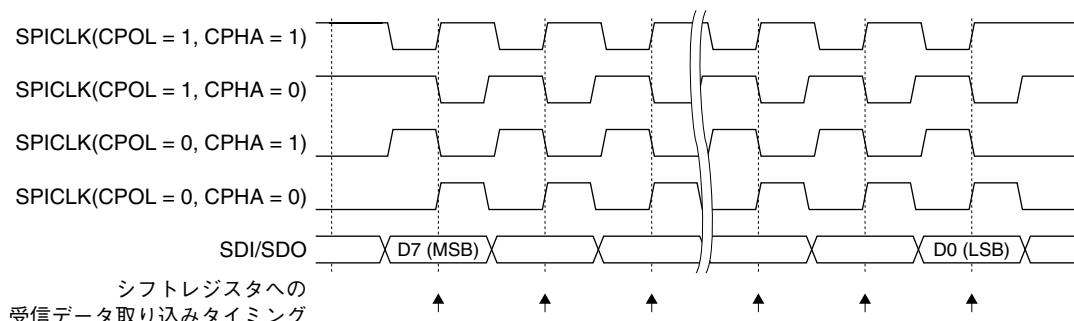

| 19.3 SPIクロック .....                                               | 237        |

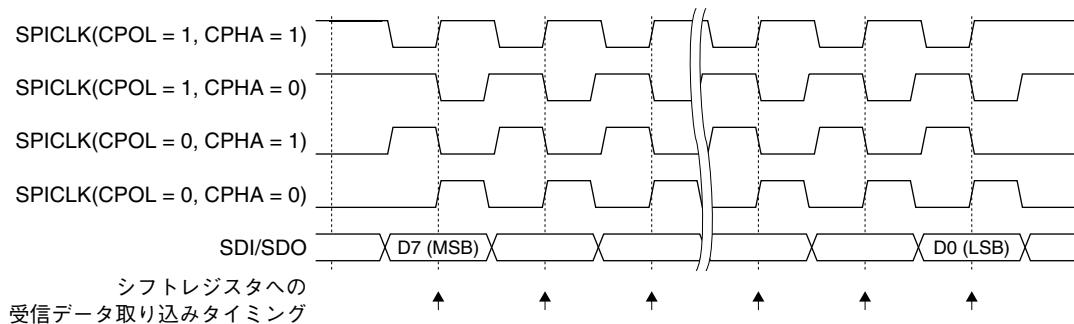

| 19.4 データ転送条件の設定 .....                                            | 238        |

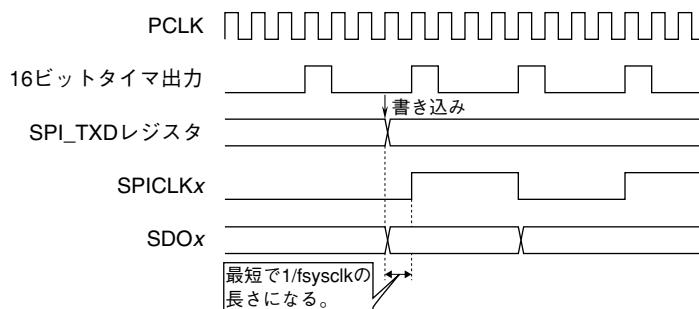

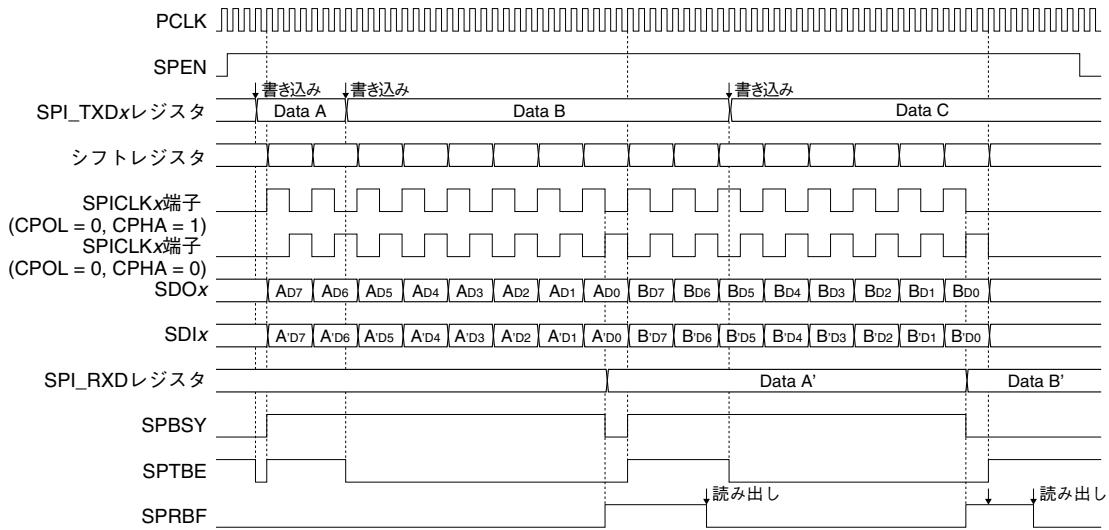

| 19.5 データ送受信の制御 .....                                             | 239        |

| 19.6 SPI割り込み .....                                               | 242        |

| 19.7 制御レジスタ詳細 .....                                              | 244        |

| 0x4320: SPI Status Register (SPI_ST) .....                       | 245        |

| 0x4322: SPI Transmit Data Register (SPI_TXD) .....               | 246        |

| 0x4324: SPI Receive Data Register (SPI_RXD) .....                | 247        |

| 0x4326: SPI Control Register (SPI_CTL) .....                     | 248        |

| 19.8 注意事項 .....                                                  | 250        |

| <b>20 I<sup>2</sup>C .....</b>                                   | <b>251</b> |

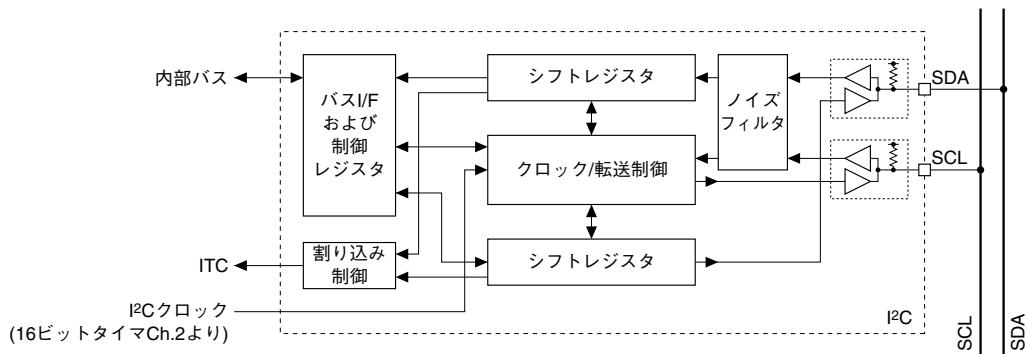

| 20.1 I <sup>2</sup> Cの構成 .....                                   | 251        |

| 20.2 I <sup>2</sup> C入出力端子 .....                                 | 252        |

---

|                                                                      |            |

|----------------------------------------------------------------------|------------|

| 20.3 I <sup>2</sup> Cクロック .....                                      | 253        |

| 20.4 データ転送前の設定項目 .....                                               | 254        |

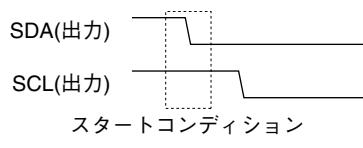

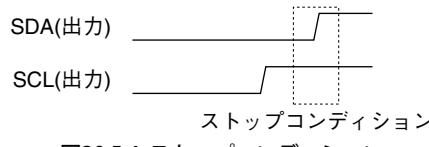

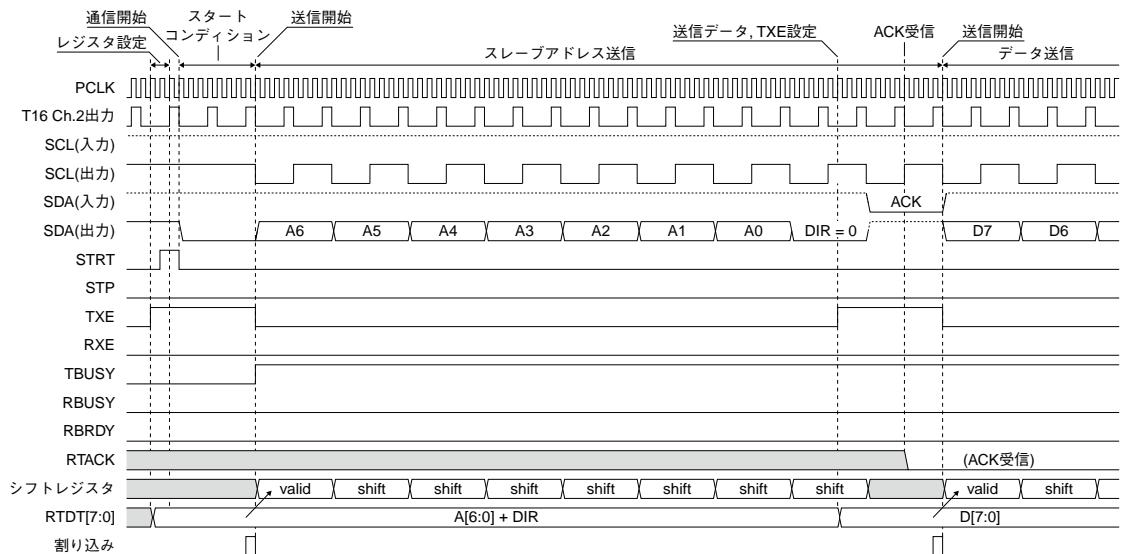

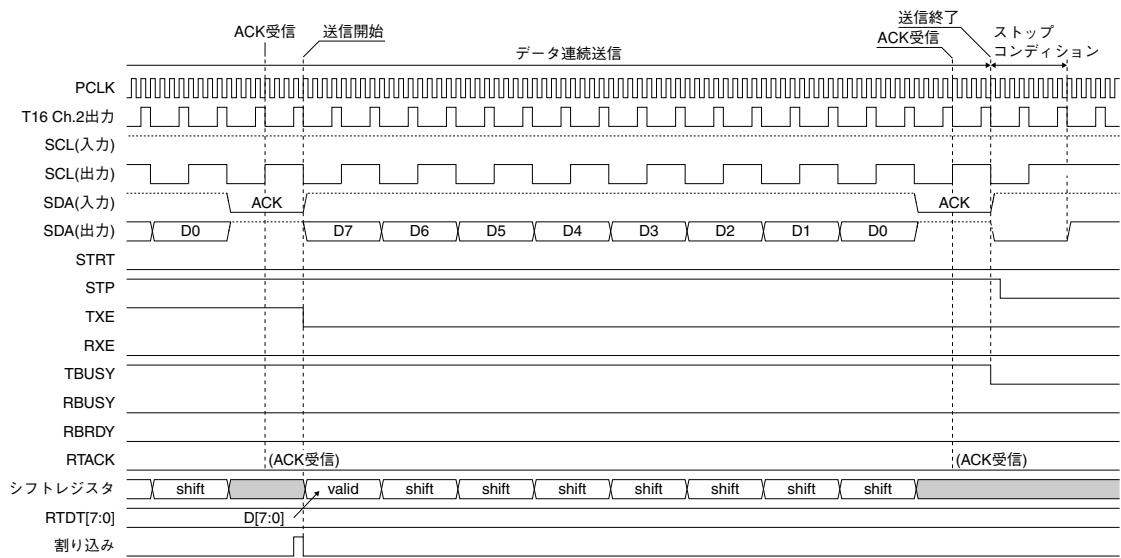

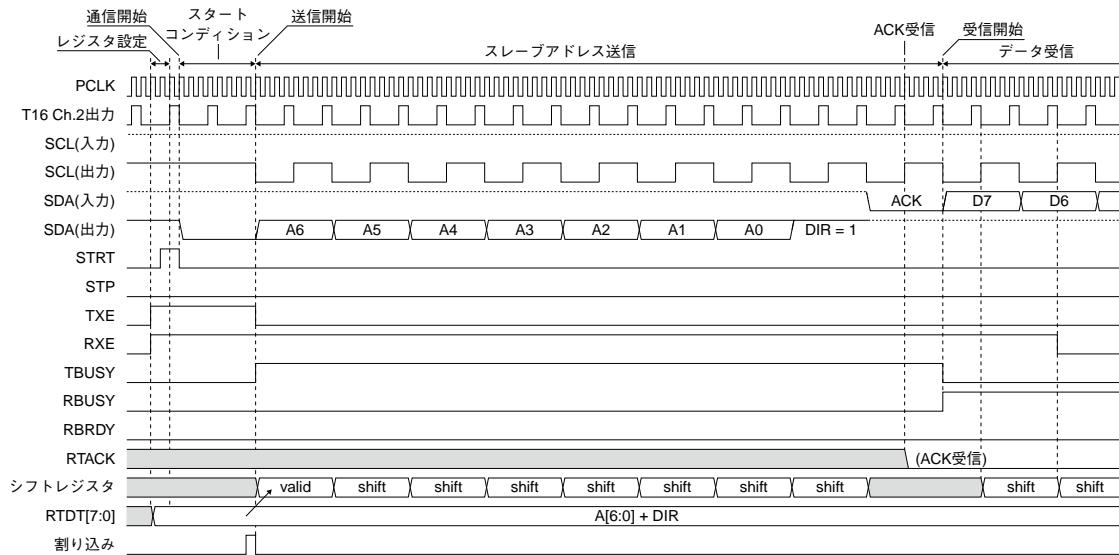

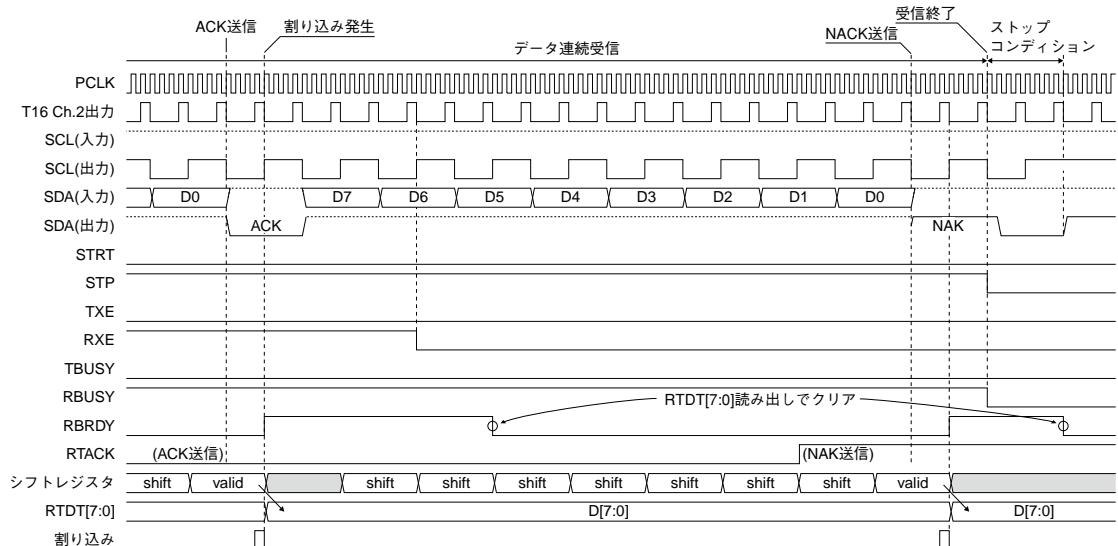

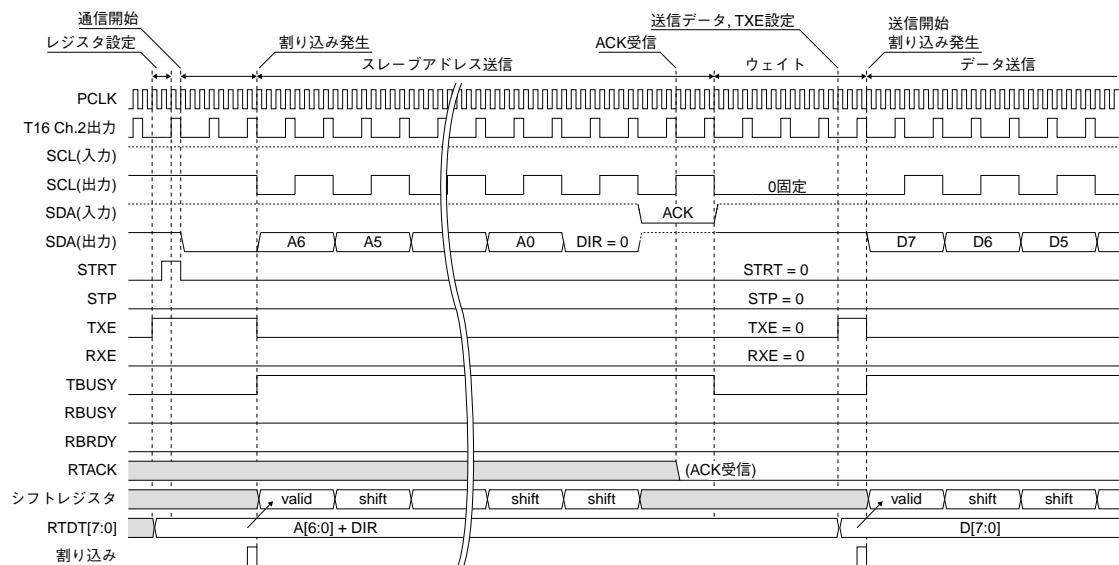

| 20.5 データ送受信の制御 .....                                                 | 255        |

| 20.6 I <sup>2</sup> C割り込み .....                                      | 262        |

| 20.7 制御レジスタ詳細 .....                                                  | 263        |

| 0x4340: I <sup>2</sup> C Enable Register (I2C_EN) .....              | 264        |

| 0x4342: I <sup>2</sup> C Control Register (I2C_CTL) .....            | 265        |

| 0x4344: I <sup>2</sup> C Data Register (I2C_DAT) .....               | 267        |

| 0x4346: I <sup>2</sup> C Interrupt Control Register (I2C_ICTL) ..... | 269        |

| <b>21 リモートコントローラ (REMC) .....</b>                                    | <b>271</b> |

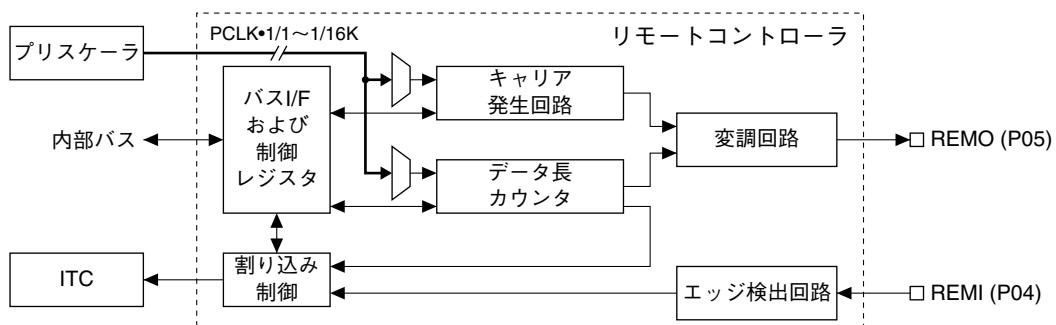

| 21.1 REMCの構成 .....                                                   | 271        |

| 21.2 REMC入出力端子 .....                                                 | 272        |

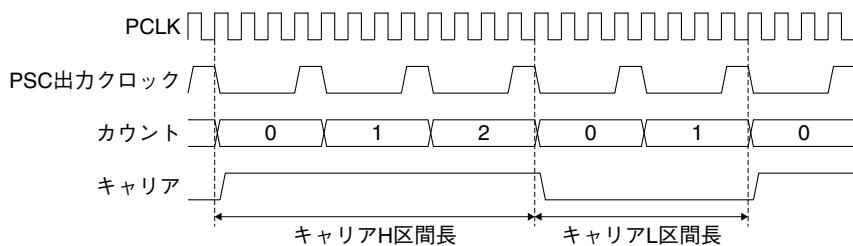

| 21.3 キャリアの生成 .....                                                   | 273        |

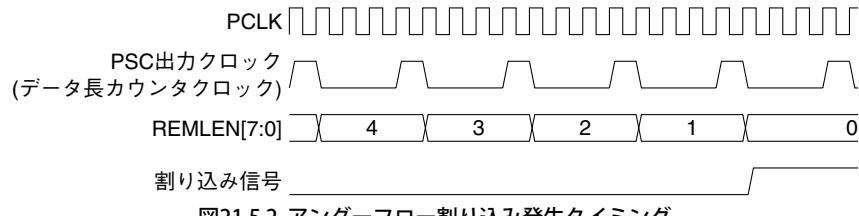

| 21.4 データ長カウンタのクロック設定 .....                                           | 274        |

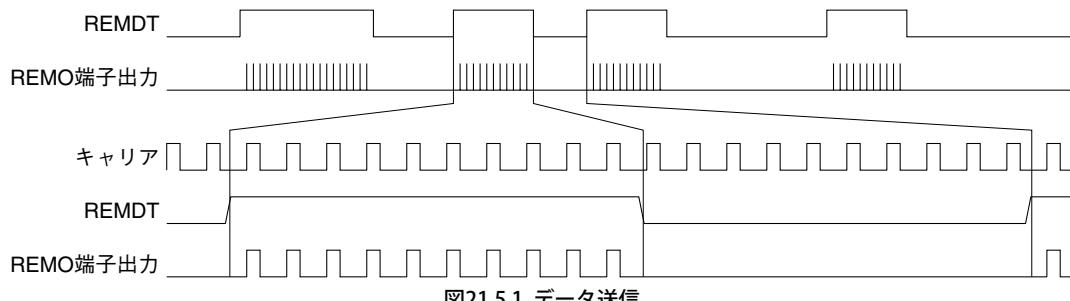

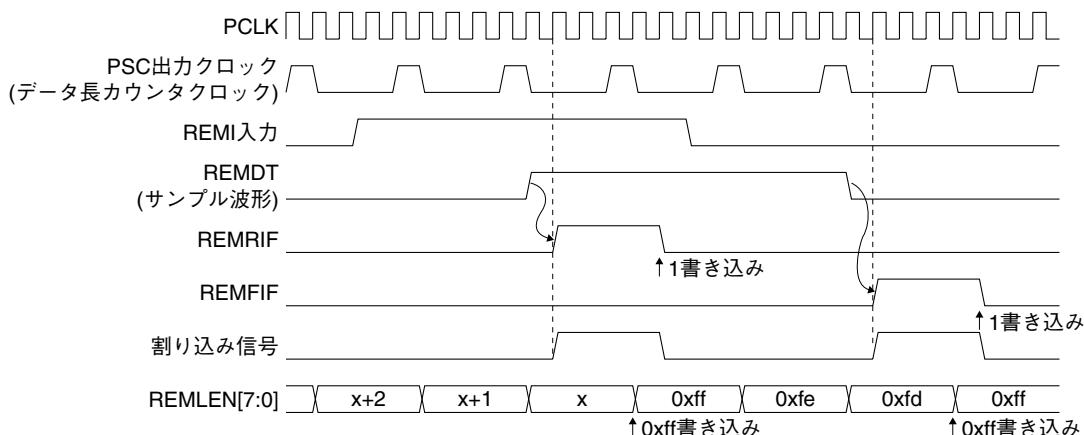

| 21.5 データ送受信の制御 .....                                                 | 275        |

| 21.6 REMC割り込み .....                                                  | 278        |

| 21.7 制御レジスタ詳細 .....                                                  | 280        |

| 0x5340: REMC Configuration Register (REMC_CFG) .....                 | 281        |

| 0x5341: REMC Prescaler Clock Select Register (REMC_PSC) .....        | 282        |

| 0x5342: REMC H Carrier Length Setup Register (REMC_CARH) .....       | 283        |

| 0x5343: REMC L Carrier Length Setup Register (REMC_CARL) .....       | 284        |

| 0x5344: REMC Status Register (REMC_ST) .....                         | 285        |

| 0x5345: REMC Length Counter Register (REMC_LCNT) .....               | 286        |

| 0x5346: REMC Interrupt Mask Register (REMC_IMSK) .....               | 287        |

| 0x5347: REMC Interrupt Flag Register (REMC_IFLG) .....               | 288        |

| 21.8 注意事項 .....                                                      | 289        |

| <b>22 オンチップデバッガ (DBG) .....</b>                                      | <b>291</b> |

| 22.1 リソース要件とデバッグツール .....                                            | 291        |

| 22.2 デバッガブレーク時の動作状態 .....                                            | 292        |

| 22.3 制御レジスタ詳細 .....                                                  | 293        |

| 0x5322: OSC1 Peripheral Control Register (MISC_OSC1) .....           | 294        |

| 0xffff90: Debug RAM Base Register (DBRAM) .....                      | 295        |

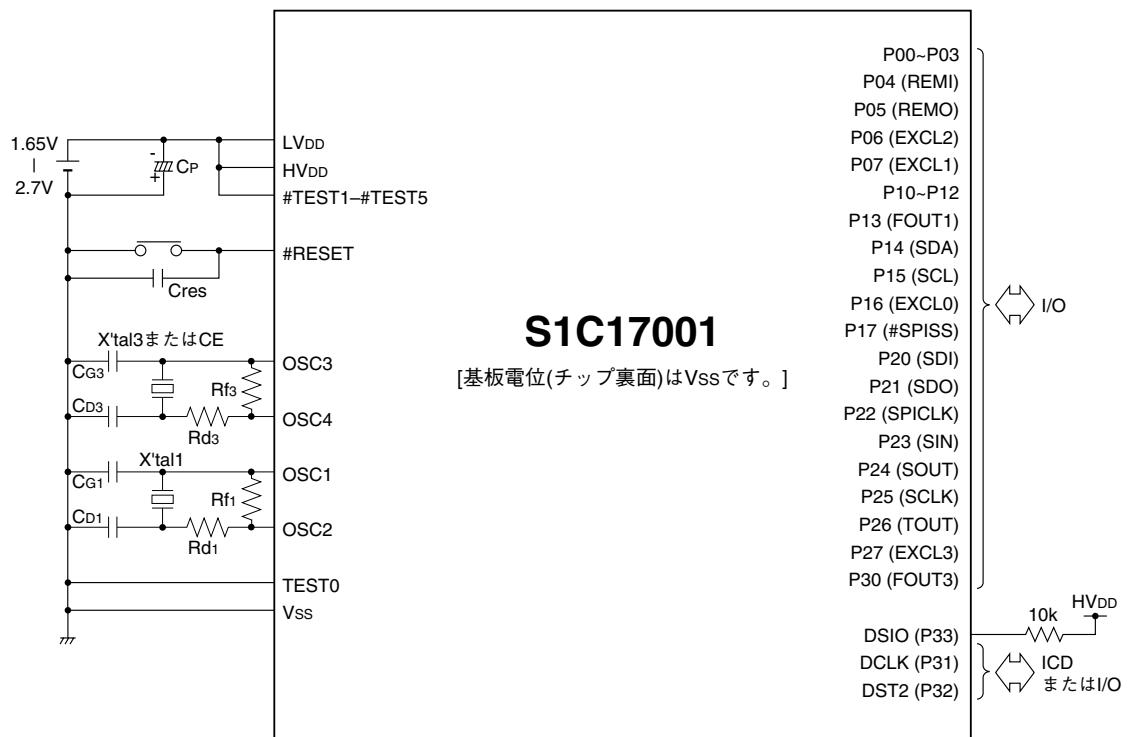

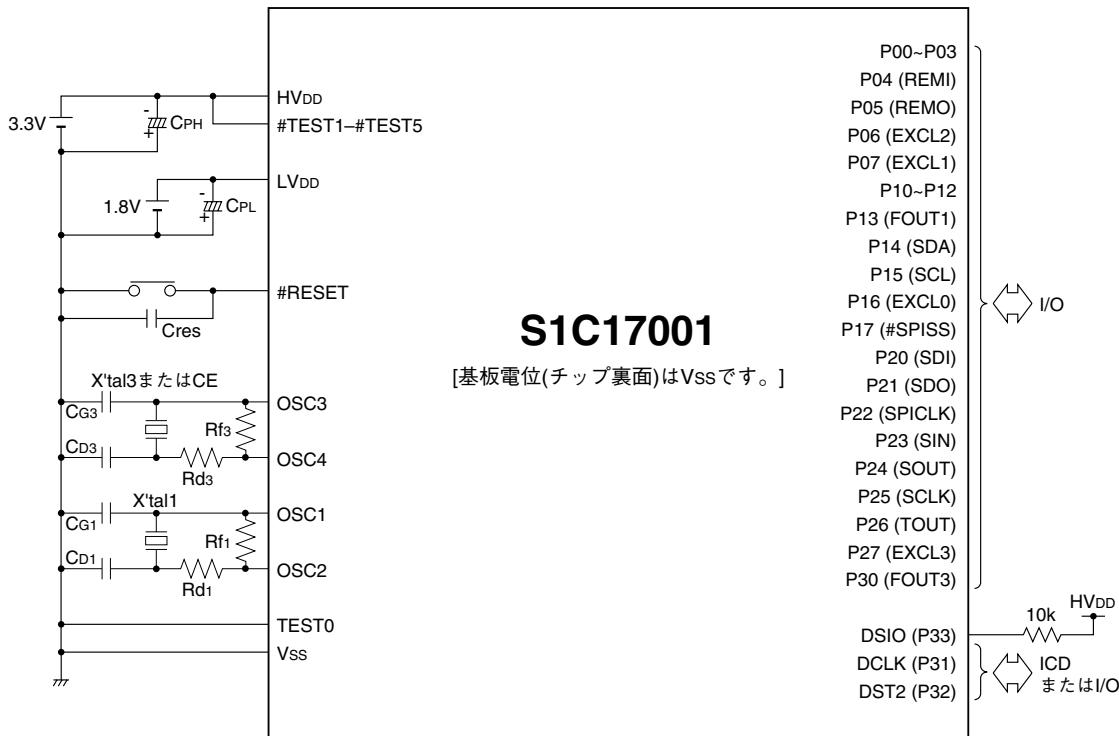

| <b>23 基本外部結線図 .....</b>                                              | <b>297</b> |

| <b>24 電気的特性 .....</b>                                                | <b>299</b> |

| 24.1 絶対最大定格 .....                                                    | 299        |

| 24.2 推奨動作条件 .....                                                    | 299        |

| 24.3 DC特性 .....                                                      | 300        |

| 24.4 消費電流 .....                                                      | 301        |

| 24.5 AC特性 .....                                                      | 302        |

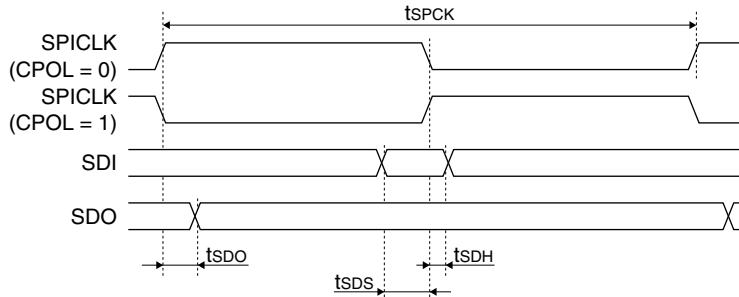

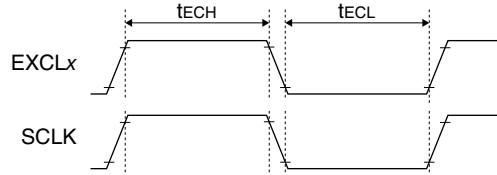

| 24.5.1 SPI AC特性 .....                                                | 302        |

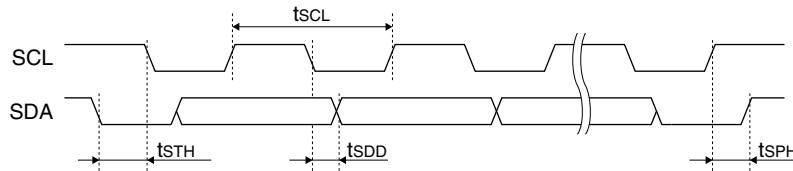

| 24.5.2 I <sup>2</sup> C AC特性 .....                                   | 302        |

| 24.5.3 外部クロック入力AC特性 .....                                            | 303        |

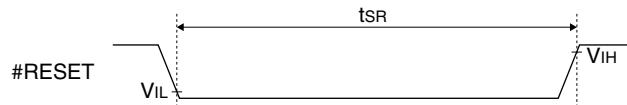

| 24.5.4 システムAC特性 .....                                                | 303        |

| 24.6 発振特性 .....                                                      | 304        |

| <b>25 パッケージ .....</b>                                                | <b>305</b> |

| <b>Appendix A I/Oレジスター一覧 .....</b>                                   | <b>307</b> |

| 0x4020              Prescaler .....                                  | 310        |

| 0x4100–0x4105      UART (with IrDA) .....                            | 311        |

| 0x4200–0x4206      8-bit Timer (with Fine Mode) .....                | 312        |

---

|                                                  |                            |     |

|--------------------------------------------------|----------------------------|-----|

| 0x4220–0x4266                                    | 16-bit Timer .....         | 313 |

| 0x4300–0x4314                                    | Interrupt Controller ..... | 315 |

| 0x4320–0x4326                                    | SPI .....                  | 317 |

| 0x4340–0x4346                                    | I <sup>2</sup> C .....     | 318 |

| 0x5000–0x5003                                    | Clock Timer .....          | 319 |

| 0x5020–0x5023                                    | Stopwatch Timer .....      | 320 |

| 0x5040–0x5041                                    | Watchdog Timer .....       | 321 |

| 0x5060–0x5065                                    | Oscillator .....           | 322 |

| 0x5080–0x5081                                    | Clock Generator .....      | 323 |

| 0x50c0–0x50c4                                    | 8-bit OSC1 Timer .....     | 324 |

| 0x5200–0x52a3                                    | P Port & Port MUX .....    | 325 |

| 0x5300–0x530c                                    | PWM & Capture Timer .....  | 327 |

| 0x5320–0x5322                                    | MISC Registers .....       | 328 |

| 0x5340–0x5347                                    | Remote Controller .....    | 329 |

| 0xfffff80–0xfffff90                              | S1C17 Core I/O .....       | 330 |

| <b>Appendix B パワーセーブ .....</b>                   | <b>331</b>                 |     |

| B.1 クロック制御によるパワーセーブ .....                        | 331                        |     |

| <b>Appendix C 実装上の注意事項 .....</b>                 | <b>334</b>                 |     |

| <b>Appendix D 初期化ルーチン .....</b>                  | <b>337</b>                 |     |

| <b>Appendix E S1C17001マスクROMコードの開発について .....</b> | <b>339</b>                 |     |

| <b>Appendix F 更新履歴 .....</b>                     | <b>340</b>                 |     |

| <b>改訂履歴表</b>                                     |                            |     |

# 1 概要

S1C17001は、高速かつ低電力動作、省サイズ、広アドレス空間、オンチップICEを実現した16ビットMCUです。S1C17 CPUコアを中心に、32KバイトのROM、2KバイトのRAM、高ビットレートおよびIrDA1.0に対応したUART、SPI、I<sup>2</sup>Cなどの各種センサに対応可能なシリアルインタフェース、8ビットタイマ、16ビットタイマ、PWM&キャプチャタイマ、計時タイマ、ストップウォッチタイマ、ウォッチドッギングタイマ、28本の汎用入出力ポートを内蔵しています。

1.8Vの動作電圧でも8.2MHzの高速動作が可能で、16ビットRISC処理により1命令を1クロックで実行します。

## 1.1 特長

以下にS1C17001の主な機能と特長を示します。

- CPU

- EPSONオリジナル16ビットRISC CPUコア S1C17

- メイン(OSC3)発振回路

- 水晶発振回路、セラミック発振回路または外部クロック入力 8.2MHz (max.)

- サブ(OSC1)発振回路

- 水晶発振回路または外部クロック入力 32.786kHz(typ.)

- 内蔵ROM

- 32Kバイト

- 内蔵RAM

- 2Kバイト

- 入出力ポート

- 最大28ビットの汎用入出力(周辺回路の入出力と端子を共用)

- シリアルインタフェース

- SPI(マスタ/スレーブ) 1ch.

- UART(IrDA1.0対応) 1ch.

- I<sup>2</sup>C(マスタ) 1ch.

- リモートコントローラ(REMC) 1ch.

- タイマ

- 8ビットタイマ(T8F) 1ch.

- 16ビットタイマ(T16) 3ch.

- PWM&キャプチャタイマ(T16E) 1ch.

- 計時タイマ(CT) 1ch.

- ストップウォッチタイマ(SWT) 1ch.

- ウオッチドッギングタイマ(WDT) 1ch.

- 8ビットOSC1タイマ(T8OSC1) 1ch.

- 割り込み

- リセット

- NMI

- ハードウェア割り込み14本(8レベル)

- 電源電圧

- コア電圧(LV<sub>DD</sub>) 1.65~2.7V

- I/O電圧(HV<sub>DD</sub>) 1.65~3.6V

- 動作温度

- -40~85°C

- 消費電流(typ.)

- SLEEP時 0.5μA

- HALT時 2.5μA (32kHz)

- 動作時 10μA (32kHz)

- 1800μA (8MHz)

- 出荷形態

- WCSP-48pinパッケージ

- マスクROMコード

- S1C17704

- 開発用Flashメモリ品

- (詳細はAppendix E参照)

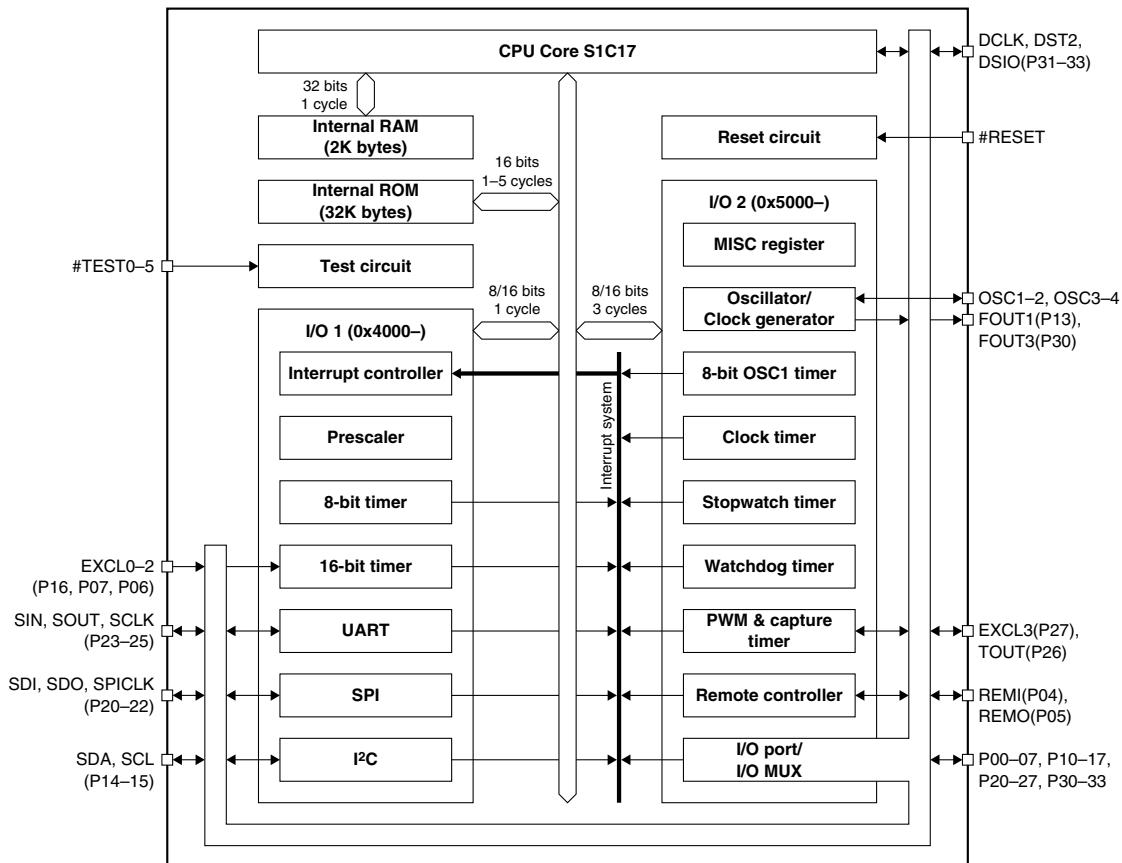

## 1.2 ブロック図

図1.2.1 ブロック図

## 1.3 端子

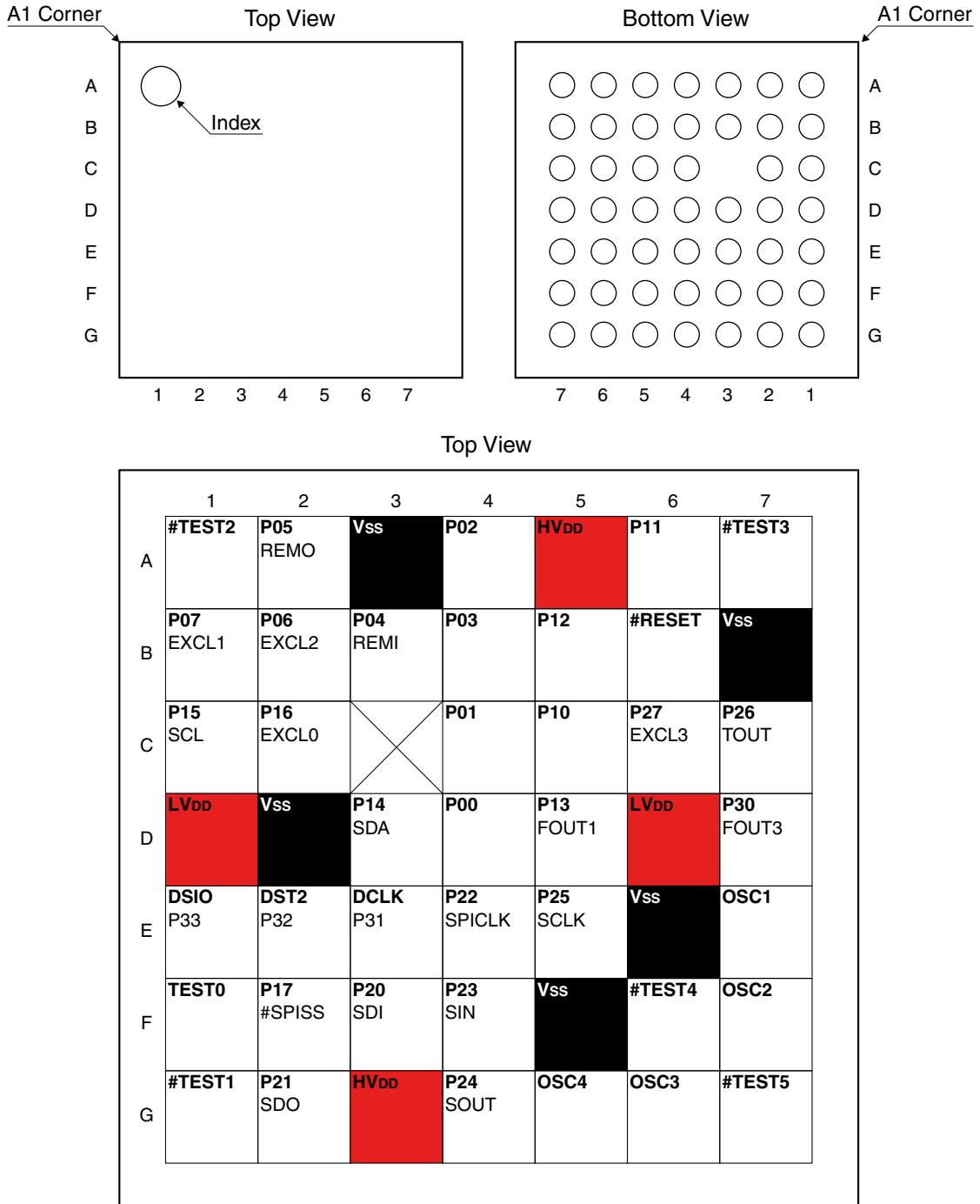

### 1.3.1 端子配置図

図1.3.1.1 端子配置図 (WCSP-48pin)

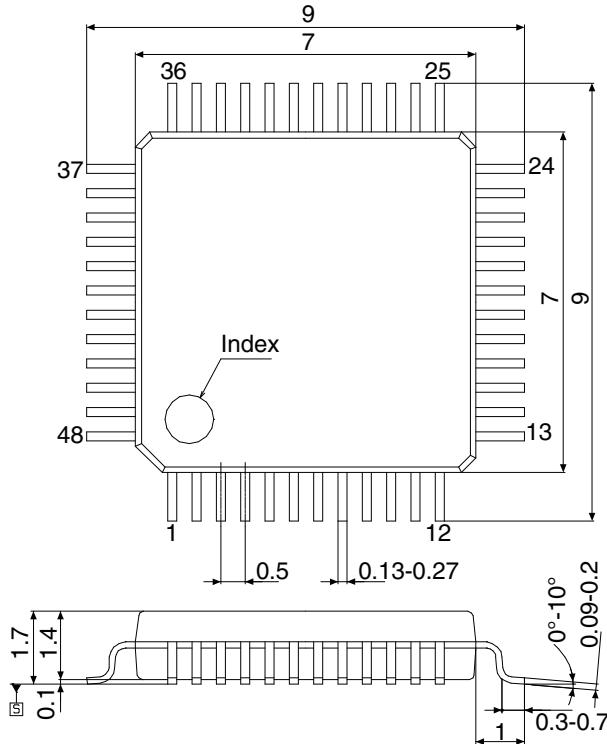

### 1.3.2 パッケージ (QFP12-48pin)

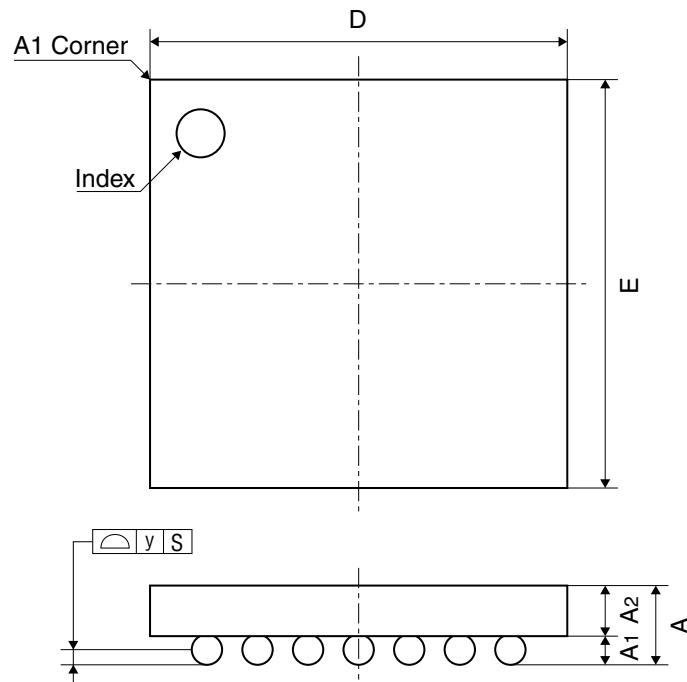

#### QFP12-48pin/パッケージ

図1.3.2.1 QFP12-48pin/パッケージ寸法

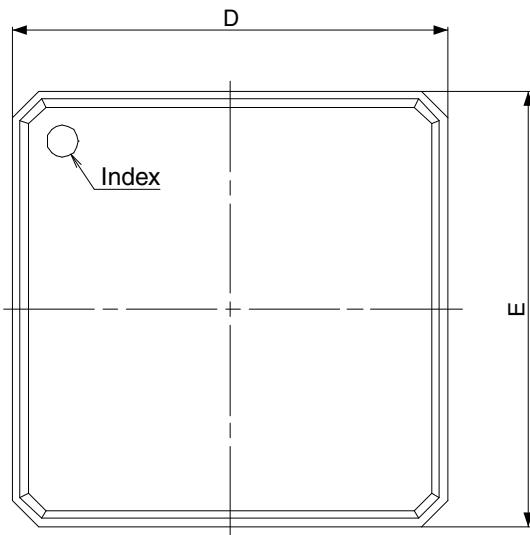

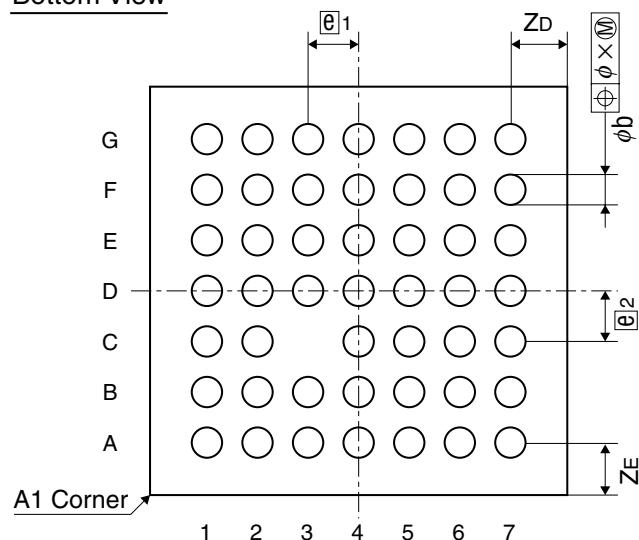

## QFN7-48pinパッケージ

Top View

Bottom View

| Symbol         | Dimension in Millimeters |     |      |

|----------------|--------------------------|-----|------|

|                | Min                      | Nom | Max  |

| D              | -                        | 7   | -    |

| E              | -                        | 7   | -    |

| A              | -                        | -   | 1    |

| A <sub>1</sub> | 0                        | -   | -    |

| b              | 0.17                     | -   | 0.3  |

| ε              | -                        | 0.5 | -    |

| L              | 0.3                      | -   | 0.5  |

| x              | -                        | -   | 0.1  |

| y              | -                        | -   | 0.08 |

図1.3.2.2 QFN7-48pin/パッケージ寸法

### 1.3.3 端子説明

表1.3.3.1 端子説明

| 端子 / ボール No.   |                 |      | 名称               | I/O | 初期状態         | 機能                                          |

|----------------|-----------------|------|------------------|-----|--------------|---------------------------------------------|

| QFN7<br>-48PIN | QFP12<br>-48PIN | WCSP |                  |     |              |                                             |

| 37             | 37              | A1   | #TEST2           | I   | I(Pull-Up)   | テスト端子(通常動作時はHighに固定)                        |

| 38             | 38              | A2   | P05/REMO         | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/リモート出力端子                  |

| 39             | 39              | B3   | P04/REMI         | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/リモート入力端子                  |

| 40             | 40              | A3   | Vss              | -   | -            | 電源端子(GND)                                   |

| 41             | 41              | B4   | P03              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 42             | 42              | A4   | P02              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 43             | 43              | C4   | P01              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 44             | 44              | D4   | P00              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 45             | 45              | A5   | HV <sub>DD</sub> | -   | -            | 電源端子(HV <sub>DD</sub> +)                    |

| 46             | 46              | B5   | P12              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 47             | 47              | A6   | P11              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 48             | 48              | C5   | P10              | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)                            |

| 1              | 1               | A7   | #TEST3           | I   | I(Pull-Up)   | テスト端子(通常動作時はHighに固定)                        |

| 2              | 2               | B6   | #RESET           | I   | I(Pull-Up)   | イニシャルセット入力端子                                |

| 3              | 3               | B7   | Vss              | -   | -            | 電源端子(GND)                                   |

| 4              | 4               | C6   | P27/EXCL3        | I/O | I(Pull-Up)   | 入出力ポート端子*/T16E 外部クロック入力端子                   |

| 5              | 5               | C7   | P26/TOUT         | I/O | I(Pull-Up)   | 入出力ポート端子*/T16E PWM 信号出力端子                   |

| 6              | 6               | D5   | P13/FOUT1        | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/OSC1 クロック出力端子             |

| 7              | 7               | D7   | P30/FOUT3        | I/O | I(Pull-Up)   | 入出力ポート端子*/OSC3 分周クロック出力端子                   |

| 8              | 8               | D6   | LV <sub>DD</sub> | -   | -            | 電源端子(LV <sub>DD</sub> +)                    |

| 9              | 9               | E6   | Vss              | -   | -            | 電源端子(GND)                                   |

| 10             | 10              | E7   | OSC1             | I   | I            | OSC1 発振入力端子(外部クロック入力可能)                     |

| 11             | 11              | F7   | OSC2             | O   | O            | OSC1 発振出力端子                                 |

| 12             | 12              | F6   | #TEST4           | I   | I(Pull-Up)   | テスト端子(通常動作時はHighに固定)                        |

| 13             | 13              | G7   | #TEST5           | I   | I(Pull-Up)   | テスト端子(通常動作時はHighに固定)                        |

| 14             | 14              | G6   | OSC3             | I   | I            | OSC3 発振入力端子(外部クロック入力可能)                     |

| 15             | 15              | G5   | OSC4             | O   | O            | OSC3 発振出力端子                                 |

| 16             | 16              | F5   | Vss              | -   | -            | 電源端子(GND)                                   |

| 17             | 17              | E5   | P25/SCLK         | I/O | I(Pull-Up)   | 入出力ポート端子*/UART クロック入力端子                     |

| 18             | 18              | G4   | P24/SOUT         | I/O | I(Pull-Up)   | 入出力ポート端子*/UART データ出力端子                      |

| 19             | 19              | F4   | P23/SIN          | I/O | I(Pull-Up)   | 入出力ポート端子*/UART データ入力端子                      |

| 20             | 20              | G3   | HV <sub>DD</sub> | -   | -            | 電源端子(HV <sub>DD</sub> +)                    |

| 21             | 21              | E4   | P22/SPICLK       | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI クロック入出力端子                     |

| 22             | 22              | G2   | P21/SDO          | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI データ出力端子                       |

| 23             | 23              | F3   | P20/SDI          | I/O | I(Pull-Up)   | 入出力ポート端子*/SPI データ入力端子                       |

| 24             | 24              | F2   | P17/#SPISS       | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/SPI スレーブセレクト入力端子          |

| 25             | 25              | G1   | #TEST1           | I   | I(Pull-Up)   | テスト端子(通常動作時はHighに固定)                        |

| 26             | 26              | F1   | TEST0            | I   | I(Pull-Down) | テスト端子(通常動作時はLowに固定)                         |

| 27             | 27              | E3   | DCLK/P31         | I/O | O(H)         | オンチップデバッガクロック出力端子*/入出力ポート端子                 |

| 28             | 28              | E2   | DST2/P32         | I/O | O(L)         | オンチップデバッガステータス出力端子*/入出力ポート端子                |

| 29             | 29              | E1   | DSIO/P33         | I/O | I(Pull-Up)   | オンチップデバッガデータ入出力端子*/入出力ポート端子                 |

| 30             | 30              | D2   | Vss              | -   | -            | 電源端子(GND)                                   |

| 31             | 31              | D1   | LV <sub>DD</sub> | -   | -            | 電源端子(LV <sub>DD</sub> +)                    |

| 32             | 32              | D3   | P14/SDA          | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/I <sup>2</sup> C データ入出力端子 |

| 33             | 33              | C1   | P15/SCL          | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/I <sup>2</sup> C クロック出力端子 |

| 34             | 34              | C2   | P16/EXCL0        | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/T16 Ch.0 外部クロック入力端子       |

| 35             | 35              | B1   | P07/EXCL1        | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/T16 Ch.1 外部クロック入力端子       |

| 36             | 36              | B2   | P06/EXCL2        | I/O | I(Pull-Up)   | 入出力ポート端子(割り込み付き)*/T16 Ch.2 外部クロック入力端子       |

注：太字の端子名、および“\*”の付いた機能がデフォルト設定の内容です。

# 2 CPU

S1C17001はコアプロセッサとしてS1C17コアを搭載しています。

S1C17コアはセイコーエプソンオリジナルの16ビットRISCプロセッサです。

低消費電力、高速動作、広いアドレス空間、主要命令の1クロック実行、省ゲート設計を特長とし、8ビットCPUがよく使われるコントローラやシーケンサ等への組み込み用に最適です。

S1C17コアの詳細については、“S1C17 Family S1C17コアマニュアル”を参照してください。

## 2.1 S1C17コアの特長

### プロセッサ形式

- セイコーエプソンオリジナル16ビットRISCプロセッサ

- 0.35～0.15μm低電力CMOSプロセステクノロジ

### 命令セット

- コード長 16ビット固定長

- 命令数 基本命令111個(全184命令)

- 実行サイクル 主要命令は1サイクルで実行

- 即値拡張命令 即値を24ビットまで拡張

- Cによる開発用に最適化されたコンパクトかつ高速な命令セット

### レジスタセット

- 24ビット汎用レジスタ × 8

- 24ビット特殊レジスタ × 2

- 8ビット特殊レジスタ × 1

### メモリ空間、バス

- 最大16Mバイトのメモリ空間(24ビットアドレス)

- 命令バス(16ビット)とデータバス(32ビット)を分離したハーバードアーキテクチャ

### 割り込み

- リセット、NMI、32種類の外部割り込みに対応

- アドレス不整割り込み

- デバッグ割り込み

- ベクタテーブルからベクタを読み込み、割り込み処理ルーチンへ直接分岐

- ベクタ番号によるソフトウェア割り込みを発生可能(全ベクタ番号を指定可能)

### パワーセーブ

- HALT(halt命令)

- SLEEP(slp命令)

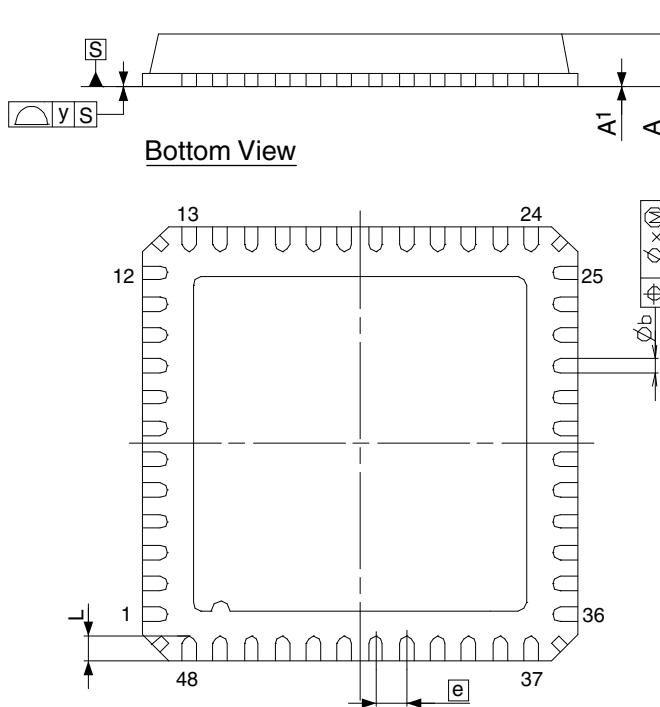

## 2.2 CPUレジスタ

S1C17コアは、8本の汎用レジスタおよび3本の特殊レジスタを内蔵しています。

図2.2.1 レジスタ

## 2.3 命令セット

S1C17コアの命令コードはすべて16ビットの固定長で、パイプライン処理を行うことによって主要な命令を1サイクルで実行します。各命令の詳細については“S1C17 Family S1C17コアマニュアル”を参照してください。

表2.3.1 S1C17コア命令一覧

| 種類    | ニーモニック          | 機能                                            |

|-------|-----------------|-----------------------------------------------|

| データ転送 | ld.b %rd, %rs   | 汎用レジスタ(16ビット) → 汎用レジスタ(符号拡張)                  |

|       | %rd, [%rb]      | メモリ(16ビット) → 汎用レジスタ(符号拡張)                     |

|       | %rd, [%rb] +    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

|       | %rd, [%rb] -    |                                               |

|       | %rd, -[%rb]     |                                               |

|       | %rd, [%sp+imm7] | スタック(16ビット) → 汎用レジスタ(符号拡張)                    |

|       | %rd, [imm7]     | メモリ(16ビット) → 汎用レジスタ(符号拡張)                     |

|       | [%rb], %rs      | 汎用レジスタ(16ビット) → メモリ                           |

|       | [%rb] +, %rs    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

|       | [%rb] -, %rs    |                                               |

|       | -[%rb], %rs     |                                               |

|       | [%sp+imm7], %rs | 汎用レジスタ(16ビット) → スタック                          |

|       | [imm7], %rs     | 汎用レジスタ(16ビット) → メモリ                           |

|       |                 |                                               |

| ld.ub | %rd, %rs        | 汎用レジスタ(16ビット) → 汎用レジスタ(ゼロ拡張)                  |

|       | %rd, [%rb]      | メモリ(16ビット) → 汎用レジスタ(ゼロ拡張)                     |

|       | %rd, [%rb] +    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

|       | %rd, [%rb] -    |                                               |

|       | %rd, -[%rb]     |                                               |

|       | %rd, [%sp+imm7] | スタック(16ビット) → 汎用レジスタ(ゼロ拡張)                    |

|       | %rd, [imm7]     | メモリ(16ビット) → 汎用レジスタ(ゼロ拡張)                     |

| ld    | %rd, %rs        | 汎用レジスタ(16ビット) → 汎用レジスタ                        |

|       | %rd, sign7      | 即値 → 汎用レジスタ(符号拡張)                             |

|       | %rd, [%rb]      | メモリ(16ビット) → 汎用レジスタ                           |

|       | %rd, [%rb] +    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

|       | %rd, [%rb] -    |                                               |

|       | %rd, -[%rb]     |                                               |

|       | %rd, [%sp+imm7] | スタック(16ビット) → 汎用レジスタ                          |

|       | %rd, [imm7]     | メモリ(16ビット) → 汎用レジスタ                           |

|       | [%rb], %rs      | 汎用レジスタ(16ビット) → メモリ                           |

|       | [%rb] +, %rs    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

| ld.a  | %rd, -[%rb]     |                                               |

|       | %rd, -[%rb]     |                                               |

|       | %rd, [%sp+imm7] | スタック(32ビット) → 汎用レジスタ (*1)                     |

|       | %rd, [imm7]     | メモリ(32ビット) → 汎用レジスタ (*1)                      |

|       | [%rb], %rs      | 汎用レジスタ(32ビット、ゼロ拡張) → メモリ (*1)                 |

|       | [%rb] +, %rs    | メモリアドレスのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能  |

|       | [%rb] -, %rs    |                                               |

|       | -[%rb], %rs     |                                               |

|       | [%sp+imm7], %rs | 汎用レジスタ(32ビット、ゼロ拡張) → スタック (*1)                |

|       | [imm7], %rs     | 汎用レジスタ(32ビット、ゼロ拡張) → メモリ (*1)                 |

|       | %rd, %sp        | SP → 汎用レジスタ                                   |

|       | %rd, %pc        | PC → 汎用レジスタ                                   |

|       | %rd, [%sp]      | スタック(32ビット) → 汎用レジスタ (*1)                     |

|       | %rd, [%sp] +    | スタックポインタのポストインクリメント、ポストデクリメント、プリデクリメント機能を使用可能 |

|       | %rd, [%sp] -    |                                               |

|       | %rd, -[%sp]     |                                               |

| 種類     | ニーモニック          | 機能                                                                  |

|--------|-----------------|---------------------------------------------------------------------|

| データ転送  | ld.a [%sp], %rs | 汎用レジスタ(32ビット、ゼロ拡張)→スタック(*1)                                         |

|        | [%sp]+, %rs     | スタックポインタのポストインクリメント、ポストデクリメント、                                      |

|        | [%sp]-, %rs     | プリデクリメント機能を使用可能                                                     |

|        | -[%sp], %rs     |                                                                     |

|        | %sp, %rs        | 汎用レジスタ(24ビット)→SP                                                    |

|        | %sp, imm7       | 即値→SP                                                               |

| 整数算術演算 | add %rd, %rs    | 汎用レジスタ間の16ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | add/c           |                                                                     |

|        | add/nc          |                                                                     |

|        | add %rd, imm7   | 汎用レジスタと即値の16ビット加算                                                   |

|        | add.a %rd, %rs  | 汎用レジスタ間の24ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | add.a/c         |                                                                     |

|        | add.a/nc        |                                                                     |

|        | add.a %sp, %rs  | SPと汎用レジスタの24ビット加算                                                   |

|        | add.a %rd, imm7 | 汎用レジスタと即値の24ビット加算                                                   |

|        | add.a %sp, imm7 | SPと即値の24ビット加算                                                       |

|        | adc %rd, %rs    | 汎用レジスタ間のキャリー付き16ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行) |

|        | adc/c           |                                                                     |

|        | adc/nc          |                                                                     |

|        | adc %rd, imm7   | 汎用レジスタと即値のキャリー付き16ビット加算                                             |

|        | sub %rd, %rs    | 汎用レジスタ間の16ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | sub/c           |                                                                     |

|        | sub/nc          |                                                                     |

|        | sub %rd, imm7   | 汎用レジスタと即値の16ビット減算                                                   |

|        | sub.a %rd, %rs  | 汎用レジスタ間の24ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | sub.a/c         |                                                                     |

|        | sub.a/nc        |                                                                     |

|        | sub.a %sp, %rs  | SPと汎用レジスタの24ビット減算                                                   |

|        | sub.a %rd, imm7 | 汎用レジスタと即値の24ビット減算                                                   |

|        | sub.a %sp, imm7 | SPと即値の24ビット減算                                                       |

|        | sbc %rd, %rs    | 汎用レジスタ間のキャリー付き16ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行) |

|        | sbc/c           |                                                                     |

|        | sbc/nc          |                                                                     |

|        | sbc %rd, imm7   | 汎用レジスタと即値のキャリー付き16ビット減算                                             |

| 論理演算   | cmp %rd, %rs    | 汎用レジスタ間の16ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | cmp/c           |                                                                     |

|        | cmp/nc          |                                                                     |

|        | cmp %rd, sign7  | 汎用レジスタと即値の16ビット比較                                                   |

|        | cmp.a %rd, %rs  | 汎用レジスタ間の24ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)       |

|        | cmp.a/c         |                                                                     |

|        | cmp.a/nc        |                                                                     |

|        | cmp.a %rd, imm7 | 汎用レジスタと即値の24ビット比較                                                   |

|        | cmc %rd, %rs    | 汎用レジスタ間のキャリー付き16ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行) |

|        | cmc/c           |                                                                     |

|        | cmc/nc          |                                                                     |

|        | cmc %rd, sign7  | 汎用レジスタと即値のキャリー付き16ビット比較                                             |

| 論理演算   | and %rd, %rs    | 汎用レジスタ間の論理積<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)           |

|        | and/c           |                                                                     |

|        | and/nc          |                                                                     |

|        | and %rd, sign7  | 汎用レジスタと即値の論理積                                                       |

|        | or %rd, %rs     | 汎用レジスタ間の論理和<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)           |

|        | or/c            |                                                                     |

|        | or/nc           |                                                                     |

|        | or %rd, sign7   | 汎用レジスタと即値の論理和                                                       |

|        | xor %rd, %rs    | 汎用レジスタ間の排他的論理和<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)        |

|        | xor/c           |                                                                     |

|        | xor/nc          |                                                                     |

|        | xor %rd, sign7  | 汎用レジスタと即値の排他的論理和                                                    |

| 論理演算   | not %rd, %rs    | 汎用レジスタ間の論理否定(1の補数)<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)    |

|        | not/c           |                                                                     |

|        | not/nc          |                                                                     |

|        | not %rd, sign7  | 汎用レジスタと即値の論理否定(1の補数)                                                |

|        |                 |                                                                     |

| 種類       | 二ーモニック  | 機能                                                 |

|----------|---------|----------------------------------------------------|

| シフト&スワップ | sr      | 右論理シフト(レジスタによるシフトビット数指定)<br>右論理シフト(即値によるシフトビット数指定) |

|          | sa      | 右算術シフト(レジスタによるシフトビット数指定)<br>右算術シフト(即値によるシフトビット数指定) |

|          | sl      | 左論理シフト(レジスタによるシフトビット数指定)<br>左論理シフト(即値によるシフトビット数指定) |

|          | swap    | 16ビット境界でバイト単位のスワップ                                 |

|          | ext     | 直後の命令のオペランドを拡張                                     |

| 即値拡張     | cv.ab   | 符号付き8ビットデータを24ビットに変換                               |

|          | cv.as   | 符号付き16ビットデータを24ビットに変換                              |

|          | cv.al   | 32ビットデータを24ビットに変換                                  |

|          | cv.la   | 24ビットデータを32ビットに変換                                  |

|          | cv.ls   | 16ビットデータを32ビットに変換                                  |

| 分岐       | jpr     | PC相対ジャンプ                                           |

|          | jpr.d   | ディレイド分岐可                                           |

|          | jpa     | 絶対ジャンプ                                             |

|          | jpa.d   | ディレイド分岐可                                           |

|          | jrgt    | PC相対条件ジャンプ 分岐条件: !Z & !(N ^ V)                     |

|          | jrgt.d  | ディレイド分岐可                                           |

|          | jrgt    | PC相対条件ジャンプ 分岐条件: !(N ^ V)                          |

|          | jrgt.d  | ディレイド分岐可                                           |

|          | jrlt    | PC相対条件ジャンプ 分岐条件: N ^ V                             |

|          | jrlt.d  | ディレイド分岐可                                           |

|          | jrlt    | PC相対条件ジャンプ 分岐条件: Z   N ^ V                         |

|          | jrlt.d  | ディレイド分岐可                                           |

|          | jrugt   | PC相対条件ジャンプ 分岐条件: !Z & !C                           |

|          | jrugt.d | ディレイド分岐可                                           |

|          | jruge   | PC相対条件ジャンプ 分岐条件: !C                                |

|          | jruge.d | ディレイド分岐可                                           |

|          | jrult   | PC相対条件ジャンプ 分岐条件: C                                 |

|          | jrult.d | ディレイド分岐可                                           |

|          | jrule   | PC相対条件ジャンプ 分岐条件: Z   C                             |

|          | jrule.d | ディレイド分岐可                                           |

|          | jreq    | PC相対条件ジャンプ 分岐条件: Z                                 |

|          | jreq.d  | ディレイド分岐可                                           |

|          | jrne    | PC相対条件ジャンプ 分岐条件: !Z                                |

|          | jrne.d  | ディレイド分岐可                                           |

| システム制御   | call    | PC相対サブルーチンコール                                      |

|          | call.d  | ディレイド分岐可                                           |

|          | calla   | 絶対サブルーチンコール                                        |

|          | calla.d | ディレイド分岐可                                           |

|          | ret     | サブルーチンからのリターン                                      |

|          | ret.d   | ディレイド分岐可                                           |

|          | int     | ソフトウェア割り込み                                         |

|          | intl    | 割り込みレベル指定付きソフトウェア割り込み                              |

|          | reti    | 割り込みからのリターン                                        |

|          | reti.d  | ディレイド分岐可                                           |

|          | brk     | デバッグ割り込み                                           |

|          | retd    | デバッグ処理からのリターン                                      |

|          | nop     | ノーオペレーション                                          |

|          | halt    | HALT                                               |

|          | slp     | SLEEP                                              |

|          | ei      | 割り込み許可                                             |

|          | di      | 割り込み禁止                                             |

\*1 l d. a命令は32ビットのメモリアクセスを行います。レジスタからメモリへのデータ転送では上位8ビットを0とした32ビットデータがメモリに書き込まれます。メモリからの読み出し時は、読み出しデータの上位8ビットが無視されます。

\*2 S1C17001はコプロセッサを内蔵していません。このため、コプロセッサ命令は予約命令となります。

表中の記号の意味は次のとおりです。

表2.3.2 記号の意味

| 記号                                   | 説明                                  |

|--------------------------------------|-------------------------------------|

| <code>%rs</code>                     | 汎用ソースレジスタ                           |

| <code>%rd</code>                     | 汎用デスティネーションレジスタ                     |

| <code>[%rb]</code>                   | 汎用レジスタで間接指定されるメモリ                   |

| <code>[%rb] +</code>                 | 汎用レジスタで間接指定されるメモリ(アドレスポストインクリメント付き) |

| <code>[%rb] -</code>                 | 汎用レジスタで間接指定されるメモリ(アドレスポストデクリメント付き)  |

| <code>-[%rb]</code>                  | 汎用レジスタで間接指定されるメモリ(アドレスプリデクリメント付き)   |

| <code>%sp</code>                     | スタックポインタ                            |

| <code>[%sp], [%sp+imm7]</code>       | スタック                                |

| <code>[%sp] +</code>                 | スタック(アドレスポストインクリメント付き)              |

| <code>[%sp] -</code>                 | スタック(アドレスポストデクリメント付き)               |

| <code>-[%sp]</code>                  | スタック(アドレスプリデクリメント付き)                |

| <code>imm3, imm5, imm7, imm13</code> | 符号なし即値(数値はビット長)                     |

| <code>sign7, sign10</code>           | 符号付き即値(数値はビット長)                     |

## 2.4 ベクターテーブル

ベクターテーブルは、割り込み処理ルーチンへのベクタ(処理ルーチン開始アドレス)を格納します。割り込みが発生すると、S1C17コアは割り込みに対応するベクタを読み出して、その処理ルーチンを実行します。ベクターテーブルの先頭には、リセット後にプログラムの実行を開始するブートアドレスを書き込んでおく必要があります。

S1C17001のベクターテーブルは、0x8000番地から配置されます。このベクターテーブルベースアドレスは0xfffff80番地のTTBR(ベクターテーブルベースレジスタ)から読み出すことができます。

表2.4.1にS1C17001のベクターテーブルを示します。

表2.4.1 ベクターテーブル

| ベクタNo./ソフトウェア割り込みNo.        | ベクタアドレス               | ハードウェア割り込み名          | ハードウェア割り込み要因                                           | 優先順位                  |

|-----------------------------|-----------------------|----------------------|--------------------------------------------------------|-----------------------|

| 0 (0x00)                    | 0x8000                | リセット                 | • #RESET端子へのLow入力<br>• ウオッチドッグタイマオーバーフロー <sup>*2</sup> | 1                     |

| 1 (0x01)                    | 0x8004                | アドレス不整割り込み           | メモリアクセス命令                                              | 2                     |

| -                           | (0xffffc00)           | デバッグ割り込み             | brk命令等                                                 | 3                     |

| 2 (0x02)                    | 0x8008                | NMI                  | ウォッチドッグタイマオーバーフロー <sup>*2</sup>                        | 4                     |

| 3 (0x03)                    | 0x800c                | reserved             | -                                                      | -                     |

| 4 (0x04)                    | 0x8010                | P0ポート割り込み            | P00~P07ポート入力                                           | 高い <sup>*1</sup><br>↑ |

| 5 (0x05)                    | 0x8014                | P1ポート割り込み            | P10~P17ポート入力                                           |                       |

| 6 (0x06)                    | 0x8018                | ストップウォッチタイマ割り込み      | • タイマ100Hz信号<br>• タイマ10Hz信号<br>• タイマ1Hz信号              |                       |

| 7 (0x07)                    | 0x801c                | 計時タイマ割り込み            | • タイマ32Hz信号<br>• タイマ8Hz信号<br>• タイマ2Hz信号<br>• タイマ1Hz信号  |                       |

| 8 (0x08)                    | 0x8020                | 8ビットOSC1タイマ割り込み      | コンペアマッチ                                                |                       |

| 9 (0x09)                    | 0x8024                | reserved             | -                                                      |                       |

| 10 (0x0a)                   | 0x8028                |                      | -                                                      |                       |

| 11 (0x0b)                   | 0x802c                | PWM&キャプチャタイマ割り込み     | • コンペアA<br>• コンペアB                                     |                       |

| 12 (0x0c)                   | 0x8030                | 8ビットタイマ割り込み          | タイマアンダーフロー                                             |                       |

| 13 (0x0d)                   | 0x8034                | 16ビットタイマCh.0割り込み     | タイマアンダーフロー                                             |                       |

| 14 (0x0e)                   | 0x8038                | 16ビットタイマCh.1割り込み     | タイマアンダーフロー                                             |                       |

| 15 (0x0f)                   | 0x803c                | 16ビットタイマCh.2割り込み     | タイマアンダーフロー                                             |                       |

| 16 (0x10)                   | 0x8040                | UART割り込み             | • 送信バッファエンブティ<br>• 受信バッファフル<br>• 受信エラー                 |                       |

| 17 (0x11)                   | 0x8044                | リモートコントローラ割り込み       | • データ長カウンタアンダーフロー<br>• 入力立ち上がりエッジ検出<br>• 入力立ち下がりエッジ検出  |                       |

| 18 (0x12)                   | 0x8048                | SPI割り込み              | • 送信バッファエンブティ<br>• 受信バッファフル                            |                       |

| 19 (0x13)                   | 0x804c                | I <sup>2</sup> C割り込み | • 送信バッファエンブティ<br>• 受信バッファフル                            |                       |

| 20 (0x14)<br>:<br>31 (0x1f) | 0x8050<br>:<br>0x807c | reserved             | -                                                      | ↓<br>低い <sup>*1</sup> |

\*1 同一の割り込みレベルが設定されている場合

\*2 ウオッチドッグタイマの割り込みは、ソフトウェアにてリセットまたはNMIのいずれかを選択

### 0xfffff80: Vector Table Base Register (TTBR)

| Register name                     | Address             | Bit    | Name       | Function                  | Setting | Init.  | R/W | Remarks |

|-----------------------------------|---------------------|--------|------------|---------------------------|---------|--------|-----|---------|

| Vector Table Base Register (TTBR) | 0xfffff80 (32 bits) | D31~24 | -          | Unused (fixed at 0)       | 0x0     | 0x0    | R   |         |

|                                   |                     | D23~0  | TTBR[23:0] | Vector table base address | 0x8000  | 0x8000 | R   |         |

## 2.5 プロセッサ情報

S1C17001はProcessor ID Register(0xffff84)を内蔵しており、アプリケーションソフトウェアからCPUコアの種類を特定することができます。

### 0xffff84: Processor ID Register (IDIR)

| Register name                | Address           | Bit  | Name      | Function                         | Setting | Init. | R/W | Remarks |

|------------------------------|-------------------|------|-----------|----------------------------------|---------|-------|-----|---------|

| Processor ID Register (IDIR) | 0xffff84 (8 bits) | D7–0 | IDIR[7:0] | Processor ID<br>0x10: S1C17 Core | 0x10    | 0x10  | R   |         |

プロセッサの機種を示すIDコードが格納されるリードオンリレジスタです。S1C17コアのIDコードは0x10です。

# 3 メモリマップ、バス制御

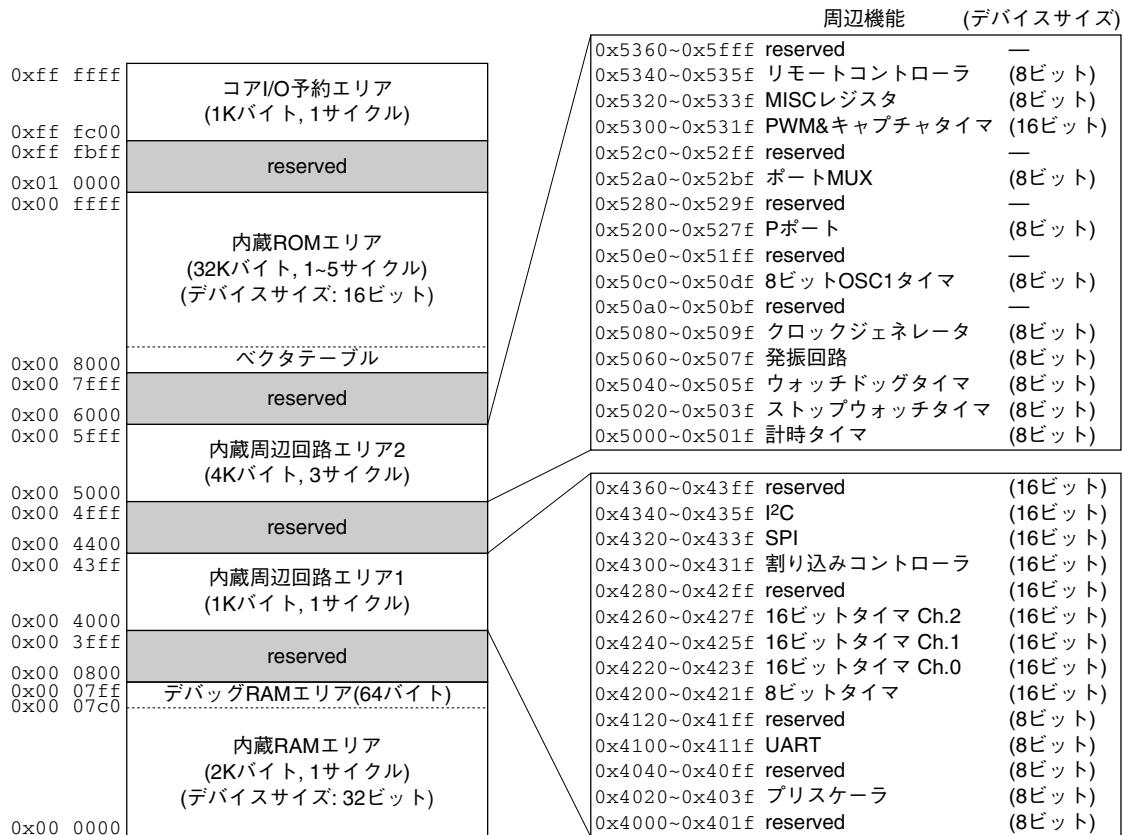

図3.1にS1C17001のメモリマップを示します。

図3.1 S1C17001メモリマップ

## 3.1 バスサイクル

CPUはCCLKを基準に動作します。CCLKについては、“8.2 CPUコアクロック(CCLK)の制御”を参照してください。

CCLKの立ち上がりから次の立ち上がりまでを1 CCLKとし、これを1バスサイクルとします。図3.1に示したとおり、1回のバスアクセスにかかるサイクル数は、周辺回路やメモリによって異なります。また、CPUの命令(アクセスサイズ)とデバイスサイズによりバスアクセス回数も変わります。

表3.1.1 バスアクセス回数

| デバイスサイズ | CPUアクセスサイズ | バスアクセス回数 |

|---------|------------|----------|

| 8ビット    | 8ビット       | 1        |

|         | 16ビット      | 2        |

|         | 32ビット*     | 4        |

| 16ビット   | 8ビット       | 1        |

|         | 16ビット      | 1        |

|         | 32ビット*     | 2        |

| 32ビット   | 8ビット       | 1        |

|         | 16ビット      | 1        |

|         | 32ビット*     | 1        |

\* 32ビットアクセス時の上位8ビットデータについて

32ビットデータは上位8ビットを0としてメモリに書き込まれます。メモリからの読み出し時は上位8ビットが無視されます。割り込み処理のスタック操作時は、PSRの値を上位8ビットに、戻アドレスを下位24ビットとした32ビットの書き込み/読み出しを行います。

### バスサイクル数の計算例

内蔵周辺回路エリア2(8ビットデバイス, 3サイクル)に、CPUから16ビットリード/ライト命令でアクセスする場合のバスサイクル数

$$3 \text{ [サイクル]} \times 2 \text{ [バスアクセス回数]} = 6 \text{ [CCLKサイクル]}$$

### 3.1.1 アクセスサイズ制限

以下に示すモジュールにはアクセスサイズに制限がありますので、プログラミングの際には使用する命令に注意してください。

#### SPI, I<sup>2</sup>C

SPIとI<sup>2</sup>Cのレジスタへのアクセスには、16ビットリード/ライト命令のみ使用可能です。

上記以外のモジュールは8ビット、16ビット、32ビットのいずれの命令でもアクセス可能です。ただし、必要のないレジスタの読み出しによって周辺回路の状態が変わり、問題が発生する場合もありますので、できるだけデバイスサイズに合わせてアクセスすることを推奨します。

### 3.1.2 命令実行サイクルの制限

以下のいずれかの条件下では命令のフェッチとデータアクセスが同時に行われず、データの存在するエリアのアクセスサイクル分、命令フェッチのサイクルが長くなります。

- 内蔵ROMエリアで命令を実行し、内蔵ROM、内蔵周辺回路エリア2(0x5000～)のデータにアクセスする場合

- 内蔵RAMエリアで命令を実行し、内蔵RAMエリアのデータにアクセスする場合

## 3.2 内蔵ROMエリア

### 3.2.1 内蔵ROM

0x8000番地から0xffff番地までの32Kバイトの領域にはROMが内蔵されており、アプリケーションプログラムやデータを書き込んでおくことができます。0x8000番地はベクターテーブルベースアドレスとして定義されていますので、この領域の先頭にベクターテーブル（“2.4 ベクターテーブル”参照）を置く必要があります。ROMの読み出しあは1～5サイクルで行われます。

### 3.2.2 ROMのリードアクセスサイクルの設定

S1C17701との互換性維持のため、IROMエリアのリードアクセスサイクルが、FLCYC[2:0](D[2:0]/MISC\_FLレジスタ)で設定できるようになっています。通常はFLCYC[2:0]を0x4に設定して使用してください。

#### 0x5320: ROM Control Register (MISC\_FL)

| Register name                  | Address         | Bit  | Name       | Function              | Setting    |            | Init. | R/W | Remarks            |

|--------------------------------|-----------------|------|------------|-----------------------|------------|------------|-------|-----|--------------------|

| ROM Control Register (MISC_FL) | 0x5320 (8 bits) | D7-3 | —          | reserved              | —          | —          | —     | —   | 0 when being read. |

|                                |                 | D2-0 | FLCYC[2:0] | ROM read access cycle | FLCYC[2:0] | Read cycle | 0x3   | R/W |                    |

|                                |                 |      |            |                       | 0x7-0x5    | reserved   |       |     |                    |

|                                |                 |      |            |                       | 0x4        | 1 cycle    |       |     |                    |

|                                |                 |      |            |                       | 0x3        | 5 cycles   |       |     |                    |

|                                |                 |      |            |                       | 0x2        | 4 cycles   |       |     |                    |

|                                |                 |      |            |                       | 0x1        | 3 cycles   |       |     |                    |

|                                |                 |      |            |                       | 0x0        | 2 cycles   |       |     |                    |

## 3.3 内蔵RAMエリア

---

### 3.3.1 内蔵RAM

0x0番地から0x7ff番地までの2Kバイトの領域にはRAMが内蔵されています。このRAMは1サイクルでアクセスされます。変数などの格納以外に、命令コードをコピーしてRAM上で高速に実行させることもできます。

注: 内蔵RAMの最後尾の64バイト(0x7c0～0x7ff)はオンチップデバッグ用に予約されています。アプリケーション開発中などデバッグ機能を使用する場合は、アプリケーションプログラムからはこの領域をアクセスしないでください。

デバッグの不要な量产品ではアプリケーション用に使用可能です。

## 3.4 内蔵周辺回路エリア

0x4000番地から始まる1Kバイトと、0x5000番地から始まる4Kバイトのエリアには、内蔵周辺回路のI/Oおよび制御レジスタが割り付けられています。

### 3.4.1 内蔵周辺回路エリア1(0x4000~)

0x4000番地から始まる内蔵周辺回路エリア1には以下の内蔵周辺機能用I/Oメモリが割り付けられており、1サイクルでアクセス可能です。

- プリスケーラ(PSC, 8ビットデバイス)

- UART(UART, 8ビットデバイス)

- 8ビットタイマ(T8F, 16ビットデバイス)

- 16ビットタイマ(T16, 16ビットデバイス)

- 割り込みコントローラ(ITC, 16ビットデバイス)

- SPI(SPI, 16ビットデバイス)

- I<sup>2</sup>C(I2C, 16ビットデバイス)

### 3.4.2 内蔵周辺回路エリア2(0x5000~)

0x5000番地から始まる内蔵周辺回路エリア2には以下の内蔵周辺機能用I/Oメモリが割り付けられており、3サイクルでアクセス可能です。

- 計時タイマ(CT, 8ビットデバイス)

- ストップウォッチタイマ(SWT, 8ビットデバイス)

- ウォッチドッグタイマ(WDT, 8ビットデバイス)

- 発振回路(OSC, 8ビットデバイス)

- クロックジェネレータ(CLG, 8ビットデバイス)

- 8ビットOSC1タイマ(T8OSC1, 8ビットデバイス)

- 入出力ポート&ポートMUX(P, 8ビットデバイス)

- PWM&キャプチャタイマ(T16E, 16ビットデバイス)

- MISCレジスタ(MISC, 8ビットデバイス)

- リモートコントローラ(REMC, 8ビットデバイス)

### 3.4.3 I/Oマップ<sup>9</sup>

内蔵周辺回路エリアのI/Oマップを以下に示します。各制御レジスタの詳細については、AppendixのI/Oレジスター一覧または各周辺回路の説明を参照してください。

注: 表中の“Reserved”で示されたアドレス、および表に記載のない周辺回路エリアの未使用領域は、アプリケーションプログラムからアクセスしないでください。

表3.4.3.1 I/Oマップ(内蔵周辺回路エリア1)

| 周辺回路                               | アドレス   | レジスタ名                 | 機能                                            |

|------------------------------------|--------|-----------------------|-----------------------------------------------|

| プリスケーラ<br>(8ビットデバイス)               | 0x4020 | PSC_CTL               | Prescaler Control Register                    |

|                                    | -      | -                     | Reserved                                      |

| UART(IrDA付き)<br>(8ビットデバイス)         | 0x4100 | UART_ST               | UART Status Register                          |

|                                    | 0x4101 | UART_TXD              | UART Transmit Data Register                   |

|                                    | 0x4102 | UART_RXD              | UART Receive Data Register                    |

|                                    | 0x4103 | UART_MOD              | UART Mode Register                            |

|                                    | 0x4104 | UART_CTL              | UART Control Register                         |

|                                    | 0x4105 | UART_EXP              | UART Expansion Register                       |

|                                    | -      | -                     | Reserved                                      |

| 8ビットタイマ<br>(Fモード付き)<br>(16ビットデバイス) | 0x4200 | T8F_CLK               | 8-bit Timer Input Clock Select Register       |

|                                    | 0x4202 | T8F_TR                | 8-bit Timer Reload Data Register              |

|                                    | 0x4204 | T8F_TC                | 8-bit Timer Counter Data Register             |

|                                    | 0x4206 | T8F_CTL               | 8-bit Timer Control Register                  |

|                                    | -      | -                     | Reserved                                      |

|                                    | -      | -                     | Reserved                                      |

|                                    | -      | -                     | Reserved                                      |

| 16ビットタイマ<br>Ch.0<br>(16ビットデバイス)    | 0x4220 | T16_CLK0              | 16-bit Timer Ch.0 Input Clock Select Register |

|                                    | 0x4222 | T16_TR0               | 16-bit Timer Ch.0 Reload Data Register        |

|                                    | 0x4224 | T16_TC0               | 16-bit Timer Ch.0 Counter Data Register       |

|                                    | 0x4226 | T16_CTL0              | 16-bit Timer Ch.0 Control Register            |

|                                    | -      | -                     | Reserved                                      |

| 16ビットタイマ<br>Ch.1<br>(16ビットデバイス)    | 0x4240 | T16_CLK1              | 16-bit Timer Ch.1 Input Clock Select Register |

|                                    | 0x4242 | T16_TR1               | 16-bit Timer Ch.1 Reload Data Register        |

|                                    | 0x4244 | T16_TC1               | 16-bit Timer Ch.1 Counter Data Register       |

|                                    | 0x4246 | T16_CTL1              | 16-bit Timer Ch.1 Control Register            |

|                                    | -      | -                     | Reserved                                      |

| 16ビットタイマ<br>Ch.2<br>(16ビットデバイス)    | 0x4260 | T16_CLK2              | 16-bit Timer Ch.2 Input Clock Select Register |

|                                    | 0x4262 | T16_TR2               | 16-bit Timer Ch.2 Reload Data Register        |

|                                    | 0x4264 | T16_TC2               | 16-bit Timer Ch.2 Counter Data Register       |

|                                    | 0x4266 | T16_CTL2              | 16-bit Timer Ch.2 Control Register            |

|                                    | -      | -                     | Reserved                                      |

| 割り込み<br>コントローラ<br>(16ビットデバイス)      | 0x4300 | ITC_IFLG              | Interrupt Flag Register                       |

|                                    | 0x4302 | ITC_EN                | Interrupt Enable Register                     |

|                                    | 0x4304 | ITC_CTL               | ITC Control Register                          |

|                                    | 0x4306 | ITC_ELV0              | External Interrupt Level Setup Register 0     |

|                                    | 0x4308 | ITC_ELV1              | External Interrupt Level Setup Register 1     |

|                                    | 0x430a | ITC_ELV2              | External Interrupt Level Setup Register 2     |

|                                    | 0x430c | ITC_ELV3              | External Interrupt Level Setup Register 3     |

|                                    | 0x430e | ITC_ILV0              | Internal Interrupt Level Setup Register 0     |

|                                    | 0x4310 | ITC_ILV1              | Internal Interrupt Level Setup Register 1     |

|                                    | 0x4312 | ITC_ILV2              | Internal Interrupt Level Setup Register 2     |

|                                    | 0x4314 | ITC_ILV3              | Internal Interrupt Level Setup Register 3     |

|                                    | -      | -                     | Reserved                                      |

|                                    | -      | -                     | Reserved                                      |

|                                    | -      | -                     | Reserved                                      |

| SPI<br>(16ビットデバイス)                 | 0x4320 | SPI_ST                | SPI Status Register                           |

|                                    | 0x4322 | SPI_TXD               | SPI Transmit Data Register                    |

|                                    | 0x4324 | SPI_RXD               | SPI Receive Data Register                     |

|                                    | 0x4326 | SPI_CTL               | SPI Control Register                          |

|                                    | -      | -                     | Reserved                                      |

| I <sup>2</sup> C<br>(16ビットデバイス)    | 0x4340 | I <sup>2</sup> C_EN   | I <sup>2</sup> C Enable Register              |

|                                    | 0x4342 | I <sup>2</sup> C_CTL  | I <sup>2</sup> C Control Register             |

|                                    | 0x4344 | I <sup>2</sup> C_DAT  | I <sup>2</sup> C Data Register                |

|                                    | 0x4346 | I <sup>2</sup> C_ICTL | I <sup>2</sup> C Interrupt Control Register   |

|                                    | -      | -                     | Reserved                                      |

|                                    | -      | -                     | Reserved                                      |

表3.4.3.2 I/Oマップ(内蔵周辺回路エリア2)

| 周辺回路                           | アドレス   | レジスタ名       | 機能                                             |

|--------------------------------|--------|-------------|------------------------------------------------|

| 計時タイマー<br>(8ビットデバイス)           | 0x5000 | CT_CTL      | Clock Timer Control Register                   |

|                                | 0x5001 | CT_CNT      | Clock Timer Counter Register                   |

|                                | 0x5002 | CT_IMSK     | Clock Timer Interrupt Mask Register            |

|                                | 0x5003 | CT_IFLG     | Clock Timer Interrupt Flag Register            |

|                                | -      | -           | Reserved                                       |

| ストップ<br>ウォッチタイマー<br>(8ビットデバイス) | 0x5020 | SWT_CTL     | Stopwatch Timer Control Register               |

|                                | 0x5021 | SWT_BCNT    | Stopwatch Timer BCD Counter Register           |

|                                | 0x5022 | SWT_IMSK    | Stopwatch Timer Interrupt Mask Register        |

|                                | 0x5023 | SWT_IFLG    | Stopwatch Timer Interrupt Flag Register        |

|                                | -      | -           | Reserved                                       |

| ウォッチドッグ<br>タイマー<br>(8ビットデバイス)  | 0x5040 | WDT_CTL     | Watchdog Timer Control Register                |

|                                | 0x5041 | WDT_ST      | Watchdog Timer Status Register                 |

|                                | -      | -           | Reserved                                       |

| 発振回路<br>(8ビットデバイス)             | 0x5060 | OSC_SRC     | Clock Source Select Register                   |

|                                | 0x5061 | OSC_CTL     | Oscillation Control Register                   |

|                                | 0x5062 | OSC_NFEN    | Noise Filter Enable Register                   |

|                                | 0x5063 | -           | Reserved                                       |

|                                | 0x5064 | OSC_FOUT    | FOUT Control Register                          |

|                                | 0x5065 | OSC_T8OSC1  | T8OSC1 Clock Control Register                  |

| クロック<br>ジェネレータ<br>(8ビットデバイス)   | 0x5080 | CLG_PCLK    | PCLK Control Register                          |

|                                | 0x5081 | CLG_CCLK    | CCLK Control Register                          |

|                                | -      | -           | Reserved                                       |

| 8ビットOSC1<br>タイマー<br>(8ビットデバイス) | 0x50c0 | T8OSC1_CTL  | 8-bit OSC1 Timer Control Register              |

|                                | 0x50c1 | T8OSC1_CNT  | 8-bit OSC1 Timer Counter Data Register         |

|                                | 0x50c2 | T8OSC1_CMP  | 8-bit OSC1 Timer Compare Data Register         |

|                                | 0x50c3 | T8OSC1_IMSK | 8-bit OSC1 Timer Interrupt Mask Register       |

|                                | 0x50c4 | T8OSC1_IFLG | 8-bit OSC1 Timer Interrupt Flag Register       |

| Pポート&<br>ポートMUX<br>(8ビットデバイス)  | -      | -           | Reserved                                       |

|                                | 0x5200 | P0_IN       | P0 Port Input Data Register                    |

|                                | 0x5201 | P0_OUT      | P0 Port Output Data Register                   |

|                                | 0x5202 | P0_IO       | P0 Port I/O Direction Control Register         |

|                                | 0x5203 | P0_PU       | P0 Port Pull-up Control Register               |

|                                | 0x5204 | -           | Reserved                                       |

|                                | 0x5205 | P0_IMSK     | P0 Port Interrupt Mask Register                |

|                                | 0x5206 | P0_EDGE     | P0 Port Interrupt Edge Select Register         |

|                                | 0x5207 | P0_IFLG     | P0 Port Interrupt Flag Register                |

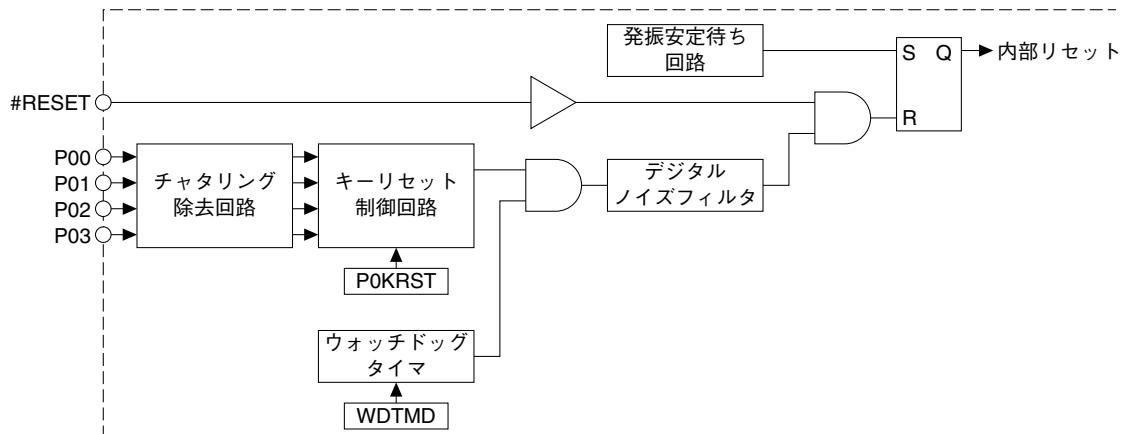

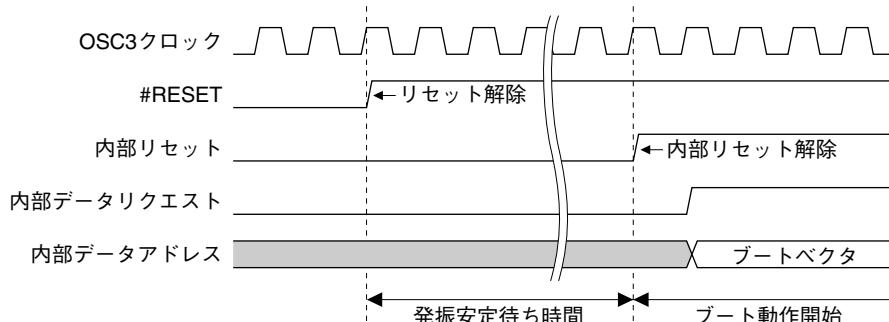

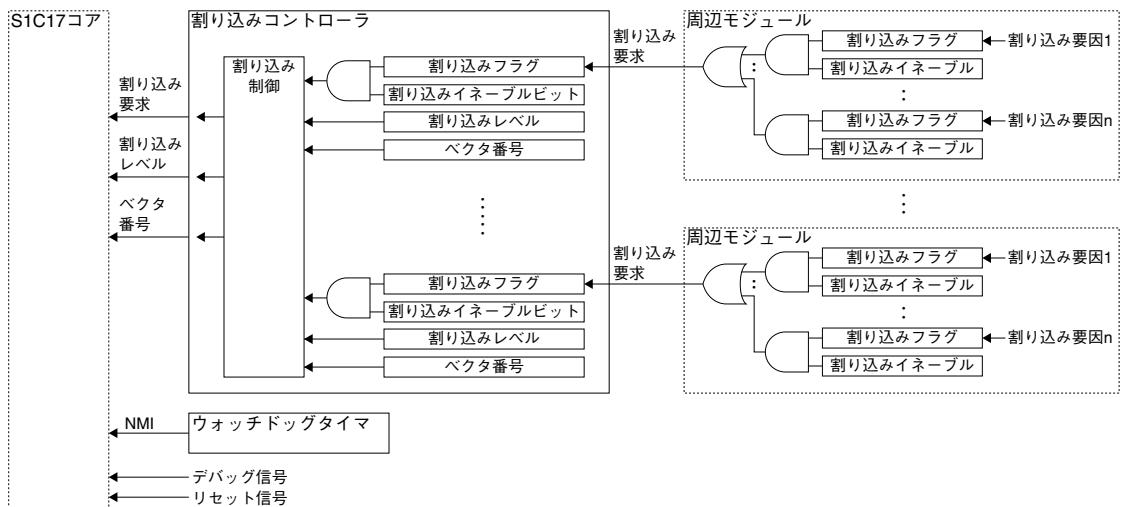

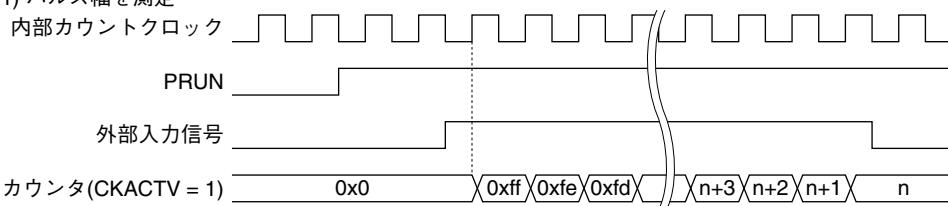

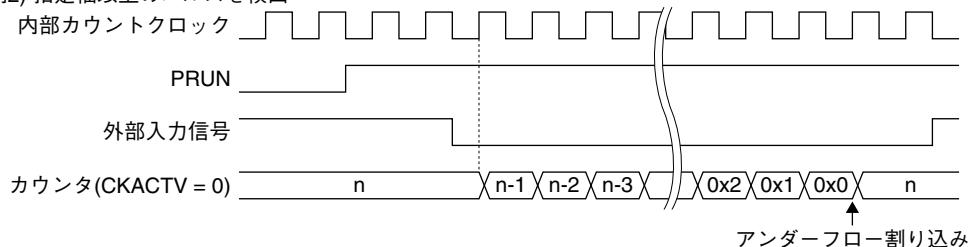

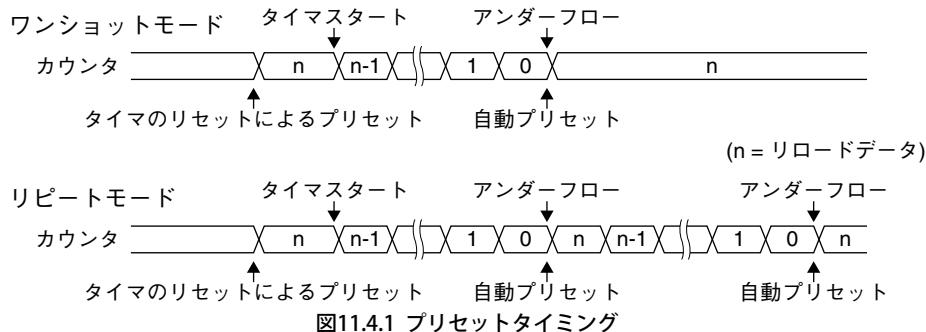

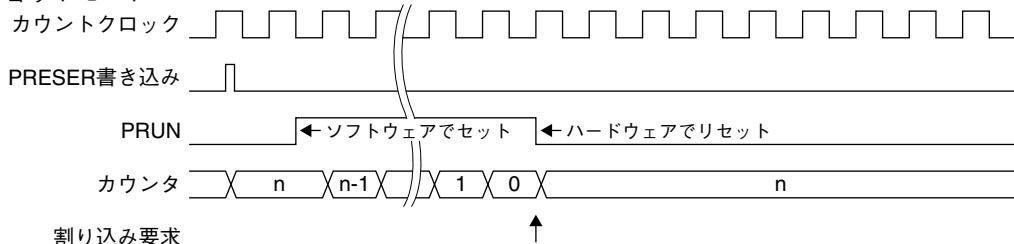

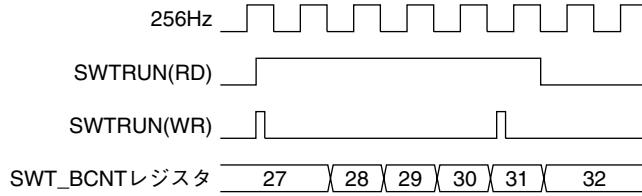

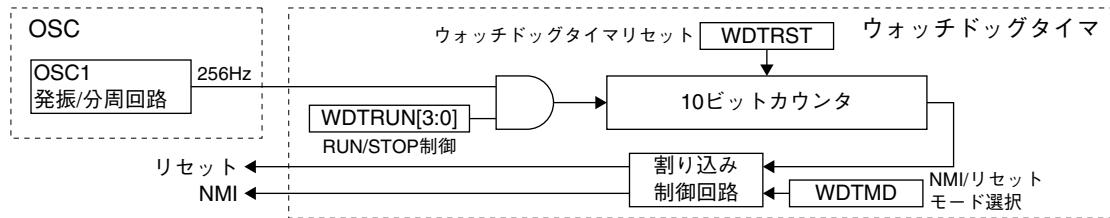

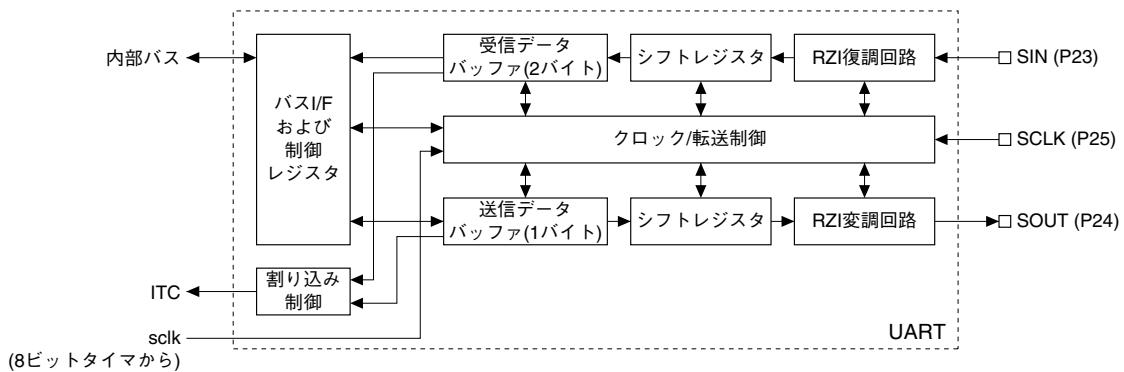

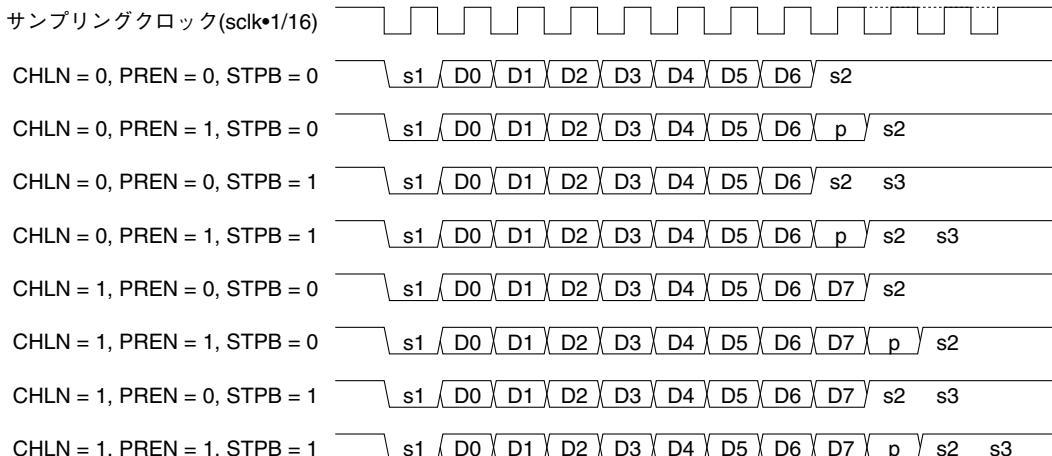

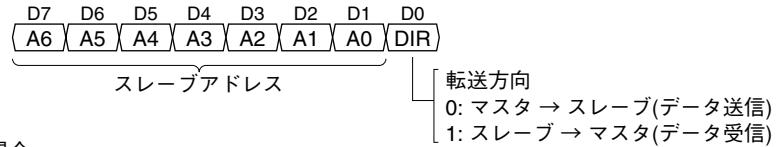

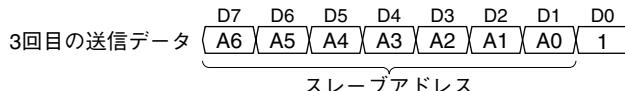

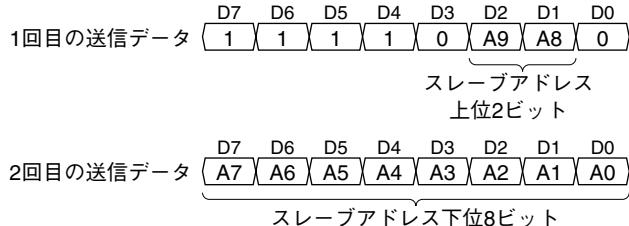

|                                | 0x5208 | P0_CHAT     | P0 Port Chattering Filter Control Register     |