# S1V30120

## ハードウェア仕様書

## 本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

©SEIKO EPSON CORPORATION 2008, All rights reserved.

Fonix DECTalk®と Fonix ロゴは Fonix Corporation の登録商標です。

ARM Powered ロゴは ARM Limited の登録商標です。

本資料に記載のその他の会社名および製品名は、各社の商標もしくは登録商標です。

## 目次

|                                     |    |

|-------------------------------------|----|

| 1. 概要 .....                         | 1  |

| 2. 特徴 .....                         | 1  |

| 3. 端子配置図（上面図） .....                 | 2  |

| 4. 端子の説明 .....                      | 3  |

| 5. 機能の説明 .....                      | 5  |

| 5.1 標準アプリケーションシステム .....            | 5  |

| 6. 電気的特性 .....                      | 6  |

| 6.1 絶対最大定格 .....                    | 6  |

| 6.2 推奨動作条件 .....                    | 6  |

| 6.3 DC特性 .....                      | 7  |

| 6.4 AC特性 .....                      | 10 |

| 6.4.1 クロックタイミング .....               | 10 |

| 6.4.2 初期化タイミング .....                | 11 |

| 6.4.2.1 パワーオン／リセット時のタイミング .....     | 11 |

| 6.4.2.2 パワーオフシーケンス .....            | 12 |

| 6.4.3 クロック同期形シリアルインタフェース（SPI） ..... | 13 |

| 6.5 フルデジタル・オーディオアンプ .....           | 14 |

| 7. 外部接続例 .....                      | 15 |

| 7.1 接続例：クロック同期形シリアルインタフェース .....    | 15 |

| 8. 外形寸法図 .....                      | 16 |

### 1. 概要

S1V30120 は、費用対効果の高いソリューションを実現する音声合成 IC です。TTS (Text-to-Speech) と ADPCM の音声処理アプリケーションがさまざまな小型機器に実装できます。高集積設計によってシステム全体のコスト削減と開発時間の短縮が実現します。必要なアナログ・コーデック、メモリ、当社の組み込みアルゴリズムをすべて備え、あらゆるアプリケーションが 1 つのシリアルインターフェース (SPI) で制御されます。そのため幅広いホストで制御できるほか、既存製品への組み込みが簡単に行えます。

### 2. 特徴

- TTS (Text-to-Speech)

- Fonix DECTalk® Version 5、フル・パラメトリックの音声合成

- 対応言語：米語、Castilian/Latin American スペイン語

- 9 種類のプリセットボイス

- サンプリングレート：11.025kHz

- 音声再生 (ADPCM)

- ADPCM デコードィング (エプソン独自フォーマット)

- ビットレート：80kbps、64kbps、48kbps、40kbps、32kbps、24kbps

- サンプリングレート：16kHz、8kHz

- ホストインターフェース

- 同期シリアルインターフェース (SPI に対応)

- コマンド制御

- 16 ビットのフルデジタルアンプ

- サンプリングレート (fs) : 16kHz、11.025kHz、8kHz

- デジタル入力：16 ビット

- 動作電圧：3.3V/1.8V

- クロック

- 32.768kHz

- パッケージ

- 64 ピン TQFP (10mm×10mm) 0.5mm ピッチ

- 電源電圧

- 3.3V (I/O 用)

- 1.8V (コア用)

### 3. 端子配置図(上面図)

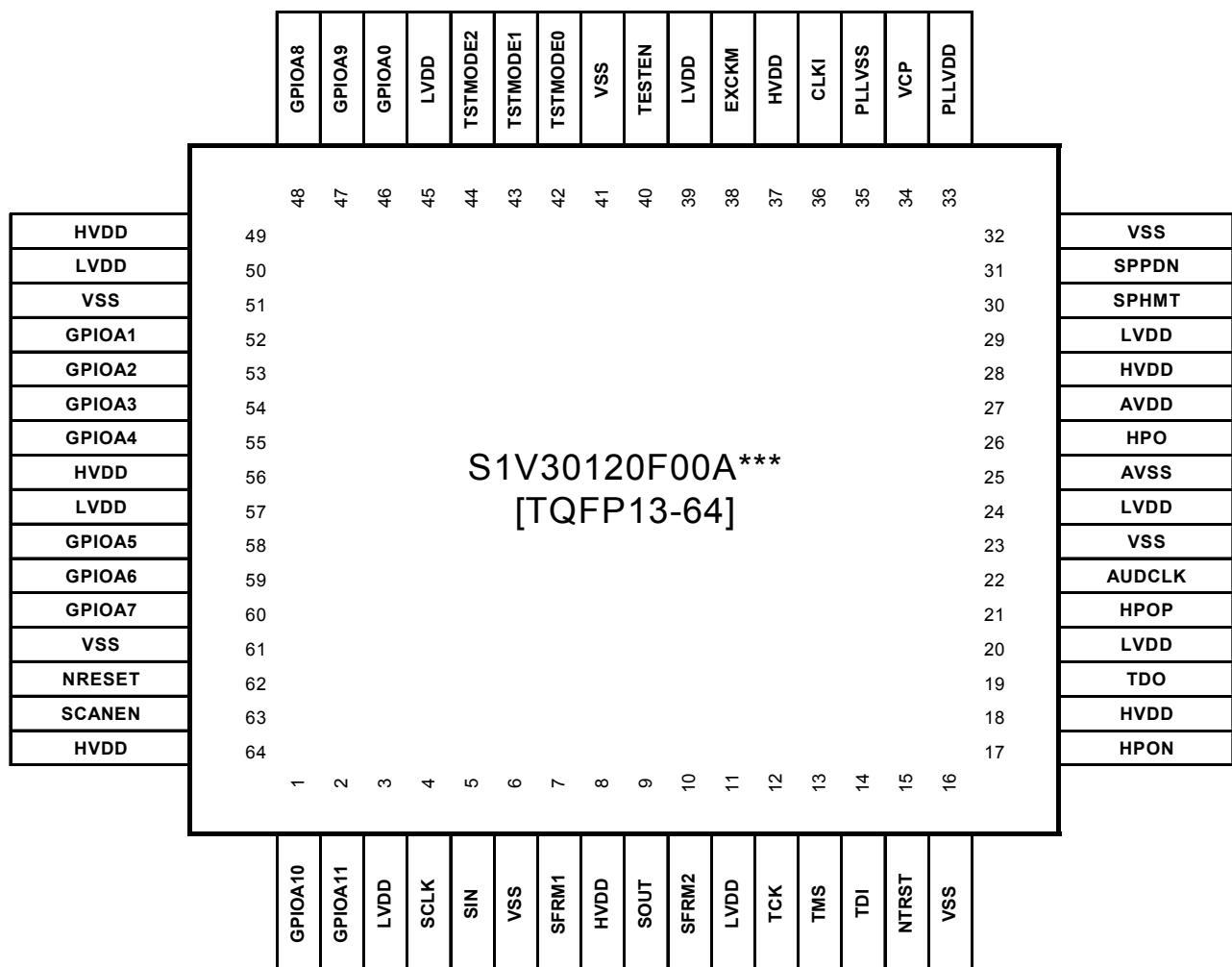

### 3. 端子配置図(上面図)

図 3-1 TQFP13-64 パッケージの端子配置

## 4. 端子の説明

- 記号

- I = 入力端子

O = 出力端子

IO = 双方向端子

P = 電源端子

Z = 高インピーダンス

### I/O セル端子

| 記号    | 機能                                                                      |

|-------|-------------------------------------------------------------------------|

| IC    | LVCMOS 入力                                                               |

| IH    | LVCMOS シュミット入力                                                          |

| ICP1  | LVCMOS 入力、プルアップ抵抗付き (3.3V で 50kΩ (typ))                                 |

| ICD2  | LVCMOS 入力、プルダウン抵抗付き (3.3V で 100kΩ (typ))                                |

| O1    | 出力バッファ (3.3V で ±2mA (typ) の出力電流)                                        |

| O3    | 出力バッファ (3.3V で ±8mA (typ) の出力電流)                                        |

| T1    | 3 ステート出力バッファ (3.3V で ±2mA (typ) の出力電流)                                  |

| BC1   | 双方向 IO バッファ (3.3V で ±2mA (typ) の出力電流)                                   |

| BC1P2 | 双方向 IO バッファ、プルアップ抵抗付き (3.3V で 100kΩ (typ))<br>(3.3V で ±2mA (typ) の出力電流) |

| BC1D2 | 双方向 IO バッファ、プルダウン抵抗付き (3.3V で 100kΩ (typ))<br>(3.3V で ±2mA (typ) の出力電流) |

| BC3D2 | 双方向 IO バッファ、プルダウン抵抗付き (3.3V で 100kΩ (typ))<br>(3.3V で ±8mA (typ) の出力電流) |

| LOT   | 透過出力                                                                    |

| ITST1 | テスト入力、プルダウン抵抗付き (1.8V (で 120kΩ (typ)))                                  |

### クロック同期形シリアルインターフェース端子

| 端子名称  | 端子 | I/O | I/O セル<br>タイプ | リセット時<br>の状態 | 電源   | 端子の説明      |

|-------|----|-----|---------------|--------------|------|------------|

| SIN   | 5  | IO  | BC1           | Z            | HVDD | シリアルデータ入力  |

| SCLK  | 4  | IO  | BC1           | Z            | HVDD | シリアルクロック入力 |

| SFRM1 | 7  | IO  | BC3P2         | Z            | HVDD | スレーブ選択入力   |

| SOUT  | 9  | IO  | BC3P2         | プルアップ        | HVDD | シリアルデータ出力  |

| SFRM2 | 10 | IO  | O3            | L            | HVDD | マスター選択出力   |

### GPIO 端子

| 端子名称        | 端子                                                 | I/O | I/O セル<br>タイプ | リセット時<br>の状態 | 電源   | 端子の説明     |

|-------------|----------------------------------------------------|-----|---------------|--------------|------|-----------|

| GPIOA[11:0] | 2, 1, 47, 48, 60,<br>59, 58, 55, 54,<br>53, 52, 46 | IO  | BC1D2         | プルダウン        | HVDD | 汎用 IO ポート |

## 4. 端子の説明

---

フルデジタル・オーディオアンプ端子

| 端子名称   | 端子 | I/O | I/O セル<br>タイプ | リセット<br>時の状態 | 電源   | 端子の説明                     |

|--------|----|-----|---------------|--------------|------|---------------------------|

| HPO    | 26 | O   | LOT           | L            | AVDD | 音声出力                      |

| HPON   | 17 | O   | O1            | L            | HVDD | 反転、バッファリングなし : HPO のデジタル版 |

| AUDCLK | 22 | O   | O1            | L            | HVDD | オーディオ PWM 用クロック           |

| HPOP   | 21 | O   | O1            | H            | HVDD | バッファリングなし : HPO のデジタル版    |

| SPPDN  | 31 | O   | O1            | L            | HVDD | オープンで使用                   |

| SPHMT  | 30 | O   | O1            | L            | HVDD | PWM 出力期間出力 (Low アクティブ)    |

クロック/リセット端子

| 端子名称   | 端子 | I/O | I/O セル<br>タイプ | リセット<br>時の状態 | 電源   | 端子の説明                |

|--------|----|-----|---------------|--------------|------|----------------------|

| CLKI   | 36 | I   | IC            | Z            | HVDD | 基準クロック入力 (32.768kHz) |

| NRESET | 62 | I   | IH            | Z            | HVDD | リセット入力 (Low アクティブ)   |

テスト

| 端子名称         | 端子               | I/O | I/O セル<br>タイプ | リセット時<br>の状態 | 電源     | 端子の説明                   |

|--------------|------------------|-----|---------------|--------------|--------|-------------------------|

| TSTMODE[2:0] | 44,<br>43,<br>42 | I   | IC            | Z            | HVDD   | テスト端子 (通常動作時に Low に設定)  |

| TESTEN       | 40               | I   | ITST1         | プルダウン        | LVDD   | テスト端子 (通常動作時に Low に設定)  |

| SCANEN       | 63               | I   | IBD2          | プルダウン        | HVDD   | テスト端子 (通常動作時に Low に設定)  |

| EXCKM        | 38               | I   | IC            | Z            | HVDD   | テスト端子 (通常動作時に Low に設定)  |

| NTRST        | 15               | I   | IH            | Z            | HVDD   | テスト端子 (通常動作時に Low に設定)  |

| TDI          | 14               | I   | ICP1          | プルアップ        | HVDD   | テスト端子 (通常動作時に High に設定) |

| TMS          | 13               | I   | ICP1          | プルアップ        | HVDD   | テスト端子 (通常動作時に High に設定) |

| TCK          | 12               | I   | ICP1          | プルアップ        | HVDD   | テスト端子 (通常動作時に High に設定) |

| TDO          | 19               | O   | T1            | Z            | HVDD   | テスト端子 (通常動作時にオープン)      |

| VCP          | 34               | O   | LOT           | Z            | PLLVDD | テスト端子 (通常動作時にオープン)      |

電源端子

| 端子名称   | 端子                        | I/O | 端子の説明                      |

|--------|---------------------------|-----|----------------------------|

| HVDD   | 8,18,28,37,49,56,64       | P   | I/O バッファ用電源端子 (3.3V)       |

| LVDD   | 3,11,20,24,29,39,45,50,57 | P   | 内部回路用電源端子 (1.8V)           |

| PLLVDD | 33                        | P   | PLL 用電源端子 (1.8V)           |

| AVDD   | 27                        | P   | フルデジタルアンプ用電源端子 (1.8V/3.3V) |

| VSS    | 6,16,23,32,41,51,61       | P   | GND 端子 (I/O、内部回路)          |

| PLLVSS | 35                        | P   | GND 端子 (PLL)               |

| AVSS   | 25                        | P   | GND 端子 (フルデジタルアンプ)         |

## 5. 機能の説明

### 5.1 標準アプリケーションシステム

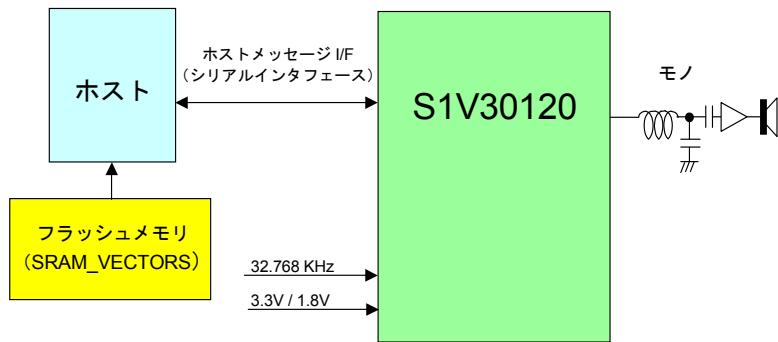

図 5-1 標準アプリケーションシステム

図 5-1 は、S1V30120 を使った標準的なアプリケーションシステムです。ホストプロセッサはシリアルインターフェースを使って S1V30120 と通信し、コマンド(メッセージプロトコル)によって組み込みアルゴリズムの制御を行います。コマンドについては「S1V30120 メッセージプロトコル仕様書」をご覧ください。

S1V30120 をリセットすると、ブートファームウェアが起動します。ホストはブートメッセージを用いて SRAM のファームウェアと ROM のファームウェアアップデート (SRAM\_VECTORS) を S1V30120 デバイスの SRAM にロードしたあと、メインモードの実行に切り替わります。この SRAM\_VECTORS は、上の図 5-1 に示した標準アプリケーションシステムではフラッシュメモリに格納されています。

S1V30120 に関するブートメッセージのメッセージプロトコル仕様については「S1V30120 メッセージプロトコル仕様書」の 4 章を、またメインモードのメッセージについては 5 章をご覧ください。

## 6. 電気的特性

### 6. 電気的特性

#### 6.1 絶対最大定格

(VSS=0[V])

| 項目                         | 記号     | 定格値              | 単位 |

|----------------------------|--------|------------------|----|

| 電源電圧                       | HVDD   | VSS-0.3~+4.0     | V  |

|                            | LVDD   | VSS-0.3~+2.5     | V  |

|                            | PLLVDD | VSS-0.3~+2.5     | V  |

|                            | AVDD   | VSS-0.3~+4.0     | V  |

| 入力電圧                       | HVI    | VSS-0.3~HVDD+0.5 | V  |

|                            | LVI    | VSS-0.3~LVDD+0.5 | V  |

| 出力電圧                       | HVO    | VSS-0.3~HVDD+0.5 | V  |

|                            | AVO    | VSS-0.3~HVDD+0.5 | V  |

| 出力電流（端子当たり）<br>(HPO を除きます) | IOUT   | ±10              | mA |

| 保管温度                       | Tstg   | -65~+150         | °C |

#### 6.2 推奨動作条件

(VSS=0[V])

| 項目   | 記号     | Min. | Typ. | Max. | 単位 |

|------|--------|------|------|------|----|

| 電源電圧 | HVDD   | 3.00 | 3.30 | 3.60 | V  |

|      | LVDD   | 1.65 | 1.80 | 1.95 | V  |

|      | PLLVDD | 1.65 | 1.80 | 1.95 | V  |

|      | AVDD   | 1.65 | 1.80 | 1.95 | V  |

|      |        | 3.00 | 3.30 | 3.60 |    |

| 入力電圧 | HVI    | VSS  | -    | HVDD | V  |

|      | LVI    | VSS  | -    | LVDD | V  |

| 周囲温度 | Ta     | -40  | 25   | 85   | °C |

ICへの電源供給をオン・オフする場合は以下の順序に従ってください。

(AVDD=1.8Vのとき)

パワーオン： LVDD/PLLVDD/AVDD => HVDD

パワーオフ： HVDD => LVDD/PLLVDD/AVDD

(AVDD=3.3Vのとき)

パワーオン： LVDD/PLLVDD => HVDD/AVDD

パワーオフ： HVDD/AVDD => LVDD/PLLVDD

注：

- LVDD、PLLVDD、AVDD の電源供給をオフにした状態で、HVDDだけに1秒以上電圧を印加しないでください。製品の信頼性が損なわれる恐れがあります。

- HVDDをオフ状態からオン状態に戻すとき、電源ノイズ等の影響により内部回路の状態は保証されません。ICへの電源供給後は NRESET によって必ず回路を初期化するようしてください。

### 6.3 DC特性

DC 入力特性（6.2「推奨動作条件」の値に基づく）

| 項目                | 記号    | 条件                                                                                        | Min. | Typ. | Max. | 単位 |

|-------------------|-------|-------------------------------------------------------------------------------------------|------|------|------|----|

| <b>電源電流</b>       |       |                                                                                           |      |      |      |    |

| 電源電流 <sup>1</sup> | IDDH  | HVDD=3.3V                                                                                 | -    | 0.05 | -    | mA |

|                   | IDDL  | LVDD=1.8V                                                                                 | -    | 20.0 | -    | mA |

|                   | IDDP  | PLLVDD=1.8V                                                                               | -    | 1.5  | -    | mA |

|                   | IDDAL | AVDD=1.8V、無負荷                                                                             | -    | 0.4  | -    | mA |

|                   | IDDAH | AVDD=3.3V、無負荷                                                                             | -    | 1.0  | -    | mA |

| <b>静止電流</b>       |       |                                                                                           |      |      |      |    |

| 静止電流 <sup>2</sup> | IDDSH | VIN = HVDD or VSS<br>HVDD=3.6V                                                            | -    | 2.0  | -    | μA |

|                   | IDDSL | LVDD=PLLVDD=1.95V                                                                         | -    | 5.0  | -    | μA |

|                   | IDDSP | AVDD=3.6V                                                                                 | -    | 0.2  | -    | μA |

|                   | IDDSA |                                                                                           | -    | 0.3  | -    | μA |

| <b>入力リーク</b>      |       |                                                                                           |      |      |      |    |

| 入力リーク電流           | IL    | HVDD=3.6V<br>LVDD=1.95V<br>PLLVDD=1.95V<br>AVDD=3.6V<br>HVIH=HVDD<br>LVIH=LVDD<br>VIL=VSS | -5   | -    | 5    | μA |

1 : 推奨動作条件 ( $T_a=25^{\circ}\text{C}$ ) における TTS 音声合成時のおよその電流値。

2 : 推奨動作条件 ( $T_a=25^{\circ}\text{C}$ ) における静止電流値。

## 6. 電気的特性

---

DC 入力特性 (6.2 「推奨動作条件」の値に基づく) (つづき)

| 項目                     | 記号                                                                                           | 条件         | Min. | Typ. | Max. | 単位 |

|------------------------|----------------------------------------------------------------------------------------------|------------|------|------|------|----|

| 入力特性 (LVC MOS)         | 端子名称 : SIN, SCLK, SFRM1, SOUT, GPIOA[11:0], CLKI, TSTMODE[2:0], SCANEN, EXCKM, TDI, TMS, TCK |            |      |      |      |    |

| H レベル入力電圧              | HVIH                                                                                         | HVDD=3.6V  | 2.2  | -    | -    | V  |

| L レベル入力電圧              | HVIL                                                                                         | HVDD=3.0V  | -    | -    | 0.8  | V  |

| 入力特性 (LVC MOS)         | 端子名称 : TESTEN                                                                                |            |      |      |      |    |

| H レベル入力電圧              | LVIH                                                                                         | LVDD=1.95V | 1.27 | -    | -    | V  |

| L レベル入力電圧              | LVIL                                                                                         | LVDD=1.65V | -    | -    | 0.57 | V  |

| シュミット入力特性<br>(LVC MOS) | 端子名称 : NRESET, NTRST                                                                         |            |      |      |      |    |

| H レベル入力電圧              | VT+                                                                                          | HVDD=3.6V  | 1.4  | -    | 2.7  | V  |

| L レベル入力電圧              | VT-                                                                                          | HVDD=3.0V  | 0.6  | -    | 1.8  | V  |

| ヒステリシス電圧               | ΔV                                                                                           | HVDD=3.0V  | 0.3  | -    | -    | V  |

| 入力特性                   | 端子名称 : TDI, TMS, TCK                                                                         |            |      |      |      |    |

| プルアップ抵抗値               | RPU1                                                                                         | VI=VSS     | 25   | 50   | 120  | kΩ |

| 入力特性                   | 端子名称 : SFRM1, SOUT                                                                           |            |      |      |      |    |

| プルアップ抵抗値               | RPU2                                                                                         | VI=VSS     | 50   | 100  | 240  | kΩ |

| 入力特性                   | 端子名称 : GPIOA[11:0], SCANEN                                                                   |            |      |      |      |    |

| プルダウン抵抗値               | RPD1                                                                                         | VI=HVDD    | 50   | 100  | 240  | kΩ |

| 入力特性                   | 端子名称 : TESTEN                                                                                |            |      |      |      |    |

| プルダウン抵抗値               | RPD2                                                                                         | VI=LVDD    | 48   | 120  | 300  | kΩ |

## 6. 電気的特性

| 項目        | 記号                                                                                          | 条件                                | Min.     | Typ. | Max.    | 単位 |

|-----------|---------------------------------------------------------------------------------------------|-----------------------------------|----------|------|---------|----|

| 出力特性      | 端子名称 : SIN, SCLK, GPIOA[11:0], AUDCLK, HPOP, SPPDN, SPHMT<br>TDO, HPON                      |                                   |          |      |         |    |

| H レベル出力電圧 | VOH1                                                                                        | HVDD=3.0V<br>IOH=-2mA             | HVDD-0.4 | -    | -       | V  |

|           | VOL1                                                                                        | HVDD=3.0V<br>IOL=2mA              | -        | -    | VSS+0.4 | V  |

| 出力特性      | 端子名称 : SOUT,SFRM1,SFRM2                                                                     |                                   |          |      |         |    |

| H レベル出力電圧 | VOH2                                                                                        | HVDD=3.0V<br>IOH=-8mA             | HVDD-0.4 | -    | -       | V  |

|           | VOL2                                                                                        | HVDD=3.0V<br>IOL=8mA              | -        | -    | VSS+0.4 | V  |

| 出力特性      | 端子名称 : SIN, SCLK, SFRM1, SFRM2, SPPDN, SPHMT, AUDCLK,<br>HPOP, HPON, SOUT, GPIOA[11:0], TDO |                                   |          |      |         |    |

| オフ状態リーケ電流 | IOZ                                                                                         | HVDD=3.6V<br>HVOH=HVDD<br>VOL=VSS | -5       | -    | 5       | μA |

| 項目      | 記号                     | 条件                                     | Min. | Typ. | Max. | 単位 |

|---------|------------------------|----------------------------------------|------|------|------|----|

| 出力特性    | 端子名称 : 全入力端子           |                                        |      |      |      |    |

| 入力端子容量  | CI                     | f=1MHz<br>HVDD=LVDD=AVDD=<br>PLLVDD=0V | -    | -    | 8    | pF |

| 端子容量    | 端子名称 : 全出力端子 (HPO を除く) |                                        |      |      |      |    |

| 出力端子容量  | CO1                    | f=1MHz<br>HVDD=LVDD=AVDD=<br>PLLVDD=0V | -    | -    | 8    | pF |

| 端子容量    | 端子名称 : 全出力端子           |                                        |      |      |      |    |

| 入出力端子容量 | CIO                    | f=1MHz<br>HVDD=LVDD=AVDD=<br>PLLVDD=0V | -    | -    | 8    | pF |

## 6. 電気的特性

### 6.4 AC特性

#### 6.4.1 クロックタイミング

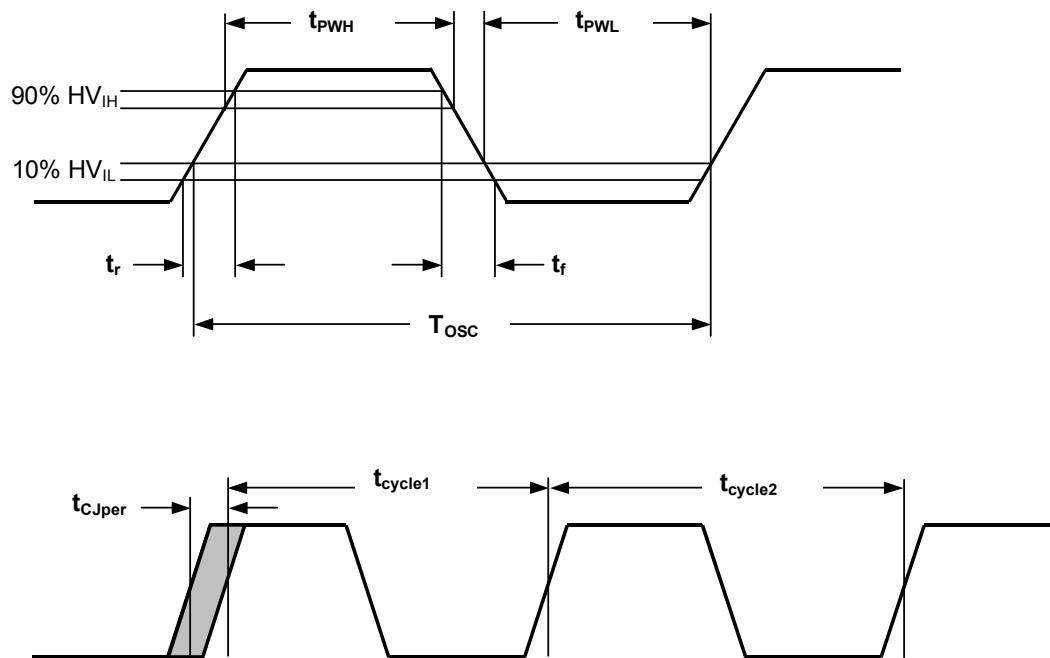

図 6-1 クロックタイミング

| 記号            | 意味                                                     | Min. | Typ.        | Max. | 単位  |

|---------------|--------------------------------------------------------|------|-------------|------|-----|

| $f_{osc}$     | 入力クロック周波数                                              | -    | 32.768      | -    | kHz |

| $T_{osc}$     | 入力クロック周期                                               | -    | $1/f_{osc}$ | -    | μs  |

| $t_{pwh}$     | 入力クロックのパルス幅 (High 区間)                                  | 5    | -           | -    | μs  |

| $t_{pwl}$     | 入力クロックのパルス幅 (Low 区間)                                   | 5    | -           | -    | μs  |

| $t_r$         | 入力クロックの立ち上がり時間 (10%→90%)                               | -    | -           | 12   | μs  |

| $t_f$         | 入力クロックの立ち下がり時間 (90%→10%)                               | -    | -           | 12   | μs  |

| $t_{CJper}$   | 入力クロックの周期ジッタ (*2、4)                                    | -10  | -           | 10   | ns  |

| $t_{CJcycle}$ | 入力クロックのサイクルジッタ (*1、3、4)                                | -10  | -           | 10   | ns  |

| *1            | $t_{CJcycle} = t_{cycle1} - t_{cycle2}$                |      |             |      |     |

| *2            | 入力クロックの周期ジッタとは、中心周期（中心周波数の逆数）からのずれのことです。               |      |             |      |     |

| *3            | 入力クロックのサイクルジッタとは、隣り合うサイクルの周期の差です。                      |      |             |      |     |

| *4            | ジッタ特性は、 $t_{CJper}$ と $t_{CJcycle}$ の両方の特性を満たす必要があります。 |      |             |      |     |

## 6.4.2 初期化タイミング

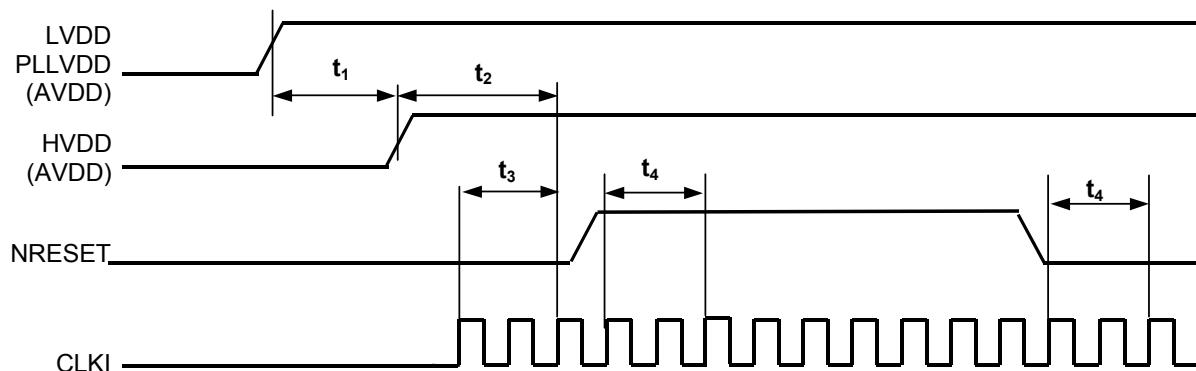

## 6.4.2.1 パワーオン／リセット時のタイミング

図 6-2 パワーオン／リセット時のタイミング

| 記号    | 項目                                                                  | Min. | Max. | 単位                      |

|-------|---------------------------------------------------------------------|------|------|-------------------------|

| $t_1$ | LVDD と PLLVDD (AVDD) のパワーオンから HVDD (AVDD) のパワーオンまでの遅延 <sup>*1</sup> | 10   | -    | μs                      |

| $t_2$ | HVDD のパワーオンから NRESET リリース前の CLK1 の立ち上がりエッジまでの最小遅延                   | 100  | -    | μs                      |

| $t_3$ | システム電源投入時の最小 RESET アサート時間                                           | 2    | -    | $T_{OSC}$ <sup>*2</sup> |

| $t_4$ | NRESET 同期時間<br>(NRESET が内部に適用されるまでのクロックサイクル数)                       | 2    | -    | $T_{OSC}$ <sup>*2</sup> |

| *1    | 6.2 「推奨動作条件」を参照してください。                                              |      |      |                         |

| *2    | $T_{OSC}$ は CLK1 のクロック周期です。                                         |      |      |                         |

## 6. 電気的特性

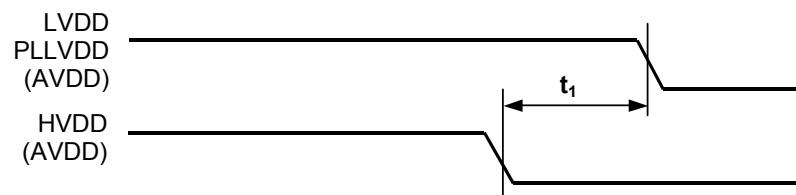

### 6.4.2.2 パワーオフシーケンス

図 6-3 パワーオフシーケンス

| Symbol | Parameter                                                           | Min. | Max. | Unit |

|--------|---------------------------------------------------------------------|------|------|------|

| $t_1$  | HVDD (AVDD) のパワーオフから LVDD と PLLVDD (AVDD) のパワーオフまでの遅延 <sup>*1</sup> | -    | 500  | μs   |

| *1     | 6.2 「推奨動作条件」を参照してください。                                              |      |      |      |

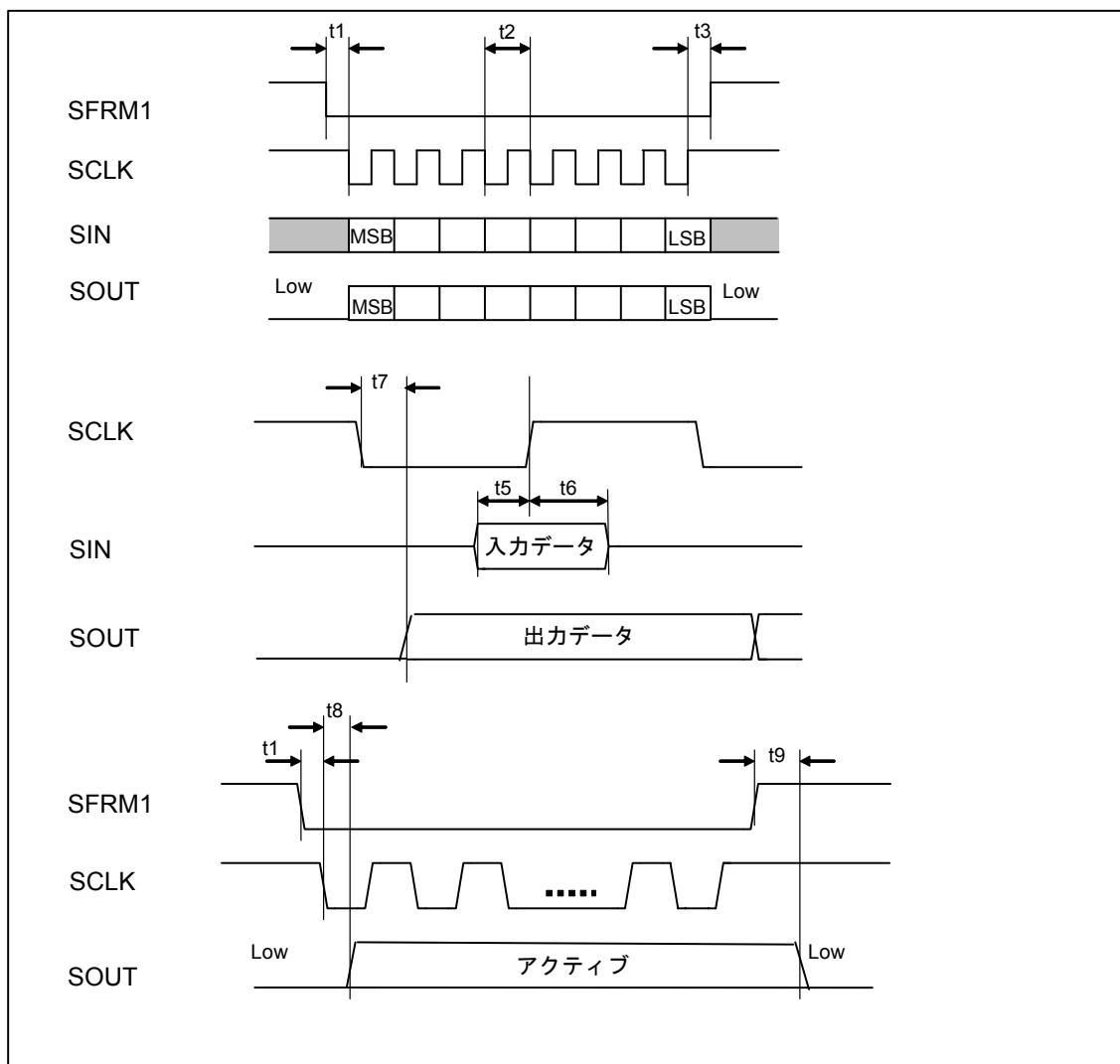

## 6.4.3 クロック同期形シリアルインタフェース (SPI)

図 6-4 クロック同期形シリアルインタフェース

| 記号             | 項目                                                 | Min. | Max. | 単位 |

|----------------|----------------------------------------------------|------|------|----|

| t <sub>1</sub> | SFRM1 の立ち下がりから SCLK の立ち下がりまでの時間                    | 200  | -    | ns |

| t <sub>2</sub> | SCLK の周期                                           | 1.0  | -    | μs |

| t <sub>3</sub> | SCLK の立ち上がりから SFRM1 の立ち上がりまでの時間                    | 200  | -    | ns |

| t <sub>5</sub> | SIN のセットアップ時間                                      | 10   | -    | ns |

| t <sub>6</sub> | SIN のホールド時間                                        | 200  | -    | ns |

| t <sub>7</sub> | SCLK の立ち下がりから SOUT がアクティブになるまでの時間                  | -    | 200  | ns |

| t <sub>8</sub> | SCLK の立ち下がりから SOUT がアクティブになるまでの時間<br>(SFRM1=L のとき) | -    | 200  | ns |

| t <sub>9</sub> | SFRM1 の立ち上がりから SOUT が Low になるまでの時間                 | -    | 250  | ns |

## 6. 電気的特性

---

### 6.5 フルデジタル・オーディオアンプ

フルデジタル・オーディオアンプの電気特性は、とくに記載のないかぎり下記となります。

- $T_a = 25^\circ\text{C}$

- $\text{HVDD} = 3.3\text{V}$ 、 $\text{LVDD} = 1.8\text{V}$ 、 $\text{PLLVDD} = 1.8\text{V}$

- 入力信号周波数 = 1kHz

- 入力信号レベル = 0dBFS

- $f_s = 32\text{kHz}$

- 測定帯域 = 20Hz～16kHz

- 負荷インピーダンス =  $16\Omega$

- 出力 (HPO) に 2 次のローパスフィルタを接続

$\text{AVDD} = 1.8\text{V}$  のとき

| 項目        | 記号    | 条件               | Min. | Typ. | Max. | 単位       |

|-----------|-------|------------------|------|------|------|----------|

| 負荷インピーダンス | $R_L$ |                  | 16   | -    | -    | $\Omega$ |

| 出力パワー     | $P_o$ |                  | 2    | 3    | -    | mW       |

| 全高調波ひずみ   | THD+N | 入力信号レベル = -6dBFS | -    | 0.13 | 0.25 | %        |

| S/N 比     | SNR   |                  | 73   | 76   | -    | dB       |

$\text{AVDD} = 3.3\text{V}$  のとき

| 項目        | 記号    | 条件               | Min. | Typ. | Max. | 単位       |

|-----------|-------|------------------|------|------|------|----------|

| 負荷インピーダンス | $R_L$ |                  | 16   | -    | -    | $\Omega$ |

| 出力パワー     | $P_o$ |                  | 8    | 11   | -    | mW       |

| 全高調波ひずみ   | THD+N | 入力信号レベル = -6dBFS | -    | 0.1  | 0.15 | %        |

| S/N 比     | SNR   |                  | 79   | 82   | -    | dB       |

- フルデジタルアンプの特性は  $\text{AVDD}$  の電圧変動によって劣化することがあります。 $\text{AVDD}$  には安定した電源をご使用ください。

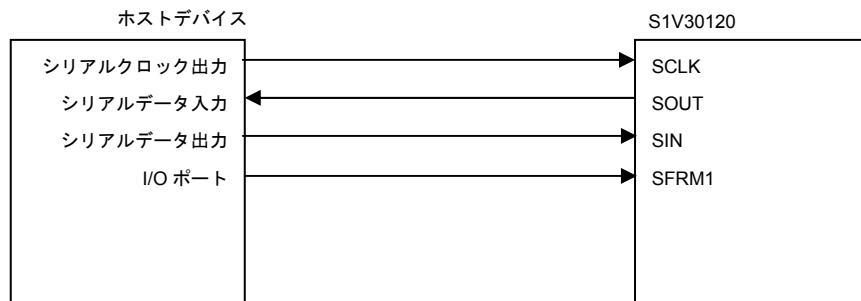

## 7. 外部接続例

### 7.1 接続例：クロック同期形シリアルインターフェース

図 7-1 クロック同期形シリアルインターフェースの接続例

注：

SFRM1 が Low のとき SOUT はアクティブに、SFRM1 が High のとき SOUT は Low に変わります。

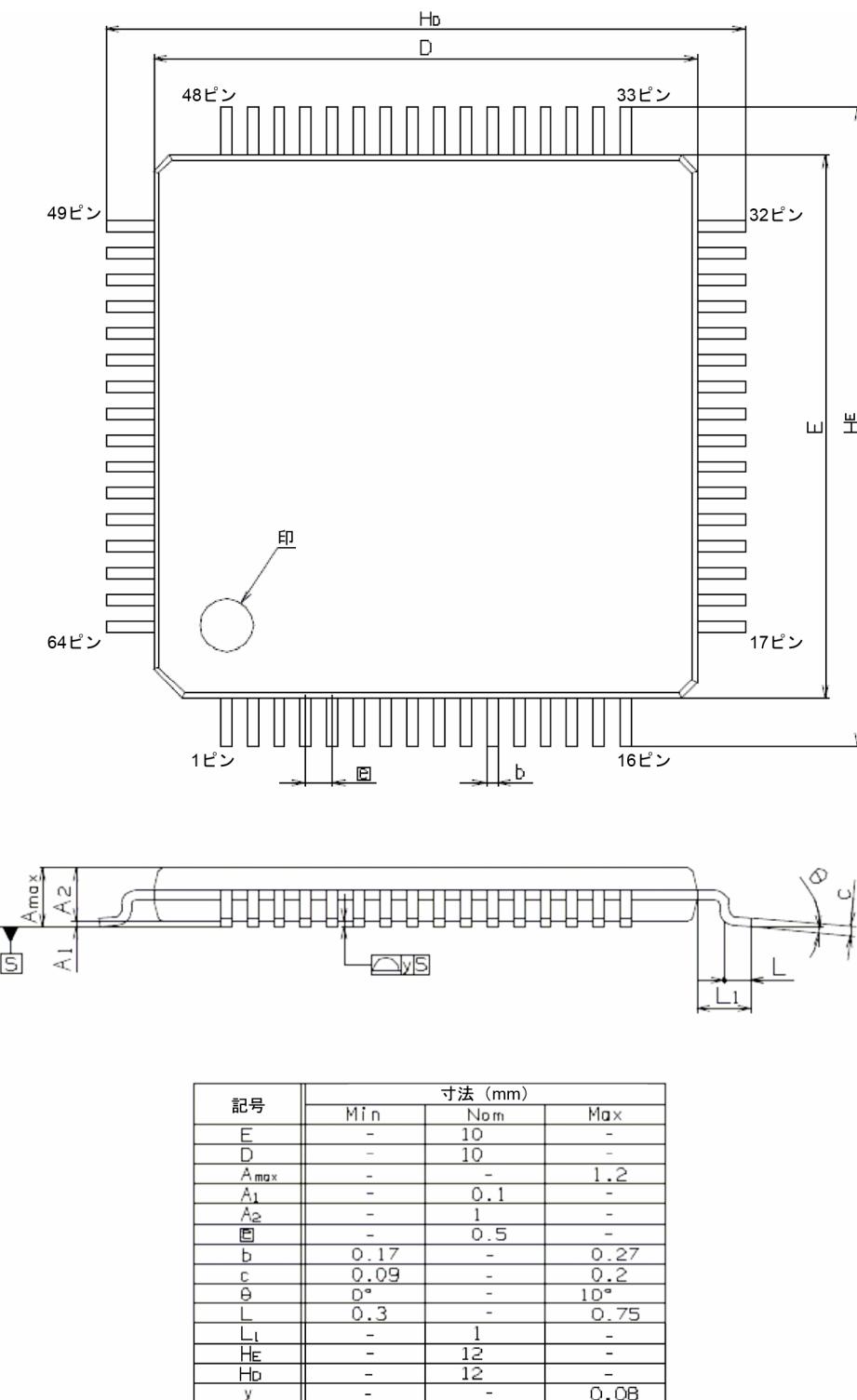

## 8. 外形寸法図

### 8. 外形寸法図

図 8-1 S1V30120F00A\*\*\*の寸法

## **セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード: 411172202

2007 年 7 月 作成

2008 年 7 月 改訂