**S1D13746**

**TV 出力 Mobile Graphics Engine**

**テクニカルマニュアル**

本資料のご使用につきましては、次の点にご留意願います。

---

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

---

# 目次

|                                                          |    |

|----------------------------------------------------------|----|

| 1. はじめに . . . . .                                        | 1  |

| 1.1 適用範囲 . . . . .                                       | 1  |

| 1.2 略語と頭字語 . . . . .                                     | 1  |

| 1.3 S1D13746 TV 出力 Mobile Graphics Engine ファミリ . . . . . | 2  |

| 2. 動作概要 . . . . .                                        | 3  |

| 2.1 TV のサポート . . . . .                                   | 3  |

| 2.1.1 ウィンドウデータの書き込み . . . . .                            | 3  |

| 2.1.2 縮小処理機能 . . . . .                                   | 4  |

| 2.1.3 ウィンドウの回転 . . . . .                                 | 4  |

| 2.1.4 複数の TV ウィンドウ . . . . .                             | 4  |

| 2.1.5 単一の TV ウィンドウ . . . . .                             | 5  |

| 2.1.6 TV ウィンドウのボーダーをサポート . . . . .                       | 5  |

| 2.1.7 TV ウィンドウのダブルバッファ処理 . . . . .                       | 5  |

| 3. 特長 . . . . .                                          | 10 |

| 3.1 内蔵ディスプレイバッファ . . . . .                               | 10 |

| 3.2 CPU インタフェース . . . . .                                | 10 |

| 3.3 入力データフォーマット . . . . .                                | 10 |

| 3.4 TV 表示のサポート . . . . .                                 | 10 |

| 3.5 TV 表示の特長 . . . . .                                   | 11 |

| 3.6 画像強化エンジン . . . . .                                   | 11 |

| 3.7 クロックソース . . . . .                                    | 11 |

| 3.8 その他 . . . . .                                        | 12 |

| 4. 機能ブロック図 . . . . .                                     | 13 |

| 5. 端子配置図 . . . . .                                       | 14 |

| 5.1 パッケージの端子マッピング . . . . .                              | 14 |

| 5.2 端子説明 . . . . .                                       | 16 |

| 5.2.1 Intel 80 ホストインターフェース . . . . .                     | 17 |

| 5.2.2 シリアル周辺インターフェース (SPI) . . . . .                     | 18 |

| 5.2.3 TV インタフェース . . . . .                               | 19 |

| 5.2.4 クロック . . . . .                                     | 20 |

| 5.2.5 その他 . . . . .                                      | 21 |

| 5.2.6 電源およびグラウンド . . . . .                               | 22 |

| 5.3 構成オプションの要約 . . . . .                                 | 23 |

| 6. 端子マッピング . . . . .                                     | 24 |

| 6.1 Intel 80 データ端子 . . . . .                             | 24 |

| 6.2 パラレル RGB データ端子 . . . . .                             | 24 |

---

|                                              |    |

|----------------------------------------------|----|

| 7. DC 特性 . . . . .                           | 25 |

| 7.1 絶対最大定格 . . . . .                         | 25 |

| 7.2 推奨動作条件 . . . . .                         | 25 |

| 7.3 電気的特性 . . . . .                          | 26 |

| 7.4 DAC 特性 . . . . .                         | 27 |

| 7.5 電力推定のガイドライン . . . . .                    | 28 |

| 8. AC 特性 . . . . .                           | 29 |

| 8.1 クロックタイミング . . . . .                      | 29 |

| 8.1.1 入力クロック . . . . .                       | 29 |

| 8.1.2 OSC クロック . . . . .                     | 30 |

| 8.1.3 PLL クロック . . . . .                     | 30 |

| 8.2 リセットタイミング . . . . .                      | 32 |

| 8.3 ホストインターフェースのタイミング . . . . .              | 33 |

| 8.3.1 Intel 80 インターフェースのタイミング . . . . .      | 33 |

| 8.4 シリアルインターフェースのタイミング . . . . .             | 36 |

| 8.4.1 3 線シリアルインターフェースのタイミング . . . . .        | 36 |

| 8.4.2 4 線シリアルインターフェース (SPI) のタイミング . . . . . | 37 |

| 8.5 パラレル RGB インターフェースのタイミング . . . . .        | 38 |

| 8.5.1 垂直タイミング . . . . .                      | 38 |

| 8.5.2 水平タイミング . . . . .                      | 39 |

| 8.5.3 PCLK に対する入力信号のタイミング . . . . .          | 39 |

| 8.6 TV のタイミング . . . . .                      | 40 |

| 8.6.1 TV 出力のタイミング . . . . .                  | 40 |

| 8.6.2 TV 出力のパラメータ . . . . .                  | 44 |

| 9. クロック . . . . .                            | 54 |

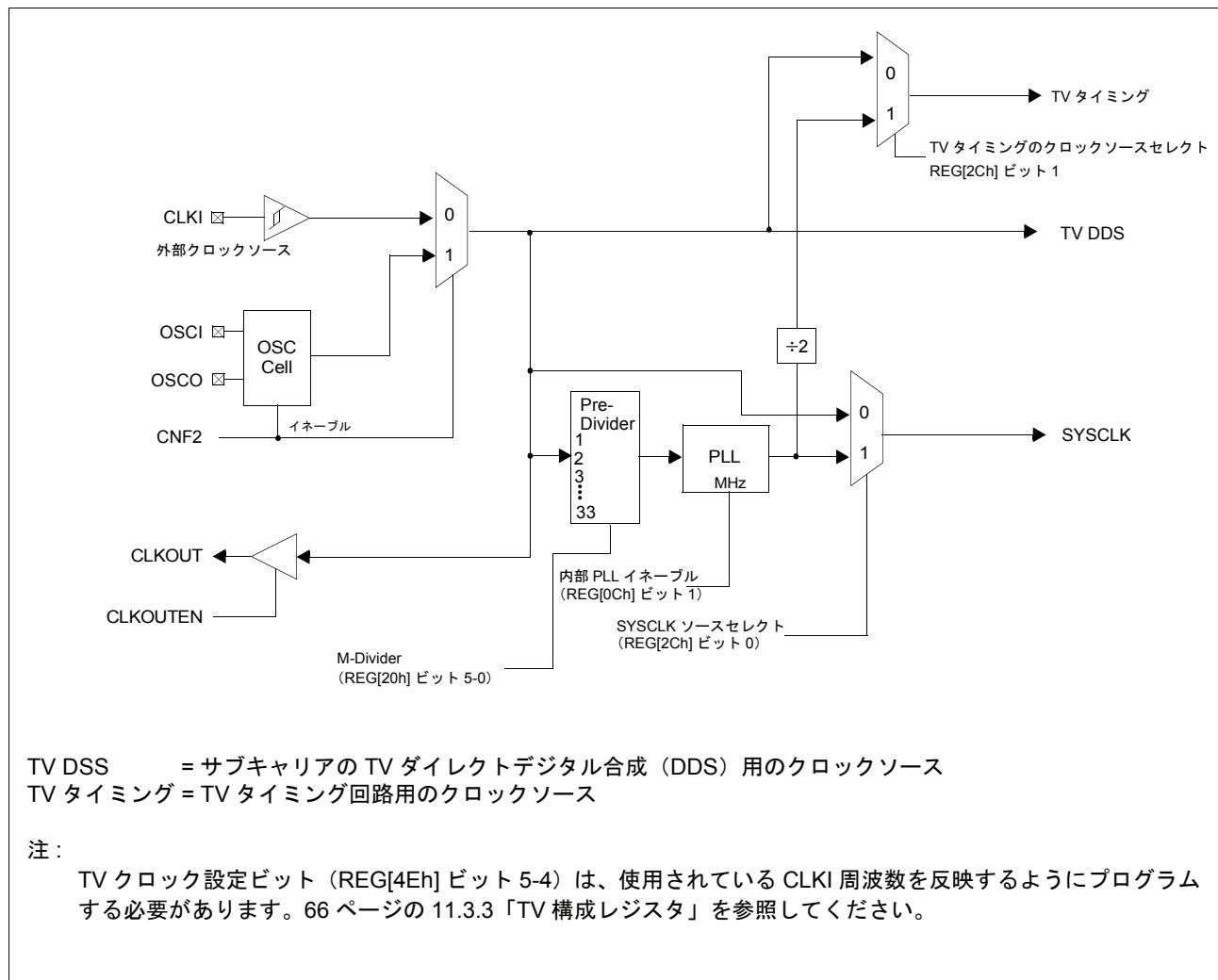

| 9.1 クロック機能ブロック図 . . . . .                    | 54 |

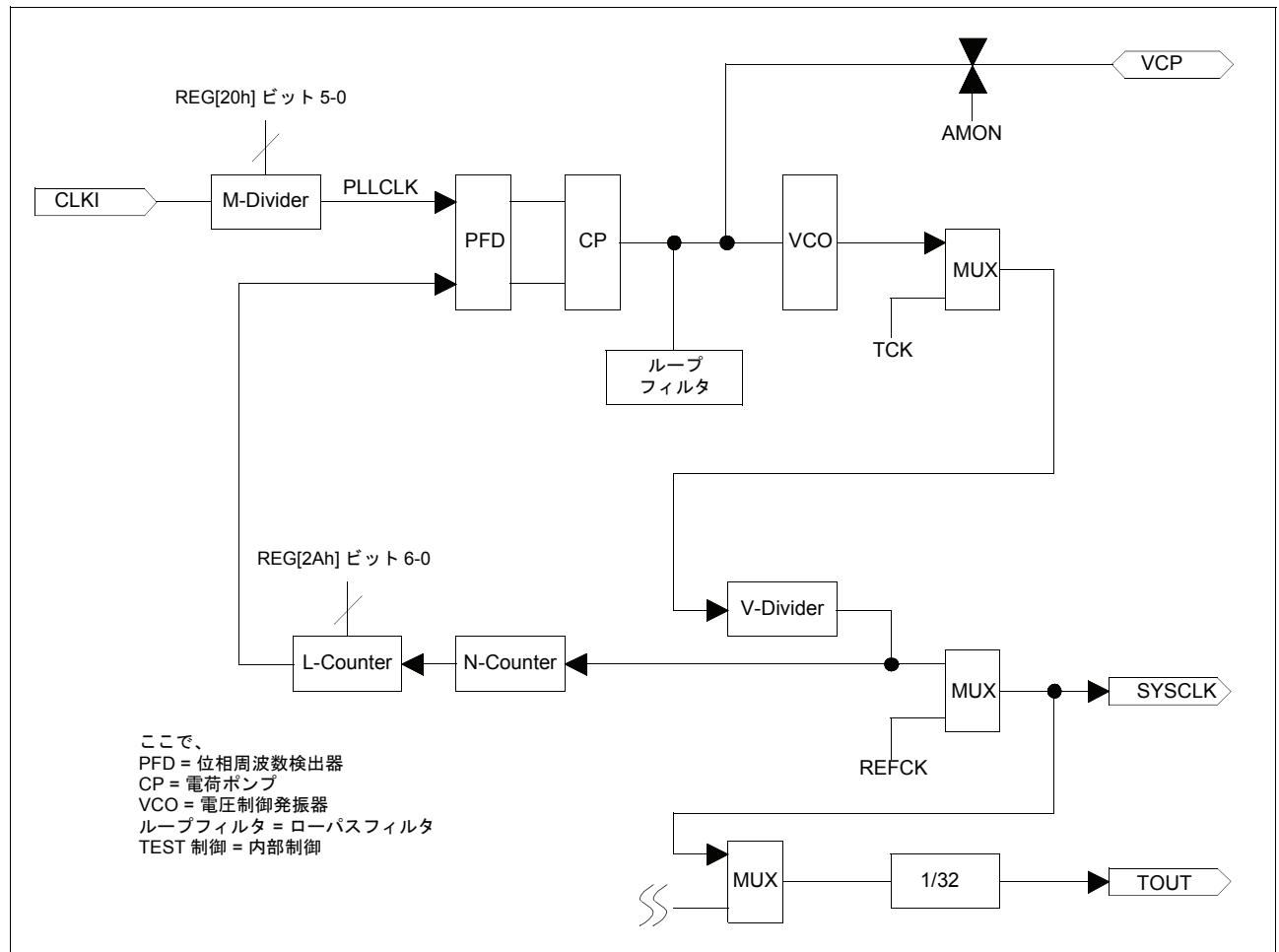

| 9.2 PLL 機能ブロック図 . . . . .                    | 55 |

| 10. メモリマップ . . . . .                         | 56 |

| 11. レジスタ . . . . .                           | 57 |

| 11.1 レジスタマッピング . . . . .                     | 57 |

| 11.2 レジスタセット . . . . .                       | 58 |

| 11.3 レジスタの説明 . . . . .                       | 60 |

| 11.3.1 製品情報レジスタ . . . . .                    | 60 |

| 11.3.2 クロック構成レジスタ . . . . .                  | 61 |

| 11.3.3 TV 構成レジスタ . . . . .                   | 66 |

| 11.3.4 入力データ制御レジスタ . . . . .                 | 82 |

| 11.3.5 表示出力制御レジスタ . . . . .                  | 91 |

| 11.3.6 表示メモリアクセスレジスタ . . . . .               | 98 |

| 11.3.7 3 × 3 ピクセルマトリックスフィルタレジスタ . . . . .    | 99 |

---

|                                                            |            |

|------------------------------------------------------------|------------|

| 11.3.8 その他のレジスタ . . . . .                                  | 110        |

| 11.3.9 汎用 IO 端子レジスタ . . . . .                              | 113        |

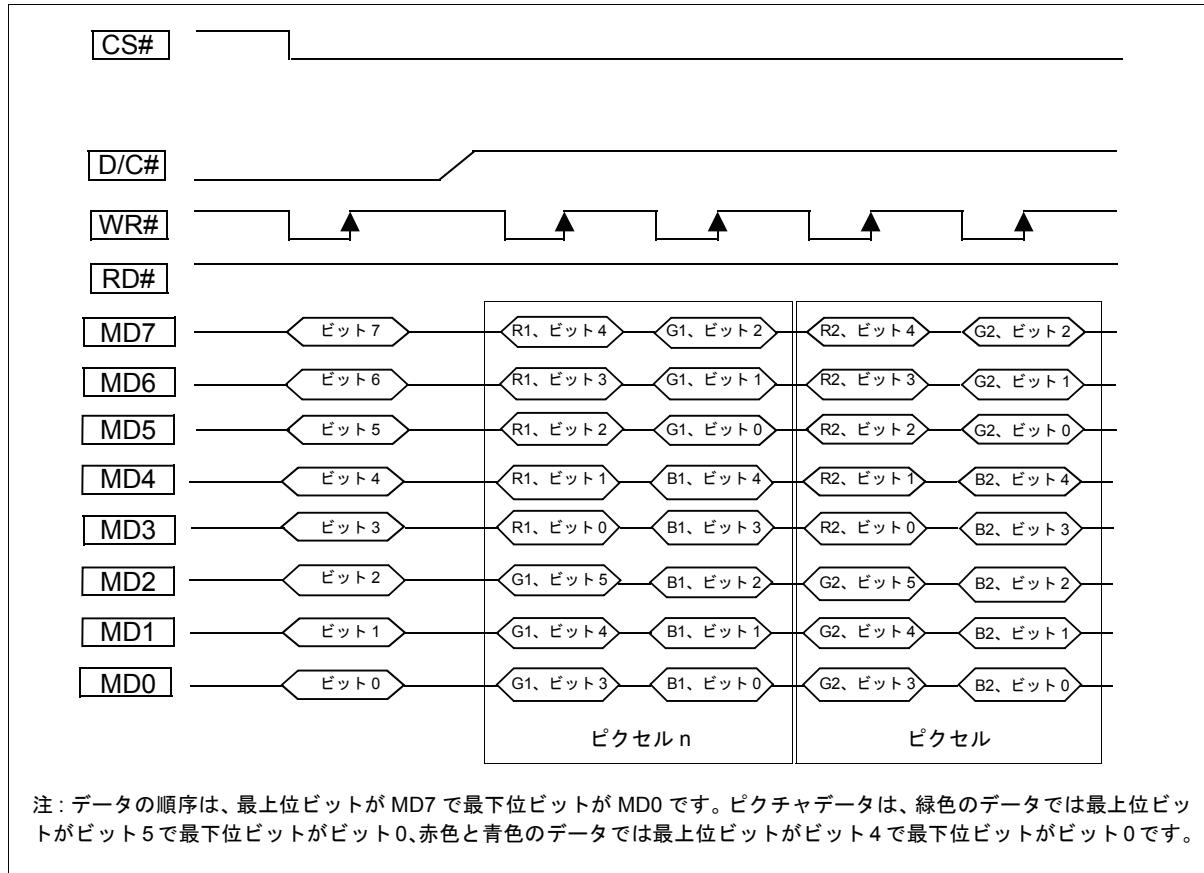

| <b>12. Intel 80、8 ビットインターフェースのカラーフォーマット . . . . .</b>      | <b>115</b> |

| 12.1 8bpp モード (RGB 3:3:2)、256 色 . . . . .                  | 115        |

| 12.2 16bpp モード (RGB 5:6:5)、65,536 色 . . . . .              | 116        |

| 12.3 18bpp (RGB 6:6:6)、262,144 色 . . . . .                 | 117        |

| 12.4 24bpp (RGB 8:8:8)、16,777,216 色 . . . . .              | 118        |

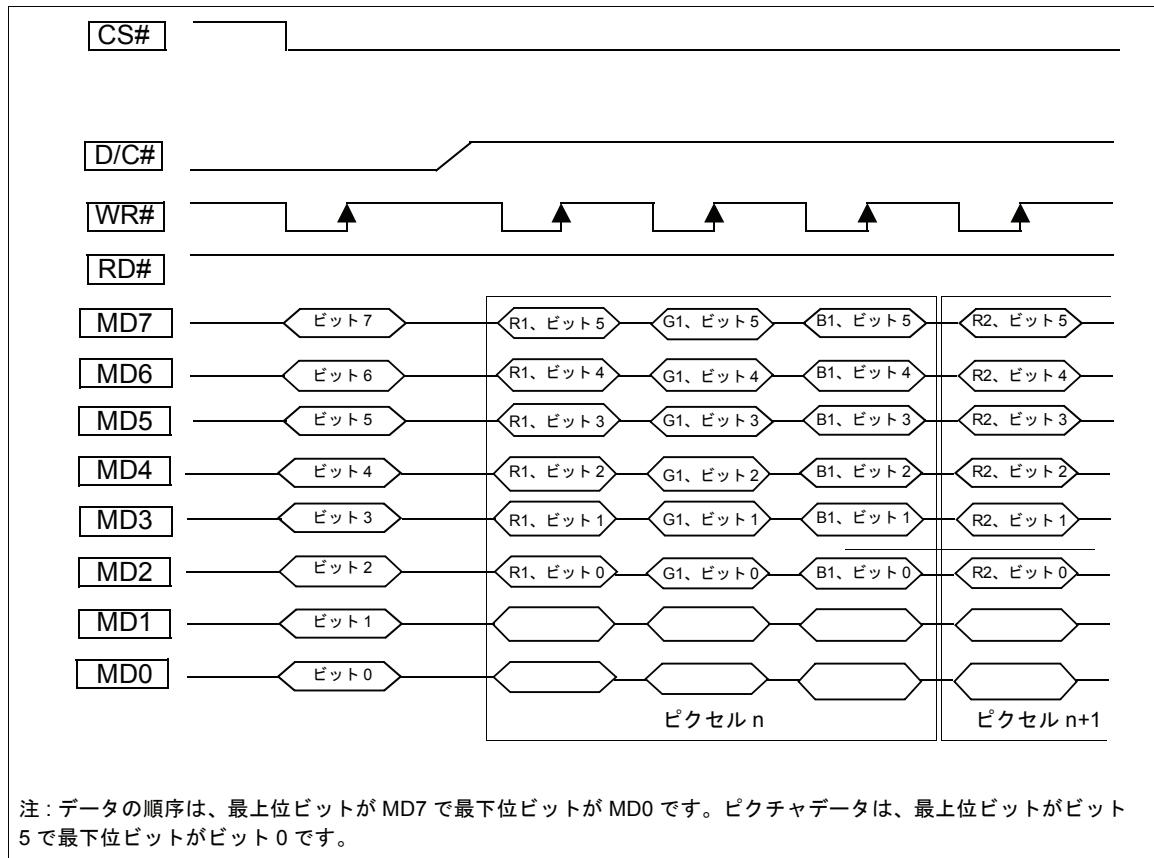

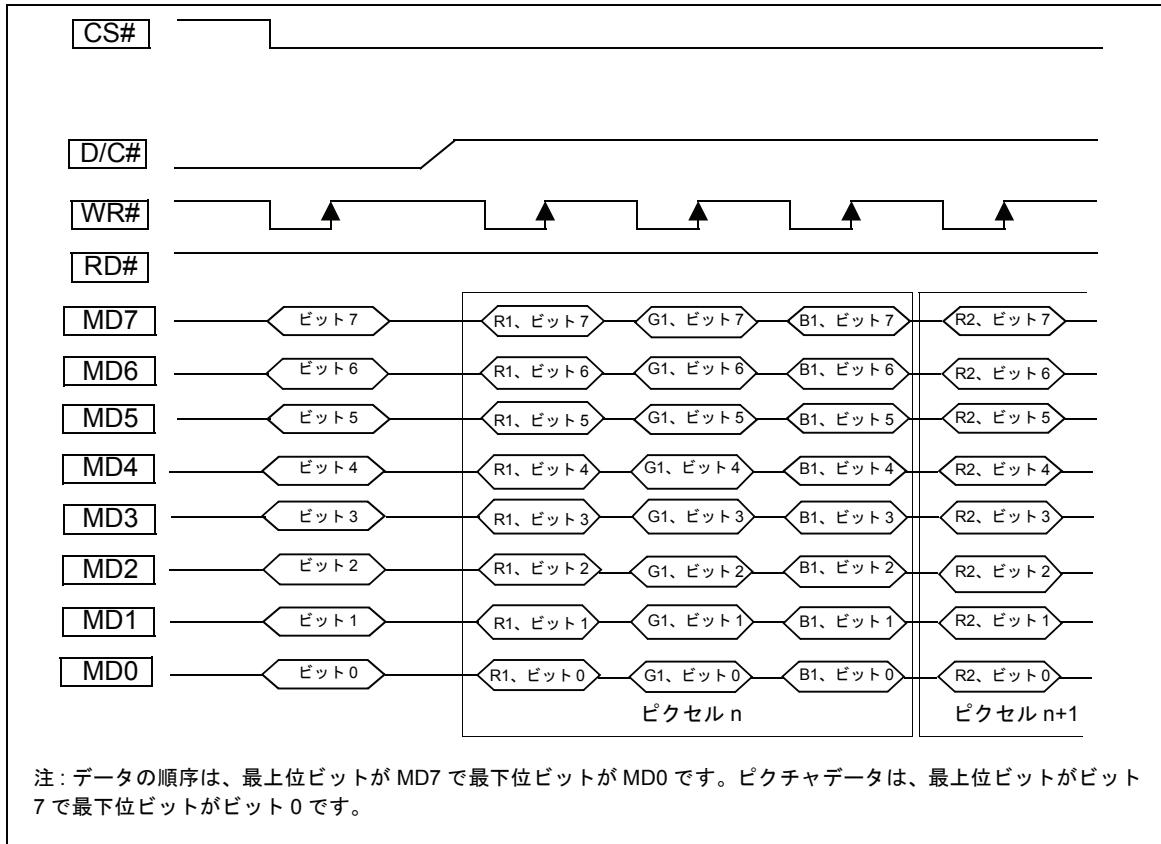

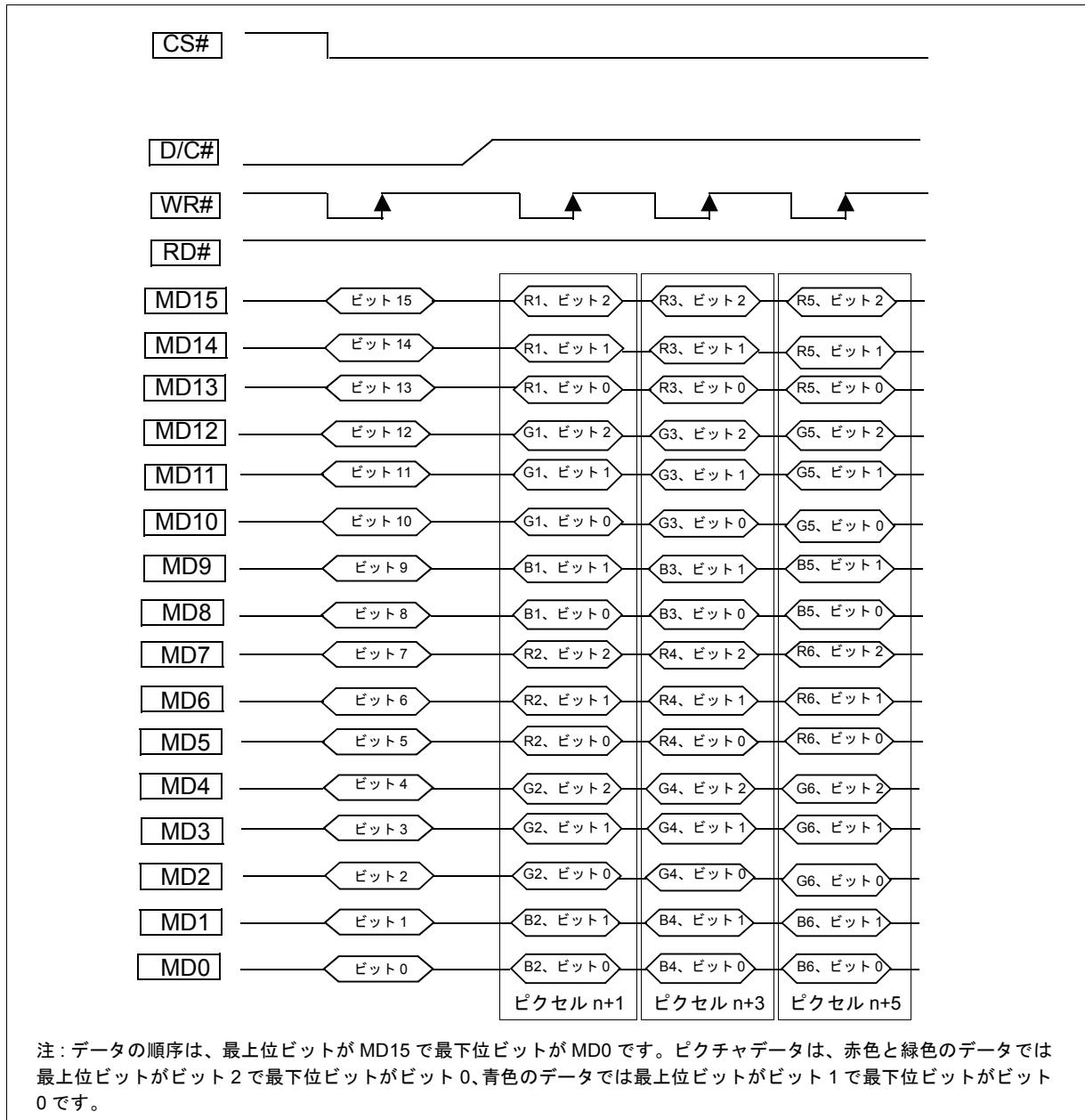

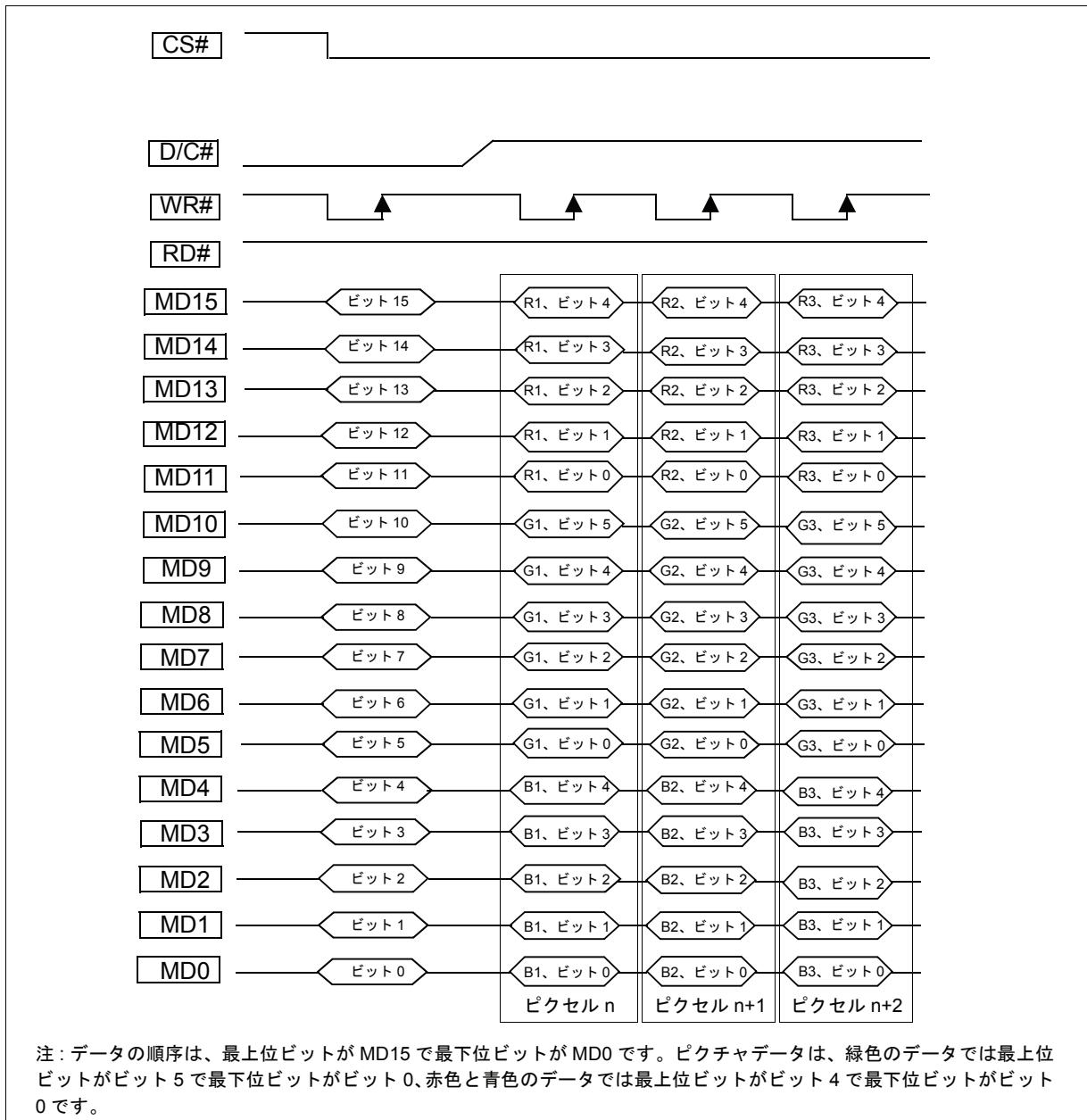

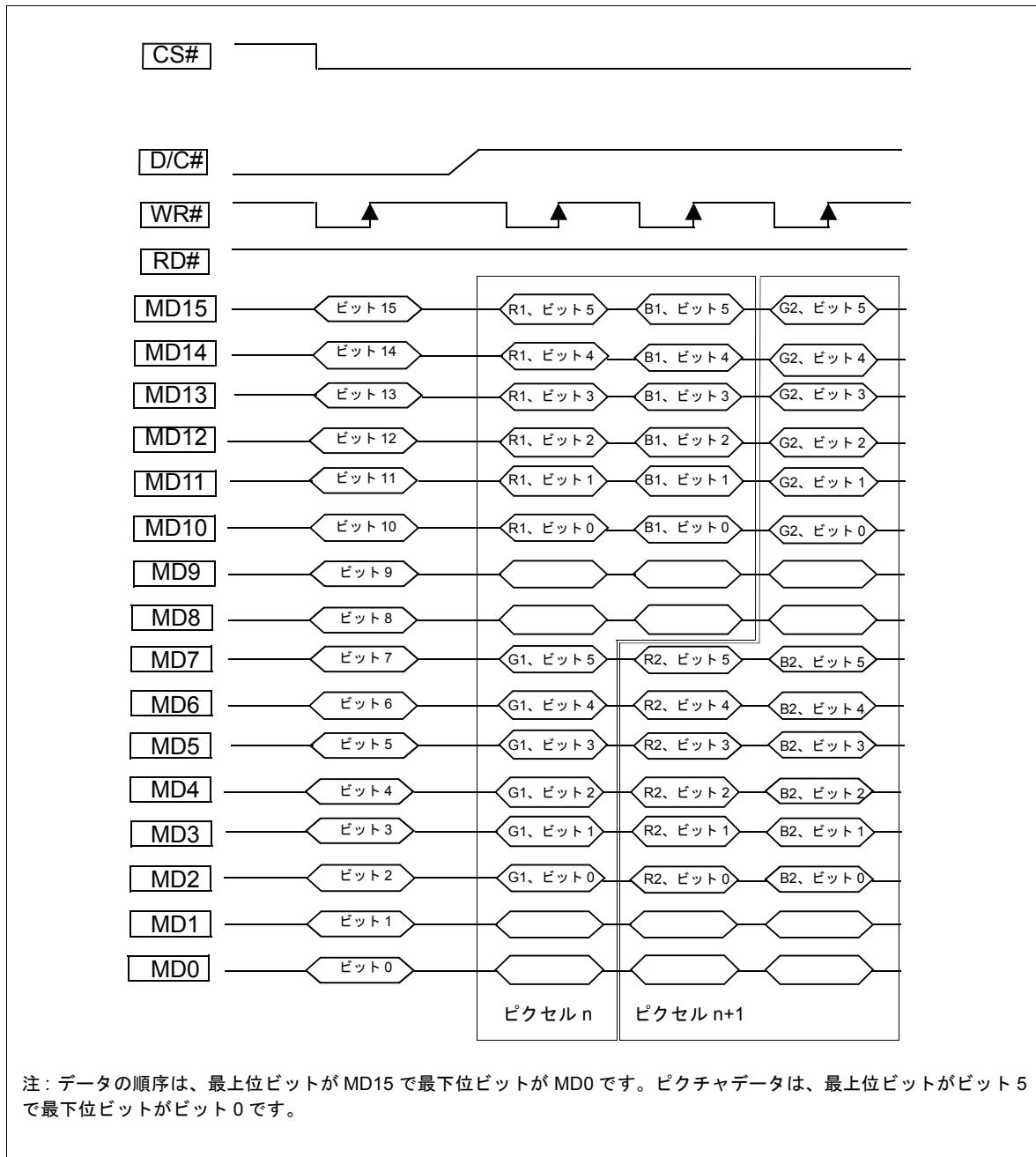

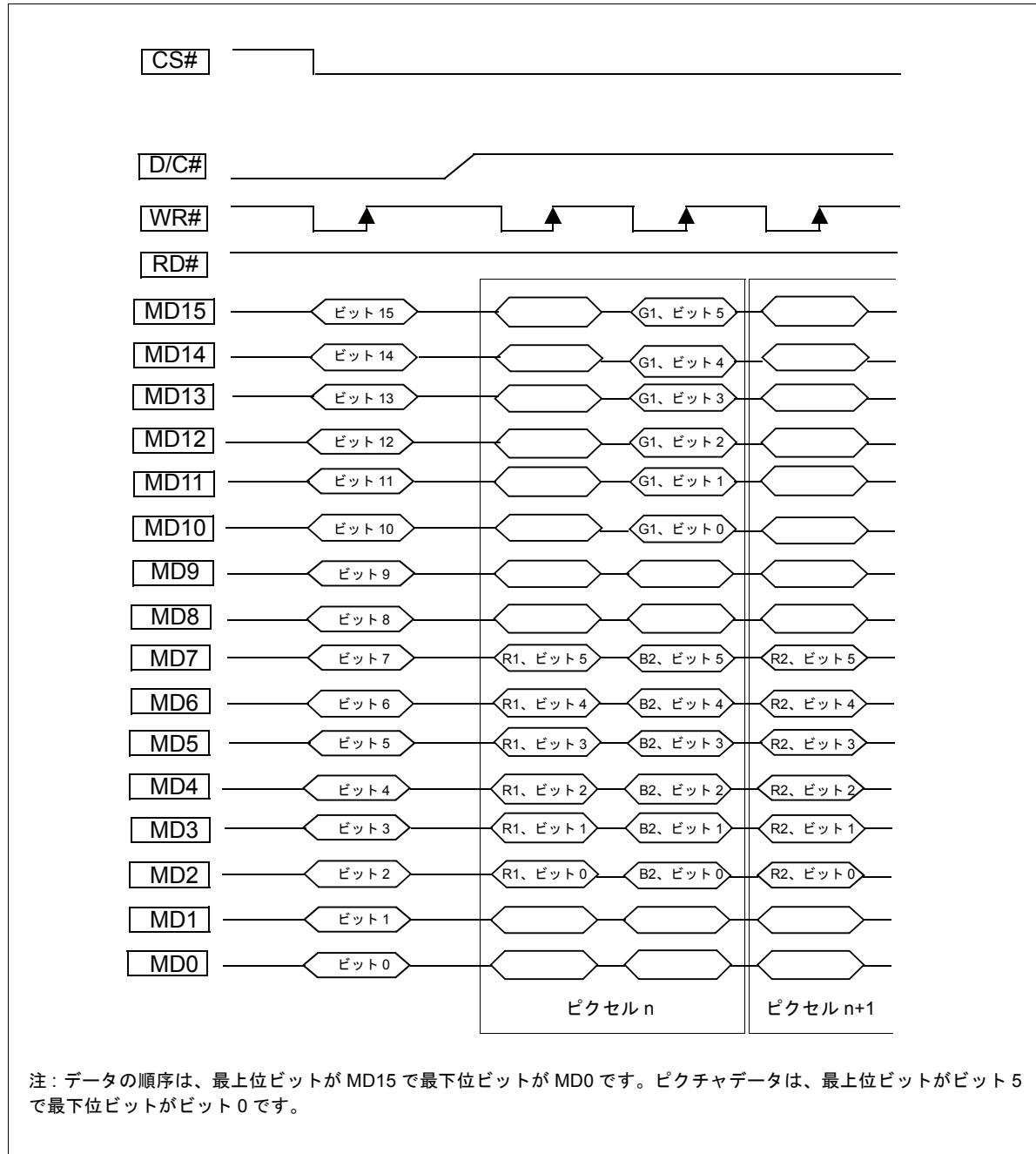

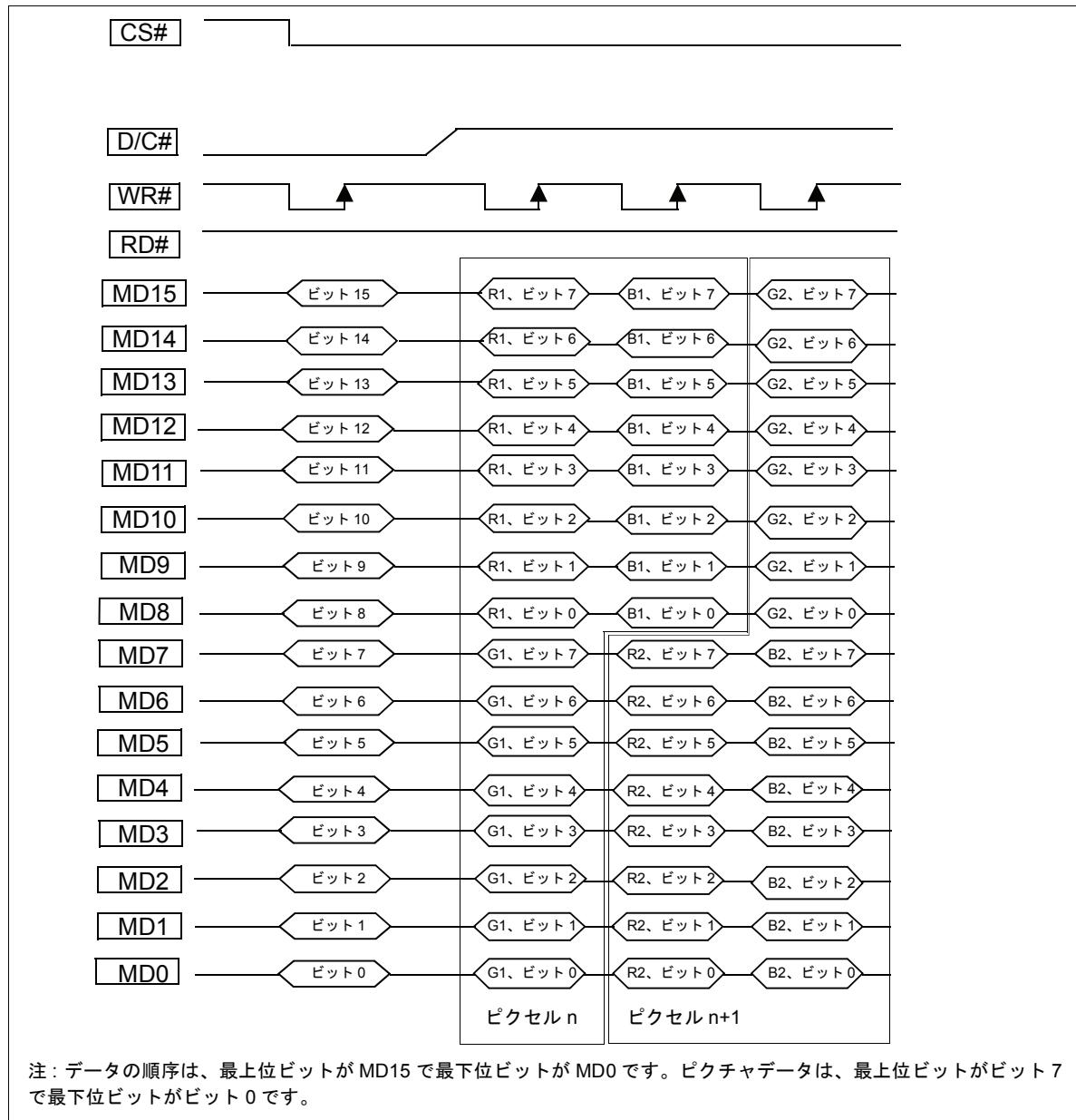

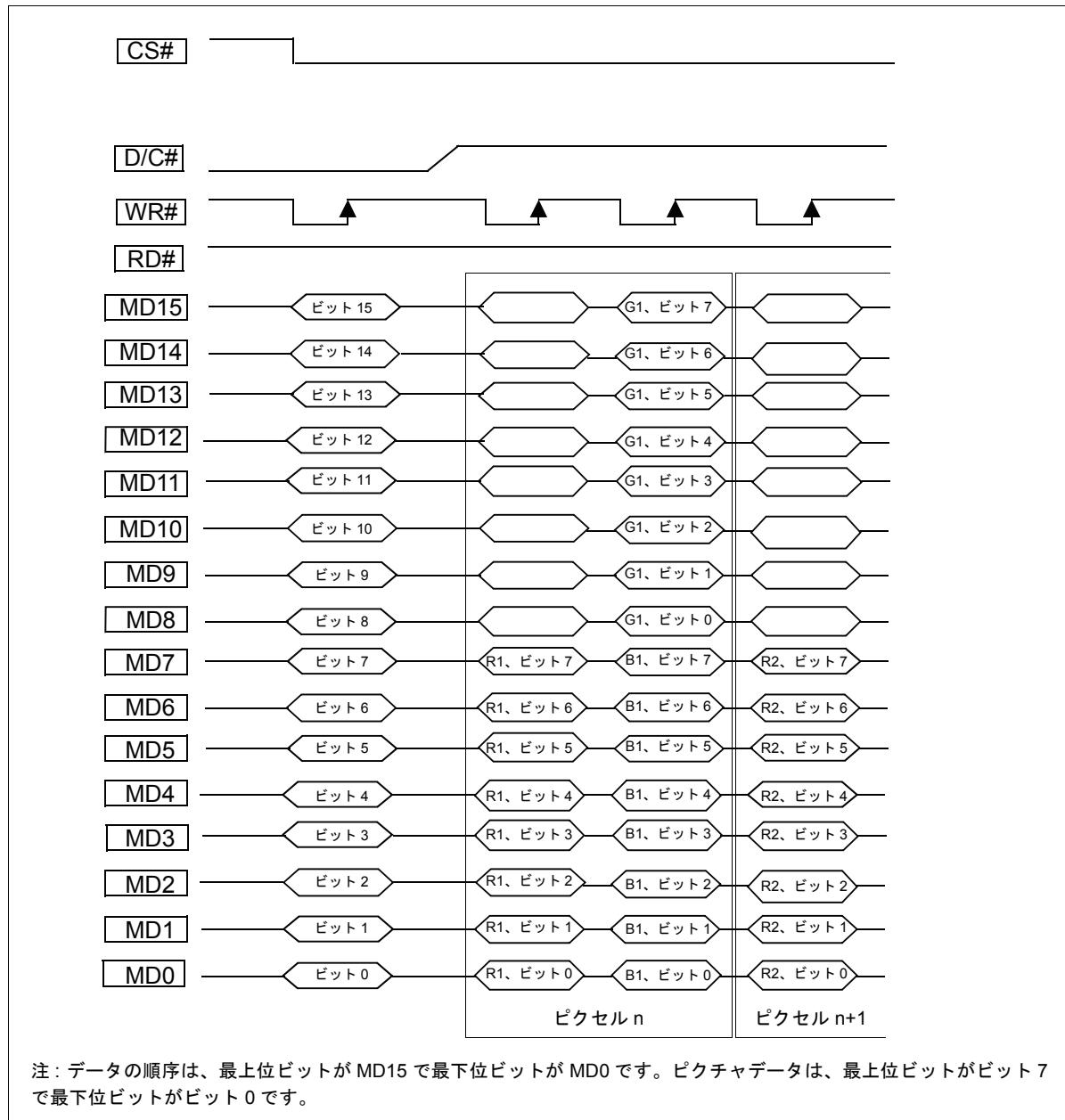

| <b>13. Intel 80、16 ビットインターフェースのカラーフォーマット . . . . .</b>     | <b>119</b> |

| 13.1 8bpp (RGB 3:3:2)、256 色 . . . . .                      | 119        |

| 13.2 16bpp (RGB 5:6:5)、65,536 色 . . . . .                  | 120        |

| 13.3 18bpp モード 1 (RGB 6:6:6)、262,144 色 . . . . .           | 121        |

| 13.4 18bpp モード 2 (RGB 6:6:6)、262,144 色 . . . . .           | 122        |

| 13.5 24bpp モード 1 (RGB 8:8:8)、16,777,216 色 . . . . .        | 123        |

| 13.6 24bpp モード 2 (RGB 8:8:8)、16,777,216 色 . . . . .        | 124        |

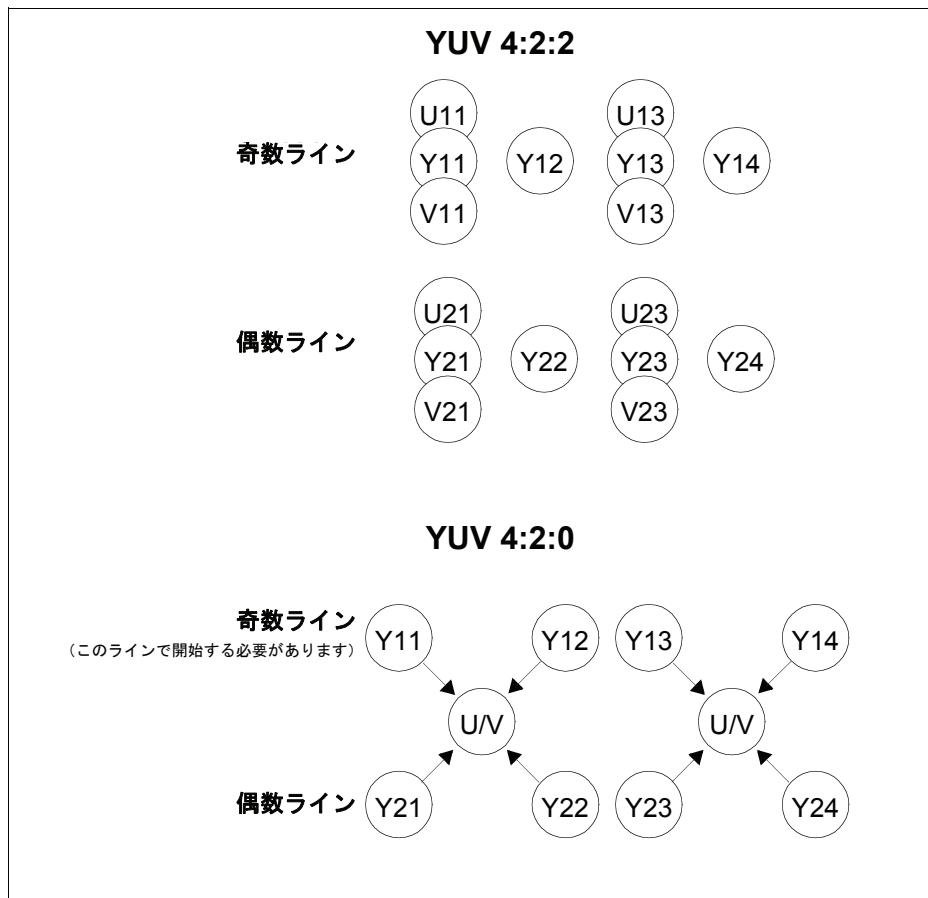

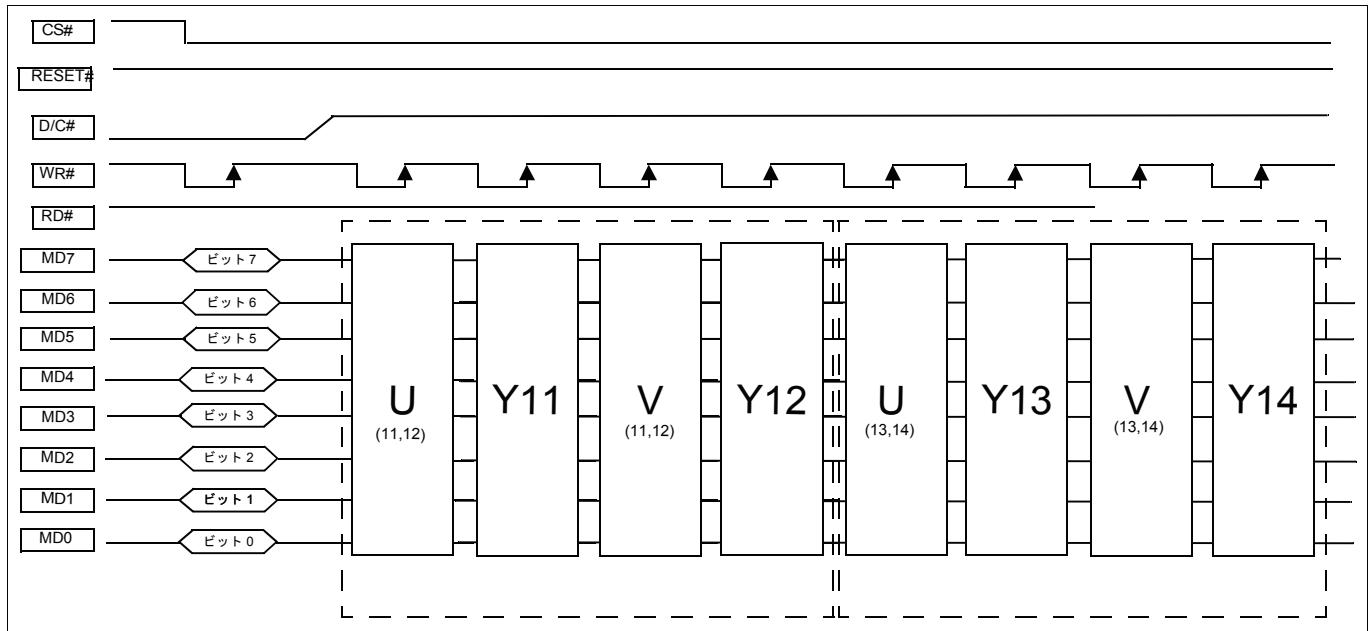

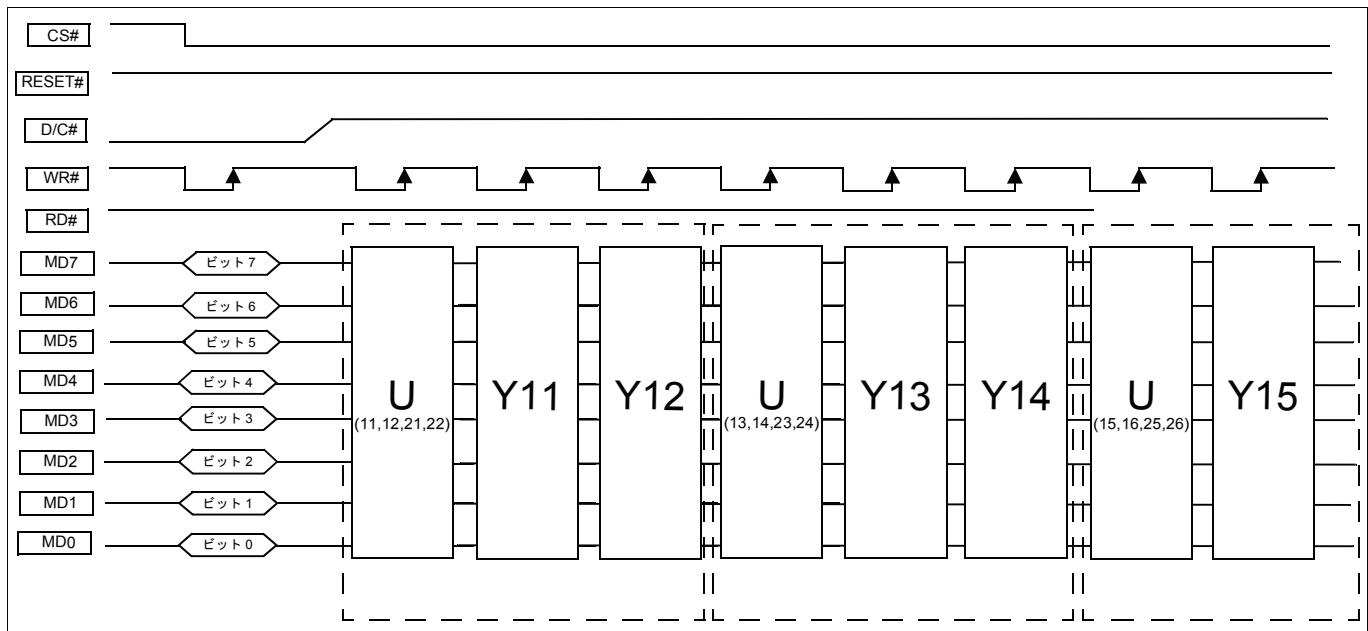

| <b>14. YUV タイミング . . . . .</b>                             | <b>125</b> |

| 14.1 Intel 80 の 8 ビットインターフェースでの YUV 4:2:2 . . . . .        | 126        |

| 14.2 Intel 80 の 8 ビットインターフェースでの YUV 4:2:0 奇数ライン . . . . .  | 126        |

| 14.3 Intel 80 の 8 ビットインターフェースでの YUV 4:2:0 偶数ライン . . . . .  | 127        |

| 14.4 Intel 80 の 16 ビットインターフェースでの YUV 4:2:2 . . . . .       | 128        |

| 14.5 Intel 80 の 16 ビットインターフェースでの YUV 4:2:0 奇数ライン . . . . . | 129        |

| 14.6 Intel 80 の 16 ビットインターフェースでの YUV 4:2:0 偶数ライン . . . . . | 130        |

| <b>15. SwivelView™ . . . . .</b>                           | <b>131</b> |

| 15.1 SwivelView™ の概念 . . . . .                             | 131        |

| 15.2 90° SwivelView™ . . . . .                             | 132        |

| 15.2.1 レジスタのプログラミング . . . . .                              | 132        |

| 15.3 180° SwivelView™ . . . . .                            | 133        |

| 15.3.1 レジスタのプログラミング . . . . .                              | 133        |

| 15.4 270° SwivelView™ . . . . .                            | 134        |

| 15.4.1 レジスタのプログラミング . . . . .                              | 134        |

| 15.5 サブウィンドウの位置 / 回転 . . . . .                             | 135        |

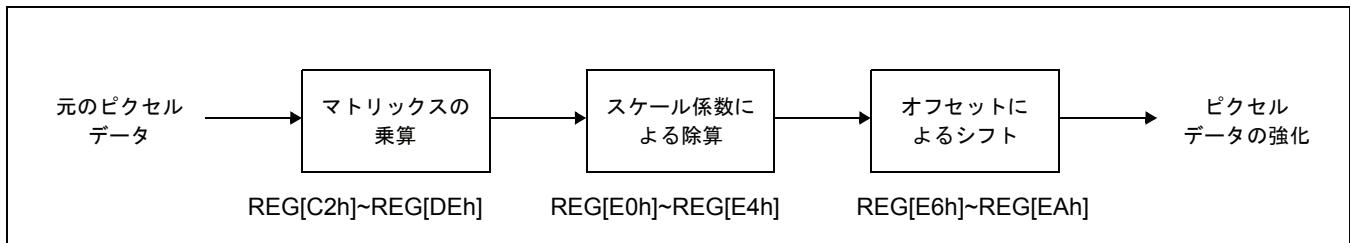

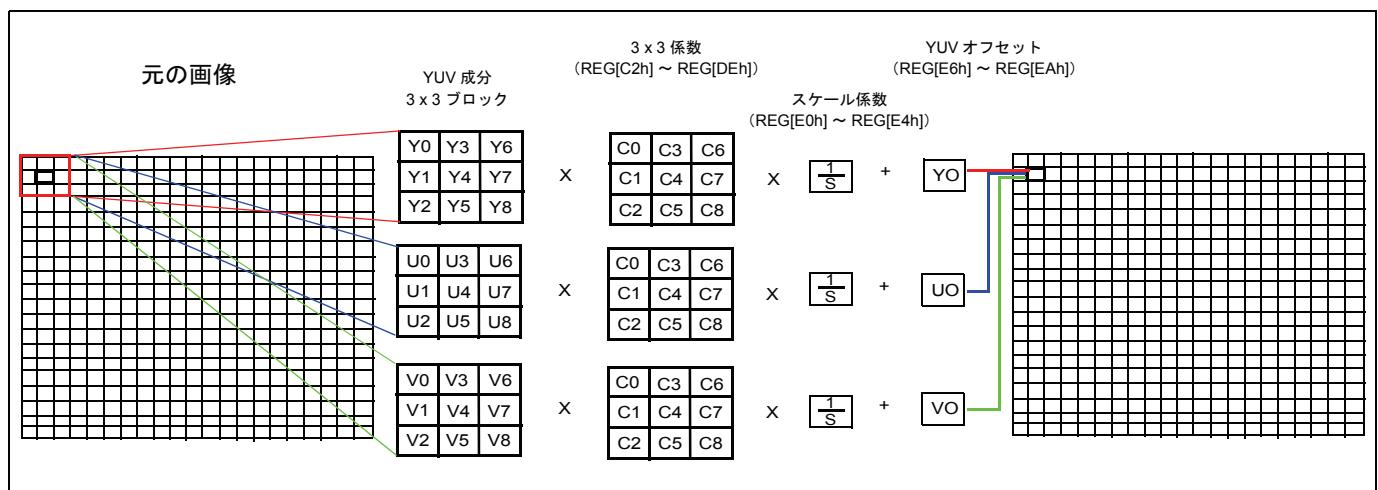

| <b>16. 画像強化エンジン . . . . .</b>                              | <b>136</b> |

| 16.1 3 x 3 フィルタ . . . . .                                  | 136        |

| 16.1.1 プログラミング値の例 . . . . .                                | 138        |

| <b>17. ホストインターフェース . . . . .</b>                           | <b>139</b> |

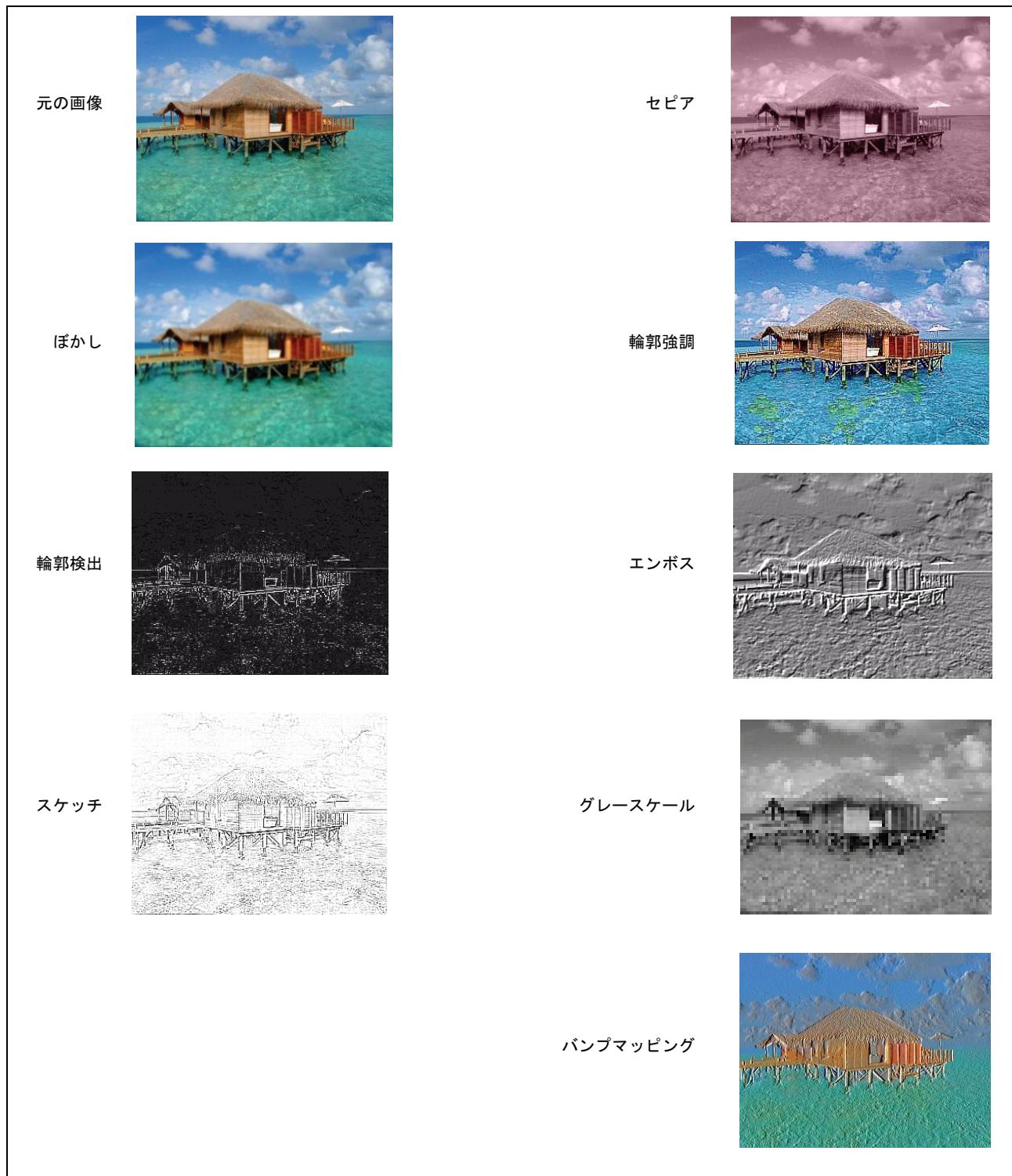

| 17.1 Intel 80 インタフェース . . . . .                            | 139        |

| 17.1.1 レジスタライト手順 . . . . .                                 | 140        |

| 17.1.2 レジスタリード手順 . . . . .                                 | 141        |

| 17.1.3 連続メモリライト手順 . . . . .                                | 142        |

| 17.2 シリアルホストインターフェース . . . . .                             | 143        |

---

|                                                   |            |

|---------------------------------------------------|------------|

| 17.2.1 3線9ビット . . . . .                           | 143        |

| 17.2.2 SPI インタフェース . . . . .                      | 146        |

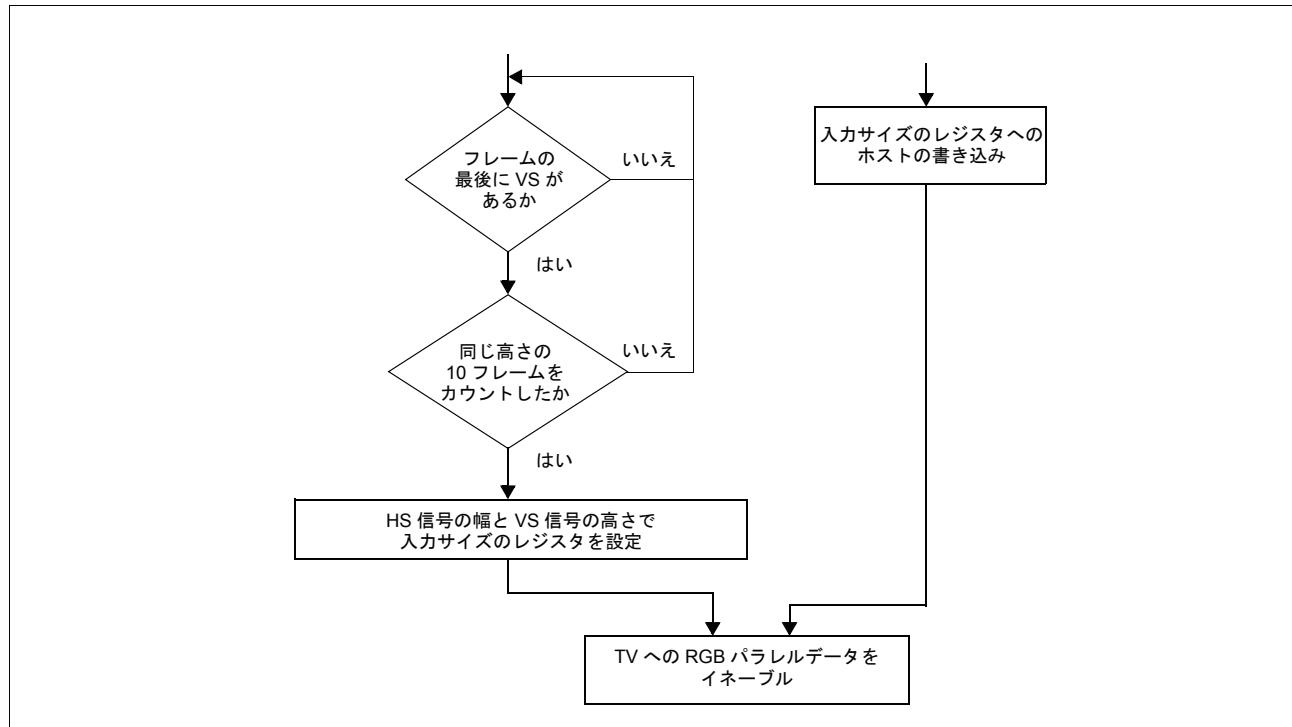

| <b>18. パラレルRGB インタフェース入力 . . . . .</b>            | <b>150</b> |

| 18.1 幅と高さの自動検出 . . . . .                          | 150        |

| <b>19. VBI とワイドスクリーンの信号送出機能 . . . . .</b>         | <b>152</b> |

| 19.1 CEA-608-B の自動モード . . . . .                   | 153        |

| 19.2 CEA-608-B の手動モード . . . . .                   | 154        |

| <b>20. 標準的な使用例の説明 . . . . .</b>                   | <b>155</b> |

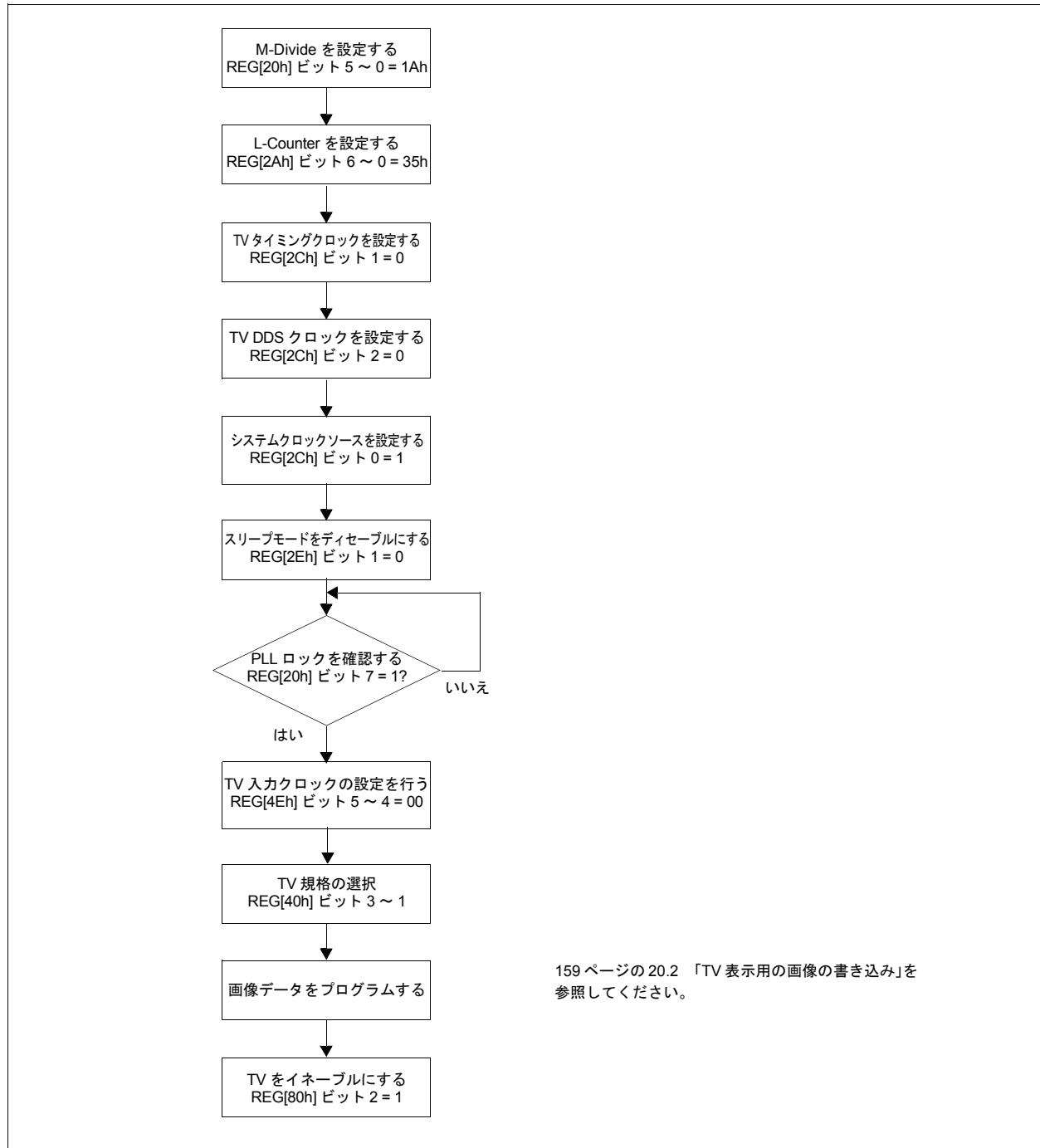

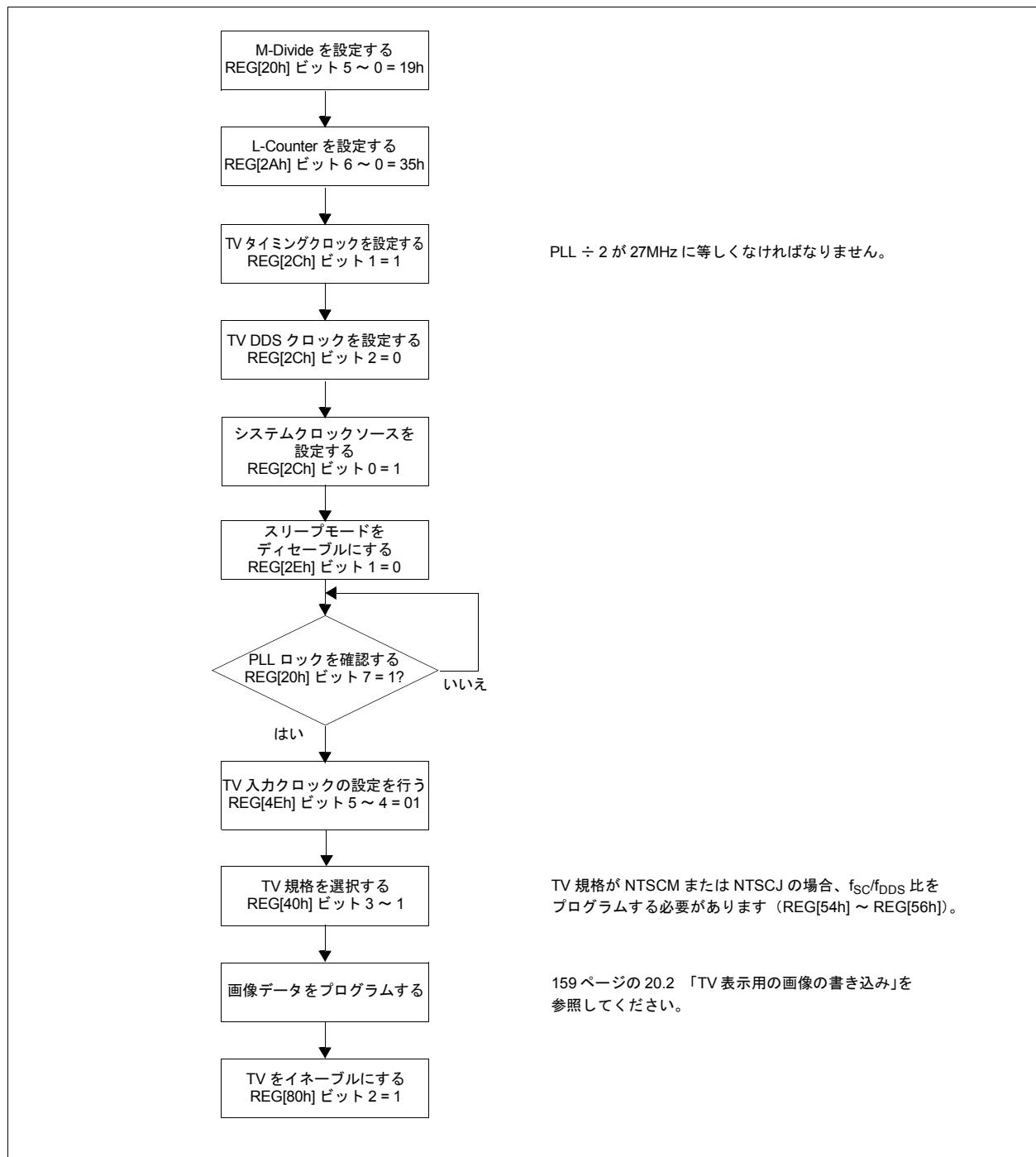

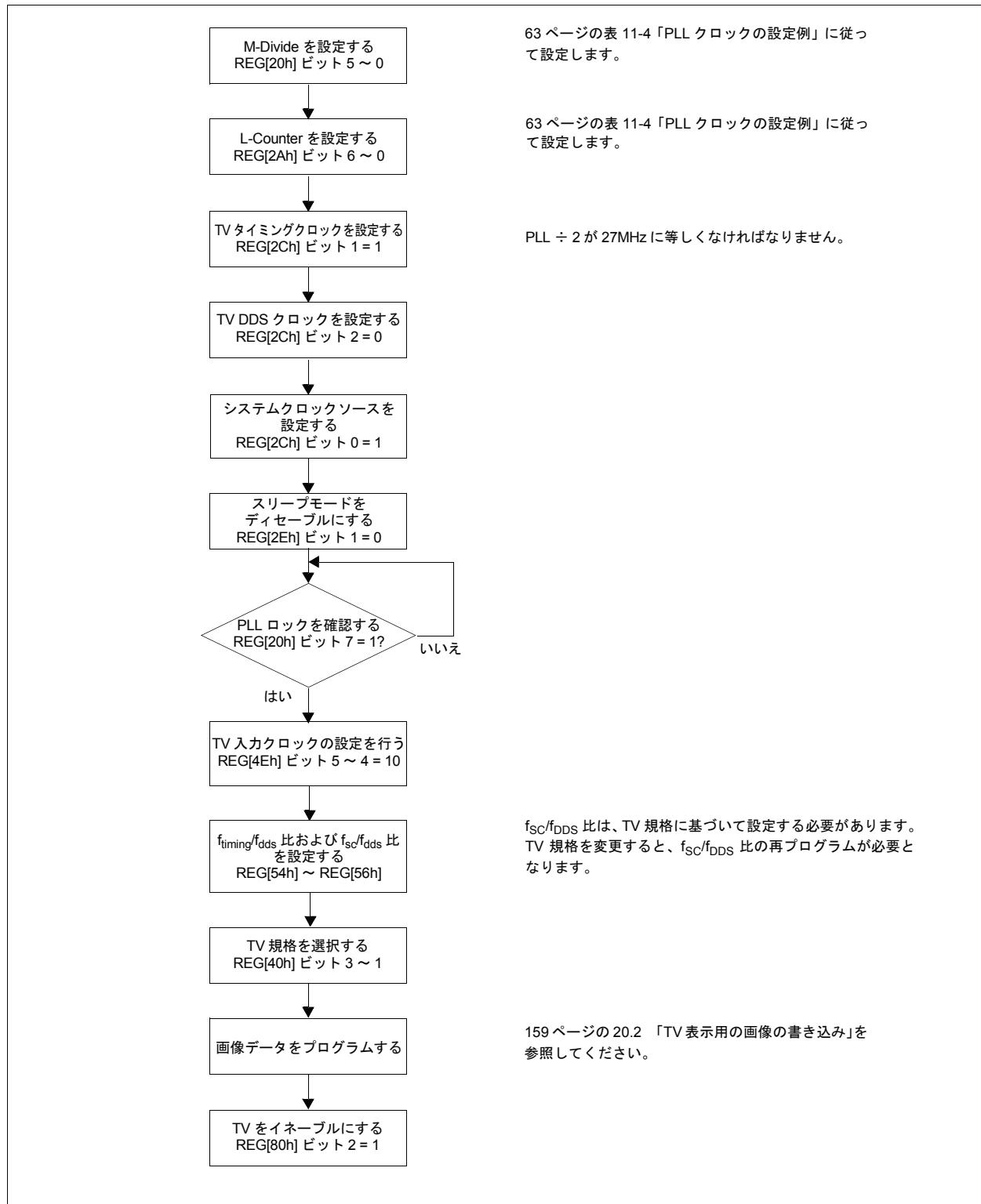

| 20.1 S1D13746 の初期化 . . . . .                      | 155        |

| 20.1.1 初期化のフローチャート . . . . .                      | 156        |

| 20.2 TV 表示用の画像の書き込み . . . . .                     | 159        |

| 20.3 使用例のフローチャート . . . . .                        | 160        |

| 20.3.1 ホストによる背景の書き込み . . . . .                    | 160        |

| 20.3.2 ホストによるオーバーレイの書き込み . . . . .                | 161        |

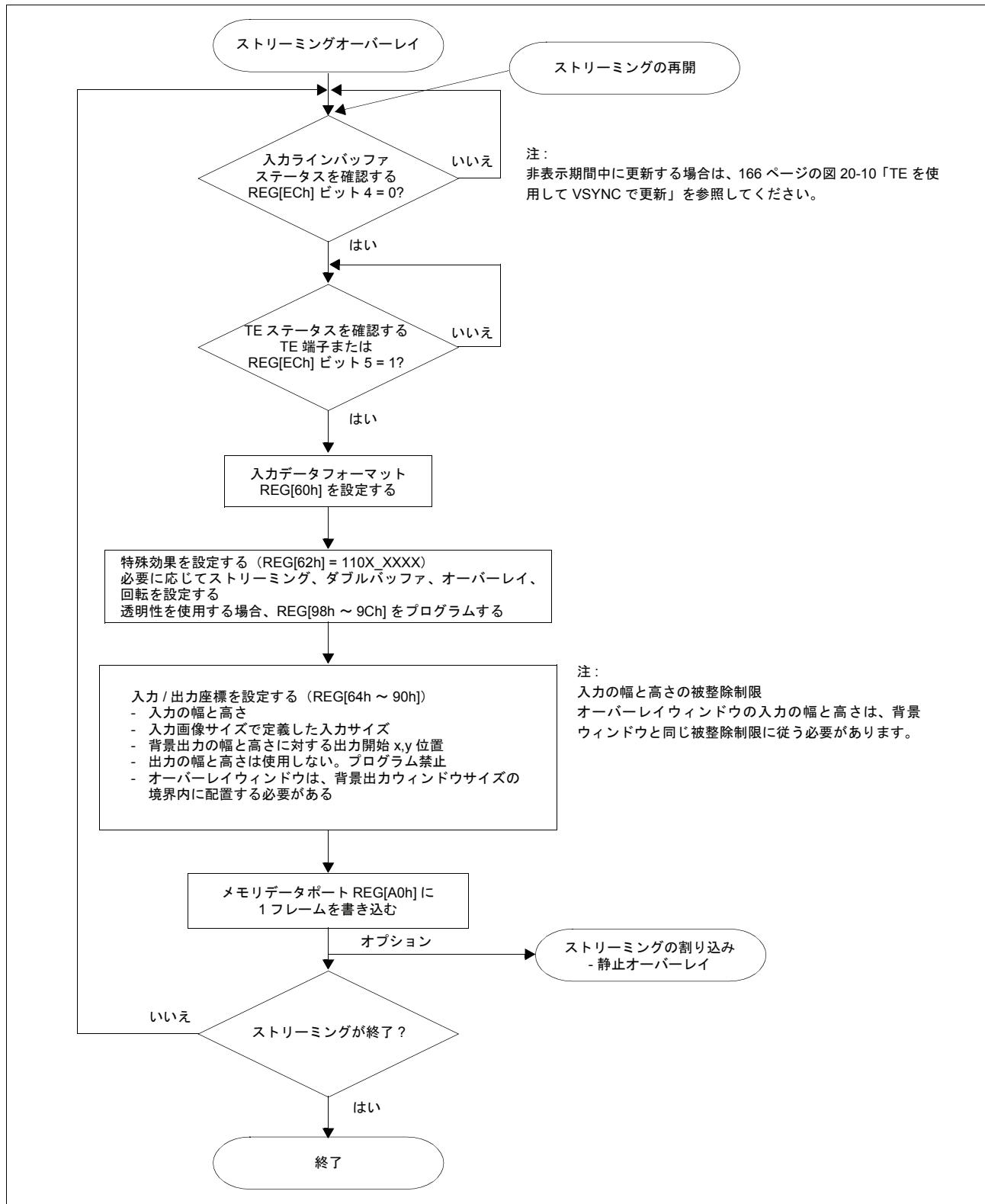

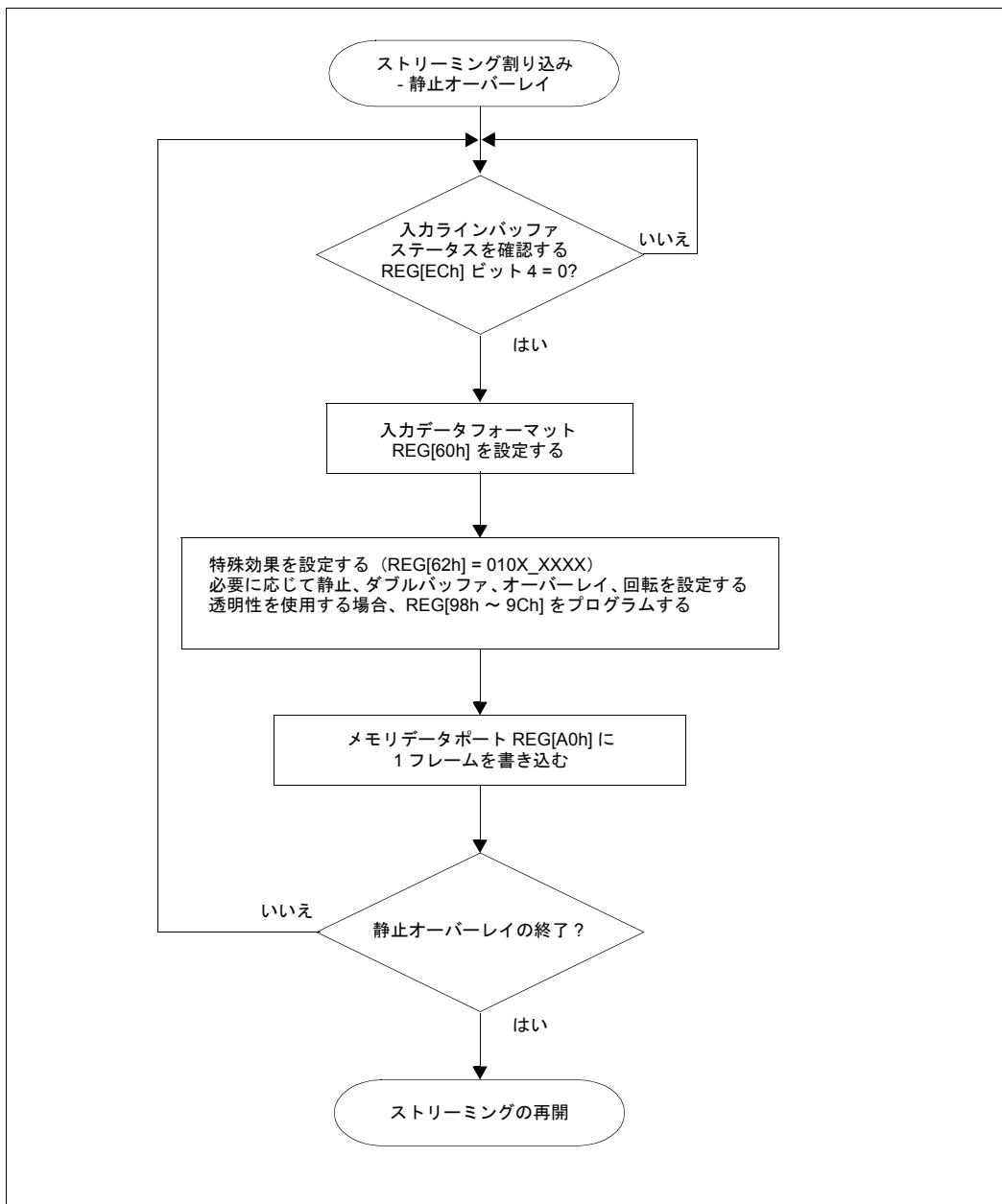

| 20.3.3 ストリーミング背景 . . . . .                        | 162        |

| 20.3.4 背景とストリーミングオーバーレイ . . . . .                 | 163        |

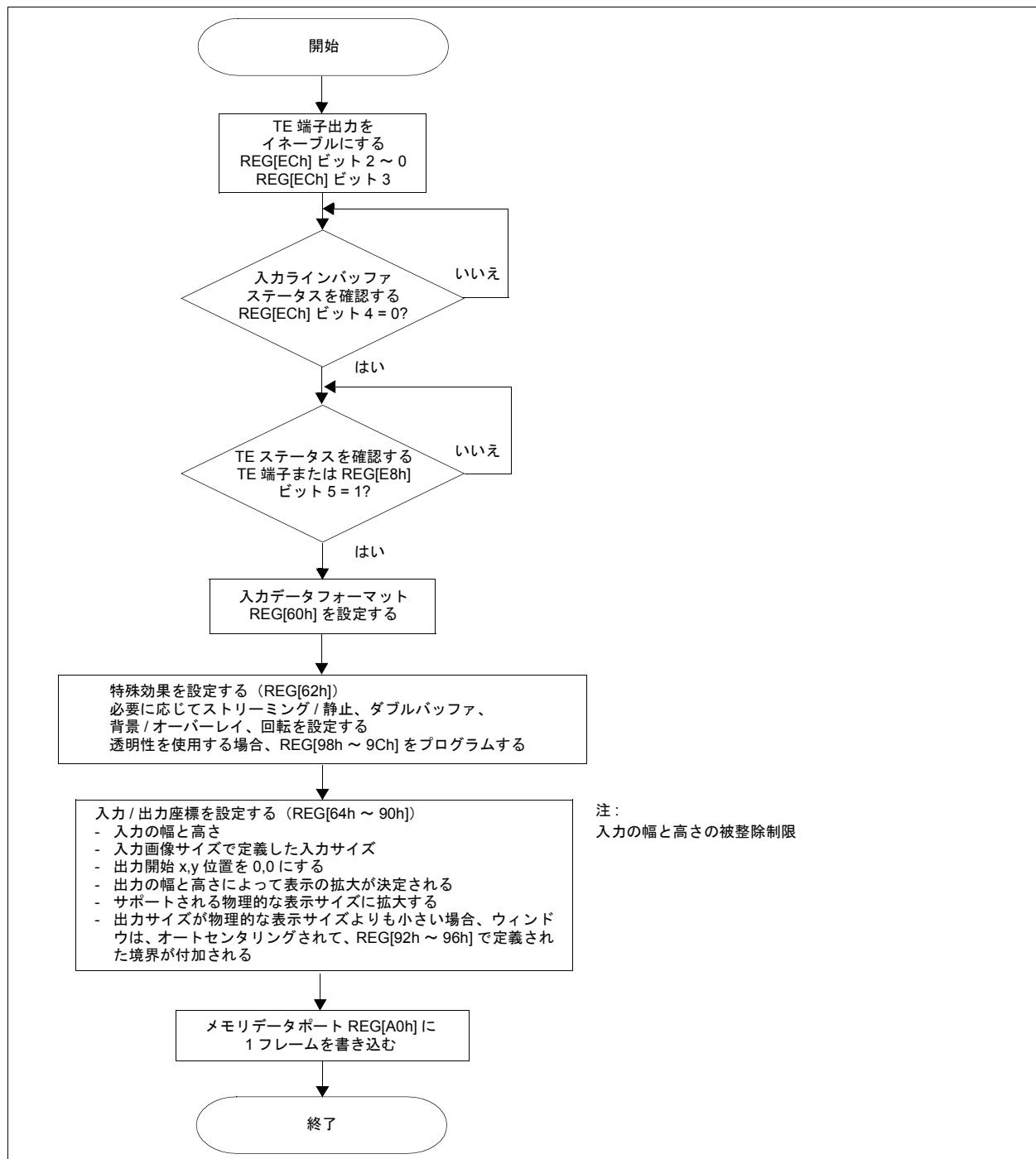

| 20.3.5 TE を使用して VSYNC で更新 . . . . .               | 166        |

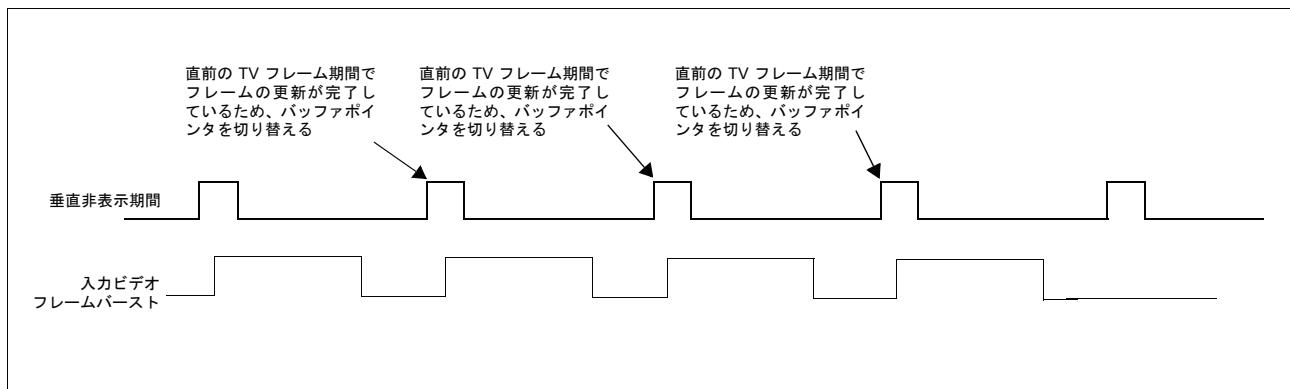

| 20.4 例: TV ウィンドウのダブルバッファ処理のイネーブル . . . . .        | 167        |

| <b>21. ダブルバッファの説明 . . . . .</b>                   | <b>169</b> |

| 21.1 ダブルバッファの制限事項 . . . . .                       | 171        |

| <b>22. TV フィルタ動作 . . . . .</b>                    | <b>172</b> |

| 22.1 ルミナンス (Y) とカラー (UV) のカスタムフィルタ係数の生成 . . . . . | 172        |

| 22.1.1 フィルタパラメータ . . . . .                        | 173        |

| <b>23. パワーセーブモード . . . . .</b>                    | <b>176</b> |

| 23.1 スリープモード . . . . .                            | 176        |

| 23.2 スタンバイモード . . . . .                           | 178        |

| <b>24. 外付け部品 . . . . .</b>                        | <b>180</b> |

| 24.1 DAC の外付け部品 . . . . .                         | 180        |

| 24.2 水晶発振器回路 . . . . .                            | 182        |

| <b>25. アナログ電源の検討事項 . . . . .</b>                  | <b>183</b> |

| 25.1 アナログ電源の配置のガイドライン . . . . .                   | 183        |

| <b>26. メカニカルデータ . . . . .</b>                     | <b>185</b> |

| <b>27. 参考資料 . . . . .</b>                         | <b>190</b> |

| <b>改訂履歴表 . . . . .</b>                            | <b>191</b> |

## 1. はじめに

### 1.1 適用範囲

本書は、LCD コントローラ S1D13746 のテクニカルマニュアルです。本書には、タイミング図、AC および DC 特性、レジスタの説明および電力管理の説明などが記載されています。

本書は、システム設計者とソフトウェア開発者を対象としています。

英語版の S1D13746 TV Out Mobile Graphics Engine Hardware Functional Specification が正規の資料であり、本書は正規英語版テクニカルマニュアルの補助的資料として、お客様のご理解を深めるために和訳したものです。製品のご検討および採用に当たりましては、必ず正規英語版の最新資料をご確認ください。

なお、本書および正規英語版は適宜改訂されています。最新版は、

[http://www.epson.jp/device/semicon/product/lcd\\_controllers/index.htm](http://www.epson.jp/device/semicon/product/lcd_controllers/index.htm)

<http://vdc.epson.com/>

からダウンロードできます。

### 1.2 略語と頭字語

本書では、以下の略語と頭字語を使用しています。

他の表示 (b は 2 進数、h は 16 進数) がない限り、数字はすべて 10 進数です。

$k = 2^{10} = 1024$  (メモリに関して使用するとき)

b = ビット

B = バイト

bpp = ビット / ピクセル

msb = 最上位ビット

lsb = 最下位ビット

IO = 入力 / 出力

LUT = ルックアップテーブル

NC = 未接続

YYC = YUV/YUV コンバータ

YRC = YUV/RGB コンバータ

RYC = RGB/YUV コンバータ

VDP = 垂直表示期間

VNDP = 垂直非表示期間

DDS = デジタルダイレクトシンセサイズ

POUT = PLL 出力

## 1.3 S1D13746 TV 出力 Mobile Graphics Engine ファミリ

S1D13746 TV 出力 Mobile Graphics Engine ファミリには現在、S1D13746B00 と S1D13746B01 があります。以下の表には、これらのデバイスの違いを記載しています。

表 I-1: S1D13746B0x の比較

| デバイス        | 機能の違い                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1D13746B00 | 基本設計                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

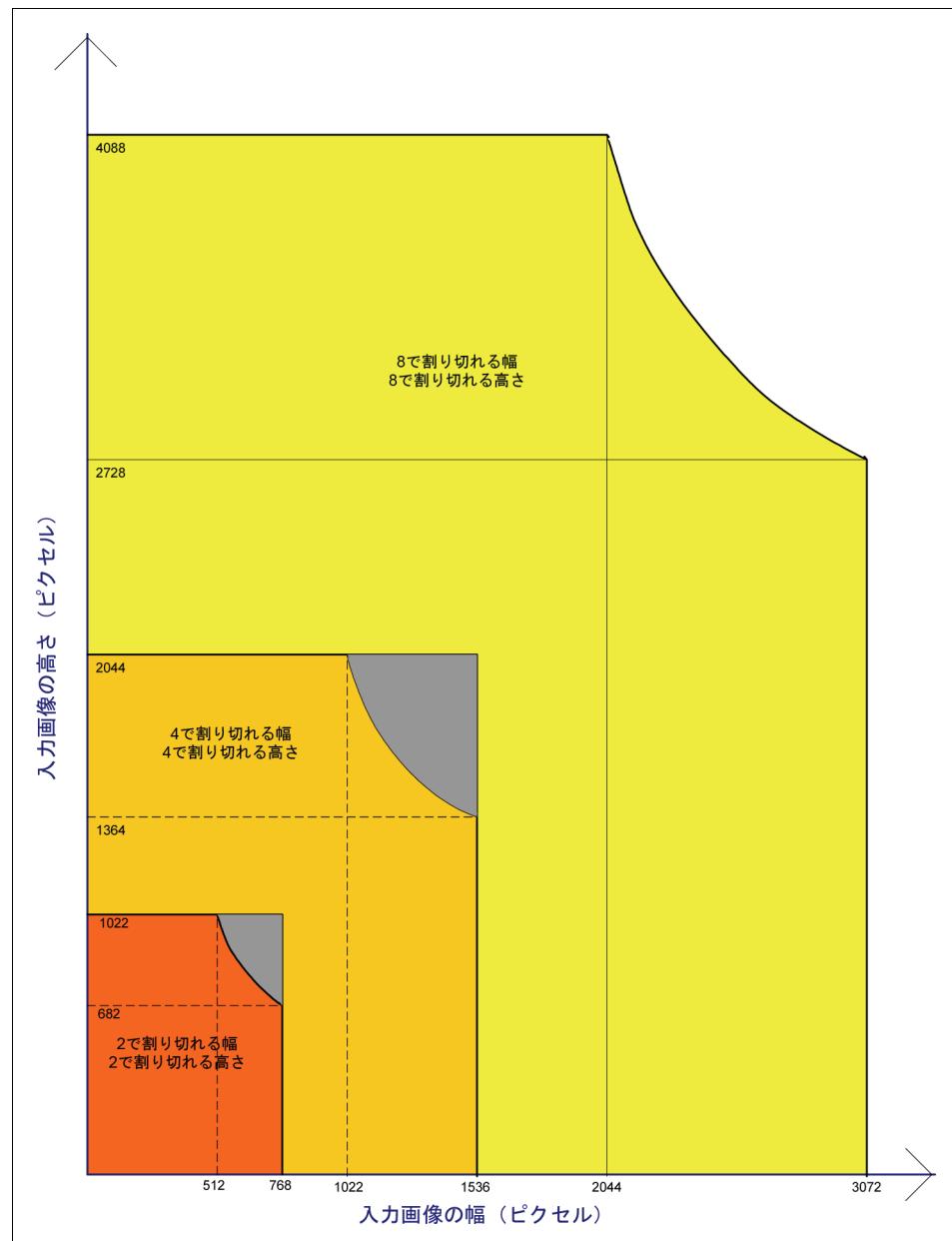

| S1D13746B01 | <p>S1D13746B00 のすべての機能に以下の機能が加わります。</p> <ul style="list-style-type: none"><li>GPIO 割り込みと GPIO レジスタは非同期であり、スリープモードで完全に機能します。</li><li>TV 出力のクロミナンスとルミナンスのフィルタを 11-TAP から 15-TAP に改良し、コンポジット出力を強化しています。</li><li>NTSC コンポジットモード用にドットクロールの削除回路を追加しています。</li><li>より鮮明な出力画像を得るために入出力スケーラを強化しています。</li><li>最大 3072 x 4092 の画像サイズを入力できるようにするために入力プレスケーラ(デシメーションスケーラ)を追加しています。</li><li>18MHz ~ 27MHz の幅広い周波数範囲で動作するように TV ブロックを変更しています。また CLKI/OSCI と 2 で除算した PLL 出力の間で TV ブロックを選択できるようにするためにクロックソースを変更しています。これにより、1MHz ~ 54MHz の範囲で CLKI/OSCI を実行することができます。</li><li>スクエアピクセルを表示する出力ウィンドウ幅を自動縮小するスクエアピクセル補正イネーブルビットを追加しています。</li><li>TE (ティアリング効果) 信号に 2 つの端子機能を追加しています。</li><li>IO セルを Fail safe タイプに変更しています。</li><li>PWRSVE 入力のプルダウン抵抗を取り除いています。</li></ul> |

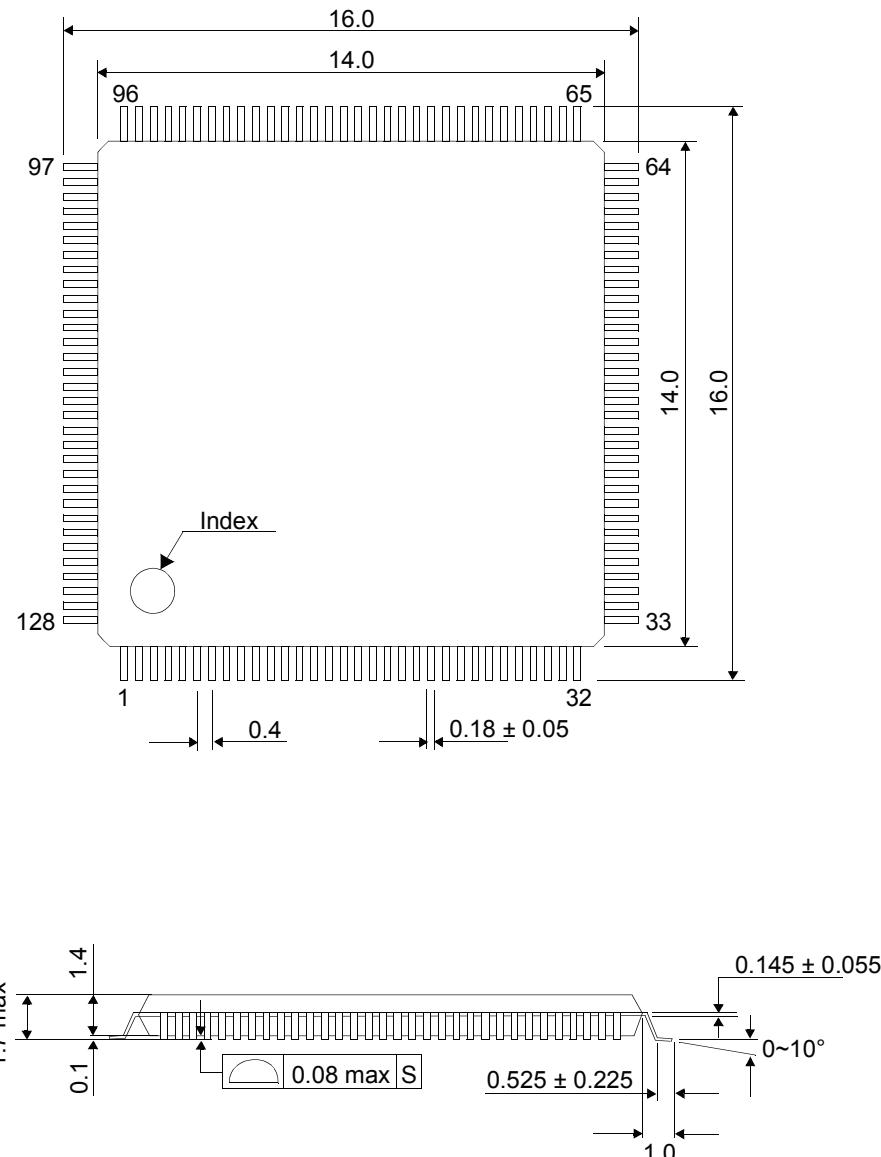

| S1D13746F01 | S1D13746B01 のすべての機能 (QFP15 128 端子パッケージ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## 2. 動作概要

S1D13746 は、複数のウィンドウと方向を表示できるようにするダイレクト TV 出力機能を備えた Mobile Graphics Engine です。

S1D13746 には、312KB のディスプレイバッファが含まれています。メモリ空間を上回る入力解像度は、メモリ空間に収まるように自動的に縮小されます。最終的な出力表示は、PAL や NTSC で定義されている標準の TV 解像度に合わせて拡大したりボーダー処理をすることができます。

ビデオのストリーミング中に画像が途切れないように TV 出力をダブルバッファ処理することができます。また TV 出力はフレームレートコンバータの機能を果たすこともできるので、PAL や NTSC の出力タイミングを維持しながら遅い入力ビデオストリーミングが可能となります。

入力データは、Intel 80 プロトコルを使用してホストプロセッサもしくは、標準の TFT ディスプレイ出力（パラレル RGB インタフェース）から得ることができます。S1D13746 は、標準の TFT ディスプレイ出力に直接接続できます。この場合、レジスタはシリアルインターフェースを使用してプログラミングされ、S1D13746 は、TV での表示に合わせて TFT 出力データを適切に変換します。

すべての画像データは、Input/Output Window Size/Position レジスタを使用し、ディスプレイメモリデータポートを使用してアクセスされます。その後のウィンドウは、destructive overlay であると見なされます。各ウィンドウは、独立した回転と位置の特性を保持することができます。

S1D13746 は、Intel 80 CPU インタフェースからの DMA バーストアクセスを受け入れるように設計されています。ディスプレイバッファへのすべてのアクセスは、ディスプレイメモリデータポートを経由して処理されます。

### 2.1 TV のサポート

S1D13746 は、解像度と出力フォーマットに関して、PAL と NTSC の両方の出力規格に準拠しています。またコンポジット出力と S ビデオ出力の両方のフォーマットに対応しています。S1D13746 は、RGB、YUV 4:2:2、および YUV 4:2:0 の複数の入力フォーマットに対応しています。すべてのデータは変換されて YUV 4:2:0 として格納されます。

#### 2.1.1 ウィンドウデータの書き込み

ウィンドウデータは、Intel 80 インタフェースを経由してホストプロセッサによって書き込まれるか、またはパラレル RGB インタフェースによって入力されます。Intel 80 プロセッサの場合、ウィンドウのサイズは不同ですが、パラレル RGB インタフェースの場合、水平と垂直の入力タイミングによってウィンドウのサイズは自動的に決まります。

## 2. 動作概要

---

### 2.1.2 縮小処理機能

- ホスト入力データは、利用可能なメモリに収まるように縮小することができます。

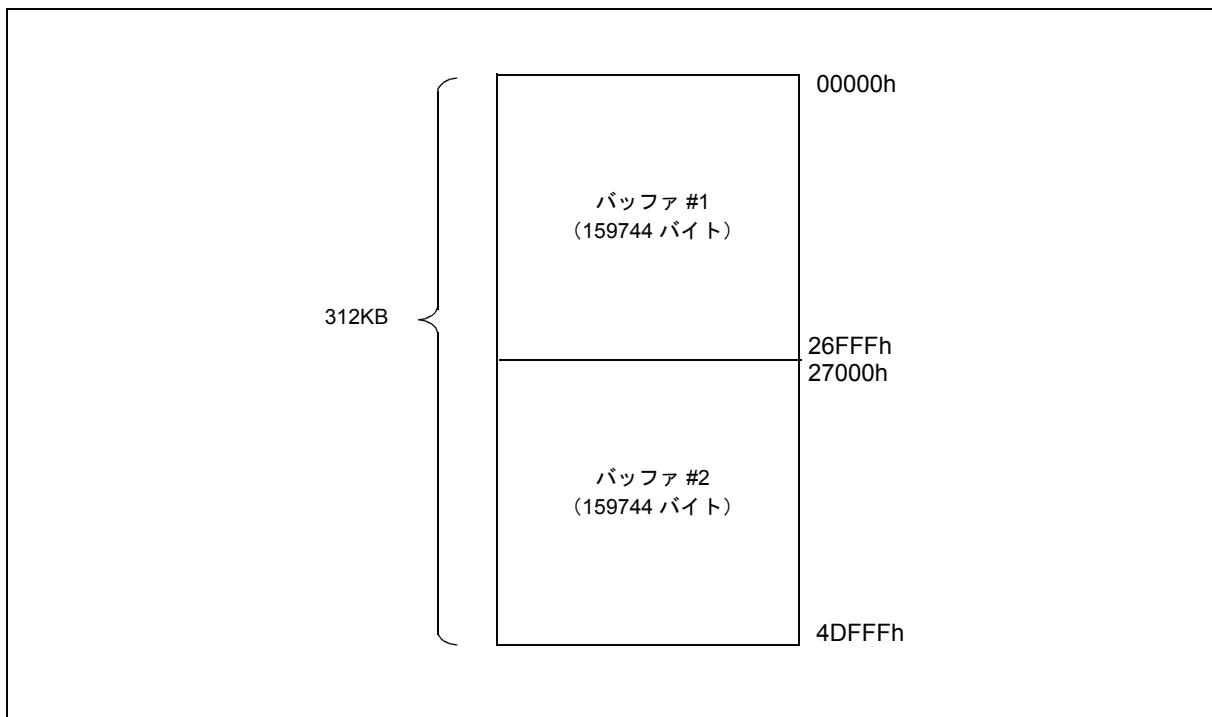

- 入力スケーラ論理回路には、入力サイズが必要であり、パラレルRGBインターフェースを使用している場合はホストによってプログラミングされるか自動的に計算されます。利用可能なメモリは、ディスプレイバッファ全体 (312KB) か、あるいはダブルバッファ機能をイネーブルにしている場合は 156KB になります。メモリに対して必要となる入力サイズの縮小率は、自動的に計算されます。

- メモリ出力データ (TV に表示するためのデータ) は、TV での表示に合わせて拡大することができます (ディスプレイ出力スケーラ)。

- 得られた拡大の解像度が、PAL や NTSC 規格で定義された最大解像度に等しくない場合、自動的にボーダーが生成され、得られた画像はそのボーダー内でセンタリングされます。

- TV に複数の画像を表示する場合、最初の背景画像によって、メモリに対する縮小率とディスプレイに対する拡大率の両方が決まります。この縮小率と拡大率が他のすべてのウィンドウで使用されます。

- TV に複数の画像を表示する場合、その後に続くすべてのウィンドウは、(オートセンタリングされた) 背景画像の左上を位置の基準としています。

### 2.1.3 ウィンドウの回転

SwipeView™ によって、ホストが書き込んだ画像ウィンドウを反時計方向に 90°、180°、および 270° にハードウェア回転させることができます。すべてのウィンドウは、メモリに書き込むときに独立した回転を保持することができます。これらのモードをイネーブルにするときに、プログラミングを追加する必要はありません。

### 2.1.4 複数の TV ウィンドウ

複数の「ウィンドウ」を TV ディスプレイに `destructive` に書き込むことができます。複数のウィンドウが必要な場合、最初に書き込んだウィンドウは「背景」と見なされます。その後のウィンドウはすべて、メモリの背景画像の上に「重ねて」格納されるので、`destructive` であると見なされます。

#### 透明性を備えた複数の TV ウィンドウ

`destructive` なウィンドウはいずれも、そのウィンドウに透明色を関連付けることができます。透明でないピクセルだけが、実際にメモリに書き込まれます。最初にウィンドウは、メモリ内に収まるように (必要に応じて) 縮小されます。スケーラの後、ピクセルは透明色用にプログラミングされた 24 ビットの YUV 値と比較されます。

透明機能を使用するモードには、次の 3 つのモードがあります。

1. 通常モード : 縮小して得られたピクセルが透明色に等しい場合、そのピクセルはメモリには書き込まれません。このモードでは、不透明色の周囲にカラーアーチファクト (画質劣化) が生じます。

2. 白黒モード：このモードでは、透明色は黒または白に限定され、可視色は反対色になります。このモードでは、すべてのピクセルが強制的に透明または不透明のいずれかにされるため、いずれのカラー・アーチファクトも最小限に抑えられます。

3. テキストモード：このモードでは、Transparency Color Register から算出される透明色の輝度範囲によってピクセルが透明か不透明かが決まります。このモードは白黒モードと同様の効果がありますが、より多くのカラー・アーチファクトが取り除かれます。

### 2.1.5 単一の TV ウィンドウ

単一のウィンドウだけが必要な場合、S1D13746 は、メモリ内に収まるように入力データを縮小したり、TV での表示に合わせて拡大したりできます。また最終出力がフルスクリーンでない場合にはオートセンタリングやオートボーダーを行うことができます。

### 2.1.6 TV ウィンドウのボーダーをサポート

得られた画像のサイズ（拡大後）が TV 出力解像度（PAL または NTSC）に等しくない場合、S1D13746 は、ウィンドウの周りにプログラム可能なボーダーカラーを生成します。このウィンドウは、ボーダー内でセンタリングされます。

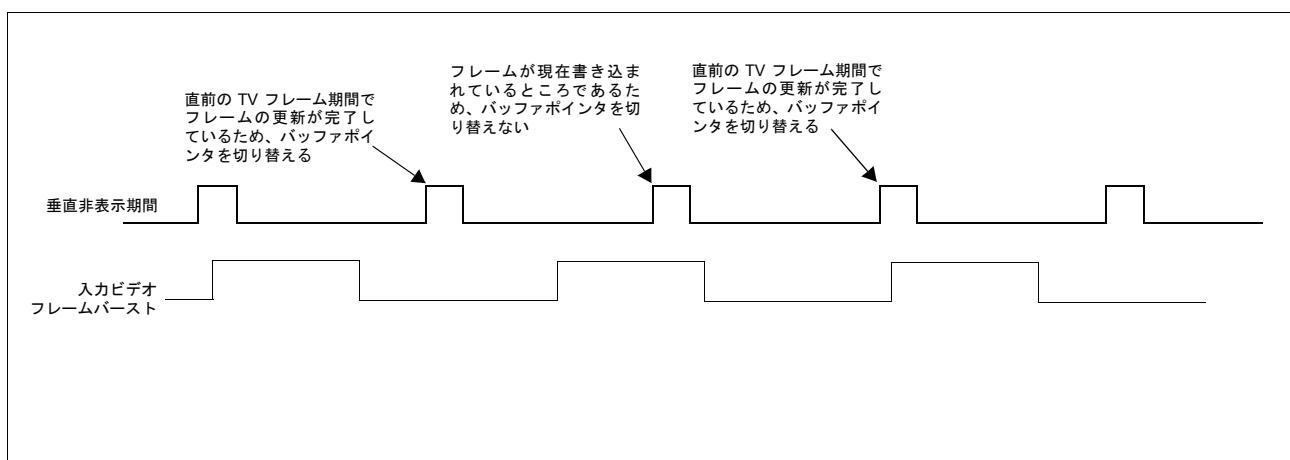

### 2.1.7 TV ウィンドウのダブルバッファ処理

単一の TV ウィンドウは、ストリーミング入力のティアリングを防止するためにダブルバッファ処理することができます。このウィンドウは、画面解像度の全体を使用することもできれば、一部だけを使用することもできます。

ストリーミングビデオのウィンドウを構成するとき、S1D13746 は、ウィンドウの座標に基づいて入力データを自動的にダブルバッファ処理します。このウィンドウが画面の一部だけの場合、「背景」の静止部分とバッファ処理されたウィンドウデータの 1 つにバッファ #1 が使用されます。バッファ #2 は、ダブルバッファ処理されたもう 1 つのウィンドウデータのみに使用され、背景の静止データはバッファ #2 には含まれません。

TV表示パイプは書き込みを完了したバッファのデータだけを使用しているので、画面上の静止情報を更新するためにストリーミングウィンドウを中断することが許されています。このため、次のバッファが準備できるまで、単一のバッファが繰り返して表示される場合があります。表示パイプがバッファ #2 を使用しているときにダブルバッファがディセーブルになると、背景情報が含まれたバッファはバッファ #1 だけであるため、表示パイプは元どおりバッファ #1 を使用します。ダブルバッファ機能は、PAL および NTSC 規格で定義された最大解像度に対応しています。

ダブルバッファ処理をイネーブルにすると、メモリは 156KB の 2 つのバンクに分割され、これまで利用可能であったメモリの半分以下に画像が収まるように、入力画像からメモリへの縮小率が大きくなります。

## 2. 動作概要

### ホスト入力データ

(メモリに書き込み)

$360 \times 288 = \sim 152\text{KB}$ 。YUV 4:2:0 として格納されます。

この場合、メモリ内に収めるための入力データの縮小はありません。

ディスプレイ出力スケーラ

高さ = 720

幅 = 576

### TV 表示

720 x 576

### ホスト入力データ

(メモリに書き込み)

$320 \times 240 = \sim 112.5\text{KB}$ 。YUV 4:2:0 として格納されます。

ディスプレイ出力スケーラ

高さ = 640

幅 = 480

### TV 表示

720 x 576

オートボーダー

### ホスト入力データ

(メモリに書き込み、シングルレバッファ)

720 x 576 = 607.5KB@4:2:0

514 x 412 = ~310KB@4:2:0

312KB 以内に

収まるように縮小

## 2. 動作概要

### ホスト入力データ

(メモリに書き込み)

720 x 576

312KB 以内に

収まるように縮小

514 x 412 = ~312KB@4:2:0

### ホスト入力データ (destructive window)

352 x 416

背景画像内に

収まるように縮小

### メモリ出力データ

拡大およびボーダー処理

### ホスト入力データ

(メモリに書き込み)

312KB 以内に

収まるように縮小

### ホスト入力データ

(透明性をイネーブル = 黒)

My Vacation

拡大およびボーダー処理

720 x 576

### 3. 特長

---

## 3. 特長

### 3.1 内蔵ディスプレイバッファ

- 312KB の SRAM ディスプレイバッファを内蔵

### 3.2 CPU インタフェース

- 8/16 ビットの Intel 80 インタフェース (表示またはレジスタデータに使用)

- パラレル RGB インタフェース (表示データ専用)

- 3 線シリアルインターフェース (レジスタデータ専用)

- チップセレクトを使用して S1D13746B01 を選択します。インアクティブのとき、入力データ / コマンドは無視されます。

### 3.3 入力データフォーマット

- RGB: 8:8:8、6:6:6、5:6:5、3:3:2

- すべての RGB 入力データは、変換されて YUV 4:2:0 として格納されます。

- YUV: 4:2:2、4:2:0

- すべての YUV 入力データは、変換されて YUV 4:2:0 として格納されます。

### 3.4 TV 表示のサポート

- PAL と NTSC の両方の TV 規格のためのコンポジット出力

- PAL と NTSC の両方の TV 規格のための S ビデオ出力

- プログラム可能な 15 タップのクロミナンス / ルミナンスフィルタ

- ワイドスクリーン信号のサポート (ITU-R BT.1119-2、ETSI EN 300 294、および IEC 61880 に準拠)

- クローズドキャプションのサポート (CEA-608-B)

### 3.5 TV 表示の特長

- 以下に示すように入力データを処理することができます。

- 利用可能なメモリに収まるように縮小することができます。

- 回転することができます。

- 透明色を関連付けることができます。

- TV での表示に合わせてメモリ出力データを拡大することができます。

- TV 画像を出力解像度に合わせて自動的に「ボーダー処理」します（拡大しない場合）。

- プログラム可能な YUV ボーダーカラー

- オートセンタリング

- 独立したアスペクト比をディスプレイ出力の高さ/幅の倍率に利用することができます。

- スクエアピクセル補正出力幅の調整

### 3.6 画像強化エンジン

- 3 x 3 ピクセルフィルタ

- ユーザー定義係数

- 各 YUV コンポーネントの個別の制御

- 表示効果には以下が含まれます。

- スムーズ、シャープ、ぼかし、ディテール、エッジ強調、エンボス、輪郭、フリッカーフィルタ、セピア

### 3.7 クロックソース

- プログラム可能な内部 PLL

- 単一の発振器入力 : CLK1 (CNF2 により決定)

- または

- 2 端子水晶のサポート : OSCI、OSCO (CNF2 により決定)

#### 注

適切な PAL と NTSC の出力タイミングを取得するためには、内部の TV DDS ロジックに 18MHz ~ 27MHz のクロックが必要となります。27MHz 以外のクロックソースについては、PLL を 54MHz 用にプログラムする必要があります。

- CLK1 を CLKOUT として利用可能 (個別の CLKOUTEN 端子を出力に関連付け)

- ディセーブルのとき出力状態 = 0

### 3. 特長

---

#### 3.8 その他

- ハードウェア / ソフトウェアのパワーセーブモード

- パワーセーブモードをイネーブル / ディセーブルにする入力端子

- 汎用の入力 / 出力端子が利用可能 (GPIO[7:0])

- 選択可能な GPIO 入力に INT 端子を関連付け

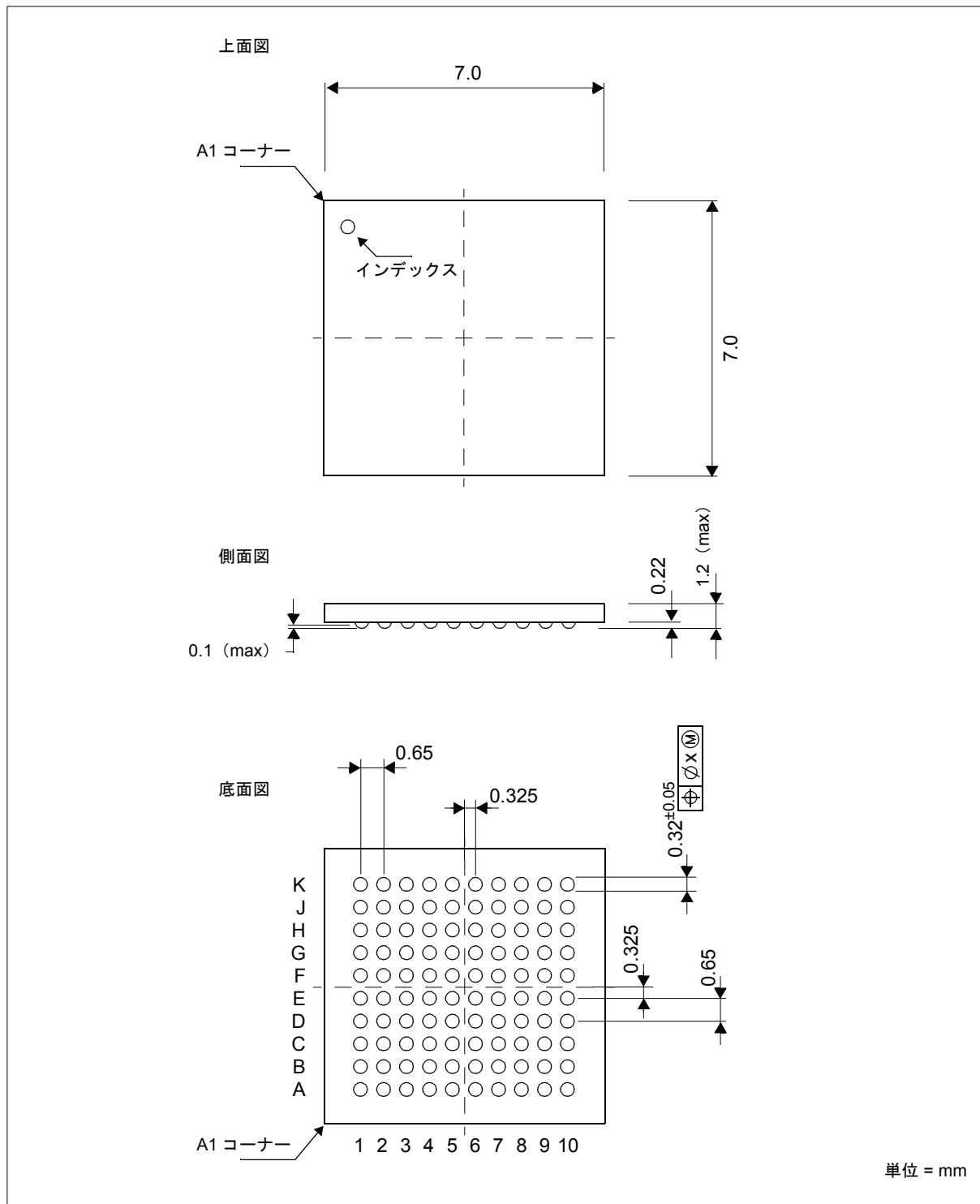

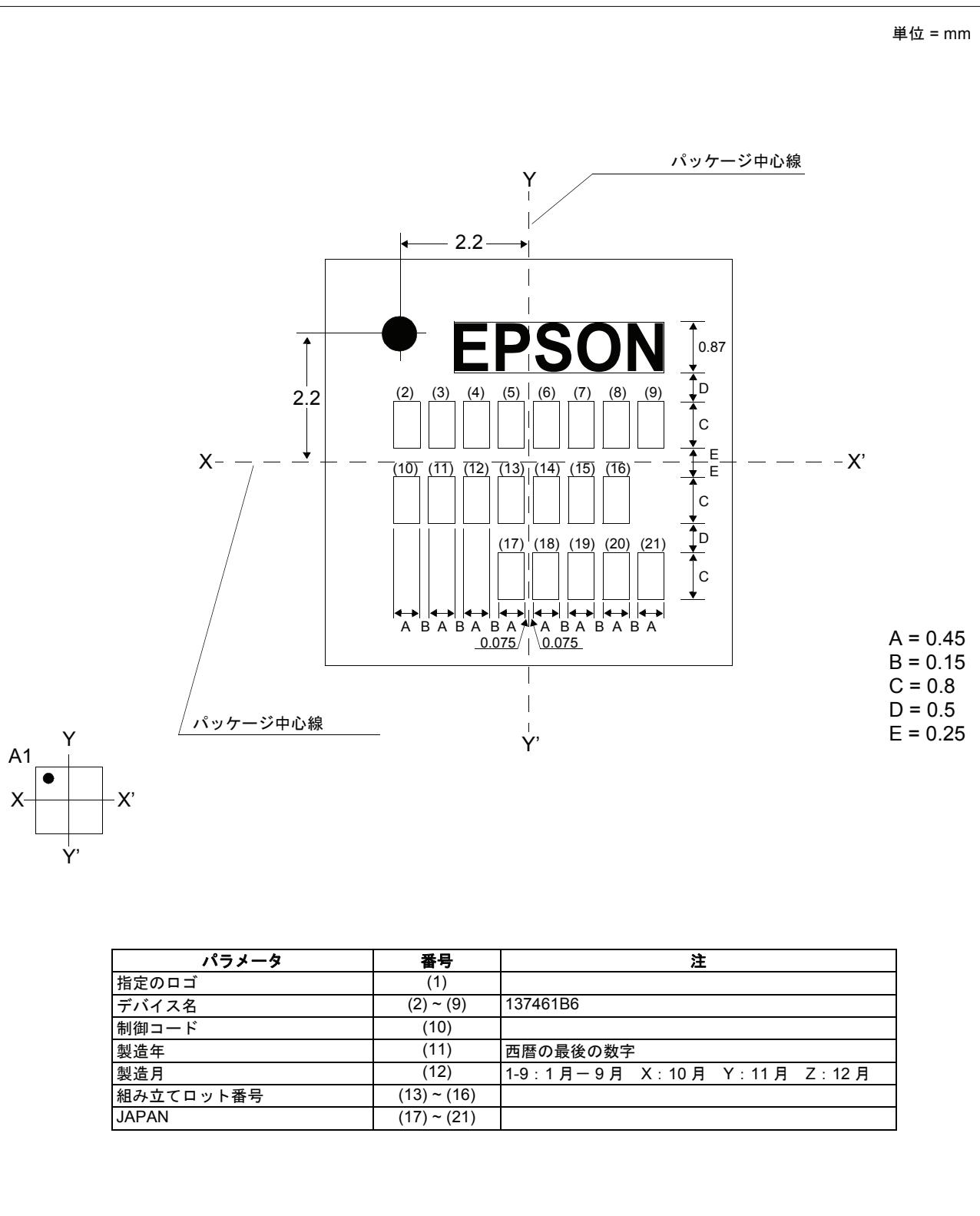

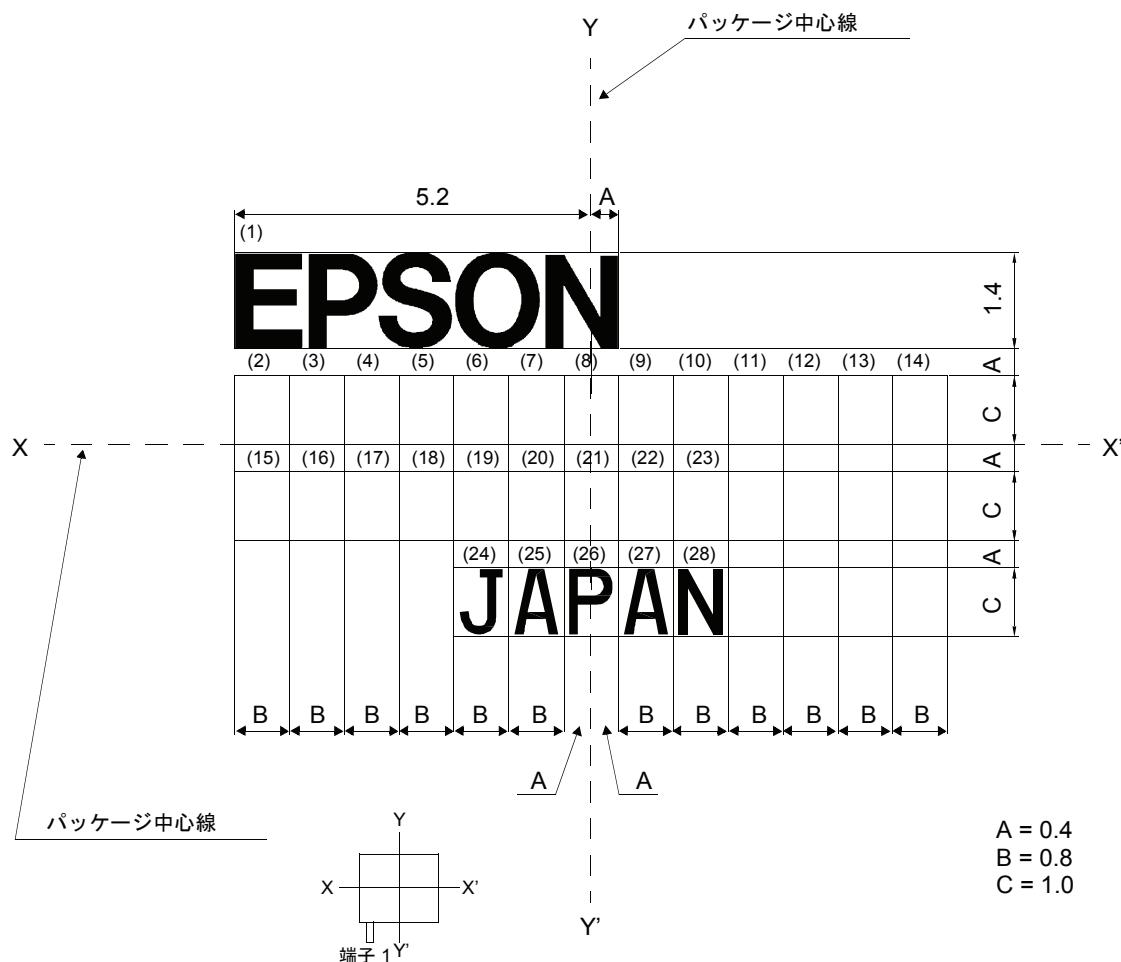

- パッケージ: **S1D13746B01B** PFBGA 100 Pin (7mm x 7mm)

**S1D13746F01A** QFP15 128 Pin

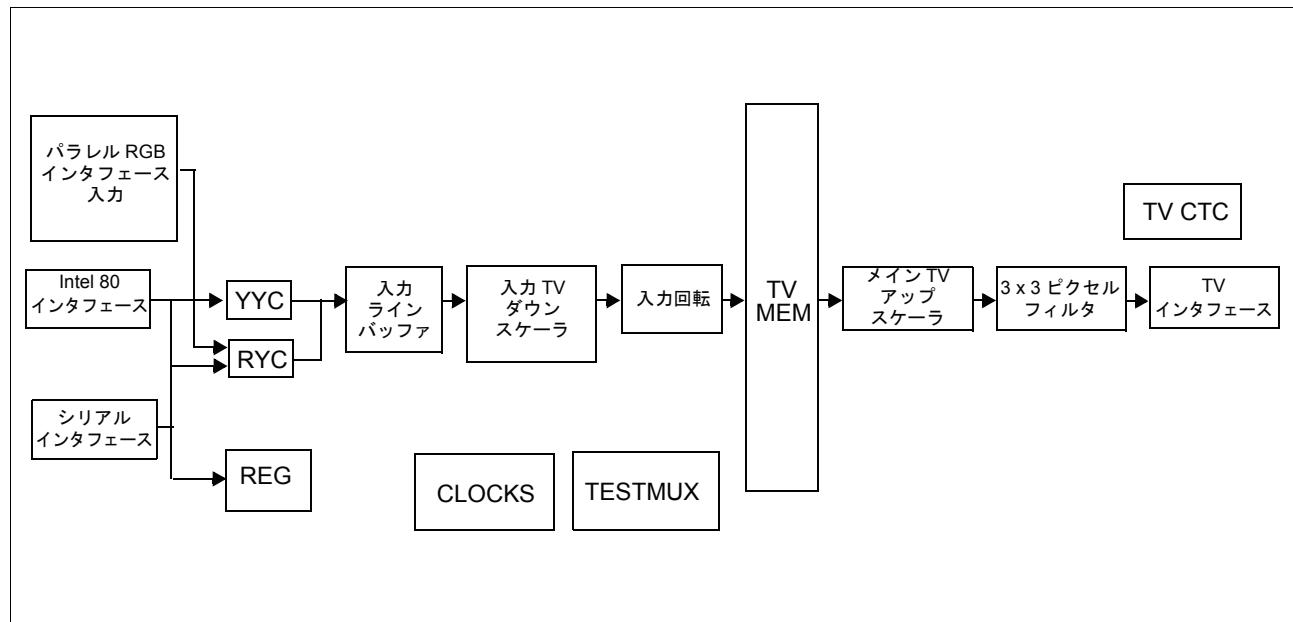

#### 4. 機能ブロック図

図 4-1: *SID13746* の機能ブロック図

## 5. 端子配置図

### 5. 端子配置図

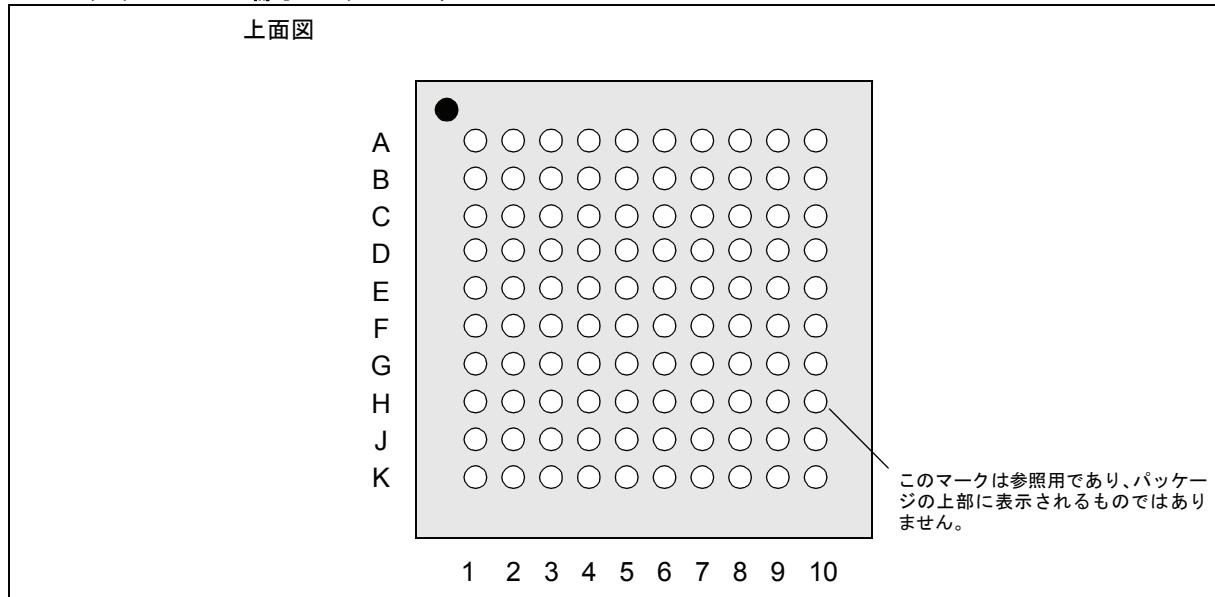

#### 5.1 パッケージの端子マッピング

図 5-1: SID13746 の端子配置図 (PFBGA-100) - Top view

表 5-1: SID13746 の端子配置図 (PFBGA-100) - Top view

| A | NC     | COREVDD | SCLK   | SO     | SI      | VSS      | PCLK   | DE     | VSS      | NC      |

|---|--------|---------|--------|--------|---------|----------|--------|--------|----------|---------|

| B | PWRSVE | TESTEN  | GPIO7  | CS#    | GPIO1   | GPIO0    | TE     | D/C#   | COREVDD  | MD15    |

| C | SCANEN | TEST0   | GPIO6  | GPIO5  | GPIO2   | GPIO_INT | GPIO4  | WE#    | VSS      | MD13    |

| D | DACVEE | DACVCC  | TEST2  | SIOVDD | GPIO3   | RESET#   | IOVDD  | MD11   | MD12     | MD9     |

| E | BOUT   | DACVCC  | DACVEE | TEST1  | CNF0    | RD#      | MD10   | MD8    | MD7      | MD6     |

| F | DACVEE | VADJ    | DACVCC | VSS    | CNF1    | IOVDD    | MD14   | MD5    | MD4      | MD3     |

| G | DACVEE | VREF    | DACVEE | VSS    | CNF3    | CNF2     | MD0    | MD1    | MD2      | COREVDD |

| H | AOUT   | DACVCC  | DACVCC | VSS    | VSS     | IOVDD    | VSS    | IOVDD  | CLKOUTEN | CLKOUT  |

| J | DACVEE | DACVEE  | DACVCC | IOVDD  | COREVDD | OSCVSS   | OSCVDD | VCP    | VSS      | CLKI    |

| k | NC     | NC      | DACVEE | VSS    | VSS     | OSCI     | OSCO   | PLLVDD | PLLVSS   | NC      |

#### 注

NC と表示された端子は使用しません。未接続のままにしておく必要があります。

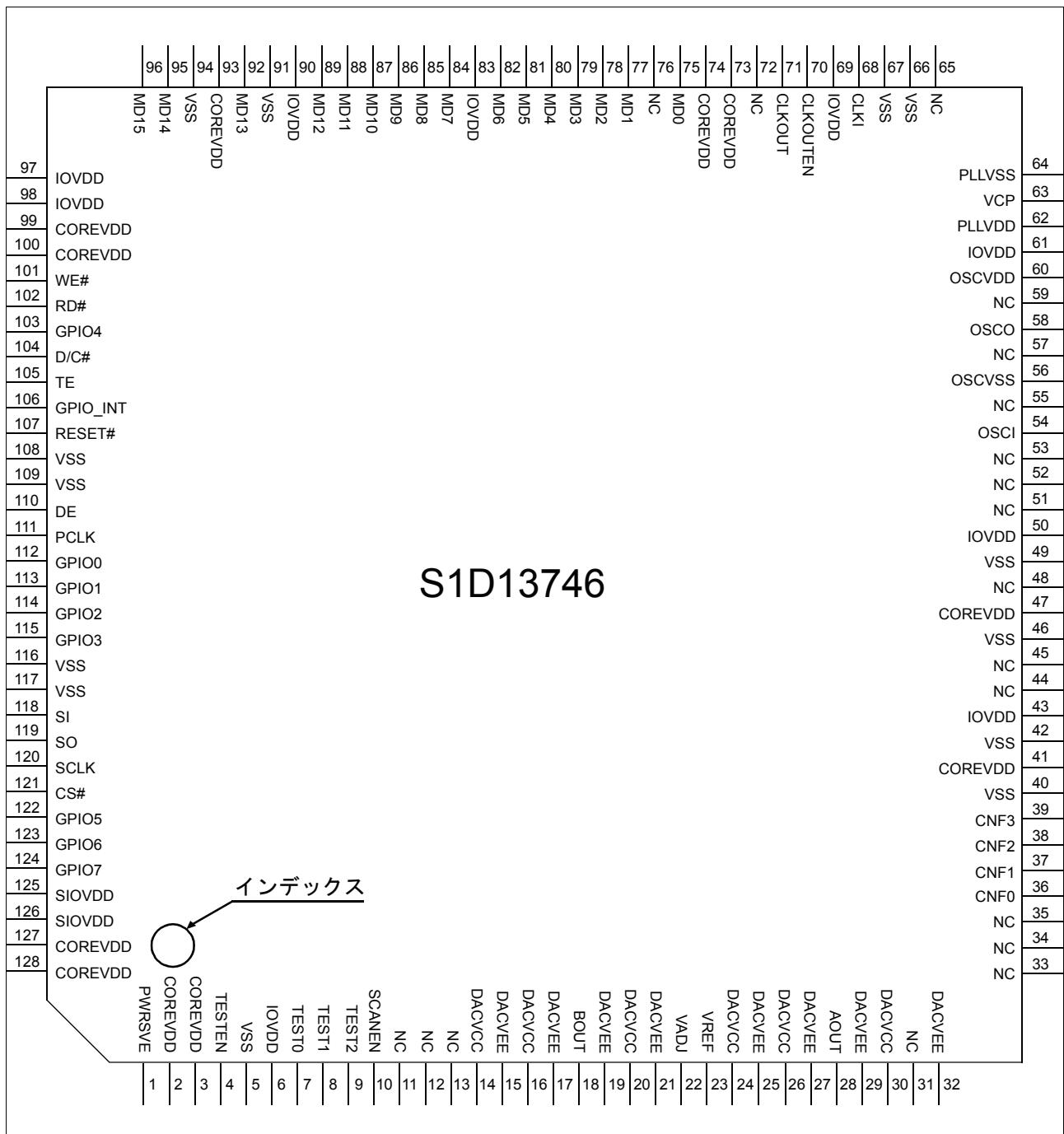

図5-2: SID13746 の端子配置図 (QFP15-128) - Top view

注

NC と表示された端子は使用しません。未接続のままにしておく必要があります。

## 5. 端子配置図

### 5.2 端子説明

略語の意味：

端子のタイプ

|    |               |

|----|---------------|

| I  | = 入力          |

| O  | = 出力          |

| IO | = 双方向（入出力）    |

| P  | = 電源端子        |

| AP | = アナログ電源端子    |

| G  | = グラウンド端子     |

| AG | = アナロググラウンド端子 |

RESET#/パワーセーブステータス

|   |                    |

|---|--------------------|

| H | = 高レベル出力           |

| L | = 低レベル出力           |

| Z | = ハイインピーダンス (Hi-Z) |

表 5-2: セルの説明

| セル   | 説明                                          |

|------|---------------------------------------------|

| HI   | H 系（注 1）LVCMOS（注 3）入力バッファ（Fail safe 付き）     |

| HIS  | H 系 LVCMOS シュミット入力バッファ（Fail safe 付き）        |

| HID  | H 系 LVCMOS 入力バッファ（プルダウン抵抗および Fail safe 付き）  |

| HO   | H 系 LVCMOS 出力バッファ（Fail safe 付き）             |

| HB   | H 系 LVCMOS 双方向バッファ（Fail safe 付き）            |

| HBD  | H 系 LVCMOS 双方向バッファ（プルダウン抵抗および Fail safe 付き） |

| LIDS | L 系（注 2）LVCMOS シュミット入力バッファ（プルダウン抵抗付き）       |

| LITR | L 系透明性入力バッファ                                |

| LOTR | L 系透明性出力バッファ                                |

| AIO  | アナログ                                        |

注

1. H 系は IOVDD および PIOVDD です（25 ページの 7.「DC 特性」を参照してください）。

2. L 系は COREVDD です（25 ページの 7.「DC 特性」を参照してください）。

3. LVCMOS は低電圧 CMOS です（25 ページの 7.「DC 特性」を参照してください）。

## 5.2.1 Intel 80 ホストインターフェース

表 5-3: ホストインターフェースの端子説明

| 端子名      | タイプ | PFBGA<br>端子 #                                                                      | QFP<br>端子 #                                                                   | セル | IO 電圧  | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                                                                                                                                                                                         |

|----------|-----|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----|--------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD[15:0] | IO  | B10, F7,<br>C10, D9,<br>D8, E7, D10,<br>E8, E9, E10,<br>F8, F9, F10,<br>G9, G8, G7 | 96, 95, 92,<br>89, 88, 87,<br>86, 85, 84,<br>82, 81, 80,<br>79, 78, 77,<br>75 | HB | IOVDD  | Z             | Z                   | <p>この端子には複数の機能があります。</p> <ul style="list-style-type: none"> <li>Intel 80 インタフェースの場合、これらの端子はデータライン MD[15:0]になります。24 ページの 6.1 「Intel 80 データ端子」を参照してください。</li> <li>パラレル RGB インタフェースの場合、これらの端子は入力データビット VD[17:2]になります。24 ページの 6.2 「パラレル RGB データ端子」を参照してください。</li> </ul>        |

| WE#      | I   | C8                                                                                 | 101                                                                           | HI | IOVDD  | —             | —                   | <p>この端子には複数の機能があります。</p> <ul style="list-style-type: none"> <li>Intel 80 インタフェースの場合、この入力端子はライトイネーブル信号 (WE#)になります。</li> <li>パラレル RGB インタフェースの場合、この入力端子はデータビット 1 (VD1)になります。</li> </ul>                                                                                      |

| RD#      | I   | E6                                                                                 | 102                                                                           | HI | IOVDD  | —             | —                   | <p>この端子には複数の機能があります。</p> <ul style="list-style-type: none"> <li>Intel 80 インタフェースの場合、この入力端子はリードイネーブル信号になります。</li> <li>パラレル RGB インタフェースの場合、この入力端子はデータビット 0 (VD0)になります。</li> </ul>                                                                                            |

| CS#      | I   | B4                                                                                 | 121                                                                           | HI | SIOVDD | —             | —                   | この入力端子は、Intel 80 ホストインターフェースとシリアルインターフェースの両方のためのチップセレクト信号です。                                                                                                                                                                                                               |

| D/C#     | I   | B8                                                                                 | 104                                                                           | HI | IOVDD  | —             | —                   | <p>この端子には複数の機能があります。</p> <ul style="list-style-type: none"> <li>Intel 80 インタフェースの場合、この入力端子はアドレスとデータ (D/C#) のいずれかを選択します。</li> <li>パラレル RGB インタフェースの場合、この入力端子は水平同期 (HS) になります。</li> </ul>                                                                                    |

| TE       | IO  | B7                                                                                 | 105                                                                           | HB | IOVDD  | L             | L                   | <p>この端子には複数の機能があります。</p> <ul style="list-style-type: none"> <li>Intel 80 インタフェースの場合、この端子はティアリング効果になります。この端子はディスプレイの VSYNC ステータスを反映します。この端子を使用して、ホストから新しいデータを安全に書き込めるタイミングを示すことにより、画像の視覚的なティアリングを防ぐことができます。</li> <li>パラレル RGB インタフェースの場合、この入力端子は垂直同期 (VS) になります。</li> </ul> |

## 5. 端子配置図

表 5-3: ホストインターフェースの端子説明

| 端子名      | タイプ | PFBGA<br>端子 # | QFP<br>端子 # | セル  | IO 電圧 | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                                                                                              |

|----------|-----|---------------|-------------|-----|-------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK     | I   | A7            | 111         | HIS | IOVDD | —             | —                   | この入力端子は、パラレル RGB インタフェースの PCLK 入力です。<br>パラレル RGB インタフェースを使用しない場合 (CNF[1:0] = 01 または 11)、この端子は VSS に接続する必要があります。                                                                 |

| DE       | I   | A8            | 110         | HI  | IOVDD | —             | —                   | この入力端子は、パラレル RGB インタフェースの DE 入力です。<br>パラレル RGB インタフェースを使用しない場合 (CNF[1:0] = 01 または 11)、この端子は VSS に接続する必要があります。                                                                   |

| GPIO_INT | O   | C6            | 106         | HO  | IOVDD | L             | L                   | この端子は、GPIO 端子が入力として構成されているときに、その GPIO 端子に関連付けられる割り込み出力です。GPIO の割り込みが発生すると、この出力端子が HIGH に駆動されます。詳細については、113 ページの 11.3.9 「汎用 IO 端子レジスタ」にある RFG[F0h] ~ REG[FAh] のレジスタの説明を参照してください。 |

| RESET#   | I   | D6            | 107         | HIS | IOVDD | —             | —                   | このアクティブ LOW 入力は、すべての内部レジスタをデフォルト状態に設定し、すべての信号を強制的にインアクティブ状態にします。                                                                                                                |

### 5.2.2 シリアル周辺インターフェース (SPI)

表 5-4: SPI の端子説明

| 端子名  | タイプ | PFBGA<br>端子 # | QFP<br>端子 # | セル  | IO 電圧  | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                          |

|------|-----|---------------|-------------|-----|--------|---------------|---------------------|-------------------------------------------------------------------------------------------------------------|

| SO   | IO  | A4            | 119         | HB  | SIOVDD | Z             | Z                   | この端子はシリアル出力です。<br>シリアルインターフェースを使用しない場合 (CNF[1:0] = 01 または 11)、この端子は抵抗を通じて SIOVDD または VSS のいずれかに接続する必要があります。 |

| SI   | I   | A5            | 118         | HI  | SIOVDD | —             | —                   | この端子はシリアル入力です。<br>シリアルインターフェースを使用しない場合 (CNF[1:0] = 01 または 11)、この端子は VSS に接続する必要があります。                       |

| SCLK | I   | A3            | 120         | HIS | SIOVDD | —             | —                   | この端子はシリアルクロックです。<br>シリアルインターフェースを使用しない場合 (CNF[1:0] = 01 または 11)、この端子は VSS に接続する必要があります。                     |

## 5.2.3 TV インタフェース

## 注

未使用のとき、これらの端子は未接続のままにしておく必要があります。

表 5-5: TV インタフェースの端子説明

| 端子名           | タイプ | PFBGA<br>端子 # | QFP<br>端子 # | セル  | IO 電圧 | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                                                                                                                                                                                                                                      |

|---------------|-----|---------------|-------------|-----|-------|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AOUT,<br>BOUT | O   | H1, E1        | 28, 18      | AIO | DAC   | —             | —                   | <p>これらは TV アナログ出力端子です。TV 出力は、二重終端された <math>75\Omega</math> の負荷 (<math>37.5\Omega</math>) を駆動するように設計されています。詳細については、180 ページの 24.1 「DAC の外付け部品」を参照してください。</p> <p>コンポジットビデオを使用するとき、AOUT を使用し、BOUT は未接続のままにしておきます。S ビデオを使用するとき、AOUT はルミナンス信号、BOUT はクロミナンス信号です。</p>                                                           |

| VREF          | IO  | G2            | 23          | AIO | DAC   | —             | —                   | <p>この入出力端子は、DAC 用の基準電圧です。VREF イネーブルビット (REG[9Eh] ビット 0) を使用して、外部または内部のいずれの VREF モードを選択するのかを決定します。</p> <p>REG[9Eh] ビット 0 = 0 のとき、外部 VREF モードが選択されるので、この端子には、1.23V の電圧を加える必要があります。</p> <p>REG[9Eh] ビット 0 = 1 のとき、内部 VREF モードが選択されるので、テスト中にこの端子を使用して、出力レベルが 1.23V であることを確認することができます。ただし通常動作では、この端子は未接続のままにしておく必要があります。</p> |

| VADJ          | IO  | F2            | 22          | AIO | DAC   | —             | —                   | <p>この入出力端子は、DAC のための基準電流の生成端子です。<math>2.06\text{k}\Omega</math> の抵抗器 (Rset) を VADJ と DACVEE の間に接続してください。詳細については、180 ページの 24.1 「DAC の外付け部品」を参照してください。</p> <p>IREF イネーブルビット = 0 (REG[9Eh] ビット 1 = 0) のとき、基準電流の内部生成はディセーブルとなり、VADJ は基準電流を制御しません。抵抗器を接続したままにしても問題はありません。</p>                                                |

## 5. 端子配置図

### 5.2.4 クロック

#### 注

クロック構造の詳細については、54 ページの 9.「クロック」を参照してください。

表 5-6: クロック入力の端子説明

| 端子名      | タイプ | PFBGA<br>端子 # | QFP<br>端子 # | セル   | IO 電圧  | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                                                                                         |

|----------|-----|---------------|-------------|------|--------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI     | I   | J10           | 68          | HIS  | IOVDD  | —             | —                   | CNF2 = 0 のとき、この端子はクロック入力になります。CNF2 = 1 のとき、この端子は VSS に接続する必要があります。                                                                                                         |

| CLKOUT   | O   | H10           | 71          | HO   | IOVDD  | (注 1)         | (注 1)               | CLKOUTEN 端子がイネーブルのとき、この端子は、CLKI 端子または OSCx 端子からのクロック信号を出力します（詳細については、54 ページの 9.1 「クロック機能ブロック図」を参照してください）。ディセーブルのとき、この端子の出力は LOW になります。<br>注：この出力端子は、各種のパワーセーブモードの影響を受けません。 |

| CLKOUTEN | I   | H9            | 70          | HI   | IOVDD  | —             | —                   | この入力端子は、CLKOUT 端子をイネーブルまたはディセーブルにします。CLKOUTEN = 0 のとき、CLKOUT はディセーブルになります。CLKOUTEN = 1 のとき、CLKOUT はイネーブルになります。                                                             |

| OSCO     | O   | K7            | 58          | LOTR | OSCVDD | (注 2)         | (注 2)               | CNF2 = 1 のとき、この出力端子は、OSCI とともに 2 端子の水晶インタフェースを構成します。内蔵の発振器を使用しないとき、または CNF2 = 0 のとき、この端子は未接続のままにしておく必要があります。                                                               |

| OSCI     | I   | K6            | 54          | LITR | OSCVDD | —             | —                   | CNF2 = 1 のとき、この入力端子は、OSCO とともに 2 端子の水晶インタフェースを構成します。内蔵の発振器を使用しないとき、または CNF2 = 0 のとき、この端子は OSCVDD に接続するか、未接続のままにしておく必要があります。                                                |

#### 注

1. CLKOUTEN = 1 のとき、この端子は CLKI (CNF2 = 1) または OSCI (CNF2 = 0) を出力します。

CLKOUTEN = 0 のとき、この端子は LOW です。

2. CNF2 = 1 のとき、この端子はアクティブです。

CNF2 = 0 のとき、この端子は HIGH です。

## 5.2.5 その他

表 5-7: その他の端子説明

| 端子名       | タイプ | PFBGA<br>端子 #            | QFP<br>端子 #                         | セル   | IO 電圧  | RESET<br># 状態 | パワー<br>セーブ<br>ステータス | 説明                                                                                                                                                                                                                               |

|-----------|-----|--------------------------|-------------------------------------|------|--------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNF[3:0]  | I   | G5, G6,<br>F5, E5        | 39, 38,<br>37, 36                   | HI   | IOVDD  | —             | —                   | これらの入力は、電源投入の構成用に使用します。詳細については、23 ページの 5.3 「構成オプションの要約」を参照してください。<br>注：これらの端子は、IO の V <sub>DD</sub> または V <sub>SS</sub> に直接接続する必要があります。                                                                                          |

| TESTEN    | I   | B2                       | 4                                   | LIDS | IOVDD  | 0             | —                   | この端子はテストイネーブル入力で、生産試験でのみ使用します。この端子は、通常動作では未接続のままにしておく必要があります。                                                                                                                                                                    |

| GPIO[7:5] | IO  | B3, C3,<br>C4            | 124,<br>123,<br>122                 | HBD  | SIOVDD | 0             | アクティブ               | これらの端子は汎用 IO 端子です。<br>これらの端子には、REG[FAh] を使用して制御できる内蔵プルダウン抵抗があります。                                                                                                                                                                |

| GPIO[4:0] | IO  | C7, D5,<br>C5, B5,<br>B6 | 103,<br>115,<br>114,<br>113,<br>112 | HBD  | IOVDD  | 0             | アクティブ               | これらの端子は汎用 IO 端子です。<br>これらの端子には、REG[FAh] を使用して制御できる内蔵プルダウン抵抗があります。                                                                                                                                                                |

| PWRSVE    | I   | B1                       | 1                                   | HI   | IOVDD  | —             | —                   | この入力端子は、選択したパワーセーブモード（スリープまたはスタンバイ）をイネーブルまたはディセーブルにします。REG[2Eh] ビット 7 により、スリープモードイネーブルビット（REG[2Eh] ビット 1）またはスタンバイモードイネーブルビット（REG[2Eh] ビット 0）のいずれかとこの端子の状態との OR をとることができます。<br>注：この端子は、外部電源によって駆動するか、または浮かないように VSS に終端する必要があります。 |

| TEST[2:0] | I   | D3, E4,<br>C2            | 9, 8, 7                             | HID  | IOVDD  | —             | —                   | これらの入力端子は生産試験でのみ使用し、通常動作では未接続のままにしておく必要があります。                                                                                                                                                                                    |

| SCANEN    | I   | C1                       | 10                                  | HID  | IOVDD  | —             | —                   | この端子はスキャニイネーブル入力であり、生産試験でのみ使用します。この端子は、通常動作では未接続のままにしておく必要があります。                                                                                                                                                                 |

| VCP       | I   | J8                       | 63                                  | LITR | PLLVDD | —             | —                   | この入力端子は生産試験用でのみ使用し、通常動作では未接続のままにしておく必要があります。                                                                                                                                                                                     |

## 5. 端子配置図

### 5.2.6 電源およびグラウンド

表 5-8: 電源およびグラウンドの端子説明

| 端子名     | タイプ | PFBGA 端子 #                                 | QFP 端子 #                                              | セル | 説明                   |

|---------|-----|--------------------------------------------|-------------------------------------------------------|----|----------------------|

| COREVDD | P   | A2, B9, G10, J5                            | 2, 3, 41, 47, 73, 74, 93, 99, 100, 127, 128           | P  | コア電源                 |

| IOVDD   | P   | D7, F6, H6, H8, J4                         | 6, 43, 50, 61, 69, 83, 90, 97, 98                     | P  | ホストインターフェース用の IO 電源  |

| SIOVDD  | P   | D4                                         | 125, 126                                              | P  | シリアルインターフェース用の IO 電源 |

| VSS     | G   | A6, A9, C9, F4, G4, H4, H5, H7, J9, K4, K5 | 5, 40, 42, 46, 49, 66, 67, 91, 94, 108, 109, 116, 117 | P  | GND                  |

| OSCVDD  | P   | J7                                         | 60                                                    | P  | 発振器 (2.5V) 用の IO 電源  |

| OSCVSS  | P   | J6                                         | 56                                                    | P  | 発振器用の GND            |

| PLLVDD  | AP  | K8                                         | 62                                                    | P  | PLL 電源               |

| PLLVSS  | AG  | K9                                         | 64                                                    | P  | PLL 用の GND           |

| DACVCC  | AP  | D2, E2, F3, H2, H3, J3                     | 14, 16, 20, 24, 26, 30                                | P  | DAC のアナログ電源          |

| DACVEE  | AG  | D1, E3, F1, G1, G3, J1, J2, K3             | 15, 17, 19, 21, 25, 27, 29, 32                        | P  | DAC のアナログ用の GND      |

### 5.3 構成オプションの要約

これらの端子は、電源投入の構成用に使用され、 $\text{IOV}_{\text{DD}}$  または  $\text{V}_{\text{SS}}$  に直接接続する必要があります。これらの端子のステータスは、 $\text{CNF}[3:0]$  ステータスピットを使用して  $\text{REG}[02\text{h}]$  で読み出すことができます。

表 5-9: 電源投入 / リセットオプションの要約

| 構成入力              | 電源投入 / リセット状態                                                                                                                                                                            |                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                   | 1 ( $\text{IOV}_{\text{DD}}$ に接続)                                                                                                                                                        | 0 ( $\text{V}_{\text{SS}}$ に接続) |

| $\text{CNF}[1:0]$ | 以下のようにホストインターフェースを選択します。<br><b>CNF1 CNF0 ホストバス</b><br>0 0 パラレル RGB インタフェース付きの 3 線シリアルホストインターフェース<br>0 1 8 ビット Intel 80<br>1 0 パラレル RGB インタフェース付きの SPI ホストインターフェース<br>1 1 16 ビット Intel 80 |                                 |

| $\text{CNF2}$     | 入力クロックとして使用する 2 端子水晶 (OSCI、OSCO 端子)                                                                                                                                                      | 入力クロックとして使用する発振器 (CLKI 端子)      |

| $\text{CNF3}$     | リセットフィルタ = 5 $\mu\text{s}$ (クロックが必要)                                                                                                                                                     | リセットフィルタ = 43ns (クロックは不要)       |

#### 注

$\text{CNF1} = 0$  のとき、すべてのレジスタアクセスは 8 ビットアクセスのみです。

$\text{CNF1} = 1$  (16 ビット) のとき、ディスプレイメモリのデータポート ( $\text{REG}[A0\text{h}]$ ) を除いてすべてのレジスタアクセスは 8 ビットアクセスのみです (データバスの最上位バイトは無視されます)。ディスプレイメモリのデータポートへのアクセスは 16 ビットアクセスです。

## 6. 端子マッピング

### 6. 端子マッピング

#### 6.1 Intel 80 データ端子

Intel 80 データ端子マッピングは、CNF[1:0] によって制御されます。CNF[1:0] の詳細については、23 ページの 5.3 「構成オプションの要約」を参照してください。

表 6-1: Intel 80 データ端子マッピング

| 端子名  | 16 ビットデータ<br>CNF[1:0] = 11 | 8 ビットデータ<br>CNF[1:0] = 01         |

|------|----------------------------|-----------------------------------|

| MD15 | MD15                       | プルダウン抵抗を通じてグラウンドに接続<br>(8bit 使用時) |

| MD14 | MD14                       |                                   |

| MD13 | MD13                       |                                   |

| MD12 | MD12                       |                                   |

| MD11 | MD11                       |                                   |

| MD10 | MD10                       |                                   |

| MD9  | MD9                        |                                   |

| MD8  | MD8                        |                                   |

| 端子名  | 16 ビットデータ<br>CNF[1:0] = 11 | 8 ビットデータ<br>CNF[1:0] = 01         |

| MD7  | MD7                        | MD7                               |

| MD6  | MD6                        | MD6                               |

| MD5  | MD5                        | MD5                               |

| MD4  | MD4                        | MD4                               |

| MD3  | MD3                        | MD3                               |

| MD2  | MD2                        | MD2                               |

| MD1  | MD1                        | MD1                               |

| MD0  | MD0                        | MD0                               |

#### 6.2 パラレル RGB データ端子

表 6-2: パラレル RGB データ端子マッピング

| S1D13746<br>端子名 | RGB<br>端子名 | RGB<br>機能 | S1D13746<br>端子名 | RGB<br>端子名 | RGB<br>機能 |

|-----------------|------------|-----------|-----------------|------------|-----------|

| MD15            | VD17       | R5        | MD4             | VD6        | G0        |

| MD14            | VD16       | R4        | MD3             | VD5        | B5        |

| MD13            | VD15       | R3        | MD2             | VD4        | B4        |

| MD12            | VD14       | R2        | MD1             | VD3        | B3        |

| MD11            | VD13       | R1        | MD0             | VD2        | B2        |

| MD10            | VD12       | R0        | WE#             | VD1        | B1        |

| MD9             | VD11       | G5        | RD#             | VD0        | B0        |

| MD8             | VD10       | G4        | D/C#            | HS         | HS        |

| MD7             | VD9        | G3        | TE              | VS         | VS        |

| MD6             | VD8        | G2        | DE              | DE         | DE        |

| MD5             | VD7        | G1        | PCLK            | PCLK       | PCLK      |

## 7. DC 特性

### 7.1 絶対最大定格

表 7-1: 絶対最大定格

| 記号                         | パラメータ                | 定格                           | 単位 |

|----------------------------|----------------------|------------------------------|----|

| $\text{COREV}_{\text{DD}}$ | コア電源電圧               | - 0.3 ~ 2.0                  | V  |

| $\text{PLLV}_{\text{DD}}$  | PLL 電源電圧             | - 0.3 ~ 2.0                  | V  |

| $\text{IOV}_{\text{DD}}$   | ホスト IO 電源電圧          | $\text{COREVDD} \sim 4.0$    | V  |

| $\text{SIOV}_{\text{DD}}$  | シリアル IO 電源電圧         | $\text{COREVDD} \sim 4.0$    | V  |

| $\text{OSCV}_{\text{DD}}$  | 水晶発振器電源電圧            | $\text{COREVDD} \sim 4.0$    | V  |

| $\text{DACV}_{\text{CC}}$  | DAC アナログ電源電圧         | $\text{COREVDD} \sim 4.0$    | V  |

| $V_{\text{IN}}$            | 入力電圧                 | - 0.3 ~ $\text{IOVDD} + 0.5$ | V  |

| $V_{\text{IN\_F}}$         | 入力電圧 (Fail safe I/O) | - 0.3 ~ 4.0                  | V  |

| $V_{\text{OUT}}$           | 出力電圧                 | - 0.3 ~ $\text{IOVDD} + 0.5$ | V  |

| $I_{\text{OUT\_IO}}$       | デジタル出力電流             | $\pm 10$                     | mA |

| $I_{\text{OUT\_DAC}}$      | DAC 出力電流             | $\pm 50$                     | mA |

| $T_{\text{STG}}$           | 保存温度                 | -65 ~ 150                    | °C |

### 7.2 推奨動作条件

以下の特性は、 $\text{VSS} = \text{PLLVSS} = \text{OSCVSS} = \text{DACVEE} = 0\text{V}$  の場合の特性です。

表 7-2: 推奨動作条件

| 記号                         | パラメータ                | Min  | Typ  | Max            | 単位 |

|----------------------------|----------------------|------|------|----------------|----|

| $\text{COREV}_{\text{DD}}$ | コア電源電圧               | 1.35 | 1.50 | 1.65           | V  |

| $\text{PLLV}_{\text{DD}}$  | PLL 電源電圧             | —    | —    | —              | —  |

| $\text{IOV}_{\text{DD}}$   | ホスト IO 電源電圧          | 1.62 | —    | 3.60           | V  |

| $\text{SIOV}_{\text{DD}}$  | シリアル IO 電源電圧         | 1.62 | —    | 3.60           | V  |

| $\text{OSCV}_{\text{DD}}$  | 水晶発振器電源電圧            | 1.62 | —    | 3.60           | V  |

| $\text{DACV}_{\text{CC}}$  | DAC アナログ電源電圧         | 2.70 | 3.00 | 3.30           | V  |

| $V_{\text{IN}}$            | 入力電圧                 | 0    | —    | $\text{IOVDD}$ | V  |

| $V_{\text{IN\_F}}$         | 入力電圧 (Fail safe I/O) | 0    | —    | 3.90           | V  |

| $T_{\text{OPR}}$           | 動作温度                 | -40  | 25   | 85             | °C |

## 7.DC 特性

### 7.3 電気的特性

以下の特性は、推奨動作条件の場合の特性です。

表 7-3:  $IOVDD$ 、 $SIOVDD$ 、または  $OSCVDD = 1.62V \sim 3.60V$ 、 $VSS = 0V$  の電気的特性

| 記号         | パラメータ      | 条件                                     | Min                 | Typ | Max                 | 単位        |

|------------|------------|----------------------------------------|---------------------|-----|---------------------|-----------|

| $I_{IZ}$   | 入カリーク電流    | —                                      | -1                  | —   | 1                   | $\mu A$   |

| $I_{OZ}$   | オフ状態リーケ電流  | —                                      | -1                  | —   | 1                   | $\mu A$   |

| $IOV_{OH}$ | 高レベル出力電圧   | $IOVDD = \text{Min}$<br>$IOH = -1.8mA$ | $IOVDD - 0.4$       | —   | —                   | V         |

| $IOV_{OL}$ | 低レベル出力電圧   | $IOVDD = \text{Min}$<br>$IOL = 1.8mA$  | —                   | —   | 0.4                 | V         |

| $V_{IH}$   | 高レベル入力電圧   | LVCMOS レベル                             | $IOVDD \times 0.7$  | —   | $IOVDD + 0.3$       | V         |

| $V_{IL}$   | 低レベル入力電圧   | LVCMOS レベル                             | -0.3                | —   | $IOVDD \times 0.3$  | V         |

| $V_{T+}$   | ポジティブトリガ電圧 | LVCMOS シュミット                           | $IOVDD \times 0.4$  | —   | $IOVDD \times 0.7$  | V         |

| $V_{T-}$   | ネガティブトリガ電圧 | LVCMOS シュミット                           | $IOVDD \times 0.25$ | —   | $IOVDD \times 0.55$ | V         |

| $\Delta V$ | ヒステリシス電圧   | LVCMOS シュミット                           | $IOVDD \times 0.1$  | —   | —                   | V         |

| $R_{PD}$   | プルダウン抵抗    | $VI = IOVDD$                           | 20                  | —   | 244                 | $k\Omega$ |

| $C_{IO}$   | 端子の静電容量    | $f = 1MHz$ ,<br>$IOVDD = 0V$           | —                   | —   | 8                   | $pF$      |

表 7-4: 消費電力

| 記号          | パラメータ        | 条件          | Min | Typ | Max | 単位      |

|-------------|--------------|-------------|-----|-----|-----|---------|

| $I_{QHVDD}$ | IO、OSC 静止電流  | —           | —   | 1   | —   | $\mu A$ |

| $I_{QLVDD}$ | コア、PLL 静止電流  | —           | —   | 20  | —   | $\mu A$ |

| $I_{QDAC}$  | DAC 静止電流     | —           | —   | 1   | —   | $\mu A$ |

| $I_{IO}$    | IOVDD 動作電流   | —           | —   | —   | 5   | $mA$    |

| $I_{OSC}$   | OSCVDD 動作電流  | 27MHz 水晶    | —   | 600 | —   | $\mu A$ |

| $I_{CORE}$  | COREVDD 動作電流 | —           | —   | —   | 33  | $mA$    |

| $I_{PLL}$   | PLLVDD 動作電流  | $f = 54MHz$ | —   | 0.8 | 2.0 | $mA$    |

| $I_{DAC}$   | DACVCC 動作電流  | S ビデオ       | —   | 90  | 100 | $mA$    |

|             |              | コンポジット      | —   | 45  | 50  | $mA$    |

## 7.4 DAC 特性

以下の特性は、 $DACVCC = 2.7V \sim 3.3V$ 、 $VSS = PLLVSS = OSCVSS = DACVEE = 0V$ 、 $T_{OPR} = -40 \sim 85^{\circ}C$ 、 $R_L = 37.5\Omega$ 、 $C_L = 30pF$ 、 $R_{ADJ} = 2060\Omega$ 、 $VREF = オープン$ の場合の特性です。

表 7-5: DAC 特性

| パラメータ         | 条件     | Min   | Typ  | Max  | 単位   |

|---------------|--------|-------|------|------|------|

| 解像度           | —      | —     | 10   | —    | bits |

| サンプルレート       | —      | —     | 27   | —    | MHz  |

| クロックデューティサイクル | —      | 40    | 50   | 60   | %    |

| 最小出力電圧        | ゼロスケール | -0.05 | 0    | 0.05 | V    |

| 最大出力電圧        | フルスケール | 1.17  | 1.30 | 1.43 | V    |

| 微分非直線性        | —      | -1    | —    | 1    | LSB  |

| 積分非直線性        | —      | -3    | —    | 3    | LSB  |

### 注

AOUT または BOUT からの TV 出力が  $75\Omega$  の二重終端（すなわち  $75\Omega$  の負荷抵抗と  $75\Omega$  の外部負荷）に接続されずに、 $75\Omega$  の単一負荷によってのみ単独で終端されている場合、出力電圧レベルは 2 倍になります。

### 7.5 電力推定のガイドライン

以下の資料は、実行可能な 3 つのモード（アクティブモード、スタンバイモード、およびスリープモード）のそれぞれについて、電力推定のガイドラインを一覧にしたもの。

これらのガイドラインは、CLKI/OSC = 27 MHz、SYSCLK = 54 MHz に基づいたものであり、結果はユーザー環境によって異なります。

表 7-6: 標準的な消費電力

| アクティブ表示（注 1）       | 消費電流         | 説明                               |

|--------------------|--------------|----------------------------------|

| Core (1.5V)        | 15mA / 20mA  | Intel 80 ホスト / パラレル RGB ホスト      |

| PLL (1.5V)         | 528μA        | —                                |

| DAC(3.0V)          | 48mA         | コンポジットビデオ出力 (REG[40h] ビット 4 = 0) |

|                    | 92mA         | S ビデオ出力 (REG[40h] ビット 4 = 1)     |

| OSCVDD(1.8V)       | 565μA        | 使用する場合。使用しない場合はゼロ。               |

| IOVDD(1.8V) (注 4)  | 80μA / 900μA | ホストアクティビティ / CLKOUT イネーブル        |

| SIOVDD(1.8V) (注 4) | 15μA         | シリアルホストレジスタアクセス                  |

| スタンバイモードイネーブル（注 2） | 消費電流  | 説明                 |

|--------------------|-------|--------------------|

| Core (1.5V)        | 820μA | —                  |

| PLL (1.5V)         | 528μA | —                  |

| DAC(3.0V)          | 0     | —                  |

| OSCVDD(1.8V)       | 565μA | 使用する場合。使用しない場合はゼロ。 |

| スリープモードイネーブル（注 3） | 消費電流         | 説明                      |

|-------------------|--------------|-------------------------|

| Core (1.5V)       | 330μA / 15μA | CLKI アクティブ / CLKI グラウンド |

| PLL (1.5V)        | 0            | —                       |

| DAC(3.0V)         | 0            | —                       |

| OSCVDD(1.8V)      | 565μA        | 使用する場合。使用しない場合はゼロ。      |

#### 注

1. アクティブ表示モードは、PWRSVE 端子が LOW で、スリープモードイネーブルビット (REG[2Eh] ビット 1) とスタンバイモードイネーブルビット (REG[2Eh] ビット 0) の両方が 0 のときです。

2. スタンバイモードは、スタンバイモードイネーブルビットが 1b (REG[2Eh] ビット 0 = 1) であるとき、または PWRSVE 入力端子機能がスタンバイモード (REG[2Eh] ビット 7 = 1) に構成されているときに PWRSVE 端子が HIGH であるときです。

3. スリープモードは、スリープモードイネーブルビットが 1b (REG[2Eh] ビット 1 = 1) であるとき、または PWRSVE 入力端子機能がスリープモード (REG[2Eh] ビット 7 = 0) に構成されているときに PWRSVE 端子が HIGH であるときです。

4. IOVDD/SIOVDD は、Intel 80 ホストインターフェース、シリアルホストインターフェース、または GPIO の動作状態によって決まります。スタンバイまたはスリープモードによる影響を受けません。

## 8. AC 特性

条件:

IOVDD = 1.62V ~ 3.60V

TOPR = -40°C ~ 85°C

シュミットと CLKI を除くすべての入力について  $T_{rise}$  と  $T_{fall}$  は  $\leq 50\text{ns}$  (10% ~ 90%) でなければなりません。

すべてのシュミットについて  $T_{rise}$  と  $T_{fall}$  は  $\leq 5\text{ms}$  (10% ~ 90%) でなければなりません。

$C_L = 8\text{pF} \sim 30\text{pF}$  (MD[15:0])

$C_L = 15\text{pF}$  (TE, GPIO\_INT, CLKOUT)

$C_L = 30\text{pF}$  (GPIO インタフェース)

### 8.1 クロックタイミング

#### 8.1.1 入力クロック

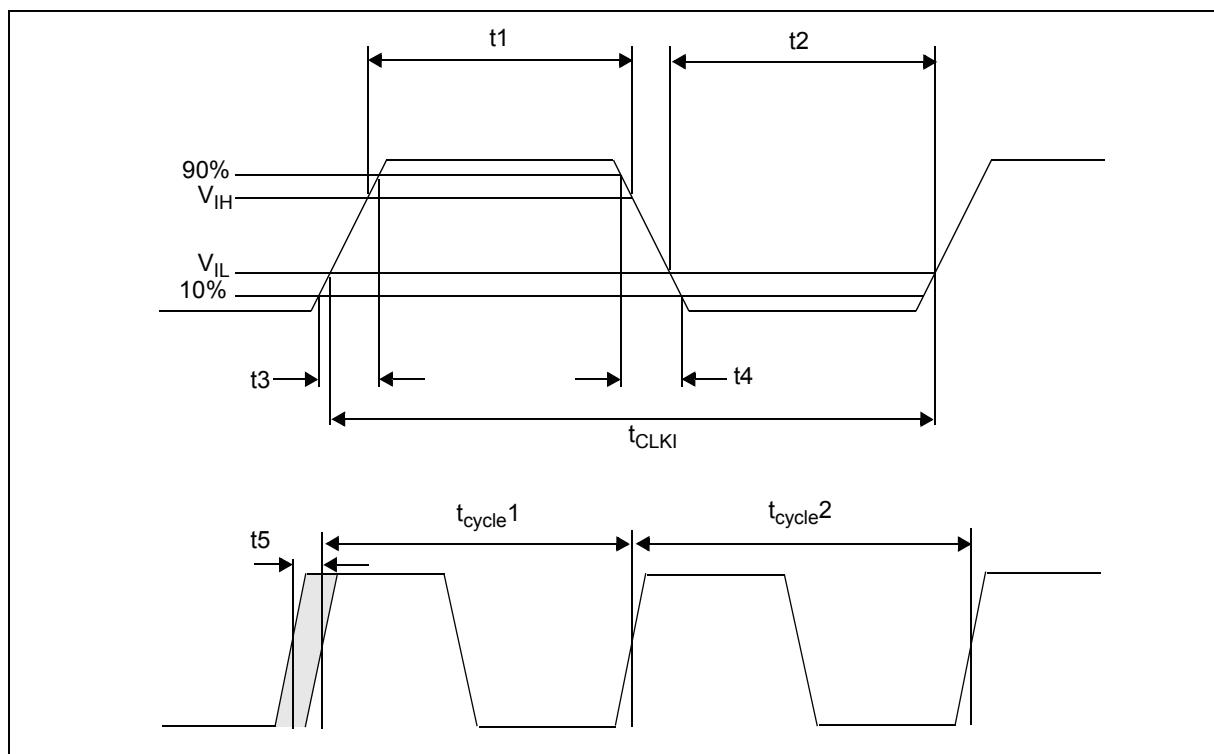

図8-1: クロック入力要件 (PLL)

## 8.AC 特性

表 8-1: クロック入力要件 (CLKI)

| 記号         | パラメータ                            | Min  | Typ          | Max  | 単位         |

|------------|----------------------------------|------|--------------|------|------------|

| $f_{CLKI}$ | 入力クロック周波数                        | 18   | 27           | 27   | MHz        |

| $t_{CLKI}$ | 入力クロック周期                         | —    | $1/f_{CLKI}$ | —    | $\mu s$    |

| $t_1$      | 入力クロック HIGH パルス幅                 | 0.45 | —            | 0.55 | $t_{CLKI}$ |

| $t_2$      | 入力クロック LOW パルス幅                  | 0.45 | —            | 0.55 | $t_{CLKI}$ |

| $t_3$      | 入力クロック立ち上がり時間 (10% ~ 90%)        | —    | —            | 5    | ns         |

| $t_4$      | 入力クロック立ち下がり時間 (10% ~ 90%)        | —    | —            | 5    | ns         |

| $t_5$      | 入力クロック周期ジッタ (注 2、4)              | -300 | —            | 300  | ps         |

| (注 1)      | 入力クロックサイクルジッタ、NTSC TV 出力 (注 3、4) | -50  | —            | 50   | ppm        |

|            | 入力クロックサイクルジッタ、PAL TV 出力 (注 3、4)  | -25  | —            | 25   | ppm        |

### 注

- $t_6 = t_{cycle1} - t_{cycle2}$

- 入力クロック周期ジッタは、クロックセンターを基準としたときの変位です。

- 入力クロックサイクルジッタは、隣接するサイクル間の周期差です。

- ジッタの特性は、 $t_5$  および  $t_6$  の両方の特性を満たす必要があります。

### 8.1.2 OSC クロック

表 8-2: OSC 水晶クロックの要件 (OSC)

| 記号        | パラメータ         | Min | Typ         | Max | 単位      |

|-----------|---------------|-----|-------------|-----|---------|

| $f_{OSC}$ | OSC 水晶クロック周波数 | 18  | 27          | 27  | MHz     |

| $t_{OSC}$ | OSC 水晶クロック周期  | —   | $1/f_{OSC}$ | —   | $\mu s$ |

### 8.1.3 PLL クロック

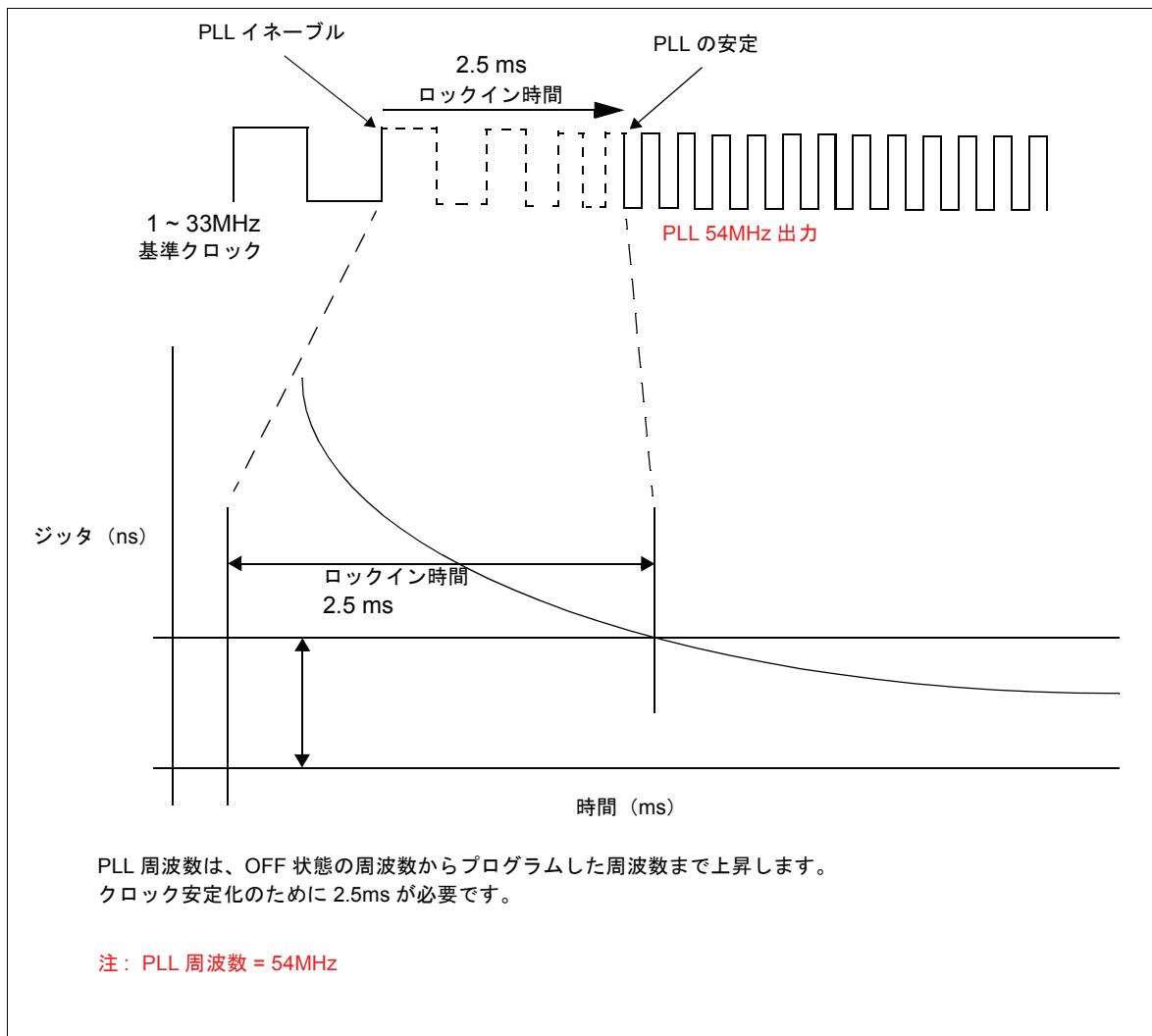

PLL 回路はアナログ回路であるため、入力クロック波形や電源に含まれるノイズに非常に敏感です。クロックや供給電源に含まれるノイズによって、PLL 回路の動作が不安定になったり、ジッタを増大させたりする恐れがあります。

このノイズの制約のため、PLL の電源トレースや電源プレーンは、他の電源のトレースやプレーンと分離することを推奨します。またフィルタリングを使用して、できるだけ電源をきれいにしてください。入力クロック波形のジッタはできるだけ少なくなるようにしてください。

PLL 周波数は、OFF 状態の周波数からプログラムした周波数まで上昇します。

クロック安定化のために 2.5ms が必要です。

注：PLL 周波数 = 54MHz

図 8-2: PLL 起動時間

表 8-3: PLL 特性

| 記号          | パラメータ                      | Min | Typ | Max | 単位  |

|-------------|----------------------------|-----|-----|-----|-----|

| $f_{PLL1}$  | M-Divider 後の PLL 入力クロック周波数 | 1   | —   | 2   | MHz |

| $f_{PLL12}$ | M-Divider 前の PLL 入力クロック周波数 | 1   | —   | 33  | MHz |

| $f_{PLLO}$  | PLL 出力クロック周波数              | —   | 54  | —   | MHz |

| $t_{Pjref}$ | PLL 出力クロック周期ジッタ            | -3  | —   | 3   | %   |

| $t_{PDuty}$ | PLL 出力クロックデューティサイクル        | 30  | —   | 70  | %   |

| $t_{PStal}$ | PLL 出力の安定時間                | —   | —   | 2.5 | ms  |

## 8.AC 特性

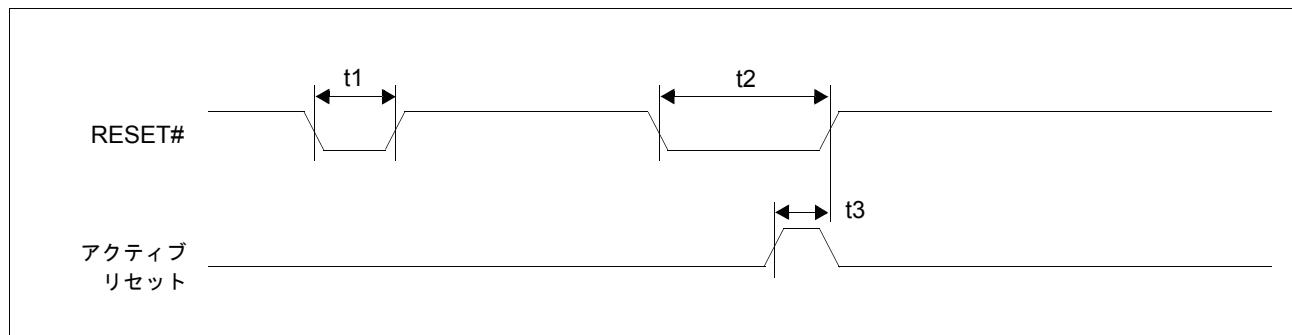

### 8.2 リセットタイミング

図 8-3: SID13746 のリセットタイミング

表 8-4: SID13746 のリセットタイミング

| CNF3 | 記号 | パラメータ                                 | Min<br>(注 1) | Max<br>(注 2) | 単位 |

|------|----|---------------------------------------|--------------|--------------|----|

| 0    | t1 | 5μs リセットフィルタがディセーブルのときに無視されるリセットパルス幅  | 43           | 138          | ns |

|      | t2 | 5μs リセットフィルタがディセーブルのときにアクティブなリセットパルス幅 | 50           | 150          | ns |

| 1    | t1 | 5μs リセットフィルタがイネーブルのときに無視されるリセットパルス幅   | 5.01         | 5.10         | μs |

|      | t2 | 5μs リセットフィルタがイネーブルのときにアクティブなリセットパルス幅  | 5.10         | 5.20         | μs |

|      | t3 | t2 - t1                               | —            | —            | —  |

#### 注

1. Min の数値は最小推奨動作条件に基づいています。

(25 ページの 7.2 「推奨動作条件」を参照してください。)

2. Max の数値は最大推奨動作条件に基づいています。

(25 ページの 7.2 「推奨動作条件」を参照してください。)

#### 注

5μs リセットフィルタには CLKI が必要であり、タイミングは 27MHz の CLKI 周波数に基づいています。

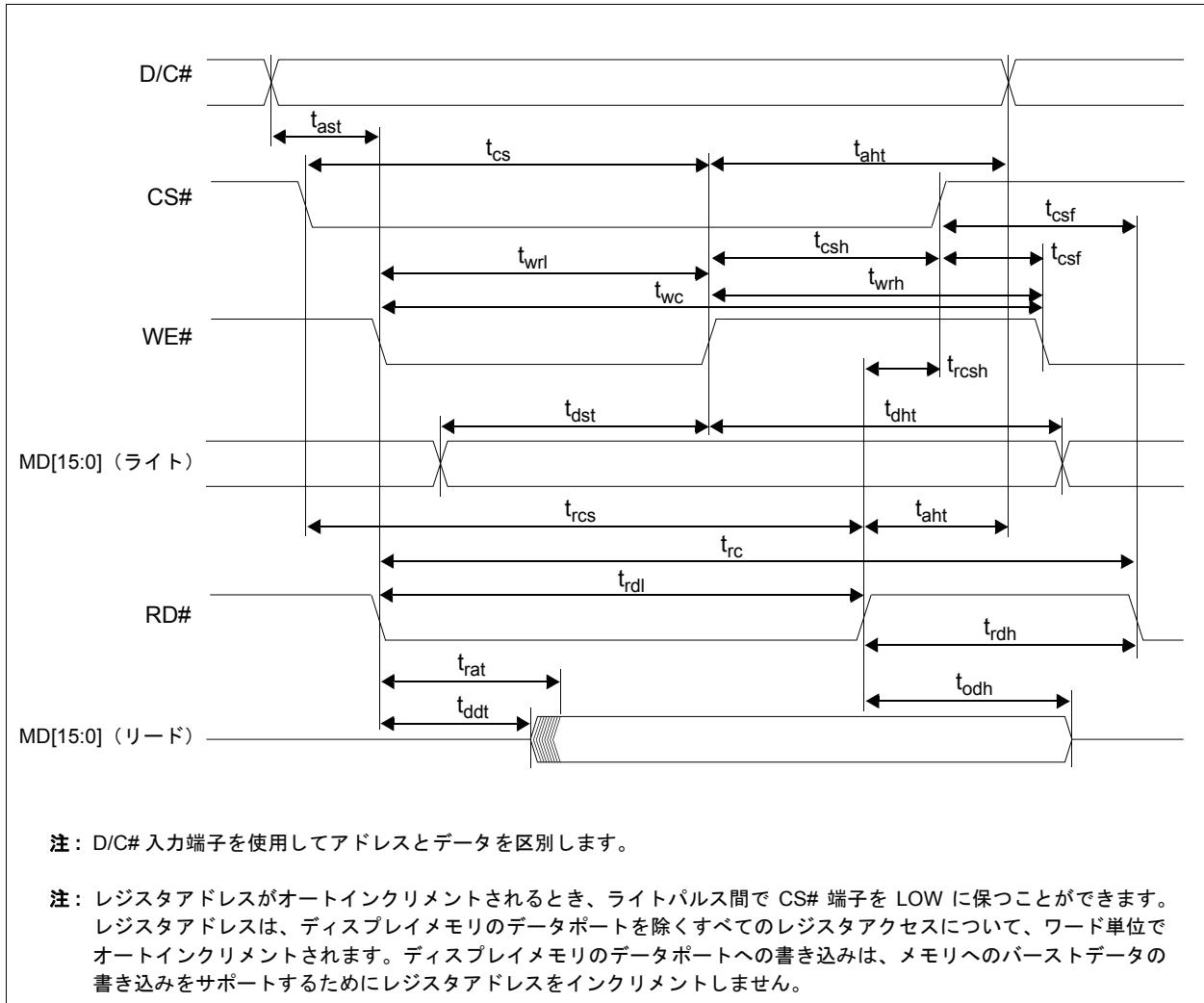

## 8.3 ホストインターフェースのタイミング

### 8.3.1 Intel 80 インタフェースのタイミング

図8-4: Intel 80 の入力 AC 特性

表 8-5: Intel 80 の入力 AC 特性

| 信号       | 記号               | パラメータ                            | Min             | Max  | 単位 | 説明                                  |

|----------|------------------|----------------------------------|-----------------|------|----|-------------------------------------|

| D/C#     | $t_{ast}$        | アドレスのセットアップ時間                    | 3.0             | —    | ns |                                     |

|          | $t_{aht}$        | アドレスのホールド時間                      | 1.0             | —    | ns |                                     |

| CS#      | $t_{cs}$         | チップセレクトのセットアップ時間 (ライト)           | $2.0 + t_{wrl}$ | —    | ns |                                     |

|          | $t_{rcs}$        | チップセレクトのセットアップ時間 (リード)           | $1.0 + t_{rdl}$ | —    | ns |                                     |

|          | $t_{csf}$        | チップセレクトの待機時間                     | 10.0            | —    | ns |                                     |

|          | $t_{csh}$        | チップセレクトのホールド時間 (ライト)             | 0               | —    | ns |                                     |

|          | $t_{rcsh}$       | チップセレクトのホールド時間 (リード)             | 0               | —    | ns |                                     |

| WE#      | $t_{wc}$         | ライトサイクル (立ち下がりエッジから次の立ち下がりエッジまで) | 2SYSCLK         | —    | ns |                                     |

|          | $t_{wrh}$        | パルス HIGH 期間                      | (注 1)           | —    | ns |                                     |

|          | $t_{wrl}$        | パルス LOW 期間                       | 1.0             | —    | ns |                                     |

| RD#      | $t_{rc}$         | レジスタのリードサイクル                     | 28.0            | —    | ns |                                     |

|          | $t_{rdh}$        | パルス HIGH 期間                      | 4.0             | —    | ns |                                     |

|          | $t_{rdl}$        | レジスタのパルス LOW 期間                  | 24.0            | —    | ns |                                     |

| MD[15:0] | $t_{dst}$        | データのセットアップ時間                     | 4.0             | —    | ns | 最大 CL = 30pF の場合<br>最小 CL = 8pF の場合 |

|          | $t_{dht}$        | データのホールド時間                       | 3.0             | —    | ns |                                     |

|          | $t_{rat}$<br>(注) | リードの立ち下がりエッジ→レジスタのデータが有効         | 5.5             | 22.5 | ns |                                     |

|          | $t_{odh}$<br>(注) | リードのホールド時間                       | 11.0            | 36.5 | ns |                                     |

|          | $t_{ddt}$<br>(注) | リード立ち下がりエッジ→データの駆動               | 4.0             | 19.0 | ns |                                     |

## 注

- $t_{wrh}$  min は、 $t_{wc}$  を満たすのに十分な長さです。

## 注

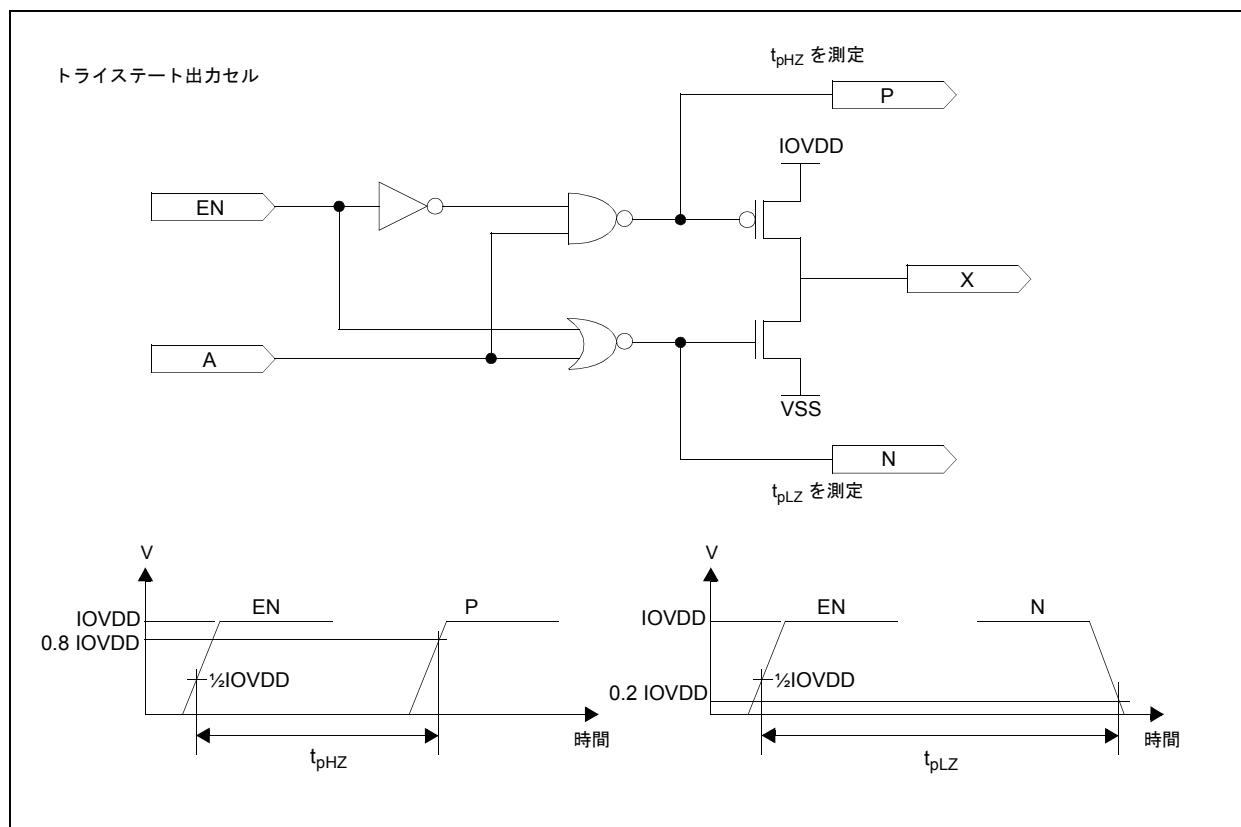

Hi-Z 状態への遷移時間の定義

高速信号のハイインピーダンス (Hi-Z) の測定は困難であるため、H/L から Hi-Z への遷移時間は以下のように規定されています。

H から Hi-Z への遷延時間 :  $t_{pHZ}$

Pch-MOSFET の最終段のゲート電圧が  $0.8 \times IOVDD$  に変わると (Pch-MOSFET がオフ) の遷延時間。Hi-Z までの総遷延時間は、次式で算出されます。

内部ロジック遷延 +  $t_{pHZ}$  (H から Hi-Z)

L から Hi-Z への遷延時間 :  $t_{pLZ}$

Nch-MOSFET の最終段のゲート電圧が  $0.2 \times IOVDD$  に変わると (Nch-MOSFET がオフ) の遷延時間。Hi-Z までの総遷延時間は、次式で算出されます。

内部ロジック遷延 +  $t_{pHZ}$  (H から Hi-Z)

トライステート出力セルの最終段の機能モデルは、図 8-5 「Hi-Z 状態への遷移時間の定義」に示されています。

### 8.4 シリアルインターフェースのタイミング

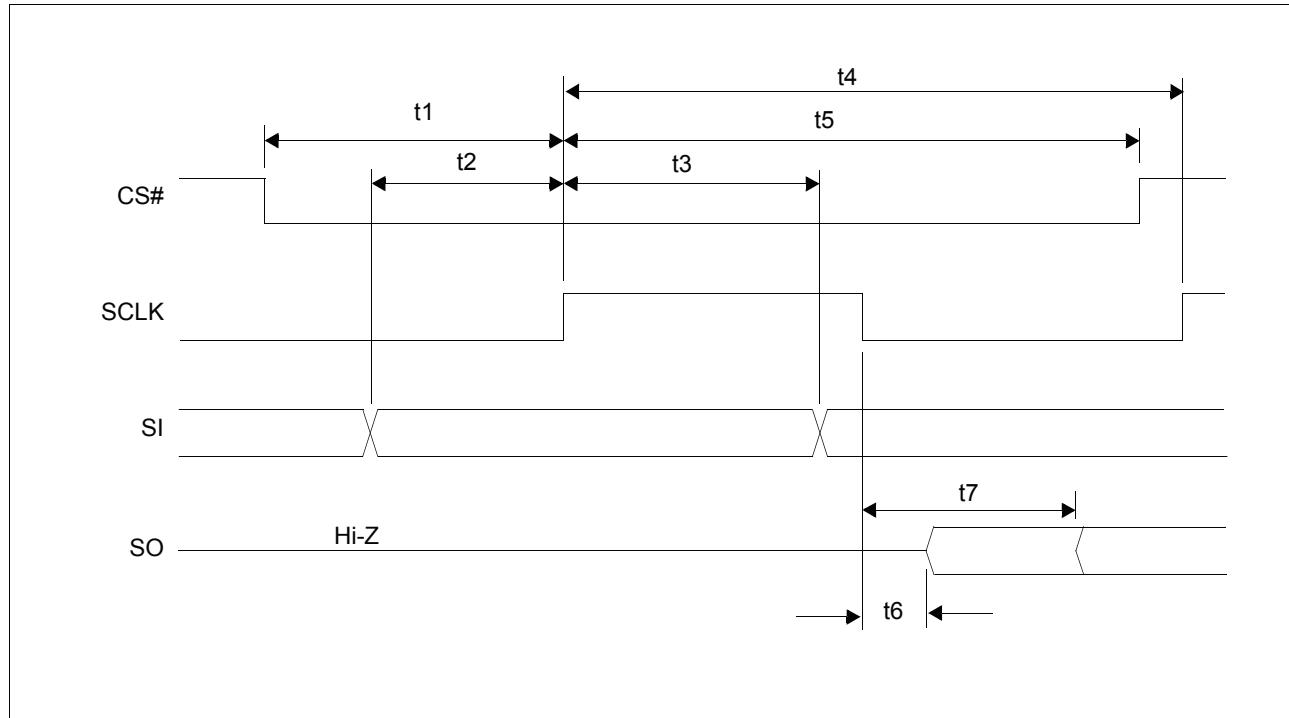

#### 8.4.1 3線シリアルインターフェースのタイミング

図8-6: 3線シリアルインターフェースのタイミング

表8-6: 3線シリアルインターフェースのタイミング

| 記号 | パラメータ                               | Min | Max | 単位   |

|----|-------------------------------------|-----|-----|------|

| t1 | CS# アクティブ → SCLK のポジティブエッジ          | 10  | —   | ns   |

| t2 | SI セットアップ → SCLK のポジティブエッジ          | 6   | —   | ns   |

| t3 | SCLK のポジティブエッジからの SI ホールド           | 8   | —   | ns   |

| t4 | SCLK の周期                            | 150 | —   | ns   |

| t5 | SCLK のポジティブエッジ → CS# HIGH           | 1   | —   | SCLK |

| t6 | SCLK のネガティブエッジ → SO の駆動 (Hi-Z ではない) | —   | 22  | ns   |

| t7 | SCLK のネガティブエッジ → SO のデータが有効         | —   | 25  | ns   |

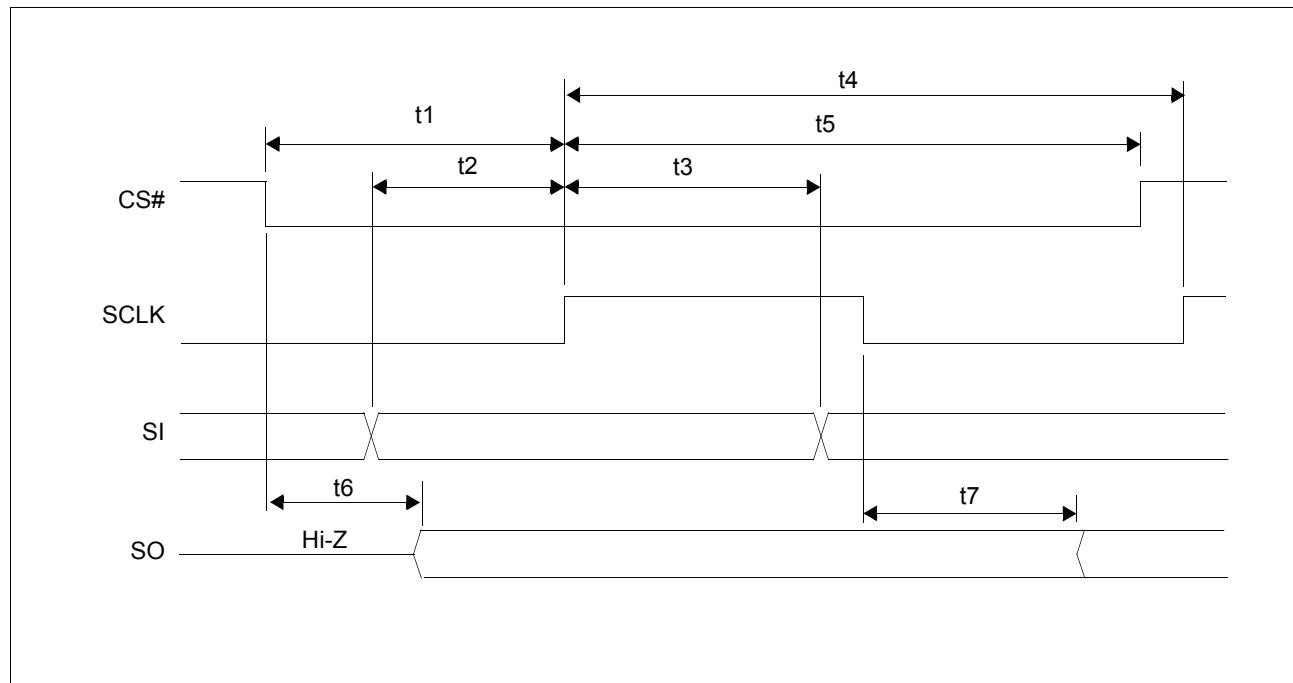

## 8.4.2 4 線シリアルインターフェース (SPI) のタイミング

図 8-7: 4 線シリアルインターフェース (SPI) のタイミング

表 8-7: 4 線シリアルインターフェース (SPI) のタイミング

| 記号 | パラメータ                        | Min | Max | 単位   |

|----|------------------------------|-----|-----|------|

| t1 | CS# アクティブ → SCLK のポジティブエッジ   | 10  | —   | ns   |

| t2 | SI セットアップ → SCLK のポジティブエッジ   | 6   | —   | ns   |

| t3 | SCLK のポジティブエッジからの SI ホールド    | 8   | —   | ns   |

| t4 | SCLK の周期                     | 100 | —   | ns   |

| t5 | SCLK のポジティブエッジ → CS# HIGH    | 1   | —   | SCLK |

| t6 | CS# LOW → SO の駆動 (Hi-Z ではない) | —   | 20  | ns   |

| t7 | SCLK のネガティブエッジ → SO のデータが有効  | —   | 25  | ns   |

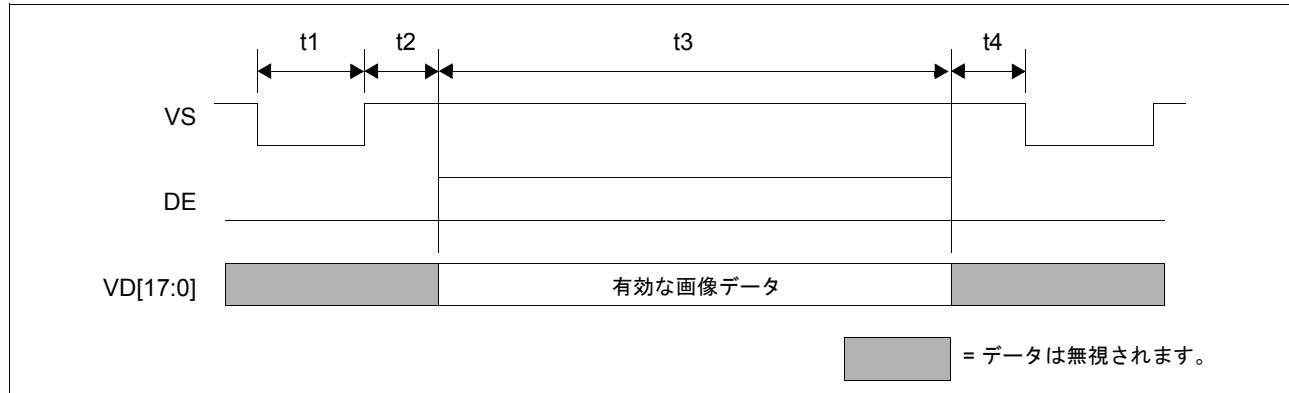

### 8.5 パラレル RGB インタフェースのタイミング

#### 8.5.1 垂直タイミング

表 8-8: パラレル RGB インタフェースの垂直タイミング

| 記号 | パラメータ         | Min | Max  | 単位  |

|----|---------------|-----|------|-----|

| t1 | 垂直同期期間        | 2   | —    | ライン |

| t2 | 垂直バックポーチ      | 2   | —    | ライン |

| t3 | 垂直アクティブフレーム期間 | 16  | 1024 | ライン |

| t4 | 垂直フロントポーチ     | 2   | —    | ライン |

## 8.5.2 水平タイミング

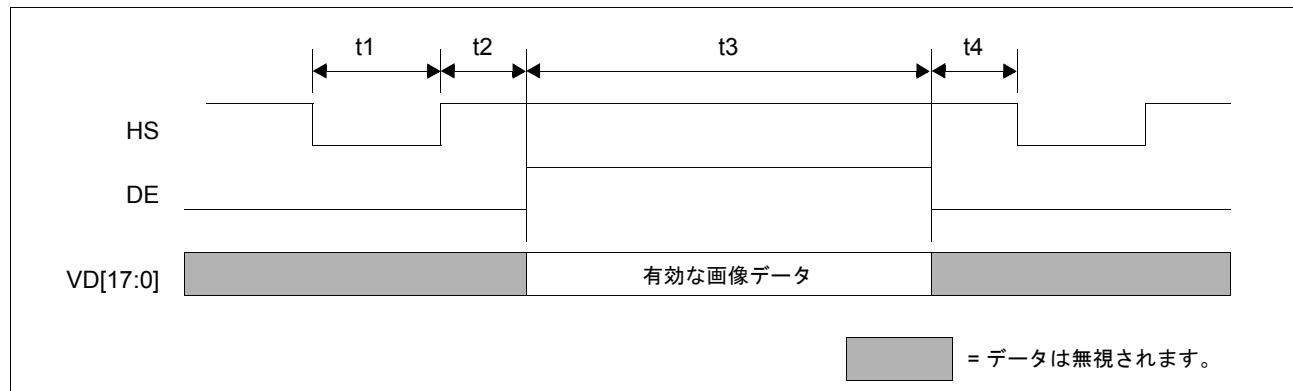

図8-9: パラレルRGB インタフェースの水平タイミング

表8-9: パラレルRGB インタフェースの水平タイミング

| 記号 | パラメータ        | Min | Max  | 単位   |

|----|--------------|-----|------|------|

| t1 | 水平同期期間       | 2   | —    | PCLK |

| t2 | 水平バックポーチ     | 2   | —    | PCLK |

| t3 | 水平アクティブライン期間 | 16  | 1024 | PCLK |

| t4 | 水平フロントポーチ    | 2   | —    | PCLK |

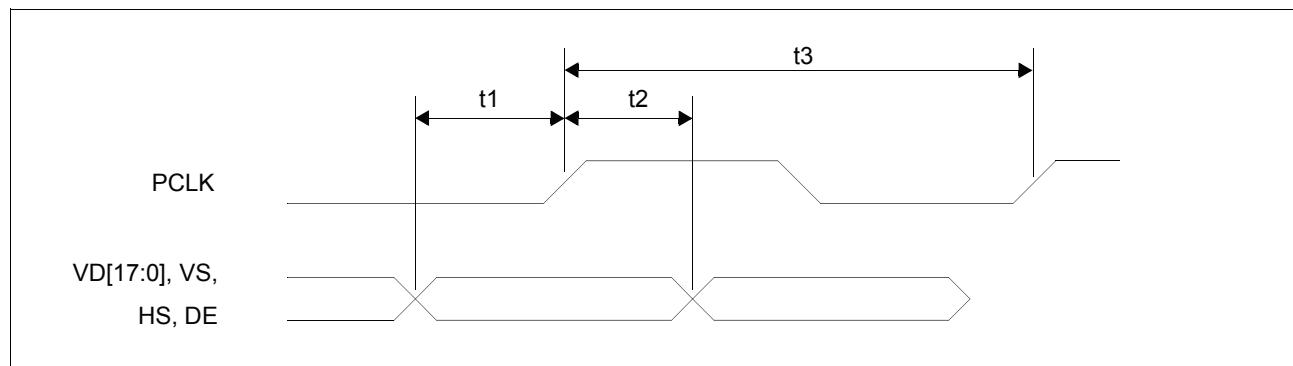

## 8.5.3 PCLK に対する入力信号のタイミング

図8-10: PCLK に対する入力信号のタイミング

表8-10: PCLK に対する入力信号のタイミング

| 記号 | パラメータ                           | Min | Max | 単位 |

|----|---------------------------------|-----|-----|----|

| t1 | VD[17:0]、VS、HS、および DE のセットアップ時間 | 5   | —   | ns |

| t2 | VD[17:0]、VS、HS、および DE のホールド時間   | 8   | —   | ns |

| t3 | PCLK の周期                        | 25  | —   | ns |

### 8.6 TV のタイミング

#### 8.6.1 TV 出力のタイミング

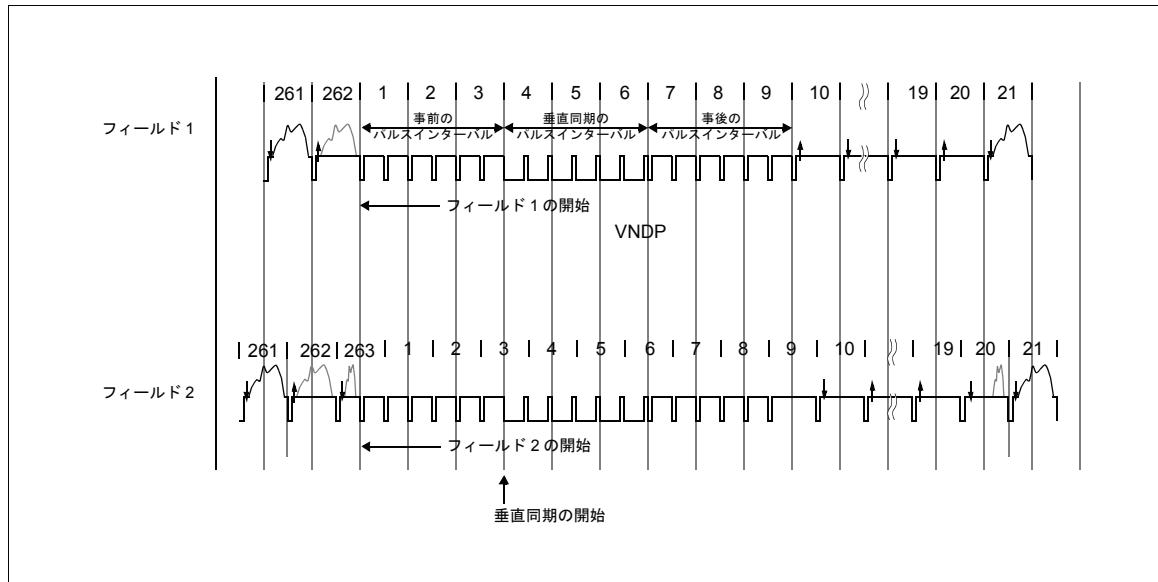

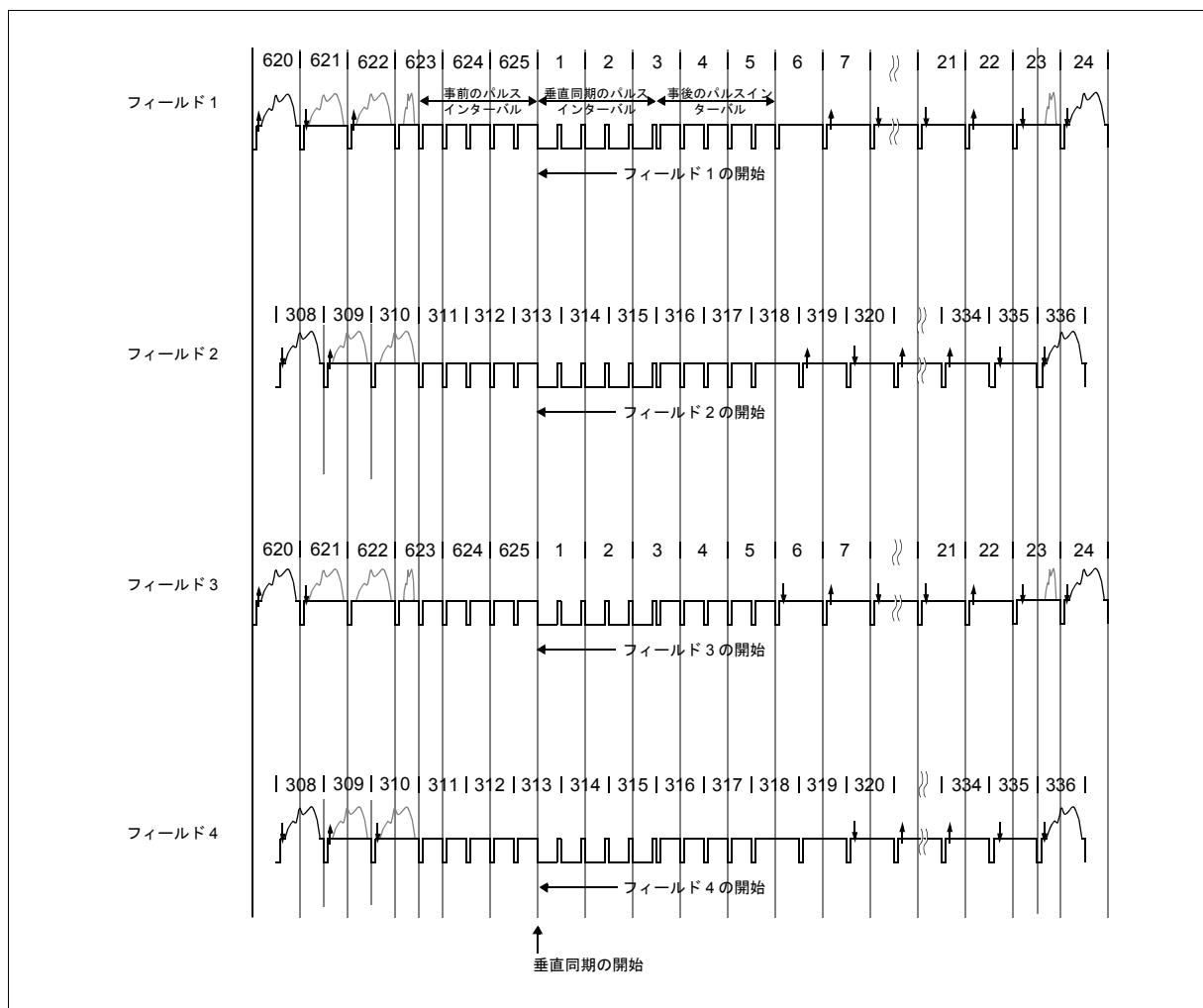

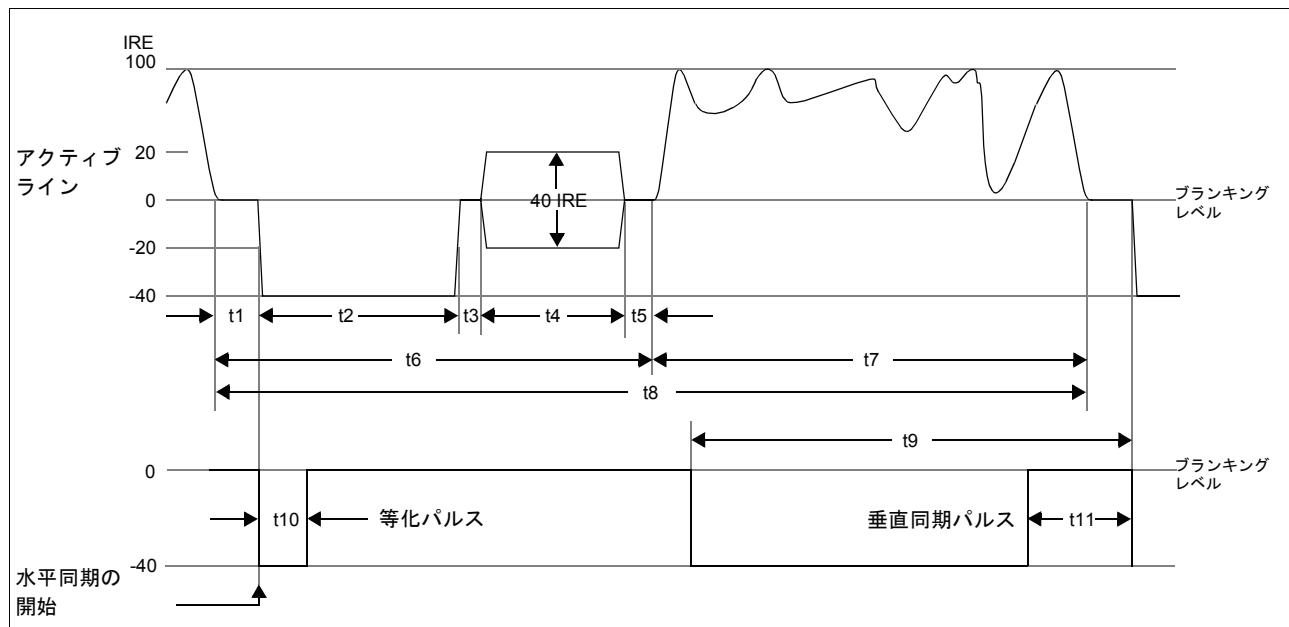

PALとNTSCの全体的なビデオのタイミングをそれぞれ図8-11と図8-12に示します。

図8-11: NTSC ビデオのタイミング

図8-12: PALビデオのタイミング

## 8.AC 特性

図 8-13: NTSC/PAL の水平タイミング

表 8-11: NTSC/PAL の水平タイミング

| 記号  | パラメータ           | NTSC M/J<br>(525 ライン) | PAL B/D/G/H/I/N<br>(625 ライン) | PAL Nc<br>(625 ライン) | PAL M<br>(525 ライン) | 単位 |

|-----|-----------------|-----------------------|------------------------------|---------------------|--------------------|----|

| t1  | フロントポーチ (注 1)   | 0.96                  | 0.96                         | 0.96                | 0.96               | μs |

| t2  | 水平同期            | 4.7                   | 4.7                          | 4.7                 | 4.7                | μs |

| t3  | ブリーズウェイ         | 0.85                  | 0.9                          | 0.9                 | 1.12               | μs |

| t4  | カラーバースト         | 2.52                  | 2.26                         | 2.52                | 2.52               | μs |

| t5  | カラーバックポーチ (注 2) | 1.19                  | 1.85                         | 1.59                | 0.96               | μs |

| t6  | 水平ブランкиング       | 10.222                | 10.667                       | 10.667              | 10.222             | μs |

| t7  | アクティブビデオ        | 53.333                | 53.333                       | 53.333              | 53.333             | μs |

| t8  | ライン期間           | 63.555                | 64                           | 64                  | 64                 | μs |

| t9  | ハーフライン期間        | 31.7777               | 32                           | 32                  | 32                 | μs |

| t10 | 等化パルス           | 2.3                   | 2.35                         | 2.35                | 2.35               | μs |

| t11 | 垂直セレーション        | 4.66                  | 4.66                         | 4.66                | 4.66               | μs |

### 注

この表の数値は、REG[9Eh] ビット 6-4 が 000 (デフォルト) に設定されているときに測定したものです。

1.  $t1 = 0.074 \times (13 \pm \text{REG}[9Eh] \text{ ビット 6-4}) \text{ } \mu\text{s}$

( $\pm$  は REG[9Eh] ビット 7 によって制御されます)

2.  $t5 = 2.15\mu\text{s} - t1$  (NTSC M/J の場合)

$= 2.81\mu\text{s} - t1$  (PAL B/D/G/H/I/N の場合)

$= 2.55\mu\text{s} - t1$  (PAL Nc の場合)

$= 1.92\mu\text{s} - t1$  (PAL M の場合)

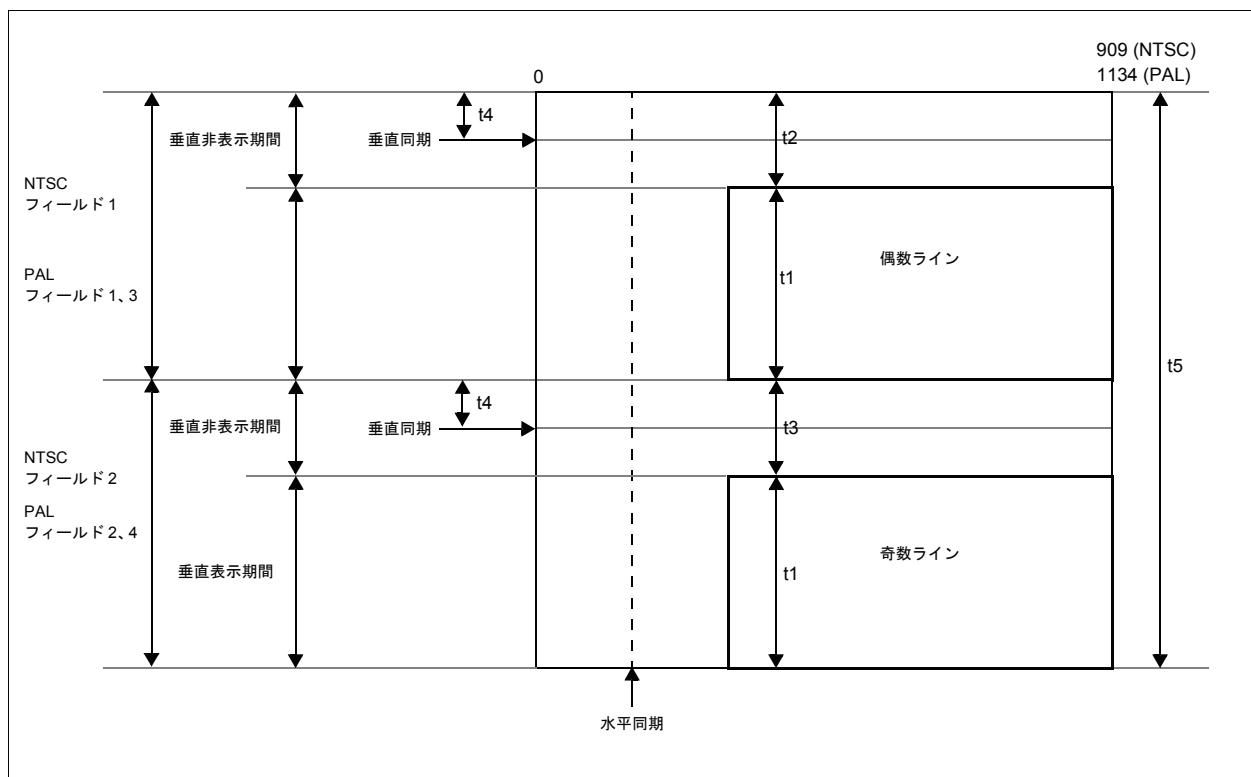

図 8-14: NTSC/PAL の垂直タイミング

表 8-12: NTSC/PAL の垂直タイミング

| 記号         | パラメータ      | NTSC M/J、PAL M | PAL B/D/G/H/I/Nc | 単位         |

|------------|------------|----------------|------------------|------------|

| $T_{LINE}$ | ライン期間      | 63.5555        | 64               | $\mu s$    |

| $t_1$      | 垂直フィールド期間  | 240            | 288              | $T_{LINE}$ |

| $t_2$      | 垂直偶数ブランキング | 22             | 24               | $T_{LINE}$ |

| $t_3$      | 垂直奇数ブランキング | 23             | 25               | $T_{LINE}$ |

| $t_4$      | 垂直同期位置 (注) | 3              | 3                | $T_{LINE}$ |

| $t_5$      | フレーム期間     | 525            | 625              | $T_{LINE}$ |

## 注

この表の数値は、REG[9Eh] ビット 3-2 が 00 (デフォルト) に設定されているときに測定したものです。

$$t_4 = 3 - \text{REG}[9Eh] \text{ ビット 3-2}$$

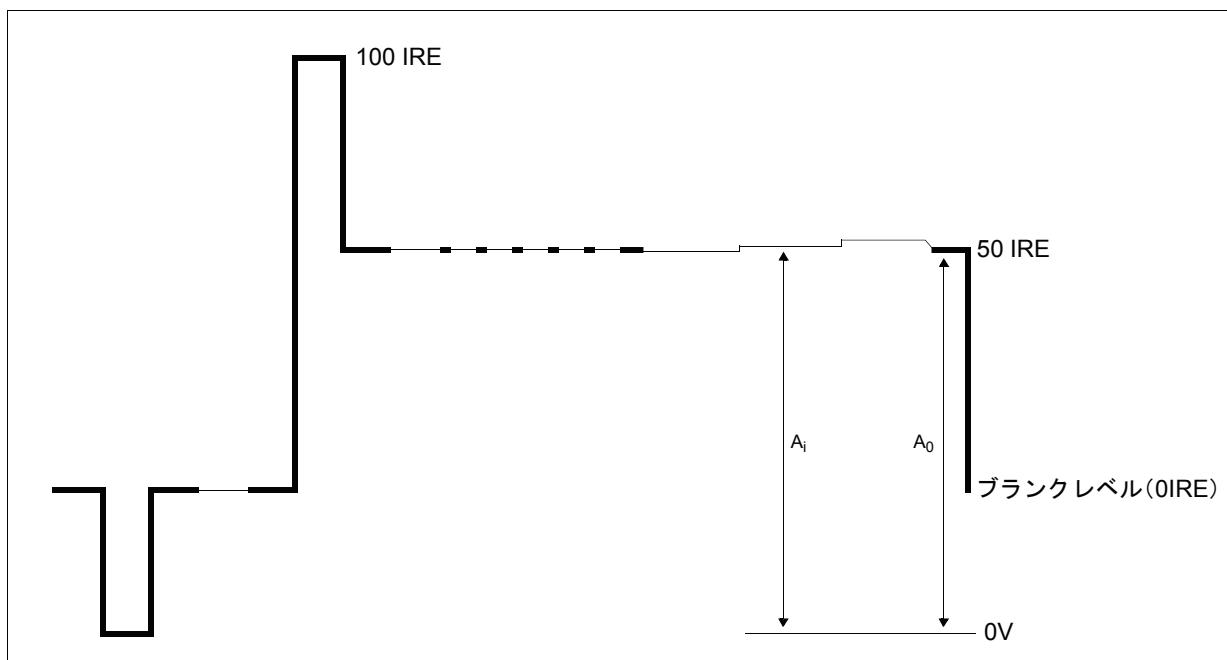

### 8.6.2 TV 出力のパラメータ

この項で得られる計算結果はすべて、コンポジットビデオ出力に関するものです。

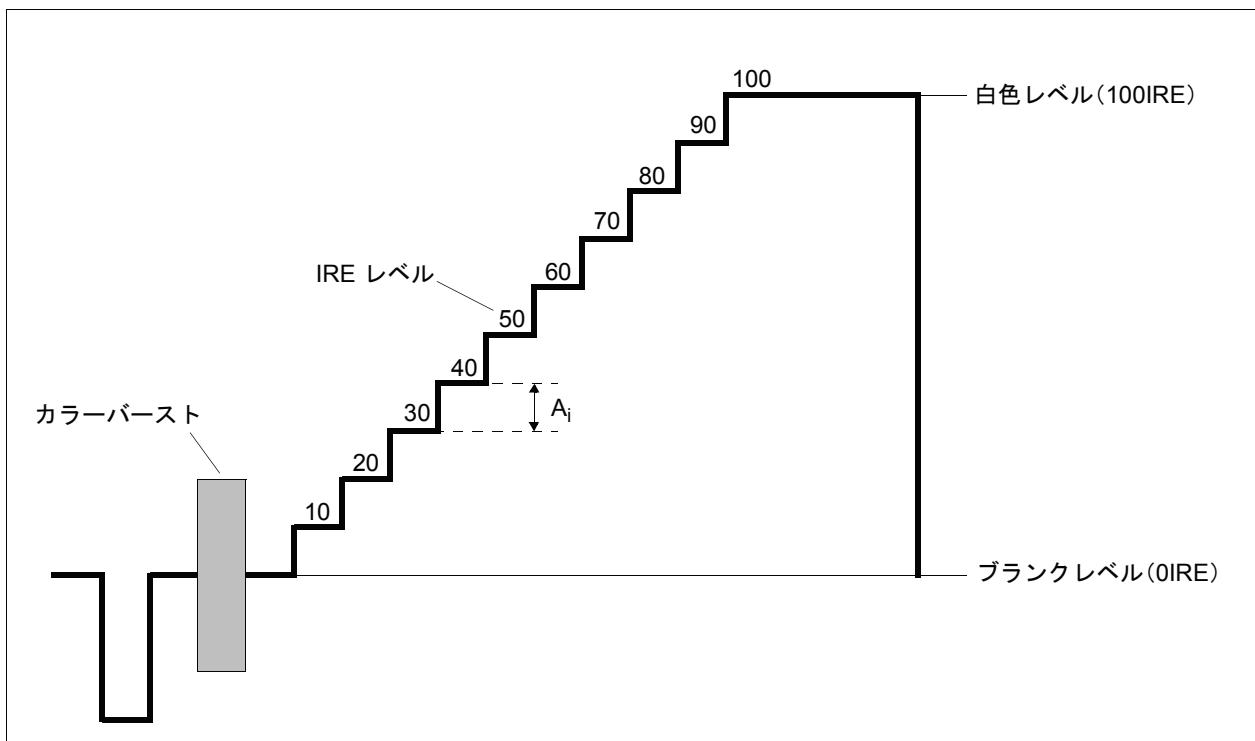

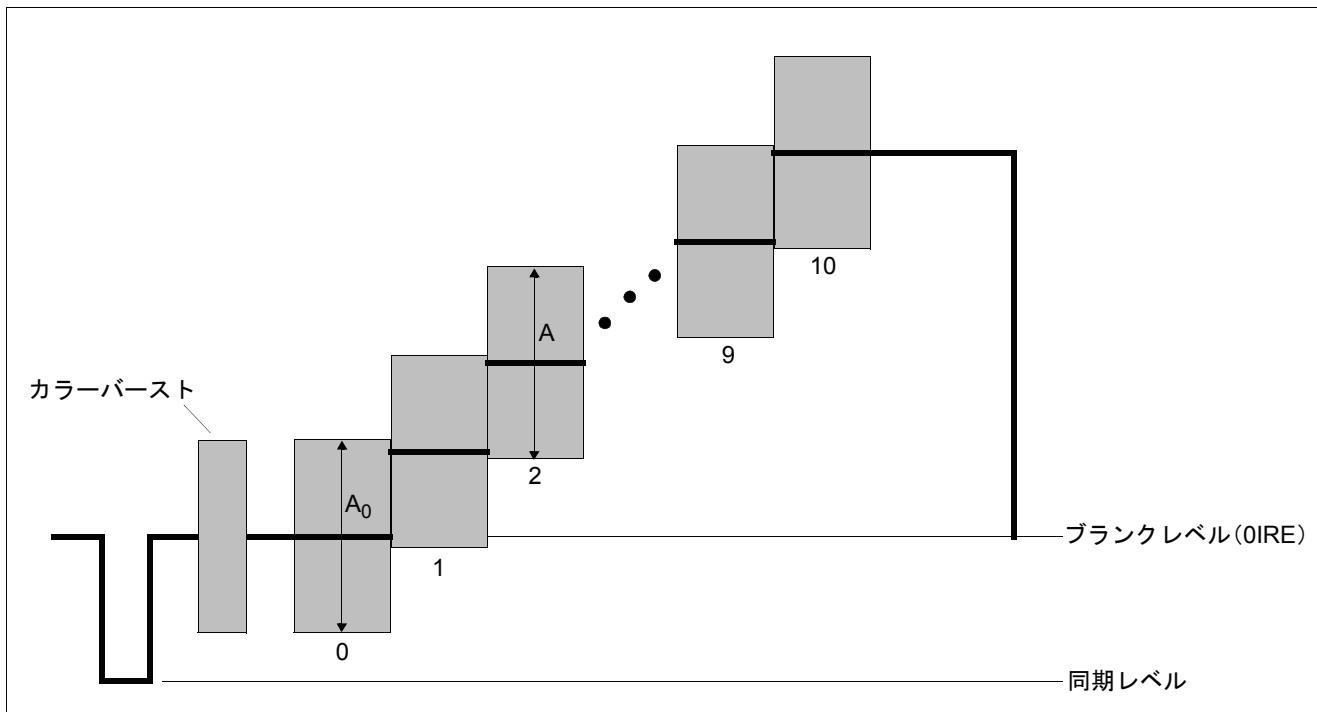

#### ルミナンスの非直線性

TV システムにおいて、ルミナンスゲインがルミナンスレベルに影響される場合、ルミナンスの非直線性が存在します。S1D13746 では、ルミナンスゲインはルミナンスレベルに影響されません。ルミナンスの非直線性は、回路と DAC 性能の丸め精度にのみ左右されます。この数字は、最悪条件の DAC パラメータを考慮しながら、10 ステップステアケースのテストパターンにおいて各ステップの振幅を比較することで計算されます。最大のステップと最小のステップとの差異が最大のステップ振幅の率として表され、ルミナンスの非直線性のひずみ量となります。

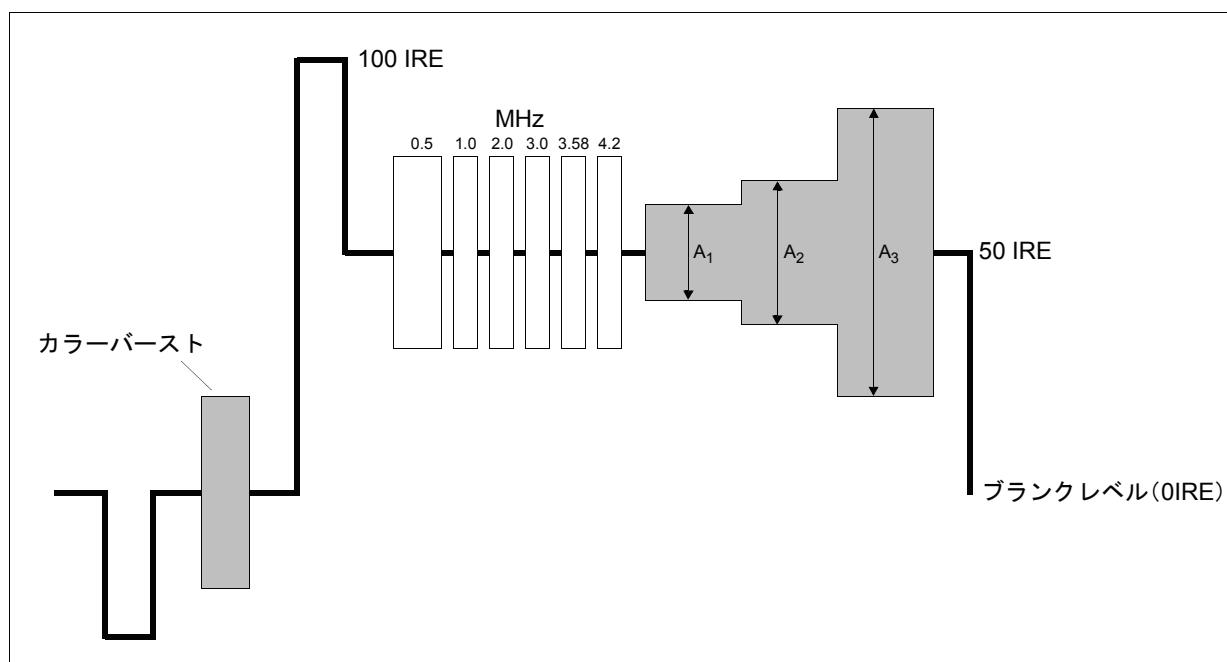

図 8-15: ルミナンスの非直線性

$$\text{ルミナンスの非直線性} = [\text{Max}(A_i) - \text{Min}(A_i)] \div \text{Max}(A_i)$$

ここで、 $i = 1 \sim 10$  ステップの各位置

表 8-13: ルミナンスの非直線性 (10 ステップステアケースによる)

|      | PAL       |        |        | NTSC   |        |

|------|-----------|--------|--------|--------|--------|

|      | B,D,G,H,I | M      | N      | Nc     | M      |

| 標準値  | 7.14%     | 0.00%  | 0.00%  | 7.14%  | 0.00%  |

| 最悪条件 | 41.18%    | 37.50% | 37.50% | 41.18% | 37.50% |

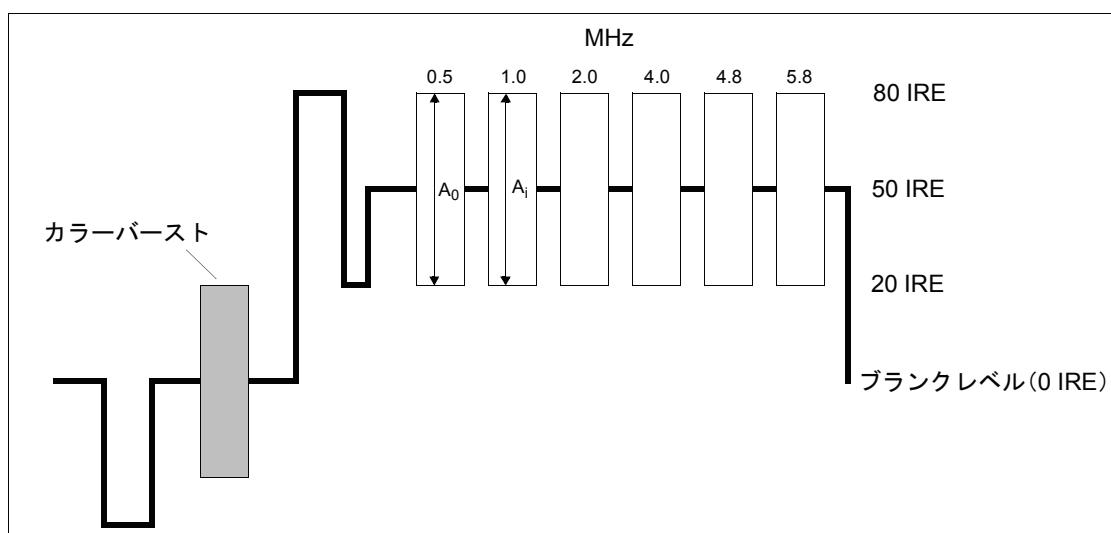

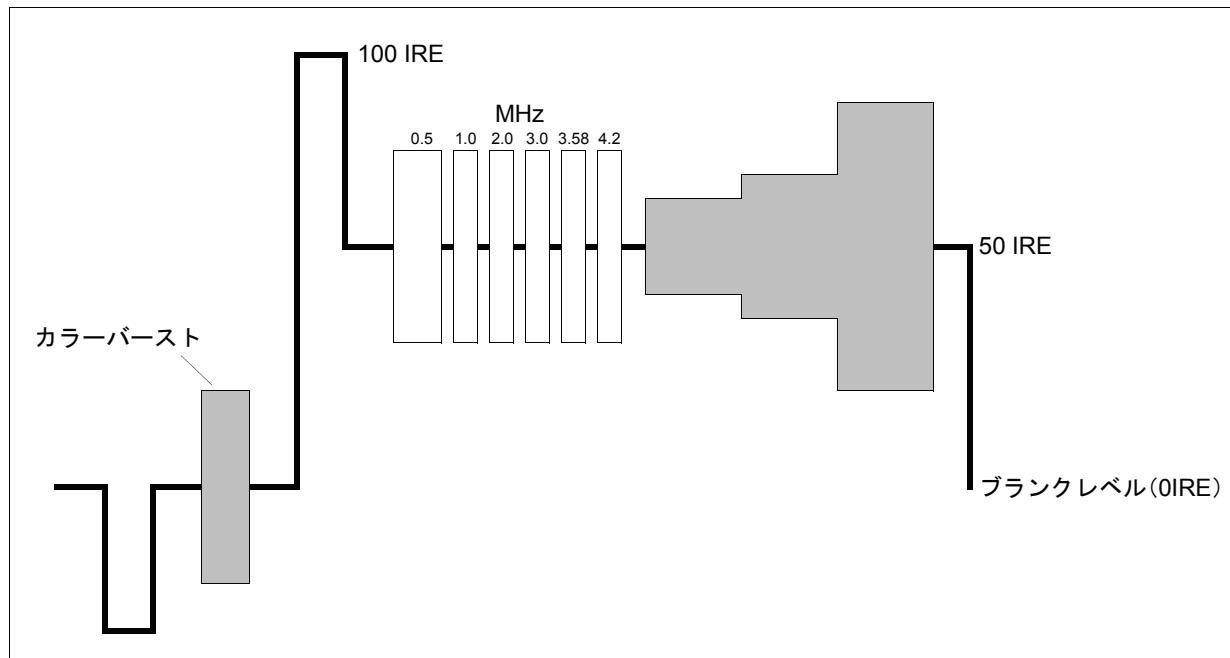

## 75%と100%のカラーバーレベル

この数字は、最悪条件の DAC パラメータを考慮しながら、75%と100%のカラーバーテストパターンに基づいて計算されます。

表 8-14: 75%と100%のカラーバーレベル

|             |          | 75%カラーバー (mV) |         |         |         |         |         | 100%カラーバー (mV) |         |         |         |         |         |         |

|-------------|----------|---------------|---------|---------|---------|---------|---------|----------------|---------|---------|---------|---------|---------|---------|

|             |          | PAL           |         |         | NTSC    |         |         | PAL            |         |         | NTSC    |         |         |         |

|             |          | B,D,G,<br>H,I | M       | N       | Nc      | M       | J       | B,D,G,<br>H,I  | M       | N       | Nc      | M       | J       |         |

| 同期チップ       | Max      | 30.75         | 30.75   | 30.75   | 30.75   | 30.75   | 30.75   | 30.75          | 30.75   | 30.75   | 30.75   | 30.75   | 30.75   |         |

|             | Typ      | 20.33         | 20.33   | 20.33   | 20.33   | 20.33   | 20.33   | 20.33          | 20.33   | 20.33   | 20.33   | 20.33   | 20.33   |         |

|             | Min      | 11.44         | 11.44   | 11.44   | 11.44   | 11.44   | 11.44   | 11.44          | 11.44   | 11.44   | 11.44   | 11.44   | 11.44   |         |

| ブランク        | Max      | 360.65        | 343.87  | 343.87  | 360.65  | 343.87  | 343.87  | 360.65         | 343.87  | 343.87  | 360.65  | 343.87  | 343.87  |         |

|             | Typ      | 320.23        | 304.99  | 304.99  | 320.23  | 304.99  | 304.99  | 320.23         | 304.99  | 304.99  | 320.23  | 304.99  | 304.99  |         |

|             | Min      | 281.35        | 267.62  | 267.62  | 281.35  | 267.62  | 267.62  | 281.35         | 267.62  | 267.62  | 281.35  | 267.62  | 267.62  |         |

| カラー<br>バースト | 高<br>チップ | Max           | 522.80  | 506.02  | 506.02  | 522.80  | 499.03  | 499.03         | 522.80  | 506.02  | 506.02  | 522.80  | 499.03  | 499.03  |

|             |          | Typ           | 467.64  | 452.39  | 452.39  | 467.64  | 446.04  | 446.04         | 467.64  | 452.39  | 452.39  | 467.64  | 446.04  | 446.04  |

|             |          | Min           | 414.02  | 400.29  | 400.29  | 414.02  | 394.57  | 394.57         | 414.02  | 400.29  | 400.29  | 414.02  | 394.57  | 394.57  |

|             | 低<br>チップ | Max           | 197.10  | 180.32  | 180.32  | 197.10  | 187.31  | 187.31         | 197.10  | 180.32  | 180.32  | 197.10  | 187.31  | 187.31  |

|             |          | Typ           | 171.55  | 156.30  | 156.30  | 171.55  | 162.66  | 162.66         | 171.55  | 156.30  | 156.30  | 171.55  | 162.66  | 162.66  |

|             |          | Min           | 147.54  | 133.81  | 133.81  | 147.54  | 139.53  | 139.53         | 147.54  | 133.81  | 133.81  | 147.54  | 139.53  | 139.53  |

| 白           | Max      | 936.56        | 944.95  | 944.95  | 936.56  | 944.95  | 930.97  | 1126.67        | 1129.46 | 1129.46 | 1126.67 | 1129.46 | 1126.67 |         |

|             | Typ      | 843.79        | 851.42  | 851.42  | 843.79  | 851.42  | 838.71  | 1016.62        | 1019.16 | 1019.16 | 1016.62 | 1019.16 | 1016.62 |         |

|             | Min      | 752.55        | 759.41  | 759.41  | 752.55  | 759.41  | 747.98  | 908.09         | 910.38  | 910.38  | 908.09  | 910.38  | 908.09  |         |

| 黄           | 高<br>チップ | Max           | 1128.06 | 1123.87 | 1123.87 | 1128.06 | 1123.87 | 1126.67        | 1375.48 | 1365.70 | 1365.70 | 1375.48 | 1365.70 | 1385.27 |

|             |          | Typ           | 1017.89 | 1014.08 | 1014.08 | 1017.89 | 1014.08 | 1016.62        | 1242.82 | 1233.92 | 1233.92 | 1242.82 | 1233.92 | 1251.71 |

|             |          | Min           | 909.24  | 905.81  | 905.81  | 909.24  | 905.81  | 908.09         | 1111.67 | 1103.67 | 1103.67 | 1111.67 | 1103.67 | 1119.68 |

|             | 低<br>チップ | Max           | 610.86  | 641.61  | 641.61  | 610.86  | 641.61  | 599.68         | 697.53  | 724.09  | 724.09  | 697.53  | 724.09  | 687.74  |

|             |          | Typ           | 547.70  | 575.66  | 575.66  | 547.70  | 575.66  | 537.54         | 626.49  | 650.64  | 650.64  | 626.49  | 650.64  | 617.60  |

|             |          | Min           | 486.07  | 511.23  | 511.23  | 486.07  | 511.23  | 476.92         | 556.98  | 578.71  | 578.71  | 556.98  | 578.71  | 548.97  |

| シアン         | 高<br>チップ | Max           | 1123.87 | 1126.67 | 1125.27 | 1123.87 | 1126.67 | 1123.87        | 1378.28 | 1369.89 | 1369.89 | 1378.28 | 1369.89 | 1385.27 |

|             |          | Typ           | 1014.08 | 1016.62 | 1015.35 | 1014.08 | 1016.62 | 1014.08        | 1245.36 | 1237.73 | 1237.73 | 1245.36 | 1237.73 | 1251.71 |

|             |          | Min           | 905.81  | 908.09  | 906.95  | 905.81  | 908.09  | 905.81         | 1113.96 | 1107.10 | 1107.10 | 1113.96 | 1107.10 | 1119.68 |

|             | 低<br>チップ | Max           | 401.18  | 438.92  | 438.92  | 401.18  | 438.92  | 378.82         | 415.16  | 451.51  | 451.51  | 415.16  | 451.51  | 396.99  |

|             |          | Typ           | 357.09  | 391.40  | 391.40  | 357.09  | 391.40  | 336.75         | 369.79  | 402.83  | 402.83  | 369.79  | 402.83  | 353.27  |

|             |          | Min           | 314.52  | 345.40  | 345.40  | 314.52  | 345.40  | 296.22         | 325.95  | 355.69  | 355.69  | 325.95  | 355.69  | 311.09  |

| 緑           | 高<br>チップ | Max           | 1035.81 | 1040.00 | 1040.00 | 1035.81 | 1040.00 | 1031.61        | 1265.05 | 1253.87 | 1253.87 | 1265.05 | 1253.87 | 1260.86 |

|             |          | Typ           | 934.02  | 937.83  | 937.83  | 934.02  | 937.83  | 930.21         | 1142.42 | 1132.26 | 1132.26 | 1142.42 | 1132.26 | 1138.61 |

|             |          | Min           | 833.75  | 837.18  | 837.18  | 833.75  | 837.18  | 830.32         | 1021.32 | 1012.17 | 1012.17 | 1021.32 | 1012.17 | 1017.89 |

|             | 低<br>チップ | Max           | 355.05  | 401.18  | 401.18  | 355.05  | 401.18  | 336.88         | 360.65  | 399.78  | 399.78  | 360.65  | 399.78  | 342.47  |

|             |          | Typ           | 315.15  | 357.09  | 357.09  | 315.15  | 357.09  | 298.63         | 320.23  | 355.82  | 355.82  | 320.23  | 355.82  | 303.71  |

|             |          | Min           | 276.77  | 314.52  | 314.52  | 276.77  | 314.52  | 261.91         | 281.35  | 313.37  | 313.37  | 281.35  | 313.37  | 266.48  |

| マゼンタ        | 高<br>チップ | Max           | 940.75  | 944.95  | 944.95  | 940.75  | 944.95  | 930.97         | 1125.27 | 1125.27 | 1125.27 | 1125.27 | 1125.27 | 1121.08 |

|             |          | Typ           | 847.61  | 851.42  | 851.42  | 847.61  | 851.42  | 838.71         | 1015.35 | 1015.35 | 1015.35 | 1015.35 | 1015.35 | 1011.53 |

|             |          | Min           | 755.98  | 759.41  | 759.41  | 755.98  | 759.41  | 747.98         | 906.95  | 906.95  | 906.95  | 906.95  | 906.95  | 903.52  |

|             | 低<br>チップ | Max           | 260.00  | 306.13  | 306.13  | 260.00  | 306.13  | 236.24         | 220.86  | 271.18  | 271.18  | 220.86  | 271.18  | 202.69  |

|             |          | Typ           | 228.74  | 270.67  | 270.67  | 228.74  | 270.67  | 207.14         | 193.16  | 238.91  | 238.91  | 193.16  | 238.91  | 176.64  |

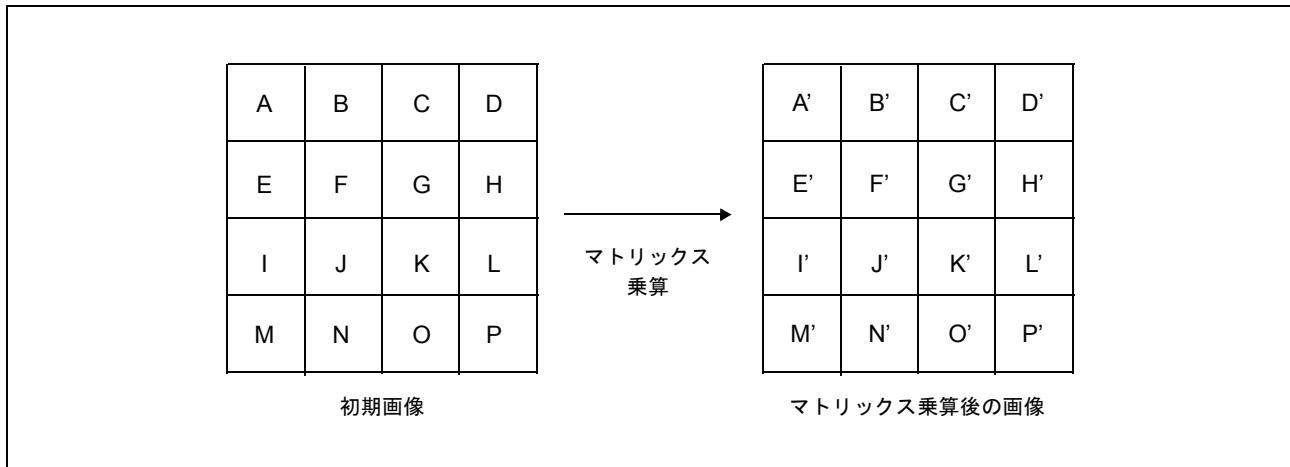

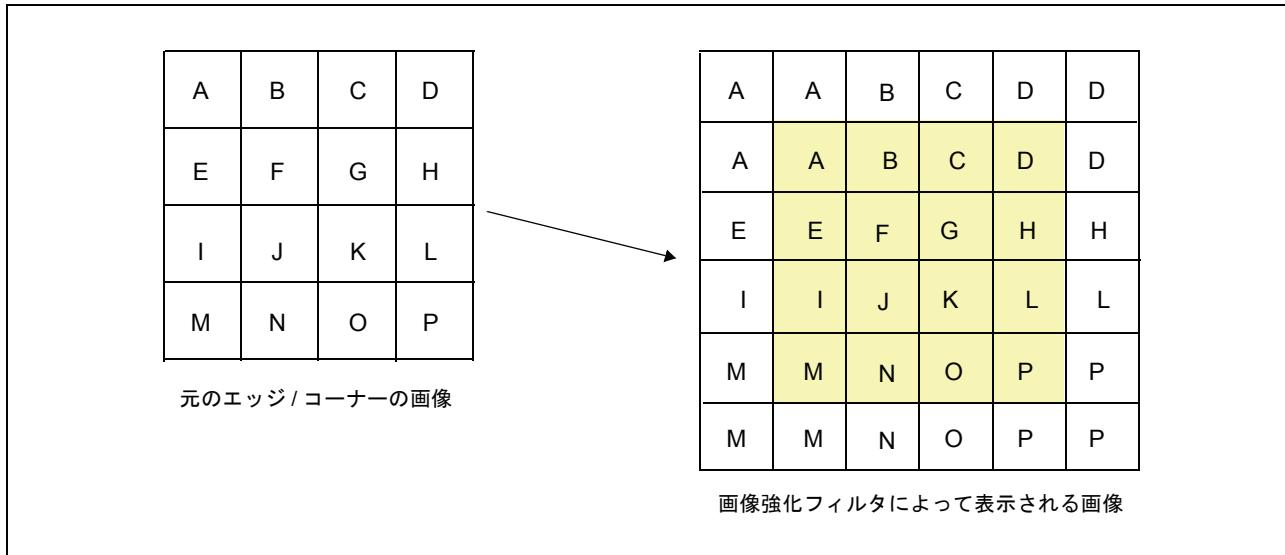

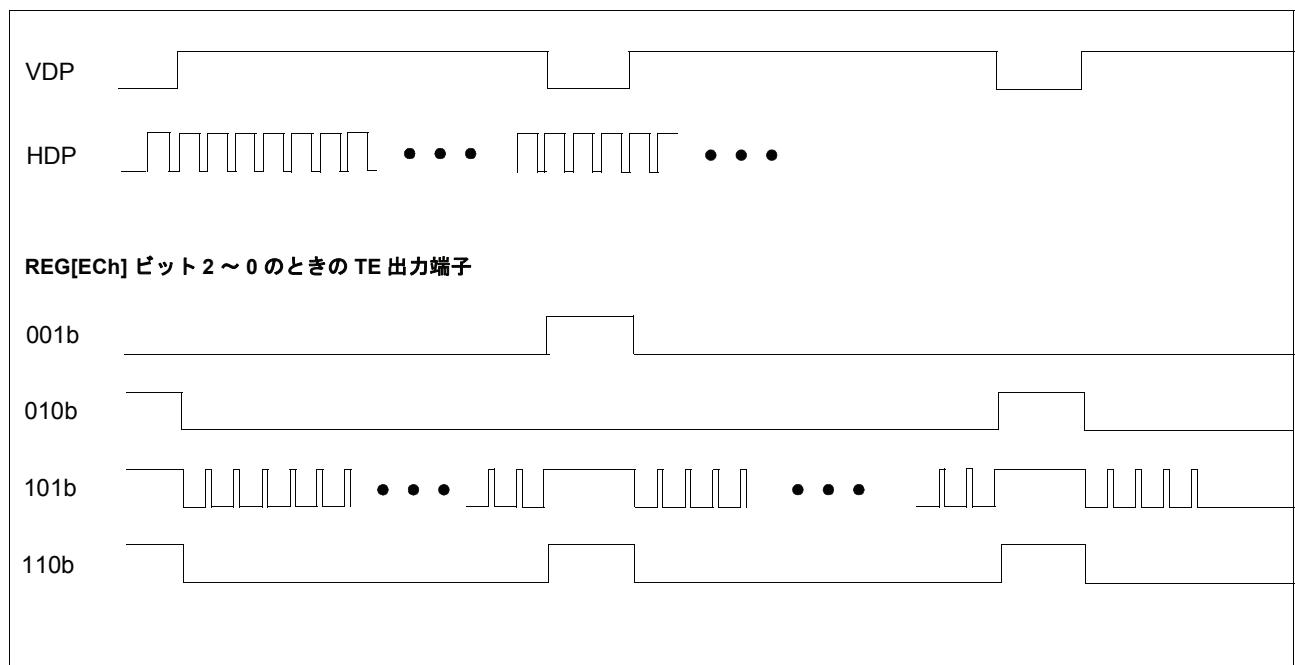

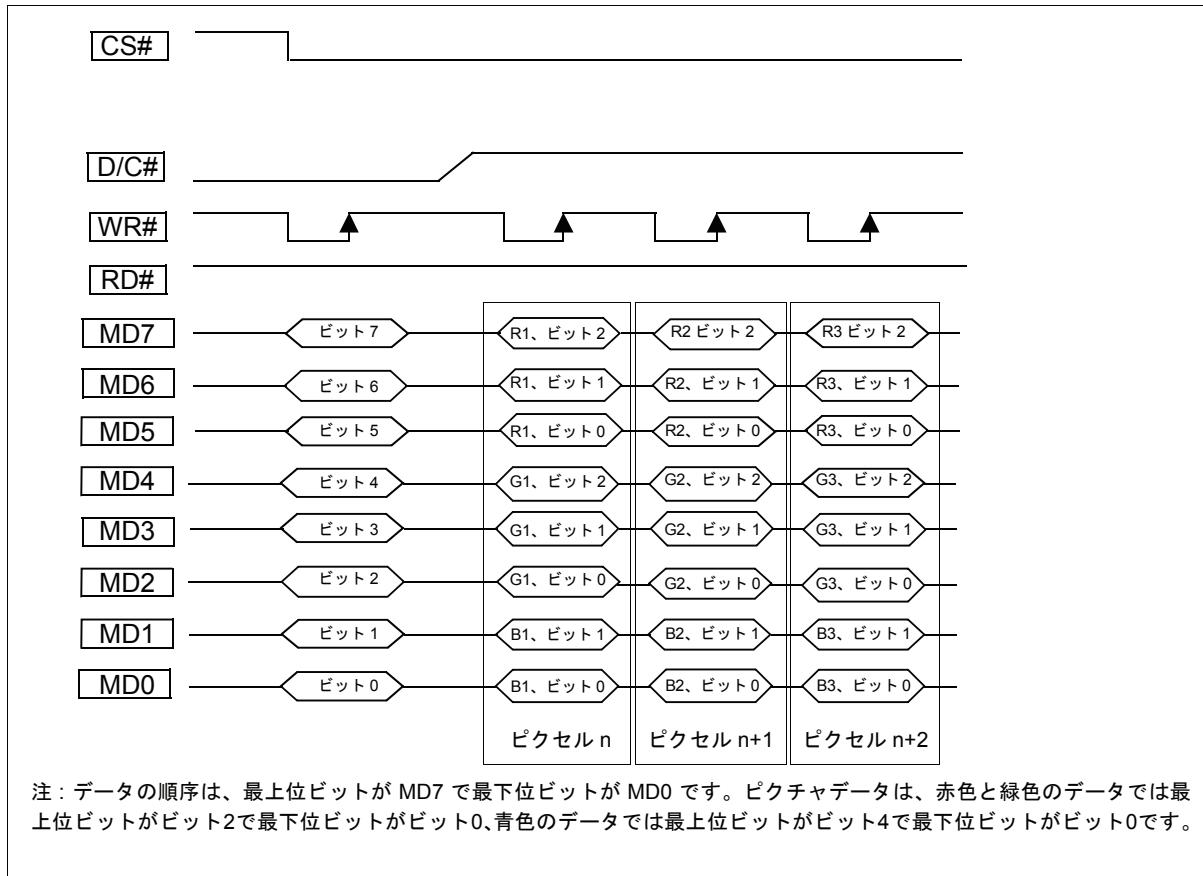

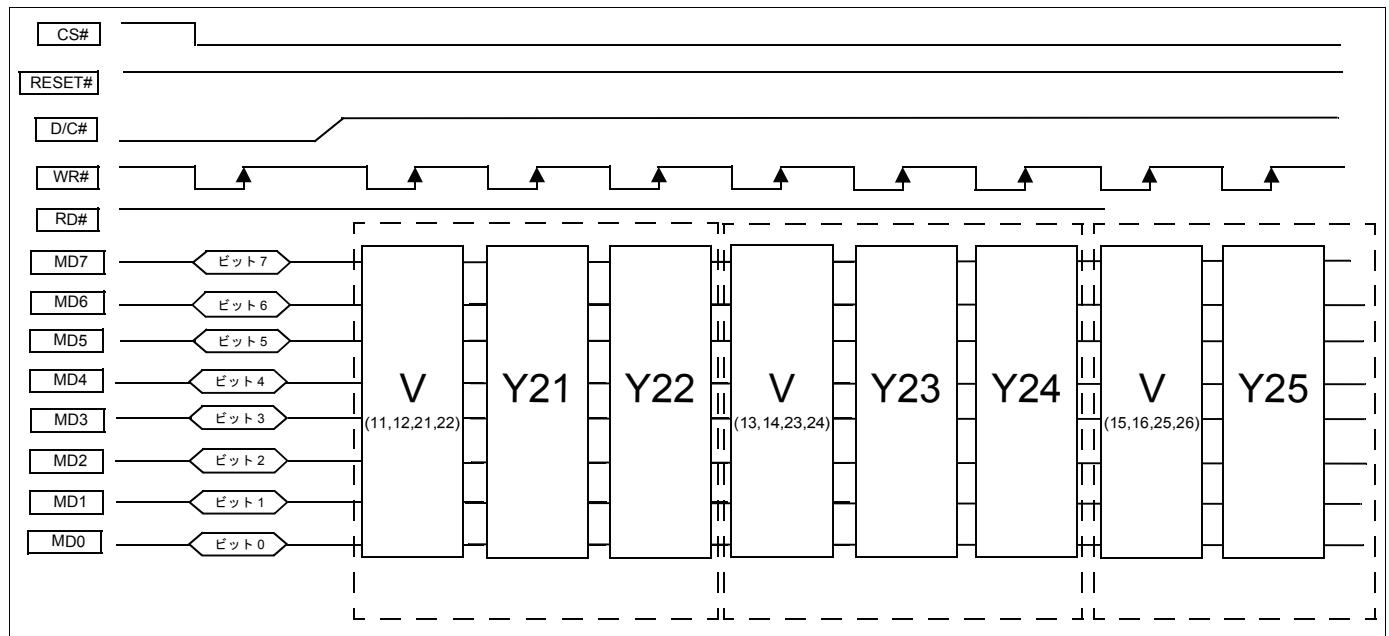

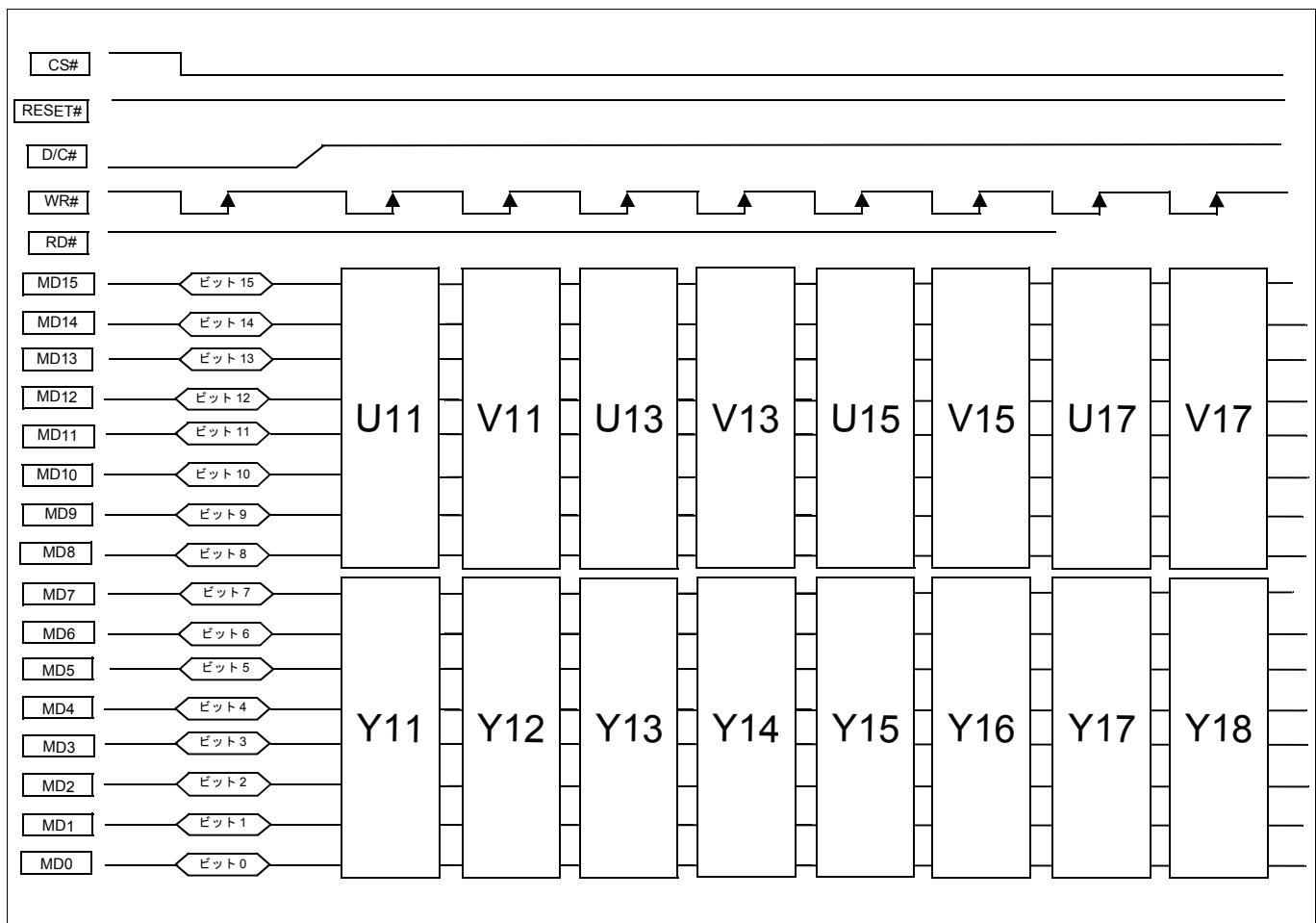

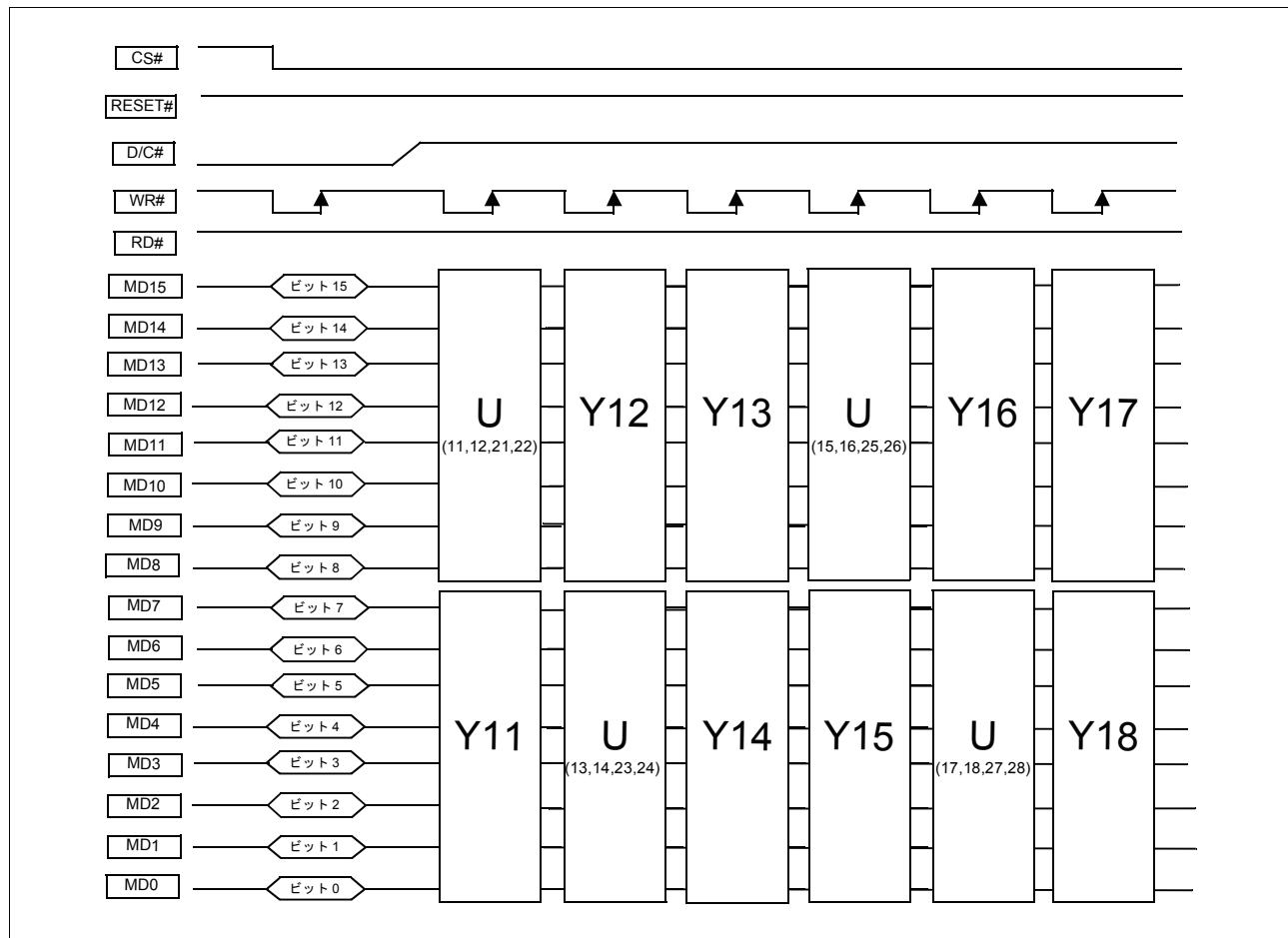

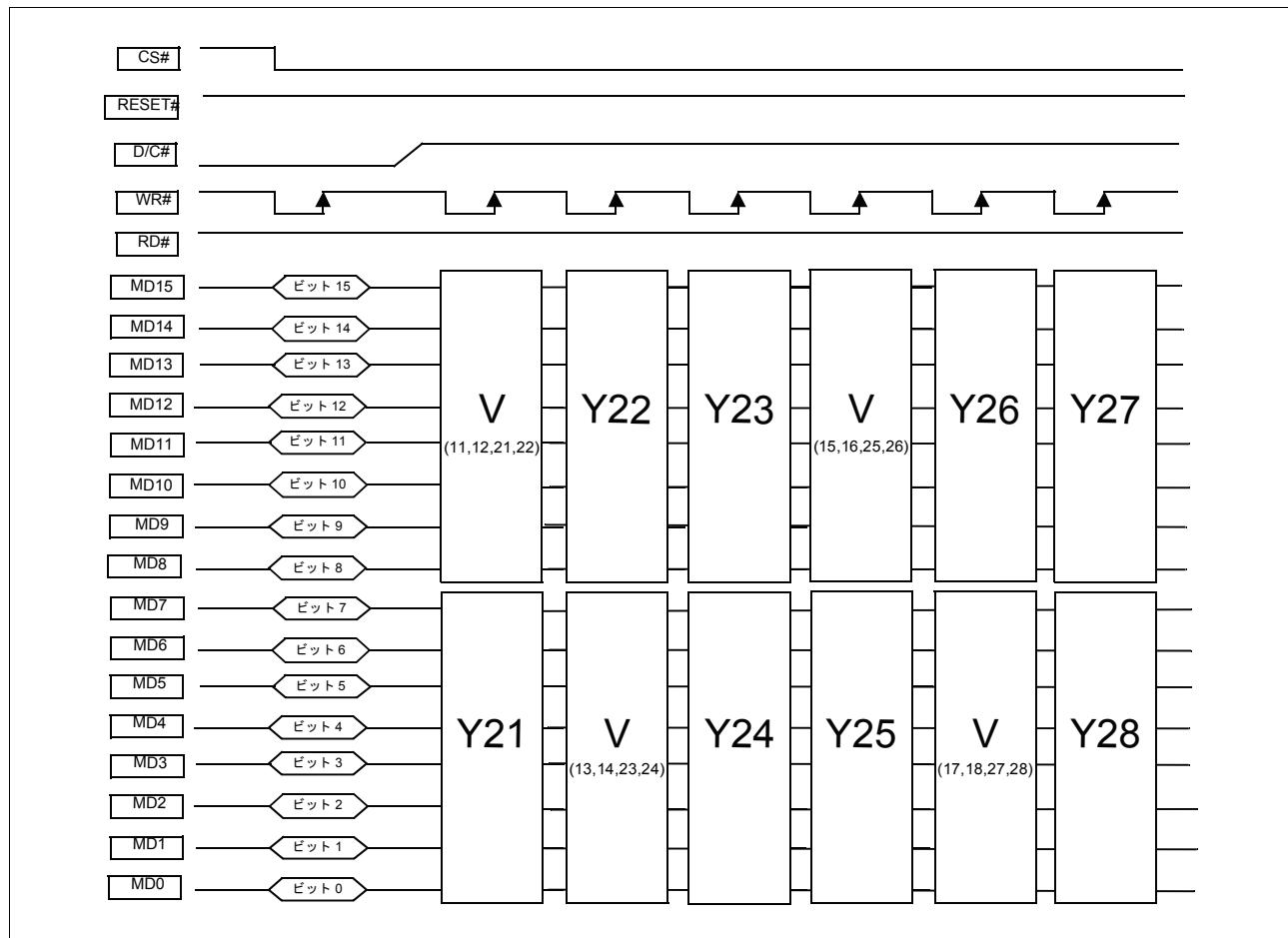

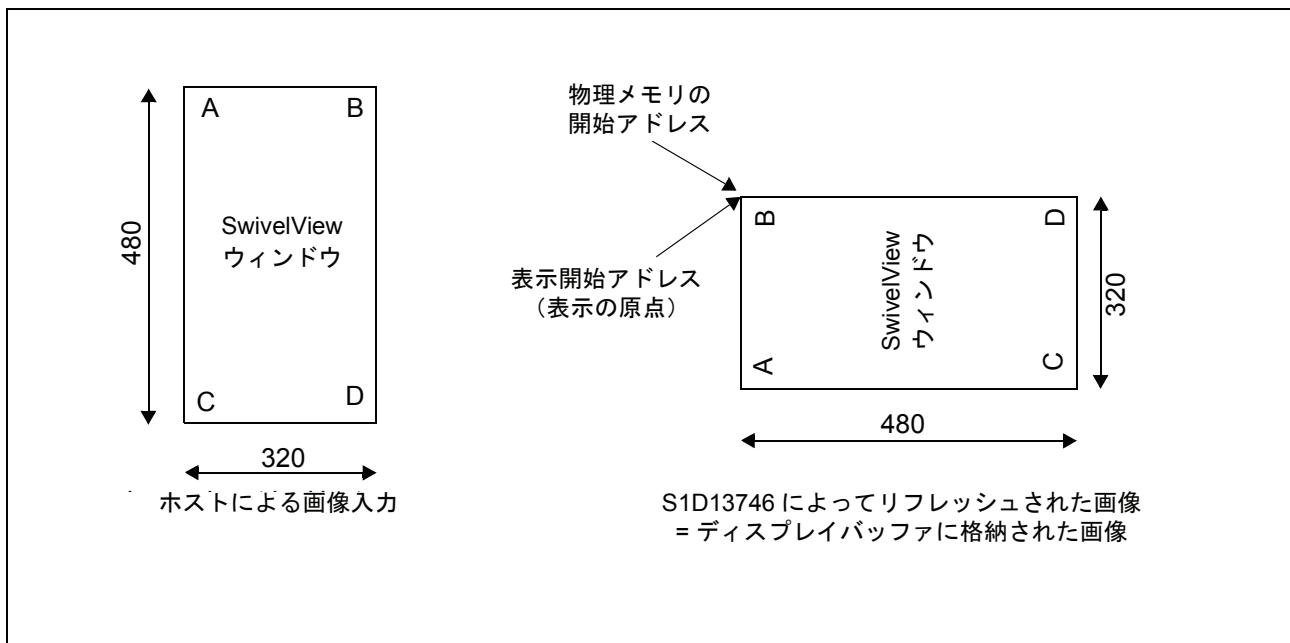

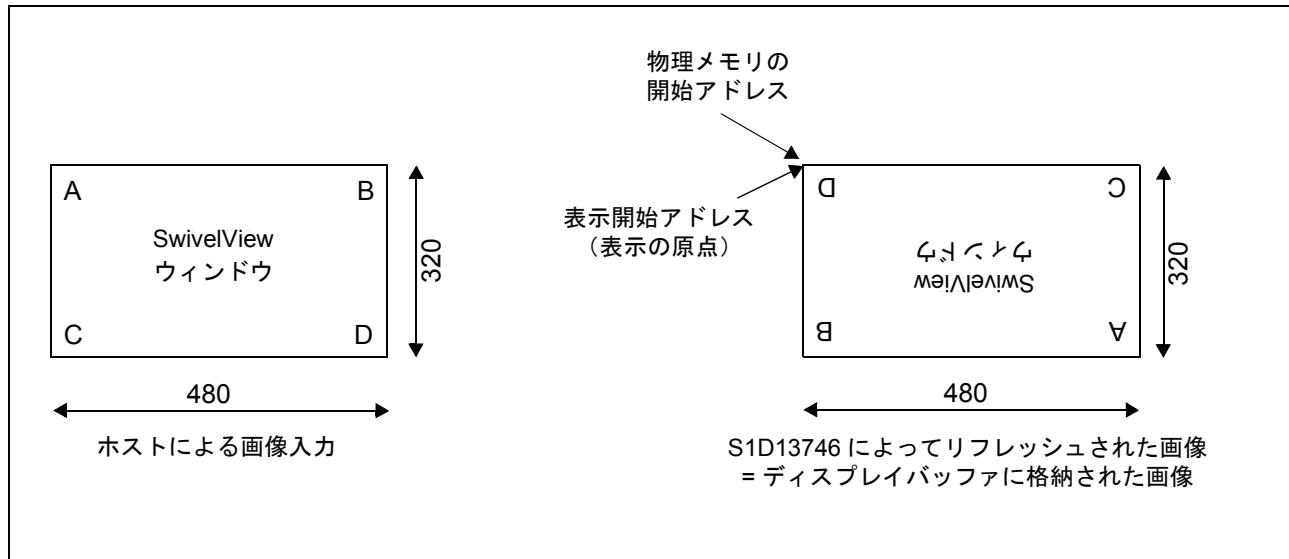

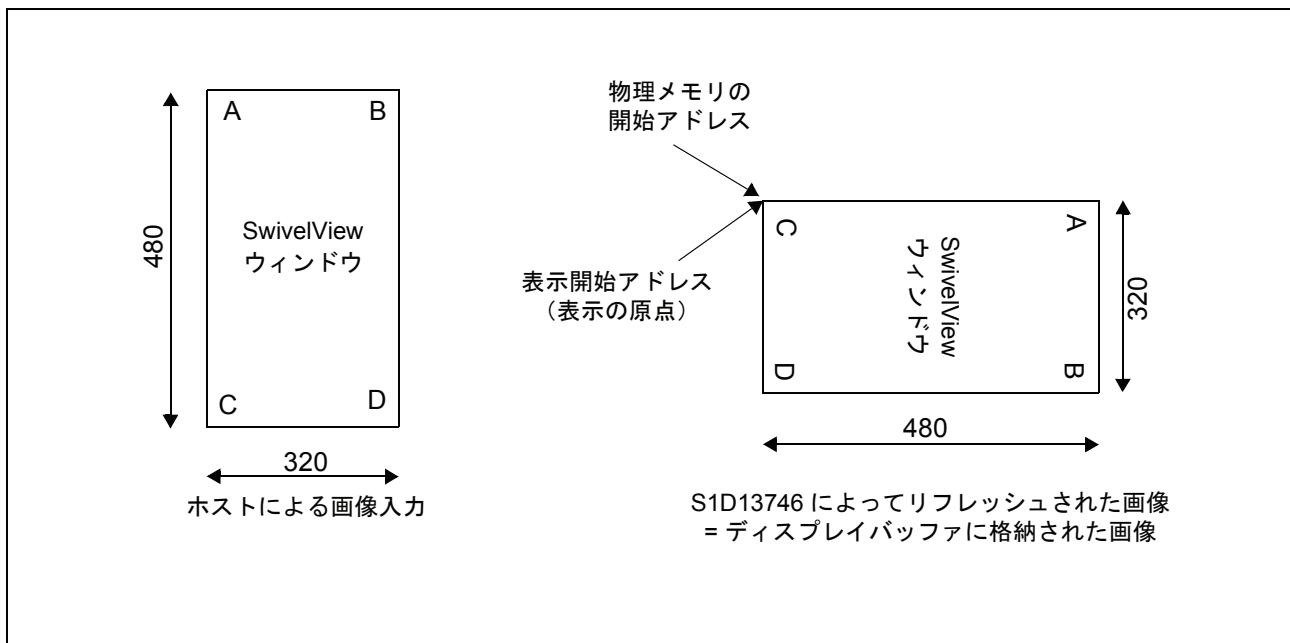

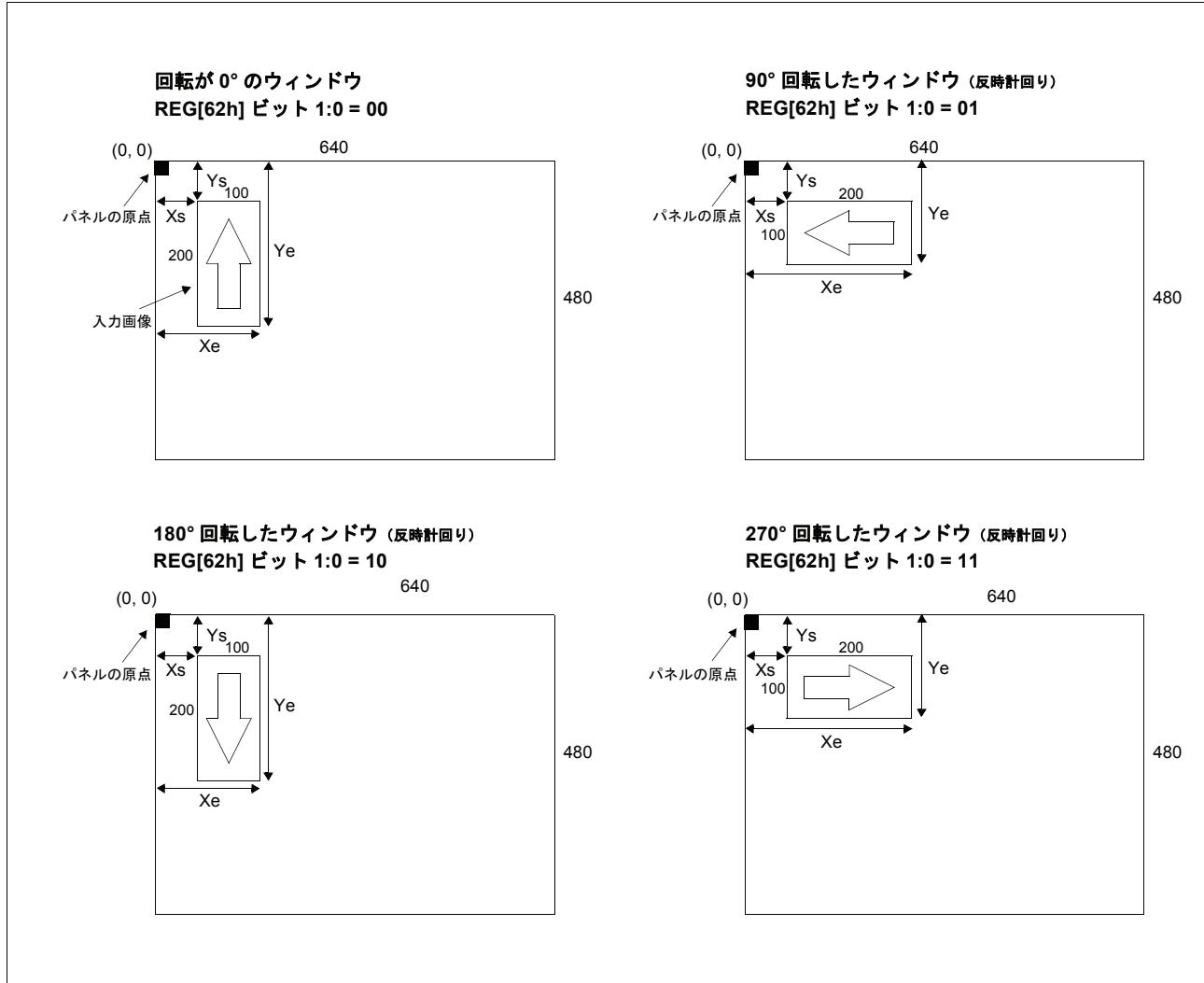

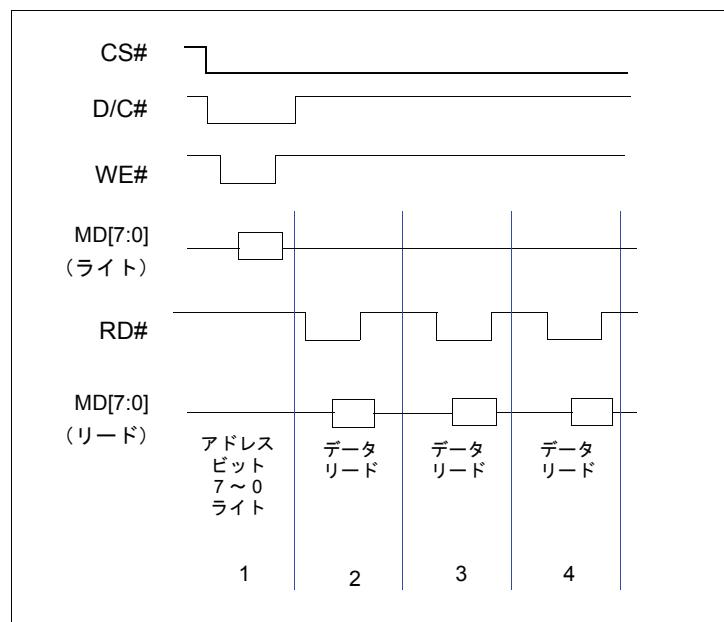

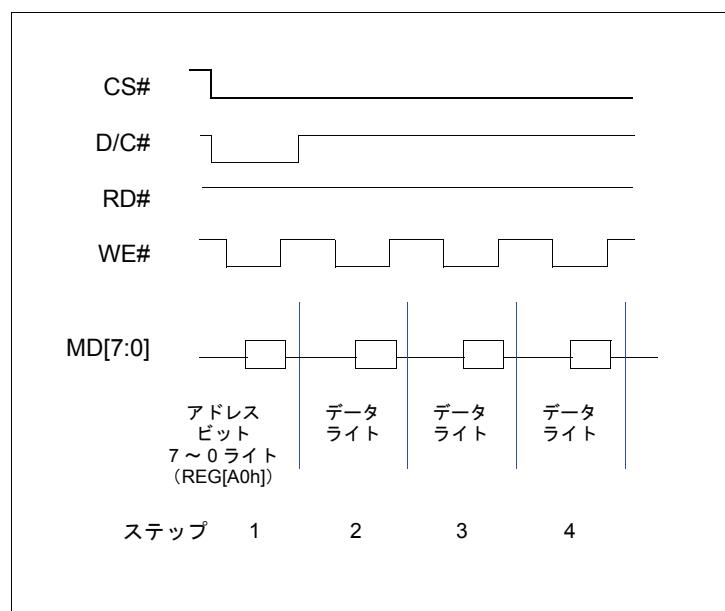

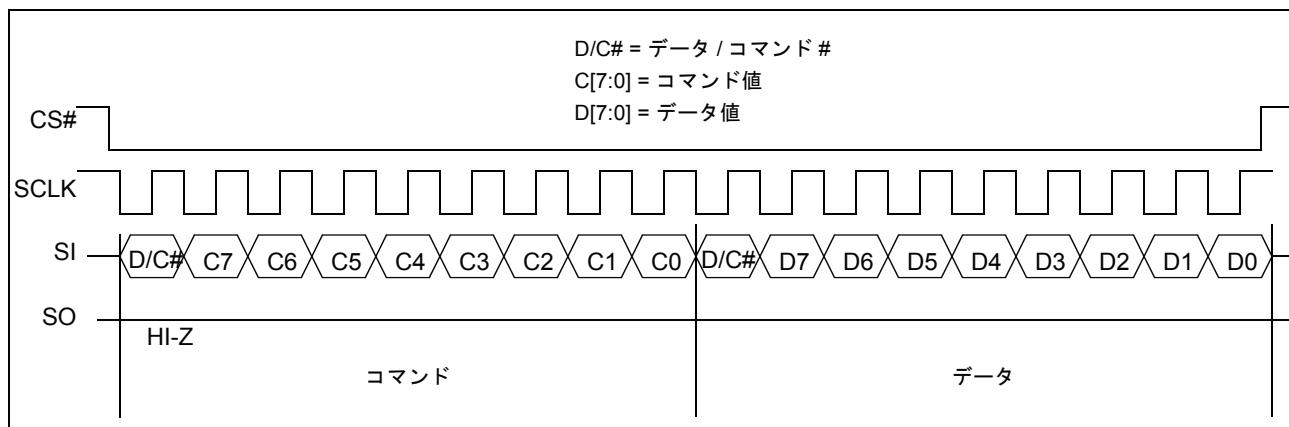

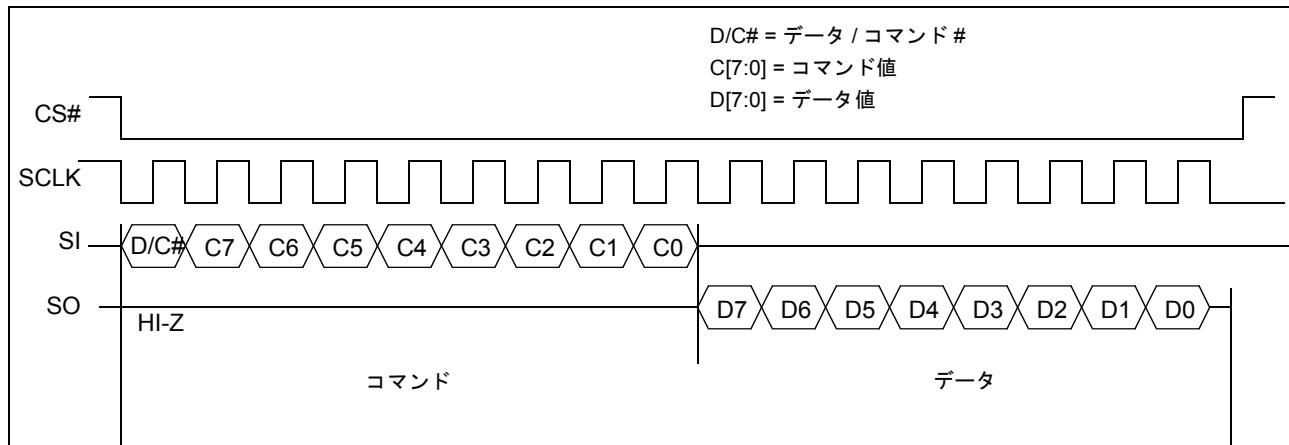

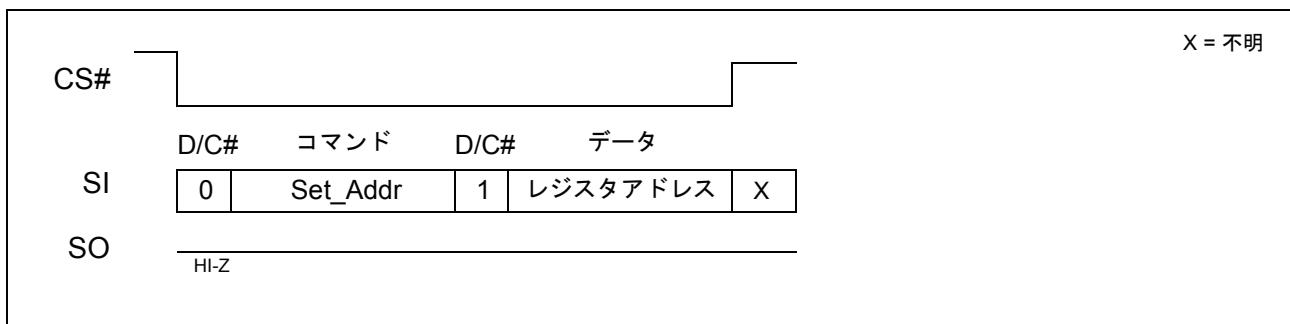

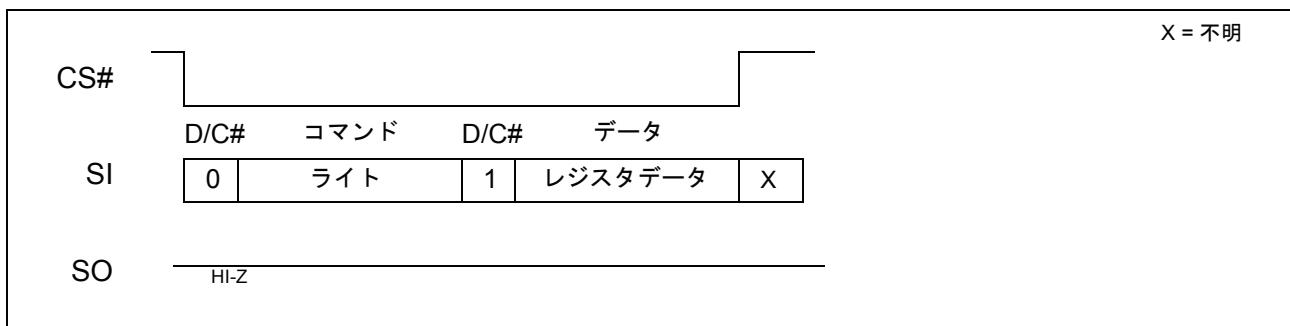

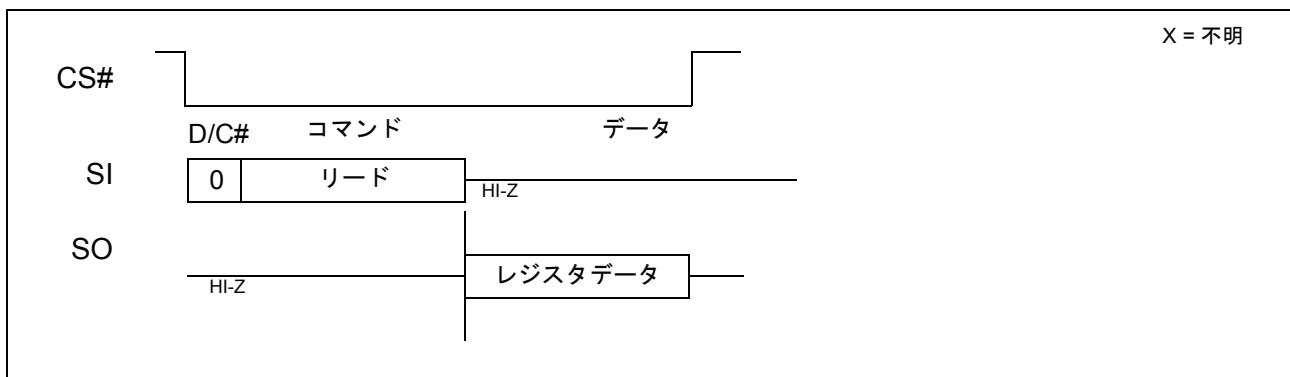

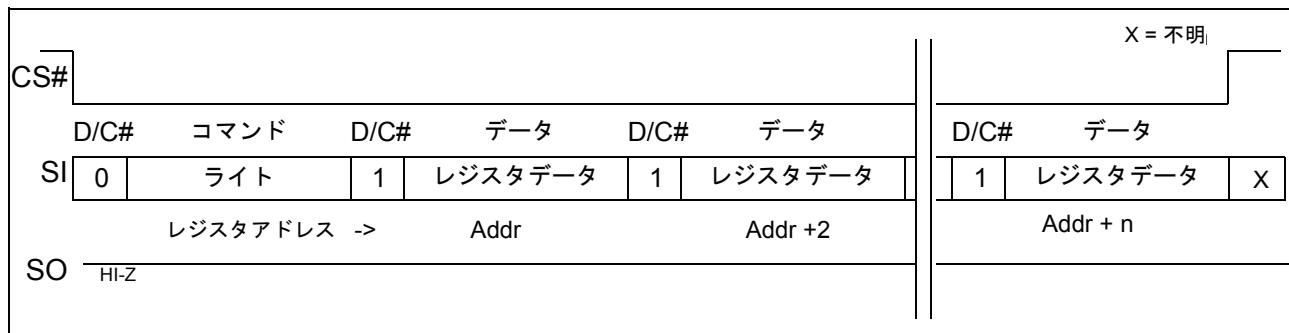

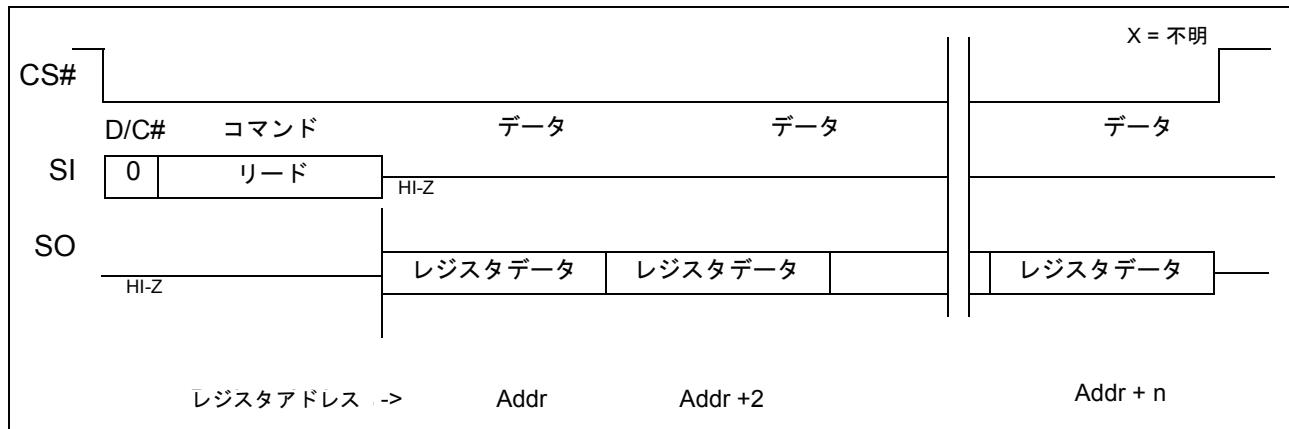

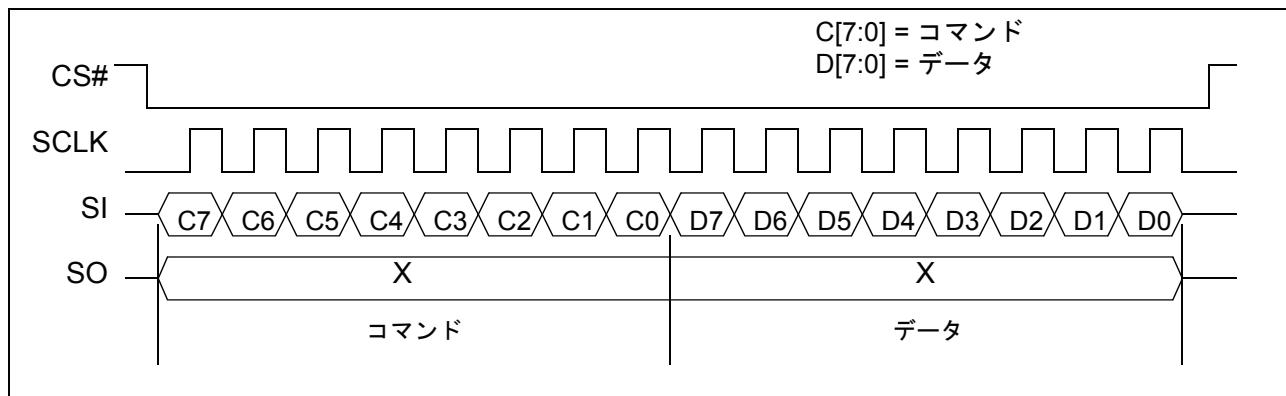

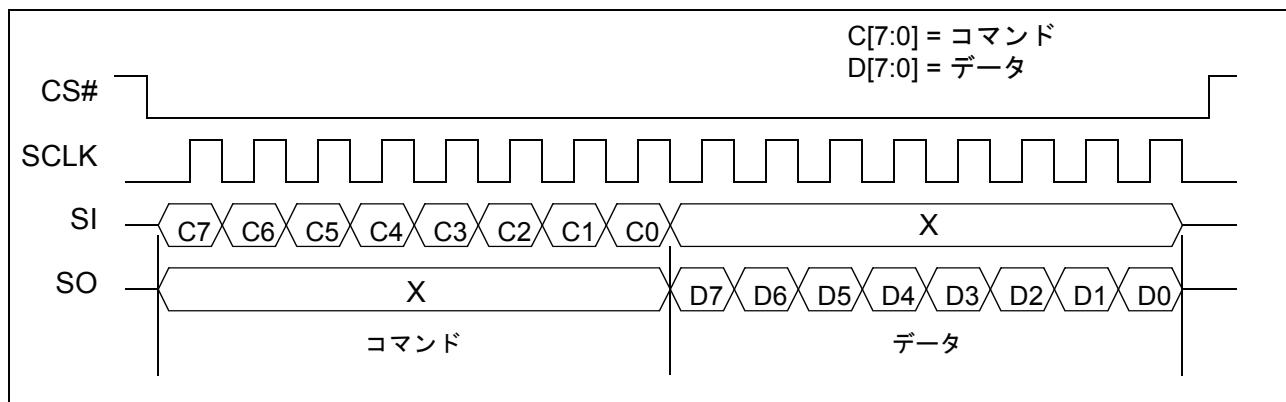

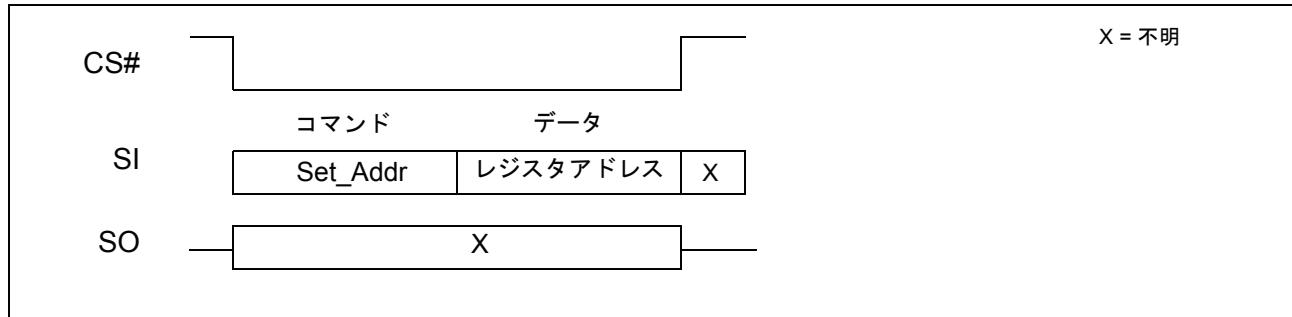

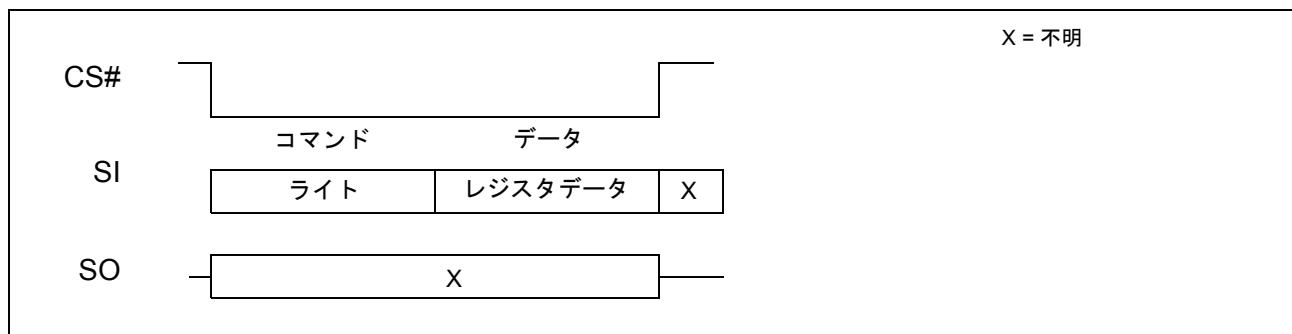

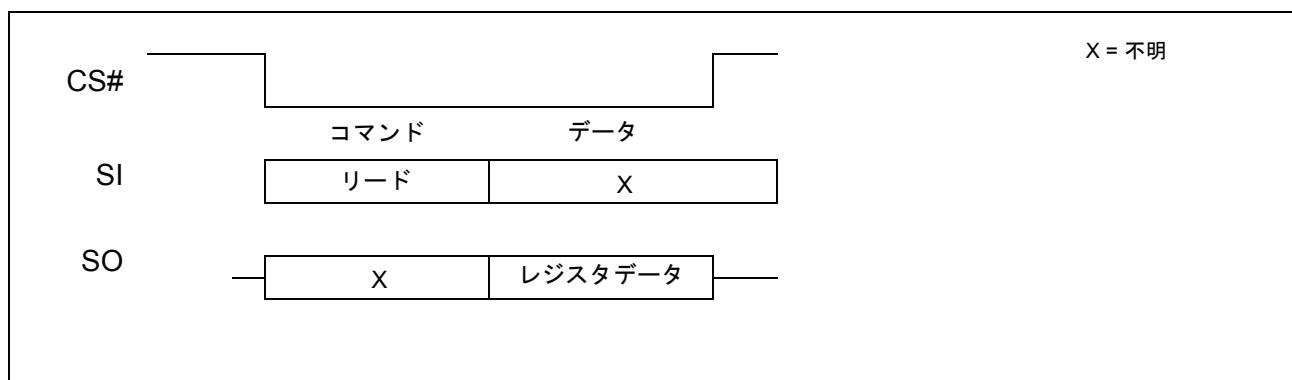

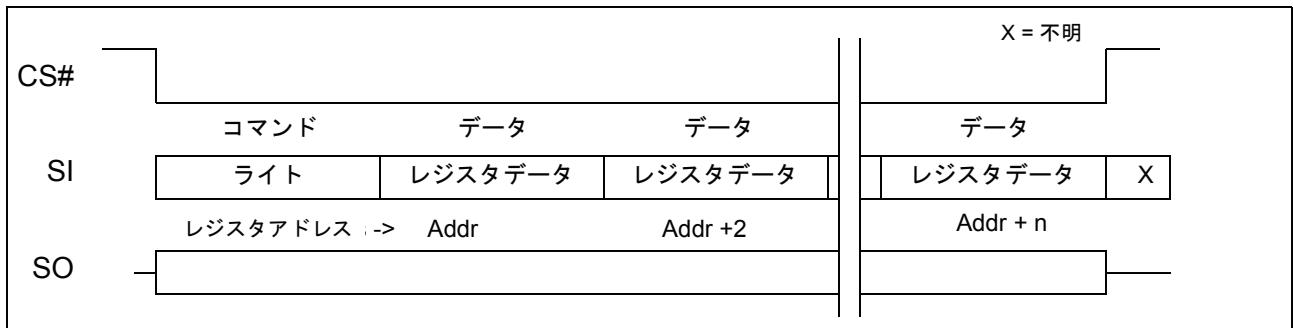

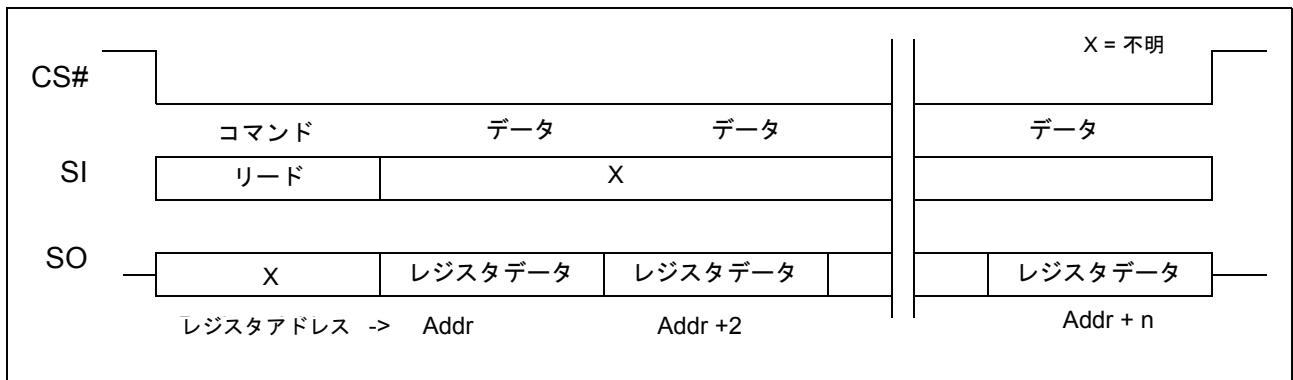

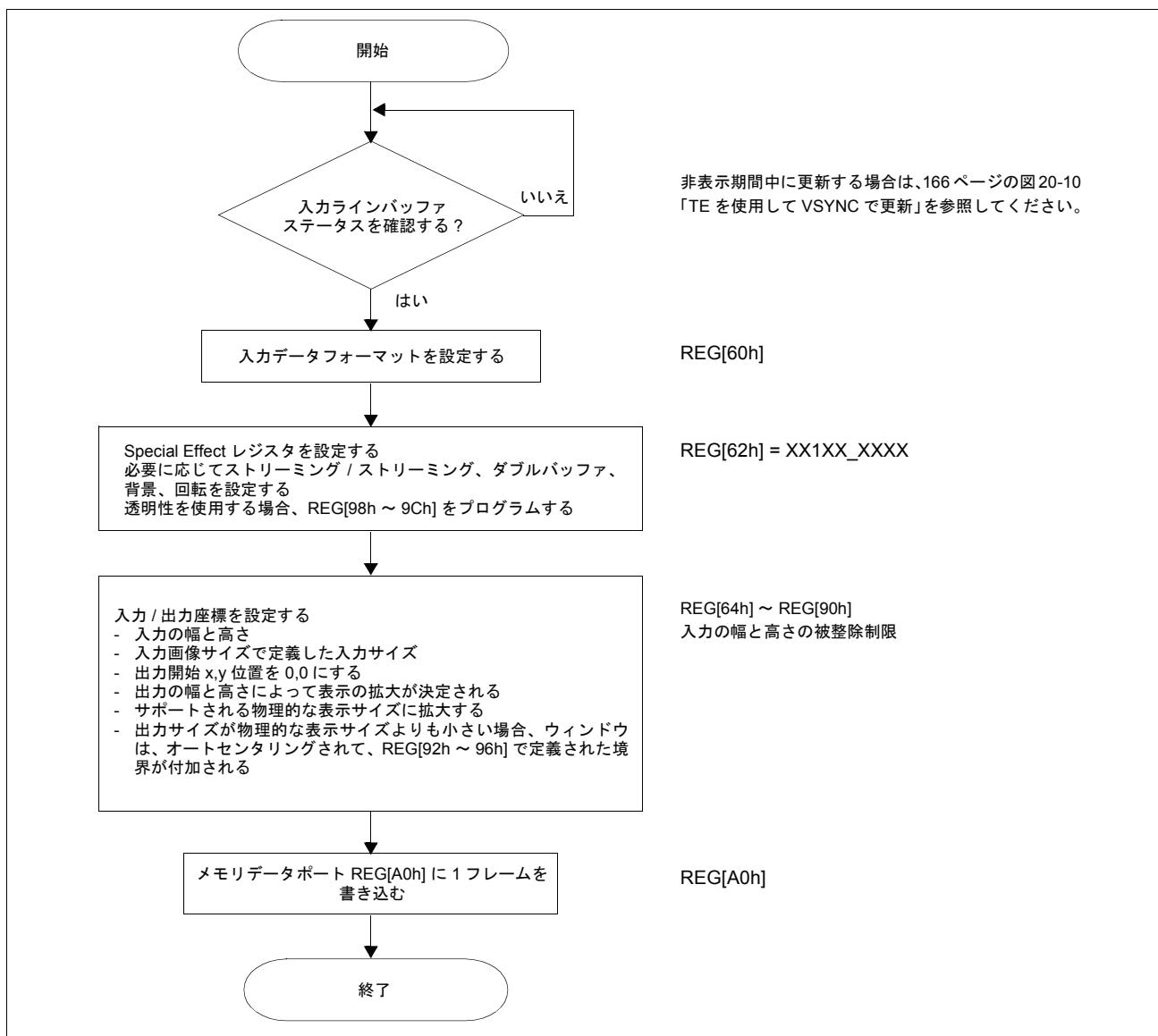

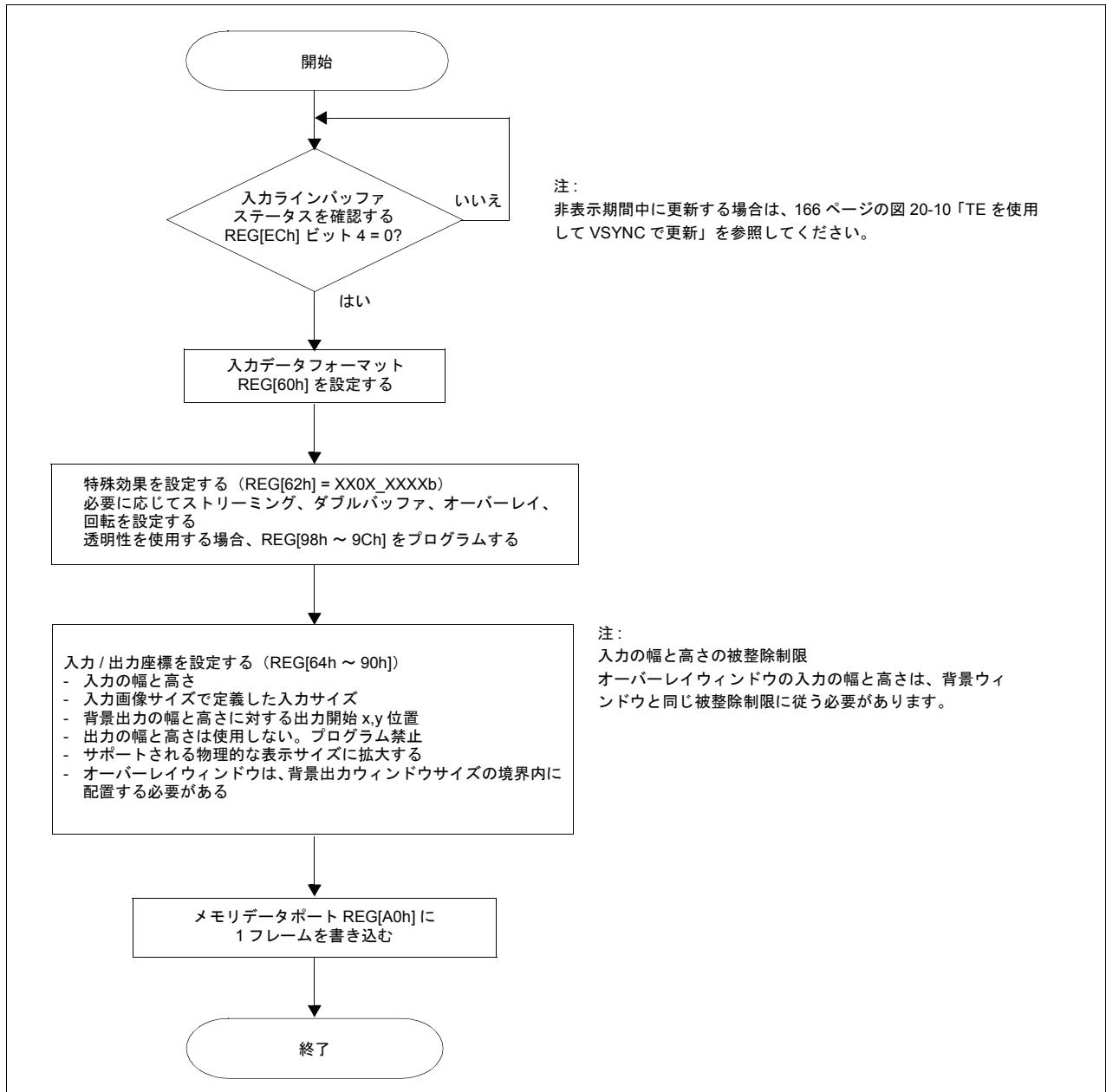

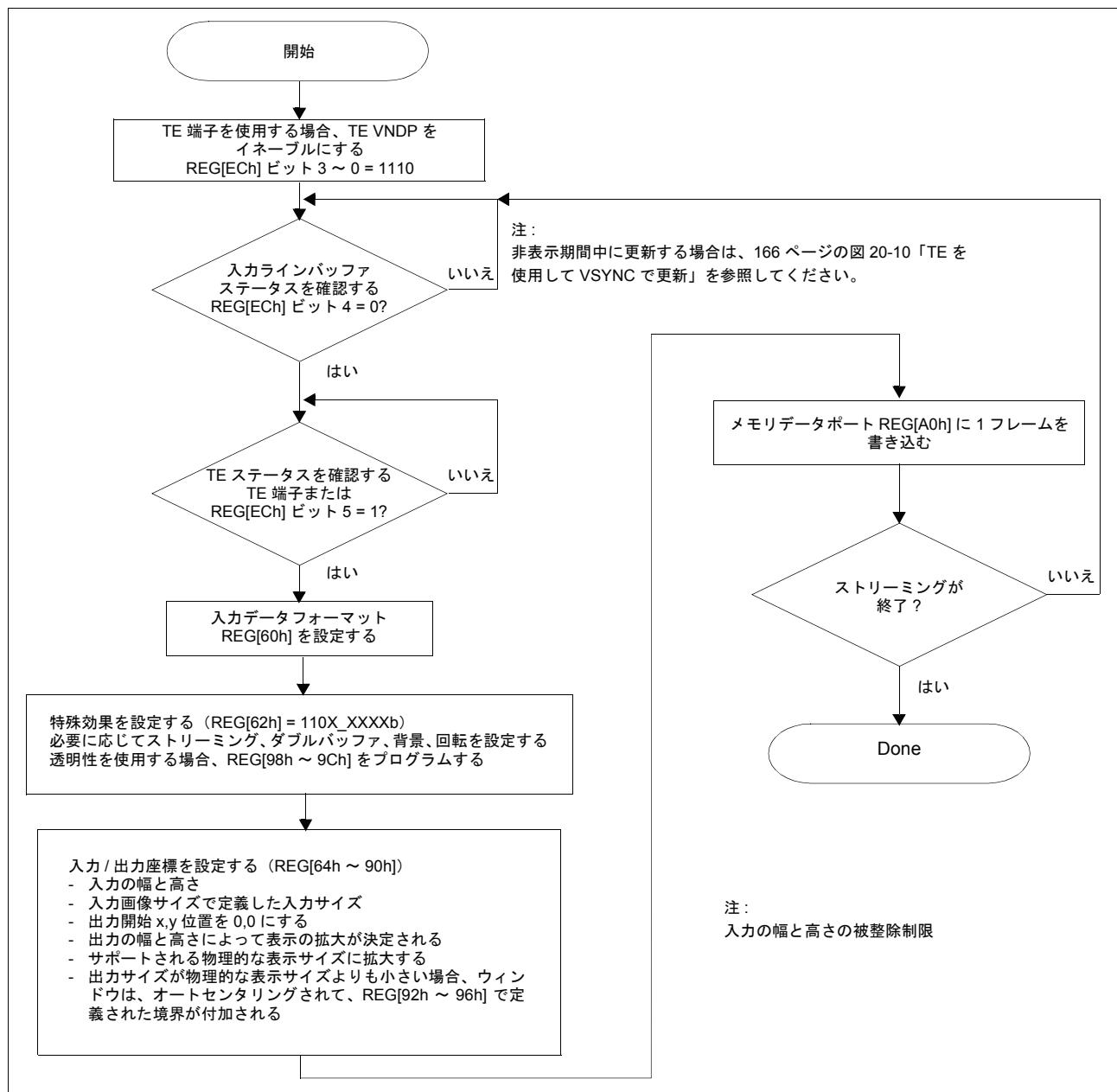

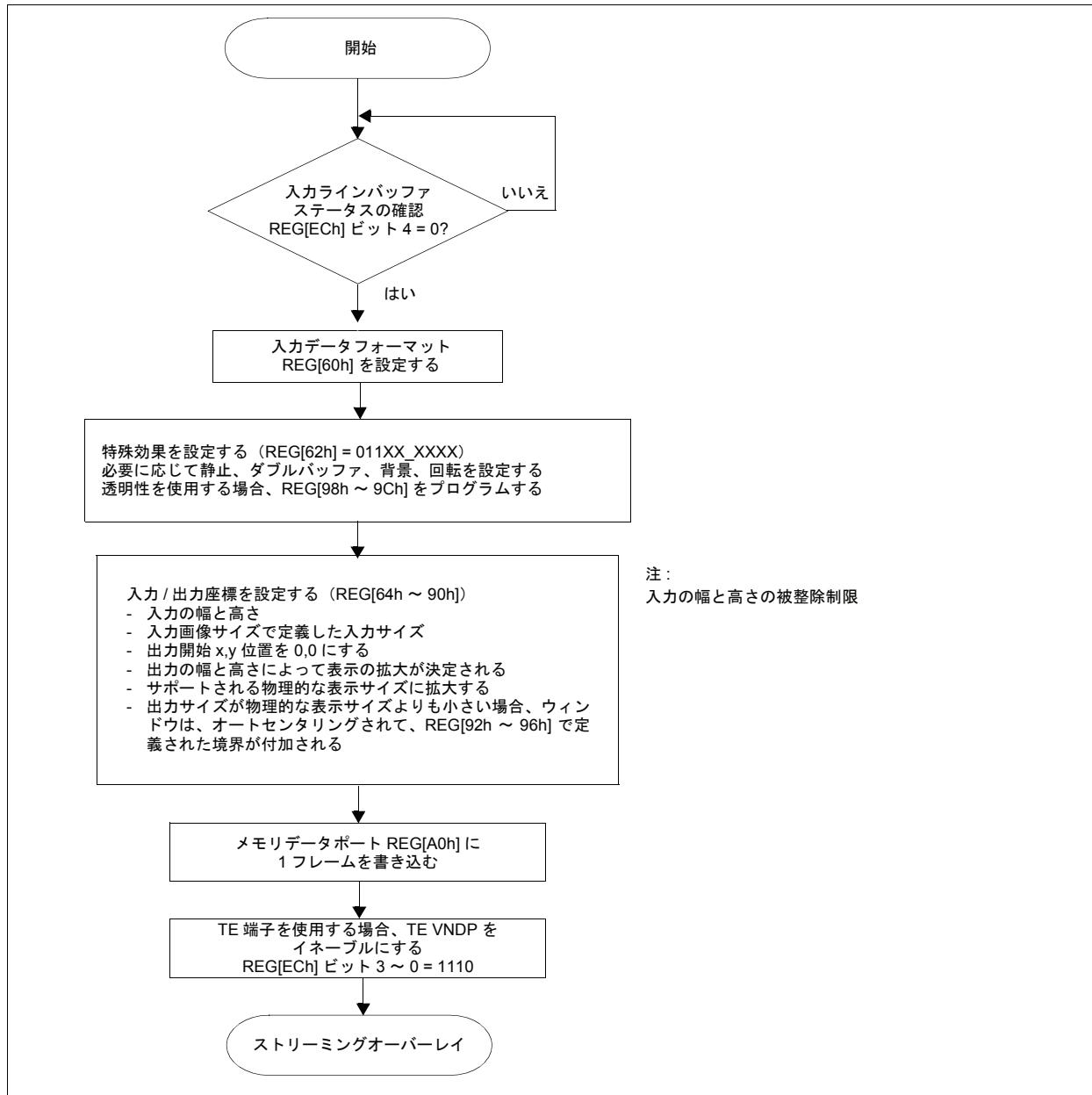

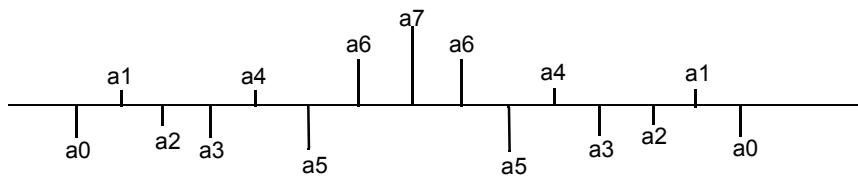

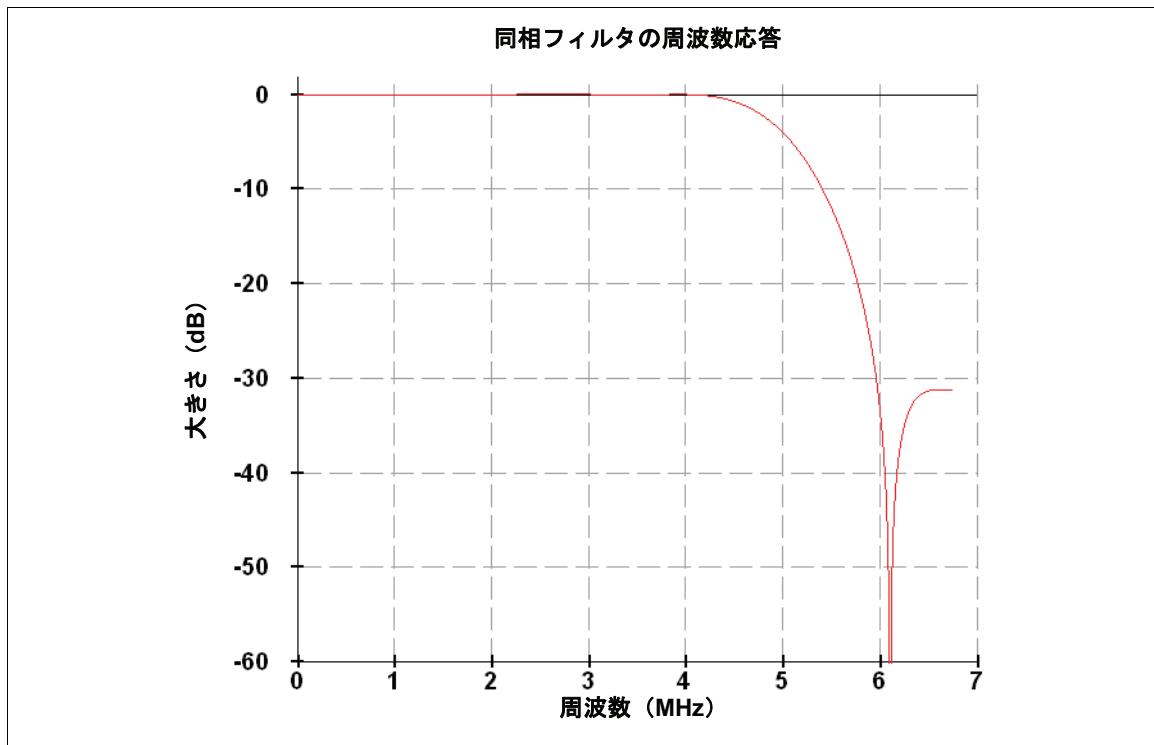

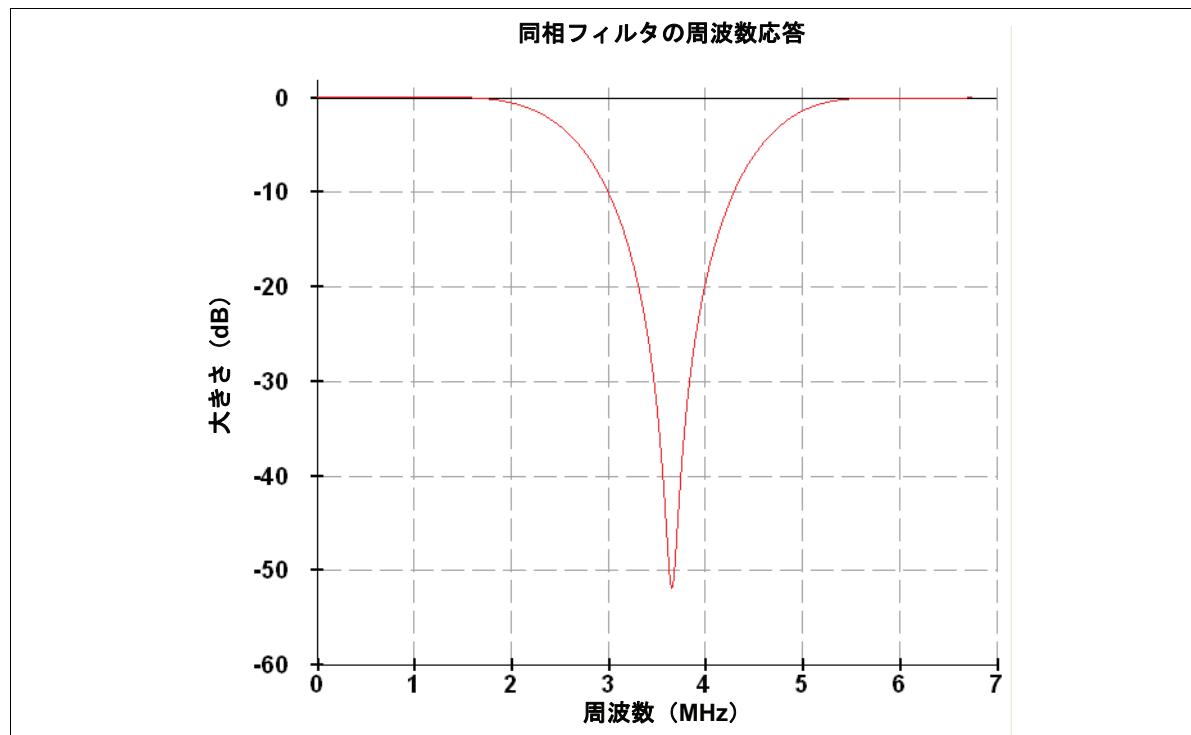

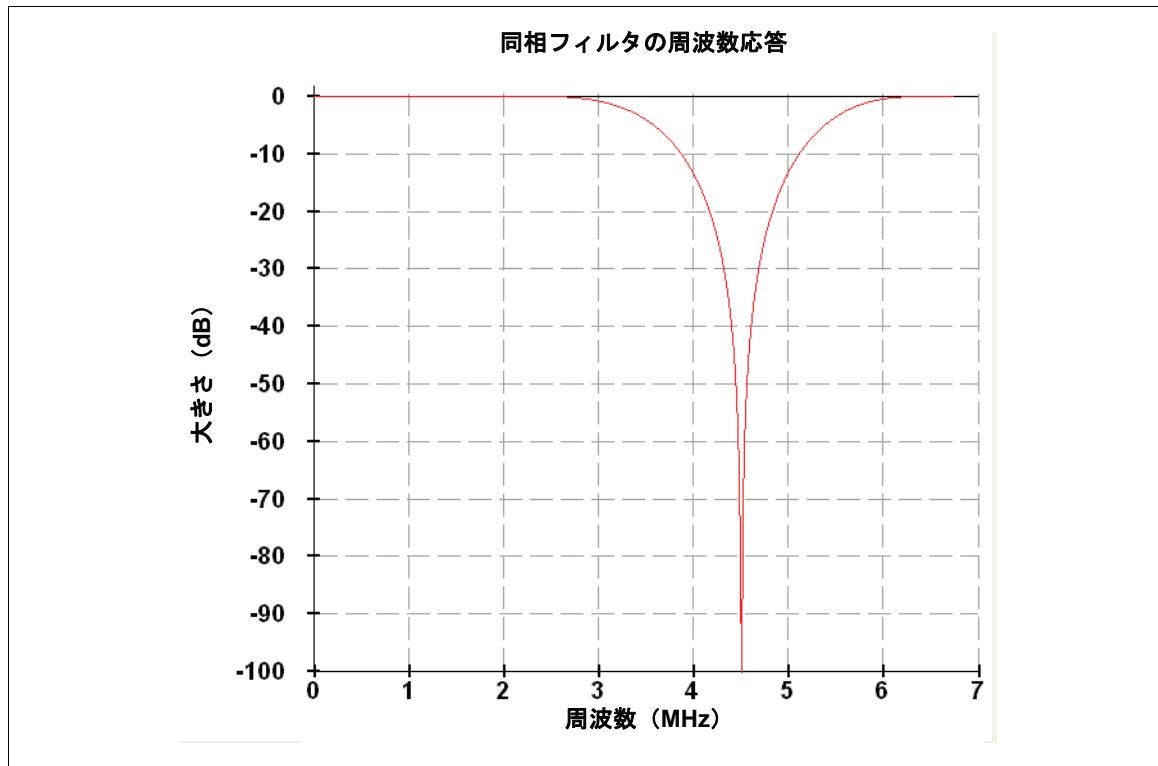

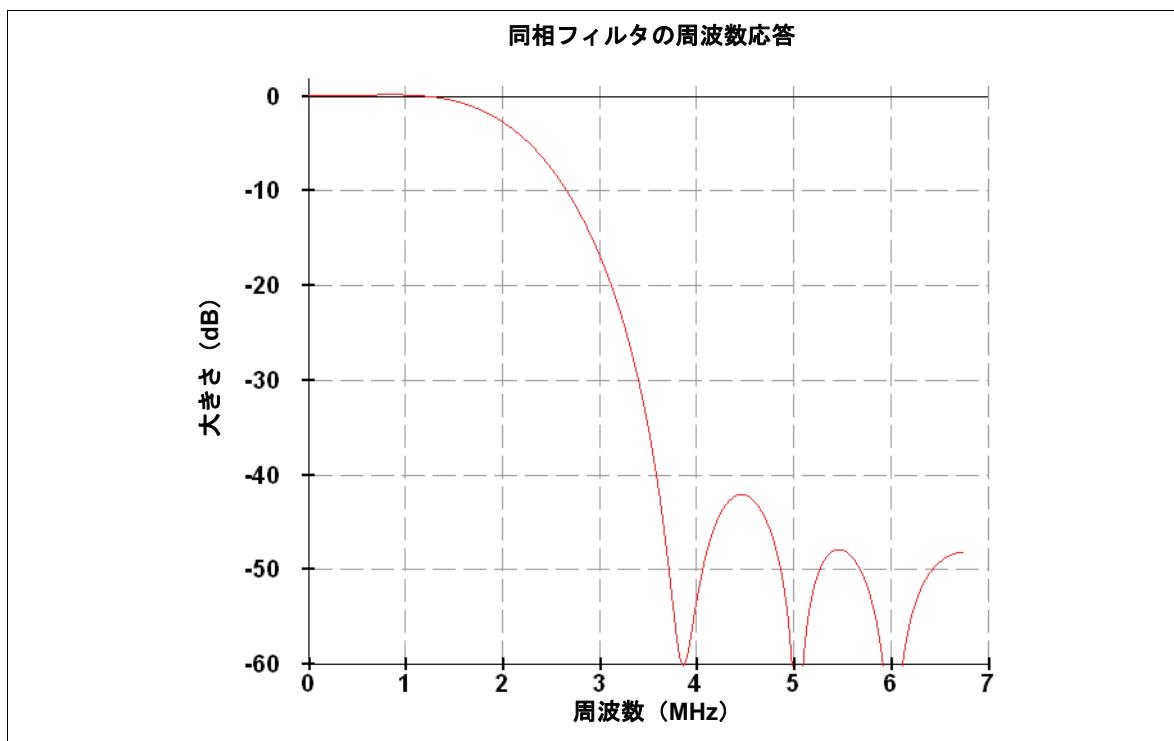

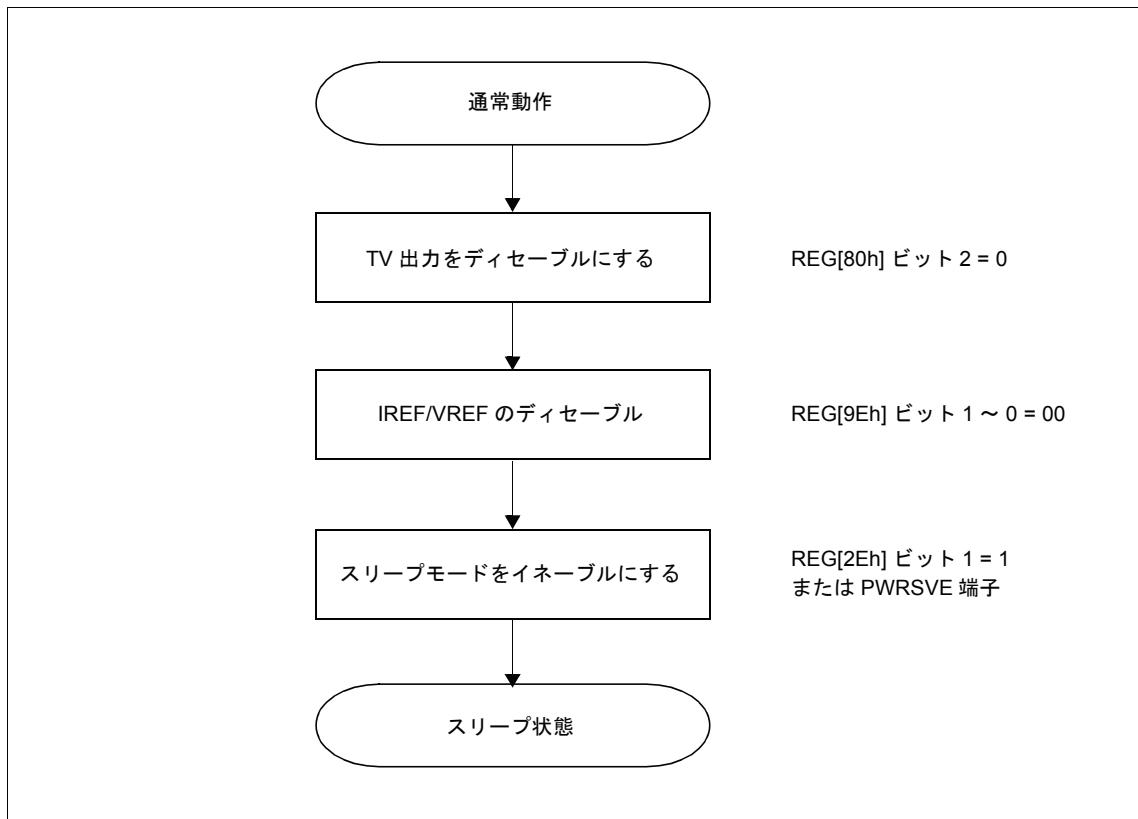

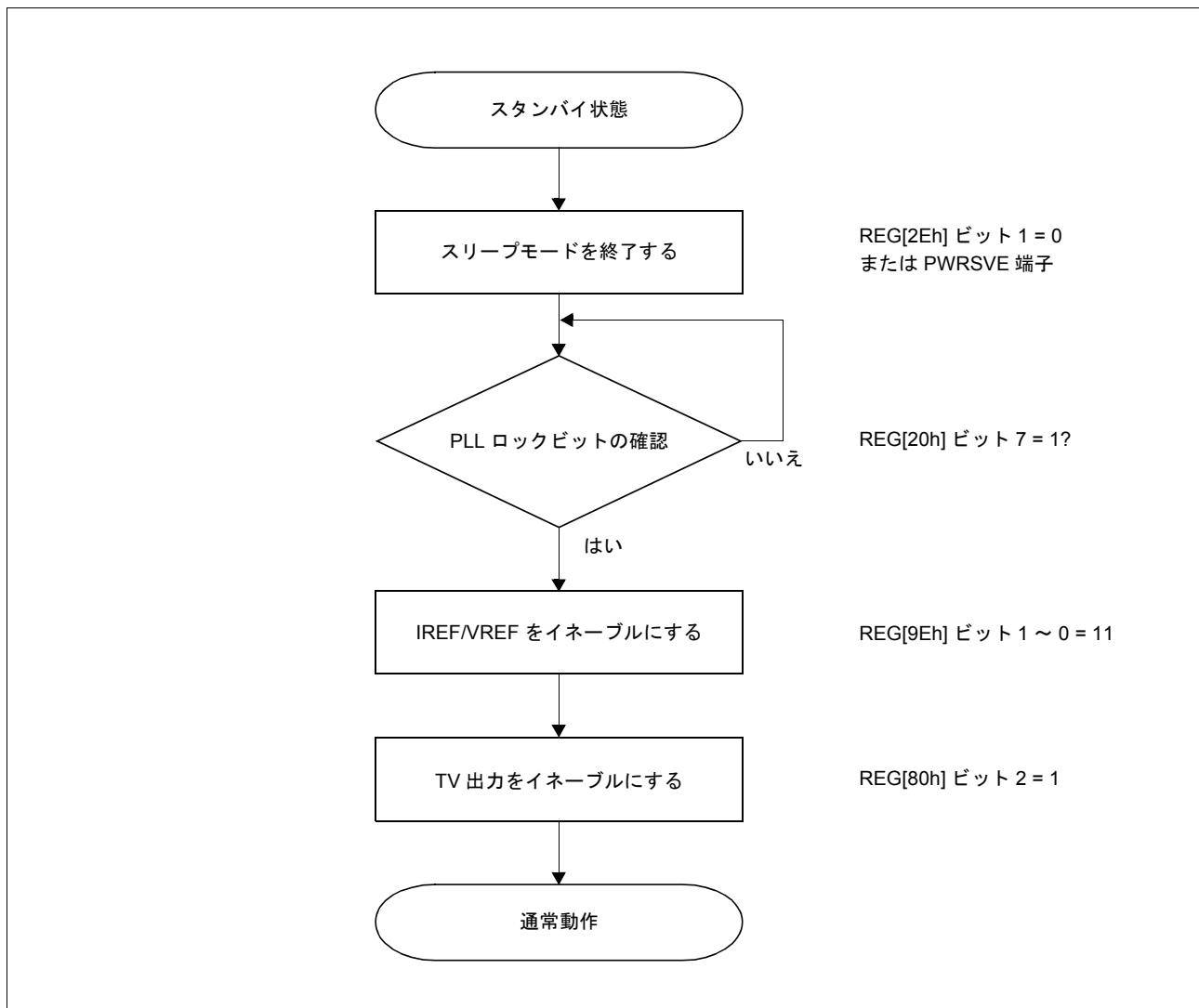

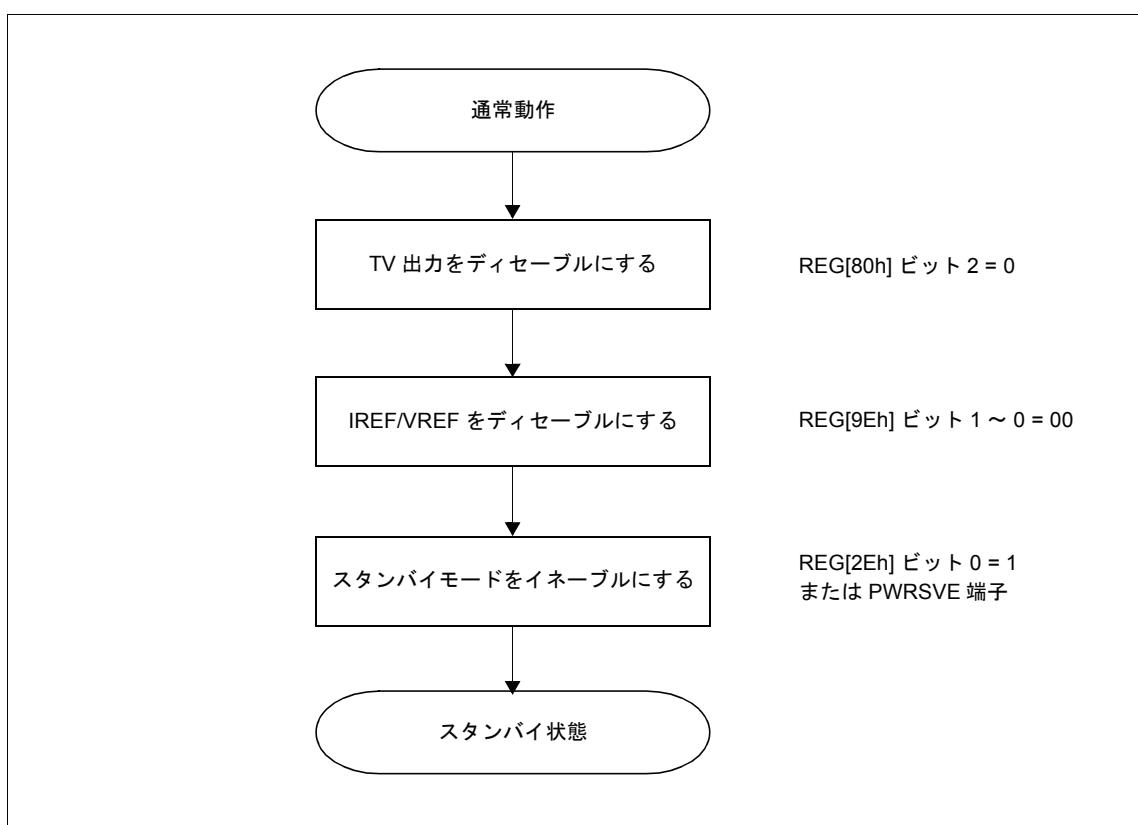

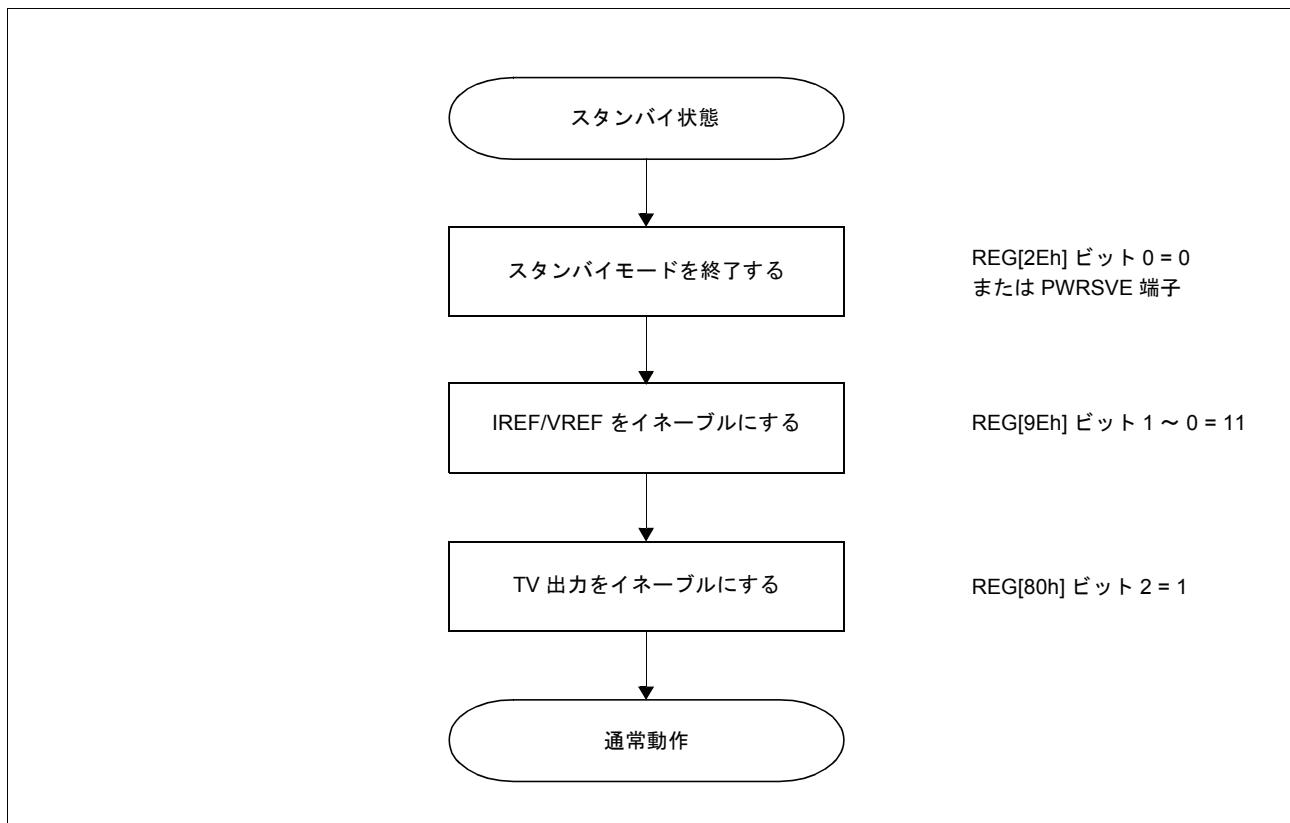

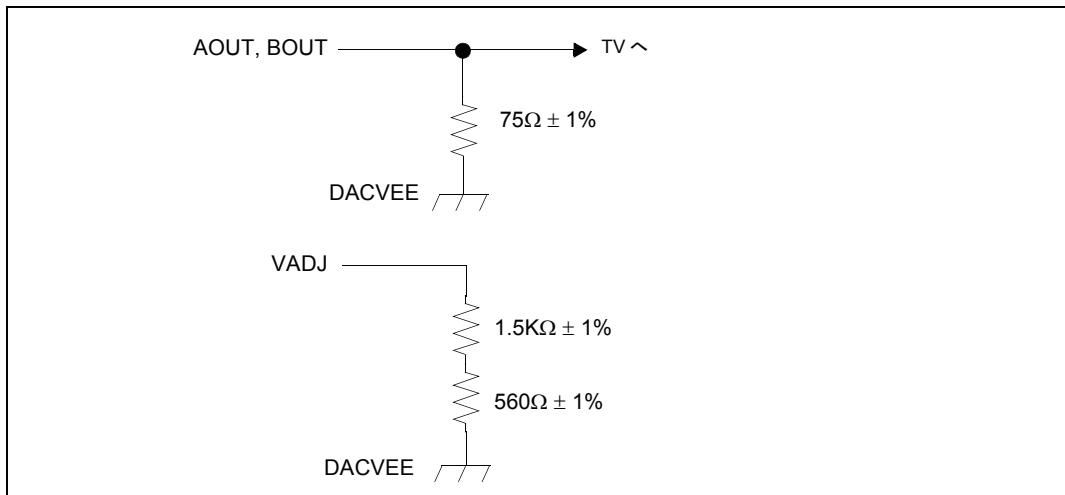

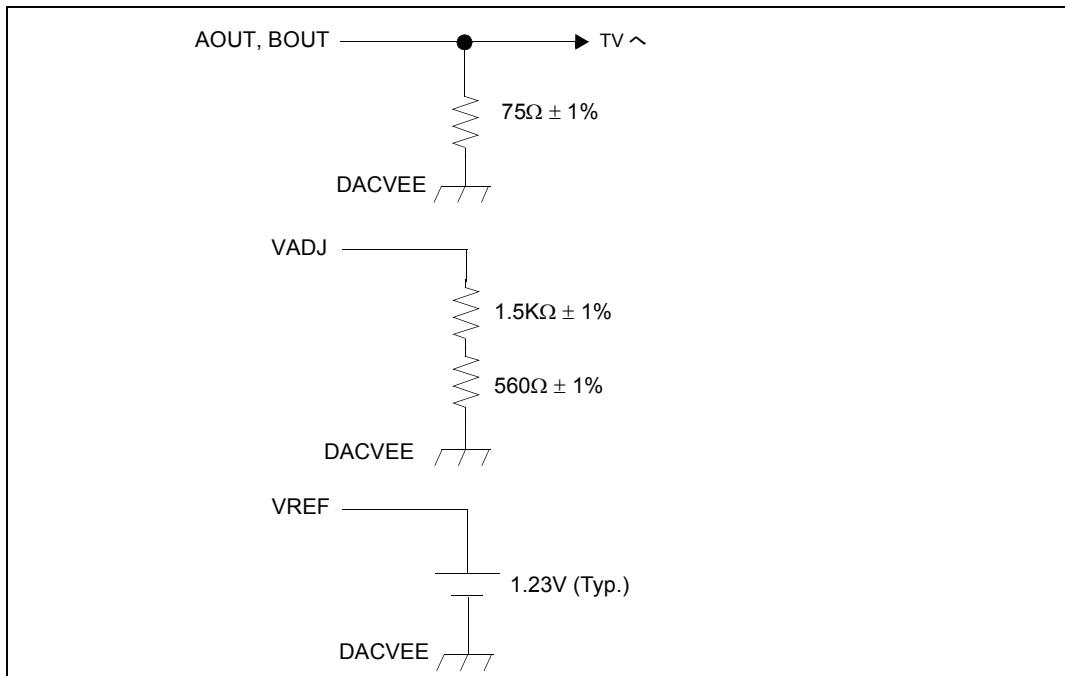

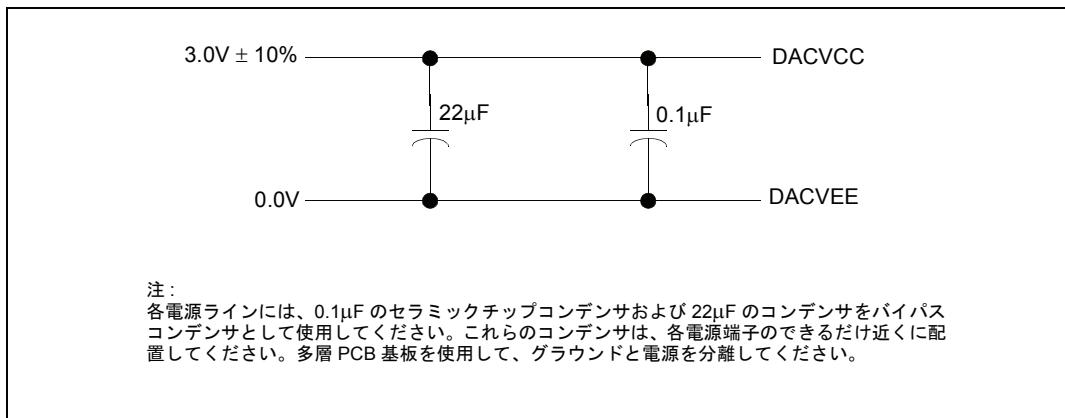

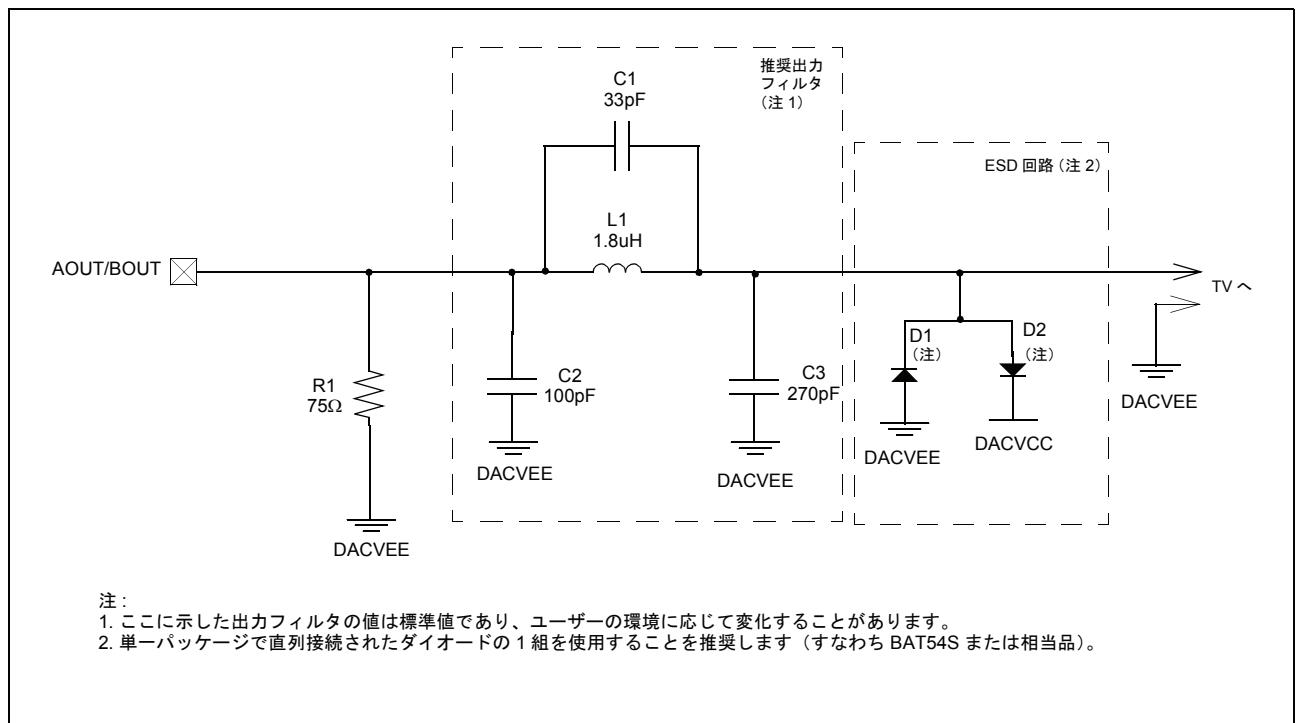

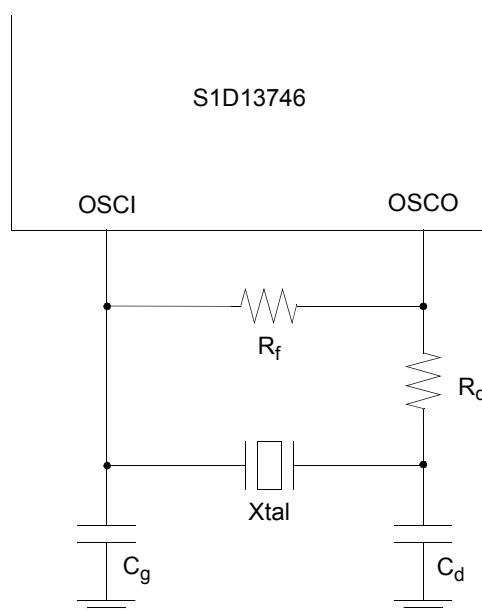

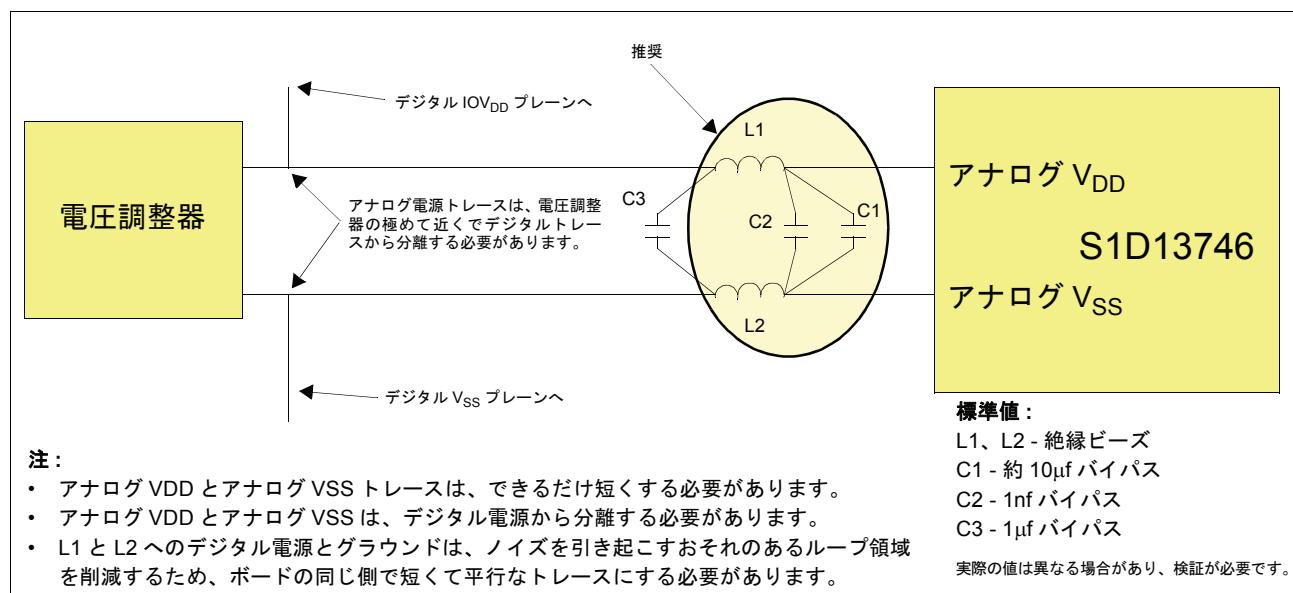

|             |          | Min           | 199.00  | 236.74  | 236.74  | 199.00  | 236.74  | 179.56         | 166.98  | 208.15  | 208.15  | 166.98  | 208.15  | 152.11  |