CMOS 32-BIT SINGLE CHIP MICROCOMPUTER

**S1C33 Family**

スタートアップマニュアル

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

Windows 2000およびWindows XPは米国マイクロソフト社の登録商標です。

PC/ATおよびIBMは米国International Business Machines社の登録商標です。

その他のブランド名または製品名は、それらの所有者の商標もしくは登録商標です。

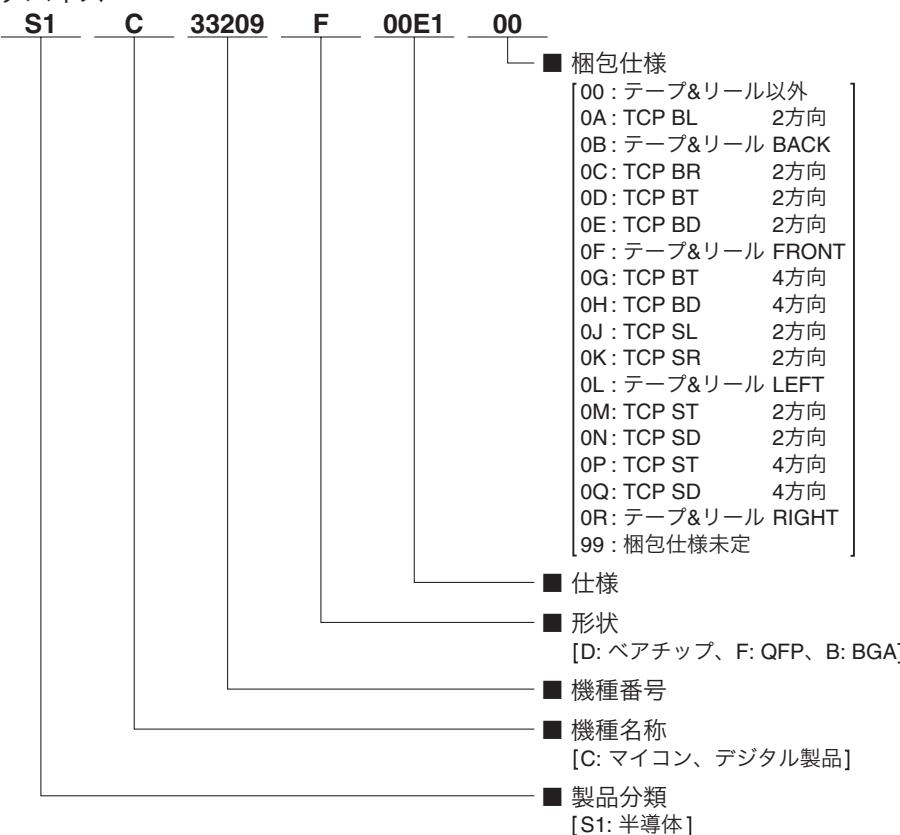

## 製品型番体系

### ●デバイス

### ●開発ツール

## — はじめに —

S1C33 Familyマイクロプロセッサ/コントローラはセイコーポンオリジナルのCMOS 32ビットRISCコアを中心に、ROM、RAM、DMA、タイマ、SIO、PLL、A/D変換器などを1チップに内蔵しています。高速動作、低消費電流、省コードサイズ、積和機能を特長とし、OA機器から携帯機器まで幅広く対応できます。また、ASICマイコン、カスタムマイコンへの展開も可能となっています。

本書はS1C33 Familyマイクロプロセッサ/コントローラを使用するアプリケーション開発者向けのマニュアルで、S1C33チップ(主にS1C3301)の基本的な組み込み用プログラミング、周辺機能のプログラミング方法などを説明します。

本書をお読みになるには、以下の内容が予備知識として必要です。

- C言語(ANSI C準拠)に関する知識およびCソースプログラムの作成方法

- GNU C、binutil、GNU makeおよびGNUリンク(ld)用リンクスクリプトに関する知識

- アセンブリ言語に関する一般的な知識

- Cコンパイラおよびアセンブラーを使用したプログラム開発全般の基礎知識

- Windows 2000またはWindows XPの基本的な操作方法

なお、本書に掲載のプログラム例は、S1C33 Family C/C++コンパイラパッケージ(S5U1C33001C)のVer. 3以降に含まれるサンプルから抜粋しています。また、Cコンパイラの詳細な仕様については、“S5U1C33001C Manual”を参照してください。

### 〈マニュアルの構成〉

本マニュアルは、以下に示す4つの章から構成されています。

1章では、組み込み用ソフトウェアを作成するための基礎知識を掲載しています。

2章では、S1C33 MCUの基本的なプログラミングについて、サンプルプログラムを使用して説明しています。

3章では、S1C33 MCUの周辺回路のサンプルプログラムについて説明しています。

4章では、S1C33 MCUのプログラミングにおける技術的な項目や注意事項について説明しています。

### 〈関連マニュアル〉

関連マニュアルは以下のとおりです。

- S1C33000コアCPUマニュアル

- S1C33 Family C33 ADVコアCPUマニュアル

- S5U1C33000C Manual(S1C33 Family Cコンパイラパッケージ) (Ver. 4)

- S5U1C33001C Manual(S1C33 Family C/C++コンパイラパッケージ) (Ver. 3)

- S1C33 Family各機種別テクニカルマニュアル

### 〈WEB公開資料〉

以下の資料をWEBに公開しています。ただし、参照にはユーザIDとパスワードが必要です。

次のアドレスよりログインしてください。

<http://www.epsondevice.com/webapp/MCUToolsDownload/entry.jsp>

1. S5U1C33001C(GNU33 Ver. 2, Ver. 3)とS5U1C33000C(CC33)との違いについて

CC33、GNU33 Ver. 2、GNU33 Ver. 3の相違点がまとめられています。

2. ツール対応表

S1C33 FamilyのCPUコア、MCU、ICD、リファレンスボード、OS、ミドルウェアの対応についてまとめています。また、各コアにおけるオプション、ライブラリ、アセンブラーなどの相違点をまとめています。

3. FAQ

よくいただく質問と回答を記載しています。

## — 目 次 —

|                                    |            |

|------------------------------------|------------|

| <b>1 組み込みの基礎知識 .....</b>           | <b>1-1</b> |

| 1.1 プログラムが動くための基本メカニズム .....       | 1-1        |

| 1.2 スタートアップ(初期化設定)ルーチン .....       | 1-2        |

| <b>2 S1C33用プログラムの書き方 .....</b>     | <b>2-1</b> |

| 2.1 ベクタテーブルとスタートアップルーチン .....      | 2-1        |

| 2.2 割り込み処理 .....                   | 2-6        |

| 2.2.1 プロトタイプ宣言 .....               | 2-6        |

| 2.2.2 NMI .....                    | 2-6        |

| 2.2.3 例外 .....                     | 2-7        |

| 2.2.4 ソフトウェア割り込み .....             | 2-7        |

| 2.2.5 割り込み要因フラグ .....              | 2-7        |

| 2.3 Cコンパイラとコードの最適化 .....           | 2-9        |

| 2.3.1 変数のアクセス .....                | 2-9        |

| 2.3.2 volatile修飾 .....             | 2-9        |

| 2.3.3 ポインタ型構造体・配列 .....            | 2-10       |

| 2.3.4 Cコンパイラの最適化オプション .....        | 2-10       |

| <b>3 S1C33基本周辺機能のプログラミング .....</b> | <b>3-1</b> |

| 3.1 BCU .....                      | 3-1        |

| 3.2 8ビットプログラマブルタイマ .....           | 3-3        |

| 3.3 16ビットプログラマブルタイマ .....          | 3-6        |

| 3.4 ウォッチドッグタイマ .....               | 3-9        |

| 3.5 計時タイマ .....                    | 3-11       |

| 3.6 シリアルインターフェース .....             | 3-14       |

| 3.7 FIFO付きシリアルインターフェース .....       | 3-25       |

| 3.8 ポート割り込み .....                  | 3-37       |

| 3.9 A/D変換 .....                    | 3-42       |

| 3.10 HSDMA転送 .....                 | 3-45       |

| 3.11 IDMA転送 .....                  | 3-48       |

| 3.12 SLEEP .....                   | 3-51       |

| <b>4 テクニカルリファレンス .....</b>         | <b>4-1</b> |

| 4.1 ブートについて .....                  | 4-1        |

| 4.1.1 外部RAMからのブート .....            | 4-1        |

| 4.1.2 フラッシュメモリからのブート .....         | 4-1        |

| 4.2 リンカスクリプトについて .....             | 4-3        |

| 4.2.1 .dataセクションの使用法 .....         | 4-3        |

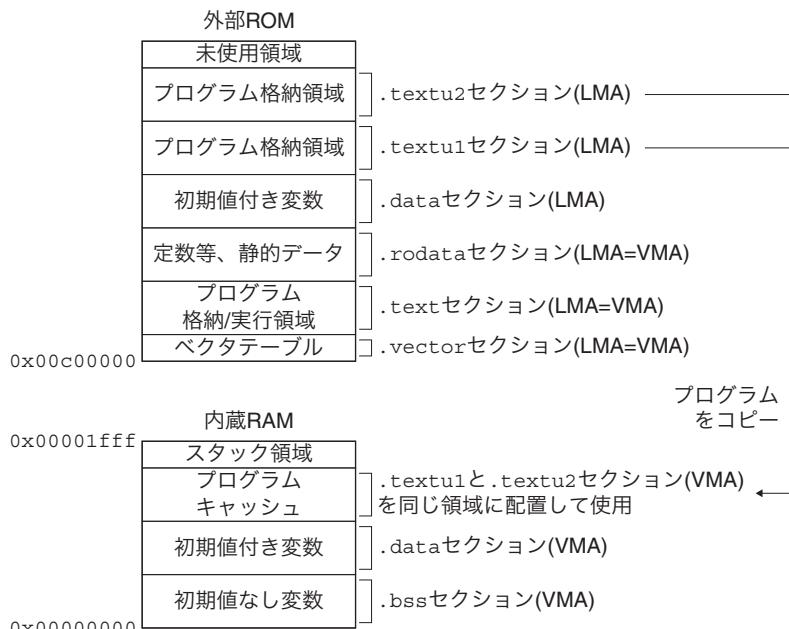

| 4.2.2 プログラムの内蔵RAMへのキャッシュ法 .....    | 4-4        |

| 4.3 Cコンパイラについて .....               | 4-5        |

| 4.3.1 引数 .....                     | 4-5        |

| 4.3.2 代入 .....                     | 4-6        |

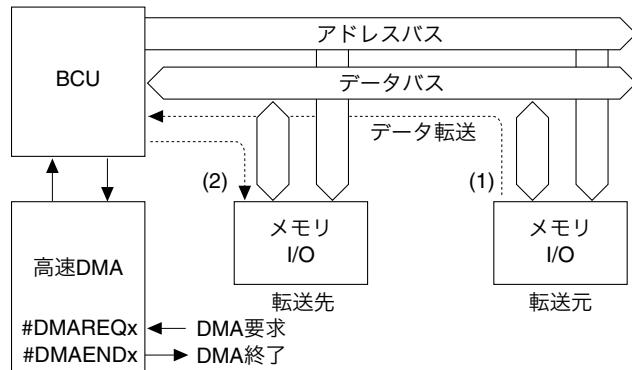

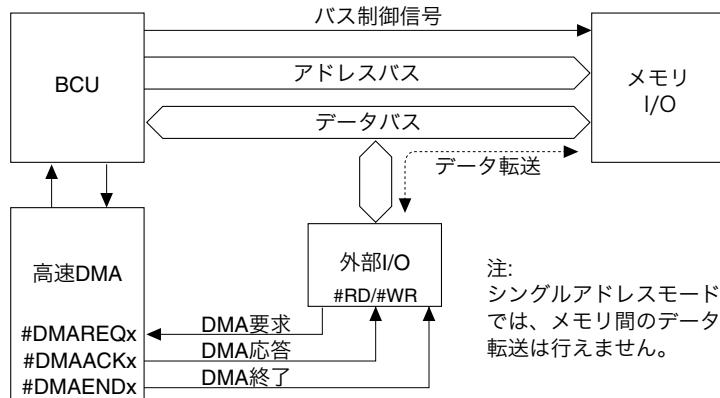

| 4.4 DMA転送について .....                | 4-7        |

# 1 組み込みの基礎知識

本章では、初めて組み込みソフトウェア開発をする方を対象に、最初に理解していただきたい、プログラムが動くための基本メカニズムやスタートアップルーチンによる初期化など、組み込みソフトウェア開発では極めて重要な考え方について説明します。

## 1.1 プログラムが動くための基本メカニズム

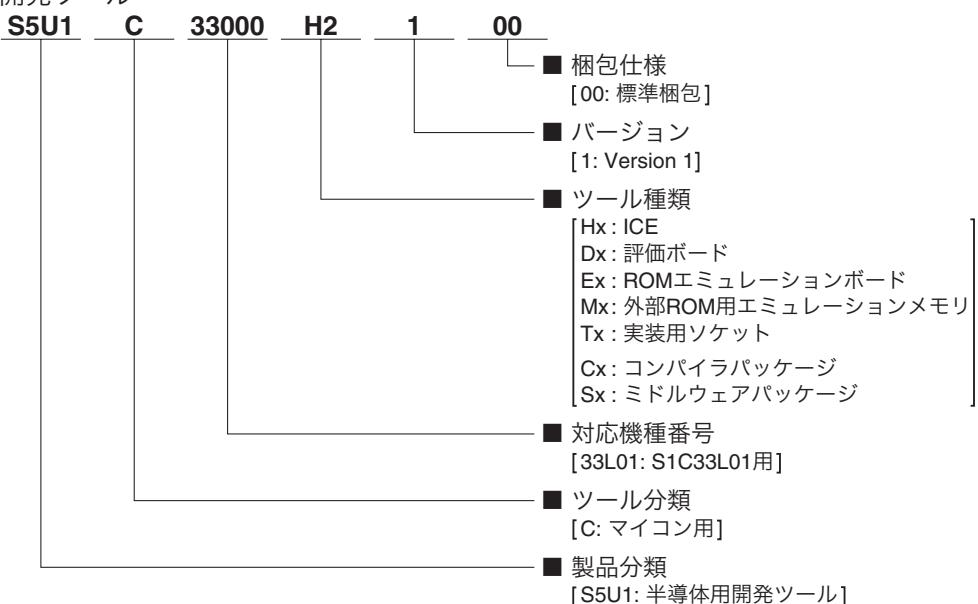

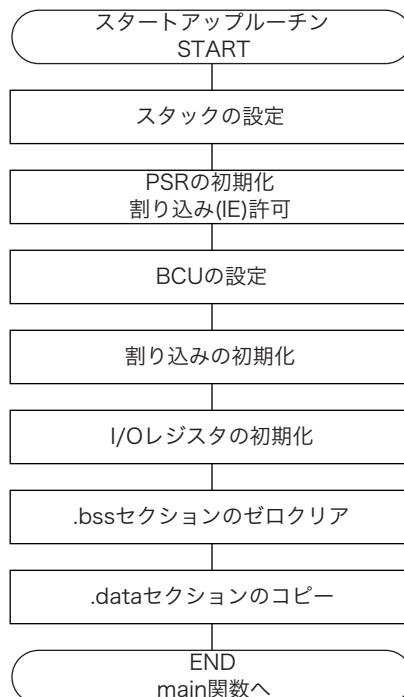

はじめに、S1C33プロセッサ(以下MCU)が動き始めるときの動作(基本メカニズム)について説明します(図1.1.1)。

図1.1.1 S1C33プロセッサ起動時の基本メカニズム

- (1)組み込み機器に電源を投入するとリセット例外が発生し、MCUは割り込みベクタ領域(トラップテーブル)内のベースアドレスの内容を読み込みます。割り込みベクタ領域は、各種例外/割り込み処理ルーチン(関数)のアドレスを書き込んでおくテーブルで、例外や割り込み発生時はここからアドレスが読み出され、対応する処理ルーチンにジャンプするようになっています。ベースアドレスにはリセット時に処理するスタートアップルーチンへのベクタ(開始アドレス)を書き込んでおきます。

- (2)MCUは(1)で読み出した内容(アドレス)にジャンプすることで、スタートアップ(初期化設定)ルーチンを呼び出します。

- (3)スタートアップルーチンは、まずスタックの設定やプログラムの実行に必要な初期化処理を行います。

- (4)初期化処理を終了後、スタートアップルーチンはmain関数を呼び出します。

組み込みアプリケーションのプログラムはmain関数からではなく、その前段階としてスタートアップルーチンというものが存在します。組み込みソフトウェアを開発するにあたって、プログラムを動かすためにはスタートアップルーチンを理解することが必要です。

## 1.2 スタートアップ(初期化設定)ルーチン

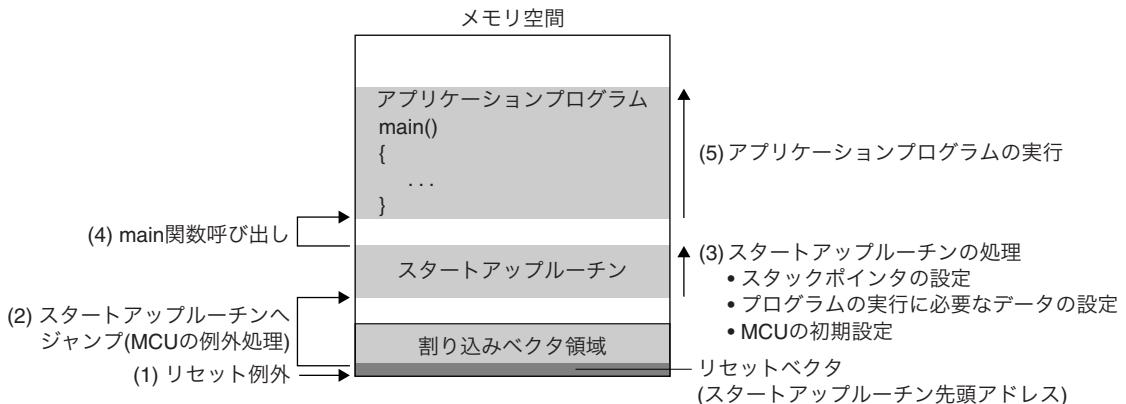

スタートアップルーチンは、mainルーチンを実行する前に必要な初期化などを行います。

WindowsやLinux/UNIXのアプリケーションプログラムを開発するときは、プログラムの実行環境がいつも同じなので(毎回変更する必要がないので)、Cコンパイラが自動的にスタートアップルーチンをリンクしています。そのため、スタートアップルーチンを意識することはありません。

しかし、組み込み機器の場合、どのようなデバイスが接続されているか、メモリがどれだけ搭載されているかなどは機器に依存します。そのため、デバイスの初期化と一言でいっても機器によってそれぞれ処理が異なります。さらに、デバイスの初期化の方法についても使用するMCUによって異なるため、組み込みシステムにおいてスタートアップルーチンの役割は重要となります。

組み込みソフトウェアのスタートアップルーチンでは、一般に次のような処理を行います。

- スタックポインタの設定

- PSRの初期化と割り込み(IE)許可

- MCU内蔵周辺回路の初期化

- BCU設定の初期化

- 割り込み設定の初期化

- I/Oレジスタ設定の初期化

- プログラムの実行に必要なデータの設定

- ROM領域からRAM領域への初期値データの転送(.dataセクションのコピー)

- 初期値を持たないメモリ領域の0クリア(.bssセクションの0クリア)

図1.2.1 スタートアップルーチン

スタックはサブルーチンや関数を呼び出す際に、処理中のデータや戻りアドレスなどを一時的に退避するのに使うRAM領域です。割り込みや例外もスタックを使用するため、スタートアップルーチンでスタック領域を確保します。

PSR(プロセッサステータスレジスタ)はCPUの状態を保持する32ビットレジスタで、実行した命令の結果によって変化します。プログラムの実行にも影響を与えるため、割り込みや例外の発生時には処理ルーチンへの分岐前にPSRの内容はスタックへ退避し、リターン後にPSRへ戻されます。スタートアップルーチンでは各ビットに0をセットして初期化を行います。またIE(割り込みイネーブル)に1をセットし、マスク可能な外部割り込みを許可します。

PSR (C33 STDコア)

|          | 31~12 | 11~8 | 7  | 6 | 5  | 4 | 3 | 2 | 1 | 0 |

|----------|-------|------|----|---|----|---|---|---|---|---|

| Reserved | IL    | MO   | DS | - | IE | C | V | Z | N |   |

- IL: 割り込みレベル (0~15: 割り込み許可レベル)

- MO: MACオーバーフロー・フラグ (1: オーバーフローあり, 0: なし)

- DS: 被除数符号・フラグ (1: 負, 0: 正)

- IE: 割り込み許可 (1: 許可, 0: 禁止)

- Z: ゼロ・フラグ (1: ゼロ, 0: ゼロ以外)

- N: ネガティブ・フラグ (1: 負, 0: 正)

- C: キャリーフラグ (1: キャリー/ボローあり, 0: なし)

- V: オーバーフロー・フラグ (1: オーバーフローあり, 0: なし)

図1.2.2 PSR

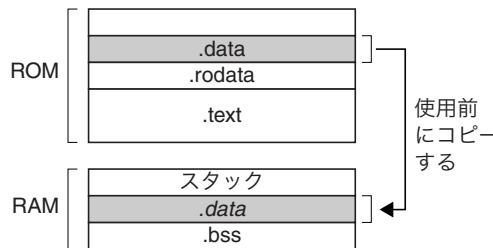

これら以外にも、プログラムの実行には初期値を持たないグローバル変数の初期化が必要になります。これらの設定はリセットによって不定となるため、初期化もしくは0クリアする必要があります(.bssセクションのクリア)。また初期値を持つグローバル変数は、初期値データをROMからRAMにコピーする必要があります(.dataセクションのコピー)。

MCUの内蔵周辺機能や割り込みに関する設定は、使用する機能や割り込みに対応して初期化を行ってください。C言語の標準ライブラリを使用する場合は、main関数を呼び出す前にライブラリの初期化を行う必要があります。

そのほかに、ソフトウェアの実行に関わる初期化だけでなく、MCUやその他のハードウェアを使用するための初期化も必要です。これらの初期化は、MCUやハードウェアのマニュアルを参照しながらコーディングを行ってください。

組み込みアプリケーションでは、このようにスタートアップルーチンを実行した後にmain関数が呼び出されます(図1.2.1)。

以上のこととを念頭におき、組み込み機器のプログラムの開発を行ってください。

このページはプランクです。

# 2 S1C33用プログラムの書き方

本章では、S1C33 Family共通のプログラムの書き方について説明します。

1章で説明したように、組み込みアプリケーションではmain関数を実行する前処理として、スタートアップルーチンを実行する必要があります。以下、スタートアップルーチンを含め、main関数を呼び出すまでの処理の流れについて、サンプルプログラムを参考に説明します。

説明内のサンプルプログラムや周辺機能は、特に指定したものを除きS1C33301の例です。機種によっては、機能や制御レジスタのアドレス等が異なる場合がありますので注意してください。

## 2.1 ベクタテーブルとスタートアップルーチン

S1C33用プログラムの実行には、ベクタテーブルとブートルーチンが最低限必要になります。

ベクタテーブルは、プログラム実行中に割り込みや例外が発生した場合に実行するトラップ(割り込み)処理ルーチンへのベクタ(分岐先アドレス)を配列として格納したテーブルです。そのため、トラップテーブルとも呼ばれます。

| ベクタアドレス         |              |

|-----------------|--------------|

| リセット            | base + 0     |

| Reserved        | base + 4~12  |

| ゼロ除算            | base + 16    |

| Reserved        | base + 20    |

| アドレス不整例外        | base + 24    |

| NMI             | base + 28    |

| Reserved        | base + 32~44 |

| ソフトウェア例外0       | base + 48    |

| :               | :            |

| ソフトウェア例外3       | base + 60    |

| マスク可能な外部割り込み0   | base + 64    |

| :               | :            |

| マスク可能な外部割り込み215 | base + 924   |

base: トラップテーブル先頭アドレス

= 0x0080000 (内蔵ROMよりのブート時)

= 0x0c00000 (外部ROMよりのブート時)

図2.1.1 ベクタテーブルの構成

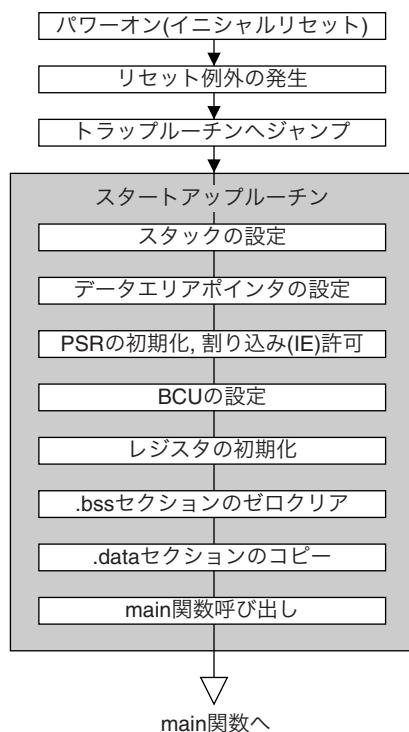

一方、スタートアップルーチンはブートルーチンとも呼ばれ、イニシャルリセット時のトラップ処理ルーチンとして呼び出されます。

S1C33 FamilyのMCUではパワーオン時にコールドリセットがかかり、リセット例外が発生します。C33コアはリセット例外に対応するベクタをベクタテーブルから読み出してそのアドレス(スタートアップルーチン)にジャンプし、main関数を実行するために必要な各種初期化の処理を開始します。

図2.1.2にS1C33 FamilyのMCUによるmain関数呼び出しまでの流れを示します。

図2.1.2 main関数呼び出しまでの実行フロー

C言語によるベクタテーブルとスタートアップルーチンの記述例として、GNU33¥sample\_ide¥std¥dmt33301¥8timer¥src¥vector.c(8ビットタイマサンプルプログラム)の内容を以下に示します。

#### ベクタテーブルとスタートアップルーチン

---

```

/* Prototype */

void boot() __attribute__((interrupt_handler));

void div0() __attribute__((interrupt_handler));

void unalign() __attribute__((interrupt_handler));

void dummy() __attribute__((interrupt_handler));

void nmi() __attribute__((interrupt_handler));

extern void int_8timer0();

extern void int_8timer1();

extern void int_8timer3();

extern void init_bcu(void);

extern void init_int(void);

extern void init_sys(void);

extern void init_ram(void);

extern void exit(void);

/* vector table */

const unsigned long vector[] = {

(unsigned long)boot,           // 0   0   Reset

(unsigned long)dummy,          // 4   1   Reserved

(unsigned long)dummy,          // 8   2   Reserved

(unsigned long)dummy,          // 12  3   Reserved

(unsigned long)div0,           // 16  4   Division by zero

(unsigned long)dummy,          // 20  5   Reserved

(unsigned long)unalign,         // 24  6   Address misaligned exception

(unsigned long)nmi,            // 28  7   NMI

(unsigned long)dummy,          // 32  8   Reserved

(unsigned long)dummy,          // 36  9   Reserved

(unsigned long)dummy,          // 40  10  Reserved

(unsigned long)dummy,          // 44  11  Reserved

(unsigned long)dummy,          // 48  12  Software exception 0

(unsigned long)dummy,          // 52  13  Software exception 1

(unsigned long)dummy,          // 56  14  Software exception 2

(unsigned long)dummy,          // 60  15  Software exception 3

}

```

```

(unsigned long) dummy, // 64 16 Port input interrupt 0

(unsigned long) dummy, // 68 17 Port input interrupt 1

(unsigned long) dummy, // 72 18 Port input interrupt 2

(unsigned long) dummy, // 76 19 Port input interrupt 3

(unsigned long) dummy, // 80 20 Key input interrupt 0

(unsigned long) dummy, // 84 21 Key input interrupt 1

(unsigned long) dummy, // 88 22 High-speed DMA Ch.0

(unsigned long) dummy, // 92 23 High-speed DMA Ch.1

(unsigned long) dummy, // 96 24 High-speed DMA Ch.2

(unsigned long) dummy, // 100 25 High-speed DMA Ch.3

(unsigned long) dummy, // 104 26 Intelligent DMA

(unsigned long) dummy, // 108 27

(unsigned long) dummy, // 112 28

(unsigned long) dummy, // 116 29

(unsigned long) dummy, // 120 30 16bit timer 0 comp B

(unsigned long) dummy, // 124 31 16bit timer 0 comp A

(unsigned long) dummy, // 128 32

(unsigned long) dummy, // 132 33

(unsigned long) dummy, // 136 34 16bit timer 1 comp B

(unsigned long) dummy, // 140 35 16bit timer 1 comp A

(unsigned long) dummy, // 144 36

(unsigned long) dummy, // 148 37

(unsigned long) dummy, // 152 38 16bit timer 2 comp B

(unsigned long) dummy, // 156 39 16bit timer 2 comp A

(unsigned long) dummy, // 160 40

(unsigned long) dummy, // 164 41

(unsigned long) dummy, // 168 42 16bit timer 3 comp B

(unsigned long) dummy, // 172 43 16bit timer 3 comp A

(unsigned long) dummy, // 176 44

(unsigned long) dummy, // 180 45

(unsigned long) dummy, // 184 46 16bit timer 4 comp B

(unsigned long) dummy, // 188 47 16bit timer 4 comp A

(unsigned long) dummy, // 192 48

(unsigned long) dummy, // 196 49

(unsigned long) dummy, // 200 50 16bit timer 5 comp B

(unsigned long) dummy, // 204 51 16bit timer 5 comp A

(unsigned long) int_8timer0, // 208 52 8bit timer 0

(unsigned long) int_8timer1, // 212 53 8bit timer 1

(unsigned long) dummy, // 216 54 8bit timer 2

(unsigned long) int_8timer3, // 220 55 8bit timer 3

(unsigned long) dummy, // 224 56 Serial interface Ch.0

(unsigned long) dummy, // 228 57 Serial interface Ch.0

(unsigned long) dummy, // 232 58 Serial interface Ch.0

(unsigned long) dummy, // 236 59

(unsigned long) dummy, // 240 60 Serial interface Ch.1

(unsigned long) dummy, // 244 61 Serial interface Ch.1

(unsigned long) dummy, // 248 62 Serial interface Ch.1

(unsigned long) dummy, // 252 63

(unsigned long) dummy, // 256 64 A/D converter

(unsigned long) dummy, // 260 65 RTC

(unsigned long) dummy, // 264 66

(unsigned long) dummy, // 268 67

(unsigned long) dummy, // 272 68 Port input interrupt 4

(unsigned long) dummy, // 276 69 Port input interrupt 5

(unsigned long) dummy, // 280 70 Port input interrupt 6

(unsigned long) dummy, // 284 71 Port input interrupt 7

(unsigned long) dummy, // 288 72 8bit timer 4

(unsigned long) dummy, // 292 73 8bit timer 5

(unsigned long) dummy, // 296 74

(unsigned long) dummy, // 300 75

(unsigned long) dummy, // 304 76 Serial interface Ch.2

(unsigned long) dummy, // 308 77 Serial interface Ch.2

(unsigned long) dummy, // 312 78 Serial interface Ch.2

(unsigned long) dummy, // 316 79

(unsigned long) dummy, // 320 80 Serial interface Ch.3

(unsigned long) dummy, // 324 81 Serial interface Ch.3

(unsigned long) dummy, // 328 82 Serial interface Ch.3

(unsigned long) dummy, // 332 83

(unsigned long) dummy, // 336 84

(unsigned long) dummy, // 340 85

(unsigned long) dummy, // 344 86

(unsigned long) dummy, // 348 87

```

## 2 S1C33用プログラムの書き方

```

(unsigned long)dummy,      // 352  88

(unsigned long)dummy,      // 356  89

(unsigned long)dummy,      // 360  90

(unsigned long)dummy,      // 364  91

(unsigned long)dummy,      // 368  92

(unsigned long)dummy,      // 372  93

(unsigned long)dummy,      // 376  94

(unsigned long)dummy,      // 380  95

(unsigned long)dummy,      // 384  96

(unsigned long)dummy,      // 388  97

(unsigned long)dummy,      // 392  98

(unsigned long)dummy,      // 396  99

(unsigned long)dummy,      // 400 100

(unsigned long)dummy,      // 404 101

(unsigned long)dummy,      // 408 102

(unsigned long)dummy,      // 412 103

(unsigned long)dummy,      // 416 104

(unsigned long)dummy,      // 420 105

(unsigned long)dummy,      // 424 106

(unsigned long)dummy,      // 428 107

(unsigned long)dummy,      // 432 108

(unsigned long)dummy,      // 436 109

(unsigned long)dummy,      // 440 110

(unsigned long)dummy,      // 444 111

(unsigned long)dummy,      // 448 112 FIFO Serial interface Ch.0

(unsigned long)dummy,      // 452 113 FIFO Serial interface Ch.0

(unsigned long)dummy,      // 456 114 FIFO Serial interface Ch.0

};

//*****************************************************************************

* boot

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Boot program.

//*****************************************************************************/

void boot(void)

{

asm("xld.w %r15,0x2000");    // Set SP in end of 8KB internal RAM      (1)

asm("ld.w %sp,%r15");

asm("ld.w %r15,0x0");        // Initialize PSR                         (2)

asm("ld.w %psr,%r15");

asm("ld.w %r15,0b10000");    // Set PSR to interrupt enable           (3)

asm("ld.w %psr,%r15");

init_bcu();                  // Initialize BCU on boot time          (4)

init_int();                  // Initialize interrupt controller       (5)

init_sys();                  // Initialize for sys.c                (6)

init_ram();                  // Initialize bss section & data section (7)

main();                      // Call main                           (8)

exit();                      // In last, go to exit                 (9)

}

//*****************************************************************************

* dummy

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Dummy interrupt program.

//*****************************************************************************/

void dummy(void)

{

INT_LOOP:

goto INT_LOOP;                  (10)

}

//*****************************************************************************

* div0

*   Type :      void

*   Ret val :    none

```

```

*   Argument : void

*   Function : Division by zero exception program.

*****void div0(void)

{

INT_LOOP:

goto INT_LOOP;

}

*****void unalign(void)

{

INT_LOOP:

goto INT_LOOP;

}

*****void nmi(void)

{

INT_LOOP:

goto INT_LOOP;

}

```

ベクターテーブルはconst型の32ビット配列として定義しています。このようにして、32ビットの分岐先アドレスをROM上に格納することができます。各ベクタのコメント(//x y z)は、テーブル先頭からのオフセットアドレス(x)とベクタ番号(y)を示す10進数と割り込み処理の説明(z)です。上記のサンプルプログラムでは、使用する8ビットタイマの割り込み処理関数を記述しています。また、使用しない割り込みについてはダミールーチン(dummy)を用意し、そこへ飛ぶようになっています。

スタートアップルーチンは、リセット例外処理関数(boot)として呼び出されます。ブートルーチンではスタックポインタの初期化(1)、PSRの初期化と割り込み許可(2、3)、BCUの初期化(4)、割り込みコントローラの初期化(5)、入力用バッファの初期化(6)、初期値を持たないグローバル変数(.bssセクション)の0クリア、初期値を持つグローバル変数(.dataセクション)の初期値データのRAMへのコピー(7)を行った後、main関数をコールします(8)。必ずしもすべてを実行しなければならない訳ではありませんので、必要に応じて処理してください。ここでは最後にすべての処理が終了したことを確認するためにexit関数を用意しています(9)。また、不当な割り込みが入るとINT\_LOOPに入るよう設定(10)しておくと、デバッグ時にブレークポイントをセットすることでデバッグが容易になります。

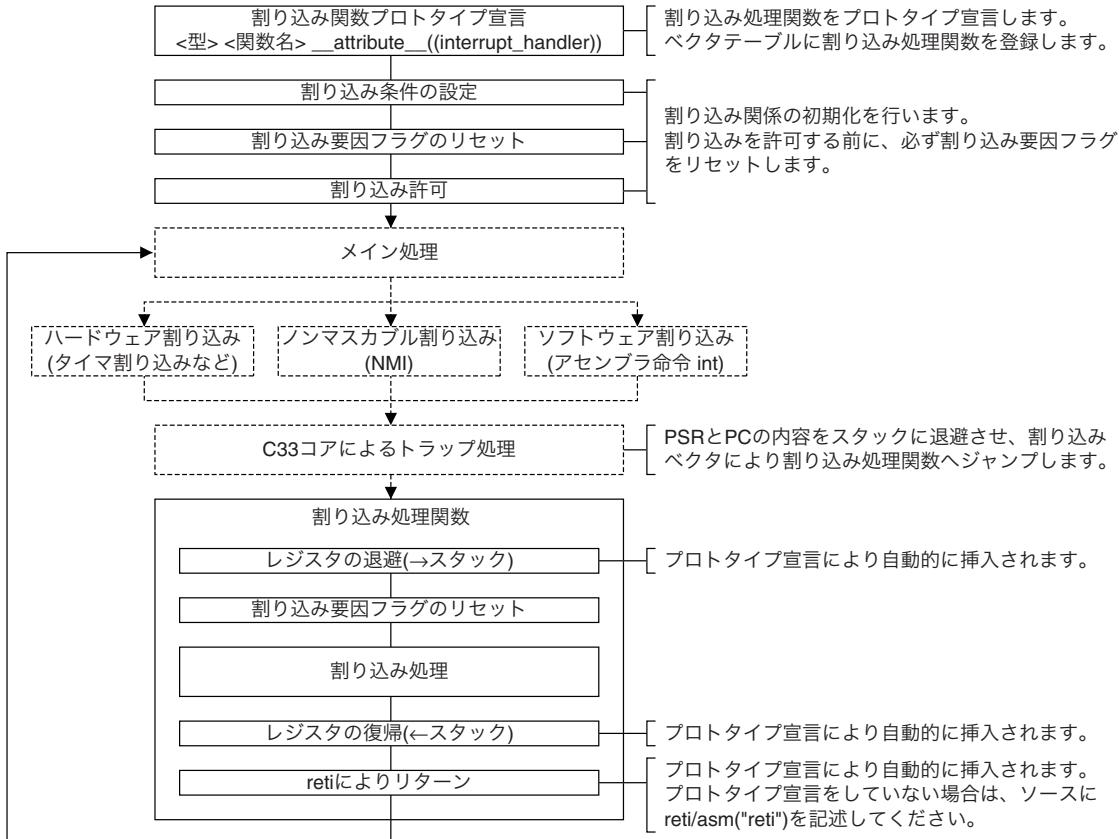

## 2.2 割り込み処理

### 2.2.1 プロトタイプ宣言

C/C++コンパイラ(S5U1C33001C)では以下の形式で`_attribute_((interrupt_handler))`による関数のプロトタイプ宣言を行うことで、その関数を割り込み処理関数に設定することができます。

<型> <関数名> `_attribute_((interrupt_handler))`;

割り込み処理関数をプロトタイプ宣言することによって、汎用レジスタの退避命令と`reti`命令がC/C++コンパイラによって自動的に組み込まれます。また、乗除算や積和演算が行われた場合は%ahr(算術演算ハイレジスタ)と%alr(算術演算ローレジスタ)の退避命令も自動的に組み込まれます。特に`reti`命令は、割り込み発生時にハードウェアが退避させたPSRとPCの内容を戻して処理ルーチンからリターンするため、プロトタイプ宣言をしない場合は必ず`reti`命令を割り込み処理関数の最後に記述してください。C言語での記述例は次のようにになります。また、コンパイル後のアセンブラーコードも記載します。

以下のサンプルプログラムは、GNU33¥sample\_ide¥std¥dmt33301¥8timer¥src¥drv\_8timer.c内の8ビットタイマ0の割り込み関数です。

#### Cコード

```

/* Prototype */

void int_8timer0() __attribute__((interrupt_handler));

/* 8bit timer0 interrupt function */

void int_8timer0(void)

{

***8ビットタイマ0割り込み処理***

}

```

#### アセンブラーコード

```

/* 8bit timer0 interrupt function */

{

pushn %r14

ld.w %0, %alr

ld.w %r1, %ahr

pushn %r1

***8ビットタイマ0割り込み処理***

popn %1

ld.w %alr, %0

ld.w %ahr, %1

popn %r14

reti

}

```

] C/C++コンパイラによって組み込まれるコード

] C/C++コンパイラによって組み込まれるコード

上記のように割り込み処理関数をプロトタイプ宣言すると、C/C++コンパイラが自動的にレジスタの退避や`reti`命令を組み込みます。不測の事態を避けるためにも、割り込み処理関数は必ずプロトタイプ宣言をするようにしてください。

### 2.2.2 NMI

割り込みにはマスク可能な割り込みとマスク不可能な割り込みがあります。

マスク不可能な割り込みをNMI(ノンマスカブル割り込み)といいます。NMIは他の割り込みに優先して、無条件にCPUに受け付けられます。

ただし、SP(スタックポインタ)設定前にNMIが発生すると誤動作するため、イニシャルリセット後はSPが設定されるまで、NMIを含む割り込みはすべてハードウェアによってマスクされます。

## 2.2.3 例外

例外はプログラムの実行中に何らかの異常が発生することをいい、S1C33 Familyでは0による除算や不正なメモリアクセスなどが例外に割り当てられています。C33コアは例外が発生するとベクターテーブルを参照し、例外処理を行います。

この中で、アドレス不正例外は16ビットのメモリリード/ライト時に奇数アドレスにアクセスした場合、または32ビットのメモリリード/ライト時にワード境界アドレス以外にアクセスした場合に発生します。C33コアではこのようなアクセスを禁止していますので注意してください。

## 2.2.4 ソフトウェア割り込み

マスク可能な割り込みにはハードウェア割り込みとソフトウェア割り込み(ソフトウェア例外)があります。タイマなど周辺回路による割り込みはハードウェア割り込みです。一方ソフトウェア割り込みは、int命令を実行することによって、任意の箇所で割り込みを発生させることができます。ソフトウェア割り込みが発生すると、C33コアはベクターテーブル内の対応するベクタ(ソフトウェア割り込み処理関数)へ飛び、割り込み処理を実行します。

以下にソフトウェア割り込みのサンプルプログラムを示します。

### ソフトウェア割り込み例

---

```

void softint1 __attribute__((interrupt_handler));

int int_num;

const unsigned long vector[] = {

:

(unsigned long)softint1,           // 52    13    software interrupt 1      (1)

:

}

int main()

{

:

asm("int 1");                  // software interrupt 1                (2)

:

}

void softint1()

{

int_num = 5;                   (3)

}

```

---

上記サンプルプログラムではmain関数の“asm("int 1")”がソフトウェア割り込み1を発生させ(2)、ベクターテーブルを介してソフトウェア割り込み1に対応する関数へ飛びます(1)。割り込み処理関数softint1では“int\_num = 5”という割り込み処理を実行し、main関数へ戻ります(3)。

## 2.2.5 割り込み要因フラグ

マスク可能なハードウェア割り込みには、それぞれ割り込み要因フラグと割り込みイネーブルレジスタが用意されています。割り込みの発生には、割り込みイネーブルレジスタにより割り込みが許可されている状態で割り込み要因フラグがセットされる必要があります。

割り込み要因フラグは、対応する割り込み要因が発生すると割り込みが発生するしない(割り込みイネーブルレジスタの設定)にかかわらず、ハードウェアによって1にセットされます。この要因フラグによって割り込み要因の発生を知ることができます。また、セットされた割り込み要因フラグはソフトウェアでリセットする必要があります。割り込み発生後、割り込み要因フラグをリセットせずにメインループに戻ると再度割り込みが発生しますので、必ず割り込み処理の中でリセットしてください。また、イニシャルリセット時も割り込み要因フラグは初期化されないため、使用する前に必ずソフトウェアでリセットしてください。

割り込み要因フラグのリセット方式には、リセットオンリーとリード/ライトの2種類があり、フラグセット/リセット方式選択レジスタ(0x4029F)で選択します。イニシャルリセット時にはリセットオンリー方式に設定されます。各方式の違いは以下のとおりです。

## ● リセットオンリー方式

割り込み要因フラグは1の書き込みによってリセットされます。0を書き込んだ場合、セットもリセットもされません。したがって、特定の要因フラグのみを確実にリセットすることができます。

## ● リード/ライト方式

割り込み要因フラグは他のレジスタと同様に、0を書き込むとリセットされ、1を書き込むとセットされます。この場合、0を書き込んだすべての要因フラグがリセットされ、1を書き込んでしまった場合は割り込み要因が発生してしまいますので注意してください。

図2.2.5.1に割り込み処理の基本フローを示します。

図2.2.5.1 基本的な割り込み処理フロー

## 2.3 Cコンパイラとコードの最適化

### 2.3.1 変数のアクセス

変数には外部変数(RAM上の変数、ROM上の定数値、static変数といった絶対アドレスを持つもの)とauto変数(スタック上に置かれる変数)があります。通常、外部変数はレジスタに変数の32ビットメモリアドレスをロードしてアクセスします。一方、auto変数はSP(スタックポインタ) + オフセットのみでアクセスできるため、以下のようなメリットがあります。

- 外部変数に比べてアクセスに必要な命令数が少なく、処理速度も速い。

- スタック上に一時的に置かれるため、RAMを常時占有せずRAMを節約できる。

- レジスタへの割り付けや不要なアクセスの消去といったCコンパイラの最適化の恩恵を受けやすい。

デメリットとしてはスタックが大きくなり、かつ上限値が予想しにくくなることが挙げられますが、あるルーチンで一時的に使用する変数はauto変数へ割り付ける方がより高いコード効率が得られます。

### 2.3.2 volatile修飾

コンパイラとプログラムによる変数へのアクセスに影響を及ぼす修飾子として、volatileがあります。一般的にCコンパイラはより高速で効率的なコードを作成するため、メモリへのアクセス回数を減らし、レジスタにロードした値をできる限り再利用して処理を行うことで最適化を行っています。ただし、この最適化によって、プログラムに記述されているメモリアクセスが実際には省略されてしまう可能性があります。この場合、ハードウェアによって変更された制御レジスタ値や、割り込み処理で変更された変数は、現在の値が反映されずに処理されてしまいます。volatile修飾子は、変数が変更されている可能性があるものとして、変数の参照のたびにその内容を取得し直すことをコンパイラに指定します。つまり、volatile宣言付きで定義した変数は、参照時に必ずメモリアクセスが発生し、最新の内容に更新された上で処理されます。

以下に、volatile宣言の有無によるアセンブラコードを比較した例を示します。

#### Cコード

```

int i_Normal_Flg; //volatile宣言なし

volatile int i_Volatile_Flg; //volatile宣言あり

while( 1 ){

/* (1)volatile宣言なし */

if( i_Normal_Flg == 1 )

{

break;

}

while( 1 ){

/* (2)volatile宣言あり */

if( i_Volatile_Flg == 2 )

{

break;

}

}

}

```

#### アセンブラコード

```

/* (1)volatile宣言なし */

cmp    %r4,0x1      ← レジスタの値を再利用して比較

jrne  0xff

/* (2)volatile宣言あり */

ld.w   %r4,[%r5]    ← 毎回メモリの値を参照して比較

cmp    %r4,0x2

jrne  0xfe

```

上記のようなプログラムの場合、たとえば割り込み処理関数内で変数の値が変更されたとき、(1)では実際のメモリを参照しないためメモリの値が更新されてもレジスタの値は更新されず、意図した結果が得られません。一方(2)ではメモリの値を確実に反映させることができます。

### 2.3.3 ポインタ型構造体・配列

前述のとおり、通常の外部変数へのアクセスはレジスタに変数の32ビットアドレスをロードして行うため、必要命令数が増えます。そこで、外部変数を構造体や配列で宣言します。これにより、構造体や配列の先頭をポインタとして各要素にはオフセットのみでアクセスできますので、外部変数への効率良いアクセスが可能となります。

### 2.3.4 Cコンパイラの最適化オプション

Cコンパイラは-00、-O、-O2、-O3、-Osいずれか1つのスイッチの指定に従って最適化処理を行います。ただし、-O2/-O3は速度のみ、-Osはサイズのみを最適化の対象にしています。スイッチが指定されない場合は最適化は行われません。-Oの数値が上がるほどコード効率が高まりますが、デバッグ情報が一部出力されないなどの問題が発生することがありますので注意してください。正常に実行できないときは、最適化の数値を下げてください。また-O2/-O3は速度の最適化を目的としていますので、-Oよりもサイズが大きくなることがあります。

通常は、-Oでコンパイルすることを推奨します。

最適化オプションについての詳しい説明は、同梱マニュアル“S5U1C33001C Manual”の“6.3.2 コマンドラインオプション”的最適化を参照してください。

# 3 S1C33基本周辺機能のプログラミング

本章では、S1C33チップの基本的な周辺機能モジュールの初期設定を中心に、プログラム方法についてサンプルプログラムを参考にしながら説明します。

以下、サンプルプログラムや周辺機能は特に指定したものを除きS1C3301の例です。機種によっては、機能や制御レジスタアドレスなどが異なる場合がありますので注意してください。

なお以下のサンプルプログラムで使用されている定数は、GNU33¥sample\_ide¥std¥dmt33301¥xxx¥includeにあるヘッダファイル内に宣言されています(xxxは周辺回路名)。

## 3.1 BCU

BCUでは、メモリエリアごとに接続するメモリや周辺I/Oデバイスの種類、サイズ、その他アクセス条件が設定できます。以下、GNU33¥sample\_ide¥std¥dmt33301¥bcu¥srcにあるサンプルプログラムを参考に、SRAMとFLASHを接続した場合の設定について説明します。

### ● 外部メモリマップとチップイネーブル

アドレス空間のエリア4～10は外部システムに解放され、エリア個々に#CE(チップイネーブル)端子が設けられています。C33 STDコアでは#CE出力端子が7本に制限されていますがエリア11～18のメモリ空間もサポートしており、#CE信号とエリアの対応をDRAMタイミング設定レジスタ(0x48130)のCEFUNC[1:0](D[A:9])で切り換えられるようになっています。

表3.1.1 #CE出力の切り換え

| 端子         | CEFUNC = 00 | CEFUNC = 01 | CEFUNC = 1x  |

|------------|-------------|-------------|--------------|

| #CE4       | #CE4        | #CE11       | #CE11+#CE12  |

| #CE5       | #CE5        | #CE15       | #CE15+#CE16  |

| #CE6       | #CE6        | #CE6        | #CE7+#CE8    |

| #CE7/#RAS0 | #CE7/#RAS0  | #CE13/#RAS2 | #CE13/#RAS2  |

| #CE8/#RAS1 | #CE8/#RAS1  | #CE14/#RAS3 | #CE14/#RAS3  |

| #CE9       | #CE9        | #CE17       | #CE17+#CE18  |

| #CE10EX    | #CE10EX     | #CE10EX     | #CE9+#CE10EX |

(デフォルト: CEFUNC = 00)

### ● SRAM、ROM、FLASH用の設定

SRAM、ROM、FLASH用の設定は、BCUレジスタで以下のエリアごとに行えます。

#### 設定エリア

18-17、16-15、14-13、12-11、10-9、8-7、6、5-4

#### 設定内容

- a) デバイスサイズ: 8または16ビット

エリア6はアドレス範囲により8、16ビットが切り換わります。

- b) ウェイト数: 0～7サイクル

書き込み時は、0ウェイトに設定しても1以上となります。

- c) 出力ディセーブル遅延時間: 0.5～3.5サイクル

異なるエリア間のアクセス時に挿入されるウェイトサイクルです。

## ● FLASH、SRAM接続プログラム

S1C33301のエリア5と8にFLASH、エリア10にSRAMが接続されている場合のBCU設定のサンプルプログラムです。

### BCU設定部

---

```

void init_bcu(void)

{

/* Set area 4-5,6 0x4812a <- 0x1111 */

/* Device size 16 bits, output disable delay 1.5, wait control 1 in area 4-5,6 */

/*(volatile unsigned short *)BCU_A4_A5_A6_ADDR =

BCU_DFH_15 | BCU_WTH_1 | BCU_SZL_16 | BCU_DFL_15 | BCU_WTL_1;          (1)

/* Set area 7-8 0x48128 <- 0x0011 */

/* Device size 16 bits, output disable delay 1.5, wait control 1, */

/* DRAM is not used in area 7-8 */

/*(volatile unsigned short *)BCU_A7_A8_ADDR =

BCU_DRAH_NOT | BCU_DRAL_NOT | BCU_SZL_16 | BCU_DFL_15 | BCU_WTL_1;      (2)

/* Set area 9-10 setting 0x48126 <- 0x0017 */

/* Device size 16 bits, disable delay 1.5, wait control 1, burst ROM not used */

/*(volatile unsigned short *)BCU_A9_A10_ADDR =

BCU_BROH_NOT | BCU_BROL_NOT | BCU_SZL_16 | BCU_DFL_15 | BCU_WTL_1;      (3)

}

```

---

このサンプルプログラムでは、エリア4-5と6(1)、7-8(2)、9-10(3)を、デバイスサイズ = 16ビット、ウェイトサイクル = 1、出力ディセーブル遅延時間 = 1.5サイクルに設定しています。

また、エリア7-8(2)ではDRAMを未使用、エリア9-10(3)ではバーストROMを未使用に設定しています。なお、2個の8ビットSRAMで16ビット幅にしている場合は上記の設定で構いませんが、16ビットSRAMを使用している場合は外部インターフェース方式設定(0x4812E•D3)を#BSL(1)にする必要があります。また、一つの設定が適用されるエリアに8ビットと16ビットのデバイスを混在して使用することはできません。

## 3.2 8ビットプログラマブルタイマ

ここでは、GNU33¥sample\_ide¥std¥dmt3301¥8timer¥src内のサンプルプログラムを例に、8ビットタイマを使用した基本的な割り込み制御プログラムについて説明します。

8ビットタイマは、8ビットプリセッタブルダウンカウンタのアンダーフロー信号を割り込みや周辺回路、IC外部に出力することができます。

### ● 8ビットタイマ割り込み制御プログラム

サンプルプログラムでは8ビットタイマ0、1、3からそれぞれ一定周期で割り込みを発生させ、その時点のカウンタ値を取得します。すべてのタイマの割り込みが発生後、取得したカウンタ値を表示します。ここではタイマ0のプログラムを抜粋して解説します。

#### 8ビットタイマ割り込みベクタ部

|                             |                        |

|-----------------------------|------------------------|

| (unsigned long)int_8timer0, | // 208 52 8bit timer 0 |

| (unsigned long)int_8timer1, | // 212 53 8bit timer 1 |

| (unsigned long)dummy,       | // 216 54 8bit timer 2 |

| (unsigned long)int_8timer3, | // 220 55 8bit timer 3 |

#### ベクタテーブルの設定

割り込みルーチンをベクタテーブルに登録します。

#### 8ビットタイマの初期設定部

```

/* Prototype */

void init_8timer0(void);

/********************* init_8timer0 ********************/

* Type : void

* Ret val : none

* Argument : void

* Function : Initialize 8bit timer0.

/*************************************************/

void init_8timer0(void)

{

unsigned char temp;

/* Set 8bit timer0 interrupt enable on interrupt controller 0x40275 */

*(volatile unsigned char *)INT_E8TU_ADDR &= ~INT_E8TU0; (1)

/* Set 8bit timer0 control 0x40160, timer stop */

*(volatile unsigned char *)T8P_PTRUN0_ADDR &= 0xfe; (2)

/* Set 8bit timer0 prescaler 0x4014d */

temp = *(volatile unsigned char *)PRESC_P8TS0_P8TS1_ADDR;

temp &= 0xF0; (3)

temp |= PRESC_PTONL_ON | PRESC_CLKDIVL_SEL7;

*(volatile unsigned char *)PRESC_P8TS0_P8TS1_ADDR = temp;

/* Set 8bit timer0 reload data 0x40161 */

*(volatile unsigned char *)T8P_RLD0_ADDR = 0x27;

// Set reload data (0x27 -> 1ms on OSC3 clock 40MHz) (4)

/* Set 8bit timer0 clock output off, preset and timer stop 0x40160 */

*(volatile unsigned char *)T8P_PTRUN0_ADDR =

T8P_PTOUT_OFF | T8P_PSET_ON | T8P_PTRUN_STOP; (5)

/* Set 8bit timer0 interrupt CPU request on interrupt controller 0x40292 */

*(volatile unsigned char *)INT_R16T5_R8TU_RS0_ADDR &= ~INT_R8TU0; (6)

// IDMA request disable and CPU request enable

/* Set 8bit timer0 interrupt priority level 3 on interrupt controller 0x40269 */

temp = *(volatile unsigned char *)INT_P8TM_PSI00_ADDR;

temp &= 0xF0; (7)

temp |= INT_PRIL_LVL3;

*(volatile unsigned char *)INT_P8TM_PSI00_ADDR = temp;

```

```

/* Reset 8bit timer0 interrupt factor flag on interrupt controller 0x40285 */

*(volatile unsigned char *)INT_F8TU_ADDR = INT_F8TU0;                                (8)

// Reset 8bit timer0 underflow interrupt factor flag

/* Set 8bit timer0 interrupt enable on interrupt controller 0x40275 */

*(volatile unsigned char *)INT_E8TU_ADDR |= INT_E8TU0;                                (9)

// Set 8bit timer0 underflow interrupt enable

}

/*********************************************

* run_8timer

* Type : void

* Ret val : none

* Argument : unsigned long reg          8bit timer run/stop register address

* Function : Run 8bit timer.

********************************************/

void run_8timer(unsigned long reg)

{

/* run timer0 0x40160 */

*(volatile unsigned char *)reg |= 0x01;                                              (10)

}

```

---

## (1)割り込みの禁止

誤動作防止のため、8ビットタイマ0割り込みを禁止します。

## (2)8ビットタイマカウンタ停止

タイマの入力クロックを設定するため、一度タイマを停止します。

## (3)入力クロックの設定、タイマへのクロック供給を開始

プリスケーラの分周クロックを設定し、タイマへのクロック供給を開始します。

サンプルプログラムではプリスケーラで動作クロックを1/256に分周しています。

## (4)リロードデータの設定

タイマがダウンカウントするデータを設定します。この値によってタイマがアンダーフローを発生する周期が決まります。アンダーフロー周期は次の式で求められます。

$$\text{アンダーフロー周期} = \frac{(\text{リロードデータ} + 1)}{(\text{プリスケーラ入力クロック周波数} \times \text{プリスケーラ分周比})}$$

サンプルプログラムではリロードデータを0x27に設定していますので、動作クロックが40MHzの場合、約250μsごとにアンダーフローが発生します。

## (5)アンダーフロー制御の設定、リロードデータのプリセット

タイマのアンダーフロー信号をIC外部に出力するか設定します。サンプルプログラムでは外部出力はしません。

同時に(4)で設定したリロードデータをダウンカウンタへプリセットします。

## (6)割り込み/IDMAリクエストの設定

アンダーフローを割り込み要因としてCPUに割り込みを要求するか、IDMAを起動するかを選択します。サンプルプログラムでは割り込み要求を行います。

## (7)プライオリティレベルの設定

割り込みのプライオリティレベルを設定します。

割り込みが同時に発生した場合、プライオリティレベルが高い割り込みが優先されます。

サンプルプログラムではプライオリティレベルを3に設定しています。

## (8)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (9)割り込みの許可

タイマの割り込みを許可します。これ以降タイマを動作させると一定周期で割り込みが発生します。

## (10)タイマスタート

タイマをスタートさせます。タイマをストップさせるまで一定周期でアンダーフローを出力します。

## 割り込み処理部

---

```

/* Prototype */

void int_8timer0(void) __attribute__((interrupt_handler));

/*********************************************************************

* int_8timer0

*   Type :      void

*   Ret val :   none

*   Argument :  void

*   Function :  8bit timer0 underflow interrupt function.

*               Read 8bit timer3 counter data and stop 8bit timer0.

*****/

```

---

```

void int_8timer0(void)

{

extern volatile unsigned char timer0;

extern volatile int t8int0_flg;

/* interrupt operation */

timer0 = read_8timer_cnt(T8P_PTD0_ADDR); (1)

stop_8timer(T8P_PTRUN0_ADDR);

t8int0_flg = TRUE;

/* Reset 8bit timer0 interrupt factor flag register 0x40285 */

*(volatile unsigned char *)INT_F8TU_ADDR = INT_F8TU0; (2)

}

```

---

(1) 割り込み処理の実行

割り込みが発生するとベクタテーブルに記述されている割り込み処理関数を実行します。

サンプルプログラムでは割り込みが発生した時点のカウンタ値を保存し、タイマを止めています。

また、割り込み確認用のソフトウェアフラグをセットしています。

(2) 割り込み要因フラグのクリア

割り込みの発生により割り込み要因フラグが1になっていますので、これをリセットします。

### 3.3 16ビットプログラマブルタイマ

ここではGNU33¥sample\_ide¥std¥dmt33301¥16timer¥src内のサンプルプログラムを例に、16ビットタイマを使用した基本的な割り込み制御プログラムについて説明します。

16ビットタイマにはコンペアデータレジスタAおよびBが設けられています。このレジスタの設定値とタイマ内のアップカウンタの値が一致するとコンペアAおよびB信号が出力され、割り込みやタイマ出力を制御します。このコンペアデータレジスタにより、割り込みの周期や出力信号のデューティ比をプログラマブルに設定できます。

#### ● 16ビットタイマ割り込み制御プログラム

サンプルプログラムは16ビットタイマ0、1、2、3の順に割り込みが発生するように設定して4つのタイマを動作させます。タイマ0、1、2の割り込みが発生した時点でタイマ3のカウント値を記録して、割り込みを発生したタイマを停止します。タイマ3の割り込みが発生したところで、タイマ0、1、および2の割り込み発生時に記録したタイマ3のカウント値を表示します。以下、タイマ0のプログラムを抜粋してタイマの制御方法を解説します。

#### 16ビットタイマ割り込みベクタ部

|                                |        |    |                      |

|--------------------------------|--------|----|----------------------|

| (unsigned long)dummy,          | // 120 | 30 | 16bit timer 0 comp B |

| (unsigned long)int_16timer_c0, | // 124 | 31 | 16bit timer 0 comp A |

| (unsigned long)dummy,          | // 128 | 32 |                      |

| (unsigned long)dummy,          | // 132 | 33 |                      |

| (unsigned long)int_16timer_u1, | // 136 | 34 | 16bit timer 1 comp B |

| (unsigned long)dummy,          | // 140 | 35 | 16bit timer 1 comp A |

| (unsigned long)dummy,          | // 144 | 36 |                      |

| (unsigned long)dummy,          | // 148 | 37 |                      |

| (unsigned long)dummy,          | // 152 | 38 | 16bit timer 2 comp B |

| (unsigned long)int_16timer_c2, | // 156 | 39 | 16bit timer 2 comp A |

| (unsigned long)dummy,          | // 160 | 40 |                      |

| (unsigned long)dummy,          | // 164 | 41 |                      |

| (unsigned long)int_16timer_u3, | // 168 | 42 | 16bit timer 3 comp B |

| (unsigned long)dummy,          | // 172 | 43 | 16bit timer 3 comp A |

#### ベクタテーブルの設定

割り込みルーチンをベクタテーブルに登録します。

#### 16ビットタイマ初期設定部

```

/* Prototype */

void init_16timer0(void);

/*********************************************

* init_16timer0

* Type : void

* Ret val : none

* Argument : void

* Function : Initialize 16bit timer0.

*****************************************/

void init_16timer0(void)

{

unsigned char temp;

/* Set 16bit timer0 interrupt enable 0x40272, compare A interrupt disable */

*(volatile unsigned char *)INT_E16T0_E16T1_ADDR &= ~INT_E16TC0;           (1)

/* Set 16bit timer0 control 0x48186, timer stop */

*(volatile unsigned char *)T16P_PRUN0_ADDR &= 0xfe;                      (2)

/* Set 16bit timer0 prescaler 0x40147, prescaler on, CLK/256 */

*(volatile unsigned char *)PRESC_P16TS0_ADDR =

PRESC_PTONL_ON | PRESC_CLKDIVL_SEL5;                                (3)

/* Set 16bit timer0 comparison match A data 0x48180, compare data A 0x4e */

*(volatile unsigned short *)T16P_CROA_ADDR = 0x9c;                      (4)

/* Set 16bit timer1 comparison match B data 0x48182, compare data B 0x9c */

*(volatile unsigned short *)T16P_CROB_ADDR = 0x138;

}

```

```

/* Set 16bit timer0 mode 0x48186 */

/* fine-mode normal, compare buffer disable, output normal, clock internal, */

/* clock output off, timer reset, timer stop */

*(volatile unsigned char *)T16P_PRUNO_ADDR =

T16P_SELFM_NOR | T16P_SELCRB_DIS | T16P_OUTINV_NOR | T16P_CKSL_INT |

T16P_PTM_OFF | T16P_PSET_ON | T16P_PRUN_STOP; (5)

/* Set 16bit timer0 interrupt CPU request 0x40290, compare A,B CPU request */

temp = *(volatile unsigned char *)INT_RPO_RHDM_R16T0_ADDR; (6)

temp &= 0x3f;

temp |= INT_RIDMA_DIS;

*(volatile unsigned char *)INT_RPO_RHDM_R16T0_ADDR = temp;

/* Set 16bit timer0 interrupt priority level 3 on interrupt controller 0x40266 */

temp = *(volatile unsigned char *)INT_P16T0_P16T1_ADDR; (7)

temp &= 0xf0;

temp |= INT_PRIL_LVL3;

*(volatile unsigned char *)INT_P16T0_P16T1_ADDR = temp;

/* Reset 16bit timer0 interrupt factor flag 0x40282, */

/* Reset compare A interrupt flag */

*(volatile unsigned char *)INT_F16T0_F16T1_ADDR = INT_F16TC0; (8)

/* Set 16bit timer0 interrupt enable 0x40272, compare A interrupt enable */

*(volatile unsigned char *)INT_E16T0_E16T1_ADDR |= INT_E16TC0; (9)

}

/*********************************************

* run_16timer

*   Type :      void

*   Ret val :   none

*   Argument :  unsigned long reg      16bit timer run/stop register address

*   Function :  Run 16bit timer.

*****************************************/

void run_16timer(unsigned long reg)

{

*(volatile unsigned char *)reg |= 0x01; (10)

}

```

## (1) 割り込みの禁止

誤動作防止のため、16ビットタイマ0割り込みを禁止します。

## (2) 16ビットタイマ0カウンタ停止

タイマの入力クロックを設定するため、一度タイマを停止します。

## (3) 入力クロックの設定、タイマへのクロック供給を開始

プリスケーラの分周クロックを設定し、タイマへのクロック供給を開始します。

サンプルプログラムではプリスケーラで動作クロックを1/256に分周しています。

## (4) コンペアデータの設定

アップカウンタと比較するデータを設定します。

コンペアデータA、Bとアップカウンタの値が一致すると、それぞれコンペアA割り込み、コンペアB割り込みが発生します。サンプルプログラムでは、コンペアデータAを0x9c、コンペアデータBを0x138に設定していますので、動作クロックが40MHzの場合は約1msでコンペアA割り込みが、約2msでコンペアB割り込みが発生します。コンペアB割り込みが発生するとアップカウンタはリセットされます。

## (5) 16ビットタイマ制御の設定

16ビットタイマの外部出力や入力クロックの設定を行います。

外部出力に関しては出力モードと信号反転の設定、外部出力開始の制御を行います。

入力クロックに関しては内部/外部クロックの選択、Run/Stopの制御を行います。

サンプルプログラムでは外部出力は行わず、入力クロックは内部クロックを選択しています。

## (6)割り込み/IDMAリクエストの設定

コンペア信号を割り込み要因としてCPUに割り込みを要求するか、IDMAを起動するかを選択します。サンプルプログラムでは割り込み要求を行います。

## (7)プライオリティレベルの設定

割り込みのプライオリティレベルを設定します。プライオリティレベルが高い割り込みが優先されます。サンプルプログラムではプライオリティレベルを3に設定しています。

## (8)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (9)割り込みの許可

タイマの割り込みを許可します。これ以降タイマを動作させると一定周期で割り込みが発生します。

## (10)タイマスタート

タイマをスタートさせます。ストップさせるまでタイマは一定周期でコンペア信号を出力します。

**割り込み処理部**

---

```

/* Prototype */

void int_16timer_c0(void) __attribute__((interrupt_handler));

/********************* Prototype Information ********************/

* int_16timer_c0

* Type : void

* Ret val : none

* Argument : void

* Function : 16bit timer0 comparison match A interrupt function.

/********************* Prototype Information End ********************/

void int_16timer_c0(void)

{

extern volatile int timer0;

/* interrupt operation */

timer0 = read_16timer_cnt(T16P_TC3_ADDR); (1)

stop_16timer(T16P_PRUNO_ADDR);

/* Reset 16bit timer0 compare A interrupt factor flag */

*(volatile unsigned char *)INT_F16T0_F16T1_ADDR = INT_F16TC0; (2)

}

```

---

## (1)割り込み処理の実行

割り込みが発生するとベクターテーブルで記述されている割り込み処理関数を実行します。サンプルプログラムでは割り込みが発生した時点のカウンタ値を保存し、タイマを止めています。

## (2)割り込み要因フラグのクリア

割り込みの発生により割り込み要因フラグが1になっていますので、これをリセットします。

## 3.4 ウオッチドッグタイマ

ここではGNU33¥sample\_ide¥std¥dmt33301¥wdt¥src内のサンプルプログラムを例に、CPUの暴走を検出するウォッチドッグタイマの制御プログラムについて説明します。

ウォッチドッグタイマは16ビットタイマ0を用いて実現します。この機能を有効にすると、タイマ0のコンペアB信号によってNMIが発生します。つまり、ソフトウェアで定期的にタイマ0をリセットしてNMIが発生しないようにすることで、その処理ルーチンを通らないようなプログラムの暴走を検出することができます。

### ● ウォッチドッグタイマ制御プログラム

このサンプルプログラムではメイン処理ループを用意し、その中で16ビットタイマ0をリセットしています。

万ータイマ0がリセットされずにコンペアB信号が出力された場合はNMIが発生しますので、CPUが暴走したと見なしてNMI処理を行います。

#### ウォッチドッグタイマの初期設定部

```

/* Prototype */

void init_wdt(void);

/*********************************************

* init_wdt

*   Type :      void

*   Ret val :   none

*   Argument : void

*   Function : Initialize WatchDogTimer function.

********************************************/

void init_wdt(void)

{

/* watchdog timer write protection 0x40170, EWD write enable */

*(volatile unsigned char *)WDT_WRWD_ADDR = WDT_WRWD_WRT;           (1)

/* watchdog timer enable 0x40171, NMI enable */

*(volatile unsigned char *)WDT_EWD_ADDR = WDT_EWD_ENABLE;          (2)

}

```

##### (1) ウォッチドッグタイマ書き込み保護の解除

不要なNMIの発生を防止するため、ウォッチドッグタイママイネーブル(EWD)ビットは書き込みが禁止されています。そこで、書き込み保護レジスタに1をセットし、書き込みを許可します。

##### (2) ウォッチドッグタイママイネーブル

ウォッチドッグタイマ機能を有効にします。

これ以降16ビットタイマ0のコンペアB信号が出力されると、NMIが発生します。

**メイン処理部**

---

```

/*********************************************

* main

*   Type :      void

*   Ret val :   none

*   Argument :  void

*   Function :  16bit timer demonstration program.

*****/

int main(void)

{

for (;;)

{

/* Main process */

. . . .

/* Reset 16bit timer0 */

*(volatile unsigned char *)T16P_PRUN0_ADDR |= T16P_PSET_ON;      (2)

}

}

```

---

## (1) メイン処理

メインルーチンの処理を実行します。

サンプルプログラムでは、このメイン処理ループを繰り返し実行するものとしています。

## (2) 16ビットタイマ0のリセット

メインルーチンの処理が終わったところで16ビットタイマ0をリセットします。リセットする前に16ビットタイマ0のコンペアB信号によってNMIが発生した場合は、CPUが暴走したと判断できます。

16ビットタイマの設定については“3.3 16ビットプログラマブルタイマ”を参考にしてください。

通常動作時にウォッチドッグタイマによるNMIが発生することのないように、コンペアマッチB信号の出力周期はメインルーチン処理の周期より長く設定しておく必要があります。

**割り込み処理部**

---

```

/* Prototype */

void nmi(void) __attribute__((interrupt_handler));

/*********************************************

* nmi

*   Type :      void

*   Ret val :   none

*   Argument :  void

*   Function :  NMI interrupt program.

*****/

void nmi(void)

{

/* Reset 16bit timer0 interrupt flag 0x40282 */

*(volatile unsigned char *)INT_F16T0_F16T1_ADDR = INT_F16TU0;

/* Stop 16bit timer0 */

stop_16timer(T16P_PRUN0_ADDR);

t16io_flg = TRUE;

write_str("**** NMI occurred by Watchdog timer ***\n");

write_str("\n");

}

```

---

## 割り込み処理

CPUが暴走した際の処理を記述します。

サンプルプログラムでは16ビットタイマ0の割り込み要因フラグをリセットしてタイマを停止し、NMIが発生したかを判定するソフトウェアフラグをセットしています。

## 3.5 計時タイマ

ここではGNU33¥sample\_ide¥std¥dmt33301¥ct¥src内のサンプルプログラムを例に、計時タイマの制御プログラムについて説明します。

計時タイマはOSC1分周信号を入力クロックとする時間カウンタを持っており、各カウンタのデータをソフトウェアによって読み出すことができます。またカウントアップによる割り込みと日時指定によるアラームを発生することができます。

### ● 計時タイマ制御プログラム

このサンプルプログラムは1Hzカウンタのカウントアップによる割り込みを制御します。以下、計時タイマの初期化設定と割り込み処理について解説します。

#### 計時タイマ割り込みベクタ部

---

```

(unsigned long)int_ct, // 260 65 RTC

```

---

#### 割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

#### 計時タイマ初期設定部

---

```

/* Prototype */

void init_ct(void);

/*********************************************************/

* init_ct

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Initialize clock timer to use real time clock.

/*********************************************************/

void init_ct(void)

{

unsigned char temp;

/* Set clock timer interrupt enable 0x40277, clock timer interrupt disable */

*(volatile unsigned char *)INT_EADE_ECTM_EP4_ADDR &= 0xfd; (1)

/* Stop clock timer 0x40151 */

*(volatile unsigned char *)CT_TCRUN_ADDR = 0x00; (2)

/* Reset clock timer 0x40151 */

*(volatile unsigned char *)CT_TCRUN_ADDR |= CT_TCRST_RST; (3)

/* Set clock timer interrupt control 0x40152, */

/* timer interrupt 1hz, timer alarm disable, factor flag reset */

*(volatile unsigned char *)CT_TCAF_ADDR =

CT_TCISE_1HZ | CT_TCASE_NONE | CT_TCIF_RST | CT_TCAF_RST; (4)

/* Set clock timer interrupt priority level 3 on interrupt controller 0x4026b */

temp = *(volatile unsigned char *)INT_PCTM_ADDR;

temp |= INT_PRIL_LVL3;

*(volatile unsigned char *)INT_PCTM_ADDR = temp; (5)

/* Reset clock timer interrupt factor flag on interrupt controller 0x40287 */

*(volatile unsigned char *)INT_FADE_FCTM_FP4_ADDR = INT_FCTM; (6)

// Reset clock timer interrupt factor flag

/* Set clock timer interrupt enable on interrupt controller 0x40277 */

*(volatile unsigned char *)INT_EADE_ECTM_EP4_ADDR |= INT_ECTM; (7)

// Set clock timer interrupt enable

}

```

---

```

/*********************************************

* main

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Clock timer demonstration program.

/********************************************/

void main()

{

/* Run clock timer */

*(volatile unsigned char *)CT_TCRUN_ADDR |= 0x01;           (8)

}

```

---

## (1)割り込みの禁止

誤動作防止のため、計時タイマ割り込みを禁止します。

## (2)計時タイマの停止

誤動作防止のため、計時タイマを停止します。

## (3)計時タイマカウンタをリセット

計時タイマのカウンタをリセットします。計時タイマの各カウンタはソフトウェアでのみリセットされます。イニシャルリセットによっては、リセットされませんので注意してください。また動作中はリセットされず、停止中にのみ受け付けられます。

リセット時、設定によっては割り込みが発生する可能性があります。したがって、先に計時タイマ割り込みを禁止してリセットしてください。

## (4)割り込み要因の選択

割り込み発生要因とする信号を選択します。

32Hz、8Hz、2Hz、1Hz、1分、1時間、1日から選択した信号の立ち下がりエッジで割り込み要因が発生します。

## (5)プライオリティレベルの設定

割り込みのプライオリティレベルを設定します。プライオリティレベルが高い割り込みが優先されます。サンプルプログラムではプライオリティレベルを3に設定しています。

## (6)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (7)割り込みの許可

タイマの割り込みを許可します。これ以降タイマを動作させると指定周期で割り込みが発生します。

## (8)計時タイマスタート

計時タイマをスタートさせます。選択した割り込み周期で、もしくは指定したアラーム日時になると割り込みが発生します。

**割り込み処理部**

---

```

/* Prototype */

void int_ct(void) __attribute__((interrupt_handler));

/*********************************************************************

* int_ct

*   Type :      void

*   Ret val :   none

*   Argument :  void

*   Function : Clock timer interrupt function.

*********************************************************************/

void int_ct(void)

{

extern volatile int ctint_flg;

/* interrupt operation */

ctint_flg = TRUE;                                (1)

/* Reset clock timer interrupt factor flag 0x40287 */

*(volatile unsigned char *)INT_FADE_FCTM_FP4_ADDR = INT_FCTM;    (2)

}

```

---

## (1) 割り込み処理の実行

割り込みが発生するとベクタテーブルで記述されている割り込み処理関数を実行します。

サンプルプログラムでは、割り込み発生の確認用に用意されたソフトウェアフラグをセットしています。

## (2) 割り込み要因フラグのリセット

割り込みの発生により割り込み要因フラグが1になっているので、これをリセットします。

## 3.6 シリアルインタフェース

ここでは、GNU33¥sample\_ide¥std¥dmt3301¥sif\_asyn/slv/mst内のサンプルプログラムを例にシリアルインターフェースの制御プログラムを説明します。

シリアルインターフェースはクロック同期式転送方式と調歩同期式転送方式に対応しています。クロック同期式転送では送受信ユニットに共通のクロックを使用し、そのクロックに同期させてデータを転送します。調歩同期式では各データの前後に同期のためのスタートビットとストップビットを附加して転送を行います。

### ●シリアルインターフェース(クロック同期式スレーブモード)プログラム

GNU33¥sample\_ide¥std¥dmt3301¥sif\_slv¥src内のサンプルプログラムでは、クロック同期式転送方式でスレーブ側(本チップ)からマスター側へ、割り込みを用いてデータを連続転送します。ここでは、シリアルインターフェースCh.1のスレーブモードへの設定や、その他の初期設定について解説します。

#### シリアルインターフェース(クロック同期式スレーブモード)割り込みベクタ部

|                               |                                 |

|-------------------------------|---------------------------------|

| (unsigned long)dummy,         | // 240 60 Serial interface Ch.1 |

| (unsigned long)dummy,         | // 244 61 Serial interface Ch.1 |

| (unsigned long)int_sif_empty, | // 248 62 Serial interface Ch.1 |

割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

#### シリアルインターフェース(クロック同期式スレーブモード)初期設定部

```

/* Prototype */

void init_sync_sif1(void);

/**********************************************************

* init_sync_sif1

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Initialize synchronous serial channel 1.

*********************************************************/

void init_sync_sif1(void)

{

unsigned char temp;

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt disable */

*(volatile unsigned char *)INT_ES_ADDR &=

~(INT_ESTX1 | INT_ESRX1 | INT_ESERR1);                                (1)

/* Set serial control 0x401e8, send disable, receive disable */

*(volatile unsigned char *)SIF_SMD1_ADDR = SIF_TXEN_DIS | SIF_RXEN_DIS;    (2)

/* Set serial interface I/O port 0x402d0, #SRDY1, #SCLK1, SOUT1, SIN1 */

*(volatile unsigned char *)IO_CFP0_ADDR |=

IO_CFP07_SRDY1 | IO_CFP06_SCLK1 | IO_CFP05_SOUT1 | IO_CFP04_SIN1;       (3)

/* Set IrDA control 0x401e9, i/f mode normal */

*(volatile unsigned char *)SIF_IRMD1_ADDR = SIF_IRMD_ORD;                  (4)

/* Set serial control 0x401e8, transfer-mode clock-syn slave */

*(volatile unsigned char *)SIF_SMD1_ADDR = SIF_SMD_SLA;                    (5)

/* Set serial control 0x401e8, send enable, receive disable, clock #SCLK */

*(volatile unsigned char *)SIF_SMD1_ADDR |=

SIF_TXEN_ENA | SIF_RXEN_DIS | SIF_SSCK_SCLK;                          (6)

/* Clear serial status */

*(volatile unsigned char *)SIF_RDBF1_ADDR = SIF_ERR_NON;                   (7)

/* Set serial interface ch.1 and A/D converter interrupt priority register */

/* 0x4026a */

temp = *(volatile unsigned char *)INT_PSI01_PAD_ADDR;

temp &= 0xf0;

temp |= INT_PRIL_LVL3;                                              (8)

```

```

*(volatile unsigned char *)INT_PSI01_PAD_ADDR = temp;

/* Set serial ch.0,1 interrupt flag 0x40286, clear serial ch.1 interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR =

INT_FSTX1 | INT_FSRX1 | INT_FSERR1;                                (9)

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt enable */

*(volatile unsigned char *)INT_ES_ADDR |=

INT_ESTX1 | INT_ESRX1 | INT_ESERR1;                                (10)

}

```

---

## (1)割り込みの禁止

誤動作防止のため、シリアルインタフェースの割り込みを禁止します。

## (2)送受信の禁止

動作中の設定変更は誤作動の原因になるため、シリアルインタフェースの送受信を禁止します。

## (3)入出力端子の設定

入出力ポート端子の機能をシリアルインタフェース用に切り換えます。

クロック同期式モードではSINx、SOUTx、#SCLKx、#SRDYx端子を使用します。

## (4)インターフェースモードの設定

通常のインターフェースかIrDAインターフェースを選択します。

イニシャルリセット時、この設定は不定になりますので初期化する必要があります。

サンプルプログラムでは通常のインターフェースを選択します。

## (5)転送モードの設定

シリアルインタフェースの転送モードを選択します。

サンプルプログラムではクロック同期式転送のスレーブとして使用します。

## (6)内部クロック、送受信許可の設定

クロック同期式のスレーブ側はマスタデバイスが出力するクロックで動作するため、動作クロックを外部クロックに設定します。よって、プリスケーラやタイマの設定をする必要はありません。また、同時にシリアルインタフェースの送受信許可の設定を行います。

サンプルプログラムではスレーブとして送信を行いますので送信のみ許可します。

クロック同期式転送では送信と受信を同時に許可することはできません。

## (7)ステータスレジスタのリセット

ステータスレジスタのエラーフラグを、0の書き込みによりリセットします。

## (8)割り込みプライオリティレベルの設定

割り込みのプライオリティレベルを設定します。

割り込みが同時に発生した場合、プライオリティレベルが高い割り込みが優先されます。

サンプルプログラムではプライオリティレベルを3に設定しています。

## (9)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (10)割り込みの許可

シリアルインタフェースの割り込みを許可します。

送信時は送信バッファエンプティ割り込みが発生します。

## シリアルインタフェース(クロック同期式スレーブモード)割り込み処理部

```

/* Prototype */

void int_sif_empty(void) __attribute__((interrupt_handler));

/*********************int_sif_empty********************

* int_sif_empty

*   Type : void

*   Ret val : none

*   Argument : void

*   Function : Serial I/F ch.1 sending buffer empty interrupt function.

*****int_sif_empty*****************************/

void int_sif_empty(void)

{

extern volatile int int_empty_flg;

extern volatile unsigned char str[10];

extern volatile int i;

if (i > 9)

{

int_empty_flg = TRUE;                                (1)

}

else

{

/* write sending data */

*(volatile unsigned char *)SIF_TXD1_ADDR = str[i];   (1)

i++;

}

/* clear serial sending buffer empty interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR = INT_FSTX1;      (2)

}

```

## (1) 割り込み処理

シリアルインタフェースでは、送信データが送信データレジスタからシフトレジスタに転送されると送信バッファエンプティ割り込み要因が発生します。割り込みが許可されていれば割り込みが発生し、割り込み処理を行います。

サンプルプログラムでは送信データを送信データレジスタへ書き込んでいます。

また、一定数のデータを送信するとソフトウェアフラグをTRUEにします。

## (2) 割り込み要因フラグのリセット

割り込みの発生により割り込み要因フラグが1になっていますので、これをリセットします。

## ● シリアルインタフェース(クロック同期式マスタモード)プログラム

GNU33¥sample\_ide¥std¥dmt33301¥sif\_mst¥src内のサンプルプログラムでは、クロック同期式転送方式でスレーブ側からマスタ側(本チップ)へ送られてくるデータを、割り込みを用いて連続受信します。ここでは、シリアルインタフェースCh.1のマスタモードへの設定や、その他の初期設定について解説します。

## シリアルインタフェース(クロック同期式マスタモード)割り込みベクタ部

|                               |        |    |                       |

|-------------------------------|--------|----|-----------------------|

| (unsigned long)int_sif_error, | // 240 | 60 | Serial interface Ch.1 |

| (unsigned long)int_sif_full,  | // 244 | 61 | Serial interface Ch.1 |

| (unsigned long)dummy,         | // 248 | 62 | Serial interface Ch.1 |

## 割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

## シリアルインターフェース(クロック同期式マスタモード)初期設定部

---

```

/* Prototype */

void init_sync_sif1(void);

/*********************************************************/

* init_sync_sif1

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Initialize synchronous serial channel 1.

/*********************************************************/

void init_sync_sif1(void)

{

unsigned char temp;

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt disable */

*(volatile unsigned char *)INT_ES_ADDR &=

~(INT_ESTX1 | INT_ESRX1 | INT_ESERR1);                                (1)

/* Set serial control 0x401e8, send disable, receive disable */

*(volatile unsigned char *)SIF_SMD1_ADDR = SIF_TXEN_DIS | SIF_RXEN_DIS;    (2)

/* Set serial interface I/O port 0x402d0, #SRDY1, #SCLK1, SOUT1, SIN1 */

*(volatile unsigned char *)IO_CFP0_ADDR |=

IO_CFP07_SRDY1 | IO_CFP06_SCLK1 | IO_CFP05_SOUT1 | IO_CFP04_SIN1;       (3)

/* Set IrDA control 0x401e9, i/f mode normal */

*(volatile unsigned char *)SIF_IRMD1_ADDR = SIF_IRMD_ORD;                  (4)

/* Set serial control 0x401e8, transfer-mode clock-syn master */

*(volatile unsigned char *)SIF_SMD1_ADDR = SIF_SMD_MAS;                    (5)

/* Set serial control 0x401e8, send disable, receive enable, clock internal */

*(volatile unsigned char *)SIF_SMD1_ADDR |=

SIF_TXEN_DIS | SIF_RXEN_ENA | SIF_SSCK_INT;                          (6)

/* Set 8bit timer3 prescaler, prescaler on, CLK/4 */

*(volatile unsigned char *)PRESC_P8TS2_P8TS3_ADDR =

PRESC_PTONH_ON | PRESC_CLKDIVH_SEL1;                                    (7)

/* Set 8bit timer3 reload data 0x4016d, reload data 0x40 */

*(volatile unsigned char *)T8P_RLD3_ADDR = 0x20;                           (8)

/* Set 8bit timer3 for serial interface ch.1 0x4016c, */

/* clock output, reload data pre-set, timer run */

*(volatile unsigned char *)T8P_PTRUN3_ADDR =

T8P_PTOUT_ON | T8P_PSET_ON | T8P_PTRUN_RUN;                         (9)

/* Clear serial status */

*(volatile unsigned char *)SIF_RDBF1_ADDR = SIF_ERR_NON;                  (10)

/* Set serial interface ch.1 and A/D converter interrupt priority register */

/* 0x4026a */

temp = *(volatile unsigned char *)INT_PSI01_PAD_ADDR;

temp &= 0xf0;                                                        (11)

temp |= INT_PRIL_LVL3;

*(volatile unsigned char *)INT_PSI01_PAD_ADDR = temp;

/* Set serial ch.0,1 interrupt flag 0x40286, clear serial ch.1 interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR =

INT_FSTX1 | INT_FSRX1 | INT_FSERR1;                                 (12)

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.1 interrupt enable */

*(volatile unsigned char *)INT_ES_ADDR |=

INT_ESTX1 | INT_ESRX1 | INT_ESERR1;                                (13)

}

```

---

## (1)割り込みの禁止

誤動作防止のため、シリアルインタフェースの割り込みを禁止します。

## (2)送受信の禁止

動作中の設定変更は誤作動の原因になるため、シリアルインタフェースの送受信を禁止します。

## (3)入出力端子の設定

入出力ポート端子の機能をシリアルインタフェース用に切り替えます。

クロック同期式モードではSINx、SOUTx、#SCLKx、#SRDYx端子を使用します。

## (4)インターフェースモードの設定

通常のインターフェースがIrDAインターフェースを選択します。

イニシャルリセット時、この設定は不定になりますので初期化する必要があります。

サンプルプログラムでは通常のインターフェースを選択します。

## (5)転送モードの設定

シリアルインタフェースの転送モードを選択します。

サンプルプログラムではクロック同期式転送のマスターとして使用します。

## (6)内部クロック、送受信の許可設定

クロック同期式のマスター mode では内部発生したクロックで動作するため、動作クロックを内部クロックに設定します。同時にシリアルインタフェースの送受信許可の設定を行います。

サンプルプログラムではマスターとして受信を行いますので受信のみ許可します。

クロック同期式転送では送信と受信を同時に許可することはできません。

## (7)～(9)入力クロック(8ビットタイマ)の設定

クロック同期式マスター mode では内部発生したクロックで動作します。

各チャネルのクロック源は次のとおりです。

Ch.0: 8ビットプログラマブルタイマ2の出力クロック

Ch.1: 8ビットプログラマブルタイマ3の出力クロック

Ch.2: 8ビットプログラマブルタイマ4の出力クロック

Ch.3: 8ビットプログラマブルタイマ5の出力クロック

ここではシリアルインタフェース Ch.1 を使用しますので、8ビットタイマ3の設定を行います。

(9)でクロック出力制御を On することで、シリアルインタフェースへクロックを供給することができます。

そのほかの8ビットタイマの設定については“3.2 8ビットプログラマブルタイマ”を参照してください。

## (10)ステータスレジスタのリセット

ステータスレジスタのエラーフラグを、0の書き込みによりリセットします。

## (11)割り込みプライオリティレベルの設定

割り込みのプライオリティレベルを設定します。

割り込みが同時に発生した場合、プライオリティレベルが高い割り込みが優先されます。

サンプルプログラムではプライオリティレベルを3に設定しています。

## (12)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (13)割り込みの許可

シリアルインタフェースの割り込みを許可します。

受信時はシリアルエラー割り込み、受信バッファフル割り込みが発生します。

## シリアルインタフェース(クロック同期式マスタモード)割り込み処理部

```

/* Prototype */

void int_sif_error(void) __attribute__((interrupt_handler));

void int_sif_full(void) __attribute__((interrupt_handler));

/*****************/

* int_sif_error

* Type : void

* Ret val : none

* Argument : void

* Function : Serial I/F ch.0 receiving error interrupt function.

/*****************/

void int_sif_error(void)

{

extern volatile int int_error_flg;

int_error_flg = TRUE;                                (1)

/* clear serial error interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR = INT_FSERRO;

}                                                       (3)

/*****************/

* int_sif_full

* Type : void

* Ret val : none

* Argument : void

* Function : Serial I/F ch.0 receiving buffer full interrupt function.

/*****************/

void int_sif_full(void)

{

extern volatile unsigned char str[10];

extern volatile int i;

/* read receiving data */

str[i] = *(volatile unsigned char *)SIF_RXD1_ADDR;

//write_hex((unsigned long)str[i]);                  (2)

/* clear serial receiving buffer full interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR = INT_FSRXI; (3)

i++;

}

```

## (1)シリアルエラー割り込み処理

シリアルインタフェースによるデータ受信の際にパリティエラー、フレーミングエラー、またはオーバーランエラーが検出されると受信エラー割り込み要因フラグがセットされます。割り込みが許可されていれば、割り込みが発生し割り込み処理を行います。クロック同期式モードではパリティエラーとフレーミングエラーは発生しません。

サンプルプログラムでは割り込み処理として、割り込み確認用のソフトウェアフラグをTRUEにしています。

## (2)受信バッファフル割り込み処理

シリアルインタフェースでは受信が完了して、受信データがシフトレジスタから受信データレジスタに転送されると受信バッファフル割り込み要因が発生します。割り込みが許可されていれば割り込みが発生し、割り込み処理を行います。

サンプルプログラムでは受信データレジスタのデータを読み出しています。

## (3)割り込み要因フラグのリセット

割り込みの発生により割り込み要因フラグが1になっていますので、これをリセットします。

以上の設定の後、クロック同期式転送を開始できます。データ送受信開始後のシリアルインタフェースの動作は以下のとおりです。

#### 受信(マスタモード)

1. スレーブ側からの#SRDY信号がLowになるまで待機します。

2. #SRDYがLowであればシリアルインタフェースへの同期クロックの入力を開始します。

3. スレーブ側からのデータをシフトレジスタへ取り込み、MSBを受信すると受信データレジスタへ転送します。

4. 受信データレジスタへ転送されると、受信バッファフル割り込みが発生し割り込み処理を行います。

#### 送信(スレーブモード)

1. 送信データレジスタへデータをセットすると#SRDY信号がLowになり、マスタ側からのクロック入力を待ちます。

2. #SCLKから同期クロックが入力されると送信データレジスタからシフトレジスタへ送信データを転送します。

3. データがシフトレジスタに転送されると、送信バッファエンプティ割り込みが発生し割り込み処理を行います。この時点で#SRDY信号はHighになります。

4. シフトレジスタのデータはクロックに同期してマスタ側へ出力されます。MSBをマスタ側へ出力すると#SRDY信号はLowになります。

サンプルプログラムでは、送信ステップ3の割り込み処理で再度データを送信データレジスタに書き込むことにより、繰り返し上記の手順でデータの連続送信を行います。

### ●シリアルインタフェース(調歩同期式転送)プログラム

GNU33¥sample\_ide¥std¥dmt33301¥sif\_asyn¥src内のサンプルプログラムでは、調歩同期式転送方式を用いて外部シリアルデバイスとの連続データ転送を行います。ここでは調歩同期式シリアルインタフェースCh.0の初期設定について解説します。

#### シリアルインタフェース(調歩同期式転送)割り込みベクタ部

---

|                               |                                 |

|-------------------------------|---------------------------------|

| (unsigned long)int_sif_error, | // 224 56 Serial interface Ch.0 |

| (unsigned long)int_sif_full,  | // 228 57 Serial interface Ch.0 |

| (unsigned long)int_sif_empty, | // 232 58 Serial interface Ch.0 |

---

#### 割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

#### シリアルインタフェース(調歩同期式受信)初期設定部

---

```

/* Prototype */

void init_async_sif0(void);

/*********************************************

* init_async_sif0

* Type : void

* Ret val : none

* Argument : void

* Function : Initialize asynchronous serial channel 0.

*****************************************/

void init_async_sif0(void)

{

unsigned char temp;

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch0 interrupt disable */

*(volatile unsigned char *)INT_ES_ADDR &=

~(INT_ESRX0 | INT_ESRRO | INT_ESERR0); (1)

/* Set serial control 0x401e3, send disable, receive disable */

*(volatile unsigned char *)SIF_SMD0_ADDR = SIF_TXEN_DIS | SIF_RXEN_DIS; (2)

/* Set serial interface I/O port 0x402d0, #SRDY0, #SCLK0, SOUT0, SINO */

*(volatile unsigned char *)IO_CFP0_ADDR |= IO_CFP01_SOUT0 | IO_CFP00_SINO; (3)

/* Set IrDA control 0x401e4, i/f mode normal */

*(volatile unsigned char *)SIF_IRMD0_ADDR = SIF_IRMD_ORD; (4)

```

---

```

/* Set serial control 0x401e3, transfer-mode clock-syn master */

*(volatile unsigned char *)SIF_SMD0_ADDR = SIF_SMD_8BIT; (5)

/* Set IrDA control 0x401e4, dividing frequency 1/16 */

*(volatile unsigned char *)SIF_IRMDO_ADDR |= SIF_DIVMD_16; (6)

/* Set serial control 0x401e3, send disable, receive enable, */

/* parity off, parity-mode even, stop-bit 1, clock internal */

*(volatile unsigned char *)SIF_SMD0_ADDR |=

SIF_TXEN_DIS | SIF_RXEN_ENA | SIF_EPR_OFF | SIF_PMD EVEN |

SIF_STPB_1 | SIF_SSCK_INT; (7)

/* Set 8bit timer2 prescaler, prescaler on, CLK/4 */

*(volatile unsigned char *)PRESC_P8TS2_P8TS3_ADDR =

PRESC_PT0NL_ON | PRESC_CLKDIVL_SEL1; (8)

/* Set 8bit timer2 reload data 0x40169, reload data 0x40 */

*(volatile unsigned char *)T8P_RLD2_ADDR = 0x20; (9)

/* Set 8bit timer2 for serial interface ch.0 0x40168, */

/* clock output, reload data pre-set, timer run */

*(volatile unsigned char *)T8P_PTRUN2_ADDR =

T8P_PTOUT_ON | T8P_PSET_ON | T8P_PTRUN_RUN; (10)

/* Clear serial status */

*(volatile unsigned char *)SIF_RDBF1_ADDR = SIF_ERR_NON; (11)

/* Set serial interface ch.0 and 8bit timer interrupt priority */

/* register 0x40269 */

temp = *(volatile unsigned char *)INT_P8TM_PSI00_ADDR;

temp &= 0x0f;

temp |= INT_PRIH_LVL3;

*(volatile unsigned char *)INT_P8TM_PSI00_ADDR = temp; (12)

/* Set serial ch.0,1 interrupt flag 0x40286, clear serial ch.0 interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR =

INT_FSTX0 | INT_FSRX0 | INT_FSERR0; (13)

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.0 interrupt enable */

*(volatile unsigned char *)INT_ES_ADDR |=

INT_ESTX0 | INT_ESRX0 | INT_ESERR0; (14)

}

```

## (1)割り込みの禁止

誤動作防止のため、シリアルインタフェースの割り込みを禁止します。

## (2)送受信の禁止

動作中の設定変更は誤作動の原因になるため、シリアルインタフェースの送受信を禁止します。

## (3)入出力端子の設定

入出力ポート端子の機能をシリアルインタフェース用に切り替えます。

調歩同期式モードではSINx、SOUTx端子を使用します。

## (4)インターフェースモードの設定

通常のインターフェースかIrDAインターフェースを選択します。

イニシャルリセット時、この設定は不定になりますので初期化する必要があります。

サンプルプログラムでは通常のインターフェースを選択します。

## (5)転送モードの設定

シリアルインターフェースの転送モードを選択します。ここでは8ビット調歩同期式として使用します。

## (6)調歩同期クロックの設定

IrDAインターフェース入出力の設定と調歩同期クロックの分周比を設定します。

サンプルプログラムではIrDAを使用せず、クロックを1/16に設定しています。

## (7) 入力クロック、送受信許可、データフォーマットの設定

調歩同期式では入力クロックとして内部クロックか外部クロックを選択します。また、同時にシリアルインタフェースの送受信許可とデータフォーマットを設定します。データフォーマットとしてデータ長、ストップビット、パリティビットが設定可能です。

サンプルプログラムでは内部クロック、データ長=8ビット、ストップビット=1ビット、パリティビットなし、受信許可に設定しています。

## (8)～(10)8ビットタイマの設定

入力クロックとして内部クロックを選択した場合は8ビットタイマで発生したクロックで動作するため、8ビットタイマのクロック出力をOnします。各チャネルのクロック源は“●シリアルインターフェース(クロック同期式マスタモード)プログラム”を参照してください。

8ビットタイマの設定については“3.2.8ビットプログラマブルタイマ”を参照してください。

## (11)ステータスレジスタのリセット

ステータスレジスタのエラーフラグを、0の書き込みによりリセットします。

## (12)割り込みプライオリティレベルの設定

割り込みのプライオリティレベルを設定します。

割り込みが同時に発生した場合、プライオリティレベルが高い割り込みが優先されます。

サンプルプログラムではプライオリティレベルを3に設定しています。

## (13)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (14)割り込みの許可

シリアルインタフェースの割り込みを許可します。

受信時はシリアルエラー割り込み、受信バッファフル割り込みが発生します。

## シリアルインターフェース(調歩同期式受信)割り込み処理部

---

```

/* Prototype */

void set_sif_mode(unsigned char);

/*********************************************

* main

* Type : void

* Ret val : none

* Argument : void

* Function : Serial interface demonstration program.

********************************************/

int main(void)

{

unsigned char sif_mode;

/* Set serial interface ch.0 transmit mode */

sif_mode = SIF_TXEN_ENA | SIF_RXEN_DIS | SIF_EPR_OFF |

SIF_PMD EVEN | SIF_STPB_1 | SIF_SSCK_INT | SIF_SMD_8BIT;           (1)

set_sif_mode(sif_mode);

/* set_sif_mode

* Type : void

* Ret val : none

* Argument : unsigned char mode      Serial mode

* Function : Set serial interface mode.

*****************************************/

void set_sif_mode(unsigned char mode)

{

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch0 interrupt disable */

*(volatile unsigned char *)INT_ES_ADDR &=

```

```

~(INT_ESTX0 | INT_ESRX0 | INT_ESERRO);                                (2)

/* Set serial control 0x401e3, send disable, receive disable */

*(volatile unsigned char *)SIF_SMD0_ADDR = SIF_TXEN_DIS | SIF_RXEN_DIS;    (3)

/* Clear serial status */

*(volatile unsigned char *) (SIF_RDBF0_ADDR) = SIF_ERR_NON;                (4)

/* Set serial control register */

*(volatile unsigned char *) (SIF_SMD0_ADDR) = mode;                         (5)

// Set serial control register

/* Set serial ch.0,1 interrupt flag 0x40286, clear serial ch.0 interrupt flag */

*(volatile unsigned char *)INT_FS_ADDR =

INT_FSTX0 | INT_FSRX0 | INT_FSERRO;                                     (6)

/* Set serial ch.0,1 interrupt enable 0x40276, serial ch.0 interrupt enable */

*(volatile unsigned char *)INT_ES_ADDR |=

INT_ESTX0 | INT_ESRX0 | INT_ESERRO;                                     (7)

}

```

---

## (1)転送モード、入力クロック、送受信許可、データフォーマットの設定

シリアルインタフェースの転送モードを選択します。調歩同期式では入力クロックとして内部クロックか外部クロックを選択します。また、同時にシリアルインタフェースの送受信許可とデータフォーマットを設定します。データフォーマットとしてデータ長、ストップビット、パリティビットが設定可能です。

サンプルプログラムでは転送モードを8ビット調歩同期式に設定し、内部クロック、データ長=8ビット、ストップビット=1ビット、パリティビットなし、送信許可に設定しています。

## (2)割り込みの禁止

誤動作防止のため、シリアルインタフェースの割り込みを禁止します。

## (3)送受信の禁止

動作中の設定変更は誤作動の原因になるため、シリアルインタフェースの送受信を禁止します。

## (4)ステータスレジスタのリセット

ステータスレジスタのエラーフラグを、0の書き込みによりリセットします。

## (5)送信パラメータのセット

(1)で用意した送信パラメータをレジスタに設定します。

## (6)割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (7)割り込みの許可

シリアルインタフェースの割り込みを許可します。

送信時は送信バッファエンプティ割り込みが発生します。

**シリアルインタフェース(調歩同期式送信)割り込み処理部**

調歩同期式転送の送信割り込み(送信バッファエンプティ)については、“シリアルインタフェース(クロック同期式スレーブモード)割り込み処理部”を参照してください。

以上の設定の後、調歩同期式転送を開始できます。データ送受信開始後のシリアルインタフェースの動作は以下のとおりです。

#### 受信

1. スタートビットの入力によりサンプリングを開始します。

2. スタートビットがサンプリングされると、各データビットを LSB から MSB までシフトレジスタへ取り込みます。

3. MSB が取り込まれると、続いてパリティビットとストップビットを取り込みます。

4. ストップビットをサンプリングするとシフトレジスタのデータは受信データレジスタへ転送されます。また、受信データレジスタへの転送時にはパリティチェックが行われ、データが転送されると受信バッファフル割り込みが発生して割り込み処理を行います。

#### 送信

1. サンプリングクロックに同期してデータを送信データレジスタからシフトレジスタへ転送します。また、同時にSOUTxよりスタートビットを送信します。

2. データがシフトレジスタに転送されると、送信バッファエンプティ割り込みが発生し割り込み処理を行います。

3. スタートビットの送信後、クロックの立ち上がりに同期して各データビットを LSB から MSB まで送信します。

4. MSB 送信後、パリティビットとストップビットを送信します。

サンプルプログラムでは、送信ステップ2の割り込み処理で再度データを送信データレジスタに書き込むことにより、繰り返し上記の手順でデータの連続送信を行います。

## 3.7 FIFO付きシリアルインタフェース

ここではGNU33¥sample\_ide¥std¥dmt33301¥fsif\_asyn/slv/mst内のサンプルプログラムを例に、FIFO付きシリアルインタフェースの制御プログラムについて説明します。

FIFO付きシリアルインタフェースでは、シリアルインタフェースの機能に加え、4バイト受信データバッファおよび2バイト送信データバッファを使用した連続受信、連続送信が可能です。

### ● FIFO付きシリアルインタフェース(クロック同期式転送スレーブモード)プログラム

GNU33¥sample\_ide¥std¥dmt33301¥fsif\_slv¥src内のサンプルプログラムは、クロック同期式転送方式でスレーブ側(本チップ)からマスター側へ、割り込みを用いてデータを連続転送します。ここでは、FIFO付きシリアルインタフェースCh.0のスレーブモードへの設定や、その他の初期設定について解説します。

#### FIFO付きシリアルインタフェース(クロック同期式スレーブモード)割り込みベクタ部

|                               |        |                                |

|-------------------------------|--------|--------------------------------|

| (unsigned long)dummy,         | // 448 | 112 FIFO Serial interface Ch.0 |

| (unsigned long)dummy,         | // 452 | 113 FIFO Serial interface Ch.0 |

| (unsigned long)int_fsif_empty | // 456 | 114 FIFO Serial interface Ch.0 |

#### 割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

#### FIFO付きシリアルインタフェース(クロック同期式スレーブモード)初期設定部

```

/* Prototype */

void init_fifo_bcu(void);

void init_sync_sif0(void);

/********************* init_fifo_bcu *************************/

* init_fifo_bcu

*   Type :      void

*   Ret val :    none

*   Argument :  void

*   Function : Initialize BCU for FIFO serial I/F.

/********************* init_fifo_bcu *************************/

void init_fifo_bcu(void)

{

unsigned short temp;

/* Set area 5-18 endian and external/internal access control 0x48132 */

temp = *(volatile unsigned short *)BCU_EC_IO_ADDR;                                (1)

temp &= 0xfd;

temp |= BCU_A6IO_INT;

*(volatile unsigned short *)BCU_EC_IO_ADDR = temp;

/* Set area 4-6 BCU register, fifo i/f selection 0x4812a */

temp = *(volatile unsigned short *)BCU_A4_A5_A6_ADDR;                            (2)

temp &= 0x0f;

temp |= BCU_WTH_1;

*(volatile unsigned short *)BCU_A4_A5_A6_ADDR = temp;

}

/********************* init_sync_sif0 *************************/

* init_sync_sif0

*   Type :      void

*   Ret val :    none

*   Argument :  void

*   Function : Initialize synchronous FIFO serial channel 0.

/********************* init_sync_sif0 *************************/

void init_sync_sif0(void)

{

/* Set FIFO serial ch.0 interrupt enable 0x402b1, */

/* FIFO serial ch.0 interrupt disable */

*(volatile unsigned char *)INT_EFS_ADDR &=

~(INT_EFSTX0 | INT_EFSRX0 | INT_EFSRRO);                                    (3)

/* Set FIFO serial interface control, each mode disable 0x300203 */

*(volatile unsigned char *)FSIF_SMD0_ADDR =

FSIF_TXEN_DIS | FSIF_RXEN_DIS;                                            (4)

}

```

### 3 S1C33基本周辺機能のプログラミング

```

/* Set P00-P03 extended function, #FSRDY0, #FSCLK0, FSOUT0, FSIN0 0x300040 */

*(volatile unsigned char *)FSIF_EFP_ADDR =

FSIF_EFP03_FSRDY | FSIF_EFP02_FSCLK | FSIF_EFP01_FSOUT |

FSIF_EFP00_FSIN; (5)

/* Set FIFO serial interface IrDA register, i/f mode normal 0x300204 */

*(volatile unsigned char *)FSIF_IRMD0_ADDR = FSIF_IRMD_ORD; (6)

/* Set FIFO serial interface control register, */

/* transfer mode clock-sync slave 0x300203 */

*(volatile unsigned char *)FSIF_SMD0_ADDR = FSIF_SMD_SLA; (7)

/* Set FIFO serial interface IrDA register, #FSRDY0 normal 0x300204 */

*(volatile unsigned char *)FSIF_IRMD0_ADDR |= FSIF_SRDYL_NML; (8)

/* Set FIFO serial interface control register, transfer enable, */

/* #FSCLK0 0x300203 */

*(volatile unsigned char *)FSIF_SMD0_ADDR |=

FSIF_TXEN_ENA | FSIF_RXEN_DIS | FSIF_SSCK_FSCLK; (9)

/* Set FIFO serial interface status register, error flag clear 0x300202 */

*(volatile unsigned char *)FSIF_RDBF0_ADDR &= 0xe3; (10)

/* Set FIFO serial interface interrupt priority level 3 on interrupt */

/* controller 0x402b0 */

*(volatile unsigned char *)INT_PFSIO_ADDR = INT_PRIH_LVL3; (11)

/* Set FIFO serial ch.0 interrupt flag 0x402b2, */

/* clear serial ch.0 interrupt flag */

*(volatile unsigned char *)INT_FFS_ADDR =

INT_FFSTX0 | INT_FFSRX0 | INT_FFSERR0; (12)

/* Set FIFO serial ch.0 interrupt enable 0x402b1, */

/* serial ch.0 interrupt enable */

*(volatile unsigned char *)INT_EFS_ADDR |=

INT_EFSTX0 | INT_EFSRX0 | INT_EFSERR0; (13)

}

```

#### (1), (2)BCUの設定

FIFO付きシリアルインタフェースの制御レジスタはエリア6の0x300200～0x300209に割り付けられているため、アクセス前にBCUレジスタを設定し、エリア6の内部デバイスがアクセスされるようにしておきます。

#### (3)割り込みの禁止

誤動作防止のため、FIFO付きシリアルインタフェースの割り込みを禁止します。

#### (4)送受信の禁止

動作中の設定変更は誤作動の原因になるため、FIFO付きシリアルインタフェースの送受信を禁止します。

#### (5)入出力端子の設定

入出力ポート端子の機能をFIFO付きシリアルインタフェース用に切り替えます。

クロック同期式モードではFSIN0、FSOUT0、#FSCLK0、#FSRDY0端子を使用します。

#### (6)インターフェースモードの設定

通常のインターフェースかIrDAインターフェースを選択します。

イニシャルリセット時、この設定は不定になりますので初期化する必要があります。

サンプルプログラムでは通常のインターフェースを選択します。

#### (7)転送モードの設定

FIFO付きシリアルインタフェースの転送モードを選択します。

サンプルプログラムではクロック同期式転送のスレーブとして使用します。

#### (8) #FSRDY0制御の設定

受信バッファフル時の#FSRDY0信号の制御内容を設定します。マスクを選択すると、受信バッファフル時に#FSRDY0信号をHighにして、オーバーランエラーの発生を回避することができます。

## (9) 内部クロック、送受信許可の設定

クロック同期式のスレーブ側はマスタデバイスが outputするクロックで動作するため、動作クロックを外部クロックに設定します。よって、プリスケーラやタイマの設定をする必要はありません。また、同時に FIFO付きシリアルインタフェースの送受信許可の設定を行います。

サンプルプログラムではスレーブとして送信を行いますので送信のみ許可します。

クロック同期式転送では送信と受信を同時に許可することはできません。

## (10) ステータスレジスタのリセット

ステータスレジスタのエラーフラグを、0の書き込みによりリセットします。

## (11) 割り込みプライオリティレベルの設定

割り込みのプライオリティレベルを設定します。

割り込みが同時に発生した場合、プライオリティレベルが高い割り込みが優先されます。

サンプルプログラムではプライオリティレベルを3に設定しています。

## (12) 割り込み要因フラグのリセット

イニシャルリセット後、割り込み要因フラグは不定となるため、割り込みを許可する前にリセットします。

## (13) 割り込みの許可

FIFO付きシリアルインタフェースの割り込みを許可します。

送信時は送信バッファエンプティ割り込みが発生します。

**FIFO付きシリアルインタフェース(クロック同期式スレーブモード)割り込み処理部**

```

/* Prototype */

void int_fsif_empty(void) __attribute__((interrupt_handler));

/*********************

* int_fsif_empty

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : FIFO serial I/F ch.0 sending buffer empty interrupt function.

****/

void int_fsif_empty(void)

{

extern volatile int int_empty_flg;

extern volatile unsigned char str[10];

extern volatile int i;

if (i > 9)

{

int_empty_flg = TRUE;                                (1)

}

else

{

/* write sending data */

*(volatile unsigned char *)FSIF_TXD0_ADDR = str[i]; (1)

i++;

}

/* clear serial sending buffer empty interrupt flag */

*(volatile unsigned char *)INT_FFS_ADDR = INT_FFSTX0; (2)

}

```

## (1) 割り込み処理

FIFO付きシリアルインタフェースでは、送信データが送信データレジスタからシフトレジスタに転送されると送信バッファエンプティ割り込み要因が発生します。割り込みが許可されていれば割り込みが発生し、割り込み処理を行います。

サンプルプログラムでは送信データを送信データレジスタへ書き込んでいます。

また、一定数のデータを送信するとソフトウェアフラグをTRUEにします。

## (2) 割り込み要因フラグのリセット

割り込みの発生によって割り込み要因フラグが1になっていますので、これをリセットします。

## ● FIFO付きシリアルインタフェース(クロック同期式マスタモード)プログラム

GNU33¥sample\_ide¥std¥dmt33301¥fsif\_mst¥src内のサンプルプログラムでは、クロック同期式転送方式でスレーブ側からマスタ側(本チップ)へ送られてくるデータを、割り込みを用いて連続受信します。ここでは、FIFO付きシリアルインタフェースCh.0のマスタモードへの設定や、その他の初期設定について解説します。

### FIFO付きシリアルインタフェース(クロック同期式マスタモード)割り込みベクタ部

|                                |        |                                |

|--------------------------------|--------|--------------------------------|

| (unsigned long)int_fsif_error, | // 448 | 112 FIFO Serial interface Ch.0 |

| (unsigned long)int_fsif_full,  | // 452 | 113 FIFO Serial interface Ch.0 |

| (unsigned long)dummy           | // 456 | 114 FIFO Serial interface Ch.0 |

### 割り込みベクタの設定

割り込みルーチンをベクタテーブルに登録します。

### FIFO付きシリアルインタフェース(クロック同期式マスタモード)初期設定部

```

/* Prototype */

void init_fifo_bcu(void);

void init_sync_sif0(void);

/*********************************************

* init_fifo_bcu

*   Type :      void

*   Ret val :    none

*   Argument :   void

*   Function : Initialize BCU for FIFO fifo-serial I/F.

*****/

void init_fifo_bcu(void)

{

unsigned short temp;

/* Set area 5-18 endian control and external/internal access control 0x48132 */

temp = *(volatile unsigned short *)BCU_EC_IO_ADDR;                                (1)

temp &= 0xffff;

temp |= BCU_A6IO_INT;

*(volatile unsigned short *)BCU_EC_IO_ADDR = temp;

/* Set area 4-6 BCU register, fifo i/f selection 0x4812a */

temp = *(volatile unsigned short *)BCU_A4_A5_A6_ADDR;                            (2)

temp &= 0xf0ff;

temp |= BCU_WTH_1;

*(volatile unsigned short *)BCU_A4_A5_A6_ADDR = temp;

}

/*********************************************

* init_sync_sif0

*   Type :      void

*   Ret val :    none

*   Argument :   void