ITU-T V.23/BELL202準拠のFSK復調回路

Bellcore"CPEアラート信号"検出

BT"アイドルトーンアラート信号"検出

低電圧動作

## 概 要

S1C05251(CAS + FSK IC)は、Call Waiting機能付き発信番号認識用CMOS ICで、S1C05250の改訂版です。Bellcore GR-30-COREに準拠したCND(Calling Number Delivery)、CNAM(Calling Name Delivery)、CIDCW(Calling Identity on Call Waiting)、あるいはBritish TelecomのCLIP(Calling Line Identification Service)、Cable Communications AssociationのCDS(Caller Display Service)など、各種発信情報通知サービスとのインターフェースを提供します。また、S1C05251にはパワーダウン回路、リング検出回路、キャリア検出回路、同期受信データ出力機能、クロック同期式シリアルインターフェースが搭載されており、以下に挙げるようなアプリケーションの構築に最適です。

- Call Waiting機能付き発信番号通知サービス

- 電話機などの補助装置

- 電話応答装置

- 多機能電話

- ファックス

- コンピュータ周辺回路

- Message Waiting電話

## 特 長

Bellcore GR-30-CORE、SR-TSV-002476に準拠 (S1C05250と同一)

British Telecom SIN227、SIN242に準拠 (S1C05250と同一)

プログラマブルなバンドパスフィルタにより、BellcoreのCPEアラート信号(CAS)、

British Telecomのアイドルトーンアラート信号を検出可能 (S1C05250と同一)

ITU-T V.23/BELL202準拠のFSK復調回路 (S1C05250と同一)

コールログレスモード信号(CPM)検出のためのフィルタバイパスモード (S1C05250と同一)

アラート信号の検出レベルをプログラマブルに設定可能 (S1C05250と同一)

キャリア/リング検出出力 (S1C05250と同一)

FSKエナジ検出モード: パワーダウン時にFSK信号検出 (S1C05251の新規追加機能)

CAS信号のシングルエンド入力可 (S1C05251の新規追加機能)

オフフック検出 (S1C05251の新規追加機能)

3.579545MHz水晶発振または外部クロック入力に対応 (S1C05250と同一)

シリアル受信データ出力 (S1C05250と同一)

シリアルホストインターフェース (S1C05250と同一)

パワーダウンモード (S1C05250と同一)

電源電圧: 2.7V ~ 5.5V (S1C05250と同一)

動作温度範囲: -20°C ~ 70°C (S1C05250と同一)

消費電流: 動作時 3mA (S1C05250と同一)

ゼロパワーモード時 1µA (S1C05250と同一)

FSKエナジ検出モード 6µA (S1C05251の新規追加機能)

出荷形態: SOP2-28pin(プラスチック)、DIP-28pin(セラミック)またはチップ (S1C05251の新規追加機能)

# S1C05251

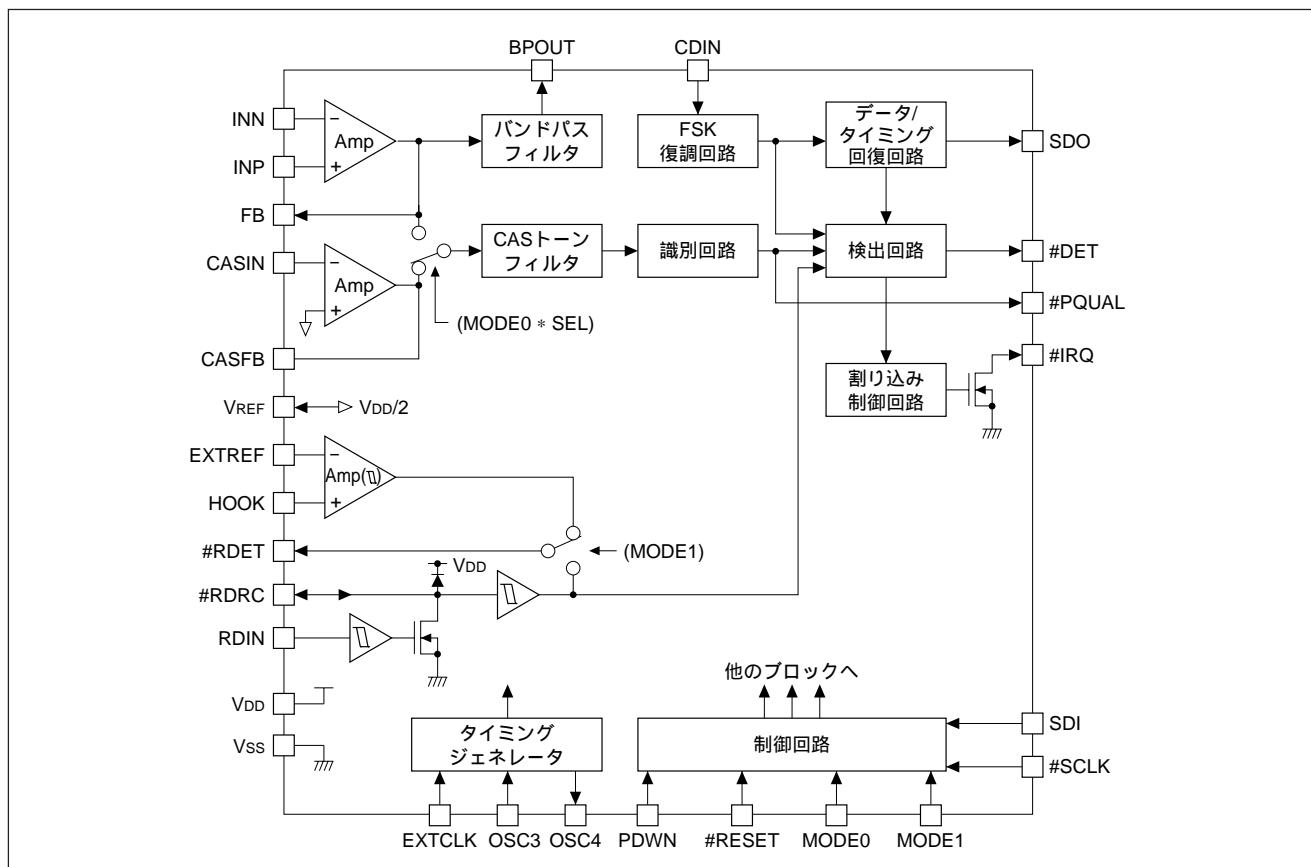

ブロック図

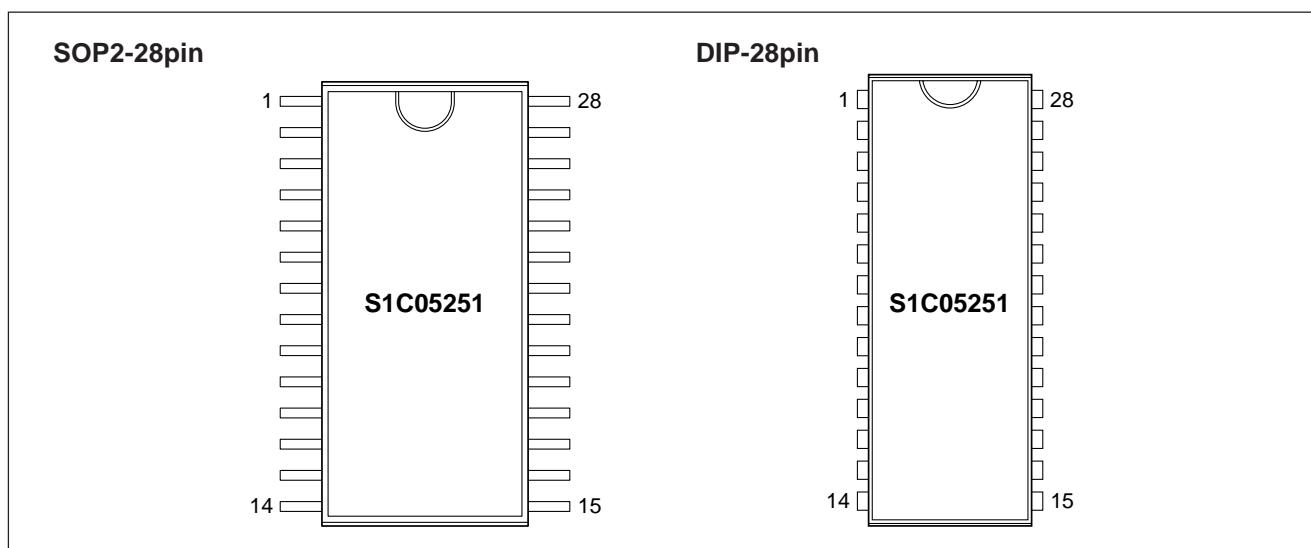

端子配置図

| No. | 端子名    | No. | 端子名    | No. | 端子名    | No. | 端子名   |

|-----|--------|-----|--------|-----|--------|-----|-------|

| 1   | INP    | 8   | HOOK   | 15  | OSC3   | 22  | #IRQ  |

| 2   | INN    | 9   | RDIN   | 16  | OSC4   | 23  | #SCLK |

| 3   | FB     | 10  | #RDRC  | 17  | EXTCLK | 24  | SDI   |

| 4   | CASIN  | 11  | #RDET  | 18  | MODE0  | 25  | SDO   |

| 5   | CASFB  | 12  | PDWN   | 19  | MODE1  | 26  | CDIN  |

| 6   | VREF   | 13  | #RESET | 20  | #PQUAL | 27  | BPOUT |

| 7   | EXTREF | 14  | Vss    | 21  | #DET   | 28  | VDD   |

## 端子説明

注: 信号名/端子名において、先頭の "#" は Low アクティブ信号/端子を表します。

| 端子名    | 端子No. | 形式                               | パワーダウン状態            | 機能                                                                                                                                                                                                                                    |

|--------|-------|----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INP    | 1     | 入力<br>アナログ                       | Off/<br>アクティブ       | +入力: アンプ非反転入力<br>入力利得設定用抵抗とDCカットコンデンサを通し、電話線に接続します。MODE1端子をLowレベルに設定すると、パワーダウンモード時に本端子は内部回路から切り離されます。MODE1端子がHighレベルの場合、#IRQ端子からホストの起動信号を出力するため、パワーダウンモード時でも本端子によるFSKエナジ検出を継続します。本端子には利得設定用抵抗以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。 |

| INN    | 2     | 入力<br>アナログ                       | Off/<br>アクティブ       | -入力: アンプ反転入力<br>入力利得設定用抵抗とDCカットコンデンサを通し、電話線に接続します。MODE1端子をLowレベルに設定すると、パワーダウンモード時に本端子は内部回路から切り離されます。MODE1端子がHighレベルの場合、#IRQ端子からホストの起動信号を出力するため、パワーダウンモード時でも本端子によるFSKエナジ検出を継続します。本端子には利得設定用抵抗以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。  |

| FB     | 3     | 出力<br>アナログ                       | High-Z/<br>アクティブ    | アンプ出力<br>本端子とINN端子間に利得を設定する帰還抵抗を接続します。MODE1端子をLowレベルに設定すると、パワーダウンモード時に本端子はハイインピーダンスとなります。MODE1端子がHighレベルの場合、#DET端子からホストの起動信号を出力するため、パワーダウンモード時でも本端子によるFSKエナジ検出を継続します。本端子には利得設定用抵抗以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。             |

| CASIN  | 4     | 入力<br>アナログ                       | Off                 | CASトーンアンプ入力<br>電話アプリケーションの場合、本端子を入力利得設定用抵抗とDCカットコンデンサを通し、電話ハイブリッド回路の出力に接続します。パワーダウンモード時、本端子は内部回路から切り離されます。本端子には利得設定用抵抗以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。                                                                        |

| CASFB  | 5     | 出力<br>アナログ                       | High-Z              | CASアンプ出力<br>本端子とCASIN端子間にCAS利得を設定する帰還抵抗を接続します。MODE1端子をLowレベルに設定すると、パワーダウンモード時、本端子はハイインピーダンスとなります。本端子には利得設定用抵抗以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。                                                                                 |

| VREF   | 6     | 出力<br>アナログ                       | High-Z/<br>VDD/2レベル | 基準電圧出力<br>VDDの1/2の電圧を出力します。本端子は0.1μFのコンデンサでVssに接続してください。MODE1端子をLowレベルに設定すると、パワーダウンモード時に本端子はハイインピーダンスとなります。MODE1端子がHighレベルの場合、パワーダウンモード時でも本端子はVDDの1/2の電圧を出力します。本端子にはVssへのバイパスコンデンサ以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。            |

| EXTREF | 7     | 入力<br>アナログ                       | アクティブ               | 外部基準電圧入力<br>外部のDC基準電圧を入力します。この入力電圧はオフフック検出のしきい値を決定します。                                                                                                                                                                                |

| HOOK   | 8     | 入力<br>アナログ                       | アクティブ               | オフフック検出入力<br>TIP/RINGラインのダイオードブリッジ出力をオフフック/オンフック検出用分割抵抗を通して接続します。                                                                                                                                                                     |

| RDIN   | 9     | ショミット<br>トリガ入力                   | アクティブ               | リング検出入力<br>リング検出のため、リング信号をアッテネートして入力します。この入力回路はパワーダウンモード時も動作します。                                                                                                                                                                      |

| #RDRC  | 10    | オープンド<br>レイン出力<br>ショミット<br>トリガ入力 | アクティブ               | リング検出RC端子<br>RCネットワークを接続して、リング信号検出のための遅延時間を設定します。この出力回路はパワーダウンモード時も動作します。                                                                                                                                                             |

| #RDET  | 11    | 出力                               | アクティブ               | リング検出出力<br>MODE1端子をLowレベルに設定すると、本端子からはショミットトリガバッファを通した#RDRC信号が出力されます。リング信号を検出すると、本端子はLowレベルとなります。MODE1端子をHighレベルに設定すると、本端子からはHOOK端子の入力を判定したオフフック検出結果が出力されます。オンフック状態で出力はHighレベル、オフフック状態でLowレベルとなります。                                   |

| PDWN   | 12    | 入力                               | アクティブ               | パワーダウン入力<br>通常動作中は、本端子をLowレベルに保つ必要があります。本端子をHighレベルに設定すると、S1C05251はパワーダウンモードになります。パワーダウンモードでは、OSC4端子はHighレベル、VREF、CASFBおよびFB端子はハイインピーダンスとなります。(FB端子およびVREF端子はMODE1端子がLowレベルの場合にのみハイインピーダンスとなります。)                                     |

| #RESET | 13    | 入力                               | アクティブ               | リセット入力<br>本端子をLowレベルに設定すると、内部レジスタがすべてデフォルト状態にリセットされます。内部レジスタに書き込みを行うには、本端子をHighレベルに設定しておく必要があります。                                                                                                                                     |

# S1C05251

| 端子名    | 端子No. | 形式         | パワーダウン状態         | 機能                                                                                                                                                                                                                                                                                                                                     |

|--------|-------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss    | 14    | 電源(-)      |                  | -電源端子<br>システムのグラウンドラインに接続します。                                                                                                                                                                                                                                                                                                          |

| OSC3   | 15    | 入力         | Off              | 水晶発振入力/外部クロック入力<br>水晶振動子を本端子とOSC4端子間に、また適切な容量を本端子とVss端子間に接続します。外部クロックを本端子に入力して使用することも可能です。パワーダウンモード時、本端子は内部回路から切り離されます。                                                                                                                                                                                                                |

| OSC4   | 16    | 出力         | Highレベル          | 水晶発振出力<br>水晶振動子を本端子とOSC3端子間に、また適切な負荷容量を本端子とVss端子間に接続します。OSC3端子に外部クロックを入力する場合は、本端子をオープンにします。パワーダウンモード時、本端子はHighレベルとなります。                                                                                                                                                                                                                |

| EXTCLK | 17    | 入力         | アクティブ            | 外部クロック入力<br>FSKエナジ検出回路のプリクオリファイロジック動作用クロック(32.768kHz Typ.)をホストより入力します。                                                                                                                                                                                                                                                                 |

| MODE0  | 18    | 入力         | アクティブ            | モード0選択入力: CASモードまたはFSK/CPMモードの選択<br>本端子をHighレベルに設定するとCASモードが選択され、CAS検出が有効、FSK機能/CPM検出が無効となります。また、この状態でホストデバイスによるSDIおよび#SCLK端子を使用した内部レジスタへの書き込みが行えます。なお、レジスタへの書き込みを行う前に本端子を一度Lowレベルに設定し、シリアルインターフェースをデータ書き込みシーケンスに同期させる必要があります。<br>本端子をLowレベルに設定するとFSK/CPMモードが選択され、CAS検出が無効、FSK機能/CPM検出が有効となります。この状態で、ホストデバイスは受信データをSDO端子から読み出すことができます。 |

| MODE1  | 19    | 入力         | アクティブ            | モード1選択入力: FSKエナジおよびオフフック検出モードの選択<br>本端子をHighレベルに設定するとFSKエナジおよびオフフック検出機能が有効になり、Lowレベルに設定すると無効となります。                                                                                                                                                                                                                                     |

| #PQUAL | 20    | 出力         | Highレベル          | プリクオリファイ出力<br>プリクオリファイ出力を本端子でモニタできます。トーン検出中以外は、本端子はHighレベルになります。                                                                                                                                                                                                                                                                       |

| #DET   | 21    | 出力         | アクティブ            | 検出出力<br>パワーダウンモード時でかつMODE1端子がLowレベルの場合は、リング信号が入力されるか、 LINERIALIZED信号により本端子がLowレベルとなります。 MODE1端子がHighレベルの場合、リング信号またはFSK信号の入力により本端子がLowレベルとなります。FSKモードでの通常動作中は、FSK信号が入力されるとLowレベルになります。CPMモードでの通常動作中は、入力したCPMトーン信号をパルス列に変換して出力します。CASモードでの通常動作中はCASトーン信号が入力されるとLowレベルになります。                                                              |

| #IRQ   | 22    | オープンドレイン出力 | アクティブ            | 割り込み要求出力<br>パワーダウンモード時は、リング信号が入力されるか、 LINERIALIZED信号によりLowレベルとなります。FSKモードでの通常動作中は、受信データが内部レジスタに取り込まれ、ホストからの読み出しが可能になるとLowレベルとなります。その後、ホストが受信データの最初のビットを読み出した時点でHighレベルに戻ります。CPMモードでの通常動作中は、CPMトーン信号が入力されるとLowレベルになります。CASモードでの通常動作中はCASトーンを検出するとLowレベルになります。CASトーン入力中はLowレベルを保持します。                                                    |

| #SCLK  | 23    | 入力         | アクティブ            | シリアルクロック入力<br>ホストが内部レジスタへの書き込みを行う場合、または受信データを読み出す場合に、ホストからクロックが本端子に供給されます。ホストに読み出される受信データは本端子に入力されるクロックの立ち下がりエッジで順次シフトします。                                                                                                                                                                                                             |

| SDI    | 24    | 入力         | アクティブ            | シリアルデータ入力<br>ホストが内部レジスタへの書き込みを行う際に、書き込みデータを入力します。                                                                                                                                                                                                                                                                                      |

| SDO    | 25    | 出力         | Highレベル          | シリアルデータ出力<br>ホストが読み出す受信データを出力します。非同期モード選択時は、非同期形式のデータが 出力されます。同期モード選択時は、ホストが#SCLK端子に供給するクロックに同期してデータが出力されます。パワーダウンモード時、CPMモード時、あるいはCASモード時、本端子はHighレベルになります。                                                                                                                                                                           |

| CDIN   | 26    | 入力<br>アナログ | V <sub>REF</sub> | コンデンサ接続端子<br>本端子とBPOUT端子間に0.1μFのコンデンサを接続します。内部動作のテストのため、この0.1μFのコンデンサを通して本端子にFSK信号を直接入力してバンドパスフィルタをバイパスすることができます。本端子にはこのコンデンサ以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。                                                                                                                                                                  |

| BPOUT  | 27    | 出力<br>アナログ | High-Z           | コンデンサ接続端子<br>本端子とCDIN端子間に0.1μFのコンデンサを接続します。内部動作のテストのため、バンドパスフィルタの出力を本端子でモニタできます。本端子にはこのコンデンサ以外は接続しないでください。本端子への過度な負荷は回路の誤動作の原因となります。                                                                                                                                                                                                   |

| VDD    | 28    | 電源(+)      |                  | +電源端子                                                                                                                                                                                                                                                                                                                                  |

## 電気的特性

### 絶対最大定格

| 項目      | 記号               | 定格値                                                       | 単位  |

|---------|------------------|-----------------------------------------------------------|-----|

| 電源電圧    | VDD              | -0.5 ~ 7                                                  | V   |

| 入力電圧    | Vi               | -0.3 to VDD+0.3                                           | V   |

| 許容総出力電流 | $\Sigma I_{VDD}$ | $\pm 10$                                                  | mA  |

| 許容損失    | Pd               | 250                                                       | mW  |

| 保存温度    | TSTG             | -65 ~ 150                                                 | °C  |

| 半田付け温度  | TSOL             | 255                                                       | °C  |

| 半田付け時間  | t <sub>SOL</sub> | 10                                                        | Sec |

| 動作温度    | TOPR             | -20 ~ 70                                                  | °C  |

| 静電気耐圧   | VE               | EIAJ試験法(C=200pF): 250V以上、MIL試験法(C=100pF,R=1.5kΩ): 1200V以上 | V   |

電圧はVss端子をグラウンドレベルとした場合の値です。

### 推奨動作条件

| 項目           | 記号   | 条件         | 単位  |

|--------------|------|------------|-----|

| 電源電圧         | VDD  | 2.7 ~ 5.5  | V   |

| 水晶/クロック周波数   | fCLK | 3.579545   | MHz |

| 水晶/クロック周波数誤差 | fERR | $\pm 0.01$ | %   |

電圧はVss端子をグラウンドレベルとした場合の値です。

### DC特性

(特記なき場合: VDD=2.7V~5.5V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C)

| 項目          | 記号    | 条件                                                   | Min.                                                                                 | Typ. | Max.   | 単位      |

|-------------|-------|------------------------------------------------------|--------------------------------------------------------------------------------------|------|--------|---------|

| 高レベル入力電圧(1) | ViH1  | OSC3, MODE0, MODE1, #SCLK, SDI, PDWN, #RESET, EXTCLK | 0.8VDD                                                                               |      | VDD    | V       |

| 高レベル入力電圧(2) | ViH2  | RDIN, #RDRC                                          | 0.7VDD                                                                               |      | VDD    | V       |

| 低レベル入力電圧(1) | ViL1  | OSC3, MODE0, MODE1, #SCLK, SDI, PDWN, #RESET, EXTCLK | 0                                                                                    |      | 0.2VDD | V       |

| 低レベル入力電圧(2) | ViL2  | RDIN, #RDRC                                          | 0                                                                                    |      | 0.3VDD | V       |

| 高レベル入力電流    | IiH   | ViH=VDD                                              | RDIN, OSC3, MODE0, MODE1, #SCLK, SDI, PDWN, #RESET, #IRQ, EXTCLK, #RDRC (RDIN = Low) | 0    | 0.5    | μA      |

| 低レベル入力電流    | IiL   | ViL=Vss                                              | RDIN, OSC3, MODE0, MODE1, #SCLK, SDI, PDWN, #RESET, #RDRC, #IRQ, EXTCLK              | -0.5 | 0      | μA      |

| 高レベル出力電流    | IoH   | VOH=0.9VDD                                           | SDO, #DET, #RDET, #PQUAL                                                             |      |        | -1.5 mA |

| 低レベル出力電流    | IoL   | VOL=0.1VDD                                           | SDO, #DET, #RDET, #PQUAL, #IRQ, #RDRC                                                | 2.5  |        | mA      |

| VREF出力電圧    | VREF  |                                                      |                                                                                      |      | VDD/2  | V       |

| 入力インピーダンス   | RIN   | INP, INN, HOOK, EXTREF, CASIN                        | 10                                                                                   |      |        | MΩ      |

|             | RCDIN | CDIN                                                 | 140                                                                                  | 200  | 260    | kΩ      |

### 消費電流

(特記なき場合: VDD=2.7V~5.5V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C)

| 項目   | 記号  | 条件                     | Min.   | Typ. | Max. | 単位     |

|------|-----|------------------------|--------|------|------|--------|

| 消費電流 | IOP | ゼロパワーモード(PDWN=High)    | VDD=5V |      | 1.0  | μA     |

|      |     | FSKエナジ検出モード(PDWN=High) | VDD=5V |      | 6.0  | 8.0 μA |

|      |     | 動作時(信号入力なし)            | VDD=5V |      | 3.0  | mA     |

|      |     |                        | VDD=3V |      | 1.8  | mA     |

### 水晶発振特性

(特記なき場合: VDD=2.7V~5.5V, Vss=0V, Cg=Cd=18pF, Ta=25°C)

| 項目     | 記号   | 条件             | Min. | Typ. | Max. | 単位   |

|--------|------|----------------|------|------|------|------|

| 発振開始時間 | tsta | 3.579545MHz振動子 |      |      | 20   | msec |

# S1C05251

## FSK復調回路特性

### FSK AC特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C)

| 項目                                 | 記号       | 条件                             | Min.  | Typ.  | Max.  | 単位  |

|------------------------------------|----------|--------------------------------|-------|-------|-------|-----|

| 転送レート                              | TRATE    |                                | 1188  | 1200  | 1212  | ボーズ |

| Bell 202マーク(論理1)周波数                | fB1      |                                | 1188  | 1200  | 1212  | Hz  |

| Bell 202スペース(論理0)周波数               | fB0      |                                | 2178  | 2200  | 2222  | Hz  |

| ITU-T V.23マーク(論理1)周波数              | fV1      |                                | 1280  | 1300  | 1320  | Hz  |

| ITU-T V.23スペース(論理0)周波数             | fV2      |                                | 2068  | 2100  | 2132  | Hz  |

| SN比                                | SNR      |                                | 20    | -     | -     | dB  |

| キャリア検出ON感度 *1<br>(TIP/RINGでの入力レベル) | CDONFSK  | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -45.0 | -43.0 | -41.0 | dBm |

|                                    |          | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -45.0 | -43.0 | -41.0 | dBm |

|                                    |          | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -47.2 | -45.2 | -43.2 | dBV |

|                                    |          | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -47.2 | -45.2 | -43.2 | dBV |

| キャリア検出OFF感度 *1                     | CDOFFFSK | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -47.0 | -45.0 | -43.0 | dBm |

|                                    |          | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -49.2 | -47.2 | -45.2 | dBm |

|                                    |          | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -47.0 | -45.0 | -43.0 | dBm |

|                                    |          | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -49.2 | -47.2 | -45.2 | dBV |

\*1: 入力アンプの利得がGAMP(dB)に設定されている場合、CDONFSKとCDOFFFSKのTyp.値は以下の式から算出できます。

$$CDONFSK \text{ [dBm]} = -GAMP - 48.0 + 20\log(\frac{VDD}{5}) \text{ [dBm]}, \quad CDONFSK \text{ [dBV]} = -GAMP - 50.2 + 20\log(\frac{VDD}{5}) \text{ [dBV]}$$

$$CDOFFFSK \text{ [dBm]} = -GAMP - 50.0 + 20\log(\frac{VDD}{5}) \text{ [dBm]}, \quad CDOFFFSK \text{ [dBV]} = -GAMP - 52.2 + 20\log(\frac{VDD}{5}) \text{ [dBV]}$$

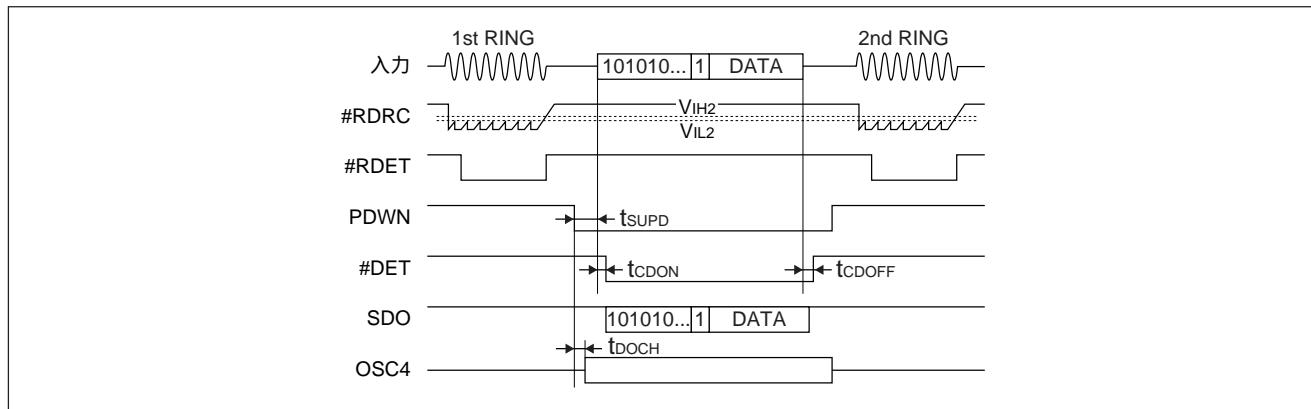

## FSKスイッチング特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C, CL=50pF)

| 項目               | 記号     | 条件               | Min. | Typ.    | Max.     | 単位   |

|------------------|--------|------------------|------|---------|----------|------|

| PDWN立ち下がり→FSK    | tSUPD  |                  |      |         | 20       | msec |

| キャリア検出開始時間       | tCDON  |                  | 5    | 10      | 15       | msec |

| データエンド→#DET立ち上がり | tCDOFF |                  | 5    | 10      | 15       | msec |

| PDWN立ち下がり→発振開始   | tDOCH  | VDD=5V<br>VDD=3V |      | 7<br>10 | 12<br>15 | msec |

## FSKエナジ検出モードAC特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C)

| 項目                                 | 記号      | 条件                             | Min.  | Typ.  | Max.  | 単位  |

|------------------------------------|---------|--------------------------------|-------|-------|-------|-----|

| 転送レート                              | TRATE   |                                | 1188  | 1200  | 1212  | ボーズ |

| Bell 202マーク(論理1)周波数                | fB1     |                                | 1188  | 1200  | 1212  | Hz  |

| Bell 202スペース(論理0)周波数               | fB0     |                                | 2178  | 2200  | 2222  | Hz  |

| ITU-T V.23マーク(論理1)周波数              | fV1     |                                | 1280  | 1300  | 1320  | Hz  |

| ITU-T V.23スペース(論理0)周波数             | fV2     |                                | 2068  | 2100  | 2132  | Hz  |

| SN比                                | SNR     |                                | 20    | -     | -     | dB  |

| キャリア検出ON感度 *1<br>(TIP/RINGでの入力レベル) | CDONFSK | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -44.0 | -41.0 | -38.0 | dBm |

|                                    |         | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -46.2 | -43.2 | -40.2 | dBV |

|                                    |         | VDD=5V<br>入力アンプ利得(GAMP)=-5dB   | -44.0 | -41.0 | -38.0 | dBm |

|                                    |         | VDD=3V<br>入力アンプ利得(GAMP)=-9.4dB | -46.2 | -43.2 | -40.2 | dBV |

\*1: 入力アンプの利得がGAMP(dB)に設定されている場合、CDONFSKのTyp.値は以下の式から算出できます。

$$CDONFSK \text{ [dBm]} = -GAMP - 46.0 + 20\log(\frac{VDD}{5}) \text{ [dBm]}, \quad CDONFSK \text{ [dBV]} = -GAMP - 48.2 + 20\log(\frac{VDD}{5}) \text{ [dBV]}$$

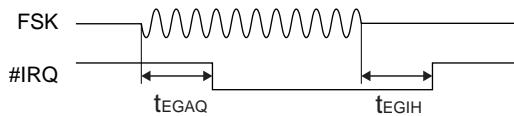

## FSKエナジ検出モードスイッチング特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C, CL=50pF)

| 項目              | 記号    | 条件     | Min. | Typ. | Max. | 単位   |

|-----------------|-------|--------|------|------|------|------|

| FSKエナジ検出取得時間    | tEGAQ | VDD=5V |      | 12   | 20   | msec |

| FSK終了→#IRQ立ち上がり | tEGIH | VDD=5V |      | 24   | 40   | msec |

## デュアルトーン(CAS)検出回路特性

## CAS AC特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C)

| 項目                               | 記号       | 条件                                                            | Min.    | Typ.  | Max.    | 単位  |

|----------------------------------|----------|---------------------------------------------------------------|---------|-------|---------|-----|

| キャリア検出感度 *1<br>(TIP/RINGでの入力レベル) | CDONTONE | VDD=5V, Bellcoreモード<br>入力アンプ利得(GAMP)=-5dB<br>トーンフィルタ利得=-4dB   | -39.9   | -35.9 | -31.9   | dBm |

|                                  |          | VDD=5V, BTモード *2<br>入力アンプ利得(GAMP)=-5dB<br>トーンフィルタ利得=-4dB      | -48.1   | -44.1 | -40.1   | dBV |

|                                  |          | VDD=3V, Bellcoreモード<br>入力アンプ利得(GAMP)=-9.4dB<br>トーンフィルタ利得=-4dB | -39.9   | -35.9 | -31.9   | dBm |

|                                  |          | VDD=3V, BTモード *2<br>入力アンプ利得(GAMP)=-9.4dB<br>トーンフィルタ利得=-4dB    | -48.1   | -44.1 | -40.1   | dBV |

| ロートーン周波数                         | fLTONE   | Bellcore(±0.5%)                                               | 2119.35 | 2130  | 2140.65 | Hz  |

|                                  |          | BT回線断状態                                                       | 2110    | 2130  | 2150    | Hz  |

|                                  |          | BT回線接続状態(±0.6%)                                               | 2117.22 | 2130  | 2142.78 | Hz  |

| ハイトーン周波数                         | fHTONE   | Bellcore(±0.5%)                                               | 2736.25 | 2750  | 2763.75 | Hz  |

|                                  |          | BT回線断状態                                                       | 2720    | 2750  | 2780    | Hz  |

|                                  |          | BT回線接続状態(±0.6%)                                               | 2733.50 | 2750  | 2766.50 | Hz  |

\*1: 入力アンプの利得がGAMP(dB)に設定されている場合、CDONTONEのTyp.値は以下の式から算出できます。

(内部のトーンフィルタ利得 = -4dB時)

$$CDONTONE \text{ [dBm]} = -GAMP - 40.9 + 20\log\left(\frac{VDD}{5}\right) \text{ [dBm]}, \quad CDONTONE \text{ [dBV]} = -GAMP - 49.1 + 20\log\left(\frac{VDD}{5}\right) \text{ [dBV]}$$

\*2: BTモードはモードレジスタ(アドレス=0h)のビット2を1に設定することで選択されます。この設定により各デュアルトーンフィルタの利得が+6dB増加し、BT用のCDレベルに調整されます。

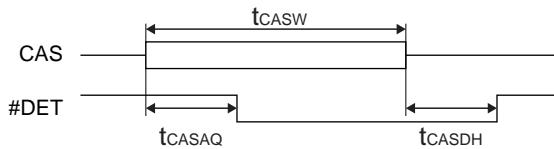

## CASスイッチング特性

(特記なき場合: VDD=5.0/3.0V, Vss=0V, fCLK=3.579545MHz, Ta=-20~70°C, CL=50pF)

| 項目               | 記号     | Min. | Typ.            | Max. | 単位   |

|------------------|--------|------|-----------------|------|------|

| CAS検出取得時間        | tCASAQ |      | 2.8×(N+2)+16.9  |      | msec |

| CASEンド→#DET立ち上がり | tCASDH |      | 2.8×(31-N)+13.1 |      | msec |

| CAS幅             | tCASW  | 75   | 80              | 85   | msec |

$$N = TH0 \times 16 + TL3 \times 8 + TL2 \times 4 + TL1 \times 2 + TL0$$

# S1C05251

## コールプログレスモード(CPM)検出回路特性

### CPM AC特性

(特記なき場合: V<sub>DD</sub>=5.0/3.0V, V<sub>SS</sub>=0V, f<sub>CLK</sub>=3.579545MHz, Ta=-20~70°C)

| 項目                                 | 記号       | 条件                   | Min.  | Typ.  | Max.  | 単位  |

|------------------------------------|----------|----------------------|-------|-------|-------|-----|

| キャリア検出ON感度 *1<br>(TIP/RINGでの入力レベル) | CDONCPM  | V <sub>DD</sub> =5V  | -45.0 | -43.0 | -41.0 | dBm |

|                                    |          | 入力アンプ利得(GAMP)=-5dB   | -47.2 | -45.2 | -43.2 | dBV |

|                                    |          | V <sub>DD</sub> =3V  | -45.0 | -43.0 | -41.0 | dBm |

|                                    |          | 入力アンプ利得(GAMP)=-9.4dB | -47.2 | -45.2 | -43.2 | dBV |

| キャリア検出OFF感度 *1                     | CDOFFCPM | V <sub>DD</sub> =5V  | -47.0 | -45.0 | -43.0 | dBm |

|                                    |          | 入力アンプ利得(GAMP)=-5dB   | -49.2 | -47.2 | -45.2 | dBV |

|                                    |          | V <sub>DD</sub> =3V  | -47.0 | -45.0 | -43.0 | dBm |

|                                    |          | 入力アンプ利得(GAMP)=-9.4dB | -49.2 | -47.2 | -45.2 | dBV |

\*1: 入力アンプの利得がGAMP(dB)に設定されている場合、CDONCPMとCDOFFCPMのTyp.値は以下の式から算出できます。

$$CDONCPM \text{ [dBm]} = -GAMP - 48.0 + 20\log\left(\frac{V_{DD}}{5}\right) \text{ [dBm]}, \quad CDONCPM \text{ [dBV]} = -GAMP - 50.2 + 20\log\left(\frac{V_{DD}}{5}\right) \text{ [dBV]}$$

$$CDOFFCPM \text{ [dBm]} = -GAMP - 50.0 + 20\log\left(\frac{V_{DD}}{5}\right) \text{ [dBm]}, \quad CDOFFCPM \text{ [dBV]} = -GAMP - 52.2 + 20\log\left(\frac{V_{DD}}{5}\right) \text{ [dBV]}$$

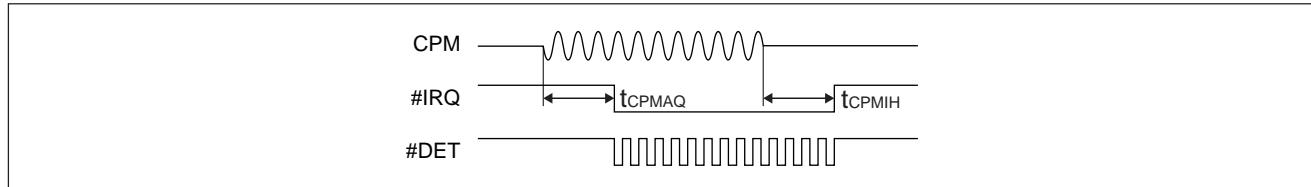

### CPMスイッチング特性

(特記なき場合: V<sub>DD</sub>=5.0/3.0V, V<sub>SS</sub>=0V, f<sub>CLK</sub>=3.579545MHz, Ta=-20~70°C)

| 項目                  | 記号                 | Min. | Typ. | Max. | 単位   |

|---------------------|--------------------|------|------|------|------|

| CPMトーン検出取得時間        | t <sub>CPMAQ</sub> |      | 25   |      | msec |

| CPMトーンエンド→#IRQ立ち上がり | t <sub>CPMIH</sub> |      | 30   |      | msec |

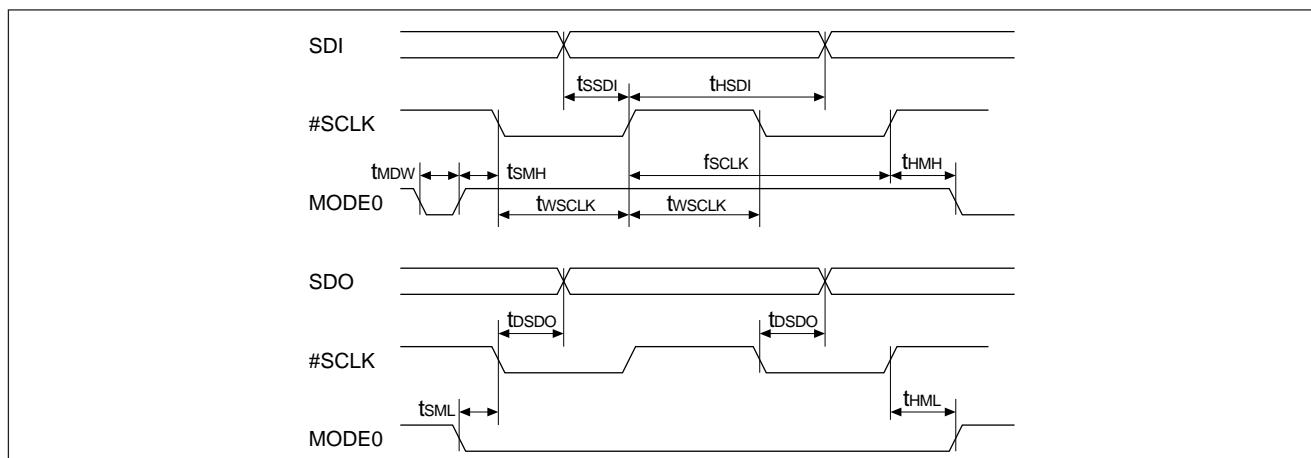

## シリアルインターフェース回路特性

### シリアルインターフェースAC特性

(特記なき場合: V<sub>DD</sub>=5.0/3.0V, V<sub>SS</sub>=0V, f<sub>CLK</sub>=3.579545MHz, Ta=-20~70°C, CL=50pF)

| 項目                 | 記号                 | Min. | Typ. | Max. | 単位   |

|--------------------|--------------------|------|------|------|------|

| #SCLK周波数           | f <sub>SCLK</sub>  |      |      | 1    | MHz  |

| #SCLKパルス幅          | t <sub>WSCLK</sub> | 400  |      |      | nsec |

| SDIセットアップ時間        | t <sub>SSDI</sub>  | 250  |      |      | nsec |

| SDIホールド時間          | t <sub>HSDI</sub>  | 500  |      |      | nsec |

| SDO遅延時間            | t <sub>DSDO</sub>  |      |      | 250  | nsec |

| MODE0 Highセットアップ時間 | t <sub>SMH</sub>   | 1    |      |      | μsec |

| MODE0 Highホールド時間   | t <sub>HMH</sub>   | 1    |      |      | μsec |

| MODE0 Lowセットアップ時間  | t <sub>ML</sub>    | 1    |      |      | μsec |

| MODE0 Lowホールド時間    | t <sub>HML</sub>   | 1    |      |      | μsec |

| MODE0 Lowパルス幅      | t <sub>MDW</sub>   | 1    |      |      | μsec |

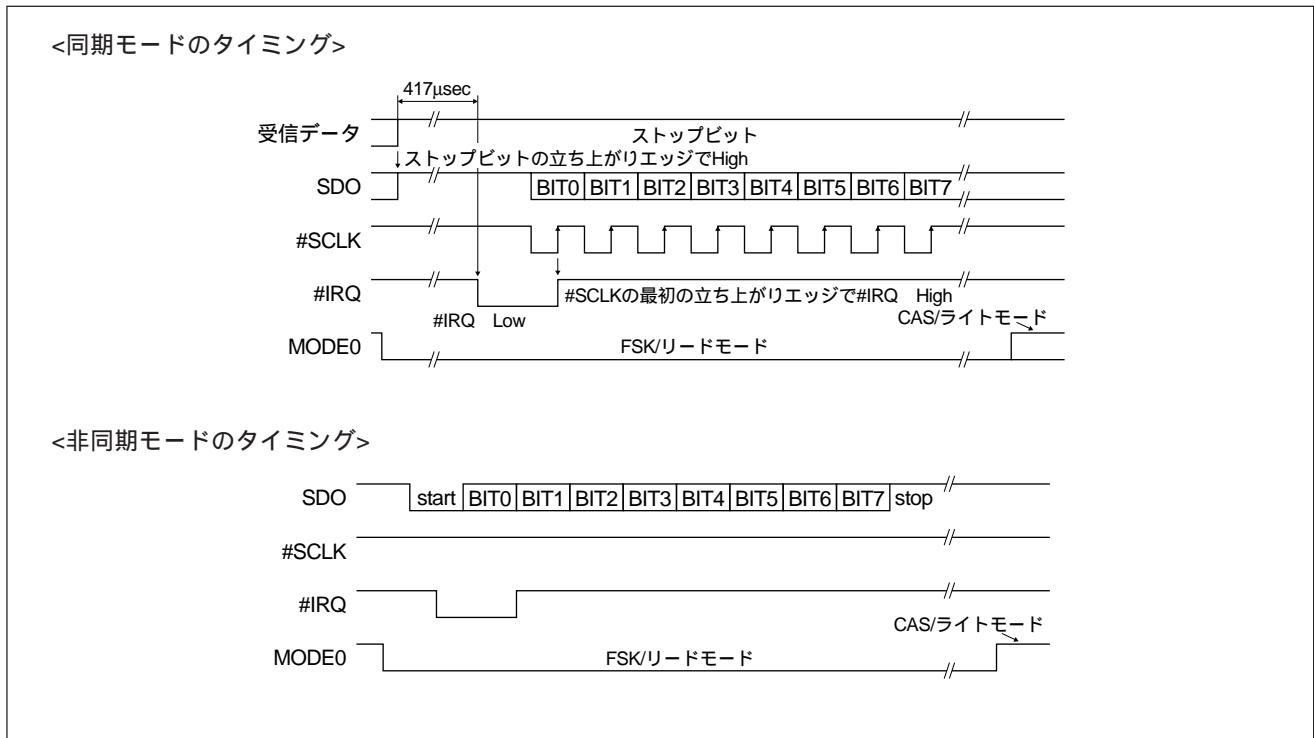

### FSK復調データリードモード

INPおよびINN端子に入力されたFSK信号は8ビット調歩同期式のデータに復調されます。その後内部の8ビットシフトレジスタにサンプルされます。データがシフトレジスタに格納されると、#IRQ端子がLowレベルとなりホストCPUからの読み出しが可能であることを示します。

MODE0端子がLowレベルで同期モードが選択されている(MDR[0] = 1)場合、ホストCPUは#SCLK端子に供給するクロックに同期して8ビットデータを読み出します。下図にそのタイミングを示します。8ビットデータの各ビットはビット0を先頭に#SCLKクロックの立ち下がりエッジに同期してSDO端子から出力されます。ホストCPUは#SCLKクロックの立ち上がりエッジで各ビットを取り込みます。

MODE0端子がLowレベルで非同期モードが選択されている(MDR[0] = 0)場合、1,200ポーの転送レートでSDO端子からデータが出力されます。ホストCPUからのクロック供給は不要です。ホストCPUはスタートビットに同期してデータを取り込みます。

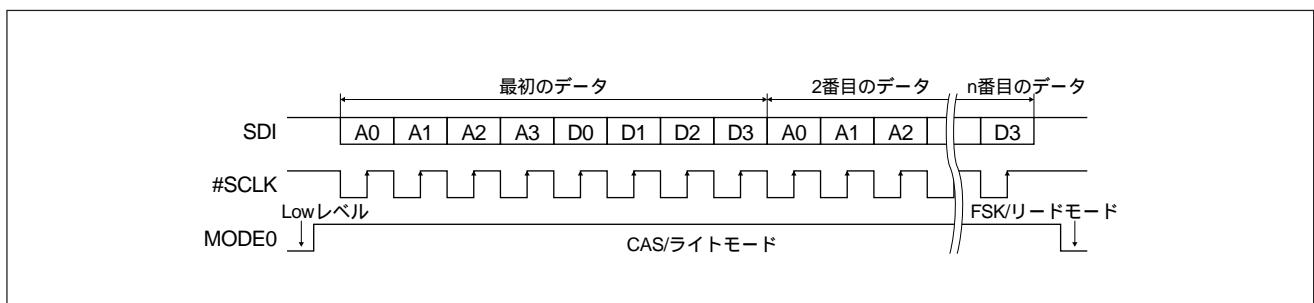

### CAS検出回路制御レジスタライトモード

ホストCPUは各制御ビットを設定するため、SDI端子を通して内部レジスタに4ビットデータを書き込むことができます。データを書き込む前に、ホストCPUはMODE0端子を一度Lowレベルに設定し、書き込み制御回路を初期化する必要があります。その後、Highレベルに設定し、データの書き込み中はHighレベルに固定します。SDI端子に入力されるデータは、同じくホストCPUが#SCLK端子に供給するクロックの立ち上がりエッジでサンプルされます。ホストCPUから送られるデータの最初の4ビットはアクセスする内部レジスタのアドレスA[3:0]で、続く4ビットは指定のレジスタに書き込むデータビットD[3:0]です。データの入力はLSBを先頭に行います。

# S1C05251

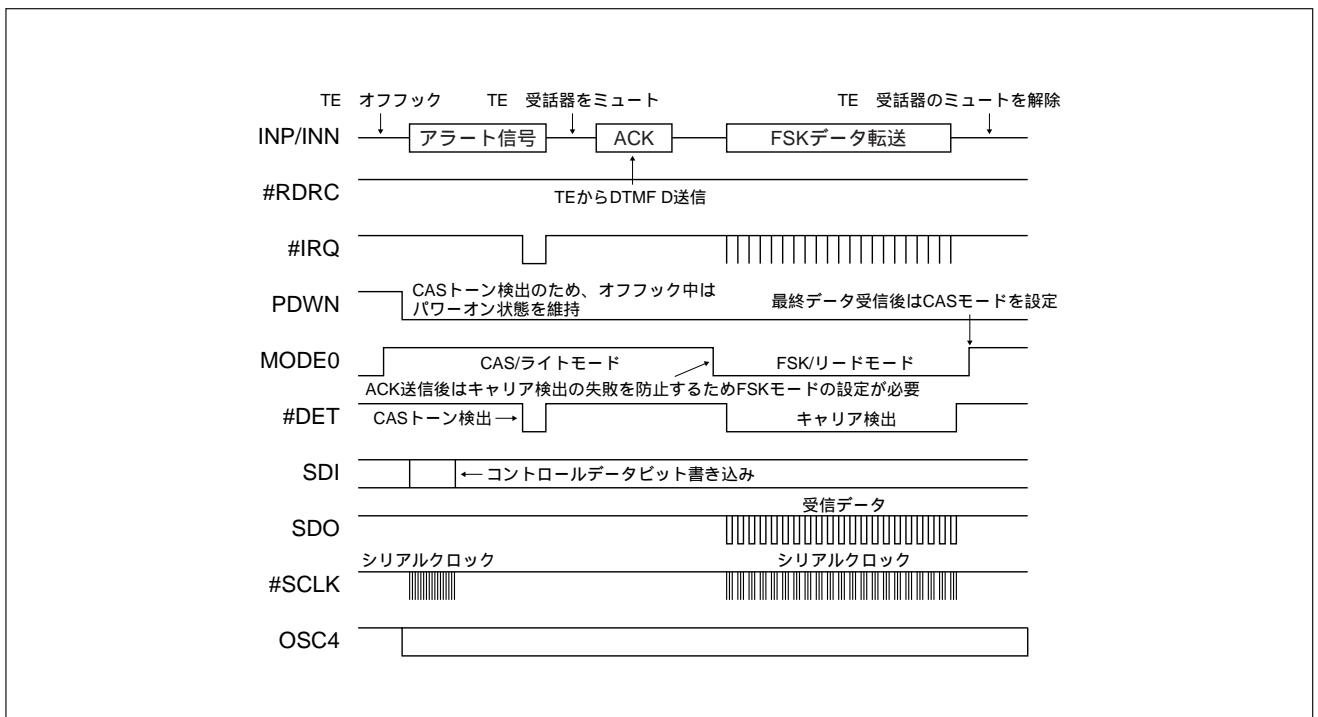

S1C05251タイミングチャート

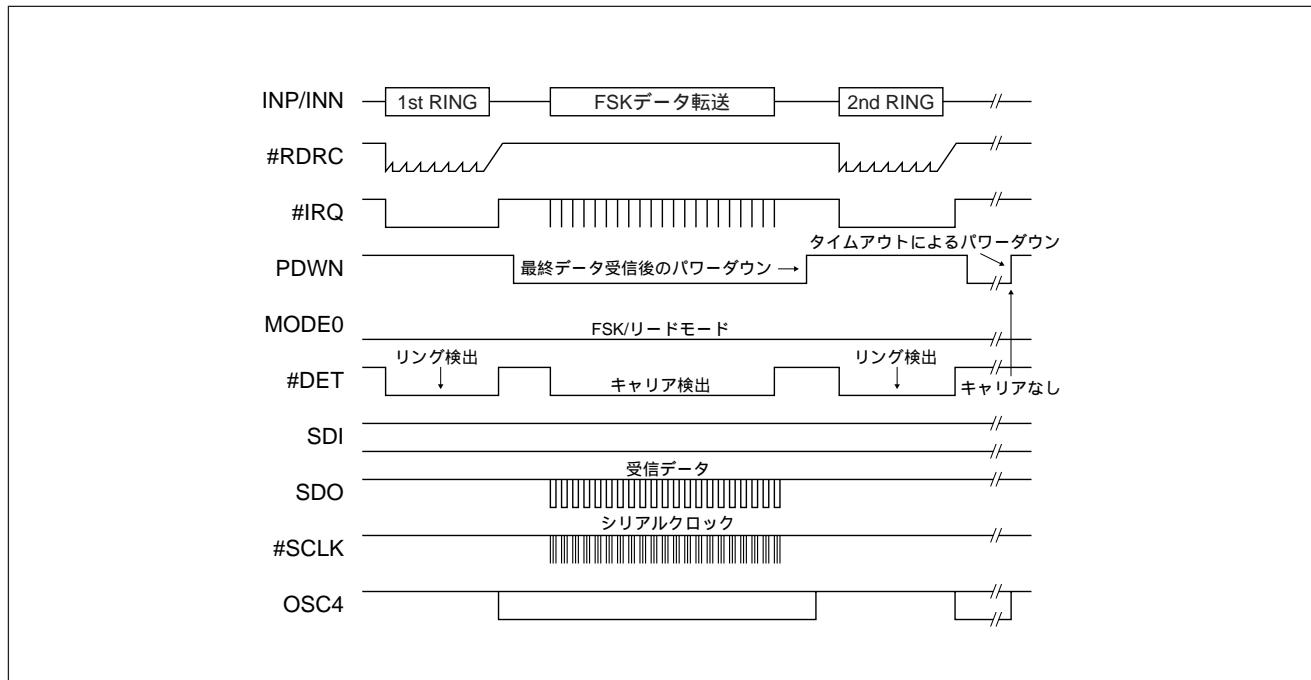

Bellcoreオンフックデータ転送

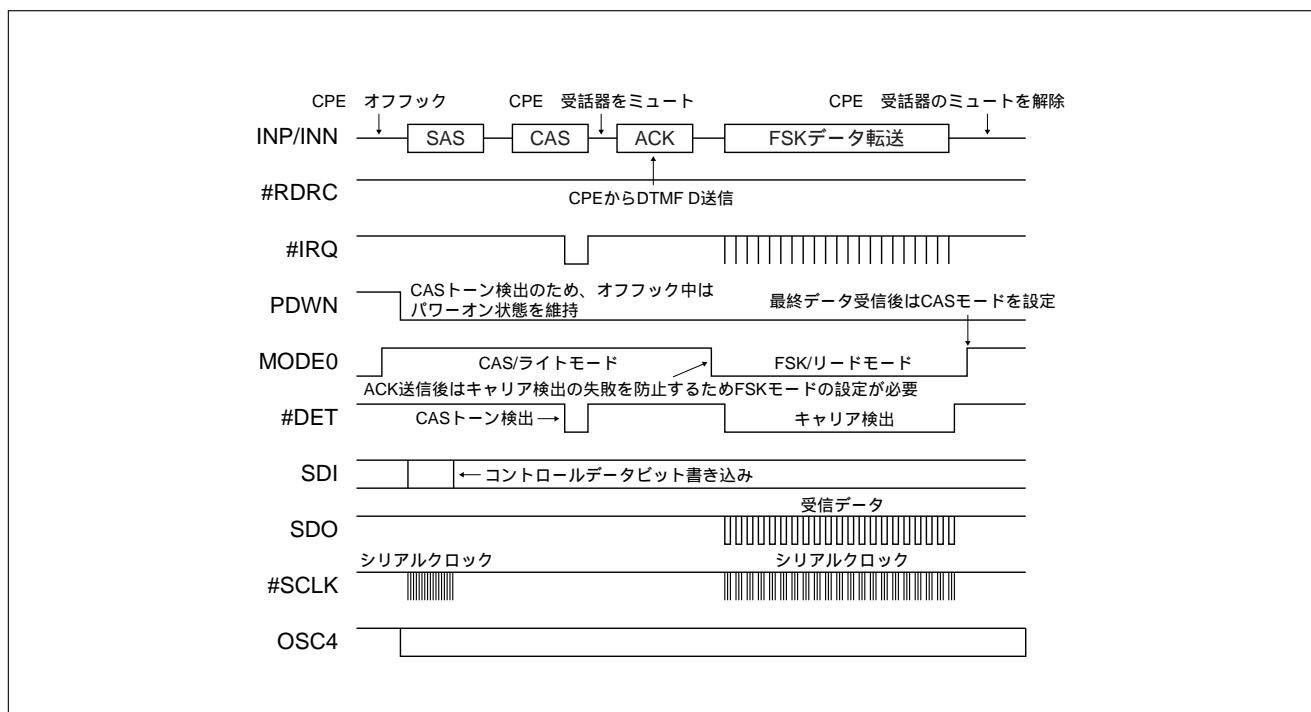

Bellcoreオフフックデータ転送

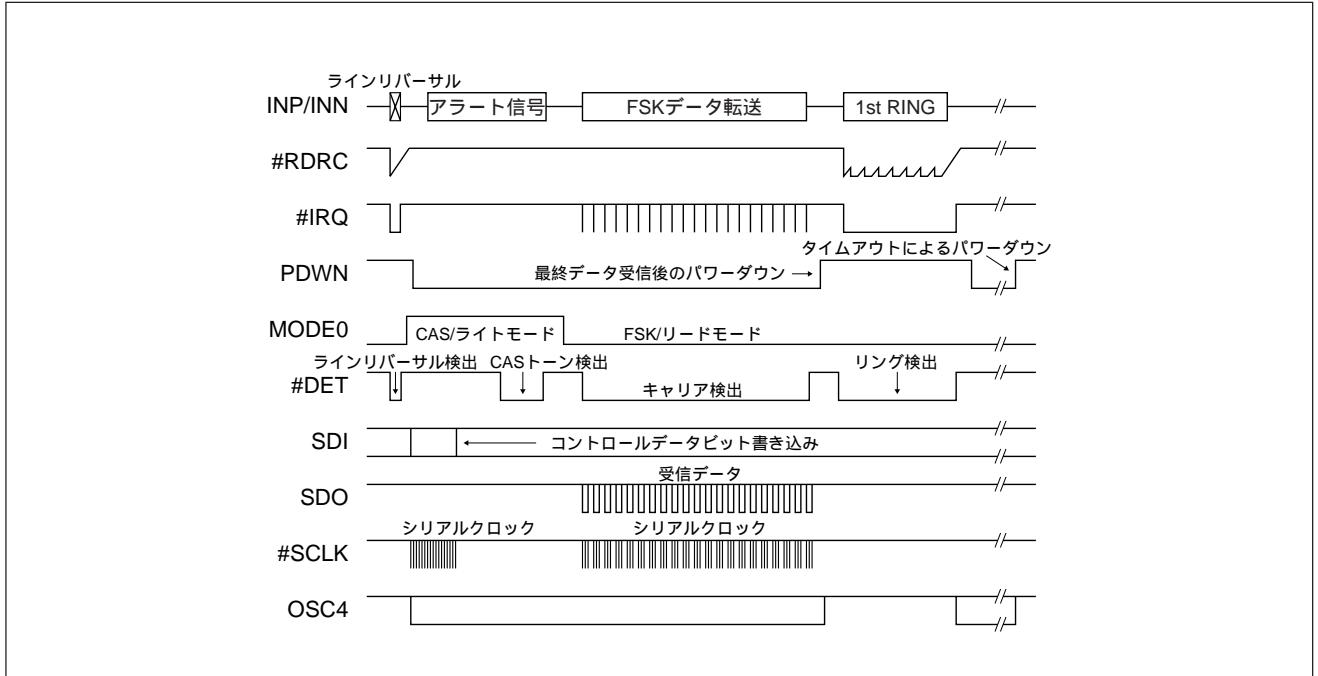

## BT Idle State CLIサービス

## BT Loop State CLIサービス

# S1C05251

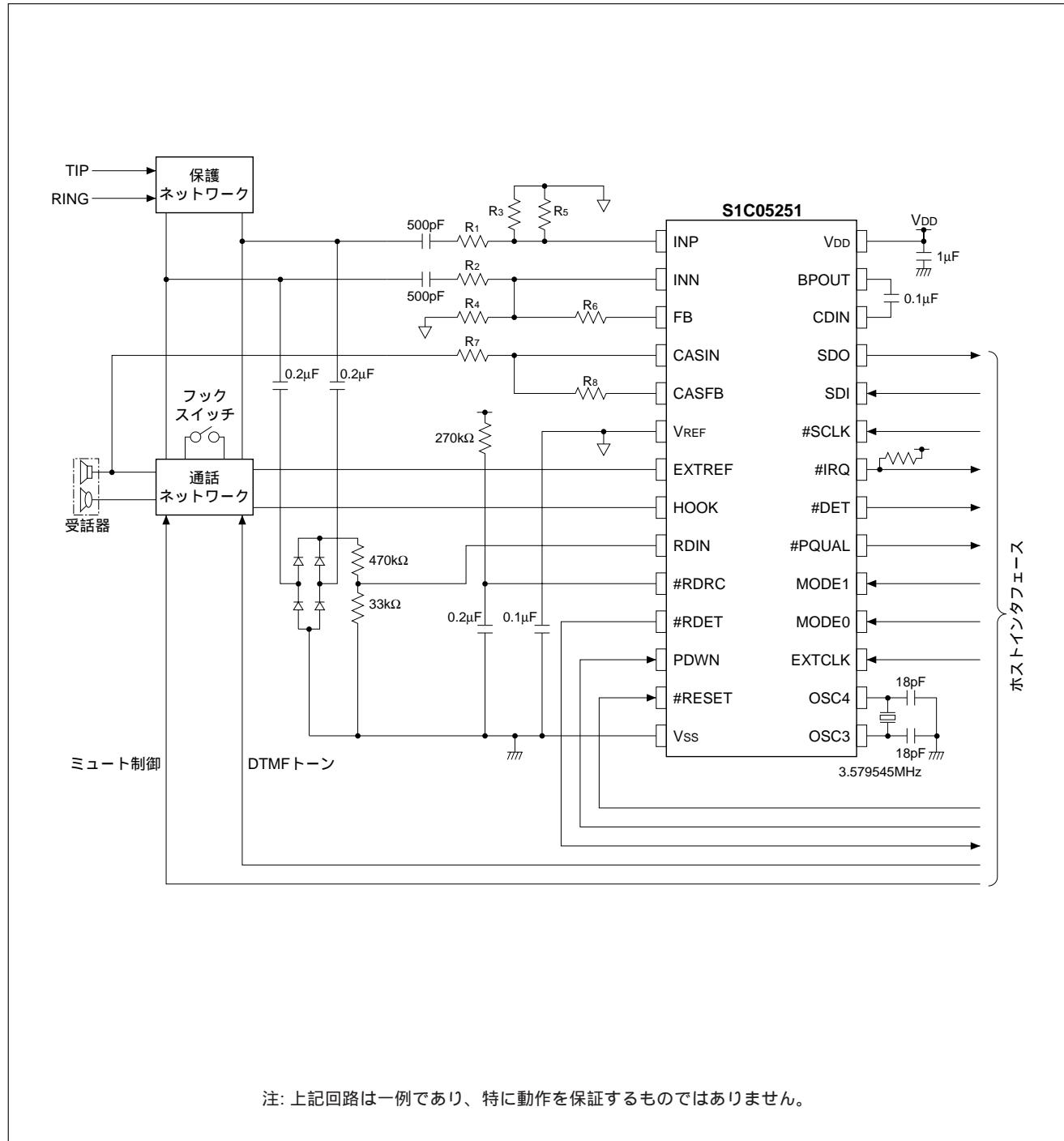

外部結線図(例)

Bellcore互換電話機回路例

## Bellcore互換補助機回路例

# S1C05251

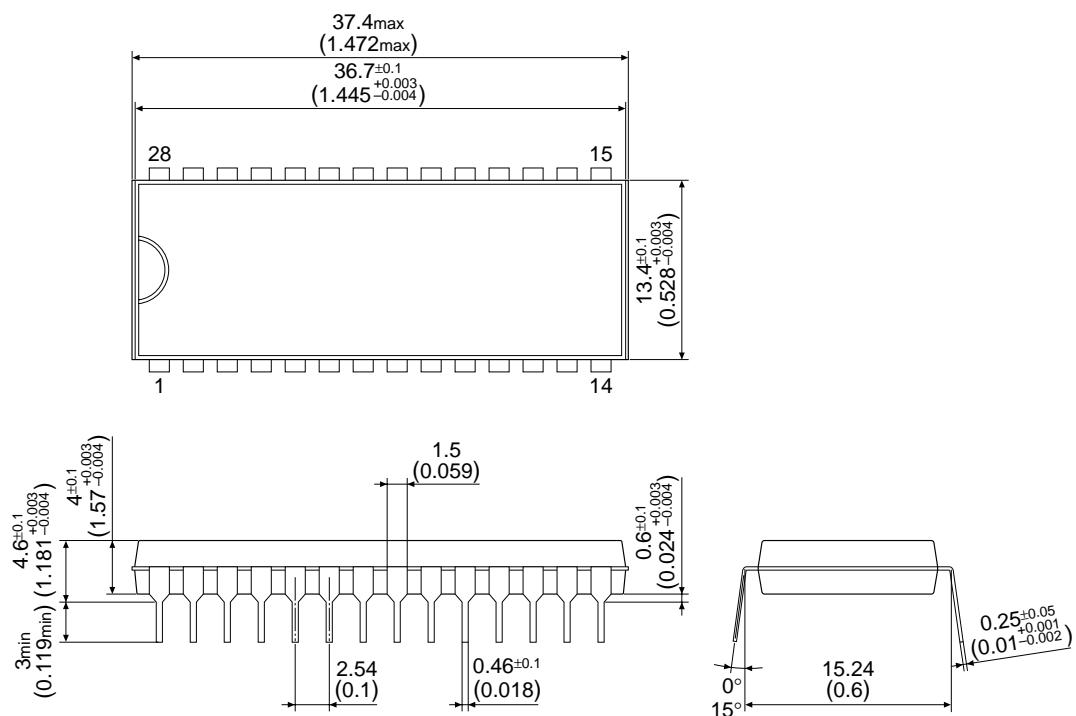

## パッケージ

### SOP2-28pin Plastic Package

### DIP-28pin Ceramic Package

単位: mm( インチ )

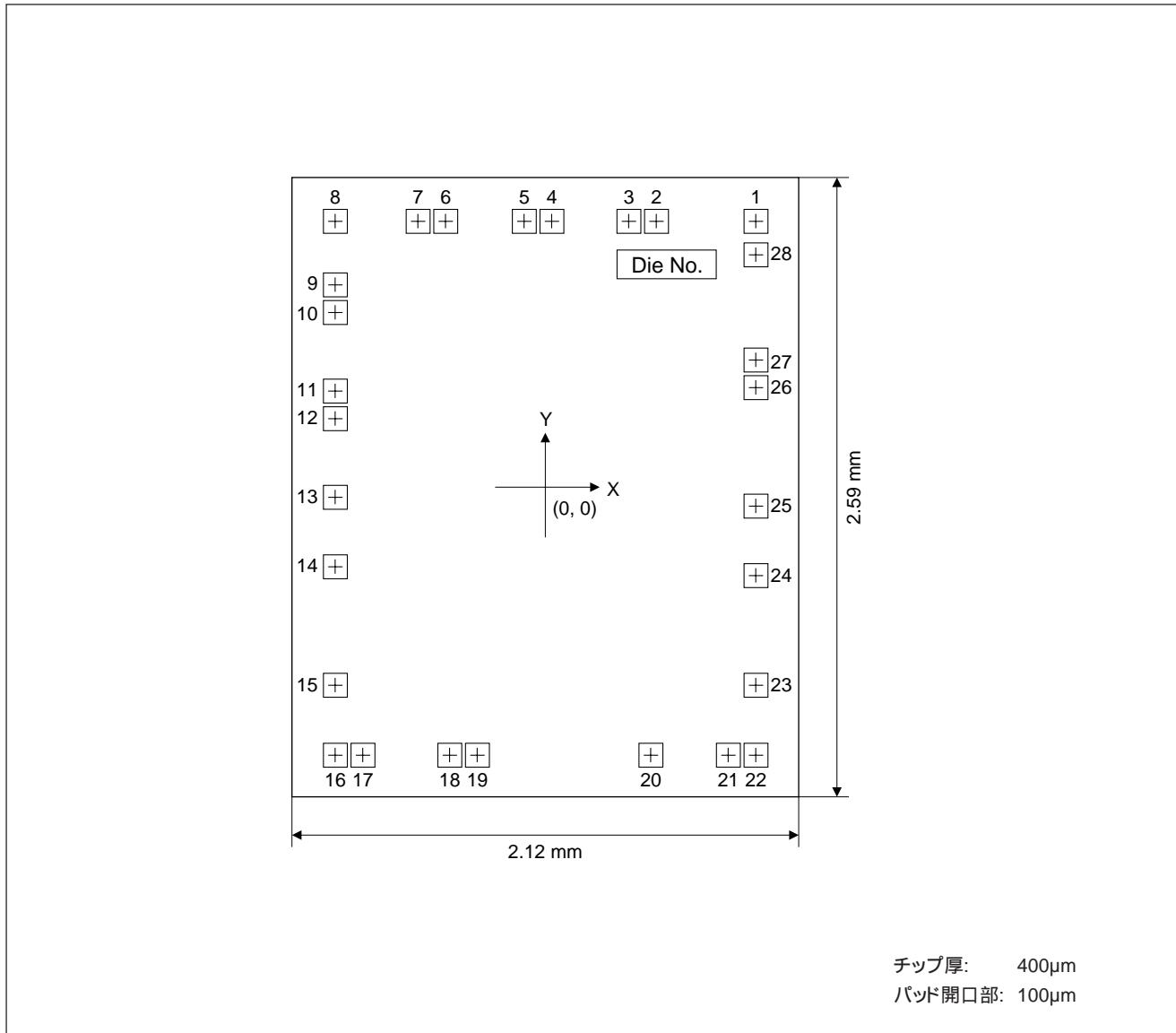

## パッド配置

## パッド配置図

## パッド座標

(単位: μm)

| パッドNo. | パッド名   | X座標    | Y座標    | パッドNo. | パッド名   | X座標    | Y座標     |

|--------|--------|--------|--------|--------|--------|--------|---------|

| 1      | SD0    | 879.9  | 1116.3 | 15     | #DET   | -879.8 | -823.8  |

| 2      | CDIN   | 463.7  | 1116.3 | 16     | PDWN   | -879.8 | -1116.4 |

| 3      | BPOUT  | 348.2  | 1116.3 | 17     | #RESET | -764.3 | -1116.4 |

| 4      | VDD    | 26.1   | 1116.3 | 18     | Vss    | -401.0 | -1116.4 |

| 5      | INP    | -89.4  | 1116.3 | 19     | OSC3   | -285.5 | -1116.4 |

| 6      | INN    | -418.1 | 1116.3 | 20     | OSC4   | 440.3  | -1116.4 |

| 7      | FB     | -533.6 | 1116.3 | 21     | EXTCLK | 764.4  | -1116.4 |

| 8      | CASIN  | -879.8 | 1116.3 | 22     | MODE0  | 879.9  | -1116.4 |

| 9      | CASFB  | -879.8 | 850.5  | 23     | MODE1  | 879.9  | -823.8  |

| 10     | VREF   | -879.8 | 735.0  | 24     | #PQUAL | 879.9  | -365.3  |

| 11     | EXTREF | -879.8 | 406.4  | 25     | #DET   | 879.9  | -74.7   |

| 12     | HOOK   | -879.8 | 290.9  | 26     | #IRQ   | 879.9  | 420.8   |

| 13     | RDIN   | -879.8 | -37.8  | 27     | #SCLK  | 879.9  | 536.3   |

| 14     | #RDRC  | -879.8 | -328.4 | 28     | SDI    | 879.9  | 976.1   |

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

© SEIKO EPSON CORPORATION 2001

## セイコーエプソン株式会社

電子デバイス営業本部

ED営業推進部 IC営業技術G

東日本

ED東京営業部 〒191-8501 東京都日野市日野421-8

東京IC営業G ☎(042)587-5313(直通) FAX(042)587-5116

西日本

〒541-0059 大阪市中央区博労町3-5-1 エプソン大阪ビル15F

ED大阪営業部 ☎(06)6120-6000(代表) FAX(06)6120-6100

東海・北陸

〒461-0005 名古屋市東区東桜1-10-24 栄大野ビル4F

ED名古屋営業部 ☎(052)953-8031(代表) FAX(052)953-8041

長野 ☎(0262)392-8502 長野県諏訪市大和3-3-5

ED長野営業部 ☎(0266)58-8171(直通) FAX(0266)58-9917

東北

〒980-0013 宮城県仙台市青葉区花京院1-1-20 花京院スクエア19F

ED仙台営業所 ☎(022)263-7975(代表) FAX(022)263-7990

インターネットによる電子デバイスのご紹介

<http://www.epson.co.jp/device/>