CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

# S1C63666

テクニカルマニュアル

S1C63666 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

## 本版で改訂または追加された箇所

| 章        | 節/項    | 頁              | 項目                      | 内容                         |

|----------|--------|----------------|-------------------------|----------------------------|

| 1        | 1.1    | 1              | 特長                      | 文章変更                       |

|          | 1.5    | 5~8            | マスクオプション                | 文章変更                       |

| 2        | 2.1.5  | 11             | LCD系電圧回路                | 図2.1.5.1変更                 |

|          | 2.2    | 12             | イニシャルリセット               | 図2.2.1変更                   |

|          | 2.2.1  | 12             | リセット端子(RESET)           | 文章追加                       |

|          | 2.2.2  | 13             | 入力ポート(K00~K03)の同時HIGH入力 | 文章変更、表2.2.2.1変更            |

| 4        | 4.1    | 17, 18, 20, 24 | メモリマップ                  | 文章変更、表4.1.1(a), (c), (g)変更 |

|          | 4.6.4  | 43~44          | 特殊出力                    | 図4.6.4.1~4.6.4.2変更         |

|          | 4.6.5  | 46             | 出力ポートのI/Oメモリ            | 文章変更                       |

|          | 4.8.1  | 53             | LCDドライバの構成              | 文章変更                       |

|          | 4.8.2  | 53             | LCD駆動電源                 | 文章変更                       |

|          | 4.8.3  | 57             | LCD表示のON/OFFとLCD駆動波形    | 文章変更、注追加                   |

|          | 4.8.5  | 58             | セグメントオプション              | 図4.8.5.1変更                 |

|          | 4.10.6 | 72             | 割り込み機能                  | 文章変更                       |

|          | 4.10.7 | 74, 75, 77     | ストップウォッチタイマのI/Oメモリ      | 表4.10.7.1変更、文章変更           |

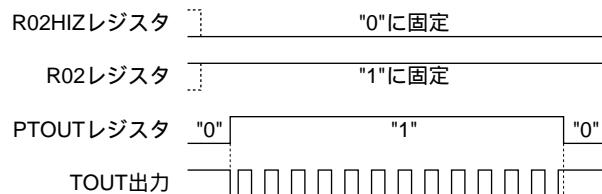

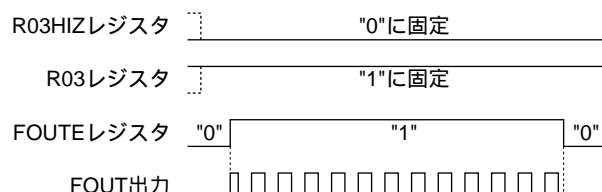

|          | 4.11.7 | 82             | TOUT出力の設定               | 図4.11.7.1~4.11.7.2変更、文章変更  |

|          | 4.11.9 | 88             | プログラマブルタイマのI/Oメモリ       | 文章変更                       |

|          | 4.15.2 | 112            | 接続端子とCR発振回路             | 文章変更、図4.15.2.3変更           |

|          | 4.15.3 | 113~114        | R/F変換                   | 文章変更、図4.15.3.1~4.15.3.2変更  |

|          | 4.15.4 | 116~117        | 割り込み機能                  | 文章変更、図4.15.4.1~4.15.4.4変更  |

|          | 4.15.5 | 118, 120       | R/FコンバータのI/Oメモリ         | 表4.15.5.1変更、文章変更           |

|          | 4.15.6 | 121            | プログラミング上の注意事項           | (4)追加                      |

|          | 4.17.2 | 124            | マスクオプション                | 文章変更                       |

|          | 4.17.3 | 125            | SVD動作                   | 文章変更                       |

|          | 4.17.4 | 126            | SVD回路のI/Oメモリ            | 表4.17.4.1変更、文章変更           |

| 5        | 4.18   | 128            | 割り込みとHALT               | 図4.18.1変更                  |

|          | 4.18.1 | 129            | 割り込みの要因                 | 表4.18.1.1変更                |

|          | 4.18.2 | 130            | 割り込みの個別マスク              | 表4.18.2.1変更                |

|          | 4.18.4 | 131~132        | 割り込みのI/Oメモリ             | 表4.18.4.1(a), (b)変更、文章変更   |

| 7        | 5.2    | 138            | 個別機能についての注意事項のまとめ       | 文章変更                       |

|          | 5.3    | 140            | 実装上の注意事項                | 文章変更                       |

| Appendix | 7.1    | 142            | 絶対最大定格                  | 表変更                        |

|          | 7.2    | 142            | 推奨動作条件                  | 表変更                        |

|          | 7.3    | 142            | DC特性                    | 表変更                        |

|          | 7.4    | 143            | アナログ回路特性・消費電流           | 表変更                        |

|          | 7.6    | 146            | シリアルインターフェースAC特性        | 図変更                        |

| Appendix | A.2    | 155            | ターゲットシステムとの接続           | 図A.2.1変更                   |

|          | A.3.2  | 158            | 実ICとの相違点                | 文章変更、図削除                   |

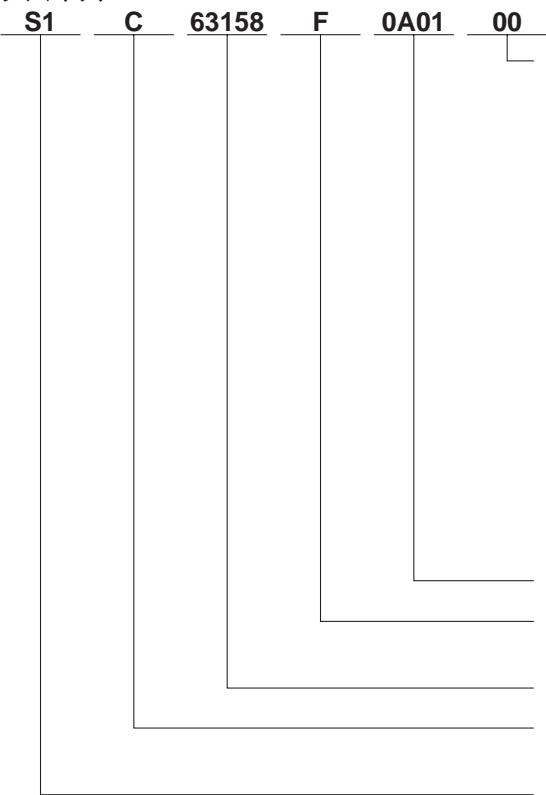

## 製品型番体系

### デバイス

#### 梱包仕様

[00 : テープ&リール以外

0A : TCP BL 2方向

0B : テープ&リール BACK

0C : TCP BR 2方向

0D : TCP BT 2方向

0E : TCP BD 2方向

0F : テープ&リール FRONT

0G : TCP BT 4方向

0H : TCP BD 4方向

0J : TCP SL 2方向

0K : TCP SR 2方向

0L : テープ&リール LEFT

0M : TCP ST 2方向

0N : TCP SD 2方向

0P : TCP ST 4方向

0Q : TCP SD 4方向

0R : テープ&リール RIGHT

99 : 梱包仕様未定]

#### 仕様

[D: ベアチップ、F: QFP、B: BGA]

#### 機種番号

[C: マイコン、デジタル製品]

#### 製品分類

[S1: 半導体]

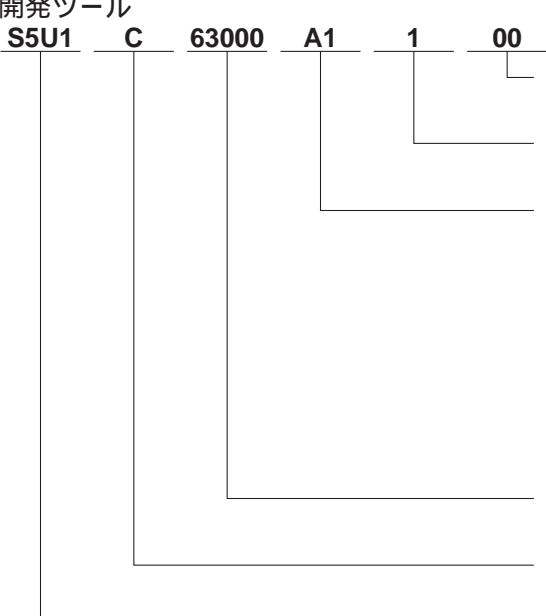

### 開発ツール

#### 梱包仕様

[00: 標準梱包]

#### バージョン

[1: Version 1]

#### ツール種類

[Hx : ICE

Ex : EVAボード

Px : ペリフェラルボード

Wx: FLASHマイコン用ROMライタ

Xx : ROMライタ周辺ボード

Cx : Cコンパイラパッケージ

Ax : アセンブラーパッケージ

Dx : 機種別ユーティリティツール

Qx : ソフトシミュレータ]

#### 対応機種番号

[63000: S1C63ファミリ共通]

#### ツール分類

[C: マイコン用]

#### 製品分類

[S5U1: 半導体用開発ツール]

## - 目 次 -

|                                   |           |

|-----------------------------------|-----------|

| <b>1 概要</b>                       | <b>1</b>  |

| 1.1 特長                            | 1         |

| 1.2 プロック図                         | 2         |

| 1.3 端子配置図                         | 3         |

| 1.4 端子説明                          | 4         |

| 1.5 マスクオプション                      | 5         |

| <b>2 電源系 および イニシャルリセット</b>        | <b>9</b>  |

| 2.1 電源系                           | 9         |

| 2.1.1 OSC1発振回路用定電圧回路              | 10        |

| 2.1.2 低速動作用定電圧回路                  | 10        |

| 2.1.3 高速動作用定電圧回路                  | 10        |

| 2.1.4 内部動作電圧VD1                   | 10        |

| 2.1.5 LCD系電圧回路                    | 10        |

| 2.1.6 降圧モードとパワーセーブ                | 11        |

| 2.1.7 アナログ回路用電源                   | 11        |

| 2.2 イニシャルリセット                     | 12        |

| 2.2.1 リセット端子( RESET )             | 12        |

| 2.2.2 入力ポート( K00 ~ K03 )の同時HIGH入力 | 13        |

| 2.2.3 イニシャルリセット時の内部レジスタ           | 13        |

| 2.2.4 イニシャルリセット時の端子設定             | 14        |

| 2.3 テスト端子( TEST )                 | 14        |

| <b>3 CPU, ROM, RAM</b>            | <b>15</b> |

| 3.1 CPU                           | 15        |

| 3.2 コードROM                        | 15        |

| 3.3 RAM                           | 15        |

| 3.4 データROM                        | 16        |

| <b>4 周辺回路と動作</b>                  | <b>17</b> |

| 4.1 メモリマップ                        | 17        |

| 4.2 電源制御                          | 25        |

| 4.2.1 電源回路の構成                     | 25        |

| 4.2.2 電源制御手順                      | 26        |

| 4.2.3 電源制御用I/Oメモリ                 | 27        |

| 4.2.4 プログラミング上の注意事項               | 29        |

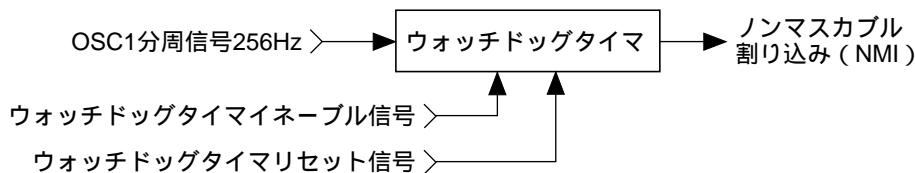

| 4.3 ウオッチドッグタイマ                    | 30        |

| 4.3.1 ウオッチドッグタイマの構成               | 30        |

| 4.3.2 割り込み機能                      | 30        |

| 4.3.3 ウオッチドッグタイマのI/Oメモリ           | 31        |

| 4.3.4 プログラミング上の注意事項               | 31        |

|        |                                            |    |

|--------|--------------------------------------------|----|

| 4.4    | 発振回路 .....                                 | 32 |

| 4.4.1  | 発振回路の構成 .....                              | 32 |

| 4.4.2  | OSC1発振回路 .....                             | 32 |

| 4.4.3  | OSC3発振回路 .....                             | 33 |

| 4.4.4  | 動作電圧切り換え .....                             | 34 |

| 4.4.5  | クロック周波数とインストラクション実行時間 .....                | 34 |

| 4.4.6  | 発振回路のI/Oメモリ .....                          | 35 |

| 4.4.7  | プログラミング上の注意事項 .....                        | 36 |

| 4.5    | 入力ポート( K00 ~ K03, K10 ~ K13 ) .....        | 37 |

| 4.5.1  | 入力ポートの構成 .....                             | 37 |

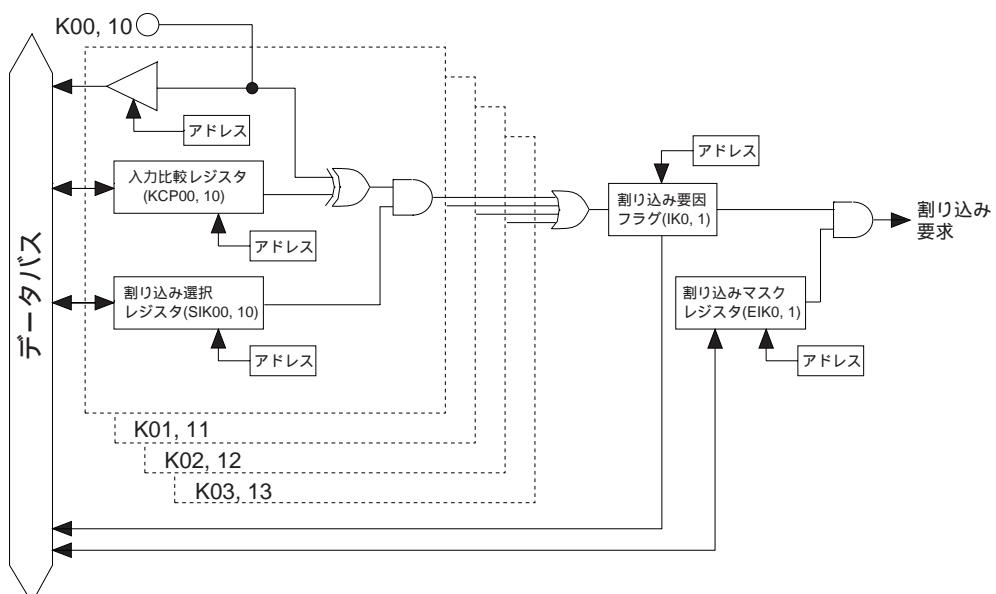

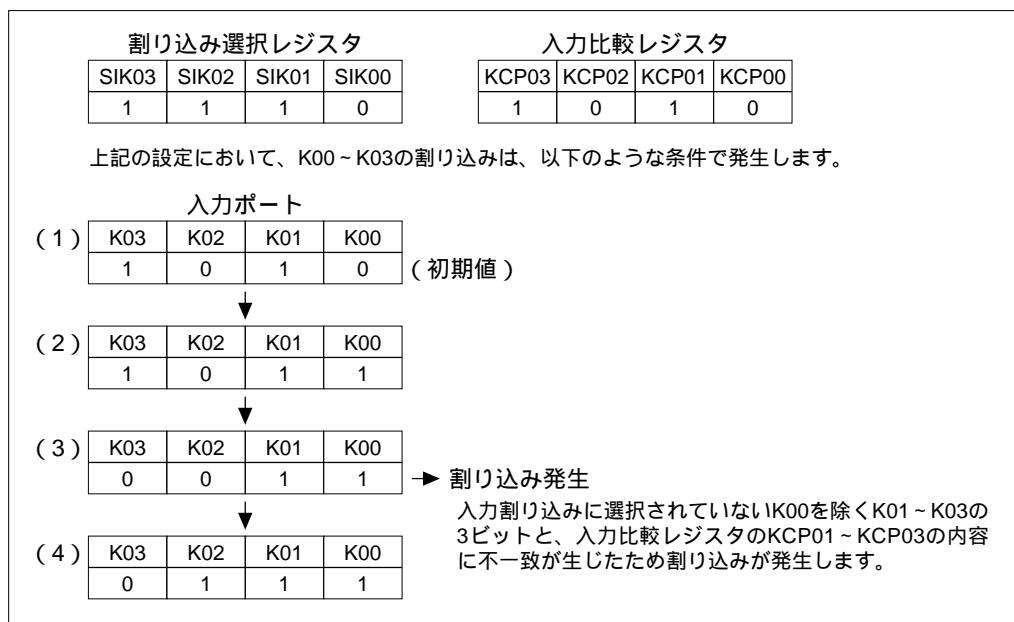

| 4.5.2  | 割り込み機能 .....                               | 37 |

| 4.5.3  | マスクオプション .....                             | 38 |

| 4.5.4  | 入力ポートのI/Oメモリ .....                         | 39 |

| 4.5.5  | プログラミング上の注意事項 .....                        | 41 |

| 4.6    | 出力ポート( R00 ~ R03, R10 ~ R13 ) .....        | 42 |

| 4.6.1  | 出力ポートの構成 .....                             | 42 |

| 4.6.2  | マスクオプション .....                             | 42 |

| 4.6.3  | ハイインピーダンス制御 .....                          | 43 |

| 4.6.4  | 特殊出力 .....                                 | 43 |

| 4.6.5  | 出力ポートのI/Oメモリ .....                         | 45 |

| 4.6.6  | プログラミング上の注意事項 .....                        | 47 |

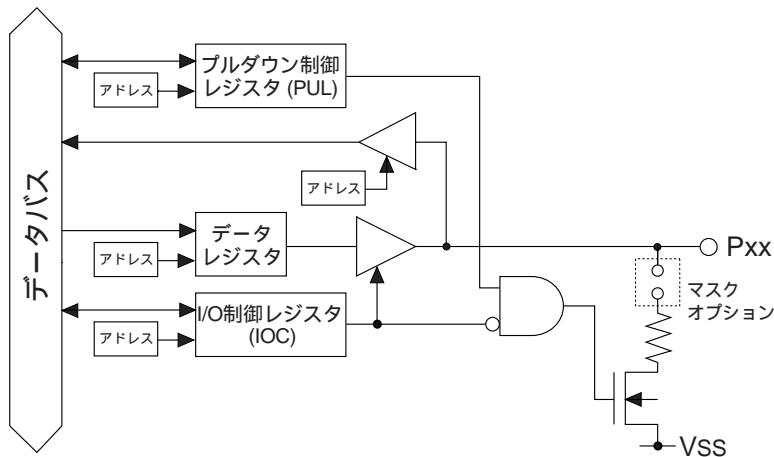

| 4.7    | 入出力兼用ポート( P00 ~ P03, P10 ~ P13 ) .....     | 48 |

| 4.7.1  | 入出力兼用ポートの構成 .....                          | 48 |

| 4.7.2  | マスクオプション .....                             | 49 |

| 4.7.3  | I/O制御レジスタと入力/出力モード .....                   | 49 |

| 4.7.4  | 入力モード時のプルダウン .....                         | 49 |

| 4.7.5  | 入出力兼用ポートのI/Oメモリ .....                      | 50 |

| 4.7.6  | プログラミング上の注意事項 .....                        | 52 |

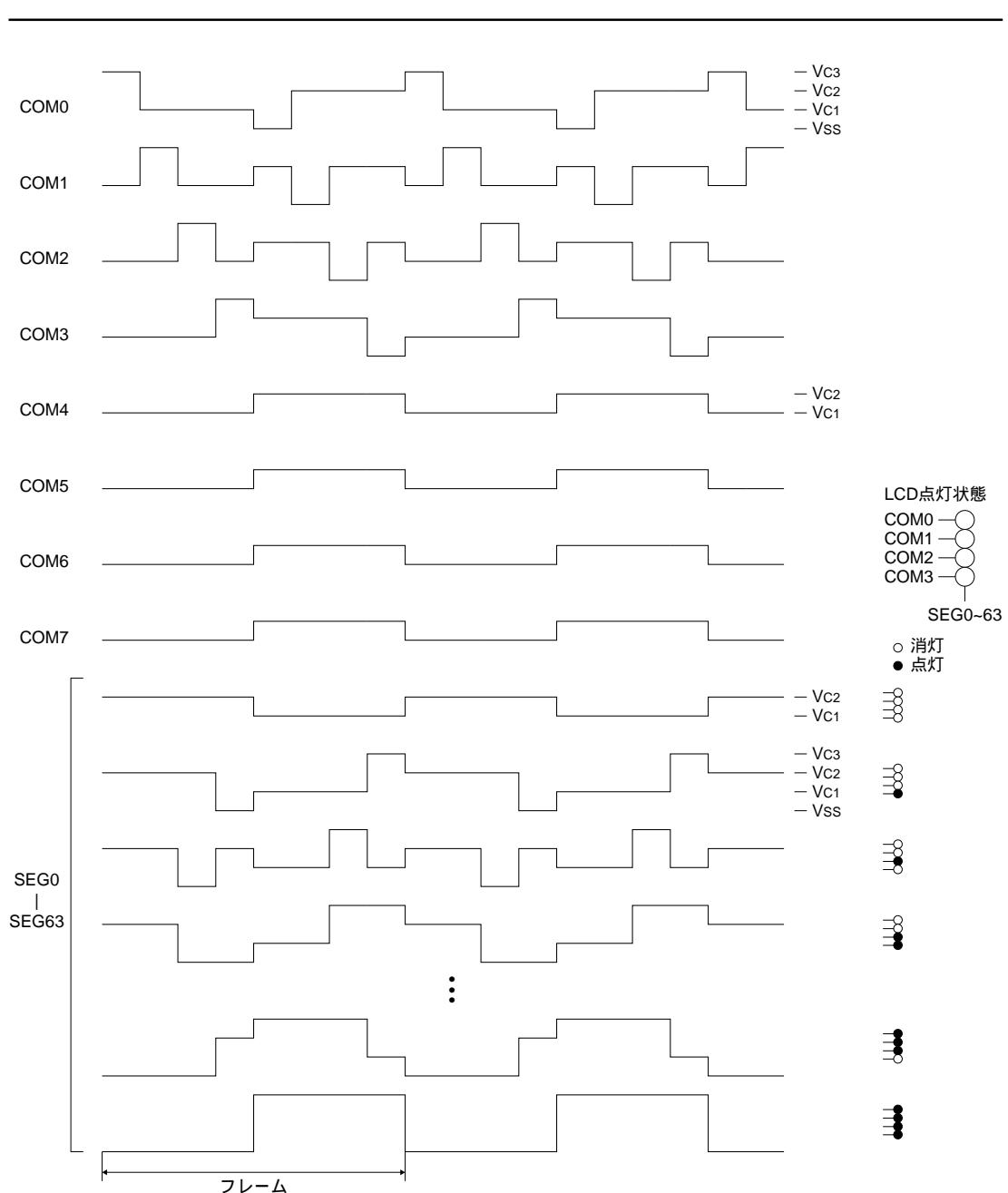

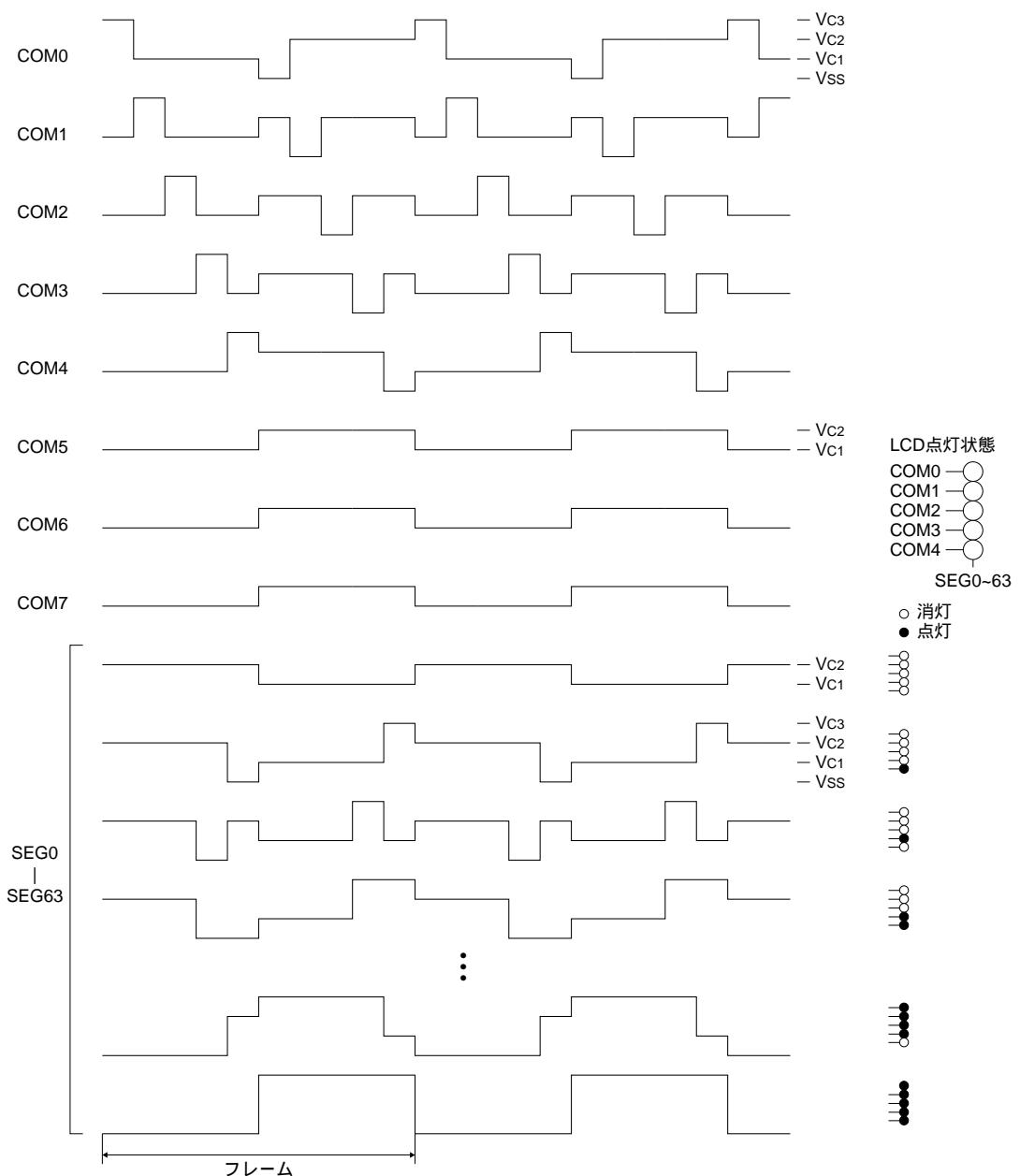

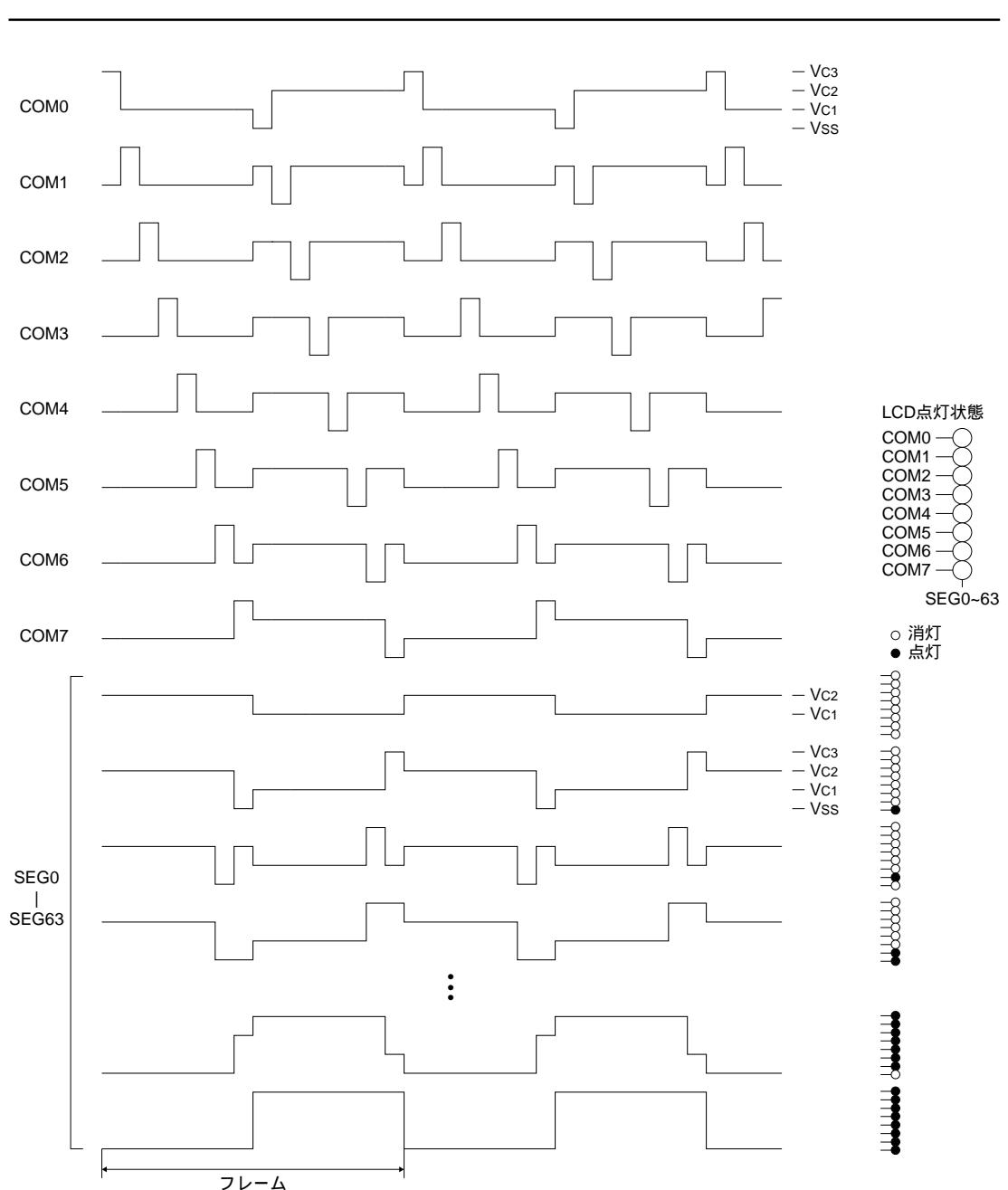

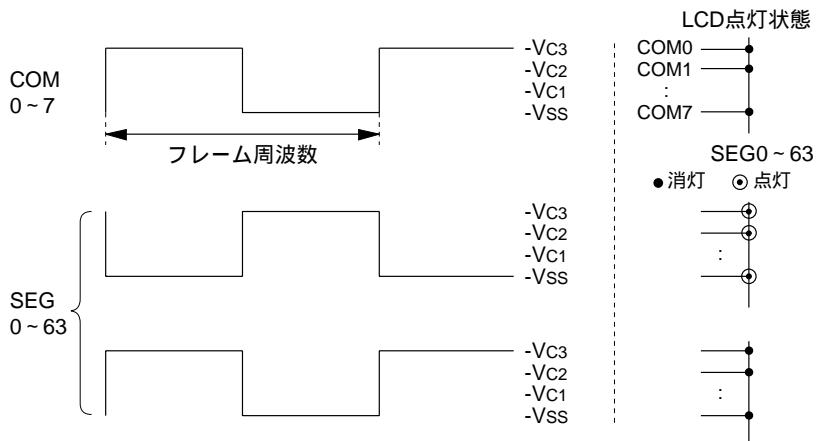

| 4.8    | LCDドライバ( COM0 ~ COM7, SEG0 ~ SEG63 ) ..... | 53 |

| 4.8.1  | LCDドライバの構成 .....                           | 53 |

| 4.8.2  | LCD駆動電源 .....                              | 53 |

| 4.8.3  | LCD表示のON/OFFとLCD駆動波形 .....                 | 53 |

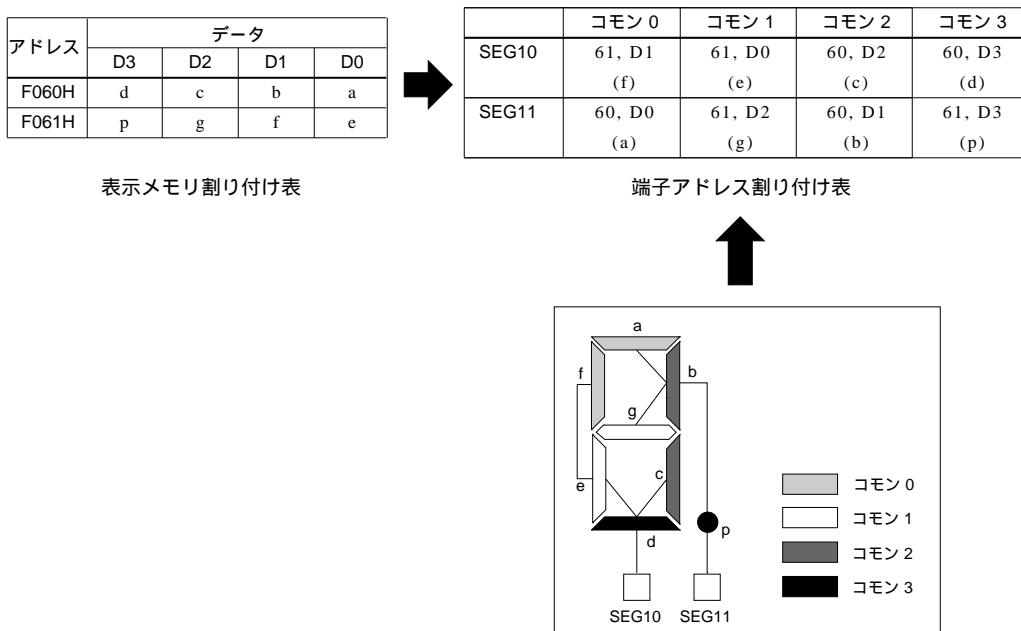

| 4.8.4  | 表示メモリ .....                                | 58 |

| 4.8.5  | セグメントオプション .....                           | 58 |

| 4.8.6  | LCDコントラスト調整 .....                          | 60 |

| 4.8.7  | LCDドライバのI/Oメモリ .....                       | 61 |

| 4.8.8  | プログラミング上の注意事項 .....                        | 62 |

| 4.9    | 計時タイマ .....                                | 63 |

| 4.9.1  | 計時タイマの構成 .....                             | 63 |

| 4.9.2  | データの読み出しとホールド機能 .....                      | 63 |

| 4.9.3  | 割り込み機能 .....                               | 64 |

| 4.9.4  | 計時タイマのI/Oメモリ .....                         | 65 |

| 4.9.5  | プログラミング上の注意事項 .....                        | 66 |

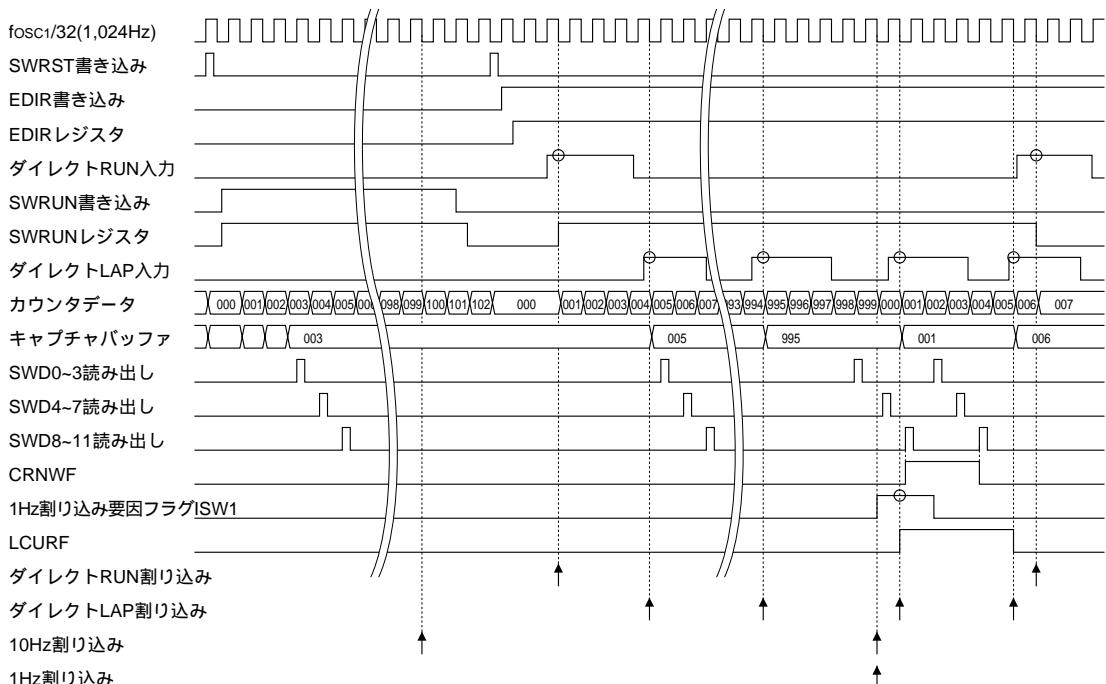

| 4.10   | ストップウォッチタイマ .....                          | 67 |

| 4.10.1 | ストップウォッチタイマの構成 .....                       | 67 |

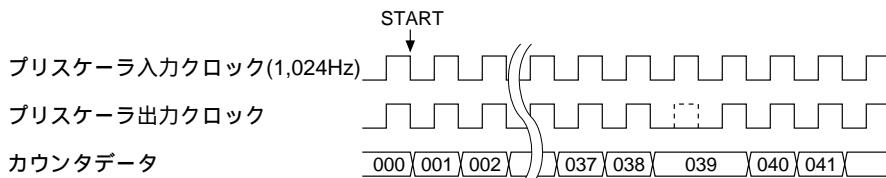

| 4.10.2 | カウンタとプリスケーラ .....                          | 67 |

|                                                  |     |

|--------------------------------------------------|-----|

| 4.10.3 キャプチャバッファとホールド機能 .....                    | 68  |

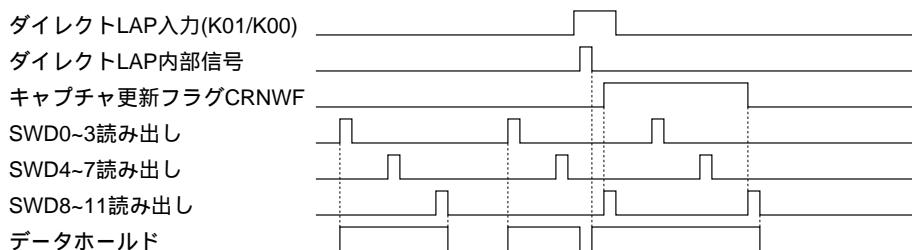

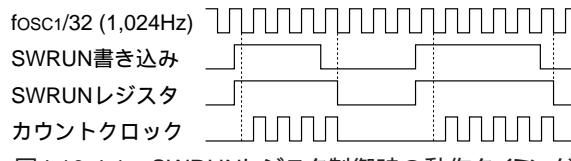

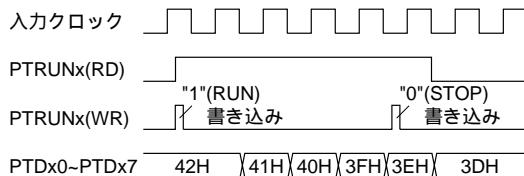

| 4.10.4 ストップウォッチタイマのRUN/STOPおよびリセット .....         | 69  |

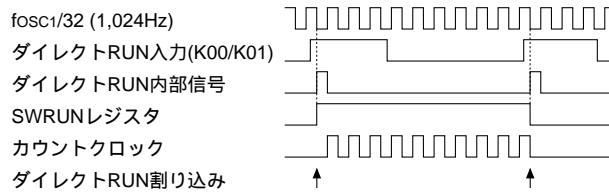

| 4.10.5 ダイレクト入力機能とキーマスク .....                     | 69  |

| 4.10.6 割り込み機能 .....                              | 72  |

| 4.10.7 ストップウォッチタイマのI/Oメモリ .....                  | 74  |

| 4.10.8 プログラミング上の注意事項 .....                       | 77  |

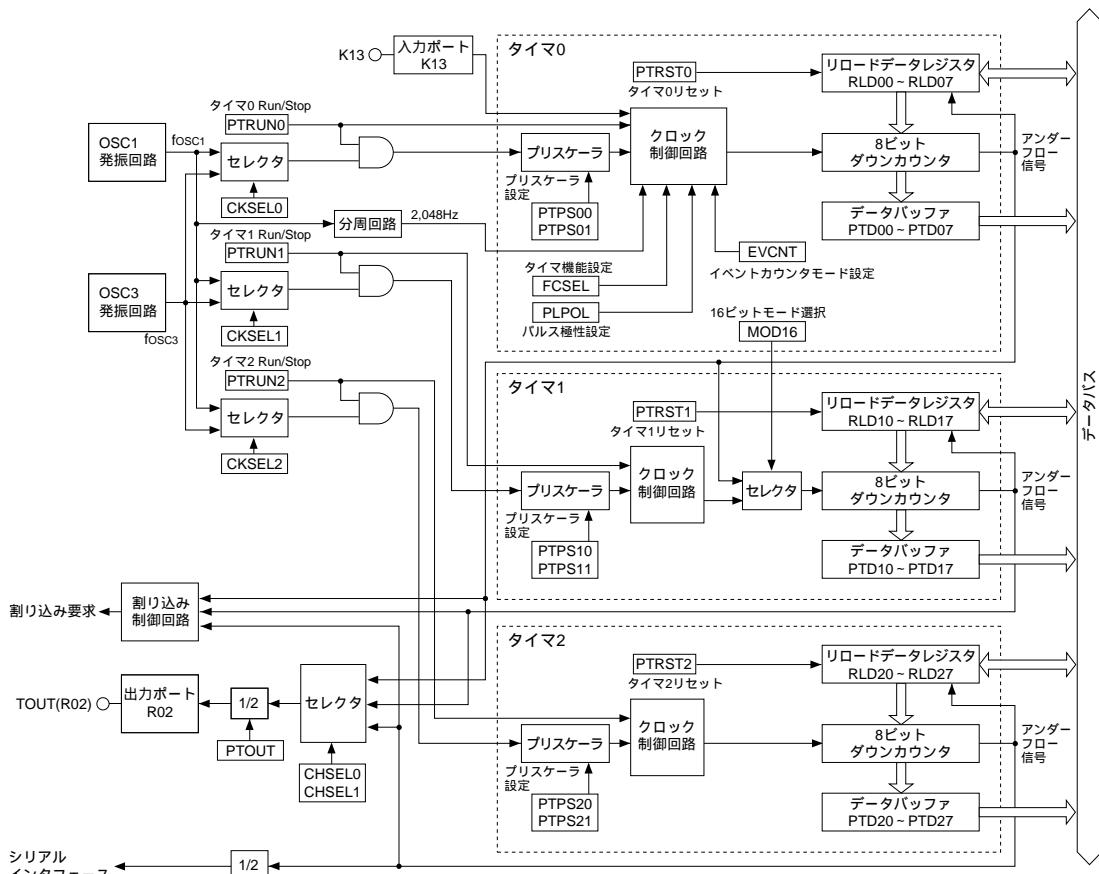

| 4.11 プログラムルタイマ .....                             | 78  |

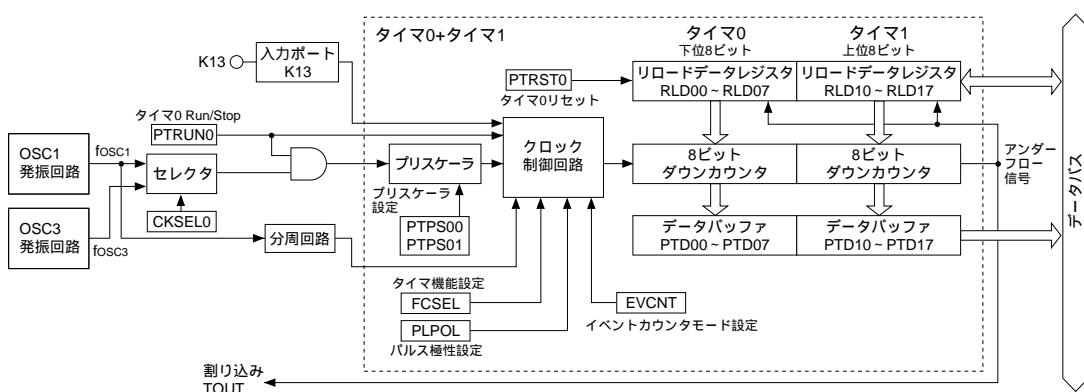

| 4.11.1 プログラムルタイマの構成 .....                        | 78  |

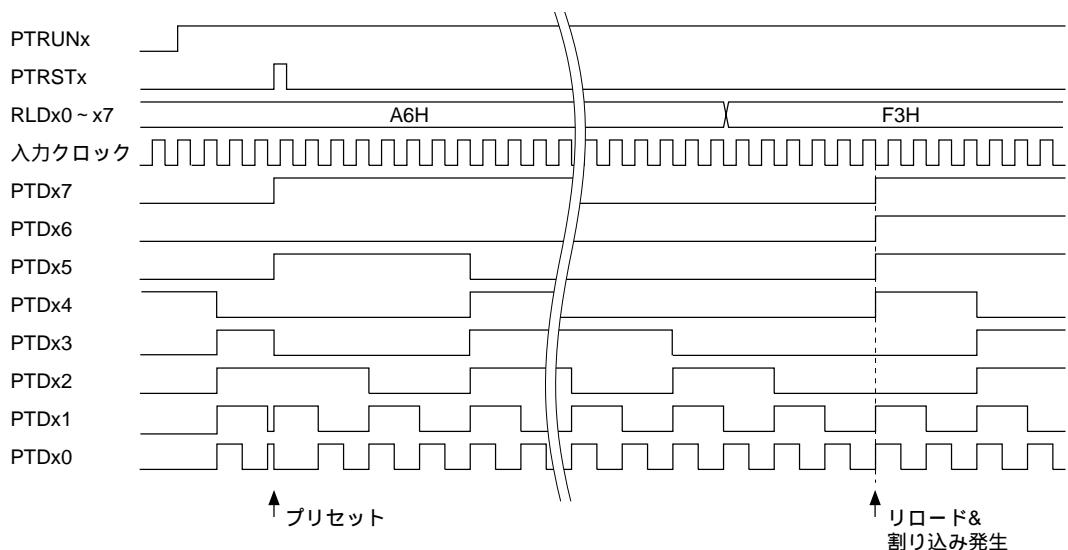

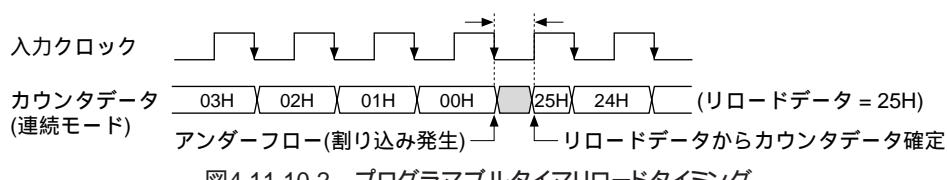

| 4.11.2 カウンタの基本動作 .....                           | 79  |

| 4.11.3 入力クロックの設定 .....                           | 80  |

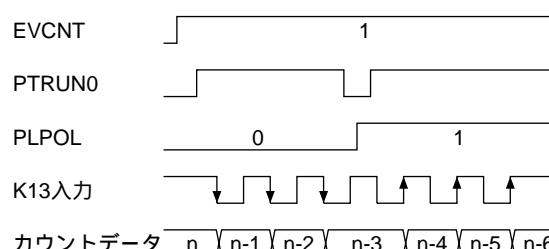

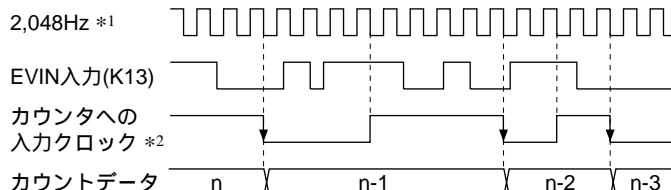

| 4.11.4 イベントカウンタモード( タイマ0) .....                  | 80  |

| 4.11.5 16ビットタイマ( タイマ0+タイマ1) .....                | 81  |

| 4.11.6 割り込み機能 .....                              | 82  |

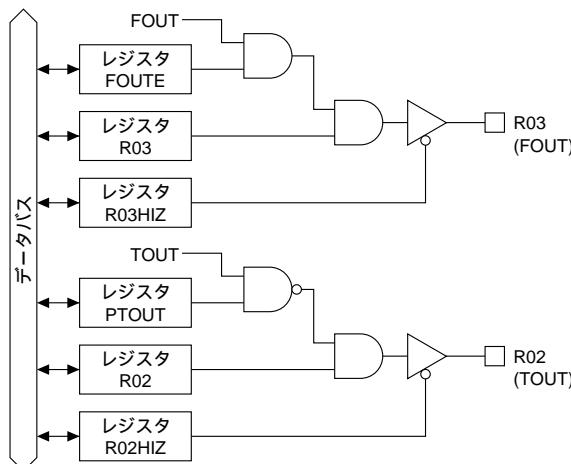

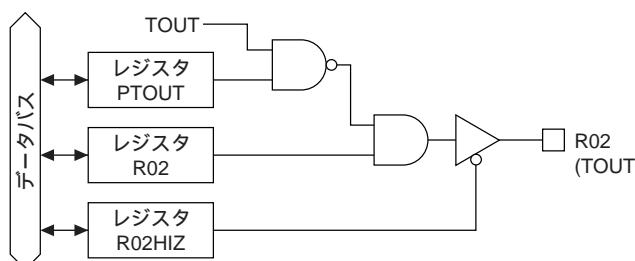

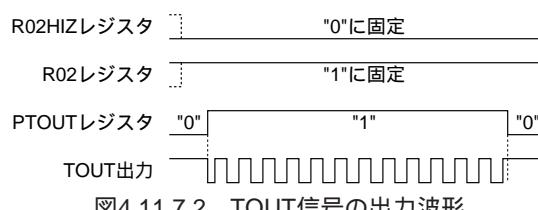

| 4.11.7 TOUT出力の設定 .....                           | 82  |

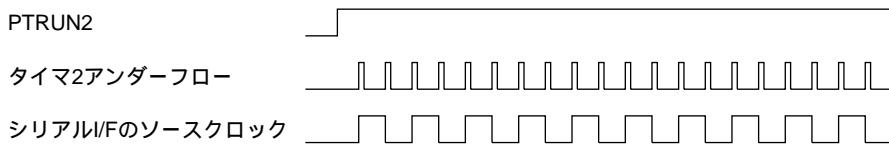

| 4.11.8 シリアルインターフェースの転送速度設定 .....                 | 83  |

| 4.11.9 プログラムルタイマのI/Oメモリ .....                    | 84  |

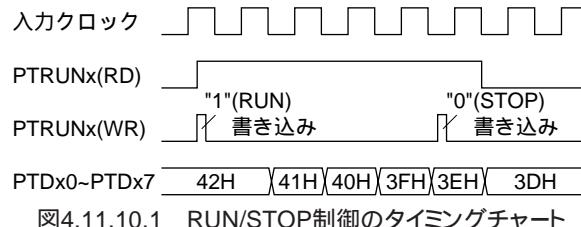

| 4.11.10 プログラミング上の注意事項 .....                      | 89  |

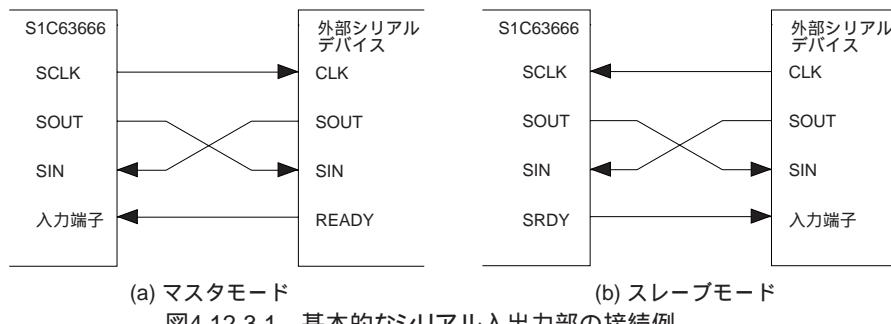

| 4.12 シリアルインターフェース( SIN, SOUT, SCLK, SRDY ) ..... | 90  |

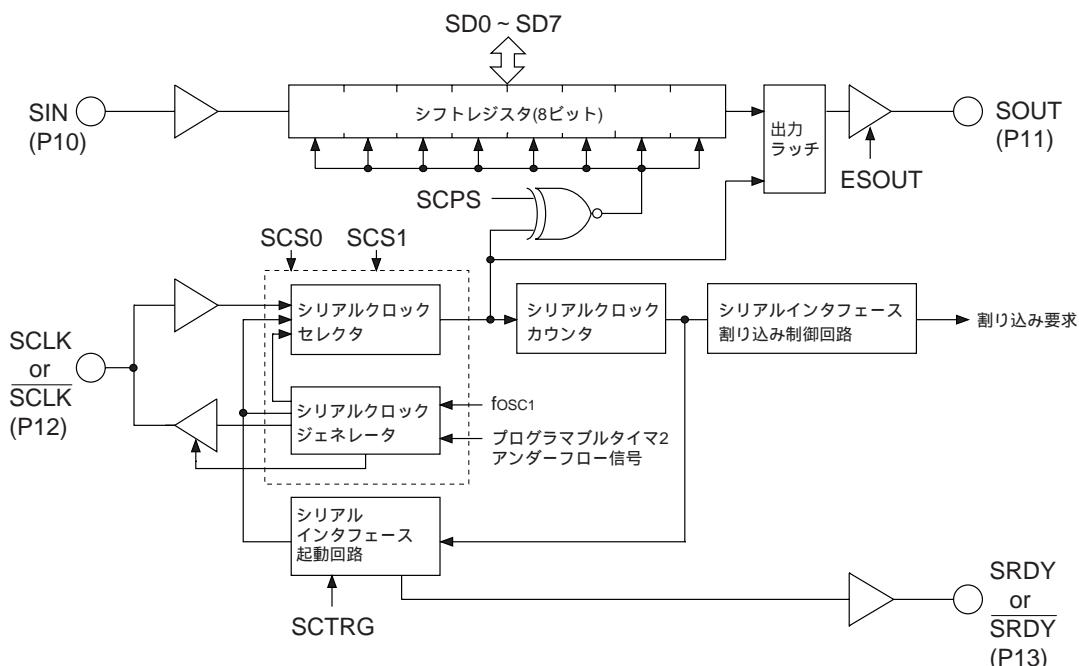

| 4.12.1 シリアルインターフェースの構成 .....                     | 90  |

| 4.12.2 マスクオプション .....                            | 91  |

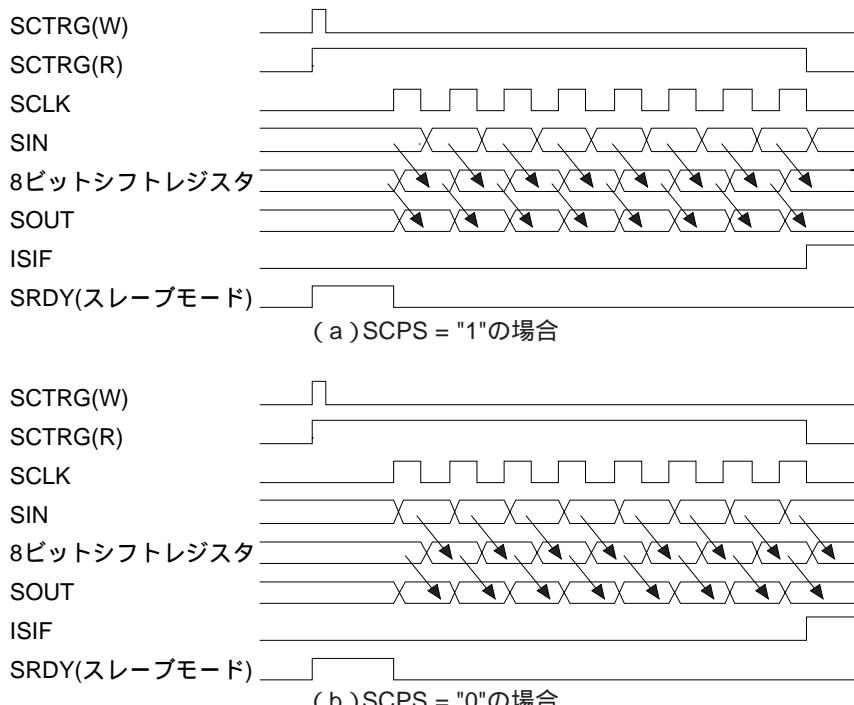

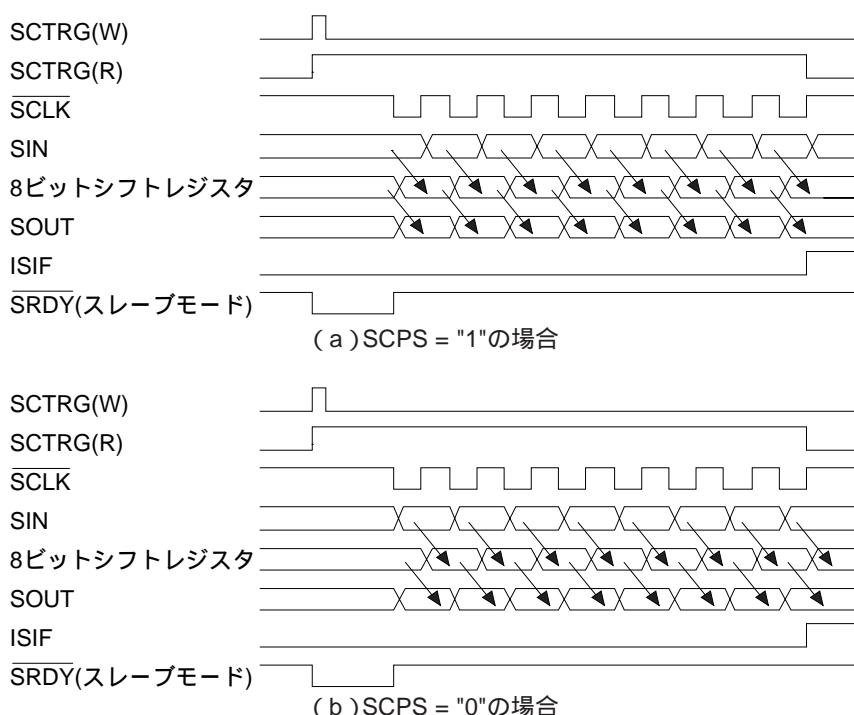

| 4.12.3 シリアルインターフェースのマスタモードとスレーブモード .....         | 91  |

| 4.12.4 データの入出力と割り込み .....                        | 92  |

| 4.12.5 シリアルインターフェースのI/Oメモリ .....                 | 95  |

| 4.12.6 プログラミング上の注意事項 .....                       | 98  |

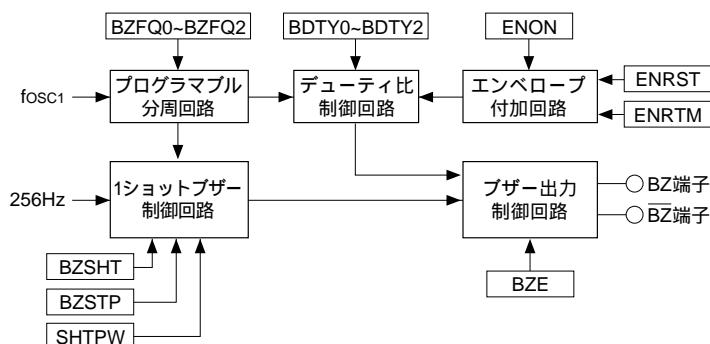

| 4.13 サウンドジェネレータ .....                            | 99  |

| 4.13.1 サウンドジェネレータの構成 .....                       | 99  |

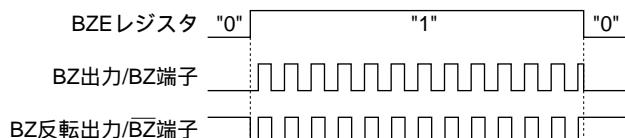

| 4.13.2 ブザー出力の制御 .....                            | 99  |

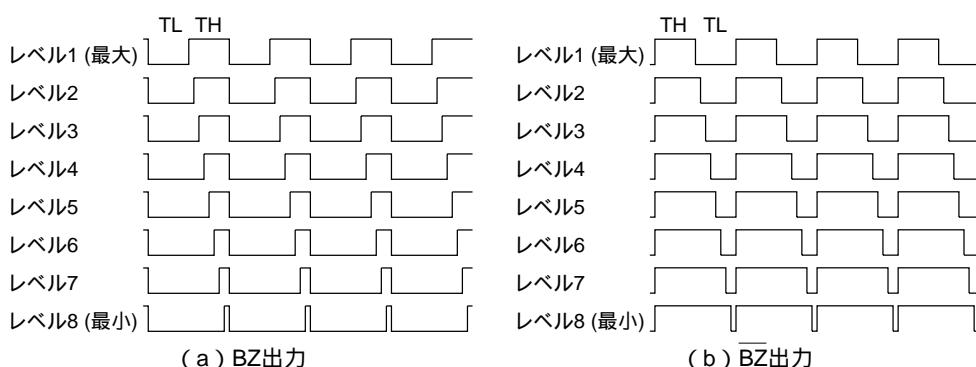

| 4.13.3 ブザー周波数と音量の設定 .....                        | 100 |

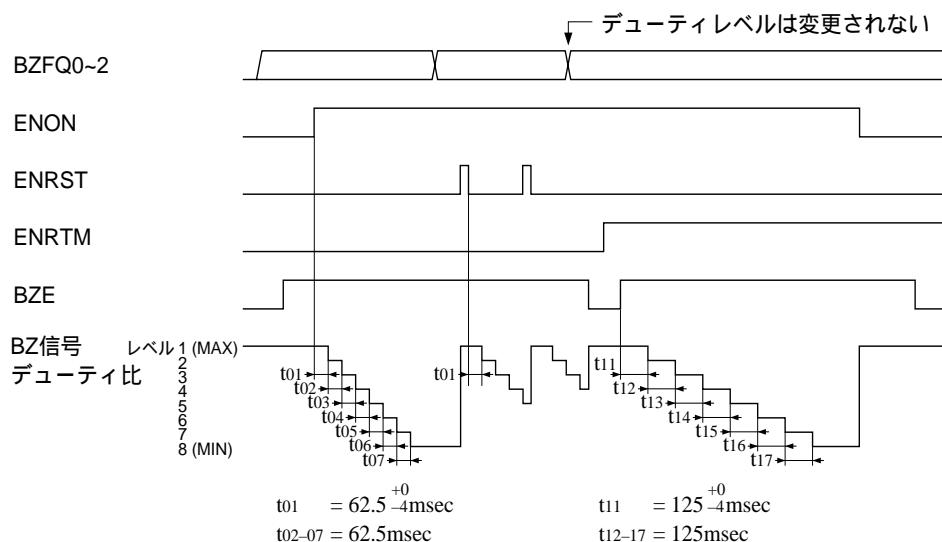

| 4.13.4 デジタルエンベロープ .....                          | 101 |

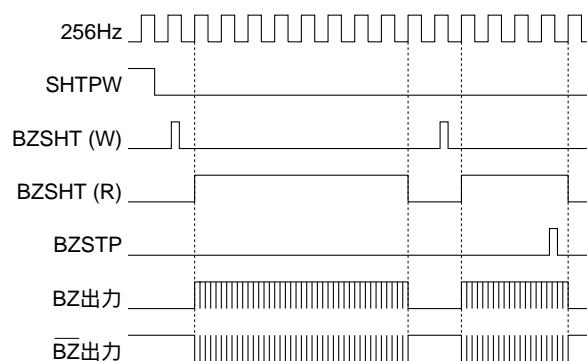

| 4.13.5 1ショット出力 .....                             | 102 |

| 4.13.6 サウンドジェネレータのI/Oメモリ .....                   | 103 |

| 4.13.7 プログラミング上の注意事項 .....                       | 105 |

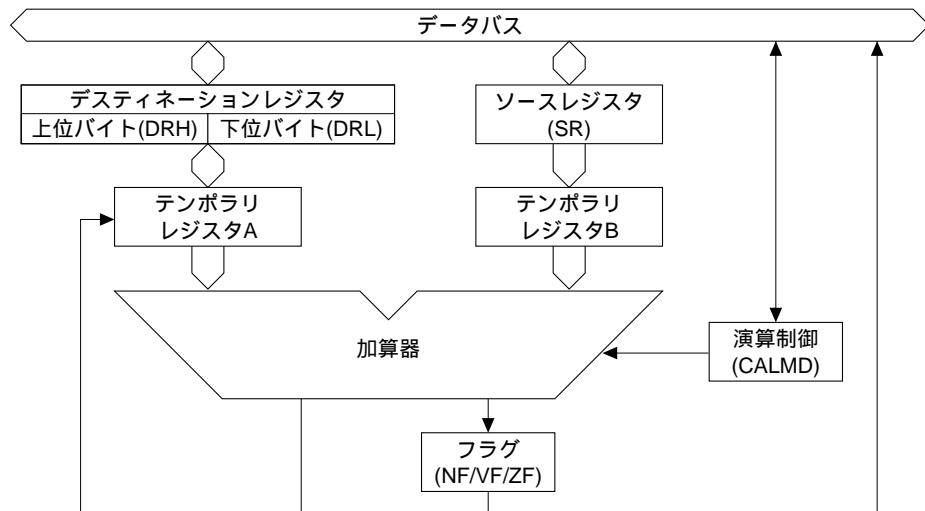

| 4.14 整数乗除算器 .....                                | 106 |

| 4.14.1 整数乗除算器の構成 .....                           | 106 |

| 4.14.2 乗算モード .....                               | 106 |

| 4.14.3 除算モード .....                               | 107 |

| 4.14.4 実行サイクル .....                              | 108 |

| 4.14.5 整数乗除算器のI/Oメモリ .....                       | 109 |

| 4.14.6 プログラミング上の注意事項 .....                       | 110 |

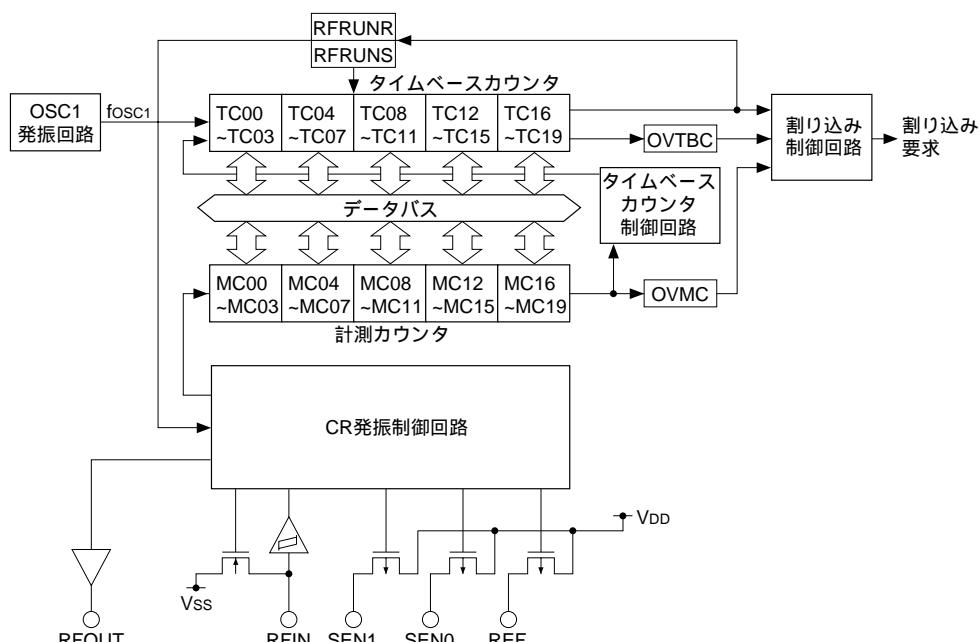

| 4.15 R/Fコンバータ .....                              | 111 |

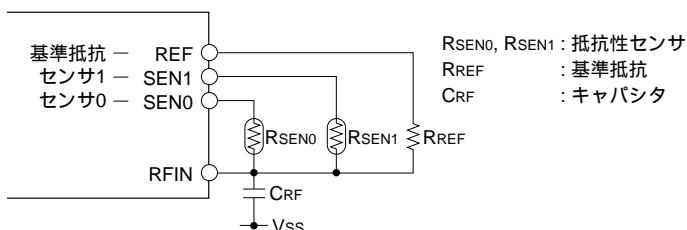

| 4.15.1 R/Fコンバータの構成 .....                         | 111 |

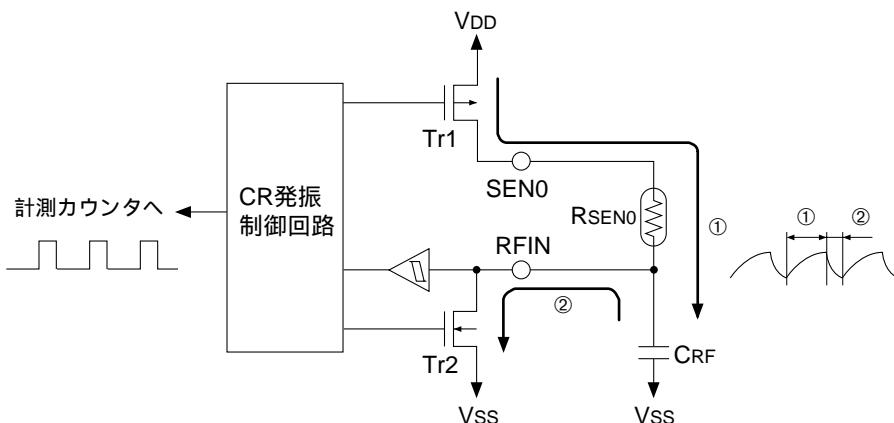

| 4.15.2 接続端子とCR発振回路 .....                         | 111 |

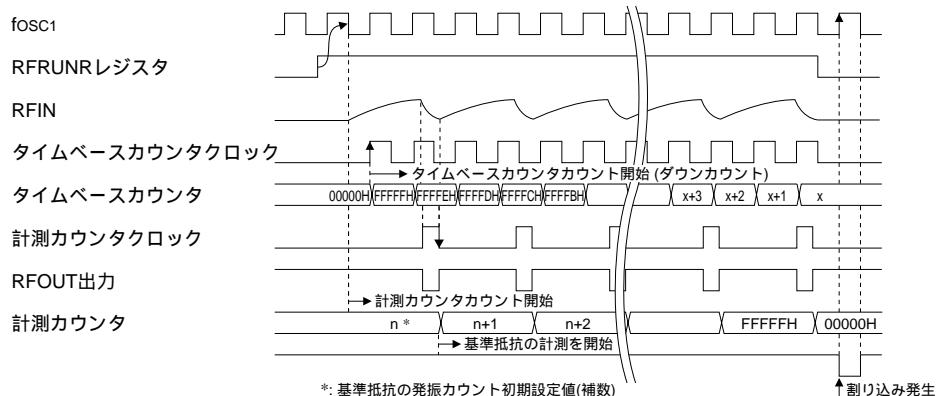

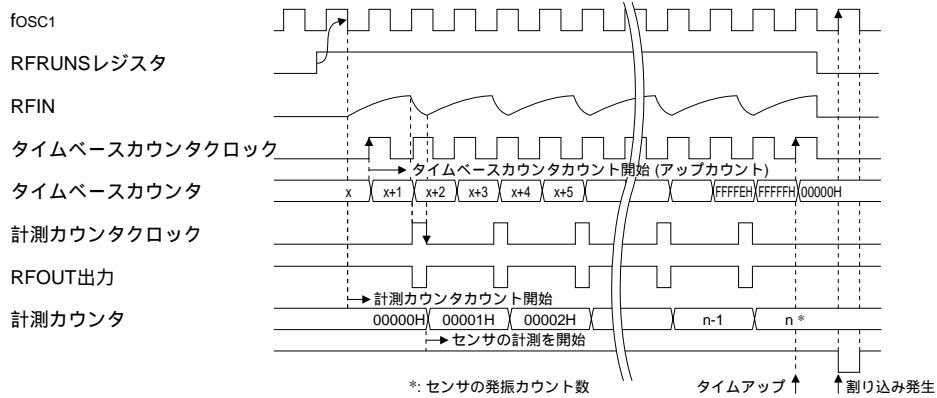

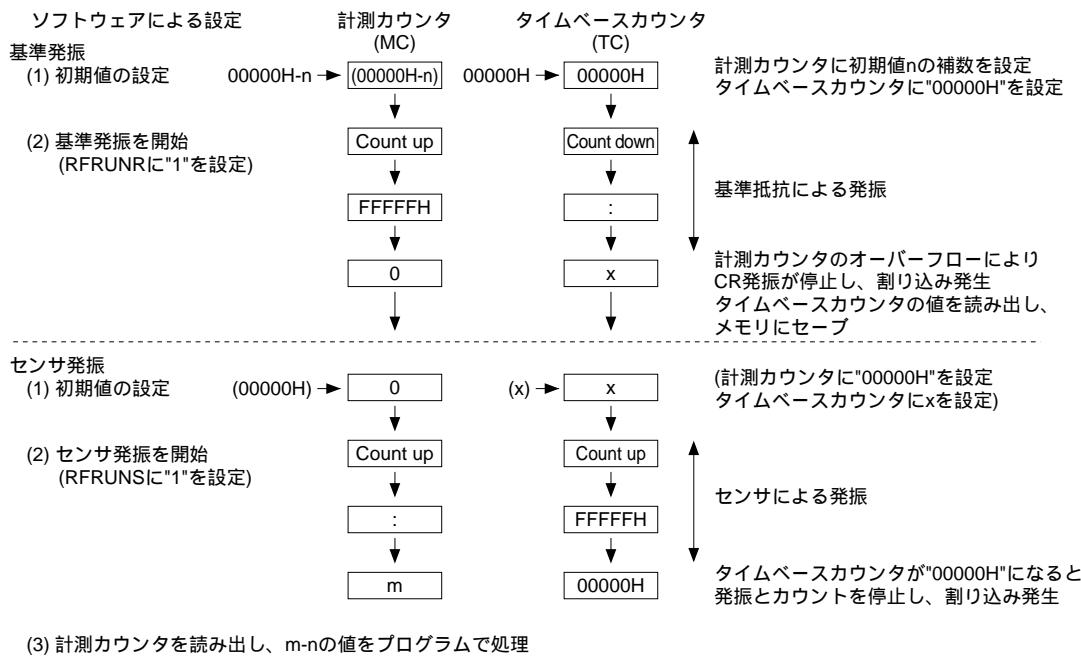

| 4.15.3 R/F変換 .....                               | 113 |

| 4.15.4 割り込み機能 .....                              | 116 |

| 4.15.5 R/FコンバータのI/Oメモリ .....                     | 118 |

| 4.15.6 プログラミング上の注意事項 .....                       | 121 |

|                                |            |

|--------------------------------|------------|

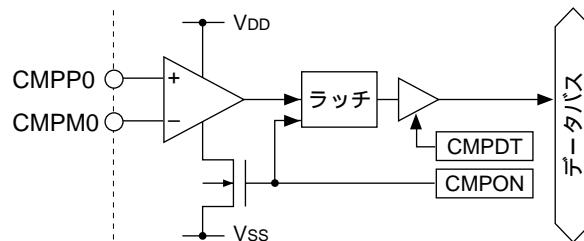

| 4.16 アナログコンパレータ .....          | 122        |

| 4.16.1 アナログコンパレータの構成 .....     | 122        |

| 4.16.2 アナログコンパレータの動作 .....     | 122        |

| 4.16.3 アナログコンパレータのI/Oメモリ ..... | 123        |

| 4.16.4 プログラミング上の注意事項 .....     | 123        |

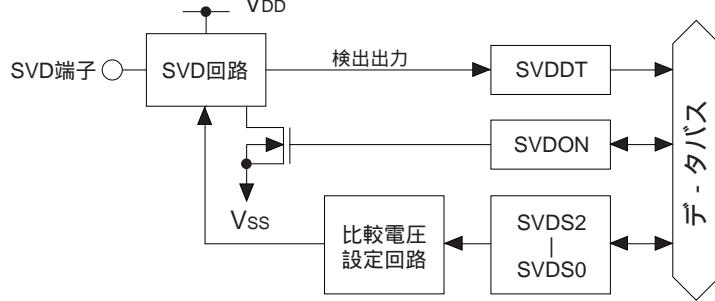

| 4.17 SVD(電源電圧検出)回路 .....       | 124        |

| 4.17.1 SVD回路の構成 .....          | 124        |

| 4.17.2 マスクオプション .....          | 124        |

| 4.17.3 SVD動作 .....             | 125        |

| 4.17.4 SVD回路のI/Oメモリ .....      | 126        |

| 4.17.5 プログラミング上の注意事項 .....     | 126        |

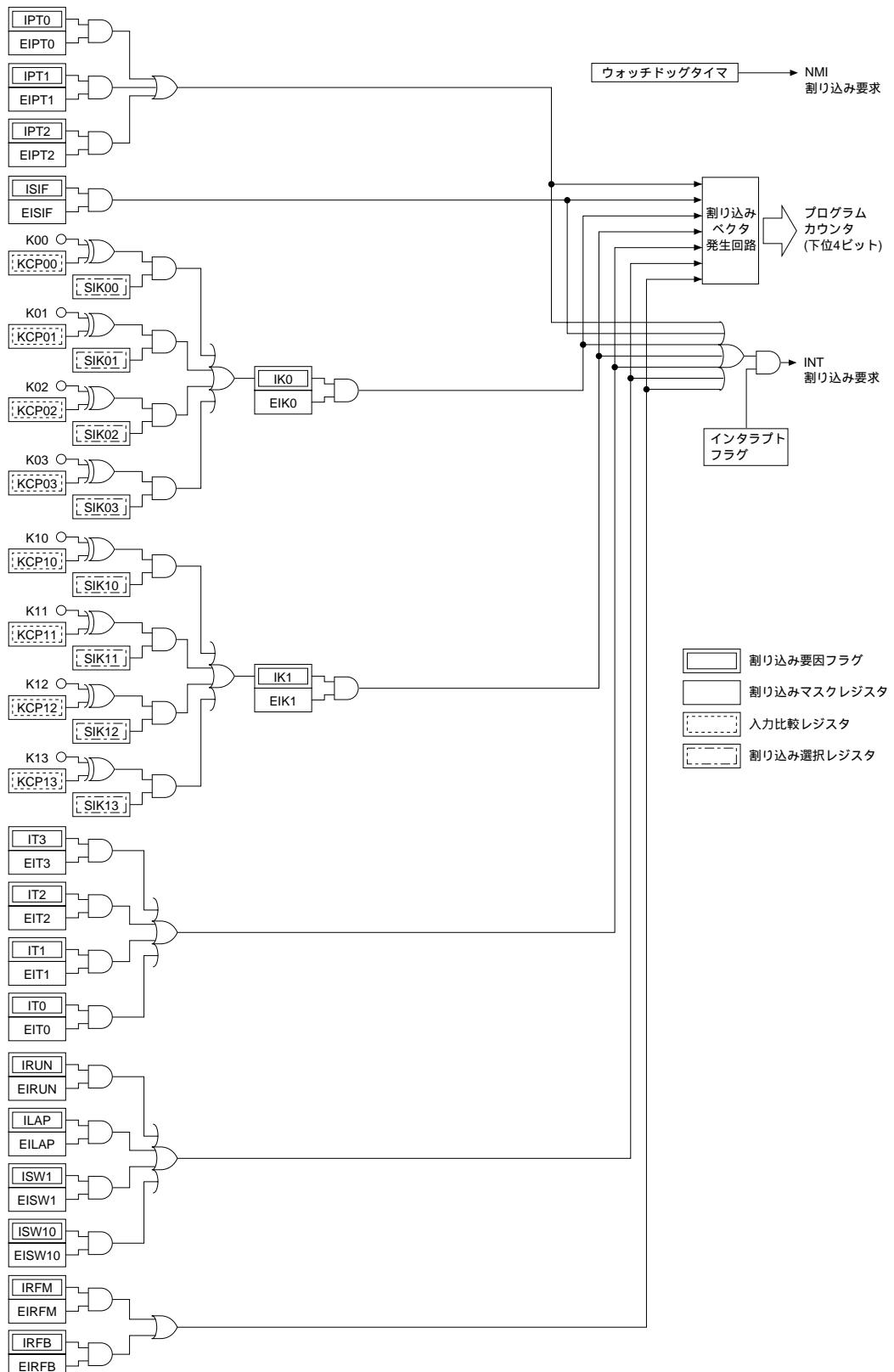

| 4.18 割り込みとHALT .....           | 127        |

| 4.18.1 割り込みの要因 .....           | 129        |

| 4.18.2 割り込みの個別マスク .....        | 130        |

| 4.18.3 割り込みベクタ .....           | 130        |

| 4.18.4 割り込みのI/Oメモリ .....       | 131        |

| 4.18.5 プログラミング上の注意事項 .....     | 133        |

| <b>5 注意事項のまとめ</b> .....        | <b>134</b> |

| 5.1 低消費電流化のための注意事項 .....       | 134        |

| 5.2 個別機能についての注意事項のまとめ .....    | 135        |

| 5.3 実装上の注意事項 .....             | 139        |

| <b>6 基本外部結線図</b> .....         | <b>141</b> |

| <b>7 電気的特性</b> .....           | <b>142</b> |

| 7.1 絶対最大定格 .....               | 142        |

| 7.2 推奨動作条件 .....               | 142        |

| 7.3 DC特性 .....                 | 142        |

| 7.4 アナログ回路特性・消費電流 .....        | 143        |

| 7.5 発振特性 .....                 | 144        |

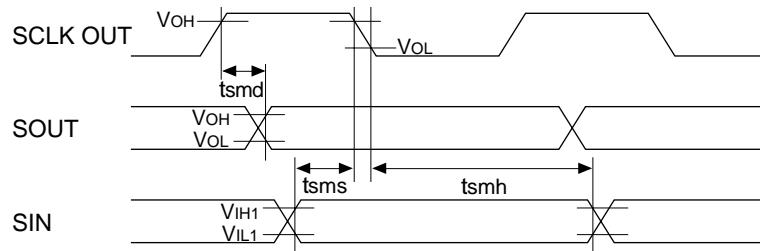

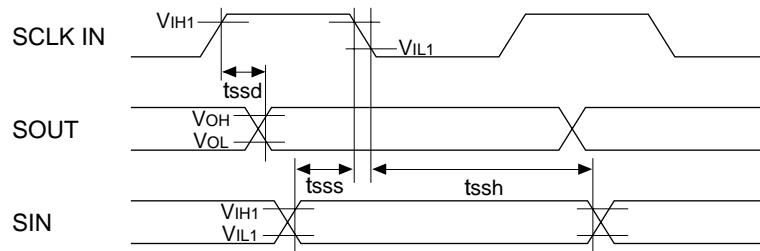

| 7.6 シリアルインタフェースAC特性 .....      | 146        |

| 7.7 タイミングチャート .....            | 147        |

| 7.8 R/Fコンバータ特性 .....           | 147        |

| <b>8 パッケージ</b> .....           | <b>148</b> |

| 8.1 プラスチックパッケージ .....          | 148        |

| 8.2 テストサンプル用セラミックパッケージ .....   | 149        |

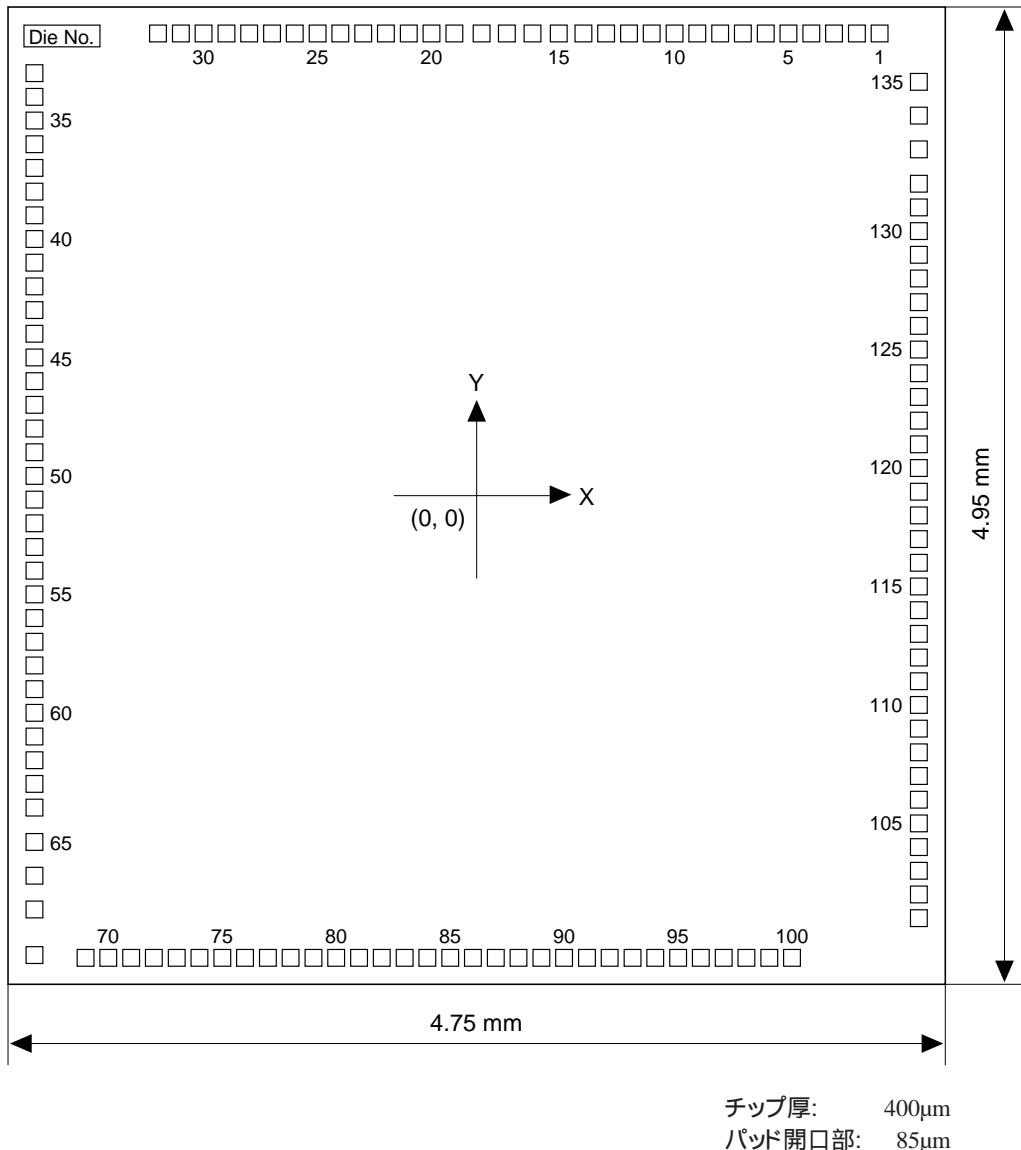

| <b>9 パッド配置</b> .....           | <b>150</b> |

| 9.1 パッド配置図 .....               | 150        |

| 9.2 パッド座標 .....                | 151        |

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

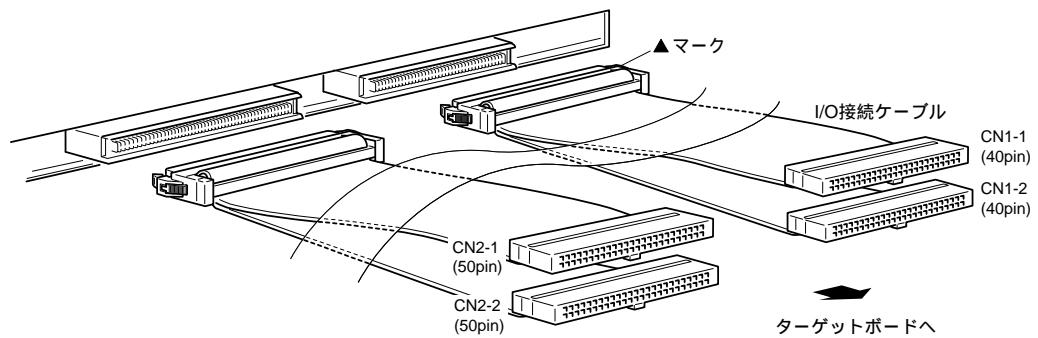

| APPENDIX S5U1C63000P1 Manual( Peripheral Circuit Board for S1C63666 ) | 152 |

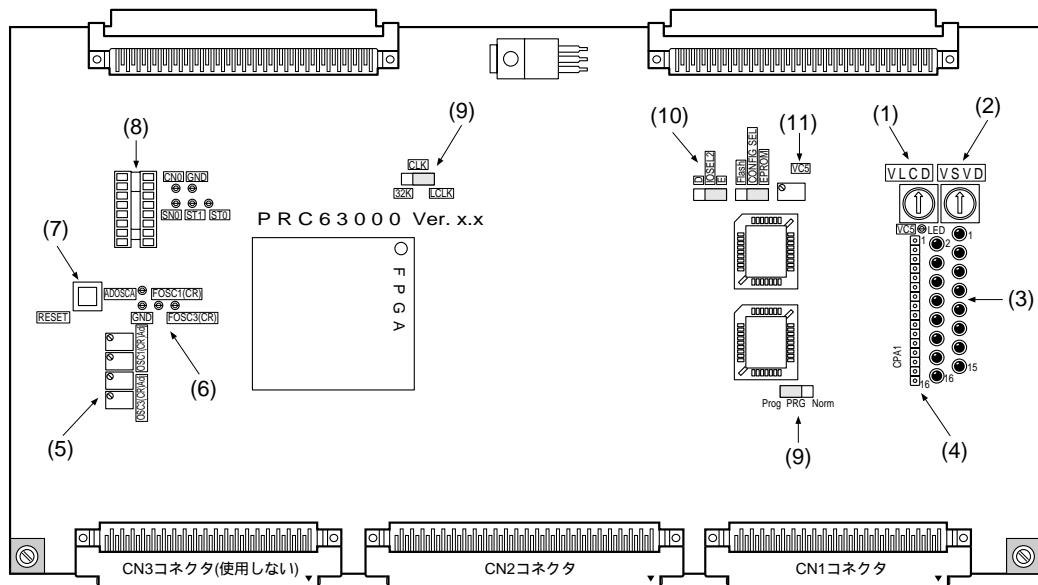

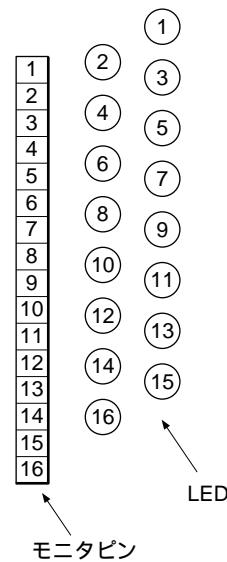

| A.1 各部の名称と機能 .....                                                    | 152 |

| A.2 ターゲットシステムとの接続 .....                                               | 155 |

| A.3 使用上の注意 .....                                                      | 157 |

| A.3.1 操作上の注意事項 .....                                                  | 157 |

| A.3.2 実ICとの相違点 .....                                                  | 157 |

# 1 概要

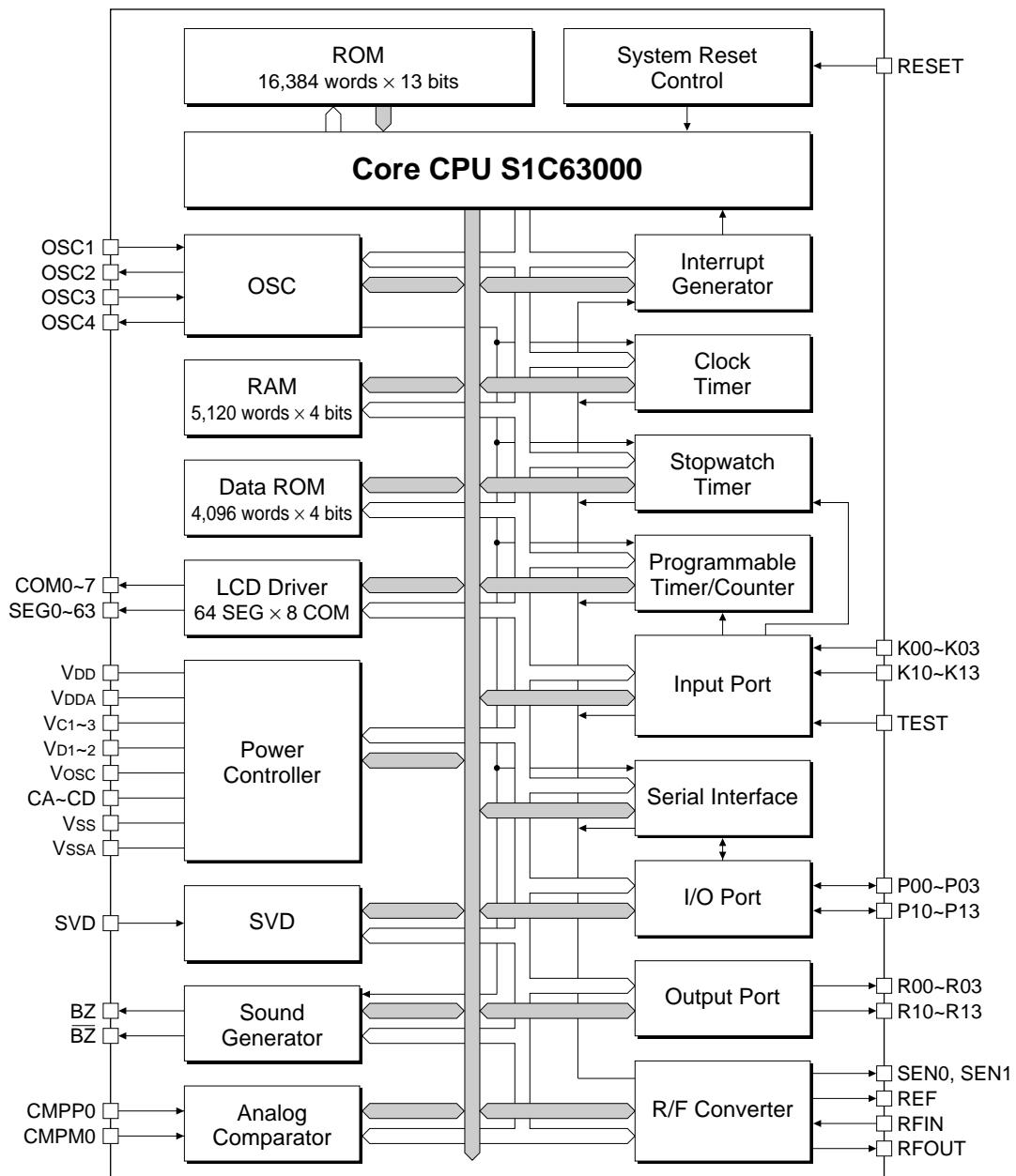

S1C63666は高性能4ビットCPU S1C63000を中心に、ワンチップ上にROM( 16,384ワード×13ビット )、RAM( 5,120ワード×4ビット )、乗除算回路、シリアルインターフェース、ウォッチドッグタイマ、プログラマブルタイマ、タイムベースカウンタ( 2系統 )、最大64セグメント×8コモンのLCDドライバ、サウンドジェネレータ、R/Fコンバータ等を内蔵したマイクロコンピュータです。低消費電流を特長とし、電池駆動を必要とするR/F変換機能付き携帯機器への応用に適しています。

## 1.1 特長

|                 |                                                                                                                                                     |                                          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| OSC1発振回路        | 32.768kHz( Typ. )                                                                                                                                   | 水晶発振回路                                   |

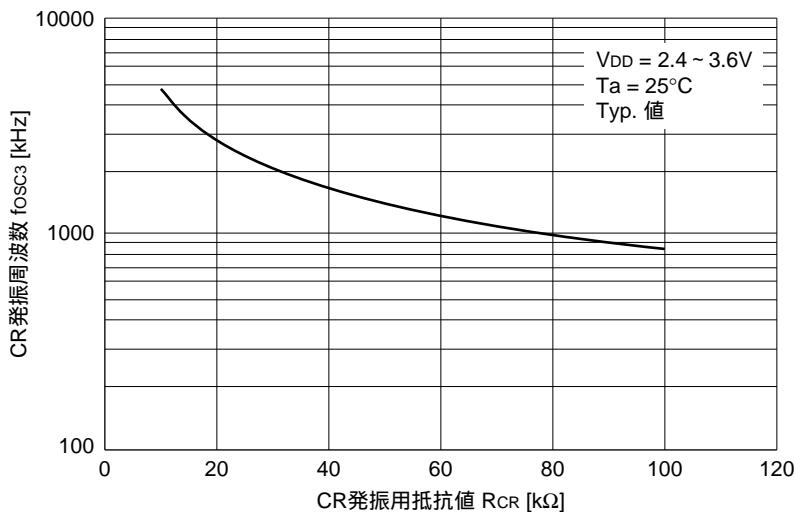

| OSC3発振回路        | 4MHz( Max. )                                                                                                                                        | セラミック発振回路、または1.1MHz( Typ. ) CR発振回路( *1 ) |

| インストラクションセット    | 基本命令 46種類( 全命令数 411種類 )                                                                                                                             | アドレスシングルモード 8種類                          |

| インストラクション実行時間   | 32.768kHz動作時: 61μsec<br>4MHz動作時: 0.5μsec<br>1μsec<br>1.5μsec                                                                                        |                                          |

| ROM容量           | 命令ROM: 16,384ワード×13ビット<br>データROM: 4,096ワード×4ビット                                                                                                     |                                          |

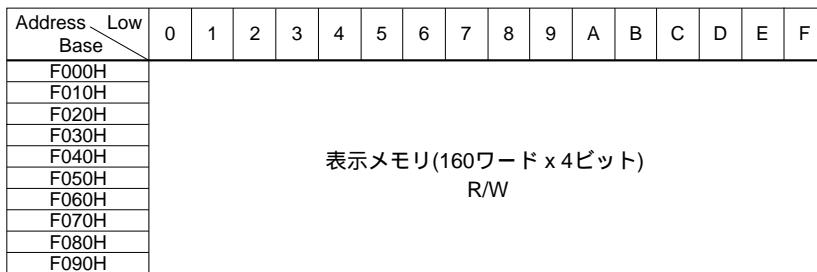

| RAM容量           | データメモリ: 5,120ワード×4ビット<br>表示メモリ: 160ワード×4ビット                                                                                                         |                                          |

| 入力ポート           | 8ビット( ブルダウントラブルの付加が可能*1 )                                                                                                                           |                                          |

| 出力ポート           | 8ビット( 2ビットを特殊出力に切り換え可能*2 )                                                                                                                          |                                          |

| 入出力兼用ポート        | 8ビット( 4ビットをシリアルI/F入出力に切り換え可能*2 )                                                                                                                    |                                          |

| シリアルインターフェース    | 1ポート( クロック同期式8ビット )                                                                                                                                 |                                          |

| LCDドライバ         | 64セグメント×4, 5、または8コモン( *2 )                                                                                                                          |                                          |

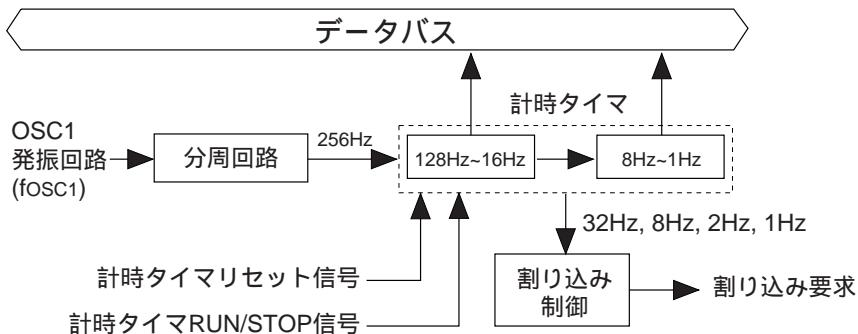

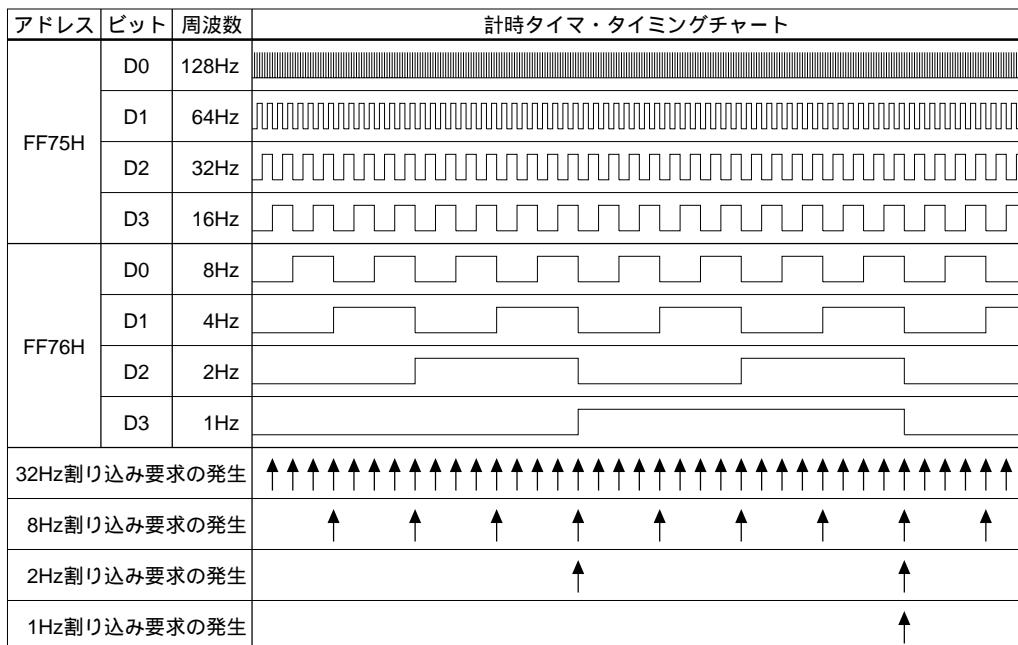

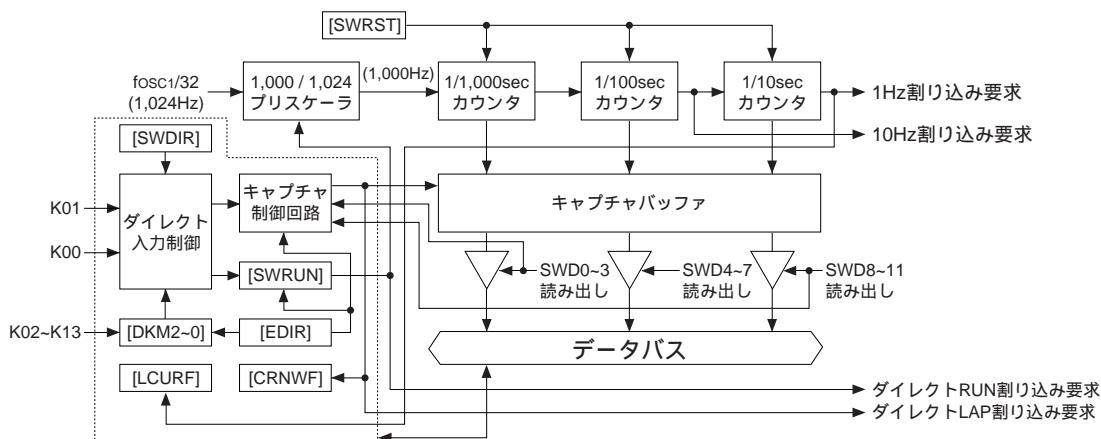

| タイムベースカウンタ      | 計時タイマ<br>ストップウォッチタイマ( 1/1000秒、ダイレクトキー入力機能付き )                                                                                                       |                                          |

| プログラマブルタイマ      | 8ビット×3ch、または16ビット×1ch + 8ビット×1ch( *2 )                                                                                                              |                                          |

| ウォッチドッグタイマ      | 内蔵                                                                                                                                                  |                                          |

| サウンドジェネレータ      | エンベロープ、1ショット出力機能付き                                                                                                                                  |                                          |

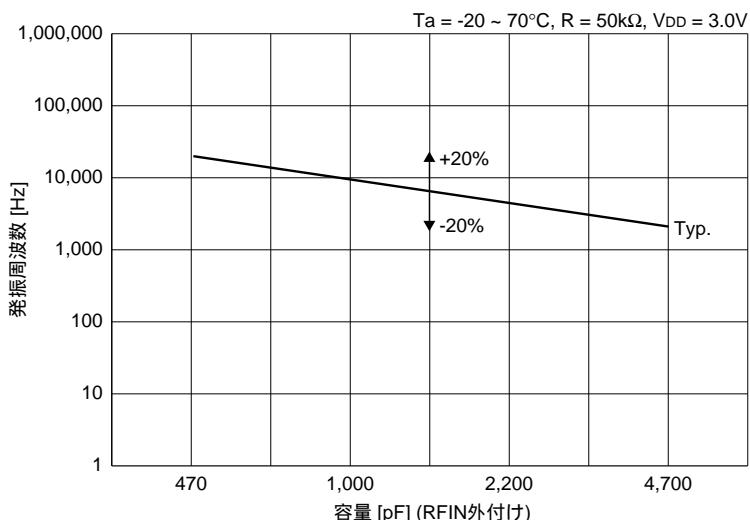

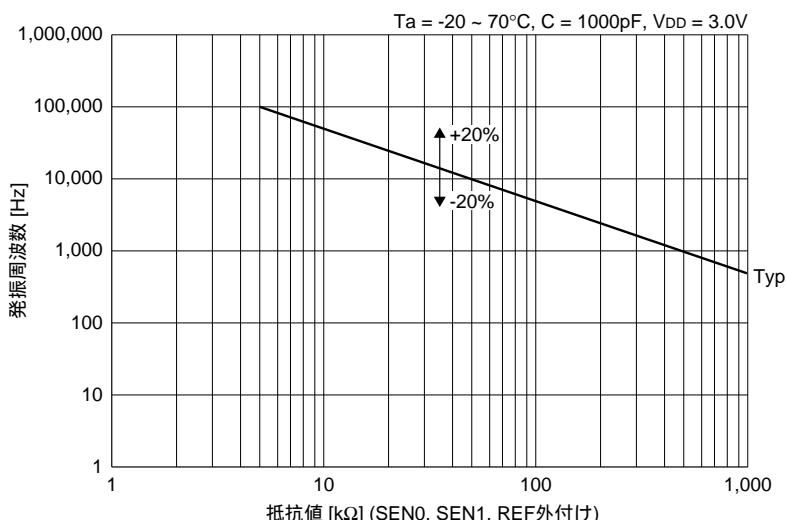

| R/Fコンバータ        | 2ch、CR発振方式、20ビットカウンタ                                                                                                                                |                                          |

| 乗除算回路           | 8ビット演算器 1ch<br>乗算: 8ビット×8ビット( 積 ) 16ビット<br>除算: 16ビット÷8ビット( 商 ) 8ビット、( 剰余 ) 8ビット                                                                     |                                          |

| アナログコンパレータ      | 1ch                                                                                                                                                 |                                          |

| 電源電圧検出( SVD )回路 | 検出電圧を8種類( 1.85V ~ 2.90V )から選択可( *2 )<br>外部入力電圧検出も可能( *1 )                                                                                           |                                          |

| 外部割り込み          | 入力ポート割り込み<br>2系統                                                                                                                                    |                                          |

| 内部割り込み          | 計時タイマ割り込み<br>4系統<br>ストップウォッチタイマ割り込み<br>4系統<br>プログラマブルタイマ割り込み<br>3系統<br>シリアルインターフェース割り込み<br>1系統<br>R/Fコンバータ割り込み<br>2系統                               |                                          |

| 電源電圧            | 2.4V ~ 3.6V 動作周波数4MHz( Max. )<br>2.4V ~ 3.6V 動作周波数32kHz<br>1.5V ~ 3.6V 動作周波数32kHz                                                                   | 通常モード<br>降圧モード<br>通常モード                  |

| 動作温度範囲          | -20°C ~ 70°C                                                                                                                                        |                                          |

| 消費電流( Typ. )    | 低速( 32kHz OSC1水晶発振 )動作時:<br>HALT時 3.0V( 液晶電源ON、降圧モード ) 0.65μA<br>動作時 3.0V( 液晶電源ON、降圧モード ) 2.5μA<br>高速( OSC3 )動作時:<br>動作時( 4MHz ) 3.0V( 液晶電源ON ) 1mA |                                          |

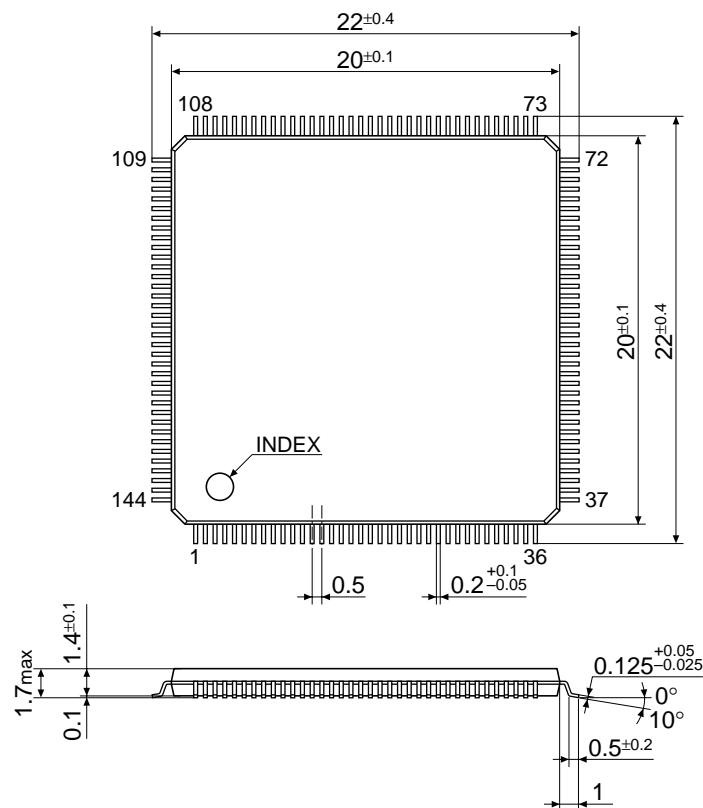

| 出荷形態            | QFP20-144pin( プラスチック 床たはチップ                                                                                                                         |                                          |

\*1: マスクオプションにより選択 \*2: ソフトウェアにより選択

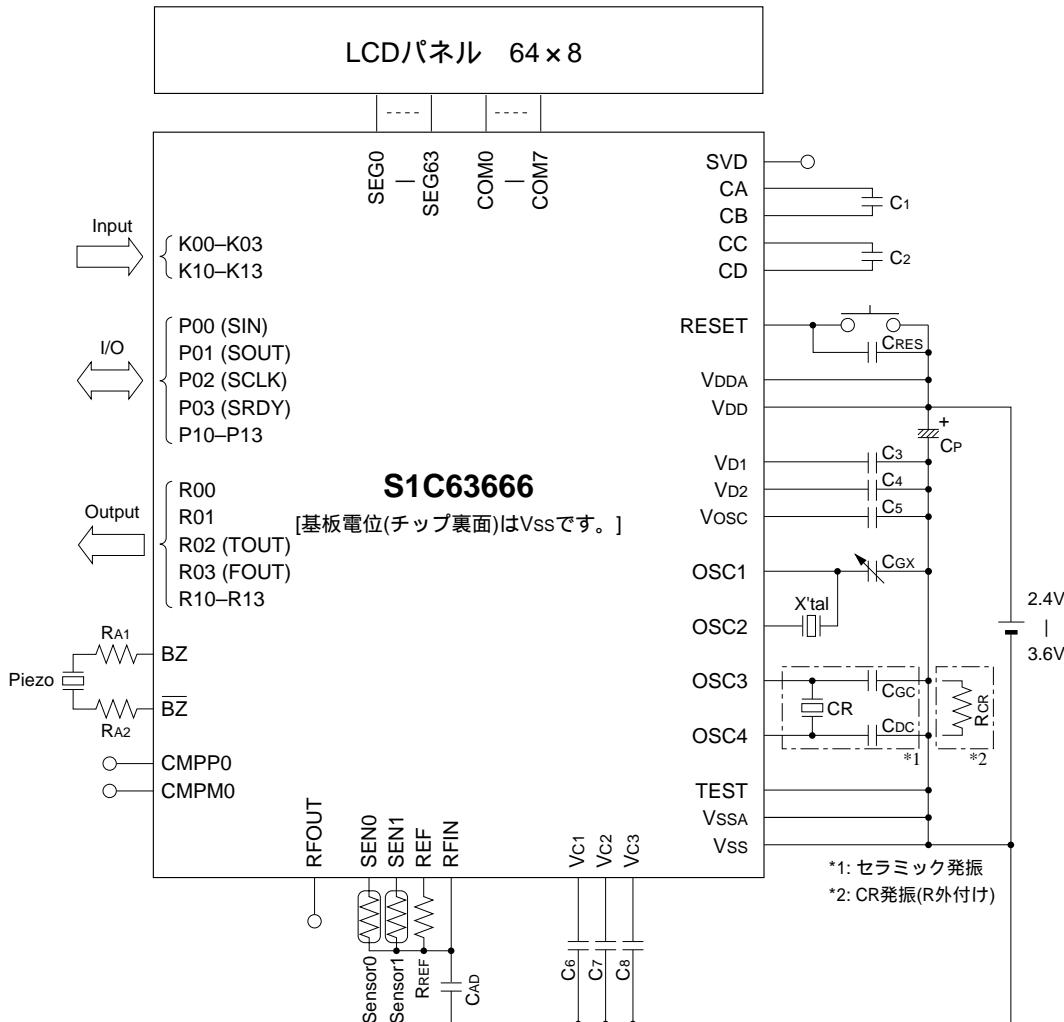

## 1.2 ブロック図

図1.2.1 ブロック図

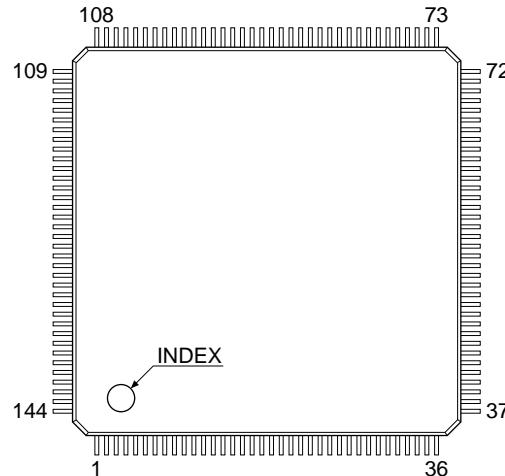

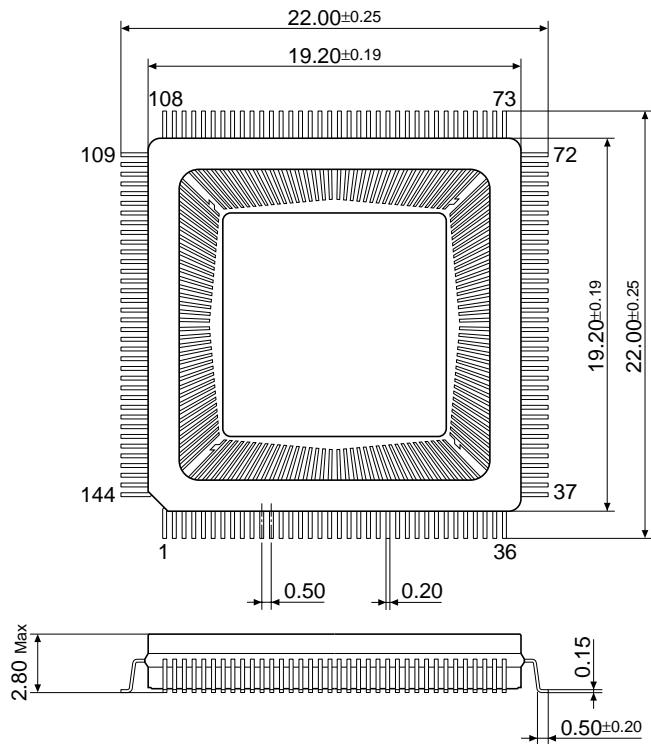

### 1.3 端子配置図

QFP20-144pin

| No. | 端子名   | No. | 端子名   | No. | 端子名  | No. | 端子名   |

|-----|-------|-----|-------|-----|------|-----|-------|

| 1   | N.C.  | 37  | N.C.  | 73  | N.C. | 109 | N.C.  |

| 2   | COM0  | 38  | SEG32 | 74  | N.C. | 110 | SEG0  |

| 3   | COM1  | 39  | SEG33 | 75  | N.C. | 111 | SEG1  |

| 4   | COM2  | 40  | SEG34 | 76  | COM4 | 112 | SEG2  |

| 5   | COM3  | 41  | SEG35 | 77  | COM5 | 113 | SEG3  |

| 6   | CA    | 42  | SEG36 | 78  | COM6 | 114 | SEG4  |

| 7   | CB    | 43  | SEG37 | 79  | COM7 | 115 | SEG5  |

| 8   | Vc1   | 44  | SEG38 | 80  | VDD  | 116 | SEG6  |

| 9   | Vc2   | 45  | SEG39 | 81  | K00  | 117 | SEG7  |

| 10  | Vc3   | 46  | SEG40 | 82  | K01  | 118 | SEG8  |

| 11  | CMPP0 | 47  | SEG41 | 83  | K02  | 119 | SEG9  |

| 12  | CMPM0 | 48  | SEG42 | 84  | K03  | 120 | SEG10 |

| 13  | SVD   | 49  | SEG43 | 85  | K10  | 121 | SEG11 |

| 14  | VSSA  | 50  | SEG44 | 86  | K11  | 122 | SEG12 |

| 15  | RFOUT | 51  | SEG45 | 87  | K12  | 123 | SEG13 |

| 16  | RFIN  | 52  | SEG46 | 88  | K13  | 124 | SEG14 |

| 17  | REF   | 53  | SEG47 | 89  | P00  | 125 | SEG15 |

| 18  | SEN0  | 54  | SEG48 | 90  | P01  | 126 | SEG16 |

| 19  | SEN1  | 55  | SEG49 | 91  | P02  | 127 | SEG17 |

| 20  | VDDA  | 56  | SEG50 | 92  | P03  | 128 | SEG18 |

| 21  | CC    | 57  | SEG51 | 93  | P10  | 129 | SEG19 |

| 22  | CD    | 58  | SEG52 | 94  | P11  | 130 | SEG20 |

| 23  | Vd2   | 59  | SEG53 | 95  | P12  | 131 | SEG21 |

| 24  | Vdd   | 60  | SEG54 | 96  | P13  | 132 | SEG22 |

| 25  | Vosc  | 61  | SEG55 | 97  | R00  | 133 | SEG23 |

| 26  | OSC1  | 62  | SEG56 | 98  | R01  | 134 | SEG24 |

| 27  | OSC2  | 63  | SEG57 | 99  | R02  | 135 | SEG25 |

| 28  | Vd1   | 64  | SEG58 | 100 | R03  | 136 | SEG26 |

| 29  | OSC3  | 65  | SEG59 | 101 | R10  | 137 | SEG27 |

| 30  | OSC4  | 66  | SEG60 | 102 | R11  | 138 | SEG28 |

| 31  | Vss   | 67  | SEG61 | 103 | R12  | 139 | SEG29 |

| 32  | TEST  | 68  | SEG62 | 104 | R13  | 140 | SEG30 |

| 33  | RESET | 69  | SEG63 | 105 | BZ   | 141 | SEG31 |

| 34  | N.C.  | 70  | N.C.  | 106 | BZ   | 142 | N.C.  |

| 35  | N.C.  | 71  | N.C.  | 107 | Vss  | 143 | N.C.  |

| 36  | N.C.  | 72  | N.C.  | 108 | N.C. | 144 | N.C.  |

N.C. : No Connection

図1.3.1 端子配置図 (QFP20-144pin)

## 1.4 端子説明

表1.4.1 端子説明

| 端子名        | 端子No.          | 入出力 | 機能                                     |

|------------|----------------|-----|----------------------------------------|

| VDD        | 24             | —   | 電源(+)端子                                |

| VSS        | 31             | —   | 電源(-)端子                                |

| VDDA       | 20             | —   | アナログ系電源(+)端子(=VDD)                     |

| VSSA       | 14             | —   | アナログ系電源(-)端子(=VSS)                     |

| VD1        | 28             | —   | 内部ロジック動作用定電圧出力端子                       |

| VD2        | 23             | —   | 1/2VDD降圧用出力端子                          |

| VOSC       | 25             | —   | OSC1発振用定電圧出力端子                         |

| VC1~VC3    | 8~10           | —   | LCD系電源端子                               |

| CA, CB     | 6, 7           | —   | LCD系昇圧コンデンサ接続端子                        |

| CC, CD     | 21, 22         | —   | 電源電圧降圧コンデンサ接続端子                        |

| OSC1       | 26             | I   | 水晶発振入力端子                               |

| OSC2       | 27             | O   | 水晶発振出力端子                               |

| OSC3       | 29             | I   | セラミックまたはCR発振入力端子(マスクオプション選択)           |

| OSC4       | 30             | O   | セラミックまたはCR発振出力端子(マスクオプション選択)           |

| K00~K03    | 81~84          | I   | 入力端子                                   |

| K10~K13    | 85~88          | I   | 入力端子                                   |

| P00        | 89             | I/O | 入出力端子(シリアルI/F SIN入力にソフト切り換え)           |

| P01        | 90             | I/O | 入出力端子(シリアルI/F SOUT出力にソフト切り換え)          |

| P02        | 91             | I/O | 入出力端子(シリアルI/F SCLK入出力にソフト切り換え)         |

| P03        | 92             | I/O | 入出力端子(シリアルI/F SRDY出力にソフト切り換え)          |

| P10~P13    | 93~96          | I/O | 入出力端子                                  |

| R00        | 97             | O   | 出力端子                                   |

| R01        | 98             | O   | 出力端子                                   |

| R02        | 99             | O   | 出力端子(TOUT信号出力にソフト切り換え)                 |

| R03        | 100            | O   | 出力端子(FOUT信号出力にソフト切り換え)                 |

| R10~R13    | 101~104        | O   | 出力端子                                   |

| COM0~COM7  | 2~5, 76~79     | O   | LCDコモン出力端子(1/4, 1/5, 1/8デューティをソフト切り換え) |

| SEG0~SEG63 | 110~141, 38~69 | O   | LCDセグメント出力端子                           |

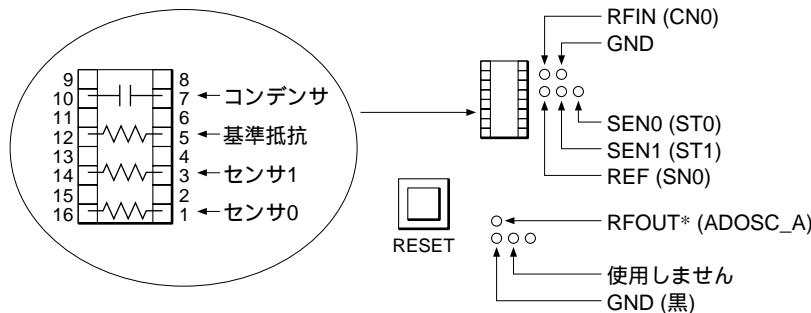

| SEN0       | 18             | O   | R/Fコンバータセンサ0 CR発振出力端子                  |

| SEN1       | 19             | O   | R/Fコンバータセンサ1 CR発振出力端子                  |

| REF        | 17             | O   | R/Fコンバータ基準抵抗用CR発振出力端子                  |

| RFIN       | 16             | I   | R/FコンバータCR発振入力端子                       |

| RFOUT      | 15             | O   | R/Fコンバータ発振周波数出力端子                      |

| CMPPO      | 11             | I   | アナログコンパレータ非反転入力端子                      |

| CMPMO      | 12             | I   | アナログコンパレータ反転入力端子                       |

| BZ         | 105            | O   | サウンド出力端子                               |

| $\bar{BZ}$ | 106            | O   | サウンド反転出力端子                             |

| SVD        | 13             | I   | SVD外部電圧入力端子                            |

| RESET      | 33             | I   | イニシャルリセット入力端子                          |

| TEST       | 32             | I   | テスト用入力端子                               |

## 1.5 マスクオプション

S1C63666には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択にはS1C63666の開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogおよびセグメントオプションジェネレータwinsogを使用します。これらのオプションジェネレータによって作成したデータをもとに最終的なICのマスクパターン生成が行われます。winfog、winsogについては"S5U1C63000A Manual"を参照してください。

### マスクオプションの概要

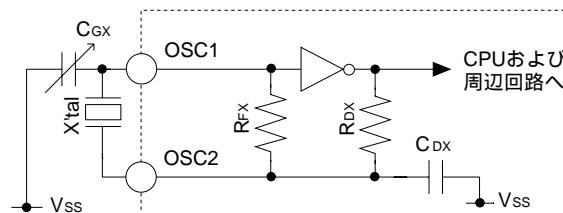

#### (1)OSC1発振回路

OSC1発振回路は、水晶発振回路に固定されています。詳細については"4.4.2 OSC1発振回路"を参照してください。

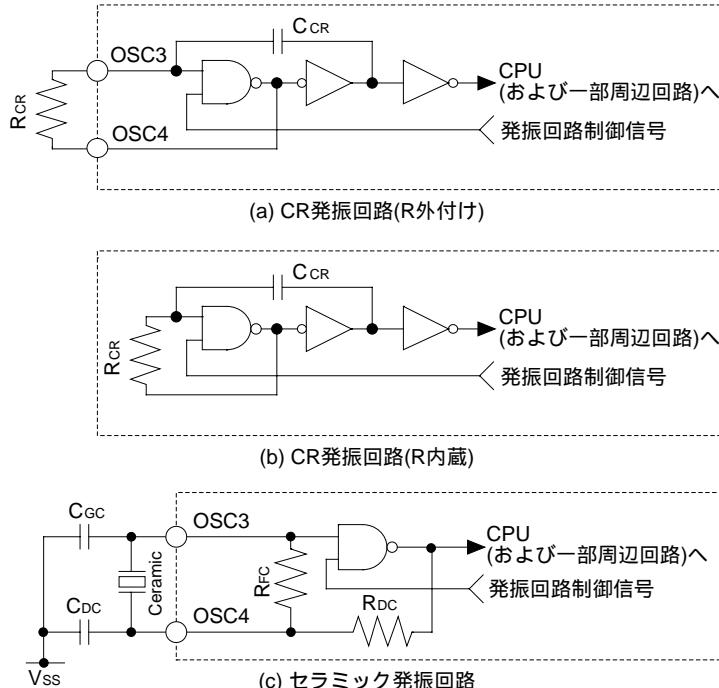

#### (2)OSC3発振回路

OSC3発振回路としてセラミック発振回路、CR発振回路( R外付け )またはCR発振回路( R内蔵 )が選択できます。詳細については"4.4.3 OSC3発振回路"を参照してください。

#### (3)SVD回路の外部電圧検出

電源電圧( VDD端子 - Vss端子 )の低下検出以外に外部電圧( SVD端子 - Vss端子 )の低下検出を選択できます。この外部電圧はSVD端子より入力します。詳細については"4.17.2 マスクオプション"を参照してください。

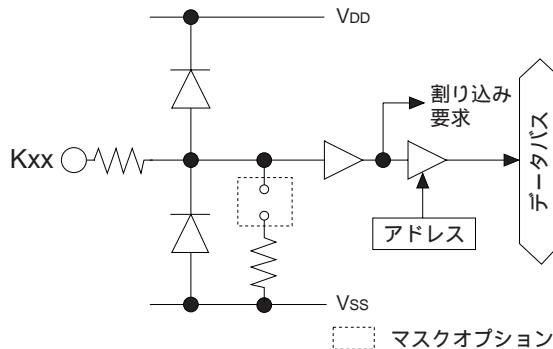

#### (4)入力ポートプルダウン抵抗

入力ポートにプルダウン抵抗を付加するかしないか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"4.5.3 マスクオプション"を参照してください。

#### (5)RESET端子プルダウン抵抗

RESET端子にプルダウン抵抗を付加するかしないか選択できます。詳細については"2.2.1 リセット端子( RESET )"を参照してください。

#### (6)入出力兼用ポートプルダウン抵抗

入出力兼用ポートP00～P03、P10～P13が入力モード時に働くプルダウン抵抗を付加するかしないか選択できます。選択は1ビット単位で行います。詳細については"4.7.2 マスクオプション"を参照してください。

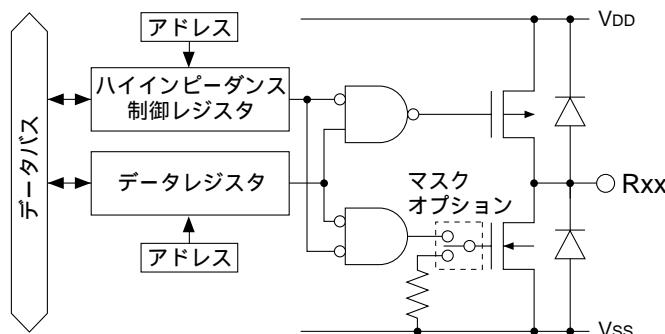

#### (7)出力ポートの出力仕様

出力ポートR00～R03、R10～R13の出力仕様として、コンプリメンタリ出力またはPチャンネルオープンドライン出力が選択できます。選択は1ビット単位で行います。詳細については"4.6.2 マスクオプション"を参照してください。

#### (8)入出力兼用ポートの出力仕様

入出力兼用ポートP00～P03、P10～P13が出力モードの際の出力仕様として、コンプリメンタリ出力またはPチャンネルオープンドライン出力が選択できます。選択は1ビット単位で行います。詳細については"4.7.2 マスクオプション"を参照してください。

#### (9)入力ポート( K00～K03 )同時HIGH入力による外部リセット

この機能は、複数キーの同時押しによってICをリセットするもので、この機能を使用するかしないかをマスクオプションで選択できます。また、使用する場合は、同時に押すキーを接続する入力ポート( K00～K03 )の組み合わせを選択します。詳細については"2.2.2 入力ポート( K00～K03 )の同時HIGH入力"を参照してください。

## ( 10 )入力ポート同時HIGH入力リセットの時間検定回路

( 9 )の外部リセット機能を使用する場合は、"時間検定回路を使用する"が選択されます。時間検定回路を使用すると、規定時間以上の同時HIGH入力があった場合のみ、リセット機能が働きます。外部リセット機能を使用しない場合、時間検定回路は使用できません。詳細については"2.2.2 入力ポート( K00 ~ K03 )の同時HIGH入力"を参照してください。

## ( 11 )シリアルインターフェースの同期クロック極性

シリアルインターフェースの同期クロックSCLKおよびスレーブモード時のSRDY信号の極性を正極性とするか負極性とするか選択できます。詳細については"4.12.2 マスクオプション"を参照してください。

## ( 12 )LCD駆動電源

LCD駆動用電源として、内蔵電源回路を使用するか外部電源を使用するか選択できます。

詳細については"4.8.2 LCD駆動電源"を参照してください。

## ( 13 )LCDセグメント仕様

SEG端子に対する表示メモリの割り付け、DC出力として使用するSEG端子の設定が行えます。

詳細については"4.8.5 セグメントオプション"を参照してください。

## オプションリスト

S1C63666のオプションリストを以下に示します。各オプション項目には、複数の選択肢が用意されていますので、システムに合った内容を選択し、印を付けてください。なお、使用しない機能についても必ず選択してください。

## 1. OSC1発振回路( OSC1 System Clock )

- 1. 水晶

## 2. OSC3発振回路( OSC3 System Clock )

- 1. CR( R内蔵 )

- 2. CR( R外付け )

- 3. セラミック

## 3. SVD回路外部電圧検出( SVD External Voltage Detection )

- 1. 使用しない

- 2. 使用する

## 4. 入力ポートプルダウン抵抗( Input Port Pull Down Resistor )

|           |       |       |

|-----------|-------|-------|

| K00 ..... | 1. あり | 2. なし |

| K01 ..... | 1. あり | 2. なし |

| K02 ..... | 1. あり | 2. なし |

| K03 ..... | 1. あり | 2. なし |

| K10 ..... | 1. あり | 2. なし |

| K11 ..... | 1. あり | 2. なし |

| K12 ..... | 1. あり | 2. なし |

| K13 ..... | 1. あり | 2. なし |

## 5. RESET端子プルダウン抵抗( Reset Port Pull Down Resistor )

- |             |       |       |

|-------------|-------|-------|

| RESET ..... | 1. あり | 2. なし |

|-------------|-------|-------|

## 6. I/Oポートプルダウン抵抗( I/O Port Pull Down Resistor )

|           |       |       |

|-----------|-------|-------|

| P00 ..... | 1. あり | 2. なし |

| P01 ..... | 1. あり | 2. なし |

| P02 ..... | 1. あり | 2. なし |

| P03 ..... | 1. あり | 2. なし |

| P10 ..... | 1. あり | 2. なし |

| P11 ..... | 1. あり | 2. なし |

| P12 ..... | 1. あり | 2. なし |

| P13 ..... | 1. あり | 2. なし |

## 7. 出力ポート出力仕様( Output Port Output Specification )

|           |             |                |

|-----------|-------------|----------------|

| R00 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R01 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R02 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R03 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R10 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R11 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R12 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| R13 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

## 8. I/Oポート出力仕様( I/O Port Output Specification )

|           |             |                |

|-----------|-------------|----------------|

| P00 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P01 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P02 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P03 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P10 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P11 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P12 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

| P13 ..... | 1. コンプリメンタリ | 2. Pchオープンドレイン |

## 9. キー同時押しリセット組み合わせ( Multiple Key Entry Reset Combination )

1. 使用しない

2. 使用する <K00, K01>

3. 使用する <K00, K01, K02>

4. 使用する <K00, K01, K02, K03>

## 10. キー同時押しリセット時間検定( Multiple Key Entry Reset Time Authorize )

1. 使用しない

2. 使用する

## 11. シリアルインターフェース極性( SIO Sync Clock &amp; SRDY )

1. 負極性

2. 正極性

## 12. LCD駆動電源( LCD Driving Power )

1. 内部電源( 3.0V/パネル )

2. 外部電源 1/3/バイアス,  $V_{DD}=V_{C2}$ ( 4.5V/パネル )

3. 外部電源 1/3/バイアス,  $V_{DD}=V_{C3}$ ( 3.0V/パネル )

4. 外部電源 1/2/バイアス,  $V_{DD}=V_{C3}$ ,  $V_{C1}=V_{C2}$ ( 3.0V/パネル )

## 13. セグメントオプション

| 端子名   | アドレス (F0xx) |   |   |      |   |   |      |   |   |      |   |   |      |   | 出力仕様 |      |   |   |      |   |   |                                                            |

|-------|-------------|---|---|------|---|---|------|---|---|------|---|---|------|---|------|------|---|---|------|---|---|------------------------------------------------------------|

|       | COM0        |   |   | COM1 |   |   | COM2 |   |   | COM3 |   |   | COM4 |   |      | COM5 |   |   | COM6 |   |   |                                                            |

|       | H           | L | D | H    | L | D | H    | L | D | H    | L | D | H    | L | D    | H    | L | D | H    | L | D |                                                            |

| SEG0  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG1  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG2  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG3  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG4  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG5  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG6  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG7  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG8  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG9  |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG10 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG11 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG12 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG13 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG14 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG15 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG16 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG17 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG18 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG19 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG20 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG21 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG22 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG23 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG24 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG25 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG26 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG27 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG28 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG29 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG30 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG31 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG32 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG33 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG34 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG35 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG36 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG37 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG38 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG39 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG40 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG41 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG42 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG43 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG44 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG45 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG46 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG47 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG48 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG49 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG50 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG51 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG52 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG53 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG54 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG55 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG56 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG57 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG58 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG59 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG60 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG61 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

| SEG62 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | SEG出力 <input type="checkbox"/> S                           |

| SEG63 |             |   |   |      |   |   |      |   |   |      |   |   |      |   |      |      |   |   |      |   |   | DC出力 <input type="checkbox"/> C <input type="checkbox"/> N |

アドレス H: RAMデータ上位アドレス (0~9)

L: RAMデータ下位アドレス (0~F)

D: データビット (0~3)

出力仕様 S: セグメント出力

C: コンプリメンタリ出力

N: Nchオープンドレイン出力

## 2 電源系 および イニシャルリセット

### 2.1 電源系

S1C63666の動作電源電圧は次のとおりです。

| 動作モード | 最大動作周波数       | 動作電源電圧      |

|-------|---------------|-------------|

| 通常モード | 4MHz(OSC3)    | 2.4V ~ 3.6V |

| 降圧モード | 32kHz(OSC1のみ) | 2.4V ~ 3.6V |

| 通常モード | 32kHz(OSC1のみ) | 1.5V ~ 3.6V |

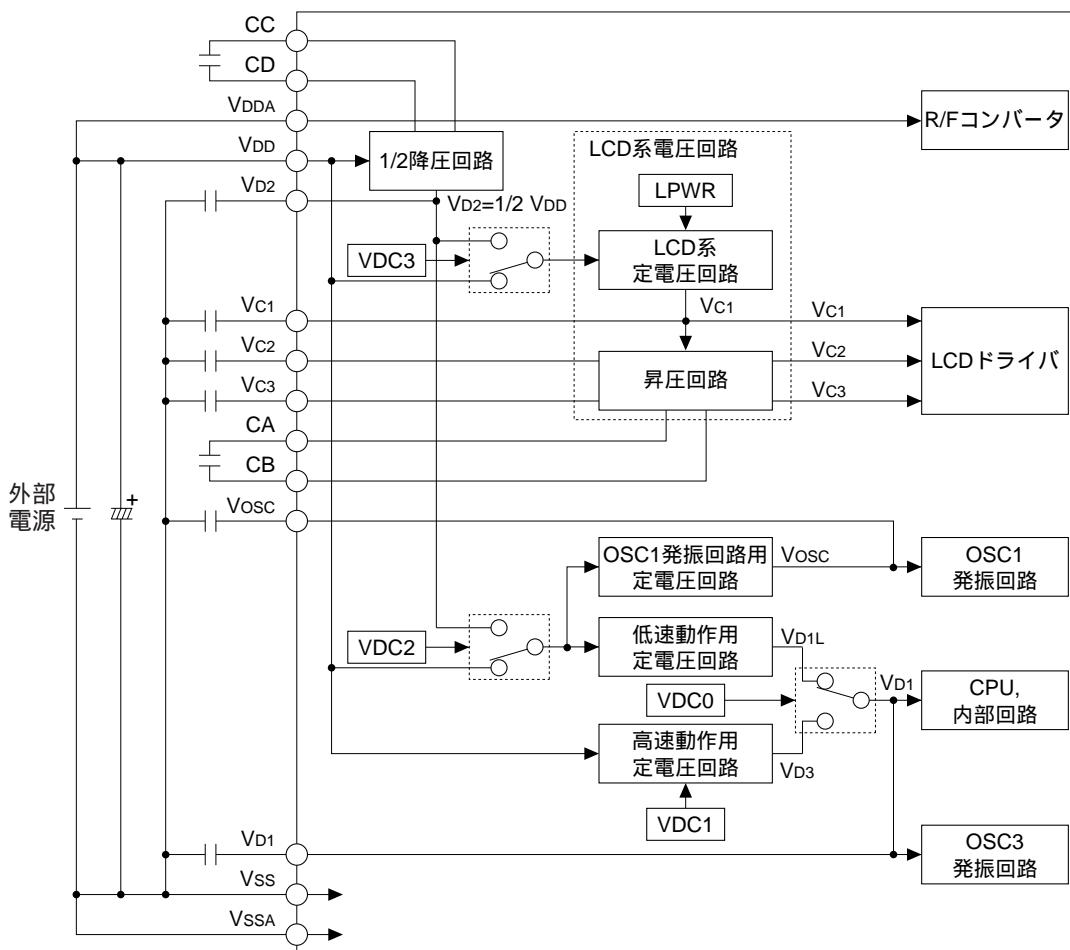

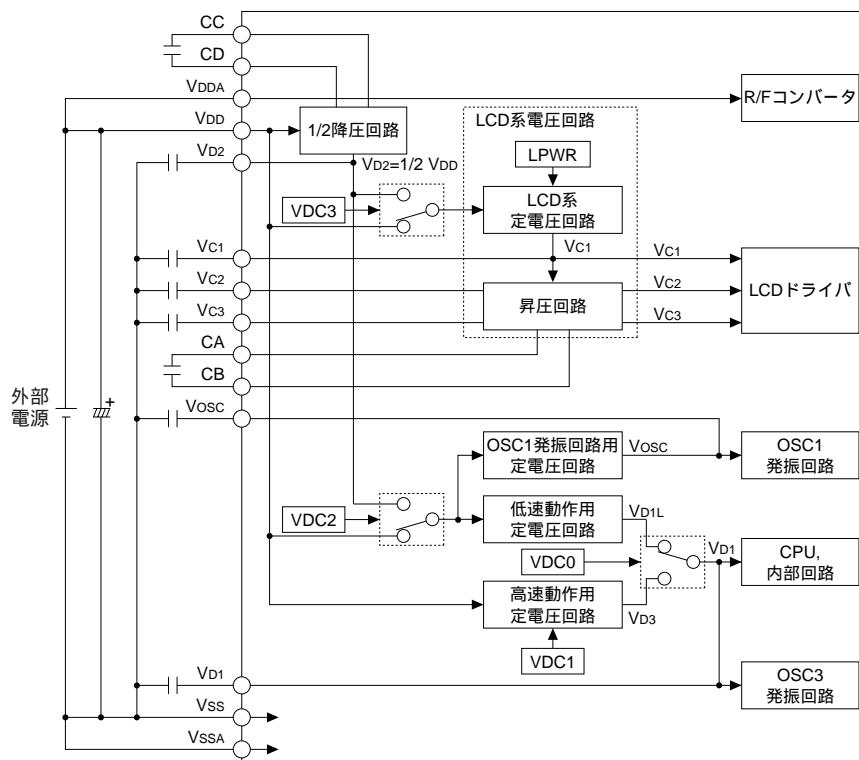

S1C63666は上記範囲の単一電源をVDD - VSS間に与えることにより動作し、内部動作に必要な電圧を内蔵の電源回路によりIC自身で発生します。

| 回路系                | 電源回路           | 出力電圧      |

|--------------------|----------------|-----------|

| OSC1発振回路           | OSC1発振回路用定電圧回路 | Vosc      |

| 内部回路(低速動作時)        | 低速用定電圧回路       | Vd1L      |

| OSC3発振、内部回路(高速動作時) | 高速用定電圧回路       | Vd3       |

| LCDドライバ            | LCD系電圧回路       | Vc1 ~ Vc3 |

- 注:

- 内部電源回路の出力電圧による外付け負荷の駆動は禁止します。

- 電圧値、駆動能力については"7 電気的特性"を参照してください。

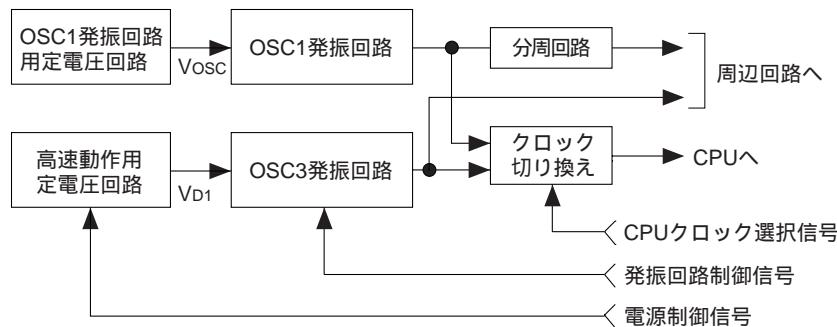

図2.1.1 電源系の構成

### 2.1.1 OSC1発振回路用定電圧回路

OSC1発振回路用定電圧回路は、OSC1発振回路の動作電圧 $V_{osc}$ ( 0.98V Typ. )を発生します。

この定電圧回路は常時動作します。

### 2.1.2 低速動作用定電圧回路

低速動作用定電圧回路は、内部ロジック回路の低速動作用の電圧 $V_{D1L}$ ( 1.25V Typ. )を発生します。

この定電圧回路は常時動作し、OSC1クロック( 32kHz )で動作させる場合に、CPUおよび内部ロジック回路の動作電圧を供給します。

### 2.1.3 高速動作用定電圧回路

高速動作用定電圧回路は、OSC3発振回路および内部ロジック回路の高速動作用の電圧 $V_{D3}$ ( 2.0V Typ. )を発生します。

この定電圧回路は通常停止しており、高速動作を開始する前にソフトウェアでONにします。

制御方法については"4.4 発振回路"を参照してください。

### 2.1.4 内部動作電圧 $V_{D1}$

CPUとその他の内部ロジック回路は内部動作電圧 $V_{D1}$ で動作します。

S1C63666はツインクロック仕様となっており、2種類の発振回路OSC1( 低速動作用 )およびOSC3( 高速動作用 )を内蔵しています。通常動作時はOSC1クロックを使用し、高速動作が必要など時にソフトウェアによってOSC3クロックに切り替えます。その際には、発振回路およびそれぞれのクロックによる内部回路の動作を安定させるため、動作電圧の値もソフトウェアによって切り換える必要があります。

低速動作時は低速動作用定電圧回路が output する $V_{D1L}$ を $V_{D1}$ として使用し、高速動作時は高速動作用定電圧回路が output する $V_{D3}$ を $V_{D1}$ として使用します。

制御方法については"4.4 発振回路"を参照してください。

### 2.1.5 LCD系電圧回路

LCD系電圧回路はLCD駆動電圧を発生します。この電圧回路はソフトウェア制御が可能で、LCDの表示を開始する前にONにします。

LCD系電圧回路は、その中の定電圧回路によって $V_{C1}$ を発生し、その電圧を昇圧して他の2電位( $V_{C2} = 2V_{C1}$ 、 $V_{C3} = 3V_{C1}$ )を発生します。 $V_{C1}$ 電圧値はソフトウェアによって16段階( 0.95V ~ 1.40V )に調整可能です。

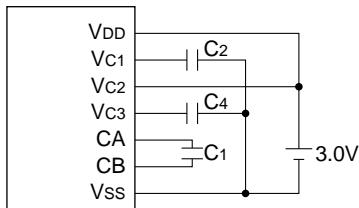

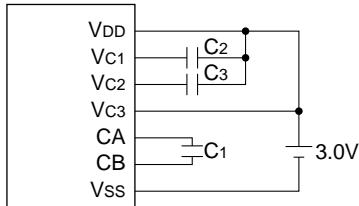

マスクオプションによりLCD系定電圧回路を使用しない構成にすることもできます。この場合、LCD系定電圧回路用のコンデンサが不要となりますので、外付け素子を削減できます。ただし、LCD系定電圧回路を使用しない場合には、使用する場合に比べて電源電圧変動( 低下 )時のLCDの表示品質が劣化します。

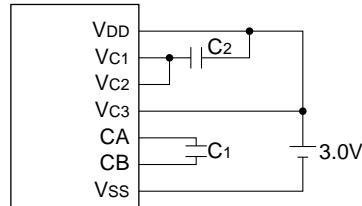

図2.1.5.1にLCD系定電圧回路を使用しない場合の外付け部品の構成を示します。

4.5V LCDパネル

1/8, 1/5または1/4デューティ, 1/3バイアス

3V LCDパネル

1/8, 1/5または1/4デューティ, 1/3バイアス

3V LCDパネル

1/8, 1/5または1/4デューティ, 1/2バイアス

図2.1.5.1 LCD系定電圧回路を使用しない場合の外付け部品の構成

LCD駆動電圧の制御方法については"4.8 LCDドライバ"を参照してください。

### 2.1.6 降圧モードとパワーセーブ

電源電圧VDDが2.4V以上の場合、VDDを1/2に降圧して低速動作用低電圧回路とLCD系電圧回路を駆動させることができます。この状態が降圧モードで、HALT時や低速動作時の消費電流を低減できます。イニシャルリセット直後はVDDを使用する通常モードに設定されますので、ソフトウェアで必要に応じて降圧モードに切り替えます。降圧モードはOSC1クロックによる低速動作に対応しており、OSC3クロックによる高速動作時に設定することはできません。

低速動作用低電圧回路とLCD系電圧回路は、それぞれ個別に降圧モードに設定可能です。

降圧モードの制御方法については"4.2 電源制御"を参照してください。

### 2.1.7 アナログ回路用電源

R/FコンバータのVDDA、VSSAは、ノイズによる変換精度への影響を低減するための専用電源端子です。ただし、入力する電圧値は、VDD、Vssと同じにしてください。

$$VDDA = VDD, VSSA = Vss$$

## 2.2 イニシャルリセット

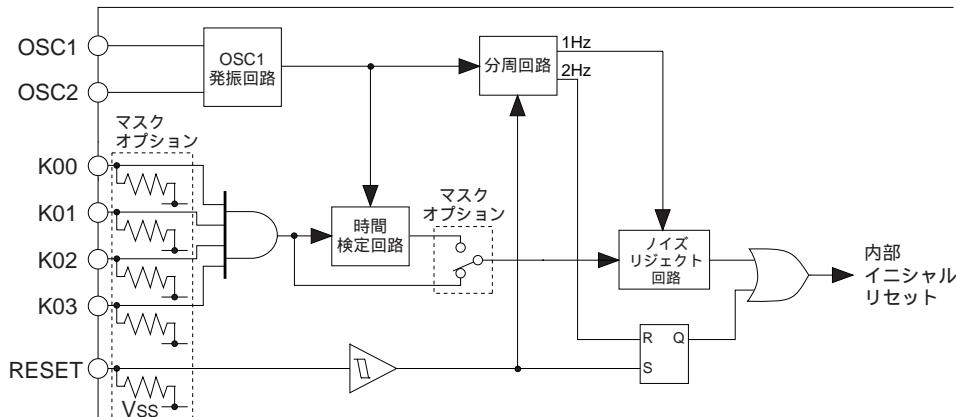

S1C63666は回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては次の2種類があります。

- (1)RESET端子による外部イニシャルリセット

- (2)K00～K03端子の同時HIGHレベル入力による外部イニシャルリセット(マスクオプションで設定)

- (1)または(2)のいずれかにより回路が初期化されます。電源投入時は必ずこのリセット機能を使用し、確実に初期化する必要があります。電源投入のみでは回路が正しく初期化される保証はありません。

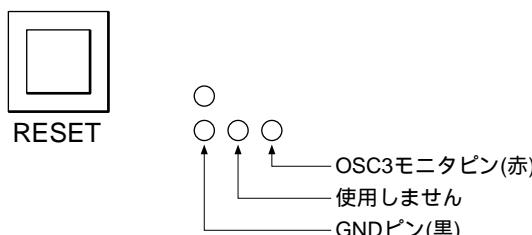

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

### 2.2.1 リセット端子( RESET )

外部よりリセット端子をHIGHレベル( V<sub>DD</sub> )にすることによりイニシャルリセットが行えます。

その後、リセット端子をLOWレベル( V<sub>SS</sub> )にすることによりイニシャルリセットは解除され、CPUが動作を開始します。

リセット入力信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチはOSC1クロックを分周した2Hz信号( HIGH )で解除されるようになっています。したがって、通常動作時はリセット端子がLOWレベルになった後、内部イニシャルリセットが解除されるまで、最大250msec( fosc1=32.768kHz時 )の時間を要します。

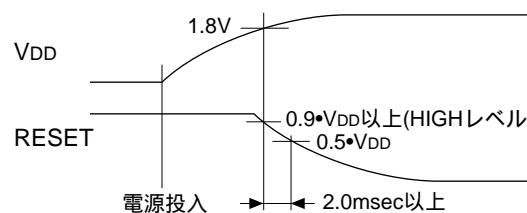

確実にイニシャルリセットを行うために、リセット入力は最低0.1msec以上、HIGHレベルを保ってください。ただし、電源投入については図2.2.1.1に示すタイミングでリセット端子をHIGHレベルにしてください。100nsec以下のリセット入力は、ノイズとして除去されます。

図2.2.1.1 電源投入時のイニシャルリセット

電源電圧が1.8V以上になるまで、リセット端子を0.9・V<sub>DD</sub>以上( HIGHレベル )とします。

その後2.0msec以上、0.5・V<sub>DD</sub>以上のレベルを保持します。

リセット端子にはプルダウン抵抗が組み込まれており、これを使用するかしないかをマスクオプションで選択することができます。

### 2.2.2 入力ポート( K00 ~ K03 )の同時HIGH入力

マスクオプションで選択された入力ポート( K00 ~ K03 )に、外部から同時にHIGH入力を与えることによりイニシャルリセットが行えます。このイニシャルリセットはノイズリジェクト回路を通るため、動作中は1.5msec( 発振周波数fOSC1=32.768kHzの場合 )以上、指定入力ポート端子をHIGHレベルに保ってください。また、電源投入時には発振が停止しているため、ノイズリジェクト回路は動作しません。このため、発振開始後、さらに1.5msec( 発振周波数fOSC1=32.768kHzの場合 )以上、指定入力ポート端子をHIGHレベルに保ってください。表2.2.2.1にマスクオプションで選択できる入力ポート( K00 ~ K03 )の組合せを示します。

表2.2.2.1 入力ポートの組合せ

|   |                 |

|---|-----------------|

| 1 | 使用しない           |

| 2 | K00*K01         |

| 3 | K00*K01*K02     |

| 4 | K00*K01*K02*K03 |

たとえば、マスクオプションで4の"K00\*K01\*K02\*K03"を選択した場合、K00 ~ K03の4ポートの入力が同時にHIGHレベルになったときにイニシャルリセットを行います。2または3の場合は、選択した入力ポートの組合せが含まれるキー入力が行われたときにイニシャルリセットがかかります。

また、このリセット機能を選択すると、同時HIGH入力の入力時間を検定し、規定時間( 1 ~ 2秒 )以上の入力があったときにイニシャルリセットを行う時間検定回路のマスクオプションも同時に選択されます。

なお、このリセット機能を使用する場合、通常動作時に指定ポートが同時にHIGHレベルにならないように注意してください。

### 2.2.3 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは表2.2.3.1のように初期化されます。

イニシャルリセットによって初期化されないレジスタ、フラグは必要に応じてプログラムで初期化する必要があります。

特にスタックポインタSP1およびSP2は必ずペアで設定してください。イニシャルリセット後は、SP1、SP2両方のスタックポインタがソフトウェアにより設定されるまでNMIを含むすべての割り込みがマスクされます。

EXTレジスタにデータを書き込むとEフラグがセットされ、次の命令が拡張アドレッシングモードで実行されます。そこに拡張アドレッシングが禁止されている命令を使用した場合、動作が保証されません。したがって、EXTレジスタの初期化のみを目的としたデータ書き込みは行わないでください。

拡張アドレッシングと使用可能な命令については"S1C63000コアCPUマニュアル"を参照してください。

表2.2.3.1 初期設定値

| CPUコア       |     |      |       |

|-------------|-----|------|-------|

| 名 称         | 記号  | ビット長 | 設定値   |

| データレジスタA    | A   | 4    | 不定    |

| データレジスタB    | B   | 4    | 不定    |

| 拡張レジスタEXT   | EXT | 8    | 不定    |

| インデックスレジスタX | X   | 16   | 不定    |

| インデックスレジスタY | Y   | 16   | 不定    |

| プログラムカウンタ   | PC  | 16   | 0110H |

| スタックポインタSP1 | SP1 | 8    | 不定    |

| スタックポインタSP2 | SP2 | 8    | 不定    |

| ゼロフラグ       | Z   | 1    | 不定    |

| キャリーフラグ     | C   | 1    | 不定    |

| インタラプトフラグ   | I   | 1    | 0     |

| 拡張フラグ       | E   | 1    | 0     |

| キューレジスタ     | Q   | 16   | 不定    |

| 周辺回路     |      |     |

|----------|------|-----|

| 名 称      | ビット長 | 設定値 |

| RAM      | 4    | 不定  |

| 表示メモリ    | 4    | 不定  |

| その他の周辺回路 | -    | *   |

\* "4.1 メモリマップ"参照

### 2.2.4 イニシャルリセット時の端子設定

S1C63666の出力ポート(R)端子、入出力兼用ポート(P)端子は特殊出力端子やシリアルインターフェースの入出力端子と兼用されており、それらの機能をソフトウェアで選択するようになっています。イニシャルリセット時、各端子はすべてが汎用出力ポート端子、汎用入出力兼用ポート端子として設定されますので、アプリケーションの初期化ルーチンでシステムに合った設定を行ってください。また、システム設計の際には、出力端子の初期状態にも注意してください。

表2.2.4.1に兼用端子設定の一覧を示します。

表2.2.4.1 兼用端子設定一覧

| 端子名     | イニシャルリセット時の<br>端子状態 | 特殊出力使用時 |      | シリアルI/F使用時 |         |

|---------|---------------------|---------|------|------------|---------|

|         |                     | TOUT    | FOUT | Master     | Slave   |

| R00     | R00 (LOW出力)         |         |      |            |         |

| R01     | R01 (LOW出力)         |         |      |            |         |

| R02     | R02 (LOW出力)         | TOUT    |      |            |         |

| R03     | R03 (LOW出力)         |         | FOUT |            |         |

| R10~R13 | R10~R13 (LOW出力)     |         |      |            |         |

| P00~P03 | P00~P03 (入力&プルダウン*) |         |      |            |         |

| P10     | P10 (入力&プルダウン*)     |         |      | SIN(I)     | SIN(I)  |

| P11     | P11 (入力&プルダウン*)     |         |      | SOUT(O)    | SOUT(O) |

| P12     | P12 (入力&プルダウン*)     |         |      | SCLK(O)    | SCLK(I) |

| P13     | P13 (入力&プルダウン*)     |         |      |            | SRDY(O) |

\* マスクオプションにて"プルダウンあり"選択時

( "プルダウンなし"選択時はハイインピーダンス )

機能の設定方法については各周辺回路の説明を参照してください。

### 2.3 テスト端子(TEST)

ICの出荷検査時に使用する端子です。通常動作時はTESTをVssに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C63666はCPU部分に4ビットコアCPU S1C63000を使用しています。

S1C63000については"S1C63000コアCPUマニュアル"を参照してください。

注: S1C63666においては、SLEEP動作を想定していないため、SLP命令は使用できません。

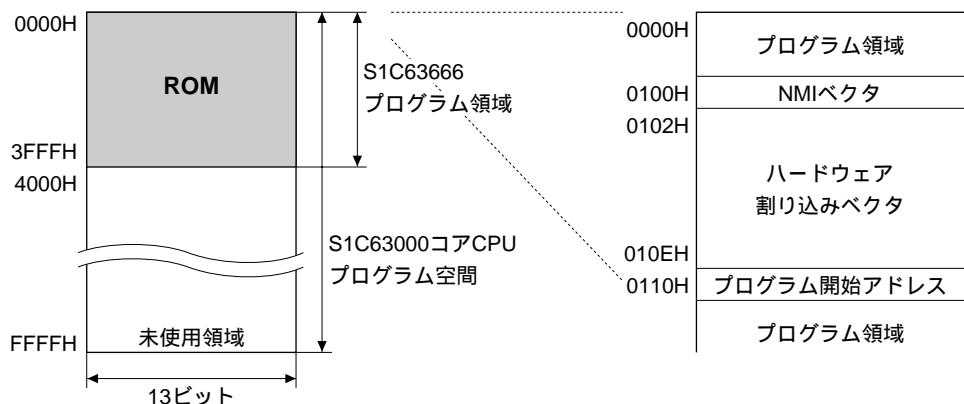

### 3.2 コードROM

内蔵コードROMはプログラム格納用のマスクROMで、16,384ステップ × 13ビットの容量があります。コアCPUのプログラム領域は0000H～FFFFHステップまでリニアにアクセス可能ですが、S1C63666では、このうち0000H～3FFFHステップがプログラム領域となります。イニシャルリセット後のプログラム開始番地が0110Hステップ、ノンマスカブル割り込み(NMI)ベクタが0100H、ハードウェア割り込みベクタが0102H～010EHステップに割り当てられています。

図3.2.1 コードROMの構成

### 3.3 RAM

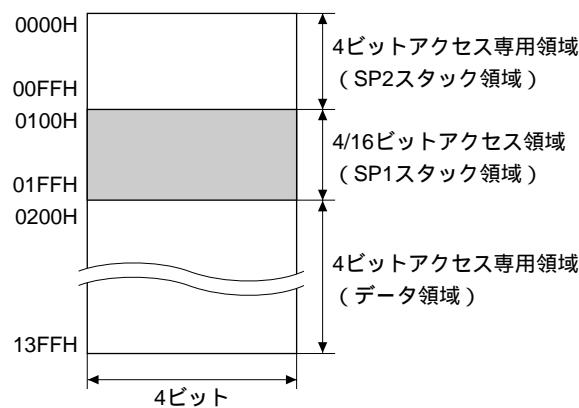

RAMは種々のデータを格納するデータメモリで、5,120ワード × 4ビットの容量があります。

RAM領域は、データメモリマップ上のアドレス0000H～13FFHに割り当てられています。

この中でアドレス0100H～01FFHが4ビット/16ビットデータアクセスが可能な領域、その他の領域は4ビットデータアクセスのみ可能な領域となっています。

プログラミングの際には以下の点に注意してください。

- (1)データメモリの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データ領域とスタック領域が重ならないように注意してください。

- (2)S1C63000コアCPUは、4ビットデータ用スタックポインタ(SP2)および16ビットデータ用スタックポインタ(SP1)によりスタック処理を行います。SP1によるスタック処理では16ビットデータアクセスが行われますので、このスタック領域の設定は4ビット/16ビットアクセスが可能な領域内(0100H～01FFH)で行ってください。スタックポインタは、SP1が0000H～03FFH、SP2が0000H～00FFHの範囲でサイクリックに動作します。このため、SP1はS1C63666の4ビット/16ビットアクセス領域を外れた0200H以上、あるいは00FFH以下の領域にも設定される可能性がありますので注意してください。SP1によるスタック操作以外のメモリアクセスは4ビットデータアクセスとなります。

- また、イニシャルリセット時は、スタックポインタSP1、SP2の両方がソフトウェアで設定されるまでNMIを含むすべての割り込みがマスクされます。また、SP1、SP2を設定後どちらか一方を再設定すると、もう一方が再設定されるまでNMIを含む割り込みは再びマスクされます。したがって、SP1およびSP2の設定は必ずペアで行ってください。

(3) サブルーチンコールでは16ビットデータ用スタック( SP1 )を4ワード( PCの退避 )消費します。

割り込みでは16ビットデータ用スタックエリアを4ワード( PCの退避 )、4ビットデータ用スタックエリアを1ワード( レジスタの退避 )消費します。

図3.3.1 データRAMの構成

### 3.4 データROM

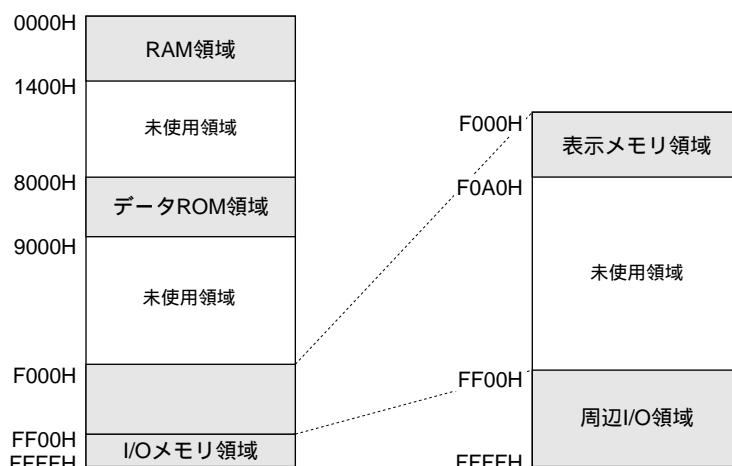

データROMはキャラクタジェネレータなどの各種固定データ格納用のマスクROMで、4,096ワード×4ビットの容量があります。データメモリマップ上のアドレス8000H～8FFFHに割り当てられており、RAMと同様にデータメモリアクセス命令でデータを読み出すことができます。

## 4 周辺回路と動作

S1C63666の周辺回路( タイマ、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

### 4.1 メモリマップ

S1C63666のデータメモリは5,120ワードのRAM、4,096ワードのデータROM、160ワードの表示メモリ、92ワードの周辺I/Oメモリで構成されます。

図4.1.1にS1C63666の全体のメモリマップ、表4.1.1に周辺回路( I/O空間 )のメモリマップを示します。

図4.1.1 メモリマップ

注：メモリマップの未使用領域にはメモリが実装されていません。また、周辺I/O領域にも非実装領域、未使用（アクセス禁止）領域が存在します。これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

周辺I/O領域については表4.1.1に示すI/Oメモリマップを参照してください。

表4.1.1(a) I/Oメモリマップ(FF00H~FF31H)

| アドレス  | レジスタ   |        |        |        | Name     | Init *1 | 1                  | 0                | 注釈                                                |   |   |   |   |   |

|-------|--------|--------|--------|--------|----------|---------|--------------------|------------------|---------------------------------------------------|---|---|---|---|---|

|       | D3     | D2     | D1     | D0     |          |         |                    |                  |                                                   |   |   |   |   |   |

| FF00H | VDC3   | VDC2   | VDC1   | VDC0   | VDC3     | 0       | 1/2V <sub>DD</sub> | V <sub>DD</sub>  | LCD系定電圧回路電源切り換え                                   |   |   |   |   |   |

|       |        |        |        |        | VDC2     | 0       | 1/2V <sub>DD</sub> | V <sub>DD</sub>  | 低速動作用定電圧回路電源切り換え                                  |   |   |   |   |   |

|       |        |        |        |        | VDC1     | 0       | On                 | Off              | 高速動作用定電圧回路On/Off                                  |   |   |   |   |   |

|       |        |        |        |        | VDC0     | 0       | V <sub>D3</sub>    | V <sub>D1L</sub> | ロジック系電源切り換え                                       |   |   |   |   |   |

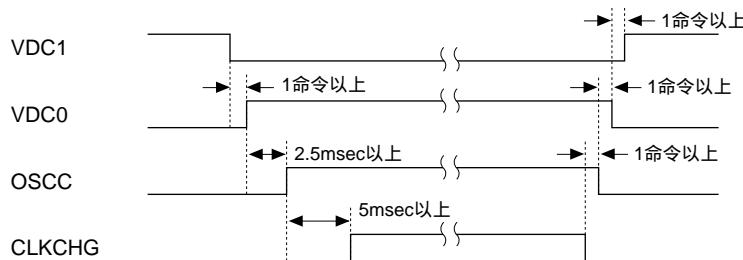

| FF01H | CLKCHG | OSCC   | 0      | 0      | CLKCHG   | 0       | OSC3 On            | OSC1 Off         | CPUクロック切り換え<br>OSC3発振On/Off                       |   |   |   |   |   |

|       |        |        |        |        | OSCC     | 0       | - *2               |                  | 未使用                                               |   |   |   |   |   |

|       |        |        | R/W    | R      | 0 *3     | - *2    |                    |                  | 未使用                                               |   |   |   |   |   |

|       |        |        |        |        | 0 *3     | - *2    |                    |                  | SVD比較電圧                                           |   |   |   |   |   |

| FF04H | 0      | SVDS2  | SVDS1  | SVDS0  | SVDS2    | 0       | [SVDS2~0] 0        | 1                | 2                                                 | 3 | 4 | 5 | 6 | 7 |

|       | R      |        | R/W    |        | SVDS1    | 0       |                    |                  |                                                   |   |   |   |   |   |

|       |        |        |        |        | SVDS0    | 0       |                    |                  |                                                   |   |   |   |   |   |

|       |        |        |        |        |          |         |                    |                  |                                                   |   |   |   |   |   |

| FF05H | CMPON  | CMPDPT | SVDDT  | SVDON  | CMPON    | 0       | On                 | Off              | アナログコンパレータOn/Off                                  |   |   |   |   |   |

|       |        |        |        |        | CMPDPT   | 0       | + > -              |                  | アナログコンパレータデータ                                     |   |   |   |   |   |

|       |        |        | R/W    | R/W    | SVDDT    | 0       | Low                | Normal           | SVD検出データ                                          |   |   |   |   |   |

|       |        |        |        |        | SVDON    | 0       | On                 | Off              | SVD回路On/Off                                       |   |   |   |   |   |

| FF06H | FOUTE  | SWDIR  | FOFQ1  | FOFQ0  | FOUTE    | 0       | Enable             | Disable          | FOUT出力イネーブル                                       |   |   |   |   |   |

|       |        |        |        |        | SWDIR    | 0       |                    |                  | ストップウォッチダイレクト入力切り換え                               |   |   |   |   |   |

|       |        |        | R/W    | R/W    | FOFQ1    | 0       |                    |                  | 0: K00=Run/Stop, K01=Lap 1: K00=Lap, K01=Run/Stop |   |   |   |   |   |

|       |        |        |        |        | FOFQ0    | 0       |                    |                  | FOUT [FOFQ1, 0] 0 1 2 3                           |   |   |   |   |   |

| FF07H | 0      | 0      | WDEN   | WDRST  | 0 *3     | - *2    |                    |                  | 周波数選択                                             |   |   |   |   |   |

|       | R      |        | R/W    | W      | 0 *3     | - *2    |                    |                  | fosc1/64 fosc1/8 fosc1 fosc3                      |   |   |   |   |   |

|       |        |        |        |        | WDEN     | 1       | Enable             | Disable          | 未使用                                               |   |   |   |   |   |

|       |        |        |        |        | WDRST *3 | Reset   | Reset              | Invalid          | 未使用                                               |   |   |   |   |   |

| FF20H | SIK03  | SIK02  | SIK01  | SIK00  | SIK03    | 0       | Enable             | Disable          | K00 ~ K03割り込み選択レジスタ                               |   |   |   |   |   |

|       |        |        |        |        | SIK02    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

|       |        |        | R/W    |        | SIK01    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

|       |        |        |        |        | SIK00    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

| FF21H | K03    | K02    | K01    | K00    | K03      | - *2    | High               | Low              | K00 ~ K03入力ポートデータ                                 |   |   |   |   |   |

|       |        |        |        |        | K02      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

|       |        |        | R      |        | K01      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

|       |        |        |        |        | K00      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

| FF22H | KCP03  | KCP02  | KCP01  | KCP00  | KCP03    | 1       | ↑                  | ↑                | K00 ~ K03入力比較レジスタ                                 |   |   |   |   |   |

|       |        |        |        |        | KCP02    | 1       | ↓                  | ↓                |                                                   |   |   |   |   |   |

|       |        |        | R/W    |        | KCP01    | 1       | ↑                  | ↓                |                                                   |   |   |   |   |   |

|       |        |        |        |        | KCP00    | 1       | ↓                  | ↑                |                                                   |   |   |   |   |   |

| FF24H | SIK13  | SIK12  | SIK11  | SIK10  | SIK13    | 0       | Enable             | Disable          | K10 ~ K13割り込み選択レジスタ                               |   |   |   |   |   |

|       |        |        |        |        | SIK12    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

|       |        |        | R/W    |        | SIK11    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

|       |        |        |        |        | SIK10    | 0       | Enable             | Disable          |                                                   |   |   |   |   |   |

| FF25H | K13    | K12    | K11    | K10    | K13      | - *2    | High               | Low              | K10 ~ K13入力ポートデータ                                 |   |   |   |   |   |

|       |        |        |        |        | K12      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

|       |        |        | R      |        | K11      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

|       |        |        |        |        | K10      | - *2    | High               | Low              |                                                   |   |   |   |   |   |

| FF26H | KCP13  | KCP12  | KCP11  | KCP10  | KCP13    | 1       | ↑                  | ↑                | K10 ~ K13入力比較レジスタ                                 |   |   |   |   |   |

|       |        |        |        |        | KCP12    | 1       | ↓                  | ↓                |                                                   |   |   |   |   |   |

|       |        |        | R/W    |        | KCP11    | 1       | ↑                  | ↓                |                                                   |   |   |   |   |   |

|       |        |        |        |        | KCP10    | 1       | ↓                  | ↑                |                                                   |   |   |   |   |   |

| FF30H | R03HIZ | R02HIZ | R01HIZ | R00HIZ | R03HIZ   | 0       | High-Z             | Output           | R03出力ハイインピーダンス制御( FOUTE=0 )                       |   |   |   |   |   |

|       |        |        |        |        | R02HIZ   | 0       | High-Z             | Output           | FOUT出力ハイインピーダンス制御( FOUTE=1 )                      |   |   |   |   |   |

|       |        |        | R/W    |        | R01HIZ   | 0       | High-Z             | Output           | R02出力ハイインピーダンス制御( PTOUT=0 )                       |   |   |   |   |   |

|       |        |        |        |        | R00HIZ   | 0       | High-Z             | Output           | TOUT出力ハイインピーダンス制御( PTOUT=1 )                      |   |   |   |   |   |

| FF31H | R03    | R02    | R01    | R00    | R03      | 0       | High               | Low              | R01出力ハイインピーダンス制御                                  |   |   |   |   |   |

|       |        |        |        |        | R02      | 0       | High               | Low              | R00出力ハイインピーダンス制御                                  |   |   |   |   |   |

|       |        |        | R/W    |        | R01      | 0       | High               | Low              | R01出力ポートデータ                                       |   |   |   |   |   |

|       |        |        |        |        | R00      | 0       | High               | Low              | R00出力ポートデータ                                       |   |   |   |   |   |

[ 注釈 ]

\*1 イニシャルリセット時の初期値 \*2 回路上設定されない \*3 読み出し時は常時"0"

表4.1.1(b) I/Oメモリマップ( FF32H ~ FF62H )

| アドレス  | レジスタ   |        |       |       | Name                             | Init *1                      | 1                                    | 0                                | 注釈                                                                    |

|-------|--------|--------|-------|-------|----------------------------------|------------------------------|--------------------------------------|----------------------------------|-----------------------------------------------------------------------|

|       | D3     | D2     | D1    | D0    |                                  |                              |                                      |                                  |                                                                       |

| FF32H | 0      | 0      | 0     | R1HIZ | 0 *3<br>0 *3<br>0 *3<br>R1HIZ    | - *2<br>- *2<br>- *2<br>0    | High-Z                               | Output                           | 未使用<br>未使用<br>未使用<br>R1出力ハイインピーダンス制御                                  |

|       | R      |        |       | R/W   |                                  |                              |                                      |                                  |                                                                       |

|       | R13    | R12    | R11   | R10   | R13<br>R12<br>R11<br>R10         | 0<br>0<br>0<br>0             | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low         | R10 ~ R13出力ポートデータ                                                     |

| FF33H | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | IOC03  | IOC02  | IOC01 | IOC00 | IOC03<br>IOC02<br>IOC01<br>IOC00 | 0<br>0<br>0<br>0             | Output<br>Output<br>Output<br>Output | Input<br>Input<br>Input<br>Input | P00 ~ P03 I/O制御レジスタ                                                   |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

| FF40H | PUL03  | PUL02  | PUL01 | PUL00 | PUL03<br>PUL02<br>PUL01<br>PUL00 | 1<br>1<br>1<br>1             | On<br>On<br>On<br>On                 | Off<br>Off<br>Off<br>Off         | P00 ~ P03プルダウン制御レジスタ                                                  |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | P03    | P02    | P01   | P00   | P03<br>P02<br>P01<br>P00         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low         | P00 ~ P03入出力兼用ポートデータ                                                  |

| FF42H | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | IOC13  | IOC12  | IOC11 | IOC10 | IOC13<br>IOC12<br>IOC11<br>IOC10 | 0<br>0<br>0<br>0             | Output<br>Output<br>Output<br>Output | Input<br>Input<br>Input<br>Input | P13 I/O制御レジスタ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                             |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

| FF44H | PUL13  | PUL12  | PUL11 | PUL10 | PUL13<br>PUL12<br>PUL11<br>PUL10 | 1<br>1<br>1<br>1             | On<br>On<br>On<br>On                 | Off<br>Off<br>Off<br>Off         | P12 I/O制御レジスタ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                           |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | P13    | P12    | P11   | P10   | P13<br>P12<br>P11<br>P10         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low         | P11 I/O制御レジスタ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                           |

| FF45H | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | P13    | P12    | P11   | P10   | P13<br>P12<br>P11<br>P10         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low         | P10 I/O制御レジスタ(ESIF=0)<br>SIF選択時、汎用レジスタとして機能                           |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

| FF46H | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | P13    | P12    | P11   | P10   | P13<br>P12<br>P11<br>P10         | - *2<br>- *2<br>- *2<br>- *2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low         | P13入出力兼用ポートデータ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                            |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

| FF60H | LDUTY1 | LDUTY0 | STCD  | LPWR  | LDUTY1<br>LDUTY0<br>STCD<br>LPWR | 0<br>0<br>0<br>0             |                                      | Dynamic<br>Static<br>On          | LCD駆動デューティ [LDUTY1, 0] 0 1 2, 3<br>切り換え<br>LCD駆動方式切り換え<br>LCD電源On/Off |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | 0      | ALOFF  | ALON  | 0     | 0 *3<br>1<br>0<br>- *2           |                              | All Off<br>All On                    | Normal<br>Normal                 | 未使用<br>LCD全消灯制御<br>LCD全点灯制御<br>未使用                                    |

| FF61H | R      | R/W    |       | R     | LC3<br>LC2<br>ALON<br>0 *3       |                              |                                      |                                  |                                                                       |

|       | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

|       | LC3    | LC2    | LC1   | LC0   | LC3<br>LC2<br>LC1<br>LC0         | 0<br>0<br>0<br>0             |                                      |                                  | LCDコントラスト調整<br>[LC3~0] 0 ~ 15<br>コントラスト 淡 ~ 濃                         |

| FF62H | R/W    |        |       |       |                                  |                              |                                      |                                  |                                                                       |

表4.1.1(c) I/Oメモリマップ( FF6CH ~ FF79H )

| アドレス  | レジスタ  |       |       |       | 注釈                                 |                              |                                    |                                                                                                                                  |                                                                                                       |

|-------|-------|-------|-------|-------|------------------------------------|------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|       | D3    | D2    | D1    | D0    | Name                               | Init *1                      | 1                                  | 0                                                                                                                                |                                                                                                       |

| FF6CH | ENRTM | ENRST | ENON  | BZE   | ENRTM<br>ENRST*3                   | 0<br>Reset                   | 1sec<br>Reset                      | 0.5sec<br>Invalid                                                                                                                | エンベローブ減衰時間選択                                                                                          |

|       | R/W   | W     | R/W   |       | ENON<br>BZE                        | 0<br>0                       | On<br>Enable                       | Off<br>Disable                                                                                                                   | エンベローブプリセット(書き込み時)<br>エンベローブOn/Off<br>BZ出力イネーブル                                                       |

| FF6DH | 0     | BZSTP | BZSHT | SHTPW | 0 *3<br>BZSTP*3                    | - *2<br>0                    | Stop<br>Trigger                    | Invalid<br>Invalid                                                                                                               | 未使用                                                                                                   |

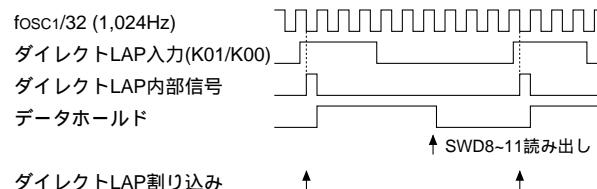

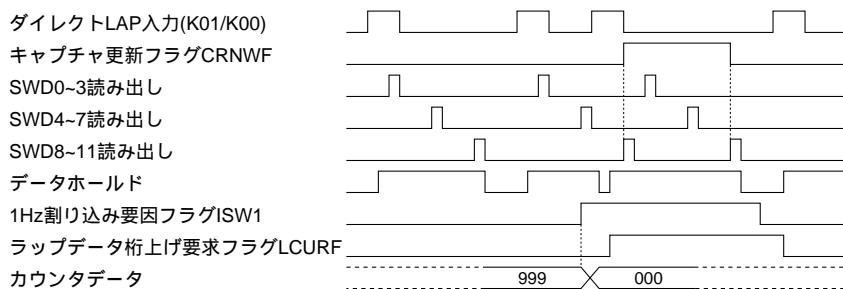

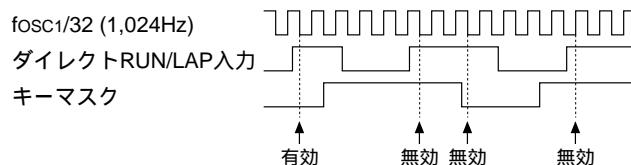

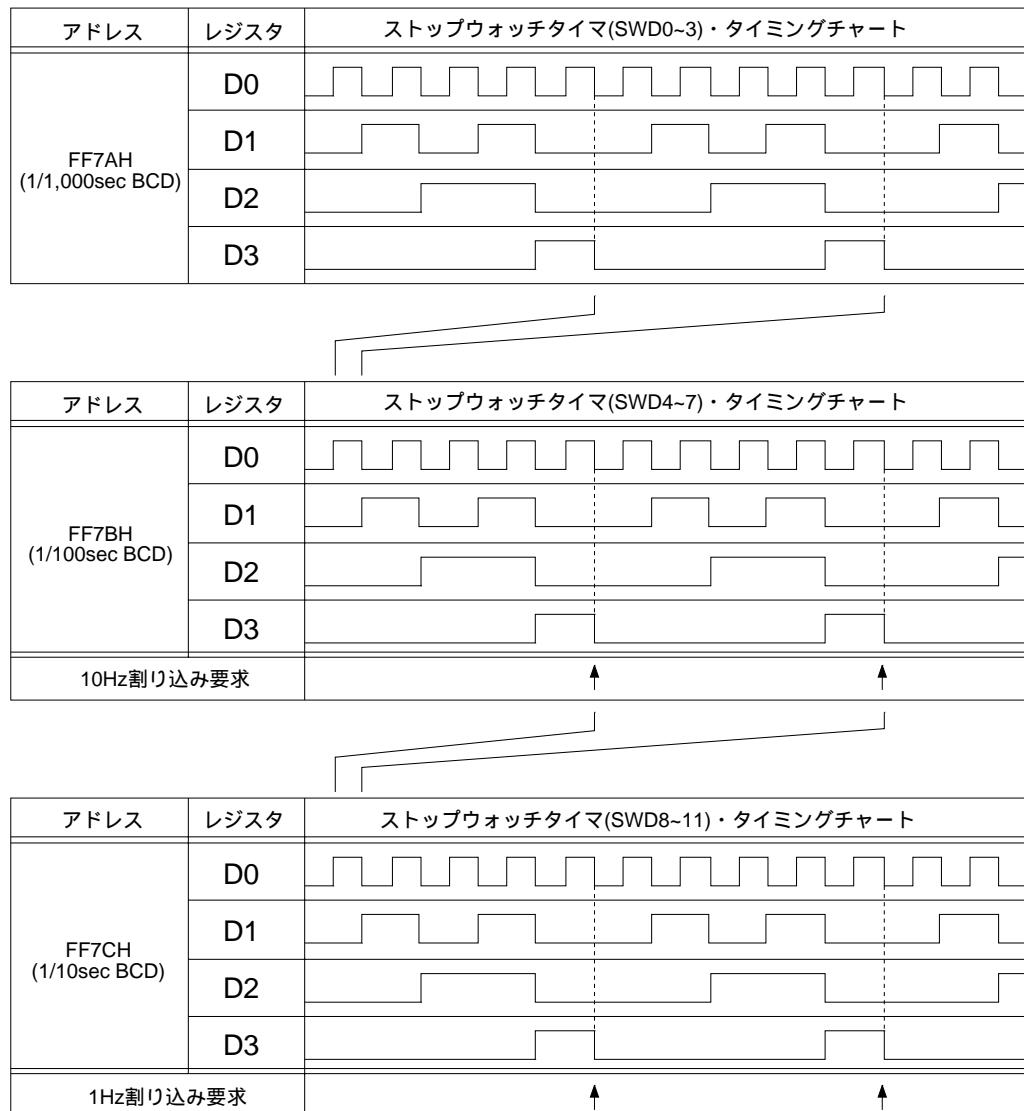

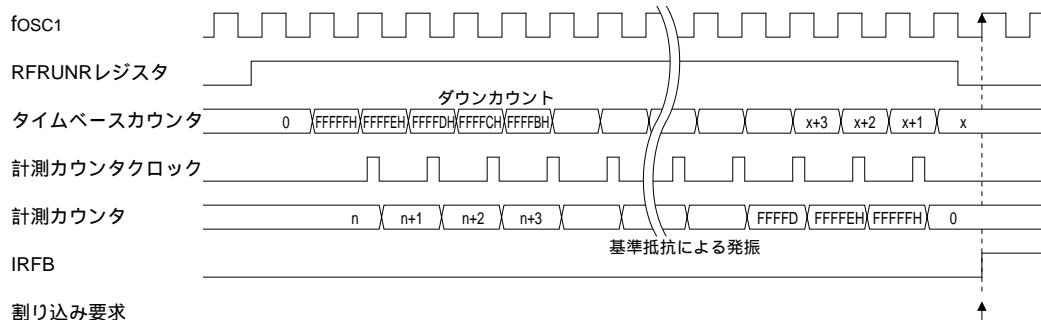

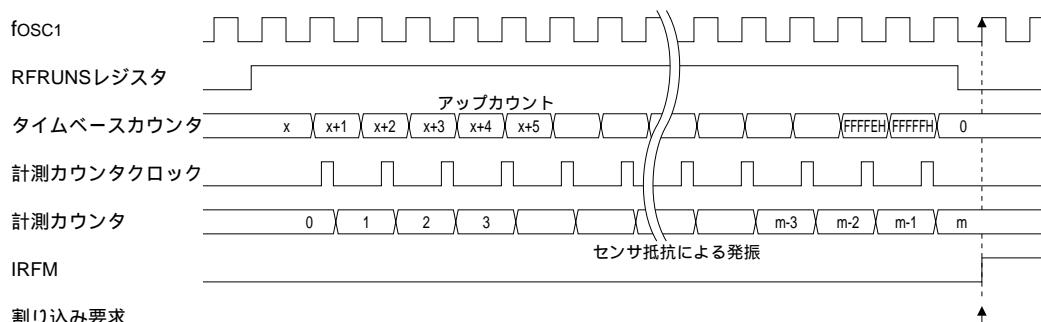

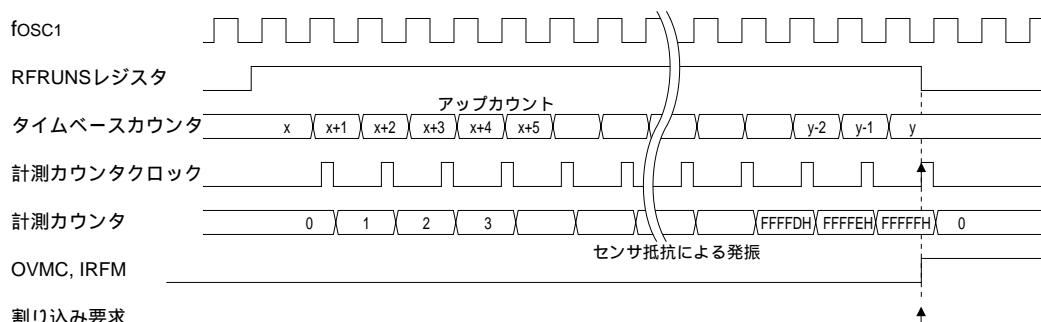

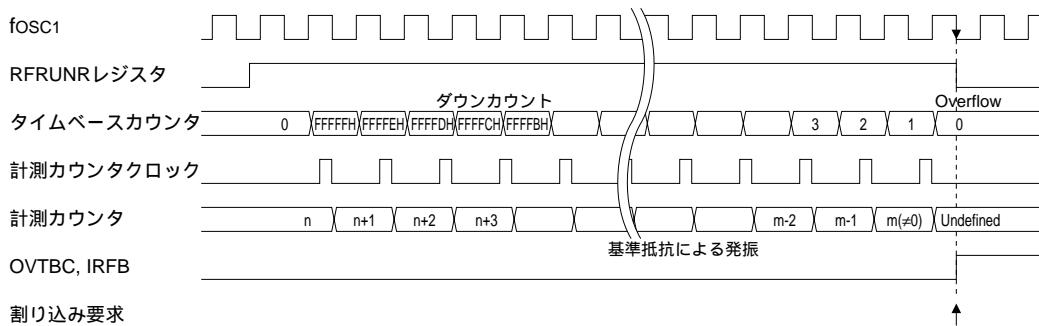

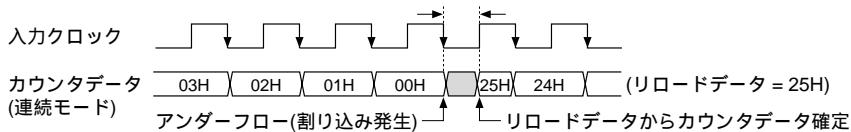

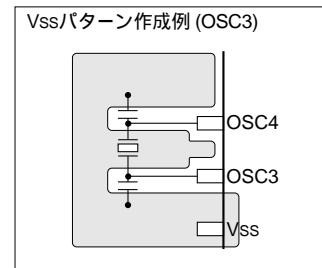

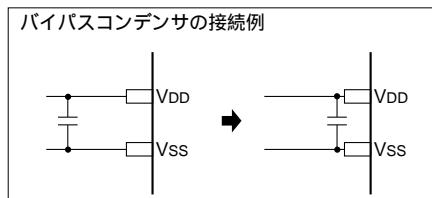

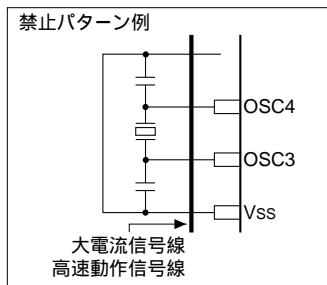

|       | R     | W     | R/W   |       | BZSHT<br>SHTPW                     | 0<br>0                       | Busy<br>31.25msec                  | Ready<br>31.25msec                                                                                                               | 1ショットブザーStop(書き込み時)<br>1ショットブザートリガ(書き込み時)<br>1ショットブザーステータス(読み出し時)<br>1ショットブザーバリス幅選択                   |