### ■ 概要

S1S65010 はインターネットカメラを構成するために最適なネットワークカメラコントローラ IC です。ネットワーク/プロトコル処理機能に加えて、カメラインターフェース、JPEG エンコーダ機能を内蔵しています。S1S65010 にカメラモジュール、Ethernet 用 PHY とファームウェアを格納した Flash ROM を接続することによりインターネットカメラが簡単に構成できます。

カメラからの画像取り込みと JPEG エンコードは、クライアントからシャッターコマンドを受けて行います。S1S65010 を LAN 上で HTTP サーバとして動作させた場合は、要求に応じて画像ファイルをクライアントに送ります。指定されたクライアントへの画像の取り込みおよび送付は、常時、あるいは内蔵タイマを使用して一定周期ごとに、または割り込み端子を使用して外部センサ等のトリガにより行うことも可能です。画像送付は電子メールの添付ファイルの形式にすることもできます。

S1S65010 は GPIO および I<sup>2</sup>C バスを搭載していますので、ネットワークからこれらのポートを経由してカメラの設定やモータなど外部機器の制御を行うことが可能です。本製品には、サンプルソフトウェアが付属します。

### ■ 特長

- PC レスでインターネットカメラの機能を実現

- S1S65000 ピン互換および S1S65000 ソフトウェア上位互換

- ネットワークカメラとして 30 fps @VGA のフレームレートを実現可能

- 2 メガピクセル（約 200 万画素）までの多様なカメラモジュールに対応

- I<sup>2</sup>S による音声／オーディオデータのサポート

- Hardware JPEG エンコーダにより JPEG 形式に圧縮（ISO 10918 準拠）

- ネットワークから各種コントロール設定が可能

- 電子メールによる画像の送付が可能

- 定期的に起動、撮影、再休止するウェイクアップモードにより、省電力化が可能

- Compact Flash Interface による CF Memory Card または無線 LAN インタフェース（802.11b/g）対応可能

- 1 Chip ソリューション：低システムコストを実現可能

- ARM720T Rev.4.3 内蔵（8KB キャッシュ付き） 50MHz

### ■ 内蔵機能

- **CPU:**

- 32bit RISC ARM720T（最大 50MHz）

- 32bit 長命令と効率よい Thumb コードと呼ばれる 16bit 長命令コードを切り替えて利用可能

- 32bit 汎用レジスタ（31 本）

- 乗算器を内蔵

- **RAM:**

- 78KB の CPU/JPEG/Ethernet Work 用内蔵 RAM

- **Camera input/JPEG encoder:**

- 8 ビットパラレルインターフェース YUV4-2-2 入力

- 解像度 1600 × 1200 程度まで（UXGA, SXGA, XGA, VGA, QVGA, CIF, QCIF）

- ITU-R BT656 形式対応

- ハードウェア JPEG エンコーダ

- Max. 30 fps @VGA, 30 fps @CIF

- カメラデータ入力用ピクセルクロック周波数は CPU クロック周波数の 2/3 未満

- **JPEG:**

- ハードウェア JPEG エンコーダ

- Resize 機能（画面切り取り可）

- 専用の Line Buffer

- JPEG エンコーダ出力に容量化変 FIFO 内蔵

- Enhanced DMA 内蔵

- **ネットワーク:**

- 10/100 BASE 全二重/半二重対応の Ethernet Mac コントローラ

- MII（Media Independent Interface, IEEE 802.3 Clause22 準拠）

- Enhanced DMA 内蔵

- **外部メモリコントローラ:**

- 16 ビットデータバス

- SDRAM 2-128MB サポート

- 3 本の Chip Select（SDRAM、Flash、他 1 本）を サポート

- **CF カードインターフェース:**

- CF+ 仕様 Rev.1.4 準拠

- 無線 LAN および PHS カードなどのインターフェースとして利用可能

- True IDE モードのサポート

- **スタンバイ機能:**

- CPU の動作が必要ない場合には CPU のクロックをとめることができる HALT 機能

- 主要な I/O ブロックごとにクロックをとめられる I/O クロックストップ機能

# S1S65010

- **タイマ、ウォッチドッグタイマ:**

- 16 bit タイマ

- リロード/Cyclic または One Shot 動作モード

- アンダーフロー出力によるトグル出力、または Port 出力をサポート

- 割り込み出力またはリセット可能なウォッチドッグタイマ

- **シリアルインターフェース:**

- UART: 16550 ソフトウェア互換 × 1 チャネル

- UART Lite: 16550 ソフトウェア下位互換 (機能限定) × 1 チャネル

- SPI: クロック同期式 × 1 チャネル

- I<sup>2</sup>C マスティンタフェース (カメラ I/F および汎用用途)

- I<sup>2</sup>S インタフェース × 2 チャネル (音声／オーディオデータ対応、I<sup>2</sup>S 規格に準拠)

- **割り込みコントローラ:**

- 32 本の IRQ と 2 本の FIQ サポート

- **リアルタイムクロック:**

- 日、時間、分、秒のサポート

- 1/128 – 1/2 までの内部タイマタップを割り込みソースとしても利用可能

- アラーム機能および割り込みをサポート

- **GPIO:**

- 汎用 I/O Port (最大 57 本)

すべてのポートに対して方向がプログラマブル設定可能

- 一部は他の I/O 機能と選択

- **電源:**

- 3.3V (I/O 電源)

- 1.8V (コア電源)

- 1.8V (PLL 用アナログ電源)

- 2.4V (Min.) - 3.6V (Max.) (カメラ I/O 電源)

- **パッケージ:**

- TQFP 144 Pin (TQFP24) 16 × 16 × 1 mm

0.4mm Pin pitch

## ■ 対応プロトコル

ARP, ICMP, IP, TCP, UDP, HTTPD, SMTP, DHCP, FTP, DNS リゾルバ, telnet

Flash EEPROM 書き換えにより対応プロトコルの追加／更新が可能。ユーザによる追加／更新も可能。

注意：サンプルソフトウェアとして、または協力会社からの提供が可能。

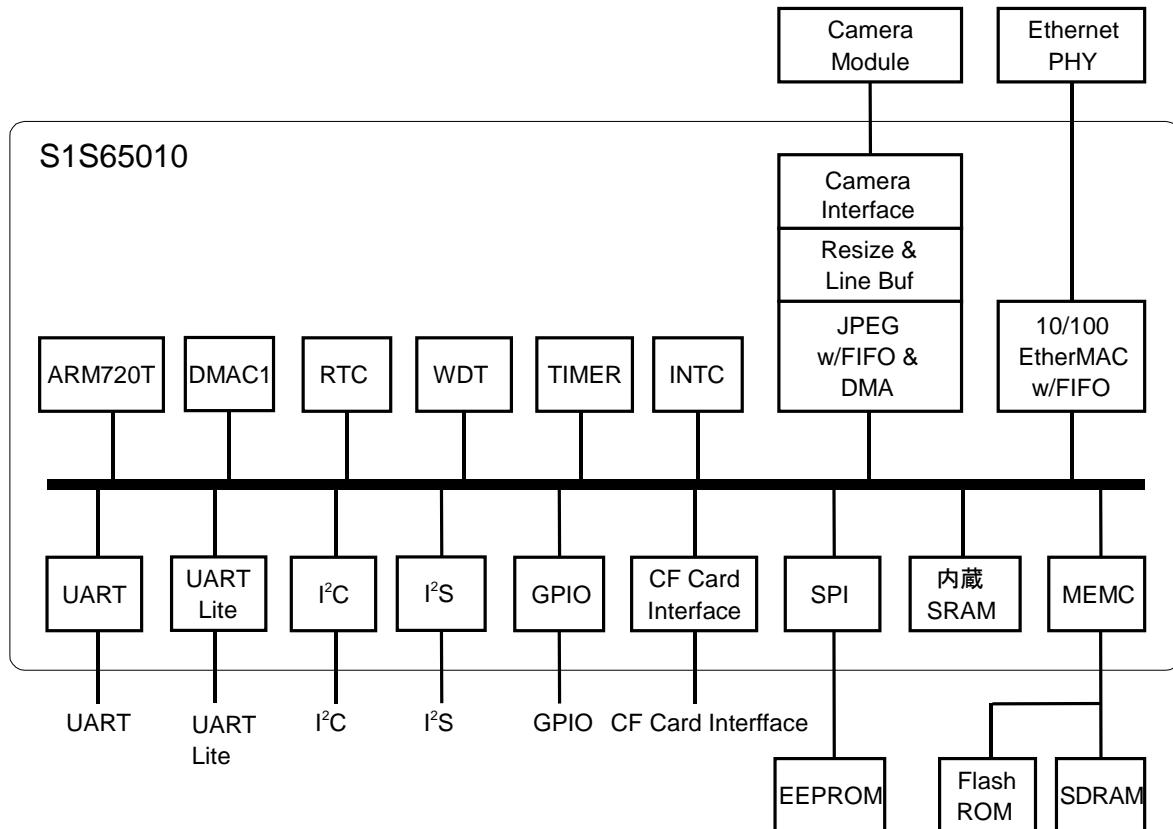

## ■ ブロック図

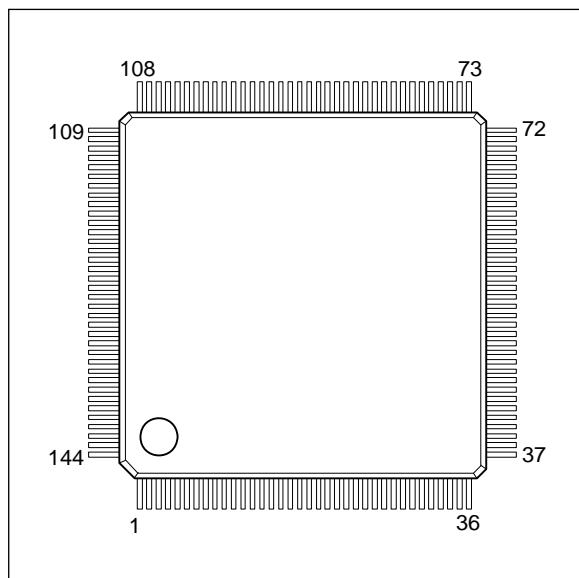

## ■ 端子配置図

| ピン No. | 端子名称   | ピン No. | 端子名称      |

|--------|--------|--------|-----------|

| 1      | MA14   | 37     | MD12      |

| 2      | MA15   | 38     | MD13      |

| 3      | MA16   | 39     | MD14      |

| 4      | MA17   | 40     | MD15      |

| 5      | MA18   | 41     | MDQML     |

| 6      | VSS    | 42     | MDQMH     |

| 7      | MA19   | 43     | HVDD1     |

| 8      | MCS2#  | 44     | VSS       |

| 9      | MCS1#  | 45     | MII_CRS   |

| 10     | MCS0#  | 46     | MII_COL   |

| 11     | LVDD   | 47     | MII_TXD3  |

| 12     | MOE#   | 48     | MII_TXD2  |

| 13     | MWE0#  | 49     | MII_TXD1  |

| 14     | MWE1#  | 50     | LVDD      |

| 15     | HVDD1  | 51     | MII_TXD0  |

| 16     | MCLKEN | 52     | MII_TXEN  |

| 17     | MCLK   | 53     | MII_TXCLK |

| 18     | VSS    | 54     | MII_RXER  |

| 19     | MRAS#  | 55     | VSS       |

| 20     | MCAS#  | 56     | HVDD1     |

| 21     | MD0    | 57     | MII_RXCLK |

| 22     | MD1    | 58     | MII_RXDV  |

| 23     | MD2    | 59     | MII_RXD0  |

| 24     | MD3    | 60     | MII_RXD1  |

| 25     | VSS    | 61     | LVDD      |

| 26     | LVDD   | 62     | MII_RXD2  |

| 27     | MD4    | 63     | MII_RXD3  |

| 28     | MD5    | 64     | MII_MDC   |

| 29     | MD6    | 65     | MII_MDIO  |

| 30     | MD7    | 66     | VSS       |

| 31     | HVDD1  | 67     | CLKI      |

| 32     | MD8    | 68     | PLLVSS    |

| 33     | MD9    | 69     | VCP       |

| 34     | MD10   | 70     | PLLVDD    |

| 35     | MD11   | 71     | RESET#    |

| 36     | VSS    | 72     | TESTEN    |

| ピン No. | 端子名称     | ピン No. | 端子名称      |

|--------|----------|--------|-----------|

| 73     | TRST#    | 109    | CMDATA5   |

| 74     | TCK      | 110    | CMDATA6   |

| 75     | TMS      | 111    | CMDATA7   |

| 76     | TDI      | 112    | VSS       |

| 77     | TDO      | 113    | LVDD      |

| 78     | VSS      | 114    | GPIOD0    |

| 79     | GPIOA0   | 115    | GPIOD1    |

| 80     | GPIOA1   | 116    | CFCE2#    |

| 81     | GPIOA2   | 117    | CFCE1#    |

| 82     | GPIOA3   | 118    | CFIORD#   |

| 83     | GPIOA4   | 119    | CFIOWR#   |

| 84     | GPIOA5   | 120    | CFIREQ    |

| 85     | GPIOA6   | 121    | CFRST     |

| 86     | GPIOA7   | 122    | VSS       |

| 87     | HVDD1    | 123    | HVDD1     |

| 88     | VSS      | 124    | CFWAIT#   |

| 89     | GPIOB0   | 125    | CFSTSCHG# |

| 90     | GPIOB1   | 126    | CFDEN#    |

| 91     | GPIOB2   | 127    | CFDDIR    |

| 92     | GPIOB3   | 128    | MA0       |

| 93     | LVDD     | 129    | MA1       |

| 94     | GPIOB4   | 130    | MA2       |

| 95     | GPIOB5   | 131    | MA3       |

| 96     | GPIOB6   | 132    | VSS       |

| 97     | GPIOB7   | 133    | LVDD      |

| 98     | VSS      | 134    | MA4       |

| 99     | CMHREF   | 135    | MA5       |

| 100    | CMVREF   | 136    | MA6       |

| 101    | CMCLKIN  | 137    | MA7       |

| 102    | CMCLKOUT | 138    | MA8       |

| 103    | CMDATA0  | 139    | HVDD1     |

| 104    | CMDATA1  | 140    | MA9       |

| 105    | HVDD2    | 141    | MA10      |

| 106    | CMDATA2  | 142    | MA11      |

| 107    | CMDATA3  | 143    | MA12      |

| 108    | CMDATA4  | 144    | MA13      |

注意: 端子名称右端の#は、ローアクティブ信号であることを示しています。

# S1S65010

## ■ 端子説明

- #: 端子名称右端の#は、そのローアクティブ信号であることを示しています。

I: 入力ピン

O: 出力ピン

IO: 双方向ピン

P: 電源

### Cell Type Description

| Cell Type | 説明                                                                           | 使用端子例                         |

|-----------|------------------------------------------------------------------------------|-------------------------------|

| ICS       | LVCMS Schmitt input                                                          | TCK, CLKI, RESET#             |

| ICD1      | LVCMS input with pull down resistor (50kΩ @3.3V)                             | TESTEN                        |

| ICU1      | LVCMS input with pull up resistor (50kΩ@3.3V)                                | TMS, TDI                      |

| ICSU1     | LVCMS Schmitt input with pull up resistor                                    | TRST#                         |

| BLNC4     | Low noise LVCMS IO buffer (±4mA)                                             | MII                           |

| BLNC4U1   | Low noise LVCMS IO buffer with pull-up resistor (50kΩ@3.3V) (±4mA)           | CF Interface                  |

| BLNC4D2   | Low noise LVCMS IO buffer with pull-down resistor (100kΩ@3.3V) (±4mA)        | MD [15:0]                     |

| BLNS4     | Low noise LVCMS Schmitt IO buffer (±4mA)                                     | GPIOA, GPIOB, GPIOD [1:0]     |

| BLNS4D1   | Low noise LVCMS Schmitt IO buffer with pull-down resistor (50kΩ@3.0V) (±4mA) | Camera Interface              |

| OLN4      | Low noise output buffer (±4mA)                                               | MEMC Interface (excluding MD) |

| OTLN4     | Low noise Tri-state output buffer (±4mA)                                     | TDO                           |

| OLTR      | Low Voltage Transparent Output                                               | VCP                           |

## 端子説明

| 端子名称         | Type  | Cell Type | ピン No.                              | 説明                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|-------|-----------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (MA [23:22]) | (I/O) | (BLNS4)   | (97, 96)                            | これらの端子の詳細については <a href="#">GPIOB[7:6]</a> をご参照ください。                                                                                                                                                                                                                                                                                                                         |

| (MA [21:20]) | (I/O) | (BLNS4)   | (114-115)                           | これらの端子の詳細については <a href="#">GPIOD[1:0]</a> をご参照ください。                                                                                                                                                                                                                                                                                                                         |

| MA [19:12]   | O     | OLN4      | 7, 1-5,<br>143-144                  | <b>アドレス出力信号[19:12]</b><br>このうち MA[15:14]は SDRAM 使用時にはバンクアドレスとして BA[1:0]になります。                                                                                                                                                                                                                                                                                               |

| MA 11        | O     | OLN4      | 142                                 | この端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li>MA11 : アドレス出力信号 11 (リセット直後の端子機能)</li> <li><b>CFREG#出力信号</b><br/>コンパクトフラッシュ(CF)インタフェース動作時は、CF インタフェースのアトリビュートおよび I/O 空間を選択する REG 信号として動作します。</li> </ul>                                                                                                                                                         |

| MA [10:0]    | O     | OLN4      | 128-131,<br>134-138,<br>140-141     | これらの端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li>MA[10:0] : アドレス出力信号[10:0] (リセット直後の端子機能)</li> <li><b>CFADDR[10:0]出力信号</b><br/>CF インタフェース動作時は、CF インタフェースのアドレス信号[10:0]となります。</li> </ul>                                                                                                                                                                         |

| MD [15:0]    | I/O   | BLNC4D2   | 21-24,<br>27-30,<br>32-35,<br>37-40 | これらの端子は以下の機能を持っています。<br><ul style="list-style-type: none"> <li><b>16Bit のメモリ用 Data Bus</b> (リセット直後の端子機能)</li> <li>CF インタフェース動作時は <b>16Bit データ</b>となります。</li> <li><b>MODESEL[15:0]</b><br/>パワーオンリセット時 (RESET#の Low から High への遷移時) に内部の動作モードを決めるためにサンプリングされます。“MODESEL 端子によるシステムコンフィギュレーション設定” の項を参照してください。この時、動作モードを決めるために外部でプルアップ抵抗が必要になる場合があります。(4.7~10kΩ程度の抵抗)</li> </ul> |

| MCS [2:0]#   | O     | OLN4      | 8-10                                | <b>メモリ (SDRAM, スタティックメモリ) 用チップセレクト信号</b> (ローアクティブ信号)<br>SDRAM 対応は MCS2#のみになります。                                                                                                                                                                                                                                                                                             |

| MOE#         | O     | OLN4      | 12                                  | この端子は以下の機能を持っています。 (ローアクティブ信号)<br><ul style="list-style-type: none"> <li>MOE# : メモリ出力用ストローブ信号 (リセット直後の端子機能)</li> <li><b>CFOE# 出力信号</b><br/>CF インタフェース動作時は、CF インタフェースのメモリおよびアトリビュート空間の出力イネーブル信号となります。</li> </ul>                                                                                                                                                             |

| 端子名称           | Type | Cell Type | ピン No.          | 説明                                                                                                                                                                                                                                                |

|----------------|------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MWE0#          | O    | OLN4      | 13              | <p>この端子は以下の機能を持っています。（ローアクティブ信号）</p> <ul style="list-style-type: none"> <li>・ <b>MWE0#</b> : メモリ用 Write Enable 信号（スタティックメモリ用）（リセット直後の端子機能）</li> <li>・ <b>CFWE# 出力信号</b><br/>CF インタフェース動作時は、CF インタフェースのメモリおよびアトリビュート空間のライトイネーブル信号となります。</li> </ul> |

| MWE1#          | O    | OLN4      | 14              | <b>メモリ用 Write Enable 信号 (SDRAM 用)</b><br>(ローアクティブ信号)                                                                                                                                                                                              |

| MCLK           | O    | OLN4      | 17              | <b>SDRAM 用クロック出力</b><br>内部動作周波数 (CPUCLK) と同じ周波数が出力されます。                                                                                                                                                                                           |

| MCLKEN         | O    | OLN4      | 16              | <b>SDRAM 用クロック・イネーブル信号</b>                                                                                                                                                                                                                        |

| MRAS#          | O    | OLN4      | 19              | <b>SDRAM 用 RAS 信号</b> (ローアクティブ信号)                                                                                                                                                                                                                 |

| MCAS#          | O    | OLN4      | 20              | <b>SDRAM 用 CAS 信号</b> (ローアクティブ信号)                                                                                                                                                                                                                 |

| MDQML<br>MDQMH | O    | OLN4      | 41-42           | <p>これらの端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>バイトイネーブル信号</b> (スタティックメモリ用)</li> <li>・ <b>SDRAM 用 DQM 信号</b><br/>MDQML が下位バイトに対応し、MDQMH が上位バイトに対応します。</li> </ul>                                                          |

| MII_TXCLK      | I/O  | BLNC4     | 53              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXCLK</b> : Media Independent Interface Ethernet PHY(以下 MII PHY)用送信データ出力用クロック TXCLK 入力(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF7 入出力</b></li> </ul>                |

| MII_TXEN       | I/O  | BLNC4     | 52              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXEN</b> : MII PHY 用送信出力イネーブル TXEN 出力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF6 入出力</b></li> </ul>                                                            |

| MII_TXD3       | I/O  | BLNC4     | 47              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXD3</b> : MII PHY 用送信データ TXD3 出力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF2 入出力</b></li> </ul>                                                                |

| MII_TXD2       | I/O  | BLNC4     | 48              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXD2</b> : MII PHY 用送信データ TXD2 出力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF3 入出力</b></li> </ul>                                                                |

| MII_TXD1       | I/O  | BLNC4     | 49              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXD1</b> : MII PHY 用送信データ TXD1 出力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF4 入出力</b></li> </ul>                                                                |

| MII_TXD0       | I/O  | BLNC4     | 51              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_TXD0</b> : MII PHY 用送信データ TXD0 出力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF5 入出力</b></li> </ul>                                                                |

| MII_RXCLK      | I/O  | BLNC4     | 57              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_RXCLK</b> : MII PHY 用受信データクロック(RXCLK)入力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOG1 入出力</b></li> </ul>                                                          |

| MII_COL        | I/O  | BLNC4     | 46              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_COL</b> : MII PHY 用コリジョン(COL)検出入力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF1 入出力</b></li> </ul>                                                                |

| MII_CRS        | I/O  | BLNC4     | 45              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_CRS</b> : MII PHY 用キャリアセンス(CRS)入力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOF0 入出力</b></li> </ul>                                                                |

| MII_RXDV       | I/O  | BLNC4     | 58              | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_RXDV</b> : MII PHY 用受信データ有効(RXDV)入力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOG2 入出力</b></li> </ul>                                                              |

| MII_RXD[3:0]   | I/O  | BLNC4     | 59-60,<br>62-63 | <p>これらの端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_RXD[3:0]</b> : MII PHY 用受信データ RXD[3:0]入力<br/>(リセット直後の端子機能；GPIO 以外の機能 1)</li> <li>・ <b>GPIOG[6:3]入出力</b></li> </ul>                                                    |

# S1S65010

| 端子名称        | Type | Cell Type | ピン No.              | 説明                                                                                                                                                                                                                                                                                                                                            |

|-------------|------|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MII_RXER    | I/O  | BLNC4     | 54                  | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_RXER</b> : MII PHY 用受信エラー(RXER)入力<br/>(リセット直後の端子機能 ; GPIO 以外の機能 1)</li> <li>・ <b>GPIOG0 入出力</b></li> </ul>                                                                                                                                                          |

| MII_MDC     | I/O  | BLNC4     | 64                  | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_MDC</b> : MII PHY 用マネージメント・インターフェース・クロック (MDC)出力 (リセット直後の端子機能 ; GPIO 以外の機能 1)</li> <li>・ <b>GPIOG7 入出力</b></li> </ul>                                                                                                                                               |

| MII_MDIO    | I/O  | BLNC4     | 65                  | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>MII_MDIO</b> : MII PHY 用マネージメント・インターフェース・データ (MDIO)入出力 (リセット直後の端子機能 ; GPIO 以外の機能 1)</li> <li>・ <b>GPIOH0 入出力</b></li> </ul>                                                                                                                                             |

| CMDATA[7:0] | I/O  | BLNS4D1   | 103-104,<br>106-111 | <p>これらの端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CMDATA[7:0]</b> : カメラ YUV データ入力<br/>これらの端子は、リセット時は GPIOC[7:0]入力になっています。CMDATA[7:0]端子として使用するためには GPIOC 端子機能レジスタのビット[15:0]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOC[7:0] 入出力</b> (リセット直後の端子機能)</li> </ul>                                                           |

| CMVREF      | I/O  | BLNS4D1   | 100                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CMVREF</b> : カメラデータ入力時の垂直同期入力<br/>この端子は、リセット時は GPIOD4 入力になっています。CMVREF 端子として使用するためには GPIOD 端子機能レジスタのビット[9:8]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD4 入出力</b> (リセット直後の端子機能)</li> </ul>                                                                             |

| CMHREF      | I/O  | BLNS4D1   | 99                  | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CMHREF</b> : カメラデータ入力時の水平同期入力<br/>この端子は、リセット時は GPIOD5 入力になっています。CMHREF 端子として使用するためには GPIOD 端子機能レジスタのビット[11:10]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD5 入出力</b> (リセット直後の端子機能)</li> </ul>                                                                           |

| CMCLKOUT    | I/O  | BLNS4D1   | 102                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CMCLKOUT</b> : カメラ用基本クロック出力<br/>この端子は、リセット時は GPIOD6 入力になっています。CMCLKOUT 端子として使用するためには GPIOD 端子機能レジスタのビット[13:12]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD6 入出力</b> (リセット直後の端子機能)</li> </ul>                                                                           |

| CMCLKIN     | I/O  | BLNS4D1   | 101                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CMCLKIN</b> : カメラデータ入力用ピクセルクロック<br/>この端子は、リセット時は GPIOD7 入力になっています。CMCLKIN 端子として使用するためには GPIOD 端子機能レジスタのビット[15:14]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD7 入出力</b> (リセット直後の端子機能)</li> </ul>                                                                        |

| CFCE2#      | I/O  | BLNC4U1   | 116                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CFCE2#</b> : Compact Flash Memory Interface 用 (以下 CF 用) カードイネーブル 2(CE2#)出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOD2 入力になっています。CFCE2# 端子として使用するためには GPIOD 端子機能レジスタのビット[5:4]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD2 入出力</b> (リセット直後の端子機能)</li> </ul>                   |

| CFCE1#      | I/O  | BLNC4U1   | 117                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CFCE1#</b> : CF 用カードイネーブル 1 (CE1#) 出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOD3 入力になっています。CFCE1# 端子として使用するためには GPIOD 端子機能レジスタのビット[7:6]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOD3 入出力</b> (リセット直後の端子機能)</li> </ul>                                                        |

| CFIORD#     | I/O  | BLNC4U1   | 118                 | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>・ <b>CFIORD#</b> : CF 用 IO Read ストローブ出力 (ロー/アクティブ信号)<br/>この端子は、リセット時は GPIOE0 入力になっています。CFIORD# 端子として使用するためには GPIOE 端子機能レジスタのビット[1:0]を“GPIO 以外の機能 1”に設定してください。</li> <li>・ <b>GPIOE0 入出力</b> (リセット直後の端子機能)</li> <li>・ <b>I2S0_SD</b> : I2S0 用シリアルデータ (GPIO 以外の機能 2)</li> </ul> |

| 端子名称      | Type | Cell Type | ピン No. | 説明                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFIOWR#   | I/O  | BLNC4U1   | 119    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFIOWR# : CF 用 IO Write ストローブ出力 (ローアクティブ信号)</li> <li>この端子は、リセット時は GPIOE1 入力になっています。CFIOWR# 端子として使用するためには GPIOE 端子機能レジスタのビット[3:2]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE1 入出力 (リセット直後の端子機能)</li> <li>I2S0_SCK : I2S0 用シリアルクロック (GPIO 以外の機能 2)</li> </ul>                            |

| CFWAIT#   | I/O  | BLNC4U1   | 124    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFWAIT# : CF 用ウェイト要求力 (ローアクティブ信号)</li> <li>この端子は、リセット時は GPIOE2 入力になっています。CFWAIT# 端子として使用するためには GPIOE 端子機能レジスタのビット[5:4]を “GPIO 以外の機能 1” に設定してください。</li> <li>MWAIT# : メモリコントローラ用ウェイト信号 (ローアクティブ信号)</li> <li>CFWAIT#信号と端子を共用 (GPIO 以外の機能 1)</li> <li>GPIOE2 入出力 (リセット直後の端子機能)</li> </ul> |

| CFRST     | I/O  | BLNC4U1   | 121    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFRST : CF カードへのリセット信号</li> <li>カードリセット時に HIGH、カードの通常動作時に LOW となります。</li> <li>この端子は、リセット時は GPIOE3 入力になっています。CFRST 端子として使用するためには GPIOE 端子機能レジスタのビット[7:6]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE3 入出力 (リセット直後の端子機能)</li> <li>I2S0_WS : I2S0 用ワードセレクト (GPIO 以外の機能 2)</li> </ul>       |

| CFIREQ    | I/O  | BLNC4U1   | 120    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFIREQ : CF カードからの割り込み要求信号</li> <li>この端子は、リセット時は GPIOE4 入力になっています。CFIREQ 端子として使用するためには GPIOE 端子機能レジスタのビット[9:8]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE4 入出力 (リセット直後の端子機能)</li> </ul>                                                                                                |

| CFSTSCHG# | I/O  | BLNC4U1   | 125    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFSTSCHG# : CF カードからのステータスチェンジ信号 (ローアクティブ信号)</li> <li>この端子は、リセット時は GPIOE5 入力になっています。CFSTSCHG#端子として使用するためには GPIOE 端子機能レジスタのビット[11:10]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE5 入出力 (リセット直後の端子機能)</li> <li>I2S1_SD : I2S1 用シリアルデータ (GPIO 以外の機能 2)</li> </ul>                          |

| CFDEN#    | I/O  | BLNC4U1   | 126    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFDEN# : CF カードの外部バッファ用データバスイネーブル信号 (ローアクティブ信号)</li> <li>この端子は、リセット時は GPIOE6 入力になっています。CFDEN# 端子として使用するためには GPIOE 端子機能レジスタのビット[13:12]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE6 入出力端子 (リセット直後の端子機能)</li> <li>I2S1_SCK : I2S1 用シリアルクロック (GPIO 以外の機能 2)</li> </ul>                     |

| CFDDIR    | I/O  | BLNC4U1   | 127    | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>CFDDIR : CF 用データバス方向指示出力</li> <li>この端子は、CF 用データのリード時に LOW となります。また、この端子はリセット時には GPIOE7 入力になっています。CFDDIR 端子として使用するためには GPIOE 端子機能レジスタのビット[15:14]を “GPIO 以外の機能 1” に設定してください。</li> <li>GPIOE7 入出力 (リセット直後の端子機能)</li> <li>I2S1_WS : I2S1 用ワードセレクト (GPIO 以外の機能 2)</li> </ul>               |

| GPIOA0    | I/O  | BLNS4     | 79     | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>GPIOA0 入出力 (リセット直後の端子機能)</li> <li>TXD0 : UART 送信データ出力 (GPIO 以外の機能 1)</li> </ul>                                                                                                                                                                                                       |

| GPIOA1    | I/O  | BLNS4     | 80     | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>GPIOA1 入出力 (リセット直後の端子機能)</li> <li>RXD0 : UART 受信データ入力 (GPIO 以外の機能 1)</li> </ul>                                                                                                                                                                                                       |

| GPIOA2    | I/O  | BLNS4     | 81     | <p>この端子は以下の機能を持っています。</p> <ul style="list-style-type: none"> <li>GPIOA2 入出力 (リセット直後の端子機能)</li> <li>SPI_SS : SPI 用チップセレクト (GPIO 以外の機能 1)</li> <li>TXD1 : UART Lite 送信データ出力 (GPIO 以外の機能 2)</li> </ul>                                                                                                                                                    |

# S1S65010

| 端子名称   | Type | Cell Type | ピン No. | 説明                                                                                                                                                                              |

|--------|------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOA3 | I/O  | BLNS4     | 82     | この端子は以下の機能を持っています。<br>• <b>GPIOA3 入出力</b> (リセット直後の端子機能)<br>• <b>SPI_SCLK</b> : SPI 用シリアルクロック (GPIO 以外の機能 1)<br>• <b>RXD1</b> : UART Lite 受信データ入力 (GPIO 以外の機能 2)                 |

| GPIOA4 | I/O  | BLNS4     | 83     | この端子は以下の機能を持っています。<br>• <b>GPIOA4 入出力</b> (リセット直後の端子機能)<br>• <b>SPI_MISO</b> : SPI 用シリアルデータマスタ入力／スレーブ出力 (GPIO 以外の機能 1)                                                          |

| GPIOA5 | I/O  | BLNS4     | 84     | この端子は以下の機能を持っています。<br>• <b>GPIOA5 入出力</b> (リセット直後の端子機能)<br>• <b>SPI_MOSI</b> : SPI 用シリアルデータマスタ出力／スレーブ入力 (GPIO 以外の機能 1)                                                          |

| GPIOA6 | I/O  | BLNS4     | 85     | この端子は以下の機能を持っています。<br>• <b>GPIOA6 入出力</b> (リセット直後の端子機能)<br>• <b>SCL</b> : I <sup>2</sup> C 用クロック入出力 (GPIO 以外の機能 1)                                                              |

| GPIOA7 | I/O  | BLNS4     | 86     | この端子は以下の機能を持っています。<br>• <b>GPIOA7 入出力</b> (リセット直後の端子機能)<br>• <b>SDA</b> : I <sup>2</sup> C 用データ入出力 (GPIO 以外の機能 1)                                                               |

| GPIOB0 | I/O  | BLNS4     | 89     | この端子は以下の機能を持っています。<br>• <b>GPIOB0 入出力</b> (リセット直後の端子機能)<br>• <b>INT0 入力</b><br>• <b>I2S0_WS</b> : I2S0 用ワードセレクト (GPIO 以外の機能 2)                                                  |

| GPIOB1 | I/O  | BLNS4     | 90     | この端子は以下の機能を持っています。<br>• <b>GPIOB1 入出力</b> (リセット直後の端子機能)<br>• <b>INT1 入力</b><br>• <b>RTS0#</b> : UART 送信要求出力 (GPIO 以外の機能 1)<br>• <b>I2S0_SCK</b> : I2S0 用シリアルクロック (GPIO 以外の機能 2) |

| GPIOB2 | I/O  | BLNS4     | 91     | この端子は以下の機能を持っています。<br>• <b>GPIOB2 入出力</b> (リセット直後の端子機能)<br>• <b>INT2 入力</b><br>• <b>CTS0#</b> : UART 送信可能入力 (GPIO 以外の機能 1)<br>• <b>I2S0_SD</b> : I2S0 用シリアルデータ (GPIO 以外の機能 2)   |

| GPIOB3 | I/O  | BLNS4     | 92     | この端子は以下の機能を持っています。<br>• <b>GPIOB3 入出力</b> (リセット直後の端子機能)<br>• <b>INT3 入力</b><br>• <b>Timer0 出力</b> (GPIO 以外の機能 1)<br>• <b>I2S1_SD</b> : I2S1 用シリアルデータ (GPIO 以外の機能 2)             |

| GPIOB4 | I/O  | BLNS4     | 94     | この端子は以下の機能を持っています。<br>• <b>GPIOB4 入出力</b> (リセット直後の端子機能)<br>• <b>INT4 入力</b><br>• <b>Timer1 出力</b> (GPIO 以外の機能 1)                                                                |

| GPIOB5 | I/O  | BLNS4     | 95     | この端子は以下の機能を持っています。<br>• <b>GPIOB5 入出力</b> (リセット直後の端子機能)<br>• <b>INT5 入力</b><br>• <b>Timer2 出力</b> (GPIO 以外の機能 1)                                                                |

| GPIOB6 | I/O  | BLNS4     | 96     | この端子は以下の機能を持っています。<br>• <b>GPIOB6 入出力</b> (リセット直後の端子機能)<br>• <b>INT6 入力</b><br>• <b>MA22</b> : アドレス出力端子 22 (GPIO 以外の機能 1)<br>• <b>I2S1_SCK</b> : I2S1 用シリアルクロック (GPIO 以外の機能 2)  |

| GPIOB7 | I/O  | BLNS4     | 97     | この端子は以下の機能を持っています。<br>• <b>GPIOB7 入出力</b> (リセット直後の端子機能)<br>• <b>INT7 入力</b><br>• <b>MA23</b> : アドレス出力端子 23 (GPIO 以外の機能 1)<br>• <b>I2S1_WS</b> : I2S1 用ワードセレクト (GPIO 以外の機能 2)    |

| GPIOD0 | I/O  | BLNS4     | 114    | この端子は以下の機能を持っています。<br>• <b>GPIOD0 入出力</b> (リセット直後の端子機能)<br>• <b>INT8 入力</b><br>• <b>MA20</b> : アドレス出力信号 20 (GPIO 以外の機能 1)                                                       |

| GPIOD1 | I/O  | BLNS4     | 115    | この端子は以下の機能を持っています。<br>• <b>GPIOD1 入出力</b> (リセット直後の端子機能)<br>• <b>MA21</b> : アドレス出力信号 21 (GPIO 以外の機能 1)                                                                           |

| 端子名称   | Type | Cell Type | ピン No.                                                           | 説明                                                                                                               |

|--------|------|-----------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| CLKI   | I    | ICS       | 67                                                               | <b>32kHz クロック入力</b><br>このチップへの基本クロック入力。内部の PLL により数十 MHz への<br>倍数が行われ、それが内部動作の基本クロックとなります。<br>シュミットトリガ入力となっています。 |

| VCP    | O    | OLTR      | 69                                                               | <b>内蔵 PLL 用テスト端子</b><br>テスト時に PLL の出力をモニタするために使用します。<br>通常使用時はオープンにしてください。                                       |

| TRST#  | I    | ICSU1     | 73                                                               | <b>JTAG Interface 用リセット (ローアクティブ信号)</b><br>プルアップ抵抗付シュミットトリガ入力となっています。                                            |

| TCK    | I    | ICS       | 74                                                               | <b>JTAG Interface 用クロック入力ピン</b><br>シュミットトリガ入力となっています。                                                            |

| TMS    | I    | ICU1      | 75                                                               | <b>JTAG Interface 用 TMS ピン</b><br>この端子はプルアップ抵抗を内蔵しています。                                                          |

| TDI    | I    | ICU1      | 76                                                               | <b>JTAG Interface 用シリアルデータ入力ピン</b><br>この端子はプルアップ抵抗を内蔵しています。                                                      |

| TDO    | O    | OTLN4     | 77                                                               | <b>JTAG Interface 用シリアルデータ出力ピン</b>                                                                               |

| TESTEN | I    | ICD1      | 72                                                               | <b>テストイネーブル (ハイアクティブ信号)</b><br>この端子はプルダウン抵抗を内蔵しています。<br>通常使用時は VSS へ接続するか、またはオープンにしてください。                        |

| RESET# | I    | ICS       | 71                                                               | <b>システムリセット信号 (ローアクティブ信号)</b><br>HVDD1 および LVDD が安定した後も 100ms の間 Reset#をアクティブ(Low) に保ってください。                     |

| HVDD1  | P    | P         | 15, 31, 43,<br>56, 87,<br>123, 139                               | <b>I/O セル用電源 : 3.3V</b><br>(カメラインタフェース以外)                                                                        |

| HVDD2  | P    | P         | 105                                                              | <b>カメラインタフェース用電源 : 3.0 (Typical)</b><br>2.4V (Min) – 3.6V (Max)                                                  |

| LVDD   | P    | P         | 11, 26, 50,<br>61, 93,<br>113, 133                               | <b>コア (内部) 用電源 : 1.8V</b>                                                                                        |

| PLLVDD | P    | P         | 70                                                               | <b>アナログ(PLL)用電源 : 1.8V</b><br>アナログ電源としての取り扱いが必要です。ノイズの少ない安定した<br>電源を供給してください。                                    |

| PLLVSS | P    | P         | 68                                                               | <b>アナログ(PLL)用グラウンド</b><br>アナログ電源としての取り扱いが必要です。ノイズの少ない安定した<br>グラウンドを供給してください。                                     |

| VSS    | P    | P         | 6, 18, 25,<br>36, 44, 55,<br>66, 78, 88,<br>98, 112,<br>122, 132 | <b>I/O セル、カメラインタフェースおよびコア電源共通グラウンド</b>                                                                           |

# S1S65010

## ■ MODESEL 端子によるシステムコンフィギュレーション設定

| 端子名  | 端子機能      | リセット時の値      |                     |

|------|-----------|--------------|---------------------|

|      |           | Low          | High                |

| MD0  | MODESEL0  | 32kHz Mode   | 予約（テスト用）*           |

| MD1  | MODESEL1  | 水晶発振安定時間（3秒） | 予約（テスト用）*           |

| MD2  | MODESEL2  | 通常動作         | 予約（テスト用）*           |

| MD3  | MODESEL3  |              | Reserved (Use "0.") |

| MD4  | MODESEL4  | USER 設定用     | USER 設定用            |

| MD5  | MODESEL5  | USER 設定用     | USER 設定用            |

| MD6  | MODESEL6  | USER 設定用     | USER 設定用            |

| MD7  | MODESEL7  | USER 設定用     | USER 設定用            |

| MD8  | MODESEL8  | USER 設定用     | USER 設定用            |

| MD9  | MODESEL9  | USER 設定用     | USER 設定用            |

| MD10 | MODESEL10 | USER 設定用     | USER 設定用            |

| MD11 | MODESEL11 | USER 設定用     | USER 設定用            |

| MD12 | MODESEL12 | USER 設定用     | USER 設定用            |

| MD13 | MODESEL13 | USER 設定用     | USER 設定用            |

| MD14 | MODESEL14 | USER 設定用     | USER 設定用            |

| MD15 | MODESEL15 | USER 設定用     | USER 設定用            |

\* 注意：予約（テスト用）と指定されている部分の設定は使用しないでください。予約（テスト用）の設定を使用した場合にはICの破壊に至ることがあります。

## ■ 物理仕様

| 項目         |                           | 特長                                                     |

|------------|---------------------------|--------------------------------------------------------|

| 電源電圧       | コアシステム電源 (LVDD)           | 1.8V ± 0.15V                                           |

|            | I/O システム電源 (HVDD1)        | 3.3V ± 0.30V                                           |

|            | カメラ Interface 用電源 (HVDD2) | 2.4V (Min.) – 3.6V (Max.)                              |

|            | PLL 電源 (PLLVDD)           | 1.8V ± 0.15V (アナログ電源)                                  |

| 動作周波数      | CPU                       | 50MHz Max.                                             |

| 消費電力 (参考値) |                           | 140mW (Typ.), 3mW (MII I/F 停止かつ HALT 時)                |

| 動作温度       |                           | T <sub>a</sub> = -40 to +85°C                          |

| パッケージ      |                           | TQFP 144 pin (TQFP24) 16 × 16 × 1 mm / 0.4mm Pin pitch |

## ■ GPIO 端子のマルチプレクス端子機能、リセット直後の端子機能

| S1S65010<br>端子名称 | リセット<br>直後の<br>端子機能 | GPIO   | INT  | アドレス<br>バス | UART/<br>UART<br>Lite | I <sup>2</sup> C | SPI /<br>I <sup>2</sup> S | タイマ      | カメラ<br>I/F          | CF<br>カード | MII |

|------------------|---------------------|--------|------|------------|-----------------------|------------------|---------------------------|----------|---------------------|-----------|-----|

| GPIOA0           | GPIOA0              | GPIOA0 |      |            | TXD0                  |                  |                           |          |                     |           |     |

| GPIOA1           | GPIOA1              | GPIOA1 |      |            | RXD0                  |                  |                           |          |                     |           |     |

| GPIOA2           | GPIOA2              | GPIOA2 |      |            | TXD1                  |                  | SPI_SS                    |          |                     |           |     |

| GPIOA3           | GPIOA3              | GPIOA3 |      |            | RXD1                  |                  | SPI_SCLK                  |          |                     |           |     |

| GPIOA4           | GPIOA4              | GPIOA4 |      |            |                       |                  | SPI_MISO                  |          |                     |           |     |

| GPIOA5           | GPIOA5              | GPIOA5 |      |            |                       |                  | SPI_MOSI                  |          |                     |           |     |

| GPIOA6           | GPIOA6              | GPIOA6 |      |            |                       | SCL              |                           |          |                     |           |     |

| GPIOA7           | GPIOA7              | GPIOA7 |      |            |                       | SDA              |                           |          |                     |           |     |

| GPIOB0           | GPIOB0              | GPIOB0 | INT0 |            |                       | I2S0_WS          |                           |          |                     |           |     |

| GPIOB1           | GPIOB1              | GPIOB1 | INT1 |            | RTS0#                 | I2S0_SCK         |                           |          |                     |           |     |

| GPIOB2           | GPIOB2              | GPIOB2 | INT2 |            | CTS0#                 | I2S0_SD          |                           |          |                     |           |     |

| GPIOB3           | GPIOB3              | GPIOB3 | INT3 |            |                       | I2S1_SD          | Timer0out                 |          |                     |           |     |

| GPIOB4           | GPIOB4              | GPIOB4 | INT4 |            |                       |                  | Timer1out                 |          |                     |           |     |

| GPIOB5           | GPIOB5              | GPIOB5 | INT5 |            |                       |                  | Timer2out                 |          |                     |           |     |

| GPIOB6           | GPIOB6              | GPIOB6 | INT6 | MA22       |                       | I2S1_SCK         |                           |          |                     |           |     |

| GPIOB7           | GPIOB7              | GPIOB7 | INT7 | MA23       |                       | I2S1_WS          |                           |          |                     |           |     |

| CMDATA0          | GPIOC0              | GPIOC0 |      |            |                       |                  |                           | CMDATA0  |                     |           |     |

| CMDATA1          | GPIOC1              | GPIOC1 |      |            |                       |                  |                           | CMDATA1  |                     |           |     |

| CMDATA2          | GPIOC2              | GPIOC2 |      |            |                       |                  |                           | CMDATA2  |                     |           |     |

| CMDATA3          | GPIOC3              | GPIOC3 |      |            |                       |                  |                           | CMDATA3  |                     |           |     |

| CMDATA4          | GPIOC4              | GPIOC4 |      |            |                       |                  |                           | CMDATA4  |                     |           |     |

| CMDATA5          | GPIOC5              | GPIOC5 |      |            |                       |                  |                           | CMDATA5  |                     |           |     |

| CMDATA6          | GPIOC6              | GPIOC6 |      |            |                       |                  |                           | CMDATA6  |                     |           |     |

| CMDATA7          | GPIOC7              | GPIOC7 |      |            |                       |                  |                           | CMDATA7  |                     |           |     |

| GPIOD0           | GPIOD0              | GPIOD0 | INT8 | MA20       |                       |                  |                           |          |                     |           |     |

| GPIOD1           | GPIOD1              | GPIOD1 |      | MA21       |                       |                  |                           |          |                     |           |     |

| CFCE2#           | GPIOD2              | GPIOD2 |      |            |                       |                  |                           |          | CFCE2#              |           |     |

| CFCE1#           | GPIOD3              | GPIOD3 |      |            |                       |                  |                           |          | CFCE1#              |           |     |

| CMVREF           | GPIOD4              | GPIOD4 |      |            |                       |                  |                           | CMVREF   |                     |           |     |

| CMHREF           | GPIOD5              | GPIOD5 |      |            |                       |                  |                           | CMHREF   |                     |           |     |

| CMCLKOUT         | GPIOD6              | GPIOD6 |      |            |                       |                  |                           | CMCLKOUT |                     |           |     |

| CMCLKIN          | GPIOD7              | GPIOD7 |      |            |                       |                  |                           | CMCLKIN  |                     |           |     |

| CFIORD#          | GPIOE0              | GPIOE0 |      |            |                       | I2S0_SD          |                           |          | CFIORD#             |           |     |

| CFIOWR#          | GPIOE1              | GPIOE1 |      |            |                       | I2S0_SCK         |                           |          | CFIOWR#             |           |     |

| CFWAIT#          | GPIOE2              | GPIOE2 |      |            |                       |                  |                           |          | CFWAIT# /<br>MWAIT# |           |     |

| CFRST            | GPIOE3              | GPIOE3 |      |            |                       | I2S0_WS          |                           |          | CFRST               |           |     |

| CFIREQ           | GPIOE4              | GPIOE4 |      |            |                       |                  |                           |          | CFIREQ              |           |     |

| CFSTSCHG#        | GPIOE5              | GPIOE5 |      |            |                       | I2S1_SD          |                           |          | CFSTSCHG#           |           |     |

| CFDEN#           | GPIOE6              | GPIOE6 |      |            |                       | I2S1_SCK         |                           |          | CFDEN#              |           |     |

| CFDDIR           | GPIOE7              | GPIOE7 |      |            |                       | I2S1_WS          |                           |          | CFDDIR              |           |     |

| MII_CRS          | MII_CRS             | GPIOF0 |      |            |                       |                  |                           |          |                     | MII_CRS   |     |

| MII_COL          | MII_COL             | GPIOF1 |      |            |                       |                  |                           |          |                     | MII_COL   |     |

| MII_TXD3         | MII_TXD3            | GPIOF2 |      |            |                       |                  |                           |          |                     | MII_TXD3  |     |

| MII_TXD2         | MII_TXD2            | GPIOF3 |      |            |                       |                  |                           |          |                     | MII_TXD2  |     |

| MII_TXD1         | MII_TXD1            | GPIOF4 |      |            |                       |                  |                           |          |                     | MII_TXD1  |     |

| MII_TXD0         | MII_TXD0            | GPIOF5 |      |            |                       |                  |                           |          |                     | MII_TXD0  |     |

| MII_TXEN         | MII_TXEN            | GPIOF6 |      |            |                       |                  |                           |          |                     | MII_TXEN  |     |

| MII_TXCLK        | MII_TXCLK           | GPIOF7 |      |            |                       |                  |                           |          |                     | MII_TXCLK |     |

| MII_RXER         | MII_RXER            | GPIOG0 |      |            |                       |                  |                           |          |                     | MII_RXER  |     |

| MII_RXCLK        | MII_RXCLK           | GPIOG1 |      |            |                       |                  |                           |          |                     | MII_RXCLK |     |

| MII_RXDV         | MII_RXDV            | GPIOG2 |      |            |                       |                  |                           |          |                     | MII_RXDV  |     |

| MII_RXD0         | MII_RXD0            | GPIOG3 |      |            |                       |                  |                           |          |                     | MII_RXD0  |     |

| MII_RXD1         | MII_RXD1            | GPIOG4 |      |            |                       |                  |                           |          |                     | MII_RXD1  |     |

| MII_RXD2         | MII_RXD2            | GPIOG5 |      |            |                       |                  |                           |          |                     | MII_RXD2  |     |

| MII_RXD3         | MII_RXD3            | GPIOG6 |      |            |                       |                  |                           |          |                     | MII_RXD3  |     |

| MII_MDC          | MII_MDC             | GPIOG7 |      |            |                       |                  |                           |          |                     | MII_MDC   |     |

| MII_MDIO         | MII_MDIO            | GPIOH0 |      |            |                       |                  |                           |          |                     | MII_MDIO  |     |

機能 1 : 機能 1

機能 2 : 機能 2

# S1S65010

## ■ リセット中およびリセット後の端子の状態

| Pin Name     | RESET 中の方向 | RESET 中の値                 | 内蔵抵抗の有無        | 説明                 |

|--------------|------------|---------------------------|----------------|--------------------|

| MA[19:0]     | 出力         | Low<br>(但し bit11 のみ High) | 無し             |                    |

| MD[15:0]     | 入力         | Low                       | Pull Down 抵抗有り | 100kΩ              |

| MCS[2]#      | 出力         | Low                       | 無し             |                    |

| MCS[1]#      | 出力         | High                      | 無し             |                    |

| MCS[0]#      | 出力         | High                      | 無し             |                    |

| MOE#         | 出力         | High                      | 無し             |                    |

| MWE0#        | 出力         | High                      | 無し             |                    |

| MWE1#        | 出力         | Low                       | 無し             |                    |

| MCLK         | 出力         | MCLK(32KHz)               | 無し             |                    |

| MCLKEN       | 出力         | High                      | 無し             |                    |

| MRAS#        | 出力         | Low                       | 無し             |                    |

| MCAS#        | 出力         | High                      | 無し             |                    |

| MDQML        | 出力         | Low                       | 無し             |                    |

| MDQMH        | 出力         | Low                       | 無し             |                    |

| MII_TXCLK    | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_TXEN     | 出力         | Low                       | 無し             |                    |

| MII_TXD[3:0] | 出力         | 不定                        | 無し             | 初期化するまで不定          |

| MII_RXCLK    | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_COL      | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_CRS      | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_RXDV     | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_RXD[3:0] | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_RXER     | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| MII_MDC      | 出力         | Low                       | 無し             |                    |

| MII_MDIO     | 入力         | High-Z                    | 無し             | 外部回路依存, 通常 MII-PHY |

| CMDATA[7:0]  | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| CMVREF       | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| CMHREF       | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| CMCLKOUT     | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| CMCLKIN      | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| CFCE2#       | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFCE1#       | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFIORD#      | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFIOWR#      | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFWAIT#      | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFRST        | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFIREQ       | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFSTSCHG#    | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFDEN#       | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| CFDDIR       | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| GPIOA[7:0]   | 入力         | High-Z                    | 無し             | 外部回路依存             |

| GPIOB[7:0]   | 入力         | High-Z                    | 無し             | 外部回路依存             |

| GPIOD[1:0]   | 入力         | High-Z                    | 無し             | 外部回路依存             |

| CLKI         | 入力         | High-Z                    | 無し             |                    |

| VCP          | 出力         | High-Z                    | 無し             | Open のまま使用する       |

| TRST#        | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| TCK          | 入力         | High-Z                    | 無し             |                    |

| TMS          | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| TDI          | 入力         | High                      | Pull Up 抵抗有り   | 50kΩ               |

| TDO          | 出力         | High-Z                    | 無し             |                    |

| TESTEN       | 入力         | Low                       | Pull Down 抵抗有り | 50kΩ               |

| RESET#       | 入力         | Low                       | 無し             |                    |

RESET 後の値は、それぞれのピンの設定内容により決まる。

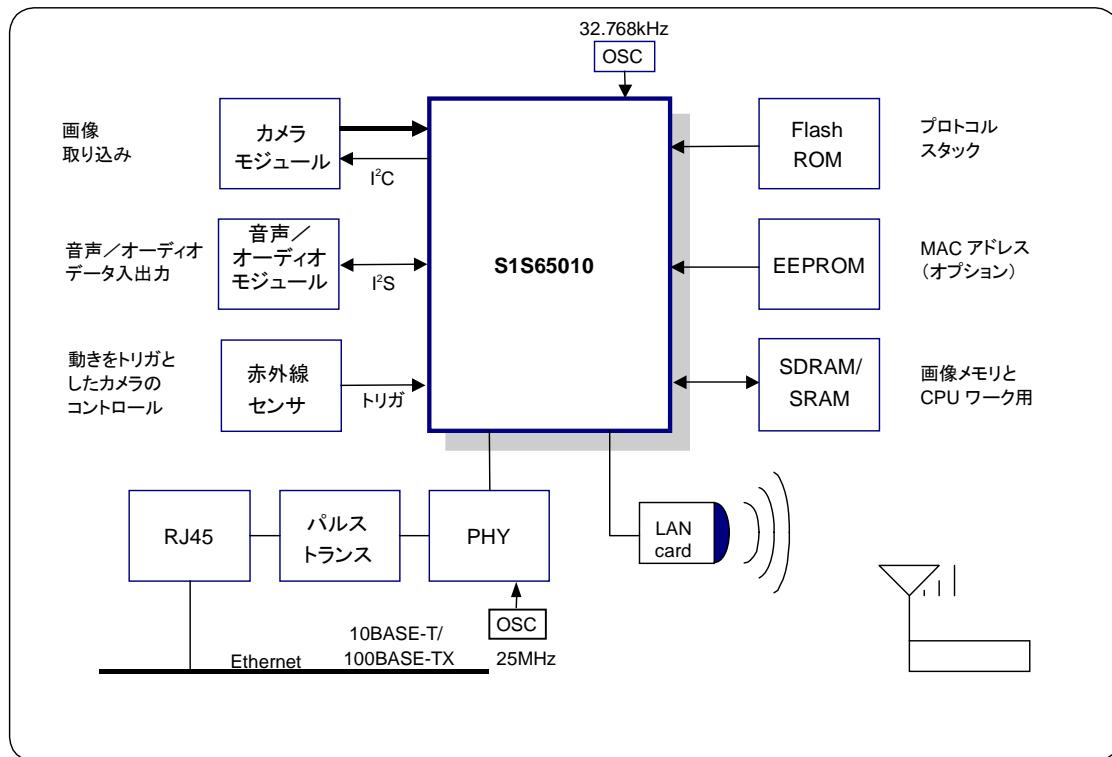

## ■ 使用例

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替法及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。

よって、弊社は本（当該）製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

POWERED

**ARM** は ARM 社の登録商標です。

CompactFlash は Sandisk 社の登録商標です。

その他記載の会社名、製品名は、それぞれの会社の商標もしくは登録商標です。

©SEIKO EPSON CORPORATION 2008

## セイコーエプソン株式会社

### 半導体事業部 IC 営業部

<IC 東日本営業部>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042)587-5313(直通) FAX (042)587-5116

<IC 西日本営業部>

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06)6120-6000(代表) FAX (06)6120-6100

インターネットによる電子デバイスのご紹介

<http://www.epson.jp/device/semicon/>

ドキュメントコード : 405160207

2004 年 6 月作成

2008 年 6 月改訂