EPSON

# ARM720T Revision 4

(AMBA AHB Bus Interface Version)

コアCPUマニュアル

本資料のご使用につきましては、次の点にご留意願います。

-

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または複製など他の目的に使用することは、堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

\* ARM は、ARM 社の登録商標です。

\* CompactFlash は Sandisk 社の登録商標です。

その他記載の会社名、製品名は、それぞれの会社の商標もしくは登録商標です。

## はじめに

## 1 概要

## 2 プログラマーズモデル

## 3 コンフィギュレーション

## 4 命令・データキャッシュ

## 5 ライトバッファ

## 6 バスインターフェース

## 7 メモリ管理ユニット

## 8 コプロセッサインターフェース

## 9 システムのデバッグ

## 10 ETMインターフェース

## 11 テストサポート

## A 信号の説明

## 用語集

## 索引

# 目次

## はじめに

|              |    |

|--------------|----|

| 本書について ..... | xi |

|--------------|----|

## 1 概要

|                             |      |

|-----------------------------|------|

| 1.1 ARM720T プロセッサについて ..... | 1-1  |

| 1.2 コプロセッサ .....            | 1-5  |

| 1.3 命令セット .....             | 1-5  |

| 1.4 シリコンレビジョン .....         | 1-18 |

## 2 プログラマーズモデル

|                                    |      |

|------------------------------------|------|

| 2.1 プロセッサの動作状態 .....               | 2-1  |

| 2.2 メモリ形式 .....                    | 2-2  |

| 2.3 命令長 .....                      | 2-3  |

| 2.4 データタイプ .....                   | 2-3  |

| 2.5 動作モード .....                    | 2-4  |

| 2.6 レジスタ .....                     | 2-5  |

| 2.7 プログラムステータスレジスタ .....           | 2-9  |

| 2.8 例外 .....                       | 2-11 |

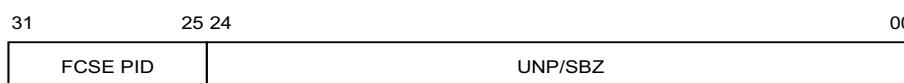

| 2.9 FCSE PID による下位仮想アドレスの再配置 ..... | 2-16 |

| 2.10 リセット .....                    | 2-17 |

| 2.11 インプリメンテーション時定義の命令動作 .....     | 2-18 |

## 3 コンフィギュレーション

|                           |     |

|---------------------------|-----|

| 3.1 コンフィギュレーションについて ..... | 3-1 |

| 3.2 内部コプロセッサ命令 .....      | 3-2 |

| 3.3 レジスタ .....            | 3-3 |

## 4 命令・データキャッシュ

|                                     |     |

|-------------------------------------|-----|

| 4.1 命令・データキャッシュについて .....           | 4-1 |

| 4.2 IDC 有効性 .....                   | 4-2 |

| 4.3 IDC イネーブル / ディセーブルおよびリセット ..... | 4-2 |

## 5 ライトバッファ

|                       |     |

|-----------------------|-----|

| 5.1 ライトバッファについて ..... | 5-1 |

| 5.2 ライトバッファ動作 .....   | 5-2 |

## 6 バスインターフェース

|                          |      |

|--------------------------|------|

| 6.1 バスインターフェースについて ..... | 6-1  |

| 6.2 バスインターフェース信号 .....   | 6-3  |

| 6.3 転送タイプ .....          | 6-5  |

| 6.4 アドレスと制御信号 .....      | 6-7  |

| 6.5 スレーブ転送応答信号 .....     | 6-9  |

| 6.6 データバス .....          | 6-10 |

| 6.7 アービトレーション .....      | 6-12 |

| 6.8 バスクロッキング .....       | 6-13 |

|     |            |      |

|-----|------------|------|

| 6.9 | リセット ..... | 6-13 |

|-----|------------|------|

## 7 メモリ管理ユニット

|     |                                |      |

|-----|--------------------------------|------|

| 7.1 | MMU について .....                 | 7-1  |

| 7.2 | MMU プログラムアクセス可能レジスタ .....      | 7-3  |

| 7.3 | アドレス変換 .....                   | 7-4  |

| 7.4 | MMU フォールトと CPU アポート .....      | 7-15 |

| 7.5 | フォールトアドレスとフォールトステータスレジスタ ..... | 7-16 |

| 7.6 | ドメインアクセス制御 .....               | 7-17 |

| 7.7 | フォールトチェックシーケンス .....           | 7-19 |

| 7.8 | 外部アポート .....                   | 7-21 |

| 7.9 | MMU とキャッシュの相互作用 .....          | 7-21 |

## 8 コプロセッサインターフェース

|     |                               |      |

|-----|-------------------------------|------|

| 8.1 | コプロセッサについて .....              | 8-1  |

| 8.2 | コプロセッサインターフェース信号 .....        | 8-3  |

| 8.3 | パイプライン監視信号 .....              | 8-4  |

| 8.4 | コプロセッサインターフェースハンドシェイキング ..... | 8-5  |

| 8.5 | コプロセッサの接続 .....               | 8-9  |

| 8.6 | 外部コプロセッサを使用しない場合 .....        | 8-10 |

| 8.7 | STC 操作 .....                  | 8-10 |

| 8.8 | 未定義命令 .....                   | 8-10 |

| 8.9 | 特権命令 .....                    | 8-10 |

## 9 システムのデバッグ

|      |                               |      |

|------|-------------------------------|------|

| 9.1  | システムのデバッグについて .....           | 9-2  |

| 9.2  | デバッグの制御 .....                 | 9-3  |

| 9.3  | デバッグ状態の開始 .....               | 9-5  |

| 9.4  | デバッグインターフェース .....            | 9-9  |

| 9.5  | ARM720T コアクロックドメイン .....      | 9-9  |

| 9.6  | EmbeddedICE-RT マクロセル .....    | 9-10 |

| 9.7  | EmbeddedICE-RT のディセーブル .....  | 9-11 |

| 9.8  | EmbeddedICE-RT レジスタマップ .....  | 9-12 |

| 9.9  | モニタモードデバッグ .....              | 9-12 |

| 9.10 | デバッグ通信チャネル .....              | 9-14 |

| 9.11 | スキャンチェインと JTAG インタフェース .....  | 9-17 |

| 9.12 | TAP コントローラ .....              | 9-19 |

| 9.13 | パブリック JTAG 命令 .....           | 9-20 |

| 9.14 | テストデータレジスタ .....              | 9-22 |

| 9.15 | スキャンタイミング .....               | 9-25 |

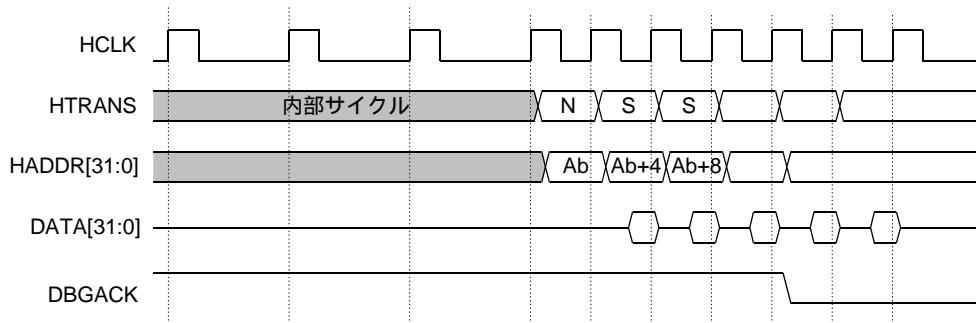

| 9.16 | デバッグ状態のコアおよびシステムの調査 .....     | 9-27 |

| 9.17 | デバッグ状態の終了 .....               | 9-29 |

| 9.18 | デバッグ時のプログラムカウンタ .....         | 9-31 |

| 9.19 | 優先順位と例外 .....                 | 9-33 |

| 9.20 | ウォッチポイントユニットレジスタ .....        | 9-34 |

| 9.21 | ブレークポイントの設定 .....             | 9-37 |

| 9.22 | ウォッチポイントの設定 .....             | 9-39 |

| 9.23 | アポートステータスレジスタ .....           | 9-40 |

| 9.24 | デバッグ制御レジスタ .....              | 9-40 |

| 9.25 | デバッグステータスレジスタ .....           | 9-42 |

| 9.26 | ブレークポイントとウォッチポイントの組み合わせ ..... | 9-44 |

| 9.27 | EmbeddedICE-RT タイミング .....    | 9-45 |

## 10 ETM インタフェース

|      |                               |      |

|------|-------------------------------|------|

| 10.1 | ETM インタフェースについて               | 10-1 |

| 10.2 | ETM7 インタフェースのイネーブル、ディセーブル     | 10-1 |

| 10.3 | ETM7 マクロセルと ARM720T プロセッサ間の接続 | 10-2 |

| 10.4 | クロックとリセット                     | 10-3 |

| 10.5 | デバッグ要求ワイヤリング                  | 10-3 |

| 10.6 | TAP インタフェースワイヤリング             | 10-3 |

## 11 テストサポート

|      |                     |      |

|------|---------------------|------|

| 11.1 | ARM720T テストレジスタについて | 11-1 |

| 11.2 | 自動テストパターン生成 (ATPG)  | 11-2 |

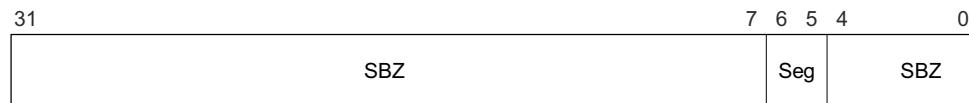

| 11.3 | テストステートレジスタ         | 11-3 |

| 11.4 | キャッシュテストレジスタと動作     | 11-3 |

| 11.5 | MMU テストレジスタと動作      | 11-8 |

## A 信号の説明

|     |                          |     |

|-----|--------------------------|-----|

| A.1 | AMBA インタフェース信号           | A-1 |

| A.2 | コプロセッサインターフェース信号         | A-2 |

| A.3 | JTAG およびテスト信号            | A-3 |

| A.4 | デバッグ信号                   | A-4 |

| A.5 | 組み込み型トレースマクロセルインターフェース信号 | A-5 |

| A.6 | ATPG テスト信号               | A-7 |

| A.7 | その他の信号                   | A-7 |

## 用語集

## 索引

# 図一覧

|        |                                  |      |

|--------|----------------------------------|------|

| 図 1-1  | ARM 720T ブロック図                   | 1-2  |

| 図 1-2  | ARM720T プロセッサ機能信号                | 1-3  |

| 図 1-3  | ARM 命令セットの形式                     | 1-7  |

| 図 1-4  | Thumb (サム) 命令セットの形式              | 1-14 |

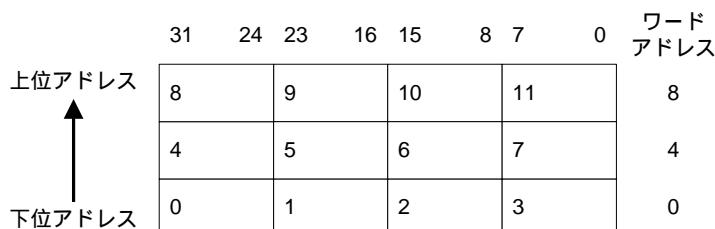

| 図 2-1  | ワード内のバイトのビッグエンディアンアドレス           | 2-2  |

| 図 2-2  | ワード内のバイトのリトルエンディアンアドレス           | 2-3  |

| 図 2-3  | ARM 状態でのレジスタ構成                   | 2-6  |

| 図 2-4  | Thumb 状態でのレジスタ構成                 | 2-7  |

| 図 2-5  | Thumb 状態レジスタから ARM 状態レジスタへのマッピング | 2-8  |

| 図 2-6  | プログラムステータスレジスタ形式                 | 2-9  |

| 図 3-1  | MRC と MCR ビットパターン                | 3-2  |

| 図 3-2  | ID レジスタリードフォーマット                 | 3-3  |

| 図 3-3  | ID レジスタライトフォーマット                 | 3-4  |

| 図 3-4  | 制御レジスタリードフォーマット                  | 3-4  |

| 図 3-5  | 制御レジスタライトフォーマット                  | 3-4  |

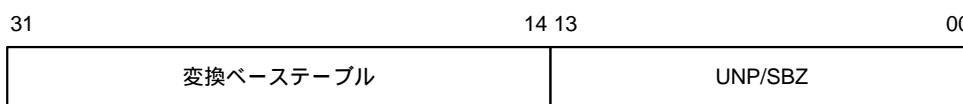

| 図 3-6  | 変換テーブルベースレジスタの形式                 | 3-5  |

| 図 3-7  | ドメインアクセス制御レジスタの形式                | 3-6  |

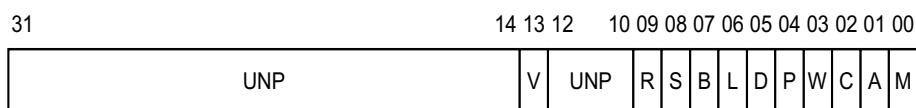

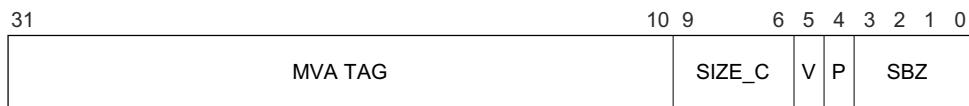

| 図 3-8  | フォールトステータスレジスタの形式                | 3-6  |

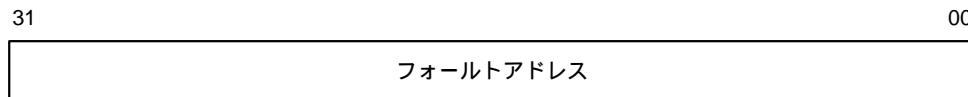

| 図 3-9  | フォールトアドレスレジスタの形式                 | 3-7  |

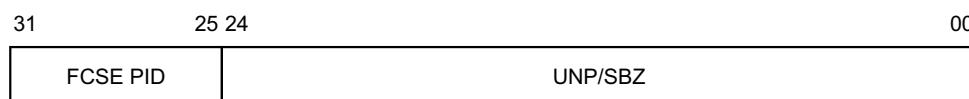

| 図 3-10 | FCSCE PID レジスタの形式                | 3-8  |

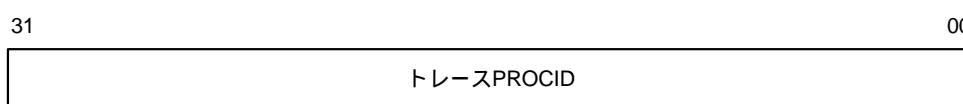

| 図 3-11 | PROCID レジスタの形式                   | 3-8  |

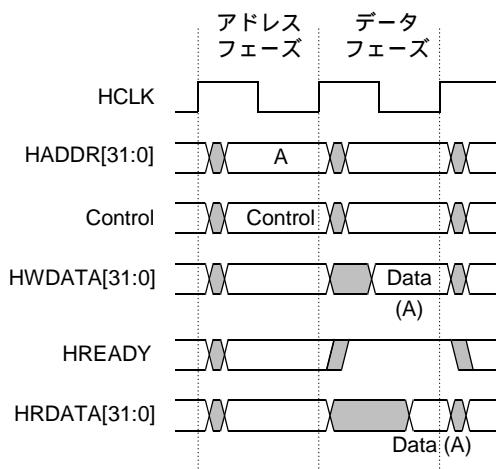

| 図 6-1  | シンプルな AHB 転送                     | 6-2  |

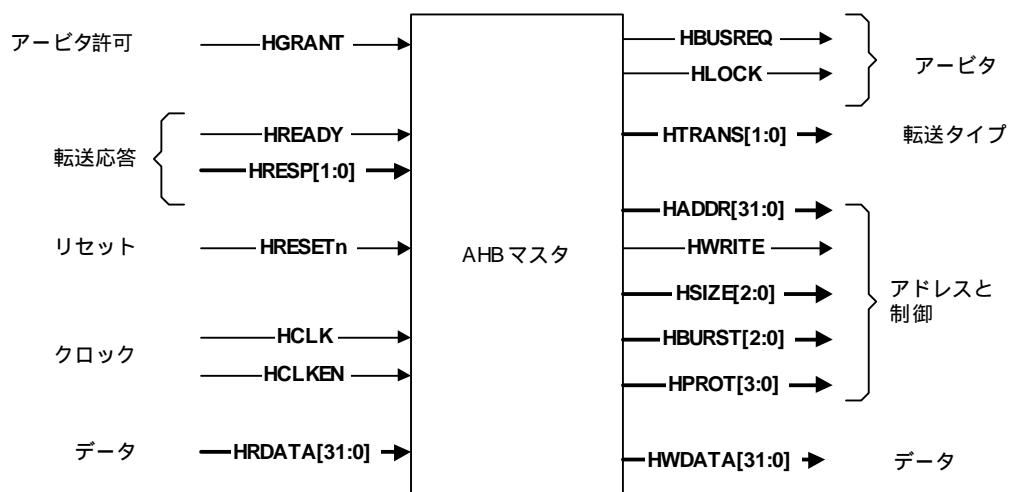

| 図 6-2  | AHB バスマスインターフェース                 | 6-4  |

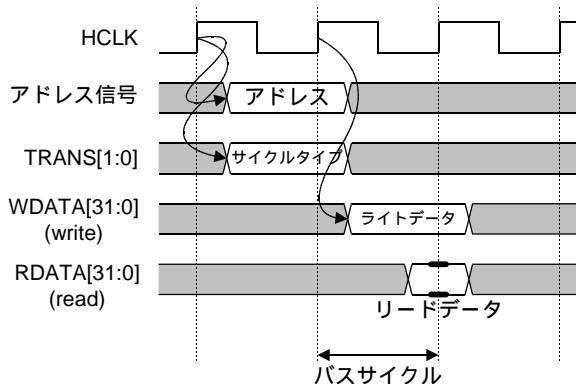

| 図 6-3  | 単純なメモリサイクル                       | 6-5  |

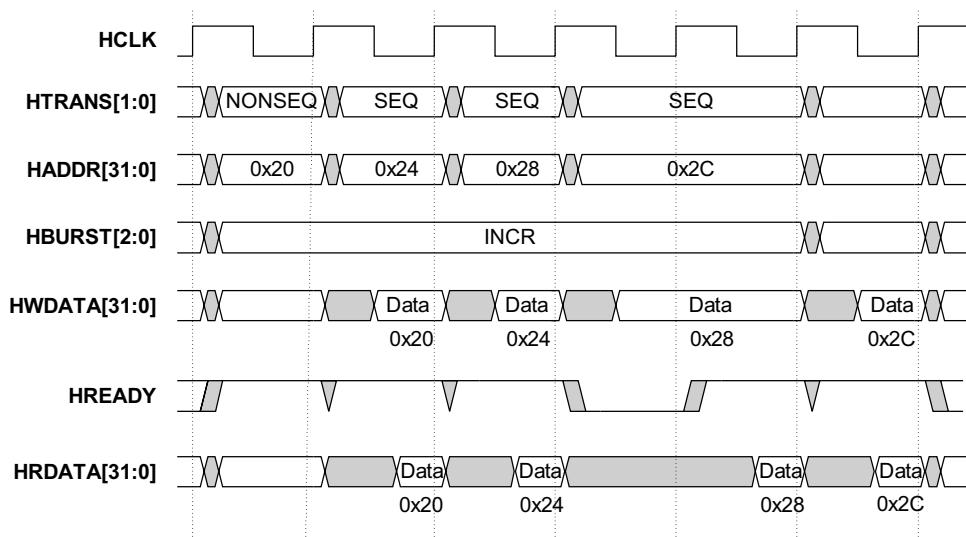

| 図 6-4  | 転送タイプの例                          | 6-6  |

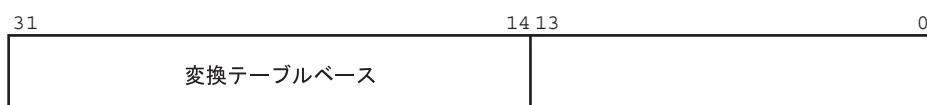

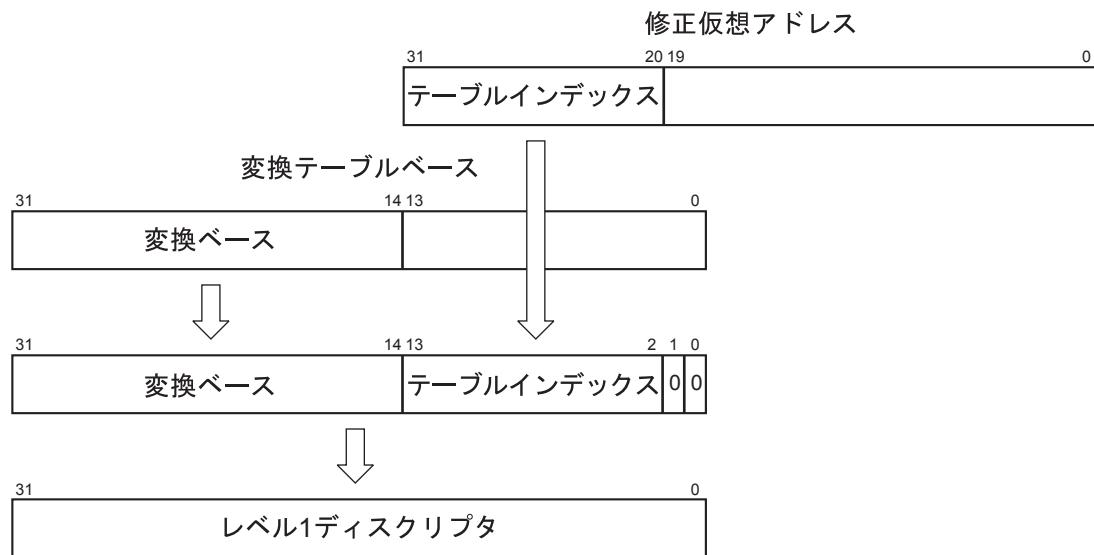

| 図 7-1  | 変換テーブルベースレジスタ                    | 7-4  |

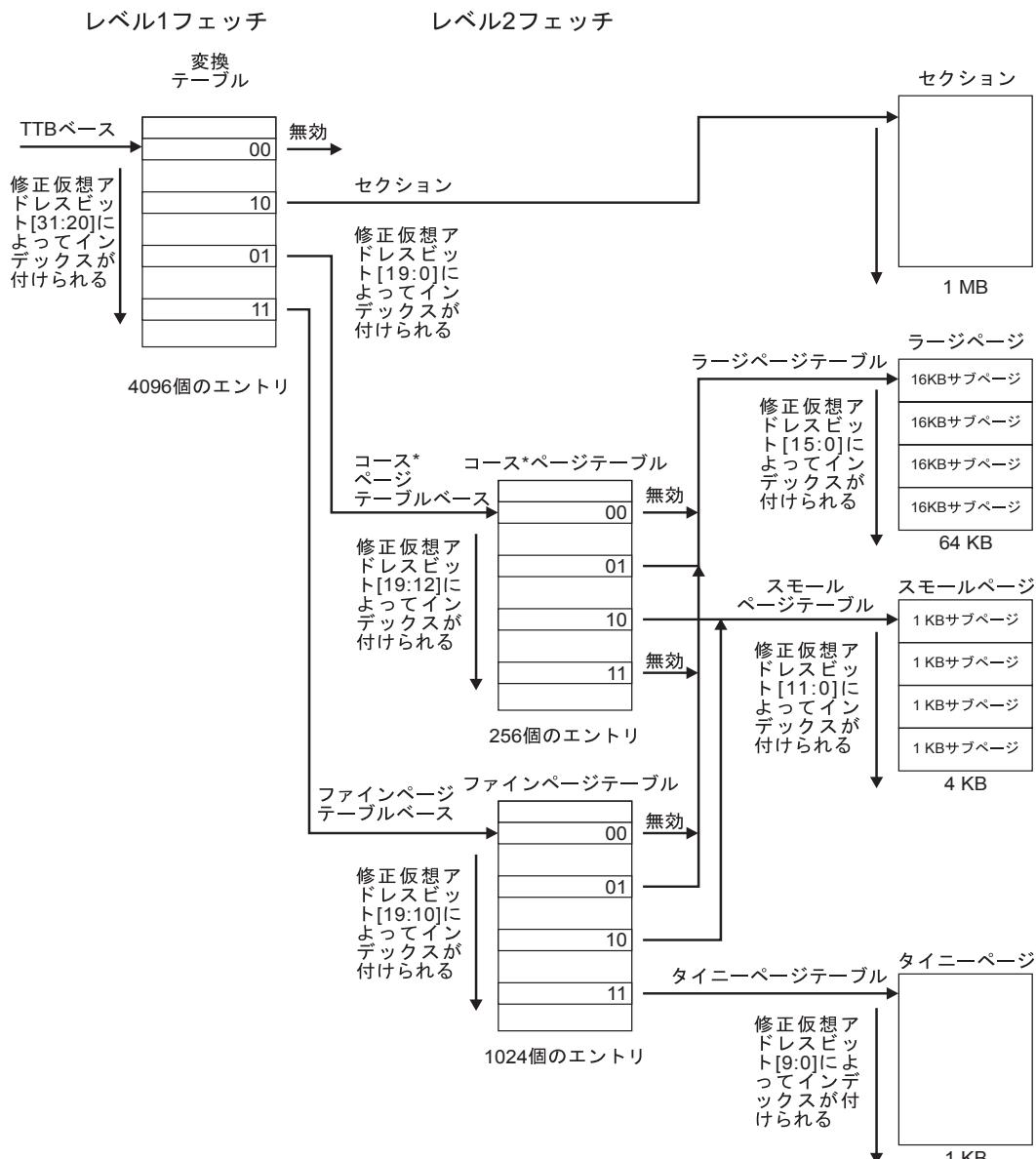

| 図 7-2  | 変換ページテーブル                        | 7-5  |

| 図 7-3  | 変換テーブルレベル 1 ディスクリプタのアクセス         | 7-6  |

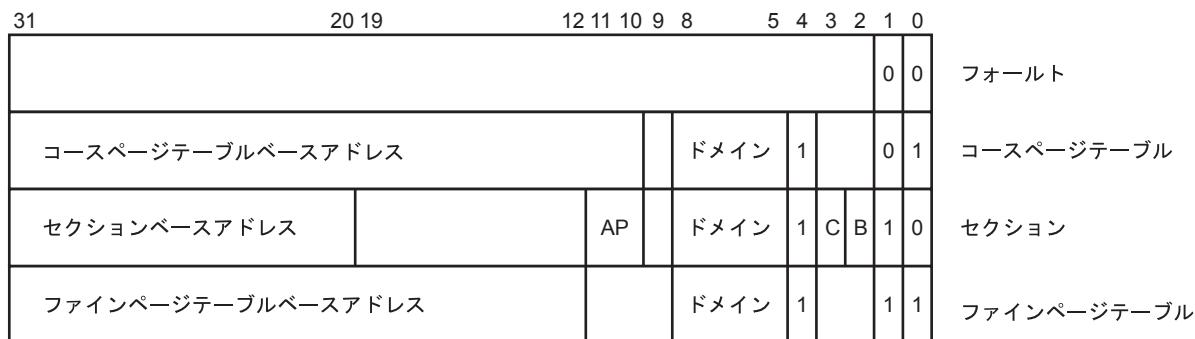

| 図 7-4  | レベル 1 ディスクリプタ                    | 7-6  |

| 図 7-5  | セクションディスクリプタ                     | 7-8  |

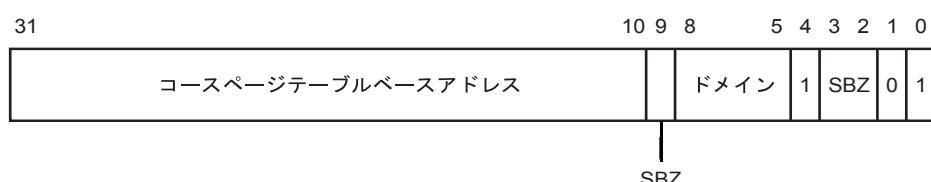

| 図 7-6  | コースページテーブルディスクリプタ                | 7-8  |

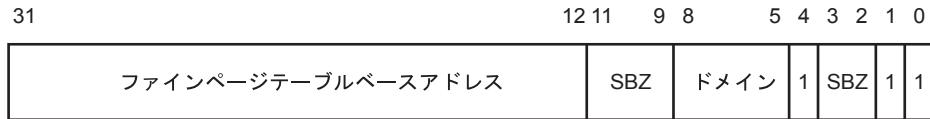

| 図 7-7  | ファインページテーブルディスクリプタ               | 7-9  |

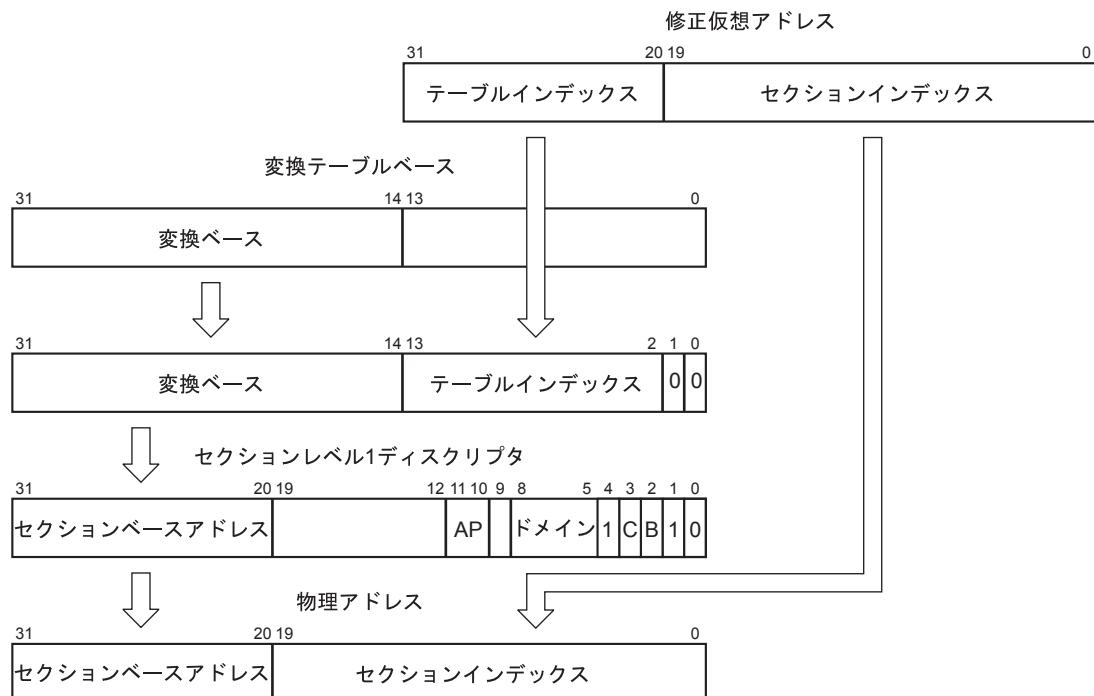

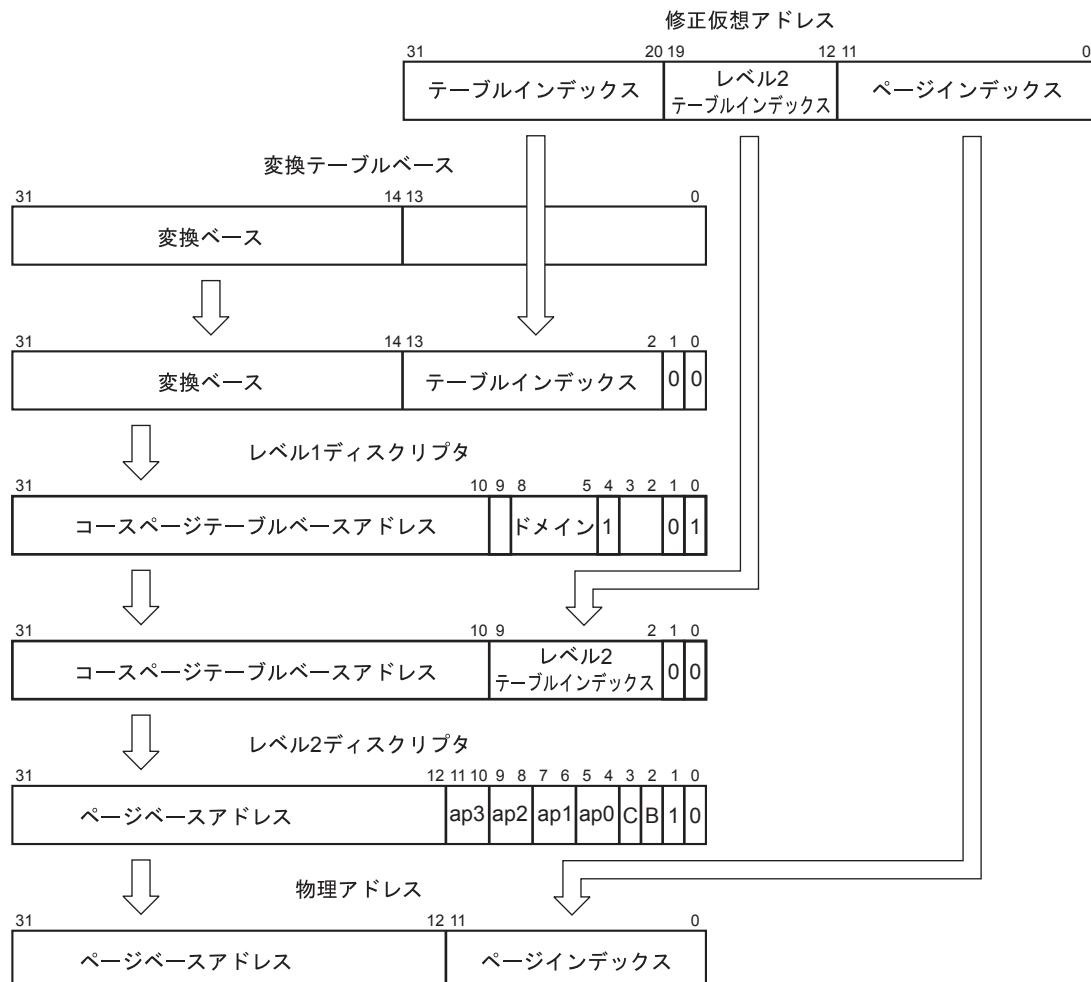

| 図 7-8  | セクション変換                          | 7-10 |

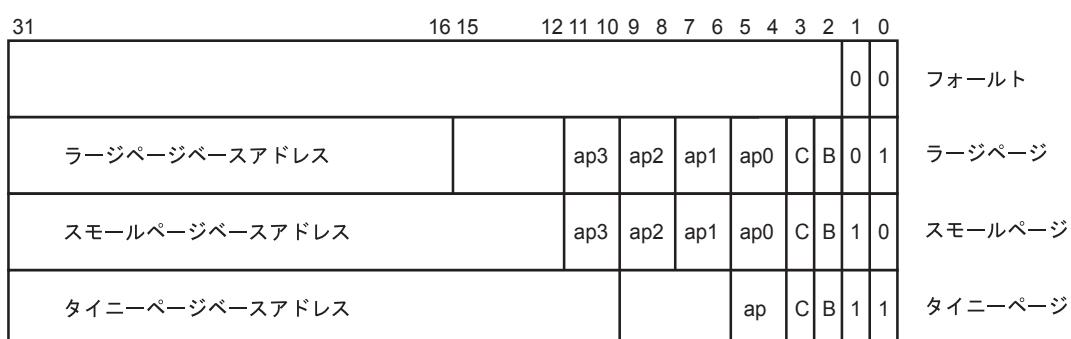

| 図 7-9  | レベル 2 ディスクリプタ                    | 7-10 |

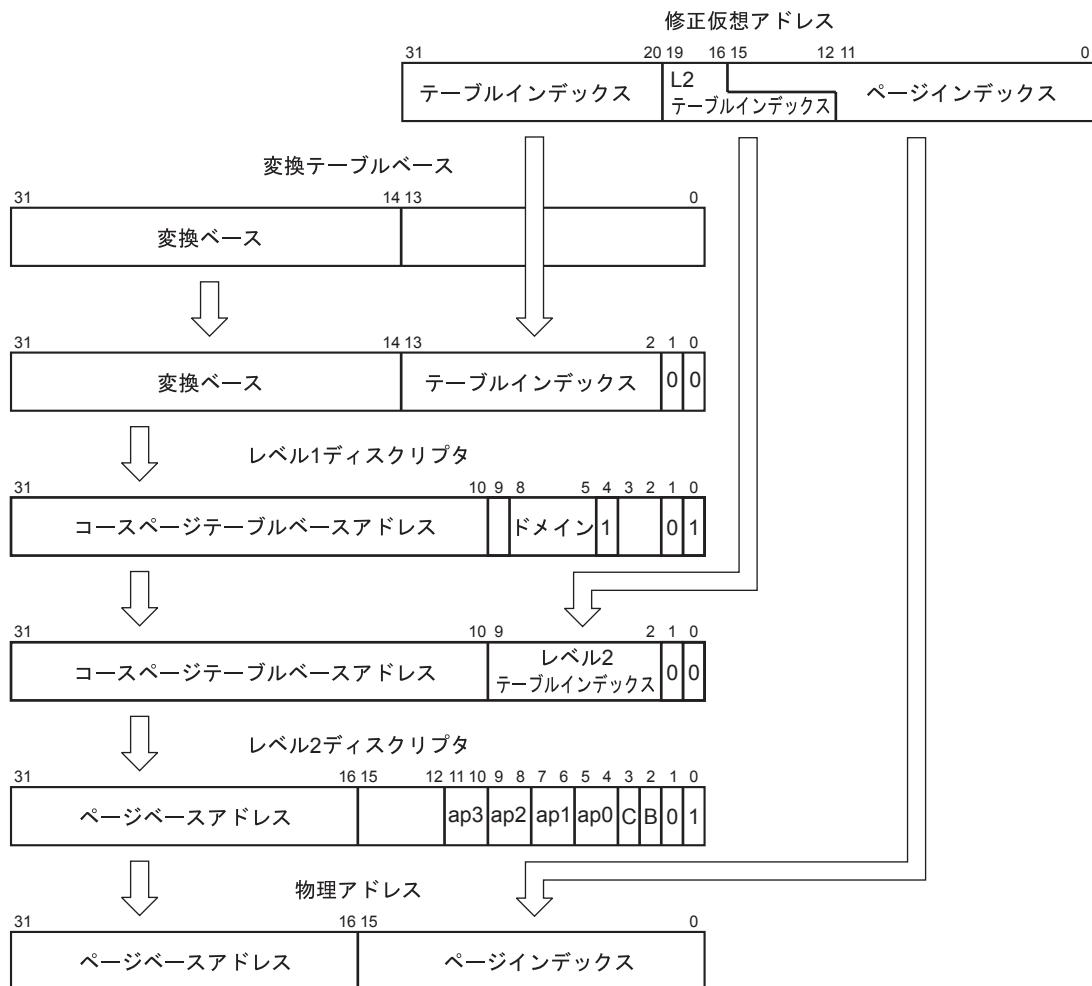

| 図 7-10 | コースページテーブルからのラージページ変換            | 7-12 |

| 図 7-11 | コースページテーブルからのスマールページ変換           | 7-13 |

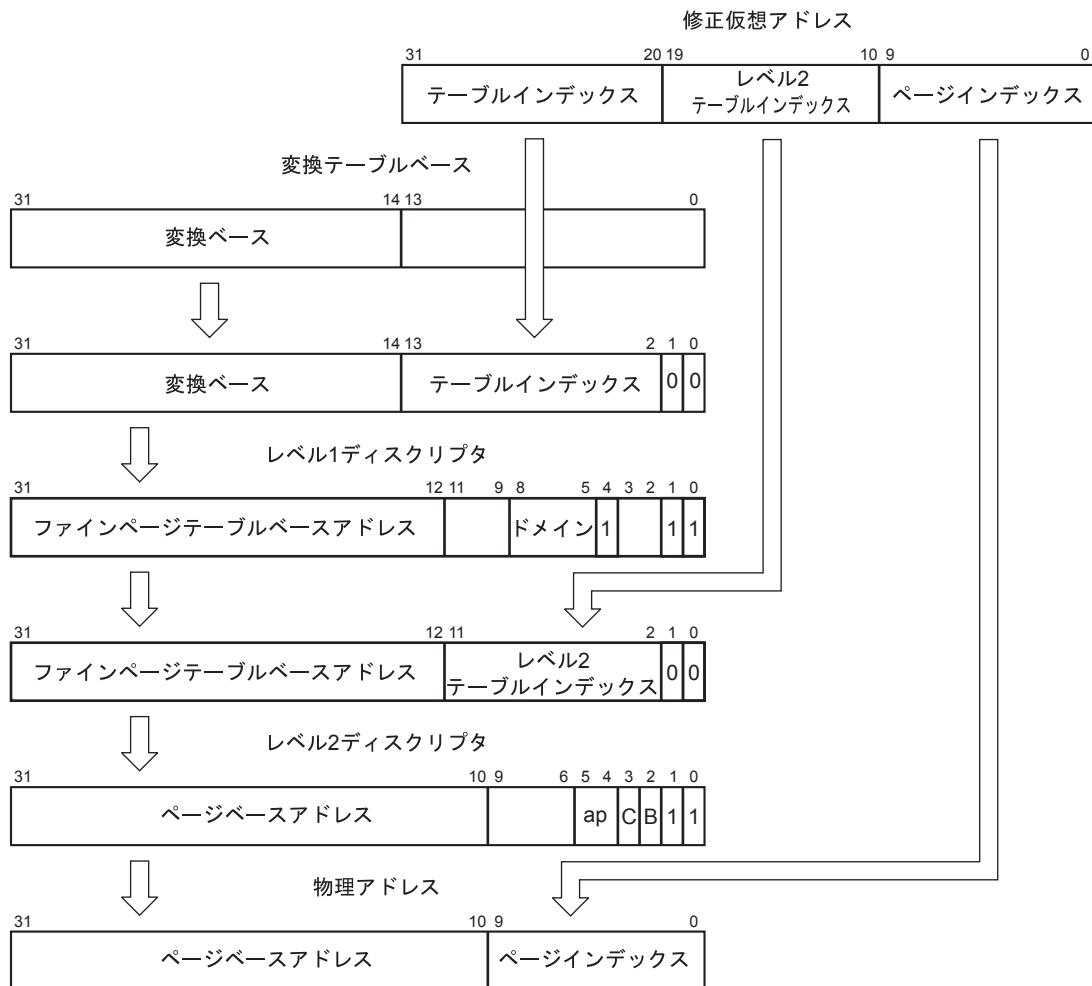

| 図 7-12 | ファインページテーブルからのタイニーページ変換          | 7-14 |

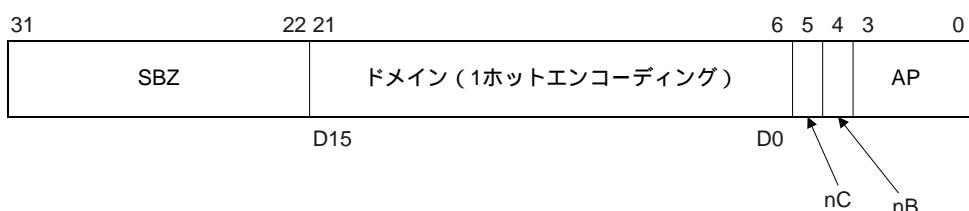

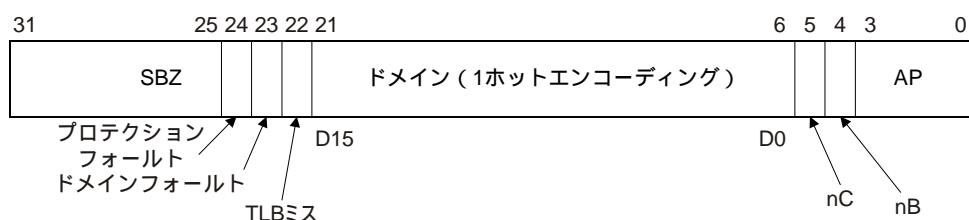

| 図 7-13 | ドメインアクセス制御レジスタの形式                | 7-17 |

| 図 7-14 | フォールトチェックシーケンス                   | 7-19 |

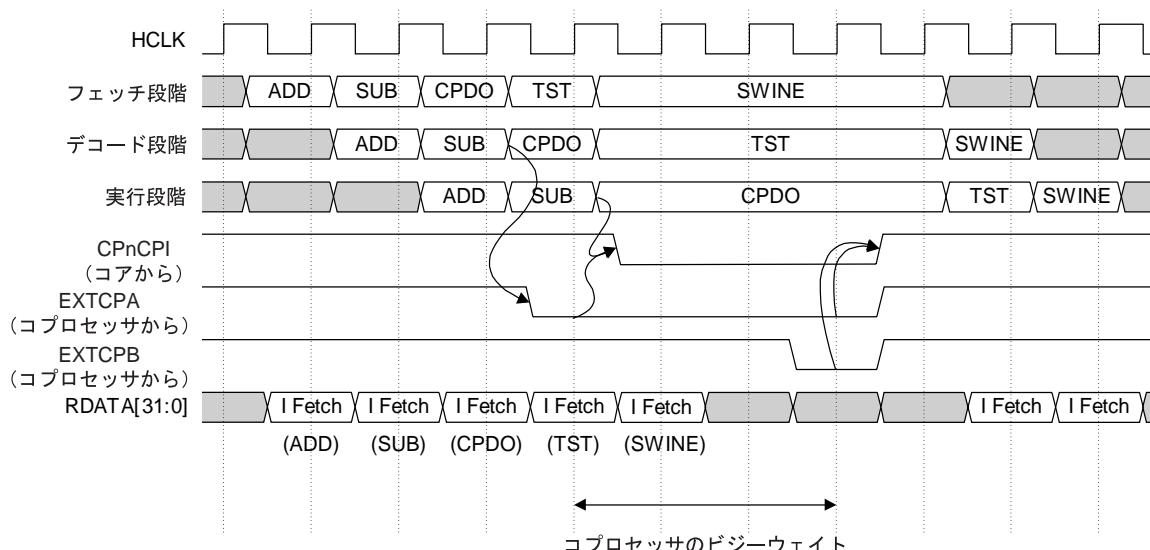

| 図 8-1  | コプロセッサのビギンウェイトシーケンス              | 8-6  |

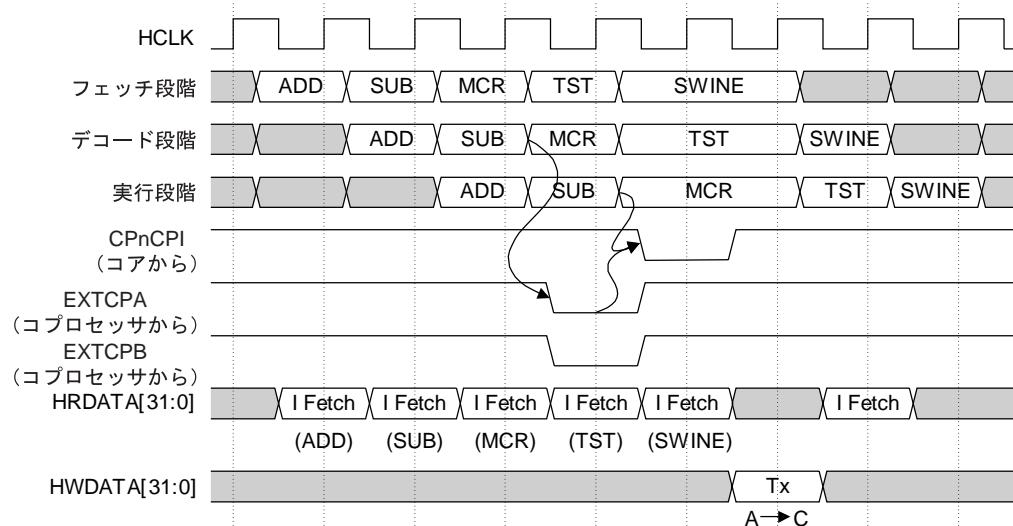

| 図 8-2  | コプロセッサのレジスタ転送シーケンス               | 8-7  |

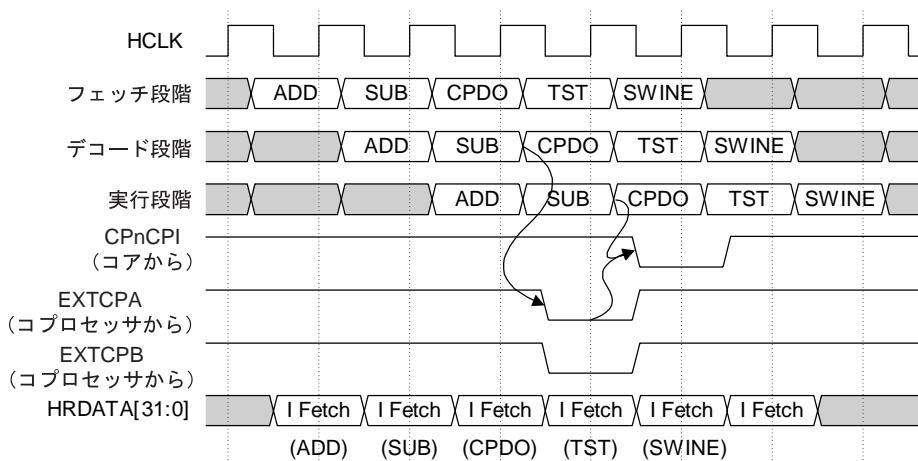

| 図 8-3  | コプロセッサのデータ操作シーケンス                | 8-7  |

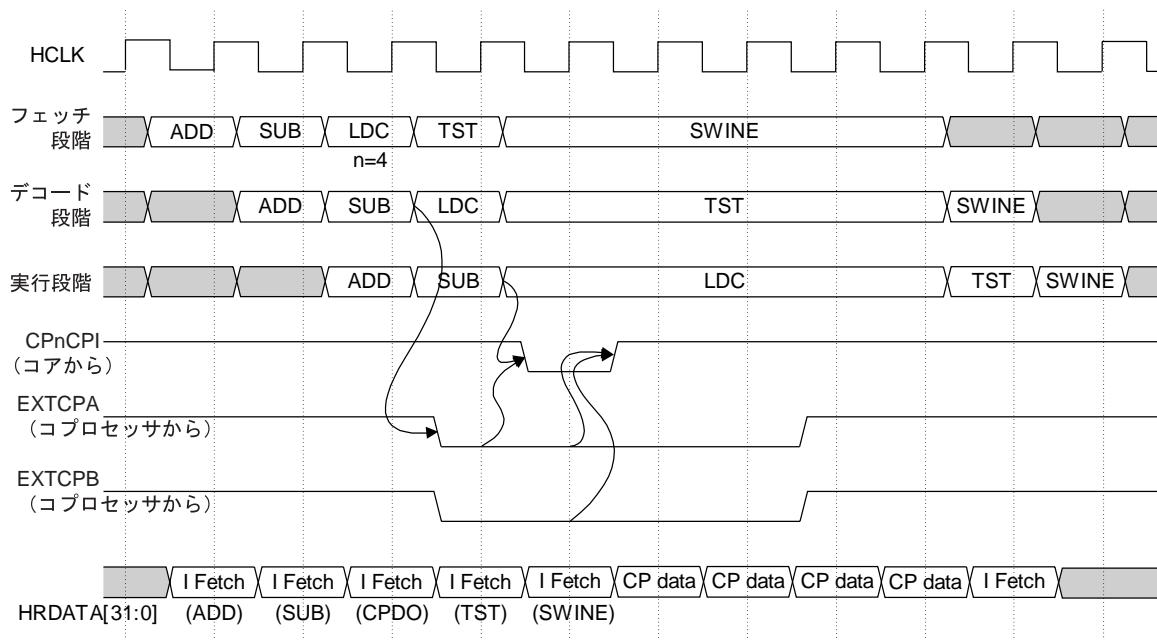

| 図 8-4  | コプロセッサのロードシーケンス                  | 8-8  |

| 図 8-5  | コプロセッサの接続例                       | 8-9  |

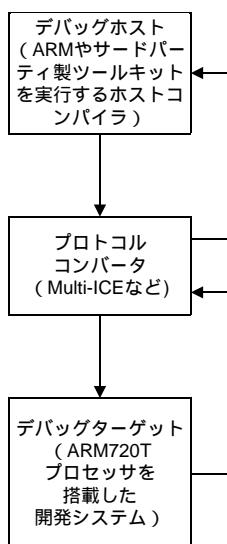

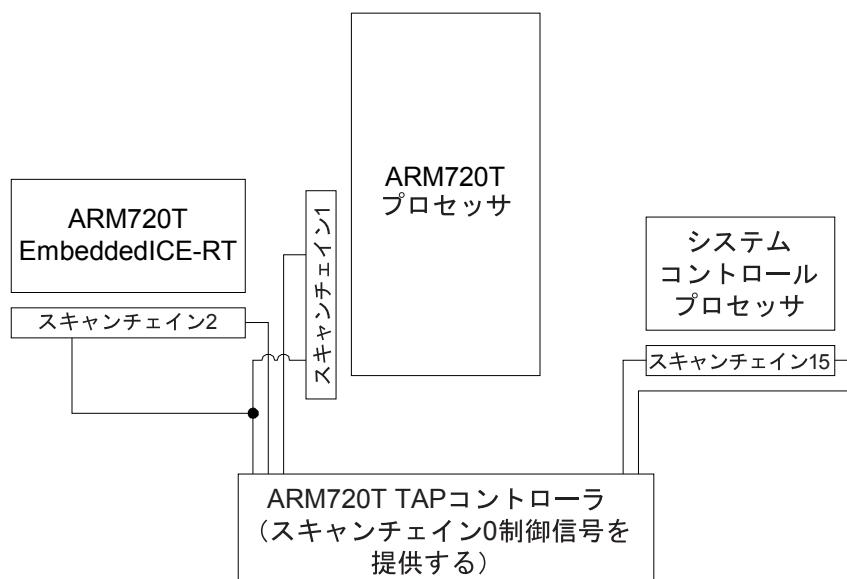

| 図 9-1  | 代表的なデバッグシステム                     | 9-2  |

| 図 9-2  | ARM720T プロセッサブロック図               | 9-3  |

| 図 9-3  | デバッグ状態の開始                        | 9-5  |

|         |                                                      |       |

|---------|------------------------------------------------------|-------|

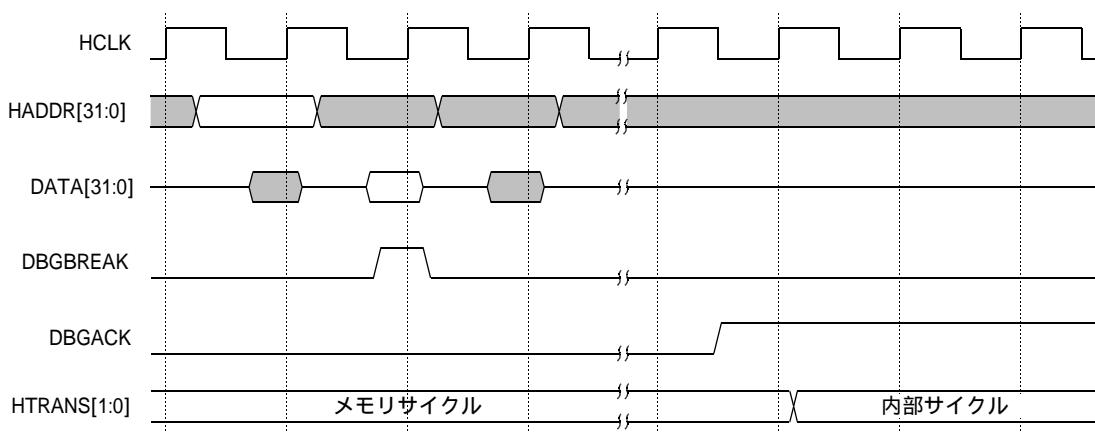

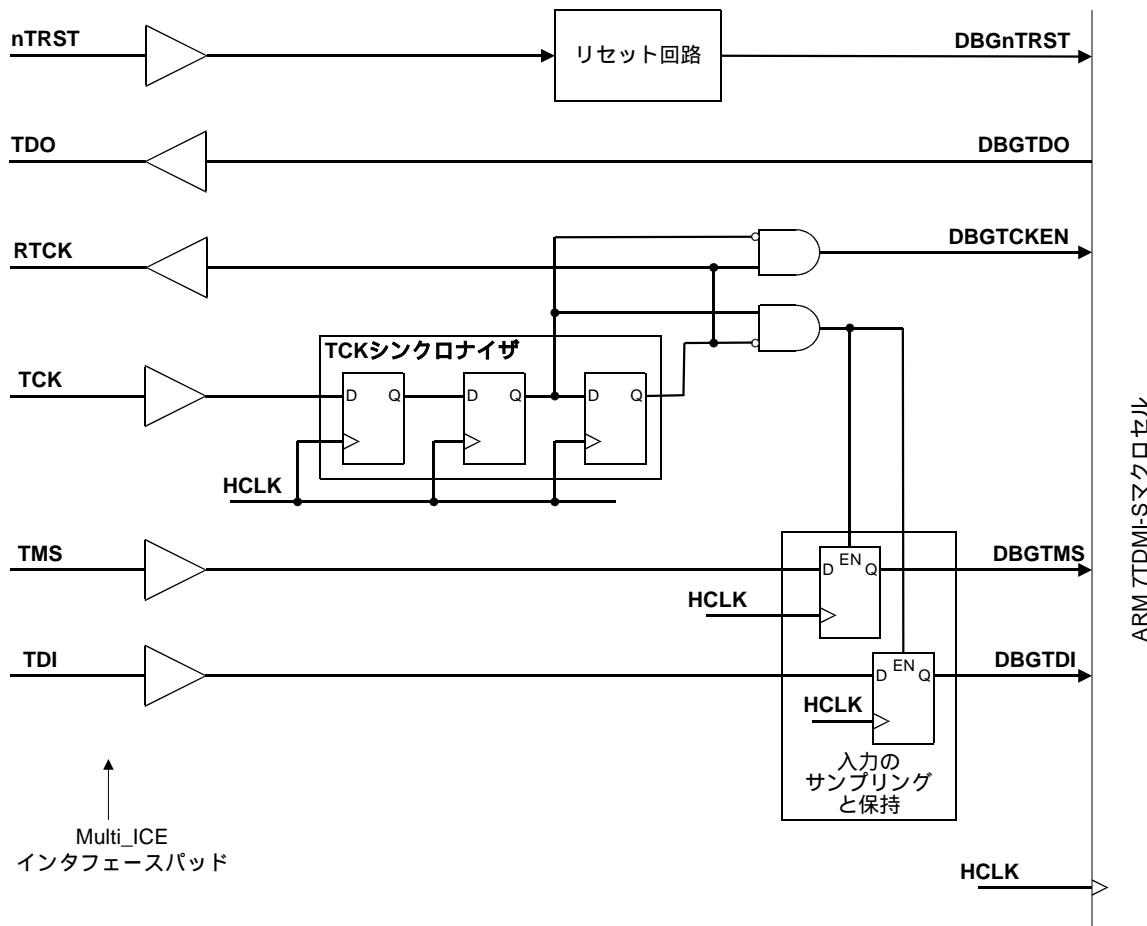

| 図 9-4   | クロックの同期化                                             | 9-8   |

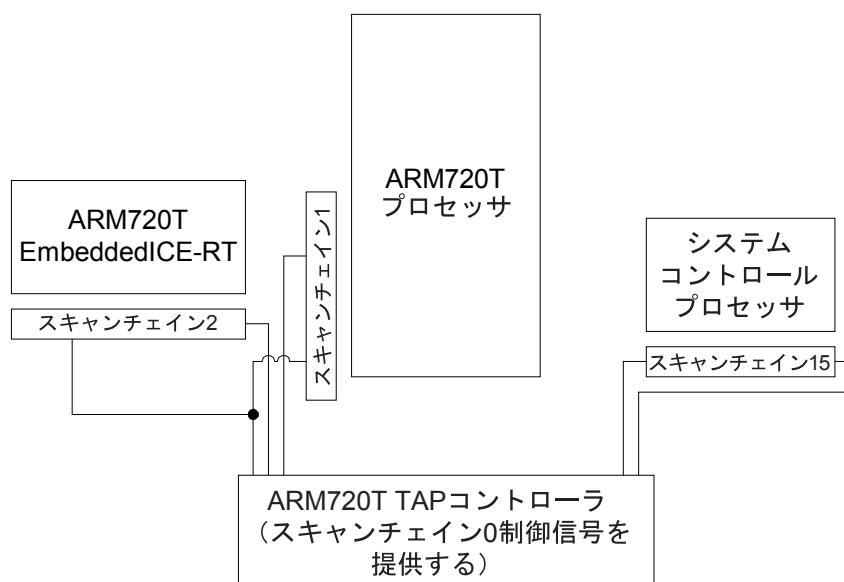

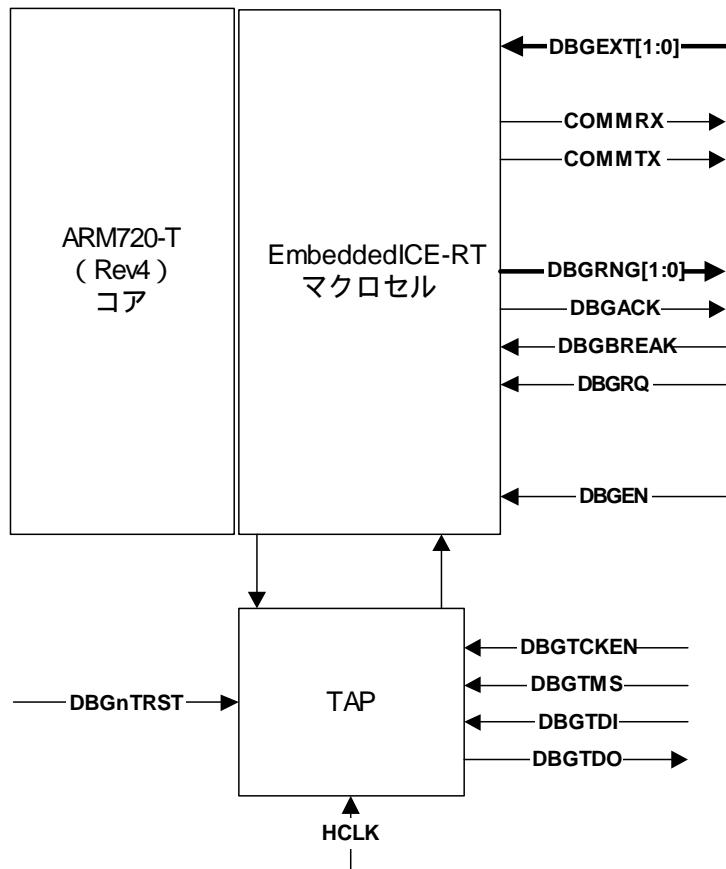

| 図 9-5   | ARM720T コア、TAP コントローラ、および<br>EmbeddedICE-RT マクロセルの関係 | 9-10  |

| 図 9-6   | ドメインアクセス制御レジスタ                                       | 9-14  |

| 図 9-7   | ARM720T プロセッサスキャンチェインの配置                             | 9-17  |

| 図 9-8   | テストアクセスポートコントローラの状態遷移                                | 9-19  |

| 図 9-9   | ID コードレジスタ形式                                         | 9-22  |

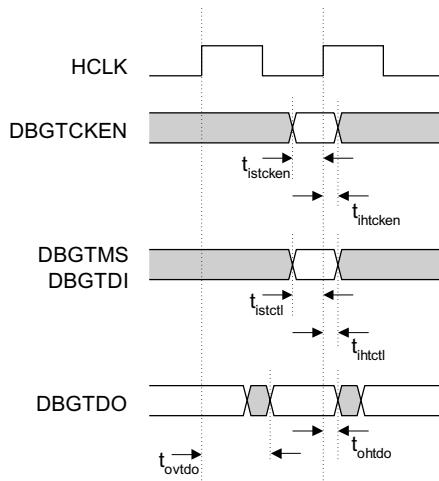

| 図 9-10  | スキャンタイミング                                            | 9-25  |

| 図 9-11  | デバッグ終了シーケンス                                          | 9-30  |

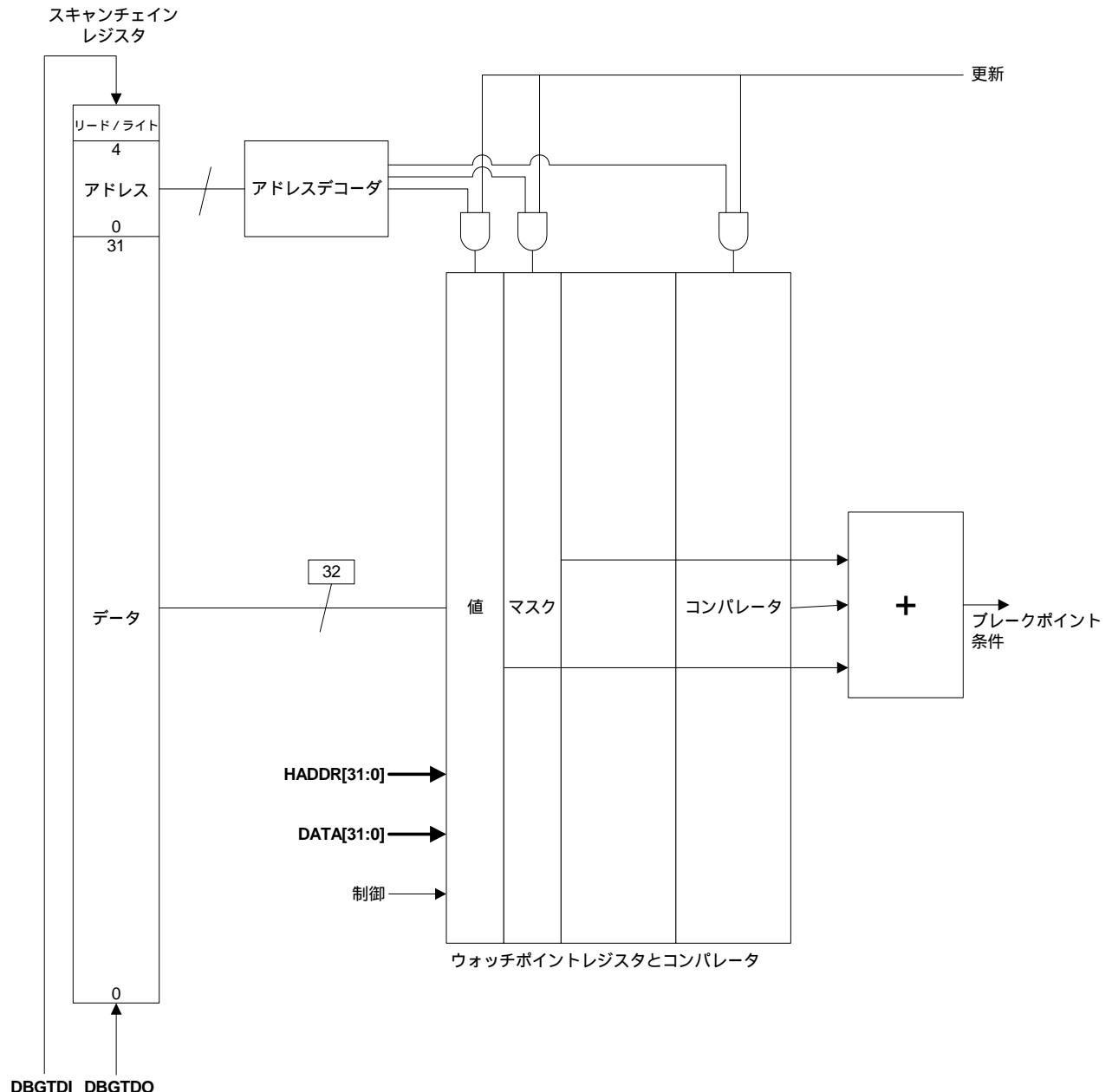

| 図 9-12  | EmbeddedICE-RT ブロック図                                 | 9-35  |

| 図 9-13  | ウォッチポイント制御値とマスク形式                                    | 9-36  |

| 図 9-14  | デバッグアポートステータスレジスタ                                    | 9-40  |

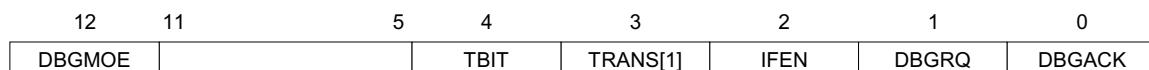

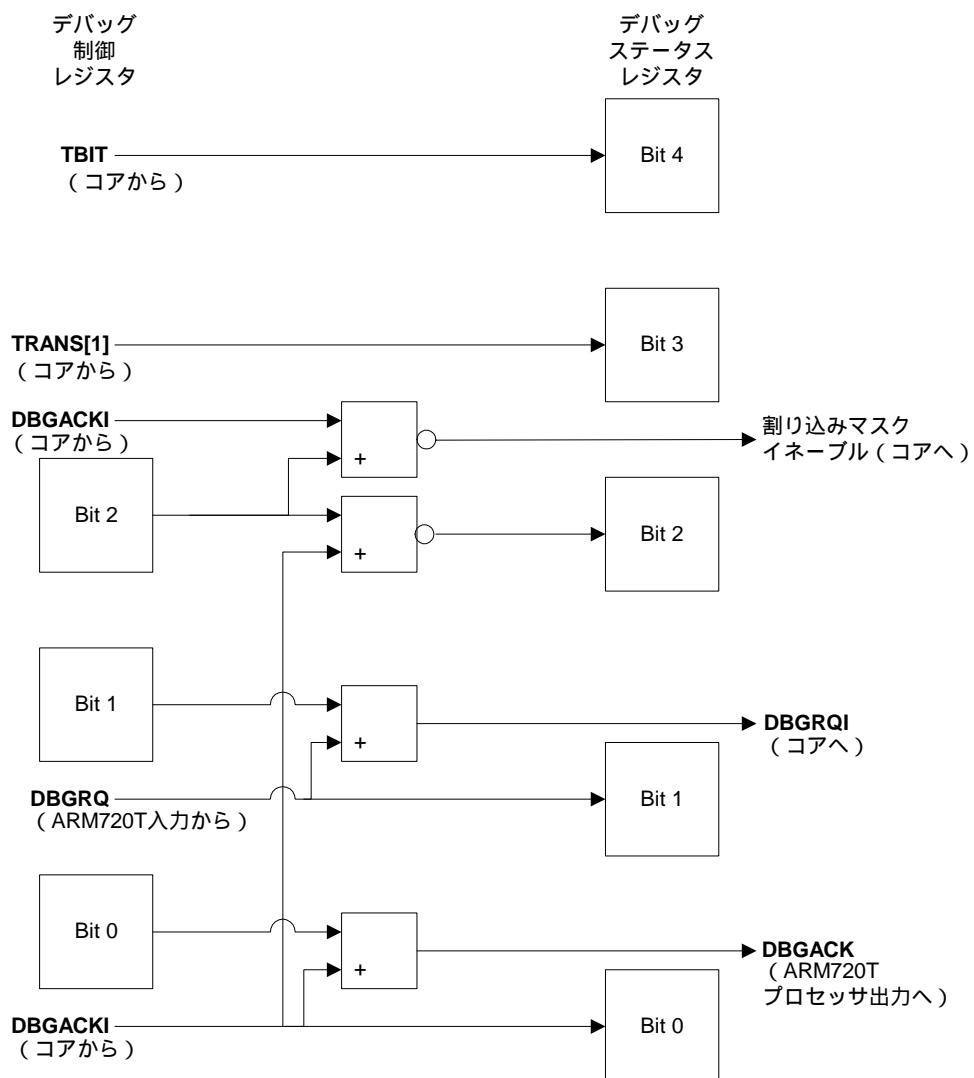

| 図 9-15  | デバッグ制御レジスタの形式                                        | 9-40  |

| 図 9-16  | デバッグステータスレジスタの形式                                     | 9-42  |

| 図 9-17  | デバッグ制御レジスタとデバッグステータスレジスタの構造                          | 9-43  |

| 図 11-1  | CP15 の MRC および MCR ビットパターン                           | 11-1  |

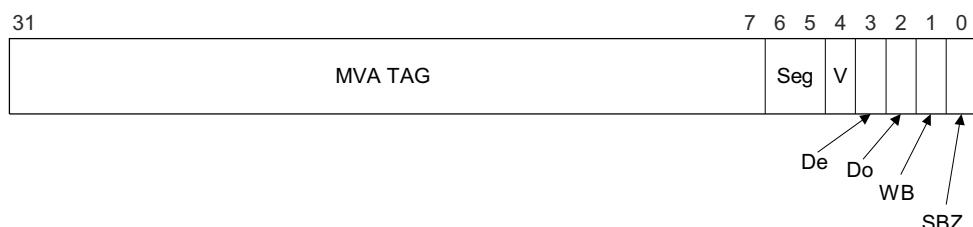

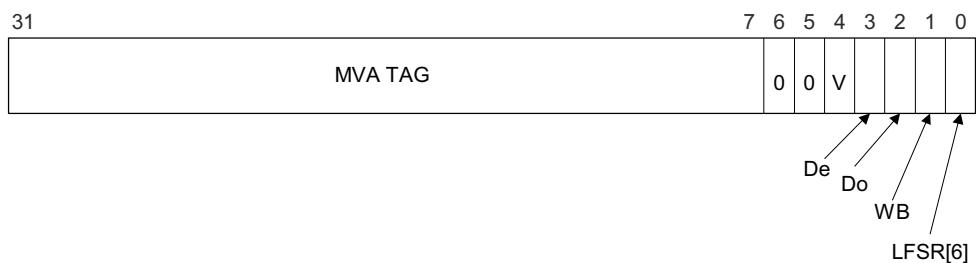

| 図 11-2  | CAM リードの Rd 形式                                       | 11-4  |

| 図 11-3  | CAM ライトの Rd 形式                                       | 11-4  |

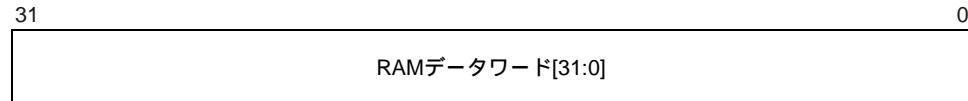

| 図 11-4  | RAM リードの Rd 形式                                       | 11-5  |

| 図 11-5  | RAM ライトの Rd 形式                                       | 11-5  |

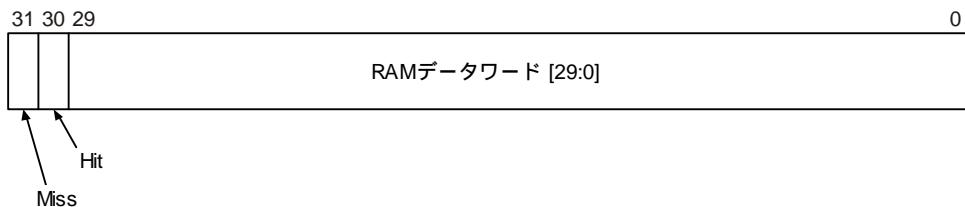

| 図 11-6  | CAM マッチと RAM リードの Rd 形式                              | 11-5  |

| 図 11-7  | CAM リードのデータ形式                                        | 11-5  |

| 図 11-8  | RAM リードのデータ形式                                        | 11-5  |

| 図 11-9  | CAM マッチと CAM リードのデータ形式                               | 11-6  |

| 図 11-10 | キャッシュビクティムとロックダウンベースライトの Rd 形式                       | 11-6  |

| 図 11-11 | キャッシュビクティムライトの Rd 形式                                 | 11-6  |

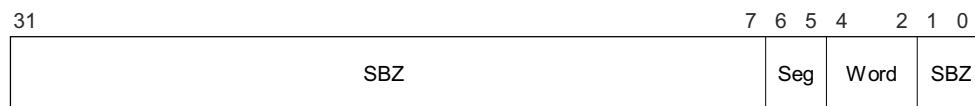

| 図 11-12 | CAM ライトの Rd 形式および CAM リードのデータ形式                      | 11-10 |

| 図 11-13 | RAM1 ライトの Rd 形式                                      | 11-10 |

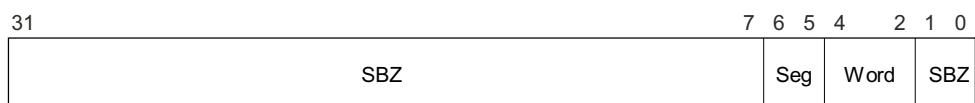

| 図 11-14 | RAM1 リードのデータ形式                                       | 11-11 |

| 図 11-15 | RAM2 ライトの Rd 形式と RAM2 リードのデータ形式                      | 11-11 |

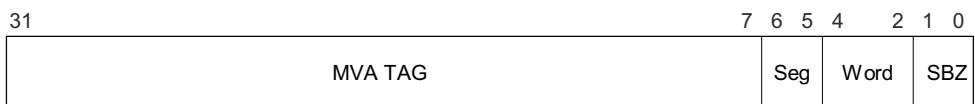

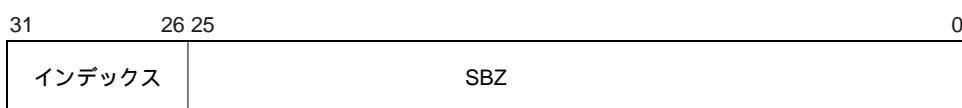

| 図 11-16 | TLB ロックダウンライトの Rd 形式                                 | 11-12 |

# 表一覧

|        |                                        |      |

|--------|----------------------------------------|------|

| 表 1-1  | 命令セットテーブルの記号 .....                     | 1-6  |

| 表 1-2  | ARM 命令一覧 .....                         | 1-8  |

| 表 1-3  | アドレスシングモード 2 .....                     | 1-10 |

| 表 1-4  | アドレスシングモード 2 ( 特権付き ) .....            | 1-11 |

| 表 1-5  | アドレスシングモード 3 .....                     | 1-11 |

| 表 1-6  | アドレスシングモード 4 ( ロード ) .....             | 1-11 |

| 表 1-7  | アドレスシングモード 4 ( ストア ) .....             | 1-12 |

| 表 1-8  | アドレスシングモード 5 .....                     | 1-12 |

| 表 1-9  | オペランド 2 .....                          | 1-12 |

| 表 1-10 | フィールド .....                            | 1-12 |

| 表 1-11 | 条件フィールド .....                          | 1-13 |

| 表 1-12 | Thumb ( サム ) 命令一覧 .....                | 1-15 |

| 表 2-1  | ARM720T の動作モード .....                   | 2-4  |

| 表 2-2  | PSR モードビット値 .....                      | 2-10 |

| 表 2-3  | 例外の開始と終了 .....                         | 2-12 |

| 表 2-4  | 例外ベクタアドレス .....                        | 2-14 |

| 表 3-1  | キャッシュと MMU 制御レジスタ .....                | 3-3  |

| 表 3-2  | キャッシュ動作 .....                          | 3-7  |

| 表 3-3  | TLB 動作 .....                           | 3-7  |

| 表 6-1  | 転送タイプエンコーディング .....                    | 6-5  |

| 表 6-2  | 転送サイズエンコーディング .....                    | 6-7  |

| 表 6-3  | バーストタイプエンコーディング .....                  | 6-8  |

| 表 6-4  | 保護制御エンコーディング .....                     | 6-8  |

| 表 6-5  | 応答エンコーディング .....                       | 6-10 |

| 表 6-6  | 32 ビットリトルエンディアンデータバスのアクティブバイトレーン ..... | 6-11 |

| 表 6-7  | 32 ビットビッグエンディアンデータバスのアクティブバイトレーン ..... | 6-12 |

| 表 7-1  | CP15 レジスタの機能 .....                     | 7-3  |

| 表 7-2  | レベル 1 ディスクリプタのビット割当 .....              | 7-7  |

| 表 7-3  | レベル 1 ディスクリプタビット [1:0] の解釈 .....       | 7-7  |

| 表 7-4  | セクションディスクリプタのビット .....                 | 7-8  |

| 表 7-5  | コースページテーブルディスクリプタのビット割当 .....          | 7-9  |

| 表 7-6  | ファインページテーブルディスクリプタのビット割当 .....         | 7-9  |

| 表 7-7  | レベル 2 ディスクリプタのビット割当 .....              | 7-11 |

| 表 7-8  | ページテーブルエントリビット [1:0] の解釈 .....         | 7-11 |

| 表 7-9  | フォールトステータスの優先順位のエンコーディング .....         | 7-16 |

| 表 7-10 | ドメインアクセス制御レジスタのアクセス制御ビットの解釈 .....      | 7-17 |

| 表 7-11 | アクセス許可 ( AP ) ビットの解釈 .....             | 7-18 |

| 表 8-1  | コプロセッサの利用 .....                        | 8-2  |

| 表 8-2  | ハンドシェイキング信号 .....                      | 8-5  |

| 表 8-3  | ハンドシェイク信号の接続 .....                     | 8-9  |

| 表 8-4  | CPnTRANS 信号の意味 .....                   | 8-10 |

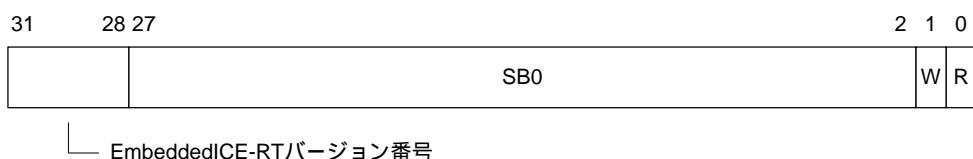

| 表 9-1  | EmbeddedICE-RT レジスタの機能とマッピング .....     | 9-12 |

| 表 9-2  | ドメインアクセス制御レジスタのビット割当 .....             | 9-15 |

| 表 9-3  | スキャンチェイン 15 の命令エンコーディング .....          | 9-18 |

| 表 9-4  | パブリック命令 .....                          | 9-20 |

| 表 9-5  | スキャンチェイン番号の割当 .....                    | 9-23 |

| 表 9-6  | スキャンチェイン 1 セル .....                    | 9-25 |

|         |                                          |       |

|---------|------------------------------------------|-------|

| 表 9-7   | デバッグ状態開始の原因の決定 .....                     | 9-33  |

| 表 9-8   | SIZE[1:0] 信号のエンコーディング .....              | 9-36  |

| 表 9-9   | デバッグ制御レジスタのビット割当 .....                   | 9-40  |

| 表 9-10  | 割り込み信号制御 .....                           | 9-41  |

| 表 9-11  | デバッグステータスレジスタのビット割当 .....                | 9-42  |

| 表 10-1  | ETM7 マクロセルと ARM720T プロセッサ間の接続 .....      | 10-2  |

| 表 11-1  | ATPG テスト信号の概要 .....                      | 11-2  |

| 表 11-2  | テストステートレジスタの動作 .....                     | 11-3  |

| 表 11-3  | CP15 レジスタ c7、c9、c15 動作の要約 .....          | 11-4  |

| 表 11-4  | キャッシュビクティムとロックダウンライト動作 .....             | 11-6  |

| 表 11-5  | CAM、RAM1、および RAM2 レジスタ c15 の動作 .....     | 11-9  |

| 表 11-6  | レジスタ c2、c3、c5、c6、c8、c10、および c15 動作 ..... | 11-9  |

| 表 11-7  | CAM メモリ領域サイズ .....                       | 11-10 |

| 表 11-8  | アクセス許可ビットの設定 .....                       | 11-11 |

| 表 11-9  | ミスおよびフォールトエンコーディング .....                 | 11-11 |

| 表 11-10 | RAM2 メモリ領域サイズ .....                      | 11-12 |

| 表 A-1   | AMBA インタフェース信号 .....                     | A-1   |

| 表 A-2   | コプロセッサインターフェース信号の説明 .....                | A-2   |

| 表 A-3   | JTAG およびテスト信号の説明 .....                   | A-3   |

| 表 A-4   | デバッガ信号の説明 .....                          | A-4   |

| 表 A-5   | ETM インタフェース信号の説明 .....                   | A-5   |

| 表 A-6   | ATPG テスト信号の説明 .....                      | A-7   |

| 表 A-7   | その他の信号の説明 .....                          | A-7   |

このページは白紙です。

はじめに

# はじめに

この「はじめに」では、*ARM720T Revision 4 (AMBA AHB Bus Interface Version)* コア CPU マニュアルを紹介します。ここでは、以下の項について記載しています。

本書について ..... xi

## 本書について

このマニュアルは、ARM720T r4p3 プロセッサのテクニカルマニュアルです。

## 対象

このマニュアルは、ARM 製品に関するアーキテクチャ、コンフィギュレーション、インテグレーション、および命令セットについての知識の有無に関係なくハードウェアおよびソフトウェアの経験豊かなエンジニア向けに作成されています。本書では、設計者がプロセッサをできるだけ速やかにターゲットシステムに組み込むことができるようにするための情報を提供しています。

## このマニュアルの使い方

このマニュアルは、以下の章から構成されています。

### 第1章「概要」

ARM720T プロセッサの概要を理解するには、この章をお読みください。

### 第2章「プログラマーズモデル」

32 ビット ARM 命令セットと 16 ビット Thumb 命令セットの説明については、この章をお読みください。

### 第3章「コンフィギュレーション」

ARM1156F-S 制御プロセッサ C15 レジスタ構成の説明およびプログラミングの詳細については、この章をお読みください。

### 第4章「命令・データキャッシュ」

命令・データ混在キャッシュの説明については、この章をお読みください。

### 第5章「ライトバッファ」

ライトバッファを使用して、ARM720T プロセッサのシステムパフォーマンスを拡張する方法に関する説明については、この章をお読みください。

### 第6章「バスインターフェース」

ARM720T プロセッサバスインターフェースの説明については、この章をお読みください。

### 第7章「メモリ管理ユニット」

メモリ管理ユニット (MMU) の機能および使用方法の説明については、この章をお読みください。

## 第8章「コプロセッサインターフェース」

ARM1156F-S コプロセッサインターフェースへのコプロセッサの接続方法に関する説明については、この章をお読みください。

## 第9章「システムのデバッグ」

ARM720T プロセッサのハードウェア拡張機能とインテグレーテッドオンチップデバッグサポートの説明については、この章をお読みください。

## 第10章「ETMインターフェース」

ARM720T プロセッサの組み込み型トレースマクロセルサポートの説明については、この章をお読みください。

## 第11章「テストサポート」

デバイス固有のテスト動作の実行方法に関する説明については、この章をお読みください。

## 付録A「信号の説明」

ARM720T プロセッサインターフェース信号の一覧については、この付録をお読みください。

## 表記規則

このマニュアルでは、以下の表記規則を使用しています。

|                         |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| ボールド体                   | ARM プロセッサ信号名、およびメニュー名などのインターフェースエレメントを強調表示しています。また、適宜記述的なリストの用語にも使用しています。 |

| イタリック体                  | 特殊な用語、クロスリファレンス、および引用を強調表示しています。                                          |

| monospace               | コマンド、ファイル名やプログラム名、およびソースコードなど、キーボードから入力することができるテキストを示しています。               |

| <u>monospace</u>        | コマンドやオプションの許容省略文字を示しています。コマンドやオプションのフルネームの代わりに、下線部のテキストを入力することができます。      |

| <i>monospace italic</i> | コマンドや関数の引数を示します。引数は、特定の値で置き換えられます。                                        |

| <b>monospace bold</b>   | 例題コード外で使用される言語キーワードを示します。                                                 |

## 製品のレビューション状態

*rnpn* 識別子は、このマニュアルで説明する製品のレビューション状態を示します。

**rn** 製品の主レビューションを識別します。

**pn** 製品の副レビューションや修正状態を識別します。

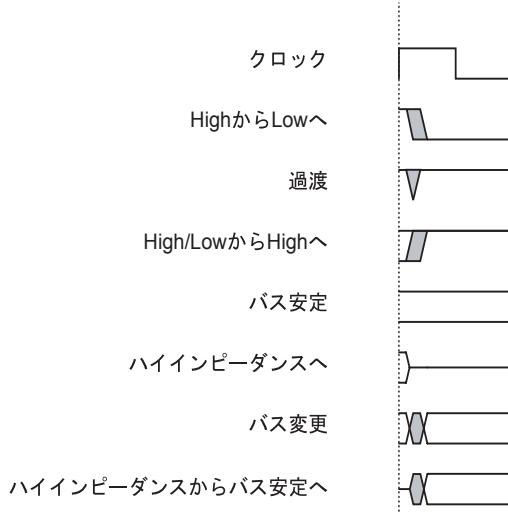

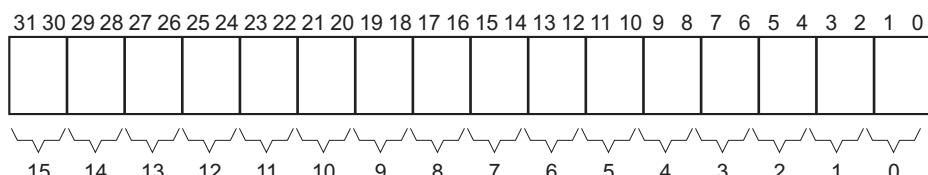

## タイミングチャート規則

このマニュアルでは、1つ以上のタイミングチャートを掲載しています。以下のキーは、これらのタイミングチャートで使用される基本的な状態を説明しています。これらの状態は明らかに、いくつかに分類されます。したがって、特に記述がないかぎりは、特別な意味が追加されることはありません。

タイミングチャートキーの規則

網掛けされているバスや信号部分は定義されていませんので、バスや信号はその時の網掛け部分で任意の値を想定することができます。実際のレベルは重要ではなく、通常の動作に影響は与えません。

## 参考文献

この項では、ARM Limited およびサードパーティ社の出版物を掲載しています。

ARM 社では、本書のアップデートや修正を定期的に行っています。最新の正誤表、追捕、ARM のFAQ（よくある質問）については、<http://www.arm.com> で確認してください。

## ARM 社の出版物

このマニュアルは、ARM720T プロセッサに固有な情報を記載しています。他の該当情報については、以下のドキュメントを参照してください。

- *ARM Architecture Reference Manual* ( ARM DDI 0100 )

- *AMBA Specification ( Rev 2.0 )* ( ARM IHI 0011 )

- *ETM7 (Rev 1) Technical Reference Manual* ( ARM DDI 0158 )

- *ARM7TDMI-S (Rev 4) Technical Reference Manual* ( ARM DDI 0234 )

## その他の出版物

この項では、サードパーティ社から出版されている関連ドキュメントをリストします。

- *Standard Test Access Port and Boundary Scan Architecture* ( IEEE Std. 1149.1-1990 )

図 9-8 ( 9-19 ページ ) は、IEEE の許可により IEEE Std. 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture Copyright 2001, by IEEE から転載されたものです。IEEE は、記載した方法により実装、使用したことによって生じるいかなる責任も負いません。

このページは白紙です。

# 1

# 概要

# 1 概要

この章では、ARM720T プロセッサの概要を説明します。ここでは、以下の項について記載しています。

|     |                   |      |

|-----|-------------------|------|

| 1.1 | ARM720T プロセッサについて | 1-1  |

| 1.2 | コプロセッサ            | 1-5  |

| 1.3 | 命令セット             | 1-5  |

| 1.4 | シリコンレビューション       | 1-18 |

## 1.1 ARM720T プロセッサについて

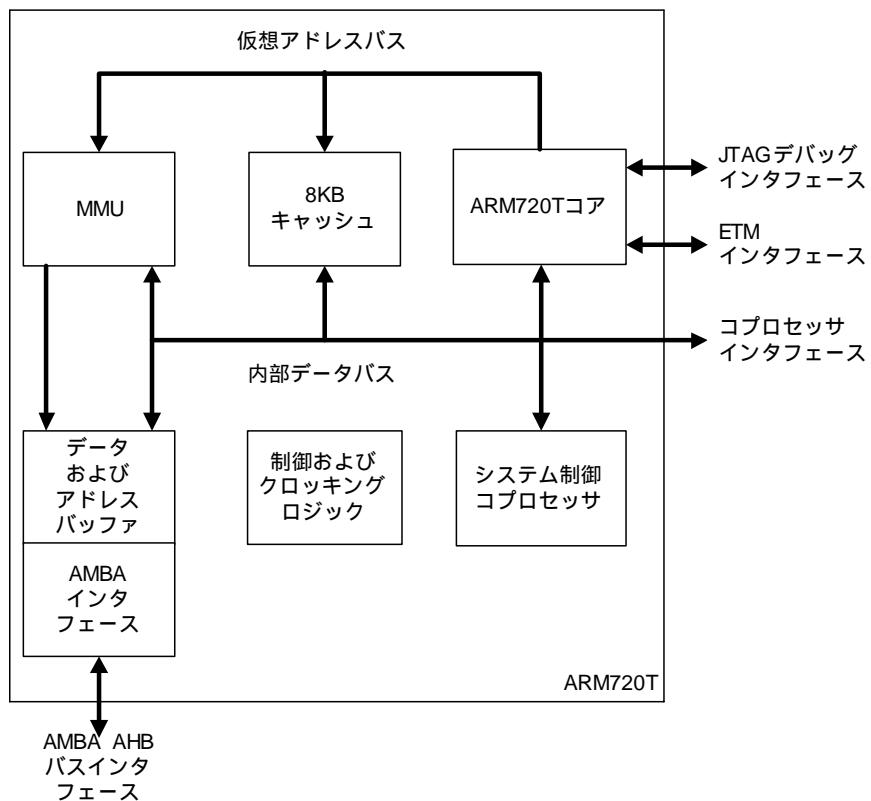

ARM720T プロセッサは、単一のチップに 8KB キャッシュ、拡張ライトバッファ、メモリ管理ユニット (MMU) を搭載した汎用 32 ビットマイクロプロセッサです。このプロセッサは ARM7TDMI-S CPU を使用しており、ARM プロセッサファミリとソフトウェアの互換性があります。

オンチップデータ・命令混在キャッシュは、ライトバッファとともに、大幅に平均実行速度を向上し、プロセッサに必要な平均メモリバンド幅を低減します。これにより、外部メモリはパフォーマンスの損失を最小限に抑えて追加プロセッサやダイレクトメモリアクセス (DMA) チャンネルに対応することができます。

MMU は、従来の 2 段階ページテーブル構造と、ハイエンドな組み込みアプリケーションや複雑なオペレーティングシステムを理想的に実行させるようにするいくつかの拡張機能をサポートしています。

異なるタスク ID により仮想アドレスを割り当てることによって、キャッシュをイネーブルにしてタスク切り換え動作のパフォーマンスを向上させています。これらの再配置仮想アドレスは、EmbeddedICE-RT ブロックによって監視されます。

メモリインターフェースは、メモリシステムに高いコストをかけずにパフォーマンスの潜在能力を実現することができます。処理速度がクリティカルな制御信号はパイプライン処理を行って、システム制御機能を標準の低電力ロジックで実現できるようにしています。これらの制御信号によって、業界標準 DRAM で提供されるページモードアクセスを活用することができます。

ARM720T プロセッサには、必要な信号を ARM コアから ARM720T プロセッサの周辺部に出力する組み込み型トレースマクロセル (ETM) インタフェースが搭載されています。これによって、標準の ETM7 マクロセルを接続することができます。

ARM720T プロセッサは完全にスタティックな部品であり、電力消費を最小限に抑えるように設計されています。これによって、MRM720T プロセッサは低電力消費が必要不可欠な携帯型アプリケーションに理想的なものになっています。

ARM720T プロセッサのアーキテクチャは、「縮小命令セットコンピュータ」(RISC) の原理に基づいています。命令セットとその関連デコードメカニズムは、マイクロプログラム化された「複雑命令セットコンピュータ」(CISC) と比べて大幅に簡略化されています。

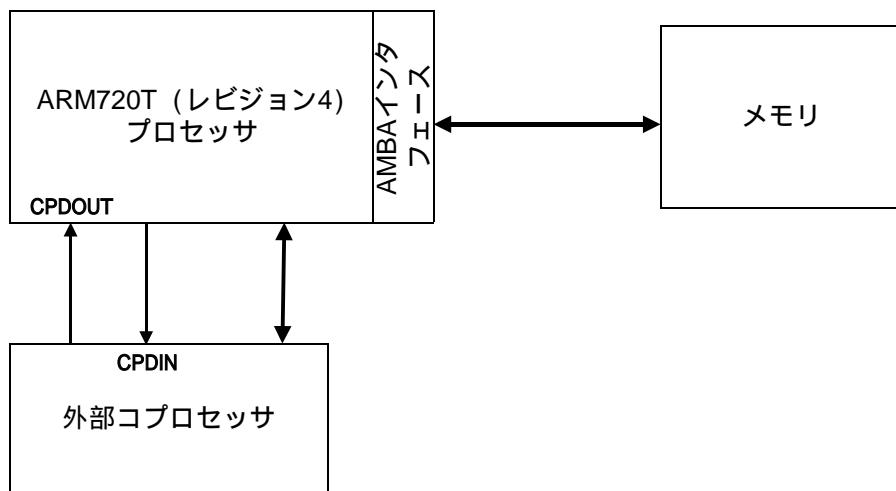

ARM720T プロセッサのブロック図を図 1-1 に示します。

図 1-1 ARM 720T ブロック図

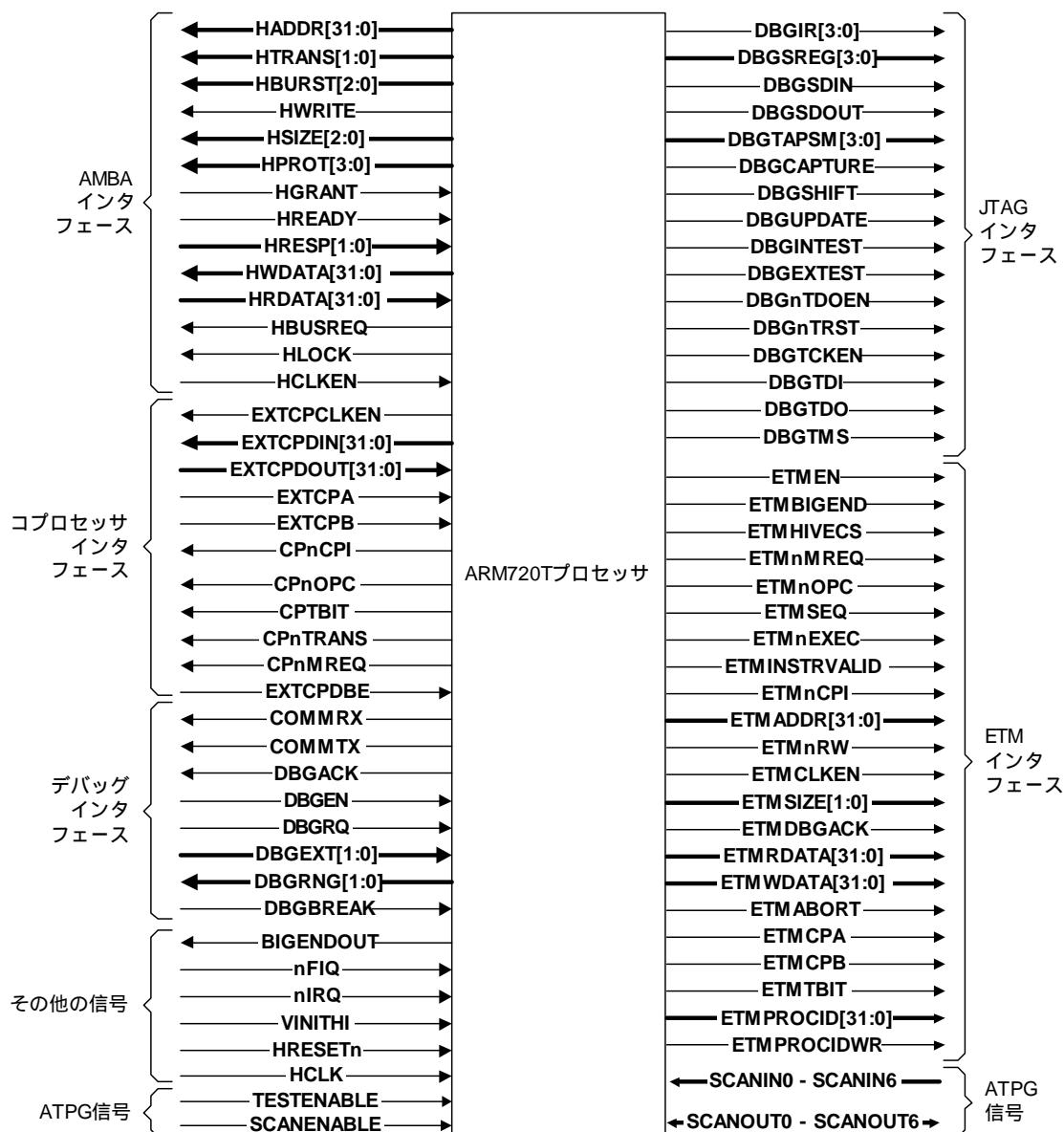

ARM720T プロセッサの機能信号を図 1-2 に示します。

図 1-2 ARM720T プロセッサ機能信号

### 1.1.1 EmbeddedICE-RT ロジック

EmbeddedICE-RT ロジックは、ARM720T コアに対してインテグレーテッドオンチップデバッグサポートを提供します。EmbeddedICE-RT ロジックにより、ブレークポイントやウォッチポイントを発生させることができる条件をプログラムすることができます。

EmbeddedICE-RT ロジックは EmbeddedICE の拡張処理系であり、監視モードでデバッグを実行することができます。監視モードでは、ARM720T コアはハルトモードのときのようにデバッグ状態になるのではなく、ブレークポイントやウォッチポイントで例外処理をとります。

ARM720T コアがウォッチポイントやブレークポイントを検出したときにデバッグ状態にならなければ、ハードウェア割り込み要求を通常通り継続して処理することができます。コアを停止させるとシステム傷害を招く可能性がある、機械的システムのフィードバックループの一部をコアが形成する場合は、監視モードでのデバッグが有効です。

EmbeddedICE-RT ロジックには、「デバッガ通信チャネル」(DCC)があります。DCC は、ターゲットとホストデバッガ間で情報を受け渡すために使用されます。EmbeddedICE-RT ロジックは、「ジョイントテストアクションングループ」(JTAG)試験アクセスポートを介して制御されます。

## プログラマーズモデルの変更

EmbeddedICE-RT マクロセルのサポートを提供するために、ARM720T プロセッサのプログラマーズモデルでは以下の変更が行われています。

### デバッグ制御レジスタ

デバッグ制御レジスタには、以下のように新しいビットが 2 つあります。

#### ビット 4

監視モードイネーブル。このビットを使用して、ブレークポイントやウォッчポイントでどのようにデバイスが対応するかを制御します。

- セットすると、ARM720T コアは命令またはデータアボート例外処理をとります。

- クリアすると、ARM720T コアはデバッグ状態になります。

#### ビット 5

EmbeddedICE-RT ディセーブル。このビットは、ウォッчポイントやブレークポイントを変更する場合に使用します。

- セットすると、このビットはブレークポイントとウォッчポイントを無効にし、ブレークポイントレジスタやウォッчポイントレジスタを有効にして新しい値を設定することができます。

- クリアすると、新しいブレークポイント値やウォッчポイント値が動作可能になります。

このレジスタの詳細については、「デバッグ制御レジスタ」の項 (9-40 ページ) を参照してください。

### コプロセッサレジスタマップ

CP14 コプロセッサレジスタマップの新しい r2 レジスタは、実際のアボートによって、あるいはブレークポイントやウォッчポイントによってプロセッサがプリフェッчまたはデータアボート例外処理に入ったかどうかを示します。この詳細については、9-40 ページの「アボートステータスレジスタ」を参照してください。

詳細については、第 9 章「システムのデバッグ」を参照してください。

## 1.2 コプロセッサ

ARM720T プロセッサには、デバイスを内部制御するための内部コプロセッサ専用 CP15 があります（第3章「コンフィギュレーション」を参照してください）。

ARM720T プロセッサには、オンチップ外部コプロセッサを接続するためのポートもあります。これによって、アーキテクチャの整合性を保ちながら ARM720T の機能を拡張させることができます。

## 1.3 命令セット

命令セットは、以下の10種類の基本命令から構成されます。

- 2種類の命令はオンチップ算術論理ユニット、バレルシフタ、乗算器を使用して、それぞれが32ビット幅の31個のレジスタから成るバンクのデータを高速で処理します。

- 3種類の命令は、メモリとレジスタ間のデータ転送を制御します。

- 1つはメモリアクセスを柔軟に最適化します。

- 1つは高速コンテキスト切り換え用です。

- 1つはデータスワッピング用です。

- 2種類の命令は、実行のフローと特権レベルを制御します。

- 3種類の命令は、外部コプロセッサの制御専用です。これらの命令によって、命令セットの機能をオーブンで統一的にオフチップに拡張することができます。

ARM 命令セットは、さまざまな高水準言語のコンパイラに適しています。クリティカルなコードセグメントが必要な場合でも、簡単にアセンブリコードプログラミングが行えます。

### 1.3.1 形式概要

この項では、ARM 命令セットと Thumb ( サム ) 命令セットの概略を説明します。

- *ARM 命令セット*、1-7 ページ

- *Thumb ( サム ) 命令セット*、1-14 ページ

命令セットテーブルの記号を表 1-1 に示します。

ARM720T プロセッサの ARM7TDMI-S コアは、ARM アーキテクチャ v4T の処理系です。2 つの命令セットの詳細については、「*ARM Architecture Reference Manual*」を参照してください。

表 1-1 命令セットテーブルの記号

| 項目           | 説明                                       |

|--------------|------------------------------------------|

| {cond}       | 表 1-11( 1-13 ページ ) を参照してください。            |

| <Oprnd2>     | 表 1-9 ( 1-12 ページ ) を参照してください。            |

| {field}      | 表 1-10( 1-12 ページ ) を参照してください。            |

| S            | 条件コードを設定する ( オプション )                     |

| B            | バイト演算 ( オプション )                          |

| H            | ハーフワード演算 ( オプション )                       |

| T            | アドレス変換を強制する。プリインデックスド・アドレスには使用することはできない。 |

| <a_mode2>    | 表 1-3 ( 1-10 ページ ) を参照してください。            |

| <a_mode2P>   | 表 1-4 ( 1-11 ページ ) を参照してください。            |

| <a_mode3>    | 表 1-5 ( 1-11 ページ ) を参照してください。            |

| <a_mode4L>   | 表 1-6 ( 1-11 ページ ) を参照してください。            |

| <a_mode4S>   | 表 1-7 ( 1-12 ページ ) を参照してください。            |

| <a_mode5>    | 表 1-8 ( 1-12 ページ ) を参照してください。            |

| #<32bit_Imm> | 8 ビット値を偶数ビット回数だけ右シフトさせて形成された32ビット定数      |

| <reglist>    | 中括弧 ( { および } ) で囲まれ、カンマで区切られたレジスタのリスト   |

### 1.3.2 ARM 命令セット

この項では、使用可能な ARM 命令の概要を説明します。これらの命令の詳細については、「*ARM Architecture Reference Manual*」を参照してください。

ARM 命令セットの形式を図 1-3 に示します。

|                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|                           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| データ処理 イミディエート             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| データ処理 イミディエートシフト          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| データ処理 レジスタシフト             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 乗算                        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 乗算ロング                     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ステータスレジスタ からの転送           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ステータスレジスタへの イミディエートの転送    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| レジスタをステータス レジスタへ転送        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 分岐 / 状態遷移 命令セット           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ロード / ストア イミディエートオフセット    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ロード / ストア レジスタオフセット       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ロード / ストア ハーフワード / 符号付バイト |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ロード / ストアハーフワード / 符号付バイト  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| スワップ / スワップバイト            |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ロード / ストア マルチブル           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| コプロセッサデータ処理               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| コプロセッサレジスタ転送              |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| コプロセッサ ロード / ストア          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 分岐とリンク付き分岐                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ソフトウェア割り込み                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 未定義                       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

図 1-3 ARM 命令セットの形式

**注意：** 命令コードの中には定義されておらず、未定義命令トラップで処理されていないものがあります。たとえばビット 6 をセットした乗算命令。これらの命令の動作は将来 ARM のインプリメントで変更される可能性がありますので、使用しないでください。

ARM 命令セットのまとめを表 1-2 に示します。

表 1-2 ARM 命令一覧

| 動作 |                       | アセンブラー                                    |

|----|-----------------------|-------------------------------------------|

| 転送 | 転送                    | MOV{cond}{S} <Rd>, <Oprnd2>               |

|    | レジスタ値の補数の転送           | MVN{cond}{S} <Rd>, <Oprnd2>               |

|    | SPSR をレジスタに転送         | MRS{cond} <Rd>, SPSR                      |

|    | CPSR をレジスタに転送         | MRS{cond} <Rd>, CPSR                      |

|    | レジスタを SPSR に転送        | MSR{cond} SPSR{field}, <Rm>               |

|    | レジスタを CPSR に転送        | MSR{cond} CPSR{field}, <Rm>               |

|    | SPSR フラグにイミディエート定数を転送 | MSR{cond} SPSR_f, #<32bit_Imm>            |

|    | CPSR フラグにイミディエート定数を転送 | MSR{cond} CPSR_f, #<32bit_Imm>            |

| 算術 | 加算                    | ADD{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | キャリー付き加算              | ADC{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 減算                    | SUB{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | キャリー付き減算              | SBC{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 逆減算                   | RSB{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | キャリー付き逆減算             | RSC{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 乗算                    | MUL{cond}{S} <Rd>, <Rm>, <Rs>             |

|    | 積和乗算                  | MLA{cond}{S} <Rd>, <Rm>, <Rs>, <Rn>       |

|    | 符号なしロングの乗算            | UMULL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs> |

|    | 符号なし積和ロングの乗算          | UMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs> |

|    | 符号付きロングの乗算            | SMULL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs> |

|    | 符号付き積和ロングの乗算          | SMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs> |

|    | 比較                    | CMP{cond} <Rd>, <Oprnd2>                  |

| 論理 | 補数の比較                 | CMN{cond} <Rd>, <Oprnd2>                  |

|    | テスト                   | TST{cond} <Rn>, <Oprnd2>                  |

|    | 等価のテスト                | TEQ{cond} <Rn>, <Oprnd2>                  |

|    | 論理積                   | AND{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 排他的論理和                | EOR{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 論理和                   | ORR{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

| 分岐 | ビットクリア                | BIC{cond}{S} <Rd>, <Rn>, <Oprnd2>         |

|    | 分岐                    | B{cond} <label>                           |

|    | リンク付き分岐               | BL{cond} <label>                          |

|    | 分岐、および命令セットの状態遷移      | BX{cond} <Rn>                             |

表 1-2 ARM 命令一覧 ( 続き )

| 動作                   |                   | アセンブラ                                      |

|----------------------|-------------------|--------------------------------------------|

| ロード                  | ワード               | LDR{cond} <Rd>, <a_mode2>                  |

|                      | ユーザモード特権付きワード     | LDR{cond}T <Rd>, <a_mode2P>                |

|                      | バイト               | LDR{cond}B <Rd>, <a_mode2>                 |

|                      | ユーザモード特権付きバイト     | LDR{cond}BT <Rd>, <a_mode2P>               |

|                      | 符号付きバイト           | LDR{cond}SB <Rd>, <a_mode3>                |

|                      | ハーフワード            | LDR{cond}H <Rd>, <a_mode3>                 |

|                      | 符号付きハーフワード        | LDR{cond}SH <Rd>, <a_mode3>                |

|                      | ロード前インクリメント       | LDM{cond}IB <Rd>{!}, <reglist>{^}          |

|                      | ロード後インクリメント       | LDM{cond}IA <Rd>{!}, <reglist>{^}          |

|                      | ロード前デクリメント        | LDM{cond}DB <Rd>{!}, <reglist>{^}          |

| マルチ<br>ブロック<br>データ操作 | ロード後デクリメント        | LDM{cond}DA <Rd>{!}, <reglist>{^}          |

|                      | スタック操作            | LDM{cond}<a_mode4L> <Rd>{!}, <reglist>     |

|                      | スタック操作と、CPSR リストア | LDM{cond}<a_mode4L> <Rd>{!}, <reglist+pc>^ |

|                      | ユーザレジスタ           | LDM{cond}<a_mode4L> <Rd>{!}, <reglist>^    |

|                      | ストア               | STR{cond} <Rd>, <a_mode2>                  |

|                      | ユーザモード特権付きワード     | STR{cond}T <Rd>, <a_mode2P>                |

|                      | バイト               | STR{cond}B <Rd>, <a_mode2>                 |

|                      | ユーザモード特権付きバイト     | STR{cond}BT <Rd>, <a_mode2P>               |

|                      | ハーフワード            | STR{cond}H <Rd>, <a_mode3>                 |

|                      | ストア前インクリメント       | STM{cond}IB <Rd>{!}, <reglist>{^}          |

| マルチ<br>ブロック<br>データ操作 | ストア後インクリメント       | STM{cond}IA <Rd>{!}, <reglist>{^}          |

|                      | ストア前デクリメント        | STM{cond}DB <Rd>{!}, <reglist>{^}          |

|                      | ストア後デクリメント        | STM{cond}DA <Rd>{!}, <reglist>{^}          |

|                      | スタック操作            | STM{cond}<a_mode4S> <Rd>{!}, <reglist>     |

|                      | ユーザレジスタ           | STM{cond}<a_mode4S> <Rd>{!}, <reglist>^    |

|                      | スワップ              | SWP{cond} <Rd>, <Rm>, [<Rn>]               |

|                      | バイト               | SWP{cond}B <Rd>, <Rm>, [<Rn>]              |

表 1-2 ARM 命令一覧 ( 続き )

| 動作         |                           | アセンブラ                                                 |

|------------|---------------------------|-------------------------------------------------------|

| コプロセッサ     | データ操作                     | CDP{cond} p<cpnum>, <op1>, <CRd>, <CRn>, <CRm>, <op2> |

|            | コプロセッサレジスタから ARM レジスタへの転送 | MRC{cond} p<cpnum>, <op1>, <Rd>, <CRn>, <CRm>, <op2>  |

|            | ARM レジスタからコプロセッサレジスタへの転送  | MCR{cond} p<cpnum>, <op1>, <Rd>, <CRn>, <CRm>, <op2>  |

|            | ロード                       | LDC{cond} p<cpnum>, <CRd>, <a_mode5>                  |

|            | ストア                       | STC{cond} p<cpnum>, <CRd>, <a_mode5>                  |

| ソフトウェア割り込み |                           | SWI <24bit_Imm>                                       |

アドレッシングモード 2 <a\_mode2> を表 1-3 に示します。

表 1-3 アドレッシングモード 2

| 動作                          | アセンブラ                                   |

|-----------------------------|-----------------------------------------|

| イミディエートオフセット                | [<Rn>, #+/-<12bit_Offset>]              |

| レジスタオフセット                   | [<Rn>, +/-<Rm>]                         |

| スケーリング済みレジスタオフセット           | [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]  |

|                             | [<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]  |

|                             | [<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]  |

|                             | [<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]  |

|                             | [<Rn>, +/-<Rm>, RRX]                    |

| プリインデックスドイミディエートオフセット       | [<Rn>, #+/-<12bit_Offset>]!             |

| プリインデックスドレジスタオフセット          | [<Rn>, +/-<Rm>]!                        |

| プリインデックスドスケーリング済みレジスタオフセット  | [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]! |

|                             | [<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]! |

|                             | [<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]! |

|                             | [<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]! |

|                             | [<Rn>, +/-<Rm>, RRX]!                   |

| ポストインデックスドイミディエートオフセット      | [<Rn>], #+/-<12bit_Offset>              |

| ポストインデックスドレジスタオフセット         | [<Rn>], +/-<Rm>                         |

| ポストインデックスドスケーリング済みレジスタオフセット | [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm>  |

|                             | [<Rn>], +/-<Rm>, LSR #<5bit_shift_imm>  |

|                             | [<Rn>], +/-<Rm>, ASR #<5bit_shift_imm>  |

|                             | [<Rn>], +/-<Rm>, ROR #<5bit_shift_imm>  |

|                             | [<Rn>, +/-<Rm>, RRX]                    |

アドレッシングモード 2 (特権付き) <a\_mode2P> を表 1-4 に示します。

表 1-4 アドレッシングモード 2 (特権付き)

| 動作                          | アセンブラ                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| イミディエートオフセット                | [<Rn>, #+/-<12bit_Offset>]                                                                                                                                                                   |

| レジスタオフセット                   | [<Rn>, +/-<Rm>]                                                                                                                                                                              |

| スケーリング済みレジスタオフセット           | [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]<br>[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]<br>[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]<br>[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]<br>[<Rn>, +/-<Rm>, RRX] |

| ポストインデックスドイミディエートオフセット      | [<Rn>], #+/-<12bit_Offset>                                                                                                                                                                   |

| ポストインデックスドレジスタオフセット         | [<Rn>], +/-<Rm>                                                                                                                                                                              |

| ポストインデックスドスケーリング済みレジスタオフセット | [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm><br>[<Rn>], +/-<Rm>, LSR #<5bit_shift_imm><br>[<Rn>], +/-<Rm>, ASR #<5bit_shift_imm><br>[<Rn>], +/-<Rm>, ROR #<5bit_shift_imm><br>[<Rn>, +/-<Rm>, RRX] |

アドレッシングモード 3( 符号付きバイト、およびハーフワードデータ転送 )<a\_mode3> を表 1-5 に示します。

表 1-5 アドレッシングモード 3

| 動作           | アセンブラ                      |

|--------------|----------------------------|

| イミディエートオフセット | [<Rn>, #+/-<8bit_Offset>]  |

| プリインデックスド    | [<Rn>, #+/-<8bit_Offset>]! |

| ポストインデックスド   | [<Rn>], #+/-<8bit_Offset>  |

| レジスタ         | [<Rn>, +/-<Rm>]            |

| プリインデックスド    | [<Rn>, +/-<Rm>]!           |

| ポストインデックスド   | [<Rn>], +/-<Rm>            |

アドレッシングモード 4 (ロード) <a\_mode4L> を表 1-6 に示します。

表 1-6 アドレッシングモード 4 (ロード)

| アドレッシングモード |           | スタックタイプ |         |

|------------|-----------|---------|---------|

| IA         | 事後インクリメント | FD      | フル下降    |

| IB         | 事前インクリメント | ED      | エンプティ下降 |

| DA         | 事後デクリメント  | FA      | フル上昇    |

| DB         | 事後デクリメント  | EA      | エンプティ上昇 |

アドレッシングモード 4(ストア) <a\_mode4S> を表 1-7 に示します。

表 1-7 アドレッシングモード 4(ストア)

| アドレッシングモード   | スタックタイプ    |

|--------------|------------|

| IA 事後インクリメント | EA エンプティ上昇 |

| IB 事前インクリメント | FA フル上昇    |

| DA 事後デクリメント  | ED エンプティ下降 |

| DB 事前デクリメント  | FD フル下降    |

アドレッシングモード 5(コプロセッサデータ転送) <a\_mode5> を表 1-8 に示します。

表 1-8 アドレッシングモード 5

| 動作           | アセンブラ                        |

|--------------|------------------------------|

| イミディエートオフセット | [<Rn>, #+/-<8bit_Offset*4>]  |

| プリインデックスド    | [<Rn>, #+/-<8bit_Offset*4>]! |

| ポストインデックスド   | [<Rn>], #+/-<8bit_Offset*4>  |

オペランド 2 <Oprnd2> を表 1-9 に示します。

表 1-9 オペランド 2

| 動作       | アセンブラ                |

|----------|----------------------|

| イミディエート値 | #<32bit_Imm>         |

| 論理左シフト   | <Rm> LSL #<5bit_Imm> |

| 論理右シフト   | <Rm> LSR #<5bit_Imm> |

| 算術右シフト   | <Rm> ASR #<5bit_Imm> |

| 右口テート    | <Rm> ROR #<5bit_Imm> |

| レジスタ     | <Rm>                 |

| 論理左シフト   | <Rm> LSL <Rs>        |

| 論理右シフト   | <Rm> LSR <Rs>        |

| 算術右シフト   | <Rm> ASR <Rs>        |

| 右口テート    | <Rm> ROR <Rs>        |

| 拡張右口テート  | <Rm> RRX             |

フィールド {field} を表 1-10 に示します。

表 1-10 フィールド

| 接尾辞 | セット                    |

|-----|------------------------|

| _c  | 制御フィールドマスクビット(ビット3)    |

| _f  | フラグフィールドマスクビット(ビット0)   |

| _s  | ステータスフィールドマスクビット(ビット1) |

| _x  | 拡張フィールドマスクビット(ビット2)    |

条件フィールド {cond} を表 1-11 に示します。

表 1-11 条件フィールド

| 接尾辞 | 内容           | 条件                                               |

|-----|--------------|--------------------------------------------------|

| EQ  | 等号           | Z セット                                            |

| NE  | 不等号          | Z クリア                                            |

| CS  | 符号なし、より高いか同じ | C セット                                            |

| CC  | 符号なし、より低い    | C クリア                                            |

| MI  | 負            | N セット                                            |

| PL  | 正またはゼロ       | N クリア                                            |

| VS  | オーバーフロー      | V セット                                            |

| VC  | オーバーフローなし    | V クリア                                            |

| HI  | 符号なし、より高い    | C セット、Z クリア                                      |

| LS  | 符号なし、より低いか同じ | C クリア、Z セット                                      |

| GE  | 以上           | N=V ( N と V セットまたは N と V クリア )                   |

| LT  | 未満           | N<V ( N セットと V クリア )または( N クリアと V セット )          |

| GT  | 超過           | Z クリア、N=V ( N と V セットまたは N と V クリア )             |

| LE  | 以下           | Z セットまたは N<V ( N セットと V クリア )または( N クリアと V セット ) |

| AL  | 常時           | 常時                                               |

### 1.3.3 Thumb (サム) 命令セット

この項では、使用可能な Thumb (サム) 命令セットの概要を説明します。これらの命令の詳細については、「*ARM Architecture Reference Manual*」を参照してください。

Thumb (サム) 命令セットの形式を図 1-4 に示します。

|                               | 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 |   |   |   |    |         |          |    |                |        |        |      |    |  |  |  |  |  |  |

|-------------------------------|-------------------------------------------------|---|---|---|----|---------|----------|----|----------------|--------|--------|------|----|--|--|--|--|--|--|

| シフトレジスタの転送                    | 01                                              | 0 | 0 | 0 | Op | Offset5 |          |    |                |        | Rs     | Rd   |    |  |  |  |  |  |  |

| 加算 / 減算                       | 02                                              | 0 | 0 | 0 | 1  | 1       | 1        | Op | Rn/<br>offset3 |        | Rs     | Rd   |    |  |  |  |  |  |  |

| イミディエート転送 /<br>比較 / 加算 / 減算   | 03                                              | 0 | 0 | 1 | Op | Rd      |          |    | Offset8        |        |        |      |    |  |  |  |  |  |  |

| ALU演算                         | 04                                              | 0 | 1 | 0 | 0  | 0       | 0        | 0  | Op             |        |        | Rs   | Rd |  |  |  |  |  |  |

| 上位レジスタの操作と分岐状態遷移              | 05                                              | 0 | 1 | 0 | 0  | 0       | 1        | Op | H1             | H2     | Rs/Hs  | RdHd |    |  |  |  |  |  |  |

| PC相対ロード                       | 06                                              | 0 | 1 | 0 | 0  | 1       | Rd       |    | Word8          |        |        |      |    |  |  |  |  |  |  |

| 相対オフセットでのロード / ストア            | 07                                              | 0 | 1 | 0 | 1  | L       | B        | 0  | Ro             |        | Rb     | Rd   |    |  |  |  |  |  |  |

| 符号拡張型バイトとハーフワードの<br>ロード / ストア | 08                                              | 0 | 1 | 0 | 1  | H       | S        | 1  | Ro             |        | Rb     | Rd   |    |  |  |  |  |  |  |

| イミディエートオフセットでの<br>ロード / ストア   | 09                                              | 0 | 1 | 1 | B  | L       | Offset5  |    |                | Rb     | Rd     |      |    |  |  |  |  |  |  |

| ハーフワードのロード / ストア              | 10                                              | 1 | 0 | 0 | 0  | L       | Offset5  |    |                | Rb     | Rd     |      |    |  |  |  |  |  |  |

| SP相対のロード / ストア                | 11                                              | 1 | 0 | 0 | 1  | L       | Rd       |    | Word8          |        |        |      |    |  |  |  |  |  |  |

| ロードアドレス                       | 12                                              | 1 | 0 | 1 | 0  | SP      | Rd       |    | Word8          |        |        |      |    |  |  |  |  |  |  |

| スタックポインタへの<br>オフセットの加算        | 13                                              | 1 | 0 | 1 | 1  | 0       | 0        | 0  | 0              | S      | SWord7 |      |    |  |  |  |  |  |  |

| レジスタのプッシュ / ポップ               | 14                                              | 1 | 0 | 1 | 1  | L       | 1        | 0  | R              | Rlist  |        |      |    |  |  |  |  |  |  |

| ロード / ストアマルチプル                | 15                                              | 1 | 1 | 0 | 0  | L       | Rb       |    | Rlist          |        |        |      |    |  |  |  |  |  |  |

| 条件分岐                          | 16                                              | 1 | 1 | 0 | 1  | Cond    |          |    | Softset8       |        |        |      |    |  |  |  |  |  |  |

| ソフトウェア割り込み                    | 17                                              | 1 | 1 | 0 | 1  | 1       | 1        | 1  | 1              | Value8 |        |      |    |  |  |  |  |  |  |

| 無条件分岐                         | 18                                              | 1 | 1 | 1 | 0  | 0       | Offset11 |    |                |        |        |      |    |  |  |  |  |  |  |

| リンク付きロング分岐                    | 19                                              | 1 | 1 | 1 | 1  | H       | Offset   |    |                |        |        |      |    |  |  |  |  |  |  |

図 1-4 Thumb (サム) 命令セットの形式

Thumb (サム) 命令セットのまとめを表 1-12 に示します。

表 1-12 Thumb (サム) 命令一覧

| 動作 |                                      | アセンブラ                                               |

|----|--------------------------------------|-----------------------------------------------------|

| 転送 | イミディエート                              | MOV <Rd>, #<8bit_Imm>                               |

|    | 上位レジスタ (R8-15) から下位レジスタ (R0-7) へ     | MOV <Rd>, <Hs>                                      |

|    | 下位レジスタ (R0-7) から上位レジスタ (R8-15) へ     | MOV <Hd>, <Rs>                                      |

|    | 上位レジスタ (R8-15) から上位レジスタ (R8-15) へ    | MOV <Hd>, <Hs>                                      |

| 算術 | 加算                                   | ADD <Rd>, <Rs>, #<3bit_Imm>                         |

|    | 下位レジスタ (R0-7) と下位レジスタ (R0-7) の加算     | ADD <Rd>, <Rs>, <Rn>                                |

|    | 上位レジスタ (R8-15) から下位レジスタ (R0-7) への加算  | ADD <Rd>, <Hs>                                      |

|    | 下位レジスタ (R0-7) から上位レジスタ (R8-15) への加算  | ADD <Hd>, <Rs>                                      |

|    | 上位レジスタ (R8-15) から上位レジスタ (R8-15) への加算 | ADD <Hd>, <Hs>                                      |

|    | イミディエート値の加算                          | ADD <Rd>, #<8bit_Imm>                               |

|    | SP への値加算                             | ADD SP, #<7bit_Imm><br>ADD SP, #-<7bit_Imm>         |

|    | キャリー付き加算                             | ADC <Rd>, <Rs>                                      |

|    | 減算                                   | SUB <Rd>, <Rs>, <Rn><br>SUB <Rd>, <Rs>, #<3bit_Imm> |

|    | イミディエート値の減算                          | SUB <Rd>, #<8bit_Imm>                               |

|    | キャリー付き減算                             | SBC <Rd>, <Rs>                                      |

|    | 否定                                   | NEG <Rd>, <Rs>                                      |

|    | 乗算                                   | MUL <Rd>, <Rs>                                      |

|    | 下位レジスタ (R0-7) と下位レジスタ (R0-7) の比較     | CMP <Rd>, <Rs>                                      |

|    | 下位レジスタ (R0-7) と上位レジスタ (R8-15) の比較    | CMP <Rd>, <Hs>                                      |

|    | 上位レジスタ (R8-15) と下位レジスタ (R0-7) の比較    | CMP <Hd>, <Rs>                                      |

|    | 上位レジスタ (R8-15) と上位レジスタ (R8-15) の比較   | CMP <Hd>, <Hs>                                      |

| 論理 | 補数の比較                                | CMN <Rd>, <Rs>                                      |

|    | イミディエート値の比較                          | CMP <Rd>, #<8bit_Imm>                               |

|    | 論理積                                  | AND <Rd>, <Rs>                                      |

|    | 排他的論理和                               | EOR <Rd>, <Rs>                                      |

表 1-12 Thumb (サム) 命令一覧 (続き)

| 動作           |                                                  | アセンブラ                                            |

|--------------|--------------------------------------------------|--------------------------------------------------|

|              | 論理和                                              | ORR <Rd>, <Rs>                                   |

|              | ビットクリア                                           | BIC <Rd>, <Rs>                                   |

|              | レジスタ値の補数の転送                                      | MVN <Rd>, <Rs>                                   |

|              | テストビット                                           | TST <Rd>, <Rs>                                   |

| シフト/<br>ロテート | 論理左シフト                                           | LSL <Rd>, <Rs>, #<5bit_shift_imm> LSL <Rd>, <Rs> |

|              | 論理右シフト                                           | LSR <Rd>, <Rs>, #<5bit_shift_imm> LSR <Rd>, <Rs> |

|              | 算術右シフト                                           | ASR <Rd>, <Rs>, #<5bit_shift_imm> ASR <Rd>, <Rs> |

|              | 右ロテート                                            | ROR <Rd>, <Rs>                                   |

| 分岐           | 条件分岐                                             |                                                  |

|              | Z セット時                                           | BEQ <label>                                      |

|              | Z クリア時                                           | BNE <label>                                      |

|              | C セット時                                           | BCS <label>                                      |

|              | C クリア時                                           | BCC <label>                                      |

|              | N セット時                                           | BMI <label>                                      |

|              | N クリア時                                           | BPL <label>                                      |

|              | V セット時                                           | BVS <label>                                      |

|              | V クリア時                                           | BVC <label>                                      |

|              | C セット、Z クリア時                                     | BHI <label>                                      |

|              | C クリア、Z セット時                                     | BLS <label>                                      |

|              | N セットと V セット時、または N クリアと V クリア時                  | BGE <label>                                      |

|              | N セットと V クリア時、または N クリアと V セット時                  | BLT <label>                                      |

|              | Z クリアおよび N または V セット時、あるいは Z クリアおよび N または V クリア時 | BGT <label>                                      |

|              | Z セットまたは N セットと V クリアあるいは N クリアと V セット時          | BLE <label>                                      |

|              | 無条件分岐                                            | B <label>                                        |

|              | リンク付きロング分岐                                       | BL <label>                                       |

|              | 任意の状態変化                                          |                                                  |

|              | 下位レジスタに保持されたアドレスへ                                | BX <Rs>                                          |

|              | 上位レジスタに保持されたアドレスへ                                | BX <Hs>                                          |

表 1-12 Thumb ( サム ) 命令一覧 ( 続き )

| 動作         |                      | アセンブラ                             |

|------------|----------------------|-----------------------------------|

| ロード        | イミディエートオフセット付き       |                                   |

|            | ワード                  | LDR <Rd>, [<Rb>, #<7bit_offset>]  |

|            | ハーフワード               | LDRH <Rd>, [<Rb>, #<6bit_offset>] |

|            | バイト                  | LDRB <Rd>, [<Rb>, #<5bit_offset>] |

|            | レジスタオフセット付き          |                                   |

|            | ワード                  | LDR <Rd>, [<Rb>, <Ro>]            |

|            | ハーフワード               | LDRH <Rd>, [<Rb>, <Ro>]           |

|            | 符号付きハーフワード           | LDRSH <Rd>, [<Rb>, <Ro>]          |

|            | バイト                  | LDRB <Rd>, [<Rb>, <Ro>]           |

|            | 符号付きバイト              | LDRSB <Rd>, [<Rb>, <Ro>]          |

| ストア        | PC 相対                | LDR <Rd>, [PC, #<10bit_offset>]   |

|            | SP 相対                | LDR <Rd>, [SP, #<10bit_offset>]   |

|            | アドレス                 |                                   |

|            | PC の使用               | ADD <Rd>, PC, #<10bit_offset>     |

|            | SP の使用               | ADD <Rd>, SP, #<10bit_offset>     |

| ストア        | マルチプル                | LDMIA Rb!, <reglist>              |

|            | イミディエートオフセット付き       |                                   |

|            | ワード                  | STR <Rd>, [<Rb>, #<7bit_offset>]  |

|            | ハーフワード               | STRH <Rd>, [<Rb>, #<6bit_offset>] |

|            | バイト                  | STRB <Rd>, [<Rb>, #<5bit_offset>] |

|            | レジスタオフセット付き          |                                   |

|            | ワード                  | STR <Rd>, [<Rb>, <Ro>]            |

|            | ハーフワード               | STRH <Rd>, [<Rb>, <Ro>]           |

|            | バイト                  | STRB <Rd>, [<Rb>, <Ro>]           |

|            | SP 相対                | STR <Rd>, [SP, #<10bit_offset>]   |

| プッシュ / ポップ | マルチプル                | STMIA <Rb>!, <reglist>            |

|            | スタックヘレジスタ値をプッシュ      | PUSH <reglist>                    |

|            | スタックヘLRおよびレジスタ値をプッシュ | PUSH <reglist, LR>                |

|            | スタックからレジスタへのポップ      | POP <reglist>                     |

| ソフトウェア割り込み | スタックからレジスタと PC へのポップ | POP <reglist, PC>                 |

|            |                      | SWI <8bit_Imm>                    |

注意：Thumb フェッチはすべて 32 ビット thumb プリフェッチバッファを使用して 32 ビットバストランザクションとして実行されます。

## 1.4 シリコンレビジョン

このマニュアルは、ARM720T マクロセルのレビジョン r4p3 に対応したものです。レビジョンナンバリングの詳細については、「製品のレビジョン状態」の項 ( xii ページ ) を参照してください。前回のレビジョンとの機能上の違いはありません。

# 2

# プログラマーズモデル

# 2 プログラマーズモデル

この章では、ARM720T プロセッサのプログラマーズモデルを説明します。ここでは、以下の項を記載しています。

|      |                          |      |

|------|--------------------------|------|

| 2.1  | プロセッサの動作状態               | 2-1  |

| 2.2  | メモリ形式                    | 2-2  |

| 2.3  | 命令長                      | 2-3  |

| 2.4  | データタイプ                   | 2-3  |

| 2.5  | 動作モード                    | 2-4  |

| 2.6  | レジスタ                     | 2-5  |

| 2.7  | プログラムステータスレジスタ           | 2-9  |

| 2.8  | 例外                       | 2-11 |

| 2.9  | FCSE PID による下位仮想アドレスの再配置 | 2-16 |

| 2.10 | リセット                     | 2-17 |

| 2.11 | インプリメンテーション時定義の命令動作      | 2-18 |

## 2.1 プロセッサの動作状態

プログラマの視点から見た場合、ARM720T は次の 2 つのいずれかの状態になります。

**ARM 状態** 32 ビットのワード境界で整列した ARM 命令を実行します。

**Thumb 状態** 16 ビットのハーフワード境界で整列した Thumb 命令で動作します。この状態では、PC はビット 1 を使用してハーフワード間の選択を行います。

### 2.1.1 プロセッサ状態間の切り換え

プロセッサ状態間で遷移が行われても、プロセッサモードやレジスタの内容には影響を与えません。

#### Thumb 状態への移行

Thumb 状態へ移行するには、オペランドレジスタの状態ビット(ビット 0)をセットして BX 命令を実行します。

プロセッサが Thumb 状態のときに例外が発生した場合、たとえば *Interrupt ReQuest* (IRQ)、*Fast Interrupt reQuest* (FIQ)、UNDEF、ABORT、あるいは *SoftWare Interrupt* (SWI) のような例外から復帰する際にも自動的に Thumb 状態へ遷移します。

#### ARM 状態への移行

以下の場合、ARM 状態へ移行します。

- オペランドレジスタの状態ビットをクリアして BX 命令を実行した場合。

- プロセッサが例外を、たとえば IRQ、FIQ、RESET、UNDEF、ABORT、または SWI を受け付けた場合。この場合、PC は例外モードのリンクレジスタに配置され、実行は例外のベクタアドレスから始まります。

## 2.2 メモリ形式

ARM720T プロセッサは、メモリを以下のように 0 から大きくなる方へ番号付けされたバイトの直線的な集まりとしてとらえます。

- バイト 0 ~ 3 最初に格納されたワードを保持します。

- バイト 4 ~ 7 2 番目に格納されたワードを保持します。

- バイト 8 ~ 11 3 番目に格納されたワードを保持します。

ワードは、次の項で説明するようにビッグエンディアンまたはリトルエンディアンとしてメモリに格納されます。

- ビッグエンディアン形式

- リトルエンディアン形式 (2-3 ページ)

使用するエンディアンは、システム制御プロセッサの制御レジスタの B ビットの状態によって異なります。詳細については、「制御レジスタ」の項 (3-4 ページ) を参照してください。

### 2.2.1 ビッグエンディアン形式

ビッグエンディアン形式では、ワードの最上位バイトが最も番号の小さいバイトに格納され、最下位バイトが最も番号の大きいバイトに格納されます。このため、メモリシステムのバイト 0 はデータライン 31 から 24 に接続されます。

ビッグエンディアン形式を図 2-1 に示します。

図 2-1 ワード内のバイトのビッグエンディアンアドレス

#### 注意 :

- 最上位バイトは、最も小さいアドレスに格納されます。

- ワードは、最上位バイトのバイトアドレスでアドレス指定されます。

## 2.2.2 リトルエンディアン形式

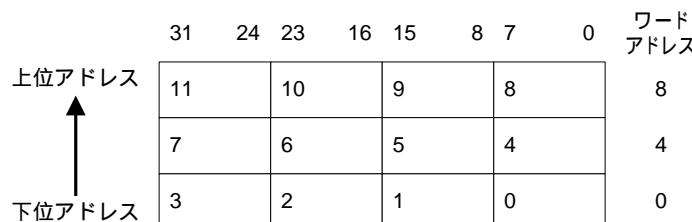

リトルエンディアン形式では、ワードの最も番号の小さいバイトがそのワードの最下位バイトとみなされ、最も番号の大きいバイトが最上位バイトとみなされます。このため、メモリシステムのバイト 0 はデータライン 7 から 0 に接続されます。

リトルエンディアン形式を図 2-2 に示します。

図 2-2 ワード内のバイトのリトルエンディアンアドレス

### 注意：

- 最下位バイトは、最も小さいアドレスに格納されます。

- ワードは、最下位バイトのバイトアドレスでアドレス指定されます。

## 2.3 命令長

命令は以下の長さを持ちます。

- ARM 状態では 32 ビット長

- Thumb 状態では 16 ビット長

## 2.4 データタイプ

ARM720T プロセッサは、以下のデータタイプをサポートしています。

- バイト (8 ビット)

- ハーフワード (16 ビット)

- ワード (32 ビット)

これらのデータタイプは、以下のように整列させます。

- ワードは 4 バイト境界に合わせる。

- ハーフワードは 2 バイト境界に合わせる。

- バイトはどのバイト境界に合わせてもよい。

## 2.5 動作モード

ARM720T プロセッサは、表 2-1 に示すように 7 種類の動作モードをサポートしています。

表 2-1 ARM720T の動作モード

| モード     | タイプ | 説明                                  |

|---------|-----|-------------------------------------|

| ユーザ     | usr | 通常の ARM プログラム実行モード                  |

| FIQ     | fiq | システムで最もパフォーマンスがクリティカルな割り込みに使用されるモード |

| IRQ     | irq | 汎用割り込み処理に使用されるモード                   |

| スーパーバイザ | svc | オペレーティングシステムのプロテクトモード               |

| アポートモード | abt | データアポートや命令プリフェッチャポート後に移行するモード       |

| システム    | sys | オペレーティングシステムの特権ユーザモード               |

| 未定義     | und | 未定義命令が実行されると移行するモード                 |

### 2.5.1 動作モードの変更

動作モードの変更は、ソフトウェアの制御によって行ったり、外部割込みによってまたは例外処理中に行ったりすることができます。大部分のアプリケーションはユーザモードで実行されます。特権モードといわれる非ユーザモードは、割り込みや例外処理を扱ったり、保護リソースにアクセスしたりする場合に移行します。

## 2.6 レジスタ

ARM720T プロセッサには、以下のように全部で 37 個のレジスタがあります。

- 31 個の汎用 32 ビットレジスタ

- 6 個のプログラムステータスレジスタ

これらのレジスタがすべて同時に使用できるわけではありません。プロセッサの状態と動作モードにより、常時プログラマが使用できるレジスタが決まります。

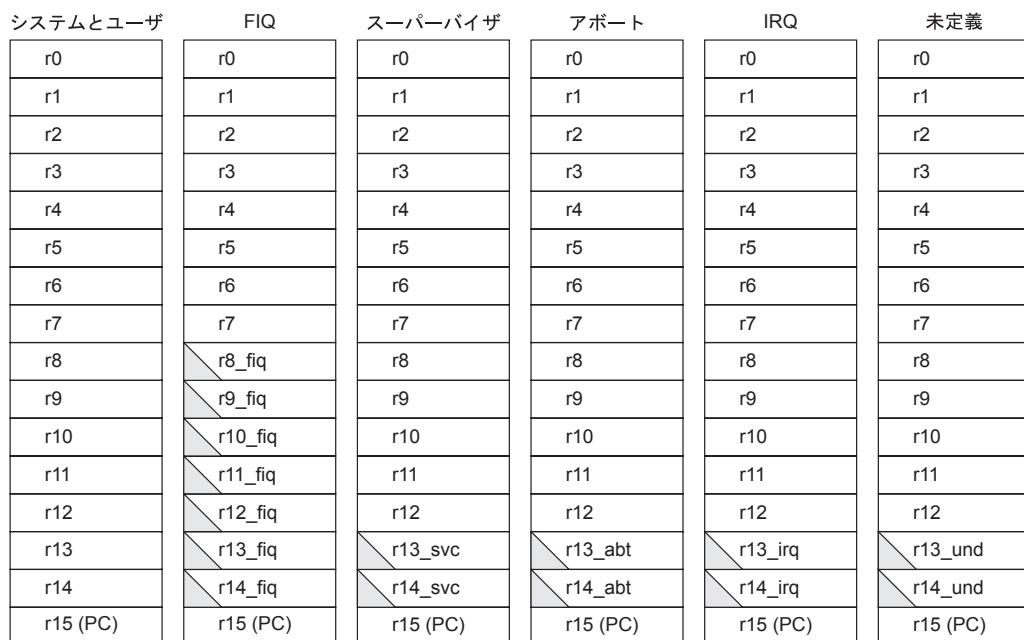

### 2.6.1 ARM 状態のレジスタセット

ARM 状態では、16 個の汎用レジスタと 1 個または 2 個のステータスレジスタを常時見ることができます。特権(非ユーザ)モードでは、モード固有のバンクレジスタに切り替わります。図 2-3 (2-6 ページ) に、各モードで使用可能なレジスタを示します。バンクレジスタには、網かけされた三角形の印がついています。

ARM 状態のレジスタセットには、16 個の直接アクセス可能なレジスタ r0 ~ r15 があります。r15 を除き、これらはすべて汎用レジスタであり、データまたはアドレス値を保持するために使用されます。また、r14 と r15 レジスタには以下のような特別な役割があります。

#### レジスタ r14

このレジスタは、サブルーチンリンクレジスタとして使用されます。このレジスタは、リンク付き分岐(BL)コード命令が実行されると r15 のコピーを受け取ります。それ以外の場合は、汎用レジスタとして扱われます。対応するバンクレジスタ r14\_svc, r14\_irq, r14\_fiq, r14\_abt、および r14\_und は、割り込みや例外が発生した場合や、割り込みルーチンや例外ルーチン内で BL 命令が実行された場合に r15 の戻り値を保持するために同じように使用されます。

#### レジスタ r15

このレジスタは、プログラムカウンタ(PC)を保持します。ARM 状態では、r15 のビット [1:0] はゼロであり、ビット [31:2] は PC 値を格納しています。Thumb 状態では、ビット 0 はゼロであり、ビット [31:1] は PC 値を格納しています。

これらに加えて、カレントプログラムステータスレジスタ(CPSR)がステータス情報を格納するために使用されます。このレジスタは、条件コードフラグと現在のモードビットを格納しています。

## 割り込みモード

FIQ モードには、r8 ~ r14 ( r8\_fiq ~ r14\_fiq ) にマップされた 7 個のバンクレジスタがあります。ARM 状態では、多数の FIQ ハンドラがこれらのバンクレジスタを使用して、レジスタをスタックに保存しなくてよいようにしています。ユーザ、IRQ、スーパーバイザ、アポート、および未定義モードには、それぞれ r13 と r14 にマップされた 2 つのバンクレジスタがあります。これらのバンクレジスタにより、これらの各モードは専用のスタックポインタとリンクレジスタを持つことができます。

ARM状態の汎用レジスタとプログラムカウンタ

ARM状態プログラムステータスレジスタ

= バンクレジスタ

図 2-3 ARM 状態でのレジスタ構成

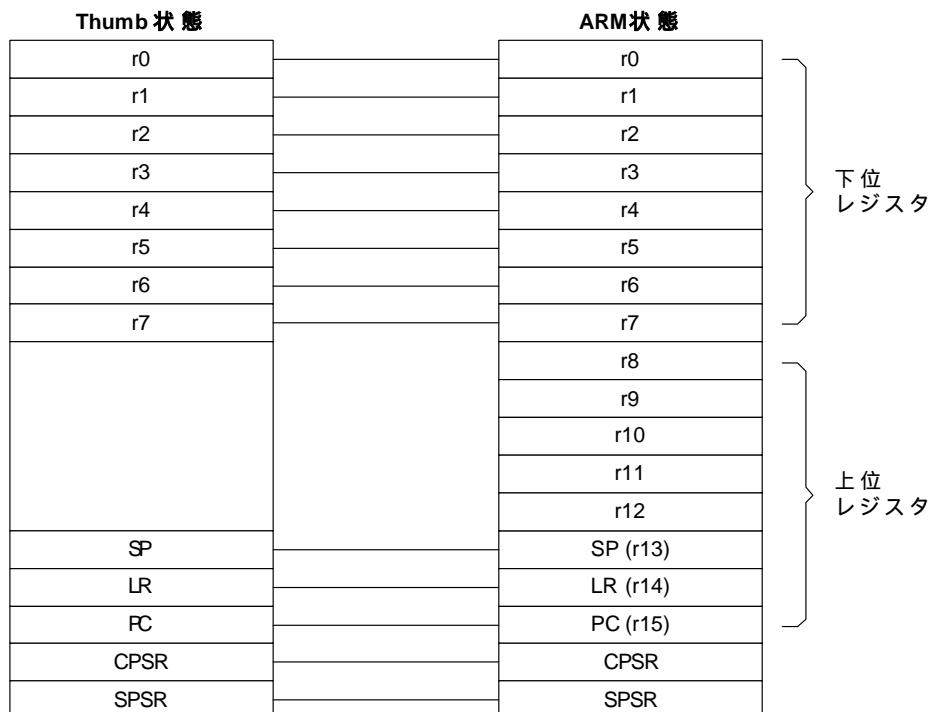

## 2.6.2 Thumb 状態のレジスタセット

Thumb 状態のレジスタセットは、ARM 状態のレジスタセットのサブセットです。以下のレジスタに直接アクセスすることができます。

- 8 個の汎用レジスタ ( r0 ~ r7 )

- PC

- スタックポインタ ( SP ) レジスタ

- リンクレジスタ ( LR )

- CPSR

各特権モードには、バンク構成の SP、LR、およびセーブプログラムステータスレジスタ ( SPSR ) があります。これを図 2-4 に示します。

Thumb 状態汎用レジスタとプログラムカウンタ

| システムとユーザ | FIQ    | スーパーバイザ | アボート   | IRQ    | 未定義    |

|----------|--------|---------|--------|--------|--------|

| r0       | r0     | r0      | r0     | r0     | r0     |

| r1       | r1     | r1      | r1     | r1     | r1     |

| r2       | r2     | r2      | r2     | r2     | r2     |

| r3       | r3     | r3      | r3     | r3     | r3     |

| r4       | r4     | r4      | r4     | r4     | r4     |

| r5       | r5     | r5      | r5     | r5     | r5     |

| r6       | r6     | r6      | r6     | r6     | r6     |

| r7       | r7     | r7      | r7     | r7     | r7     |

| SP       | SP_fiq | SP_svc  | SP_abt | SP_irq | SP_und |

| LR       | LR_fiq | LR_svc  | LR_abt | LR_irq | LR_und |

| PC       | PC     | PC      | PC     | PC     | PC     |

Thumb 状態プログラムステータスレジスタ

|      |                  |                  |                  |                  |                  |

|------|------------------|------------------|------------------|------------------|------------------|

| CPSR | CPSR<br>SPSR_fiq | CPSR<br>SPSR_svc | CPSR<br>SPSR_abt | CPSR<br>SPSR_irq | CPSR<br>SPSR_und |

|------|------------------|------------------|------------------|------------------|------------------|

= バンクレジスタ

図 2-4 Thumb 状態でのレジスタ構成

### 2.6.3 ARM 状態レジスタと Thumb 状態レジスタ間の関係

Thumb 状態のレジスタは、以下のように ARM 状態のレジスタと関係しています。

- Thumb 状態レジスタ r0 ~ r7 と ARM 状態レジスタ r0 ~ r7 は同じです。

- Thumb 状態 CPSR、SPSR と ARM 状態 CPSR、SPSR は同じです。

- Thumb 状態 SP は、ARM 状態 r13 レジスタに対応します。

- Thumb 状態 LR は、ARM 状態 r14 レジスタに対応します。

- Thumb 状態 PC は、ARM 状態 PC (r15) に対応します。

この関係を図 2-5 に示します。

図 2-5 Thumb 状態レジスタから ARM 状態レジスタへのマッピング

### 2.6.4 Thumb 状態の上位レジスタへのアクセス

Thumb 状態では、ARM レジスタ r8 ~ r15 (上位レジスタ) は標準のレジスタセットの一部ではありませんが、アセンブリ言語プログラマは制限付きでこれらのレジスタにアクセスして、高速の一時記憶用に使用できます。

値は、特殊な形式の MOV 命令を使用して r0 ~ r7 の範囲のレジスタ (下位レジスタ) から上位レジスタへ、また上位レジスタから下位レジスタへ値を転送することができます。上位レジスタの値は、CMP 命令や ADD 命令を使用して下位レジスタと比較したり、下位レジスタに加算したりすることもできます。上位レジスタの動作の詳細については、「*ARM Architecture Reference Manual*」を参照してください。

## 2.7 プログラムステータスレジスタ

ARM720T プロセッサには、CPSR と、例外ハンドラによって使用される 5 つの SPSR があります。これらのレジスタは以下の動作を行います。

- ALU 演算で実行された最新の情報を保持する。

- 割り込みのイネーブル、ディセーブルを制御する。

- プロセッサの動作モードを設定する。

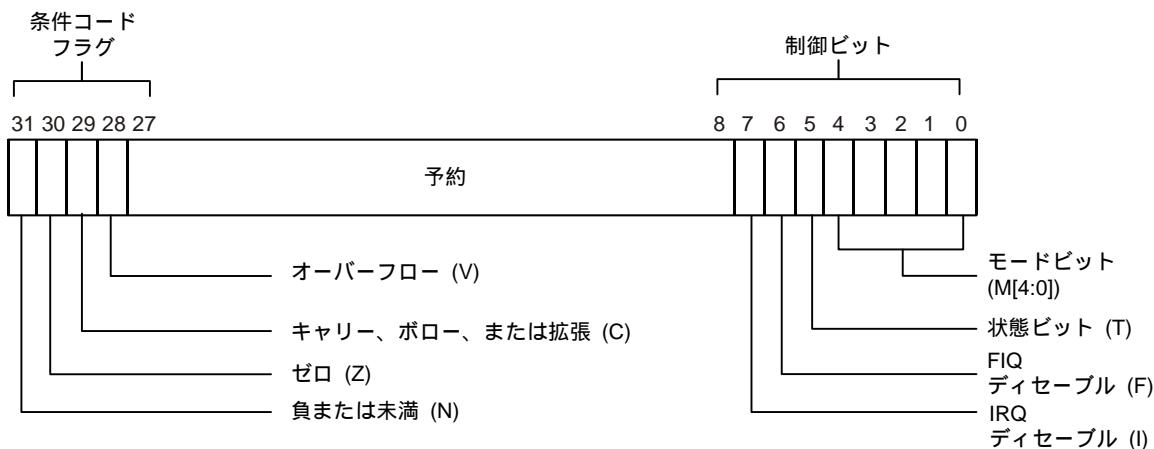

図 2-6 はビット配列を示します。

図 2-6 プログラムステータスレジスタ形式

### 2.7.1 条件コードフラグ

N、Z、C、V ビットは条件コードフラグです。これらのビットは、算術演算や論理演算の結果変更されたり、命令を実行すべきかどうかを決定するために調べられたりします。

ARM 状態では、すべての命令を条件付で実行できます。Thumb 状態では、分岐命令のみが条件付で実行できます。詳細については、「*ARM Architecture Reference Manual*」を参照してください。

### 2.7.2 制御ビット

PSR の下位 8 ビット (I、F、T、および M[4:0] を含む) は、ひとまとめに制御ビットといわれています。これらのビットは、例外が発生すると変化します。プロセッサが特権モードで動作している場合、これらのビットはソフトウェアから操作することもできます。

**I、F ビット** これらのビットは、割り込みディセーブルビットです。セットされると、それぞれ IRQ、FIQ 割り込みを無効にします。

**T ビット** このビットは動作状態を反映します。このビットがセットされると、プロセッサは Thumb 状態で実行しており、セットされていなければ ARM 状態で実行しています。これは、CPTBIT 外部信号に反映されます。ソフトウェアは、CPSR の CPTBIT の状態を変更してはいけません。変更した場合、プロセッサは予期できない状態になります。

**M[4:0] ビット** これらのビットはモードビットです。これらは、表 2-2 (2-10 ページ) に示すようにプロセッサの動作モードを決定します。すべてのモードビットの組み合わせが有効なプロセッサモードを定義するわけではありません。明示された組み合わせのみ使用することができます。

**注意：** モードビット M[4:0] に不当な値を設定すると、プロセッサは予期できない状態になります。このような場合はリセットを行ってください。

### 2.7.3 予約ビット

PSR の残りのビットは予約されています。PSR のフラグや制御ビットを変更する場合は、これらの未使用のビットが変更されていないことを確認してください。また、将来プロセッサがこれらのビットを 1 または 0 として読み出す可能性がありますので、プログラムは特定の値を格納したこれらのビットに頼ることはできません。

表 2-2 PSR モードビット値

| M[4:0] | モード         | 使用可能なThumb 状態レジスタ                                  | 使用可能なARM 状態レジスタ                                       |

|--------|-------------|----------------------------------------------------|-------------------------------------------------------|

| b10000 | ユーザ         | r7 to r0,<br>LR, SP<br>PC, CPSR                    | r14 to r0,<br>PC, CPSR                                |

| b10001 | FIQ         | r7 to r0,<br>LR_fiq, SP_fiq<br>PC, CPSR, SPSR_fiq  | r7 to r0,<br>r14_fiq..r8_fiq,<br>PC, CPSR, SPSR_fiq   |

| b10010 | IRQ         | r7 to r0,<br>LR_irq, SP_irq<br>PC, CPSR, SPSR_irq  | r12 to r0,<br>r14_irq, r13_irq,<br>PC, CPSR, SPSR_irq |

| b10011 | スーパー<br>バイザ | r7 to r0,<br>LR_svc, SP_svc,<br>PC, CPSR, SPSR_svc | r12 to r0,<br>r14_svc, r13_svc,<br>PC, CPSR, SPSR_svc |

| b10111 | アボート        | r7 to r0,<br>LR_abt, SP_abt,<br>PC, CPSR, SPSR_abt | r12 to r0,<br>r14_abt..r13_abt,<br>PC, CPSR, SPSR_abt |

| b11011 | 未定義         | r7 to r0<br>LR_und, SP_und,<br>PC, CPSR, SPSR_und  | r12 to r0,<br>r14_und, r13_und,<br>PC, CPSR, SPSR_und |

| b11111 | システム        | r7 to r0,<br>LR, SP<br>PC, CPSR                    | r14 to r0,<br>PC, CPSR                                |

## 2.8 例外

例外は、通常のプログラムフローを一時的に停止しなければならない時に必ず発生します。たとえば、周辺機器からの割り込みを処理する場合がそうです。例外を処理する前には、ハンドラーチンが終了した時に元のプログラムを再開できるように現在のプロセッサ状態が保存されます。

複数の例外が同時に発生することがありますが、この場合は、決まった順序で処理されます。詳細については、「例外の優先順位」の項（2-15 ページ）を参照してください。

例外動作は、以下の項で説明しています。

- 例外開始時の動作

- 例外終了時の動作、2-12 ページ

- 例外の開始／終了の概要、2-12 ページ

- 高速割り込み要求、2-13 ページ

- 割り込み要求、2-13 ページ

- アポート、2-13 ページ

- ソフトウェア割り込み、2-14 ページ

- 未定義命令、2-14 ページ

- 例外ベクタ、2-14 ページ

- 例外の優先順位、2-15 ページ

- 例外の制限、2-15 ページ

### 2.8.1 例外開始時の動作

例外を処理する場合、ARM720T プロセッサは以下のように動作します。

- 1 該当する LR に次の命令のアドレスを保存します。

- a. ARM 状態で例外が発生すると、次の命令のアドレスは LR ( すなわち、例外により現在の PC+4 または PC+8 ) にコピーされます。詳細については、表 2-3 ( 2-12 ページ ) を参照してください。

- b. Thumb 状態で例外が発生すると、LR に書き込まれた値は、例外から戻ったときにプログラムが正しい場所から再開できるような値でオフセットされた現在の PC 値になります。これは、例外ハンドラが、どの状態で例外が発生したかを決める必要がないことを意味しています。

たとえば、SWI の場合 :

MOVS PC, r14\_svc

この命令は、SWI が ARM 状態か Thumb 状態で実行されたかにかかわらず必ず次の命令に戻します。

- 2 CPSR の内容を該当する SPSR にコピーします。

- 3 強制的に CPSR モードビットを例外に対応した値にします。

- 4 強制的に PC に、該当する例外ベクタから次の命令をフェッチさせます。

また、制御不可能な例外のネスティングを妨ぐために割り込みディセーブルフラグを設定することもできます。

例外が発生したときにプロセッサが Thumb 状態の場合は、PC に例外ベクタアドレスがロードされると自動的に ARM 状態に切り換わります。

## 2.8.2 例外終了時の動作

例外終了時、例外ハンドラは以下の動作を行います。

- 1 必要に応じてオフセットをマイナスして、LR の内容を PC に移します。オフセットは例外のタイプによって異なります。

- 2 SPSR の内容を CPSR に書き戻します。

- 3 例外発生時に割り込みディセーブルフラグがセットされていた場合は、それらをクリアします。

**注意：**Thumb 状態に切り換える必要はまったくありません。それは、SPSR の内容を CPSR にリストアすることによって、T ビットが例外の直前に保持していた値に自動的にセットされるからです。

## 2.8.3 例外の開始 / 終了の概要

表 2-3 は、例外開始時に該当する r14 レジスタに保存される PC 値と、例外ハンドラを終了するための推奨命令をまとめたものです。

表 2-3 例外の開始と終了

| 例外                 | リターン命令               | 例外発生前の状態  |             |

|--------------------|----------------------|-----------|-------------|

|                    |                      | ARM r14_x | Thumb r14_x |

| BL <sup>a</sup>    | MOV PC, r14          | PC + 4    | PC + 2      |

| SWI <sup>a</sup>   | MOVS PC, r14_svc     | PC + 4    | PC + 2      |

| UDEF <sup>a</sup>  | MOVS PC, r14_und     | PC + 4    | PC + 2      |

| FIQ <sup>b</sup>   | SUBS PC, r14_fiq, #4 | PC + 4    | PC + 4      |

| IRQ <sup>b</sup>   | SUBS PC, r14_irq, #4 | PC + 4    | PC + 4      |

| PABT <sup>a</sup>  | SUBS PC, r14_abt, #4 | PC + 4    | PC + 4      |

| DABT <sup>c</sup>  | SUBS PC, r14_abt, #8 | PC + 8    | PC + 8      |

| RESET <sup>d</sup> | NA                   | -         | -           |

- a. PC は、プリフェッチャポートを発生した BL、SWI、未定義命令、またはフェッチのアドレスです。

- b. PC は、FIQ または IRQ が優先されたために実行されなかつた命令のアドレスです。

- c. PC は、データアポートを発生させたロードまたはストア命令のアドレスです。

- d. リセット時に r14\_svc に保存される値は、予測不可能です。

## 2.8.4 高速割り込み要求

FIQ 例外は、システムの中で最もパフォーマンスが重要な割り込みに使用されます。ARM 状態では、プロセッサはレジスタ退避の必要がないように十分な専用レジスタを備えていますので、コンテキスト切り換えのオーバーヘッドが最小限に抑えられます。

FIQ は、外部で **nFIQ** 入力を Low にすることにより発生します。**nFIQ** と **nIRQ** は非同期とみなされますので、割り込みがプロセッサフローに影響を及ぼす前に同期化のためのサイクル遅延が発生します。

例外が ARM 状態から、あるいは Thumb 状態から発生したかにかかわらず、FIQ ハンドラは次の命令を実行して割り込みを終了しなければなりません。

SUBS PC, r14\_fiq, #4

FIQ は、CPSR の F フラグをセットすることによって無効にすることができます。

**注意：** この操作は、ユーザモードでは行えません。

F フラグがクリアされると、ARM720T プロセッサは各命令の終了時に FIQ 同期回路の出力が Low レベルになっているかどうかをチェックします。

## 2.8.5 割り込み要求

IRQ 例外は、**nIRQ** 入力が Low レベルのときに発生する通常の割り込みです。IRQ は FIQ よりも優先順位が低いため、FIQ シーケンスが開始されるとマスクされます。IRQ は CPSR の I ビットをセットすることによりいつでも無効にすることができますが、これは特権（非ユーザ）モードからしか行うことができません。

例外が ARM 状態から、あるいは Thumb 状態から発生したかどうかにかかわらず、IRQ ハンドラは次の命令を実行して割り込みから戻らなければなりません。

SUBS PC, r14\_irq, #4

## 2.8.6 アポート

アポートは、現在のメモリアクセスを完了できないことを示しています。アポートは、プロテクションユニットが、または **HRESP** バスのいずれかによって信号を送ることができます。ARM720T プロセッサは、メモリアクセスサイクル中にアポート例外が発生していないかどうかをチェックします。

アポートには、以下の 2 つのタイプがあります。

**プリフェッチャアポート** このアポートは、命令プリフェッチ時に発生します。プリフェッチャ命令は無効にすることができますが、例外は命令がパイプラインの先頭に来るまで実行されません。たとえば、命令がパイプラインにあるときに分岐が発生したために命令が実行されなかった場合、アポートは発生しません。

**データアポート** このアポートは、データアクセス中に発生します。実行される動作は、以下のように命令タイプによって異なります。

- シングルデータ転送命令 (LDR、STR) は、変更されたベースレジスタを書き戻します。アポートハンドラは、このことを認識していなければなりません。

- スワップ命令 (SWP) は、あたかも実行されなかったかのようにアポートされます。

- ロックデータ転送命令 (LDM、STM) は完了します。ライトバックが設定されると、ベースは更新されます。命令がデータによってベースを上書きしようとする（すなわち、転送リストにベースがあると）上書きは阻止されます。アポートが示された後、すべてのレジスタの上書きは行われません。これは、特に r15 (常に、最後に転送されるレジスタ) は LDM 命令がアポートされても保存されることを意味しています。

アポートの原因が解決された後、ハンドラはプロセッサの状態 (ARM または Thumb) にかかわらず以下の命令を実行しなければなりません。

プリフェッチアポートの場合 : SUBS PC, r14\_abt, #4

データアポートの場合 : SUBS PC, r14\_abt, #8

これによって、PC と CPSR の両方がリストアされ、アポートされた命令を再試行します。

**注意 :** 外部アポート信号の使用に関しては制限があります。詳細については、「外部アポート」の項 (7-21 ページ) を参照してください。

## 2.8.7 ソフトウェア割り込み

SWI 命令はスーパーバイザモードを開始するために使用され、通常特定のスーパーバイザ機能を要求します。SWI ハンドラは、プロセッサの状態 (ARM または Thumb) にかかわりなく以下の命令を実行することによって復帰しなければなりません。

MOV PC, r14\_svc

これによって PC と CPSR の両方がリストアされ、SWI の次の命令に復帰します。

## 2.8.8 未定義命令

ARM720T プロセッサは処理することができない命令を検出した場合、未定義命令トラップを使用します。このメカニズムを使用して、ソフトウェアエミュレーションによって設定されているThumb 命令か ARM 命令のいずれかを拡張することができます。

実行に失敗した命令をエミュレートした後、トラップハンドラはプロセッサの状態 (ARM または Thumb) にかかわりなく以下の命令を実行しなければなりません。

MOVS PC, r14\_und

これによって CPSR がリストアされ、未定義命令の次の命令に復帰します。

## 2.8.9 例外ベクタ

ARM720T プロセッサは、システム制御コプロセッサの制御レジスタの V ビットで制御される下位アドレスか上位アドレスのいずれかにマップされた例外ベクタを持つことができます (「制御レジスタ」の項 (3-4 ページ) を参照してください)。表 2-4 に、例外ベクタアドレスを示します。

表 2-4 例外ベクタアドレス

| 上位アドレス     | 下位アドレス     | 例外           | エントリーモード |

|------------|------------|--------------|----------|

| 0xFFFF0000 | 0x00000000 | リセット         | スーパーバイザ  |

| 0xFFFF0004 | 0x00000004 | 未定義命令        | 未定義      |

| 0xFFFF0008 | 0x00000008 | ソフトウェア割り込み   | スーパーバイザ  |

| 0xFFFF000C | 0x0000000C | アポート(プリフェッチ) | アポート     |

| 0xFFFF0010 | 0x00000010 | アポート(データ)    | アポート     |

| 0xFFFF0014 | 0x00000014 | 予約           | 予約       |

| 0xFFFF0018 | 0x00000018 | IRQ          | IRQ      |

| 0xFFFF001C | 0x0000001C | FIQ          | FIQ      |

**注意 :** 下位アドレスはデフォルトです。

## 2.8.10 例外の優先順位

複数の例外が同時に発生した場合、決められた優先順位システムによって処理される順番は以下のように決まっています。

- 1 リセット（最も優先順位が高い）

- 2 データアポート

- 3 FIQ

- 4 IRQ

- 5 プリフェッチャアポート

- 6 未定義命令、SWI（最も優先順位が低い）

## 2.8.11 例外の制限

未定義命令と SWI は同時に指定できません。それぞれが現在の命令の特定の（非オーバラッピング）デコーディングに対応しているためです。

データアポートが FIQ と同時に発生し、かつ FIQ が有効になっている、すなわち CPSR の F フラグがクリアされている場合、ARM720T プロセッサはデータアポートハンドラを開始し、その後すぐに FIQ ベクタ処理に移ります。FIQ から正常復帰すると、データアポートハンドラは実行を再開します。データアポートの優先順位を FIQ よりも高く設定して、転送エラーの検出が確実に行われるようになります。この例外開始に要する時間は、最悪の場合を想定した FIQ レイテンシの計算に加えてください。

## 2.9 FCSE PID による下位仮想アドレスの再配置

ARM720T プロセッサは高速コンテキスト切り換え拡張機能 (FCSE) というメカニズムを提供して、FCSE プロセス識別子 (PID) の現在の値に基づいて仮想アドレスを物理アドレスに変換します。

プロセッサコアによって生成される IDC、MMU への仮想アドレスは、仮想アドレスの下位 32MB に存在する場合再配置させることができます。すなわち、CP15 コプロセッサの FCSE PID レジスタの 7 ビット [31:25] で置き換えることによって、仮想アドレスビット [31:25] = b0000000 になります。

以下の場合、FCSE PID が変更されると、遅延分岐と同様な動作を示します。

- FCSE PID を変更するための命令のすぐ後でフェッチされた 2 つの命令は、以前の FCSE PID に再配置されてフェッチされる。

- フェッチ中の命令のアドレスは、再配置するアドレスの範囲内にある。

リセット時、FCSE PID レジスタビット [31:25] は b0000000 にセットされ、すべての再配置を無効にします。このことから、下位アドレスリセット例外ベクタは、このメカニズムでは効果的に再配置されません。

**注意：** プロセッサコアによって生成されるすべてのアドレスは、適切なアドレスレンジに入っている限りこの変換にかけられます。例外ベクタが仮想メモリマップの下位に来るよう構成されている場合は、例外ベクタもこれに含まれます。この構成は、CP15 制御レジスタ c1 の V ビットによって決定されます。

## 2.10 リセット

**HRESETn** 信号が Low になると、ARM720T プロセッサは以下の動作を行います。

- 1 実行中の命令を中止します。

- 2 キャッシュとトランスレーションルックアサイド/バッファ (TLB) をフラッシュします。

- 3 ライト/バッファ (WB) キャッシュ、MMU をディセーブルにします。

- 4 FCSE PID をリセットします。

- 5 インクリメントするワードアドレスから命令フェッチを継続します。

**HRESETn** 信号が Low になると、プロセッサは **VINITHI** 外部入力をサンプリングし、その結果を CP15 レジスタ 1 の V ビットに格納します。

**HRESETn** 信号が再度 High になると、ARM720T プロセッサは以下の動作を行います。

- 1 PC と CPSR の現在の値をコピーして r14\_svc と SPSR\_svc を上書きします。保存された PC と SPSR の値は、定義されていません。

- 2 強制的に M[4:0] を b10011 にし(スーパーバイザモード) CPSR の I ビットと F ビットをセットし、CPSR の T ビットをクリアします。

- 3 強制的に PC にリセット例外ベクタから次の命令をフェッチさせます。例外ベクタは、CP15 レジスタ 1 の V ビット状態に応じて上位アドレスか下位アドレスのいずれかに再配置されます (LOW = 下位アドレス、HIGH = 上位アドレス)。

- 4 ARM 状態で実行を再開します。

## 2.11 インプリメンテーション時定義の命令動作

“*ARM Architecture Reference Manual*”では、ARM720T プロセッサの命令セットが定義されています。

- “*ARM Architecture Reference Manual*”でインプリメンテーション時定義としてみなされる命令の動作については、「データアポート時のインデックスドアドレッシング」の項を参照してください。

- ARM720T プロセッサでの符号付き早期終了、符号なし早期終了を定義するこれらの機能については、「早期終了」の項を参照してください。

### 2.11.1 データアポート時のインデックスドアドレッシング

プリインデックスドアドレッシングやポストインデックスドアドレッシングでデータアポートが発生した場合、Rn にある値は、以下の命令について更新されたベースレジスタ値として定義されます。

- LDC

- LDM

- LDR

- LDRB

- LDRBT

- LDRH

- LDRSB

- LDRSH

- LDRT

- STC

- STM

- STR

- STRB

- STRBT

- STRH

- STRT.

### 2.11.2 早期終了

ARM720T では、早期終了を以下のように定義しています。

- |                     |          |

|---------------------|----------|

| <b>MLA、MUL</b>      | 符号付き早期終了 |

| <b>SMULL、SMLAL</b>  | 符号付き早期終了 |

| <b>UMULL, UMLAL</b> | 符号なし早期終了 |

3

コンフィギュレーション

# 3 コンフィギュレーション

この章では、ARM720T プロセッサのコンフィギュレーションについて説明します。ここでは、以下の項を記載しています。

|     |                 |     |

|-----|-----------------|-----|

| 3.1 | コンフィギュレーションについて | 3-1 |

| 3.2 | 内部コプロセッサ命令      | 3-2 |

| 3.3 | レジスタ            | 3-3 |

## 3.1 コンフィギュレーションについて

ARM720T プロセッサの動作とコンフィギュレーションは、以下のように制御されます。

- 直接、システム制御コプロセッサ CP15 へのコプロセッサ命令を使用

- 間接的に MMU ページテーブルを使用