**EPSON**

CMOS 8-BIT SINGLE CHIP MICROCOMPUTER

# S1C88848

テクニカルマニュアル

S1C88848 Technical Hardware

**セイコーエプソン株式会社**

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

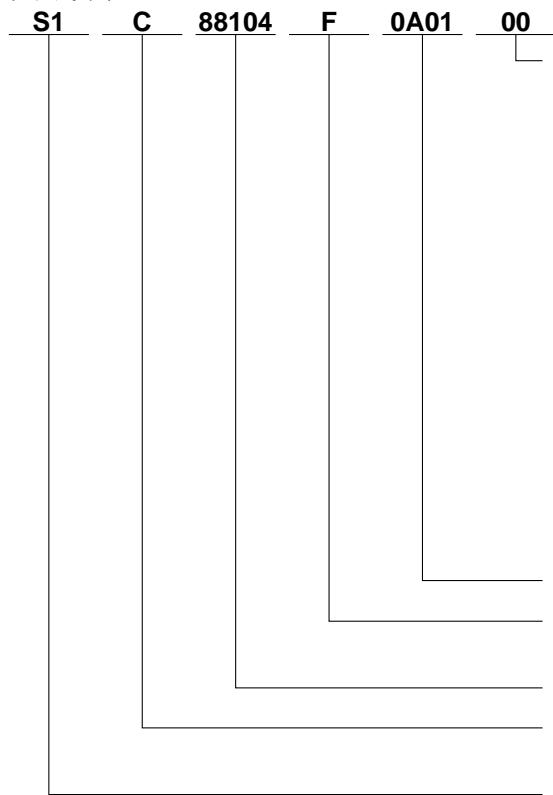

## 製品型番体系

デバイス

### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

### 仕様

[D: ベアチップ、F: QFP]

### 機種番号

### 機種名称

[C: マイコン、デジタル製品]

### 製品分類

[S1: 半導体]

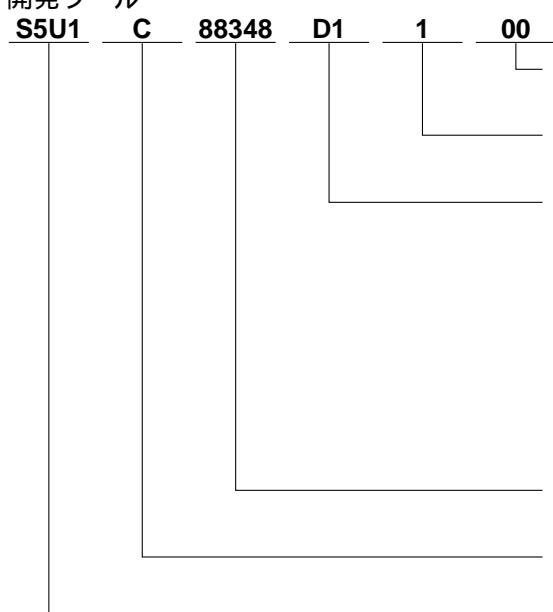

開発ツール

### 梱包仕様

[00: 標準梱包]

### バージョン

[1: Version 1]

### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ペリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

### 対応機種番号

[88348: S1C88348用]

### ツール分類

[C: マイコン用]

### 製品分類

[S5U1: 半導体用開発ツール]

## 一 目 次 一

|       |                                 |    |

|-------|---------------------------------|----|

| 1     | 概要 .....                        | 1  |

| 1.1   | 特長 .....                        | 1  |

| 1.2   | ブロック図 .....                     | 2  |

| 1.3   | 端子 .....                        | 3  |

| 1.3.1 | 端子配置図 .....                     | 3  |

| 1.3.2 | 端子説明 .....                      | 4  |

| 1.4   | マスクオプション .....                  | 5  |

| 2     | 電源 .....                        | 8  |

| 2.1   | 動作電圧 .....                      | 8  |

| 2.2   | 内部電源回路 .....                    | 8  |

| 3     | CPUとメモリの構成 .....                | 9  |

| 3.1   | CPU .....                       | 9  |

| 3.2   | 内蔵メモリ .....                     | 9  |

| 3.2.1 | ROM .....                       | 9  |

| 3.2.2 | RAM .....                       | 9  |

| 3.2.3 | I/Oメモリ .....                    | 9  |

| 3.2.4 | 表示メモリ .....                     | 9  |

| 3.3   | 例外処理ベクタ .....                   | 10 |

| 3.4   | CC(カスタマイズコンディションフラグ) .....      | 10 |

| 4     | イニシャルリセット .....                 | 11 |

| 4.1   | イニシャルリセット要因 .....               | 11 |

| 4.1.1 | RESET端子 .....                   | 12 |

| 4.1.2 | 入力ポート(K00~K03)の同時LOWレベル入力 ..... | 12 |

| 4.1.3 | イニシャルリセットシーケンス .....            | 12 |

| 4.2   | イニシャルリセット時の初期設定 .....           | 13 |

| 5     | 周辺回路と動作 .....                   | 14 |

| 5.1   | I/Oメモリマップ .....                 | 14 |

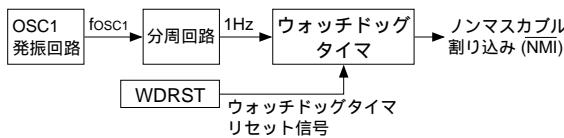

| 5.2   | ウォッチドッグタイマ .....                | 25 |

| 5.2.1 | ウォッチドッグタイマの構成 .....             | 25 |

| 5.2.2 | 割り込み機能 .....                    | 25 |

| 5.2.3 | ウォッチドッグタイマの制御方法 .....           | 25 |

| 5.2.4 | プログラミング上の注意事項 .....             | 25 |

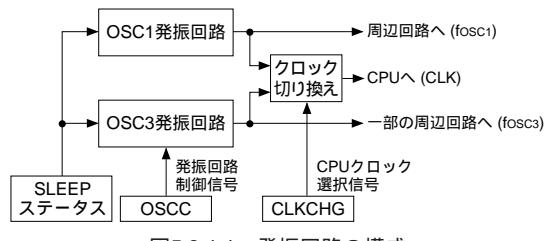

| 5.3   | 発振回路 .....                      | 26 |

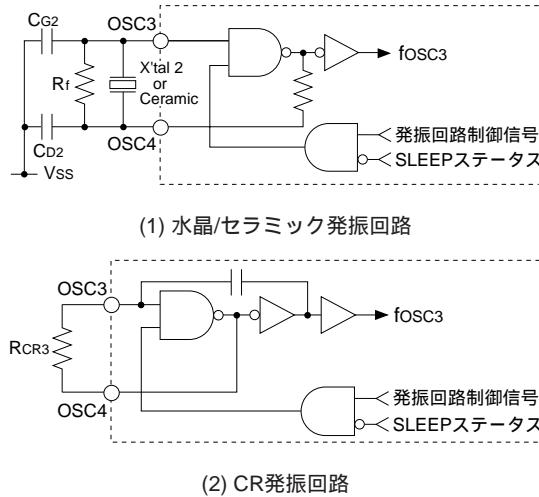

| 5.3.1 | 発振回路の構成 .....                   | 26 |

| 5.3.2 | マスクオプション .....                  | 26 |

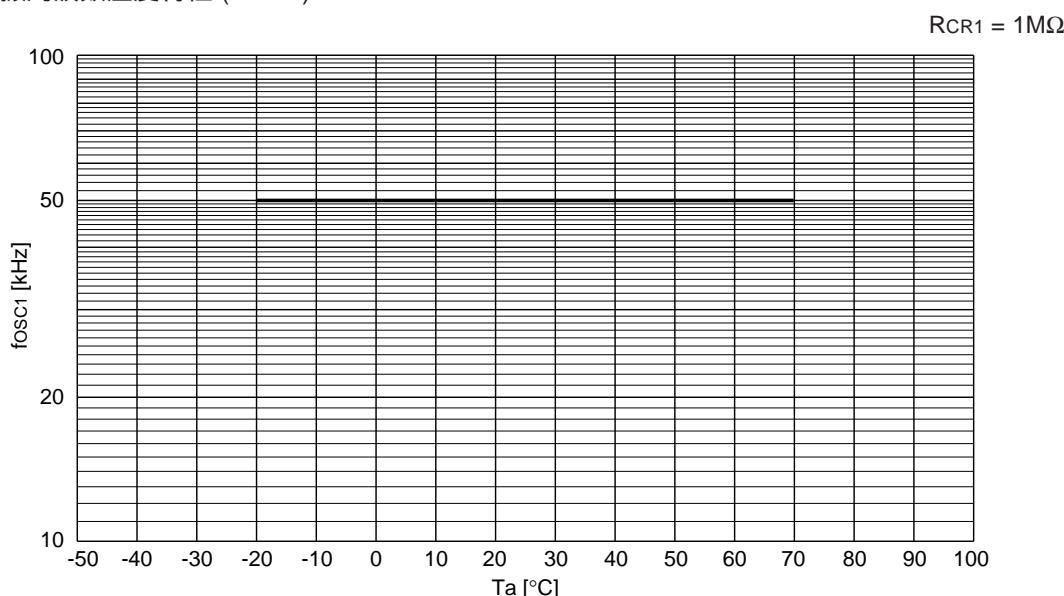

| 5.3.3 | OSC1発振回路 .....                  | 26 |

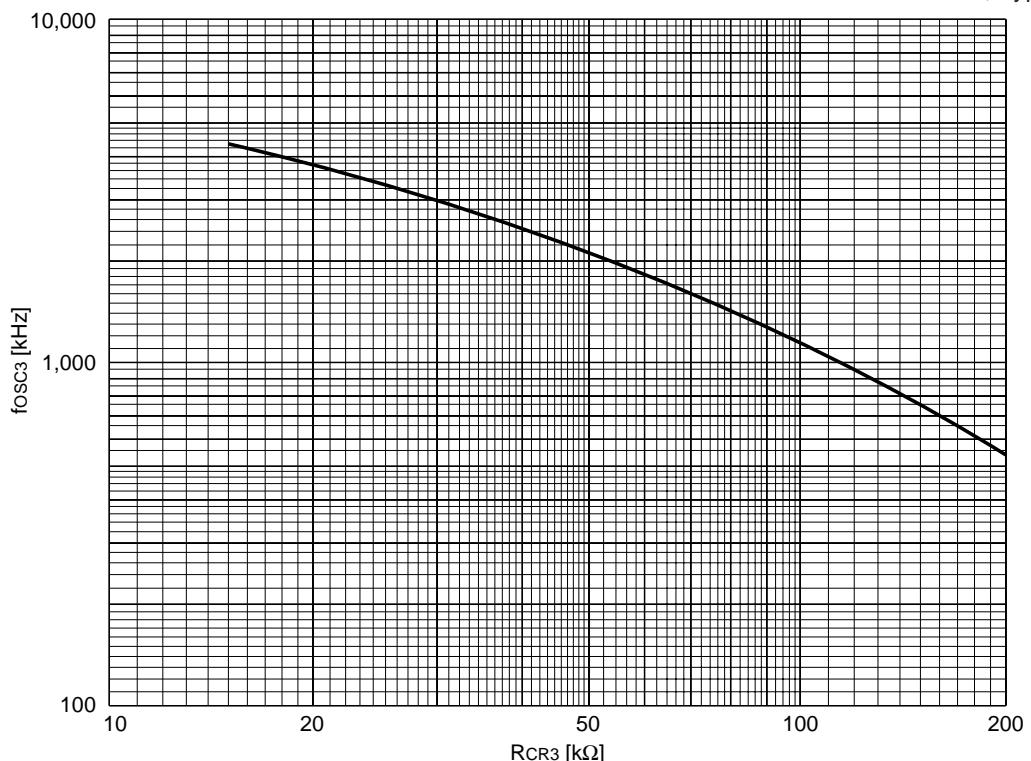

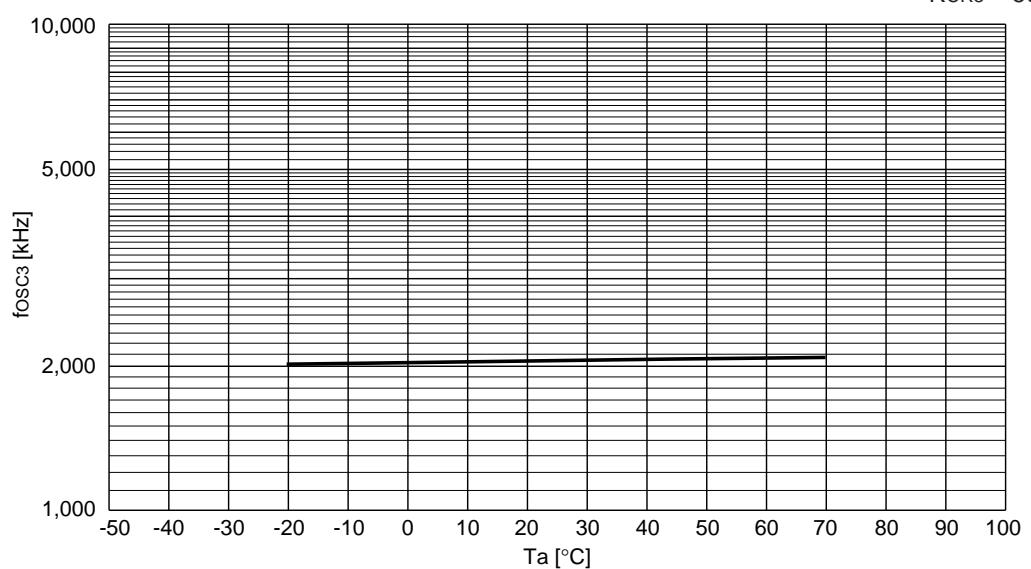

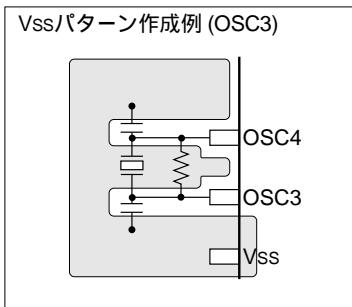

| 5.3.4 | OSC3発振回路 .....                  | 27 |

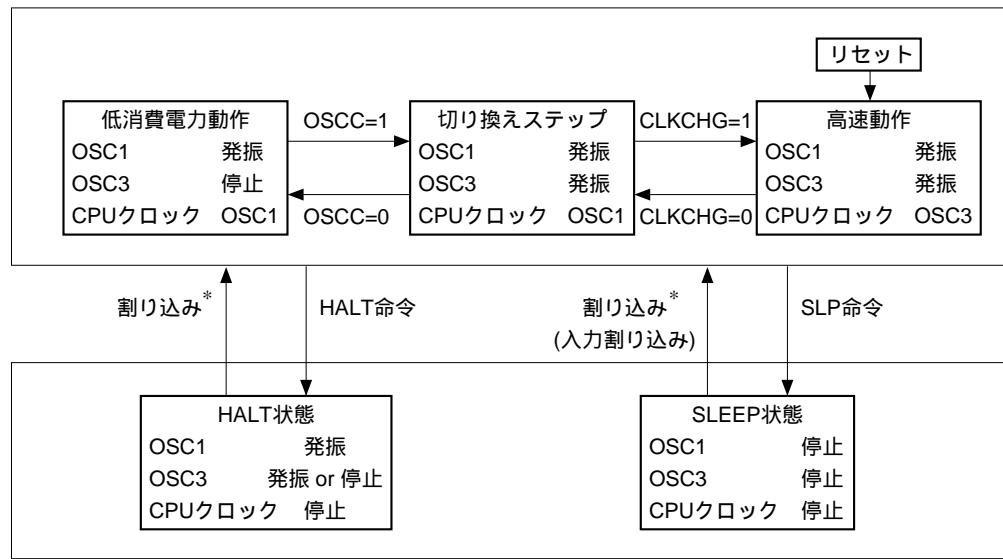

| 5.3.5 | CPUクロックの切り換え .....              | 27 |

| 5.3.6 | 発振回路の制御方法 .....                 | 28 |

| 5.3.7 | プログラミング上の注意事項 .....             | 28 |

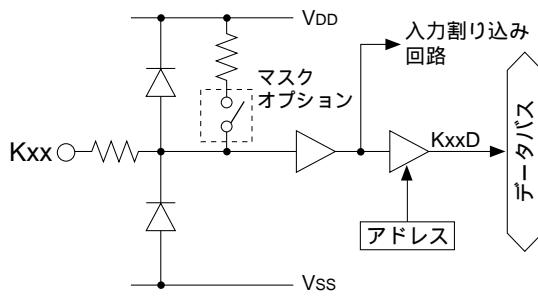

| 5.4   | 入力ポート(Kポート) .....               | 29 |

| 5.4.1 | 入力ポートの構成 .....                  | 29 |

| 5.4.2 | マスクオプション .....                  | 29 |

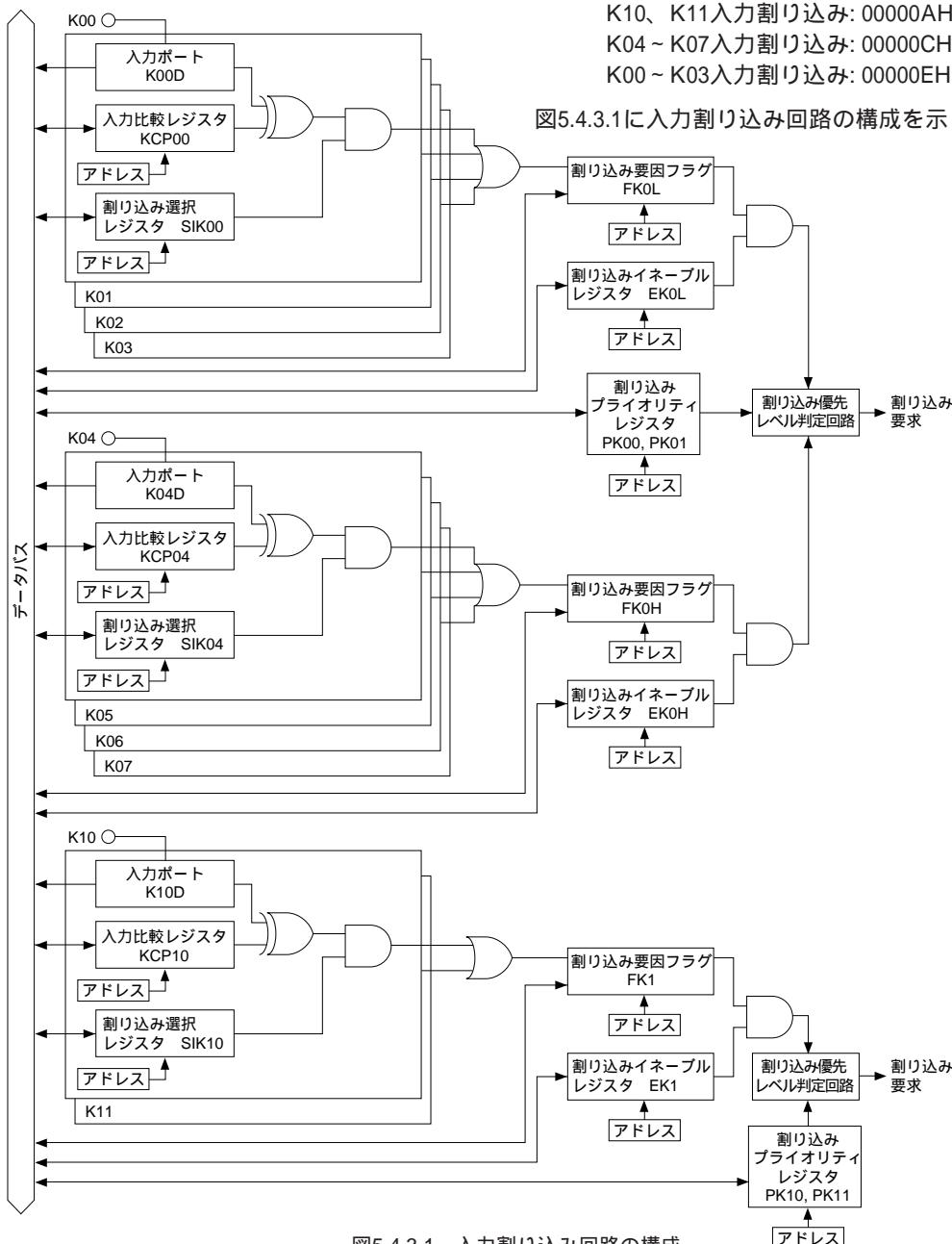

| 5.4.3 | 割り込み機能と入力比較レジスタ .....           | 30 |

|                                    |    |

|------------------------------------|----|

| 5.4.4 入力ポートの制御方法 .....             | 32 |

| 5.4.5 プログラミング上の注意事項 .....          | 34 |

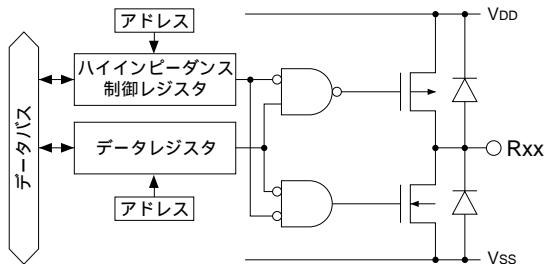

| 5.5 出力ポート (Rポート) .....             | 35 |

| 5.5.1 出力ポートの構成 .....               | 35 |

| 5.5.2 マスクオプション .....               | 35 |

| 5.5.3 ハイインピーダンス制御 .....            | 35 |

| 5.5.4 DC出力 .....                   | 35 |

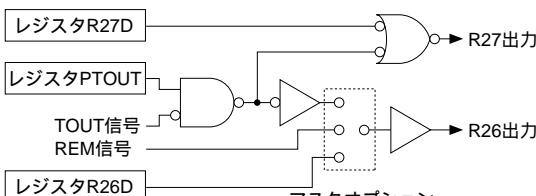

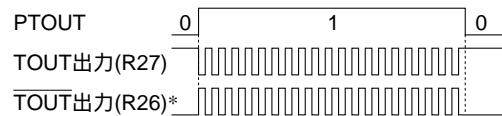

| 5.5.5 特殊出力 .....                   | 36 |

| 5.5.6 出力ポートの制御方法 .....             | 38 |

| 5.5.7 プログラミング上の注意事項 .....          | 41 |

| 5.6 入出力兼用ポート (Pポート) .....          | 42 |

| 5.6.1 入出力兼用ポートの構成 .....            | 42 |

| 5.6.2 マスクオプション .....               | 42 |

| 5.6.3 I/Oコントロールレジスタと入力/出力モード ..... | 42 |

| 5.6.4 入出力兼用ポートの制御方法 .....          | 43 |

| 5.6.5 プログラミング上の注意事項 .....          | 43 |

| 5.7 シリアルインタフェース .....              | 44 |

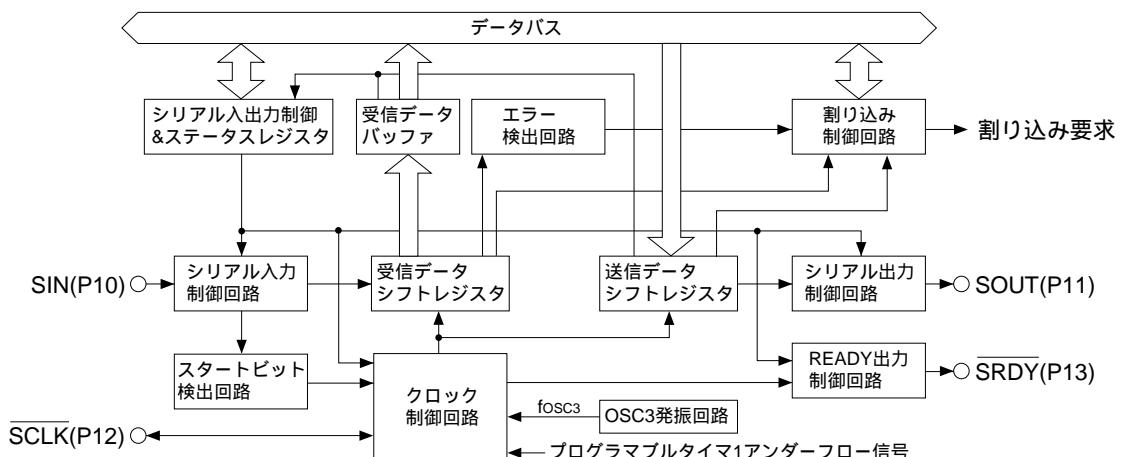

| 5.7.1 シリアルインタフェースの構成 .....         | 44 |

| 5.7.2 マスクオプション .....               | 45 |

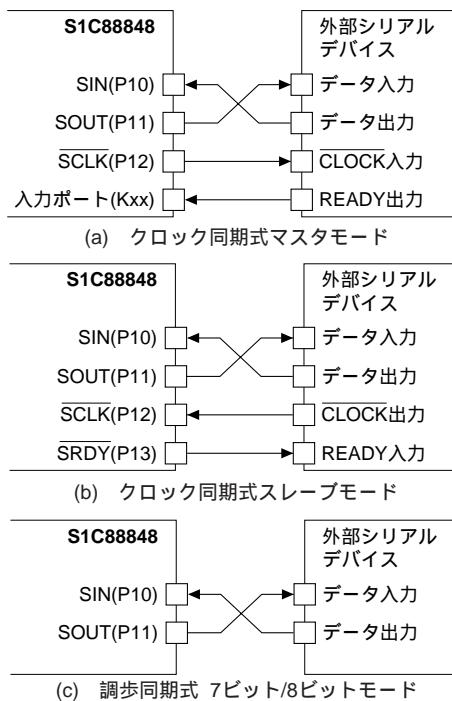

| 5.7.3 転送モード .....                  | 45 |

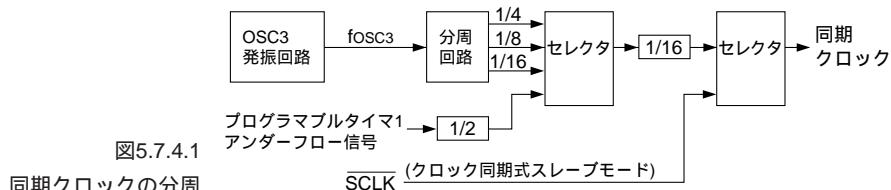

| 5.7.4 クロック源 .....                  | 46 |

| 5.7.5 送受信の制御 .....                 | 47 |

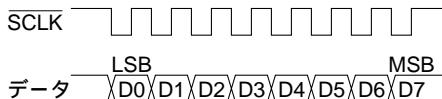

| 5.7.6 クロック同期式転送の動作 .....           | 48 |

| 5.7.7 調歩同期式転送の動作 .....             | 52 |

| 5.7.8 割り込み機能 .....                 | 56 |

| 5.7.9 シリアルインタフェースの制御方法 .....       | 58 |

| 5.7.10 プログラミング上の注意事項 .....         | 62 |

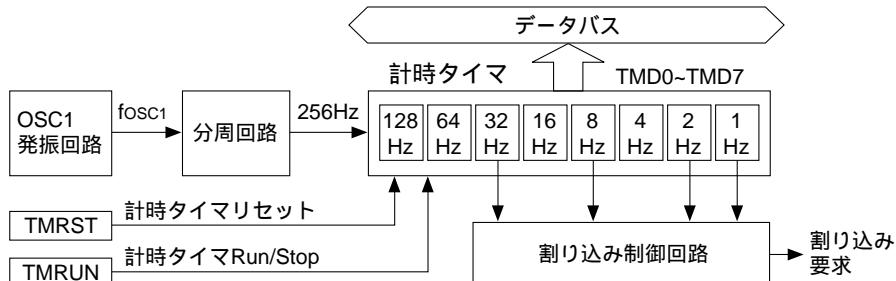

| 5.8 計時タイマ .....                    | 63 |

| 5.8.1 計時タイマの構成 .....               | 63 |

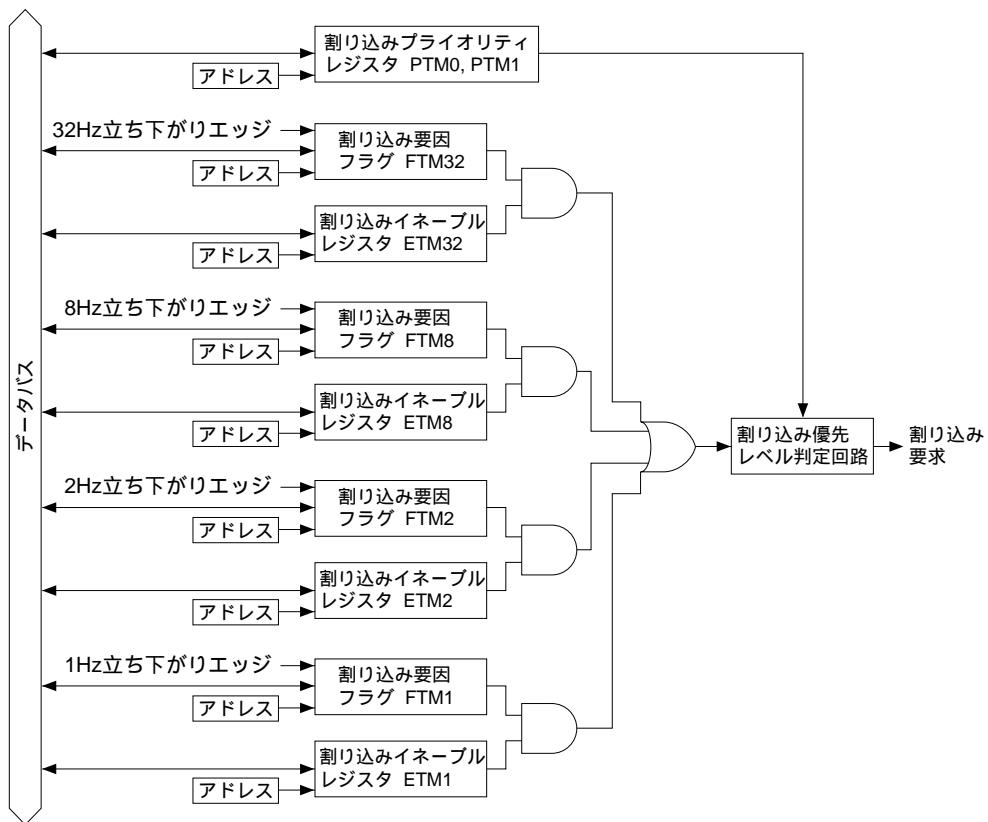

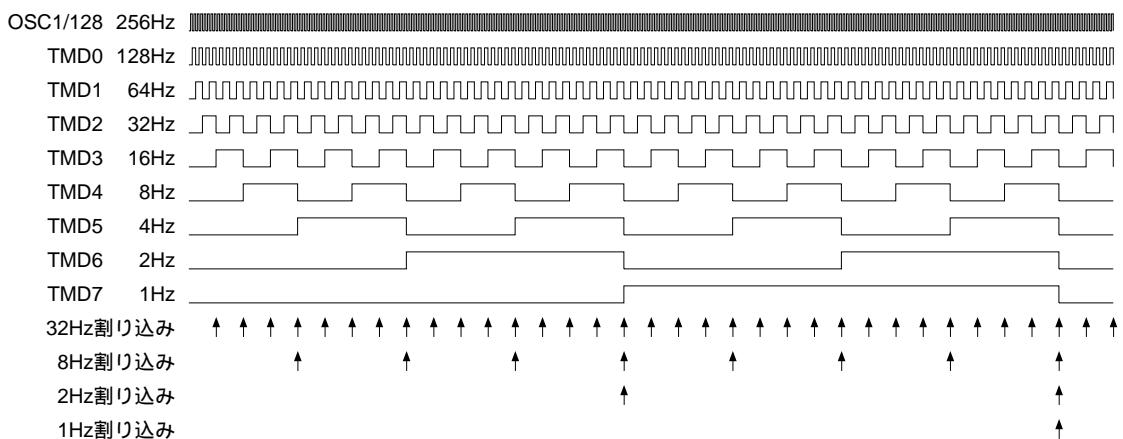

| 5.8.2 割り込み機能 .....                 | 63 |

| 5.8.3 計時タイマの制御方法 .....             | 65 |

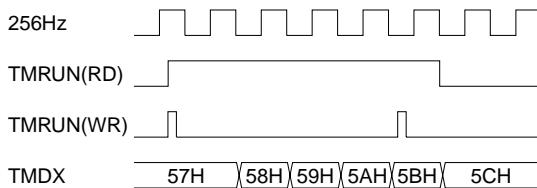

| 5.8.4 プログラミング上の注意事項 .....          | 67 |

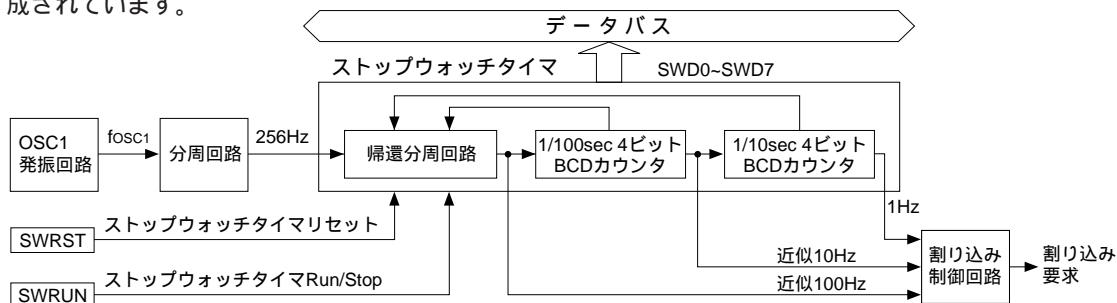

| 5.9 ストップウォッチタイマ .....              | 68 |

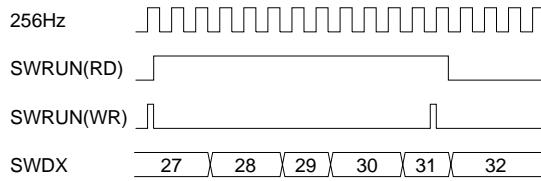

| 5.9.1 ストップウォッチタイマの構成 .....         | 68 |

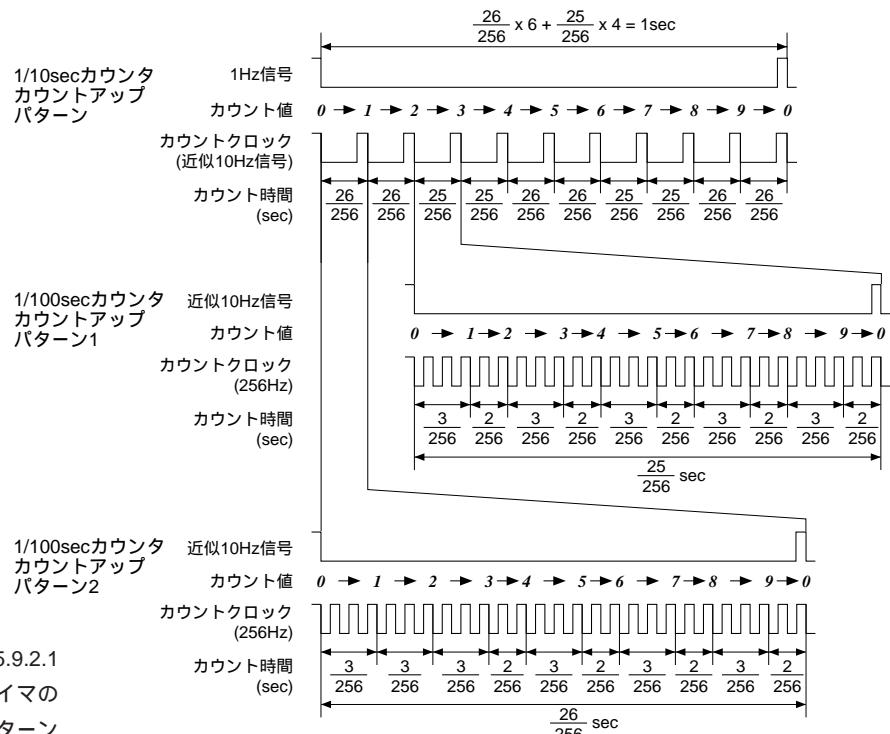

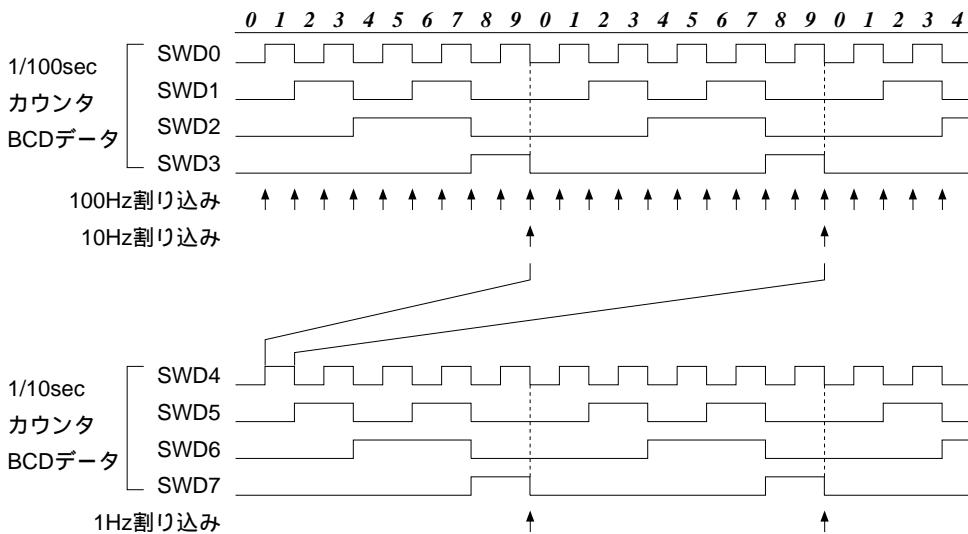

| 5.9.2 カウントアップパターン .....            | 68 |

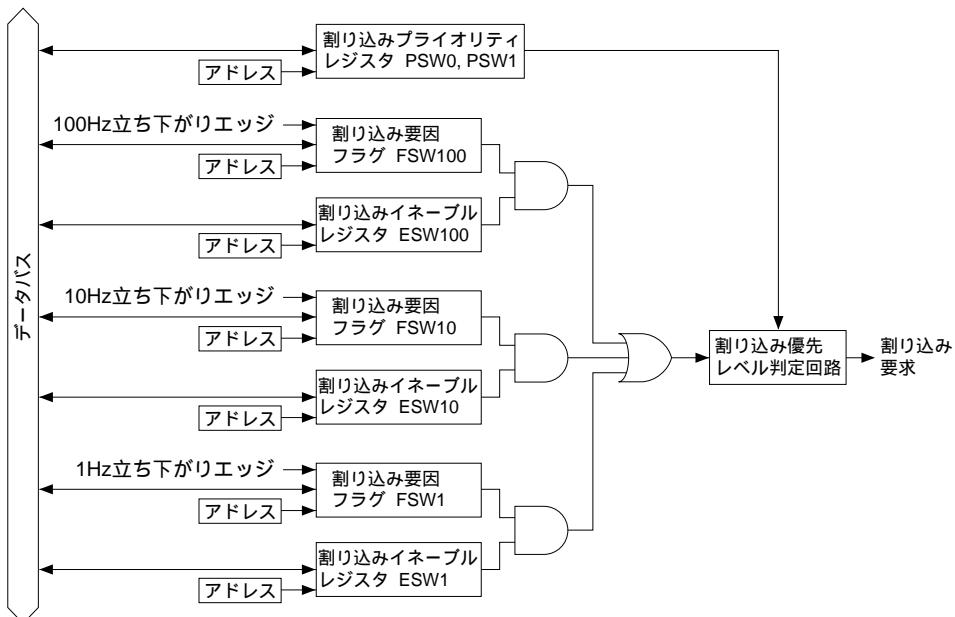

| 5.9.3 割り込み機能 .....                 | 69 |

| 5.9.4 ストップウォッチタイマの制御方法 .....       | 70 |

| 5.9.5 プログラミング上の注意事項 .....          | 72 |

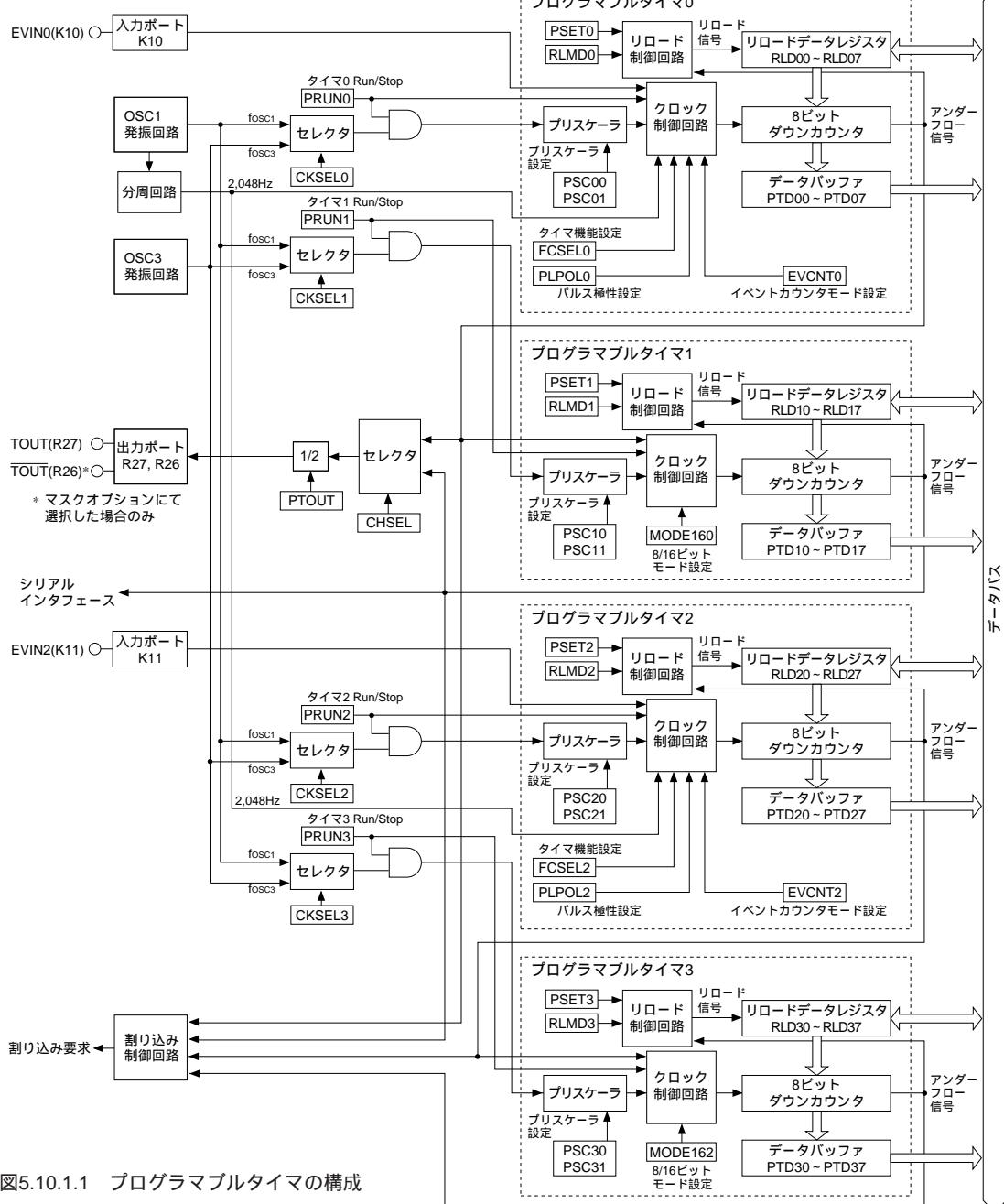

| 5.10 プログラマブルタイマ .....              | 73 |

| 5.10.1 プログラマブルタイマの構成 .....         | 73 |

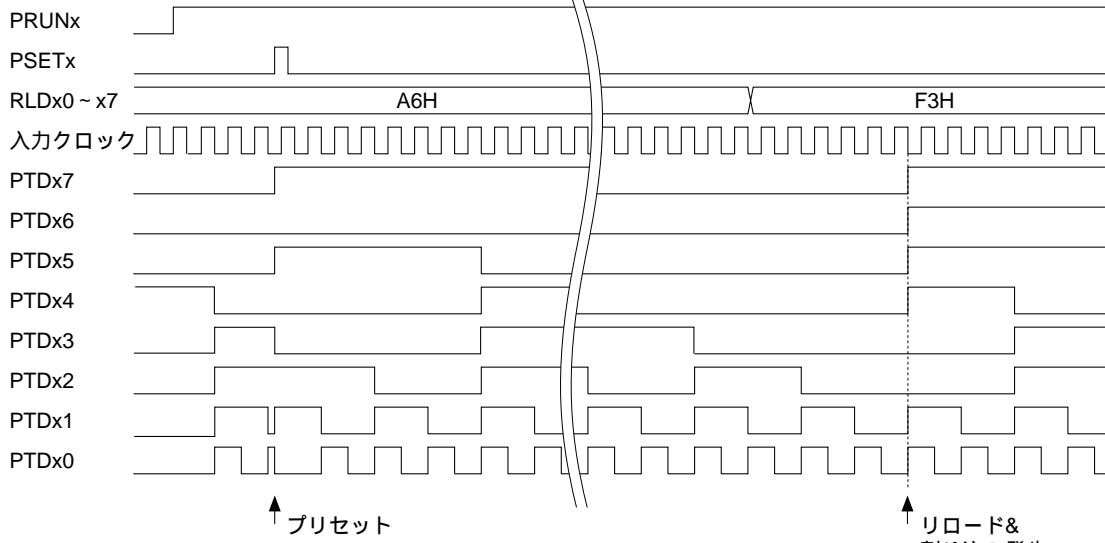

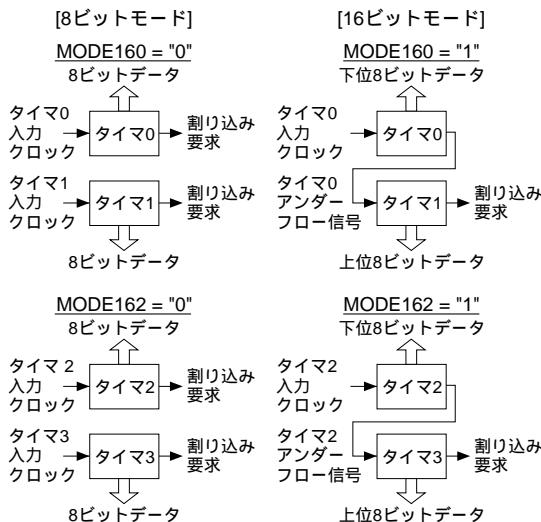

| 5.10.2 カウント動作と基本モード設定 .....        | 74 |

| 5.10.3 入力クロックの設定 .....             | 75 |

| 5.10.4 タイマモード .....                | 76 |

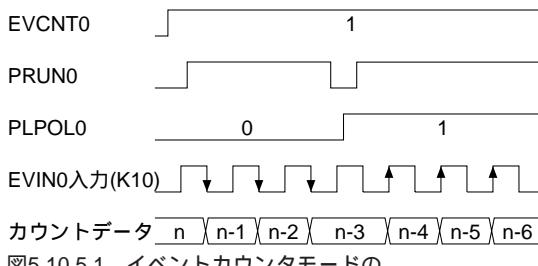

| 5.10.5 イベントカウンタモード .....           | 76 |

| 5.10.6 パルス幅測定タイマモード .....          | 76 |

| 5.10.7 割り込み機能 .....                | 77 |

| 5.10.8 TOUT出力の設定 .....             | 78 |

| 5.10.9 シリアルインタフェースの転送速度設定 .....    | 78 |

|                                        |     |

|----------------------------------------|-----|

| 5.10.10 プログラマブルタイマの制御方法 .....          | 79  |

| 5.10.11 プログラミング上の注意事項 .....            | 86  |

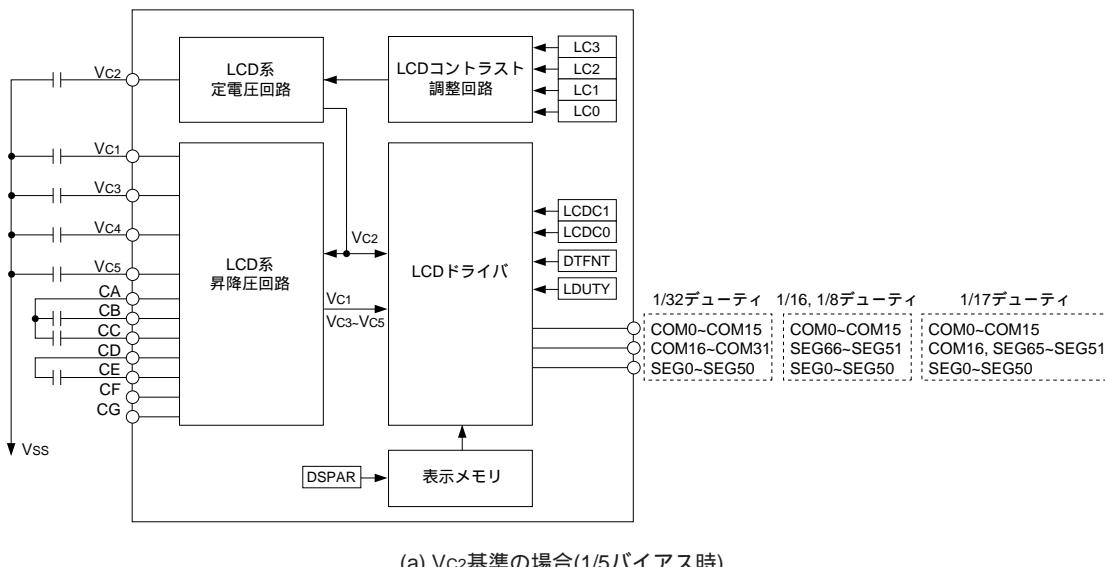

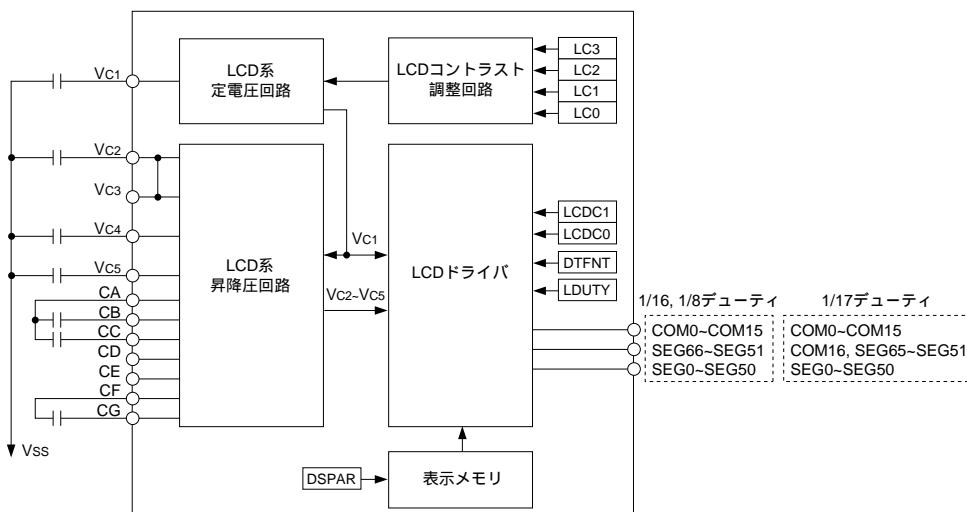

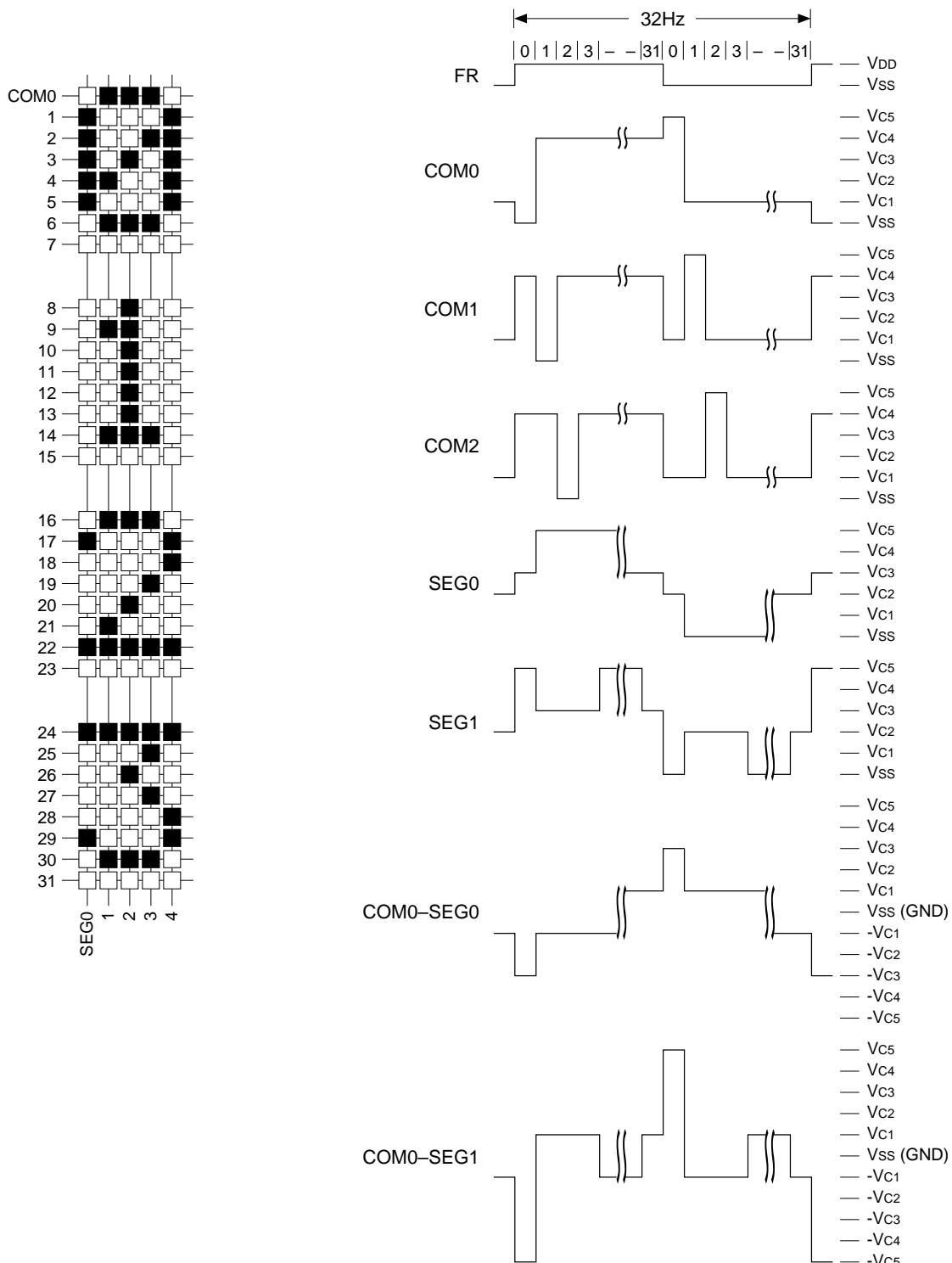

| 5.11 LCDコントローラ .....                   | 88  |

| 5.11.1 LCDコントローラの構成 .....              | 88  |

| 5.11.2 マスクオプション .....                  | 89  |

| 5.11.3 LCDドライバ .....                   | 90  |

| 5.11.4 表示の制御 .....                     | 95  |

| 5.11.5 表示メモリ .....                     | 95  |

| 5.11.6 LCDコントローラの制御方法 .....            | 104 |

| 5.11.7 プログラミング上の注意事項 .....             | 105 |

| 5.12 サウンドジェネレータ .....                  | 106 |

| 5.12.1 サウンドジェネレータの構成 .....             | 106 |

| 5.12.2 ブザー出力の制御 .....                  | 106 |

| 5.12.3 ブザー周波数と音量の設定 .....              | 107 |

| 5.12.4 デジタルエンベロープ .....                | 108 |

| 5.12.5 ワンショット出力 .....                  | 108 |

| 5.12.6 サウンドジェネレータの制御方法 .....           | 109 |

| 5.12.7 プログラミング上の注意事項 .....             | 111 |

| 5.13 リモートコントローラ(REM) .....             | 112 |

| 5.13.1 リモートコントローラの構成 .....             | 112 |

| 5.13.2 マスクオプション .....                  | 113 |

| 5.13.3 キャリア(搬送波) .....                 | 113 |

| 5.13.4 ソフトタイマ方式 .....                  | 114 |

| 5.13.5 ハードタイマ方式とREM割り込み .....          | 114 |

| 5.13.6 リモートコントローラの制御方法 .....           | 118 |

| 5.13.7 プログラミング上の注意事項 .....             | 121 |

| 5.14 電源電圧検出(SVD)回路 .....               | 122 |

| 5.14.1 SVD回路の構成 .....                  | 122 |

| 5.14.2 SVD動作 .....                     | 122 |

| 5.14.3 SVD回路の制御方法 .....                | 123 |

| 5.14.4 プログラミング上の注意事項 .....             | 123 |

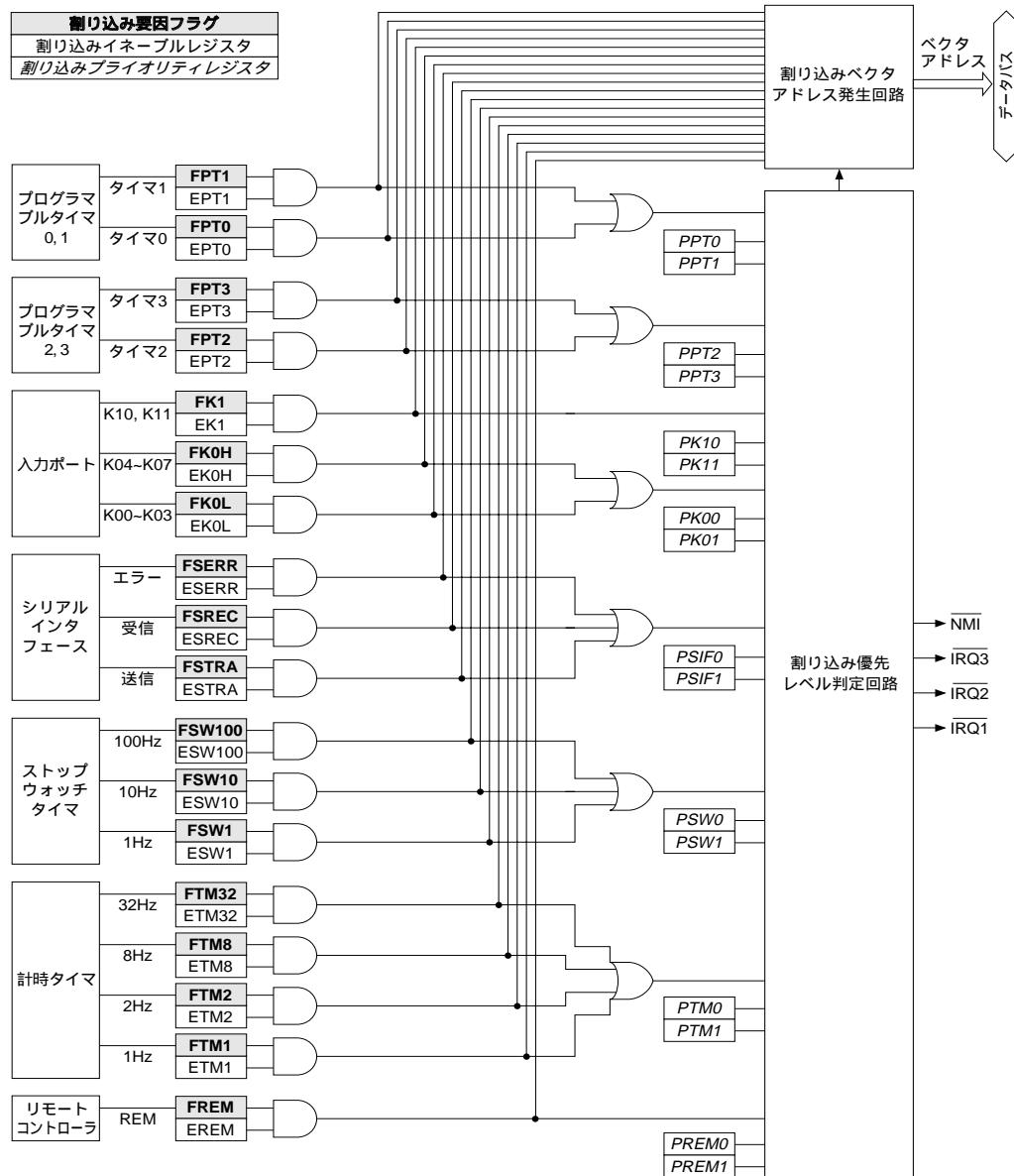

| 5.15 割り込みとスタンバイ状態 .....                | 124 |

| 5.15.1 割り込み発生条件 .....                  | 125 |

| 5.15.2 割り込み要因フラグ .....                 | 125 |

| 5.15.3 割り込みイネーブルレジスタ .....             | 126 |

| 5.15.4 割り込みプライオリティレジスタと割り込み優先レベル ..... | 126 |

| 5.15.5 例外処理ベクタ .....                   | 127 |

| 5.15.6 割り込みの制御 .....                   | 128 |

| 5.15.7 プログラミング上の注意事項 .....             | 129 |

| 5.16 低消費電力化のための注意事項 .....              | 130 |

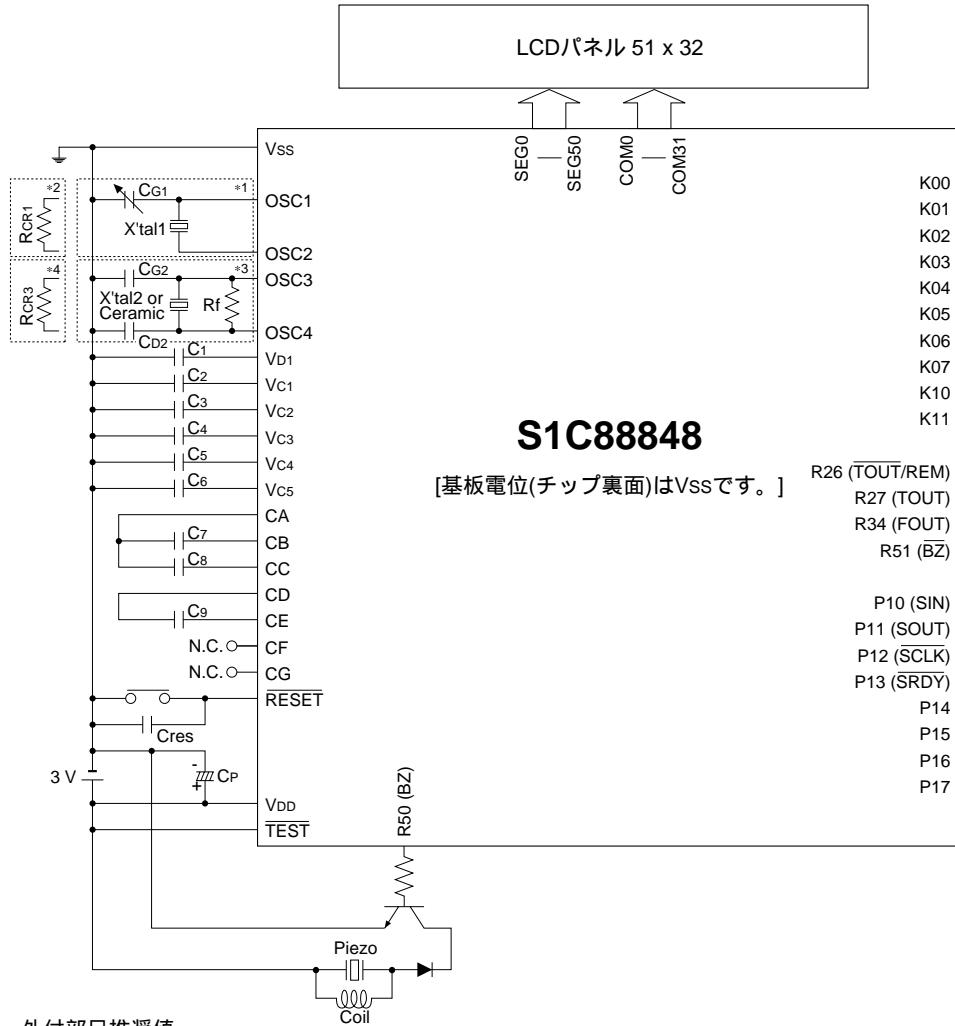

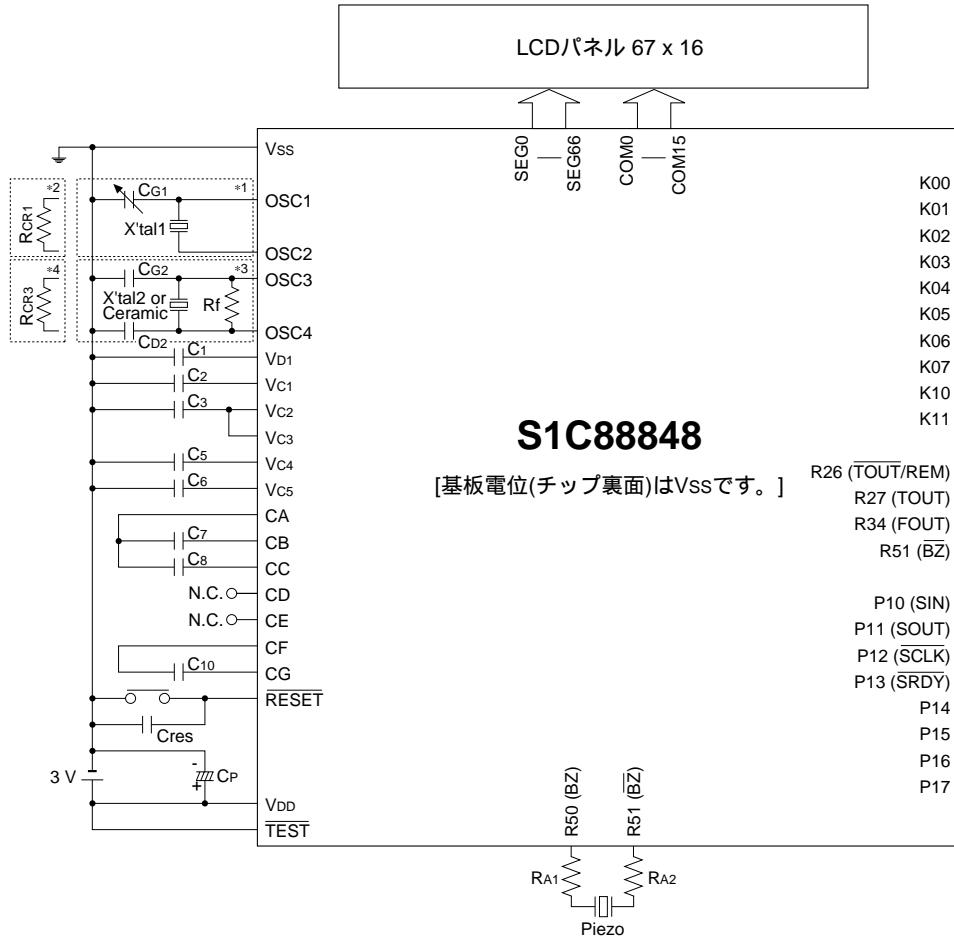

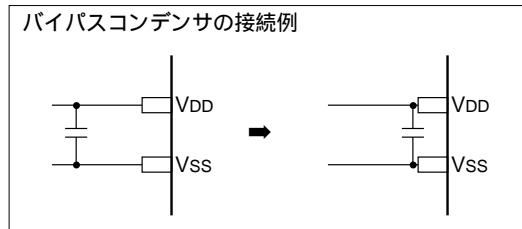

| 6 基本外部結線図 .....                        | 131 |

| 7 電気的特性 .....                          | 133 |

| 7.1 絶対最大定格 .....                       | 133 |

| 7.2 推奨動作条件 .....                       | 133 |

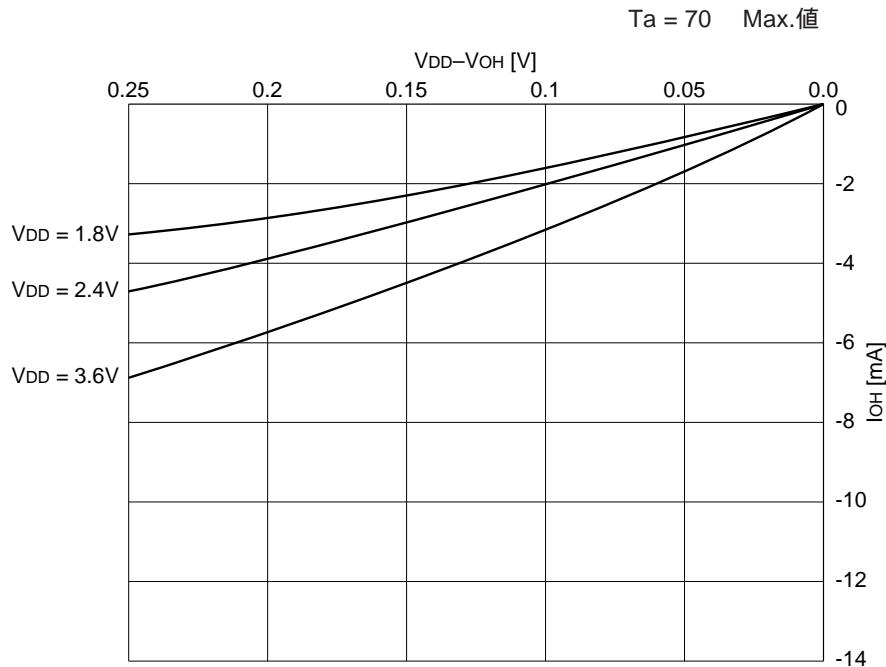

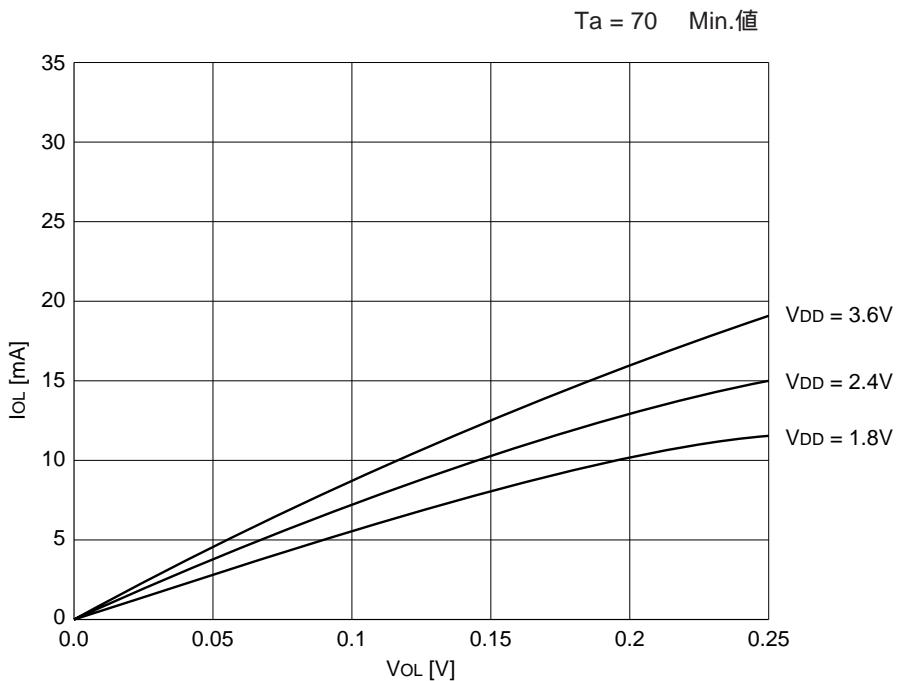

| 7.3 DC特性 .....                         | 134 |

| 7.4 アナログ回路特性 .....                     | 135 |

| 7.5 消費電流 .....                         | 137 |

|                                                                                        |     |

|----------------------------------------------------------------------------------------|-----|

| 7.6 AC特性 .....                                                                         | 138 |

| 7.7 発振特性 .....                                                                         | 142 |

| 7.8 特性グラフ(参考値) .....                                                                   | 143 |

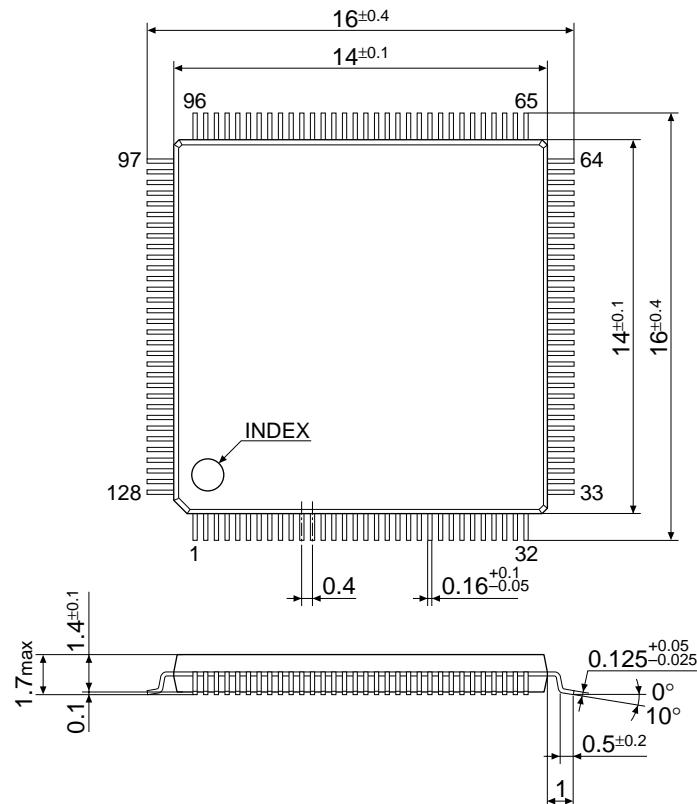

| 8 パッケージ .....                                                                          | 150 |

| 8.1 プラスチックパッケージ .....                                                                  | 150 |

| 8.2 セラミックパッケージ .....                                                                   | 151 |

| 9 パッド配置 .....                                                                          | 152 |

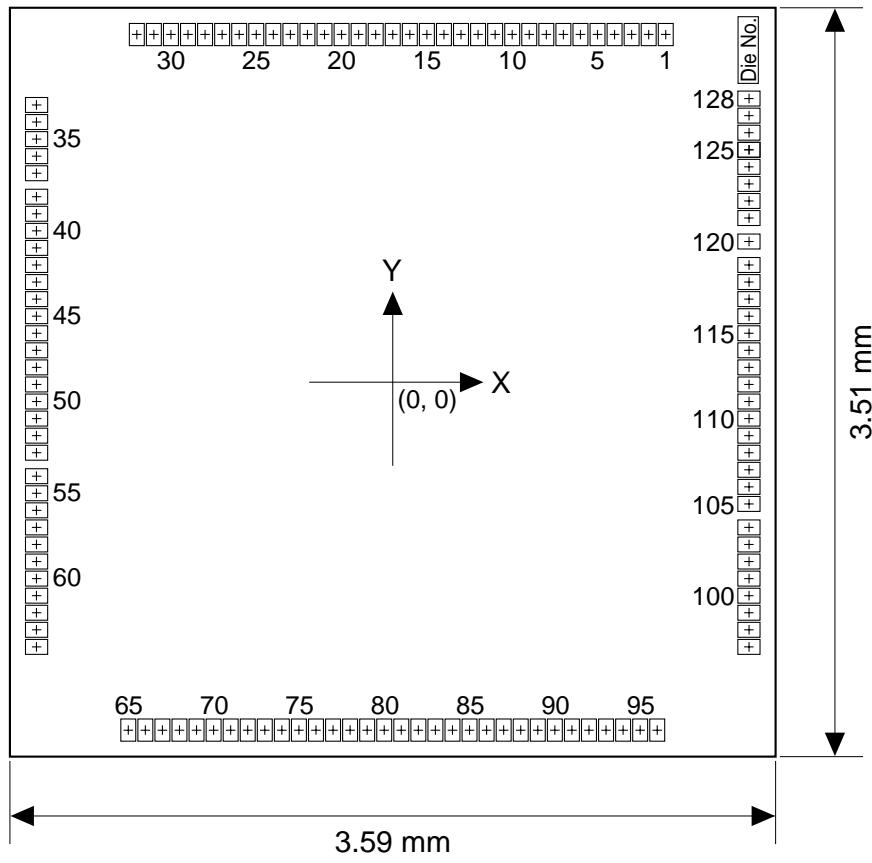

| 9.1 パッド配置図 .....                                                                       | 152 |

| 9.2 パッド座標 .....                                                                        | 153 |

| 10 実装上の注意事項 .....                                                                      | 154 |

| Appendix A S5U1C88000P1&S5U1C88816P2 Manual (Peripheral Circuit Board for S1C88848) .. | 156 |

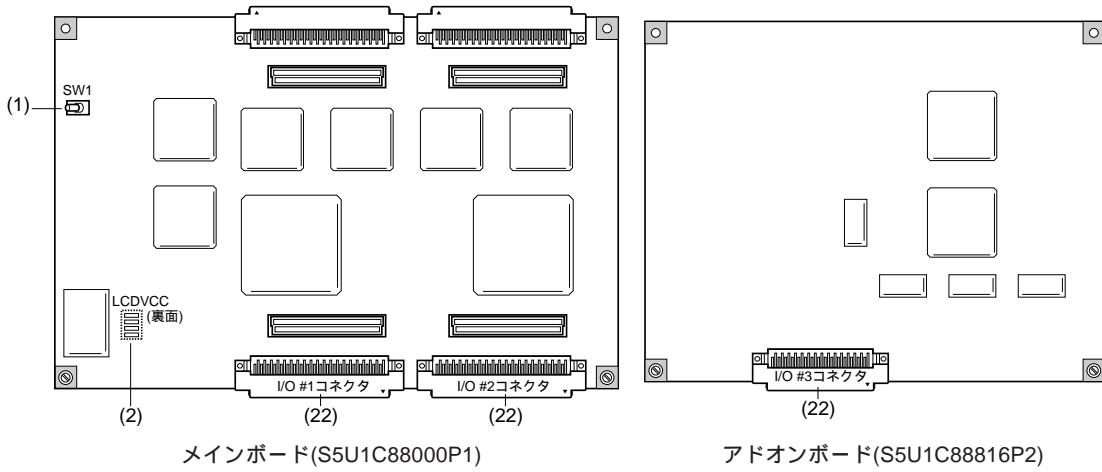

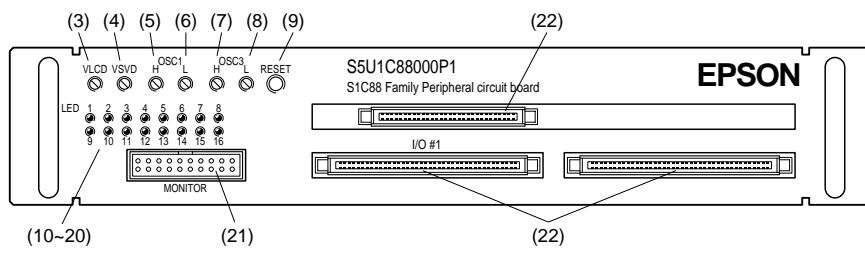

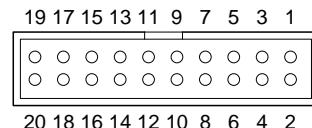

| A.1 各部の名称と機能 .....                                                                     | 156 |

| A.2 使用上の注意 .....                                                                       | 158 |

| A.2.1 操作上の注意事項 .....                                                                   | 158 |

| A.2.2 実際のICとの相違点 .....                                                                 | 158 |

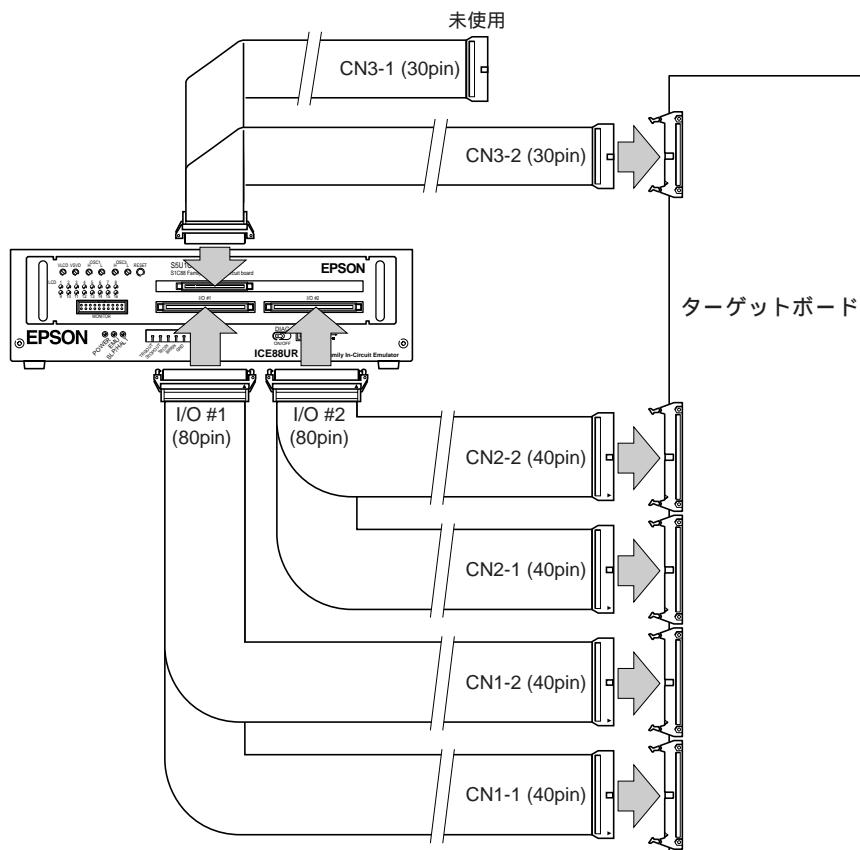

| A.3 ターゲットシステムとの接続 .....                                                                | 161 |

| Appendix B FlashマイコンS1C8F360との違い .....                                                 | 164 |

# 1 概要

S1C88848は、CMOS 8ビットコアCPU S1C88 (MODEL3)を中心に、ROM、RAM、赤外線リモコンキャリア出力、最大1,632ピクセルを駆動可能なドットマトリクスLCDコントローラ/ドライバ、3種類のタイマ、調歩同期/クロック同期が選択可能なシリアルインターフェースなどを内蔵したマイクロコンピュータです。

動作電圧範囲が広く、低電圧(1.8V Min.)から安定した動作が可能です。

また、低消費電流(スタンバイ時 $1.7\mu\text{A}$ )というS1C Familyの特長も合わせ持っています。<sup>\*4</sup>

電池電圧の低下を検出するSVD回路も内蔵し、家電機器のリモコンなどへの応用に最適です。

## 1.1 特長

表1.1.1にS1C88848の特長を示します。

表1.1.1 特長

|                    |                                                                                                                                                                                                                                      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| コアCPU              | CMOS 8ビットコアCPU S1C88 (MODEL3)                                                                                                                                                                                                        |

| メイン(OSC3)発振回路      | 水晶発振回路/セラミック発振回路/CR発振回路 <sup>*1</sup> Max. 8.2MHz (スタートクロックソース)                                                                                                                                                                      |

| サブ(OSC1)発振回路       | 水晶発振回路/CR発振回路 <sup>*1</sup> Typ. 32.768kHz                                                                                                                                                                                           |

| 命令セット              | 608種類(乘除算命令使用可能)                                                                                                                                                                                                                     |

| 最小命令実行時間           | 0.244μsec/8.2MHz (2クロック)                                                                                                                                                                                                             |

| 内蔵ROM容量            | 48Kバイト                                                                                                                                                                                                                               |

| 内蔵RAM容量            | 1.5Kバイト/RAM 402バイト/表示メモリ                                                                                                                                                                                                             |

| 入力ポート              | 10ビット(2ビットをイベントカウンタの外部クロック入力に設定可能)<br>プルアップ抵抗を付加可能 <sup>*1</sup>                                                                                                                                                                     |

| 出力ポート              | 5ビット(ブザー出力 <sup>*2</sup> 、TOUT信号出力 <sup>*2</sup> 、FOUT出力 <sup>*2</sup> 、赤外線リモコンキャリア出力 <sup>*1</sup> 端子に設定可能)<br>SEG40～SEG50をDC出力ポートに設定可能 <sup>*1</sup>                                                                               |

| 入出力兼用ポート           | 8ビット(4ビットをシリアルI/F入出力に設定可能 <sup>*2</sup> )<br>プルアップ抵抗を付加可能 <sup>*1</sup>                                                                                                                                                              |

| LCD ドライバ           | ドットマトリクス方式( $5 \times 8$ または $5 \times 5$ ドットフォント対応可能 <sup>*2</sup> )<br>51セグメント×32コモン <sup>*1, *2</sup><br>66セグメント×17コモン <sup>*1</sup><br>67セグメント×16コモン <sup>*1, *2</sup><br>67セグメント×8コモン <sup>*1</sup><br>LCD電源回路内蔵(5電位/4電位昇降圧タイプ) |

| リモートコントローラ         | 赤外線リモコンキャリア出力およびDC出力                                                                                                                                                                                                                 |

| シリアルインターフェース       | 1ch(クロック同期式/調歩同期式の選択が可能 <sup>*2</sup> )                                                                                                                                                                                              |

| タイマ                | プログラマブルタイマ: 16ビット×2chまたは8ビット×4ch <sup>*2</sup> 、イベントカウンタ機能付き<br>計時タイマ: 8ビット×1ch<br>ストップウォッチタイマ: 8ビット×1ch                                                                                                                             |

| サウンドジェネレータ         | エンベロープ機能、音量調整機能付き                                                                                                                                                                                                                    |

| ウォッチドッグタイマ         | 内蔵                                                                                                                                                                                                                                   |

| 電源電圧検出回路(SVD)      | 16値プログラマブル(1.8～4.35V) <sup>*2</sup>                                                                                                                                                                                                  |

| 割り込み               | 外部割り込み: 入力割り込み 2系統(3種類)<br>内部割り込み: 計時タイマ割り込み 1系統(4種類)<br>ストップウォッチタイマ割り込み 1系統(3種類)<br>プログラマブルタイマ割り込み 2系統(4種類)<br>シリアルインターフェース割り込み 1系統(3種類)<br>リモコン出力制御割り込み 1系統(1種類)                                                                   |

| 電源電圧               | 1.8V～5.5V <sup>*3</sup>                                                                                                                                                                                                              |

| 消費電流 <sup>*4</sup> | SLEEP時: 1μA(Typ.)<br>HALT時(32kHz 水晶発振): 1.7μA(Typ.)<br>HALT時(8MHz セラミック発振): 100μA(Typ.)<br>動作時(32kHz 水晶発振): 4μA(Typ.)<br>動作時(8MHz セラミック発振): 700μA(Typ.)                                                                              |

| 出荷形態               | QFP15-128pinまたはチップ                                                                                                                                                                                                                   |

\*1 マスクオプションで選択 \*2 ソフトウェアで選択 \*3 2.4V未満の電源電圧ではLCDの濃淡に影響がでます。

\*4 イニシャルリセット後、OSC1、OSC3が共にONし、CPUはOSC3で動作します。また、マスクオプションの選択にかかわらずリモートコントローラもOSC3で動作します。リモートコントローラを使用しない場合は低消費電流化のため、イニシャルリセット後の初期化ルーチンでリモートコントローラをOFF(REMC = "0")にしてください。

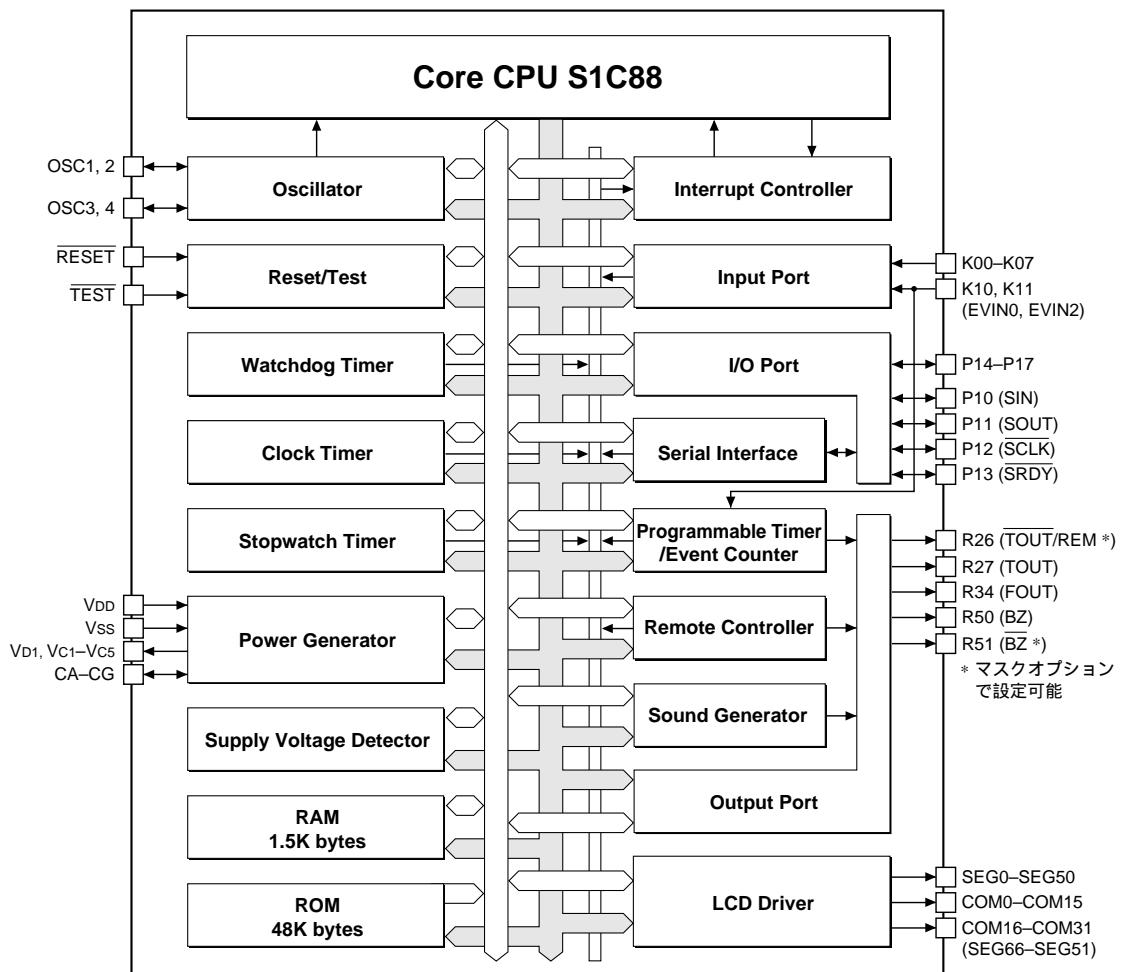

## 1.2 ブロック図

図1.2.1 ブロック図

## 1.3 端子

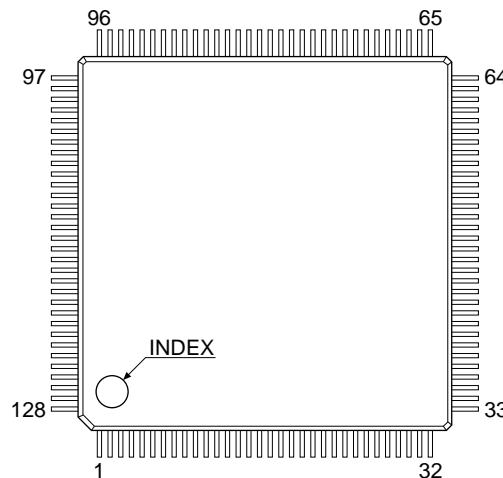

### 1.3.1 端子配置図

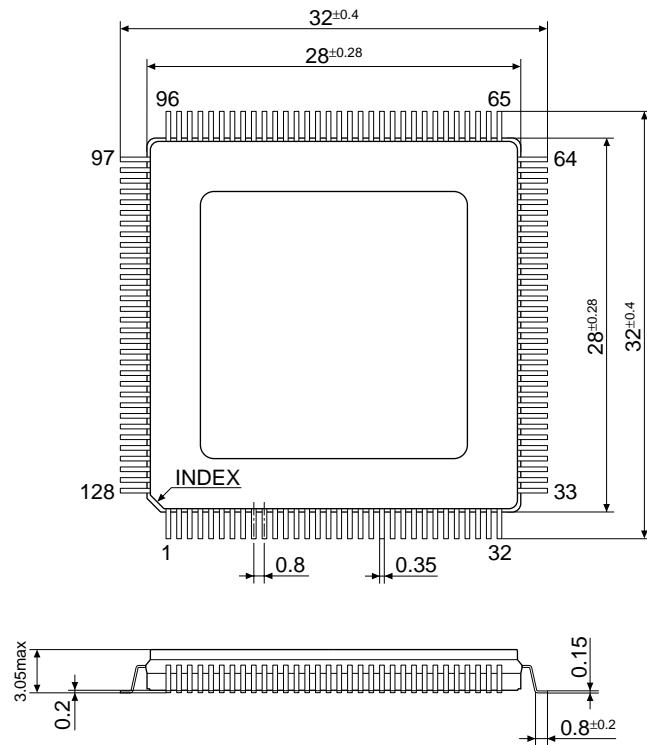

QFP15-128pin

| 端子No. | 端子名   | 端子No. | 端子名         | 端子No. | 端子名       | 端子No. | 端子名          |

|-------|-------|-------|-------------|-------|-----------|-------|--------------|

| 1     | SEG11 | 33    | SEG43       | 65    | Vc3       | 97    | R26/TOUT/REM |

| 2     | SEG12 | 34    | SEG44       | 66    | Vc2       | 98    | R27/TOUT     |

| 3     | SEG13 | 35    | SEG45       | 67    | Vc1       | 99    | R34/FOUT     |

| 4     | SEG14 | 36    | SEG46       | 68    | OSC3      | 100   | R50/BZ       |

| 5     | SEG15 | 37    | SEG47       | 69    | OSC4      | 101   | R51/BZ       |

| 6     | SEG16 | 38    | SEG48       | 70    | Vd1       | 102   | COM0         |

| 7     | SEG17 | 39    | SEG49       | 71    | Vdd       | 103   | COM1         |

| 8     | SEG18 | 40    | SEG50       | 72    | Vss       | 104   | COM2         |

| 9     | SEG19 | 41    | COM31/SEG51 | 73    | OSC1      | 105   | COM3         |

| 10    | SEG20 | 42    | COM30/SEG52 | 74    | OSC2      | 106   | COM4         |

| 11    | SEG21 | 43    | COM29/SEG53 | 75    | TEST      | 107   | COM5         |

| 12    | SEG22 | 44    | COM28/SEG54 | 76    | RESET     | 108   | COM6         |

| 13    | SEG23 | 45    | COM27/SEG55 | 77    | K11/EVIN2 | 109   | COM7         |

| 14    | SEG24 | 46    | COM26/SEG56 | 78    | K10/EVINO | 110   | COM8         |

| 15    | SEG25 | 47    | COM25/SEG57 | 79    | K07       | 111   | COM9         |

| 16    | SEG26 | 48    | COM24/SEG58 | 80    | K06       | 112   | COM10        |

| 17    | SEG27 | 49    | COM23/SEG59 | 81    | K05       | 113   | COM11        |

| 18    | SEG28 | 50    | COM22/SEG60 | 82    | K04       | 114   | COM12        |

| 19    | SEG29 | 51    | COM21/SEG61 | 83    | K03       | 115   | COM13        |

| 20    | SEG30 | 52    | COM20/SEG62 | 84    | K02       | 116   | COM14        |

| 21    | SEG31 | 53    | COM19/SEG63 | 85    | K01       | 117   | COM15        |

| 22    | SEG32 | 54    | COM18/SEG64 | 86    | K00       | 118   | SEG0         |

| 23    | SEG33 | 55    | COM17/SEG65 | 87    | P17       | 119   | SEG1         |

| 24    | SEG34 | 56    | COM16/SEG66 | 88    | P16       | 120   | SEG2         |

| 25    | SEG35 | 57    | N.C.        | 89    | P15       | 121   | SEG3         |

| 26    | SEG36 | 58    | CE *1       | 90    | P14       | 122   | SEG4         |

| 27    | SEG37 | 59    | CD *1       | 91    | P13/SRDY  | 123   | SEG5         |

| 28    | SEG38 | 60    | CC          | 92    | P12/SCLK  | 124   | SEG6         |

| 29    | SEG39 | 61    | CB          | 93    | P11/SOUT  | 125   | SEG7         |

| 30    | SEG40 | 62    | CA          | 94    | P10/SIN   | 126   | SEG8         |

| 31    | SEG41 | 63    | Vc5         | 95    | CF *2     | 127   | SEG9         |

| 32    | SEG42 | 64    | Vc4         | 96    | CG *2     | 128   | SEG10        |

\*1: Vc1基準(1/4バイアス)で駆動する場合はN.C.

N.C.: No Connection

\*2: Vc2基準(1/5バイアス)で駆動する場合はN.C.

図1.3.1.1 端子配置図

### 1.3.2 端子説明

表1.3.2.1 端子説明

| 端子名                              | 端子No.         | In/Out | 機能                                                                                                                              |

|----------------------------------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| VDD                              | 71            | -      | 電源(+)端子                                                                                                                         |

| VSS                              | 72            | -      | 電源(-)端子                                                                                                                         |

| V <sub>D1</sub>                  | 70            | -      | 内部動作電圧出力端子                                                                                                                      |

| V <sub>C1</sub> ~V <sub>C5</sub> | 67~63         | O      | LCD駆動電圧出力端子                                                                                                                     |

| CA~CG                            | 62~58, 95, 96 | -      | LCD系昇降圧コンデンサ接続端子                                                                                                                |

| OSC1                             | 73            | I      | OSC1発振入力端子(水晶/CR発振をマスクオプションで選択)                                                                                                 |

| OSC2                             | 74            | O      | OSC1発振出力端子                                                                                                                      |

| OSC3                             | 68            | I      | OSC3発振入力端子(水晶/セラミック/CR発振をマスクオプションで選択)                                                                                           |

| OSC4                             | 69            | O      | OSC3発振出力端子                                                                                                                      |

| K00~K07                          | 86~79         | I      | 入力ポート(K00~K07)端子                                                                                                                |

| K10/EVIN0                        | 78            | I      | 入力ポート(K10)端子<br>またはイベントカウンタ外部クロック(EVIN0)入力端子                                                                                    |

| K11/EVIN2                        | 77            | I      | 入力ポート(K11)端子<br>またはイベントカウンタ外部クロック(EVIN2)入力端子                                                                                    |

| R26/TOUT/REM                     | 97            | O      | 出力ポート(R26)端子<br>プログラマブルタイマアンダーフロー反転信号(TOUT)出力端子<br>またはリモコンキャリア信号(REM)出力端子(マスクオプションで選択)                                          |

| R27/TOUT                         | 98            | O      | 出力ポート(R27)端子<br>またはプログラマブルタイマアンダーフロー信号(TOUT)出力端子                                                                                |

| R34/FOUT                         | 99            | O      | 出力ポート(R34)端子<br>またはクロック(FOUT)出力端子                                                                                               |

| R50/BZ                           | 100           | O      | 出力ポート(R50)端子<br>またはブザー信号(BZ)出力端子                                                                                                |

| R51/ $\overline{BZ}$             | 101           | O      | 出力ポート(R51)端子<br>またはブザー反転信号( $\overline{BZ}$ )出力端子(マスクオプションで選択)                                                                  |

| P10/SIN                          | 94            | I/O    | 入出力兼用ポート(P10)端子<br>またはシリアルI/Fデータ入力(SIN)端子                                                                                       |

| P11/SOUT                         | 93            | I/O    | 入出力兼用ポート(P11)端子<br>またはシリアルI/Fデータ出力(SOUT)端子                                                                                      |

| P12/SCLK                         | 92            | I/O    | 入出力兼用ポート(P12)端子<br>またはシリアルI/Fクロック(SCLK)入出力端子                                                                                    |

| P13/ $\overline{SRDY}$           | 91            | I/O    | 入出力兼用ポート(P13)端子<br>またはシリアルI/Fレディ信号( $\overline{SRDY}$ )出力端子                                                                     |

| P14~P17                          | 90~87         | I/O    | 入出力兼用ポート(P14~P17)端子                                                                                                             |

| COM0~COM15                       | 102~117       | O      | LCDコモン出力端子                                                                                                                      |

| COM16~COM31<br>/SEG66~SEG51      | 56~41         | O      | LCDコモン出力端子またはLCDセグメント出力端子<br>COM16~COM31 (1/32デューティ選択時)<br>SEG66~SEG51 (1/16または1/8デューティ選択時)<br>COM16、SEG65~SEG51 (1/17デューティ選択時) |

| SEG0~SEG39                       | 118~128, 1~29 | O      | LCDセグメント出力端子                                                                                                                    |

| SEG40~SEG50                      | 30~40         | O      | LCDセグメント出力端子またはDC出力端子(マスクオプションで選択)                                                                                              |

| RESET                            | 76            | I      | イニシャルリセット入力端子                                                                                                                   |

| TEST *1                          | 75            | I      | テスト用入力端子                                                                                                                        |

\*1 TEST端子はICの出荷検査時に使用する端子です。通常動作時は必ずVDDに接続してください。

## 1.4 マスクオプション

S1C88848には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択にはS1C88848の開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogを使用します。winfogによって作成したデータをもとに最終的なICのマスクパターン生成が行われます。winfogについては、"S5U1C88000C Manual II"を参照してください。

### S1C88848のマスクオプション

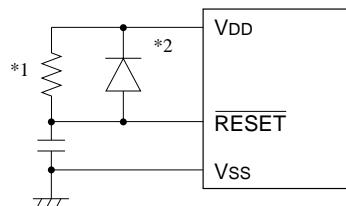

#### (1) RESET端子ブルアップ抵抗

RESET端子にブルアップ抵抗を付加するかしないか選択できます。

#### (2) 入力ポート(K00 ~ K03)同時LOW入力による外部リセット

この機能は、複数キーの同時押しによってICをリセットするもので、この機能を使用するかしないかをマスクオプションで選択できます。また、使用する場合は、同時に押すキーを接続する入力ポート(K00 ~ K03)の組み合わせを選択します。詳細については"4.1.2 入力ポート(K00 ~ K03)の同時LOWレベル入力"を参照してください。

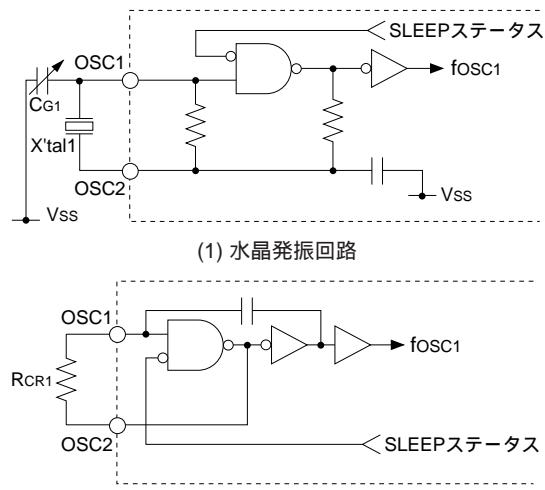

#### (3) OSC1発振回路

OSC1発振回路の種類を、水晶発振とCR発振から選択できます。詳細については、"5.3.3 OSC1発振回路"を参照してください。

#### (4) OSC3発振回路

OSC3発振回路の種類を、水晶発振、セラミック発振、CR発振から選択できます。詳細については、"5.3.4 OSC3発振回路"を参照してください。

#### (5) 入力ポートブルアップ抵抗

入力(K)ポートにブルアップ抵抗を付加するかしないか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"5.4 入力ポート(Kポート)"を参照してください。

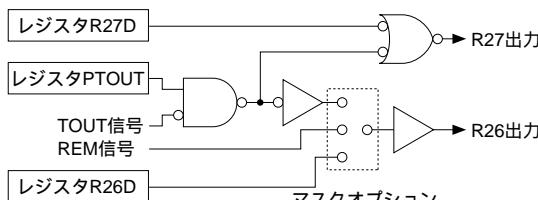

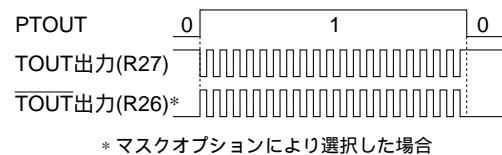

#### (6) R26、R51出力ポート仕様

R26ポートを、汎用DC出力、TOUT出力(TOUT反転出力)あるいはREM出力(リモコンキャリア出力)として使用するか選択できます。同様に、R51ポートを汎用DC出力として使用するか、BZ出力(ブザー反転信号出力)として使用するか選択できます。詳細については"5.5 出力ポート(Rポート)"を参照してください。

#### (7) 入出力兼用ポートブルアップ抵抗

入出力兼用(P)ポートが入力モード時に働くブルアップ抵抗を付加するかしないか選択できます。この選択は入出力兼用ポートの各ビットごとに行えます。詳細については"5.6 入出力兼用ポート(Pポート)"を参照してください。

なお、P10～P13はシリアルインターフェースの入出力端子と兼用されており、P10およびP12端子の選択は、それぞれシリアル入力(SIN)端子、シリアルクロック入力(クロック同期式スレーブモード選択時のSCLK)端子にも適用されます。詳細については"5.7 シリアルインターフェース"を参照してください。

#### (8) LCD駆動デューティ

内蔵LCDドライバの駆動デューティを1/32と1/16のソフトウェア切り換えとするか、1/17固定あるいは1/8固定とするか選択できます。詳細については"5.11 LCDコントローラ"を参照してください。

#### (9) LCD駆動電源

LCDの駆動に内部電源を使用するか、外部電源を使用するか選択できます。さらに、内部電源を使用する場合は、駆動電圧を4.5V LCDパネル用または5.5V LCDパネル用に、駆動バイアスを1/5または1/4に設定できます。詳細については"5.11 LCDコントローラ"を参照してください。

#### (10) SEG40～SEG50ポート仕様

SEG40～SEG50をLCDセグメント出力、あるいは汎用DC出力として使用するか選択できます。LCDセグメント出力の詳細については"5.11 LCDコントローラ"を、DC出力の詳細については"5.5 出力ポート(Rポート)"を参照してください。

## オプションリスト

S1C88848には以下のオプションが設定可能です。各オプション項目には複数の仕様が用意されていますので、システムに合った内容を選択し、**印**をつけてください。

このオプションリストを参照して、S1C88848の持つマスクオプション選択をwinfogの画面上で行います。

### S5U1C88000Pオプションリスト

#### A OSC1発振回路 ... OSC1 SYSTEM CLOCK

- 1. 内部クロック

- 2. ユーザクロック

#### B OSC3発振回路 ... OSC3 SYSTEM CLOCK

- 1. 内部クロック

- 2. ユーザクロック

### S1C88848マスクオプションリスト(1/2)

#### 1 OSC1発振回路 ... OSC1 SYSTEM CLOCK

- 1. 水晶発振回路

- 2. CR発振回路

#### 2 OSC3発振回路 ... OSC3 SYSTEM CLOCK

- 1. 水晶発振回路

- 2. セラミック発振回路

- 3. CR発振回路

#### 3 キー同時押しリセット ... MULTIPLE KEY ENTRY RESET

- ・組み合わせ ..... 1. 使用しない

- 2. 使用する K00, K01

- 3. 使用する K00, K01, K02

- 4. 使用する K00, K01, K02, K03

#### 4 入力ポート プルアップ抵抗 ... INPUT PORT PULL UP RESISTOR

- |              |       |       |

|--------------|-------|-------|

| ・K00 .....   | 1. あり | 2. なし |

| ・K01 .....   | 1. あり | 2. なし |

| ・K02 .....   | 1. あり | 2. なし |

| ・K03 .....   | 1. あり | 2. なし |

| ・K04 .....   | 1. あり | 2. なし |

| ・K05 .....   | 1. あり | 2. なし |

| ・K06 .....   | 1. あり | 2. なし |

| ・K07 .....   | 1. あり | 2. なし |

| ・K10 .....   | 1. あり | 2. なし |

| ・K11 .....   | 1. あり | 2. なし |

| ・RESET ..... | 1. あり | 2. なし |

#### 5 入出力兼用ポート プルアップ抵抗 ... I/O PORT PULL UP RESISTOR

- |            |       |       |

|------------|-------|-------|

| ・P10 ..... | 1. あり | 2. なし |

| ・P11 ..... | 1. あり | 2. なし |

| ・P12 ..... | 1. あり | 2. なし |

| ・P13 ..... | 1. あり | 2. なし |

| ・P14 ..... | 1. あり | 2. なし |

| ・P15 ..... | 1. あり | 2. なし |

| ・P16 ..... | 1. あり | 2. なし |

| ・P17 ..... | 1. あり | 2. なし |

## S1C88848マスクオプションリスト(2/2)

- 6 LCD駆動デューティ ... LCD DRIVING DUTY

- 1. 1/32 & 1/16デューティ

- 2. 1/17デューティ

- 3. 1/8デューティ

- 7 LCD駆動電源 ... LCD POWER SUPPLY

- 1. 内部駆動 タイプA (Vc2基準, 1/5バIAS, 4.5V)

- 2. 外部駆動

- 3. 内部駆動 タイプB (Vc2基準, 1/5バIAS, 5.5V)

- 4. 内部駆動 タイプD (Vc1基準, 1/4バIAS, 4.5V)

- 8 R51出力ポート仕様 ... R51 OUTPUT PORT SPECIFICATION

- 1.  $\overline{BZ}$ あり (Use)

- 2.  $\overline{BZ}$ なし (Not Use)

- 9 R26出力ポート仕様 ... R26 OUTPUT PORT SPECIFICATION \*1

- 1. REM出力

- 2.  $\overline{TOUT}$ 出力

- 3. DC出力

- 10 SEG40 ~ SEG50ポート仕様 ... SEG40-SEG50 PORT SPECIFICATIONS

|               |          |         |

|---------------|----------|---------|

| • SEG40 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG41 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG42 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG43 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG44 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG45 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG46 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG47 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG48 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG49 ..... | 1. SEG出力 | 2. DC出力 |

| • SEG50 ..... | 1. SEG出力 | 2. DC出力 |

\*1 REM出力を選択しない場合も、イニシャルリセット後にリモートコントローラはOSC3で動作します。リモートコントローラを使用しない場合は低消費電流化のため、イニシャルリセット後の初期化ルーチンでリモートコントローラをOFF(REMC = "0")にしてください。

# 2 電源

ここでは、S1C88848の動作電圧、および内部電源回路の構成について説明します。

## 2.1 動作電圧

S1C88848の動作電源電圧V<sub>DD</sub>は次のとおりです。

$$V_{DD} = 1.8V \sim 5.5V$$

ただし、2.4V未満の電源電圧ではLCD表示の濃淡に影響がでます(注!参照)。

## 2.2 内部電源回路

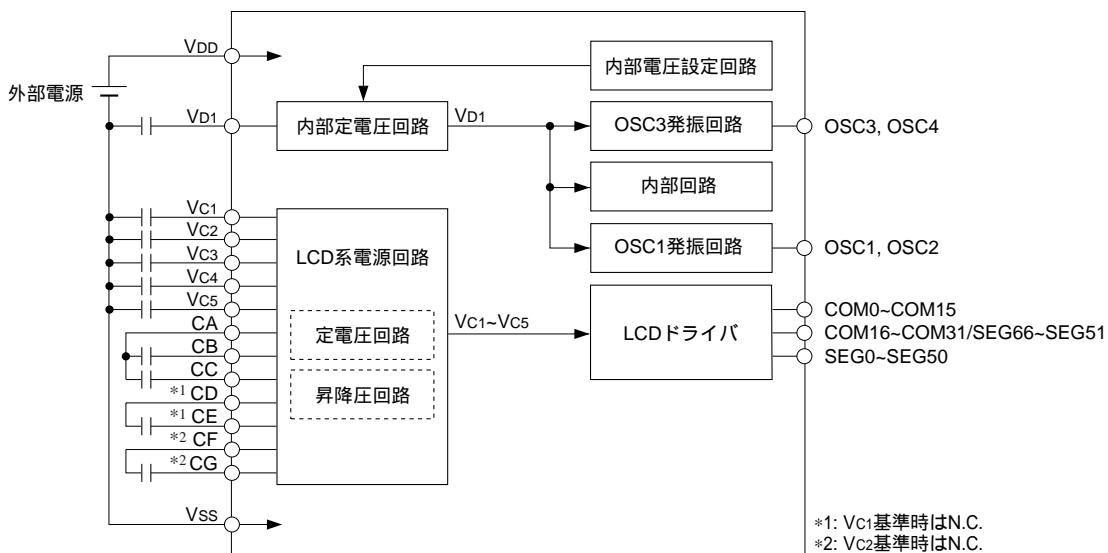

S1C88848は図2.2.1に示す電源回路を内蔵しており、前記の範囲内の電圧をV<sub>DD</sub>(+)、V<sub>SS</sub>(GND)間に供給することによって内部回路に必要なすべての電圧をIC内部で発生します。

電源回路は大きく2つに分けられます。

内部定電圧回路は、内部回路とOSC3、OSC1発振回路の動作電圧<V<sub>D1</sub>>を発生します。

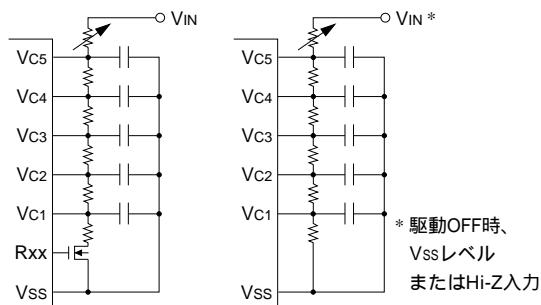

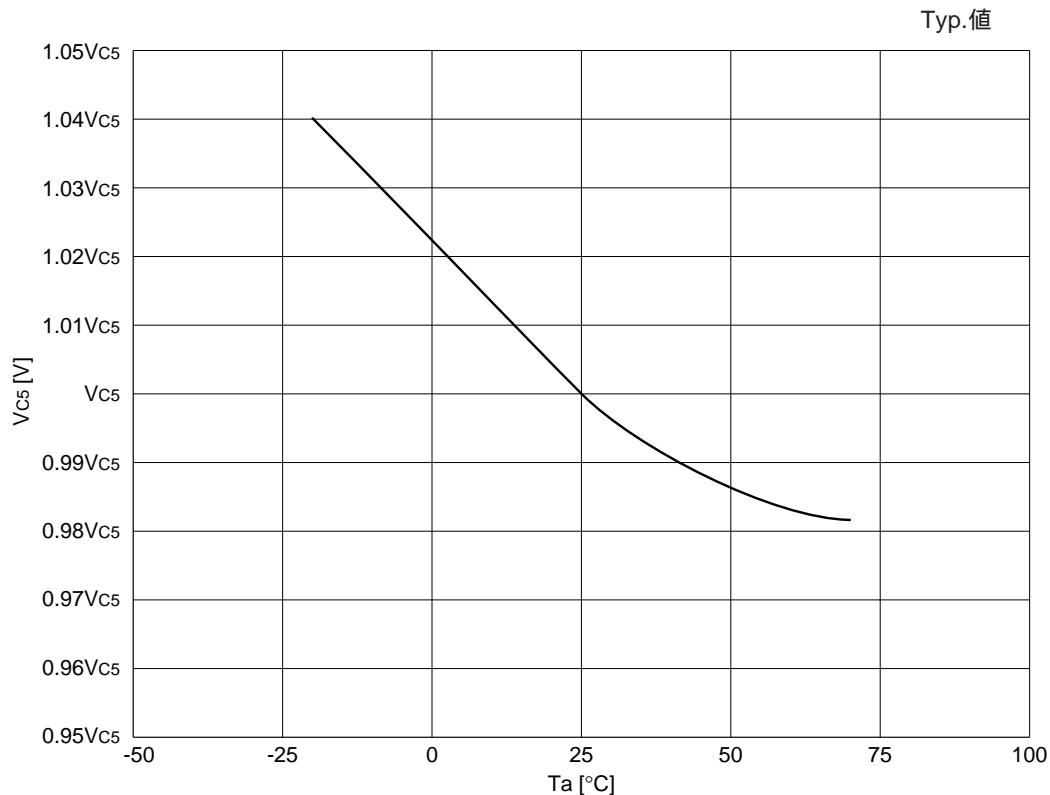

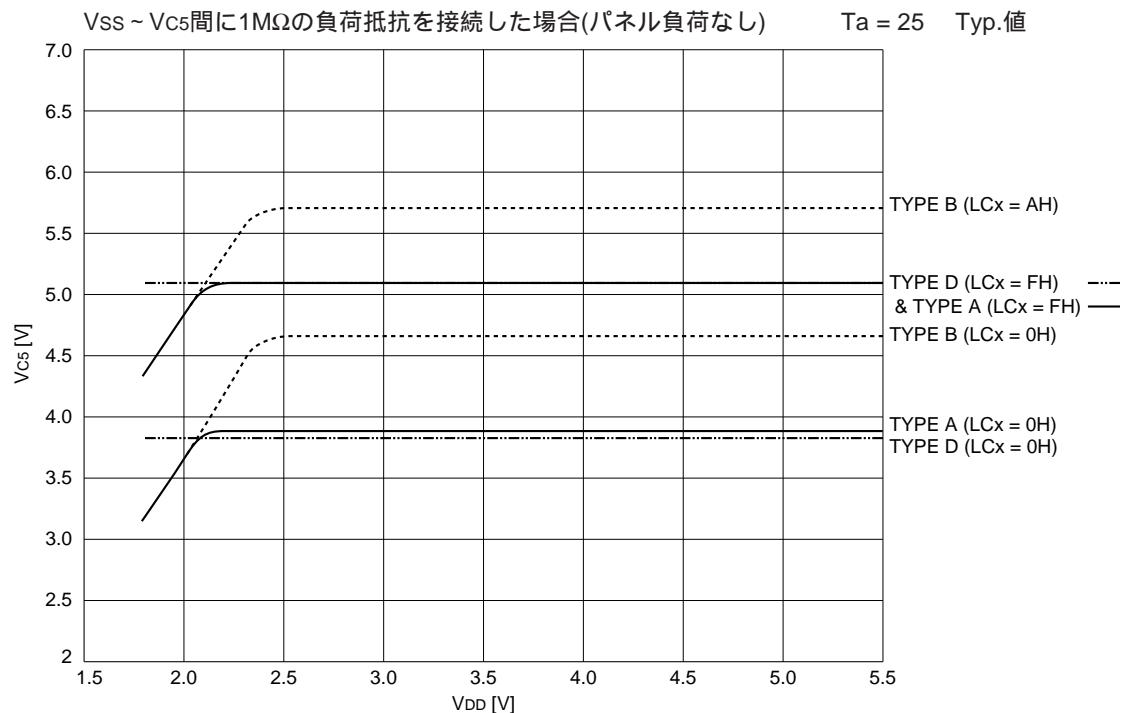

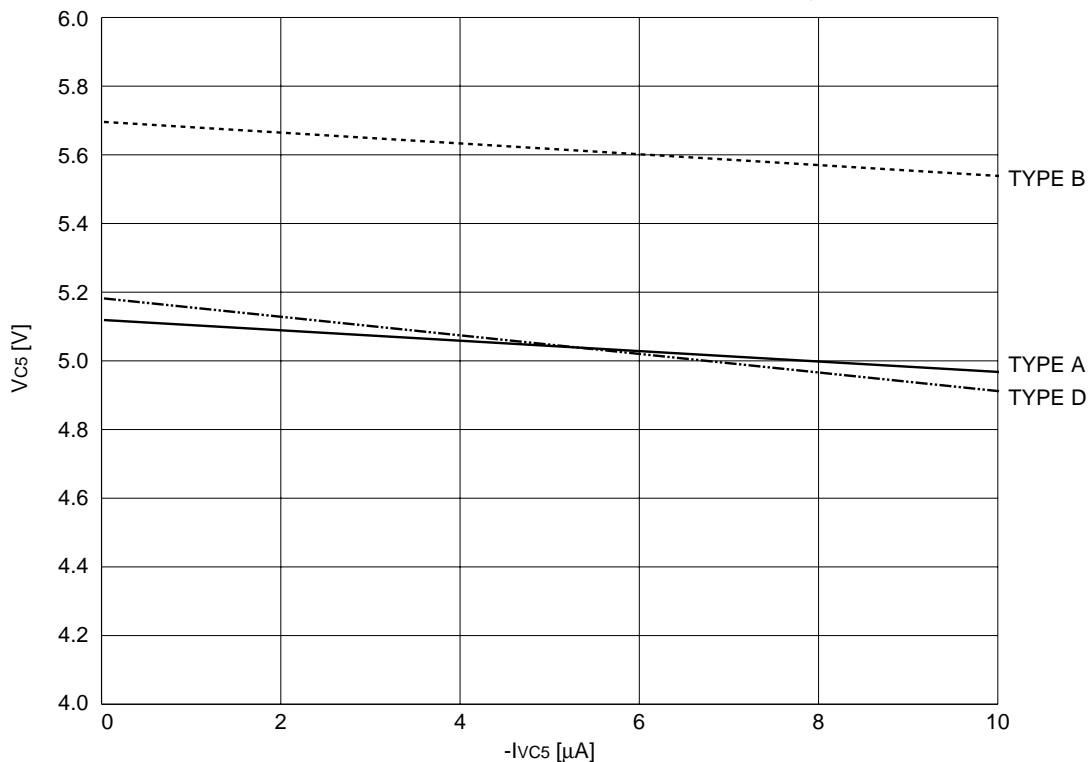

LCD系電源回路はLCDの駆動電圧<V<sub>C1</sub>~<V<sub>C5</sub>>を発生します。1/5バイアス時は、LCD系定電圧回路の出力V<sub>C2</sub>を降圧してV<sub>C1</sub>を、昇圧してV<sub>C3</sub>~V<sub>C5</sub>を発生しています。この5電位はマスクオプションにより外部から供給することも可能です。

また、マスクオプションにより1/4バイアス用の駆動電圧としても使用でき、この場合はV<sub>C2</sub> = V<sub>C3</sub>となります。1/4バイアス時は、V<sub>C1</sub>を昇圧してV<sub>C2</sub>~V<sub>C5</sub>を発生しています。

各電圧値については"7 電気的特性"を参照してください。

S1C88848では、内蔵されたLCDドライバにこのLCD駆動電圧が供給され、コモン/セグメント端子に接続されたLCDパネルを駆動します。

注! • 内部電源回路の出力を外部回路の駆動には絶対に使用しないでください。

- 1/5バイアス時、V<sub>DD</sub> < 2.4Vとなる電源電圧ではV<sub>C2</sub>の電圧値はほぼV<sub>DD</sub>と同じになります。V<sub>C2</sub>の電圧値はLCDの濃淡に影響しますので、安定した表示品質を得るにはV<sub>DD</sub> 2.4Vを満たす電源電圧を与える必要があります。

1/4バイアスではV<sub>C1</sub>を昇圧してV<sub>C2</sub>~V<sub>C5</sub>を発生させるため、V<sub>C1</sub>が最大でも1.4V以上になりません。したがって、1/4バイアス時はV<sub>DD</sub> = 1.8V ~ 5.5Vの範囲ではLCDの濃淡に影響がでることはありません。

図2.2.1 電源回路の構成

# 3 CPUとメモリの構成

ここでは、CPUとメモリの構成について説明します。

## 3.1 CPU

S1C88848はCPUとして8ビットコアCPU S1C88を使用しており、レジスタ構成、命令等は他のS1C88を使用したファミリプロセッサとほぼ同様です。S1C88については"S1C88コアCPUマニュアル"を参照してください。

使用しているS1C88のCPUモデルはMODEL3/ミニマムモードで、物理空間000000Hから00FFFFHまでの領域中、内部メモリが配置されたアドレスのみアクセスの対象として有効となります。

## 3.2 内蔵メモリ

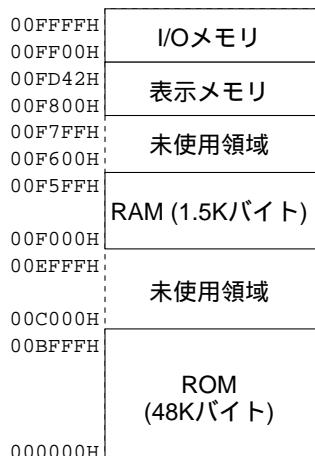

S1C88848は図3.2.1に示すROMおよびRAMを内蔵しています。

図3.2.1 内蔵メモリマップ

### 3.2.1 ROM

内蔵ROMの容量は次のとおりです。

ROM容量: 48Kバイト

アドレス: 000000H ~ 00BFFFH

### 3.2.2 RAM

内蔵RAMの容量は次のとおりです。

RAM容量: 1.5Kバイト

アドレス: 00F000H ~ 00F5FFFH

### 3.2.3 I/Oメモリ

S1C88848では、内蔵する周辺回路とのインターフェースにメモリマップドI/O方式を採用しています。各周辺回路の制御ビットやデータレジスタはメモリ空間上に配置され、通常のメモリアクセスによって制御およびデータのやりとりが行えます。I/Oメモリが配置されている領域は00FF00H ~ 00FFFFHです。I/Oメモリの詳細については"5.1 I/Oメモリマップ"を参照してください。

### 3.2.4 表示メモリ

S1C88848はLCDドライバの表示データを保持する表示メモリを内蔵しています。表示メモリが配置されている領域は00F800H ~ 00FD42H(未使用領域を含む)です。表示メモリの詳細については"5.11 LCDコントローラ"を参照してください。

### 3.3 例外処理ベクタ

S1C88848ではプログラム領域の000000H～000029Hが例外処理ベクタとして割り当てられています。また、00002CH～0000FFHまでは任意の偶数番地から始まる2バイトにソフトウェア割り込みのベクタを割り付けることができます。

表3.3.1にベクタアドレスと例外処理要因の対応を示します。

表3.3.1 ベクタアドレスと例外処理要因の対応

| ベクタアドレス | 例外処理要因               | 優先順位 |

|---------|----------------------|------|

| 000000H | リセット                 | 高い   |

| 000002H | ゼロ除算                 |      |

| 000004H | ウォッチドッグタイマ(NMI)      |      |

| 000006H | プログラマブルタイマ1割り込み      |      |

| 000008H | プログラマブルタイマ0割り込み      |      |

| 00000AH | K10, K11入力割り込み       |      |

| 00000CH | K04～K07入力割り込み        |      |

| 00000EH | K00～K03入力割り込み        |      |

| 000010H | シリアルI/Fエラー割り込み       |      |

| 000012H | シリアルI/F受信完了割り込み      |      |

| 000014H | シリアルI/F送信完了割り込み      |      |

| 000016H | ストップウォッチタイマ100Hz割り込み |      |

| 000018H | ストップウォッチタイマ1Hz割り込み   |      |

| 00001AH | ストップウォッチタイマ1Hz割り込み   |      |

| 00001CH | 計時タイマ32Hz割り込み        |      |

| 00001EH | 計時タイマ8Hz割り込み         |      |

| 000020H | 計時タイマ2Hz割り込み         |      |

| 000022H | 計時タイマ1Hz割り込み         |      |

| 000024H | リモコンキャリア出力割り込み       |      |

| 000026H | プログラマブルタイマ3割り込み      |      |

| 000028H | プログラマブルタイマ2割り込み      |      |

| 00002AH | システム予約(使用不可)         |      |

| 00002CH |                      |      |

| ：       |                      |      |

| 0000FEH | ソフトウェア割り込み           | なし   |

各ベクタアドレスとその次のアドレスに、例外処理ルーチンの先頭アドレスを下位、上位の順に格納しておきます。例外処理要因が発生すると、設定されたアドレスから始まる例外処理ルーチンを実行します。

同時に複数の例外処理が発生した場合は優先順位の高いものから先に実行されます。

なお、表3.3.1に示された割り込みの優先順位は、割り込み優先レベルがすべて同じ場合のものです。各割り込みの優先レベルは系列ごとにソフトウェアで設定することができます。("5.15 割り込みとスタンバイ状態"参照)

注! リセット以外の例外処理ではSC(システムコンディションフラグ)およびPC(プログラムカウンタ)をスタックに退避させ、各例外処理ルーチンに分岐します。したがって、例外処理ルーチンからメインルーチンに戻す際にはRETE命令を使用してください。

例外処理要因発生時のCPUの動作については "S1C88コアCPUマニュアル" を参照してください。

### 3.4 CC(カスタマイズコンディションフラグ)

S1C88848ではコアCPU内のカスタマイズコンディションフラグ(CC)を使用していません。したがって、条件付き分岐命令(JRS、CARS)の分岐条件として使用することはできません。

# 4 イニシャルリセット

S1C88848は回路を初期化するためにイニシャルリセットを必要とします。

ここでは、イニシャルリセットの要因と内部レジスタ等の初期設定について説明します。

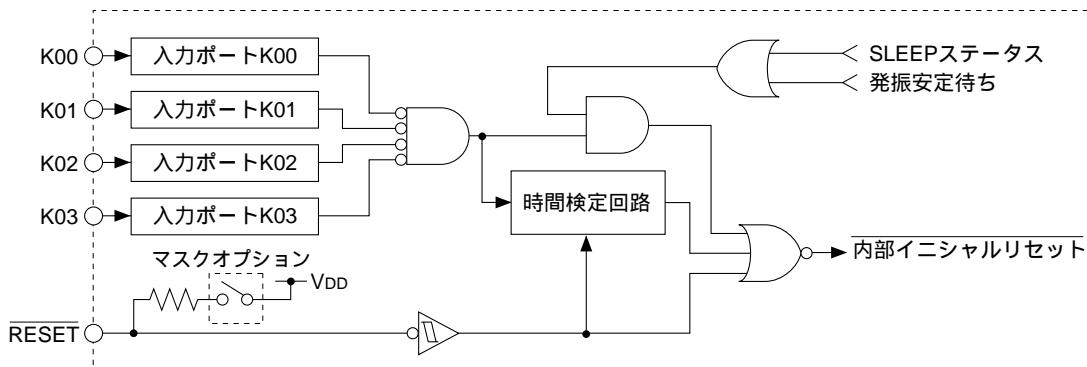

## 4.1 イニシャルリセット要因

S1C88848のイニシャルリセット要因としては以下の2種類があります。

(1) RESET端子

(2) 入力ポート(K00～K03端子)の同時LOWレベル

入力

図4.1.1にイニシャルリセット回路の構成を示します。

イニシャルリセット要因によってCPUおよび周辺回路が初期化され、要因が解除されるとCPUはリセット例外処理を開始します。("S1C88コアCPUマニュアル"参照)

これによって、バンク0先頭(000000H～000001H)のリセット例外処理ベクタが読み出され、その読み出されたアドレスから始まるプログラム(初期化ルーチン)の実行を開始します。

図4.1.1 イニシャルリセット回路の構成

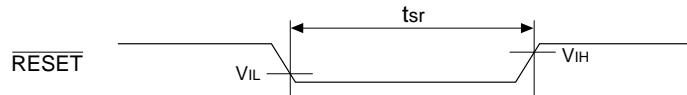

### 4.1.1 RESET端子

外部からRESET端子にLOWレベルを入力することでイニシャルリセットが行えます。

S1C88848を確実に初期化するため、電源電圧立ち上がり後規定の時間RESET端子をLOWレベルに保持してください。

また、電源投入時の初回のイニシャルリセットは必ずRESET端子を使用してください。RESET端子の内蔵プルアップ抵抗はマスクオプションで使用するかしないかを選択することができます。

### 4.1.2 入力ポート(K00～K03)の同時LOWレベル入力

マスクオプションで選択された入力ポート(K00～K03)に、外部から同時にLOWレベルを入力することでイニシャルリセットが行えます。本イニシャルリセット手段は時間検定回路を内蔵しているため、2秒(発振周波数 $f_{osc1}=32.768\text{kHz}$ の場合)以上、指定入力ポート端子をLOWレベルに保つ必要があります。

ただし、SLEEP(スタンバイ)状態時、および電源投入時の発振安定待ち期間中は時間検定回路がバイパスされるため、指定入力ポートへのLOWレベル同時入力直後にイニシャルリセットがかかります。マスクオプションで選択できる入力ポート(K00～K03)の組合せは次のとおりです。

- (1) 使用しない

- (2) K00 & K01

- (3) K00 & K01 & K02

- (4) K00 & K01 & K02 & K03

たとえば、マスクオプションで(4)の"K00 & K01 & K02 & K03"を選択した場合、K00～K03の4ポートの入力が同時にLOWレベルになったときにイニシャルリセットがかかります。

この機能を使用する場合、通常動作時に指定入力ポートが同時にLOWレベルにならないように注意してください。

### 4.1.3 イニシャルリセットシーケンス

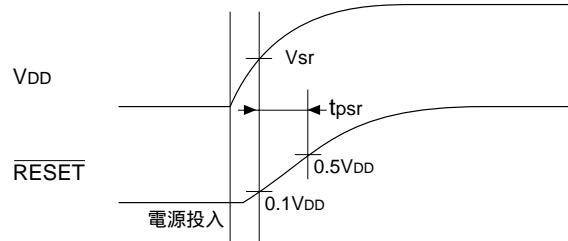

電源投入時のRESET端子へのLOWレベル入力解除後、発振安定待ち時間( $128/f_{osc1}$ 秒)が経過するまでCPUの起動は待たれます。

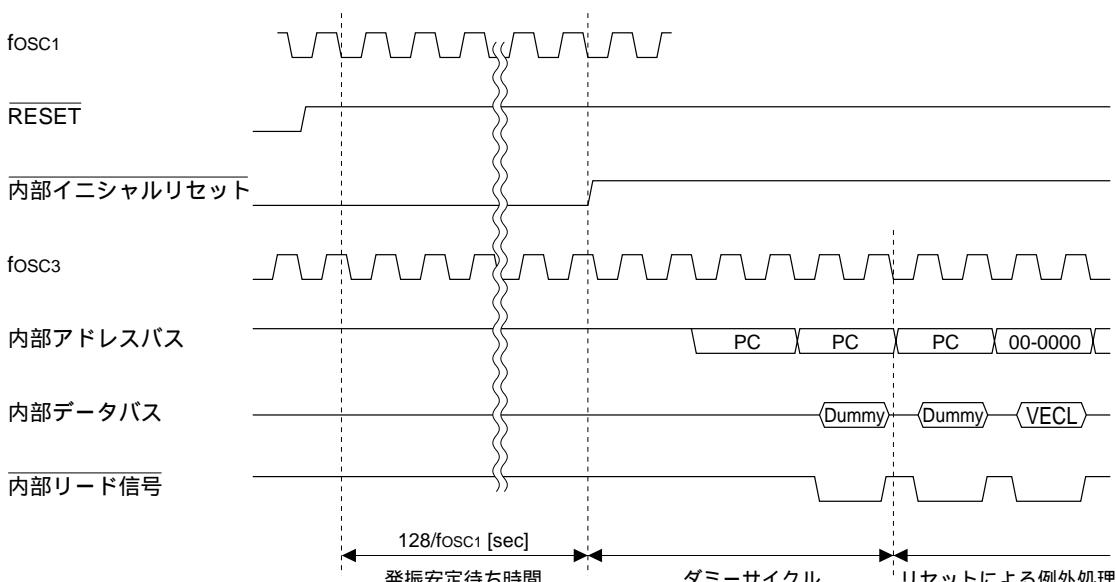

図4.1.3.1にイニシャルリセット解除後の動作シーケンスを示します。

なお、入力ポート(K00～K03)への同時LOWレベル入力によるイニシャルリセット手段を使用する場合は、次の点に注意してください。

- (1) SLEEP状態時、および電源投入時の発振安定待ち期間中は時間検定回路がバイパスされるため、LOWレベル同時入力直後にイニシャルリセットがかかります。この場合、LOWレベル同時入力解除後に発振安定時間を使ってCPUが起動されます。

- (2) (1)の状態以外はLOWレベル同時入力1～2秒後にイニシャルリセットがかかります。この場合は、S1C88848内部でリセット微分パルス(256/ $f_{osc1}$ 秒)が発生されるため、LOWレベル同時入力状態を解除しなくてもCPUは起動されます。

図4.1.3.1 イニシャルリセット解除後の動作シーケンス

## 4.2 イニシャルリセット時の初期設定

イニシャルリセットによりCPUの内部レジスタは以下のように初期化されます。

表4.2.1 初期設定値

| レジスタ名称           | 記号 | ビット長 | 初期値 |

|------------------|----|------|-----|

| データレジスタA         | A  | 8    | 不定  |

| データレジスタB         | B  | 8    | 不定  |

| インデックス(データ)レジスタL | L  | 8    | 不定  |

| インデックス(データ)レジスタH | H  | 8    | 不定  |

| インデックスレジスタIX     | IX | 16   | 不定  |

| インデックスレジスタIY     | IY | 16   | 不定  |

| プログラムカウンタ        | PC | 16   | 不定* |

| スタックポインタ         | SP | 16   | 不定  |

| ベースレジスタ          | BR | 8    | 不定  |

| ゼロフラグ            | Z  | 1    | 0   |

| キャリーフラグ          | C  | 1    | 0   |

| オーバーフロー/フラグ      | V  | 1    | 0   |

| ネガティブフラグ         | N  | 1    | 0   |

| デシマルフラグ          | D  | 1    | 0   |

| アンパックフラグ         | U  | 1    | 0   |

| インタラプトフラグ0       | IO | 1    | 1   |

| インタラプトフラグ1       | II | 1    | 1   |

| ニューコードバンクレジスタ    | NB | 8    | 01H |

| コードバンクレジスタ       | CB | 8    | 不定* |

| エクスパンドページレジスタ    | EP | 8    | 00H |

| IX用エクスパンドページレジスタ | XP | 8    | 00H |

| IY用エクスパンドページレジスタ | YP | 8    | 00H |

\* リセット例外処理によって、0バンクのメモリの先頭(000000H ~ 000001H)に格納されている値がPCにロードされます。また、このとき同時にNBの初期値01HがCBにロードされます。

イニシャルリセット時に初期化されない(不定)レジスタはソフトウェアで初期化してください。

内蔵RAMおよび表示メモリについてもイニシャルリセット時に初期化されませんので、同様にソフトウェアで初期化してください。

内蔵の周辺回路については、それぞれ所定の初期化が行われます。必要に応じてソフトウェアで初期化してください。

イニシャルリセット時の初期値については、次章のI/Oメモリマップまたは各周辺回路の説明を参照してください。

# 5 周辺回路と動作

S1C88848の周辺回路はメモリマップI/O方式でCPUとインターフェースされています。このため、他のメモリアクセスと同様にI/Oメモリを操作して周辺回路を制御することができます。以下、各周辺回路別にその動作と制御方法を説明します。

## 5.1 I/Oメモリマップ

表5.1.1(a) I/Oメモリマップ(00FF00H ~ 00FF10H)

| アドレス   | ビット | 名称     | 機能             | 1         | 0         | SR | R/W | 注釈            |

|--------|-----|--------|----------------|-----------|-----------|----|-----|---------------|

| 00FF00 | D7  | BSMD1  | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ<br>(注) |

|        | D6  | BSMD0  | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D5  | CEMD1  | 汎用レジスタ         |           |           | 1  | R/W |               |

|        | D4  | CEMD0  | 汎用レジスタ         |           |           | 1  | R/W |               |

|        | D3  | CE3    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D2  | CE2    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D1  | CE1    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D0  | CE0    | 汎用レジスタ         |           |           | 0  | R/W |               |

| 00FF01 | D7  | SPP7   | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ<br>(注) |

|        | D6  | SPP6   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D5  | SPP5   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D4  | SPP4   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D3  | SPP3   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D2  | SPP2   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D1  | SPP1   | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D0  | SPP0   | 汎用レジスタ         |           |           | 0  | R/W |               |

| 00FF02 | D7  | EBR    | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ        |

|        | D6  | WT2    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D5  | WT1    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D4  | WT0    | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D3  | CLKCHG | CPU動作クロック切り換え  | OSC3      | OSC1      | 1  | R/W |               |

|        | D2  | OSCC   | OSC3発振On/Off制御 | On        | Off       | 1  | R/W |               |

|        | D1  | VD1C1  | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ        |

|        | D0  | VD1C0  | 汎用レジスタ         |           |           | 0  | R/W |               |

| 00FF10 | D7  | -      | -              | -         | -         | -  | -   | 読み出し時は常時"0"   |

|        | D6  | -      | -              | -         | -         | -  | -   |               |

|        | D5  | -      | -              | -         | -         | -  | -   |               |

|        | D4  | LCCLK  | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ        |

|        | D3  | LCFRM  | 汎用レジスタ         |           |           | 0  | R/W |               |

|        | D2  | DTFNT  | LCDドットフォント選択   | 5x5ドット    | 5x8ドット    | 0  | R/W |               |

|        | D1  | LDUTY  | LCD駆動デューティ選択   | 1/16デューティ | 1/32デューティ | 0  | R/W | *1            |

|        | D0  | SGOUT  | 汎用レジスタ         | 1         | 0         | 0  | R/W | 予約レジスタ        |

\*1 マスクオプションで1/8デューティまたは1/17デューティを選択している場合は、本レジスタの設定は無効となります。

(注) S1C88 FamilyのデバッグツールICE(S5U1C88000H5)にペリフェラルボード(S5U1C88000P)を装着してデバッグを行う場合は、アドレス"00FF00H"および"00FF01H"に任意の値をそれぞれ書き込むまで、NMIを含めたすべての割り込みはマスクされます。

表5.1.1(b) I/Oメモリマップ(00FF11H ~ 00FF21H)

| アドレス   | ビット | 名称    | 機能                               | 1                                                              | 0                                                                                                                                                  | SR       | R/W      | 注釈                                    |  |

|--------|-----|-------|----------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------------------------------------|--|

| 00FF11 | D7  | -     | -                                | -                                                              | -                                                                                                                                                  | -        | -        | 読み出し時は"0"<br>SLP命令実行時に<br>(0, 0)にリセット |  |

|        | D6  | DSPAR | LCD表示メモリ領域選択                     | 表示領域1                                                          | 表示領域0                                                                                                                                              | 0        | R/W      |                                       |  |

|        | D5  | LCDC1 | LCD表示制御                          | LCD表示<br>全点灯<br>全消灯<br>通常表示<br>駆動Off                           | 0<br>R/W                                                                                                                                           | 0<br>R/W | R/W      |                                       |  |

|        | D4  | LCDC0 | LCDC1<br>LCDC0                   |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D3  | LC3   | LCDコントラスト調整                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D2  | LC2   | LC3<br>LC2<br>LC1<br>LC0         | コントラスト<br>濃                                                    |                                                                                                                                                    |          |          |                                       |  |

|        | D1  | LC1   | 1<br>1<br>1<br>0                 | :                                                              |                                                                                                                                                    |          |          |                                       |  |

|        | D0  | LC0   | :<br>:<br>:<br>:                 | 淡                                                              |                                                                                                                                                    |          |          |                                       |  |

|        | D7  | -     | -                                | -                                                              | -                                                                                                                                                  | -        | -        |                                       |  |

|        | D6  | -     | -                                | -                                                              | -                                                                                                                                                  | -        | -        |                                       |  |

| 00FF12 | D5  | SVDDT | SVD検出データ                         | Low                                                            | Normal                                                                                                                                             | 0        | R        | 読み出し時は常時"0"                           |  |

|        | D4  | SVDON | SVD回路On/Off                      | On                                                             | Off                                                                                                                                                | 0        | R/W      |                                       |  |

|        | D3  | SVDS3 | SVD比較電圧設定                        | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0                               | 電圧<br>4.35V<br>4.17V<br>4.00V<br>3.83V<br>3.67V<br>3.50V<br>3.33V<br>3.17V<br>3.00V<br>2.83V<br>2.67V<br>2.50V<br>2.33V<br>2.17V<br>2.00V<br>1.83V | 0<br>R/W | 0<br>R/W |                                       |  |

|        | D2  | SVDS2 | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0 |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D1  | SVDS1 | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0 |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D0  | SVDS0 | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0 |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D7  | PK01  | K00 ~ K07割り込み                    | PK01<br>PK00<br>PSIF1<br>PSIF0<br>PSW1<br>PSW0<br>PTM1<br>PTM0 | 優先<br>レベル<br>3<br>2<br>1<br>0<br>レバ<br>ル3<br>レバ<br>ル2<br>レバ<br>ル1<br>レバ<br>ル0                                                                      | 0<br>R/W | 0<br>R/W |                                       |  |

|        | D6  | PK00  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D5  | PSIF1 | シリアルインターフェース割り込み                 |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D4  | PSIF0 | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D3  | PSW1  | ストップウォッチタイマ割り込み                  |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D2  | PSW0  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D1  | PTM1  | 計時タイマ割り込み                        |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D0  | PTM0  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

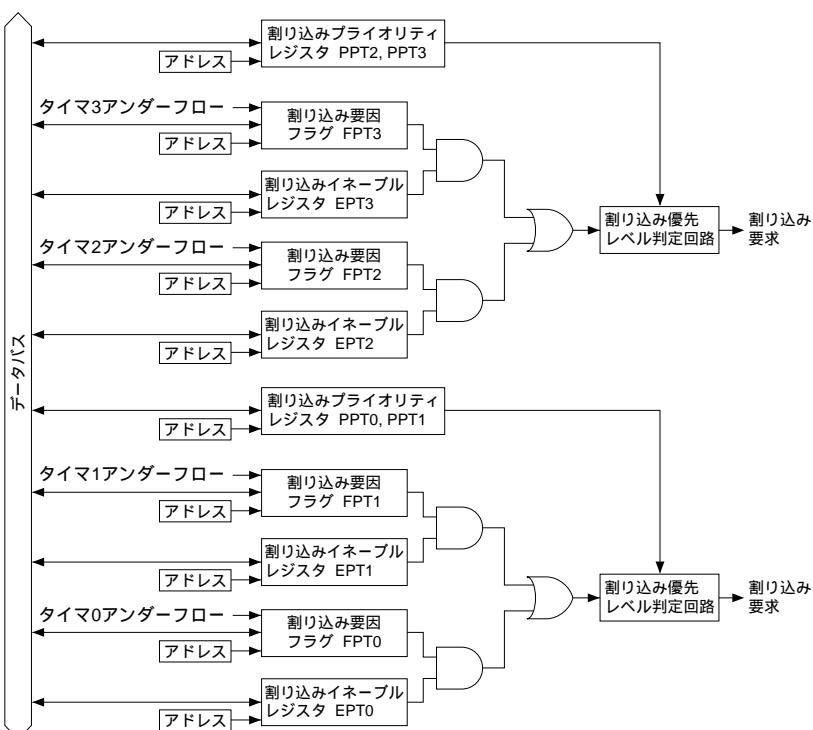

| 00FF21 | D7  | PREM1 | REMキャリア割り込み                      | PREM1<br>PREM0<br>PPT3<br>PPT2<br>PPT1<br>PPT0<br>PK11<br>PK10 | 優先<br>レベル<br>3<br>2<br>1<br>0<br>レバ<br>ル3<br>レバ<br>ル2<br>レバ<br>ル1<br>レバ<br>ル0                                                                      | 0<br>R/W | 0<br>R/W |                                       |  |

|        | D6  | PREM0 | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D5  | PPT3  | プログラマブルタイマ2, 3割り込み               |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D4  | PPT2  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D3  | PPT1  | プログラマブルタイマ0, 1割り込み               |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D2  | PPT0  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D1  | PK11  | K10, K11割り込み                     |                                                                |                                                                                                                                                    |          |          |                                       |  |

|        | D0  | PK10  | プライオリティレジスタ                      |                                                                |                                                                                                                                                    |          |          |                                       |  |

表5.1.1(c) I/Oメモリマップ(00FF22H ~ 00FF27H)

| アドレス   | ビット | 名称     | 機能                         | 1                   | 0                   | SR | R/W | 注釈              |

|--------|-----|--------|----------------------------|---------------------|---------------------|----|-----|-----------------|

| 00FF22 | D7  | -      | -                          | -                   | -                   | -  |     | 読み出し時は"0"       |

|        | D6  | ESW100 | ストップウォッチ100Hz割り込みイネーブルレジスタ | 割り込み<br>許可          | 割り込み<br>禁止          | 0  | R/W |                 |

|        | D5  | ESW10  | ストップウォッチ10Hz割り込みイネーブルレジスタ  |                     |                     | 0  | R/W |                 |

|        | D4  | ESW1   | ストップウォッチ1Hz割り込みイネーブルレジスタ   |                     |                     | 0  | R/W |                 |

|        | D3  | ETM32  | 計時タイマ32Hz割り込みイネーブルレジスタ     |                     |                     | 0  | R/W |                 |

|        | D2  | ETM8   | 計時タイマ8Hz割り込みイネーブルレジスタ      |                     |                     | 0  | R/W |                 |

|        | D1  | ETM2   | 計時タイマ2Hz割り込みイネーブルレジスタ      |                     |                     | 0  | R/W |                 |

|        | D0  | ETM1   | 計時タイマ1Hz割り込みイネーブルレジスタ      |                     |                     | 0  | R/W |                 |

| 00FF23 | D7  | EPT1   | プログラマブルタイマ1割り込みイネーブルレジスタ   | 割り込み<br>許可          | 割り込み<br>禁止          | 0  | R/W |                 |

|        | D6  | EPT0   | プログラマブルタイマ0割り込みイネーブルレジスタ   |                     |                     | 0  | R/W |                 |

|        | D5  | EK1    | K10, K11割り込みイネーブルレジスタ      |                     |                     | 0  | R/W |                 |

|        | D4  | EK0H   | K04 ~ K07割り込みイネーブルレジスタ     |                     |                     | 0  | R/W |                 |

|        | D3  | EK0L   | K00 ~ K03割り込みイネーブルレジスタ     |                     |                     | 0  | R/W |                 |

|        | D2  | ESERR  | シリアルI/F(エラー)割り込みイネーブルレジスタ  |                     |                     | 0  | R/W |                 |

|        | D1  | ESREC  | シリアルI/F(受信)割り込みイネーブルレジスタ   |                     |                     | 0  | R/W |                 |

|        | D0  | ESTRA  | シリアルI/F(送信)割り込みイネーブルレジスタ   |                     |                     | 0  | R/W |                 |

| 00FF24 | D7  | -      | -                          | -                   | -                   | -  |     | 読み出し時は"0"       |

|        | D6  | FSW100 | ストップウォッチ100Hz割り込み要因フラグ     | (R)<br>割り込み<br>要因あり | (R)<br>割り込み<br>要因なし | 0  | R/W |                 |

|        | D5  | FSW10  | ストップウォッチ10Hz割り込み要因フラグ      |                     |                     | 0  | R/W |                 |

|        | D4  | FSW1   | ストップウォッチ1Hz割り込み要因フラグ       |                     |                     | 0  | R/W |                 |

|        | D3  | FTM32  | 計時タイマ32Hz割り込み要因フラグ         | (W)<br>リセット         | (W)<br>無効           | 0  | R/W |                 |

|        | D2  | FTM8   | 計時タイマ8Hz割り込み要因フラグ          |                     |                     | 0  | R/W |                 |

|        | D1  | FTM2   | 計時タイマ2Hz割り込み要因フラグ          |                     |                     | 0  | R/W |                 |

|        | D0  | FTM1   | 計時タイマ1Hz割り込み要因フラグ          |                     |                     | 0  | R/W |                 |

| 00FF25 | D7  | FPT1   | プログラマブルタイマ1割り込み要因フラグ       | (R)<br>割り込み<br>要因あり | (R)<br>割り込み<br>要因なし | 0  | R/W |                 |

|        | D6  | FPT0   | プログラマブルタイマ0割り込み要因フラグ       |                     |                     | 0  | R/W |                 |

|        | D5  | FK1    | K10, K11割り込み要因フラグ          |                     |                     | 0  | R/W |                 |

|        | D4  | FK0H   | K04 ~ K07割り込み要因フラグ         |                     |                     | 0  | R/W |                 |

|        | D3  | FK0L   | K00 ~ K03割り込み要因フラグ         | (W)<br>リセット         | (W)<br>無効           | 0  | R/W |                 |

|        | D2  | FSERR  | シリアルI/F(エラー)割り込み要因フラグ      |                     |                     | 0  | R/W |                 |

|        | D1  | FSREC  | シリアルI/F(受信)割り込み要因フラグ       |                     |                     | 0  | R/W |                 |

|        | D0  | FSTRA  | シリアルI/F(送信)割り込み要因フラグ       |                     |                     | 0  | R/W |                 |

| 00FF26 | D7  | EPT3   | プログラマブルタイマ3割り込みイネーブルレジスタ   | 割り込み<br>許可          | 割り込み<br>禁止          | 0  | R/W | 読み出し時は<br>常時"0" |

|        | D6  | EPT2   | プログラマブルタイマ2割り込みイネーブルレジスタ   |                     |                     | 0  | R/W |                 |

|        | D5  | EREM   | REMキャリア割り込みイネーブルレジスタ       |                     |                     | 0  | R/W |                 |

|        | D4  | REMC   | REMキャリア発生On/Off            | On                  | Off                 | 1  | R/W |                 |

|        | D3  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D2  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D1  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D0  | -      | -                          | -                   | -                   | -  |     |                 |

| 00FF27 | D7  | FPT3   | プログラマブルタイマ3割り込み要因フラグ       | (R)要因あり             | (R)要因なし             | 0  | R/W | 読み出し時は<br>常時"0" |

|        | D6  | FPT2   | プログラマブルタイマ2割り込み要因フラグ       |                     |                     | 0  | R/W |                 |

|        | D5  | FREM   | REMキャリア割り込み要因フラグ           | (W)リセット             | (W)無効               | 0  | R/W |                 |

|        | D4  | REMSO  | REM強制出力On/Off              |                     |                     | On | Off |                 |

|        | D3  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D2  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D1  | -      | -                          | -                   | -                   | -  |     |                 |

|        | D0  | -      | -                          | -                   | -                   | -  |     |                 |

表5.1.1(d) I/Oメモリマップ(00FF28H ~ 00FF30H)

| アドレス   | ビット | 名称      | 機能                                                                                                                                                                                                                                                                                                    | 1        | 0        | SR | R/W | 注釈          |

|--------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----|-----|-------------|

| 00FF28 | D7  | -       | -                                                                                                                                                                                                                                                                                                     | -        | -        | -  | -   | 読み出し時は"0"   |

|        | D6  | RT1     | REMτ周期設定<br>RT1 RT0 分割比<br>1 1 1/32<br>1 0 1/20<br>0 1 1/16<br>0 0 1/12                                                                                                                                                                                                                               |          |          | 0  | R/W |             |

|        | D5  | RT0     |                                                                                                                                                                                                                                                                                                       |          |          | 0  | R/W |             |

|        | D4  | RCDIV   | REMキャリア周期設定                                                                                                                                                                                                                                                                                           | fosc3/96 | fosc3/64 | 0  | R/W |             |

|        | D3  | RCDUTY3 | REMキャリアデューティ設定<br>RCDUTYx デューティ<br>3 2 1 0 (RCDIV = 0) (RCDIV = 1)<br>1 0 1 1 - 12/24<br>1 0 1 0 - 11/24<br>1 0 0 1 - 10/24<br>1 0 0 0 - 9/24<br>0 1 1 1 - 8/24<br>0 1 1 0 - 7/24<br>0 1 0 1 - 6/24<br>0 1 0 0 - 5/24<br>0 0 1 1 4/8 4/24<br>0 0 1 0 3/8 3/24<br>0 0 0 1 2/8 2/24<br>0 0 0 0 1/8 1/24 |          |          | 0  | R/W | *2          |

|        | D2  | RCDUTY2 |                                                                                                                                                                                                                                                                                                       |          |          | 0  | R/W |             |

|        | D1  | RCDUTY1 |                                                                                                                                                                                                                                                                                                       |          |          | 0  | R/W |             |

|        | D0  | RCDUTY0 |                                                                                                                                                                                                                                                                                                       |          |          | 0  | R/W |             |

| 00FF29 | D7  | RIC3    | REM割り込み発生カウンタ設定                                                                                                                                                                                                                                                                                       |          |          | -  | W   | *1          |

|        | D6  | RIC2    | (0 ~ 0EH: 0 ~ 14τクロック)                                                                                                                                                                                                                                                                                |          |          | -  | W   | 読み出し時は常時"0" |

|        | D5  | RIC1    | 書き込みにより1回のみ動作し、その後0FHにリセット                                                                                                                                                                                                                                                                            |          |          | -  | W   |             |

|        | D4  | RIC0    |                                                                                                                                                                                                                                                                                                       |          |          | -  | W   |             |

|        | D3  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D2  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   | 読み出し時は常時"0" |

|        | D1  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D0  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

| 00FF2A | D7  | ROUT1   | REM出力On時間設定(0 ~ 3: 0 ~ 3τ)                                                                                                                                                                                                                                                                            |          |          | 0  | R/W | *1          |

|        | D6  | ROUT0   | 書き込みにより1回のみ動作                                                                                                                                                                                                                                                                                         |          |          | 0  | R/W |             |

|        | D5  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D4  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D3  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   | 読み出し時は常時"0" |

|        | D2  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D1  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

|        | D0  | -       |                                                                                                                                                                                                                                                                                                       | -        | -        | -  | -   |             |

| 00FF30 | D7  | -       | -                                                                                                                                                                                                                                                                                                     | -        | -        | -  | -   | 読み出し時は常時"0" |

|        | D6  | -       | -                                                                                                                                                                                                                                                                                                     | -        | -        | -  | -   |             |

|        | D5  | -       | -                                                                                                                                                                                                                                                                                                     | -        | -        | -  | -   |             |

|        | D4  | MODE160 | 8/16ビットモード選択(タイマ0/1)                                                                                                                                                                                                                                                                                  | 16ビットx1  | 8ビットx2   | 0  | R/W |             |

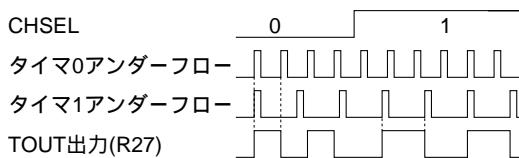

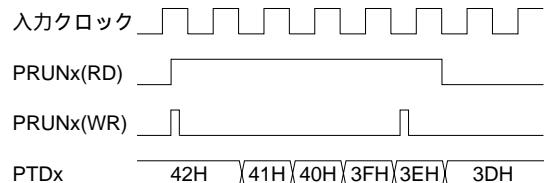

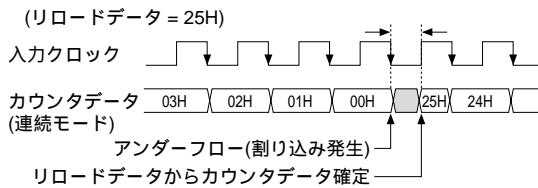

|        | D3  | CHSEL   | TOUT出力チャンネル選択                                                                                                                                                                                                                                                                                         | タイマ1     | タイマ0     | 0  | R/W |             |

|        | D2  | PTOUT   | TOUT出力制御                                                                                                                                                                                                                                                                                              | On       | Off      | 0  | R/W |             |

|        | D1  | CKSEL1  | プリスケーラ1原振クロック選択                                                                                                                                                                                                                                                                                       | fosc3    | fosc1    | 0  | R/W |             |

|        | D0  | CKSEL0  | プリスケーラ0原振クロック選択                                                                                                                                                                                                                                                                                       | fosc3    | fosc1    | 0  | R/W |             |

\*1 ハードタイマ方式のみ有効。ソフトタイマ方式では書き込み禁止

\*2 RCDIV = "1"の場合、RCDUTYxが"1100"以上ではREM出力しません。

RCDIV = "0"の場合、RCDUTYxが"0100"以上の設定は"0011"と同じとなります。

表5.1.1(e) I/Oメモリマップ(00FF31H ~ 00FF35H)

| アドレス   | ビット   | 名称                  | 機能                       | 1                                                                                                                                                                                                                                                                                         | 0               | SR    | R/W       | 注釈          |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

|--------|-------|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----------|-------------|---|-------------|---|---|-------------|---|---|------------|---|---|------------|--|---|-----|

| 00FF31 | D7    | EVCNT0              | タイマ0カウンタモード選択            | イベントカウント                                                                                                                                                                                                                                                                                  | タイマ             | 0     | R/W       |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

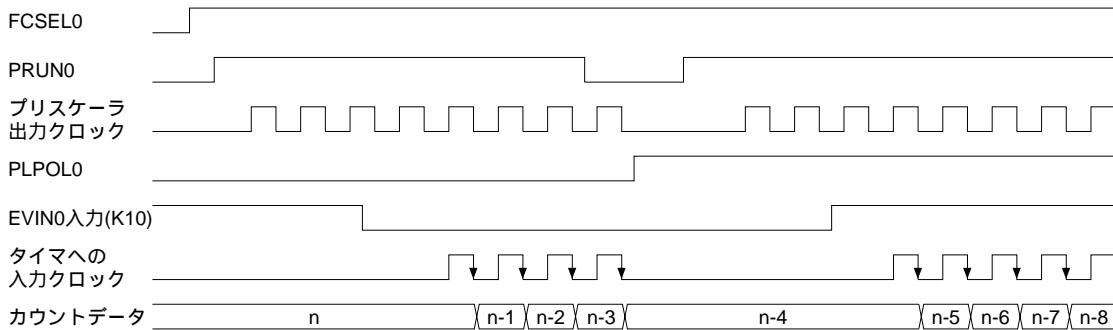

|        | D6    | FCSEL0<br>機能選択      | タイマ0モード時                 | パルス幅測定                                                                                                                                                                                                                                                                                    | 通常モード           | 0     | R/W       |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

|        |       |                     | イベントカウンタモード時             | ノイズリジエクタ付き                                                                                                                                                                                                                                                                                | ノイズリジエクタなし      |       |           |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

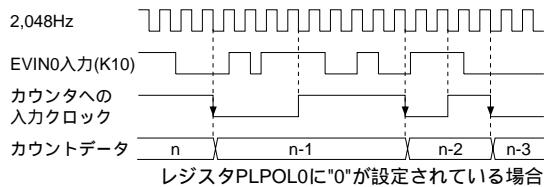

|        | D5    | PLPOL0<br>パルス極性選択   | イベントカウンタモードのダウンカウントタイミング | K10入力の立ち上がり                                                                                                                                                                                                                                                                               | K10入力の立ち下がり     | 0     | R/W       |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

|        |       |                     | パルス幅測定モード時               | K10入力のHighレベル幅測定                                                                                                                                                                                                                                                                          | K10入力のLowレベル幅測定 |       |           |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |

|        | D4    | PSC01               | タイマ0プリスケーラ分周比選択          | <table border="1"> <tr><td>PSC01</td><td>PSC00</td><td>プリスケーラ分周比</td></tr> <tr><td>1</td><td>1</td><td>原振クロック / 64</td></tr> <tr><td>1</td><td>0</td><td>原振クロック / 16</td></tr> <tr><td>0</td><td>1</td><td>原振クロック / 4</td></tr> <tr><td>0</td><td>0</td><td>原振クロック / 1</td></tr> </table> | PSC01           | PSC00 | プリスケーラ分周比 | 1           | 1 | 原振クロック / 64 | 1 | 0 | 原振クロック / 16 | 0 | 1 | 原振クロック / 4 | 0 | 0 | 原振クロック / 1 |  | 0 | R/W |

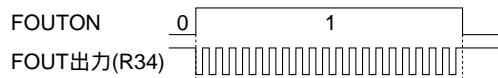

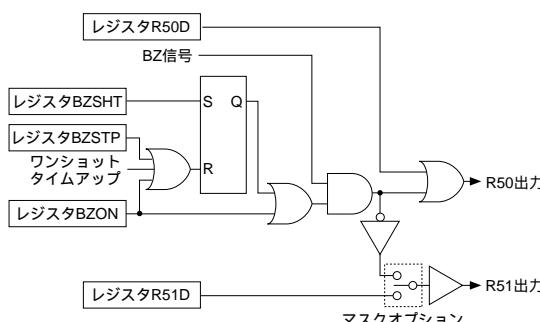

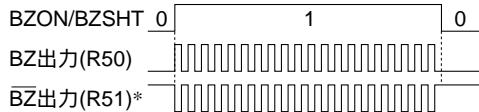

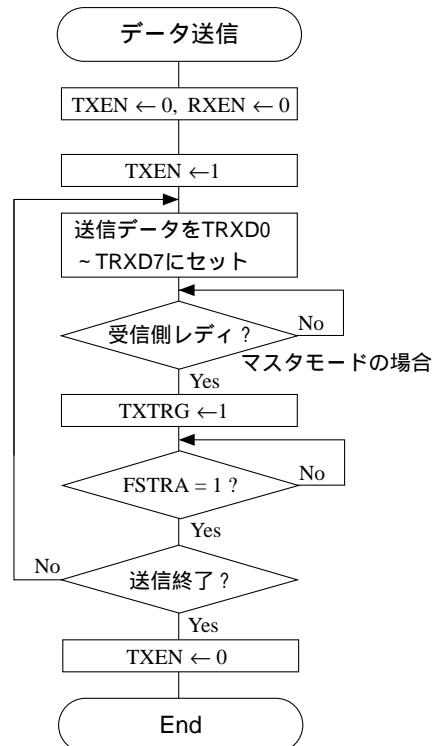

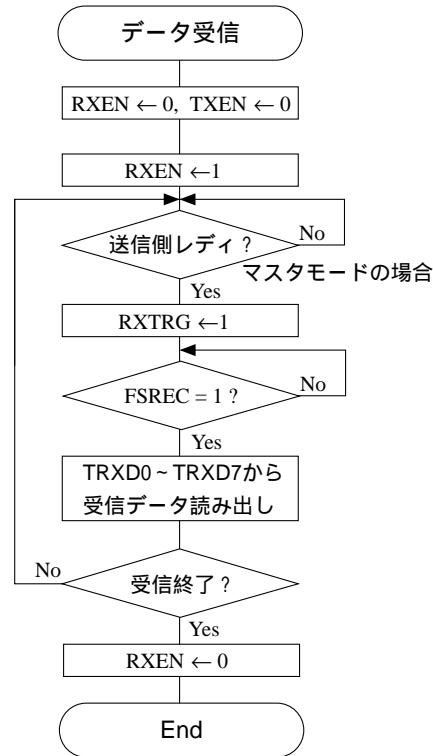

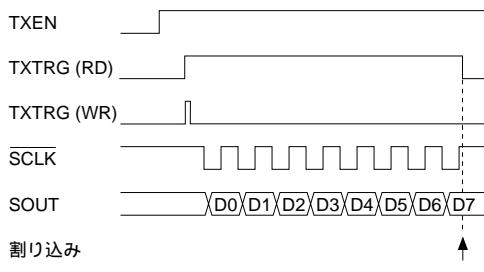

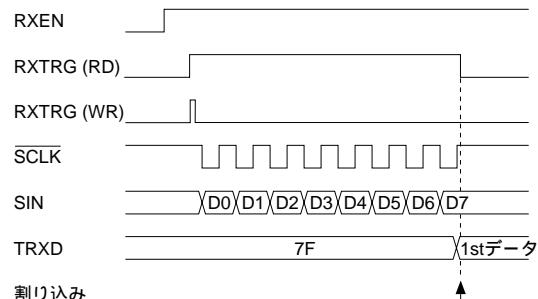

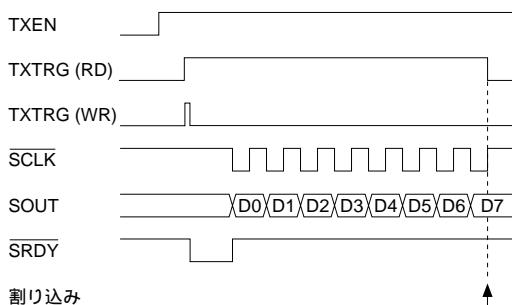

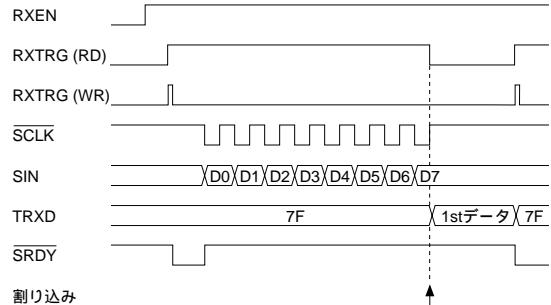

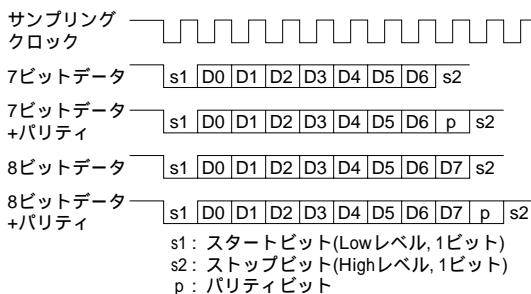

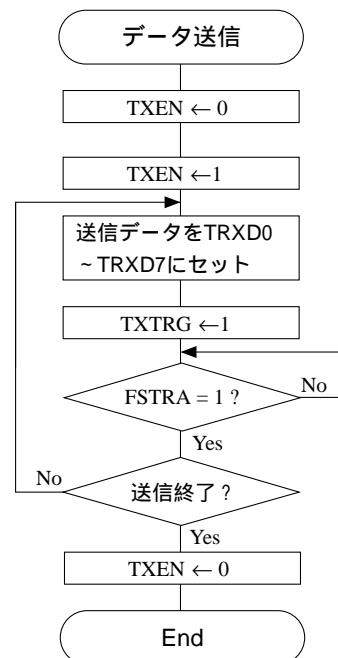

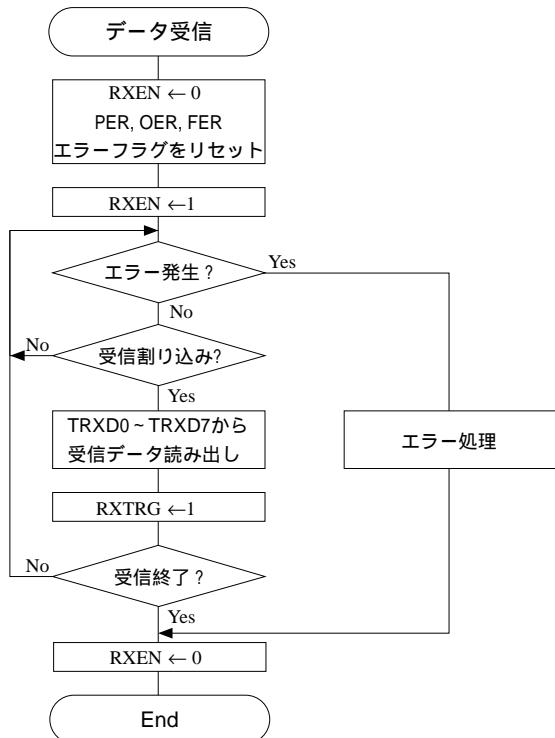

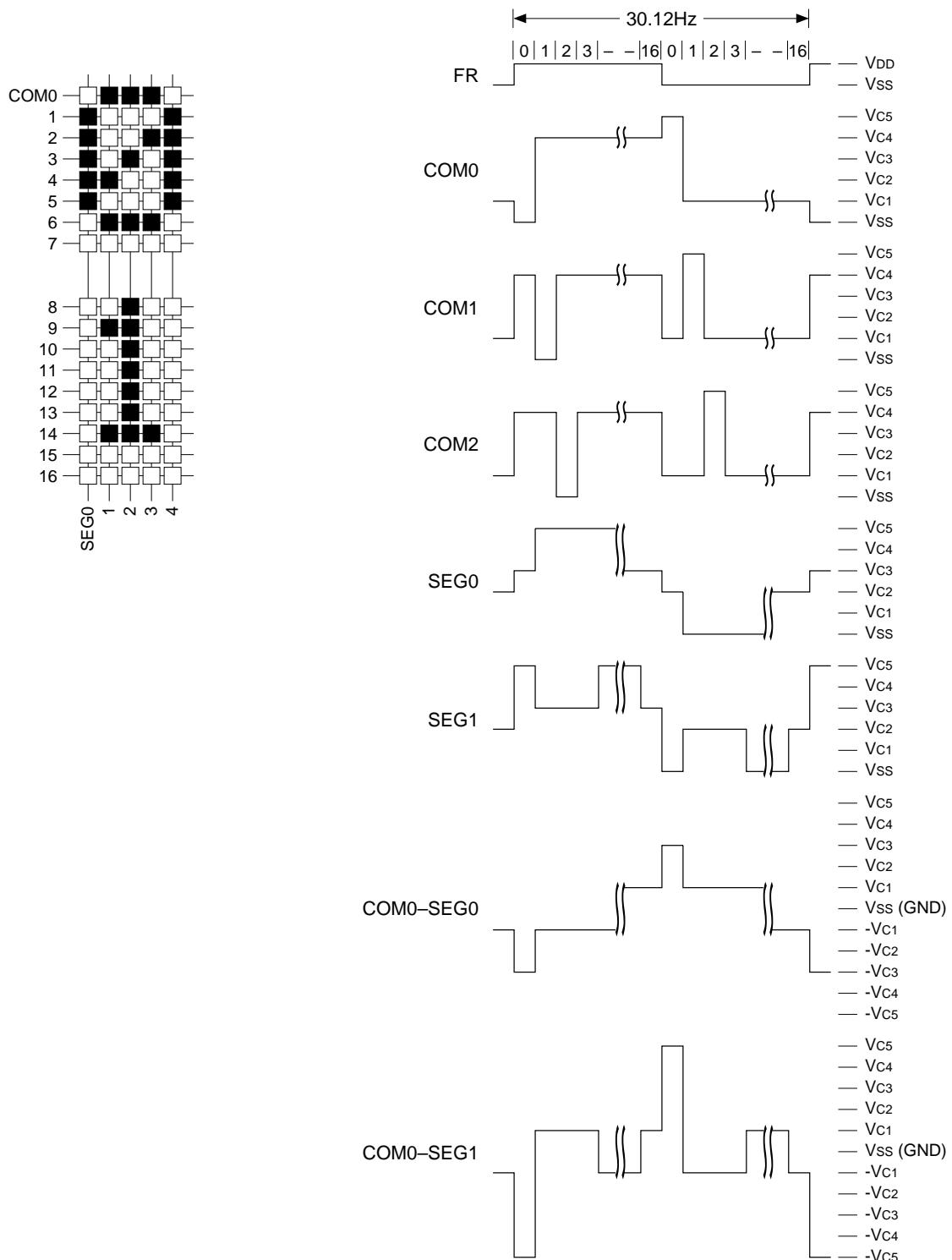

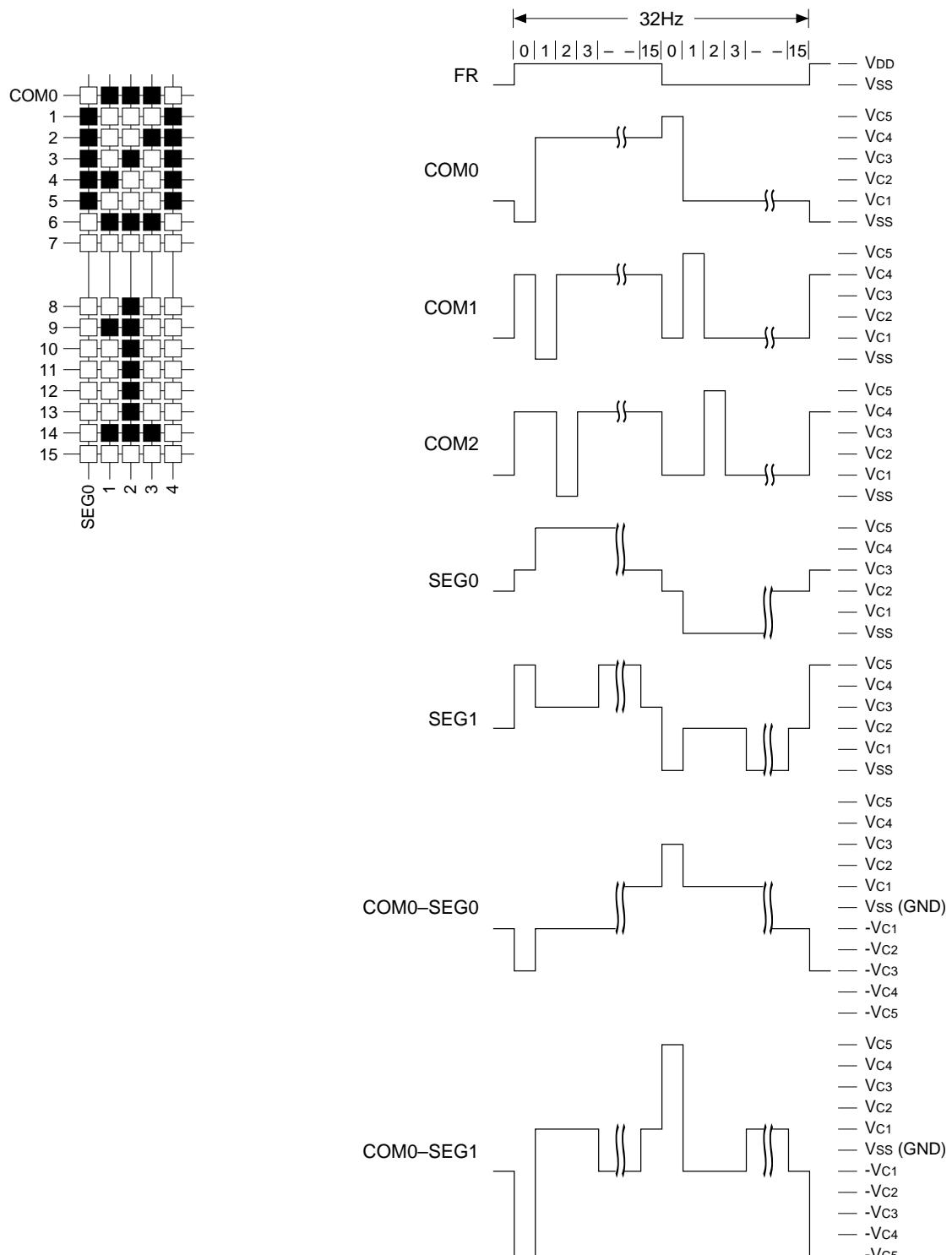

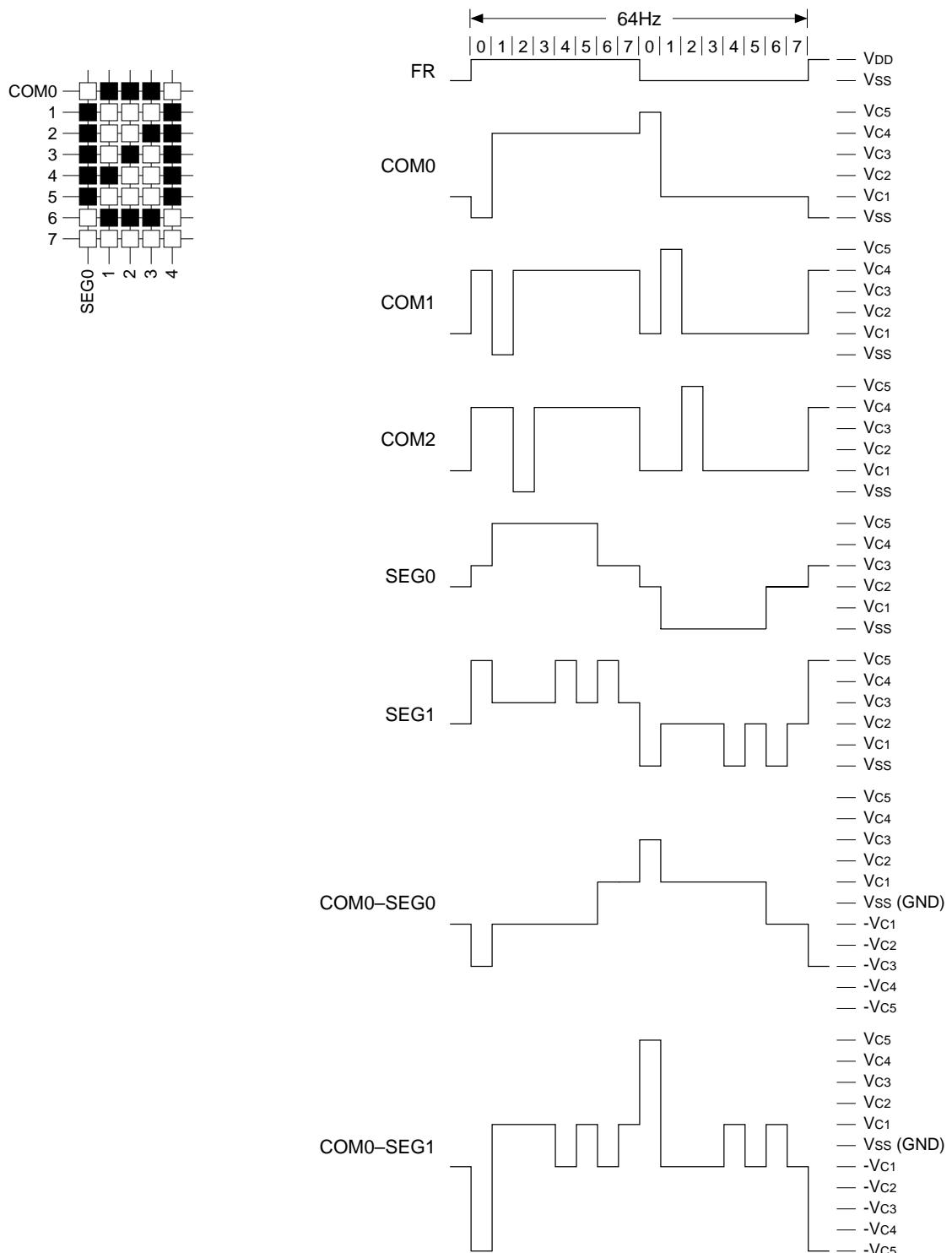

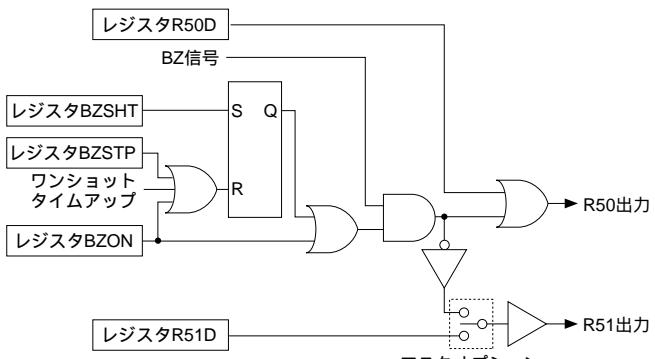

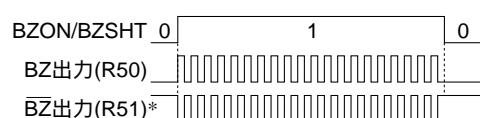

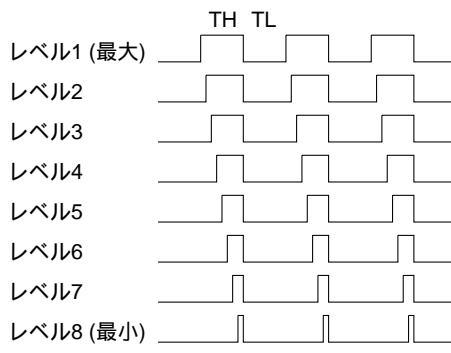

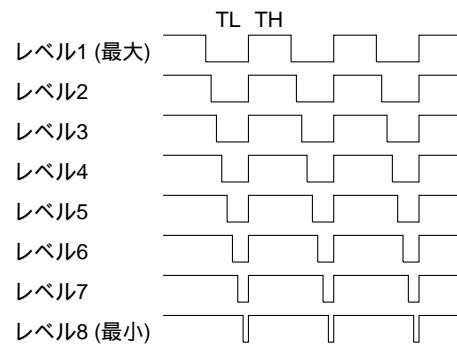

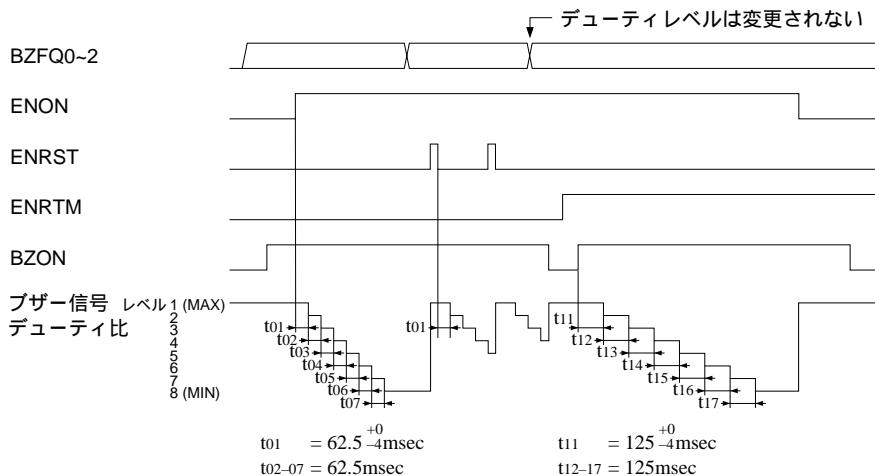

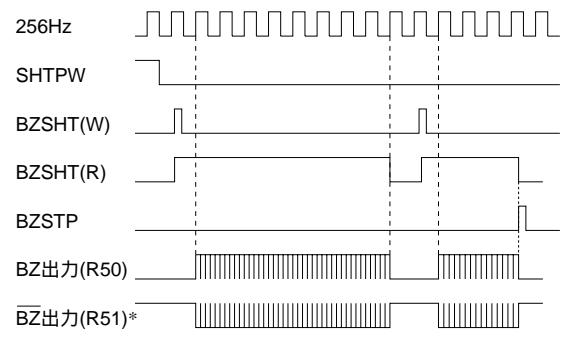

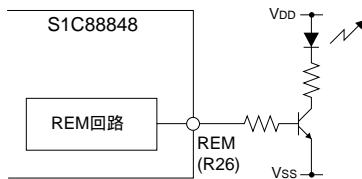

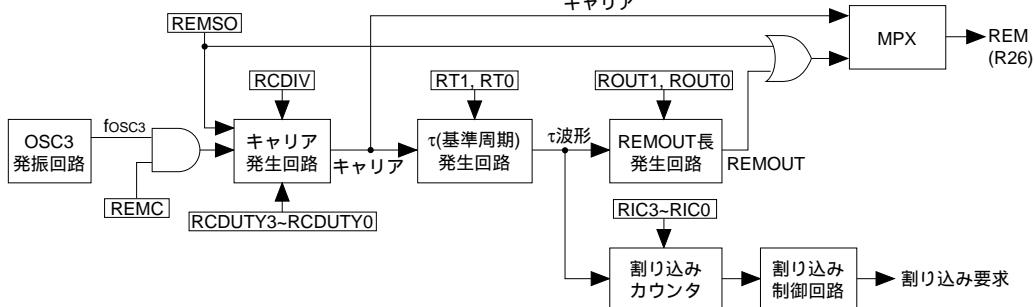

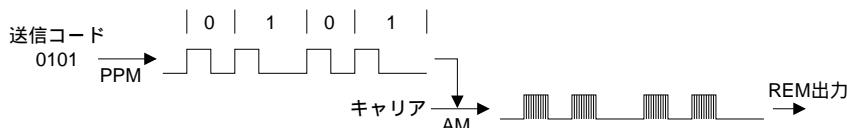

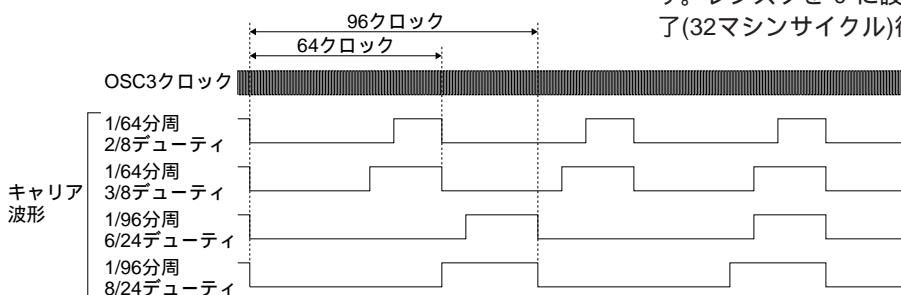

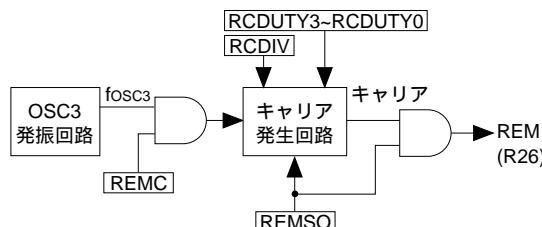

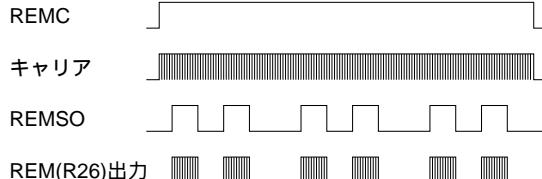

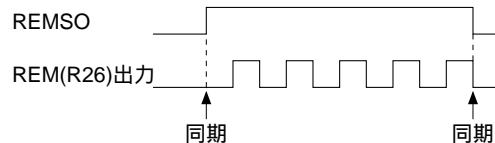

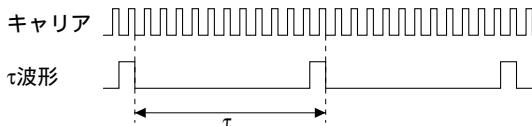

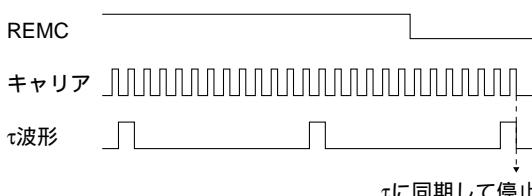

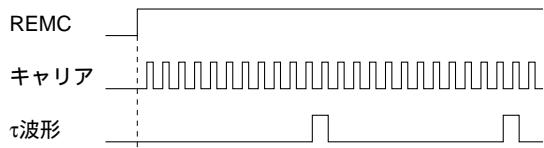

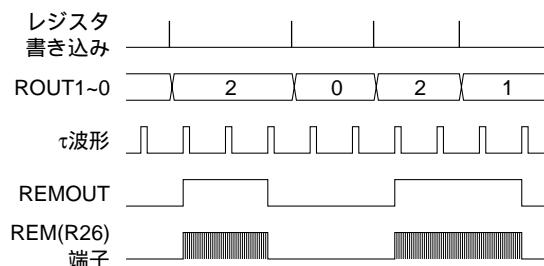

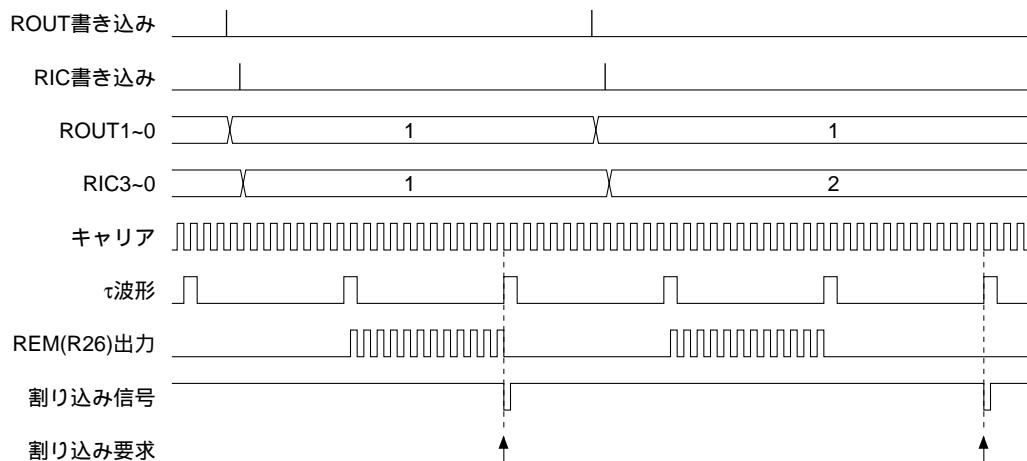

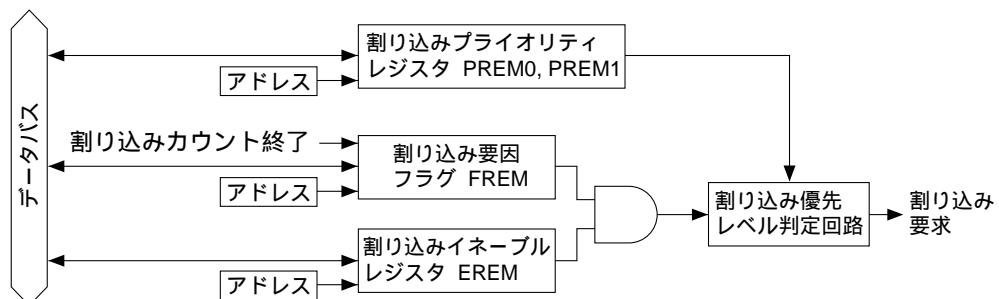

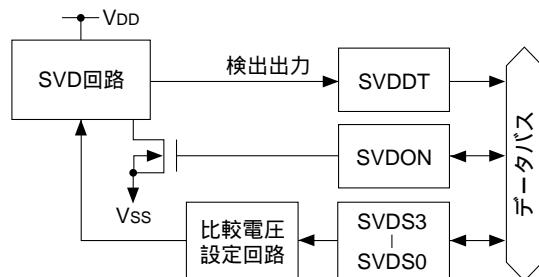

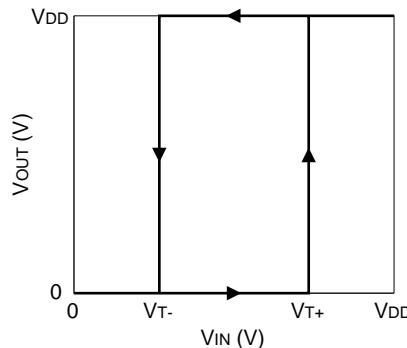

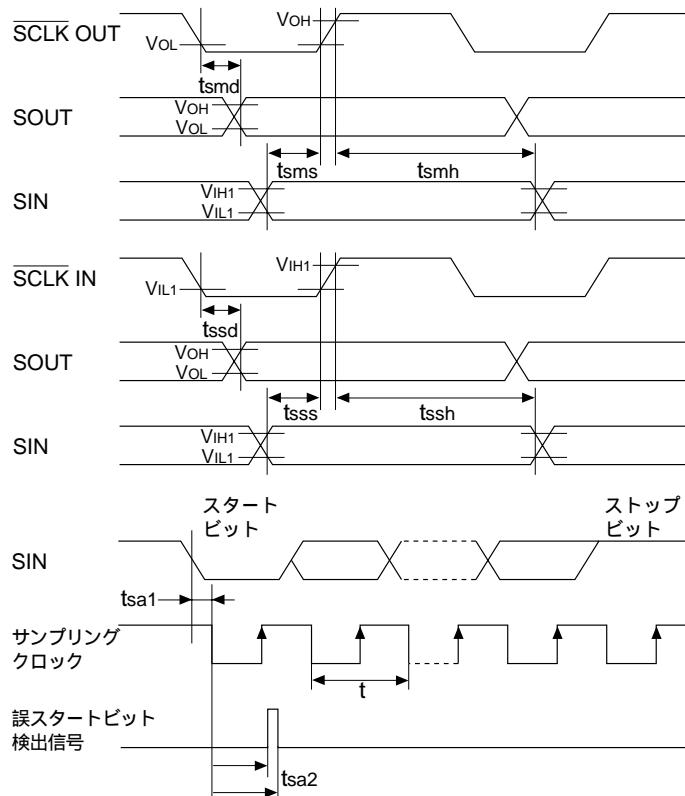

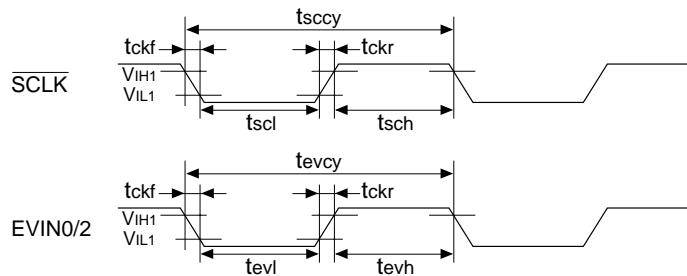

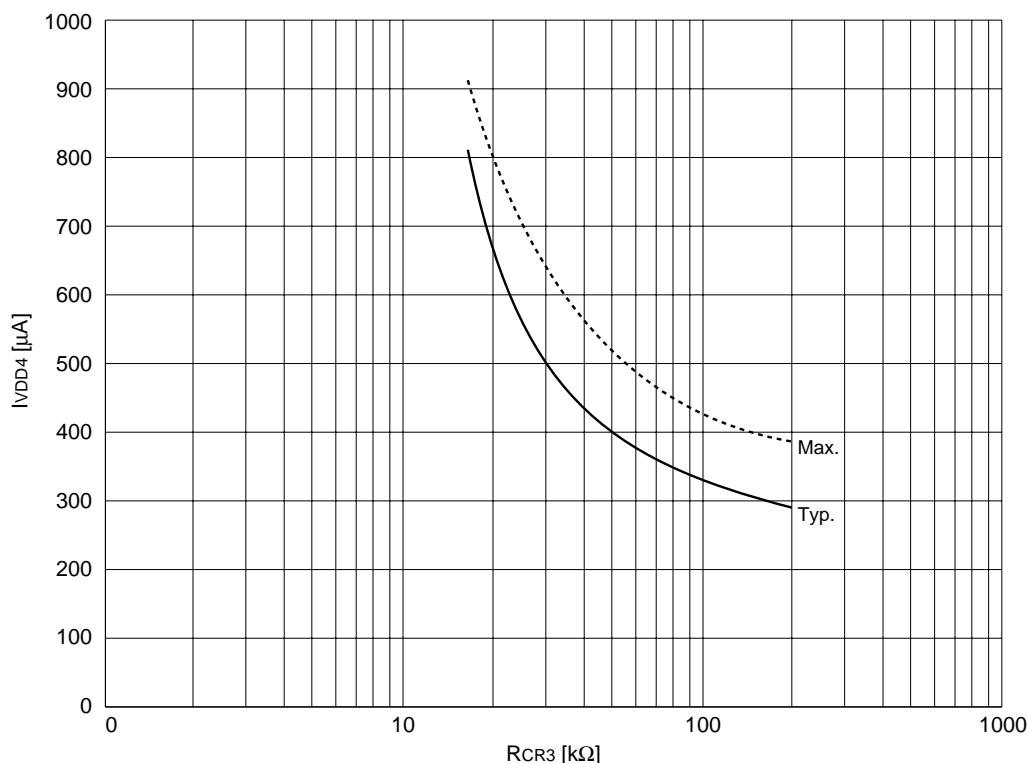

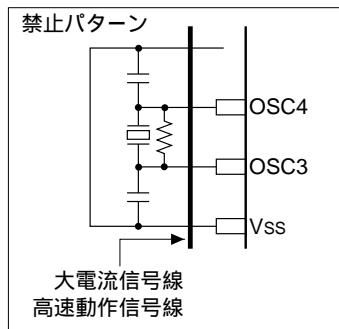

| PSC01  | PSC00 | プリスケーラ分周比           |                          |                                                                                                                                                                                                                                                                                           |                 |       |           |             |   |             |   |   |             |   |   |            |   |   |            |  |   |     |