# S1S60000

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

-

1. 本資料の内容については、予告無く変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施件の許諾を行うものではありません。

4. 特性値の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

<登録商標>

ブランド名、製品名は各社の商標もしくは登録商標です。

本製品は Silicon Storage Technology, Inc.よりライセンスされた SuperFlash®テクノロジーを使用しています。

©SEIKO EPSON CORPORATION 2005, All rights reserved.

## 製品型番体系

# 目 次

|                                     |           |

|-------------------------------------|-----------|

| <b>1. 概要</b>                        | <b>1</b>  |

| 1.1 特徴                              | 1         |

| 1.2 主な仕様                            | 1         |

| 1.3 ブロック図                           | 2         |

| 1.4 端子説明                            | 3         |

| 1.4.1 端子配置図                         | 3         |

| 1.4.2 端子機能                          | 4         |

| <b>2. ハードウェア仕様</b>                  | <b>9</b>  |

| 2.1 コア CPU                          | 9         |

| 2.1.1 ROM とポートアドレス                  | 9         |

| 2.1.2 RAM                           | 9         |

| 2.2 周辺回路                            | 9         |

| 2.3 シリアルインタフェース                     | 10        |

| 2.3.1 ハードウェア制御モード                   | 10        |

| 2.3.2 シリアルエミュレーションモード               | 10        |

| 2.4 電源                              | 11        |

| 2.4.1 動作電圧                          | 11        |

| 2.5 パワーオンリセット                       | 12        |

| 2.6 OSC3 クロック                       | 12        |

| <b>3. ネットワークインターフェース</b>            | <b>13</b> |

| 3.1 MII インタフェース                     | 13        |

| 3.2 マネジメントインターフェース                  | 14        |

| 3.3 PHY チップとの接続                     | 14        |

| 3.4 通信モード                           | 15        |

| <b>4. ホストインターフェース</b>               | <b>16</b> |

| 4.1 制御信号                            | 16        |

| 4.2 ホストインターフェースポート                  | 17        |

| 4.2.1 コマンドポート                       | 17        |

| 4.2.2 ステータスポート                      | 17        |

| 4.2.3 データポート                        | 17        |

| 4.2.4 フラグポート                        | 17        |

| 4.3 ホストインターフェースタイプ                  | 19        |

| 4.4 エンディアンによるデータ入れ替え                | 25        |

| 4.5 アクセスタイミング                       | 26        |

| <b>5. ハードウェア制御</b>                  | <b>28</b> |

| 5.1 制御方法                            | 28        |

| 5.1.1 ネットワークからの制御                   | 28        |

| 5.1.2 ホストインターフェースからの制御              | 31        |

| 5.1.3 外部 I <sup>2</sup> C マスターからの制御 | 31        |

| 5.1.4 シリアルインターフェースからの制御             | 31        |

| 5.2 内蔵レジスタ                          | 34        |

| 5.2.1 REVID                         | 35        |

| 5.2.2 MAC0,MAC1,MAC2                | 35        |

| 5.2.3 GENCR                         | 36        |

| 5.2.4 HIFCR                         | 37        |

|             |                               |    |

|-------------|-------------------------------|----|

| 5.2.5       | I2CSADR .....                 | 37 |

| 5.2.6       | I2CCONF .....                 | 38 |

| 5.2.7       | GPALT .....                   | 39 |

| 5.2.8       | GPCFG .....                   | 40 |

| 5.2.9       | GPDAT .....                   | 40 |

| 5.2.10      | GPMSK .....                   | 41 |

| 5.2.11      | EPMSK .....                   | 41 |

| 5.2.12      | I2CMSK .....                  | 42 |

| 5.2.13      | PMWAIT .....                  | 43 |

| 5.2.14      | PHYMODE .....                 | 43 |

| 5.2.15      | ANEGR .....                   | 44 |

| 5.2.16      | IPADDRH,IPADRL .....          | 45 |

| 5.2.17      | SNMSKH,SNMSKL .....           | 45 |

| 5.2.18      | DGWH,DGWL .....               | 45 |

| 5.2.19      | DADRnH,DADRnL .....           | 45 |

| 5.2.20      | PORT .....                    | 45 |

| 5.2.21      | DPORT .....                   | 45 |

| 5.2.22      | SERMODE .....                 | 46 |

| 5.2.23      | TMOUT .....                   | 46 |

| 5.2.24      | SOPAR .....                   | 47 |

| 5.2.25      | COMN0,COMN1,COMN2,COMN3 ..... | 48 |

| 5.3         | GPIO .....                    | 49 |

| 5.3.1       | 割り込み通知機能 .....                | 50 |

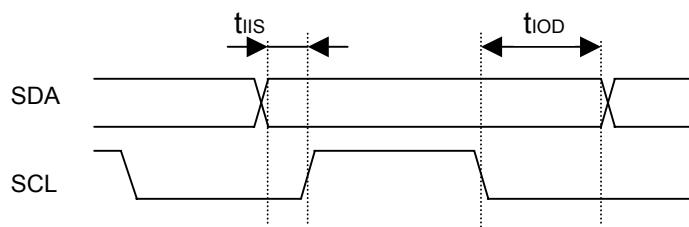

| 5.4         | I <sup>2</sup> C .....        | 51 |

| 5.4.1       | マスター機能 .....                  | 51 |

| 5.4.2       | スレーブ機能 .....                  | 53 |

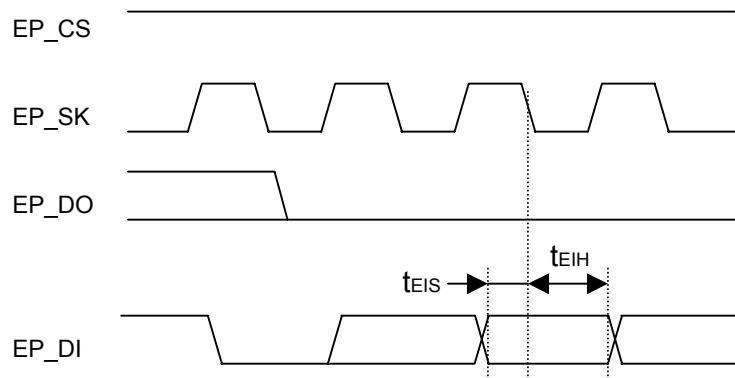

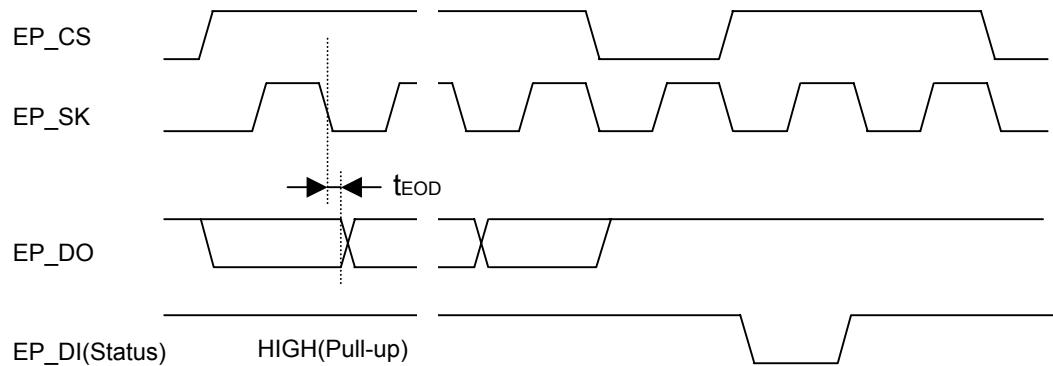

| 5.5         | EEPROM .....                  | 56 |

| 5.5.1       | EEPROM 仕様 .....               | 56 |

| 5.5.2       | 格納データ .....                   | 56 |

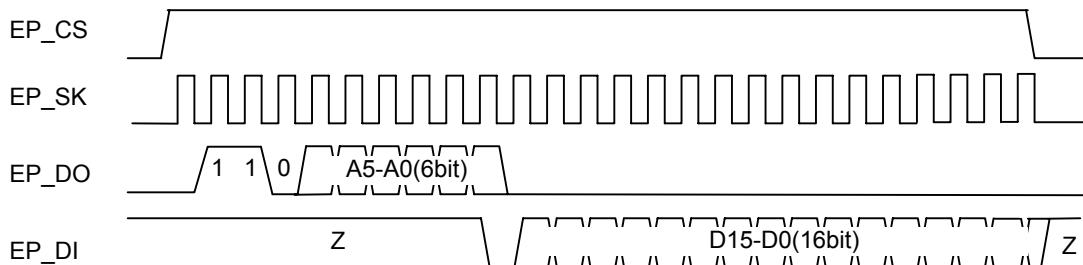

| 5.5.3       | 送受信フォーマット .....               | 57 |

| 5.5.4       | 自動読み込み .....                  | 57 |

| 6.          | パワーマネジメント制御 .....             | 58 |

| 7.          | 実装上の注意事項 .....                | 59 |

| 8.          | 電気的特性 .....                   | 60 |

| 8.1         | 絶対最大定格 .....                  | 60 |

| 8.2         | 推奨動作条件 .....                  | 60 |

| 8.3         | DC 特性 .....                   | 61 |

| 8.4         | 消費電流 .....                    | 61 |

| 8.5         | AC 特性 .....                   | 61 |

| 8.5.1       | 記号説明 .....                    | 61 |

| 8.5.2       | AC 特性測定条件 .....               | 61 |

| 8.5.3       | AC 特性表 .....                  | 62 |

| 8.5.4       | AC 特性タイミングチャート .....          | 63 |

| 8.6         | 発振特性 .....                    | 67 |

| 8.7         | PLL 特性 .....                  | 67 |

| 9.          | パッケージ .....                   | 68 |

| APPENDIX A. | 参考回路 .....                    | 69 |

| APPENDIX B. | 端子特性一覧 .....                  | 72 |

## 1. 概要

S1S60000 はプロトコル処理機能を内蔵した組み込み機器向けのインテリジェント・ネットワークコントローラです。TCP/IP 接続に必要な ARP, ICMP, IP, TCP, UDP 等のプロトコル処理を S1S60000 内部で処理するため、ホスト CPU からは簡単なコマンドとデータを渡すだけで TCP/IP 通信が行なえます。物理層とのインターフェースは MII (Media Independent Interface)を採用し、MII 対応 PHY チップと組み合わせることで容易に 10Base-T/100Base-TX 等のネットワーク対応機器が実現できます。高機能 OS やソフトウェアベンダが提供するプロトコルスタックの必要なしに、8/16 ビットクラスの CPU 使用機器をネットワーク接続対応にするのに最適です。

また多種多様なホスト CPU に追加ロジックなしで直接接続が可能です。PCI、ISA などの汎用バスや外部バスを持たない機器でも容易に使用できます。

### 1.1 特徴

- OSI モデル L4 層までのプロトコル処理を内部処理

- 簡単なコマンド操作によりネットワーク接続を実現

- 独自開発のプロトコルスタック使用によりライセンス費用が不要

- 汎用 I/O ピン、I<sup>2</sup>C バスにより、ネットワークからホスト CPU なしで簡単なハードウェア制御が可能

- 単独で RS232 Ethernet 変換機能を実現

- 対応プロトコルは Flash ROM の書き換えにより追加、変更が可能

### 1.2 主な仕様

|                       |                                                                                                                             |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| • 対応プロトコル             | ARP, ICMP, IP, TCP, UDP, HTTP <sup>1</sup> , DHCP, TFTP <sup>2</sup> , SNMP                                                 |

| • 物理層インターフェース         | Media Independent Interface (IEEE 802.3 Clause 22 準拠)<br>10Base-T/全二重、10Base-T/半二重、100Base-TX/半二重<br>( 100Base-TX/全二重は非対応 ) |

| • 実効転送速度              | 最大約 5.5Mbps (UDP 転送時)                                                                                                       |

| • ホストインターフェース         | 8/16 ビットパラレル                                                                                                                |

| • 直接接続可能タイプ           | SH-3/4, EPSON S1C33, MC68000, MC68030, Philips PR31500/PR31700, Toshiba TX3912, NEC VR4121, PC Card(PCMCIA), ISA 他          |

| • エンディアン              | Little/Big 切り替え                                                                                                             |

| • ホストコマンド体系           | EPSON Standard Code for Network                                                                                             |

| • 汎用 I/O              | 最大 16 本(ネットワークから制御可能、8 本はシリアルインターフェースと共に)                                                                                   |

| • EEPROM Interface    | 93C46 互換 3-wire interface, 16bit 幅 (一部はユーザ使用可能)                                                                             |

| • I <sup>2</sup> C バス | マスター機能(マルチマスター、10bit スレーブ対応、Fast/Normal モード)<br>/スレーブ機能内蔵                                                                   |

| • コア CPU              | EPSON S1C33240 50MHz                                                                                                        |

| • 内蔵 Flash ROM        | 128KB (1KB × 128 ブロック)                                                                                                      |

| • 電源                  | +3.3V, 120mA(Max.)                                                                                                          |

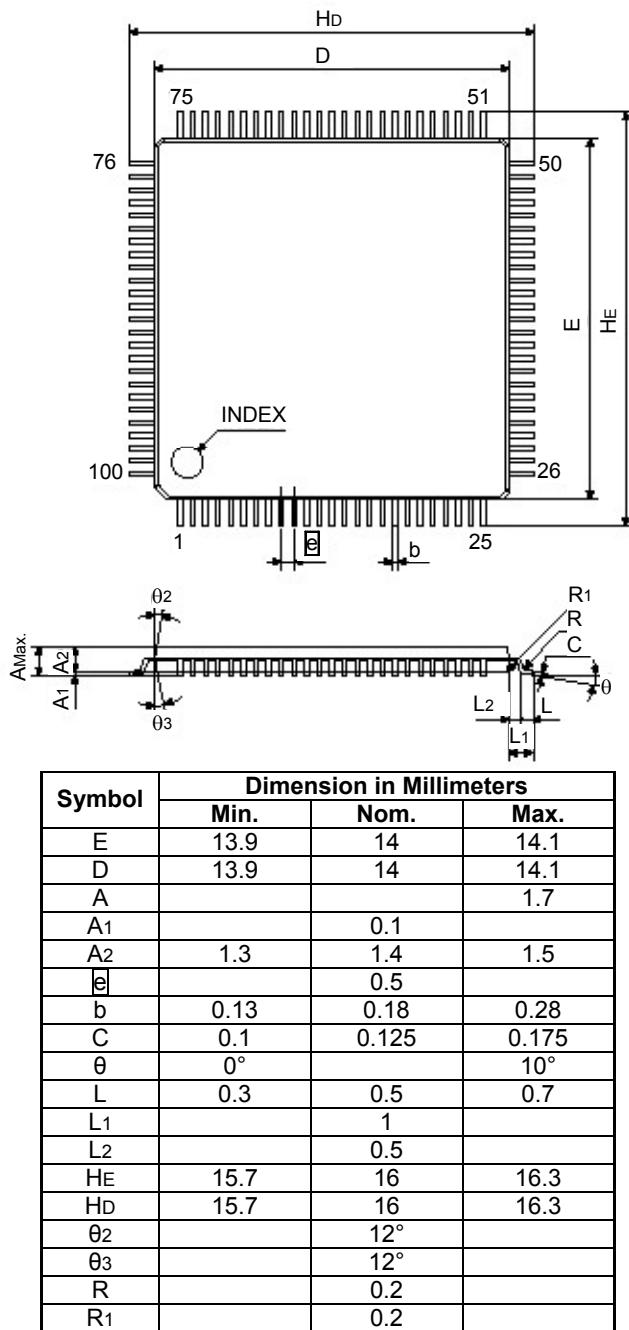

| • パッケージ               | QFP15-100pin                                                                                                                |

S1S60000 シリーズ (EPSON Network Controller for Embedded System) はプロトコルスタック内蔵ネットワーク IC の総称です。S1S60000 は S1S60000 シリーズの最初の製品です。

<sup>1</sup> ハードウェア制御にのみ使用可能です

<sup>2</sup> ネットワークからの Flash ROM アップデートにのみ使用可能です

# 1. 概要

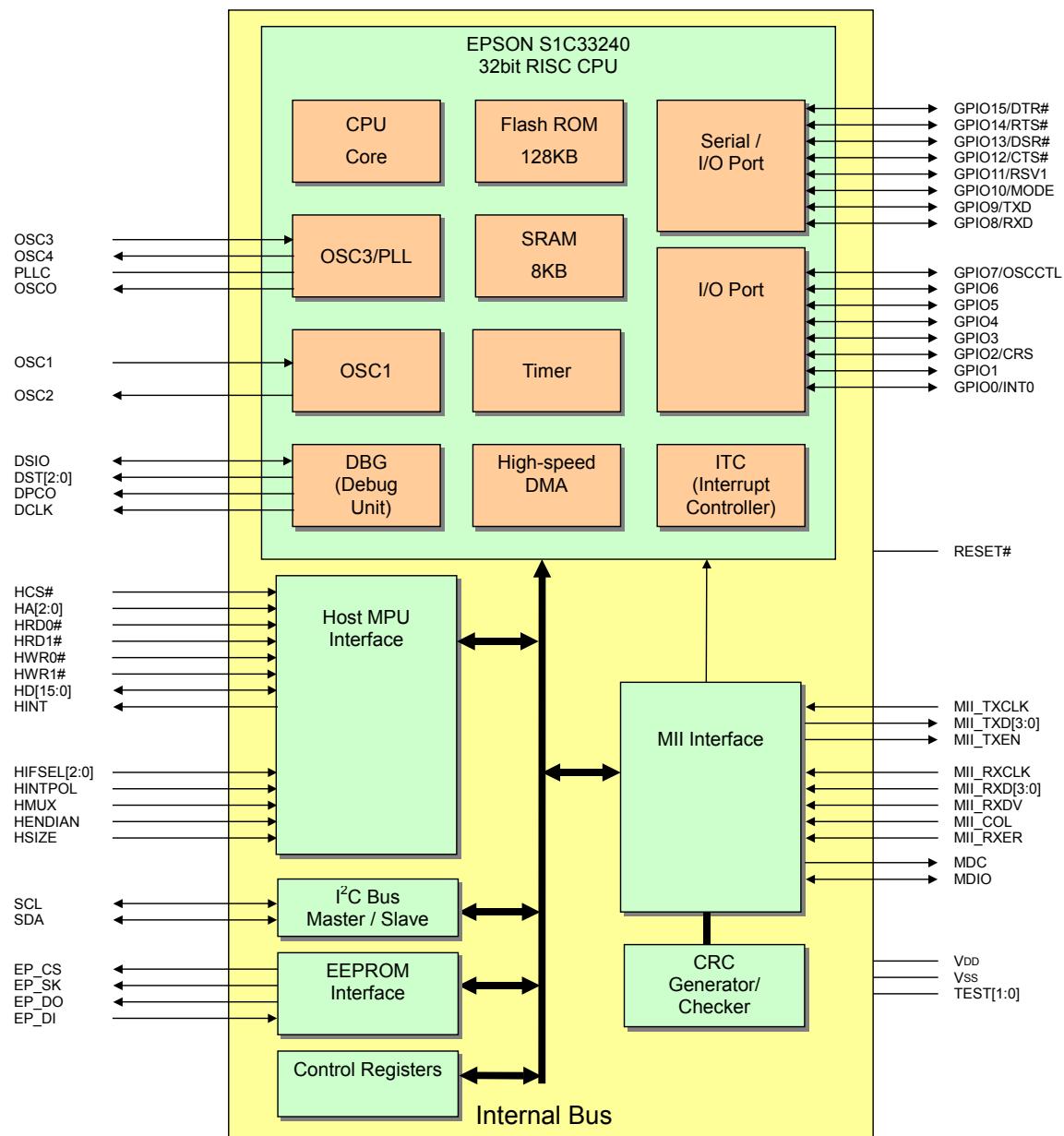

## 1.3 ブロック図

図 1.1 S1S60000 ブロック図

## 1.4 端子説明

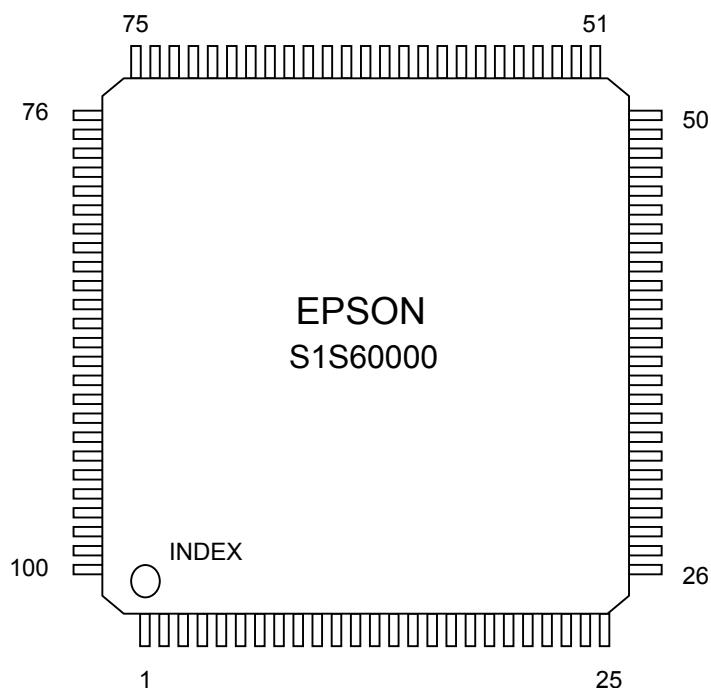

### 1.4.1 端子配置図

QFP15-100pin

| No. | 端子名          | No. | 端子名       | No. | 端子名   | No. | 端子名     |

|-----|--------------|-----|-----------|-----|-------|-----|---------|

| 1   | GPIO15/DTR#  | 26  | MII_COL   | 51  | HA2   | 76  | Reserve |

| 2   | GPIO14/RTS#  | 27  | MII_TXD3  | 52  | Vss   | 77  | Reserve |

| 3   | GPIO13/DSR#  | 28  | MII_TXD2  | 53  | HD0   | 78  | HIFSEL0 |

| 4   | GPIO12/CTS#  | 29  | MII_TXD1  | 54  | HD1   | 79  | VDD     |

| 5   | GPIO11/RSV1  | 30  | MII_TXD0  | 55  | HD2   | 80  | PLLC    |

| 6   | GPIO10/MODE  | 31  | MII_TXEN  | 56  | HD3   | 81  | TEST0   |

| 7   | GPIO9/TXD    | 32  | VDD       | 57  | HD4   | 82  | HIFSEL1 |

| 8   | GPIO8/RXD    | 33  | MII_TXCLK | 58  | HD5   | 83  | HIFSEL2 |

| 9   | Vss          | 34  | MII_RXER  | 59  | HD6   | 84  | HMUX    |

| 10  | GPIO7/OSCCTL | 35  | MII_RXCLK | 60  | HD7   | 85  | HINTPOL |

| 11  | GPIO6        | 36  | MII_RXDV  | 61  | VDD   | 86  | TEST1   |

| 12  | GPIO5        | 37  | MII_RXD0  | 62  | HD8   | 87  | OSC4    |

| 13  | GPIO4        | 38  | MII_RXD1  | 63  | HD9   | 88  | Vss     |

| 14  | GPIO3        | 39  | MII_RXD2  | 64  | HD10  | 89  | OSC3    |

| 15  | GPIO2/CRS    | 40  | MII_RXD3  | 65  | HD11  | 90  | VDD     |

| 16  | GPIO1        | 41  | MDC       | 66  | HD12  | 91  | RESET#  |

| 17  | GPIO0/INT0   | 42  | MDIO      | 67  | HD13  | 92  | HENDIAN |

| 18  | VDD          | 43  | OSC2      | 68  | HD14  | 93  | HSIZE   |

| 19  | EP_CS        | 44  | VDD       | 69  | HD15  | 94  | OSCO    |

| 20  | EP_SK        | 45  | VSS       | 70  | Vss   | 95  | DSIO    |

| 21  | EP_DI        | 46  | OSC1      | 71  | HRD0# | 96  | DST0    |

| 22  | EP_DO        | 47  | VDD       | 72  | HRD1# | 97  | DST1    |

| 23  | SCL          | 48  | HCS#      | 73  | HWR0# | 98  | DST2    |

| 24  | SDA          | 49  | HA0       | 74  | HWR1# | 99  | DPCO    |

| 25  | Vss          | 50  | HA1       | 75  | HINT  | 100 | DCLK    |

図 1.2 端子配置図

## 1. 概要

---

### 1.4.2 端子機能

以下に S1S60000 の端子を示します。信号名の “#” は負論理である事を示し、“[15:0]” 等の表記は複数の信号線をまとめた信号である事を示します。各端子の詳細特性は「Appendix B 端子特性一覧」を参照してください。

#### 1.4.2.1 電源系端子

表 1.1 電源系端子一覧

| 端子名 | 端子 No.               | I/O | 機能                                         |

|-----|----------------------|-----|--------------------------------------------|

| VDD | 18,32,44,47,61,79,90 | —   | 内部ロジック電源(+)電源端子です。必ず全ての端子に+3.3V を供給してください。 |

| Vss | 9,25,45,52,70,88     | —   | 電源(-) GND GND 端子。必ず全ての端子を GND に接続してください。   |

#### 1.4.2.2 ホストインターフェース信号

ホスト CPU と接続するためのインターフェースです。I/O を含む全ての入力端子にはプルアップ抵抗が内蔵され、HCS#, HA[2:0], HD[15:0], HRD0#, HRD1#, HWR0#, HWR1# は 5V 入力が可能です。出力は 3.3V CMOS 出力、または 3 ステート出力になります。

表 1.2 ホストインターフェース信号一覧

| 端子名         | 端子 No.              | I/O | 機能                                                                                                                                                                                                                                                                                            |

|-------------|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCS#        | 48                  | I   | Host Chip Select:<br>ホストインターフェース・アクセス制御信号です。この信号が LOW 状態の間、ホストインターフェースへのアクセスが可能になります。<br>この端子にはプルアップ抵抗が内蔵されています。5V 入力が可能です。                                                                                                                                                                   |

| HA[2:0]     | 51,50,49            | I   | Host Address:<br>ホストインターフェース・ポート選択信号です。HCS#=LOW の間アクセスするポートを選択します。選択されるポートは以下のとおりです。<br>LLx:コマンドポート(書き込み)/ステータスポート(読み出し)<br>Lhx:データポート(読み出し/書き込み)<br>Hxx:フラグポート(読み出し/書き込み)<br>この端子にはプルアップ抵抗が内蔵されています。5V 入力が可能です。<br>HA0 は 8bit インタフェース時に上位/下位バイトの切り替えに使用します。16bit インタフェース時には常に LOW 状態にしてください。 |

| HD[15:0]    | 69 ~ 62,<br>60 ~ 53 | I/O | Host Data:<br>ホストインターフェースのデータ信号線です。8 ビットインターフェース時には、HDATA[7:0]のみが有効で、HDATA[15:8]は駆動されません。<br>この端子にはプルアップ抵抗が内蔵されています。5V 入力が可能です。<br>出力は 3.3V CMOS 出力です。                                                                                                                                        |

| HRD0#       | 71                  | I   | Host Read/Host Write:<br>ホストインターフェースの R/W 制御信号です。HIFCR レジスタの HIFSEL[2:0]ビットの状態により機能が変更されます。詳細は「4 ホストインターフェース」の章を参照してください。<br>この端子にはプルアップ抵抗が内蔵されています。5V 入力が可能です。                                                                                                                               |

| HRD1#       | 72                  | I   |                                                                                                                                                                                                                                                                                               |

| HWR0#       | 73                  | I   |                                                                                                                                                                                                                                                                                               |

| HWR1#       | 74                  | I   | Host Interrupt:<br>S1S60000 からホストインターフェースに対する割り込み線です。割り込み要因はフラグポートの内容により判断してください。割り込みの極性はリセット時の HINTPOL 線状態により変更可能です。<br>この信号は 3.3V/3 ステート出力信号ですので、HINTPOL=L の場合にはプルアップ、HINTPOL=H の場合にはプルダウン抵抗を外部に接続してください。                                                                                   |

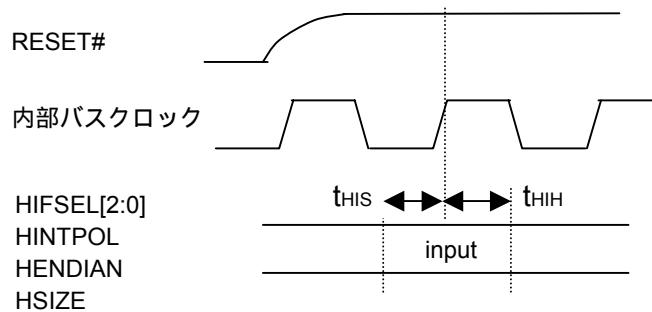

| HIFSEL[2:0] | 83,82,78            | I   |                                                                                                                                                                                                                                                                                               |

| 端子名     | 端子 No. | I/O | 機能                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HMUX    | 84     | I   | <p>Host Bus Multiplex<br/>ホストインターフェースのアドレスバスとデータバスが、時分割でマルチブレクスされているかどうかの設定を行ないます。マルチブレクスの場合、HA[2:0]の替わりにラッチされた HD[2:0]が使用されます。ラッチに使用する制御線は、HIFSEL で選択された CPU タイプにより異なります。</p> <p>L:Multiplex bus, H:Separate bus<br/>このピンは Rev.1.3 以前の仕様では未使用ピンだったため、何も接続されていない場合には分離バスタイプの設定となります。マルチブレクスバスを使用する場合のみ、このピンを GND に接続してください。リセット時に HIFCR レジスタにこのピンの状態が取り込まれます。この端子にはプルアップ抵抗が内蔵されています。</p> |

| HINTPOL | 85     | I   | <p>Host Interrupt Polarity Select:<br/>HINT のアクティブ時の極性設定端子です。<br/>L:LOW active, H:HIG active<br/>リセット時に HIFCR レジスタにこのピンの状態が取り込まれます。この端子にはプルアップ抵抗が内蔵されています。</p>                                                                                                                                                                                                                           |

| HENDIAN | 92     | I   | <p>Host Interface Endian Select:<br/>エンディアン設定端子です。使用的する CPU に応じて適切に設定することにより、コマンド/ステータスポート、データポート上の上位/下位データの入れ換えを行ないます。<br/>L:Little Endian, H:Big Endian<br/>リセット時に HIFCR レジスタにこのピンの状態が取り込まれます。この端子にはプルアップ抵抗が内蔵されています。</p>                                                                                                                                                              |

| HSIZE   | 93     | I   | <p>Host Bus Size Select:<br/>インターフェースサイズ設定端子です。ポートアクセス時のデータバス幅を指定します。<br/>L:16bit, H:8bit<br/>リセット時に HIFCR レジスタにこのピンの状態が取り込まれます。この端子にはプルアップ抵抗が内蔵されています。</p>                                                                                                                                                                                                                              |

#### 1.4.2.3 MII インタフェース信号

表 1.3 MII インタフェース信号一覧

| 端子名          | 端子 No.  | I/O | 機能                                                                                                                                       |

|--------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| MII_RXCLK    | 35      | I   | <p>MII Receive Clock:<br/>PHY チップからの受信クロック入力です。MII_RXD[3:0], MII_RXDV の基準となるクロックで、10Base-T の場合は 2.5MHz、100Base-TX の場合は 25MHz となります</p>   |

| MII_RXD[3:0] | 40 ~ 37 | I   | <p>MII Receive Data:<br/>PHY チップからの受信データ入力です。</p>                                                                                        |

| MII_RXDV     | 36      | I   | <p>MII Receive Data Valid:<br/>PHY チップからの入力信号で、MII_RXCLK の立ち上がり時に HIGH レベルの場合、MII_RXD[3:0]が有効であることを示します。</p>                             |

| MII_TXCLK    | 33      | I   | <p>MII Transmit Clock:<br/>PHY チップからの送信クロック入力です。MII_TXD[3:0], MII_TXEN の基準となるクロックで、10Base-T の場合は 2.5MHz、100Base-TX の場合は 25MHz となります。</p> |

| MII_TXD[3:0] | 27 ~ 30 | O   | <p>MII Transmit Data:<br/>PHY チップへの送信データ出力です</p>                                                                                         |

| MII_TXEN     | 31      | O   | <p>MII Transmit Enable:<br/>PHY チップへの出力信号で、MII_TXCLK の立ち上がり時に HIGH レベルの場合、MII_TXD[3:0]が有効であることを示します。</p>                                 |

| MII_RXER     | 34      | I   | <p>MII Receive Error:<br/>PHY チップからの入力信号で、受信データにエラーがあったことを示します。100Base-TX 時のみ有効で、10Base-T では無視されます。</p>                                  |

| MII_COL      | 26      | I   | <p>MII Collision Detect:<br/>半二重通信を行なっている場合、信号の衝突が発生したことを示します。</p>                                                                       |

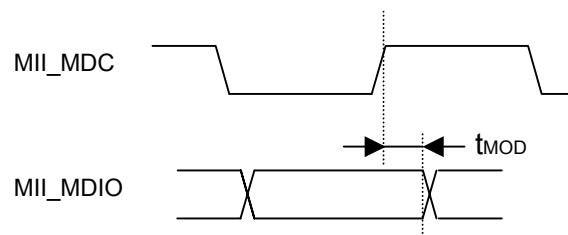

| MDC          | 41      | O   | <p>MII Management Interface Clock:<br/>PHY チップの機能設定、制御およびステータス読み出しのためのクロックです。S1S60000 からの出力で、このクロックに同期にして MDIO 端子でデータが送受信されます。</p>       |

## 1. 概要

---

| 端子名       | 端子 No. | I/O | 機能                                                                                                                                                                                                                  |

|-----------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIO      | 42     | I/O | MII Management Interface Data I/O<br>PHY チップの機能設定、制御およびステータス読み出しのためのデータです。PHY チップの機能設定、制御のためのデータは MDC に同期してこの端子から PHY チップに送られます。また PHY チップからステータスを読み出す場合は MDC に同期して PHY チップからのデータがこの端子から読み込まれます。<br>外部でプルアップしてください。 |

| GPIO2/CRS | 15     | I   | MII Carrier Sense<br>GPIO2 の別機能を選択した場合、CRS 入力端子となり、半二重通信を行なう場合キャリア状態を入力します。半二重通信を行なわない場合には使用しません。                                                                                                                   |

### 1.4.2.4 外部素子制御信号

表 1.4 外部素子制御端子

| 端子名   | 端子 No. | I/O  | 機能                                                                                                                                                                                |

|-------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EP_CS | 19     | O    | EEPROM Chip Select:<br>EEPROM のチップセレクト端子です。                                                                                                                                       |

| EP_SK | 20     | O    | EEPROM Serial Clock:<br>EEPROM のクロック端子です。                                                                                                                                         |

| EP_DI | 21     | I    | EEPROM Data In:<br>EEPROM のデータ入力端子です。                                                                                                                                             |

| EP_DO | 22     | O    | EEPROM Data Out:<br>EEPROM のデータ出力端子です。                                                                                                                                            |

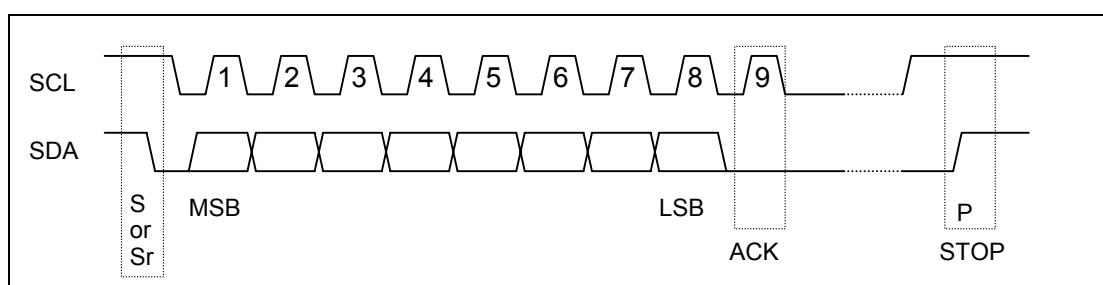

| SCL   | 23     | OD/I | I <sup>2</sup> C Serial Clock:<br>I <sup>2</sup> C バスシリアルクロック端子です。マスタ設定の場合には出力、スレーブ設定の場合は入力となります。<br>この端子はオープンドレイン出力のため、外部にプルアップ抵抗が必要です。プルアップ抵抗値はバス上の負荷、ノイズ環境により最適な値を選択する必要があります。 |

| SDA   | 24     | OD/I | I <sup>2</sup> C Serial Data:<br>I <sup>2</sup> C バスデータ入出力端子です。データ入出力、ACK 入出力のための双方向信号です。<br>この端子はオープンドレイン出力のため、外部にプルアップ抵抗が必要です。プルアップ抵抗値はバス上の負荷、ノイズ環境により最適な値を選択する必要があります。         |

### 1.4.2.5 汎用入出力端子

表 1.5 汎用入出力端子一覧

| 端子名          | 端子 No. | I/O | 機能                                                                                                                                                                                                                                       |

|--------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0/INT0   | 17     | I/O |                                                                                                                                                                                                                                          |

| GPIO1        | 16     | I/O |                                                                                                                                                                                                                                          |

| GPIO2/CRS    | 15     | I/O |                                                                                                                                                                                                                                          |

| GPIO3        | 14     | I/O |                                                                                                                                                                                                                                          |

| GPIO4        | 13     | I/O |                                                                                                                                                                                                                                          |

| GPIO5        | 12     | I/O |                                                                                                                                                                                                                                          |

| GPIO6        | 11     | I/O |                                                                                                                                                                                                                                          |

| GPIO7/OSCCTL | 10     | I/O | General Purpose I/O [7:0]:<br>汎用入出力端子です。5V 入力が可能です。<br>GPIO0 は割り込み端子として使用し、あらかじめ指定した宛て先に対して割り込み通知を送ることができます。GPIO2 は半二重通信を行なう場合の CRS 入力端子として使用します。GPIO7 はスリープモード時に OSC 制御端子として使用することができます。詳細は 5.3 章を参照してください。<br>ハードウェアリセット後は全て入力設定となります。 |

| GPIO8/RXD    | 8      | I/O |                                                                                                                                                                                                                                          |

| GPIO9/TXD    | 7      | I/O |                                                                                                                                                                                                                                          |

| GPIO10/MODE  | 6      | I/O |                                                                                                                                                                                                                                          |

| GPIO11/RSV1  | 5      | I/O |                                                                                                                                                                                                                                          |

| GPIO12/CTS#  | 4      | I/O |                                                                                                                                                                                                                                          |

| GPIO13/DSR#  | 3      | I/O |                                                                                                                                                                                                                                          |

| GPIO14/RTS#  | 2      | I/O |                                                                                                                                                                                                                                          |

| GPIO15/DTR#  | 1      | I/O | General Purpose I/O [15:8]:<br>汎用 I/O 入出力端子です。3.3V CMOS レベル専用で、シユミット入力です。GPALT レジスタの設定により、調歩同期シリアル端子となります。詳細は 2.3 章を参照してください。<br>ハードウェアリセット後は全て入力設定となります。                                                                                |

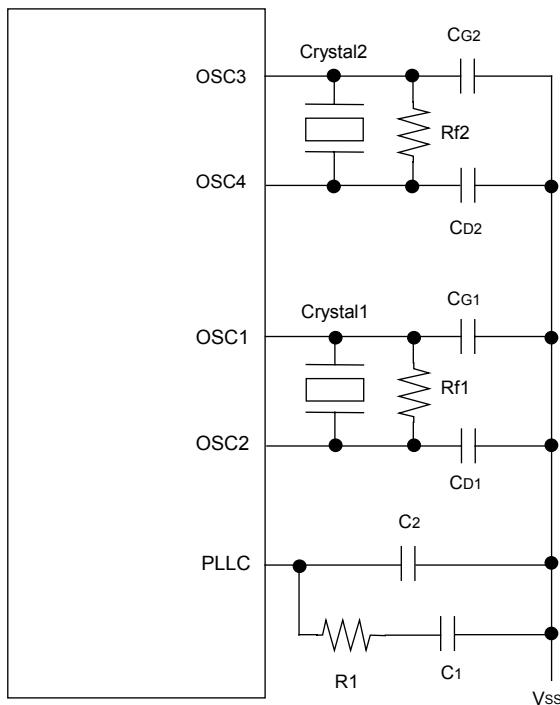

### 1.4.2.6 クロックジェネレータ端子

表 1.6 クロックジェネレータ端子一覧

| 端子名  | 端子 No. | I/O | 機能                                                                                                                                                                                                   |

|------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1 | 46     | I   | OSC1 クロック端子                                                                                                                                                                                          |

| OSC2 | 43     | O   | パワーマネジメントでスリープモードを使用する場合、32.768kHz の水晶を接続するために使用します。S1S60000 がスリープモードに入ると、このクロックで動作します。スリープモードを使用しない場合は、OSC1 を Vss に接続、OSC2 を開放してください。                                                               |

| OSC3 | 89     | I   | OSC3 クロック端子（水晶/セラミック発振、または外部クロック入力）                                                                                                                                                                  |

| OSC4 | 87     | O   | S1S60000 の動作クロック用発振端子です。10 ~ 25MHz の水晶振動子を接続します。外部からクロックを入力する場合は OSC3 に 10 ~ 25MHz のクロックを入力し、OSC4 は開放してください。<br>通常は 25MHz のクロックを使用してください。それ以外の周波数を使用した場合、100Base-TX での通信や、パワーセーブモードが使用できない場合があります。   |

| OSCO | 94     | O   | OSC 出力端子<br>OSC3 入力をバッファ出力する端子です。OSC3 入力と同じ周波数が本端子から出力されます。PHY チップにクロックを供給する場合、この端子から供給することで PHY 用の発振器を削減することができます。<br>【注意】本端子からクロックを供給する場合、PHY チップで必要な周波数精度を満足する水晶発振器を使用してください。通常は 50ppm 以下の精度とします。 |

| PLLC | 80     | —   | PLL 用コンデンサ接続端子<br>OSC3 周波数を内部 PLL で 2 適倍するためのコンデンサ接続端子です。必ず図 1.3 に示す R、C を接続してください。接続がされていない場合、本 IC は正常に動作しません。                                                                                      |

## 1. 概要

---

図 1.3 クロックジェネレータ接続図

|          |        |                           |

|----------|--------|---------------------------|

| Crystal1 | 水晶振動子  | 32.768kHz Ci (Max.) =34kΩ |

| CG1      | ゲート容量  | 10pF                      |

| Cd1      | ドレイン容量 | 10pF                      |

| Rf1      | 帰還抵抗   | 10MΩ                      |

| Crystal2 | 水晶振動子  | 25MHz                     |

| CG2      | ゲート容量  | 10pF                      |

| Cd2      | ドレイン容量 | 10pF                      |

| Rf2      | 帰還抵抗   | 1MΩ                       |

| R1       | 抵抗     | 4.7kΩ                     |

| C1       | コンデンサ  | 100pF                     |

| C2       | コンデンサ  | 5pF                       |

### 1.4.2.7 その他の端子

表 1.7 その他の端子

| 端子名         | 端子 No.   | I/O | 機能                                                                                                                  |

|-------------|----------|-----|---------------------------------------------------------------------------------------------------------------------|

| DSIO        | 95       | I/O | これらの端子はデバッグツールICD33との通信に使用します。ICD33は主にS1S60000のFlashメモリを書きかえる場合に使用します。                                              |

| DST[2:0]    | 98,97,96 | O   | 通常は何も接続しないで下さい。ただしノイズの多い環境で使用すると、DSIO端子のレベル変動によりICがデバッグ状態に入り、通常動作が停止する場合があります。その場合には外部に10kΩ以下の抵抗を付けてVDDにプルアップして下さい。 |

| DPCO        | 99       | O   |                                                                                                                     |

| DCLK        | 100      | O   |                                                                                                                     |

| RESET#      | 91       | I   | Hardware Reset Input:<br>LOWレベルを入力するとS1S60000がリセットされます。この端子にはプルアップ抵抗が内蔵されています。                                      |

| TEST1,TEST0 | 86,81    | I   | Test Input:<br>本ICのテスト用端子です。通常動作時は開放にして下さい。この端子にはプルダウン抵抗が内蔵されています。                                                  |

| Reserve     | 77,76    | —   | 将来の拡張用に予約されています。通常は何も接続しないで下さい。                                                                                     |

## 2. ハードウェア仕様

### 2.1 コア CPU

コア CPU にはセイコーホームオーディオの 32 ビットマイクロコンピュータ S1C33240 相当品を使用しています。ただし、ADC は内蔵していません。

CPU 動作クロックは常に内部バスクロックと同じで、初期設定後は OSC3 入力の 2 倍のクロックとなります。GENCR レジスタの PSEN ビット (bit11) を設定した場合には通常動作時の 1/4 クロックとなり、消費電流を削減します。

内部では Little Endian により処理が行なわれます。

#### 2.1.1 ROM とポートアドレス

S1S60000 は 128K バイトのフラッシュ ROM を内蔵しています。リセット後、Flash ROM 領域であるエリア 10 のアドレス 0x0C000000 から起動します。128K バイトのうち、127K バイトはシステムファームウェア領域、1K バイトはユーザ使用可能領域です。ユーザ使用可能領域は 0xC1FC00 から 0xC1FFFF となります。

システムファームウェア領域の書き換えにはデバッグシリアル端子、またはネットワークを使用して行ないます。書き換えには専用ツール、プログラムを使用します。

ユーザ使用可能領域の書き換えにはデバッグシリアル端子、またはホストインターフェースを使用し、ホストインターフェース・コマンドにより行ないますので、絶対アドレス指定は不要です。なお、この領域はデータ領域としてのみ使用可能です。プログラムを置いて実行させることはできません。

#### 2.1.2 RAM

S1S60000 は 8K バイトの RAM を内蔵しています。内蔵 RAM のデバイスサイズは 32 ビットで、バイト、ハーフワード、ワードデータが 1 サイクルで読み出し/書き込み可能です。この RAM は全て S1S60000 内部で使用しているため、ユーザが操作することはできません。

### 2.2 周辺回路

S1S60000 では内蔵コア CPU である S1C33240 の周辺ブロックのうち、以下の内蔵周辺回路を使用しています。各周辺回路の詳細については、“S1C33 Family ASIC Macro Manual”を参照してください。

- C33 コアブロック

- CPU 32 ビット RISC 型 CPU S1C33000

- BCU バスコントロールユニット

- ITC 割り込みコントローラ

- CLG クロックジェネレータ

- DBG ICD33(In-Circuit Debugger for S1C33 Family)によるデバッグ用機能ブロック

- C33 周辺回路ブロック

- プリスケーラ 周辺回路用クロックをプログラマブルに設定可能

- 16 ビットプログラマブルタイマ

- シリアルインターフェース

- 入出力ポート

- 計時タイマ

- C33DMA ブロック

- HSDMA(高速 DMA) 4 チャネル

S1S60000 の内蔵 I/O メモリマップは S1C33240 のメモリマップに準じます。詳細は「S1C33240 テクニカルマニュアル」を参照してください。

## 2. ハードウェア仕様

### 2.3 シリアルインタフェース

GPIO[15:8]は、以下の2つの条件を満たす場合に、シリアルインタフェース端子となります。

- GPALT レジスタ bit[15:8]=FFh

- GENCR レジスタ bit[10:8] ( SERCONF ) = “000” or “010” or “011”

その場合には、SERCONF 設定と GPIO10 端子 ( MODE 端子 ) の状態により、動作モードが切り替わります。表 2.1 に設定と、動作モードの関係を示します。

表 2.1 シリアルインタフェース動作モード設定

| GPALT[15:8] | SERCONF[2:0] | MODE | モード                           | 通信条件   |

|-------------|--------------|------|-------------------------------|--------|

| FFh         | 000          | —    | ハードウェア制御モード                   | 固定(*1) |

|             | 010          | HIGH | ハードウェア制御モード                   | 固定(*1) |

|             |              | LOW  | シリアルエミュレーションモード(Active Open)  | 可変(*2) |

|             | 011          | HIGH | ハードウェア制御モード                   | 固定(*1) |

|             |              | LOW  | シリアルエミュレーションモード(Passive Open) | 可変(*2) |

|             | 上記以外         | —    | 予約状態。設定しないでください。              | —      |

| 00h         | —            | —    | GPIO[15:8]として使用               | —      |

| 上記以外        | —            | —    | 無効。いずれの動作も行なわれません。            | —      |

\*1: 調歩同期シリアル、9600baud,8bit data,1Stop bit,No parity,No flow control

\*2: SERMODE レジスタで設定:

**【注意】各モードの切り換え後、100ms はシリアルインタフェースに対するアクセスは行なわないでください。**

#### 2.3.1 ハードウェア制御モード

表 2.1 で「ハードウェア制御モード」に設定された場合、シリアルインタフェースはハードウェア制御モードで動作します。このモードを使用することにより、シリアルインタフェースから各種ハードウェア ( EEPROM / I<sup>2</sup>C / GPIO ) の状態変更や確認が行なえます。ホスト CPU を接続しない状態で EEPROM の設定を変更する場合や、シリアルインタフェースから GPIO の状態を確認したい場合などに、このモードを使用してください。

ハードウェア制御モードに設定されると、通信条件は以下に固定されます。

調歩同期シリアル、9600Baud、8 ビットデータ、1STOP ビット、パリティなし、フロー制御なし

このモードの詳細については 5.1.4 章を参照してください。

#### 2.3.2 シリアルエミュレーションモード

表 2.1 で「シリアルエミュレーションモード」に設定された場合、シリアルインタフェースはシリアルエミュレーションモードで動作します。このモードでは、シリアルインタフェースの送受信データは、ネットワーク上の接続相手との間で送受信されます。[ RS232 Ethernet コンバート機能 ] 従来の RS232 インタフェースを持つ機器のデータを、イーサネット上の他の機器に対して送受信する場合に特に有効です。接続は TCP/IP で行なわれます。RTS/CTS 制御を有効にすることで、フロー制御をすることも可能です。通信条件は SERMODE レジスタにより設定されます。

##### 【コネクションの確立】

S1S60000 は、GPIO[15:8]をシリアルエミュレーションモードに設定した場合、ホストインターフェースから System Open コマンドと TCP Open コマンドを送ったと同等の処理を自動的に行ないます。System Open 時のパラメータには SOPAR レジスタの内容が使用されます。また TCP Open 時、SERCONF(bit[10:8])=010 の場合は Active Open, 011 の場合は Passive Open 処理が行なわれます。

Active Open ( クライアント動作 ) の場合、EEPROM にあらかじめ設定された接続相手先の IP アドレス ( DADROH,DADR0L レジスタにより設定 ) ポート ( PORT レジスタにより設定 ) に対して接続要求を行なって接続を確立します。その後相手先によりコネクションが切断された場合、自動的に再接続が行なわれます。

Passive Open ( サーバー動作 ) の場合、あらかじめ設定された自らの通信ポート ( PORT レジスタにより設定 ) をオープンして接続待ち ( リスン状態 ) になります。外部から接続要求があった場合、コネクションが確立します。

**【シリアルインタフェースからネットワークへの送信】**

シリアルインタフェースから受信されたシリアルデータは、最後の受信データを受け取ってから 100 データ転送時間の間受信データがなかった場合、または 1 パケット分 (536 バイト) のデータを受け取った時点でネットワークに対して出力されます。

**【ネットワークからシリアルインタフェースへの送信】**

ネットワークから受け取ったデータは、S1S60000 内部でエラーチェック、ヘッダ情報の除去が行なわれた後、データ部のみがシリアルインタフェースに送信されます。

各端子の機能は表 2.2 のとおりとなります。

表 2.2 調歩同期シリアル設定時の端子機能

| 端子     | Pin | 名称   | In/Out | 機能                                                                                                                                                                                    |

|--------|-----|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO15 | 1   | DTR# | O      | Data Terminal Ready<br>受信可能状態の表示。LOW アクティブ信号です。シリアルエミュレーションモード時、初期化が終了すると LOW 状態となります。ハードウェア制御モードでは常に HIGH 状態です。                                                                      |

| GPIO14 | 2   | RTS# | O      | Request to Send<br>送信可能状態の表示。LOW アクティブ信号です。シリアルエミュレーションモード時、受信可能な時に LOW 状態となります。ハードウェア制御モードでは常に LOW 状態です。                                                                             |

| GPIO13 | 3   | DSR# | I      | Data Set Ready<br>外部からの送信可能状態入力。現在は未使用です。                                                                                                                                             |

| GPIO12 | 4   | CTS# | I      | Clear to Send<br>外部からの受信可能状態入力。LOW アクティブ信号です。この端子が HIGH 状態の時には送信を一時的に停止し、LOW 状態になると送信を再開します。制御は割り込みによるソフトウェア制御によるため、信号変化後の送信停止/再開までの時間は不定です。したがって外部デバイス側はある程度バッファ容量に余裕のある時点で制御してください。 |

| GPIO11 | 5   | —    | —      | —                                                                                                                                                                                     |

| GPIO10 | 6   | MODE | I      | Mode Select<br>通常モード/ハードウェア制御モードの切り換えを行ないます。シリアルエミュレーションモードでは LOW にしてください。                                                                                                            |

| GPIO9  | 7   | TXD  | O      | Transmit Data<br>シリアル送信データ                                                                                                                                                            |

| GPIO8  | 8   | RXD  | I      | Receive Data<br>シリアル受信データ                                                                                                                                                             |

TXD、RXD は調歩同期シリアル送受信端子となり、内蔵 S1C33240 のシリアルインタフェース Ch.0 の機能により送受信されます。詳細機能は S1C33240 テクニカルマニュアルのシリアルインタフェース仕様を参照してください。それ以外の制御線はソフトウェアにより制御されます。CTS#信号は内部割込みにより処理されます。

## 2.4 電源

### 2.4.1 動作電圧

S1S60000 は VDD ~ Vss 間に供給される電源電圧によって動作します。この動作電圧は次のとおりです。

$$VDD = 3.3 \pm 0.3V (Vss = GND)$$

**【注意】** S1S60000 は 7 本の VDD 端子と 6 本の Vss 端子を持っています。これらすべての端子を電源に接続し、開放しないでください。

## 2. ハードウェア仕様

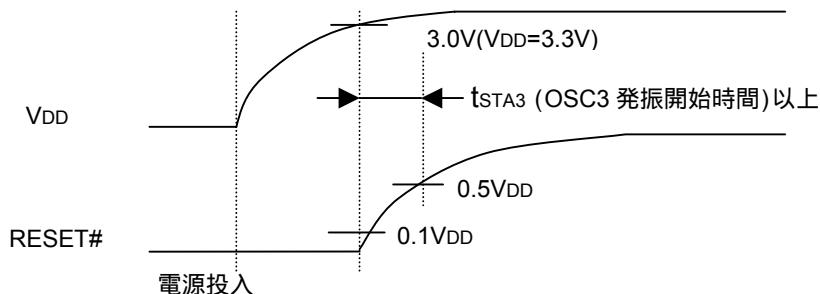

### 2.5 パワーオンリセット

電源投入時は、確実に動作を開始させるため、必ずイニシャルリセットを行なってください。RESET#端子はシュミット入力です。

イニシャルリセット( RESET#=LOW )により OSC3 発振回路が発振を開始し、リセット信号の立ち上がりで CPU が OSC3 クロックにより動作を開始します。OSC3 発振回路は動作開始後に発振が安定するまでの時間 ( VDD=3V 、標準動作条件の発振安定時間 : Max . 10ms ) を要しますので、CPU を確実に起動させるには、この発振安定時間が経過後にイニシャルリセットを解除することが必要です。イニシャルリセットパルス幅は発振安定時間を超えるように決定してください。

図 2.1 にパワーオンリセット時のタイミングチャートを示します

図 2.1 パワーオンリセットタイミング

電源投入後、電源電圧が発振開始電圧 ( 3.0V ) 以上になるまでは、RESET#端子を 0.1 · VDD 以下 ( LOW レベル ) としてください。また、OSC3 発振回路の発振が安定するまで、RESET#端子を 0.5 · VDD 以下のレベルとしておくことが必要です。

**【注意】** OSC3 発振回路の発振開始時間は使用する素子や基板パターンおよび動作環境により変化しますので、リセット解除時間には十分な余裕を取ってください。

#### ・リセットパルス

S1S60000 が動作中は、RESET#端子に LOW レベルのパルスを入力してイニシャルリセットを行なうことが可能ですが、ただし、“ AC 特性 ” に記載の最小リセットパルス幅以上のパルスを入力してください。また、OSC3 発振回路が停止中にリセットパルスを入力する場合は、パワーオンリセットと同様に発振安定時間以上 RESET#端子を LOW レベルに設定する必要があります。

#### ・リセット動作の確認

正常にリセットが行なわれ、S1S60000 のハードウェアが動作を始めた場合、EEPROM の接続確認のため EP\_SK,EP\_CS 信号が変化します。また、S1S60000 のソフトウェアが動作を開始した場合、PHY チップの接続確認のため、MII\_MDC,MII\_MDIO 信号が変化します。これらの信号が変化しない場合、電源、OSC3 クロック、RESET#端子状態、PLLC 端子設定などを確認してください。

ファームウェアによる初期化が完了すると、ホストインターフェースから BOOT ステータス ( 000Bh ) が読み出せます。( ただし、端子 HIFSEL[2:0]= “ 111 ” で、かつ HIFCR レジスタの HIFSEL[2:0]= “ 111 ” の場合を除きます。この設定の場合、「ホストインターフェース未接続」と解釈されます。)

### 2.6 OSC3 クロック

OSC3 端子には S1S60000 の動作用のクロックを入力します。内部バスクロックと CPU 動作クロックは、OSC3 から入力されたクロックを 2 倍したクロックが使用されます。通常は 25MHz クロックを入力してください。入力可能な最低周波数は 10MHz です。

パワーセーブモード時、内部バスクロックと CPU 動作クロックは通常の 1/4 ( OSC3 入力の 1/2 ) となります。

100Base-TX で動作させる場合には、必ず OSC3 に 25MHz を入力し、常に Normal モードで動作させてください。パワーセーブモードでは動作しません。

## 3. ネットワークインターフェース

### 3.1 MII インタフェース

S1S60000 は物理層 (PHY チップ) との間に MII (Media Independent Interface) を使用しており、MII に対応した各種のネットワーク PHY チップと接続が可能です。MII の詳細については IEEE 802.3 Clause22 (IEEE 802.3u) を参照してください。ただし、以下の点で注意が必要です。

- CRS(Carrier Sense) 信号

この信号は全二重通信設定の場合には使用されません。半二重通信を行なう場合のみ GPIO2 端子に CRS 信号を接続してください。また、PHY を強制的に半二重通信に設定する場合には GENCR の設定を半二重設定にしてください。

- TX\_ER 信号

この信号は RX\_ER で受け取ったエラー状態を伝播するために使用しますが、S1S60000 は中継機能は持たないため使用しません。

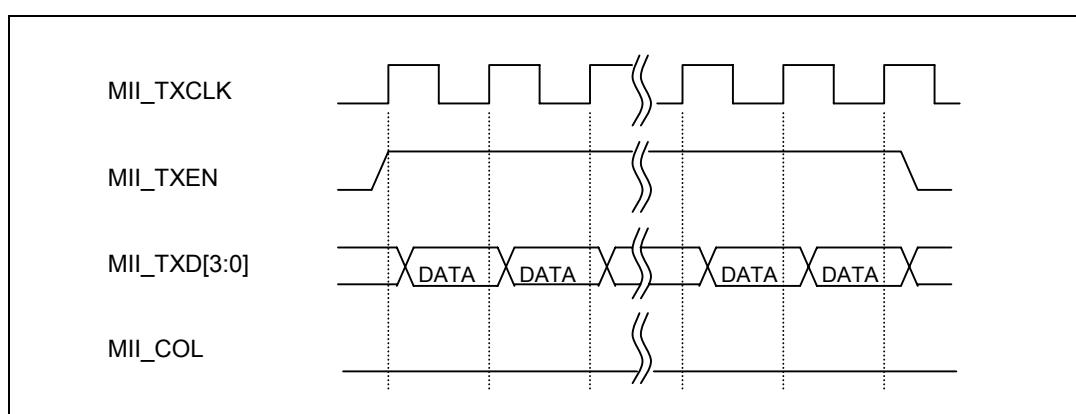

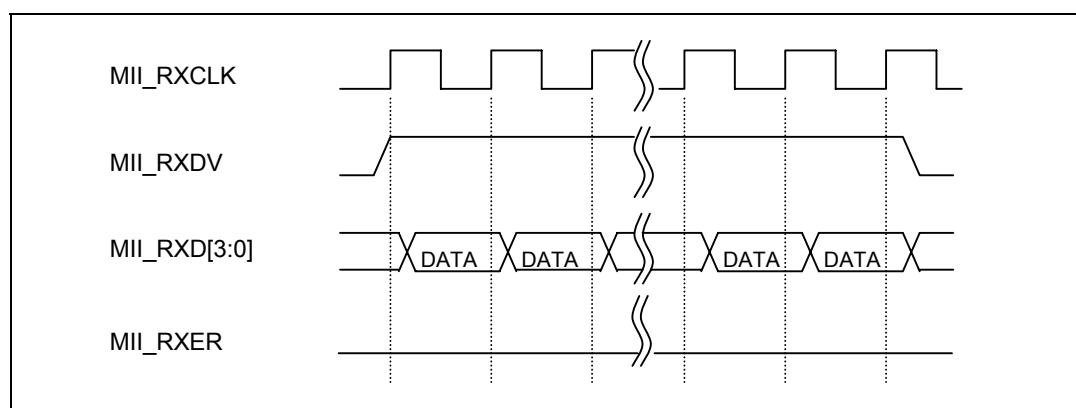

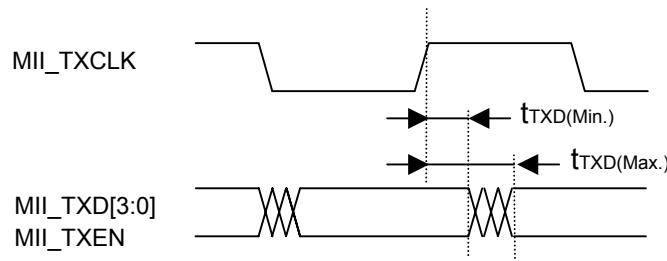

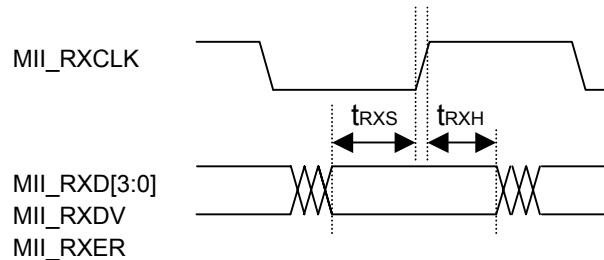

図 3.1 に MII 送信波形を、図 3.2 に MII 受信波形を示します。

送信時は MII\_TXEN を HIGH レベルにした後、MII\_RXCLK の立ち上がり後に MII\_TXD を変化させます。半二重通信時に MII\_COL が HIGH レベルになると S1S60000 内部では割り込みが発生し、MII\_TXEN を LOW レベルに落として送信を中断し、一定時間待ってから再送を行ないます。

受信時は、MII\_RXDV が HIGH レベルになった後の MII\_RXCLK の立ち上がりで MII\_RXD が取り込まれます。100Base-TX 通信中に MII\_RXER が HIGH レベルになると、受信終了後に FCS エラーがセットされ、受信したフレームは廃棄されます。

図 3.1 MII 送信波形

図 3.2 MII 受信波形

### 3. ネットワークインターフェース

### 3.2 マネジメントインターフェース

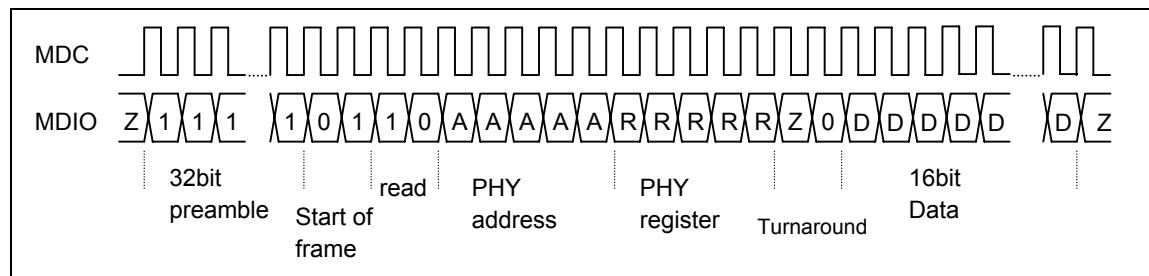

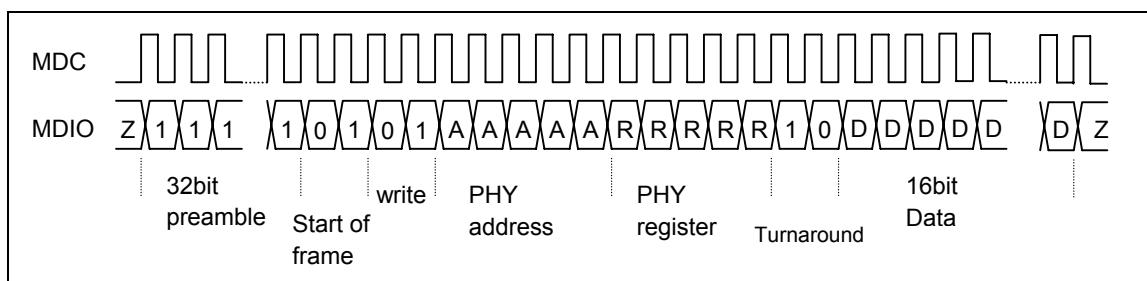

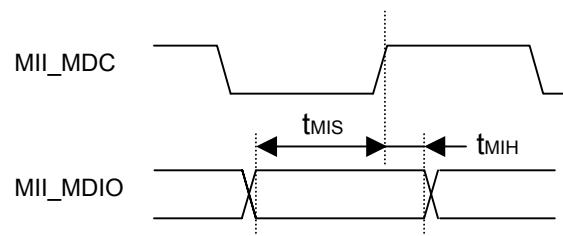

S1S60000 は MII マネジメントインターフェースに対応しており、このインターフェースを通じて PHY 内のレジスタを R/W できます。図 3.3 に読み出し時の波形を、図 3.4 に書き込み時の波形を示します。

図 3.3 MII マネジメントインターフェース読み出し動作

図 3.4 MII マネジメントインターフェース書き込み動作

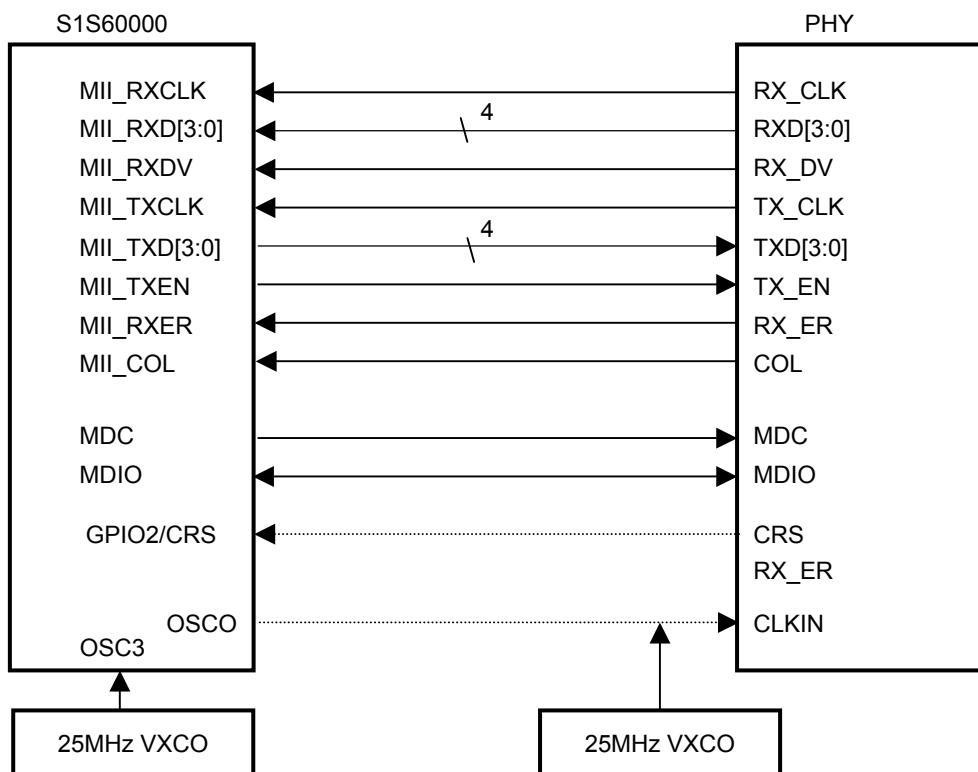

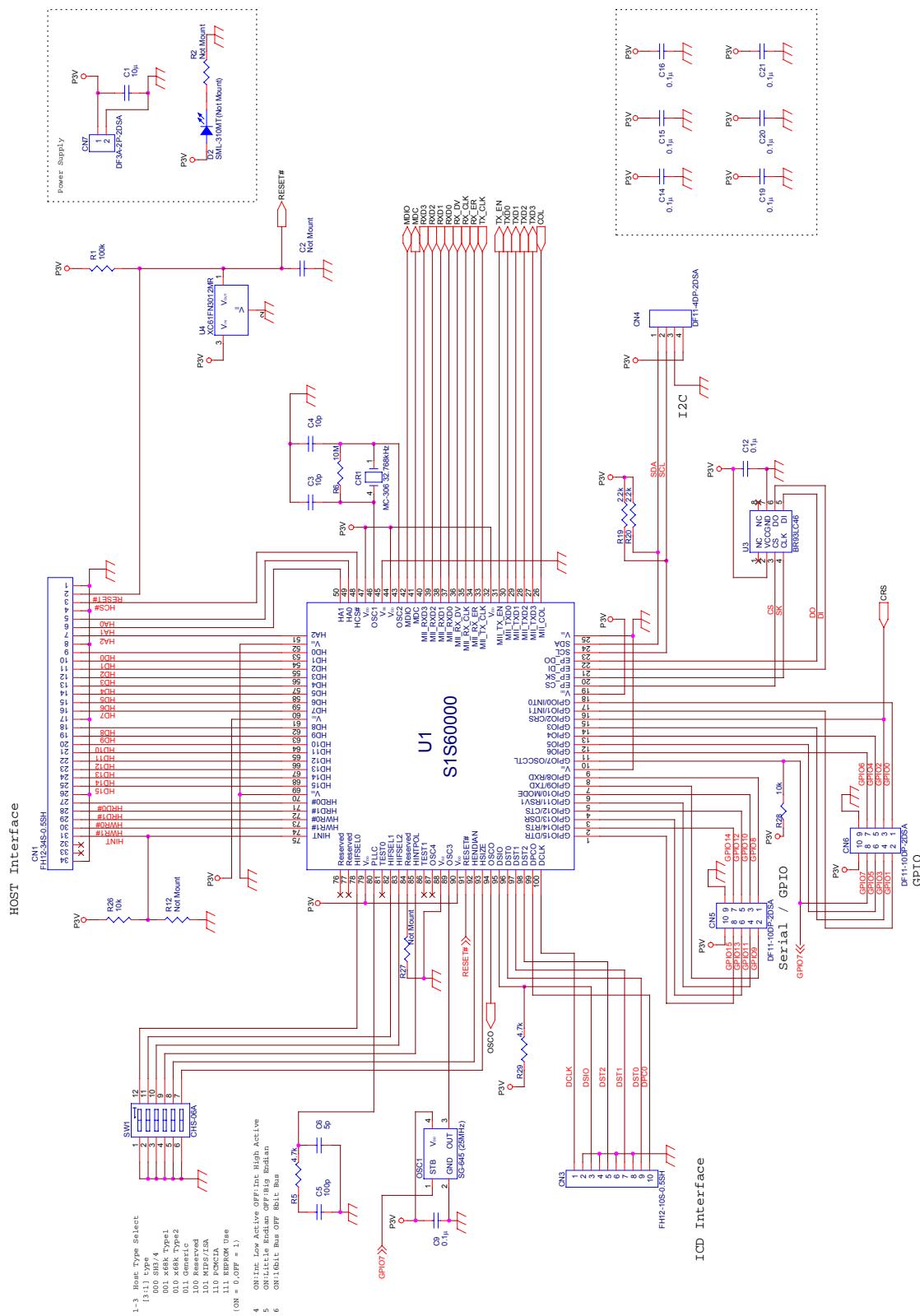

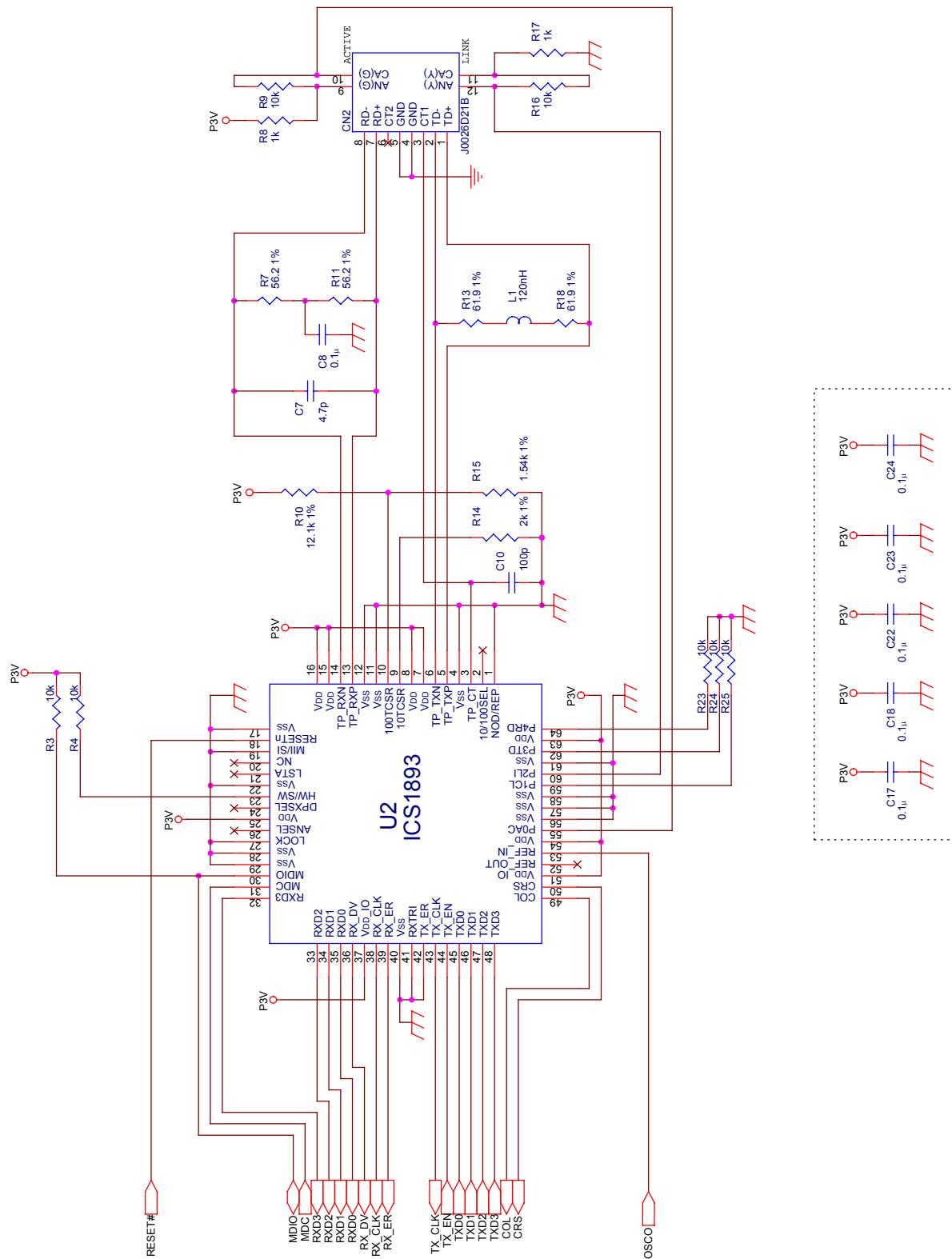

### 3.3 PHY チップとの接続

S1S60000 と PHY チップとの接続は、図 3.5 のように行ないます。

CRS は全二重通信のみを行なう場合には接続する必要はありません。また、TX\_ER 信号は接続しません。

**【重要】**PHY チップのアドレスは必ず 0x01 になるように設定してください。他の設定を行なった場合の動作は保証されません。

S1S60000 の OSCO 端子からは、通常動作時とパワーセーブモード時は OSC3 入力をバッファリングした信号が出力されています。したがって OSC3 入力に 25MHz の水晶発振器を接続し、OSCO を PHY のクロック入力に接続することで、1 つの水晶発振器で S1S60000 と PHY の両方を動作させることができます。

**【注意】** OSCO から PHY へクロック供給する場合には、PHY の要求するクロック精度を満たす事を確認してください。また、接続パターン長は最短とし、クロック波形が PHY の仕様を満たす事を確認してください。

ファームウェア Version 1, Revision 22 ( 製品型番 : S1S60000F00A500, IC マーキング S1S60000F00A5 ) 以降の製品の場合、以下に述べる ANEGR レジスタの設定は必要ありません。設定値は無視されます。Revision 22 より前の製品をお使いの場合には、以下を参考に ANEGR の設定を行ってください。( Realtek 社 RTL8201L は Version 1, Revision 22 以降のファームウェアで使用できます。)

使用する PHY チップが決まつたら、そのデータシートからオートネゴシエーションの結果、リンクが確立したスピード(100Base/10Base)モード(全二重/半二重)を示すビットの情報を取得し、それが ANEGR レジスタに反映されるようにしてください。

・ ANEGR レジスタ値の取得方法

- (1) オートネゴシエーションの結果が格納されるレジスタを探します。通常は 16 ~ 19, または 24, 25 にあります。

- (2) レジスタのオフセットから 16 を引いた値を、LSOFF ビットにセットします。

- (3) 結果の格納方法により、DINV, SINV をセットします。

- (4) 結果の格納ビット位置により、DUPLEX, SPEED の各ビットを設定します。

S1S60000 との接続で推奨する PHY は以下のものです。

| メーカー名 | 型番          | ANEGR 値 |

|-------|-------------|---------|

| ICS   | ICS1893Y-10 | 10EFh   |

| TDK   | 78Q2120-64T | 20BAh   |

図 3.5 PHY との結線図

### 3.4 通信モード

S1S60000 を使用する場合、通常は 10Base-T/全二重設定でご使用ください。S1S60000 は 100Base-TX/全二重通信には対応しておりません。

PHY チップのオートネゴシエーション機能を使用して通信モードを決定する場合、S1S60000 は 100Base-TX/半二重、10Base-T/全二重、10Base-T/半二重の順でオートネゴシエーションを行ない、最初にリンクが確立したモードで通信を行ないます。

PHYMODE レジスタの設定により、リンクする条件を限定することも可能です。

#### 通信モードの設定フロー

- (1) 100Base-TX/Half-Duplex でオートネゴシエーションを実行し、成功すれば 100Base-TX/Half-Duplex で決定。終了。それ以外は次へ。

- (2) 10Base-T/Full-Duplex でオートネゴシエーションを実行し、成功すれば 10Base-T/Full-Duplex で決定。終了。それ以外は次へ。

- (3) 10Base-T/Half-Duplex でオートネゴシエーションを実行し、成功すれば 10Base-T/Half-Duplex で決定。終了。(オートネゴシエーションに対応していない場合でも、この状態ではリンクすることが規定されているため、接続が正しければここでリンクする。)

- (4) 上記のいずれも成功しなかった場合、Link が不成立と判断する。

## 4. ホストインターフェース

### 4. ホストインターフェース

ホストインターフェースは、S1S60000 を外部の CPU と接続するためのインターフェースであり、8 ビット、または 16 ビットのパラレルインターフェースです。ホストインターフェースは設定により、6 タイプの CPU を直接接続できます。

#### 4.1 制御信号

表 4.1 にホストインターフェース信号を示します。I/O を含む全ての入力端子にはプルアップ抵抗が内蔵され、HCS#, HA[2:0], HD[15:0], HRD0#, HRD1#, HWR0#, HWR1# は 5V 入力が可能です。出力は 3.3V CMOS 出力、または 3 ステート出力になります。ホストインターフェースを使用しない場合（例：単独で GPIO 制御のみを行なう場合）などは、ホストインターフェースの全ての信号を未接続としてください。

表 4.1 ホストインターフェース信号

| 端子名         | I/O | 機能                                                                  |

|-------------|-----|---------------------------------------------------------------------|

| HCS#        | I   | アクセス有効信号。LOW 状態でアクセス可能。                                             |

| HA[2:0]     | I   | ポート選択信号                                                             |

| HD[15:0]    | I/O | 入出力データバス                                                            |

| HRD0#       | I   | R/W 制御信号。HIFSEL[2:0] の状態により機能変化                                     |

| HRD1#       | I   | R/W 制御信号。HIFSEL[2:0] の状態により機能変化                                     |

| HWR0#       | I   | R/W 制御信号。HIFSEL[2:0] の状態により機能変化                                     |

| HWR1#       | I   | R/W 制御信号。HIFSEL[2:0] の状態により機能変化                                     |

| HINT        | Tri | 割込み信号。極性設定可能                                                        |

| HIFSEL[2:0] | I   | ホストインターフェース種別設定信号                                                   |

| HMUX        | I   | ホストインターフェース・バスマルチプレクス（リセット時のみ有効）<br>L:Multiplex bus, H:Separate bus |

| HINTPOL     | I   | ホスト割り込み線極性設定（リセット時のみ有効）<br>L:LOW active, H:HIGH active              |

| HENDIAN     | I   | ホストインターフェース・エンディアン設定（リセット時のみ有効）<br>L:Little Endian, H:Big Endian    |

| HSIZE       | I   | ホストインターフェースサイズ設定（リセット時のみ有効）<br>L:16bit, H:8bit                      |

Tri: 3 ステート出力

HCS#が LOW 時の HA[2:0] の状態により、アクセスポートが選択されます。ポート割り当ては以下のとおりです。

##### (1) 16 ビットインターフェース設定時

| HA[2:0] | 選択ポート                         |

|---------|-------------------------------|

| LLL     | コマンドポート（Write）/ステータスポート（Read） |

| LHL     | データポート                        |

| HxL     | フラグポート                        |

注) フラグポートアクセス時、上位 8 ビットと下位 8 ビットには同じ内容が出力されます

##### (2) 8 ビットインターフェース設定時

| HA[2:0] | 選択ポート                             |

|---------|-----------------------------------|

| LLL     | コマンド下位ポート（Write）/ステータス下位ポート（Read） |

| LLH     | コマンド上位ポート（Write）/ステータス上位ポート（Read） |

| LHL     | データ下位ポート                          |

| LHH     | データ上位ポート                          |

| Hxx     | フラグポート                            |

注) 8 ビットインターフェース時には上位、下位の両ポートのアクセスを行なった時点でのデータ転送が終了します。上位、下位のアクセス順は任意です。フラグポートには上位/下位はありません。

## 4.2 ホストインターフェースポート

### 4.2.1 コマンドポート

ホスト CPU から S1S60000 に対してコマンドを送るポートです。このポートは 16 ビット幅のため、8 ビットインターフェースの場合には上位アドレスと下位アドレスの 2 回のアクセスが必要です。コマンド内容の詳細は「S1S60000 シリーズ ホストインターフェース仕様書」を参照してください。

### 4.2.2 ステータスポート

S1S60000 からホスト CPU に対してステータスを返すポートです。このポートは 16 ビット幅のため、8 ビットインターフェースの場合には上位アドレスと下位アドレスの 2 回のアクセスが必要です。ステータス内容の詳細は「S1S60000 シリーズ ホストインターフェース仕様書」を参照してください。

### 4.2.3 データポート

ホスト CPU と S1S60000 間でデータを送受信するポートです。このポートは 16 ビット幅のため、8 ビットインターフェースの場合には上位アドレスと下位アドレスの 2 回のアクセスが必要です。コマンドやステータスに付随するオプション部もこのポートを使用して送受信されます。オプションの内容の詳細は「S1S60000 シリーズ ホストインターフェース仕様書」を参照してください。

ホスト CPU からデータポートへ書き込みを行なう場合、SEND コマンドに対し、WRITE ステータスが返されてから書き込みを行ないます。そのさい、書き込みごとにフラグポートの HSTREN(bit4)および H2CDV/H2CDC(bit3)の状態を確認して書き込むようにしてください。

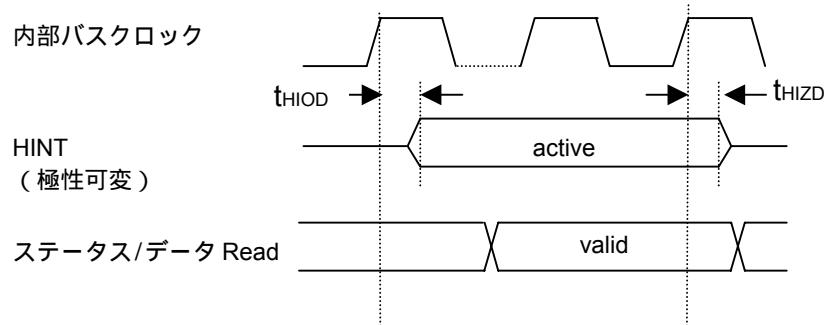

### 4.2.4 フラグポート

ホストインターフェース上のコマンド、ステータス、データの処理状態を示すポートです。

bit[1:0]の状態が HINT 信号のアクティブ要因となり、いずれかのビットが 1 の場合 HINT 信号がアクティブ状態となります（信号極性は変更可能です）。ホスト側ではステータスやデータの読み出しを行なうと、対応する要因がクリアされ、全ての要因がなくなった場合に HINT 信号は非アクティブとなります。またホスト側から S1S60000 内部のデータ処理状態を調べる場合は、bit[3:2]の状態で判断します。このポートは 8 ビット幅のため、16 ビットインターフェースの場合、または 8 ビットインターフェースで上位アドレスと下位アドレス 2 回のアクセスを行なった場合には、上位と下位には同じデータが読み出されます。

## 4. ホストインターフェース

---

表 4.2 フラグポートビット割り当て

| bit | 解説                                                                     |

|-----|------------------------------------------------------------------------|

| 7:5 | 未使用。値は0                                                                |

| 4   | HSTREN データポート受信回路状態(R/O)<br>0: データポート受信回路が無効である<br>1: データポート受信回路が有効である |

| 3   | H2CDV 書き込みデータ処理状態(R/O)<br>0: データ書き込み可能<br>1: データ読み出し待ち                 |

| 2   | H2CCV コマンド処理状態(R/O)<br>0: コマンド書き込み可能<br>1: コマンド処理待ち                    |

| 1   | C2HDV 読み出しデータ準備状態(R/O)<br>0: 読み出しデータなし<br>1: 読み出しデータあり(読み出いでクリア)       |

| 0   | C2HSV ステータス準備状態(R/O)<br>0: 読み出시스テータスなし<br>1: 読み出ysisテータスあり(読み出いでクリア)   |

注: ホストインターフェースが 16 ビット幅の場合、bit[15:8]には bit[7:0]と同じ内容が出力されます。

書き込みは bit[7:0]側への書き込みのみが有効です。

### 4.3 ホストインターフェースタイプ

ハードウェアリセット時の HIFSEL[2:0]端子状態、および EEPROM 内 HIFCR データによりホストインターフェースタイプが選択されます。ホストインターフェースタイプの割り当ては表 4.3 のとおりです

表 4.3 ホストインターフェースタイプ

| HIFSEL[2:0] | Type   | ホスト CPU 例 (8/16bit bus)                         |

|-------------|--------|-------------------------------------------------|

| 000         | Type 0 | Renesas Technology SH-3/4, EPSON S1C33          |

| 001         | Type 1 | MC68000/10                                      |

| 010         | Type 2 | MC68030/40                                      |

| 011         | Type 3 | Generic                                         |

| 100         | Type 4 | Reserved                                        |

| 101         | Type 5 | MIPS, ISA, NEC VR4121(16bit)                    |

| 110         | Type 6 | PCMCIA, Philips PR31500/PR31700, Toshiba TX3912 |

| 111         | EEPROM | EEPROM 内 HIFCR データにより Type0 ~ Type6 を選択         |

- Type0 独立したバイト単位のライト信号と、単独のリード信号によりアクセス制御を行なうタイプ。ルネサステクノロジ SH-3/4, EPSON S1C33 はこのタイプです。

- Type1 UDS#/LDS#などの上位/下位バイト選択信号と、リード/ライト選択信号の組み合わせによりアクセス制御を行なうタイプ。フリースケール・セミコンダクタの MC68000 はこのタイプです。この場合、上位バイト選択信号を HWR0#に、下位バイト選択信号を HWR1#に、リード/ライト選択を HRD1#に結線し、RD0#は未結線にしてください。

- Type2 データ転送サイズ表示信号と、リード/ライト選択信号の組み合わせによりアクセス制御を行なうタイプ。MC68030/40 などがこのタイプです。この場合、SIZ0 信号を HWR0#に、SIZ1 信号を HRD0#に、リード/ライト選択を HRD1#に、HWR1#は未結線にしてください。

- Type3 汎用タイプ。いずれのタイプも当てはまらない場合などに、外部でアクセス信号を生成して接続する場合に使用します。この場合、HWR0#に下位バイトの書き込み信号を、HWR1#に上位バイトの書き込み信号を、HRD0#に下位バイトの読み出し信号を、HRD1#に上位バイトの読み出し信号を接続します。

- Type4 このタイプは将来の拡張用に予約されています。指定しないでください。

- Type5 上位/下位バイト選択に複数の信号を使用し、独立したリード信号、ライト信号によりアクセス制御を行なうタイプ。MIPS、ISA バスはこのタイプです。この場合、ライト信号を HWR0#に、上位バイト指定信号を HWR1#に、リード信号を HRD0#に、RD1#は未結線にしてください。

- Type6 独立したバイトイネーブル信号と、独立したリード信号、ライト信号によりアクセス制御を行なうタイプ。PCMCIA インタフェースがこのタイプです。この場合ライト信号を HWR0#に、リード信号を HRD0#に、下位バイトイネーブル信号を HWE1#に、上位バイトイネーブル信号を HRD1#に接続してください。

- EEPROM シリアル EEPROM 内の HIFCR データによりタイプを選択します。設定可能なタイプは Type0 から Type6 までです。EEPROM 内データが “111” の場合、または EEPROM が接続されていない場合は S1S60000 はホスト CPU が接続されていないと判断します。

#### •マルチプレクスバスについて

一部の CPU では、アドレス線の一部または全部を、データバスと時分割で共用します。このような CPU を S1S60000 に接続する場合には、HMUX 端子を LOW にしてマルチプレクスバス設定とする必要があります。この設定にした場合、アドレスとして HA[2:0]の替わりに、HD[2:0]をラッチした信号が使用されます。ラッチ信号にはアドレス出力期間中 HIGH となり、アドレスが確定している期間中に LOW へ変化する信号を使用し、タイプごとに以下の信号線に入力してください。

Type0=HRD1#, Type1=HRD0#, Type2=HWR1#, Type5=HRD1#

ただし、Type3(Generic)と Type6(PCMCIA)ではマルチプレクスバス設定にすることはできません。

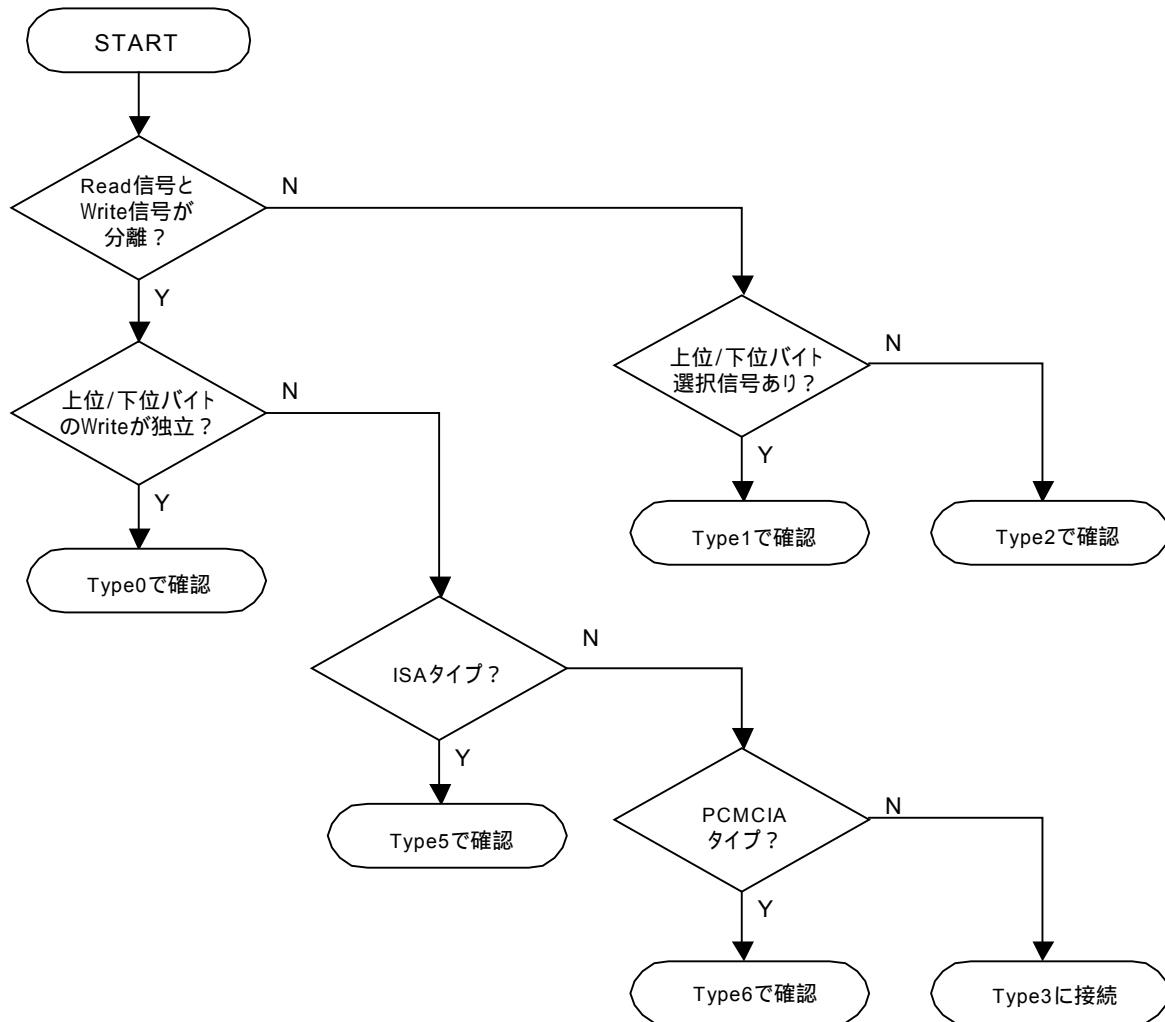

## 4. ホストインターフェース

図 4.1 に CPU タイプ選択フローチャートを示します。使用する CPU の持つ信号線から対応する CPU のタイプを選択した後、表 4.5 から表 4.10 の各 CPU の信号パターンを参照し、適切なアクセス状態となるかを確認してください。もし選択したパターンでの信号パターンが合致しない場合は、外部で Type3 の Generic、または似たパターンの CPU タイプに合うようにデコードを行なってください。

図 4.1 ホストインターフェースタイプ選択フローチャート

表 4.4 CPU 別信号結線表

| Type  | Manufacturer            | Model              | HCS#  | HA[2:0]    | HD[15:0]              | HWR0#      | HWR1#      | HRD0#      | HRD1#      | RESET#         | Re-mark        |

|-------|-------------------------|--------------------|-------|------------|-----------------------|------------|------------|------------|------------|----------------|----------------|

| Type0 | Renesas Technology      | SH-3               | (*)1) | A[2:0]     | D[15:0]               | WE0#       | WE1#       | RD#        | -/(ASTB)   | RESET#         |                |

|       |                         | SH-4               | (*)1) | A[2:0]     | D[15:0]               | WE0#       | WE1#       | RD#        | -/(ASTB)   | RESET#         |                |

|       | EPSON                   | S1C33              | (*)1) | A[2:0]     | D[15:0]               | #WRL       | #WRH       | #RD        | -/(ASTB)   | #RESET         |                |

| Type1 | Freescale Semiconductor | MC68000<br>MC68010 | (*)1) | A[2:1], NC | D[15:0]               | UDS#       | LDS#       | -/(ASTB)   | R/W#       | RESET#         | 16bit bus only |

|       |                         | MC68008            | (*)1) | A[2:0]     | D[7:0]                | —          | DS#        | -/(ASTB)   | R/W#       | RESET#         | 8bit bus only  |

|       |                         | MC68HC001          | (*)1) | A[2:0]     | D[15:0]               | UDS#       | LDS#       | -/(ASTB)   | R/W#       | RESET#         |                |

|       |                         | MC68030<br>MC68040 | (*)1) | A[2:0]     | D[31:16]              | SIZ0       | -/(ASTB)   | SIZ1       | R/W#       | RESET#         |                |

| Type2 | Freescale Semiconductor | MC68040            | (*)1) | A[2:0]     | D[31:16]              | SIZ0       | -/(ASTB)   | SIZ1       | R/W#       | RESET#         |                |

| Type3 | —                       | Generic            | (*)1) | A[2:0]     | —                     | WR0#       | WR1#       | RD0#       | RD1#       | RESET#         |                |

| Type5 | —                       | MIPS               | (*)1) | SA[2:0]    | SD[15:0]              | MEMW#      | SBHE#      | MEMR#      | -/(ASTB)   | inverted RESET |                |

|       | IBM                     | ISA                | (*)1) | SA[2:0]    | SD[15:0]              | MEMW#      | SBHE#      | MEMR#      | -/(ASTB)   | inverted RESET |                |

|       | NEC                     | VR4121             | (*)1) | ADD [2:0]  | DATA [15:0]           | IOW#       | SHB#       | IOR#       | -/(ASTB)   | RSTSW#         |                |

| Type6 | Philips                 | PR31500<br>PR31700 | GND   | A[2:0]     | D[23:16],<br>D[31:24] | /CARD IOWR | /CARD xCSL | /CARD IORD | /CARD xCSH | /PON           |                |

|       | Toshiba                 | TX3912             | GND   | A[2:0]     | D[23:16],<br>D[31:24] | CARD IOWR* | CARD xCSL* | CARD IORD* | CARD xCSH* | PON*           |                |

|       | PCMCIA                  | PC Card            | GND   | A[2:0]     | D[15:0]               | -WE        | -CE1       | -RD        | -CE2       | inverted RESET |                |

- : No Connection

-/(ASTB): バス分離タイプの CPU を接続する場合には NC。マルチブレクスタイプの CPU を接続する場合にはアドレス ラッチ信号を接続。

\*1: 必要に応じてデコードしたものを入力。Active LOW。

**【注意】**この表の結線での動作を保証するものではありません。使用する条件（バスサイズ、バスクロック、信号タイミング等）により適切な結線が変わる場合がありますので、必ずタイプ別の信号パターンに照らして確認をお願いします。

## 4. ホストインターフェース

表 4.5 Type0 の信号パターン

|       |        |       |      | S1S60000 信号線 |       |       |            |     |

|-------|--------|-------|------|--------------|-------|-------|------------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#        | HWR1# | HRD0# | HRD1# (*1) | HA0 |

| Write | Little | 16bit | Word | L            | L     | H     | H          | L   |

|       |        |       | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | H            | L     | H     | H          | H   |

|       |        |       | 8bit | LOW          | L     | H     | H          | L   |

|       |        | 16bit | HIGH | L            | H     | H     | H          | H   |

|       |        |       | Word | L            | L     | H     | H          | L   |

|       | Big    | 16bit | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | H            | L     | H     | H          | H   |

|       |        |       | 8bit | LOW          | L     | H     | H          | L   |

|       |        |       | HIGH | L            | H     | H     | H          | H   |

| Read  | Little | 16bit | Word | H            | H     | L     | H          | L   |

|       |        |       | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

|       | Big    | 16bit | Word | H            | H     | L     | H          | L   |

|       |        |       | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

\*1 : HRD1#は内部プルアップ抵抗により常に HIGH です。マルチプレクスバスの場合、ここにラッチ信号を接続することで、LOWへの変化点で HD[2:0]をラッチしてアドレスとします。

表 4.6 Type1 の信号パターン

|       |        |       |      | S1S60000 信号線 |       |            |       |     |

|-------|--------|-------|------|--------------|-------|------------|-------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#        | HWR1# | HRD0# (*1) | HRD1# | HA0 |

| Write | Little | 16bit | Word | L            | L     | H          | L     | L   |

|       |        |       | LOW  | H            | L     | H          | L     | L   |

|       |        |       | HIGH | L            | H     | H          | L     | H   |

|       |        |       | 8bit | LOW          | H     | L          | L     | L   |

|       |        | 16bit | HIGH | H            | L     | H          | L     | H   |

|       |        |       | Word | L            | L     | H          | L     | L   |

|       | Big    | 16bit | LOW  | H            | L     | H          | L     | L   |

|       |        |       | HIGH | L            | H     | H          | L     | H   |

|       |        |       | 8bit | LOW          | H     | L          | L     | L   |

|       |        |       | HIGH | H            | L     | H          | L     | H   |

| Read  | Little | 16bit | Word | L            | L     | H          | H     | L   |

|       |        |       | LOW  | H            | L     | H          | H     | L   |

|       |        |       | HIGH | L            | H     | H          | H     | H   |

|       |        | 8bit  | LOW  | H            | L     | H          | L     | L   |

|       |        |       | HIGH | H            | L     | H          | L     | H   |

|       | Big    | 16bit | Word | L            | L     | H          | H     | L   |

|       |        |       | LOW  | H            | L     | H          | H     | L   |

|       |        |       | HIGH | H            | L     | H          | H     | H   |

|       |        | 8bit  | LOW  | H            | L     | H          | L     | L   |

|       |        |       | HIGH | H            | L     | H          | L     | H   |

HRD0#は内部プルアップ抵抗により常に HIGH です。マルチプレクスバスの場合、ここにラッチ信号を接続することで、LOWへの変化点で HD[2:0]をラッチしてアドレスとします。

表 4.7 Type2 の信号パターン

|       |        |       |      | S1S60000 信号線  |       |       |       |     |

|-------|--------|-------|------|---------------|-------|-------|-------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#<br>(*1) | HWR1# | HRD0# | HRD1# | HA0 |

| Write | Little | 16bit | Word | L             | H     | H     | L     | L   |

|       |        |       | LOW  | H             | H     | L     | L     | L   |

|       |        |       | HIGH | H             | H     | L     | L     | H   |

|       |        | 8bit  | LOW  | H             | H     | L     | L     | L   |

|       |        |       | HIGH | H             | H     | L     | L     | H   |

|       | Big    | 16bit | Word | L             | H     | H     | L     | L   |

|       |        |       | LOW  | H             | H     | L     | L     | L   |

|       |        |       | HIGH | H             | H     | L     | L     | H   |

|       |        | 8bit  | LOW  | H             | H     | L     | L     | L   |

|       |        |       | HIGH | H             | H     | L     | L     | H   |

| Read  | Little | 16bit | Word | L             | H     | H     | H     | L   |

|       |        |       | LOW  | H             | H     | L     | H     | L   |

|       |        |       | HIGH | H             | H     | L     | H     | H   |

|       |        | 8bit  | LOW  | H             | H     | L     | H     | L   |

|       |        |       | HIGH | H             | H     | L     | H     | H   |

|       | Big    | 16bit | Word | L             | H     | H     | H     | L   |

|       |        |       | LOW  | H             | H     | L     | H     | L   |

|       |        |       | HIGH | H             | H     | L     | H     | H   |

|       |        | 8bit  | LOW  | H             | H     | L     | H     | L   |

|       |        |       | HIGH | H             | H     | L     | H     | H   |

HWR1#は内部プルアップ抵抗により常に HIGH です。マルチプレクスバスの場合、ここにラッチ信号を接続することで、LOWへの変化点で HD[2:0]をラッチしてアドレスとします。

表 4.8 Type3 の信号パターン

|       |        |       |      | S1S60000 信号線 |       |       |       |     |

|-------|--------|-------|------|--------------|-------|-------|-------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#        | HWR1# | HRD0# | HRD1# | HA0 |

| Write | Little | 16bit | Word | L            | L     | H     | H     | L   |

|       |        |       | LOW  | L            | H     | H     | H     | L   |

|       |        |       | HIGH | H            | L     | H     | H     | H   |

|       |        | 8bit  | LOW  | L            | H     | H     | H     | L   |

|       |        |       | HIGH | L            | H     | H     | H     | H   |

|       | Big    | 16bit | Word | L            | L     | H     | H     | L   |

|       |        |       | LOW  | L            | H     | H     | H     | L   |

|       |        |       | HIGH | H            | L     | H     | H     | H   |

|       |        | 8bit  | LOW  | L            | H     | H     | H     | L   |

|       |        |       | HIGH | L            | H     | H     | H     | H   |

| Read  | Little | 16bit | Word | H            | H     | L     | L     | L   |

|       |        |       | LOW  | H            | H     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | H     | L     | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | L     | H     | H   |

|       | Big    | 16bit | Word | H            | H     | L     | L     | L   |

|       |        |       | LOW  | H            | H     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | H     | L     | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | L     | H     | H   |

## 4. ホストインターフェース

表 4.9 Type5 の信号パターン

|       |        |       |      | S1S60000 信号線 |       |       |            |     |

|-------|--------|-------|------|--------------|-------|-------|------------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#        | HWR1# | HRD0# | HRD1# (*1) | HA0 |

| Write | Little | 16bit | Word | L            | L     | H     | H          | L   |

|       |        |       | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | L            | L     | H     | H          | H   |

|       |        | 8bit  | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | L            | H     | H     | H          | H   |

|       | Big    | 16bit | Word | L            | L     | H     | H          | L   |

|       |        |       | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | L            | L     | H     | H          | H   |

|       |        | 8bit  | LOW  | L            | H     | H     | H          | L   |

|       |        |       | HIGH | L            | H     | H     | H          | H   |

| Read  | Little | 16bit | Word | H            | L     | L     | H          | L   |

|       |        |       | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | L     | L     | H          | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

|       | Big    | 16bit | Word | H            | L     | L     | H          | L   |

|       |        |       | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | L     | L     | H          | H   |

|       |        | 8bit  | LOW  | H            | H     | L     | H          | L   |

|       |        |       | HIGH | H            | H     | L     | H          | H   |

HRD1#は内部プルアップ抵抗により常にHIGHです。マルチプレクスバスの場合、ここにラッチ信号を接続することで、LOWへの変化点でHD[2:0]をラッチしてアドレスとします。

表 4.10 Type6 の信号パターン

|       |        |       |      | S1S60000 信号線 |       |       |       |     |

|-------|--------|-------|------|--------------|-------|-------|-------|-----|

| R/W   | Endian | バス幅   | 操作   | HWR0#        | HWR1# | HRD0# | HRD1# | HA0 |

| Write | Little | 16bit | Word | L            | L     | H     | L     | L   |

|       |        |       | LOW  | L            | L     | H     | H     | L   |

|       |        |       | HIGH | L            | H     | H     | L     | H   |

|       |        | 8bit  | LOW  | L            | L     | H     | H     | L   |

|       |        |       | HIGH | L            | L     | H     | H     | H   |

|       | Big    | 16bit | Word | L            | L     | H     | L     | L   |

|       |        |       | LOW  | L            | L     | H     | H     | L   |

|       |        |       | HIGH | L            | H     | H     | L     | H   |

|       |        | 8bit  | LOW  | L            | L     | H     | H     | L   |

|       |        |       | HIGH | L            | L     | H     | H     | H   |

| Read  | Little | 16bit | Word | H            | L     | L     | L     | L   |

|       |        |       | LOW  | H            | L     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | L     | L     | H   |

|       |        | 8bit  | LOW  | H            | L     | L     | H     | L   |

|       |        |       | HIGH | H            | L     | L     | H     | H   |

|       | Big    | 16bit | Word | H            | L     | L     | L     | L   |

|       |        |       | LOW  | H            | L     | L     | H     | L   |

|       |        |       | HIGH | H            | H     | L     | L     | H   |

|       |        | 8bit  | LOW  | H            | L     | L     | H     | L   |

|       |        |       | HIGH | H            | L     | L     | H     | H   |

#### 4.4 エンディアンによるデータ入れ替え

S1S60000 内部では Little Endian 形式でデータ処理が行なわれます。一方、Big Endian の CPU の接続に対応するため、S1S60000 ではエンディアン設定とアクセスするポートにより、必要に応じてデータの swapping を行ない、ホスト CPU 側のデータ入れ替え負荷を軽減しています。適切なエンディアン設定、バス幅設定をしていれば swapping を意識する必要はありません。実際にどのような場合に swapping が行なわれるかを以下に示します。

- コマンド/ステータスポートへのアクセス時

コマンド/ステータスポートでは、ホスト CPU 内の 16 ビットレジスタ上と S1S60000 内部レジスタ上で同じビット順となるように変換が行なわれます。具体的には Big エンディアン、8 ビットバス幅設定の場合に swapping が行なわれます。

- データポートへのアクセス時

データポートにアクセスする場合には、メモリ上の連続したバイト列を転送した場合にホスト CPU 側と S1S60000 側で同じバイト順となるように変換を行ないます。具体的には Big エンディアン、16 ビットバス幅設定の場合に交換が行なわれます。

表 4.11 にホスト CPU から書き込んだ内容を S1S60000 で取得した場合のデータ状態を、表 4.12 に S1S60000 から書き込んだ内容をホスト CPU で取得した場合のデータ状態を示します。

表 4.11 書き込み時の S1S60000 取り込みデータ

| R/W   | Endian | バス幅   | 操作        | コマンドポート<br>1234h 書きこみ操作 | データポート<br>5678h 書き込み操作 |

|-------|--------|-------|-----------|-------------------------|------------------------|

| Write | Little | 16bit | Word      | 1234                    | 5678                   |

|       |        |       | LOW Byte  | xx34                    | xx78                   |

|       |        |       | HIGH Byte | 12xx                    | 56xx                   |

|       |        | 8bit  | LOW Byte  | xx34                    | xx78                   |

|       |        |       | HIGH Byte | xx12                    | xx56                   |

|       | Big    | 16bit | Word      | 1234                    | 7856(*1)               |

|       |        |       | LOW Byte  | 12xx                    | 78xx(*1)               |

|       |        |       | HIGH Byte | xx34                    | xx56(*1)               |

|       |        | 8bit  | LOW Byte  | xx12(*1)                | xx78                   |

|       |        |       | HIGH Byte | xx34(*1)                | xx56                   |

xx: 不定

\*1: swapping 操作により上位/下位バイトが入れ替えられます

表 4.12 読み出し時のホスト CPU 取得データ

| R/W  | Endian | バス幅   | 操作        | ステータスポート<br>1234h 読み出し操作 | データポート<br>5678h 読み出し操作   |

|------|--------|-------|-----------|--------------------------|--------------------------|

| Read | Little | 16bit | Word      | 1234                     | 5678                     |

|      |        |       | LOW Byte  | zz34                     | zz78<br>5678(*2)         |

|      |        |       | HIGH Byte | 12zz                     | 56zz<br>5678(*2)         |

|      |        | 8bit  | LOW Byte  | zz34                     | zz78                     |

|      |        |       | HIGH Byte | zz12                     | zz56                     |

|      | Big    | 16bit | Word      | 1234                     | 7856(*1)                 |

|      |        |       | LOW Byte  | 12zz                     | 78zz(*1)<br>7856(*1, *2) |

|      |        |       | HIGH Byte | zz34                     | zz56(*1)<br>7856(*1, *2) |

|      |        | 8bit  | LOW Byte  | zz12(*1)                 | zz78                     |

|      |        |       | HIGH Byte | zz34(*1)                 | zz56                     |

zz: ハイインピーダンスですが、プルアップにより FFh となります。

\*1: swapping 操作により上位/下位バイトが入れ替えられます。

\*2: Type0 の場合、バス上には 16bit データが出力されますが、ホスト CPU 側では 8bit のみ取り込まれます。

## 4. ホストインターフェース

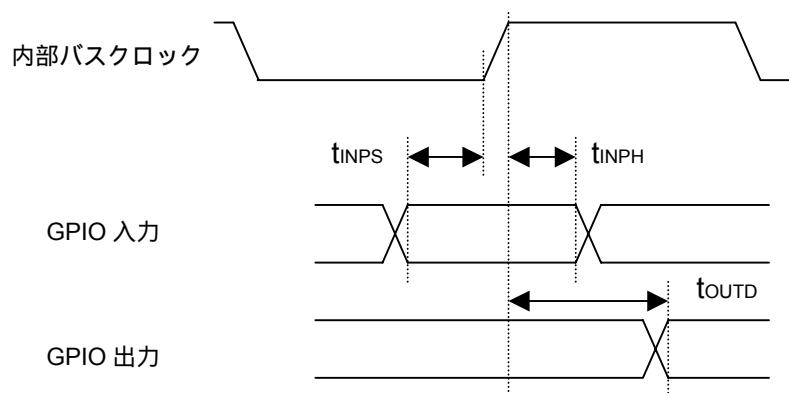

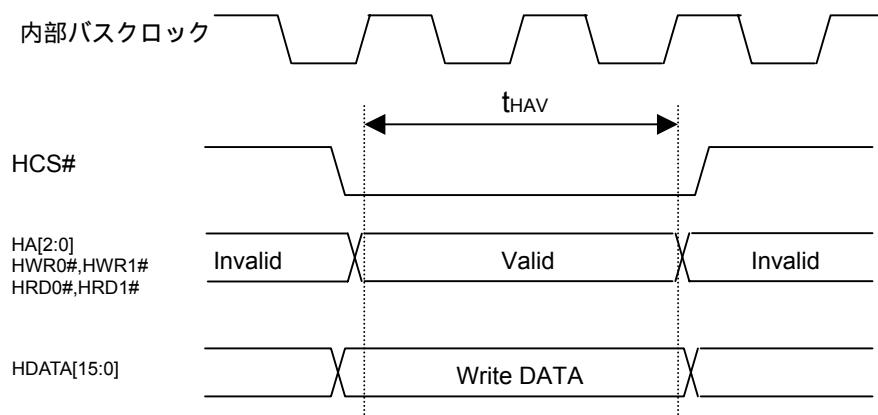

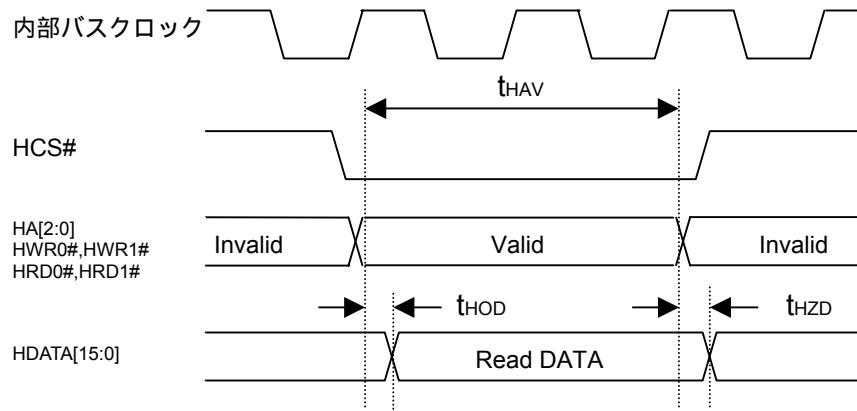

### 4.5 アクセスタイミング

ホストインターフェースからの S1S60000 へ書き込みは非同期に行なわれ、各信号は S1S60000 の内部バスクロックとは独立して変化します。そのため S1S60000 では内部バスクロックでホストインターフェース信号状態を連続してサンプリングし、アクセス状態が認識された後、最初に非アクセス状態になったタイミングで書き込み処理を行ないます。したがってホスト CPU では最低 3 回以上のサンプリング（内部バスクロックで 2 周期 + セットアップタイム以上）が行なわれるようバスサイクル設定を行なってください。サンプリングタイミングは内部バスクロックにより周期が変わるため、S1S60000 を低い内部バスクロックで動作させる場合には特に注意してください。

表 4.13 動作状態による必要アクセス時間

| OSC3 入力 | 動作モード  | 内部バスクロック | 最小アクセス期間(ns)(*1) |

|---------|--------|----------|------------------|

| 25MHz   | Normal | 50MHz    | 45               |

| 25MHz   | パワーセーブ | 12.5MHz  | 165              |

| 20MHz   | Normal | 40MHz    | 55               |

| 10MHz   | Normal | 20MHz    | 105              |

\*1: ホストインターフェース入力信号がアクセス状態で確定している期間

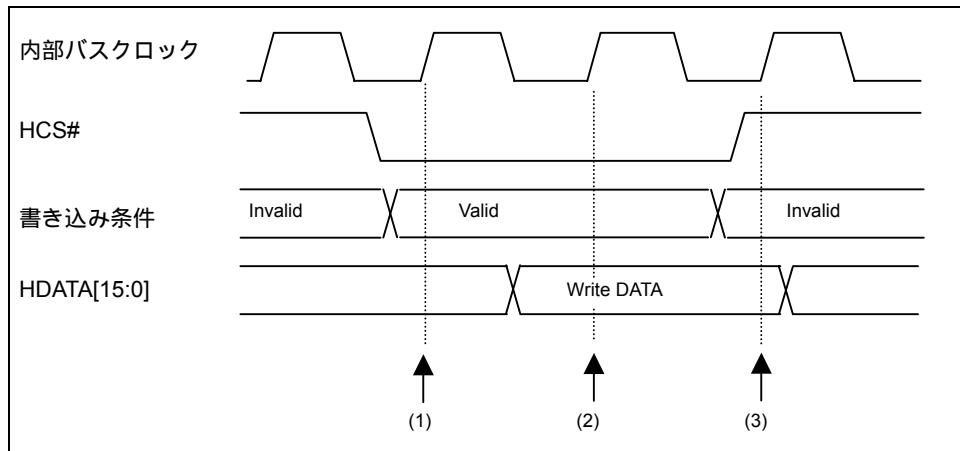

図 4.2 に書き込みサンプリングタイミングを示します。

図 4.2 書き込みサンプリングタイミング

- (1): 最初に書き込み条件が成立したタイミング。データの取り込みが行なわれ、一時的に保持されます。

- (2): 2 回目に書き込み条件が成立したタイミング。再度データの取り込みが行なわれ、(1)のデータを上書きし、一時的に保持されます。

- (3): 最初の非アクセス状態を検出したタイミング。この時点のデータは取り込まれません。このタイミングまでに取り込まれていたデータが S1S60000 内部に取り込まれます。

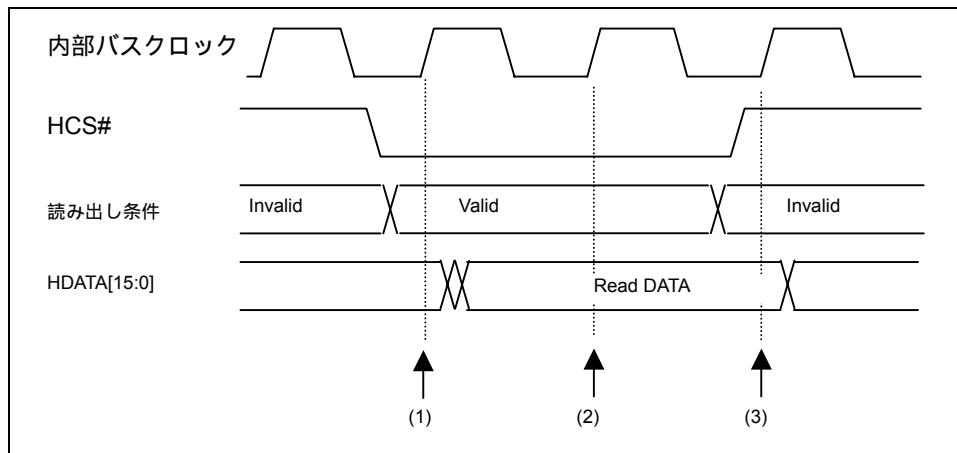

読み出しタイミングではデータバス駆動タイミングが異なりますが、基本的な動作は書き込み時と同じです。図 4.3 にサンプリングタイミングを示します。

図 4.3 読み出しサンプリングタイミング

- (1): 最初に読み出し条件が成立したタイミング。データバス駆動が開始されます。

- (2): 2回目に読み出し条件が成立したタイミング。データバス駆動は保持されます。

- (3): 最初の非アクセス状態を検出したタイミング。このタイミングでバス駆動が解除されます。

アクセス条件の成立には書き込み条件または読み出し条件に加えて  $HCS\#=LOW$  の成立が必要ですが、その成立の順番は任意です。またサンプリングタイミング直前で信号が変化してセットアップタイムを満足していない場合には、そのサンプリングでは条件が成立せず、次のサンプリングで有効なアクセスとなります。

### 5. ハードウェア制御

S1S60000 は GPIO、I<sup>2</sup>C バスマスター等を内蔵しており、これらを利用することで簡単なハードウェア制御が行なえます。制御可能ハードウェアは以下のとおりです。

- 内蔵レジスタ [5.2 章にて解説]

- GPIO (General Purpose Input/Output) [5.3 章にて解説]

- I<sup>2</sup>C スレーブデバイス [5.4.2 章にて解説]

- EEPROM [5.5 章にて解説]

- Flash ROM - ユーザが使用可能な 1K バイト領域

#### 5.1 制御方法

ユーザによる S1S60000 の内蔵ハードウェア制御は、以下の方法により可能です。

- ネットワークからの制御

- ホストインターフェースからの制御

- 外部 I<sup>2</sup>C マスターからの制御

- シリアルインターフェースからの制御

表 5.1 に制御方法と制御可能ハードウェア対象の関係を示します。

表 5.1 制御方法と対象の関係

| 制御方法                       | 内蔵レジスタ | GPIO | I <sup>2</sup> C Slave | EEPROM | Flash ROM |

|----------------------------|--------|------|------------------------|--------|-----------|

| ネットワークから                   | ×      | ○    | ○                      | △      | ×         |

| ホストインターフェースから              | ○      | ○    | ○                      | ○      | ○         |

| 外部 I <sup>2</sup> C マスターから | ○      | ○    | —                      | ×      | ×         |

| シリアルインターフェースから             | ×      | ○    | ○                      | ○      | ×         |

○: アクセス可能    △: 一部可能    ×: アクセス不可

##### 5.1.1 ネットワークからの制御

S1S60000 はプロトコル処理機能を内蔵しているため、ネットワークからの URI 指定により、GPIO や I<sup>2</sup>C などの読み出しや出力制御が行なえます。URI の指定形式は以下のとおりで、全て ASCII 文字です。大文字、小文字の区別はありません。

指定形式      http://Address:8080/Target[/Destination][?Data]

Address      S1S60000 に割り当てた IP アドレス。アクセス先のポート番号は必ず 8080 になります。

Target      次のいずれかの指定（アクセス対象）

GPIO, I<sup>2</sup>C, EEPROM

不適切な書き換えを防ぐため、ネットワークからの書換禁止設定が可能です。詳しくは 5.2.10、5.2.11、5.2.12 の各章を参照してください。

Destination      実際に Read/Write する対象のメモリ、レジスタ等。Target により異なります。

Data      Destination に対する操作を示すデータ。Destination により異なります。

“ & ” で区切ることにより、データを複数指定可能です。

制御要求に対して S1S60000 は返信中の以下の 3 個所で戻り値を返します。3 個所の戻り値のいずれにもすべて同じ ASCII 文字列が設定されています。

HTTP レスポンスヘッダ中      X-DEVICE-VALUE: 戻り値

HTML の HEAD エレメント中      <META NAME=“ DEVICE-VALUE ” CONTENT=“ 戻り値 ” >

HTML の BODY エレメント中      <DIV CLASS=“ DEVICE-VALUE ” > 戻り値 </DIV>

ネットワークからのハードウェア制御に失敗した場合、S1S60000 は HTTP レスポンスヘッダのステータスラインでエラーを返します。

## (1) GPIO アクセス

GPIO を制御する場合、Target には “GPIO” を、Destination には GPIO のポート番号を、Data にはポートへ出力するデータなどを指定します。

表 5.2 に 1 ポート単位の GPIO アクセス、表 5.3 に 16 ポート単位の GPIO アクセスの場合の指定形式を示します。マスク指定で操作対象とする GPIO に対応するビットを“1”にし、対象外を“0”とすることで特定の GPIO のみの操作が可能です。

表 5.2 GPIO アクセス形式 (1 ポート単位)

| 操作       | ポート指定 |               | 出力データ指定 |         | 戻り値 |

|----------|-------|---------------|---------|---------|-----|

|          | 桁     | 指定可能値         | 桁       | 指定可能値   |     |

| 1port 入力 | 2     | “00”~“0F”(*1) | —       | なし      | 1   |

| 1port 出力 | 2     | “00”~“0F”(*1) | 1       | “0”,“1” | 1   |

\*1：対応する GPIO を、2 桁の 16 進数で指定します。

表 5.3 GPIO アクセス形式 (16 ポート単位)

| 操作        | ポート指定 |       | 入出力指定 |          | マスク指定 |              | 出力値指定 |         | 戻り値 |

|-----------|-------|-------|-------|----------|-------|--------------|-------|---------|-----|

|           | 桁     | 指定可能値 | 桁     | 指定可能値    | 桁     | 指定可能値        | 桁     | 指定可能値   |     |

| 16port 入力 | 2     | “0X”  | 1     | “R” (*1) | 16    | “0”,“1” (*2) | —     | なし      | 16  |

| 16port 出力 | 2     | “0X”  | 1     | “W”      | 16    | “0”,“1” (*2) | 16    | “0”,“1” | 16  |

\*1：省略可能です。

\*2：省略可能です。省略した場合、“1111111111111111”を指定したことになります。

16 桁指定をする場合（マスク指定、出力値指定、戻り値指定時）上位が GPIO15、下位が GPIO0 の順に並びます。データ/戻り値の状態を表 5.4 に示します。

表 5.4 GPIO データ指定/戻り値

| 戻り値 | 内 容                                                             |

|-----|-----------------------------------------------------------------|

| “0” | 出力設定がされており、LOW 出力中である。またはマスクならばポートを操作対象外に、出力値ならばポートに LOW 出力する。  |

| “1” | 出力設定がされており、HIGH 出力中である。またはマスクならばポートを操作対象に、出力値ならばポートに HIGH 出力する。 |

| “L” | 入力設定がされており、LOW 入力状態である                                          |

| “H” | 入力設定がされており、HIGH 入力状態である                                         |

| “U” | GPIO として設定がされていない。別機能として使用している。                                 |

| “P” | ネットワークからの制御が禁止されている。                                            |

【例 1】IP アドレス 192.168.1.1 の GPIO0 に HIGH を出力する。

URI: <http://192.168.1.1:8080/GPIO/00?1>

返信(HIGH 出力中): <DIV NAME=“DEVICE-VALUE”>1</DIV>

【例 2】IP アドレス 192.168.1.1 の GPIO1 の入出力設定&入力状態を調べる。

URI: <http://192.168.1.1:8080/GPIO/01>

返信(LOW 入力中): <DIV NAME=“DEVICE-VALUE”>L</DIV>

【例 3】IP アドレス 192.168.1.1 の GPIO0 に LOW を、GPIO4 に HIGH を出力する。

URI: <http://192.168.1.1:8080/GPIO/0X?W&0000000000010001&00000000000010000>

返信: <DIV NAME=“DEVICE-VALUE”>LLLLPPPLLL1PLL0</DIV>

【例 4】IP アドレス 192.168.1.1 の GPIO0 から GPIO15 の入出力設定 & 入力状態を調べる。

URI: <http://192.168.1.1:8080/GPIO/0X>

返信: <DIV NAME=“DEVICE-VALUE”>LLLLPPPLLL0PLL0</DIV>

## 5. ハードウェア制御

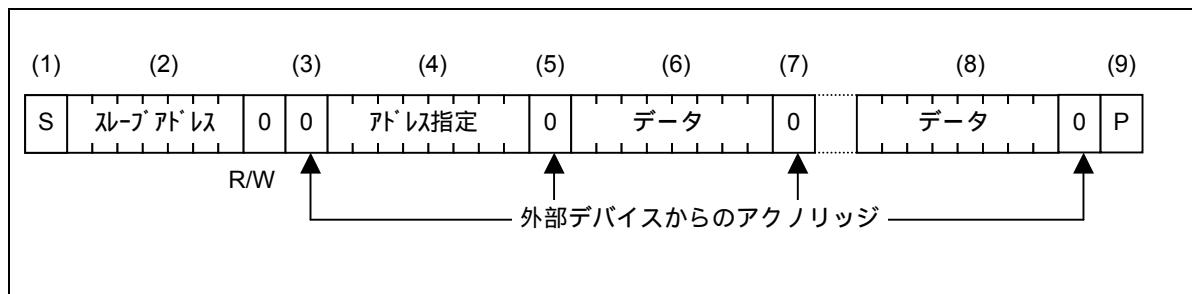

### (2) I<sup>2</sup>C

I<sup>2</sup>C マスタ機能を制御する場合、Target 部には“ I<sup>2</sup>C ”を、Data 部には制御データ列を指定します。Destination 部は存在しません。

制御データ列には、I<sup>2</sup>C バスに出力する値、再 Start のタイミング、I<sup>2</sup>C バスから入力を受け取るタイミングとそのバイト数を指定できます。制御データ列は次のように記述します。

表 5.5 I<sup>2</sup>C 制御データ列の記述方法

| 制御データ列の要素                                       | 指定方法                                                                                                                                                                                                                                           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slave アドレス指定                                    | 制御データの先頭、再 Start 後は必ずこの指定を行なう。<br>7 ビットアドレス指定の場合は bit[7:1]=Adr[6:0] を、bit0 に R/W ビット(1:Read,0:Write)を指定。<br>10 ビットアドレス指定の場合は最初のバイトの bit[7:3]=“ 11110 ” , bit[2:1]=Adr[9:8], bit0 に R/W ビット(1:Read,0:Write)を指定し、2 番目のバイトで bit[7:0]=Adr[7:0]を指定。 |

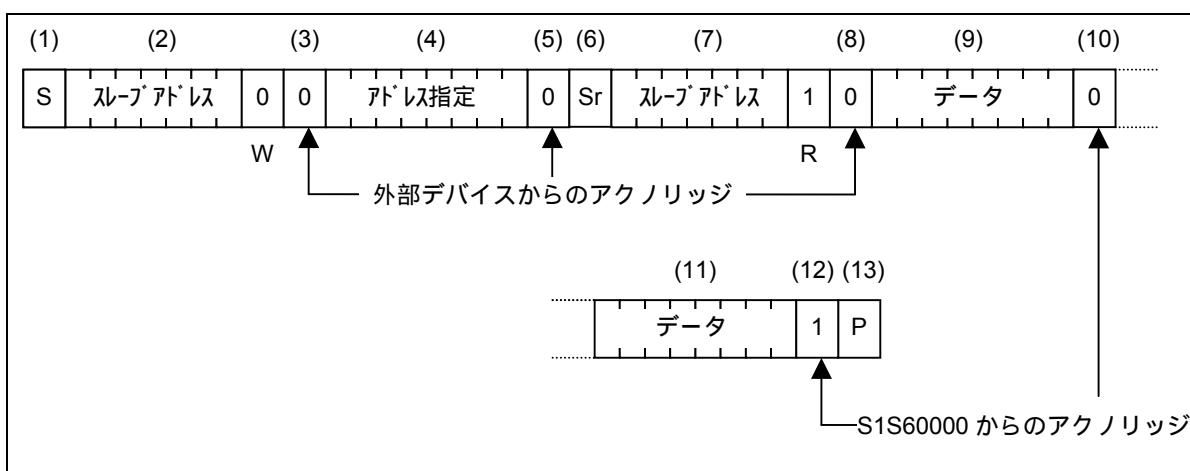

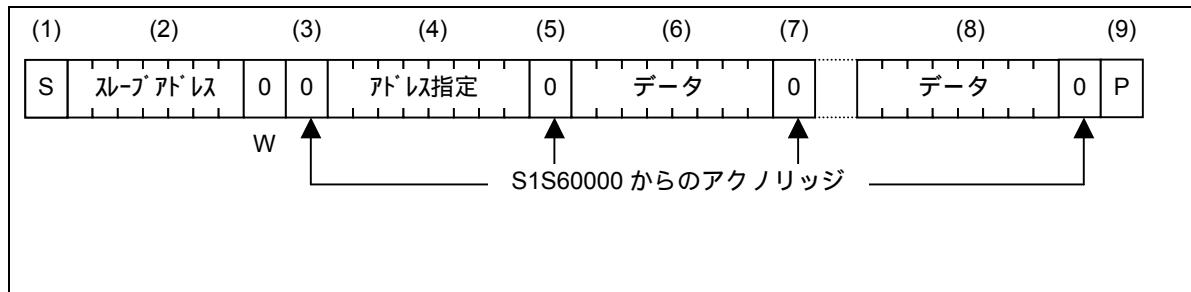

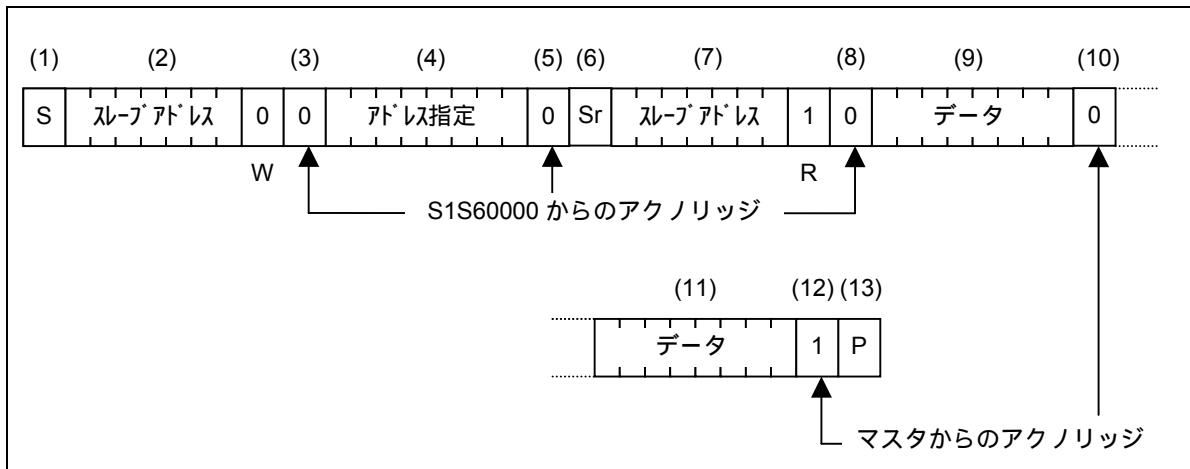

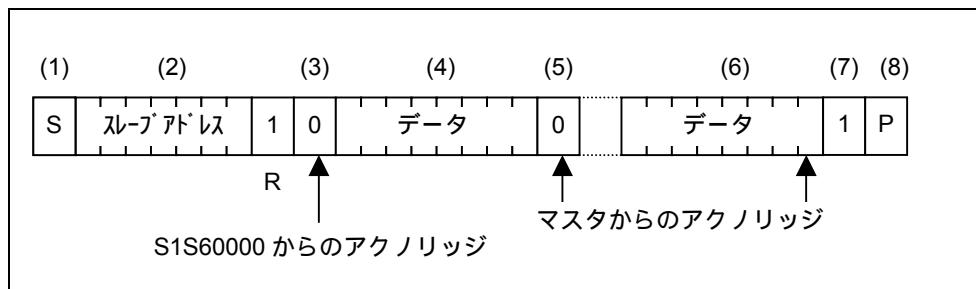

| I <sup>2</sup> C バスに出力する値                       | 1 バイトごとに 2 衔の 16 進数“ 00 ” ~“ FF ”                                                                                                                                                                                                              |