### **CMOS 16-BIT SINGLE CHIP MICROCONTROLLER**

# S1C17711 テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

- 1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

- 2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

- 3. 特性値の数値の大小は、数直線上の大小関係で表しています。

- 4. 本資料に掲載されている製品のうち、「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、 輸出する場合、同法に基づく輸出許可が必要です。

- 5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

- 6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

本製品はSilicon Storage Technology, Inc.よりライセンスされたSuperFlash®テクノロジを使用しています。

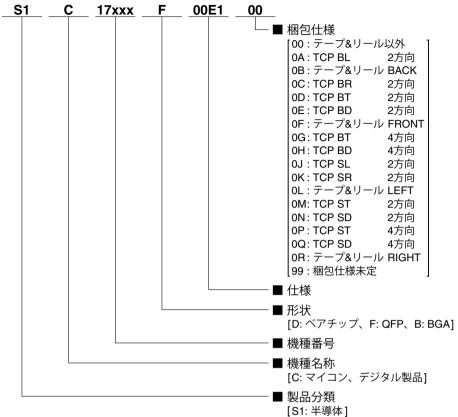

### 製品型番体系

### ●デバイス

#### ●開発ツール

# - 目 次 -

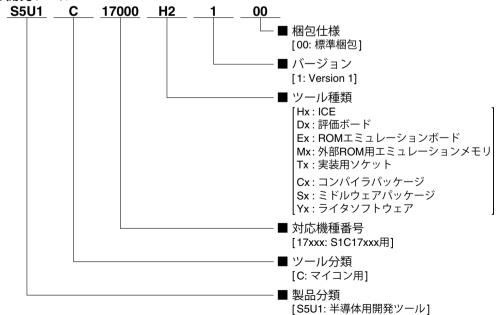

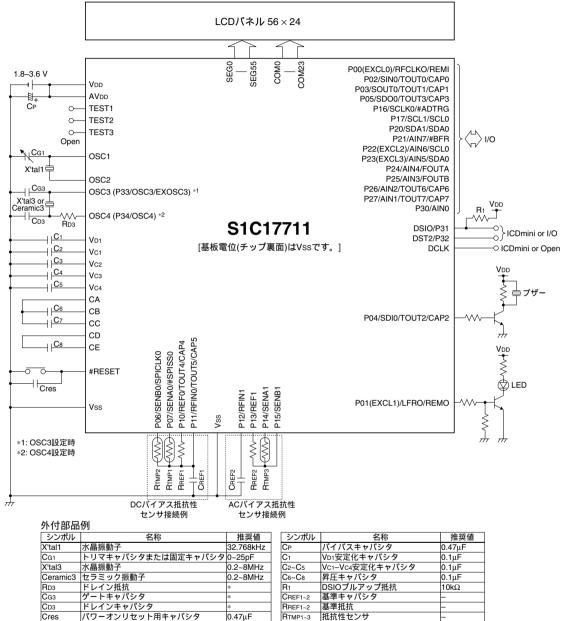

| 1  | 概要        |                      | 1-1                                          |

|----|-----------|----------------------|----------------------------------------------|

|    | 1.1       | 特長                   | 1-1                                          |

|    |           |                      | 1-3                                          |

|    |           | ·                    | 1-4                                          |

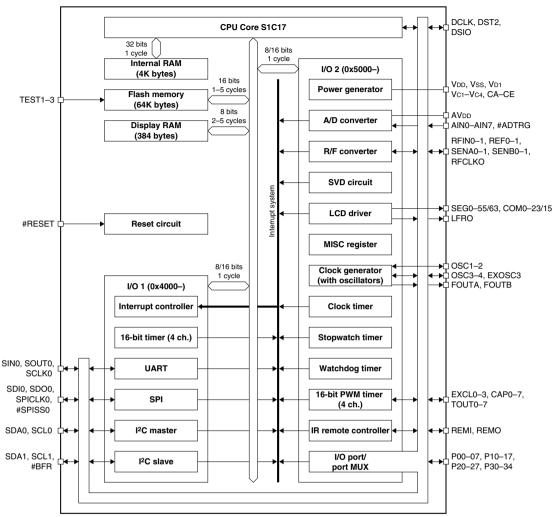

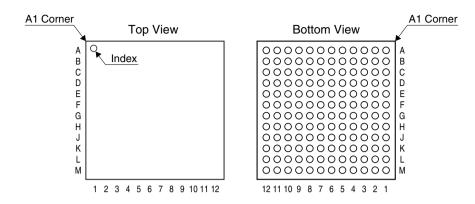

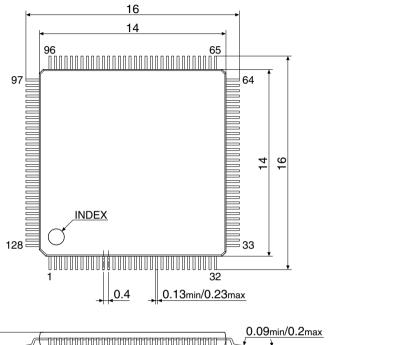

|    | 1.0       |                      | QFP15-128pin)1-4                             |

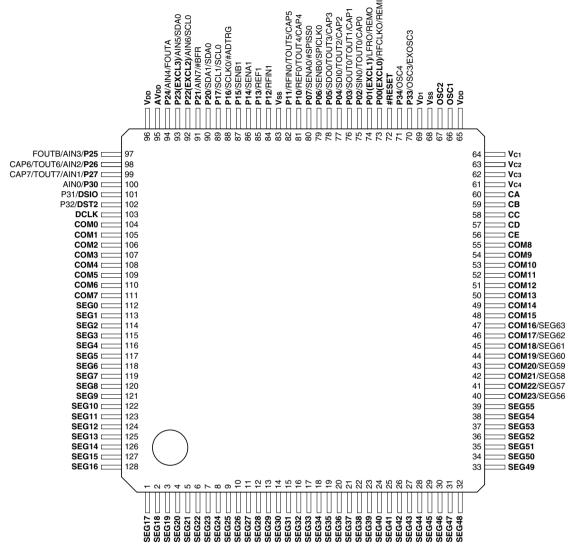

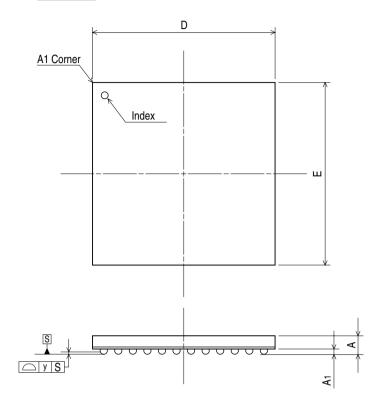

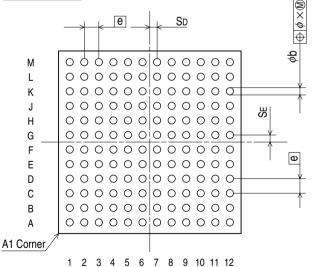

|    |           |                      | FBGA10H-144)1-5                              |

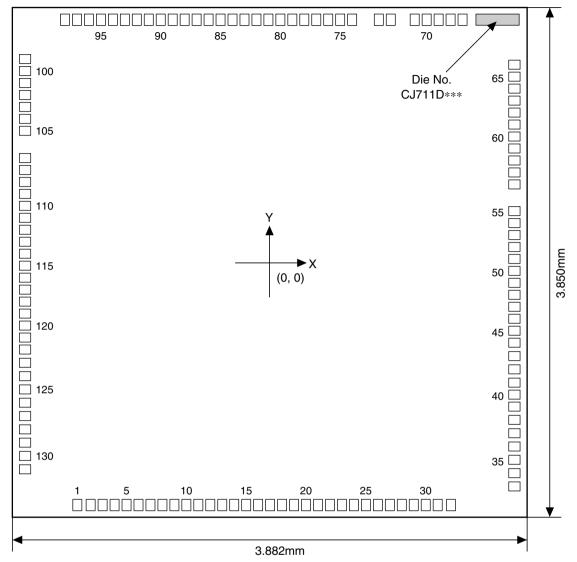

|    |           |                      | (チップ)1-6                                     |

|    |           |                      | 1-8                                          |

| ^  | CDII      |                      |                                              |

| 2  |           |                      | 2-1                                          |

|    |           |                      | 2-1                                          |

|    |           |                      | 2-2                                          |

|    |           |                      | 2-2                                          |

|    |           |                      | 2-5                                          |

|    | 2.5       | プロセッサ情報              | 2-6                                          |

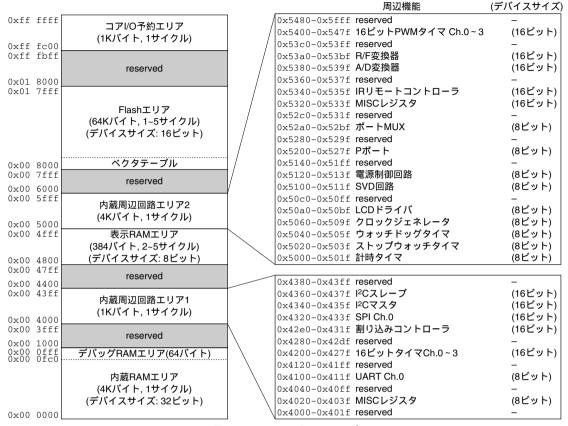

| 3  | メモリ       | マップ, バス制御            | 3-1                                          |

|    |           |                      | 3-1                                          |

|    | 0.1       |                      | ブ制限                                          |

|    |           |                      | クルの制限                                        |

|    | 3.2       |                      | 3-2                                          |

|    | 0         |                      | ٠٠                                           |

|    |           |                      | シミング                                         |

|    |           |                      | ット3-3                                        |

|    |           | Flash Protect Bits   | 3-3                                          |

|    |           | 3.2.4 Flashコントロ      | ーラのアクセス制御3-3                                 |

|    |           |                      | ntrol Register (MISC_FL)                     |

|    | 3.3       |                      | 3-4                                          |

|    |           |                      | 3-4                                          |

|    |           |                      | gister (MISC_IRAMSZ)                         |

|    | 3.4       |                      | 3-5                                          |

|    |           |                      |                                              |

|    |           |                      | コーラのアクセス制御3-5<br>ntrol Register (MISC_FL)3-5 |

|    | 3.5       |                      |                                              |

|    | 0.5       |                      | エリア1(0x4000~)                                |

|    |           |                      | エリア2(0x5000~)                                |

|    | 3.6       |                      | ア                                            |

|    |           |                      |                                              |

| 4  |           |                      | 4-1                                          |

|    |           |                      | 4-1                                          |

|    |           |                      | 王(AV <sub>DD</sub> )4-1                      |

|    |           |                      | 4-1                                          |

|    |           |                      | 4-2                                          |

|    | 4.5       | 重負荷保護機能              | 4-3                                          |

|    | 4.6       |                      | 4-3                                          |

|    |           |                      | (VD1_CTL)4-3                                 |

|    |           | LCD Voltage Regulate | or Control Register (LCD_VREG)4-4            |

| 5  |           |                      | 5-1                                          |

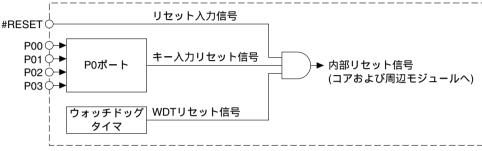

|    | 5.1       | イニシャルリセット要           | 因5-1                                         |

|    |           |                      | 5-1                                          |

| S1 | C17711 TE | CHNICAL MANUAL       | Seiko Epson Corporation i                    |

|   |     | 5.1.2 POポートキー入力リセット                                                    | .5-1  |

|---|-----|------------------------------------------------------------------------|-------|

|   |     | 5.1.3 ウォッチドッグタイマによるリセット                                                | .5-2  |

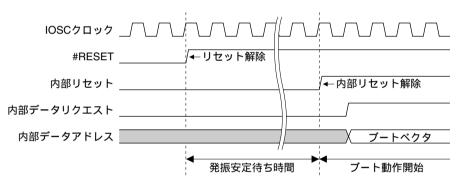

|   | 5.2 | イニシャルリセットシーケンス                                                         | .5-2  |

|   | 5.3 | イニシャルリセット時の初期設定                                                        | .5-2  |

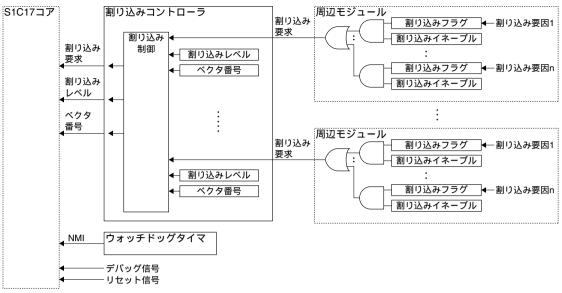

| 6 | 割り込 | みコントローラ (ITC)                                                          | .6-1  |

|   | 6.1 | ITCモジュールの概要                                                            | .6-1  |

|   |     | ベクタテーブル                                                                |       |

|   |     | Vector Table Address Low/High Registers (MISC_TTBRL, MISC_TTBRH)       | . 6-3 |

|   | 6.3 | マスク可能割り込みの制御                                                           | .6-4  |

|   |     | 6.3.1 周辺モジュールの割り込み制御ビット                                                | .6-4  |

|   |     | 6.3.2 ITCの割り込み要求処理                                                     |       |

|   |     | 6.3.3 S1C17コアの割り込み処理                                                   |       |

|   |     | NMI                                                                    |       |

|   |     | ソフトウェア割り込み                                                             |       |

|   |     | HALT, SLEEPモードの解除                                                      |       |

|   | 6.7 | 制御レジスタ詳細                                                               |       |

|   |     | Interrupt Level Setup Register x (ITC_LVx)                             | . 6-7 |

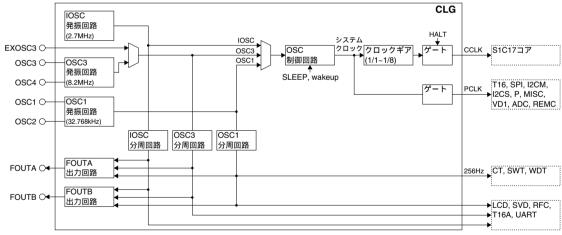

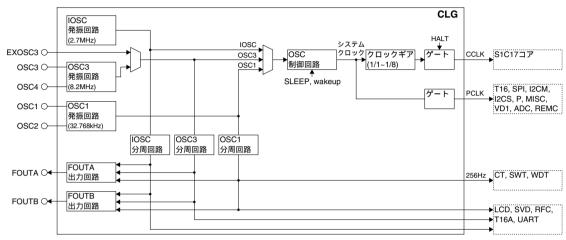

| 7 | クロッ | クジェネレータ(CLG)                                                           | .7-1  |

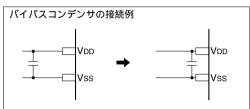

|   | 7.1 | CLGモジュールの概要                                                            | .7-1  |

|   | 7.2 | CLG入出力端子                                                               | .7-2  |

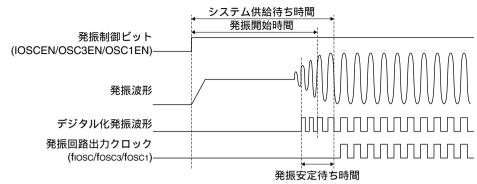

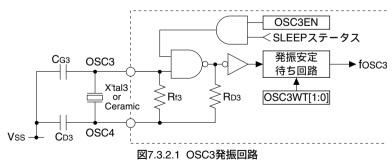

|   | 7.3 | 発振回路                                                                   | .7-2  |

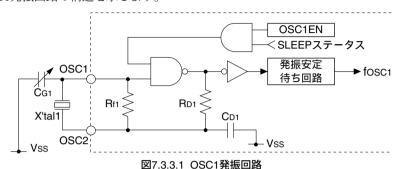

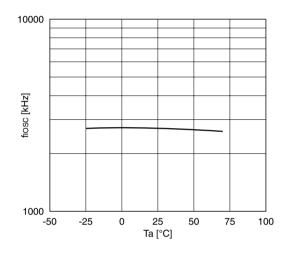

|   |     | 7.3.1 IOSC発振回路                                                         | .7-2  |

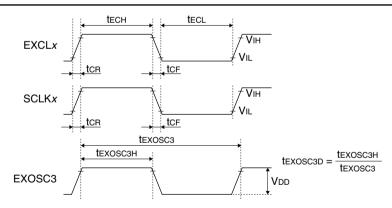

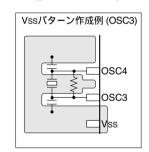

|   |     | 7.3.2 OSC3発振回路                                                         | .7-3  |

|   |     | 7.3.3 OSC1発振回路                                                         |       |

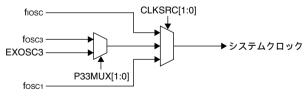

|   |     | システムクロックの切り換え                                                          |       |

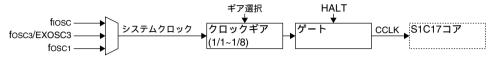

|   |     | CPUコアクロック (CCLK) の制御                                                   |       |

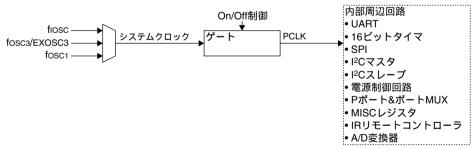

|   |     | 周辺モジュールクロック (PCLK) の制御                                                 |       |

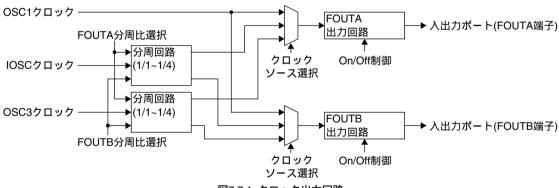

|   |     | クロック外部出力(FOUTA, FOUTB)                                                 |       |

|   | 7.8 | 制御レジスタ詳細                                                               |       |

|   |     | Clock Source Select Register (CLG_SRC)                                 |       |

|   |     | Oscillation Control Register (CLG_CTL)                                 |       |

|   |     | FOUTA Control Register (CLG_FOUTA)  FOUTB Control Register (CLG_FOUTB) |       |

|   |     | PCLK Control Register (CLG_PCLK)                                       |       |

|   |     | CCLK Control Register (CLG_CCLK)                                       |       |

| 8 | 入出力 | ポート(P)                                                                 | .8-1  |

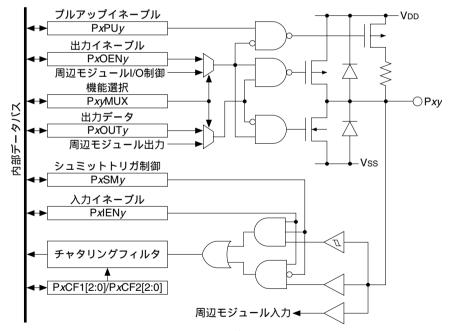

|   |     | Pモジュールの概要                                                              |       |

|   |     | 入出力端子機能の選択(ポートMUX)                                                     |       |

|   |     | データの入出力                                                                |       |

|   |     | プルアップ制御                                                                |       |

|   |     | 入力インタフェースレベル                                                           |       |

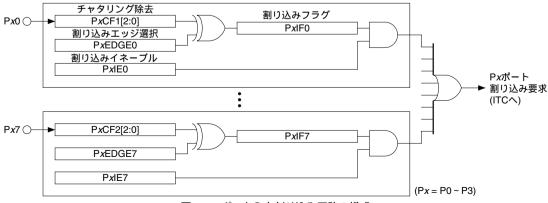

|   |     | P0~P3ポートのチャタリング除去機能                                                    |       |

|   |     | ポート入力割り込み                                                              |       |

|   |     | P0ポートキー入力リセット                                                          |       |

|   |     | 制御レジスタ詳細                                                               |       |

|   | 0.9 | Px Port Input Data Registers (Px_IN)                                   |       |

|   |     | Px Port Output Data Registers (Px_OUT)                                 |       |

|   |     | Px Port Output Enable Registers (Px_OEN)                               | . 8-7 |

|   |     | Px Port Pull-up Control Registers (Px_PU)                              |       |

|   |     | Px Port Schmitt Trigger Control Registers (Px_SM)                      | . 8-8 |

| Px Port Interrupt Mask Registers (Px_IMSK)                                        |       |

|-----------------------------------------------------------------------------------|-------|

| Px Port Interrupt Edge Select Registers (Px_EDGE)                                 | 8-9   |

| Px Port Interrupt Flag Registers (Px_IFLG)                                        |       |

| Px Port Chattering Filter Control Registers (Px_CHAT)                             |       |

| P0 Port Key-Entry Reset Configuration Register (P0_KRST)                          |       |

| Px Port Input Enable Registers (Px_IEN)                                           |       |

| P0[3:0] Port Function Select Register (P00_03PMUX)                                |       |

| P0[7:4] Port Function Select Register (P04_07PMUX)                                |       |

| P1[3:0] Port Function Select Register (P10_13PMUX)                                |       |

| P1[7:4] Port Function Select Register (P14_17PMUX)                                |       |

| P2[3:0] Port Function Select Register (P20_23PMUX)                                |       |

| P2[7:4] Port Function Select Register (P24_27PMUX)                                |       |

| P3[3:0] Port Function Select Register (P30_33PMUX)                                |       |

| P34 Port Function Select Register (P34PMUX)                                       |       |

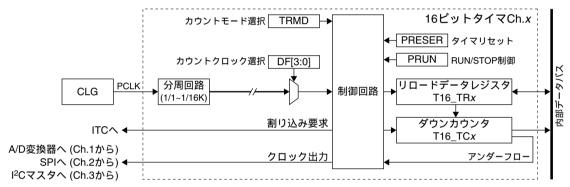

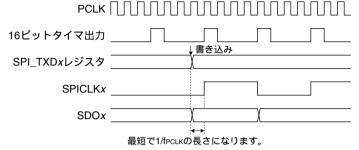

| 9 16ビットタイマ(T16)                                                                   | 9-1   |

| 9.1 T16モジュールの概要                                                                   | 9-1   |

| 9.2 カウントクロック                                                                      | 9-2   |

| 9.3 カウントモード                                                                       |       |

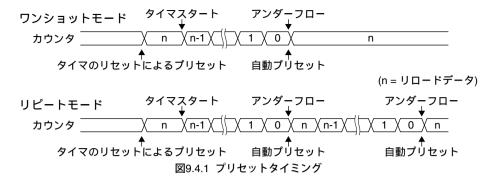

| 9.4 リロードデータレジスタとアンダーフロー周期                                                         |       |

|                                                                                   |       |

| 9.5 タイマのリセット                                                                      |       |

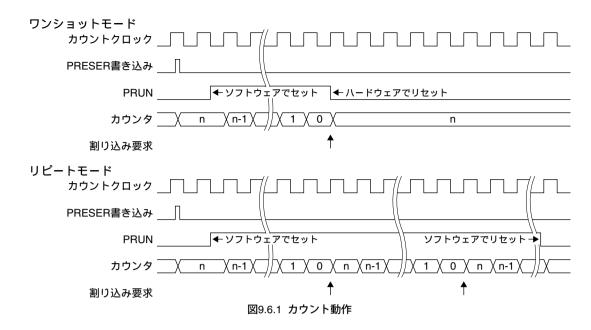

| 9.6 タイマRUN/STOP制御                                                                 | 9-3   |

| 9.7 T16出力信号                                                                       | 9-4   |

| 9.8 T16割り込み                                                                       | 9-4   |

| 9.9 制御レジスタ詳細                                                                      |       |

| T16 Ch.x Count Clock Select Registers (T16_CLKx)                                  |       |

|                                                                                   |       |

| T16 Ch.x Reload Data Registers (T16_TRx)T16 Ch.x Counter Data Registers (T16_TCx) |       |

| T16 Ch.x Control Registers (T16_CTLx)                                             |       |

| T16 Ch.x Interrupt Control Registers (T16_INTx)                                   |       |

|                                                                                   |       |

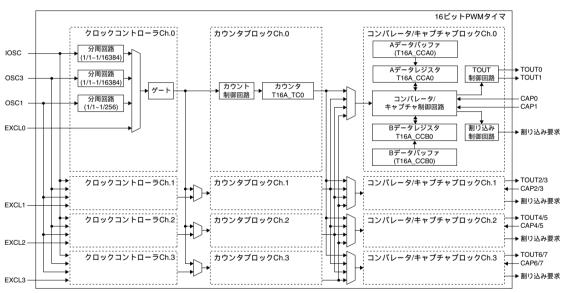

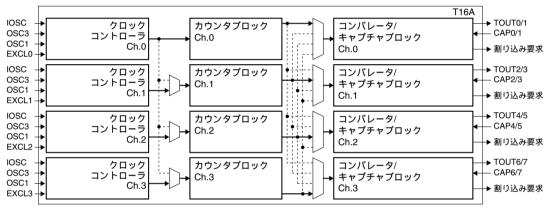

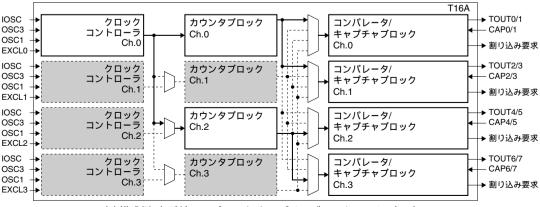

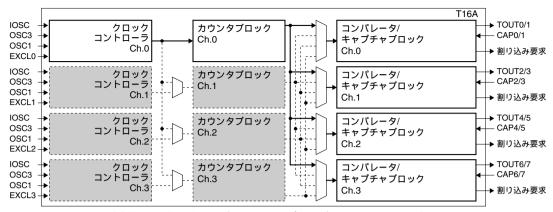

| 10 16ビットPWMタイマ(T16A)                                                              |       |

| 10.1 T16Aモジュールの概要                                                                 |       |

| 10.2 T16A入出力端子                                                                    | 10-2  |

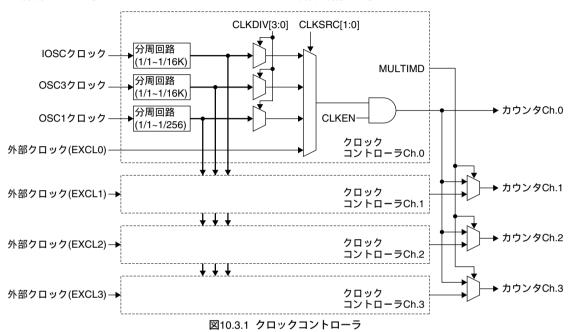

| 10.3 カウントクロック                                                                     | 10-3  |

| 10.4 T16Aの動作モード                                                                   |       |

| 10.4.1 コンパレータモードとキャプチャモード                                                         |       |

| 10.4.2 リピートモードとワンショットモード                                                          |       |

| 10.4.2 グレードモードとフランョッドモード<br>10.4.3 ノーマルチャネルモードとマルチコンパレータ/キャプチャモード                 |       |

|                                                                                   |       |

| 10.5 カウンタの制御                                                                      |       |

| 10.5.1 カウンタのリセット                                                                  |       |

| 10.5.2 カウンタRUN/STOP制御                                                             |       |

| 10.5.3 カウンタ値の読み出し                                                                 |       |

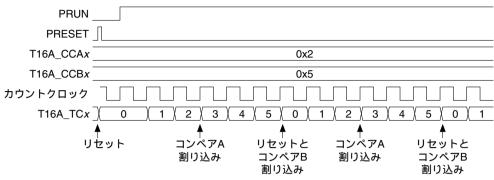

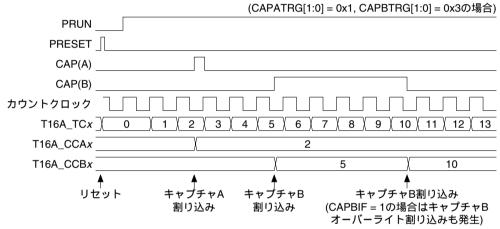

| 10.5.4 タイミングチャート                                                                  |       |

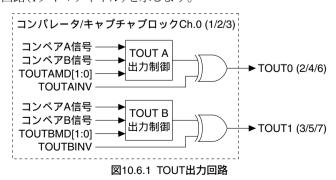

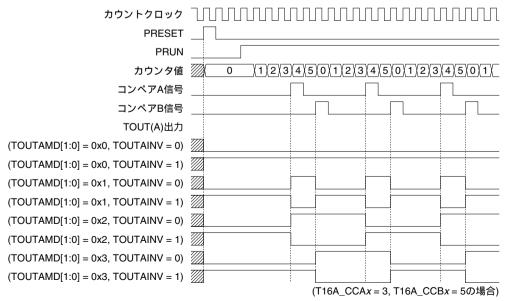

| 10.6 タイマ出力の制御                                                                     | 10-9  |

| 10.7 T16A割り込み                                                                     | 10-11 |

| 10.8 制御レジスタ詳細                                                                     | 10-12 |

| T16A Clock Control Register Ch.x (T16A_CLKx)                                      |       |

| T16A Counter Ch.x Control Registers (T16A_CTLx)                                   |       |

| T16A Counter Ch.x Data Registers (T16A_TCx)                                       |       |

| T16A Comparator/Capture Ch.x Control Registers (T16A_CCCTLx)                      |       |

| T16A Comparator/Capture Ch.x A Data Registers (T16A_CCAx)                         |       |

| T16A Comparator/Capture Ch.x B Data Registers (T16A_CCBx)                         | 10-18 |

| T16A Comparator/Capture Ch.x Interrupt Enable Registers (T16A_IENx)               | 10-19 |

| T16A Comparator/Capture Ch.x Interrupt Flag Registers (T16A_IFLGx)                |       |

| 11 | 計時タ                                                  | イマ(CT)                                                                                                                                                                                                                                                                                                                         | 11-1                                                                                                                             |

|----|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

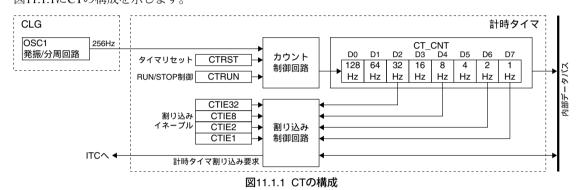

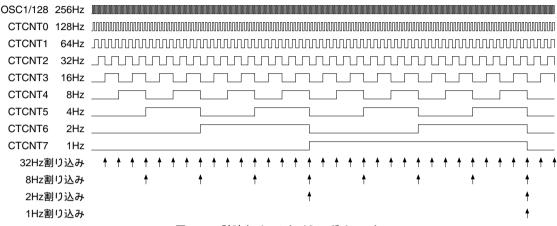

|    | 11.1                                                 | CTモジュールの概要                                                                                                                                                                                                                                                                                                                     | .11-1                                                                                                                            |

|    | 11.2                                                 | 動作クロック                                                                                                                                                                                                                                                                                                                         | .11-1                                                                                                                            |

|    | 11.3                                                 | タイマのリセット                                                                                                                                                                                                                                                                                                                       | 11-1                                                                                                                             |

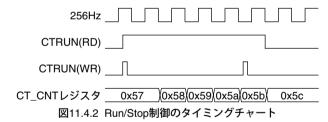

|    | 11.4                                                 | タイマRUN/STOP制御                                                                                                                                                                                                                                                                                                                  | 11-1                                                                                                                             |

|    | 11.5                                                 | CT割り込み                                                                                                                                                                                                                                                                                                                         | 11-2                                                                                                                             |

|    | 11.6                                                 | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                       | .11-3                                                                                                                            |

|    |                                                      | Clock Timer Control Register (CT_CTL)                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|    |                                                      | Clock Timer Counter Register (CT_CNT)                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|    |                                                      | Clock Timer Interrupt Mask Register (CT_IMSK)                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

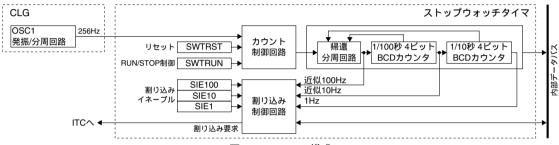

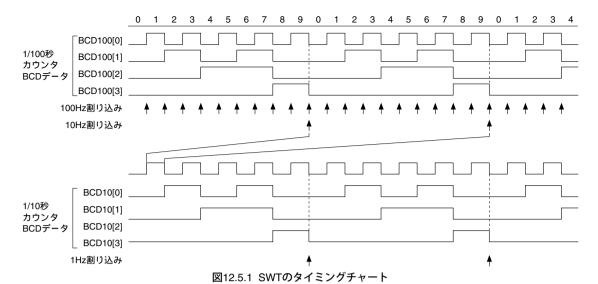

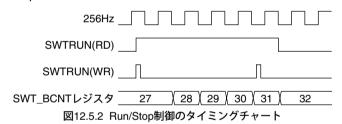

| 10 | 7 h w                                                | プウォッチタイマ(SWT)                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| 12 |                                                      | フフォフファイ * (GWT)                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

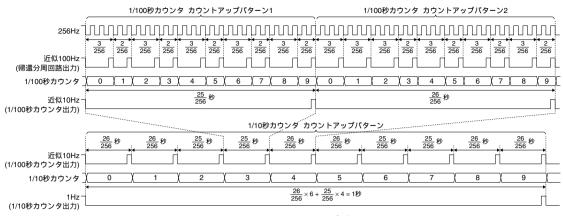

|    |                                                      | 動作クロック                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

|    |                                                      | BCDカウンタ                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|    |                                                      | タイマのリセット                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

|    |                                                      | タイマRUN/STOP制御                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|    |                                                      | SWT割り込み                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|    |                                                      | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

|    | 12.7                                                 | By Stopwatch Timer Control Register (SWT_CTL)                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|    |                                                      | Stopwatch Timer BCD Counter Register (SWT_BCNT)                                                                                                                                                                                                                                                                                |                                                                                                                                  |

|    |                                                      | Stopwatch Timer Interrupt Mask Register (SWT_IMSK)                                                                                                                                                                                                                                                                             |                                                                                                                                  |

|    |                                                      | Stopwatch Timer Interrupt Flag Register (SWT_IFLG)                                                                                                                                                                                                                                                                             |                                                                                                                                  |

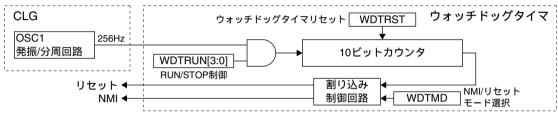

| 13 | ウォッ                                                  | チドッグタイマ(WDT)                                                                                                                                                                                                                                                                                                                   | 13-1                                                                                                                             |

|    |                                                      | WDTモジュールの概要                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

|    | 13.2                                                 | 動作クロック                                                                                                                                                                                                                                                                                                                         | .13-1                                                                                                                            |

|    | 13.3                                                 | WDTの制御                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

|    |                                                      | 13.3.1 NMI/リセットモードの選択                                                                                                                                                                                                                                                                                                          | .13-1                                                                                                                            |

|    |                                                      | 13.3.2 WDTのRUN/STOP制御                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|    |                                                      | 13.3.3 WDTのリセット<br>13.3.4 HALT, SLEEPモード時の動作                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|    |                                                      | 1334 DALL SLEEPT T CHOURITE                                                                                                                                                                                                                                                                                                    | . 13-2                                                                                                                           |

|    | 13.4                                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

|    | 13.4                                                 | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                       | 13-2                                                                                                                             |

|    | 13.4                                                 |                                                                                                                                                                                                                                                                                                                                | .13-2<br>13-2                                                                                                                    |

| 14 | 13.4                                                 | 制御レジスタ詳細<br>Watchdog Timer Control Register (WDT_CTL)<br>Watchdog Timer Status Register (WDT_ST)                                                                                                                                                                                                                               | .13-2<br>13-2<br>13-3                                                                                                            |

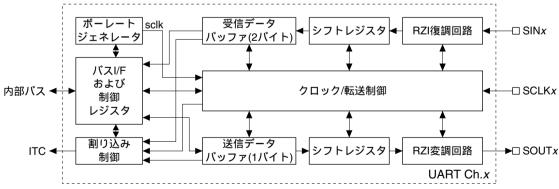

| 14 | UART.                                                | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                       | 13-2<br>13-2<br>13-3<br><b>14-1</b>                                                                                              |

| 14 | <b>UART.</b><br>14.1                                 | 制御レジスタ詳細<br>Watchdog Timer Control Register (WDT_CTL)<br>Watchdog Timer Status Register (WDT_ST)<br>UARTモジュールの概要                                                                                                                                                                                                               | .13-2<br>13-2<br>13-3<br><b>14-1</b><br>.14-1                                                                                    |

| 14 | <b>UART.</b><br>14.1<br>14.2                         | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                       | 13-2<br>13-3<br>13-1<br>14-1<br>14-1                                                                                             |

| 14 | <b>UART.</b> 14.1 14.2 14.3                          | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL)  Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子                                                                                                                                                                                                          | 13-2<br>13-3<br>14-1<br>14-1<br>14-2<br>14-2                                                                                     |

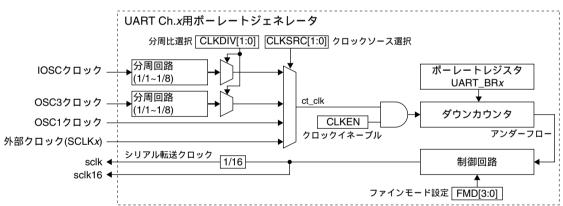

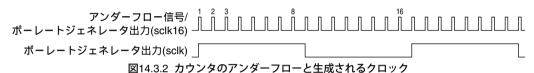

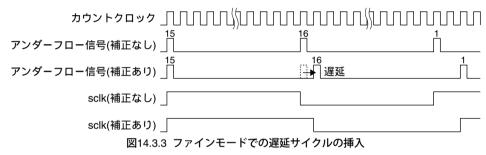

| 14 | UART.<br>14.1<br>14.2<br>14.3<br>14.4                | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL) Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ                                                                                                                                                                                               | 13-2<br>13-3<br>14-1<br>14-1<br>14-2<br>14-2                                                                                     |

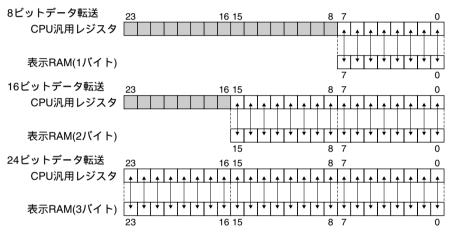

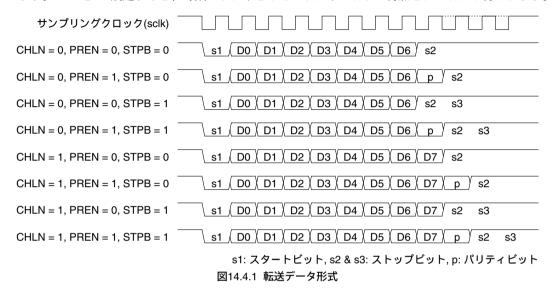

| 14 | UART.<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5        | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL) Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ 転送データの設定                                                                                                                                                                                      | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>.14-4                                                                     |

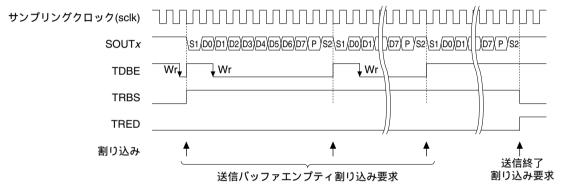

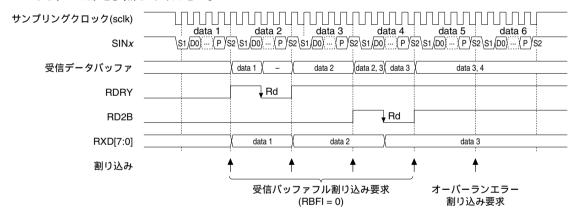

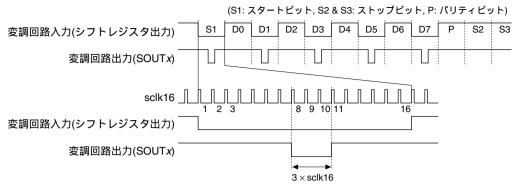

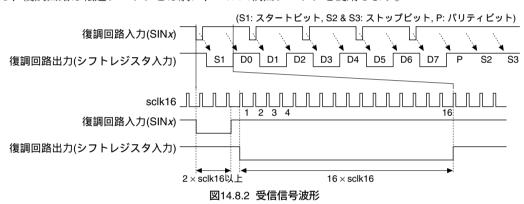

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6         | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL) Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ 転送データの設定 データ送受信の制御                                                                                                                                                                            | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8                                                      |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL)  Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子  ボーレートジェネレータ  転送データの設定  データ送受信の制御  受信エラー                                                                                                                                                                 | 13-2<br>13-3<br><b>14-1</b><br>.14-1<br>.14-2<br>.14-2<br>.14-4<br>.14-5<br>.14-8                                                |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL) Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ 転送データの設定 データ送受信の制御 受信エラー  UART割り込み                                                                                                                                                            | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8<br>14-8                                              |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL) Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ 転送データの設定 データ送受信の制御 受信エラー  UART割り込み  IrDAインタフェース  制御レジスタ詳細  UART Ch.x Status Register (UART_STx)                                                                                               | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8<br>14-9<br>14-10<br>14-11                            |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL)  Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ  転送データの設定  データ送受信の制御  受信エラー  UART割り込み  IrDAインタフェース  制御レジスタ詳細  UART Ch.x Status Register (UART_STx)  UART Ch.x Transmit Data Register (UART_TXDx)                                             | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8<br>14-8<br>14-9<br>14-10<br>14-11<br>14-12           |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL)  Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ 転送データの設定  データ送受信の制御  受信エラー  UART割り込み  IrDAインタフェース  制御レジスタ詳細  UART Ch.x Status Register (UART_STx)  UART Ch.x Transmit Data Register (UART_RXDx)  UART Ch.x Receive Data Register (UART_RXDx) | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8<br>14-8<br>14-9<br>14-10<br>14-11<br>14-12<br>14-13  |

| 14 | 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>14.7 | 制御レジスタ詳細  Watchdog Timer Control Register (WDT_CTL)  Watchdog Timer Status Register (WDT_ST)  UARTモジュールの概要  UART入出力端子 ボーレートジェネレータ  転送データの設定  データ送受信の制御  受信エラー  UART割り込み  IrDAインタフェース  制御レジスタ詳細  UART Ch.x Status Register (UART_STx)  UART Ch.x Transmit Data Register (UART_TXDx)                                             | 13-2<br>13-3<br><b>14-1</b><br>14-1<br>14-2<br>14-2<br>14-4<br>14-5<br>14-8<br>14-8<br>14-10<br>14-11<br>14-12<br>14-13<br>14-13 |

|    |                    | UART Ch.x Baud Rate Register (UART_BRx)                        |      |

|----|--------------------|----------------------------------------------------------------|------|

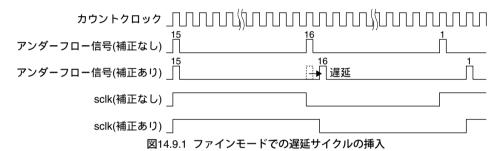

|    |                    | UART Ch.x Fine Mode Register (UART_FMDx)                       |      |

|    |                    | UART Ch.x Clock Control Register (UART_CLKx)                   |      |

| 15 |                    |                                                                |      |

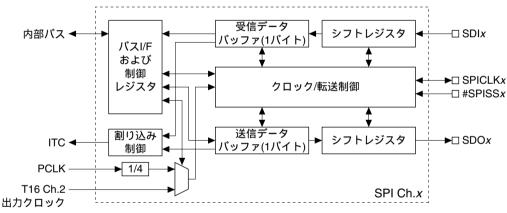

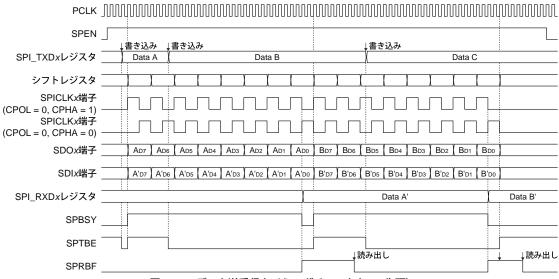

|    |                    | SPIモジュールの概要                                                    |      |

|    |                    | SPI入出力端子                                                       |      |

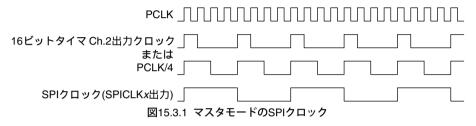

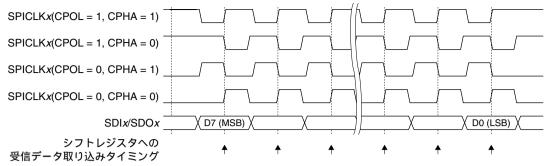

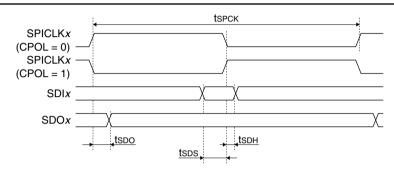

|    | 15.3               | SPIクロック                                                        | 15-2 |

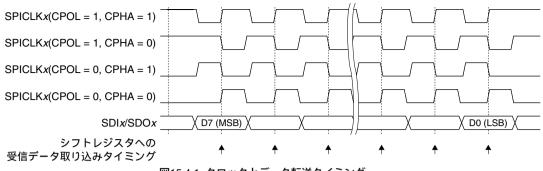

|    | 15.4               | データ転送条件の設定                                                     | 15-2 |

|    | 15.5               | データ送受信の制御                                                      | 15-3 |

|    | 15.6               | SPI割り込み                                                        | 15-5 |

|    | 15.7               | 制御レジスタ詳細                                                       | 15-6 |

|    |                    | SPI Ch.x Status Register (SPI_STx)                             |      |

|    |                    | SPI Ch.x Transmit Data Register (SPI_TXDx)                     |      |

|    |                    | SPI Ch. x Receive Data Register (SPI_RXDx)                     |      |

|    | .20-7              | SPI Ch.x Control Register (SPI_CTLx)                           |      |

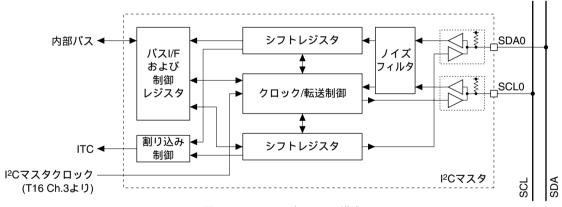

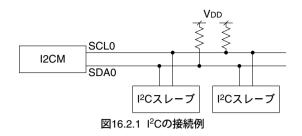

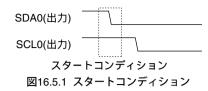

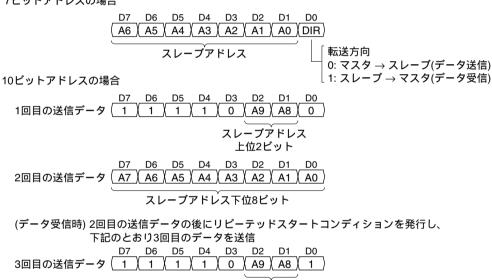

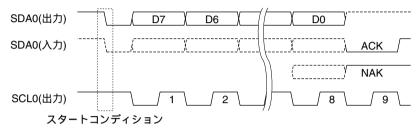

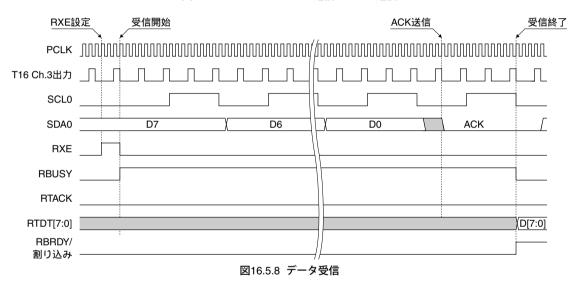

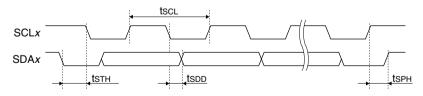

| 16 |                    | 9 (I2CM)                                                       |      |

|    |                    | I2CMモジュールの概要                                                   |      |

|    |                    | I2CM入出力端子                                                      |      |

|    |                    | 同期クロック                                                         |      |

|    |                    | データ転送前の設定項目                                                    |      |

|    |                    | データ送受信の制御                                                      |      |

|    |                    | I2CM割り込み                                                       |      |

|    | 16.7               | 制御レジスタ詳細                                                       |      |

|    |                    | I <sup>2</sup> C Master Enable Register (I2CM_EN)              |      |

|    |                    | I <sup>2</sup> C Master Control Register (I2CM_CTL)            |      |

|    |                    | I <sup>2</sup> C Master Interrupt Control Register (I2CM_ICTL) |      |

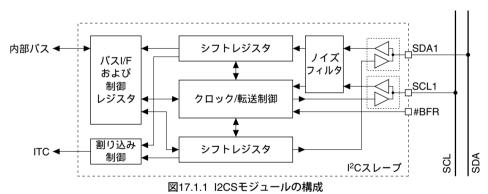

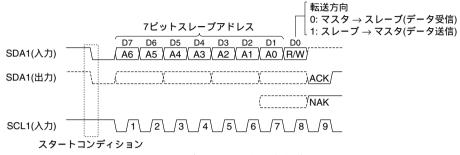

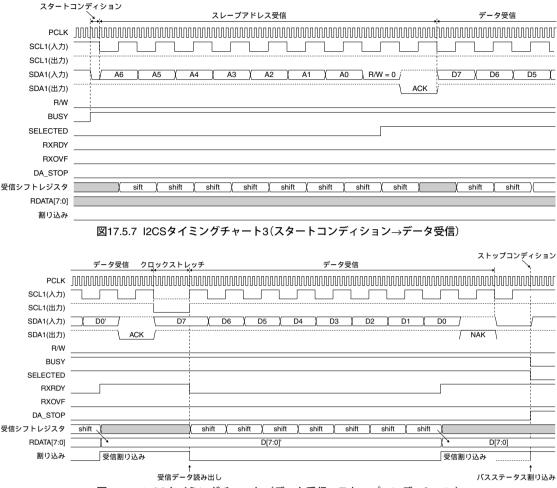

| 17 | I <sup>2</sup> Cスレ | ·一ブ(I2CS)                                                      |      |

|    |                    | I2CSモジュールの概要                                                   |      |

|    |                    | I2CS入出力端子                                                      |      |

|    |                    | 動作クロック                                                         |      |

|    |                    | 12CSの初期設定                                                      |      |

|    |                    | 17.4.1 リセット                                                    |      |

|    |                    | 17.4.2 スレーブアドレスの設定                                             |      |

|    |                    | 17.4.3 オプション機能                                                 |      |

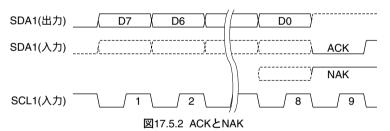

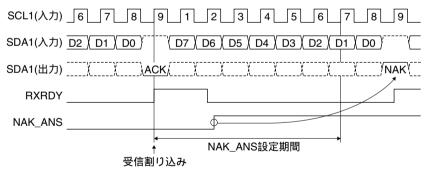

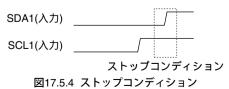

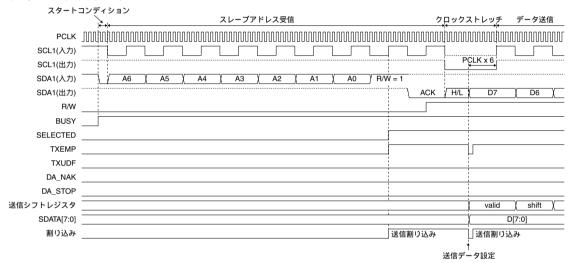

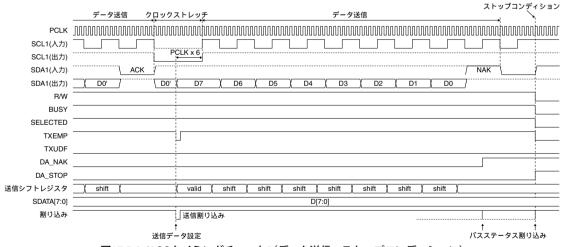

|    | 17.5               | データ送受信の制御                                                      | 17-3 |

|    | 17.6               | I2CS割り込み                                                       | 17-8 |

|    | 17.7               | 制御レジスタ詳細                                                       | 17-9 |

|    |                    | I <sup>2</sup> C Slave Transmit Data Register (I2CS_TRNS)      |      |

|    |                    | I <sup>2</sup> C Slave Receive Data Register (I2CS_RECV)       |      |

|    |                    | I <sup>2</sup> C Slave Address Setup Register (I2CS_SADRS)     |      |

|    |                    | I <sup>2</sup> C Slave Control Register (I2CS_CTL)             |      |

|    |                    | I <sup>2</sup> C Slave Access Status Register (I2CS_ASTAT)     |      |

|    |                    | I <sup>2</sup> C Slave Interrupt Control Register (I2CS_ICTL)  |      |

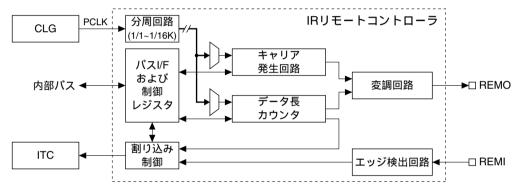

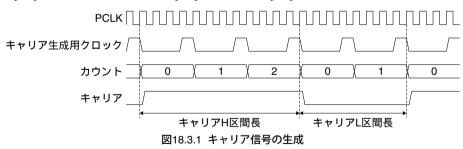

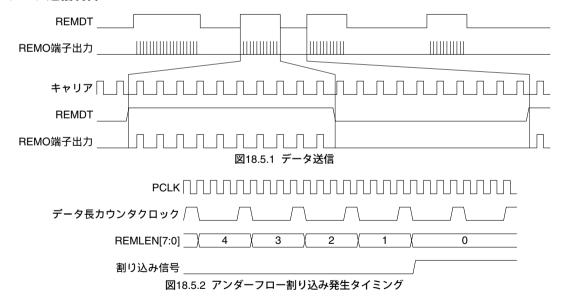

| 18 | IRリモ               | ートコントローラ(REMC)                                                 | 18-1 |

|    |                    | REMCモジュールの概要                                                   |      |

|    |                    | REMC入出力端子                                                      |      |

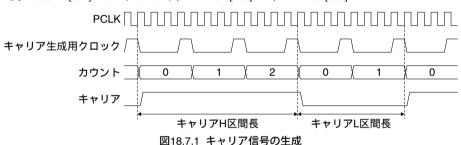

|    |                    | キャリアの生成                                                        |      |

|    |                    | データ長カウンタのクロック設定                                                |      |

|    |                    |                                                                |      |

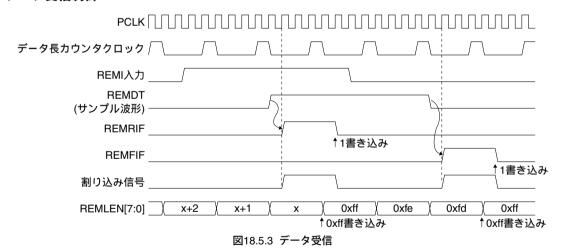

|    | 18.5  | データ送受信の制御                                                                                  | 18-3  |

|----|-------|--------------------------------------------------------------------------------------------|-------|

|    | 18.6  | REMC割り込み                                                                                   | 18-5  |

|    | 18.7  | 制御レジスタ詳細                                                                                   | 18-6  |

|    |       | REMC Configuration Register (REMC_CFG)                                                     | 18-6  |

|    |       | REMC Carrier Length Setup Register (REMC_CAR)                                              | 18-7  |

|    |       | REMC Length Counter Register (REMC_LCNT)                                                   |       |

|    |       | REMC Interrupt Control Register (REMC_INT)                                                 | 18-9  |

| 19 | LCD F | ライバ(LCD)                                                                                   | 19-1  |

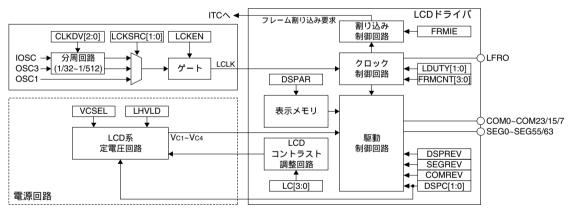

|    | 19.1  | LCDモジュールの概要                                                                                | 19-1  |

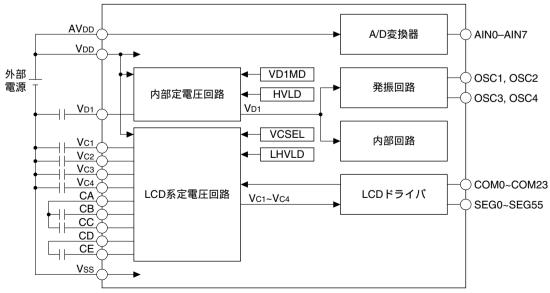

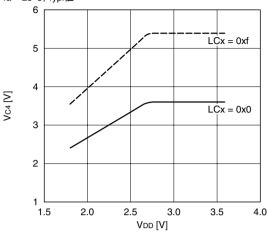

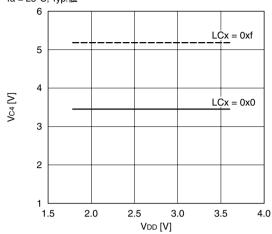

|    | 19.2  | LCD電源                                                                                      | 19-2  |

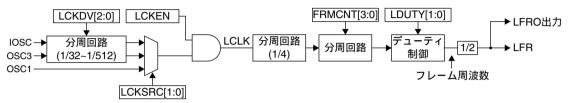

|    | 19.3  | LCDクロック                                                                                    | 19-2  |

|    |       | 19.3.1 LCD動作クロック(LCLK)                                                                     |       |

|    |       | 19.3.2 フレーム信号                                                                              |       |

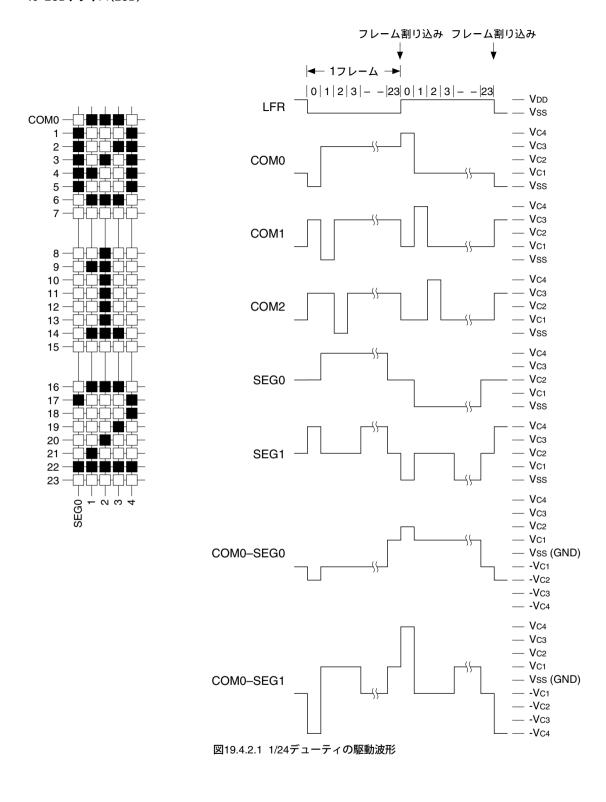

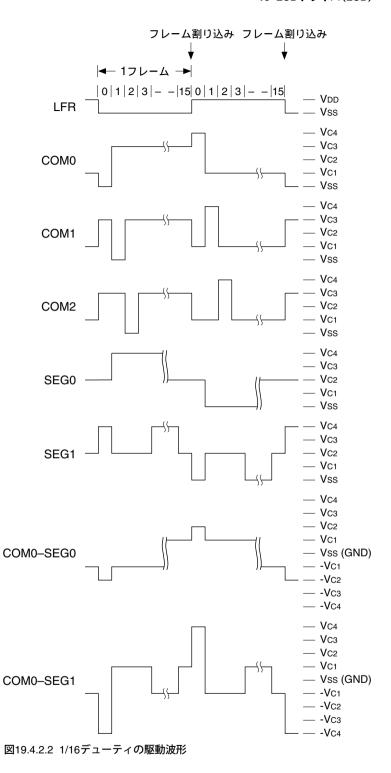

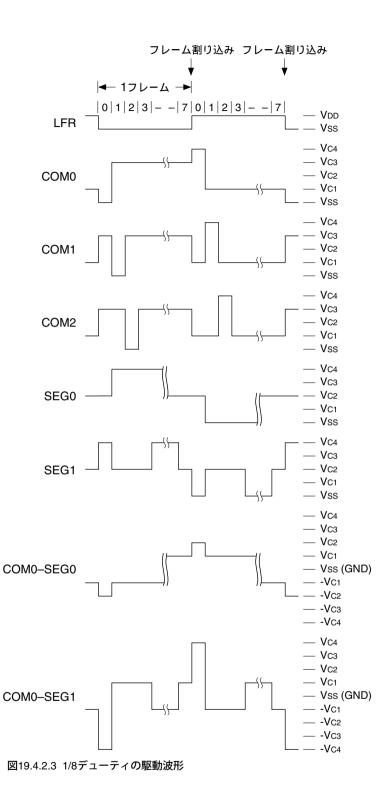

|    | 19.4  | 駆動デューティ制御                                                                                  | 19-3  |

|    |       | 19.4.1 駆動デューティの切り換え                                                                        | 19-3  |

|    |       | 19.4.2 駆動波形                                                                                | 19-3  |

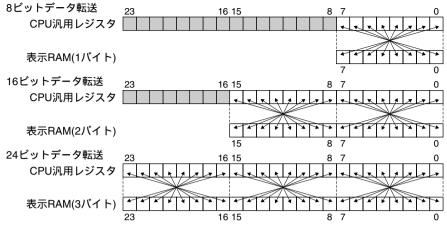

|    | 19.5  | 表示メモリ                                                                                      | 19-7  |

|    | 19.6  | 表示の制御                                                                                      | 19-11 |

|    |       | 19.6.1 表示のOn/Off                                                                           | 19-11 |

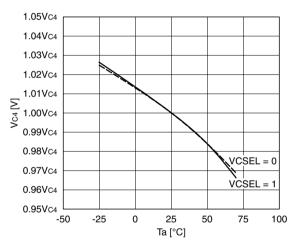

|    |       | 19.6.2 LCDコントラスト調整                                                                         | 19-11 |

|    |       | 19.6.3 反転表示                                                                                |       |

|    |       | 19.6.4 階調表示の制御                                                                             |       |

|    | 19.7  | LCD割り込み                                                                                    | 19-12 |

|    | 19.8  | 制御レジスタ詳細                                                                                   | 19-12 |

|    |       | LCD Clock Select Register (LCD_CLK)                                                        |       |

|    |       | LCD Display Control Register (LCD_DCTL)                                                    |       |

|    |       | LCD Contrast Adjustment Register (LCD_CADJ)                                                |       |

|    |       | LCD Clock Control Register (LCD_CCTL)<br>LCD Voltage Regulator Control Register (LCD_VREG) |       |

|    |       | LCD Interrupt Mask Register (LCD_IMSK)                                                     |       |

|    |       | LCD Interrupt Flag Register (LCD_IFLG)                                                     |       |

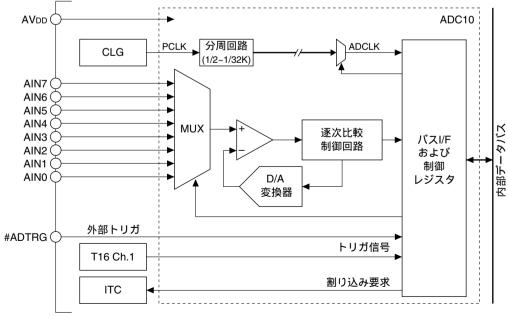

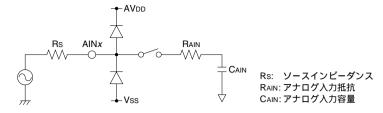

| 20 | A/D変料 | <b>奐器 (ADC10)</b>                                                                          | 20-1  |

|    |       | ADC10モジュールの概要                                                                              |       |

|    |       | ADC10入力端子                                                                                  |       |

|    |       | A/D変換器の設定                                                                                  |       |

|    | 20.0  | 20.3.1 A/D変換クロックの設定                                                                        |       |

|    |       | 20.3.2 A/D変換開始チャネル/終了チャネルの選択                                                               |       |

|    |       | 20.3.3 A/D変換モードの設定                                                                         |       |

|    |       | 20.3.4 トリガの選択                                                                              |       |

|    |       | 20.3.5 サンプリング時間の設定                                                                         |       |

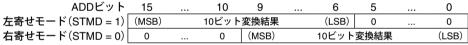

|    |       | 20.3.6 変換結果格納モードの設定                                                                        |       |

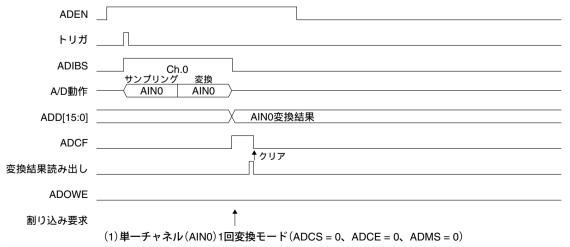

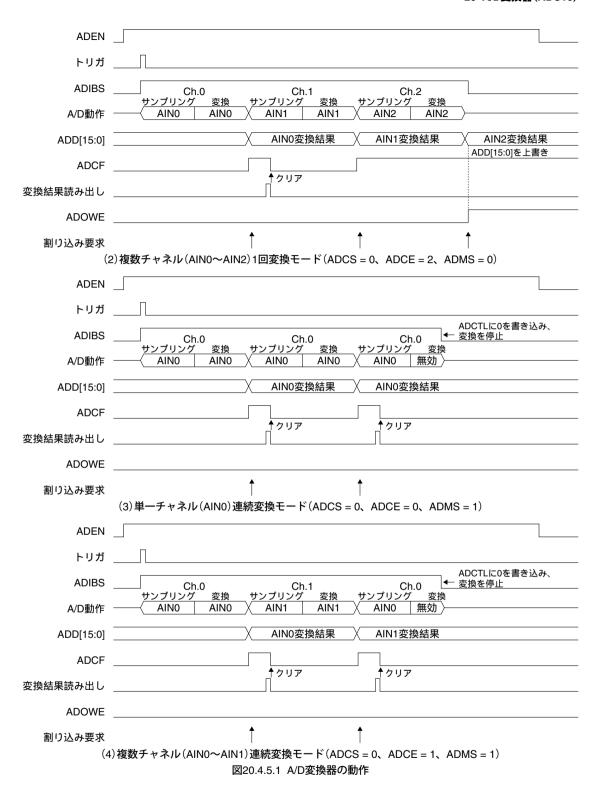

|    | 20.4  | A/D変換の制御と動作                                                                                | 20-5  |

|    |       | 20.4.1 A/D変換器の起動                                                                           | 20-5  |

|    |       | 20.4.2 A/D変換の開始                                                                            |       |

|    |       | 20.4.3 A/D変換結果の読み出し                                                                        |       |

|    |       | 20.4.4 A/D変換の終了                                                                            |       |

|    |       | 20.4.5 タイミングチャート                                                                           |       |

|    |       | A/D変換器割り込み                                                                                 |       |

|    | 20.6  | 制御レジスタ詳細                                                                                   |       |

|    |       | A/D Conversion Result Register (ADC10_ADD)                                                 |       |

|    |       | A/D Trigger/Channel Select Register (ADC10, TRG)                                           | つい-0  |

|    |                                                             | A/D Control/Status Register (ADC10_CTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

|----|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|    |                                                             | A/D Clock Control Register (ADC10_CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

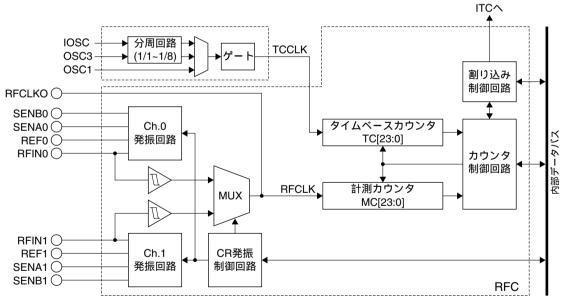

| 21 | R/F変換                                                       | 2器(RFC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21-1                         |

|    | 21.1                                                        | RFCモジュールの概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21-1                         |

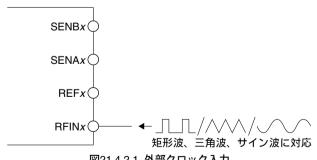

|    | 21.2                                                        | RFC入出力端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21-2                         |

|    | 21.3                                                        | 動作クロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21-2                         |

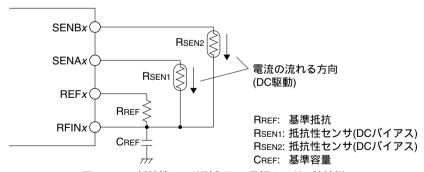

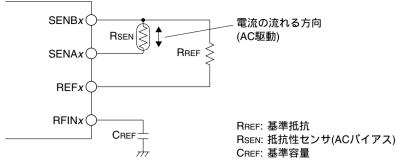

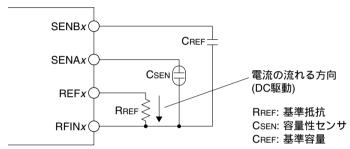

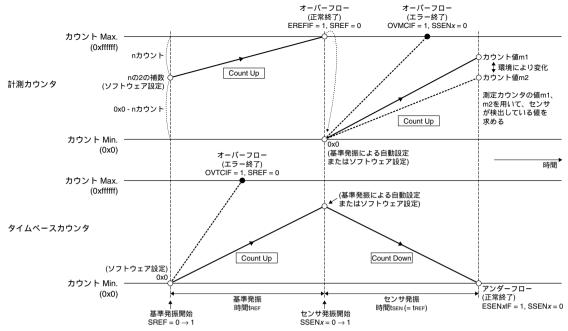

|    | 21.4                                                        | 動作モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21-3                         |

|    |                                                             | 21.4.1 発振モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21-3                         |

|    |                                                             | 21.4.2 外部クロック入力モード(イベントカウンタモード)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21-4                         |

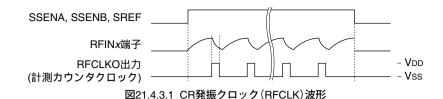

|    |                                                             | 21.4.3 CR発振クロック周波数測定用機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21-4                         |

|    | 21.5                                                        | RFCカウンタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21-5                         |

|    | 21.6                                                        | 変換動作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21-5                         |

|    |                                                             | 21.6.1 初期設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21-6                         |

|    |                                                             | 21.6.2 基準発振の制御                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |

|    |                                                             | 21.6.3 センサ発振の制御                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|    |                                                             | 21.6.4 強制終了                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

|    | o., =                                                       | 21.6.5 変換誤差について                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|    |                                                             | RFC割り込み                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

|    | 21.8                                                        | 制御レジスタ詳細                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

|    |                                                             | RFC Clock Control Register (RFC_CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |

|    |                                                             | RFC Control Register (RFC_CTL)RFC Oscillation Trigger Register (RFC_TRG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |

|    |                                                             | RFC Measurement Counter Low and High Registers (RFC_MCL, RFC_MCH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

|    |                                                             | RFC Time Base Counter Low and High Registers (RFC_TCL, RFC_TCH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|    |                                                             | RFC Interrupt Mask Register (RFC_IMSK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|    |                                                             | RFC Interrupt Flag Register (RFC_IFLG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

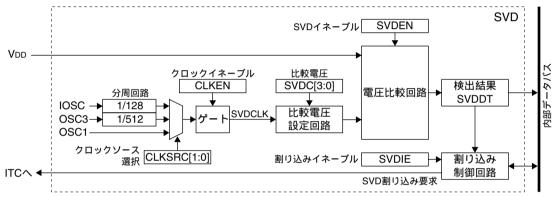

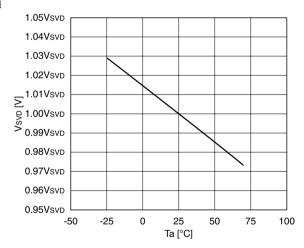

| 22 |                                                             | 王検出回路(SVD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                              |

|    |                                                             | SVDモジュールの概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

|    | 22.2                                                        | 動作クロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

|    |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              |

|    |                                                             | <b>助TFプロック 比較電圧の設定</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

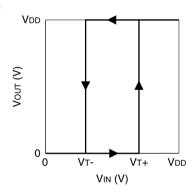

|    | 22.3                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22-2                         |

|    | 22.3<br>22.4                                                | 比較電圧の設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22-2<br>22-2                 |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22-2<br>22-2<br>22-3         |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定<br>SVDの制御<br>SVD割り込み<br>制御レジスタ詳細<br>SVD Clock Control Register (SVD_CLK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22-2<br>22-2<br>22-3<br>22-3 |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22-222-322-322-3             |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN) SVD Comparison Voltage Register (SVD_CMP)                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN) SVD Comparison Voltage Register (SVD_CMP) SVD Detection Result Register (SVD_RSLT)                                                                                                                                                                                                                                                                                                                                                                                         |                              |

|    | 22.3<br>22.4<br>22.5                                        | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN) SVD Comparison Voltage Register (SVD_CMP) SVD Detection Result Register (SVD_RSLT) SVD Interrupt Mask Register (SVD_IMSK)                                                                                                                                                                                                                                                                                                                                                  |                              |

| 23 | 22.3<br>22.4<br>22.5<br>22.6                                | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN) SVD Comparison Voltage Register (SVD_CMP) SVD Detection Result Register (SVD_RSLT) SVD Interrupt Mask Register (SVD_IMSK) SVD Interrupt Flag Register (SVD_IFLG)                                                                                                                                                                                                                                                                                                           |                              |

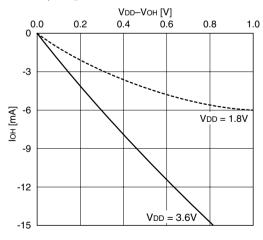

| 23 | 22.3<br>22.4<br>22.5<br>22.6                                | 比較電圧の設定 SVDの制御 SVD割り込み 制御レジスタ詳細 SVD Clock Control Register (SVD_CLK) SVD Enable Register (SVD_EN) SVD Comparison Voltage Register (SVD_CMP) SVD Detection Result Register (SVD_RSLT) SVD Interrupt Mask Register (SVD_IMSK) SVD Interrupt Flag Register (SVD_IFLG)                                                                                                                                                                                                                                                                                                           |                              |