## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 出荷形態の一部新規受付終了                                                        |           |      |     |

|-------------------------------------------------------------------------|-----------|------|-----|

| 対象マニュアル                                                                 | 発行 No.    | 項目   | ページ |

| S1C17704 テクニカルマニュアル                                                     | 411511804 | 出荷形態 | 1-2 |

| (誤)                                                                     |           |      |     |

| ●出荷形態                                                                   |           |      |     |

| • TQFP24-144pinプラスチックパッケージ<br>(16mm × 16mm × 1.0mm、リードピッチ: 0.4mm)       |           |      |     |

| • PFBGA6U96パッケージ <sup>(注)</sup><br>(6mm × 6mm × 1.0mm、ポールピッチ: 0.5mm)    |           |      |     |

| • VFBGA7H-161パッケージ<br>(7mm × 7mm × 1.0mm、ポールピッチ: 0.5mm)                 |           |      |     |

| • VFBGA10H-144パッケージ<br>(10mm × 10mm × 1.0mm、ポールピッチ: 0.8mm)              |           |      |     |

| • チップ                                                                   |           |      |     |

| (正)                                                                     |           |      |     |

| ●出荷形態                                                                   |           |      |     |

| • TQFP24-144pinプラスチックパッケージ<br>(16mm × 16mm × 1.0mm、リードピッチ: 0.4mm)       |           |      |     |

| • PFBGA6U96パッケージ <sup>(注)</sup><br>(6mm × 6mm × 1.0mm、ポールピッチ: 0.5mm) #1 |           |      |     |

| • VFBGA7H-161パッケージ<br>(7mm × 7mm × 1.0mm、ポールピッチ: 0.5mm)                 |           |      |     |

| • VFBGA10H-144パッケージ<br>(10mm × 10mm × 1.0mm、ポールピッチ: 0.8mm)              |           |      |     |

| • チップ                                                                   |           |      |     |

| #1 : PFBGA6U96 は新規受付終了                                                  |           |      |     |

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 LCD 駆動電圧             |           |                 |       |

|-------------------------|-----------|-----------------|-------|

| 対象マニュアル                 | 発行 No.    | 項目              | ページ   |

| S1C17701 テクニカルマニュアル     | 412445600 | 26.4 アナログ回路特性   | 26-3  |

| S1C17702 テクニカルマニュアル     | 411602402 | 27.4 アナログ回路特性   | 27-3  |

| S1C17704 テクニカルマニュアル     | 411511804 | 26.4 アナログ回路特性   | 26-3  |

| S1C17705/703 テクニカルマニュアル | 411706502 | 25.9 LCD ドライバ特性 | 25-10 |

| S1C17706 テクニカルマニュアル     | 412026301 | 27.9 LCD ドライバ特性 | 27-7  |

|                         |           |                 |       |

(誤)

特記なき場合:  $V_{DD} = 1.8\text{--}3.6V$ ,  $V_{SS} = 0V$ ,  $T_a = 25^\circ\text{C}$ ,  $C_1\text{--}C_{11} = 0.1\mu\text{F}$ , 市松模様出力時, パネル負荷なし

| 項目      | 記号       | 条件                                                 | Min.            | Typ. | Max.         | 単位 |

|---------|----------|----------------------------------------------------|-----------------|------|--------------|----|

| LCD駆動電圧 | $V_{C1}$ | $V_{SS}\text{--}V_{C1}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.18V_{C5}$    |      | $0.22V_{C5}$ | V  |

|         | $V_{C2}$ | $V_{SS}\text{--}V_{C2}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.39V_{C5}$    |      | $0.43V_{C5}$ | V  |

|         | $V_{C3}$ | $V_{SS}\text{--}V_{C3}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.59V_{C5}$    |      | $0.63V_{C5}$ | V  |

|         | $V_{C4}$ | $V_{SS}\text{--}V_{C4}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.79V_{C5}$    |      | $0.83V_{C5}$ | V  |

|         | $V_{C5}$ | $V_{SS}\text{--}V_{C5}$ 間に $1M\Omega$ の負荷<br>抵抗を接続 | $LC[3:0] = 0x0$ |      | 4.20         | V  |

|         |          |                                                    | $LC[3:0] = 0x1$ |      | 4.30         | V  |

(正)

特記なき場合:  $V_{DD} = 1.8\text{--}3.6V$ ,  $V_{SS} = 0V$ ,  $T_a = 25^\circ\text{C}$ ,  $C_1\text{--}C_{11} = 0.1\mu\text{F}$ , 市松模様出力時, パネル負荷なし

| 項目      | 記号       | 条件                                                 | Min.            | Typ. | Max.         | 単位 |

|---------|----------|----------------------------------------------------|-----------------|------|--------------|----|

| LCD駆動電圧 | $V_{C1}$ | $V_{SS}\text{--}V_{C1}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.18V_{C5}$    |      | $0.22V_{C5}$ | V  |

|         | $V_{C2}$ | $V_{SS}\text{--}V_{C2}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.39V_{C5}$    |      | $0.43V_{C5}$ | V  |

|         | $V_{C3}$ | $V_{SS}\text{--}V_{C3}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.59V_{C5}$    |      | $0.63V_{C5}$ | V  |

|         | $V_{C4}$ | $V_{SS}\text{--}V_{C4}$ 間に $1M\Omega$ の負荷抵抗を接続     | $0.79V_{C5}$    |      | $0.83V_{C5}$ | V  |

|         | $V_{C5}$ | $V_{SS}\text{--}V_{C5}$ 間に $1M\Omega$ の負荷<br>抵抗を接続 | $LC[3:0] = 0x0$ |      | 4.20         | V  |

|         |          |                                                    | $LC[3:0] = 0x1$ |      | 4.30         | V  |

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 I2CM 入出力端子       |           |                    |        |

|---------------------|-----------|--------------------|--------|

| 対象マニュアル             | 発行 No.    | 項目                 | ページ    |

| S1C17601 テクニカルマニュアル | 411806001 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17611 テクニカルマニュアル | 411882201 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17701 テクニカルマニュアル | 411089703 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17704 テクニカルマニュアル | 411511803 | 20.2 I2C 入出力端子     | 20-2   |

| S1C17706 テクニカルマニュアル | 412026301 | 17.2 I2CM 入出力端子    | 17-1   |

| S1C17001 テクニカルマニュアル | 411412002 | 20.2 I2C 入出力端子     | 252    |

| S1C17002 テクニカルマニュアル | 411554302 | V.2.2 I2C マスタ入出力端子 | V-2-2  |

| S1C17003 テクニカルマニュアル | 411635002 | 20.2 I2C マスタ入出力端子  | 20-2   |

| S1C17501 テクニカルマニュアル | 411525502 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17801 テクニカルマニュアル | 411390602 | VI.2.2 I2C 入出力端子   | VI-2-2 |

| S1C17803 テクニカルマニュアル | 411820701 | 20.2 I2CM 入出力端子    | 20-1   |

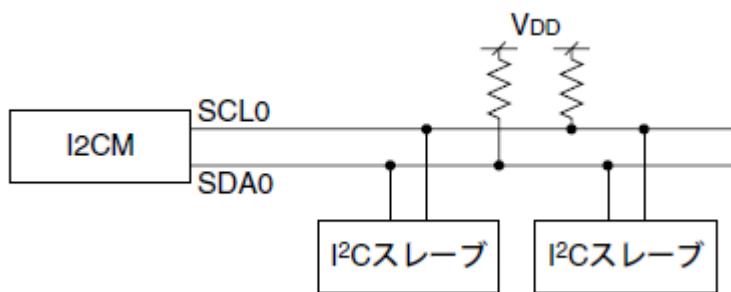

(追加)

注: ポート機能切り換え時は、端子がハイインピーダンスになります。High レベルは出力しませんので、SCL と SDA ラインは外部で VDD レベルにプルアップしてください。なお、VDD を超える電圧値にはプルアップしないでください。

## S1C17 ファミリテクニカルマニュアル正誤表

| 項目 T16E フайнモードについて                                                                                                                                                                            |           |                |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|------|

| 対象マニュアル                                                                                                                                                                                        | 発行 No.    | 項目             | ページ  |

| S1C17001 テクニカルマニュアル                                                                                                                                                                            | 411412003 | 13.6 クロック出力の制御 | 13-8 |

| S1C17003 テクニカルマニュアル                                                                                                                                                                            | 411635002 | 13.6 クロック出力の制御 | 13-8 |

| S1C17624/604/622/602/621 テクニカルマニュアル                                                                                                                                                            | 411014802 | 12.7 クロック出力の制御 | 12-6 |

| S1C17701 テクニカルマニュアル                                                                                                                                                                            | 411089704 | 13.6 クロック出力の制御 | 13-8 |

| S1C17702 テクニカルマニュアル                                                                                                                                                                            | 411602402 | 13.6 クロック出力の制御 | 13-8 |

| S1C17704 テクニカルマニュアル                                                                                                                                                                            | 411511804 | 13.6 クロック出力の制御 | 13-8 |

| <b>150 ページ</b> S1C17001 テクニカルマニュアル<br><b>13-8 ページ</b> S1C17003 テクニカルマニュアル<br><b>13-8 ページ</b> S1C17701 テクニカルマニュアル<br><b>13-8 ページ</b> S1C17702 テクニカルマニュアル<br><b>13-8 ページ</b> S1C17704 テクニカルマニュアル |           |                |      |

| <b>「クロック出力ファインモードの設定」の注意事項に、以下の記載を追加</b><br>(3) フайнモードは、T16EDF = 0x0 (PCLK 1/1)のみで使用してください。                                                                                                   |           |                |      |

| <b>12-6 ページ</b> S1C17624/604/622/602/621 テクニカルマニュアル                                                                                                                                            |           |                |      |

| <b>「クロック出力ファインモードの設定」の注意事項に、以下の記載を追加</b><br>(4) フайнモードは、T16EDF = 0x0 (PCLK 1/1)のみで使用してください。                                                                                                   |           |                |      |

## S1C17 マニュアル 正誤表

| 項目 T8OSC1 使用時の HALT からの復帰                                                                                  |           |                   |       |

|------------------------------------------------------------------------------------------------------------|-----------|-------------------|-------|

| 対象マニュアル                                                                                                    | 発行 No.    | 項目                | ページ   |

| S1C17701 テクニカルマニュアル                                                                                        | 411089704 | 14 ビット OSC1 タイマ   | 14-7  |

| S1C17704 テクニカルマニュアル                                                                                        | 411511804 | Appendix C パワーセーブ | AP-31 |

|                                                                                                            |           |                   | AP-32 |

|                                                                                                            |           |                   |       |

|                                                                                                            |           |                   |       |

|                                                                                                            |           |                   |       |

| (誤)                                                                                                        |           |                   |       |

| 注: 不要な割り込みの発生を防止するため、T8OIE によって 8 ビット OSC1 タイマ割り込みを許可する前に、T8OIF をリセットしてください。                               |           |                   |       |

| (正)                                                                                                        |           |                   |       |

| 注: 不要な割り込みの発生を防止するため、T8OIE によって 8 ビット OSC1 タイマ割り込みを許可する前に、T8OIF をリセットしてください。                               |           |                   |       |

| ・PCLK を OFF にしていると、カウンタがコンペアデータレジスタの設定値に一致しても T8OIF がセットされず、割り込みが発生しません。割り込みを使用する場合には PCLK を ON で使用してください。 |           |                   |       |

(誤)

PCLK で動作する周辺モジュール

- プリスケーラ (PWM&キャプチャタイマ、リモートコントローラ、P ポート)

- UART

- 8 ビットタイマ

- 16 ビットタイマ Ch.0~2

- 割り込みコントローラ

- SPI

- I2C

- SVD 回路

- 電源制御回路

- P ポート&ポート MUX (制御レジスタ、チャタリング除去)

- PWM&キャプチャタイマ

- MISC レジスタ

- リモートコントローラ

(正)

PCLK で動作する周辺モジュール

- プリスケーラ (PWM&キャプチャタイマ、リモートコントローラ、P ポート)

- UART

- 8 ビットタイマ

- 16 ビットタイマ Ch.0~2

- 割り込みコントローラ

- SPI

- I2C

- SVD 回路

- 電源制御回路

- P ポート&ポート MUX (制御レジスタ、チャタリング除去)

- PWM&キャプチャタイマ

- MISC レジスタ

- リモートコントローラ

- 8 ビット OSC1 タイマ

(誤)

以下の周辺モジュールは制御レジスタへのアクセスを除き、**PCLK** 以外のクロックで動作します。

したがって、制御レジスタを設定して動作を開始後は **PCLK** は必要ありません。

- 計時タイマ

- ストップウォッチタイマ

- ウォッチドッグタイマ

- 8 ビット OSC1 タイマ

- LCD ドライバ

(正)

以下の周辺モジュールは制御レジスタへのアクセスを除き、**PCLK** 以外のクロックで動作します。

したがって、制御レジスタを設定して動作を開始後は **PCLK** は必要ありません。

- 計時タイマ

- ストップウォッチタイマ

- ウォッチドッグタイマ

- 8 ビット OSC1 タイマ

- LCD ドライバ

## S1C17 マニュアル 正誤表

| 項目 | 対象マニュアル             | 発行 No.    | 項目            | ページ |

|----|---------------------|-----------|---------------|-----|

|    | S1C17701 テクニカルマニュアル | 411089704 | 8 クロックジェネレーター | 8-1 |

|    | S1C17704 テクニカルマニュアル | 411511804 |               | 8-2 |

|    |                     |           |               | 8-4 |

|    |                     |           |               | 8-6 |

|    |                     |           |               |     |

|    |                     |           |               |     |

|    |                     |           |               |     |

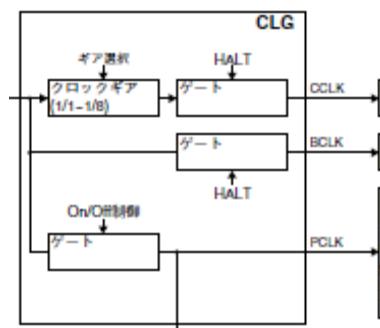

(誤)

(正)

(クロックギア部を削除)

(誤)

(正)

(クロックギア部を削除)

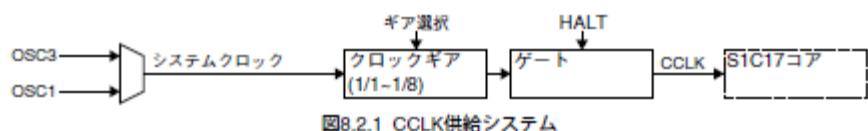

(誤)

**クロックギアの設定**

CCLKGR[1:0](D[1:0]/CLG\_CCLKレジスタ)でシステムクロックを減速するギア比を選択します。

\* CCLKGR[1:0]: CCLK Clock Gear Ratio Select Bits in the CCLK Control (CLG\_CCLK) Register (D[1:0]/0x5081)

表8.2.1 CCLKギア比の選択

| CCLKGR[1:0] | ギア比 |

|-------------|-----|

| 0x3         | 1/8 |

| 0x2         | 1/4 |

| 0x1         | 1/2 |

| 0x0         | 1/1 |

(デフォルト:0x0)

(正)

(記述を全て削除)

(誤)

表8.4.1 CLGレジスター一覧

| アドレス   | レジスター名   |                       | 機能         |

|--------|----------|-----------------------|------------|

| 0x5080 | CLG_PCLK | PCLK Control Register | PCLK供給制御   |

| 0x5081 | CLG_CCLK | CCLK Control Register | CCLK分周比の設定 |

(正)

(0x5081 番地を削除)

(誤)

**0x5081: CCLK Control Register (CLG\_CCLK)**

| Register name                    | Address | Bit  | Name     | Function | Setting | Init. | R/W | Remarks            |

|----------------------------------|---------|------|----------|----------|---------|-------|-----|--------------------|

| CCLK Control Register (CLG_CCLK) | 0x5081  | D7-2 | reserved |          | -       | -     | -   | 0 when being read. |

D[7:2] Reserved

D[1:0] CCLKGR[1:0]: CCLK Clock Gear Ratio Select Bits

システムクロックを減速するギア比を選択し、SIC17コアを動作させるCCLKクロックの速度を設定します。できるだけ低速なクロックでSIC17コアを動作させることで消費電流を抑えることができます。

表8.4.3 CCLKギア比の選択

| CCLKGR[1:0] | ギア比 |

|-------------|-----|

| 0x3         | 1/8 |

| 0x2         | 1/4 |

| 0x1         | 1/2 |

| 0x0         | 1/1 |

(デフォルト:0x0)

(正)

(記述を全て削除)

## S1C17 マニュアル 正誤表

| 項目 8 ビット OSC1 タイマ, 計時タイマ, ストップウォッチタイマの割り込みイネーブル動作 |           |                      |                |

|---------------------------------------------------|-----------|----------------------|----------------|

| 対象マニュアル                                           | 発行 No.    | 項目                   | ページ            |

| S1C17701 テクニカルマニュアル                               | 411089704 | 8 ビット OSC1 タイマ       | 14-13          |

| S1C17704 テクニカルマニュアル                               | 411511804 | 計時タイマ<br>ストップウォッチタイマ | 15-10<br>16-11 |

|                                                   |           |                      |                |

|                                                   |           |                      |                |

|                                                   |           |                      |                |

|                                                   |           |                      |                |

(誤)

D0 T8OIE: 8-bit OSC1 Timer Interrupt Enable Bit

コンペアマッチによる割り込みを許可または禁止します。

1(R/W): 割り込み許可

0(R/W): 割り込み禁止(デフォルト)

T8OIE を 1 に設定すると ITC への 8 ビット OSC1 タイマ割り込み要求が許可され、0 に設定すると割り込みが禁止されます。なお、割り込みを発生させるには、ITC の 8 ビット OSC1 タイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

(正)

D0 T8OIE: 8-bit OSC1 Timer Interrupt Enable Bit

コンペアマッチによる割り込みフラグのセットを許可または禁止します。

1(R/W): 割り込みフラグセット許可

0(R/W): 割り込みフラグセット禁止(デフォルト)

T8OIE を 1 に設定すると ITC への 8 ビット OSC1 タイマ割り込み要求フラグのセットが許可され、0 に設定すると割り込みフラグのセットが禁止されます。なお、割り込みを発生させるには、ITC の 8 ビット OSC1 タイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

注: T8OIF (D0/T8OSC1\_IFLG レジスタ)が 1 の場合に本ビットを 0 に設定しても、CPU への割り込みリクエストは禁止されません。割り込みリクエストの禁止を行なう場合は、割り込みコントローラー(ITC)のマスク機能を使用してください。

(誤)

本レジスタは、計時タイマの 32Hz、8Hz、2Hz、1Hz 信号による割り込み要求を個々に許可または禁止します。CTIE\*ビットを 1 に設定すると、対応する周波数の信号の立ち下がりエッジによる計時タイマ割り込み要求が許可され、0 に設定すると割り込みが禁止されます。

なお、割り込みを発生させるには、ITC の計時タイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

**D[7:4] Reserved**

**D3 CTIE32: 32 Hz Interrupt Enable Bit**

32Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

**D2 CTIE8: 8 Hz Interrupt Enable Bit**

8Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

**D1 CTIE2: 2 Hz Interrupt Enable Bit**

2Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

**D0 CTIE1: 1 Hz Interrupt Enable Bit**

1Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

(正)

本レジスタは、計時タイマの 32Hz、8Hz、2Hz、1Hz 信号による割り込み要求フラグのセットを個々に許可または禁止します。CTIE\*ビットを 1 に設定すると、対応する周波数の信号の立ち下がりエッジによる計時タイマ割り込み要求フラグのセットが許可され、0 に設定すると割り込みフラグのセットが禁止されます。

なお、割り込みを発生させるには、ITC の計時タイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

**D[7:4] Reserved**

**D3 CTIE32: 32 Hz Interrupt Enable Bit**

32Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**D2 CTIE8: 8 Hz Interrupt Enable Bit**

8Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**D1 CTIE2: 2 Hz Interrupt Enable Bit**

2Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**D0 CTIE1: 1 Hz Interrupt Enable Bit**

1Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**注: CTIF32, CTIF8, CTIF2, CTIF1 (D[3:0]/CT\_JFLG レジスタ)が 1 の場合に、上記ビットの対応するものを 0 に設定しても、CPU への割り込みリクエストは禁止されません。割り込みリクエストの禁止を行なう場合は、割り込みコントローラー(ITC)のマスク機能を使用してください。**

**この場合は、要因毎の個別の割り込み禁止は出来ません。**

(誤)

本レジスタは、ストップウォッチタイマの 100Hz、10Hz、1Hz 信号による割り込み要求を個々に許可または禁止します。SIE\*ビットを 1 に設定すると、対応する周波数の信号の立ち下がりエッジによるストップウォッチタイマ割り込み要求が許可され、0 に設定すると割り込みが禁止されます。

なお、割り込みを発生させるには、ITC のストップウォッチタイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

**D[7:3] Reserved****D2 SIE1: 1 Hz Interrupt Enable Bit**

1Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

**D1 SIE10: 10 Hz Interrupt Enable Bit**

10Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

**D0 SIE100: 100 Hz Interrupt Enable Bit**

100Hz 信号による割り込みを許可または禁止します。

1 (R/W) : 割り込み許可

0 (R/W) : 割り込み禁止 (デフォルト)

(正)

本レジスタは、ストップウォッチタイマの 100Hz、10Hz、1Hz 信号による割り込み要求フラグのセットを個々に許可または禁止します。SIE\*ビットを 1 に設定すると、対応する周波数の信号の立ち下がりエッジによるストップウォッチタイマ割り込み要求フラグのセットが許可され、0 に設定すると割り込みフラグのセットが禁止されます。

なお、割り込みを発生させるには、ITC のストップウォッチタイマ割り込みイネーブルビットも割り込み許可に設定する必要があります。

**D[7:3] Reserved****D2 SIE1: 1 Hz Interrupt Enable Bit**

1Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**D1 SIE10: 10 Hz Interrupt Enable Bit**

10Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**D0 SIE100: 100 Hz Interrupt Enable Bit**

100Hz 信号による割り込みフラグのセットを許可または禁止します。

1 (R/W) : 割り込みフラグのセット許可

0 (R/W) : 割り込みフラグのセット禁止 (デフォルト)

**注: SIF1, SIF10, SIF100 (D[2:0]/SWT\_JFLG レジスタ)が 1 の場合に、上記ビットの対応するものを 0 に設定しても、CPU への割り込みリクエストは禁止されません。割り込みリクエストの禁止を行なう場合は、割り込みコントローラー(ITC)のマスク機能を使用してください。**

**この場合は、要因毎の個別の割り込み禁止は出来ません。**