# **CMOS 16-BIT SINGLE CHIP MICROCONTROLLER**

# S1C17F63

テクニカルマニュアル

- 1. 本評価ボード・キット、開発ツールは、お客様での技術的評価、動作の確認および開発のみに用いられることを 想定し設計されています。それらの技術評価・開発等の目的以外には使用しないでください。本品は、完成品に 対する設計品質に適合していません。

- 2. 本評価ボード・キット、開発ツールは、電子エンジニア向けであり、消費者向け製品ではありません。お客様において、適切な使用と安全に配慮願います。弊社は、本品を用いることで発生する損害や火災に対し、いかなる責も負いかねます。通常の使用においても、異常がある場合は使用を中止してください。

- 3. 本評価ボード・キット、開発ツールに用いられる部品は、予告なく変更されることがあります。

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

- 1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

- 2. 弊社製品のご購入およびご使用にあたりましては、事前に弊社営業窓口で最新の情報をご確認いただきますとと もに、弊社ホームページなどを通じて公開される最新情報に常にご注意ください。

- 3. 本資料に掲載されている応用回路、プログラム、使用方法などはあくまでも参考情報です。お客様の機器・システムの設計において、応用回路、プログラム、使用方法などを使用する場合には、お客様の責任において行ってください。これらに起因する第三者の知的財産権およびその他の権利侵害ならびに損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

- 4. 弊社は常に品質、信頼性の向上に努めていますが、一般的に半導体製品は誤作動または故障する場合があります。 弊社製品のご使用にあたりましては、弊社製品の誤作動や故障により生命・身体に危害を及ぼすこと又は財産が 侵害されることのないように、お客様の責任において、お客様のハードウエア、ソフトウエア、システムに必要 な安全設計を行うようお願いします。なお、設計および使用に際しては、弊社製品に関する最新の情報(本資料、 仕様書、データシート、マニュアル、弊社ホームページなど)をご確認いただき、それに従ってください。また、 上記資料などに掲載されている製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他 応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価を行い、お客様の 責任において適用可否の判断をお願いします。

- 5. 弊社は、正確さを期すために慎重に本資料およびプログラムを作成しておりますが、本資料およびプログラムに掲載されている情報に誤りがないことを保証するものではありません。万一、本資料およびプログラムに掲載されている情報の誤りによってお客様に損害が生じた場合においても、弊社は一切その責任を負いかねます。

- 6. 弊社製品の分解、解析、リバースエンジニアリング、改造、改変、翻案、複製などは堅くお断りします。

- 7. 弊社製品は、一般的な電子機器(事務機器、通信機器、計測機器、家電製品など)および本資料に個別に掲載されている用途に使用されることを意図して設計、開発、製造されています(一般用途)。特別な品質、信頼性が要求され、その誤動作や故障により生命・身体に危害を及ぼす恐れ、膨大な財産侵害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある以下の特定用途に使用されることを意図していません。お客様に置かれましては、弊社製品を一般用途に使用されることを推奨いたします。もし一般用途以外の用途で弊社製品のご使用およびご購入を希望される場合、弊社はお客様の特定用途に弊社製品を使用されることへの商品性、適合性、安全性について、明示的・黙示的に関わらずいかなる保証を行うものではありません。お客様が特定用途での弊社製品の使用を希望される場合は、弊社営業窓口まで事前にご連絡の上、承諾を得てください。

#### 【特定用途】

宇宙機器(人工衛星・ロケットなど)/輸送車両並びにその制御機器(自動車・航空機・列車・船舶など) 医療機器(本資料に個別に掲載されている用途を除く)/海底中継機器/発電所制御機器/防災・防犯装置 交通用機器/金融関連機器

上記と同等の信頼性を必要とする用途

- 8. 本資料に掲載されている弊社製品および当該技術を国内外の法令および規制により製造・使用・販売が禁止されている機器・システムに使用することはできません。また、弊社製品および当該技術を大量破壊兵器等の開発および軍事利用の目的その他軍事用途等に使用しないでください。弊社製品または当該技術を輸出または海外に提供する場合は、「外国為替及び外国為替法」、「米国輸出管理規則(EAR)」、その他輸出関連法令を遵守し、係る法令の定めるところにより必要な手続きを行ってください。

- 9. お客様が本資料に掲載されている諸条件に反したことに起因して生じたいかなる損害(直接・間接を問わず)に関して、弊社は一切その責任を負いかねます。

- 10.お客様が弊社製品を第三者に譲渡、貸与などをしたことにより、損害が発生した場合、弊社は一切その責任を負いかねます。

- 11. 本資料についての詳細に関するお問合せ、その他お気付きの点などがありましたら、弊社営業窓口までご連絡ください。

- 12.本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

(Rev. J1.0, 2021.9)

## はじめに

本書はS1C17F63を使用する製品を開発される設計者、プログラマを対象とした技術マニュアルで、ICの機能、内蔵周辺回路の動作、およびその制御方法を説明します。

CPUの機能と命令については"S1C17 Family S1C17コアマニュアル"を、デバッグツールの機能と操作方法については各ツールのマニュアルを参照してください。(マニュアルは、弊社WEBサイト"製品情報: ドキュメントダウンロード"からダウンロード可能です。)

# 本書内の表記や記号について

#### レジスタのアドレス

各周辺回路の説明には制御レジスタのアドレスは記載されておりません。レジスタのアドレスは"メモリ,バス"の章の"周辺回路エリア"、またはAppendixの"周辺回路制御レジスタ一覧"を参照してください。

## レジスタと制御ビットの表記

説明の中では、レジスタや制御ビットを信号名や端子名と区別するため、次のように記載します。

XXXレジスタ: 1つのレジスタの全体を示します。

XXX.YYYビット: XXXレジスタ内にある1ビットの制御ビットYYYを示します。

XXX.ZZZ[1:0]ビット: XXXレジスタ内にある2ビットの制御ビットZZZ1とZZZ0を示します。

#### レジスタ表の内容と記号

Initial: 初期化時の値

Reset: 初期化条件。初期化条件はリセットグループ(H0、H1、S0)により決まります。リセットグループについては、"電源, リセット, クロック"の章の"初期化条件(リセットグループ)" を参照してください。

R/W: R = 読み出し可能 W = 書き込み可能

WP = 書き込み可能(MSCPROT.PROT[15:0]ビットによる書き込み保護あり)

R/W = 読み書き可能

R/WP = 読み書き可能(MSCPROT.PROT[15:0]ビットによる書き込み保護あり)

#### 制御ビットの読み出し/書き込み値

本書では1ビット値を除き、制御ビットの値を16進数で記載します(説明上、10進数や2進数が必要な場合を除く)。制御ビットのビット幅により次のように記載します。

1ビット: 0または1 2~4ビット: 0x0~0xf 5~8ビット: 0x00~0xff 9~12ビット: 0x000~0xfff 13~16ビット: 0x0000~0xffff

10進数: 0~9999...

2進数: 0b0000...~0b1111...

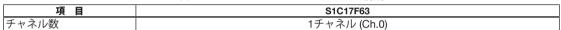

#### チャネル番号

周辺回路によっては複数チャネルの機能を搭載可能な場合があります(例: 16ビットタイマなど)。 これらの周辺回路の章は実装されているチャネル数にかかわらず、レジスタ名や端子名などに付いているチャネル番号を表す数値を'n'と記述しています。基本的に、説明は全チャネルに適用されます。機能が異なるチャネルについてはチャネル番号を明記しています。

例) 16ビットタイマのT16 nCTLレジスタ

1チャネル搭載機種(Ch.0のみ): T16\_nCTL = T16\_0CTLのみ 2チャネル搭載機種(Ch.0とCh.1): T16\_nCTL = T16\_0CTLとT16\_1CTL

本ICの周辺回路の搭載チャネル数は、"概要"の章の"特長"を参照してください。

# - 目 次 -

|   | V | はじ  | めに    |                                              | i   |

|---|---|-----|-------|----------------------------------------------|-----|

|   |   |     |       | 日や記号について                                     |     |

|   |   |     |       |                                              |     |

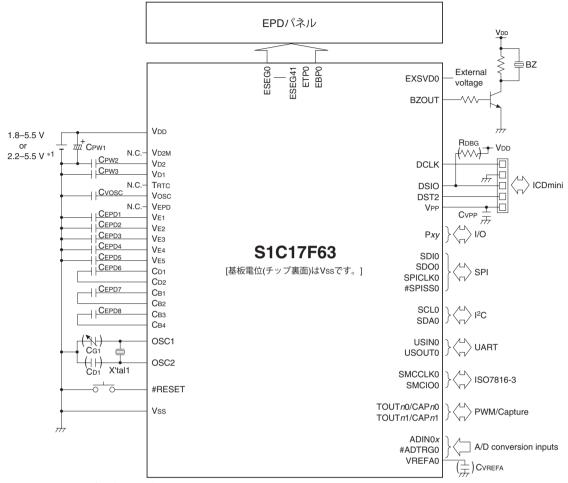

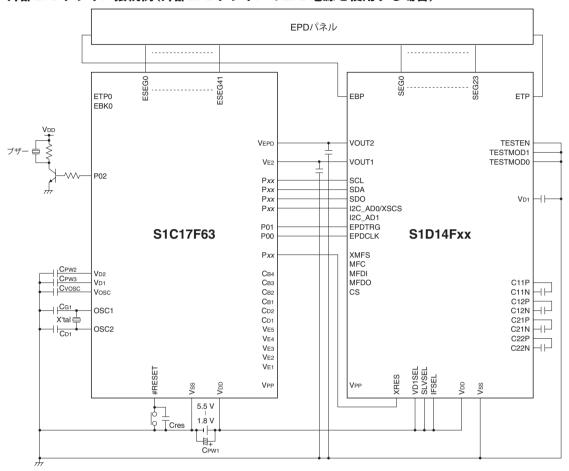

| 1 |   |     |       |                                              |     |

|   | 1 | 1.1 | 特長    |                                              | 1-1 |

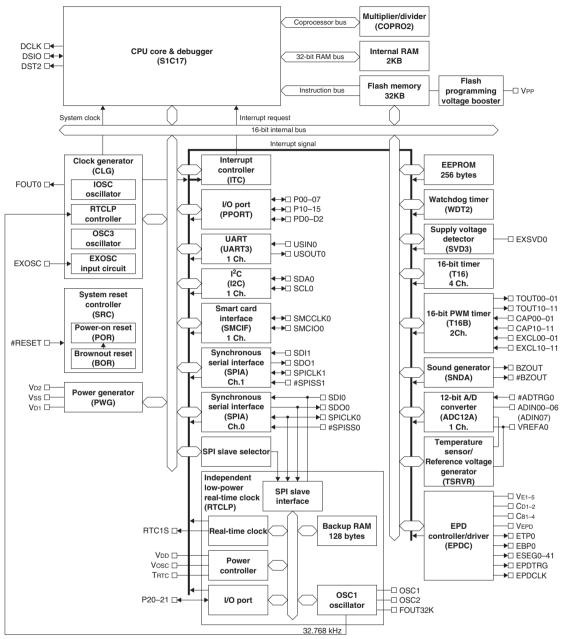

|   | 1 | 1.2 | ブロック  | 7図                                           | 1-4 |

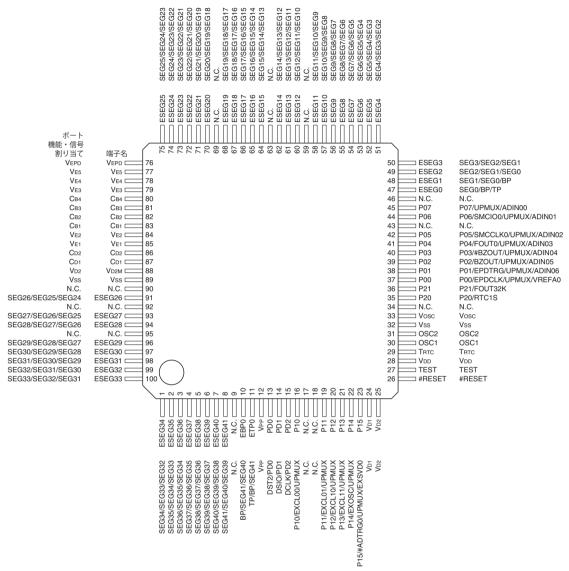

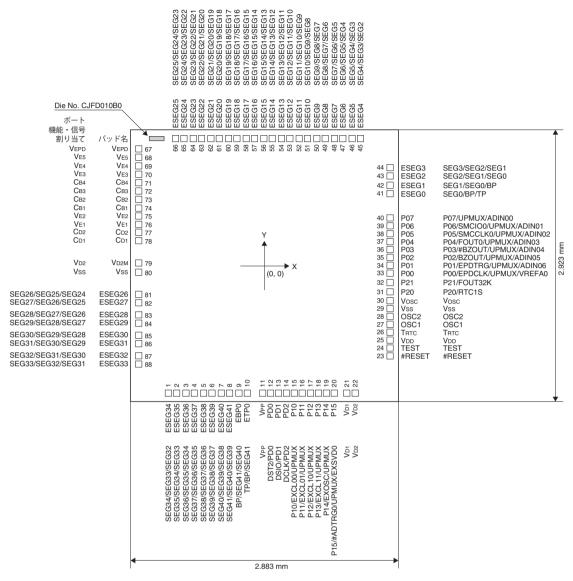

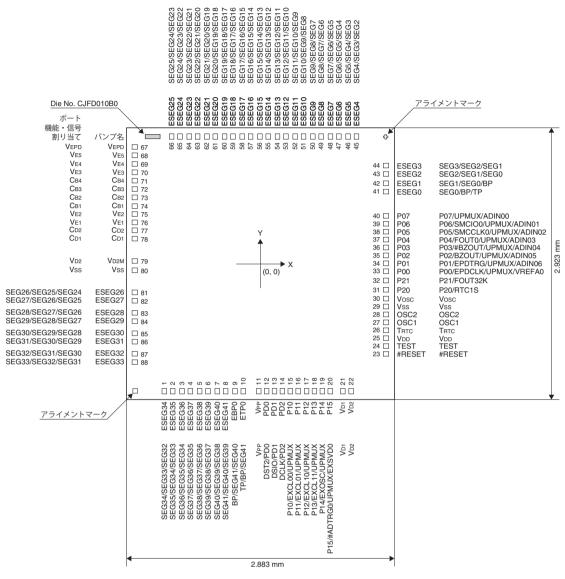

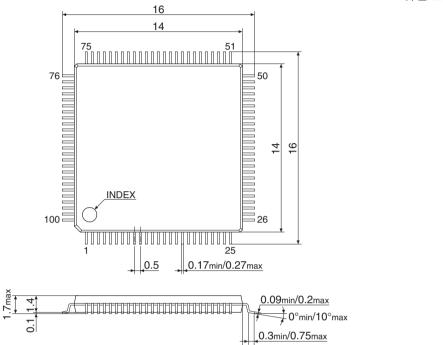

|   | 1 | 1.3 | 端子    |                                              | 1-5 |

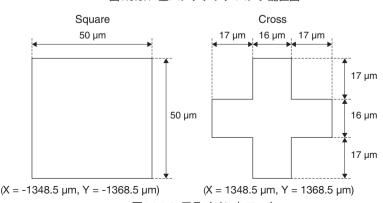

|   |   |     |       | QFP15-100PIN                                 |     |

|   |   |     |       | アルミパッドチップ                                    |     |

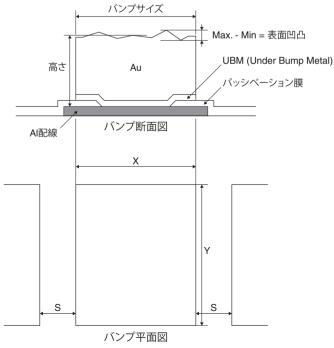

|   |   |     |       | 金バンプチップ                                      |     |

|   |   |     |       | 端子説明                                         |     |

| _ |   |     |       |                                              |     |

| 2 |   | •   |       | クロック                                         |     |

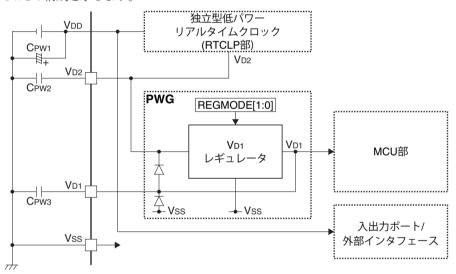

|   | 2 | 2.1 |       | シェネレータ(PWG)                                  |     |

|   |   |     | 2.1.1 | 概要                                           | 2-1 |

|   |   |     |       | 端子                                           |     |

|   |   |     | 2.1.3 | VD1レギュレータの動作モード                              | 2-2 |

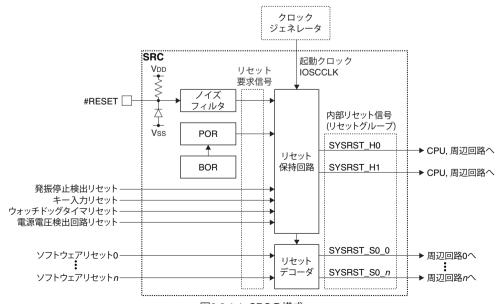

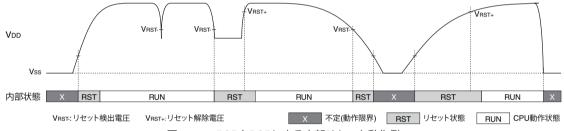

|   | 2 | 2.2 | システム  | ムリセットコントローラ(SRC)                             | 2-2 |

|   |   |     | 2.2.1 | 概要                                           | 2-2 |

|   |   |     | 2.2.2 | 入力端子                                         | 2-3 |

|   |   |     |       | リセットソース                                      |     |

|   |   |     |       | 初期化条件(リセットグループ)                              |     |

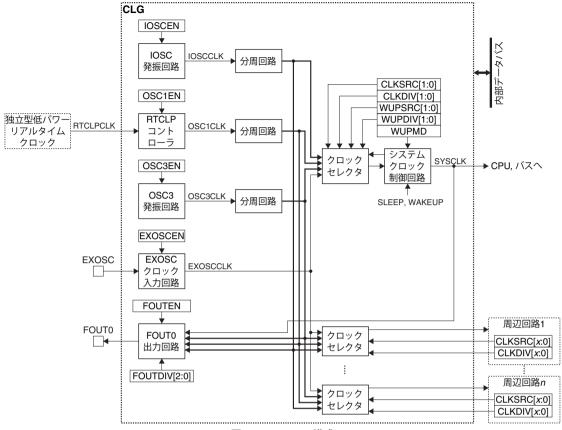

|   | 2 | 2.3 |       | プジェネレータ(CLG)                                 |     |

|   | - |     |       | 概要                                           |     |

|   |   |     |       | 入出力端子                                        |     |

|   |   |     |       | クロックソース                                      |     |

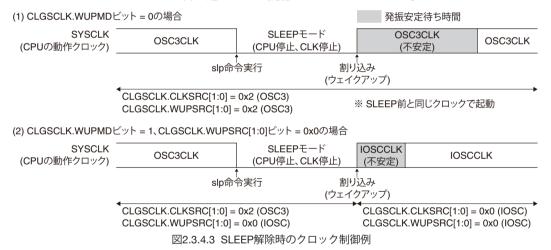

|   |   |     |       | 動作                                           |     |

|   | , | 2 4 |       | <del>=</del> 11F                             |     |

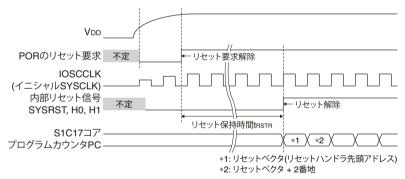

|   | 4 | 2.4 |       | - Mイニシャル起動シーケンス                              |     |

|   |   |     |       |                                              |     |

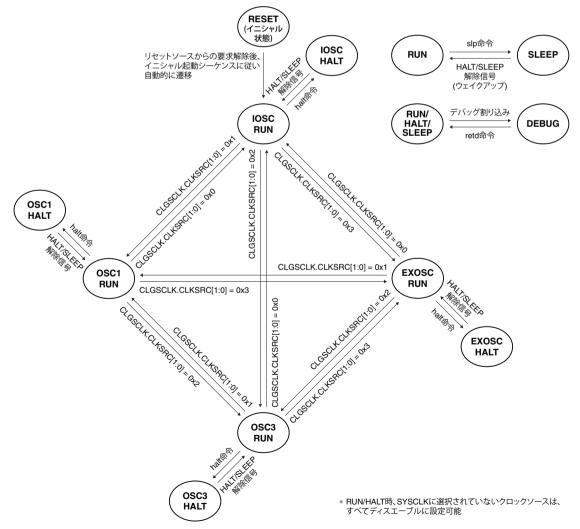

|   |   |     |       | 動作モードの遷移                                     |     |

|   |   |     |       | F                                            |     |

|   | 2 | 2.6 |       | <sup>ÿ</sup> スタ                              |     |

|   |   |     |       | G VD1 Control Register                       |     |

|   |   |     |       | System Clock Control Register                |     |

|   |   |     |       | Oscillation Control Register                 |     |

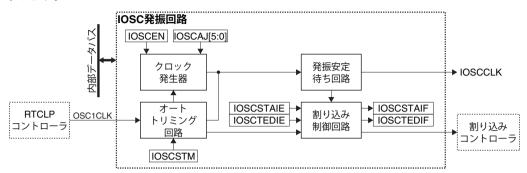

|   |   |     |       | IOSC Control Register                        |     |

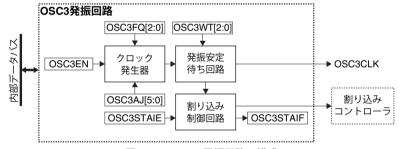

|   |   |     |       | OSC1 Trimming Register OSC3 Control Register |     |

|   |   |     |       | Interrupt Flag Register                      |     |

|   |   |     |       | Interrupt Enable Register                    |     |

|   |   |     |       | FOUT Control Register 0                      |     |

|   |   |     |       | Oscillation Frequency Trimming Register      |     |

| _ |   |     |       |                                              |     |

| 3 |   | -   |       |                                              |     |

|   | 3 | 3.1 | 概要    |                                              | 3-1 |

|   | 3 | 3.2 |       | 7                                            |     |

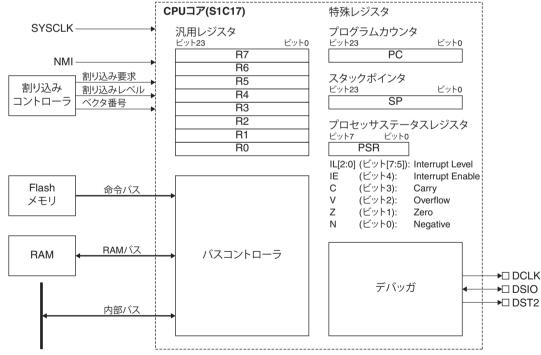

|   |   |     | 3.2.1 | CPUレジスタ                                      | 3-2 |

|   |   |     |       | 命令セット                                        |     |

|   |   |     |       | PSRの読み出し                                     |     |

|   |   |     |       | S1C17コア予約I/Oエリア                              |     |

|   |   | 3.3 |       | ÿ                                            |     |

|   | • |     |       | デバッグ機能                                       |     |

|   |   |     |       |                                              |     |

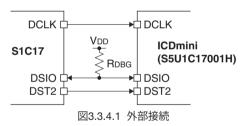

|   |           | 3.3.2 必要リソースとデバッグツール                                 |       |

|---|-----------|------------------------------------------------------|-------|

|   |           | 3.3.3 デバッガ入出力端子一覧                                    | 3-3   |

|   |           | 3.3.4 外部接続                                           |       |

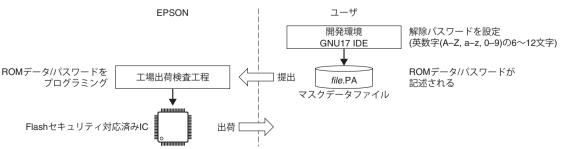

|   |           | 3.3.5 Flashセキュリティ機能                                  | 3-3   |

|   | 3.4       | 制御レジスタ                                               | 3-4   |

|   |           | MISC PSR Register                                    | . 3-4 |

|   |           | Debug RAM Base Register                              | . 3-4 |

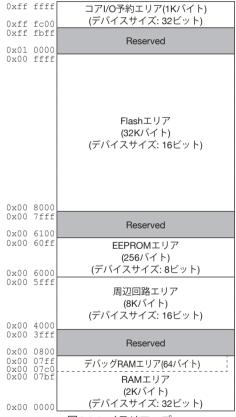

| 4 | メモリ.      | バス                                                   | .4-1  |

| • |           | 概要                                                   |       |

|   |           | バスアクセスサイクル                                           |       |

|   |           |                                                      |       |

|   | 4.3       | Flashメモリ                                             |       |

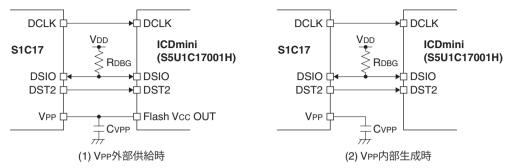

|   |           | 4.3.1 Flashメモリ端子                                     |       |

|   |           | 4.3.2 Flashバスアクセスサイクルの設定                             | 4-2   |

|   |           | 4.3.3 Flashプログラミング                                   |       |

|   | 4.4       | EEPROM                                               |       |

|   |           | 4.4.1 EEPROM端子                                       |       |

|   |           | 4.4.2 EEPROM操作                                       |       |

|   |           | 4.4.3 割り込み                                           |       |

|   |           | RAM                                                  |       |

|   | 4.6       | 周辺回路制御レジスタ                                           | 4-5   |

|   |           | 4.6.1 システムプロテクト機能                                    | 4-9   |

|   | 4.7       | 制御レジスタ                                               | 4-9   |

|   |           | MISC System Protect Register                         | . 4-9 |

|   |           | MISC IRAM Size Register                              |       |

|   |           | FLASHC Flash Read Cycle Register                     |       |

|   |           | EEPROMC Control Register 0                           |       |

|   |           | EEPROMC Control Register 1  EEPROMC Address Register |       |

|   |           | EEPROMC Write Data Register                          |       |

|   |           | EEPROMC Interrupt Flag Register                      |       |

|   |           | EEPROMC Interrupt Enable Register                    |       |

| _ | 空川 4127 1 | みコントローラ(ITC)                                         |       |

| Э |           | • •                                                  |       |

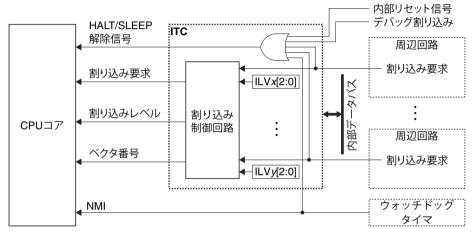

|   |           | 概要                                                   |       |

|   | 5.2       | ベクタテーブル                                              |       |

|   |           | 5.2.1 ベクタテーブルベースアドレス(TTBR)                           |       |

|   | 5.3       | 初期設定                                                 | 5-3   |

|   | 5.4       | マスク可能割り込みの制御と動作                                      |       |

|   |           | 5.4.1 周辺回路の割り込み制御                                    |       |

|   |           | 5.4.2 ITCの割り込み要求処理                                   |       |

|   |           | 5.4.3 CPUの割り込み要求受領条件                                 | 5-4   |

|   | 5.5       | NMI                                                  | 5-4   |

|   | 5.6       | ソフトウェア割り込み                                           | 5-4   |

|   | 5.7       | CPUによる割り込み処理                                         | 5-4   |

|   |           | 制御レジスタ                                               |       |

|   | 0.0       | MISC Vector Table Address Low Register               |       |

|   |           | MISC Vector Table Address High Register              |       |

|   |           | ITC Interrupt Level Setup Register x                 |       |

| 6 | አ !!! ታን  | ポート(PPORT)                                           | 6-1   |

| J |           | •                                                    |       |

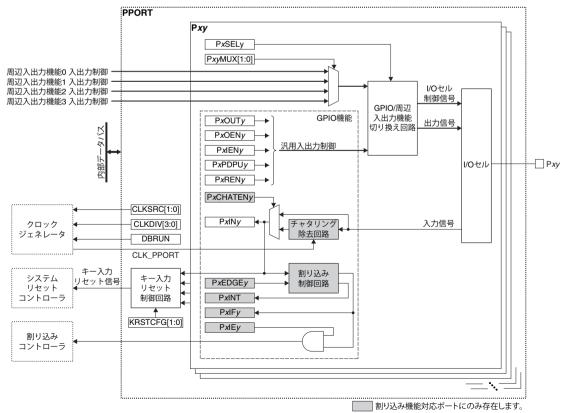

|   |           | 概要                                                   |       |

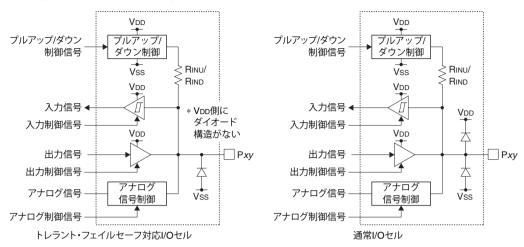

|   | 6.2       | I/Oセルの構造と機能                                          | 6-2   |

|   |           | N 2 L 2 J 2 W N A 11                                 | n-')  |

|   |                                                                                         | 6.2.2 トレラント・フェイルセーフ                                                                                                                                                                                                                                                                                                                                                                               | 6.0                                                                         |

|---|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|   |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         | 6.2.3 プルアップ/プルダウン                                                                                                                                                                                                                                                                                                                                                                                 | 6-2                                                                         |

|   |                                                                                         | 6.2.4 CMOS出力とハイインピーダンス状態                                                                                                                                                                                                                                                                                                                                                                          | 6-3                                                                         |

|   | 6.3                                                                                     | クロック設定                                                                                                                                                                                                                                                                                                                                                                                            | 6-3                                                                         |

|   |                                                                                         | 6.3.1 PPORTの動作クロック                                                                                                                                                                                                                                                                                                                                                                                | 6-3                                                                         |

|   |                                                                                         | 6.3.2 SLEEPモード時のクロック供給                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

|   |                                                                                         | 6.3.3 DEBUGモード時のクロック供給                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

|   | 6.4                                                                                     | 動作                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

|   | 0.4                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         | 6.4.1 初期設定                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

|   |                                                                                         | 6.4.2 ポートの入出力制御                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   | 6.5                                                                                     | 割り込み                                                                                                                                                                                                                                                                                                                                                                                              | 6-6                                                                         |

|   | 6.6                                                                                     | 制御レジスタ                                                                                                                                                                                                                                                                                                                                                                                            | 6-7                                                                         |

|   |                                                                                         | Px Port Data Register                                                                                                                                                                                                                                                                                                                                                                             |                                                                             |

|   |                                                                                         | Px Port Enable Register                                                                                                                                                                                                                                                                                                                                                                           |                                                                             |

|   |                                                                                         | Px Port Pull-up/down Control Register                                                                                                                                                                                                                                                                                                                                                             |                                                                             |

|   |                                                                                         | Px Port Interrupt Flag Register                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         | Px Port Interrupt Control Register                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

|   |                                                                                         | Px Port Chattering Filter Enable Register                                                                                                                                                                                                                                                                                                                                                         |                                                                             |

|   |                                                                                         | Px Port Mode Select Register                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |

|   |                                                                                         | Px Port Function Select Register                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |

|   |                                                                                         | P Port Clock Control Register                                                                                                                                                                                                                                                                                                                                                                     |                                                                             |

|   |                                                                                         | P Port Interrupt Flag Group Register                                                                                                                                                                                                                                                                                                                                                              |                                                                             |

|   | 6.7                                                                                     | 本ICの制御レジスタ/ポート機能の構成                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |

|   | 0.7                                                                                     | 4.7.1 POポートグループ                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         | 6.7.2 P1ポートグループ                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         | 6.7.3 Pdポートグループ                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

|   |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                   | C 11                                                                        |

|   |                                                                                         | 6.7.4 ポートグループ共通                                                                                                                                                                                                                                                                                                                                                                                   | 0-14                                                                        |

| 7 | ユニバ                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

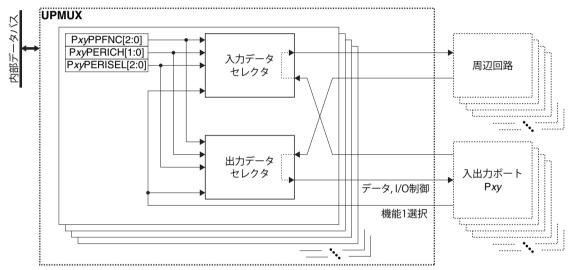

| 7 |                                                                                         | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | .7-1                                                                        |

| 7 | 7.1                                                                                     | ーサルポートマルチプレクサ(UPMUX)<br>概要                                                                                                                                                                                                                                                                                                                                                                        | . <b>7-1</b><br>7-1                                                         |

| 7 | 7.1<br>7.2                                                                              | <b>ーサルポートマルチプレクサ(UPMUX)</b><br>概要<br>周辺入出力機能の割り当て                                                                                                                                                                                                                                                                                                                                                 | . <b>7-1</b><br>7-1<br>7-1                                                  |

| 7 | 7.1<br>7.2                                                                              | <b>ーサルポートマルチプレクサ(UPMUX)</b><br>概要<br>周辺入出力機能の割り当て<br>制御レジスタ                                                                                                                                                                                                                                                                                                                                       | 7-1<br>7-1<br>7-1<br>7-2                                                    |

| 7 | 7.1<br>7.2                                                                              | <b>ーサルポートマルチプレクサ(UPMUX)</b><br>概要<br>周辺入出力機能の割り当て                                                                                                                                                                                                                                                                                                                                                 | 7-1<br>7-1<br>7-1<br>7-2                                                    |

|   | 7.1<br>7.2<br>7.3                                                                       | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | . <b>7-1</b><br>7-1<br>7-1<br>7-2<br>.7-2                                   |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b>                                                         | ーサルポートマルチプレクサ(UPMUX)<br>概要<br>周辺入出力機能の割り当て<br>制御レジスタ<br>Pxy-xz Universal Port Multiplexer Setting Register<br>チドッグタイマ(WDT2)                                                                                                                                                                                                                                                                       | 7-1<br>7-1<br>7-1<br>7-2<br>7-2                                             |

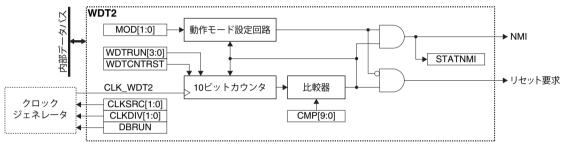

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1                                                  | ーサルポートマルチプレクサ(UPMUX)<br>概要<br>周辺入出力機能の割り当て<br>制御レジスタ<br>Pxy-xz Universal Port Multiplexer Setting Register<br>チドッグタイマ(WDT2)                                                                                                                                                                                                                                                                       | .7-1<br>7-1<br>7-1<br>7-2<br>.7-2<br>.8-1                                   |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1                                                  | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | .7-1<br>7-1<br>7-2<br>.7-2<br>.8-1<br>8-1                                   |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1                                                  | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | .7-1<br>7-1<br>7-2<br>.7-2<br>.8-1<br>8-1<br>8-1                            |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1                                                  | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | .7-1<br>7-1<br>7-2<br>.7-2<br>.8-1<br>8-1<br>8-1                            |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | . <b>7-1</b> 7-1 7-2 .7-2 .8-1 8-1 8-1 8-1 8-1                              |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | ーサルポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ  Pxy-xz Universal Port Multiplexer Setting Register  チドッグタイマ(WDT2)  概要  クロック設定  8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作                                                                                                                                                                                                                          | .7-1<br>7-1<br>7-2<br>.7-2<br>.8-1<br>8-1<br>8-1<br>8-1<br>8-2              |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | ーサルポートマルチプレクサ(UPMUX)                                                                                                                                                                                                                                                                                                                                                                              | .7-1<br>7-1<br>7-2<br>.7-2<br>.8-1<br>8-1<br>8-1<br>8-1<br>8-2<br>8-2       |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | ーサルポートマルチプレクサ(UPMUX) 概要                                                                                                                                                                                                                                                                                                                                                                           | 7-1 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-1 8-2 8-2 8-3                         |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | ーサルポートマルチプレクサ(UPMUX)         概要       周辺入出力機能の割り当て         制御レジスタ       Pxy-xz Universal Port Multiplexer Setting Register         チドッグタイマ(WDT2)         概要         クロック設定       8.2.1 WDT2の動作クロック         8.2.2 DEBUGモード時のクロック供給       動作         8.3.1 WDT2の制御       8.3.2 HALT, SLEEPモード時の動作         制御レジスタ       制御レジスタ                                                                       | 7-1 7-1 7-1 7-2 .7-2 .7-2 .8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3                  |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | 世界の表示を表現しています。 一世のポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ  Pxy-xz Universal Port Multiplexer Setting Register  チドッグタイマ(WDT2)  概要  クロック設定  8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作  8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ  WDT2 Clock Control Register                                                                                                                               | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3                         |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | 世界の表示を表現します。 一世のポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ  Pxy-xz Universal Port Multiplexer Setting Register.  チドッグタイマ(WDT2) 概要  クロック設定  8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作 8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ WDT2 Clock Control Register WDT2 Control Register                                                                                                             | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4                     |

|   | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2                                           | 世界の表示を表現しています。 一世のポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ  Pxy-xz Universal Port Multiplexer Setting Register  チドッグタイマ(WDT2)  概要  クロック設定  8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作  8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ  WDT2 Clock Control Register                                                                                                                               | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4                     |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3                                    | 世界の表示を表現します。 一世のポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ  Pxy-xz Universal Port Multiplexer Setting Register.  チドッグタイマ(WDT2) 概要  クロック設定  8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作 8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ WDT2 Clock Control Register WDT2 Control Register                                                                                                             | 7-1 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-3 8-4 8-4         |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3                                    | 根要                                                                                                                                                                                                                                                                                                                                                                                                | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 8-4                 |

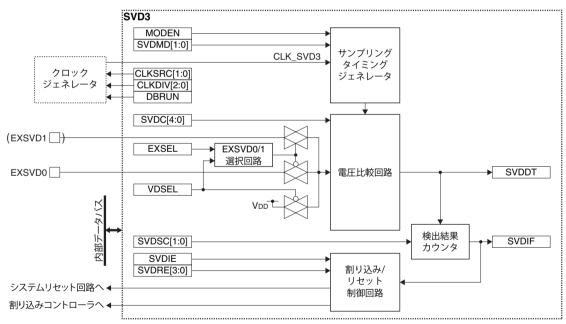

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1        | 根要                                                                                                                                                                                                                                                                                                                                                                                                | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 9-1                 |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1        | 世界の表示のでは、 一サルポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て                                                                                                                                                                                                                                                                                                                                                   | 7-1 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 9-1 9-1         |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1        | 世界の表別の表別の表別の表別の表別の表別の表別の表別の表別の表別の表別の表別の表別の                                                                                                                                                                                                                                                                                                                                                        | 7-1 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 9-1 9-2 9-2     |

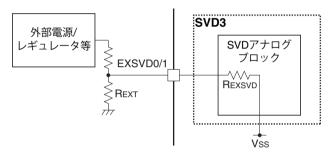

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1<br>9.2 | 一サルポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ Pxy-xz Universal Port Multiplexer Setting Register.  チドッグタイマ(WDT2) 概要 クロック設定 8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作 8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ WDT2 Clock Control Register WDT2 Control Register WDT2 Counter Compare Match Register. WDT2 Counter Compare Match Register.  E検出回路(SVD3) 概要 入力端子と外部接続 9.2.1 入力端子 9.2.2 外部との接続 | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-4 8-4 9-1 9-2 9-2         |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1<br>9.2 | 一サルポートマルチプレクサ(UPMUX) 概要                                                                                                                                                                                                                                                                                                                                                                           | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 9-1 9-2 9-2 9-2 9-2 |

| 8 | 7.1<br>7.2<br>7.3<br><b>ウォッ</b><br>8.1<br>8.2<br>8.3<br>8.4<br><b>電源電</b><br>9.1<br>9.2 | 一サルポートマルチプレクサ(UPMUX) 概要  周辺入出力機能の割り当て 制御レジスタ Pxy-xz Universal Port Multiplexer Setting Register.  チドッグタイマ(WDT2) 概要 クロック設定 8.2.1 WDT2の動作クロック 8.2.2 DEBUGモード時のクロック供給 動作 8.3.1 WDT2の制御 8.3.2 HALT, SLEEPモード時の動作 制御レジスタ WDT2 Clock Control Register WDT2 Control Register WDT2 Counter Compare Match Register. WDT2 Counter Compare Match Register.  E検出回路(SVD3) 概要 入力端子と外部接続 9.2.1 入力端子 9.2.2 外部との接続 | 7-1 7-1 7-2 7-2 8-1 8-1 8-1 8-1 8-2 8-2 8-3 8-3 8-3 8-4 9-1 9-2 9-2 9-2 9-2 |

|    | 9.3.3 DEBUGモード時のクロック供給                  | 9-3  |

|----|-----------------------------------------|------|

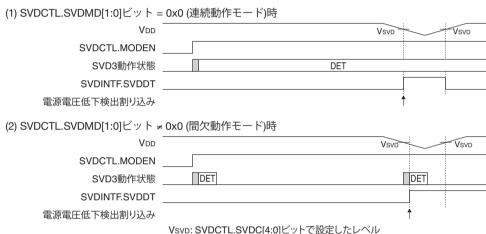

|    | 9.4 動作                                  | 9-3  |

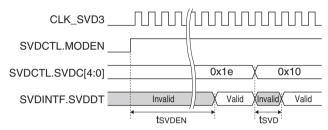

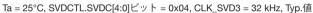

|    | 9.4.1 SVD3の制御                           | 9-3  |

|    | 9.4.2 SVD3の動作                           | 9-4  |

|    | 9.5 SVD3割り込みとリセット                       | 9-4  |

|    | 9.5.1 SVD3割り込み                          |      |

|    | 9.5.2 SVD3リセット                          |      |

|    | 9.6 制御レジスタ                              |      |

|    | SVD3 Clock Control Register             |      |

|    | SVD3 Control Register                   |      |

|    | SVD3 Status and Interrupt Flag Register |      |

|    | SVD3 Interrupt Enable Register          | 9-8  |

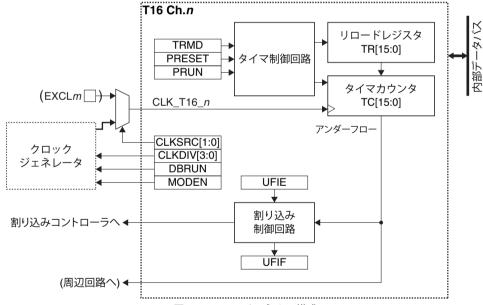

| 10 | 6ビットタイマ(T16)                            | 10-1 |

|    | 10.1 概要                                 |      |

|    | 10.2 入力端子                               |      |

|    | 10.3 クロック設定                             |      |

|    | 10.3.1 T16の動作クロック                       |      |

|    | 10.3.2 SLEEPモード時のクロック供給                 |      |

|    | 10.3.2 SLEEPモード時のクロック供給                 |      |

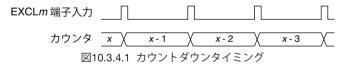

|    | 10.3.4 イベントカウンタクロック                     |      |

|    |                                         |      |

|    | 10.4 動作                                 |      |

|    | 10.4.1 初期設定<br>10.4.2 カウンタのアンダーフロー      |      |

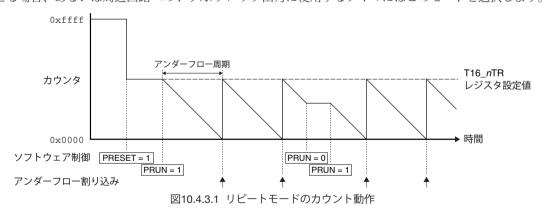

|    | 10.4.3 リピートモードの動作                       |      |

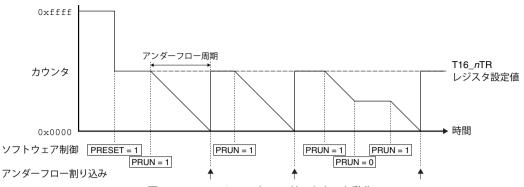

|    | 10.4.4 ワンショットモードの動作                     |      |

|    | 10.4.5 カウンタ値のリード                        |      |

|    | 10.5 割り込み                               |      |

|    |                                         |      |

|    | 10.6 制御レジスタ                             |      |

|    | T16 Ch.n Clock Control Register         |      |

|    | T16 Ch.n Control Register               |      |

|    | T16 Ch.n Reload Data Register           |      |

|    | T16 Ch.n Counter Data Register          |      |

|    | T16 Ch.n Interrupt Flag Register        | 10-6 |

|    | T16 Ch.n Interrupt Enable Register      | 10-7 |

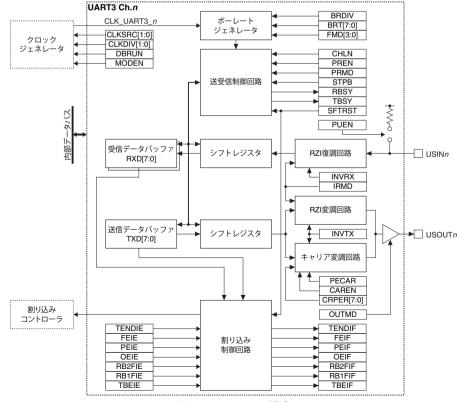

| 11 | ART(UART3)                              | 11-1 |

| •  | 11.1 概要                                 |      |

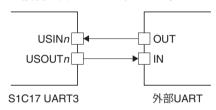

|    | 11.2 入出力端子と外部接続                         |      |

|    | 11.2.1 入出力端子一覧                          |      |

|    | 11.2.2 外部との接続                           |      |

|    | 11.2.3 入力端子のプルアップ機能                     | 11-2 |

|    | 11.2.4 出力端子のオープンドレイン出力機能                | 11-2 |

|    | 11.2.5 入出力信号の反転機能                       |      |

|    | 11.3 クロック設定                             |      |

|    | 11.3.1 UART3の動作クロック                     |      |

|    | 11.3.2 SLEEPモード時のクロック供給                 |      |

|    | 11.3.3 DEBUGモード時のクロック供給                 |      |

|    | 11.3.4 ボーレートジェネレータ                      |      |

|    | 11.4 データフォーマット                          |      |

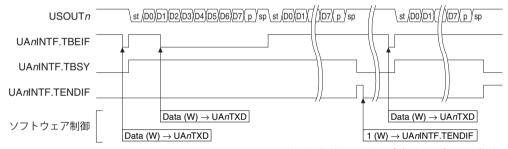

|    | 11.5 動作                                 |      |

|    | 11.5.1 初期設定                             |      |

|    |                                         | 11-4 |

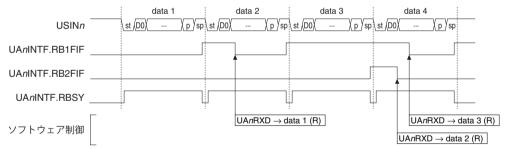

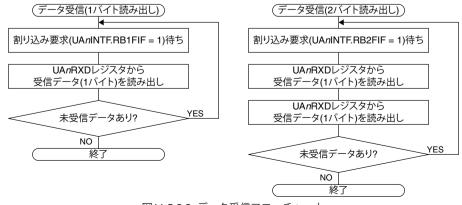

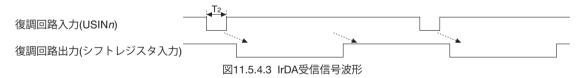

|                         | 11.5.3 データ受信                                                         | . 11-6  |

|-------------------------|----------------------------------------------------------------------|---------|

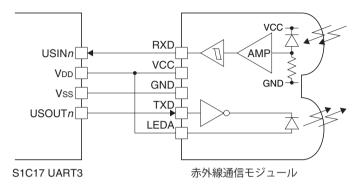

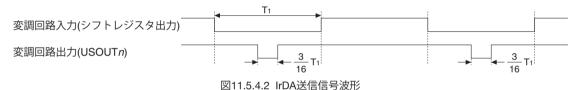

|                         | 11.5.4 IrDAインタフェース                                                   |         |

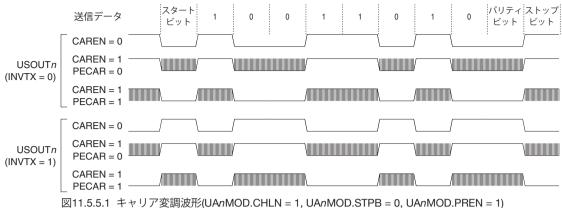

|                         | 11.5.5 キャリア変調                                                        |         |

| 11.6                    | 受信エラー                                                                | . 11-8  |

|                         | 11.6.1 フレーミングエラー                                                     |         |

|                         | 11.6.2 パリティエラー                                                       |         |

|                         | 11.6.3 オーバーランエラー                                                     |         |

| 11 7                    | 割り込み                                                                 |         |

|                         | 制御レジスタ                                                               |         |

| 11.0                    | UART3 Ch.n Clock Control Register                                    |         |

|                         | UART3 Ch.n Mode Register                                             |         |

|                         | UART3 Ch.n Baud-Rate Register                                        |         |

|                         | UART3 Ch.n Control Register                                          |         |

|                         | UART3 Ch.n Transmit Data Register                                    |         |

|                         | UART3 Ch.n Receive Data Register                                     |         |

|                         | UART3 Ch.n Status and Interrupt Flag Register                        |         |

|                         | UART3 Ch.n Interrupt Enable Register                                 |         |

|                         | UART3 Ch.n Carrier Waveform Register                                 | . 11-14 |

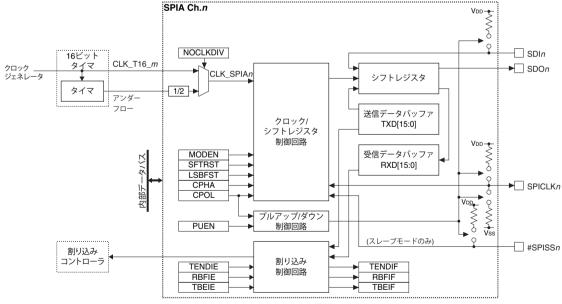

| 12 同期式                  | シリアルインタフェース(SPIA)                                                    | .12-1   |

| 12.1                    | 概要                                                                   | . 12-1  |

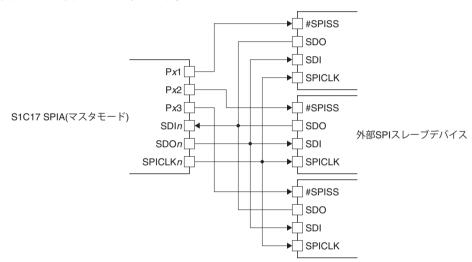

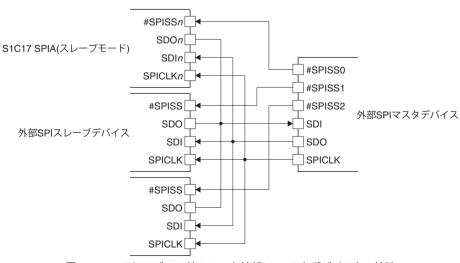

|                         | 入出力端子と外部接続                                                           |         |

|                         | 12.2.1 入出力端子一覧                                                       |         |

|                         | 12.2.2 外部との接続                                                        | . 12-2  |

|                         | 12.2.3 マスタモードとスレーブモードの端子機能                                           | . 12-3  |

|                         | 12.2.4 入力端子のプルアップ/プルダウン機能                                            | . 12-3  |

| 12.3                    | クロック設定                                                               | . 12-3  |

|                         | 12.3.1 SPIAの動作クロック                                                   |         |

|                         | 12.3.2 DEBUGモード時のクロック供給                                              |         |

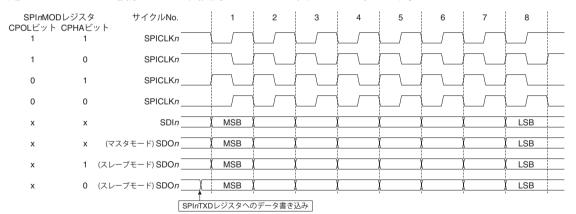

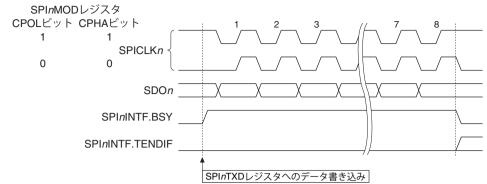

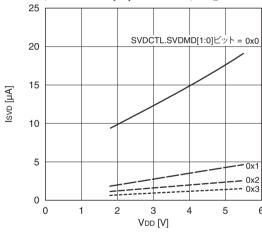

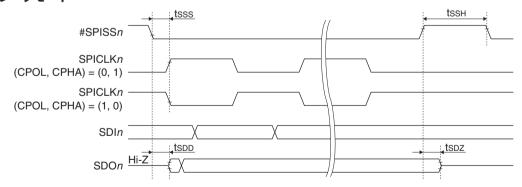

|                         | 12.3.3 SPIクロック(SPICLKn)の位相と極性                                        |         |

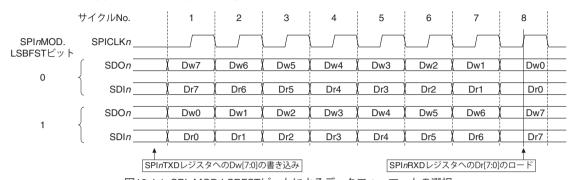

| 12.4                    | データフォーマット                                                            | . 12-5  |

| 12.5                    | 動作                                                                   | . 12-5  |

|                         |                                                                      |         |

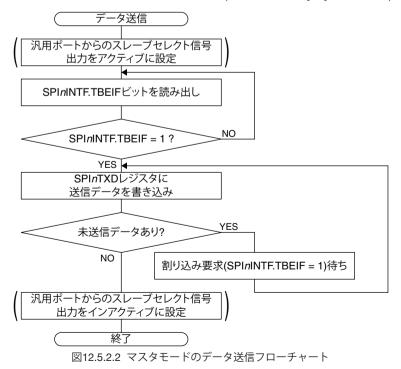

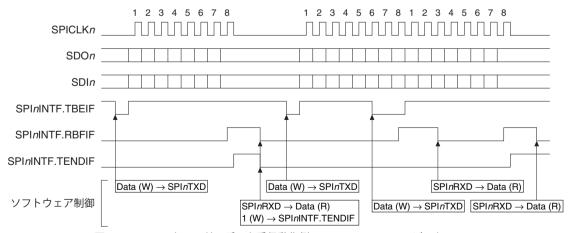

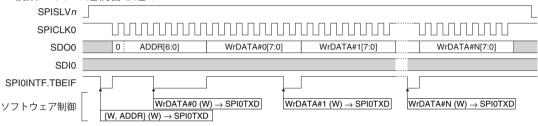

|                         | 12.5.2 マスタモードのデータ送信                                                  |         |

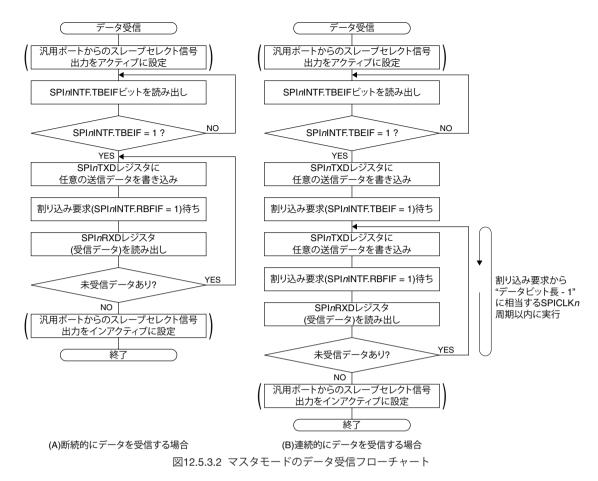

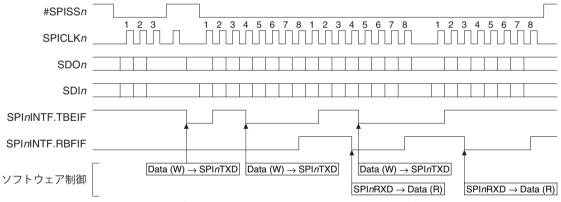

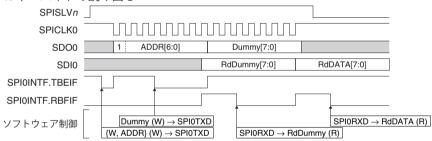

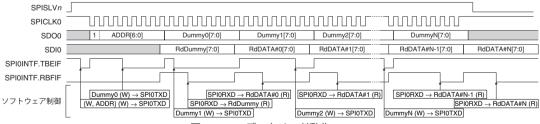

|                         | 12.5.3 マスタモードのデータ受信                                                  | . 12-7  |

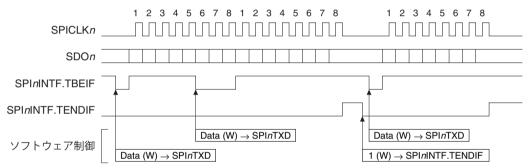

|                         | 12.5.4 マスタモードのデータ送受信終了                                               | . 12-8  |

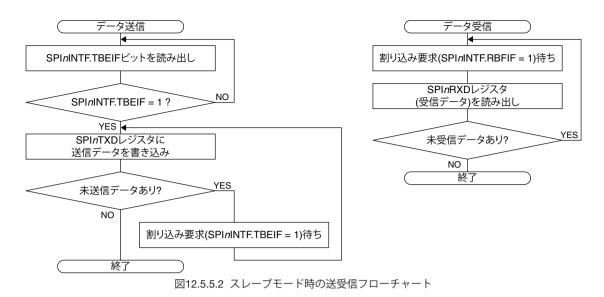

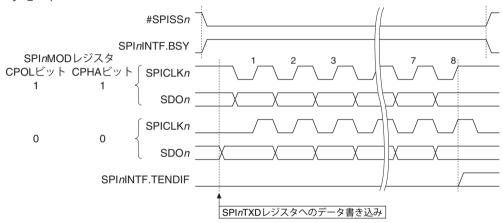

|                         | 12.5.5 スレーブモードのデータ送受信                                                | . 12-8  |

|                         | 12.5.6 スレーブモードのデータ送受信終了                                              | 12-10   |

| 12.6                    | 割り込み                                                                 | 12-10   |

| 12.7                    | 制御レジスタ                                                               | 12-11   |

|                         | SPIA Ch.n Mode Register                                              |         |

|                         | SPIA Ch.n Control Register                                           |         |

|                         | SPIA Ch.n Transmit Data Register                                     |         |

|                         | SPIA Ch.n Receive Data Register                                      |         |

|                         | SPIA Ch.n Interrupt Flag RegisterSPIA Ch.n Interrupt Enable Register |         |

|                         |                                                                      |         |

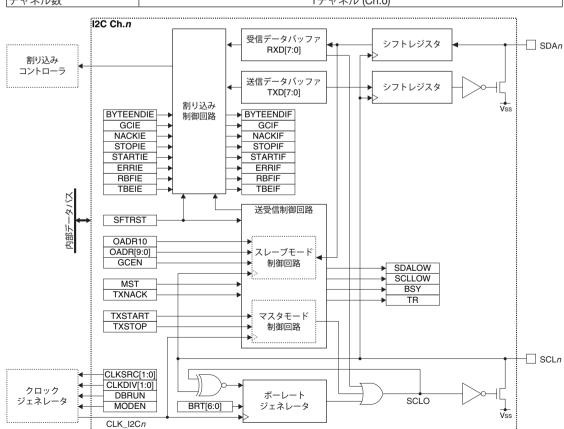

| 13 I <sup>2</sup> C(I20 | C)                                                                   | .13-1   |

|                         | 概要                                                                   |         |

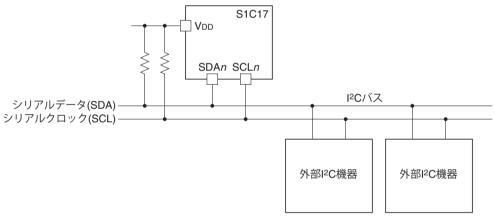

| 13.2                    | 入出力端子と外部接続                                                           |         |

|                         | 13.2.1 入出力端子一覧                                                       |         |

|                         | 13.2.2 外部との接続                                                        |         |

| 13.3                    | クロック設定                                                               |         |

|                         | 13.3.1 I2Cの動作クロック                                                    |         |

|                         | 13.3.2 DEBUGモード時のクロック供給                                              | 13-3    |

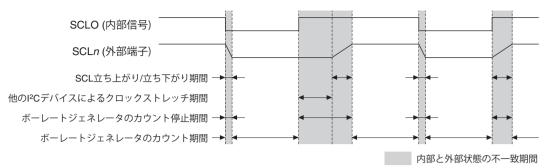

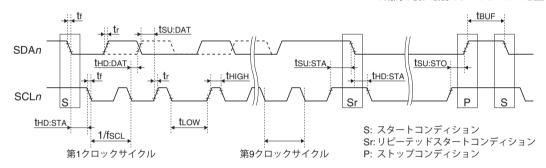

|      |      | 13.3.3 ボーレートジェネレータ                            | 13-3  |

|------|------|-----------------------------------------------|-------|

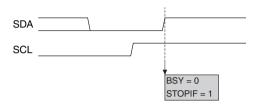

|      | 13.4 | 動作                                            |       |

|      |      | 13.4.1 初期設定                                   | 13-4  |

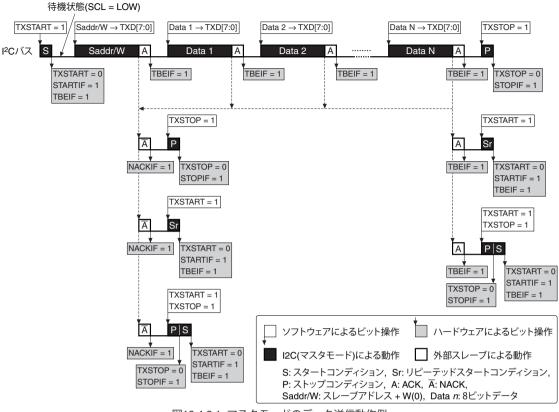

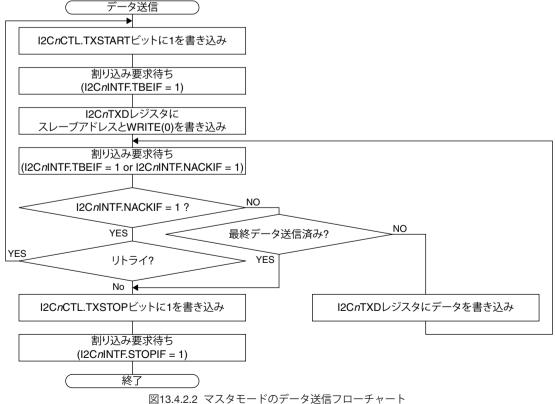

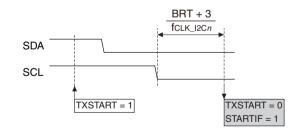

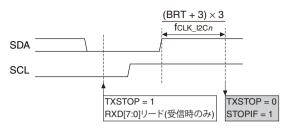

|      |      | 13.4.2 マスタモードのデータ送信                           | 13-5  |

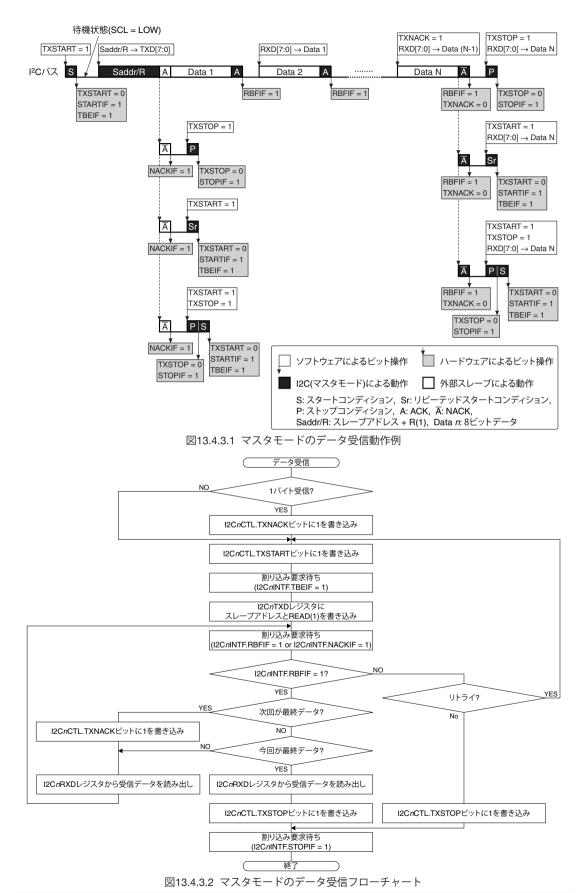

|      |      | 13.4.3 マスタモードのデータ受信                           | 13-7  |

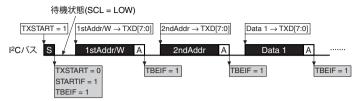

|      |      | 13.4.4 マスタモードでの10ビットアドレス指定                    |       |

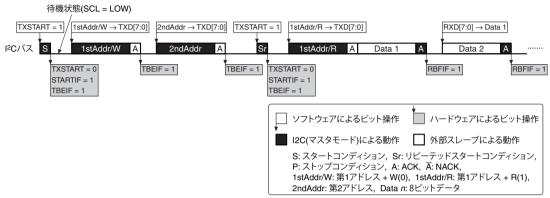

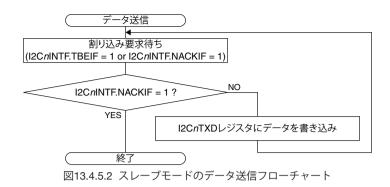

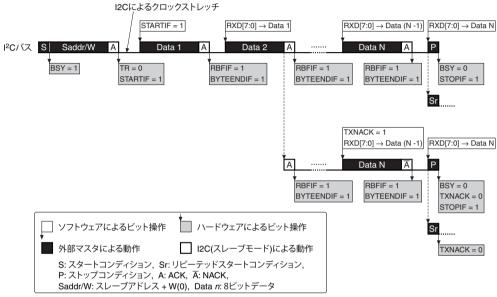

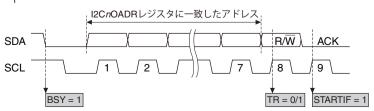

|      |      | 13.4.5 スレーブモードのデータ送信                          | 13-10 |

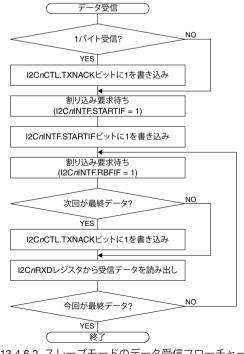

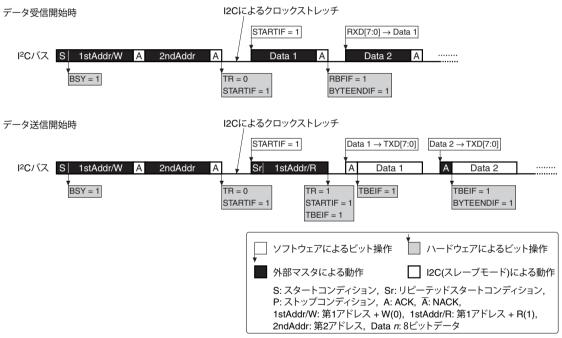

|      |      | 13.4.6 スレーブモードのデータ受信                          | 13-12 |

|      |      | 13.4.7 10ビットアドレスモードのスレーブ動作                    |       |

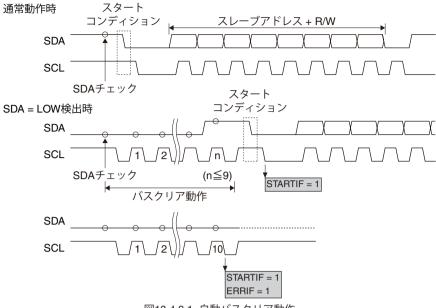

|      |      | 13.4.8 自動バスクリア動作                              |       |

|      |      | 13.4.9 エラー検出                                  | 13-15 |

|      | 13.5 | 割り込み                                          | 13-16 |

|      | 13.6 | 制御レジスタ                                        | 13-17 |

|      |      | I2C Ch.n Clock Control Register               | 13-17 |

|      |      | I2C Ch.n Mode Register                        |       |

|      |      | I2C Ch.n Baud-Rate Register                   |       |

|      |      | I2C Ch.n Own Address Register                 |       |

|      |      | I2C Ch.n Control Register                     |       |

|      |      | I2C Ch.n Transmit Data Register               |       |

|      |      | I2C Ch.n Receive Data Register                |       |

|      |      | I2C Ch.n Status and Interrupt Flag Register   |       |

|      |      |                                               |       |

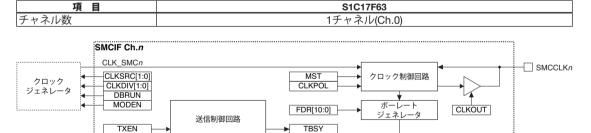

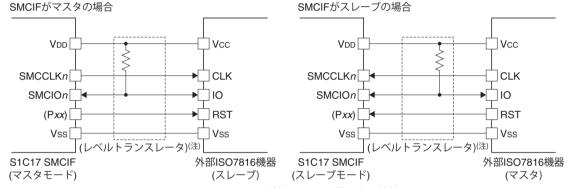

| 14 ス |      | トカードインタフェース(SMCIF)                            |       |

|      |      | 概要                                            |       |

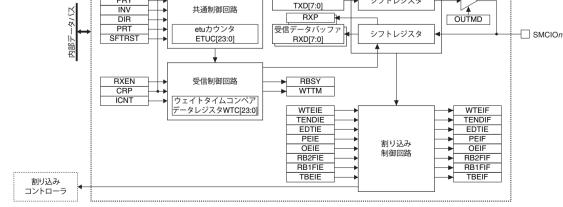

|      | 14.2 | 入出力端子と外部接続                                    | 14-2  |

|      |      | 14.2.1 入出力端子一覧                                |       |

|      |      | 14.2.2 外部との接続                                 |       |

|      |      | 14.2.3 出力端子のプッシュプル/オープンドレイン選択                 | 14-2  |

|      | 14.3 | クロック設定                                        | 14-2  |

|      |      | 14.3.1 SMCIFの動作クロック                           | 14-2  |

|      |      | 14.3.2 SLEEPモード時のクロック供給                       | 14-3  |

|      |      | 14.3.3 DEBUGモード時のクロック供給                       | 14-3  |

|      |      | 14.3.4 SMCCLKn端子出力停止機能                        | 14-3  |

|      |      | 14.3.5 ボーレートジェネレータの設定                         |       |

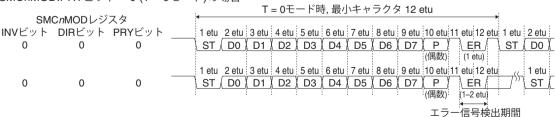

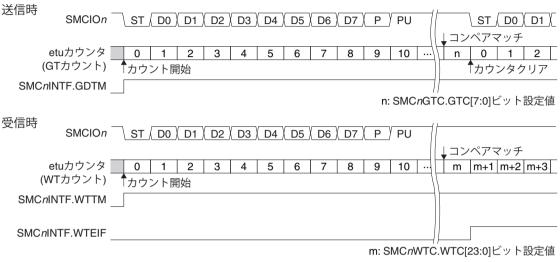

|      | 14.4 | データフォーマット                                     | 14-4  |

|      |      | ガードタイムとウェイトタイムの設定                             |       |

|      |      | 動作                                            |       |

|      |      | 14.6.1 初期設定                                   |       |

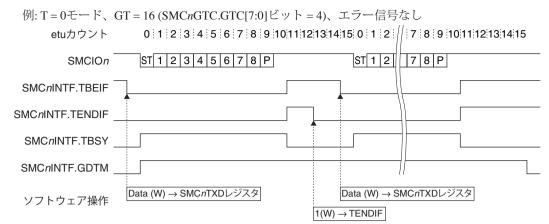

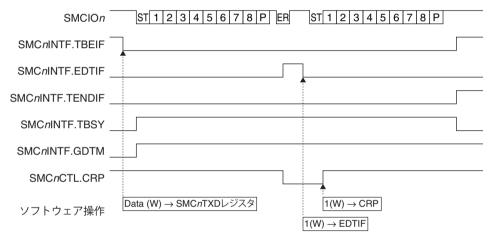

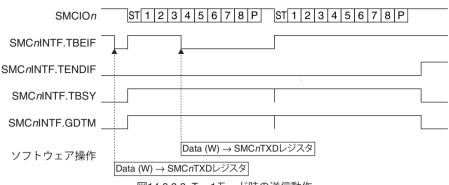

|      |      | 14.6.2 データ送信                                  |       |

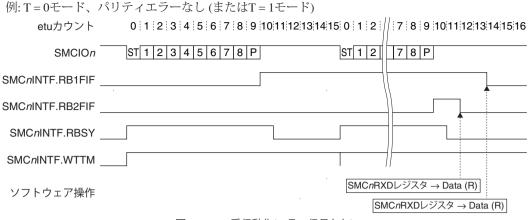

|      |      | 14.6.3 データ受信                                  |       |

|      | 14 7 | 割り込み                                          |       |

|      |      | 制御レジスタ                                        |       |

|      | 14.0 | SMCIF Ch.n Clock Control Register             |       |

|      |      | SMCIF Ch.n Mode Register                      |       |

|      |      | SMCIF Ch.n Baud Rate Register                 |       |

|      |      | SMCIF Ch.n Control Register                   | 14-12 |

|      |      | SMCIF Ch.n Transmit Data Register             |       |

|      |      | SMCIF Ch.n Receive Data Register              |       |

|      |      | SMCIF Ch.n Wait Time Compare Data Register 0  |       |

|      |      | SMCIF Ch.n Wait Time Compare Data Register 1  |       |

|      |      | SMCIF Ch.n Guard Time Compare Data Register   |       |

|      |      | SMCIF Ch.n Status and Interrupt Flag Register |       |

|      |      |                                               |       |

|    |      | SMCIF Ch.n Etu Counter Data Register 1          | 14-17 |

|----|------|-------------------------------------------------|-------|

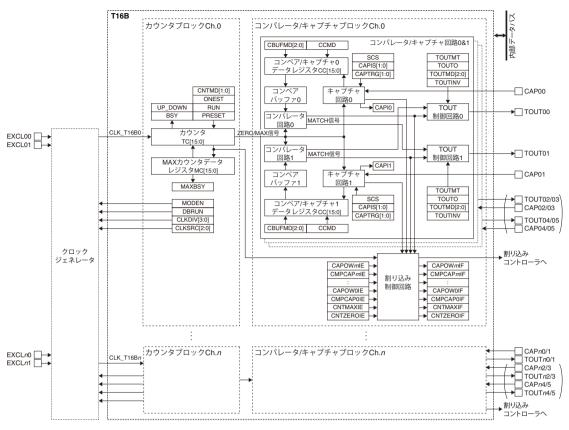

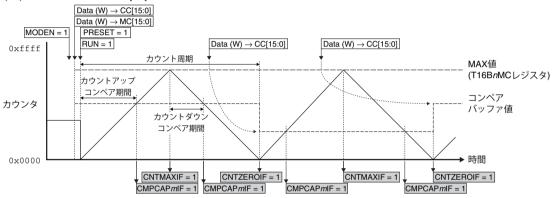

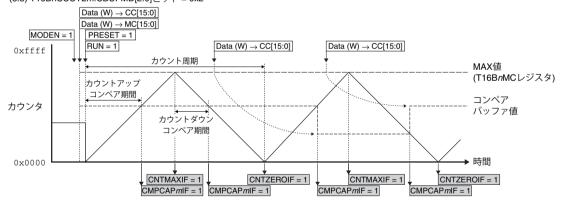

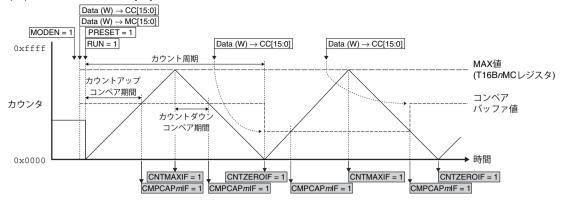

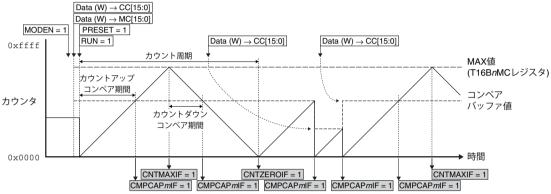

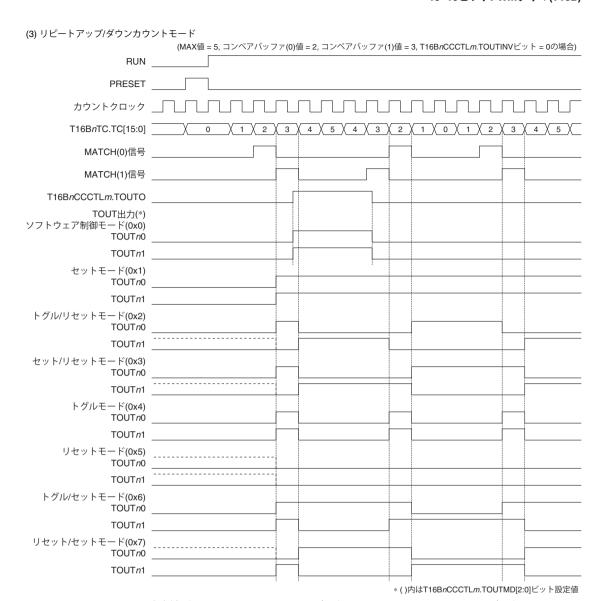

| 15 | 16ビッ | トPWMタイマ(T16B)                                   | 15-1  |

|    |      | 概要                                              |       |

|    |      | 入出力端子                                           |       |

|    |      | クロック設定                                          |       |

|    | 10.0 | フロック設定                                          |       |

|    |      | 15.3.2 SLEEPモード時のクロック供給                         | 15-3  |

|    |      | 15.3.3 DEBUGモード時のクロック供給                         |       |

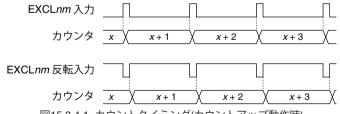

|    |      | 15.3.4 イベントカウンタクロック                             | 15-3  |

|    | 15.4 | 動作                                              |       |

|    | 10.4 | 15.4.1 初期設定                                     |       |

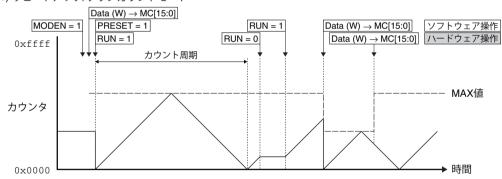

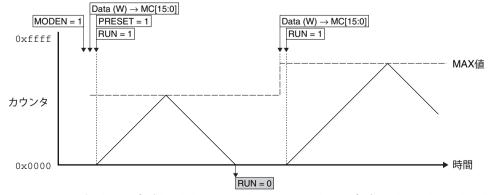

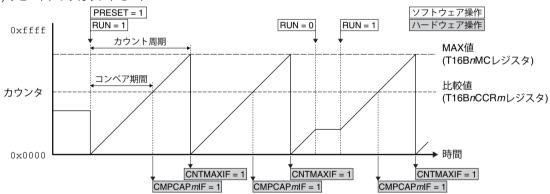

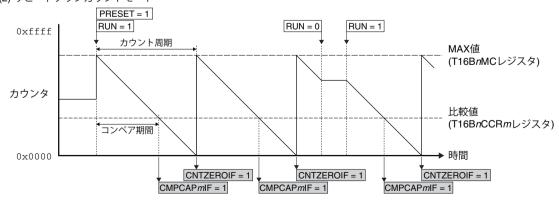

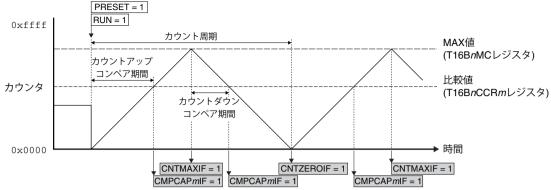

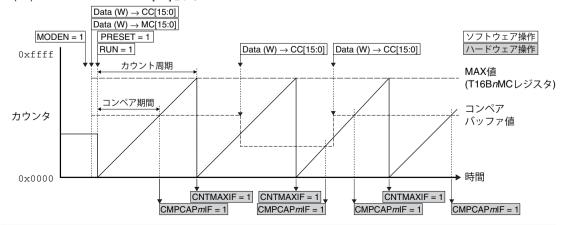

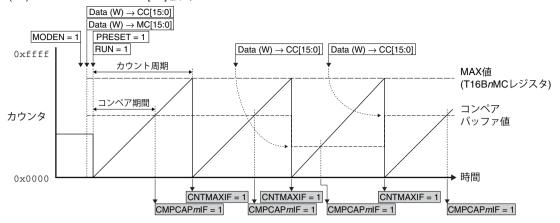

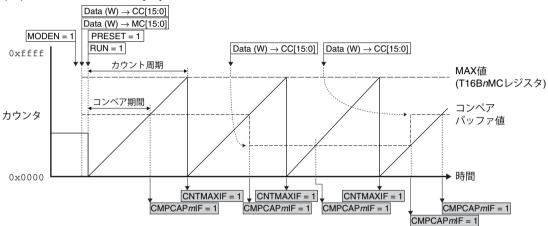

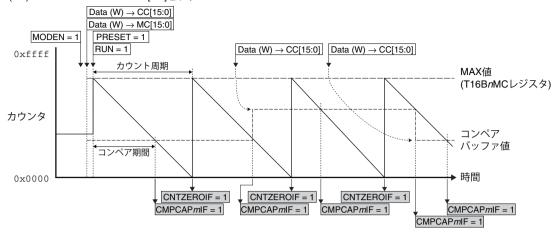

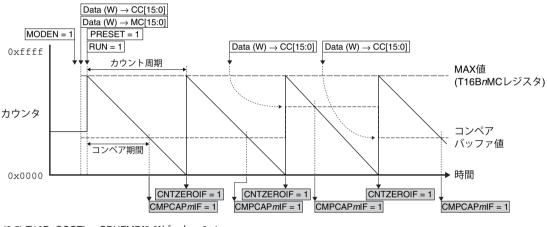

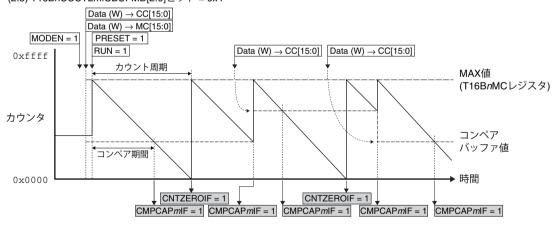

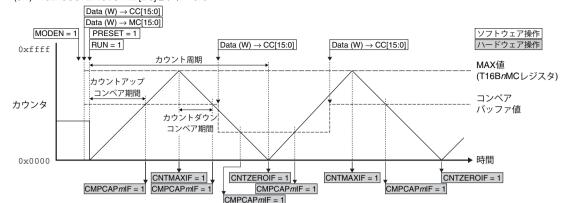

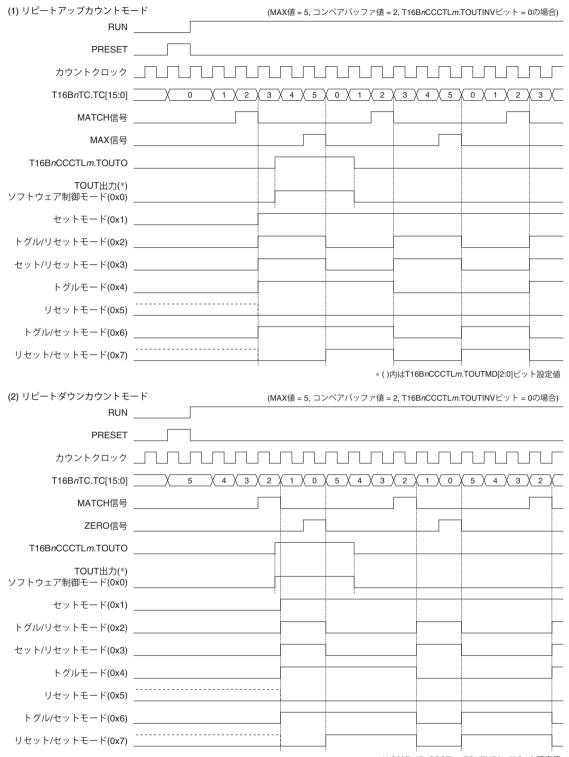

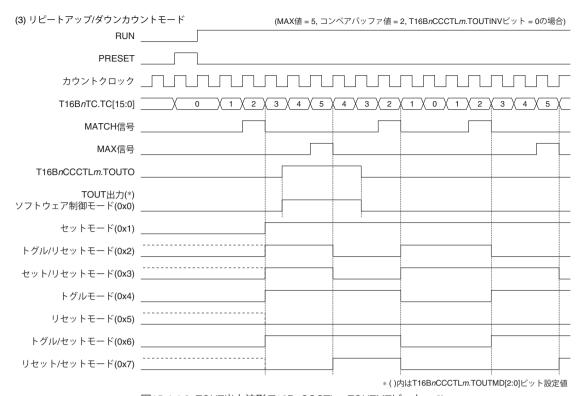

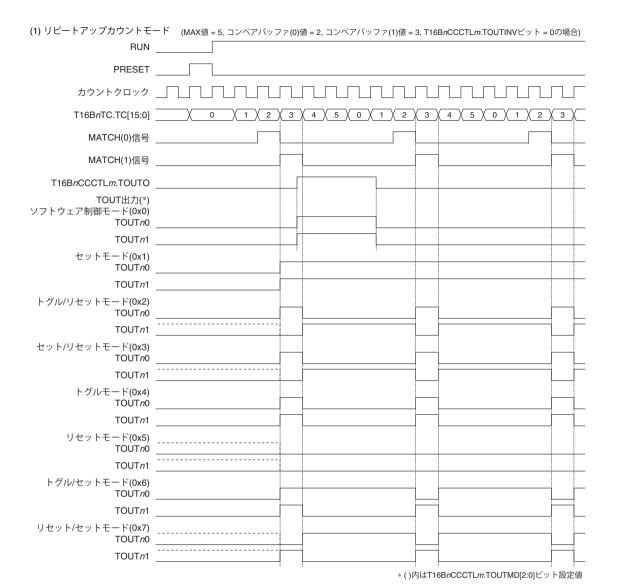

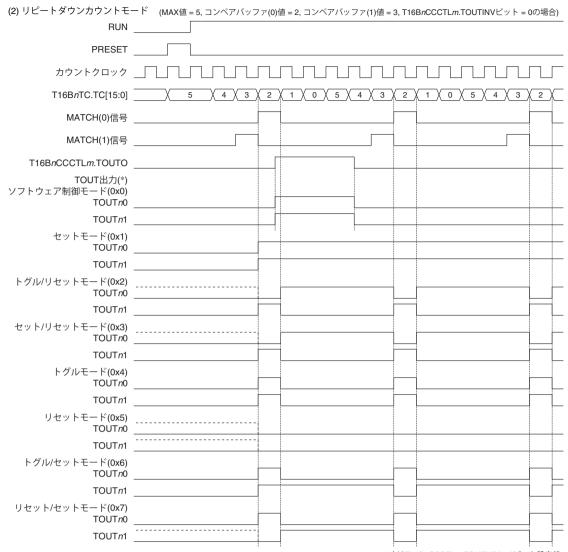

|    |      | 15.4.2 カウンタブロックの動作                              |       |

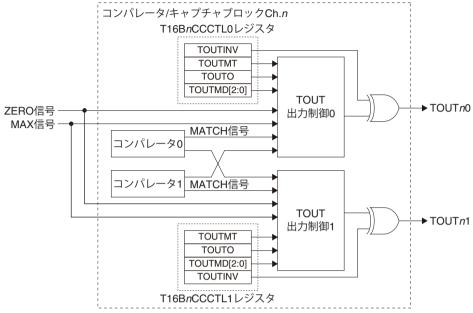

|    |      | 15.4.3 コンパレータ/キャプチャブロックの動作                      |       |

|    |      | 15.4.4 TOUT出力の制御                                |       |

|    | 15.5 | 割り込み                                            |       |

|    |      | 制御レジスタ                                          |       |

|    | 13.0 | T16B Ch.n Clock Control Register                |       |

|    |      | T16B Ch.n Counter Control Register              |       |

|    |      | T16B Ch.n Max Counter Data Register             |       |

|    |      | T16B Ch.n Timer Counter Data Register           | 15-25 |

|    |      | T16B Ch.n Counter Status Register               |       |

|    |      | T16B Ch.n Interrupt Flag Register               |       |

|    |      | T16B Ch.n Interrupt Enable Register             |       |

|    |      | T16B Ch.n Comparator/Capture m Control Register |       |

|    |      |                                                 |       |

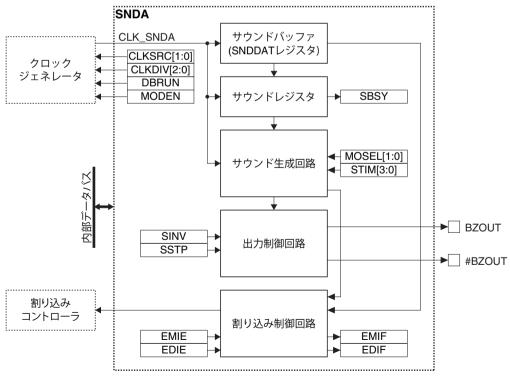

| 16 |      | ドジェネレータ(SNDA)                                   |       |

|    |      | 概要                                              |       |

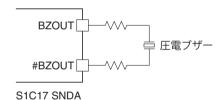

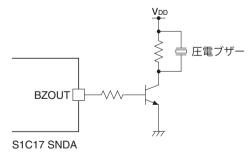

|    | 16.2 | 出力端子と外部接続                                       |       |

|    |      | 16.2.1 出力端子一覧                                   |       |

|    |      | 16.2.2 出力端子の駆動モード                               |       |

|    |      | 16.2.3 外部との接続                                   |       |

|    | 16.3 | クロック設定                                          |       |

|    |      | 16.3.1 SNDAの動作クロック                              |       |

|    |      | 16.3.2 SLEEPモード時のクロック供給                         | 16-3  |

|    |      | 16.3.3 DEBUGモード時のクロック供給                         |       |

|    | 16.4 | 動作                                              |       |

|    |      | 16.4.1 初期設定                                     | 16-3  |

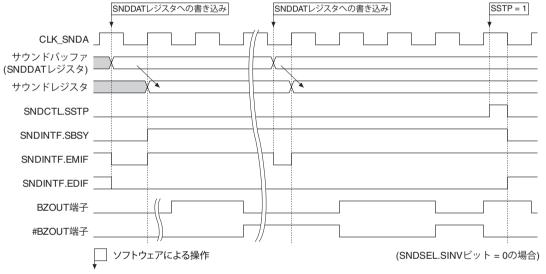

|    |      | 16.4.2 ノーマルブザーモードのブザー出力                         |       |

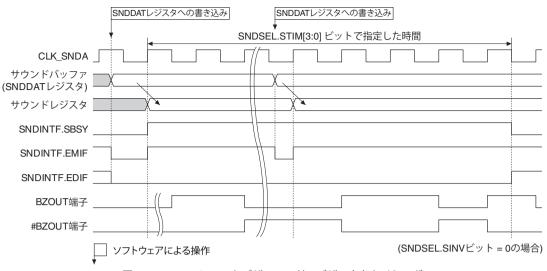

|    |      | 16.4.3 ワンショットブザーモードのブザー出力                       |       |

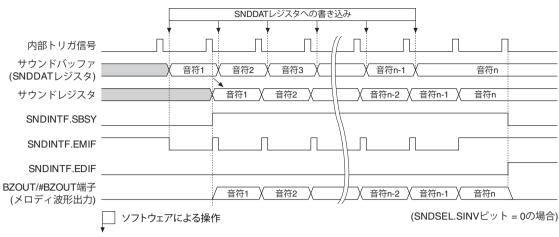

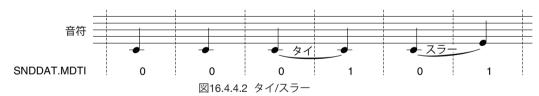

|    |      | 16.4.4 メロディモードの出力                               |       |

|    |      | 割り込み                                            |       |

|    | 16.6 | 制御レジスタ                                          |       |

|    |      | SNDA Clock Control Register                     |       |

|    |      | SNDA Select Register                            |       |

|    |      | SNDA Control Register                           |       |

|    |      | SNDA Data RegisterSNDA Interrupt Flag Register  |       |

|    |      | SNDA Interrupt Flag Register                    |       |

| 47 | 4012 |                                                 |       |

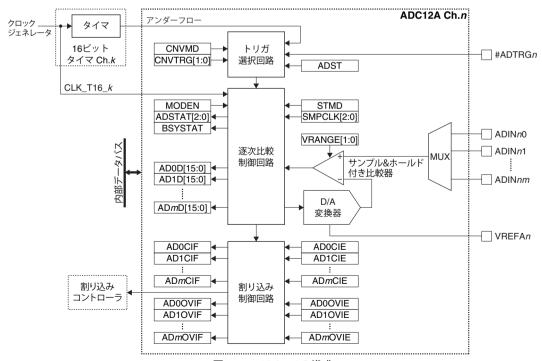

| 1/ |      | トA/D変換器(ADC12A)                                 |       |

|    |      | 概要                                              |       |

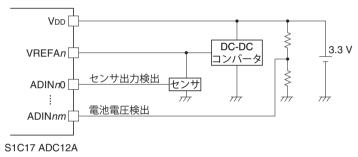

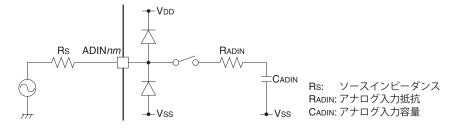

|    | 17.2 | 入力端子と外部接続                                       |       |

|    |      | 17.2.1 入力端子一覧                                   | 17-2  |

|    |                                      | 17.2.2 外部との接続                                                                                                                                                                                                |                                                                                                                                                                                               |

|----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 17.3                                 | クロック設定                                                                                                                                                                                                       |                                                                                                                                                                                               |

|    |                                      | 17.3.1 ADC12Aの動作クロック                                                                                                                                                                                         |                                                                                                                                                                                               |

|    |                                      | 17.3.2 サンプリング時間                                                                                                                                                                                              | . 17-2                                                                                                                                                                                        |

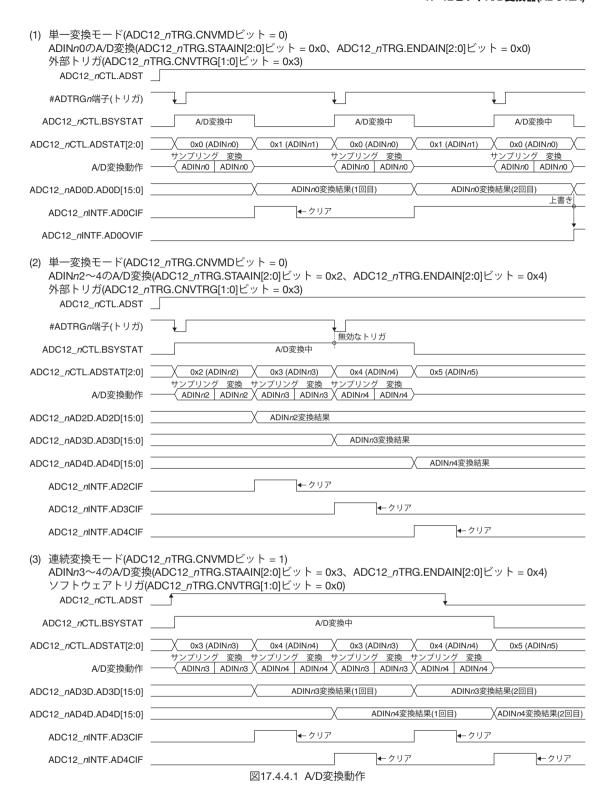

|    | 17.4                                 | 動作                                                                                                                                                                                                           | . 17-3                                                                                                                                                                                        |

|    |                                      | 17.4.1 初期設定                                                                                                                                                                                                  | . 17-3                                                                                                                                                                                        |

|    |                                      | 17.4.2 変換開始トリガソース                                                                                                                                                                                            | . 17-3                                                                                                                                                                                        |

|    |                                      | 17.4.3 変換動作モードと変換を行うアナログ入力端子の設定                                                                                                                                                                              | . 17-4                                                                                                                                                                                        |

|    |                                      | 17.4.4 A/D変換動作と制御手順                                                                                                                                                                                          | . 17-4                                                                                                                                                                                        |

|    | 17.5                                 | 割り込み                                                                                                                                                                                                         |                                                                                                                                                                                               |

|    |                                      | 制御レジスタ                                                                                                                                                                                                       |                                                                                                                                                                                               |

|    | 17.0                                 | ADC12A Ch. <i>n</i> Control Register                                                                                                                                                                         |                                                                                                                                                                                               |

|    |                                      | ADC12A Ch.n Trigger/Analog Input Select Register                                                                                                                                                             |                                                                                                                                                                                               |

|    |                                      | ADC12A Ch.n Configuration Register                                                                                                                                                                           |                                                                                                                                                                                               |

|    |                                      | ADC12A Ch.n Interrupt Flag Register                                                                                                                                                                          |                                                                                                                                                                                               |

|    |                                      | ADC12A Ch.n Interrupt Enable Register                                                                                                                                                                        |                                                                                                                                                                                               |

|    |                                      | ADC12A Ch.n Result Register m                                                                                                                                                                                |                                                                                                                                                                                               |

| 40 | 油中上                                  | ンサ/甘淮電圧化成同致/TCDVD)                                                                                                                                                                                           | 40.4                                                                                                                                                                                          |

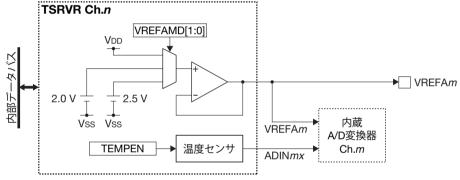

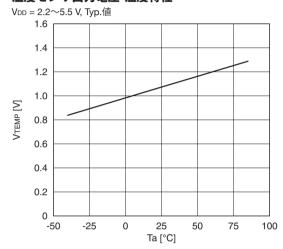

| 10 |                                      | ンサ/基準電圧生成回路(TSRVR)                                                                                                                                                                                           |                                                                                                                                                                                               |

|    |                                      | 概要                                                                                                                                                                                                           |                                                                                                                                                                                               |

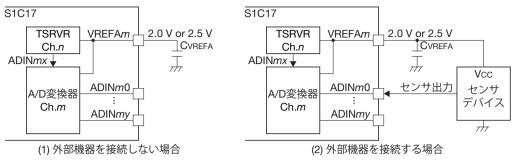

|    | 18.2                                 | 出力端子と外部接続                                                                                                                                                                                                    |                                                                                                                                                                                               |

|    |                                      | 18.2.1 出力端子                                                                                                                                                                                                  |                                                                                                                                                                                               |

|    |                                      | 18.2.2 外部との接続                                                                                                                                                                                                | . 18-2                                                                                                                                                                                        |

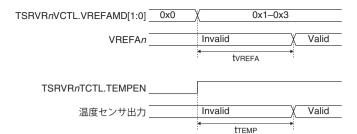

|    | 18.3                                 | 動作                                                                                                                                                                                                           | . 18-2                                                                                                                                                                                        |

|    |                                      | 18.3.1 基準電圧の設定                                                                                                                                                                                               | . 18-2                                                                                                                                                                                        |

|    |                                      | 18.3.2 温度センサの設定                                                                                                                                                                                              |                                                                                                                                                                                               |

|    | 10.4                                 | 制御レジスタ                                                                                                                                                                                                       |                                                                                                                                                                                               |

|    | 18.4                                 | 刑御レンスタ                                                                                                                                                                                                       | . 10-o                                                                                                                                                                                        |

|    | 18.4                                 |                                                                                                                                                                                                              |                                                                                                                                                                                               |

|    | 18.4                                 | TSRVR Ch.n Temperature Sensor Control Register                                                                                                                                                               | 18-3                                                                                                                                                                                          |

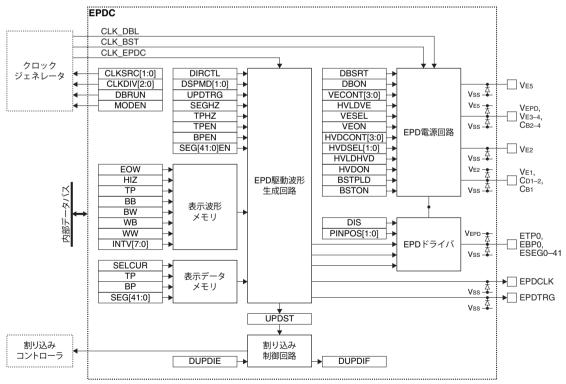

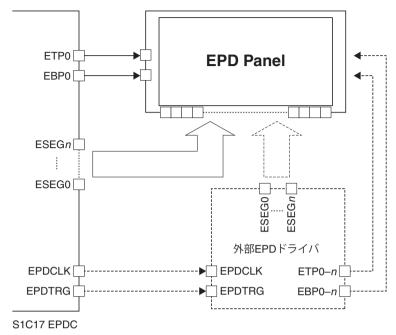

| 10 |                                      | TSRVR Ch.n Temperature Sensor Control Register                                                                                                                                                               | 18-3<br>18-3                                                                                                                                                                                  |