# **S1V50300**

## **ハードウェアマニュアル**

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

は、ARM 社の登録商標です。

# 目次

|                                    |    |

|------------------------------------|----|

| 1. 概要                              | 1  |

| 2. 特長                              | 2  |

| 3. ピン配置                            | 3  |

| 3.1 QFP13-64                       | 3  |

| 4. 端子                              | 4  |

| 4.1 端子説明                           | 4  |

| 4.2 端子状態                           | 7  |

| 5. 機能説明                            | 9  |

| 5.1 標準アプリケーションシステム                 | 9  |

| 5.2 動作モード                          | 10 |

| 5.3 ホストインターフェース                    | 11 |

| 6. 電気的特性                           | 12 |

| 6.1 絶対最大定格                         | 12 |

| 6.2 推奨動作条件                         | 12 |

| 6.3 DC 特性                          | 13 |

| 6.3.1 電源電圧 $3.3\pm0.3V$ における DC 特性 | 13 |

| 6.4 AC 特性                          | 15 |

| 6.4.1 システムクロックタイミング                | 15 |

| 6.4.2 電源投入／リセットタイミング               | 16 |

| 6.4.3 電源切断タイミング                    | 17 |

| 6.4.4 メッセージ受付タイミング                 | 18 |

| 6.4.5 ホストインターフェース（クロック同期式（SPI））    | 19 |

| 6.4.6 外部シリアル Flash メモリインターフェース     | 20 |

| 7. 外部接続例                           | 21 |

| 7.1 ホストインターフェース                    | 21 |

| 7.1.1 クロック同期式（SPI）                 | 21 |

| 7.1.2 調歩同期式（UART）                  | 22 |

| 7.2 アナログコーデックインターフェース              | 23 |

| 7.3 外部シリアル Flash メモリインターフェース       | 24 |

| 8. 外形寸法図                           | 25 |

| 8.1 QFP13-64                       | 25 |

| 9. 参考資料                            | 26 |

| 9.1 応用回路例                          | 26 |

| 9.2 電源に関する注意事項                     | 27 |

| 9.3 クロック直接入力に関する注意事項               | 28 |

|                      |    |

|----------------------|----|

| 9.4 実装上の注意事項.....    | 29 |

| 9.4.1 リセット回路 .....   | 29 |

| 9.4.2 電源回路.....      | 29 |

| 9.4.3 信号線の配置 .....   | 29 |

| 9.4.4 ノイズによる誤動作..... | 30 |

| 9.5 製品型番体系.....      | 31 |

| 改訂履歴表 .....          | 32 |

### 1. 概要

S1V50300 は、EPSON の高性能音声認識エンジンを搭載した LSI です。音声認識機能に加え、高音質高压縮音声フォーマットを採用した音声再生機能も搭載しているため、お客様のシステムに音声による双方向（会話）コミュニケーションの搭載を実現できます。

ホストとのコミュニケーションはシリアルインターフェースによるコマンド制御で行うため、既存のシステムに容易に Add-On 可能です。

S1V50300 を使用することで、声による人と機器のコミュニケーション “Voice Human Interface” を容易に実現できます。

## 2. 特長

---

### 2. 特長

- 音声認識機能 ※1

- サポート言語：（言語で型番が異なります）

**型番：S1V50300F05R000：日本語音声認識**

**型番：S1V50300F05S000：英語音声認識**

- 不特定話者認識 ※2

- 1回の認識あたりの最大選択肢数：50

- 登録可能語彙：無制限

- 音声再生機能

- サンプリング周波数：16kHz

- ビットレート：16, 24, 32, 40kbps

- シーケンサ（音声フレーズ間接続）機能に対応

- フレーズ間のディレイを設定可能

- 最大 64 フレーズのシーケンス設定可能（組み合わせ制限なし）

- ホストインターフェース

- クロック同期式（SPI）

- 調歩同期式（UART）

- シナリオライブラリー格納領域

- 外部シリアル Flash メモリ

- ホスト（ストリーミング転送）：音声再生はクロック同期式（SPI）のみ対応

- アナログコーデックインターフェース

- 推奨アナログコーデック LSI 専用

- I<sup>2</sup>S：音声データ入出力

- I<sup>2</sup>C：アナログコーデック設定用

- 外部シリアル Flash メモリインターフェース

- システムクロック

- 32.768kHz

- パッケージ

- QFP 64pin (10mm×10mm) 0.5mm Pin ピッチ

- 電源電圧

- IO : 3.3±0.3V

- Core : 1.8±0.15V

※1 S1V50300 は高音声認識性能を示しますが、認識率を保証するものではありません。

※2 S1V50300 は 16 歳以上の男女に対して最適化しています。

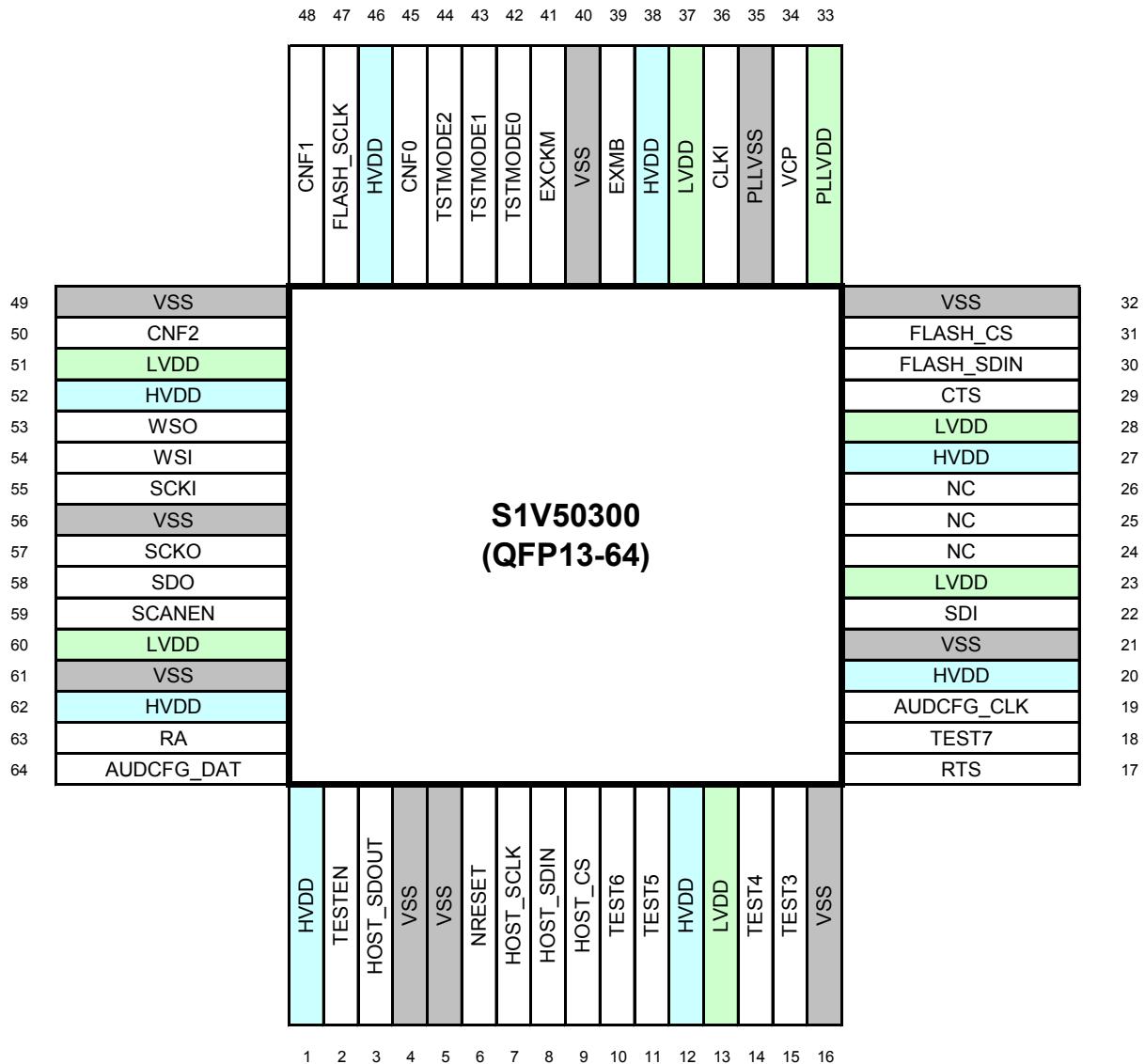

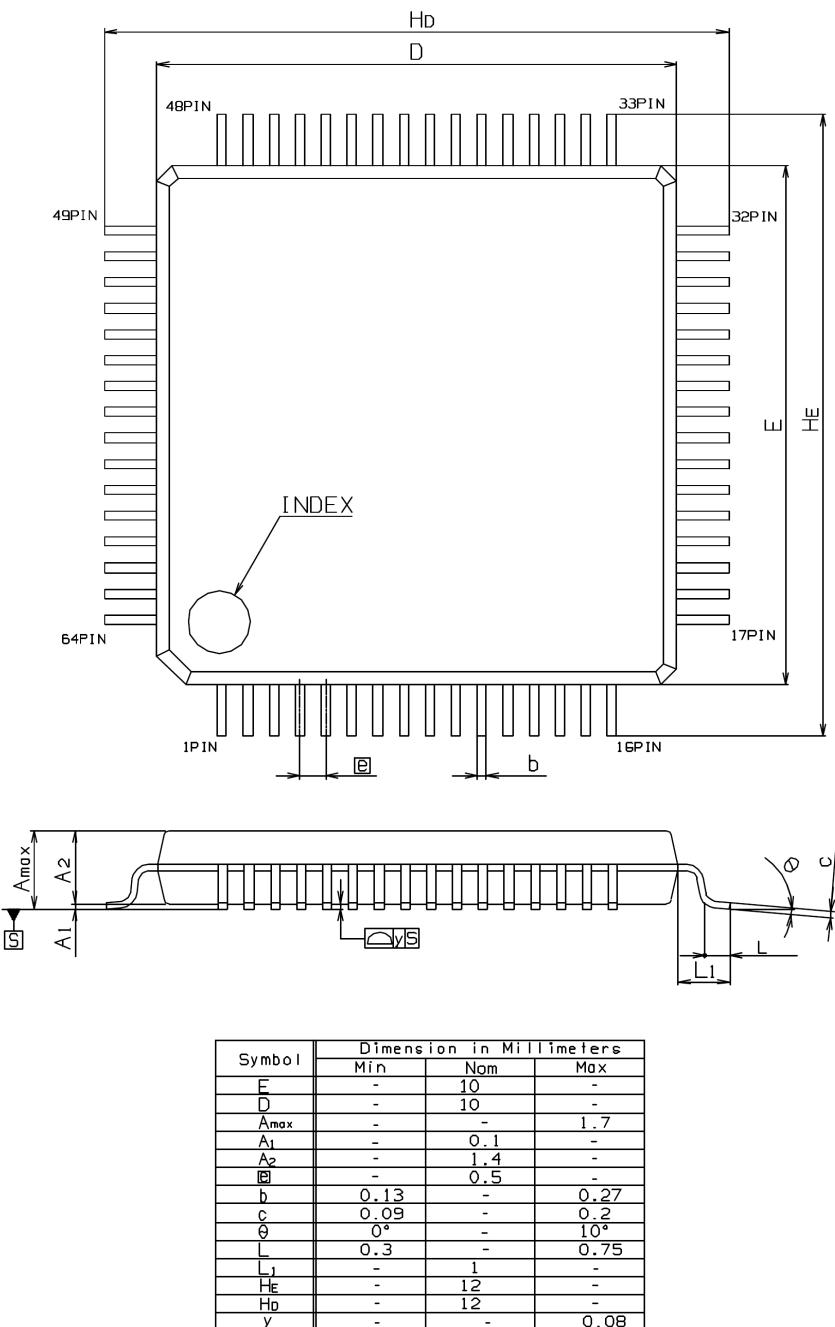

### 3. ピン配置

#### 3.1 QFP13-64

図 3.1 ピン配置 (QFP13-64)

## 4. 端子

### 4. 端子

#### 4.1 端子説明

- 凡例

I = 入力端子

O = 出力端子

IO = 双方向端子

P = 電源端子

Z = ハイインピーダンス

- I/O セル種類

| 記号    | 機能                                                                |

|-------|-------------------------------------------------------------------|

| IC    | LVCMOS 入力                                                         |

| IH    | LVCMOS シュミット入力                                                    |

| ICP1  | プルアップ抵抗 (50kΩ@3.3V(typ.)) 付き LVCMOS 入力                            |

| ICD2  | プルダウン抵抗 (100kΩ@3.3V(typ.)) 付き LVCMOS 入力                           |

| IHD2  | プルダウン抵抗 (100kΩ@3.3V(typ.)) 付き LVCMOS シュミット入力                      |

| O1    | 出力バッファ (出力電流 2mA / -2mA@3.3V(typ.))                               |

| T1    | 3-state 出力バッファ (出力電流 2mA / -2mA@3.3V(typ.))                       |

| BC1   | 双方向バッファ (出力電流 2mA / -2mA@3.3V(typ.))                              |

| BC3   | 双方向バッファ (出力電流 8mA / -8mA@3.3V(typ.))                              |

| BC1P2 | プルアップ抵抗 (100kΩ@3.3V(typ.)) 付き双方向バッファ (出力電流 2mA / -2mA@3.3V(typ.)) |

| BC1D2 | プルダウン抵抗 (100kΩ@3.3V(typ.)) 付き双方向バッファ (出力電流 2mA / -2mA@3.3V(typ.)) |

| BC3P2 | プルアップ抵抗 (100kΩ@3.3V(typ.)) 付き双方向バッファ (出力電流 8mA / -8mA@3.3V(typ.)) |

| LOT   | Transparent Output                                                |

| ITST1 | プルダウン抵抗 (120kΩ@1.8V(typ.)) 付きテスト入力                                |

| 端子名称        | Pin | I/O セル種類 | I/O 電源 | 機能                                         |

|-------------|-----|----------|--------|--------------------------------------------|

| ホストインターフェース |     |          |        |                                            |

| HOST_SCLK   | 7   | BC3      | HVDD   | 【SPI】クロック入力<br>【UART】H レベルに固定              |

| HOST_SDIN   | 8   | BC1D2    | HVDD   | 【SPI】データ入力<br>【UART】データ入力                  |

| HOST_SDOUT  | 3   | BC3P2    | HVDD   | 【SPI】データ出力<br>【UART】データ出力                  |

| HOST_CS     | 9   | BC3P2    | HVDD   | 【SPI】チップセレクト入力 (L アクティブ)<br>【UART】H レベルに固定 |

| RTS         | 17  | BC1D2    | HVDD   | 送信要求信号出力 (H アクティブ)                         |

| CTS         | 29  | BC1D2    | HVDD   | 送信許可信号入力 (H アクティブ)                         |

| RA          | 63  | BC1D2    | HVDD   | 音声認識アクティブ出力 (H アクティブ)                      |

| アナログコーデックインターフェース (I <sup>2</sup> S) |    |       |        |                                                                                                                           |

|--------------------------------------|----|-------|--------|---------------------------------------------------------------------------------------------------------------------------|

| SCKI                                 | 55 | BC1D2 | HVDD   | I <sup>2</sup> S(In) ビットクロック入力                                                                                            |

| WSI                                  | 54 | BC1D2 | HVDD   | I <sup>2</sup> S(In) ワードクロック入力                                                                                            |

| SDI                                  | 22 | ICD2  | HVDD   | I <sup>2</sup> S(In) データ入力                                                                                                |

| SCKO                                 | 57 | BC1D2 | HVDD   | I <sup>2</sup> S(Out) ビットクロック入力                                                                                           |

| WSO                                  | 53 | BC1D2 | HVDD   | I <sup>2</sup> S(Out) ワードクロック入力                                                                                           |

| SDO                                  | 58 | O1    | HVDD   | I <sup>2</sup> S(Out) データ出力                                                                                               |

| アナログコーデックインターフェース (I <sup>2</sup> C) |    |       |        |                                                                                                                           |

| AUDCFG_CLK                           | 19 | BC1D2 | HVDD   | クロック出力                                                                                                                    |

| AUDCFG_DAT                           | 64 | BC1P2 | HVDD   | データ出力                                                                                                                     |

| アナログコーデックインターフェース (基準クロック)           |    |       |        |                                                                                                                           |

| CNF2<br>(EXAUDCK)                    | 50 | BC1D2 | HVDD   | 基準クロック出力 (16.59MHz)<br>ハードウェアリセット後の一定期間は起動時動作モード設定入力 (CNF2) として機能します。                                                     |

| 外部シリアル Flash メモリインターフェース             |    |       |        |                                                                                                                           |

| FLASH_SCLK                           | 47 | BC1D2 | HVDD   | クロック出力                                                                                                                    |

| FLASH_SDIN                           | 30 | BC1D2 | HVDD   | データ入力                                                                                                                     |

| CNF1<br>(FLASH_SDOUT)                | 48 | BC1D2 | HVDD   | データ出力<br>ハードウェアリセット後の一定期間は起動時動作モード設定入力 (CNF1) として機能します。                                                                   |

| FLASH_CS                             | 31 | BC1P2 | HVDD   | チップセレクト出力                                                                                                                 |

| システムクロック                             |    |       |        |                                                                                                                           |

| CLKI                                 | 36 | IC    | HVDD   | クロック入力                                                                                                                    |

| ハードウェアリセット                           |    |       |        |                                                                                                                           |

| NRESET                               | 6  | IH    | HVDD   | ハードウェアリセット入力 (L アクティブ)                                                                                                    |

| 起動時動作モード設定                           |    |       |        |                                                                                                                           |

| CNF0                                 | 45 | BC1D2 | HVDD   | 起動時動作モード設定入力[0] (5.2 項を参照)                                                                                                |

| CNF1<br>(FLASH_SDOUT)                | 48 | BC1D2 | HVDD   | 起動時動作モード設定入力[1] (5.2 項を参照)<br>起動時動作モード設定完了後は FLASH_SDOUT 端子として機能しますので、プルアップ/プルダウン抵抗を用いて設定して下さい。直接 HVDD または VSS への接続は禁じます。 |

| CNF2<br>(EXAUDCK)                    | 50 | BC1D2 | HVDD   | 起動時動作モード設定入力[2] (5.2 項を参照)<br>起動時動作モード設定完了後は EXAUDCK 端子として機能しますので、プルアップ/プルダウン抵抗を用いて設定して下さい。直接 HVDD または VSS への接続は禁じます。     |

| テスト入出力                               |    |       |        |                                                                                                                           |

| TESTEN                               | 2  | ITST1 | LVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| TSTMODE0                             | 42 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| TSTMODE1                             | 43 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| TSTMODE2                             | 44 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| SCANEN                               | 59 | IHD2  | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| EXCKM                                | 41 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| EXMB                                 | 39 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| VCP                                  | 34 | LOT   | PLLVDD | テスト端子 (通常使用時は Open)                                                                                                       |

| TEST3                                | 15 | IH    | HVDD   | テスト端子 (通常使用時は VSS に接続)                                                                                                    |

| TEST4                                | 14 | ICP1  | HVDD   | テスト端子 (通常使用時は HVDD に接続)                                                                                                   |

| TEST5                                | 11 | ICP1  | HVDD   | テスト端子 (通常使用時は HVDD に接続)                                                                                                   |

| TEST6                                | 10 | ICP1  | HVDD   | テスト端子 (通常使用時は HVDD に接続)                                                                                                   |

| TEST7                                | 18 | T1    | HVDD   | テスト端子 (通常使用時は Open)                                                                                                       |

## 4. 端子

---

| 端子名称   | Pin                              | 機能              |

|--------|----------------------------------|-----------------|

| 電源     |                                  |                 |

| HVDD   | 1, 12, 20, 27, 38, 46, 52, 62    | I/O 電源 (3.3V)   |

| LVDD   | 13, 23, 28, 37, 51, 60           | Core 電源 (1.8V)  |

| PLLVDD | 33                               | PLL 電源 (1.8V)   |

| VSS    | 4, 5, 16, 21, 32, 40, 49, 56, 61 | GND (I/O, Core) |

| PLLVSS | 35                               | GND (PLL)       |

| 未使用端子  |                                  |                 |

| NC     | 24, 25, 26                       | 未使用端子           |

## 4.2 端子状態

| 端子名称                                 | I/O 電源 | I/O セル種類 | 端子状態      |                                                          |

|--------------------------------------|--------|----------|-----------|----------------------------------------------------------|

|                                      |        |          | NRESET=L  | 通常動作時                                                    |

| ホストインターフェース                          |        |          |           |                                                          |

| HOST_SCLK                            | HVDD   | BC3      | Z         | Z                                                        |

| HOST_SDIN                            | HVDD   | BC1D2    | Pull-down | Z                                                        |

| HOST_SDOUT                           | HVDD   | BC3P2    | Pull-up   | 【SPI】Output (HOST_CS=L)<br>Z (HOST_CS=H)<br>【UART】Output |

| HOST_CS                              | HVDD   | BC3P2    | Pull-up   | Z                                                        |

| RTS                                  | HVDD   | BC1D2    | Pull-down | Output                                                   |

| CTS                                  | HVDD   | BC1D2    | Pull-down | Z                                                        |

| RA                                   | HVDD   | BC1D2    | Pull-down | Output                                                   |

| アナログコーデックインターフェース (I <sup>2</sup> S) |        |          |           |                                                          |

| SCKI                                 | HVDD   | BC1D2    | Pull-down | Pull-down                                                |

| WSI                                  | HVDD   | BC1D2    | Pull-down | Pull-down                                                |

| SDI                                  | HVDD   | ICD2     | Pull-down | Pull-down                                                |

| SCKO                                 | HVDD   | BC1D2    | Z         | Pull-down                                                |

| WSO                                  | HVDD   | BC1D2    | Pull-down | Pull-down                                                |

| SDO                                  | HVDD   | O1       | L         | Output                                                   |

| アナログコーデックインターフェース (I <sup>2</sup> C) |        |          |           |                                                          |

| AUDCFG_CLK                           | HVDD   | BC1D2    | Pull-down | Output                                                   |

| AUDCFG_DAT                           | HVDD   | BC1P2    | Pull-up   | Output                                                   |

| アナログコーデックインターフェース (基準クロック)           |        |          |           |                                                          |

| CNF2<br>(EXAUDCK)                    | HVDD   | BC1D2    | Z         | Output<br>(16.59MHz)                                     |

| 外部シリアル Flash メモリインターフェース             |        |          |           |                                                          |

| FLASH_SCLK                           | HVDD   | BC1D2    | Z         | Z<br>(外部シリアル Flash メモリアクセス後は Output)                     |

| FLASH_SDIN                           | HVDD   | BC1D2    | Pull-down | Pull-down                                                |

| CNF1<br>(FLASH_SDOUT)                | HVDD   | BC1D2    | Z         | Z<br>(外部シリアル Flash メモリアクセス後は Output)                     |

| FLASH_CS                             | HVDD   | BC1P2    | H         | Output                                                   |

| システムクロック                             |        |          |           |                                                          |

| CLKI                                 | HVDD   | IC       | Z         | Z                                                        |

| ハードウェアリセット                           |        |          |           |                                                          |

| NRESET                               | HVDD   | IH       | Z         | Z                                                        |

| 起動時動作モード設定                           |        |          |           |                                                          |

| CNF0                                 | HVDD   | BC1D2    | Z         | Z                                                        |

| CNF1<br>(FLASH_SDOUT)                | HVDD   | BC1D2    | Z         | Z<br>(外部シリアル Flash メモリアクセス後は Output)                     |

| CNF2<br>(EXAUDCK)                    | HVDD   | BC1D2    | Z         | Output<br>(16.59MHz)                                     |

## 4. 端子

| テスト入出力   |        |       |           |           |

|----------|--------|-------|-----------|-----------|

| TESTEN   | LVDD   | ITST1 | Pull-down | Pull-down |

| TSTMODE0 | HVDD   | IH    | Z         | Z         |

| TSTMODE1 | HVDD   | IH    | Z         | Z         |

| TSTMODE2 | HVDD   | IH    | Z         | Z         |

| SCANEN   | HVDD   | IHD2  | Pull-down | Pull-down |

| EXCKM    | HVDD   | IH    | Z         | Z         |

| EXMB     | HVDD   | IH    | Z         | Z         |

| VCP      | PLLVDD | LOT   | Z         | Z         |

| TEST3    | HVDD   | IH    | Z         | Z         |

| TEST4    | HVDD   | ICP1  | Pull-up   | Pull-up   |

| TEST5    | HVDD   | ICP1  | Pull-up   | Pull-up   |

| TEST6    | HVDD   | ICP1  | Pull-up   | Pull-up   |

| TEST7    | HVDD   | T1    | Z         | Z         |

## 5. 機能説明

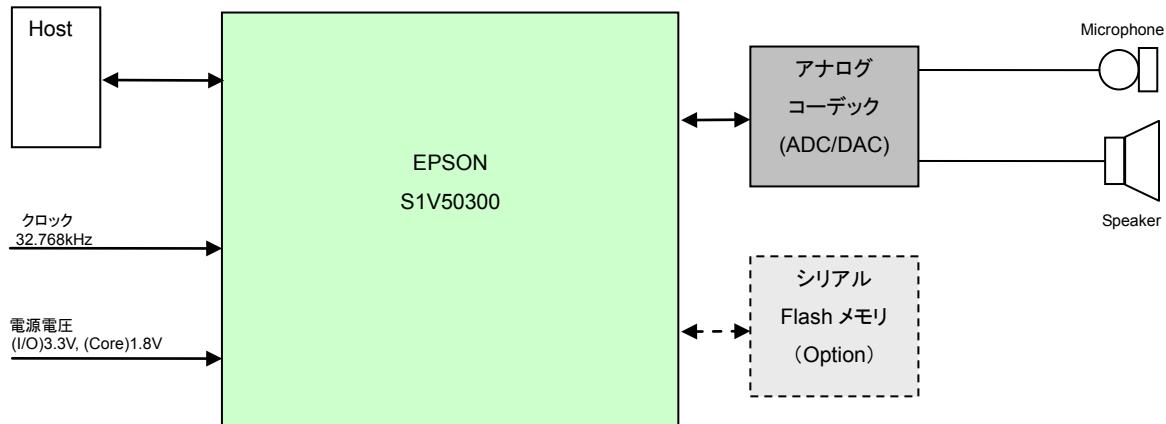

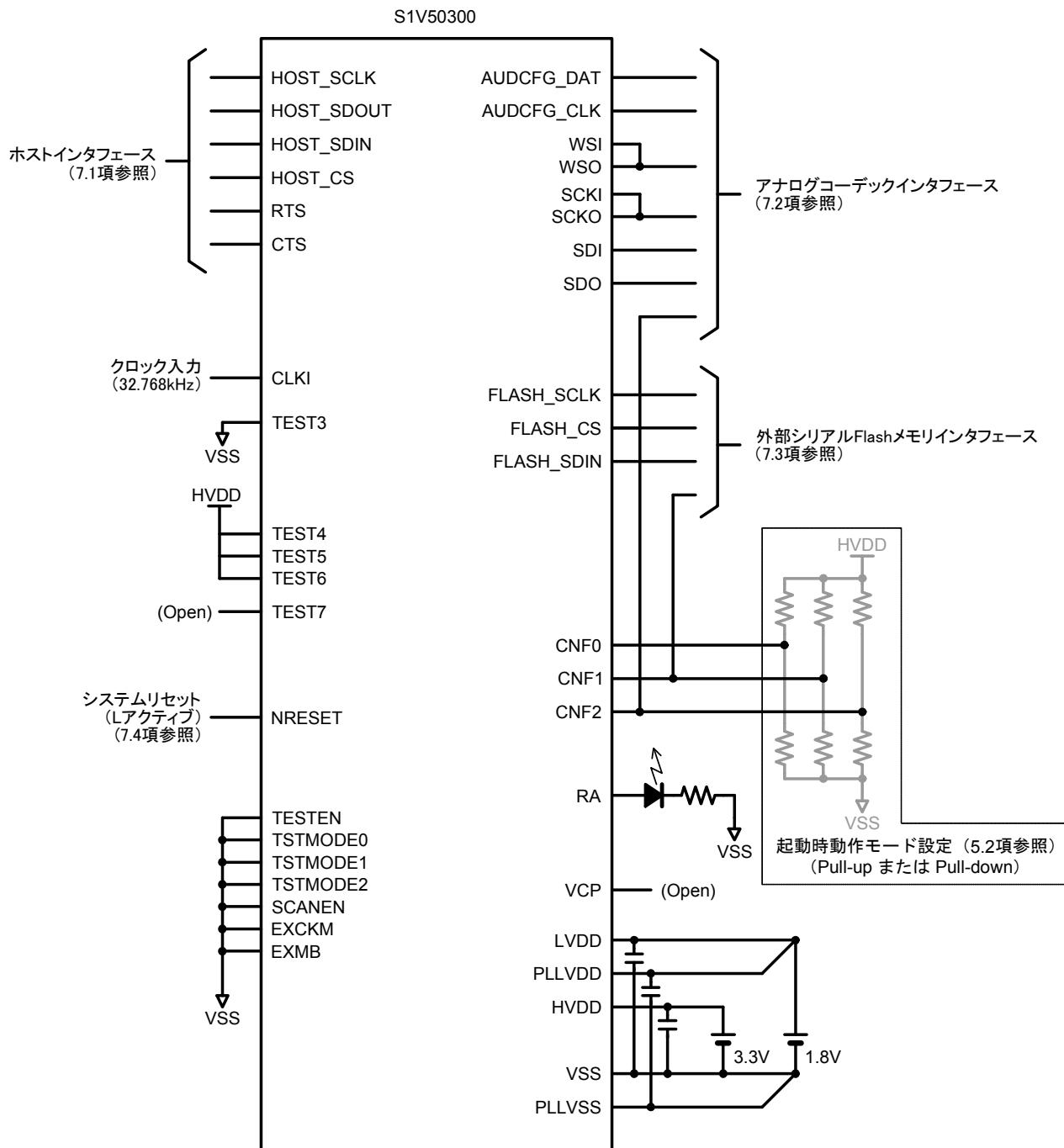

### 5.1 標準アプリケーションシステム

図 5.1 標準アプリケーションシステム

S1V50300 の標準アプリケーションシステムを図 5.1 に示します。ホストはシリアルインターフェースを介したコマンド制御（メッセージプロトコル）により S1V50300 を制御します。S1V50300 は Power On Reset 後、ホストからシリアルインターフェース経由で設定されるメッセージに従い音声認識を実行し認識結果をホストに返す、または音声データのデコードを行い音声再生を開始するなどの処理を行い、音声対話機能を実現します。シナリオライブラリーの格納領域として、外部シリアル Flash メモリを接続することも可能です。

メッセージの詳細は、『S1V50300 メッセージプロトコルマニュアル』を参照願います。

## 5. 機能説明

### 5.2 動作モード

S1V50300 は 2 種類の動作モードがあります。

- ブートモード

UART の通信条件の設定などを行う動作モードです。

設定を完了した後、メインモードに移行して下さい。

- メインモード

音声認識と音声再生による音声対話を実行する動作モードです。

起動時の動作モードは S1V50300 のハードウェアリセット解除時における CNF0,CNF1,CNF2 端子のレベルで決定します。同時にホストインターフェースの種類 (SPI または UART) も設定されます。一旦メインモードに移行した後は、ハードウェアリセットを実行しない限りブートモードに移行できません。

表 5.1 に CNF0,CNF1,CNF2 端子の設定値と起動時動作モードの対応を示します。

表 5.1 起動時動作モード

| モード設定端子    |            |            | 起動時動作モード | インターフェース                                                                                                                                                                                                                 | 備考                  |

|------------|------------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| CNF2       | CNF1       | CNF0       |          |                                                                                                                                                                                                                          |                     |

| 0<br>プルダウン | 1<br>プルアップ | 1<br>プルアップ | ブートモード   | SPI                                                                                                                                                                                                                      | -                   |

| 1<br>プルアップ | 0<br>プルダウン | 1<br>プルアップ | ブートモード   | UART                                                                                                                                                                                                                     | 通信条件はブートモードで変更できます。 |

| 1<br>プルアップ | 1<br>プルアップ | 0<br>プルダウン | メインモード   | 外部シリアル Flash ブート<br>外部シリアル Flash に格納されたホストインターフェース<br>設定データと初期化データを読み込むモードです。電源投<br>入後自動的にホストインターフェース設定データと初期化<br>データの読み込みを開始し、その後メインモードで起動し<br>ます。<br>ホストインターフェースと通信条件は、ホストインターフェー<br>ス設定データ内で指定されたインターフェースが選択され<br>ます。 |                     |

| 上記以外       |            |            | 設定禁止     |                                                                                                                                                                                                                          |                     |

注意)

- CNF1, CNF2 端子は起動時動作モード設定完了後、出力状態となりますので、必ずプルアップ/プルダウン抵抗を用いて設定して下さい。直接 HVDD または VSS への接続は動作に支障を及ぼすため絶対に行わないで下さい。

- CNF1, CNF2 端子からプルアップ/プルダウン抵抗までの配線長は極力短くして下さい。

### 5.3 ホストインターフェース

S1V50300 のホストインターフェースは、クロック同期式 (SPI) 、調歩同期式 (UART) のいずれかを選択することができます。

- クロック同期式 (SPI)

- スレーブモードに対応

- データ長 : 8 ビット固定、MSB ファースト

- 調歩同期式 (UART)

- データ長 : 8 ビット固定、LSB ファースト

- スタートビット : 1 ビット固定

- ストップビット : 1 ビットまたは 2 ビットを選択可能 (初期値 : 2 ビット)

- パリティビット : 偶数、奇数、または なし を選択可能 (初期値 : なし)

- ボーレート [baud] : 9.6k, 14.4k, 19.2k, 28.8k, 38.4k, 57.6k, 115.2k を選択可能 (初期値 : 9.6k)

ホストインターフェースの種類 (SPI または UART) は起動時動作モードの設定と同時に選択されます。詳細は 5.2 項を参照願います。

表 5.2 に、ホストインターフェースの端子設定を示します。

表 5.2 ホストインターフェース 端子設定

| インターフェース      | シリアル通信    |           |            |                | ハンドシェイク      |              |

|---------------|-----------|-----------|------------|----------------|--------------|--------------|

|               | HOST_SCLK | HOST_SDIN | HOST_SDOUT | HOST_CS        | RTS          | CTS          |

| クロック同期式 (SPI) | クロック入力    | データ入力     | データ出力      | スレーブ選択<br>信号入力 | 送信要求<br>信号出力 | 送信許可<br>信号入力 |

| 調歩同期式 (UART)  | H レベル固定   |           |            | H レベル固定        |              |              |

(注意)

- UART インタフェースは、ホストからのストリーミング転送による音声再生に対応していません。

- ホストからのストリーミング転送による音声再生を行う場合は、SPI インタフェースを選択願います。

- ホストからのストリーミング転送による音声再生を行う場合、使用する転送レートによっては音飛びが発生する可能性があります。音飛びの発生は、転送レートを上げることで回避できます。

## 6. 電気的特性

### 6. 電気的特性

#### 6.1 絶対最大定格

| ( VSS = 0V ) |        |                    |    |

|--------------|--------|--------------------|----|

| 項目           | 記号     | 定格値                | 単位 |

| 電源電圧         | HVDD   | VSS-0.3 ~ 4.0      | V  |

|              | LVDD   | VSS-0.3 ~ 2.5      | V  |

|              | PLLVDD | VSS-0.3 ~ 2.5      | V  |

| 入力電圧         | HVI    | VSS-0.3 ~ HVDD+0.5 | V  |

|              | LVI    | VSS-0.3 ~ LVDD+0.5 | V  |

| 出力電圧         | HVO    | VSS-0.3 ~ HVDD+0.5 | V  |

|              | LVO    | VSS-0.3 ~ LVDD+0.5 | V  |

| 出力電流／端子      | IOUT   | ±10                | mA |

| 保存温度         | Tstg   | -65 ~ +150         | °C |

#### 6.2 推奨動作条件

| ( VSS = 0V ) |        |      |      |      |    |

|--------------|--------|------|------|------|----|

| 項目           | 記号     | Min. | Typ. | Max. | 単位 |

| 電源電圧         | HVDD   | 3.00 | 3.30 | 3.60 | V  |

|              | LVDD   | 1.65 | 1.80 | 1.95 | V  |

|              | PLLVDD | 1.65 | 1.80 | 1.95 | V  |

| 入力電圧         | HVI    | VSS  | -    | HVDD | V  |

|              | LVI    | VSS  | -    | LVDD | V  |

| 周囲温度         | Ta     | -40  | 25   | 85   | °C |

本 LSI は、下記順序で電源投入・切断を行って下さい。

電源投入時 : LVDD・PLLVDD ⇒ HVDD

電源切断時 : HVDD ⇒ LVDD・PLLVDD

注意)

- LVDD 及び PLLVDD が切断されている状態で、HVDD のみを継続的に (1sec.以上) 印加することは、本 LSI の信頼性上問題がありますので避けて下さい。

- 電源をオフ状態からオン状態へ復帰させる場合には、電源ノイズ等の影響により、内部回路の状態を保証できませんので、電源投入後は必ずハードウェアリセットを実行し内部回路の初期化を行ってください。

## 6.3 DC 特性

6.3.1 電源電圧  $3.3 \pm 0.3V$  における DC 特性( HVDD =  $3.3 \pm 0.3V$ , VSS = 0V, Ta =  $-40^{\circ}C \sim 85^{\circ}C$  )

| 項目                                                                                                                                                                                            | 記号       | 条件                                 | Min.                                             | Typ. | Max. | 単位 |    |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------|--------------------------------------------------|------|------|----|----|--|--|--|--|

| 電源電流                                                                                                                                                                                          |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| 静止電流<br>(※1)                                                                                                                                                                                  | LVDD 系   | IDDSL                              | HVDD=3.3V<br>LVDD=1.8V<br>PLLVDD=1.8V<br>Ta=25°C | -    | 3    | -  | μA |  |  |  |  |

|                                                                                                                                                                                               | HVDD 系   | IDDSH                              |                                                  | -    | 4    | -  | μA |  |  |  |  |

|                                                                                                                                                                                               | PLLVDD 系 | IDDSP                              |                                                  | -    | 1    | -  | μA |  |  |  |  |

| 消費電流<br>音声再生時<br>(※2)                                                                                                                                                                         | LVDD 系   | IDDPL                              | HVDD=3.3V<br>LVDD=1.8V<br>PLLVDD=1.8V<br>Ta=25°C | -    | 21   | -  | mA |  |  |  |  |

|                                                                                                                                                                                               | HVDD 系   | IDDPH                              |                                                  | -    | 4    | -  | mA |  |  |  |  |

|                                                                                                                                                                                               | PLLVDD 系 | IDDPP                              |                                                  | -    | 2    | -  | mA |  |  |  |  |

| 消費電流<br>音声認識時<br>(※3)                                                                                                                                                                         | LVDD 系   | IDDRL                              | HVDD=3.3V<br>LVDD=1.8V<br>PLLVDD=1.8V<br>Ta=25°C | -    | 30   | -  | mA |  |  |  |  |

|                                                                                                                                                                                               | HVDD 系   | IDDRH                              |                                                  | -    | 4    | -  | mA |  |  |  |  |

|                                                                                                                                                                                               | PLLVDD 系 | IDDRP                              |                                                  | -    | 2    | -  | mA |  |  |  |  |

| 入力リーク電流                                                                                                                                                                                       |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| 入力リーク電流                                                                                                                                                                                       |          | HVI=HVDD or VSS<br>LVI=LVDD or VSS | -5                                               | -    | 5    | μA |    |  |  |  |  |

|                                                                                                                                                                                               |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| 入力特性 (LVC MOS)                                                                                                                                                                                |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| 端子名:HOST_SCLK, HOST_SDIN, HOST_SDOUT, HOST_CS, RTS, CTS, RA, SCKI, WSI, SDI, SCKO, WSO, AUDCFG_CLK, AUDCFG_DAT, FLASH_SCLK, FLASH_SDIN, FLASH_CS, CLKI, CNF0, CNF1, CNF2, TEST4, TEST5, TEST6 |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| H レベル入力電圧                                                                                                                                                                                     | HVIH1    | HVDD=3.6V                          | 2.2                                              | -    | -    | V  |    |  |  |  |  |

| L レベル入力電圧                                                                                                                                                                                     | HVIL1    | HVDD=3.0V                          | -                                                | -    | 0.8  | V  |    |  |  |  |  |

| 入力特性 (LVC MOS) 端子名:TESTEN                                                                                                                                                                     |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| H レベル入力電圧                                                                                                                                                                                     | LVIH1    | LVDD=1.95V                         | 1.27                                             | -    | -    | V  |    |  |  |  |  |

| L レベル入力電圧                                                                                                                                                                                     | LVIL1    | LVDD=1.65V                         | -                                                | -    | 0.57 | V  |    |  |  |  |  |

| シュミット入力特性 (LVC MOS) 端子名:NRESET, TSTMODE0, TSTMODE1, TSTMODE2, SCANEN, EXCKM, EXMB, TEST3                                                                                                      |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| H レベル入力電圧                                                                                                                                                                                     | HVIH2    | HVDD=3.6V                          | 1.4                                              | -    | 2.7  | V  |    |  |  |  |  |

| L レベル入力電圧                                                                                                                                                                                     | HVIL2    | HVDD=3.0V                          | 0.6                                              | -    | 1.8  | V  |    |  |  |  |  |

| ヒステリシス電圧                                                                                                                                                                                      | ΔV       | HVDD=3.0V                          | 0.3                                              | -    | -    | V  |    |  |  |  |  |

| 入力特性 (LVC MOS) 端子名:TEST4, TEST5, TEST6                                                                                                                                                        |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| プルアップ抵抗                                                                                                                                                                                       | HRPU1    | HVI=VSS                            | 25                                               | 50   | 120  | kΩ |    |  |  |  |  |

| 入力特性 (LVC MOS) 端子名:HOST_SDOUT, HOST_CS, AUDCFG_DAT, FLASH_CS                                                                                                                                  |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| プルアップ抵抗                                                                                                                                                                                       | HRPU2    | HVI=VSS                            | 50                                               | 100  | 240  | kΩ |    |  |  |  |  |

| 入力特性 (LVC MOS) 端子名:HOST_SDIN, RTS, CTS, RA, SCKI, WSI, SDI, SCKO, WSO, AUDCFG_CLK, FLASH_SCLK, FLASH_SDIN, CNF0, CNF1, CNF2, SCANEN                                                           |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| プルダウン抵抗                                                                                                                                                                                       | HRPD2    | HVI=HVDD                           | 50                                               | 100  | 240  | kΩ |    |  |  |  |  |

| 入力特性 (LVC MOS) 端子名:TESTEN                                                                                                                                                                     |          |                                    |                                                  |      |      |    |    |  |  |  |  |

| プルダウン抵抗                                                                                                                                                                                       | LRPD2    | LVI=LVDD                           | 48                                               | 120  | 300  | kΩ |    |  |  |  |  |

| (次頁に続く)                                                                                                                                                                                       |          |                                    |                                                  |      |      |    |    |  |  |  |  |

## 6. 電気的特性

|            |       |                                                                                                                                                                      |          |   |   |         |    |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---|---------|----|

| 出力特性       |       | 端子名:HOST_SDIN, RTS, CTS, RA, SCKI, WSI, SCKO, WSO, SDO, AUDCFG_CLK, AUDCFG_DAT, FLASH_SCLK, FLASH_SDIN, FLASH_CS, CNF0, CNF1, CNF2, TEST7                            |          |   |   |         |    |

| H レベル出力電圧  | HVOH1 | HVDD=3.0V<br>IOH=-2mA                                                                                                                                                | HVDD-0.4 | - | - | -       | V  |

| L レベル出力電圧  | HVOL1 | HVDD=3.0V<br>IOL=2mA                                                                                                                                                 | -        | - | - | VSS+0.4 | V  |

| 出力特性       |       | 端子名:HOST_SCLK, HOST_SDOUT, HOST_CS                                                                                                                                   |          |   |   |         |    |

| H レベル出力電圧  | HVOH3 | HVDD=3.0V<br>IOH=-8mA                                                                                                                                                | HVDD-0.4 | - | - | -       | V  |

| L レベル出力電圧  | HVOL3 | HVDD=3.0V<br>IOL=8mA                                                                                                                                                 | -        | - | - | VSS+0.4 | V  |

| 出力特性       |       | 端子名:HOST_SCLK, HOST_SDIN, HOST_SDOUT, HOST_CS, RTS, CTS, RA, SCKI, WSI, SCKO, WSO, AUDCFG_CLK, AUDCFG_DAT, FLASH_SCLK, FLASH_SDIN, FLASH_CS, CNF0, CNF1, CNF2, TEST7 |          |   |   |         |    |

| カスケートリード電流 | IOZ   | HVO=HVDD or VSS                                                                                                                                                      | -5       | - | - | 5       | μA |

| 端子容量       |       | 端子名: 全入力端子                                                                                                                                                           |          |   |   |         |    |

| 入力端子容量     | CI    | f=1MHz<br>HVDD=0V                                                                                                                                                    | -        | - | - | 8       | pF |

| 端子容量       |       | 端子名: 全出力端子                                                                                                                                                           |          |   |   |         |    |

| 出力端子容量     | CO    | f=1MHz<br>HVDD=0V                                                                                                                                                    | -        | - | - | 8       | pF |

| 端子容量       |       | 端子名: 全入出力端子                                                                                                                                                          |          |   |   |         |    |

| 入出力端子容量    | CIO   | f=1MHz<br>HVDD=0V                                                                                                                                                    | -        | - | - | 8       | pF |

※1 推奨動作条件 (Ta=25°C) における、全入出力信号が静止状態の消費電流

※2 推奨動作条件 (Ta=25°C) における、EOV 形式音声ファイル再生実行中の消費電流

※3 推奨動作条件 (Ta=25°C) における、音声認識実行中の消費電流

## 6.4 AC 特性

## • 条件

特記なき場合は、以下の条件に従います。

電源電圧 : LVDD=1.8V±0.15V, PLLVDD=1.8V±0.15V, HVDD=3.3V±0.3V

周囲温度 : Ta=-40°C~85°C

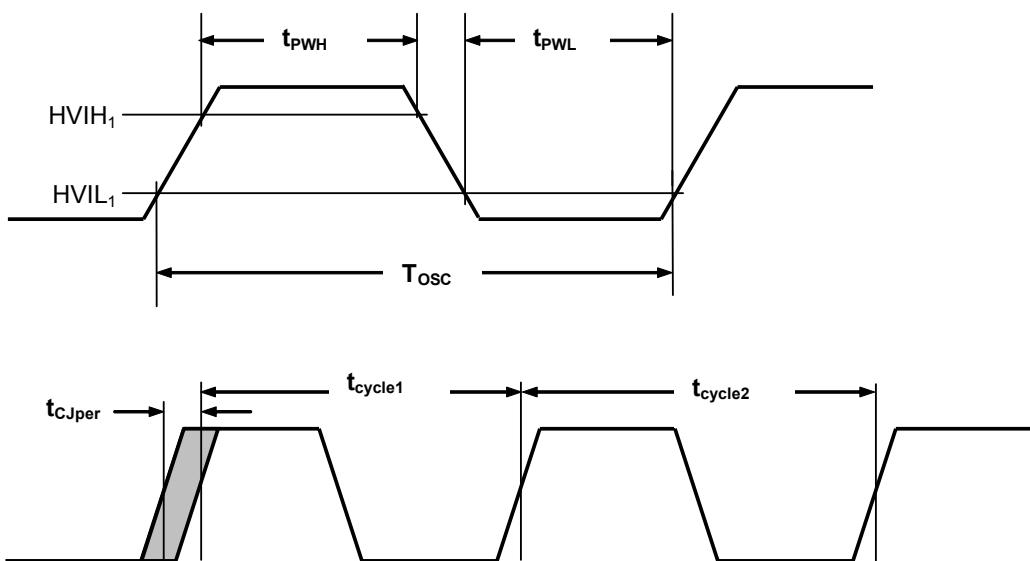

## 6.4.1 システムクロックタイミング

図 6.1 システムクロックタイミング

| 記号            | 項目                                                  | Min.            | Typ.         | Max.            | 単位  |

|---------------|-----------------------------------------------------|-----------------|--------------|-----------------|-----|

| $F_{CLKI}$    | 入力クロック周波数                                           | -               | 32.768       | -               | kHz |

| $T_{CLKI}$    | 入力クロック周期                                            | -               | $1/F_{CLKI}$ | -               | ms  |

| $t_{pwh}$     | 入力クロック H レベルパルス幅                                    | $0.45*T_{CLKI}$ | -            | $0.55*T_{CLKI}$ | ms  |

| $t_{pwl}$     | 入力クロック L レベルパルス幅                                    | $0.45*T_{CLKI}$ | -            | $0.55*T_{CLKI}$ | ms  |

| $t_{CJper}$   | 入力クロック周期ジッタ (※2, 4)                                 | -5.0            | -            | 5.0             | ns  |

| $t_{CJcycle}$ | 入力クロックサイクルジッタ (※1, 3, 4)                            | -5.0            | -            | 5.0             | ns  |

| ※1            | $t_{CJcycle} = t_{cycle1} - t_{cycle2}$             |                 |              |                 |     |

| ※2            | 入力クロック周期ジッタは、中心周期（中心周波数の逆数）からの変化です。                 |                 |              |                 |     |

| ※3            | 入力クロックサイクルジッタは、隣接するサイクル間における周期の差分です。                |                 |              |                 |     |

| ※4            | ジッタ特性は $t_{CJper}$ 及び $t_{CJcycle}$ の両方を満たす必要があります。 |                 |              |                 |     |

| ※5            | クロックは極力オーバーシュート／アンダーシュートがないようにして下さい。                |                 |              |                 |     |

## 6. 電気的特性

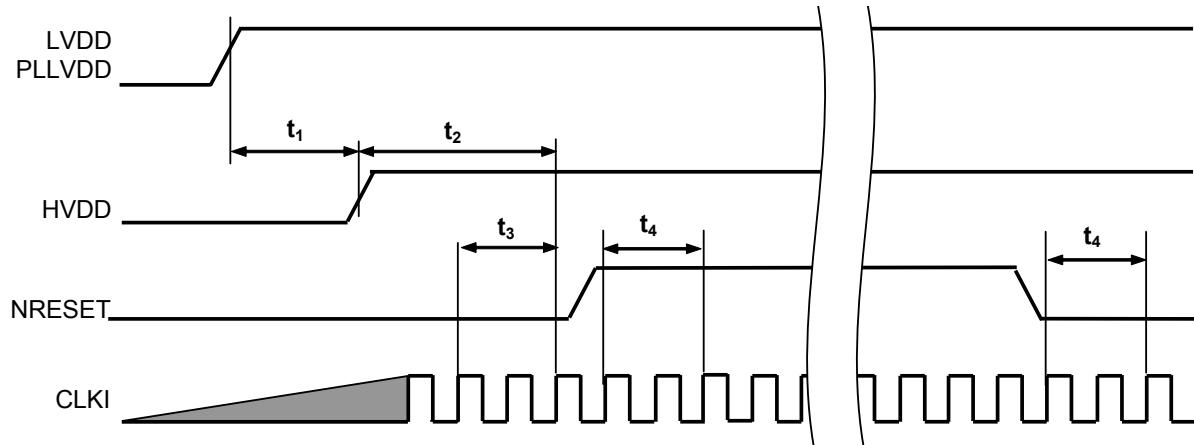

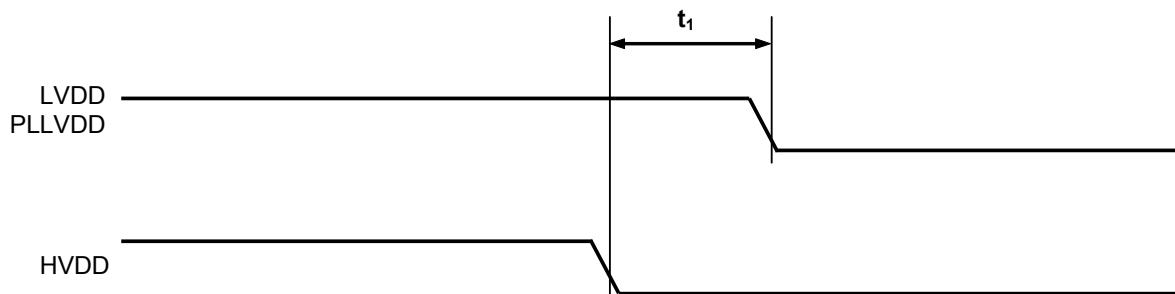

### 6.4.2 電源投入／リセットタイミング

図 6.2 電源投入／リセットタイミング

| 記号    | 項目                                                  | Min. | Max. | 単位              |

|-------|-----------------------------------------------------|------|------|-----------------|

| $t_1$ | LVDD・PLLVDD 系電源の投入から HVDD 系電源投入までの時間                | 0    | -    | s               |

| $t_2$ | HVDD 系電源投入から、NRESET 解除直前における CLKI 立ち上がりエッジまでの時間（※1） | 100  | -    | μs              |

| $t_3$ | 電源投入時における最小リセット幅                                    | 2    | -    | $T_{CLKI}$ （※2） |

| $t_4$ | NRESET 内部同期時間<br>(リセット信号が内部回路に適用されるまでの時間)           | 2    | -    | $T_{CLKI}$ （※2） |

| ※1    | CLKI は十分に安定した状態であること。                               |      |      |                 |

| ※2    | $T_{CLKI}$ は CLKI の周期です。                            |      |      |                 |

注意)

LVDD 及び PLLVDD が切断されている状態で、HVDD のみを継続的に（1sec.以上）印加することは、本 LSI の信頼性上問題がありますので避けて下さい。

電源をオフ状態からオン状態へ復帰させる場合には、電源ノイズ等の影響により、内部回路の状態を保証できませんので、電源投入後は必ずハードウェアリセット（NRESET）を実行し回路の初期化を行って下さい。

## 6.4.3 電源切断タイミング

図 6.3 電源切断タイミング

| 記号    | 項目                                   | Min. | Max. | 単位 |

|-------|--------------------------------------|------|------|----|

| $t_1$ | HVDD 系電源切断から LVDD・PLLVDD 系電源の切断までの時間 | 0    | -    | s  |

## 注意)

LVDD 及び PLLVDD が切断されている状態で、HVDD のみを継続的に（1sec.以上）印加することは、本 LSI の信頼性上問題がありますので避けて下さい。

## 6. 電気的特性

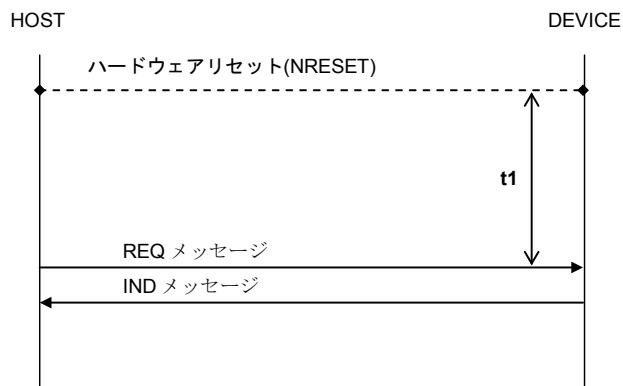

### 6.4.4 メッセージ受付タイミング

図 6.4 メッセージ受付タイミング

ハードウェアリセット後、 $t_1$  時間を経過してからシステムが立ち上ります。

S1V50300 は  $t_1$  時間経過後にメッセージを受付可能となります。

| 記号    | 項目                               | Min. | Max. | 単位 |

|-------|----------------------------------|------|------|----|

| $t_1$ | 初期化からメッセージ受付可能となるまでの時間 (※1)      | 160  | -    | ms |

| ※1    | $t_1$ 時間にパディングバイトを送信しても問題はありません。 |      |      |    |

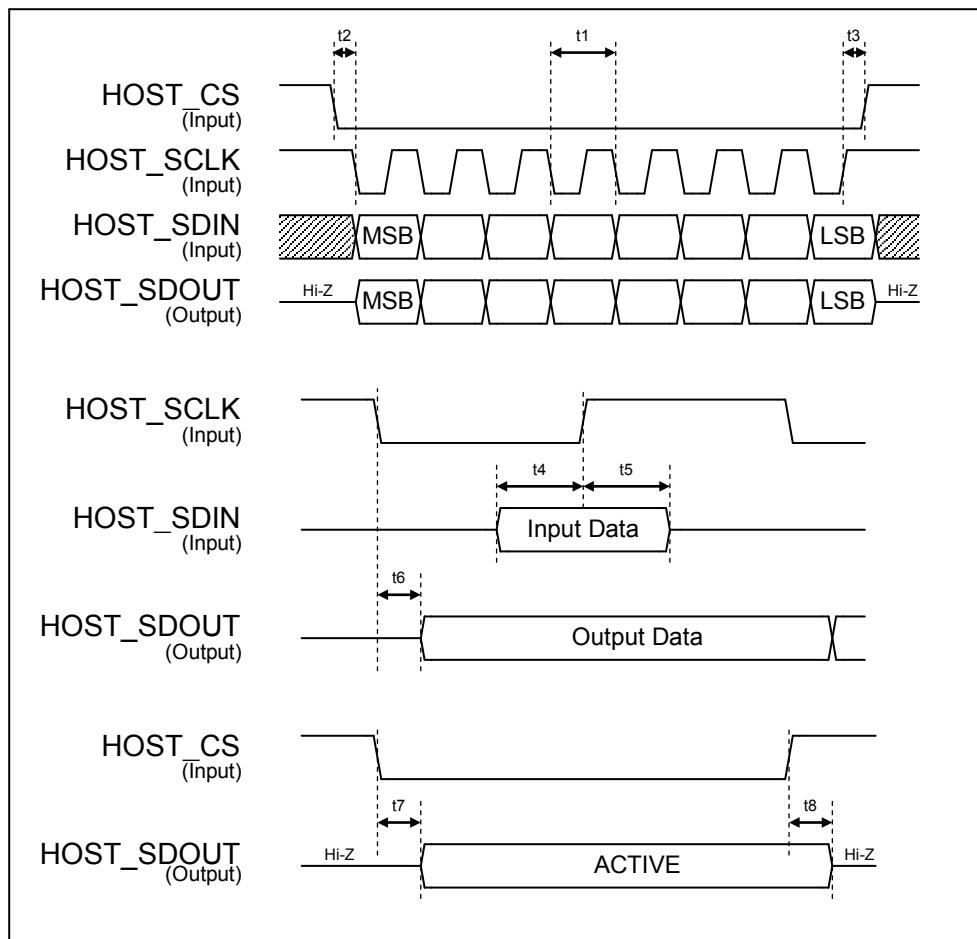

## 6.4.5 ホストインターフェース（クロック同期式（SPI））

図 6.5 ホストインターフェース（クロック同期式（SPI））アクセスタイミング

| 記号    | 項目                                        | Min. | Max. | 単位 |

|-------|-------------------------------------------|------|------|----|

| $t_1$ | HOST_SCLK サイクル時間                          | 1.0  | 20   | μs |

| $t_2$ | HOST_CS セットアップ時間                          | 200  | -    | ns |

| $t_3$ | HOST_CS ホールド時間                            | 50   | -    | ns |

| $t_4$ | HOST_SDIN セットアップ時間                        | 50   | -    | ns |

| $t_5$ | HOST_SDIN ホールド時間                          | 50   | -    | ns |

| $t_6$ | HOST_SDOUT 出力遅延時間（※1）                     | -    | 200  | ns |

| $t_7$ | HOST_CS 立ち下がりから HOST_SDOUT 駆動までの時間（※1）    | -    | 200  | ns |

| $t_8$ | HOST_CS 立ち上がりから HOST_SDOUT Hi-Z までの時間（※1） | -    | 200  | ns |

| ※1    | HOST_SDOUT 端子の負荷容量 $C_L=15pF$             |      |      |    |

## 6. 電気的特性

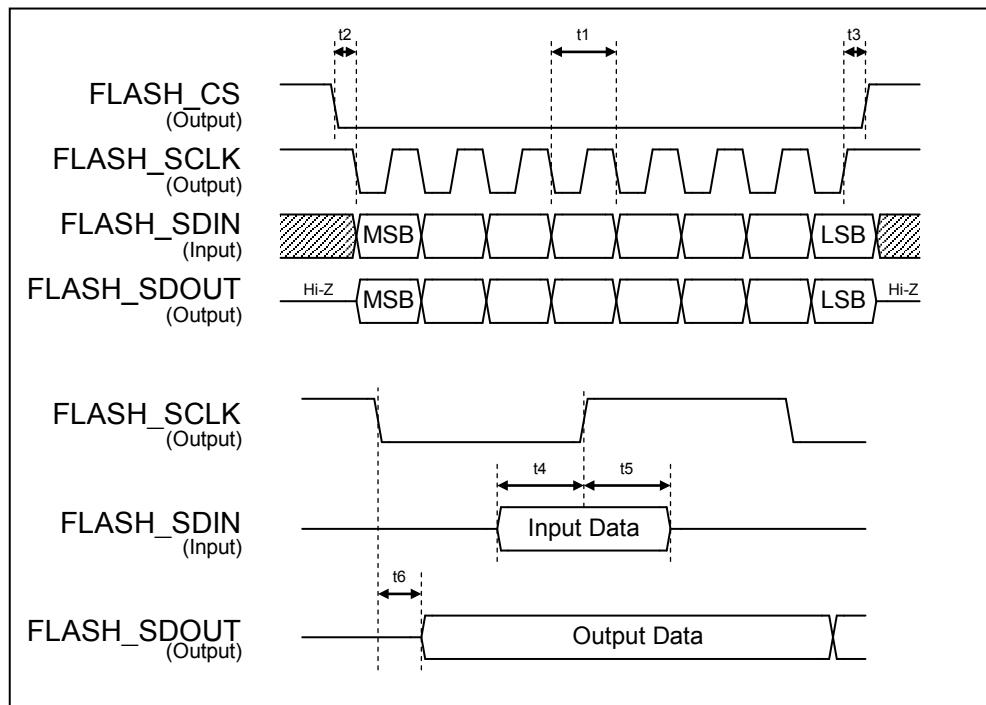

### 6.4.6 外部シリアル Flash メモリインタフェース

図 6.6 外部シリアル Flash メモリインタフェース アクセスタイミング

| 記号    | 項目                                                   | Min. | Max. | 単位 |

|-------|------------------------------------------------------|------|------|----|

| $t_1$ | FLASH_SCLK サイクル時間                                    | 950  | -    | ns |

| $t_2$ | FLASH_CS セットアップ時間 (※1)                               | 100  | -    | ns |

| $t_3$ | FLASH_CS ホールド時間 (※1)                                 | 100  | -    | ns |

| $t_4$ | FLASH_SDIN セットアップ時間                                  | 10   | -    | ns |

| $t_5$ | FLASH_SDIN ホールド時間                                    | 10   | -    | ns |

| $t_6$ | FLASH_SDOUT 出力遅延時間 (※1)                              | -    | 30   | ns |

| ※1    | FLASH_SCLK, FLASH_CS, FLASH_SDOUT 端子の負荷容量 $C_L=15pF$ |      |      |    |

## 7. 外部接続例

### 7.1 ホストインターフェース

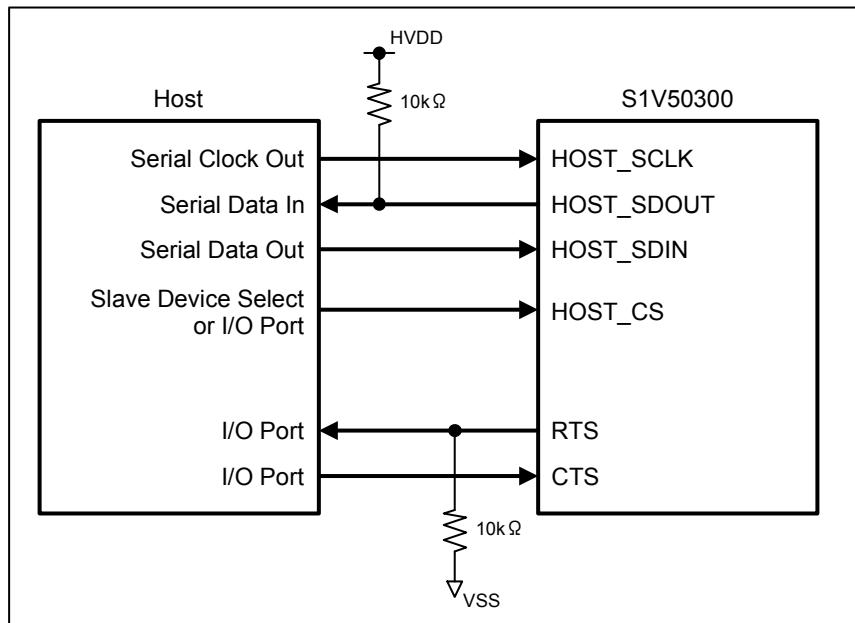

#### 7.1.1 クロック同期式 (SPI)

図 7.1 シリアルインターフェース外部接続例 (SPI)

図 7.1 に SPI によるホストとの接続例を示します。

HOST\_CS が Low レベルの場合は、HOST\_SDOUT はアクティブとなります。HOST\_CS が High レベルの場合は、HOST\_SDOUT はハイインピーダンスとなります。HOST\_CS を図 7.1 のように、汎用出力ポートまたはホスト側シリアルインターフェースのスレーブデバイス選択信号により制御することで、複数のスレーブデバイスの接続が可能となります。HOST\_CS 端子をホストの汎用ポート等で制御する場合は、メッセージの送信直前に Low レベルに設定し、メッセージの受信が完了したら High レベルに設定してください。AC 特性は 6.4.5 項を参照ください。

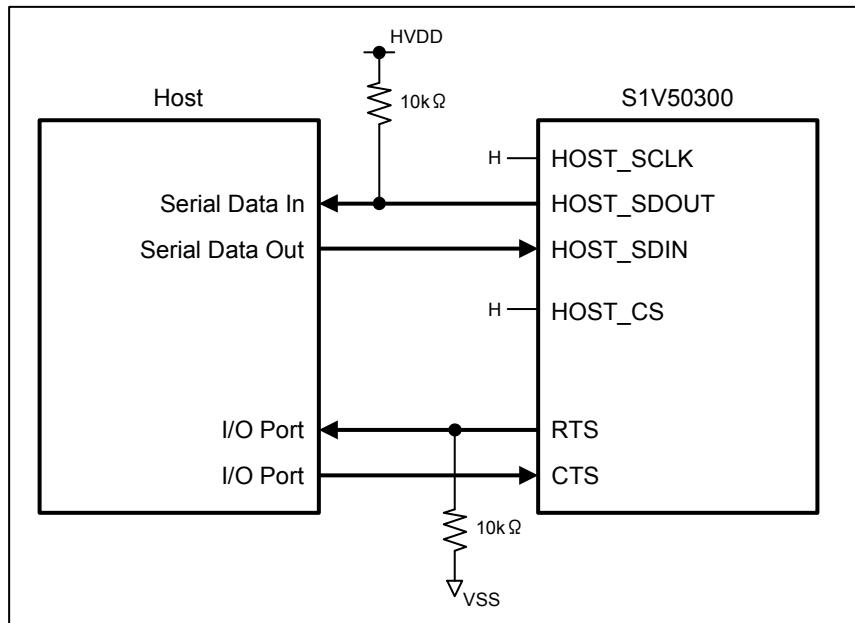

### 7.1.2 調歩同期式 (UART)

図 7.2 シリアルインタフェース外部接続例 (UART)

図 7.2 に UART によるホストとの接続例を示します。

UART インタフェースの通信設定の初期値は、以下の通りです。

スタートビット長： 1bit

ストップビット長： 2bit

パリティビット： なし

ボーレート： 9.6kbaud

通信設定はブートモードメッセージ ISC\_BOOT\_SYS\_CONFIG\_REQ メッセージで変更することができます。同メッセージで設定した通信設定はハードウェアリセットを実行するまで保持されます。ハードウェアリセットを実行した場合、通信設定は上記の初期値となりますので、必要に応じ ISC\_BOOT\_SYS\_CONFIG\_REQ メッセージを実行して下さい。詳細は『S1V50300 メッセージプロトコルマニュアル』を参照ください。

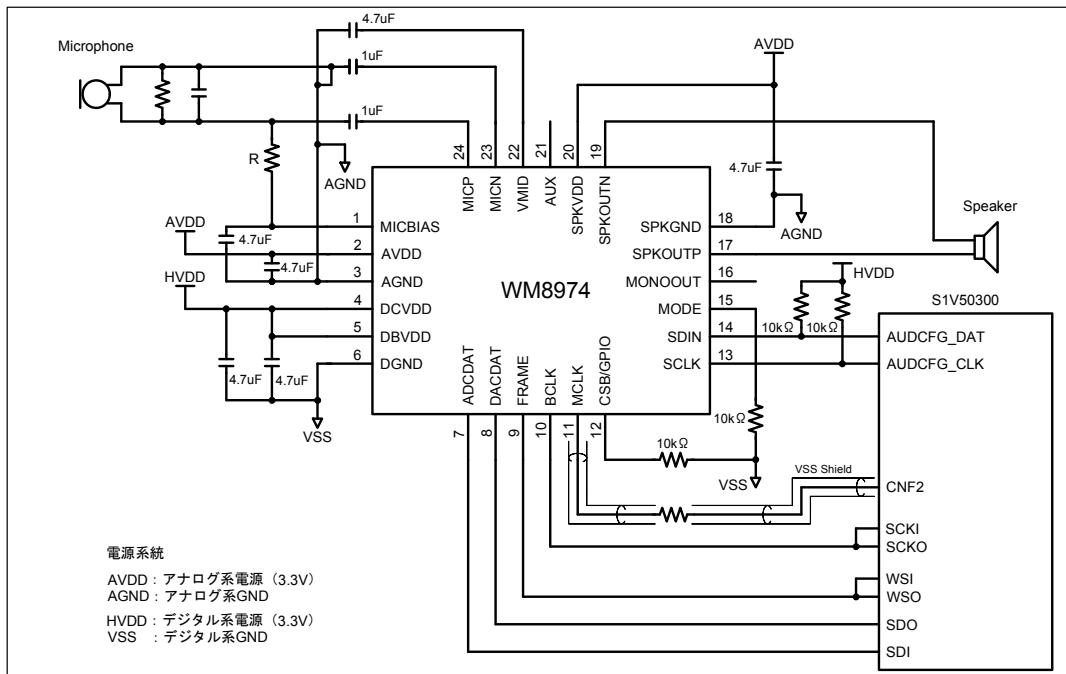

## 7.2 アナログコーデックインターフェース

図 7.3 アナログコーデックインターフェース外部接続例

S1V50300 はアナログコーデックを接続する必要があります。アナログコーデックは Wolfson 社の WM8974 を使用することができます。図 7.3 にアナログコーデックとの接続例を示します。

アナログコーデックの電源は、S1V50300 をはじめとするデジタル系の電源系統と分離してください。電源系統を分離しない場合、アナログコーデックの電気的特性に影響を与えることがあります。

MCLK 端子と CNF2(EXAUDCK)端子との配線は極力短く、かつデジタル系電源系統の GND でシールドして下さい。CNF2(EXAUDCK)端子は起動時動作モード（5.2 項参照）の設定完了後、アナログコーデックに供給する基準クロック信号（16.59MHz）を出力します。

MICP 端子, MICBIAS 端子の配線と他のデジタル信号との配線は、極力並走または交差することのないようご配慮願います。

MICBIAS 端子の抵抗  $R$  は、エレクトレットコンデンサマイクロфонに電源を供給する場合に接続します。抵抗  $R$  の定数はマイクロфонの仕様書をご参照下さい。

その他、アナログコーデックの実装に関する注意事項は、WM8974 の設計資料をご参照ください。

## 7. 外部接続例

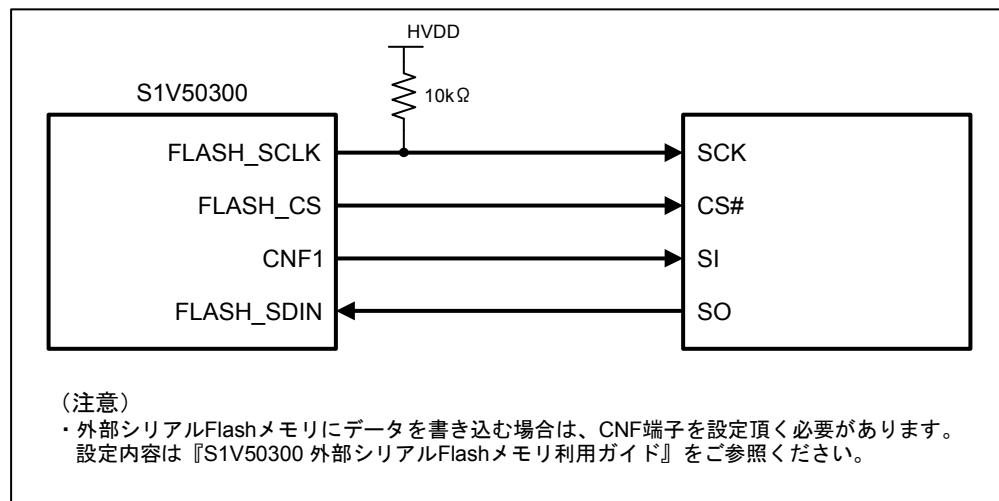

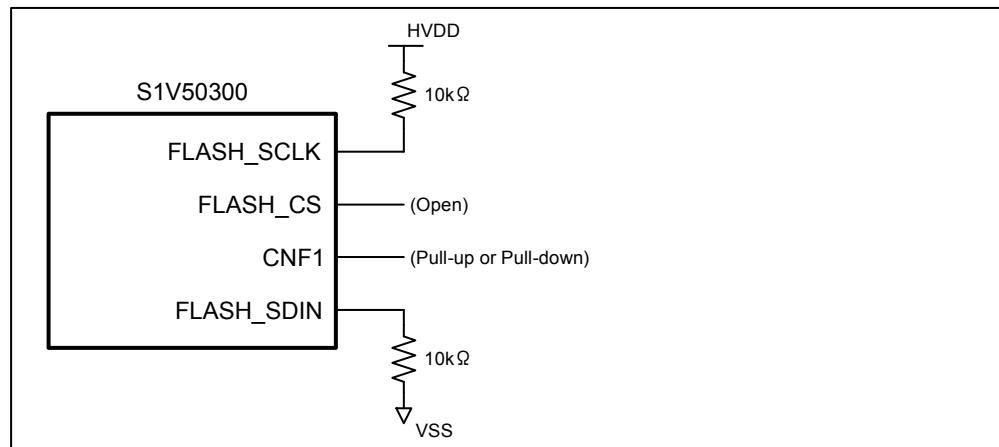

### 7.3 外部シリアル Flash メモリインタフェース

図 7.4 外部シリアル Flash メモリインタフェース外部接続例

S1V50300 にシリアル Flash メモリを外部接続することで、シナリオライブラリーを格納することができます。図 7.4 に外部シリアル Flash メモリインタフェースの外部接続例を示します。AC 特性は 6.4.6 項を参照ください。外部シリアル Flash メモリにデータを書き込む場合は、CNF 端子を設定頂く必要があります。設定内容は『S1V50300 外部シリアル Flash メモリ利用ガイド』をご参照ください。

図 7.4 に外部シリアル Flash メモリを接続しない場合の各端子の処理を示します。

図 7.5 外部シリアル Flash メモリ非接続時の端子処理

## 8. 外形寸法図

## 8.1 QFP13-64

1 = 1mm

## 9. 參考資料

## 9.1 應用回路例

図 9.1 S1V50300 應用回路例

### 9.2 電源に関する注意事項

電源をオフ状態からオン状態へ復帰させる場合には、電源ノイズ等の影響により、内部回路の状態を保証できませんので、電源投入後は必ず NRESET により回路の初期化を行って下さい。

CMOS 構造のデバイスは、ラッチアップと呼ばれる状態になることがあります。これは、CMOS IC が内蔵する PNPN 接合（サイリスタ構造）が導通し、HVDD – VSS 間に大電流が流れ破壊に至る現象です。

ラッチアップは、入力・出力端子への電圧印加が定格を超えて、内部素子に大きな電流が流れた場合、あるいは HVDD 端子の電圧が定格を超えて内部素子が降伏状態となったときに起こります。この場合、定格外の電圧印加が瞬間的なものであっても、一旦ラッチアップ状態になると HVDD – VSS 間の大電流が保持され、発熱や発煙のおそれもあるため、次の点に注意して下さい。

- (1) 入出力端子の電圧レベルを電気的特性に指定された範囲を超えて電源電圧より上げない、または VSS より下げないで下さい。

- (2) 異常ノイズがデバイスに加わらないようにして下さい。

- (3) 未使用の入力端子の電位を HVDD または VSS に固定して下さい。

- (4) 出力を短絡しないで下さい。

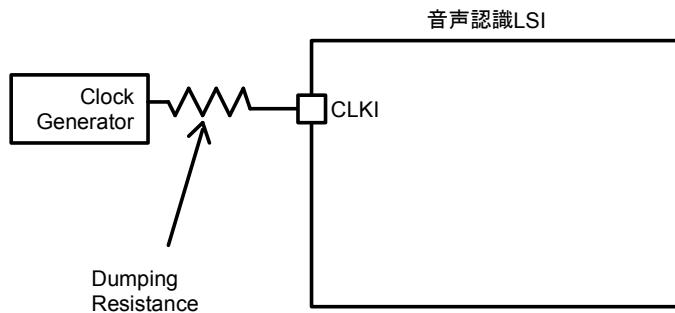

### 9.3 クロック直接入力に関する注意事項

外部からの直接クロック入力時、クロックにオーバーシュート／アンダーシュートが大きいと、電源にノイズが入ります。内部回路の破壊や誤動作につながる可能性があります。

クロックのオーバーシュート／アンダーシュートは、6.1 項 絶対最大定格 で示す入力電圧の範囲内に収めてください。オーバーシュート／アンダーシュートがある場合には、ダンピング抵抗や Low Pass Filter を付けるなどの対策をとってください。

図 10.2 クロック入力 オーバーシュート／アンダーシュート対策例

なお、クロック以外の外部信号 HOST\_SCLK、SCKI、SCKO、WSI、WSO 各端子についても同様の配慮が必要になります。

## 9.4 実装上の注意事項

基板の設計、及びICを実装する際の注意事項を以下に示します。

### 9.4.1 リセット回路

電源投入時、NRESET端子に入力されるリセット信号は、諸条件（電源の立ち上がり時間、使用部品、基板パタン等）により変化します。容量や抵抗などの定数は応用製品にて十分確認を行い、適切なものを選んでください。NRESET端子のプルアップ抵抗については、インピーダンスが高い場合ノイズによる誤動作が生じることがありますので、抵抗値のばらつきを十分考慮した定数設定が必要です。

### 9.4.2 電源回路

ノイズによる急激な電源変動は誤動作の原因となります。これを防止するため、以下の点に配慮してください。

- 電源からHVDD,LVDD,VSS端子へはできるだけ短く太いパタンで接続してください。

- HVDD or LVDD – VSS間のバイパスコンデンサを接続する場合、HVDD端子またはLVDD端子とVSS端子をできるだけ最短で接続してください。

なおバイパスコンデンサは、システムによって異なりますが、数μF～数十μFを目安としてください。

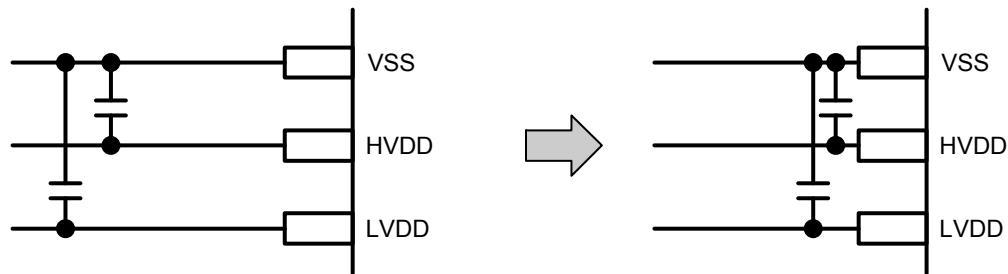

図 10.3 バイパスコンデンサ 接続例

### 9.4.3 信号線の配置

相互インダクタンスによって生じる電磁誘導ノイズを防止するために、発振部などのノイズに弱い回路の近くには、大電流信号線を配置しないでください。

高速動作する信号線と、長くかつ平行に、または交差させて別の信号線を配置することは、信号間の相互干渉によって発生するノイズにより誤動作の原因になります。特に、発振部などのノイズに弱い回路の近くには、高速に動作する信号線を配置しないでください。

### 9.4.4 ノイズによる誤動作

ノイズによる IC の誤動作が考えられる場合、以下の点について確認してみてください。

- **NRESET 端子**

この端子に Low レベルのノイズが入ると、IC がリセットされます。ただし、入力波形によっては正常なリセット動作が行えない場合があります。回路設計上、リセット入力が High 状態でのインピーダンスが高いときに起こりやすくなります。

- **HOST\_SCLK 端子**

この端子は、クロック同期式シリアルインターフェースの同期クロック入力端子です。この端子にノイズが入ると、入力波形によっては有効なデータと認識し、誤動作の原因となります。シリアルインターフェース (HOST\_SCLK, HOST\_SDIN, HOST\_SDOUT, HOST\_CS) の配線はできるだけ最短で接続してください。

- **CNF2(EXAUDCK)端子**

この端子は、アナログコーデックに供給する基準クロック信号 (16.59MHz) を出力します。この端子の信号にノイズが入ると、アナログコーデックの誤動作や、電気的特性に影響を与える恐れがあります。CNF2(EXAUDCK)端子からアナログコーデックのクロック入力端子までの配線は極力短く、かつデジタル系電源系統の GND でシールドして下さい。

- **電源**

規定の電圧を下回るようなノイズが入った場合、その瞬間に IC が誤動作します。基板の電源系のベタパタン化、ノイズ除去用デカップリングコンデンサの追加、電源ラインへのサージ/ノイズ対策部品の追加など、基板上の対策をお願いします。

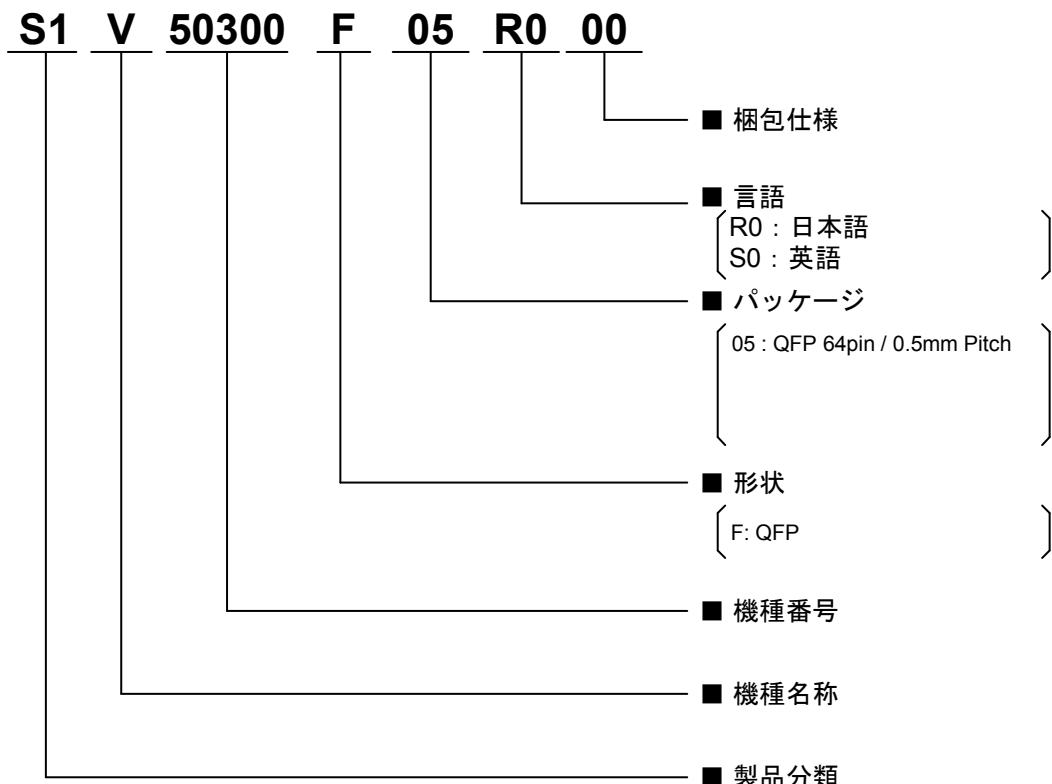

## 9.5 製品型番体系

## 改訂履歴表

### 改訂履歴表

| 年月日        | Rev. | 改訂内容 |          |                                                                                                                                                           |

|------------|------|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |      | 頁    | 種別       | 内 容                                                                                                                                                       |

| 2011/11/22 | 1.0  | 全頁   | 新規       | 新規制定                                                                                                                                                      |

| 2012/02/27 | 1.1  | 2    | 追加       | 注釈 ※1, ※2 を追加                                                                                                                                             |

|            |      | 10   | 追加       | 5.2 項: 表 5.1 に外部シリアル Flash ブートに関する記述を追加                                                                                                                   |

|            |      | 13   | 追加       | 6.3.1 項: 静止電流、消費電流の項目に電源系統の記述を追加                                                                                                                          |

|            |      | 24   | 追加       | 7.3 項: 外部シリアル Flash メモリのデータ書き込みに関する記述を追加                                                                                                                  |

| 2015/03/18 | 2.0  | 2    | 追加<br>削除 | 英語音声認識型番を追加<br>シナリオライブラリ格納場所としての内蔵 MASK ROM を削除                                                                                                           |

|            |      | 5    | 変更       | 入力音声解析用端子を削除<br>TEST 端子 3(pulldown から VSS 接続へ変更)<br>TEST 端子 4(pullup から HVDD 接続へ変更)<br>TEST 端子 5(pullup から HVDD 接続へ変更)<br>TEST 端子 6(pullup から HVDD 接続へ変更) |

|            |      | 25   | 削除       | 入力音声解析用端子説明を削除                                                                                                                                            |

|            |      | 26   | 変更       | TEST 端子 3,4,5,6 の接続を変更                                                                                                                                    |

|            |      | 31   | 追加<br>修正 | 英語音声認識を追加<br>誤記 QFP48 を QFP64 に修正                                                                                                                         |

|            |      |      |          |                                                                                                                                                           |

|            |      |      |          |                                                                                                                                                           |

## セイコーエプソン株式会社

### マイクロデバイス事業部 デバイス営業部

---

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 412253602

2011 年 11 月 作成 ⑧

2015 年 6 月 改訂