# S7R77021

## *Analog Front End*

## *Application Notes*

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告無く変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性値の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

© SEIKO EPSON Corporation 2007, All rights reserved.

- 目 次 -

|                            |    |

|----------------------------|----|

| <b>1. 概要</b>               | 4  |

| <b>2. 基本構成</b>             | 4  |

| 2.1. 内部構成                  | 4  |

| 2.2. 内部クロック系構成             | 4  |

| 2.3. システム構成                | 5  |

| 2.3.1. TGCK/RXCLKP/N供給システム | 5  |

| 2.3.2. TGCK/CLKIN供給システム    | 5  |

| 2.3.3. TGCK供給システム          | 5  |

| <b>3. インタフェース</b>          | 6  |

| 3.1. Host IF               | 6  |

| 3.1.1. TGCK                | 6  |

| 3.1.2. CLKIN               | 6  |

| 3.1.3. RXCLKP/N            | 6  |

| 3.1.4. TXSYNCP/N           | 6  |

| 3.1.5. TXD[7:0]P/N         | 6  |

| 3.1.6. シリアル・インターフェース       | 7  |

| 3.1.7. SYNC                | 7  |

| 3.1.8. D [7:0]             | 7  |

| 3.2. Image IF              | 7  |

| 3.2.1. SHn, SNCKn          | 7  |

| 3.2.2. nINP                | 8  |

| <b>4. シリアルアクセス</b>         | 8  |

| 4.1. アクセス方法                | 8  |

| 4.2. 注意事項                  | 8  |

| <b>5. レジスタ制御</b>           | 9  |

| 5.1. 設定順序                  | 9  |

| 5.2. 参考設定手順                | 9  |

| 5.3. 設定考慮事項                | 9  |

| 5.3.1. 制限事項                | 9  |

| 5.3.2. アクセス制限              | 10 |

| 5.3.3. SNCKn出力設定           | 10 |

| 5.3.4. 設定範囲                | 10 |

| 5.3.5. 排他的設定               | 11 |

| 5.3.6. 調整用レジスタ             | 11 |

|                              |           |

|------------------------------|-----------|

| <b>6. 制御機能 .....</b>         | <b>11</b> |

| 6.1. 動作状態 .....              | 11        |

| 6.2. 出力制御 .....              | 12        |

| 6.3. クロック制御 .....            | 12        |

| 6.3.1. 同期方法 .....            | 12        |

| 6.3.2. 周波数範囲 .....           | 12        |

| 6.3.3. 内部基準クロック精度 .....      | 13        |

| 6.4. 適倍・分周・ステート .....        | 13        |

| 6.4.1. 適倍設定と分周設定 .....       | 13        |

| 6.4.2. ステート .....            | 13        |

| 6.5. 駆動制御 .....              | 14        |

| 6.5.1. AC特性 .....            | 14        |

| 6.5.2. SHnタイミング .....        | 14        |

| 6.5.3. SNCKnタイミング .....      | 15        |

| 6.5.4. TGCKタイミング .....       | 16        |

| 6.6. 遅延制御 .....              | 17        |

| 6.6.1. SHn遅延 .....           | 17        |

| 6.6.2. SNCKn遅延 .....         | 17        |

| <b>7. 動作制御 .....</b>         | <b>18</b> |

| 7.1. イメージセンサー制御モード .....     | 18        |

| 7.2. サンプリング・モード .....        | 18        |

| 7.2.1. CDSモード(ピットクランプ) ..... | 19        |

| 7.2.2. S/Hモード(差電圧入力) .....   | 19        |

| 7.3. 画像転送モード .....           | 20        |

| 7.3.1. モード .....             | 20        |

| 7.3.2. 同期化 .....             | 20        |

| 7.4. テスト・モード .....           | 21        |

| 7.5. 内部同期 .....              | 22        |

| 7.6. モニタ・モード .....           | 22        |

| <b>8. 用語解説 .....</b>         | <b>23</b> |

| <b>9. 技術情報 .....</b>         | <b>24</b> |

| <b>10. 改定履歴表 .....</b>       | <b>25</b> |

## 1. 概要

弊社製 CCD クロック生成機能搭載アナログフロントエンド S7R77021 (以下、AFE と記載します) の Application Notes です。本書では、AFE の制御方法や動作モードなど、スキャナシステムを構築する際に必要となる技術情報を説明します。

本 AFE には、QFP と BGA の 2 種類のパッケージが用意されています、パッケージ毎に制約がありますので、ご注意ください。

尚、レジスタおよびビット説明で記載された「TGSTART ビット(0x50)」の(0x50)は、開発仕様書の「7.2 レジスタマップ」、「7.3 ビットマップ」および「7.4 レジスタ詳細説明」に「No.」で記載された値を意味しています。

## 2. 基本構成

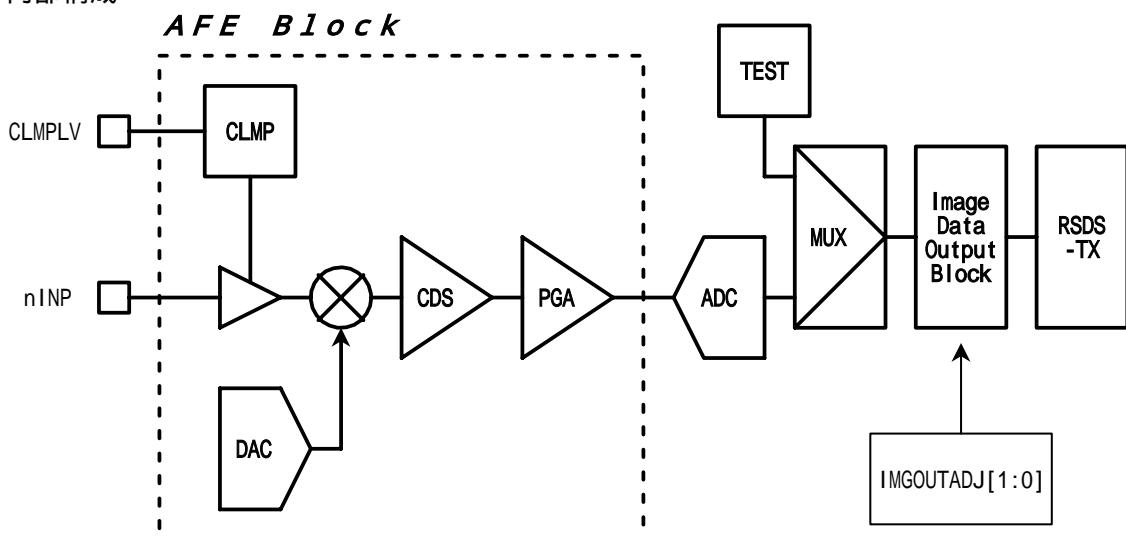

### 2.1. 内部構成

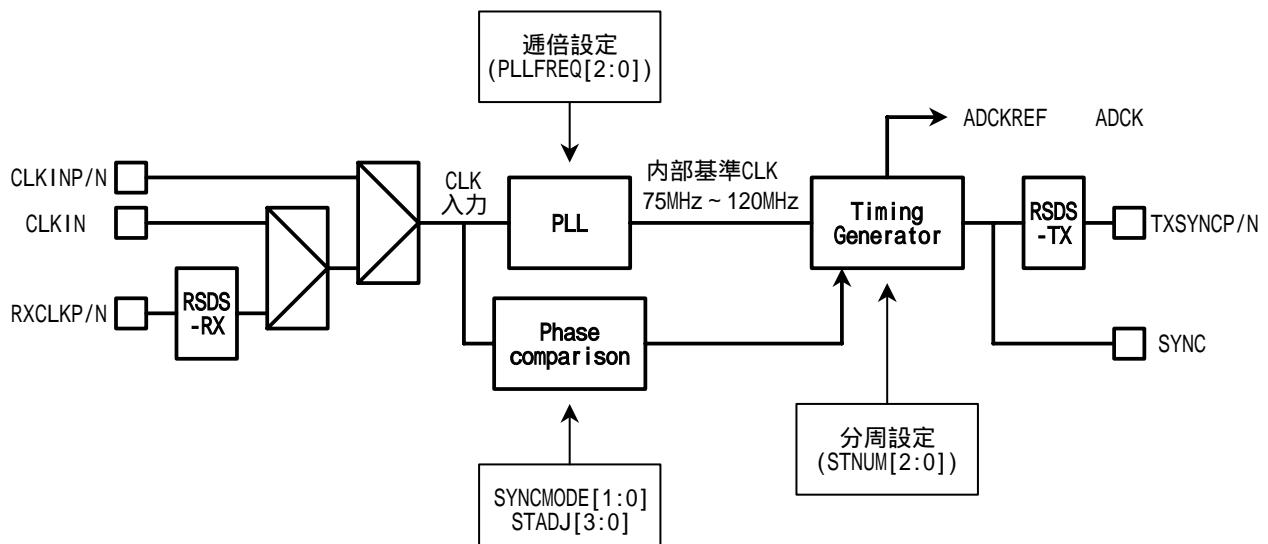

### 2.2. 内部クロック系構成

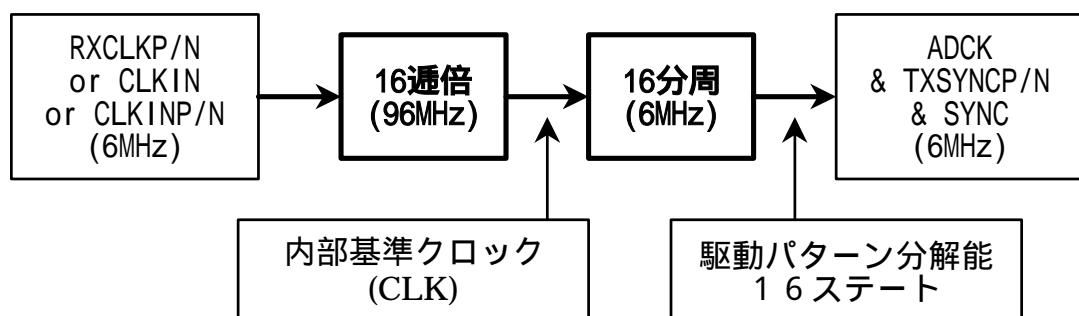

本 AFE では、内部クロックとして ADCK, ADCKREF, SYNCOUT を有しています。

ADCKREF は内部ステートに同期した仮想クロックを意味しており、内部ステートとの関係を説明する場合に使用されています。

### 2.3. システム構成

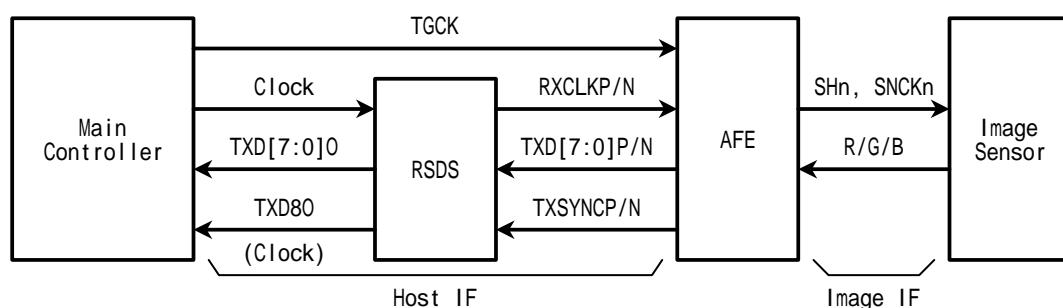

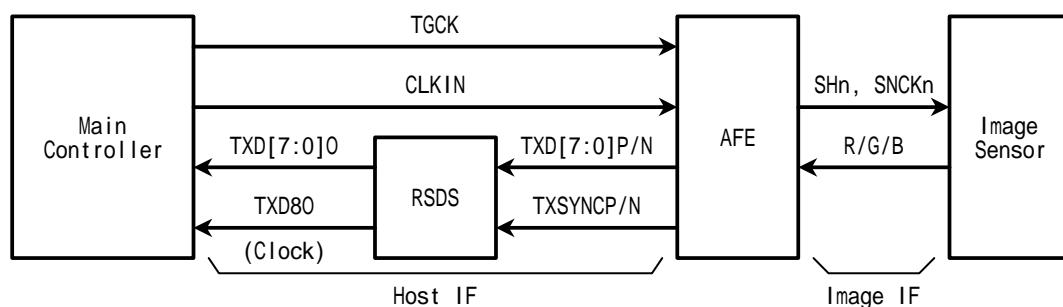

代表的な簡易システム構成を示します。

下記以外の構成も準備されていますので、詳細は開発仕様書をご覧ください。

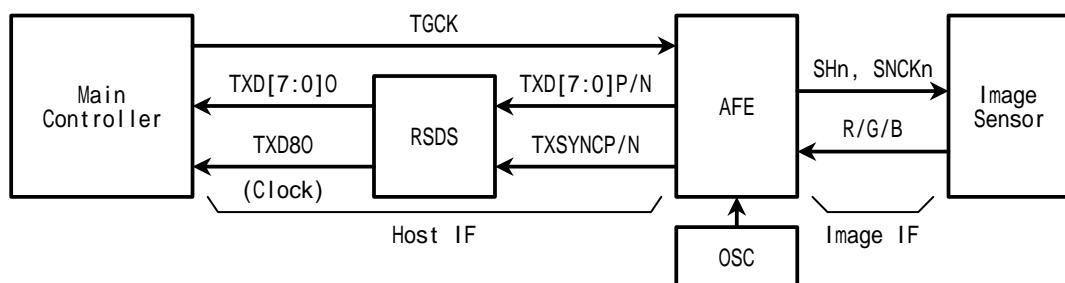

本 AFE は、Main Controller とのホスト・インターフェース(以下、Host IF と記載します)とイメージセンサー・インターフェース(以下、Image IF と記載します)を有しています。詳細は、

「3. インタフェース」をご覧ください。

尚、弊社製 RSDS トランスマッタ / レシーバ (以下、RSDS デバイスと記載します)を使用することで容易に実現することができます。

#### 2.3.1. TGCK/RXCLKP/N 供給システム

TGCK および RXCLKP/N(デファレンシャル)を AFE へ供給することでシステムが構成できます。

#### 2.3.2. TGCK/CLKIN 供給システム

TGCK および CLKIN(シングルエンド)を AFE へ供給することでシステムが構成できます。

#### 2.3.3. TGCK 供給システム

TGCK のみを AFE へ供給することでシステムが構成できます。

本システムでは、振動子または発振器を AFE に接続します。

### 3. インタフェース

#### 3.1. Host IF

Host IF は、RSDS の差動(デファレンシャル: RXCLKP/N, TXSYNCP/N, TXD[7:0]P/N)入出力が搭載されています。システム構成にあわせて必要なインターフェースをご使用ください。

尚、RSDS に関する技術情報は、「S7R77021 Analog Front End PCB Design Guide」をご覧ください。

(1) 共通端子      TGCK, CLKIN, RXCLKP/N, TXSYNCP/N, TXD[7:0]P/N

シリアル・インターフェース(XCS,SCLK,SDIO)

(2) BGA 専用端子    SYNC, D[7:0]

##### 3.1.1. TGCK

TGCK は、本 AFE におけるライン周期の基準信号となります。

外部から入力された TGCK は、内部基準クロックで約 2 クロック遅延します。

INTGCK ビット(0x54) で内部生成することも可能です。この場合、TGPERIOD レジスタ(0x20,0x21) にてライン周期を設定してください。

内部生成時は、TGCK 波形が出力されます。

##### 3.1.2. CLKIN

シングルエンド用のクロック入力端子です。

本 AFE は、多様なクロック構成を有しておりますので、ご使用になられるシステムに柔軟な対応が可能です。詳細は、「6.3.1. 同期方法」をご覧ください。

##### 3.1.3. RXCLKP/N

デファレンシャル用のクロック入力端子です。

本 AFE は、多様なクロック構成を有しておりますので、ご使用になられるシステムに柔軟な対応が可能です。詳細は、「6.3.1. 同期方法」をご覧ください。

##### 3.1.4. TXSYNCP/N

デファレンシャル画像データのサンプリング用クロック出力端子です。

本 AFE は、多様なクロック構成を有しておりますので、ご使用になられるシステムに柔軟な対応が可能です。詳細は、「6.3.1. 同期方法」をご覧ください。

##### 3.1.5. TXD[7:0]P/N

TXSYNCP/N に同期した画像データが出力されます。

画像データを転送するモードは、複数準備されておりますので「7.2. 画像転送モード」をご覧ください。

### 3.1.6. シリアル・インターフェース

XCS, SCLK, SDIO から構成され、本 AFE のレジスタ設定を行います。

詳細は、「4. シリアルアクセス」をご覧ください。

### 3.1.7. SYNC

BGA 専用のシングルエンド画像データのサンプリング用クロック出力端子です。

SYNC は、クロックの入力構成によらず出力されます。クロック信号を出力させない場合は、

SYNC 端子を汎用ポートに設定してください。

### 3.1.8. D [7:0]

BGA 専用で SYNC に同期した画像データが出力されます。

画像データを転送するモードは、複数準備されておりるので「7.2. 画像転送モード」をご

覧ください。

## 3.2. Image IF

Image IF は、ラインパルス(以下、SHn と記載します)とクロックパルスパターン(以下、SNCKn

と記載します)のイメージセンサー駆動用出力端子と、イメージセンサーからの入力端子(以下、

nINP と記載します)を有しています。

イメージセンサーにあわせて必要なインターフェースをご使用ください。

### 3.2.1. SHn , SNCKn

SHn (SHR/G/B, SH, LEDR/G/B)は、TGCK に同期したラインパルスです。

SNCKn (SNCK1A ~ 1D, SNCK2 ~ 4)は、Sub Pixel (1 副画素)単位での駆動パターンです。

イメージセンサーにあわせて、必要な信号を使用してください。

詳細は、「6.5. 駆動制御」、「6.6. 遅延制御」をご覧ください。

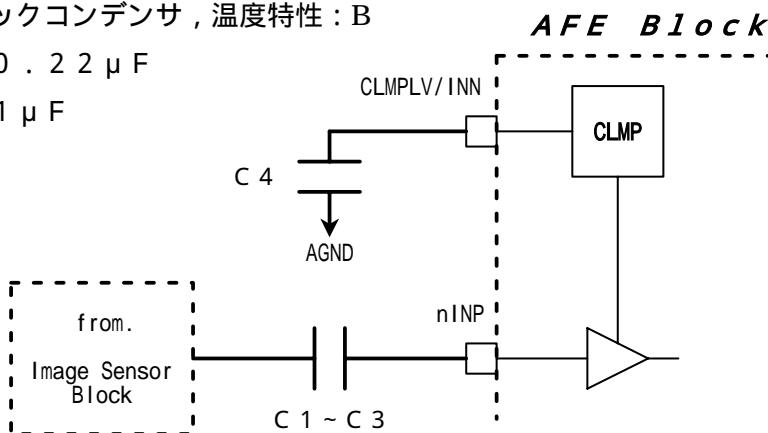

### 3.2.2. nINP

イメージセンサーの出力を入力してください。

イメージセンサーが CCD の場合、AC カップリング・コンデンサ(RINP,GINP,BINP: C1 ~ C3)を介して入力する必要があります。また、入力信号を内部で適正にクランプさせるために、CLMPLV/INN 端子にコンデンサ(C4)を接続する必要があります。

下記推奨値はイメージセンサーおよび、ご使用になられる環境によっては他の定数の方が特性が改善される場合がありますので、お客様の評価にて判断してください。

#### [推奨コンデンサ]

チップ・セラミックコンデンサ、温度特性：B

C1 ~ C3 : 0 . 2 2  $\mu$  F

C4 : 1  $\mu$  F

## 4. シリアルアクセス

本 AFE は制御機能を有しており、シリアル・インターフェースによってレジスタ設定することで容易に制御することができます。

### 4.1. アクセス方法

シリアルアクセスを有効(XCS = 'L')にして、識別ビットを設定(L=Write Access, H=Read Access)後、クロック(SCLK)を 'L' → 'H' (内部でラッチ)、'H' → 'L' にします。続けてアドレス(A[7:1])とデータ(D[15:0])の順で同様に処理してください。1回のシリアルアクセス(ライトまたはリード)終了後、必ずシリアルアクセスを無効(XCS = 'H')にしてください。

### 4.2. 注意事項

- (1) 本シリアルアクセスで指定するアドレス(A[7:1])は、開発仕様書の「7.2 レジスタマップ」、「7.3 ビットマップ」および「7.4 レジスタ詳細説明」に「No.」で記載された値を使用してください。

- (2) シリアルアクセス用の端子はシミュット入力になっていますが、本 AFE へ接続されるまでに波形の鈍りなどが生じると誤動作する可能性がありますので、ご使用になられる環境で十分な評価をお願いします。特に、クロック(SCLK)の立ち上がりエッジにてデータをラッチしていますので、クロック(SCLK)の波形には注意が必要です。

- (3) 1回のシリアルアクセス(ライトまたはリード)の度に、必ず XCS = 'H' にしてシリアルアクセスを無効にしてください。

## 5. レジスタ制御

### 5.1. 設定順序

xPD\_PLL ビット(0x70)の PLL パワーダウン解除後、安定した発振出力まで最大 10 ms を必要としますので、レジスタアクセスを含めて注意してください。

その他のレジスタに関しては、特に設定順序としての制約はありませんので、ご使用になられる環境に応じて最適な設定順序を決定願います。

### 5.2. 参考設定手順

参考として以下に、電源投入直後から画像読み取りに至るまでのレジスタ設定手順を示します。

| 順            | No.  | Register Name  | Bit Symbol       | 内容           |

|--------------|------|----------------|------------------|--------------|

| 1            | 0x7F | PLL_IMGSIG_CTL | -                | Clock/PLL 設定 |

| 2            | 0x51 | STCTL          | STNUM[1:0]       | 分周設定         |

| 3            | 0x70 | ANA_RESET      | xPD_PLL          | normal に設定   |

| ~            |      |                |                  | (任意の設定)      |

| a-1          | 0x50 | TGCTL          | ADCKEN           | disable 設定   |

| a            | 0x50 | TGCTL          | MEMEN            | invert 設定    |

| a+1          | 0xXX | SNCK_PATXX     | SNCK_PATXX[15:0] | パターン設定       |

| ~            |      |                |                  | (パターン設定)     |

| b-1          | 0xZZ | SNCK_PATZZ     | SNCK_PATZZ[15:0] | パターン設定       |

| b            | 0x50 | TGCTL          | MEMEN            | normal 設定    |

| ~            |      |                |                  | (任意の設定)      |

| c-1          | 0x50 | TGCTL          | ADCKEN           | enable 設定    |

| c            | 0x50 | TGCTL          | TGSTART          | reverse 設定   |

| ~ 画像読み取り期間 ~ |      |                |                  |              |

| c+1          | 0x50 | TGCTL          | TGSTART          | normal 設定    |

| ~            |      |                |                  | (任意の設定)      |

補足 1. 英大字で示された 'XX', 'ZZ' は 00 ~ 1F の任意の値です。

2. 手順 a+1 から b-1 に至るまでの制約はありませんので、任意に設定可能です。

### 5.3. 設定考慮事項

レジスタ設定時に考慮する必要がある事項について説明します。

#### 5.3.1. 制限事項

(1) 画像読み取り状態でのレジスタ設定は、TGSTART ビット(0x50)のみ変更可能です。

TGSTART ビット以外を変更した場合、正常に動作しない場合があります。

(2) ANA\_RESET(0x70)の設定は、xPD\_VREF ビットのみを Power Down にしないでください。

(3) 下記レジスタは、PLL 停止時にリードアクセスできません。

| No.  | Register Name |

|------|---------------|

| 0x50 | TGCTL         |

| 0x51 | STCTL         |

| 0x54 | CCAEMODE      |

(4) QFP パッケージには汎用ポート 2 の機能はありませんので下記設定が必要です。

| No.  | Register Name | 設定値    |

|------|---------------|--------|

| 0x64 | GPIO2EN       | 0x01FF |

| 0x65 | GPIO2DIR      | 0x01F0 |

| 0x66 | GPIO2ST       | 0x0000 |

(5) reserved のレジスタおよびビットには、内部検査用として使用している部分がありますので Write Access しないようしてください。

### 5.3.2. アクセス制限

SNCKn 設定レジスタ(0x00 ~ 0x1F)へアクセスする前に、ADCKEN ビット(0x50)を disable = '0' にして、MEMEN ビット(0x50)を invert = '1' に設定する必要があります。また、アクセス終了後に MEMEN ビットを normal = '0' に設定する必要があります。

### 5.3.3. SNCKn 出力設定

SNCKn をパルスを出力させるためには、下記レジスタの設定が必要です。

下記は、全て出力に設定した場合です。(英大字の X は任意の値)

| No.  | Register Name | 設定値    |

|------|---------------|--------|

| 0x53 | SNCKCTL       | 0xXX00 |

| 0x60 | GPIOEN        | 0x0X00 |

| 0x61 | GPIODIR       | 0xFX7F |

### 5.3.4. 設定範囲

- (1) 開発仕様書の「7.5.2 レジスタ設定制限」に記載された設定範囲内で使用願います。

- (2) 下記レジスタは、駆動パターン分解能(分周)および動作チャネルモードによって設定範囲が異なります。

| No.  | Register Name | Bit Symbol    |

|------|---------------|---------------|

| 0x26 | SH_RISE       | SH_ADJ[3:0]   |

| 0x31 | SHR2_RISE_H   | SHR2_ADJ[3:0] |

| 0x35 | SHG2_RISE_H   | SHG2_ADJ[3:0] |

| 0x39 | SHB2_RISE_H   | SHB2_ADJ[3:0] |

| 0x51 | STCTL         | STADJ[3:0]    |

注 . 開発仕様書の No.85 に記載された「制限注意事項」は誤記です。

ADSP[3:0]は存在しませんので、ご注意ください。

### 5.3.5. 排他的設定

下記レジスタのビット設定は、同時設定禁止または、設定内容に依存して制約されますので注意してください。([page]欄は開発仕様書に記載されているページです)

| No.  | Bit Symbol     | vs | No.          | Bit Symbol                    | page  |

|------|----------------|----|--------------|-------------------------------|-------|

| 0x78 | xPD_VREF       | 制約 | 0x78         | xPD_AFE<br>xPD_ADC<br>xPD_PLL | -     |

| 0x7F | PLL_IMGSIG_CTL | 制約 | 0x70         | xPD_PLL                       | No.19 |

| 0x51 | SYNCMODE[1:0]  | 制約 | 0x51<br>0x7F | STNUM[2:0]<br>PLLFREQ[2:0]    | No.37 |

### 5.3.6. 調整用レジスタ

最適な画像読み取りを実現するために、下記レジスタが用意されています。使用状態にあわせて適切な設定を、お願いします。尚、SYNCMODE[1:0]ビット(0x51)と STADJ[3:0]ビット(0x51)による内部動作は、「7.3. 内部同期」をご覧ください。

- (1) SYNCMODE[1:0](0x51) [常時同期化]で Sub Pixel にシーケンス異常が生じた場合は、[TGCK の立ち上がり検出時のみ同期化]に設定してください。

- (2) STADJ[3:0] (0x51) CLK 入力(RXCLKP/N, CLKIN, CLKINP/N)と内部ステートの位相を調整できます。

- (3) IMGOUTADJ[1:0] (0x7F) TXSYNCP/N および SYNCOUT に対して、画像データ出力を遅延させることができます。

## 6. 制御機能

### 6.1. 動作状態

- (1) ADCKEN ビット(0x50)を enable = '1' に設定することで、ADCK(ADCKREF)および SNCKn を生成して動作状態になります。

- (2) TGSTART ビット(0x50)を reverse = '1' に設定することで、画像読み取り状態になります。

- (3) TGCK が入力(外部入力の場合)されると、TGCK のライン周期に応じた画像データが出力されます。詳細は、「6.5.4. TGCK タイミング」をご覧ください。

## 6.2. 出力制御

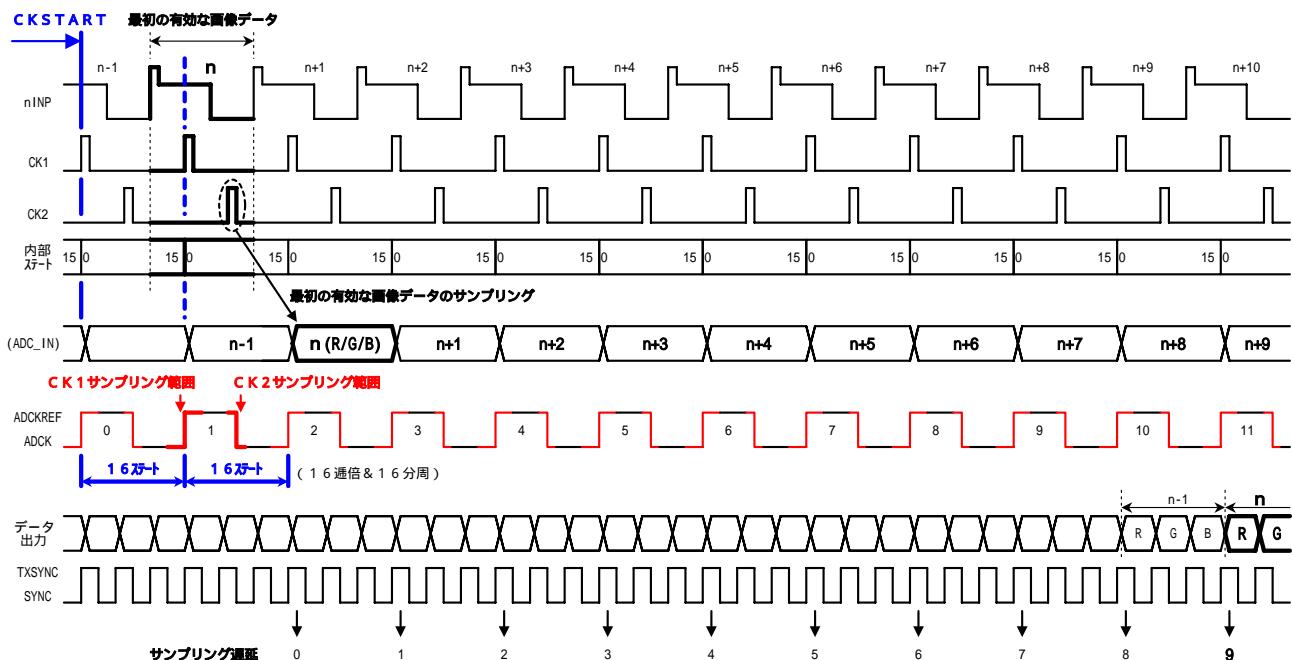

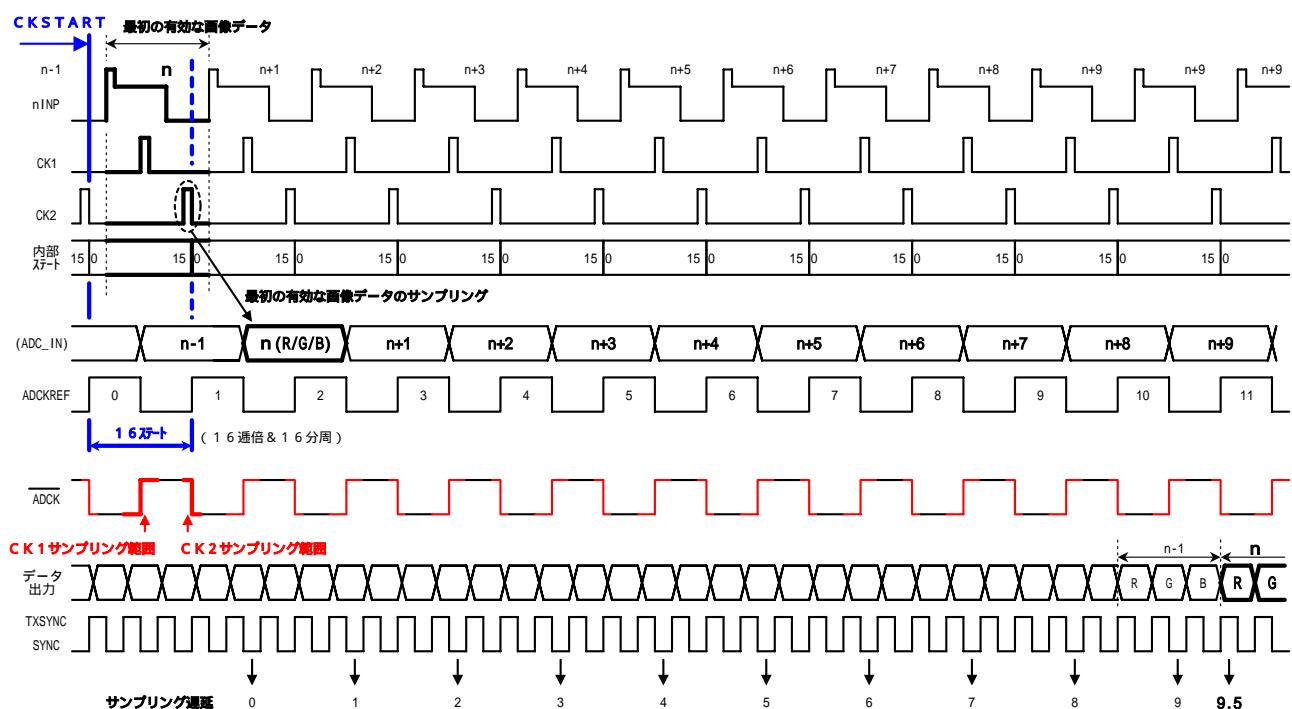

- (1) CK1,CK2 でサンプリングされた画像データは、9 クロック遅延して出力されます。

ADCK を反転させた場合は、9 . 5 クロック遅延して出力されます。

詳細は、「6.5.3. SNCKn タイミング」をご覧ください。

- (2) CKSTART レジスタ(0x24)で設定されたタイミングからイメージセンサーの駆動を開始しますので、Main Controller にて画像データを取得してください。

- (3) Main Controller における最適な画像データのサンプルポイント設定に関しましては、「5.3.6. 調整用レジスタ」、「6.5.3. SNCKn タイミング」をご覧ください。また、サンプルポイントの調整用にテスト・モードが用意されています。

詳細は、「7.6. テスト・モード」をご覧ください。

- (4) 画像レベルの調整につきましては、各色のオフセットおよびゲインにて調整してください。

尚、画像データのサンプルポイントが Main Controller において不適切な場合、画像レベルの調整ができませんのでご注意ください。

## 6.3. クロック制御

### 6.3.1. 同期方法

本 AFE ではクロック同期方法が 2 種類(クロック入力または出力)準備されています。

入力クロックに対する内部の同期については、「7.4. 内部同期」をご覧ください。

- (1) クロック入力の場合は、CLKIN または RXCLKP/N にクロックを入力してください。

入力クロックに対して、内部クロック(ADCK など)は 6 クロック遅延しています。

STADJ[3:0]ビット(0x51) で位相差を調整可能です。

- (2) クロック出力の場合は、TXSYNCP/N または SYNC(BGA 専用)を使用願います。

この場合、CLKIN への発振器入力か、CLKINP/N からの発振回路入力の何れかを選択することができます。

発振回路入力へは、水晶振動子またはセラミック振動子などが接続可能です。但し、ご使用になられる状態で評価が必要となりますので、最終的にはお客様の評価にて判断する必要があります。

- (3) 下記にて入力クロックを選択してください。

| 入力<br>クロック | レジスタ設定 |          | 端子処理     |          |        |          |        |

|------------|--------|----------|----------|----------|--------|----------|--------|

|            | OSCSEL | RXCLKSEL | CLKIN    | RXCLKP   | RXCLKN | CLKINP   | CLKINN |

| 発振器        | 0      | 0        | Clock IN | L        | H      | L        | Open   |

| 差動         | 0      | 1        | L        | Clock IN |        | L        | Open   |

| 振動子        | 1      | -        | L        | L        | H      | Clock IN |        |

### 6.3.2. 周波数範囲

PLL の内部基準クロック(CLK)周波数範囲が 75 MHz ~ 120 MHz となるように入力クロックの周波数選定および倍率設定が必要です。

倍率については、「6.4. 倍率・分周・ステート」をご覧ください。

### 6.3.3. 内部基準クロック精度

遙倍の設定方法による精度の違いはありませんので、入力クロックに応じた遙倍設定が可能です。遙倍については「6.4. 遙倍・分周・ステート」をご覧ください。

例 CLKIN 入力クロックと遙倍後の内部クロックの関係を示します。

|                       |           |

|-----------------------|-----------|

| 1 . CLKIN=6MHz, 16 遙倍 | CLK=96MHz |

| 2 . CLKIN=8MHz, 12 遙倍 | CLK=96MHz |

| 3 . CLKIN=12MHz, 8 遙倍 | CLK=96MHz |

| 4 . CLKIN=24MHz, 4 遙倍 | CLK=96MHz |

## 6.4. 遙倍・分周・ステート

### 6.4.1. 遙倍設定と分周設定

本 AFE は入力クロック(RXCLKP/N,CLKIN,CLKINP/N)を遙倍することによって内部処理動作の 1 ステート時間[内部基準クロック(CLK)]を決定します。また、分周設定によって Sub Pixel (1 チャネル)の駆動パターン分解能(ADCKREF 1 サイクルに対する分解能)を決定します。尚、遙倍と分周の設定が異なる場合は、SYNCMODE[1:0]ビット(0x51)を「常時同期化」以外の設定にする必要があります。

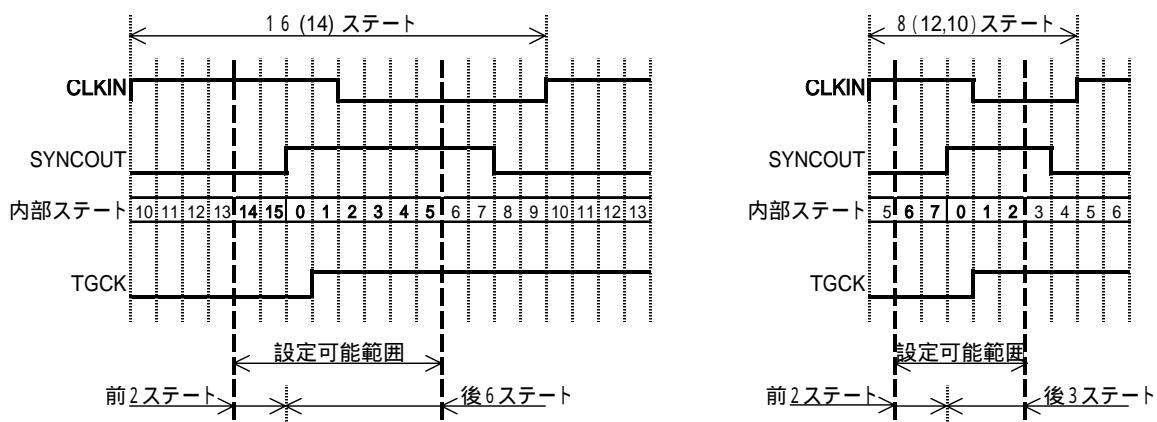

### 6.4.2. ステート

ステートは、ADCKREF に同期しています。チャネルによるステート数の違いはありません。

## 6.5. 駆動制御

### 6.5.1. AC 特性

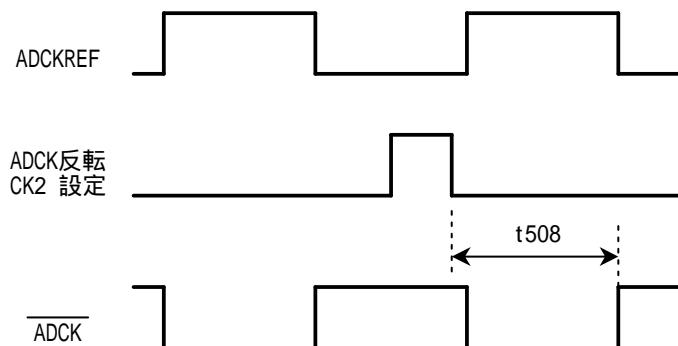

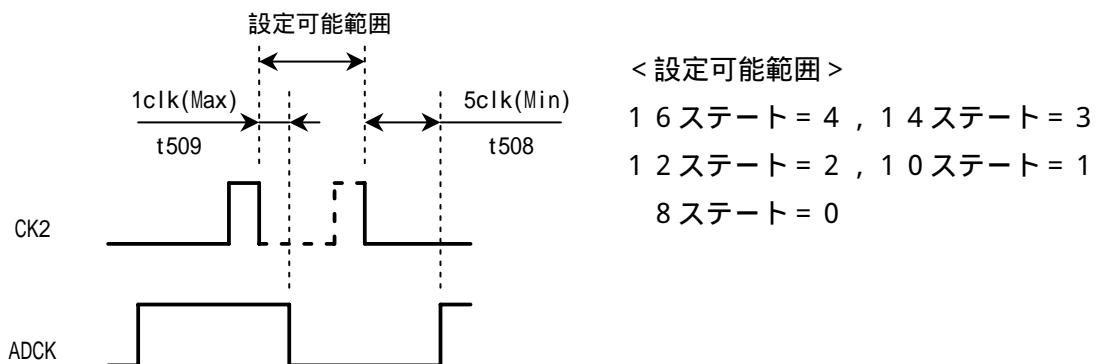

ADCK\_POL ビット(0x54)に invert = '1' を設定することで、入力クロック(RXCLKP/N, CLKIN, CLKINP/N)に対して ADCK が反転(ADCKREF および SYNCOUT は非反転)します。 詳細は「6.5.3. SNCKn タイミング」をご覧ください。

ADCK を反転した場合、開発仕様書の「8.4.5 CDS モードサンプリングタイミング」、「8.4.6 S / H モード(差電圧入力)サンプリングタイミング」は反転した後の波形で規定されることになります。

以下に、CDS モードの t508 の例を示します。

### 6.5.2. SHn タイミング

本AFEではサンプリング・モードによって下記のSHnでイメージセンサー制御が可能です。

サンプリング・モードについては、「7.1. サンプリング・モード」をご覧ください。

- (1) CDS モード 3 本 : SHR, SHG, SHB

- (2) S/H モード 4 本 : LEDR, LEDG, LEDB, SH

### 6.5.3. SNCKn タイミング

本 AFE では最大 7 本(SNCK1A ~ SNCK4)でイメージセンサー制御が可能であり、SNCK1A ~ SNCK1D については、Sub Pixel 単位で Odd と Even を別のパターンに設定可能です。SNCKn 設定レジスタ(0x00 ~ 0x1F)にて各タイミングを設定します。

使用するチャネル数によってステート数が異なりますので、SNCKn も各ステート数に応じて設定する必要があります。

(1) CDS モードにおける 3 チャンネルでの設定および動作の詳細を示します。

(2) 同様に ADCK\_POL ビット(0x54)に invert = '1' を設定した場合の動作を示します。

(3) CK2 タンミングの設定は下記範囲で設定してください。

尚、8ステートの場合は、ピンポイントの設定になります。

(4) CK1,CK2 以外の SNCKn も各ステート数に応じて設定する必要があります。

ご使用になるイメージセンサーの駆動に合わせて設定してください。

未使用の SNCKn およびステート範囲外については、'0' を設定してください。

(5) ダミーパターンのステート数はチャネル数によらず一定で、No.0x10 を先頭に分周設定のステート数まで出力されます。16ステートの場合は No.0x1F が最終となり、14ステートの場合は No.0x1D が最終となります。

SNCKn 同様に未使用および、ステート範囲外については '0' を設定してください。

また、CIS モード時は全て '0' を設定してください。

#### 6.5.4. TGCK タイミング

TGCK 外部入力時におけるタイミングは、ADCK の立ち下りに対して下記仕様で設定してください。

## 6.6. 遅延制御

本 AFE は、SHn と SNCKn に遅延を加えて出力することが可能です。

### 6.6.1. SHn 遅延

SHn の遅延設定は、Sub Pixel (ADCKREF 1 サイクル)内をステート数に応じて設定することになります。遅延は SHn の立ち上がりと立ち下がり双方に適用されます。

### 6.6.2. SNCKn 遅延

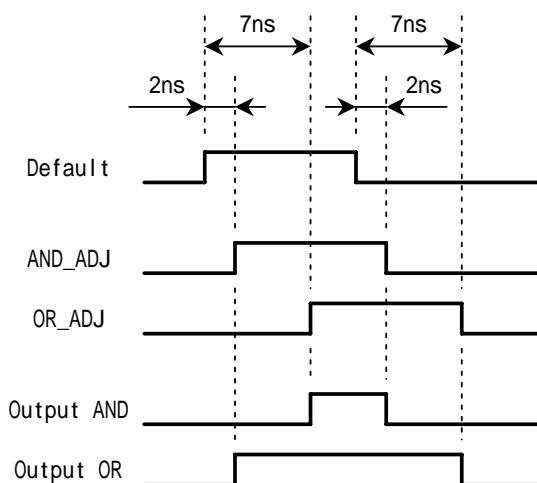

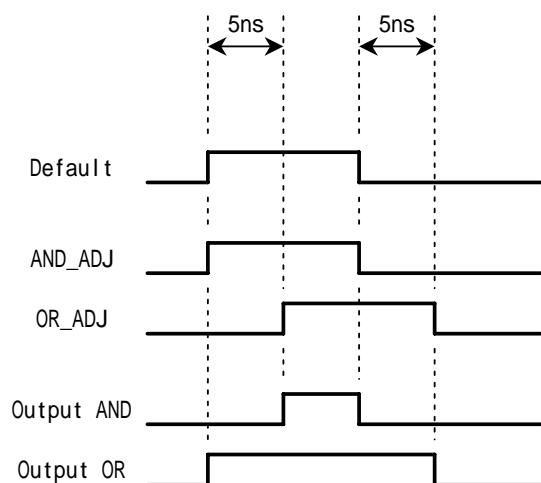

SNCKn の遅延設定は、下表のレジスタ設定にて 2 種類の遅延を組み合わせて時間で設定することになります。遅延は SNCKn の立ち上がりと立ち下がり双方に適用されます。

但し、遅延回路には誤差があり、外部要因などの影響によって、意図した遅延を正確に得ることが困難な場合もありますので、ご注意ください。

| No.       | Bit Symbol     | Description                |

|-----------|----------------|----------------------------|

| 0x40<br>~ | n_AND_ADJ[1:0] | 遅延時間(なし, 2ns, 5ns, 7ns)を選択 |

|           | n_OR_ADJ[1:0]  | 遅延時間(なし, 2ns, 5ns, 7ns)を選択 |

| 0x44      | ANDxORn        | 遅延回路(AND, OR)を選択           |

下記の例のように、出力は論理和と論理積になっていますので、論理演算を必要としない場合(例 5ns 遅延させたい場合など)は、n\_AND\_ADJ[1:0] と n\_OR\_ADJ[1:0] に同じ値を設定してください。

例 1 . AND=2ns, OR=7ns

$$\begin{aligned} n\_AND\_ADJ[1:0] &= '01' \\ n\_OR\_ADJ[1:0] &= '11' \end{aligned}$$

例 2 . AND=なし, OR=5ns

$$\begin{aligned} n\_AND\_ADJ[1:0] &= '00' \\ n\_OR\_ADJ[1:0] &= '10' \end{aligned}$$

## 7. 動作制御

### 7.1. イメージセンサー制御モード

本 AFE は、CCD 制御モードと CIS 制御モード（線順次出力センサ）に対応しております。

ご使用になられるイメージセンサーに応じて、制御モードを選択してください。

また、下表に示しましたように、制御モードによって使用できる SHn が異なりますので注意してください。

| 端子       | CCD 制御モード | CIS 制御モード |

|----------|-----------|-----------|

| SHR/LEDR | SHR       | LEDR      |

| SHG/LEDG | SHG       | LEDG      |

| SHB/LEDB | SHB       | LEDB      |

### 7.2. サンプリング・モード

アナログ入力のサンプリング・モードには、CDS モードと S/H モード(差電圧入力)があります。

「7.1. イメージセンサー制御モード」に合わせてサンプリング・モードを選択してください。

また、サンプリング・モードとイメージセンサー制御モードの設定は下表によります。

| サンプリング・モード |             | イメージセンサー制御モード |

|------------|-------------|---------------|

| CDS        | ビットクランプ(BC) | CCD           |

| S/H        | 差電圧入力(DVI)  | CIS           |

注 1. 括弧内の記号は、略称を意味しています。

2. CCD および CIS は一般的な仕様を意図しています。

各モードの設定は下表によります。

| モード       |     | CIS<br>(0x54) | xCDS<br>(0x7E) | CLMPEN<br>(0x7E) |

|-----------|-----|---------------|----------------|------------------|

| CDS (BC)  | CCD | 0             | 0              | 1                |

| S/H (DVI) | CIS | 1             | 1              | 0                |

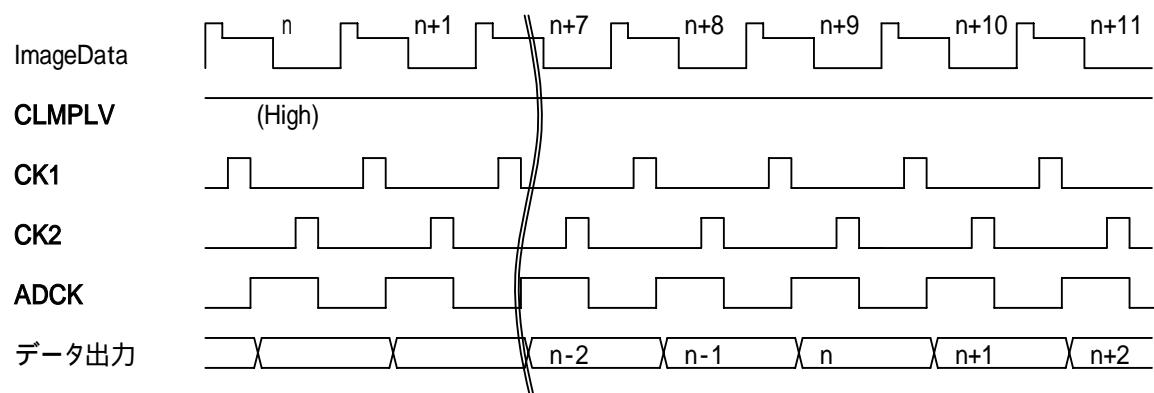

### 7.2.1. CDS モード(ピットクランプ)

CDS モードは、CK1 でクランプレベル(黒レベル)をサンプリングします。CK2 の 'H' 期間に画像データレベル(白レベル)をサンプリングします。

CDS モードのクランプ動作は、ピットクランプになります。

以下に動作タイミングを示します。

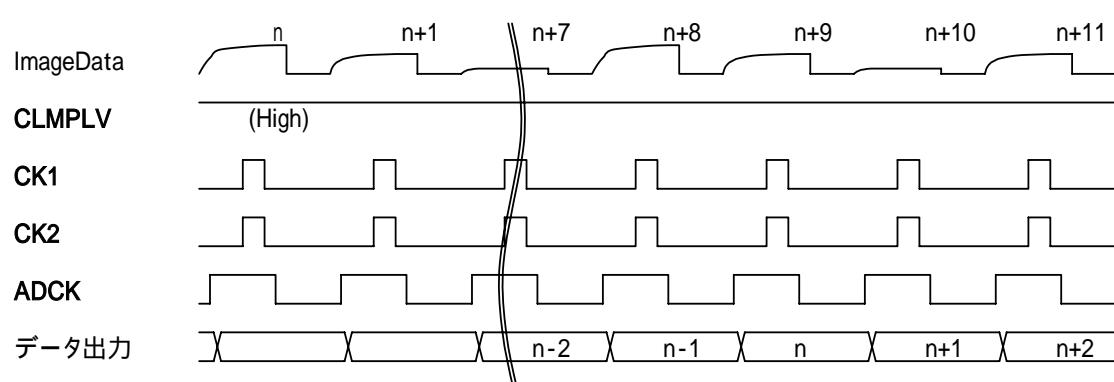

### 7.2.2. S/H モード(差電圧入力)

S/H モード(差電圧入力)は、CK1,CK2 で基準電圧レベル(黒レベル)と画像データレベル(白レベル)を同時にサンプリングします。

CLMPLV/INN 端子への基準電圧レベル入力は、AV<sub>I</sub>=AGND ~ AVDD の範囲で入力してください。

SHR2\_RISE レジスタ(0x30-0x31) および SHR2\_FALL レジスタ(0x32-0x33) の設定によって LCLMP が内部生成されますので、'0' (Low) にするため下記設定にしてください。

SHR2\_RISE > TGPERIOD または TGCK 周期

SHR2\_FALL > SHR2\_RISE

以下に動作タイミングを示します。

### 7.3. 画像転送モード

#### 7.3.1. モード

画像転送モードを IMGOUT4 ビット (0x7F)で選択してください。

デファレンシャル転送モードの受信用として、弊社製 RSDS デバイス(S1R77081)が用意されています。

尚、シングルエンドの転送モードは BGA 専用のため、QFP では使用することができませんので注意してください。尚、QFP の場合は「5.3.1. 制限事項 (4)」の設定が必要になりますので確認願います。

| 転送モード    | ビット構成     | 出力端子            | xPD_RSDS<br>(0x70) | IMGOUT4<br>(0x7F) |

|----------|-----------|-----------------|--------------------|-------------------|

| デファレンシャル | 8 ビット × 2 | TXD[7:0]P/N     | 1                  | 0                 |

|          | 4 ビット × 4 | TXD[6,4,2,0]P/N | 1                  | 1                 |

| シングルエンド  | 8 ビット × 2 | D[7:0]          | 0                  | 0                 |

|          | 4 ビット × 4 | D[6,4,2,0]      | 0                  | 1                 |

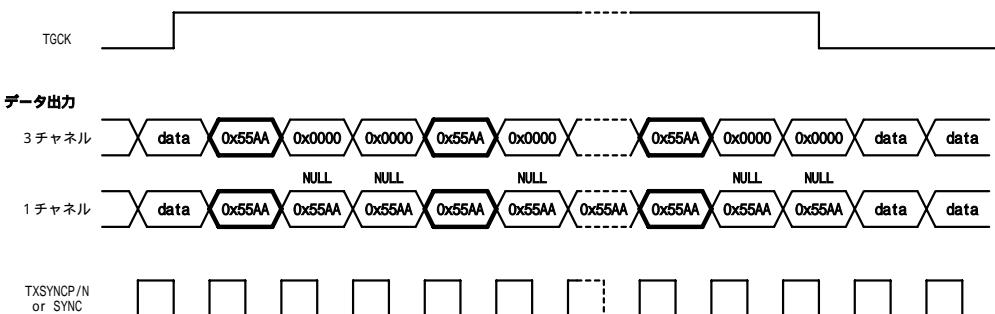

#### 7.3.2. 同期化

TGCK 外部入力時には INDEX ビット(0x54) に INDEX = ‘1’ を設定することで、TGCK ‘H’ 期間に固定データを出力しますので、Main Controller との同期用として使用することができます。

(1) TGCK は外部入力に限定されます。INTGCK ビット(0x54) : external input = ‘0’ にしてください。

(2) 同期化のために固定値出力設定 INDEX ビット(0x54) = ‘1’ にして、固定値出力チャンネルを INDEXMODE[1:0]ビット(0x54) で選択する必要があります。

1 チャンネルの場合、MONOMODE[1:0]ビット(0x54)で選択されたチャンネルに合わせてください。3 チャンネルの場合は、RGBMODE[1:0]ビットおよび MUXSEQ ビット(0x54)で選択された先頭チャンネルに合わせてください。固定値データのチャンネルが相違していると NULL 出力になりますので注意してください。

#### 7.4. テスト・モード

Main Controller における画像サンプリングなどの調整用としてテスト・モードが用意されています。テスト・モード設定後、「6.1. 動作状態」の設定により画像転送状態となります。

##### (1) 固定値モード

ADTD\_MD ビット(0x5F) に mode1 = '1' を設定することで固定値モードになります。

出力データの上位(8 ビット)と下位(8 ビット)は、ADTD\_DT[7:0]ビット(0x5F) に設定された同値になります。

ADTD\_DT[7:0]ビットは、TGCK 外部入力時における 'H' 期間の固定値出力と兼用になっていますので注意が必要です。詳細は「7.3.2. 同期化」をご覧ください。

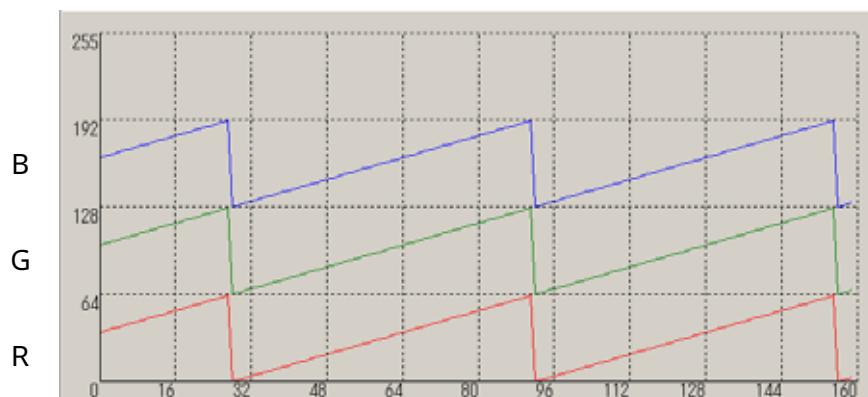

##### (2) インクリメント・モード

ADTD\_MD ビット(0x5F) に mode0 = '0' を設定することでインクリメント・モードになります。出力のイメージを下図に示します。

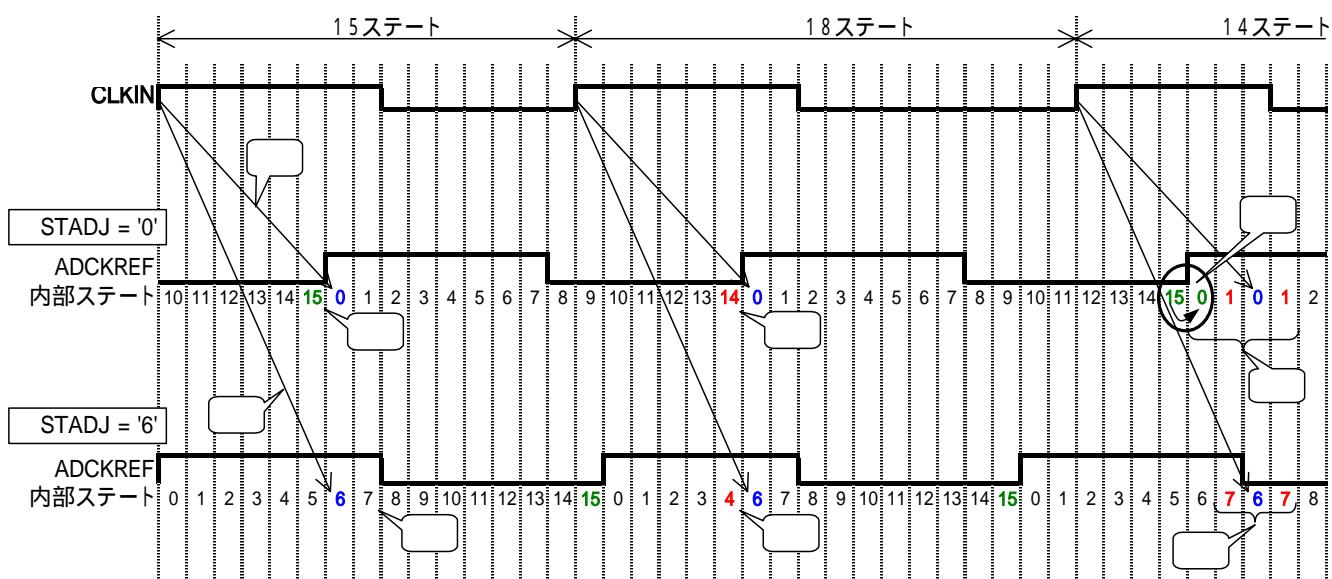

## 7.5. 内部同期

外部入力クロックに対してジッタ成分を強調した場合の内部同期は、下図に示すような動作になります。下図は1チャネル、16分周、SYNCMODE[1:0]ビット(0x51)‘00’「常時同期化」の動作例です。動作の詳細を以下に記載します。

CLKIN の立ち上がりから 6 クロック遅延して内部ステートが強制リセットされます。

STADJ[1:0]ビット(0x51)の設定によって、下記のリセット状態になります。

STADJ = ‘0’ : 0 にリセット

STADJ = ‘6’ : 6 にリセット

内部ステートが 0 カウント時に ADCKREF のレベルに対応して、ADCKREF が L H に変化します。

によって 15 が欠落し、内部ステートは 14 0 に強制リセットされます。

カウントフルのため内部ステートがリセットされます。

カウントフルの後に強制リセットされるため、内部ステートは 0 1 0 1 の繰り返しになります。

内部ステートが 7 カウント後に ADCKREF のレベルに対応して、ADCKREF が H L に変化します。

によって 5 が欠落し、内部ステートは 4 6 に強制リセットされます。

内部ステートが 7 カウント後に、によって内部ステートが 7 6 に強制リセットされますが、後段の 7 ステートで ADCKREF は変化しません。

## 7.6. モニタ・モード

本 AFE の内部波形をモニタ(AFECK1-AFECK4)することができます。

イメージセンサーとのタイミング調整用としてモニタ・モードが用意されています。

## 8. 用語解説

### A

|         |                                                     |

|---------|-----------------------------------------------------|

| ADC     | Analog Digital Converter (A/D コンバータ)の略です。           |

| ADCK    | ADC 変換クロックを意味しています。                                 |

| ADCKREF | 内部ステートに同期した仮想クロック(=ADCK)を意味しています。                   |

| AFE     | Analog Front End の略です。<br>本 AFE はスキャナシステム用の AFE です。 |

| AGND    | アナロググランドを意味しています。                                   |

| AVDD    | アナログ電源を意味しています。                                     |

### C

|      |                                                                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCD  | Charge Coupled Device (電荷結合素子)の略です。                                                                                                                                               |

| CDS  | Correlated Double Samplers (相関二重サンプリング)の略です。<br>イメージセンサー出力信号に含まれるノイズで支配的であるリセットノイズを除去する回路です。イメージセンサー出力の各 Sub Pixel 信号のうち、映像信号期間をサンプリングしたものと、基準期間をサンプリングしたものとを引き算することによりノイズを除去します。 |

| CIS  | Contact Image Sensor の略です。<br>線順次出力センサとも呼ばれ、LED を光源としており CCD と比較すると消費電力が低い特徴があります。CMOS イメージセンサーとも呼ばれています。                                                                         |

| CLMP | Clamp の略です。<br>Image Data の黒レベルを固定する動作を意味しています。                                                                                                                                   |

### D

|     |                                           |

|-----|-------------------------------------------|

| DAC | Digital Analog Converter (D/A コンバータ)の略です。 |

|-----|-------------------------------------------|

### E

|     |                                                                                        |

|-----|----------------------------------------------------------------------------------------|

| EMI | Electro Magnetic Interference (電磁妨害, 放射ノイズ) の略です。<br>電子機器の外部に対する電磁的な妨害・干渉などの放出現象の総称です。 |

|-----|----------------------------------------------------------------------------------------|

### I

|              |                                                                                          |

|--------------|------------------------------------------------------------------------------------------|

| Image Data   | イメージセンサーの出力データを意味しています。                                                                  |

| Image Sensor | 撮像デバイス（固体撮像素子）を意味しています。<br>リニアイメージセンサー、エリアイメージセンサーがあります。<br>本 AFE は、リニアイメージセンサーに対応しています。 |

|              |                                                                                          |

### M

|     |                 |

|-----|-----------------|

| MUX | multiplex の略です。 |

|-----|-----------------|

### N

|      |                                                          |

|------|----------------------------------------------------------|

| NULL | 何のデータも含まない空の値を意味しています。<br>データの ‘0’ と区別する必要がある場合に明示しています。 |

|------|----------------------------------------------------------|

**O**

OB Optical Black の略です。

**P**

PGA Programmable Gain Amp の略です。

Pixel Sub Pixel で構成され、色情報(色調)を持った画素を意味しています。

PLL Phase-locked loop (位相同期回路)の略です。

**R**

RSDS Reduced Swing Differential Signaling (RSDS™インターフェース) の略です。

低電圧差動信号方式を利用して、低 EMI となるようにしたドライバ LSI 用インターフェースの規格です。

**S**

S/H Sample & Hold の略です。

イメージセンサー(CIS など)出力の各 Sub Pixel 信号を、映像信号期間と基準期間を同時にサンプリングする方式です。

SHn SHR/G/B, SH2/3/4, LEDR/G/B, SH 信号の総称です。

SNCKn SNCK1A ~ 1D, SNCK2 ~ 5 信号の総称です。

Sub Pixel Pixel (画素)を構成する、単色(R, G, B)を意味しています。

**T**

TEST テスト・モード用の回路ブロックを意味しています。

TGCK ライン周期の基準信号を意味しています。

## 9. 技術情報

本 AFE に関する技術情報の検索や最新版の入手は、下記 URL をご覧ください。

【URL】 <http://www.epsondevice.com/semicon/index.html>

[アナログフロントエンド(AFE)] [AFE ポータルサイト]

## 10. 改定履歴表

| Rev | 改定日        | 改定内容 |

|-----|------------|------|

| 1.0 | 2007/05/29 | 初版制定 |

|     |            |      |