**S1R72V シリーズ向け**

**USB2.0 Hi-Speed 用**

**PCB 設計ガイドライン**

## 適用範囲 SCOPE

本ガイドラインは、弊社製 S1R72V シリーズ(及びその派生機種)製品(以下、USB2.0 コントローラ IC)に適用します。

なお USB2.0 トランシーバマクロ部に関する、各信号名、各電源名については弊社開発時の固有名を用いておりま

すので、実際の USB2.0 コントローラ IC での端子名称につきましては、各製品に準じます。

本ガイドラインで示す様々な図、部品及び値に関しては、あくまでも参考であり、保証するものではありません。

また、本ガイドラインは予告無く改訂されることがあります。

## 目次

|                                               |    |

|-----------------------------------------------|----|

| 1. 目的 PURPOSE .....                           | 4  |

| 2. アートワークガイドライン BOARD DESIGN GUIDELINES ..... | 5  |

| 2.1. DP/DM 信号配線 .....                         | 5  |

| 2.1.1. コモンモードチョークコイル(CMCC)の使用について .....       | 5  |

| 2.1.2. チップバリスタの使用について .....                   | 5  |

| 2.1.3. DP/DM 端子の外付け部品について .....               | 5  |

| 2.1.4. 基板レイアウト例 .....                         | 7  |

| 2.1.5. 基板層構成例 .....                           | 10 |

| 2.2. USB 周回回路 .....                           | 11 |

| 2.2.1. 電源間デカップリング容量と VDD・GND プレーン .....       | 12 |

| 2.2.2. VBUS 保護回路 .....                        | 13 |

| 2.2.3. VBUS 供給回路 .....                        | 14 |

| 2.3. 発振回路 .....                               | 16 |

| 3. 差動信号特性事例 EYE DIAGRAM .....                 | 17 |

## 1. 目的 PURPOSE

本ガイドラインは、弊社製 S1R72V シリーズ(及びその派生機種)製品をご使用されるお客様が基板設計を行う際に、USB2.0 トランシーバマクロ周辺部のガイドラインとして用いていただくことを目的としております。したがいまして、USB2.0 機能の実現に特化した内容となっており、一般的な基板設計における注意事項は特に含まれていません。

また本ガイドラインと併せて、USB Implementers Forum(USB-IF)から公開されている基板アートワーク、認証試験のドキュメントもあわせてご覧いただけますようお願いいたします。

## 2. アートワークガイドライン BOARD DESIGN GUIDELINES

### 2.1. DP/DM 信号配線

DP/DM 信号に対し、次の項目に配慮して配線を行ってください。

DP/DM の差動インピーダンスが 90 Ω になること。

信号ラインは短く配線し、基板上での信号伝搬遅延が 1ns 以内におさるように配線すること。

スキューの防止、差動インピーダンスの安定化を図るため、等長かつ平行に配線すること。

直下の内層は完全な GND ベタ面とし、ベタ面分離をしないこと。

近接して他の信号は配線しないこと。特に高速信号やクロック信号からは遠ざけて配線し、安定した特性インピーダンスが得られるようにすること。

配線を曲げる場合、信号の反射を極力抑えるため R 处理を行うこと。

VBUS ラインは、DP/DM 信号ラインの差動インピーダンスを妨害しないだけの距離をあけて配線すること。

配線長が長くなる場合や、IC と USB コネクタ間に他のコネクタが挿入される場合には、特性インピーダンスの合わせ込みに特に配慮すること。

送信波形の調整のために、DP-GND 及び DM-GND 間にチップコンデンサ実装用のパターンをご用意いただくことを推奨します。なお、下記でご紹介いたしております、静電気・サージ保護用のチップバリスタの選定によって、波形を調整いただくことが可能です。

#### 2.1.1. コモンモードチョークコイル (CMCC) の使用について

CMCC の使用により、スキューの改善、不要輻射ノイズの低減等の効果が得られます。その一方で差動信号特性(FS 送信波形等)が劣化する恐れがあります。USB2.0 コントローラ IC では CMCC の使用による差動信号特性の影響はわずかであるため、必要に応じて使用することが可能です。

CMCC を使用する場合、以下の製品を推奨いたします。

なお、下記 CMCC を使用した際の不要輻射ノイズの低減効果は、お客様でご確認されますようお願いいたします。また CMCC の実装位置などの技術的なご質問に関しては各供給元にお問い合わせ下さい。

[ TDK 製 コモンモードフィルタ ACM2012-900-2P ]

[ 村田製作所製 チップコモンモードチョークコイル DLW21SN900SQ2 ]

[ TOKO 製 コモンモードチョーク 985BH - 1007 ]

#### 2.1.2. チップバリスタの使用について

DP/DM 端子の静電気・サージ保護のため、チップバリスタをご使用下さい。

USB2.0 の High-Speed 転送に対応した、チップバリスタとしては、下記のような製品がございます。なお、チップバリスタの実装位置は、一般的にはコネクタ近傍が効果的と考えられますが、各供給元にお問い合わせの上で決定して下さい。

[ TDK 製 チップバリスタ AVR シリーズ]

[ 松下電器産業製 チップバリスタ EZJJZ シリーズ]

#### 2.1.3. DP/DM 端子の外付け部品について

DP/DM 端子について、下記のような場合において、差動信号特性(HS 送信波形等)が劣化する恐れがあり、アイパターん波形品質に悪影響を与える場合があります。お客様製品においての各部品の必要性を十分ご検討され、製品機能、差動信号特性との総合評価を行ってください。

- 認証を取得していないレセプタクルやケーブル、コネクタ等をご使用になる場合。

- 1 対の DP/DM 信号線に対して、複数のレセプタクルをご使用になる場合。

弊社の 72V\*\* シリーズ USB コントローラ LSI は、High-Speed の波形品質を特長の一つとしており、良好な接続性をご提

供しています。High-Speed の通信では、PCB 上でフレキシブルケーブル等による中継や基板間接続、保護素子の付加等をされると、特に送信波形が劣化して通信が確保されにくくなる傾向が有ります。弊社の 72V\*\*シリーズ USB コントローラ LSI では、このように DP/DM ラインに寄生容量が付加されることを前提として、PCB での調整自由度を確保できるように送信特性を比較的急峻に調整しています。その反面、結果として、PCB のアートワークに依存して、USB コンプライアンス試験にて  $T_r/T_f$  の規定値( )を満たせない可能性があることにご配慮下さい。弊社では、判定時の測定において、本特性の測定値が、測定環境に大きく依存することを確認しており、LSI で完全に対処することは出来ないと結論しております。

したがいまして、静電保護バリスタをご使用されない場合にも、波形調整を目的に、バリスタを実装できるランドパターンを設けていただくことをご推奨いたします。

: min.500ps, USB2.0 規格 7.1.2.2

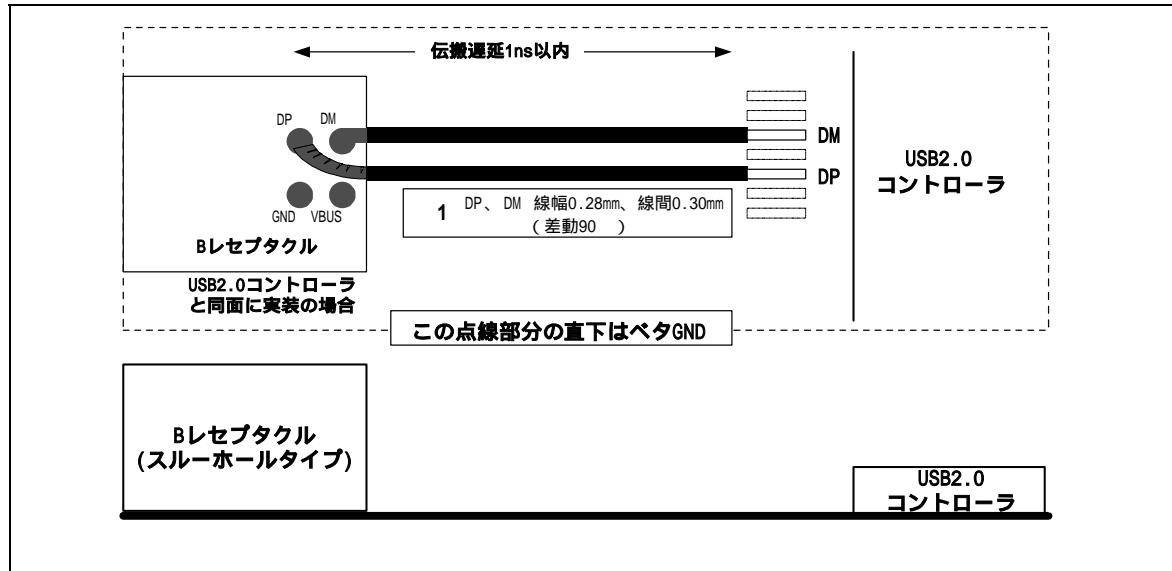

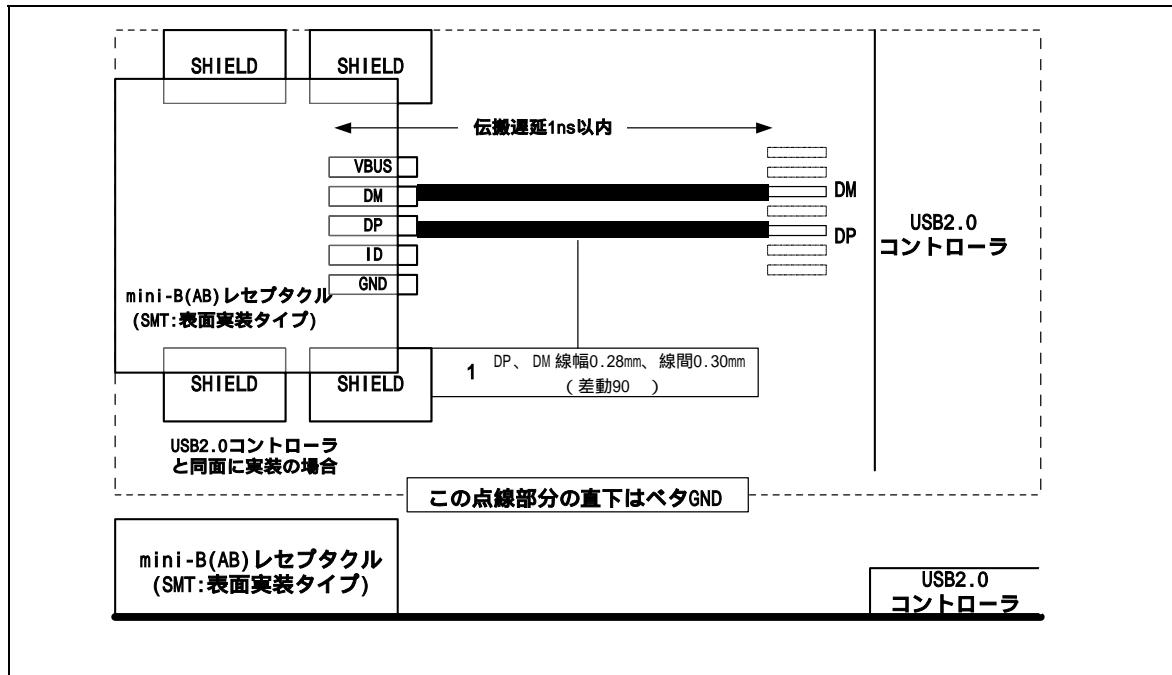

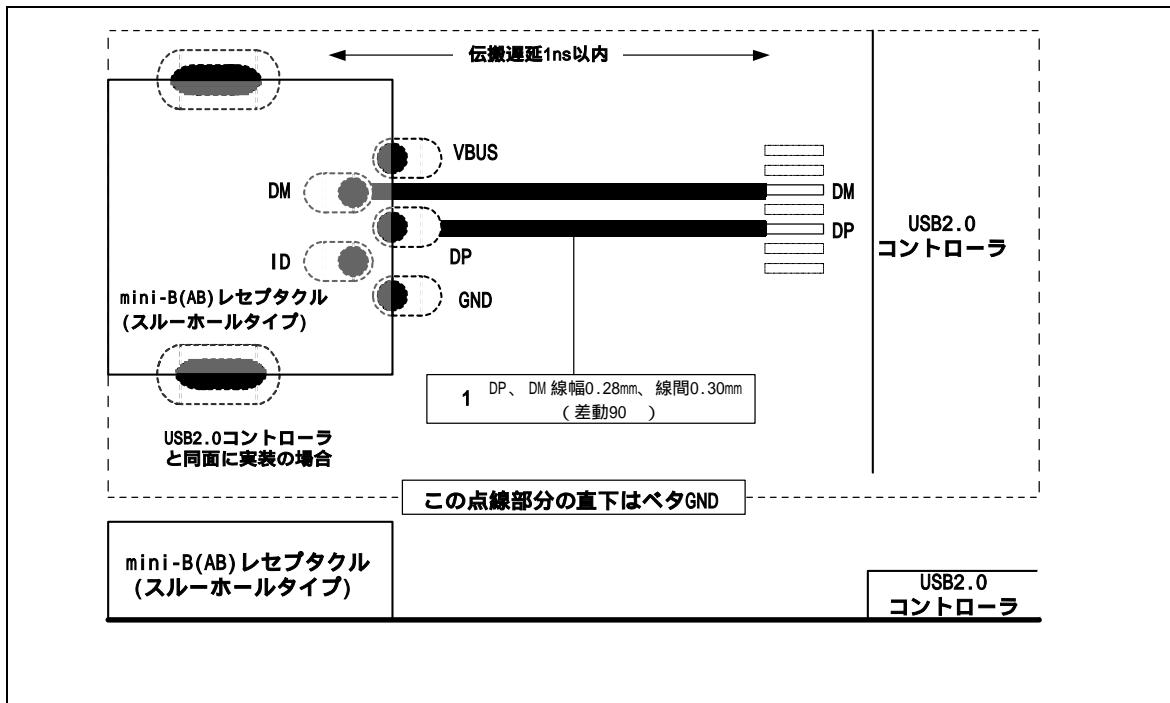

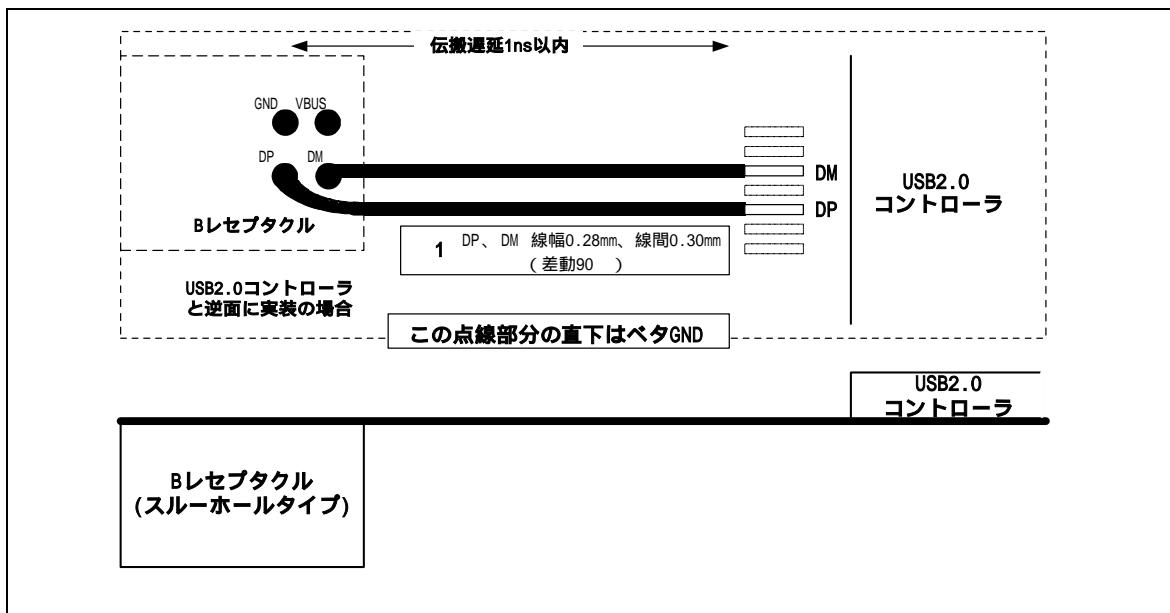

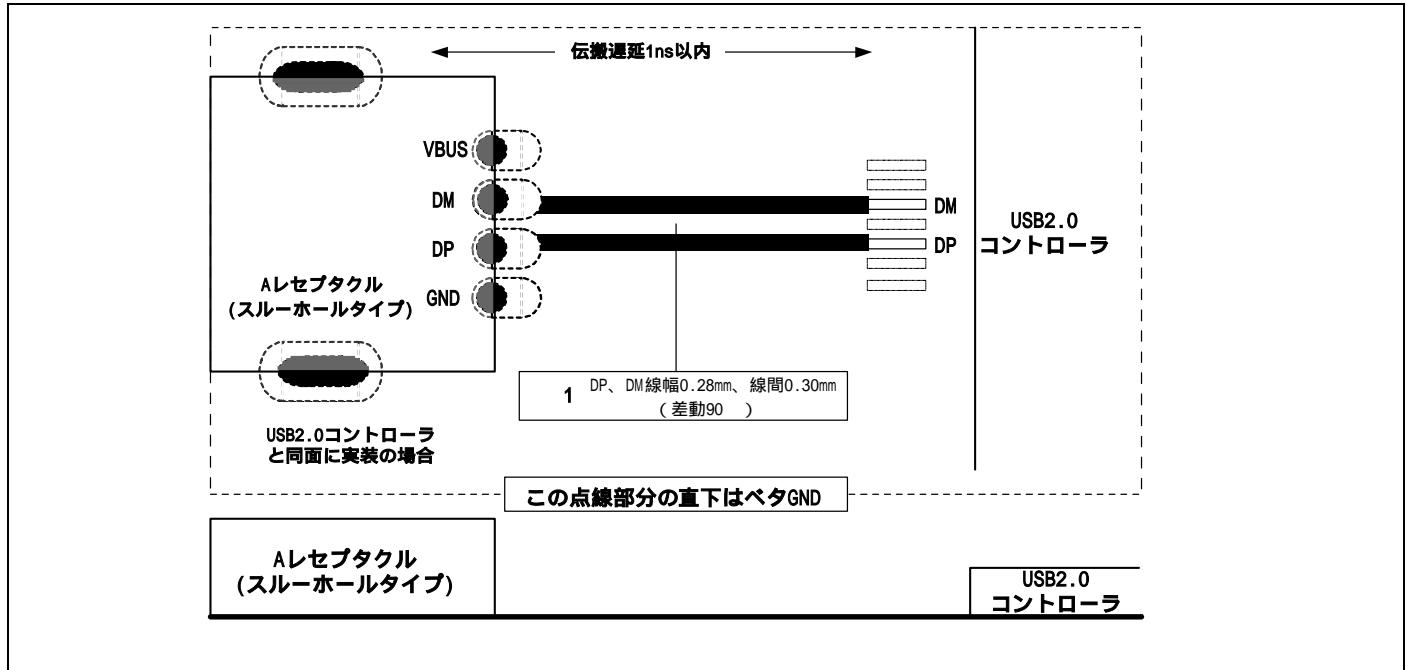

#### 2.1.4. 基板レイアウト例

以下に、USB2.0 コントローラ IC とレセプタクル間の DP/DM 配線例を示します。

各寸法は、弊社 USB2.0 特性確認用評価ボード（「株式会社キヨウデン」製）における製造実績に基づいています。お客様の基板製造時に差動インピーダンス特性を整えるための適切な加工条件を、基板メーカーへご確認ください。

なお、CMC やチップバリスタなどの外付け部品につきましては、本レイアウト例では割愛しております。CMC は DP/DM ラインに直線的に配置されるよう、また、チップバリスタは DP/DM ラインからの分岐が最短となるようにご注意ください。

図 2-1 基板レイアウト例 [B レセプタクル(スルーホールタイプ) : 同面実装]

図 2-2 基板レイアウト例 [mini-B または mini-AB レセプタクル(SMT タイプ) : 同面実装]

図 2-3 基板レイアウト例【mini-B または mini-AB レセプタクル(スルーホールタイプ)：同面実装】

図 2-4 基板レイアウト例【B レセプタクル(スルーホールタイプ)：逆面実装】

図 2-5 基板レイアウト例【A レセプタクル(スルーホールタイプ)：同面実装】

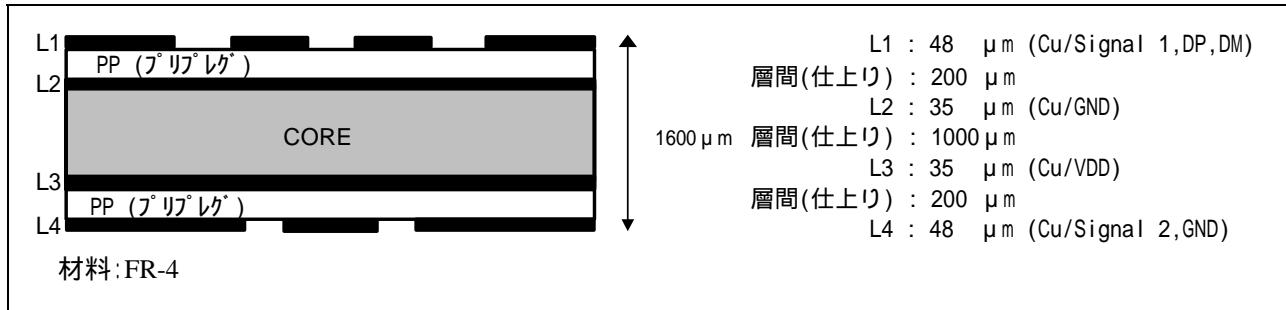

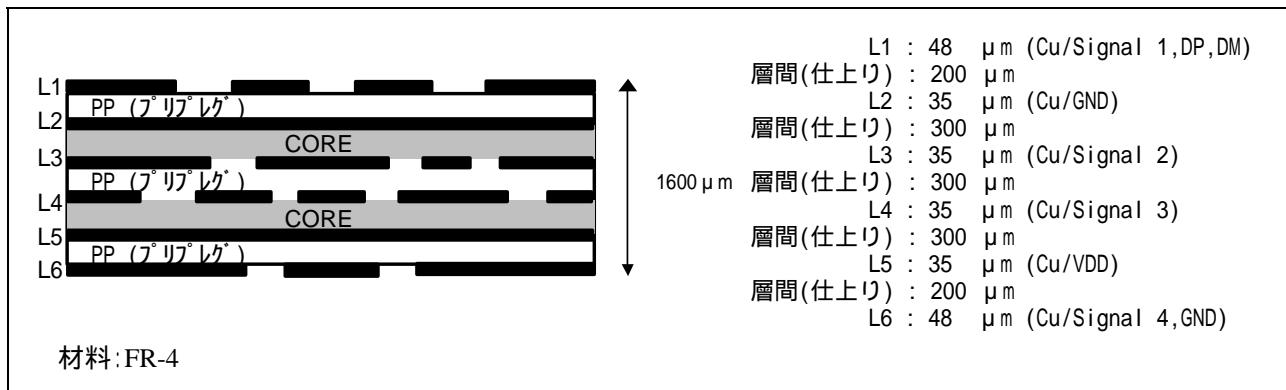

### 2.1.5. 基板層構成例

以下に、4層もしくは6層構造の1.6mm厚プリント基板の参考例を示します。

各寸法は、弊社USB2.0特性確認用評価ボード(「株式会社キヨウデン」製)における製造実績に基づいています。お客様の基板製造時には、差動インピーダンス特性を整えるための適切な加工条件を、基板メーカーへご確認ください。

図 2-6 4層対応プリント基板構成図

図 2-7 6層対応プリント基板構成図

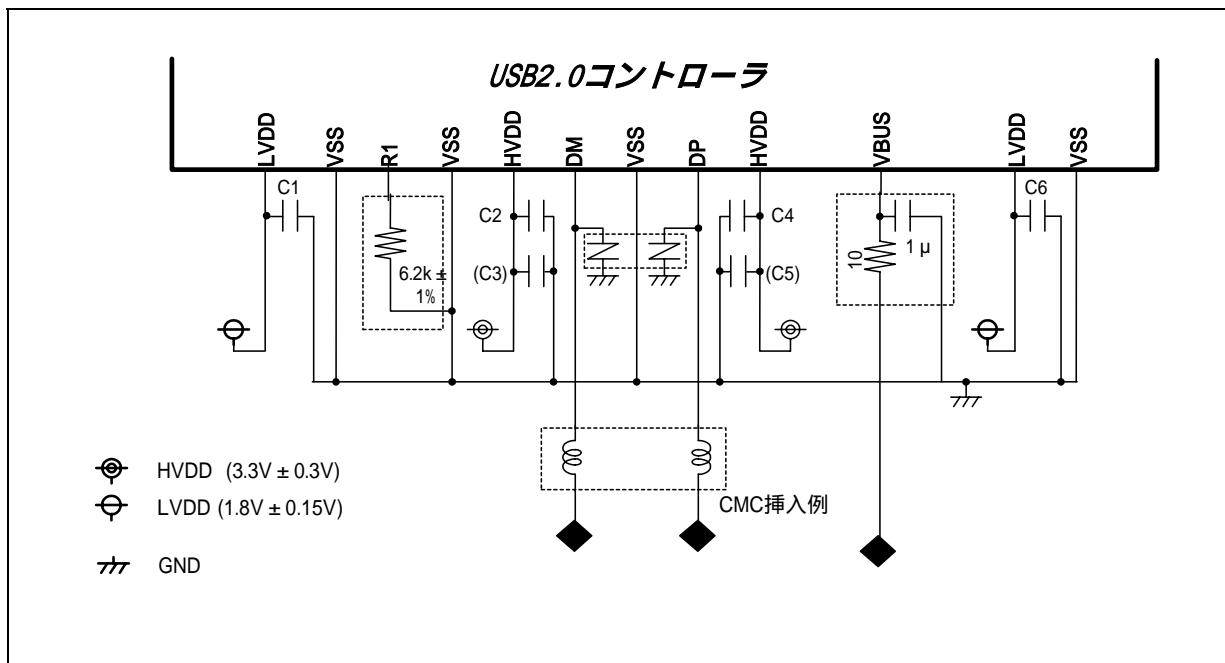

## 2.2. USB 周辺回路

USB2.0 コントローラ IC の周辺回路については、以下の項目に配慮し部品配置を行ってください。

- R1 端子に接続する  $6.2k \pm 1\%$  の抵抗は、可能な限り R1 端子近傍に配置すること。

- USB2.0 トランシーバマクロ部に属する VSS は、分離せずに共通 GND に低インピーダンスで落とすこと。

- 各デカップリングコンデンサは対応する電源端子の近傍に配置すること(推奨)。

- C3,C5 は必要に応じて使用すること(詳細は「2.2.1 電源間デカップリング容量と VDD・GND プレーン」を参照)。

図 2-8 に USB 周辺回路例を示します。

実際の端子配置、端子名は、製品によって変更されていることもありますので、部品配置や端子との接続に関しましては各製品の開発仕様書の USB 接続例をご覧下さい。

図 2-8 USB 周辺回路例

### 2.2.1. 電源間デカップリング容量と VDD・GND プレーン

各電源間デカップリングコンデンサの容量の参考値を示します。

**表 2-1 電源間デカップリングコンデンサの容量**

| 容量名(図 2-8) | C1        | C2, C4      | C6        |

|------------|-----------|-------------|-----------|

| 参考値        | 1 $\mu$ F | 0.1 $\mu$ F | 1 $\mu$ F |

VDD プレーン・GND プレーンの特性が良好でないと、ジッターの増加など差動信号特性に影響を及ぼします。これらを回避するため、次の点に配慮してください。

- スイッチングレギュレータを使用する場合、スイッチングレギュレータのノイズの影響を十分調査するとともに、スイッチングノイズが小さくなるよう考慮して、プリント基板を設計してください。

- プリント基板の状況によっては、C2 および C4 に比べて容量の大きなコンデンサを C3 および C5 の箇所に配置することにより、ジッターを良好にできることがあります。その場合、C2, C4 は C3, C5 よりも HVDD 端子近傍に寄せて配置してください。

- コンデンサの容量は、回路基板、部品配置、部品点数、実施可能コスト、信号品質等を考慮し、最適な値を決定してください。

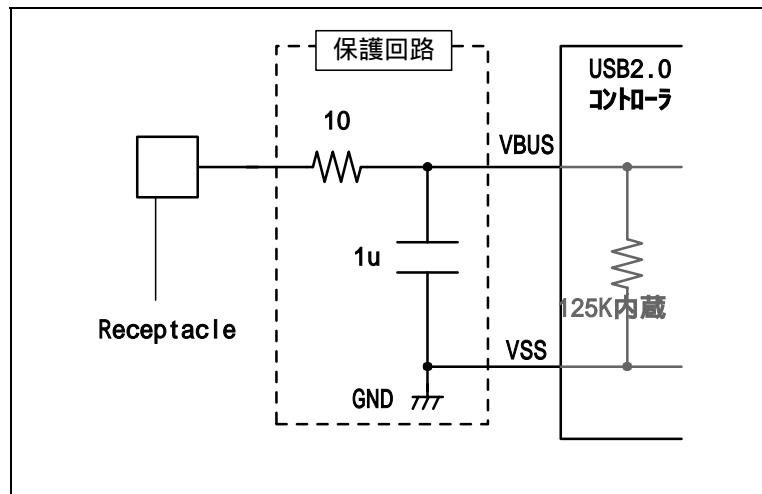

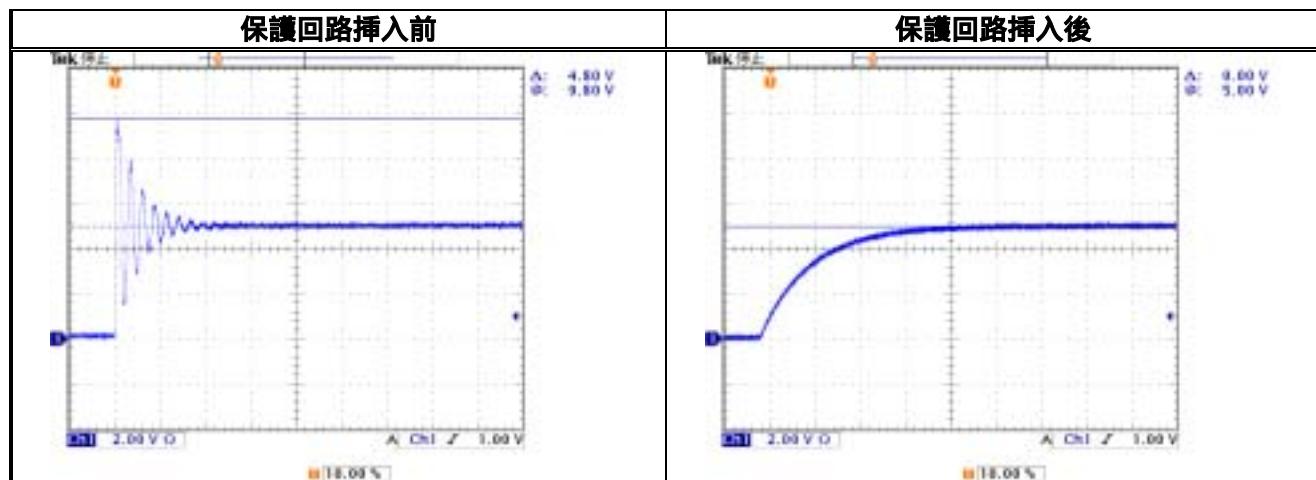

### 2.2.2. VBUS 保護回路

USB2.0 コントローラ IC が USB デバイスである場合において、USB ケーブル接続時に VBUS 端子に VBUS 規格電圧(5V)を大きく超える電圧が生じ、これにより IC の絶対最大定格を超え VBUS 端子を破壊することが考えられます。そこで、破壊を回避するため、以下のような保護回路を必ず使用してください。

図 2-9 VBUS 保護回路

青色 ————— : VBUS 端子電圧

図 2-10 VBUS 端子の印加電圧立ち上がり波形

### 2.2.3. VBUS 供給回路

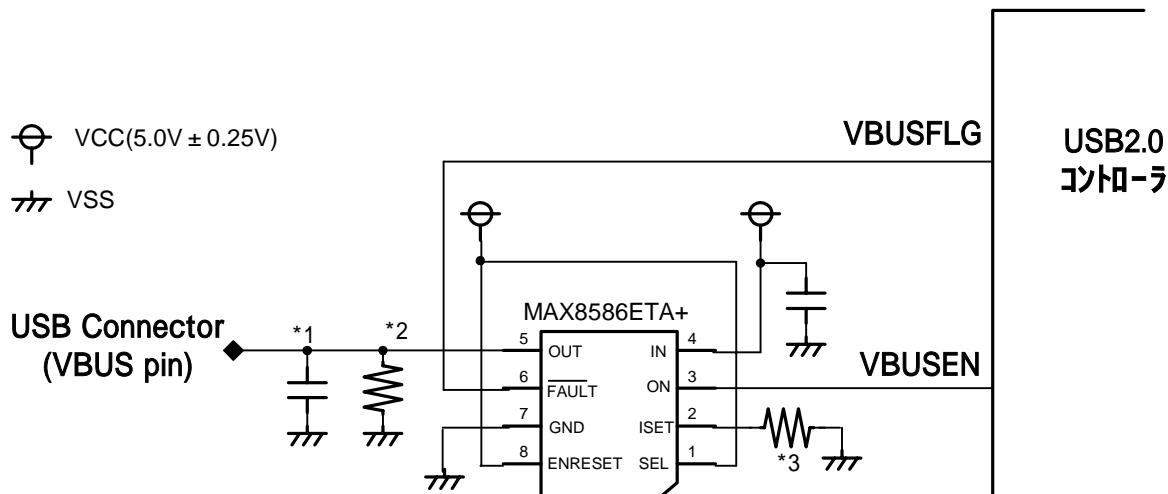

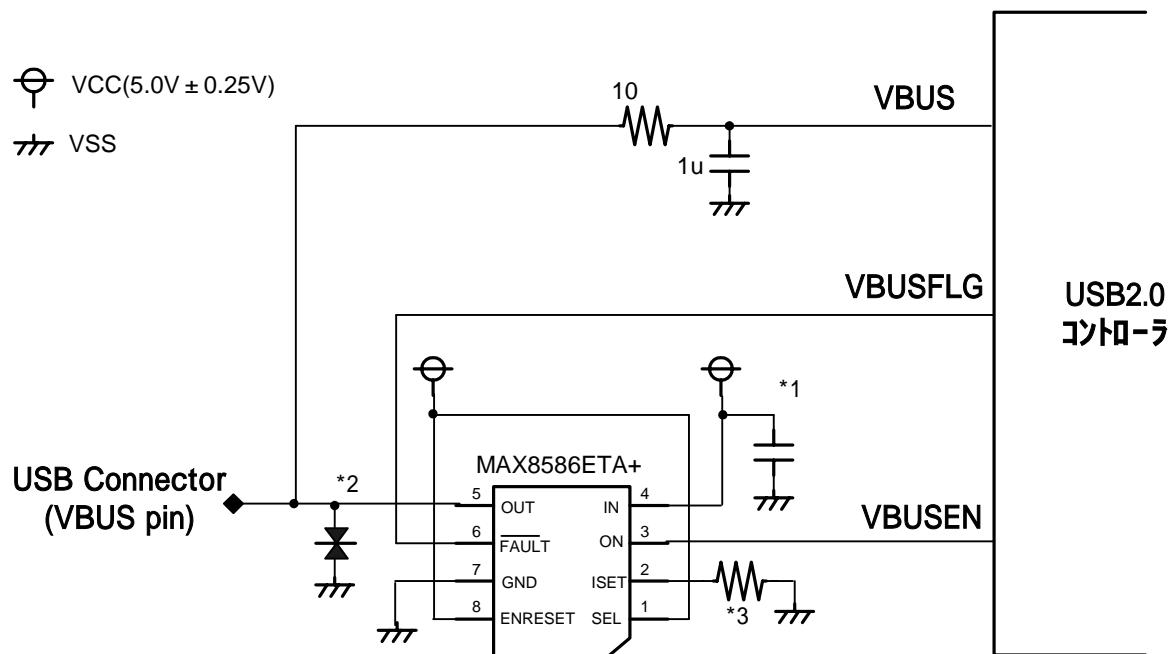

USB ホスト機能を持つ弊社 USB2.0 コントローラ IC において、USB コネクタより VBUS 電源(+5V)を供給するための回路例を示します。ここでは、過電流保護機能および逆電流保護機能( )付き USB パワースイッチ IC として、Maxim 社製 MAX8586ETA+を用いた場合の接続例を示しておりますが、お客様のシステムでの動作を保証するものではありません。実際には、お使いになるパワースイッチ IC の仕様、過電流保護の方法、等を十分ご検討の上、お客様のシステムに合わせた部品および回路方式を選定してください。

逆電流保護機能を持たない USB パワースイッチ IC を使用する場合、下記の点に注意してください。

例えば機器の電源が投入されていない状態で USB コネクタの VBUS 端子に外部から電圧が印加された場合、USB パワースイッチ IC の OUT 端子側から IN 端子側への逆電流が生じることが考えられます。これは、機器の電源が予期せぬ投入状態になる要因となります。

USB ホスト機能と USB デバイス機能を兼ね備える構成において、ホスト専用の USB コネクタを備える場合、およびデバイス用 USB コネクタと兼用する場合、各々の回路例を示します。

#### ホスト専用の USB コネクタを備える場合

\*1: Universal Serial Bus Specification (Revision 2.0) では、7.2.4 項において、「USB ダウンストリーム側ポートの VBUS ラインは、 $120 \mu F$  以上の容量でバイパスすること」が規定されています。弊社評価ボードでは、 $122 \mu F$  相当を実装しております。

\*2: 上記した  $120 \mu F$  以上のコンデンサに蓄積された電荷をディスチャージするための抵抗です。弊社評価ボードでは、 $100k$  を実装しております。

\*3: 過電流検出値を決める抵抗です。詳細は、USB パワースイッチ IC の仕様書をご覧ください。

図 2-11 VBUS 供給回路例\_1

デバイス用 USB コネクタと兼用する場合

\*1: Universal Serial Bus Specification (Revision 2.0) では、7.2.4 項において、「USB ダウンストリーム側ポートの VBUS ラインは、 $120 \mu F$  以上の容量でバイパスすること」が規定されています。弊社評価ボードでは、 $122 \mu F$  相当を実装しております。

\*2: USB コネクタを介して定格以上の VBUS 電圧を供給する機器と接続された場合に、USB パワースイッチ IC を保護することを目的とします。必要に応じて適切な部品をご使用ください。

\*3: 過電流検出値を決める抵抗です。詳細は、USB パワースイッチ IC の仕様書をご覧ください。

図 2-12 VBUS 供給回路例\_2

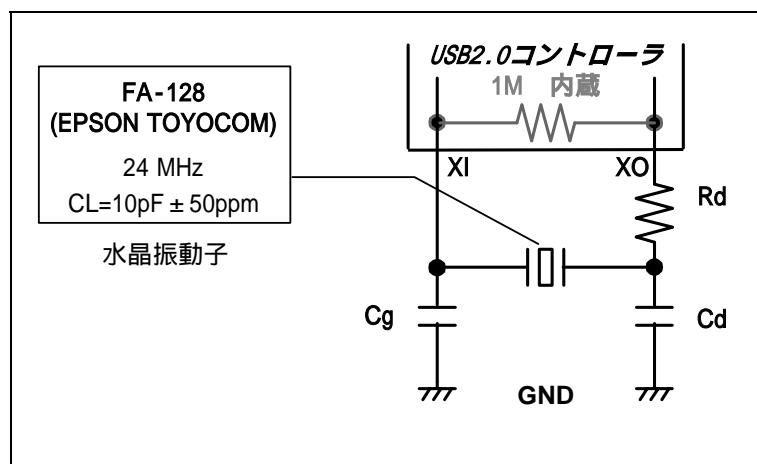

## 2.3. 発振回路

ノイズによる発振クロックの乱れは誤動作の原因となるため、以下の点に配慮してください。

- 発振回路近くには大電流信号線や高速動作信号線を配置しないこと。

- XI、XO 信号は最短で配線すること。

- 水晶発振子の周波数精度は、概ね 100ppm 以下のものを選択すること。

図 2-13、表 2-2 にエプソントヨコム社製水晶振動子 FA-128 を使用した場合の発振回路の参考構成例を示します。

ただし発振特性は諸条件（使用部品、基板パターン）により変化するため、周辺回路定数は、振動子メーカーへ評価を依頼し、基板ごとに適切な定数を決定されますようお願いいたします。

図 2-13 水晶振動子接続例

表 2-2 弊社 EVA ボードでの回路定数

| エプソントヨコム社製<br>水晶振動子(CL=10pF ± 50ppm) | 発振周波数<br>(MHz) | 推奨回路定数  |         |        |

|--------------------------------------|----------------|---------|---------|--------|

|                                      |                | Cg (pF) | Cd (pF) | Rd ( ) |

| FA-128                               | 24             | 15      | 15      | 470    |

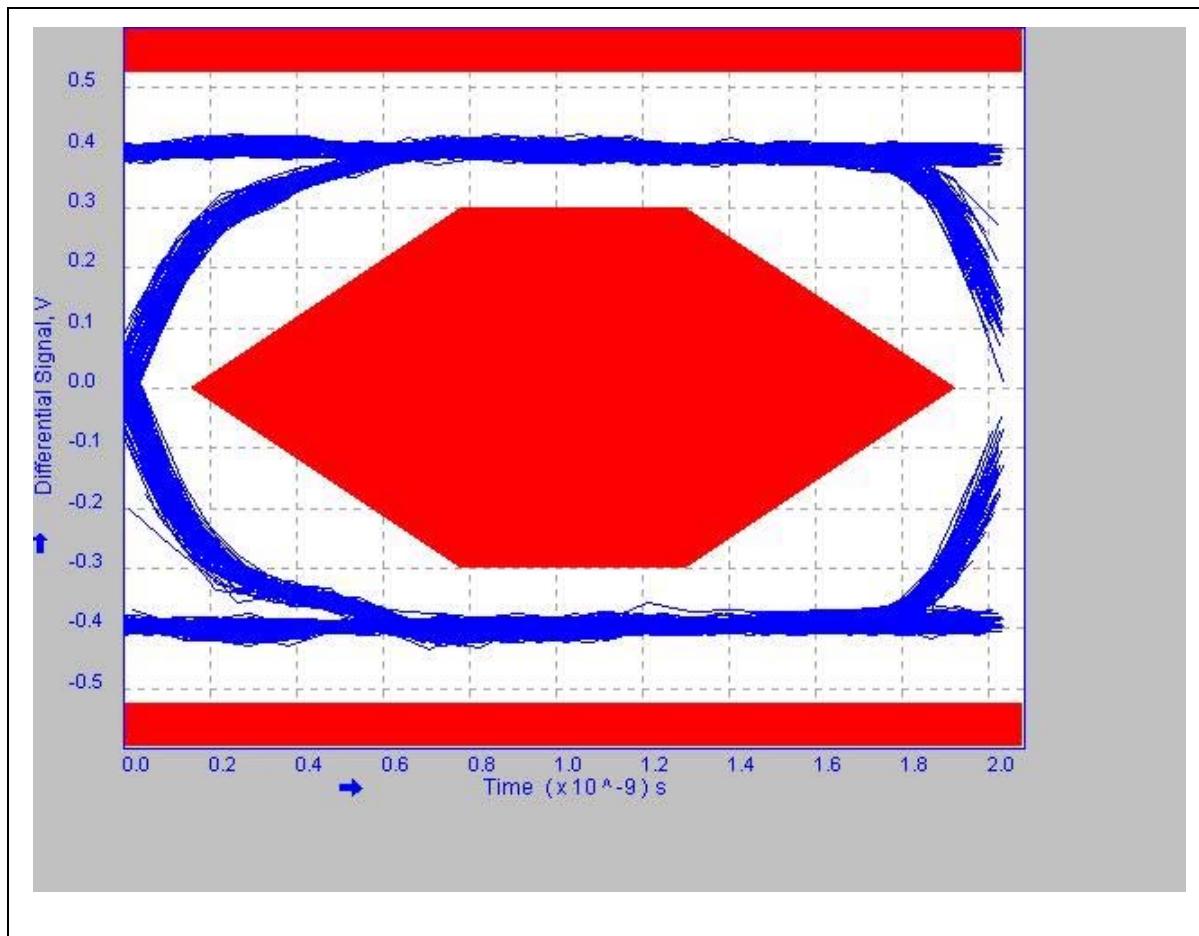

### 3. 差動信号特性事例 EYE DIAGRAM

本ガイドラインに沿って設計された USB2.0 コントローラ IC Evaluation Board における Hi-Speed アイパターの観測事例を図 3-1 に示します。

図 3-1 アイパターの波形(Hi-Speed)

アイパターの波形は、基板上の伝送線路特性並びに電源特性、および測定環境等によって観測される波形が異なります。

## 改訂履歴

| 年月日      | 改訂内容  |           |    |                                                      |

|----------|-------|-----------|----|------------------------------------------------------|

|          | Rev.  | 項<br>(旧版) | 種別 | 内 容                                                  |

| 05/10/14 | 2.0   | 全項        | 新規 | 新規制定                                                 |

| 06/03/01 | 2.1   | 2.2       | 修正 | C2,C4 に関する項目を削除                                      |

|          |       |           | 修正 | C3,C5 に関する項目を追加                                      |

|          |       |           | 修正 | 図 2-8 において、C3 (C3), C5 (C5)                          |

|          | 2.2.1 |           | 修正 | 表 2-1 において、C3, C5 を削除                                |

|          |       |           | 修正 | C3,C5 を使用する場合の配慮項目を追加                                |

|          |       |           | 修正 | コンデンサ容量決定に関する配慮項目を追加                                 |

| 06/04/10 | 2.2   | 2.1       | 追記 | 波形調整に関する記載を追加                                        |

|          |       | 2.1.2     | 追記 | チップバリスタに関する項を追加し、2.1.2 とした                           |

|          |       | 2.1.3     | 修正 | 上記に伴い項番を更新<br>注記を一部削除<br>波形調整に関する記載を追加               |

|          |       | 2.1.4     | 追記 | 外付け部品に関する注記を追加                                       |

|          |       | 2.2       | 追記 | 図にバリスタ及び CMC を追加                                     |

| 07/05/11 | 2.3   | 2.2.3     | 追記 | 項全体を追加                                               |

|          |       | 2.3       | 修正 | 水晶振動子の型番を FA-365 から FA-128 へ修正<br>2.2.3 挿入に伴い、図番号を更新 |