# S1R72V17

## CPU 接続ガイド

## 本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## 適用範囲

本ドキュメントは、USB2.0 ホスト／デバイスコントローラ LSI 「S1R72V17」に適用されます。

# 目次

|                                           |    |

|-------------------------------------------|----|

| 1. はじめに.....                              | 1  |

| 1.1 概要 .....                              | 1  |

| 1.2 関連資料 .....                            | 1  |

| 2. 一般的なCPUとの接続例 .....                     | 2  |

| 3. 16bitバス幅接続時の、エンディアン設定について .....        | 4  |

| 3.1 ビックエンディアンCPUとの接続 .....                | 4  |

| 3.2 リトルエンディアンCPUとの接続 .....                | 7  |

| 4. CPUIF検証手順.....                         | 10 |

| 5. iMX21(FreeScale社製)との接続例 .....          | 14 |

| 5.1 接続例 .....                             | 14 |

| 5.2 iMX21 のバスサイクル設定例 .....                | 15 |

| 5.3 S1R72V17 のACスペックとiMX21 バスサイクルの確認..... | 17 |

## 1. はじめに

### 1.1 概要

本資料は、お客様が S1R72V17 を実際に使用する際に必要な情報の中で、制御 CPU と S1R72V17 を接続する際に必要な内容に特化してまとめた資料です。

本資料に記載されている内容は、接続方法の一例であり、内容を保証するものではありません。お客様のシステム環境に合わせて、接続方法を変更する必要があります。

また、本資料の内容は、予告なく改定されることがあります。

### 1.2 関連資料

- S1R72V17 テクニカルマニュアル（ハードウェア仕様書）

## 2. 一般的な CPU との接続例

ここでは、一般的な CPU との接続例を示します。

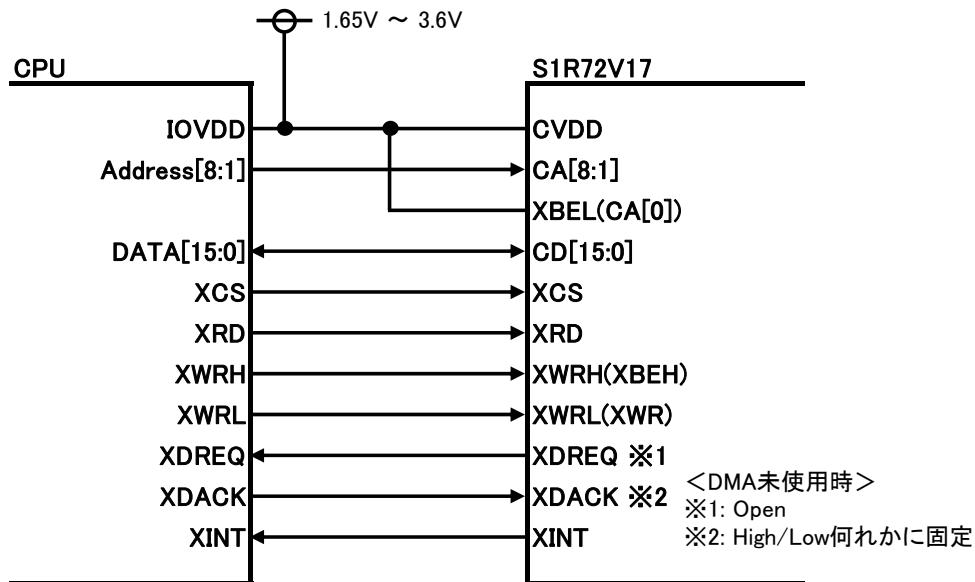

### 1) 16bit バス、Strobe mode における接続例

CPU\_Config レジスタ (0x075h 番地) の BusMode ビット="0"、Bus8x16 ビット="0"を設定。

図 2-1 16bit バス、Strobe mode における接続例

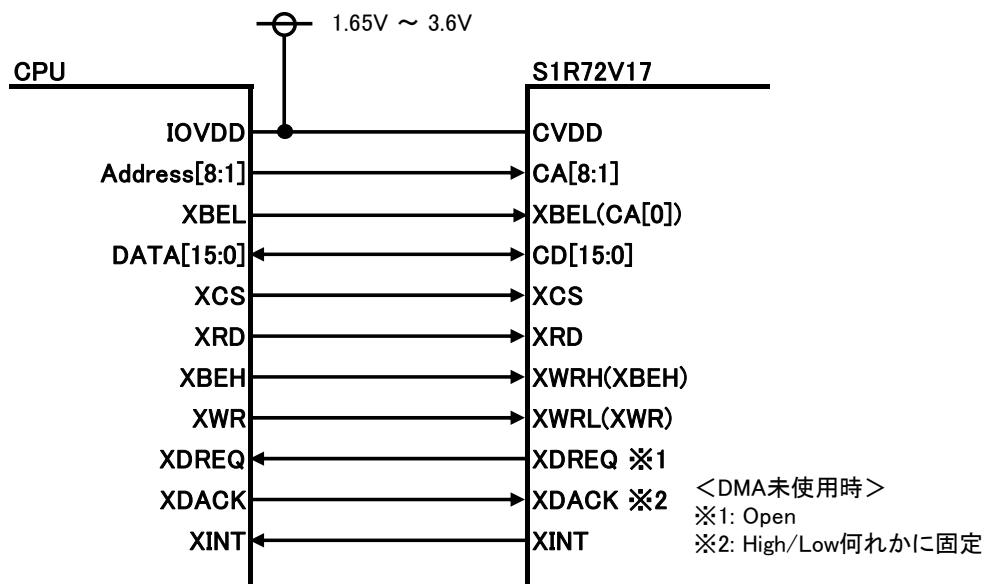

### 2) 16bit バス、BE mode における接続例

CPU\_Config レジスタ (0x075h 番地) の BusMode ビット="1"、Bus8x16 ビット="0"を設定。

図 2-2 16bit バス、BE mode における接続例

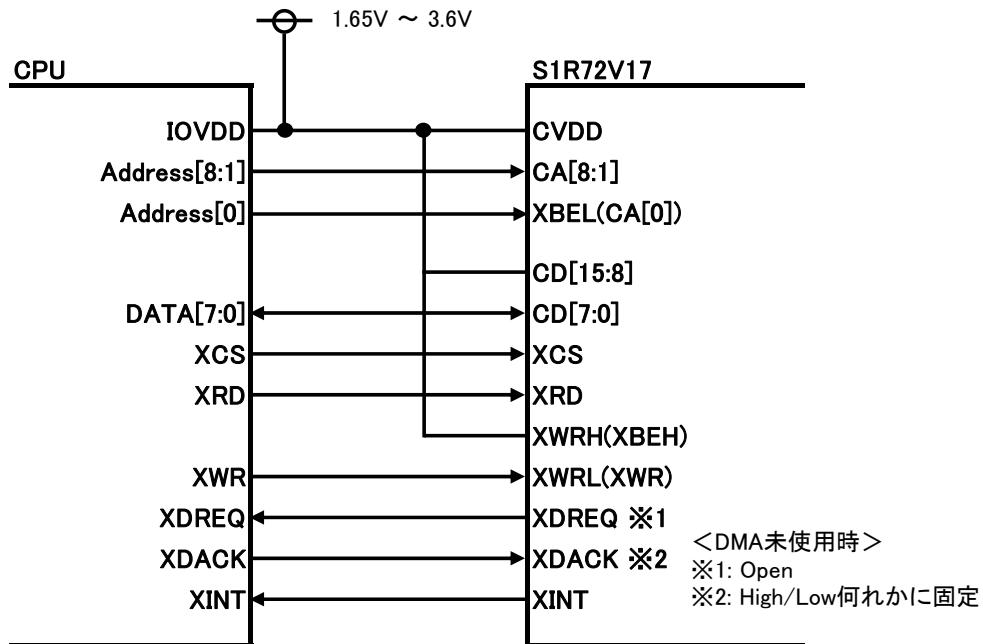

### 3) 8bit バスモードにおける接続例

CPU\_Config レジスタ (0x075h 番地) の BusMode ビット="0"、Bus8x16 ビット="1"を設定。

図 2-3 8bit バスモードにおける接続例

### 3. 16bit バス幅接続時の、エンディアン設定について

ここでは、CPU と 16bit バス幅で接続した場合の、エンディアン設定について説明します。

S1R72V17 のレジスタを、下記の 3 タイプに分けて説明します。レジスタの詳細は、S1R72V17 テクニカルマニュアルを参照してください。

- 1) Word レジスタ： レジスタ名称の末尾に、\_H/\_L/\_HH/\_HL/\_LH/\_LL がつくレジスタが該当します。

- 2) Byte レジスタ： Word レジスタ/FIFO レジスタ以外のレジスタが該当します。

- 3) FIFO レジスタ： RAM\_Rd\_00~\_1F / RAM\_WrDoor\_0,1 / FIFO\_Rd\_0,1 / FIFO\_Wr\_0,1 / FIFO\_ByteRd レジスタが該当します。

#### 3.1 ビックエンディアンCPUとの接続

基本的に、CPU\_Config レジスタ (0x075h 番地) の CPU\_Endian ビットに“0”をセットしたモードで、アクセスします。

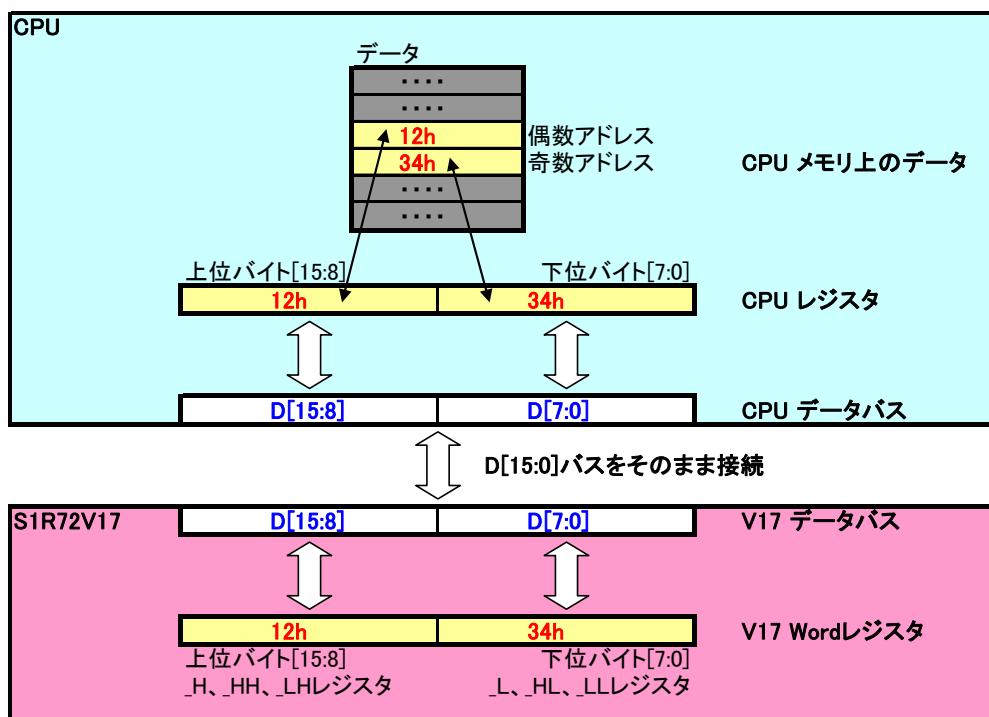

- 1) Word レジスタへのアクセス

S1R72V17 は、D[15:8]バスを Word レジスタの上位バイト、D[7:0]バスを Word レジスタの下位バイトと接続します。

ここでは、Word レジスタに対して 0x1234h のデータをライトして、リードする場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ（12h）が、S1R72V17 の Word レジスタの上位バイトに保存されます。

リード時： S1R72V17 の Word レジスタの上位バイトデータ（12h）が、CPU メモリ上の偶数アドレスに保存されます。

図 3-1 Word レジスタへのアクセス（ビックエンディアン C P U）

### 3. 16bit バス幅接続時の、エンディアン設定について

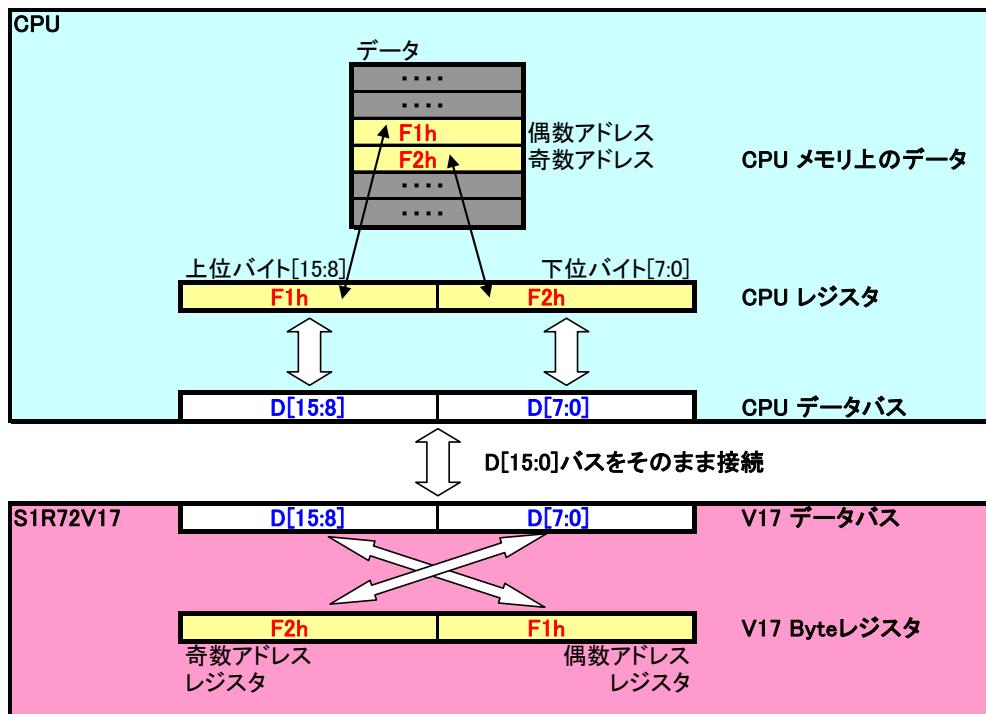

#### 2) Byte レジスタへのアクセス

S1R72V17は、CPU\_Endian ビット=“0”設定により D[15:8]バスを偶数アドレスレジスタ、D[7:0]バスを奇数アドレスレジスタと接続します。

ここでは、Byte レジスタの偶数アドレスレジスタに F1h／奇数アドレスレジスタに F2h をライトして読み出す場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ（F1h）が、S1R72V17 の偶数アドレスレジスタに保存されます。

リード時： S1R72V17 の偶数アドレスレジスタのデータ（F1h）が、CPU メモリ上の偶数アドレスに保存されます。

図 3-2 Byte レジスタへのアクセス（ビックエンディアン CPU）

### 3. 16bit バス幅接続時の、エンディアン設定について

#### 3) FIFO レジスタへのアクセス

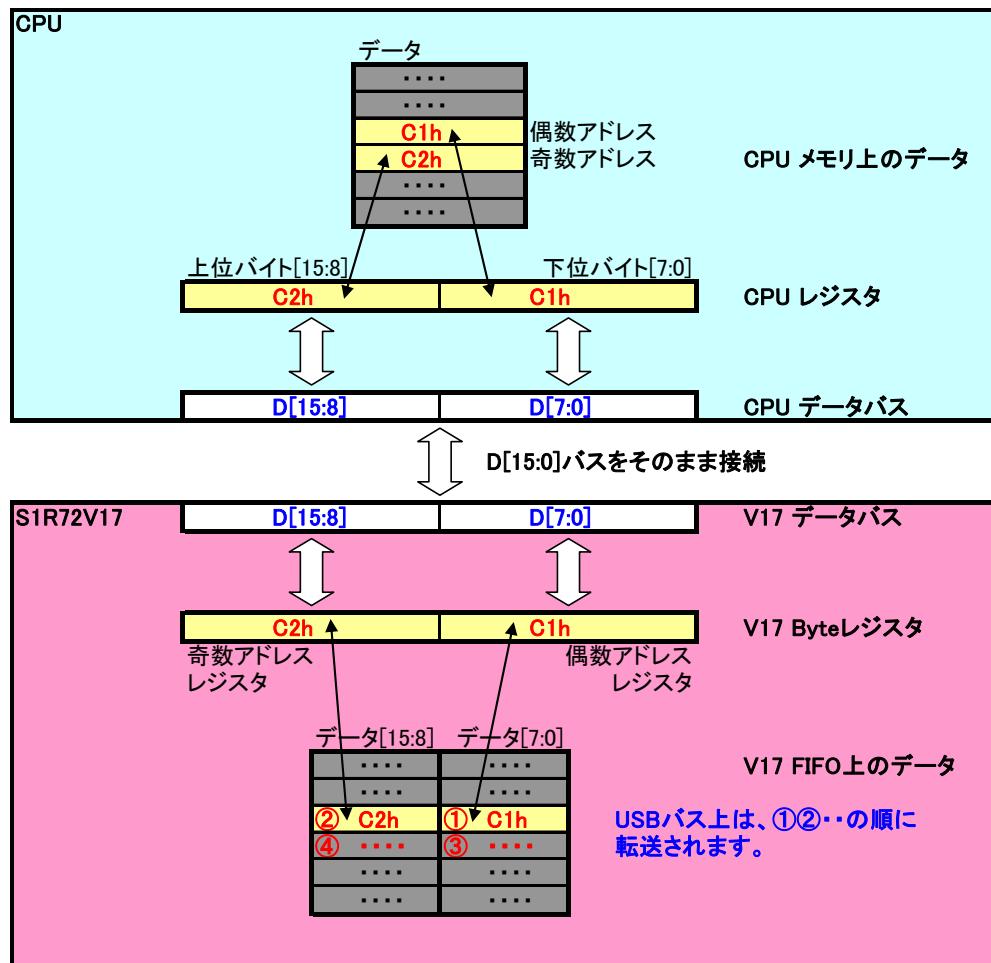

S1R72V17は、CPU\_Endian ビット="0"設定により D[15:8]バスを偶数アドレスレジスタ、D[7:0]バスを奇数アドレスレジスタと接続します。

ここでは、USB バスから C1h/C2h の順番に送信し、C1h/C2h の順番に受信する場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ (C1h) が、USB バスから最初のデータとして送信されます。

リード時： USB バスから最初に受信したデータ (C1h) が、CPU メモリ上の偶数アドレスに保存されます。

図 3-3 FIFO レジスタへのアクセス（ビックエンディアン CPU）

### 3.2 リトルエンディアンCPUとの接続

基本的に、CPU\_Config レジスタ (0x075h 番地) の CPU\_Endian ビットに“1”をセットしたモードで、アクセスします。

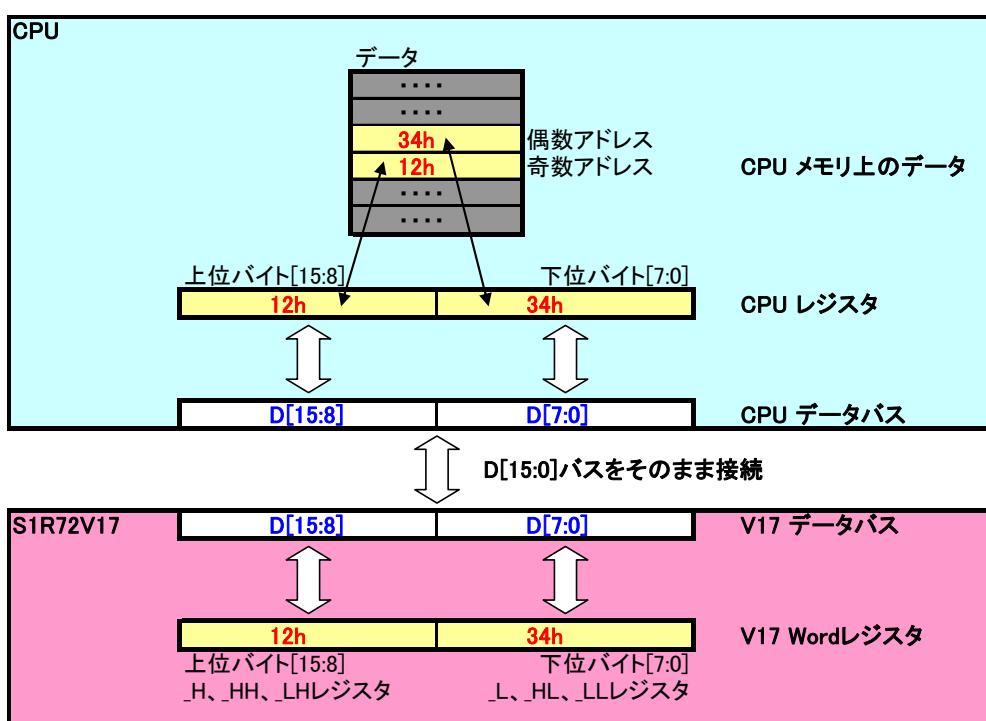

#### 1) Word レジスタへのアクセス

S1R72V17 は、D[15:8]バスを Word レジスタの上位バイト、D[7:0]バスを Word レジスタの下位バイトと接続します。

ここでは、Word レジスタに対して 0x1234h のデータをライトして、リードする場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ (34h) が、S1R72V17 の Word レジスタの下位バイトに保存されます。

リード時： S1R72V17 の Word レジスタの下位バイトデータ (34h) が、CPU メモリ上の偶数アドレスに保存されます。

図 3-4 Word レジスタへのアクセス（リトルエンディアン CPU）

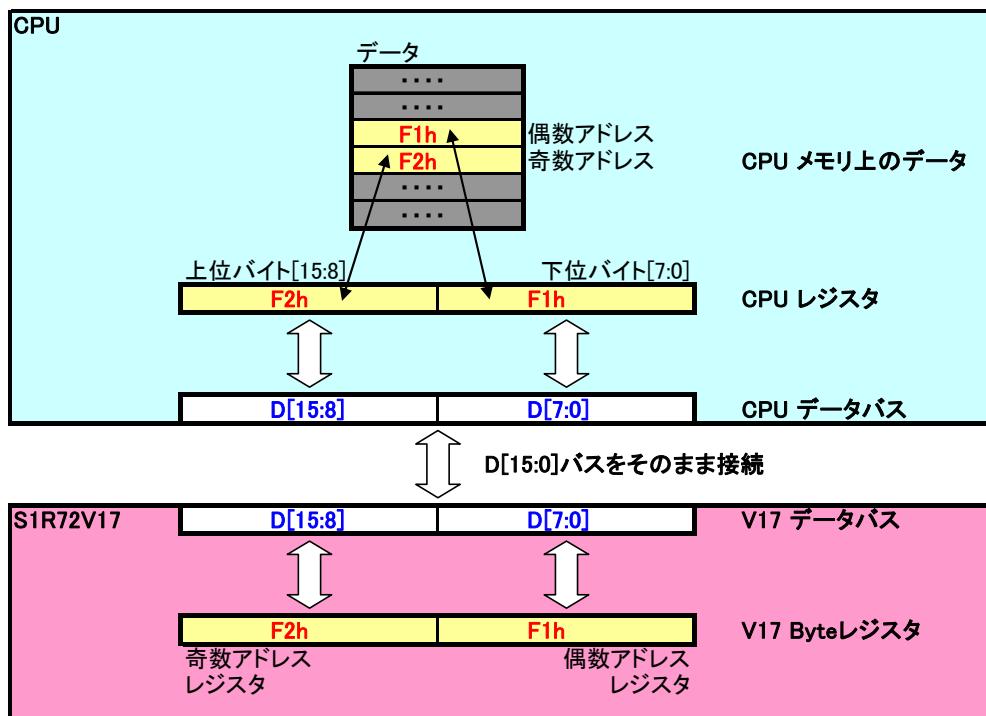

### 3. 16bit バス幅接続時の、エンディアン設定について

#### 2) Byte レジスタへのアクセス

S1R72V17 は、CPU\_Endian ビット=“1”設定により D[7:0]バスを偶数アドレスレジスタ、D[15:8]バスを奇数アドレスレジスタと接続します。

ここでは、Byte レジスタの偶数アドレスレジスタに F1h／奇数アドレスレジスタに F2h をライトして読み出す場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ（F1h）が、S1R72V17 の偶数アドレスレジスタに保存されます。

リード時： S1R72V17 の偶数アドレスレジスタのデータ（F1h）が、CPU メモリ上の偶数アドレスに保存されます。

図 3-5 Byte レジスタへのアクセス（リトルエンディアン CPU）

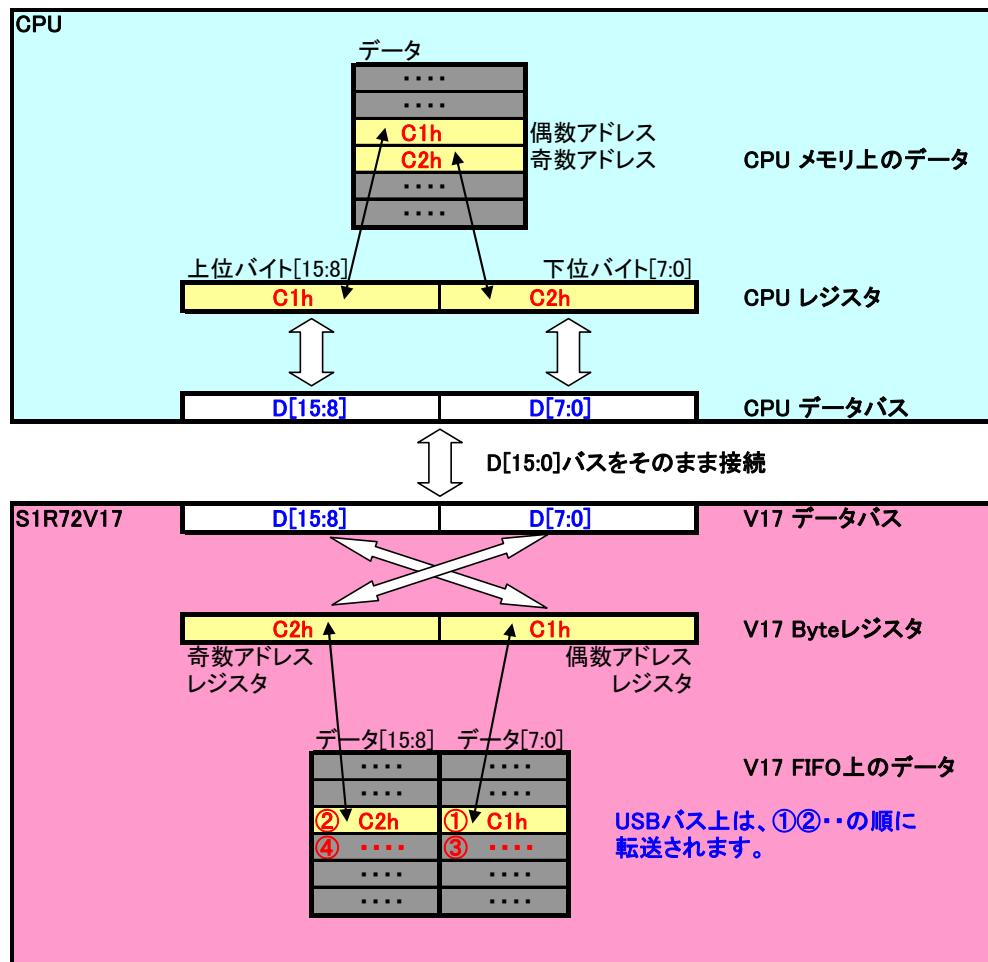

### 3. 16bit バス幅接続時の、エンディアン設定について

#### 3) FIFO レジスタへのアクセス

S1R72V17 は、CPU\_Endian ビット="1" 設定により D[7:0] バスを偶数アドレスレジスタ、D[15:8] バスを奇数アドレスレジスタと接続します。

ここでは、USB バスから C1h/C2h の順番に送信し、C1h/C2h の順番に受信する場合の例を下記に示します。

ライト時： CPU メモリ上の偶数アドレスのデータ (C1h) が、USB バスから最初のデータとして送信されます。

リード時： USB バスから最初に受信したデータ (C1h) が、CPU メモリ上の偶数アドレスに保存されます。

図 3-6 FIFO レジスタへのアクセス（リトルエンディアン CPU）

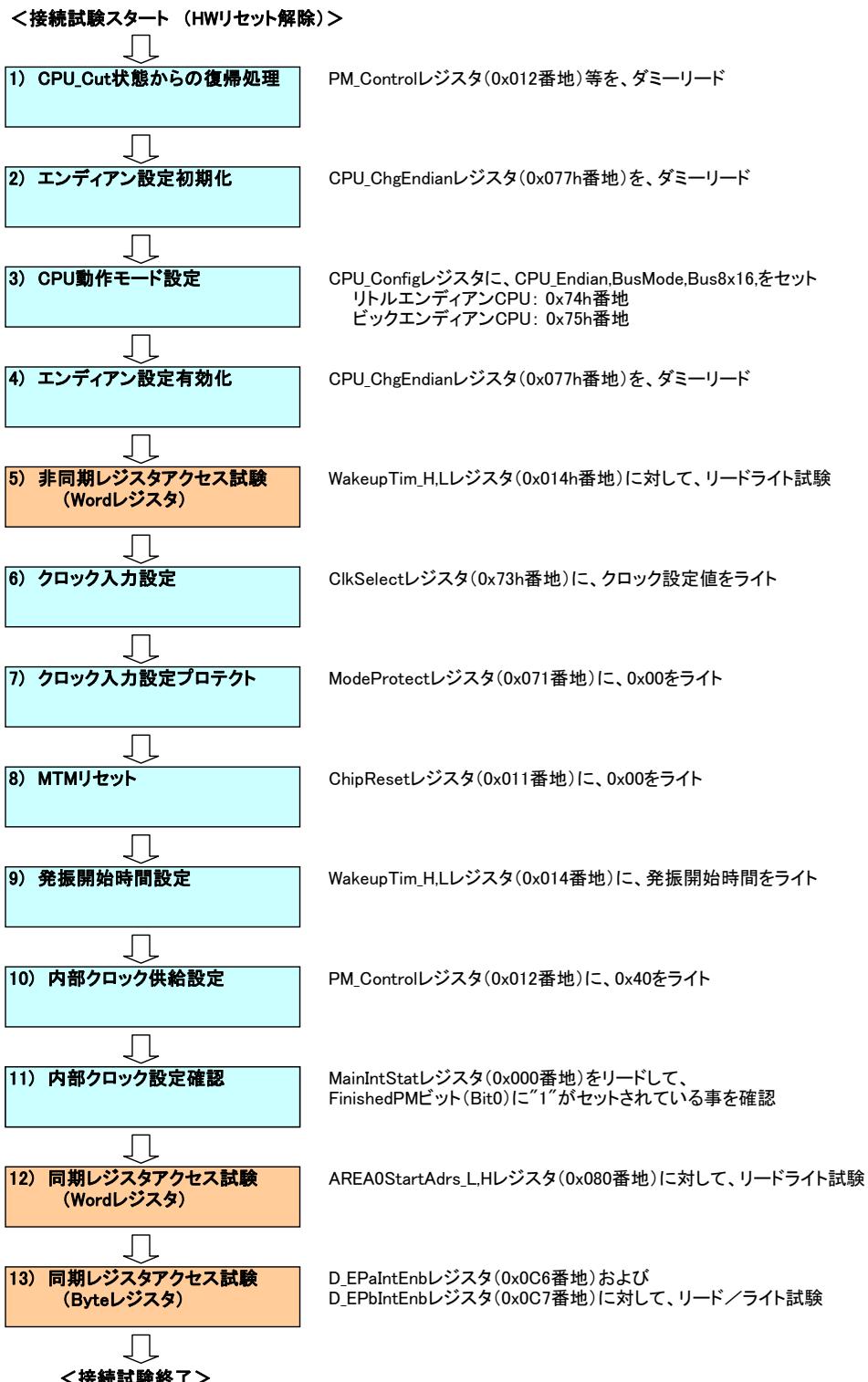

## 4. CPUIF 検証手順

ここでは、S1R72V17 と CPU が適切に接続されているかをチェックする手順を示します。本 LSI を制御する CPU の ICE 等を使用して、以下の手順を実行してください。

図 4-1 CPU-IF 検証手順

### 1) CPU\_Cut 状態からの復帰処理

PM\_Control レジスタ（0x012h 番地）等を、ダミーリードしてください。

本 LSI は、リセット解除後は CPU\_Cut 状態になっています。このダミーリード動作により、CPU\_Cut 状態を終了させ、SLEEP 状態にします。SLEEP 状態では、全ての非同期レジスタに対してリード／ライト動作が可能です。

### 2) エンディアン設定初期化

CPU\_ChgEndian レジスタ（0x077h 番地）を、ダミーリードしてください。

ChipReset レジスタ（0x011h 番地）の AllReset ビットに“1”をセットすることで本 LSI をリセットした場合、リセットされた CPU\_Config レジスタの CPU\_Endian 設定値が有効となるのは、本レジスタをダミーリードした後になります。

### 3) CPU 動作モード設定

CPU\_Config レジスタの、CPU\_Endian、BusMode、Bus8x16 ビットに、ご使用のモード設定値をライトしてください。

リトルエンディアン CPU : 0x074h 番地

ビックエンディアン CPU : 0x075h 番地

このレジスタのアドレス番地は、0x075h 番地に割り当てられています。S1R72V17 は、本設定を行うまでは初期状態であるビックエンディアンで動作しているため、リトルエンディアン CPU にてアクセスする場合は、0x074h 番地にアクセスしてください。

**表 4-1 CPU\_Config レジスタ設定値**

| Bus モード           | CPU エンディアン    | 設定値  |

|-------------------|---------------|------|

| 16bit Strobe mode | Little Endian | 0x04 |

|                   | Big Endian    | 0x00 |

| 16bit BE mode     | Little Endian | 0x06 |

|                   | Big Endian    | 0x02 |

| 8bit mode         | -             | 0x01 |

### 4) エンディアン設定有効化

CPU\_ChgEndian レジスタ（0x077h 番地）を、ダミーリードしてください。

本レジスタをリードすることで、3)で設定した CPU\_Endian ビットの設定が有効になります。

### 5) 非同期レジスタアクセス試験 (Word レジスタ)

WakeupTim\_L,H レジスタ（0x014 番地）に対して、リード／ライト試験を実行してください。

このレジスタは、SLEEP 状態でのリード／ライトが可能で、全ビットが有効です。

このレジスタのリード／ライト試験によって、CPU のデータバスが正確に接続されているか否かを確認できます。もし、このリード／ライト動作が正常に行われない場合には、CPU との物理的な接続を確認してください。

**6) クロック入力設定**

ClkSelect レジスタ(0x073h 番地)に、クロック入力設定値をライトして下さい。

本 LSI で使用するクロック入力方法と、その周波数を設定します。表 4-2 から設定する値を決定してください。

**表 4-2 ClkSelect レジスタ設定値**

| クロック入力方法 |        |           |

|----------|--------|-----------|

| クロック周波数  | 外付け振動子 | 外部クロックソース |

| 12MHz    | 0x00   | 0x80      |

| 24MHz    | 0x01   | 0x81      |

| 48MHz    | 使用不可   | 0x83      |

**7) クロック入力設定のプロテクト**

ModeProtect レジスタ (0x071 番地) に、0x00 をライトして下さい。

このレジスタに 0x56 以外の値を書き込むことで、ClkSelect レジスタの書き込み保護が有効となります。

**8) MTM リセット**

ChipReset レジスタ (0x011 番地) に対して、0x00 をライトして下さい。

bit7 の ResetMTM ビットを“0”にクリアすることで、USB Transceiver Macro のリセットが解除され、本 LSI に内蔵された PLL の発振が可能となります。

**9) 発振開始時間設定**

WakeupTim\_H,L レジスタ (0x014 番地) に、発振開始時間をライトして下さい。

外部クロックソースの場合 :

0x0010 をライトしてください。ただし、外部クロックソースの発振が安定していることを前提とします。

外付け振動子の場合 :

クロック周波数の±10%に入る時間を基準としますが、選択する振動子、回路基板、外付け部品等により値は大きく変化します。ここでは、接続チェックということで、一義に 0x2500 をライトしてください。

**10) 内部クロック供給設定**

PM\_Control レジスタ (0x012 番地) に、0x40 をライトしてください。

bit6 の GoActive ビットに“1”にセットすることで、内部クロックが動作開始 (OSC、PLL が起動) し、内部回路へのクロック供給が開始されます。

### 11) 内部クロック供給確認

MainIntStat レジスタ（0x000 番地）をリードして、FinishedPM ビット（bit0）に“1”がセットされていることを確認してください。

もし、本ビットがセットされない場合には、外部クロックソース選択時は外部クロックからのクロックが供給されていないことが考えられ、外付け振動子選択時は振動子が正確に発振していないことが考えられます。

この時、0x008 番地（MainIntEnb レジスタ）のビット 0（EnFinishedPM ビット）を“1”にセットしてください。このことにより XINT 出力ピンが“Low”にアサートされます。次に同ビットを“0”にクリアすると、XINT 出力ピンが“High”にネゲートされます。この動作を行い、CPU に割り込みが発生するか、確認してください。

MainIntStat レジスタ（0x000 番地）のビット 0（FinishedPM ビット）に“1”をライトすることで、このステータスはクリアされますので、再度 MainIntStat レジスタ（0x000 番地）のビット 0（FinishedPM ビット）をリードし、“0”にクリアされていることを確認してください。

### 12) 同期レジスタアクセス試験（Word レジスタ）

AREA0StartAdrs\_L,H レジスタ（0x080 番地）に対して、リード／ライト試験を実行してください。

これらのレジスタは、ACTIVE 状態でのリード／ライトが可能です。

上位 3 ビット（ビット[15:13]）、下位 2 ビット（ビット[1:0]）はライトできず、常に”0”がリードされます。

### 13) 同期レジスタアクセス試験（Byte レジスタ）

D\_EPAIntEnb レジスタ（0x0C6 番地）及び、D\_EPbIntEnb レジスタ（0x0C7 番地）に対して、リード／ライト試験を実行してください。

これらのレジスタは、ACTIVE 状態でのリード／ライトが可能です。

D\_EPAIntEnb レジスタ、及び D\_EPbIntEnb レジスタは、上位 1 ビット（ビット[7]）がライトできず、常に”0”がリードされます。

< 以上で、接続確認終了です。 >

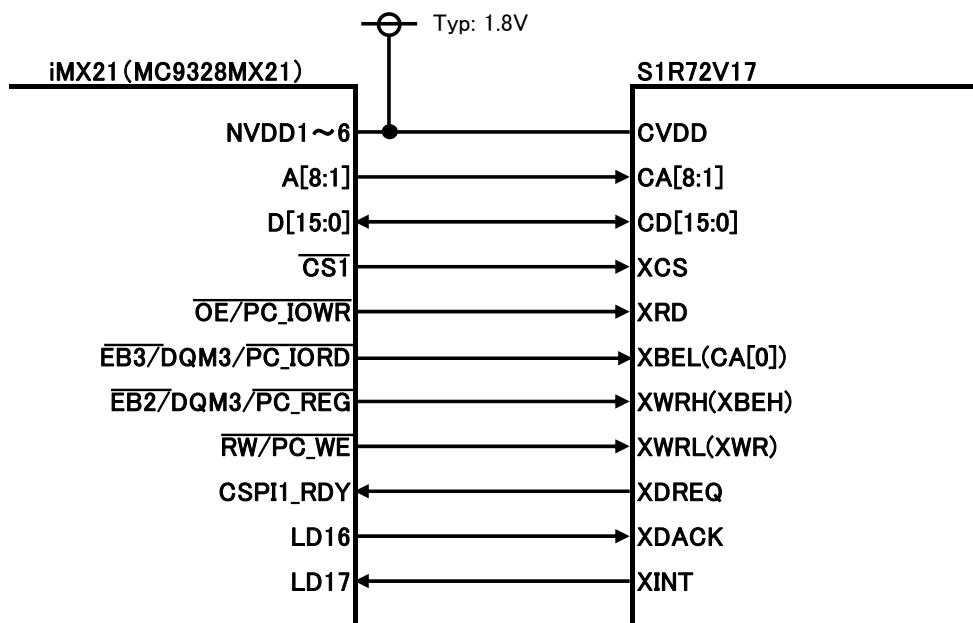

## 5. iMX21(FreeScale 社製)との接続例

### 5.1 接続例

ここでは、iMX21 と S1R72V17 の接続実績のある CPU-IF の接続例を示します。

S1R72V17 のバスモードを 16bit BE mode で接続しています。

図 5-1 iMX21 との接続例

#### 1) CPU-IF 電源電圧

本接続例では、CPU-IF 用電源電圧として、Typ : 1.8V で接続しています。

iMX21 の IO 電源電圧 (NVDD1~6) : 1.7V~3.3V

S1R72V17 の CPU-IF 電源電圧 (CVDD) : 1.65V~3.6V

#### 2) iMX21 の兼用端子設定

本接続例では、iMX21 の兼用端子を、以下のように設定して使用しています。

表 5-1 iMX21 兼用端子設定

| iMX21端子名         | iMX21端子機能            |

|------------------|----------------------|

| NVDD1~NVDD6      | NVDD1~NVDD6          |

| A[8:1]           | A[8:1]               |

| D[15:0]          | D[15:0]              |

| CS1              | CS1                  |

| OE/PC_IOWR       | OE                   |

| EB3/DQM3/PC_IORD | EB3                  |

| EB2/DQM2/PC_REG  | EB2                  |

| RW/PC_WE         | RW                   |

| CSPI1_RDY        | EXT_DMAREQ           |

| LD16             | EXT_DMAGRANT         |

| LD17             | PA23(GPIOをXINTとして使用) |

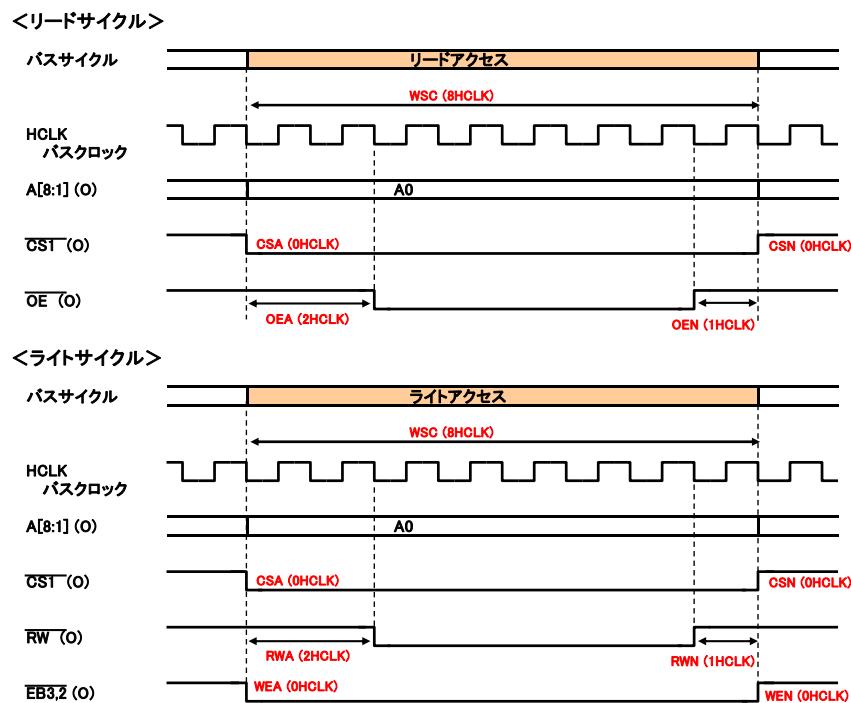

## 5.2 iMX21 のバスサイクル設定例

- **iMX21 クロック設定**

本接続例では、iMX21 内のクロック設定値を下記のようにしています。

システムクロック : 264MHz

CPU-IF バスクロック (HCLK) : 88MHz (システムクロックの 3 分周)

- **バスサイクル設定**

| CS1ULレジスタ(0xDF001008番地)        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 設定値: 0x0402_0700 |     |     |     |     |     |      |      |  |  |  |  |  |  |  |  |  |

|--------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------------------|-----|-----|-----|-----|-----|------|------|--|--|--|--|--|--|--|--|--|

| 31                             | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | SP               | WP  | DCT | RWA | PSZ | PME | SYNC | RWN  |  |  |  |  |  |  |  |  |  |

| 15                             | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | CNC              | WSC | EW  | WWS | EDC |     |      |      |  |  |  |  |  |  |  |  |  |

| <b>CS1LLレジスタ(0xDF00100C番地)</b> |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                  |     |     |     |     |     |      |      |  |  |  |  |  |  |  |  |  |

| 31                             | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | OEA              | OEN | WEA | WEN |     |     |      |      |  |  |  |  |  |  |  |  |  |

| 15                             | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | CSA              | EBC | DSZ | CSN | PSR | CRE | WRAP | CSEN |  |  |  |  |  |  |  |  |  |

| 設定値説明 |           |                            |

|-------|-----------|----------------------------|

| レジスタ  | 設定値       | 説明                         |

| RWA   | 4'b0100   | RW出力アサートタイミング。(2HCLK)      |

| SYNC  | 1'b0      | 同期転送モード。(無効)               |

| RWN   | 4'b0010   | RW出力ネゲートタイミング。(1HCLK)      |

| WSC   | 6'b000011 | アクセスサイクル。(8HCLK)           |

| WWS   | 3'b000    | ライト時のWaitサイクル。(0HCLK)      |

| OEA   | 4'b0100   | OE出力アサートタイミング。(2HCLK)      |

| OEN   | 4'b0010   | OE出力ネゲートタイミング。(1HCLK)      |

| WEA   | 4'b0000   | EBx出力アサートタイミング。(0HCLK)     |

| WEN   | 4'b0000   | EBx出力ネゲートタイミング。(0HCLK)     |

| CSA   | 4'b0000   | CS1出力アサートタイミング。(0HCLK)     |

| EBC   | 1'b1      | リード時のEB3.2出力モード。(無効)       |

| DSZ   | 3'b101    | データバスサイズ。(16bit D[15:0]使用) |

| CSN   | 4'b0000   | CS1出力アサートタイミング。(0HCLK)     |

| CSEN  | 1'b1      | CS1イネーブル。(有効)              |

図 5-2 バスサイクル設定レジスタ

- バスサイクル波形

図 5-3 iMX21 バスサイクル波形

### 5.3 S1R72V17 のACスペックとiMX21 バスサイクルの確認

下記に、S1R72V17 の AC スペック規定値と iMX21 のバスサイクル設定値の比較表を記載します。

S1R72V17 の AC スペックの詳細に関しては、S1R72V17 テクニカルマニュアルの CPU/DMA IF アクセスタイミング（8.4.3.1 章 基本サイクル）を参照してください。

表 5-2 AC スペック比較表

| 記号   | 項目                        | S1R72V17 CPU/DMA IF アクセスタイミング |     |      |      | iMX21 設定値              |  |

|------|---------------------------|-------------------------------|-----|------|------|------------------------|--|

|      |                           | min                           | max | サイクル | unit | iMX21 設定レジスタ           |  |

| tcas | アドレスセットアップ時間              | 6                             | -   | 2    | HCLK | RWA, OEA               |  |

| tcah | アドレスホールド時間(ストローブネゲーションから) | 6                             | -   | 1    | HCLK | RWN, OEN               |  |

| tsah | アドレスホールド時間(ストローブアサーションから) | 55                            | -   | 6    | HCLK | WSC-(RWA, OEA)         |  |

| tccs | XCSセットアップ時間               | 6                             | -   | 2    | HCLK | RWA, OEA               |  |

| tcch | XCSホールド時間                 | 6                             | -   | 1    | HCLK | RWN, OEN               |  |

| trcy | リードサイクル                   | 80                            | -   | 8    | HCLK | WSC                    |  |

| tras | リードストローブアサート時間            | 40                            | -   | 5    | HCLK | WSC-(OEA+OEN)          |  |

| trng | リードストローブネゲート時間            | 25                            | -   | 3    | HCLK | OEA+OEN                |  |

| trbd | リードデータ出力開始時間              | 1                             | -   | —    |      |                        |  |

| trdf | リードデータ確定時間                | -                             | 35  | 5    | HCLK | WSC-(OEA+OEN)          |  |

| trdh | リードデータホールド時間              | 3                             | -   | —    |      |                        |  |

| trbh | リードデータ出力遅延時間              | -                             | 9   | —    |      |                        |  |

| twcy | ライトサイクル                   | 80                            | -   | 8    | HCLK | WSC                    |  |

| twas | ライトストローブアサート時間            | 40                            | -   | 5    | HCLK | WSC-(RWA+RWN)          |  |

| twng | ライトストローブネゲート時間            | 25                            | -   | 3    | HCLK | RWA+RWN                |  |

| twbs | ライトバイトイネーブルセットアップ時間       | 6                             | -   | 2    | HCLK | RWA                    |  |

| twbh | ライトバイトイネーブルホールド時間         | 6                             | -   | 1    | HCLK | RWN                    |  |

| twds | ライトデータセットアップ時間            | 0                             | -   | 1.5  | HCLK | RWA - 0.5HCLK(データ出力開始) |  |

| twdh | ライトデータホールド時間              | 0                             | -   | 1    | HCLK | RWN                    |  |

| tdrn | XDREQネゲート遅延時間             | -                             | 35  | —    |      |                        |  |

| tdaa | XDREQセットアップ時間             | 6                             | -   | —    |      |                        |  |

| tdan | XDREQホールド時間               | 6                             | -   | —    |      |                        |  |

( C<sub>L</sub>=30pf )

1HCLK=11.36ns(88MHz)

## 改訂履歴

| 年月日        | Rev. | 頁  | 種別 | 改訂内容 |  |

|------------|------|----|----|------|--|

|            |      |    |    | 内 容  |  |

| 2008/06/06 | 1.0  | 全頁 | 新規 | 新規制定 |  |

|            |      |    |    |      |  |

|            |      |    |    |      |  |

## **セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 411528500

2008 年 6 月 作成