# S1R72V18

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

---

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## 適用範囲

本ドキュメントは、USB2.0 デバイス・ホストコントローラ LSI 「S1R72V18」 に適用されます。

# 目次

|                                           |          |

|-------------------------------------------|----------|

| <b>1. 機能説明 .....</b>                      | <b>1</b> |

| 1.1    USBポート .....                       | 1        |

| 1.2    USBデバイス／ホスト選択 .....                | 2        |

| 1.2.1    USBデバイス／ホスト機能選択方法 .....          | 2        |

| 1.2.2    USBポート状態変化検出ステータス .....          | 2        |

| 1.2.2.1    USBポート状態変化検出ステータスの使用例 .....    | 2        |

| 1.2.2.1.1    デバイスポート変化ステータス .....         | 2        |

| 1.2.2.1.2    ホストポート変化ステータス .....          | 3        |

| 1.2.2.2    信号ライン変化ステータスの使用方法 .....        | 3        |

| 1.3    USBデバイス制御 .....                    | 5        |

| 1.3.1    エンドポイント .....                    | 5        |

| 1.3.2    トランザクション .....                   | 7        |

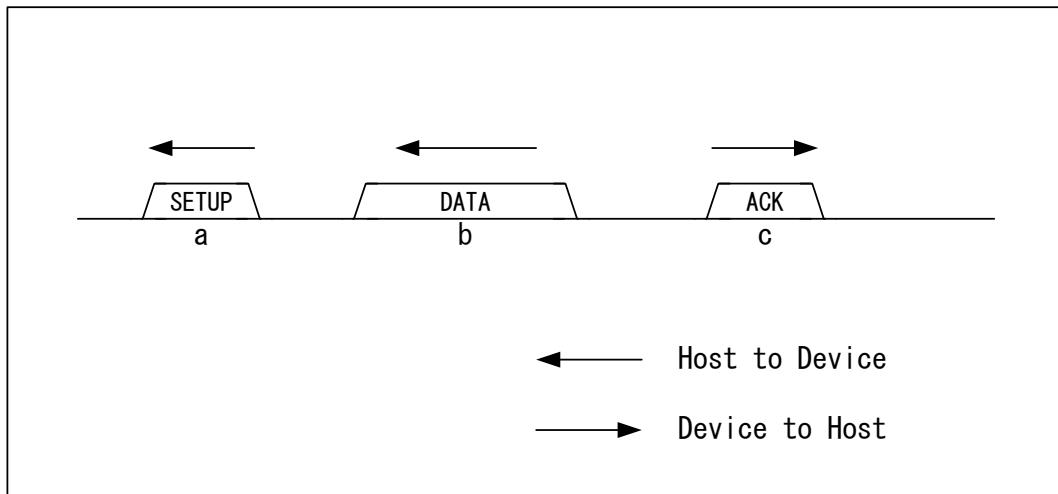

| 1.3.2.1    SETUPトランザクション .....            | 9        |

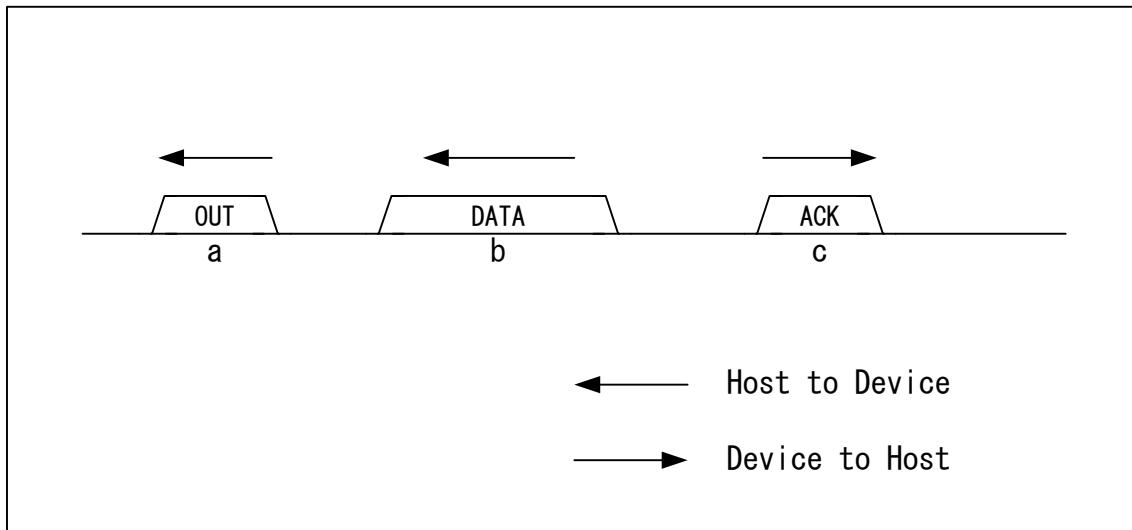

| 1.3.2.2    バルク／インタラプトOUTトランザクション .....    | 10       |

| 1.3.2.3    アイソクロナスOUTトランザクション .....       | 11       |

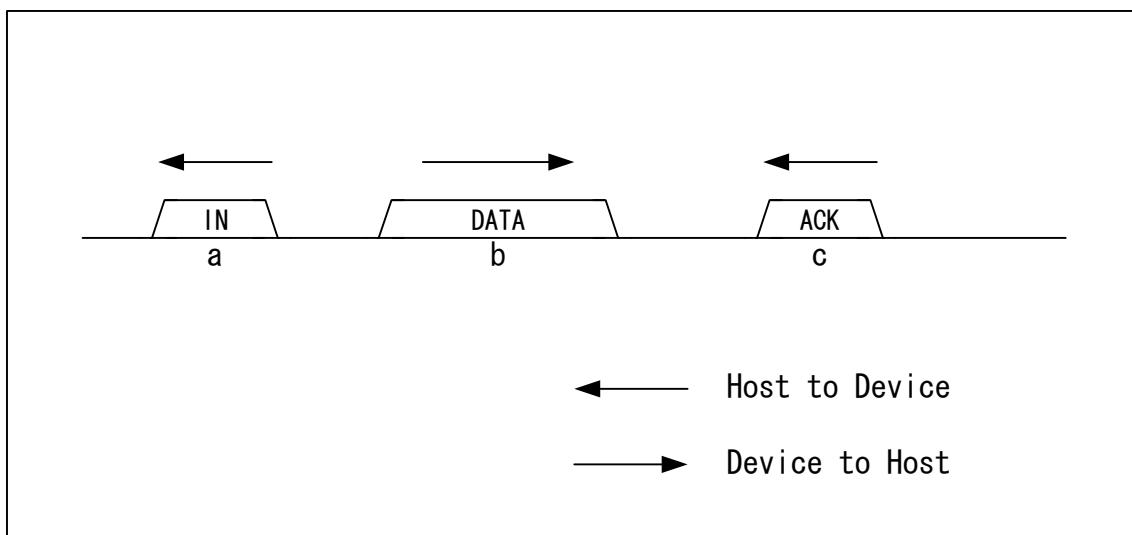

| 1.3.2.4    バルク／インタラプトINトランザクション .....     | 11       |

| 1.3.2.5    アイソクロナスINトランザクション .....        | 12       |

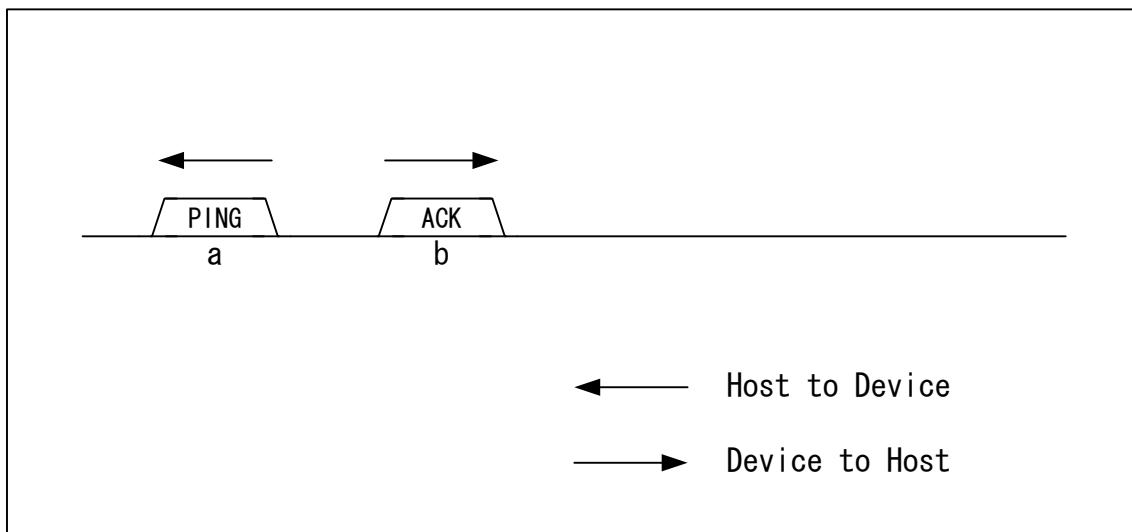

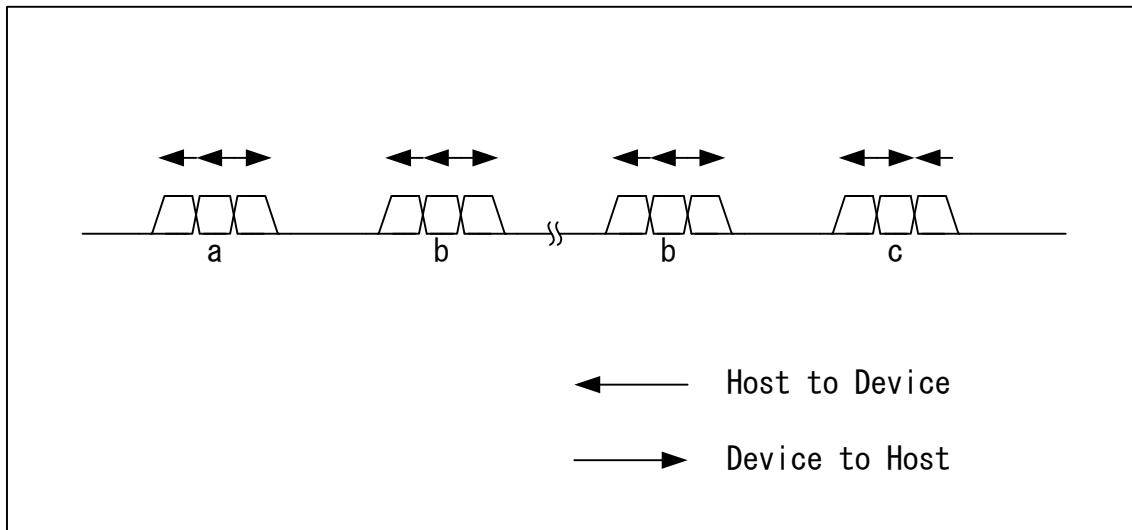

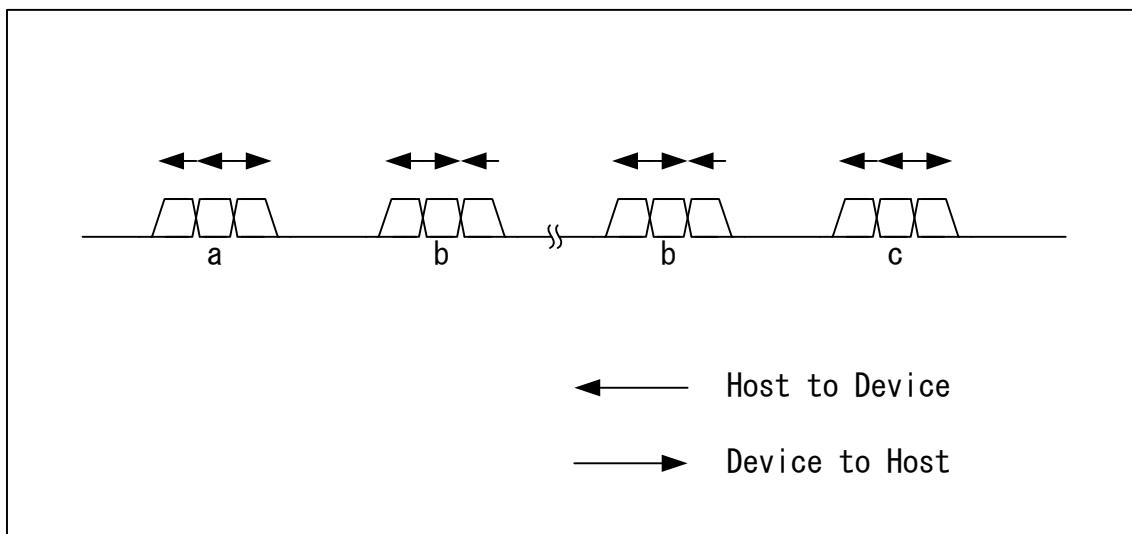

| 1.3.2.6    PINGトランザクション .....             | 13       |

| 1.3.3    コントロール転送 .....                   | 13       |

| 1.3.3.1    セットアップステージ .....               | 15       |

| 1.3.3.2    データステージ／ステータスステージ .....        | 15       |

| 1.3.3.3    自動アドレス設定機能 .....               | 15       |

| 1.3.3.4    デスクリプタ返信機能 .....               | 15       |

| 1.3.4    バルク転送／インタラプト転送／アイソクロナス転送 .....   | 16       |

| 1.3.5    データフロー .....                     | 16       |

| 1.3.5.1    OUT転送 .....                    | 16       |

| 1.3.5.2    IN転送 .....                     | 17       |

| 1.3.6    バルクオンリーサポート .....                | 17       |

| 1.3.6.1    CBWサポート .....                  | 17       |

| 1.3.6.2    CSWサポート .....                  | 18       |

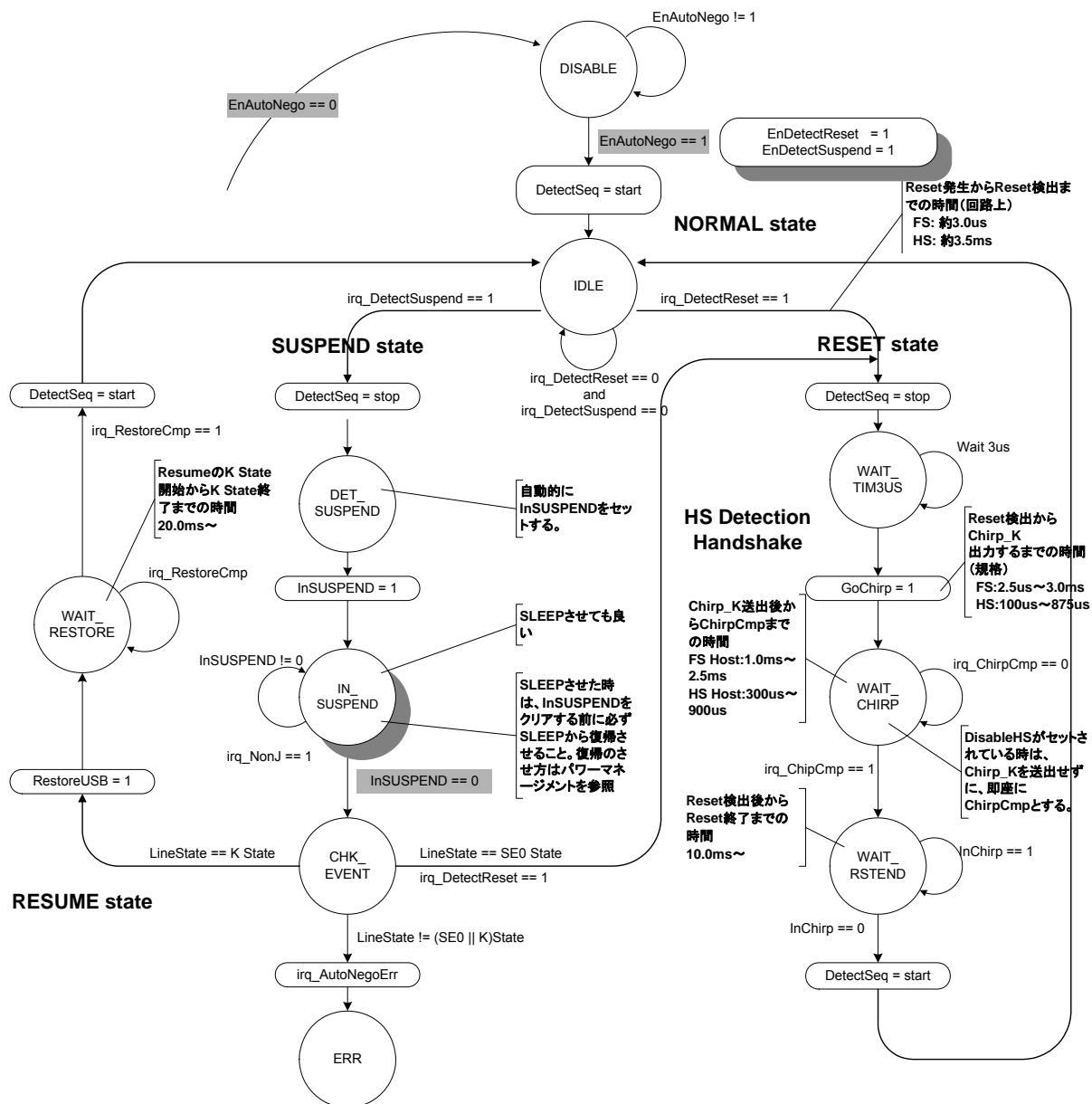

| 1.3.7    ケーブルネゴシエーション機能(オート・ネゴシエータ) ..... | 19       |

| 1.3.7.1    オート・ネゴシエータ .....               | 20       |

| 1.3.7.1.1    DISABLE .....                | 20       |

| 1.3.7.1.2    IDLE .....                   | 20       |

| 1.3.7.1.3    WAIT_TIM3US .....            | 20       |

|             |                                  |    |

|-------------|----------------------------------|----|

| 1.3.7.1.4   | WAIT_CHIRP .....                 | 20 |

| 1.3.7.1.5   | WAIT_RSTEND .....                | 21 |

| 1.3.7.1.6   | DET_SUSPEND .....                | 21 |

| 1.3.7.1.7   | IN_SUSPEND .....                 | 21 |

| 1.3.7.1.8   | CHK_EVENT .....                  | 21 |

| 1.3.7.1.9   | WAIT_RESTORE .....               | 21 |

| 1.3.7.1.10  | ERR .....                        | 22 |

| 1.3.7.2     | 各バスイベント発生時の動作 .....              | 22 |

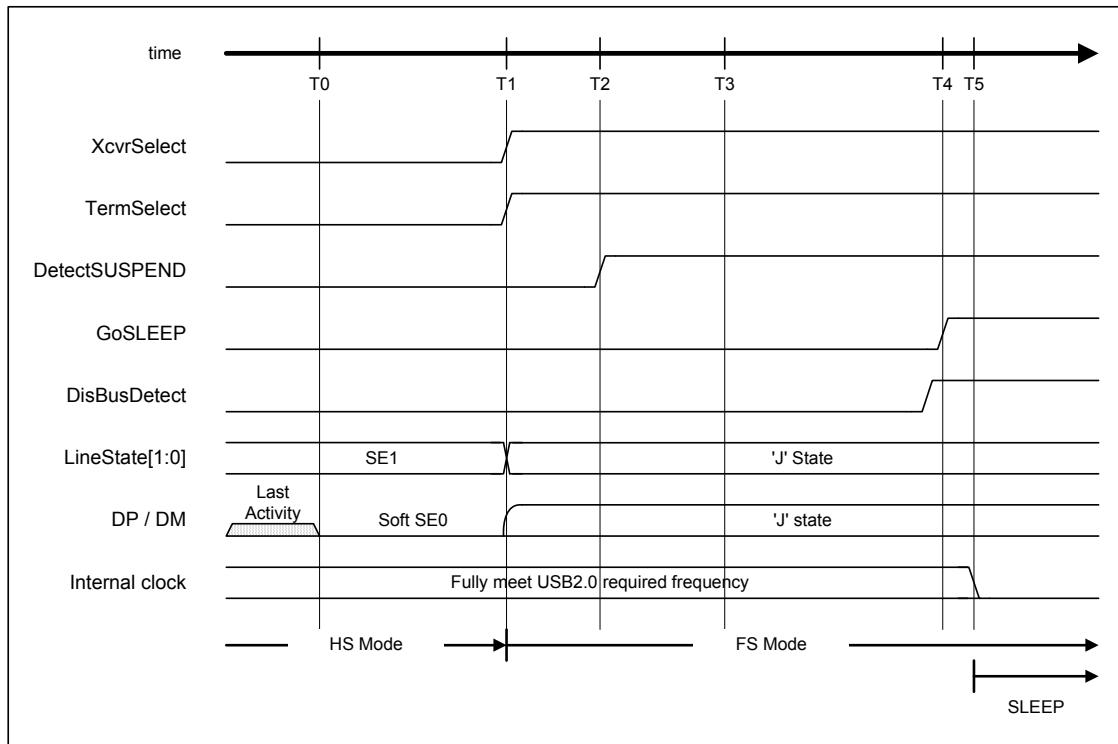

| 1.3.7.2.1   | HSモードにおけるサスPEND検出 .....          | 22 |

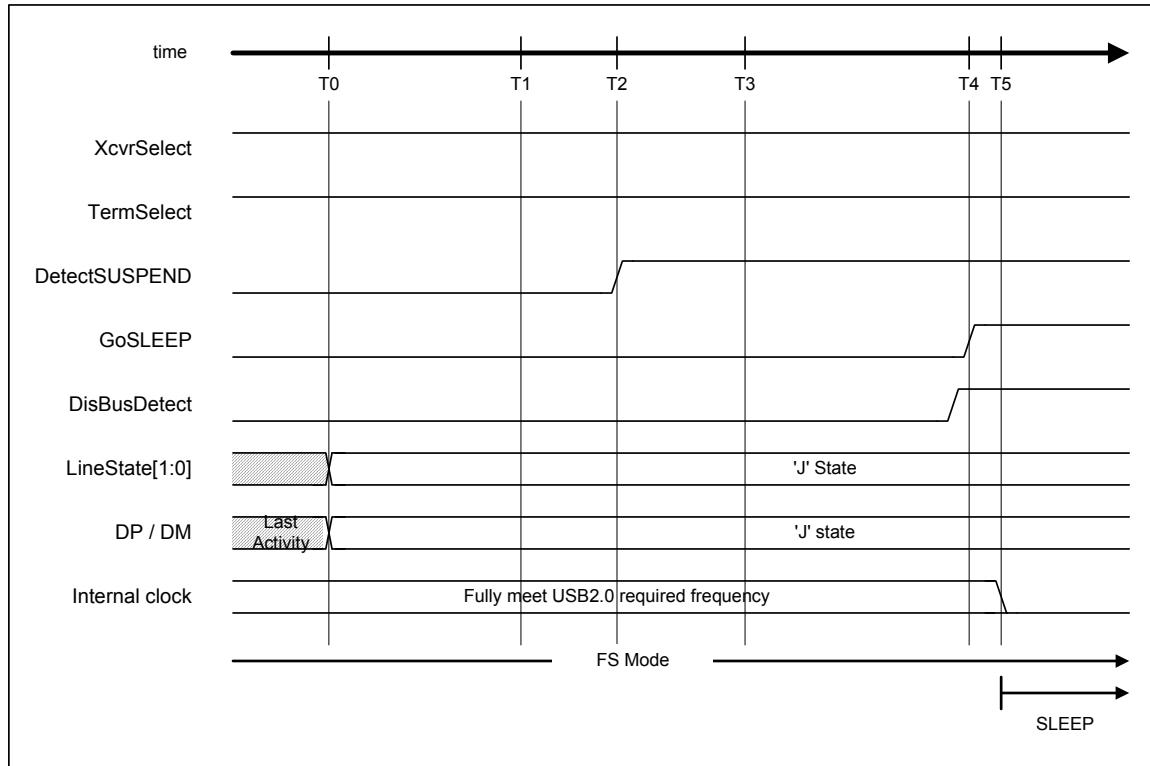

| 1.3.7.2.2   | FSモードにおけるサスPEND検出 .....          | 23 |

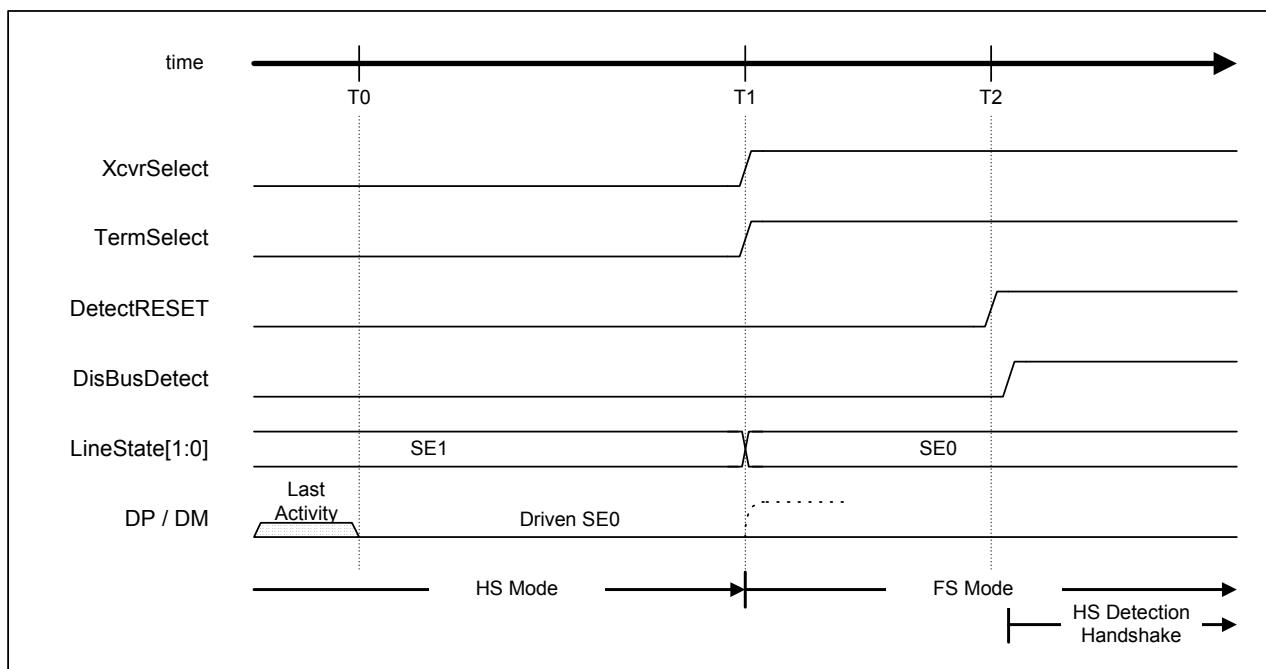

| 1.3.7.2.3   | HSモードにおけるリセット検出 .....            | 25 |

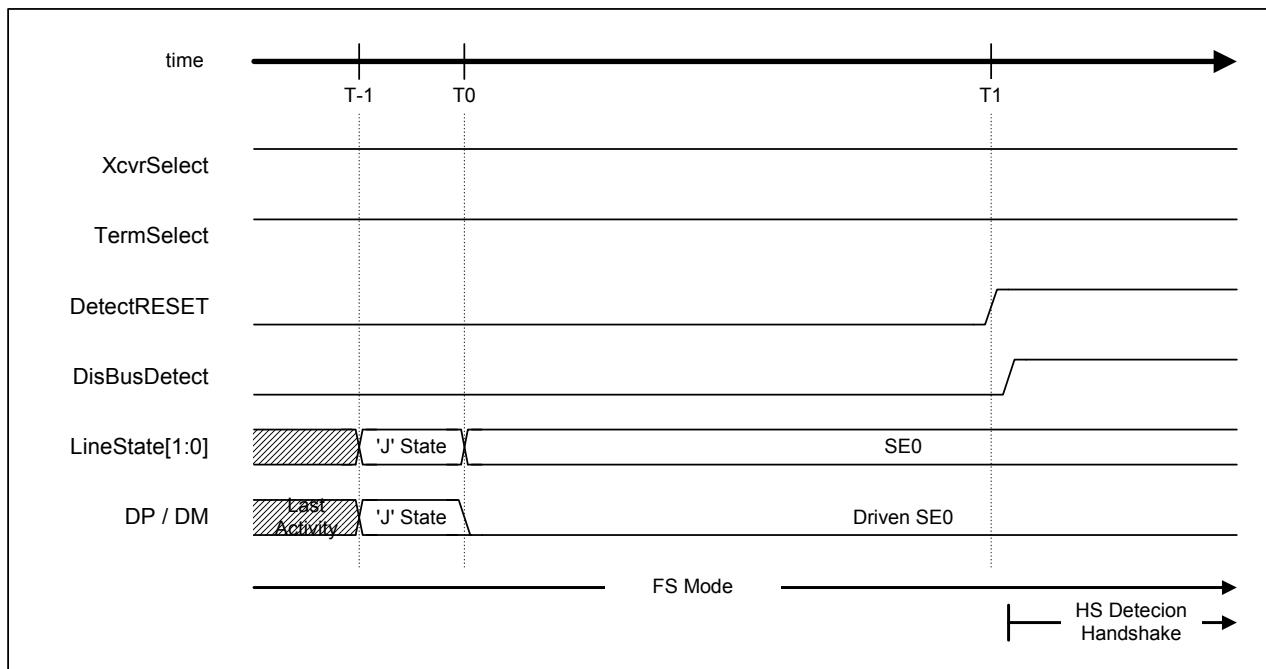

| 1.3.7.2.4   | FSモードにおけるリセット検出 .....            | 26 |

| 1.3.7.2.5   | HS Detection Handshake .....     | 27 |

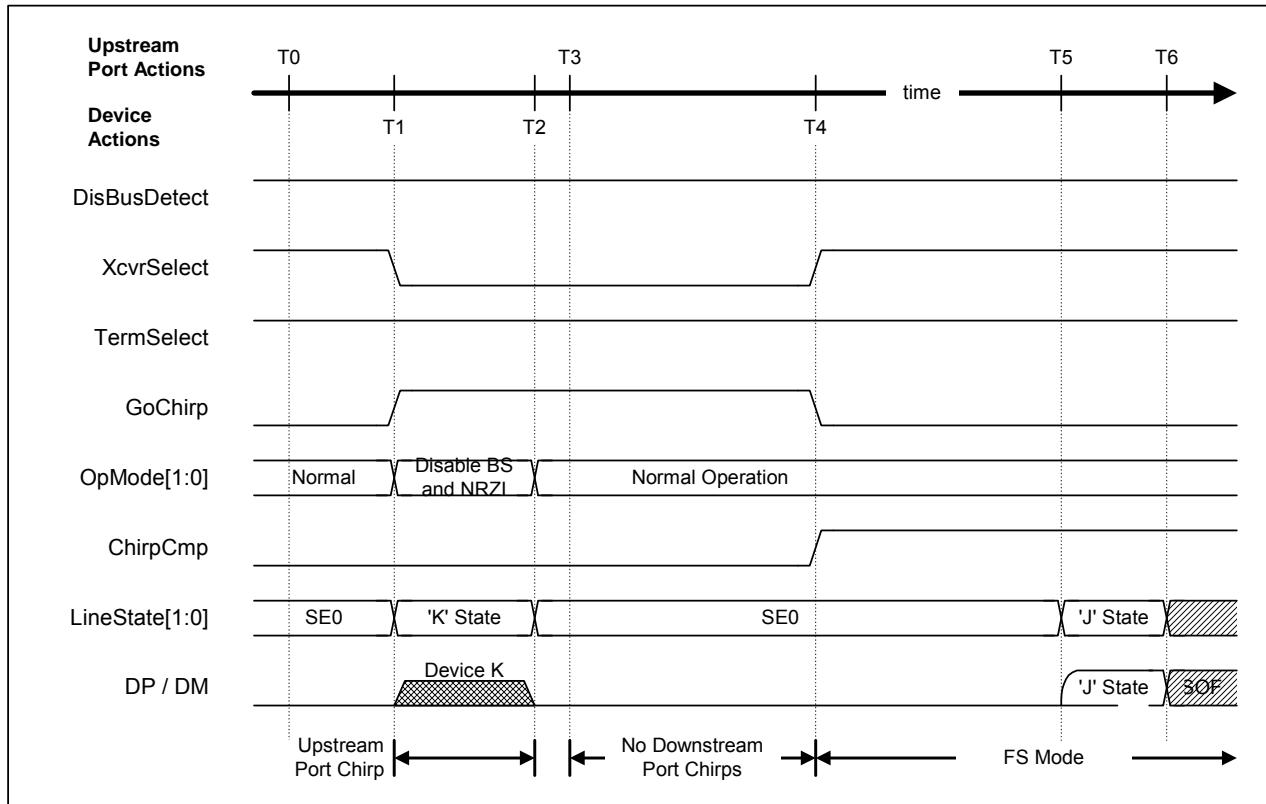

| 1.3.7.2.5.1 | FSのホストダウンストリームポートに繋がれた場合 .....   | 27 |

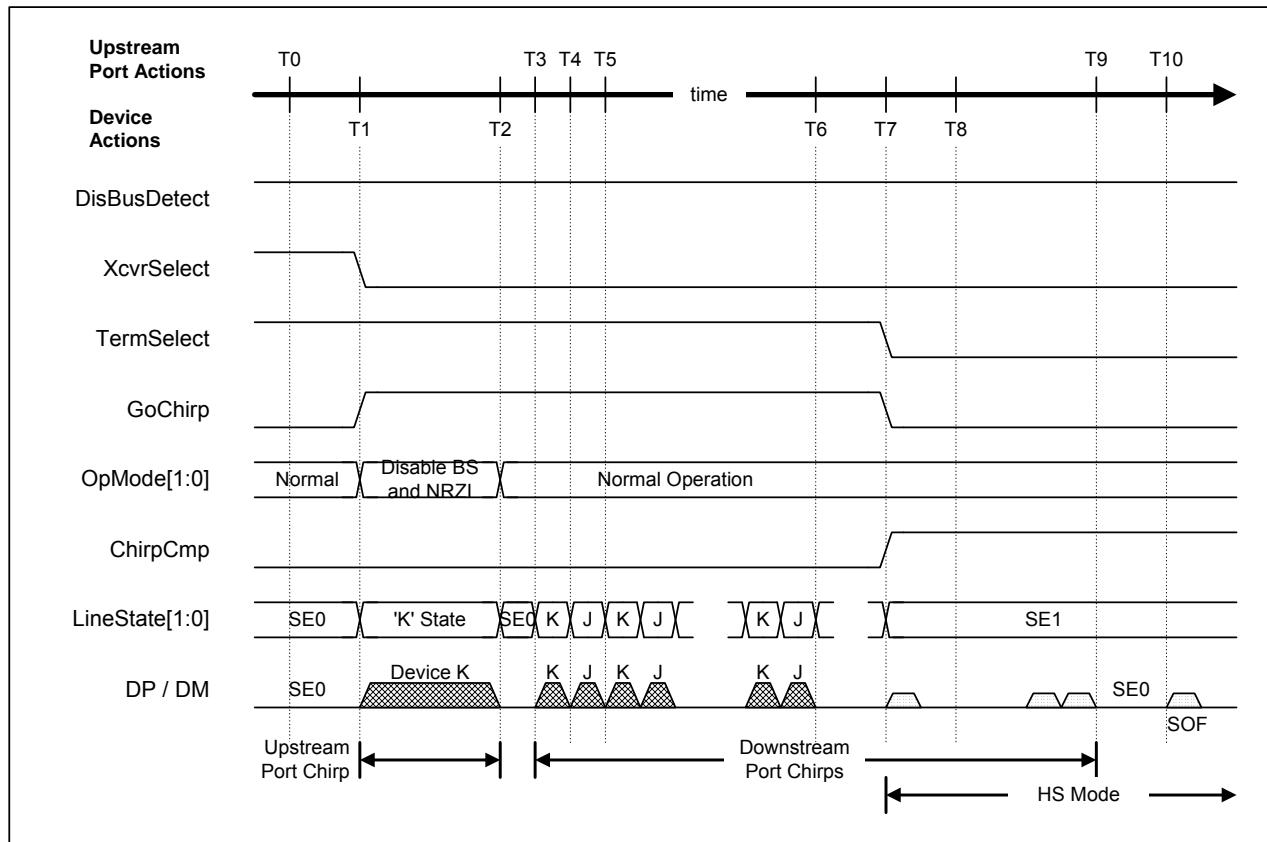

| 1.3.7.2.5.2 | HSのホストダウンストリームポートに繋がれた場合 .....   | 29 |

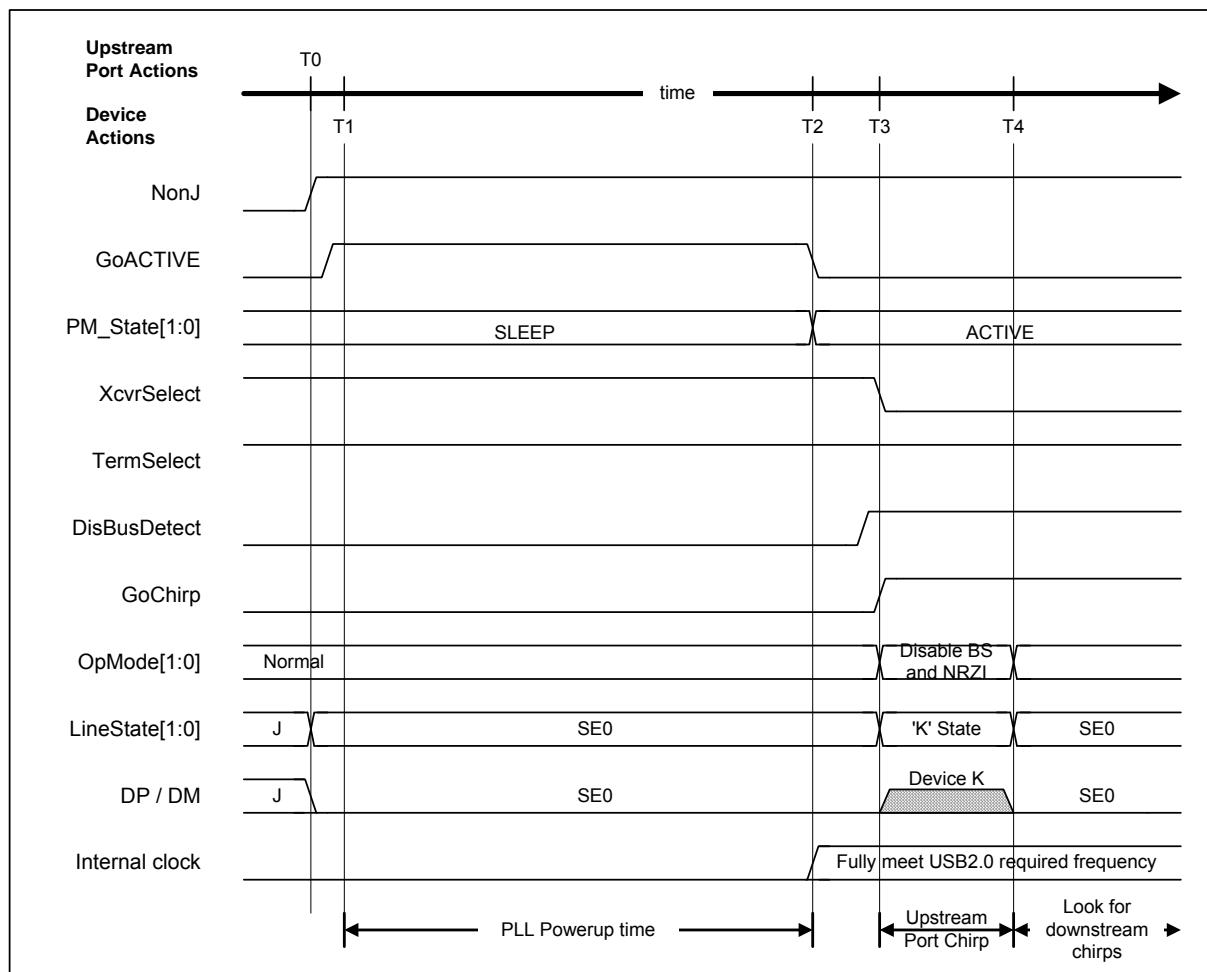

| 1.3.7.2.5.3 | スリープ中にリセットされた場合 .....            | 31 |

| 1.3.7.2.6   | レジュームの発行 .....                   | 32 |

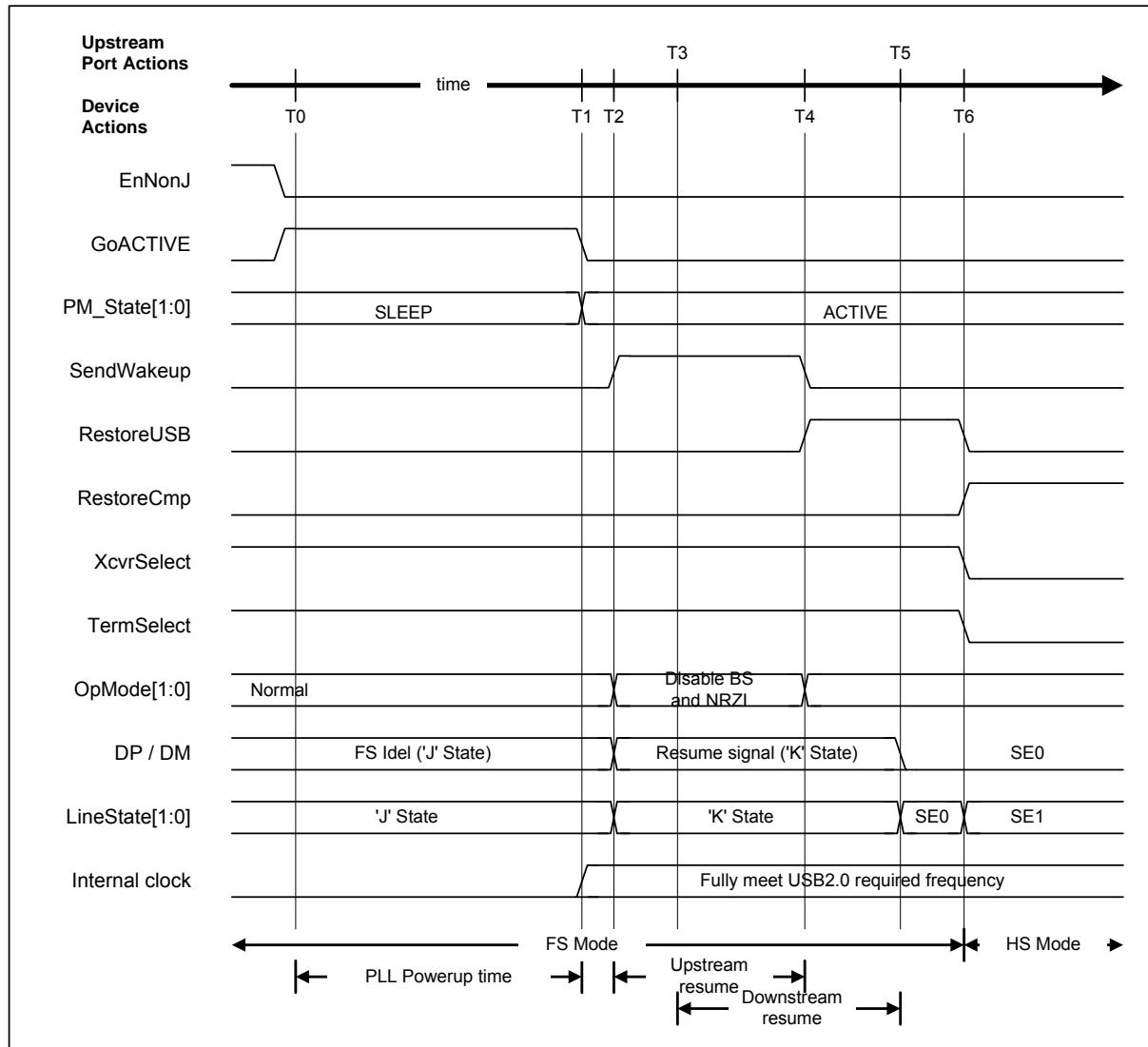

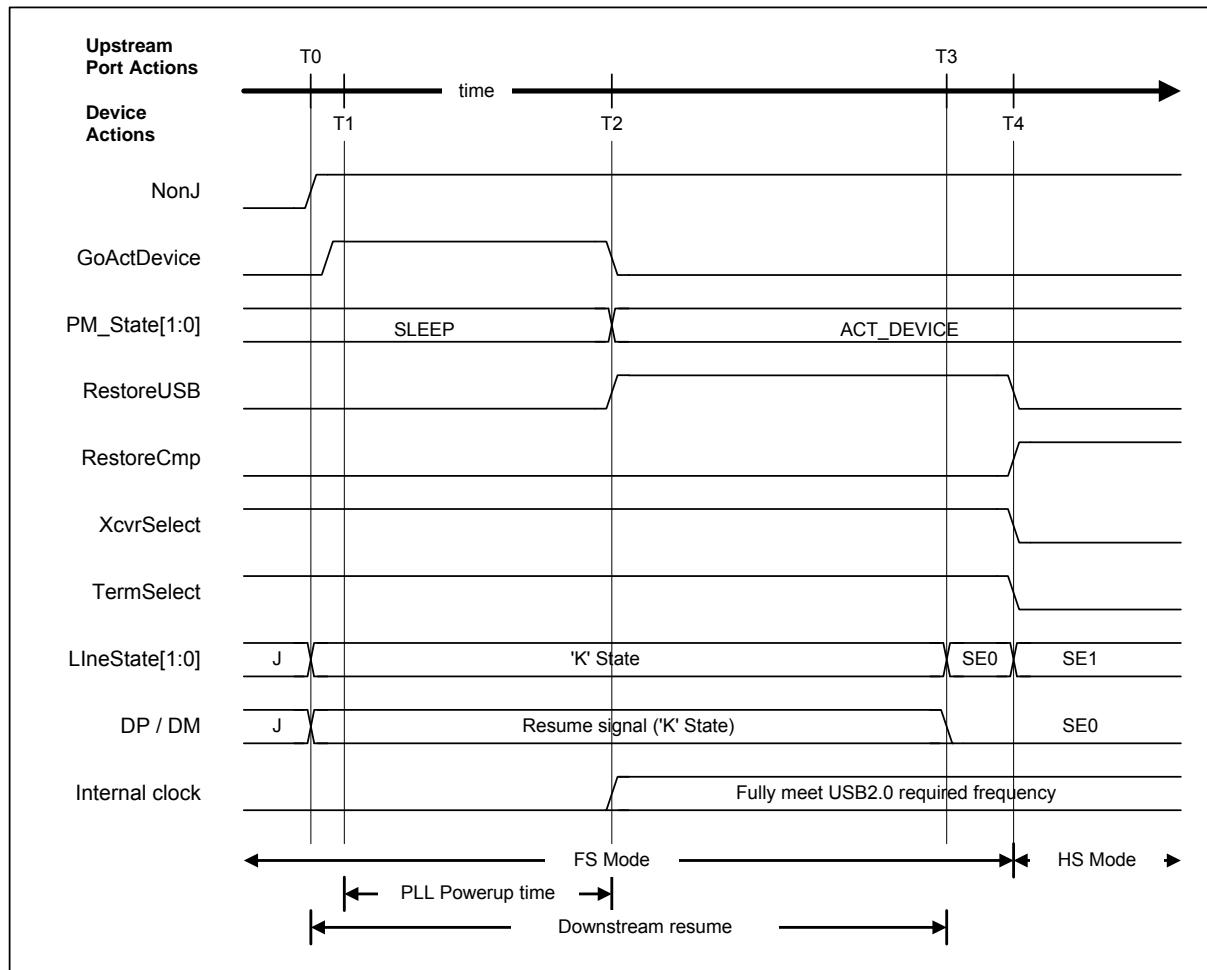

| 1.3.7.2.7   | レジュームの検出 .....                   | 34 |

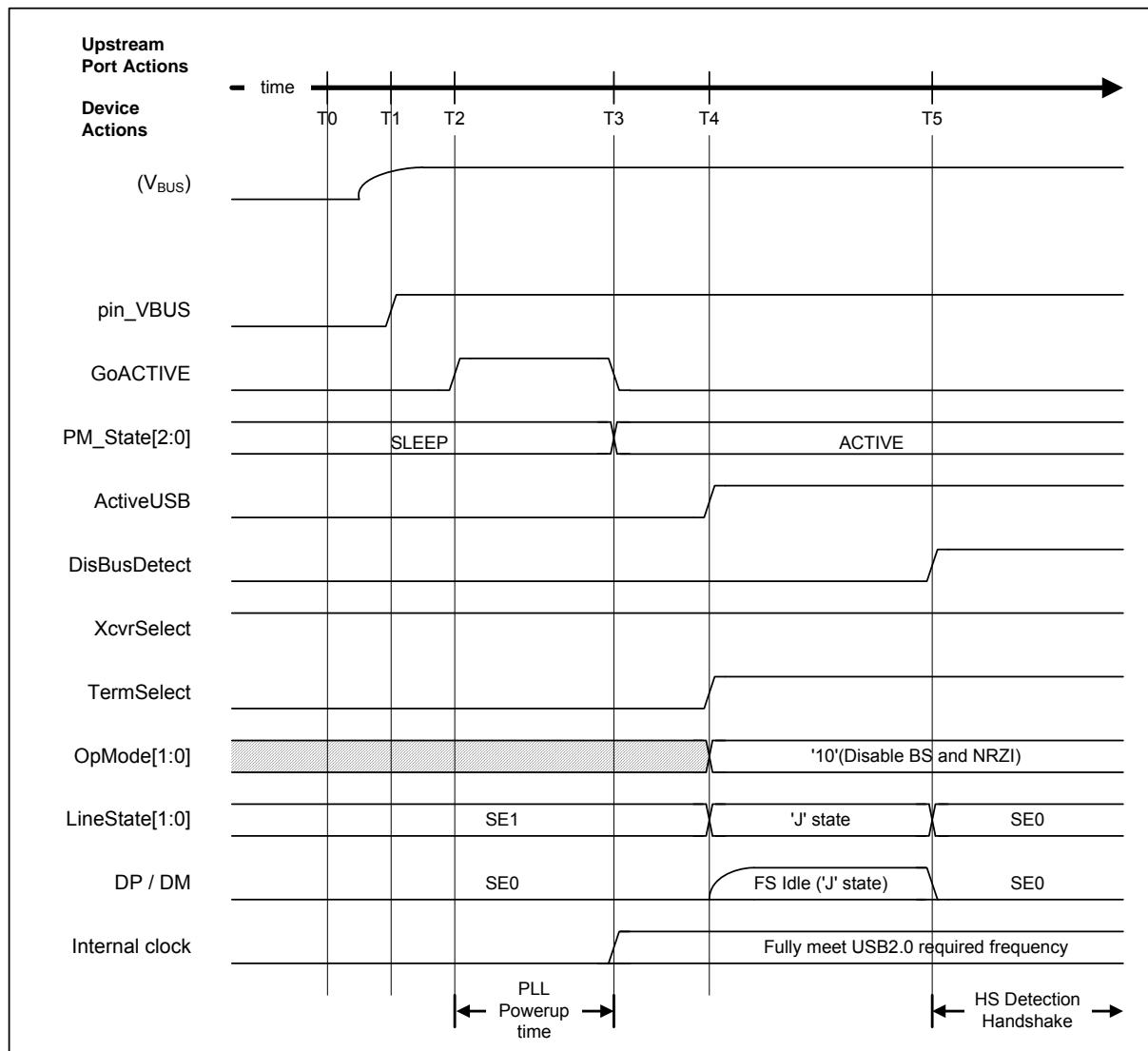

| 1.3.7.2.8   | ケーブル挿入 .....                     | 36 |

| 1.4         | USBホスト制御 .....                   | 38 |

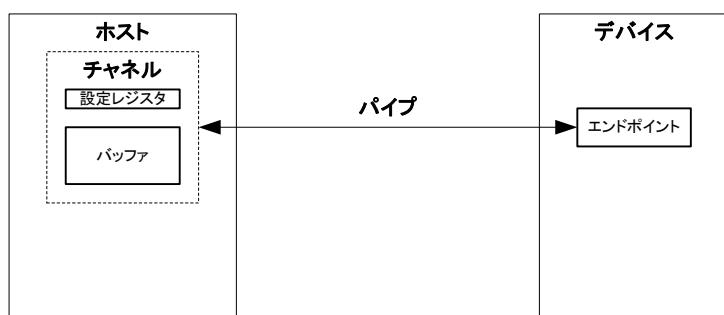

| 1.4.1       | チャネル .....                       | 38 |

| 1.4.1.1     | チャネル概要 .....                     | 38 |

| 1.4.1.2     | コントロール専用チャネル .....               | 40 |

| 1.4.1.3     | 汎用チャネル .....                     | 41 |

| 1.4.1.4     | チャネル使用例 .....                    | 42 |

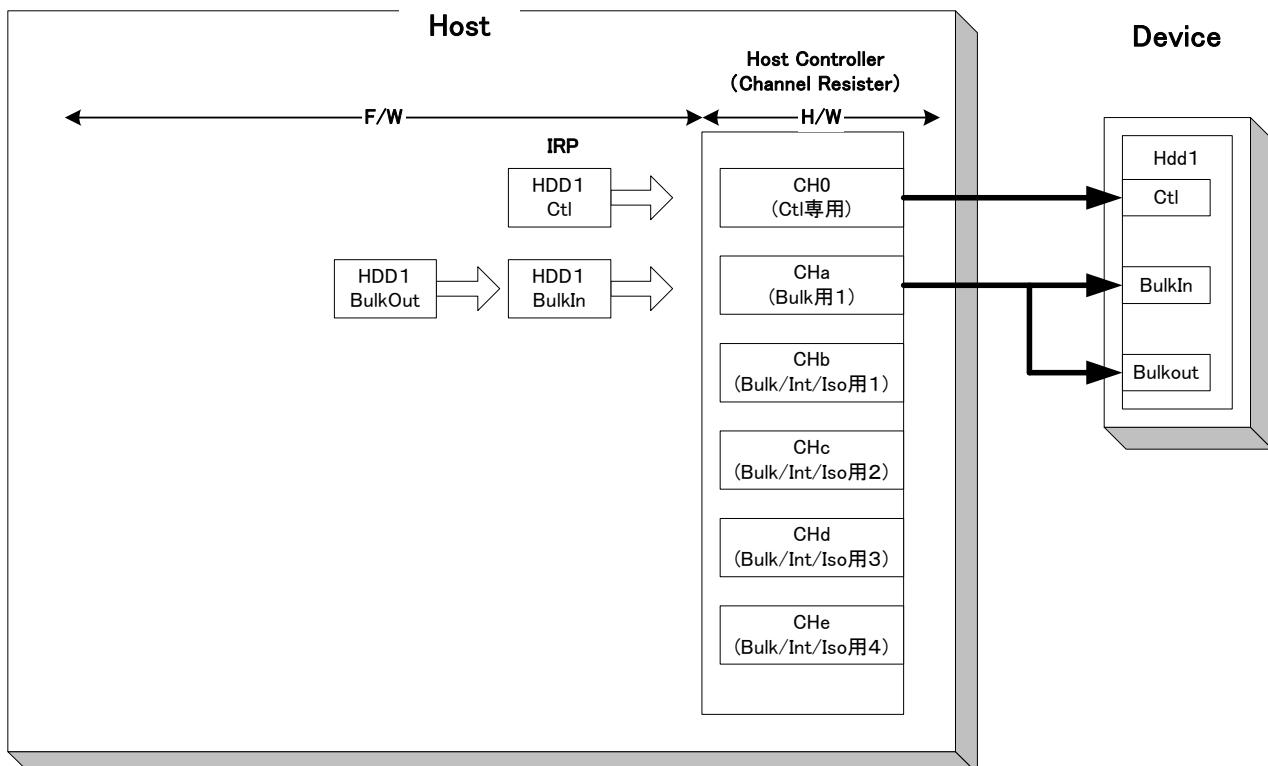

| 1.4.1.4.1   | ストレージデバイスを1台接続した場合 .....         | 42 |

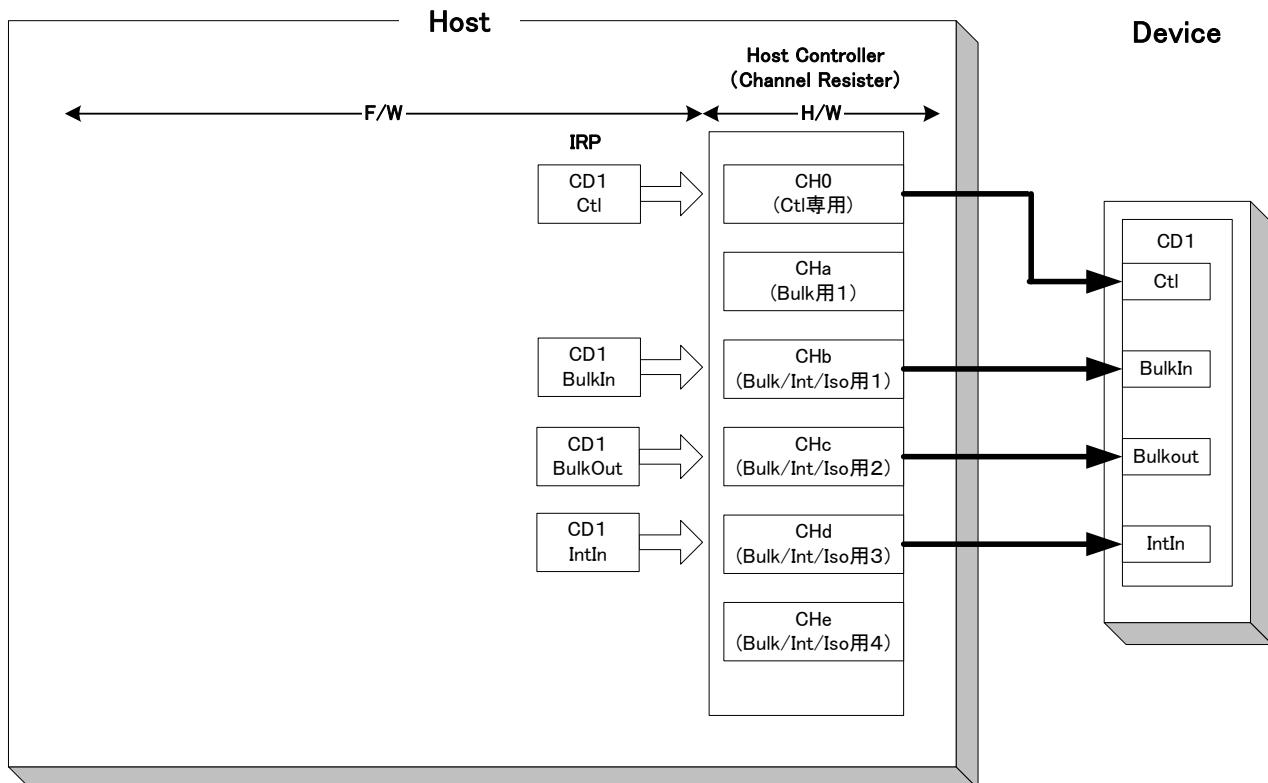

| 1.4.1.4.2   | コミュニケーションデバイスを1台接続した場合 .....     | 43 |

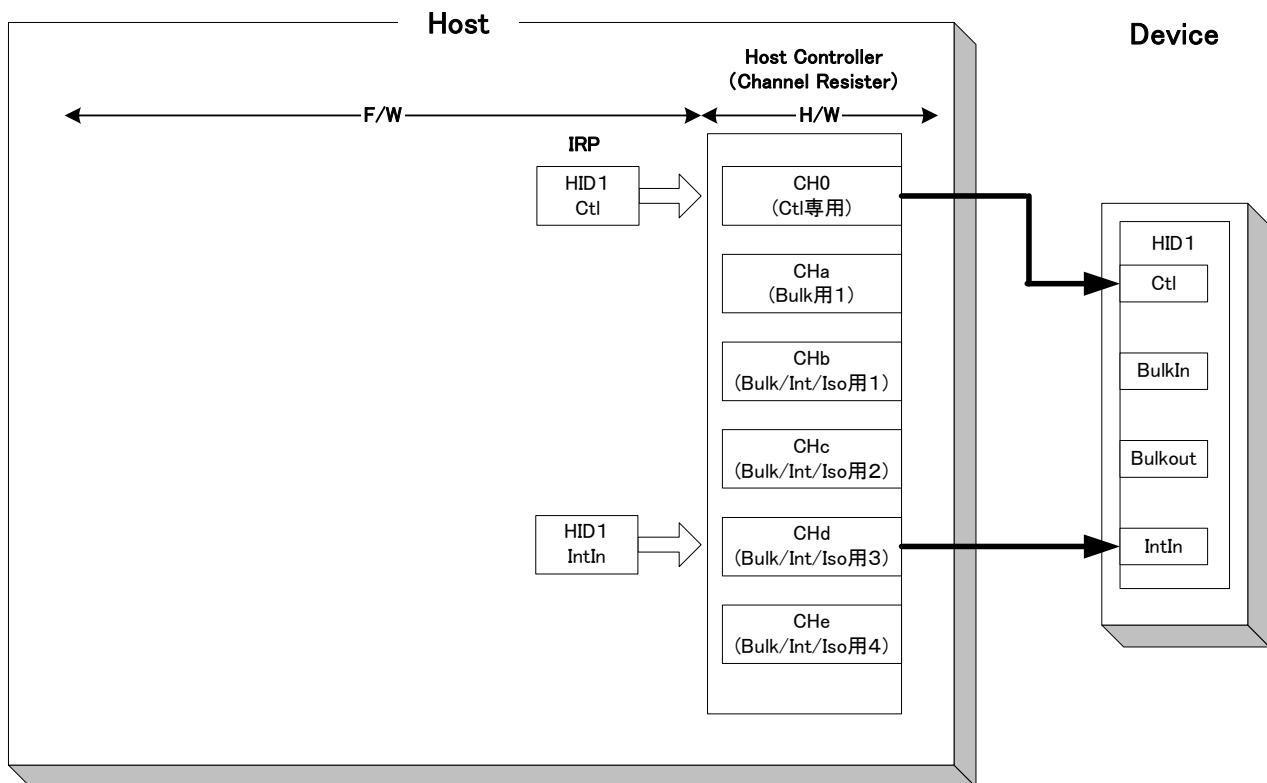

| 1.4.1.4.3   | ヒューマンインターフェイスデバイスを1台接続した場合 ..... | 44 |

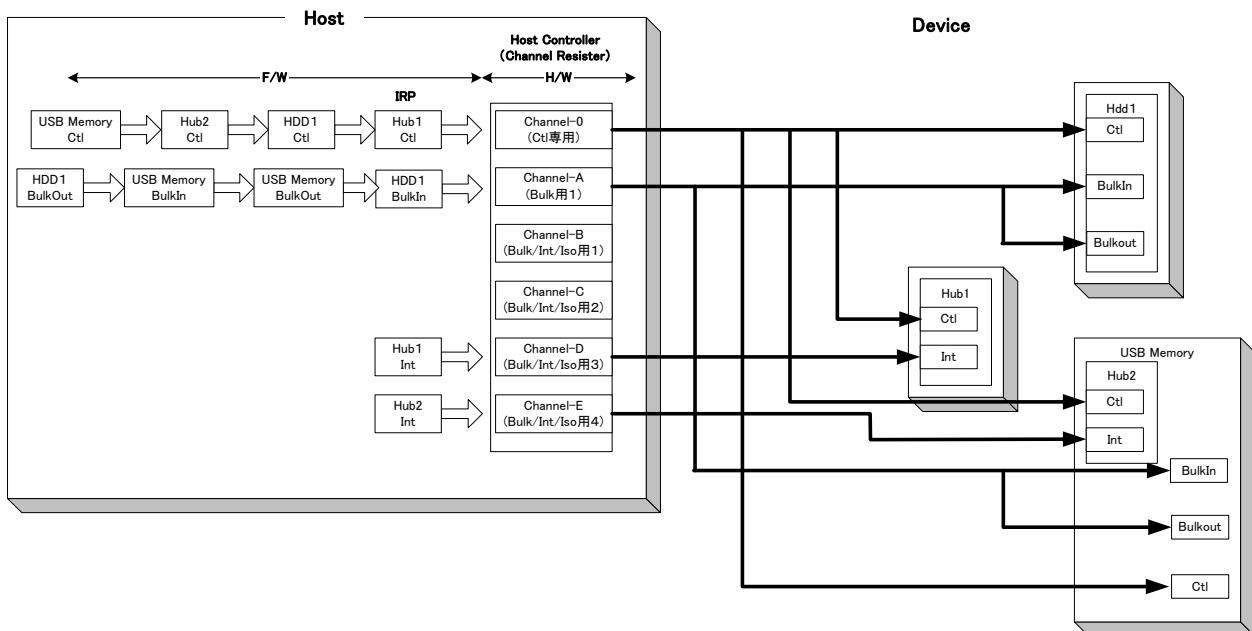

| 1.4.1.4.4   | ハブを介してストレージデバイスを2台接続した場合 .....   | 45 |

| 1.4.2       | スケジューリング .....                   | 46 |

| 1.4.3       | トランザクション .....                   | 47 |

| 1.4.3.1     | SETUPトランザクション .....              | 48 |

| 1.4.3.2     | バルクOUTトランザクション .....             | 49 |

| 1.4.3.3     | インタラプトOUTトランザクション .....          | 50 |

| 1.4.3.4     | アイソクロナスOUTトランザクション .....         | 51 |

| 1.4.3.5     | バルクINトランザクション .....              | 52 |

| 1.4.3.6     | インタラプトINトランザクション .....           | 54 |

| 1.4.3.7     | アイソクロナスINトランザクション .....          | 55 |

|              |                                     |    |

|--------------|-------------------------------------|----|

| 1.4.3.8      | PING トランザクション .....                 | 57 |

| 1.4.3.9      | low-speed(LS)トランザクション .....         | 58 |

| 1.4.3.10     | スプリットトランザクション .....                 | 60 |

| 1.4.4        | コントロール転送 .....                      | 61 |

| 1.4.4.1      | セットアップステージ .....                    | 62 |

| 1.4.4.2      | データステージ／ステータスステージ .....             | 62 |

| 1.4.4.3      | コントロール転送サポート機能 .....                | 63 |

| 1.4.5        | バルク転送／インタラプト転送／アイソクロナス転送 .....      | 66 |

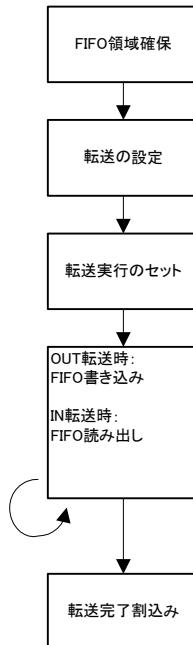

| 1.4.6        | データフロー .....                        | 66 |

| 1.4.6.1      | OUT転送 .....                         | 66 |

| 1.4.6.2      | IN転送 .....                          | 66 |

| 1.4.7        | ゼロ長パケット自動発行機能 .....                 | 67 |

| 1.4.7.1      | バルク／インタラプトOUT転送のゼロ長パケット自動発行機能 ..... | 67 |

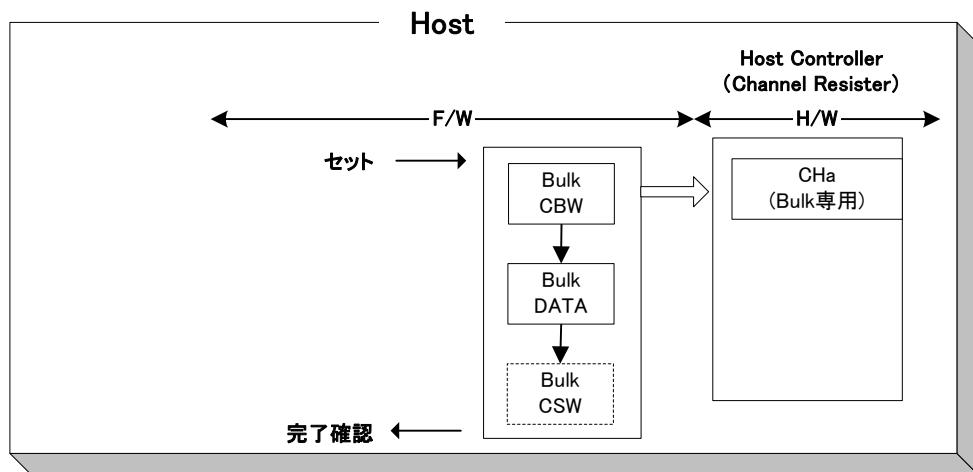

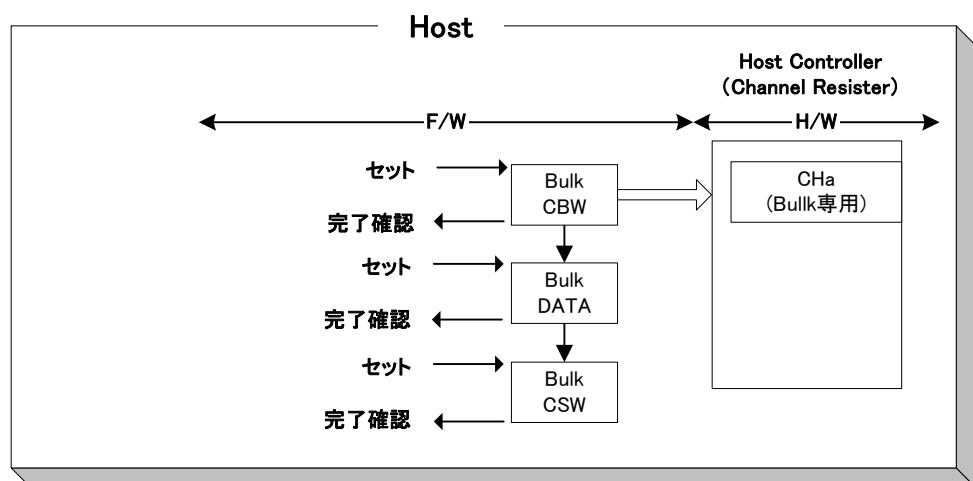

| 1.4.8        | バルクオンリーサポート機能 .....                 | 68 |

| 1.4.9        | オーディオクラス・アシスト機能 .....               | 72 |

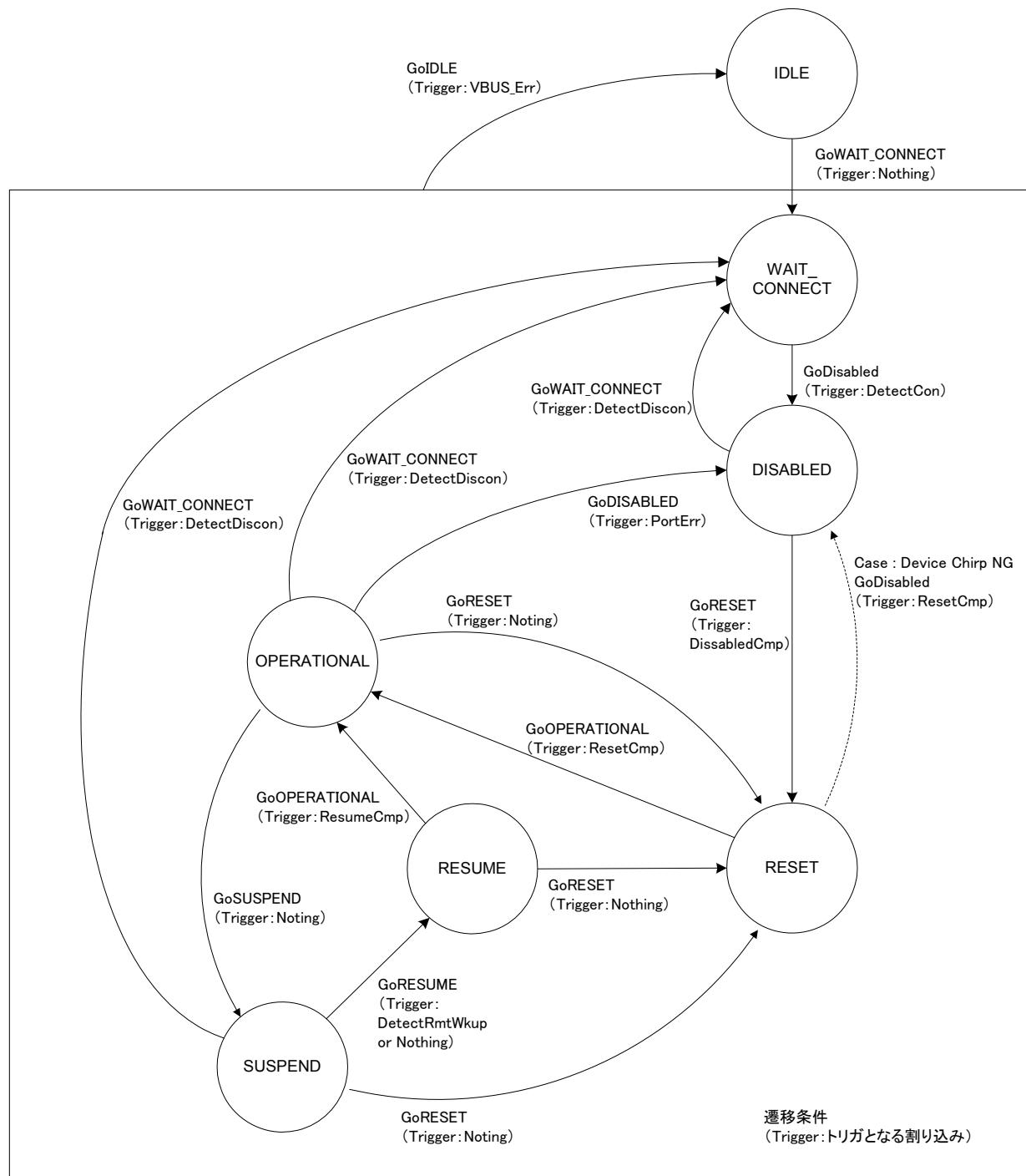

| 1.4.10       | ホストステート管理サポート機能 .....               | 73 |

| 1.4.10.1     | ホストステート .....                       | 73 |

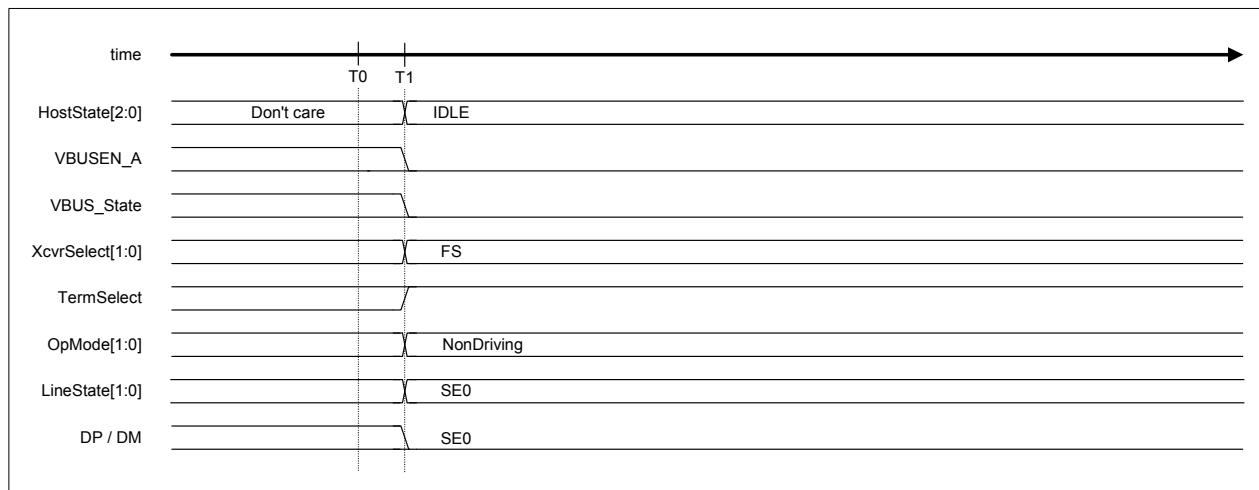

| 1.4.10.1.1   | IDLE .....                          | 75 |

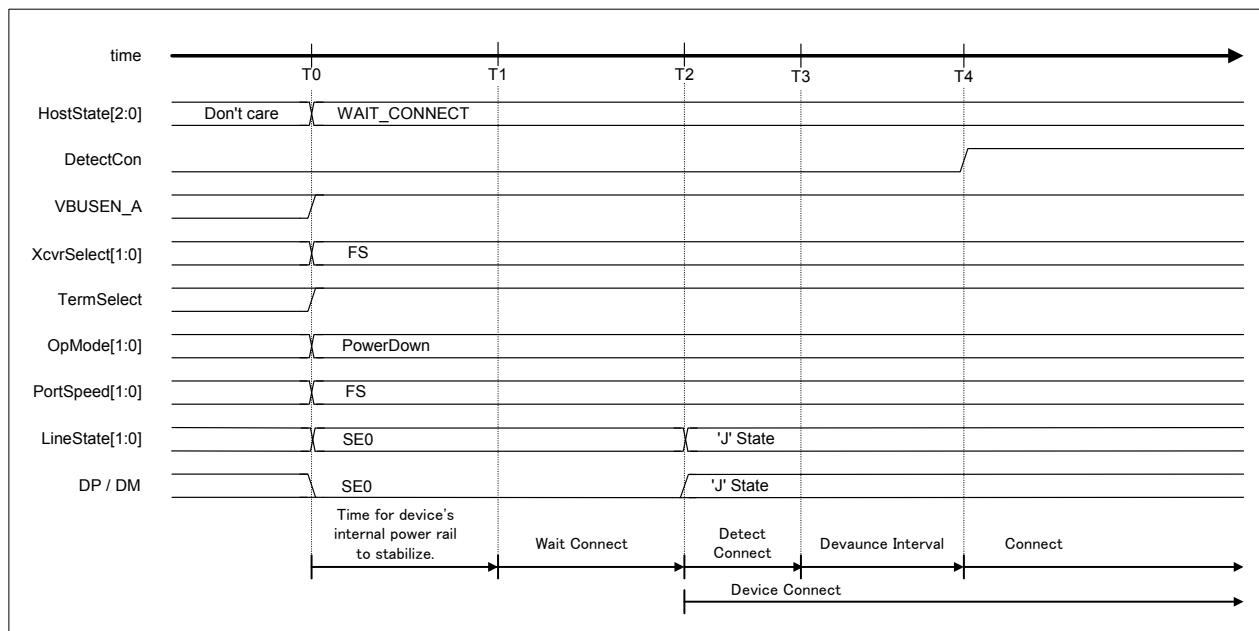

| 1.4.10.1.2   | WAIT_CONNECT .....                  | 76 |

| 1.4.10.1.3   | DISABLED .....                      | 76 |

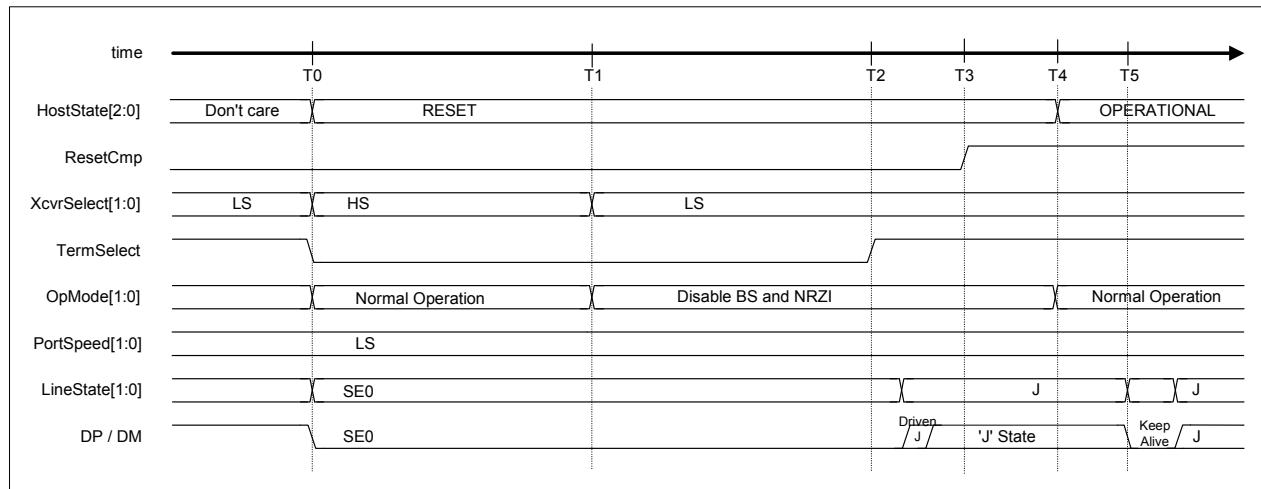

| 1.4.10.1.4   | RESET .....                         | 77 |

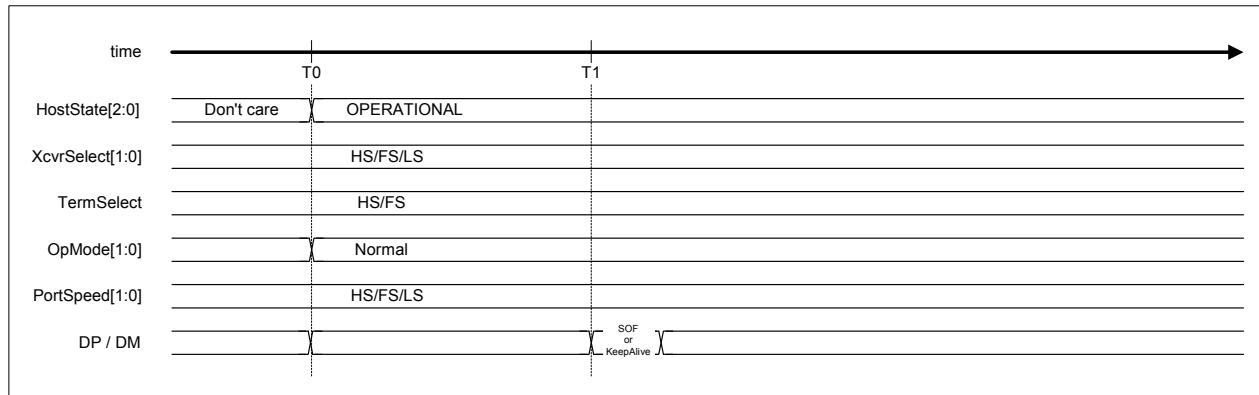

| 1.4.10.1.5   | OPERATIONAL .....                   | 78 |

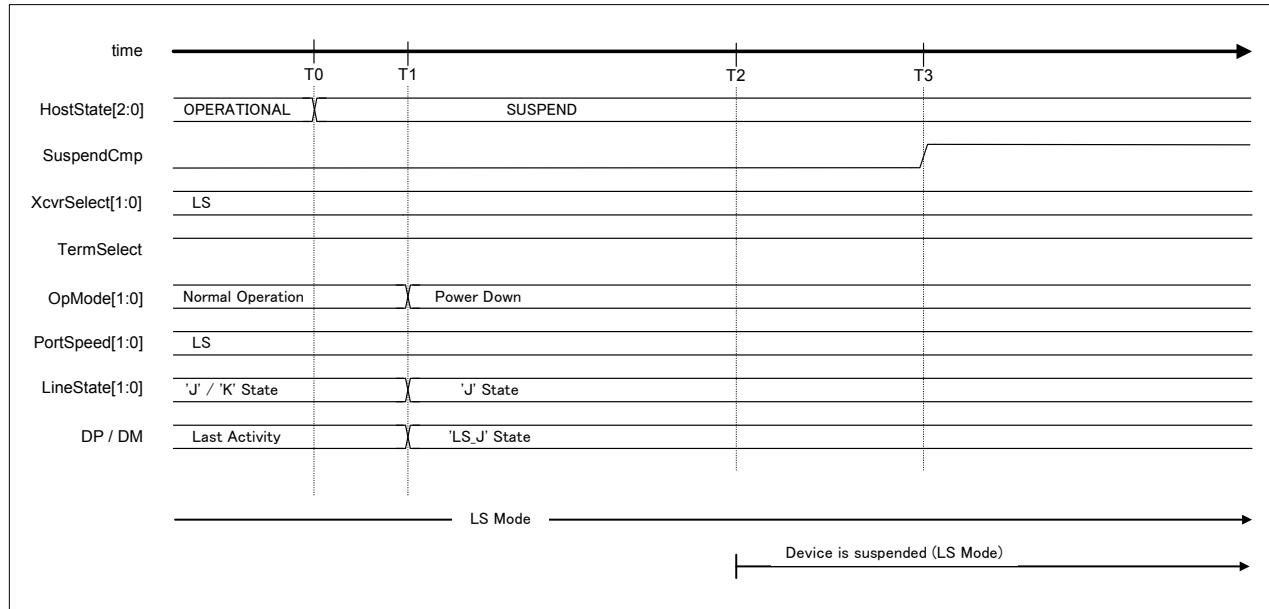

| 1.4.10.1.6   | SUSPEND .....                       | 78 |

| 1.4.10.1.7   | RESUME .....                        | 79 |

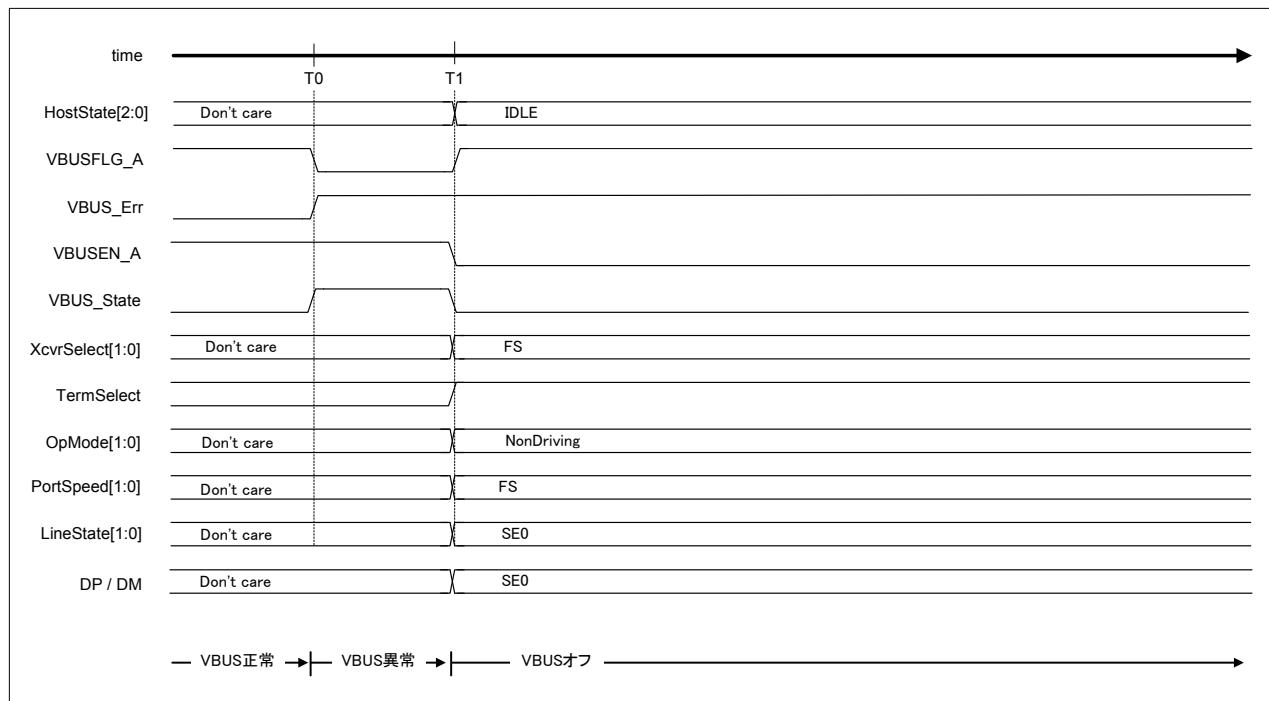

| 1.4.10.2     | 検出機能 .....                          | 80 |

| 1.4.10.2.1   | VBUS異常検出 .....                      | 80 |

| 1.4.10.2.2   | 切断検出 .....                          | 82 |

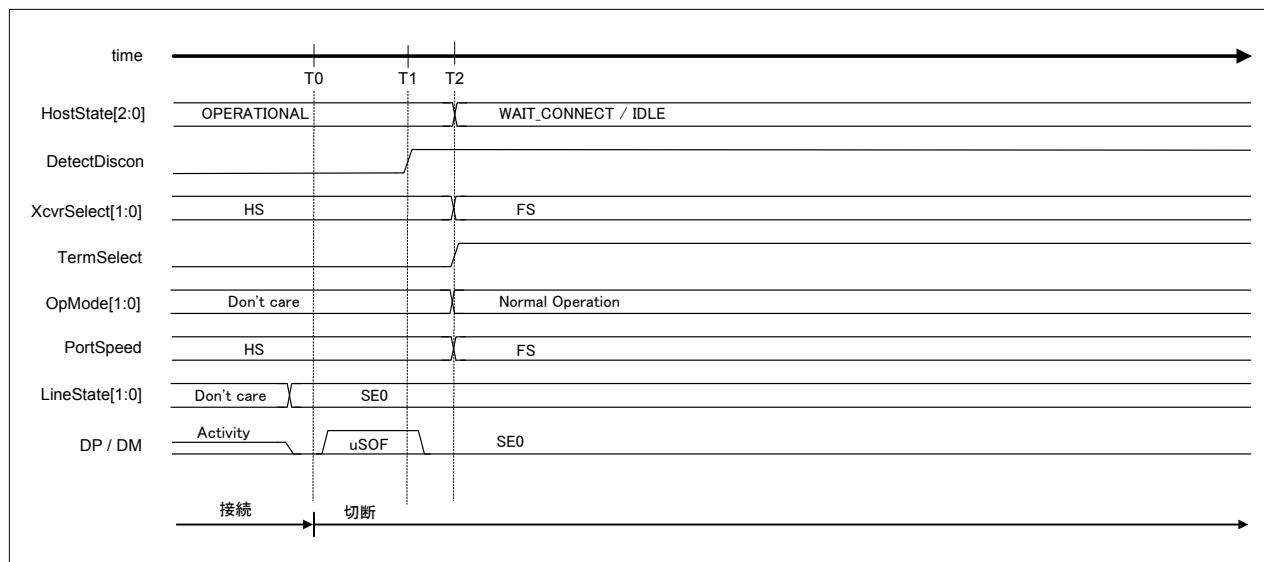

| 1.4.10.2.2.1 | HSデバイスが切断された場合 .....                | 82 |

| 1.4.10.2.2.2 | FSまたはLSデバイスが切断された場合 .....           | 83 |

| 1.4.10.2.3   | リモート・ウェークアップ検出 .....                | 84 |

| 1.4.10.2.3.1 | HSデバイスが接続されている場合 .....              | 84 |

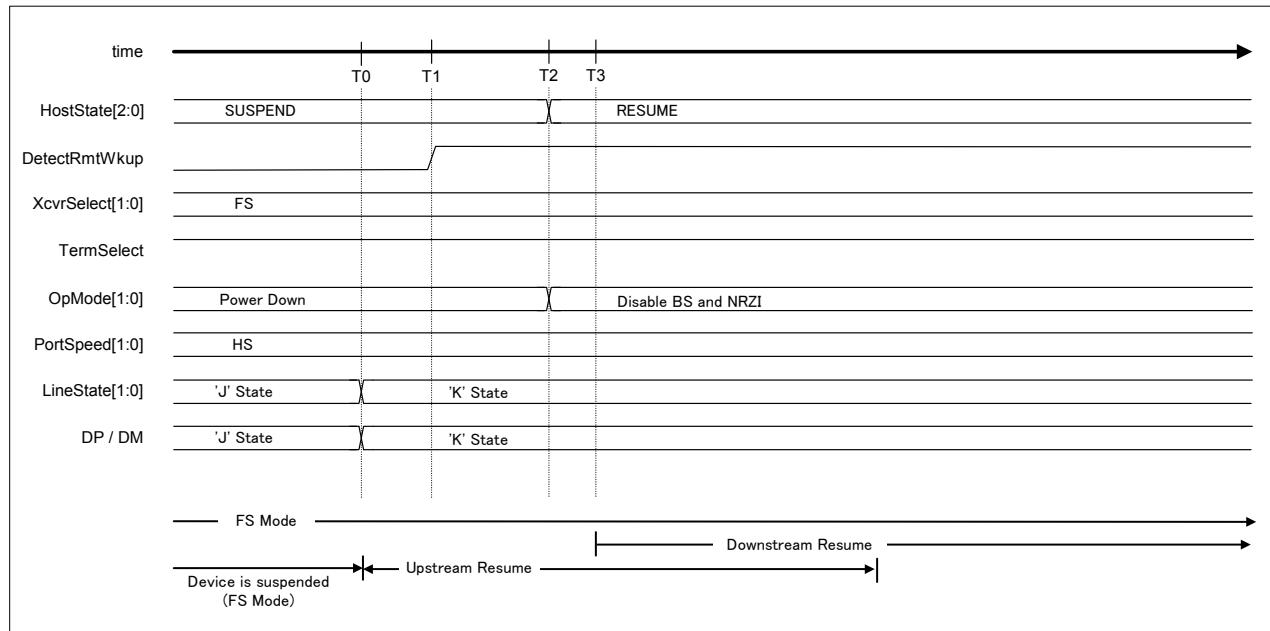

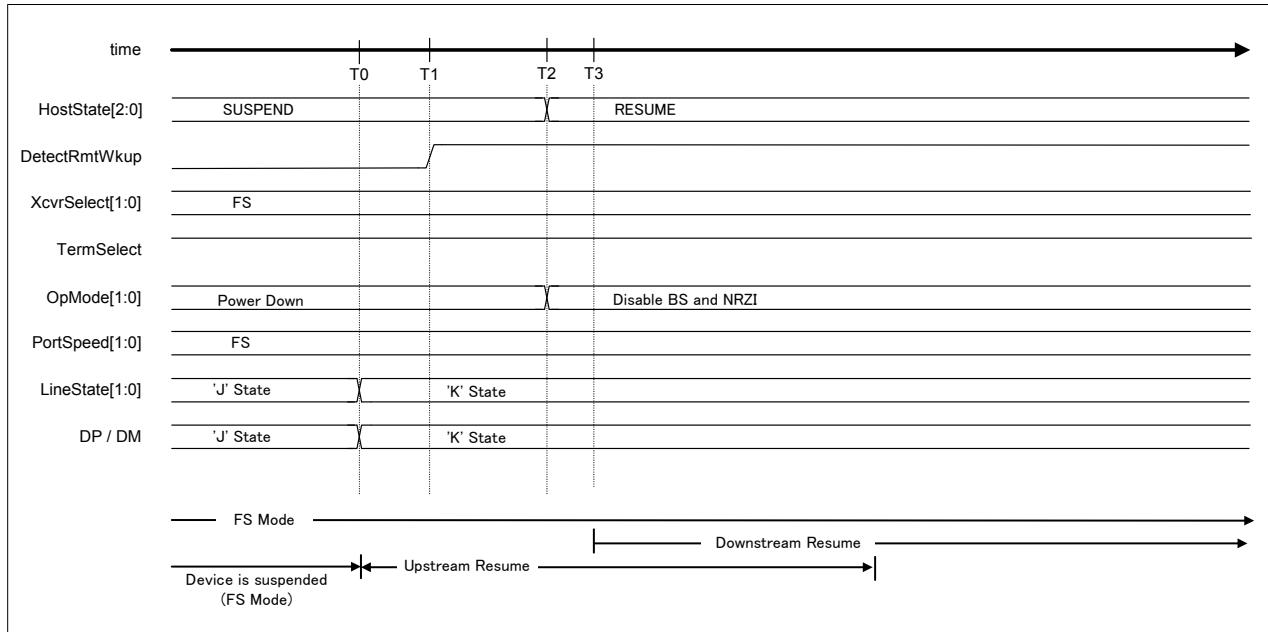

| 1.4.10.2.3.2 | FSデバイスが接続されている場合 .....              | 85 |

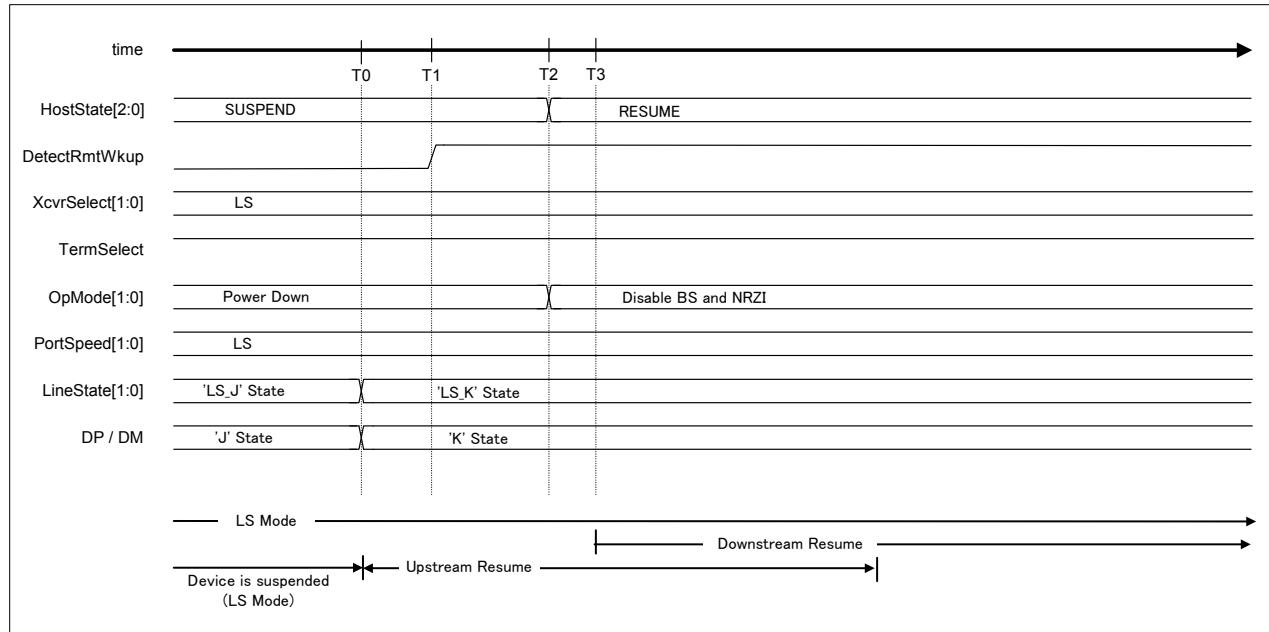

| 1.4.10.2.3.3 | LSデバイスが接続されている場合 .....              | 86 |

| 1.4.10.2.4   | デバイスチャープ検出機能 .....                  | 87 |

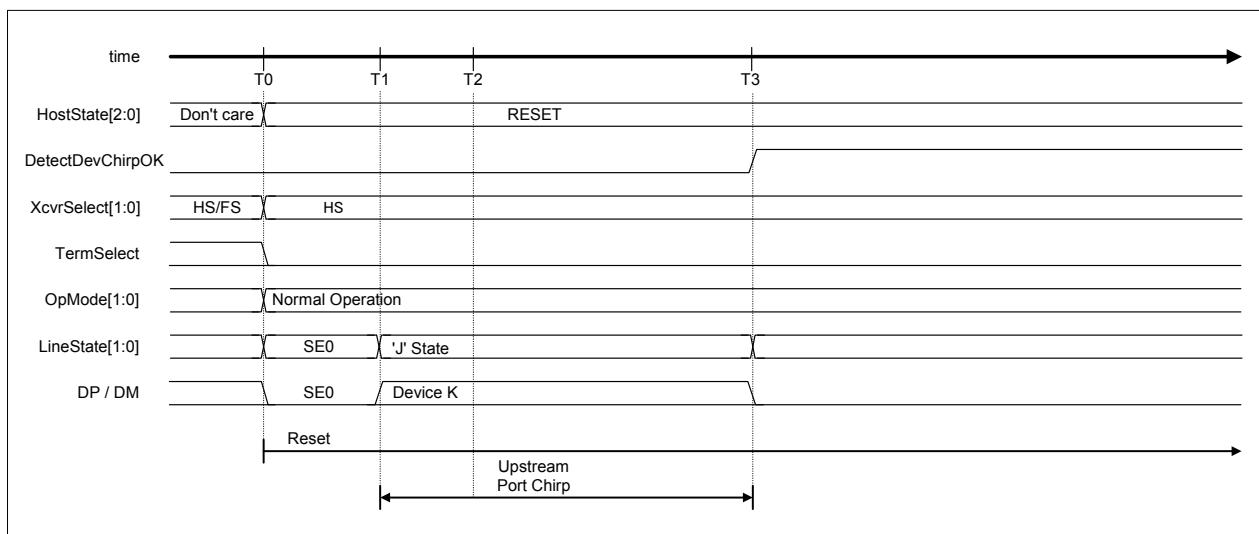

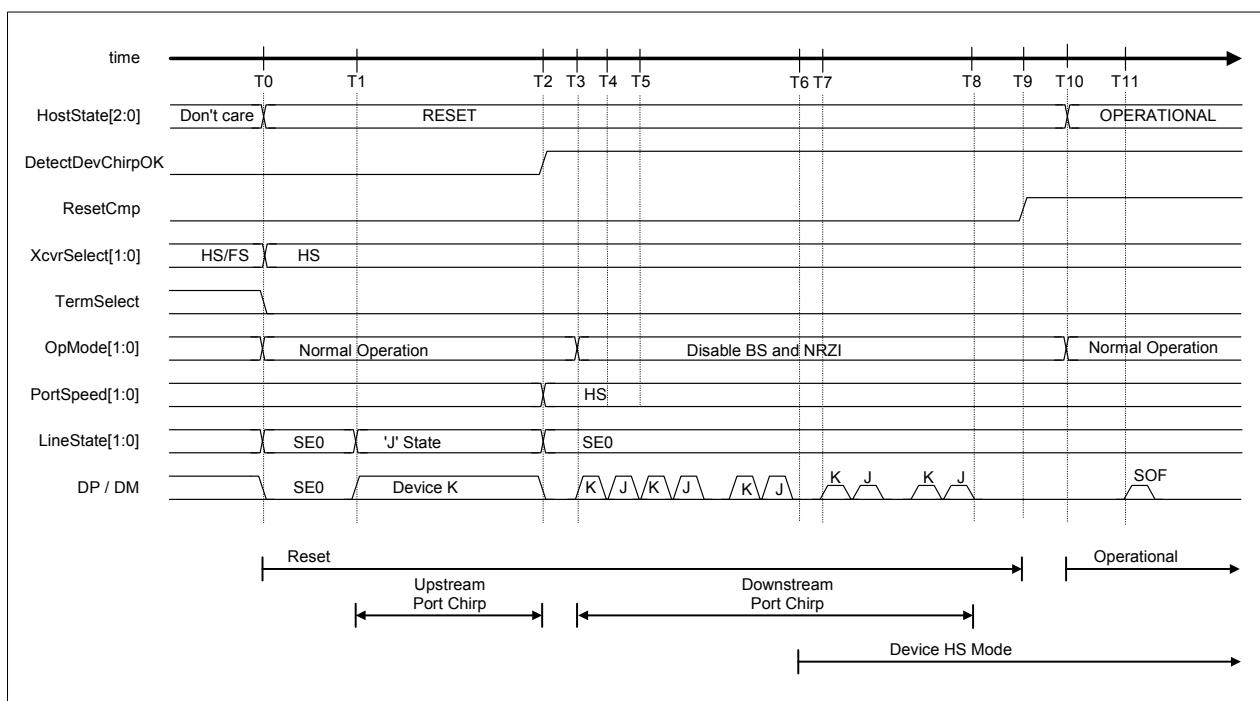

| 1.4.10.2.4.1 | 正しいデバイスのChirpを検出した場合 .....          | 87 |

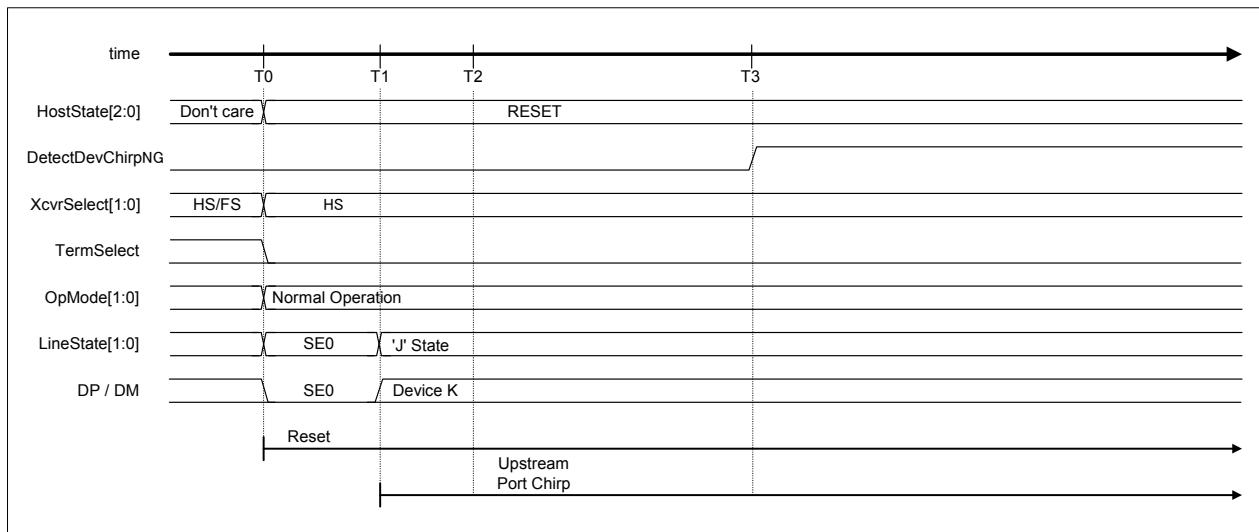

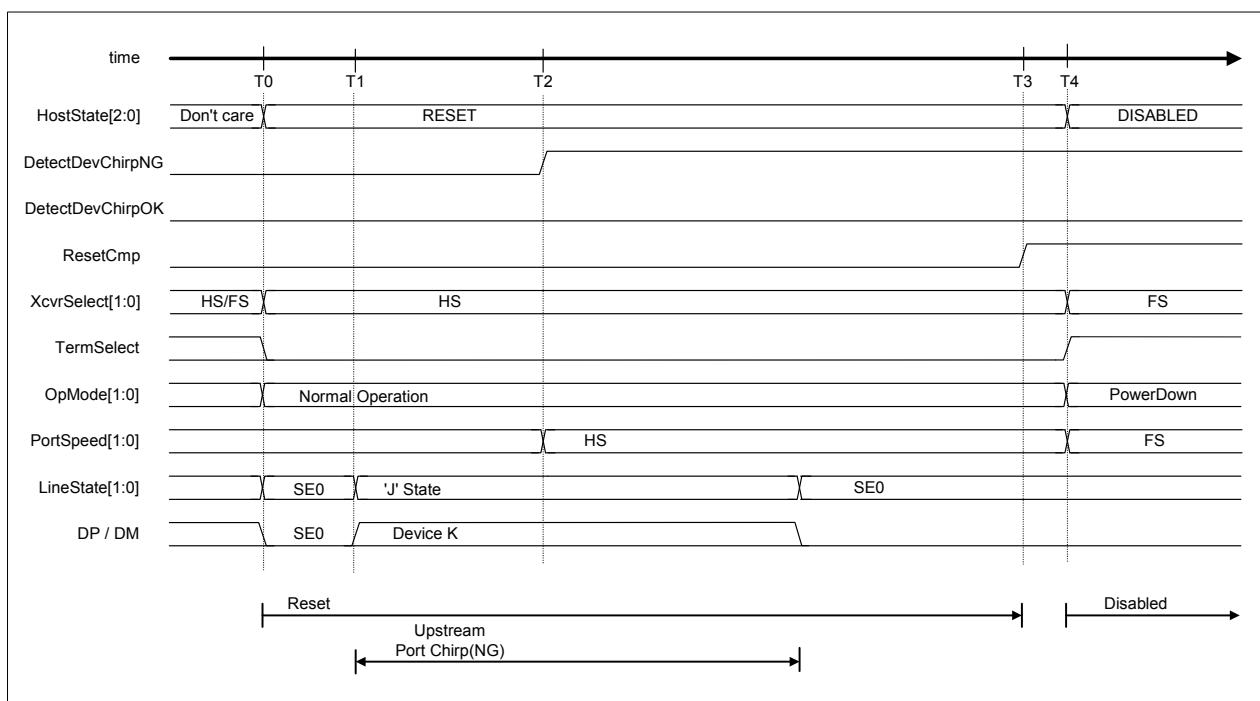

| 1.4.10.2.4.2 | 異常なデバイスのChirpを検出した場合 .....          | 88 |

| 1.4.10.2.5   | ポートエラー検出 .....                      | 89 |

| 1.4.10.3     | ホストステート管理サポート機能の単体説明 .....          | 90 |

|                |                                                                 |     |

|----------------|-----------------------------------------------------------------|-----|

| 1.4.10.3.1     | GoIDLE.....                                                     | 90  |

| 1.4.10.3.2     | GoWAIT_CONNECT.....                                             | 92  |

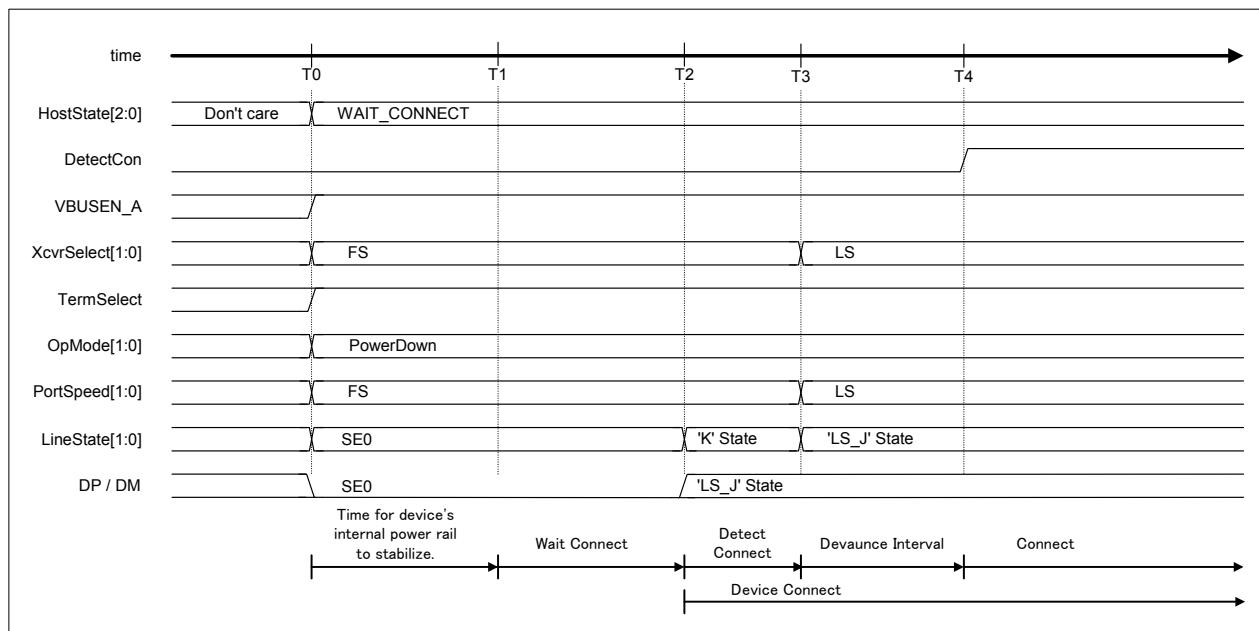

| 1.4.10.3.2.1   | FSデバイスが接続された場合 .....                                            | 92  |

| 1.4.10.3.2.2   | LSデバイスが接続された場合 .....                                            | 94  |

| 1.4.10.3.3     | GoDISABLED .....                                                | 96  |

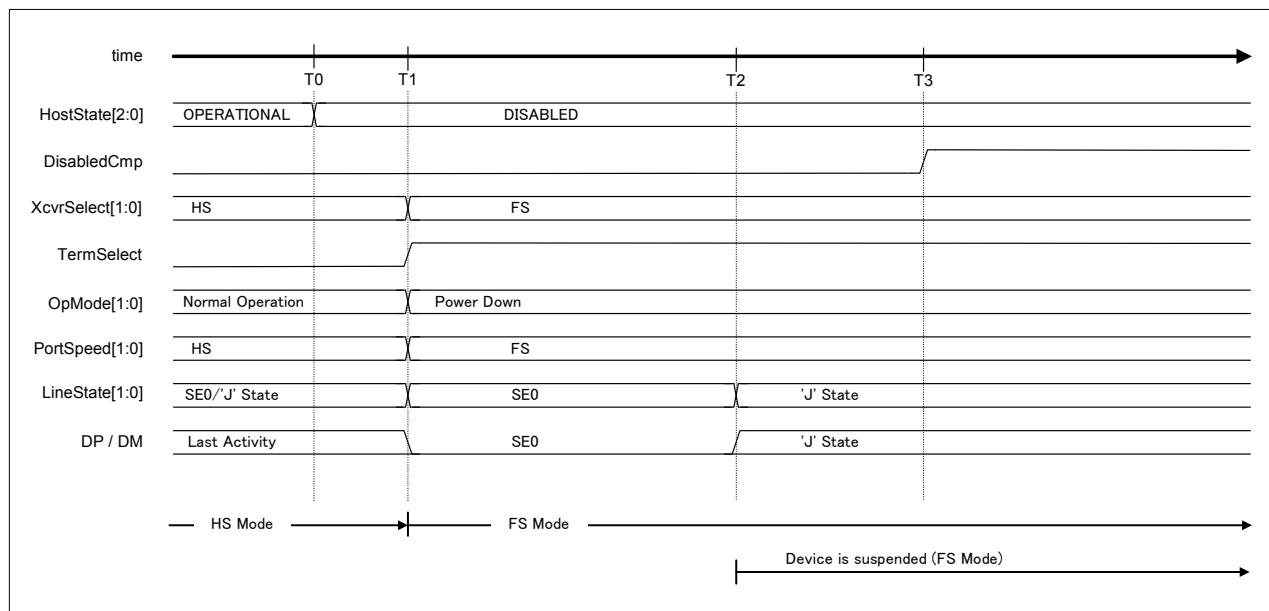

| 1.4.10.3.3.1   | HSデバイスが接続されている場合 .....                                          | 96  |

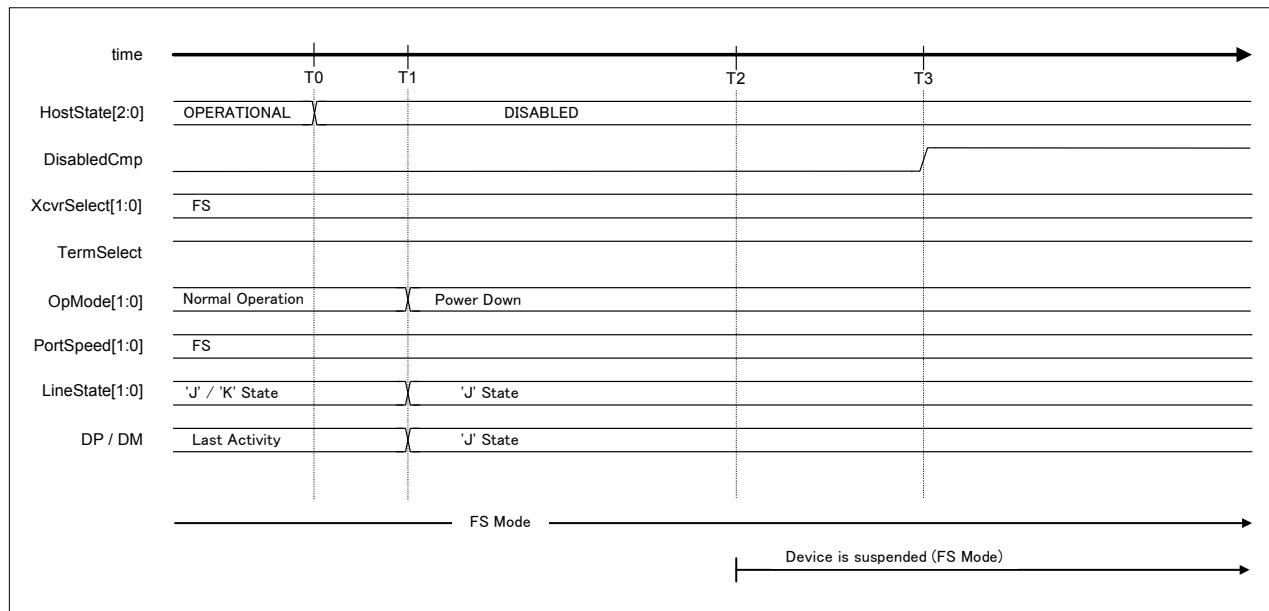

| 1.4.10.3.3.2   | FSデバイスが接続されている場合.....                                           | 98  |

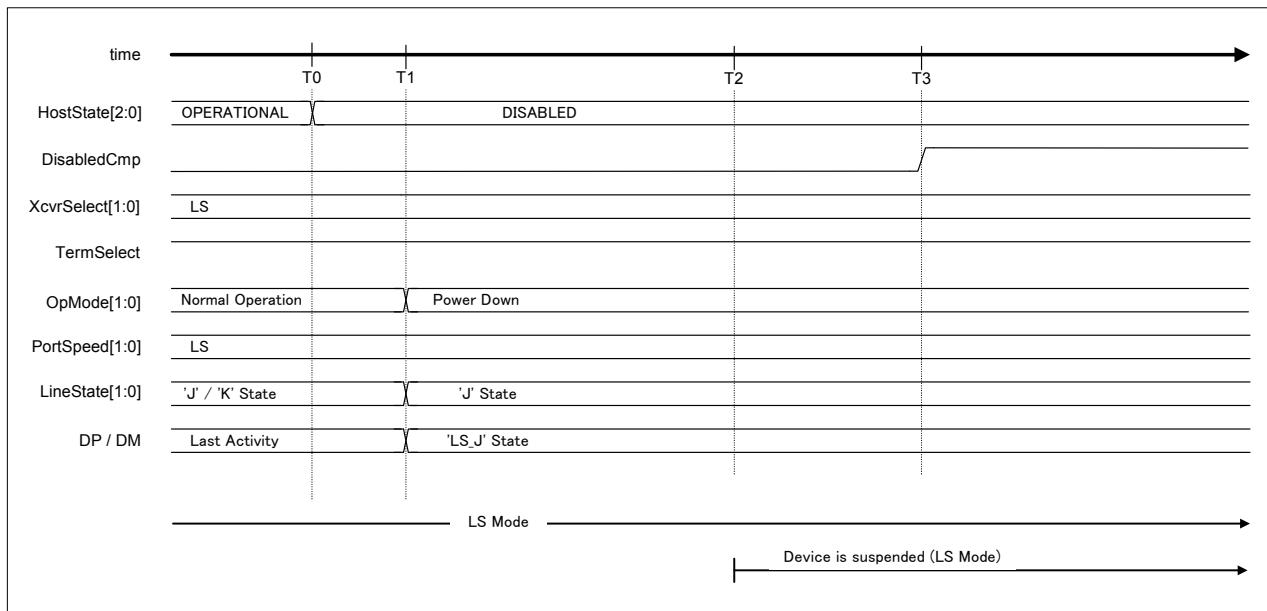

| 1.4.10.3.3.3   | LSデバイスが接続されている場合 .....                                          | 99  |

| 1.4.10.3.4     | GoRESET.....                                                    | 100 |

| 1.4.10.3.4.1   | HSデバイスに対するリセット .....                                            | 100 |

| 1.4.10.3.4.2   | 異常なデバイスのChirp検出.....                                            | 102 |

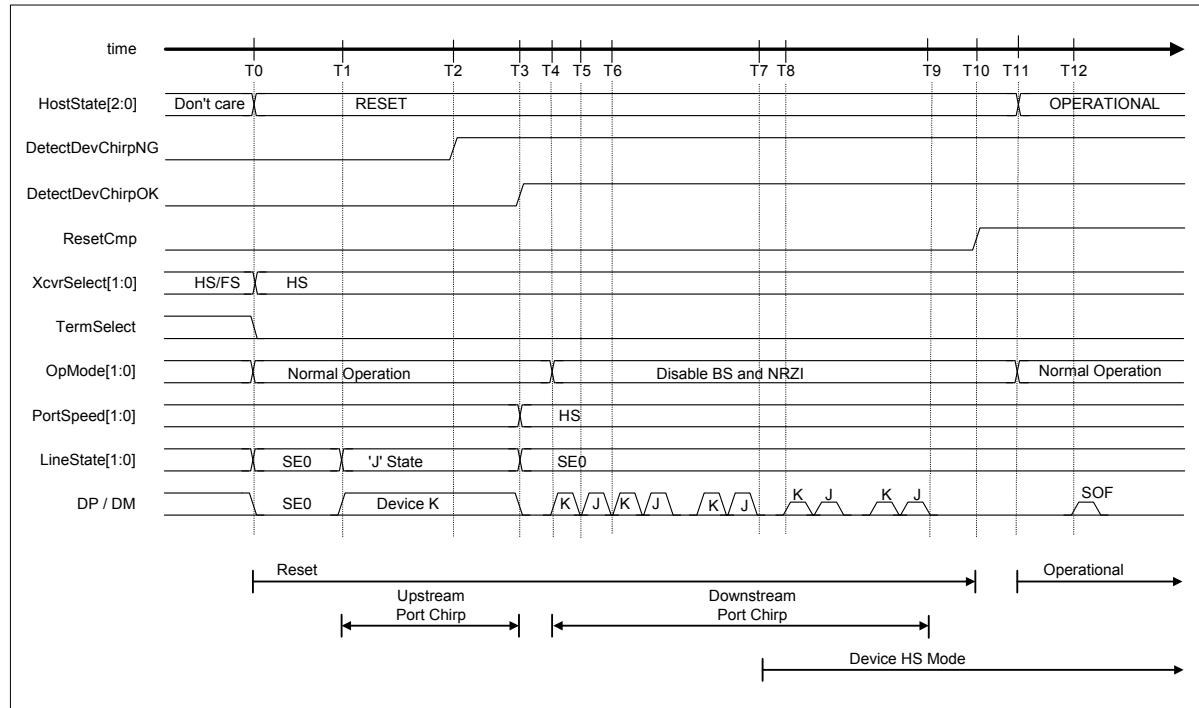

| 1.4.10.3.4.2.1 | チャープ完了ディセーブル<br>(H_NegoControl_1.DisChirpFinish)設定が 0 の場合 ..... | 102 |

| 1.4.10.3.4.2.2 | チャープ完了ディセーブル<br>(H_NegoControl_1.DisChirpFinish)設定が 1 の場合 ..... | 104 |

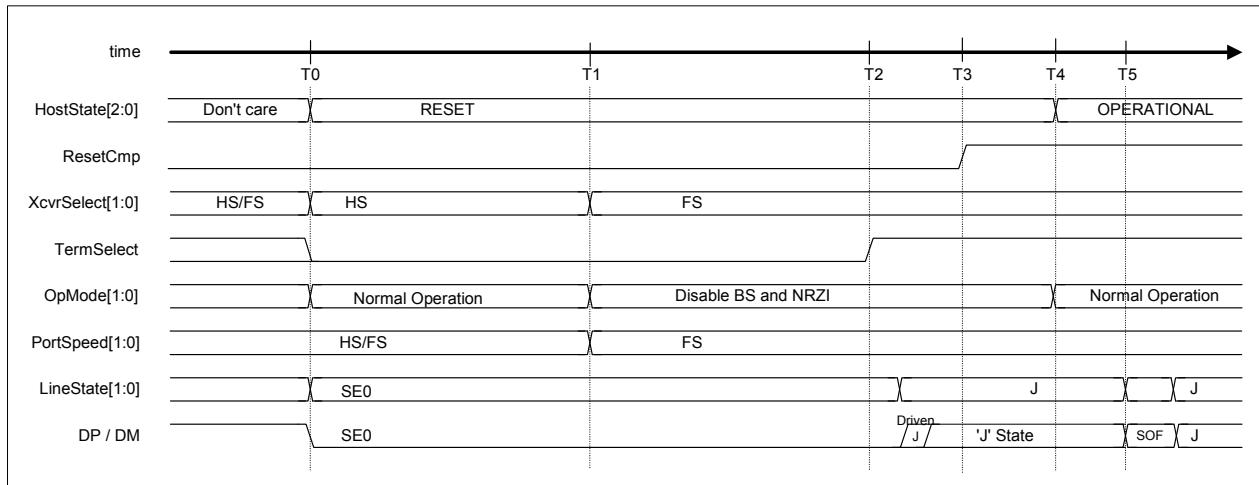

| 1.4.10.3.4.3   | FSデバイスに対するリセット .....                                            | 106 |

| 1.4.10.3.4.4   | LSデバイスに対するリセット .....                                            | 108 |

| 1.4.10.3.5     | GoOPERATIONAL .....                                             | 109 |

| 1.4.10.3.6     | GoSUSPEND .....                                                 | 110 |

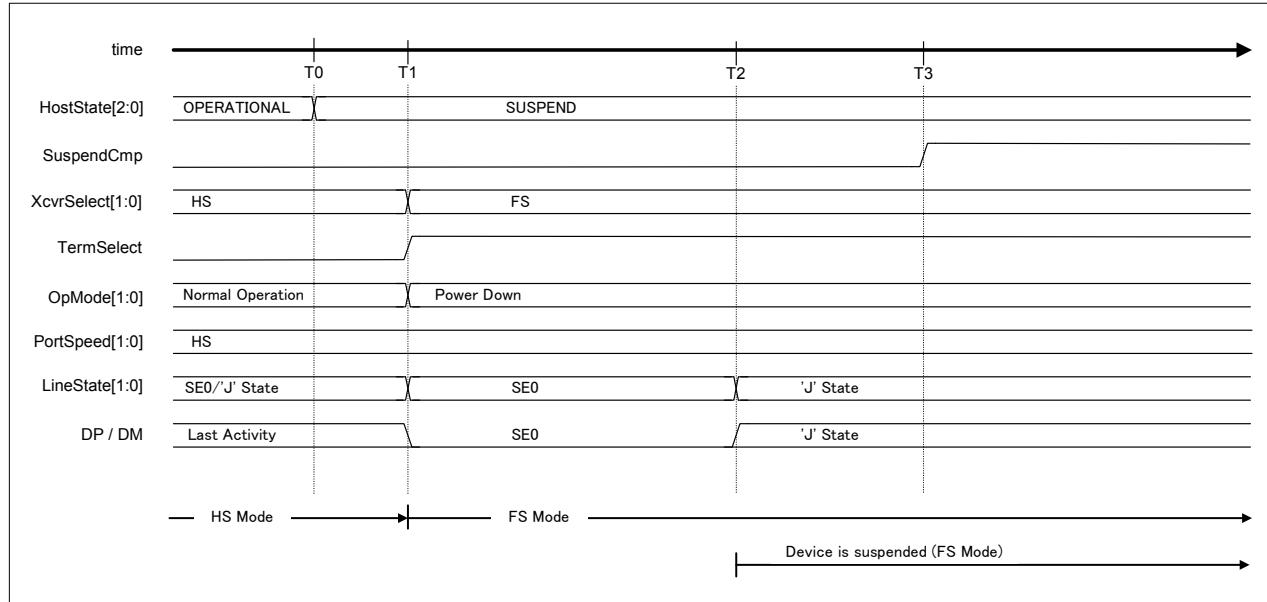

| 1.4.10.3.6.1   | HSデバイスが接続されている場合 .....                                          | 110 |

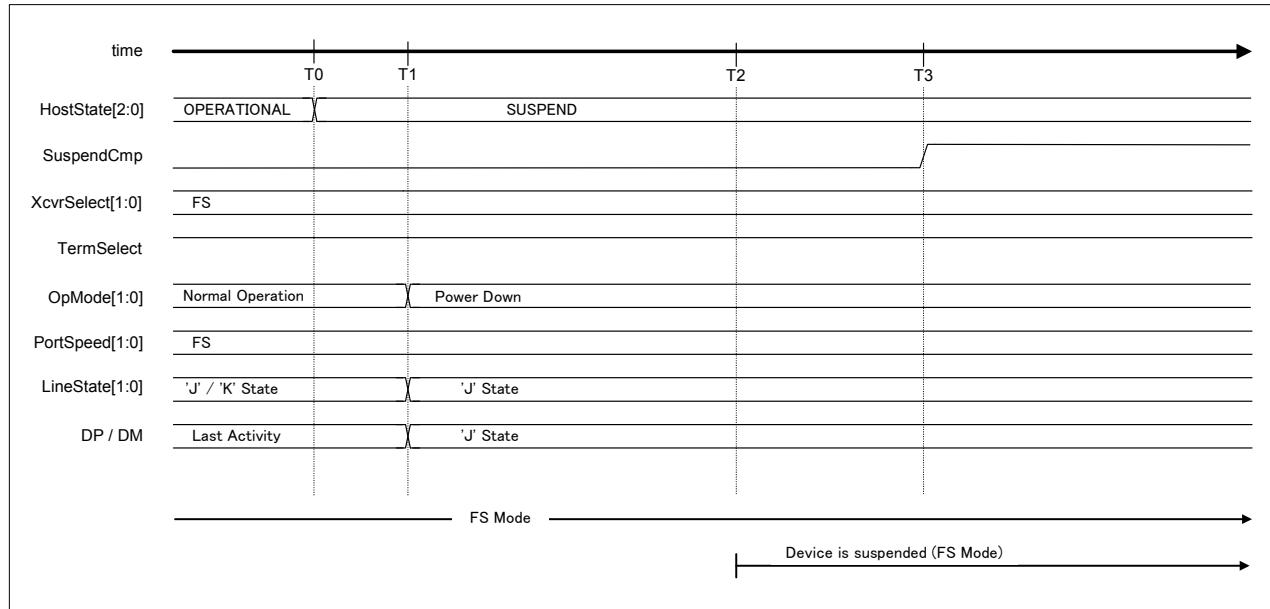

| 1.4.10.3.6.2   | FSデバイスが接続されている場合.....                                           | 112 |

| 1.4.10.3.6.3   | LSデバイスが接続されている場合 .....                                          | 114 |

| 1.4.10.3.7     | GoRESUME.....                                                   | 116 |

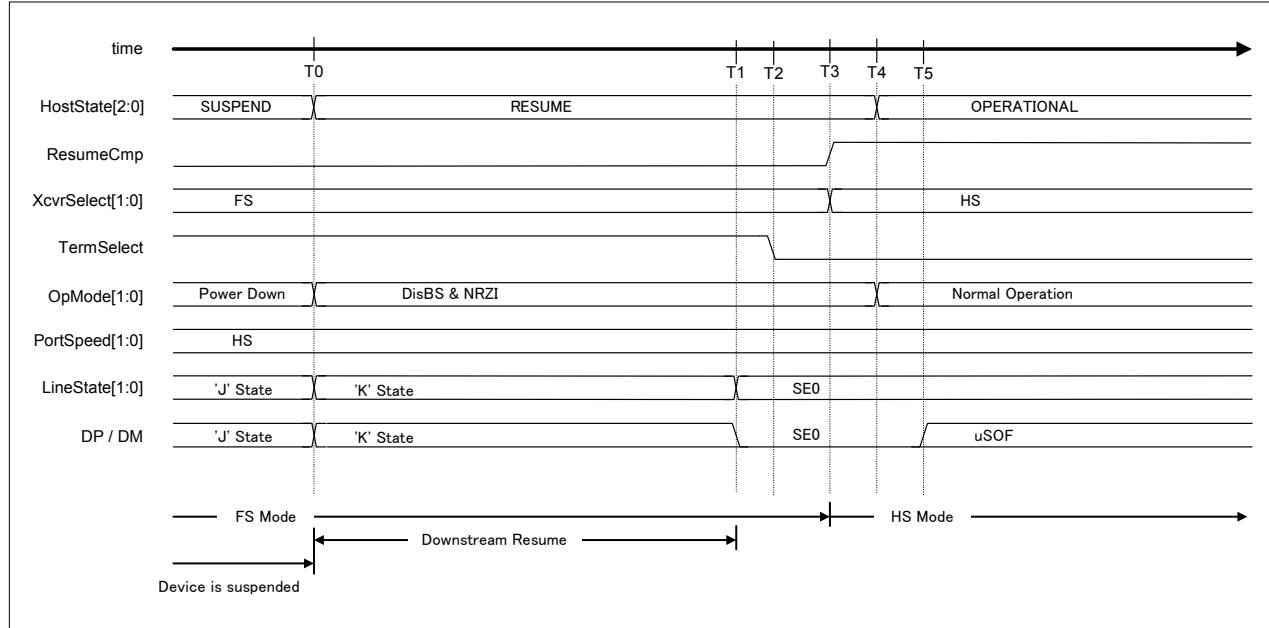

| 1.4.10.3.7.1   | HSデバイスが接続されている場合 .....                                          | 116 |

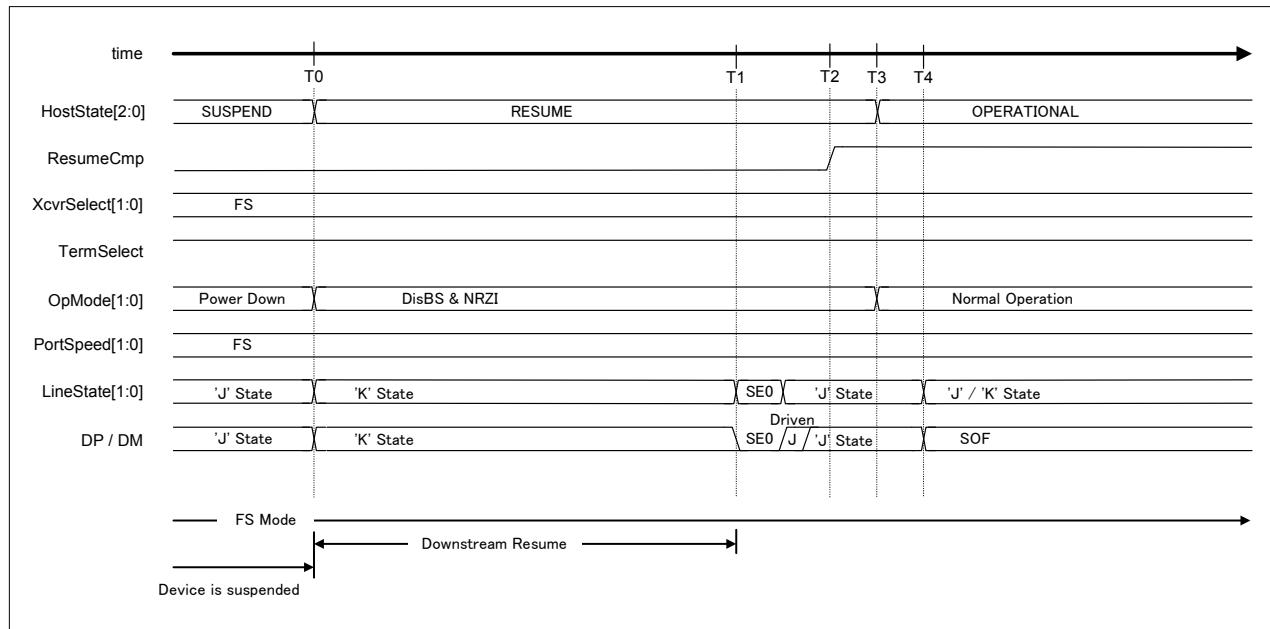

| 1.4.10.3.7.2   | FSデバイスが接続されている場合.....                                           | 118 |

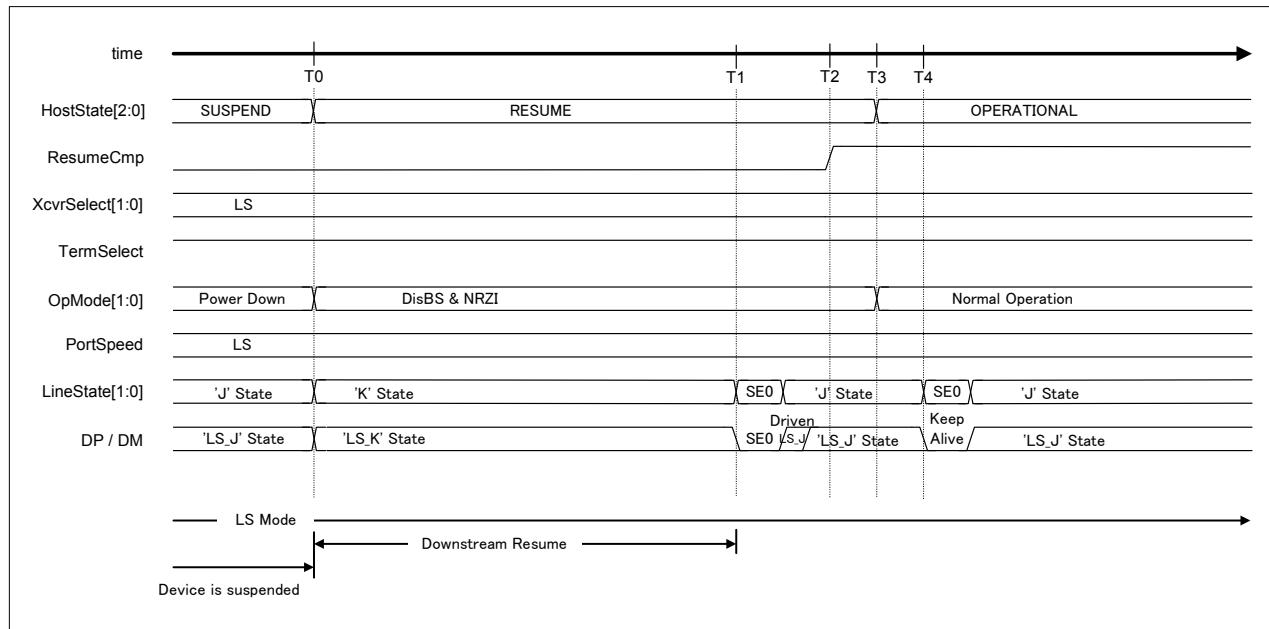

| 1.4.10.3.7.3   | LSデバイスが接続されている場合 .....                                          | 120 |

| 1.4.10.3.8     | GoWAIT_CONNECTtoDIS.....                                        | 122 |

| 1.4.10.3.9     | GoWAIT_CONNECTtoOP.....                                         | 123 |

| 1.4.10.3.9.1   | HSデバイスが接続されている場合 .....                                          | 123 |

| 1.4.10.3.9.2   | FSまたはLSデバイスが接続されている場合 .....                                     | 125 |

| 1.4.10.3.10    | GoRESETtoOP .....                                               | 127 |

| 1.4.10.3.10.1  | HSデバイスが接続されている場合 .....                                          | 127 |

| 1.4.10.3.10.2  | FSまたはLSデバイスが接続されている場合 .....                                     | 128 |

| 1.4.10.3.11    | GoSUSPENDtoOP .....                                             | 129 |

| 1.4.10.3.12    | GoRESUMETOOP .....                                              | 130 |

| 1.5            | パワーマネージメント機能 .....                                              | 131 |

| 1.5.1          | SLEEP(スリープ) .....                                               | 132 |

|           |                                  |     |

|-----------|----------------------------------|-----|

| 1.5.2     | ACTIVE(アクティブ) .....              | 132 |

| 1.6       | FIFO管理 .....                     | 133 |

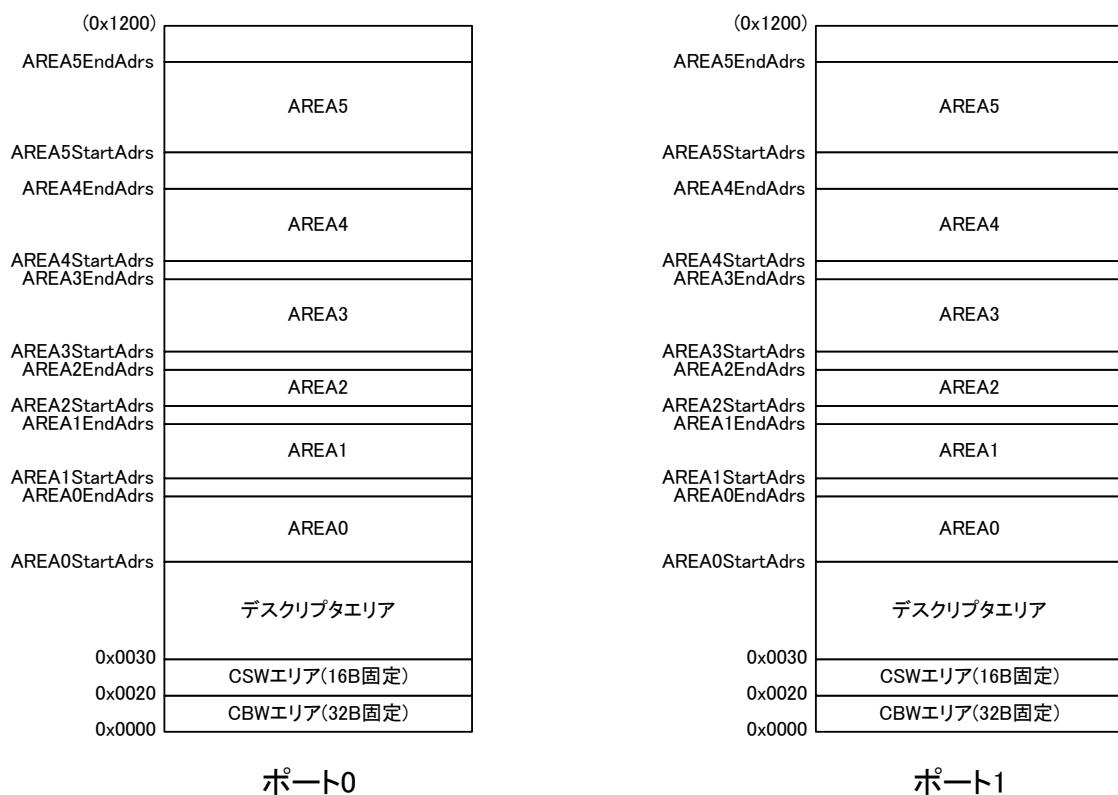

| 1.6.1     | FIFOメモリマップ .....                 | 133 |

| 1.6.2     | デスクリプタエリア .....                  | 134 |

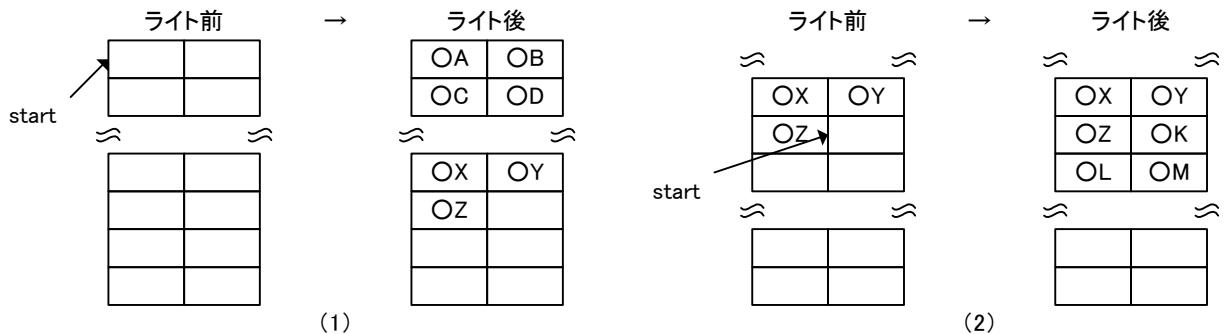

| 1.6.2.1   | デスクリプタエリアへのデータの書き込み .....        | 134 |

| 1.6.2.2   | デスクリプタエリアでのデータステージ(IN)の実行 .....  | 134 |

| 1.6.3     | CBWエリア .....                     | 135 |

| 1.6.3.1   | CBWエリア(USBデバイス時) .....           | 135 |

| 1.6.3.2   | CBWエリア(USBホスト時) .....            | 135 |

| 1.6.4     | CSWエリア .....                     | 135 |

| 1.6.4.1   | CSWエリア(USBデバイス時) .....           | 135 |

| 1.6.4.2   | CSWエリア(USBホスト時) .....            | 136 |

| 1.6.5     | FIFOへのアクセス方法 .....               | 136 |

| 1.6.5.1   | RAMアクセスの方法(RAM_Rd) .....         | 136 |

| 1.6.5.2   | RAMアクセスの方法(RAM_WrDoor) .....     | 136 |

| 1.6.5.3   | FIFOアクセスの方法(レジスタアクセス) .....      | 137 |

| 1.6.5.4   | FIFOアクセスの方法(DMA) .....           | 137 |

| 1.6.5.5   | FIFOアクセスの制限 .....                | 137 |

| 1.7       | CPUIF .....                      | 139 |

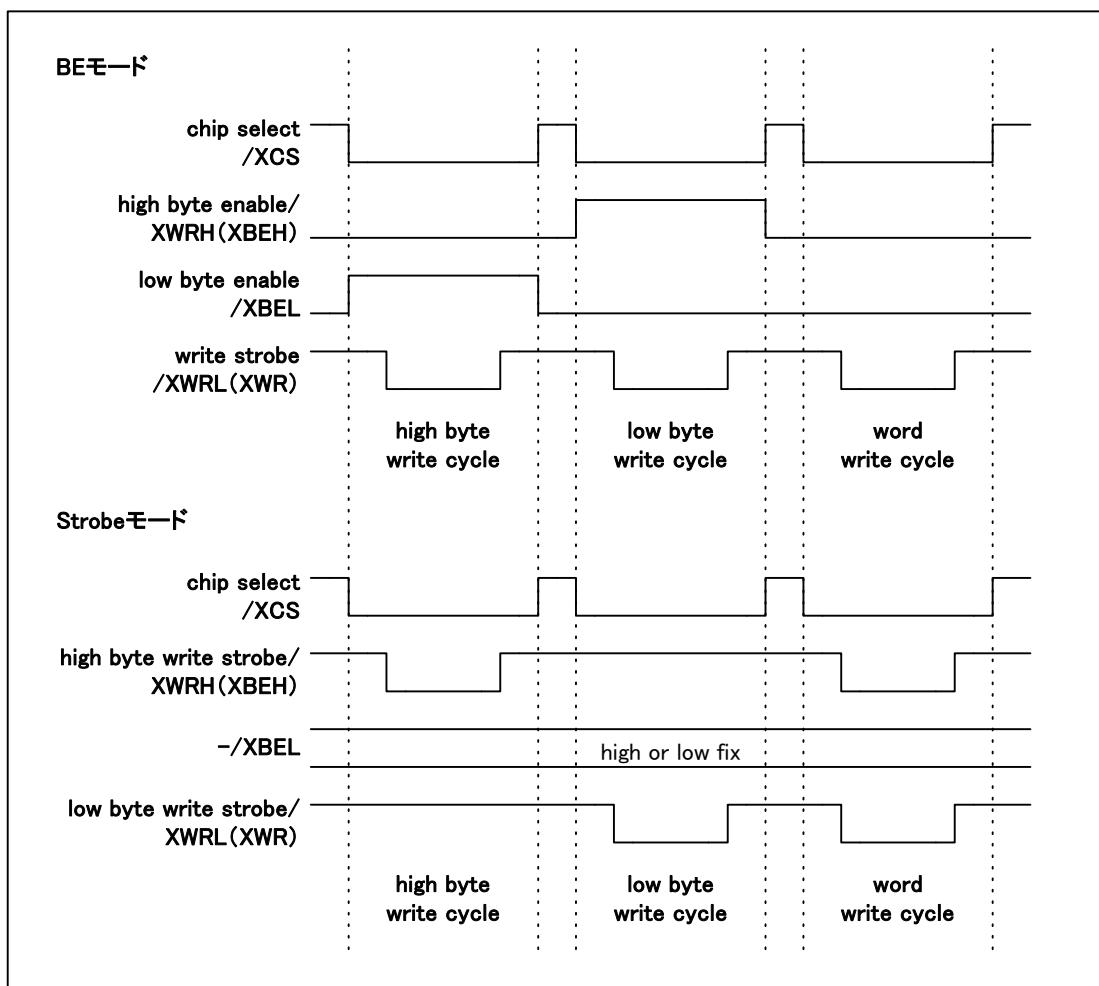

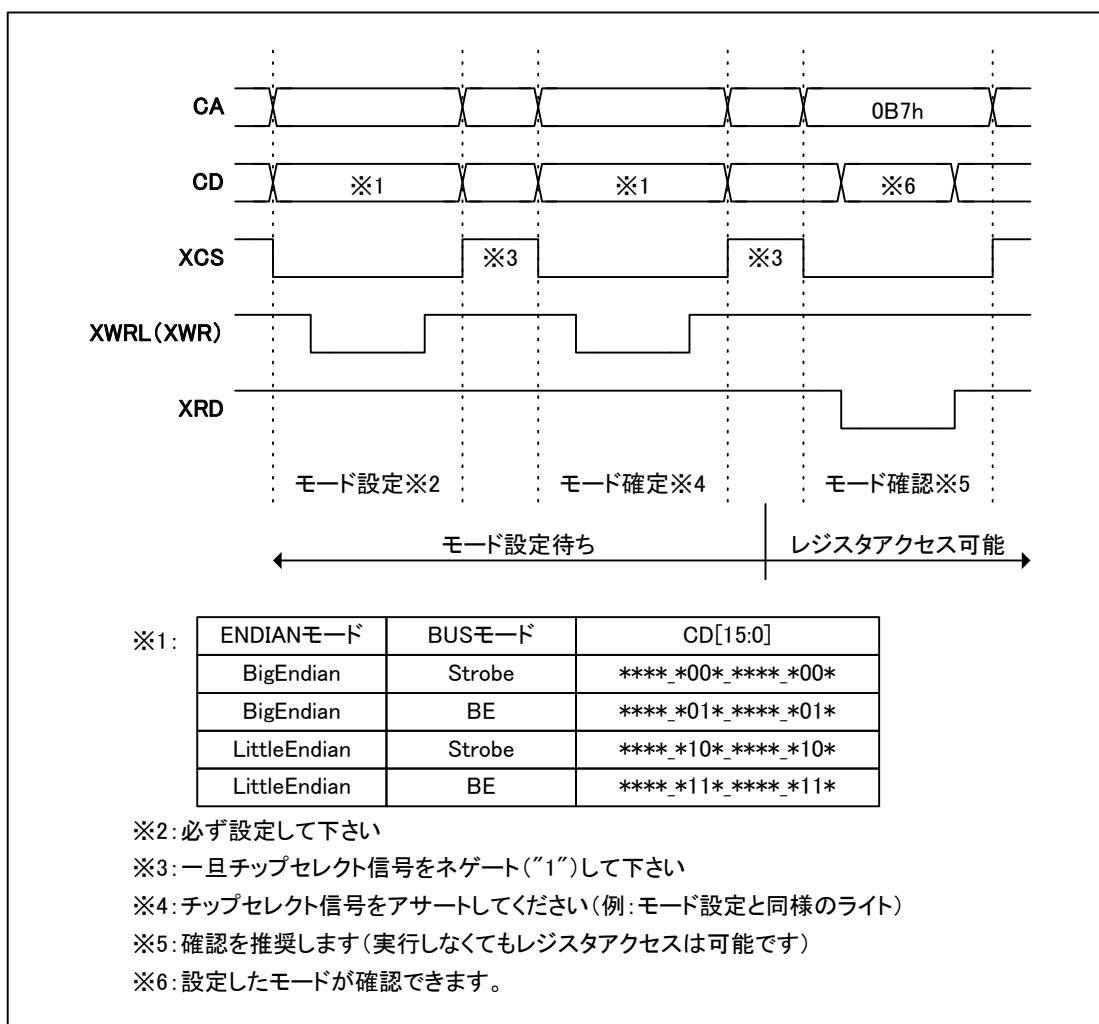

| 1.7.1     | CPUIFモード .....                   | 139 |

| 1.7.2     | CPUIFのモード設定 .....                | 140 |

| 1.7.3     | ブロック構成 .....                     | 141 |

| 1.7.3.1   | REG(Registers) .....             | 141 |

| 1.7.3.1.1 | 同期レジスタアクセス(ライト) .....            | 141 |

| 1.7.3.1.2 | 同期レジスタアクセス(リード) .....            | 141 |

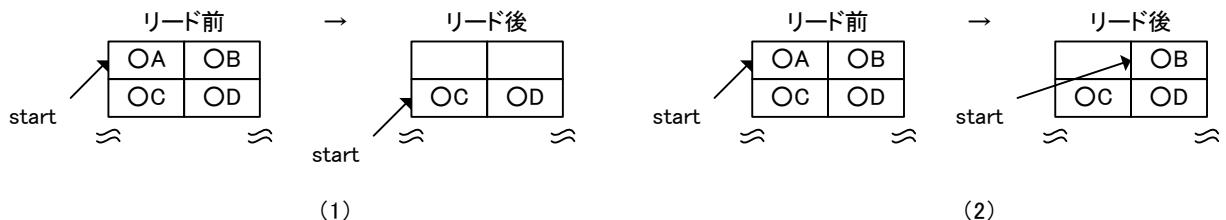

| 1.7.3.1.3 | FIFOアクセス(ライト) .....              | 141 |

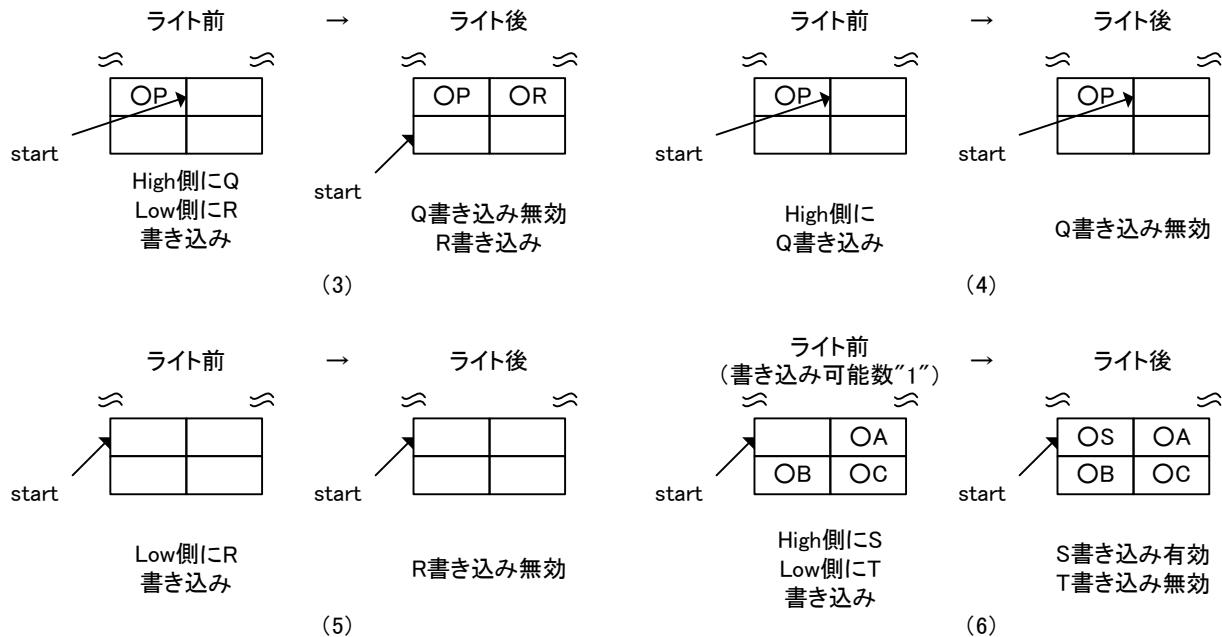

| 1.7.3.1.4 | FIFOアクセス(リード) .....              | 142 |

| 1.7.3.1.5 | FIFOアクセスの端数処理 .....              | 143 |

| 1.7.3.1.6 | RAM_Rdアクセス .....                 | 145 |

| 1.7.3.1.7 | 非同期レジスタアクセス(ライト) .....           | 145 |

| 1.7.3.1.8 | 非同期レジスタアクセス(リード) .....           | 145 |

| 1.7.3.2   | DMA0/DMA1(DMA ch.0 / ch.1) ..... | 146 |

| 1.7.3.2.1 | 基本機能 .....                       | 146 |

| 1.7.3.2.2 | 端子設定 .....                       | 147 |

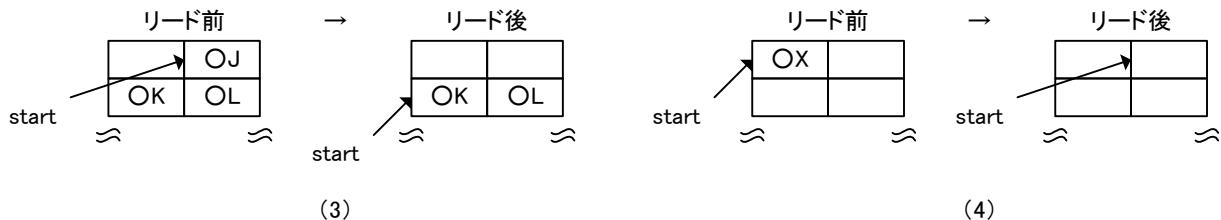

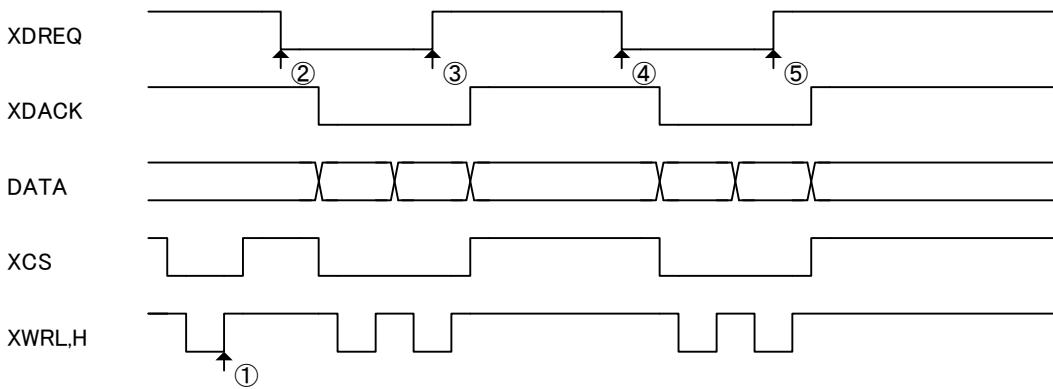

| 1.7.3.2.3 | カウントモード(ライト) .....               | 147 |

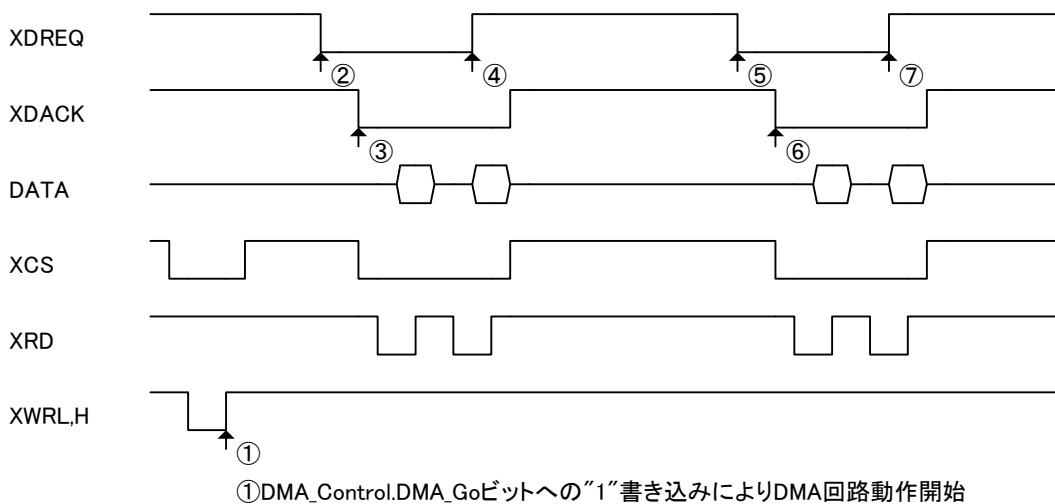

| 1.7.3.2.4 | カウントモード(リード) .....               | 149 |

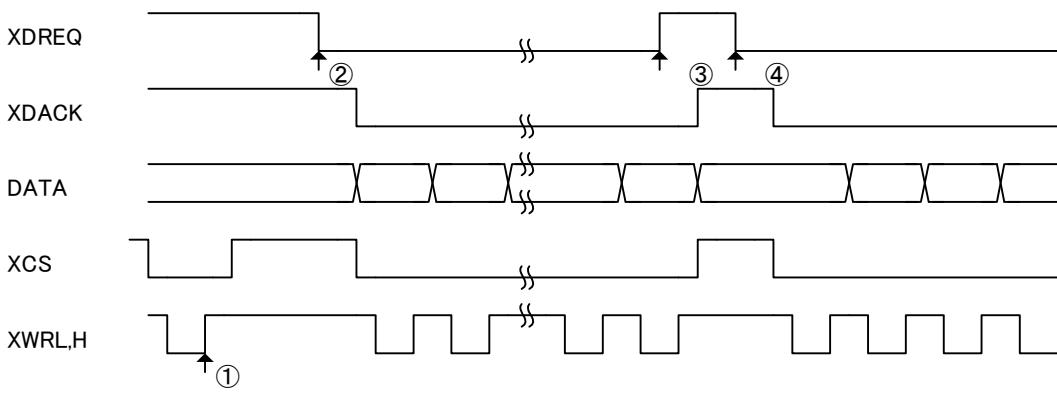

| 1.7.3.2.5 | フリーランモード(ライト) .....              | 151 |

| 1.7.3.2.6 | フリーランモード(リード) .....              | 151 |

|           |                                                                                      |            |

|-----------|--------------------------------------------------------------------------------------|------------|

| 1.7.3.2.7 | REQアサートカウントオプション(ライト) .....                                                          | 152        |

| 1.7.3.2.8 | REQアサートカウントオプション(リード) .....                                                          | 153        |

| 1.7.3.2.9 | DMAのFIFOアクセス端数処理 .....                                                               | 153        |

| <b>2.</b> | <b>レジスタマップ .....</b>                                                                 | <b>154</b> |

| 2.1       | レジスタ構成 .....                                                                         | 154        |

| 2.2       | 初期レジスタマップ .....                                                                      | 155        |

| 2.3       | ポート0 レジスタマップ .....                                                                   | 156        |

| 2.3.1     | デバイス／ホスト共通レジスタマップ .....                                                              | 156        |

| 2.3.2     | デバイスレジスタマップ .....                                                                    | 162        |

| 2.3.3     | ホストレジスタマップ .....                                                                     | 166        |

| 2.4       | ポート1 レジスタマップ .....                                                                   | 171        |

| 2.4.1     | デバイス／ホスト共通レジスタマップ .....                                                              | 171        |

| 2.4.2     | ホストレジスタマップ .....                                                                     | 177        |

| <b>3.</b> | <b>レジスタ詳細説明 .....</b>                                                                | <b>182</b> |

| 3.1       | デバイス／ホスト共通レジスタ詳細説明 .....                                                             | 182        |

| 3.1.1     | Port0:000h / Port1:200h <i>MainIntStat (Main Interrupt Status)</i> .....             | 183        |

| 3.1.2     | Port0:001h / Port1:N/A <i>USB_DeviceIntStat (USB Device Interrupt Status)</i> .....  | 185        |

| 3.1.3     | Port0:002h / Port1:202h <i>USB_HostIntStat (USB Host Interrupt Status)</i> .....     | 187        |

| 3.1.4     | Port0:003h / Port1:203h <i>CPU_IntStat (CPU Interrupt Status)</i> .....              | 189        |

| 3.1.5     | Port0:004h / Port1:204h <i>FIFO_IntStat (FIFO Interrupt Status)</i> .....            | 190        |

| 3.1.6     | Port0:006h / Port1:206h <i>RootIntStat (Root Interrupt Status)</i> .....             | 191        |

| 3.1.7     | Port0:008h / Port1:208h <i>MainIntEnb (Main Interrupt Enable)</i> .....              | 192        |

| 3.1.8     | Port0:009h / Port1:N/A <i>USB_DeviceIntEnb (Device Interrupt Enable)</i> .....       | 193        |

| 3.1.9     | Port0:00Ah / Port1:20Ah <i>USB_HostIntEnb (Host Interrupt Enable)</i> .....          | 194        |

| 3.1.10    | Port0:00Bh / Port1:20Bh <i>CPU_IntEnb (CPU Interrupt Enable)</i> .....               | 195        |

| 3.1.11    | Port0:00Ch / Port1:20Ch <i>FIFO_IntEnb (FIFO Interrupt Enable)</i> .....             | 196        |

| 3.1.12    | Port0:010h / Port1:210h <i>RevisionNum (Revision Number)</i> .....                   | 197        |

| 3.1.13    | Port0:011h / Port1:211h <i>ChipReset (Chip Reset)</i> .....                          | 198        |

| 3.1.14    | Port0:012h / Port1:212h <i>PM_Control (Power Management Control)</i> .....           | 199        |

| 3.1.15    | Port0:014h-015h / Port1:214h-215h <i>WakeupTim_H,L (Wakeup Time High, Low)</i> ..... | 201        |

| 3.1.16    | Port0:016h / Port1:216h <i>H_USB_Control (Host USB Control)</i> .....                | 202        |

| 3.1.17    | Port0:017h / Port1:217h <i>H_XcvrControl (Host Xcvr Control)</i> .....               | 203        |

| 3.1.18    | Port0:018h / Port1:N/A <i>D_USB_Status (Device USB Status)</i> .....                 | 205        |

| 3.1.19    | Port0:019h / Port1:219h <i>H_USB_Status (Host USB Status)</i> .....                  | 206        |

| 3.1.20    | Port0:01Bh / Port1 <i>MTM_Config (Multi Transceiver Macro Config)</i> .....          | 207        |

| 3.1.21    | Port0:01Fh / Port1:21Fh <i>HostDeviceSel (Host Device Select)</i> .....              | 208        |

| 3.1.22    | Port0:020h / Port1:220h <i>FIFO_Rd_0 (FIFO Read 0)</i> .....                         | 209        |

|        |                                   |                                                         |     |

|--------|-----------------------------------|---------------------------------------------------------|-----|

| 3.1.23 | Port0:021h / Port1:221h           | FIFO_Rd_1 (FIFO Read 1) .....                           | 209 |

| 3.1.24 | Port0:022h / Port1:222h           | FIFO_Wr_0(FIFO Write 0).....                            | 210 |

| 3.1.25 | Port0:023h / Port1:223h           | FIFO_Wr_1(FIFO Write 1).....                            | 210 |

| 3.1.26 | Port0:024h-025h / Port1:224h-225h | FIFO_RdRemain_H.L<br>(FIFO Read Remain High, Low) ..... | 211 |

| 3.1.27 | Port0:026h-027h / Port1:226h-227h | FIFO_WrRemain_H.L (FIFO Write Remain High, Low) ...     | 212 |

| 3.1.28 | Port0:028h / Port1:228h           | FIFO_BytRd(FIFO Byte Read) .....                        | 213 |

| 3.1.29 | Port0:02Ah / Port1:22Ah           | FIFO_BytWr(FIFO Byte Write).....                        | 214 |

| 3.1.30 | Port0:030h-031h / Port1:230h-231h | RAM_RdAdrs_H,L (RAM Read Address High, Low) ....        | 215 |

| 3.1.31 | Port0:032h / Port1:232h           | RAM_RdControl (RAM Read Control) .....                  | 216 |

| 3.1.32 | Port0:035h / Port1:235h           | RAM_RdCount (RAM Read Counter) .....                    | 217 |

| 3.1.33 | Port0:038h-039h / Port1:238h-239h | RAM_WrAdrs_H,L (RAM Write Address High, Low) ...        | 218 |

| 3.1.34 | Port0:03Ah / Port1:23Ah           | RAM_WrDoor_0 (RAM Write Door 0).....                    | 219 |

| 3.1.35 | Port0:03Bh / Port1:23Bh           | RAM_WrDoor_1 (RAM Write Door 1).....                    | 219 |

| 3.1.36 | Port0:040h / Port1:240h           | RAM_Rd_00 (RAM Read 00).....                            | 220 |

| 3.1.37 | Port0:041h / Port1:241h           | RAM_Rd_01 (RAM Read 01).....                            | 220 |

| 3.1.38 | Port0:042h / Port1:242h           | RAM_Rd_02 (RAM Read 02).....                            | 220 |

| 3.1.39 | Port0:043h / Port1:243h           | RAM_Rd_03 (RAM Read 03).....                            | 220 |

| 3.1.40 | Port0:044h / Port1:244h           | RAM_Rd_04 (RAM Read 04).....                            | 220 |

| 3.1.41 | Port0:045h / Port1:245h           | RAM_Rd_05 (RAM Read 05).....                            | 220 |

| 3.1.42 | Port0:046h / Port1:246h           | RAM_Rd_06 (RAM Read 06).....                            | 220 |

| 3.1.43 | Port0:047h / Port1:247h           | RAM_Rd_07 (RAM Read 07).....                            | 220 |

| 3.1.44 | Port0:048h / Port1:248h           | RAM_Rd_08 (RAM Read 08).....                            | 220 |

| 3.1.45 | Port0:049h / Port1:249h           | RAM_Rd_09 (RAM Read 09).....                            | 220 |

| 3.1.46 | Port0:04Ah / Port1:24Ah           | RAM_Rd_0A (RAM Read 0A) .....                           | 220 |

| 3.1.47 | Port0:04Bh / Port1:24Bh           | RAM_Rd_0B (RAM Read 0B) .....                           | 220 |

| 3.1.48 | Port0:04Ch / Port1:24Ch           | RAM_Rd_0C (RAM Read 0C) .....                           | 220 |

| 3.1.49 | Port0:04Dh / Port1:24Dh           | RAM_Rd_0D (RAM Read 0D) .....                           | 220 |

| 3.1.50 | Port0:04Eh / Port1:24Eh           | RAM_Rd_0E (RAM Read 0E).....                            | 220 |

| 3.1.51 | Port0:04Fh / Port1:24Fh           | RAM_Rd_0F (RAM Read 0F).....                            | 220 |

| 3.1.52 | Port0:050h / Port1:250h           | RAM_Rd_10 (RAM Read 10).....                            | 220 |

| 3.1.53 | Port0:051h / Port1:251h           | RAM_Rd_11 (RAM Read 11).....                            | 220 |

| 3.1.54 | Port0:052h / Port1:252h           | RAM_Rd_12 (RAM Read 12).....                            | 220 |

| 3.1.55 | Port0:053h / Port1:253h           | RAM_Rd_13 (RAM Read 13).....                            | 220 |

| 3.1.56 | Port0:054h / Port1:254h           | RAM_Rd_14 (RAM Read 14).....                            | 220 |

| 3.1.57 | Port0:055h / Port1:255h           | RAM_Rd_15 (RAM Read 15).....                            | 220 |

| 3.1.58 | Port0:056h / Port1:256h           | RAM_Rd_16 (RAM Read 16).....                            | 220 |

| 3.1.59 | Port0:057h / Port1:257h           | RAM_Rd_17 (RAM Read 17).....                            | 220 |

|        |                                   |                                                                         |     |

|--------|-----------------------------------|-------------------------------------------------------------------------|-----|

| 3.1.60 | Port0:058h / Port1:258h           | RAM_Rd_18 (RAM Read 18).....                                            | 220 |

| 3.1.61 | Port0:059h / Port1:259h           | RAM_Rd_19 (RAM Read 19).....                                            | 220 |

| 3.1.62 | Port0:05Ah / Port1:25Ah           | RAM_Rd_1A (RAM Read 1A) .....                                           | 220 |

| 3.1.63 | Port0:05Bh / Port1:25Bh           | RAM_Rd_1B (RAM Read 1B).....                                            | 220 |

| 3.1.64 | Port0:05Ch / Port1:25Ch           | RAM_Rd_1C (RAM Read 1C).....                                            | 220 |

| 3.1.65 | Port0:05Dh / Port1:25Dh           | RAM_Rd_1D (RAM Read 1D).....                                            | 220 |

| 3.1.66 | Port0:05Eh / Port1:25Eh           | RAM_Rd_1E (RAM Read 1E).....                                            | 220 |

| 3.1.67 | Port0:05Fh / Port1:25Fh           | RAM_Rd_1F (RAM Read 1F).....                                            | 220 |

| 3.1.68 | Port0:061h / Port1:261h           | DMA_Config (DMA Config) .....                                           | 222 |

| 3.1.69 | Port0:062h / Port1:262h           | DMA_Control (DMA Control).....                                          | 224 |

| 3.1.70 | Port0:064h-065h / Port1:264h-265h | DMA_Remain_H,L (DMA FIFO Remain High, Low)....                          | 225 |

| 3.1.71 | Port0:068h-069h / Port1:268h-269h | DMA_Count_HH,HL<br>(DMA Transfer Byte Counter High/High, High/Low)..... | 226 |

| 3.1.72 | Port0:06Ah-06Bh / Port1:26Ah-26Bh | DMA_Count_LH,LL<br>(DMA Transfer Byte Counter Low/High, Low/Low) .....  | 226 |

| 3.1.73 | Port0:06Ch / Port1:26Ch           | DMA_RdData_0 (DMA Read Data 0) .....                                    | 228 |

| 3.1.74 | Port0:06Dh / Port1:26Dh           | DMA_RdData_1 (DMA Read Data 1).....                                     | 228 |

| 3.1.75 | Port0:06Eh / Port1:26Eh           | DMA_WrData_0 (DMA Write Data 0).....                                    | 229 |

| 3.1.76 | Port0:06Fh / Port1:26Fh           | DMA_WrData_1 (DMA Write Data 1).....                                    | 229 |

| 3.1.77 | Port0:071h / Port1:271h           | <i>ModeProtect (Mode Protection)</i> .....                              | 230 |

| 3.1.78 | Port0:073h / Port1:273h           | <i>ClkSelect (Clock Select)</i> .....                                   | 231 |

| 3.1.79 | 075h                              | <i>CPU_Config (CPU Configuration)</i> .....                             | 232 |

| 3.1.80 | Port0:07E-07Fh / Port1:27Eh-27Fh  | <i>CPUIF_MODE (CPUIF Mode)</i> .....                                    | 234 |

| 3.1.81 | Port0:080h-081h / Port1:280h-281h | AREA0StartAdrs_H,L<br>(AREA 0 Start Address High, Low).....             | 235 |

| 3.1.82 | Port0:084h-085h / Port1:284h-285h | AREA1StartAdrs_H,L<br>(AREA 1 Start Address High, Low).....             | 235 |

| 3.1.83 | Port0:088h-089h / Port1:288h-289h | AREA2StartAdrs_H,L<br>(AREA 2 Start Address High, Low).....             | 235 |

| 3.1.84 | Port0:08Ch-08Dh / Port1:28Ch-28Dh | AREA3StartAdrs_H,L<br>(AREA 3 Start Address High, Low).....             | 235 |

| 3.1.85 | Port0:090h-091h / Port1:290h-291h | AREA4StartAdrs_H,L<br>(AREA 4 Start Address High, Low).....             | 235 |

| 3.1.86 | Port0:094h-095h / Port1:294h-295h | AREA5StartAdrs_H,L<br>(AREA 5 Start Address High, Low).....             | 235 |

| 3.1.87 | Port0:082h-083h / Port1:282h-283h | AREA0EndAdrs_H,L<br>(AREA 0 End Address High, Low).....                 | 237 |

| 3.1.88 | Port0:086h-087h / Port1:286h-287h | AREA1EndAdrs_H,L<br>(AREA 1 End Address High, Low).....                 | 237 |

| 3.1.89 | Port0:08Ah-08Bh / Port1:28Ah-28Bh | AREA2EndAdrs_H,L<br>(AREA 2 End Address High, Low).....                 | 237 |

|         |                                   |                                                                             |     |

|---------|-----------------------------------|-----------------------------------------------------------------------------|-----|

| 3.1.90  | Port0:08Eh-08Fh / Port1:28Eh-28Fh | AREA3EndAdrs_H,L<br>(AREA 3 End Address High, Low).....                     | 237 |

| 3.1.91  | Port0:092h-093h / Port1:292h-293h | AREA4EndAdrs_H,L<br>(AREA 4 End Address High, Low).....                     | 237 |

| 3.1.92  | Port0:096h-097h / Port1:296h-297h | AREA5EndAdrs_H,L<br>(AREA 5 End Address High, Low).....                     | 237 |

| 3.1.93  | Port0:09Fh / Port1:29Fh           | AREAnFIFO_Clr (AREA n FIFO Clear) .....                                     | 239 |

| 3.1.94  | Port0:0A0h / Port1:2A0h           | AREA0Join_0 (AREA 0 Join 0) .....                                           | 240 |

| 3.1.95  | Port0:0A2h / Port1:2A2h           | AREA1Join_0 (AREA 1 Join 0) .....                                           | 240 |

| 3.1.96  | Port0:0A4h / Port1:2A4h           | AREA2Join_0 (AREA 2 Join 0) .....                                           | 240 |

| 3.1.97  | Port0:0A6h / Port1:2A6h           | AREA3Join_0 (AREA 3 Join 0) .....                                           | 240 |

| 3.1.98  | Port0:0A8h / Port1:2A8h           | AREA4Join_0 (AREA 4 Join 0) .....                                           | 240 |

| 3.1.99  | Port0:0AAh / Port1:2Aah           | AREA5Join_0 (AREA 5 Join 0) .....                                           | 240 |

| 3.1.100 | Port0:0A1h / Port1:2A1h           | AREA0Join_1 (AREA 0 Join 1) .....                                           | 241 |

| 3.1.101 | Port0:0A3h / Port1:2A3h           | AREA1Join_1 (AREA 1 Join 1) .....                                           | 241 |

| 3.1.102 | Port0:0A5h / Port1:2A5h           | AREA2Join_1 (AREA 2 Join 1) .....                                           | 241 |

| 3.1.103 | Port0:0A7h / Port1:2A7h           | AREA3Join_1 (AREA 3 Join 1) .....                                           | 241 |

| 3.1.104 | Port0:0A9h / Port1:2A9h           | AREA4Join_1 (AREA 4 Join 1) .....                                           | 241 |

| 3.1.105 | Port0:0ABh / Port1:2Abh           | AREA5Join_1 (AREA 5 Join 1) .....                                           | 241 |

| 3.1.106 | Port0:0AEh / Port1:2Aeh           | ClrAREAnJoin_0 (Clear AREA n Join 0) .....                                  | 243 |

| 3.1.107 | Port0:0AFh / Port1:2Afh           | ClrAREAnJoin_1 (Clear AREA n Join 1) .....                                  | 244 |

| 3.2     | デバイスレジスタ詳細説明                      | .....                                                                       | 245 |

| 3.2.1   | Port0:0B0h / Port1:N/A            | D_SIE_IntStat (Device SIE Interrupt Status) .....                           | 246 |

| 3.2.2   | Port0:0B3h / Port1:N/A            | D_BulkIntStat (Device Bulk Interrupt Status) .....                          | 248 |

| 3.2.3   | Port0:0B4h / Port1:N/A            | D_EPrIntStat (Device EPr Interrupt Status) .....                            | 249 |

| 3.2.4   | Port0:0B5h / Port1:N/A            | D_EP0IntStat (Device EP0 Interrupt Status) .....                            | 251 |

| 3.2.5   | Port0:0B6h / Port1:N/A            | D_EPaIntStat (Device EPa Interrupt Status) .....                            | 253 |

| 3.2.6   | Port0:0B7h / Port1:N/A            | D_EPbIntStat (Device EPb Interrupt Status) .....                            | 253 |

| 3.2.7   | Port0:0B8h / Port1:N/A            | D_EPcIntStat (Device EPc Interrupt Status) .....                            | 253 |

| 3.2.8   | Port0:0B9h / Port1:N/A            | D_EPdIntStat (Device EPd Interrupt Status) .....                            | 253 |

| 3.2.9   | Port0:0BAh / Port1:N/A            | D_EPeIntStat (Device EPe Interrupt Status) .....                            | 253 |

| 3.2.10  | Port0:0BCh-0BDh / Port1:N/A       | D_AlarmIN_IntStat_H,L<br>(Device AlarmIN Interrupt Status High, Low).....   | 255 |

| 3.2.11  | Port0:0BEh-0BFh / Port1:N/A       | D_AlarmOUT_IntStat_H,L<br>(Device AlarmOUT Interrupt Status High, Low)..... | 256 |

| 3.2.12  | Port0:0C0h / Port1:N/A            | D_SIE_IntEnb (Device SIE Interrupt Enable) .....                            | 257 |

| 3.2.13  | Port0:0C3h / Port1:N/A            | D_BulkIntEnb (Device Bulk Interrupt Enable) .....                           | 258 |

| 3.2.14  | Port0:0C4h / Port1:N/A            | D_EPrIntEnb (Device EPr Interrupt Enable) .....                             | 259 |

| 3.2.15  | Port0:0C5h / Port1:N/A            | D_EP0IntEnb (Device EP0 Interrupt Enable) .....                             | 260 |

| 3.2.16  | Port0:0C6h / Port1:N/A            | D_EPaIntEnb (Device EPa Interrupt Enable) .....                             | 261 |

|        |                             |                                                                             |     |

|--------|-----------------------------|-----------------------------------------------------------------------------|-----|

| 3.2.17 | Port0:0C7h / Port1:N/A      | D_EPbIntEnb (Device EPb Interrupt Enable) .....                             | 261 |

| 3.2.18 | Port0:0C8h / Port1:N/A      | D_EPcIntEnb (Device EPc Interrupt Enable) .....                             | 261 |

| 3.2.19 | Port0:0C9h / Port1:N/A      | D_EPdIntEnb (Device EPd Interrupt Enable) .....                             | 261 |

| 3.2.20 | Port0:0CAh / Port1:N/A      | D_EPeIntEnb (Device EPe Interrupt Enable) .....                             | 261 |

| 3.2.21 | Port0:0CCh-0CDh / Port1:N/A | D_AlarmIN_IntEnb_H,L<br>(Device AlarmIN Interrupt Enable High, Low) .....   | 262 |

| 3.2.22 | Port0:0CEh-0CFh / Port1:N/A | D_AlarmOUT_IntEnb_H,L<br>(Device AlarmOUT Interrupt Enable High, Low) ..... | 263 |

| 3.2.23 | Port0:0D0h / Port1:N/A      | D_NegoControl (Device Negotiation Control) .....                            | 264 |

| 3.2.24 | Port0:0D3h / Port1:N/A      | D_XcvrControl (Device Xcvr Control) .....                                   | 266 |

| 3.2.25 | Port0:0D4h / Port1:N/A      | D_USB_Test (Device USB_Test) .....                                          | 267 |

| 3.2.26 | Port0:0D6h / Port1:N/A      | D_EPnControl (Device Endpoint Control) .....                                | 269 |

| 3.2.27 | Port0:0D8h / Port1:N/A      | D_BulkOnlyControl (Device BulkOnly Control) .....                           | 270 |

| 3.2.28 | Port0:0D9h / Port1:N/A      | D_BulkOnlyConfig (Device BulkOnly Configuration) .....                      | 271 |

| 3.2.29 | Port0:0E0h / Port1:N/A      | D_EP0SETUP_0 (Device EP0 SETUP 0) .....                                     | 273 |

| 3.2.30 | Port0:0E1h / Port1:N/A      | D_EP0SETUP_1 (Device EP0 SETUP 1) .....                                     | 273 |

| 3.2.31 | Port0:0E2h / Port1:N/A      | D_EP0SETUP_2 (Device EP0 SETUP 2) .....                                     | 273 |

| 3.2.32 | Port0:0E3h / Port1:N/A      | D_EP0SETUP_3 (Device EP0 SETUP 3) .....                                     | 273 |

| 3.2.33 | Port0:0E4h / Port1:N/A      | D_EP0SETUP_4 (Device EP0 SETUP 4) .....                                     | 273 |

| 3.2.34 | Port0:0E5h / Port1:N/A      | D_EP0SETUP_5 (Device EP0 SETUP 5) .....                                     | 273 |

| 3.2.35 | Port0:0E6h / Port1:N/A      | D_EP0SETUP_6 (Device EP0 SETUP 6) .....                                     | 273 |

| 3.2.36 | Port0:0E7h / Port1:N/A      | D_EP0SETUP_7 (Device EP0 SETUP 7) .....                                     | 273 |

| 3.2.37 | Port0:0E8h / Port1:N/A      | D_USB_Address (Device USB Address) .....                                    | 274 |

| 3.2.38 | Port0:0EAh / Port1:N/A      | D_SETUP_Control (Device SETUP Control) .....                                | 275 |

| 3.2.39 | Port0:0EEh-0EFh / Port1:N/A | D_FrameNumber_H,L (Device FrameNumber High, Low) .....                      | 276 |

| 3.2.40 | Port0:0F0h / Port1:N/A      | D_EP0MaxSize (Device EP0 Max Packet Size) .....                             | 277 |

| 3.2.41 | Port0:0F1h / Port1:N/A      | D_EP0Control (Device EP0 Control) .....                                     | 278 |

| 3.2.42 | Port0:0F2h / Port1:N/A      | D_EP0ControlIN (Device EP0 Control IN) .....                                | 279 |

| 3.2.43 | Port0:0F3h / Port1:N/A      | D_EP0ControlOUT (Device EP0 Control OUT) .....                              | 281 |

| 3.2.44 | Port0:0F8h-0F9h / Port1:N/A | D_EPaMaxSize_H,L (Device EPa Max Packet Size High, Low) .....               | 283 |

| 3.2.45 | Port0:100h-101h / Port1:N/A | D_EPbMaxSize_H,L (Device EPb Max Packet Size High, Low) .....               | 283 |

| 3.2.46 | Port0:108h-109h / Port1:N/A | D_EPcMaxSize_H,L (Device EPc Max Packet Size High, Low) .....               | 283 |

| 3.2.47 | Port0:110h-111h / Port1:N/A | D_EPdMaxSize_H,L (Device EPd Max Packet Size High, Low) .....               | 283 |

| 3.2.48 | Port0:118h-119h / Port1:N/A | D_EPeMaxSize_H,L (Device EPe Max Packet Size High, Low) .....               | 283 |

| 3.2.49 | Port0:0FAh / Port1:N/A      | D_EPaConfig (Device EPa Configuration) .....                                | 284 |

| 3.2.50 | Port0:102h / Port1:N/A      | D_EPbConfig (Device EPb Configuration) .....                                | 284 |

| 3.2.51 | Port0:10Ah / Port1:N/A      | D_EPcConfig (Device EPc Configuration) .....                                | 284 |

| 3.2.52 | Port0:112h / Port1:N/A      | D_EPdConfig (Device EPd Configuration) .....                                | 284 |

| 3.2.53 | Port0:11Ah / Port1:N/A      | D_EPeConfig (Device EPe Configuration) .....                                | 284 |

|        |                             |                                                                               |     |

|--------|-----------------------------|-------------------------------------------------------------------------------|-----|

| 3.2.54 | Port0:0FCh / Port1:N/A      | D_EPaControl (Device EPa Control).....                                        | 286 |

| 3.2.55 | Port0:104h / Port1:N/A      | D_EPbControl (Device EPb Control) .....                                       | 286 |

| 3.2.56 | Port0:10Ch / Port1:N/A      | D_EPcControl (Device EPc Control).....                                        | 286 |

| 3.2.57 | Port0:114h / Port1:N/A      | D_EPdControl (Device EPd Control) .....                                       | 286 |

| 3.2.58 | Port0:11Ch / Port1:N/A      | D_EPeControl (Device EPc Control).....                                        | 286 |

| 3.2.59 | Port0:120h-121h / Port1:N/A | D_DescAdrs_H,L (Device Descriptor Address High, Low).....                     | 288 |

| 3.2.60 | Port0:122h-123h / Port1:N/A | D_DescSize_H,L (Device Descriptor Size High, Low).....                        | 289 |

| 3.2.61 | Port0:126h / Port1:N/A      | D_EP_DMA_Ctrl (Device EP DMA Control) .....                                   | 290 |

| 3.2.62 | Port0:128h-129h / Port1:N/A | D_EnEP_IN_H,L (Device Enable Endpoint-IN High, Low).....                      | 291 |

| 3.2.63 | Port0:12Ah-12Bh / Port1:N/A | D_EnEP_OUT_H,L (Device Enable Endpoint-OUT High, Low)...                      | 292 |

| 3.2.64 | Port0:12Ch-12Dh / Port1:N/A | D_EnEP_IN_ISO_H,L<br>(Device Enable Endpoint-IN Isocronouse High, Low).....   | 293 |

| 3.2.65 | Port0:12Eh-12Fh / Port1:N/A | D_EnEP_OUT_ISO_H,L<br>(Device Enable Endpoint-OUT Isocronouse High, Low)..... | 294 |

| 3.3    | ホストレジスタ詳細説明 .....           |                                                                               | 295 |

| 3.3.1  | Port0:140h / Port1:340h     | H_SIE_IntStat_0 (Host SIE Interrupt Status 0) .....                           | 296 |

| 3.3.2  | Port0:141h / Port1:341h     | H_SIE_IntStat_1 (SIE Host Interrupt Status 1) .....                           | 298 |

| 3.3.3  | Port0:143h / Port1:343h     | H_FrameIntStat (Host Frame Interrupt Status ).....                            | 299 |

| 3.3.4  | Port0:144h / Port1:344h     | H_CHrIntStat (Host CHr Interrupt Status) .....                                | 300 |

| 3.3.5  | Port0:145h / Port1:345h     | H_CH0IntStat (Host CH0 Interrupt Status).....                                 | 301 |

| 3.3.6  | Port0:146h / Port1:346h     | H_CHaIntStat (Host CHa Interrupt Status) .....                                | 303 |

| 3.3.7  | Port0:147h / Port1:347h     | H_CHbIntStat (Host CHb Interrupt Status).....                                 | 305 |

| 3.3.8  | Port0:148h / Port1:348h     | H_CHcIntStat (Host CHc Interrupt Status) .....                                | 305 |

| 3.3.9  | Port0:149h / Port1:349h     | H_CHdIntStat (Host CHd Interrupt Status).....                                 | 305 |

| 3.3.10 | Port0:14Ah / Port1:34Ah     | H_CHeIntStat (Host CHe Interrupt Status).....                                 | 305 |

| 3.3.11 | Port0:150h / Port1:350h     | H_SIE_IntEnb_0 (Host SIE Interrupt Enable) .....                              | 307 |

| 3.3.12 | Port0:151h / Port1:351h     | H_SIE_IntEnb_1(SIE Host Interrupt Enable 1) .....                             | 308 |

| 3.3.13 | Port0:153h / Port1:353h     | H_FrameIntEnb(Host Frame Interrupt Enable ) .....                             | 309 |

| 3.3.14 | Port0:154h / Port1:354h     | H_CHrIntEnb(Host CHr Interrupt Enable).....                                   | 310 |

| 3.3.15 | Port0:155h / Port1:355h     | H_CH0IntEnb(Host CH0 Interrupt Enable) .....                                  | 311 |

| 3.3.16 | Port0:156h / Port1:356h     | H_CHaIntEnb (Host CHa Interrupt Enable).....                                  | 312 |

| 3.3.17 | Port0:157h / Port1:357h     | H_CHbIntEnb (Host CHb Interrupt Enable) .....                                 | 313 |

| 3.3.18 | Port0:158h / Port1:358h     | H_CHcIntEnb (Host CHc Interrupt Enable).....                                  | 313 |

| 3.3.19 | Port0:159h / Port1:359h     | H_CHdIntEnb (Host CHd Interrupt Enable) .....                                 | 313 |

| 3.3.20 | Port0:15Ah / Port1:35Ah     | H_CHeIntEnb (Host CHe Interrupt Enable) .....                                 | 313 |

| 3.3.21 | Port0:160h / Port1:360h     | H_NegoControl_0 (Host NegoControl 0).....                                     | 314 |

| 3.3.22 | Port0:162h / Port1:362h     | H_NegoControl_1 (Host NegoControl 1).....                                     | 316 |

| 3.3.23 | Port0:164h / Port1:364h     | H_USB_Test (Host USB_Test).....                                               | 317 |

| 3.3.24 | Port0:170h / Port1:370h     | H_CH0SETUP_0 (Host CH0 SETUP 0).....                                          | 319 |

|        |                                   |                                                                                         |     |

|--------|-----------------------------------|-----------------------------------------------------------------------------------------|-----|

| 3.3.25 | Port0:171h / Port1:371h           | H_CH0SETUP_1 (Host CH0 SETUP 1).....                                                    | 319 |

| 3.3.26 | Port0:172h / Port1:372h           | H_CH0SETUP_2 (Host CH0 SETUP 2).....                                                    | 319 |

| 3.3.27 | Port0:173h / Port1:373h           | H_CH0SETUP_3 (Host CH0 SETUP 3).....                                                    | 319 |

| 3.3.28 | Port0:174h / Port1:374h           | H_CH0SETUP_4 (Host CH0 SETUP 4).....                                                    | 319 |

| 3.3.29 | Port0:175h / Port1:375h           | H_CH0SETUP_5 (Host CH0 SETUP 5).....                                                    | 319 |

| 3.3.30 | Port0:176h / Port1:376h           | H_CH0SETUP_6 (Host CH0 SETUP 6).....                                                    | 319 |

| 3.3.31 | Port0:177h / Port1:377h           | H_CH0SETUP_7 (Host CH0 SETUP 7).....                                                    | 319 |

| 3.3.32 | Port0:17Eh-17Fh / Port1:37Eh-37Fh | H_FrameNumber_H,L<br>(Host FrameNumber High, Low).....                                  | 320 |

| 3.3.33 | Port0:180h / Port1:380h           | H_CH0Config_0(Host Channel 0 Configuration0).....                                       | 321 |

| 3.3.34 | Port0:181h / Port1:381h           | H_CH0Config_1(Host Channel 0 Configuration1).....                                       | 323 |

| 3.3.35 | Port0:183h / Port1:383h           | H_CH0MaxPktSize (Host Channel 0 Max Packet Size) .....                                  | 324 |

| 3.3.36 | Port0:186h-187h / Port1:386h-387h | H_CH0TotalSize_H,L<br>(Host Channel 0 Total Size High, Low).....                        | 325 |

| 3.3.37 | Port0:188h / Port1:388h           | H_CH0HubAdrs (Host Channel 0 Hub Address) .....                                         | 326 |

| 3.3.38 | Port0:189h / Port1:389h           | H_CH0FuncAdrs (Host Channel 0 Function Address).....                                    | 327 |

| 3.3.39 | Port0:18Bh / Port1:38Bh           | H_CTL_SupportControl (Host ControlTransfer Support Control).....                        | 328 |

| 3.3.40 | Port0:18Eh / Port1:38Eh           | H_CH0ConditionCode (Host Channel 0 Condition Code).....                                 | 329 |

| 3.3.41 | Port0:190h / Port1:390h           | H_CHaConfig_0(Host Channel a Configuration0) .....                                      | 330 |

| 3.3.42 | Port0:191h / Port1:391h           | H_CHaConfig_1(Host Channel a Configuration1) .....                                      | 332 |

| 3.3.43 | Port0:192h-193h / Port1:392h-393h | H_CHaMaxPktSize_H,L<br>(Host Channel a Max Packet Size High, Low) .....                 | 333 |

| 3.3.44 | Port0:194h-195h / Port1:394h-395h | H_CHaTotalSize_HH,HL<br>(Host Channel a Total Size High-High, High-Low).....            | 334 |

| 3.3.45 | Port0:196h-197h / Port1:396h-397h | H_CHaTotalSize_LH,LL<br>(Host Channel a Total Size Low-High, Low-Low).....              | 334 |

| 3.3.46 | Port0:198h / Port1:398h           | H_CHaHubAdrs (Host Channel a Hub Address).....                                          | 336 |

| 3.3.47 | Port0:199h / Port1:399h           | H_CHaFuncAdrs (Host Channel a Function Address) .....                                   | 337 |

| 3.3.48 | Port0:19Ah / Port1:39Ah           | H_CHaBO_SupportCtl<br>(Host CHa Bulk Only Transfer Support Control) .....               | 338 |

| 3.3.49 | Port0:19Bh / Port1:39Bh           | H_CHaBO_CSW_RcvSize<br>(Host CHa Bulk Only Transfer Support CSW Receive Data Size)..... | 340 |

| 3.3.50 | Port0:19Ch / Port1:39Ch           | H_CHaBO_OUT_EP_Ctl<br>(Host CHa Bulk Only Transfer Support OUT Endpoint Control).....   | 341 |

| 3.3.51 | Port0:19Dh / Port1:39Dh           | H_CHaBO_IN_EP_Ctl<br>(Host CHa Bulk Only Transfer Support IN Endpoint Control).....     | 342 |

| 3.3.52 | Port0:19Eh / Port1:39Eh           | H_CHaConditionCode (Host Channel a Condition Code) .....                                | 343 |

| 3.3.53 | Port0:1A0h / Port1:3A0h           | H_CHbConfig_0(Host Channel b Configuration0) .....                                      | 344 |

| 3.3.54 | Port0:1B0h / Port1:3B0h           | H_CHcConfig_0(Host Channel c Configuration0) .....                                      | 344 |

| 3.3.55 | Port0:1C0h / Port1:3C0h           | H_CHdConfig_0(Host Channel d Configuration0).....                                       | 344 |

| 3.3.56 | Port0:1D0h / Port1:3D0h           | H_CHeConfig_0(Host Channel e Configuration0).....                                       | 344 |

|        |                                   |                                                                               |     |

|--------|-----------------------------------|-------------------------------------------------------------------------------|-----|

| 3.3.57 | Port0:1A1h / Port1:3A1h           | H_CHbConfig_1(Host Channel b Configuration1) .....                            | 346 |

| 3.3.58 | Port0:1B1h / Port1:3B1h           | H_CHcConfig_1(Host Channel c Configuration1) .....                            | 346 |

| 3.3.59 | Port0:1C1h / Port1:3C1h           | H_CHdConfig_1(Host Channel d Configuration1) .....                            | 346 |

| 3.3.60 | Port0:1D1h / Port1:3D1h           | H_CHeConfig_1(Host Channel e Configuration1) .....                            | 346 |

| 3.3.61 | Port0:1A2h-1A3h / Port1:3A2h-3A3h | H_CHbMaxPktSize_H,L<br>(Host Channel b Max Packet Size High, Low) .....       | 348 |

| 3.3.62 | Port0:1B2h-1B3h / Port1:3B2h-3B3h | H_CHcMaxPktSize_H,L<br>(Host Channel c Max Packet Size High, Low) .....       | 348 |

| 3.3.63 | Port0:1C2h-1C3h / Port1:3C2h-3C3h | H_CHdMaxPktSize_H,L<br>(Host Channel d Max Packet Size High, Low) .....       | 348 |

| 3.3.64 | Port0:1D2h-1D3h / Port1:3D2h-3D3h | H_CHeMaxPktSize_H,L<br>(Host Channel e Max Packet Size High, Low) .....       | 348 |

| 3.3.65 | Port0:1A4h-1A5h / Port1:3A4h-3A5h | H_CHbTotalSize_HH,HL<br>(Host Channel b Total Size High-High, High-Low) ..... | 350 |

| 3.3.66 | Port0:1A6h-1A7h / Port1:3A6h-3A7h | H_CHbTotalSize_LH,LL<br>(Host Channel b Total Size Low-High, Low-Low) .....   | 350 |

| 3.3.67 | Port0:1B4h-1B5h / Port1:3B4h-3B5h | H_CHcTotalSize_HH,HL<br>(Host Channel c Total Size High-High, High-Low) ..... | 350 |

| 3.3.68 | Port0:1B6h-1B7h / Port1:3B6h-3B7h | H_CHcTotalSize_LH,LL<br>(Host Channel c Total Size Low-High, Low-Low) .....   | 350 |

| 3.3.69 | Port0:1C4h-1C5h / Port1:3C4h-3C5h | H_CHdTotalSize_HH,HL<br>(Host Channel d Total Size High-High, High-Low) ..... | 350 |

| 3.3.70 | Port0:1C6h-1C7h / Port1:3C6h-3C7h | H_CHdTotalSize_LH,LL<br>(Host Channel d Total Size Low-High, Low-Low) .....   | 350 |

| 3.3.71 | Port0:1D4h-1D5h / Port1:3D4h-3D5h | H_CHeTotalSize_HH,HL<br>(Host Channel e Total Size High-High, High-Low) ..... | 350 |

| 3.3.72 | Port0:1D6h-1D7h / Port1:3D6h-3D7h | H_CHeTotalSize_LH,LL<br>(Host Channel e Total Size Low-High, Low-Low) .....   | 350 |

| 3.3.73 | Port0:1A8h / Port1:3A8h           | H_CHbHubAdrs (Host Channel b Hub Address) .....                               | 352 |

| 3.3.74 | Port0:1B8h / Port1:3B8h           | H_CHcHubAdrs (Host Channel c Hub Address) .....                               | 352 |

| 3.3.75 | Port0:1C8h / Port1:3C8h           | H_CHdHubAdrs (Host Channel d Hub Address) .....                               | 352 |

| 3.3.76 | Port0:1D8h / Port1:3D8h           | H_CHeHubAdrs (Host Channel e Hub Address) .....                               | 352 |

| 3.3.77 | Port0:1A9h / Port1:3A9h           | H_CHbFuncAdrs (Host Channel b Function Address) .....                         | 353 |

| 3.3.78 | Port0:1B9h / Port1:3B9h           | H_CHcFuncAdrs (Host Channel c Function Address) .....                         | 353 |

| 3.3.79 | Port0:1C9h / Port1:3C9h           | H_CHdFuncAdrs (Host Channel d Function Address) .....                         | 353 |

| 3.3.80 | Port0:1D9h / Port1:3D9h           | H_CHeFuncAdrs (Host Channel d Function Address) .....                         | 353 |

| 3.3.81 | Port0:1AAh-1ABh / Port1:3AAh-3ABh | H_CHbInterval_H,L<br>(Host Channel b Interval High, Low) .....                | 354 |

| 3.3.82 | Port0:1BAh-1BBh / Port1:3BAh-3BBh | H_CHcInterval_H,L<br>(Host Channel c Interval High, Low) .....                | 354 |

| 3.3.83 | Port0:1CAh-1CBh / Port1:3CAh-3CBh | H_CHdInterval_H,L<br>(Host Channel d Interval High, Low) .....                | 354 |

|                                            |                                                                                                 |            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------|------------|

| 3.3.84                                     | Port0:1DAh-1DBh / Port1:3DAh-3DBh H_CHeInterval_H,L<br>(Host Channel e Interval High, Low)..... | 354        |

| 3.3.85                                     | Port0:1ACh / Port1:3ACh H_CHbTranPause (Host Channel b Transaction Pause).....                  | 355        |

| 3.3.86                                     | Port0:1BCh / Port1:3BCh H_CHcTranPause (Host Channel c Transaction Pause).....                  | 355        |

| 3.3.87                                     | Port0:1CCh / Port1:3CCh H_CHdTranPause (Host Channel d Transaction Pause) .....                 | 355        |

| 3.3.88                                     | Port0:1DCh / Port1:3DCh H_CHeTranPause (Host Channel e Transaction Pause) .....                 | 355        |

| 3.3.89                                     | Port0:1AEh / Port1:3AEh H_CHbConditionCode (Host Channel b Condition Code) .....                | 356        |

| 3.3.90                                     | Port0:1BEh / Port1:3BEh H_CHcConditionCode (Host Channel c Condition Code) .....                | 356        |

| 3.3.91                                     | Port0:1CEh / Port1:3CEh H_CHdConditionCode (Host Channel d Condition Code).....                 | 356        |

| 3.3.92                                     | Port0:1DEh / Port1:3DEh H_CHeConditionCode (Host Channel e Condition Code).....                 | 356        |

| <b>Appendix A. リトルエンディアンのCPUとの接続 .....</b> |                                                                                                 | <b>358</b> |

## 1. 機能説明

本 LSI の動作について説明します。

以下では、レジスタについて下記のルールで標記します。

- ポート毎のレジスタ区別

本 LSI は、2 つの USB Port のそれぞれに、同一機能のレジスタセットを持ちます。

(Port 1 にはデバイス機能のレジスタ群は有りません。)

特に Port 別の説明が必要な場合に限り、

レジスタ名+(ポート番号)と標記します。

例：「MainIntStat(0)レジスタ」

- 1 アドレス分のレジスタを指す場合の名称

レジスタ名+レジスタと標記します。

例：「MainIntStat レジスタ」

- 個々のビットを指す場合の名称

レジスタ名. ビット名+ビット、或いは、ビット名+ビットと標記します。

例：「MainIntStat.CPU\_IntStat ビット」

- デバイスエンドポイント毎にあるレジスタ

D\_EPx{x=... }～レジスタと標記します。

例：「D\_EPx{x=0,a-e}IntStat レジスタ」

- ホストチャネル毎にあるレジスタ

H\_CHx{x=... }～レジスタと標記します。

例：「H\_CHx{x=0,a-e}IntStat レジスタ」

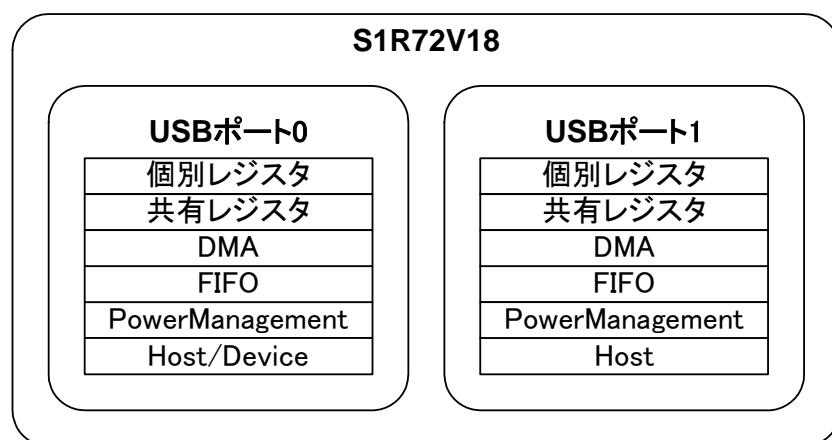

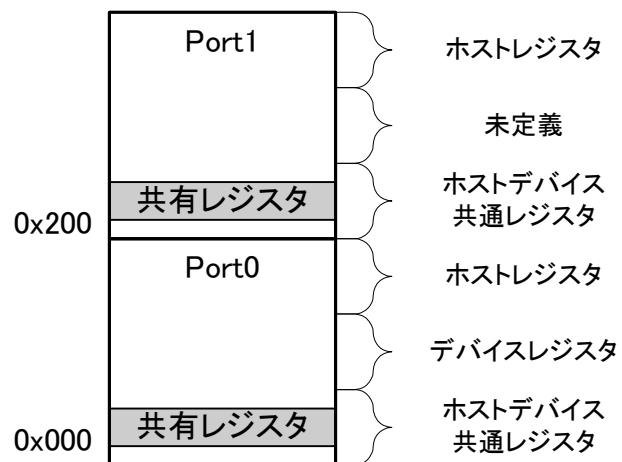

### 1.1 USBポート

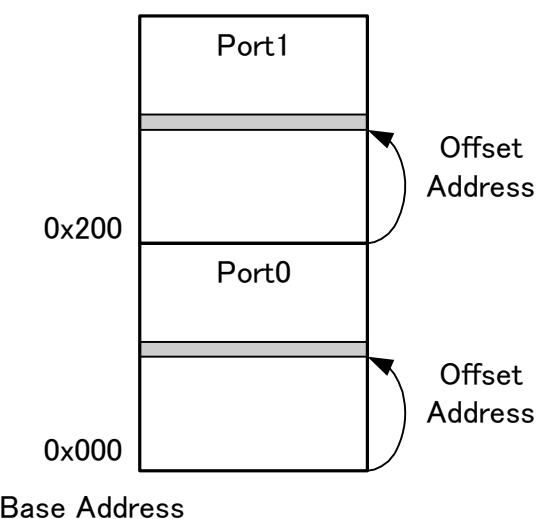

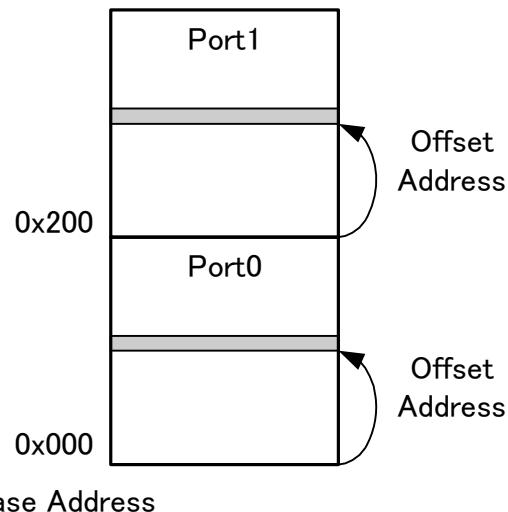

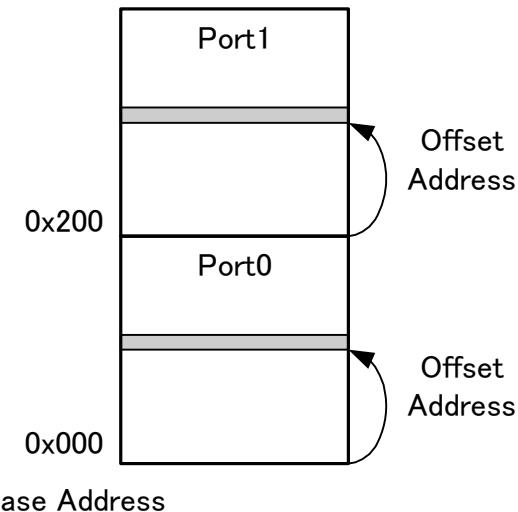

本 LSI は、USB ポートを 2 つ備え、それぞれ USB ポート 0、USB ポート 1 と呼びます。USB ポート 0 では USB ホスト及び USB デバイスの機能を切り替えて使用できます。USB ポート 1 では USB ホストの機能を使用できます。各 USB ポートは、それぞれに USB 機能と制御インターフェイスを持ちます。各ポートに属さないチップ固有の機能は、各ポートの制御インターフェイスの中にミラー配置されている、共有レジスタにより制御します。

図 1-1 ブロックイメージ

# 1. 機能説明

## 1.2 USBデバイス／ホスト選択

USB Port 0 を使用する場合、USB デバイス機能と USB ホスト機能のいずれか一方を選択して下さい。USB Port 1 は USB ホスト機能のみを使用可能です。

USB デバイス機能を選択した場合（以下デバイスマード）、共通レジスタおよびデバイスレジスタのレジスタビット及び機能が有効となります。

USB ホスト機能を選択した場合（以下ホストモード）、共通レジスタおよびホストレジスタのレジスタビット及び機能が有効となります。

### 1.2.1 USBデバイス／ホスト機能選択方法

USB Port 0 では、HostDeviceSel(0).HOSTxDEVICE ビットをクリアした場合にはデバイス機能が、セットした場合にはホスト機能が使用可能となります。ホストモードとデバイスマードとの相互のモード切り替えは、Port 0 のパワーマネジメントステートが SLEEP である時に行えます。USB デバイス／ホスト選択の設定項目を表 1-1 に示します。

表 1-1 USB デバイス／ホスト機能選択の設定項目

| 項目             | レジスタ／ビット                     | 説明                                                                               |

|----------------|------------------------------|----------------------------------------------------------------------------------|

| USB デバイス／ホスト選択 | HostDeviceSel(0).HOSTxDEVICE | USB デバイスマードとホストモードのいずれかを選択します。選択した側のレジスタ、及び機能が使用可能です。<br>1: ホストモード<br>0: デバイスマード |

### 1.2.2 USBポート状態変化検出ステータス

本 LSI には、USB ポート状態の検出機能があります。

本機能は SLEEP / ACTIVE（「1.5 パワーマネージメント機能」項を参照）の両ステートで使用できます。

#### 1.2.2.1 USBポート状態変化検出ステータスの使用例

デバイスポート変化ステータスおよびホストポート変化ステータスの使用例を示します。

##### 1.2.2.1.1 デバイスポート変化ステータス

本ステータスは、USB Port 0 のデバイスマードにおいて、VBUS\_0 端子の状態が変化したことを示します。

デバイスポート変化ステータス関連レジスタを表 1-2 に示します。

表 1-2 デバイスポート変化ステータス関連レジスタ

| 項目                  | レジスタ／ビット                           | 説明                                                                                  |

|---------------------|------------------------------------|-------------------------------------------------------------------------------------|

| VBUS 端子変化ステータス      | USB_DeviceIntStat(0).VBUS_Changed  | デバイスポートの VBUS_0 端子の状態が変化したことを示します。                                                  |

| VBUS 端子変化ステータスイネーブル | USB_DeviceIntEnb(0).EnVBUS_Changed | USB_DeviceIntStat.VBUS_Changed による MainIntStat.USB_DeviceIntStat ビットのアサートを許可／禁止します。 |

| VBUS 端子状態           | D_USB_Status(0).VBUS               | デバイスポートの VBUS_0 端子の状態を示します。                                                         |

デバイスポート変化ステータスを使用する場合、F/W は (1) 、 (2) 、 (4) ~ (7) の処理を行います。

- (1) VBUS 端子変化ステータスをクリアします。また、MainIntEnb.EnUSB\_DeviceIntStat ビットをセットします。(割り込みを使用する場合)

- (2) VBUS 端子変化ステータスイネーブルをセットします。

- (3) VBUS の供給があると、VBUS 端子変化ステータスが発行されます。

- (4) VBUS 端子変化ステータスを確認します。

- (5) VBUS 端子変化ステータスをクリアします。

- (6) VBUS 端子変化ステータスイネーブルをクリアします。

- (7) VBUS 端子状態を確認します。VBUS 端子状態が“1”であれば、VBUS が供給されている（ホストまたはハブが接続されている）状態と判断します。

#### 1.2.2.1.2 ホストポート変化ステータス

本ステータスは、USB Port 0 のホストモード、及び USB Port 1 において、VBUS 給電を制御しているパワードライバの状態を示します。

ホストポート変化ステータス関連レジスタを表 1-3 に示します。

表 1-3 ホストポート変化ステータス関連レジスタ

| 項目                  | レジスタ／ビット                  | 説明                                                                          |

|---------------------|---------------------------|-----------------------------------------------------------------------------|

| VBUS 異常検出ステータス      | USB_HostIntStat.VBUS_Err  | VBUS に異常が発生したことを示します。                                                       |

| VBUS 異常検出ステータスイネーブル | USB_HostIntEnb.EnVBUS_Err | USB_HostIntStat.VBUS_Err による MainIntStat.USB_HostIntStat ビットのアサートを許可／禁止します。 |

| VBUS イネーブル          | H_USB_Control.VBUS_Enb    | 外部 USB パワースイッチをイネーブルにします。                                                   |

| ホストポート VBUS 状態      | H_USB_Status.VBUS_State   | ホストポートの VBUS の状態（正常／異常）を示します。                                               |

VBUS 異常検出ステータスを検出した場合には、直ちに VBUS イネーブルを OFF にして VBUS のドライブを停止してください。

#### 1.2.2.2 信号ライン変化ステータスの使用方法

本ステータスは、USB Port 0 のホストモードにおいて、及び USB Port 1 において、DP 端子 (DP\_0, DP\_1) および DM 端子 (DM\_0, DM\_1) の状態が変化したことを示します。

信号ライン変化ステータス関連レジスタを表 1-4 に示します。

## 1. 機能説明

表 1-4 信号ライン変化ステータス関連レジスタ

| 項目                      | レジスタ/ビット                          | 説明                                                                 |

|-------------------------|-----------------------------------|--------------------------------------------------------------------|

| 信号ライン変化ステータス            | USB_HostIntStat.LineStateChanged  | ホストポートの DP 端子および DM 端子の状態が変化したことを示します。                             |

| 信号ライン変化ステータス割り込みイネーブル   | USB_HostIntEnb.EnLineStateChanged | 信号ライン変化ステータスによる MainIntStat.USB_HostIntStat ビットのアサートを許可／禁止します。     |

| VBUS 異常検出ステータス          | USB_HostIntStat.VBUS_Err          | VBUSFLG 端子(VBUSFLG_0, VBUSFLG_1)をモニタし、VBUS 給電に異常が発生したことを示します。      |

| VBUS 異常検出ステータス割り込みイネーブル | USB_HostIntEnb.EnVBUS_Err         | VBUS 異常検出ステータスによる MainIntStat.USB_HostIntStat ビットのアサートを許可／禁止します。   |

| オペレーションモード              | H_XcvrControl.OpMode[1:0]         | トランシーバマクロのオペレーションモードを設定します。                                        |

| VBUS イネーブル              | H_USB_Control.VBUS_Enb            | 外部 USB パワースイッチをイネーブルにするよう、VBUSEN 端子(VBUSEN_0, VBUSEN_1)から信号を出力します。 |

| ホストポート VBUS 状態          | H_USB_Status.VBUS_State           | ホストポートの VBUSFLG 端子(VBUSFLG_0, VBUSFLG_1)の状態(正常／異常)を示します。           |

| ホストポート信号ライン状態           | H_USB_Status.LineState[1:0]       | USB ケーブル上の信号状態を示します。                                               |

| ホストステート遷移実行             | H_NegoControl_0.AutoMode[3:0]     | 遷移させるホストステートを設定します。                                                |

信号ライン変化ステータスは、USB ホストとして動作中の接続検出ステータスとは異なり、USB ホスト機能を使用していないとき、すなわち、SLEEP ステート(「1.5 パワーマネージメント機能」参照)において、ホストポートの信号ライン変化を検出するための特殊なステータスです。USB ホスト動作時に USB\_HostIntEnb.EnLineStateChanged がイネーブルとなっていると、本ステータスは頻繁にアサートされます。そのため、USB ホストモードでの動作時は USB\_HostIntEnb.EnLineStateChanged をディセーブルにしてください。

また、USB ホストモードでの動作時以外で VBUS 異常検出ステータスを検出した場合には、直ちに VBUS イネーブルを OFF して VBUS のドライブを停止してください。

信号ライン変化ステータスを使用する際に、ファームウェアは(1)～(4)、(6)～(9)の処理を行います。

- (1) 信号ライン変化ステータスおよび VBUS 異常検出ステータスをクリアします。

- (2) 信号ライン変化ステータスイネーブルおよび VBUS 異常検出ステータスイネーブルをセットします。また、MainIntEnb.EnUSB\_HostIntStat ビットをセットします。(割り込みを使用する場合)

- (3) H\_XcvrControl レジスタに 0x93 を設定します。

- (4) VBUS イネーブルを ON します。

- (5) ホストポートにデバイスの接続があるとラインステートが SE0 から変化し、信号ライン変化ステータスが発行されます。

- (6) 信号ライン変化ステータスを確認します。

- (7) 信号ライン変化ステータスをクリアします。

- (8) 信号ライン変化ステータスイネーブルをクリアします。

- (9) ホストポート信号ライン状態を確認します。“01”または“10”であれば、ホストポートにデバイスが接続されている状態と判断します。

このあと、ホスト・モードを選択した際に、H\_XcvrControl レジスタと VBUS\_Enb ビットは、ここで設定した値が保持されています。これらの設定は、ファームウェアがホストステート遷移実行レジスタに適切なコードを設定することで、設定したホストステートに応じてハードウェアが自動設定します。詳細は、「1.4.10 ホストステート管理サポート機能」を参照してください。

### 1.3 USBデバイス制御

本 LSI の USB デバイス機能について説明します。

#### 1.3.1 エンドポイント

本 LSI はコントロール転送用のエンドポイント(EP0)と、5 本の汎用エンドポイント(EPa, EPb, EPc, EPd, EPe)を持ちます。エンドポイント EPa, EPb, EPc, EPd, EPe は、それぞれに、バルク、インタラプトまたはアイソクロナス転送用のエンドポイントとして使用できます。さらに、USB ホストからトランザクションが発行された時に、アラームを発生するアラームエンドポイント機能により、エンドポイント EP0 を除き、最大 15 の IN エンドポイントと最大 15 の OUT エンドポイントを持つことが可能です。アラームエンドポイント機能は、EPa,EPb,EPc,EPd,EPe に設定されたアクティブなエンドポイント以外の、任意のエンドポイントに対して発行されたトランザクションに対して、NAK 応答し、F/W に通知することができます。

本 LSI のハードウェアは、エンドポイントを提供し、トランザクションの管理を行います。一方、USB に定義されるインターフェイス(以下、USB 定義インターフェイス)の管理機能を提供しません。USB 定義インターフェイスは、ファームウェアで実装して下さい。デバイス固有のデスクリプタ定義に沿って、エンドポイントを適宜設定し、組み合わせて、USB 定義インターフェイスを構成してください。

各エンドポイントには、USB 定義インターフェイスによって決定される固定の基本設定項目と、転送毎に制御を行う可変の制御項目及びステータスがあります。基本設定項目は、チップ初期化時、または、USB 定義インターフェイスの切り替え時等に設定して下さい。

表 1-5 にエンドポイント EP0(デフォルトコントロールパイプ)の基本設定項目を示します。

エンドポイント EP0 は、IN 方向と OUT 方向とで、レジスタセットや FIFO 領域を共有します。エンドポイント EP0 におけるデータステージ及びステータスステージでは、その実行に際して、ファームウェアによって、適宜データトランザクションの方向を設定して下さい。

後述する FIFO エリアに関連付けることにより、トランザクションを実行することが出来るようになります。まず、FIFO 領域を AREA{x=0-5}StartAdrs\_H,L 及び AREA{x=0-5}EndAdrs\_H,L で確保し、AREAnFIFO\_Clr で FIFO 領域を初期化した後、AREA{x=0-5}Join\_1.JoinEP0CH0 をセットして下さい。このジョイン処理によって関連付けが行われるまで、FIFO を使用してのデータ転送が行えません。

表 1-5 エンドポイント EP0 の基本設定項目

| 項目              | レジスタ/ビット                                           | 説明                                                                                                                       |

|-----------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| マックスパケット<br>サイズ | D_EP0MaxSize                                       | マックスパケットサイズを、FS 動作時には 8,16,32,64 のいずれかの値に設定します。また、HS 動作時には 64 に設定します。<br>エンドポイント EP0 を FIFO の AREA0 領域に<br>関連付けて使用して下さい。 |

| FIFO 領域         | AREA{x=0-5}StartAdrs_H,L<br>AREA{x=0-5}EndAdrs_H,L | AREA0 領域に割り当てる FIFO 領域を、アドレスで指定します。FIFO 領域には、マックスパケットサイズ以上を確保してください。                                                     |

| FIFO 関連付け       | AREA{x=0-5}Join_1.JoinEP0CH0                       | エンドポイント EP0 を FIFO 領域に関連付け、<br>EP0 におけるデータ転送を行えるようにします。                                                                  |

## 1. 機能説明

表 1-6 に汎用エンドポイント(EPa, EPb, EPc, EPd, EPe)の基本設定項目を示します。エンドポイント EPa, EPb, EPc, EPd, EPe は、トランザクション方向とエンドポイントナンバーを任意に設定出来ますので、5 本までの独立したエンドポイントを使用できます。USB 定義インターフェイスの定義内容に合わせて適宜設定し、また有効にすることによって、USB 定義インターフェイスを構成して下さい。

エンドポイント EPa, EPb, EPc, EPd, EPe は、それぞれ FIFO 領域に関連付けられることによって、トランザクションを実行できるようになります。FIFO 領域を AREAx{x=0-5}StartAdrs\_H,L 及び AREAx{x=0-5}EndAdrs\_H,L レジスタにより確保し、AREAnFIFO\_Clr にて FIFO を初期化した後、AREAx{x=0-5}Join\_1 レジスタを適宜セットして下さい。このジョイン処理によって関連付けが行われて居ないエンドポイントは、トランザクションを実行しません。従って、使用しないエンドポイントでは、ジョイン処理をしないで下さい。

表 1-6 汎用エンドポイントの基本設定項目

| 項目          | レジスタ/ビット                                             | 説明                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| トランザクション方向  | D_EPx{x=a-e}Config_0.INxOUT                          | 各エンドポイントの転送方向を設定します。                                                                                                                                                                                                                            |

| マックスパケットサイズ | D_EPx{x=a-e}MaxSize_H,<br>D_EPx{x=a-e}MaxSize_L      | 各エンドポイントのマックスパケットサイズを、8Byte,16Byte,32Byte,64Byte,512Byte のいずれかの値に設定します。<br>但し、バルク転送を行うエンドポイントでは、FS モード時は 8/16/32/64Byte のいずれか、HS モード時は 512Byte に設定して下さい。<br>また、アイソクロナス転送を行うエンドポイントでは、FS モード時は 1~1023Byte のいずれか、HS モード時は 1~1024Byte のいずれかに設定します。 |

| エンドポイントナンバー | D_EPx{x=a-e}Config_0.EndpointNumber                  | 各エンドポイントのエンドポイントナンバーを 0x1~0xF の間の任意の値に設定します。                                                                                                                                                                                                    |

| トグルモード      | D_EPx{x=a-e}Config_0.IntEP_Mode                      | インターラプト転送の動作モードを設定します。バルク転送を行うエンドポイントでは、方向に関らず、“0”に設定して下さい。<br>IN 方向のエンドポイントでは、トグルシーケンスのモードを設定します。<br>OUT 方向のエンドポイントでは、インターラプト転送を行う場合に、“1”にセットして下さい。                                                                                            |

| アイソクロナスマード  | D_EPx{x=a-e}Config_0.ISO                             | アイソクロナス転送を行うエンドポイントで、1 にセットして下さい。                                                                                                                                                                                                               |

| FIFO 領域     | AREAx{x=0-5}StartAdrs_H,L<br>AREAx{x=0-5}EndAdrs_H,L | 領域をアドレスで指定して確保します。各領域は、関連付けるエンドポイントのマックスパケットサイズ以上のサイズを確保してください。また、FIFO のサイズは転送のスループットに影響する場合があります。                                                                                                                                              |

| FIFO 関連付け   | AREAx{x=0-5}Join_1                                   | 各エンドポイントと FIFO 領域とを関連付けます。                                                                                                                                                                                                                      |

表 1-7 にアラームエンドポイントの基本設定項目を示します。このアラームエンドポイントは、現在汎用エンドポイントに割り当てられてはいないが、USB 定義インターフェースにて定義したエンドポイントを実装するものです。USB 定義インターフェイスの定義内容に合わせて適宜設定し、また有効にすることによって、USB 定義インターフェイスを構成して下さい。

このアラームエンドポイントには、FIFO 領域は必要ありません。

表 1-7 アラームエンドポイントの基本設定項目

| 項目                | レジスタ/ビット                                                                                                                                                      | 説明                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| アラームエンド<br>ポイント有効 | D_EnEP_IN_H.EnEPn{n=8-15}IN,<br>D_EnEP_IN_L.EnEPn{n=1-7}IN,<br>D_EnEP_OUT_H.EnEPn{n=8-15}OUT,<br>D_EnEP_OUT_L.EnEPn{n=1-7}OUT                                 | アラームエンドポイント有効にします。                                                       |

| アイソクロナス<br>モード    | D_EnEP_IN_ISO_H.EnEPn{n=8-15}IN_ISO,<br>D_EnEP_IN_ISO_L.EnEPn{n=1-7}IN_ISO,<br>D_EnEP_OUT_ISO_H.EnEPn{n=8-15}OUT_ISO,<br>D_EnEP_OUT_ISO_L.EnEPn{n=1-7}OUT_ISO | アイソクロナス転送モードに設定する際に“1”に設定します。バルク転送、インターバルト転送に設定するエンドポイントでは、“0”に設定してください。 |

### 1.3.2 トランザクション

本 LSI は H/W でトランザクション実行機能と、ファームウェアに対するトランザクション実行のためのインターフェイスを提供します。ファームウェアに対するインターフェイスは、制御レジスタとステータスレジスタ、及び、ステータスによりアサートされる割り込み信号として実装されています。ステータスにより割り込みをアサートする設定については、「2 レジスタ」を参照して下さい。

本 LSI は個々のトランザクション毎に、ファームウェアに対してステータスを発行します。しかしながら、ファームウェアは必ずしも、個々のトランザクションを管理する必要はありません。LSI はトランザクションへの応答を行う時に、FIFO を参照し、そのデータ数または空き数によって、データ転送を行えるか否かを判断して自動的に処理を行います。

例えば、OUT のエンドポイントであれば、ファームウェアは、CPU インタフェイス(DMA リードまたはレジスタリード)により、FIFO からデータを読み出して FIFO に空き領域を作り出すことによって、OUT トランザクションを自動的に連続して実行させることができます。また、IN のエンドポイントであれば、ファームウェアは、CPU インタフェイス(DMA ライトまたはレジスタライト)により、FIFO にデータを書き込んで FIFO に有効データを作り出すことによって、IN トランザクションを自動的に連続して実行させることができます。

## 1. 機能説明

表1-8にエンドポイントEP0のトランザクション制御に関する制御項目及びステータスを示します。

表1-8 エンドポイントEP0の制御項目及びステータス

| 項目                     | レジスタ/ビット                                                                                                                                                                           | 説明                                                                                                                                                                         |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| トランザクション方向             | D_EP0Control.INxOUT                                                                                                                                                                | データステージ及びステータスステージにおいて、転送方向を設定します。                                                                                                                                         |

| デスクリプタ返信イネーブル          | D_EP0Control.ReplyDescriptor                                                                                                                                                       | デスクリプタの自動応答を起動します。                                                                                                                                                         |

| デスクリプタ返信アドレス           | D_DescAdrs_H, DescAdrs_L                                                                                                                                                           | デスクリプタの自動応答によって、返信を行うデータの FIFO 上の先頭アドレスを指定します。                                                                                                                             |

| デスクリプタサイズ              | D_DescSize_H, DescSize_L                                                                                                                                                           | デスクリプタの自動応答によって、返信を行うデータ数を指定します。                                                                                                                                           |

| 制御禁止                   | D_SETUP_Control.ProtectEP0                                                                                                                                                         | このビットがセットされていると、EP0ControlIN 及び EP0ControlOUT レジスタの ForceNAK ビットと ForceSTALL ビットへのアクセスが行えません。<br>このビットは、RcvEP0SETUP ステータスが立つと、LSI の h/w によってセットされ、CPU によるレジスタアクセスでクリアできます。 |

| ショートパケット送信イネーブル        | D_EP0ControlIN.EnShortPkt                                                                                                                                                          | マックスパケットサイズに満たない、ショートパケットの送信を有効にします。ショートパケットを送信した IN トランザクションが完結すると、クリアされます。                                                                                               |

| トグルシーケンスビット            | D_EP0ControlIN.ToggleStat, D_EP0ControlOUT.ToggleStat                                                                                                                              | トグルシーケンスビットの状態を示します。SETUP ステージにより、自動的に初期化されます。                                                                                                                             |

| トグルセット                 | D_EP0ControlIN.ToggleSet, D_EP0ControlOUT.ToggleSet                                                                                                                                | トグルシーケンスビットをセットします。                                                                                                                                                        |

| トグルクリア                 | D_EP0ControlIN.ToggleClr, D_EP0ControlOUT.ToggleClr                                                                                                                                | トグルシーケンスビットをクリアします。                                                                                                                                                        |

| 強制NAK応答                | D_EP0ControlIN.ForceNAK, D_EP0ControlOUT.ForceNAK                                                                                                                                  | FIFO のデータ数／空き数に関わらず、IN 又は OUT(PING を含む)トランザクションに NAK 応答します。                                                                                                                |

| STALL応答                | D_EP0ControlIN.ForceSTALL, D_EP0ControlOUT.ForceSTALL                                                                                                                              | IN 又は OUT(PING を含む)トランザクションに STALL 応答します。                                                                                                                                  |

| 自動ForceNAKセット          | D_EP0ControlOUT.AutoForceNAK                                                                                                                                                       | OUT トランザクションの完結毎に、D_EP0ControlOUT.ForceNAK ビットをセットします。                                                                                                                     |

| SETUP受信ステータス           | USB_DeviceIntStat.RcvEP0SETUP                                                                                                                                                      | SETUP トランザクションが実行されたことを示します。                                                                                                                                               |

| トランザクションステータス          | D_EP0IntStat.OUT_ShortACK, D_EP0IntStat.IN_TranACK, D_EP0IntStat.OUT_TranACK, D_EP0IntStat.IN_TranNAK, D_EP0IntStat.OUT_TranNAK, D_EP0IntStat.IN_TranErr, D_EP0IntStat.OUT_TranErr | トランザクションの結果を示します。                                                                                                                                                          |

| デスクリプタ返信データステージ終了ステータス | D_EP0IntStat.DescriptorCmp                                                                                                                                                         | デスクリプタ自動応答のデータステージが終了したことを示します。                                                                                                                                            |

表 1-9 に、汎用エンドポイント EPa, EPb, EPc, EPd, EPe のトランザクション処理に関する制御項目とステータスを示します。

表 1-9 汎用エンドポイントの制御項目とステータス

| 項目                              | レジスタ/ビット                                                                                                                                                                                                                                              | 説明                                                                                                                                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 自動 ForceNAK セット                 | D_EPx{x=a-e}Control.AutoForceNAK                                                                                                                                                                                                                      | OUT トランザクションの完結毎に、そのエンドポイントの D_EPx{x=a-e}Control.ForceNAK ビットをセットします。                                                               |

| ショートパケット送信イネーブル                 | D_EPx{x=a-e}Control.EnShortPkt                                                                                                                                                                                                                        | IN トランザクションに対し、マックスパケットサイズに満たない、ショートパケットの送信を有効にします。ショートパケットを送信した IN トランザクションが完結すると、クリアされます。                                         |

| ショートパケット受信による自動 ForceNAK セットの禁止 | D_EPx{x=a-e}Control.DisAF_NAK_Short                                                                                                                                                                                                                   | OUT トランザクションにおいて、ショートパケットを受信すると、自動的にそのエンドポイントの D_EPx{x=a-e}Control.ForceNAK ビットをセットする機能(※)を禁止します。<br>※ : このビットにより禁止しない場合は有効になっています。 |

| トグルシーケンスビット                     | D_EPx{x=a-e}Control.ToggleStat                                                                                                                                                                                                                        | トグルシーケンスビットの状態を示します。                                                                                                                |

| トグルセット                          | D_EPx{x=a-e}Control.ToggleSet                                                                                                                                                                                                                         | トグルシーケンスビットをセットします。                                                                                                                 |

| トグルクリア                          | D_EPx{x=a-e}Control.ToggleClr                                                                                                                                                                                                                         | トグルシーケンスビットをクリアします。                                                                                                                 |

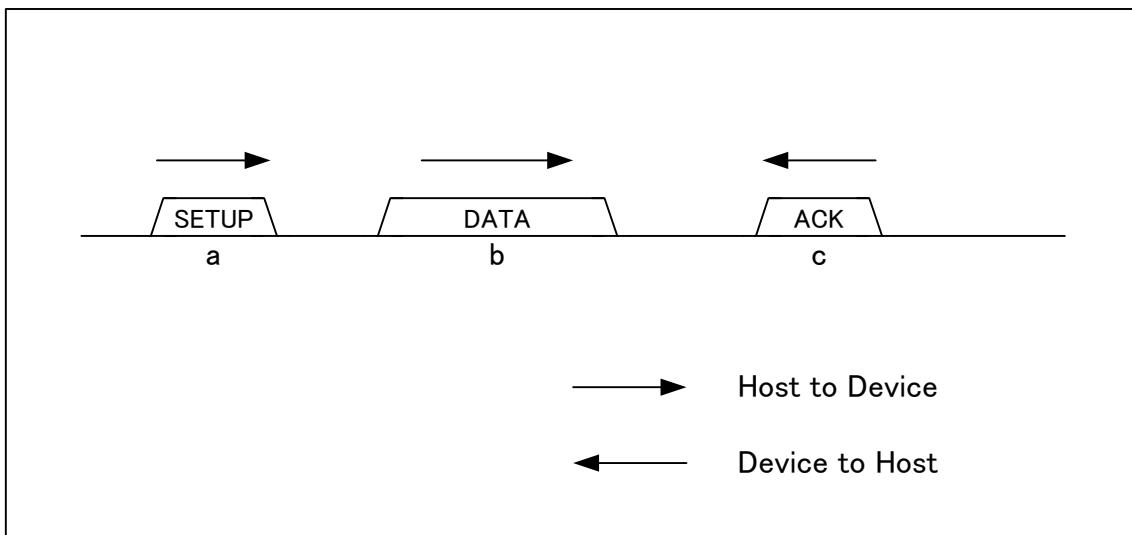

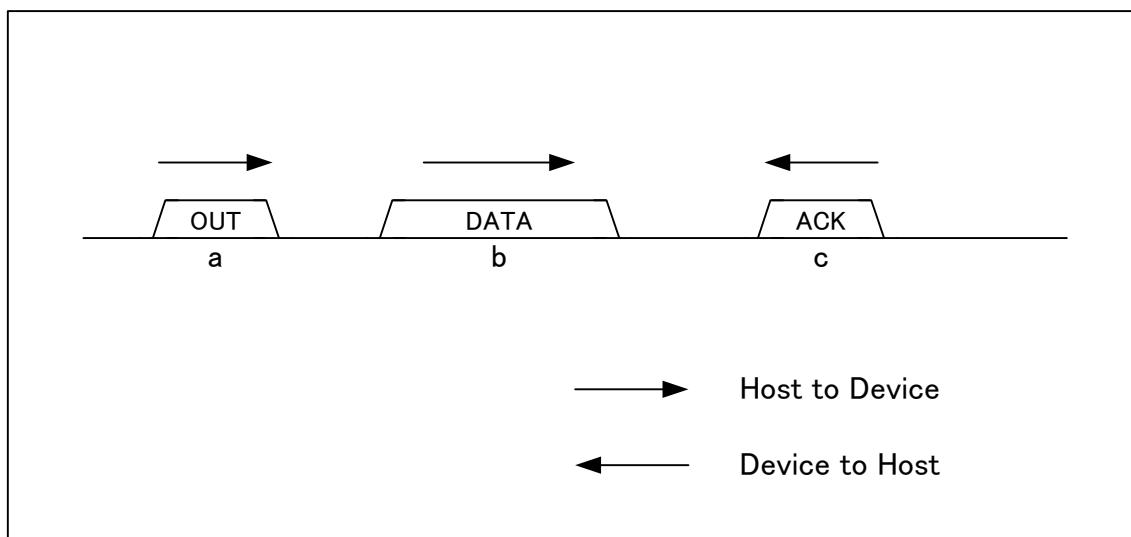

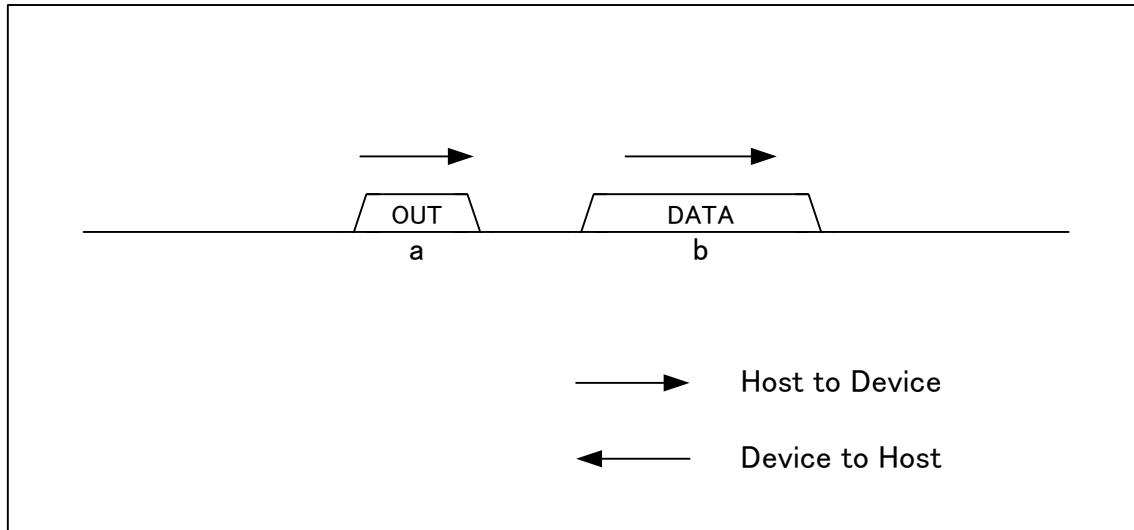

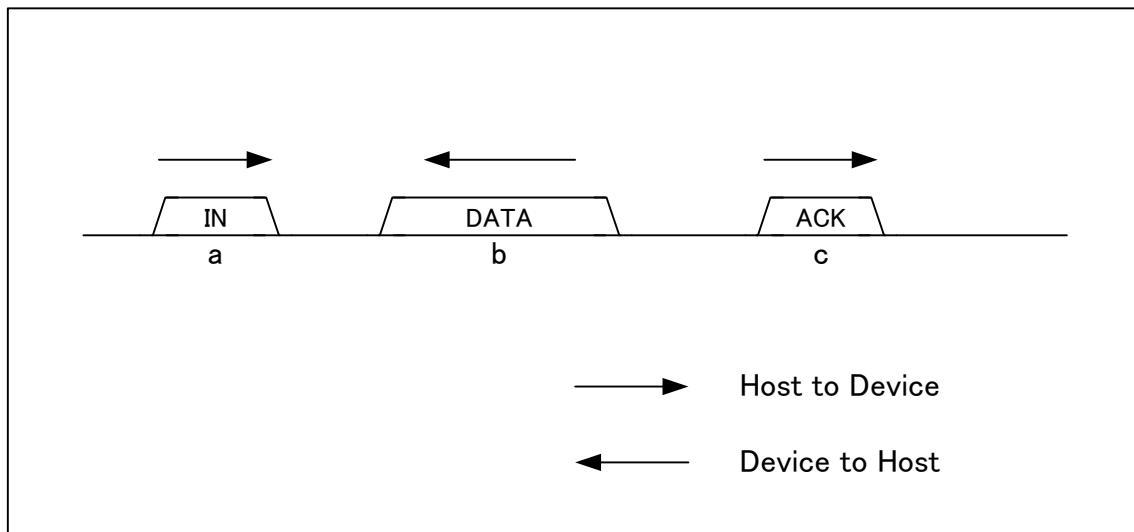

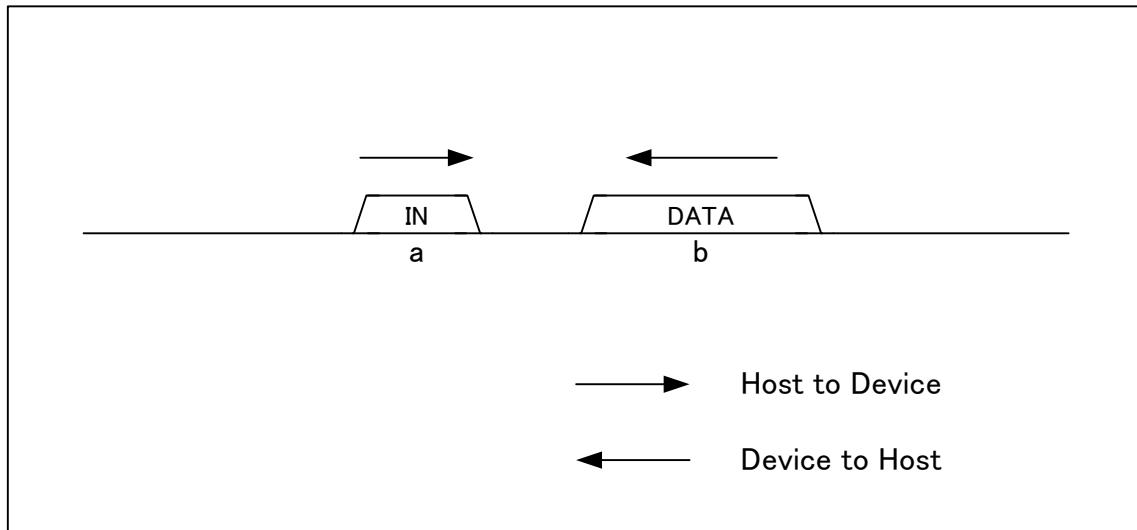

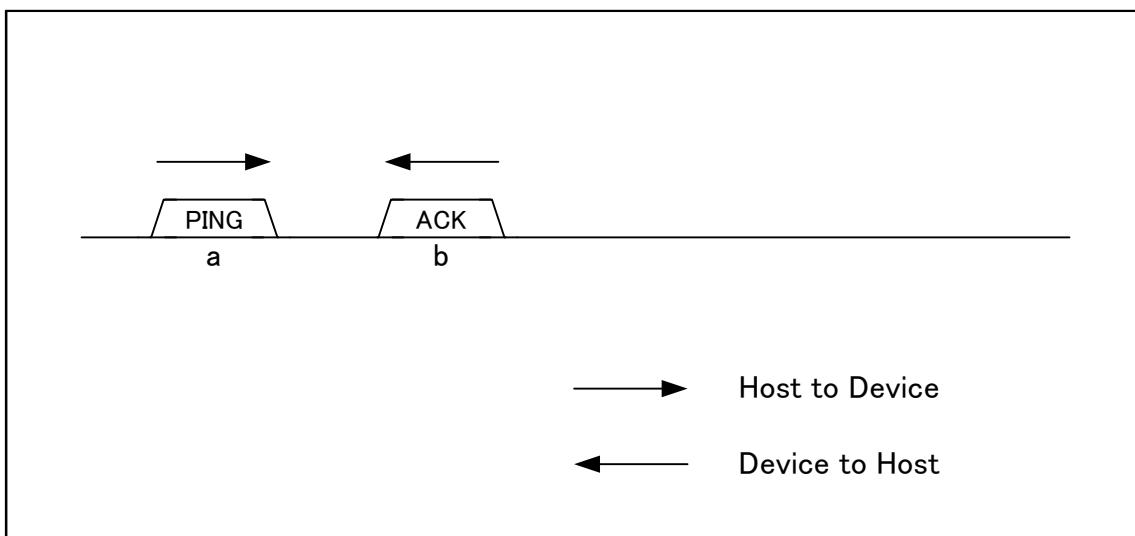

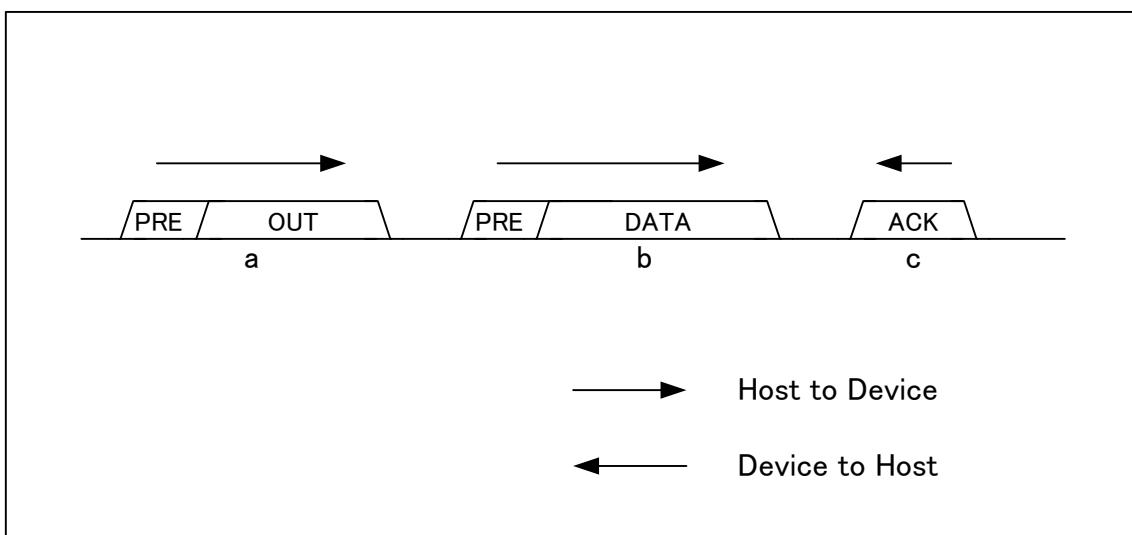

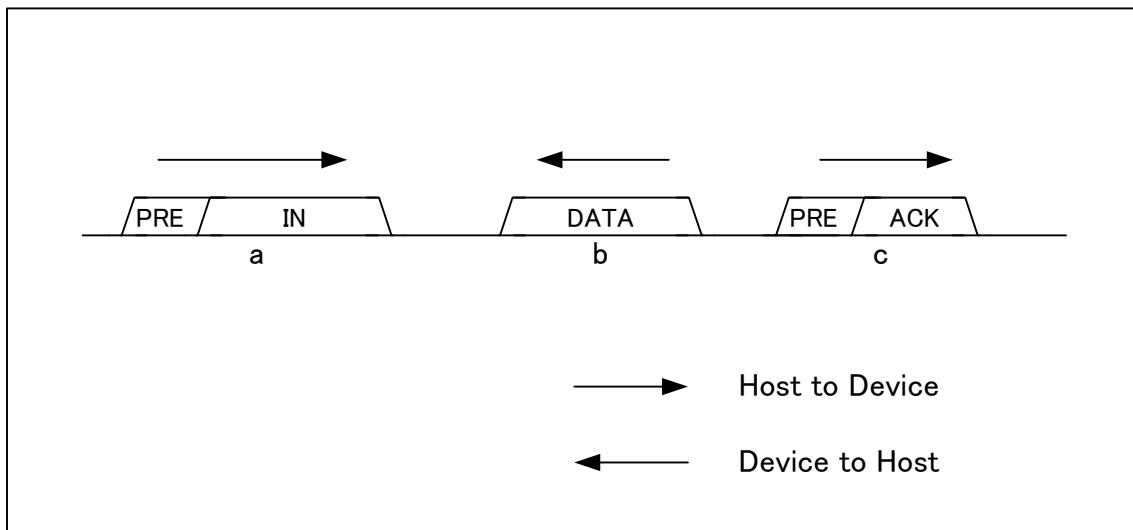

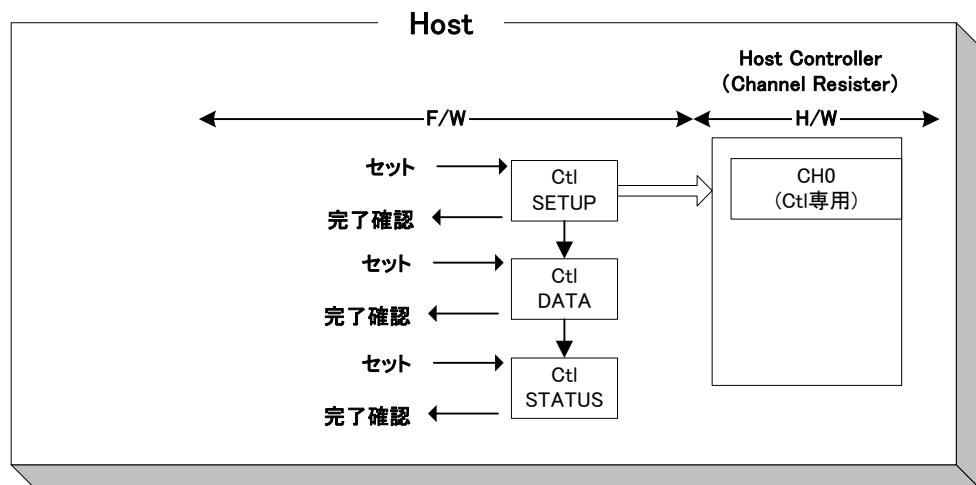

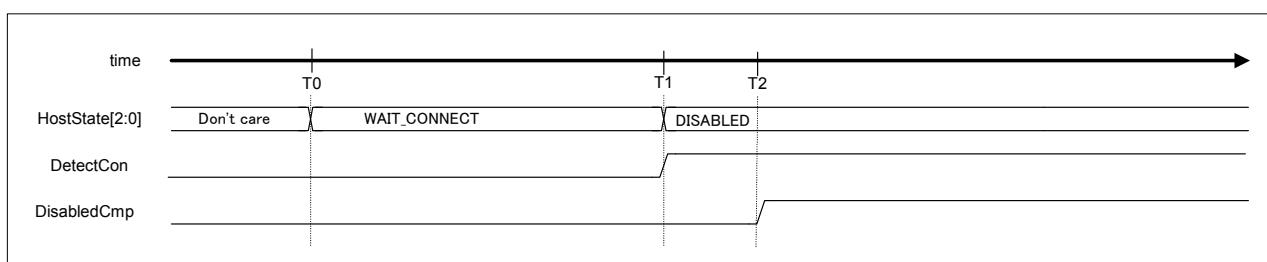

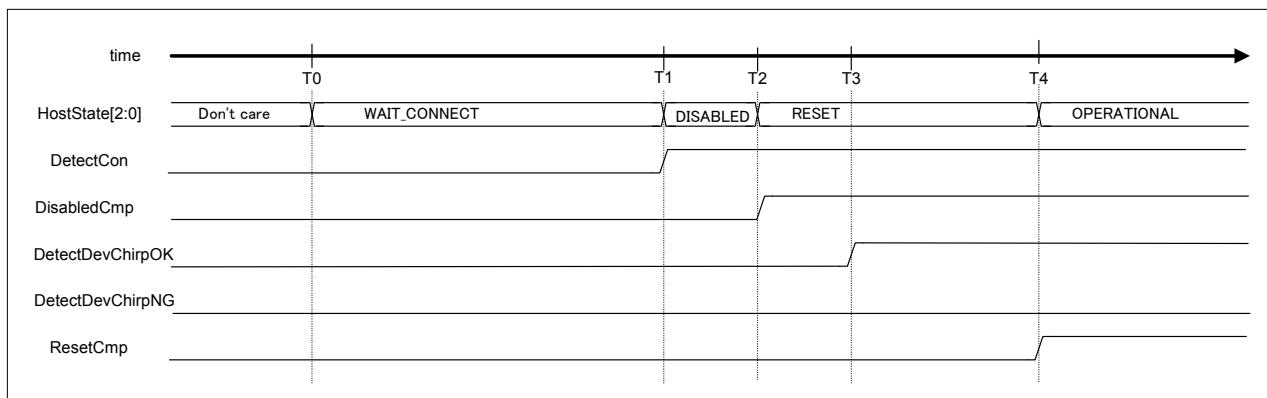

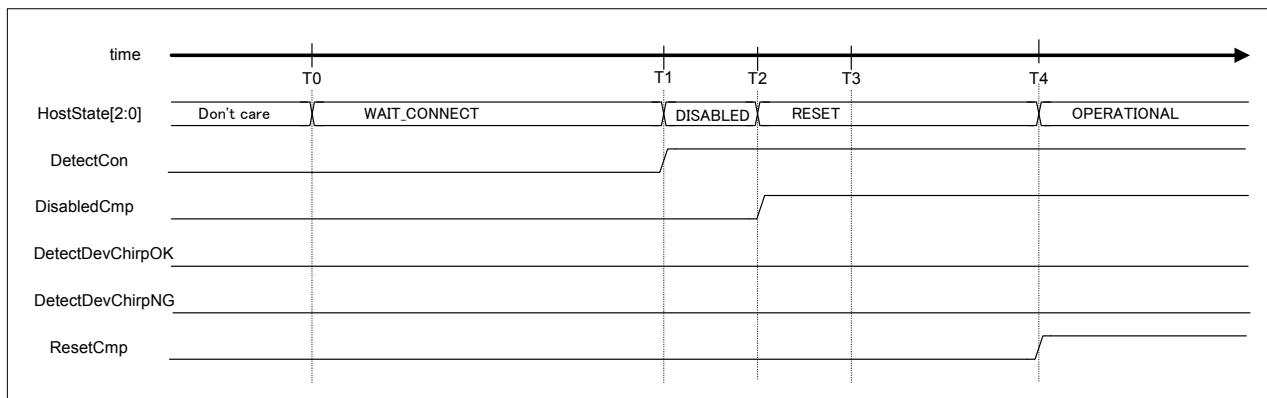

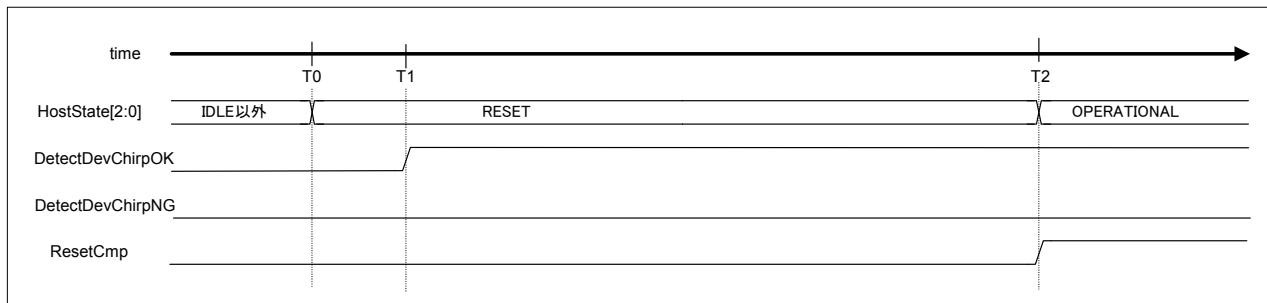

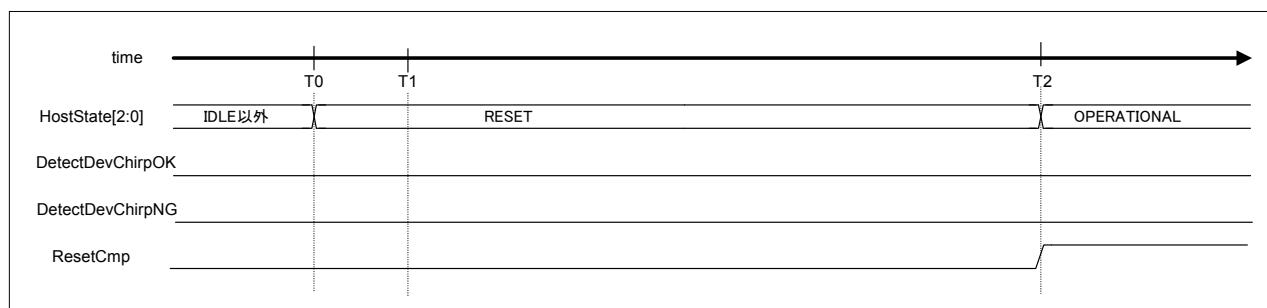

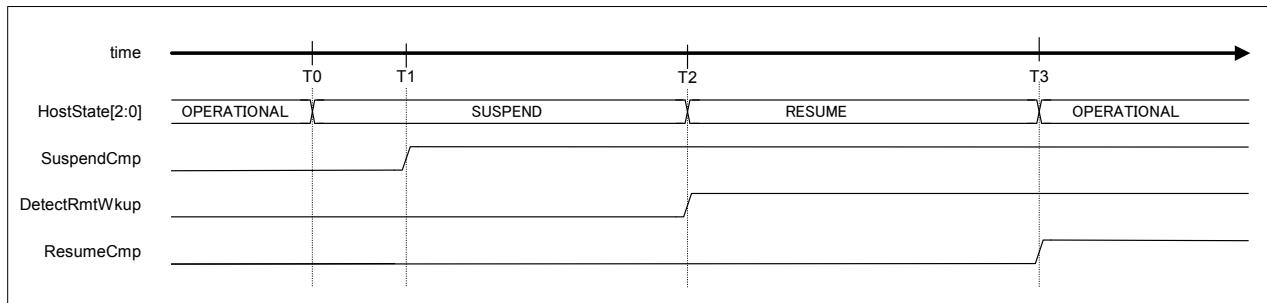

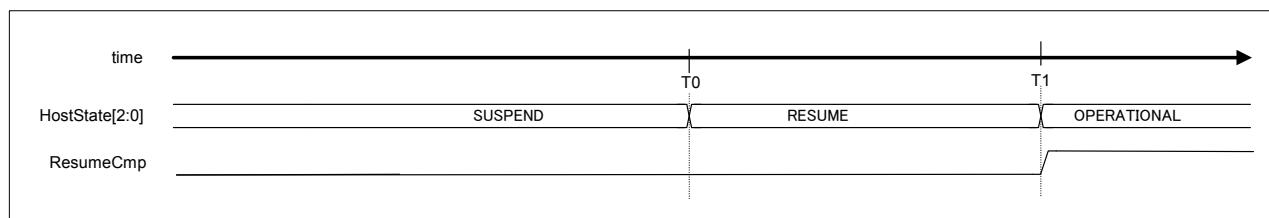

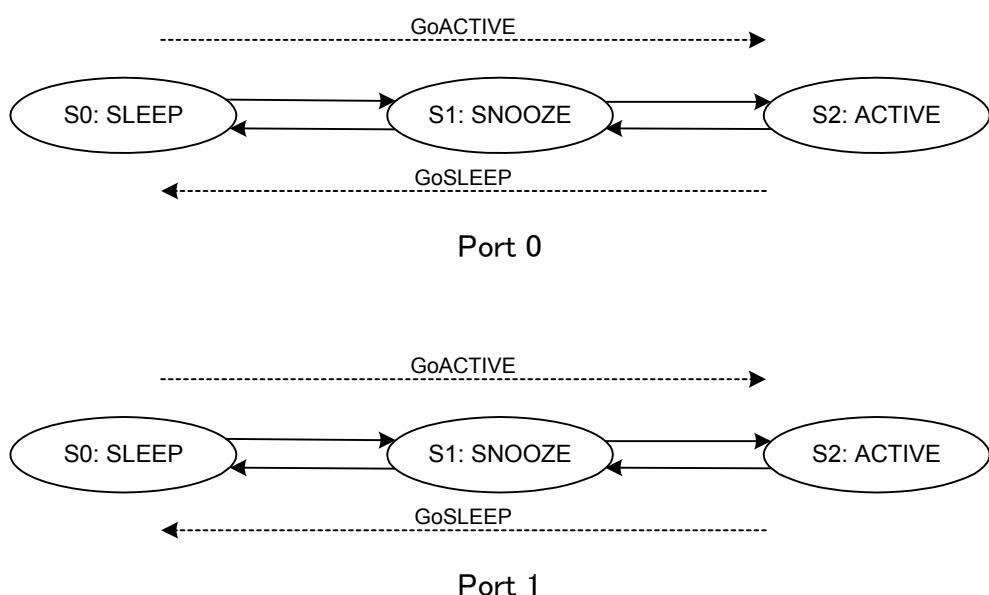

| 強制 NAK 応答                       | D_EPx{x=a-e}Control.ForceNAK                                                                                                                                                                                                                          | FIFO のデータ数／空き数に関わらず、トランザクションに NAK 応答します。                                                                                            |