CMOS 4-BIT SINGLE CHIP MICROCONTROLLER

**S1C63003/004/008/016**

テクニカルマニュアル

#### 評価ボード・キット、開発ツールご使用上の注意事項

1. 本評価ボード・キット、開発ツールは、お客様での技術的評価、動作の確認および開発のみに用いられることが想定し設計されています。それらの技術評価・開発等の目的以外には使用しないでください。本品は、完成品に対する設計品質に適合していません。

2. 本評価ボード・キット、開発ツールは、電子エンジニア向けであり、消費者向け製品ではありません。お客様において、適切な使用と安全に配慮願います。弊社は、本品を用いることで発生する損害や火災に対し、いかなる責も負いかねます。通常の使用においても、異常がある場合は使用を中止してください。

3. 本評価ボード・キット、開発ツールに用いられる部品は、予告なく変更されることがあります。

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告なく変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 製品および弊社が提供する技術を輸出等するにあたっては「外国為替および外国貿易法」を遵守し、当該法令の定める手続きが必要です。大量破壊兵器の開発等およびその他の軍事用途に使用する目的をもって製品および弊社が提供する技術を費消、再販売または輸出等しないでください。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

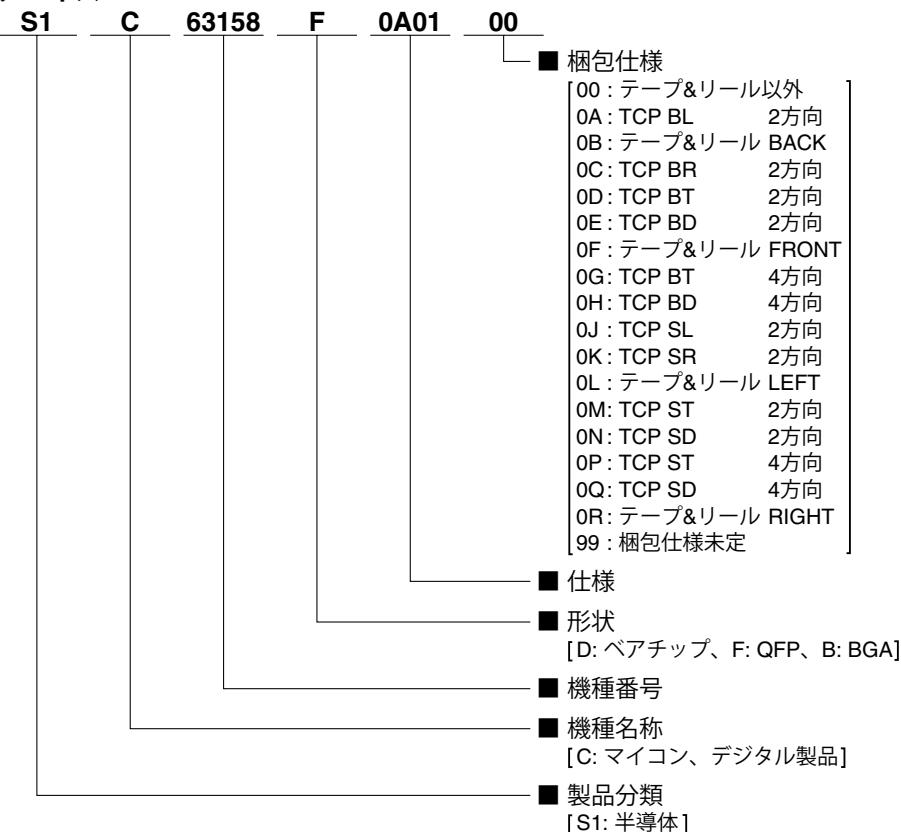

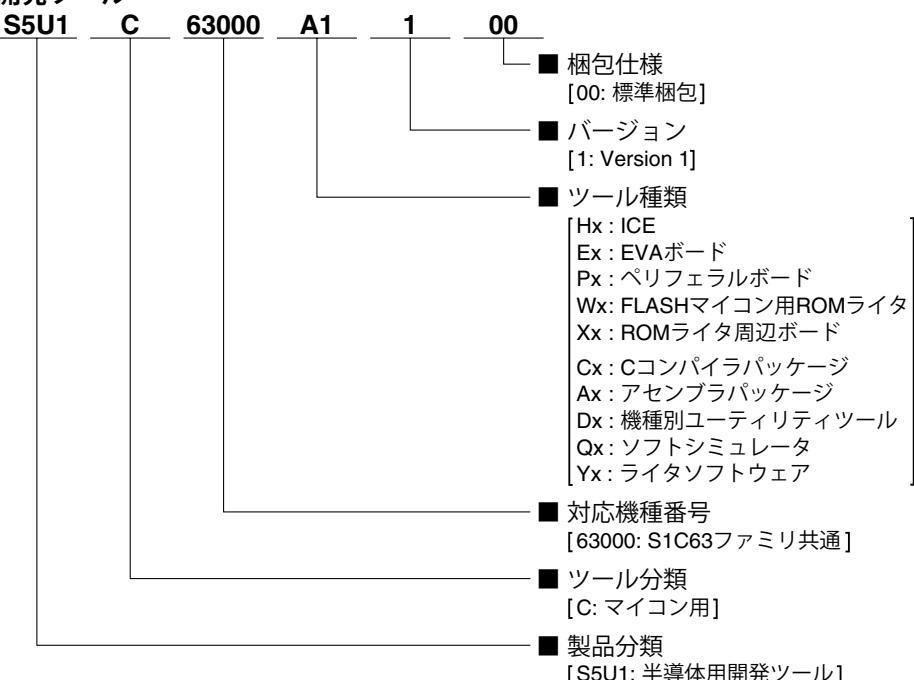

## 製品型番体系

### ●デバイス

### ●開発ツール

## - 目 次 -

|                                    |            |

|------------------------------------|------------|

| <b>1 概要 .....</b>                  | <b>1-1</b> |

| 1.1 特長 .....                       | 1-1        |

| 1.2 ブロック図 .....                    | 1-2        |

| 1.3 マスクオプション .....                 | 1-6        |

| <b>2 端子とパッケージ .....</b>            | <b>2-1</b> |

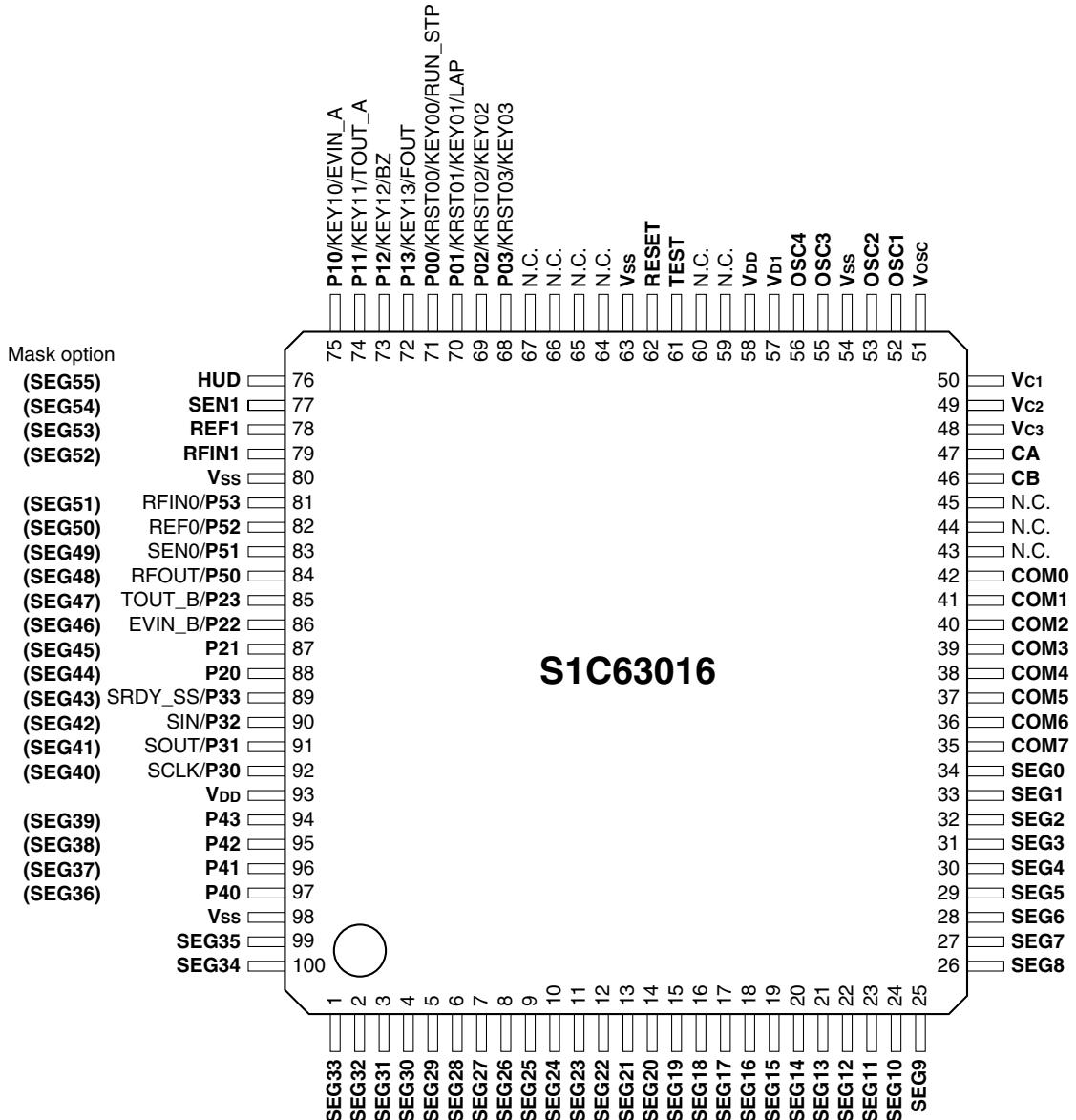

| 2.1 S1C63016端子 .....               | 2-1        |

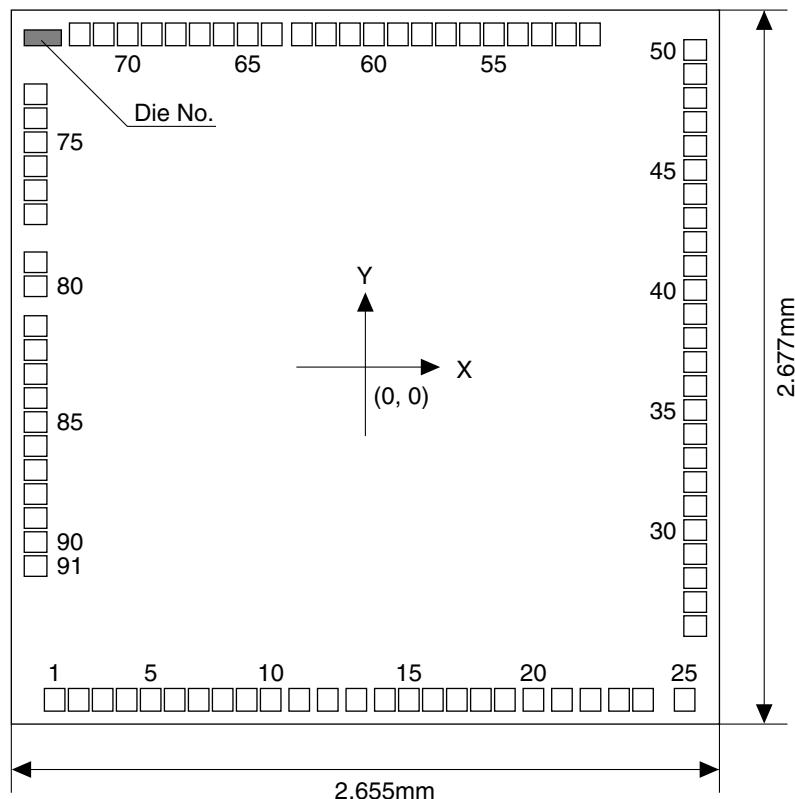

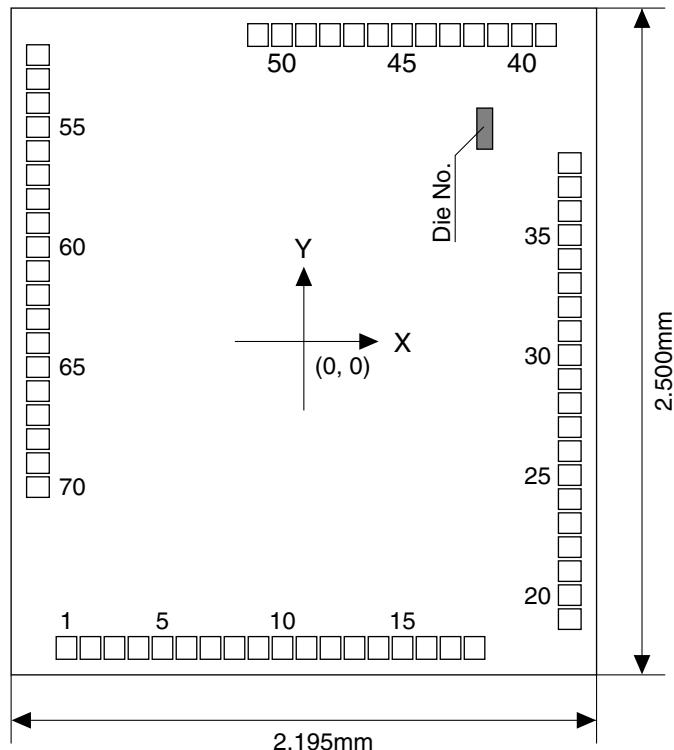

| 2.1.1 S1C63016端子/パッド配置図 .....      | 2-1        |

| 2.1.2 S1C63016端子説明 .....           | 2-4        |

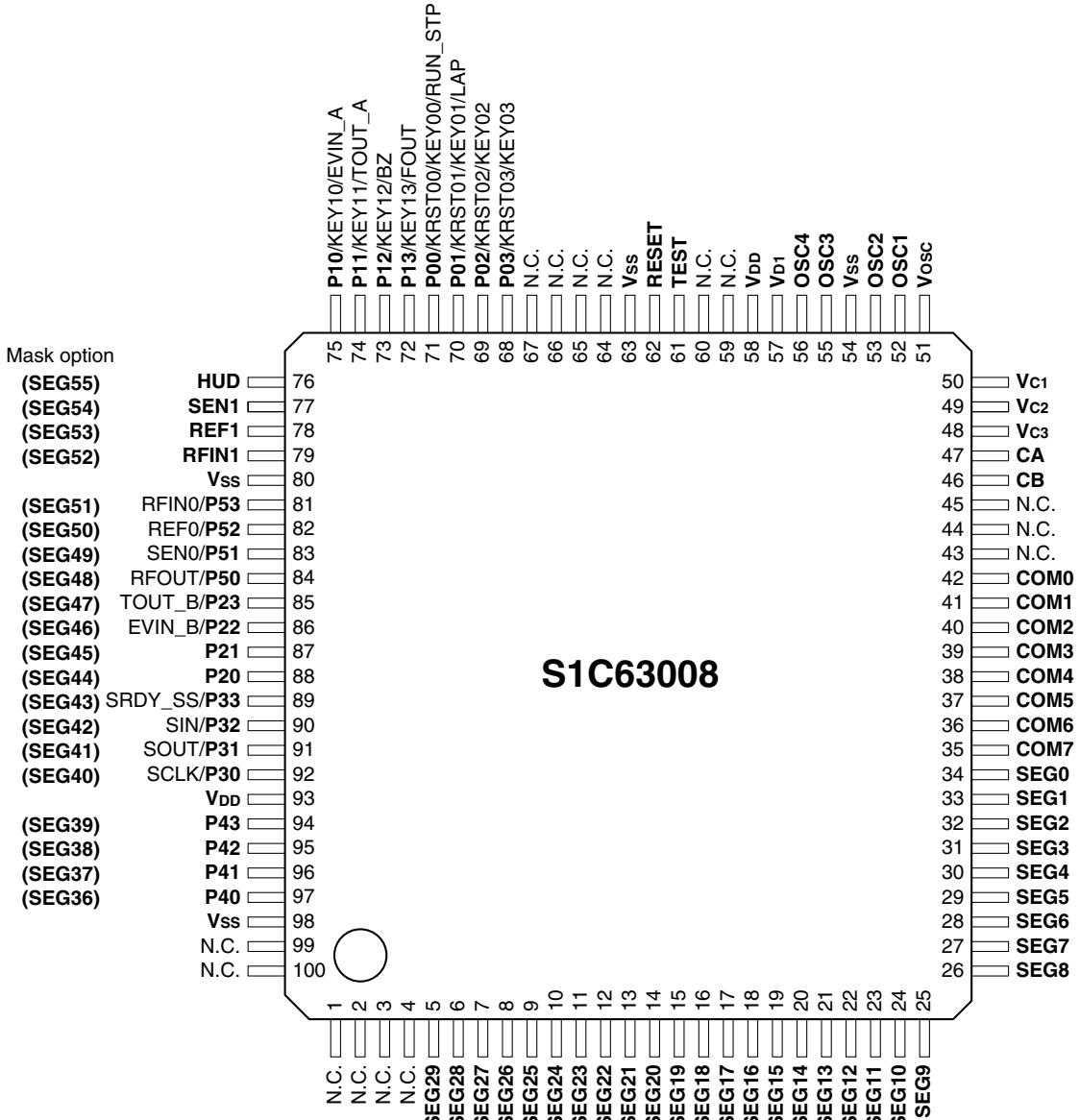

| 2.2 S1C63008端子 .....               | 2-6        |

| 2.2.1 S1C63008端子/パッド配置図 .....      | 2-6        |

| 2.2.2 S1C63008端子説明 .....           | 2-9        |

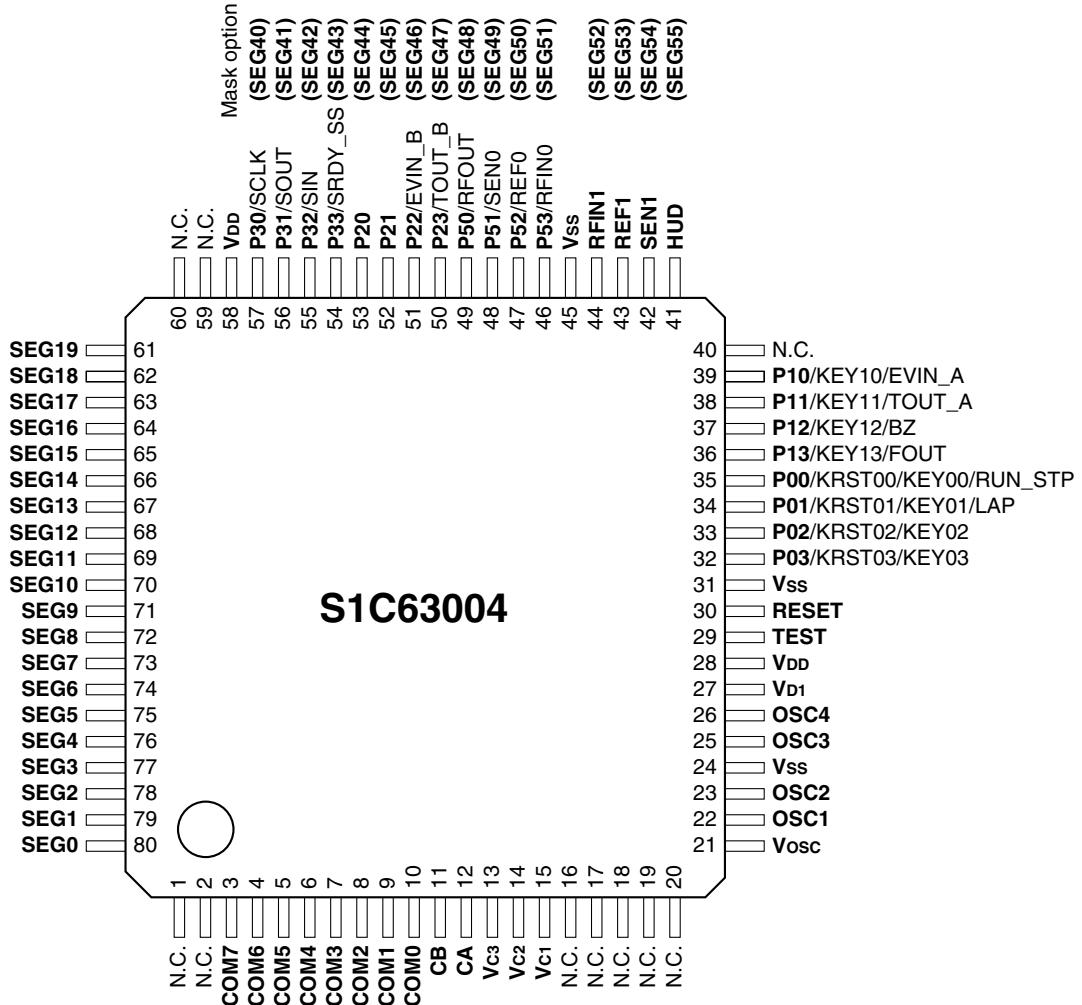

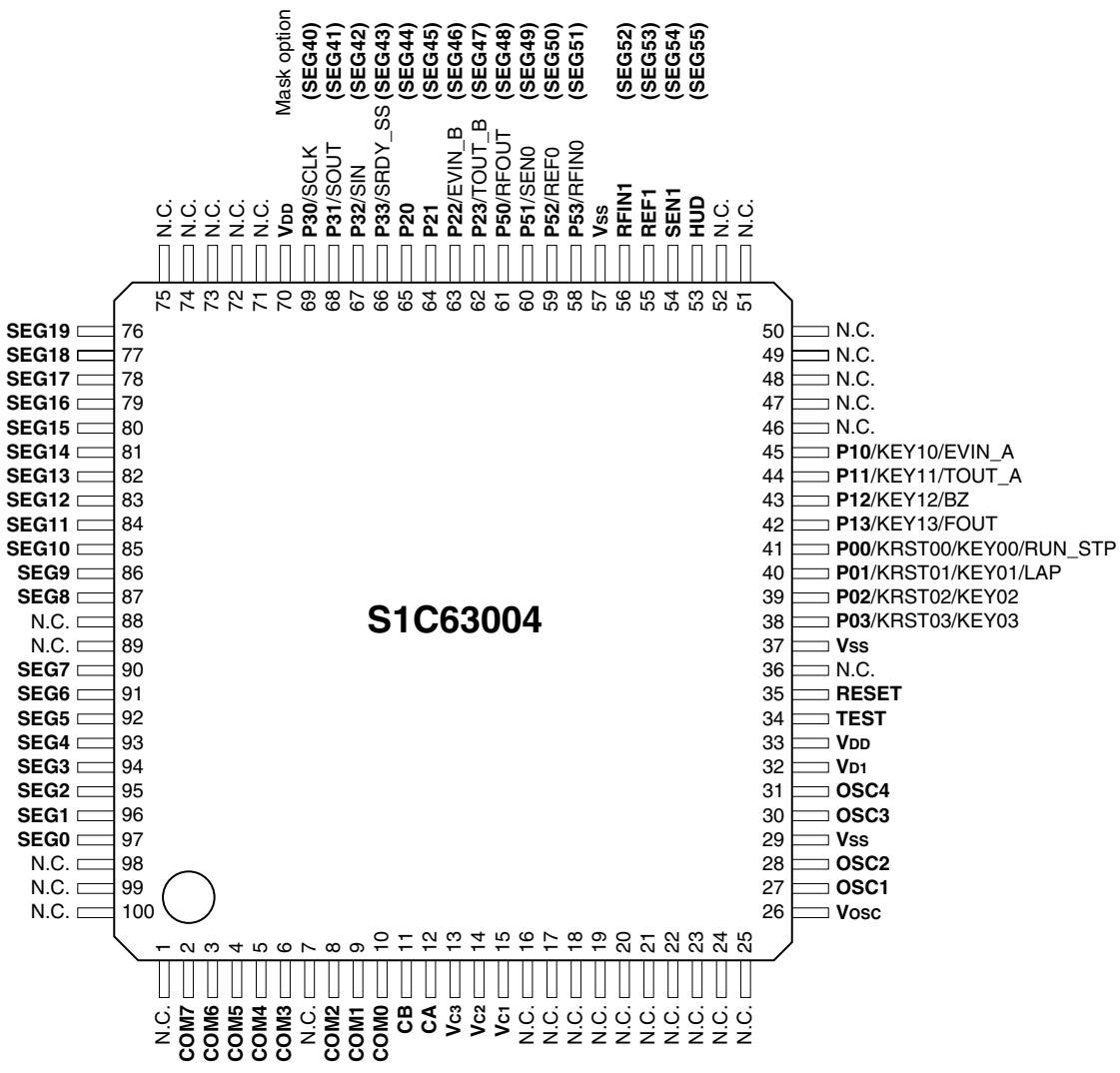

| 2.3 S1C63004端子 .....               | 2-11       |

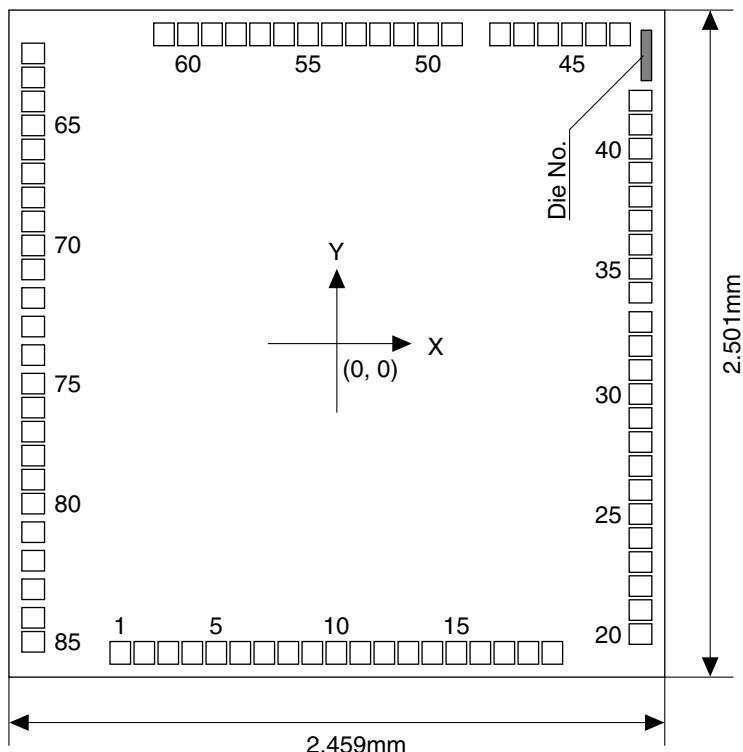

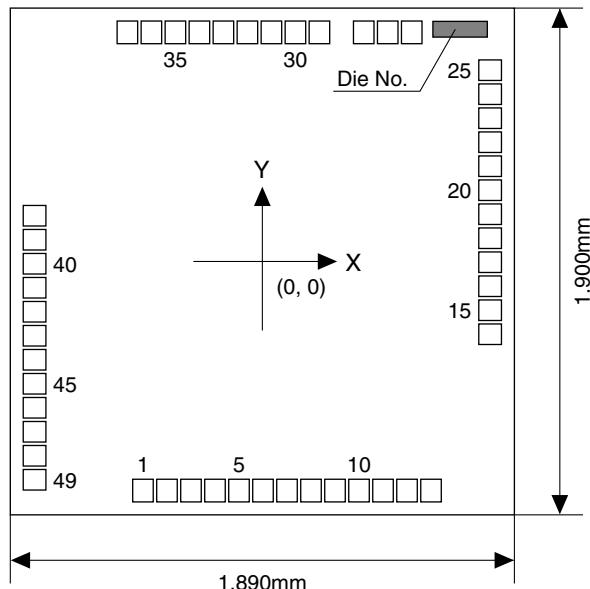

| 2.3.1 S1C63004端子/パッド配置図 .....      | 2-11       |

| 2.3.2 S1C63004端子説明 .....           | 2-15       |

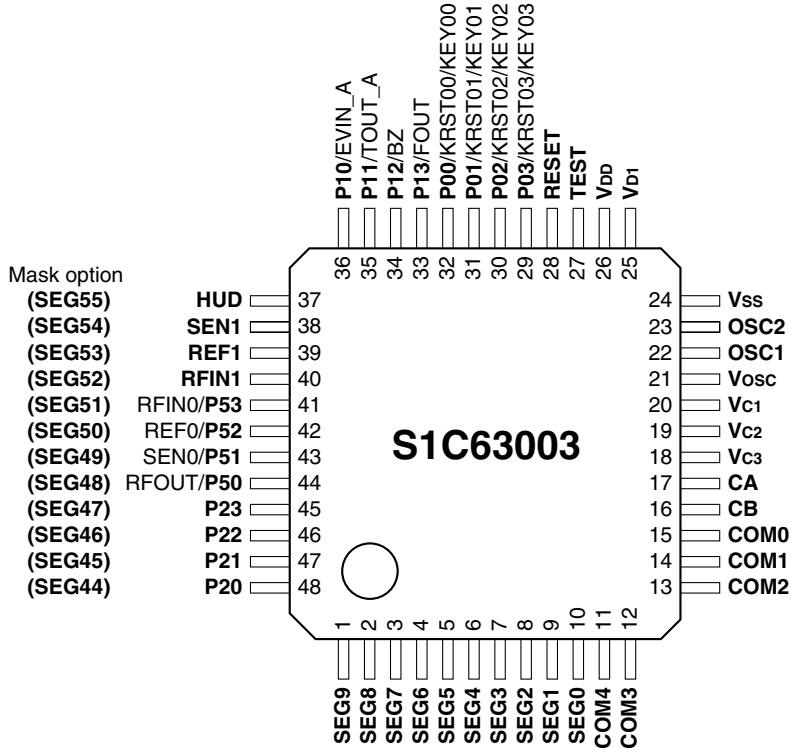

| 2.4 S1C63003端子 .....               | 2-17       |

| 2.4.1 S1C63003端子/パッド配置図 .....      | 2-17       |

| 2.4.2 S1C63003端子説明 .....           | 2-19       |

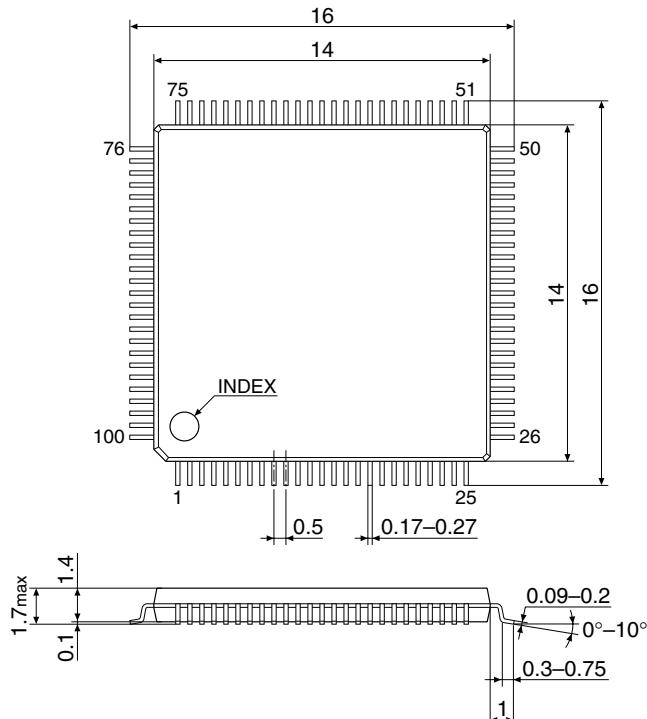

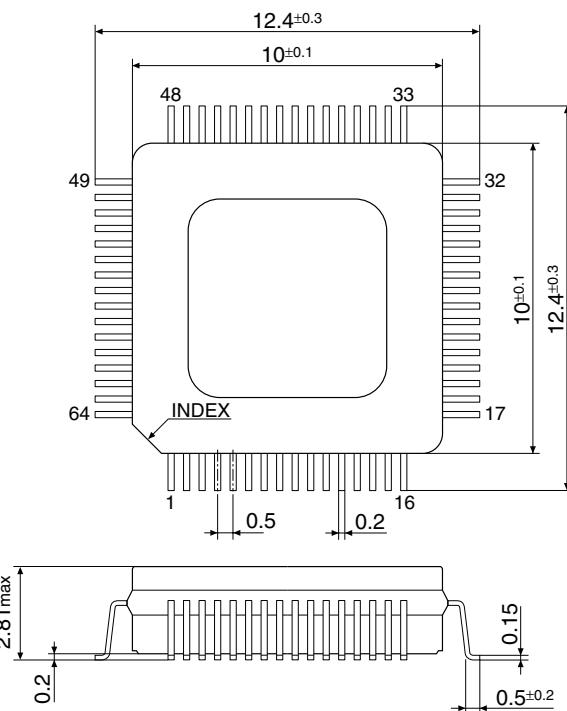

| 2.5 パッケージ .....                    | 2-20       |

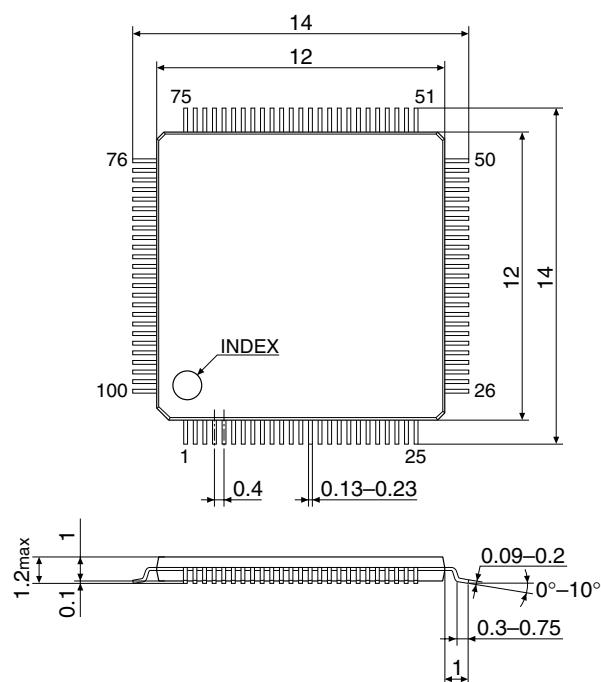

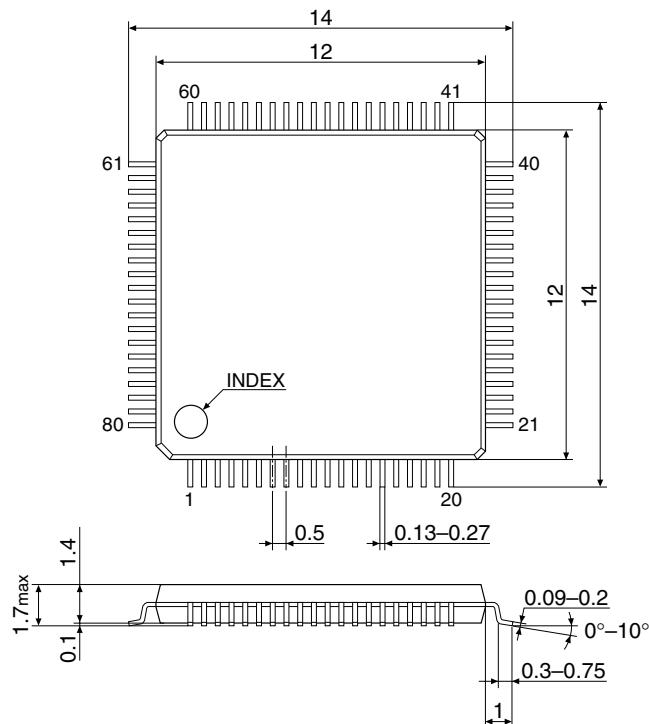

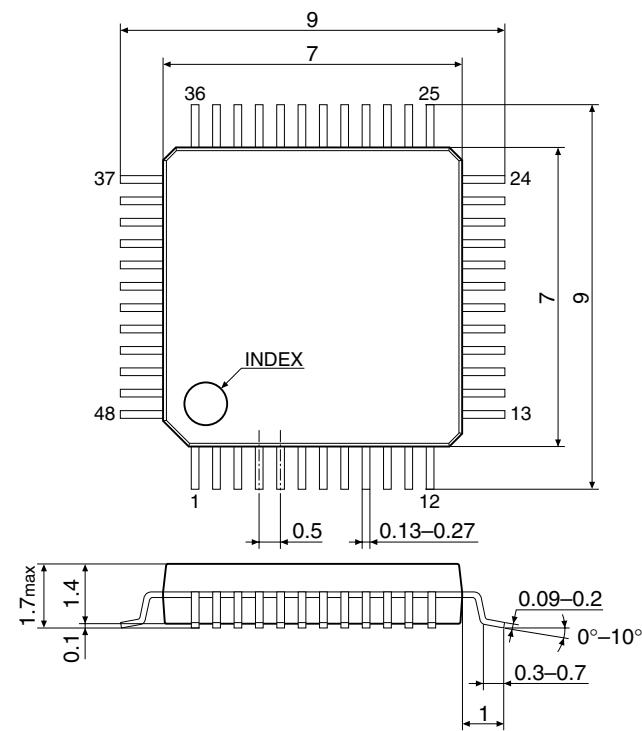

| 2.5.1 プラスチックパッケージ .....            | 2-20       |

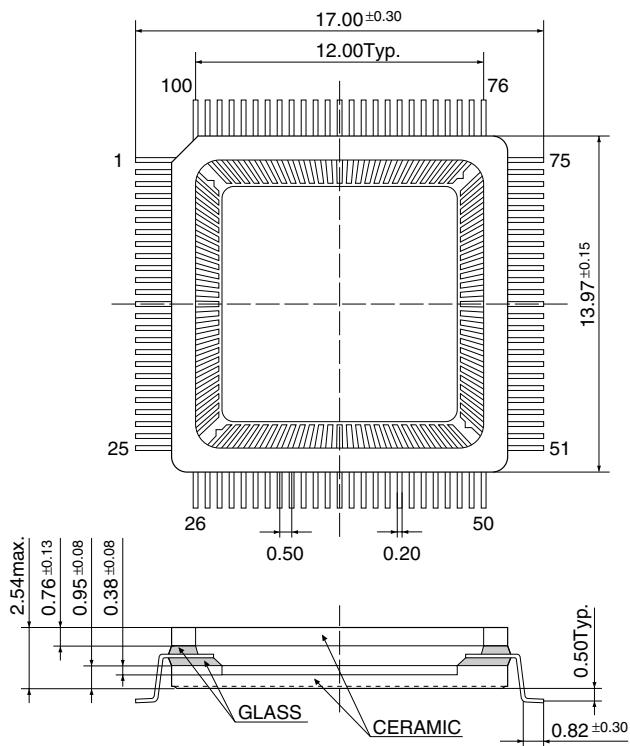

| 2.5.2 テストサンプル用セラミックパッケージ .....     | 2-22       |

| <b>3 CPUとメモリ .....</b>             | <b>3-1</b> |

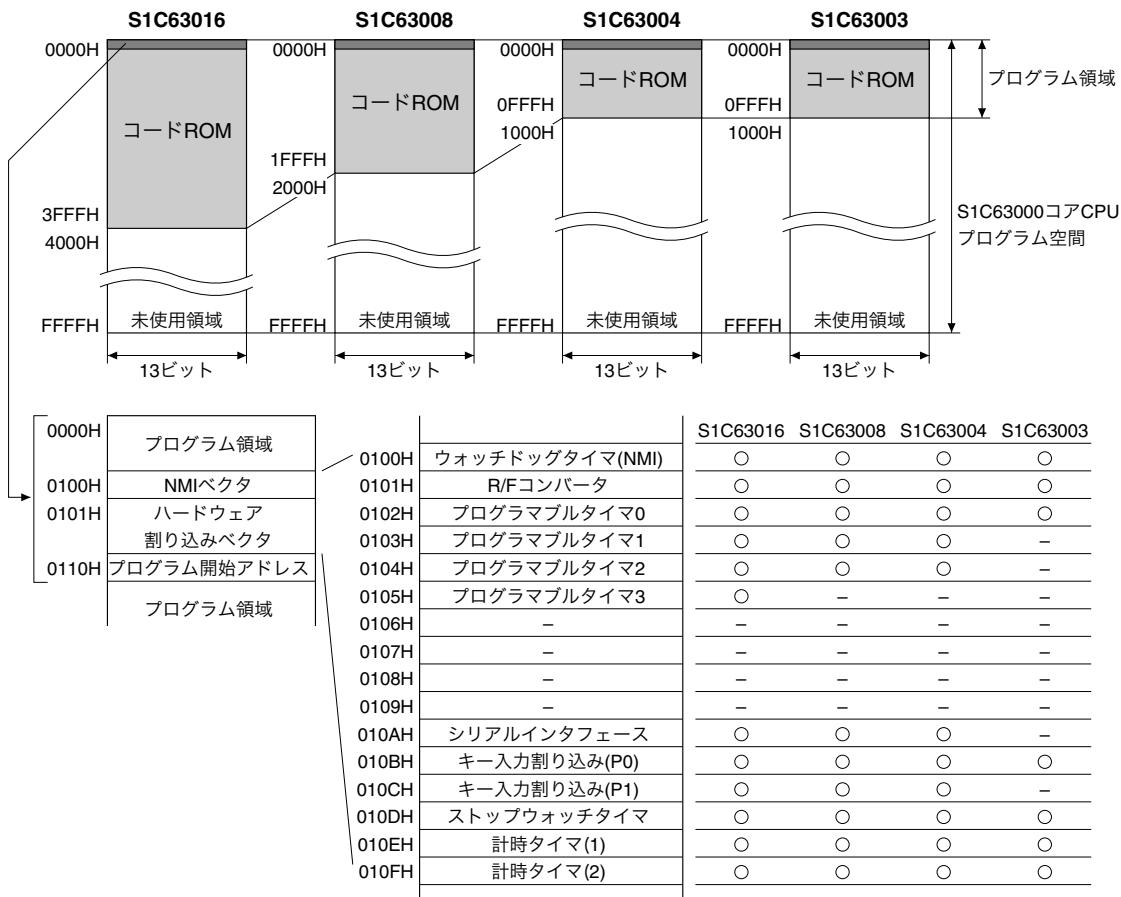

| 3.1 CPU .....                      | 3-1        |

| 3.2 コードメモリ領域 .....                 | 3-1        |

| 3.2.1 コードROM .....                 | 3-1        |

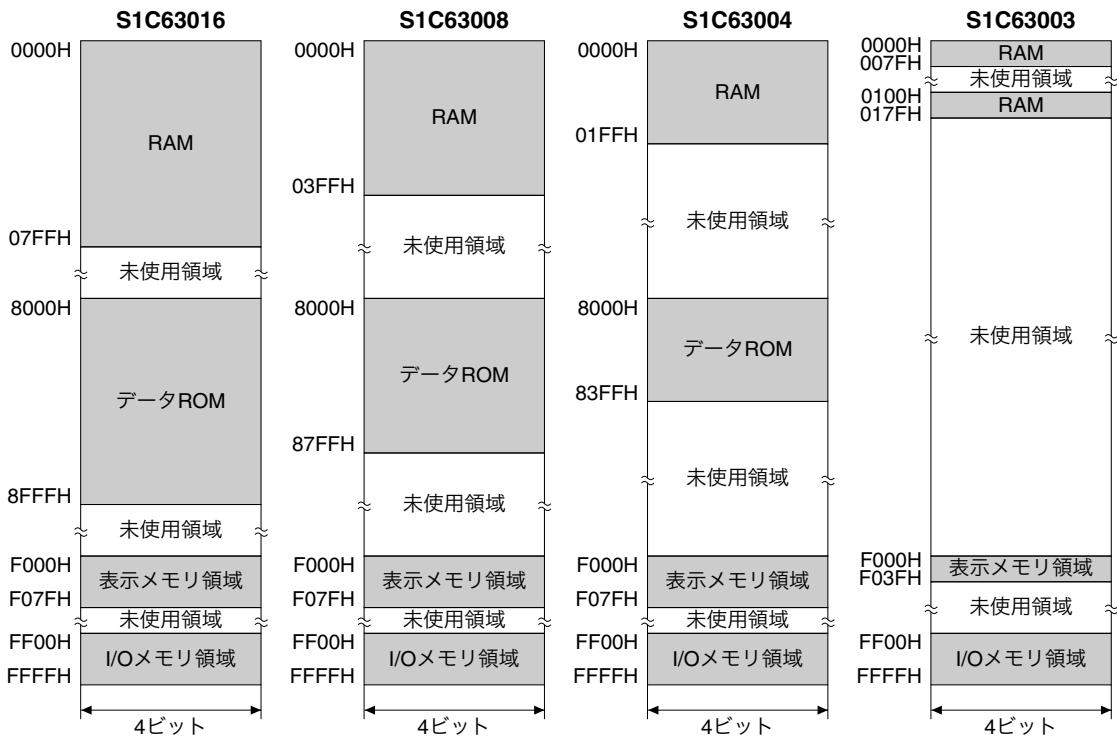

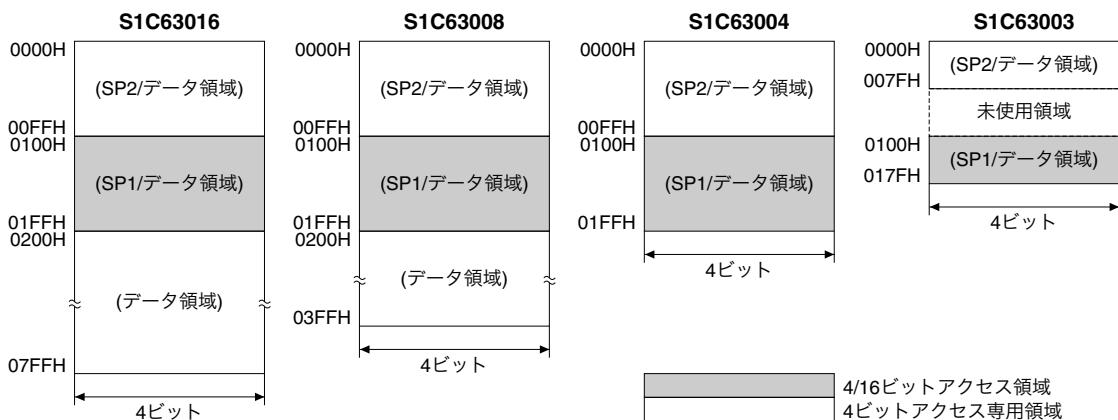

| 3.3 データメモリ領域 .....                 | 3-2        |

| 3.3.1 RAM .....                    | 3-2        |

| 3.3.2 データROM .....                 | 3-3        |

| 3.3.3 表示メモリ .....                  | 3-3        |

| 3.3.4 I/Oメモリ .....                 | 3-4        |

| <b>4 イニシャルリセット .....</b>           | <b>4-1</b> |

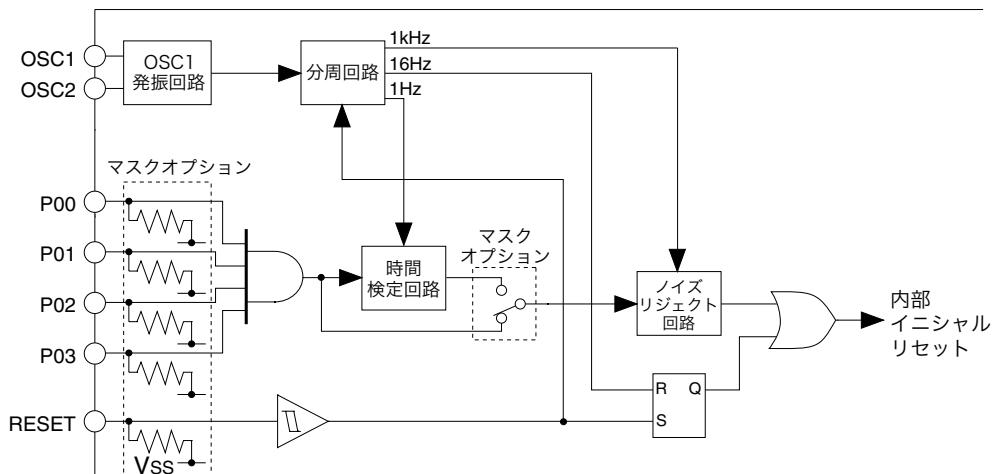

| 4.1 イニシャルリセット回路 .....              | 4-1        |

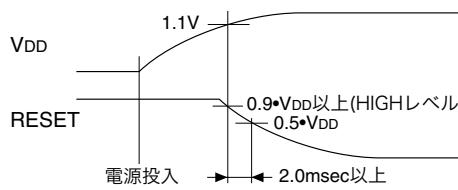

| 4.2 リセット端子(RESET) .....            | 4-1        |

| 4.3 P0xポート(P00～P03)の同時HIGH入力 ..... | 4-2        |

| 4.4 イニシャルリセット時の内部レジスタ .....        | 4-2        |

| 4.5 イニシャルリセット時の端子設定 .....          | 4-3        |

| <b>5 電源 .....</b>                  | <b>5-1</b> |

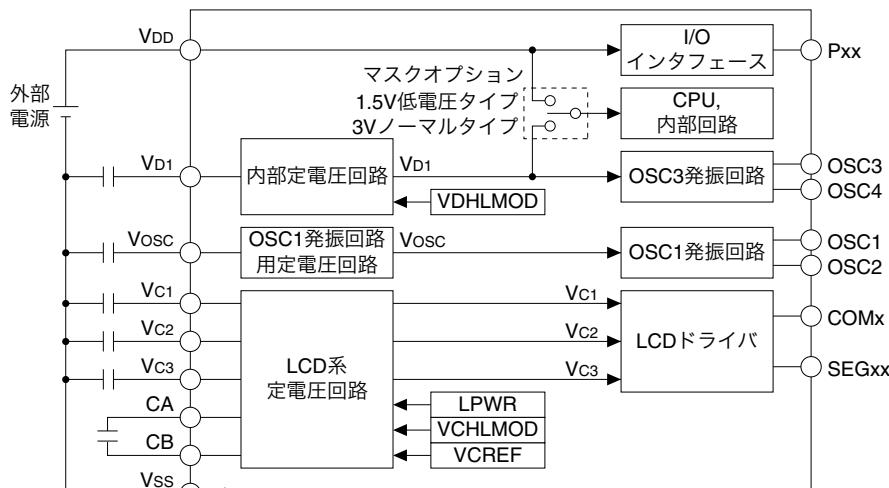

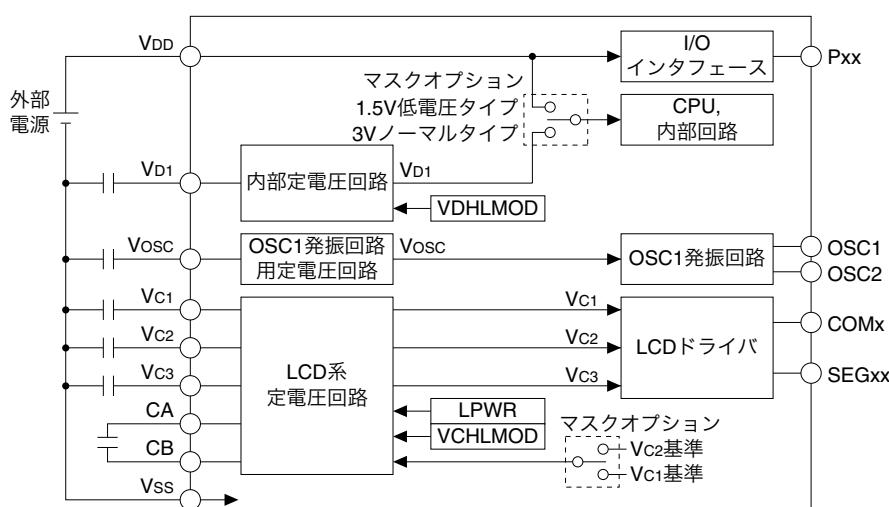

| 5.1 動作電圧 .....                     | 5-1        |

| 5.2 内蔵電源回路 .....                   | 5-1        |

| 5.3 LCD電源の制御 .....                 | 5-3        |

| 5.4 重負荷保護機能 .....                  | 5-3        |

| 5.5 電源回路のI/Oメモリ .....              | 5-4        |

| 5.6 注意事項 .....                     | 5-5        |

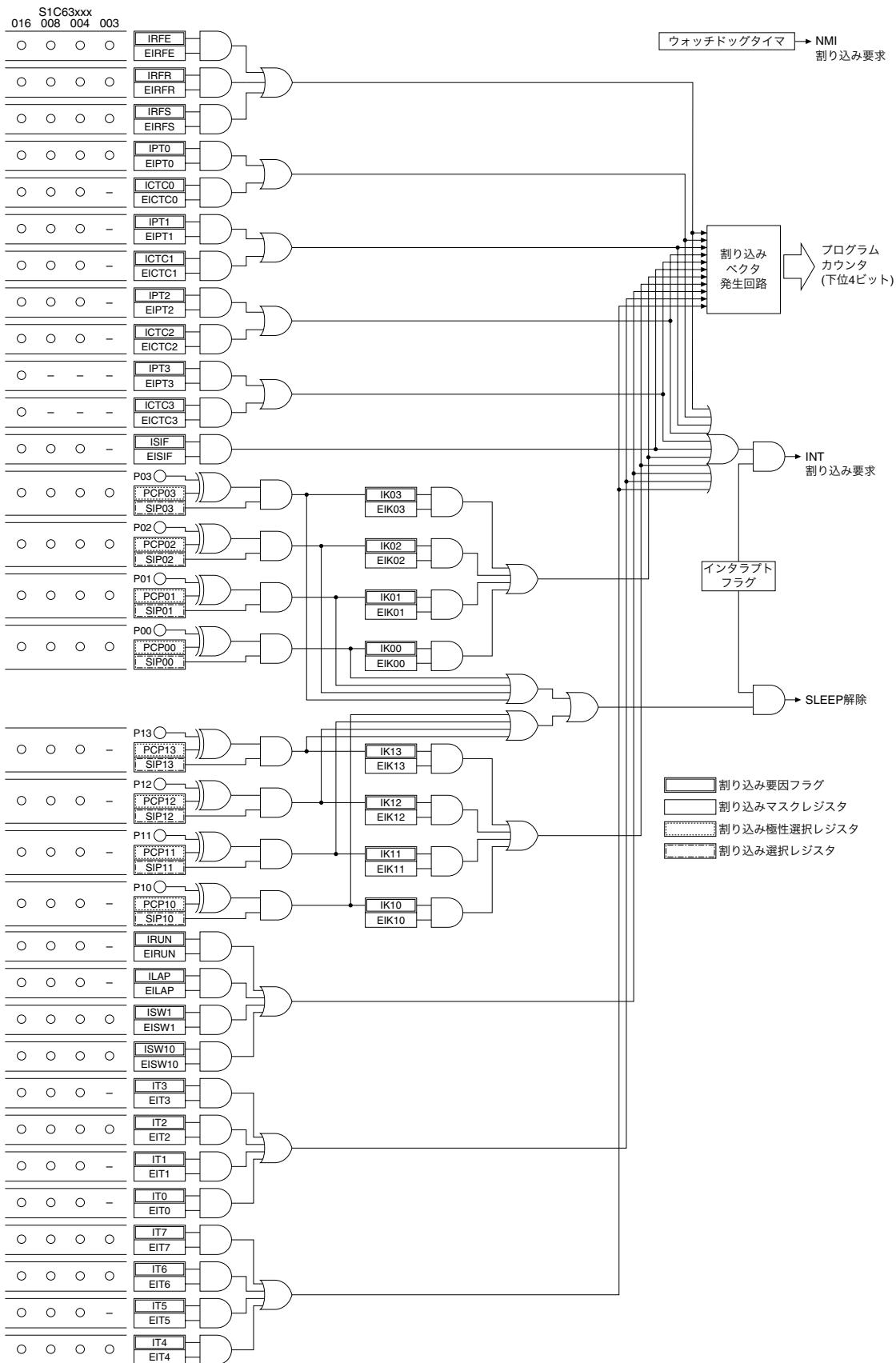

| <b>6 割り込みコントローラ .....</b>          | <b>6-1</b> |

| 6.1 割り込みコントローラの構成 .....            | 6-1        |

| 6.2 割り込みの要因 .....                  | 6-3        |

| 6.3 割り込みの個別マスク .....               | 6-3        |

## 目次

|                                                          |             |

|----------------------------------------------------------|-------------|

| 6.4 割り込みベクタ .....                                        | 6-4         |

| 6.5 割り込みコントローラのI/Oメモリ .....                              | 6-5         |

| 6.6 注意事項 .....                                           | 6-8         |

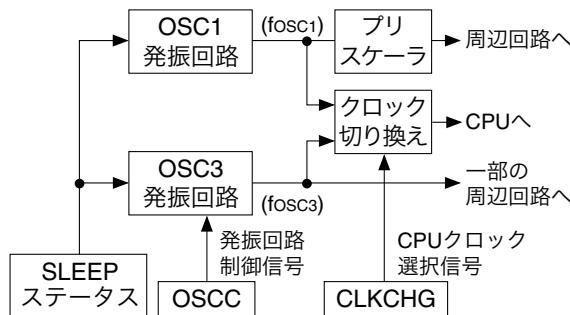

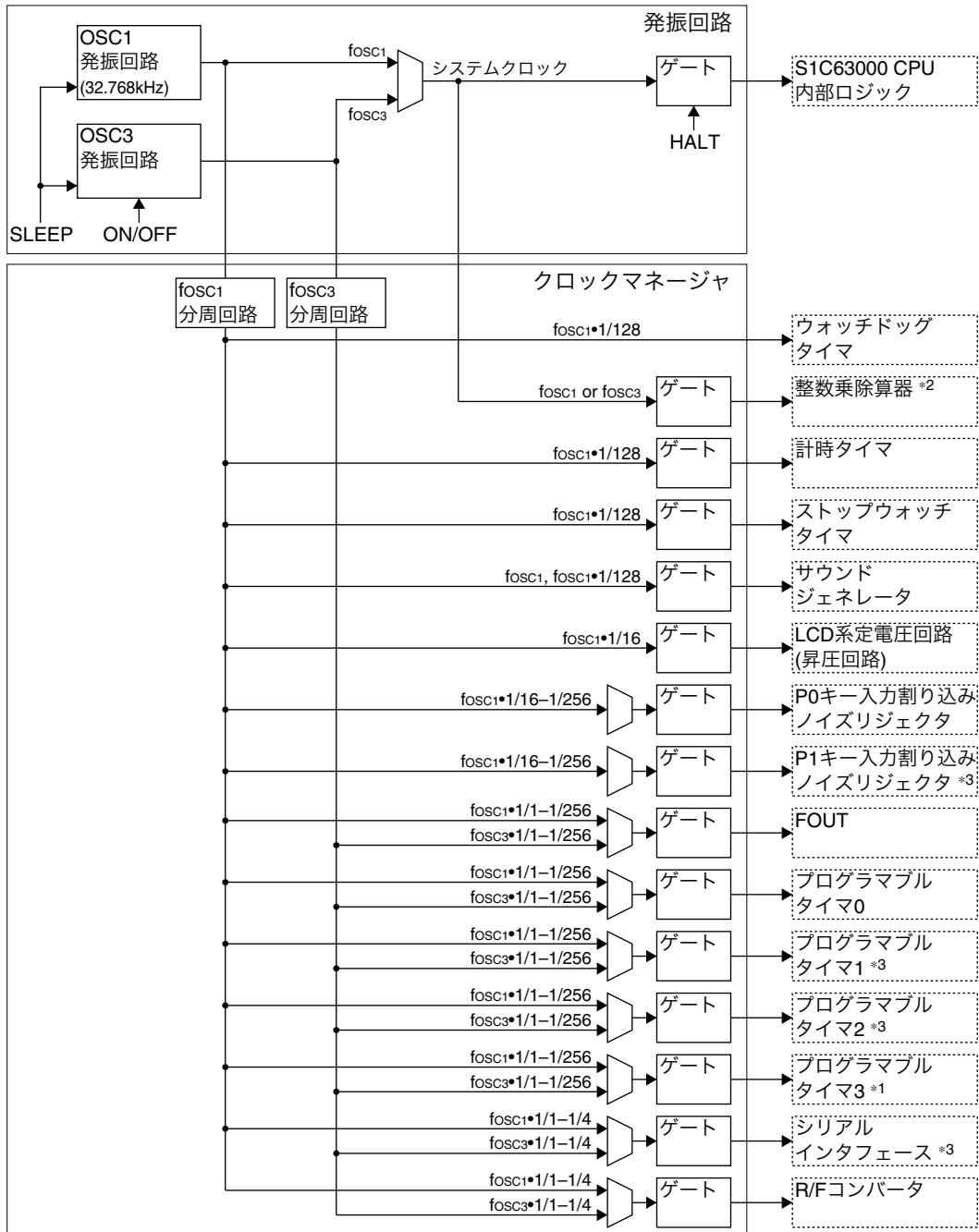

| <b>7 発振回路とクロック制御 .....</b>                               | <b>7-1</b>  |

| 7.1 発振回路 .....                                           | 7-1         |

| 7.1.1 発振回路の構成 .....                                      | 7-1         |

| 7.1.2 マスクオプション .....                                     | 7-1         |

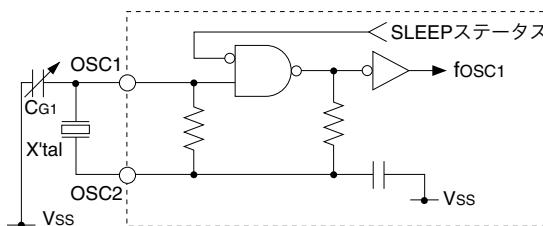

| 7.1.3 OSC1発振回路 .....                                     | 7-1         |

| 7.1.4 OSC3発振回路 .....                                     | 7-2         |

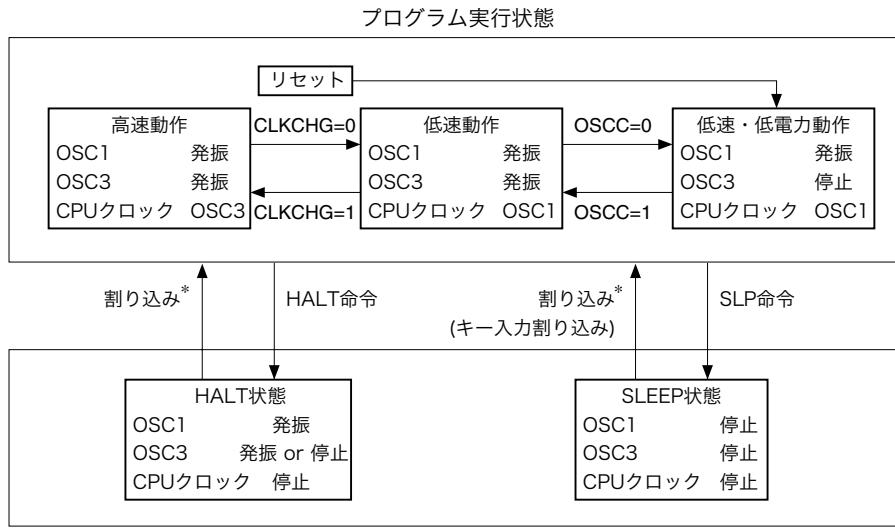

| 7.2 CPUクロックの切り換え .....                                   | 7-2         |

| 7.3 HALTとSLEEP .....                                     | 7-3         |

| 7.4 周辺回路用クロックの制御 .....                                   | 7-4         |

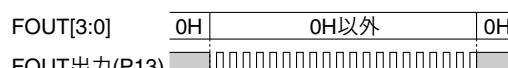

| 7.5 クロック出力(FOUT) .....                                   | 7-4         |

| 7.6 発振回路/クロック出力制御のI/Oメモリ .....                           | 7-5         |

| 7.7 注意事項 .....                                           | 7-6         |

| <b>8 ウオッチドッグタイマ .....</b>                                | <b>8-1</b>  |

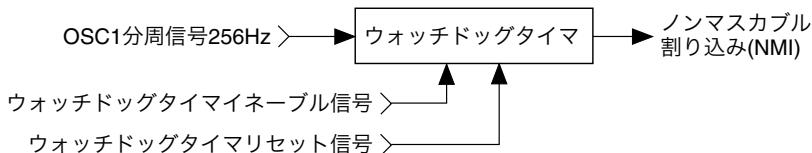

| 8.1 ウオッチドッグタイマの構成 .....                                  | 8-1         |

| 8.2 割り込み機能 .....                                         | 8-1         |

| 8.3 ウオッチドッグタイマのI/Oメモリ .....                              | 8-1         |

| 8.4 注意事項 .....                                           | 8-2         |

| <b>9 計時タイマ .....</b>                                     | <b>9-1</b>  |

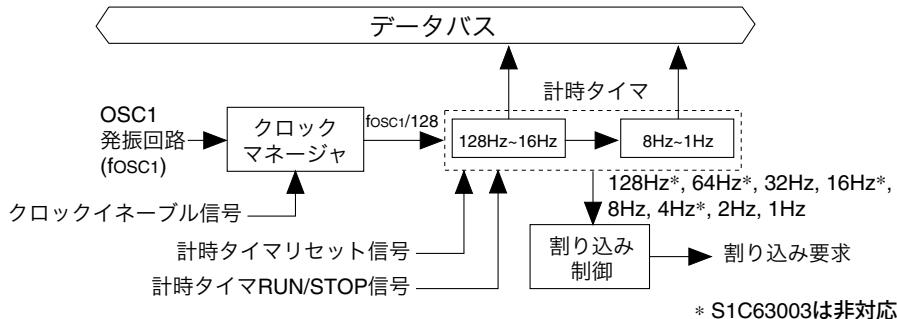

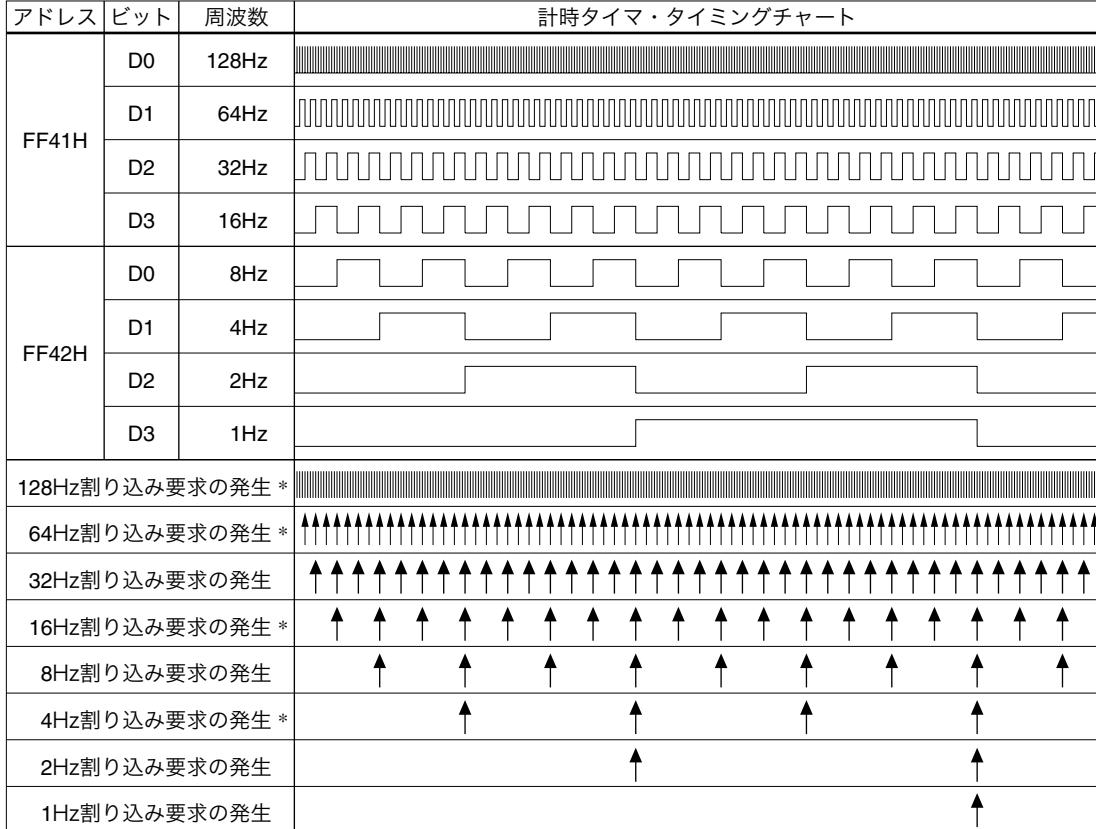

| 9.1 計時タイマの構成 .....                                       | 9-1         |

| 9.2 動作クロックの制御 .....                                      | 9-1         |

| 9.3 データの読み出しとホールド機能 .....                                | 9-1         |

| 9.4 割り込み機能 .....                                         | 9-2         |

| 9.5 計時タイマのI/Oメモリ .....                                   | 9-2         |

| 9.6 注意事項 .....                                           | 9-4         |

| <b>10 ストップウォッチタイマ .....</b>                              | <b>10-1</b> |

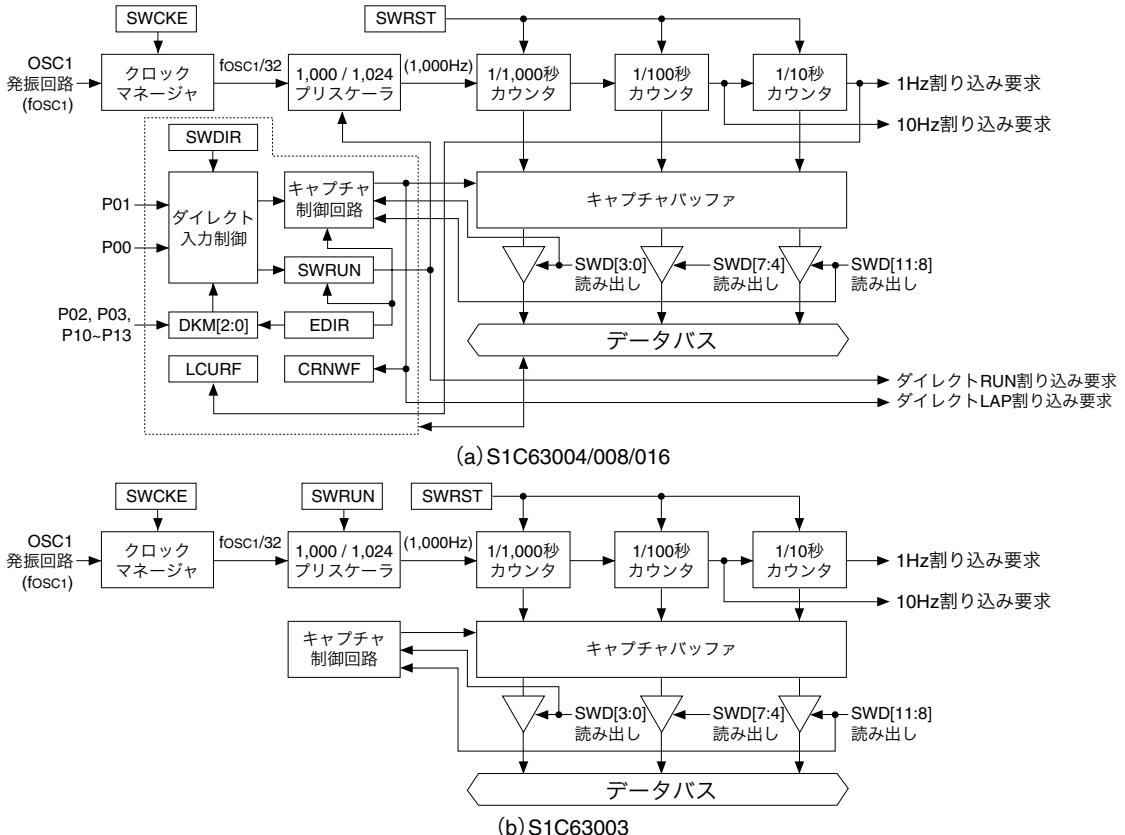

| 10.1 ストップウォッチタイマの構成 .....                                | 10-1        |

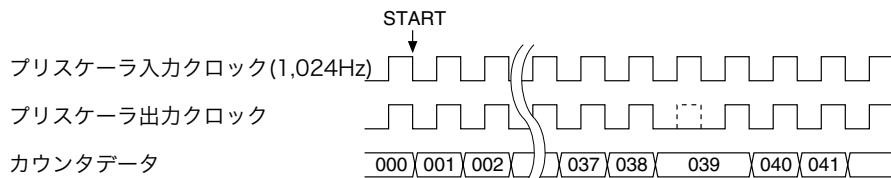

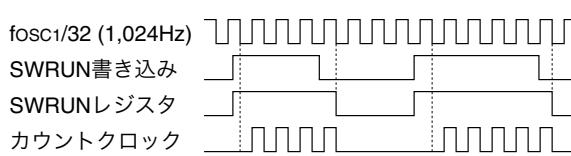

| 10.2 動作クロックの制御 .....                                     | 10-1        |

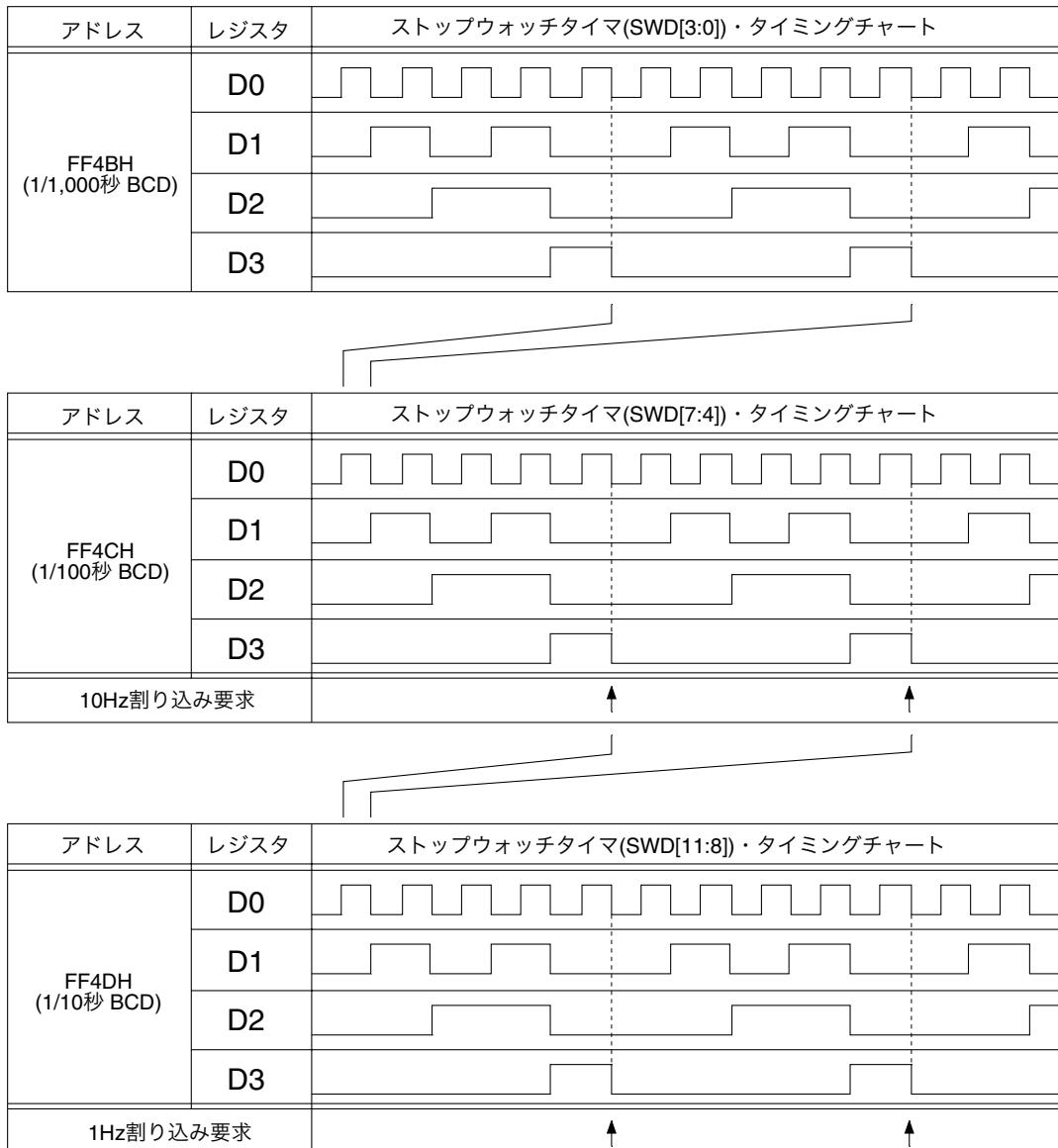

| 10.3 カウンタとプリスケーラ .....                                   | 10-2        |

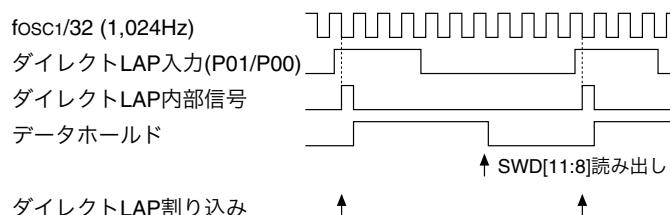

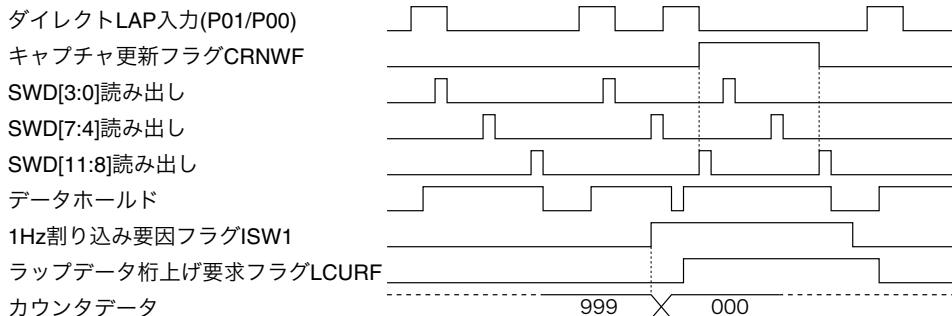

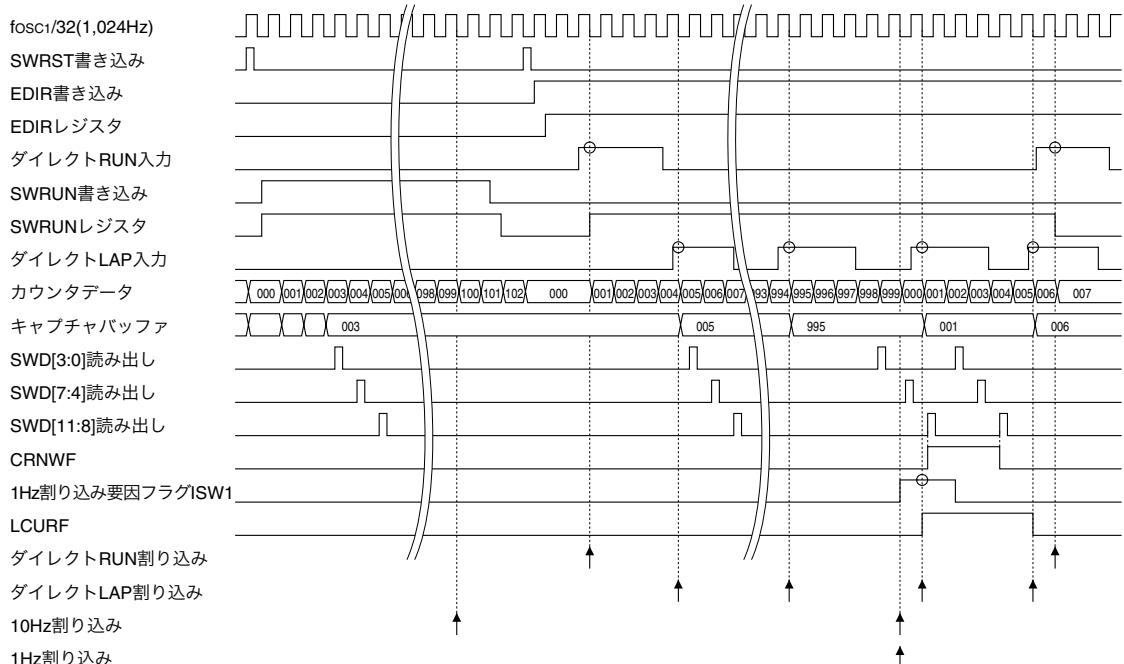

| 10.4 キャプチャバッファとホールド機能 .....                              | 10-2        |

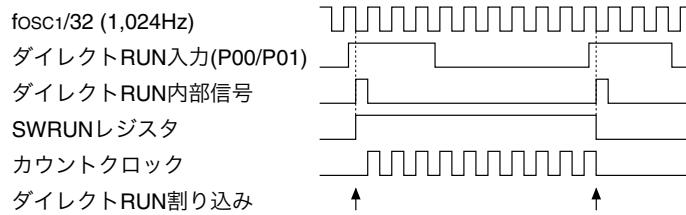

| 10.5 ストップウォッチタイマのRUN/STOPおよびリセット .....                   | 10-3        |

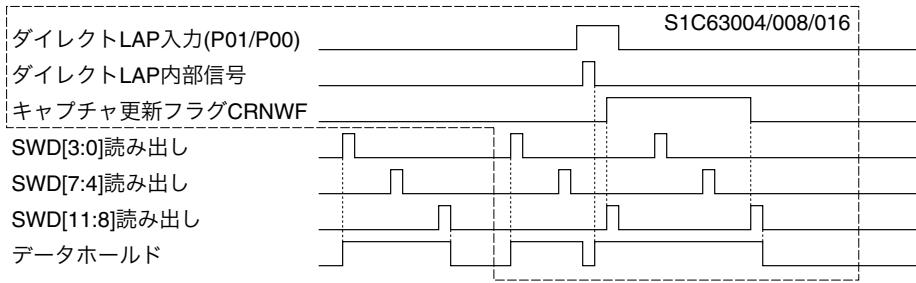

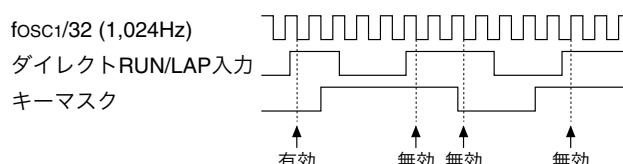

| 10.6 ダイレクト入力機能とキーマスク [S1C63004/008/016] .....            | 10-3        |

| 10.7 割り込み機能 .....                                        | 10-6        |

| 10.8 ストップウォッチタイマのI/Oメモリ .....                            | 10-7        |

| 10.9 注意事項 .....                                          | 10-10       |

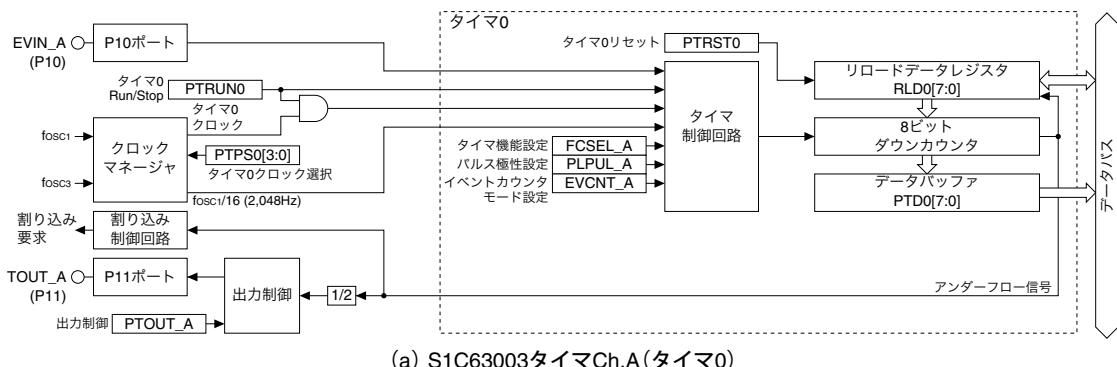

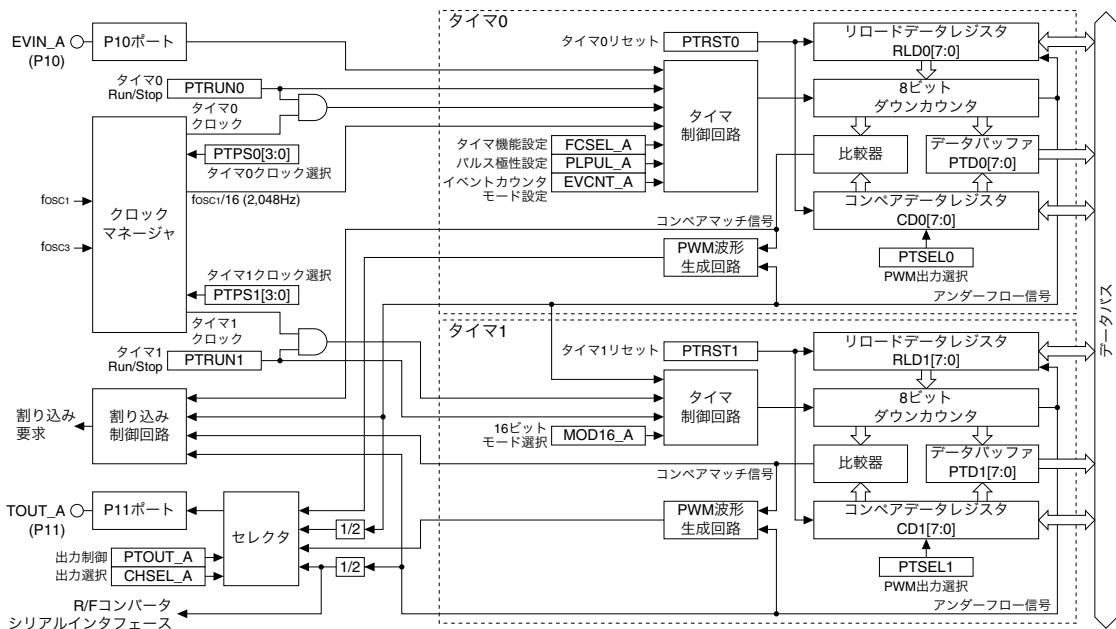

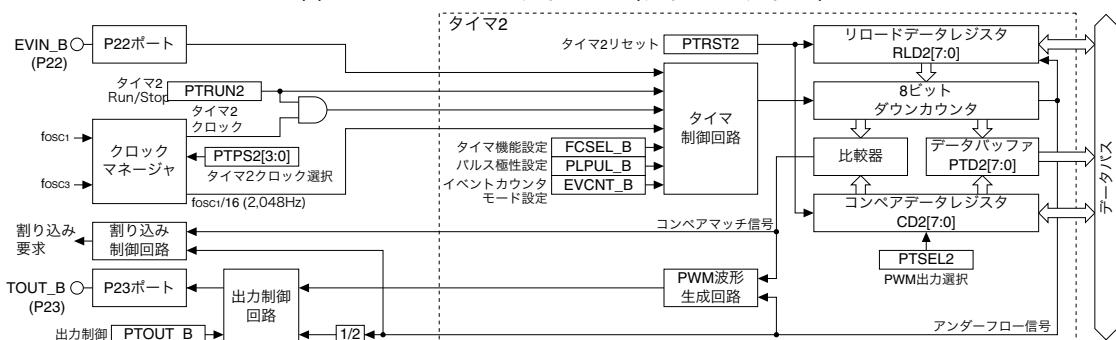

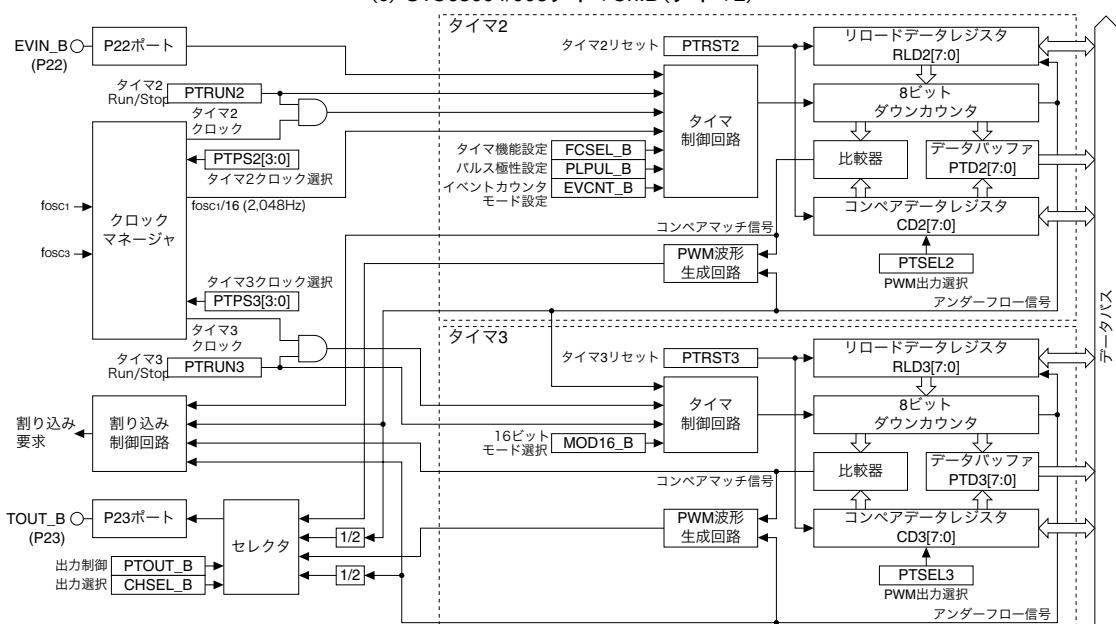

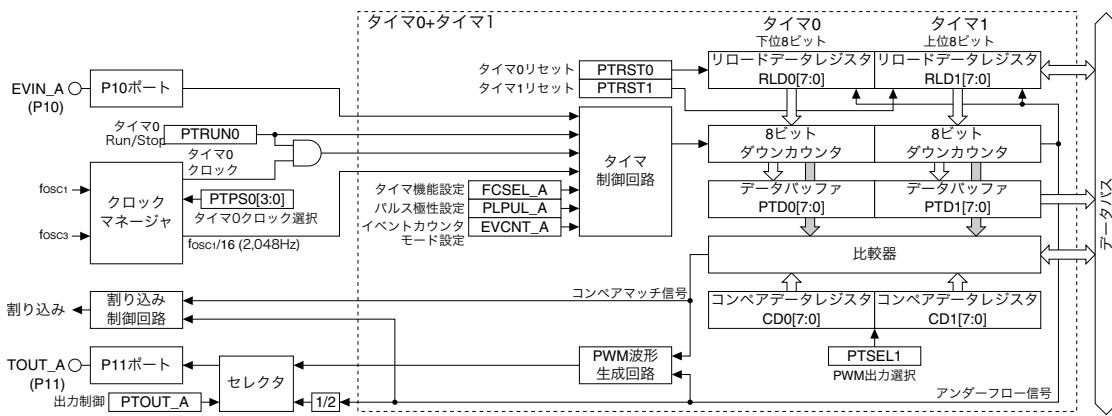

| <b>11 プログラムルタイマ .....</b>                                | <b>11-1</b> |

| 11.1 プログラムルタイマの構成 .....                                  | 11-1        |

| 11.2 動作クロックの制御 .....                                     | 11-3        |

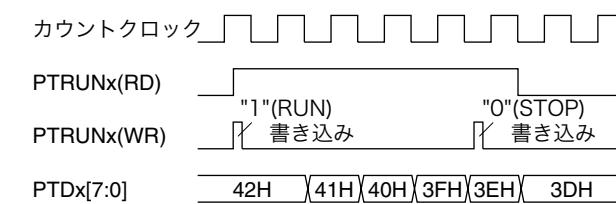

| 11.3 カウンタの基本動作 .....                                     | 11-4        |

| 11.4 イベントカウンタモード(タイマ0、タイマ2) .....                        | 11-4        |

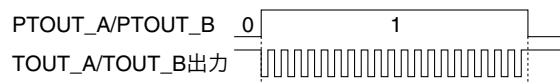

| 11.5 PWMモード(タイマ0～タイマ3) [S1C63004/008/016] .....          | 11-5        |

| 11.6 16ビットタイマモード(タイマ0+1、タイマ2+3) [S1C63004/008/016] ..... | 11-6        |

| 11.7 割り込み機能 .....                                        | 11-7        |

| 11.8 TOUT出力の設定 .....                                     | 11-7        |

|                                                             |             |

|-------------------------------------------------------------|-------------|

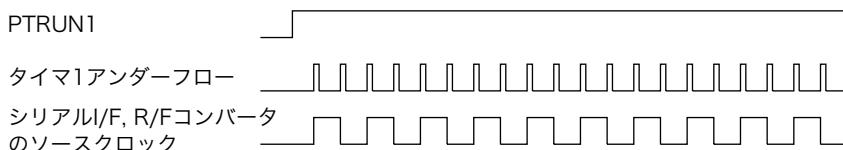

| 11.9 シリアルインタフェース, R/Fコンバータへのクロック出力 [S1C63004/008/016] ..... | 11-8        |

| 11.10 プログラマブルタイマのI/Oメモリ .....                               | 11-8        |

| 11.11 注意事項.....                                             | 11-15       |

| <b>12 入出力兼用ポート .....</b>                                    | <b>12-1</b> |

| 12.1 入出力兼用ポートの構成.....                                       | 12-1        |

| 12.2 マスクオプション .....                                         | 12-2        |

| 12.3 I/O制御レジスタと入力/出力モード .....                               | 12-3        |

| 12.4 入力インターフェースレベル .....                                    | 12-3        |

| 12.5 入力モード時のプルダウン .....                                     | 12-3        |

| 12.6 キー入力割り込み機能 .....                                       | 12-3        |

| 12.7 入出力兼用ポートのI/Oメモリ .....                                  | 12-5        |

| 12.8 注意事項.....                                              | 12-10       |

| <b>13 シリアルインタフェース [S1C63004/008/016] .....</b>              | <b>13-1</b> |

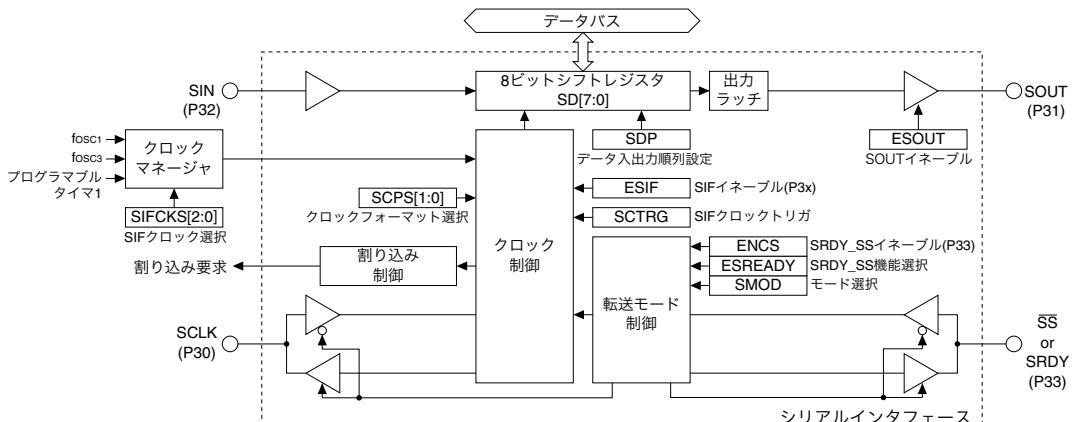

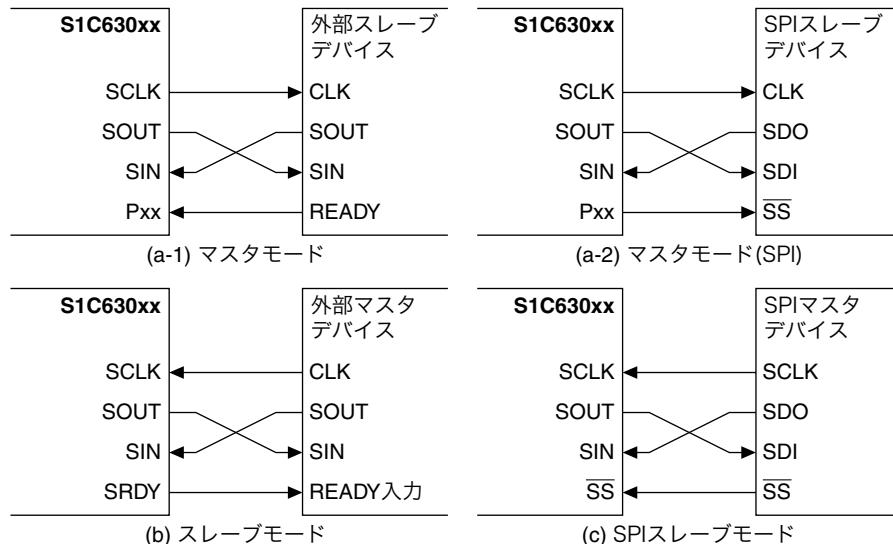

| 13.1 シリアルインタフェースの構成.....                                    | 13-1        |

| 13.2 シリアルインタフェース入出力端子.....                                  | 13-1        |

| 13.3 マスクオプション .....                                         | 13-2        |

| 13.4 シリアルインタフェースの動作モード .....                                | 13-2        |

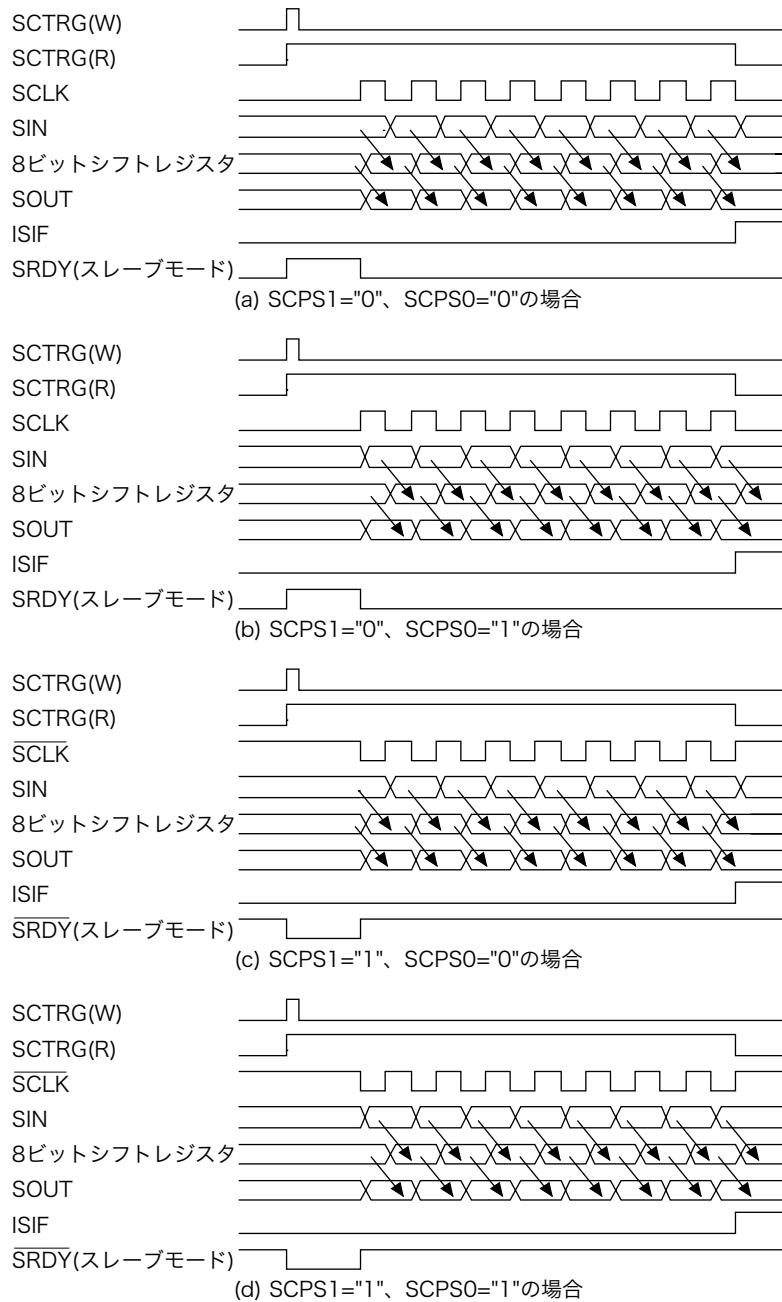

| 13.5 同期クロックの設定 .....                                        | 13-4        |

| 13.5.1 ソースクロックの選択.....                                      | 13-4        |

| 13.5.2 同期クロックフォーマットの選択.....                                 | 13-4        |

| 13.6 データの入出力と割り込み .....                                     | 13-5        |

| 13.6.1 シリアルデータの出力と割り込み .....                                | 13-5        |

| 13.6.2 シリアルデータの入力と割り込み .....                                | 13-5        |

| 13.6.3 シリアルデータの入出力順列 .....                                  | 13-6        |

| 13.6.4 SRDY信号 .....                                         | 13-6        |

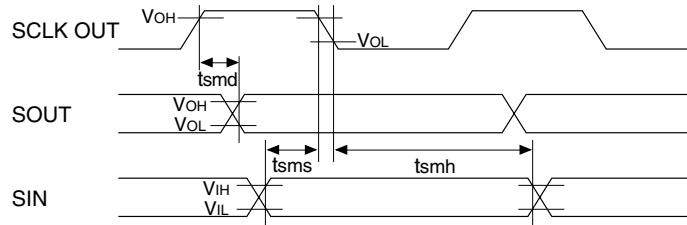

| 13.6.5 タイミングチャート.....                                       | 13-6        |

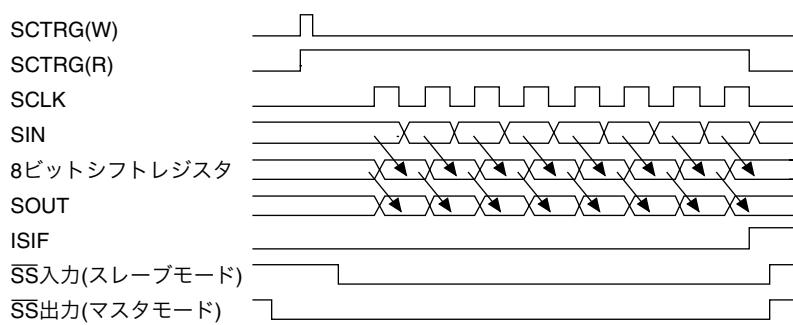

| 13.7 SPI方式のデータ転送 .....                                      | 13-8        |

| 13.8 シリアルインタフェースのI/Oメモリ .....                               | 13-9        |

| 13.9 注意事項.....                                              | 13-12       |

| <b>14 LCDドライバ .....</b>                                     | <b>14-1</b> |

| 14.1 LCDドライバの構成.....                                        | 14-1        |

| 14.2 マスクオプション .....                                         | 14-1        |

| 14.2.1 SEG/GPIO/RFC端子切り換え .....                             | 14-1        |

| 14.2.2 LCD駆動電源 .....                                        | 14-2        |

| 14.2.3 セグメントオプション .....                                     | 14-2        |

| 14.3 LCD表示の制御 .....                                         | 14-7        |

| 14.3.1 表示モードの選択 .....                                       | 14-7        |

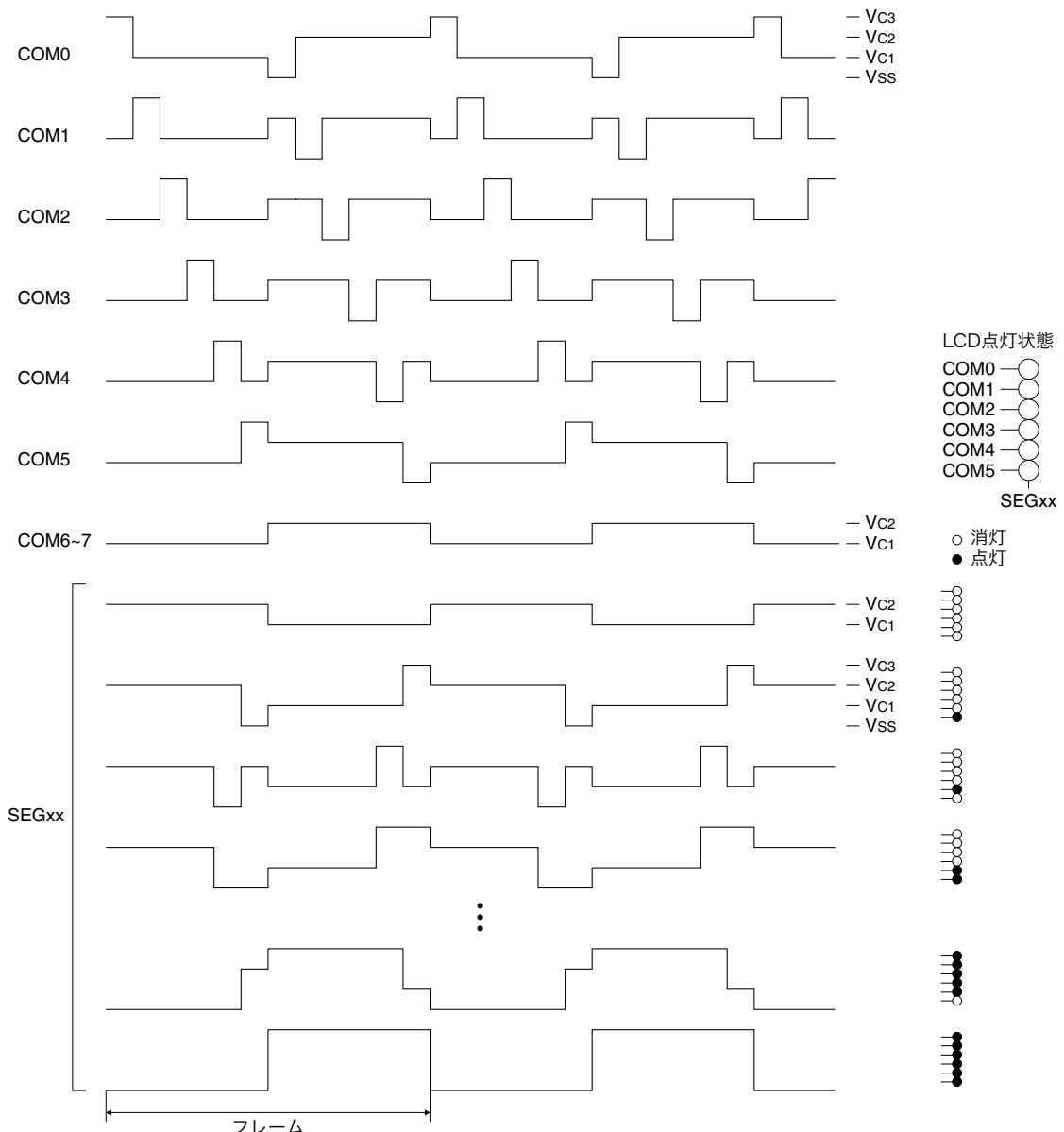

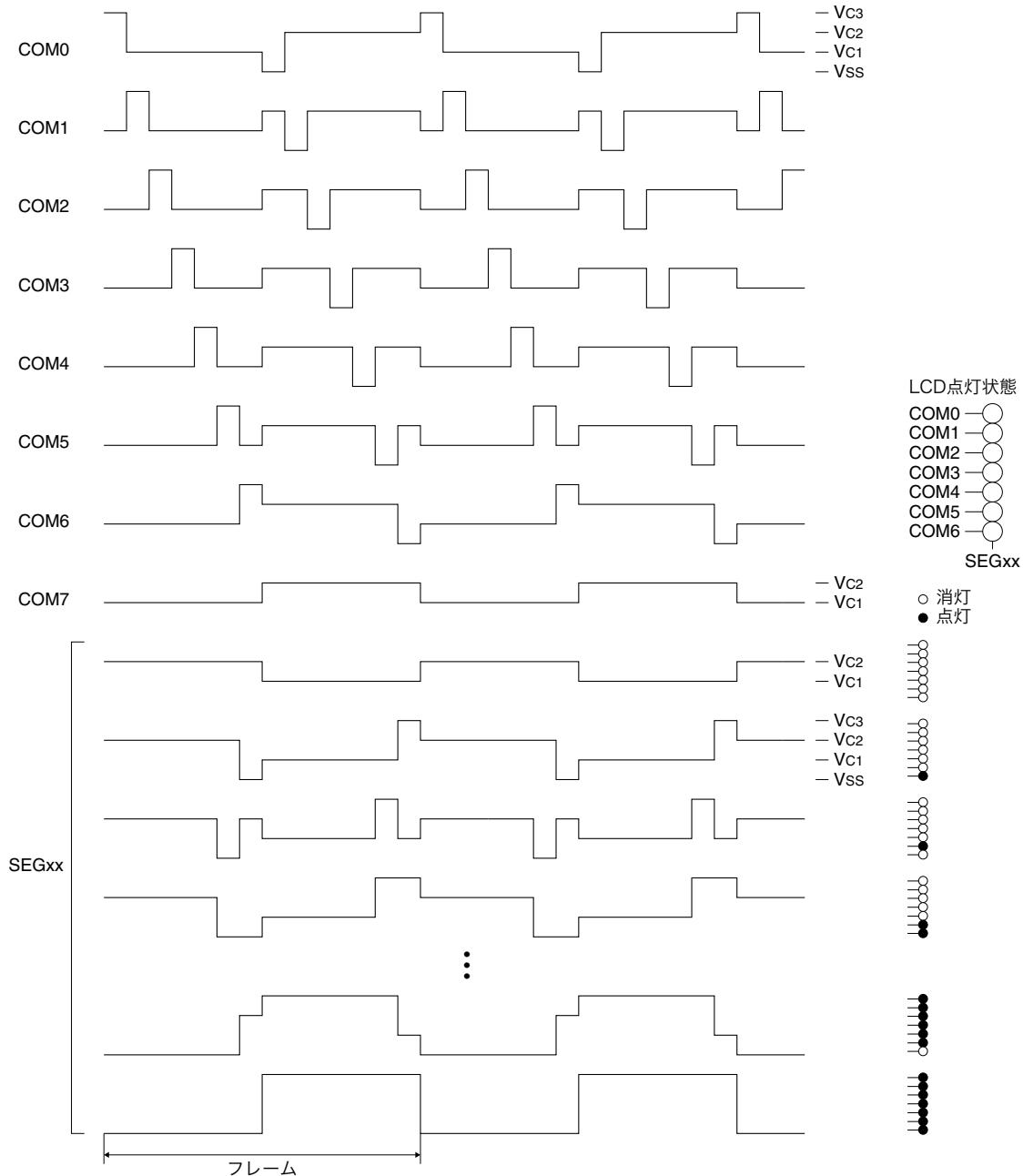

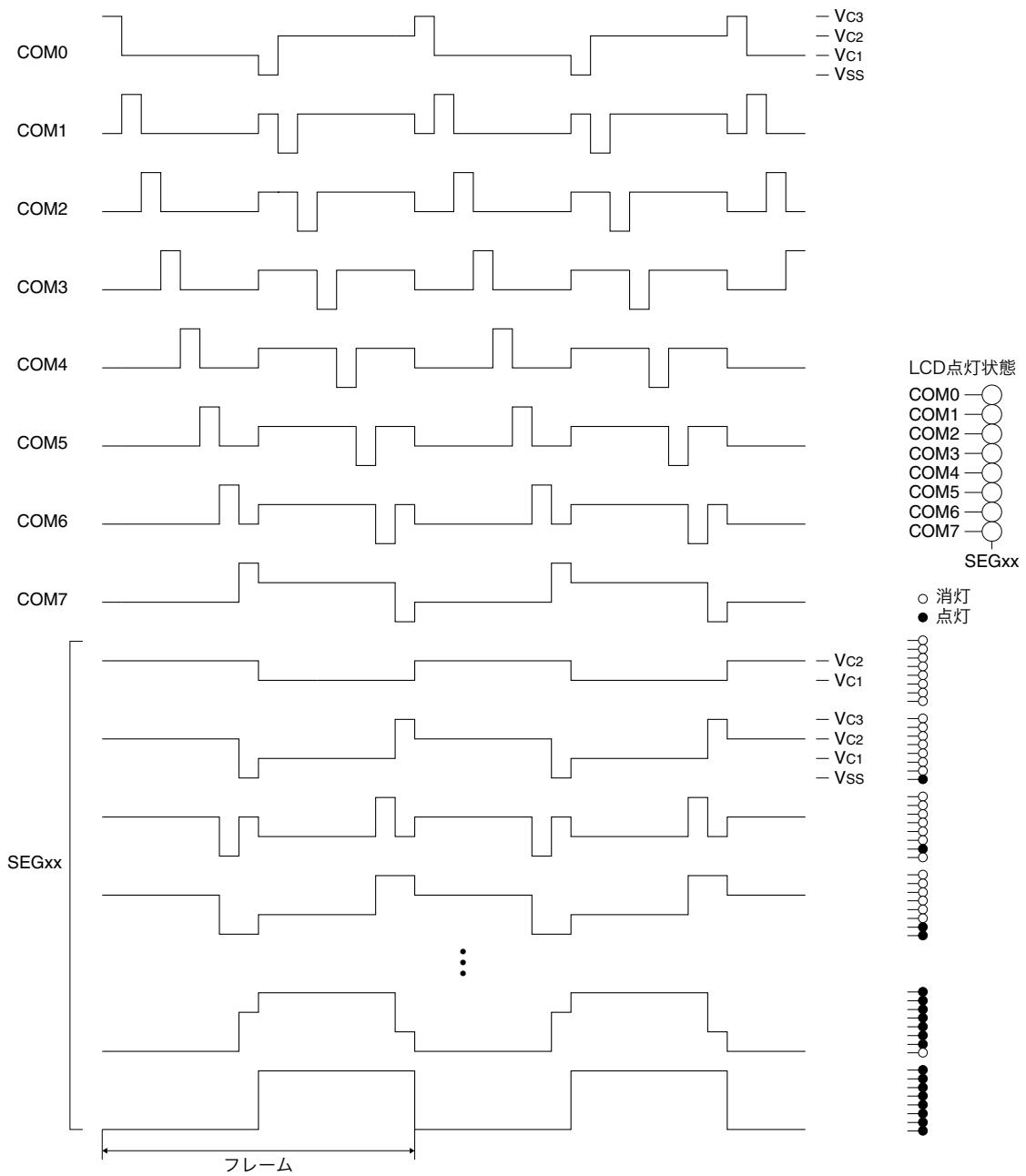

| 14.3.2 駆動デューティの切り換え .....                                   | 14-7        |

| 14.3.3 フレーム周波数の切り換え .....                                   | 14-7        |

| 14.3.4 駆動波形 .....                                           | 14-8        |

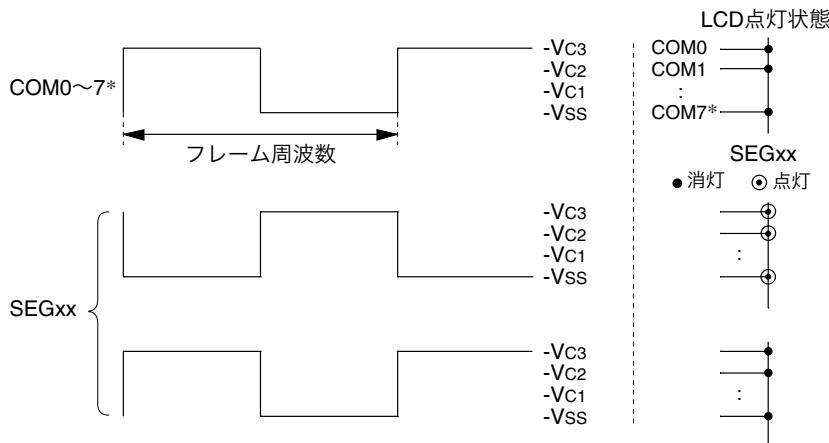

| 14.3.5 スタティック駆動 .....                                       | 14-14       |

| 14.3.6 LCDコントラスト調整 [S1C63004/008/016] .....                 | 14-14       |

| 14.4 表示メモリ .....                                            | 14-15       |

| 14.5 LCDドライバのI/Oメモリ .....                                   | 14-15       |

| 14.6 注意事項.....                                              | 14-17       |

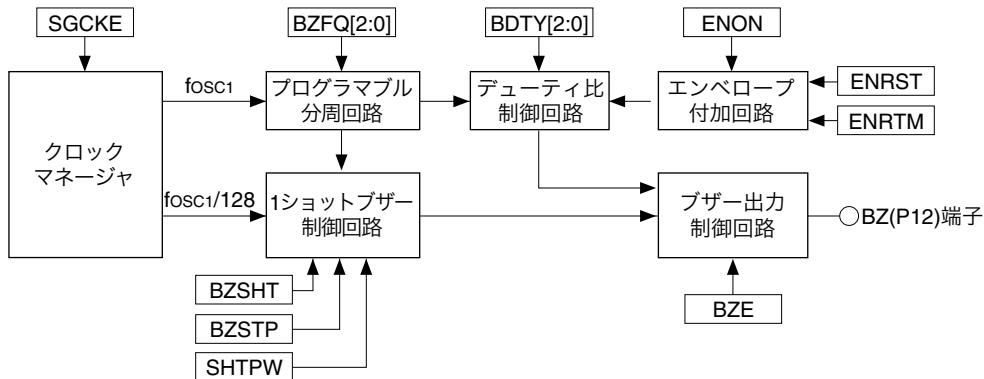

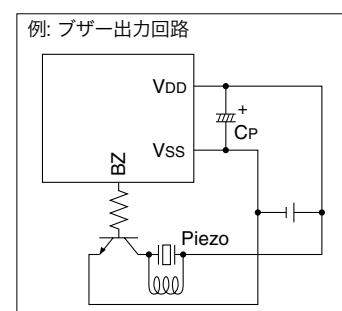

| <b>15 サウンドジェネレータ .....</b>                                  | <b>15-1</b> |

| 15.1 サウンドジェネレータの構成 .....                                    | 15-1        |

| 15.2 動作クロックの制御.....                                         | 15-1        |

## 目次

|                                                  |               |

|--------------------------------------------------|---------------|

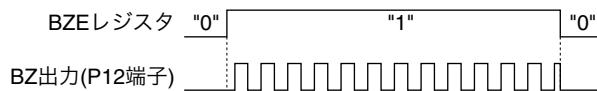

| 15.3 ブザー出力の制御 .....                              | 15-1          |

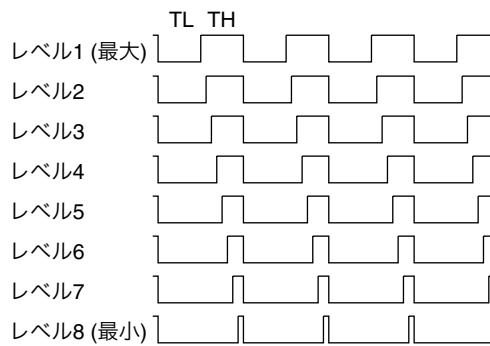

| 15.4 ブザー周波数と音量の設定 .....                          | 15-2          |

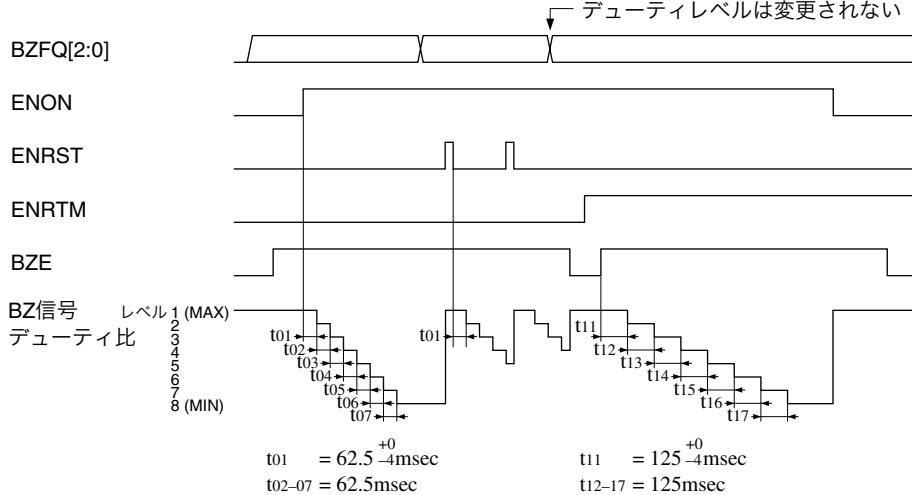

| 15.5 デジタルエンベロープ .....                            | 15-3          |

| 15.6 1ショット出力 .....                               | 15-3          |

| 15.7 サウンドジェネレータのI/Oメモリ .....                     | 15-4          |

| 15.8 注意事項 .....                                  | 15-7          |

| <b>16 R/Fコンバータ .....</b>                         | <b>16-1</b>   |

| 16.1 R/Fコンバータの構成 .....                           | 16-1          |

| 16.2 動作クロックの制御 .....                             | 16-1          |

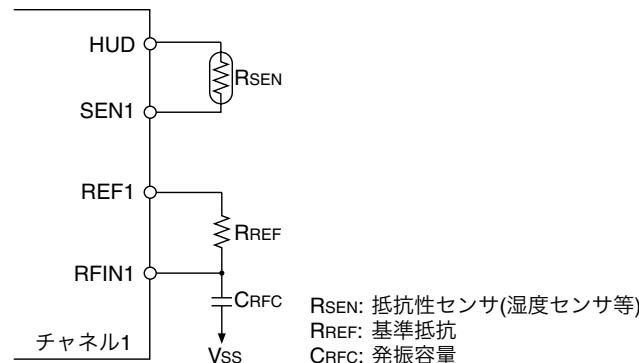

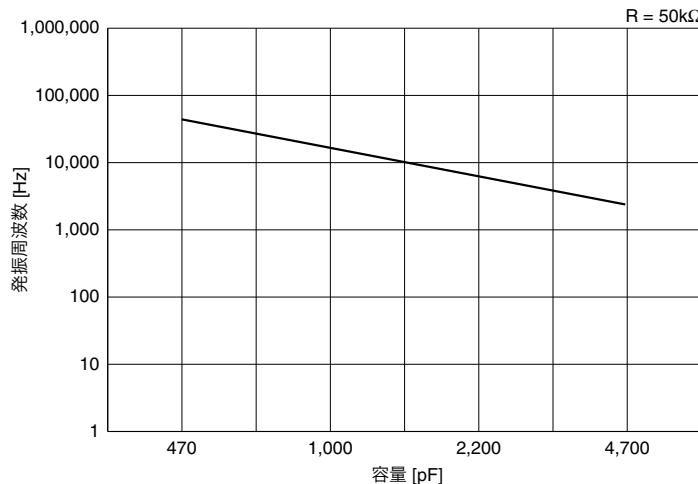

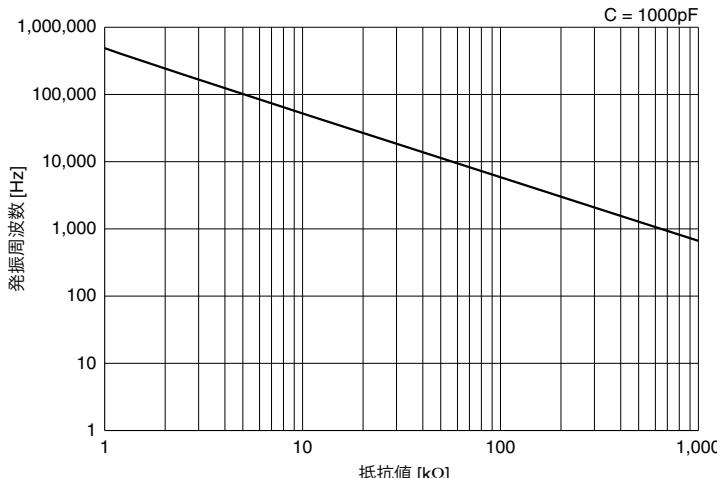

| 16.3 接続端子とCR発振回路 .....                           | 16-2          |

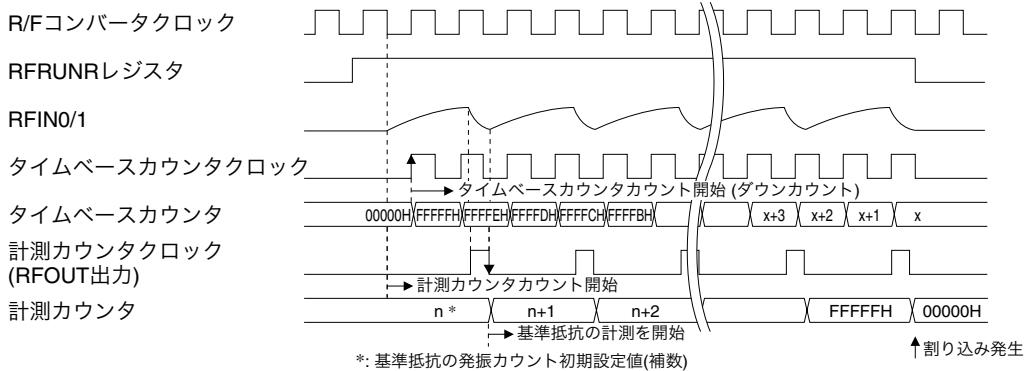

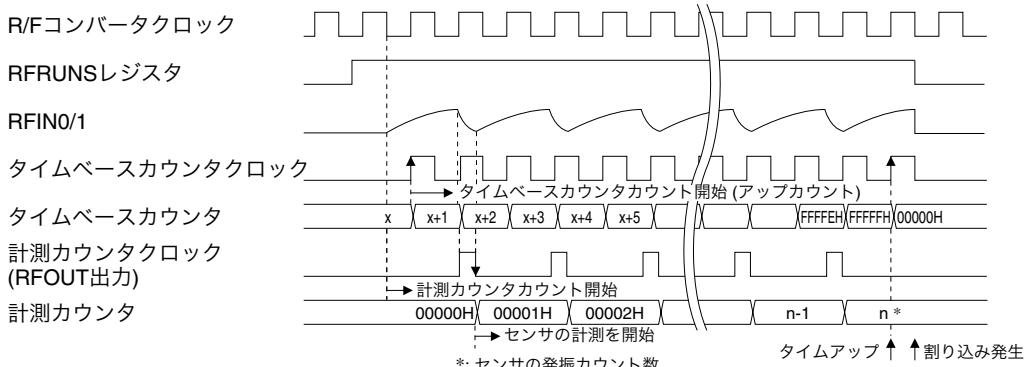

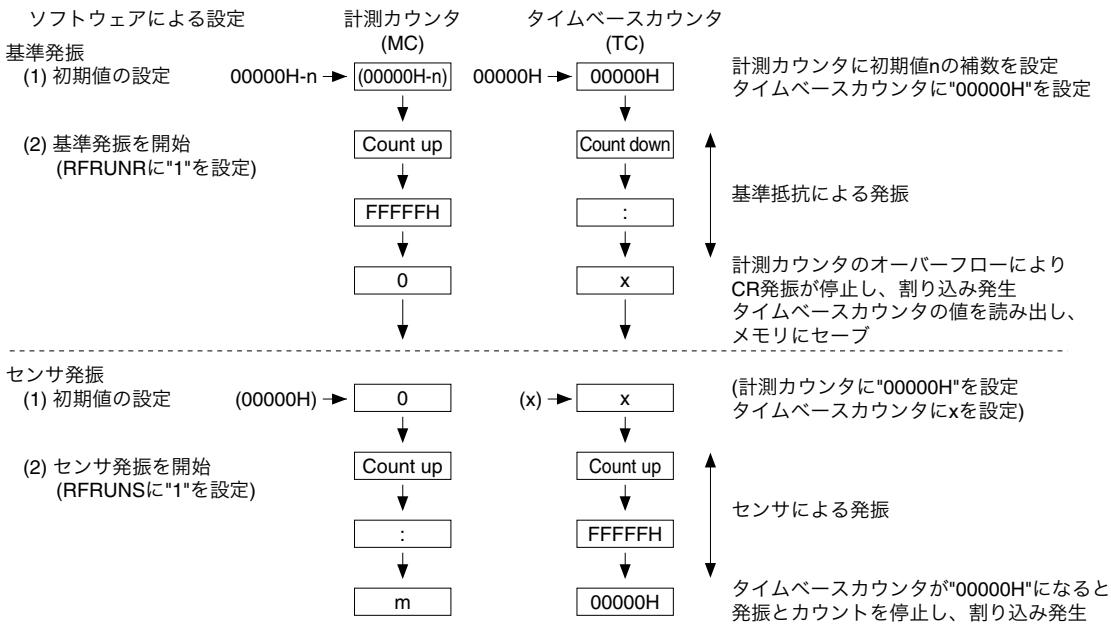

| 16.4 R/F変換 .....                                 | 16-4          |

| 16.5 割り込み機能 .....                                | 16-6          |

| 16.6 連続発振機能 .....                                | 16-8          |

| 16.7 R/FコンバータのI/Oメモリ .....                       | 16-8          |

| 16.8 注意事項 .....                                  | 16-11         |

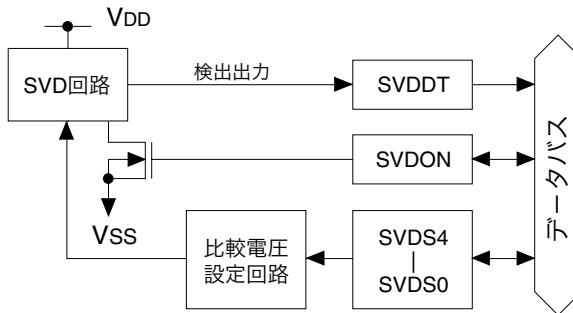

| <b>17 SVD(電源電圧検出)回路 [S1C63004/008/016] .....</b> | <b>17-1</b>   |

| 17.1 SVD回路の構成 .....                              | 17-1          |

| 17.2 SVD動作 .....                                 | 17-1          |

| 17.3 SVD回路のI/Oメモリ .....                          | 17-2          |

| 17.4 注意事項 .....                                  | 17-2          |

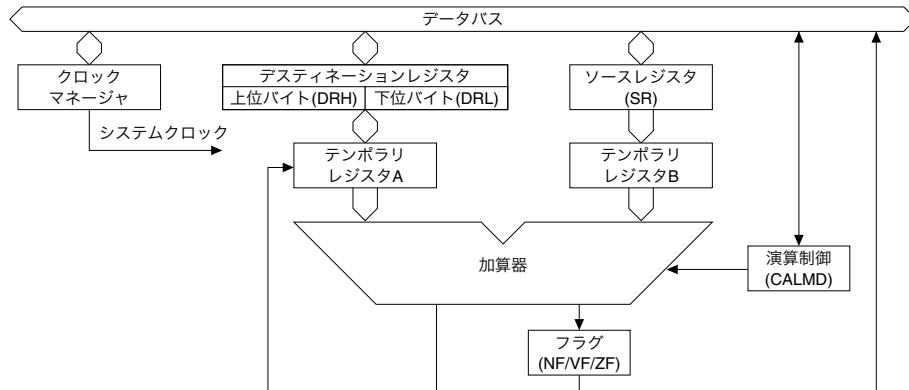

| <b>18 整数乗除算器 [S1C63008/016] .....</b>            | <b>18-1</b>   |

| 18.1 整数乗除算器の構成 .....                             | 18-1          |

| 18.2 動作クロックの制御 .....                             | 18-1          |

| 18.3 乗算モード .....                                 | 18-1          |

| 18.4 除算モード .....                                 | 18-2          |

| 18.5 実行サイクル .....                                | 18-2          |

| 18.6 整数乗除算器のI/Oメモリ .....                         | 18-3          |

| 18.7 注意事項 .....                                  | 18-5          |

| <b>19 電気的特性 .....</b>                            | <b>19-1</b>   |

| 19.1 絶対最大定格 .....                                | 19-1          |

| 19.2 推奨動作条件 .....                                | 19-1          |

| 19.3 DC特性 .....                                  | 19-2          |

| 19.4 アナログ回路特性・消費電流 .....                         | 19-3          |

| 19.4.1 LCD ドライバ .....                            | 19-3          |

| 19.4.2 SVD回路 [S1C63004/008/016] .....            | 19-4          |

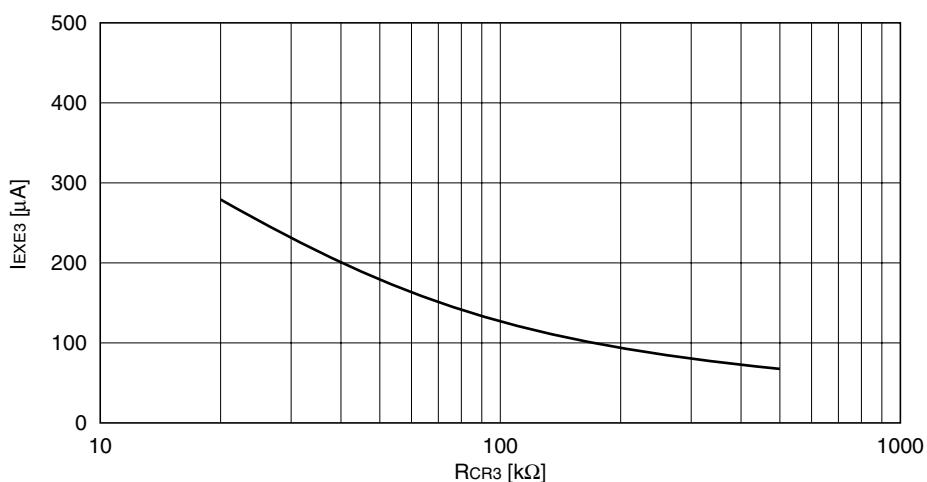

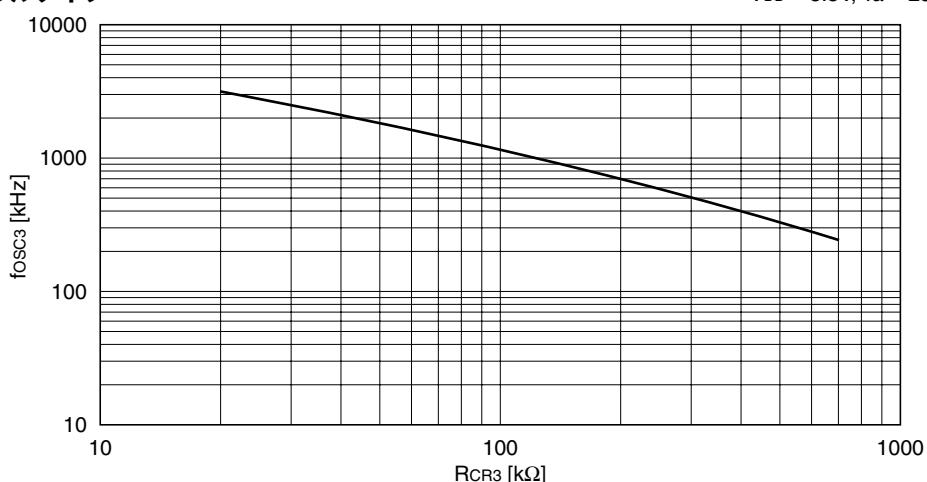

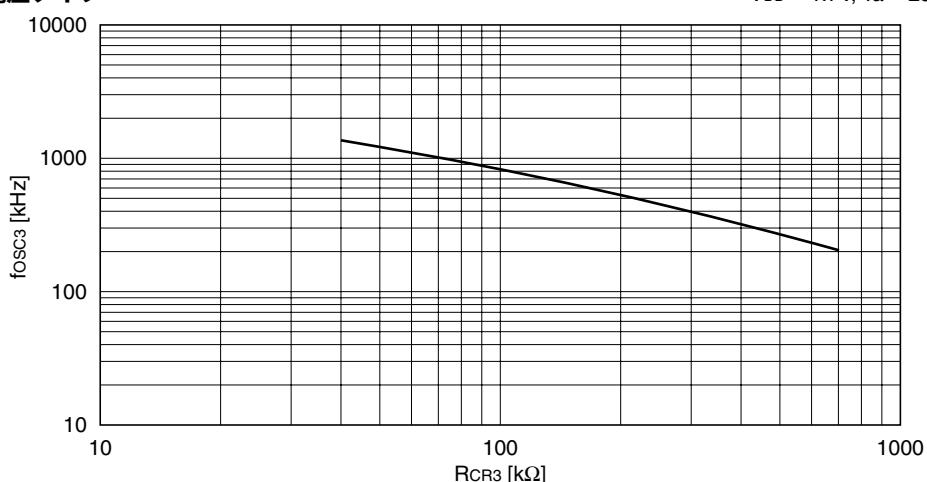

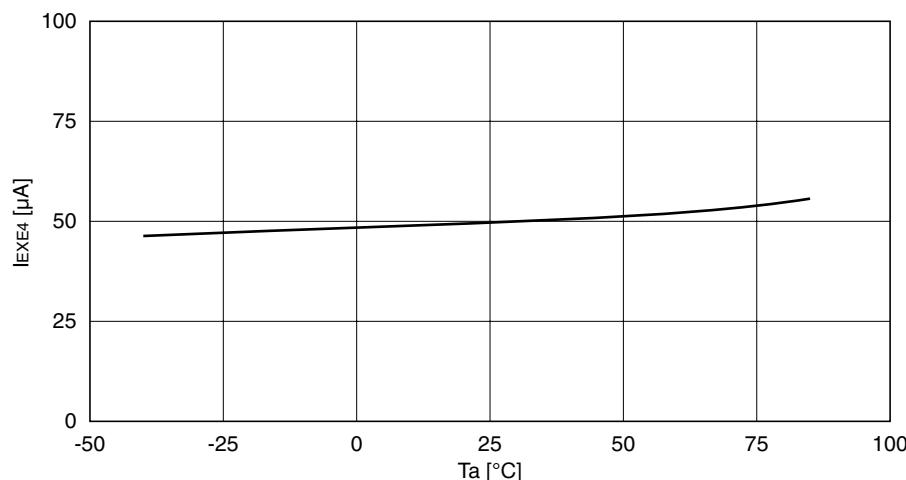

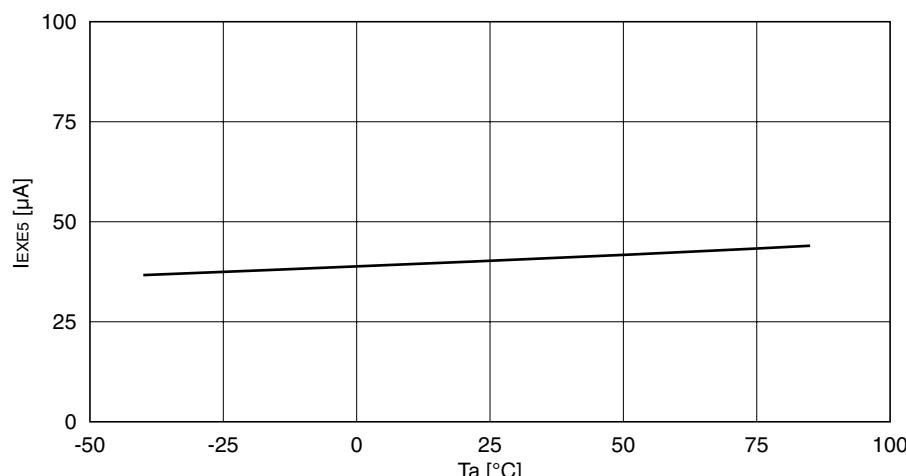

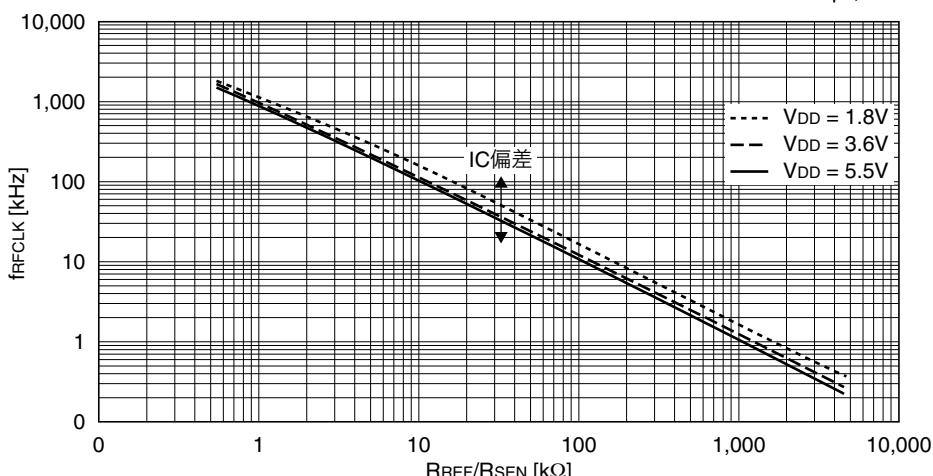

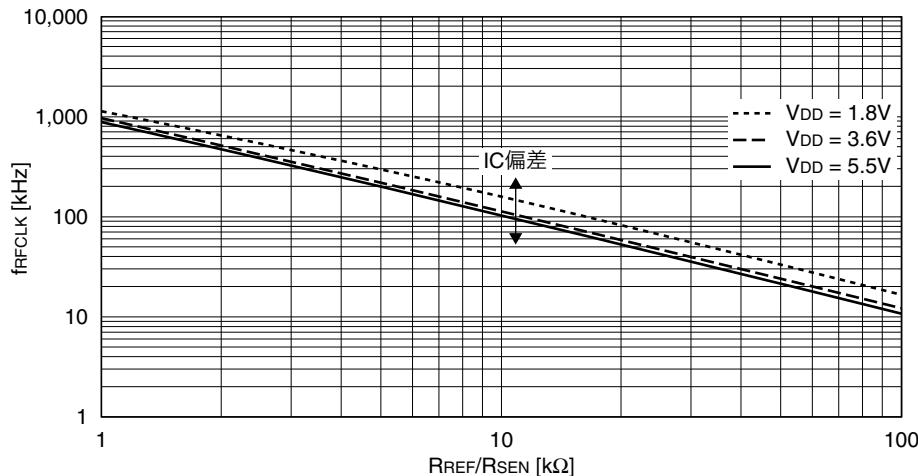

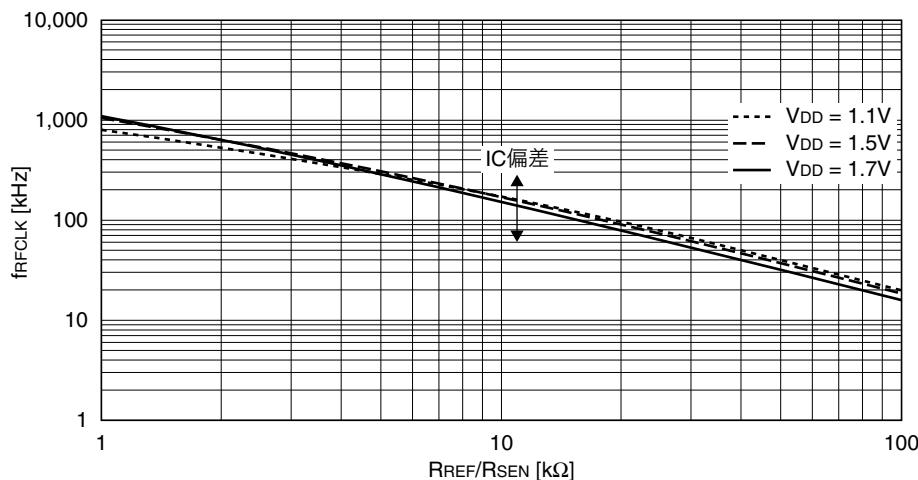

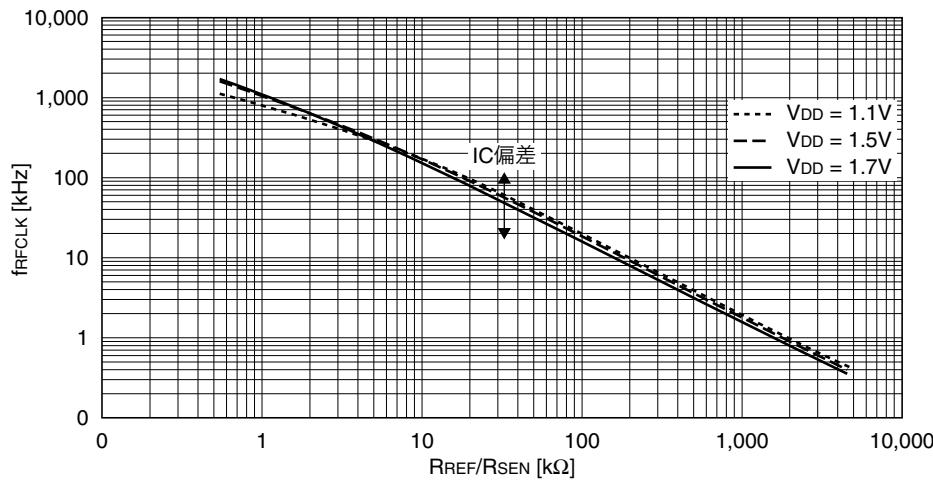

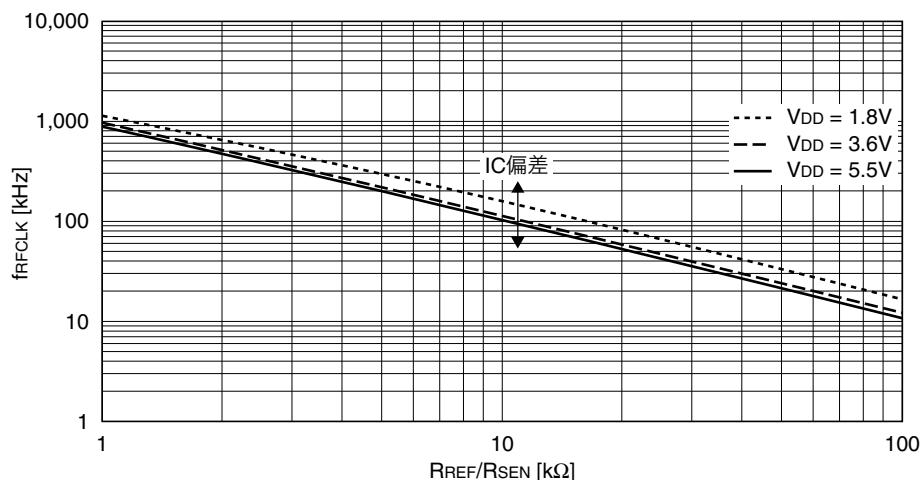

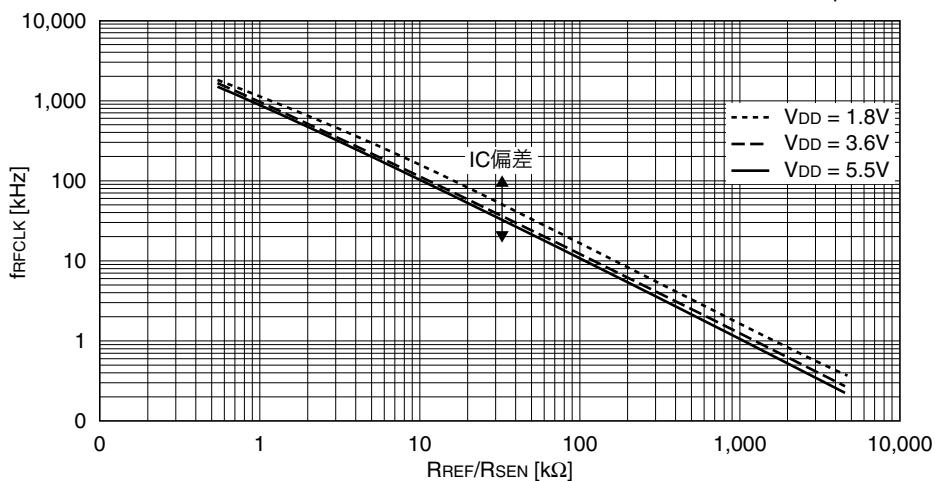

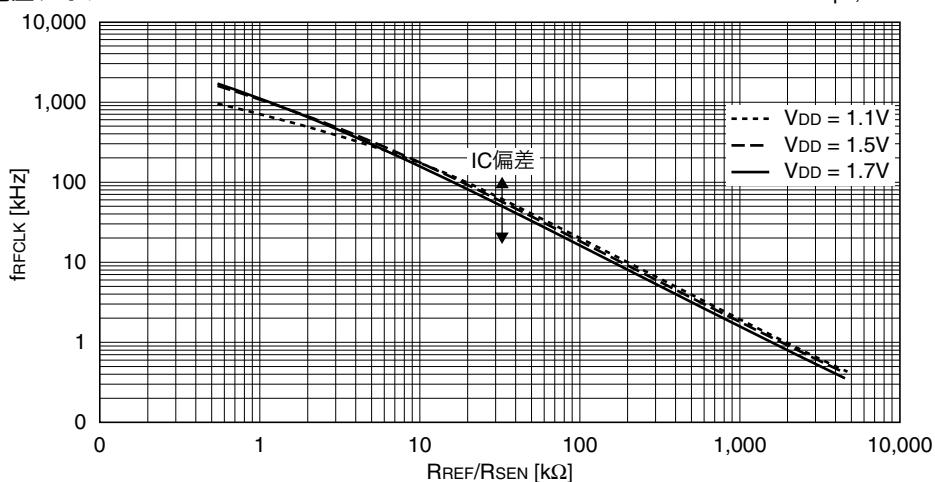

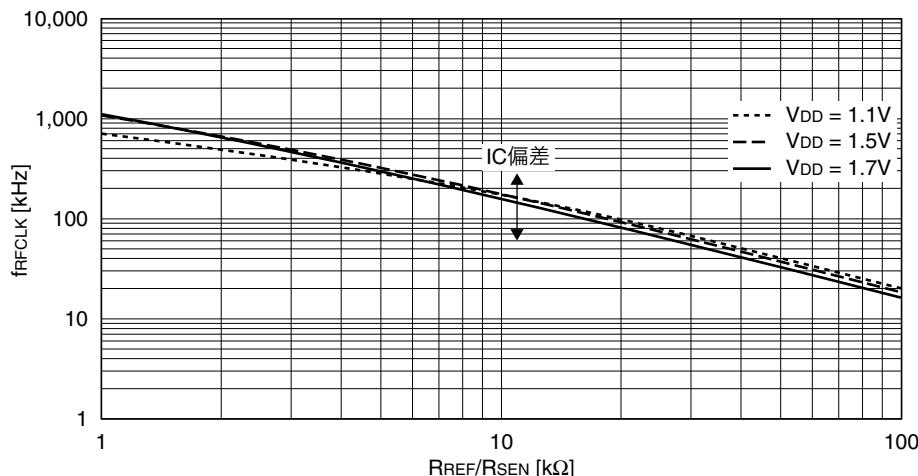

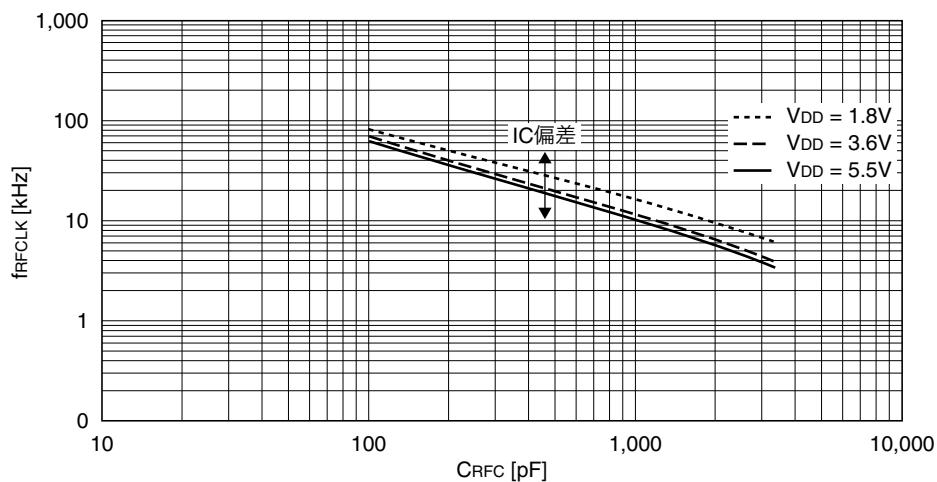

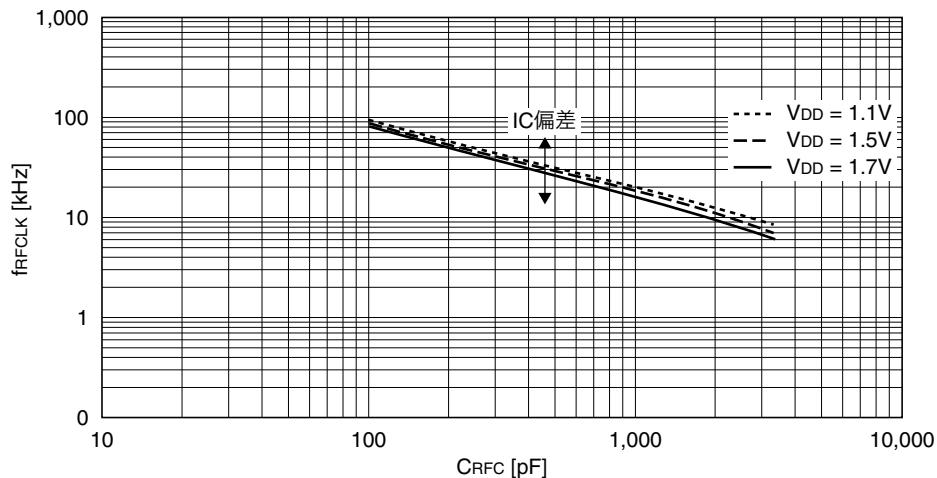

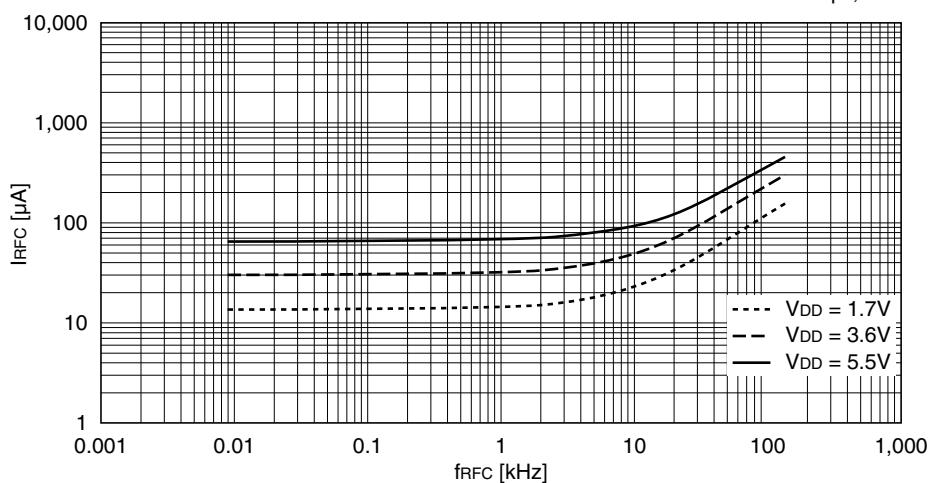

| 19.4.3 R/Fコンバータ回路 .....                          | 19-5          |

| 19.4.4 消費電流 .....                                | 19-5          |

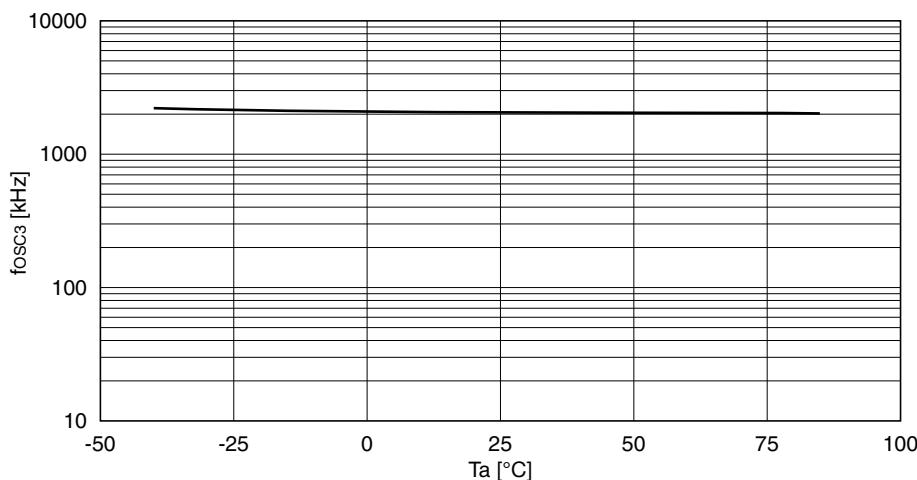

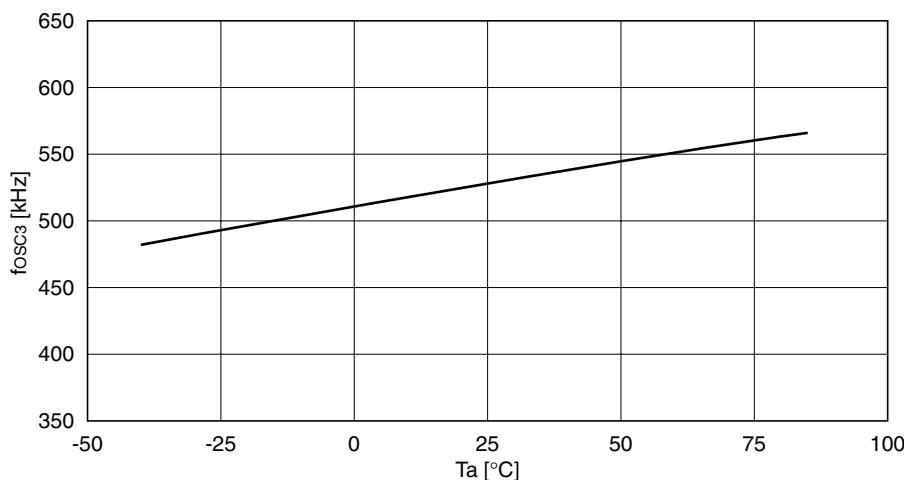

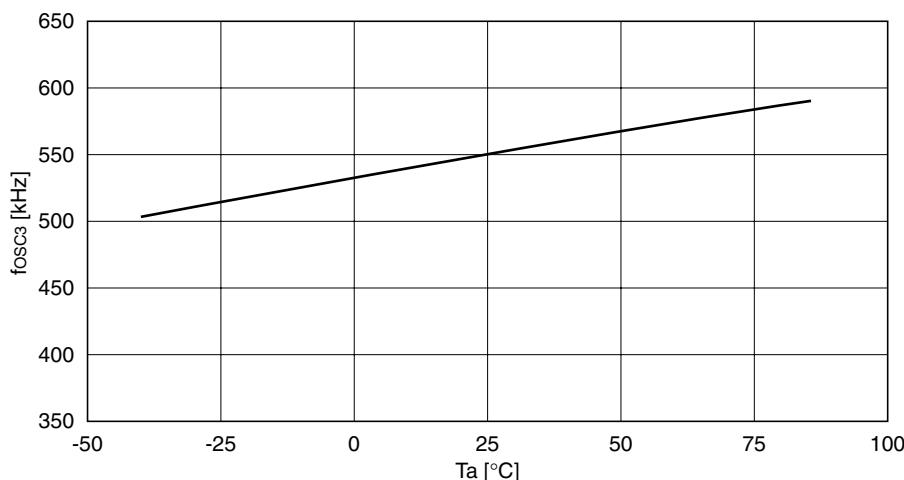

| 19.5 発振特性 .....                                  | 19-6          |

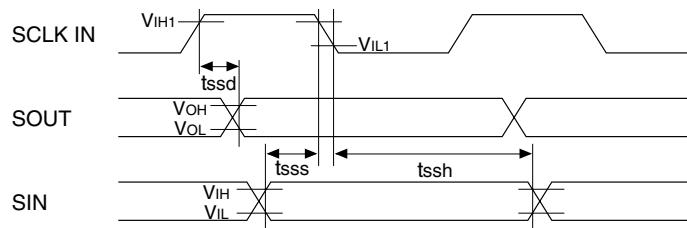

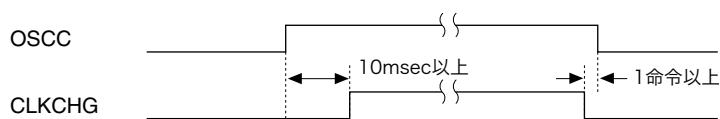

| 19.6 シリアルインターフェースAC特性 [S1C63004/008/016] .....   | 19-7          |

| 19.7 タイミングチャート .....                             | 19-8          |

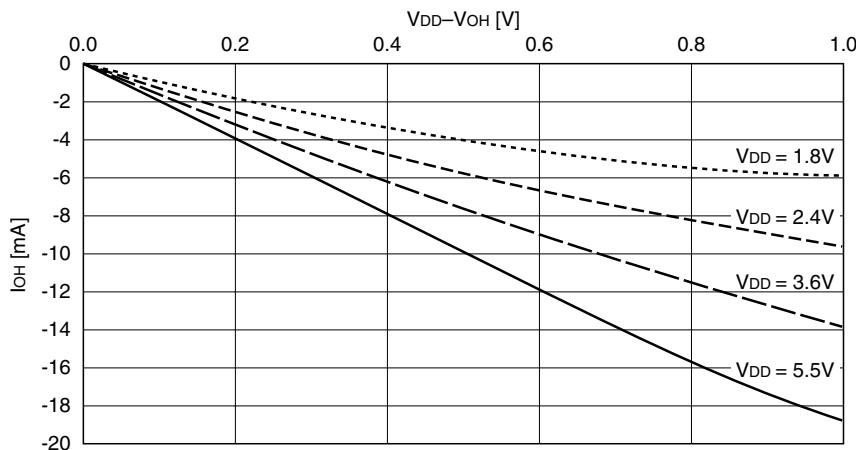

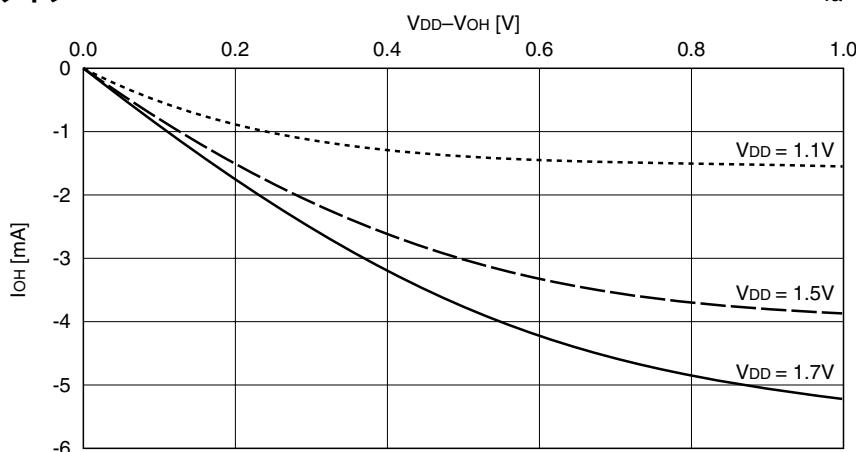

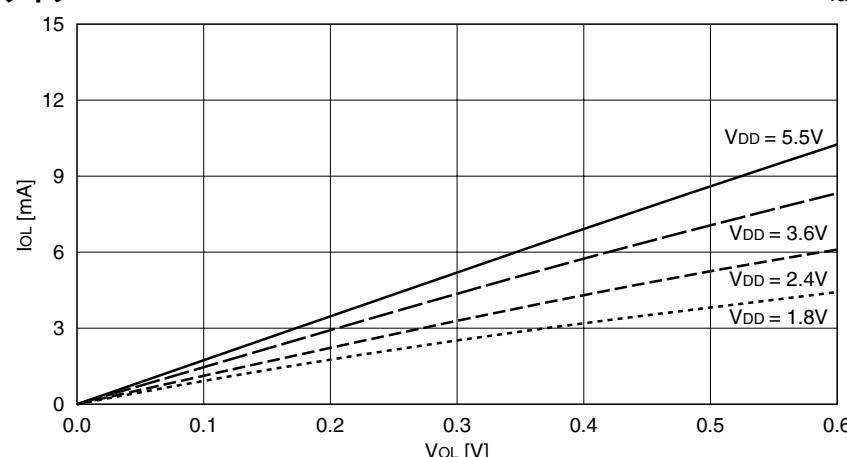

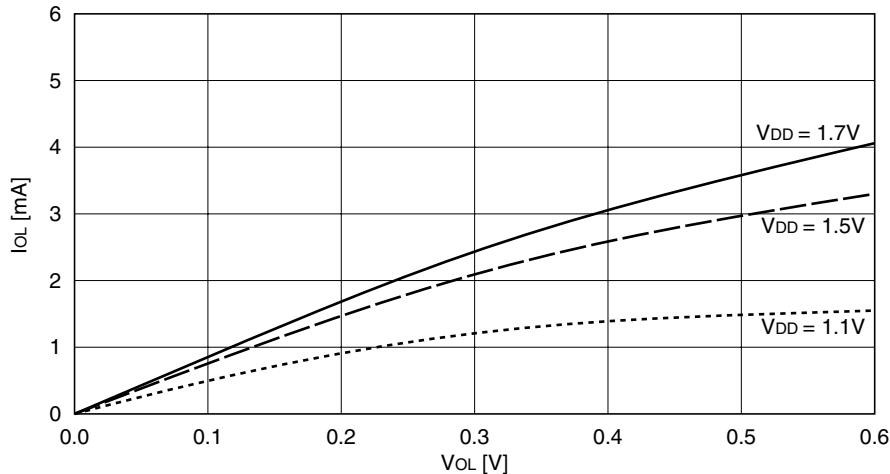

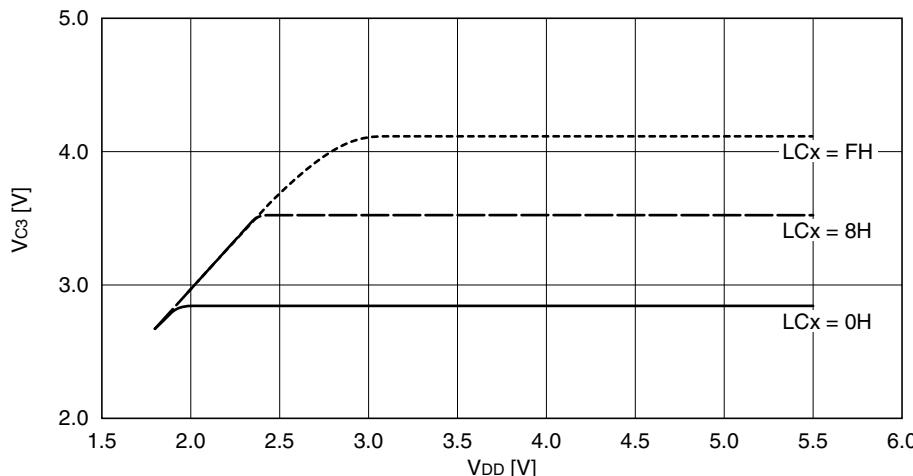

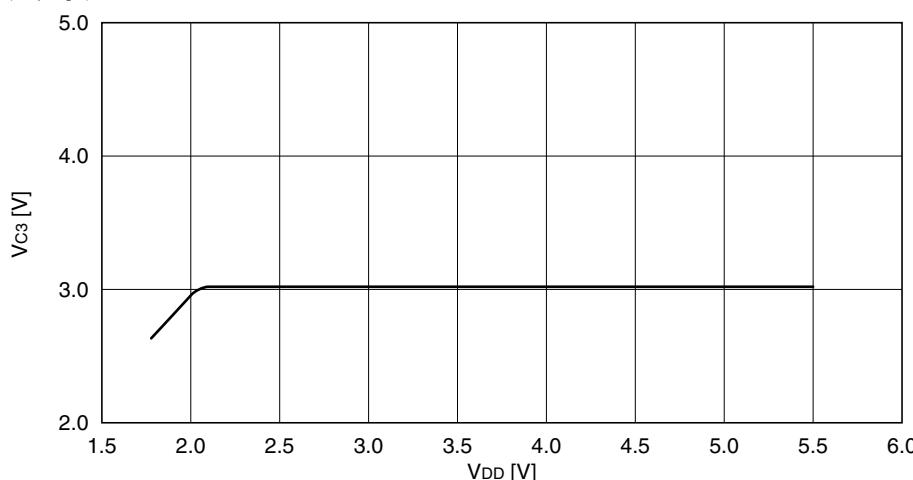

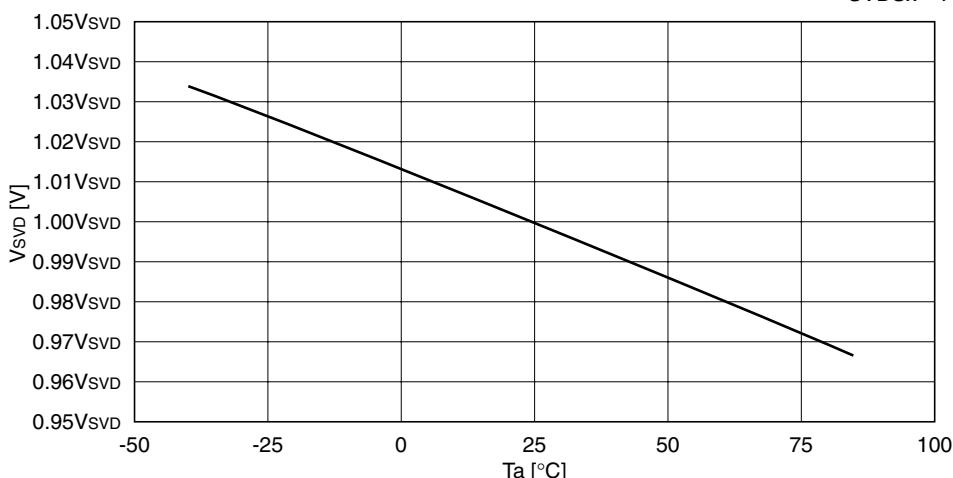

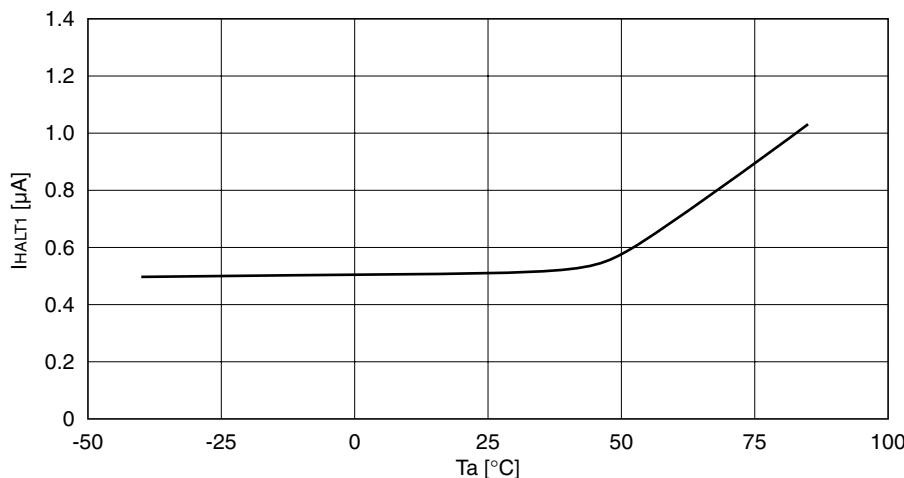

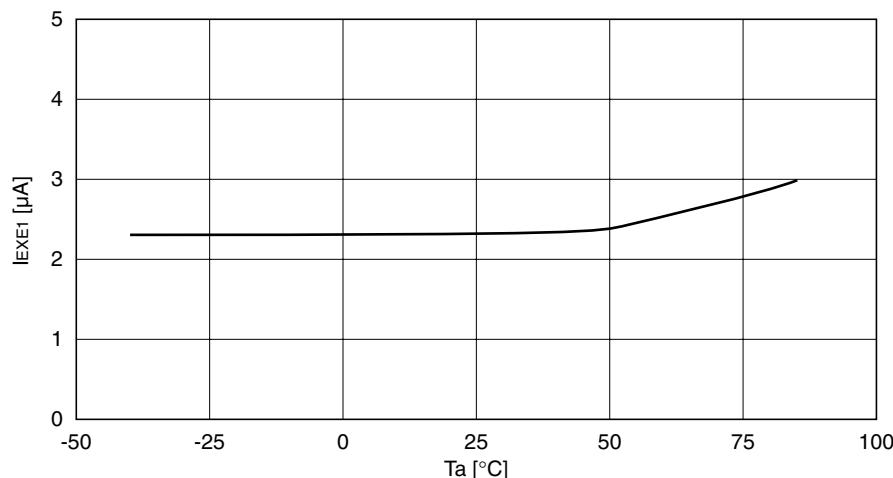

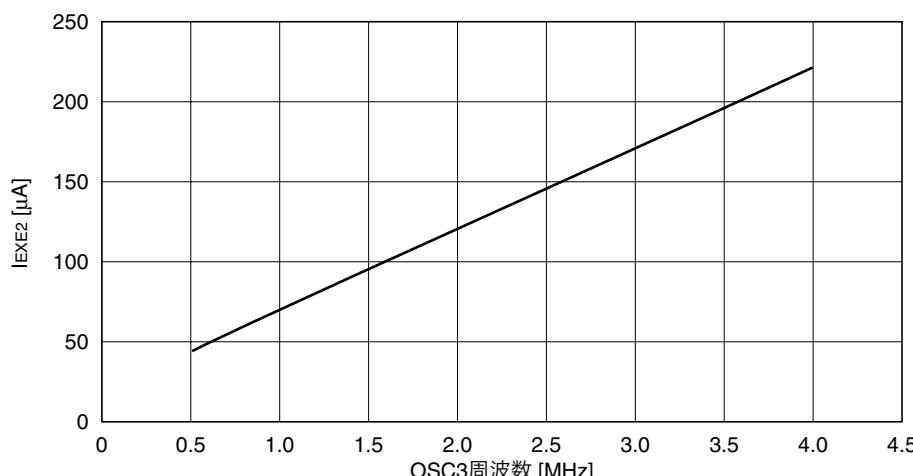

| 19.8 特性グラフ(参考値) .....                            | 19-9          |

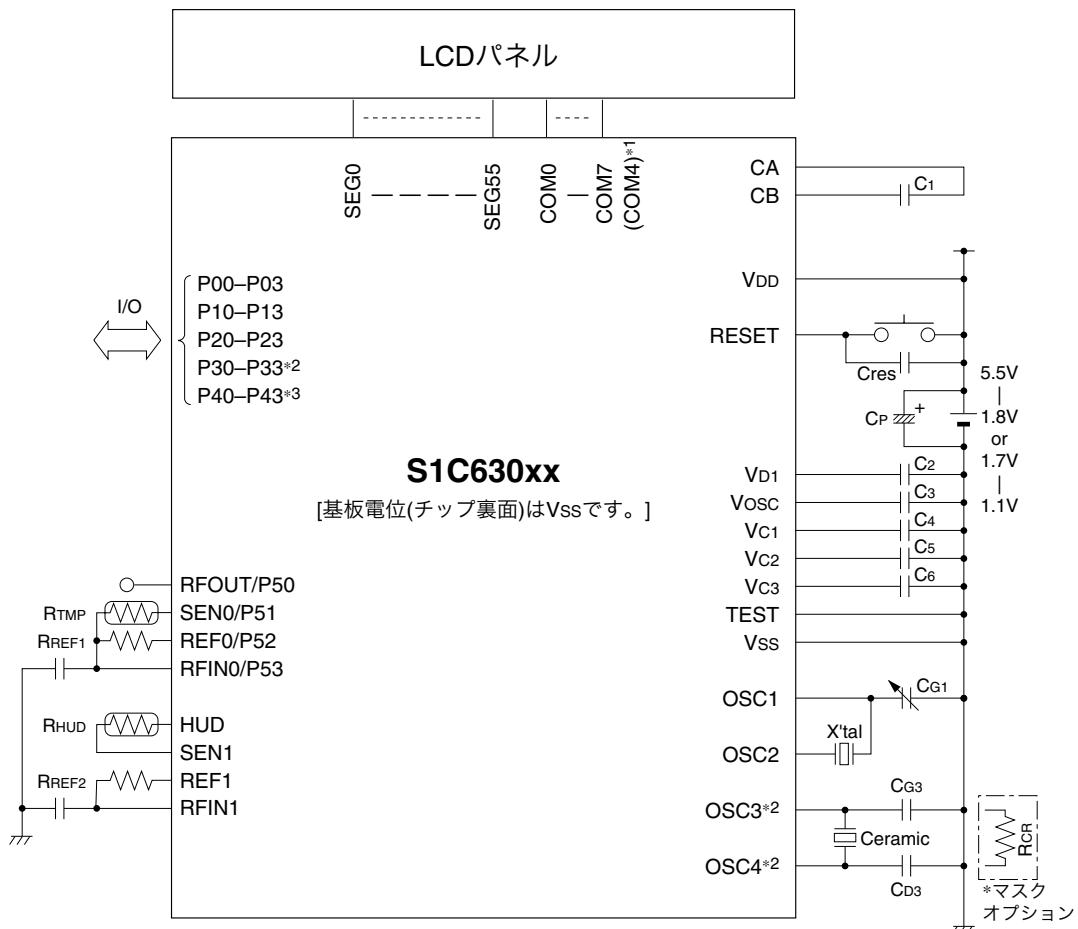

| <b>20 基本外部結線図 .....</b>                          | <b>20-1</b>   |

| <b>Appendix A I/Oレジスター一覧 .....</b>               | <b>AP-A-1</b> |

| FF00H                  発振回路 .....                | AP-A-1        |

| FF01H                  ウオッチドッグタイム .....          | AP-A-1        |

| FF02H–FF03H          電源回路 .....                  | AP-A-1        |

|                                                              |                    |        |

|--------------------------------------------------------------|--------------------|--------|

| FF04H–FF05H                                                  | SVD回路 .....        | AP-A-1 |

| FF10H–FF1BH                                                  | クロックマネージャ .....    | AP-A-1 |

| FF20H–FF3FH                                                  | 入出力兼用ポート .....     | AP-A-2 |

| FF40H–FF42H                                                  | 計時タイマ .....        | AP-A-4 |

| FF44H–FF47H                                                  | サウンドジェネレータ .....   | AP-A-4 |

| FF48H–FF4DH                                                  | ストップウォッチタイマ .....  | AP-A-5 |

| FF50H–FF52H                                                  | LCDドライバ .....      | AP-A-5 |

| FF58H–FF5CH                                                  | シリアルインターフェース ..... | AP-A-5 |

| FF60H–FF6BH                                                  | R/Fコンバータ .....     | AP-A-6 |

| FF70H–FF76H                                                  | 整数乗除算器 .....       | AP-A-7 |

| FF80H–FF9FH                                                  | プログラマブルタイマ .....   | AP-A-7 |

| FFE1H–FFFFH                                                  | 割り込みコントローラ .....   | AP-A-9 |

| <b>Appendix B Peripheral Circuit Board for S1C6F016.....</b> | <b>AP-B-1</b>      |        |

| B.1 各部の名称と機能 .....                                           | AP-B-1             |        |

| B.1.1 S5U1C63000P6.....                                      | AP-B-1             |        |

| B.1.2 S5U1C6F016P2 .....                                     | AP-B-3             |        |

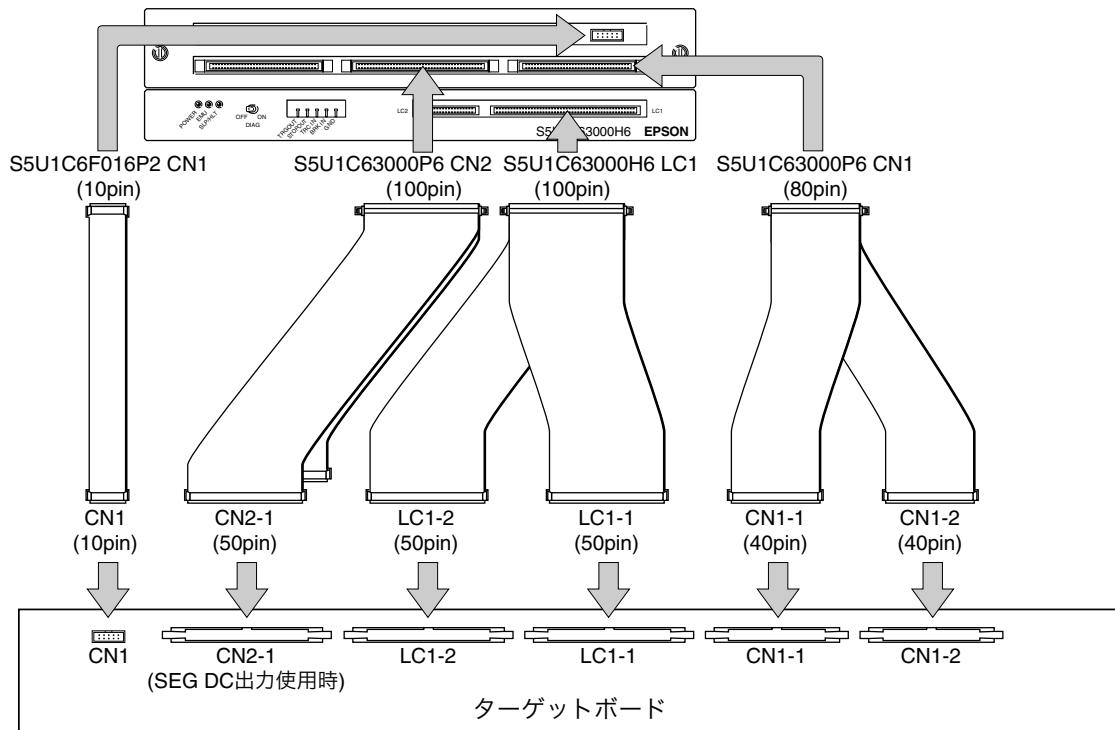

| B.2 ターゲットシステムとの接続 .....                                      | AP-B-5             |        |

| B.3 S5U1C63000P6へのダウンロード .....                               | AP-B-8             |        |

| B.4 使用上の注意 .....                                             | AP-B-9             |        |

| B.4.1 操作上の注意事項.....                                          | AP-B-9             |        |

| B.4.2 実ICとの相違点 .....                                         | AP-B-9             |        |

| B.5 製品の仕様 .....                                              | AP-B-12            |        |

| B.5.1 S5U1C63000P6の仕様.....                                   | AP-B-12            |        |

| B.5.2 S5U1C6F016P2の仕様.....                                   | AP-B-12            |        |

| <b>Appendix C パワーセーブ .....</b>                               | <b>AP-C-1</b>      |        |

| C.1 クロック制御によるパワーセーブ .....                                    | AP-C-1             |        |

| C.2 電源制御によるパワーセーブ .....                                      | AP-C-3             |        |

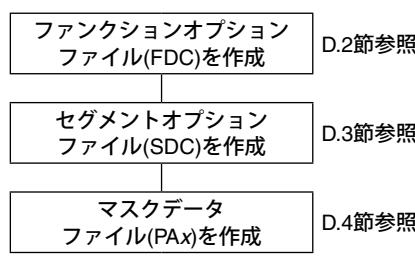

| <b>Appendix D マスクデータ作成手順.....</b>                            | <b>AP-D-1</b>      |        |

| D.1 マスクデータ作成フロー .....                                        | AP-D-1             |        |

| D.2 ファンクションオプションファイルの作成方法 .....                              | AP-D-1             |        |

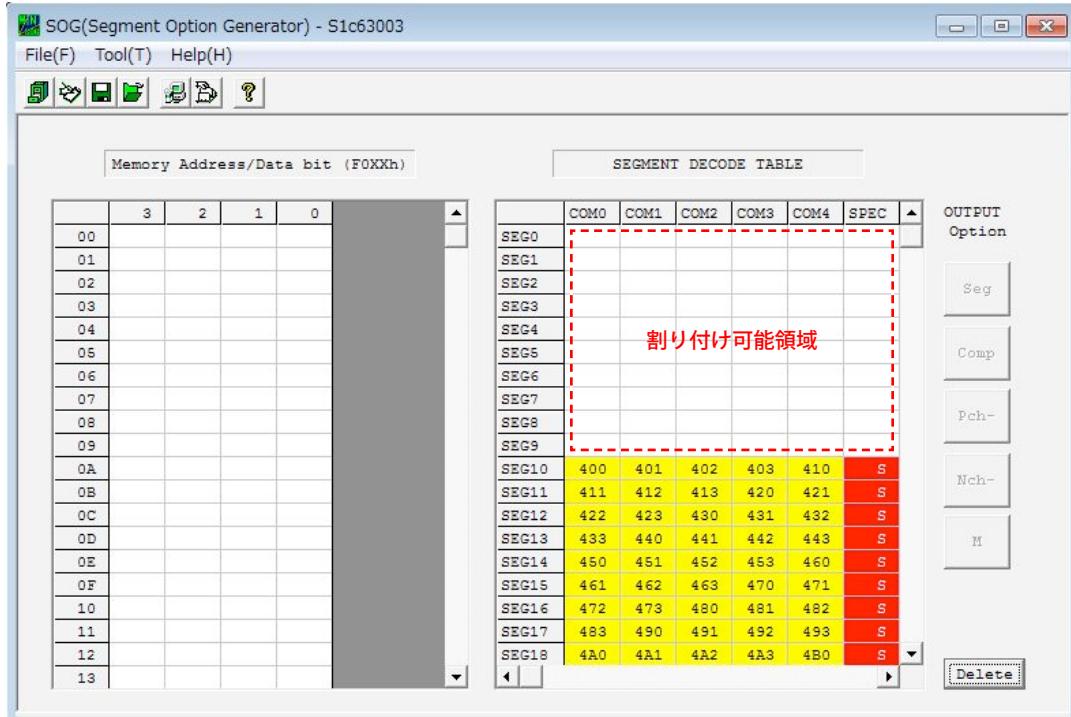

| D.3 セグメントオプションファイルの作成方法 .....                                | AP-D-1             |        |

| D.4 マスクデータファイルの作成方法 .....                                    | AP-D-2             |        |

| <b>Appendix E 注意事項のまとめ .....</b>                             | <b>AP-E-1</b>      |        |

| E.1 個別機能についての注意事項のまとめ .....                                  | AP-E-1             |        |

| E.2 実装上の注意事項 .....                                           | AP-E-5             |        |

## 改訂履歴表

# 1 概要

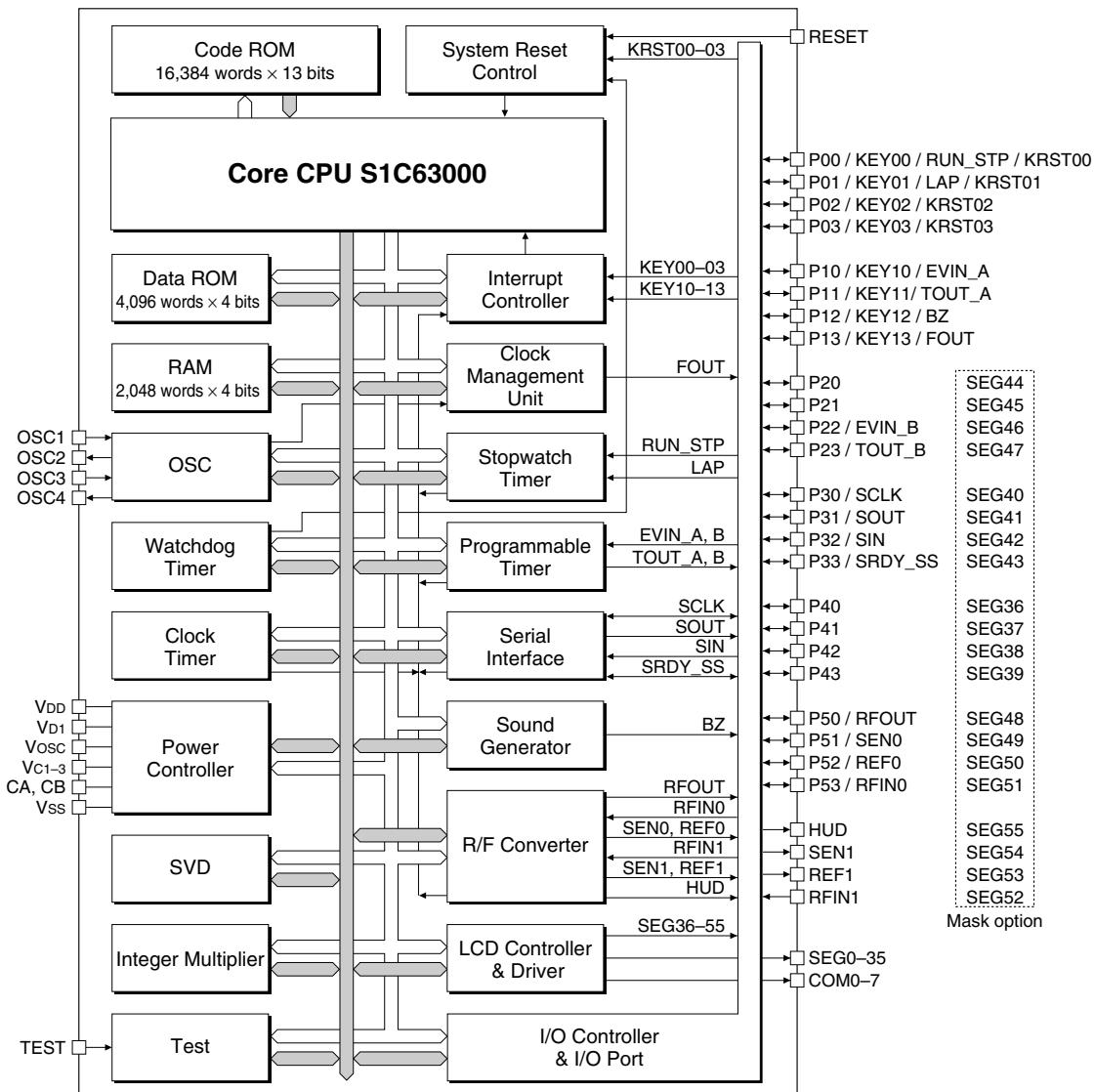

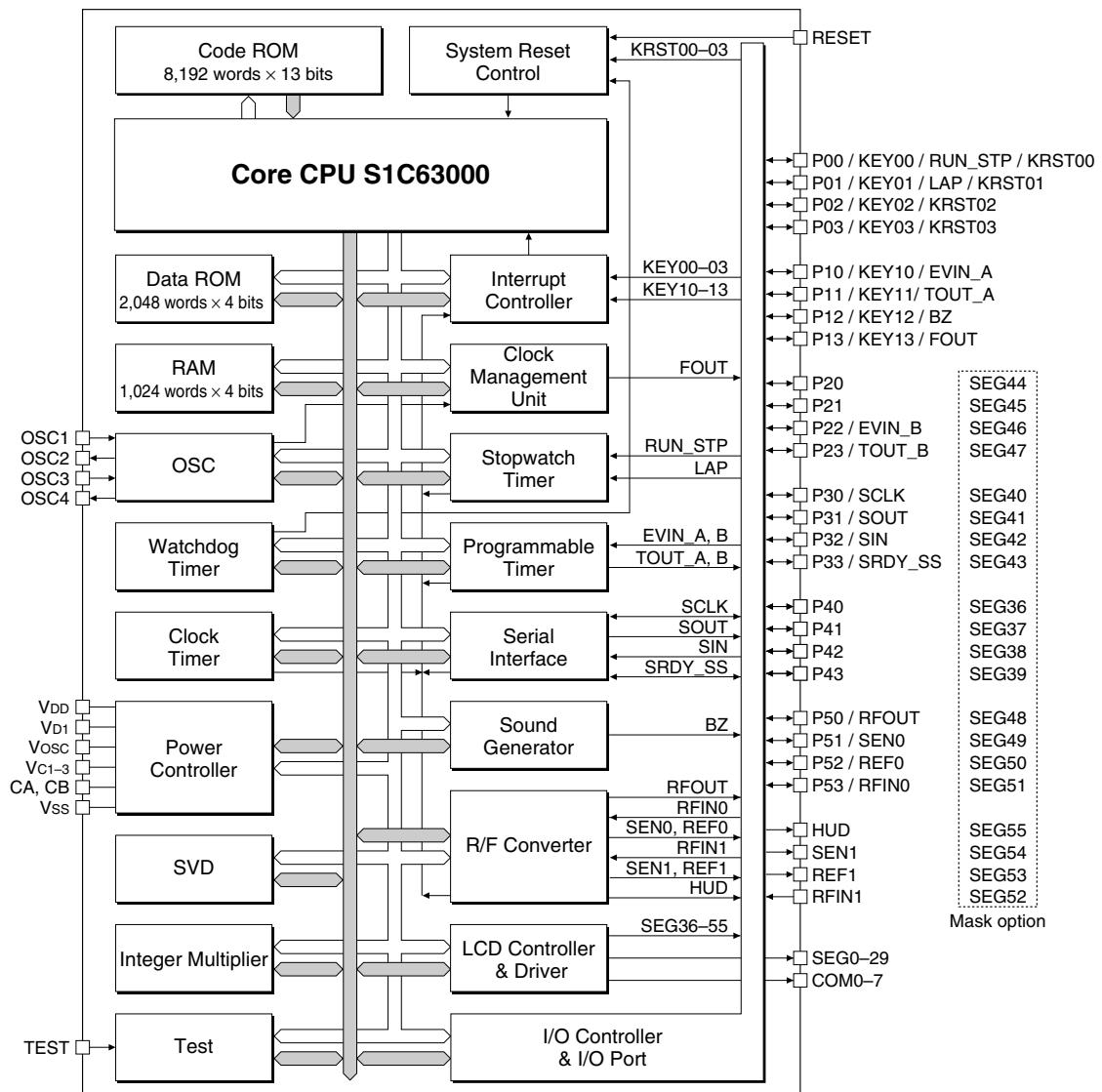

S1C630 Series(S1C63003/004/008/016)は低電圧動作、低消費電流を特長とする4ビットマイクロコントローラです。高性能4ビットコアCPU S1C63000を中心に、ワンチップ上にROM(最大16Kワード×13ビット)、RAM(最大2Kワード×4ビット)、タイマ、サウンドジェネレータなどで構成されています。また、最大56セグメント×8コモンのLCDパネルを駆動可能なセグメントLCDコントローラ/ドライバ、サーミスタなどのセンサを接続することで温度や湿度を測定可能なR/Fコンバータを内蔵しています。S1C630 Seriesは電池駆動を必要とする温度/湿度計測機能付きのクロックやウォッチへの応用に適しています。

※ 本書はS1C630 SeriesのマスクROM版の4機種、S1C63016、S1C63008、S1C63004、S1C63003の機能を解説します。特に機種名の指定がない限り、説明内容は4機種に共通です。

## 1.1 特長

表1.1.1 各機種の特長

| 機能            | S1C63016                                                                                                                                                          | S1C63008                                                 | S1C63004                         | S1C63003                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--------------------------------------------|

| コア            | 4ビットコアCPU S1C63000                                                                                                                                                |                                                          |                                  |                                            |

| OSC1発振回路      | 32.768kHz(Typ.)水晶発振回路                                                                                                                                             |                                                          |                                  |                                            |

| OSC3発振回路      | 4.0MHz(Typ., 3V版)/1.0MHz(Typ., 1.5V版)セラミック発振回路、<br>1.8MHz(Typ., 3V版)/500kHz(Typ., 1.5V版)CR発振回路(R外付け)、または<br>500kHz(Typ., 3V版)/500kHz(Typ., 1.5V版)CR発振回路(R内蔵) (*1) | 550kHz(Typ., 3V版)/<br>550kHz(Typ., 1.5V版)<br>CR発振回路(R内蔵) |                                  |                                            |

| インストラクションセット  | 基本命令 47種類(全命令数 411種類)、アドレッシングモード 8種類                                                                                                                              |                                                          |                                  |                                            |

| インストラクション     | 32.768kHz動作時: 61μsec                                                                                                                                              | 122μsec                                                  | 183μsec                          |                                            |

| 実行時間          | 4MHz動作時:<br>0.5μsec                                                                                                                                               | 1μsec                                                    | 1.5μsec                          |                                            |

| ROM容量         | コードROM<br>16,384ワード×13ビット                                                                                                                                         | 8,192ワード×13ビット                                           | 4,096ワード×13ビット                   |                                            |

|               | データROM<br>4,096ワード×4ビット                                                                                                                                           | 2,048ワード×4ビット                                            | 1,024ワード×4ビット                    | なし                                         |

| RAM容量         | データメモリ<br>2,048ワード×4ビット                                                                                                                                           | 1,024ワード×4ビット                                            | 512ワード×4ビット                      | 256ワード×4ビット                                |

|               | 表示メモリ<br>448ビット                                                                                                                                                   | 400ビット                                                   | 288ビット                           | 110ビット                                     |

| 入出力兼用ポート      | 24ビット                                                                                                                                                             | 24ビット                                                    | 20ビット                            | 16ビット                                      |

|               | ブルダウントラクション抵抗の付加が可能(*1)、周辺回路入出力に切り替え可能(*2)                                                                                                                        |                                                          |                                  |                                            |

| シリアルインターフェース  | 1ポート(クロック同期式8ビット、SPIに対応)                                                                                                                                          |                                                          |                                  | なし                                         |

| LCDドライバ       | 56セグメント(Max., *1)<br>×3~8コモン(*2)                                                                                                                                  | 50セグメント(Max., *1)<br>×3~8コモン(*2)                         | 36セグメント(Max., *1)<br>×3~8コモン(*2) | 22セグメント(Max., *1)<br>×3~5コモン(*2)           |

| タイムベースカウンタ    | 計時タイマ<br>1/1000秒ストップウォッチタイマ(ダイレクトキー入力機能付き)                                                                                                                        |                                                          |                                  | 計時タイマ<br>1/1000秒ストップウォッチタイマ(ダイレクトキー入力機能なし) |

| プログラマブルタイマ    | 8ビットタイマ<br>×4チャネル<br>(16ビットタイマ×2<br>または16ビットタイマ×<br>1+8ビットタイマ×2と<br>して使用可能) (*2)                                                                                  | 8ビットタイマ×3チャネル<br>(16ビットタイマ×1+8ビットタイマ×1として使<br>用可能) (*2)  |                                  | 8ビットタイマ<br>×1チャネル                          |

| ウォッチドッグタイマ    | 内蔵                                                                                                                                                                |                                                          |                                  |                                            |

| サウンドジェネレータ    | エンペロープ、1ショット出力機能付き                                                                                                                                                |                                                          |                                  |                                            |

| R/Fコンバータ      | 2チャネル、CR発振方式、20ビットカウンタ、湿度センサに対応                                                                                                                                   |                                                          |                                  |                                            |

| 乗除算回路         | 8ビット演算器<br>乗算: 8ビット×8ビット →(積)16ビット<br>除算: 16ビット÷8ビット<br>→(商)8ビット、(余数)8ビット                                                                                         |                                                          | なし                               |                                            |

| 電源電圧検出(SVD)回路 | 検出電圧を29種類から選択可能(*2)                                                                                                                                               |                                                          |                                  | なし                                         |

| 外部割り込み        |                                                                                                                                                                   |                                                          |                                  |                                            |

| キー入力          | 8系統                                                                                                                                                               |                                                          |                                  | 4系統                                        |

| 内部割り込み        |                                                                                                                                                                   |                                                          |                                  |                                            |

| ウォッチドッグタイマ    | 1系統(NMI)                                                                                                                                                          | 1系統(NMI)                                                 |                                  | 1系統(NMI)                                   |

| 計時タイマ         | 8系統                                                                                                                                                               | 8系統                                                      |                                  | 4系統                                        |

| ストップウォッチタイマ   | 4系統                                                                                                                                                               | 4系統                                                      |                                  | 2系統                                        |

| プログラマブルタイマ    | 8系統                                                                                                                                                               | 6系統                                                      |                                  | 1系統                                        |

| シリアルインターフェース  | 1系統                                                                                                                                                               | 1系統                                                      |                                  | なし                                         |

| R/Fコンバータ      | 3系統                                                                                                                                                               | 3系統                                                      |                                  | 3系統                                        |

| 機能          | S1C63016                                                        | S1C63008                                                                                                                      | S1C63004                                 | S1C63003                                  |

|-------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------|

| 電源電圧        | 1.8V~5.5V(3Vノーマルタイプ)または1.1V~1.7V(1.5V低電圧タイプ) (*1)               |                                                                                                                               |                                          |                                           |

| 動作温度範囲      | -40°C~85°C                                                      |                                                                                                                               |                                          |                                           |

| 消費電流 (Typ.) | SLEEP時 (32kHz)<br>HALT時 (32kHz)<br>動作時 (32kHz)<br>動作時 (4M/1MHz) | 0.1µA (3V版)/0.1µA (1.5V版)<br>0.5µA (3V版)/0.5µA (1.5V版)<br>2.3µA (3V版)/2.0µA (1.5V版)<br>220µA (4MHz、3V版)/<br>60µA (1MHz、1.5V版) |                                          | 40µA (550kHz、3V版)/<br>30µA (550kHz、1.5V版) |

| 出荷形態        | QFP15-100pin、TQFP14-100pin、またはチップ                               |                                                                                                                               | QFP14-80pin、<br>TQFP14-100pin、<br>またはチップ | QFP12-48pin<br>またはチップ                     |

\*1: マスクオプションにより選択 \*2: ソフトウェアにより選択

## 1.2 ブロック図

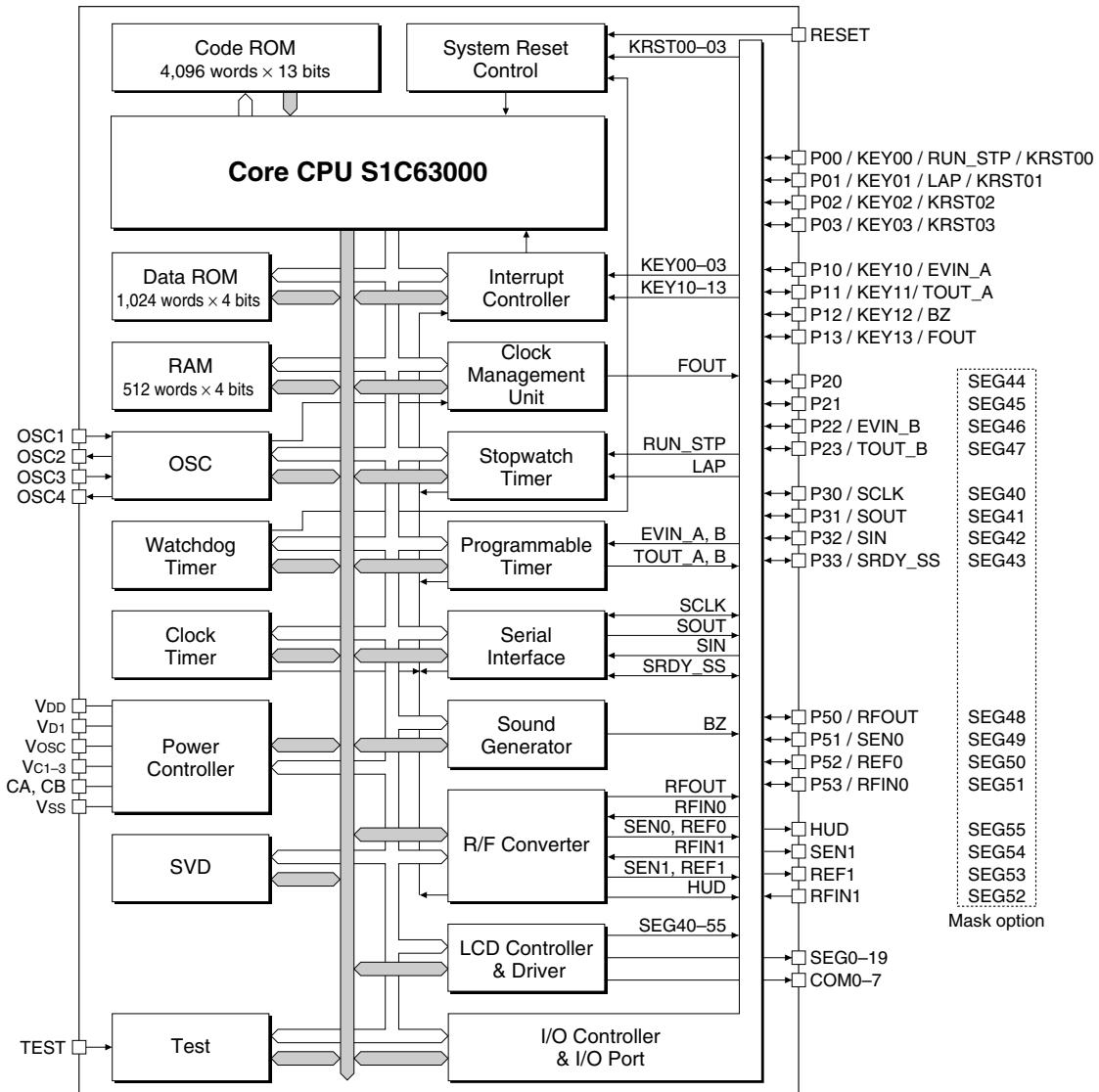

### S1C63016

図1.2.1 S1C63016ブロック図

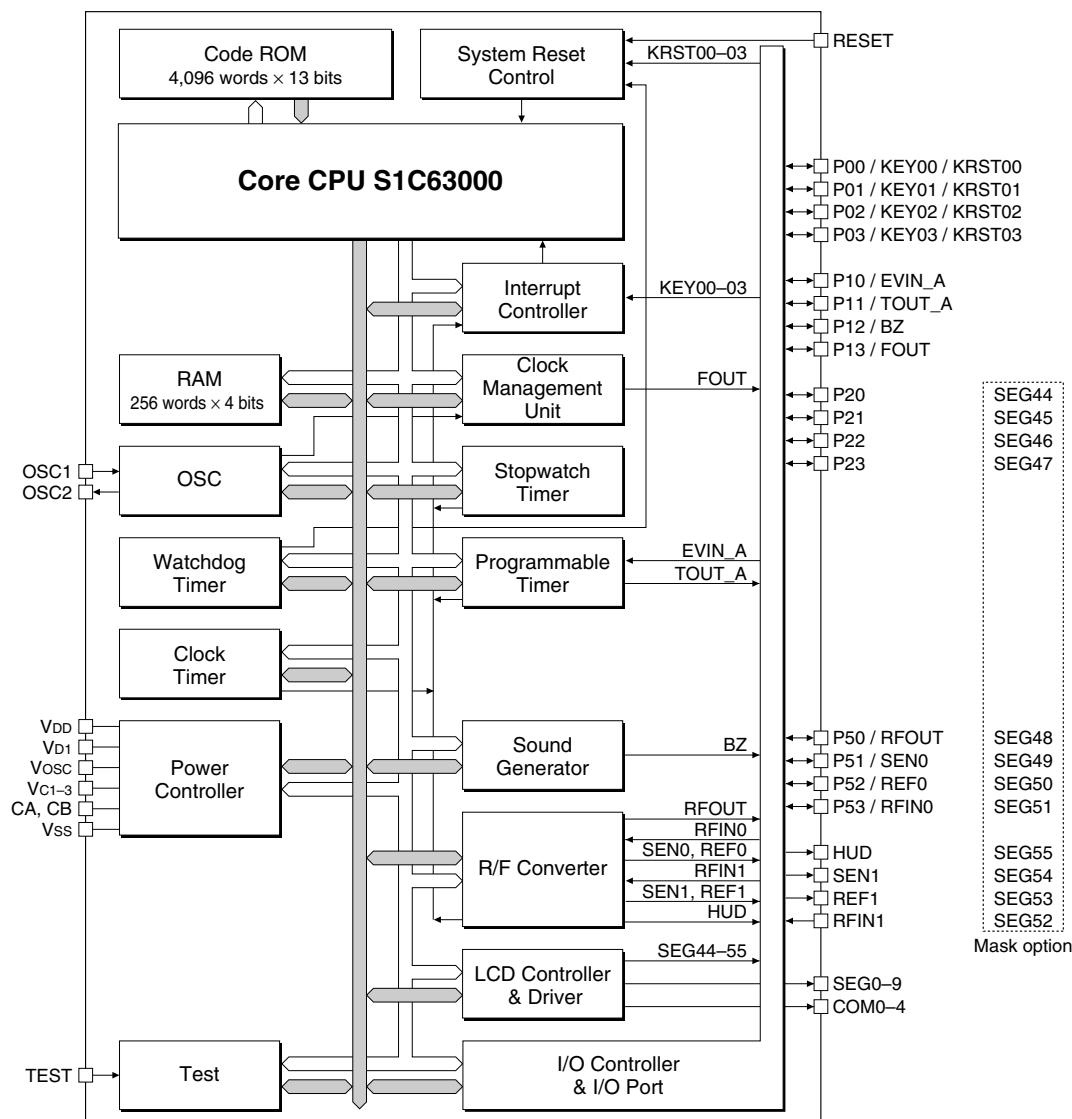

**S1C63008**

図1.2.2 S1C63008ブロック図

## S1C63004

図1.2.3 S1C63004ブロック図

**S1C63003**

図1.2.4 S1C63003ブロック図

## 1.3 マスクオプション

S1C63003/004/008/016には、以下に示すマスクオプションが用意されています。各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択には開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogおよびセグメントオプションジェネレータwinsogを使用します。winfogおよびwinsogで作成したデータをもとに最終的なICのマスクパターンが生成されます。winfogおよびwinsogについては"S5U1C63000A Manual"を参照してください。

### 〈マスクオプションの概要〉

#### (1)動作電源タイプ

動作電源の種類として3Vノーマルタイプ(1.8V～5.5V)と1.5V低電圧タイプ(1.1V～1.7V)が選択できます。

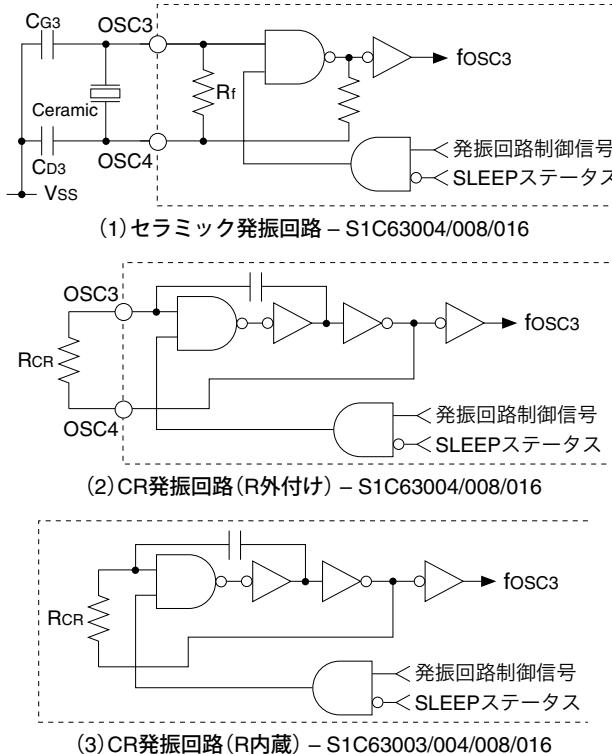

#### (2)OSC3発振回路

S1C63004/008/016では、OSC3発振回路としてセラミック発振回路、CR発振回路(R外付け)、またはCR発振回路(R内蔵)が選択できます。S1C63003はCR発振回路(R内蔵)に固定されています。詳細については"発振回路とクロック制御"の章の"OSC3発振回路"を参照してください。

#### (3)RESET端子プルダウン抵抗

RESET端子にプルダウン抵抗を付加するか否かを選択できます。詳細については"イニシャルリセット"の章の"リセット端子(RESET)"を参照してください。

#### (4)SEG/GPIO/RFC選択

入出力兼用ポートP20～P53およびR/F変換器の入出力端子がSEG出力端子を兼用しています。これらの端子を入出力兼用ポートまたはR/F変換器用として使用するか、SEG出力端子として使用するか選択できます。選択は1ビット単位で行います。詳細については"LCD ドライバ"の章の"マスクオプション"を参照してください。

#### (5)入出力兼用ポートプルダウン抵抗

入出力兼用ポートP00～P53が入力モード時に働くプルダウン抵抗を付加するか否かを選択できます。選択は1ビット単位で行います。詳細については"入出力兼用ポート"の章の"マスクオプション"を参照してください。

#### (6)入出力兼用ポートの出力仕様

入出力兼用ポートP00～P53が出力モードの際の出力仕様として、コンプリメンタリ出力またはPチャネルオープンドレイン出力が選択できます。選択は1ビット単位で行います。詳細については"入出力兼用ポート"の章の"マスクオプション"を参照してください。

R/F変換器(チャネル0)を使用する場合は、P50～P53ポートの出力仕様に"Pチャネルオープンドレイン出力"を選択しないでください。

#### (7)P0xポート同時HIGH入力による外部リセット

複数キーの同時押しによってICをリセットする機能を使用するか否かを選択できます。また、使用する場合は、同時に押すキーを接続するP0xポート(P00～P03)の組み合わせを選択します。詳細については"イニシャルリセット"の章の"P0xポート(P00～P03)の同時HIGH入力"を参照してください。

#### (8)P0xポート同時HIGH入力リセットの時間検定回路

(7)の外部リセット機能を使用する場合は、時間検定回路を使用するか否かについても選択できます。時間検定回路を使用すると、規定時間以上の同時HIGH入力があった場合のみ、リセット機能が働きます。外部リセット機能を使用しない場合、時間検定回路は使用できません。詳細については"イニシャルリセット"の章の"P0xポート(P00～P03)の同時HIGH入力"を参照してください。

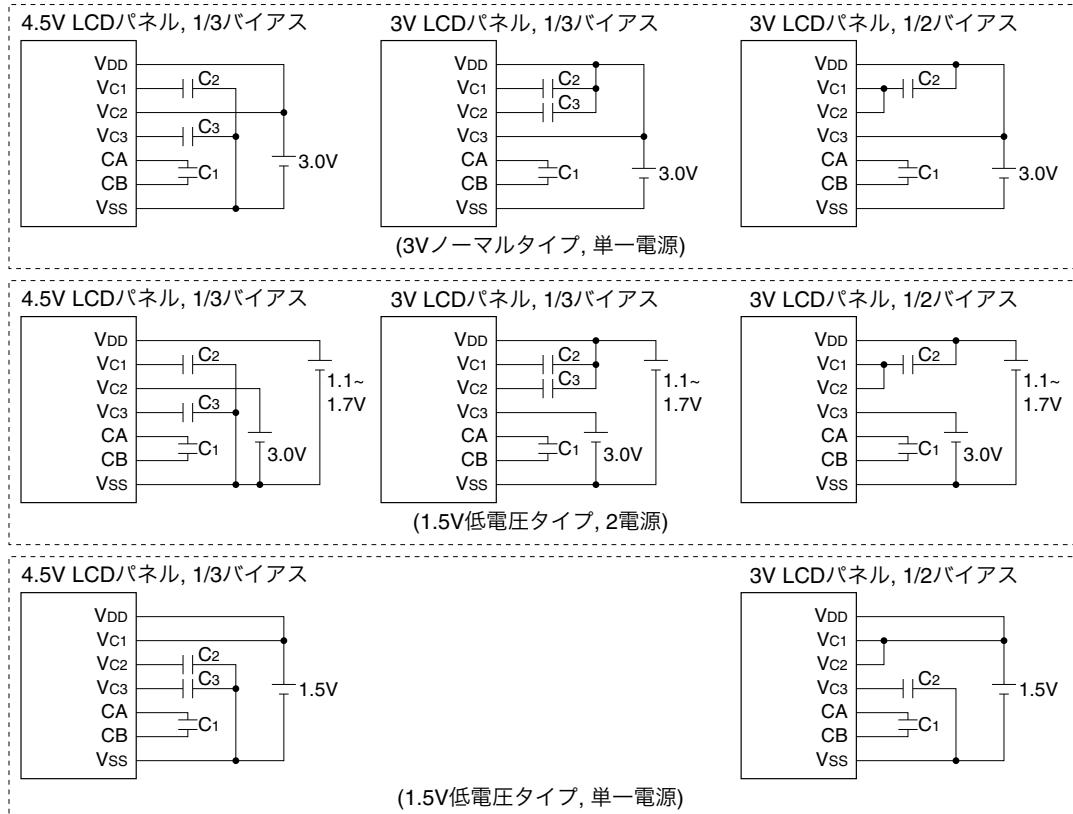

#### (9)LCD駆動電源

S1C63004/008/016では、LCD駆動用電源として内部電源または外部電源を選択できます。内部電源選択時の昇圧用基準電圧(Vc1またはVc2)はレジスタで設定します。S1C63003でも、マスクオプションにより内部電源と外部電源の選択が可能です。また、内部電源使用時の昇圧用基準電圧(Vc1またはVc2)についてもマスクオプションで選択します。詳細については"LCD ドライバ"の章の"マスクオプション"を参照してください。

## (10) LCDセグメント仕様

SEG端子に対する表示メモリの割り付け、DC出力として使用するSEG端子の選択が行えます。詳細については"LCD ドライバ"の章の"マスクオプション"を参照してください。

表1.3.1 オプションリスト(S1C63008/016)

# 1 概要

| 項目                        | オプション                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 入出力兼用ポート<br>出力仕様          | P22                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P23                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P30                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P31                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P32                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P33                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P40                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P41                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P42                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P43                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P50                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P51                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P52                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P53                                                                                                                                                                                                                                                                                                                                                                                     | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

| P0xポートキー同時押し<br>リセット組み合わせ | <input type="checkbox"/> 1. Not Use<br><input type="checkbox"/> 2. Use <P00, P01><br><input type="checkbox"/> 3. Use <P00, P01, P02><br><input type="checkbox"/> 4. Use <P00, P01, P02, P03>                                                                                                                                                                                            |                                                                                        |

|                           | <input type="checkbox"/> 1. Not Use <input type="checkbox"/> 2. Use                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| LCD駆動電源                   | <input type="checkbox"/> 1. Internal 1/3 bias<br><input type="checkbox"/> 2. External 1/3 bias, V <sub>DD</sub> = V <sub>C2</sub> (4.5 V panel)<br><input type="checkbox"/> 3. External 1/3 bias, V <sub>DD</sub> = V <sub>C3</sub> (3.0 V panel)<br><input type="checkbox"/> 4. External 1/2 bias, V <sub>DD</sub> = V <sub>C3</sub> , V <sub>C1</sub> = V <sub>C2</sub> (3.0 V panel) |                                                                                        |

□選択可能 ■固定

\* R/Fコンバータ(チャネル0)を使用する場合は、P50～P53ポートの出力仕様に"Pch Open Drain"を選択しないでください。

表1.3.2 オプションリスト(S1C63004)

| 項目                  | オプション                                                                                                                                       |                                                                     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 動作電源タイプ             | <input type="checkbox"/> 1. Normal Type (1.8–5.5 V)                                                                                         | <input type="checkbox"/> 2. Low Voltage Type (1.1–1.7 V)            |

| OSC3発振回路            | <input type="checkbox"/> 1. CR (built-in R)<br><input type="checkbox"/> 2. CR (external R)<br><input type="checkbox"/> 3. Ceramic (4.0 MHz) |                                                                     |

| RESET端子プルダウン抵抗      | <input type="checkbox"/> 1. Use                                                                                                             | <input type="checkbox"/> 2. Not Use                                 |

| SEG/GPIO/RFC選択      | P20                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P21                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P22                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P23                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P30                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P31                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P32                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P33                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P50                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P51                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P52                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P53                                                                                                                                         | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | RFIN1                                                                                                                                       | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | REF1                                                                                                                                        | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | SEN1                                                                                                                                        | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | HUD                                                                                                                                         | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

| 入出力兼用ポート<br>プルダウン抵抗 | P00                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P01                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P02                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P03                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P10                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P11                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P12                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P13                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P20                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P21                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P22                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P23                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P30                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P31                                                                                                                                         | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

| 項目                        | オプション                                                                                                                                                                                                                                                                                  |                                                                                        |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 入出力兼用ポート<br>ブルダウン抵抗       | P32                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P33                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P50                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P51                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P52                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P53                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

| 入出力兼用ポート<br>出力仕様          | P00                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P01                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P02                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P03                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P10                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P11                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P12                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P13                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P20                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P21                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P22                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P23                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P30                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P31                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

| P0xポートキー同時押し<br>リセット組み合わせ | P32                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P33                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

| P50～P53ポートの出力仕様           | P50                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P51                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P52                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

|                           | P53                                                                                                                                                                                                                                                                                    | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain * |

| P0xポートキー同時押し<br>リセット時間検定  | <input type="checkbox"/> 1. Not Use                                                                                                                                                                                                                                                    | <input type="checkbox"/> 2. Use                                                        |

| LCD駆動電源                   | <input type="checkbox"/> 1. Internal 1/3 bias<br><input type="checkbox"/> 2. External 1/3 bias, VDD = VC2 (4.5 V panel)<br><input type="checkbox"/> 3. External 1/3 bias, VDD = VC3 (3.0 V panel)<br><input type="checkbox"/> 4. External 1/2 bias, VDD = VC3, VC1 = VC2 (3.0 V panel) |                                                                                        |

□選択可能 ■固定

\* R/Fコンバータ(チャネル0)を使用する場合は、P50～P53ポートの出力仕様に"Pch Open Drain"を選択しないでください。

表1.3.3 オプションリスト(S1C63003)

| 項目                  | オプション                                                                                                                                                  |                                                                     |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 動作電源タイプ             | <input type="checkbox"/> 1. Normal Type (1.8–5.5 V)                                                                                                    | <input type="checkbox"/> 2. Low Voltage Type (1.1–1.7 V)            |

| OSC3発振回路            | <input checked="" type="checkbox"/> 1. CR (built-in R)<br><input type="checkbox"/> 2. CR (external R)<br><input type="checkbox"/> 3. Ceramic (4.0 MHz) |                                                                     |

| RESET端子ブルダウン抵抗      | <input type="checkbox"/> 1. Use                                                                                                                        | <input type="checkbox"/> 2. Not Use                                 |

| SEG/GPIO/RFC選択      | P20                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P21                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P22                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P23                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P50                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P51                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P52                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | P53                                                                                                                                                    | <input type="checkbox"/> 1. I/O <input type="checkbox"/> 2. SEG     |

|                     | RFIN1                                                                                                                                                  | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | REF1                                                                                                                                                   | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | SEN1                                                                                                                                                   | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

|                     | HUD                                                                                                                                                    | <input type="checkbox"/> 1. RFC <input type="checkbox"/> 2. SEG     |

| 入出力兼用ポート<br>ブルダウン抵抗 | P00                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P01                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P02                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P03                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P10                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

|                     | P11                                                                                                                                                    | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use |

## 1 概要

| 項目                        | オプション                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 入出力兼用ポート<br>ブルダウン抵抗       | P12                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P13                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P20                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P21                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P22                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P23                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P50                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P51                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P52                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

|                           | P53                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Use <input type="checkbox"/> 2. Not Use                    |

| 入出力兼用ポート<br>出力仕様          | P00                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P01                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P02                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P03                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

|                           | P10                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |

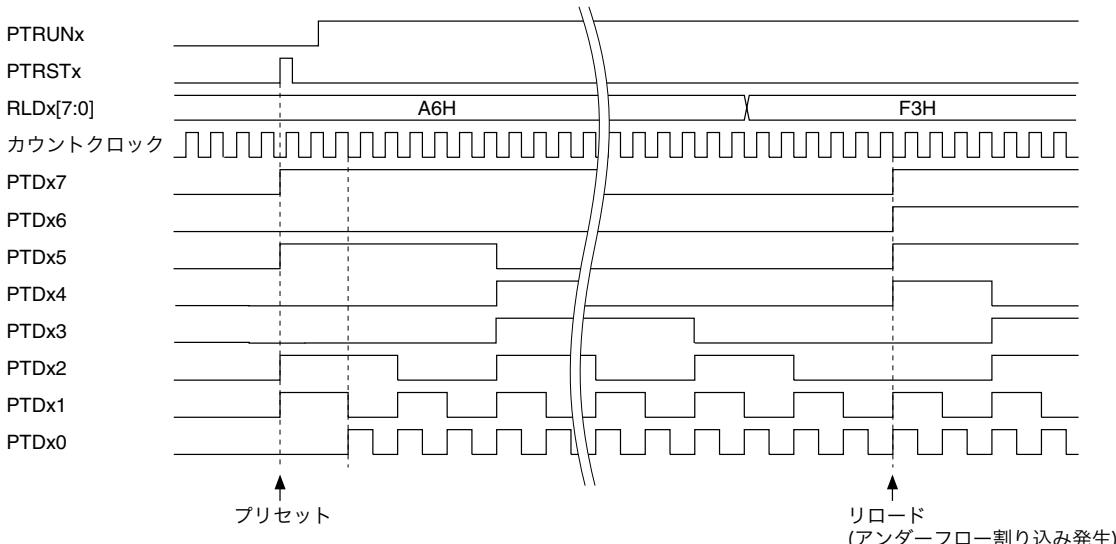

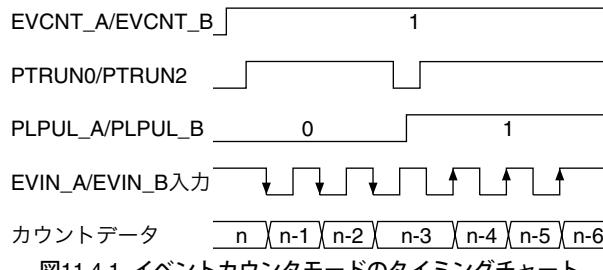

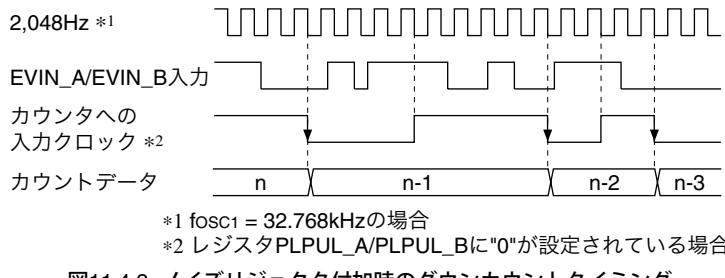

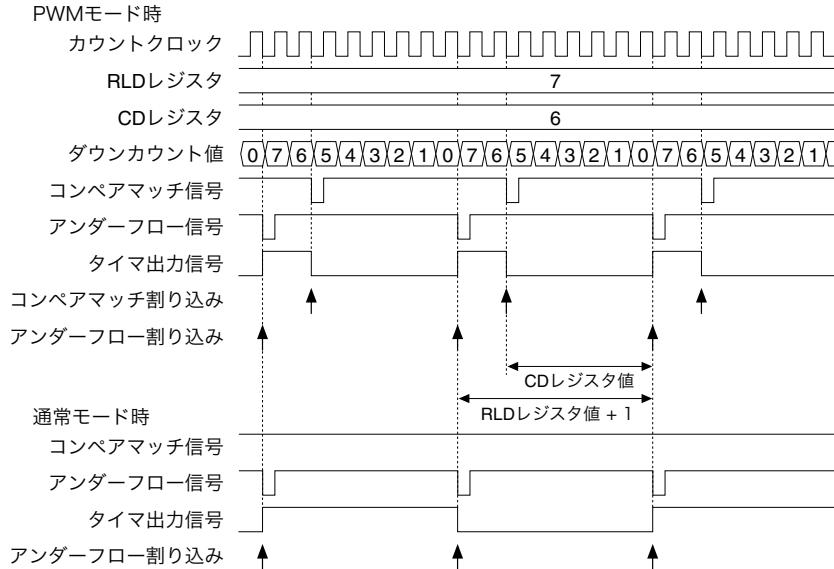

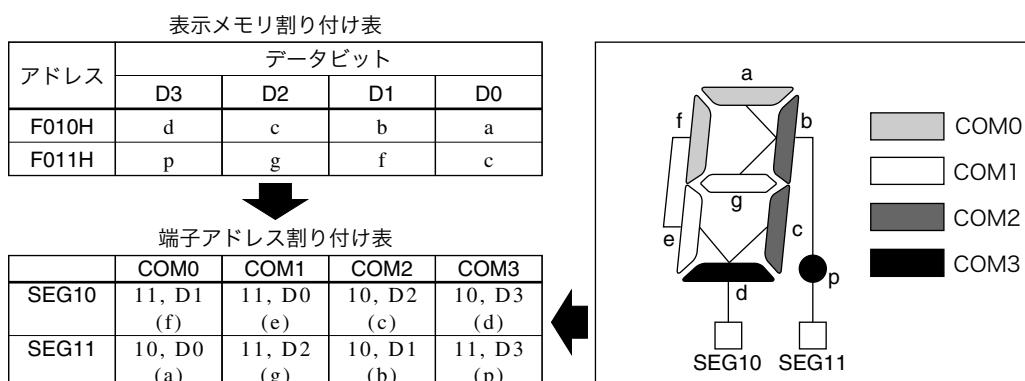

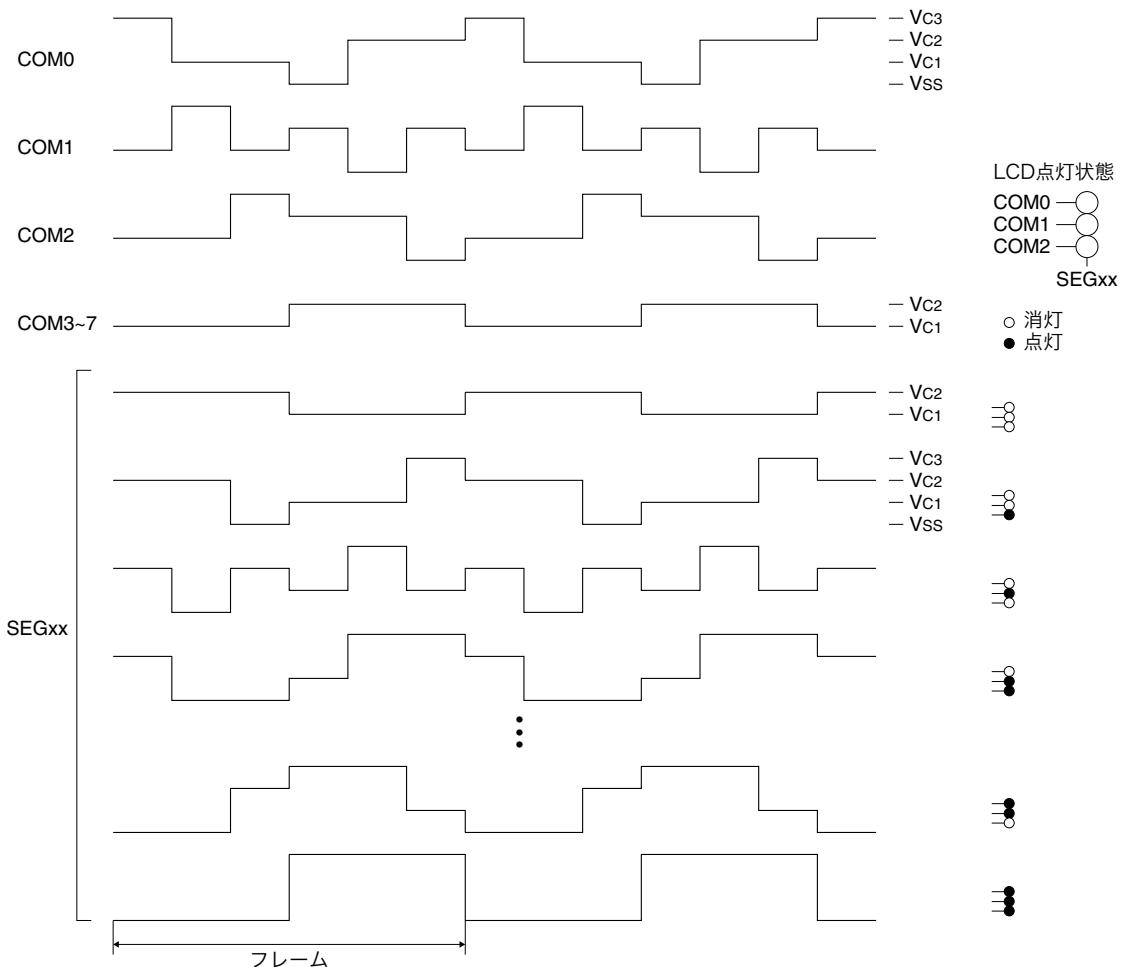

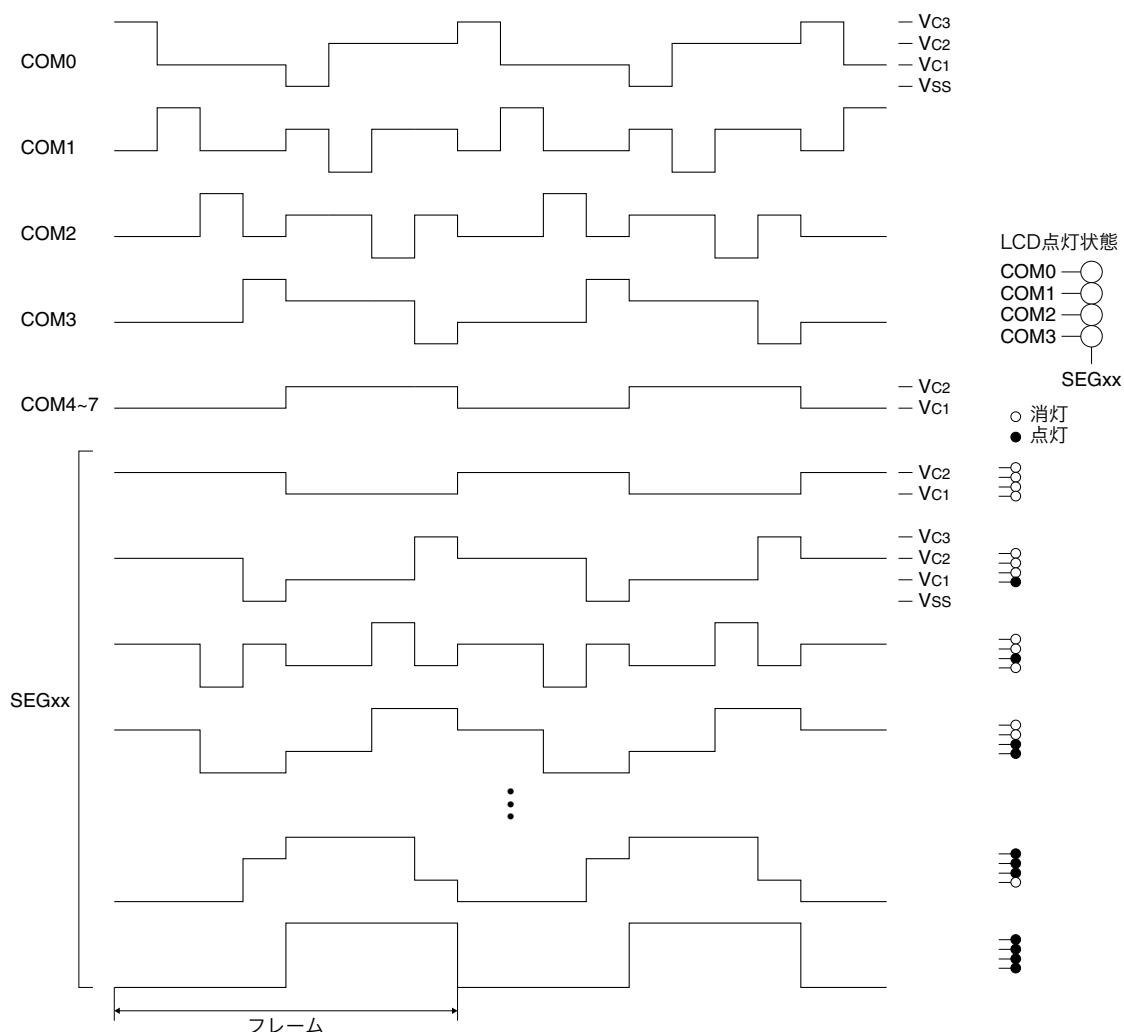

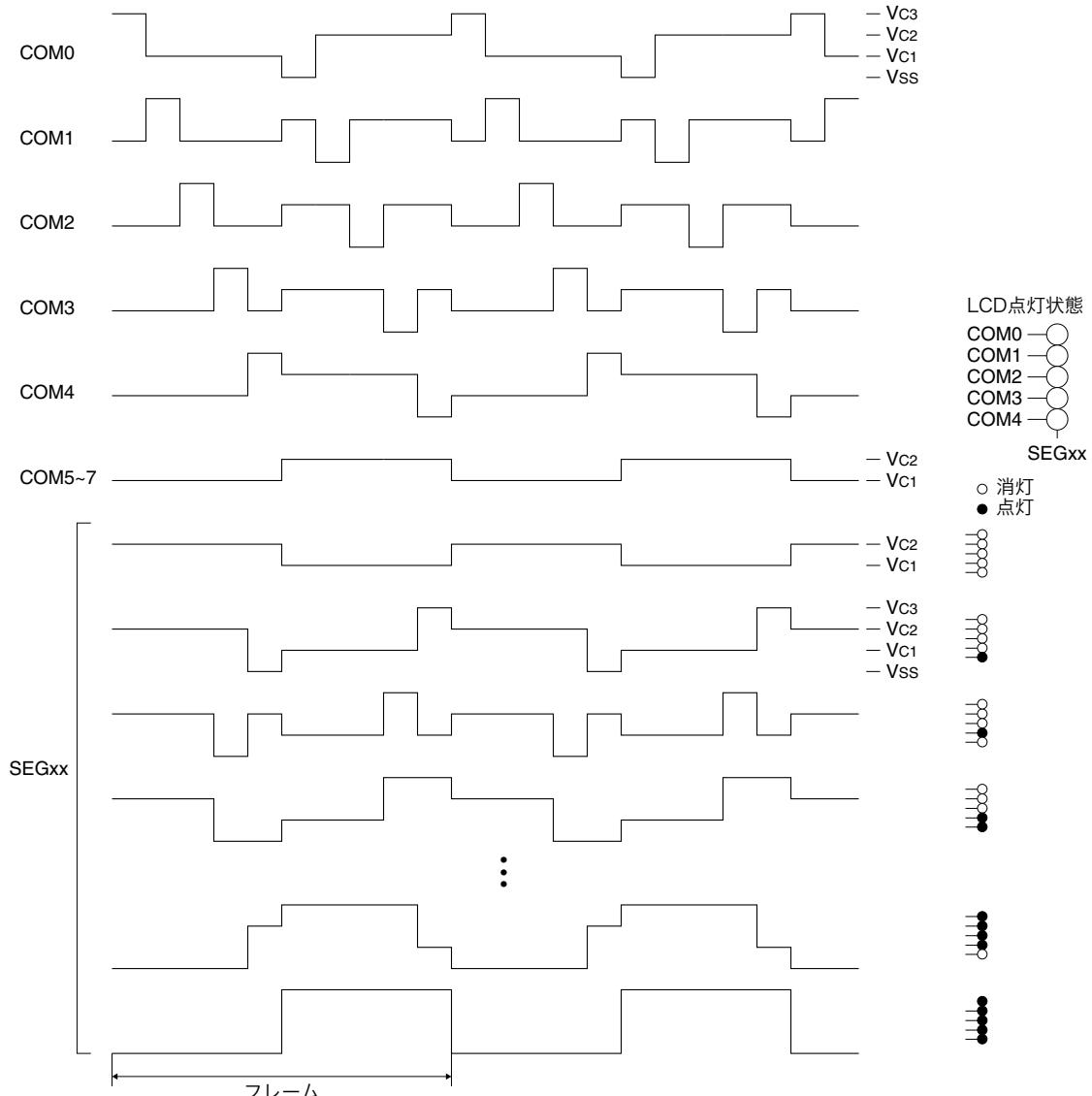

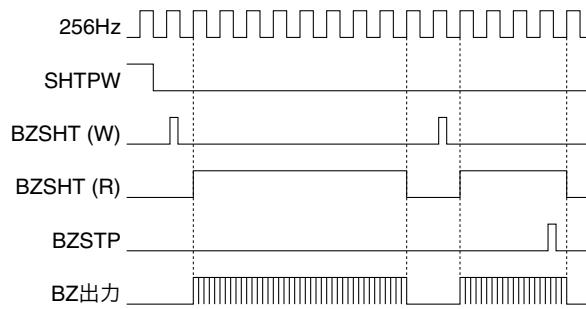

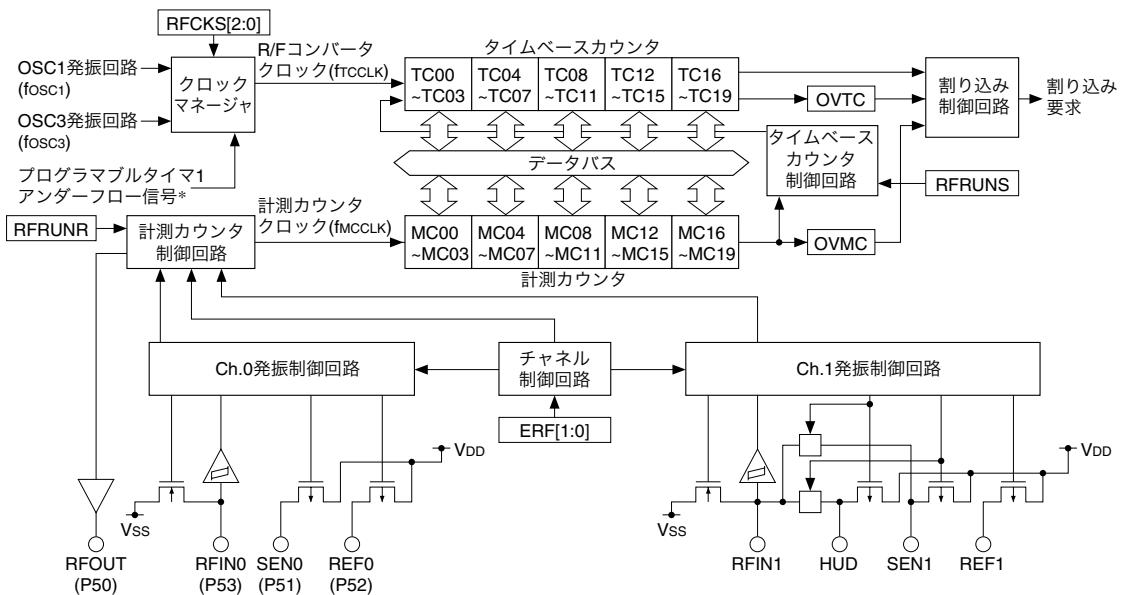

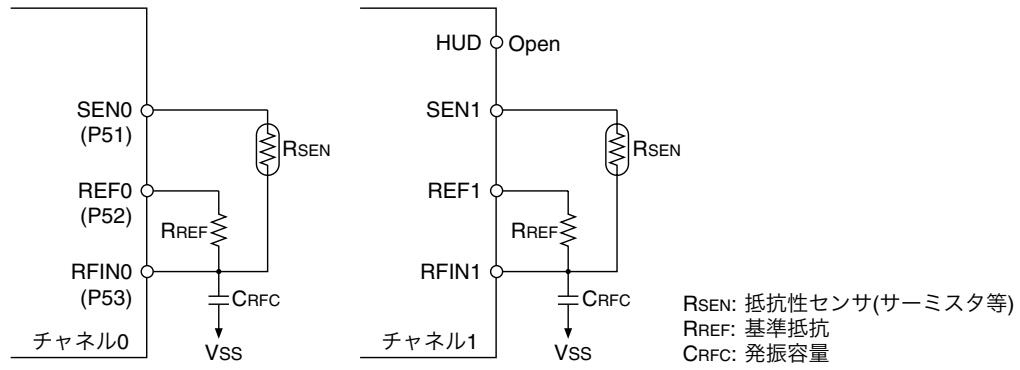

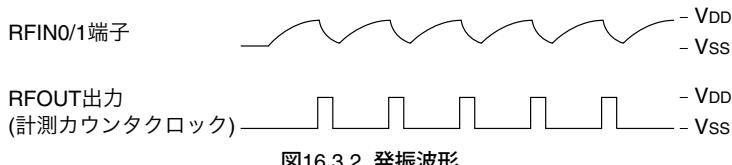

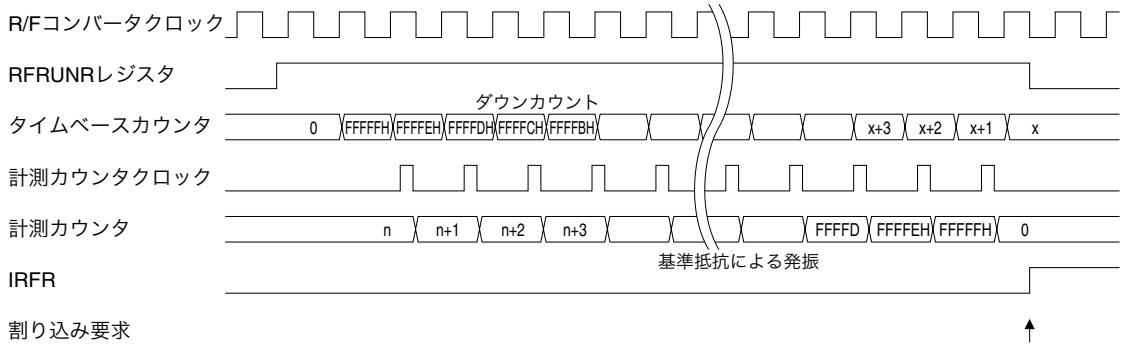

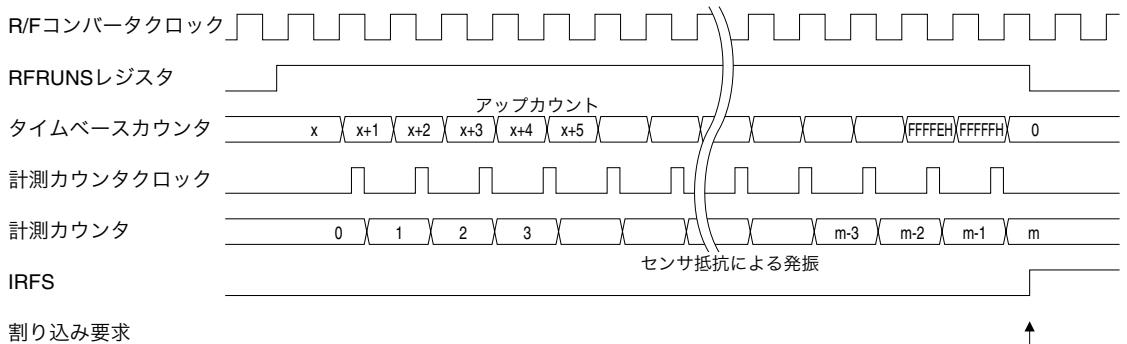

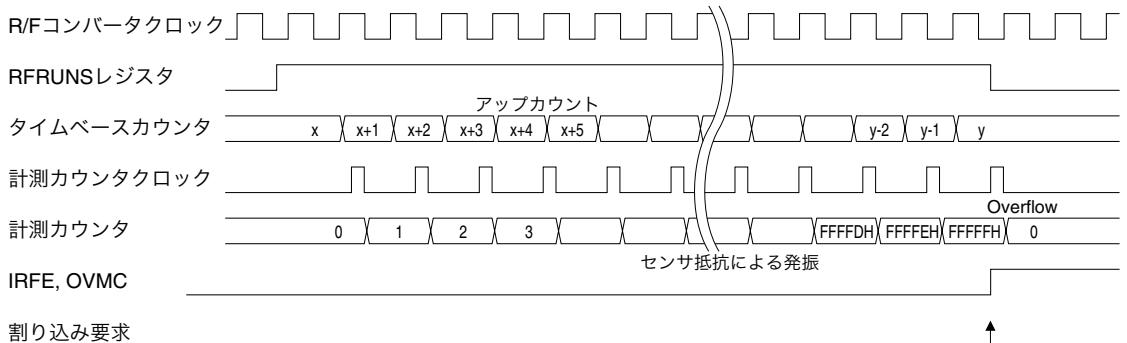

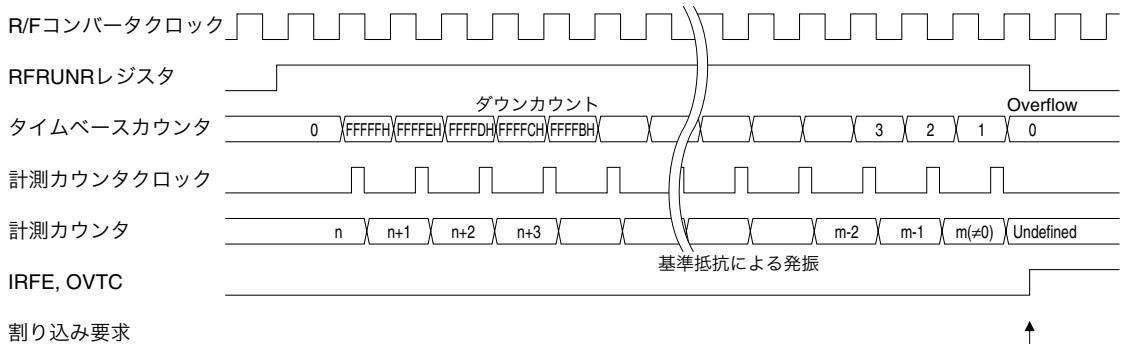

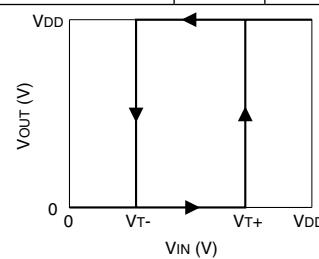

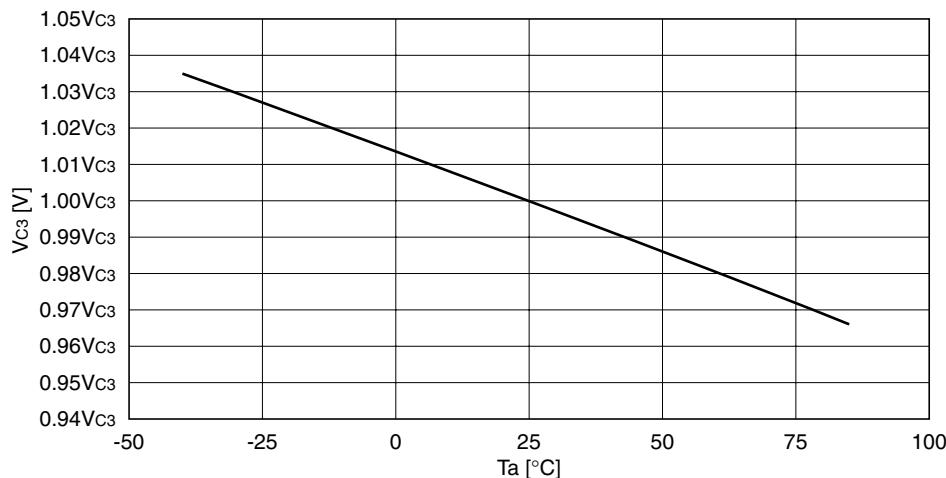

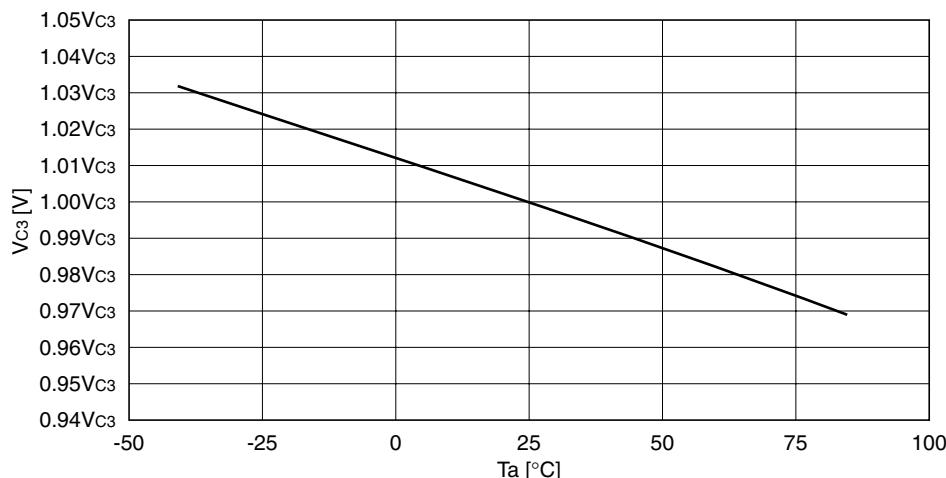

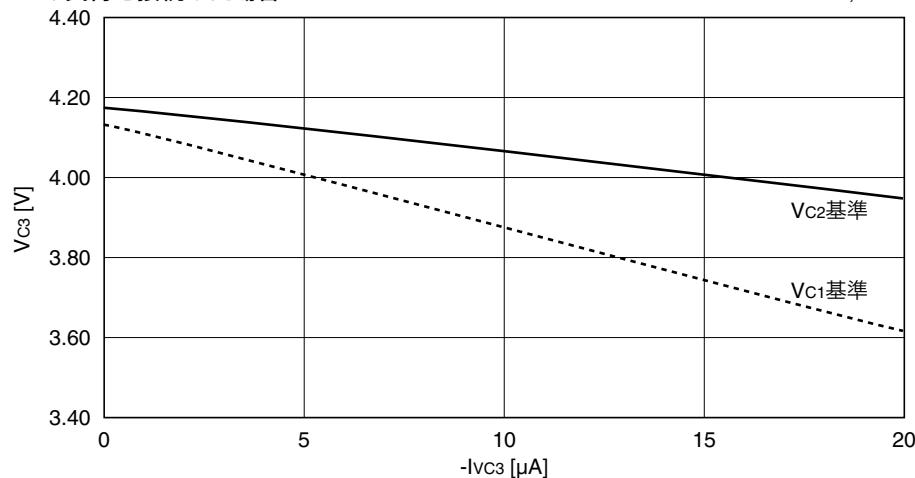

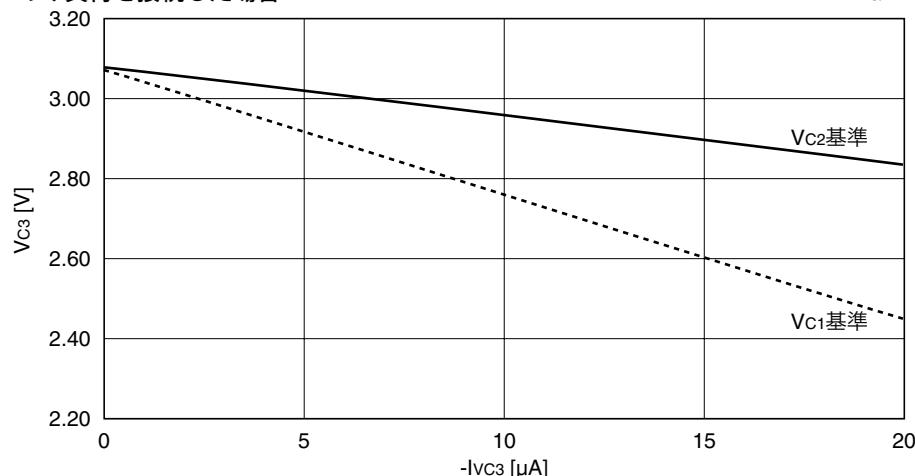

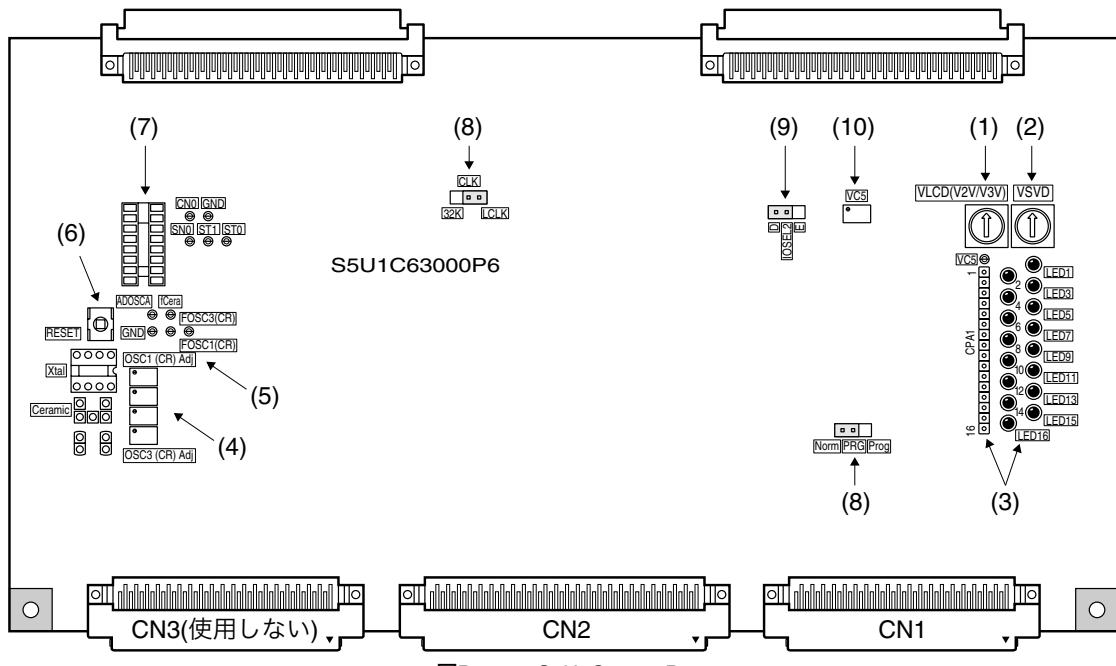

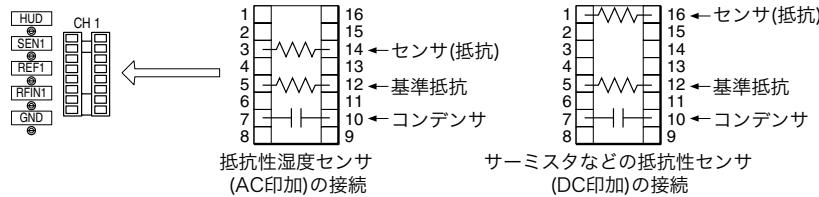

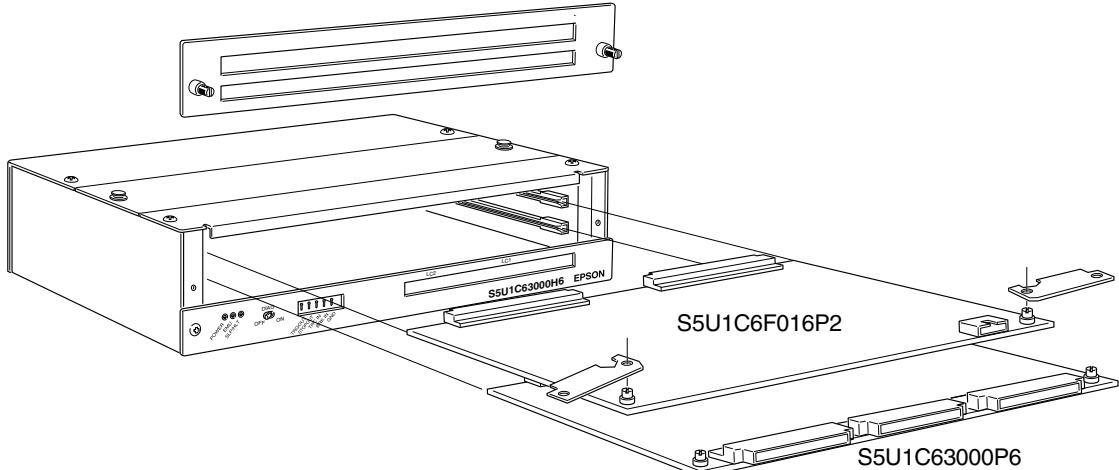

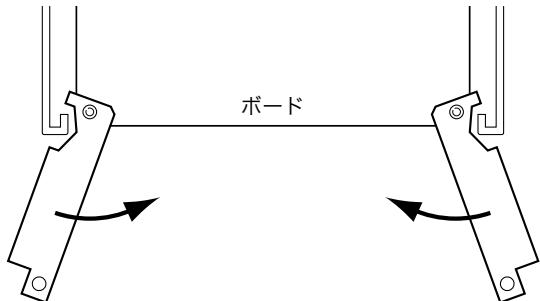

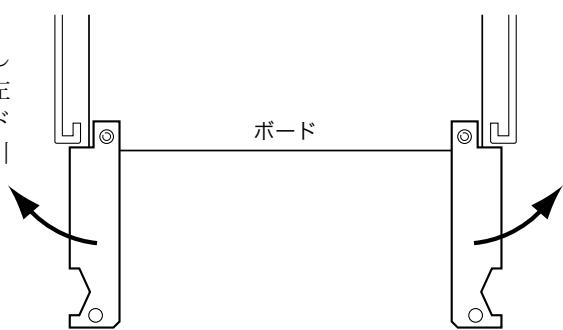

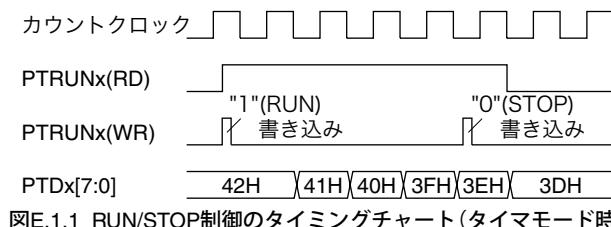

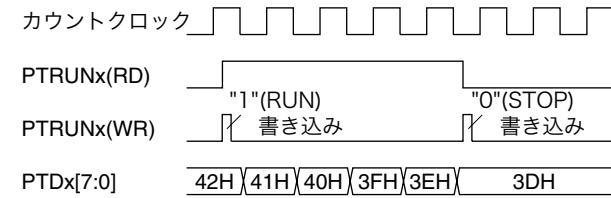

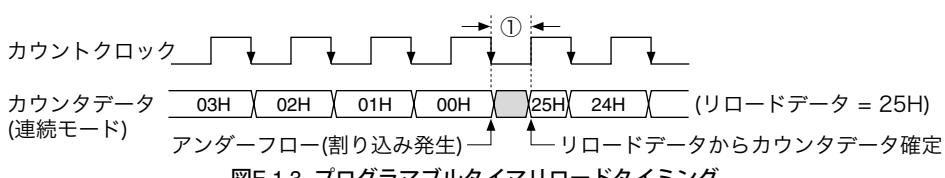

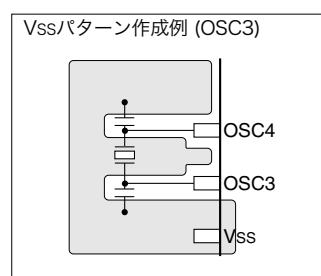

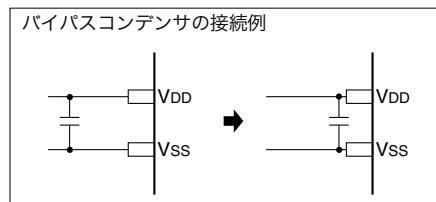

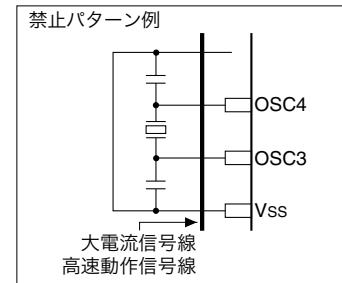

|                           | P11                                                                                                                                                                                                                                                                                                                                                                                                 | <input type="checkbox"/> 1. Complementary <input type="checkbox"/> 2. Pch Open Drain   |