CMOS 16-BIT SINGLE CHIP MICROCONTROLLER

**S1C17003**

テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

---

本資料の内容については、予告なく変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の知的財産権およびその他の権利侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち、「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

6. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

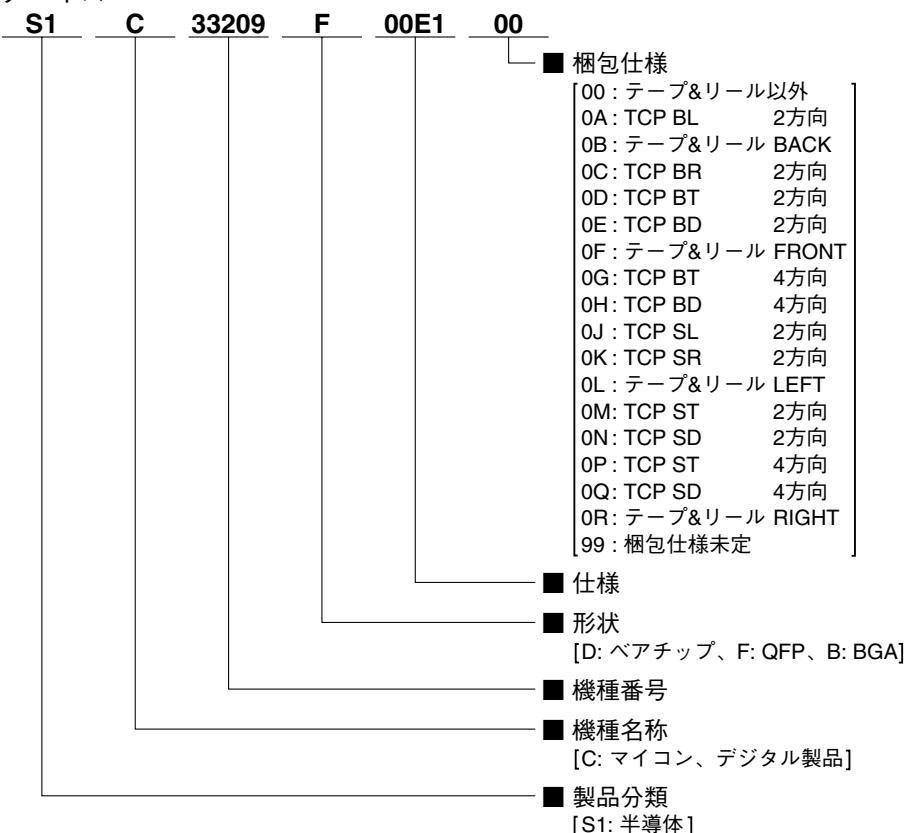

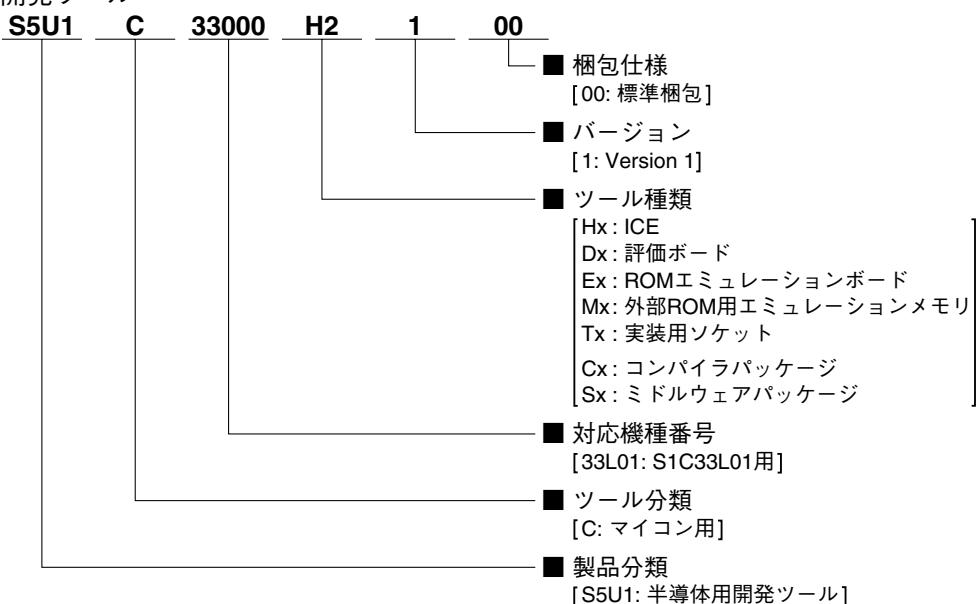

## 製品型番体系

### ●デバイス

### ●開発ツール

## - 目 次 -

|                                                 |     |

|-------------------------------------------------|-----|

| <b>1 概要</b>                                     | 1-1 |

| 1.1 特長                                          | 1-2 |

| 1.2 ブロック図                                       | 1-3 |

| 1.3 端子                                          | 1-4 |

| 1.3.1 端子配置                                      | 1-4 |

| 1.3.2 端子説明                                      | 1-8 |

| <b>2 CPU</b>                                    | 2-1 |

| 2.1 S1C17コアの特長                                  | 2-1 |

| 2.2 CPUレジスタ                                     | 2-2 |

| 2.3 命令セット                                       | 2-3 |

| 2.4 ベクタテーブル                                     | 2-7 |

| 2.5 PSRの読み出し                                    | 2-8 |

| 2.6 プロセッサ情報                                     | 2-9 |

| <b>3 メモリマップ, バス制御</b>                           | 3-1 |

| 3.1 バスサイクル                                      | 3-2 |

| 3.1.1 アクセスサイズ制限                                 | 3-2 |

| 3.1.2 命令実行サイクルの制限                               | 3-2 |

| 3.2 内蔵ROMエリア                                    | 3-3 |

| 3.2.1 内蔵ROM                                     | 3-3 |

| 3.2.2 ROMのリードアクセスサイクルの設定                        | 3-3 |

| 0x5320: ROM Control Register (MISC_FL)          | 3-3 |

| 3.3 内蔵RAMエリア                                    | 3-4 |

| 3.3.1 内蔵RAM                                     | 3-4 |

| 0x5326: IRAM Size Select Register (MISC_IRAMSZ) | 3-4 |

| 3.4 内蔵周辺回路エリア                                   | 3-5 |

| 3.4.1 内蔵周辺回路エリア1 (0x4000~)                      | 3-5 |

| 3.4.2 内蔵周辺回路エリア2 (0x5000~)                      | 3-5 |

| 3.5 コアI/O予約エリア                                  | 3-6 |

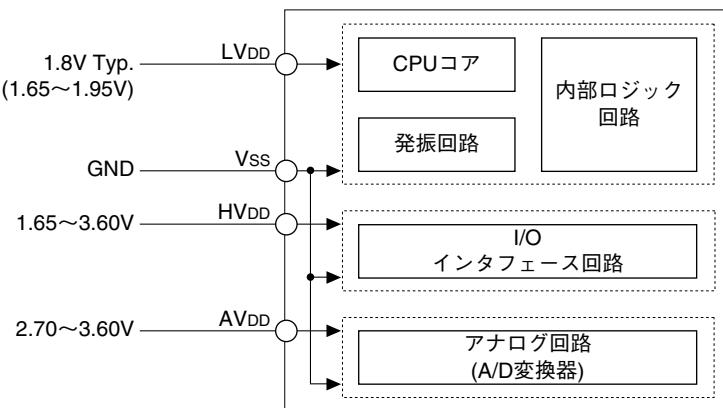

| <b>4 電源</b>                                     | 4-1 |

| 4.1 電源端子                                        | 4-1 |

| 4.2 動作電圧 (LV <sub>DD</sub> , V <sub>SS</sub> )  | 4-2 |

| 4.3 I/Oインターフェース電源 (HV <sub>DD</sub> )           | 4-2 |

| 4.4 アナログ回路用電源 (AV <sub>DD</sub> )               | 4-2 |

| 4.5 電源に関する注意事項                                  | 4-3 |

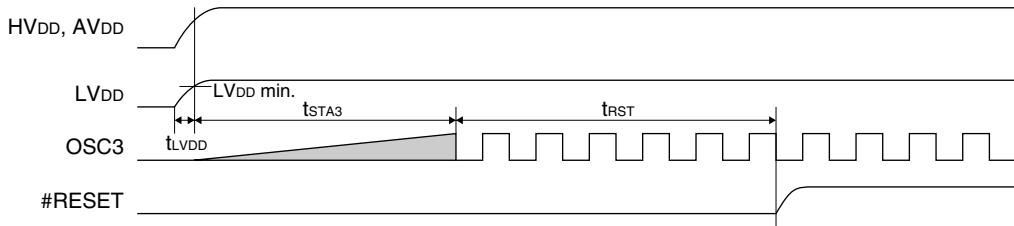

| <b>5 イニシャルリセット</b>                              | 5-1 |

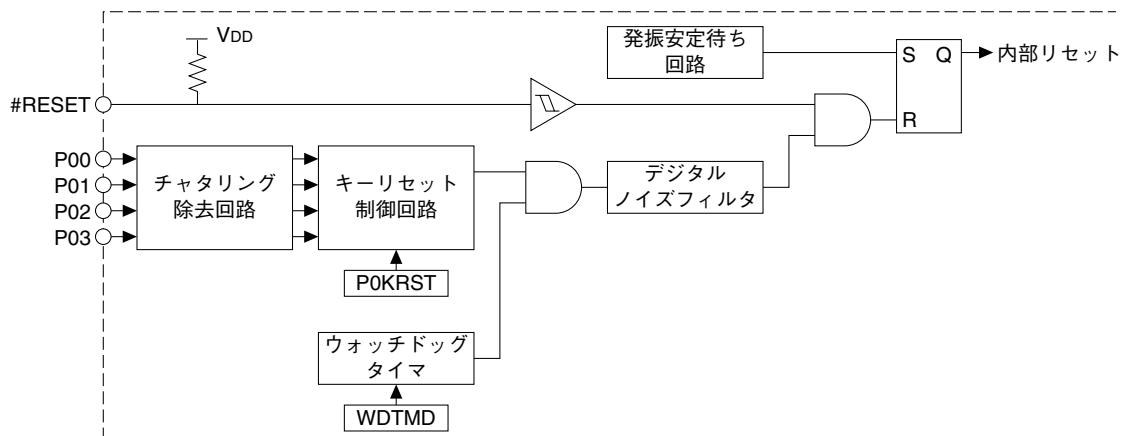

| 5.1 イニシャルリセット要因                                 | 5-1 |

| 5.1.1 #RESET端子                                  | 5-1 |

| 5.1.2 P0ポートキー入力リセット                             | 5-2 |

| 5.1.3 ウォッチドッグタイマによるリセット                         | 5-2 |

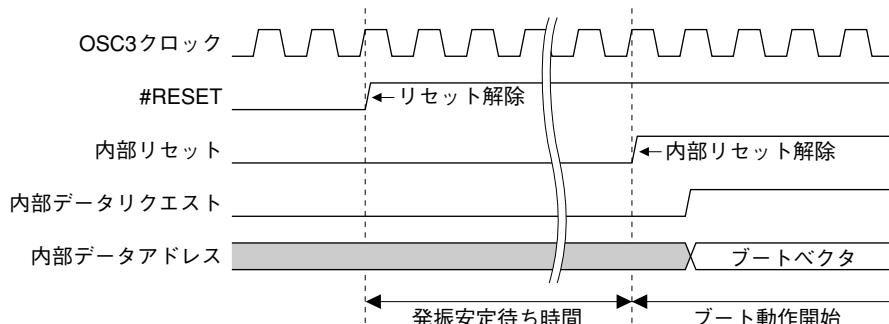

| 5.2 イニシャルリセットシーケンス                              | 5-3 |

| 5.3 イニシャルリセット時の初期設定                             | 5-4 |

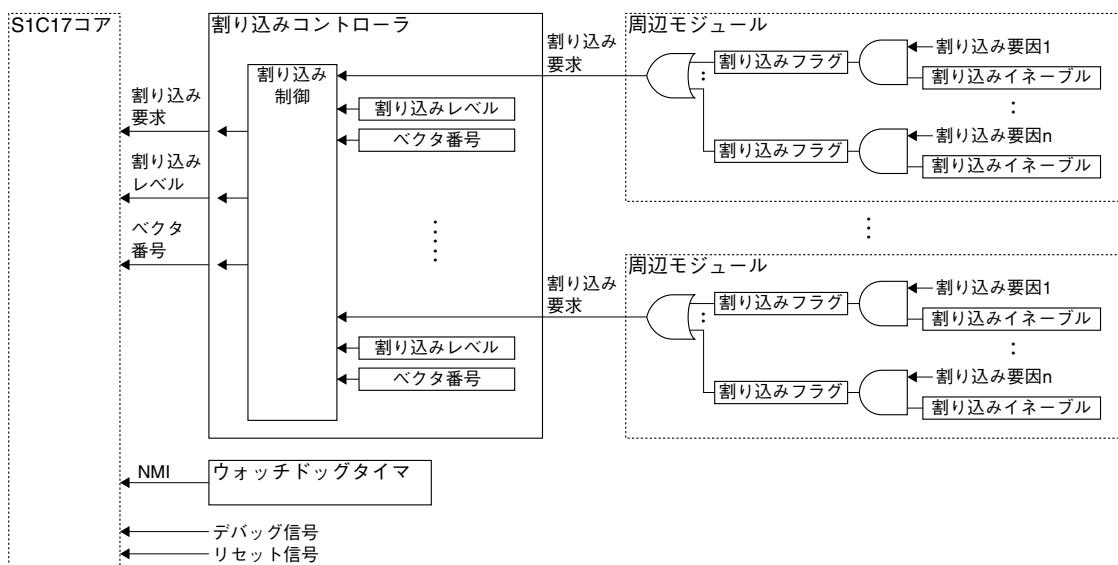

| <b>6 割り込みコントローラ (ITC)</b>                       | 6-1 |

| 6.1 ITCの構成                                      | 6-1 |

| 6.2 ベクタテーブル                                     | 6-2 |

| 6.3 マスク可能割り込みの制御                                | 6-3 |

| 6.3.1 周辺モジュールの割り込み制御ビット                         | 6-3 |

|                                                          |             |

|----------------------------------------------------------|-------------|

| 6.3.2 ITCの割り込み要求処理.....                                  | 6-3         |

| 6.3.3 S1C17コアの割り込み処理.....                                | 6-4         |

| 6.4 NMI.....                                             | 6-5         |

| 6.5 ソフトウェア割り込み .....                                     | 6-6         |

| 6.6 HALT, SLEEPモードの解除.....                               | 6-7         |

| 6.7 制御レジスタ詳細 .....                                       | 6-8         |

| 0x4306: Interrupt Level Setup Register 0 (ITC_LV0).....  | 6-9         |

| 0x4308: Interrupt Level Setup Register 1 (ITC_LV1).....  | 6-10        |

| 0x430a: Interrupt Level Setup Register 2 (ITC_LV2).....  | 6-11        |

| 0x430c: Interrupt Level Setup Register 3 (ITC_LV3).....  | 6-12        |

| 0x430e: Interrupt Level Setup Register 4 (ITC_LV4).....  | 6-13        |

| 0x4310: Interrupt Level Setup Register 5 (ITC_LV5).....  | 6-14        |

| 0x4312: Interrupt Level Setup Register 6 (ITC_LV6).....  | 6-15        |

| 0x4314: Interrupt Level Setup Register 7 (ITC_LV7).....  | 6-16        |

| 0x4316: Interrupt Level Setup Register 8 (ITC_LV8).....  | 6-17        |

| 0x4318: Interrupt Level Setup Register 9 (ITC_LV9).....  | 6-18        |

| 6.8 注意事項.....                                            | 6-19        |

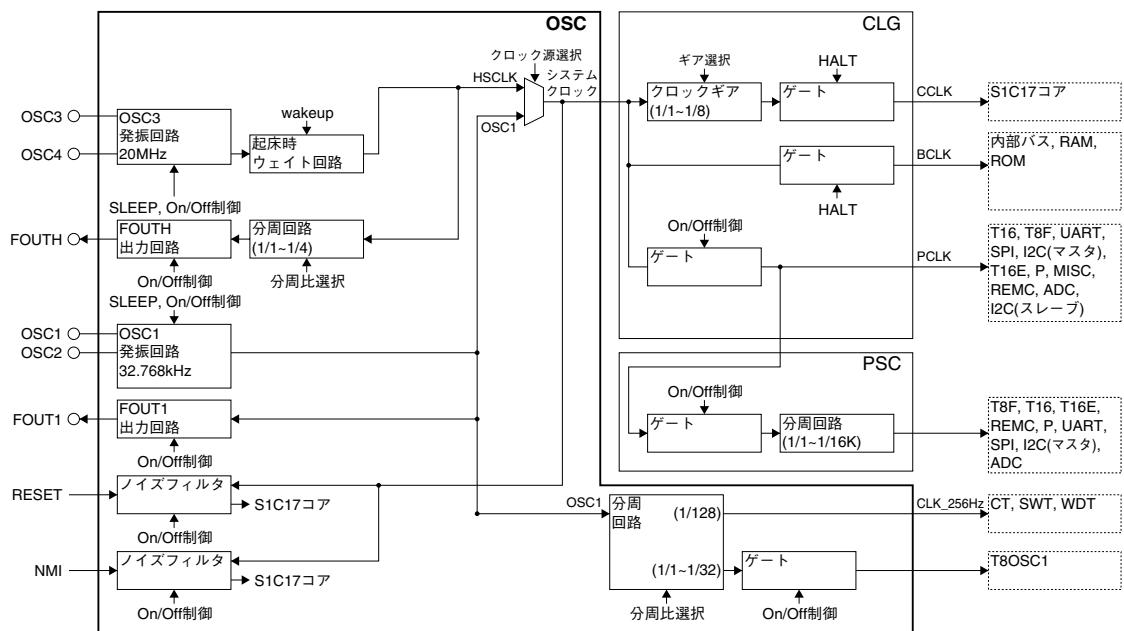

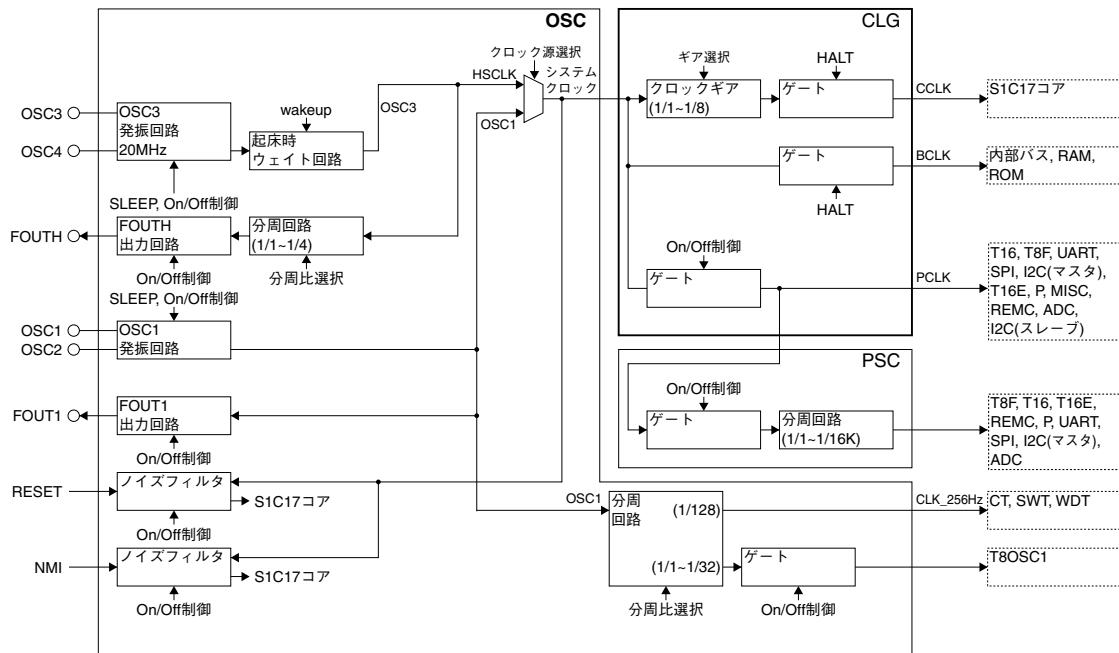

| <b>7 発振回路 (OSC) .....</b>                                | <b>7-1</b>  |

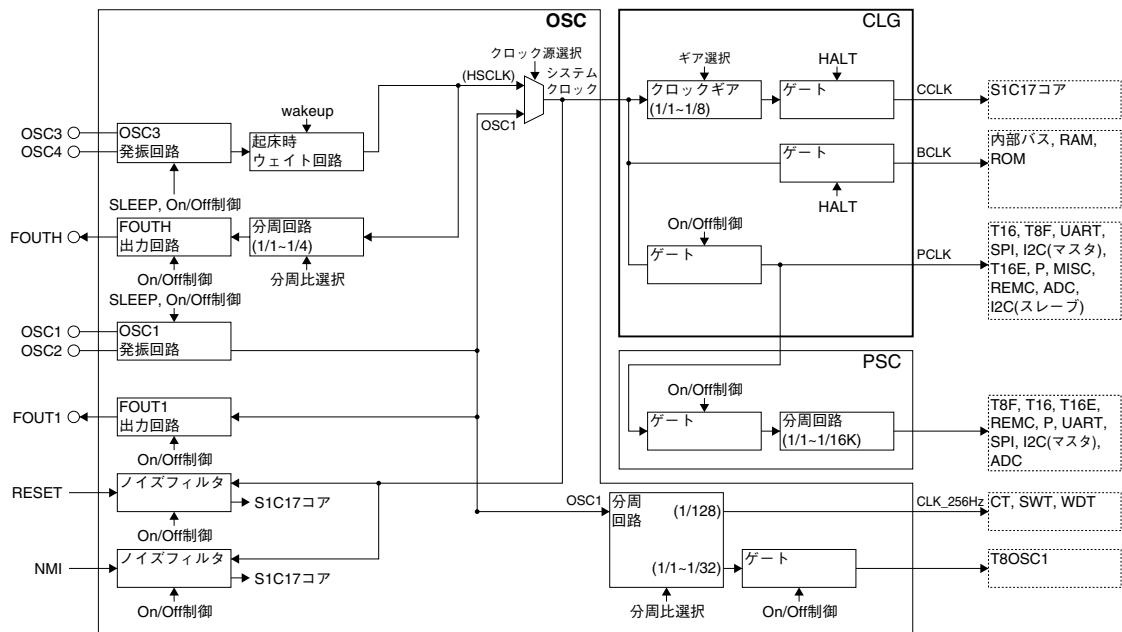

| 7.1 OSCモジュールの構成.....                                     | 7-1         |

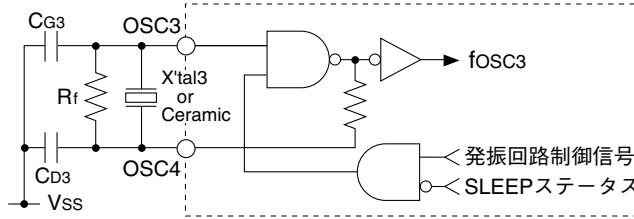

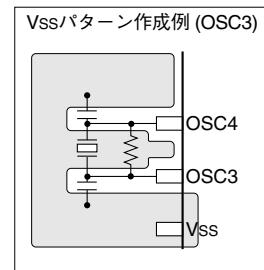

| 7.2 OSC3発振回路 .....                                       | 7-2         |

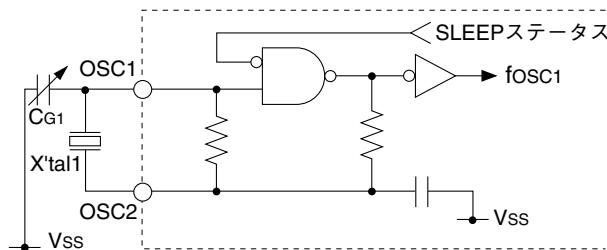

| 7.3 OSC1発振回路 .....                                       | 7-3         |

| 7.4 クロックの切り換え .....                                      | 7-4         |

| 7.5 8ビットOSC1タイマクロックの制御.....                              | 7-5         |

| 7.6 クロック外部出力 (FOUTH, FOUT1) .....                        | 7-6         |

| 7.7 RESET, NMI入力ノイズフィルタ .....                            | 7-8         |

| 7.8 制御レジスタ詳細 .....                                       | 7-9         |

| 0x5060: Clock Source Select Register (OSC_SRC) .....     | 7-10        |

| 0x5061: Oscillation Control Register (OSC_CTL) .....     | 7-11        |

| 0x5062: Noise Filter Enable Register (OSC_NFEN) .....    | 7-12        |

| 0x5064: FOUT Control Register (OSC_FOUT) .....           | 7-13        |

| 0x5065: T8OSC1 Clock Control Register (OSC_T8OSC1) ..... | 7-14        |

| 7.9 注意事項.....                                            | 7-15        |

| <b>8 クロックジェネレータ (CLG) .....</b>                          | <b>8-1</b>  |

| 8.1 クロックジェネレータの構成 .....                                  | 8-1         |

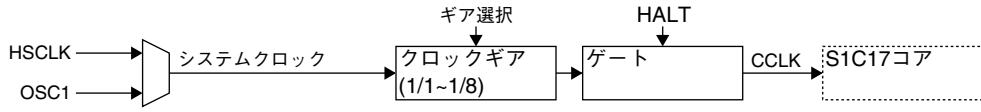

| 8.2 CPUコアクロック (CCLK) の制御 .....                           | 8-2         |

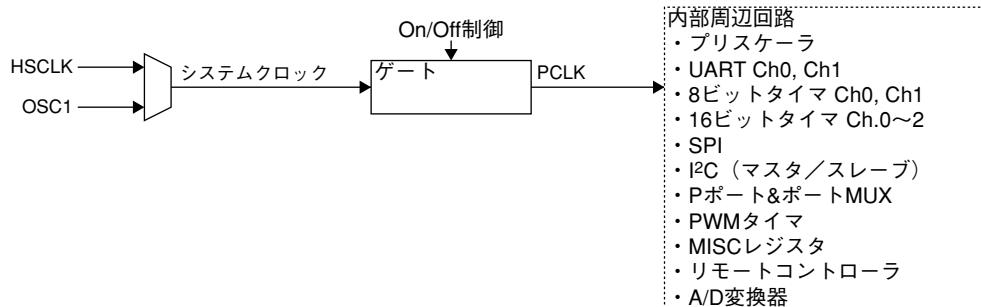

| 8.3 周辺モジュールクロック (PCLK) の制御 .....                         | 8-3         |

| 8.4 制御レジスタ詳細 .....                                       | 8-4         |

| 0x5080: PCLK Control Register (CLG_PCLK) .....           | 8-5         |

| 0x5081: CCLK Control Register (CLG_CCLK) .....           | 8-6         |

| 8.5 注意事項.....                                            | 8-7         |

| <b>9 プリスケーラ (PSC) .....</b>                              | <b>9-1</b>  |

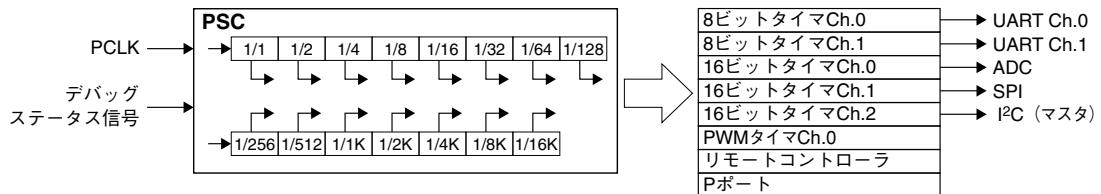

| 9.1 プリスケーラの構成 .....                                      | 9-1         |

| 9.2 制御レジスタ詳細 .....                                       | 9-2         |

| 0x4020: Prescaler Control Register (PSC_CTL) .....       | 9-2         |

| 9.3 注意事項.....                                            | 9-3         |

| <b>10 入出力ポート (P) .....</b>                               | <b>10-1</b> |

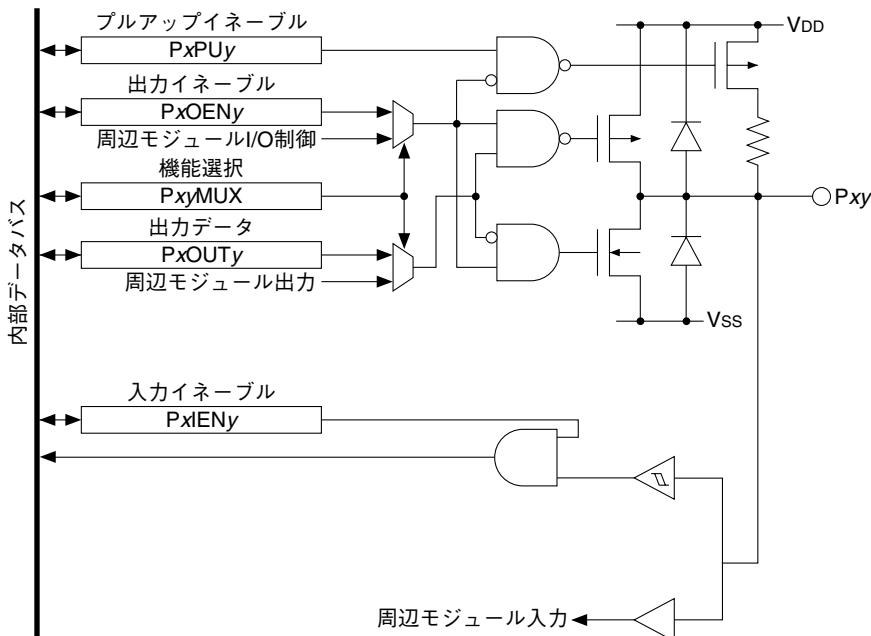

| 10.1 入出力ポートの構成 .....                                     | 10-1        |

| 10.2 入出力端子機能の選択 (ポートMUX) .....                           | 10-2        |

| 10.3 データの入出力 .....                                       | 10-3        |

| 10.4 プルアップ制御 .....                                       | 10-5        |

|                                                                                       |             |

|---------------------------------------------------------------------------------------|-------------|

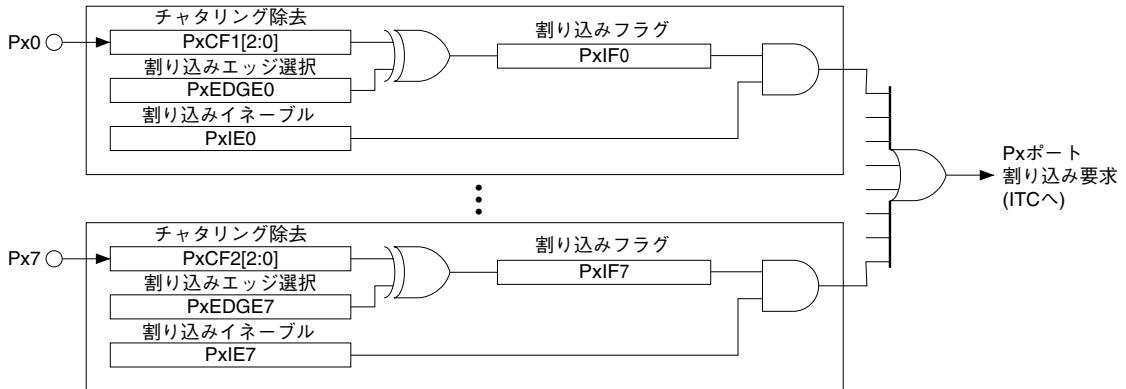

| 10.5 P0/P1ポートのチャタリング除去機能 .....                                                        | 10-6        |

| 10.6 ポート入力割り込み .....                                                                  | 10-7        |

| 10.7 制御レジスタ詳細 .....                                                                   | 10-9        |

| 0x5200/0x5210/0x5220/0x5230/0x5240: Px Port Input Data Registers (Px_IN).....         | 10-10       |

| 0x5201/0x5211/0x5221/0x5231/0x5241: Px Port Output Data Registers (Px_OUT).....       | 10-11       |

| 0x5202/0x5212/0x5222/0x5232/0x5242: Px Port Output Enable Registers (Px_OEN) .....    | 10-12       |

| 0x5203/0x5213/0x5223/0x5233/0x5243: Px Port Pull-up Control Registers (Px_PU) .....   | 10-13       |

| 0x5205/0x5215: Px Port Interrupt Mask Registers (Px_IMSK) .....                       | 10-14       |

| 0x5206/0x5216: Px Port Interrupt Edge Select Registers (Px_EDGE) .....                | 10-15       |

| 0x5207/0x5217: Px Port Interrupt Flag Registers (Px_IFLG) .....                       | 10-16       |

| 0x5208/0x5218: P0/P1 Port Chattering Filter Control Register (Px_CHAT) .....          | 10-17       |

| 0x5209: P0 Port Key-Entry Reset Configuration Register (P0_KRST) .....                | 10-19       |

| 0x520a/0x521a/0x522a/0x523a/0x524a: Px Port Input Enable Registers (Px_IEN) .....     | 10-20       |

| 0x52a0: P0 Port Function Select Register (P0_PMUX) .....                              | 10-21       |

| 0x52a1: P0 Port Function Select Register (P0_PMUX) .....                              | 10-22       |

| 0x52a2: P1 Port Function Select Register (P1_PMUX) .....                              | 10-23       |

| 0x52a3: P1 Port Function Select Register (P1_PMUX) .....                              | 10-24       |

| 0x52a4: P2 Port Function Select Register (P2_PMUX) .....                              | 10-25       |

| 0x52a5: P2 Port Function Select Register (P2_PMUX) .....                              | 10-26       |

| 0x52a6: P3 Port Function Select Register (P3_PMUX) .....                              | 10-27       |

| 0x52a7: P3 Port Function Select Register (P3_PMUX) .....                              | 10-28       |

| 0x52a8: P4 Port Function Select Register (P4_PMUX) .....                              | 10-29       |

| 10.8 注意事項 .....                                                                       | 10-30       |

| <b>11 16ビットタイマ (T16) .....</b>                                                        | <b>11-1</b> |

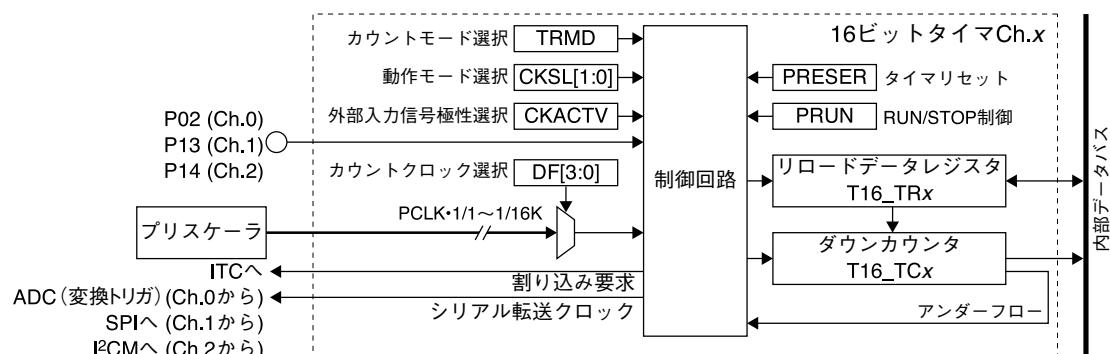

| 11.1 16ビットタイマの概要 .....                                                                | 11-1        |

| 11.2 16ビットタイマの動作モード .....                                                             | 11-2        |

| 11.2.1 内部クロックモード .....                                                                | 11-2        |

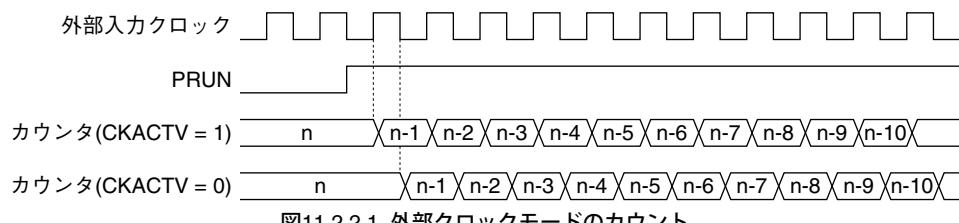

| 11.2.2 外部クロックモード .....                                                                | 11-3        |

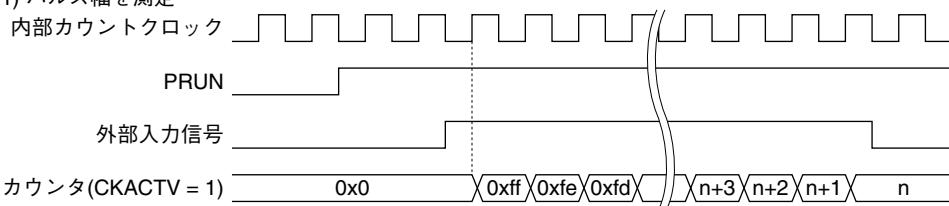

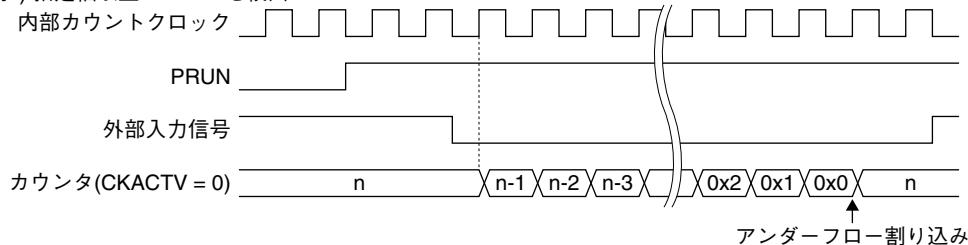

| 11.2.3 パルス幅測定モード .....                                                                | 11-4        |

| 11.3 カウントモード .....                                                                    | 11-5        |

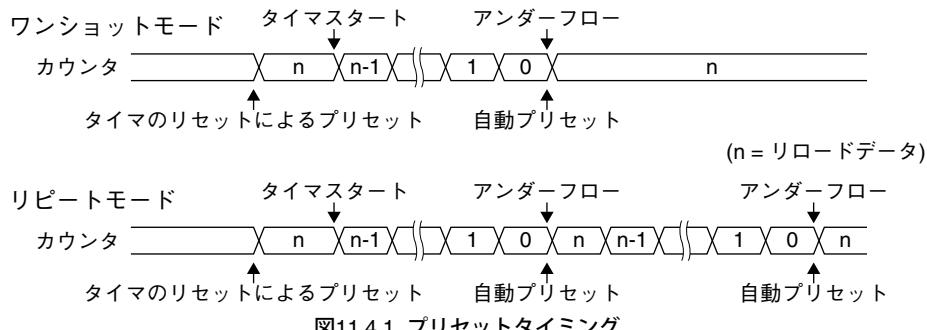

| 11.4 16ビットタイマリロードレジスタとアンダーフロー周期 .....                                                 | 11-6        |

| 11.5 16ビットタイマのリセット .....                                                              | 11-7        |

| 11.6 16ビットタイマRUN/STOP制御 .....                                                         | 11-8        |

| 11.7 16ビットタイマ出力信号 .....                                                               | 11-9        |

| 11.8 16ビットタイマ割り込み .....                                                               | 11-10       |

| 11.9 制御レジスタ詳細 .....                                                                   | 11-11       |

| 0x4220/0x4240/0x4260: 16-bit Timer Ch.x Input Clock Select Registers (T16_CLKx) ..... | 11-12       |

| 0x4222/0x4242/0x4262: 16-bit Timer Ch.x Reload Data Registers (T16_TRx) .....         | 11-13       |

| 0x4224/0x4244/0x4264: 16-bit Timer Ch.x Counter Data Registers (T16_TCx) .....        | 11-14       |

| 0x4226/0x4246/0x4266: 16-bit Timer Ch.x Control Registers (T16_CTLx) .....            | 11-15       |

| 0x4228/0x4248/0x4268: 16-bit Timer Ch.x Interrupt Control Registers (T16_INTx) .....  | 11-17       |

| 11.10 注意事項 .....                                                                      | 11-18       |

| <b>12 8ビットタイマ (T8F) .....</b>                                                         | <b>12-1</b> |

| 12.1 8ビットタイマの概要 .....                                                                 | 12-1        |

| 12.2 8ビットタイマのカウントモード .....                                                            | 12-2        |

| 12.3 カウントクロック .....                                                                   | 12-3        |

| 12.4 8ビットタイマリロードレジスタとアンダーフロー周期 .....                                                  | 12-4        |

| 12.5 8ビットタイマのリセット .....                                                               | 12-5        |

| 12.6 8ビットタイマRUN/STOP制御 .....                                                          | 12-6        |

| 12.7 8ビットタイマ出力信号 .....                                                                | 12-7        |

| 12.8 フайнモード .....                                                                    | 12-8        |

| 12.9 8ビットタイマ割り込み .....                                                                | 12-9        |

|                                                                                     |             |

|-------------------------------------------------------------------------------------|-------------|

| 12.10 制御レジスタ詳細 .....                                                                | 12-10       |

| 0x4200/0x4280: 8-bit Timer Ch. $x$ Input Clock Select Register (T8F_CLK $x$ ) ..... | 12-11       |

| 0x4202/0x4282: 8-bit Timer Ch. $x$ Reload Data Register (T8F_TR $x$ ) .....         | 12-12       |

| 0x4204/0x4284: 8-bit Timer Ch. $x$ Counter Data Register (T8F_TC $x$ ) .....        | 12-13       |

| 0x4206/0x4286: 8-bit Timer Ch. $x$ Control Register (T8F_CTL $x$ ) .....            | 12-14       |

| 0x4208/0x4288: 8-bit Timer Ch. $x$ Interrupt Control Register (T8F_INT $x$ ) .....  | 12-16       |

| 12.11 注意事項 .....                                                                    | 12-17       |

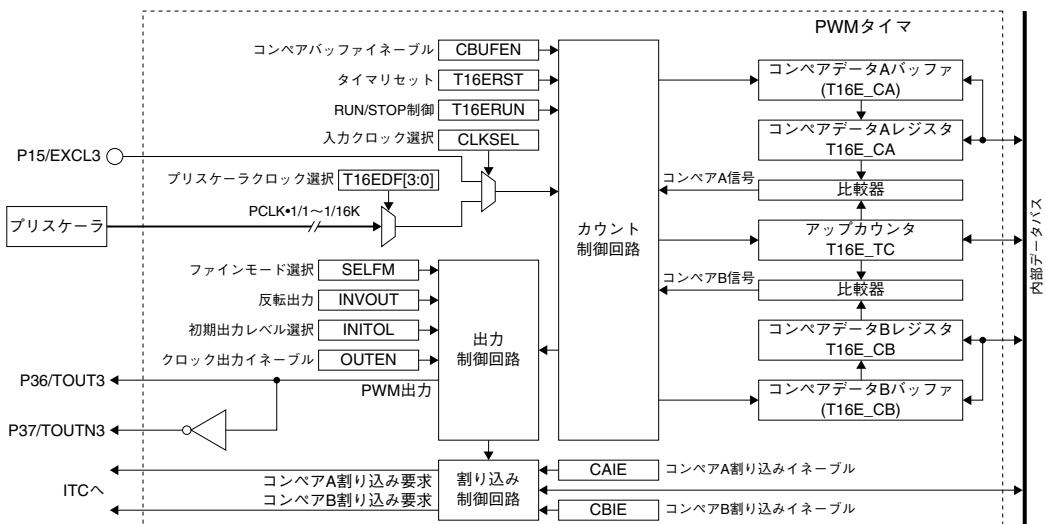

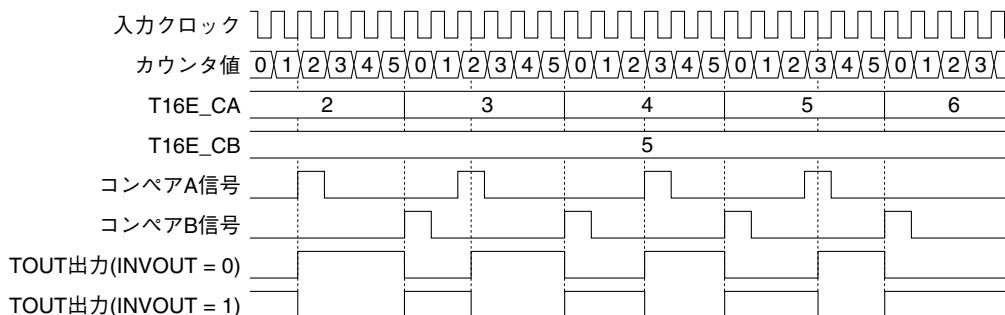

| <b>13 PWMタイマ (T16E) .....</b>                                                       | <b>13-1</b> |

| 13.1 PWMタイマの概要 .....                                                                | 13-1        |

| 13.2 PWMタイマの動作モード .....                                                             | 13-2        |

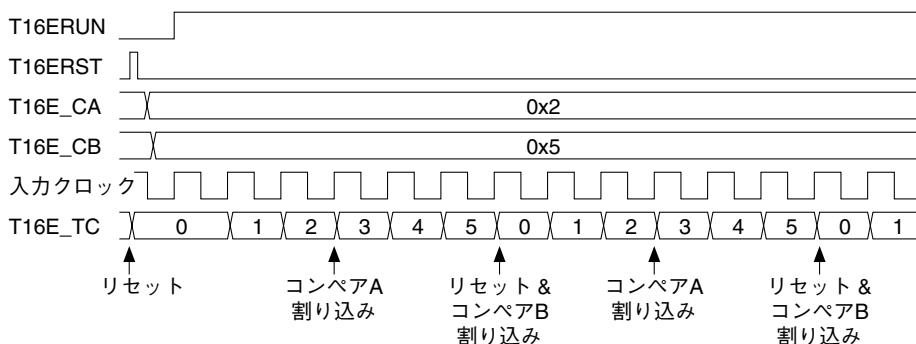

| 13.3 カウンタ値のセット/リセット .....                                                           | 13-3        |

| 13.4 コンペアデータの設定 .....                                                               | 13-4        |

| 13.5 PWMタイマRUN/STOP制御 .....                                                         | 13-5        |

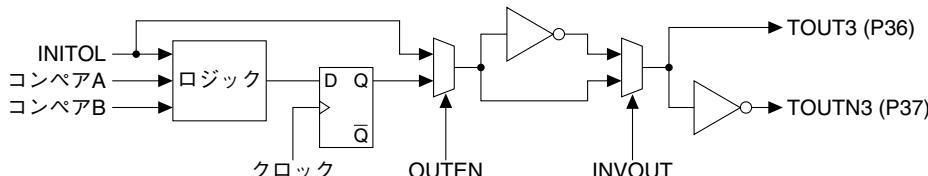

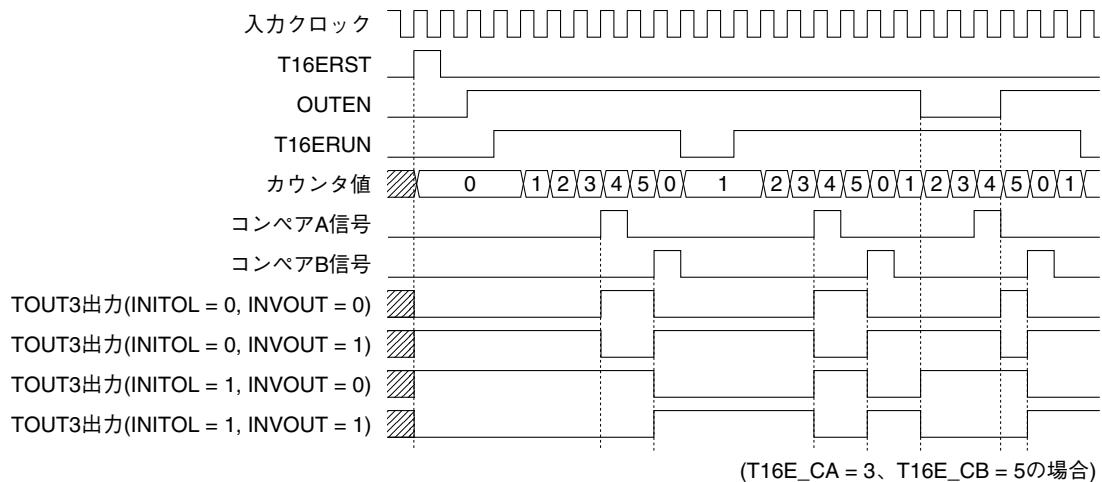

| 13.6 クロック出力の制御 .....                                                                | 13-6        |

| 13.7 PWMタイマ割り込み .....                                                               | 13-9        |

| 13.8 制御レジスタ詳細 .....                                                                 | 13-11       |

| 0x5300: PWM Timer Compare Data A Registers (T16E_CA) .....                          | 13-12       |

| 0x5302: PWM Timer Compare Data B Registers (T16E_CB) .....                          | 13-13       |

| 0x5304: PWM Timer Counter Data Registers (T16E_TC) .....                            | 13-14       |

| 0x5306: PWM Timer Control Registers (T16E_CTL) .....                                | 13-15       |

| 0x5308: PWM Timer Input Clock Select Registers (T16E_CLK) .....                     | 13-17       |

| 0x530a: PWM Timer Interrupt Mask Registers (T16E_IMSK) .....                        | 13-18       |

| 0x530c: PWM Timer Interrupt Flag Registers (T16E_IFLG) .....                        | 13-19       |

| 13.9 注意事項 .....                                                                     | 13-20       |

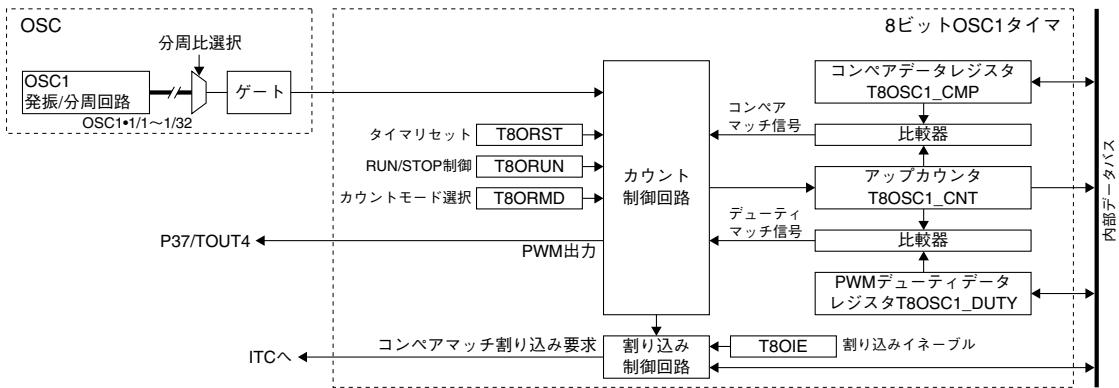

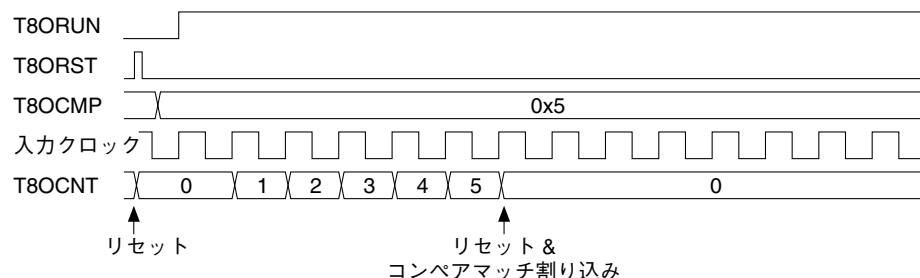

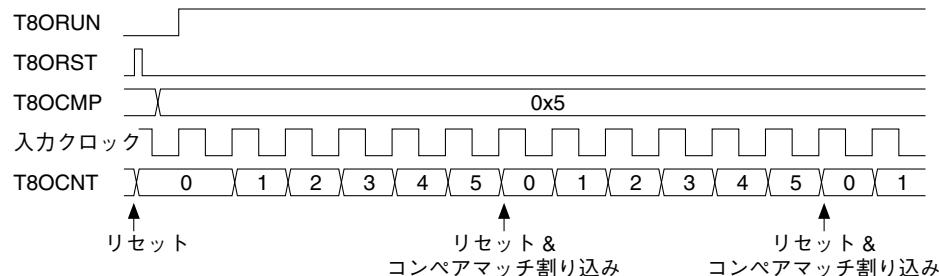

| <b>14 8ビットOSC1タイマ (T8OSC1) .....</b>                                                | <b>14-1</b> |

| 14.1 8ビットOSC1タイマの概要 .....                                                           | 14-1        |

| 14.2 8ビットOSC1タイマのカウントモード .....                                                      | 14-2        |

| 14.3 カウントクロック .....                                                                 | 14-3        |

| 14.4 8ビットOSC1タイマのリセット .....                                                         | 14-4        |

| 14.5 コンペアデータの設定 .....                                                               | 14-5        |

| 14.6 8ビットOSC1タイマRUN/STOP制御 .....                                                    | 14-6        |

| 14.7 8ビットOSC1タイマ割り込み .....                                                          | 14-7        |

| 14.8 PWM出力 .....                                                                    | 14-8        |

| 14.9 制御レジスタ詳細 .....                                                                 | 14-9        |

| 0x50c0: 8-bit OSC1 Timer Control Register (T8OSC1_CTL) .....                        | 14-10       |

| 0x50c1: 8-bit OSC1 Timer Counter Data Register (T8OSC1_CNT) .....                   | 14-11       |

| 0x50c2: 8-bit OSC1 Timer Compare Data Register (T8OSC1_CMP) .....                   | 14-12       |

| 0x50c3: 8-bit OSC1 Timer Interrupt Mask Register (T8OSC1_IMSK) .....                | 14-13       |

| 0x50c4: 8-bit OSC1 Timer Interrupt Flag Register (T8OSC1_IFLG) .....                | 14-14       |

| 0x50c5: 8-bit OSC1 Timer PWM Duty Data Register (T8OSC1_DUTY) .....                 | 14-15       |

| 14.10 注意事項 .....                                                                    | 14-16       |

| <b>15 計時タイマ (CT) .....</b>                                                          | <b>15-1</b> |

| 15.1 計時タイマの概要 .....                                                                 | 15-1        |

| 15.2 動作クロック .....                                                                   | 15-2        |

| 15.3 計時タイマのリセット .....                                                               | 15-3        |

| 15.4 計時タイマRUN/STOP制御 .....                                                          | 15-4        |

| 15.5 計時タイマ割り込み .....                                                                | 15-5        |

| 15.6 制御レジスタ詳細 .....                                                                 | 15-6        |

| 0x5000: Clock Timer Control Register (CT_CTL) .....                                 | 15-7        |

| 0x5001: Clock Timer Counter Register (CT_CNT) .....                                 | 15-8        |

| 0x5002: Clock Timer Interrupt Mask Register (CT_IMSK) .....                         | 15-9        |

|                                                                    |             |

|--------------------------------------------------------------------|-------------|

| 0x5003: Clock Timer Interrupt Flag Register (CT_IFLG).....         | 15-10       |

| 15.7 注意事項.....                                                     | 15-11       |

| <b>16 ストップウォッチタイマ (SWT) .....</b>                                  | <b>16-1</b> |

| 16.1 ストップウォッチタイマの概要.....                                           | 16-1        |

| 16.2 BCDカウンタ .....                                                 | 16-2        |

| 16.3 動作クロック .....                                                  | 16-3        |

| 16.4 ストップウォッチタイマのリセット .....                                        | 16-4        |

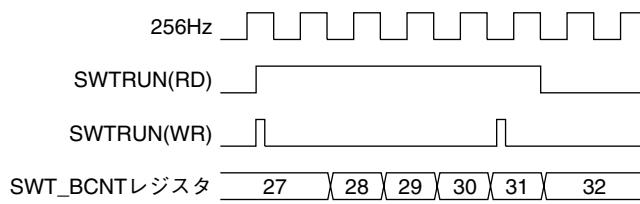

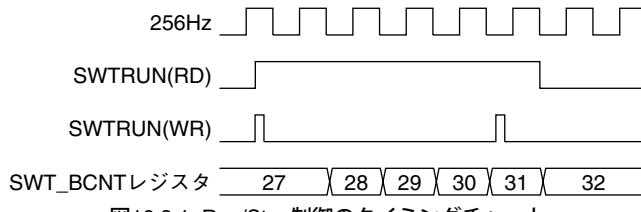

| 16.5 ストップウォッチタイマRUN/STOP制御 .....                                   | 16-5        |

| 16.6 ストップウォッチタイマ割り込み .....                                         | 16-6        |

| 16.7 制御レジスタ詳細 .....                                                | 16-7        |

| 0x5020: Stopwatch Timer Control Register (SWT_CTL).....            | 16-8        |

| 0x5021: Stopwatch Timer BCD Counter Register (SWT_BCNT) .....      | 16-9        |

| 0x5022: Stopwatch Timer Interrupt Mask Register (SWT_IMSK).....    | 16-10       |

| 0x5023: Stopwatch Timer Interrupt Flag Register (SWT_IFLG).....    | 16-11       |

| 16.8 注意事項.....                                                     | 16-12       |

| <b>17 ウオッチドッグタイマ (WDT) .....</b>                                   | <b>17-1</b> |

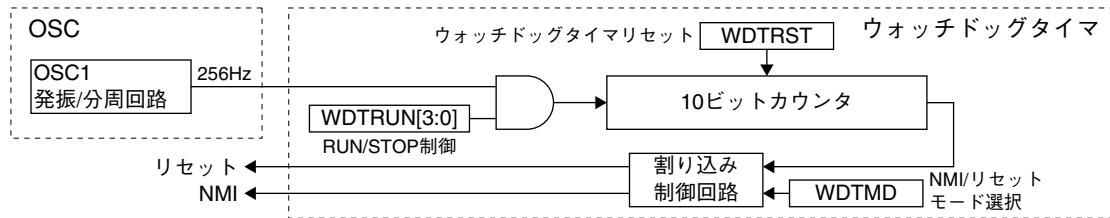

| 17.1 ウオッチドッグタイマの概要 .....                                           | 17-1        |

| 17.2 動作クロック .....                                                  | 17-2        |

| 17.3 ウオッチドッグタイマの制御 .....                                           | 17-3        |

| 17.3.1 NMI/リセットモードの選択 .....                                        | 17-3        |

| 17.3.2 ウオッチドッグタイマのRUN/STOP制御 .....                                 | 17-3        |

| 17.3.3 ウオッチドッグタイマのリセット .....                                       | 17-3        |

| 17.3.4 スタンバイモード時の動作 .....                                          | 17-3        |

| 17.4 制御レジスタ詳細 .....                                                | 17-4        |

| 0x5040: Watchdog Timer Control Register (WDT_CTL).....             | 17-5        |

| 0x5041: Watchdog Timer Status Register (WDT_ST) .....              | 17-6        |

| 17.5 注意事項.....                                                     | 17-7        |

| <b>18 UART.....</b>                                                | <b>18-1</b> |

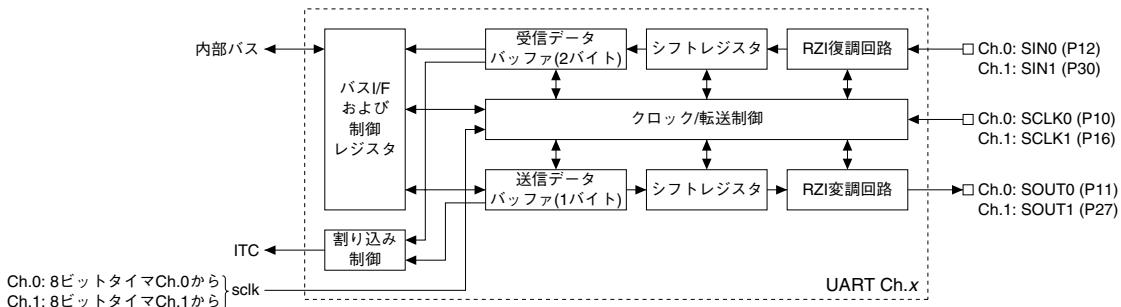

| 18.1 UARTの構成 .....                                                 | 18-1        |

| 18.2 UART端子 .....                                                  | 18-2        |

| 18.3 転送クロック .....                                                  | 18-3        |

| 18.4 転送データの設定 .....                                                | 18-4        |

| 18.5 データ送受信の制御 .....                                               | 18-5        |

| 18.6 受信エラー .....                                                   | 18-8        |

| 18.7 UART割り込み .....                                                | 18-9        |

| 18.8 IrDAインターフェース .....                                            | 18-11       |

| 18.9 制御レジスタ詳細 .....                                                | 18-13       |

| 0x4100/0x4120: UART Ch.x Status Registers (UART_STx) .....         | 18-14       |

| 0x4101/0x4121: UART Ch.x Transmit Data Registers (UART_TDXx) ..... | 18-16       |

| 0x4102/0x4122: UART Ch.x Receive Data Registers (UART_RXDx) .....  | 18-17       |

| 0x4103/0x4123: UART Ch.x Mode Registers (UART_MODx) .....          | 18-18       |

| 0x4104/0x4124: UART Ch.x Control Registers (UART_CTLx) .....       | 18-19       |

| 0x4105/0x4125: UART Ch.x Expansion Registers (UART_EXPx) .....     | 18-20       |

| 18.10 注意事項 .....                                                   | 18-21       |

| <b>19 SPI.....</b>                                                 | <b>19-1</b> |

| 19.1 SPIの構成 .....                                                  | 19-1        |

| 19.2 SPI入出力端子 .....                                                | 19-2        |

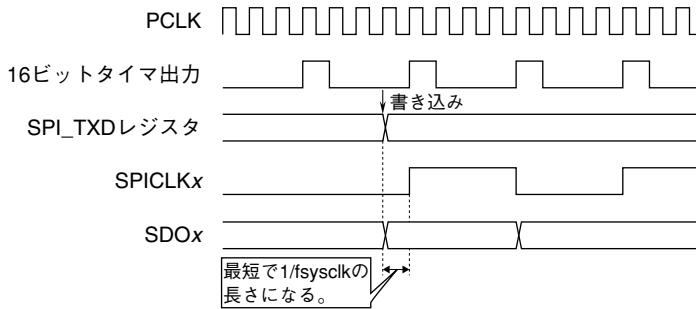

| 19.3 SPIクロック .....                                                 | 19-3        |

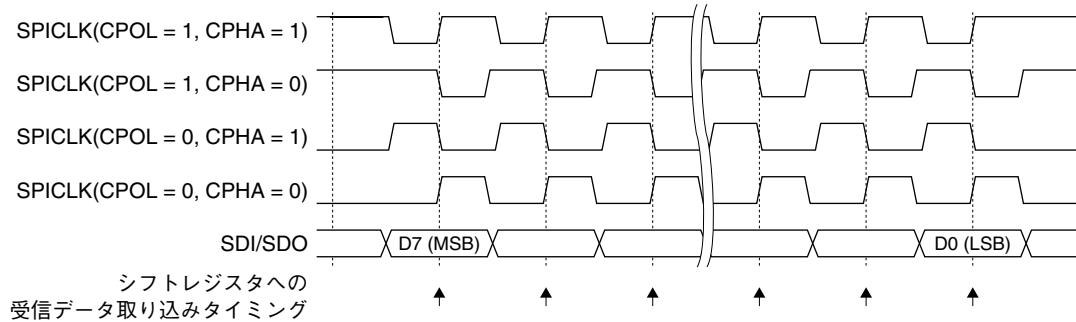

| 19.4 データ転送条件の設定 .....                                              | 19-4        |

|                                                                       |             |

|-----------------------------------------------------------------------|-------------|

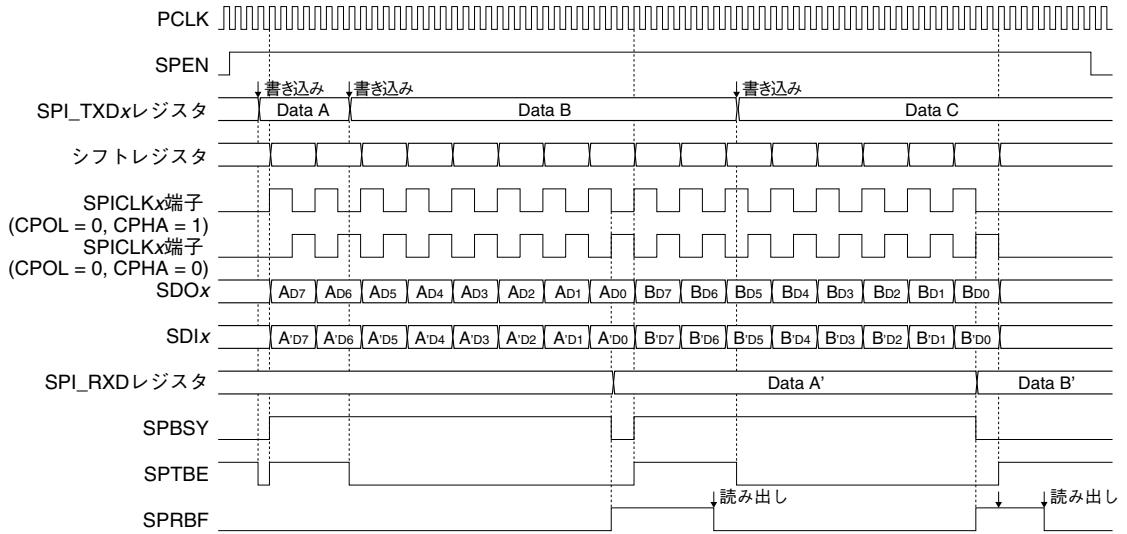

| 19.5 データ送受信の制御                                                        | 19-5        |

| 19.6 SPI割り込み                                                          | 19-8        |

| 19.7 制御レジスタ詳細                                                         | 19-9        |

| 0x4320: SPI Status Register (SPI_ST)                                  | 19-10       |

| 0x4322: SPI Transmit Data Register (SPI_TXD)                          | 19-11       |

| 0x4324: SPI Receive Data Register (SPI_RXD)                           | 19-12       |

| 0x4326: SPI Control Register (SPI_CTL)                                | 19-13       |

| 19.8 注意事項                                                             | 19-15       |

| <b>20 I<sup>2</sup>Cマスタ (I<sup>2</sup>CM)</b>                         | <b>20-1</b> |

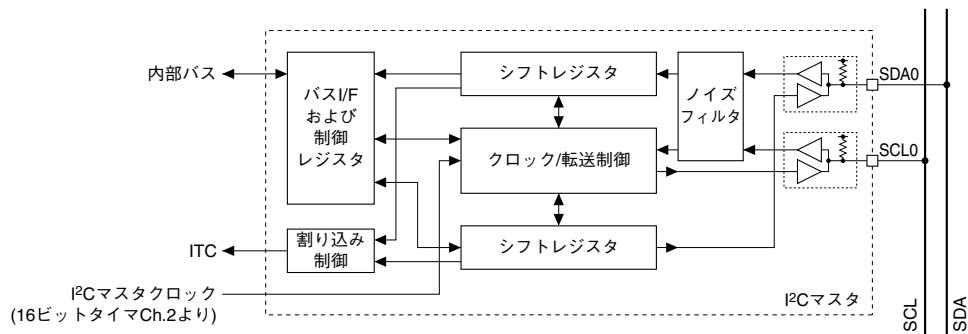

| 20.1 I <sup>2</sup> Cマスタの構成                                           | 20-1        |

| 20.2 I <sup>2</sup> Cマスタ入出力端子                                         | 20-2        |

| 20.3 I <sup>2</sup> Cマスタクロック                                          | 20-3        |

| 20.4 データ転送前の設定項目                                                      | 20-4        |

| 20.5 データ送受信の制御                                                        | 20-5        |

| 20.6 I <sup>2</sup> Cマスタ割り込み                                          | 20-10       |

| 20.7 制御レジスタ詳細                                                         | 20-11       |

| 0x4340: I <sup>2</sup> C Enable Register (I2C_EN)                     | 20-12       |

| 0x4342: I <sup>2</sup> C Control Register (I2C_CTL)                   | 20-13       |

| 0x4344: I <sup>2</sup> C Data Register (I2C_DAT)                      | 20-15       |

| 0x4346: I <sup>2</sup> C Interrupt Control Register (I2C_ICTL)        | 20-17       |

| <b>21 I<sup>2</sup>Cスレーブ (I<sup>2</sup>CS)</b>                        | <b>21-1</b> |

| 21.1 I <sup>2</sup> Cスレーブの構成                                          | 21-1        |

| 21.2 I <sup>2</sup> Cスレーブ入出力端子                                        | 21-2        |

| 21.3 I <sup>2</sup> Cスレーブクロック                                         | 21-3        |

| 21.4 I <sup>2</sup> Cスレーブの初期設定                                        | 21-4        |

| 21.4.1 リセット                                                           | 21-4        |

| 21.4.2 スレーブアドレスの設定                                                    | 21-4        |

| 21.4.3 オプション機能                                                        | 21-4        |

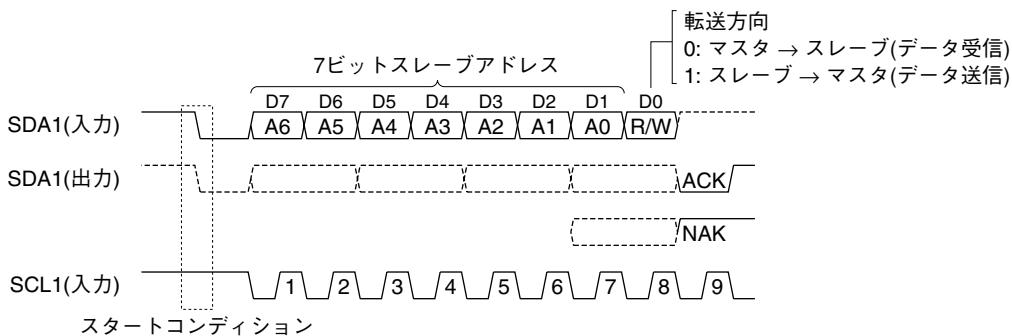

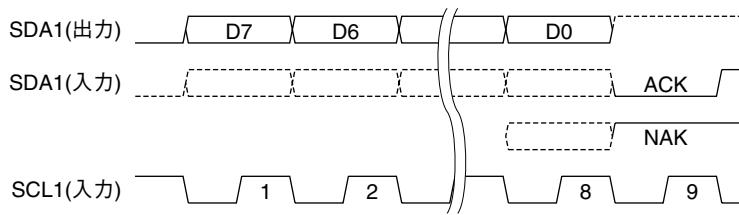

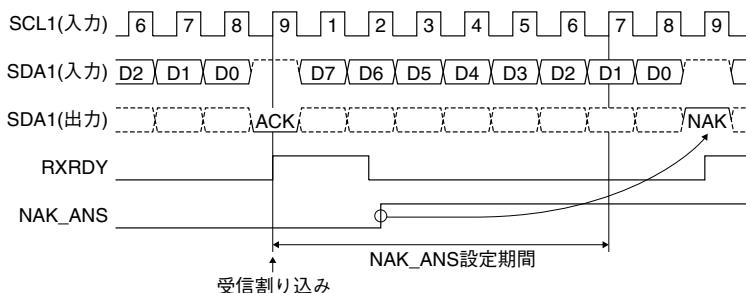

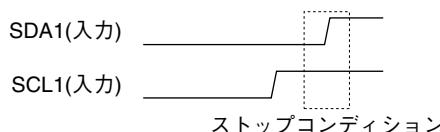

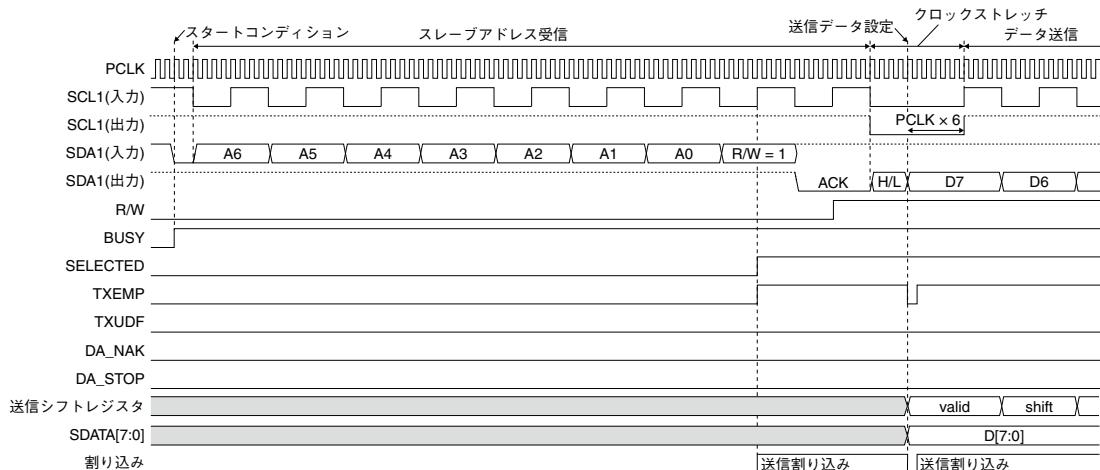

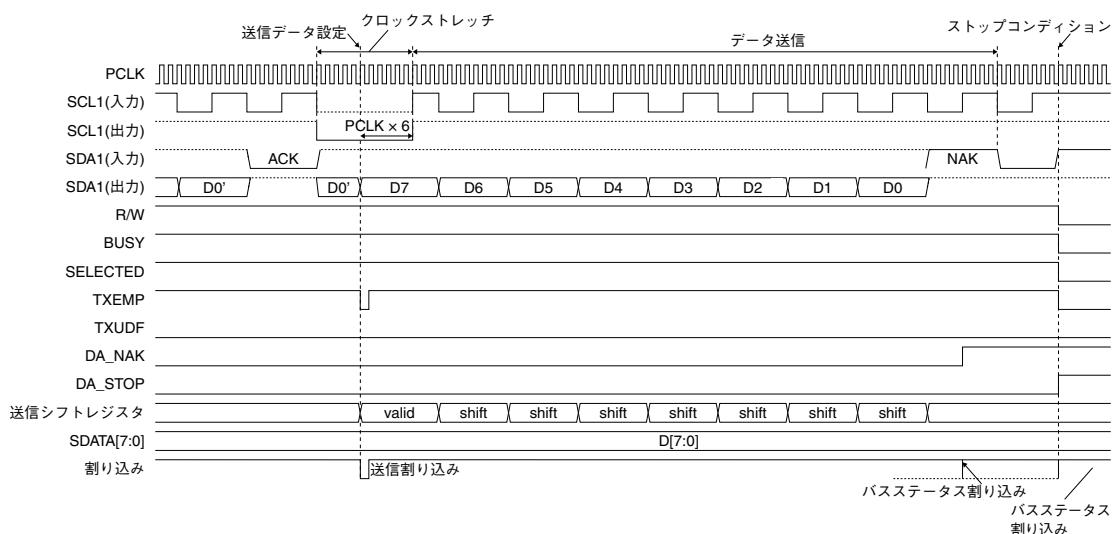

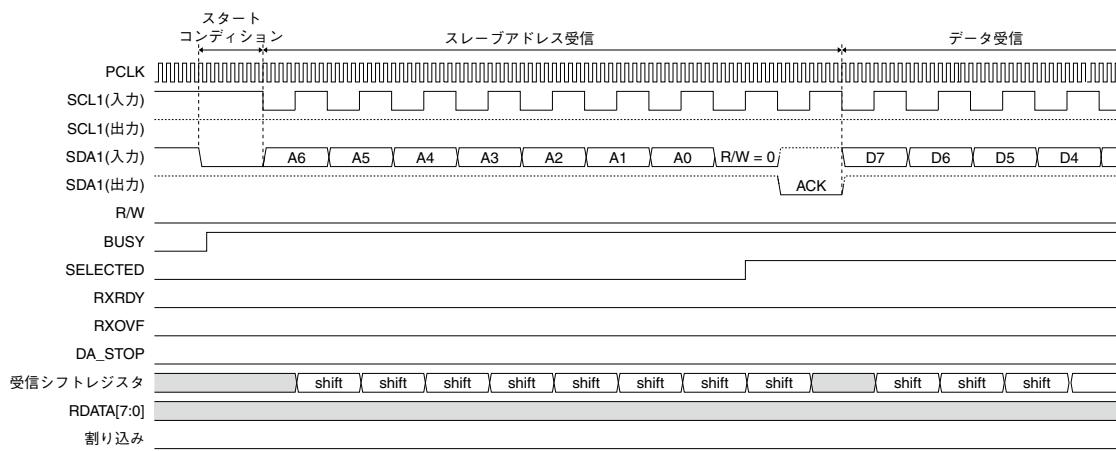

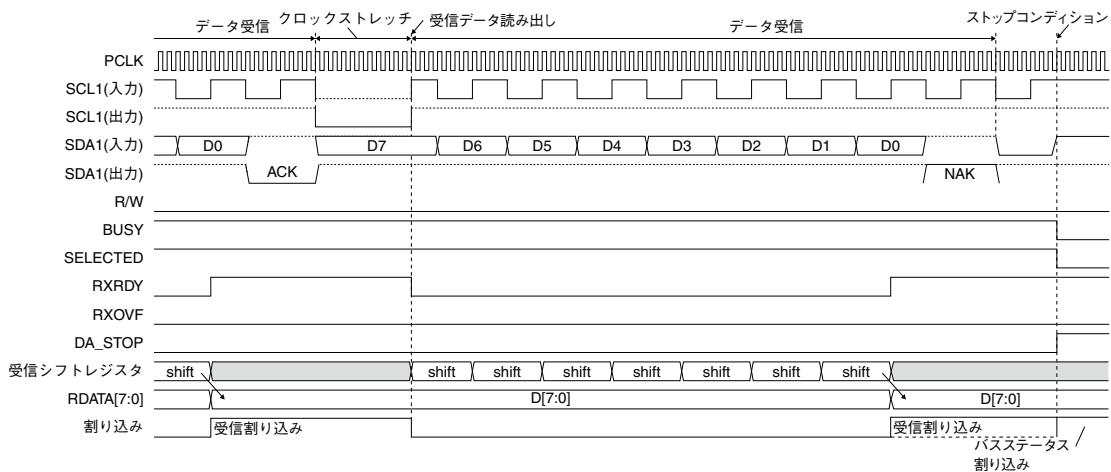

| 21.5 データ送受信の制御                                                        | 21-6        |

| 21.6 I <sup>2</sup> Cスレーブ割り込み                                         | 21-11       |

| 21.7 制御レジスタ詳細                                                         | 21-13       |

| 0x4360: I <sup>2</sup> C Slave Transmit Data Register (I2CS_TRNS)     | 21-14       |

| 0x4362: I <sup>2</sup> C Slave Receive Data Register (I2CS_RECV)      | 21-15       |

| 0x4364: I <sup>2</sup> C Slave Address Setup Register (I2CS_SADRS)    | 21-16       |

| 0x4366: I <sup>2</sup> C Slave Control Register (I2CS_CTL)            | 21-17       |

| 0x4368: I <sup>2</sup> C Slave Status Register (I2CS_STAT)            | 21-20       |

| 0x436a: I <sup>2</sup> C Slave Access Status Register (I2CS_ASTAT)    | 21-23       |

| 0x436c: I <sup>2</sup> C Slave Interrupt Control Register (I2CS_ICTL) | 21-24       |

| 21.8 注意事項                                                             | 21-25       |

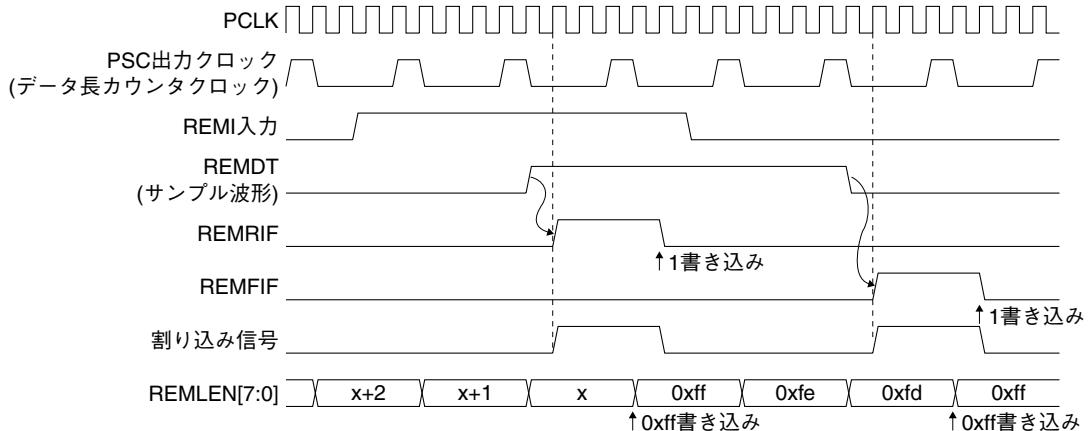

| <b>22 リモートコントローラ (REMC)</b>                                           | <b>22-1</b> |

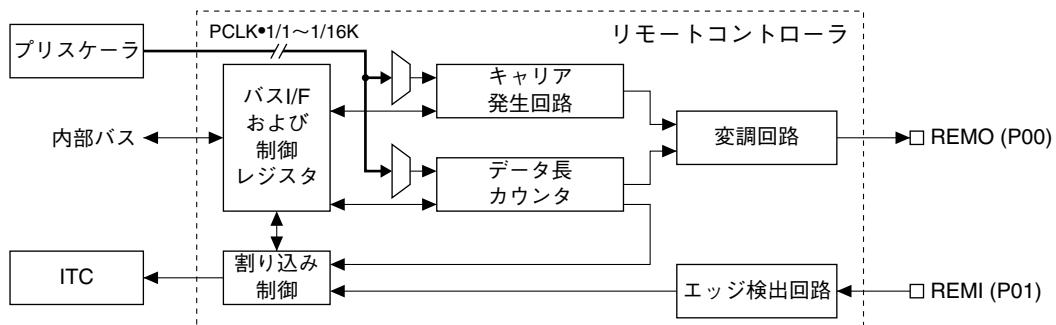

| 22.1 REMCの構成                                                          | 22-1        |

| 22.2 REMC入出力端子                                                        | 22-2        |

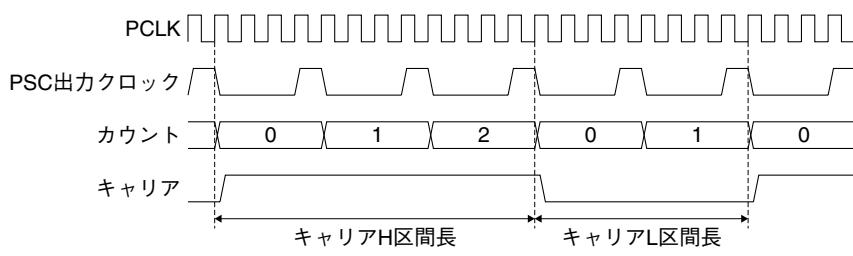

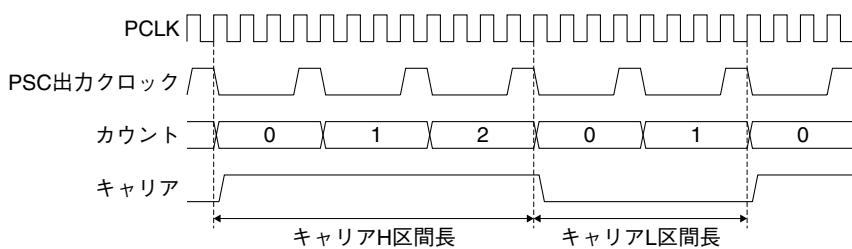

| 22.3 キャリアの生成                                                          | 22-3        |

| 22.4 データ長カウンタのクロック設定                                                  | 22-4        |

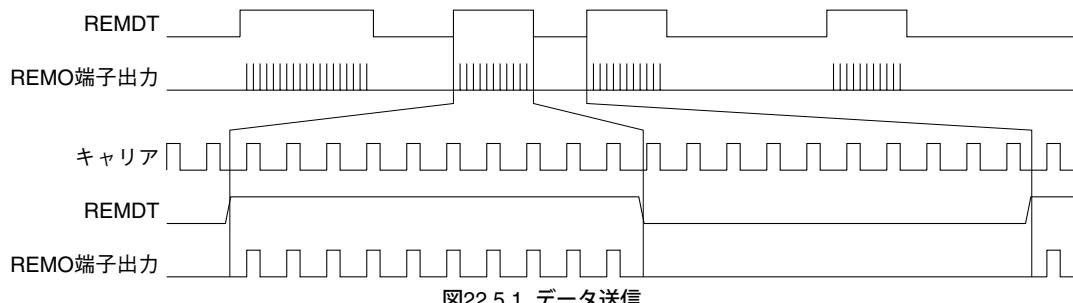

| 22.5 データ送受信の制御                                                        | 22-5        |

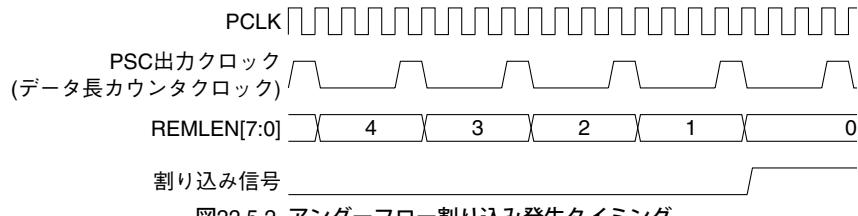

| 22.6 REMC割り込み                                                         | 22-8        |

| 22.7 制御レジスタ詳細                                                         | 22-10       |

| 0x5340: REMC Configuration Register (REMC_CFG)                        | 22-11       |

| 0x5342: REMC Carrier Length Setup Register (REMC_CAR)                 | 22-13       |

| 0x5344: REMC Length Counter Register (REMC_LCNT)                      | 22-14       |

| 0x5346: REMC Interrupt Control Register (REMC_INT)                    | 22-15       |

|                                                                 |             |

|-----------------------------------------------------------------|-------------|

| 22.8 注意事項.....                                                  | 22-17       |

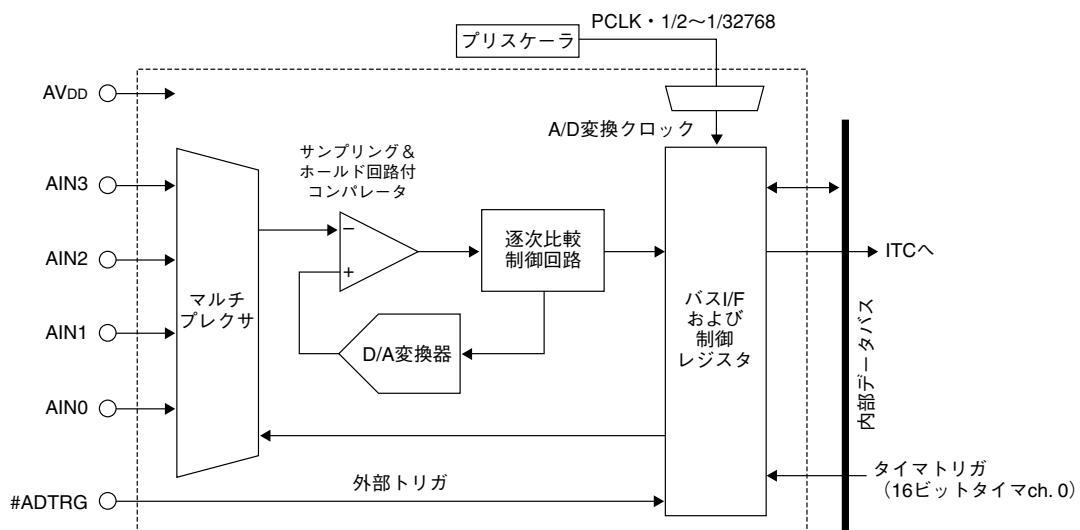

| <b>23 A/D変換器 (ADC10SA) .....</b>                                | <b>23-1</b> |

| 23.1 A/D変換器の概要.....                                             | 23-1        |

| 23.2 ADC端子 .....                                                | 23-2        |

| 23.3 A/D変換器の設定.....                                             | 23-3        |

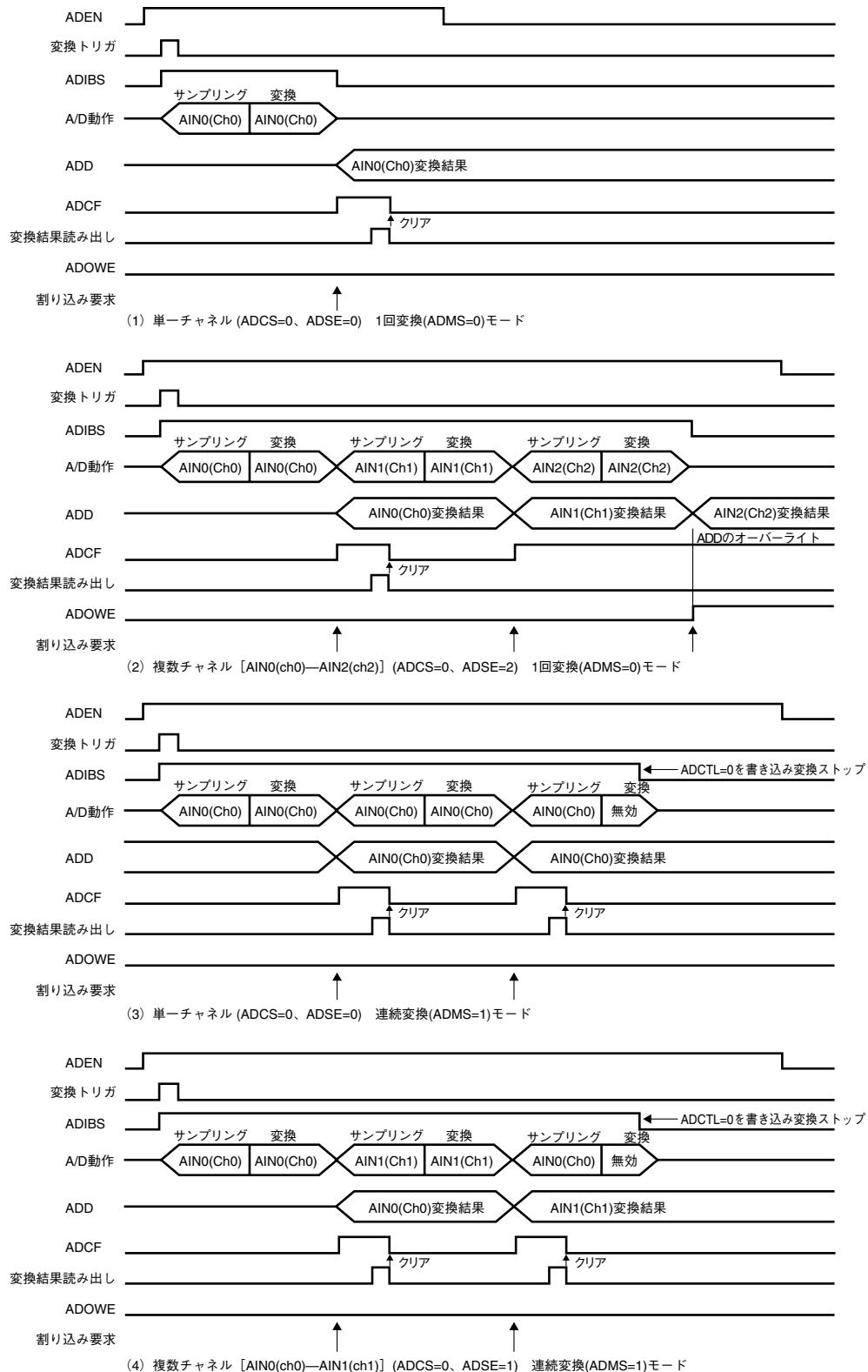

| 23.4 A/D変換の制御と動作 .....                                          | 23-6        |

| 23.5 A/D変換器割り込み .....                                           | 23-9        |

| 23.6 制御レジスタ詳細 .....                                             | 23-11       |

| 0x5380: ADC10 Conversion Result Register (ADC10_ADD) .....      | 23-12       |

| 0x5382: ADC10 Trigger/Channel Select Register (ADC10_TRG) ..... | 23-13       |

| 0x5384: ADC10 Control/Status Register (ADC10_CTL) .....         | 23-15       |

| 0x5386: ADC10 Divided Frequency Register (ADC10_DIV) .....      | 23-17       |

| 23.7 注意事項.....                                                  | 23-18       |

| <b>24 オンチップデバッガ (DBG) .....</b>                                 | <b>24-1</b> |

| 24.1 リソース要件とデバッグツール.....                                        | 24-1        |

| 24.2 デバッグブレーク時の動作状態.....                                        | 24-2        |

| 24.3 追加デバッガ機能 .....                                             | 24-3        |

| 24.4 制御レジスタ詳細 .....                                             | 24-4        |

| 0x5322: OSC1 Peripheral Control Register (MISC_OSC1).....       | 24-5        |

| 0x5326: IRAM Size Select Register (MISC_IRAMSZ).....            | 24-6        |

| 0xfffff90: Debug RAM Base Register (DBRAM) .....                | 24-7        |

| 0xfffffa0: Debug Control Register (DCR) .....                   | 24-8        |

| 0xfffffb8: Instruction Break Address Register 2 (IBAR2) .....   | 24-10       |

| 0xfffffbc: Instruction Break Address Register 3 (IBAR3).....    | 24-11       |

| 0xfffffd0: Instruction Break Address Register 4 (IBAR4) .....   | 24-12       |

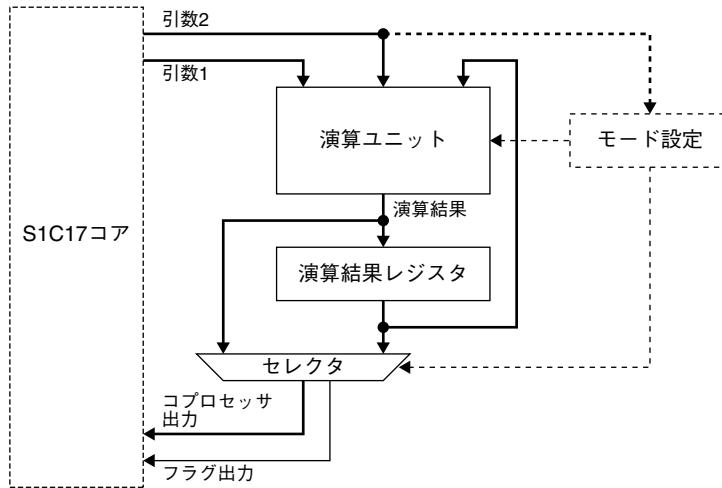

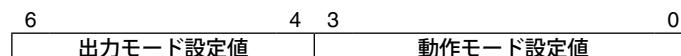

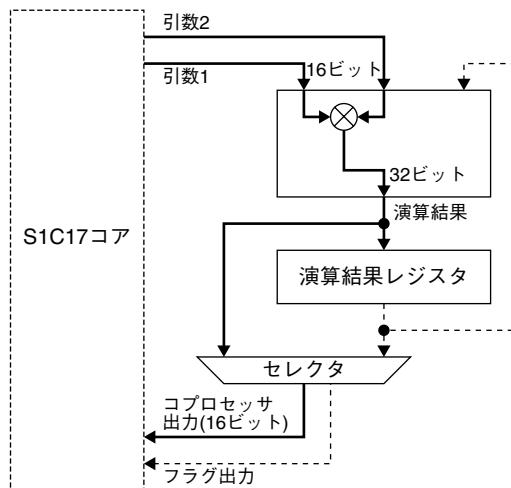

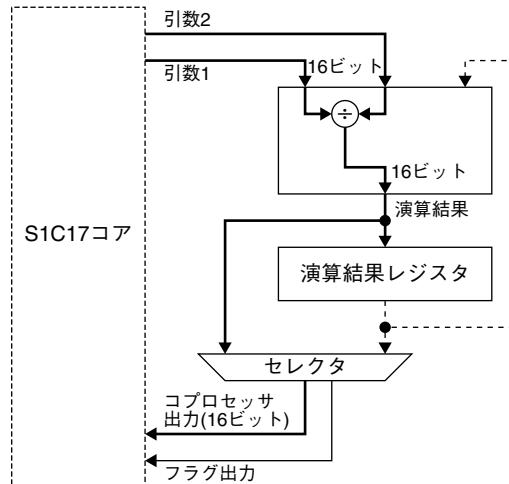

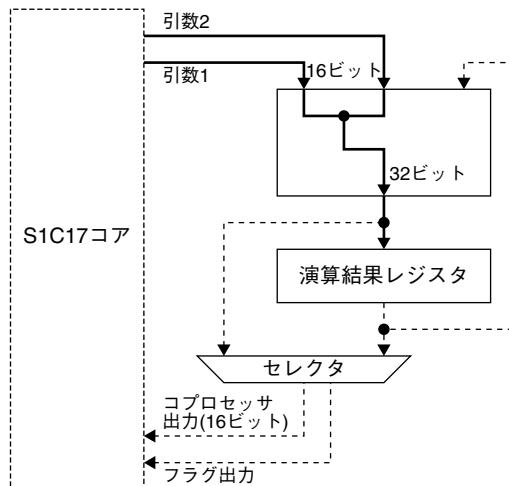

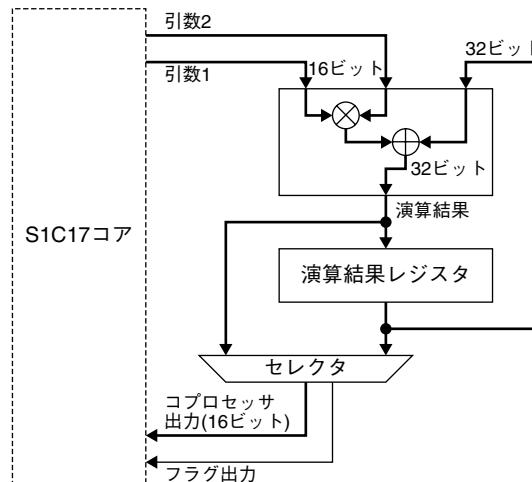

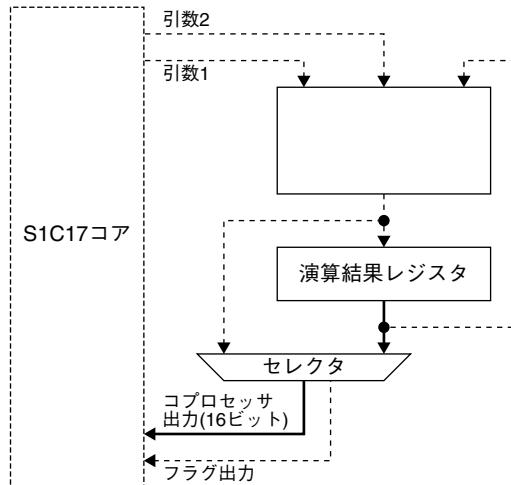

| <b>25 乗除算器 .....</b>                                            | <b>25-1</b> |

| 25.1 概要 .....                                                   | 25-1        |

| 25.2 動作モードと出力モード .....                                          | 25-2        |

| 25.3 乗算 .....                                                   | 25-3        |

| 25.4 除算 .....                                                   | 25-4        |

| 25.5 積和演算 .....                                                 | 25-5        |

| 25.6 演算結果の読み出し .....                                            | 25-7        |

| <b>26 電気的特性 .....</b>                                           | <b>26-1</b> |

| 26.1 絶対最大定格.....                                                | 26-1        |

| 26.2 推奨動作電圧.....                                                | 26-1        |

| 26.3 消費電流 .....                                                 | 26-2        |

| 26.4 入出力端子特性 .....                                              | 26-3        |

| 26.5 A/D変換器特性 .....                                             | 26-4        |

| 26.6 SPI特性 .....                                                | 26-5        |

| 26.7 I <sup>2</sup> C特性 .....                                   | 26-5        |

| 26.8 発振特性 .....                                                 | 26-6        |

| 26.9 外部クロック入力特性 .....                                           | 26-6        |

| <b>27 基本外部結線図 .....</b>                                         | <b>27-1</b> |

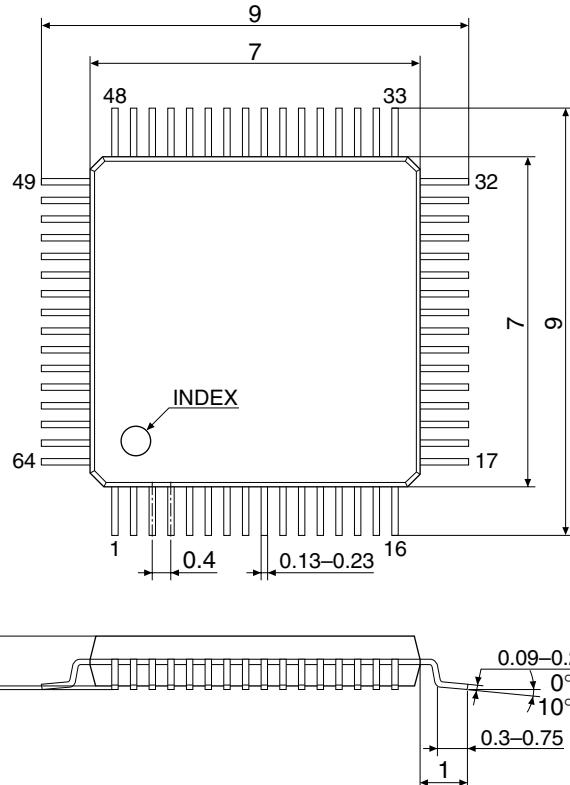

| <b>28 パッケージ .....</b>                                           | <b>28-1</b> |

| 28.1 TQFP12-64pin/パッケージ .....                                   | 28-1        |

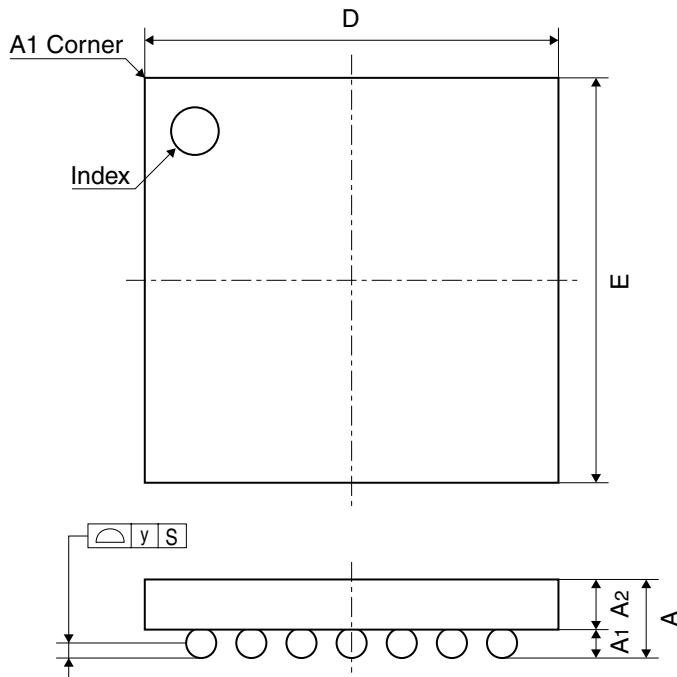

| 28.2 W CSP-48パッケージ .....                                        | 28-2        |

| 28.3 パッケージの熱抵抗 .....                                            | 28-3        |

| 28.4 パッド配置 .....                                                | 28-4        |

|                                                      |              |

|------------------------------------------------------|--------------|

| 28.4.1 パッド配置図 .....                                  | 28-4         |

| <b>Appendix A I/Oレジスター一覧 .....</b>                   | <b>AP-1</b>  |

| 0x4020 Prescaler.....                                | AP-5         |

| 0x4100–0x4125 UART (with IrDA).....                  | AP-6         |

| 0x4200–0x4208 8-bit Timer (with Fine Mode) Ch.0..... | AP-8         |

| 0x4220–0x4268 16-bit Timer .....                     | AP-9         |

| 0x4280–0x4288 8-bit Timer (with Fine Mode) Ch.1..... | AP-11        |

| 0x4306–0x4318 Interrupt Controller.....              | AP-12        |

| 0x4320–0x4326 SPI .....                              | AP-13        |

| 0x4340–0x4346 I <sup>2</sup> C Master .....          | AP-14        |

| 0x4360–0x436c I <sup>2</sup> C Slave .....           | AP-15        |

| 0x5000–0x5003 Clock Timer .....                      | AP-16        |

| 0x5020–0x5023 Stopwatch Timer .....                  | AP-17        |

| 0x5040–0x5041 Watchdog Timer.....                    | AP-18        |

| 0x5060–0x5065 Oscillator .....                       | AP-19        |

| 0x5080–0x5081 Clock Generator.....                   | AP-20        |

| 0x50c0–0x50c5 8-bit OSC1 Timer .....                 | AP-21        |

| 0x5200–0x52a8 P Port & Port MUX .....                | AP-22        |

| 0x5300–0x530c PWM & Capture Timer .....              | AP-26        |

| 0x5320–0x532c MISC Registers.....                    | AP-27        |

| 0x5340–0x5346 Remote Controller.....                 | AP-28        |

| 0x5380–0x5386 ADC10SA.....                           | AP-29        |

| 0xfffff84–0xfffffd0 S1C17 Core I/O .....             | AP-30        |

| <b>Appendix B パワーセーブ .....</b>                       | <b>AP-31</b> |

| B.1 クロック制御によるパワーセーブ .....                            | AP-31        |

| <b>Appendix C 実装上の注意事項 .....</b>                     | <b>AP-34</b> |

| <b>Appendix D マスクROMコードの開発について .....</b>             | <b>AP-38</b> |

## 改訂履歴表

# 1 概要

S1C17003は、高速かつ低電力動作、省サイズ、広アドレス空間、オンチップICEを実現した16ビットMCUです。A/D変換器を内蔵しており、各種アナログI/Fのセンサを接続することができます。電池駆動で小規模、高精細な表示を必要とするセンサ付きヘルスケア製品、スポーツウォッチ、メータモジュールなどの機器への応用に適しています。

## 1.1 特長

以下にS1C17003の主な機能と特長を示します。

- CPU

- EPSONオリジナル16ビットRISC CPUコア S1C17

16ビット×16ビット + 32ビット積和演算器、

16ビット÷16ビット除算器

- OSC3

- 20MHz (max.) 内蔵発振回路(水晶/セラミック)または外部クロック入力

- OSC1

- 32.768kHz(typ.) 内蔵発振回路(水晶)または外部クロック入力

- 内蔵Mask ROM

- 64Kバイト

- 内蔵RAM

- 4Kバイト

- A/D変換器

- 10ビット分解能 4ch

- 入出力ポート

- 最大30ビットの汎用入出力ポート、4ビットの入力専用ポート

- シリアルインタフェース

- SPI(マスター/スレーブ) 1ch.

- I<sup>2</sup>C(マスター) 1ch.

- I<sup>2</sup>C(スレーブ) 1ch.

- UART(460800bps, IrDA1.0対応) 2ch.

- リモートコントローラ(REMC) 1ch.

- タイマ

- 8ビットタイマ(T8F) 2ch.

- 16ビットタイマ(T16) 3ch.

- PWMタイマ(T16E) 1ch.

- 計時タイマ(CT) 1ch.

- ストップウォッチタイマ(SWT) 1ch.

- ウォッチドッグタイマ(WDT) 1ch.

- 8ビットOSC1 PWMタイマ(T8OSC1) 1ch.

- 割り込み

- NMI、Pポート入力割り込み 3系統

- シリアルインタフェース割り込み 5系統

- タイマ割り込み 9系統

- 電源電圧

- HV<sub>DD</sub>(I/O) : 1.65~3.6V

- LV<sub>DD</sub>(コア) : 1.65~1.95V

- AV<sub>DD</sub>(I/O) : 2.7V~3.6V

- 動作温度

- -40~85°C

- 消費電流

- SLEEP時 1μA (typ.)Off/1.8V

- HALT時 3.3μA (typ.)32kHz/1.8V

- 動作時 4.0mA (typ.)20MHz/1.8V

- 出荷形態

- TQFP12-64pin(7mm×7mm×1.2mm、端子ピッチ：0.4mm)

- WCSP-48pin(3.124mm×3.124mm×0.78mm、ボールピッチ：0.4mm)

- チップ(3.124mm×3.124mm×0.40mm)

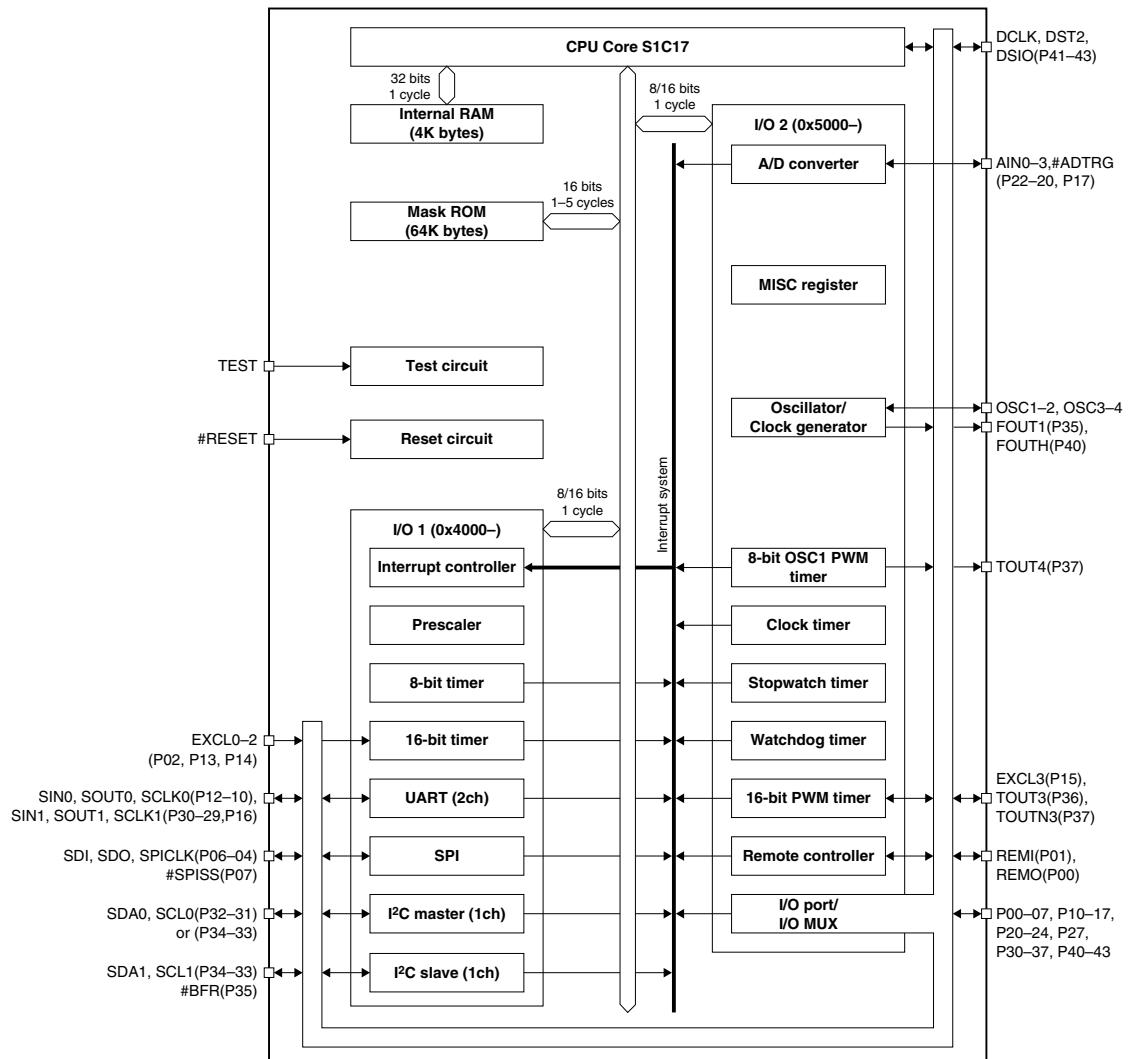

## 1.2 ブロック図

図1.2.1 ブロック図

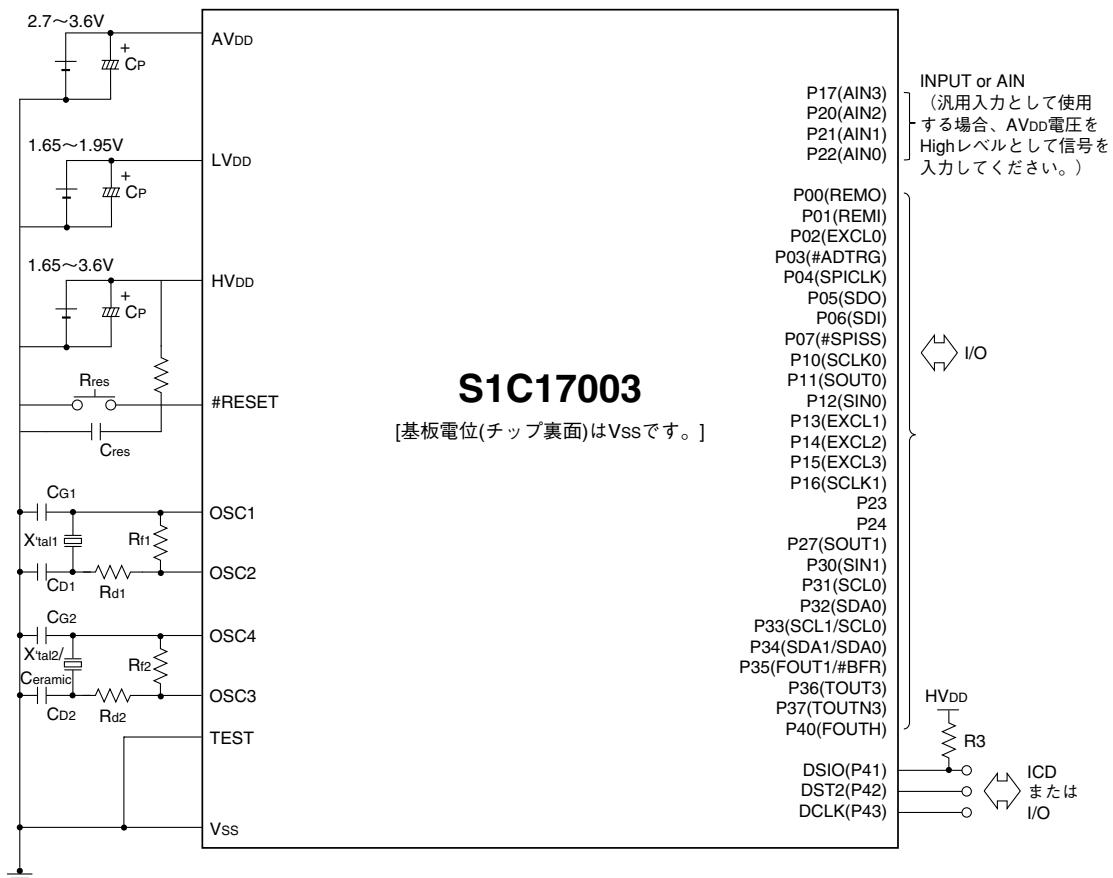

## 1.3 端子

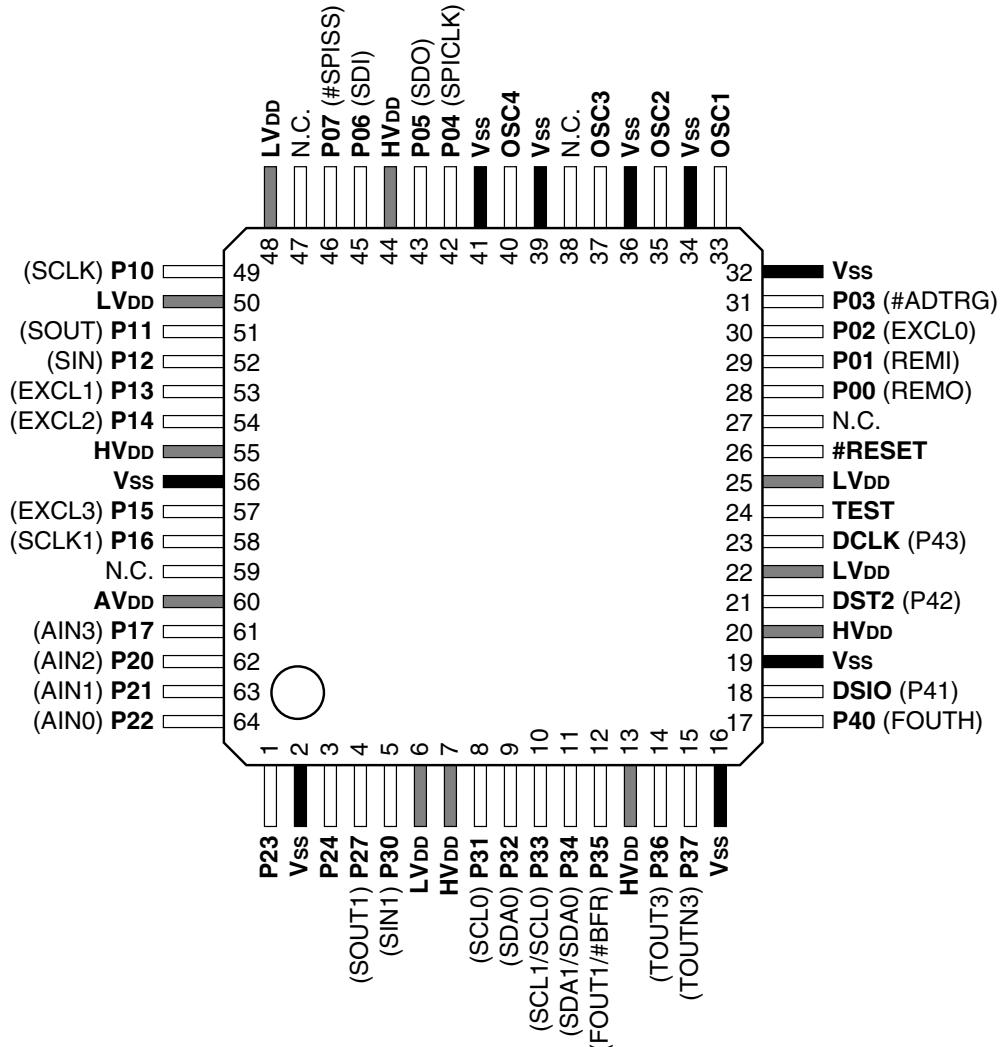

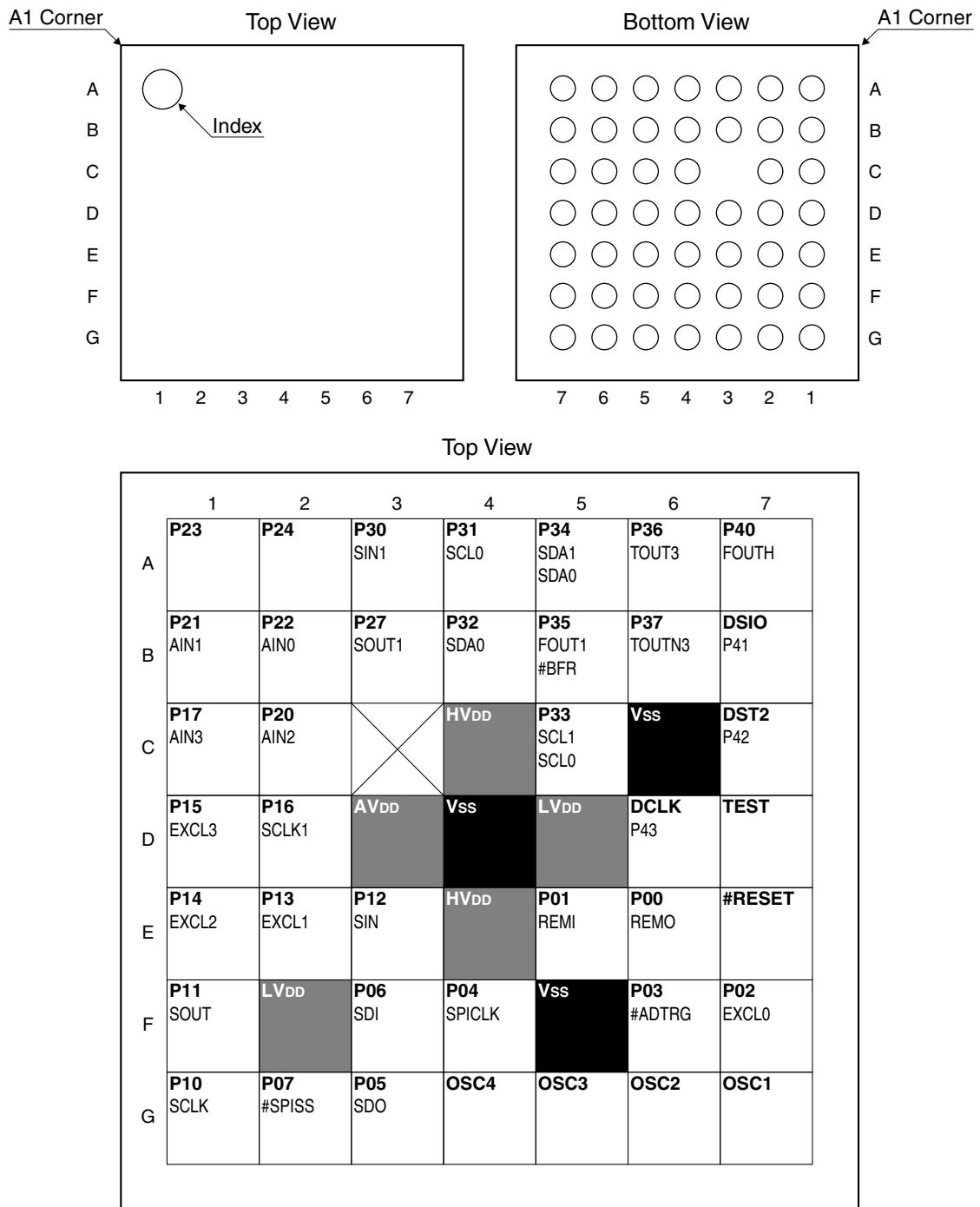

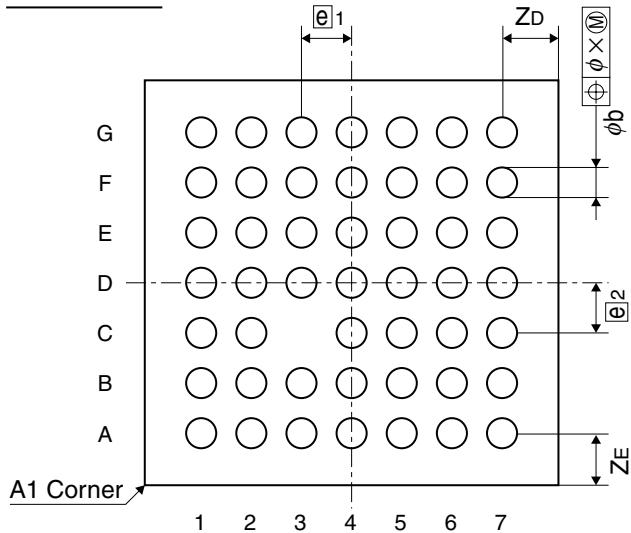

### 1.3.1 端子配置

S1C17003は、TQFP12-64pinまたはWCSP-48パッケージを採用しています。

#### TQFP12-64pin/パッケージ

図1.3.1.1 端子配置図(TQFP12-64pin)

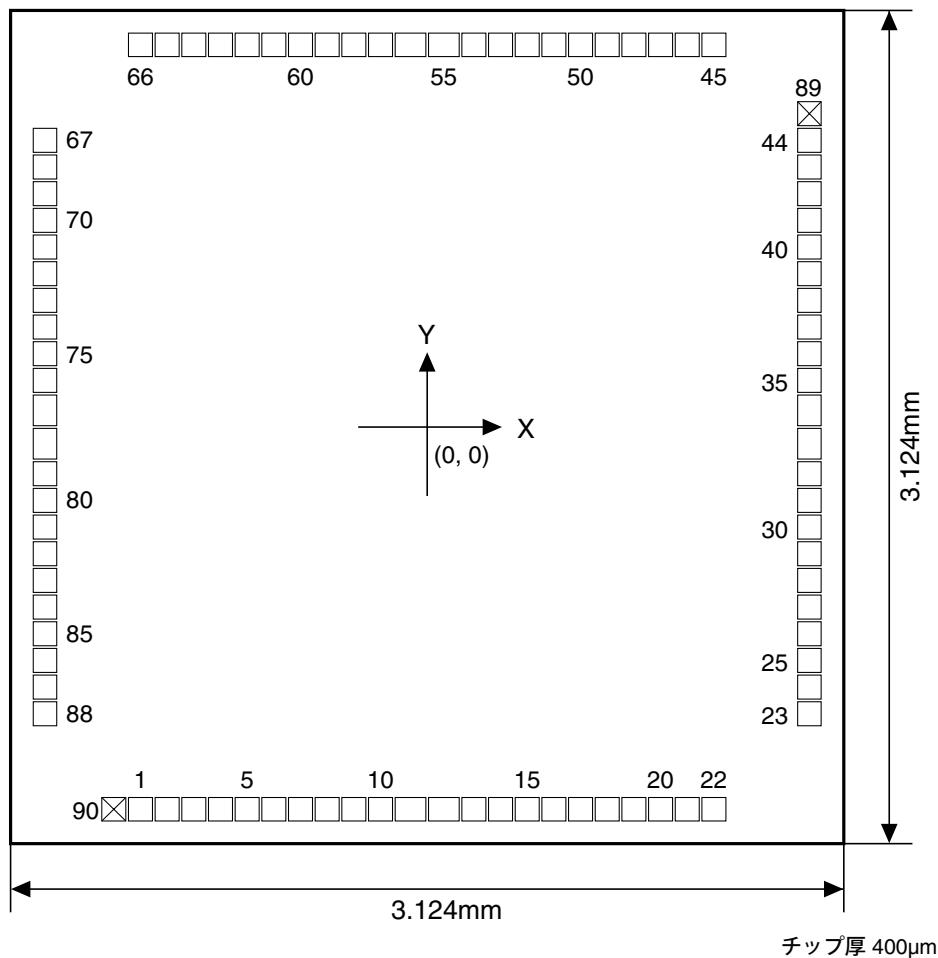

## WCSP-48パッケージ

図1.3.1.2 端子配置図(WCSP-48)

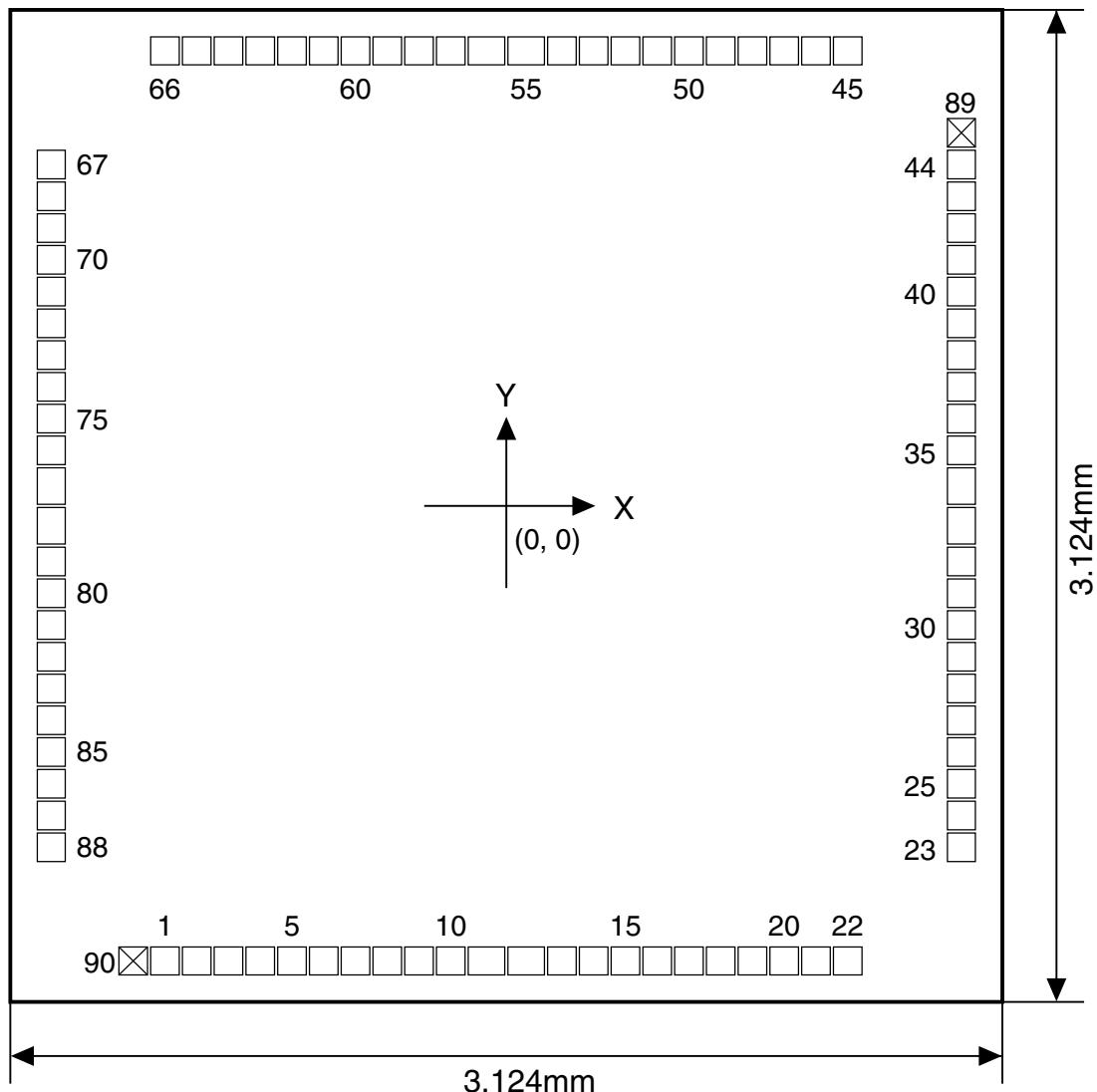

## CHIP-88pad

## パッド開口部

Pad No. 1~10, 13~22, 45~54, 57~66 :  $90\text{ }\mu\text{m} \times 88\text{ }\mu\text{m}$

Pad No. 11, 12, 55, 56 :  $115\text{ }\mu\text{m} \times 88\text{ }\mu\text{m}$

Pad No. 23~32, 35~44, 67~76, 79~88 :  $88\text{ }\mu\text{m} \times 90\text{ }\mu\text{m}$

Pad No. 33, 34, 77, 78 :  $88\text{ }\mu\text{m} \times 115\text{ }\mu\text{m}$

## チップ厚

$400\text{ }\mu\text{m}$

## パッド座標

| PAD No. | X (mm) | Y (mm) | 割り当て             | PAD No. | X (mm) | Y (mm) | 割り当て             |

|---------|--------|--------|------------------|---------|--------|--------|------------------|

| 1       | -1.075 | -1.433 | P23              | 45      | 1.433  | 1.075  | NC               |

| 2       | -0.975 | -1.433 | V <sub>ss</sub>  | 46      | 1.075  | 1.433  | OSC1             |

| 3       | -0.875 | -1.433 | V <sub>ss</sub>  | 47      | 0.975  | 1.433  | V <sub>ss</sub>  |

| 4       | -0.775 | -1.433 | P24              | 48      | 0.875  | 1.433  | V <sub>ss</sub>  |

| 5       | -0.675 | -1.433 | NC               | 49      | 0.775  | 1.433  | OSC2             |

| 6       | -0.575 | -1.433 | P27              | 50      | 0.675  | 1.433  | NC               |

| 7       | -0.475 | -1.433 | P30              | 51      | 0.475  | 1.433  | V <sub>ss</sub>  |

| 8       | -0.375 | -1.433 | LV <sub>DD</sub> | 52      | 0.375  | 1.433  | OSC3             |

| 9       | -0.275 | -1.433 | LV <sub>DD</sub> | 53      | 0.275  | 1.433  | NC               |

| 10      | -0.175 | -1.433 | HV <sub>DD</sub> | 54      | 0.175  | 1.433  | V <sub>ss</sub>  |

| 11      | -0.063 | -1.433 | HV <sub>DD</sub> | 55      | 0.063  | 1.433  | OSC4             |

| 12      | 0.063  | -1.433 | P31              | 56      | -0.063 | 1.433  | V <sub>ss</sub>  |

| 13      | 0.175  | -1.433 | P32              | 57      | -0.175 | 1.433  | NC               |

| 14      | 0.275  | -1.433 | P33              | 58      | -0.275 | 1.433  | P04              |

| 15      | 0.375  | -1.433 | P34              | 59      | -0.375 | 1.433  | P05              |

| 16      | 0.475  | -1.433 | P35              | 60      | -0.475 | 1.433  | HV <sub>DD</sub> |

| 17      | 0.575  | -1.433 | HV <sub>DD</sub> | 61      | -0.575 | 1.433  | P06              |

| 18      | 0.675  | -1.433 | P36              | 62      | -0.675 | 1.433  | P07              |

| 19      | 0.775  | -1.433 | P37              | 63      | -0.775 | 1.433  | NC               |

| 20      | 0.875  | -1.433 | V <sub>ss</sub>  | 64      | -0.875 | 1.433  | LV <sub>DD</sub> |

| 21      | 0.975  | -1.433 | V <sub>ss</sub>  | 65      | -0.975 | 1.433  | NC               |

| 22      | 1.075  | -1.433 | NC               | 66      | -1.075 | 1.433  | NC               |

| 23      | 1.433  | -1.075 | NC               | 67      | -1.433 | 1.075  | P10              |

| 24      | 1.433  | -0.975 | P40              | 68      | -1.433 | 0.975  | NC               |

| 25      | 1.433  | -0.875 | NC               | 69      | -1.433 | 0.875  | LV <sub>DD</sub> |

| 26      | 1.433  | -0.775 | DSIO             | 70      | -1.433 | 0.775  | LV <sub>DD</sub> |

| 27      | 1.433  | -0.675 | V <sub>ss</sub>  | 71      | -1.433 | 0.675  | P11              |

| 28      | 1.433  | -0.575 | V <sub>ss</sub>  | 72      | -1.433 | 0.575  | P12              |

| 29      | 1.433  | -0.475 | HV <sub>DD</sub> | 73      | -1.433 | 0.475  | P13              |

| 30      | 1.433  | -0.375 | DST2             | 74      | -1.433 | 0.375  | P14              |

| 31      | 1.433  | -0.275 | LV <sub>DD</sub> | 75      | -1.433 | 0.275  | HV <sub>DD</sub> |

| 32      | 1.433  | -0.175 | DCLK             | 76      | -1.433 | 0.175  | V <sub>ss</sub>  |

| 33      | 1.433  | -0.063 | TEST             | 77      | -1.433 | 0.063  | P15              |

| 34      | 1.433  | 0.063  | LV <sub>DD</sub> | 78      | -1.433 | -0.063 | V <sub>ss</sub>  |

| 35      | 1.433  | 0.175  | LV <sub>DD</sub> | 79      | -1.433 | -0.175 | P16              |

| 36      | 1.433  | 0.275  | #RESET           | 80      | -1.433 | -0.275 | AV <sub>DD</sub> |

| 37      | 1.433  | 0.375  | NC               | 81      | -1.433 | -0.375 | NC               |

| 38      | 1.433  | 0.475  | P00              | 82      | -1.433 | -0.475 | AV <sub>DD</sub> |

| 39      | 1.433  | 0.575  | P01              | 83      | -1.433 | -0.575 | P17/AIN3         |

| 40      | 1.433  | 0.675  | P02              | 84      | -1.433 | -0.675 | P20/AIN2         |

| 41      | 1.433  | 0.775  | NC               | 85      | -1.433 | -0.775 | AV <sub>DD</sub> |

| 42      | 1.433  | 0.875  | P03              | 86      | -1.433 | -0.875 | P21/AIN1         |

| 43      | 1.433  | 0.975  | V <sub>ss</sub>  | 87      | -1.433 | -0.975 | P22/AIN0         |

| 44      | 1.433  | 1.075  | V <sub>ss</sub>  | 88      | -1.433 | -1.075 | NC               |

## 1.3.2 端子説明

| PAD / 端子 / ボール No. |      |      | 名称                    | I/O | 初期状態       | 機能 (デフォルト機能 / 設定による兼用機能)                  |

|--------------------|------|------|-----------------------|-----|------------|-------------------------------------------|

| CHIP               | TQFP | WCSP |                       |     |            |                                           |

| 1                  | 1    | A1   | <b>P23</b>            | I/O | I(Pull-UP) | 入出力兼用ポート                                  |

| *2                 | 2    | *2   | <b>VSS</b>            | -   | -          | 電源(-)                                     |

| 4                  | 3    | A2   | <b>P24</b>            | I/O | I(Pull-UP) | 入出力兼用ポート                                  |

| 6                  | 4    | B3   | <b>P27/SOUT1</b>      | I/O | I(Pull-UP) | 入出力兼用ポート *1/ UART Ch1 データ出力               |

| 7                  | 5    | A3   | <b>P30/SIN1</b>       | I/O | I(Pull-UP) | 入出力兼用ポート *1/ UART Ch1 データ入力               |

| *3                 | 6    | *3   | <b>LVDD</b>           | -   | -          | コア電源(+)                                   |

| *4                 | 7    | *4   | <b>HVDD</b>           | -   | -          | I/O電源(+)                                  |

| 12                 | 8    | A4   | <b>P31/SCL0</b>       | I/O | I(Pull-UP) | 入出力兼用ポート *1/I2Cマスタクロック出力                  |

| 13                 | 9    | B4   | <b>P32/SDA0</b>       | I/O | I(Pull-UP) | 入出力兼用ポート *1/I2Cマスタデータ入出力                  |

| 14                 | 10   | C5   | <b>P33/SCL1/SCL0</b>  | I/O | I(Pull-UP) | 入出力兼用ポート<br>*1/I2Cスレーブクロック入力/I2Cマスタクロック出力 |

| 15                 | 11   | A5   | <b>P34/SDA1/SDA0</b>  | I/O | I(Pull-UP) | 入出力兼用ポート<br>*1/I2Cスレーブデータ入出力/I2Cマスタデータ入出力 |

| 16                 | 12   | B5   | <b>P35/FOUT1/#BFR</b> | I/O | I(Pull-UP) | 入出力兼用ポート<br>*1/OSC1外部クロック出力/I2Cスレーブバス開放   |

| *4                 | 13   | *4   | <b>HVDD</b>           | -   | -          | I/O電源(+)                                  |

| 18                 | 14   | A6   | <b>P36/TOUT3</b>      | I/O | I(Pull-UP) | 入出力兼用ポート *1/T16E Ch0 PWM信号出力(非反転)         |

| 19                 | 15   | B6   | <b>P37/TOUTN3</b>     | I/O | I(Pull-UP) | 入出力兼用ポート *1/T16E Ch0 PWM信号出力(反転)          |

| *2                 | 16   | *2   | <b>VSS</b>            | -   | -          | 電源(-)                                     |

| 24                 | 17   | A7   | <b>P40/FOUTH</b>      | I/O | I(Pull-UP) | 入出力兼用ポート *1/HSCLKクロック出力(分周あり)             |

| 26                 | 18   | B7   | <b>DSIO/P41</b>       | I/O | I(Pull-UP) | オンチップデバッガデータ入出力 *1/入出力兼用ポート               |

| *2                 | 19   | *2   | <b>VSS</b>            | -   | -          | 電源(-)                                     |

| *4                 | 20   | *4   | <b>HVDD</b>           | -   | -          | I/O電源(+)                                  |

| 30                 | 21   | C7   | <b>DST2/P42</b>       | I/O | O(L)       | オンチップデバッガステータス出力 *1/入出力兼用ポート              |

| *3                 | 22   | *3   | <b>LVDD</b>           | -   | -          | コア電源(+)                                   |

| 32                 | 23   | D6   | <b>DCLK/P43</b>       | I/O | O(H)       | オンチップデバッガクロック出力 *1/入出力兼用ポート               |

| 33                 | 24   | D7   | <b>TEST</b>           | I   | I(Pull-DN) | テスト端子(通常動作時はVSSに固定のこと)                    |

| *3                 | 25   | *3   | <b>LVDD</b>           | -   | -          | コア電源(+)                                   |

| 36                 | 26   | E7   | <b>#RESET</b>         | I   | I(Pull-UP) | イニシャルセット入力(ノイズフィルタ付き)                     |

| -                  | 27   | -NC  |                       | -   | -          | -                                         |

| 38                 | 28   | E6   | <b>P00/REMO</b>       | I/O | I(Pull-UP) | 入出力兼用ポート(割り込みあり) *1/REMC 出力               |

| 39                 | 29   | E5   | <b>P01/REMI</b>       | I/O | I(Pull-UP) | 入出力兼用ポート(割り込みあり) *1/REMC 入力               |

| 40                 | 30   | F7   | <b>P02/EXCL0</b>      | I/O | I(Pull-UP) | 入出力兼用ポート(割り込みあり)<br>*1/T16 Ch0外部クロック入力    |

| 42                 | 31   | F6   | <b>P03/#ADTRG</b>     | I/O | I(Pull-UP) | 入出力兼用ポート(割り込みあり) *1/AD変換外部トリガ             |

| *2                 | 32   | *2   | <b>VSS</b>            | -   | -          | 電源(-)                                     |

| 46                 | 33   | G7   | <b>OSC1</b>           | I   | I          | OSC1発振入力*6                                |

| *2                 | 34   | *2   | <b>VSS</b>            | -   | -          | 電源(-)                                     |

| 49                 | 35   | G6   | <b>OSC2</b>           | O   | O          | OSC1発振出力                                  |

| PAD / 端子 / ボール No. |      |      | 名称                | I/O | 初期状態       | 機能 (デフォルト機能 / 設定による兼用機能)                             |

|--------------------|------|------|-------------------|-----|------------|------------------------------------------------------|

| CHIP               | TQFP | WCSP |                   |     |            |                                                      |

| *2                 | 36   | *2   | <b>VSS</b>        | -   | -          | 電源(-)                                                |

| 52                 | 37   | G5   | <b>OSC3</b>       | I   | I          | OSC3発振入力 <sup>*6</sup>                               |

| -                  | 38   | -    | <b>-NC</b>        | -   | -          | -                                                    |

| *2                 | 39   | *2   | <b>VSS</b>        | -   | -          | 電源(-)                                                |

| 55                 | 40   | G4   | <b>OSC4</b>       | O   | O          | OSC3発振出力                                             |

| *2                 | 41   | *2   | <b>VSS</b>        | -   | -          | 電源(-)                                                |

| 58                 | 42   | F4   | <b>P04/SPICLK</b> | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり) <sup>*1</sup> /SPIクロック入出力          |

| 59                 | 43   | G3   | <b>P05/SDO</b>    | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり) <sup>*1</sup> /SPIデータ出力            |

| *4                 | 44   | *4   | <b>HVDD</b>       | -   | -          | I/O電源(+)                                             |

| 61                 | 45   | F3   | <b>P06/SDI</b>    | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり) <sup>*1</sup> /SPIデータ入力            |

| 62                 | 46   | G2   | <b>P07/#SPISS</b> | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /SPIスレーブセレクト入力    |

| -                  | 47   | -    | <b>-NC</b>        | -   | -          | -                                                    |

| *3                 | 48   | *3   | <b>LVDD</b>       | -   | -          | コア電源(+)                                              |

| 67                 | 49   | G1   | <b>P10/SCLK</b>   | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /UART Ch0クロック入力   |

| *3                 | 50   | *3   | <b>LVDD</b>       | -   | -          | コア電源(+)                                              |

| 71                 | 51   | F1   | <b>P11/SOUT</b>   | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /UART Ch0データ出力    |

| 72                 | 52   | E3   | <b>P12/SIN</b>    | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり) <sup>*1</sup> /UART Ch0データ入力       |

| 73                 | 53   | E2   | <b>P13/EXCL1</b>  | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /T16 Ch1外部クロック入力  |

| 74                 | 54   | E1   | <b>P14/EXCL2</b>  | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /T16 Ch2外部クロック入力  |

| *4                 | 55   | *4   | <b>HVDD</b>       | -   | -          | I/O電源(+)                                             |

| *2                 | 56   | *2   | <b>VSS</b>        | -   | -          | 電源(-)                                                |

| 77                 | 57   | D1   | <b>P15/EXCL3</b>  | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /T16E Ch0外部クロック入力 |

| 79                 | 58   | D2   | <b>P16/SCLK1</b>  | I/O | I(Pull-UP) | 入出力兼用ポート (割り込みあり)<br><sup>*1</sup> /UART Ch1 クロック入力  |

| -                  | 59   | -    | <b>-NC</b>        | -   | -          | -                                                    |

| *5                 | 60   | D3   | <b>AVDD</b>       | -   | -          | アナログ電源(+)                                            |

| 83                 | 61   | C1   | <b>P17/AIN3</b>   | I   | I          | 入力兼用ポート (割り込みあり) <sup>*1</sup> / AD変換器 Ch3 入力        |

| 84                 | 62   | C2   | <b>P20/AIN2</b>   | I   | I          | 入力兼用ポート <sup>*1</sup> / AD変換器 Ch2 入力                 |

| 86                 | 63   | B1   | <b>P21/AIN1</b>   | I   | I          | 入力兼用ポート <sup>*1</sup> / AD変換器 Ch1 入力                 |

| 87                 | 64   | B2   | <b>P22/AIN0</b>   | I   | I          | 入力兼用ポート <sup>*1</sup> / AD変換器 Ch0 入力                 |

\*1 デフォルト設定の機能です。

\*2 VssのPAD No. : 2, 3, 20, 21, 27, 28, 43, 44, 47, 48, 51, 54, 56, 76, 78

VssのBALL No. : C6, D4, F5

\*3 LV<sub>DD</sub>のPAD No. : 8, 9, 31, 34, 35, 64, 69, 70

LV<sub>DD</sub>のBALL No. : D5, F2

\*4 HV<sub>DD</sub>のPAD No. : 10, 11, 17, 29, 60, 75

HV<sub>DD</sub>のBALL No. : C4, E4

\*5 AV<sub>DD</sub>のPAD No. : 80, 82, 85

\*6 OSC3、OSC1端子に外部クロックを入力する場合、クロックの電圧レベルはLV<sub>DD</sub>としてください。

注：NC pin (TQFPはNCと記載、CHIP/WCSPはNo.記載の無い端子)には、ボンディングを行わないで下さい。

# 2 CPU

S1C17003はコアプロセッサとしてS1C17コアを搭載しています。

S1C17コアはセイコーエプソンオリジナルの16ビットRISCプロセッサです。

低消費電力、高速動作、広いアドレス空間、主要命令の1クロック実行、省ゲート設計を特長とし、8ビットCPUがよく使われるコントローラやシーケンサ等への組み込み用に最適です。

S1C17コアの詳細については、“S1C17 Family S1C17コアマニュアル”を参照してください。

## 2.1 S1C17コアの特長

---

### プロセッサ形式

- セイコーエプソンオリジナル16ビットRISCプロセッサ

- 0.35～0.15μm低電力CMOSプロセステクノロジ

### 命令セット

- コード長 16ビット固定長

- 命令数 基本命令111個(全184命令)

- 実行サイクル 主要命令は1サイクルで実行

- 即値拡張命令 即値を24ビットまで拡張

- Cによる開発用に最適化されたコンパクトかつ高速な命令セット

### レジスタセット

- 24ビット汎用レジスタ × 8

- 24ビット特殊レジスタ × 2

- 8ビット特殊レジスタ × 1

### メモリ空間、バス

- 最大16Mバイトのメモリ空間(24ビットアドレス)

- 命令バス(16ビット)とデータバス(32ビット)を分離したハーバードアーキテクチャ

### 割り込み

- リセット、NMI、32種類の外部割り込みに対応

- アドレス不整割り込み

- デバッグ割り込み

- ベクタテーブルからベクタを読み込み、割り込み処理ルーチンへ直接分岐

- ベクタ番号によるソフトウェア割り込みを発生可能(全ベクタ番号を指定可能)

### パワーセーブ

- HALT(halt命令)

- SLEEP(slp命令)

### コプロセッサインターフェース

- 16ビット × 16ビット + 32ビット積和演算器

- 16ビット ÷ 16ビット除算器

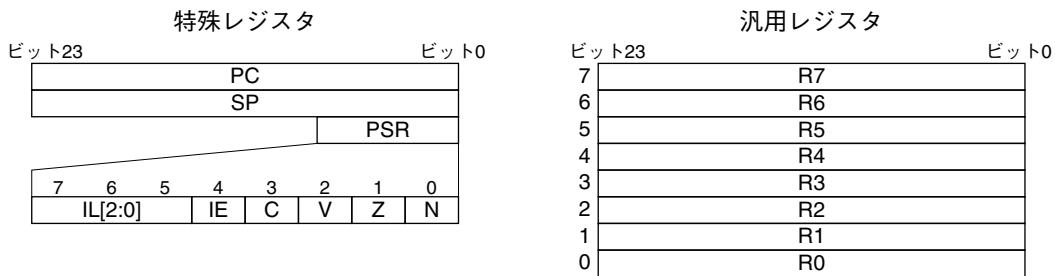

## 2.2 CPUレジスタ

S1C17コアは、8本の汎用レジスタおよび3本の特殊レジスタを内蔵しています。

図2.2.1 レジスタ

## 2.3 命令セット

S1C17コアの命令コードはすべて16ビットの固定長で、パイプライン処理を行うことによって主要な命令を1サイクルで実行します。各命令の詳細については“S1C17 Family S1C17コアマニュアル”を参照してください。

表2.3.1 S1C17コア命令一覧

| 種類    | ニーモニック | 機能                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| データ転送 | ld.b   | 汎用レジスタ(バイト) → 汎用レジスタ(符号拡張)<br>メモリ(バイト) → 汎用レジスタ(符号拡張)<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>メモリ(バイト) → 汎用レジスタ(符号拡張)<br>メモリ(バイト) → 汎用レジスタ(符号拡張)<br>汎用レジスタ(バイト) → メモリ<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>汎用レジスタ(バイト) → スタック<br>汎用レジスタ(バイト) → メモリ                                                                                                                                                                         |

|       | ld.ub  | 汎用レジスタ(バイト) → 汎用レジスタ(ゼロ拡張)<br>メモリ(バイト) → 汎用レジスタ(ゼロ拡張)<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>メモリ(バイト) → 汎用レジスタ(ゼロ拡張)<br>メモリ(バイト) → 汎用レジスタ(ゼロ拡張)                                                                                                                                                                                                                                                                                             |

|       | ld     | 汎用レジスタ(16ビット) → 汎用レジスタ<br>即値 → 汎用レジスタ(符号拡張)<br>メモリ(16ビット) → 汎用レジスタ<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>メモリ(16ビット) → 汎用レジスタ<br>汎用レジスタ(16ビット) → メモリ<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>汎用レジスタ(16ビット) → スタック<br>汎用レジスタ(16ビット) → メモリ                                                                                                                                                                                     |

|       | ld.a   | 汎用レジスタ(24ビット) → 汎用レジスタ<br>即値 → 汎用レジスタ(ゼロ拡張)<br>メモリ(32ビット) → 汎用レジスタ (*1)<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>メモリ(32ビット) → 汎用レジスタ (*1)<br>メモリ(32ビット) → 汎用レジスタ (*1)<br>汎用レジスタ(32ビット、ゼロ拡張) → メモリ (*1)<br>メモリアドレスのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能<br>汎用レジスタ(32ビット、ゼロ拡張) → スタック (*1)<br>汎用レジスタ(32ビット、ゼロ拡張) → メモリ (*1)<br>SP → 汎用レジスタ<br>PC → 汎用レジスタ<br>スタック(32ビット) → 汎用レジスタ (*1)<br>スタックポインタのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能 |

| 種類     | ニーモニック      | 機能                                                                                  |

|--------|-------------|-------------------------------------------------------------------------------------|

| データ転送  | ld.a        | 汎用レジスタ(32ビット、ゼロ拡張) → スタック (*1)<br>スタックポインタのポストインクリメント、ポストデクリメント、<br>プリデクリメント機能を使用可能 |

|        | [%sp], %rs  |                                                                                     |

|        | [%sp]+, %rs |                                                                                     |

|        | [%sp]-, %rs |                                                                                     |

|        | -[%sp], %rs |                                                                                     |

|        | %sp, %rs    | 汎用レジスタ(24ビット) → SP                                                                  |

| 整数算術演算 | %sp, imm7   | 即値 → SP                                                                             |

|        | add         | 汎用レジスタ間の16ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | add/c       |                                                                                     |

|        | add/nc      |                                                                                     |

|        | add         | 汎用レジスタと即値の16ビット加算                                                                   |

|        | add.a       | 汎用レジスタ間の24ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | add.a/c     |                                                                                     |

|        | add.a/nc    |                                                                                     |

|        | add.a       | SPと汎用レジスタの24ビット加算                                                                   |

|        | %sp, %rs    |                                                                                     |

|        | %rd, imm7   | 汎用レジスタと即値の24ビット加算                                                                   |

|        | %sp, imm7   | SPと即値の24ビット加算                                                                       |

|        | adc         | 汎用レジスタ間のキャリー付き16ビット加算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                 |

|        | adc/c       |                                                                                     |

|        | adc/nc      |                                                                                     |

|        | adc         | 汎用レジスタと即値のキャリー付き16ビット加算                                                             |

|        | sub         | 汎用レジスタ間の16ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | sub/c       |                                                                                     |

|        | sub/nc      |                                                                                     |

|        | sub         | 汎用レジスタと即値の16ビット減算                                                                   |

| 論理演算   | sub.a       | 汎用レジスタ間の24ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | %sp, %rs    | SPと汎用レジスタの24ビット減算                                                                   |

|        | %rd, imm7   | 汎用レジスタと即値の24ビット減算                                                                   |

|        | %sp, imm7   | SPと即値の24ビット減算                                                                       |

|        | sbc         | 汎用レジスタ間のキャリー付き16ビット減算<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                 |

|        | sbc/c       |                                                                                     |

|        | sbc/nc      |                                                                                     |

|        | sbc         | 汎用レジスタと即値のキャリー付き16ビット減算                                                             |

|        | cmp         | 汎用レジスタ間の16ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | cmp/c       |                                                                                     |

|        | cmp/nc      |                                                                                     |

|        | cmp         | 汎用レジスタと即値の16ビット比較                                                                   |

| 論理演算   | cmp.a       | 汎用レジスタ間の24ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                       |

|        | %rd, sign7  |                                                                                     |

|        | cmp.a/c     |                                                                                     |

|        | cmp.a/nc    |                                                                                     |

|        | cmp.a       | 汎用レジスタと即値の24ビット比較                                                                   |

|        | cmc         | 汎用レジスタ間のキャリー付き16ビット比較<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                 |

|        | cmc/c       |                                                                                     |

|        | cmc/nc      |                                                                                     |

|        | cmc         | 汎用レジスタと即値のキャリー付き16ビット比較                                                             |

|        | %rd, sign7  |                                                                                     |

|        | and         | 汎用レジスタ間の論理積<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                           |

|        | and/c       |                                                                                     |

|        | and/nc      |                                                                                     |

|        | and         | 汎用レジスタと即値の論理積                                                                       |

| 論理演算   | %rd, sign7  |                                                                                     |

|        | or          | 汎用レジスタ間の論理和<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                           |

|        | or/c        |                                                                                     |

|        | or/nc       |                                                                                     |

|        | or          | 汎用レジスタと即値の論理和                                                                       |

|        | %rd, sign7  |                                                                                     |

|        | xor         | 汎用レジスタ間の排他的論理和<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                        |

|        | xor/c       |                                                                                     |

|        | xor/nc      |                                                                                     |

|        | xor         | 汎用レジスタと即値の排他的論理和                                                                    |

|        | %rd, sign7  |                                                                                     |

|        | not         | 汎用レジスタ間の論理否定(1の補数)<br>条件実行に対応(/c: C = 1の場合に実行, /nc: C = 0の場合に実行)                    |

|        | %rd, sign7  |                                                                                     |

|        | not/c       |                                                                                     |

|        | not/nc      |                                                                                     |

|        | not         | 汎用レジスタと即値の論理否定(1の補数)                                                                |

| 種類       | ニーモニック   | 機能                                                 |

|----------|----------|----------------------------------------------------|

| シフト&スワップ | sr       | 右論理シフト(レジスタによるシフトビット数指定)<br>右論理シフト(即値によるシフトビット数指定) |

|          | sa       | 右算術シフト(レジスタによるシフトビット数指定)<br>右算術シフト(即値によるシフトビット数指定) |

|          | sl       | 左論理シフト(レジスタによるシフトビット数指定)<br>左論理シフト(即値によるシフトビット数指定) |

|          | swap     | 16ビット境界でバイト単位のスワップ                                 |

|          | ext      | 直後の命令のオペランドを拡張                                     |

| 即値拡張     | cv.ab    | 符号付き8ビットデータを24ビットに変換                               |

|          | cv.as    | 符号付き16ビットデータを24ビットに変換                              |

|          | cv.al    | 32ビットデータを24ビットに変換                                  |

|          | cv.la    | 24ビットデータを32ビットに変換                                  |

|          | cv.ls    | 16ビットデータを32ビットに変換                                  |

| 分岐       | jpr      | PC相対ジャンプ                                           |

|          | jpr.d    | ディレイド分岐可                                           |

|          | jpa      | 絶対ジャンプ                                             |

|          | jpa.d    | ディレイド分岐可                                           |

|          | jrgt     | PC相対条件ジャンプ 分岐条件: !Z & !(N ^ V)                     |

|          | jrgt.d   | ディレイド分岐可                                           |

|          | jrgt.e   | PC相対条件ジャンプ 分岐条件: !(N ^ V)                          |

|          | jrgt.d.e | ディレイド分岐可                                           |

|          | jrlt     | PC相対条件ジャンプ 分岐条件: N ^ V                             |

|          | jrlt.d   | ディレイド分岐可                                           |

|          | jrlt.e   | PC相対条件ジャンプ 分岐条件: Z   N ^ V                         |

|          | jrlt.d.e | ディレイド分岐可                                           |

|          | jrugt    | PC相対条件ジャンプ 分岐条件: !Z & !C                           |

|          | jrugt.d  | ディレイド分岐可                                           |

|          | jruge    | PC相対条件ジャンプ 分岐条件: !C                                |

|          | jruge.d  | ディレイド分岐可                                           |

|          | jrule    | PC相対条件ジャンプ 分岐条件: C                                 |

|          | jrule.d  | ディレイド分岐可                                           |

|          | jreq     | PC相対条件ジャンプ 分岐条件: Z                                 |

|          | jreq.d   | ディレイド分岐可                                           |

|          | jrne     | PC相対条件ジャンプ 分岐条件: !Z                                |

|          | jrne.d   | ディレイド分岐可                                           |

| システム制御   | call     | PC相対サブルーチンコール                                      |

|          | call.d   | ディレイド分岐可                                           |

|          | calla    | 絶対サブルーチンコール                                        |

|          | calla.d  | ディレイド分岐可                                           |

|          | ret      | サブルーチンからのリターン                                      |

|          | ret.d    | ディレイド分岐可                                           |

|          | int      | ソフトウェア割り込み                                         |

|          | intl     | 割り込みレベル指定付きソフトウェア割り込み                              |

|          | reti     | 割り込みからのリターン                                        |

|          | reti.d   | ディレイド分岐可                                           |

| コプロセッサ制御 | brk      | デバッグ割り込み                                           |

|          | retd     | デバッグ処理からのリターン                                      |

|          | nop      | ノーオペレーション                                          |

|          | halt     | HALT                                               |

|          | slp      | SLEEP                                              |

| コプロセッサ制御 | ei       | 割り込み許可                                             |

|          | di       | 割り込み禁止                                             |

|          | ld.cw    | コプロセッサへのデータ転送                                      |

|          | ld.ca    | コプロセッサへのデータ転送、結果とフラグ状態の取得                          |

|          | ld.cf    | コプロセッサへのデータ転送、フラグ状態の取得                             |

\*1 1d.a命令は32ビットのメモリアクセスを行います。レジスタからメモリへのデータ転送では上位8ビットを0とした32ビットデータがメモリに書き込まれます。メモリからの読み出し時は、読み出しデータの上位8ビットが無視されます。

表中の記号の意味は次のとおりです。

表2.3.2 記号の意味

| 記号                                   | 説明                                  |

|--------------------------------------|-------------------------------------|

| <code>%rs</code>                     | 汎用ソースレジスタ                           |

| <code>%rd</code>                     | 汎用デスティネーションレジスタ                     |

| <code>[%rb]</code>                   | 汎用レジスタで間接指定されるメモリ                   |

| <code>[%rb]+</code>                  | 汎用レジスタで間接指定されるメモリ(アドレスポストインクリメント付き) |

| <code>[%rb]-</code>                  | 汎用レジスタで間接指定されるメモリ(アドレスポストデクリメント付き)  |

| <code>-[%rb]</code>                  | 汎用レジスタで間接指定されるメモリ(アドレスプリデクリメント付き)   |

| <code>%sp</code>                     | スタックポインタ                            |

| <code>[%sp], [%sp+imm7]</code>       | スタック                                |

| <code>[%sp]+</code>                  | スタック(アドレスポストインクリメント付き)              |

| <code>[%sp]-</code>                  | スタック(アドレスポストデクリメント付き)               |

| <code>-[%sp]</code>                  | スタック(アドレスプリデクリメント付き)                |

| <code>imm3, imm5, imm7, imm13</code> | 符号なし即値(数値はビット長)                     |

| <code>sign7, sign10</code>           | 符号付き即値(数値はビット長)                     |

## 2.4 ベクターテーブル

ベクターテーブルは、割り込み処理ルーチンへのベクタ(処理ルーチン開始アドレス)を格納します。割り込みが発生すると、S1C17コアは割り込みに対応するベクタを読み出して、その処理ルーチンを実行します。ベクターテーブルの先頭には、リセット後にプログラムの実行を開始するブートアドレスを書き込んでおく必要があります。

ベクターテーブルは“6. 割り込みコントローラ(ITC)”を参照してください。

割り込みベクタを書き込んでおくベクターテーブルのベース(先頭)アドレスは、MISC\_TTBRLとMISC\_TTBRHレジスタ(0x5328、0x532a)によって設定することができます。表の“TTBR”はこれらのレジスタに設定された値を意味します。イニシャルリセット後、MISC\_TTBRL/MISC\_TTBRHレジスタは0x8000番地に設定されます。したがって、ベクターテーブルの位置を変更する場合でも、リセットベクタのみは上記のアドレスに書き込んでおくことが必要です。MISC\_TTBRLレジスタのビット7~0は0に固定されます。このため、ベクターテーブルの先頭アドレスは常に256バイト境界アドレスから始まります。

### 0x5328–0x532a: Vector Table Address Low/High Registers (MISC\_TTBRL, MISC\_TTBRH)

| Register name                                   | Address | Bit                | Name               | Function                                                                              | Setting         | Init.       | R/W      | Remarks            |

|-------------------------------------------------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------|-----------------|-------------|----------|--------------------|

| Vector Table Address Low Register (MISC_TTBRL)  | 0x5328  | D15–8<br>(16 bits) | TTBR[15:8]<br>D7–0 | Vector table base address A[15:8]<br>Vector table base address A[7:0]<br>(fixed at 0) | 0x0–0xff<br>0x0 | 0x80<br>0x0 | R/W<br>R |                    |

| Vector Table Address High Register (MISC_TTBRH) | 0x532a  | D15–8<br>(16 bits) | –<br>D7–0          | reserved<br>TTBR[23:16]                                                               | –<br>0x0–0xff   | –<br>0x0    | –<br>R/W | 0 when being read. |

注: MISC\_TTBRL/MISC\_TTBRHレジスタは書き込み保護されています。これらのレジスタを書き換えるには、MISC Protect Register(0x5324)に0x96を書き込んで、書き込み保護を解除する必要があります。なお、MISC\_TTBRL/MISC\_TTBRHの不要な書き換えはシステムの誤動作につながりますので、書き換え時以外はMISC Protect Register(0x5324)を0x96以外に設定してください。

## 2.5 PSRの読み出し

S1C17003にはS1C17コアのPSR(Processor Status Register)の内容を読み出すためのPSR Register(0x532c)が設けられています。このレジスタを読み出すことにより、アプリケーションソフトウェアからPSRの内容を確認することができます。ただし、PSRへの書き込みは行えません。

### 0x532c: PSR Register (MISC\_PSR)

| Register name              | Address             | Bit   | Name       | Function                      | Setting      |               | Init. | R/W | Remarks            |

|----------------------------|---------------------|-------|------------|-------------------------------|--------------|---------------|-------|-----|--------------------|

| PSR Register<br>(MISC_PSR) | 0x532c<br>(16 bits) | D15–8 | —          | reserved                      | —            | —             | —     | —   | 0 when being read. |

|                            |                     | D7–5  | PSRIL[2:0] | PSR interrupt level (IL) bits | 0x0 to 0x7   |               | 0x0   | R   |                    |

|                            |                     | D4    | PSRIE      | PSR interrupt enable (IE) bit | 1 1 (enable) | 0 0 (disable) | 0     | R   |                    |

|                            |                     | D3    | PSRC       | PSR carry (C) flag            | 1 1 (set)    | 0 0 (cleared) | 0     | R   |                    |

|                            |                     | D2    | PSRV       | PSR overflow (V) flag         | 1 1 (set)    | 0 0 (cleared) | 0     | R   |                    |

|                            |                     | D1    | PSRZ       | PSR zero (Z) flag             | 1 1 (set)    | 0 0 (cleared) | 0     | R   |                    |

|                            |                     | D0    | PSRN       | PSR negative (N) flag         | 1 1 (set)    | 0 0 (cleared) | 0     | R   |                    |

#### D[7:5] PSRIL[2:0]: PSR Interrupt Level (IL) Bits

PSRのILビットの値(割り込みレベル)が読み出せます。(デフォルト: 0x0)

#### D4 PSRIE: PSR Interrupt Enable (IE) Bit

PSRのIEビットの値(割り込みイネーブル)が読み出せます。

1(R): 1(割り込み許可)

0(R): 0(割り込み禁止) (デフォルト)

#### D3 PSRC: PSR Carry (C) Flag

PSRのC(キャリー)フラグの値が読み出せます。

1(R): 1

0(R): 0(デフォルト)

#### D2 PSRV: PSR Overflow (V) Flag

PSRのV(オーバーフロー)フラグの値が読み出せます。

1(R): 1

0(R): 0(デフォルト)

#### D1 PSRZ: PSR Zero (Z) Flag

PSRのZ(ゼロ)フラグの値が読み出せます。

1(R): 1

0(R): 0(デフォルト)

#### D0 PSRN: PSR Negative (N) Flag

PSRのN(ネガティブ)フラグの値が読み出せます。

1(R): 1

0(R): 0(デフォルト)

## 2.6 プロセッサ情報

S1C17003はProcessor ID Register(0xfffff84)を内蔵しており、アプリケーションソフトウェアからCPUコアの種類を特定することができます。

### 0xfffff84: Processor ID Register (IDIR)

| Register name                | Address               | Bit  | Name      | Function                         | Setting | Init. | R/W | Remarks |

|------------------------------|-----------------------|------|-----------|----------------------------------|---------|-------|-----|---------|

| Processor ID Register (IDIR) | 0xfffff84<br>(8 bits) | D7-0 | IDIR[7:0] | Processor ID<br>0x10: S1C17 Core | 0x10    | 0x10  | R   |         |

プロセッサの機種を示すIDコードが格納されるリードオンリレジスタです。S1C17コアのIDコードは0x10です。

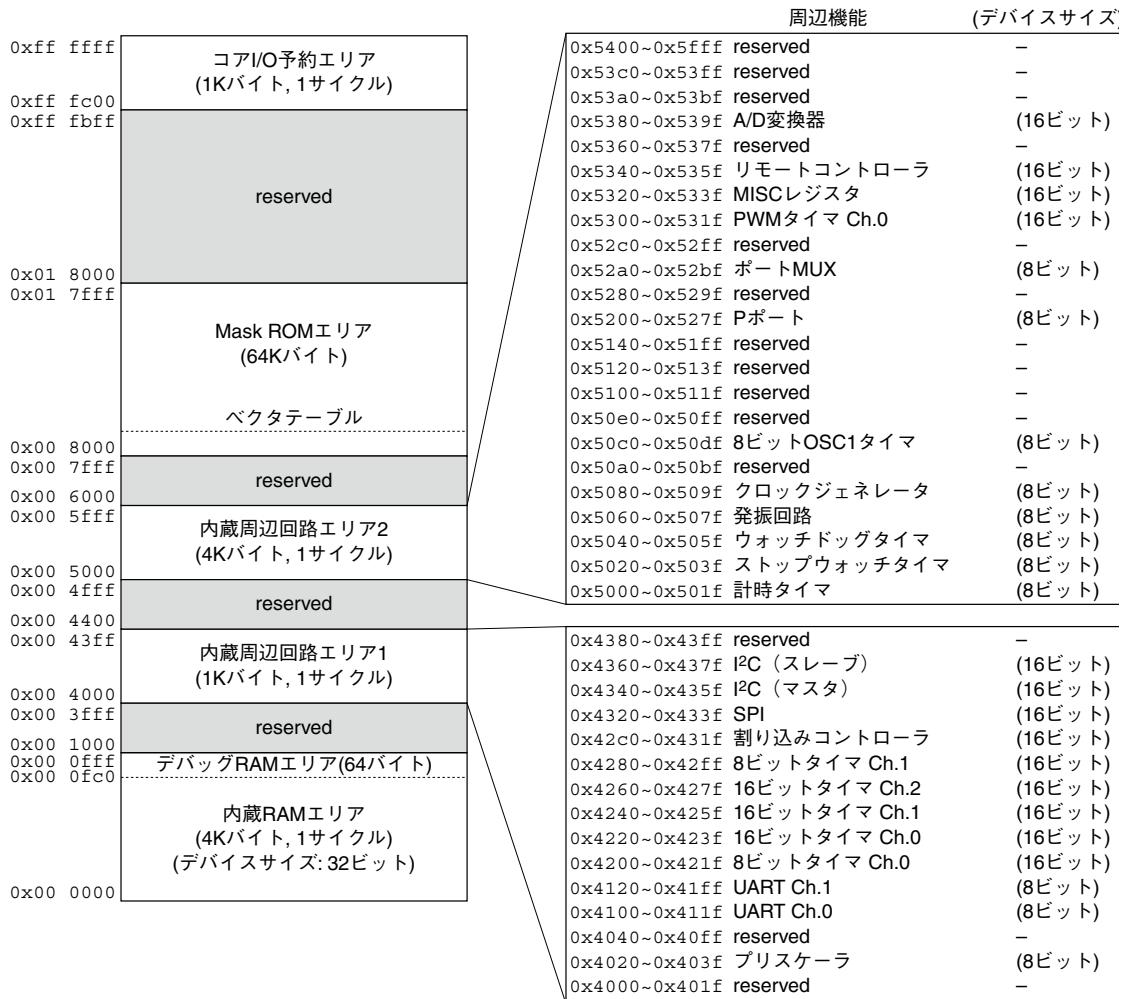

# 3 メモリマップ, バス制御

図3.1にS1C17003のメモリマップを示します。

図3.1 S1C17003メモリマップ

## 3.1 バスサイクル

CPUはCCLKを基準に動作します。CCLKについては、“8.2 CPUクロック(CCLK)の制御”を参照してください。

CCLKの立ち上がりから次の立ち上がりまでを1 CCLKとし、これを1バスサイクルとします。図3.1に示したとおり、1回のバスアクセスにかかるサイクル数は、周辺回路やメモリによって異なります。また、CPUの命令(アクセスサイズ)とデバイスサイズによりバスアクセス回数も変わります。

表3.1.1 バスアクセス回数

| デバイスサイズ | CPUアクセスサイズ | バスアクセス回数 |

|---------|------------|----------|

| 8ビット    | 8ビット       | 1        |

|         | 16ビット      | 2        |

|         | 32ビット*     | 4        |

| 16ビット   | 8ビット       | 1        |

|         | 16ビット      | 1        |

|         | 32ビット*     | 2        |

| 32ビット   | 8ビット       | 1        |

|         | 16ビット      | 1        |

|         | 32ビット*     | 1        |

\* 32ビットアクセス時の上位8ビットデータについて

32ビットデータは上位8ビットを0としてメモリに書き込まれます。メモリからの読み出し時は上位8ビットが無視されます。割り込み処理のスタック操作時は、PSRの値を上位8ビットに、戻りアドレスを下位24ビットとした32ビットの書き込み/読み出しを行います。

### 3.1.1 アクセスサイズ制限

全てのモジュールは8ビット、16ビット、32ビットのいずれの命令でもアクセス可能です。ただし、必要なないレジスタの読み出しによって周辺回路の状態が変わり、問題が発生する場合もありますので、できるだけデバイスサイズに合わせてアクセスすることを推奨します。

### 3.1.2 命令実行サイクルの制限

以下のいずれかの条件下では命令のフェッチとデータアクセスが同時に行われず、データの存在するエリアのアクセスサイクル分、命令フェッチのサイクルが長くなります。

- 内蔵RAMエリアで命令を実行し、内蔵RAMエリアのデータにアクセスする場合

## 3.2 内蔵ROMエリア

### 3.2.1 内蔵ROM

0x8000番地から0x17fff番地までの64Kバイトの領域にはROMが内蔵されており、予めアプリケーションプログラムやデータを書き込んでおくことができます。0x8000番地はベクタテーブルベースアドレスとして定義されていますので、この領域の先頭にベクタテーブル(“2.4 ベクタテーブル”参照)をおく必要があります。ベクターブルアドレスはMISC\_TTBRL/MISC\_TTBRLレジスタ(0x5328、0x532a)で変更可能です。

ROMの読み出しがは、1~5サイクルで行われます。

### 3.2.2 ROMのリードアクセスサイクルの設定

S1C17602との互換性維持のため、ROMエリアのリードアクセスサイクルが、FLCYC[2:0](D[2:0]/MISC\_FLレジスタ)で設定できるようになっています。通常はFLCYC[2:0]を0x4に設定して使用してください。

#### 0x5320: ROM Control Register (MISC\_FL)

| Register name                  | Address         | Bit   | Name       | Function                 | Setting    |            | Init. | R/W | Remarks            |

|--------------------------------|-----------------|-------|------------|--------------------------|------------|------------|-------|-----|--------------------|

| ROM Control Register (MISC_FL) | 0x5320 (16bits) | D15-3 | —          | reserved                 | —          |            | —     | —   | 0 when being read. |

|                                |                 | D2-0  | FLCYC[2:0] | FLASHC read access cycle | FLCYC[2:0] | Read cycle | 0x3   | R/W |                    |

|                                |                 |       |            |                          | 0x7-0x5    | reserved   |       |     |                    |

|                                |                 |       |            |                          | 0x4        | 1 cycle    |       |     |                    |

|                                |                 |       |            |                          | 0x3        | 5 cycles   |       |     |                    |

|                                |                 |       |            |                          | 0x2        | 4 cycles   |       |     |                    |

|                                |                 |       |            |                          | 0x1        | 3 cycles   |       |     |                    |

|                                |                 |       |            |                          | 0x0        | 2 cycles   |       |     |                    |

#### D[2:0] FLCYC[2:0]: FLASHC Read Access Cycle Setup Bits

ROMのリードアクセスサイクル数を設定します。

表3.2.2.1 ROMのリードアクセスサイクルの設定

| FLCYC[2:0] | リードアクセスサイクル数 | CCLK周波数    |

|------------|--------------|------------|

| 0x7~0x5    | Reserved     | —          |

| 0x4        | 1サイクル        | 20MHz max. |

| 0x3        | 5サイクル        | 20MHz max. |

| 0x2        | 4サイクル        | 20MHz max. |

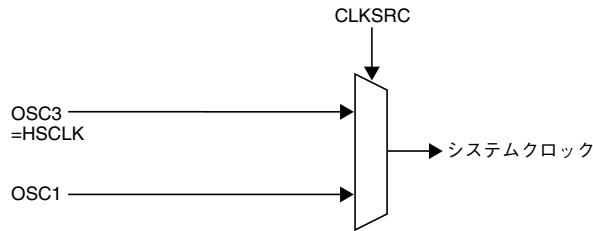

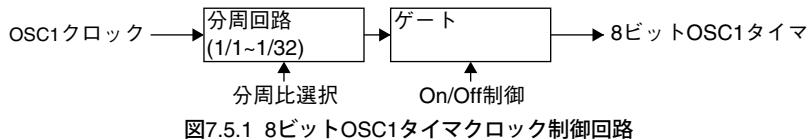

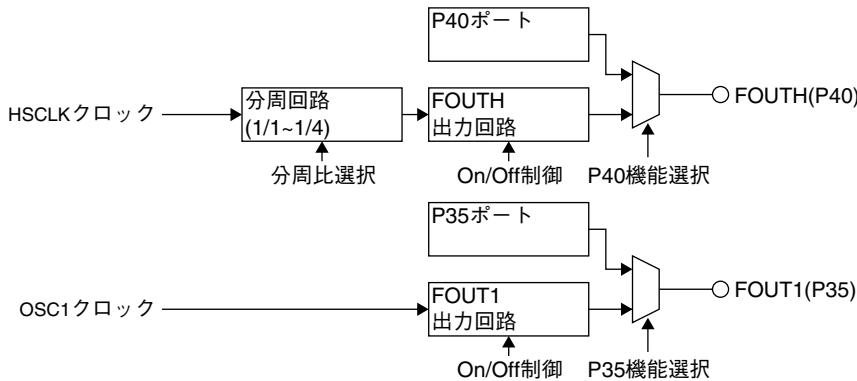

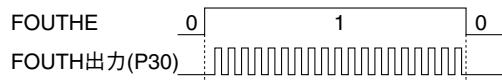

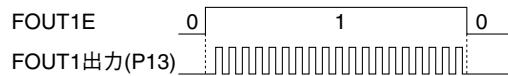

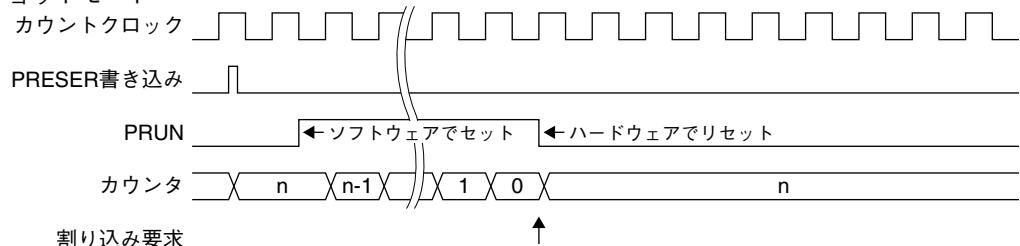

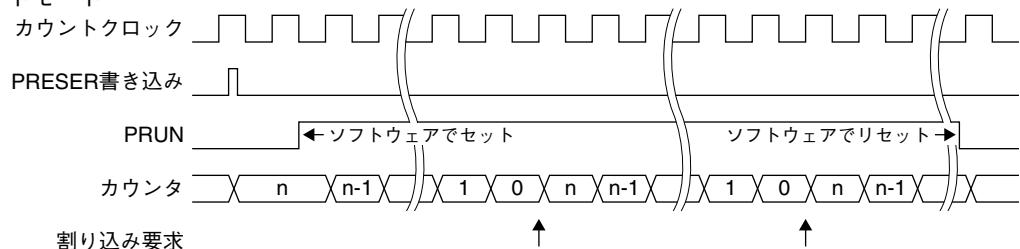

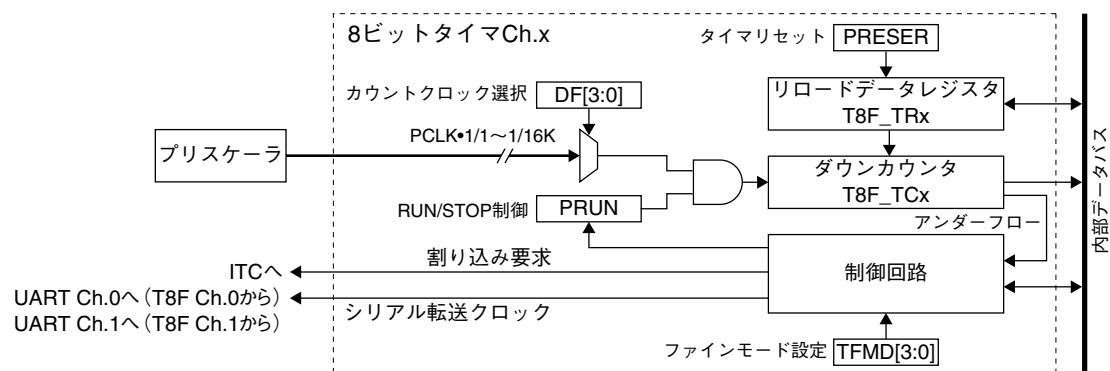

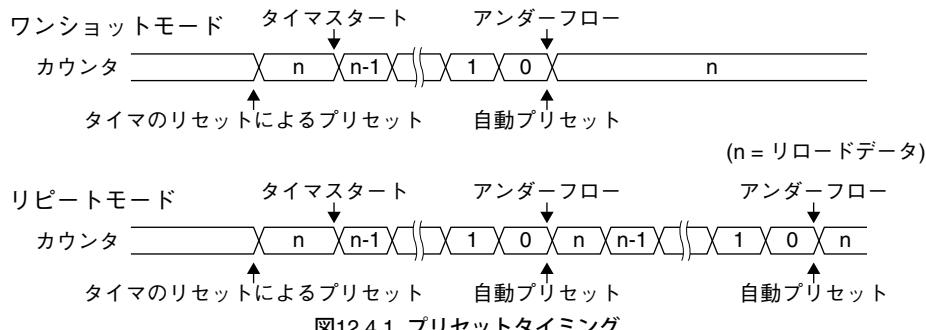

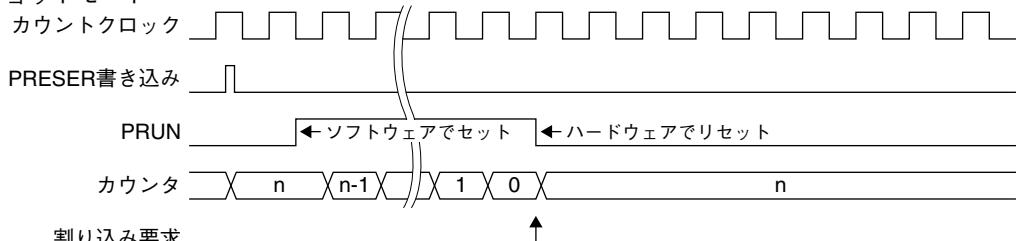

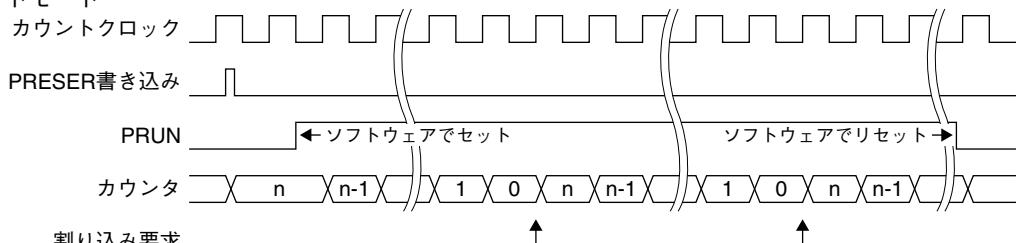

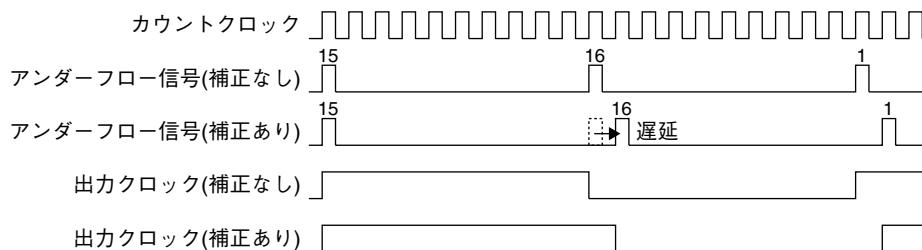

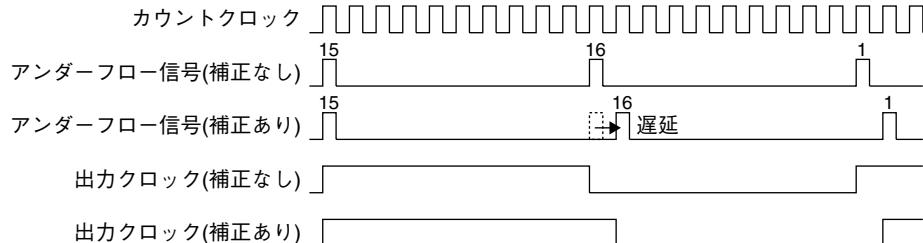

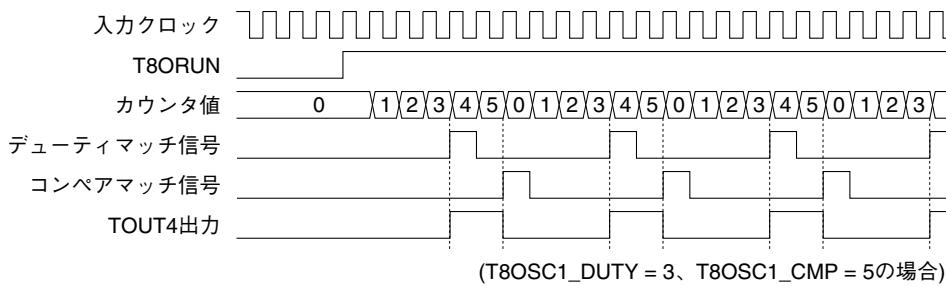

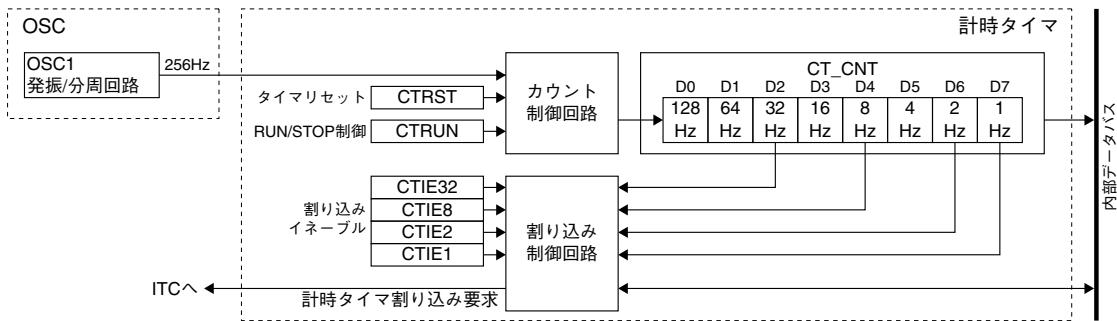

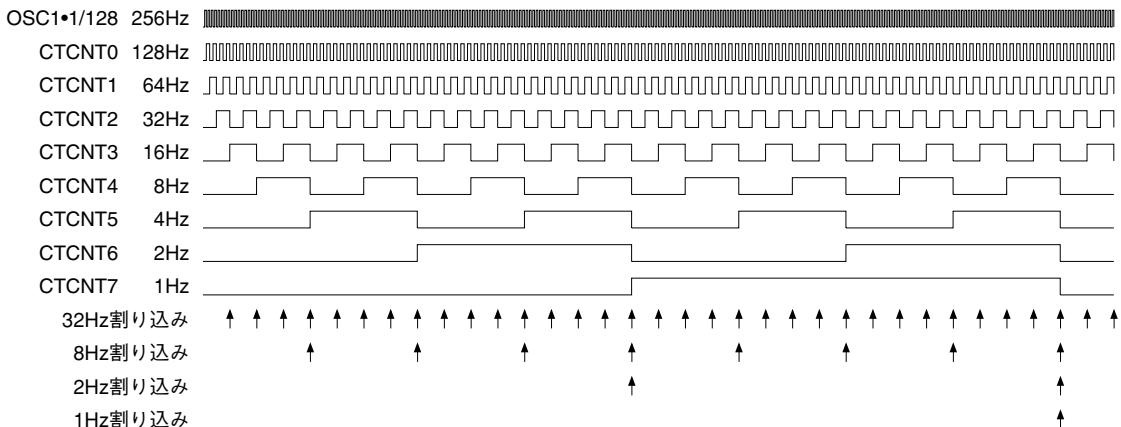

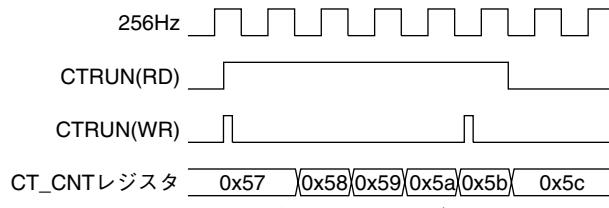

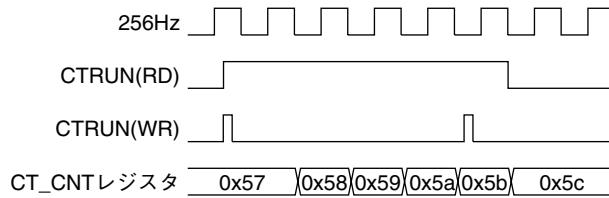

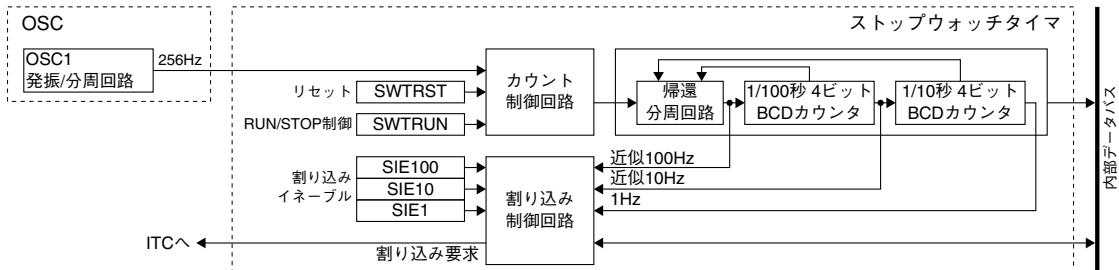

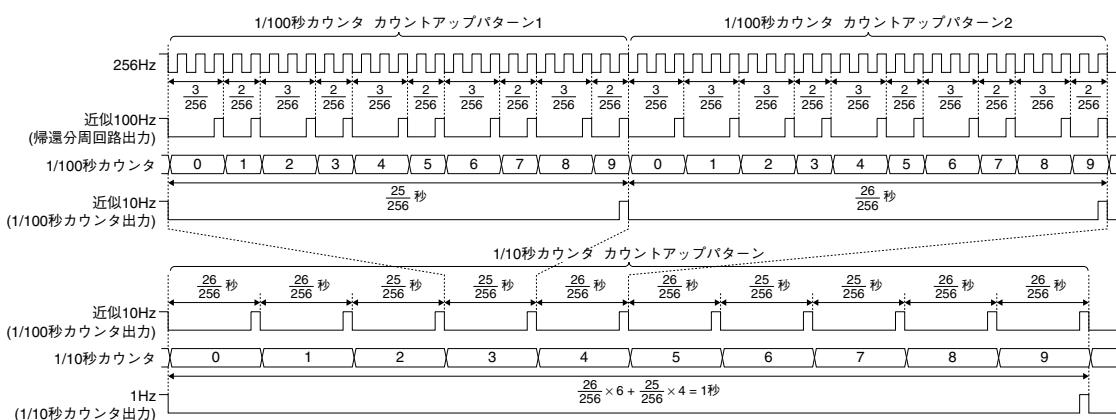

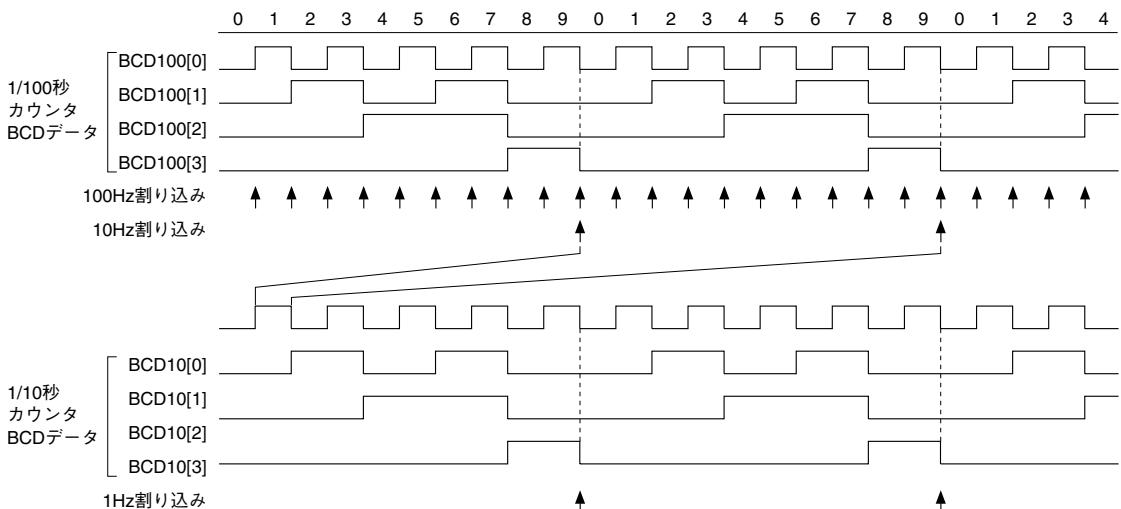

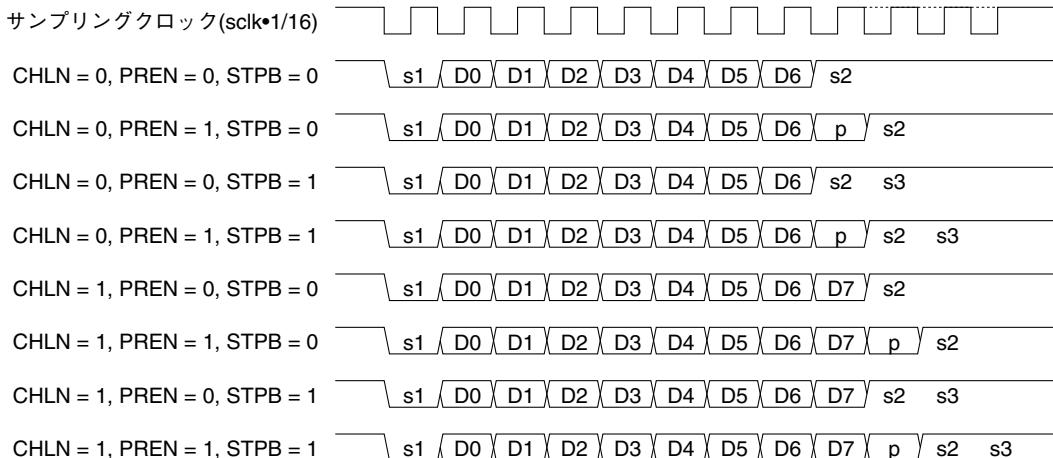

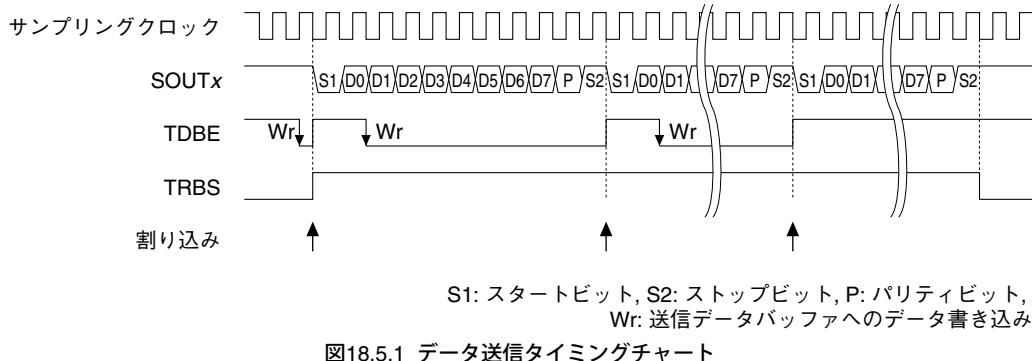

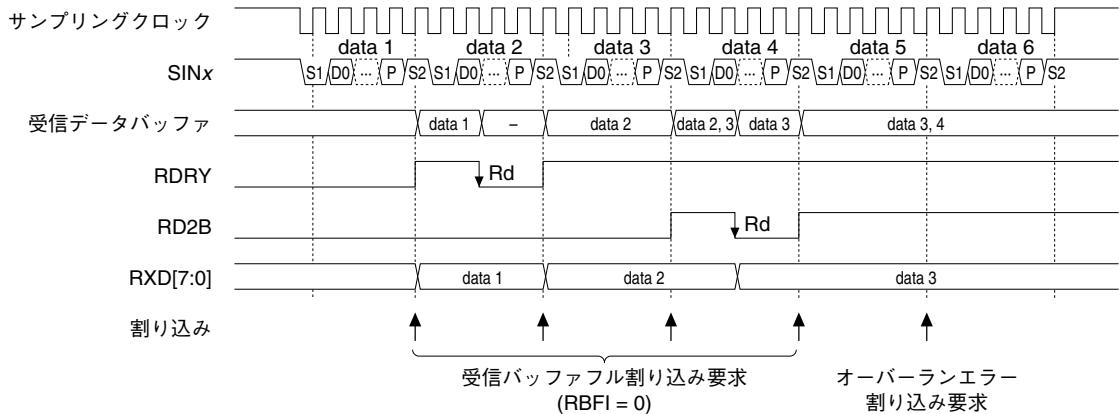

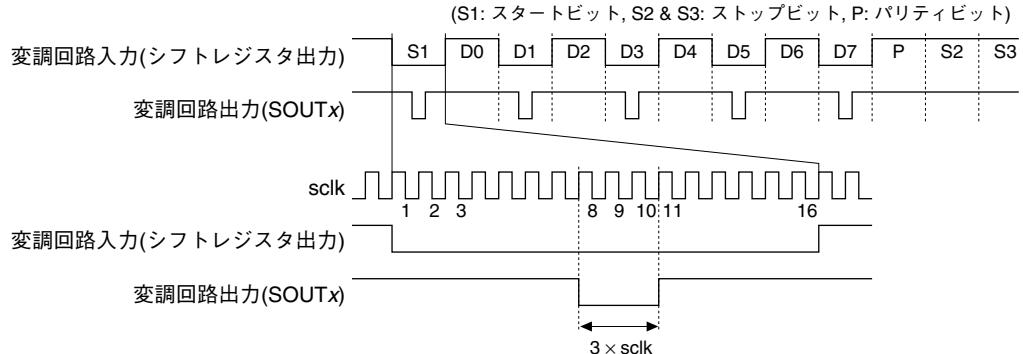

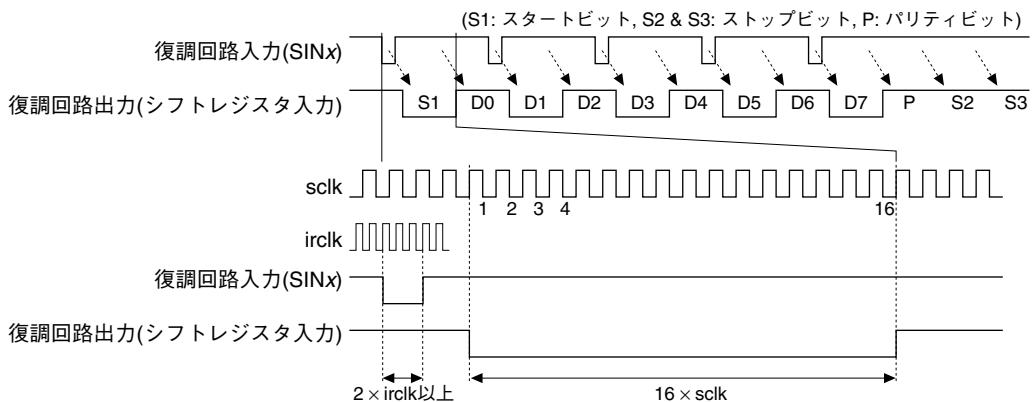

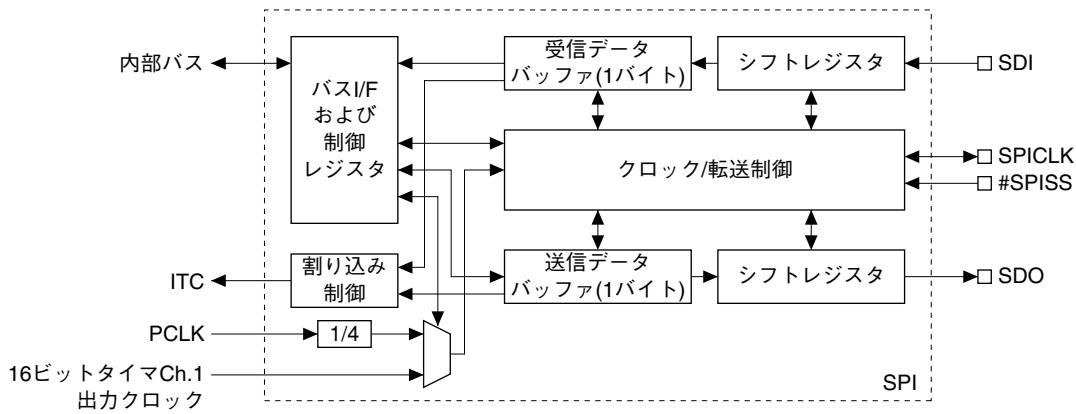

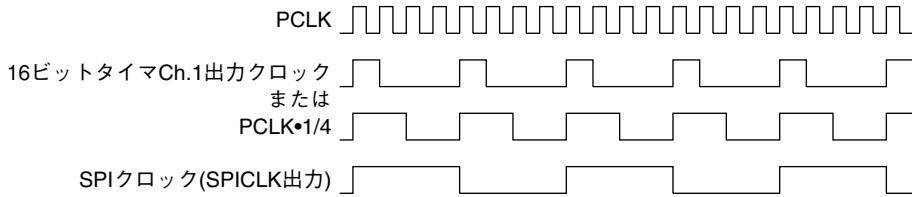

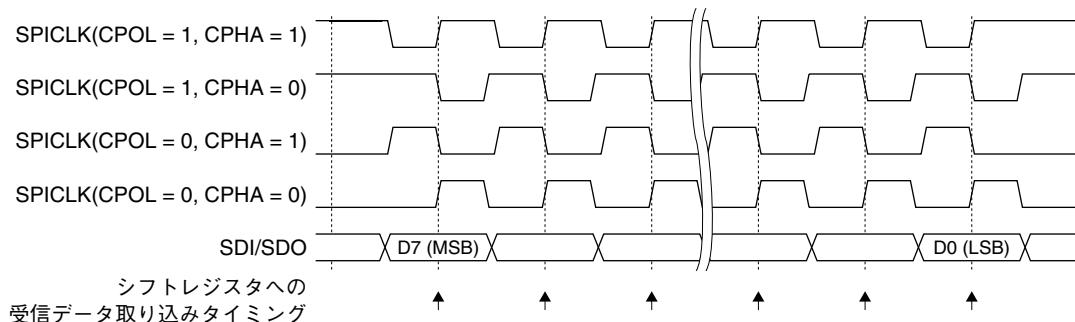

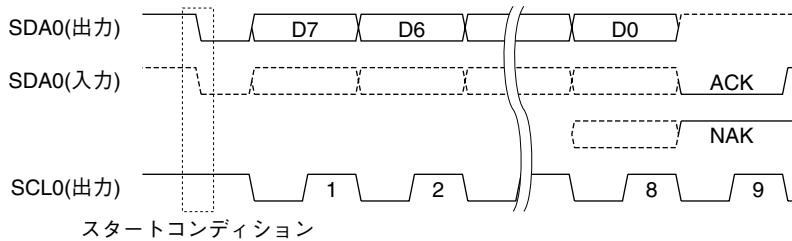

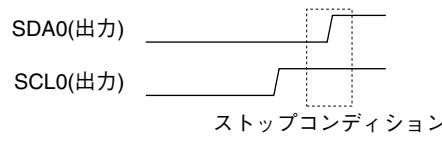

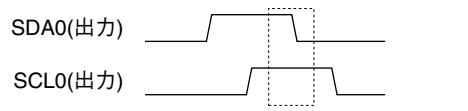

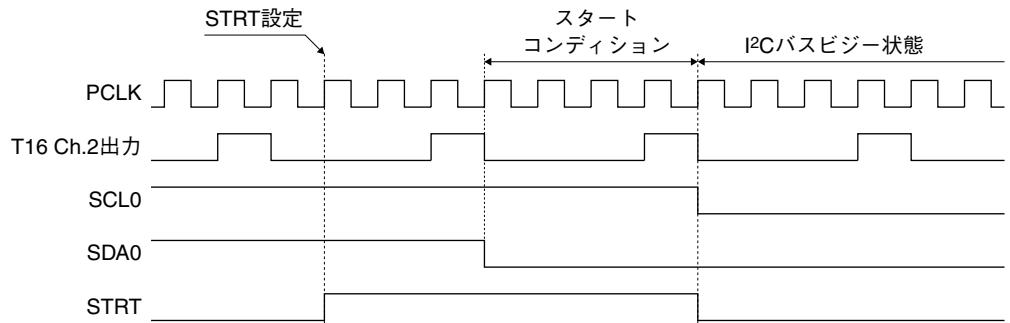

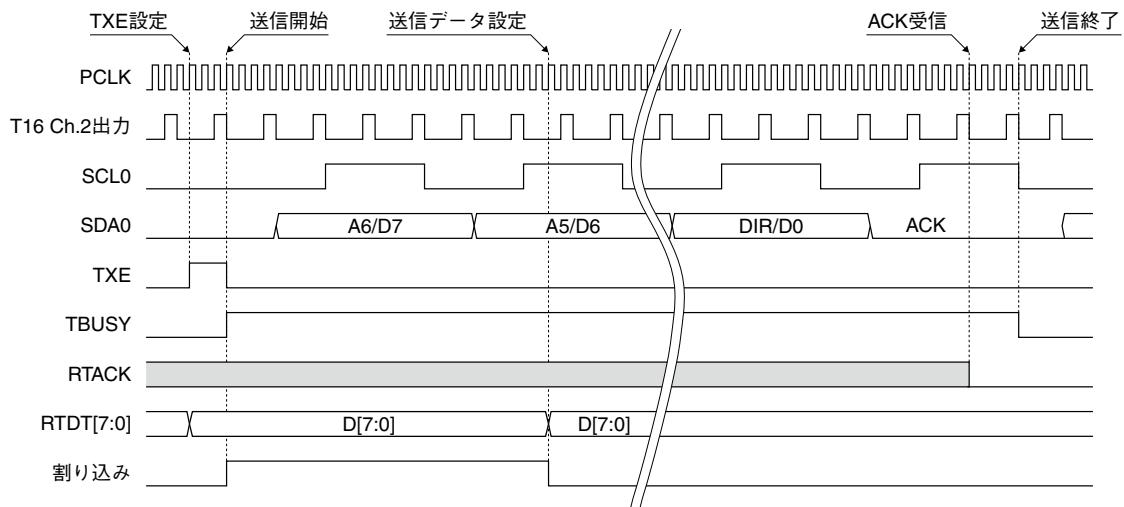

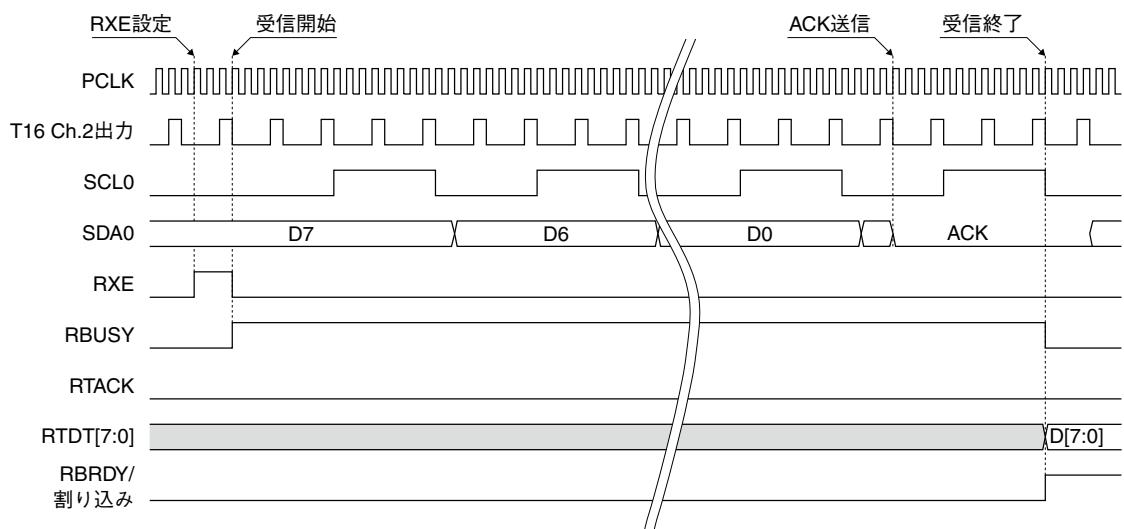

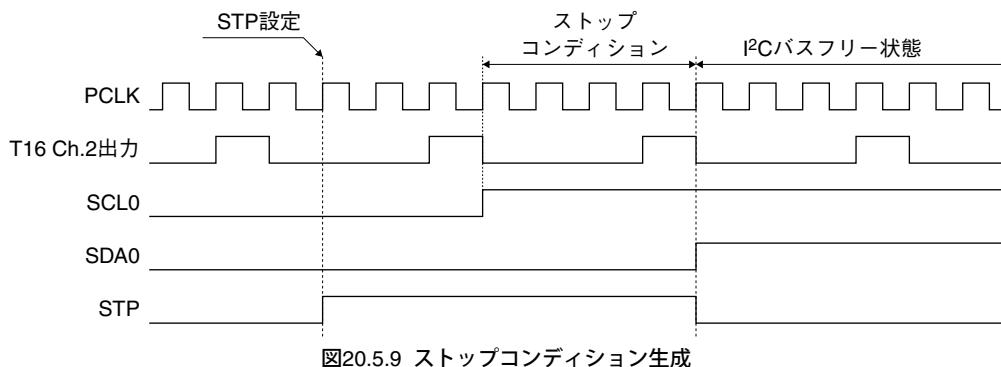

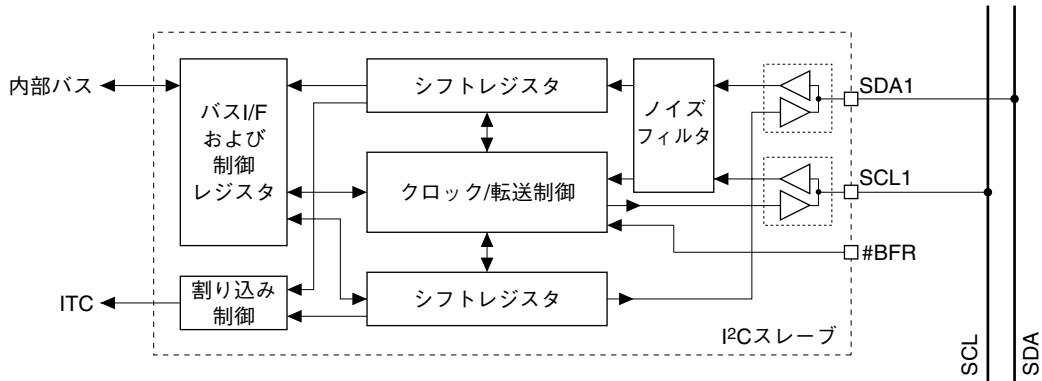

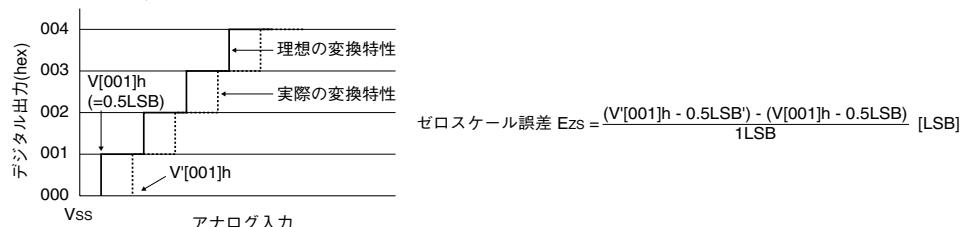

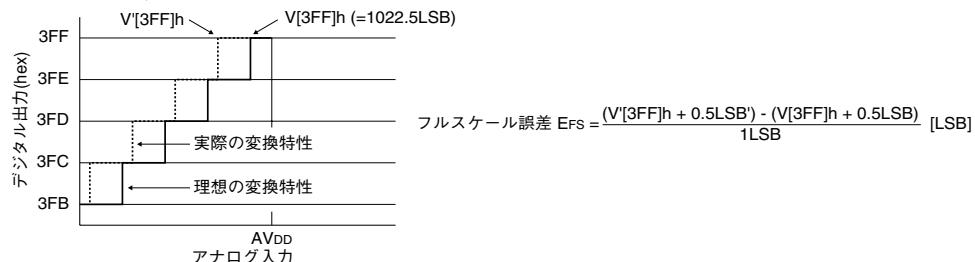

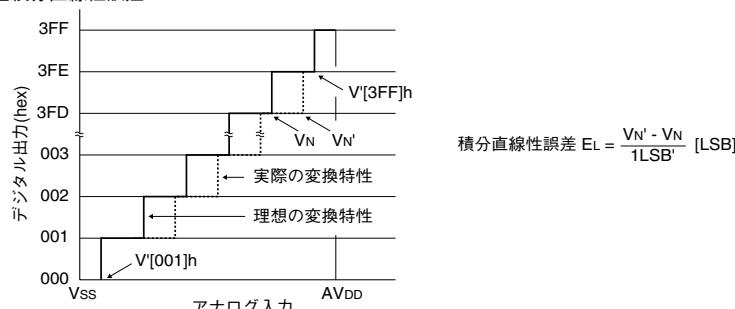

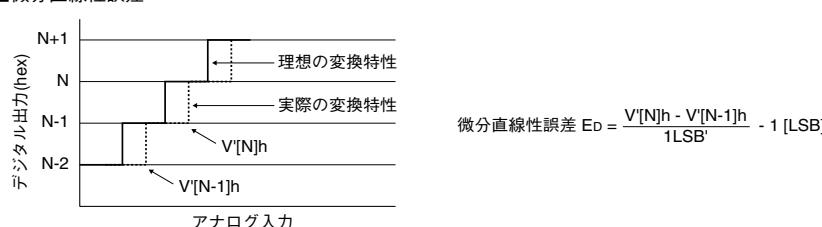

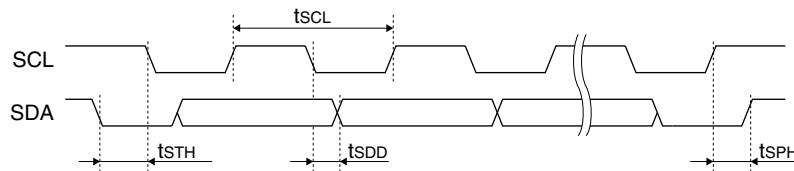

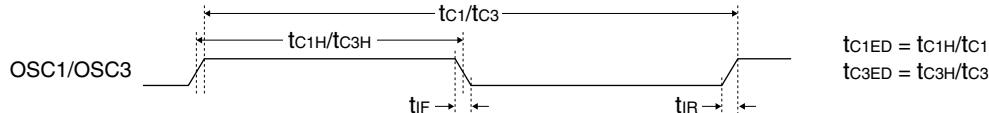

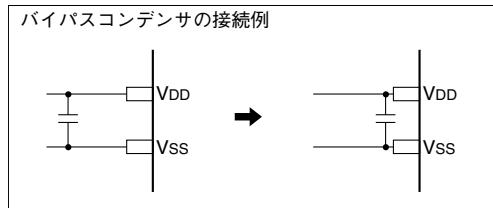

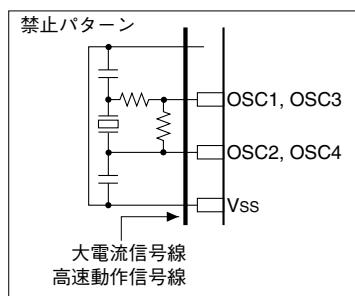

| 0x1        | 3サイクル        | 20MHz max. |