## LCD Controller

### ■ 概要

S1D13715 は、デュアルポートのカメラインターフェースとハードウェア JPEG エンコーダ／デコーダおよび外部の MPEG コーデックとインターフェースできる LCD コントローラです。ダイレクトまたはインダイレクトの CPU インターフェースに接続することで、最大 2 つの LCD パネルをコントロールできます。また、標準的 TFT パネルタイプと多くの拡張 TFT パネルタイプをサポートしています。320KB の内蔵 SRAM と豊富な機能セットを備える本製品は、移動通信機器や PDA (携帯情報端末) など、デジタルビデオを必要とする組込み市場のニーズに応える低消費電力のシングルチップソリューションです。

S1D13715 は、デジタルビデオ機能を必要とする携帯端末などのモバイルシステムを強力にサポートします。CPU の種類やオペレーティングシステムに依存しないため、非常に多様なアプリケーションに対して理想的な LCD コントローラを提供します。

### ■ 特長

- 320KB の内蔵 SRAM ディスプレイバッファ

- 低動作電圧

- ダイレクトおよびインダイレクトの CPU インターフェース

- 2 つのパネルが使用可能 (LCD2 は RAM 内蔵)

- RGB、シリアルおよびパラレルインターフェースのパネルをサポート

- HR-TFT を含む拡張 TFT インターフェース

- 内部 PLL またはデジタルクロック入力

- デュアルポートのカメラインターフェース

- ハードウェア JPEG エンコーダ／デコーダ

- YUV-RGB 変換

- SwivelView™ (ハードウェアによる表示画像の 90°、180°、270° 回転)

- (米国特許第 5,734,875 号、同第 5,956,049 号、同第 6,262,751 号)

- 「Picture-in-Picture Plus」 (PIP+)

- 2D ハードウェアアクセラレータ

- ソフトウェアによるパワーセーブモード

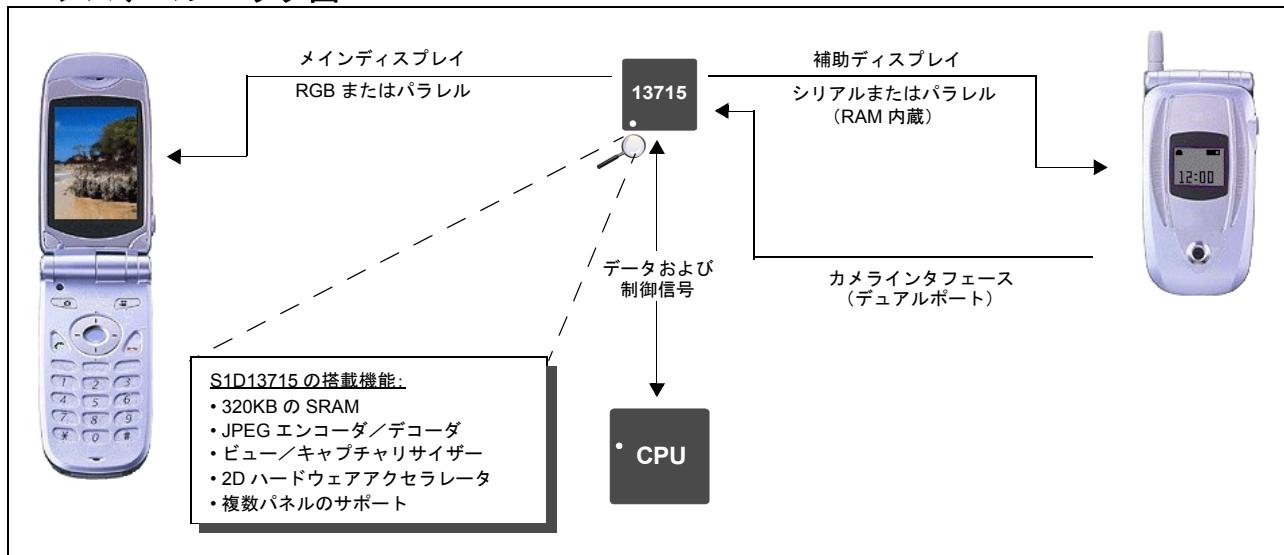

### ■ システムブロック図

# S1D13715

## ■ 仕様

### 内蔵ディスプレイバッファ

- 320KBの内蔵SRAM

- 1つの線形アドレス空間としてアドレス指定可能

### CPU インタフェース

- 16ビットの汎用非同期CPUインターフェース

- 間接および直接アドレス指定

### パネルのサポート

- 最大2つのLCDパネルをサポート

- LCD1 : 9/12/18/24ビットのRGBパネル

LCD2 : 8/9ビットのRAM内蔵シリアルパネル

- LCD1 : 8/16/18/24ビットのRAM内蔵パラレルパネル

LCD2 : 8/9ビットのRAM内蔵シリアルパネル

- LCD1 : 8/16/18/24ビットのRAM内蔵パラレルパネル

LCD2 : 8/16/18/24ビットのRAM内蔵パラレルパネル

- LCD1 : 9/12/18/24ビットのRGBパネル

LCD2 : 8ビットのRAM内蔵パラレルパネル

- TFT、HR-TFT、カシオ製TFT、 $\alpha$ -TFT、ND-TFD、拡張TFT

- 標準的な解像度：

最大320×480 (16bpp)

最大320×240 (32bpp)

### 高速化

- 2D BitBLTエンジン

- SwivelView : ハードウェアによる表示画像の90°、180°、270°回転

- ミラー表示 : ハードウェアによるミラー画像

### 表示機能

- 8/16/32bpp (ビット/ピクセル) をサポート

- Picture-in-Picture Plus (PIP+) : 背景画像の上に可変サイズウインドウを表示

- オーバレイ機能

- ピクセルダブリング : 有効解像度を2倍に

- ビデオ反転 : 表示データを反転

### デジタルビデオ

- デュアルポートのカメラインターフェース (YUV 4:2:2)

- ハードウェアJPEGエンコーダ (YUV 4:2:2、4:1:1、4:2:0)

- ハードウェアJPEGデコーダ (YUV 4:4:4、4:2:2、4:1:1、4:2:0)

- YUVの表示/キャプチャ (YUV 4:2:2、4:2:0)

- メモリ画像に対するJPEGエンコード (YUV 4:2:2、4:1:1、4:2:0)

- ビュー側およびキャプチャ側のハードウェアリサイズ (トリミングと縮小の機能あり)

- YUV-RGB変換とRGB-YUV変換

- 外部MPEGコーデックインターフェースをサポート

### その他

- 内部PLLまたはデジタルクロック入力

- ソフトウェアによるパワーセーブモード

- 複数の汎用IO端子

- CORE<sub>VDD</sub>は1.8V、IO<sub>VDD</sub>は3.0V

- FCBGAおよびPFBGAの160ピンパッケージ

- QFP 176ピンパッケージ

総合設計ツールについては、最寄りの営業担当者までご連絡ください。

|            |                        |       |                         |

|------------|------------------------|-------|-------------------------|

| テクニカルマニュアル | CPUに依存しないソフトウェアユーティリティ | 評価ボード | ロイヤリティフリーのソースレベルドライバコード |

|------------|------------------------|-------|-------------------------|

本資料のご使用につきましては、次の点にご留意願います。

- 本資料の内容については、予告なく変更することがあります。

- 本資料の一部、または全部を弊社に無断で転載、または複製など他の目的に使用することは堅くお断りします。

- 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

- 特性表の数値の大小は、数直線上の大小関係で表しています。

- 本資料に掲載されている製品のうち、「外国為替法及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合同法に基づく輸出許可が必要です。

- 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。

## セイコーエプソン株式会社

### 半導体事業部 IC 営業部

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042)587-5816(直通) FAX (042)587-5624

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06)6120-6000(代表) FAX (06)6120-6100

インターネットによる電子デバイスのご紹介

<http://www.epson.jp/device/semicon/>

ドキュメントコード: 411510900

2008年7月作成