21bit Channel Link LVDS レシーバー

**S1R77084F00A000**

テクニカルマニュアル

Preliminary

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## 目 次

|                       |    |

|-----------------------|----|

| 1. 概要                 | 1  |

| 2. 特長                 | 1  |

| 3. ブロック図              | 1  |

| 4. 端子配置図              | 2  |

| 5. 端子説明               | 3  |

| 5.1 LVDS 入力端子         | 3  |

| 5.2 LVDS 出力端子         | 3  |

| 5.3 設定端子              | 3  |

| 5.4 電源関連端子            | 4  |

| 6. 機能説明               | 5  |

| 6.1 LVDS データマッピング     | 5  |

| 6.2 LVDS 入力 Hi-Z 検出回路 | 5  |

| 6.3 終端抵抗              | 5  |

| 7. 電気的特性              | 6  |

| 7.1 絶対最大定格            | 6  |

| 7.2 推奨動作条件            | 6  |

| 7.3 CMOS 入出力特性        | 6  |

| 7.4 LVDS 入力特性         | 6  |

| 7.5 LVDS 入力タイミング特性    | 7  |

| 7.6 クロック入力／出力遅延特性     | 8  |

| 7.7 クロック入力／データ出力遅延特性  | 8  |

| 7.8 出力クロックデューティ       | 8  |

| 7.9 DLL ロックアップタイム特性   | 8  |

| 7.10 消費電流             | 8  |

| 8. 外形寸法図              | 9  |

| 9. 改訂履歴表              | 10 |

## 1. 概要

本 IC 「S1R77084」は LVDS レシーバ IC です。

S1R77084 は、3 チャンネルの LVDS データストリームを受け、21bits の CMOS/TTL データに復元します。

トランスマッタクロック周波数が 115MHz の場合、21bits の CMOS/TTL データは LVDS 1 チャンネルあたり 805Mbps で転送されます。115MHz のクロックを使った場合のトータルスループットは 2.415Gbps(301Mbyte/s)になります。

LVDS トランスマッタ IC としては、「S1R77094」の使用を推奨します。

また、「アナログフロントエンド IC」とセットで使用することにより、高速スキャナシステムに最適なチップセットが実現できます。

## 2. 特長

- 3 チャンネル LVDS 入力を 21bits CMOS/TTL 出力へ変換

- ワイドレンジクロック周波数：20MHz～115MHz

- 301Mbytes/s のスループット

- 3.3V 単一電源

- パワーダウン機能

- ローパワーCMOS プロセス

- QFP-48 ピンパッケージ

☆ 耐放射線性設計はされておりません

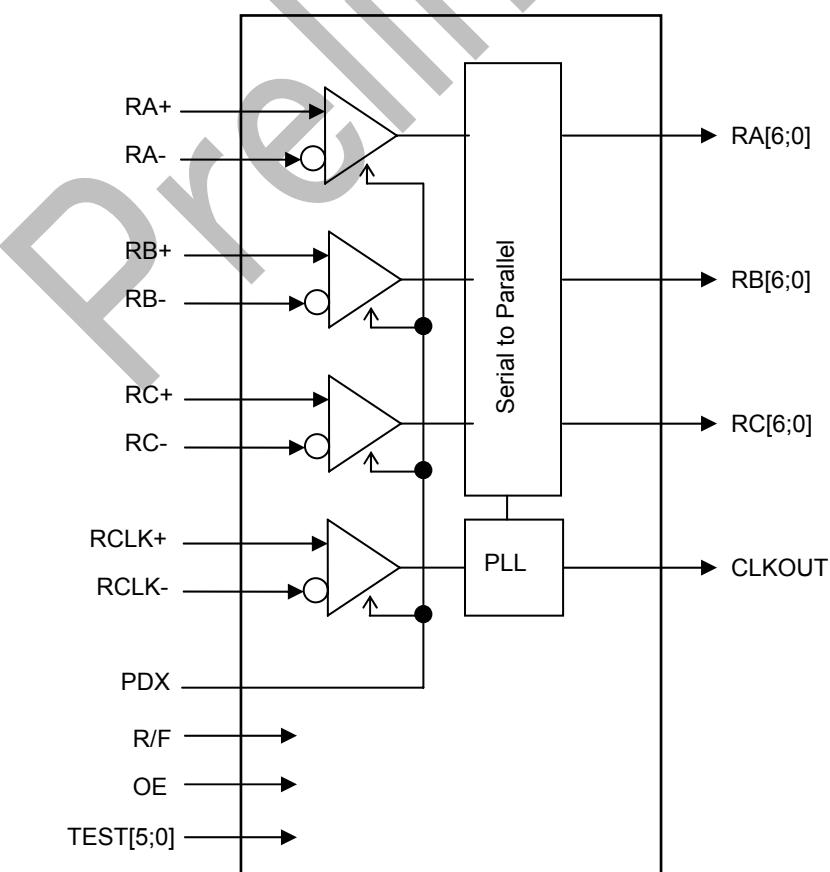

## 3. ブロック図

## 4. 端子配置図

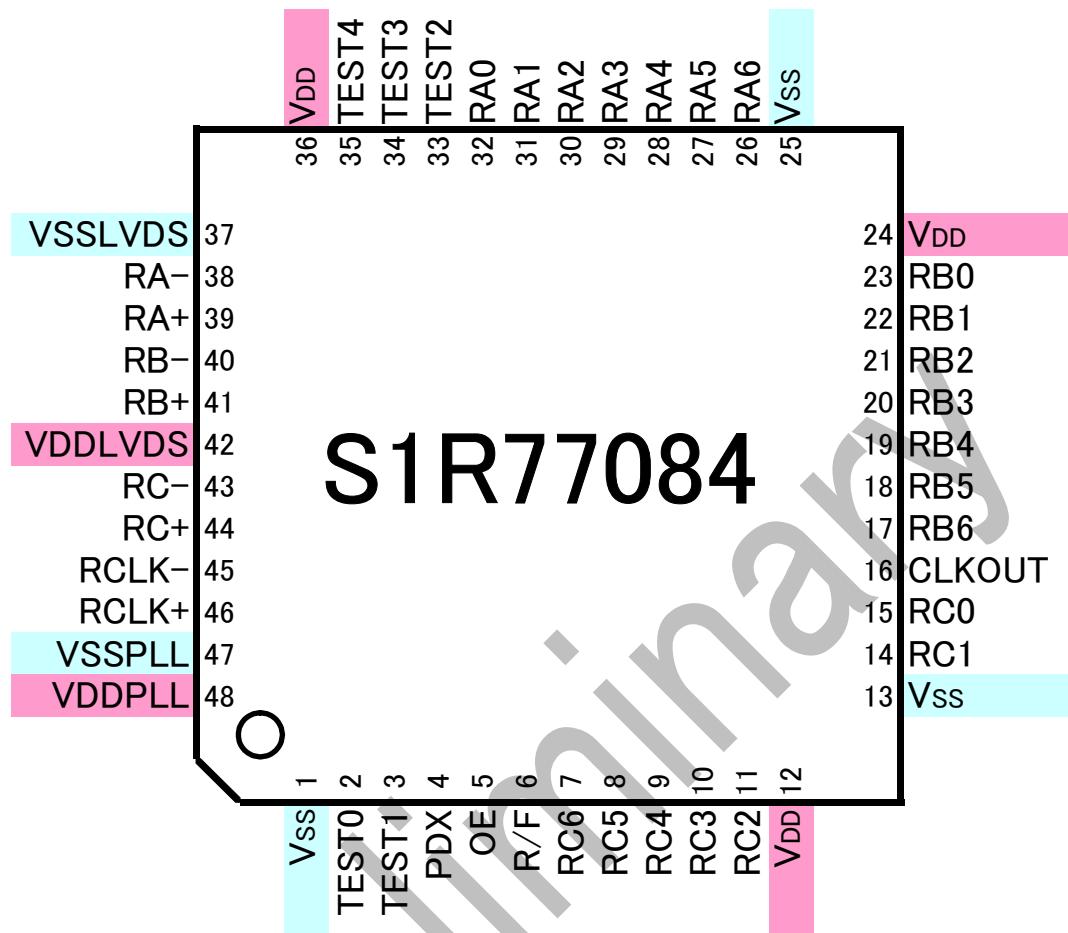

### 4. 端子配置図

## 5. 端子説明

### 5.1 LVDS 入力端子

| 端子名     | I/O | No.    | 説明                                         | 端子数 |

|---------|-----|--------|--------------------------------------------|-----|

| RA+/-   | I   | 39, 38 | LVDS 差動データ入力端子です。<br>+/-端子間に終端抵抗を挿入して下さい。  | 2   |

| RB+/-   | I   | 41, 40 | LVDS 差動データ入力端子です。<br>+/-端子間に終端抵抗を挿入して下さい。  | 2   |

| RC+/-   | I   | 44, 43 | LVDS 差動データ入力端子です。<br>+/-端子間に終端抵抗を挿入して下さい。  | 2   |

| RCLK+/- | I   | 46, 45 | LVDS 差動クロック入力端子です。<br>+/-端子間に終端抵抗を挿入して下さい。 | 2   |

### 5.2 LVDS 出力端子

| 端子名     | I/O | No.                              | 説明                  | 端子数 |

|---------|-----|----------------------------------|---------------------|-----|

| RA[6;0] | O   | 26, 27, 28,<br>29, 30, 31,<br>32 | LVDS パラレルデータ出力端子です。 | 7   |

| RB[6;0] | O   | 17, 18, 19,<br>20, 21, 22,<br>23 | LVDS パラレルデータ出力端子です。 | 7   |

| RC[6;0] | O   | 7, 8, 9,<br>10, 11, 14,<br>15    | LVDS パラレルデータ出力端子です。 | 7   |

| CLKOUT  | O   | 16                               | LVDS クロック出力端子です。    | 1   |

### 5.3 設定端子

| 端子名       | I/O | No.                 | 説明                                                           | 端子数 |

|-----------|-----|---------------------|--------------------------------------------------------------|-----|

| PDX       | I   | 4                   | パワーダウン設定の入力端子です。<br>H: ノーマル動作 L: パワーダウン                      | 1   |

| OE        | I   | 5                   | 出力イネーブル設定の入力端子です。<br>H: 出力イネーブル (ノーマル動作) L: 出力ディスエーブル (Hi-Z) | 1   |

| R/F       | I   | 6                   | 出力クロックのエッジトリガ設定の入力端子です。<br>H: Rising Edge L: Falling Edge    | 1   |

| TEST[4;0] | I   | 35, 34, 33,<br>3, 2 | 出荷時のテスト専用の入力端子です。<br>通常は Low 固定にして下さい。                       | 5   |

## 5. 端子説明

### 5.4 電源関連端子

| 端子名     | I/O | No.        | 説明                                                             | 端子数 |

|---------|-----|------------|----------------------------------------------------------------|-----|

| VDDLVDS | 電源  | 42         | LVDS のアナログ回路用の電源端子です。<br>外部電源 3.3V を供給して下さい。 他の電源端子とは分離して下さい。  | 1   |

| VDDPLL  | 電源  | 48         | PLL のアナログ回路用の電源端子です。<br>外部電源 3.3V を供給して下さい。 他の電源端子とは分離して下さい。   | 1   |

| VSSLVDS | 電源  | 37         | LVDS のアナログ回路用の接地端子です。<br>GND に接続される 0V の端子です。 他の接地端子とは分離して下さい。 | 1   |

| VSSPLL  | 電源  | 47         | PLL のアナログ回路用の接地端子です。<br>GND に接続される 0V の端子です。 他の接地端子とは分離して下さい。  | 1   |

| VDD     | 電源  | 12, 24, 36 | デジタル回路用の電源端子です。<br>外部電源 3.3V を供給して下さい。 他の電源端子とは分離して下さい。        | 3   |

| Vss     | 電源  | 1, 13, 25  | デジタル回路用の接地端子です。<br>GND に接続される 0V の端子です。 他の接地端子とは分離して下さい。       | 3   |

## 6. 機能説明

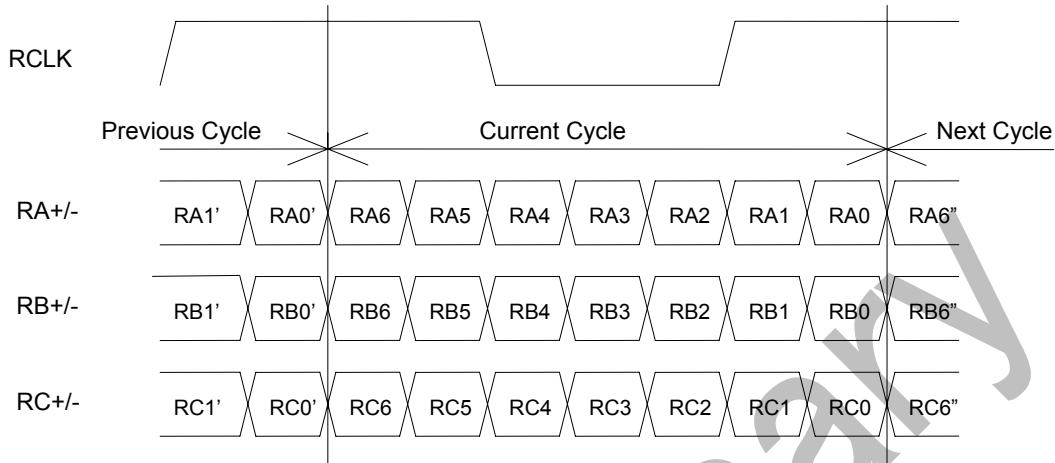

### 6.1 LVDS データマッピング

LVDS 信号は 7 ビットのシリアルデータで、以下の入出力マッピングとなります。

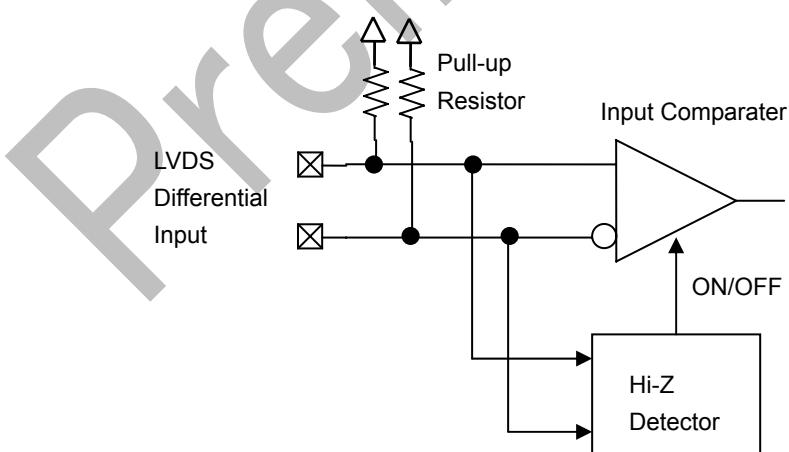

### 6.2 LVDS 入力 Hi-Z 検出回路

LVDS の差動入力信号が Hi-Z 状態の場合に内部回路が不安定にならないように、その Hi-Z 状態を検出する回路を内蔵しています。

LVDS の差動入力端子にはプルアップ抵抗がついています。差動入力信号が Hi-Z になった場合にはこのプルアップ抵抗によって差動ラインが High/High の状態になります。通常の差動でなくなつた High/High のレベルを検出して内部回路を停止させます。

### 6.3 終端抵抗

受信チャネル外部端子の直近に  $100\Omega$  の終端抵抗を接続してください。また、送信チャネルにおいても受信デバイスの入力端子直近にて  $100\Omega$  で終端してください。

#### 「制限注意事項」

終端抵抗は公差  $\pm 1.0\%$  以下を推奨します。

また、基板実装は本 IC とスルーホール等を介さず同一面に実装してください。

## 7. 電気的特性

### 7. 電気的特性

#### 7.1 絶対最大定格

| Item                | Symbol | Min            | Unit |

|---------------------|--------|----------------|------|

| Supply Voltage      | Vdd    | -0.3 ~ 4.0     | V    |

| Storage Temperature | Tstg   | -65 ~ 150      | °C   |

| Input Voltage       | Vin    | -0.5 ~ VDD+0.5 | V    |

#### 7.2 推奨動作条件

| Item                  | Symbol | Condition               | Min. | Typ. | Max. | Unit |

|-----------------------|--------|-------------------------|------|------|------|------|

| Supply Voltage        | Vdd1   | VDDLVDS,<br>VDDPLL, VDD | 3.0  | 3.3  | 3.6  | V    |

| Supply Voltage        | Vdd2   | VDDLVDS,<br>VDDPLL, VDD | 2.7  | 3.0  | 3.3  | V    |

| Operating Temperature | Topr   | —                       | -40  | 25   | 85   | °C   |

| Input Clock Frequency | Fin1   | Vdd=3.3±0.3V            | 20   | —    | 115  | MHz  |

| Input Clock Frequency | Fin2   | Vdd=3.0±0.3V            | 20   | —    | 85   | MHz  |

#### 7.3 CMOS 入出力特性

| Item                      | Symbol | Condition                           | Min.    | Typ. | Max. | Unit |

|---------------------------|--------|-------------------------------------|---------|------|------|------|

| High Level Input Voltage  | Vih    | VDD=Max.                            | 2.0     | —    | —    | V    |

| Low Level Input Voltage   | Vil    | VDD=Min.                            | VSS     | —    | 0.8  | V    |

| High Level Output Voltage | Voh    | IoH=-2mA (Data)<br>IoH=-6mA (Clock) | VDD-0.4 | —    | —    | V    |

| Low Level Output Voltage  | Vol    | IoH=2mA (Data)<br>IoH=6mA (Clock)   | —       | —    | 0.4  | V    |

| Input Leak Current        | Iil    | —                                   | -1      | —    | 1    | μA   |

#### 7.4 LVDS 入力特性

| Item                              | Symbol | Condition | Min.        | Typ. | Max. | Unit |

|-----------------------------------|--------|-----------|-------------|------|------|------|

| Differential Input High Threshold | Vth    | Vcm=1.25V | —           | —    | +100 | mV   |

| Differential Input Low Threshold  | Vtl    | Vcm=1.25V | -100        | —    | —    | mV   |

| Differential Input Voltage        | Vid    | —         | 100         | 350  | 600  | mV   |

| Common Mode Voltage               | Vcm1   | VDD>3.0V  | 0 +  Vid /2 | 1.25 | 2.0  | V    |

| Common Mode Voltage               | Vcm2   | VDD<3.0V  | 0 +  Vid /2 | 1.25 | 1.8  | V    |

| Input Pull-up Resistor            | Rpu    | —         | 100         | 200  | 600  | kΩ   |

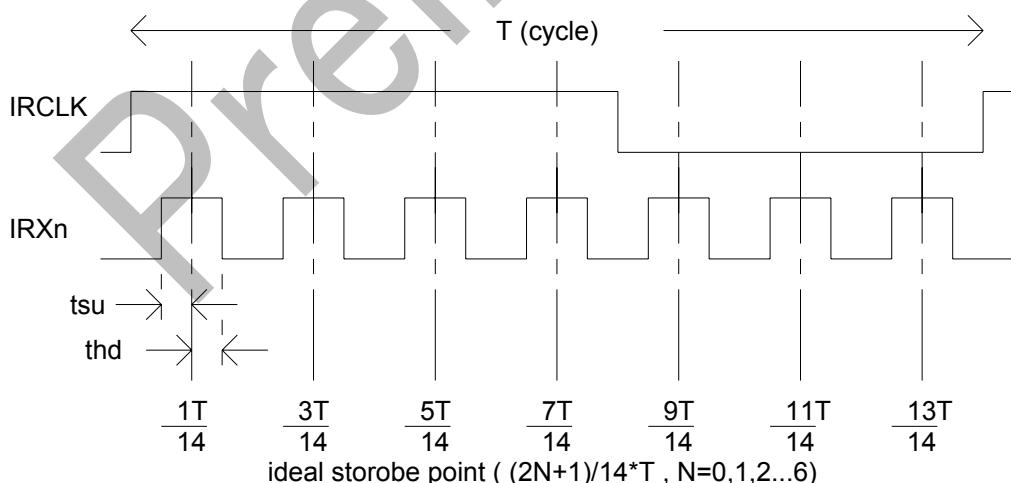

## 7.5 LVDS 入力タイミング特性

VDD=3.3V±0.3V、Ta=-40～+85°C

| Item             | Symbol | Condition           | Min. | Typ. | Max. | Unit |

|------------------|--------|---------------------|------|------|------|------|

| Data Setup Time1 | tsu1   | Tin=9ns, Vcm=1.25V  | 250  | —    | —    | ps   |

| Data Hold Time1  | thd1   | Tin=9ns, Vcm=1.25V  | 400  | —    | —    | ps   |

| Data Setup Time2 | tsu2   | Tin=12ns, Vcm=1.25V | 350  | —    | —    | ps   |

| Data Hold Time2  | thd2   | Tin=12ns, Vcm=1.25V | 350  | —    | —    | ps   |

| Data Setup Time3 | tsu3   | Tin=15ns, Vcm=1.25V | 400  | —    | —    | ps   |

| Data Hold Time3  | thd3   | Tin=15ns, Vcm=1.25V | 400  | —    | —    | ps   |

| Data Setup Time4 | tsu4   | Tin=18ns, Vcm=1.25V | 550  | —    | —    | ps   |

| Data Hold Time4  | thd4   | Tin=18ns, Vcm=1.25V | 550  | —    | —    | ps   |

| Data Setup Time5 | tsu5   | Tin=25ns, Vcm=1.25V | 1050 | —    | —    | ps   |

| Data Hold Time5  | thd5   | Tin=25ns, Vcm=1.25V | 1050 | —    | —    | ps   |

VDD=3.0V±0.3V、Ta=-40～+85°C

| Item             | Symbol | Condition           | Min. | Typ. | Max. | Unit |

|------------------|--------|---------------------|------|------|------|------|

| Data Setup Time1 | tsu1   | Tin=9ns, Vcm=1.25V  | —    | —    | —    | ps   |

| Data Hold Time1  | thd1   | Tin=9ns, Vcm=1.25V  | —    | —    | —    | ps   |

| Data Setup Time2 | tsu2   | Tin=12ns, Vcm=1.25V | 350  | —    | —    | ps   |

| Data Hold Time2  | thd2   | Tin=12ns, Vcm=1.25V | 350  | —    | —    | ps   |

| Data Setup Time3 | tsu3   | Tin=15ns, Vcm=1.25V | 400  | —    | —    | ps   |

| Data Hold Time3  | thd3   | Tin=15ns, Vcm=1.25V | 400  | —    | —    | ps   |

| Data Setup Time4 | tsu4   | Tin=18ns, Vcm=1.25V | 550  | —    | —    | ps   |

| Data Hold Time4  | thd4   | Tin=18ns, Vcm=1.25V | 550  | —    | —    | ps   |

| Data Setup Time5 | tsu5   | Tin=25ns, Vcm=1.25V | 1150 | —    | —    | ps   |

| Data Hold Time5  | thd5   | Tin=25ns, Vcm=1.25V | 1150 | —    | —    | ps   |

(注) VDD=3.0V 未満では Tin=9ns の動作保証は不可となります。

## 7. 電気的特性

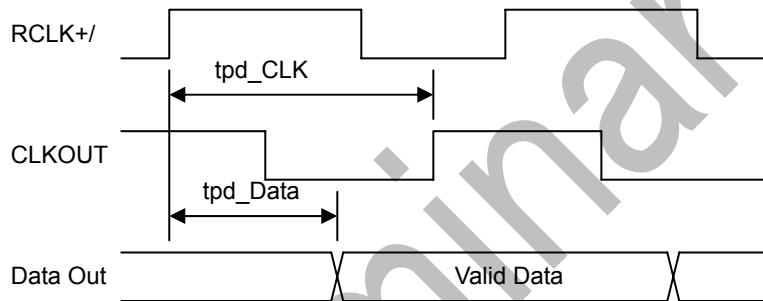

### 7.6 クロック入力／出力遅延特性

| Item         | Symbol  | Condition            | Min.          | Typ.          | Max.          | Unit |

|--------------|---------|----------------------|---------------|---------------|---------------|------|

| CLKOUT Delay | tpd_CLK | 3.3V±0.3V, 0~+70°C   | 1.98+(T/14)×8 | 3.31+(T/14)×8 | 5.29+(T/14)×8 | ns   |

|              |         | 3.0V±0.3V, 0~+70°C   | 2.19+(T/14)×8 | 3.59+(T/14)×8 | 5.89+(T/14)×8 | ns   |

|              |         | 3.3V±0.3V, -40~+85°C | 1.92+(T/14)×8 | 3.31+(T/14)×8 | 5.52+(T/14)×8 | ns   |

|              |         | 3.0V±0.3V, -40~+85°C | 2.08+(T/14)×8 | 3.59+(T/14)×8 | 6.10+(T/14)×8 | ns   |

### 7.7 クロック入力／データ出力遅延特性

| Item              | Symbol   | Condition            | Min.          | Typ.          | Max.          | Unit |

|-------------------|----------|----------------------|---------------|---------------|---------------|------|

| Data Output Delay | tpd_Data | 3.3V±0.3V, 0~+70°C   | 2.37+(T/14)×4 | 3.95+(T/14)×4 | 6.32+(T/14)×4 | ns   |

|                   |          | 3.0V±0.3V, 0~+70°C   | 2.62+(T/14)×4 | 4.29+(T/14)×4 | 7.04+(T/14)×4 | ns   |

|                   |          | 3.3V±0.3V, -40~+85°C | 2.29+(T/14)×4 | 3.95+(T/14)×4 | 6.59+(T/14)×4 | ns   |

|                   |          | 3.0V±0.3V, -40~+85°C | 2.49+(T/14)×4 | 4.29+(T/14)×4 | 7.30+(T/14)×4 | ns   |

### 7.8 出力クロックデューティ

| Item        | Symbol   | Condition | Min. | Typ. | Max. | Unit |

|-------------|----------|-----------|------|------|------|------|

| CLKOUT Duty | Duty_CLK | —         | 45   | 50   | 55   | %    |

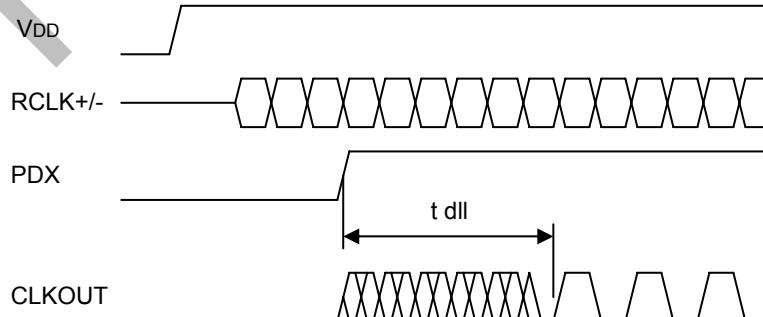

### 7.9 DLL ロックアップタイム特性

| Item          | Symbol | Condition | Min. | Typ. | Max. | Unit |

|---------------|--------|-----------|------|------|------|------|

| DLL Lock Time | tdll   | —         | —    | 1    | 10   | ms   |

### 7.10 消費電流

| Item                | Symbol     | Condition                                | Min. | Typ. | Max. | Unit |

|---------------------|------------|------------------------------------------|------|------|------|------|

| Current Consumption | Pd_VDDLVDs | Tin=15nS、<br>VDDLVDs=VDDPLL=<br>VDD=3.3V | —    | TBD  | —    | mA   |

|                     | Pd_VDDPLL  |                                          | —    | TBD  | —    |      |

|                     | Pd_VDD     |                                          | —    | TBD  | —    |      |

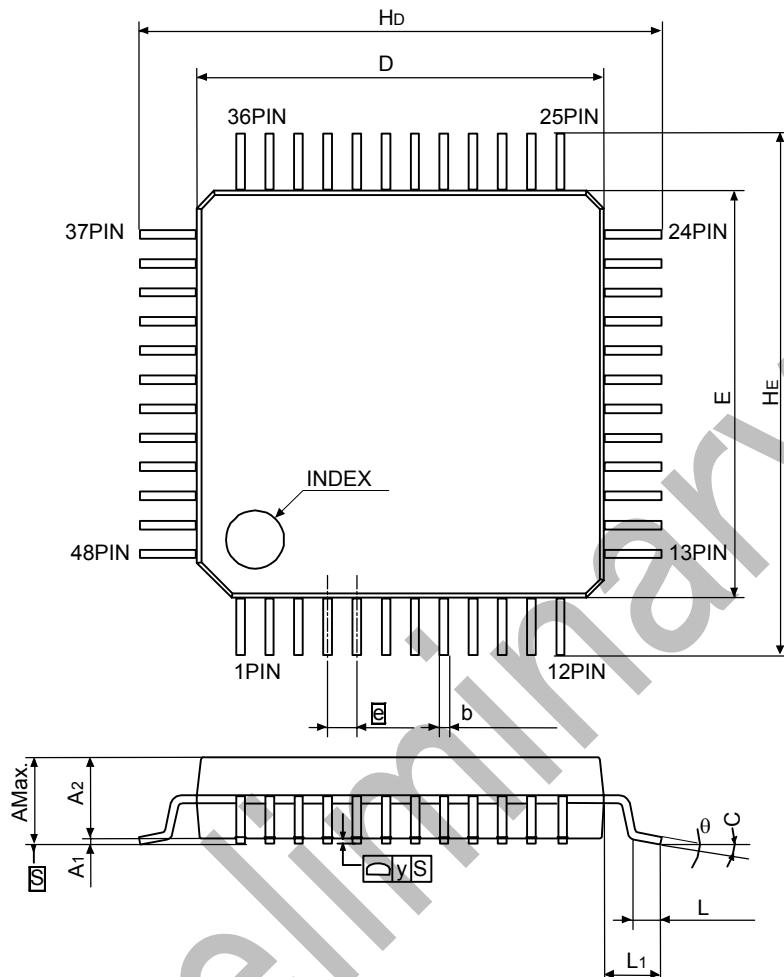

## 8. 外形寸法図

| Symbol           | Dimension in Millimeters |      |      |

|------------------|--------------------------|------|------|

|                  | Min.                     | Nom. | Max. |

| E                | —                        | 7    | —    |

| D                | —                        | 7    | —    |

| A <sub>max</sub> | —                        | —    | 1.7  |

| A <sub>1</sub>   | —                        | 0.1  | —    |

| A <sub>2</sub>   | —                        | 1.4  | —    |

| $\bar{e}$        | —                        | 0.5  | —    |

| b                | 0.13                     | —    | 0.27 |

| c                | 0.09                     | —    | 0.2  |

| $\theta$         | 0°                       | —    | 10°  |

| L                | 0.3                      | —    | 0.7  |

| L <sub>1</sub>   | —                        | 1    | —    |

| H <sub>E</sub>   | —                        | 9    | —    |

| H <sub>D</sub>   | —                        | 9    | —    |

| y                | —                        | —    | 0.08 |

Unit:mm

LQFP12-48PIN

## 9. 改訂履歴表

### 9. 改訂履歴表

| 年月日       | レビジョン   | 改訂内容 |     |      |                                                                                                                        |                                                                                                                                                            |

|-----------|---------|------|-----|------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |         | 適用   | ページ | 該当項目 | 旧内容                                                                                                                    | 新内容                                                                                                                                                        |

| '07/6/25  | Rev.0.1 | 新規   | 全項  | —    | —                                                                                                                      | 新規制定                                                                                                                                                       |

| '07/11/22 | Rev.0.2 | 改定   | P1  | 概要   | 本 IC「S1R77084」は、LVDS 信号を受ける LVDS レシーバ IC です。CCD 駆動クロック搭載アナログフロントエンド IC と組み合わせることで、EMI 特性に優れた高速スキャナシステムを容易に実現することができます。 | 「本 IC「S1R77084」は LVDS レシーバ IC です。S1R77084 は、3 チャンネルの LVDS データストリームを受け、21bit の CMOS/TTL データに復元します。」<br>(一部抜粋)                                               |

|           |         |      |     | 特長   | LVDS 3 チャンネル内蔵<br>パワーダウン機能<br>3.3V 単一電源<br>ローパワー CMOS プロセス<br>QFP-48 ピンパッケージ                                           | 3 チャンネル LVDS 入力を 21bit CMOS/TTL 出力へ変換<br>ワイドレンジクロック周波数 : 20MHz~115MHz<br>301Mbyte/s のスループット<br>3.3V 単一電源<br>パワーダウン機能<br>ローパワー CMOS プロセス<br>QFP-48 ピン パッケージ |

|           |         | 追加   | P4  | 追加   | —                                                                                                                      | 6.3 終端抵抗                                                                                                                                                   |

**セイコーエプソン株式会社**

**半導体事業部 IC 営業部**

---

<IC 国内営業グループ>

東京 〒191-8501 東京都日野市日野 421-8

TEL (042) 587-5313 (直通) FAX (042) 587-5116

大阪 〒541-0059 大阪市中央区博労町 3-5-1 エプソン大阪ビル 15F

TEL (06) 6120-6000 (代表) FAX (06) 6120-6100

---

ドキュメントコード : 411269400

2007 年 12 月 作成