# S1R72H74

## テクニカルマニュアル

本資料のご使用につきましては、次の点にご留意願います。

本資料の内容については、予告無く変更することがあります。

1. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りいたします。

2. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これら起因する第三者の権利（工業所有権を含む）侵害あるいは損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

3. 特性値の数値の大小は、数直線上の大小関係で表しています。

4. 本資料に掲載されている製品のうち「外国為替及び外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

5. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提といたしません。よって、弊社は本（当該）製品をこれらの用途に用いた場合のいかなる責任についても負いかねます。

## **適用範囲**

本ドキュメントは、ATA ホストコントローラ LSI 「S1R72H74」に適用されます。

# 目 次

|                                                      |          |

|------------------------------------------------------|----------|

| <b>1. 概要 .....</b>                                   | <b>1</b> |

| <b>2. 特長 .....</b>                                   | <b>2</b> |

| <b>3. ブロック図 .....</b>                                | <b>3</b> |

| 3.1 PLL60.....                                       | 4        |

| 3.2 FIFO Endpoint / FIFO Controller / FIFO RAM ..... | 4        |

| 3.3 CPU I/F Controller.....                          | 4        |

| 3.4 DMA Controller .....                             | 4        |

| 3.5 IDE Master Controller.....                       | 4        |

| 3.6 TestMUX .....                                    | 4        |

| <b>4. 端子配置図 .....</b>                                | <b>5</b> |

| 4.1 端子配置図 (QFP パッケージ) .....                          | 5        |

| <b>5. 端子機能説明.....</b>                                | <b>6</b> |

| <b>6. 機能説明 .....</b>                                 | <b>9</b> |

| 6.1 互換性.....                                         | 9        |

| 6.2 パワーマネージメント機能 .....                               | 9        |

| 6.2.1 SLEEP (スリープ) .....                             | 10       |

| 6.2.2 SNOOZE (スヌーズ) .....                            | 11       |

| 6.2.3 ACTIVE60 (アクティブ 60) .....                      | 11       |

| 6.3 FIFO 管理 .....                                    | 12       |

| 6.3.1 FIFO 管理 .....                                  | 12       |

| 6.3.1.1 FIFO メモリマップ .....                            | 12       |

| 6.3.2 FIFO へのアクセス方法 .....                            | 12       |

| 6.3.2.1 FIFO へのアクセス方法 (PIO アクセス) .....               | 12       |

| 6.3.2.2 FIFO へのアクセス方法 (DMA) .....                    | 13       |

| 6.3.2.3 FIFO へのアクセス方法(IDE).....                      | 13       |

| 6.3.2.4 FIFO へのアクセス制限 .....                          | 13       |

| 6.4 CPUIF.....                                       | 14       |

| 6.4.1 モード切り替え .....                                  | 14       |

| 6.4.2 モード切り替えに際して .....                              | 14       |

| 6.4.2.1 16bit BE mode をご使用の場合 .....                  | 14       |

| 6.4.2.2 8bit mode をご使用の場合 .....                      | 16       |

| 6.4.3 ブロック構成 .....                                   | 16       |

| 6.4.3.1 REG (S1R72H74 Registers) .....               | 16       |

| 6.4.3.1.1 同期レジスタアクセス (ライト) .....                     | 16       |

| 6.4.3.1.2 同期レジスタアクセス (リード) .....                     | 16       |

| 6.4.3.1.3 FIFO アクセス (ライト) .....                      | 16       |

| 6.4.3.1.4 FIFO アクセス (リード) .....                      | 17       |

| 6.4.3.1.5 FIFO アクセスの端数処理 .....                       | 17       |

| 6.4.3.1.6 非同期レジスタアクセス (ライト) .....                    | 19       |

| 6.4.3.1.7 非同期レジスタアクセス (リード) .....                    | 19       |

| 6.4.3.2 DMA0/DMA1 (DMA ch.0 / ch.1) .....            | 19       |

| 6.4.3.2.1 基本機能 .....                                 | 19       |

| 6.4.3.2.2 端子設定 .....                                 | 21       |

| 6.4.3.2.3 アクセスマード設定 .....                            | 22       |

| 6.4.3.2.4 カウントモード (ライト) .....                        | 22       |

| 6.4.3.2.5 カウントモード (リード) .....                        | 23       |

| 6.4.3.2.6 フリーランモード (ライト) .....                       | 24       |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 6.4.3.2.7 フリーランモード(リード) .....                               | 25        |

| 6.4.3.2.8 REQ アサートカウントオプション(ライト) .....                      | 25        |

| 6.4.3.2.9 REQ アサートカウントオプション(リード) .....                      | 26        |

| 6.4.3.2.10 DMA の FIFO アクセス端数処理 .....                        | 26        |

| <b>6.5 IDE I/F .....</b>                                    | <b>26</b> |

| 6.5.1 IDE タスクファイルレジスタへのアクセス .....                           | 27        |

| 6.5.1.1 IDE タスクファイルレジスタからのリード .....                         | 27        |

| 6.5.1.2 IDE タスクファイルレジスタへのライト .....                          | 27        |

| 6.5.1.3 IDE タスクファイルレジスタへのシーケンシャルライト .....                   | 27        |

| 6.5.1.4 IDE タスクファイルレジスタからのオートステータスレジスタリード .....             | 27        |

| 6.5.2 PIO アクセス .....                                        | 28        |

| 6.5.2.1 PIO リード DMA .....                                   | 28        |

| 6.5.2.2 PIO ライト DMA .....                                   | 28        |

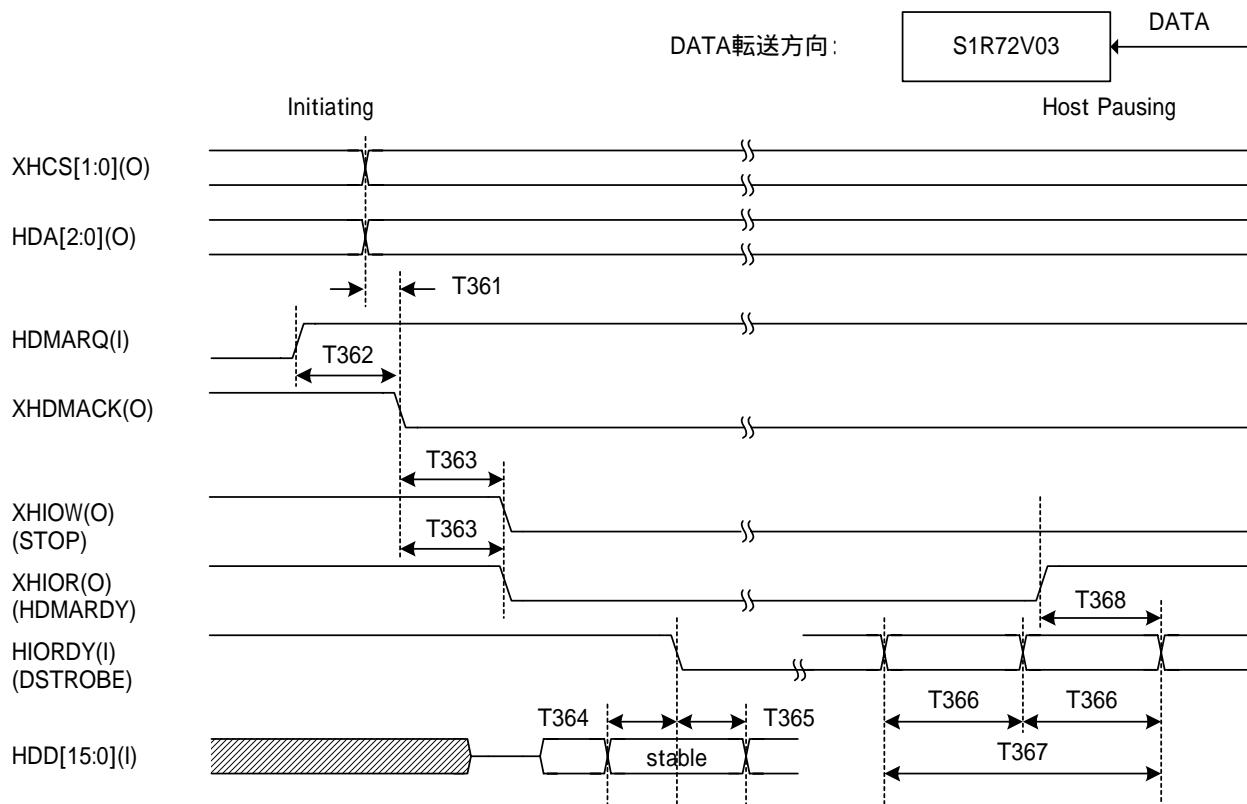

| 6.5.3 Multi-Word DMA .....                                  | 28        |

| 6.5.3.1 Multi-Word DMA リード .....                            | 28        |

| 6.5.3.2 Multi-Word DMA ライト .....                            | 29        |

| 6.5.4 Ultra DMA .....                                       | 30        |

| 6.5.4.1 Ultra DMA リード .....                                 | 30        |

| 6.5.4.2 Ultra DMA ライト .....                                 | 30        |

| 6.5.5 IDE 転送モードの設定について .....                                | 31        |

| <b>6.6 バウンダリスキャン (JTAG) .....</b>                           | <b>32</b> |

| 6.6.1 対応インストラクション .....                                     | 32        |

| 6.6.2 DEVICE_CODE について .....                                | 32        |

| 6.6.3 バウンダリスキャン除外端子 .....                                   | 32        |

| <b>7. レジスタ .....</b>                                        | <b>33</b> |

| <b>7.1 レジスタマップ .....</b>                                    | <b>33</b> |

| <b>7.2 レジスタ詳細説明 .....</b>                                   | <b>41</b> |

| 7.2.1 00h MainIntStat (Main Interrupt Status) .....         | 41        |

| 7.2.2 02h SIE_IntStat (SIE Interrupt Status) .....          | 42        |

| 7.2.3 03h CPU_IntStat (CPU Interrupt Status) .....          | 43        |

| 7.2.4 04h FIFO_IntStat (FIFO Interrupt Status) .....        | 44        |

| 7.2.5 06h IDE_IntStat (IDE Interrupt Status) .....          | 45        |

| 7.2.6 10h MainIntEnb (Main Interrupt Enable) .....          | 45        |

| 7.2.7 12h SIE_IntEnb (SIE Interrupt Enable) .....           | 45        |

| 7.2.8 13h CPU_IntEnb (CPU Interrupt Enable) .....           | 45        |

| 7.2.9 14h FIFO_IntEnb (FIFO Interrupt Enable) .....         | 45        |

| 7.2.10 16h IDE_IntEnb (IDE Interrupt Enable) .....          | 45        |

| 7.2.11 20h RevisionNum (Revision Number) .....              | 45        |

| 7.2.12 21h ChipReset (Chip Reset) .....                     | 45        |

| 7.2.13 22h PM_Control (Power Management Control) .....      | 45        |

| 7.2.14 29h EPrxFIFO_Clr (Endpoint FIFO Clear) .....         | 45        |

| 7.2.15 2Ah ClrAllJoin (Clear All Join) .....                | 45        |

| 7.2.16 2Eh WakeupTim_H (Wakeup Time High) .....             | 45        |

| 7.2.17 2Fh WakeupTim_L (Wakeup Time Low) .....              | 45        |

| 7.2.18 5Ah EPbConfig_0 (EPb Configuration 0) .....          | 45        |

| 7.2.19 5Dh EPbJoin (End Point b Join) .....                 | 45        |

| 7.2.20 62h EPcConfig_0 (EPc Configuration 0) .....          | 45        |

| 7.2.21 65h EPcJoin (End Point c Join) .....                 | 45        |

| 7.2.22 70h EPnFIFO_Rd_H (EPn FIFO Read High) .....          | 45        |

| 7.2.23 71h EPnFIFO_Rd_L (EPn FIFO Read Low) .....           | 45        |

| 7.2.24 72h EPnFIFO_Wr_H (EPn FIFO Write High) .....         | 45        |

| 7.2.25 73h EPnFIFO_Wr_L (EPn FIFO Write Low) .....          | 45        |

| 7.2.26 74h EPnRdRemain_H (EPn FIFO Read Remain High) .....  | 45        |

| 7.2.27 75h EPnRdRemain_L (EPn FIFO Read Remain Low) .....   | 45        |

| 7.2.28 76h EPnWrRemain_H (EPn FIFO Write Remain High) ..... | 45        |

| 7.2.29 77h EPnWrRemain_L (EPn FIFO Write Remain Low) .....  | 45        |

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| 7.2.30 7Ch EPnFIFO_ByteRd(EPn FIFO Byte Read) .....                            | 45        |

| 7.2.31 80h DMA0_FIFO_Control (DMA0 FIFO Control) .....                         | 45        |

| 7.2.32 81h DMA0_Config (DMA0 Config) .....                                     | 45        |

| 7.2.33 82h DMA0_Control (DMA0 Control) .....                                   | 45        |

| 7.2.34 84h DMA0_Remain_H (DMA0 FIFO Remain High) .....                         | 45        |

| 7.2.35 85h DMA0_Remain_L (DMA0 FIFO Remain Low) .....                          | 45        |

| 7.2.36 88h DMA0_Count_HH (DMA0 Transfer Byte Counter High/High) .....          | 45        |

| 7.2.37 89h DMA0_Count_HL (DMA0 Transfer Byte Counter High/Low) .....           | 45        |

| 7.2.38 8Ah DMA0_Count_LH (DMA0 Transfer Byte Counter Low/High) .....           | 45        |

| 7.2.39 8Bh DMA0_Count_LL (DMA0 Transfer Byte Counter Low/Low) .....            | 45        |

| 7.2.40 8Ch DMA0_RdData_H (DMA0 Read Data High) .....                           | 45        |

| 7.2.41 8Dh DMA0_RdData_L (DMA0 Read Data Low) .....                            | 45        |

| 7.2.42 8Eh DMA0_WrData_H (DMA0 Write Data High) .....                          | 45        |

| 7.2.43 8Fh DMA0_WrData_L (DMA0 Write Data Low) .....                           | 45        |

| 7.2.44 90h DMA1_FIFO_Control (DMA1 FIFO Control) .....                         | 45        |

| 7.2.45 91h DMA1_Config (DMA0 Config) .....                                     | 45        |

| 7.2.46 92h DMA1_Control (DMA1 Control) .....                                   | 45        |

| 7.2.47 94h DMA1_Remain_H (DMA1 FIFO Remain High) .....                         | 45        |

| 7.2.48 95h DMA1_Remain_L (DMA1 FIFO Remain Low) .....                          | 45        |

| 7.2.49 98h DMA1_Count_HH (DMA1 Transfer Byte Counter High/High) .....          | 45        |

| 7.2.50 99h DMA1_Count_HL (DMA1 Transfer Byte Counter High/Low) .....           | 45        |

| 7.2.51 9Ah DMA1_Count_LH (DMA1 Transfer Byte Counter Low/High) .....           | 45        |

| 7.2.52 9Bh DMA1_Count_LL (DMA1 Transfer Byte Counter Low/Low) .....            | 45        |

| 7.2.53 9Ch DMA1_RdData_H (DMA1 Read Data High) .....                           | 45        |

| 7.2.54 9Dh DMA1_RdData_L (DMA1 Read Data Low) .....                            | 45        |

| 7.2.55 9Eh DMA1_WrData_H (DMA1 Write Data High) .....                          | 45        |

| 7.2.56 9Fh DMA1_WrData_L (DMA1 Write Data Low) .....                           | 45        |

| 7.2.57 A0h IDE_Status (IDE Status) .....                                       | 45        |

| 7.2.58 A1h IDE_Control (IDE Control) .....                                     | 45        |

| 7.2.59 A2h IDE_Config_0 (IDE Configuration 0) .....                            | 45        |

| 7.2.60 A3h IDE_Config_1 (IDE Configuration 1) .....                            | 45        |

| 7.2.61 A4h IDE_Rmod (IDE Register Mode) .....                                  | 45        |

| 7.2.62 A5h IDE_Tmod (IDE Transfer Mode) .....                                  | 45        |

| 7.2.63 A6h IDE_Umod (IDE Ultra-DMA Transfer Mode) .....                        | 45        |

| 7.2.64 AAh IDE_CRC_H (IDE CRC High) .....                                      | 45        |

| 7.2.65 ABh IDE_CRC_L (IDE CRC Low) .....                                       | 45        |

| 7.2.66 ADh IDE_Count_H (IDE Transfer Byte Counter High) .....                  | 45        |

| 7.2.67 AEh IDE_Count_M (IDE Transfer Byte Counter Middle) .....                | 45        |

| 7.2.68 AFh IDE_Count_L (IDE Transfer Byte Counter Low) .....                   | 45        |

| 7.2.69 B0h IDE_RegAdrs (IDE Register Address) .....                            | 45        |

| 7.2.70 B2h IDE_RdRegValue_H (IDE Register Read Value High) .....               | 45        |

| 7.2.71 B3h IDE_RdRegValue_L (IDE Register Read Value Low) .....                | 45        |

| 7.2.72 B4h IDE_WrRegValue_H (IDE Register Write Value High) .....              | 45        |

| 7.2.73 B5h IDE_WrRegValue_L (IDE Register Write Value Low) .....               | 45        |

| 7.2.74 B6h IDE_SeqWrRegControl (IDE Sequential Register Write Control) .....   | 45        |

| 7.2.75 B7h IDE_SeqWrRegCnt (IDE Sequential Register Write Counter) .....       | 45        |

| 7.2.76 B8h IDE_SeqWrRegAdrs (IDE Sequential Register Write Address FIFO) ..... | 45        |

| 7.2.77 B9h IDE_SeqWrRegValue (IDE Sequential Register Write Value FIFO) .....  | 45        |

| 7.2.78 BCh IDE_RegConfig (IDE Register Configuration) .....                    | 45        |

| 7.2.79 EBh ModeProtect (Mode Protection) .....                                 | 45        |

| 7.2.80 EDh ClkSelect (Clock Select) .....                                      | 45        |

| 7.2.81 EFh ChipConfig (Chip Configuration) .....                               | 45        |

| <b>8. 電気的特性 .....</b>                                                          | <b>45</b> |

| <b>8.1 絶対最大定格 .....</b>                                                        | <b>45</b> |

| <b>8.2 推奨動作条件 .....</b>                                                        | <b>45</b> |

| <b>8.3 DC 特性 .....</b>                                                         | <b>45</b> |

|                                                     |           |

|-----------------------------------------------------|-----------|

| <b>8.4 AC 特性 .....</b>                              | <b>45</b> |

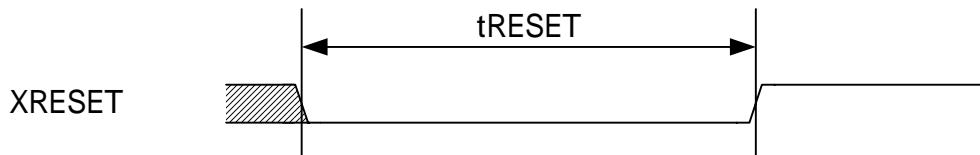

| 8.4.1 RESET タイミング .....                             | 45        |

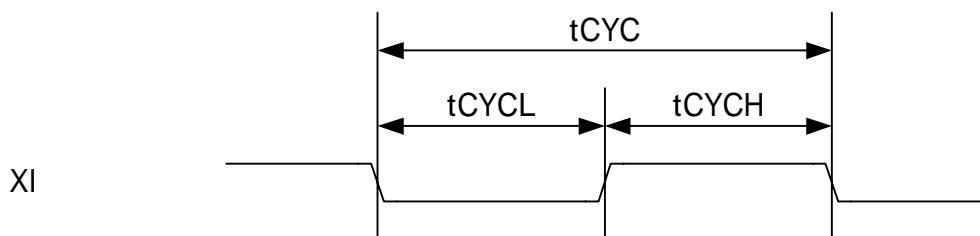

| 8.4.2 クロックタイミング .....                               | 45        |

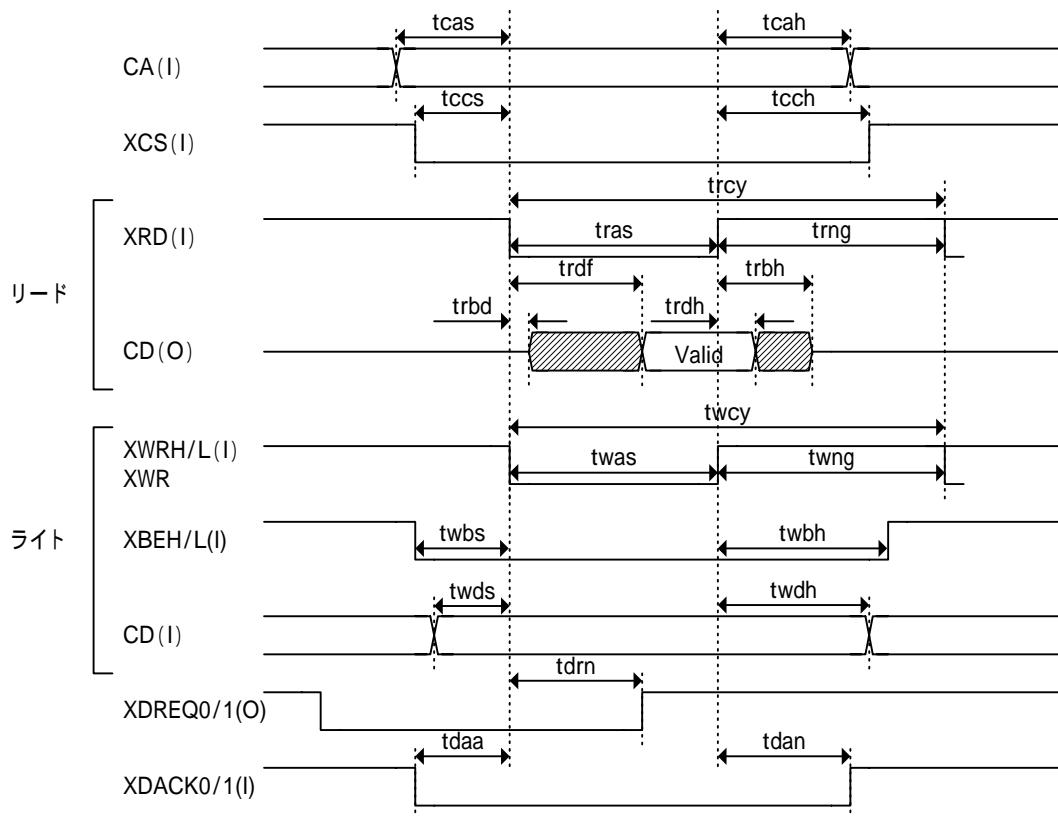

| 8.4.3 CPU/DMA I/F アクセスタイミング .....                   | 45        |

| 8.4.4 IDE I/F タイミング .....                           | 45        |

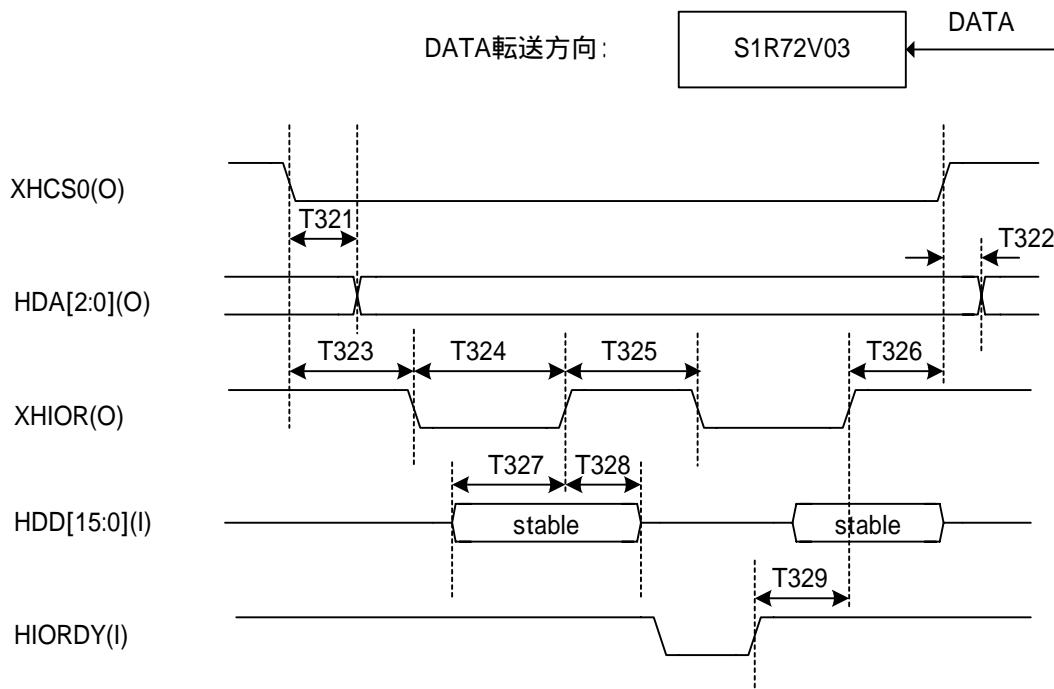

| 8.4.4.1 PIO Read Timing .....                       | 45        |

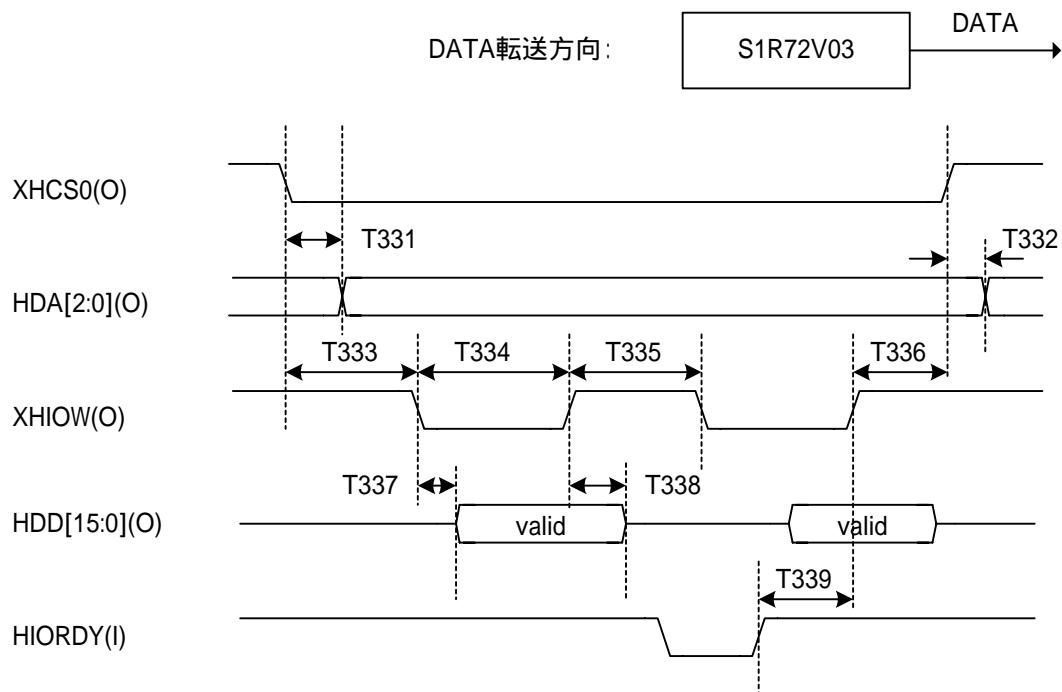

| 8.4.4.2 PIO Write Timing .....                      | 45        |

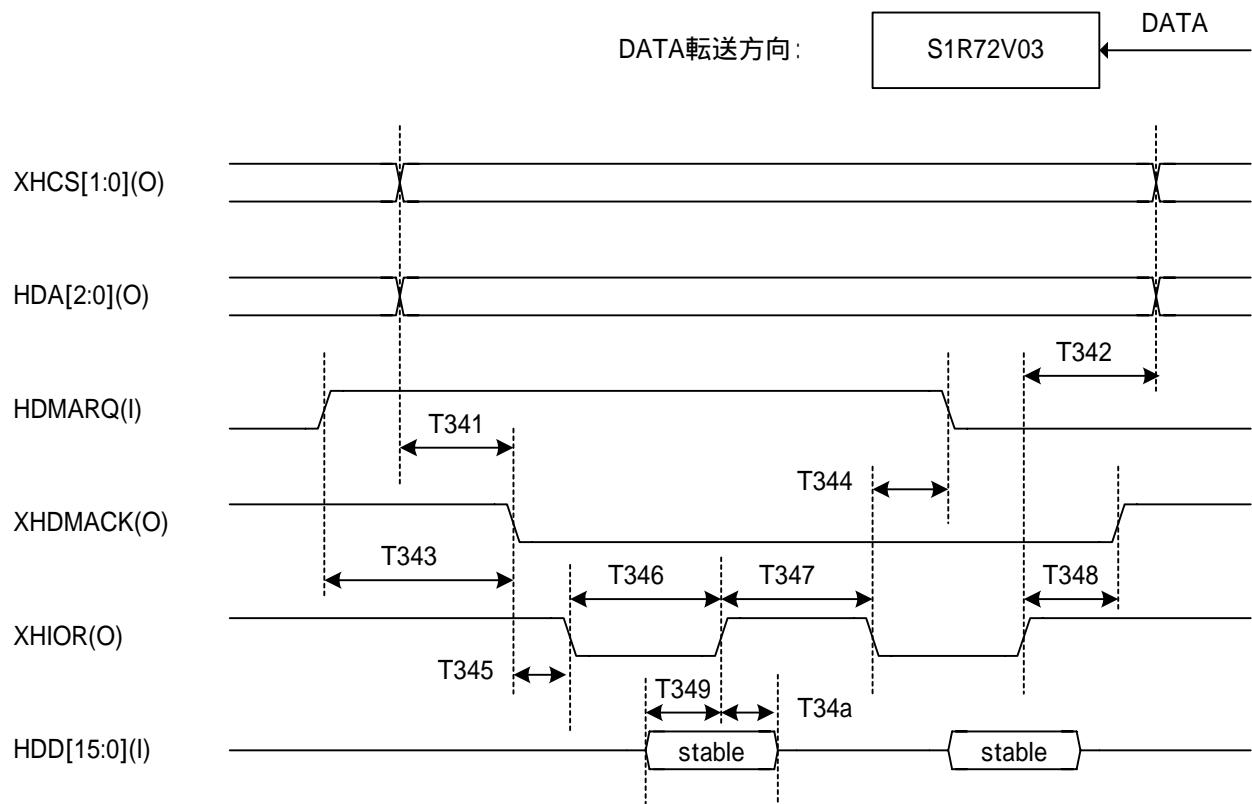

| 8.4.4.3 DMA Read Timing .....                       | 45        |

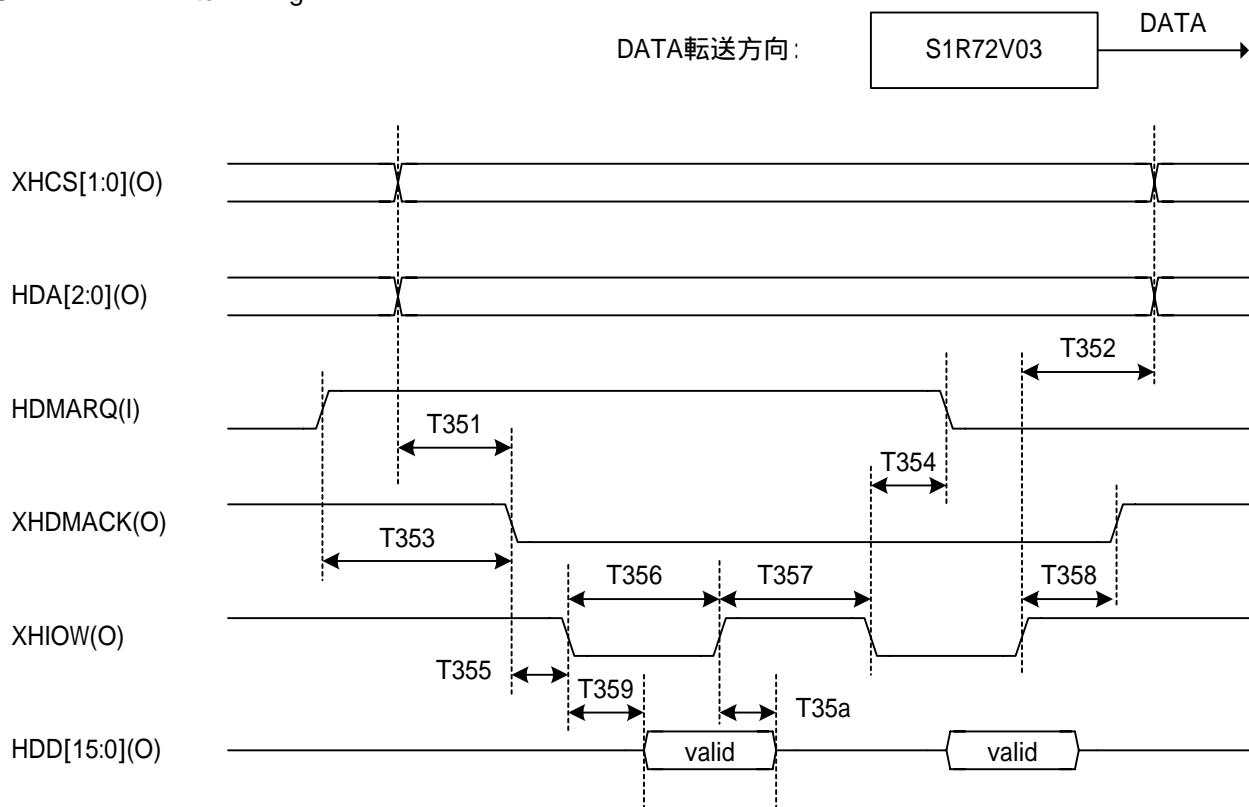

| 8.4.4.4 DMA Write Timing .....                      | 45        |

| 8.4.4.5 Ultra DMA Read Timing .....                 | 45        |

| 8.4.4.6 Ultra DMA Write Timing .....                | 45        |

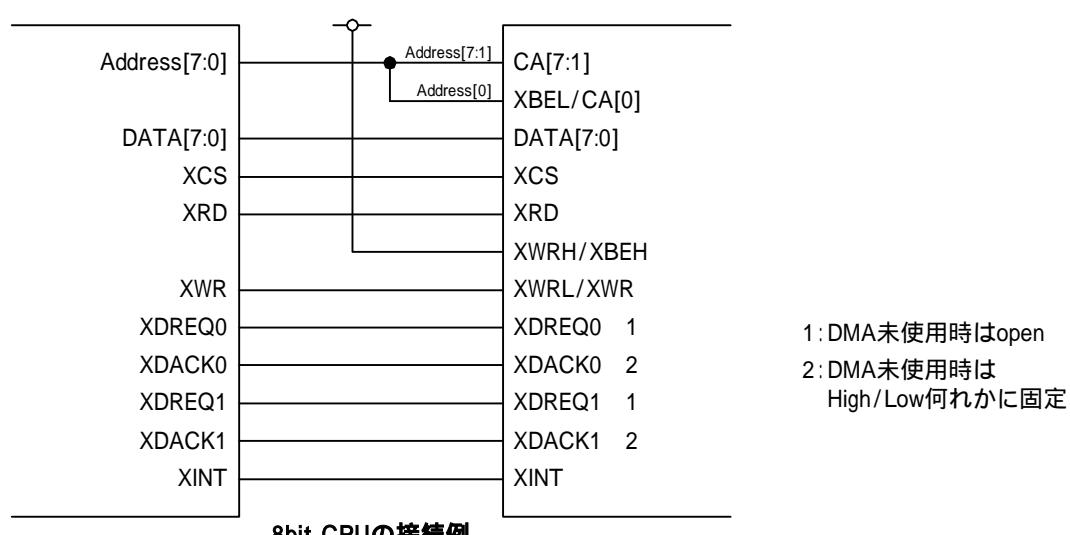

| <b>9. 接続例 .....</b>                                 | <b>45</b> |

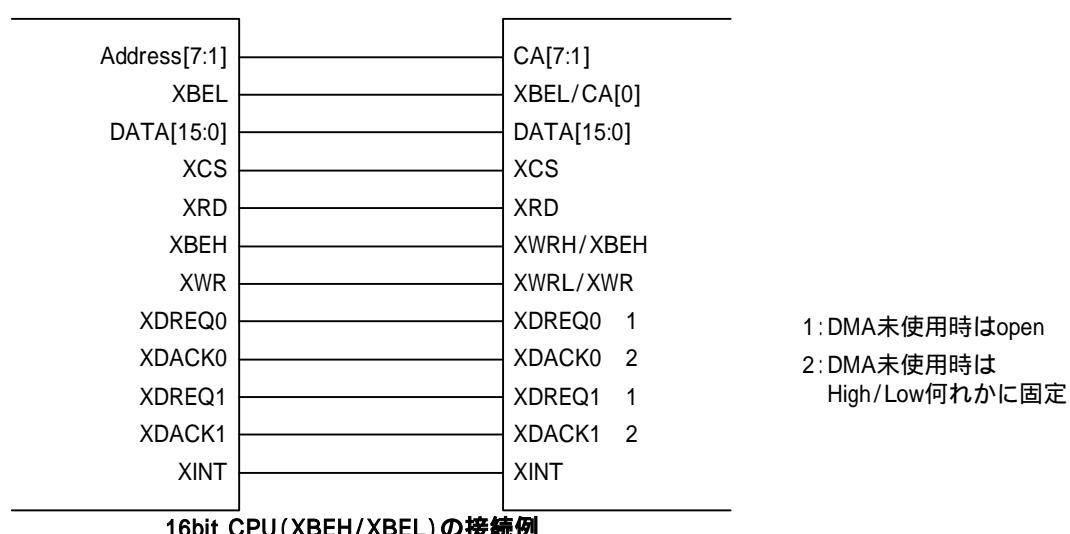

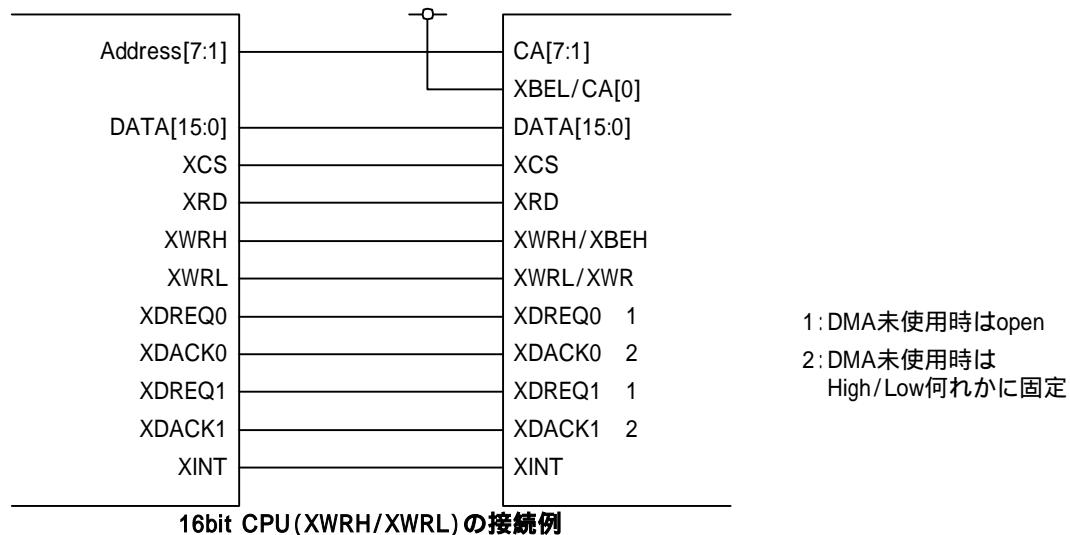

| <b>9.1 CPU I/F 接続例 .....</b>                        | <b>45</b> |

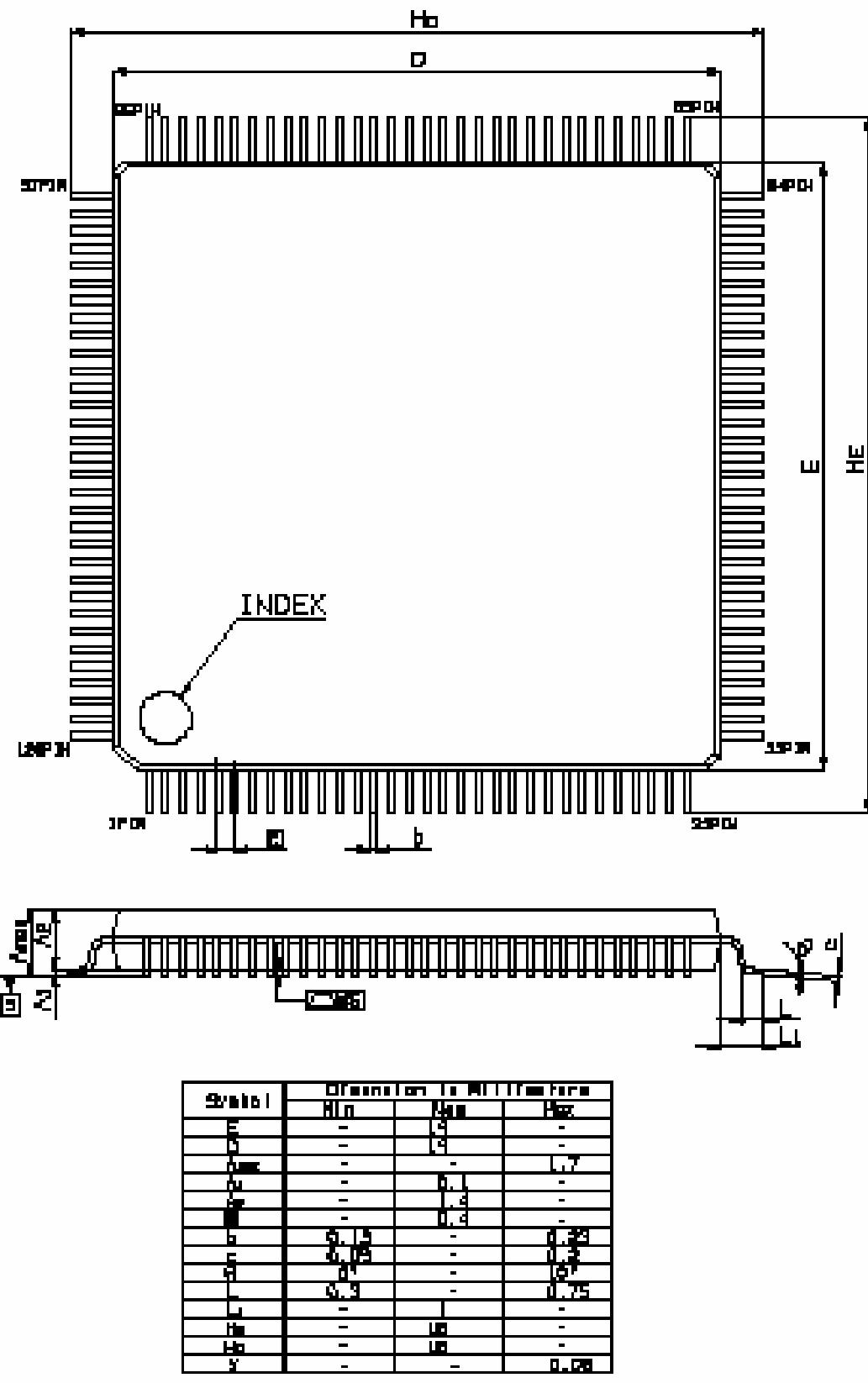

| <b>10. 外形寸法図 .....</b>                              | <b>45</b> |

| <b>10.1 QFP パッケージ .....</b>                         | <b>45</b> |

| <b>11. Appendix A IDE_Config_1.Swap ビット設定 .....</b> | <b>45</b> |

| <b>12. Appendix B リトルエンディアンの CPU への接続 .....</b>     | <b>45</b> |

| <b>改訂履歴表 .....</b>                                  | <b>45</b> |

### 1. 概要

S1R72H74\*\*は ATA/ATAPI6 に対応する ATA ホストコントローラ LSI です。HDD を内蔵するポータブル機器に適した特長を持ちます。

## 2. 特長

---

### 2. 特長

#### 《 CPU I/F 》

- 16bit 又は 8bit 幅の、汎用 CPU I/F に対応

- DMA 2ch. 搭載 (Multi-word 手順)

- Big Endian(Little Endian の CPU に対応するためのバススワップ機能を搭載)

- I/F 電圧変更可能(3.3V or 1.8V)

#### 《 IDE I/F 》

- ATA/ATAPI6 に対応

PIO モード 0 ~ 4, Multi word DMA, UDMA モード 0 ~ 5

#### 《 互換性 》

- USB デバイスコントローラ S1R72V03 と互換

- USB を除く機能互換

- USB を除くレジスタ互換

- 端子互換

#### 《 その他 》

- クロック入力 12MHz, 24MHz、水晶発振子対応。(発振回路及び帰還抵抗 1M 内蔵)

- 電源電圧 3.3V と 1.8V、及び CPU I/F 電源の 3 電圧系統

- パッケージタイプ QFP15-128

- 動作保証温度範囲 -40 ~ 85

耐放射設計はされておりません

## 3. ブロック図

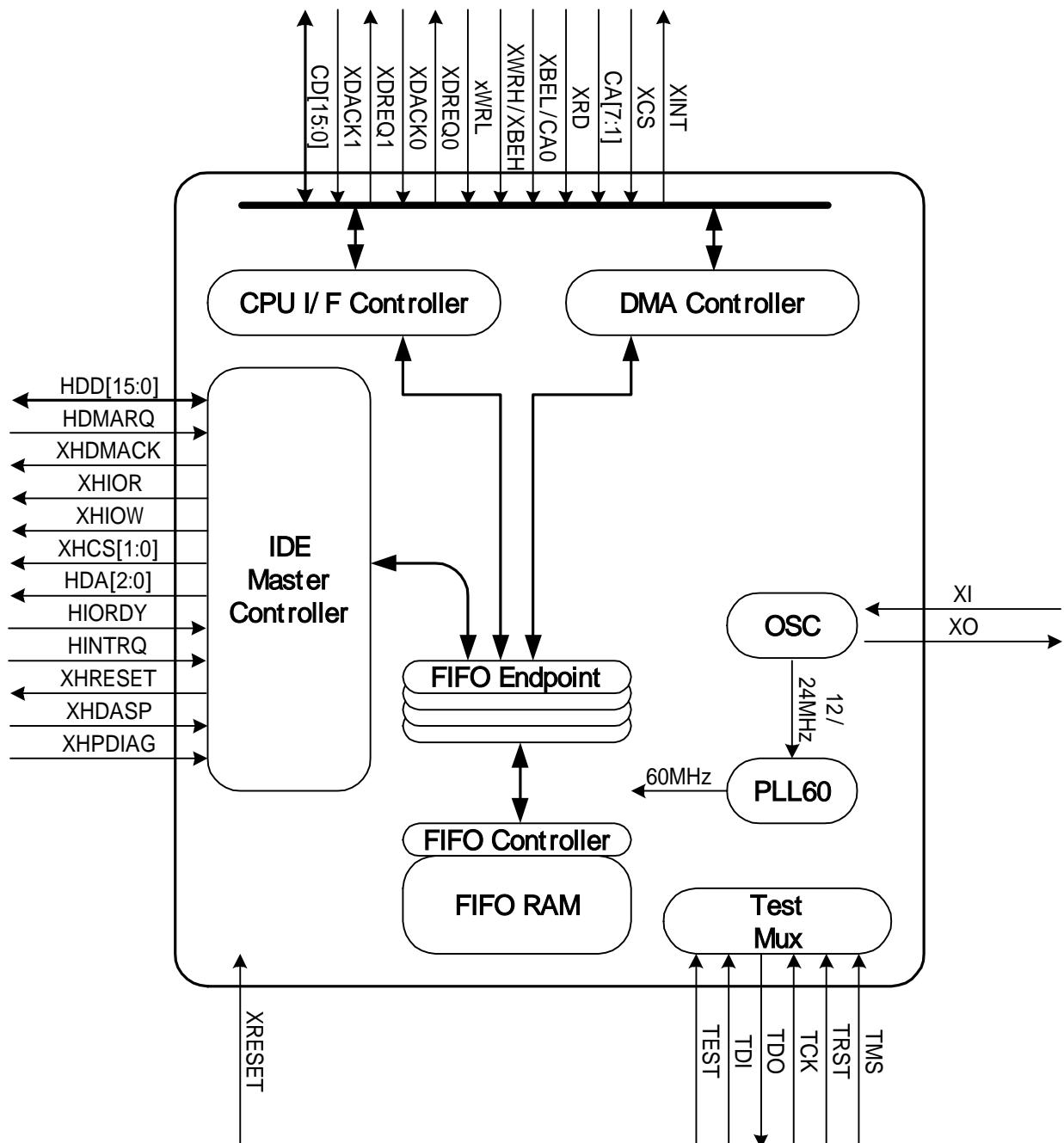

図 3.1 全体ブロック図

### **3. ブロック図**

---

#### **3.1 PLL60**

内部ロジック動作に必要な 60MHz クロックを生成します。発振回路の入力クロックは 12/24MHz の水晶発振子に対応可能です。

#### **3.2 FIFO Endpoint / FIFO Controller / FIFO RAM**

データ転送用バッファ（計 2kB）です。

#### **3.3 CPU I/F Controller**

CPU I/F のタイミングを制御し、レジスタアクセスを可能にします。

#### **3.4 DMA Controller**

CPU I/F の DMA タイミングを制御し、FIFO アクセスを可能にします。2 チャンネルの DMA を搭載します。

#### **3.5 IDE Master Controller**

ATA/ATAPI6 に対応する IDE インタフェースです。

PIO モード 0 ~ 4, Multi word DMA, UDMA モード 0 ~ 5 に対応します。

#### **3.6 TestMUX**

テスト回路です。

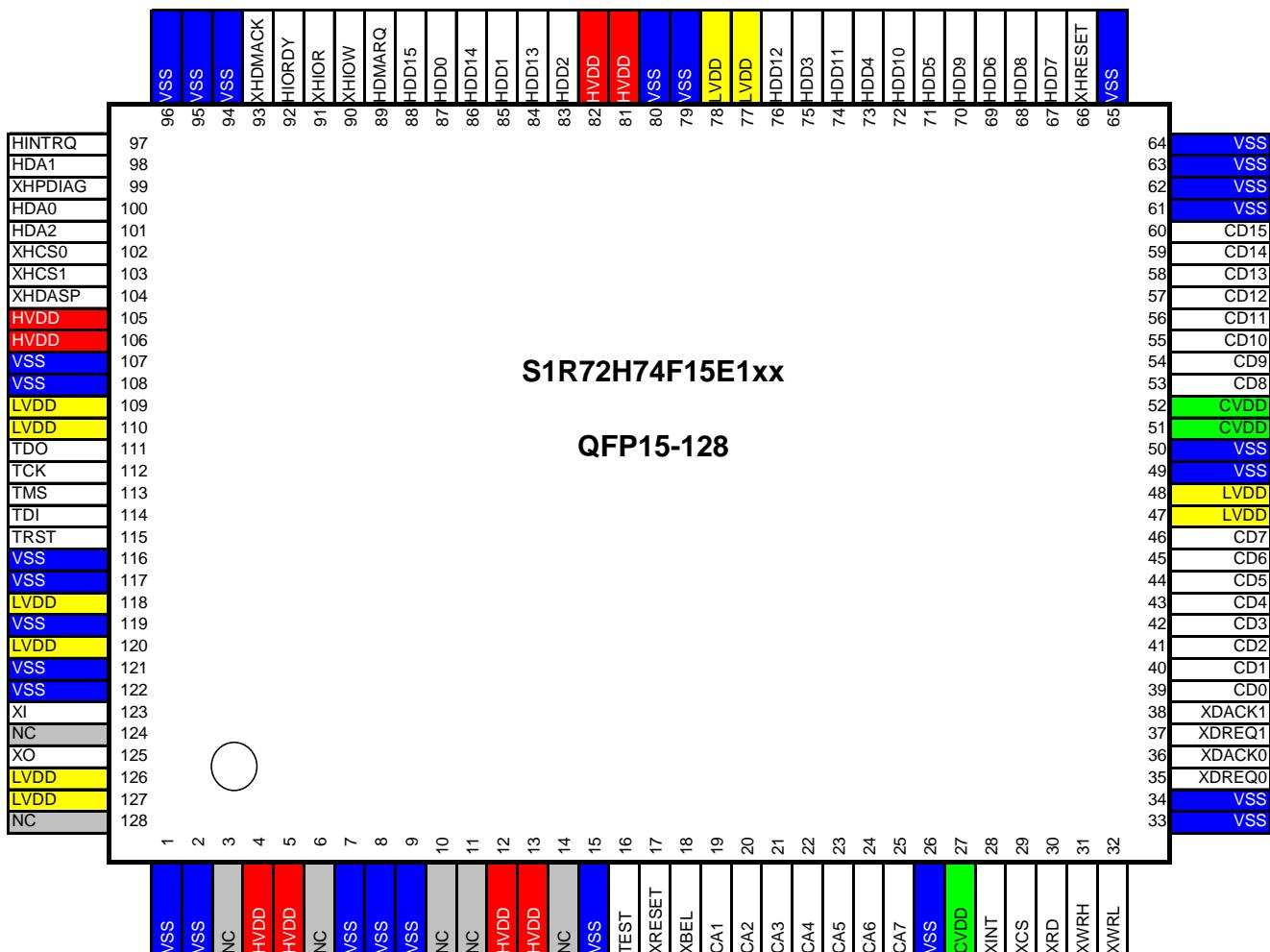

## 4. 端子配置図

### 4.1 端子配置図 (QFP パッケージ)

図 4.1 QFP パッケージ端子配置図

## 5. 端子機能説明

---

### 5. 端子機能説明

| Pin | 名称     | I/O | RESET | 端子タイプ  | 端子説明                     |

|-----|--------|-----|-------|--------|--------------------------|

| 17  | XRESET | IN  | -     | -      | リセット信号                   |

| 123 | XI     | IN  | -     | Analog | 内部発振回路用入力<br>12MHz/24MHz |

| 125 | XO     | OUT | -     | Analog | 内部発振回路用出力                |

XRESET は CVDD 電源系に属します。

XI,XO は LVDD 電源系に属します。

| Pin | 名称   | I/O | RESET | 端子タイプ | 端子説明          |

|-----|------|-----|-------|-------|---------------|

| 16  | TEST | IN  | -     |       | テスト端子(Low 固定) |

| 111 | TDO  | OUT | Hi-Z  | 2mA   | JTAG TDO 端子   |

| 112 | TCK  | IN  | -     |       | JTAG TCK 端子   |

| 113 | TMS  | IN  | -     |       | JTAG TMS 端子   |

| 114 | TDI  | IN  | -     |       | JTAG TDI 端子   |

| 115 | TRST | IN  | -     |       | JTAG TRST 端子  |

TEST は CVDD 電源系に属します。

上記の他の端子は HVDD 電源系に属します。

JTAG 機能を使用しない場合は、TEST, TCK, TMS, TDI, TRST の各端子は Low 固定、TDO 端子はオーブンとして処理してください。

| Pin | 名称          | I/O | RESET | 端子タイプ           | 端子説明              |                 |           |

|-----|-------------|-----|-------|-----------------|-------------------|-----------------|-----------|

|     |             |     |       | Bus Mode        | 16bit Strobe mode | 16bit BE mode   | 8bit mode |

| 30  | XRD         | IN  | -     | -               | リード・ストローブ         |                 |           |

| 32  | XWRL (XWR)  | IN  | -     | -               | ライト・ストローブ<br>下位   | ライト・ストローブ       |           |

| 31  | XWRH (XBEP) | IN  | -     | -               | ライト・ストローブ<br>上位   | ハイ・バイト<br>イネーブル | High 固定   |

| 29  | XCS         | IN  | -     | -               | チップセレクト信号         |                 |           |

| 28  | XINT        | OUT | High  | 2mA<br>TriState | 割り込み出力信号          |                 |           |

| 35  | XDREQ0      | OUT | High  | 2mA             | DMA0 リクエスト        |                 |           |

| 36  | XDACK0      | IN  | -     | -               | DMA0 アクノリッジ       |                 |           |

| 37  | XDREQ1      | OUT | High  | 2mA             | DMA1 リクエスト        |                 |           |

| 38  | XDACK1      | IN  | -     | -               | DMA1 アクノリッジ       |                 |           |

| 18  | XBEL (CA0)  | IN  | -     | -               | High or Low 固定    | ロー・バイト<br>イネーブル | アドレス 0    |

| 19  | CA1         | IN  | -     | -               | CPU パスアドレス        |                 |           |

| 20  | CA2         | IN  | -     | -               |                   |                 |           |

| 21  | CA3         | IN  | -     | -               |                   |                 |           |

| 22  | CA4         | IN  | -     | -               |                   |                 |           |

| 23  | CA5         | IN  | -     | -               |                   |                 |           |

| 24  | CA6         | IN  | -     | -               |                   |                 |           |

| 25  | CA7         | IN  | -     | -               |                   |                 |           |

| 39  | CD0         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 40  | CD1         | BI  | Hi-Z  | 2mA             | CPU データ・バス        |                 |           |

| 41  | CD2         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 42  | CD3         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 43  | CD4         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 44  | CD5         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 45  | CD6         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 46  | CD7         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 53  | CD8         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 54  | CD9         | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 55  | CD10        | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 56  | CD11        | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 57  | CD12        | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 58  | CD13        | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 59  | CD14        | BI  | Hi-Z  | 2mA             |                   |                 |           |

| 60  | CD15        | BI  | Hi-Z  | 2mA             |                   |                 |           |

上記の端子は CVDD 電源系に属します。

## 5. 端子機能説明

| Pin | 名称             | I/O            | RESET       | 端子タイプ    | 端子説明                    |

|-----|----------------|----------------|-------------|----------|-------------------------|

| 101 | HDA2           | OUT            | Hi-Z        | 4mA      |                         |

| 98  | HDA1           | OUT            | Hi-Z        | 4mA      | IDE レジスタ・アドレス           |

| 100 | HDA0           | OUT            | Hi-Z        | 4mA      |                         |

| 103 | XHCS1          | OUT            | Hi-Z        | 4mA      | コントロールレジスタアクセス用チップセレクト  |

| 102 | XHCS0          | OUT            | Hi-Z        | 4mA      | コマンドロックレジスタアクセス用チップセレクト |

| 91  | XHIOR          | OUT            | Hi-Z        | 4mA      | IDE リード・ストローブ           |

| 90  | XHIOW          | OUT            | Hi-Z        | 4mA      | IDE ライト・ストローブ           |

| 89  | HDMARQ         | IN (PD)        | (PD)        | -        | DMA 転送要求                |

| 93  | XHDMACK        | OUT            | Hi-Z        | 4mA      | DMA 転送許可                |

| 92  | HIORDY         | IN (PU)        | (PU)        | -        | IDE レジスタレディ信号           |

| 97  | HINTRQ         | IN (PU)        | (PU)        | -        | IDE 割り込み要求              |

| 66  | XHRESET        | OUT            | Hi-Z        | 4mA      | IDE バスリセット              |

| 104 | XHDASP         | IN (PU)        | (PU)        | -        | ドライブ有効 / スレーブドライブ有り     |

| 99  | <b>XHPDIAG</b> | <b>IN (PU)</b> | <b>(PU)</b> | <b>-</b> | <b>診断シーケンス終了信号</b>      |

| 88  | HDD15          | BI (PU)        | (PU)        | 4mA      |                         |

| 86  | HDD14          | BI (PU)        | (PU)        | 4mA      |                         |

| 84  | HDD13          | BI (PU)        | (PU)        | 4mA      |                         |

| 76  | HDD12          | BI (PU)        | (PU)        | 4mA      |                         |

| 74  | HDD11          | BI (PU)        | (PU)        | 4mA      |                         |

| 72  | HDD10          | BI (PU)        | (PU)        | 4mA      |                         |

| 70  | HDD9           | BI (PU)        | (PU)        | 4mA      |                         |

| 68  | HDD8           | BI (PU)        | (PU)        | 4mA      |                         |

| 67  | HDD7           | BI (PD)        | (PD)        | 4mA      | IDE データ・バス              |

| 69  | HDD6           | BI (PU)        | (PU)        | 4mA      |                         |

| 71  | HDD5           | BI (PU)        | (PU)        | 4mA      |                         |

| 73  | HDD4           | BI (PU)        | (PU)        | 4mA      |                         |

| 75  | HDD3           | BI (PU)        | (PU)        | 4mA      |                         |

| 83  | HDD2           | BI (PU)        | (PU)        | 4mA      |                         |

| 85  | HDD1           | BI (PU)        | (PU)        | 4mA      |                         |

| 87  | HDD0           | BI (PU)        | (PU)        | 4mA      |                         |

上記の端子は HVDD 電源系に属します。

PD: Pull Down

PU: Pull Up

### POWER

| Pin                                                                                                                                | 名称   | 電圧        | 端子説明                  |

|------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-----------------------|

| 4, 5, 12, 13, 81,<br>82, 105, 106                                                                                                  | HVDD | 3.3V      | IDE, TEST I/O 用電源     |

| 27, 51, 52                                                                                                                         | CVDD | 3.3V/1.8V | CPU I/F I/O 用電源       |

| 47, 48, 77, 78,<br>109, 110, 118,<br>120, 126, 127                                                                                 | LVDD | 1.8V      | 内部電源                  |

| 1, 2, 7, 8, 9, 15,<br>26, 33, 34, 49,<br>50, 61, 62, 63,<br>64, 65, 79, 80,<br>94, 95, 96, 107,<br>108, 116, 117,<br>119, 121, 122 | VSS  | 0V        | GND                   |

| 3, 6, 10, 11, 14,<br>124, 128                                                                                                      | NC   | 0V        | NC ( GND に固定してください。 ) |

## 6. 機能説明

本 LSI の動作について説明します。

以下では、レジスタについて下記のルールで標記します。

- ・1 アドレス分のレジスタを指す場合の名称

レジスタ名 + レジスタと上記します。

例：「MainIntStat レジスタ」

- ・個々のビットを指す場合の名称

レジスタ名 . ビット名 + ビット、或いは、ビット名 + ビットと標記します。

例：「MainIntStat.FIFO\_IntStat ビット」「MainIntStat レジスタの FIFO\_IntStat ビット」

- ・FIFO エンドポイント毎にあるレジスタ

EPx{ $x=b-c$ } ~ レジスタ、EPx{ $x=b-c$ } ~ レジスタ等と標記します。

例：「EPx{ $x=b-c$ }Config レジスタ」

- ・DMA チャネル毎にあるレジスタ

DMAx{ $x=0,1$ } ~ レジスタ等と標記します。

例：「DMAx{ $x=0,1$ }Config レジスタ」「EPx{ $x=b-c$ }Join.JoinDMAx{ $x=0,1$ }\_Wr ビット」

### 6.1 互換性

本 LSI は、USB デバイスコントローラ LSI 「S1R72V03」との互換性を持ちます。S1R72V03 は、USB デバイス機能と ATA ホスト機能を持ちます。本 LSI は、物理的 I/F 及び論理的 I/F において、S1R72V03 から USB 機能を除いた構成となっています。

また、ソフトウェアのソースコードの互換性を保持するため、S1R72V03 の USB に関連するレジスタ名称を継承しています。

### 6.2 パワーマネージメント機能

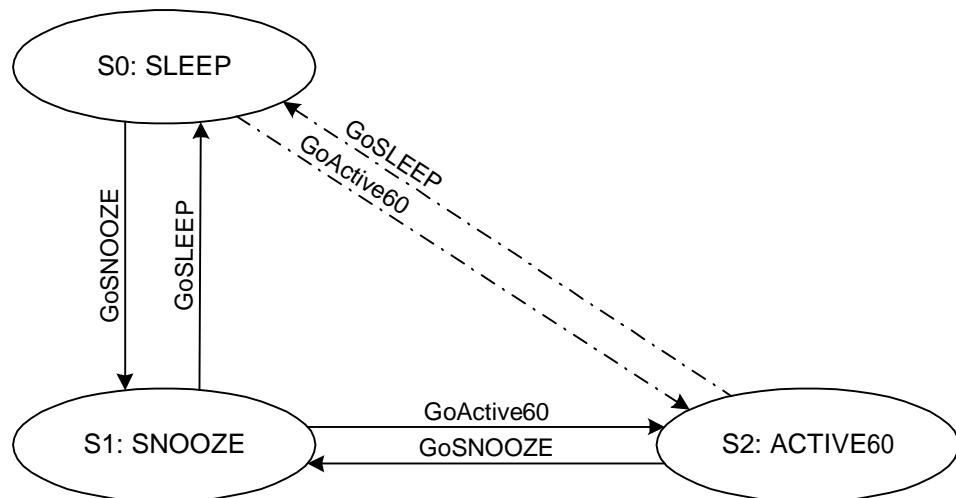

オシレータ及び PLL の動作を制御し、スリープ、スヌーズ、アクティブ 60 の 3 ステートを遷移します。他のステートに遷移する場合には、PM\_Control.GoSLEEP、PM\_Control.GoSNOOZE、PM\_Control.GoActive60 ビットをセットすることで開始され、任意の処理を行います。現在、どのステートにいるかを確認するには、PM\_Control.PM\_State[2:0]を確認してください。また遷移終了時、PM\_IntStat(SIE\_IntStat).FinishedPM イベントを発生します。この時、PM\_IntEnb(SIE\_IntEnb).EnFinishedPM ビットをセットし、かつ MainIntEnb.EnPM\_IntStat(EnSIE\_IntStat)ビットをセットしていれば、割り込み XINT が発生します。

全てのステートから他のステートへ遷移することが可能で、アクティブ 60 ステート時に PM\_Control.GoSLEEP ビットをセットした場合は、スヌーズステートを経由してスリープステートに遷移し、遷移終了した時点で PM\_IntStat(SIE\_IntStat).FinishedPM イベントを発生します。またスリープステート時に PM\_Control.GoActive60 ビットをセットした場合も、スヌーズステートを経由して、アクティブ 60 ステートに遷移し、遷移終了した時点で PM\_IntStat(SIE\_IntStat).FinishedPM イベントを発生します。

## 6. 機能説明

一点鎖線の遷移は、実際には実線を通って遷移する。

図 6.1 パワーマネージメント

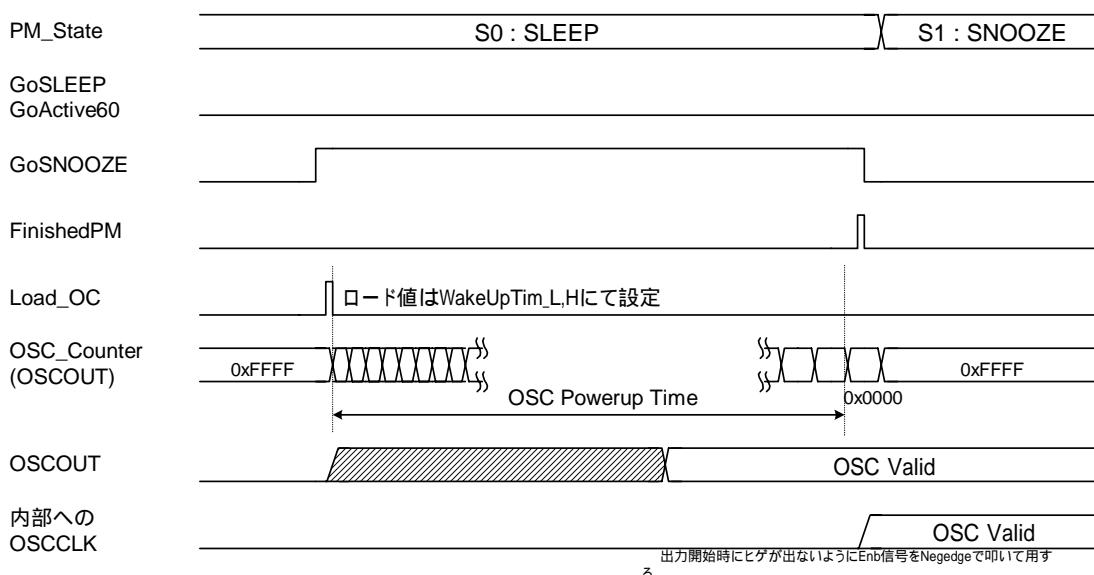

### 6.2.1 SLEEP (スリープ)

オシレータが発振していない状態です。したがいまして、この状態では、PLL も発振していません。

スヌーズ状態及びアクティブ 60 状態中に PM\_Control.GoSLEEP ビットをセットし、スリープに遷移する場合は、まず PLL60 を停止し、次に、OSCCLK の出力を停めた後にオシレータの発振を停止します。

逆に、スリープ状態中に PM\_Control.GoSNOOZE または PM\_Control.GoActive60 ビットをセットすると、オシレータが安定して発振するまで内部回路には OSCCLK を与えないように、発振安定時間ゲートしています。この発振安定時間は、発振セル、発振子、周辺回路及び基板によって変化しますので、WakeUpTim\_H,L レジスタを用いて設定してください。

図 6.2 SLEEP ステートからの離脱 (GoSNOOZE 時)

## 6.2.2 SNOOZE (スヌーズ)

オシレータは発振している状態で、PLL が発振していないステートです。

アクティブ60ステート中にPM\_Control.GoSNOOZE ビットをセットし、スヌーズに遷移する場合は、出力しているクロックを停止した後、PLL60 を停止します。

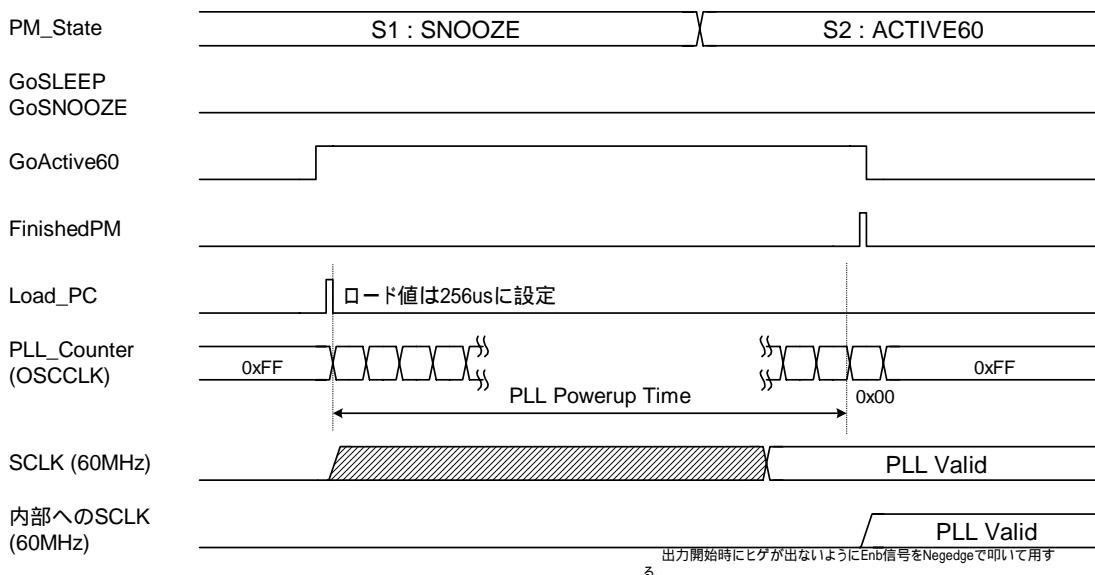

また、スヌーズステート中に PM\_Control.GoActive60 ビットをセットし、スヌーズからアクティブへ離脱する時には、PLL が安定して発振するまで内部回路には SCLK を与えないように、PLL 安定時間（約 250us）ゲートします。

図 6.3 SNOOZE ステートからの離脱 ( GoActive60 時 )

## 6.2.3 ACTIVE60 (アクティブ 60)

オシレータ及び PLL60 が動作しているステートです。レジスタマップの斜体太字のレジスタ及びビットはスヌーズ及びスリープ時でも読み書き可能なレジスタです。斜体文字以外のレジスタについては、アクティブ 60 ステートで無ければ読み書きできません。

IDE 並びに CPU 回路は、アクティブ 60 ステートで動作します。

## 6. 機能説明

### 6.3 FIFO 管理

#### 6.3.1 FIFO 管理

FIFO 管理について説明します。

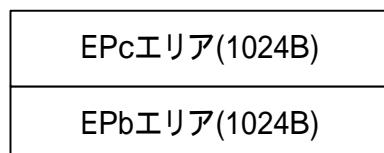

##### 6.3.1.1 FIFO メモリマップ

FIFO のメモリマップを以下に示します。

図 6.4 FIFO メモリマップ

FIFO のメモリは、EPb エリア、EPc エリアに分割され、それぞれに固定領域が割り当てられています。

EPb エリア及び EPc エリアは、IN(IDE Read)または OUT(IDE Write)の方向を任意に設定できる汎用 FIFO エンドポイントのエリアです。EPb エリア、EPc エリアは 1024 バイトが確保されており、IDE のリードまたはライト転送に使用することが出来ます。

IN(IDE Read)方向に設定された FIFO エンドポイントでは、IDE リードのデータ転送が可能です。また、OUT(IDE Write)方向に設定された FIFO エンドポイントでは、IDE ライトのデータ転送が可能です。CPU I/F からの PIO 及び DMA による FIFO アクセスは、IN または OUT の設定に依りません。(6.3.2.1, 6.3.2.2 を参照)

EPb エリア及び EPc エリアは、FIFO として制御されており、データ格納数が保持されています。この保持された状態をクリアするためには、EPnControl.AllFIFO\_Clr ビットか、または、各領域に対応した、EPrFIFO\_Clr.EPx{x=b-c}FIFO\_Clr の各ビットをセットしてください。

#### 6.3.2 FIFO へのアクセス方法

FIFO へのアクセス要因には、CPU(PIO), CPU(DMA), IDE が有ります。

##### 6.3.2.1 FIFO へのアクセス方法 ( PIO アクセス )

FIFO に CPU のレジスタアクセスによってリードアクセスする場合には、いずれか 1 つの FIFO エンドポイントに対して、EPx{x=b-c}Join.JoinCPU\_Rd に 1 をセットし、EPnFIFO\_Rd レジスタ、または、EPnFIFO\_ByteRd レジスタにて読み出しを行います。

また、FIFO に CPU のレジスタアクセスによってライトアクセスする場合には、いずれか 1 つの FIFO エンドポイントに対して、EPx{x=b-c}Join.JoinCPU\_Wr に 1 をセットし、EPnFIFO\_Wr レジスタに書き込みを行います。

EPnRdRemain\_H,L レジスタは、EPx{x=b-c}Join.JoinCPU\_Rd にてただ 1 つ設定された FIFO エンドポイントにおいて、FIFO から読み出し可能なデータの残り数を表しています。また、EPnWrRemain\_H,L レジスタは、EPx{x=b-c}Join.JoinCPU\_Wr にてただ 1 つ設定された FIFO エンドポイントにおいて、FIFO に書き込み可能なエリアの残り数を表しています。

ICE 等を使用してファームウェアのデバッグを行うに際し、レジスタのダンプ等を行う場合に、EPx{x=b-c}Join.JoinCPU\_Rd レジスタのいずれかがセットされていると、レジスタのダンプ時に FIFO からデータを読み出されてしまうことに注意してください。

### 6.3.2.2 FIFO へのアクセス方法 (DMA)

FIFO に CPU の DMA アクセスによってリードアクセスする場合には、DMA の各チャネルにつき、いずれか 1 つの FIFO エンドポイントの、 $EPn\{n=b-c\}Join.JoinDMAx\{x=0,1\}_Rd$  レジスタに 1 をセットし、DMA 手順を実行して読み出しを行います。

また、FIFO に CPU の DMA アクセスによってライトアクセスする場合には、DMA の各チャネルにつき、いずれか 1 つの FIFO エンドポイントの、 $EPn\{n=b-c\}Join.JoinDMAx\{x=0,1\}_Wr$  レジスタに 1 をセットし、DMA 手順を実行して書き込みを行います。

$DMAx\{x=0,1\}_Remain_H,L$  レジスタは、DMA の各チャネルについて、 $EPn\{n=b-c\}Join.JoinDMAx\{x=0,1\}_Rd$  にて、ただ 1 つ設定された FIFO エンドポイントにおいて、FIFO から読み出し可能なデータの残り数を表しています。また、DMA の各チャネルについて、 $EPn\{n=b-c\}Join.JoinDMAx\{x=0,1\}_Wr$  にて、ただ 1 つ設定された FIFO エンドポイントにおいて、FIFO に書き込み可能なエリアの残り数を表しています。

### 6.3.2.3 FIFO へのアクセス方法(IDE)

FIFO に IDE がアクセスする場合には、いずれか 1 つの FIFO エンドポイントに対して、 $EPx\{x=b-c\}Join.JoinIDE$  に 1 をセットし、IDE 手順を実行してデータ転送を行います。IDE 転送の方向は接続されている FIFO エンドポイントの方向に応じて設定されます。FIFO エンドポイントの方向設定が IN( $EPn\{n=b-c\}Config_0.INxOUT=1$ ) である時、その FIFO エンドポイントでは、IDE リードアクセスが行われます。また、FIFO エンドポイントの方向設定が OUT( $EPn\{n=b-c\}Config_0.INxOUT=0$ ) である時、その FIFO エンドポイントでは、IDE ライトアクセスが行われます。

### 6.3.2.4 FIFO へのアクセス制限

本 LSI の FIFO には、CPU バスからの PIO または DMA 書き込み、読み出し、IDE との送受信が同時に行われます。また、CPU バスからの読み出しについては、先読み処理を行っています。

これらのことから、それぞれの FIFO エンドポイントにおける、FIFO へのアクセス設定方法(Join)に対し、基本的に下記の排他ルールがあります。

- ・ 1 つの FIFO エンドポイントには、 $JoinCPU_Wr$ ,  $JoinCPU_Rd$ ,  $JoinDMAx\{x=0,1\}_Wr$ ,  $JoinDMAx\{x=0,1\}_Rd$  のうちの 1 つしか設定できない。

- ・  $JoinIDE$ ,  $JoinCPU_Wr$ ,  $JoinCPU_Rd$ ,  $JoinDMAx\{x=0,1\}_Wr$ ,  $JoinDMAx\{x=0,1\}_Rd$  は、それぞれ、同時に 1 つの FIFO エンドポイントにしか設定できない。

- ・  $JoinCPU_Wr$  と  $JoinCPU_Rd$  は同時に設定出来ない。

## 6. 機能説明

### 6.4 CPUIF

#### 6.4.1 モード切り替え

本 LSI の CPUIF は非同期 CPU に対応し、以下の 3 つの動作モードを持っております。

表 6.1 CPUIF 動作モード設定

| 動作モード             | BusMode | Bus8x16 | 備考               |

|-------------------|---------|---------|------------------|

| 16bit Strobe mode | 0       | 0       | デフォルト            |

| 16bit BE mode     | 1       | *       | BusMode ビットの設定優先 |

| 8bit mode         | 0       | 1       |                  |

各動作モードの切り替えは ChipConfig レジスタの BusMode ビット、Bus8x16 ビットの設定によって行います。ChipConfig レジスタの値は ModeProtect レジスタの設定によって誤書き込みに対するプロテクトをかけることができます。

実使用時には、電源投入直後、第一に ChipConfig レジスタの設定を行い動作モードを決定してください。その後、ModeProtect レジスタにより設定を保護してください。

また、本 LSI の CPUIF はバスの Swap 機能を持ちます。この機能を使用する場合は ChipConfig レジスタの初期設定時に ChipConfig.CPU\_BusSwap ビットを設定してください。Swap 機能は CPU\_BusSwap ビットを設定した後、E9h 番地をリードする事で有効になります。ChipConfig レジスタの設定では上記に加え、XINT の論理レベル及び出力モードの設定、XDREQ0,1、XDACK0,1 の論理レベル設定、DMA0,1 の CS\_Mode の設定を行う事が出来ます。

以下の説明においては、特に断りの無い限りデフォルト設定の 16bit Strobe mode、Bus Swap なしを基本として説明致します。

#### 6.4.2 モード切り替えに際して

本 LSI は ChipConfig レジスタにより、ご使用の CPU に適合する CPU バスの動作モードに設定することができます。チップの初期状態は 16bit Strobe mode で動作しておりますので、16bit BE mode、または 8bit mode に切り替える際には以下の点にご注意ください。

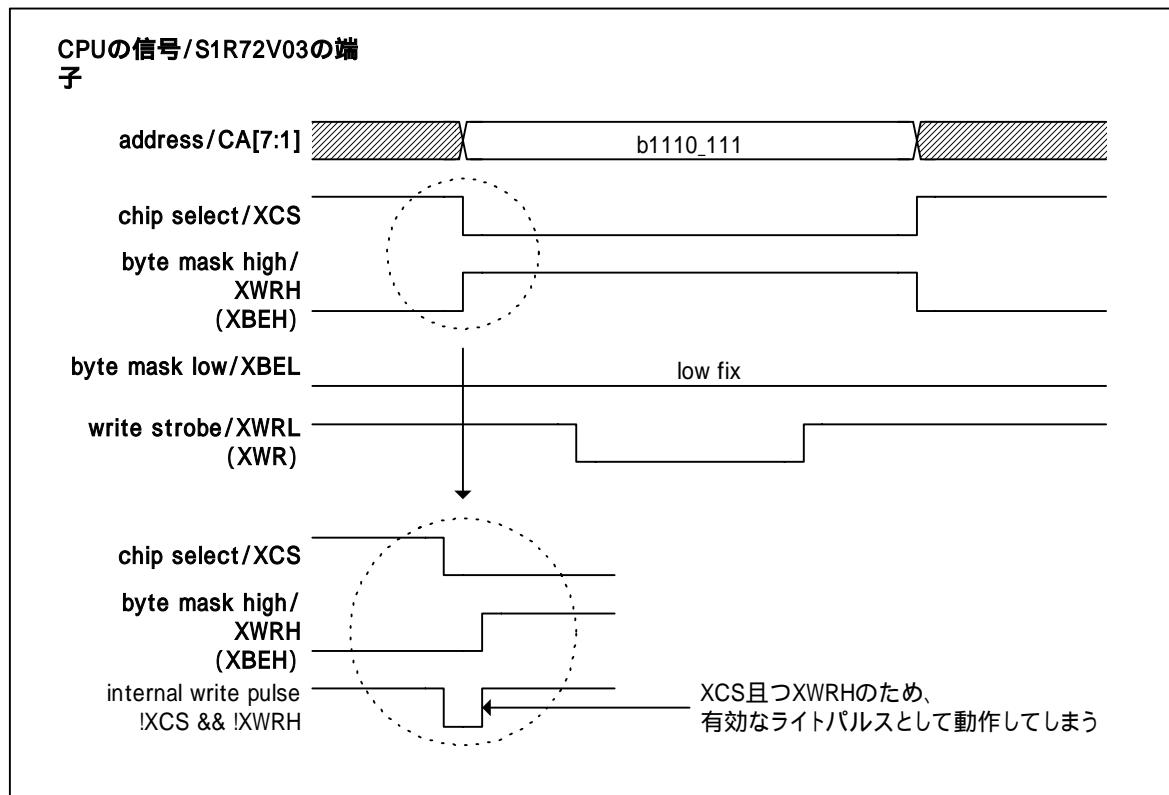

##### 6.4.2.1 16bit BE mode をご使用の場合

ご使用の CPU に合わせて 16bit BE mode を使用する場合、0 に示す通り、ChipConfig レジスタへの設定を第一に行ってください。また、その際には図 6.5 に示す通り、必ず EFh 番地に対するバイトライトを行ってください。この時、本 LSI は初期状態の 16bit Strobe mode で動作しており、CPU の chip select 信号と byte mask high 信号 ( XCS と XWRH ) に下図に示すようなスキューブがある場合、有効なライト期間と見なして内部的に動作してしまう可能性があります。本 LSI ではこの様なスキューブを除去する為のフィルタ回路 ( min:1ns ) を内蔵しておりますが、ご使用の CPU の AC 特性をご確認の上、基板上で処理等により、この様なスキューブが生じないようにしてください。

図 6.5 ChipConfig レジスタの初期設定

動作モードの設定完了後は内部的なライトパルス (internal write pulse) の生成条件が更新されますので、この様な制限はございません。

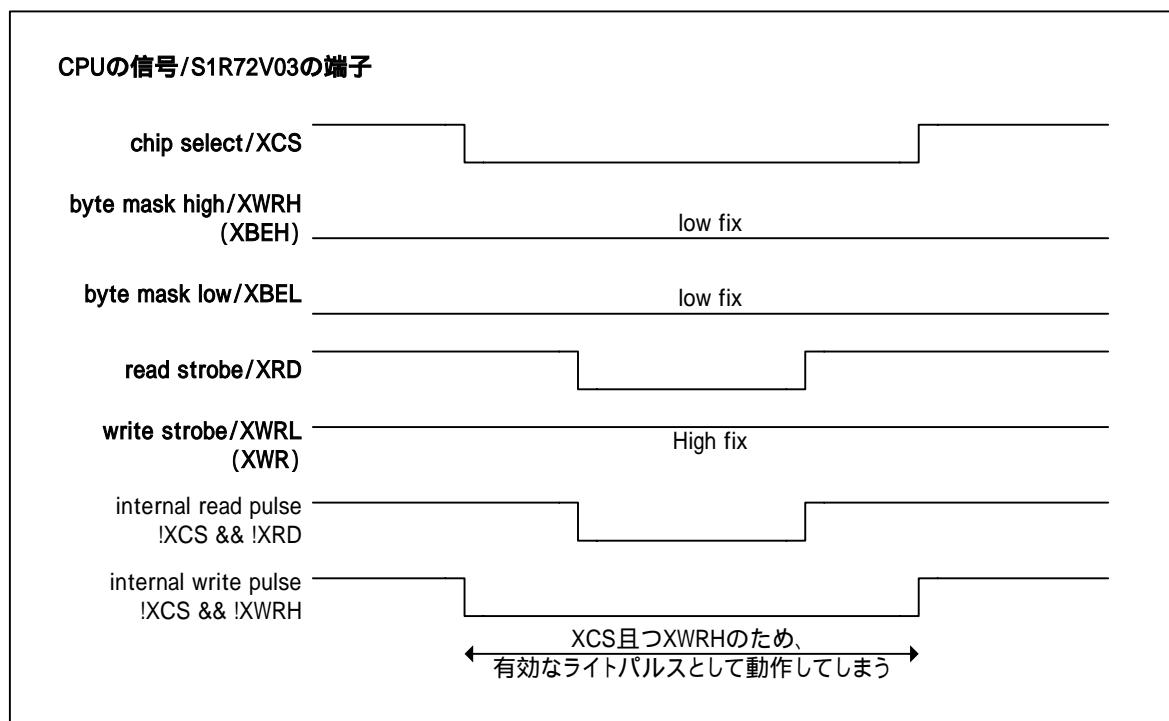

また、ChipConfig レジスタの設定前に、本 LSI にリードアクセスを行った場合、図 6.6 に示す通り、チップの内部ではリード動作とライト動作を同時に実行ってしまいます。この場合の動作は保証されませんので、必ず ChipConfig レジスタの設定を第一に行ってください。

図 6.6 ChipConfig レジスタの初期設定前のリードアクセス

## 6. 機能説明

### 6.4.2.2 8bit mode をご使用の場合

ご使用の CPU に合わせて 8bit mode を使用する場合、0 に示す通り、ChipConfig レジスタへの設定を第一に行ってください。ChipConfig レジスタの設定の前に、本 LSI にリードアクセスを行った場合、本 LSI は初期状態の 16bit Strobe mode で動作しておりますので、CD[15:0]全端子が出力状態になります。CD[15:8]を Pull Up/Pull Down 処理されている場合は特に問題ありませんが、これらの端子を VDD/GND に直結している場合、電流消費が大幅に増大します。これを回避する為、必ず ChipConfig レジスタの設定を第一に行ってください。

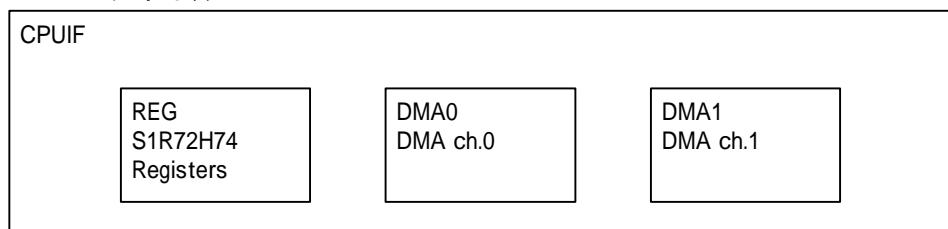

### 6.4.3 ブロック構成

本 LSI の CPUIF (以下、CPUIF) のブロック構成を図 6.7 に示します。

REG/DMA0/DMA1 の 3 ブロックから構成されます。

- REG : 本 LSI レジスタ領域へのアクセス制御

- DMA0 : DMA チャネル 0

- DMA1 : DMA チャネル 1

図 6.7 ブロック構成

#### 6.4.3.1 REG ( S1R72H74 Registers )

本 LSI のレジスタ領域へのアクセスを制御します。以下のアクセス機能が含まれます。

- 同期レジスタアクセス

- FIFO アクセス

- 非同期レジスタアクセス

##### 6.4.3.1.1 同期レジスタアクセス（ライト）

内部クロックに同期して外部バスのデータをレジスタへ書き込みます。

##### 6.4.3.1.2 同期レジスタアクセス（リード）

リード (XCS、XRD 共にアサート) 期間を出力イネーブル期間としてレジスタのデータを外部バスへ出力します。

レジスタのリード動作において、カウント値など 3 バイト以上 (8bit mode の場合 2 バイト以上) で意味を成すレジスタでは、アクセスサイクル間のカウント値の桁上がり等により誤ったカウント値をリードしない様、最上位バイトのリードタイミングで下位バイトのレジスタの値を保持し、下位バイトのリード時には、この値を外部バスへ出力します。

##### 6.4.3.1.3 FIFO アクセス（ライト）

FIFO ライトアクセスは EPnFIFO\_Wr\_H,L レジスタへの書き込みを意味します。8bit mode 動作の場合は EPnFIFO\_Wr\_H,L レジスタのどちらにアクセスを行っても FIFO への書き込みを行うことができます。

FIFO アクセス（ライト）には以下の制限事項があります。

- EPx{x=b-c}Join.JoinCPU\_Wr ビットを設定した後、EPnWrRemain\_H,L レジスタで書き込み可能

なデータ数を確認した上でアクセスを行ってください。

- 16bit CPU を使用の場合は、基本的にワード(2バイト)単位でアクセスを行ってください。端数(奇数)バイトの書き込みを行う場合は FIFO のバイト境界を意識してストローブ信号を制御してください。詳細は”FIFO アクセスの端数処理”をご参照ください。

- EPnFIFO\_Wr\_H,L レジスタへのライト直後に EPnWrRemain\_H,L レジスタを確認しても正確な FIFO の空き領域を確認することが出来ません。必ず 1CPU サイクル以上の間隔を空けて確認してください。

#### 6.4.3.1.4 FIFO アクセス(リード)

FIFO リードアクセスは EPnFIFO\_Rd\_H,L レジスタ、EPnFIFO\_ByteRd レジスタの読み出しを意味します。8bit mode 動作の場合は EPnFIFO\_Rd\_H,L レジスタ、EPnFIFO\_ByteRd レジスタのどのレジスタにアクセスを行っても同様に FIFO からの読み出しを行うことができます。

FIFO リードアクセスには、以下の制限事項があります。

- EPx{x=b-c}Join.JoinCPU\_Rd ビットを設定した後、EPnRdRemain\_H,L レジスタで読み出し可能データ数及び RdRemainValid ビットを確認した上でアクセスを行ってください。

- 16bit mode で使用の場合、ワード読みを行いう場合は EPnFIFO\_Rd\_H,L レジスタを用いて行ってください。バイト読みを行いう場合は EPnFIFO\_ByteRd レジスタを用いて行ってください。バイト境界が存在する場合はバイト読みを行ってください。この場合に EPnFIFO\_Rd\_H,L レジスタを用いてワード読みを行った場合は片側にのみ有効なデータが出力されます。詳細は”FIFO アクセスの端数処理”をご参照ください。

#### 6.4.3.1.5 FIFO アクセスの端数処理

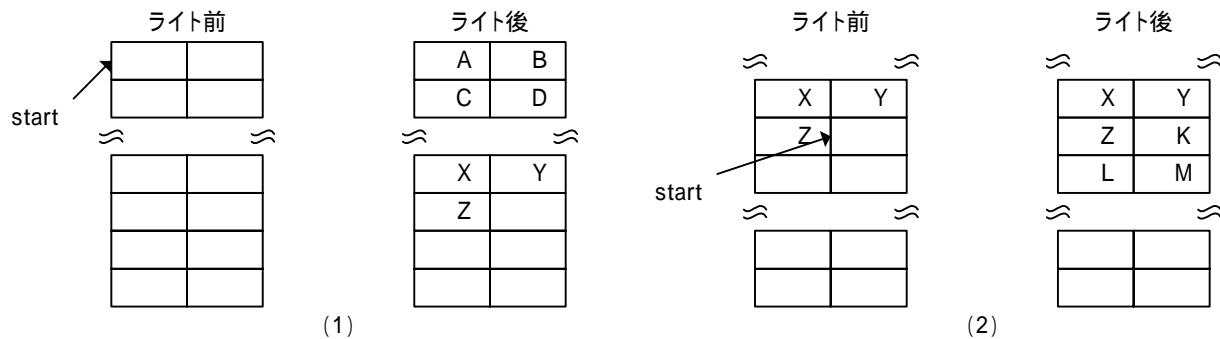

端数(奇数)データを扱う場合の FIFO へのデータの格納状態と FIFO アクセスの関係を説明します。実際の FIFO は 4byte 幅ですが、この章の説明では簡易化のため 2byte 幅で表記致します。4byte/2byte による動作の相違はありません。

##### 【ライト動作】

基本的にはバイト境界の存在しない状態から書き込み動作を行う事を推奨致します。

EPxFIFO\_Clr.EPx{x=b-c}FIFO\_Clr ビットをセットする等行って、バイト境界の存在しない状態からワード書き込みを行い、奇数データが存在する場合は、連続するデータの最終バイト(データ Z)のみ High 側に書き込んでください。この状態を図 6.8 の(1)に示します。IDE IF 等からはデータ A, B, C, D, … X, Y, Z の順に出力されます。

FIFO にバイト境界がある状態から書き込みを行う場合は、最初に Low 側にデータを書き込み(データ K の書き込み)バイト境界を解消した後、ワード書き込み(データ L, M)を行ってください。この状態を図 6.8 の(2)に示します。

以上は、正常な書き込み動作です。

A: FIFO にデータ A が存在する様

空: FIFO にデータが存在しない様

start: 書き込み開始ポイント

図 6.8 FIFO ライト処理(正常動作)

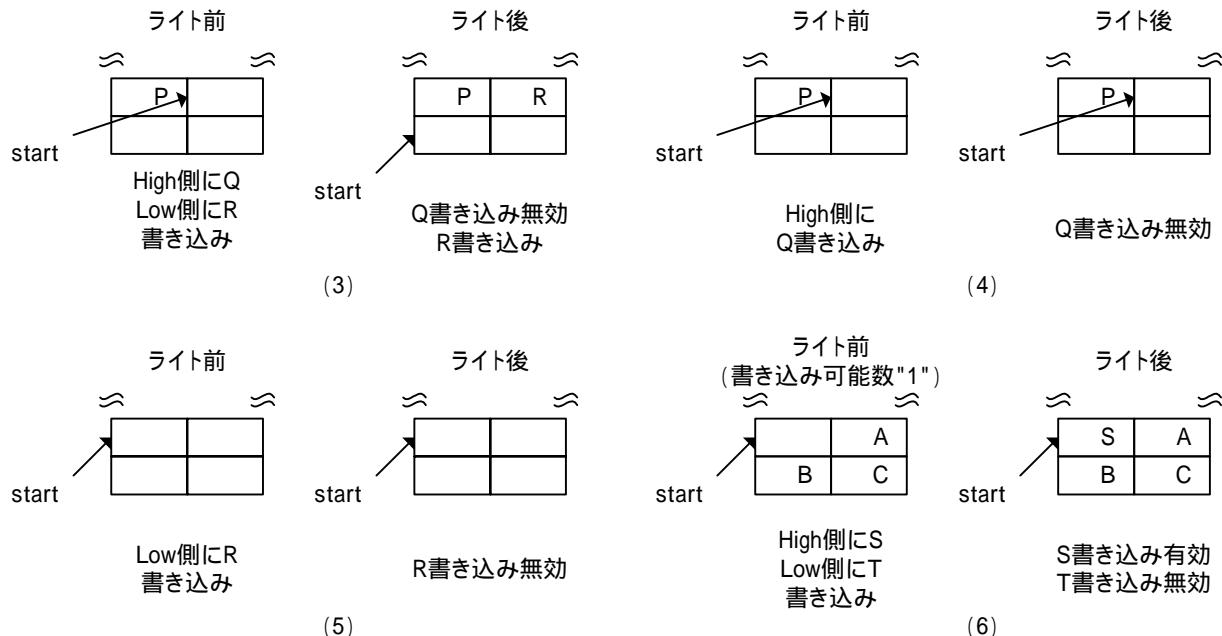

以下は注意が必要な書き込みを行った場合の動作です。

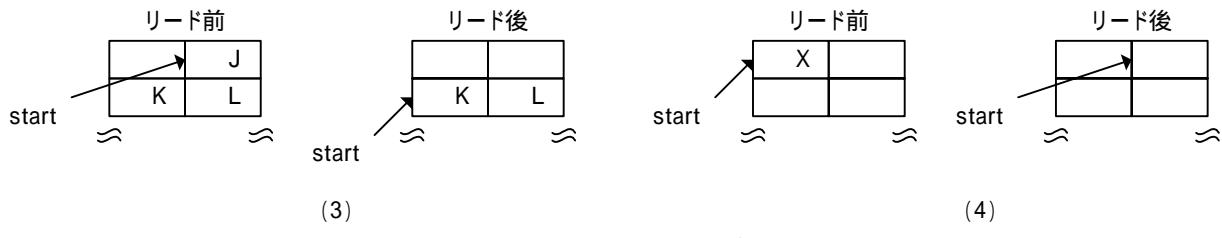

FIFO にバイト境界がある状態からワード書き込みを行った場合、High 側の書き込みは無視され Low

## 6. 機能説明

側のみ書き込みが行われます（図 6.9 の（3））。つまり、Low 側にバイト書き込みを行ったときと同じ動作を行います。また、FIFO にバイト境界のある状態から High 側にのみ書き込みを行った場合、その書き込みは無視されます（図 6.9 の（4））。

FIFO にバイト境界が無い状態から Low 側にのみ書き込みを行った場合、その書き込みは無視されます（図 6.9 の（5））。また、FIFO にバイト境界が無く、且つ書き込み可能数が”1”の状態からワード書き込みを行った場合、Low 側の書き込みは無視され、High 側のみ書き込みが行われます（図 6.9 の（6））。つまり、High 側にバイト書き込みを行ったときと同じ動作を行います。

図 6.9 FIFO ライト処理（注意が必要な動作）

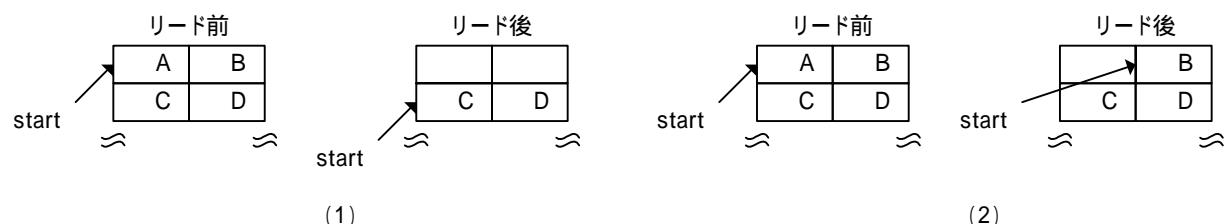

### 【リード動作】

バイト境界が無い場合は、EPnFIFO\_Rd\_H,L レジスタを用いたワード読み出し、EPnFIFO\_ByteRd レジスタを用いたバイト読み出し何れを行っても問題ありません。バイト境界がある場合は、EPnFIFO\_ByteRd レジスタを用いたバイト読み出しを行ってください。一旦バイト境界を解消した後はワード読み出し、バイト読み出し何れを行っても問題ありません。

バイト境界が無い状態からのワード読み出しの様子を図 6.10 の（1）に示します。アクセス毎にデータ A, B データ C, D と読み出されます。また、バイト読み出しの様子を図 6.10 の（2）に示します。アクセス毎にデータ A データ B データ C データ D と読み出されます。以上は正常な読み出し動作です。

図 6.10 FIFO リード処理（正常動作）

以下は注意が必要な読み出しを行った場合の動作です。

図 6.11 の（3）はバイト境界がある状態から、EPnFIFO\_Rd\_H,L レジスタを用いてワード読み出しを行った場合の動作です。High 側には不定のデータが出力され、Low 側にデータ J が出力されます。リードのポインタは 1 バイト分のみ進みます。図 6.11 の（4）はバイト境界が無いが残りデータが 1 バイトの状態から、EPnFIFO\_Rd\_H,L レジスタを用いてワード読み出しを行った場合の動作です。High 側にはデータ X が出力され、Low 側には不定データが出力されます。リードのポインタは 1 バイト分のみ進みます。

図 6.11 FIFO リード処理（注意が必要な動作）

上記より、端数処理のリード動作を行う場合の例を説明します。

- 1) FIFO に 64 バイト有るデータを 31 バイト 33 バイトで読み出したい場合。

CPUIF は 64 バイトのレディをラッチして一連のリードシーケンスを開始する。

30 バイト分のデータを EPnFIFO\_Rd\_H,L レジスタでワード読み、もしくは EPnFIFO\_ByteRd レジスタでバイト読みする。

31 バイト目のデータを EPnFIFO\_ByteRd レジスタでバイト読みする。 バイト境界発生。

32 バイト目のデータをバイト読みする。この場合 EPnFIFO\_ByteRd レジスタでのバイト読みを推奨します。EPnFIFO\_Rd\_H,L レジスタでのワード読みを行った場合は Low 側にデータが出力されます。 バイト境界解消。

残り 32 バイトのデータを EPnFIFO\_Rd\_H,L レジスタでワード読み、もしくは EPnFIFO\_ByteRd レジスタでバイト読みする。

- 2) 31 バイトのデータが有る時点で JoinCPU\_Rd をセットして読み出しを開始した後、続けて書き込まれたデータを EPnFIFO\_Rd\_H,L レジスタでワード読みしたい場合。

31 バイトのデータが有る状態で JoinCPU\_Rd を設定した時点で、CPUIF は 31 バイトのレディをラッチして一連の動作シーケンスを開始する。

30 バイト分のデータをワード読みする。

キャッシュされている 31 バイト目のデータ（バイト境界）を解消するため、一旦ジョインを切り離す。

再度ジョインする。

CPUIF は残るデータ数のレディをラッチして一連の動作シーケンスを開始する。

残りのデータをワード読みする。

#### 6.4.3.1.6 非同期レジスタアクセス（ライト）

外部ライト信号（XCS、XWRL,H）からライトパルスを作成して外部バスのデータをレジスタへ書き込みます。

#### 6.4.3.1.7 非同期レジスタアクセス（リード）

同期レジスタリードと同様、リード（XCS、XRD 共にアサート）期間を出力イネーブル期間としてレジスタのデータを外部バスへ出力します。

#### 6.4.3.2 DMA0/DMA1 ( DMA ch.0 / ch.1 )

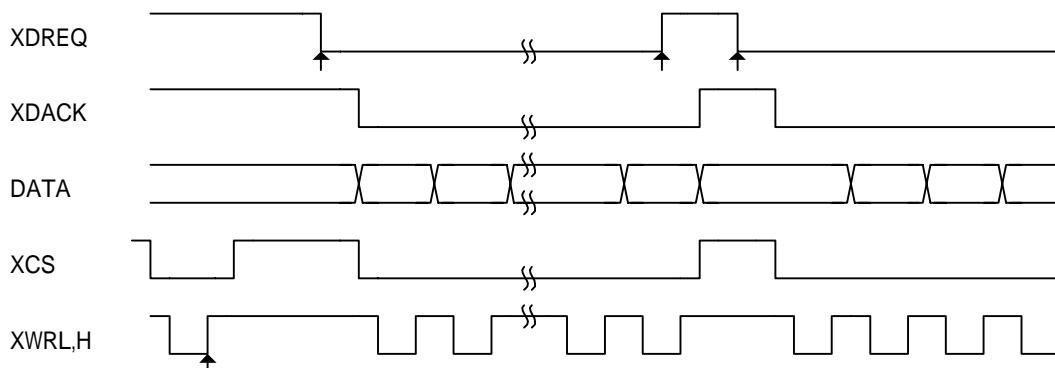

##### 6.4.3.2.1 基本機能

DMA の基本動作は以下の通りです。

###### 【ライト動作】

FIFO に書き込み可能な空き領域がある場合に XDREQ をアサートし DMA 転送が可能になります。

###### 【リード動作】

FIFO に読み出し可能なデータがあり、読み出し動作可能になると XDREQ をアサートし DMA 転送が可能になります。

DMA は二つの動作モードと一つの動作オプションを持ちます。

###### カウントモード

設定されたカウント数分の DMA 転送を行います。

## 6. 機能説明

---

内部 FIFO に書き込み可能な空き領域 / 読み出し可能なデータがあり、且つ DMAx{ $x=0,1$ }\_Count\_HH,HL,LH,LL レジスタに残りカウントがある場合に XDREQ をアサートし DMA 転送が可能になります。

### フリーランモード

内部 FIFO に書き込み可能な空き領域 / 読み出し可能なデータがある場合に XDREQ をアサートし DMA 転送が可能になります。

### REQ アサートカウントオプション

CPU のバーストストリード / バーストライトに対応するためのオプションです。このオプションは、カウントモード / フリーランモード何れでも使用が可能です。DMAx{ $x=0,1$ }\_Config.ReqAssertCount [1:0]ビットに設定されたアサートカウント数以上の、書き込み可能な空き領域 / 読み出し可能なデータが FIFO にある場合に XDREQ をアサートし DMA 転送が可能になります。従って、基本的には一旦 XDREQ がアサートされると、設定されたアサートカウント数分の転送が保証されることになります。ただし、FIFO の空き領域 / データが設定されたアサートカウント数未満の場合も、カウントモードに設定され、且つ FIFO の空き領域 / データが残りカウント数以上の場合、XDREQ がアサートされます。この場合の保証される転送数は残りカウント数となります。

16bit mode の場合、DMA の基本はワード単位でのデータ処理となります。バイト単位でのデータ処理はカウントモードで且つ残りカウント数が”1”の時のみ行うことが出来ます。各々の動作モード、オプションにおける XDREQ のアサート条件、また XDREQ アサート時の転送可能数の関係を下表に示します。

表 6.2 動作モード、オプションと転送開始条件一覧

## カウントモード・ReqAssertCountオプション使用時(16bit / 8bitモード動作時共)

| 条件    | カウントモード(Count > 0) |     |             |       |       |

|-------|--------------------|-----|-------------|-------|-------|

|       | Count Req          |     | Count < Req |       |       |

|       | Ready              | Req | Ready < Req | Ready | Count |

| XDREQ | アサート               |     | ネゲート        | アサート  | ネゲート  |

| 転送可能数 | Req                | -   |             | Count | -     |

## フリーランモード・ReqAssertCountオプション使用時(16bit / 8bitモード動作時共)

| 条件    | フリーランモード |      |             |

|-------|----------|------|-------------|

|       | -        |      |             |

|       | Ready    | Req  | Ready < Req |

| XDREQ | アサート     | ネゲート |             |

| 転送可能数 | Req      | -    |             |

## カウントモード・ReqAssertCountオプション未使用時(16bitモード動作時)

| 条件    | カウントモード(Count > 0)         |      |               |       |       |

|-------|----------------------------|------|---------------|-------|-------|

|       | Count Ready                |      | Count < Ready |       |       |

|       | Ready                      | 2    | Ready < 2     | Ready | Count |

| XDREQ | アサート                       | ネゲート | アサート          |       |       |

| 転送可能数 | Ready(Readyが奇数の場合はReady-1) |      | -             | Count |       |

## フリーランモード・ReqAssertCountオプション未使用時(16bitモード動作時)

| 条件    | フリーランモード                   |      |           |

|-------|----------------------------|------|-----------|

|       | -                          |      |           |

|       | Ready                      | 2    | Ready < 2 |

| XDREQ | アサート                       | ネゲート |           |

| 転送可能数 | Ready(Readyが奇数の場合はReady-1) | -    |           |

## カウントモード・ReqAssertCountオプション未使用時(8bitモード動作時)

| 条件    | カウントモード(Count > 0) |      |               |       |       |

|-------|--------------------|------|---------------|-------|-------|

|       | Count Ready        |      | Count < Ready |       |       |

|       | Ready              | 1    | Ready < 1     | Ready | Count |

| XDREQ | アサート               | ネゲート | アサート          |       |       |

| 転送可能数 | Ready              |      | -             | Count |       |

## フリーランモード・ReqAssertCountオプション未使用時(8bitモード動作時)

| 条件    | フリーランモード |      |           |

|-------|----------|------|-----------|

|       | -        |      |           |

|       | Ready    | 1    | Ready < 1 |

| XDREQ | アサート     | ネゲート |           |

| 転送可能数 | Ready    | -    |           |

表中の Req は DMAx{x=0,1}Config.ReqAssertCount の設定値を、Ready は FIFO の空き領域 / データ数を、Count は DMAx { x=0,1 } Count\_HH,HL,LH,LL の値を指しています。

## 6.4.3.2.2 端子設定

ChipConfig レジスタの設定により、XDREQx{x=1,0}の論理レベル、XDACKx{x=1,0}の論理レベルを設定する事が出来ます。以下の説明では特に断りの無い限り、XDREQ,XDACK 共に負論理で記述しております。

## 6. 機能説明

### 6.4.3.2.3 アクセスマード設定

ChipConfig.CS\_Mode ビット及び DMAx{x=1,0}\_Config.DMA\_Mode ビットの設定により、DMA アクセスと見なす動作条件を設定する事が出来ます。

表 6.3 アクセスマード設定

| CS_Mode | DMA_Mode | 説明                                                            |

|---------|----------|---------------------------------------------------------------|

| 0       | 0        | XDREQ に対し XDACK がアサートされることで DMA アクセスと見なします                    |

| 1       | 0        | XDREQ に対し XDACK 及び XCS がアサートされることで DMA アクセスと見なします             |

| *       | 1        | XDREQ に対し DMAx{x=1,0}_Rd/WrData レジスタにアクセスされる事で DMA アクセスと見なします |

以下の説明では特に断りの無い限り、XDACK 及び XCS のアサートを動作条件と見なすアクセスマードで記述しております。

### 6.4.3.2.4 カウントモード（ライト）

#### 【動作開始】

DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタにカウント値を設定した後、DMAx{x=0,1}\_Control.DMA\_Go ビットに”1”をセットしてください。内部 FIFO に書き込み可能な空き領域 (DMA\_Ready) が 2 バイト以上 (8bit mode の場合 1 バイト以上) あり、且つ残りカウントがある場合に XDREQ をアサートし DMA 転送が可能になります。FIFO に残り 1 バイトの空き領域しかない場合は、カウントモードに設定され、且つ残りカウント数が”1”的のみ XDREQ がアサートされます。

奇数バイトの書き込みを行って FIFO にバイト境界が発生した場合には、FIFO が空になった後、FIFO クリアを行ってバイト境界を解消し、次のライト動作を開始してください。

動作停止となるまで DMAx{x=0,1}\_Control.DMA\_Running ビットに”1”が読みます。

#### 【動作停止】

動作停止条件は以下の 2 つです。

- DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタに設定したカウント数分の DMA 転送が完了

- DMAx{x=0,1}\_Control.DMA\_Stop ビットに”1”をライト

DMA 動作停止時に CPU\_IntStat..DMAx{x=0,1}\_Cmp ビットがセットされます。

DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタによる転送停止時は最終アクセスのストローブアサート期間に XDREQ をネゲートします。

DMA\_Stop ビットによる転送停止時は、同期レジスタアクセスのライトタイミングでチップ内部動作を停止し、XDREQ をネゲートします。DMA\_Stop ビットによる DMA の停止を行う場合は、CPU 側の DMAC (マスター) を先に停止してください。

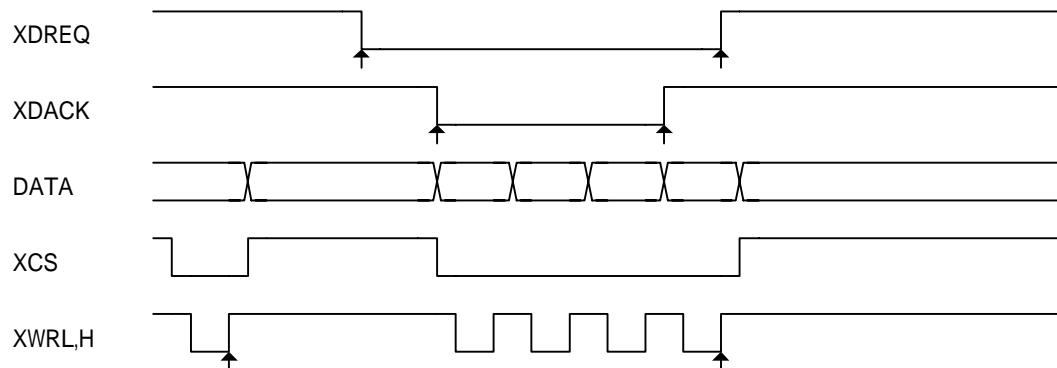

カウントモードで転送を開始し、設定されたカウント数の転送完了前に DMAx{x=0,1}\_Control.DMA\_Stop ビットで転送を停止した場合の動作タイミングを図 6.12 に示します。

ex1.【転送開始条件】カウント(8バイト) < FIFOの空き容量(16バイト) 【転送停止条件】DMA\_Stop

DMA\_Control.DMA\_Goビットへの"1"書き込みによりDMA回路動作開始

データが転送されて、FIFOに空き領域(DMA\_Ready)が出来、

DMA\_Readyを受けてXDREQをアサート

XDACKがアサートされDMA転送開始

カウントモードの転送数完了前に、マスタ側を停止、XDACKをネゲート

DMA\_Control.DMA\_Stopビットへの"1"書き込みによりDMA回路停止

DMA回路停止を受けてXDREQネゲート

図 6.12 カウントモードライトタイミング 1

カウントモードで転送を開始し、設定されたカウント数分の転送を完了し DMA 転送が終了する場合の動作タイミングを図 6.13 に示します。

ex2.【転送開始条件】カウント(8バイト) > FIFOの空き容量(4バイト) 【転送停止条件】カウント0

DMA\_Control.DMA\_Goビットへの"1"書き込みによりDMA回路動作開始

データが転送される事によりFIFOに空き領域(DMA\_Ready)が出来、

DMA\_Readyを受けてXDREQをアサート

DMA\_ReadyがなくなるタイミングでXDREQをネゲート

データが転送される事によりFIFOに空き領域(DMA\_Ready)が出来、

DMA\_Readyを受けてXDREQをアサート

DMA\_Countの最終データタイミングでXDREQをネゲート

DMA\_Count数分の転送終了によりDMA回路停止

図 6.13 カウントモードライトタイミング 2

#### 6.4.3.2.5 カウントモード（リード）

##### 【動作開始】

DMax{x=0,1}\_Count\_HH,HL,LH,LL レジスタにカウント値を設定した後、DMax{x=0,1}\_Control.DMA\_Go ビットに”1”をセットしてください。内部 FIFO に読み出し可能なデータが 2 バイト以上 (8bit mode 動作時は 1 バイト以上) あり、且つ残りカウントがある場合に、外部か

## 6. 機能説明

らのリードに対応可能になると XDREQ をアサートします。FIFO に残り 1 バイトしかデータがない場合はカウントモードに設定され、且つ残りカウント数が”1”の時のみ XDREQ がアサートされます。

奇数バイトのリードを行ってバイト境界が発生した場合には、FIFO クリアを行ってバイト境界を解消してから次の転送を行ってください。

動作停止となるまで DMAx{x=0,1}\_Control.DMA\_Running ビットに”1”が読みます。

### 【動作停止】

動作停止条件は以下の 2 つです。

- DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタに設定したカウント数分の DMA 転送が完了

- DMAx{x=0,1}\_Control.DMA\_Stop ビットに”1”をライト

DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタによる転送停止は最終アクセスのストローブ信号アサート期間に XDREQ をネゲートします。

DMA\_Stop ビットによる転送停止は、同期レジスタアクセスのライトタイミングでチップ内部動作を停止し、XDREQ をネゲートします。DMA\_Stop ビットによる DMA の停止を行う場合は、CPU 側の DMAC (マスター) を先に停止してください。

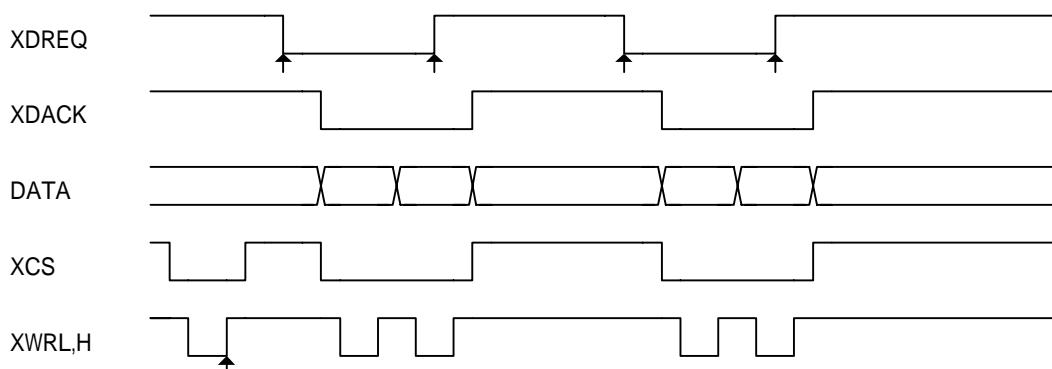

カウントモードで転送を開始し、設定されたカウント数分の転送を完了して DMA 転送が終了する場合の動作タイミングを図 6.14 に示します。

ex.【転送開始】カウント(8バイト) > FIFOのデータ(4バイト) 【転送停止】カウント0

DMA\_Control.DMA\_Go ビットへの "1" 書き込みにより DMA 回路動作開始

FIFO にデータが書き込まれ

外部からデータ読み出し可能になることで XDREQ をアサート

XDACK がアサートされ DMA 転送開始

FIFO データが空になるタイミングで XDREQ ネゲート

FIFO にデータが書き込まれ

外部からデータ読み出し可能になることで XDREQ をアサート

XDACK がアサートされ DMA 転送開始

DMA\_Count の最終データタイミングで XDREQ ネゲート

図 6.14 カウントモードリードタイミング

### 6.4.3.2.6 フリー郎モード (ライト)

#### 【動作開始】

DMAx{x=0,1}\_Config.FreeRun ビットをセットした後、DMAx{x=0,1}\_Control.DMA\_Go ビットに”1”を書き込んでください。内部 FIFO に書き込み可能な空き領域が 2 バイト以上 (8bit mode 動作時は 1 バイト以上) ある場合に XDREQ をアサートし DMA 転送が可能になります。FIFO に残り 1 バイトの空き領域しかない場合はフリー郎モードでは XDREQ がアサートされません。転送を行う場合はカウントモードの説明をご参照ください。

動作停止となるまで DMAx{x=0,1}\_Control.DMA\_Running ビットに”1”が読みます。

**【動作停止】**

動作停止条件は以下です。

- DMAx{x=0,1}\_Control.DMA\_Stop ビットに”1”をライト

DMA\_Stop ビットによる転送停止は、同期レジスタアクセスのライトタイミングでチップ内部動作を停止し、XDREQ をネゲートします。DMA\_Stop ビットによる DMA の停止を行う場合は、CPU 側の DMAC (マスター) を先に停止してください。

フリーランモードの DMA 転送中に DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタの値がオーバーフローすると、CPU\_IntStat. DMAx{x=0,1}\_Countup ビットがセットされます。この場合も DMA 転送は継続され、DMAx{x=0,1}\_Count\_HH,HL,LH,LL も継続してカウントされます。

動作タイミングは DMAx{x=0,1}\_Count\_HH,HL,LH,LL による制限が無い事を除き、カウントモードと同等です。

#### 6.4.3.2.7 フリーランモード (リード)

**【動作開始】**

DMAx{x=0,1}\_Config.FreeRun ビットをセットした後、DMAx{x=0,1}\_Control.DMA\_Go ビットに”1”をセットしてください。内部 FIFO に読み出し可能なデータが 2 バイト以上 (8bit mode 動作時は 1 バイト以上) あり、外部からのリードに対応可能になると XDREQ をアサートします。FIFO に残り 1 バイトしか有効なデータがない場合は DMA 動作を開始しません。転送を行う場合はカウントモードの説明をご参照ください。

動作停止となるまで DMAx{x=0,1}\_Control.DMA\_Running ビットに”1”が読めます。

**【動作停止】**

動作停止条件は以下です。

- DMAx{x=0,1}\_Control.DMA\_Stop ビットに”1”をライト

DMA\_Stop ビットによる転送停止は、同期レジスタアクセスのライトタイミングでチップ内部動作を停止し、XDREQ をネゲートします。DMA\_Stop ビットによる DMA の停止を行う場合は、CPU 側の DMAC (マスター) を先に停止してください。

フリーランモードの DMA 転送中に DMAx{x=0,1}\_Count\_HH,HL,LH,LL レジスタの値がオーバーフローすると、CPU\_IntStat. DMAx{x=0,1}\_Countup ビットがセットされます。この場合も DMA 転送は継続され、DMAx{x=0,1}\_Count\_HH,HL,LH,LL も継続してカウントされます。

動作タイミングは DMAx{x=0,1}\_Count\_HH,HL,LH,LL による制限が無い事を除き、カウントモードと同等です。

#### 6.4.3.2.8 REQ アサートカウントオプション (ライト)

**【動作開始】**

DMAx{x=0,1}\_Config.ReqAssertCount [1:0] ビットでアサートカウント数を設定した後、DMAx{x=0,1}\_Control.DMA\_Go ビットに”1”をセットしてください。内部 FIFO に設定されたアサートカウント数以上の書き込み可能な空き領域がある場合に XDREQ をアサートし DMA 転送が可能になります。従って、一旦 XDREQ がアサートされると、設定されたアサートカウント数分の転送が保証されることになります。ただし、空き領域がアサートカウント数に満たない場合でも、カウントモードに設定され且つ残りカウント数以上の空き領域がある場合は XDREQ をアサートします。この場合、転送可能数は、残りカウント数となります。

このモードでは、ReqAssertCount [1:0] ビットに設定された転送数毎に一旦 XDREQ がネゲートされます。

動作停止となるまで DMAx{x=0,1}\_Control.DMA\_Running ビットに”1”が読めます。

**【動作停止】**

動作停止条件はカウントモード、フリーランモードの説明をご参照ください。

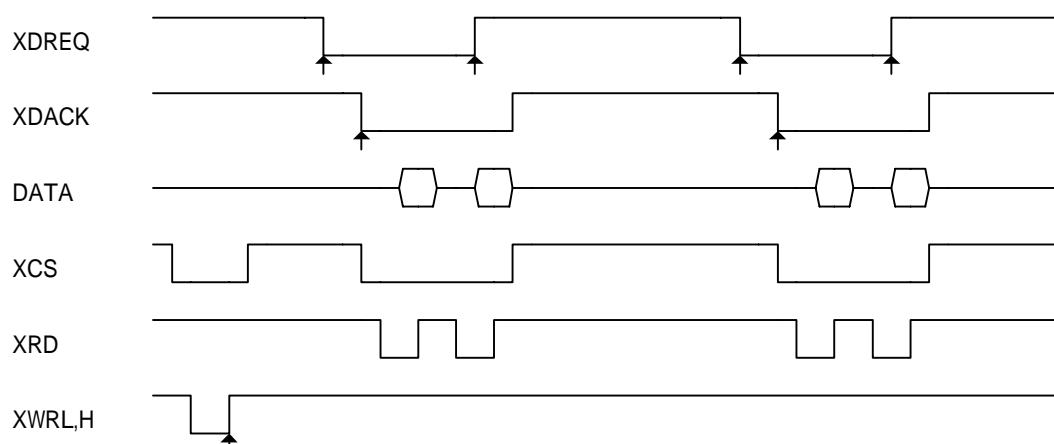

## 6. 機能説明

ex.【転送開始】REQアサートカウント(8beat:16byte)

DMA\_Control.DMA\_Goビットへの"1"書き込みによりDMA回路動作開始

DMA\_Readyの値が連続転送数に満たないためXDREQはアサートしない

データが転送され、FIFOに連続転送数以上の有効な空き領域

(DMA\_Ready)が出来、DMA\_Readyを受けてXDREQをアサート

連続転送数(REQアサートカウント)終了のタイミングでXDREQネゲート

1回目の連続転送終了時点で、次の連続転送分の空き領域(DMA\_Ready)がある

DMA\_Readyを受けてDREQをアサート

図 6.15 REQ アサートカウントオプションライトタイミング

### 6.4.3.2.9 REQ アサートカウントオプション(リード)

#### 【動作開始】

DMAX{x=0,1}\_Config.ReqAssertCount [ [1:0] ビットでアサートカウント数を設定した後、

DMAX{x=0,1}\_Control.DMA\_Go ビットに"1"をセットしてください。内部 FIFO に設定されたアサートカウン

ト数以上の読み出し可能なデータがあり外部からのリードに対応可能になると XDREQ をアサートし DMA

転送が可能になります。したがって、一旦 XDREQ がアサートされると、設定されたアサートカウント数分

の転送が保証されることになります。ただし、FIFO のデータが REQ アサートカウント数に満たない場合も、

カウントモードに設定され且つ残りカウント数以上のデータがある場合は、XDREQ をアサートします。こ

の場合、転送可能数は、残りカウント数となります。

このモードでは、ReqAssertCount [1:0] ビットに設定された転送数毎に一旦 XDREQ がネゲートされます。

動作停止となるまで DMAX{x=0,1}\_Control.DMA\_Running ビットに"1"が読みます。

#### 【動作停止】

動作停止条件はカウントモード、フリーランモードの説明をご参照ください。

動作タイミングは図 6.14、図 6.15 をご参照ください。

### 6.4.3.2.10 DMA の FIFO アクセス端数処理

6.4.3.1.5“FIFO アクセスの端数処理”をご参照ください。DMA にはバイト読み出しの口はございませんのでご注意ください。

## 6.5 IDE I/F

ここでは、IDE I/F 機能について説明します。

IDE I/F 機能を使用する際は、IDE\_Config\_1.ActiveIDE ビットにあらかじめ"1"を書き込む必要があります。

また、IDE デバイスとの通信におけるエンディアンを正しく設定するために、

IDE\_Config\_1.Swap ビットに"1"を書き込んでください。以下では、特に断らない限り、

IDE\_Config\_1.Swap ビットが"1"にセットされている前提で説明します。なお、IDE\_Config\_1.Swap ビット

につきましては、レジスタ詳細説明及び Appendix A をご参照ください。

### 6.5.1 IDE タスクファイルレジスタへのアクセス

IDE タスクファイルレジスタへのアクセス方法について説明します。

ファームウェアは IDE\_RegAdrs レジスタから IDE\_RegConfig レジスタまでのレジスタ群を介して、IDE タスクファイルレジスタにアクセスすることが出来ます。IDE バス上のリードライトシーケンスは、動作完了まで LSI のハードウェアが行うため、ファームウェアはコマンドをセットした後ポーリングまたは割り込みでシーケンス終了が通知されるまで、この IDE タスクファイルレジスタへのアクセス動作から解放されます。

IDE タスクファイルレジスタへアクセスする際には、IDE バスの XHCS0=0/HDA[2:0]=0 の時は IDE\_Tmod レジスタの設定値が、それ以外のアドレスでは IDE\_Rmod レジスタの設定値が使われて転送が行われるため、IDE の転送モードに応じて IDE\_Rmod/IDE\_Tmod レジスタにあらかじめ適切な値を設定する必要があります。

#### 6.5.1.1 IDE タスクファイルレジスタからのリード

IDE\_RegAdrs.IDE\_RegAddress[3:0] ビットに、アクセスしたいアドレスをあらかじめまたは同時にセットし、IDE\_RegAdrs.IDE\_RdReg ビットに”1”をライトすることにより、IDE タスクファイルレジスタからのリード動作が行われます。

IDE\_RegAdrs.IDE\_RdReg ビットが”0”になり、かつ IDE\_IntStat.IDE\_RegCmp ビットが”1”になりリード動作が終了します。

IDE タスクファイルレジスタからリードされたデータは IDE\_RdRegValue レジスタに格納されます。

#### 6.5.1.2 IDE タスクファイルレジスタへのライト

IDE\_WrRegValue レジスタにあらかじめライトしたいデータをセットし、IDE\_RegAdrs.IDE\_RegAddress[3:0] ビットにアクセスしたいアドレスをあらかじめまたは同時にセットし、IDE\_RegAdrs.IDE\_WrReg ビットに”1”をライトすることにより、IDE タスクファイルレジスタへのライト動作が行われます。

IDE\_RegAdrs.IDE\_WrReg ビットが”0”になり、かつ IDE\_IntStat.IDE\_RegCmp ビットが”1”になりライト動作が終了します。

#### 6.5.1.3 IDE タスクファイルレジスタへのシーケンシャルライト

IDE\_SeqWrRegControl レジスタを使うことにより、あらかじめセットしておいた最大 16 組のアドレス・データで IDE タスクファイルレジスタへシーケンシャルライトすることが出来ます。

あらかじめ IDE\_SeqWrRegAdrs.IDE\_SeqWrRegAddress[3:0] ビットにライトしたいアドレスを、IDE\_SeqWrRegValue レジスタにライトしたいバイトデータを対で最大 16 組ライトします。XHCS0=0/HDA[2:0]=0 のアドレスの時はワードアクセスになるため、下位(HDD[15:8]側) / 上位(HDD[7:0]側)の順(IDE\_Config\_1.Swap=”1”的時にデータを 2 回書き込む必要があり、アドレス・データ対は 2 組使用されます。その後 IDE\_SeqWrRegControl.IDE\_SeqWrReg ビットに”1”を書き込むとシーケンシャルライト動作が行われます。IDE\_SeqWrRegControl.IDE\_SeqWrReg ビットが”0”になり、かつ IDE\_IntStat.IDE\_SeqWrRegCmp ビットが”1”になりシーケンシャルライト動作が終了します。

シーケンシャルライト動作の起動前に、あらかじめセットしておいたアドレス・データが不要になった場合は、IDE\_SeqWrRegControl.IDE\_SeqWrRegClr ビットに”1”をライトしてアドレス・データを破棄することが出来ます。

シーケンシャルライト動作中にファームウェアが通常の IDE タスクファイルレジスタのリードライト動作を行うと、IDE\_IntStat.IDE\_RegErr ビットが”1”になり、そのリードライトは無視されます。

#### 6.5.1.4 IDE タスクファイルレジスタからのオートステータスレジスタリード

IDE バスの HINTRQ がセットされた場合、IDE\_RegConfig.EnAutoStsRd ビットに”1”が書き込まれていると、LSI は自動で IDE ステータスレジスタ(XHCS0=0,HDA[2:0]=7)をリードし、リードしたデータを IDE\_RdRegValue レジスタに格納した後、IDE\_IntStat.IDE\_CompleteINTRQ ビットが”1”になります。

オートステータスレジスタリード動作からファームウェアが IDE\_RdRegValue\_L レジスタを読み出

## 6. 機能説明

---

までの期間に、ファームウェアが通常のIDEタスクファイルレジスタのリードライト動作を行うと、IDE\_IntStat.IDE\_RegErrビットが”1”になり、そのリードライトは無視されます。

### 6.5.2 PIO アクセス

PIO モードによる DMA 機能について説明します。

PIO モードによる DMA では、IDE\_Tmod レジスタの設定値が使われて DMA 転送が行われるため、IDE の転送モードに応じて IDE\_Tmod レジスタにあらかじめ適切な値を設定する必要があります。

#### 6.5.2.1 PIO リード DMA

PIO リード DMA は以下の手順で動作します。

IDE\_Config\_0.DMA ビット及び IDE\_Config\_0.Ultra ビット両方に”0”を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE の DMA 動作と IDE からリードしたデータの内部 FIFO への書き込みが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時内部 FIFO まで転送したデータは有効ですが、回路の中間バッファに溜まったデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。

#### 6.5.2.2 PIO ライト DMA

PIO ライト DMA は以下の手順で動作します。

IDE\_Config\_0.DMA ビット及び IDE\_Config\_0.Ultra ビット両方に”0”を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE への DMA ライトが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時までに IDE にライトしたデータは有効ですが、回路の中間バッファに溜まったデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。

### 6.5.3 Multi-Word DMA

Multi-Word DMA モードによる DMA 機能について説明します。

Multi-Word DMA モードによる DMA では、IDE\_Tmod レジスタの設定値が使われて DMA 転送が行われるため、IDE の転送モードに応じて IDE\_Tmod レジスタにあらかじめ適切な値を設定する必要があります。

#### 6.5.3.1 Multi-Word DMA リード

Multi-Word DMA リードは以下の手順で動作します。

IDE\_Config\_0.DMA ビットに”1”を、IDE\_Config\_0.Ultra ビットに”0”を書き込みます。

IDE\_Config\_1.DelayStrobe ビット、IDE\_Config\_1.InterLock ビットに適切な値を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

りません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE の DMA 動作と IDE からリードしたデータの内部 FIFO への書き込みが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時内部 FIFO まで転送したデータは有効ですが、回路の中間バッファに溜まったデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。

### 6.5.3.2 Multi-Word DMA ライト

Multi-Word DMA ライトは以下の手順で動作します。

IDE\_Config\_0.DMA ビットに”1”を、IDE\_Config\_0.Ultra ビットに”0”を書き込みます。

IDE\_Config\_1.DelayStrobe ビット、IDE\_Config\_1.InterLock ビットに適切な値を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE への DMA ライトが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時までに IDE にライトしたデータは有効ですが、回路の中間バッファに溜まったデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。

## 6. 機能説明

---

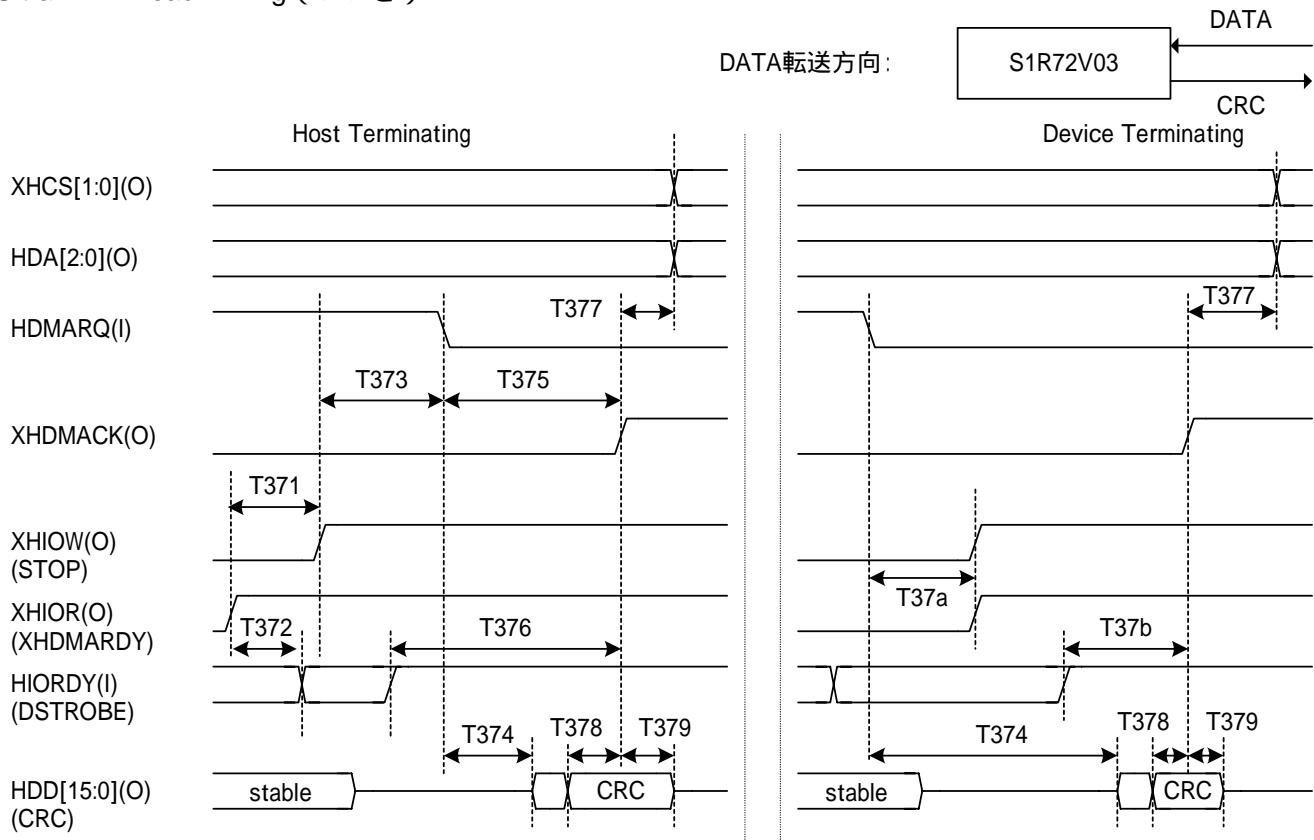

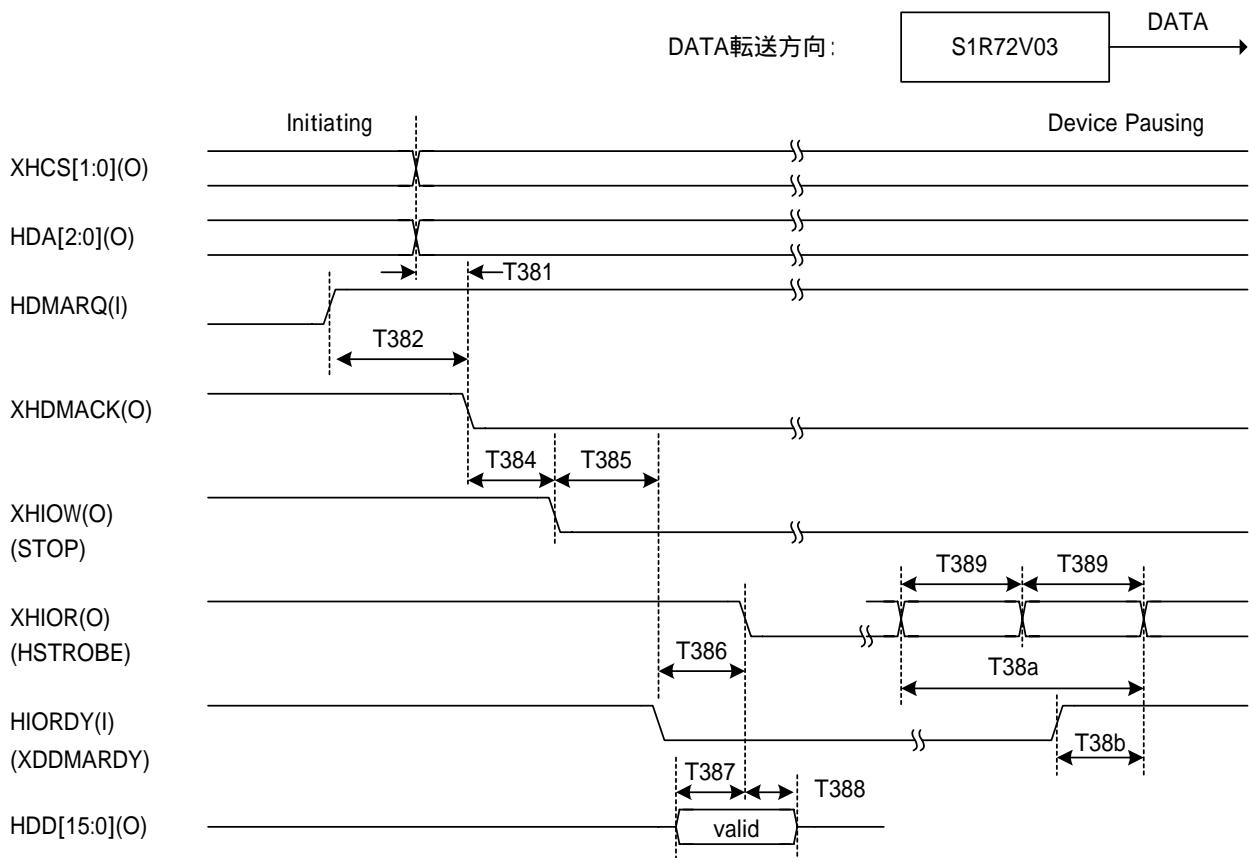

### 6.5.4 Ultra DMA

Ultra DMA モードによる DMA 機能について説明します。

Ultra DMA モードによる DMA では、IDE\_Umod レジスタの設定値が使われて DMA 転送が行われるため、IDE の転送モードに応じて IDE\_Umod レジスタにあらかじめ適切な値を設定する必要があります。

#### 6.5.4.1 Ultra DMA リード

Ultra DMA リードは以下の手順で動作します。

IDE\_Config\_0.DMA ビット及び IDE\_Config\_0.Ultra ビットに”1”を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE の DMA 動作と IDE からリードしたデータの内部 FIFO への書き込みが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時内部 FIFO まで転送したデータは有効ですが、回路の中間バッファに溜まつたデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。また、この場合接続された IDE デバイスにはホストターミネートを通知します。

DMA 転送中にデバイスター・ミネートが発生した場合、IDE\_IntStat.DetectTerm ビットが”1”になり接続された IDE デバイスは転送を止めてしまいますが、起動した DMA は終了しませんので IDE\_Control.IDE\_Go ビットに”0”を書き込んで DMA を終了させる必要があります。

#### 6.5.4.2 Ultra DMA ライト

Ultra DMA ライトは以下の手順で動作します。

IDE\_Config\_0.DMA ビット及び IDE\_Config\_0.Ultra ビットに”1”を書き込みます。

IDE\_CountH/M/L レジスタに転送バイト数を設定します。

IDE\_Control.IDE\_Clr ビットに”1”を書き込み、IDE 回路を初期状態にします。(必ずしも必要ではありません)

IDE\_Control.IDE\_Go ビットに”1”を書き込むと DMA 動作が開始され、転送とともに IDE\_CountH/M/L レジスタの内容が減っていき、カウントが 0 になって IDE への DMA ライトが全て終了すると、IDE\_Control.IDE\_Go ビットが”0”になり、かつ IDE\_IntStat.IDE\_Cmp ビットが”1”になり DMA 動作が終了します。

DMA 転送中に IDE\_Control.IDE\_Go ビットに”0”を書き込むと DMA 動作が中断されて DMA が終了します。その時までに IDE にライトしたデータは有効ですが、回路の中間バッファに溜まつたデータは捨てられるため、IDE の転送バイト数を正確に管理することは出来ません。また、この場合接続された IDE デバイスにはホストターミネートを通知します。

DMA 転送中にデバイスター・ミネートが発生した場合、IDE\_IntStat.DetectTerm ビットが”1”になり接続された IDE デバイスは転送を止めてしまいますが、起動した DMA は終了しませんので IDE\_Control.IDE\_Go ビットに”0”を書き込んで DMA を終了させる必要があります。

## 6.5.5 IDE 転送モードの設定について

IDE 転送の各モードにする設定値を下表に示します。

Register Mode ( XHCS0=0,HDA=0 以外のファームウェアによる IDE タスクファイルレジスタへのアクセス時 )

| Mode | レジスタ設定値(必須)        |                  | レジスタ設定値(推奨) |

|------|--------------------|------------------|-------------|

|      | IDE_Config_0.Ultra | IDE_Config_0.DMA |             |

| 0    | 影響しない              | 影響しない            | FFh         |

| 1    | 影響しない              | 影響しない            | F1h         |

| 2    | 影響しない              | 影響しない            | F0h         |

| 3    | 影響しない              | 影響しない            | 22h         |

| 4    | 影響しない              | 影響しない            | 10h         |

PIO Mode ( XHCS0=0,HDA=0 のファームウェアによる IDE タスクファイルレジスタへのアクセス時 )

| Mode | レジスタ設定値(必須)        |                  | レジスタ設定値(推奨) |

|------|--------------------|------------------|-------------|

|      | IDE_Config_0.Ultra | IDE_Config_0.DMA |             |

| 0    | 影響しない              | 影響しない            | FFh         |

| 1    | 影響しない              | 影響しない            | 88h         |

| 2    | 影響しない              | 影響しない            | 44h         |

| 3    | 影響しない              | 影響しない            | 22h         |

| 4    | 影響しない              | 影響しない            | 10h         |

PIO Mode ( DMA 転送時 )

| Mode | レジスタ設定値(必須)        |                  | レジスタ設定値(推奨) |

|------|--------------------|------------------|-------------|

|      | IDE_Config_0.Ultra | IDE_Config_0.DMA |             |

| 0    | 0                  | 0                | FFh         |

| 1    | 0                  | 0                | 88h         |

| 2    | 0                  | 0                | 44h         |

| 3    | 0                  | 0                | 22h         |

| 4    | 0                  | 0                | 10h         |

Multi-word DMA Mode ( DMA 転送時 )

| Mode | レジスタ設定値(必須)        |                  | レジスタ設定値(推奨) |

|------|--------------------|------------------|-------------|

|      | IDE_Config_0.Ultra | IDE_Config_0.DMA |             |

| 0    | 0                  | 1                | BBh         |

| 1    | 0                  | 1                | 20h         |

| 2    | 0                  | 1                | 10h         |

Ultra Mode ( DMA 転送時、DATA-OUT 時 )

| Mode | レジスタ設定値(必須)        |                  | レジスタ設定値(推奨) |

|------|--------------------|------------------|-------------|

|      | IDE_Config_0.Ultra | IDE_Config_0.DMA |             |

| 0    | 1                  | 1                | 06h         |

| 1    | 1                  | 1                | 04h         |

| 2    | 1                  | 1                | 03h         |

| 3    | 1                  | 1                | 02h         |

| 4    | 1                  | 1                | 01h         |

| 5    | 1                  | 1                | 00h         |

注：Ultra ModeにおいてIDEバスからデータを入力するDATA-IN時は、IDE\_Umodレジスタの設定によらず全てのモードでデータ受信可能です。

## 6. 機能説明

### 6.6 バウンダリスキャン ( JTAG )

バウンダリスキャン ( JTAG ) は、TEST 端子を L ( デフォルト ) の時使用可能です。バウンダリスキャンは、JTAG ( IEEE 1149.1 ) 仕様に準拠した、BSR ( Boundary Scan Register ) それを繋ぐスキャンパスおよび TAP コントローラで構成されます。バウンダリスキャンの接続情報は、BSDL フォーマットにて提供可能です。

#### 6.6.1 対応インストラクション

本 LSI の JTAG インストラクションビット幅は 4 ビットとなっており、以下の JTAG インストラクションに対応致します。

表 6.4 JTAG インストラクションコード

| インストラクション      | 説明                           | コード  |

|----------------|------------------------------|------|

| SAMPLE/PRELOAD | LSI 内部状態の BSR への取り込み及びデータ設定。 | 0010 |

| BYPASS         | BSR によるスキャンパスをバイパスする。        | 1111 |

| EXTEST         | デバイスの物理的な接続チェック。             | 0000 |

| CLAMP          | 出力値を保持しながら、スキャンパスをバイパスする。    | 0011 |

| HIGHZ          | 出力を全て Hi-Z に固定する。            | 0100 |

| IDCODE         | 定められた DEVICE_CODE の出力。       | 0001 |

#### 6.6.2 DEVICE\_CODE について

IDCODE インストラクションに対する DEVICE\_CODE の構成要素は以下のとおりとなります。

表 6.5 DEVICE\_CODE

|              |        |

|--------------|--------|

| Version      | 1      |

| Part Number  | 0x000E |

| Manufacturer | 0x0BE  |

従って、IDCODE インストラクションに対する DEVICE\_CODE 応答は、

0001\_0000000000001110\_00010111110\_1

となります。

#### 6.6.3 バウンダリスキャン除外端子

本 LSI の端子のうち、XI、XO、および、TEST にはバウンダリスキャンセルが挿入されていないため、スキャン対象外となります。従って XO 端子は、HIGHZ インストラクションを実行することによっては High-Z にはなりません。

## 7. レジスタ

S1R72H74 は、S1R72V03 との互換性を保持するため、レジスタ名称を継承します。そのため、USB 固有の名称が使用されている場合が有ります。S1R72V03 でレジスタ定義され、S1R72H74 ではレジスタ定義されていないレジスタ・ビットについては、"Don't care"または"Don't touch"と明示しています。

### 7.1 レジスタマップ

スリープ / スヌーズ時にでも読み書きできるレジスタを**太字斜体**で示します。

| Byte Addr. | Register Name      | R/W   | Reset | bit15              | bit14        | bit13             | bit12         | bit11        | bit10        | bit9         | bit8         |

|------------|--------------------|-------|-------|--------------------|--------------|-------------------|---------------|--------------|--------------|--------------|--------------|

|            |                    |       |       | bit7               | bit6         | bit5              | bit4          | bit3         | bit2         | bit1         | bit0         |

| 0x00       | <i>MainIntStat</i> | R/(W) | 0x00  | <i>SIE_IntStat</i> | (Don't care) | CPU_IntStat       | FIFO_IntStat  | (Don't care) | IDE_IntStat  | (Don't care) | (Don't care) |

| 0x01       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x02       | <i>SIE_IntStat</i> | R/(W) | 0x00  | (Don't care)       | (Don't care) | <i>FinishedPM</i> | (Don't care)  | (Don't care) | (Don't care) | (Don't care) | (Don't care) |

| 0x03       | CPU_IntStat        | R/(W) | 0x00  |                    | (Don't care) | DMA1_Countup      | DMA1_Cmp      |              |              | DMA0_Countup | DMA0_Cmp     |

| 0x04       | FIFO_IntStat       | R/(W) | 0x00  | (Don't care)       | (Don't care) | FIFO_IDE_Cmp      | FIFO1_Cmp     | FIFO_Full    | FIFO_Empty   |              | FIFO0_Cmp    |

| 0x05       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x06       | IDE_IntStat        | R/(W) | 0x00  | IDE_RegCmp         | IDE_RegErr   | IDE_SeqWrRegCmp   | CompleteINTRQ |              | IDE_Cmp      | DetectINTRQ  | DetectTerm   |

| 0x07       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x08       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x09       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0A       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0B       | (Don't care)       |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0C       |                    |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0D       |                    |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0E       |                    |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| 0x0F       |                    |       | 0xXX  |                    |              |                   |               |              |              |              |              |

| Byte Addr. | Register Name     | R/W | Reset | bit15                | bit14         | bit13               | bit12           | bit11         | bit10         | bit9           | bit8          |

|------------|-------------------|-----|-------|----------------------|---------------|---------------------|-----------------|---------------|---------------|----------------|---------------|

|            |                   |     |       | bit7                 | bit6          | bit5                | bit4            | bit3          | bit2          | bit1           | bit0          |

| 0x10       | <i>MainIntEnb</i> | R/W | 0x00  | <i>EnSIE_IntStat</i> | (Don't touch) | EnCPU_IntStat       | EnFIFO_IntStat  | (Don't touch) | EnIDE_IntStat | (Don't touch)  | (Don't touch) |

| 0x11       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x12       | <i>SIE_IntEnb</i> | R/W | 0x00  | (Don't touch)        | (Don't touch) | <i>EnFinishedPM</i> | (Don't touch)   | (Don't touch) | (Don't touch) | (Don't touch)  | (Don't touch) |

| 0x13       | CPU_IntEnb        | R/W | 0x00  |                      | (Don't touch) | EnDMA1_Countup      | EnDMA1_Cmp      |               |               | EnDMA0_Countup | EnDMA0_Cmp    |

| 0x14       | FIFO_IntEnb       | R/W | 0x00  | (Don't touch)        | (Don't touch) | EnFIFO_IDE_Cmp      | EnFIFO1_Cmp     | EnFIFO_Full   | EnFIFO_Empty  |                | EnFIFO0_Cmp   |

| 0x15       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x16       | IDE_IntEnb        | R/W | 0x00  | EnIDE_RegCmp         | EnIDE_RegErr  | En_SeqWrRegCmp      | EnCompleteINTRQ |               | EnIDE_Cmp     | EnDetectINTRQ  | EnDetectTerm  |

| 0x17       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x18       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x19       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1A       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1B       | (Don't touch)     |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1C       |                   |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1D       |                   |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1E       |                   |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

| 0x1F       |                   |     | 0xXX  |                      |               |                     |                 |               |               |                |               |

## 7. レジスタ

スリープ / スヌーズ時にでも読み書きできるレジスタを**太字斜体**で示します。

| Byte<br>Addr<br>. | Register<br>Name   | R/W  | Rese<br>t | bit15                   | bit14                 | bit13          | bit12          | bit11          | bit10          | bit9          | bit8          |          |  |  |

|-------------------|--------------------|------|-----------|-------------------------|-----------------------|----------------|----------------|----------------|----------------|---------------|---------------|----------|--|--|

|                   |                    |      |           | bit7                    | bit6                  | bit5           | bit4           | bit3           | bit2           | bit1          | bit0          |          |  |  |

| 0x20              | <i>RevisionNum</i> | R    | 0x30      | <i>Revision Number</i>  |                       |                |                |                |                |               |               |          |  |  |

| 0x21              | <i>ChipReset</i>   | W    | 0xXX      | (Don't touch)           |                       |                |                |                |                |               |               | AllReset |  |  |

| 0x22              | <i>PM_Control</i>  | R/W  | 0x00      | <i>PM_State [2:0]</i>   |                       |                |                | GoSLEEP        | GoSNOOZE       | GoActive60    | (Don't touch) |          |  |  |

| 0x23              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x24              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x25              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x26              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x27              |                    | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x28              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x29              | EPrFIFO_Clr        | W    | 0xXX      |                         |                       |                |                |                | EPcFIFO_Clr    | EPbFIFO_Clr   | (Don't touch) |          |  |  |

| 0x2A              | ClrAllJoin         | W    | 0xXX      | ClrJoinIDE              | ClrJoinFIFOStatu<br>s | ClrJoinDMA0_Rd | ClrJoinDMA0_Wr | ClrJoinDMA1_Rd | ClrJoinDMA1_Wr | ClrJoinCPU_Rd | ClrJoinCPU_Wr |          |  |  |

| 0x2B              |                    |      |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x2C              | (Don't touch)l     | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x2D              | (Don't touch)      | 0xXX |           |                         |                       |                |                |                |                |               |               |          |  |  |

| 0x2E              | <i>WakeupTim_H</i> | R/W  | 0x00      | <i>WakeupTim [15:8]</i> |                       |                |                |                |                |               |               |          |  |  |

| 0x2F              | <i>WakeupTim_L</i> | R/W  | 0x00      | <i>WakeupTim [7:0]</i>  |                       |                |                |                |                |               |               |          |  |  |

| Byte<br>Addr<br>. | Register<br>Name | R/W  | Rese<br>t | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 |

|-------------------|------------------|------|-----------|-------|-------|-------|-------|-------|-------|------|------|

|                   |                  |      |           | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1 | bit0 |

| 0x30              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x31              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x32              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x33              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x34              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x35              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x36              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x37              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x38              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x39              |                  | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3A              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3B              |                  | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3C              |                  | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3D              |                  | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3E              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

| 0x3F              | (Don't care)     | 0xXX |           |       |       |       |       |       |       |      |      |

スリープ / スヌーズ時にでも読み書きできるレジスタを**太字斜体**で示します。

| Byte Addr. | Register Name | R/W | Reset | bit15 | bit14 | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 |

|------------|---------------|-----|-------|-------|-------|-------|-------|-------|-------|------|------|

|            |               |     |       | bit7  | bit6  | bit5  | bit4  | bit3  | bit2  | bit1 | bit0 |

| 0x40       | (Don't care)  |     | 0xXX  |       |       |       |       |       |       |      |      |

| 0x41       | (Don't touch) |     | 0xXX  |       |       |       |       |       |       |      |      |

| 0x42       | (Don't care)  |     | 0xXX  |       |       |       |       |       |       |      |      |

| 0x43       | (Don't care)  |     | 0xXX  |       |       |       |       |       |       |      |      |

| 0x44       |               |     |       |       |       |       |       |       |       |      |      |