# S1D13506F00A

## Color LCD/CRT/TV Controller

### 概要

S1D13506 は、各種のCPUおよび表示装置に幅広く対応可能なカラーLCD/CRT/TV用グラフィックコントローラで、OA機器やモバイル通信機器あるいはWindows® CEを主要OSとするハンドヘルドパソコンなど、組み込み機器の市場要求に合ったアーキテクチャで設計されています。

S1D13506 は、マルチCPU、LCDパネルのすべてのタイプ、CRT/TVをサポートし、さらに多様な機能を提供します。デジタルカメラの入力が必要な製品では、WINNOV VideumCam™ デジタルインターフェースを直接サポートしておりますので、大変便利です。EPSON独立型同時表示装置(EISD)では、ユーザが2つの違った表示装置に、それぞれ違った画像を表示させる設定を行うことができます。さらに、SwivelView™、ハードウェアソール、インクレイヤそしてBitBLTエンジンでは、重要なパフォーマンスを一層向上させることができます。

### 特長

#### ●メモリインターフェース

##### •16ビットDRAMインターフェース:

- 最大データ転送速度40MHzまでのEDO-DRAMに対応(80Mバイト/秒)

- 最大データ転送速度25MHzまでのFPM-DRAMに対応(50Mバイト/秒)

##### •メモリサイズオプション:

- 256K × 16ビットを1個使用した場合: 512Kバイト

- 1M × 16ビットを1個使用した場合: 2Mバイト

##### •コンフィグレーションレジスタは、DRAMのメモリ制御出力タイミングの調整等、パフォーマンス向上させるプログラミングが可能

##### •全2MB表示バッファのアドレス領域は、21ビットアドレスバスが直接に、また連続して使用可能

#### ●CPUインターフェース

##### •各種インターフェースに対応:

- EPSON S1C33(32ビットマイクロプロセッサへの16ビットインターフェース)

- 16ビット日立SH-4バスインターフェース

- 16ビット日立SH-3バスインターフェース

- MIPSバス

- モトローラMC68000

- (16/32ビットマイクロプロセッサ/マイクロコントローラへの16ビットインターフェース)

- モトローラMC68030

- (16/32ビットマイクロプロセッサ/マイクロコントローラへの16ビットインターフェース)

- モトローラPowerPC MPC82x(32ビットマイクロプロセッサへの16ビットインターフェース)

–プログラム可能なREADYのあるMPUバスインターフェース

–NEC VR41xx(MIPS)

–PCカード(PCMCIA)

–フィリップスPR31500/31700(MIPS)

–東芝TX39xx(MIPS)

–StrongARM(PCカード)

•CPUから最小ウェイトサイクルで書き込み可能な、ワンステージ書き込みバッファ

•メモリ割り当てレジスタ(M/R#端子により表示バッファとレジスタアドレス空間を選択)

#### ●表示サポート

•シングルパネル、シングル駆動表示装置への4/8ビットモノクロまたは4/8/16ビットカラーLCDインターフェース

•ディアルパネル、デュアル駆動表示装置への8ビットモノクロまたは8/16ビットカラーLCDインターフェース

•最大64K色をサポートする9/12ビットTFT/D-TFD、18ビットTFT/D-TFDを直接サポート

•組み込み型RAMDACを使用する最大64K色CRTを直接サポート

•組み込み型RAMDACを使用するNTSC/PAL信号出力のTVを直接サポート

#### ●表示モード

•4/8/15/16ビット/ピクセル(bpp)色深度

•フレームレート調整(FRM)とディザーを使用するパッセンブリモノクロLCDパネルでの最大64階調グレースケール

# S1D13506F00A

- ディザーを使用するパッシブカラー LCD パネルで

15/16 bpp モードで最大 32k/64k 色

- TFT/D-TFD、CRT そして TV 上で最大 64K 色

- 4/8 bpp 色深度は、256 × 4 ルックアップテーブル

(LUT)を使用してマッピングし、4096 色以内の 16/

256 色のカラー表示が可能

- LCD と CRT/TV 表示には別々の LUT を使用

- 15/16 bpp 色深度は、LUT を使用せずに直接マッピング

- 解像度例:

- 16 bpp で 320 × 240

- 16 bpp で 640 × 240

- 16 bpp で 640 × 480

- 16 bpp で 800 × 600

## ●表示特長

- SwivelView™: 表示画像の 90 度、180 度、270 度の

ハードウェア回転

- EPSON 独立同時表示装置(EISD): それぞれの画像を

違った表示装置で表示 (CRT または TV とパッシブ

または TFT/D-TFD パネル)

- 仮想表示サポート: パニングやスクロールを使用して

パネルサイズより大きく画像を表示させます。

- ハードウェアカーソル/インクレイヤ: LCD と CRT/

TV 両方に対して別々の 64 × 64 × 2 ハードウェア

カーソルまたは 2-ビットインクレイヤ

- ダブルバッファリング/多重ページ: スムーズな動画

と瞬間的の画面の更新

## ●クロックソース

- メモリクロックは、CLKI または BUSCLK 端子より取

得し、内部で 2 分周することができます。

- ピクセルクロックは、CLKI, CLKI2 または BUSCLK

端子より取得し、内部で 2, 3, 4 分周することができます。

- バスクロックは、BUSCLK または(BUSCLK) / 2 であ

り、すなわち 2x クロックが使用されます。

## ●加 速

- 2D エンジンは、以下の 2 ROP BitBlit を含みます:

Write BLT.

Move BLT.

Solid Fill.

Pattern Fill.

Transparent Write BLT.

Transparent Move BLT.

Read BLT.

Color Expansion.

Move BLT with Color Expansion.

## ●MediaPlug インタフェース

- WINNOV MediaPlug インタフェース内蔵

- VideumCam により 30 fps で 320 × 240 × 256 色の

解像度をサポート

## ●その他

- メモリデータバス MD[15:0]は、電源投入時の状態に

よりチップ内部の構成を設定。

- 上位メモリアドレスピンに非対称 DRAM サポートが

必要でない場合、3 つの汎用 I/O ピンと、GPIO[3:1]

が利用可能です。

- パワーセーブモードは、ソフトウェアによって初期

化します。

- 動作電圧として 2.7V から 5.5V までをサポートして

います。

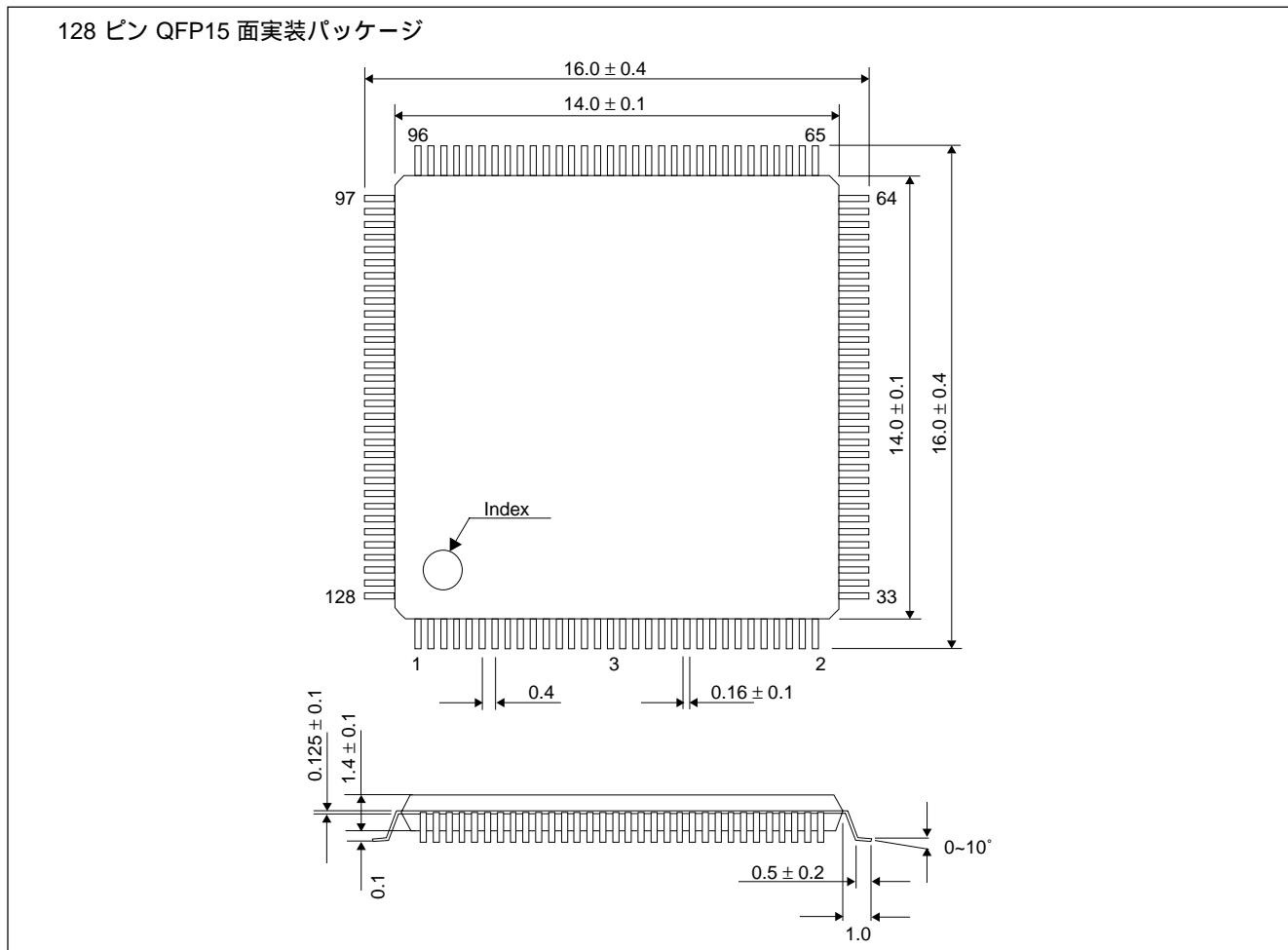

- 128 ピン QFP15 面実装パッケージ

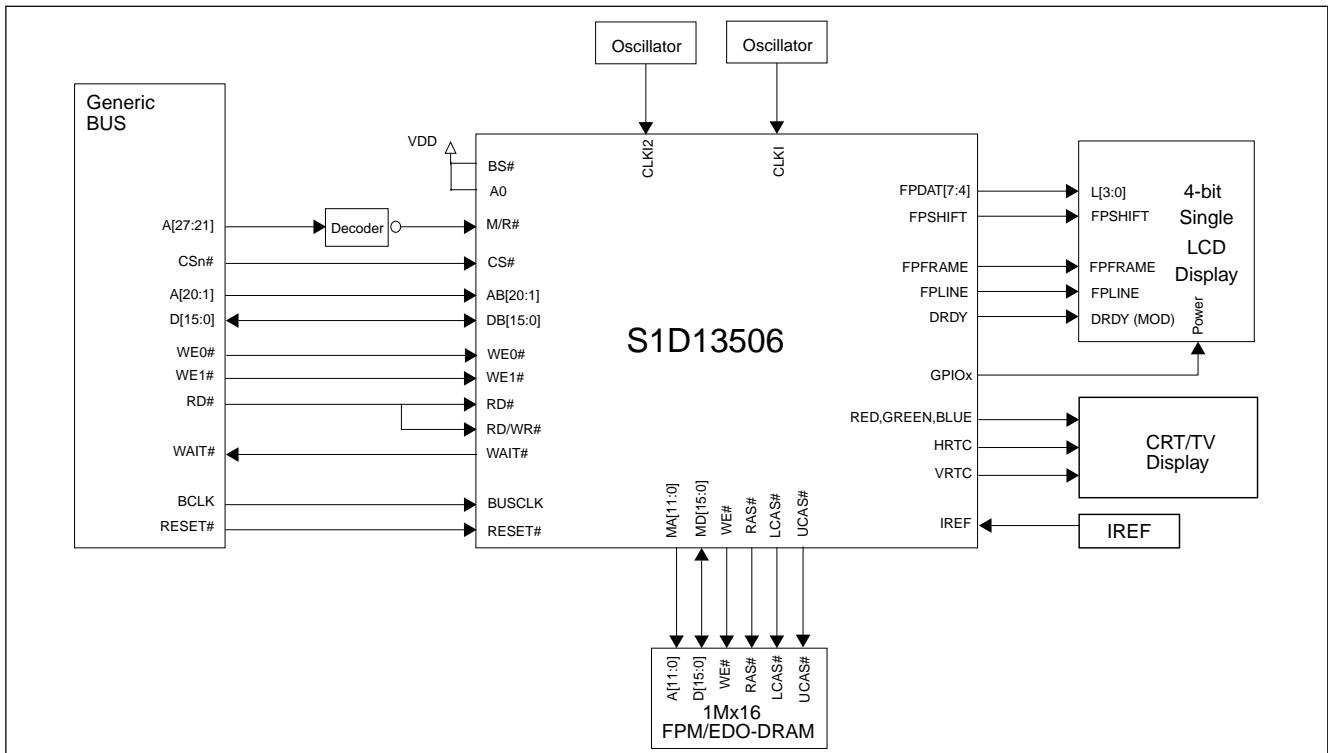

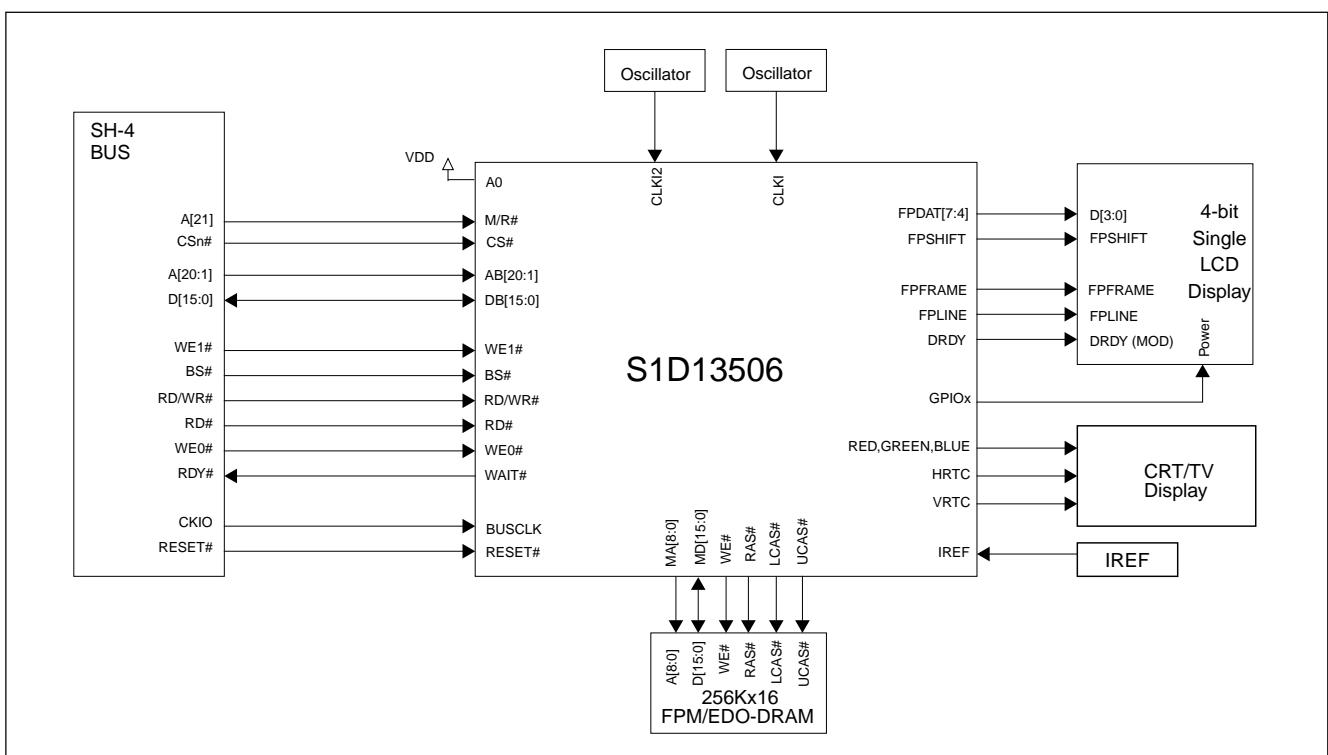

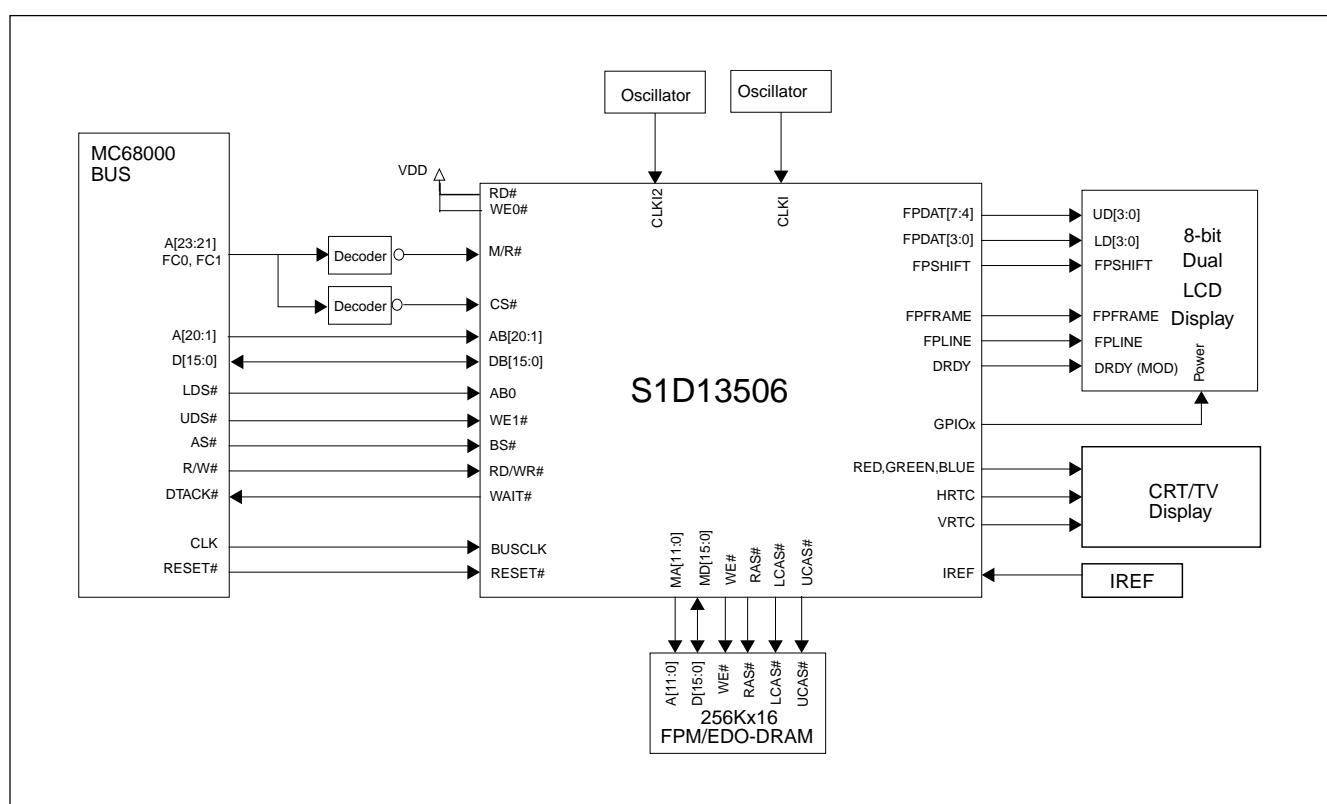

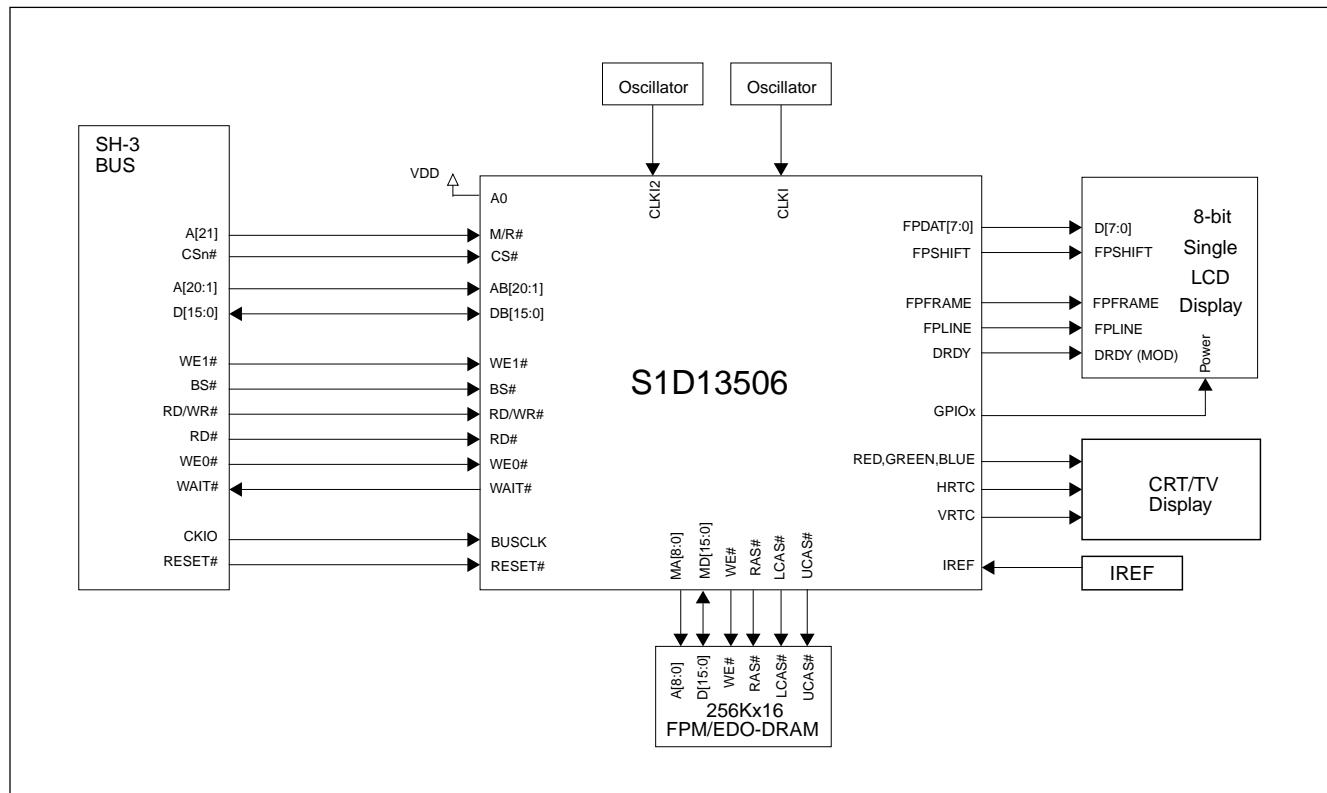

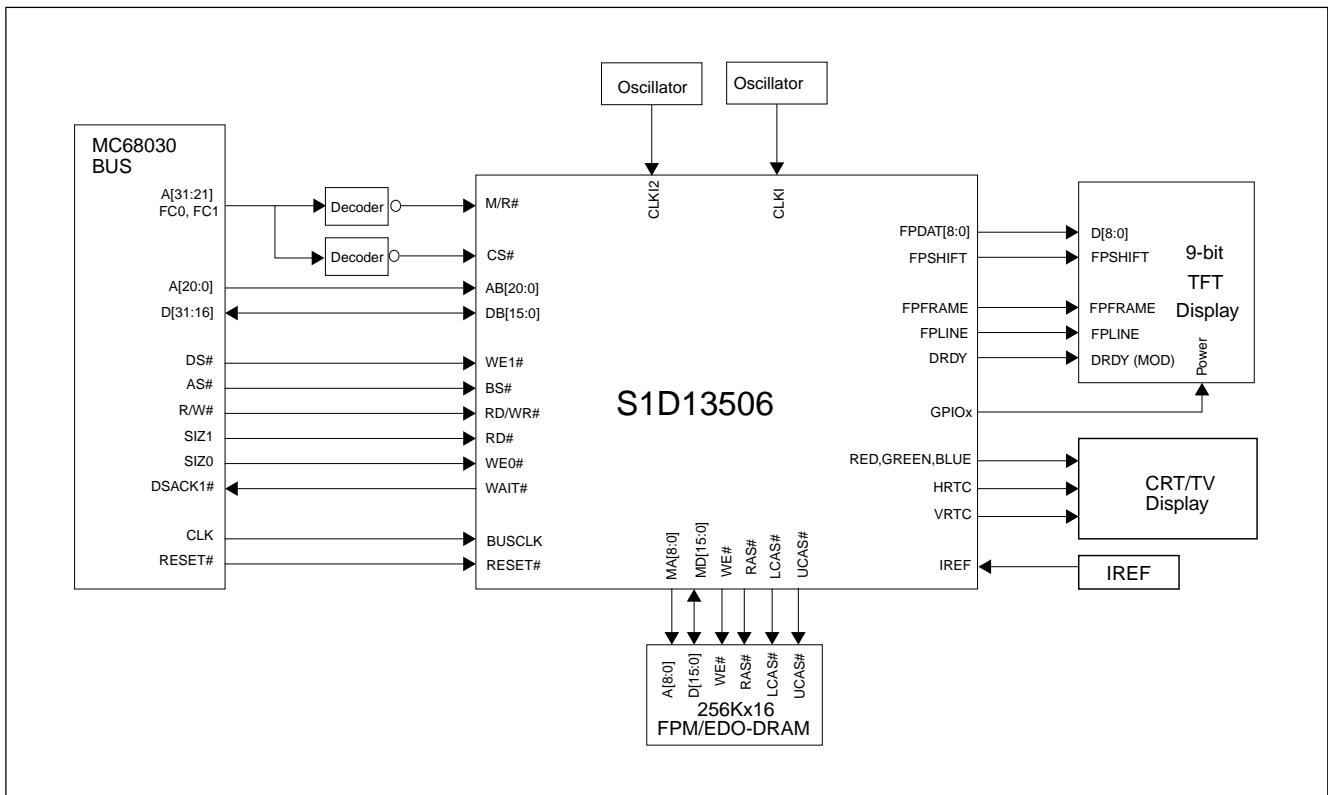

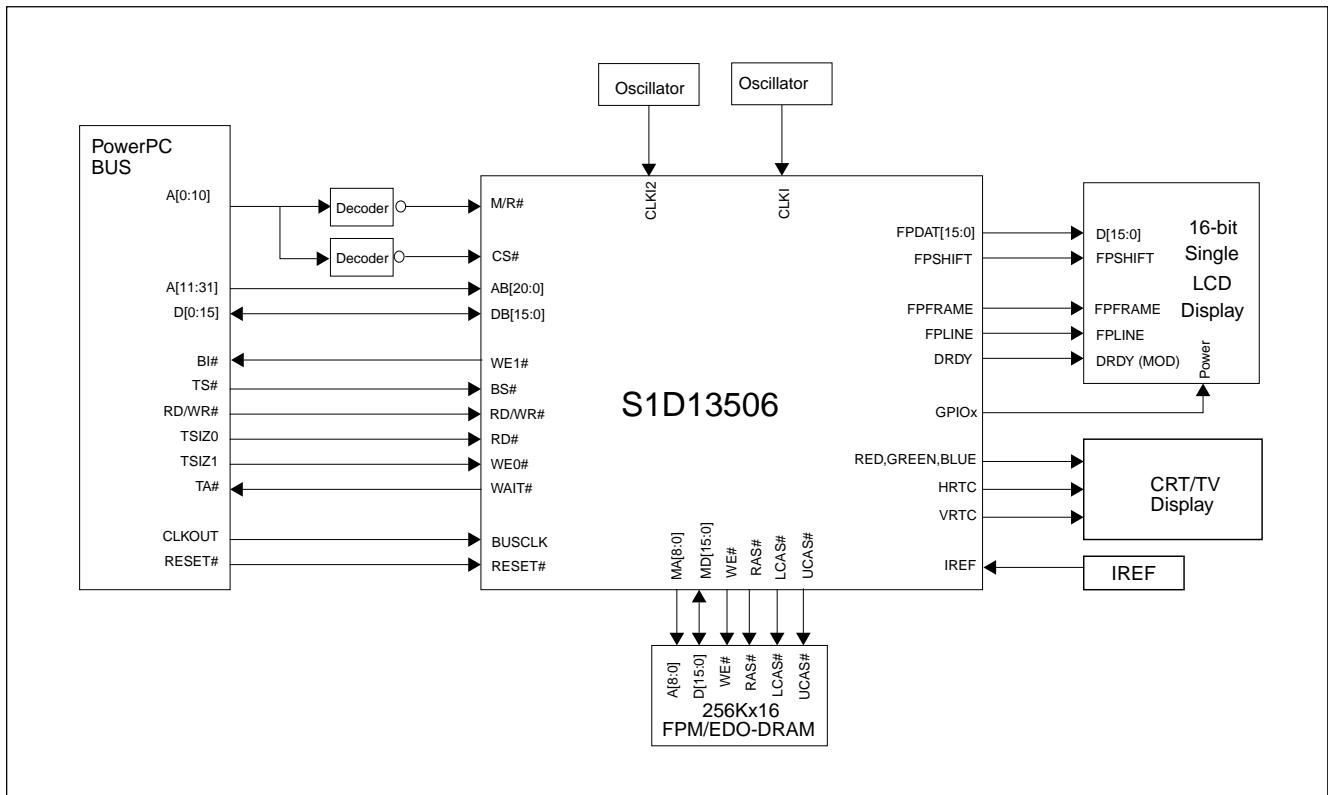

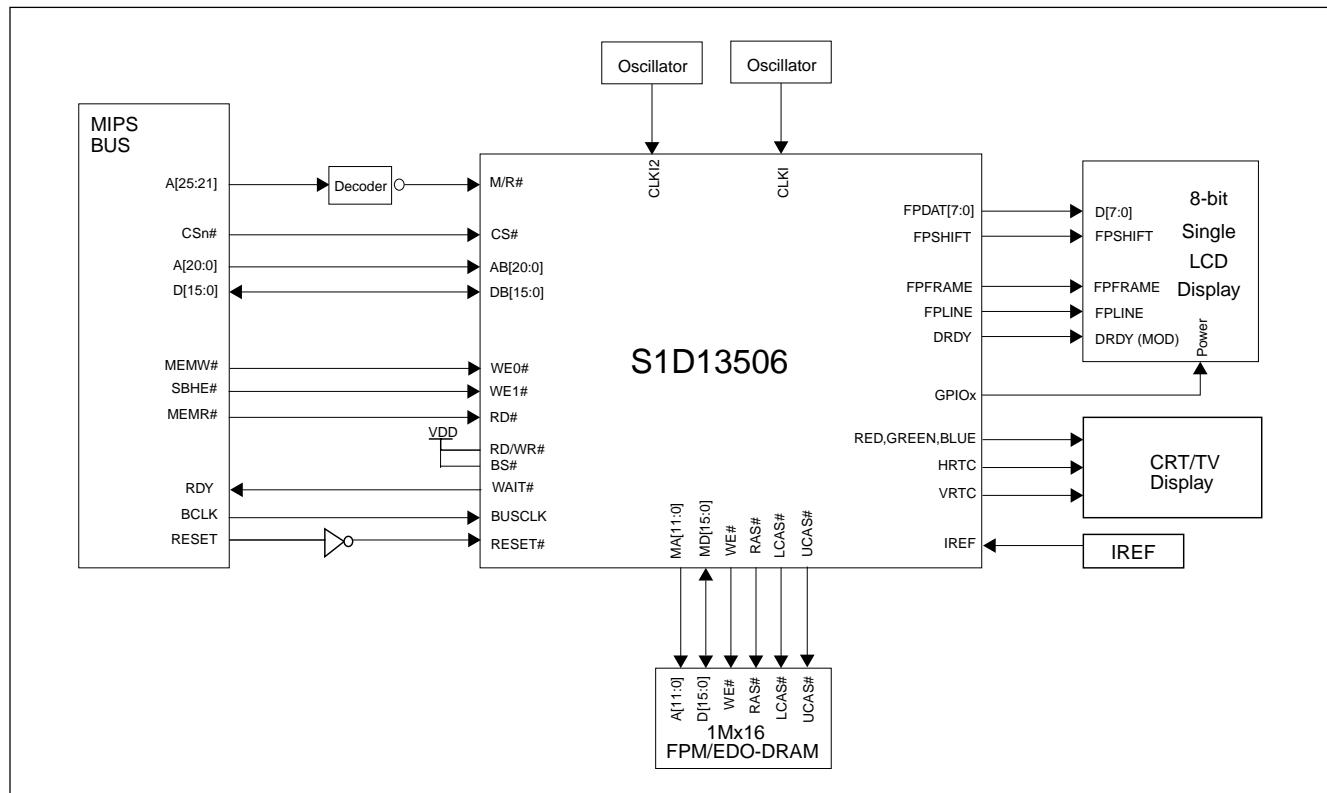

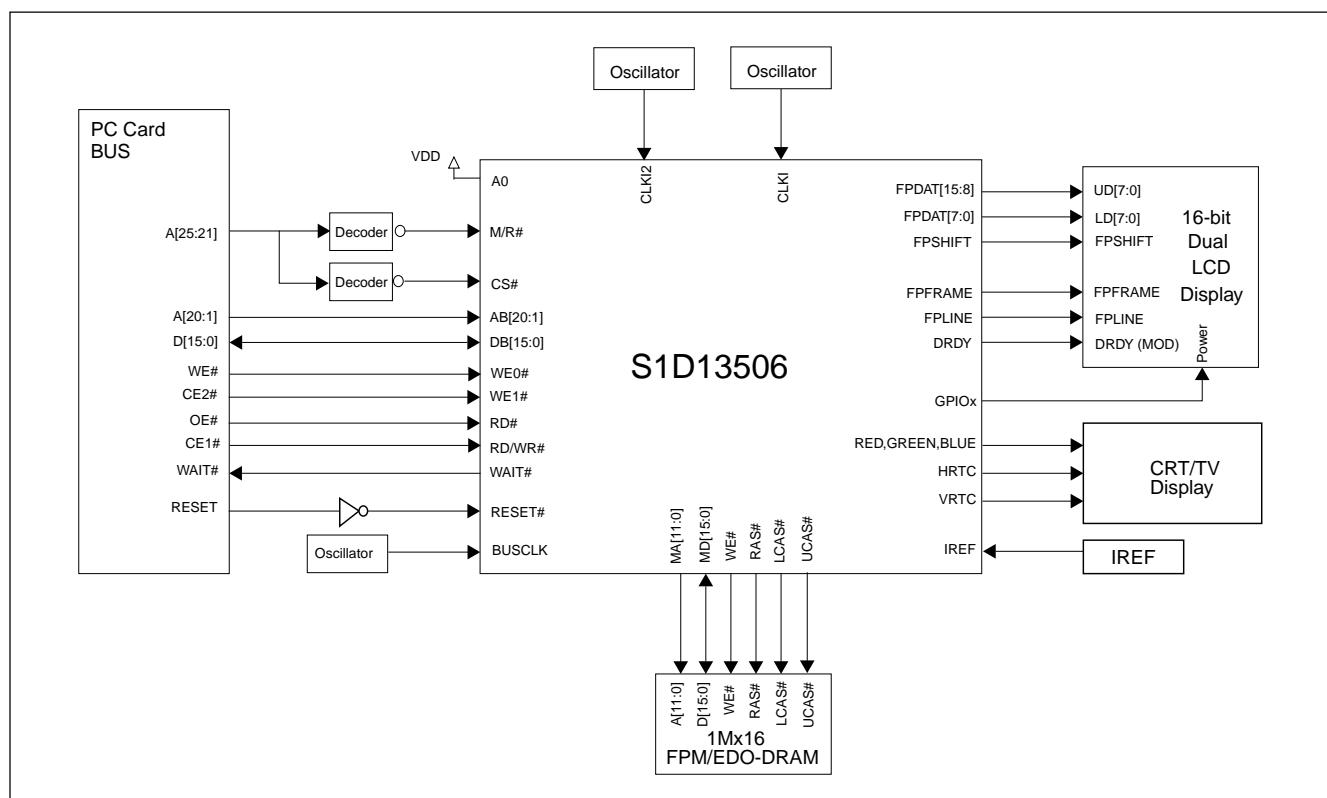

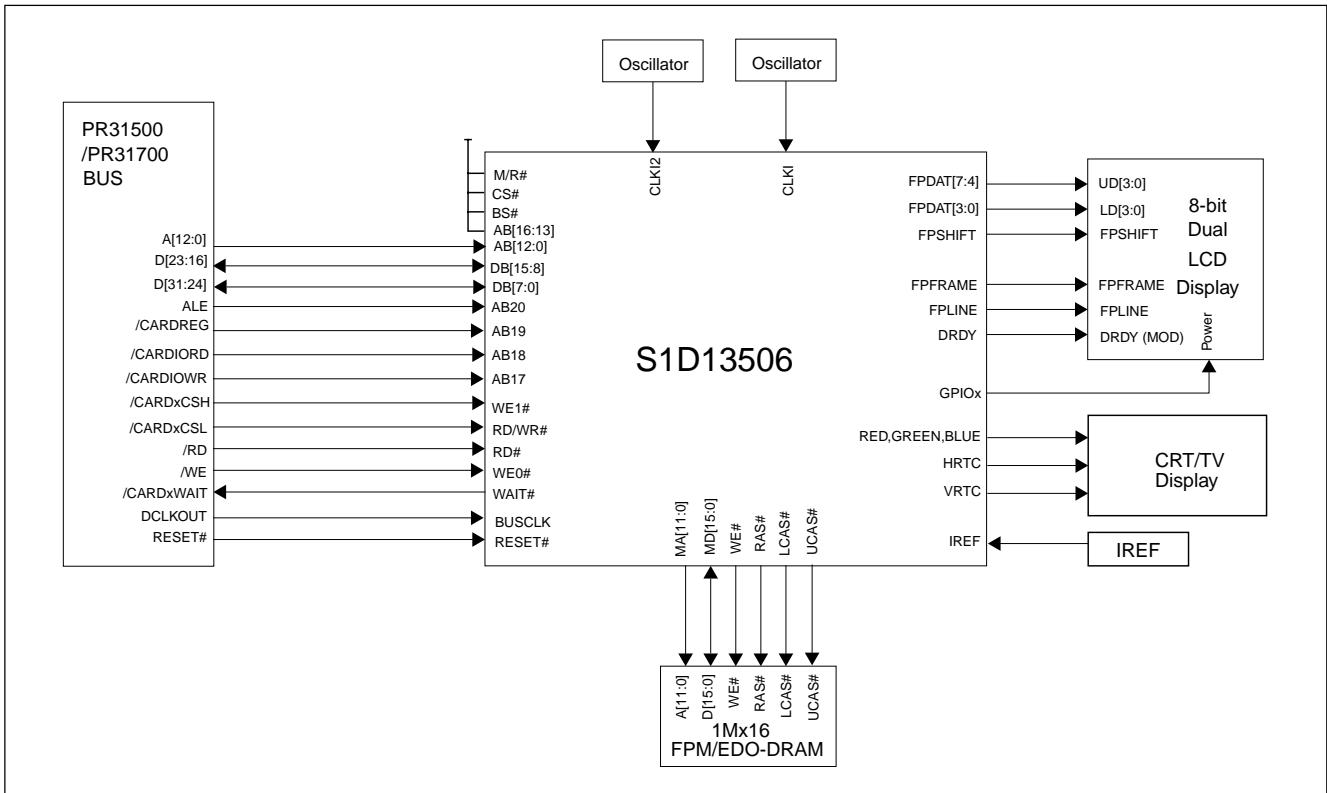

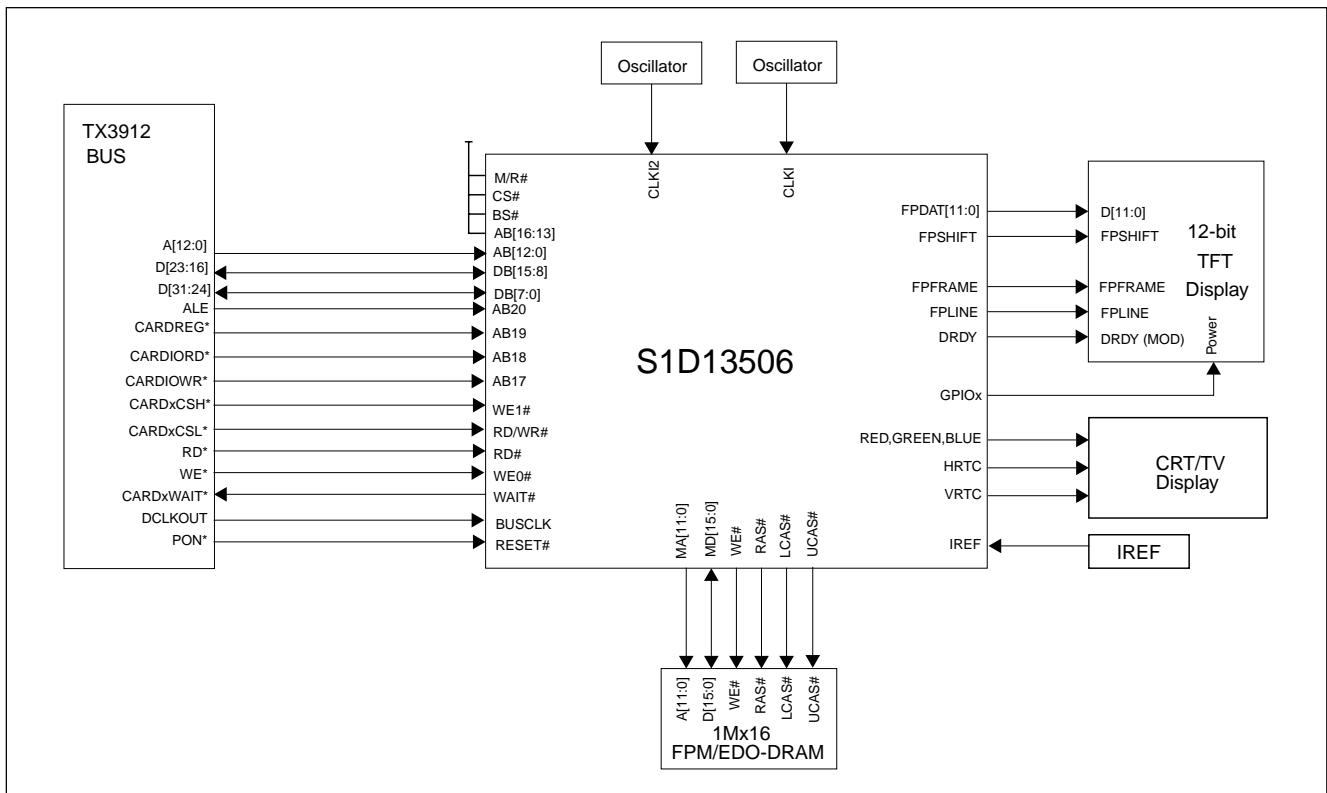

## 基本システムブロック図

以下のブロック図は、S1D13506 の代表的なシステム構成例を示しています。詳細については、表 “CPU インタフェース端子の割り付け”(21 ページ) を参照してください。

基本システム構成例 (汎用バス)

基本システム構成例 (日立SH-4バス)

# S1D13506F00A

基本システム構成例 ( MC68Kバス2、モトローラ32-Bit 68030 )

基本システム構成例 ( モトローラPowerPCバス )

# S1D13506F00A

基本システム構成例 (NEC VR41xx MIPS/バス)

基本システム構成例 (PCカードバス)

基本システム構成例 ( フィリップスMIPS PR31500/PR31700バス )

基本システム構成例 ( 東芝MIPS TX3912バス )

# S1D13506F00A

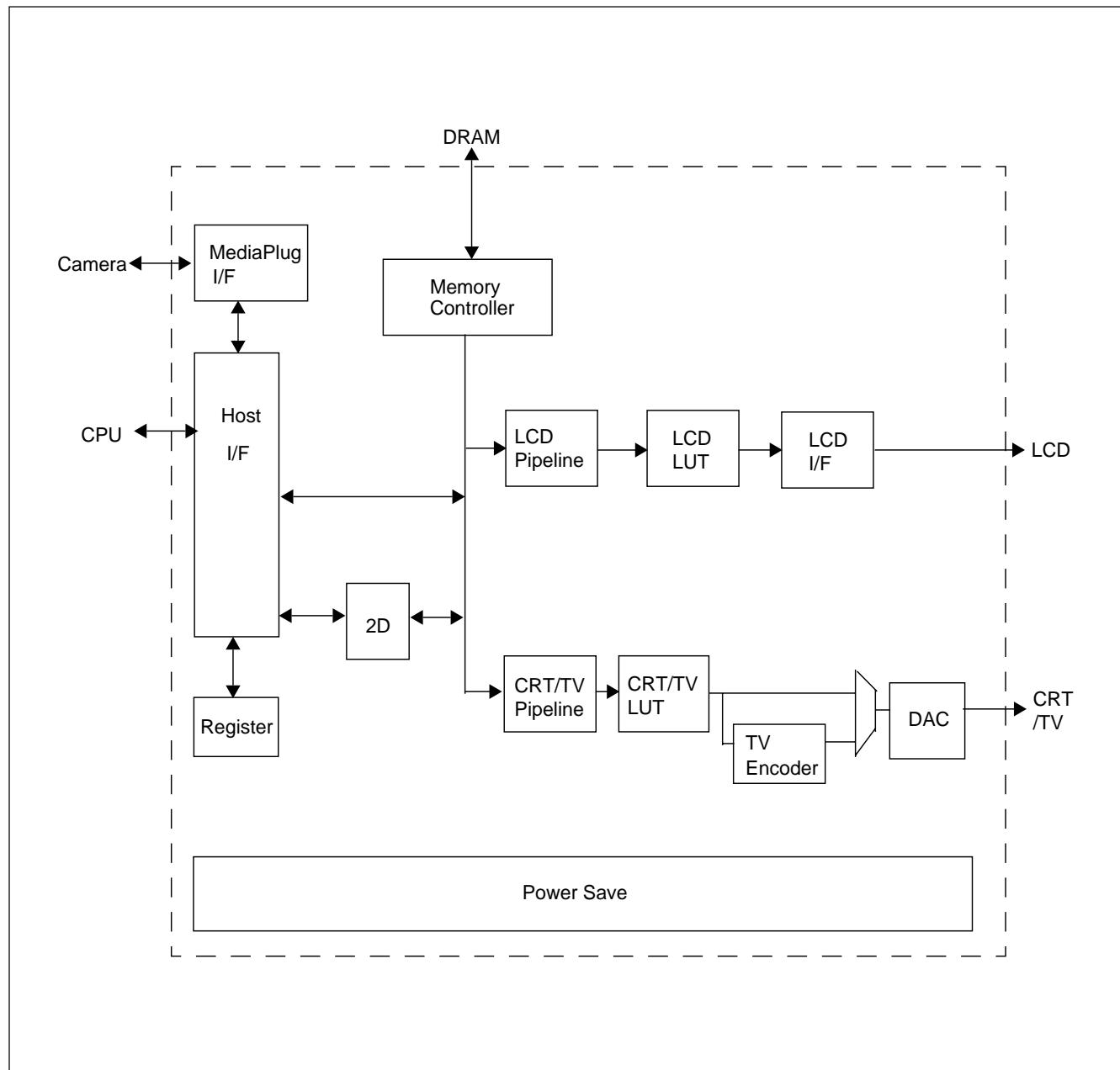

## 内部ブロックの概要

### 機能ブロック図とデータライン

S1D13506F00A機能ブロック図

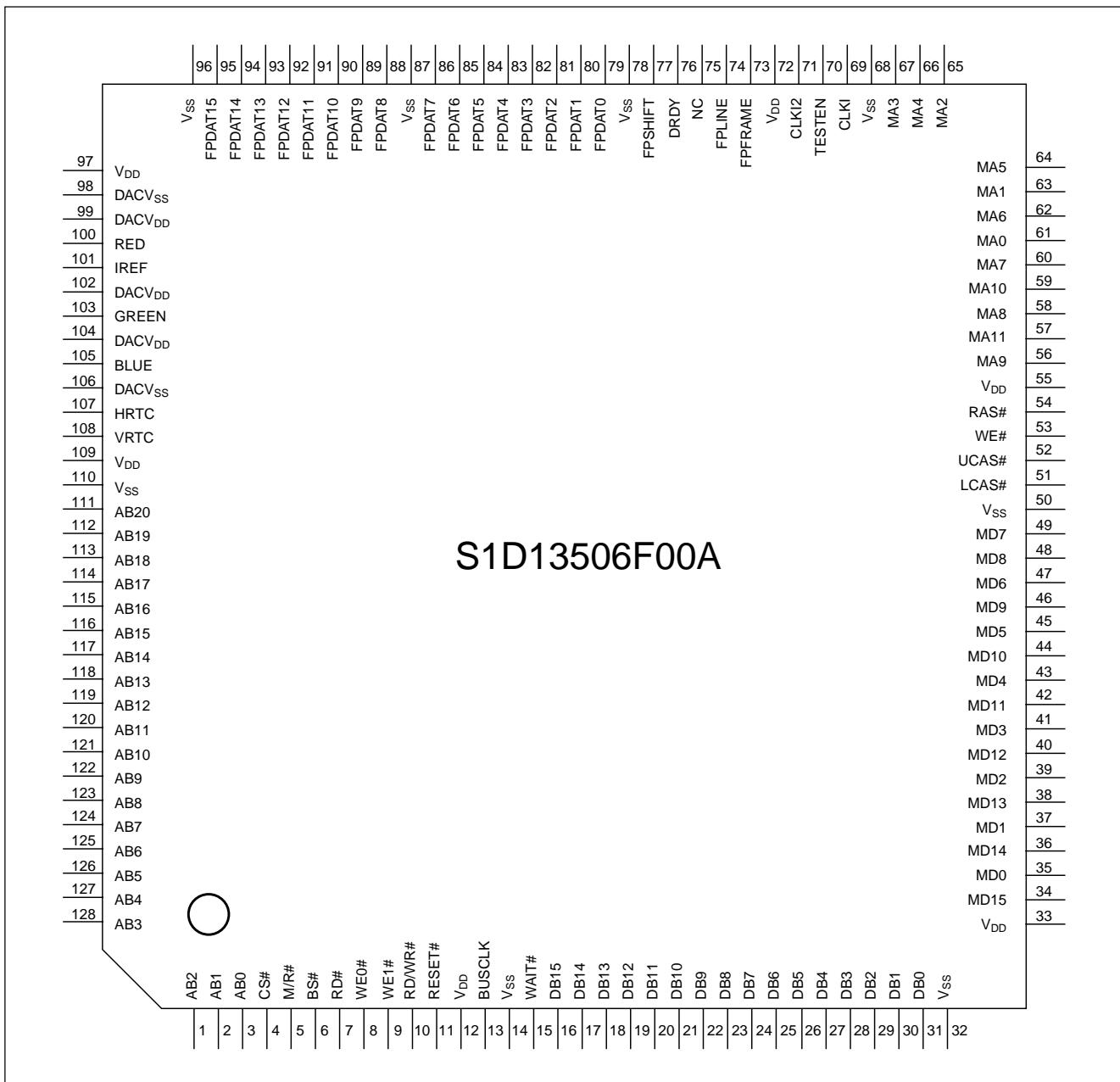

## 端子構成

## 端子配置図

128 ピン QFP15 面実装パッケージ

# S1D13506F00A

## 端子説明

Key:

|      |                                                                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

| I    | = 入力                                                                                                                              |

| O    | = 出力                                                                                                                              |

| IO   | = 双方向 ( 入力 / 出力 )                                                                                                                 |

| A    | = アナログ                                                                                                                            |

| P    | = 電源端子                                                                                                                            |

| C    | = CMOS レベル入力                                                                                                                      |

| CD   | = プルダウン抵抗付き CMOS レベル入力<br>( 5V/3.3V それぞれのプルダウン抵抗 Typ. 値は 50k /90k )                                                               |

| CS   | = CMOS レベルシュミット入力                                                                                                                 |

| COx  | = CMOS 出力ドライバ。<br>x はドライバの種類を示します。 ( 5V で 1=4/-4mA 、 2=8/-8mA 、 3=12/-12mA )                                                      |

| TSx  | = 3- ステート CMOS 出力ドライバ。<br>x はドライバの種類を示します。 ( 5V で 1 = 4/-4mA 、 2 = 8/-8mA 、 3 = 12/-12mA )                                        |

| TSu  | = プルアップ抵抗付き TSx<br>( 5V/3.3V それぞれの Typ. 値は 100k /180k )                                                                           |

| TSxD | = プルダウン抵抗付き TSx。<br>x はドライバの種類を示します。 ( 5V で 1 = 4/-4mA 、 2 = 8/-8mA 、 3 = 12/-12mA ) ( 5V で 100k の Typ. 値、 3.3V で 180k の Typ. 値 ) |

| CNx  | = CMOS ローノイズ出力ドライバ。<br>x はドライバの種類を示します。 ( 5V で 1 = 4/-4mA 、 2 = 8/-8mA 、 3 = 12/-12mA )                                           |

| CNxU | = プルアップ抵抗付き CNx。<br>x はドライバの種類を示します。 ( 5V で 1 = 4/-4mA 、 2 = 8/-8mA 、 3 = 12/-12mA )                                              |

| CNxD | = プルダウン抵抗付き CNx。<br>x はドライバの種類を示します。 ( 5V で 1 = 4/-4mA 、 2 = 8/-8mA 、 3 = 12/-12mA )                                              |

## ● ホストインターフェース

### ホストインターフェース端子一覧

| 端子名      | 入出力<br>タイプ | 端子No.            | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------|------------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB0      | I          | 3                | CS        | Hi-Z         | <ul style="list-style-type: none"><li>SH-3/SH-4バス:V<sub>SS</sub>またはV<sub>DD</sub>端子用接続端子</li><li>MC68Kバス1:下位データストローブ(LDS#)入力端子</li><li>MC68Kバス2:システムアドレスバスのビット0 (A0)入力端子</li><li>汎用バス:VSSまたはVDD端子用接続端子</li><li>MIPS/ISAバス:システムアドレスバスのビット0 (A0)入力端子</li><li>フィリップスPR31500/31700バス:システムアドレスバスのビット0 (A0)入力端子</li><li>東芝TX3912/バス:システムアドレスバスのビット0 (A0)入力端子</li><li>PowerPCバス:システムアドレスバスのビット31 (A31)入力端子</li><li>PC Card (PCMCIA)バス:V<sub>SS</sub>またはV<sub>DD</sub>端子用接続端子</li></ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

| AB[12:1] | I          | 119-128,<br>1, 2 | C         | Hi-Z         | <ul style="list-style-type: none"><li>PowerPCバス:システムアドレスバスのビット19~30 (A[19:30])入力端子</li><li>他のすべてのバス:システムアドレスバスのビット12~1 (A[12:1])入力端子</li></ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                                                                                                                                                                                                                                                  |

## ホストインターフェース端子一覧

| 端子名       | 入出力<br>タイプ | 端子No.   | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------|---------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB[16:13] | I          | 115-118 | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700バス: V<sub>DD</sub>端子用接続端子</li> <li>• 東芝TX3912バス: V<sub>DD</sub>端子用接続端子</li> <li>• PowerPCバス: システムアドレスバスのビット15~18 (A[15:18])入力端子</li> <li>• 他のすべてのバス: システムアドレスバスのビット16~13 (A[16:13])入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                       |

| AB17      | I          | 114     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700バス: I/Oライトコマンド (/CARDIOWR)入力端子</li> <li>• 東芝TX3912バス: I/Oライトコマンド (CARDIOWR*)入力端子</li> <li>• PowerPCバス: システムアドレスバスのビット14 (A14)入力端子</li> <li>• 他のすべてのバス: システムアドレスバスのビット17 (A17)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                             |

| AB18      | I          | 113     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700バス: I/Oリードコマンド (/CARDIORD)入力端子</li> <li>• 東芝TX3912バス: I/Oリードコマンド (CARDIORD*)入力端子</li> <li>• PowerPCバス: システムアドレスバスのビット13 (A13)入力端子</li> <li>• 他のすべてのバス: システムアドレスバスのビット18 (A18)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                             |

| AB19      | I          | 112     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700バス: カード制御レジスタアクセス (/CARDREG)入力端子</li> <li>• 東芝TX3912バス: カード制御レジスタアクセス (CARDREG*)入力端子</li> <li>• PowerPCバス: システムアドレスバスのビット12 (A12)入力端子</li> <li>• 他のすべてのバス: システムアドレスバスのビット19 (A19)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                         |

| AB20      | I          | 111     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• MIPS/ISAバス: システムアドレスバスのビット20(A20)入力端子。<br/>ISAバスについては、AB20への入力の前にラッチを解除されたLA20が最初にラッチされなければならない点に注意してください。</li> <li>• フィリップスPR31500/31700バス: アドレスラッチイネーブル(ALE)入力端子</li> <li>• 東芝TX3912バス: アドレスラッチイネーブル(ALE)入力端子</li> <li>• PowerPCバス: システムアドレスバスのビット11 (A11)入力端子</li> <li>• 他のすべてのバス: システムアドレスバスのビット20 (A20)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

# S1D13506F00A

## ホストインターフェース端子一覧

| 端子名      | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------------|-------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB[15:0] | IO         | 16-31 | C/TS2     | Hi-Z         | <p>システムデータバス<br/>8ビットバスモードで使用しない端子は<math>V_{DD}</math>に接続してください。</p> <ul style="list-style-type: none"> <li>• SH-3/SH-4バス: システムデータバスのD[15:0]に接続</li> <li>• MC68Kバス1: システムデータバスのD[15:0]に接続</li> <li>• MC68Kバス2: 32ビットデバイス(MC68030等)の場合はシステムデータバスのD[31:16]に、16ビットデバイス(MC68340等)の場合はシステムデータバスのD[15:0]に接続</li> <li>• 汎用バス: システムデータバスのD[15:0]に接続</li> <li>• MIPS/ISAバス: システムデータバスのSD[15:0]に接続</li> <li>• フィリップス PR31500/31700 バス: 端子DB[15:8]は、端子DB[23:16]に接続し、端子DB[7:0]は、端子DB[31:24]に接続</li> <li>• 東芝 TX3912 バス: 端子DB[15:8]は、端子DB[23:16]に接続し、端子DB[7:0]は、端子DB[31:24]に接続</li> <li>• PowerPCバス: システムデータバスのD[0:15]に接続</li> <li>• PCカード(PCMCIA) バス: システムデータバスのD[15:0]に接続</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

| WE1#     | IO         | 9     | CS/TS2    | Hi-Z         | <p>インターフェースの種類により機能が異なります。</p> <ul style="list-style-type: none"> <li>• SH-3/SH-4バス: 上位データバイトのライトイネーブル(WE1#)入力端子</li> <li>• MC68Kバス1: 上位データストローブ(UDS#)入力端子</li> <li>• MC68Kバス2: データストローブ(DS#)入力端子</li> <li>• 汎用バス: 上位データバイトのライトイネーブル(WE1#)入力端子</li> <li>• MIPS/ISAバス: システムバイトハイイネーブル信号(SBHE#)入力端子</li> <li>• フィリップスPR31500/31700バス: 奇数バイトアクセシイネーブル信号(/CARDxCSH)の入力端子</li> <li>• 東芝 TX3912 バス: 奇数バイトアクセシイネーブル信号(/CARDxCSH*)の入力端子</li> <li>• PowerPCバス: バースト禁止信号(BI#)出力端子</li> <li>• PCカード (PCMCIA) バス: カードイネーブル2信号(-CE2)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                                                    |

| M/R#     | I          | 5     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• 東芝 TX3912 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• すべてのバスについて、この入力ピンは表示バッファおよびS1D13506のレジスタアドレス空間のどちらを選択するかに使用します。M/R#は、表示バッファにアクセスするにはハイに設定し、レジスタにアクセスするにはローに設定します。レジスタマッピングを参照してください。</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。</p>                                                                                                                                                                                                                                                                                                                                                                                                  |

## ホストインターフェース端子一覧

| 端子名    | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|------------|-------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#    | I          | 4     | C         | Hi-Z         | <ul style="list-style-type: none"> <li>• フィリップスPR31500/31700 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• 東芝 TX3912 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• すべてのバスについて、<br/>これはチップ選択入力となります。</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                                                                                                                                                                                                                                             |

| BUSCLK | I          | 13    | C         | Hi-Z         | <p>このピンは、システムバスクロックを入力します。2xクロックを適用し内部的にそれを2で割ることは可能です - “設定オプション一覧”のMD12を参照してください。</p> <ul style="list-style-type: none"> <li>• SH-3/SH-4バス: CKIOに接続</li> <li>• MC68Kバス1: CLKに接続</li> <li>• MC68Kバス2: CLKIに接続</li> <li>• 汎用バス: BCLKに接続</li> <li>• MIPS/ISAバス: CLKIに接続</li> <li>• フィリップスPR31500/31700 バス: DCLKOUT端子用接続端子</li> <li>• 東芝 TX3912 バス: DCLKOUT端子用接続端子</li> <li>• PowerPCバス: CLKOUTに接続</li> <li>• PCカード(PCMCIA)バス: 入力クロックに接続(CLKI)</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                            |

| BS#    | I          | 6     | CS        | Hi-Z         | <p>インターフェースの種類により機能が異なります。</p> <ul style="list-style-type: none"> <li>• SH-3/SH-4バス: バススタート信号(BS#)入力端子</li> <li>• MC68Kバス1: アドレスストローブ(AS#)入力端子</li> <li>• MC68Kバス2: アドレスストローブ(AS#)入力端子</li> <li>• 汎用バス: <math>V_{DD}</math>に接続</li> <li>• MIPS/ISAバス: <math>V_{DD}</math>に接続</li> <li>• フィリップスPR31500/31700 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• 東芝 TX3912 バス: <math>V_{DD}</math>端子用接続端子</li> <li>• PowerPCバス: 伝送開始信号(TS#)入力端子</li> <li>• PCカード(PCMCIA)バス: <math>V_{DD}</math>に接続</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

## ホストインターフェース端子一覧

| 端子名    | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|------------|-------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD/WR# | I          | 10    | CS        | Hi-Z         | <p>インターフェースの種類により機能が異なります。</p> <ul style="list-style-type: none"> <li>SH-3/SH-4バス: 読み出し/書き込み信号(RD/WR#)入力端子。S1D13506では、この信号をバスサイクルの初期に読み出しておく必要があります。</li> <li>MC68Kバス1: 読み出し/書き込み信号(R/W#)入力端子</li> <li>MC68Kバス2: 読み出し/書き込み信号(R/W#)入力端子</li> <li>汎用バス: 上位データバイトのリードコマンド(RD1#)入力端子</li> <li>MIPS/ISAバス: <math>V_{DD}</math>に接続</li> <li>フィリップスPR31500/31700 バス: 偶数バイトアクセス可能信号(/CARDxCSL)の入力端子</li> <li>東芝 TX3912 バス: 偶数バイトアクセス可能信号(/CARDxCSL*)の入力端子</li> <li>PowerPCバス: 読み出し/書き込み信号(RD/WR#)入力端子</li> <li>PCカード(PCMCIA)バス: カードイネーブル1信号(-CE1)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

| RD#    | I          | 7     | CS        | Hi-Z         | <p>インターフェースの種類により機能が異なります。</p> <ul style="list-style-type: none"> <li>SH-3/SH-4バス: 読み出し信号(RD#)入力端子</li> <li>MC68Kバス1: <math>V_{DD}</math>に接続してください。</li> <li>MC68Kバス2: バスサイズビット1(SIZ1)入力端子</li> <li>汎用バス: 下位データバイトの読み出しコマンド(RD0#)入力端子</li> <li>MIPS/ISAバス: メモリ読み出し信号(MEMR#)入力端子</li> <li>フィリップスPR31500/31700 バス: メモリ読み出しコマンド(/RD)入力端子</li> <li>東芝 TX3912 バス: メモリ読み出しコマンド(/RD*)入力端子</li> <li>PowerPCバス: 伝送サイズ0信号(TSIZ0)入力端子</li> <li>PCカード(PCMCIA)バス: 出力イネーブル信号(-OE)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                                       |

| WE0#   | I          | 8     | CS        | Hi-Z         | <p>インターフェースの種類により機能が異なります。</p> <ul style="list-style-type: none"> <li>SH-3/SH-4バス: 下位データバイトの書き込みイネーブル(WE0#)入力端子</li> <li>MC68Kバス1: <math>V_{DD}</math>に接続してください。</li> <li>MC68Kバス2: バスサイズビット0(SIZ0)入力端子</li> <li>汎用バス: 下位データバイトの書き込みイネーブル(WE0#)入力端子</li> <li>MIPS/ISAバス: メモリ書き込み信号(MEMW#)入力端子</li> <li>フィリップスPR31500/31700 バス: メモリ書き込みコマンド(/WE)入力端子</li> <li>東芝 TX3912 バス: メモリ書き込みコマンド(WE*)入力端子</li> <li>PowerPCバス: 伝送サイズ1信号(TSIZ1)入力端子</li> <li>PCカード(PCMCIA)バス: 書き込みイネーブル信号(-WE)入力端子</li> </ul> <p>概要については表“CPUインターフェース端子の割り付け”(21ページ)を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p>                                                        |

## ホストインターフェース端子一覧

| 端子名    | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態                                                         | 端子説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------------|-------|-----------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT#  | ○          | 15    | TS2       | Hi-Z <sup>*a</sup><br>or<br>1 <sup>*b</sup><br>or<br>0 <sup>*c</sup> | <p>WAIT#出力のアクティブ極性を設定することができます。 ;<br/>RESET#の上昇点のMD5の状態はWAIT#のアクティブ極性を定義します - “設定オプション一覧” (20ページ) を参照してください。</p> <ul style="list-style-type: none"> <li>• SH-3バス: ウェイト要求(WAIT#)出力端子。リセット時、MD5端子は内蔵プルダウン抵抗でローに設定してください。</li> <li>• SH-4バス: レディ信号(RDY#)出力端子。リセット時、MD5端子は外付けプルアップ抵抗でハイに設定してください。</li> <li>• MC68Kバス1: データ転送確認(DTACK#)出力端子。リセット時、MD5端子は外部のプルアップ抵抗でハイに設定してください。</li> <li>• MC68Kバス2: データ転送確認ビット1 (DSACK1#)出力端子。リセット時、MD5端子は外部のプルアップ抵抗でハイに設定してください。</li> <li>• 汎用バス: ウェイト要求(WAIT#)出力端子。リセット時、MD5端子は内蔵プルダウン抵抗でローに設定してください。</li> <li>• MIPS/ISAバス: I/Oチャネルレディ信号(IOCHRDY)出力端子。リセット時、MD5端子は内蔵プルダウン抵抗でローに設定してください。</li> <li>• フィリップスPR31500/31700 バス: ウェイトステート信号(CARDxWAIT)出力端子。リセット時、MD5端子は内部プルダウン抵抗でローに設定してください。</li> <li>• 東芝 TX3912 バス: ウェイトステート信号(CARDxWAIT*)出力端子。リセット時、MD5端子は内部プルダウン抵抗でローに設定してください。</li> <li>• PowerPCバス: 伝送確認信号(TA#)出力端子。リセット時、MD5端子は外付けプルアップ抵抗でハイに設定してください。</li> <li>• PCカード(PCMCIA)バス: ウェイト信号(-WAIT)出力端子。リセット時、MD5端子は内部プルダウン抵抗でローに設定してください。</li> </ul> <p>概要については表 “CPUインターフェース端子の割り付け” (21ページ) を参照してください。詳細な機能については、それぞれのACタイミング図を参照してください。</p> |

| RESET# | ।          | 11    | CS        | 0                                                                    | アクティブロー入力により、内部レジスタがクリアされ、すべての信号がインアクティブ状態となります。アクティブハイのRESET信号は、このピンへ入力する前に反転します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

\* a. RESET# での MD 設定は、WAIT# が3-ステートになるよう設定してください。

b. RESET# での MD 設定は、WAIT# が常に出力し、アクティブローになるよう設定してください。

c. RESET# での MD 設定は、WAIT# が常に出力し、アクティブハイになるよう設定してください。

# S1D13506F00A

## ●メモリインターフェース

メモリインターフェース端子一覧

| 端子名      | 入出力<br>タイプ | 端子No.                                                                         | セル<br>タイプ  | リセット時<br>の状態                              | 端子説明                                                                                                                                                                                                                                                                                                                      |

|----------|------------|-------------------------------------------------------------------------------|------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCAS#    | O          | 51                                                                            | CO1        | 1                                         | <ul style="list-style-type: none"> <li>• 2CAS方式: 下位バイトのコラムアドレスストローブ(LCAS#)出力端子</li> <li>• WE方式: コラムアドレスストローブ(CAS#)出力端子</li> </ul> <p>概要については表“メモリインターフェース端子の割り付け”(22ページ)を参照してください。</p>                                                                                                                                    |

| UCAS#    | O          | 52                                                                            | CO1        | 1                                         | <p>DRAMの方式により機能が異なります。</p> <ul style="list-style-type: none"> <li>• 2CAS方式: 上位バイトのコラムアドレスストローブ(UCAS#)出力端子</li> <li>• WE方式: 上位バイトの書き込みイネーブル(UWE#)出力端子</li> </ul> <p>概要については表“メモリインターフェース端子の割り付け”(22ページ)を参照してください。</p>                                                                                                      |

| WE#      | O          | 53                                                                            | CO1        | 1                                         | <ul style="list-style-type: none"> <li>• 2CAS方式: 書き込みイネーブル(WE#)出力端子</li> <li>• WE方式: 下位バイトの書き込みイネーブル(LWE#)出力端子</li> </ul> <p>概要については表“メモリインターフェース端子の割り付け”(22ページ)を参照してください。</p>                                                                                                                                            |

| RAS#     | O          | 54                                                                            | CO1        | 1                                         | ローアドレスストローブ(RAS#)出力端子                                                                                                                                                                                                                                                                                                     |

| MD[15:0] | IO         | 34, 36, 38,<br>40, 42, 44,<br>46, 48, 49,<br>47, 45, 43,<br>41, 39, 37,<br>35 | C/<br>TS1D | Hi-Z<br>(pull 0)                          | 双方向メモリデータバス<br>リセット中、これらのピンは、入力として使用され、RESET#の立ち上がりエッジでのステータスは、チップの設定に使用されます。“設定オプション一覧”(20ページ)を参照してください。内部プルダウン抵抗(5Vで100kΩのTyp.値、3.3Vで180kΩのTyp.値)は、リセットステータスを“0”に落とします。外付けプルアップ抵抗でリセットステータスを“1”に上げることができます。                                                                                                             |

| MA[8:0]  | O          | 58, 60, 62,<br>64, 66, 67,<br>65, 63, 61                                      | CO1        | 0                                         | 多重化メモリアドレスバス                                                                                                                                                                                                                                                                                                              |

| MA9      | IO         | 56                                                                            | C/TS1      | 0 <sup>a</sup><br>or<br>Hi-Z <sup>b</sup> | <p>DRAMの方式により機能が異なります。</p> <ul style="list-style-type: none"> <li>• 2MB DRAM : メモリアドレスビット9(MA9)入力端子</li> <li>• 非対称512KB DRAM : メモリアドレスビット9(MA9)入力端子</li> <li>• 対称512KB DRAM : 汎用入出力(GPIO3)として使用可能</li> </ul> <p>他に設定が行われないのであれば、このピンのデフォルトは入力であり、有効な論理レベルに設定します。</p> <p>概要については表“メモリインターフェース端子の割り付け”(22ページ)を参照してください。</p> |

## メモリインターフェース端子一覧

| 端子名  | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態                                                         | 端子説明                                                                                                                                                                                                                                                    |

|------|------------|-------|-----------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA10 | IO         | 59    | C/TS1     | 0 <sup>*c</sup><br>or<br>Hi-Z <sup>*d</sup>                          | DRAMの方式により機能が異なります。<br>• 非対称2MB DRAM : メモリアドレスピット10 (MA10)入力端子<br>• 対称2MB DRAM : 汎用入出力(GPIO1)として使用可能<br>• 512KB DRAM : 汎用入出力(GPIO1)として使用可能<br>他に設定が行われないのであれば、このピンのデフォルトは入力で<br>あり、有効な論理レベルに設定します。<br>概要については表“メモリインターフェース端子の割り付け”(22ペ<br>ージ)を参照してください。 |

| MA11 | IO         | 57    | C/TS1     | 0 <sup>*e</sup><br>or<br>Hi-Z <sup>*f</sup><br>or<br>1 <sup>*g</sup> | DRAMの方式により機能が異なります。<br>• 非対称2MB DRAM : メモリアドレスピット11 (MA11)入力端子<br>• 対称2MB DRAM : 汎用入出力(GPIO2)として使用可能<br>• 512KB DRAM : 汎用入出力(GPIO2)として使用可能<br>他に設定が行われないのであれば、このピンのデフォルトは入力で<br>あり、有効な論理レベルに設定します。<br>概要については表“メモリインターフェース端子の割り付け”(22ペ<br>ージ)を参照してください。 |

- \*: a.RESET#でのMD設定は、FPDAT9がFPDAT9として使用されるよう設定してください。

b.RESET#でのMD設定は、FPDAT9がVMRCTLとして使用されるよう設定してください。

c.RESET#でのMD設定は、FPDAT[13:10]がFPDAT[13:10]として使用されるよう設定してください。

d.RESET#でのMD設定は、FPDAT[13:10]がVMPD[3:0]として使用されるよう設定してください。

e.RESET#でのMD設定は、DRDYがDRDY(MOD)として使用されるよう設定してください。

f.RESET#でのMD設定は、DRDYがVMPEPWRとして使用されるよう設定してください。

# S1D13506F00A

## ●LCD インタフェース

LCDインターフェース端子一覧

| 端子名          | 入出力<br>タイプ | 端子No.     | セル<br>タイプ | リセット時<br>の状態                                | 端子説明                                                                                                                                                                                                                                                                                                   |

|--------------|------------|-----------|-----------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPDAT[8:0]   | O          | 88, 86-79 | CN3       | 0                                           | パネルデータバス<br>いくつかのパネルについては、すべてのピンが使われるわけではありません。詳細は表“LCDインターフェース端子の割り付け”(22ページ)を参照してください。FPDAT[15:8]は、MediaPlugインターフェースとして設定することができます。詳細は、表“MediaPlugインターフェース端子割り付け”(23ページ)を参照してください。                                                                                                                   |

| FPDAT9       | O          | 89        | CN3D      | 0 <sup>*a</sup><br>or<br>Hi-Z <sup>*b</sup> | パネルデータバス<br>いくつかのパネルについては、すべてのピンが使われるわけではありません。詳細は表“LCDインターフェース端子の割り付け”(22ページ)を参照してください。使われないピンはローに設定されます。FPDAT[15:8]は、MediaPlugインターフェースとして設定することができます。詳細は、表“MediaPlugインターフェース端子割り付け”(23ページ)を参照してください。                                                                                                 |

| FPDAT[13:10] | IO         | 93-90     | C/TS3U    | 0 <sup>*c</sup><br>or<br>Hi-Z <sup>*d</sup> | Panel data bus.いくつかのパネルについては、すべてのピンが使われるわけではありません。詳細は表“LCDインターフェース端子の割り付け”(22ページ)を参照してください。使われないピンはローに設定されます。FPDAT[15:8]は、MediaPlugインターフェースとして設定することができます。詳細は、表“MediaPlugインターフェース端子割り付け”(23ページ)を参照してください。                                                                                              |

| FPDAT[15:14] | O          | 95,94     | CN3       | 0                                           | Panel data bus.いくつかのパネルについては、すべてのピンが使われるわけではありません。詳細は表“LCDインターフェース端子の割り付け”(22ページ)を参照してください。使われないピンはローに設定されます。FPDAT[15:8]は、MediaPlugインターフェースとして設定することができます。詳細は、表“MediaPlugインターフェース端子割り付け”(23ページ)を参照してください。                                                                                              |

| FPFRAME      | O          | 73        | CN3       | 0                                           | フレームパルス                                                                                                                                                                                                                                                                                                |

| FPLINE       | O          | 74        | CN3       | 0                                           | ラインパルス                                                                                                                                                                                                                                                                                                 |

| FPSHIFT      | O          | 77        | CO3       | 0                                           | シフトクロック                                                                                                                                                                                                                                                                                                |

| DRDY         | O          | 76        | CO3       | 0 <sup>*e</sup><br>or<br>1 <sup>*f</sup>    | 使用するパネルの種類により機能が自動的に選択されます。<br>• TFT/D-TFDパネル: 表示イネーブル(DRDY)出力端子<br>• パッシブLCDの形式1:2ndシフトクロック(FPSHIFT2)出力端子<br>• その他のパネル: LCDバックプレーンバイアス信号(MOD)出力端子<br>詳細は表“LCDインターフェース端子の割り付け”(22ページ)とREG[030h]を参照してください。この端子は、MediaPlug電源端子VMPEPWRとして設定することができます。詳細は、表“MA11, MA10, MA9およびDRDY端子割り付け”(23ページ)を参照してください。 |

- \*: a.RESET#でのMD設定は、FPDAT9がFPDAT9として使用されるよう設定してください。

- b.RESET#でのMD設定は、FPDAT9がVMRCTLとして使用されるよう設定してください。

- c.RESET#でのMD設定は、FPDAT[13:10]がFPDAT[13:10]として使用されるよう設定してください。

- d.RESET#でのMD設定は、FPDAT[13:10]がVMPD[3:0]として使用されるよう設定してください。

- e.RESET#でのMD設定は、DRDYがDRDY(MOD)として使用されるよう設定してください。

- f.RESET#でのMD設定は、DRDYがVMPEPWRとして使用されるよう設定してください。

## ●CRT インタフェース

CRTインターフェース端子一覧

| 端子名   | 入出力<br>タイプ | 端子No. | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                     |

|-------|------------|-------|-----------|--------------|----------------------------------------------------------|

| HRTC  | O          | 107   | CN3       | 0            | CRT用の水平方向リトレース信号                                         |

| VRTC  | O          | 108   | CN3       | 0            | CRT用の垂直方向リトレース信号                                         |

| RED   | O          | 100   | A         | 電流出力<br>無し   | CRT赤色用のアナログ出力/ S-ビデオ輝度                                   |

| GREEN | O          | 103   | A         | 電流出力<br>無し   | CRT緑色用のアナログ出力/複合ビデオ出力信号                                  |

| BLUE  | O          | 105   | A         | 電流出力<br>無し   | CRT青色用のアナログ出力/ S-ビデオ色度                                   |

| IREF  | I          | 101   | A         | -            | DACカレントリファレンス<br>このピンはDACが必要でない場合は、未接続のままにしておかなければなりません。 |

## ●その他

その他のインターフェース端子一覧

| 端子名                | 入出力<br>タイプ | 端子No.                                 | セル<br>タイプ | リセット時<br>の状態 | 端子説明                                                                     |

|--------------------|------------|---------------------------------------|-----------|--------------|--------------------------------------------------------------------------|

| CLKI               | I          | 69                                    | C         | -            | 選択可能な入力クロック<br>内部ピクセルクロック(PCLK)、メモリクロック(MCLK)とMediaPlugクロックを使用することができます。 |

| CLKI2              | I          | 71                                    | C         | -            | 選択可能な入力クロック<br>内部ピクセルクロック(PCLK)とMediaPlugクロックを使用することができます。               |

| TESTEN             | I          | 70                                    | CD        | -            | テストイネーブル入力端子<br>通常動作時は、V <sub>SS</sub> に接続してください。                        |

| V <sub>DD</sub>    | P          | 12, 33, 55,<br>72, 97, 109            | P         | -            | V <sub>DD</sub>                                                          |

| DACV <sub>DD</sub> | P          | 99, 102,<br>104                       | P         | -            | DACV <sub>DD</sub>                                                       |

| V <sub>SS</sub>    | P          | 14, 32, 50,<br>68, 78, 87,<br>96, 110 | P         | -            | V <sub>SS</sub>                                                          |

| DACV <sub>SS</sub> | P          | 98, 106                               | P         | -            | DACV <sub>SS</sub>                                                       |

| NC                 | -          | 75                                    |           | -            | 未使用                                                                      |

# S1D13506F00A

## ●設定オプション一覧

### パワーオン/リセットオプション

| 端子名              | RESET#立ち上がり時の端子状態: (1/0)                                                                                                                                                                                                                                                                                                                                     |                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                  | 1                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                |

| MD0              | 未使用。RESET#の立ち上がりエッジでピンの値は、REG[00Ch]ビット0で読み出すことができます。                                                                                                                                                                                                                                                                                                         |                                                                                                                  |

| MD11,<br>MD[3:1] | ホストバスインターフェースを選択してください。( MD11 = 0 の時)<br>000 = SH-4/SH-3バスインターフェース<br>001 = MC68Kバス1<br>010 = MC68Kバス2<br>011 =汎用<br>100 =リザーブ<br>101 =MIPS/ISA<br>110 =PowerPC<br>111 =PC カード(PCMCIA)またはフィリップスPR31500/PR31700 /オルタネイトホストバスの時は、<br>東芝 TX3912 バス<br>インターフェース選択 ( MD11 = 1 )                                                                                   |                                                                                                                  |

| MD4              | リトルエンディアン                                                                                                                                                                                                                                                                                                                                                    | ビッグエンディアン                                                                                                        |

| MD5              | WAIT#信号論理 = アクティブハイ<br>(WAIT# = 1でウェイトサイクル挿入)                                                                                                                                                                                                                                                                                                                | WAIT#信号論理 = アクティブロー<br>(WAIT# = 0でウェイトサイクル挿入)                                                                    |

| MD[7:6]          | メモリアドレス/汎用入出力(GPIO)の設定:<br>(表“MA11, MA10, MA9およびDRDY端子割り付け”(23ページ)を参照してください。)<br>00 =対称256K × 16 DRAM。MA[8:0] = DRAMアドレス。MA[11:9]は、GPIO2, 1, 3端子として使用できます。<br>01 =対称1M × 16 DRAM。MA[9:0] = DRAMアドレス。MA[11:10]は、GPIO2, 1端子として使用できます。<br>10 =非対称256K × 16 DRAM。MA[9:0] = DRAMアドレス。MA[11:10] は、GPIO2, 1端子として使用できます。<br>11 =非対称1M × 16 DRAM。MA[11:0] = DRAMアドレス。 |                                                                                                                  |

| MD8              | 未使用、RESET#の立ち上がりエッジでこの端子の値は、REG[00Dh]ビット0で読み出すことができます。                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

| MD9              | 未使用、RESET#の立ち上がりエッジでこの端子の値は、REG[00Dh]ビット1で読み出すことができます。                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

| MD10             | 未使用、RESET#の立ち上がりエッジでこの端子の値は、REG[00Dh]ビット2で読み出すことができます。                                                                                                                                                                                                                                                                                                       |                                                                                                                  |

| MD12             | 2分周したBUSCLK                                                                                                                                                                                                                                                                                                                                                  | 分周されないBUSCLK                                                                                                     |

| MD13             | FPDAT[15:8]をMediaPlugインターフェースに設定してください。16-ビットパッシブパネルをサポートする必要がある外付けラッч。                                                                                                                                                                                                                                                                                      | 16-ビットパッシブパネルを直接サポート                                                                                             |

| MD14             | DRDYまたはMA11は、MediaPlugの省電力端子(VMPEPWR)として設定します。(表“MA11, MA10, MA9およびDRDY端子割り付け”(23ページ)を参照してください。)                                                                                                                                                                                                                                                             | DRDYは、通常のLCDインターフェース出力端子として設定します。MA11は、メモリアドレスかGPIO2かどうかを設定します(表“MA11, MA10, MA9およびDRDY端子割り付け”(23ページ)を参照してください。) |

| MD15             | WAIT#は、常に出力                                                                                                                                                                                                                                                                                                                                                  | WAIT#は、チップがホストにアクセスされない時、3-ステートです。                                                                               |

## ● インタフェース別端子構成

CPUインターフェース端子の割り付け

| S1D13506<br>端子名 | 汎用                        | 日立<br>SH-4/SH-3           | MIPS/ISA                | モトローラ<br>MC68K<br>Bus 1 | モトローラ<br>MC68K<br>Bus 2 | モトローラ<br>PowerPC | PCカード                     | フィリップス<br>PR31500<br>/PR31700 | 東芝<br>TX3912        |

|-----------------|---------------------------|---------------------------|-------------------------|-------------------------|-------------------------|------------------|---------------------------|-------------------------------|---------------------|

| AB20            | A20                       | A20                       | LatchA20                | A20                     | A20                     | A11              | A20                       | ALE                           | ALE                 |

| AB19            | A19                       | A19                       | SA19                    | A19                     | A19                     | A12              | A19                       | /CARDREG                      | CARDREG*            |

| AB18            | A18                       | A18                       | SA18                    | A18                     | A18                     | A13              | A18                       | /CARDIORD                     | CARDIORD*           |

| AB17            | A17                       | A17                       | SA17                    | A17                     | A17                     | A14              | A17                       | /CARDIOWR                     | CARDIOWR*           |

| AB[16:13]       | A[16:13]                  | A[16:13]                  | SA[16:13]               | A[16:13]                | A[16:13]                | A[15:18]         | A[16:13]                  | V <sub>DD</sub> へ接続           | V <sub>DD</sub> へ接続 |

| AB[12:1]        | A[12:1]                   | A[12:1]                   | SA[12:1]                | A[12:1]                 | A[12:1]                 | A[19:30]         | A[12:1]                   | A[12:1]                       | A[12:1]             |

| AB0             | V <sub>DD</sub> *1へ<br>接続 | V <sub>DD</sub> *1へ<br>接続 | SA0                     | LDS#                    | A0                      | A31              | V <sub>DD</sub> *1へ<br>接続 | A0                            | A0                  |

| DB[15:8]        | D[15:0]                   | D[15:8]                   | SD[15:0]                | D[15:8]                 | D[31:24]                | D[0:7]           | D[15:0]                   | D[23:16]                      | D[23:16]            |

| DB[7:0]         | D[7:0]                    | D[7:0]                    | SD[7:0]                 | D[7:0]                  | D[23:16]                | D[8:15]          | D[7:0]                    | D[31:24]                      | D[31:24]            |

| WE1#            | WE1#                      | WE1#                      | SBHE#                   | UDS#                    | DS#                     | BI               | CE2#                      | /CARDxCSH                     | CARDxCSH*           |

| M/R#            | 外付けデコード                   |                           |                         |                         |                         |                  | V <sub>DD</sub> へ接続       | V <sub>DD</sub> へ接続           |                     |

| CS#             | 外付けデコード                   |                           |                         |                         |                         |                  | V <sub>DD</sub> へ接続       | V <sub>DD</sub> へ接続           |                     |

| BUSCLK          | BCLK                      | CKIO                      | CLK                     | CLK                     | CLK                     | CLKOUT           | CLK                       | DCLKOUT                       | DCLKOUT             |

| BS#             | V <sub>DD</sub> へ<br>接続   | BS#                       | V <sub>DD</sub> へ<br>接続 | AS#                     | AS#                     | TS               | V <sub>DD</sub> へ<br>接続   | V <sub>DD</sub> へ接続           | V <sub>DD</sub> へ接続 |

| RD/WR#          | RD1#                      | RD/WR#                    | V <sub>DD</sub> へ<br>接続 | R/W#                    | R/W#                    | RD/WR            | CE1#                      | /CARDxCSL                     | CARDxCSL*           |

| RD#             | RD0#                      | RD#                       | MEMR#                   | V <sub>DD</sub> へ<br>接続 | SIZ1                    | TSIZ0            | OE#                       | /RD                           | RD*                 |

| WE0#            | WE0#                      | WE0#                      | MEMW#                   | V <sub>DD</sub> へ<br>接続 | SIZ0                    | TSIZ1            | WE#                       | /WE                           | WE*                 |

| WAIT#           | WAIT#                     | RDY#<br>/WAIT#            | IOCHRDY                 | DTACK#                  | DSACK1#                 | TA               | WAIT#                     | /CARDxWAIT                    | CARDxWAIT*          |

| RESET#          | RESET#                    | RESET#                    | inverted<br>RESET       | RESET#                  | RESET#                  | RESET#           | inverted<br>RESET         | RESET#                        | PON*                |

\* : GPIO 端子はすべて、リセット時に入力にデフォルト設定されます。特に設定していない限り、これらの端子は使用していない場合は V<sub>SS</sub> または IOV<sub>DD</sub> に接続してください。

\* 1 : AB0 はこれらのバスについては内部で使用されていませんので、V<sub>SS</sub> または V<sub>DD</sub> に接続してください。

\* 2 : S1D13506 を PC カードバスに接続する場合の詳細については、PC カードバスへの接続(X25B-G-005-xx) を参照してください。

# S1D13506F00A

## メモリインターフェース端子の割り付け

| S1D13506<br>端子名    | FPM/EDO-DRAM        |       |               |       |            |       |             |       |  |  |  |

|--------------------|---------------------|-------|---------------|-------|------------|-------|-------------|-------|--|--|--|

|                    | 対称型256K × 16        |       | 非対称型256K × 16 |       | 対称型1M × 16 |       | 非対称型1M × 16 |       |  |  |  |

|                    | 2-CAS#              | 2-WE# | 2-CAS#        | 2-WE# | 2-CAS#     | 2-WE# | 2-CAS#      | 2-WE# |  |  |  |

| MD[15:0]           | D[15:0]             |       |               |       |            |       |             |       |  |  |  |

| MA[8:0]            | A[8:0]              |       |               |       |            |       |             |       |  |  |  |

| MA9 <sup>*1</sup>  | GPIO3 <sup>*2</sup> |       | A9            |       |            | A9    |             |       |  |  |  |

| MA10 <sup>*1</sup> | GPIO1 <sup>*2</sup> |       |               |       |            |       | A10         |       |  |  |  |

| MA11 <sup>*1</sup> | GPIO2 <sup>*2</sup> |       |               |       |            |       | A11         |       |  |  |  |

| UCAS#              | UCAS#               | UWE#  | UCAS#         | UWE#  | UCAS#      | UWE#  | UCAS#       | UWE#  |  |  |  |

| LCAS#              | LCAS#               | CAS#  | LCAS#         | CAS#  | LCAS#      | CAS#  | LCAS#       | CAS#  |  |  |  |

| WE#                | WE#                 | LWE#  | WE#           | LWE#  | WE#        | LWE#  | WE#         | LWE#  |  |  |  |

| RAS#               | RAS#                |       |               |       |            |       |             |       |  |  |  |

- \* 1: MA9, MA10 と MA11 の機能について、表 “ MA11, MA10, MA9 および DRDY 端子割り付け ”( 23 ページ ) を参照してください。

- \* 2: 全 GPIO 端子は、リセット時でデフォルト設定は、入力です。また、それらは特にプログラムが組まれておらず使用されないのであれば、V<sub>SS</sub> または IOV<sub>DD</sub> のいずれかに接続してください。

## LCDインターフェース端子の割り付け

| S1D13506<br>端子名 | モノクロパッシブパネル |      | カラーパッシブパネル |             |             |      |       |      | カラーティフ/D-TFD<br>パネル |      |       |       |

|-----------------|-------------|------|------------|-------------|-------------|------|-------|------|---------------------|------|-------|-------|

|                 | シングル        | デュアル | シングル       | シングル<br>形式1 | シングル<br>形式2 | シングル | デュアル  |      |                     |      |       |       |

|                 | 4ビット        | 8ビット | 8ビット       | 4ビット        | 8ビット        | 8ビット | 16ビット | 8ビット | 16ビット               | 9ビット | 12ビット | 18ビット |

| FPFRAME         | FPFRAME     |      |            |             |             |      |       |      |                     |      |       |       |

| FPLINE          | FPLINE      |      |            |             |             |      |       |      |                     |      |       |       |

| FPSHIFT         | FPSHIFT     |      |            |             |             |      |       |      |                     |      |       |       |

| DRDY            | MOD         |      |            | FPSHIFT2    | MOD         |      |       | DRDY |                     |      |       |       |

| FPDAT0          | 0出力         | D0   | LD0        | 0出力         | D0          | D0   | D0    | LD0  | LD0                 | R2   | R3    | R5    |

| FPDAT1          | 0出力         | D1   | LD1        | 0出力         | D1          | D1   | D1    | LD1  | LD1                 | R1   | R2    | R4    |

| FPDAT2          | 0出力         | D2   | LD2        | 0出力         | D2          | D2   | D2    | LD2  | LD2                 | R0   | R1    | R3    |

| FPDAT3          | 0出力         | D3   | LD3        | 0出力         | D3          | D3   | D3    | LD3  | LD3                 | G2   | G3    | G5    |

| FPDAT4          | D0          | D4   | UD0        | D0          | D4          | D4   | D4    | UD0  | UD0                 | G1   | G2    | G4    |

| FPDAT5          | D1          | D5   | UD1        | D1          | D5          | D5   | D5    | UD1  | UD1                 | G0   | G1    | G3    |

| FPDAT6          | D2          | D6   | UD2        | D2          | D6          | D6   | D6    | UD2  | UD2                 | B2   | B3    | B5    |

| FPDAT7          | D3          | D7   | UD3        | D3          | D7          | D7   | D7    | UD3  | UD3                 | B1   | B2    | B4    |

| FPDAT8          | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D8    | 0出力  | LD4                 | B0   | B1    | B3    |

| FPDAT9          | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D9    | 0出力  | LD5                 | 0出力  | R0    | R2    |

| FPDAT10         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D10   | 0出力  | LD6                 | 0出力  | 0出力   | R1    |

| FPDAT11         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D11   | 0出力  | LD7                 | 0出力  | G0    | G2    |

| FPDAT12         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D12   | 0出力  | UD4                 | 0出力  | 0出力   | G1    |

| FPDAT13         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D13   | 0出力  | UD5                 | 0出力  | 0出力   | G0    |

| FPDAT14         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D14   | 0出力  | UD6                 | 0出力  | B0    | B2    |

| FPDAT15         | 0出力         | 0出力  | 0出力        | 0出力         | 0出力         | 0出力  | D15   | 0出力  | UD7                 | 0出力  | 0出力   | B1    |

注: DRDY と FPDAT[15:8] は、MediaPlug が使用可能である時、MediaPlug インタフェースで使用されます。

MediaPlug インタフェース端子の割り付けについては、表 “ MediaPlug インタフェース端子割り付け ”( 23 ページ ) を参照してください。

## MA11, MA10, MA9およびDRDY端子割り付け

| MD14, MD7, MD6 | MA11    | MA10  | MA9   | DRDY   |

|----------------|---------|-------|-------|--------|

| 000            | GPIO2   | GPIO1 | GPIO3 | DRDY   |

| 001            | GPIO2   | GPIO1 | MA9   | DRDY   |

| 010            | GPIO2   | GPIO1 | MA9   | DRDY   |

| 011            | MA11    | MA10  | MA9   | DRDY   |

| 100            | VMPEPWR | GPIO1 | GPIO3 | DRDY   |

| 101            | VMPEPWR | GPIO1 | MA9   | DRDY   |

| 110            | VMPEPWR | GPIO1 | MA9   | DRDY   |

| 111            | MA11    | MA10  | MA9   | VMPEPW |

## MediaPlugインターフェース端子割り付け

| S1D13506端子名                | OI タイプ | MediaPlug I/F ( リセット時 MD13=1 ) |

|----------------------------|--------|--------------------------------|

| FPDAT8                     | O      | VMPLCTL                        |

| FPDAT9                     | I      | VMPRCTL                        |

| FPDAT10                    | IO     | VMPD 0                         |

| FPDAT11                    | IO     | VMPD 1                         |

| FPDAT12                    | IO     | VMPD 2                         |

| FPDAT13                    | IO     | VMPD 3                         |

| FPDAT14                    | O      | VMPCLK                         |

| FPDAT15                    | O      | VMPCLKN                        |

| DRDY or MA11 <sup>*1</sup> | O      | VMPEPW                         |

\* 1: DRDY または MA11 は、VMPEPWR に使用することができます (表 “MA11, MA10, MA9 および DRDY 端子割り付け”を参照してください)。DRDY が LCD インタフェースで必要で、MA11 も DRAM インタフェースで必要ならば、VMPEPWR は使用できません。

# S1D13506F00A

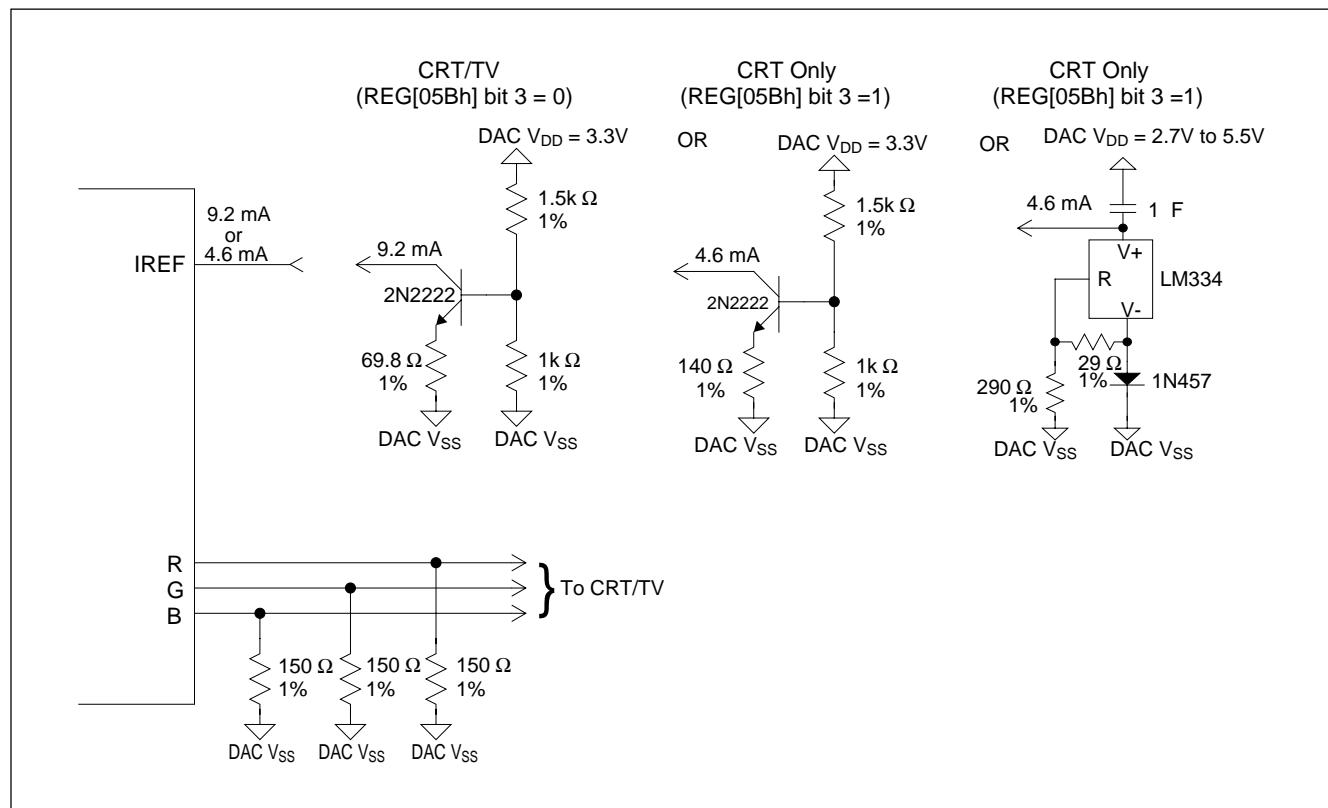

## ●CRT/TV インタフェース

CRT/TV インタフェースの外付け回路を下図に示します。

CRT/TVインターフェースの外付け回路

注:上記の構成例では、個々の回路の特性が、実際の IREF 電流に影響を与えます。

## DC特性

## 絶対最大定格

| 記号           | 項目        | 定格                               | 単位 |

|--------------|-----------|----------------------------------|----|

| $V_{DD}$     | 電源電圧      | $V_{SS} - 0.3 \sim 6.0$          | V  |

| DAC $V_{DD}$ | 電源電圧      | $V_{SS} - 0.3 \sim 6.0$          | V  |

| $V_{IN}$     | 入力電圧      | $V_{SS} - 0.3 \sim V_{DD} + 0.5$ | V  |

| $V_{OUT}$    | 出力電圧      | $V_{SS} - 0.3 \sim V_{DD} + 0.5$ | V  |

| $T_{STG}$    | 保存温度      | -65 ~ 150                        |    |

| $T_{SOL}$    | 半田付け温度/時間 | 260 /リード部で最大10sec.               |    |

## 推奨動作条件

| 記号        | 項目   | 定格                     | Min. | Typ.        | Max. | 単位 |

|-----------|------|------------------------|------|-------------|------|----|

| $V_{DD}$  | 電源電圧 | $V_{SS} = 0 \text{ V}$ | 2.7  | 3.0/3.3/5.0 | 5.5  | V  |

| $V_{IN}$  | 入力電圧 | $V_{SS}$               |      | $V_{DD}$    |      | V  |

| $T_{OPR}$ | 動作温度 |                        | -40  | 25          | 85   |    |

電気的特性( $V_{DD} = 5.0$ , Typ.)

| 記号        | 項目       | 定格                                                                                                                                   | Min.           | Typ. | Max. | 単位               |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------------------|

| $I_{DDS}$ | 静的消費電流   | 静止状態                                                                                                                                 |                |      | 400  | uA               |

| $I_{IZ}$  | 入力リーケ電流  |                                                                                                                                      | -1             |      | 1    | $\mu\text{A}$    |

| $I_{OZ}$  | 出力リーケ電流  |                                                                                                                                      | -1             |      | 1    | $\mu\text{A}$    |

| $V_{OH}$  | 高レベル出力電圧 | $V_{DD} = \text{Min.}$<br>$I_{OZ} = -4\text{mA} \text{ (Type1)},$<br>$-8\text{mA} \text{ (Type2)}$<br>$-12\text{mA} \text{ (Type3)}$ | $V_{DD} - 0.4$ |      |      | V                |

| $V_{OL}$  | 低レベル出力電圧 | $V_{DD} = \text{Min.}$<br>$I_{OZ} = 4\text{mA} \text{ (Type1)},$<br>$8\text{mA} \text{ (Type2)}$<br>$12\text{mA} \text{ (Type3)}$    |                |      | 0.4  | V                |

| $V_{IH}$  | 高レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Max.}$                                                                                                   | 3.5            |      |      | V                |

| $V_{IL}$  | 低レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Min.}$                                                                                                   |                |      | 1.0  | V                |

| $V_{T+}$  | 高レベル入力電圧 | CMOSシユミット、<br>$V_{DD} = 5.0\text{V}$                                                                                                 |                |      | 4.0  | V                |

| $V_{T-}$  | 低レベル入力電圧 | CMOSシユミット、<br>$V_{DD} = 5.0\text{V}$                                                                                                 | 0.8            |      |      | V                |

| $V_{H1}$  | ヒステリシス電圧 | CMOSシユミット、<br>$V_{DD} = 5.0\text{V}$                                                                                                 | 0.3            |      |      | V                |

| $R_{PD}$  | プルダウン抵抗  | $V_I = V_{DD}$                                                                                                                       | 50             | 100  | 200  | $\text{k}\Omega$ |

| $C_I$     | 入力ピン容量   |                                                                                                                                      |                |      | 12   | $\text{pF}$      |

| $C_O$     | 出力ピン容量   |                                                                                                                                      |                |      | 12   | $\text{pF}$      |

| $C_{IO}$  | 双方向ピン容量  |                                                                                                                                      |                |      | 12   | $\text{pF}$      |

# S1D13506F00A

電気的特性 ( $V_{DD} = 3.3$ , Typ.)

| 記号       | 項目       | 定格                                                                                                           | Min.           | Typ. | Max. | 単位 |

|----------|----------|--------------------------------------------------------------------------------------------------------------|----------------|------|------|----|

| $I_{DD}$ | 静的消費電流   | 静止状態                                                                                                         |                |      | 290  | μA |

| $I_{IZ}$ | 入力リーク電流  |                                                                                                              | -1             |      | 1    | μA |

| $I_{OZ}$ | 出力リーク電流  |                                                                                                              | -1             |      | 1    | μA |

| $V_{OH}$ | 高レベル出力電圧 | $V_{DD} = \text{Min.}$<br>$I_{OL} = -2\text{mA}$ (Type1),<br>$-4\text{mA}$ (Type2),<br>$-6\text{mA}$ (Type3) | $V_{DD} - 0.3$ |      |      | V  |

| $V_{OL}$ | 低レベル入力電圧 | $V_{DD} = \text{Min.}$<br>$I_{OL} = 2\text{mA}$ (Type1),<br>$4\text{mA}$ (Type2),<br>$6\text{mA}$ (Type3)    |                |      | 0.3  | V  |

| $V_{IH}$ | 高レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Max.}$                                                                           | 2.2            |      |      | V  |

| $V_{IL}$ | 低レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Min.}$                                                                           |                |      | 0.8  | V  |

| $V_{T+}$ | 高レベル入力電圧 | CMOSシュミット、<br>$V_{DD} = 3.3V$                                                                                |                |      | 2.4  | V  |

| $V_{T-}$ | 低レベル入力電圧 | CMOSシュミット<br>$V_{DD} = 3.3V$                                                                                 | 0.6            |      |      | V  |

| $V_{H1}$ | ヒステリシス電圧 | CMOSシュミット<br>$V_{DD} = 3.3V$                                                                                 | 0.1            |      |      | V  |

| $R_{PD}$ | プルダウン抵抗  | $V_I = V_{DD}$                                                                                               | 90             | 180  | 360  | kΩ |

| $C_I$    | 入力ピン容量   |                                                                                                              |                |      | 12   | pF |

| $C_O$    | 出力ピン容量   |                                                                                                              |                |      | 12   | pF |

| $C_{IO}$ | 双方向ピン容量  |                                                                                                              |                |      | 12   | pF |

電気的特性 ( $V_{DD} = 3.0$ , Typ.)

| 記号       | 項目       | 定格                                                                                                                  | Min.           | Typ. | Max. | 単位 |

|----------|----------|---------------------------------------------------------------------------------------------------------------------|----------------|------|------|----|

| $I_{DD}$ | 静的消費電流   | 静止状態                                                                                                                |                |      | 260  | uA |

| $I_{IZ}$ | 入力リーク電流  |                                                                                                                     | -1             |      | 1    | μA |

| $I_{OZ}$ | 出力リーク電流  |                                                                                                                     | -1             |      | 1    | μA |

| $V_{OH}$ | 高レベル出力電圧 | $V_{DD} = \text{Min.}$<br>$I_{\alpha} = -1.8\text{mA (Type1),}$<br>$-3.5\text{mA (Type2)}$<br>$-5\text{mA (Type3)}$ | $V_{DD} - 0.3$ |      |      | V  |

| $V_{OL}$ | 低レベル出力電圧 | $V_{DD} = \text{Min.}$<br>$I_{\alpha} = 1.8\text{mA (Type1),}$<br>$3.5\text{mA (Type2)}$<br>$5\text{mA (Type3)}$    |                |      | 0.3  | V  |

| $V_{IH}$ | 高レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Max.}$                                                                                  | 2.0            |      |      | V  |

| $V_{IL}$ | 低レベル入力電圧 | CMOSレベル、<br>$V_{DD} = \text{Min.}$                                                                                  |                |      | 0.8  | V  |

| $V_{T+}$ | 高レベル入力電圧 | CMOSシュミット、<br>$V_{DD} = 3.0V$                                                                                       |                |      | 2.3  | V  |

| $V_{T-}$ | 低レベル入力電圧 | CMOSシュミット、<br>$V_{DD} = 3.0V$                                                                                       | 0.5            |      |      | V  |

| $V_{H1}$ | ヒステリシス電圧 | CMOSシュミット、<br>$V_{DD} = 3.0V$                                                                                       | 0.1            |      |      | V  |

| $R_{PD}$ | プルダウン抵抗  | $V_I = V_{DD}$                                                                                                      | 100            | 200  | 400  | kΩ |

| $C_I$    | 入力ピン容量   |                                                                                                                     |                |      | 12   | pF |

| $C_O$    | 出力ピン容量   |                                                                                                                     |                |      | 12   | pF |

| $C_{IO}$ | 双方向ピン容量  |                                                                                                                     |                |      | 12   | pF |

# S1D13506F00A

## パッケージ外形図

パッケージ外形図 QDP15

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

© SEIKO EPSON CORPORATION 2001

セイコーエプソン株式会社

電子デバイス営業本部

ED営業推進部 IC営業技術G

東日本

ED東京営業部 〒191-8501 東京都日野市日野421-8

TEL(042)687-5313(直通) FAX(042)687-5116

西日本

〒541-0059 大阪市中央区博労町3-5-1 エプソン大阪ビル15F

ED大阪営業部

TEL(06)6120-6000(代表) FAX(06)6120-6100

東海・北陸

〒461-0005 名古屋市東区東桜1-10-24 栄大野ビル4F

ED名古屋営業部

TEL(052)953-8031(代表) FAX(052)953-8041

長野

〒392-8502 長野県諏訪市大和3-3-5

ED長野営業部

TEL(0266)68-8171(直通) FAX(0266)68-9917

東北

〒980-0013 宮城県仙台市青葉区花京院1-1-20 花京院スクエア19F

ED仙台営業所

TEL(022)263-7975(代表) FAX(022)263-7990

インターネットによる電子デバイスのご紹介

<http://www.epsondevice.com>