CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

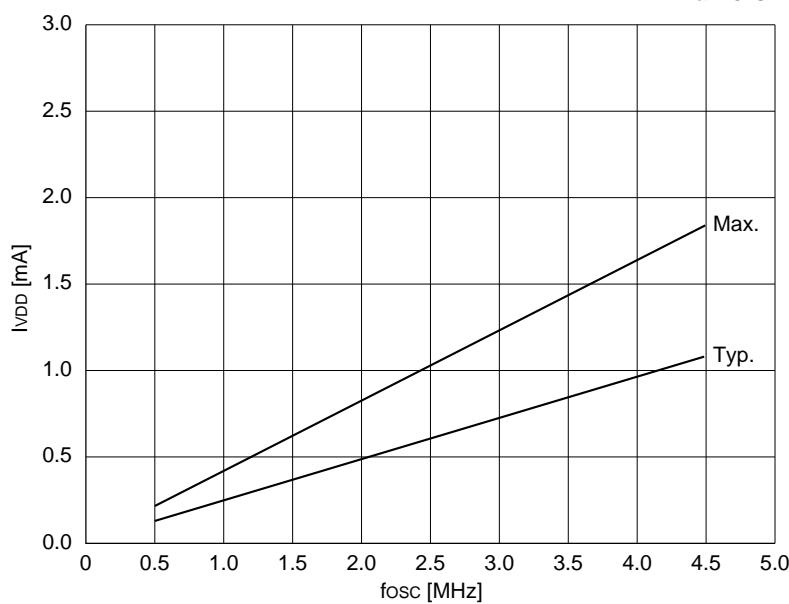

**S1C63256**

テクニカルマニュアル

S1C63256 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

## 本版で改訂または追加された箇所

| 章 | 節/項   | 頁  | 項目                              | 内容    |

|---|-------|----|---------------------------------|-------|

| 4 | 4.6.3 | 39 | LCD表示と駆動波形の制御<br>(1)表示のON/OFF   | 文章変更  |

|   | 4.8.8 | 66 | プログラミング上の注意事項                   | (5)追加 |

| 5 |       | 84 | プログラミング上の注意事項のまとめ<br>プログラマブルタイマ | (4)追加 |

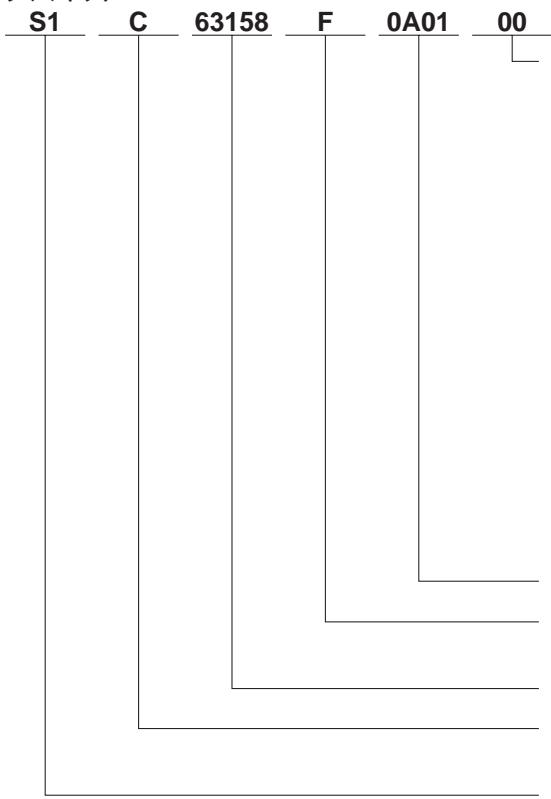

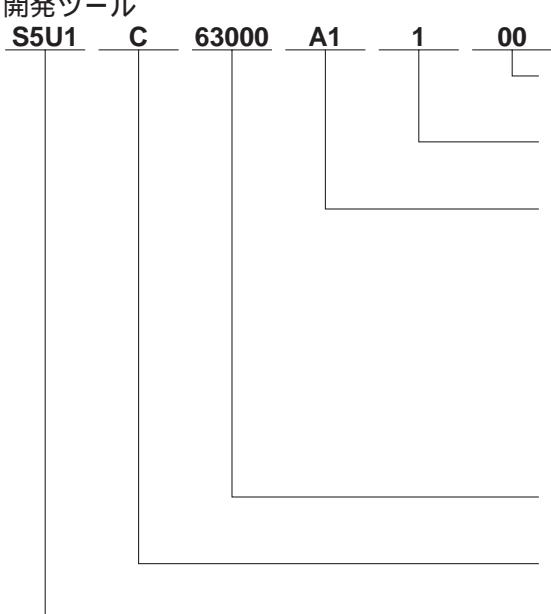

## 製品型番体系

### デバイス

#### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

#### 仕様

[D: ペアチップ、F: QFP]

#### 機種番号

[C: マイコン、デジタル製品]

#### 製品分類

[S1: 半導体]

### 開発ツール

#### 梱包仕様

[00: 標準梱包]

#### バージョン

[1: Version 1]

#### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ペリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

#### 対応機種番号

[63000: S1C63ファミリ共通]

#### ツール分類

[C: マイコン用]

#### 製品分類

[S5U1: 半導体用開発ツール]

## - 目 次 -

|                                           |           |

|-------------------------------------------|-----------|

| <b>1 概要</b>                               | <b>1</b>  |

| 1.1 特長                                    | 1         |

| 1.2 プロック図                                 | 2         |

| 1.3 端子配置図                                 | 3         |

| 1.4 端子説明                                  | 3         |

| 1.5 マスクオプション                              | 4         |

| <b>2 電源系 および イニシャルリセット</b>                | <b>7</b>  |

| 2.1 電源系                                   | 7         |

| 2.1.1 発振回路および内部回路用電圧<VD1>                 | 7         |

| 2.1.2 LCD駆動用電圧<Vc1, Vc2, Vc3>             | 7         |

| 2.2 イニシャルリセット                             | 9         |

| 2.2.1 リセット端子( $\overline{\text{RESET}}$ ) | 9         |

| 2.2.2 入力ポート( K00 ~ K03 )の同時LOW入力          | 10        |

| 2.2.3 イニシャルリセット時の内部レジスタ                   | 11        |

| 2.2.4 イニシャルリセット時の端子設定                     | 12        |

| 2.3 テスト端子( $\overline{\text{TEST}}$ )     | 12        |

| <b>3 CPU, ROM, RAM</b>                    | <b>13</b> |

| 3.1 CPU                                   | 13        |

| 3.2 コードROM                                | 13        |

| 3.3 RAM                                   | 14        |

| <b>4 周辺回路と動作</b>                          | <b>15</b> |

| 4.1 メモリマップ                                | 15        |

| 4.2 発振回路とプリスケーラ                           | 20        |

| 4.2.1 発振回路の構成                             | 20        |

| 4.2.2 発振回路の種類                             | 20        |

| 4.2.3 プリスケーラ                              | 21        |

| 4.2.4 クロック周波数とインストラクション実行時間               | 22        |

| 4.2.5 プリスケーラのI/Oメモリ                       | 22        |

| 4.2.6 プログラミング上の注意事項                       | 22        |

| 4.3 入力ポート( K00 ~ K03 )                    | 23        |

| 4.3.1 入力ポートの構成                            | 23        |

| 4.3.2 割り込み機能                              | 23        |

| 4.3.3 マスクオプション                            | 24        |

| 4.3.4 入力ポートのI/Oメモリ                        | 25        |

| 4.3.5 プログラミング上の注意事項                       | 27        |

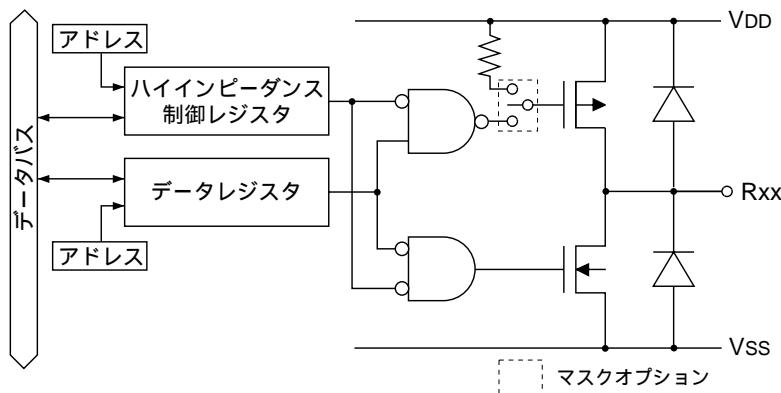

| 4.4 出力ポート( R00 ~ R03 )                    | 28        |

| 4.4.1 出力ポートの構成                            | 28        |

| 4.4.2 マスクオプション                            | 28        |

|                                                |    |

|------------------------------------------------|----|

| 4.4.3 ハインピーダンス制御 .....                         | 29 |

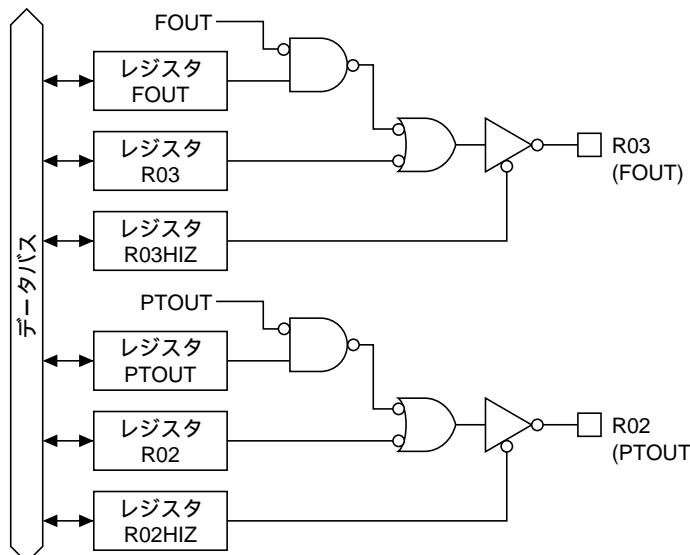

| 4.4.4 特殊出力 .....                               | 29 |

| 4.4.5 出力ポートのI/Oメモリ .....                       | 31 |

| 4.4.6 プログラミング上の注意事項 .....                      | 32 |

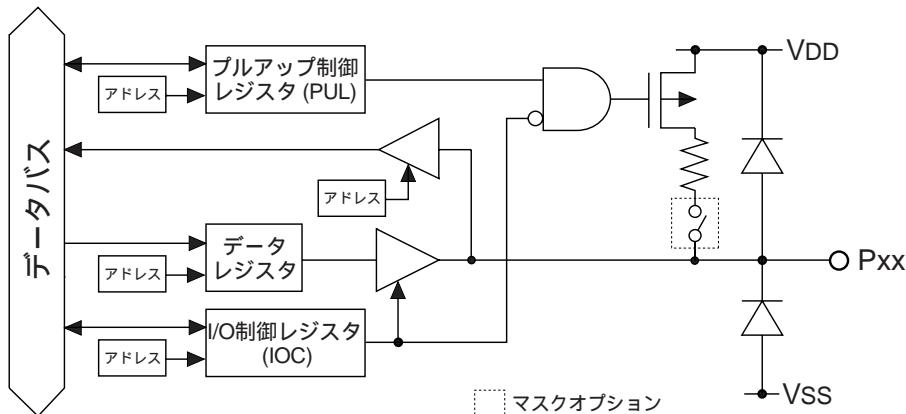

| 4.5 入出力兼用ポート( P20 ~ P23, P40 ~ P43 ) .....     | 33 |

| 4.5.1 入出力兼用ポートの構成 .....                        | 33 |

| 4.5.2 マスクオプション .....                           | 34 |

| 4.5.3 I/O制御レジスタと入力/出力モード .....                 | 34 |

| 4.5.4 入力モード時のプルアップ .....                       | 34 |

| 4.5.5 入出力兼用ポートのI/Oメモリ .....                    | 35 |

| 4.5.6 プログラミング上の注意事項 .....                      | 37 |

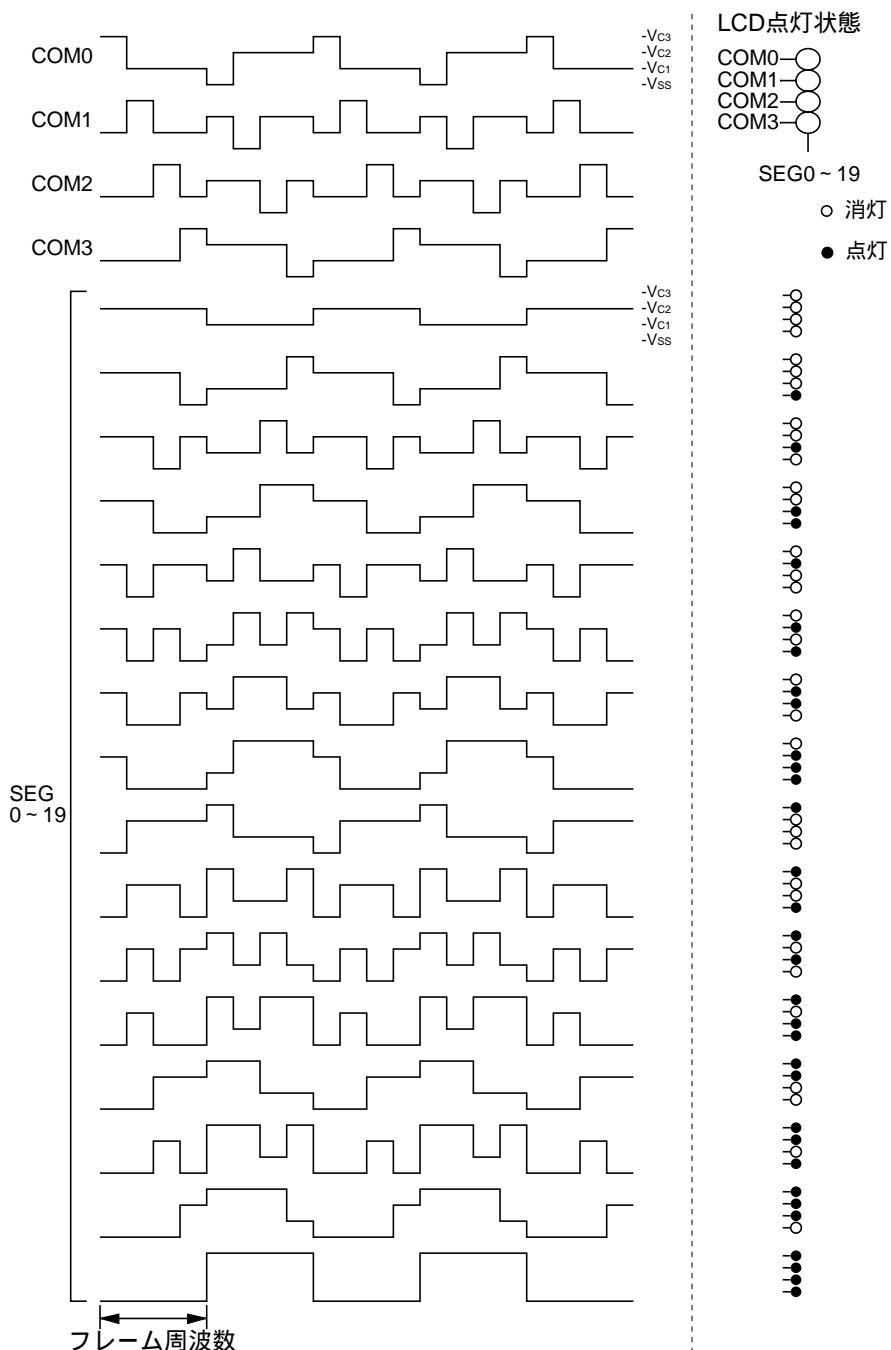

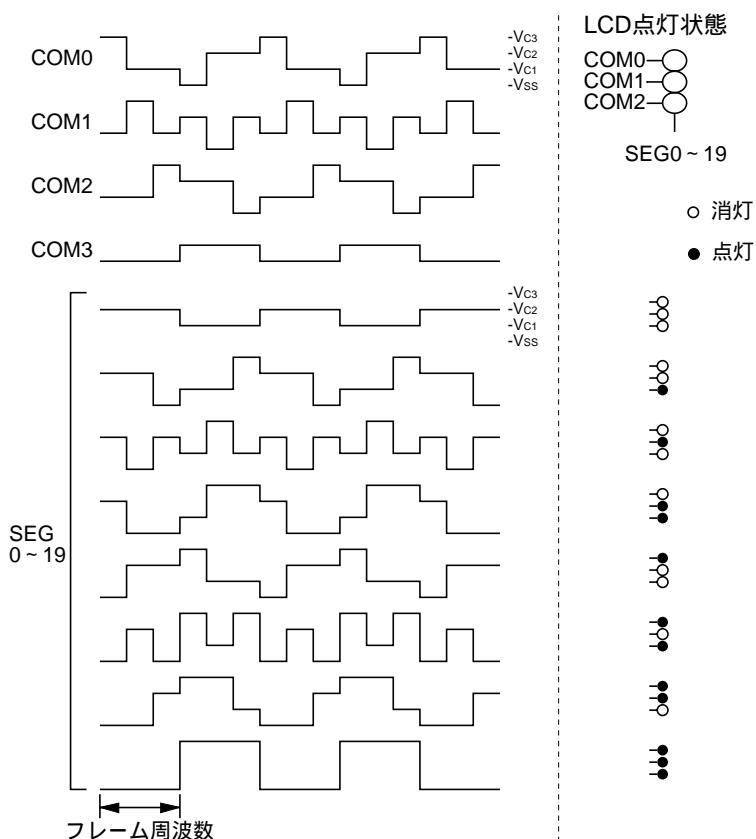

| 4.6 LCDドライバ( COM0 ~ COM3, SEG0 ~ SEG19 ) ..... | 38 |

| 4.6.1 LCDドライバの構成 .....                         | 38 |

| 4.6.2 LCD駆動電源/駆動バイアス .....                     | 38 |

| 4.6.3 LCD表示と駆動波形の制御 .....                      | 39 |

| 4.6.4 マスクオプション .....                           | 45 |

| 4.6.5 LCDドライバのI/Oメモリ .....                     | 46 |

| 4.6.6 プログラミング上の注意事項 .....                      | 48 |

| 4.7 計時タイマとウォッチドッグタイマ .....                     | 49 |

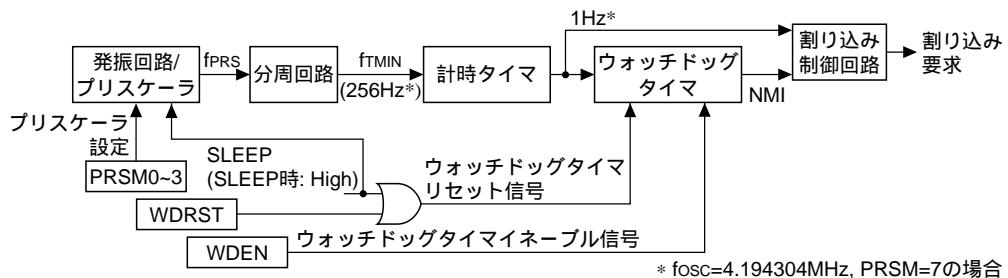

| 4.7.1 計時タイマとウォッチドッグタイマの構成 .....                | 49 |

| 4.7.2 計時タイマの動作 .....                           | 49 |

| 4.7.3 ウォッチドッグタイマの動作 .....                      | 50 |

| 4.7.4 計時タイマとウォッチドッグタイマのI/Oメモリ .....            | 51 |

| 4.7.5 プログラミング上の注意事項 .....                      | 52 |

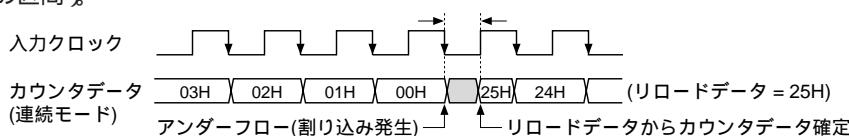

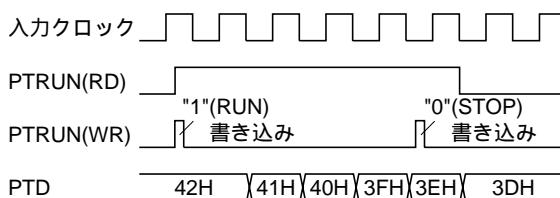

| 4.8 プログラマブルタイマ .....                           | 53 |

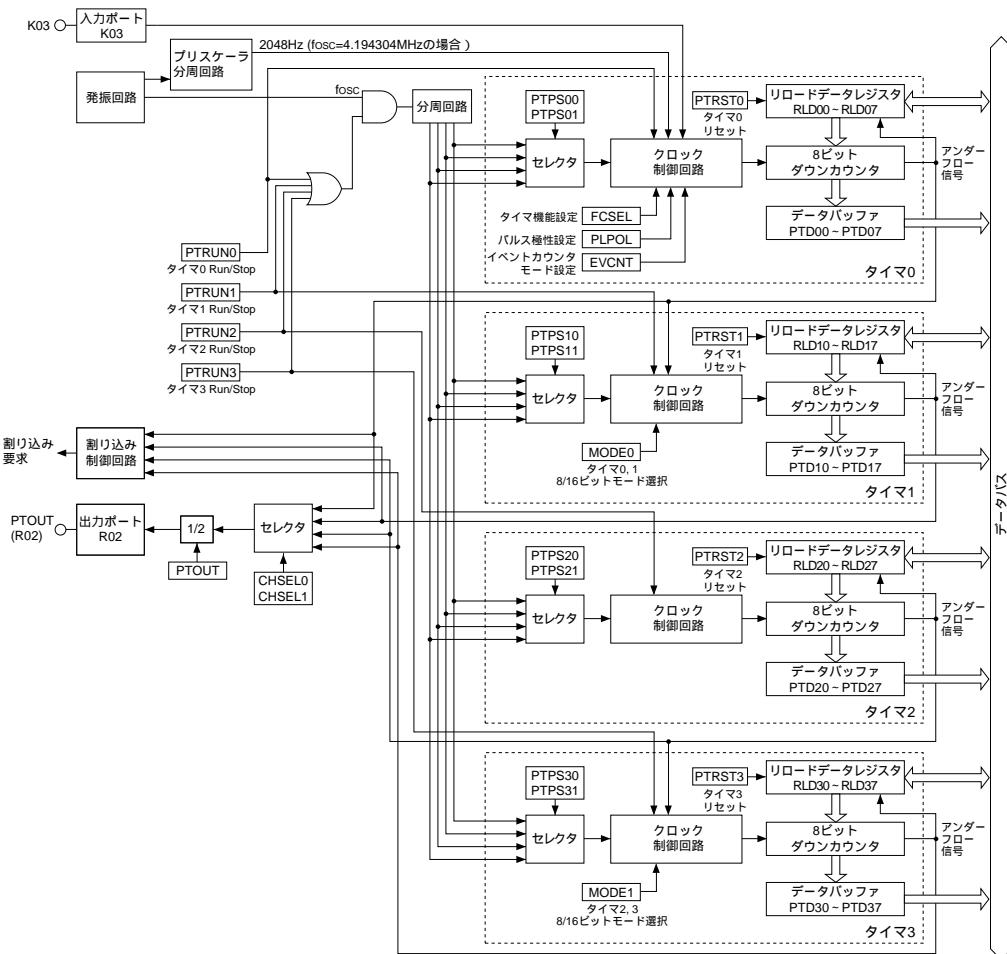

| 4.8.1 プログラマブルタイマの構成 .....                      | 53 |

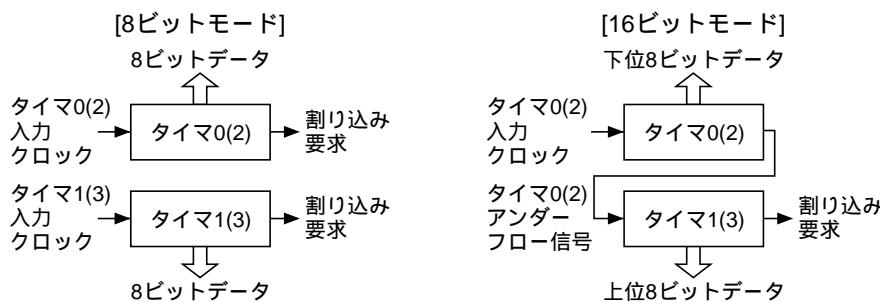

| 4.8.2 8/16ビットモード .....                         | 54 |

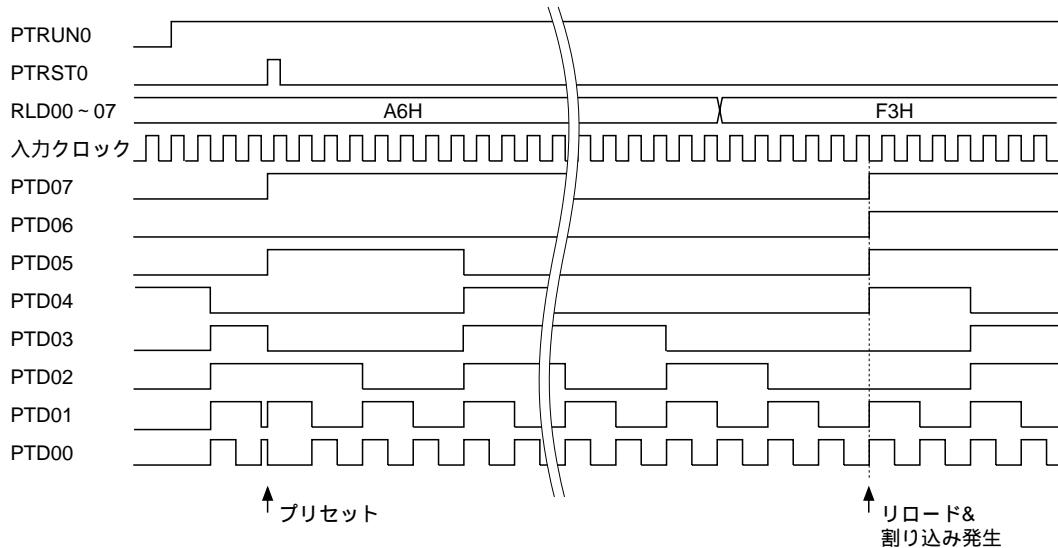

| 4.8.3 プログラマブルタイマの動作 .....                      | 54 |

| 4.8.4 割り込み機能 .....                             | 57 |

| 4.8.5 イベントカウンタ機能 .....                         | 57 |

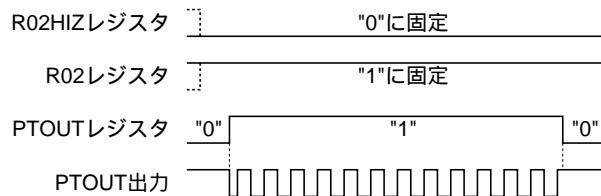

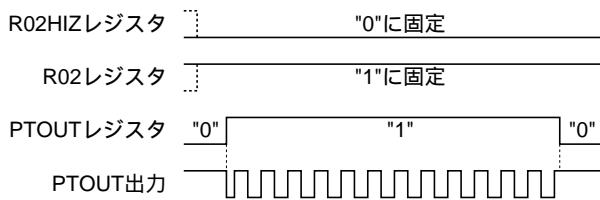

| 4.8.6 PTOUT出力の設定 .....                         | 59 |

| 4.8.7 プログラマブルタイマのI/Oメモリ .....                  | 60 |

| 4.8.8 プログラミング上の注意事項 .....                      | 66 |

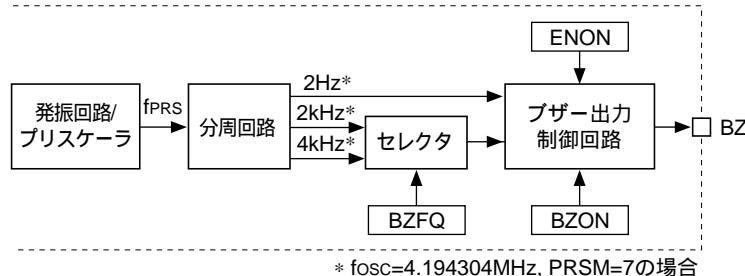

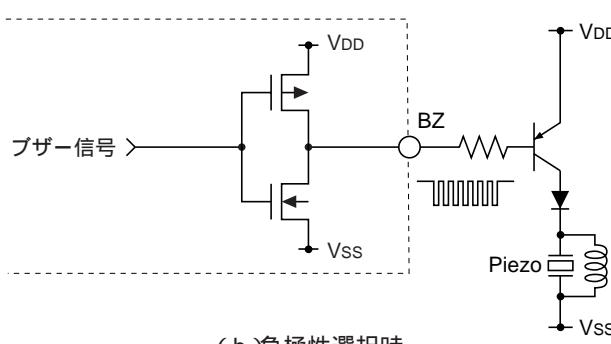

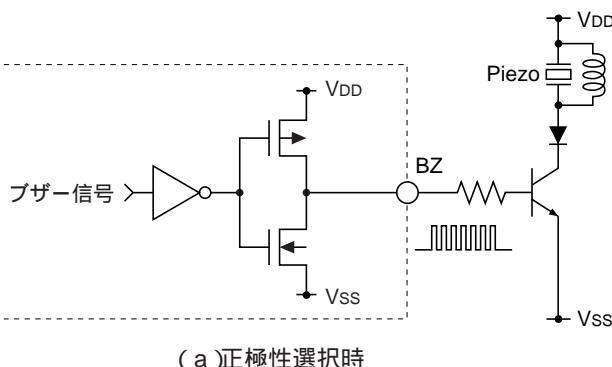

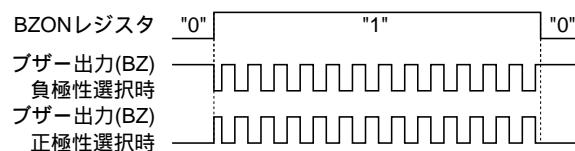

| 4.9 ブザー出力回路 .....                              | 67 |

| 4.9.1 ブザー出力回路の構成 .....                         | 67 |

| 4.9.2 マスクオプション .....                           | 67 |

| 4.9.3 ブザー出力の制御 .....                           | 68 |

| 4.9.4 ブザー出力回路のI/Oメモリ .....                     | 69 |

| 4.9.5 プログラミング上の注意事項 .....                      | 69 |

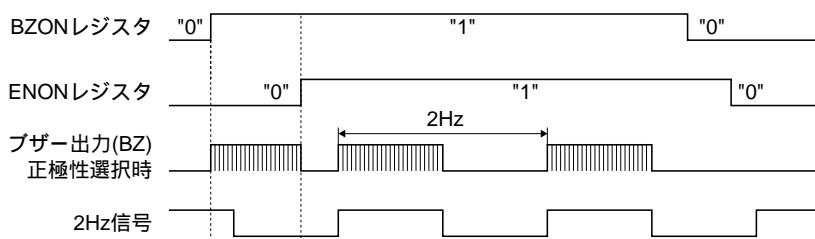

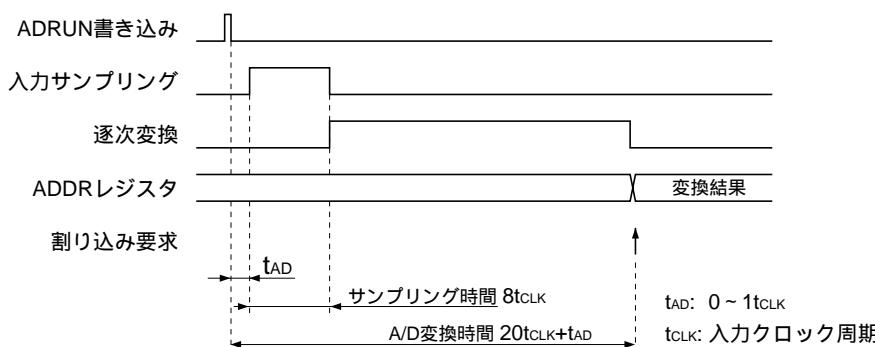

| 4.10 A/D変換器 .....                              | 70 |

| 4.10.1 A/D変換器の特徴と構成 .....                      | 70 |

| 4.10.2 A/D変換器の端子構成 .....                       | 70 |

| 4.10.3 マスクオプション .....                          | 71 |

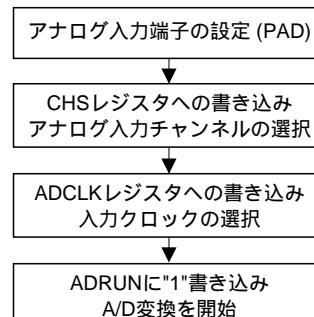

| 4.10.4 A/D変換の制御 .....                          | 71 |

| 4.10.5 割り込み機能 .....                            | 73 |

| 4.10.6 A/D変換器のI/Oメモリ .....                     | 73 |

| 4.10.7 プログラミング上の注意事項 .....                     | 75 |

|        |                          |     |

|--------|--------------------------|-----|

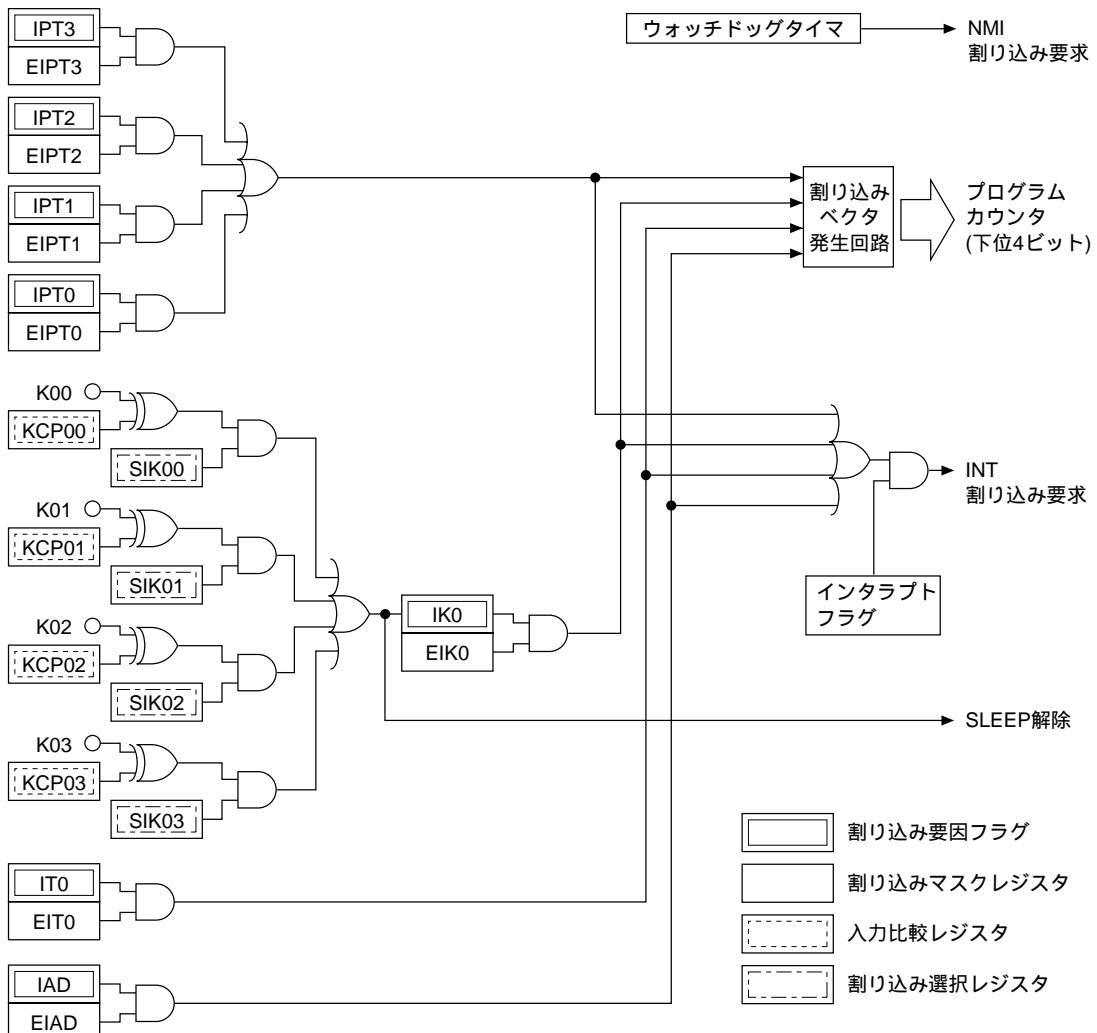

| 4.11   | 割り込みとHALT/SLEEP .....    | 76  |

| 4.11.1 | 割り込みの要因 .....            | 78  |

| 4.11.2 | 割り込みの個別マスク .....         | 78  |

| 4.11.3 | 割り込みベクタ .....            | 79  |

| 4.11.4 | 割り込みのI/Oメモリ .....        | 80  |

| 4.11.5 | プログラミング上の注意事項 .....      | 81  |

| 5      | プログラミング上の注意事項のまとめ .....  | 82  |

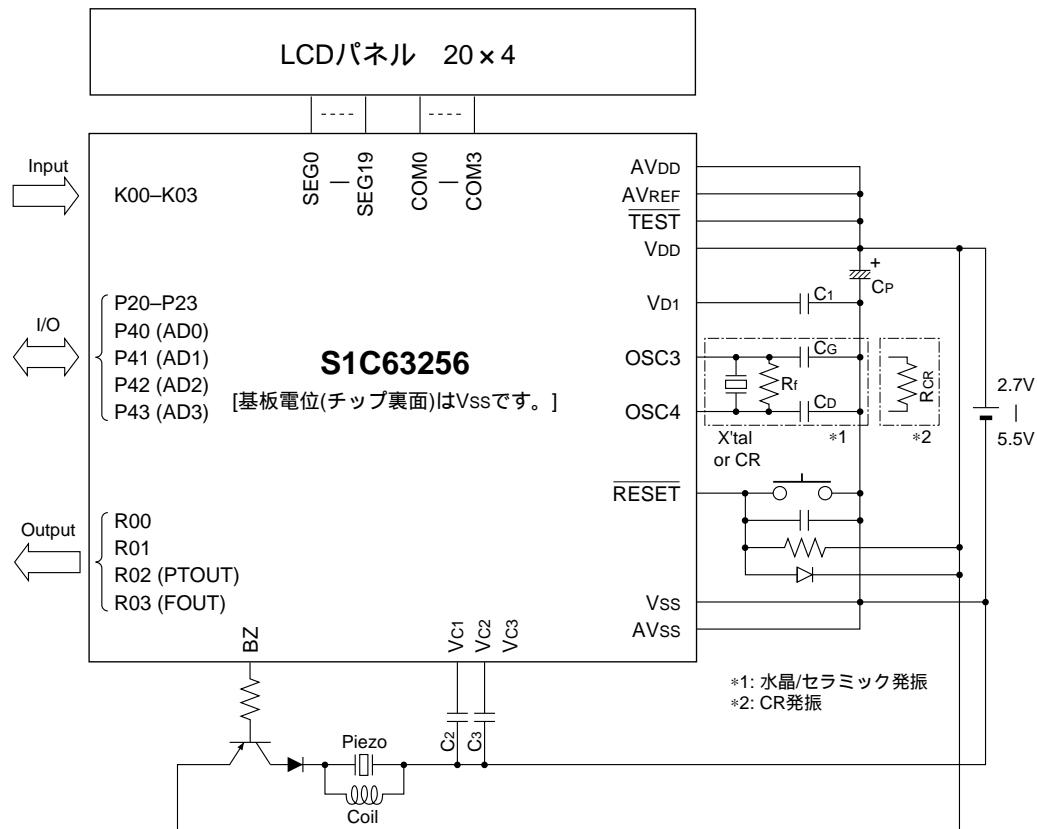

| 6      | 基本外部結線図 .....            | 85  |

| 7      | 電気的特性 .....              | 86  |

| 7.1    | 絶対最大定格 .....             | 86  |

| 7.2    | 推奨動作条件 .....             | 86  |

| 7.3    | DC特性 .....               | 87  |

| 7.3.1  | 入力特性 .....               | 87  |

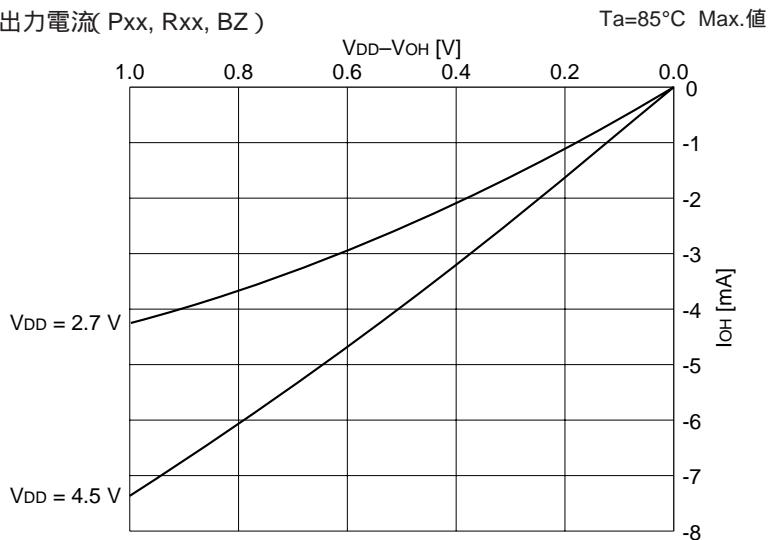

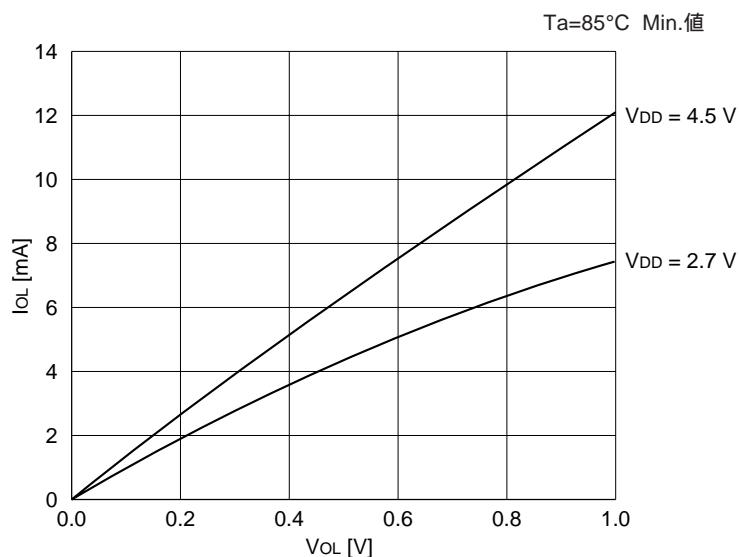

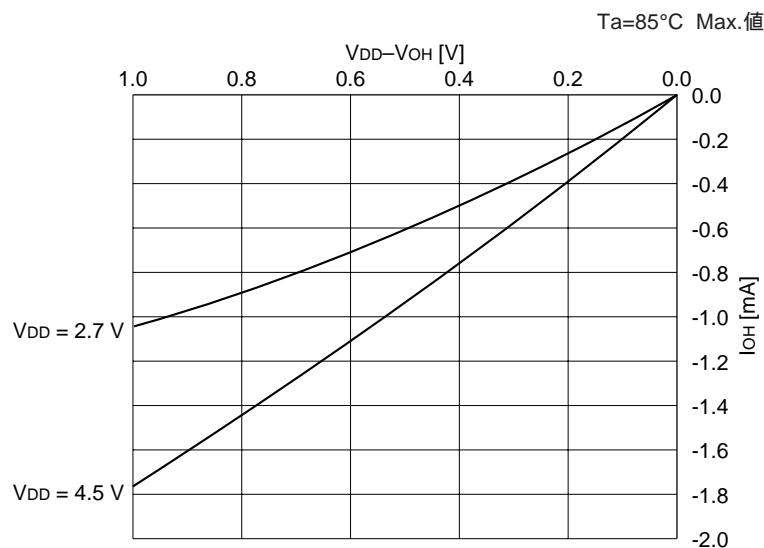

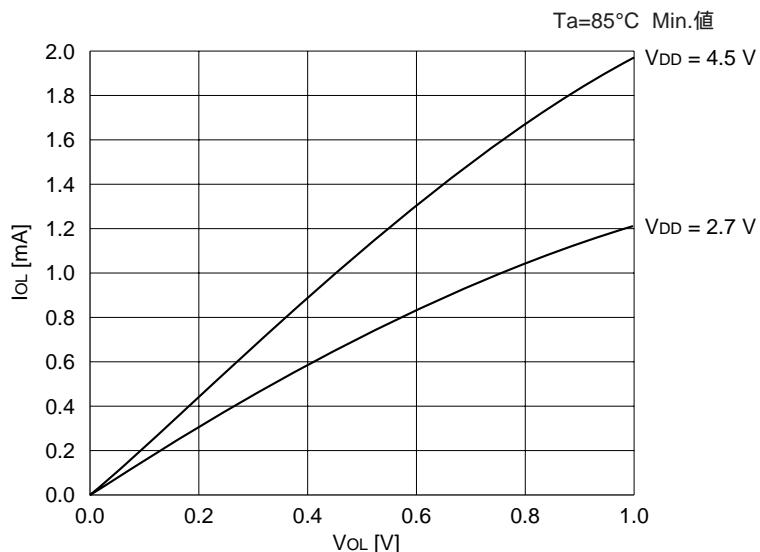

| 7.3.2  | 出力特性 .....               | 87  |

| 7.4    | アナログ回路特性 .....           | 88  |

| 7.4.1  | LCD駆動電源特性 .....          | 88  |

| 7.4.2  | A/D変換特性 .....            | 88  |

| 7.5    | 消費電流 .....               | 89  |

| 7.6    | AC特性 .....               | 90  |

| 7.6.1  | 動作範囲 .....               | 90  |

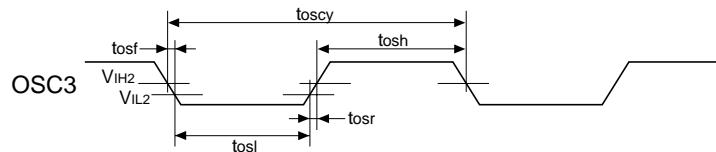

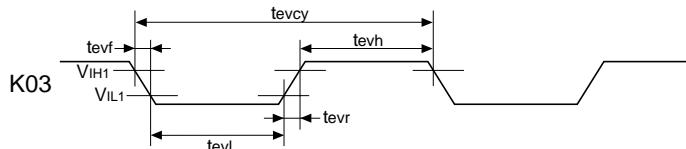

| 7.6.2  | 入力クロック .....             | 90  |

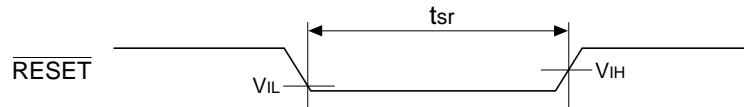

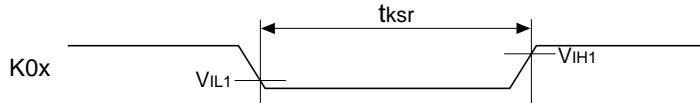

| 7.6.3  | パワーオンリセット .....          | 91  |

| 7.6.4  | A/D変換特性 .....            | 91  |

| 7.7    | 発振特性 .....               | 92  |

| 7.7.1  | 水晶発振回路 .....             | 92  |

| 7.7.2  | セラミック発振回路 .....          | 92  |

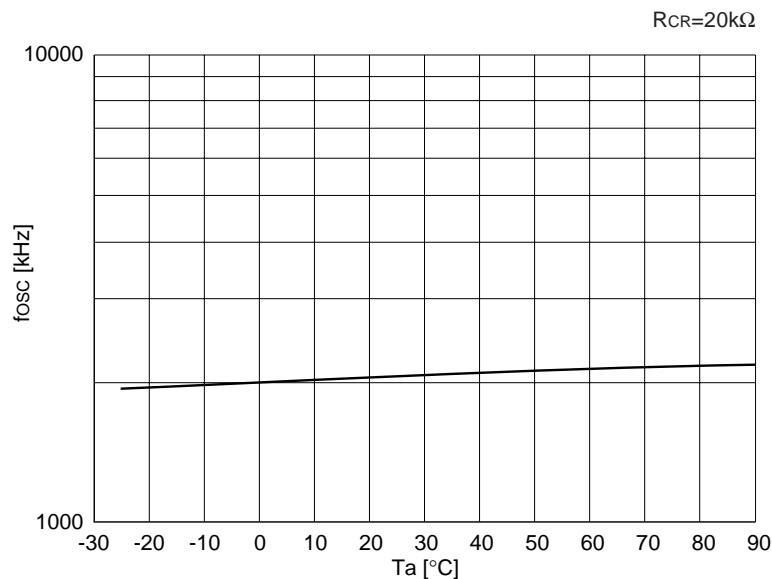

| 7.7.3  | CR発振回路 .....             | 92  |

| 7.8    | 特性グラフ(参考値) .....         | 93  |

| 7.8.1  | 出力電流特性 .....             | 93  |

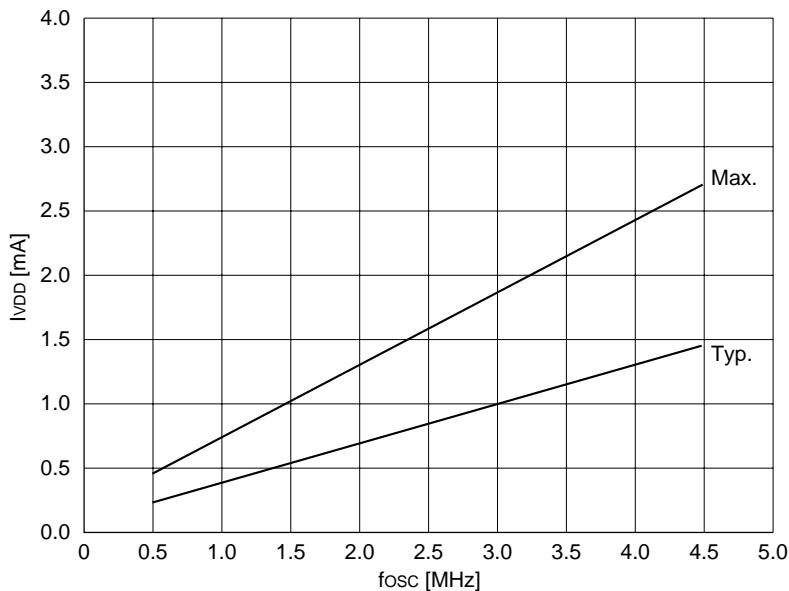

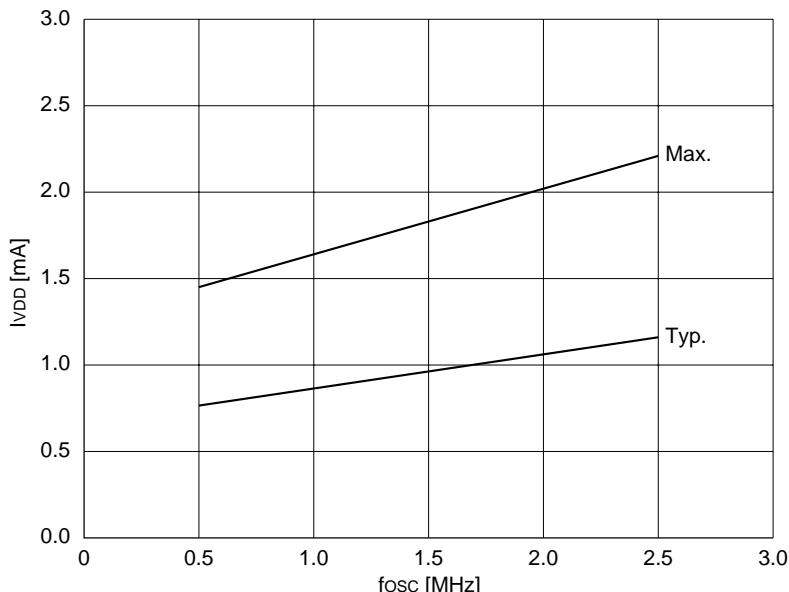

| 7.8.2  | 電源電流-周波数特性 .....         | 95  |

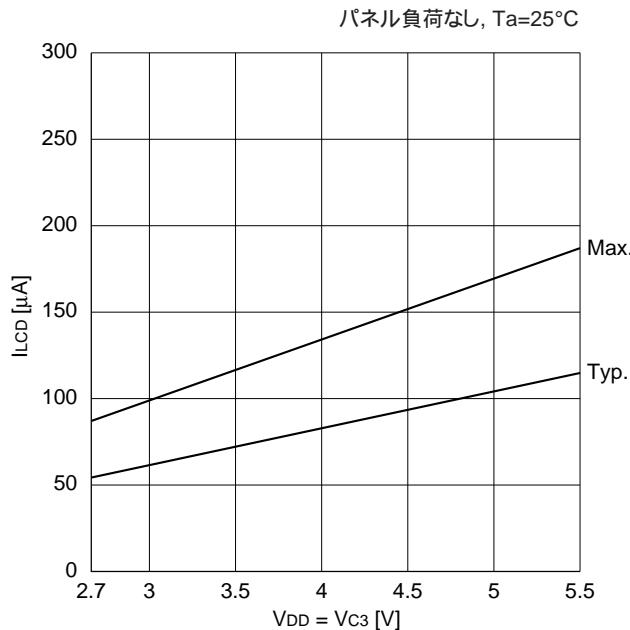

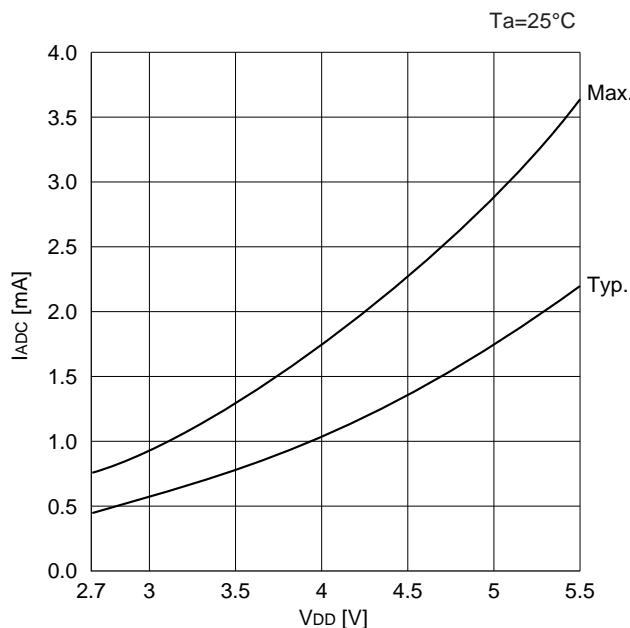

| 7.8.3  | アナログ系動作電流-電圧特性 .....     | 97  |

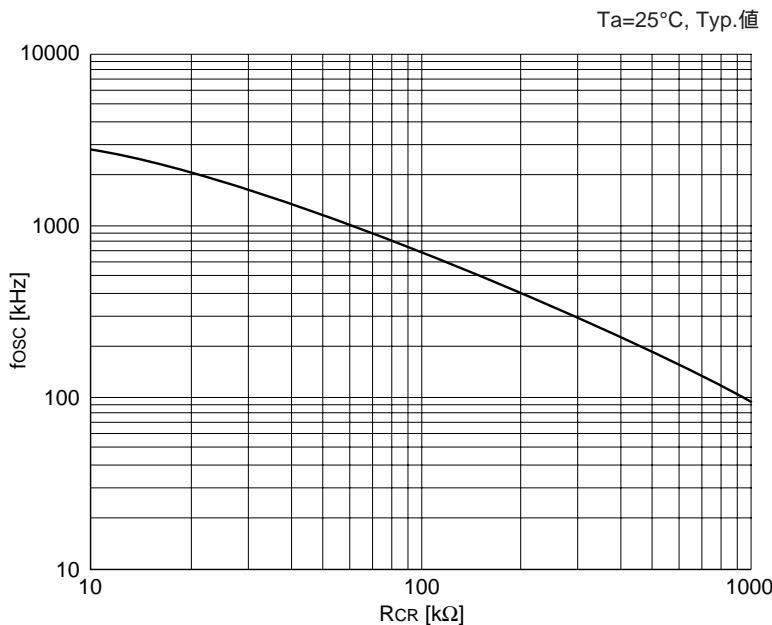

| 7.8.4  | CR発振周波数特性 .....          | 98  |

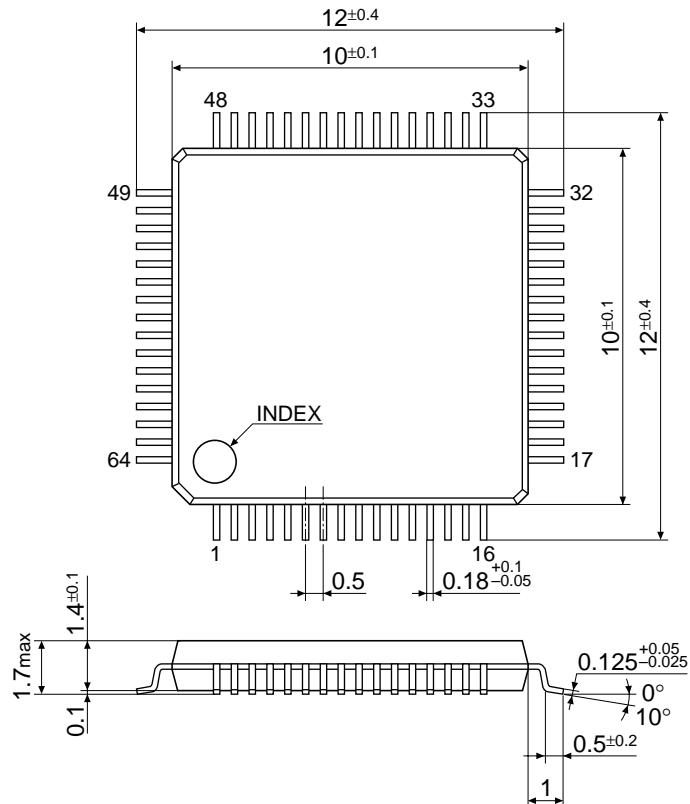

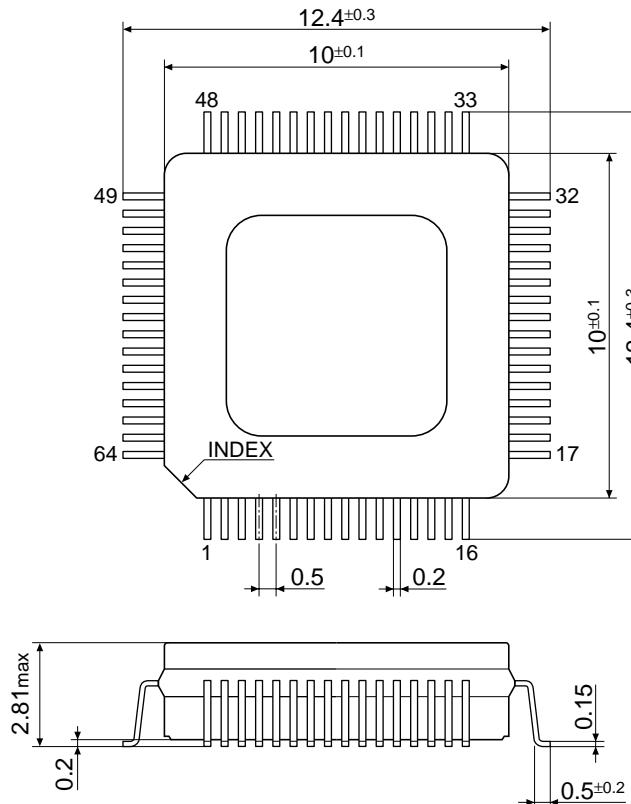

| 8      | パッケージ .....              | 99  |

| 8.1    | プラスチックパッケージ .....        | 99  |

| 8.2    | テストサンプル用セラミックパッケージ ..... | 100 |

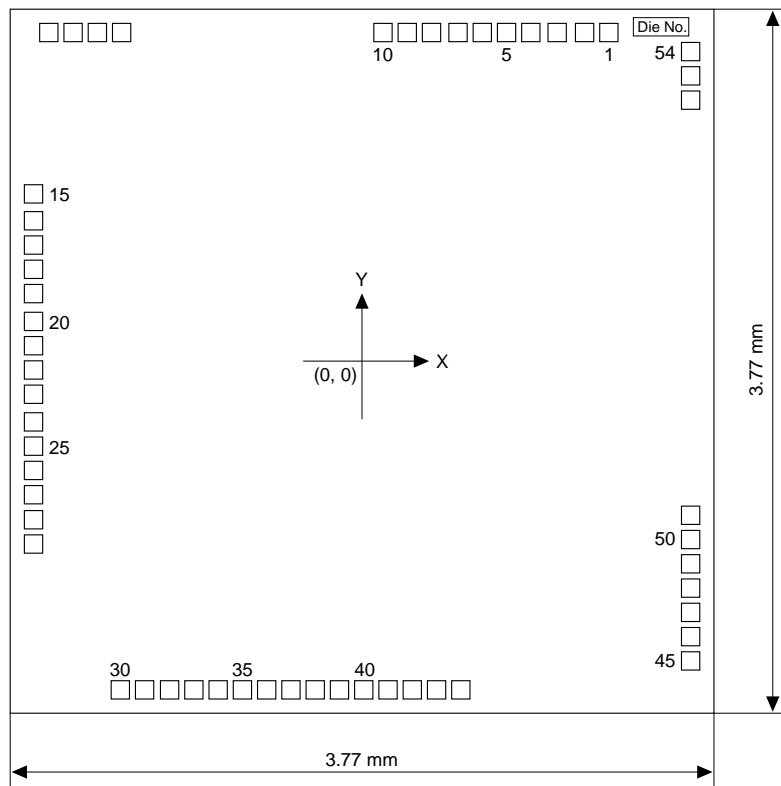

| 9      | パッド配置 .....              | 101 |

| 9.1    | パッド配置図 .....             | 101 |

| 9.2    | パッド座標 .....              | 101 |

| 10     | 実装上の注意事項 .....           | 102 |

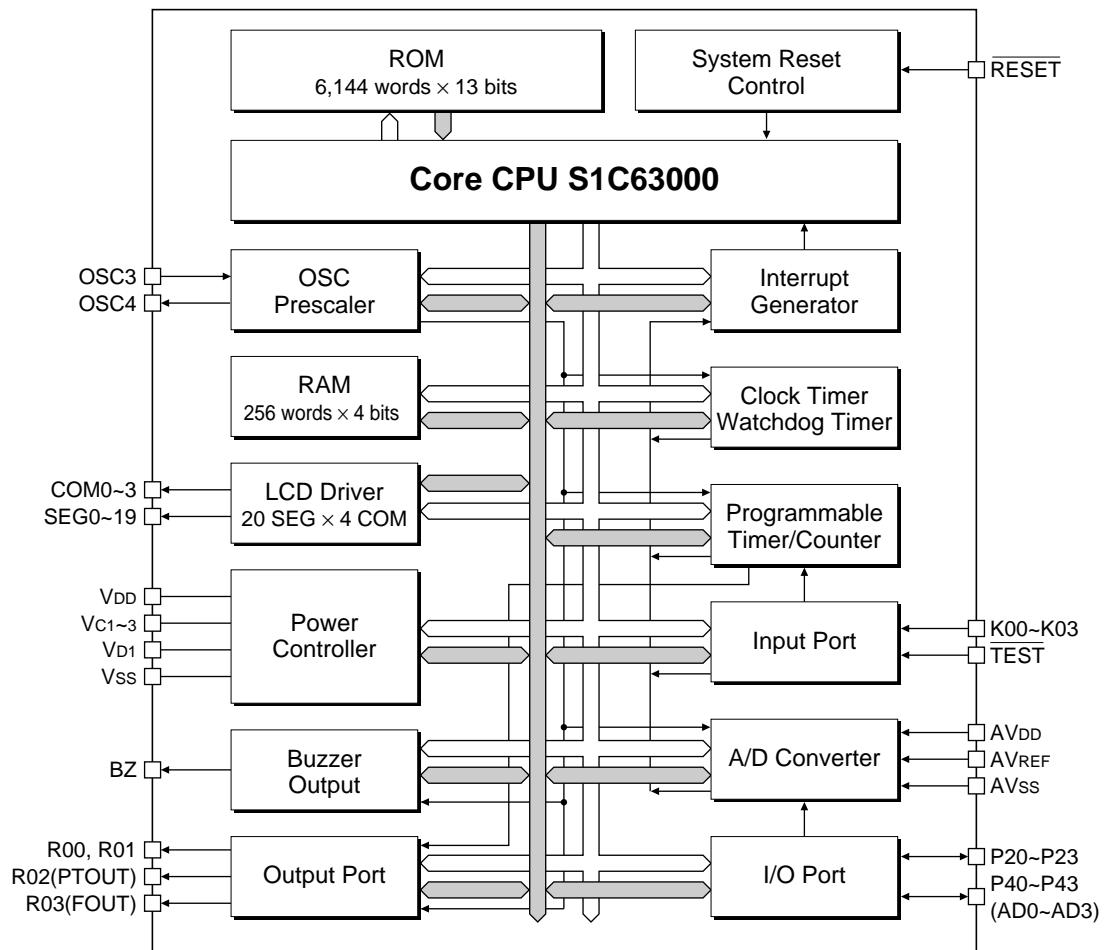

# 1 概要

---

S1C63256は高性能4ビットCPU S1C63000を中心に、ワンチップ上にROM( 6,144ワード×13ビット ) RAM( 256ワード×4ビット ) 計時タイマ、ウォッチドッグタイマ、プログラマブルタイマ、最大20セグメント×4コモンのLCD駆動回路、A/D変換器等を内蔵したマイクロコンピュータです。広範囲な動作電圧( 2.7 ~ 5.5V )と動作周波数( 0.5 ~ 4.5MHz )が特長で、A/D変換と液晶表示が必要な家電製品の制御ユニット等への応用に最適です。

## 1.1 特長

|               |                                                                                  |                                                                                                                |

|---------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 発振回路          | 0.5 ~ 4.5MHz                                                                     | 水晶、セラミック、CR発振回路または外部クロック入力(*1)                                                                                 |

| インストラクションセット  | 基本命令 47種類( 全命令数 411種類 )                                                          | アドレスシングルモード 8種類                                                                                                |

| インストラクション実行時間 | 2MHz動作時:                                                                         | 1μsec      2μsec      3μsec                                                                                    |

|               | 4.194304MHz動作時:                                                                  | 0.48μsec      0.95μsec      1.43μsec                                                                           |

| ROM容量         | 命令ROM:                                                                           | 6,144ワード×13ビット                                                                                                 |

| RAM容量         | データメモリ:                                                                          | 256ワード×4ビット<br>表示メモリ: 20ワード×4ビット                                                                               |

| 入力ポート         | 4ビット( ブルアップ抵抗の付加が可能*1 )                                                          |                                                                                                                |

| 出力ポート         | 4ビット( 2ビットをクロック出力に切り替え可能*2 )                                                     |                                                                                                                |

| 入出力兼用ポート      | 8ビット( 4ビットをA/D変換器入力に切り替え可能*2 )                                                   |                                                                                                                |

| LCDドライバ       | 20セグメント×4, 3または2コモン(*2)                                                          |                                                                                                                |

|               | 1/3または1/2バイアス駆動(*1)                                                              |                                                                                                                |

| タイムベースカウンタ    | 計時タイマ( 発振周波数4.194304MHz時 )                                                       |                                                                                                                |

| プログラマブルタイマ    | 8ビット×4ch内蔵、イベントカウンタ、クロック出力機能付き<br>8ビット×4ch、8ビット×2ch & 16ビット×1ch、16ビット×2chとして使用可能 |                                                                                                                |

| ウォッチドッグタイマ    | 内蔵                                                                               |                                                                                                                |

| ブザー出力         | ブザー周波数: 2kHzまたは4kHz(*2)                                                          |                                                                                                                |

| A/D変換器        | 分解能: 8ビット、アナログ入力: 4ch                                                            |                                                                                                                |

| 外部割り込み        | 入力ポート割り込み                                                                        | 1系統                                                                                                            |

| 内部割り込み        | 計時タイマ割り込み<br>プログラマブルタイマ割り込み                                                      | 1系統<br>4系統                                                                                                     |

|               | A/D変換器割り込み                                                                       | 1系統                                                                                                            |

| 電源電圧          | 2.7V ~ 5.5V                                                                      |                                                                                                                |

| 動作温度範囲        | -20°C ~ 85°C                                                                     |                                                                                                                |

| 消費電流( Typ. )  | SLEEP時                                                                           | 0.3μA                                                                                                          |

|               | HALT時(*3)                                                                        |                                                                                                                |

|               | 4.194304MHz:<br>( 水晶発振 )<br>4MHz:<br>( セラミック発振 )<br>2MHz:<br>( CR発振 )            | 3.0V      620μA<br>5.0V      660μA<br>3.0V      670μA<br>5.0V      710μA<br>3.0V      740μA<br>5.0V      780μA |

|               | 動作時(*3)                                                                          |                                                                                                                |

|               | 4.194304MHz:<br>( 水晶発振 )<br>4MHz:<br>( セラミック発振 )<br>2MHz:<br>( CR発振 )            | 3.0V      1.5mA<br>5.0V      1.5mA<br>3.0V      1.5mA<br>5.0V      1.5mA<br>3.0V      1.2mA<br>5.0V      1.2mA |

| 出荷形態          | QFP13-64pin( プラスチック )またはチップ                                                      |                                                                                                                |

\*1: マスクオプションにより選択

\*2: ソフトウェアにより選択

\*3: A/D変換動作電流は含みません。

## 1.2 ブロック図

図1.2.1 ブロック図

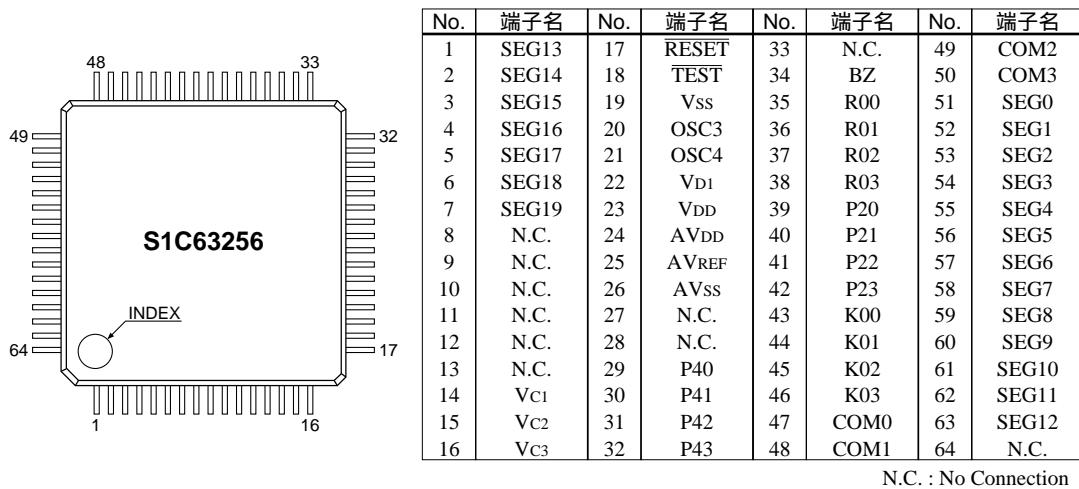

## 1.3 端子配置図

QFP13-64pin

図1.3.1 端子配置図

## 1.4 端子説明

表1.4.1 端子説明

| 端子名           | 端子No.      | 入出力 | 機能                                     |

|---------------|------------|-----|----------------------------------------|

| VDD           | 23         | -   | 電源(+)端子                                |

| VSS           | 19         | -   | 電源(-)端子                                |

| AVDD          | 24         | -   | アナログ系電源(+)端子                           |

| AVSS          | 26         | -   | アナログ系電源(-)端子                           |

| AVREF         | 25         | I   | アナログ系基準電圧入力端子                          |

| Vd1           | 22         | -   | 発振および内部ロジック系定電圧出力端子                    |

| VC1, VC2, VC3 | 14, 15, 16 | -   | LCD系電源端子 1/3または1/2バイアス(マスクオプション選択)     |

| OSC3          | 20         | I   | 水晶/セラミック/CR発振/外部クロック入力端子(マスクオプション選択)   |

| OSC4          | 21         | O   | 水晶/セラミック/CR発振出力端子(マスクオプション選択)          |

| K00~K03       | 43~46      | I   | 入力端子                                   |

| P20~P23       | 39~42      | I/O | 入出力端子                                  |

| P40~P43       | 29~32      | I/O | 入出力端子(A/D変換器入力にソフト切り換え)                |

| R00           | 35         | O   | 出力端子                                   |

| R01           | 36         | O   | 出力端子                                   |

| R02           | 37         | O   | 出力端子(PTOUT信号出力にソフト切り換え)                |

| R03           | 38         | O   | 出力端子(FOUT信号出力にソフト切り換え)                 |

| COM0~COM3     | 47~50      | O   | LCDコモン出力端子(1/4, 1/3, 1/2デューティをソフト切り換え) |

| SEG0~SEG19    | 51~63, 1~7 | O   | LCDセグメント出力端子                           |

| BZ            | 34         | O   | ブザー出力端子                                |

| RESET         | 17         | I   | イニシャルリセット入力端子                          |

| TEST          | 18         | I   | テスト用入力端子                               |

## 1.5 マスクオプション

S1C63256には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択にはS1C63256の開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogおよびセグメントオプションジェネレータwinsogを使用します。これらのオプションジェネレータによって作成したデータをもとに最終的なICのマスクパターン生成が行われます。winfog、winsogについては"S5U1C63000A Manual"を参照してください。

### S1C63256のマスクオプション

#### (1) 入力ポート(K00 ~ K03)同時LOW入力による外部リセット

この機能は、複数キーの同時押しによってICをリセットするもので、この機能を使用するかしないかをマスクオプションで選択できます。また、使用する場合は、同時に押すキーを接続する入力ポート(K00 ~ K03)の組み合わせを選択します。詳細については"2.2.2 入力ポート(K00 ~ K03)の同時LOW入力"を参照してください。

#### (2) 入力ポート同時LOW入力リセットの時間検定回路

(1)の外部リセット機能を使用する場合に時間検定回路を使用するかしないか選択できます。時間検定回路を使用すると、規定時間以上の同時LOW入力があった場合のみ、リセット機能が働きます。詳細については"2.2.2 入力ポート(K00 ~ K03)の同時LOW入力"を参照してください。

#### (3) 入力ポートブルアップ抵抗

入力ポートにブルアップ抵抗を付加するかしないか選択できます。この選択は入力ポートの各ビットごとに行えます。詳細については"4.3.3 マスクオプション"を参照してください。

#### (4) 出力ポートの出力仕様

出力ポートの出力仕様としてコンプリメンタリ出力またはNチャンネルオープンドレイン出力が選択できます。選択は出力ポートの各ビットごとに行えます。詳細については"4.4.2 マスクオプション"を参照してください。

#### (5) 入出力兼用ポートの出力仕様/ブルアップ抵抗

入出力兼用ポートが出力モードの際の出力仕様としてコンプリメンタリ出力またはNチャンネルオープンドレイン出力が選択できます。また入力モード時に働くブルアップ抵抗を付加するかしないか選択できます。選択は入出力兼用ポートの各ビットごとに行えます。詳細については"4.5.2 マスクオプション"を参照してください。

#### (6) LCD電源/駆動バイアス

LCD駆動に内部電源を使用するか、外部電源を使用するか選択できます。また、駆動方式として1/3バイアスまたは1/2バイアスのどちらかを選択できます。詳細については"2.1.2 LCD駆動用電圧<VC1, VC2, VC3>"を参照してください。

#### (7) LCDセグメント仕様

SEG端子に対する表示メモリの割り付け、DC出力として使用するSEG端子の設定が行えます。詳細については"4.6.4 マスクオプション"を参照してください。

#### (8) ブザー出力信号の極性

BZ端子から出力するブザー信号の極性が選択できます。駆動用外付けトランジスタに合わせ、正極性または負極性を選択します。詳細については"4.9.2 マスクオプション"を参照してください。

#### (9) 発振回路

発振回路の種類を水晶/セラミック発振、CR発振、外部クロック入力の中から選択できます。詳細については"4.2.2 発振回路の種類"を参照してください。

#### (10) RESET端子ブルアップ抵抗

RESET端子にブルアップ抵抗を付加するかしないか選択できます。

## マスクオプションリスト

S1C63256のオプションリストを以下に示します。各オプション項目には、複数の選択肢が用意されていますので、4章の"周辺回路と動作"を参照してシステムに合った内容を選択してください。使用しない機能についてもオプション設定が必要です。このオプションリストを参照しながら、S1C63256のオプション設定をS5U1C63000A内のwinfogの画面上で行ってください。詳細については"S5U1C63000A Manual"を参照してください。

### 1. OSC発振回路( OSC system clock )

1. 水晶発振回路

2. セラミック発振回路

3. CR発振回路

4. 外部クロック

### 2. キー同時押しリセット組み合わせ( Multiple key entry reset combination )

1. 使用しない

2. 使用する <K00, K01, K02, K03>

3. 使用する <K00, K01, K02>

4. 使用する <K00, K01>

### 3. キー同時押しリセット時間検定( Multiple key entry reset time authorize )

1. 使用しない

2. 使用する

### 4. 入力ポートプルアップ抵抗( Input port pull up resistor )

|           |       |       |

|-----------|-------|-------|

| K00 ..... | 1. あり | 2. なし |

| K01 ..... | 1. あり | 2. なし |

| K02 ..... | 1. あり | 2. なし |

| K03 ..... | 1. あり | 2. なし |

### 5. 出力ポート出力仕様( Output port output specification )

|           |             |                |

|-----------|-------------|----------------|

| R00 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R01 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R02 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R03 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

### 6. I/Oポート出力仕様( I/O port output specification )

|           |             |                |

|-----------|-------------|----------------|

| P20 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P21 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P22 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P23 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P40 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P41 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P42 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P43 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

### 7. I/Oポートプルアップ抵抗( I/O port pull up resistor )

|           |       |       |

|-----------|-------|-------|

| P20 ..... | 1. あり | 2. なし |

| P21 ..... | 1. あり | 2. なし |

| P22 ..... | 1. あり | 2. なし |

| P23 ..... | 1. あり | 2. なし |

| P40 ..... | 1. あり | 2. なし |

| P41 ..... | 1. あり | 2. なし |

| P42 ..... | 1. あり | 2. なし |

| P43 ..... | 1. あり | 2. なし |

### 8. LCD駆動電源( LCD driving power )

1. 内部電圧電源 (  $V_{C3} =$ 外部電圧電源 )

2. 内部電圧電源 (  $V_{C3} = V_{DD}$  )

3. 外部電圧電源

4. 使用しない

9. LCD駆動バイアス( LCD driving bias )

1. 内部電圧電源 1/3バイアス

2. 内部電圧電源 1/2バイアス

3. 外部電圧電源 1/3バイアス

4. 外部電圧電源 1/2バイアス

5. 使用しない

10. ブザー出力極性( Buzzer polarity for output )

1. 正極性

2. 負極性

11. リセットプルアップ抵抗( /Reset pull up resistor )

1. あり

2. なし

## 2 電源系 および イニシャルリセット

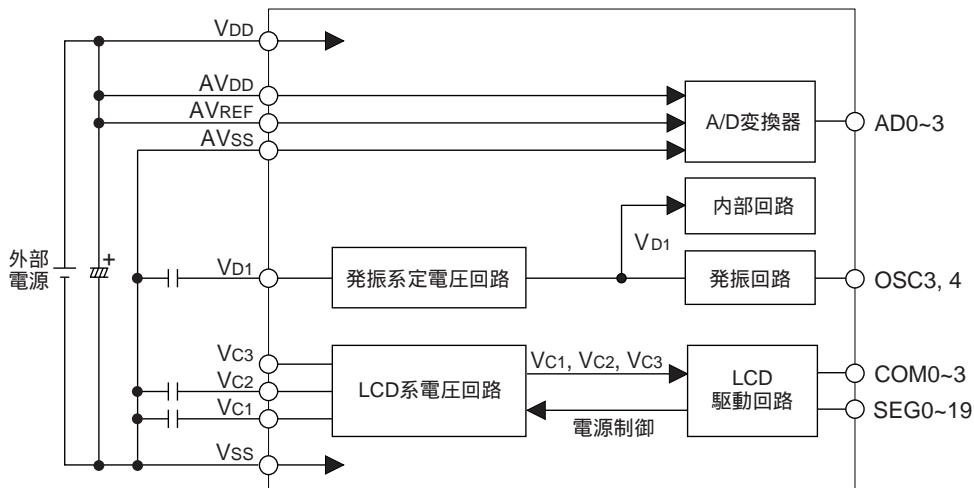

### 2.1 電源系

S1C63256の動作電源電圧は次のとおりです。

2.7V ~ 5.5V

S1C63256は上記範囲の単一電源をVDD - Vss間に与えることにより動作し、内部に必要な電圧を内蔵された以下の電源回路によりIC自身で発生します。

| 回路系     | 電源回路     | 入力電圧 | 出力電圧     |

|---------|----------|------|----------|

| 発振、内部回路 | 発振系定電圧回路 | VDD  | VD1      |

| LCD駆動回路 | LCD系電圧回路 | VC3  | VC1, VC2 |

上記の電源電圧の他に、内蔵のA/D変換器用の電源端子AVDD、AVssも用意されています。

- 注:

- 内部電源回路の出力電圧による外付け負荷の駆動は禁止します。

- 1/2バイアスのLCD駆動を選択した場合、VC1とVC2は短絡します。

- AVssはVssと短絡してください。

- 電圧値、駆動能力については"7 電気的特性"を参照してください。

図2.1.1 電源系の構成

#### 2.1.1 発振回路および内部回路用電圧<VD1>

VD1は発振回路および内部ロジック回路用の電圧で、発振を安定させるため発振系定電圧回路で発生しています。

発振系定電圧回路が outputする VD1は2.4V(Typ.)です。

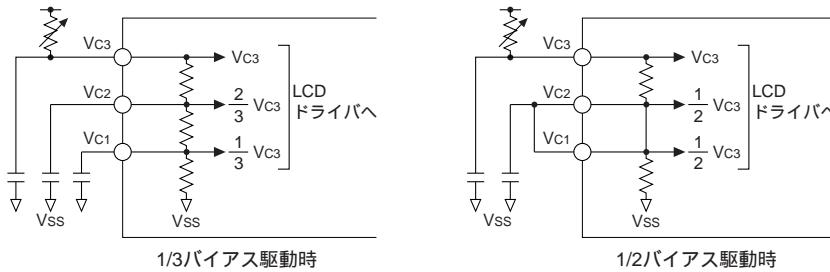

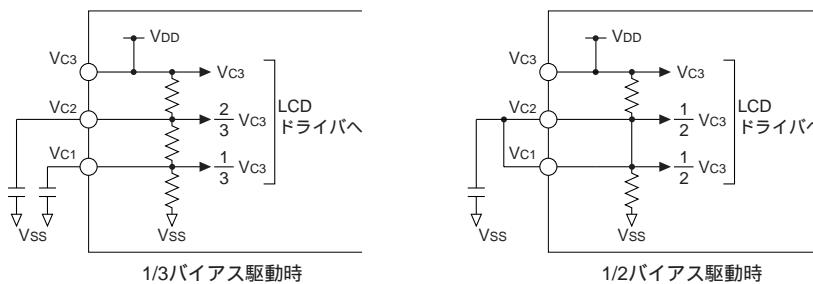

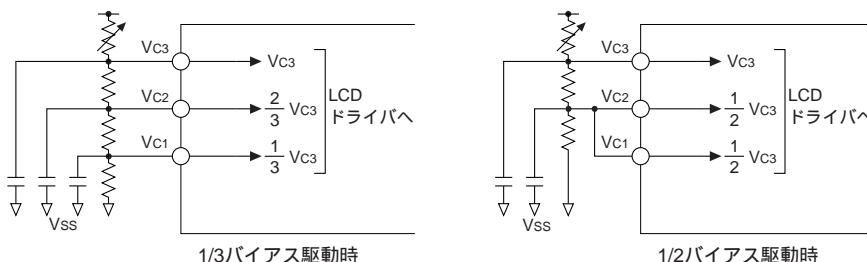

#### 2.1.2 LCD駆動用電圧<VC1, VC2, VC3>

VC1 ~ VC3はLCD駆動用の電圧です。LCD駆動にはマスクオプションによって1/3バイアスまたは1/2バイアスが選択でき、その選択により各電圧は次のようになります。

1/3バイアス選択時:  $VC1 = VC3 \times 1/3$ ,  $VC2 = VC3 \times 2/3$

1/2バイアス選択時:  $VC1 = VC2 = VC3 \times 1/2$

$V_{C1} \sim V_{C3}$ はマスクオプションによって内部のLCD系電圧回路で発生するか、外部電源より供給するか選択できます。マスクオプションの選択項目は次の3種類です。

#### ( 1 ) 内部電源( $V_{C3}$ 外部印加あり )

このオプションを選択した場合は外部より  $V_{C3}$ を供給します。 $V_{C1}$ と $V_{C2}$ は抵抗分割によりIC内部で発生します。外部電源で  $V_{C3}$ を設定できるため、LCDパネルの選択の幅が広がります。また、 $V_{C3}$ の制御によりコントラストの調整も可能となります。ただし、 $V_{C3}$ 端子には2.7V ~ 5.5Vの範囲内の電圧を供給してください。この範囲外の電圧を印加することは禁止します。

図2.1.2.1 オプション1( 内部電源/ $V_{C3}$ 外部印加 )

#### ( 2 ) 内部電源( $V_{C3}$ 外部印加なし, $V_{C3} = V_{DD}$ )

このオプションを選択した場合は  $V_{C1} \sim V_{C3}$ をすべてIC内部で発生しますので、外部の部品点数を削減できます。この場合、 $V_{C3}$ 端子は電源電圧  $V_{DD}$ と同電位になりますので開放してください。

図2.1.2.2 オプション2( 内部電源/ $V_{C3} = V_{DD}$  )

#### ( 3 ) 外部電源

このオプションを選択した場合は  $V_{C1} \sim V_{C3}$ をすべて外部より供給します。表示品質を優先する場合に選択してください。なお、2.7V ~ 5.5Vかつ  $V_{SS} < V_{C1} < V_{C2} < V_{C3}$ の条件を満たしてください。

図2.1.2.3 オプション3( 外部電源 )

内部のLCD系電圧回路を使用する場合には、電源制御レジスタLPWRに"1"を書き込むことによってLCD駆動用電圧を内部発生します。"0"が書き込まれているときには  $V_{C1} = V_{C2} = V_{SS}$ となり、SEGおよびCOM端子の出力はすべて  $V_{SS}$ レベルとなります。

注: 外部電源選択時にも、LPWRに"1"を書き込むことが必要です。

## 2.2 イニシャルリセット

S1C63256は回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては以下の2種類があります。

- (1)  $\overline{\text{RESET}}$ 端子による外部イニシャルリセット

- (2) K00～K03端子の同時LOWレベル入力による外部イニシャルリセット(マスクオプションで設定)

電源投入時は上記いずれかのリセット機能を使用し、ICを確実に初期化してください。電源投入のみでは動作が保証できません。

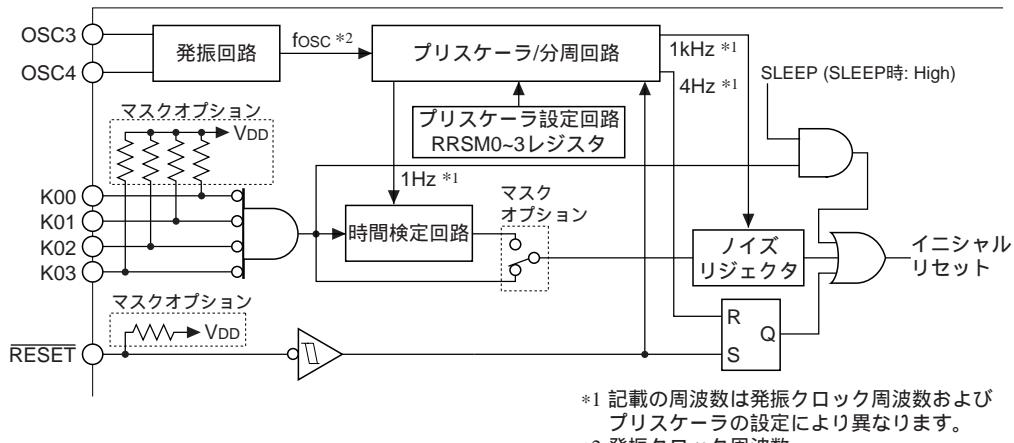

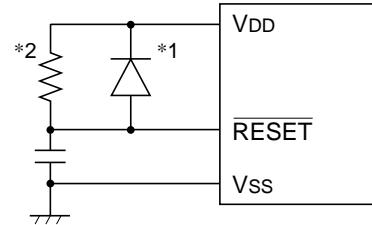

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

### 2.2.1 リセット端子( $\overline{\text{RESET}}$ )

外部よりリセット端子をLOWレベル( $V_{ss}$ )にすることによりイニシャルリセットが行えます。その後、リセット端子をHIGHレベル( $V_{dd}$ )にすることによりイニシャルリセットは解除され、CPUが動作を開始します。

なお、リセット端子にはマスクオプションでプルアップ抵抗を付加することができます。

#### (1) リセット入力ラッチ

リセット入力信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチはfoscを分周したクロック信号の立ち上がりエッジで解除されるようになっています。このラッチ解除クロックの周波数はfosc/1048576です。

ラッチ解除クロックの例

fosc = 4.194304MHzの場合: 4Hz

fosc = 2MHzの場合: 1.9Hz

この例の場合、リセット端子がHIGHレベルになった後、内部イニシャルリセットが解除されるまで、それぞれ最大125msec、264msecの時間を要します。

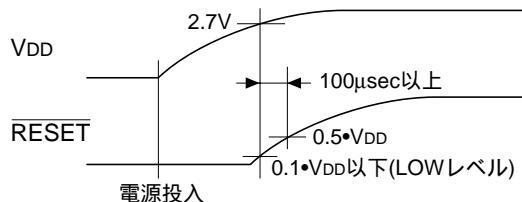

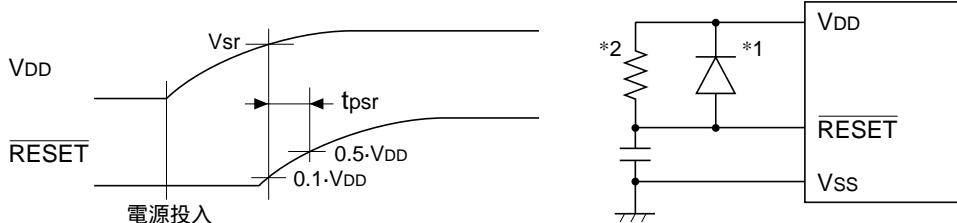

#### (2) 電源投入時のリセット

電源投入時にICを確実にイニシャルリセットするためには、図2.2.1に示すタイミングでリセット端子をLOWレベルにしてください。

図2.2.1.1 電源投入時のイニシャルリセット

電源電圧が2.7V以上になるまでリセット端子は0.1・VDD以下(LOWレベル)とします。

その後100μsec以上、0.5・VDD以下のレベルを保持してください。

リセット端子がHIGHレベルになった後は、前述のラッチにより内部イニシャルリセットが解除されます。

### (3)動作中のリセット

動作中にイニシャルリセットを確実に行うためには、最低0.1msec以上、リセット入力をLOWレベルに保ってください。

リセット端子がHIGHレベルになった後は、前述のラッチにより内部イニシャルリセットが解除されます。

## 2.2.2 入力ポート( K00 ~ K03 )の同時LOW入力

マスクオプションで選択された入力ポート( K00 ~ K03 )に、外部から同時にLOW入力を与えることによりイニシャルリセットが行えます。このイニシャルリセットはノイズリジェクト回路を通り、 $256 \cdot n/fosc$  (nはプリスケーラの分周用パラメータで、PRSMレジスタ[FF02H]の設定値+1の値です)以下のリセットパルスをノイズとして除去します。よって、動作中はリジェクトパルス幅の3倍以上、指定入力ポート端子をLOWレベルに保ってください。

電源投入時には発振が停止しているため、ノイズリジェクト回路は動作しません。このため、発振開始後、上記の時間が経過するまで指定入力ポート端子をLOWレベルに保ってください。表2.2.2.1にマスクオプションで選択できる入力ポート( K00 ~ K03 )の組合せを示します。

表2.2.2.1 入力ポートの組合せ

|   |                 |

|---|-----------------|

| 1 | 使用しない           |

| 2 | K00*K01*K02*K03 |

| 3 | K00*K01*K02     |

| 4 | K00*K01         |

たとえば、マスクオプションで2の"K00\*K01\*K02\*K03"を選択した場合、K00 ~ K03の4ポートの入力が同時にLOWレベルになったときにイニシャルリセットを行います。3または4の場合は、選択した入力ポートの組合せが含まれるキー入力が行われたときにイニシャルリセットがかかります。なお、このリセット機能を使用する場合、通常動作時に指定ポートが同時にLOWレベルにならないように注意してください。

また、同時LOW入力の入力時間を検定し、規定時間以上の入力があったときにイニシャルリセットを行う時間検定回路をマスクオプションで選択できます。

検定時間は、プリスケーラの設定により $[524288 \cdot n/fosc] \sim [1048576 \cdot n/fosc]$ となります( n: PRSM設定値+1 )。

### 検定時間の例

$fosc = 4.194304\text{MHz}$ , PRSM = 7の場合: Min.  $524288 \cdot 8/4194304 = 1\text{sec}$ , Max.  $1048576 \cdot 8/4194304 = 2\text{sec}$

$fosc = 2\text{MHz}$ , PRSM = 3の場合: Min.  $524288 \cdot 4/2000000 = 1.0\text{sec}$ , Max.  $1048576 \cdot 4/2000000 = 2.1\text{sec}$

SLEEP状態では発振回路が停止するため、ノイズリジェクト回路および時間検定回路はバイパスされます。

### 2.2.3 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは表2.2.3.1のように初期化されます。

イニシャルリセットによって初期化されないレジスタ、フラグは必要に応じてプログラムで初期化する必要があります。

特にスタックポインタSP1およびSP2は必ずペアで設定してください。イニシャルリセット後は、SP1、SP2両方のスタックポインタがソフトウェアにより設定されるまでNMIを含むすべての割り込みがマスクされます。

EXTレジスタにデータを書き込むとEフラグがセットされ、次の命令が拡張アドレッシングモードで実行されます。そこに拡張アドレッシングが禁止されている命令を使用した場合、動作が保証されません。したがって、EXTレジスタの初期化のみを目的としたデータ書き込みは行わないでください。

拡張アドレッシングと使用可能な命令については"S1C63000コアCPUマニュアル"を参照してください。

表2.2.3.1 初期設定値

| CPUコア       |     |      |       |

|-------------|-----|------|-------|

| 名 称         | 記号  | ビット長 | 設定値   |

| データレジスタA    | A   | 4    | 不定    |

| データレジスタB    | B   | 4    | 不定    |

| 拡張レジスタEXT   | EXT | 8    | 不定    |

| インデックスレジスタX | X   | 16   | 不定    |

| インデックスレジスタY | Y   | 16   | 不定    |

| プログラムカウンタ   | PC  | 16   | 0110H |

| スタックポインタSP1 | SP1 | 8    | 不定    |

| スタックポインタSP2 | SP2 | 8    | 不定    |

| ゼロフラグ       | Z   | 1    | 不定    |

| キャリーフラグ     | C   | 1    | 不定    |

| インタラプトフラグ   | I   | 1    | 0     |

| 拡張フラグ       | E   | 1    | 0     |

| キューレジスタ     | Q   | 16   | 不定    |

| 周辺回路     |      |     |

|----------|------|-----|

| 名 称      | ビット長 | 設定値 |

| RAM      | 4    | 不定  |

| 表示メモリ    | 4    | 不定  |

| その他の周辺回路 | —    | *   |

\* "4.1 メモリマップ"参照

### 2.2.4 イニシャルリセット時の端子設定

S1C63256の出力ポート(R)端子、入出力兼用ポート(P)端子は特殊出力端子やA/D変換器の入力端子と兼用されており、それらの機能をソフトウェアで選択するようになっています。イニシャルリセット時、各端子はすべてが汎用出力ポート端子、汎用入出力兼用ポート端子として設定されますので、アプリケーションの初期化ルーチンでシステムに合った設定を行ってください。また、システム設計の際には、出力端子の初期状態にも注意してください。

表2.2.4.1に兼用端子設定の一覧を示します。

表2.2.4.1 兼用端子設定一覧

| 端子名     | イニシャルリセット時の<br>端子状態   | 特殊出力使用時 |      | A/D変換器<br>使用時 |

|---------|-----------------------|---------|------|---------------|

|         |                       | PTOUT   | FOUT |               |

| R00     | R00 ( HIGH出力 )        |         |      |               |

| R01     | R01 ( HIGH出力 )        |         |      |               |

| R02     | R02 ( HIGH出力 )        | PTOUT   |      |               |

| R03     | R03 ( HIGH出力 )        |         | FOUT |               |

| P20~P23 | P20~P23 ( 入力&プルアップ* ) |         |      |               |

| P40     | P40 ( 入力&プルアップ* )     |         |      | AD0(I)        |

| P41     | P41 ( 入力&プルアップ* )     |         |      | AD1(I)        |

| P42     | P42 ( 入力&プルアップ* )     |         |      | AD2(I)        |

| P43     | P43 ( 入力&プルアップ* )     |         |      | AD3(I)        |

\* マスクオプションにて"プルアップあり"選択時

("プルアップなし"選択時はハイインピーダンス)

機能の設定方法については各周辺回路の説明を参照してください。

### 2.3 テスト端子( TEST )

ICの出荷検査時に使用する端子です。通常動作時はTESTをVDDに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C63256はCPU部分に4ビットコアCPU S1C63000を使用しています。

S1C63000については"S1C63000コアCPUマニュアル"を参照してください。

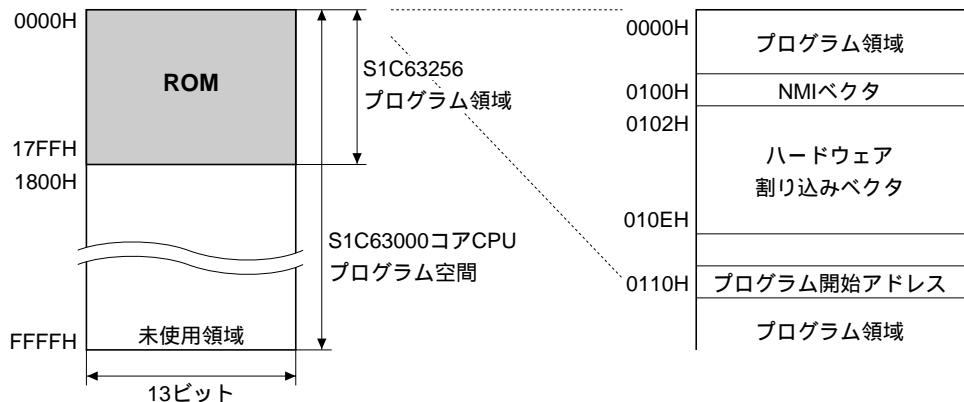

### 3.2 コードROM

内蔵コードROMはプログラム格納用のマスクROMで、6,144ステップ×13ビットの容量があります。コアCPUのプログラム領域は0000H～FFFFHステップまでリニアにアクセス可能ですが、S1C63256では、このうち0000H～17FFHステップがプログラム領域となります。イニシャルリセット後のプログラム開始番地が0110Hステップ、ノンマスカブル割り込み(NMI)ベクタが0100H、ハードウェア割り込みベクタが0102H～010EHステップに割り当てられています。

図3.2.1 コードROMの構成

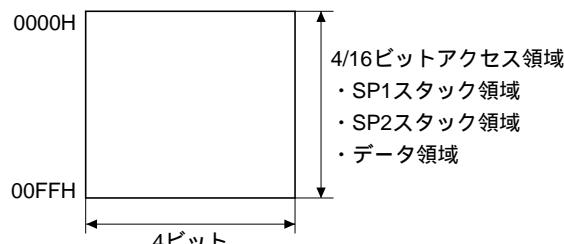

### 3.3 RAM

RAMは種々のデータを格納するデータメモリで、256ワード×4ビットの容量があります。RAM領域は、データメモリマップ上のアドレス0000H～00FFHに割り当てられています。この全領域に渡って4ビット/16ビットデータアクセスが可能です。プログラミングの際には以下の点に注意してください。

- (1)データメモリの全領域をサブルーチンコールやレジスタ退避時のスタック領域としても使用できますので、データ領域とスタック領域が重ならないように注意してください。

- (2)S1C63000コアCPUは、4ビットデータ用スタックポインタ(SP2)および16ビットデータ用スタックポインタ(SP1)によりスタック処理を行います。スタックポインタは、SP1が0000H～03FFH、SP2が0000H～00FFHの範囲でサイクリックに動作します。このため、SP1はS1C63256のRAM領域を外れた0100H以上にも設定される可能性がありますので注意してください。SP1によるスタック操作以外のメモリアクセスは4ビットデータアクセスとなります。また、イニシャルリセット時は、スタックポインタSP1、SP2の両方がソフトウェアで設定されるまでNMIを含むすべての割り込みがマスクされます。また、SP1、SP2を設定後どちらか一方を再設定すると、もう一方が再設定されるまでNMIを含む割り込みは再びマスクされます。したがって、SP1およびSP2の設定は必ずペアで行ってください。

- (3)サブルーチンコールでは16ビットデータ用スタック(SP1)を4ワード(PCの退避)消費します。割り込みでは16ビットデータ用スタックエリアを4ワード(PCの退避)、4ビットデータ用スタックエリアを1ワード(Fレジスタの退避)消費します。

図3.3.1 データRAMの構成

## 4 周辺回路と動作

S1C63256の周辺回路( タイマ、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

### 4.1 メモリマップ

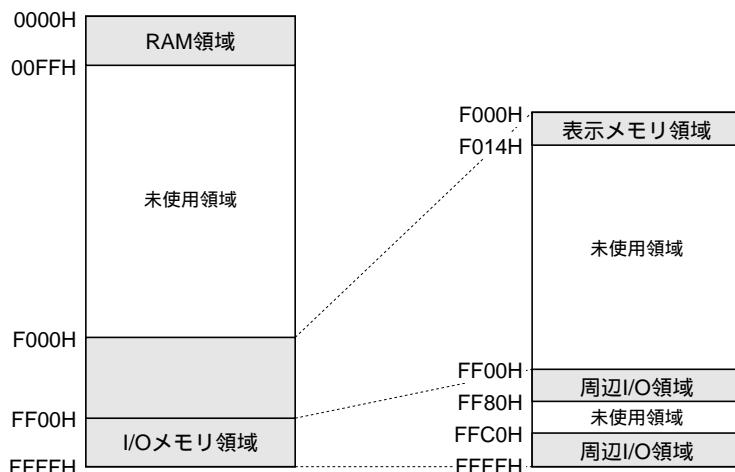

S1C63256のデータメモリは256ワードのRAM、20ワードの表示メモリ、52ワードの周辺I/Oメモリ領域で構成されます。

図4.1.1にS1C63256の全体のメモリマップ、表4.1.1(a)~(d)に周辺回路( I/O空間 )のメモリマップを示します。

図4.1.1 メモリマップ

注：メモリマップの未使用領域にはメモリが実装されていません。また、周辺I/O領域にも非実装領域、未使用（アクセス禁止）領域が存在します。これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

周辺I/O領域については表4.1.1(a)~(d)に示すI/Oメモリマップを参照してください。

表4.1.1(a) I/Oメモリマップ(FF02H ~ FF52H)

| アドレス  | レジスタ   |        |        |         | Name    | Init *1 | 1       | 0                                                      | 注釈                                                                                                                                                   |  |

|-------|--------|--------|--------|---------|---------|---------|---------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | D3     | D2     | D1     | D0      |         |         |         |                                                        |                                                                                                                                                      |  |

| FF02H | PRSM3  | PRSM2  | PRSM1  | PRSM0   | PRSM3   | 1       |         |                                                        | プリスケーラ設定<br>プリスケーラ出力 $f_{PRS} = \frac{f_{OSC}}{2 \cdot (PRSM+1)}$<br>PRSM設定条件:<br>$240Hz < f_{OSC}/(2048 \cdot (PRSM+1)) < 530Hz$                    |  |

|       | R/W    |        |        |         | PRSM2   | 1       |         |                                                        |                                                                                                                                                      |  |

|       | FOUT   | 0      | FOFQ1  | FOFQ0   | PRSM1   | 1       |         |                                                        |                                                                                                                                                      |  |

|       |        | R/W    | R/W    | FOFQ1   | PRSM0   | 1       |         |                                                        |                                                                                                                                                      |  |

| FF06H | FOUT   | 0      | FOFQ1  | FOFQ0   | FOUT    | 0       | Enable  | Disable                                                | FOUT出力イネーブル<br>未使用 [FOFQ1, 0] 0 1 2 3<br>周波数 fosc fprs fprs 64 512<br>周波数選択 fosc=4.19MHz → 262kHz 4kHz 512Hz                                         |  |

|       | R/W    | R      | R/W    |         | FOFQ1   | 0       |         |                                                        |                                                                                                                                                      |  |

|       |        | FOFQ0  |        |         | FOFQ0   | 0       |         |                                                        |                                                                                                                                                      |  |

|       | R/W    |        |        |         | WDEN    | 0 *3    | - *2    | 未使用<br>未使用<br>ウォッチドッグタイマイネーブル<br>ウォッチドッグタイマリセット(書き込み時) |                                                                                                                                                      |  |

| FF07H | 0      | 0      | WDEN   | WDRST   | WDEN    | 0 *3    | - *2    | 未使用<br>未使用<br>ウォッチドッグタイマイネーブル<br>ウォッチドッグタイマリセット(書き込み時) |                                                                                                                                                      |  |

|       | R      | R/W    | W      | WDRST*3 | WDRST*3 | 1       | Enable  | Disable                                                |                                                                                                                                                      |  |

|       |        |        |        | Reset   | Reset   | 1       | Reset   | Invalid                                                |                                                                                                                                                      |  |

| FF20H | SIK03  | SIK02  | SIK01  | SIK00   | SIK03   | 0       | Enable  | Disable                                                | K00 ~ K03割り込み選択レジスタ                                                                                                                                  |  |

|       | R/W    |        |        |         | SIK02   | 0       | Enable  | Disable                                                |                                                                                                                                                      |  |

|       | SIK01  | SIK00  | SIK00  | SIK01   | 0       | Enable  | Disable |                                                        |                                                                                                                                                      |  |

|       | R/W    |        |        |         | SIK00   | 0       | Enable  | Disable                                                |                                                                                                                                                      |  |

| FF21H | K03    | K02    | K01    | K00     | K03     | - *2    | High    | Low                                                    | K00 ~ K03入力ポートデータ                                                                                                                                    |  |

|       | R      | R/W    | W      | K02     | K02     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       |        |        |        | K01     | K01     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | K00     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

| FF22H | KCP03  | KCP02  | KCP01  | KCP00   | KCP03   | 1       | ↑       | ↑                                                      | K00 ~ K03入力比較レジスタ                                                                                                                                    |  |

|       | R/W    | W      | W      | KCP02   | KCP02   | 1       | ↓       | ↑                                                      |                                                                                                                                                      |  |

|       |        |        |        | KCP01   | KCP01   | 1       | ↓       | ↑                                                      |                                                                                                                                                      |  |

|       | R/W    |        |        |         | KCP00   | 1       | ↓       | ↑                                                      |                                                                                                                                                      |  |

| FF30H | R03HIZ | R02HIZ | R01HIZ | R00HIZ  | R03HIZ  | 0       | High-Z  | Output                                                 | R03/FOUT出力ハイインピーダンス制御<br>R02/PTOUT出力ハイインピーダンス制御<br>R01出力ハイインピーダンス制御<br>R00出力ハイインピーダンス制御                                                              |  |

|       | R/W    | W      | W      | R02HIZ  | R02HIZ  | 0       | High-Z  | Output                                                 |                                                                                                                                                      |  |

|       |        |        |        | R01HIZ  | R01HIZ  | 0       | High-Z  | Output                                                 |                                                                                                                                                      |  |

|       | R/W    |        |        |         | R00HIZ  | 0       | High-Z  | Output                                                 |                                                                                                                                                      |  |

| FF31H | R03    | R02    | R01    | R00     | R03     | 1       | High    | Low                                                    | R03出力ポートデータ(FOUT=0) FOUT出力時は1に固定<br>R02出力ポートデータ(PTOUT=0) PTOUT出力時は1に固定<br>R01出力ポートデータ<br>R00出力ポートデータ                                                 |  |

|       | R/W    | W      | W      | R02     | R02     | 1       | High    | Low                                                    |                                                                                                                                                      |  |

|       |        |        |        | R01     | R01     | 1       | High    | Low                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | R00     | 1       | High    | Low                                                    |                                                                                                                                                      |  |

| FF48H | IOC23  | IOC22  | IOC21  | IOC20   | IOC23   | 0       | Output  | Input                                                  | P20 ~ P23 I/O制御レジスタ                                                                                                                                  |  |

|       | R/W    | W      | W      | IOC22   | IOC22   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

|       |        |        |        | IOC21   | IOC21   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

|       | R/W    |        |        |         | IOC20   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

| FF49H | PUL23  | PUL22  | PUL21  | PUL20   | PUL23   | 1       | On      | Off                                                    | P20 ~ P23 プルアップ制御レジスタ                                                                                                                                |  |

|       | R/W    | W      | W      | PUL22   | PUL22   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

|       |        |        |        | PUL21   | PUL21   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | PUL20   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

| FF4AH | P23    | P22    | P21    | P20     | P23     | - *2    | High    | Low                                                    | P20 ~ P23入出力兼用ポートデータ                                                                                                                                 |  |

|       | R/W    | W      | W      | P22     | P22     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       |        |        |        | P21     | P21     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | P20     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

| FF50H | IOC43  | IOC42  | IOC41  | IOC40   | IOC43   | 0       | Output  | Input                                                  | P43 I/O制御(PAD3=0) 汎用レジスタ(PAD3=1)<br>P42 I/O制御(PAD2=0) 汎用レジスタ(PAD2=1)<br>P41 I/O制御(PAD1=0) 汎用レジスタ(PAD1=1)<br>P40 I/O制御(PAD0=0) 汎用レジスタ(PAD0=1)         |  |

|       | R/W    | W      | W      | IOC42   | IOC42   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

|       |        |        |        | IOC41   | IOC41   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

|       | R/W    |        |        |         | IOC40   | 0       | Output  | Input                                                  |                                                                                                                                                      |  |

| FF51H | PUL43  | PUL42  | PUL41  | PUL40   | PUL43   | 1       | On      | Off                                                    | P43 プルアップ制御(PAD3=0) 汎用レジスタ(PAD3=1)<br>P42 プルアップ制御(PAD2=0) 汎用レジスタ(PAD2=1)<br>P41 プルアップ制御(PAD1=0) 汎用レジスタ(PAD1=1)<br>P40 プルアップ制御(PAD0=0) 汎用レジスタ(PAD0=1) |  |

|       | R/W    | W      | W      | PUL42   | PUL42   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

|       |        |        |        | PUL41   | PUL41   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | PUL40   | 1       | On      | Off                                                    |                                                                                                                                                      |  |

| FF52H | P43    | P42    | P41    | P40     | P43     | - *2    | High    | Low                                                    | P43ポートデータ(PAD3=0) 汎用レジスタ(PAD3=1)<br>P42ポートデータ(PAD2=0) 汎用レジスタ(PAD2=1)<br>P41ポートデータ(PAD1=0) 汎用レジスタ(PAD1=1)<br>P40ポートデータ(PAD0=0) 汎用レジスタ(PAD0=1)         |  |

|       | R/W    | W      | W      | P42     | P42     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       |        |        |        | P41     | P41     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

|       | R/W    |        |        |         | P40     | - *2    | High    | Low                                                    |                                                                                                                                                      |  |

## [注釈]

\*1 イニシャルリセット時の初期値 \*2 回路上設定されない \*3 読み出し時は常時"0"

表4.1.1(b) I/Oメモリマップ( FF60H ~ FFD0H )

| アドレス  | レジスタ   |        |        |        | Name      | Init *1 | 1            | 0            | 注釈                              |                               |                                          |                             |                             |

|-------|--------|--------|--------|--------|-----------|---------|--------------|--------------|---------------------------------|-------------------------------|------------------------------------------|-----------------------------|-----------------------------|

|       | D3     | D2     | D1     | D0     |           |         |              |              |                                 |                               |                                          |                             |                             |

| FF60H | LDUTY1 | LDUTY0 | 0      | LPWR   | LDUTY1    | 0       | On           | Off          | LCD駆動デューティ [LDUTY1, 0] 0 1 2, 3 | LCD駆動デューティ 1/4 1/3 1/2        | LCD駆動デューティ [LDUTY1, 0] 0 1 2, 3          | LCD駆動デューティ 1/4 1/3 1/2      |                             |

|       | R/W    | R      | R/W    | 0 *3   | LDUTY0    | 0       |              |              | 切り換え                            |                               |                                          |                             |                             |

|       |        |        |        | LPWR   | 0 *3      | - *2    |              |              | 未使用                             |                               |                                          |                             |                             |

| FF61H | 0      | ALOFF  | ALON   | STCD   | 0 *3      | - *2    | All Off      | Normal       | 未使用                             | LCD全消灯制御                      | LCD全点灯制御                                 | コモン出力信号制御                   | LCD全消灯制御                    |

|       | R      | R/W    |        |        | ALOFF     | 1       | 0            | Normal       | LCD全消灯制御                        |                               |                                          |                             |                             |

|       |        |        |        | STCD   | ALON      | 0       | All On       | Normal       | LCD全点灯制御                        |                               |                                          |                             |                             |

| FF64H | 0      | ENON   | BZFQ   | BZON   | 0 *3      | - *2    | Off          | Off          | 未使用                             | 2HzインターバルOn/Off               | ブザー周波数選択                                 | ブザー出力On/Off制御               | ブザー出力On/Off制御               |

|       | R      | R/W    |        |        | BZFQ      | 0       | 2kHz         | 4kHz         | 2HzインターバルOn/Off                 |                               |                                          |                             |                             |

|       |        |        |        | BZON   | 0         | On      | On           | Off          | ブザー周波数選択                        |                               |                                          |                             |                             |

| FF68H | ADRUN  | ADCLK  | CHS1   | CHS0   | ADRUN *3  | 0       | Start fosc/2 | Invalid fPRS | A/D変換制御                         | A/D変換制御                       | 入力チャンネル [CHS1, 0] 0 1 2 3                | 入力チャンネル [CHS1, 0] 0 1 2 3   | 入力チャンネル [CHS1, 0] 0 1 2 3   |

|       | R      | R/W    |        |        | ADCLK     | 0       |              |              | 入力クロック選択                        |                               |                                          |                             |                             |

|       |        |        |        | CHS0   | 0         | 0       |              |              | 選択                              |                               |                                          |                             |                             |

| FF69H | PAD3   | PAD2   | PAD1   | PAD0   | PAD3      | 0       | A/D          | I/O          | A/D-Ch3イネーブル(P43端子)             | A/D-Ch3イネーブル(P43端子)           | A/D-Ch2イネーブル(P42端子)                      | A/D-Ch1イネーブル(P41端子)         | A/D-Ch0イネーブル(P40端子)         |

|       | R/W    |        |        |        | PAD2      | 0       | A/D          | I/O          | A/D-Ch2イネーブル(P42端子)             |                               |                                          |                             |                             |

|       |        |        |        |        | PAD1      | 0       | A/D          | I/O          | A/D-Ch1イネーブル(P41端子)             |                               |                                          |                             |                             |

| FF6AH | ADDR3  | ADDR2  | ADDR1  | ADDR0  | ADDR3     | - *2    | Start fosc/2 | Invalid fPRS | A/D変換データ(下位4ビット)                | A/D変換データ(下位4ビット)              | LSB                                      | LSB                         | LSB                         |

|       | R      |        |        |        | ADDR2     | - *2    |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | ADDR1     | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FF6BH | ADDR7  | ADDR6  | ADDR5  | ADDR4  | ADDR7     | - *2    |              |              |                                 |                               |                                          |                             |                             |

|       | R      |        |        |        | ADDR6     | - *2    |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | ADDR5     | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FFC0H | 0      | 0      | MODE1  | MODE0  | 0 *3      | - *2    | 16bit x 2    | 8bit x 2     | 未使用                             | 未使用                           | 8/16ビットモード選択(プログラマブルタイマ2,3)              | 8/16ビットモード選択(プログラマブルタイマ0,1) | 8/16ビットモード選択(プログラマブルタイマ0,1) |

|       | R/W    |        |        |        | 0 *3      | - *2    |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | MODE1     | 0       |              |              |                                 |                               |                                          |                             |                             |

| FFC1H | 0      | EVCNT  | FCSEL  | PLPOL  | 0 *3      | - *2    |              |              |                                 |                               |                                          |                             |                             |

|       | R/W    |        |        |        | EVCNT     | 0       | Event ct.    | Timer        | 未使用                             | タイマ0カウンタモード選択                 | タイマ0機能選択(イベントカウンタモード時)                   | タイマ0パルス極性選択(イベントカウンタモード時)   | タイマ0パルス極性選択(イベントカウンタモード時)   |

|       |        |        |        |        | FCSEL     | 0       | With NR      | No NR        |                                 |                               |                                          |                             |                             |

| FFC2H | 0      | PTOUT  | CHSEL1 | CHSEL0 | 0 *3      | - *2    | On           | Off          | 未使用                             | PTOUT出力                       | [CHSEL1, 0] 0 1 2 3                      | [CHSEL1, 0] 0 1 2 3         | [CHSEL1, 0] 0 1 2 3         |

|       | R/W    |        |        |        | PTOUT     | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | CHSEL1    | 0       |              |              |                                 |                               |                                          |                             |                             |

| FFC4H | PTPS01 | PTPS00 | PTRST0 | PTRUN0 | PTPS01    | 0       | Reset Run    | Invalid Stop | 未使用                             | タイマ0クロック [PTPS01, 00] 0 1 2 3 | 分周比選択 分周比 fosc/1 fosc/4 fosc/32 fosc/256 | タイマ0リセット(リロード)              | タイマ0Run/Stop                |

|       | R/W    |        |        |        | PTPS00    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | PTRST0 *3 | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FFC5H | PTPS11 | PTPS10 | PTRST1 | PTRUN1 | PTPS11    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       | R/W    |        |        |        | PTPS10    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | PTRST1 *3 | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FFC6H | PTPS21 | PTPS20 | PTRST2 | PTRUN2 | PTPS21    | 0       | Reset Run    | Invalid Stop | 未使用                             | タイマ2クロック [PTPS21, 20] 0 1 2 3 | 分周比選択 分周比 fosc/1 fosc/4 fosc/32 fosc/256 | タイマ2リセット(リロード)              | タイマ2Run/Stop                |

|       | R/W    |        |        |        | PTPS20    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | PTRST2 *3 | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FFC7H | PTPS31 | PTPS30 | PTRST3 | PTRUN3 | PTPS31    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       | R/W    |        |        |        | PTPS30    | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | PTRST3 *3 | - *2    |              |              |                                 |                               |                                          |                             |                             |

| FFD0H | RLD03  | RLD02  | RLD01  | RLD00  | RLD03     | 0       | Reset Run    | Invalid Stop | 未使用                             | タイマ3クロック [PTPS31, 30] 0 1 2 3 | 分周比選択 分周比 fosc/1 fosc/4 fosc/32 fosc/256 | タイマ3リセット(リロード)              | タイマ3Run/Stop                |

|       | R/W    |        |        |        | RLD02     | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | RLD01     | 0       |              |              |                                 |                               |                                          |                             |                             |

|       |        |        |        |        | RLD00     | 0       |              |              |                                 |                               |                                          |                             |                             |

表4.1.1(c) I/Oメモリマップ(FFD1H~FFDFH)

| アドレス  | レジスタ  |       |       |       | Name  | Init *1 | 1 | 0 | 注釈                         |

|-------|-------|-------|-------|-------|-------|---------|---|---|----------------------------|

|       | D3    | D2    | D1    | D0    |       |         |   |   |                            |

| FFD1H | RLD07 | RLD06 | RLD05 | RLD04 | RLD07 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD06 | 0       |   |   | プログラマブルタイマ0リロードデータ(上位4ビット) |

|       | R/W   |       |       |       | RLD05 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD04 | 0       |   |   |                            |

| FFD2H | RLD13 | RLD12 | RLD11 | RLD10 | RLD13 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD12 | 0       |   |   | プログラマブルタイマ1リロードデータ(下位4ビット) |

|       | R/W   |       |       |       | RLD11 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD10 | 0       |   |   |                            |

| FFD3H | RLD17 | RLD16 | RLD15 | RLD14 | RLD17 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD16 | 0       |   |   | プログラマブルタイマ1リロードデータ(上位4ビット) |

|       | R/W   |       |       |       | RLD15 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD14 | 0       |   |   |                            |

| FFD4H | RLD23 | RLD22 | RLD21 | RLD20 | RLD23 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD22 | 0       |   |   | プログラマブルタイマ2リロードデータ(下位4ビット) |

|       | R/W   |       |       |       | RLD21 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD20 | 0       |   |   |                            |

| FFD5H | RLD27 | RLD26 | RLD25 | RLD24 | RLD27 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD26 | 0       |   |   | プログラマブルタイマ2リロードデータ(上位4ビット) |

|       | R/W   |       |       |       | RLD25 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD24 | 0       |   |   |                            |

| FFD6H | RLD33 | RLD32 | RLD31 | RLD30 | RLD33 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD32 | 0       |   |   | プログラマブルタイマ3リロードデータ(下位4ビット) |

|       | R/W   |       |       |       | RLD31 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD30 | 0       |   |   |                            |

| FFD7H | RLD37 | RLD36 | RLD35 | RLD34 | RLD37 | 0       |   |   | MSB                        |

|       |       |       |       |       | RLD36 | 0       |   |   | プログラマブルタイマ3リロードデータ(上位4ビット) |

|       | R/W   |       |       |       | RLD35 | 0       |   |   | LSB                        |

|       |       |       |       |       | RLD34 | 0       |   |   |                            |

| FFD8H | PTD03 | PTD02 | PTD01 | PTD00 | PTD03 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD02 | 0       |   |   | プログラマブルタイマ0データ(下位4ビット)     |

|       | R     |       |       |       | PTD01 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD00 | 0       |   |   |                            |

| FFD9H | PTD07 | PTD06 | PTD05 | PTD04 | PTD07 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD06 | 0       |   |   | プログラマブルタイマ0データ(上位4ビット)     |

|       | R     |       |       |       | PTD05 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD04 | 0       |   |   |                            |

| FFDAH | PTD13 | PTD12 | PTD11 | PTD10 | PTD13 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD12 | 0       |   |   | プログラマブルタイマ1データ(下位4ビット)     |

|       | R     |       |       |       | PTD11 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD10 | 0       |   |   |                            |

| FFDBH | PTD17 | PTD16 | PTD15 | PTD14 | PTD17 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD16 | 0       |   |   | プログラマブルタイマ1データ(上位4ビット)     |

|       | R     |       |       |       | PTD15 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD14 | 0       |   |   |                            |

| FFDCH | PTD23 | PTD22 | PTD21 | PTD20 | PTD23 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD22 | 0       |   |   | プログラマブルタイマ2データ(下位4ビット)     |

|       | R     |       |       |       | PTD21 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD20 | 0       |   |   |                            |

| FFDDH | PTD27 | PTD26 | PTD25 | PTD24 | PTD27 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD26 | 0       |   |   | プログラマブルタイマ2データ(上位4ビット)     |

|       | R     |       |       |       | PTD25 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD24 | 0       |   |   |                            |

| FFDEH | PTD33 | PTD32 | PTD31 | PTD30 | PTD33 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD32 | 0       |   |   | プログラマブルタイマ3データ(下位4ビット)     |

|       | R     |       |       |       | PTD31 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD30 | 0       |   |   |                            |

| FFDFH | PTD37 | PTD36 | PTD35 | PTD34 | PTD37 | 0       |   |   | MSB                        |

|       |       |       |       |       | PTD36 | 0       |   |   | プログラマブルタイマ3データ(上位4ビット)     |

|       | R     |       |       |       | PTD35 | 0       |   |   | LSB                        |

|       |       |       |       |       | PTD34 | 0       |   |   |                            |

表4.1.1(d) I/Oメモリマップ( FFE2H ~ FFFF7H )

| アドレス  | レジスタ  |       |       |       | Name  | Init *1 | 1      | 0       | 注釈                         |

|-------|-------|-------|-------|-------|-------|---------|--------|---------|----------------------------|

|       | D3    | D2    | D1    | D0    |       |         |        |         |                            |

| FFE2H | EIPT3 | EIPT2 | EIPT1 | EIPT0 | EIPT3 | 0       | Enable | Mask    | 割り込みマスクレジスタ( プログラマブルタイマ3 ) |

|       |       |       |       |       | EIPT2 | 0       | Enable | Mask    | 割り込みマスクレジスタ( プログラマブルタイマ2 ) |

|       | R/W   |       |       |       | EIPT1 | 0       | Enable | Mask    | 割り込みマスクレジスタ( プログラマブルタイマ1 ) |

|       |       |       |       |       | EIPT0 | 0       | Enable | Mask    | 割り込みマスクレジスタ( プログラマブルタイマ0 ) |

| FFE4H | 0     | 0     | 0     | EIK0  | 0 *3  | - *2    |        |         | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | EIK0  | 0       | Enable | Mask    | 割り込みマスクレジスタ( K00 ~ K03 )   |

| FFE6H | 0     | 0     | 0     | EITO  | 0 *3  | - *2    |        |         | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | EITO  | 0       | Enable | Mask    | 割り込みマスクレジスタ( 計時タイマ1Hz )    |

| FFE7H | 0     | 0     | 0     | EIAD  | 0 *3  | - *2    |        |         | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    |        |         | 未使用                        |

|       |       |       |       |       | EIAD  | 0       | Enable | Mask    | 割り込みマスクレジスタ( A/D変換器 )      |

| FFF2H | IPT3  | IPT2  | IPT1  | IPT0  | IPT3  | 0       | (R)    | (R)     | 割り込み要因フラグ( プログラマブルタイマ3 )   |

|       | R/W   |       |       |       | IPT2  | 0       | Yes    | No      | 割り込み要因フラグ( プログラマブルタイマ2 )   |

|       |       |       |       |       | IPT1  | 0       | (W)    | (W)     | 割り込み要因フラグ( プログラマブルタイマ1 )   |

|       |       |       |       |       | IPT0  | 0       | Reset  | Invalid | 割り込み要因フラグ( プログラマブルタイマ0 )   |

| FFF4H | 0     | 0     | 0     | IK0   | 0 *3  | - *2    | (R)    | (R)     | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    | Yes    | No      | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    | (W)    | (W)     | 未使用                        |

|       |       |       |       |       | IK0   | 0       | Reset  | Invalid | 割り込み要因フラグ( K00 ~ K03 )     |

| FFF6H | 0     | 0     | 0     | ITO   | 0 *3  | - *2    | (R)    | (R)     | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    | Yes    | No      | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    | (W)    | (W)     | 未使用                        |

|       |       |       |       |       | ITO   | 0       | Reset  | Invalid | 割り込み要因フラグ( 計時タイマ1Hz )      |

| FFF7H | 0     | 0     | 0     | IAD   | 0 *3  | - *2    | (R)    | (R)     | 未使用                        |

|       | R     |       |       | R/W   | 0 *3  | - *2    | Yes    | No      | 未使用                        |

|       |       |       |       |       | 0 *3  | - *2    | (W)    | (W)     | 未使用                        |

|       |       |       |       |       | IAD   | 0       | Reset  | Invalid | 割り込み要因フラグ( A/D変換器 )        |

## 4.2 発振回路とプリスケーラ

### 4.2.1 発振回路の構成

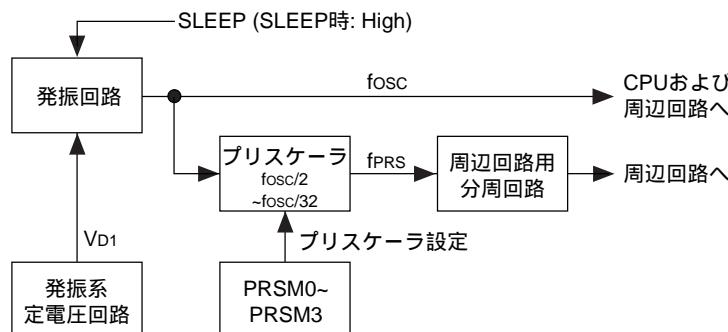

S1C63256は発振回路を内蔵しており、CPUおよび周辺回路に動作クロックを供給します。

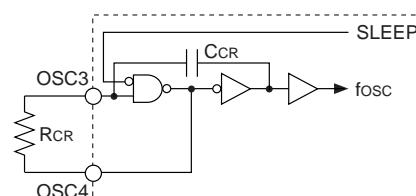

発振回路の種類としては、水晶/セラミック発振、CR発振、外部クロック入力の中から1つをマスクオプションで選択することができます。発振周波数は0.5MHz ~ 4.5MHz( CR発振はMax. 2.5MHz )まで対応しています。この広範囲な周波数から周辺回路の動作クロックを生成するため、発振回路の後段にはプリスケーラが設けられています。プリスケーラの分周比は発振周波数に合わせてソフトウェアで設定可能です。図4.2.1.1に発振系のブロック図を示します。

図4.2.1.1 発振系のブロック図

### 4.2.2 発振回路の種類

S1C63256では発振回路の種類として水晶/セラミック発振、CR発振、外部クロック入力の1つをマスクオプションで選択できます。発振周波数はCR発振が0.5MHz ~ 2.5MHzまで、その他は0.5MHz ~ 4.5MHzまで対応しています。この発振回路はSLEEP時に停止します。

注: 計時機能を使用する場合は、4.194304MHzの水晶発振回路を推奨します。

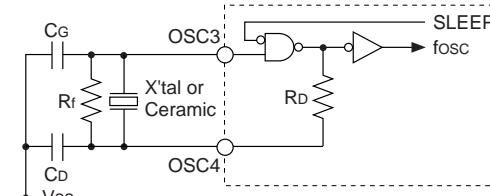

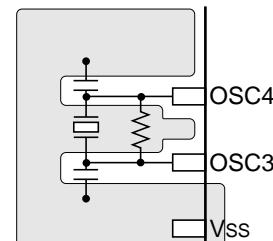

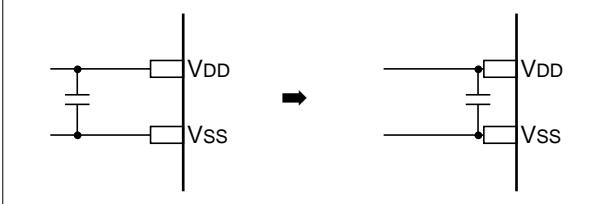

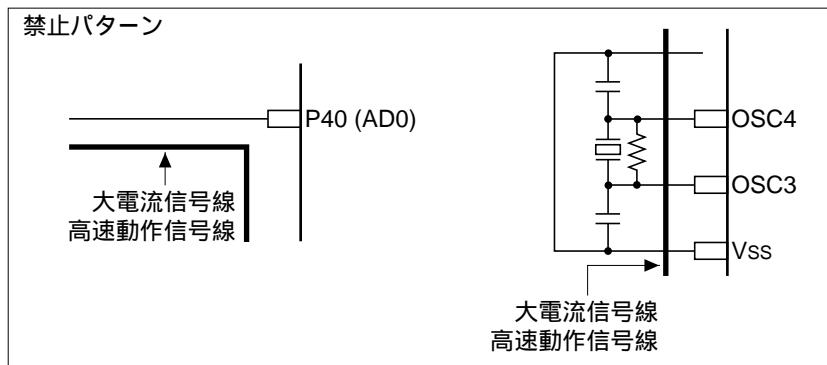

#### (1) 水晶/セラミック発振回路

図4.2.2.1に示すとおり、OSC3端子とOSC4端子間に水晶振動子(X'tal)またはセラミック振動子(Ceramic)を接続し、Rf (帰還抵抗)とCd (ゲートキャパシタ)をそれぞれ接続することにより、容易に水晶発振回路を構成することができます。セラミック発振の場合は、水晶振動子の代わりにセラミック振動子をOSC3端子とOSC4端子間に接続します。各素子の推奨値については"7 電気的特性"を参照してください。

図4.2.2.1 水晶/セラミック発振回路

#### (2) CR発振回路

図4.2.2.2に示すとおり、OSC3端子とOSC4端子間に抵抗(RCR)を接続するだけでCR発振回路を構成できます。抵抗値については"7 電気的特性"を参照してください。

図4.2.2.2 CR発振回路

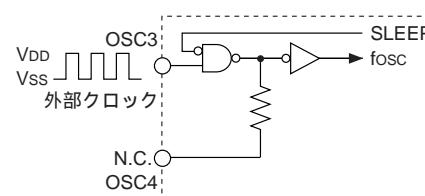

#### (3) 外部クロック入力

外部クロック入力を選択した場合はOSC4端子を開放し、OSC3端子に矩形波のクロックを入力してください。

図4.2.2.3 外部クロック入力

### 4.2.3 プリスケーラ

0.5MHz ~ 4.5MHzまでの発振周波数に対応するため、発振回路の後段にはプリスケーラが設けられています。このプリスケーラによって、周辺回路の動作クロックを一定範囲に設定します。プリスケーラの分周比はPRSMレジスタによって次のように設定できます。

表4.2.3.1 プリスケーラの分周比

| PRSM3 | PRSM2 | PRSM1 | PRSM0 | fPRS    | PRSM3 | PRSM2 | PRSM1 | PRSM0 | fPRS    |

|-------|-------|-------|-------|---------|-------|-------|-------|-------|---------|

| 1     | 1     | 1     | 1     | fosc/32 | 0     | 1     | 1     | 1     | fosc/16 |

| 1     | 1     | 1     | 0     | fosc/30 | 0     | 1     | 1     | 0     | fosc/14 |

| 1     | 1     | 0     | 1     | fosc/28 | 0     | 1     | 0     | 1     | fosc/12 |

| 1     | 1     | 0     | 0     | fosc/26 | 0     | 1     | 0     | 0     | fosc/10 |

| 1     | 0     | 1     | 1     | fosc/24 | 0     | 0     | 1     | 1     | fosc/8  |

| 1     | 0     | 1     | 0     | fosc/22 | 0     | 0     | 1     | 0     | fosc/6  |

| 1     | 0     | 0     | 1     | fosc/20 | 0     | 0     | 0     | 1     | fosc/4  |

| 1     | 0     | 0     | 0     | fosc/18 | 0     | 0     | 0     | 0     | fosc/2  |

fPRS: プリスケーラの出力クロック周波数=fosc/2n( n: PRSM設定値+1 )

fosc: 発振クロック周波数

設定は次の条件を満たすように行ってください。

$$240\text{Hz} < \frac{\text{fosc}}{2048 \cdot n} < 530\text{Hz} \quad ( n: \text{PRSM設定値}+1 )$$

例: fosc = 4.194304MHzの場合: fosc/(2048・8) = 256Hz PRSM = 7 fPRS = 262.144kHz

fosc = 2MHzの場合: fosc/(2048・4) = 244Hz PRSM = 3 fPRS = 250kHz

注: 実際にはfoscの周波数偏差も考慮した設定が必要です。記載例は周波数偏差を考慮していません。

周波数偏差については"7 電気的特性"を参照してください。

プリスケーラの設定が影響する周辺回路は以下のとおりです。

- ・計時タイマとウォッチドッグタイマ( カウントクロック )

- ・LCDドライバ( フレーム周波数 )

- ・ブザー出力回路( ブザー周波数、2Hzインターバル )

- ・出力ポート特殊出力( FOUT周波数 )

- ・イニシャルリセット回路( 時間検定回路、ノイズリジェクタ )

- ・プログラマブルタイマ( ノイズリジェクタ、データホールド時間 )

- ・A/D変換クロック

これらの周辺回路の動作クロックは、プリスケーラの出力( fPRS )を分周して生成します。

表4.2.3.2に各周辺回路用クロックの分周比と周波数の例を示します。4.19MHzの例はPRSMを7に設定、2MHzの例はPRSMを3に設定した場合のものです。

表4.2.3.2 周辺回路用クロック周波数

| 周辺回路/信号                       | 分周比          | 周波数/時間           |           |

|-------------------------------|--------------|------------------|-----------|

|                               |              | fosc=4.194304MHz | fosc=2MHz |

| 計時タイマカウントクロック                 | fPRS/1024    | 256Hz            | 244Hz     |

| 計時タイマ1Hz割り込み(WDTクロック)         | fPRS/262144  | 1Hz              | 0.95Hz    |

| ウォッチドッグタイマリセット周期Min.          | 786432/fPRS  | 3sec             | 3.15sec   |

| ウォッチドッグタイマリセット周期Max.          | 1048576/fPRS | 4sec             | 4.19sec   |

| LCDドライバフレーム周波数(1/4, 1/2デューティ) | fPRS/4096    | 64Hz             | 61.0Hz    |

| LCDドライバフレーム周波数(1/3デューティ)      | fPRS/3072    | 85.3Hz           | 81.4Hz    |

| ブザー信号(2kHz)                   | fPRS/128     | 2048Hz           | 1953Hz    |

| ブザー信号(4kHz)                   | fPRS/64      | 4096Hz           | 3906Hz    |

| ブザー2Hzインターバル                  | fPRS/131072  | 2Hz              | 1.9Hz     |

| FOUT周波数0                      | fOSC         | 4.194304MHz      | 2MHz      |

| FOUT周波数1                      | fPRS         | 262.144kHz       | 250kHz    |

| FOUT周波数2                      | fPRS/64      | 4096Hz           | 3906Hz    |

| FOUT周波数3                      | fPRS/512     | 512Hz            | 488Hz     |

| イニシャルリセットノイズリジェクトパルス幅         | 128/fPRS     | 0.49msec         | 0.51msec  |

| 入力ポート同時Lowリセット検定時間Min.        | 262144/fPRS  | 1sec             | 1.05sec   |

| 入力ポート同時Lowリセット検定時間Max.        | 524288/fPRS  | 2sec             | 2.1sec    |

| プログラマブルタイマノイズリジェクトパルス幅        | 128/fPRS     | 0.49msec         | 0.51msec  |

| プログラマブルタイマデータホールド時間(8ビット)     | 128/fPRS     | 0.49msec         | 0.51msec  |

| プログラマブルタイマデータホールド時間(16ビット)    | 256/fPRS     | 0.98msec         | 1.02msec  |

| A/D変換クロック                     | fPRS         | 262.144kHz       | 250kHz    |

#### 4.2.4 クロック周波数とインストラクション実行時間

CPUは発振クロックfoscで動作します。

表4.2.4.1にクロック周波数によるインストラクションの実行時間の例を示します。

表4.2.4.1 クロック周波数とインストラクション実行時間

| クロック周波数     | インストラクション実行時間( $\mu$ sec ) |         |         |

|-------------|----------------------------|---------|---------|

|             | 1サイクル命令                    | 2サイクル命令 | 3サイクル命令 |

| 4.194304MHz | 0.48                       | 0.95    | 1.43    |

| 2MHz        | 1                          | 2       | 3       |

#### 4.2.5 プリスケーラのI/Oメモリ

表4.2.5.1にプリスケーラの制御ビットとそのアドレスを示します。

表4.2.5.1 プリスケーラの制御ビット

| アドレス  | レジスタ  |       |       |       | Name  | Init *1 | 1 | 0 | 注 粹                                                               |

|-------|-------|-------|-------|-------|-------|---------|---|---|-------------------------------------------------------------------|

|       | D3    | D2    | D1    | D0    |       |         |   |   |                                                                   |

| FF02H | PRSM3 | PRSM2 | PRSM1 | PRSM0 | PRSM3 | 1       |   |   | プリスケーラ設定<br>プリスケーラ出力 $f_{PRS} = \frac{f_{OSC}}{2 \cdot (PRSM+1)}$ |

|       |       |       |       |       | PRSM2 | 1       |   |   | PRSM設定条件:<br>$240Hz < f_{OSC}/(2048 \cdot (PRSM+1)) < 530Hz$      |

|       | R/W   |       |       |       | PRSM1 | 1       |   |   |                                                                   |

|       |       |       |       |       | PRSM0 | 1       |   |   |                                                                   |

\*1 イニシャルリセット時の初期値

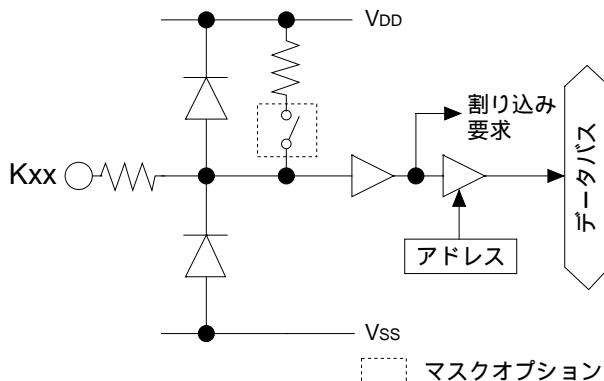

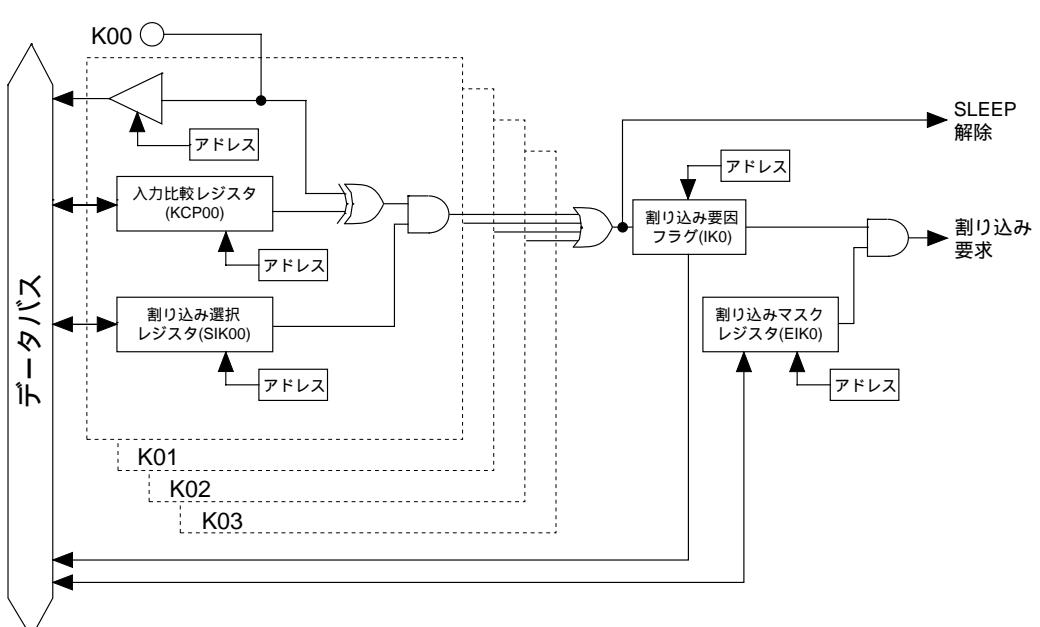

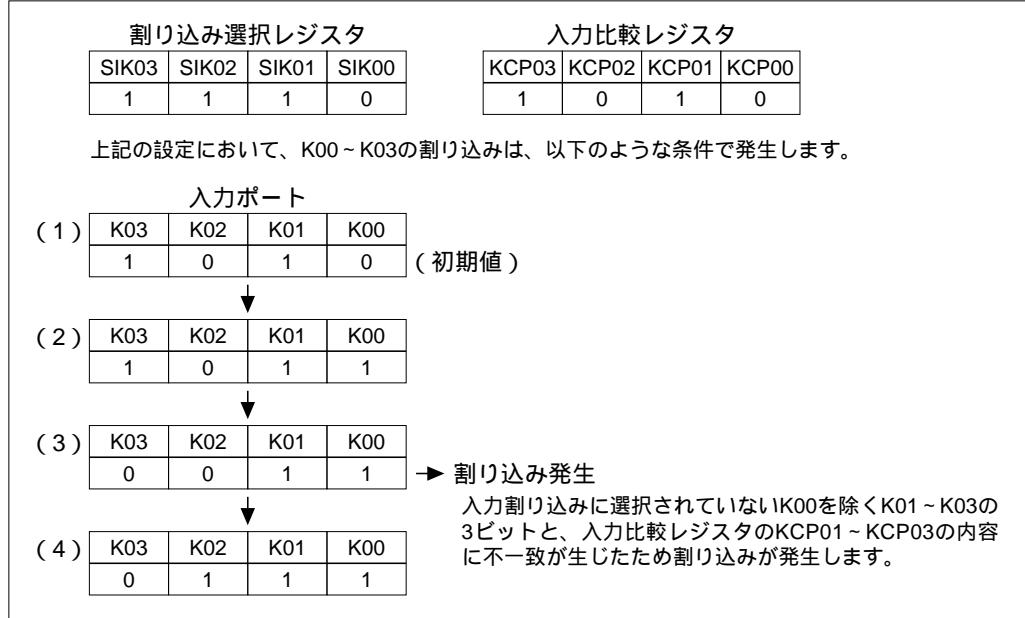

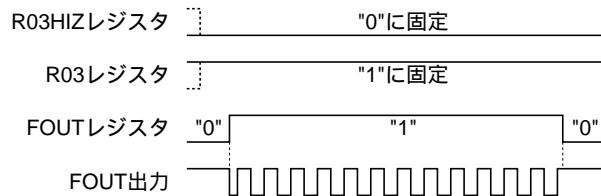

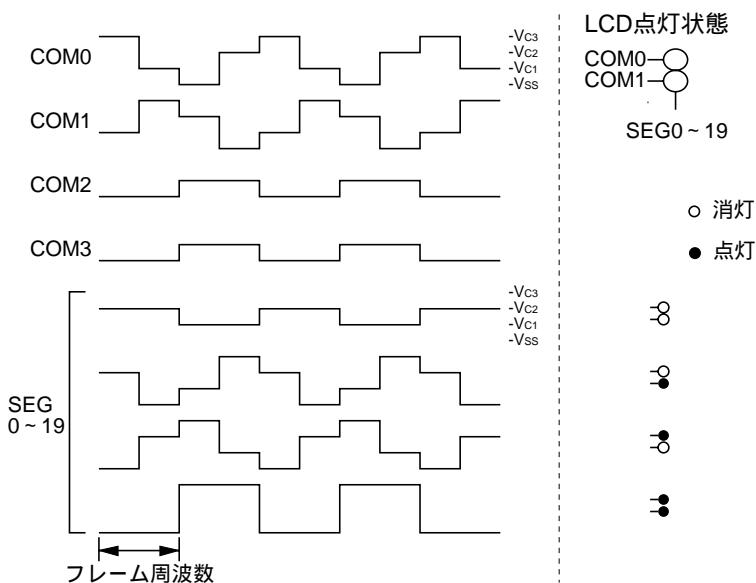

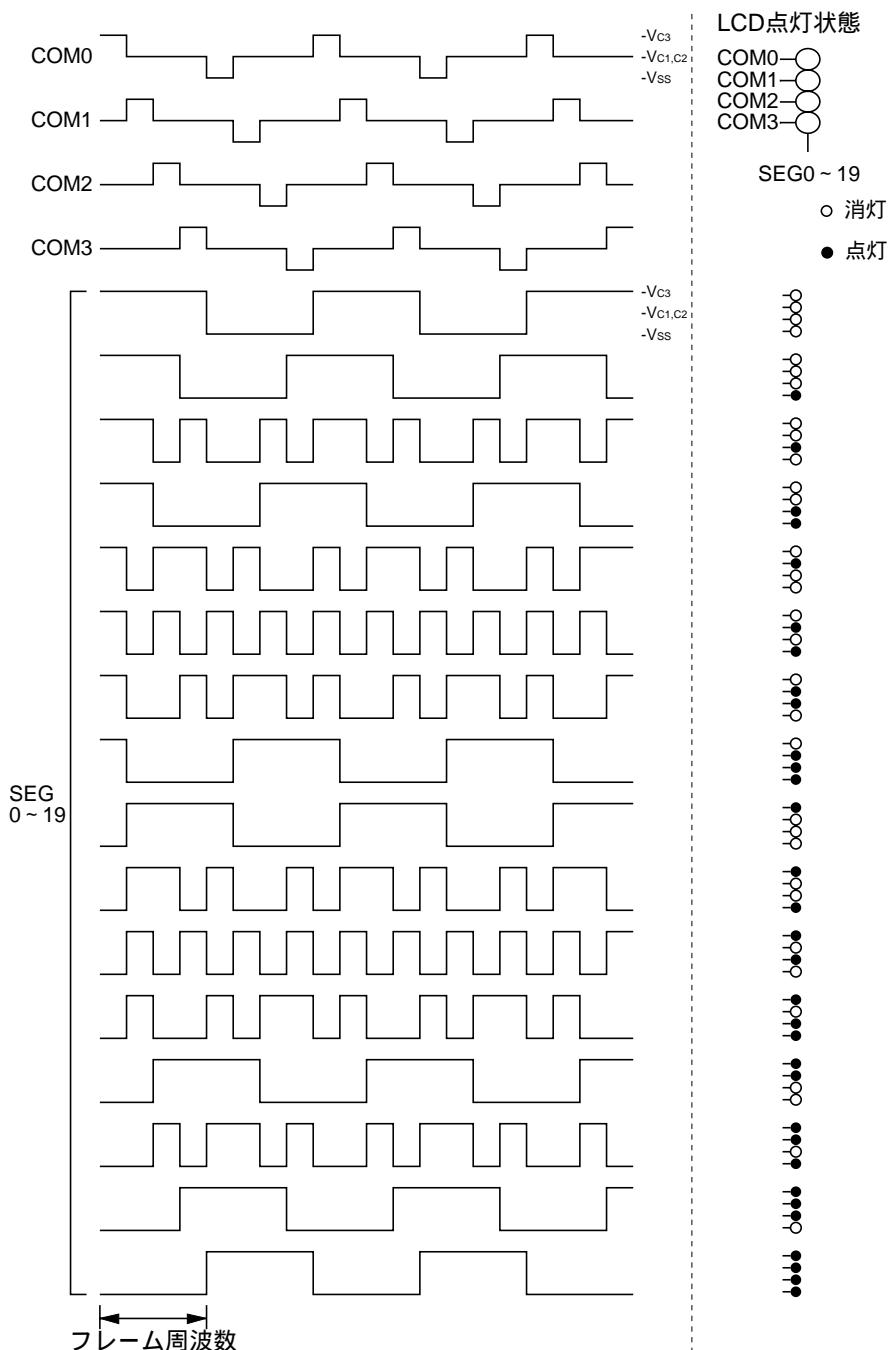

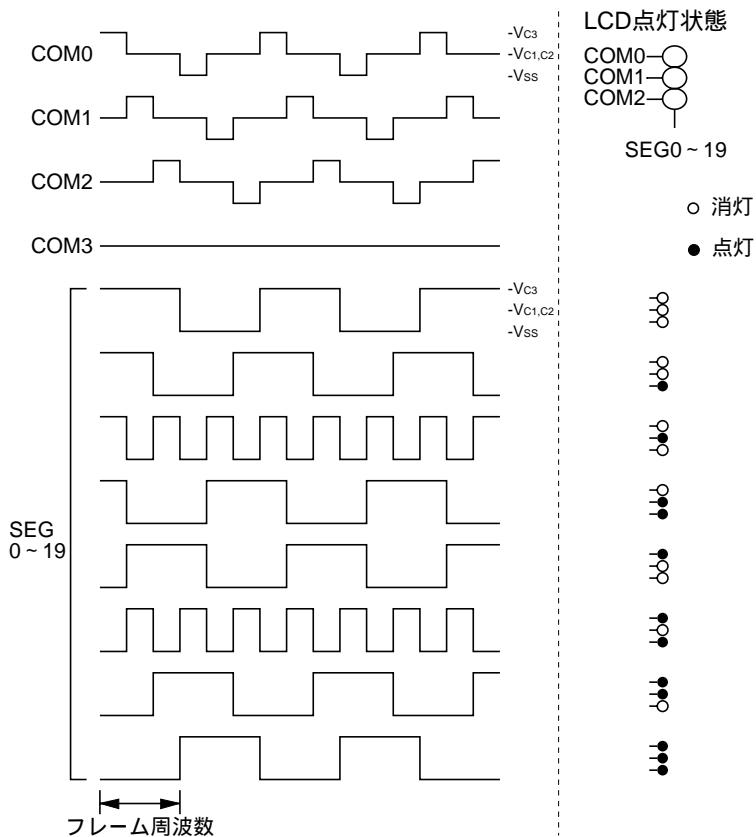

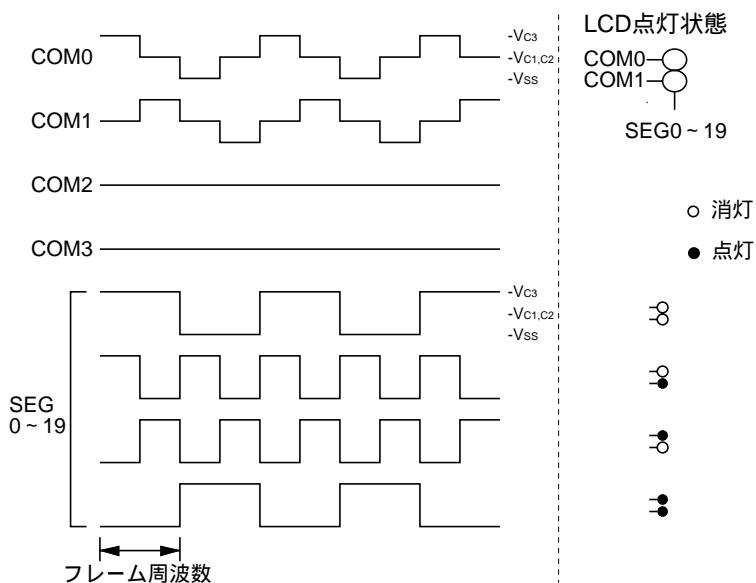

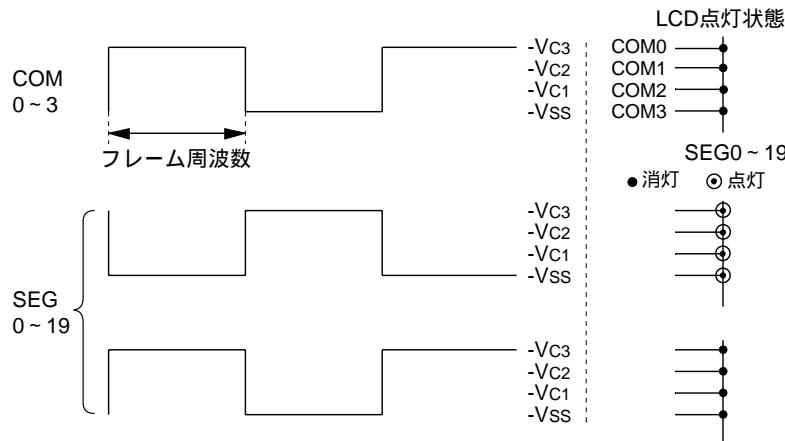

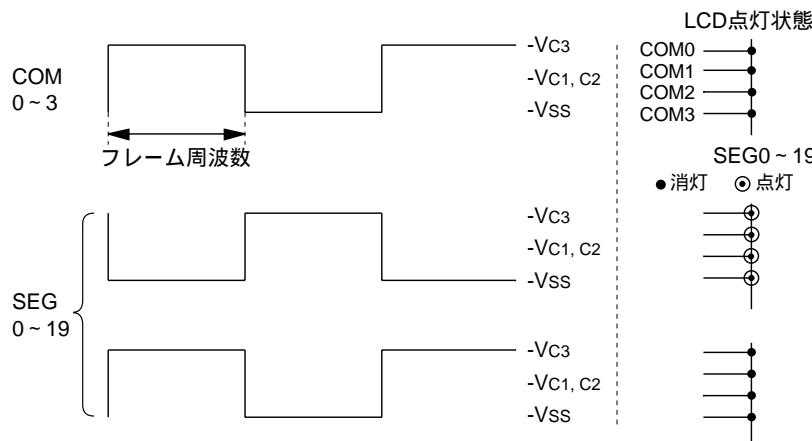

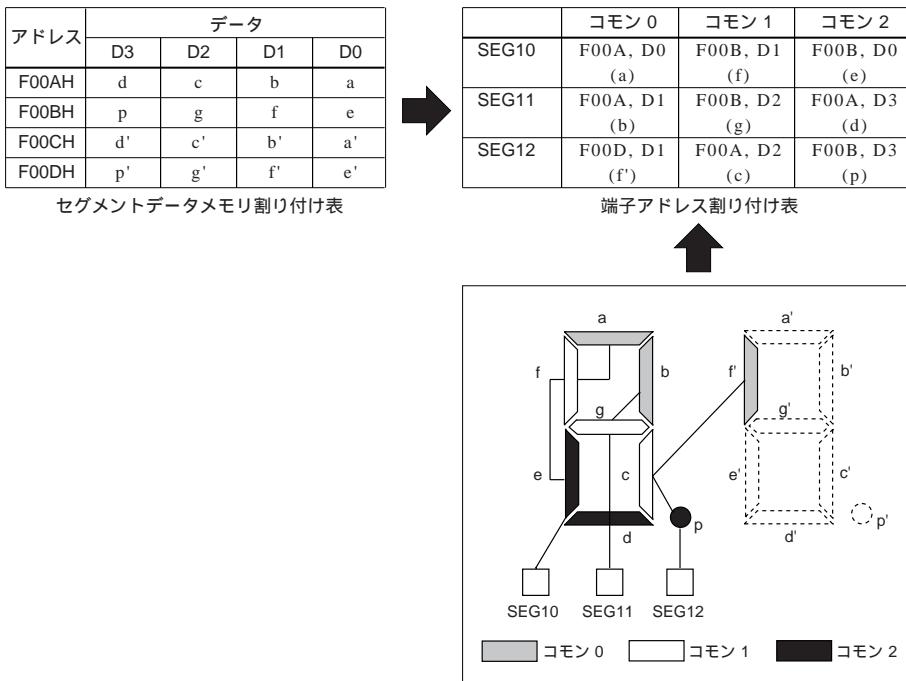

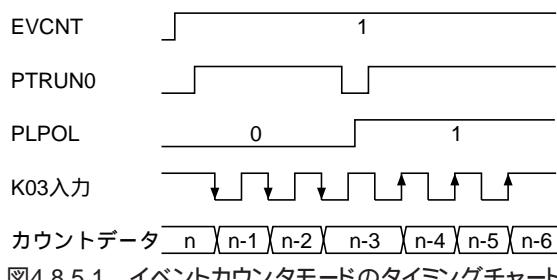

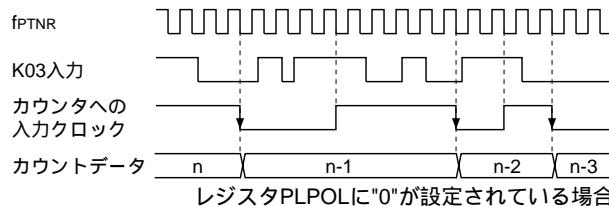

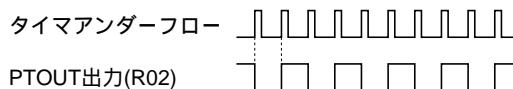

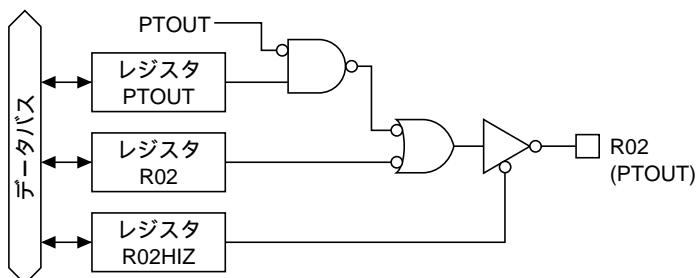

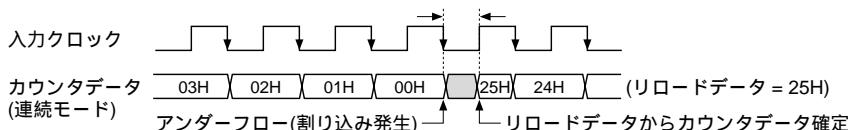

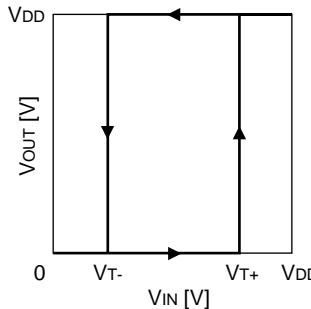

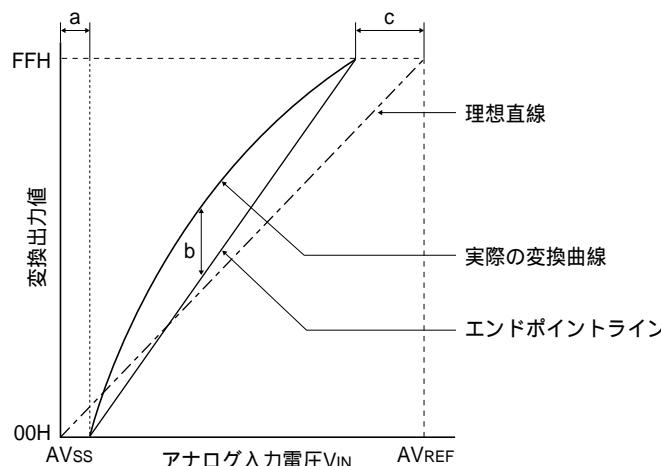

\*2 回路上設定されない