CMOS 8-BIT SINGLE CHIP MICROCOMPUTER

**S1C88**

コアCPUマニュアル

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

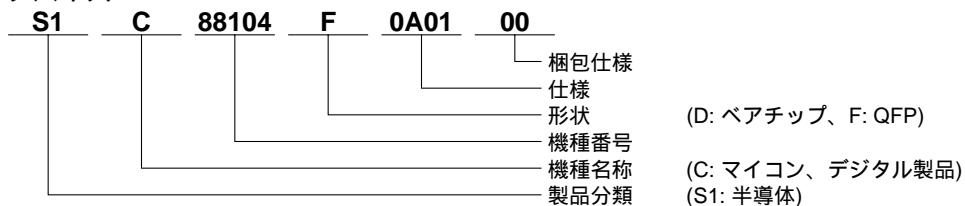

## 製品型番変更のご案内

2001年4月1日より、弊社半導体製品の製品型番が以下のとおり変更となりますので、4月1日以降のご発注につきましては変更後の製品型番にてお願い申し上げます。

なお、製品型番の詳細仕様につきましては、弊社営業担当にお問い合わせください。

## 製品型番体系

### デバイス

### 開発ツール

\*1: ツールの種類は、新旧型番対応表を参照してください。(マニュアル類には一桁で記載されているものもあります。)

\*2: マニュアル類には、実際のバージョンは記載されておりません。

## 新旧型番対応表

### S1C88ファミリ

| 旧型番       | 新型番      | 旧型番       | 新型番      |

|-----------|----------|-----------|----------|

| E0C88104  | S1C88104 | E0C88365  | S1C88365 |

| E0C88112  | S1C88112 | E0C88F360 | S1C8F360 |

| E0C88308  | S1C88308 | E0C88408  | S1C88408 |

| E0C88316  | S1C88316 | E0C88409  | S1C88409 |

| E0C88317  | S1C88317 | E0C88816  | S1C88816 |

| E0C88348  | S1C88348 | E0C88832  | S1C88832 |

| E0C88P348 | S1C8P348 | E0C88862  | S1C88862 |

| E0C88349  | S1C88349 | E0C88F816 | S1C8F816 |

## 開発ツール新旧型番対応表

### S1C88ファミリ関係の開発ツール

| 旧型番      | 新型番          | 旧型番         | 新型番          |

|----------|--------------|-------------|--------------|

| 881SAIF  | S5U1C88000H4 | DEV88816    | S5U1C88816D  |

| ADP88348 | S5U1C88348X  | DEV88832    | S5U1C88832D  |

| ADP88360 | S5U1C88360X  | DEV88862    | S5U1C88862D  |

| DEV88104 | S5U1C88104D  | DMT88348-DB | S5U1C88348T  |

| DEV88112 | S5U1C88112D  | ICE88UR     | S5U1C88000H5 |

| DEV88308 | S5U1C88308D  | PRC88316    | S5U1C88316P  |

| DEV88316 | S5U1C88316D  | PRC88348    | S5U1C88348P  |

| DEV88317 | S5U1C88317D  | PRC88365    | S5U1C88365P  |

| DEV88348 | S5U1C88348D  | PRC88409    | S5U1C88409P  |

| DEV88365 | S5U1C88365D  | PRC88816    | S5U1C88816P  |

| DEV88408 | S5U1C88408D  | SAP88       | S5U1C88000S  |

| DEV88409 | S5U1C88409D  | URS88348    | S5U1C88348Y  |

### S1C63/88ファミリ関係の開発ツール

| 旧型番      | 新型番          |

|----------|--------------|

| ADS00002 | S5U1C88000X1 |

| GWH00002 | S5U1C88000W2 |

| URM00002 | S5U1C88000W1 |

CMOS 8-bit Single Chip Microcomputer

# **S1C88 Core CPU Manual**

はじめに 本書はCMOS 8ビットシングルチップマイクロコンピュータS1C88 FamilyのコアCPU S1C88のアーキテクチャとその動作および命令セットについて解説します。

なお、S1C88 Familyの各デバイスごとにメモリ構成や周辺回路の構成が異なりますので、基本機能以外の内容についてはそれぞれのマニュアルをご覧ください。

## - 目 次 -

|                                    |    |

|------------------------------------|----|

| <b>1 概要</b>                        | 1  |

| 1.1 特長                             | 1  |

| 1.2 命令セットの特長                       | 1  |

| 1.3 ブロック図                          | 1  |

| 1.4 入出力信号                          | 2  |

| <b>2 アーキテクチャ</b>                   | 4  |

| 2.1 アドレス空間とCPUモデル                  | 4  |

| 2.2 演算部とレジスタ                       | 5  |

| 2.2.1 ALU                          | 5  |

| 2.2.2 レジスタ構成                       | 5  |

| 2.2.3 フラグ                          | 6  |

| 2.2.4 補数演算とオーバーフロー                 | 8  |

| 2.2.5 10進演算とアンパック演算                | 9  |

| 2.2.6 乗除算                          | 11 |

| 2.3 プログラムメモリ                       | 12 |

| 2.3.1 プログラムメモリの構成                  | 12 |

| 2.3.2 PC(プログラムカウンタ)とCB(コードバンク)レジスタ | 12 |

| 2.3.3 バンク管理                        | 13 |

| 2.3.4 分岐命令                         | 13 |

| 2.4 データメモリ                         | 16 |

| 2.4.1 データメモリの構成                    | 16 |

| 2.4.2 ページレジスタEP、XP、YP              | 16 |

| 2.4.3 スタック                         | 17 |

| 2.4.4 メモリマップドI/O                   | 18 |

| <b>3 CPUの動作と処理状態</b>               | 19 |

| 3.1 タイミングジェネレータとバス制御               | 19 |

| 3.1.1 バスサイクル                       | 19 |

| 3.1.2 ウェイトステート                     | 20 |

| 3.2 処理状態の概要                        | 21 |

| 3.3 リセット状態                         | 22 |

|                           |           |

|---------------------------|-----------|

| 3.4 プログラム実行状態 .....       | 23        |

| 3.5 例外処理状態 .....          | 23        |

| 3.5.1 例外処理の種類と優先度 .....   | 24        |

| 3.5.2 例外処理要因とベクタ .....    | 24        |

| 3.5.3 割り込み .....          | 24        |

| 3.5.4 例外処理のシーケンス .....    | 25        |

| 3.6 パス権解放状態 .....         | 28        |

| 3.7 スタンバイ状態 .....         | 29        |

| 3.7.1 HALT状態 .....        | 29        |

| 3.7.2 SLEEP状態 .....       | 30        |

| <b>4 命令セット .....</b>      | <b>31</b> |

| 4.1 アドレッシングモード .....      | 31        |

| 4.2 命令のフォーマット .....       | 34        |

| 4.3 命令セット一覧表 .....        | 35        |

| 4.3.1 機能分類 .....          | 35        |

| 4.3.2 記号の意味 .....         | 36        |

| 4.3.3 機能別命令一覧表 .....      | 37        |

| 4.4 命令の詳細説明 .....         | 54        |

| <b>APPENDIX</b>           |           |

| A. オペコードマップ .....         | 179       |

| B. アドレッシングモード別命令一覧表 ..... | 182       |

| C. 命令索引 .....             | 194       |

# 1 概要

S1C88はEPSONオリジナルのアーキテクチャを採用したCMOS 8ビットシングルチップマイクロコンピュータS1C88 FamilyのコアCPUです。

最大16Mバイトのアドレス空間と高速・豊富な命令セットを持ち、広範囲な動作電圧に対応するとともに低消費電力を特長としています。

また、統一アーキテクチャのもとにメモリマップドI/O方式の周辺回路インターフェースを採用しており、今後のFamily拡充にも柔軟に対応します。

## 1.1 特長

S1C88は以下の特長を持っています。

アドレス空間 最大16Mバイト

命令サイクル 1~15サイクル(1サイクル=2クロック)

命令セット 608種類

レジスタ構成 データレジスタ 2

インデックスレジスタ 3

(1つはデータレジスタとして使用可)

プログラムカウンタ

スタックポインタ

システムコンディションフラグ

カスタマイズコンディションフラグ

例外処理要因 リセット、ゼロ除算、割り込み

例外処理ベクタ 最大128ベクタ

スタンバイ機能 HALT/SLEEP

周辺回路インターフェース メモリマップドI/O方式

## 1.2 命令セットの特長

- (1) マシンサイクル効率の高い、高速かつ豊富な命令セットを採用しています。

- (2) 12種類のアドレッシングモードにより、メモリ管理が容易に行えます。

- (3) アドレス計算などに有効な16ビット演算機能を持っています。

- (4) 10進演算モード、パック/アンパック命令など、強力な10進演算機能があります。

- (5) カストマイズドフラグ命令により、各種の特定用途向けマイコンの実現をサポートしています。

- (6) リロケータブルプログラミングが可能な命令体系となっており、ソフトウェアのライブラリ化が容易に実現できます。

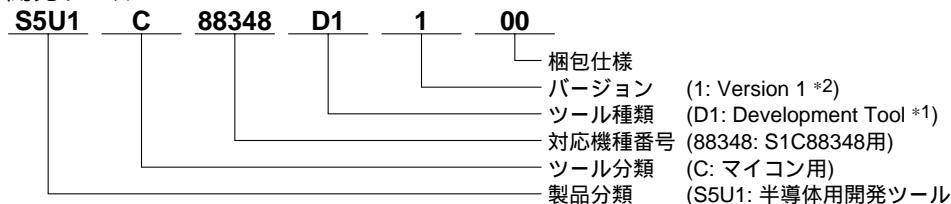

## 1.3 ブロック図

図1.3.1にS1C88のブロック図を示します。

図1.3.1 S1C88ブロック図

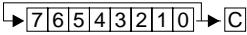

## 1.4 入出力信号

表1.4.1(a)、表1.4.1(b)にS1C88と周辺回路間の入出力信号を示します。

表1.4.1(a) 入出力信号一覧 (1)

| 種 別      | 名 称                      | 信 号 名     | 入出力 | 機 能                                                                                                                           |

|----------|--------------------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 電源       | 電源                       | VDD       | 入力  | + 側電源を入力します。                                                                                                                  |

|          | グランド                     | VSS       | 入力  | - 側電源(GND)を入力します。                                                                                                             |

| クロック     | クロック入力                   | CLK       | 入力  | 周辺回路からのシステムクロックを入力します。                                                                                                        |

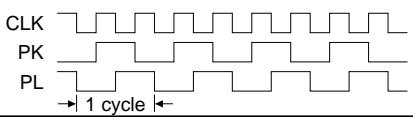

|          | クロック出力                   | PK<br>PL  | 出力  | CLK端子に入力されるシステムクロックの2相分周信号を以下の位相で出力します。<br> |

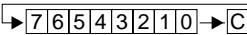

| アドレスバス   | アドレスバス                   | A00~A23   | 出力  | 24ビットのアドレスバスです。                                                                                                               |

| データバス    | データバス                    | D0~D7     | 入出力 | 8ビットの双方向データバスです。                                                                                                              |

| バス制御信号   | ウェイト                     | WAIT      | 入力  | メモリアクセス時のアクセスタイム伸長用ウェイストートの挿入を制御します。<br>LOWレベルの入力で有効です。                                                                       |

|          | リード                      | RD        | 出力  | メモリ(周辺回路)リード信号です。<br>データの読み出し時にLOWレベルとなります。                                                                                   |

|          | ライト                      | WR        | 出力  | メモリ(周辺回路)ライト信号です。<br>データの書き込み時にLOWレベルとなります。                                                                                   |

|          | リード割り込み<br>ベクタアドレス       | RDIV      | 出力  | 割り込みベクタアドレスリード信号です。ベクタアドレスの読み出し時にLOWレベルとなります。                                                                                 |

|          | リセット                     | SR        | 入力  | LOWレベルの入力によりCPUがリセット状態となります。                                                                                                  |

| システム制御信号 | モード設定                    | MODE      | 入力  | CPUの動作モードを周辺回路より設定します。<br>LOW: ミニマムモード<br>HIGH: マキシマムモード                                                                      |

|          | カスタマイズ<br>コンディション<br>フラグ | F0~F3     | 入力  | 周辺回路より入力されるステータス信号です。<br>周辺回路により信号の意味が異なります。                                                                                  |

|          | マイクロ<br>スリープ             | USLP      | 出力  | CPUがSLP(SLEEP)命令によりSLEEP状態に入る1サイクル前にHIGHレベルとなります。本信号をもとに周辺回路は発振停止の制御を行います。                                                    |

|          | バス権要求                    | BREQ      | 入力  | 周辺回路がDMA転送を行う場合のバス権要求信号です。本端子へのLOWレベル入力によりCPUはバスを解放します。アドレスバス、データバス、およびリード/ライト信号がハイインピーダンス状態となります。                            |

|          | バス権要求<br>アクノリッジ          | BACK      | 出力  | バス権を周辺回路に解放したことを示す応答信号です。バス権解放時にLOWレベルとなります。                                                                                  |

|          | スタック<br>ポインタページ          | SPP0~SPP7 | 入力  | 周辺回路により指定されるスタックポインタのページアドレスです。スタックポインタがメモリをアクセスする際に、このアドレスがアドレスバスのページ部(AD16~AD23)に出力されます。                                    |

各信号のタイミング等については、3章の"CPUの動作と処理状態"を参照してください。

表1.4.1(b) 入出力信号一覧 (2)

| 種別      | 名称            | 信号名            | 入出力 | 機能                                                                                                                                                                                                                                                                                                                     |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|---------|---------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---|---|-----------|---|---|----------------|---|---|--------|---|---|--------|

| 割り込み信号  | ノンマスカブル割り込み   | NMI            | 入力  | ソフトウェアによるマスクが不可能な割り込み信号です。入力は立ち下がりエッジにてセンスされます。                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 割り込み要求3       | IRQ3           | 入力  | ソフトウェアによるマスクが可能な割り込み信号です。割り込み優先度はレベル3で、入力はLOWレベルにてセンスされます。                                                                                                                                                                                                                                                             |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 割り込み要求2       | IRQ2           | 入力  | ソフトウェアによるマスクが可能な割り込み信号です。割り込み優先度はレベル2で、入力はLOWレベルにてセンスされます。                                                                                                                                                                                                                                                             |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 割り込み要求1       | IRQ1           | 入力  | ソフトウェアによるマスクが可能な割り込み信号です。割り込み優先度はレベル1で、入力はLOWレベルにてセンスされます。                                                                                                                                                                                                                                                             |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 割り込みマスク       | IMASK          | 入力  | 周辺回路より入力される割り込みマスク信号です。周辺回路部に構成されるスタックポインタのページ部等をアクセスする際に本端子にLOWレベルが入力され、以下の割り込みがマスクされます。<br>NMI, IRQ3, IRQ2, IRQ1                                                                                                                                                                                                     |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 割り込みアクノリッジ    | IACK           | 出力  | 割り込み要求を受け付けたことを示す応答信号です。割り込み受け付け時にLOWレベルとなります。周辺回路は本信号を受けてベクタアドレスをホールドします。なお、本信号はリセットおよびゼロ除算による例外処理の実行時においてもLOWレベルとなります。                                                                                                                                                                                               |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | インターラプトフラグ    | I0F<br>I1F     | 出力  | システムコンディションフラグ(SC)内のインターラプトフラグ(I0, I1)をモニタ出力しています。                                                                                                                                                                                                                                                                     |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

| ステータス信号 | 第1オペコードフェッチ信号 | SYNC           | 出力  | CPUが第1オペコードをフェッチする際にアクティブとなる信号です。第1オペコードフェッチのバスサイクル期間中、HIGHレベルとなります。<br>また、本信号の立ち上がりエッジにて割り込みがサンプリングされます。                                                                                                                                                                                                              |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | 停止信号          | STOP           | 出力  | CPUが以下の状態に入ったとき、LOWレベルとなります。<br>・HALT命令によるCPUの停止<br>・SLP命令によるCPUの停止<br>・BREQへのLOWレベル入力によるバスの解放                                                                                                                                                                                                                         |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         | データバスステータス    | DBS0<br>DBS1   | 出力  | データバスの状態を以下のとおり示す2ビットのステータス信号です。                                                                                                                                                                                                                                                                                       |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

|         |               |                |     | <table> <thead> <tr> <th>DSB1</th> <th>DSB0</th> <th>ステート</th> </tr> </thead> <tbody> <tr> <td>0</td> <td>0</td> <td>ハイインピーダンス</td> </tr> <tr> <td>0</td> <td>1</td> <td>割り込みベクタアドレスリード</td> </tr> <tr> <td>1</td> <td>0</td> <td>メモリライト</td> </tr> <tr> <td>1</td> <td>1</td> <td>メモリリード</td> </tr> </tbody> </table> | DSB1 | DSB0 | ステート | 0 | 0 | ハイインピーダンス | 0 | 1 | 割り込みベクタアドレスリード | 1 | 0 | メモリライト | 1 | 1 | メモリリード |

| DSB1    | DSB0          | ステート           |     |                                                                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

| 0       | 0             | ハイインピーダンス      |     |                                                                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

| 0       | 1             | 割り込みベクタアドレスリード |     |                                                                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

| 1       | 0             | メモリライト         |     |                                                                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

| 1       | 1             | メモリリード         |     |                                                                                                                                                                                                                                                                                                                        |      |      |      |   |   |           |   |   |                |   |   |        |   |   |        |

注! 入出力信号はS1C88 Familyの各デバイスによって周辺回路の信号の追加など、表の内容と異なる場合があります。それらの信号については各デバイスのマニュアルを参照してください。

# 2 アーキテクチャ

S1C88は最大16Mバイトのアドレス空間を持ち、大規模なアプリケーションにも対応できます。ここでは、このアドレス空間とメモリ管理、レジスタの構成等について説明します。

## 2.1 アドレス空間とCPUモデル

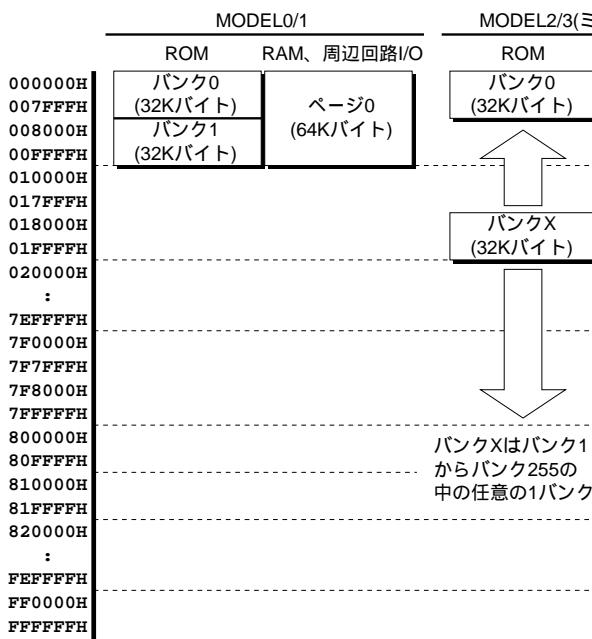

S1C88にはアドレス空間の大きさと乗除算命令のありなしにより、MODEL0～MODEL3の4種類のCPUモデルが設定されています。各モデルの違いは表2.1.1のとおりで、マイコンの用途、アプリケーションの規模によって選択できるようになっています。

MODEL2、MODEL3については、さらにプログラミング領域を最大64Kバイトとするミニマムモードと最大8MバイトとするマキシマムモードのいずれかがコアCPUのMODE端子の設定によって選択できます。

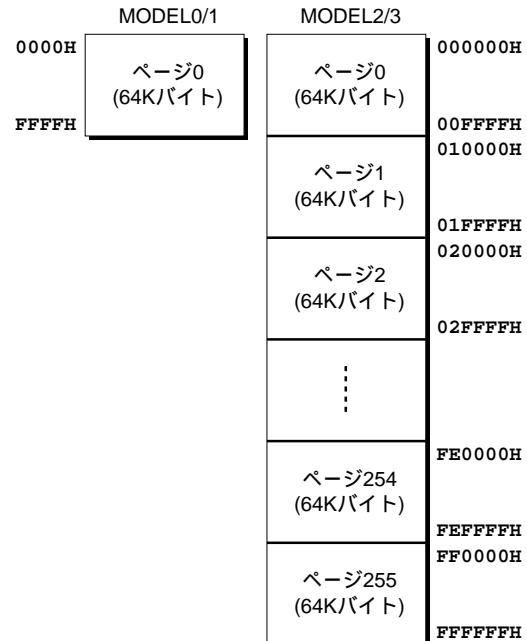

各CPUモデルに対するメモリマップの概念を図2.1.1に示します。

表2.1.1 CPUモデル

| CPUモデル | アドレス空間 | 乗除算命令 |

|--------|--------|-------|

| MODEL0 | 64Kバイト | なし    |

| MODEL1 | 64Kバイト | あり    |

| MODEL2 | 16Mバイト | なし    |

| MODEL3 | 16Mバイト | あり    |

表2.1.2 動作モードの設定(MODEL2、MODEL3)

| MODE | 動作モード    | プログラミング領域 |

|------|----------|-----------|

| 0    | ミニマムモード  | 最大64Kバイト  |

| 1    | マキシマムモード | 最大8Mバイト   |

図2.1.1 メモリマップ

プログラムメモリは32Kバイトごとのパンク、データメモリは64Kバイトごとのページに分けて管理されます。

☞ "2.3 プログラムメモリ"、"2.4 データメモリ"

注! S1C88 Familyの各デバイスによってメモリの構成が異なります。各デバイスのマニュアルを参照してください。

## 2.2 演算部とレジスタ

### 2.2.1 ALU ///////////////////////////////////////////////////

ALU(算術論理演算ユニット)は2種類のテンポラリレジスタTEMP 0とTEMP 1にストアされた8ビットまたは16ビットデータ間の演算を行います。

ALUの機能は表2.2.1.1のとおりです。

演算結果は16ビットのテンポラリレジスタTEMP 2に一旦ストアされた後、演算命令にしたがったレジスタ/メモリにストアされるか、アドレスデータとして使用されます。

また、演算結果によりZ(ゼロ)フラグ、C(キャリー)フラグ、V(オーバーフロー)フラグ、N(ネガティブ)フラグがセット/リセットされます。

☞ "2.2.3 フラグ"

### 2.2.2 レジスタ構成 ///////////////////////////////////////////////////

S1C88のレジスタ構成を図2.2.2.1に示します。

表2.2.1.1 ALUの演算機能

| 演算機能      | 演算命令               | 16ビット演算 |

|-----------|--------------------|---------|

| 加算        | ADD, ADC           |         |

| 減算        | SUB, SBC           |         |

| 論理積       | AND                |         |

| 論理和       | OR                 |         |

| 排他的論理和    | XOR                |         |

| 比較        | CP                 |         |

| ビットテスト    | BIT                |         |

| 1加算/減算    | INC, DEC           |         |

| 乗算        | MLT                |         |

| 除算        | DIV                |         |

| 補数        | CPL, NEG           |         |

| ローテート     | RL, RLC, RR, RRC   |         |

| シフト       | SLA, SLL, SRA, SRL |         |

| パック/アンパック | PACK, UPCK         |         |

| 符号拡張      | SEP                |         |

標準部 (MODEL0 ~ MODEL3共通)

|                            |                |                          |

|----------------------------|----------------|--------------------------|

| 7 (15) <b>B</b>            | 0 7 <b>A</b> 0 | データレジスタ A、B、(BA)         |

| 7 (15) <b>H</b>            | 0 7 <b>L</b> 0 | インデックス(データ)レジスタ HL、(H、L) |

| 15 <b>IX</b>               | 0              | インデックスレジスタ IX            |

| 15 <b>IY</b>               | 0              | インデックスレジスタ IY            |

| 15 <b>PC</b>               | 0              | プログラムカウンタ                |

| 15 <b>SP</b>               | 0              | スタックポインタ                 |

| 7 <b>BR</b>                | 0              | ベースレジスタ                  |

| SC <b>I1 0 U D N V C Z</b> |                | システムコンディションフラグ           |

| CC <b>F3 F2 F1 F0</b>      |                | カスタマイズコンディションフラグ         |

拡張部 (MODEL2、MODEL3)

|             |   |                  |

|-------------|---|------------------|

| 7 <b>NB</b> | 0 | ニューコードバンクレジスタ    |

| 7 <b>CB</b> | 0 | コードバンクレジスタ       |

| 7 <b>EP</b> | 0 | エクスパンドページレジスタ    |

| 7 <b>XP</b> | 0 | IX用エクスパンドページレジスタ |

| 7 <b>YP</b> | 0 | IY用エクスパンドページレジスタ |

図2.2.2.1 レジスタ構成

#### Aレジスタ、Bレジスタ

Aレジスタ、Bレジスタはそれぞれ8ビットのデータレジスタで、他のレジスタやデータメモリとのデータ転送や演算、即値データの転送、演算が行えます。8ビット転送/演算においてはそれ単独に、16ビット転送/演算においてはBレジスタを上位8ビットとするBAペアで使用します。

#### HLレジスタ

HLレジスタは16ビットのインデックスレジスタで、データメモリの間接アドレッシングに使用します(ページ内のアドレスを指定)。他のレジスタやデータメモリとの16ビットデータ転送や演算が行えます。また、Hレジスタ、Lレジスタの8ビットずつに分けてデータレジスタとしても使用できます。この場合のLレジスタはIXレジスタ、IYレジスタによる間接アドレッシングの際のディスプレースメントとして使用することもできます。

☞ "2.4 データメモリ"

☞ "4.1 アドレッシングモード"

#### IXレジスタ、IYレジスタ

IXレジスタ、IYレジスタはそれぞれ16ビットのインデックスレジスタで、データメモリの間接アドレッシングに使用します(ページ内のアドレスを指定)。他のレジスタやデータメモリとの16ビットデータ転送や演算が行えます。

☞ "2.4 データメモリ"

☞ "4.1 アドレッシングモード"

#### PC(プログラムカウンタ)

PCはプログラムメモリのアドレッシングを行う16ビットのカウンタレジスタで、次に実行する命令のアドレスを示します。

☞ "2.3 プログラムメモリ"

#### SP(スタックポインタ)

SPは16ビットのカウンタレジスタでスタックアドレス(スタックページ内のアドレス)を示します。他のレジスタやデータメモリとの16ビットデータ転送や演算が行えます。

☞ "2.4.3 スタック"

**BR(ベースレジスタ)**

BRは8ビットのインデックスレジスタで、8ビット絶対アドレッシング(アドレスの下位8ビットを指定)の際にページ内の上位8ビットのアドレス指定に使用されます。

☞ "4.1 アドレッシングモード"

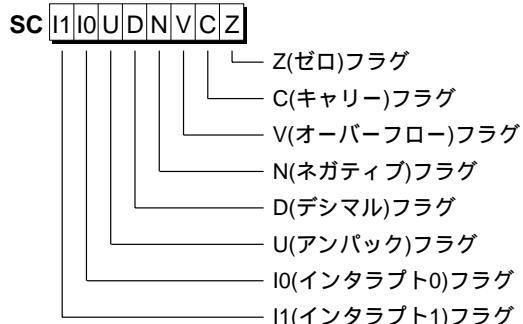

**SC(システムコンディションフラグ)**

SCは8ビットのフラグで、演算結果を示すZ、C、V、Nフラグ、演算モードを設定するD、Uフラグ、割り込み優先レベルを設定するI0、I1フラグで構成されます。

☞ "2.2.3 フラグ"

**CC(カスタマイズコンディションフラグ)**

CCは周辺回路によって設定された各種の状態を示す4ビットのフラグで、周辺回路によってセット/リセットされ、分岐命令の条件の1つとして使用されます。

☞ "2.2.3 フラグ"

**NB(ニューコードバンクレジスタ)**

NBレジスタはプログラムメモリのバンクを指定する8ビットのレジスタです。NBレジスタはCPUモデルのMODEL2およびMODEL3に設定されています。

☞ "2.3 プログラムメモリ"

**CB(コードバンクレジスタ)**

CBレジスタはプログラムメモリの現在選択されているバンクを示す8ビットのレジスタです。NBレジスタにデータを設定した場合、そのデータがCBレジスタにロードされ、新たなバンクが選択されます。CBレジスタはCPUモデルのMODEL2およびMODEL3に設定されています。

☞ "2.3 プログラムメモリ"

**EP、XP、YP(エクスパンドページレジスタ)**

これらのレジスタはデータメモリのページを指定する8ビットのレジスタです。

EPレジスタはHLレジスタによる間接アドレッシング、あるいは即値データによる絶対アドレッシングの際に使用されます。

XPレジスタはIXレジスタによる間接アドレッシング、YPレジスタはIYレジスタによる間接アドレッシングの際に使用されます。

これらのレジスタはCPUモデルのMODEL2およびMODEL3に設定されています。

☞ "2.4.2 ページレジスタEP、XP、YP"

☞ "4.1 アドレッシングモード"

**2.2.3 フラグ**

S1C88にはCPU内部の演算結果の状態などを表すシステムコンディションフラグ(SC)と周辺回路の状態を表すカスタマイズコンディションフラグ(CC)が設定されています。

**システムコンディションフラグ (SC)**

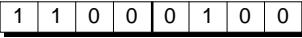

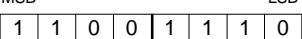

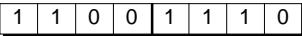

図2.2.3.1 システムコンディションフラグ (SC)

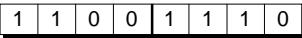

システムコンディションフラグは図2.2.3.1に示すとおり、8ビットのフラグで構成されたレジスタSCとなっています。

システムコンディションフラグのZ(ゼロ)、C(キャリー)、V(オーバーフロー)、N(ネガティブ)フラグは演算の結果によりセット/リセットされ、I0、I1(インタラプト)フラグは割り込みによりセット/リセットされます。また、これらのフラグは以下の命令によっても操作できます。

|            |               |

|------------|---------------|

| AND SC,#nn | (任意のフラグをリセット) |

| OR SC,#nn  | (任意のフラグをセット)  |

| XOR SC,#nn | (任意のフラグを反転)   |

| LD SC,#nn  | (フラグのライト)     |

| LD SC,A    | (フラグのライト)     |

| POP SC     | (フラグの復帰)      |

| RETE       | (フラグの復帰)      |

Z、C、V、NフラグはJRS命令やCARS命令などの条件ジャンプ/コール命令実行の際の条件判定に使用されます。

☞ "4.4 命令の詳細説明"

以下、各フラグについて説明します。

**(1) Z(ゼロ)フラグ**

Zフラグは演算命令の実行結果が'0'になった場合に'1'にセット、結果が'0'以外の場合に'0'にリセットされます。

## (2) C(キャリー)フラグ

Cフラグは加算命令の実行によりキャリー(最上位ビットから桁上げ)が発生した場合、または減算命令/比較命令の実行によりボロー(最上位ビットに借り)が発生した場合に'1'にセット、それ以外の場合に'0'にリセットされます。ただし、1加減算命令(INC、DEC命令)の実行ではCフラグは変化しません。

また、ローテート/シフト命令の実行によってもCフラグは変化します。

乗除算命令(MLT、DIV命令)を実行した場合は'0'にリセットされます。

## (3) V(オーバーフロー)フラグ

Vフラグは演算を行った結果が8ビットまたは16ビットで補数表現可能な範囲を越えた場合に'1'にセット、範囲内の場合に'0'にリセットされます。補数表現の範囲は8ビットが-128～127、16ビットが-32768～32767になります。

ただし、演算命令の中でも論理演算命令(デステイニエーションがSCの場合を除くAND、OR、XOR命令)、ビット操作命令(BIT命令)、1加減算命令(INC、DEC命令)の実行ではVフラグは変化しません。乗算命令(MLT命令)を実行した場合は'0'にリセットされます。除算命令(DIV命令)を実行した場合は、商が8ビットを越えるときに'1'にセットされます。

Cフラグが絶対値演算のオーバー(アンダー)フローを示すのに対し、Vフラグは補数演算のオーバーフローを示します。オーバーフローが起こりうる補数演算を行う場合はVフラグをチェックして、'1'のときには演算結果を補正する必要があります。

☞ "2.2.4 補数演算とオーバーフロー"

## (4) N(ネガティブ)フラグ

Nフラグは演算を行った結果がマイナス(最上位ビットが'1')になった場合に'1'にセット、プラス(最上位ビットが'0')の場合に'0'にリセットされます。ただし、1加減算命令(INC、DEC命令)の実行ではNフラグは変化しません。

## (5) D(デシマル)フラグ

Dフラグは8ビット加減算命令の実行の際に10進演算(演算結果が10進補正される)を行うように設定するビットで、'1'を設定することにより10進演算を行い、'0'で16進演算を行います。

☞ "2.2.5 10進演算とアンパック演算"

## (6) U(アンパック)フラグ

Uフラグは8ビット加減算の実行の際にアンパック演算(上位4ビットを'0'として演算)を行うように設定するビットで、'1'を設定することによりアンパック演算を行い、'0'で通常の8ビット演算を行います。

☞ "2.2.5 10進演算とアンパック演算"

## (7) I0、I1(インタラプト)フラグ

I0およびI1フラグは割り込み優先レベルを設定するビットで、この2ビットで設定したレベルより高いレベルの割り込みのみCPUは受け付けます。

また、割り込みが発生した際にも、そのレベル以下の割り込みをマスクするよう、新たな値が自動設定されます。

☞ "3.5.3 割り込み"

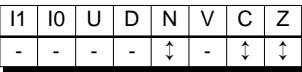

命令セット一覧表等では命令の実行により変化するフラグを"↑"を付けて示しています。Dフラグ、Uフラグは"↑"を付けて、その命令が10進演算、アンパック演算可能であることを示しています。

## カスタマイズコンディションフラグ (CC)

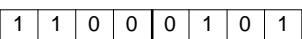

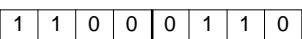

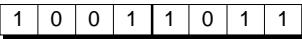

図2.2.3.2 カスタマイズコンディションフラグ (CC)

カスタマイズコンディションフラグは図2.2.3.2に示すとおり、4ビットのフラグで構成されたレジスタCCとなっています。

CCの各フラグはF0～F3の名称となっており、周辺回路からS1C88のF0～F3端子に入力される信号によって変化します。ここには周辺回路の状態を示す信号が入力されますので、各フラグに反映された周辺回路の状態によってプログラムを分岐させることができます。

S1C88はCCフラグによって特定用途向けマイコンが容易に実現できるように配慮されています。

CCフラグはJRS命令やCARS命令の条件ジャンプ/コール命令実行の際の条件判定に使用されます。

☞ "4.4 命令の詳細説明"

2.2.4 補数演算とオーバーフロー//////////

S1C88内部ではマイナスのデータを扱うために補数表現が用いられます。以下に補数表現と補数を用いた演算について説明します。

### 補数

マイクロコンピュータでマイナス(負)の数を扱う場合、一般的には補数表現が用いられます。補数には2の補数と1の補数の2種類の表現方法があり、通常単に補数といった場合、2の補数を指します。S1C88でもマイナスの数は2の補数で表しています。

任意の数Nの補数は以下の式で表され、2の補数表現が可能な範囲は8ビットの場合が-128 ~ 127、16ビットの場合が-32768 ~ 32767になります。1の補数表現が可能な範囲は8ビットの場合が-127 ~ 127、16ビットの場合が-32767 ~ 32767になります。

#### ----- 2の補数 -----

8ビット  $-N = 2^8 - N = 256 - N$

127 = 0111 1111b

126 = 0111 1110b

:

2 = 0000 0010b

1 = 0000 0001b

0 = 0000 0000b

-1 = 1111 1111b (= 1 0000 0000b - 0000 0001b)

-2 = 1111 1110b (= 1 0000 0000b - 0000 0010b)

:

-127 = 1000 0001b (= 1 0000 0000b - 0111 1111b)

-128 = 1000 0000b (= 1 0000 0000b - 1000 0000b)

#### ----- 16ビット -----

16ビット  $-N = 2^{16} - N = 65536 - N$

32767 = 0111 1111 1111 1111b

32766 = 0111 1111 1111 1110b

:

2 = 0000 0000 0000 0010b

1 = 0000 0000 0000 0001b

0 = 0000 0000 0000 0000b

-1 = 1111 1111 1111 1111b

(= 1 0000 0000 0000 0000b - 0000 0000 0000 0001b)

-2 = 1111 1111 1111 1110b

(= 1 0000 0000 0000 0000b - 0000 0000 0000 0010b)

:

-32767 = 1000 0000 0000 0001b

(= 1 0000 0000 0000 0000b - 0111 1111 1111 1111b)

-32768 = 1000 0000 0000 0000b

(= 1 0000 0000 0000 0000b - 1000 0000 0000 0000b)

補数表現した場合、マイナスの数の最上位ビットは必ず'1'になります。この最上位ビットの内容がN(ネガティブ)フラグに反映されます。

なお、8ビットのデータを補数に変換するための命令として"CPL"命令(1の補数に変換)と"NEG"命令(2の補数に変換)が、8ビットの補数を16ビットに拡張するための命令として"SEP"命令が用意されています。

#### 例: NEG命令とSEP命令

| 命令        | B reg.    | A reg.    | Nフラグ |

|-----------|-----------|-----------|------|

| LD A,#127 | 0000 0000 | 0111 1111 | 0    |

| NEG A     | 0000 0000 | 1000 0001 | 1    |

| SEP       | 1111 1111 | 1000 0001 | 1    |

#### ----- 1の補数 -----

8ビット  $-N = 2^8 - 1 - N = 255 - N (= \bar{N})$

127 = 0111 1111b

126 = 0111 1110b

:

2 = 0000 0010b

1 = 0000 0001b

0 = 0000 0000b

-1 = 1111 1110b (= 1111 1111b - 0000 0001b)

-2 = 1111 1101b (= 1111 1111b - 0000 0010b)

:

-126 = 1000 0001b (= 1111 1111b - 0111 1110b)

-127 = 1000 0000b (= 1111 1111b - 0111 1111b)

#### ----- 16ビット -----

16ビット  $-N = 2^{16} - 1 - N = 65535 - N (= \bar{N})$

32767 = 0111 1111 1111 1111b

32766 = 0111 1111 1111 1110b

:

2 = 0000 0000 0000 0010b

1 = 0000 0000 0000 0001b

0 = 0000 0000 0000 0000b

-1 = 1111 1111 1111 1111b

(= 1111 1111 1111 1111b - 0000 0000 0000 0001b)

-2 = 1111 1111 1111 1101b

(= 1111 1111 1111 1111b - 0000 0000 0000 0010b)

:

-32767 = 1000 0000 0000 0001b

(= 1111 1111 1111 1111b - 0111 1111 1111 1111b)

-32768 = 1000 0000 0000 0000b

(= 1111 1111 1111 1111b - 0111 1111 1111 1111b)

## 補数演算とV(オーバーフロー)フラグ

アドレス計算などの絶対値による演算の場合、8ビットでは0~255、16ビットでは0~65535の範囲で正しい演算結果が得られます。演算によりオーバーフローあるいはアンダーフローが発生し範囲を外れた場合は、C(キャリー)フラグが'1'にセットされます。

演算数、被演算数が補数になっている場合の正しい演算結果の範囲は、8ビットが-128~127、16ビットが-32768~32767となり、Cフラグのみでは演算結果が正しいかどうか判断できません。この判断を行うためにV(オーバーフロー)フラグが設定されており、補数表現の範囲を越えた場合にVフラグが'1'にセットされます。

なお、ALUは絶対値演算、補数演算を区別してはいませんので、Cフラグ、Vフラグのセット/リセットは単に演算結果が上記の範囲内にあるかどうかで行われます。したがって、絶対値演算においてもVフラグが'1'にセットされる場合があります。この場合のVフラグは意味を持ちませんので、プログラムでVフラグを確認する必要はありません。Vフラグでオーバーフローが判断できるのは補数演算の場合に限られますので、アプリケーションで扱うデータが符号付きかどうかを判断してください。

以下に8ビットの演算例とその演算結果によるVフラグ、Cフラグの変化を示します。

### 例: "ADD A,B"命令による加算例

| A reg.    | B reg.    | 結果(A reg.) | Vフラグ | Cフラグ |

|-----------|-----------|------------|------|------|

| 0101 1010 | 1010 0101 | 1111 1111  | 0    | 0    |

| 0101 1011 | 1010 0101 | 0000 0000  | 0    | 1    |

| 0101 1011 | 0010 0101 | 1000 0000  | 1    | 0    |

### "SUB A,B"命令による減算例

| A reg.    | B reg.    | 結果(A reg.) | Vフラグ | Cフラグ |

|-----------|-----------|------------|------|------|

| 0101 1010 | 0101 1010 | 0000 0000  | 0    | 0    |

| 0101 1010 | 0101 1011 | 1111 1111  | 0    | 1    |

| 0101 1010 | 1101 1010 | 1000 0000  | 1    | 1    |

## 2.2.5 10進演算とアンパック演算 ///////////////

S1C88では以下の8ビット演算命令実行時、通常の16進演算の他に10進演算、アンパック演算、およびその組み合わせによって演算を行うように設定することができます。この設定はD(デシマル)フラグ、U(アンパック)フラグによって行います。

### 10進演算とアンパック演算が可能な演算命令

|     |     |     |     |     |

|-----|-----|-----|-----|-----|

| ADD | ADC | SUB | SBC | NEG |

|-----|-----|-----|-----|-----|

いずれも8ビット演算命令で、命令セット一覧表等ではDフラグ、Uフラグの部分に" "を付けて、10進演算、アンパック演算が可能であることを示しています。

### 10進演算

Dフラグを'1'にセットして8ビット算術演算(ADD、ADC、SUB、SBC、NEG)命令を実行すると、2桁の10進演算が行われます。演算結果はBCD(2進化10進数)コードで得られます。

10進演算を行う場合は演算命令の実行前に"OR SC,#00010000B"命令等でDフラグを'1'に設定します。また、演算数および被演算数はBCDコードが対象となりますので、BCDコードを設定してから演算を実行してください。BCDコードになっていない場合は、正しい結果が得られません。

### 10進演算時のSCフラグ

10進演算実行後、演算結果によってSCのN/V/C/Zフラグは下記のように設定されます。

N: 常時 リセット(0)

V: 常時 リセット(0)

C: 2桁の10進数に対して

桁上げまたは桁借りがあったとき セット(1)

桁上げまたは桁借りがないとき リセット(0)

Z: 演算結果=0のとき セット(1)

演算結果≠0のとき リセット(0)

### 例: "ADD A,B"命令による10進演算例

| A reg. | B reg. | A reg.(和) | SC |   |   |   |

|--------|--------|-----------|----|---|---|---|

|        |        |           | N  | V | C | Z |

| 55     | 28     | 83        | 0  | 0 | 0 | 0 |

| 74     | 98     | 72        | 0  | 0 | 1 | 0 |

### "SUB A,B"命令による10進演算例

| A reg. | B reg. | A reg.(差) | SC |   |   |   |

|--------|--------|-----------|----|---|---|---|

|        |        |           | N  | V | C | Z |

| 55     | 55     | 00        | 0  | 0 | 0 | 1 |

| 55     | 28     | 27        | 0  | 0 | 0 | 0 |

| 74     | 98     | 76        | 0  | 0 | 1 | 0 |

### アンパック演算

Uフラグを'1'にセットして8ビット算術演算(ADD、ADC、SUB、SBC、NEG)命令を実行すると、下記に示すアンパック形式での演算を行うことができます。

アンパック演算は、上位4ビットのデータを無視し、下位4ビットのみを対象に演算を行います。実行後は下位4ビットのみの演算結果が出力され、上位4ビットは'0'が出力されます。

アンパック演算は、メモリ1アドレスに対して1桁のデータを格納するため、演算項の桁合わせが容易に行えます。(この場合の桁合わせはメモリアドレスのポインティングのみとなります。)

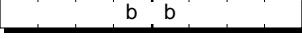

#### <ADD命令の例>

|   | MSB | 2 <sup>4</sup> | 2 <sup>3</sup> | LSB |             |

|---|-----|----------------|----------------|-----|-------------|

|   |     | 不定データ          | 被加数            |     | レジスタ or メモリ |

| + |     | 不定データ          | 加数             |     | レジスタ or メモリ |

|   |     | 0              | 結果(和)          |     | レジスタ or メモリ |

#### アンパック演算時のSCフラグ

アンパック演算は下位4ビットデータのみを対象にしますので、SCフラグも下位4ビットの演算結果によって変化します。

アンパック演算実行後、演算結果によってSCのN/V/C/Zフラグは下記のように設定されます。

N: 2<sup>3</sup>ビットが'1'のとき セット(1)

2<sup>3</sup>ビットが'0'のとき リセット(0)

V: 4ビットの補数表現(-8 ~ 7)

を越えたとき セット(1)

以内のとき リセット(0)

C: 2<sup>3</sup>ビットからの桁上げ、2<sup>3</sup>ビットへの桁借りが

あったとき セット(1)

ないとき リセット(0)

Z: 下位4ビット=0のとき セット(1)

下位4ビット≠0のとき リセット(0)

### アンパック演算補助命令

アンパック形式とパック形式(通常の8ビットデータ形式)を相互に変換する"PACK"、"UPCK"命令が用意されており、容易にフォーマット変換ができます。

PACK命令: BAレジスタのアンパック形式データをパック形式に変換し、Aレジスタに格納します。

| B reg. | A reg. | A reg. |

|--------|--------|--------|

| * m *  | n      | m n    |

#### 例: PACKの実行例

| 設定値              | 結果            | SC            |

|------------------|---------------|---------------|

| BA reg.<br>38C4H | A reg.<br>84H | N V C Z<br>不变 |

UPCK命令: Aレジスタの8ビットデータをアンパック形式に変換し、BAレジスタに格納します。

| A reg. | B reg. | A reg. |

|--------|--------|--------|

| m n    | 0 m 0  | n      |

#### 例: UPCKの実行例

| 設定値           | 結果               | SC            |

|---------------|------------------|---------------|

| A reg.<br>84H | BA reg.<br>0804H | N V C Z<br>不变 |

#### 例: "ADD A,B"命令によるアンパック演算例

| 設定値           | 結果            | SC               |

|---------------|---------------|------------------|

| A reg.<br>20H | B reg.<br>D0H | A reg.(和)<br>00H |

| 0             | 0             | N                |

| 0             | 0             | V                |

| 0             | 0             | C                |

| 1             | 0             | Z                |

2.2.6 乗除算 ////////////////////////////////////////////////

S1C88のMODEL1およびMODEL3は乗除算機能を持っています。MODEL0およびMODEL2ではこの機能および以下に説明する乗除算命令は使用できません。

### 乗算

乗算はMLT命令によって行います。

MLT命令を実行すると、Lレジスタ×Aレジスタの演算が行われ、積がHLレジスタに格納されます。この演算結果により、SCのN/V/C/Zフラグは次のように設定されます。

N: HLレジスタ(積)の最上位ビットが

'1'のとき セット(1)

'0'のとき リセット(0)

V: 常時 リセット(0)

C: 常時 リセット(0)

Z: HLレジスタ(積)が

0000Hのとき セット(1)

0000H以外のとき リセット(0)

以下にMLT命令の実行例を示します。

| 設定値    |        |            | 結果 SC |   |   |   |

|--------|--------|------------|-------|---|---|---|

| L reg. | A reg. | HL reg.(積) | N     | V | C | Z |

| 00H    | 64H    | 0000H      | 0     | 0 | 0 | 1 |

| 64H    | 58H    | 2260H      | 0     | 0 | 0 | 0 |

| C8H    | 58H    | 44C0H      | 0     | 0 | 0 | 0 |

| A5H    | 93H    | 5EBFH      | 0     | 0 | 0 | 0 |

| C8H    | A5H    | 80E8H      | 1     | 0 | 0 | 0 |

乗算は上記の設定値を符号なし8ビットデータとして扱い、符号なしの演算を行いますので、演算結果により設定されるNフラグは符号を表しません。したがって、上記例のC8H×A5Hのように負の数どうしの乗算を行った場合でも、Nフラグが'0'に設定されないことがあります。

### 除算

除算はDIV命令によって行います。

DIV命令を実行すると、HLレジスタ÷Aレジスタの演算が行われ、商がLレジスタに、剰余がHレジスタに格納されます。

商が8ビットを越える場合はV(オーバーフロー)フラグがセットされ、HLレジスタの内容は被除数が保持されます。

Aレジスタに'0'を設定してDIV命令を実行した場合はゼロ除算例外処理が発生します。

この演算結果により、SCのN/V/C/Zフラグは次のように設定されます。

N: Lレジスタ(商)の最上位ビットが

'1'のとき セット(1)

'0'のとき リセット(0)

V: 商が8ビット以内に

納まらないとき セット(1)

納まるとき リセット(0)

C: 常時 リセット(0)

Z: Lレジスタ(商)が

00Hのとき セット(1)

00H以外のとき リセット(0)

### SCの動作例

| 設定値     |        | SC |   |   |   | 備考     |

|---------|--------|----|---|---|---|--------|

| HL reg. | A reg. | N  | V | C | Z |        |

| nz      | nz     | ↑  | ↑ | 0 | ↑ |        |

| 0000H   | nz     | 0  | 0 | 0 | 1 |        |

| nz      | 00H    | 1  | 1 | 0 | 0 | ゼロ除算   |

| 0000H   | 00H    | 1  | 1 | 0 | 0 | 例外処理発生 |

nzは'0'以外の8ビットまたは16ビットデータを表します。

### 除算実行例

以下にDIV命令の実行例を示します。

| 設定値     |        | 結果 SC |       |        |   |   |   |   |

|---------|--------|-------|-------|--------|---|---|---|---|

| HL reg. | A reg. | L(商)  | H(剰余) | A reg. | N | V | C | Z |

| 1A16H   | 64H    | 42H   | 4EH   | 64H    | 0 | 0 | 0 | 0 |

| 332CH   | 64H    | 83H   | 00H   | 64H    | 1 | 0 | 0 | 0 |

| 0000H   | 58H    | 00H   | 00H   | 58H    | 0 | 0 | 0 | 1 |

| 0301H   | 02H    | 01H   | 03H   | 02H    | 1 | 1 | 0 | 0 |

上記例の0301H ÷ 02Hは商が8ビットを越えるため、HLレジスタの値が保持され結果が出力されません。このような場合は、下記のように被除数を上位8ビット、下位8ビットに分離して除算を行います。

### <0301H ÷ 02Hの実行例>

```

LD  HL,#0003H ;被除数=上位8ビット

LD  A,#02H      ;除数

DIV                      ;L=商, H=剰余

LD  [hhll],L          ;商(上位8ビット)をメモリに格納

LD  L,#01H          ;被除数=Hレジスタ+下位8ビット

DIV                      ;

```

| 設定値     |        | 結果 SC |       |        |   |   |   |   |

|---------|--------|-------|-------|--------|---|---|---|---|

| HL reg. | A reg. | L(商)  | H(剰余) | A reg. | N | V | C | Z |

| 0003H   | 02H    | 01H   | 01H   | 02H    | 0 | 0 | 0 | 0 |

| 0101H   | 02H    | 80H   | 01H   | 02H    | 1 | 0 | 0 | 0 |

商 : 0180H

剰余: 01H

## 2.3 プログラムメモリ

### 2.3.1 プログラムメモリの構成

S1C88のアドレス空間16Mバイトの中で前半の8Mバイト(アドレス000000H ~ 7FFFFFFH)がプログラミング領域として使用できるようになっています。ただし、MODEL0とMODEL1についてはアドレス空間が最大64Kバイトのため、プログラミング領域もそれ以内に制限されます。

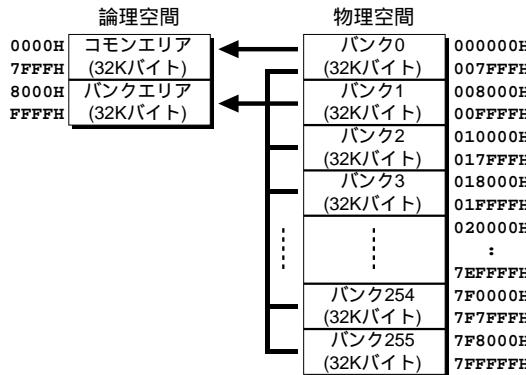

8ビットCPUの論理空間64Kバイトを越えるメモリを管理するため、S1C88ではバンクマッピング方式を採用しています。最大8Mバイトのプログラムメモリはバンク0 ~ バンク255まで、それぞれ32Kバイトのバンクに分割されます。

64Kバイトの論理空間上には2つのバンクがアドレス0000H ~ FFFFHとして論理的に連続するように配置され、そのアドレス空間内でプログラムを実行します。論理空間内のアドレスングはPC(プログラムカウンタ)が行います。

論理空間のアドレス0000H ~ 7FFFHにはコモンバンクとしてバンク0(アドレス000000H ~ 007FFFH)が配置され、この物理アドレスは常時固定となります。アドレス000000H ~ 0000FFHは例外処理(割り込み等)のベクタが割り付けられます。

#### ☞ "3.5.2 例外処理要因とベクタ"

コモンエリアが固定のため、各バンクに例外処理ベクタを割り付ける必要はありません。また、汎用的なサブルーチン等もコモンエリアに記述することができます。

後半のアドレス8000H ~ FFFFHのバンクエリアにはCB(コードバンク)レジスタで選択されるバンクが配置されます。この部分に配置するバンクはプログラムで任意に選択できます。ただし、MODEL0とMODEL1についてはバンク1に固定、MODEL2とMODEL3のミニマムモードについては任意に選択された1つのバンクに固定されます。

### 2.3.2 PC(プログラムカウンタ)と

#### CB(コードバンク)レジスタ

PC(プログラムカウンタ)は実行するプログラムのアドレスを保持しています。PCの内容は64Kバイトの論理空間内のアドレスで、物理アドレスが連続しない32Kずつのコモンエリアとバンクエリアを論理的に連続したプログラムメモリとしてアドレスングしています。

コモンエリアは物理アドレスのバンク0に固定されていますが、バンクエリアは256バンクの中から任意の1バンクを選択できるようになっています。(MODEL2とMODEL3)

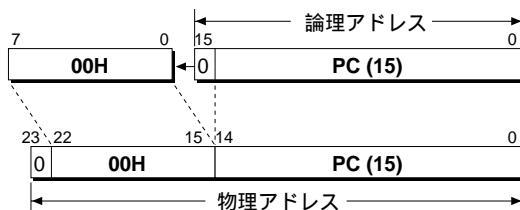

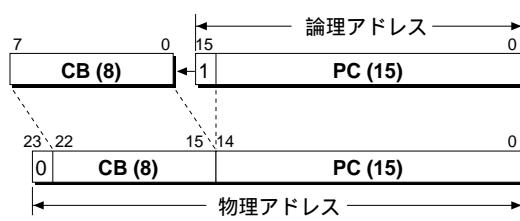

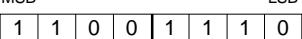

このバンクエリアに割り当てるバンクアドレス(0 ~ 255)を示すレジスタがCB(コードバンク)です。実際にメモリをアクセスするためにアドレスバスに出力される物理アドレスはCPU内部で図2.3.2.1のように生成されます。

#### コモンエリアのアクセス (0000H ~ 7FFFH)

#### バンクエリアのアクセス (8000H ~ FFFFH)

図2.3.2.1 論理アドレスと物理アドレス(MODEL2/3)

図に示すとおり、16ビットのPCの中でアドレスバスに出力されるのは最上位ビットを除く15ビットです。その内容はアドレスバスのA00 ~ A14に出力されます。PCの最上位ビットは'0'でコモンエリア、'1'でバンクエリアを示しており、この内容によってCBをアドレスバスに出力するかどうかを決定します。コモンエリアの場合はアドレスバスのA15 ~ A22に00Hが出力され、バンクエリアの場合はCBの内容8ビットが出力されます。アドレスバスのA23はデータメモリ領域専用で、最大8Mバイトのプログラムメモリアクセス時には常時'0'を出力します。以上のようにPCの最上位ビットはアドレスバスに出力されませんので、システム開発時には注意してください。

MODEL0とMODEL1についてはアドレスバスが16ビットのため、PCの内容がそのまま出力されます。

"LD BA,PC"命令、"LD HL,PC"命令のPC値

"LD BA,PC"命令、"LD HL,PC"命令はPC値をBAレジスタおよびHLレジスタに読み込む命令です。読み込むPC値を"PC"、本命令の置かれている先頭アドレスを"PC"とすると、

$$\text{PC} \quad \text{PC} + 2$$

で示されるPC値がBAおよびHLレジスタに読み込まれます。たとえば、"LD BA,PC"命令が100H番地に置かれているとすると、BAレジスタには102Hが読み込まれます。

### 2.3.3 バンク管理

プログラムの実行は基本的に論理空間に割り当てられたバンク内に限られています。バンクが変更されるのは、プログラムによって分岐命令が実行される時点での他のバンクが指定されている場合です。

注! プログラムの実行によりPCのカウントがオーバーフローした場合でもCBは更新されません。再びコモンエリアの先頭からの実行となります。

以下にバンク指定の方法と、分岐命令実行時の動作について説明します。

なお、バンク変更にかかる記載事項はMODEL2およびMODEL3にのみ摘要されます。

#### リセット時のバンク設定

イニシャルリセット時にCBは'1'に初期化され、バンクエリアにはバンク1が割り当てられます。

コモンエリアはバンク0に固定されますので、論理アドレスは物理アドレスと同様になります。

この設定は別のバンクがプログラムで指定され、分岐命令によって実際に分岐が行われるまで変更されません。

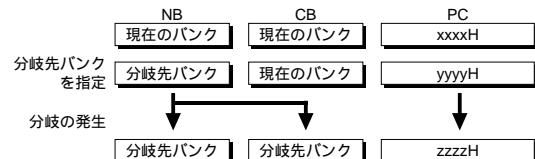

#### バンクの指定

選択されているバンクを示すCBはプログラムによって直接変更することはできません。

バンク指定用にはNB(ニューコードバンク)レジスタが用意されており、分岐命令実行直前に分岐先のバンクアドレス(0~255)を以下の命令によって書き込んでおきます。

LD NB,A (Aレジスタによる指定)

LD NB,#bb(8ビット即値データによる指定)

NBの内容はその直後の分岐命令の実行により実際に分岐が行われる時点でCBにロードされ、新たなバンクがバンクエリアに選択されます。条件ジャンプなどにおいて条件が合わずに分岐が行われない場合は、CBの内容が逆にNBにロードされます。

したがって、NBに値を設定せずに分岐命令を実行した場合はその時点の論理空間内に分岐するようになっています。

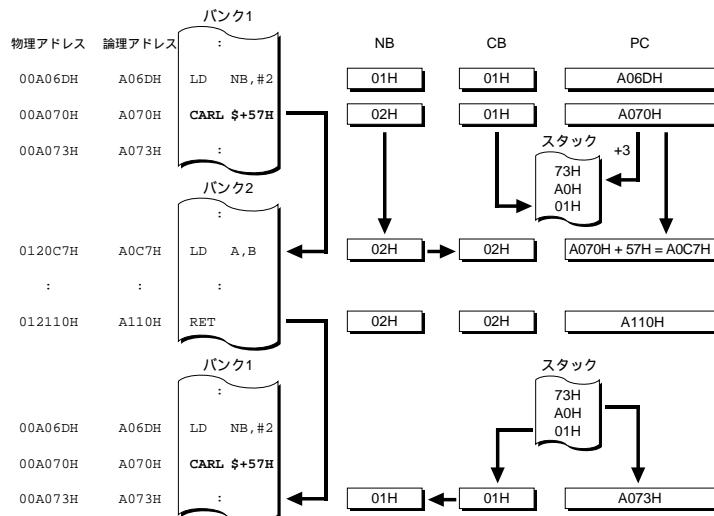

図2.3.3.1 バンクの変更

### 2.3.4 分岐命令

分岐命令はPCとCBを変更してプログラムを任意のアドレスに分岐させます。分岐命令の種類は動作の違いにより、以下のように分類されます。

表2.3.4.1 分岐命令の種類

| 種類         | 条件     | 命令            |

|------------|--------|---------------|

| PC相対ジャンプ   | 条件/無条件 | JRS、JRL、DJR   |

| 間接ジャンプ     | 無条件    | JP            |

| PC相対コール    | 条件/無条件 | CARS、CARL     |

| 間接コール      | 無条件    | CALL          |

| リターン       | 無条件    | RET、RETS、RETE |

| ソフトウェア割り込み | 無条件    | INT           |

上記の分岐命令それぞれの中にも無条件に分岐する無条件分岐命令とフラグの状態によって分岐する数種類の条件分岐命令があります。

条件分岐命令の条件が満たされていない場合は、分岐が行われずにその分岐命令の次の命令を実行します。

☞ "4.4 命令の詳細説明"

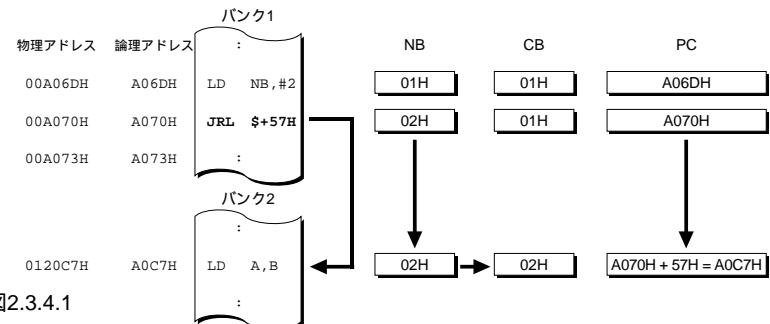

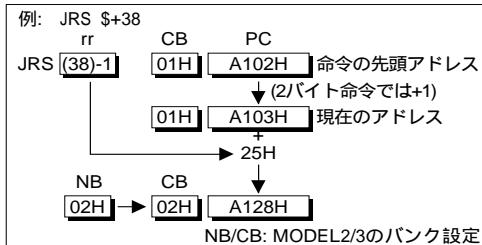

#### PC相対ジャンプ命令(JRS、JRL、DJR)

PC相対ジャンプはPCにオペランドで指定された相対アドレスを加え、そのアドレスに分岐させる命令で、リロケータブルなプログラミングを可能にしています。

相対アドレスは分岐実行時のアドレスから分岐先アドレスまでのディスプレースメントで、1または2バイトで指定します。

指定できる相対アドレスは"JRS"命令、"DJR"命令が8ビット補数表現の-128~127、"JRL"命令が16ビット補数表現の-32768~32767の範囲です。

なお、この相対アドレスはPCに加算されるため分岐先のアドレスは論理アドレスとなります。直前のNBの設定によって他のバンクにも分岐できますが、分岐先はあくまでも論理空間内で物理的な相対アドレスの指定はできません。

図2.3.4.1にPC相対ジャンプの動作を示します。

"JRS"命令は無条件ジャンプと20種類の条件ジャンプ命令が設定されています。

"JRL"命令は無条件ジャンプと4種類の条件ジャンプ命令が設定されています。

図2.3.4.1

PC相対ジャンプの動作 (MODEL2/3の例)

"DJR NZ,rr"命令はBレジスタの'1'減算を行い、その結果が"0"以外の場合に"JRS"の無条件ジャンプ命令を実行します。この命令によって、Bレジスタをカウンタとしたその初期値分の繰り返しルーチンが簡単に記述できます。

例: 50 cycle時間のウェイトルーチン

LD B,#12 ;初期値をBレジスタにセット(2 cycle)

DJR NZ,\$ ;Bレジスタが0になるまで繰り返す(48 cycle)

### 間接ジャンプ命令(JP)

間接ジャンプは分岐先のアドレスを間接的に指定する命令です。

"JP [kk]"命令はアドレス00kk(kk=00H ~ FFH、ページは'0'固定)のメモリの内容をPCの下位8ビットに、アドレス00kk+1のメモリの内容をPCの上位8ビットにそれぞれロードして、そのアドレスに無条件に分岐します。ここで指定するアドレス00kkは例外処理やソフトウェア割り込みのベクタ領域となっています。

"JP HL"命令はHLレジスタの内容をアドレスとして無条件に分岐します。この命令は演算結果等をそのまま分岐先アドレスにすることができるため、ジャンプテーブルの作成などに有効です。

### PC相対コール命令(CARS、CARL)

PC相対コールはPCにオペランドで指定された相対アドレスを加え、そのアドレスからのサブルーチンをコールする命令です。

相対アドレスは分岐実行時のアドレスから分岐先アドレスまでのディスプレースメントで、1または2バイトで指定します。

指定できる相対アドレスは"CARS"命令が8ビット補数表現の-128 ~ 127、"CARL"命令が16ビット補数表現の-32768 ~ 32767の範囲です。

なお、この相対アドレスはPCに加算されるため分岐先のアドレスは論理アドレスとなります。直前のNBの設定によって他のバンクにも分岐できますが、分岐先はあくまでも論理空間内で物理的な相対アドレスの指定はできません。

サブルーチンコール実行時にはリターン情報としてPC値(コール命令の次の命令の先頭アドレス)がスタックに退避されます。

MODEL2/3のマキシマムモードではPC値以外にCB値もスタックに退避され、リターン時にはコール元のバンクに戻るようになっています。

MODEL2/3のミニマムモードではMODEL0/1と同様、PC値のみのスタックとなるため、64Kバイト以上のプログラムメモリを使用することはできません。

図2.3.4.2にPC相対コールの動作を示します。

"CARS"命令は無条件コールと20種類の条件コール命令が設定されています。

"CARL"命令は無条件コールと4種類の条件コール命令が設定されています。

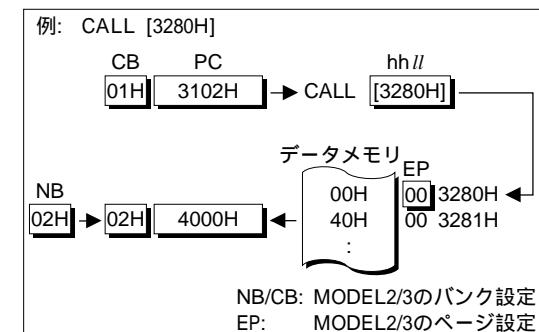

### 間接コール命令(CALL)

間接コールはサブルーチンのアドレスを間接的に指定するコール命令です。

"CALL [hhll]"命令はアドレスhhll(hhll=0000H ~ FFFFH、ページはEPレジスタによって指定)のメモリの内容をPCの下位8ビットに、アドレスhhll+1のメモリの内容をPCの上位8ビットにそれぞれロードして、そのアドレスのサブルーチンを無条件にコールします。

サブルーチンコール実行時にはPC相対コールと同様、リターン情報としてPC値(コール命令の次の命令の先頭アドレス)とCB値(MODEL2/3マキシマムモードの場合)がスタックに退避されます。

### リターン命令(RET、RETS、RETE)

リターン命令はコール命令によって呼び出されたサブルーチンからコール元のルーチンに戻るための命令です。

リターン命令はサブルーチンコール実行時にスタックに退避されているPC値(コール命令の次の命令の先頭アドレス)を元に戻します。MODEL2/3のマキシマムモードではCB値の復帰も行われ、コールしたバンクに戻ります。

MODEL2/3のミニマムモードではMODEL0/1と同様、PC値のみ復帰します。

図2.3.4.2 PC相対コールの動作 (MODEL2/3マキシマムモードの例)

ミニマムモードでコール命令の実行時、または実行後にバンクの変更を行っている場合は、リターン命令を実行しても正常なアドレスへ戻ることはできません。

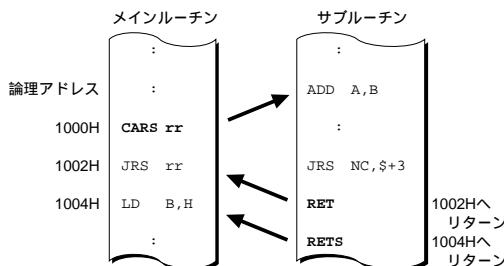

"RET"命令はリターン情報そのままに、コール命令の次の命令の先頭アドレスに処理を戻します。

"RETS"命令はリターン情報のPC値に'2'を加えてリターンしますので、コール命令の次の2バイト命令をスキップすることができます。

図2.3.4.3 サブルーチンからのリターン

"RETE"命令はソフトウェア割り込みルーチンや例外処理ルーチン専用のリターン命令で、リターン情報にSC(システムコンディションフラグ)の内容が含まれていることが"RET"命令との違いです。

☞ "3.5 例外処理状態"

#### ソフトウェア割り込み命令(INT)

ソフトウェア割り込み"INT [kk]"はアドレス00kk (kk=00H ~ FFH、ページは0'固定)のベクタアドレスを指定して、その割り込みルーチンを実行させる命令です。間接コール命令の一種ですが、分岐前にSC(システムコンディションフラグ)もスタックに退避されます。したがって、この命令により実行される割り込みルーチンは必ず"RETE"命令でリターンする必要があります。

☞ "3.5 例外処理状態"

#### 相対分岐命令のPC値

JRS命令、CARS命令、DJR命令

JRS命令、CARS命令、DJR命令は符号付き8ビットPC相対ジャンプ命令で、PC値に相対値rr(-128 ~ 127)を符号付きで加算し分岐先を決定します。分岐先アドレスを"PC"、本命令の置かれている先頭アドレスを"PC"とすると、

$$PC \quad PC' + rr + (n-1)$$

となります。

ここでnは命令のバイト数を示します。たとえば、"JRS LE,rr"命令が100H番地に置かれているとすると分岐先アドレスは102H+rr番地となります。

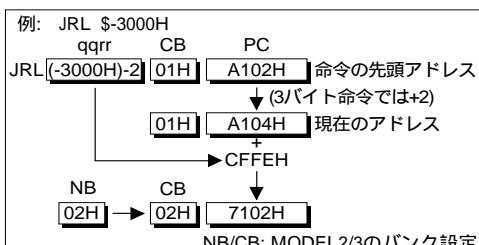

JRL命令、CARL命令

JRL命令、CARL命令は符号付き16ビットPC相対ジャンプ命令で、PC値に相対値qqrr(-32768 ~ 32767)を符号付きで加算し分岐先を決定します。分岐先アドレスを"PC"、本命令の置かれている先頭アドレスを"PC"とすると、

$$PC \quad PC' + qqrr + 2$$

となります。

たとえば、"JRL C,qqrr"命令が100H番地に置かれているとすると分岐先アドレスは102H+qqrr番地となります。

## 2.4 データメモリ

### 2.4.1 データメモリの構成 ///////////////

S1C88のアドレス空間(最大16Mバイト)の中でプログラムメモリとして使用する領域を除くすべてをデータメモリとして使用することができます。データメモリ領域にはRAMや表示メモリ、周辺回路を制御するI/Oメモリなどが配置されます。データメモリは64Kバイトを1つのページとして管理します。

図2.4.1.1にデータメモリの構成を示します。

MODEL0/1においてはアドレス空間が64Kバイトのため、ページによる管理を考慮する必要はありません。MODEL2/3は最大で256ページの構成となります。

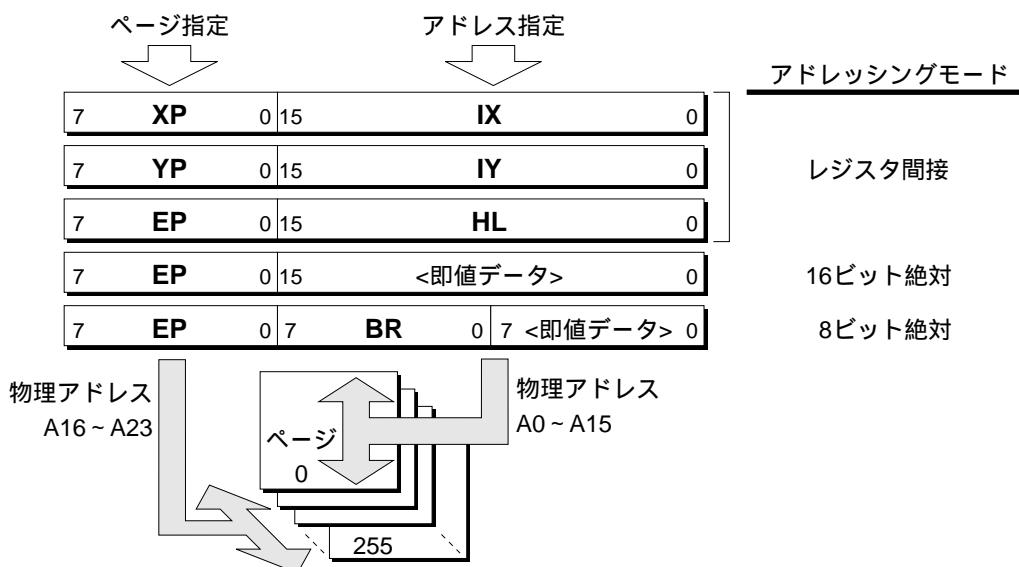

### 2.4.2 ページレジスタEP、XP、YP ///////////////

データメモリの物理空間は64Kバイトのページに論理的に区切られています。したがって、物理アドレスの上位8ビットがページ部、下位16ビットが論理アドレスとして管理されます。ページ内のアドレス指定はアレッシングモードにしたがってインデックスレジスタ、即値データ等によって行います。MODEL2とMODEL3にはページ部の指定用として3組のページレジスタEP、XP、YPが設定されており、アレッシングモードの指定にしたがって使い分けられます。図2.4.2.1にアレッシングモードとページレジスタの対応を示します。

☞ "4.1 アレッシングモード"

図2.4.1.1 データメモリの構成

図2.4.2.1 データメモリのアレッシング

### 2.4.3 スタック ////////////////

スタックはLIFO(Last In, First Out)形式でアクセスされるメモリで、S1C88ではデータメモリのRAM領域に割り当てられます。

スタックはサブルーチンコールや例外処理(割り込み)などが発生した場合にCPUのレジスタ情報を退避するのに使用されます。またプログラムの任意の場所でレジスタの退避等を行うことができます。以下、スタックにデータを記憶させることを"プッシュ"、記憶したデータを取り出すことを"ポップ"と記述します。

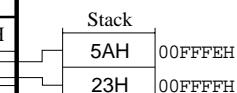

#### スタックポインタSP

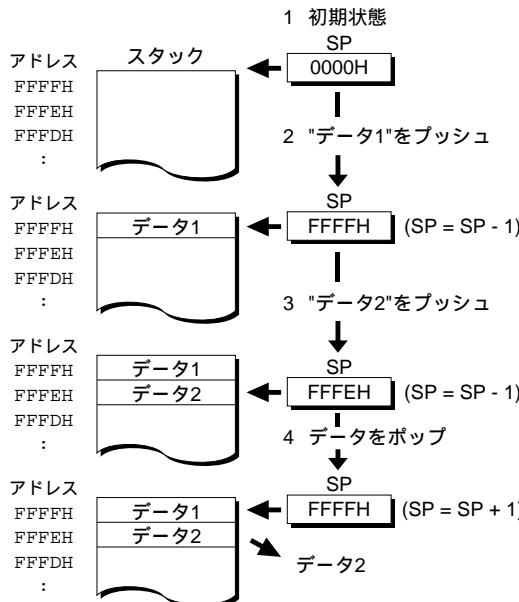

データはスタックの最上位アドレスから順番にプッシュされ、逆にデータを取り出すときには最後にプッシュされたデータから順にポップされます。このプッシュとポップを行うスタックのアドレスを示すレジスタがSP(スタックポインタ)です。

SPは1バイトデータのプッシュにより'1'減算(プリデクリメント)され、1バイトデータのポップにより'1'加算(ポストインクリメント)されます。

図2.4.3.1 スタックの動作

物理メモリ内でのスタックの位置は周辺回路からコアCPUに入力されるSPP0～SPP7(スタックポインタページ)信号によってページアドレスが決定され、スタックアクセス時にはSPP0～SPP7の内容がそのままアドレスバスのページ部(A16～A23)に出力されます。そのページ内のアドレスはSPによって指定されます。一般的にはSPの初期値としてアドレス0000Hを設定することにより、そのページの最終アドレスFFFFHから下位のアドレスに向かってデータが順にプッシュされます。

注! SP(スタックポインタ)はイニシャルリセット時は不定ですので、スタックが使用される前に必ずプログラム("LD SP, \*\*"命令)で初期化を行ってください。

#### サブルーチンコールとスタック

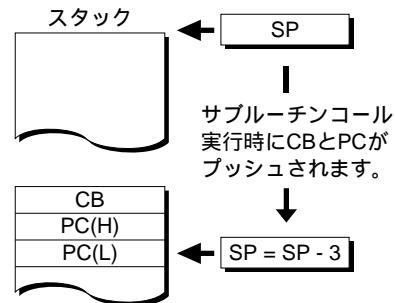

コール命令を実行すると、サブルーチンに分岐する前にリターンアドレスとしてコール命令の次の命令の先頭アドレスとCB(MODEL2/3のマキシマムモードの場合)がスタックにプッシュされます。スタックにプッシュされたリターン情報はリターン命令の実行によりポップされ、PCとCBに再設定されます。

サブルーチンの中からさらに別のサブルーチンをコールするようなネスティングはスタックが割り当てられたページの使用可能なメモリの範囲内で何レベルまででも可能です。

図2.4.3.2 サブルーチンコール実行時のスタック消費

MODEL2/3のマキシマムモードでは、サブルーチンコールによりスタックを3バイト(CB, PC)消費します。MODEL0/1およびMODEL2/3のミニマムモードではCBを除くPCの2バイト分を消費します。

#### 例外処理とスタック

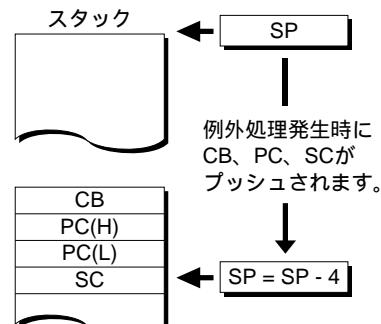

例外処理(割り込み等)発生時もサブルーチンコールと同様にリターン情報がスタックにプッシュされます。このときのリターン情報にはリターンアドレスPCとCB(MODEL2/3のマキシマムモード)のほかにSCも含まれます。

図2.4.3.3 例外処理発生時のスタック消費

MODEL2/3のマキシマムモードでは、例外処理の発生によりスタックを4バイト(CB、PC、SC)消費します。MODEL0/1およびMODEL2/3のミニマムモードではCBを除くPCとSCの3バイト分を消費します。

### その他のスタック操作

サブルーチンコールや例外処理(割り込み等)でのリターン情報のプッシュは自動的に行われますが、汎用レジスタのプッシュは行われません。サブルーチンや例外処理ルーチンから汎用レジスタの内容を分岐前の状態にして戻りたい場合は、ルーチンの最初と最後にそれぞれレジスタの内容をプッシュ/ポップする命令を配置する必要があります。

レジスタのプッシュ/ポップは"PUSH"命令と"POP"命令によって行えます。この命令によってプッシュ/ポップできるレジスタは以下のとおりです。

A、B、L、H、BR、SC、EP\*、IP(XPとYP)\*、

BA、HL、IX、IY

\*はMODEL0/1にはありません。

また、上記のSCを除くすべてのレジスタを1命令でプッシュする"PUSH ALL"、"PUSH ALE"命令と、1命令でポップする"POP ALL"、"POP ALE"命令も用意されています。

|            |                |           |               |

|------------|----------------|-----------|---------------|

| PUSH ALL = | <u>PUSH BA</u> | POP ALL = | <u>POP BR</u> |

|            | PUSH HL        |           | POP IY        |

|            | PUSH IX        |           | POP IX        |

|            | PUSH IY        |           | POP HL        |

|            | PUSH BR        |           | POP BA        |

| PUSH ALE = | <u>PUSH BA</u> | POP ALE = | <u>POP IP</u> |

|            | PUSH HL        |           | POP EP        |

|            | PUSH IX        |           | POP BR        |

|            | PUSH IY        |           | POP IY        |

|            | PUSH BR        |           | POP IX        |

|            | PUSH EP        |           | POP HL        |

|            | PUSH IP        |           | POP BA        |

オペランドの"All"はMODEL0/1用で、"ALE"はMODEL2/3で拡張されているレジスタEPとIP(XPとYP)のプッシュ/ポップも行います。

構造化プログラミングにおいてはサブルーチンに渡す引数などをスタック領域にストアするといったことがよく行われますが、上記の"PUSH"命令や"POP"命令を使用せずにSPを操作したりスタック領域の直接アクセスが容易に行える命令等も用意されています。

ADD、SUB、CP、INC、DEC、LD

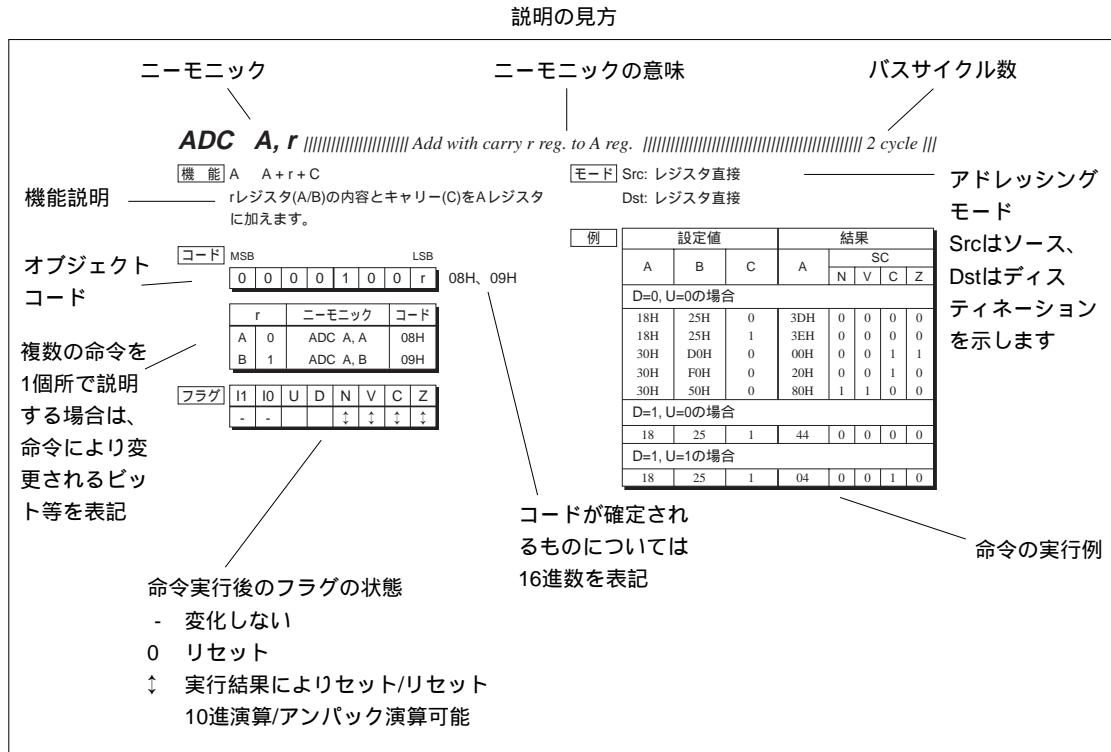

### 4.4 命令の詳細説明

注! スタックは汎用RAM領域に割り当てられますので、データ領域とスタック領域が重ならないよう注意してください。

### 2.4.4 メモリマップドI/O ///////////////////////////////

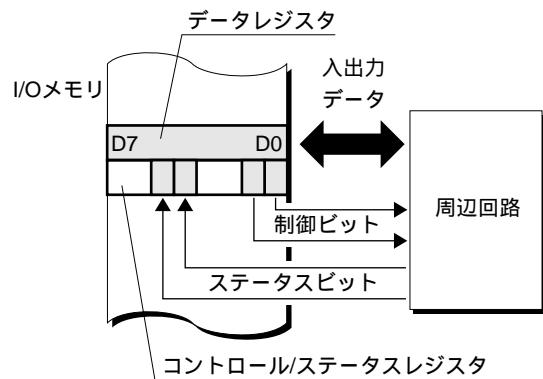

S1C88 FamilyはS1C88をコアCPUとして、その周辺に入出力ポート等、各種の回路を内蔵します。

S1C88では、それらの周辺回路の制御にメモリマップドI/O方式を採用しており、周辺回路の制御ビットやデータをやり取りするためのレジスタがデータメモリ領域に配置されます。

このメモリ領域を汎用RAMと区別するためにI/Oメモリと呼びますが、ページの管理やアクセスの方法はデータメモリと共通ですので、通常のメモリアクセスの命令を使って周辺回路を制御することができます。

図2.4.4.1 周辺回路とメモリマップドI/O

LCD ドライバ内蔵の機種ではデータメモリの一部をセグメントデータ用の表示メモリとして使用します。表示メモリ領域の各ビットはセグメントと1対1に対応し、ビットをオン/オフさせることにより対応したセグメントが点灯/消灯します。

このセグメントの制御も通常のメモリアクセスの命令で行うことができます。

注! 機種によってはI/Oメモリの一部や表示メモリがライトオンリーになっている場合があります。その場合、その部分を論理演算および算術演算命令等で直接ビット操作(リード/モディファイ/ライト)を行うことはできません。ビット操作を行う場合は同じ内容のバッファをリード/ライト可能なメモリ上に設定しておき、バッファ上でデータを変更してから本来のメモリに書き込みを行う必要があります。

周辺回路とI/Oメモリおよび表示メモリの詳細についてはS1C88 Familyの各機種のマニュアルを参照してください。

# 3 CPUの動作と処理状態

CPUはシステムクロックに同期して動作します。また、CPUの処理にはプログラムをシーケンシャルに実行している状態やスタンバイ状態等各種の状態があります。

ここでは割り込みなども含む各種の処理状態と、動作のタイミングについて説明します。

## 3.1 タイミングジェネレータとバス制御

はじめに、CPU動作の基準となるクロックとバスの制御について説明します。

### 3.1.1 バスサイクル

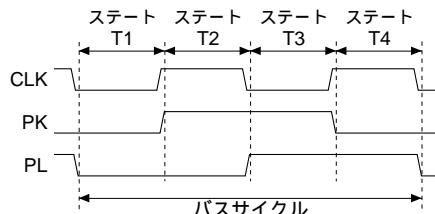

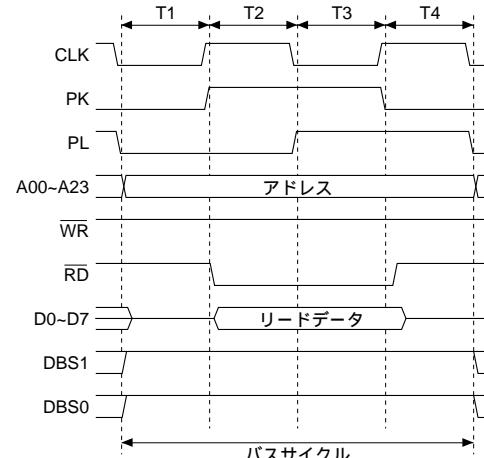

S1C88のタイミングジェネレータは入力されたクロックCLKから2相分周した信号PK、PLを作りCLKをステートに分解します。1ステートはCLKの1/2サイクルとなり、命令実行の単位となる1バスサイクルは4ステートの構成となります。

図3.1.1.1 ステートとバスサイクル

命令セット一覧表などでサイクルとして示された数値はこのバスサイクル数を表しています。

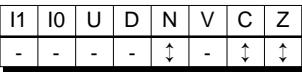

S1C88では各バスサイクルでのデータバスの状態を2ビットのステータス信号DBS0、DBS1で外部に出力しています。周辺回路はこの信号によってバスドライバの方向制御等を容易に行うことができます。

DBS0、DBS1により示されるデータバスのステートは表3.1.1.1のとおりです。

表3.1.1.1 データバスのステート

| DBS1 | DBS0 | ステート           |

|------|------|----------------|

| 0    | 0    | ハイインピーダンス      |

| 0    | 1    | 割り込みベクタアドレスリード |

| 1    | 0    | メモリライト         |

| 1    | 1    | メモリリード         |

以下に各バスサイクルのタイミングチャートを示します。

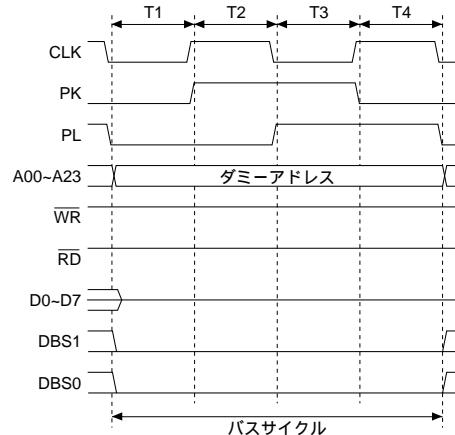

### ハイインピーダンス

内部レジスタアクセス時にはデータバスがハイインピーダンスとなります。また、読み出し信号RDと書き込み信号WRが共にHIGHレベルに固定され、アドレスバスはバスサイクルの期間中ダミーアドレスを出力します。

図3.1.1.2 内部レジスタアクセス時のバスサイクル

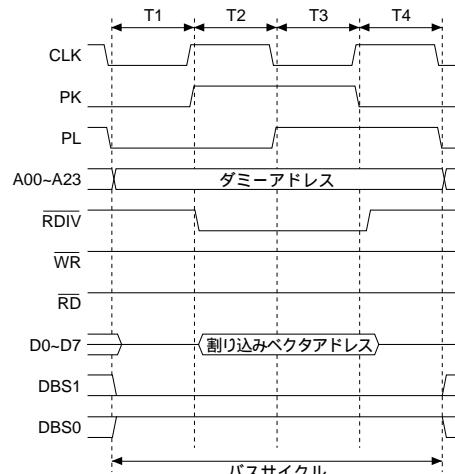

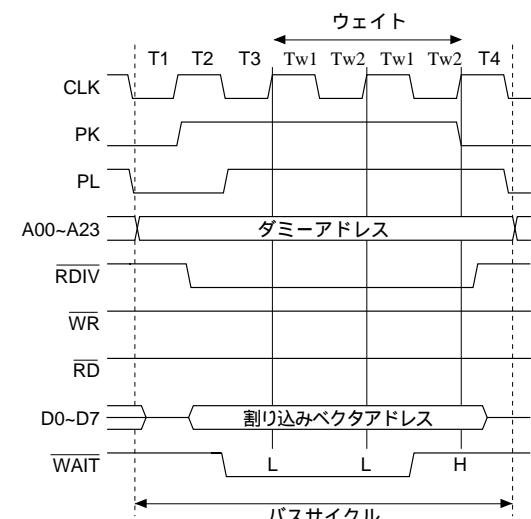

### 割り込みベクタアドレスリード

割り込みベクタアドレスはT2～T3ステートの間にデータバスから読み込まれます。

このリードに際しては読み出し信号RDが outputされず、割り込みベクタアドレス専用のリード信号RDIVが outputされます。アドレスバスはバスサイクルの期間中ダミーアドレスを出力します。

図3.1.1.3 割り込みベクタアドレスリード時のバスサイクル

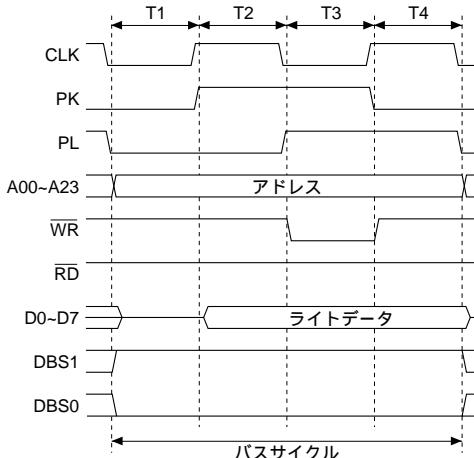

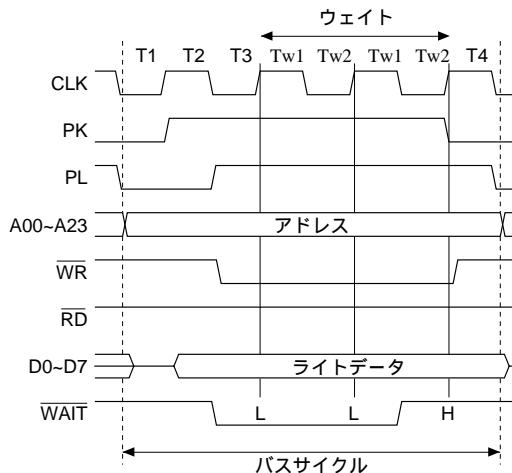

### メモリライト

メモリライト時はT2～T4ステートの間データバスに書き込みデータが出力され、T3ステートにおいて書き込み信号WRが出力されます。アドレスバスはバスサイクルの期間中対象アドレスを出力します。

図3.1.1.4 メモリライト時のバスサイクル

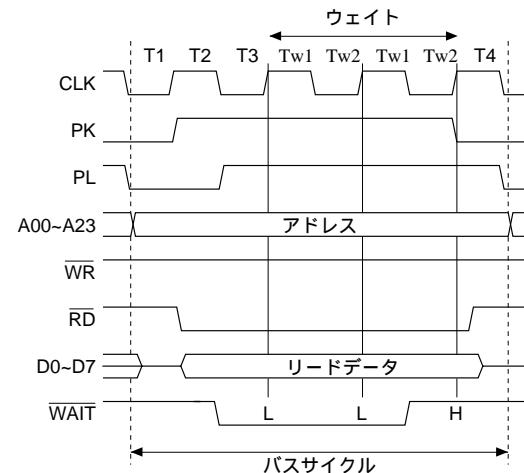

### メモリリード

メモリリード時はT2～T3ステートの間読み出し信号RDが出力され、データバス上のデータを読み込みます。アドレスバスはバスサイクルの期間中対象アドレスを出力します。

図3.1.1.5 メモリリード時のバスサイクル

### 3.1.2 ウェイットステート

S1C88はバスラインに接続された低速デバイスのアクセスを確実に行うために、ウェイットステートを挿入してバスサイクルを伸ばすことができます。

S1C88ではウェイットステートとしてアクセスタイム伸長用のウェイトを挿入する機能を持っており、WAIT端子の入力信号によってその制御を行います。

WAIT信号のサンプリングは、T3ステートのCLKの立ち上がりエッジで行われます。このときのWAIT信号がLOWレベルの場合にT3ステートとT4ステートの間にウェイットステートTw1、Tw2を挿入し、アクセスタイムを伸ばします。WAIT信号がHIGHレベルの場合、ウェイットステートは挿入されません。ウェイットステートTw1、Tw2はWAIT信号がLOWレベルの間、連続して挿入されます。ウェイットステートの挿入を解除するためのサンプリングはTw2ステートのCLKの立ち上がりエッジで行われ、WAIT信号がHIGHレベルに戻っている場合は以降のウェイットステートが挿入されずにT4ステートを開始します。

なお、ウェイットステートはメモリ空間上に接続されたデバイスをアクセスするときにのみ挿入され、内部レジスタをアクセスするときには挿入されません。

以下に、割り込みベクタアドレスリード、メモリライト、メモリリードの各サイクルにおけるウェイットステート挿入のタイミングチャートを示します。

図3.1.2.1 割り込みベクタアドレスリードサイクルのウェイット挿入

図3.1.2.2 メモリライトサイクルのウェイト挿入

図3.1.2.3 メモリリードサイクルのウェイト挿入

### 3.2 処理状態の概要

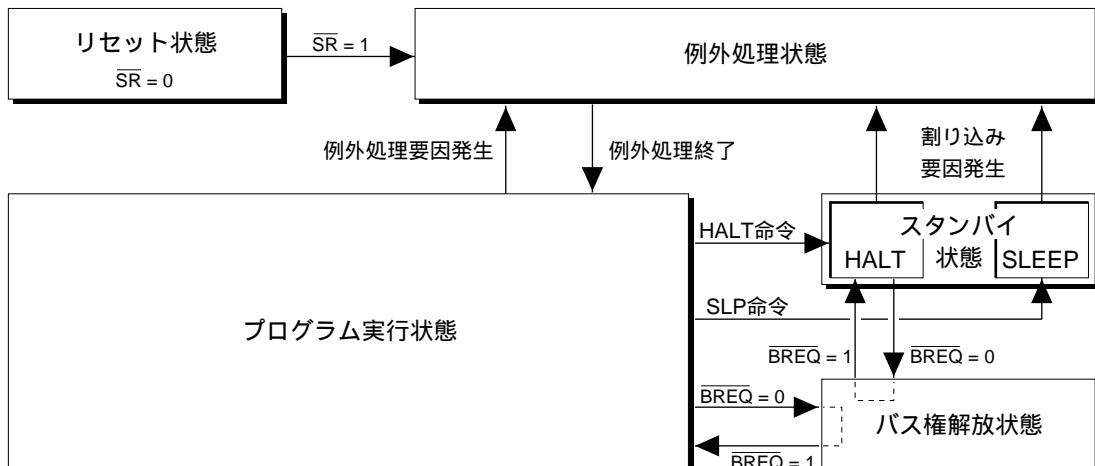

S1C88の動作をその処理の内容により分類するリセット状態、プログラム実行状態、例外処理状態、バス権解放状態、スタンバイ状態の5種類になります。

表3.2.1に処理状態の分類を、図3.2.1に状態遷移図を示します。

表3.2.1 処理状態の分類

| 処理状態      |       | 概 要                                                                                |

|-----------|-------|------------------------------------------------------------------------------------|

| リセット状態    |       | CPUがリセットされ、停止している状態                                                                |

| プログラム実行状態 |       | CPUがプログラムを順次実行している状態                                                               |

| 例外処理状態    |       | リセット、割り込み等の例外処理要因によって起動される例外処理(ペクタアドレスのフェッチ、PCとSCの退避、PCに対する分岐アドレスの設定)を実行している過渡的な状態 |

| バス権解放状態   |       | 外部からのバス権要求信号により外部バスを解放している状態                                                       |

| スタンバイ状態   | HALT  | CPUを停止し、消費電力を低減させている状態                                                             |

|           | SLEEP | CPUおよび周辺回路を停止し、消費電力を低減させている状態                                                      |

図3.2.1 状態遷移図

### 3.3 リセット状態

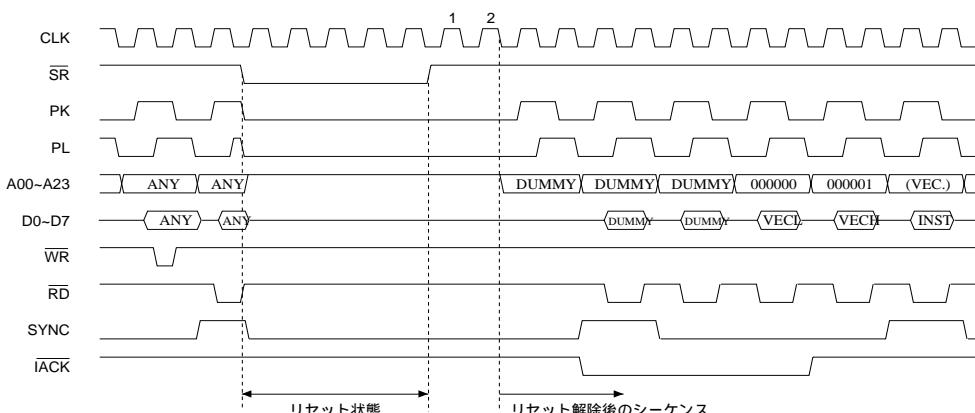

リセット状態とは、S1C88がリセットされ停止している状態を示します。SR端子にLOWレベルを入力することによりS1C88がリセットされます。リセットはCLKと非同期に行われますので、すべての処理状態から即時リセット状態に移行します。

リセットにより一部の内部レジスタが初期化されます。表3.3.1にレジスタの初期設定値を示します。

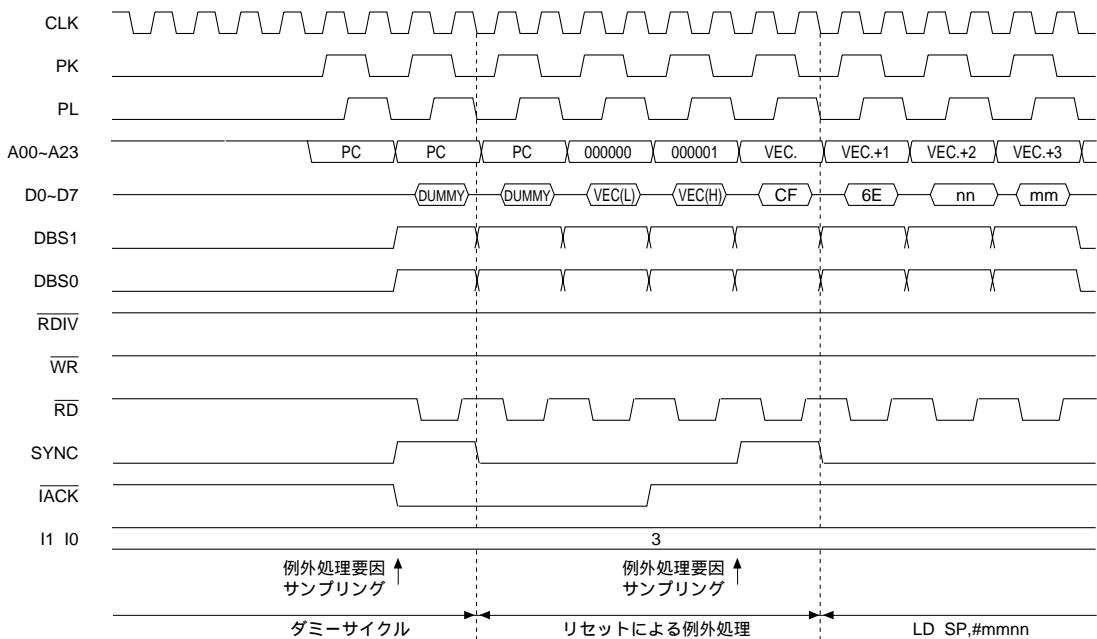

図3.3.1にリセット状態とリセット解除後のシーケンスを示します。

SR端子がLOWレベルのリセット期間中はアドレスバス、データバス、リード/ライト信号がハイインピーダンスになります。ただし、アドレスバスとリード/ライト信号はCPU内部でブルアップされるため、HIGHレベルが出力されます。

SR端子がHIGHレベルになるとリセットが解除され、CLKの立ち下がりエッジが2回入力された時点で最初のバスサイクルを開始します。このバスサイクルではアドレスバスにダミーアドレスが出力され、次のバスサイクルで割り込みアクノリッジIACKがイネーブルになります。

これにより、ベクタテーブルに格納されているスタートアドレスを、不定の状態にあるPC(プログラムカウンタ)にロードするリセットの例外処理を開始します。また、このときにNB(ニューコードバンクレジスタ)の初期値01HをCB(コードバンクレジスタ)にロードする処理も同時に進行します。このため、リセット後のバンクエリアにはバンク1(008000H～00FFFFH)が選択されます。

以上の処理により、イニシャルリセット後は000000H～000001Hのメモリに格納されたスタートアドレスからプログラムの実行を開始します。

表3.3.1 内部レジスタの初期設定値

| レジスタ名称           | 記号 | ビット長 | 初期値 |

|------------------|----|------|-----|

| データレジスタA         | A  | 8    | 不定  |

| データレジスタB         | B  | 8    | 不定  |

| インデックス(データ)レジスタL | L  | 8    | 不定  |

| インデックス(データ)レジスタH | H  | 8    | 不定  |

| インデックスレジスタIX     | IX | 16   | 不定  |

| インデックスレジスタIY     | IY | 16   | 不定  |

| プログラムカウンタ        | PC | 16   | 不定* |

| スタックポインタ         | SP | 16   | 不定  |

| ベースレジスタ          | BR | 8    | 不定  |

| ゼロフラグ            | Z  | 1    | 0   |

| キャリーフラグ          | C  | 1    | 0   |

| オーバーフローフラグ       | V  | 1    | 0   |

| ネガティブフラグ         | N  | 1    | 0   |

| デシマルフラグ          | D  | 1    | 0   |

| アンパックフラグ         | U  | 1    | 0   |

| インタラプトフラグ0       | IO | 1    | 1   |

| インタラプトフラグ1       | I1 | 1    | 1   |

| ニューコードバンクレジスタ    | NB | 8    | 01H |

| コードバンクレジスタ       | CB | 8    | 不定* |

| エクスパンドページレジスタ    | EP | 8    | 00H |

| IX用エクスパンドページレジスタ | XP | 8    | 00H |

| IY用エクスパンドページレジスタ | YP | 8    | 00H |

\* リセット例外処理によって、0バンクのメモリの先頭(000000H～000001H)に格納されている値がPCにロードされます。また、このとき同時にNBの初期値01HがCBにロードされます。

レジスタNB、CB、EP、XPおよびYPはMODEL2/3にのみ設定されており、MODEL0/1にはありません。

注! リセットで初期化されないレジスタは、必要に応じてプログラムで初期化を行う必要があります。

図3.3.1 リセット状態とリセット解除後のシーケンス

### 3.4 プログラム実行状態

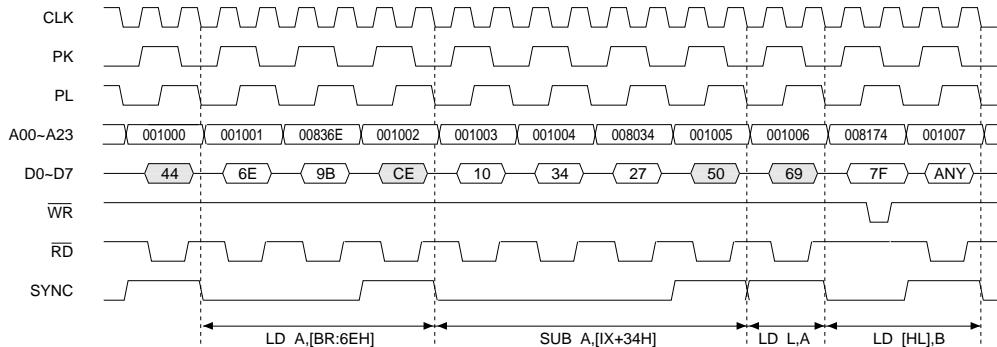

プログラム実行状態とは、S1C88がプログラムを順次実行している状態を示します。

S1C88では、命令の第1オペコードのフェッチが直前の命令の最終サイクルに重複して行われます。したがって、S1C88の1命令の実行サイクルは第2オペコードのフェッチサイクル、第1オペランドのリードサイクル、第1実行サイクルのいずれか(命令により異なる)から始まり、次の命令の第1オペコードのフェッチサイクルで完了します。1サイクル命令については、次の命令の第1オペコードのフェッチサイクルのみとなります。また、オペランドのリードサイクル後、実行サイクルをはさまずに第1オペコードのフェッチサイクルに移行する場合もあります。

第1オペコードのフェッチサイクルでは、その期間中SYNC信号がHIGHレベルになります。

図3.4.1に以下のプログラムと条件による命令の実行サイクルの例を示します。

| プログラムリスト |    |    |     |             |

|----------|----|----|-----|-------------|

| 001000   | 44 | 6E | LD  | A, [BR:6EH] |

| 001002   | CE | 10 | SUB | A, [IX+34H] |

| 001005   | 50 |    | LD  | L,A         |

| 001006   | 69 |    | LD  | [HL],B      |

| レジスタおよびメモリの条件 |   |       |  |  |

|---------------|---|-------|--|--|

| B             | = | 7FH   |  |  |

| H             | = | 81H   |  |  |

| BR            | = | 83H   |  |  |

| IX            | = | 8000H |  |  |

| EP            | = | 00H   |  |  |

| XP            | = | 00H   |  |  |

| M(008034H)    | = | 27H   |  |  |

| M(00836EH)    | = | 9BH   |  |  |

図3.4.1 命令の実行サイクル例

〈第1オペコード〉

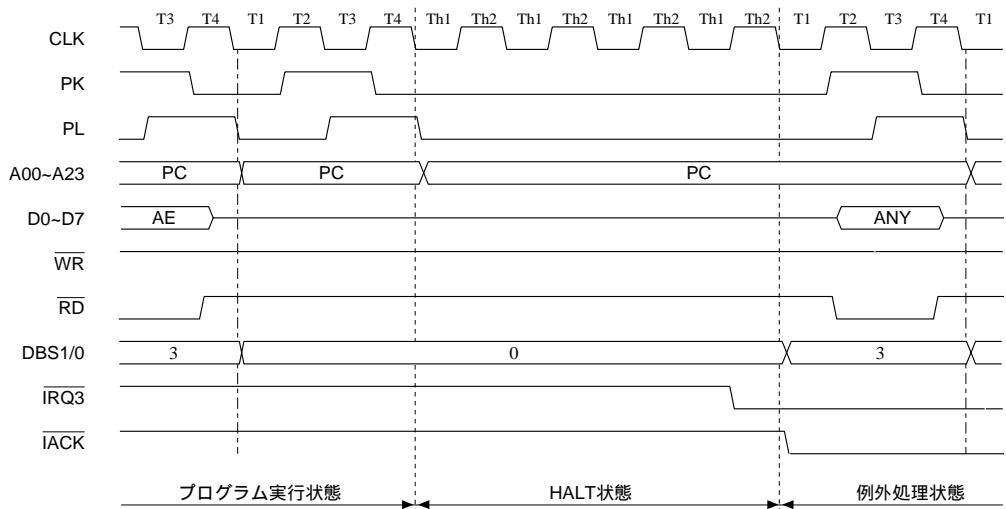

### 3.5 例外処理状態

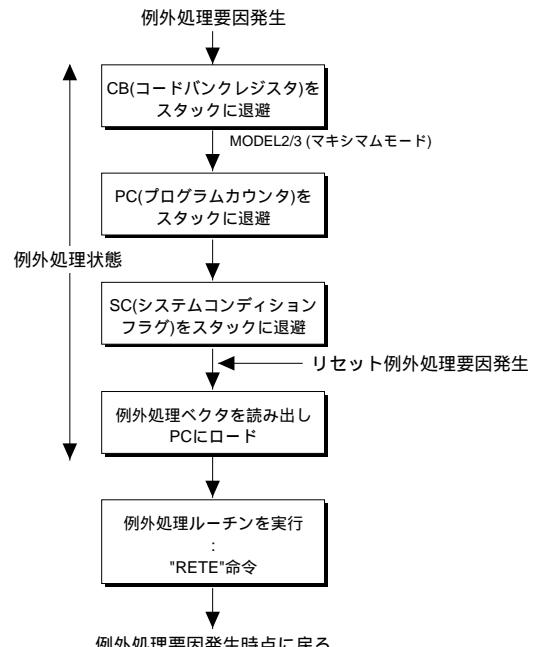

例外処理状態とは、割り込みなどの例外処理要因によってS1C88が通常のプログラム実行を中断して処理の流れを変える過渡的な状態を示します。

例外処理のシーケンスを図3.5.1に示します。

例外処理は例外処理要因が発生した時点で実行している命令のサイクル終了時に開始されます。

例外処理フローに示すとおり、中断したルーチンを再開するためのリターン情報をスタックに退避後、例外処理要因に対応したベクタアドレスから例外処理ルーチン(ユーザーが設定した処理ルーチン)のスタートアドレスをPCにロードしてその処理ルーチンに分岐します。ただし、リセット例外処理についてはリターン情報の退避は行われません。

この例外処理ルーチンに分岐するまでの過渡的な状態が例外処理状態で、分岐後は通常のプログラム実行状態になります。

ユーザーが作成する例外処理ルーチンはサブルーチンの形式を取りますが、スタックにSCが退避されるためリターン命令は必ず"RETE"命令を使用する必要があります。"RETE"命令により、例外処理で中断されていたルーチンの実行を再開します。

図3.5.1 例外処理フロー

## 3.5.1 例外処理の種類と優先度 ////////////////

例外処理の種類と優先度を表3.5.1.1に示します。

表3.5.1.1 例外処理の種類と優先度

| 優先度              | 種類    | 例外処理の開始タイミング                                             |

|------------------|-------|----------------------------------------------------------|

| 高<br>↑<br>↓<br>低 | リセット  | SR端子がLOWレベルからHIGHレベルに変化後の最初のフェッチサイクル                     |

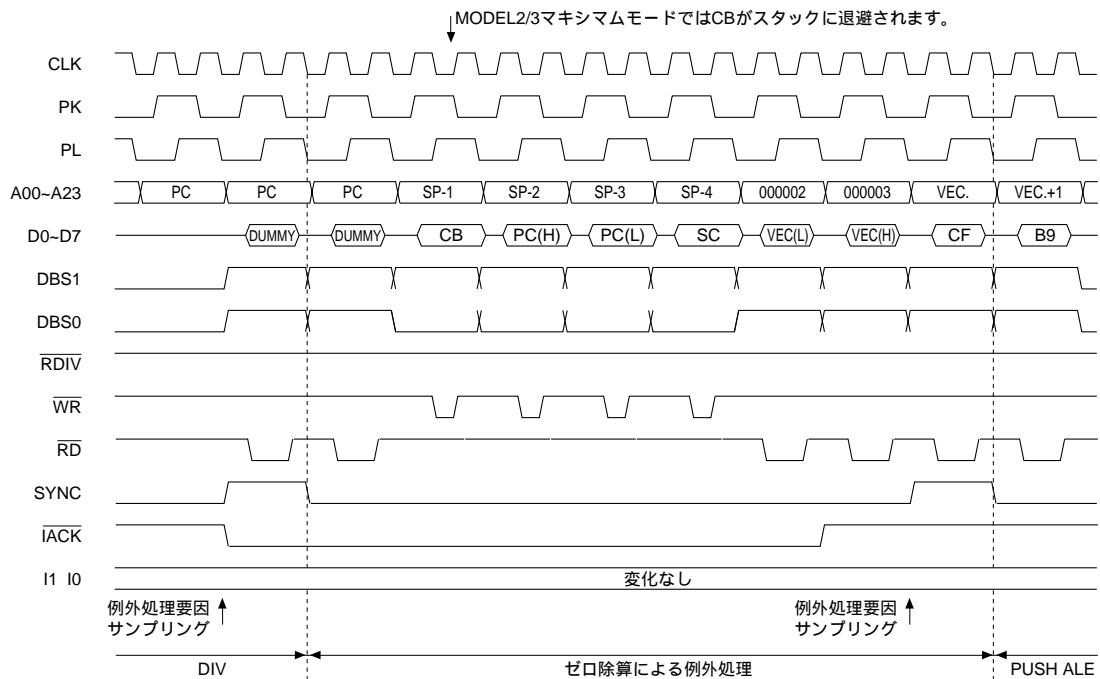

|                  | ゼロ除算  | 除数ゼロでDIV命令(除算)を実行した場合のDIV命令実行直後                          |

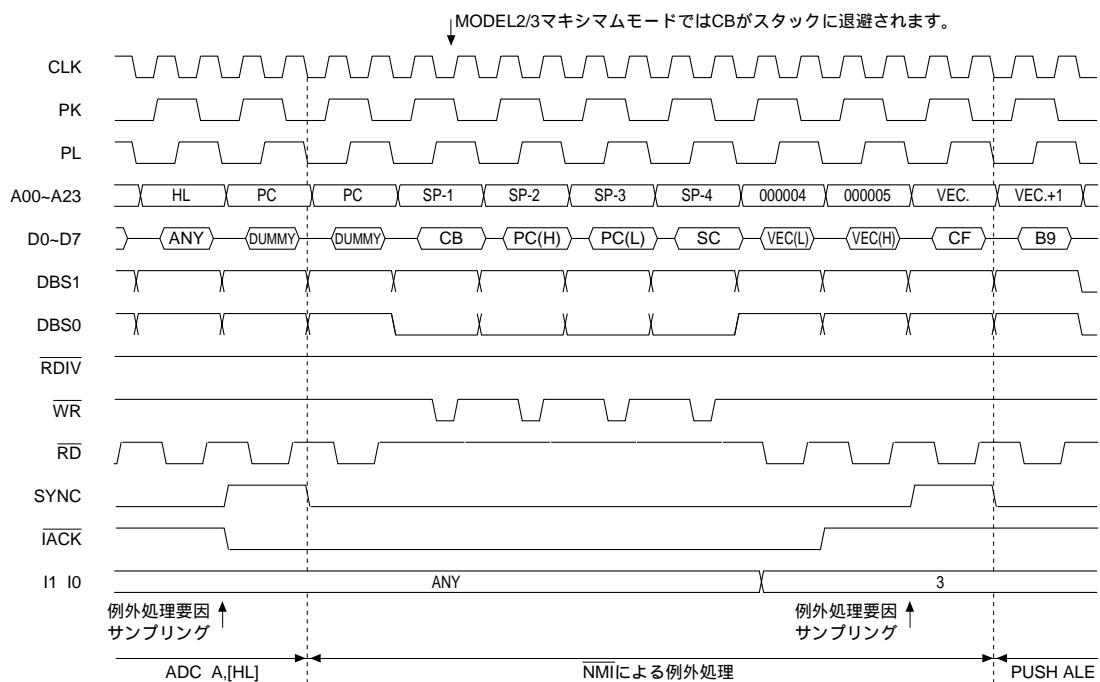

|                  | NMI   | <ノンマスカブル割り込み><br>NMI端子に立ち下がりエッジが入力された時点で実行中の命令または例外処理終了時 |

|                  | IRQ3  | <割り込み要求3><br>IRQ3端子にLOWレベルが入力された時点で実行中の命令または例外処理終了時      |

|                  | IRQ2  | <割り込み要求2><br>IRQ2端子にLOWレベルが入力された時点で実行中の命令または例外処理終了時      |

|                  | IRQ1  | <割り込み要求1><br>IRQ1端子にLOWレベルが入力された時点で実行中の命令または例外処理終了時      |

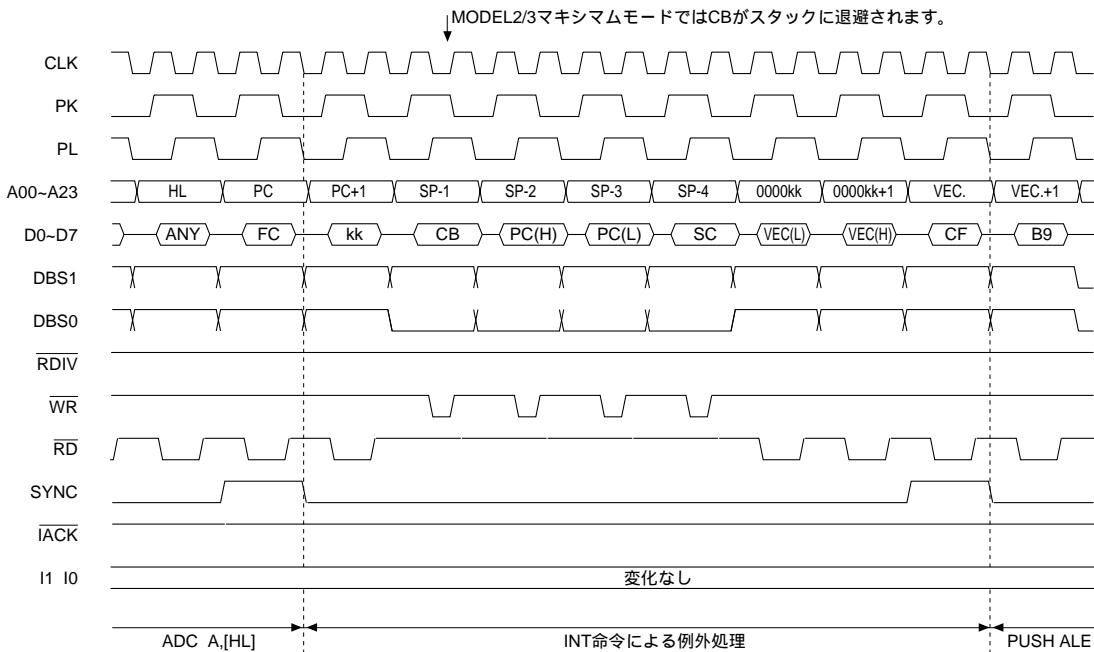

|                  | INT命令 | <ソフトウェア割り込み><br>INT命令の実行                                 |

例外処理要因には優先順位が設定されており、複数の要因が同時に発生した場合は優先度の高い例外処理が先に実行されます。

また、例外処理状態において新たな例外処理要因が発生した場合は、その時点の例外処理終了後(例外処理ルーチンの実行前)に新たな例外処理が実行されます。

たとえば、IRQ3の例外処理中にNMIが発生した場合、IRQ3の例外処理の最後にNMIのサンプリングが行われ、ユーザーの処理ルーチンとしてはNMI処理ルーチンがIRQ3処理ルーチンより先に実行されます。IRQ3の処理ルーチンはNMIの処理ルーチン終了後に実行されます。

このため、割り込みによる例外処理ではその割り込みより優先度の低い割り込みがマスクされるようになっています。

INT命令による例外処理はプログラムによって開始できますので、優先度は設定されません。

## 3.5.2 例外処理要因とベクタ ////////////////

例外処理ルーチンのスタートアドレスは、各例外処理要因に対応したベクタアドレスにベクタとして設定しておきます。

このベクタが例外処理の最後にPCにロードされ、例外処理ルーチンへ分岐します。

表3.5.2.1に例外処理要因とベクタアドレスの対応を示します。

ベクタはCPUモデルにかかわらず論理アドレスを示す2バイトのアドレス情報に固定されています。MODEL2/3においてもユーザーが作成した例外処理ルーチンのバンクをベクタにより指定することはできません。したがって、どのバンクのプログラムを実行している場合でも共通の例外処理ルーチンに分

表3.5.2.1 例外処理要因とベクタアドレスの対応

| 例外処理要因      | ベクタアドレス           | ベクタアドレス発生元 |

|-------------|-------------------|------------|

| リセット        | 000000H ~ 000001H | CPU内部      |

| ゼロ除算        | 000002H ~ 000003H | CPU内部      |

| NMI         | 000004H ~ 000005H | CPU内部      |

| IRQ1 ~ IRQ3 | 000006H ~ 0000FFH | 周辺回路       |

| INT命令       | 000000H ~ 0000FFH | 命令のオペランド   |

岐させるために、ベクタにより指定される例外処理ルーチンの先頭をコモンエリア内(000000H ~ 007FFFFH)に配置する必要があります。

IRQ1 ~ IRQ3のベクタアドレスは周辺回路によって設定されます。INT命令の場合は命令のオペランドがそのままベクタアドレスとなり、他の例外処理要因も含めると最大128ベクタまで確保できます。

## 3.5.3 割り込み ////////////////

割り込みにはNMI、IRQ3、IRQ2、IRQ1の4種類があり、それぞれには表3.5.3.1に示す割り込み優先レベルが設定されています。

表3.5.3.1 割り込み優先レベル

| 優先度              | 割り込み優先レベル | 割り込み要因 |

|------------------|-----------|--------|

| 高<br>↑<br>↓<br>低 | 4         | NMI    |

|                  | 3         | IRQ3   |

|                  | 2         | IRQ2   |

|                  | 1         | IRQ1   |

割り込みはインターフラグI0、I1によってマスク(割り込みを受け付けないように設定)することができます。プログラムによってI0、I1の2ビットに割り込み優先レベルを設定すると、それより高い優先レベルの割り込みのみが受け付けられます。このうち、レベル4の優先度を持っているNMIはI0とI1の設定にかかわらず常時受け付けられます。

また、割り込み要因の発生により例外処理が実行されるときI0とI1は受け付けた割り込みと同じレベルに設定され、同一レベル以下の割り込みがマスクされます。このマスクの設定はSC(システムコンディションフラグ)のスタック退避後に行われますので、割り込み処理ルーチンを"RETE"命令で終了した時点でSCが元の状態に戻り、割り込みマスクも元の優先レベルに戻ります。

割り込み処理ルーチン内で同一レベル以下の多重割り込みを許可したい場合は、そのルーチンの中で再度優先レベルの設定を行ってください。

なお、NBおよびSCの内容を変更する命令を実行している最中は割り込みを受け付けません。その間に発生した割り込みの例外処理は、次の命令終了後に開始されます。

### 3.5.4 例外処理のシーケンス

例外処理のサンプリングはSYNC信号の立ち上がりエッジ(命令の第1オペコードフェッチサイクル開始時)で行われます。ここで例外処理要因が発生している場合、CPUは割り込みアクノリッジ信号IACKを出力し例外処理を開始します。IRQ1～IRQ3割り込みの場合、割り込みを発生させた周辺回路はIACK信号を受けてベクタアドレスをホールドします。

以下に各例外処理のシーケンスを示します。

図3.5.4.1 例外処理のシーケンス - リセット -

表3.5.3.2 割り込みマスクの設定

| I1 | I0 | 受け付け可能な割り込み        |

|----|----|--------------------|

| 1  | 1  | NMI                |

| 1  | 0  | NMI IRQ3           |

| 0  | 1  | NMI IRQ3 IRQ2      |

| 0  | 0  | NMI IRQ3 IRQ2 IRQ1 |

表3.5.3.3 割り込み受け付け後のI0とI1

| 受け付けた割り込み要因 | I1 | I0 |

|-------------|----|----|

| NMI         | 1  | 1  |

| IRQ3        | 1  | 1  |

| IRQ2        | 1  | 0  |

| IRQ1        | 0  | 1  |

### 3 CPUの動作と処理状態

図3.5.4.2 例外処理のシーケンス - ゼロ除算 -

図3.5.4.3 例外処理のシーケンス - NMI -

図3.5.4.4 例外処理のシーケンス - IRQ1 ~ IRQ3 -

図3.5.4.5 例外処理のシーケンス - INT命令 -

### 3.6 バス権解放状態

S1C88ではDMA(Direct Memory Access)転送など、CPU外部からのバス権要求に対してバスを解放する機能を持っています。この外部からの要求に応答してバスを解放している状態をバス権解放状態といいます。

バス権解放状態ではアドレスバス(A00～A23)、データバス(D0～D7)、およびリード/ライト信号(RD/WR)がハイインピーダンスとなり、バスマスター(バス権解放要求を出したCPU外部のデバイス)がバスに接続されたメモリなどの他のデバイスを直接アクセスすることができます。

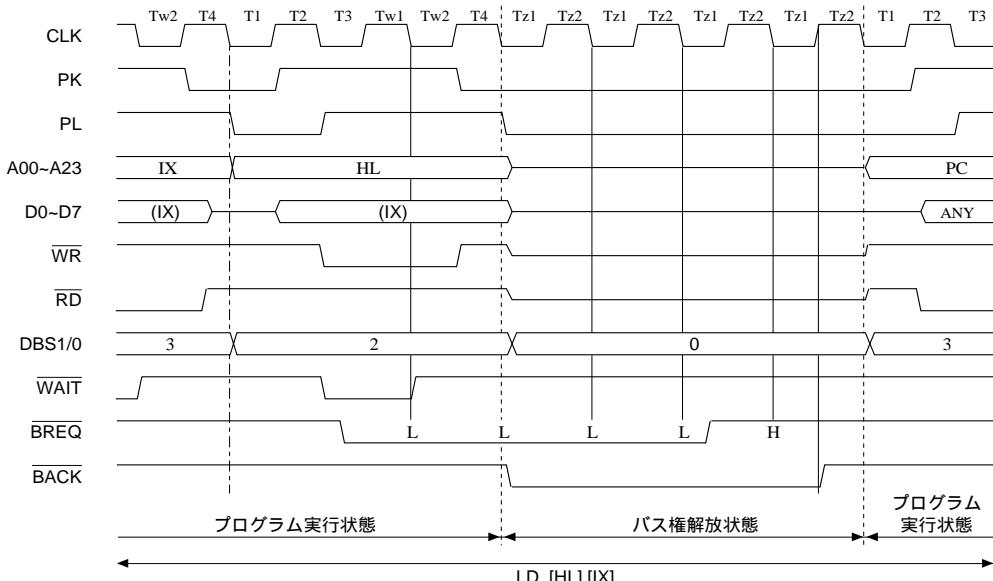

図3.6.1にプログラム実行状態からのバス権解放のシーケンスを示します。

バスマスターとなるデバイスはCPUのBREQ端子にLOWレベルを入力して、バス権の解放を要求します。

この信号に対してCPUは各バスサイクルのT2ステート(ウェイトが挿入されている場合はTw1ステート)のCLKの立ち下がりエッジおよびT4ステートのCLKの立ち下がりエッジで2度のサンプリングを行います。T4ステートのサンプリングの時点でT2ステートに引き続きBREQ信号がLOWレベルだった場合、CPUは実行中の命令をそのバスサイクルで中断し、BACK信号をLOWレベルにしてバス権解放状態に移行します。外部バスマスターはこのBACK信号を受けてバスの制御を開始します。

なお、外部バスマスターはバス権解放要求からバスの使用が終了するまでBREQ信号をLOWレベルで保持しておく必要があります。

バス権解放状態移行後、CPUはTz1およびTz2ステートを挿入し、Tz2ステートのCLKの立ち下がりエッジでBREQ信号のサンプリングを行います。このサンプリングでHIGHレベルが検出されるまでTz1/Tz2ステートは連続して挿入されます。HIGHレベルを検出した場合、CPUは次のTz2ステートのCLKの立ち上がりエッジでBACK信号をHIGHレベルに戻し、そのTz2ステート終了直後に通常のバスサイクルに復帰して中断していた処理を再開します。

前記の例外処理状態が各命令の区切りで挿入できるのに対し、バス権解放状態はバスサイクルの区切りで挿入することができます。ただし、IACK信号を出力する例外処理(INT命令以外)を実行中で、IACK信号がLOWレベルとなっている期間はバス権解放要求を受け付けません。

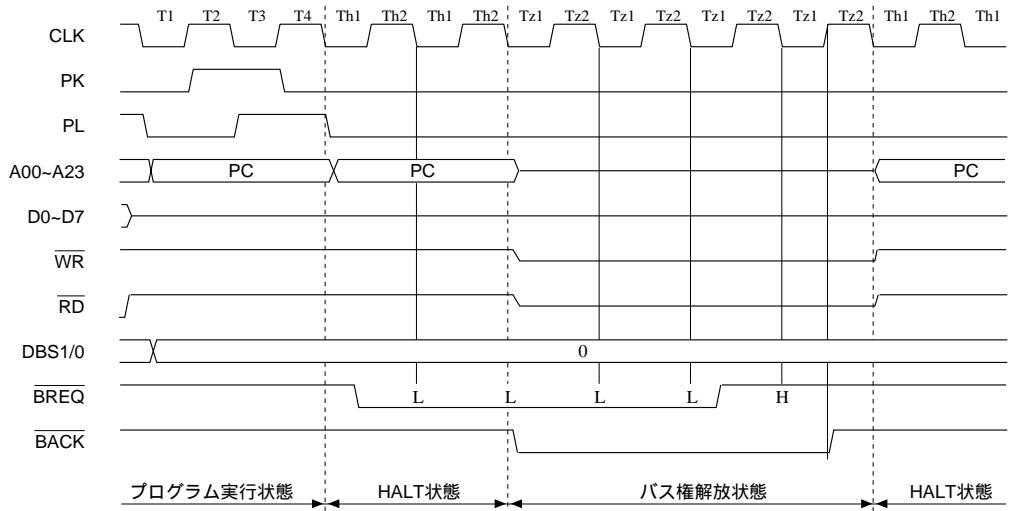

以上、プログラム実行状態からバス権解放状態への移行について説明しましたが、スタンバイ状態でもHALT状態からはバス権解放状態に移行することができます。

HALT状態でのバス解放要求信号のサンプリングが、Th2ステート(後述)のCLKの立ち下がりエッジで行われる点がプログラム実行状態とは異なります。図3.6.2にHALT状態からのバス権解放のシーケンスを示します。

図3.6.1 プログラム実行状態からのバス権解放シーケンス

図3.6.2 HALT状態からのバス権解放シーケンス

### 3.7 スタンバイ状態

S1C88にはCPUの動作を停止させる機能があり、これによって消費電力を大幅に低減することができます。アプリケーションプログラムがある期間CPUに実行させる処理がない場合にこの機能を用いてCPUを停止させることができます。低消費電力化のためにCPUを停止させた状態がスタンバイ状態で、この状態にも以下に説明するHALT状態とSLEEP状態の2種類があります。

#### 3.7.1 HALT状態

HALT状態はCPUのみが停止するもので、"HALT"命令によって移行することができます。

HALT状態からはリセットまたは任意の割り込み(NMI、IRQ1 ~ IRQ3)によって例外処理に移行することができ、割り込みによる再起動の場合は例外処

理ルーチン実行後"RETE"命令によって"HALT"命令の次の命令からプログラムの実行を再開できます。発振回路などの周辺回路はHALT状態の間も動作しているため、MCU(S1C88 Family)の外部にCPU再起動用の割り込み回路などを設ける必要もなく、再起動も瞬時に行われます。

CPU内のレジスタ等は"HALT"命令実行時点の内容がHALT状態の間も保持されます。

図3.7.1.1にHALT状態への移行と再起動のシーケンスを示します。

HALT状態ではTh1およびTh2ステートが連続して挿入されます。この間Th2ステートのCLKの立ち下がりエッジで割り込みのサンプリングが行われ、割り込み要因の発生により即時例外処理に移行します。

図3.7.1.1 HALT状態への移行と再起動のシーケンス

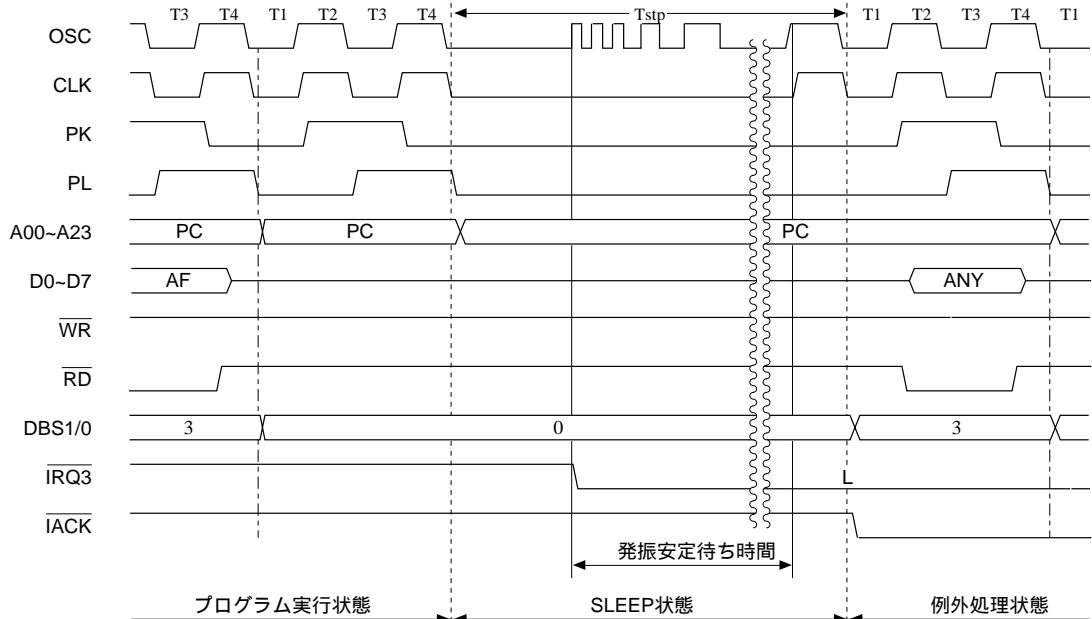

## 3.7.2 SLEEP状態 ///////////////////////////////////////////////////////////////////

SLEEP状態はCPUとMCU内部の周辺回路の動作が停止するもので、"SLP"命令によって移行することができます。

SLEEP状態からはリセットまたはMCU外部からの割り込み(NMI、 $\overline{\text{IRQ1}} \sim \overline{\text{IRQ3}}$ )によって例外処理に移行することができ、割り込みによる再起動の場合は例外処理ルーチン実行後"RETE"命令によって"SLP"命令の次の命令からプログラムの実行を再開できます。

SLEEP状態では発振回路などの周辺回路も停止するため、HALT状態に比べて消費電力が大幅に低減できます。ただし、再起動の際に発振回路の安定待ち時間が必要となりますので、瞬時の立ち上げの必要のない長時間のスタンバイに有効です。

SLEEP状態でも規定電圧の印加によりCPU内のレジスタ等は"SLP"命令実行時点の内容が保持されます。

図3.7.2.1にSLEEP状態への移行と再起動のシーケンスを示します。

SLEEP状態で外部割り込みが発生すると、周辺回路が動作を開始し発振回路も発振を開始します。発振開始時はCPUへのCLK入力が周辺回路によってマスクされ、ある程度の安定待ち時間(数10msec ~ 数sec)経過後にCPUへの入力が開始されます。CPUは最初に入力されたCLKの立ち下がりエッジで割り込みをサンプリングし例外処理を開始します。

図3.7.2.1 SLEEP状態への移行と再起動のシーケンス

# 4 命令セット

S1C88はマシンサイクル効率が高い、高速かつ豊富な命令セットを持っています。命令の数は608個(MODEL3)でリロケータブルプログラミングが可能な命令体系となっています。ここでは、メモリ管理のためのアドレッシングモードと各命令の詳細について説明します。

## 4.1 アドレッシングモード

S1C88は以下に説明する12種類のアドレッシングモードを持っており、いろいろな状況に応じたアドレス指定が簡潔かつ的確に行えます。

以下の説明と例は、基本的にソース側を対象としています。

表4.1.1 アドレッシングモードの種類

| No. | アドレッシングモード                |

|-----|---------------------------|

| 1   | 即値データアドレッシング              |

| 2   | レジスタ直接アドレッシング             |

| 3   | レジスタ間接アドレッシング             |

| 4   | ディスプレースメント付きレジスタ間接アドレッシング |

| 5   | インデックスレジスタ付きレジスタ間接アドレッシング |

| 6   | 8ビット絶対アドレッシング             |

| 7   | 16ビット絶対アドレッシング            |

| 8   | 8ビット間接アドレッシング             |

| 9   | 16ビット間接アドレッシング            |

| 10  | 符号付き8ビットPC相対アドレッシング       |

| 11  | 符号付き16ビットPC相対アドレッシング      |

| 12  | インプライドレジスタアドレッシング         |

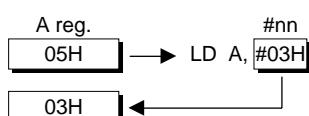

### 即値データアドレッシング

即値データアドレッシングは演算や転送のソースデータに即値データを用いる場合のアドレッシングモードです。命令のソースオペランドを="#"で続く8ビット即値データ、または16ビット即値データで直接ソースデータとして指定します。

命令セットの表記においては、以下の記号によって即値データを表します。

表4.1.2 即値データのシンボル

| 記号    | 用途     | サイズ   | 指定範囲    |

|-------|--------|-------|---------|

| #nn   | 汎用データ  | 8ビット  | 0~255   |

| #hh   | BR設定用  | 8ビット  | 0~255   |

| #bb   | NB設定用  | 8ビット  | 0~255   |

| #pp   | ページ設定用 | 8ビット  | 0~255   |

| #mmnn | 汎用データ  | 16ビット | 0~65535 |

例: LD A, #03H

図4.1.1 即値データアドレッシング

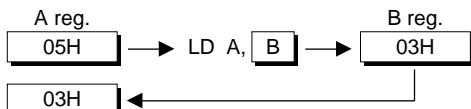

### レジスタ直接アドレッシング

レジスタ直接アドレッシングは、ソースまたはディスティネーションにレジスタを指定する場合のアドレッシングモードです。

命令セットの表記においては、オペランドに以下のレジスタ名をそのまま使用します。

### レジスタ表記の種類

8ビット: A、B、L、H、BR、SC、NB、EP、XP、YP

16ビット: BA、HL、IX、IY、PC、SP、IP(XP&YP)

NB、EP、XP、YP、IPについてはMODEL2/3のみ使用可能です。

ソースオペランドにこのモードを用いた場合、指定したレジスタの内容が演算や転送のソースデータになります。ディスティネーションオペランドに用いた場合は、そのレジスタに対してデータのストアや演算などの操作が行われます。

例: LD A,B

図4.1.2 レジスタ直接アドレッシング

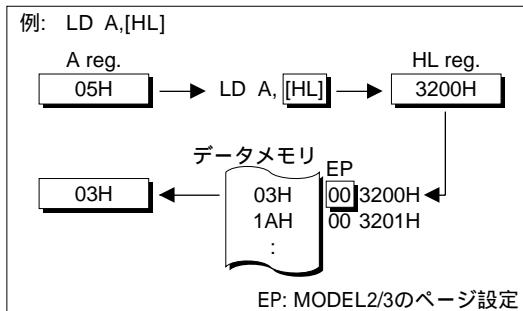

### レジスタ間接アドレッシング

レジスタ間接アドレッシングはデータメモリをアクセスするためのアドレッシングモードで、インデックスレジスタによってデータメモリのアドレスを間接的に指定します。

アドレス指定に使用するインデックスレジスタはHL、IX、IYの3種類で、その内容がアクセスされるデータメモリのアドレスとなります。

命令セットにおいては、インデックスレジスタ名を[]で囲んで[HL]、[IX]、[IY]と表記します。

ソースオペランドにこのモードを用いた場合、指定したインデックスレジスタの内容がデータメモリのアドレスとなり、そのアドレスにストアされている内容がソースデータとなります。ディスティネーションオペランドに用いた場合は、指定されたデータメモリに対してデータのストアや演算などの操作が行われます。

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタEP(HL用)、XP(IX用)、YP(IY用)が使用されます。

図4.1.3 レジスタ間接アドレッシング

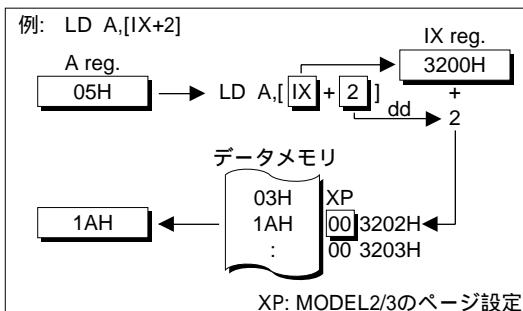

### ディスプレースメント付きレジスタ間接

#### アドレッシング

ディスプレースメント付きレジスタ間接アドレッシングはデータメモリをアクセスするためのアドレッシングモードで、レジスタとディスプレースメントによってデータメモリのアドレスを指定します。データメモリのアドレスは、指定したレジスタの内容にディスプレースメント(符号付き8ビットデータ、-128～127)を加算した値となります。

アドレス指定に使用するレジスタはIX、IY、SPで、命令セットにおいては、符号付き8ビットデータによるディスプレースメントに記号ddを使用し、[IX+dd]、[IY+dd]、[SP+dd]と表記します。

ソースオペランドにこのモードを用いた場合、指定されたレジスタの内容にディスプレースメントを加算した値がデータメモリのアドレスとなり、そのアドレスにストアされている内容がソースデータとなります。ディスティネーションオペランドに用いた場合は、指定されたデータメモリに対してデータのストアや演算などの操作が行われます。

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタXP(IX用)、YP(IY用)が使用されます。SP(スタックポインタ)を使用する場合のページ指定は各機種ごとに周辺回路上で設定されるSP用のページレジスタの内容がそのまま用いられます。

図4.1.4 ディスプレースメント付き

レジスタ間接アドレッシング

### インデックスレジスタ付きレジスタ間接

#### アドレッシング

インデックスレジスタ付きレジスタ間接アドレッシングは、ディスプレースメント付きレジスタ間接アドレッシングと同様のモードで、ディスプレースメントに8ビットデータではなくLレジスタの内容を使用します。

この場合、Lレジスタの内容は符号付き8ビットデータ(-128～127)として扱われます。

アドレス指定にはインデックスレジスタIXとIYを使用し、ディスプレースメントとして使用されるレジスタはLレジスタに固定されます。命令セットにおいては、[IX+L]、[IY+L]と表記します。

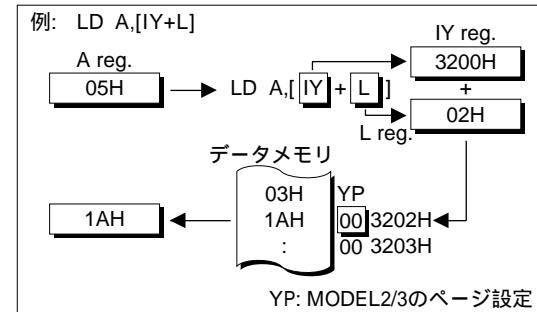

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタXP(IX用)、YP(IY用)が使用されます。

図4.1.5 インデックスレジスタ付き

レジスタ間接アドレッシング

### 8ビット絶対アドレッシング

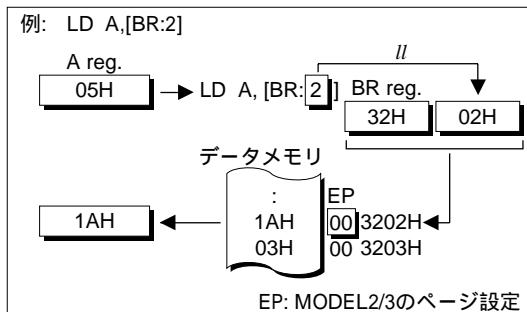

8ビット絶対アドレッシングはデータメモリをアクセスするためのアドレッシングモードで、8ビット絶対アドレスによってアドレスの下位8ビットを直接指定します。アドレスの上位8ビットはBRレジスタの内容により間接的に指定されます。

命令セットにおいては、アドレス指定を行う8ビット絶対アドレス(0～255)に記号//を使用し、[BR://]と表記します。

ソースオペランドにこのモードを用いた場合、BRレジスタの内容をアドレスの上位8ビット、指定した8ビット絶対アドレスを下位8ビットとしてアドレス指定されたデータメモリにストアされている内容がソースデータとなります。ディスティネーションオペランドに用いた場合は、指定されたデータメモリに対してデータのストアや演算などの操作が行われます。

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタEPが使用されます。

図4.1.6 8ビット絶対アドレッシング

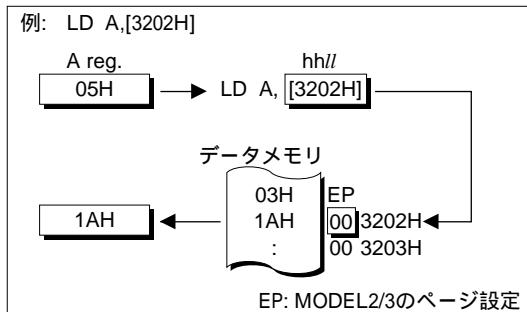

### 16ビット絶対アドレッシング

16ビット絶対アドレッシングはデータメモリをアクセスするためのアドレッシングモードで、16ビット絶対アドレスによってアドレスを直接指定します。命令セットにおいては、アドレス指定を行う16ビット絶対アドレス(0 ~ 65535)に記号hh//lを使用し、[hh//l]と表記します。

ソースオペランドにこのモードを用いた場合、指定した16ビット絶対アドレスが直接データメモリのアドレスとなり、そのアドレスにストアされている内容がソースデータとなります。ディスティネーションオペランドに用いた場合は、指定されたデータメモリに対してデータのストアや演算などの操作が行われます。

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタEPが使用されます。

図4.1.7 16ビット絶対アドレッシング

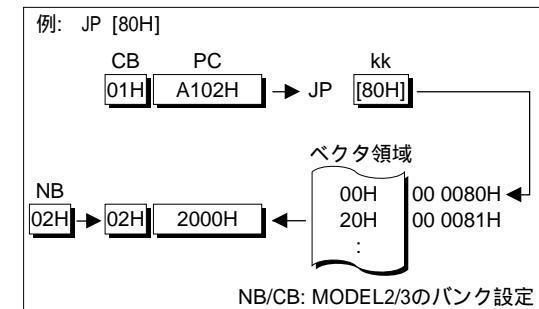

### 8ビット間接アドレッシング

8ビット間接アドレッシングは分岐命令における分岐先アドレスにベクタ領域(000000H ~ 0000FFH)の内容を使用するアドレッシングモードで、ベクタアドレスを8ビット絶対アドレスで指定します。指定したメモリアドレスの内容をPC(プログラムカウンタ)の下位8ビット、次のアドレスの内容をPCの上位8ビットにそれぞれロードして分岐を行います。

MODEL2/3ではNBレジスタの設定により分岐先バンクの選択も行われます。

命令セットにおいては、アドレス指定を行う8ビット絶対アドレス(0 ~ 255)に記号kkを使用し、[kk]と表記します。

このアドレッシングモードの命令は"JP [kk]"、"INT [kk]"の2種類です。

図4.1.8 8ビット間接アドレッシング

### 16ビット間接アドレッシング

16ビット間接アドレッシングは"CALL [hh//l]"命令のアドレッシングモードで、分岐先アドレスを16ビット絶対アドレス(0 ~ 65535)で間接的に指定します。指定したデータメモリアドレスの内容をPC(プログラムカウンタ)の下位8ビット、次のアドレスの内容をPCの上位8ビットにそれぞれロードして分岐を行います。

MODEL2/3ではページ部の指定も必要になり、これにはエクスパンドページレジスタEPが使用されます。また、NBレジスタの設定により分岐先バンクの選択も行われます。

図4.1.9 16ビット間接アドレッシング

### 符号付き8ビットPC相対アドレッシング

符号付き8ビットPC相対アドレッシングは分岐命令で使用されるアドレッシングモードです。オペランドで指定された符号付き8ビット相対アドレス(-128 ~ 127)が分岐実行時のPCに加算され、そのアドレスに分岐します。

分岐実行時のPC値は次のようにになっています。

2バイト命令: PC = 命令の先頭アドレス + 1

3バイト命令: PC = 命令の先頭アドレス + 2

命令セットの表記においては、符号付き8ビット相対アドレス(-128 ~ 127)に記号rrを使用します。

MODEL2/3ではNBレジスタの設定により分岐先バンクの選択も行われます。

図4.1.10 符号付き8ビットPC相対アドレッシング

### 符号付き16ビットPC相対アドレッシング

符号付き16ビットPC相対アドレッシングは分岐命令で使用されるアドレッシングモードです。オペランドで指定された符号付き16ビット相対アドレス(-32768 ~ 32767)が分岐実行時のPCに加算され、そのアドレスに分岐します。

分岐実行時のPC値は命令の先頭アドレス+2となります。

命令セットの表記においては、符号付き16ビット相対アドレス(-32768 ~ 32767)に記号qqrrを使用します。

MODEL2/3ではNBレジスタの設定により分岐先バンクの選択も行われます。

図4.1.11 符号付き16ビットPC相対アドレッシング

### インプライドレジスタアドレッシング

インプライドレジスタアドレッシングはオペランドを持たずに、暗黙的にレジスタが指定されるレジスタ直接アドレッシングモードです。

このアドレッシングモードの命令はMLT、DIV、SEP、PACK、UPCKの5種類です。

## 4.2 命令のフォーマット

S1C88の1命令は1バイトから4バイトのコードで次のように構成されています。

- 1 オペコード

- 2 オペコード オペコード

(CEH/CFH)

- 3 オペコード オペランド

- 4 オペコード オペコード オペランド

(CEH/CFH)

- 5 オペコード オペランド オペランド

- 6 オペコード オペコード オペランド オペランド

(CEH/CFH)

図4.2.1 命令のフォーマット

### オペコード

S1C88の命令セットは608種類(MODEL3)あり、1バイトのオペコードではすべての命令を表現できません。そこで、コードのCEHとCFHを拡張コードとして第1オペコードに使用し、続く1バイトを第2オペコードとして命令を拡張しています。16ビット演算/転送命令およびスタック操作命令をコードCFHで、その他の命令をコードCEHでそれぞれ拡張しています。

また、各命令のアドレッシングモードは、第1または第2オペコードの下位3ビットで指定されます。レジスタ直接アドレッシング、レジスタ間接アドレッシング、インデックスレジスタ付きレジスタ間接アドレッシングの命令がオペコードのみで構成されます。

### オペランド

8ビットの即値データアドレッシング、ディスプレースメント付きレジスタ間接アドレッシング、8ビット絶対アドレッシング(ソースをレジスタで指定している場合)、8ビット間接アドレッシング、符号付き8ビットPC相対アドレッシングの命令は1バイトのオペランドを持っており、8ビットデータによる指定値がそのままオペランドとなります。

16ビットの即値データアドレッシング、8ビット絶対アドレッシング(ソースを即値で指定している場合)、16ビット絶対アドレッシング、16ビット間接アドレッシング、符号付き16ビットPC相対アドレッシングの命令は2バイトのオペランドを持っており、16ビットデータによる指定値の下位8ビットが第1オペランド、上位8ビットが第2オペランドとなります。(8ビット絶対アドレッシングの場合は、アドレス指定が第1オペランド、即値データが第2オペランドとなります。)

## 4.3 命令セット一覧表

ここではS1C88の命令セットを機能別に分類した一覧表を掲載しています。

なお、"APPENDIX"にもアドレッシングモード別一覧表が掲載されていますので、必要に応じて参照してください。

### 4.3.1 機能分類

命令の機能分類を表4.3.1.1に示します。

表4.3.1.1 命令の機能分類

| 機能分類           | 二ーモニック | オペレーション      | 機能分類          | 二ーモニック  | オペレーション    |

|----------------|--------|--------------|---------------|---------|------------|

| 8ビット<br>算術論理演算 | ADD    | 加算           | 16ビット<br>算術演算 | ADD     | 加算         |

|                | ADC    | キャリー付き加算     |               | ADC     | キャリー付き加算   |

|                | SUB    | 減算           |               | SUB     | 減算         |

|                | SBC    | キャリー付き減算     |               | SBC     | キャリー付き減算   |

|                | AND    | 論理積          |               | CP      | 比較         |

|                | OR     | 論理和          |               | INC     | 1加算        |

|                | XOR    | 排他的論理和       |               | DEC     | 1減算        |

|                | CP     | 比較           |               | BIT     | ビットテスト     |

|                | INC    | 1加算          |               | LD      | ロード        |

|                | DEC    | 1減算          |               | EX      | ワード交換      |

|                | MLT    | 乗算           |               | STACK制御 | PUSH プッシュ  |

|                | DIV    | 除算           |               | POP ポップ |            |

|                | CPL    | 1の補数         |               | JRS     | 相対ショートジャンプ |

|                | NEG    | 2の補数         |               | JRL     | 相対ロングジャンプ  |

| 8ビット転送         | LD     | ロード          |               | JP      | 間接ジャンプ     |

|                | EX     | バイト交換        |               | DJR     | ループ        |

|                | SWAP   | ニブル交換        |               | CARS    | 相対ショートコール  |

| ローテート<br>/シフト  | RL     | キャリー付き左ローテート |               | CARL    | 相対ロングコール   |

|                | RLC    | 左ローテート       |               | CALL    | 間接コール      |

|                | RR     | キャリー付き右ローテート |               | RET     | リターン       |

|                | RRC    | 右ローテート       |               | RETE    | 例外処理リターン   |

|                | SLA    | 算術左シフト       |               | RETS    | スキップリターン   |

|                | SLL    | 論理左シフト       |               | INT     | ソフトウェア割り込み |

|                | SRA    | 算術右シフト       |               |         |            |

|                | SRL    | 論理右シフト       |               |         |            |

| 演算補助           | PACK   | パック          | システム制御        | NOP     | ノーオペレーション  |

|                | UPCK   | アンパック        |               | HALT    | HALT状態移行   |

|                | SEP    | 符号拡張         |               | SLP     | SLEEP状態移行  |

## 4.3.2 記号の意味 //////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

次項の機能別命令一覧表で使われている記号の意味を表4.3.2.1に示します。

表4.3.2.1 記号の意味

| レジスタ関係 |                         | メモリ関係   |                       |

|--------|-------------------------|---------|-----------------------|

| A      | データレジスタA                | [HL]    | HLレジスタで指定されるメモリ       |

| A(H)   | Aレジスタの上位4ビット            | [HL](H) | [HL]の上位4ビット           |

| A(L)   | Aレジスタの下位4ビット            | [HL](L) | [HL]の下位4ビット           |

| B      | データレジスタB                | [IX]    | IXレジスタで指定されるメモリ       |

| BA     | BAペアレジスタ                | [IX+dd] | IXレジスタ+ddで指定されるメモリ    |

| H      | データレジスタH                | [IX+L]  | IXレジスタ+Lレジスタで指定されるメモリ |

| L      | データレジスタL                | [IY]    | IYレジスタで指定されるメモリ       |

| HL     | インデックスレジスタHL            | [IY+dd] | IYレジスタ+ddで指定されるメモリ    |

| IX     | インデックスレジスタIX            | [IY+L]  | IYレジスタ+Lレジスタで指定されるメモリ |

| IX(H)  | IXレジスタの上位8ビット           | [BR://] | BRレジスタと"//で指定されるメモリ   |

| IX(L)  | IXレジスタの下位8ビット           | [hh//]  | "hh//で指定されるメモリ        |

| IY     | インデックスレジスタIY            | [kk]    | "kk"で指定されるベクタ         |

| IY(H)  | IYレジスタの上位8ビット           | [SP]    | SPで指定されるスタック          |

| IY(L)  | IYレジスタの下位8ビット           | [SP+dd] | SP+ddで指定されるスタック       |

| SP     | スタックポインタSP              | フラグ関係   |                       |

| BR     | ベースレジスタBR               | Z       | ゼロフラグ                 |

| SC     | システムコンディションフラグSC        | C       | キャリーフラグ               |

| CC     | カスタマイズコンディションフラグCC      | V       | オーバーフローフラグ            |

| PC     | プログラムカウンタPC             | N       | ネガティブフラグ              |

| PC(H)  | PCの上位8ビット               | D       | デシマルフラグ               |

| PC(L)  | PCの下位8ビット               | U       | アンパックフラグ              |

| NB     | ニューコードバンクレジスタNB         | I0      | インタラプトフラグ0            |

| CB     | コードバンクレジスタCB            | I1      | インタラプトフラグ1            |

| EP     | エクスパンドページレジスタEP         | ↑       | フラグのセット/リセット          |

| XP     | IX用エクスパンドページレジスタXP      | -       | 変化なし                  |

| YP     | IY用エクスパンドページレジスタYP      | 0       | フラグのリセット              |

| IP     | XPおよびYPレジスタ             | F0      | カスタマイズコンディションフラグF0    |

| 即値データ  |                         | F1      | カスタマイズコンディションフラグF1    |

| nn     | 8ビット即値データ(符号なし)         | F2      | カスタマイズコンディションフラグF2    |

| hh     | 絶対アドレス上位8ビット設定データ(符号なし) | F3      | カスタマイズコンディションフラグF3    |

| ll     | 絶対アドレス下位8ビット設定データ(符号なし) | 演算、その他  |                       |

| pp     | ページ設定データ(符号なし)          | +       | 加算                    |

| bb     | バンク設定データ(符号なし)          | -       | 減算                    |

| dd     | 符号付き8ビットディスプレースメント      | *       | 乗算                    |

| rr     | 8ビット相対アドレス設定データ(符号付き)   | /       | 除算                    |

| kk     | ベクタアドレス設定データ(符号なし)      | ^       | 論理積                   |

| mmnn   | 16ビット即値データ(符号なし)        | ∨       | 論理和                   |

| hh ll  | 16ビット絶対アドレス設定データ(符号なし)  | ▽       | 排他的論理和                |

| qqrr   | 16ビット相対アドレス設定データ(符号付き)  | ★       | 10進演算/アンパック演算可能な命令    |

## 4.3.3 機能別命令一覧表 //////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

表4.3.3.1(a) 機能別命令一覧表 (8ビット転送命令 1/3)

## 8ビット転送命令

| ニーモニック | コード       | オペレーション     | サイ<br>クル  | バイト | SC |    |   |   |   |   | 備 考 | ページ |     |

|--------|-----------|-------------|-----------|-----|----|----|---|---|---|---|-----|-----|-----|

|        |           |             |           |     | I1 | I0 | U | D | N | V | C   | Z   |     |

| LD     | A,A       | 40          | A←A       | 1   | 1  | —  | — | — | — | — | —   | —   | 101 |

|        | A,B       | 41          | A←B       | 1   | 1  | —  | — | — | — | — | —   | —   | 101 |

|        | A,L       | 42          | A←L       | 1   | 1  | —  | — | — | — | — | —   | —   | 101 |

|        | A,H       | 43          | A←H       | 1   | 1  | —  | — | — | — | — | —   | —   | 101 |

|        | A,BR      | CE,C0       | A←BR      | 2   | 2  | —  | — | — | — | — | —   | —   | 101 |

|        | A,SC      | CE,C1       | A←SC      | 2   | 2  | —  | — | — | — | — | —   | —   | 101 |

|        | A,#nn     | B0,nn       | A←nn      | 2   | 2  | —  | — | — | — | — | —   | —   | 108 |

|        | A,[BR:ll] | 44,ll       | A←[BR:ll] | 3   | 2  | —  | — | — | — | — | —   | —   | 111 |

|        | A,[hhll]  | CE,D0,ll,hh | A←[hhll]  | 5   | 4  | —  | — | — | — | — | —   | —   | 113 |

|        | A,[HL]    | 45          | A←[HL]    | 2   | 1  | —  | — | — | — | — | —   | —   | 113 |

|        | A,[IX]    | 46          | A←[IX]    | 2   | 1  | —  | — | — | — | — | —   | —   | 115 |