CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

**S1C63406/408**

テクニカルマニュアル

S1C63406/408 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

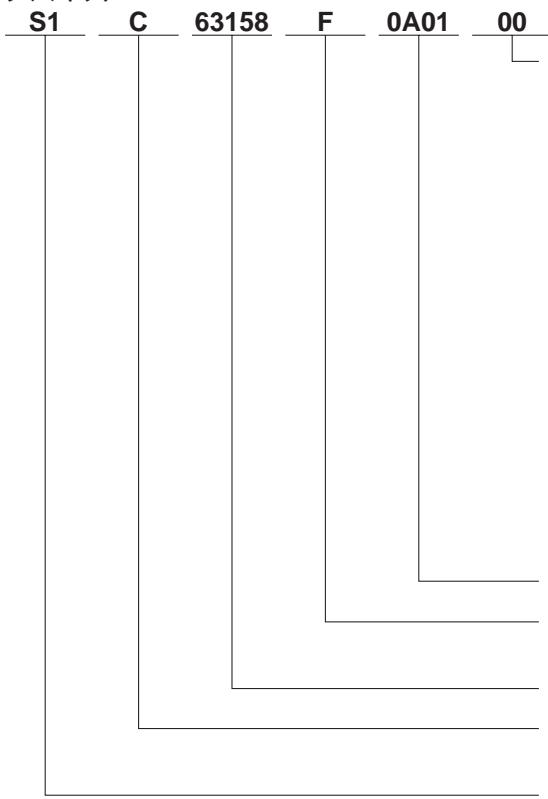

## 製品型番体系

### デバイス

#### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

#### 仕様

[D: ペアチップ、F: QFP]

#### 機種番号

[C: マイコン、デジタル製品]

#### 製品分類

[S1: 半導体]

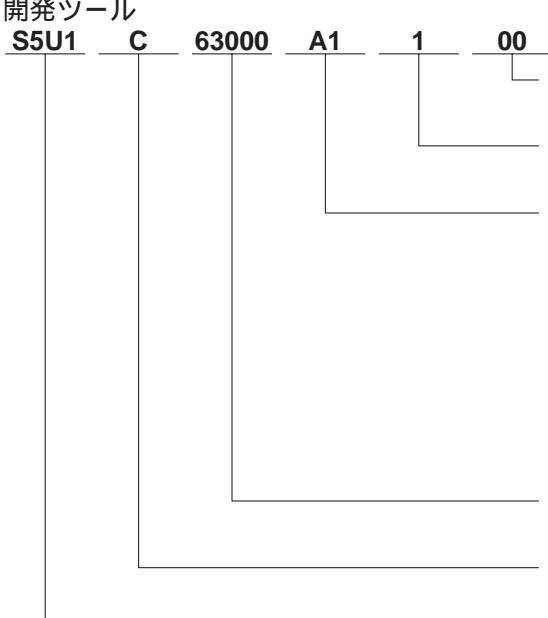

### 開発ツール

#### 梱包仕様

[00: 標準梱包]

#### バージョン

[1: Version 1]

#### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ベリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

#### 対応機種番号

[63000: S1C63ファミリ共通]

#### ツール分類

[C: マイコン用]

#### 製品分類

[S5U1: 半導体用開発ツール]

- 目 次 -

|          |                              |           |

|----------|------------------------------|-----------|

| <b>1</b> | <b>概要</b>                    | <b>1</b>  |

| 1.1      | 特長                           | 1         |

| 1.2      | ブロック図                        | 3         |

| 1.3      | 端子配置図                        | 5         |

| 1.4      | 端子説明                         | 7         |

| 1.5      | マスクオプション                     | 9         |

| <b>2</b> | <b>電源系 および イニシャルリセット</b>     | <b>11</b> |

| 2.1      | 電源系                          | 11        |

| 2.1.1    | 内部回路用電圧<VD1>                 | 12        |

| 2.1.2    | OSC1発振回路用電圧<Vosc>            | 12        |

| 2.1.3    | LCD駆動用電圧<Vc1, Vc2, Vc4, Vc5> | 12        |

| 2.2      | イニシャルリセット                    | 13        |

| 2.2.1    | リセット端子( RESET )              | 13        |

| 2.2.2    | K00 ~ K03端子への同時LOW入力         | 14        |

| 2.2.3    | 内蔵リセット回路                     | 14        |

| 2.2.4    | イニシャルリセット時の内部レジスタ            | 15        |

| 2.2.5    | イニシャルリセット時の端子設定              | 15        |

| 2.3      | テスト端子( TEST )                | 15        |

| <b>3</b> | <b>CPU, ROM, RAM</b>         | <b>16</b> |

| 3.1      | CPU                          | 16        |

| 3.2      | コードROM                       | 16        |

| 3.3      | RAM                          | 17        |

| 3.4      | データROM                       | 17        |

| <b>4</b> | <b>周辺回路と動作</b>               | <b>18</b> |

| 4.1      | メモリマップ                       | 18        |

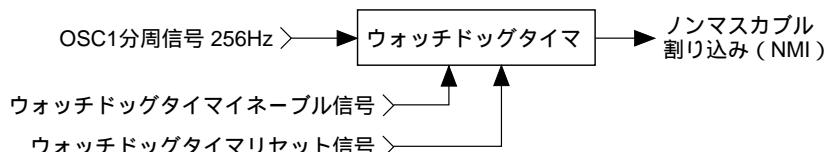

| 4.2      | ウォッチドッグタイマ                   | 23        |

| 4.2.1    | ウォッチドッグタイマの構成                | 23        |

| 4.2.2    | 割り込み機能                       | 23        |

| 4.2.3    | ウォッチドッグタイマのI/Oメモリ            | 24        |

| 4.2.4    | プログラミング上の注意事項                | 24        |

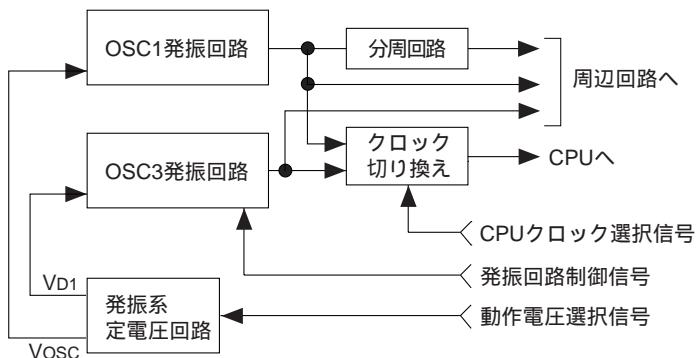

| 4.3      | 発振回路                         | 25        |

| 4.3.1    | 発振回路の構成                      | 25        |

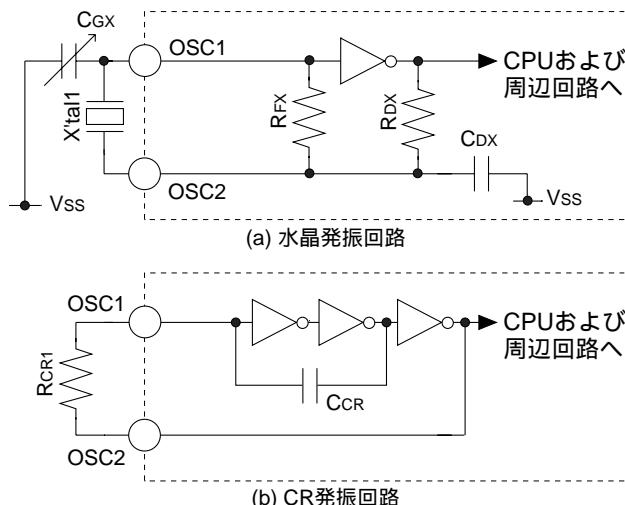

| 4.3.2    | OSC1発振回路                     | 26        |

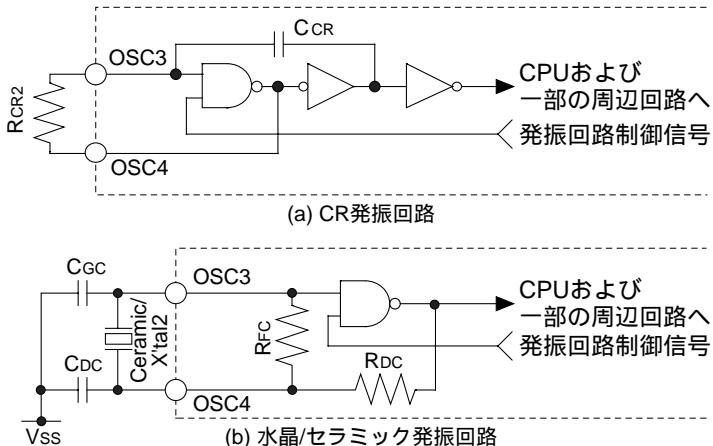

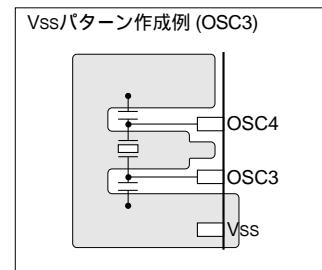

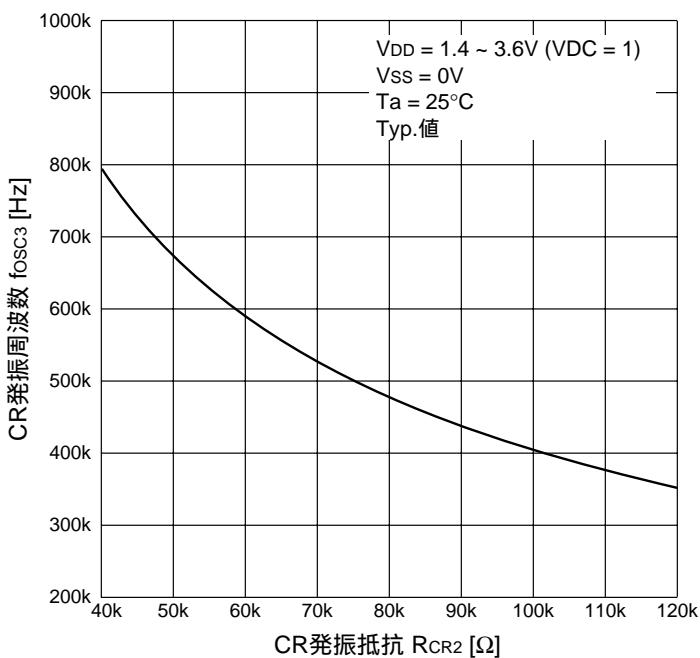

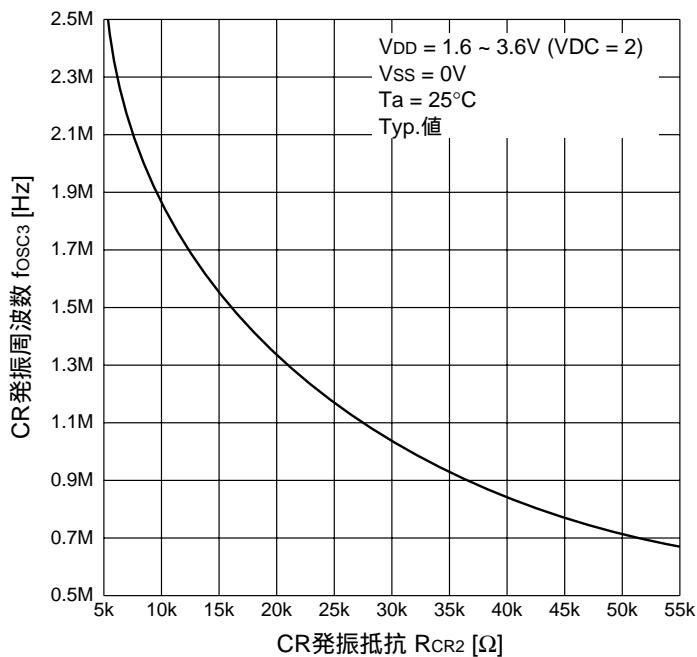

| 4.3.3    | OSC3発振回路                     | 27        |

| 4.3.4    | 動作電圧切り換え                     | 28        |

| 4.3.5    | クロック周波数とインストラクション実行時間        | 28        |

| 4.3.6    | 発振回路のI/Oメモリ                  | 29        |

| 4.3.7    | プログラミング上の注意事項                | 30        |

|          |                                         |    |

|----------|-----------------------------------------|----|

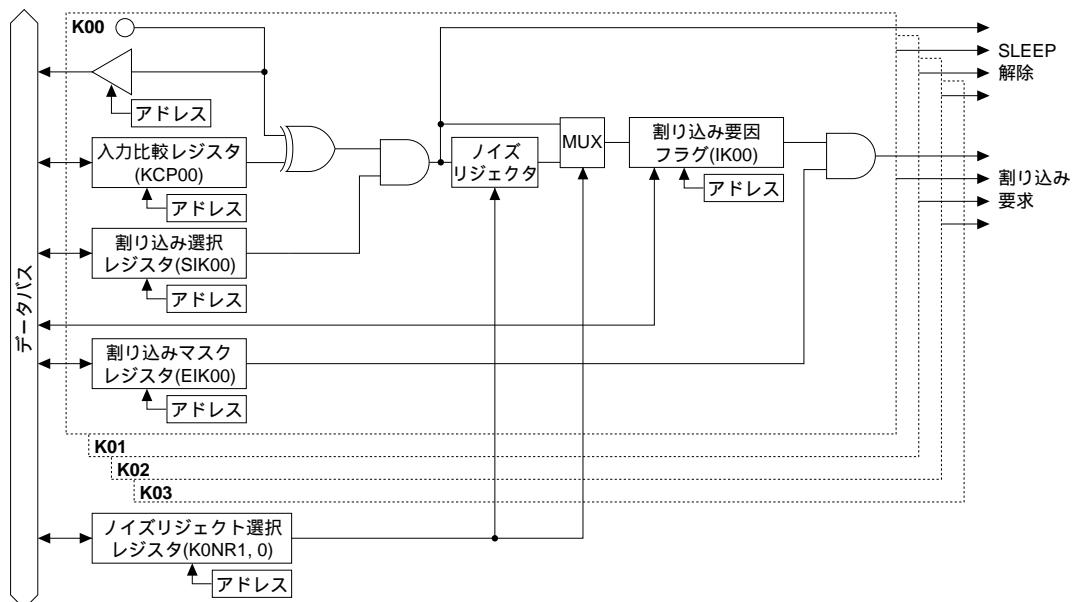

| 4.4      | 入力ポート( K00 ~ K03 ) .....                | 31 |

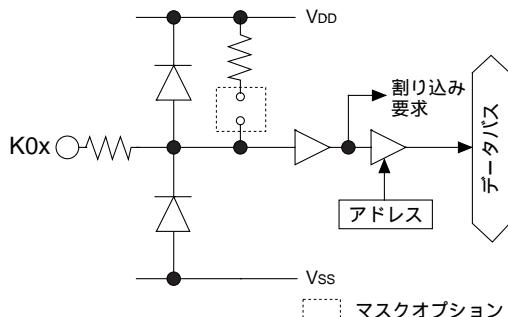

| 4.4.1    | 入力ポートの構成 .....                          | 31 |

| 4.4.2    | マスクオプション .....                          | 31 |

| 4.4.3    | 割り込み機能 .....                            | 31 |

| 4.4.4    | 入力ポートのI/Oメモリ .....                      | 33 |

| 4.4.5    | プログラミング上の注意事項 .....                     | 35 |

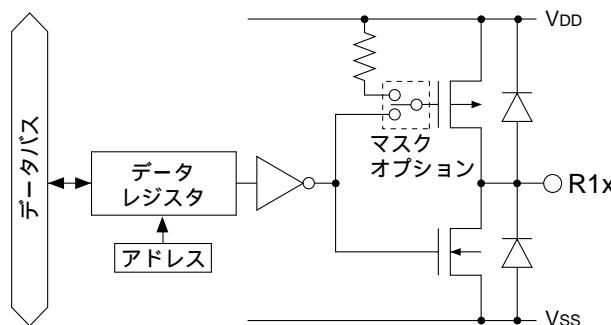

| 4.5      | 出力ポート( R10 ~ R13 ) .....                | 36 |

| 4.5.1    | 出力ポートの構成 .....                          | 36 |

| 4.5.2    | マスクオプション .....                          | 36 |

| 4.5.3    | DC出力 .....                              | 36 |

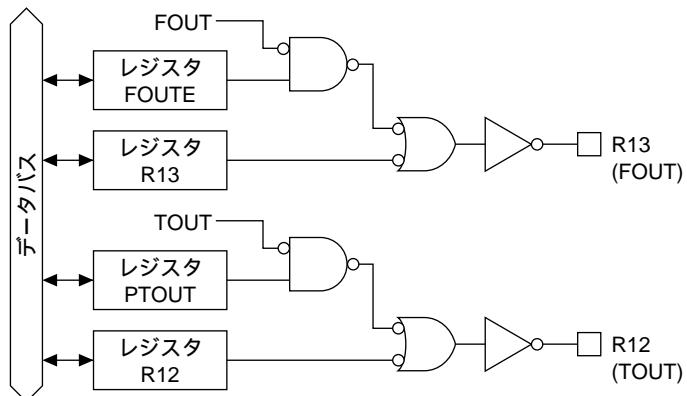

| 4.5.4    | 特殊出力 .....                              | 37 |

| 4.5.5    | 出力ポートのI/Oメモリ .....                      | 39 |

| 4.5.6    | プログラミング上の注意事項 .....                     | 40 |

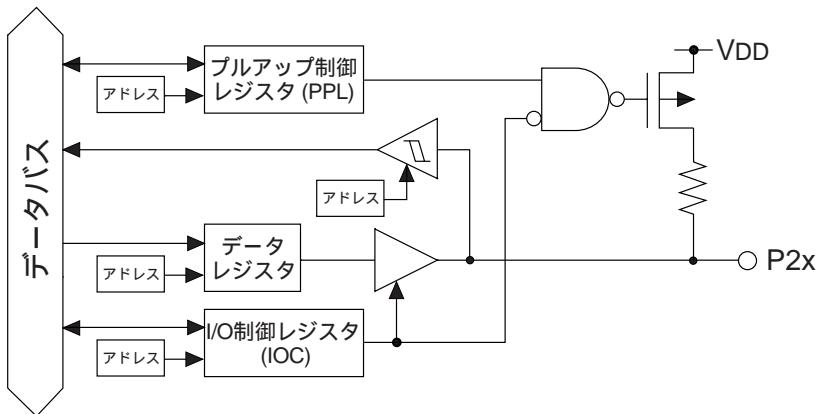

| 4.6      | 入出力兼用ポート( P20 ~ P23 ) .....             | 41 |

| 4.6.1    | 入出力兼用ポートの構成 .....                       | 41 |

| 4.6.2    | マスクオプション .....                          | 42 |

| 4.6.3    | I/O制御レジスタと入力/出力モード .....                | 42 |

| 4.6.4    | 入力モード時のプルアップ .....                      | 42 |

| 4.6.5    | 入出力兼用ポートのI/Oメモリ .....                   | 43 |

| 4.6.6    | プログラミング上の注意事項 .....                     | 45 |

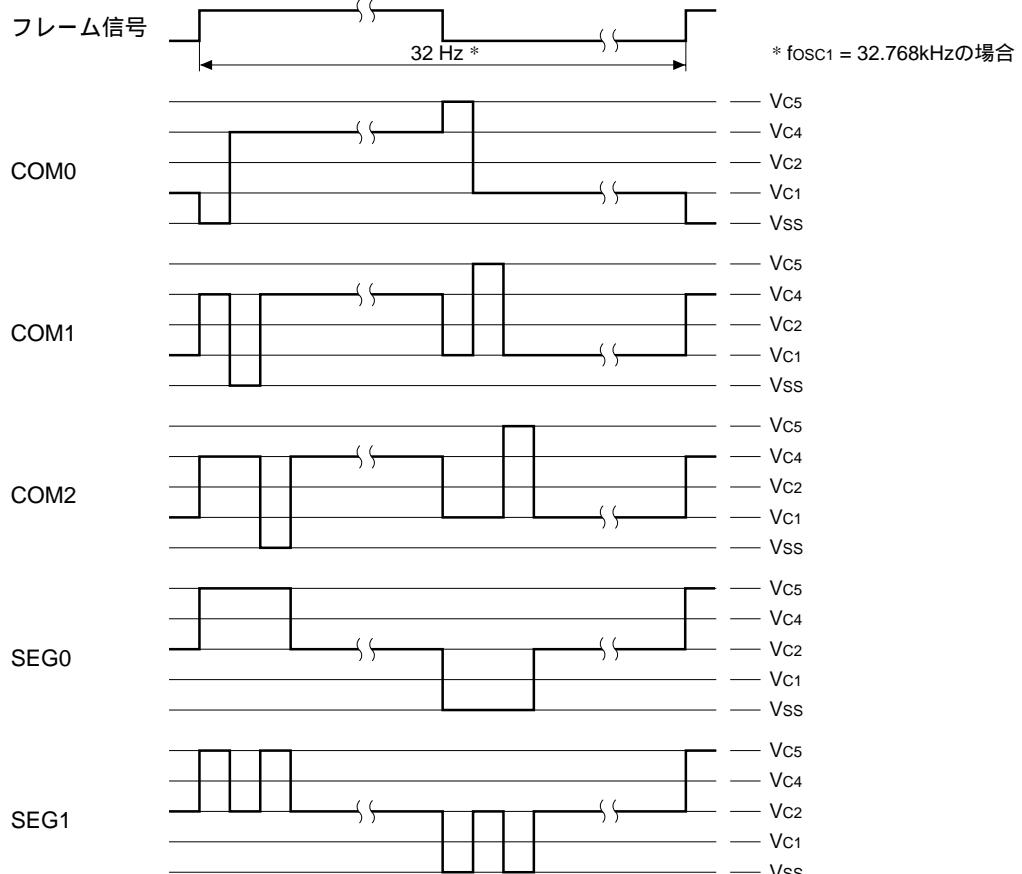

| 4.7      | LCDドライバ .....                           | 46 |

| 4.7.1    | LCDドライバの構成 .....                        | 46 |

| 4.7.2    | LCD駆動電源 .....                           | 46 |

| 4.7.3    | LCD表示のON/OFFとデューティの切り換え .....           | 46 |

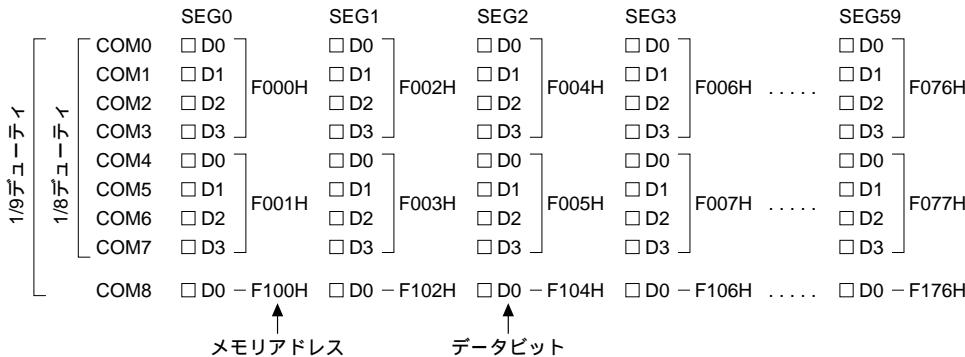

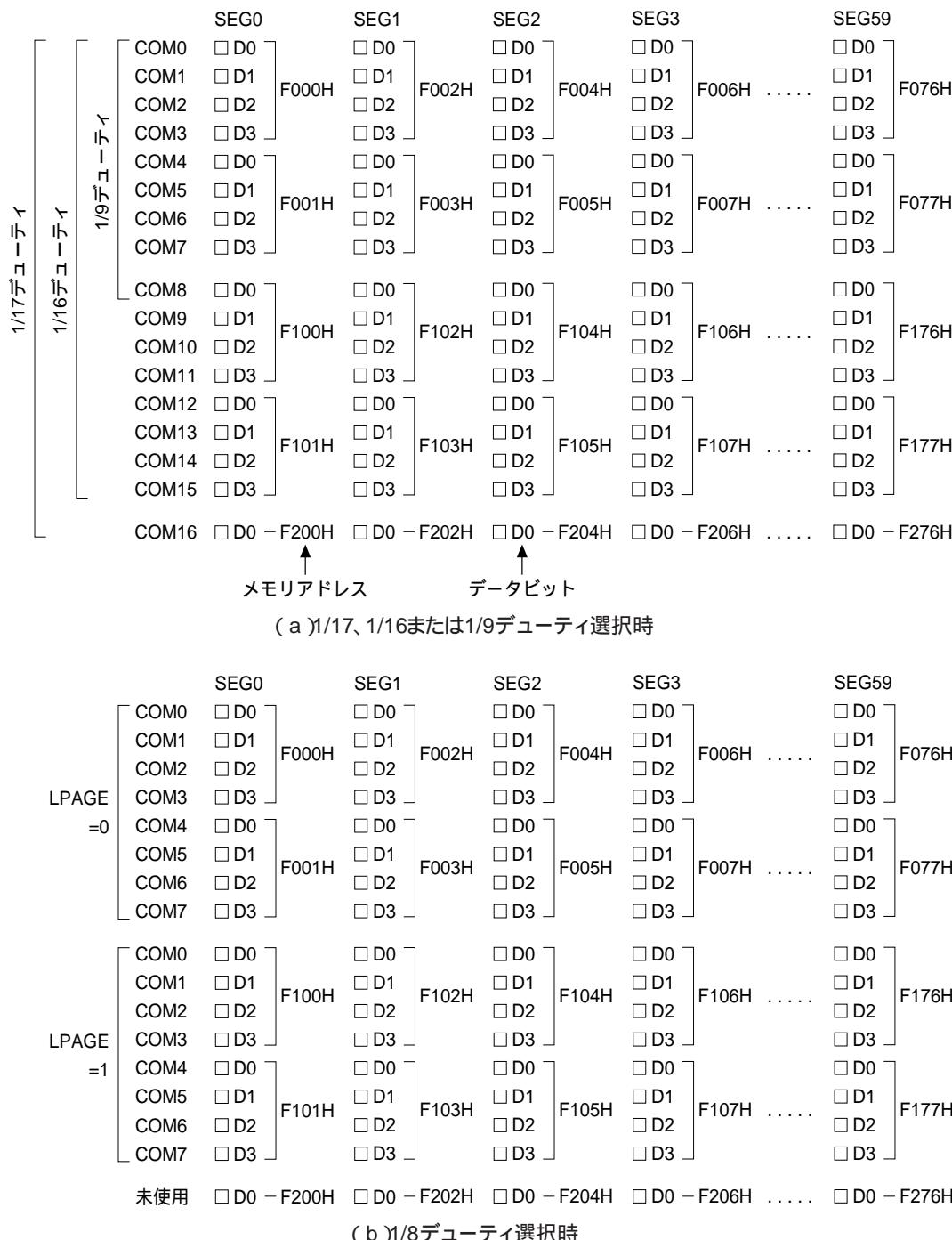

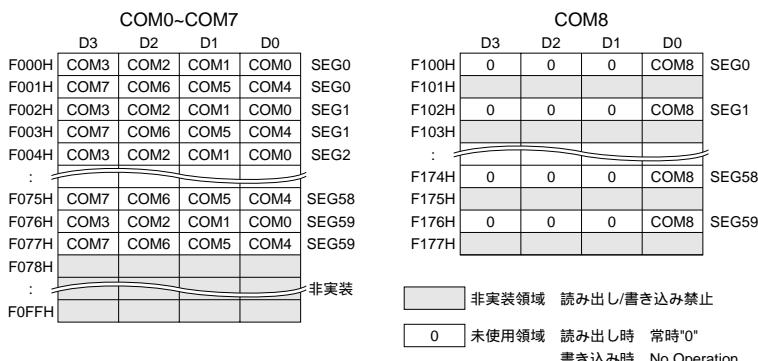

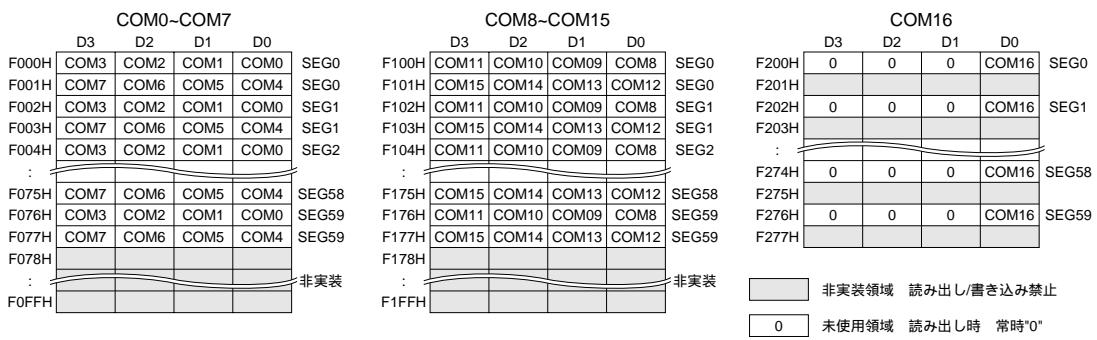

| 4.7.4    | 表示メモリ .....                             | 48 |

| 4.7.5    | LCDコントラスト調整 .....                       | 50 |

| 4.7.6    | LCDドライバのI/Oメモリ .....                    | 51 |

| 4.7.7    | プログラミング上の注意事項 .....                     | 53 |

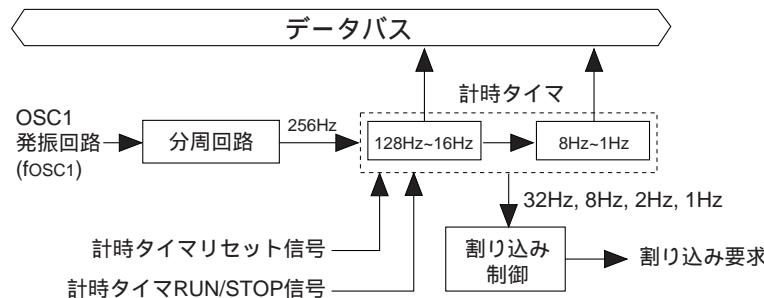

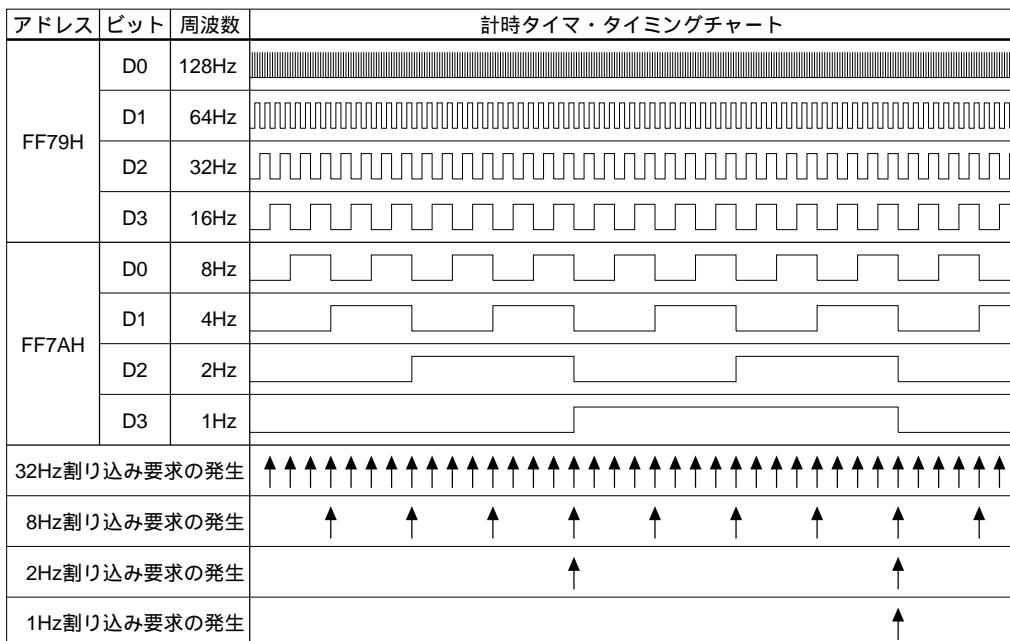

| 4.8      | 計時タイマ .....                             | 54 |

| 4.8.1    | 計時タイマの構成 .....                          | 54 |

| 4.8.2    | データの読み出しとホールド機能 .....                   | 54 |

| 4.8.3    | 割り込み機能 .....                            | 55 |

| 4.8.4    | 計時タイマのI/Oメモリ .....                      | 56 |

| 4.8.5    | プログラミング上の注意事項 .....                     | 58 |

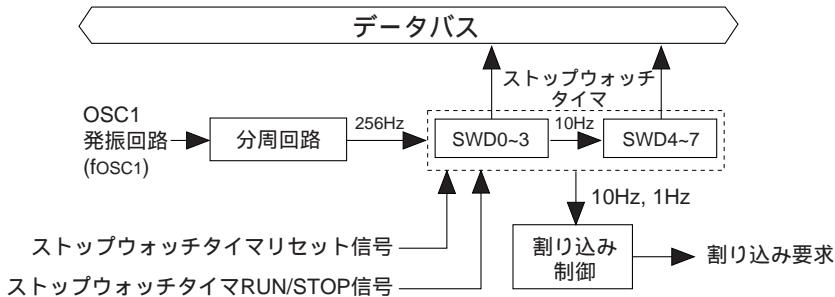

| 4.9      | ストップウォッチタイマ .....                       | 59 |

| 4.9.1    | ストップウォッチタイマの構成 .....                    | 59 |

| 4.9.2    | カウントアップパターン .....                       | 59 |

| 4.9.3    | 割り込み機能 .....                            | 60 |

| 4.9.4    | ストップウォッチタイマのI/Oメモリ .....                | 61 |

| 4.9.5    | プログラミング上の注意事項 .....                     | 62 |

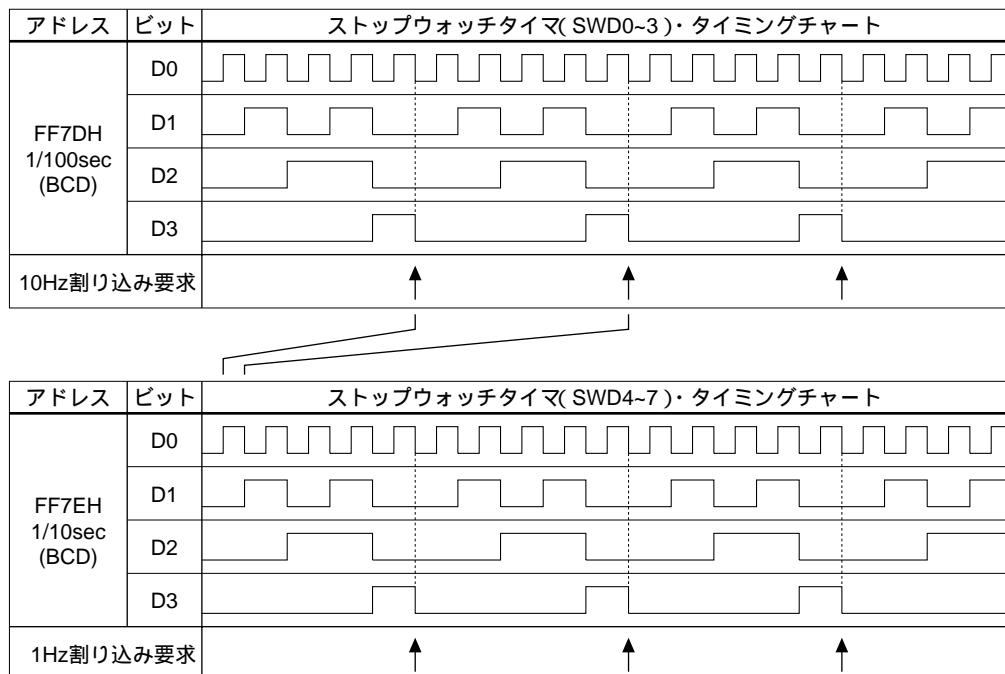

| 4.10     | プログラマブルタイマ .....                        | 63 |

| 4.10.1   | プログラマブルタイマの構成 .....                     | 63 |

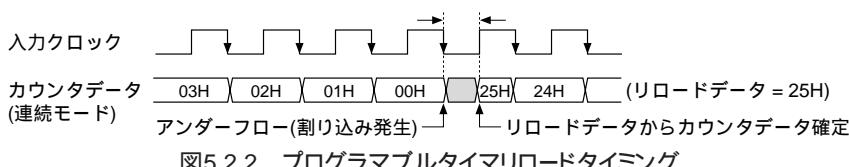

| 4.10.2   | 2チャンネル×8ビットタイマ( MODE16 = "0" )の動作 ..... | 64 |

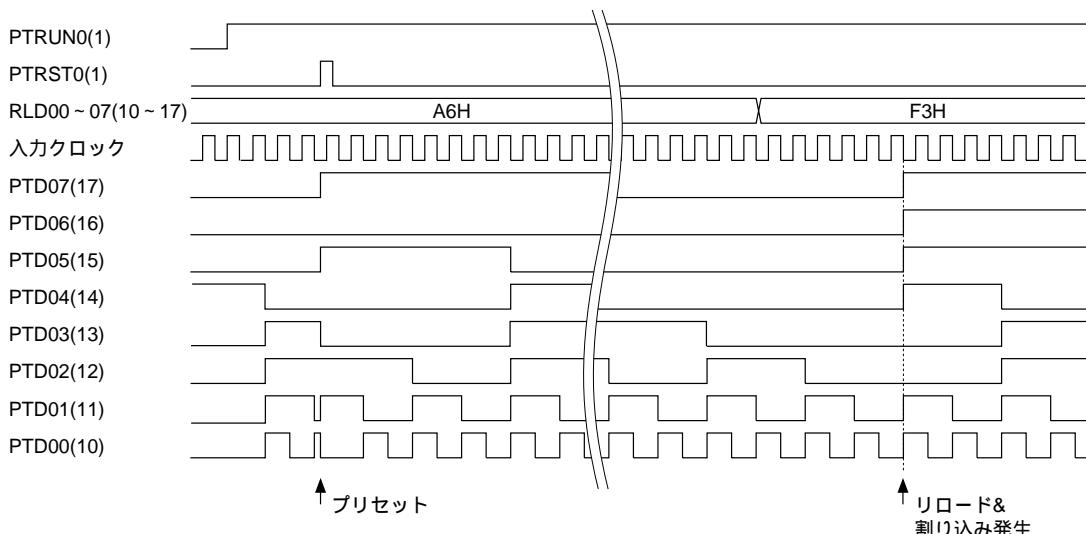

| 4.10.2.1 | カウンタ初期値の設定とダウンカウント動作 .....              | 64 |

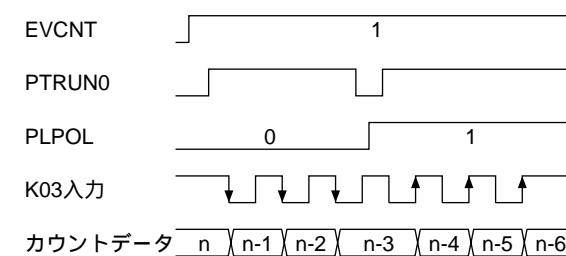

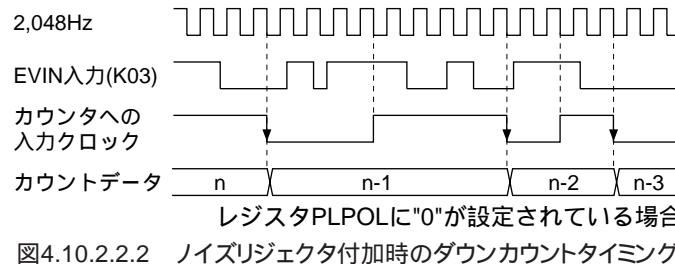

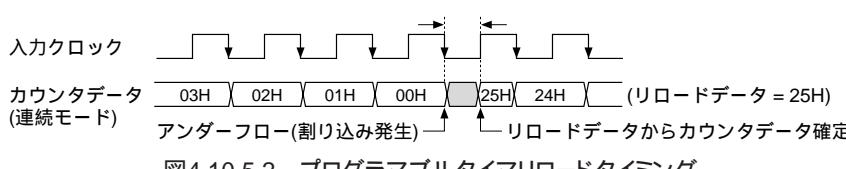

| 4.10.2.2 | カウンタモード .....                           | 65 |

| 4.10.2.3 | タイマモード入力クロックの設定 .....                   | 66 |

| 4.10.2.4 | 割り込み機能 .....                            | 67 |

|                                               |     |

|-----------------------------------------------|-----|

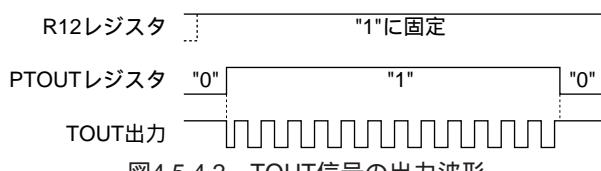

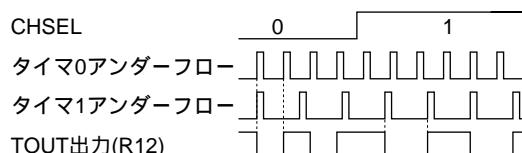

| 4.10.2.5 TOUT出力の設定 .....                      | 67  |

| 4.10.2.6 シリアルインタフェースの転送速度設定 .....             | 68  |

| 4.10.3 1チャンネル×16ビットタイマ(MODE16 = "1")の動作 ..... | 68  |

| 4.10.3.1 カウンタ初期値の設定とダウンカウント動作 .....           | 68  |

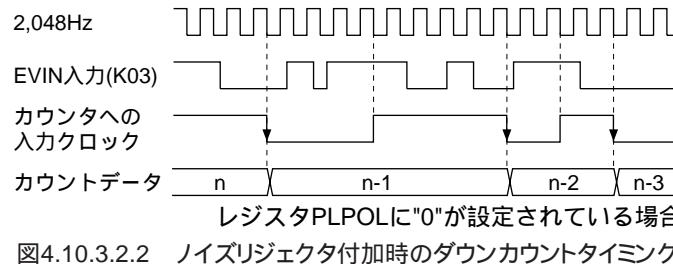

| 4.10.3.2 カウンタモード .....                        | 69  |

| 4.10.3.3 タイマモード入力クロックの設定 .....                | 70  |

| 4.10.3.4 割り込み機能 .....                         | 71  |

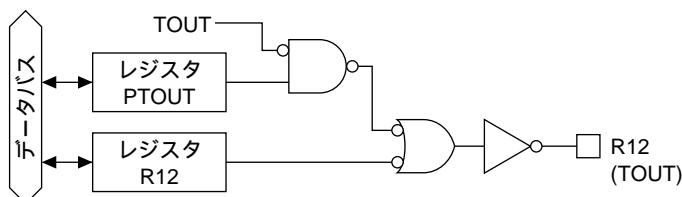

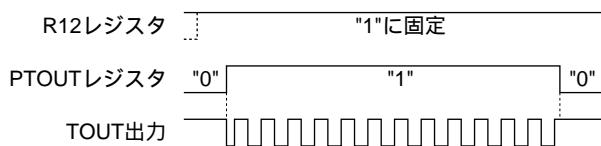

| 4.10.3.5 TOUT出力の設定 .....                      | 71  |

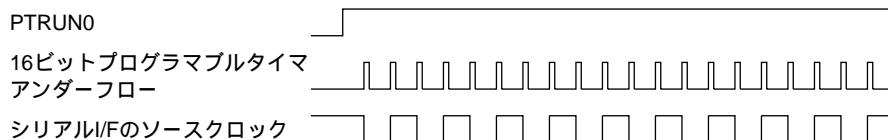

| 4.10.3.6 シリアルインタフェースの転送速度設定 .....             | 72  |

| 4.10.4 プログラマブルタイマのI/Oメモリ .....                | 73  |

| 4.10.5 プログラミング上の注意事項 .....                    | 78  |

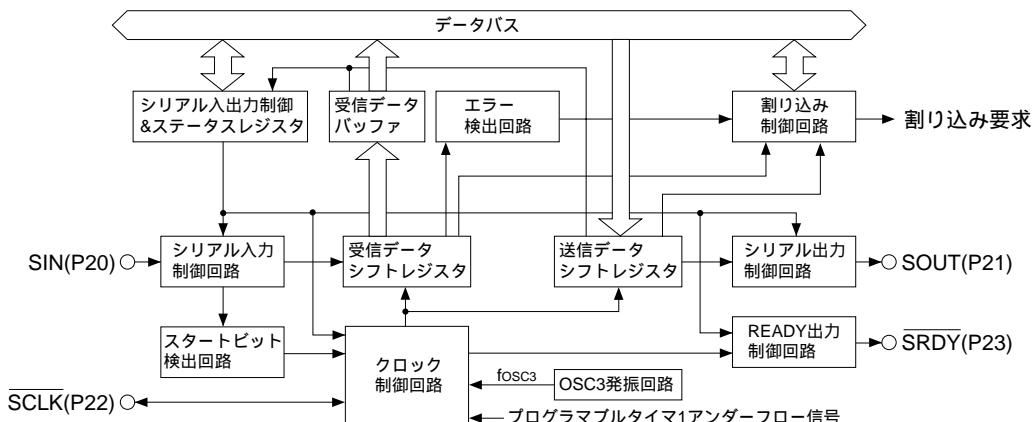

| 4.11 シリアルインタフェース .....                        | 79  |

| 4.11.1 シリアルインタフェースの構成 .....                   | 79  |

| 4.11.2 マスクオプション .....                         | 80  |

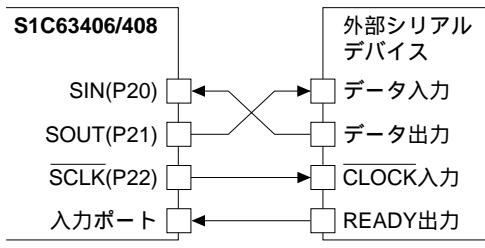

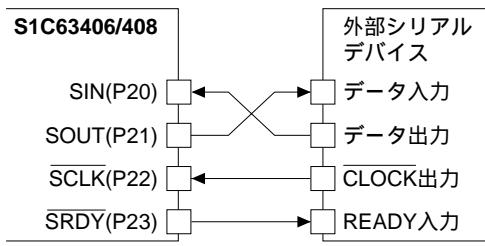

| 4.11.3 転送モード .....                            | 80  |

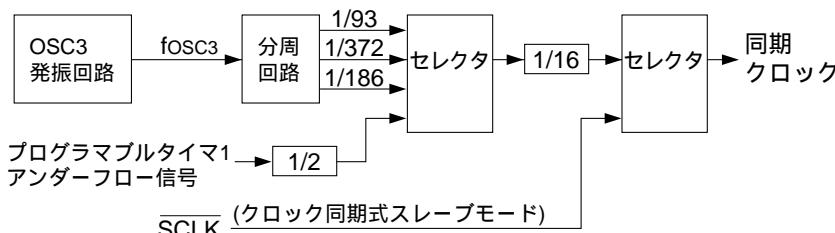

| 4.11.4 クロック源 .....                            | 82  |

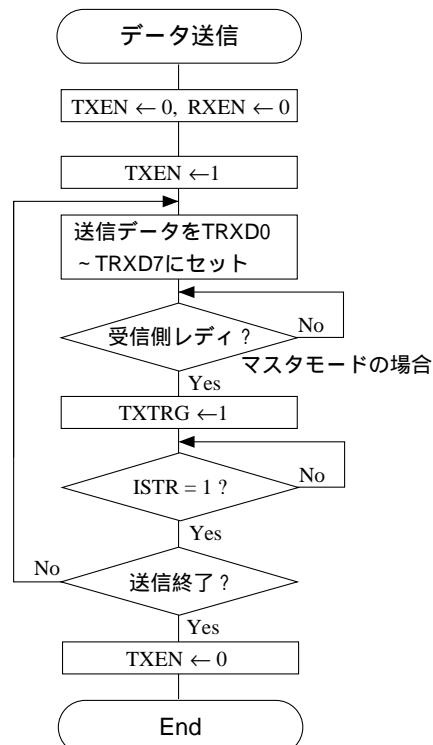

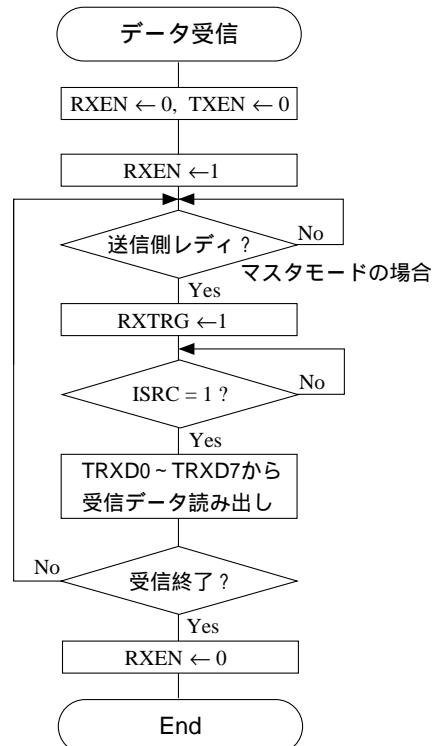

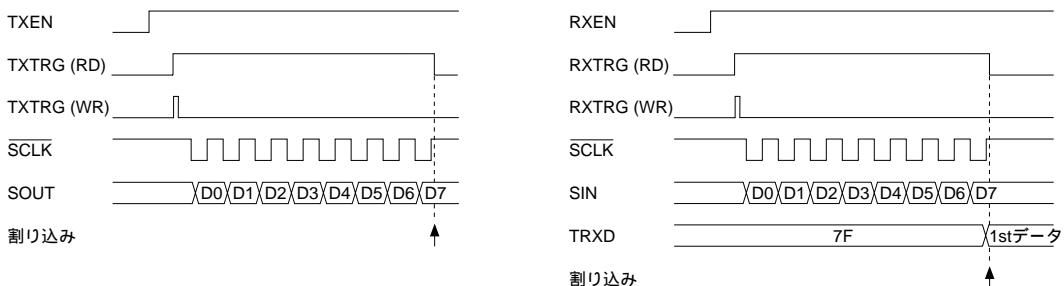

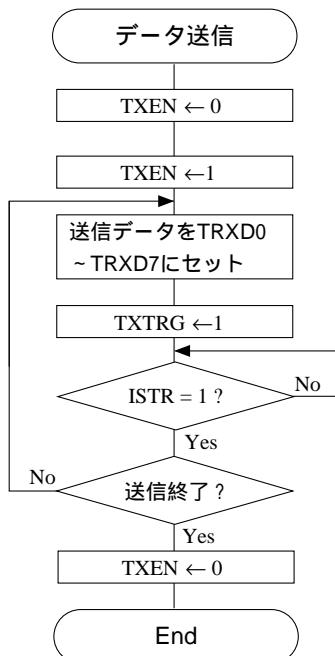

| 4.11.5 送受信の制御 .....                           | 83  |

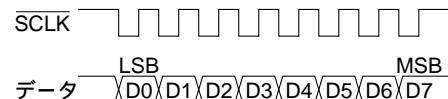

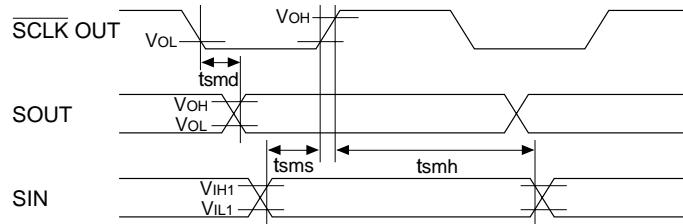

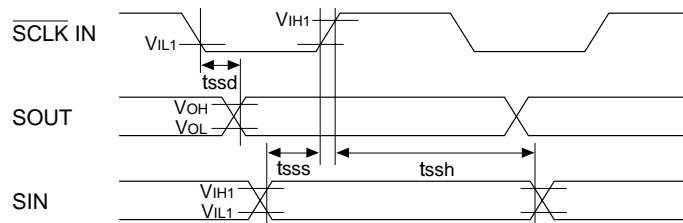

| 4.11.6 クロック同期式転送の動作 .....                     | 84  |

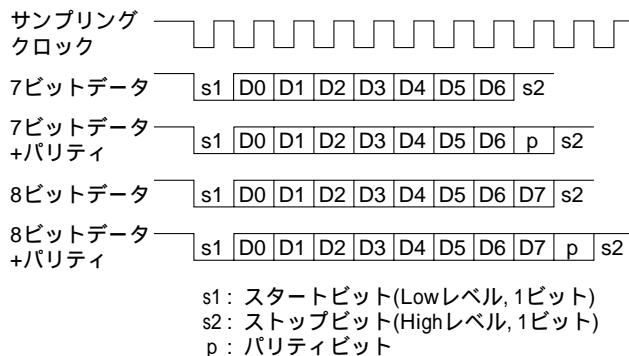

| 4.11.7 調歩同期式転送の動作 .....                       | 88  |

| 4.11.8 割り込み機能 .....                           | 92  |

| 4.11.9 シリアルインタフェースのI/Oメモリ .....               | 94  |

| 4.11.10 プログラミング上の注意事項 .....                   | 100 |

| 4.12 SVD(電源電圧検出)回路 .....                      | 101 |

| 4.12.1 SVD回路の構成 .....                         | 101 |

| 4.12.2 SVD動作 .....                            | 101 |

| 4.12.3 SVD回路のI/Oメモリ .....                     | 102 |

| 4.12.4 プログラミング上の注意事項 .....                    | 102 |

| 4.13 重負荷保護機能 .....                            | 103 |

| 4.13.1 重負荷保護モード .....                         | 103 |

| 4.13.2 重負荷保護機能のI/Oメモリ .....                   | 103 |

| 4.13.3 プログラミング上の注意事項 .....                    | 103 |

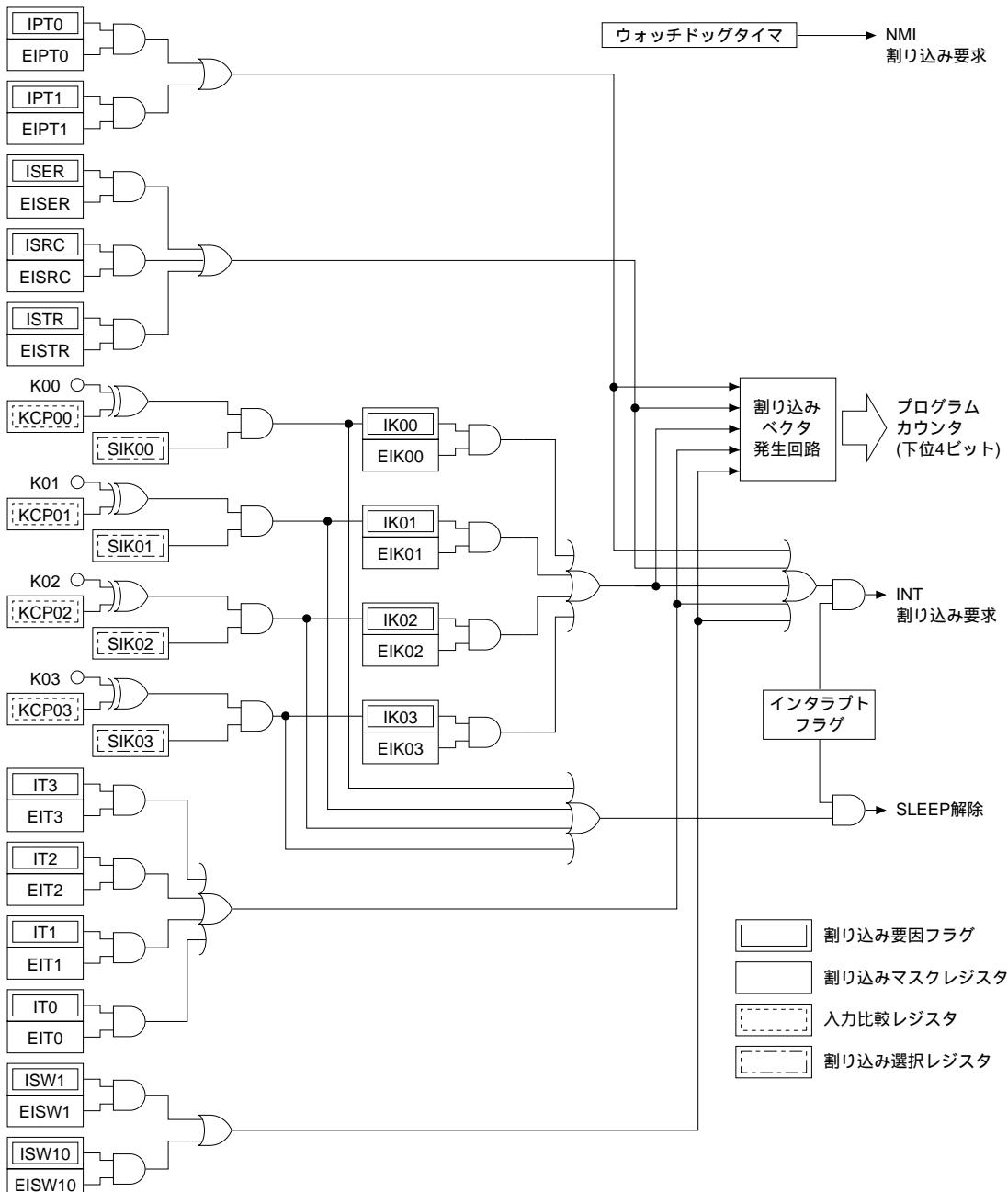

| 4.14 割り込みとHALT/SLEEP .....                    | 104 |

| 4.14.1 割り込みの要因 .....                          | 106 |

| 4.14.2 割り込みの個別マスク .....                       | 107 |

| 4.14.3 割り込みベクタ .....                          | 107 |

| 4.14.4 割り込みのI/Oメモリ .....                      | 108 |

| 4.14.5 プログラミング上の注意事項 .....                    | 109 |

| 5 注意事項のまとめ .....                              | 110 |

| 5.1 低消費電流化のための注意事項 .....                      | 110 |

| 5.2 個別機能についての注意事項のまとめ .....                   | 111 |

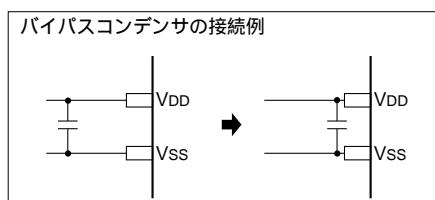

| 5.3 実装上の注意事項 .....                            | 115 |

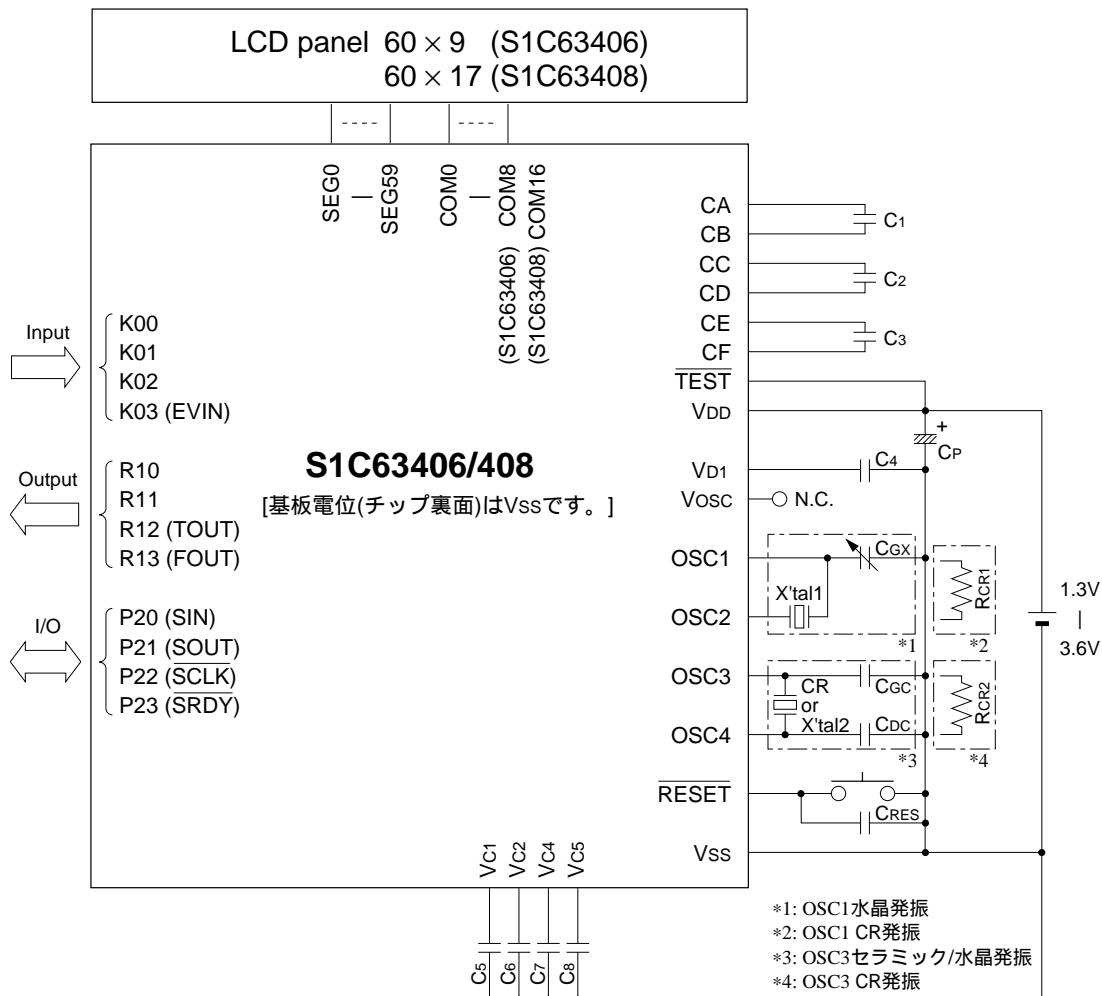

| 6 基本外部結線図 .....                               | 117 |

|                                               |     |

|-----------------------------------------------|-----|

| 7 電気的特性                                       | 118 |

| 7.1 絶対最大定格                                    | 118 |

| 7.2 推奨動作条件                                    | 118 |

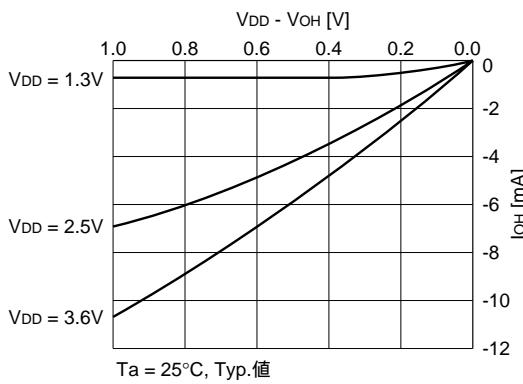

| 7.3 DC特性                                      | 119 |

| 7.4 アナログ回路特性/消費電流                             | 120 |

| 7.5 発振特性                                      | 123 |

| 7.6 シリアルインターフェースAC特性                          | 126 |

| 7.7 タイミングチャート                                 | 127 |

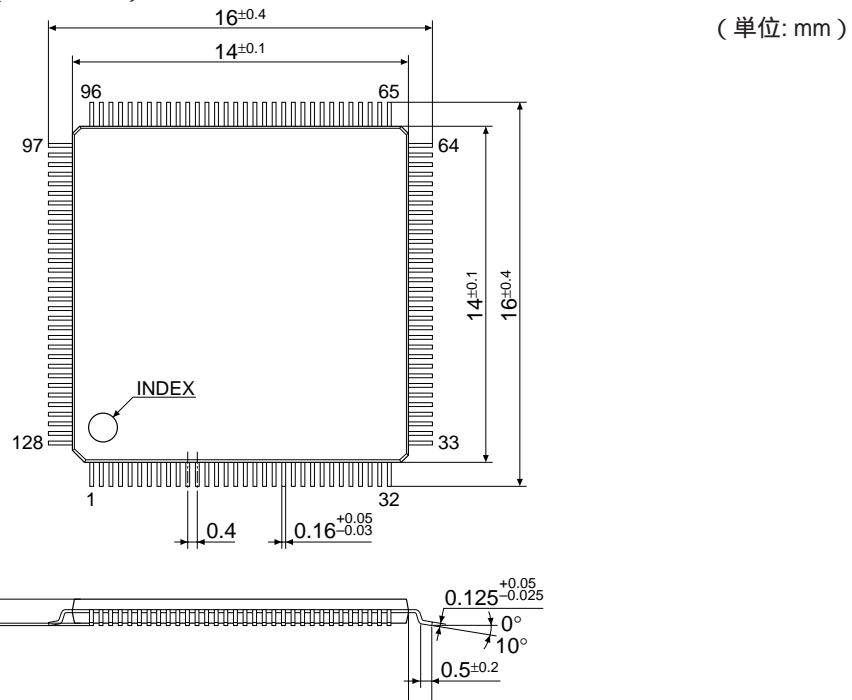

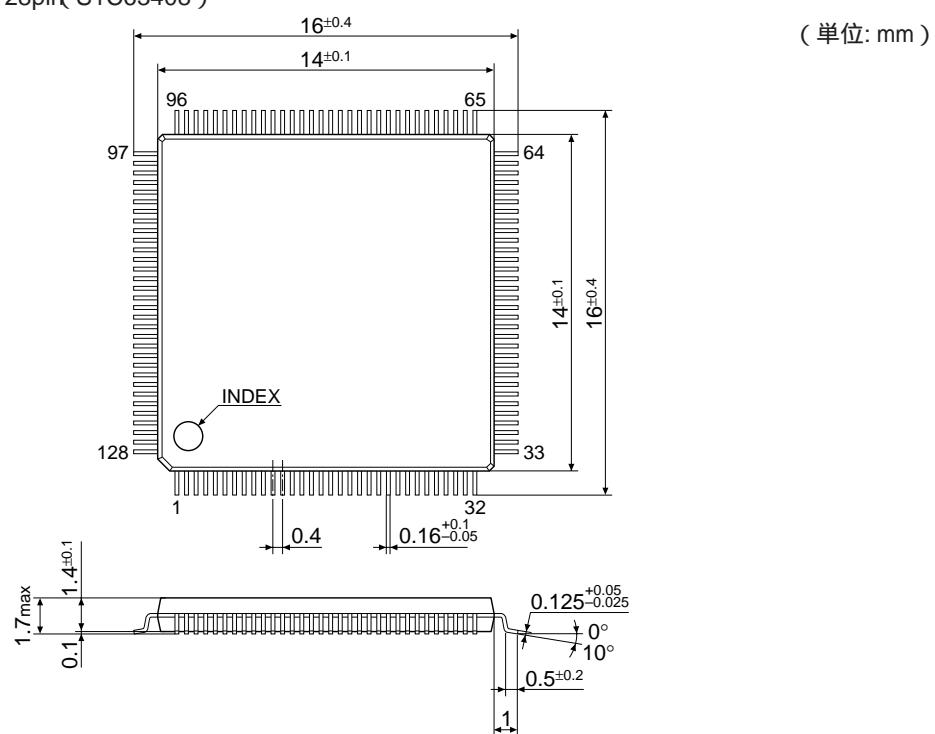

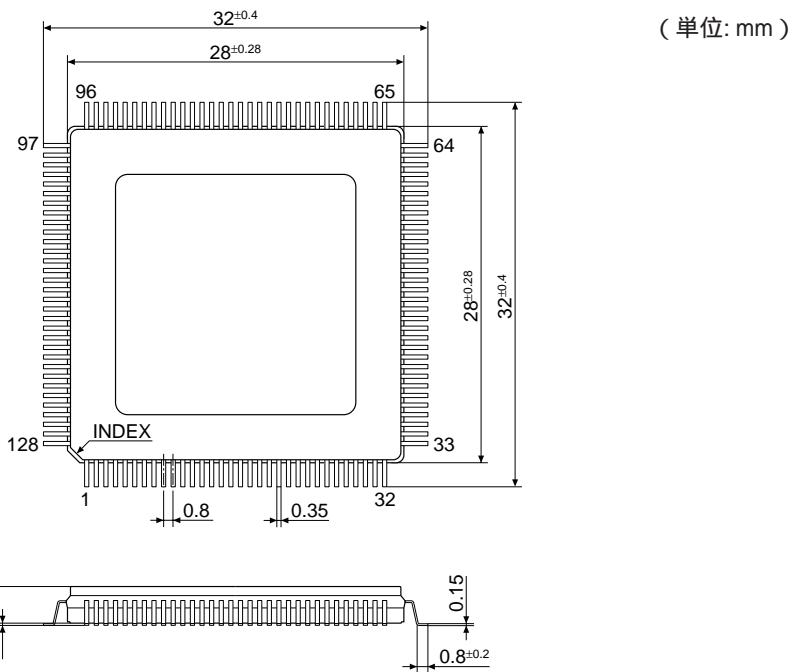

| 8 パッケージ                                       | 128 |

| 8.1 プラスチックパッケージ                               | 128 |

| 8.2 テストサンプル用セラミックパッケージ                        | 129 |

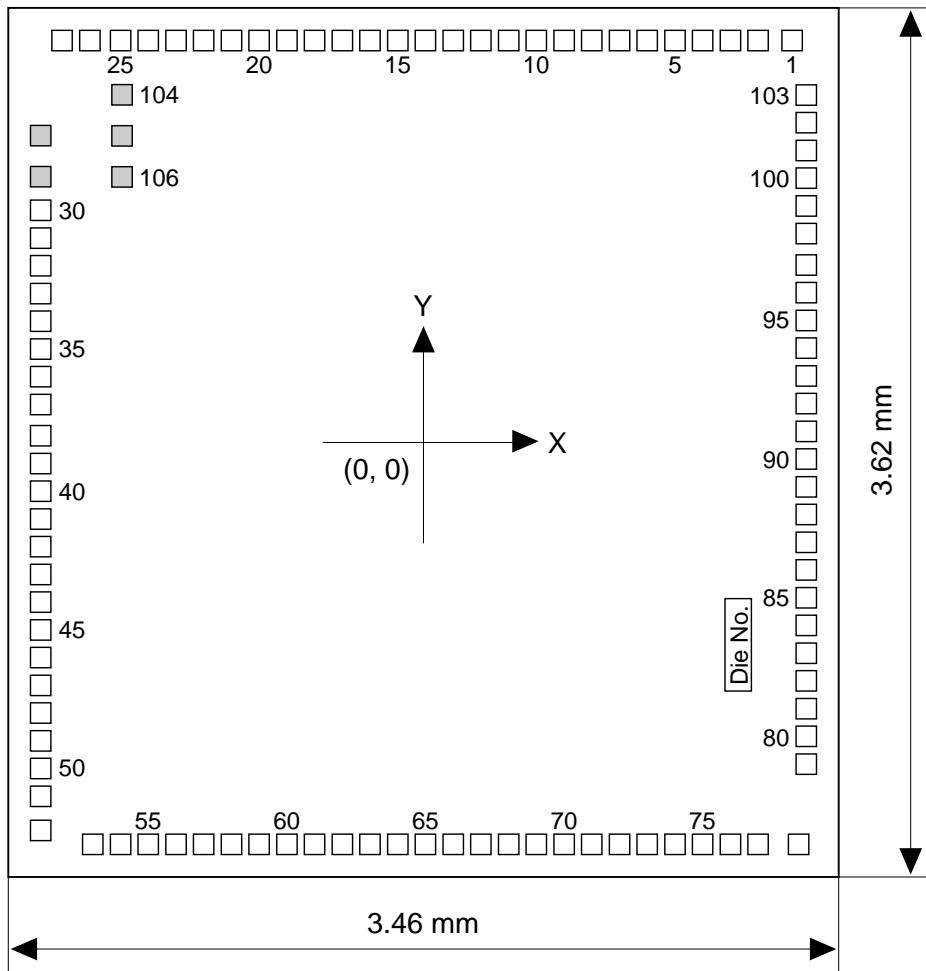

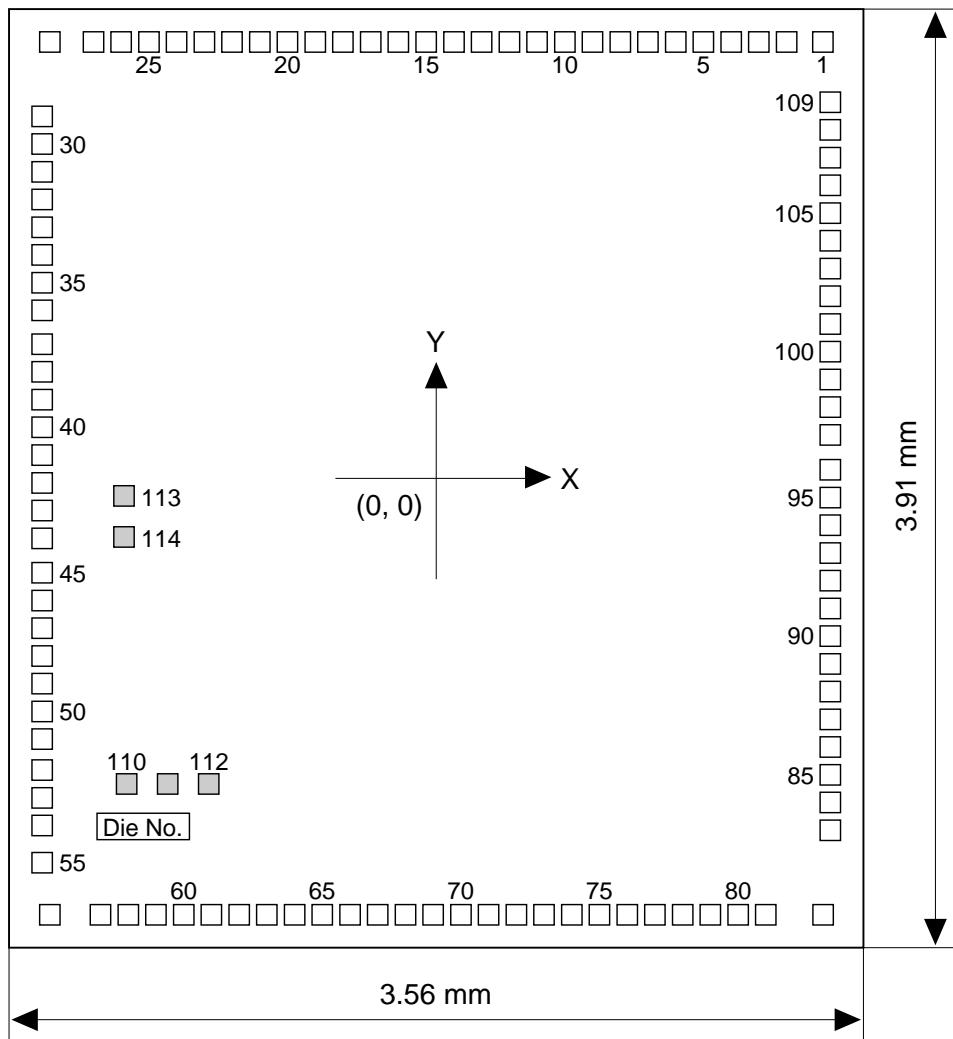

| 9 パッド配置                                       | 130 |

| 9.1 パッド配置図                                    | 130 |

| 9.2 パッド座標                                     | 132 |

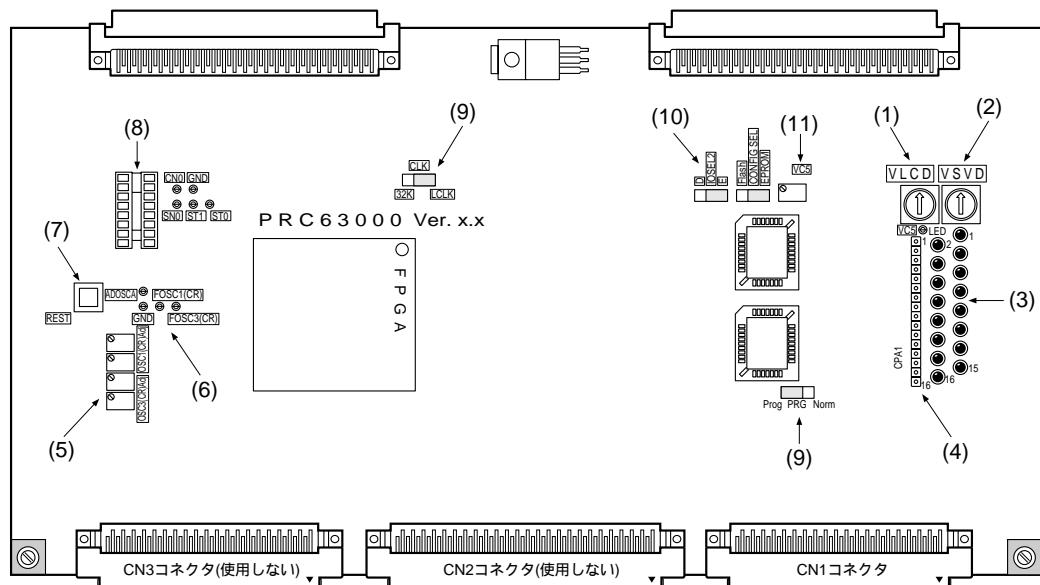

| APPENDIX S5U1C63000P Manual                   |     |

| ( Peripheral Circuit Board for S1C63406/408 ) | 134 |

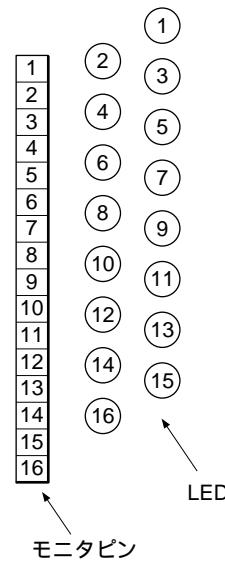

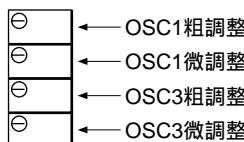

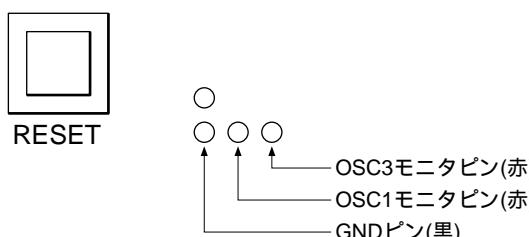

| A.1 各部の名称と機能                                  | 134 |

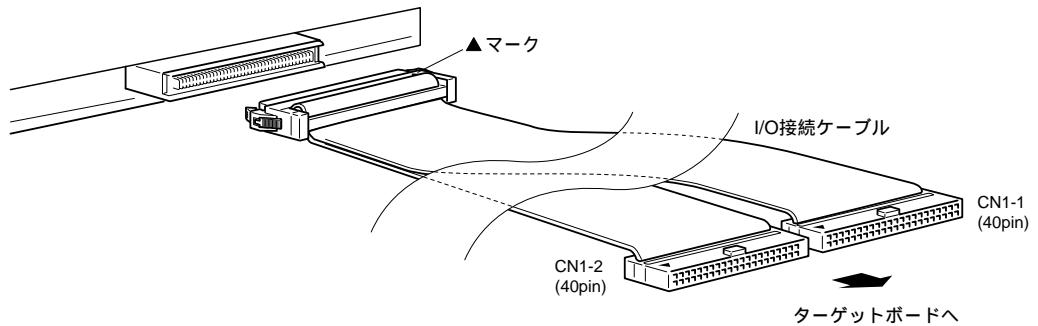

| A.2 ターゲットシステムとの接続                             | 137 |

| A.3 使用上の注意                                    | 139 |

| A.3.1 操作上の注意事項                                | 139 |

| A.3.2 実ICとの相違点                                | 139 |

# 1 概要

S1C63406/408は高性能4ビットCPU S1C63000を中心に、ワンチップ上に命令ROM、RAM、データROM、シリアルインターフェース、ウォッチドッグタイマ、プログラマブルタイマ、タイムベースカウンタ(2系統)、ドットマトリクスLCD駆動回路等を内蔵したマイクロコンピュータです。また、電源投入時や電源瞬断時に電源電圧を検出し、マイクロコンピュータシステムをリセットするリセット回路(パワーオンリセット機能付き)を内蔵しています。低動作電圧(1.3V~3.6V)による高速動作および低消費電流等の特長を持ち、電池駆動を必要とするポータブルMD/CDプレイヤー等への応用に適しています。

表1.1にS1C63406とS1C63408の相違点を示します。

表1.1 S1C63406とS1C63408の相違点

| 機種       | S1C63406            | S1C63408                  |

|----------|---------------------|---------------------------|

| 命令ROM容量  | 6,144ワード×13ビット      | 8,192ワード×13ビット            |

| データROM容量 | 3,072ワード×4ビット       | 4,096ワード×4ビット             |

| RAM容量    | 1,024ワード×4ビット       | 1,024ワード×4ビット             |

| 表示メモリ容量  | 540ビット              | 1,020ビット                  |

| LCDドライバ  | 60セグメント<br>8または9コモン | 60セグメント<br>8、9、16または17コモン |

## 1.1 特長

|               |                                                                                                                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1発振回路      | 32.768kHz( Typ. )水晶発振、または60kHz( Typ. )CR発振回路(*1)                                                                                                                                  |

| OSC3発振回路      | 4MHz( Typ. )水晶発振、3.58MHz( Typ. )セラミック発振、<br>または2MHz( Typ. )CR発振回路(*1)                                                                                                             |

| インストラクションセット  | 基本命令 47種類(全命令数 411種類)アドレッシングモード 8種類                                                                                                                                               |

| インストラクション実行時間 | 32.768kHz動作時: 61μsec 122μsec 183μsec<br>60kHz動作時: 33μsec 67μsec 100μsec<br>2MHz動作時: 1μsec 2μsec 3μsec<br>3.58MHz動作時: 0.56μsec 1.12μsec 1.68μsec<br>4MHz動作時: 0.5μsec 1μsec 1.5μsec |

| ROM容量         | 命令ROM: 6,144ワード×13ビット(S1C63406)<br>8,192ワード×13ビット(S1C63408)<br>データROM: 3,072ワード×4ビット(S1C63406)<br>4,096ワード×4ビット(S1C63408)                                                         |

| RAM容量         | データメモリ: 1,024ワード×4ビット<br>表示メモリ: 540ビット(120ワード×4ビット+60×1ビット、S1C63406)<br>1,020ビット(240ワード×4ビット+60×1ビット、S1C63408)                                                                    |

| 入力ポート         | 4ビット(プルアップ抵抗の付加が可能 *1)                                                                                                                                                            |

| 出力ポート         | 4ビット(2ビットを特殊出力に切り換え可能 *2)                                                                                                                                                         |

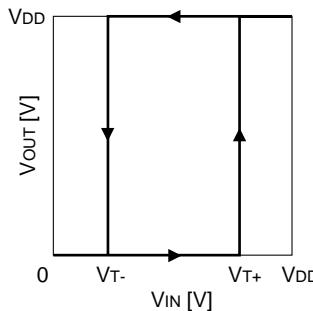

| 入出力兼用ポート      | 4ビット シュミットトリガ入力対応(プルアップ抵抗の付加が可能 *2、<br>シリアルI/F出入力に切り換え可能 *2)                                                                                                                      |

| シリアルインターフェース  | 1ポート(8ビットクロック同期式または調歩同期式 *2)                                                                                                                                                      |

| LCDドライバ       | 60セグメント×8または9コモン(S1C63406 *2)<br>60セグメント×8、9、16または17コモン(S1C63408 *2)                                                                                                              |

| タイムベースカウンタ    | 2系統(計時タイマ、ストップウォッチタイマ)                                                                                                                                                            |

| プログラマブルタイマ    | 内蔵(2入力×8ビットまたは1入力×16ビット、イベントカウンタ機能付き)                                                                                                                                             |

| ウォッチドッグタイマ    | 内蔵                                                                                                                                                                                |

| 電源電圧検出(SVD)回路 | 16値プログラマブル(1.30V~2.80V)                                                                                                                                                           |

| リセット回路        | 内蔵(1.8V、1.6Vまたは1.4V *1)パワーオンリセット機能付き                                                                                                                                              |

| 外部割り込み        | 入力ポート割り込み 4系統                                                                                                                                                                     |

| 内部割り込み        | 計時タイマ割り込み 4系統<br>ストップウォッチタイマ割り込み 2系統<br>プログラマブルタイマ割り込み 2系統<br>シリアルインターフェース割り込み 3系統                                                                                                |

---

|              |                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 電源電圧 .....   | 1.3V ~ 3.6V<br>( 700kHz (Max.) OSC3 CR発振回路を使用する場合はMin. 1.4V )<br>( 2.2MHz (Max.) OSC3 CR発振回路を使用する場合はMin. 1.6V )<br>( 4.2MHz (Max.) OSC3発振回路を使用する場合はMin. 1.8V ) |

| 動作温度範囲 ..... | -40°C ~ 85°C                                                                                                                                                   |

| 消費電流 .....   | 低電力動作( *3 )                                                                                                                                                    |

|              | SLEEP時 1.2µA( Typ. )                                                                                                                                           |

|              | HALT時( 32kHz, 水晶発振 )                                                                                                                                           |

|              | 3.6V( 液晶電源OFF ) 1.3µA( Typ. )                                                                                                                                  |

|              | 3.6V( 液晶電源ON, Vc1基準 ) 3.0µA( Typ. )                                                                                                                            |

|              | 3.6V( 液晶電源ON, Vc2基準 ) 2.5µA( Typ. )                                                                                                                            |

|              | 動作時( 32kHz, 水晶発振 )                                                                                                                                             |

|              | 3.6V( 液晶電源OFF ) 3.0µA( Typ. )                                                                                                                                  |

|              | HALT時( 60kHz, CR発振 )                                                                                                                                           |

|              | 3.6V( 液晶電源OFF ) 3.5µA( Typ. )                                                                                                                                  |

|              | 3.6V( 液晶電源ON, Vc1基準 ) 6.2µA( Typ. )                                                                                                                            |

|              | 3.6V( 液晶電源ON, Vc2基準 ) 4.6µA( Typ. )                                                                                                                            |

|              | 動作時( 60kHz, CR発振 )                                                                                                                                             |

|              | 3.6V( 液晶電源OFF ) 7.0µA( Typ. )                                                                                                                                  |

|              | 高速動作:                                                                                                                                                          |

|              | 動作時( 500kHz, CR発振 )                                                                                                                                            |

|              | 3.6V( 液晶電源OFF ) 90µA( Typ. )                                                                                                                                   |

|              | 動作時( 1MHz, CR発振 )                                                                                                                                              |

|              | 3.6V( 液晶電源OFF ) 200µA( Typ. )                                                                                                                                  |

|              | 動作時( 2MHz, CR発振 )                                                                                                                                              |

|              | 3.6V( 液晶電源OFF ) 350µA( Typ. )                                                                                                                                  |

|              | 動作時( 3.58MHz, セラミック発振 )                                                                                                                                        |

|              | 3.6V( 液晶電源OFF ) 500µA( Typ. )                                                                                                                                  |

|              | 動作時( 4MHz, 水晶発振 )                                                                                                                                              |

|              | 3.6V( 液晶電源OFF ) 550µA( Typ. )                                                                                                                                  |

| 出荷形態 .....   | TQFP15-128pin( プラスチック )またはチップ( S1C63406 )<br>QFP15-128pin( プラスチック )またはチップ( S1C63408 )                                                                          |

\*1: マスクオプションにより選択

\*2: ソフトウェアにより選択

\*3: リセット回路オプション非選択時( 選択時はリセット回路の消費電流が加算されます )

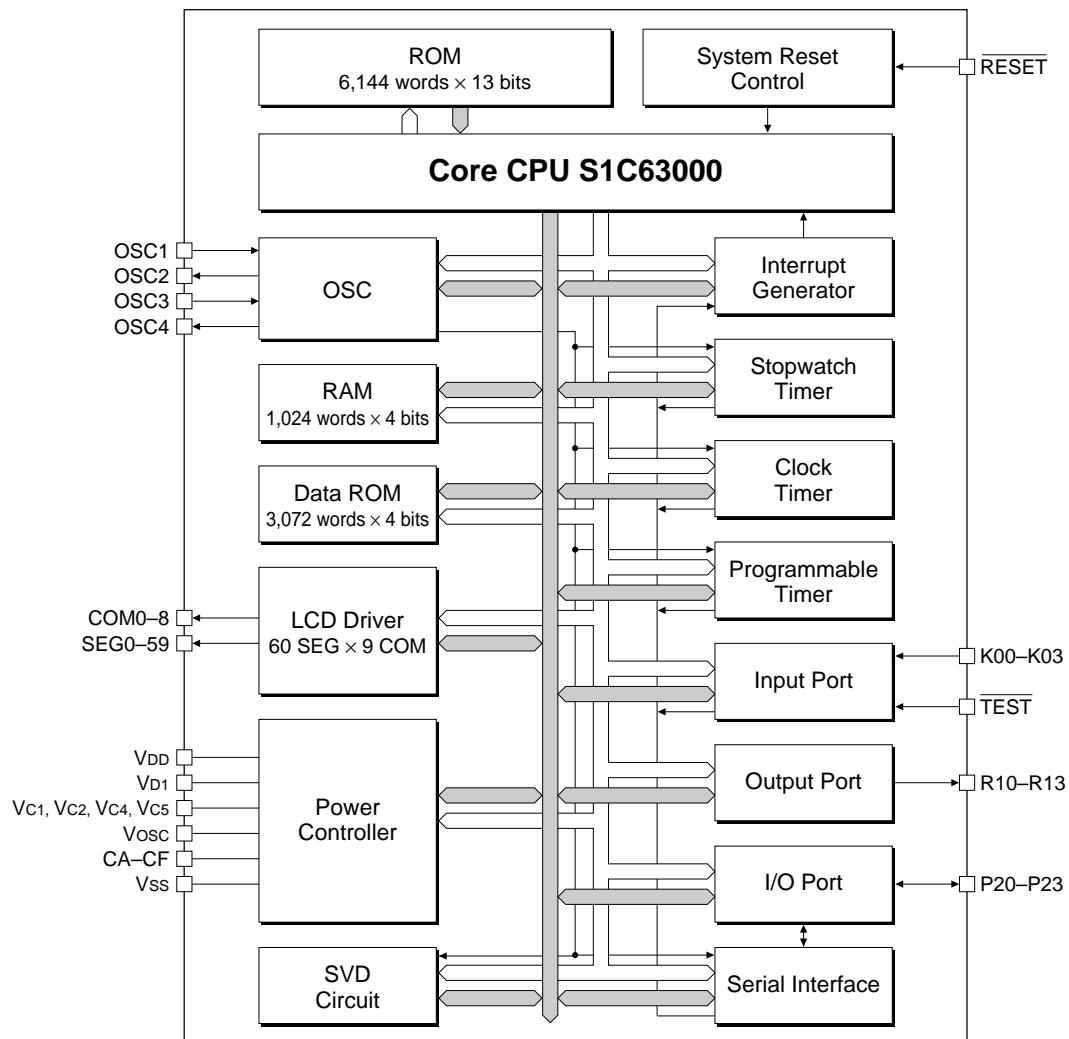

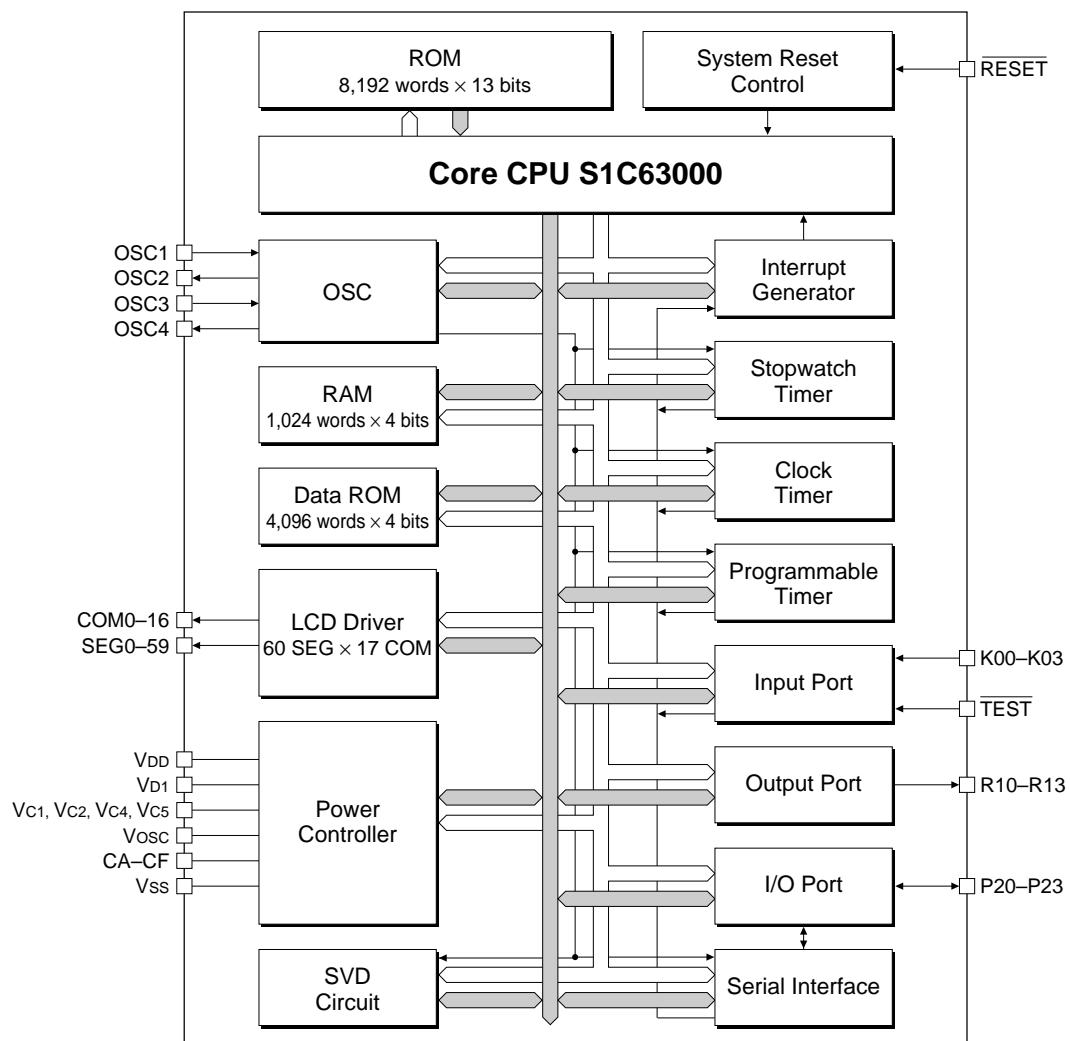

## 1.2 ブロック図

S1C63406

図1.2.1 S1C63406ブロック図

**S1C63408**

図1.2.2 S1C63408ブロック図

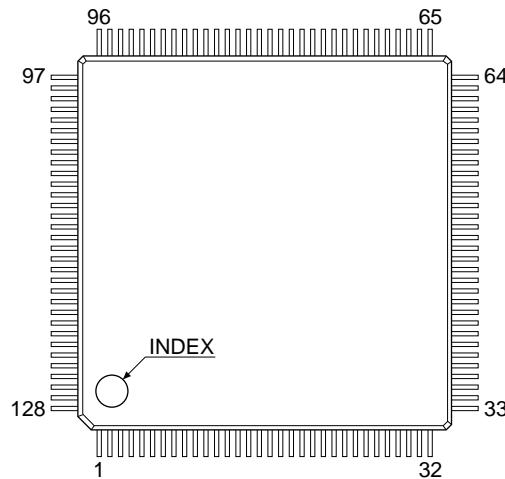

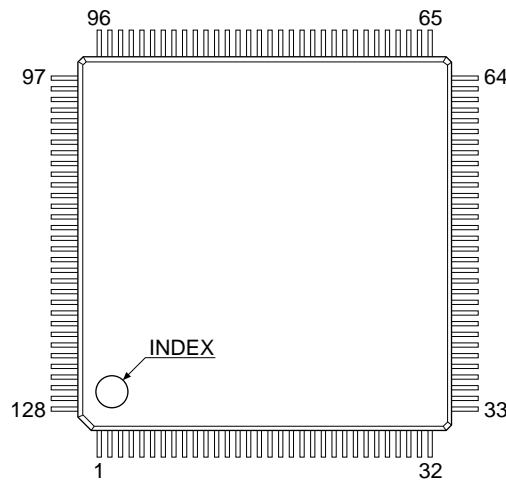

### 1.3 端子配置図

**S1C63406 (TQFP15-128pin)**

| No. | 端子名   | No. | 端子名              | No. | 端子名   | No. | 端子名   |

|-----|-------|-----|------------------|-----|-------|-----|-------|

| 1   | N.C.  | 33  | CF               | 65  | N.C.  | 97  | SEG15 |

| 2   | SEG41 | 34  | V <sub>C5</sub>  | 66  | N.C.  | 98  | SEG16 |

| 3   | SEG42 | 35  | V <sub>C4</sub>  | 67  | N.C.  | 99  | SEG17 |

| 4   | SEG43 | 36  | V <sub>C2</sub>  | 68  | N.C.  | 100 | SEG18 |

| 5   | SEG44 | 37  | V <sub>C1</sub>  | 69  | COM0  | 101 | SEG19 |

| 6   | SEG45 | 38  | K00              | 70  | COM1  | 102 | SEG20 |

| 7   | SEG46 | 39  | K01              | 71  | COM2  | 103 | SEG21 |

| 8   | SEG47 | 40  | K02              | 72  | COM3  | 104 | SEG22 |

| 9   | SEG48 | 41  | N.C.             | 73  | COM4  | 105 | SEG23 |

| 10  | SEG49 | 42  | N.C.             | 74  | N.C.  | 106 | N.C.  |

| 11  | N.C.  | 43  | K03              | 75  | N.C.  | 107 | N.C.  |

| 12  | N.C.  | 44  | R10              | 76  | N.C.  | 108 | N.C.  |

| 13  | N.C.  | 45  | R11              | 77  | COM5  | 109 | N.C.  |

| 14  | SEG50 | 46  | R12              | 78  | COM6  | 110 | SEG24 |

| 15  | SEG51 | 47  | R13              | 79  | COM7  | 111 | SEG25 |

| 16  | SEG52 | 48  | P20              | 80  | SEG0  | 112 | SEG26 |

| 17  | SEG53 | 49  | P21              | 81  | SEG1  | 113 | SEG27 |

| 18  | SEG54 | 50  | P22              | 82  | SEG2  | 114 | SEG28 |

| 19  | N.C.  | 51  | P23              | 83  | SEG3  | 115 | SEG29 |

| 20  | N.C.  | 52  | N.C.             | 84  | N.C.  | 116 | SEG30 |

| 21  | N.C.  | 53  | N.C.             | 85  | N.C.  | 117 | SEG31 |

| 22  | SEG55 | 54  | N.C.             | 86  | SEG4  | 118 | SEG32 |

| 23  | SEG56 | 55  | V <sub>DD</sub>  | 87  | SEG5  | 119 | N.C.  |

| 24  | SEG57 | 56  | V <sub>D1</sub>  | 88  | SEG6  | 120 | N.C.  |

| 25  | SEG58 | 57  | OSC4             | 89  | SEG7  | 121 | SEG33 |

| 26  | SEG59 | 58  | OSC3             | 90  | SEG8  | 122 | SEG34 |

| 27  | COM8  | 59  | V <sub>Osc</sub> | 91  | SEG9  | 123 | SEG35 |

| 28  | CA    | 60  | OSC2             | 92  | SEG10 | 124 | SEG36 |

| 29  | CB    | 61  | OSC1             | 93  | SEG11 | 125 | SEG37 |

| 30  | CC    | 62  | V <sub>ss</sub>  | 94  | SEG12 | 126 | SEG38 |

| 31  | CD    | 63  | <u>RESET</u>     | 95  | SEG13 | 127 | SEG39 |

| 32  | CE    | 64  | <u>TEST</u>      | 96  | SEG14 | 128 | SEG40 |

N.C. : No Connection

図1.3.1 S1C63406端子配置図

**S1C63408 (QFP15-128pin)**

| No. | 端子名   | No. | 端子名   | No. | 端子名   | No. | 端子名   |

|-----|-------|-----|-------|-----|-------|-----|-------|

| 1   | N.C.  | 33  | N.C.  | 65  | N.C.  | 97  | N.C.  |

| 2   | N.C.  | 34  | N.C.  | 66  | N.C.  | 98  | N.C.  |

| 3   | N.C.  | 35  | CE    | 67  | COM0  | 99  | SEG19 |

| 4   | SEG46 | 36  | CF    | 68  | COM1  | 100 | N.C.  |

| 5   | SEG47 | 37  | Vc5   | 69  | COM2  | 101 | SEG20 |

| 6   | SEG48 | 38  | Vc4   | 70  | N.C.  | 102 | SEG21 |

| 7   | SEG49 | 39  | Vc2   | 71  | COM3  | 103 | SEG22 |

| 8   | SEG50 | 40  | Vc1   | 72  | COM4  | 104 | SEG23 |

| 9   | SEG51 | 41  | K00   | 73  | COM5  | 105 | SEG24 |

| 10  | SEG52 | 42  | K01   | 74  | COM6  | 106 | SEG25 |

| 11  | SEG53 | 43  | K02   | 75  | COM7  | 107 | SEG26 |

| 12  | SEG54 | 44  | K03   | 76  | SEG0  | 108 | SEG27 |

| 13  | SEG55 | 45  | R10   | 77  | SEG1  | 109 | SEG28 |

| 14  | SEG56 | 46  | R11   | 78  | SEG2  | 110 | SEG29 |

| 15  | SEG57 | 47  | R12   | 79  | SEG3  | 111 | SEG30 |

| 16  | SEG58 | 48  | R13   | 80  | SEG4  | 112 | SEG31 |

| 17  | SEG59 | 49  | P20   | 81  | SEG5  | 113 | SEG32 |

| 18  | COM8  | 50  | P21   | 82  | SEG6  | 114 | SEG33 |

| 19  | COM9  | 51  | P22   | 83  | SEG7  | 115 | SEG34 |

| 20  | COM10 | 52  | P23   | 84  | SEG8  | 116 | SEG35 |

| 21  | COM11 | 53  | VDD   | 85  | SEG9  | 117 | SEG36 |

| 22  | COM12 | 54  | Vd1   | 86  | SEG10 | 118 | SEG37 |

| 23  | COM13 | 55  | OSC4  | 87  | SEG11 | 119 | SEG38 |

| 24  | COM14 | 56  | OSC3  | 88  | SEG12 | 120 | SEG39 |

| 25  | COM15 | 57  | Vosc  | 89  | SEG13 | 121 | SEG40 |

| 26  | COM16 | 58  | OSC2  | 90  | SEG14 | 122 | SEG41 |

| 27  | CA    | 59  | OSC1  | 91  | SEG15 | 123 | SEG42 |

| 28  | CB    | 60  | Vss   | 92  | SEG16 | 124 | SEG43 |

| 29  | CC    | 61  | RESET | 93  | SEG17 | 125 | SEG44 |

| 30  | CD    | 62  | TEST  | 94  | N.C.  | 126 | SEG45 |

| 31  | N.C.  | 63  | N.C.  | 95  | SEG18 | 127 | N.C.  |

| 32  | N.C.  | 64  | N.C.  | 96  | N.C.  | 128 | N.C.  |

N.C. : No Connection

図1.3.2 S1C63408端子配置図

## 1.4 端子説明

### S1C63406

表1.4.1 S1C63406端子説明

| 端子名                | 端子No.                                                     | 入出力 | 機能                                    |

|--------------------|-----------------------------------------------------------|-----|---------------------------------------|

| VDD                | 55                                                        | -   | 電源(+)端子                               |

| VSS                | 62                                                        | -   | 電源(-)端子                               |

| VDI                | 56                                                        | -   | 内部ロジック系定電圧出力端子                        |

| VOSC               | 59                                                        | -   | 発振系定電圧出力端子                            |

| Vc1, Vc2, Vc4, Vc5 | 37, 36, 35, 34                                            | -   | LCD系電源端子(1/4バイアス)                     |

| CA-CF              | 28~33                                                     | -   | LCD系昇降圧コンデンサ接続端子                      |

| OSC1               | 61                                                        | I   | 水晶またはCR発振入力端子(マスクオプション選択)             |

| OSC2               | 60                                                        | O   | 水晶またはCR発振出力端子(マスクオプション選択)             |

| OSC3               | 58                                                        | I   | 水晶、セラミックまたはCR発振入力端子(マスクオプション選択)       |

| OSC4               | 57                                                        | O   | 水晶、セラミックまたはCR発振出力端子(マスクオプション選択)       |

| K00~K02            | 38~40                                                     | I   | 入力ポート                                 |

| K03                | 43                                                        | I   | 入力ポートまたはEVIN信号入力端子(ソフトウェア選択)          |

| R10, R11           | 44, 45                                                    | O   | 出力ポート                                 |

| R12                | 46                                                        | O   | 出力ポートまたはTOUT信号出力端子(ソフトウェア選択)          |

| R13                | 47                                                        | O   | 出力ポートまたはFOUT信号出力端子(ソフトウェア選択)          |

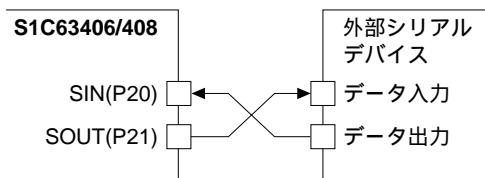

| P20                | 48                                                        | I/O | 入出力兼用ポートまたはシリアルI/Fデータ入力端子(ソフトウェア選択)   |

| P21                | 49                                                        | I/O | 入出力兼用ポートまたはシリアルI/Fデータ出力端子(ソフトウェア選択)   |

| P22                | 50                                                        | I/O | 入出力兼用ポートまたはシリアルI/Fクロック入出力端子(ソフトウェア選択) |

| P23                | 51                                                        | I/O | 入出力兼用ポートまたはシリアルI/Fレディ信号出力端子(ソフトウェア選択) |

| COM0~COM8          | 69~73, 77~79, 27                                          | O   | LCDコモン出力端子(1/8, 1/9デューティをソフト切り換え)     |

| SEG0~SEG59         | 80~83, 86~105,<br>110~118, 121~128,<br>2~10, 14~18, 22~26 | O   | LCDセグメント出力端子                          |

| RESET              | 63                                                        | I   | イニシャルリセット入力端子                         |

| TEST               | 64                                                        | I   | テスト用入力端子                              |

**S1C63408**

表1.4.2 S1C63408端子説明

| 端子名                | 端子No.                           | 入出力 | 機能                                            |

|--------------------|---------------------------------|-----|-----------------------------------------------|

| VDD                | 53                              | -   | 電源(+)端子                                       |

| VSS                | 60                              | -   | 電源(-)端子                                       |

| VDI                | 54                              | -   | 内部ロジック系定電圧出力端子                                |

| VOSC               | 57                              | -   | 発振系定電圧出力端子                                    |

| VC1, VC2, VC4, VCS | 40, 39, 38, 37                  | -   | LCD系電源端子(1/4バイアス)                             |

| CA~CF              | 27~30, 35, 36                   | -   | LCD系昇降圧コンデンサ接続端子                              |

| OSC1               | 59                              | I   | 水晶またはCR発振入力端子(マスクオプション選択)                     |

| OSC2               | 58                              | O   | 水晶またはCR発振出力端子(マスクオプション選択)                     |

| OSC3               | 56                              | I   | 水晶、セラミックまたはCR発振入力端子(マスクオプション選択)               |

| OSC4               | 55                              | O   | 水晶、セラミックまたはCR発振出力端子(マスクオプション選択)               |

| K00~K02            | 41~43                           | I   | 入力ポート                                         |

| K03                | 44                              | I   | 入力ポートまたはEVIN信号入力端子(ソフトウェア選択)                  |

| R10, R11           | 45, 46                          | O   | 出力ポート                                         |

| R12                | 47                              | O   | 出力ポートまたはTOUT信号出力端子(ソフトウェア選択)                  |

| R13                | 48                              | O   | 出力ポートまたはFOUT信号出力端子(ソフトウェア選択)                  |

| P20                | 49                              | I/O | 入出力兼用ポートまたはシリアルI/Fデータ入力端子(ソフトウェア選択)           |

| P21                | 50                              | I/O | 入出力兼用ポートまたはシリアルI/Fデータ出力端子(ソフトウェア選択)           |

| P22                | 51                              | I/O | 入出力兼用ポートまたはシリアルI/Fクロック入出力端子(ソフトウェア選択)         |

| P23                | 52                              | I/O | 入出力兼用ポートまたはシリアルI/Fレディ信号出力端子(ソフトウェア選択)         |

| COM0~COM16         | 67~69, 71~75, 18~26             | O   | LCDコモン出力端子(1/8, 1/9, 1/16, 1/17デューティをソフト切り換え) |

| SEG0~SEG59         | 76~93, 95, 99,<br>101~126, 4~17 | O   | LCDセグメント出力端子                                  |

| RESET              | 61                              | I   | イニシャルリセット入力端子                                 |

| TEST               | 62                              | I   | テスト用入力端子                                      |

## 1.5 マスクオプション

S1C63406/408には以下に示すマスクオプションが設定されています。

各マスクオプションには複数のハードウェア仕様が用意されており、アプリケーションに合わせて選択することができます。この選択にはS1C63406/408の開発ソフトウェアツールとして用意されているファンクションオプションジェネレータwinfogを使用します。winfogによって作成したデータをもとに最終的なICのマスクパターン生成が行われます。winfogについては"S5U1C63000A Manual"を参照してください。

### マスクオプションリスト

S1C63406/408のオプションリストを以下に示します。各オプション項目には、複数の選択肢が用意されていますので、4章の"周辺回路と動作"を参照してシステムに合った内容を選択し、に印を付けてください。なお、使用しない機能についても解説に従って必ず選択してください。

#### 1. OSC1発振回路( OSC1 System Clock )

- 1. 水晶( 32.768kHz )

- 2. CR( 60kHz )

#### 2. OSC3発振回路( OSC3 System Clock )

- 1. CR

- 2. セラミック( 3.58MHz )

- 3. 水晶( 4MHz )

#### 3. リセット回路( Reset Circuit )

- 1. 使用する( 1.8V )

- 2. 使用する( 1.6V )

- 3. 使用する( 1.4V )

- 4. 使用しない

#### 4. キー同時押しリセット組み合わせ( Multiple Key Entry Reset Combination )

- 1. 使用しない

- 2. 使用する <K00, K01, K02, K03>

- 3. 使用する <K00, K01, K02>

- 4. 使用する <K00, K01>

#### 5. キー同時押しリセット時間検定( Multiple Key Entry Reset Time Authorize )

- 1. 使用しない

- 2. 使用する

#### 6. 入力ポートプルアップ抵抗( Input port pull up resistor )

|           |       |       |

|-----------|-------|-------|

| K00 ..... | 1. あり | 2. なし |

| K01 ..... | 1. あり | 2. なし |

| K02 ..... | 1. あり | 2. なし |

| K03 ..... | 1. あり | 2. なし |

#### 7. 出力ポート出力仕様( Output port output specification )

|           |             |                |

|-----------|-------------|----------------|

| R10 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R11 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R12 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| R13 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

#### 8. 入出力兼用ポート出力仕様( I/O port output specification )

|           |             |                |

|-----------|-------------|----------------|

| P20 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P21 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P22 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

| P23 ..... | 1. コンプリメンタリ | 2. Nchオープンドレイン |

## マスクオプションの概要

### (1) OSC1発振回路

OSC1発振回路として水晶発振またはCR発振が選択できます。

詳細については"4.3.2 OSC1発振回路"を参照してください。

### (2) OSC3発振回路

OSC3発振回路としてCR発振、セラミック発振または水晶発振が選択できます。

水晶振動子を使用する場合は3を、セラミック振動子を使用する場合は2を選択してください。( )内の周波数は推奨値(Typ.)です。

詳細については"4.3.3 OSC3発振回路"を参照してください。

### (3) 内蔵リセット回路

内蔵リセット回路を使用するかしないか選択できます。使用する場合は、発振周波数に従った最小電源電圧値を選択します。詳細については"2.2.3 内蔵リセット回路"を参照してください。

### (4) 入力ポート( K00 ~ K03 )同時LOW入力による外部リセット

この機能は、複数キーの同時押しによってICをリセットするもので、この機能を使用するかしないかをマスクオプションで選択できます。また、使用する場合は、同時に押すキーを接続する入力端子( K00 ~ K03 )の組み合わせを選択します。詳細については"2.2.2 K00 ~ K03端子への同時LOW入力"を参照してください。

### (5) 同時LOW入力リセットの時間検定回路

(4)の外部リセット機能を使用する場合に時間検定回路を使用するかしないか選択できます。時間検定回路を使用すると、規定時間以上の同時LOW入力があった場合のみ、リセット機能が働きます。詳細については"2.2.2 K00 ~ K03端子への同時LOW入力"を参照してください。

### (6) 入力ポートプルアップ抵抗

入力( K )ポートにプルアップ抵抗を付加するかしないか選択できます。選択はビット単位で行います。詳細については"4.4.2 マスクオプション"を参照してください。

### (7) 出力ポートの出力仕様

出力( R )ポートの出力仕様として、コンプリメンタリ出力またはNチャンネルオーブンドレイン出力が選択できます。選択はビット単位で行います。詳細については"4.5.2 マスクオプション"を参照してください。

### (8) 入出力兼用ポートの出力仕様

入出力兼用( P )ポートが出力モードの際の出力仕様として、コンプリメンタリ出力またはNチャンネルオーブンドレイン出力が選択できます。選択はビット単位で行います。

詳細については"4.6.2 マスクオプション"を参照してください。

## 2 電源系 および イニシャルリセット

### 2.1 電源系

S1C63406/408の動作電源電圧は次のとおりです。

表2.1.1 動作電源電圧

| OSC1クロック                  | OSC3クロック                     | 動作電源電圧      | CPU動作電圧 (V <sub>D1</sub> )                           |

|---------------------------|------------------------------|-------------|------------------------------------------------------|

| Max. 80kHz<br>(水晶またはCR発振) | 使用しない                        | 1.3V ~ 3.6V | 1.1V                                                 |

|                           | Max. 700kHz (CR発振)           | 1.4V ~ 3.6V | 1.1V / 1.3V                                          |

|                           | Max. 2.2MHz (CR発振)           | 1.6V ~ 3.6V | 1.1V / 1.3V / 1.5V                                   |

|                           | Max. 4.2MHz(水晶、セラミックまたはCR発振) | 1.8V ~ 3.6V | 1.1V / 1.3V / 1.5V / 1.7V<br>(V <sub>C1</sub> 基準選択時) |

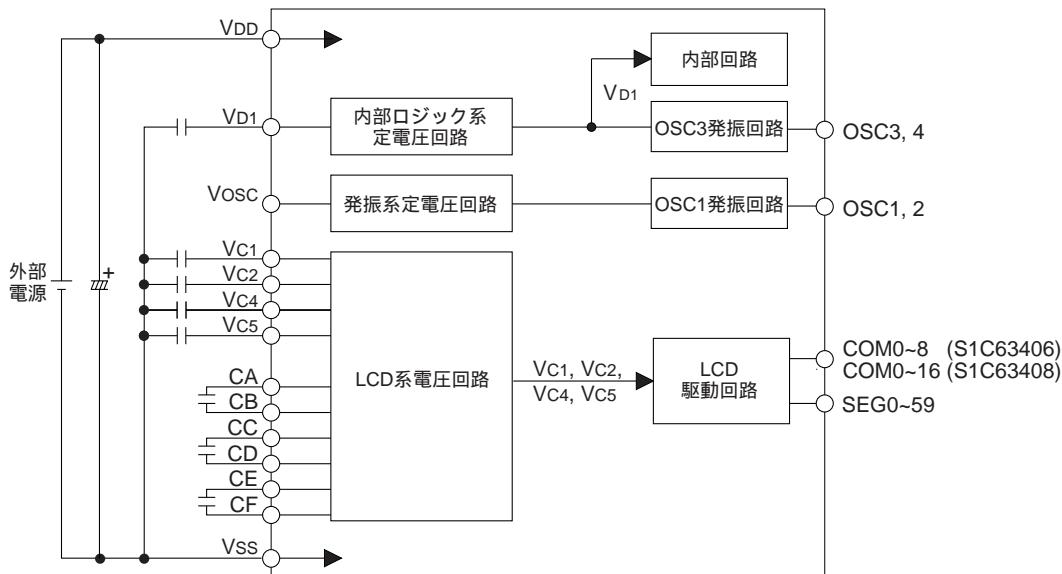

S1C63406/408は上記範囲の単一電源をV<sub>DD</sub> - V<sub>SS</sub>間に与えることにより動作し、内部に必要な電圧を、内蔵された以下の電源回路によりIC自身で発生します。

表2.1.2 電源回路

| 回路系         | 電源回路         | 出力電圧                                                                  |

|-------------|--------------|-----------------------------------------------------------------------|

| OSC1発振回路    | 発振系定電圧回路     | V <sub>osc</sub>                                                      |

| OSC3発振、内部回路 | 内部ロジック系定電圧回路 | V <sub>D1</sub>                                                       |

| LCD駆動回路     | LCD系電圧回路     | V <sub>C1</sub> , V <sub>C2</sub> , V <sub>C4</sub> , V <sub>C5</sub> |

- 注:

- 内部電源回路の出力電圧による外付け負荷の駆動は禁止します。

- 電圧値、駆動能力については"7 電気的特性"を参照してください。

図2.1.1 電源系の構成

### 2.1.1 内部回路用電圧<VD1>

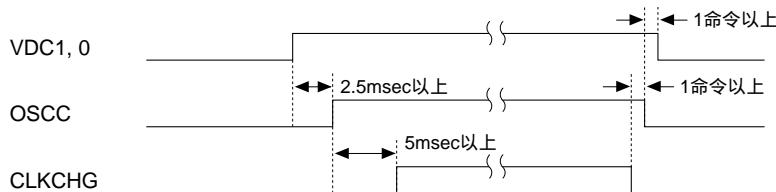

VD1はOSC3発振回路および内部ロジック回路用の電圧で、内部ロジック系定電圧回路で発生しています。S1C63406/408はツインクロック仕様となっており、2種類の発振回路OSC1およびOSC3を内蔵しています。通常動作時はOSC1クロックを使用し、高速動作が必要なときにソフトウェアによってOSC3クロックに切り替えます。その際には、発振回路および内部回路の動作を安定させるため、動作電圧VD1もソフトウェアによって切り換える必要があります。発振系定電圧回路はVD1の電圧値として以下の4種類が出力可能で、ソフトウェアにより発振回路と発振周波数にしたがった値に設定します。

VD1 = 1.1V: 低電力動作時( OSC3発振回路がOFFの場合 )

VD1 = 1.3V: 高速動作時( Max. 700kHz OSC3 CR発振回路がONの場合 )

VD1 = 1.5V: 高速動作時( Max. 2.2MHz OSC3 CR発振回路がONの場合 )

VD1 = 1.7V: 高速動作時( Max. 4.2MHz OSC3 水晶/セラミック/CR発振回路がONの場合 )

VD1の切り換え方法については"4.3 発振回路"を参照してください。

### 2.1.2 OSC1発振回路用電圧<Vosc>

VoscはOSC1発振回路用の電圧で、発振を安定させるため発振系定電圧回路で発生しています。

### 2.1.3 LCD駆動用電圧<VC1, VC2, VC4, VC5>

VC1、VC2、VC4、VC5はLCD駆動用の電圧で、LCD系電圧回路によって内部発生します。

LCD系電圧回路は、その中の定電圧回路によってVC1またはVC2を発生し、その電圧を昇圧または降圧して他の3電位を発生します。表2.1.3.1にVC1、VC2、VC4、VC5の電圧値と昇降圧の状態を示します。

表2.1.3.1 内部発生時のLCD駆動電圧

| LCD駆動電圧             | VDD=1.3V~3.6V | VDD=2.5V~3.6V |

|---------------------|---------------|---------------|

| VC1 ( 0.975V~1.2V ) | VC1 ( 基準 )    | 1/2 × VC2     |

| VC2 ( 1.950V~2.4V ) | 2 × VC1       | VC2 ( 基準 )    |

| VC4 ( 2.925V~3.6V ) | 3 × VC1       | 3/2 × VC2     |

| VC5 ( 3.900V~4.8V ) | 4 × VC1       | 2 × VC2       |

注 )LCD駆動電圧はソフトウェア( 4.7.5項参照 )により調整できます。

表の数値はTYP値です。

VC1基準、VC2基準のどちらを使用するかは、電源電圧にしたがってソフトウェアで選択します。

VC2基準とすると表示品質の向上と共に低消費電流化が図れます。電源電圧VDDが2.5V以上である必要があります。

LCD駆動電圧の制御方法については"4.7 LCDドライバ"を参照してください。

## 2.2 イニシャルリセット

S1C63406/408は回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては次の3種類があります。

- (1)  $\overline{\text{RESET}}$ 端子による外部イニシャルリセット

- (2) K00～K03端子の同時LOWレベル入力による外部イニシャルリセット( マスクオプションで設定 )

- (3) リセット回路による内部イニシャルリセット( マスクオプションで設定 )

電源投入時は必ず上記のリセット機能を使用し、確実に初期化する必要があります。

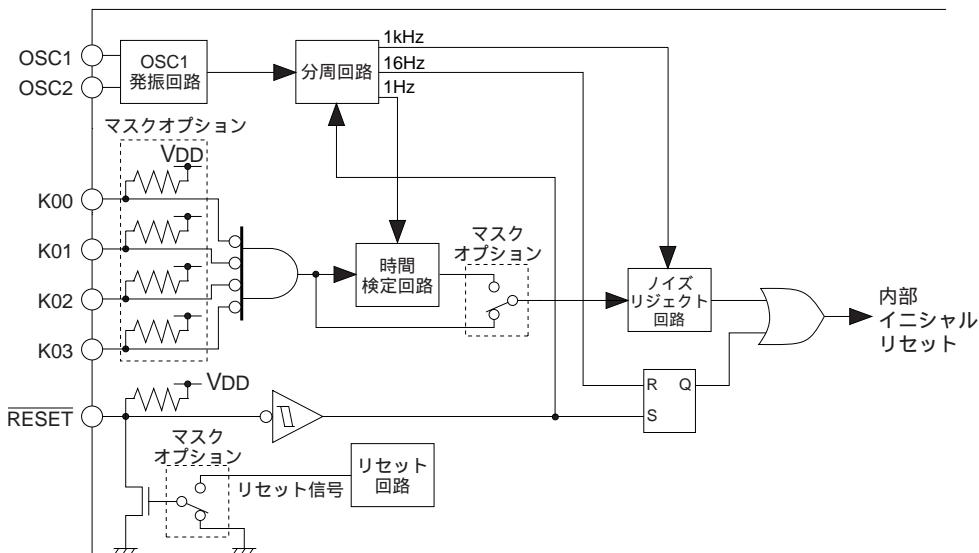

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

### 2.2.1 リセット端子( $\overline{\text{RESET}}$ )

外部よりリセット端子をLOWレベル(  $V_{ss}$  )にすることによりイニシャルリセットが行えます。

その後、リセット端子をHIGHレベル(  $V_{DD}$  )にすることによりイニシャルリセットは解除され、CPUが動作を開始します。

リセット入力信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチはOSC1クロックを分周した16Hz信号( HIGH )で解除されるようになっています。したがって、通常動作時はリセット端子がHIGHレベルになった後、内部イニシャルリセットが解除されるまで、最大1024/fosc1秒( fosc1=32.768 kHzの場合は32msec )の時間を要します。

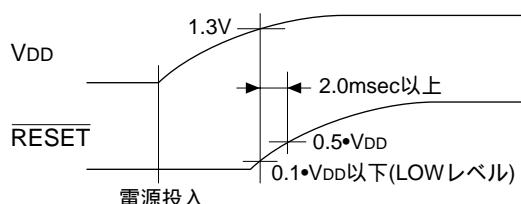

確実にイニシャルリセットを行うために、リセット入力は最低0.1msec以上、LOWレベルを保ってください。ただし、電源投入時については図2.2.1.1に示すタイミングでリセット端子をLOWレベルにしてください。

図2.2.1.1 電源投入時のイニシャルリセット

電源電圧が1.3V以上になるまで、リセット端子を0.1・ $V_{DD}$ 以下( LOWレベル )とします。その後2.0msec以上、0.5・ $V_{DD}$ 以下のレベルを保持します。

### 2.2.2 K00 ~ K03端子への同時LOW入力

マスクオプションで選択した入力ポート( K00 ~ K03 )に、外部から同時にLOW入力を与えることによりイニシャルリセットが行えます。このイニシャルリセットはノイズリジェクト回路を通るため、動作中は1.5msec( 発振周波数fosc1=32.768kHzの場合 )以上、指定入力端子をLOWレベルに保ってください。また、電源投入時には発振が停止しているため、ノイズリジェクト回路は動作しません。このため、発振開始後、さらに1.5msec( 発振周波数fosc1=32.768kHzの場合 )以上、指定入力端子をLOWレベルに保ってください。表2.2.2.1にマスクオプションで選択できる入力ポート( K00 ~ K03 )の組合せを示します。

表2.2.2.1 入力ポートの組合せ

|   |                 |

|---|-----------------|

| 1 | 使用しない           |

| 2 | K00*K01*K02*K03 |

| 3 | K00*K01*K02     |

| 4 | K00*K01         |

たとえば、マスクオプションで2の"K00\*K01\*K02\*K03"を選択した場合、K00 ~ K03の4ポートの入力が同時にLOWレベルになったときにイニシャルリセットを行います。3または4の場合は、選択したポートの組合せが含まれるキー入力が行われたときにイニシャルリセットがかかります。

また、同時LOW入力の入力時間を検定し、規定時間( 1 ~ 2秒 )以上の入力があったときにイニシャルリセットを行う時間検定回路をマスクオプションで選択できます。なお、このリセット機能を使用する場合、通常動作時に指定ポートが同時にLOWレベルにならないように注意してください。

### 2.2.3 内蔵リセット回路

S1C63406/408はマスクオプションで設定可能なリセット回路を内蔵しています。このリセット回路は、電源投入時のパワーオンリセット機能を実現し、電源の瞬断時や低下時に確実にシステムリセットを行います。

表2.2.3.1 リセットオプション

|   |           |

|---|-----------|

| 1 | 使用する 1.8V |

| 2 | 使用する 1.6V |

| 3 | 使用する 1.4V |

| 4 | 使用しない     |

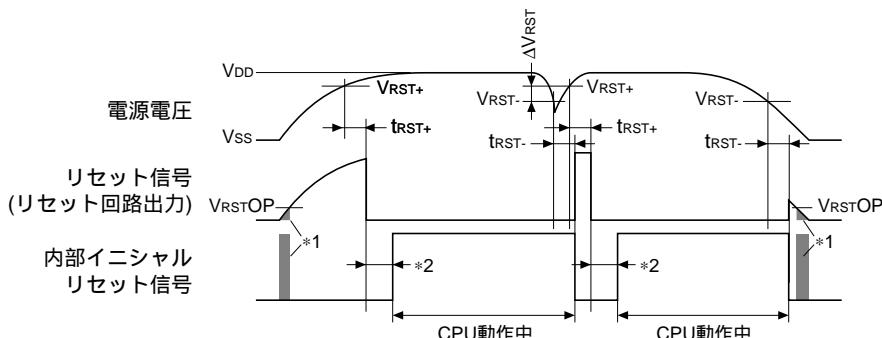

マスクオプションで"使用する"を選択すると、リセット回路は電源投入からVDD端子がリセット解除レベルになるまで、リセット信号を出力します。電源OFFあるいは電源電圧低下時においても、VDDがリセットレベル以下になるとリセット信号を出力します。詳細なリセットタイミングチャートは、"7 電気的特性"を参照してください。

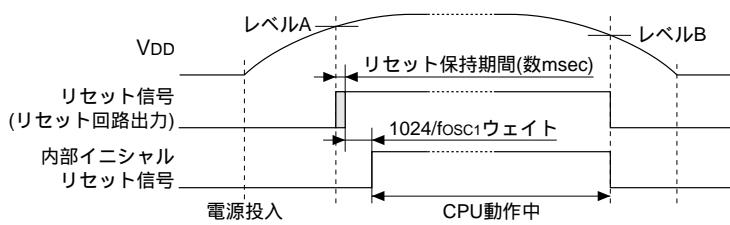

リセット信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチはOSC1クロックを分周した16Hz信号( HIGH )で解除されるようになっています。したがって、通常動作時はリセット信号がHIGHレベルになった後、内部イニシャルリセットが解除されるまで、最大1024/fosc1秒( fosc1=32.768kHzの場合は32msec )の時間を要します。

図2.2.3.1 内部リセットタイミング

リセット回路を使用する場合、マスクオプションで電圧値( 1.8、1.6または1.4V )を最小動作電圧( 表2.1.1参照 )に合わせて選択します。この選択により、リセット解除レベル( レベルA )とリセットレベル( レベルB )がリセット回路にプリセットされます。レベルAとレベルBは、40mV( Typ. )のヒステリシス電圧を持ちます。これらのレベルについての詳細は"7 電気的特性"を参照してください。リセット回路を使用した場合、消費電流が増加します。また、リセット状態での消費電流は大きくなります。詳細は"7 電気的特性"を参照してください。

マスクオプションで"使用しない"を選択すると、リセット回路は電源ON/OFFや電圧低下時にリセット信号を出力しません。

- 注:

- リセット回路使用時は、リセット端子に必ずコンデンサ( 推奨値: 0.01μF )を接続してください。コンデンサがないと、リセット回路が正しく動作しない可能性があります。また、大電流が流れてしまいしますので、リセット端子をHIGHレベルに固定しないでください。

- リセット回路使用時は、リセット端子によるイニシャルリセットは必要ありません。

## 2.2.4 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは表2.2.4.1のように初期化されます。

イニシャルリセットによって初期化されないレジスタ、フラグは必要に応じてプログラムで初期化する必要があります。

特にスタックポインタSP1およびSP2は必ずペアで設定してください。イニシャルリセット後は、SP1、SP2両方のスタックポインタがソフトウェアにより設定されるまでNMIを含むすべての割り込みがマスクされます。

EXTレジスタにデータを書き込むとEフラグがセットされ、次の命令が拡張アドレッシングモードで実行されます。そこに拡張アドレッシングが禁止されている命令を使用した場合、動作が保証されません。したがって、EXTレジスタの初期化のみを目的としたデータ書き込みは行わないでください。

拡張アドレッシングと使用可能な命令については"S1C63000コアCPUマニュアル"を参照してください。

表2.2.4.1 初期設定値

| CPUコア       |     |      |       | 周辺回路     |      |     |

|-------------|-----|------|-------|----------|------|-----|

| 名 称         | 記号  | ビット長 | 設定値   | 名 称      | ビット長 | 設定値 |

| データレジスタA    | A   | 4    | 不定    | RAM      | 4    | 不定  |

| データレジスタB    | B   | 4    | 不定    | 表示メモリ    | 4    | 不定  |

| 拡張レジスタEXT   | EXT | 8    | 不定    | その他の周辺回路 | -    | *   |

| インデックスレジスタX | X   | 16   | 不定    |          |      |     |

| インデックスレジスタY | Y   | 16   | 不定    |          |      |     |

| プログラムカウンタ   | PC  | 16   | 0110H |          |      |     |

| スタックポインタSP1 | SP1 | 8    | 不定    |          |      |     |

| スタックポインタSP2 | SP2 | 8    | 不定    |          |      |     |

| ゼロフラグ       | Z   | 1    | 不定    |          |      |     |

| キャリーフラグ     | C   | 1    | 不定    |          |      |     |

| インタラプトフラグ   | I   | 1    | 0     |          |      |     |

| 拡張フラグ       | E   | 1    | 0     |          |      |     |

| キューレジスタ     | Q   | 16   | 不定    |          |      |     |

\* "4.1 メモリマップ"参照

## 2.2.5 イニシャルリセット時の端子設定

S1C63406/408の出力ポートR 端子、入出力兼用ポートP 端子は特殊出力端子やシリアルインターフェースの入出力端子と兼用されており、それらの機能をソフトウェアで選択するようになっています。イニシャルリセット時、各端子はすべてが汎用出力ポート端子、汎用入出力兼用ポート端子として設定されますので、アプリケーションの初期化ルーチンでシステムに合った設定を行ってください。また、システム設計の際には、出力端子の初期状態にも注意してください。

表2.2.5.1に兼用端子設定の一覧を示します。

表2.2.5.1 兼用端子設定一覧

| 端子名 | イニシャルリセット時の<br>端子状態 | 特殊出力使用時 |      | シリアルインターフェース使用時 |                  |                 |

|-----|---------------------|---------|------|-----------------|------------------|-----------------|

|     |                     | TOUT    | FOUT | Async.          | Clk-sync. Master | Clk-sync. Slave |

| R10 | R10 (HIGH出力)        |         |      |                 |                  |                 |

| R11 | R11 (HIGH出力)        |         |      |                 |                  |                 |

| R12 | R12 (HIGH出力)        | TOUT    |      |                 |                  |                 |

| R13 | R13 (HIGH出力)        |         | FOUT |                 |                  |                 |

| P20 | P20 (入力&プルアップ)      |         |      | SIN(I)          | SIN(I)           | SIN(I)          |

| P21 | P21 (入力&プルアップ)      |         |      | SOUT(O)         | SOUT(O)          | SOUT(O)         |

| P22 | P22 (入力&プルアップ)      |         |      |                 | SCLK(O)          | SCLK(I)         |

| P23 | P23 (入力&プルアップ)      |         |      |                 |                  | SRDY(O)         |

機能の設定方法については各周辺回路の説明を参照してください。

## 2.3 テスト端子( TEST )

ICの出荷検査時に使用する端子です。通常動作時はTESTをVDDに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C63406/408はCPU部分に4ビットコアCPU S1C63000を使用しています。

S1C63000については"S1C63000コアCPUマニュアル"を参照してください。

S1C63406/408ではSLP命令も使用できます。

### 3.2 コードROM

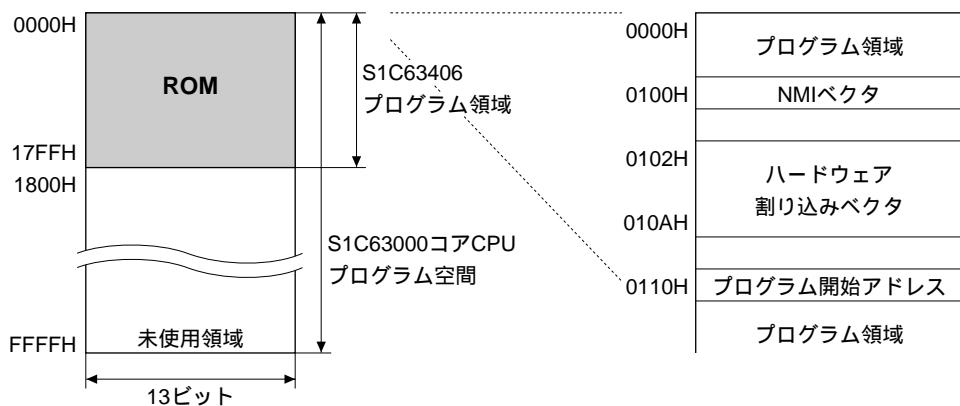

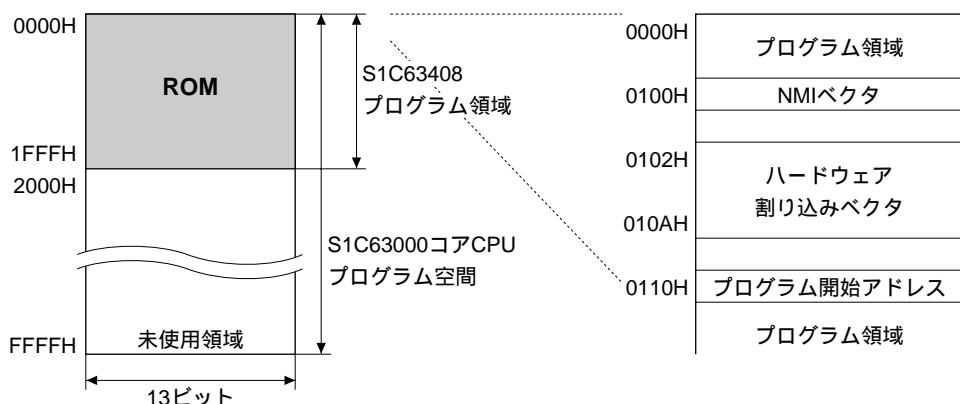

内蔵コードROMはプログラム格納用のマスクROMで、S1C63406は6,144ステップ×13ビット、S1C63408は8,192ステップ×13ビットの容量があります。コアCPUのプログラム領域は0000H～FFFFHステップまでリニアにアクセス可能ですが、S1C63406では0000H～17FFHステップが、S1C63408では0000H～1FFFHステップがプログラム領域となります。イニシャルリセット後のプログラム開始番地が0110Hステップ、ノンマスカブル割り込み(NMI)ベクタが0100H、ハードウェア割り込みベクタが0102H～010AHステップに割り当てられています。

**S1C63406**

**S1C63408**

図3.2.1 コードROMの構成

### 3.3 RAM

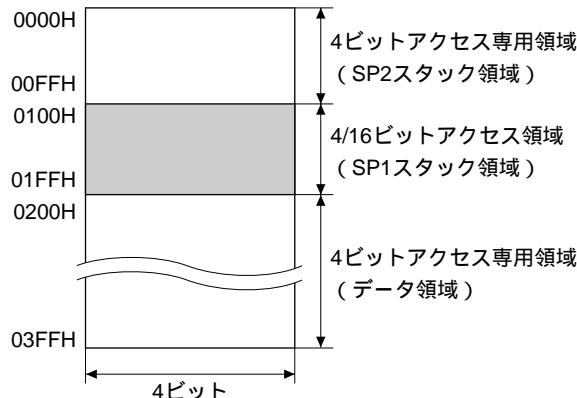

RAMは種々のデータを格納するデータメモリで、1,024ワード×4ビットの容量があります。

RAM領域は、データメモリマップ上のアドレス0000H～03FFHに割り当てられています。

この中でアドレス0100H～01FFHが4ビット/16ビットデータアクセスが可能な領域、その他の領域は4ビットデータアクセスのみ可能な領域となっています。

プログラミングの際には以下の点に注意してください。

- (1) データメモリの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データ領域とスタック領域が重ならないように注意してください。

- (2) S1C63000コアCPUは、4ビットデータ用スタックポインタ(SP2)および16ビットデータ用スタックポインタ(SP1)によりスタック処理を行います。SP1によるスタック処理では16ビットデータアクセスが行われますので、このスタック領域の設定は4ビット/16ビットアクセスが可能な領域内(0100H～01FFH)で行ってください。スタックポインタは、SP1が0000H～03FFH、SP2が0000H～00FFHの範囲でサイクリックに動作します。このため、SP1はS1C63406/408の4ビット/16ビットアクセス領域を外れた0200H以上、あるいは00FFH以下の領域にも設定される可能性がありますので注意してください。SP1によるスタック操作以外のメモリアクセスは4ビットデータアクセスとなります。

また、イニシャルリセット時は、スタックポインタSP1、SP2の両方がソフトウェアで設定されるまでNMIを含むすべての割り込みがマスクされます。また、SP1、SP2を設定後どちらか一方を再設定すると、もう一方が再設定されるまでNMIを含む割り込みは再びマスクされます。したがって、SP1およびSP2の設定は必ずペアで行ってください。

- (3) サブルーチンコールでは16ビットデータ用スタック(SP1)を4ワード(PCの退避)消費します。

割り込みでは16ビットデータ用スタックエリアを4ワード(PCの退避)4ビットデータ用スタックエリアを1ワード(Fレジスタの退避)消費します。

図3.3.1 データRAMの構成

### 3.4 データROM

データROMはキャラクタジェネレータなどの各種固定データ格納用のマスクROMで、RAMと同様にデータメモリアクセス命令でデータを読み出すことができます。

S1C63406は3,072ワード×4ビットの容量があり、データメモリマップ上のアドレス8000H～8BFFHに割り当てられています。

S1C63408は4,096ワード×4ビットの容量があり、データメモリマップ上のアドレス8000H～8FFFHに割り当てられています。

## 4 周辺回路と動作

S1C63406/408の周辺回路( タイマ、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

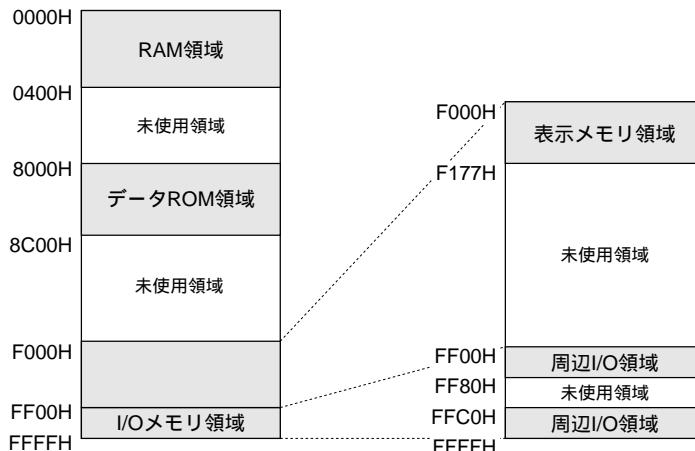

### 4.1 メモリマップ

S1C63406のデータメモリは1,024ワードのRAM、3,072ワードのデータROM、540ビットの表示メモリ、50ワードの周辺I/Oメモリで構成されます。

S1C63408のデータメモリは1,024ワードのRAM、4,096ワードのデータROM、1,020ビットの表示メモリ、50ワードの周辺I/Oメモリで構成されます。

図4.1.1にS1C63406/408の全体のメモリマップ、表4.1.1(a)~(d)に周辺回路( I/O空間 )のメモリマップを示します。

**S1C63406**

**S1C63408**

図4.1.1 メモリマップ

注：メモリマップの未使用領域にはメモリが実装されていません。また、表示メモリ領域および周辺I/O領域にも非実装領域( アクセス禁止 )領域が存在します。これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

表示メモリについては“4.7.4 表示メモリ”を、周辺I/O領域については表4.1.1(a)~(d)に示すI/Oメモリマップを参照してください。

表4.1.1(a) I/Oメモリマップ(FF00H ~ FF4AH)

| アドレス  | レジスタ           |                |               |              | Name   | Init *1 | 注 釈     |                                                                                      |

|-------|----------------|----------------|---------------|--------------|--------|---------|---------|--------------------------------------------------------------------------------------|

|       | D3             | D2             | D1            | D0           |        |         | 1       | 0                                                                                    |

| FF00H | CLKCHG         | OSCC           | VDC1          | VDC0         | CLKCHG | 0       | OSC3 On | CPUクロック切り換え<br>OSC3発振On/Off                                                          |

|       |                |                |               |              | OSCC   | 0       | Off     |                                                                                      |

|       |                |                |               |              | VDC1   | 0       |         | CPU動作電圧 [VDC1, 0] 0 1 2 3<br>切り換え VDI (V) 1.1 1.3 1.5 1.7                            |

|       |                |                |               |              | VDC0   | 0       |         |                                                                                      |

| FF04H | R/W            |                |               |              | SVDS3  | 0       |         | SVD比較電圧設定 [SVDS3-0] 0 1 2 3 4 5 6 7<br>電圧(V) 1.30 1.40 1.50 1.60 1.70 1.80 1.90 2.00 |

|       | SVDS3          | SVDS2          | SVDS1         | SVDS0        | SVDS2  | 0       |         | [SVDS3-0] 8 9 10 11 12 13 14 15<br>電圧(V) 2.10 2.20 2.30 2.40 2.50 2.60 2.70 2.80     |

|       |                |                |               |              | SVDS1  | 0       |         |                                                                                      |

|       |                |                |               |              | SVDS0  | 0       |         |                                                                                      |

| FF05H | R/W            |                |               |              | 0 *3   | - *2    |         | 未使用                                                                                  |

|       | 0              | 0              | SVDDT         | SVDON        | 0 *3   | - *2    |         | 未使用                                                                                  |

|       |                |                |               |              | SVDDT  | 0       | Low     | SVD検出データ                                                                             |

|       |                |                |               |              | SVDON  | 0       | On      | SVD回路On/Off                                                                          |

| FF06H | R/W            |                |               |              | FOUT   | 0       | Enable  | FOUT出力イネーブル [FOFQ2-0] 0 1 2 3                                                        |

|       | FOUT           | FOFQ2          | FOFQ1         | FOFQ0        | FOFQ2  | 0       |         | [FOFQ2-0] 周波数 fosc1/64 fosc1/32 fosc1/16 fosc1/8                                     |

|       |                |                |               |              | FOFQ1  | 0       |         | 周波数 [FOFQ2-0] 4 5 6 7                                                                |

|       |                |                |               |              | FOFQ0  | 0       |         | 選択 周波数 fosc1/4 fosc1 fosc3/2 fosc3                                                   |

| FF07H | R/W            |                |               |              | HLMOD  | 0 *3    | On      | 重負荷保護モード                                                                             |

|       | HLMOD          | 0              | WDEN          | WDRST        | 0 *3   | - *2    | Off     | 未使用                                                                                  |

|       |                | R              | R/W           | W            | WDEN   | 1       | Enable  | ウォッチドッグタイマイネーブル                                                                      |

|       |                |                |               |              | WDRST  | *3      | Reset   | ウォッチドッグタイマリセット(書き込み時)                                                                |

| FF42H | R/W            |                |               |              | K03    | - *2    | High    |                                                                                      |

|       | K03            | K02            | K01           | K00          | K02    | - *2    | High    | Low                                                                                  |

|       |                |                |               |              | K01    | - *2    | High    | Low                                                                                  |

|       |                |                |               |              | K00    | - *2    | High    | Low                                                                                  |

| FF43H | R/W            |                |               |              | K03    | - *2    |         | K00 ~ K03入力ポートデータ                                                                    |

|       | 0              | 0              | K0NR1         | K0NR0        | K02    | - *2    |         |                                                                                      |

|       |                |                |               |              | K01    | 0       |         |                                                                                      |

|       |                |                |               |              | K00    | 0       |         |                                                                                      |

| FF46H | R/W            |                |               |              | R13    | 1       | High    | R13出力ポートデータ(FOUTE=0)                                                                 |

|       | R13            | R12            | R11           | R10          | R12    | 1       | High    | FOUT出力時は1に固定(FOUTE=1)                                                                |

|       |                |                |               |              | R11    | 1       | High    | R12出力ポートデータ(PTOUT=0)                                                                 |

|       |                |                |               |              | R10    | 1       | High    | TOUT出力時は1に固定(PTOUT=1)                                                                |

| FF48H | R/W            |                |               |              | R13    | 1       | High    | R11出力ポートデータ                                                                          |

|       | IOC23          | IOC22          | IOC21         | IOC20        | R12    | 1       | High    | R10出力ポートデータ                                                                          |

|       |                |                |               |              | R11    | 1       | High    |                                                                                      |

|       |                |                |               |              | R10    | 1       | High    |                                                                                      |

| FF49H | R/W            |                |               |              | IOC23  | 0       | Output  | P23 I/O制御レジスタ                                                                        |

|       | PPL23          | PPL22          | PPL21         | PPL20        | IOC22  | 0       | Output  | SIF クロック同期式スレーブ 選択時、汎用レジスタとして機能                                                      |

|       |                |                |               |              | IOC21  | 0       | Output  | P22 I/O制御レジスタ                                                                        |

|       |                |                |               |              | IOC20  | 0       | Output  | SIF クロック同期式のみ 選択時、汎用レジスタとして機能                                                        |

| FF4AH | R/W            |                |               |              | PPL23  | 1       | On      | P21 I/O制御レジスタ( ESIF=0 )                                                              |

|       | P23<br>(XSRDY) | P22<br>(XSCLK) | P21<br>(SOUT) | P20<br>(SIN) | PPL22  | 1       | On      | SIF選択時、汎用レジスタとして機能                                                                   |

|       |                |                |               |              | PPL21  | 1       | On      | P20 I/O制御レジスタ( ESIF=0 )                                                              |

|       |                |                |               |              | PPL20  | 1       | On      | SIF選択時、SINブルアップ制御レジスタ                                                                |

| FF4AH | R/W            |                |               |              | P23    | - *2    | High    | P23入出力兼用ポートデータ                                                                       |

|       | P23<br>(XSRDY) | P22<br>(XSCLK) | P21<br>(SOUT) | P20<br>(SIN) | P22    | - *2    | High    | SIF クロック同期式スレーブ 選択時、汎用レジスタとして機能                                                      |

|       |                |                |               |              | P21    | - *2    | High    | P22入出力兼用ポートデータ                                                                       |

|       |                |                |               |              | P20    | - *2    | High    | SIF クロック同期式のみ 選択時、汎用レジスタとして機能                                                        |

[ 注 釈 ]

\*1 イニシャルリセット時の初期値 \*2 回路上設定されない \*3 読み出し時は常時"0"

表4.1.1( b ) I/Oメモリマップ( FF54H ~ FF7AH )

| アドレス  | レジスタ   |        |       |       | Name    | Init *1 | 1                                                                                                                                                                                                  | 0                                                                                                                                     | 注釈                                                                                                                                       |

|-------|--------|--------|-------|-------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|       | D3     | D2     | D1    | D0    |         |         |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

| FF54H | SIK03  | SIK02  | SIK01 | SIK00 | SIK03   | 0       | Enable                                                                                                                                                                                             | Disable                                                                                                                               | K00 ~ K03割り込み選択レジスタ<br>R/W                                                                                                               |

|       |        |        |       |       | SIK02   | 0       | Enable                                                                                                                                                                                             | Disable                                                                                                                               |                                                                                                                                          |

|       |        |        |       |       | SIK01   | 0       | Enable                                                                                                                                                                                             | Disable                                                                                                                               |                                                                                                                                          |

|       |        |        |       |       | SIK00   | 0       | Enable                                                                                                                                                                                             | Disable                                                                                                                               |                                                                                                                                          |

| FF55H | KCP03  | KCP02  | KCP01 | KCP00 | KCP03   | 1       | ↓                                                                                                                                                                                                  | ↑                                                                                                                                     | K00 ~ K03入力比較レジスタ<br>R/W                                                                                                                 |

|       |        |        |       |       | KCP02   | 1       | ↓                                                                                                                                                                                                  | ↑                                                                                                                                     |                                                                                                                                          |

|       |        |        |       |       | KCP01   | 1       | ↓                                                                                                                                                                                                  | ↑                                                                                                                                     |                                                                                                                                          |

|       |        |        |       |       | KCP00   | 1       | ↓                                                                                                                                                                                                  | ↑                                                                                                                                     |                                                                                                                                          |

| FF60H | LDUTY1 | LDUTY0 | VCCHG | LPWR  | LDUTY1  | 0       | LCD駆動デューティ<br>切り換え<br>LCD定電圧切り換え<br>LCD電源On/Off                                                                                                                                                    | Vc2<br>On                                                                                                                             | LCD駆動デューティ [LDUTY1, 0] 0 1 2* 3*<br>デューティ 1/9 1/8 1/17 1/16<br>(* S1C63408のみ)                                                            |

|       |        |        |       |       | LDUTY0  | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | VCCHG   | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | LPWR    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

| FF61H | EXLCDC | ALOFF  | ALON  | LPAGE | EXLCDC  | 0       | 1                                                                                                                                                                                                  | 0                                                                                                                                     | 汎用レジスタ<br>LCD全消灯制御<br>LCD全点灯制御<br>表示メモリ領域選択( S1C63408で1/8デューティ選択時 )<br>S1C63408で1/17、1/16、1/9デューティ選択時、<br>およびS1C63406では汎用レジスタとして機能       |

|       |        |        |       |       | ALOFF   | 1       | All Off                                                                                                                                                                                            | Normal                                                                                                                                |                                                                                                                                          |

|       |        |        |       |       | ALON    | 0       | All On                                                                                                                                                                                             | Normal                                                                                                                                |                                                                                                                                          |

|       |        |        |       |       | LPAGE   | 0       | F100-F177                                                                                                                                                                                          | F000-F077                                                                                                                             |                                                                                                                                          |

| FF62H | LC3    | LC2    | LC1   | LC0   | LC3     | - *2    | LCDコントラスト調整<br>[LC3~0] 0 ~ 15<br>コントラスト 淡 ~ 濃                                                                                                                                                      |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | LC2     | - *2    |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | LC1     | - *2    |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | LC0     | - *2    |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

| FF70H | 0      | SMD1   | SMD0  | ESIF  | 0 *3    | - *2    | 未使用<br>シリアルI/F<br>モード選択                                                                                                                                                                            | [SMD1, 0] 0 1<br>モード Clk-sync. master Clk-sync. slave<br>[SMD1, 0] 2 3<br>モード Async. 7-bit Async. 8-bit<br>シリアルI/Fイネーブル( P2xポート機能選択 ) | I/O                                                                                                                                      |

|       |        |        |       |       | SMD1    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       | R      |        |       |       | SMD0    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | ESIF    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

| FF71H | EPR    | PMD    | SCS1  | SCS0  | EPR     | 0       | Enable                                                                                                                                                                                             | Disable                                                                                                                               | シリアルI/Fパリティ機能選択<br>シリアルI/Fパリティモード選択<br>シリアルI/F [SCS1, 0] 0 1 2 3<br>クロック源選択 モード 1200bps 600bps 2400bps PT                                |

|       |        |        |       |       | PMD     | 0       | Odd                                                                                                                                                                                                | Even                                                                                                                                  |                                                                                                                                          |

|       |        |        |       |       | SCS1    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

|       |        |        |       |       | SCS0    | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

| FF72H | RXTRG  | RXEN   | TXTRG | TXEN  | RXTRG   | 0       | Run                                                                                                                                                                                                | Stop                                                                                                                                  | シリアルI/F受信ステータス( 読み出し時 )<br>シリアルI/F受信トリガ( 書き込み時 )<br>シリアルI/F受信イネーブル<br>シリアルI/F送信ステータス( 読み出し時 )<br>シリアルI/F送信トリガ( 書き込み時 )<br>シリアルI/F送信イネーブル |

|       |        |        |       |       | RXEN    | 0       | Trigger                                                                                                                                                                                            | Disable                                                                                                                               |                                                                                                                                          |

|       |        |        |       |       | TXTRG   | 0       | Enable                                                                                                                                                                                             | Run                                                                                                                                   |                                                                                                                                          |

|       |        |        |       |       | TXEN    | 0       | Trigger                                                                                                                                                                                            | Stop                                                                                                                                  |                                                                                                                                          |

| FF73H | 0      | FER    | PER   | OER   | 0 *3    | - *2    | 未使用<br>SIFフレーミングエラーフラグステータス( 読み出し時 )<br>SIFフレーミングエラーフラグリセット( 書き込み時 )<br>SIFパリティエラーフラグステータス( 読み出し時 )<br>SIFパリティエラーフラグリセット( 書き込み時 )<br>SIFオーバーランエラーフラグステータス( 読み出し時 )<br>SIFオーバーランエラーフラグリセット( 書き込み時 ) | No error<br>-<br>No error<br>-<br>No error<br>-                                                                                       | Error<br>Reset<br>Error<br>Reset<br>Error<br>Reset                                                                                       |

|       |        |        |       |       | FER     | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |

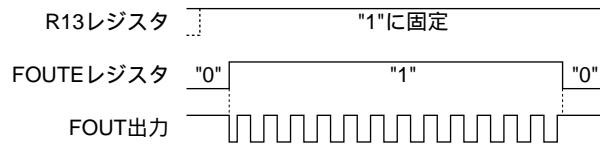

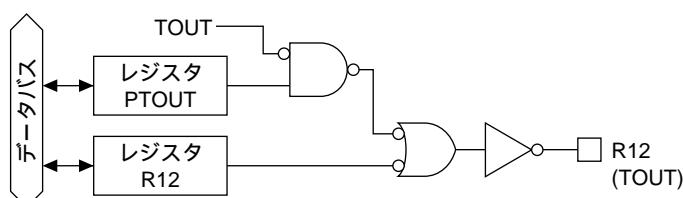

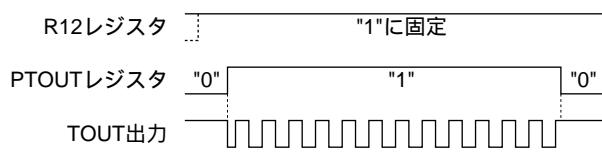

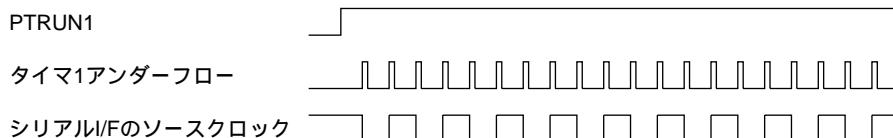

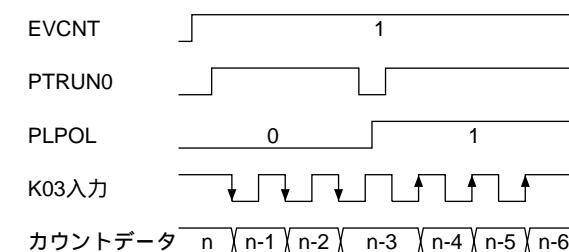

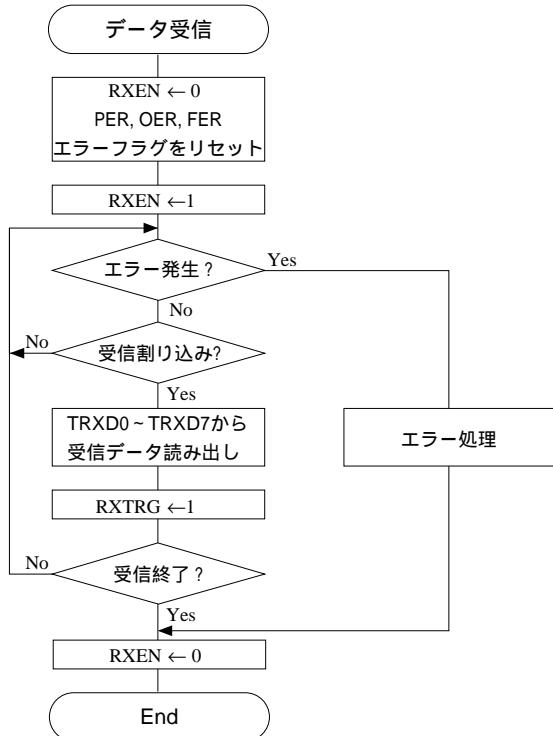

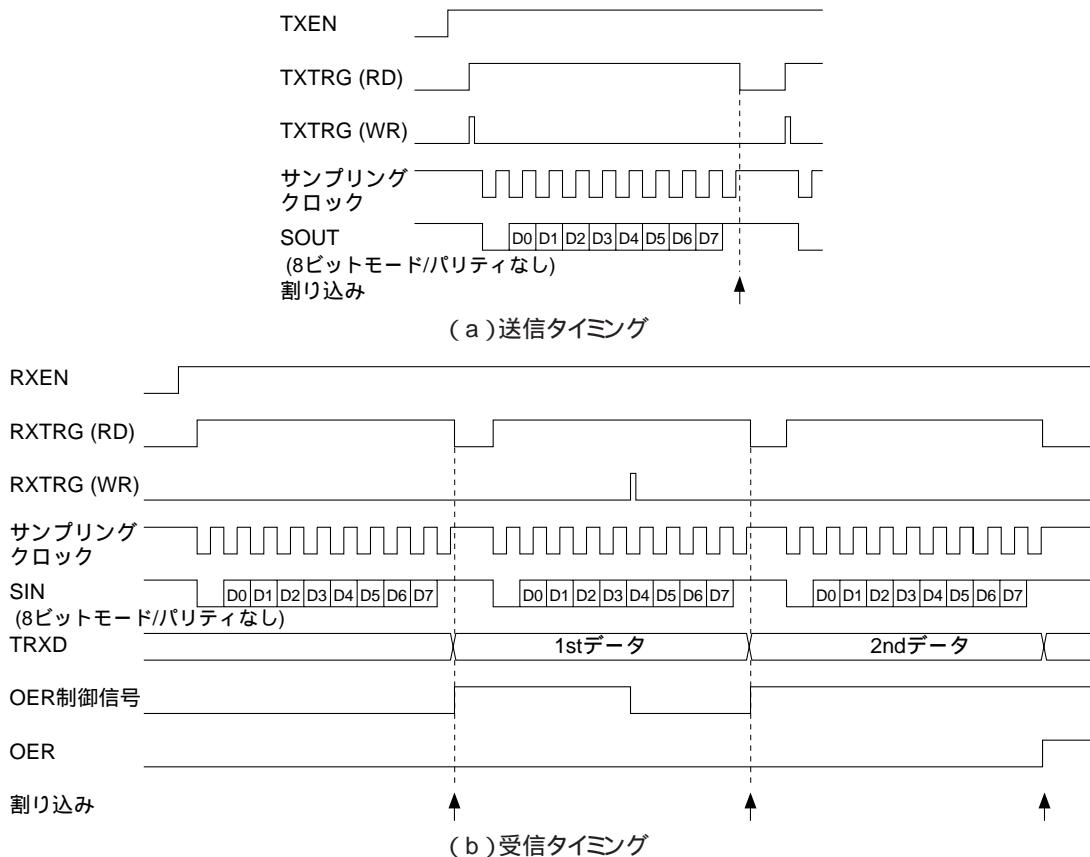

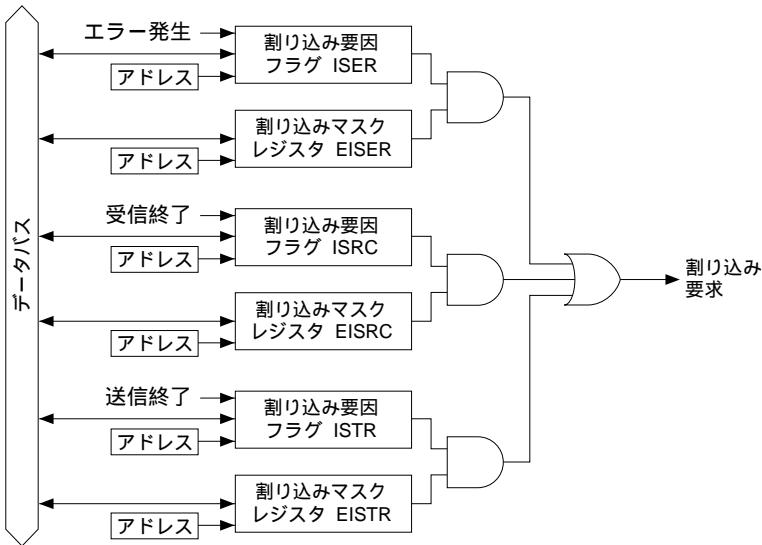

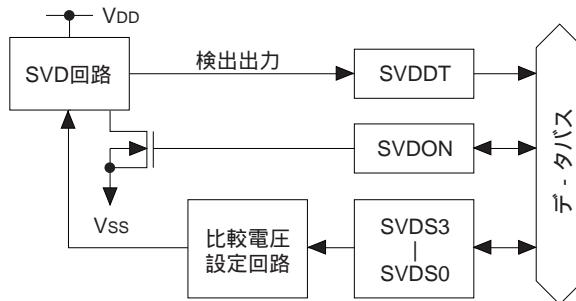

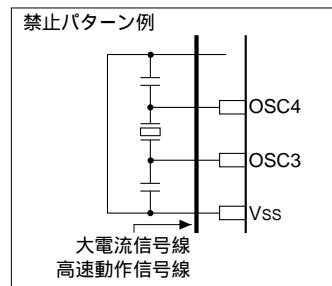

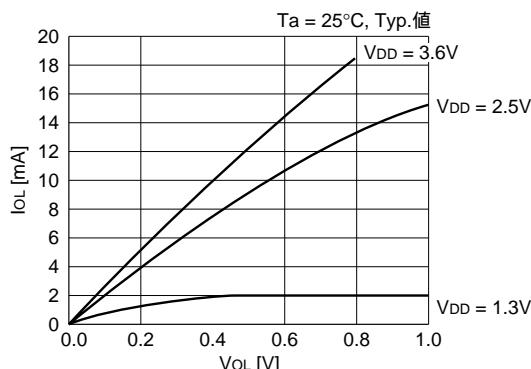

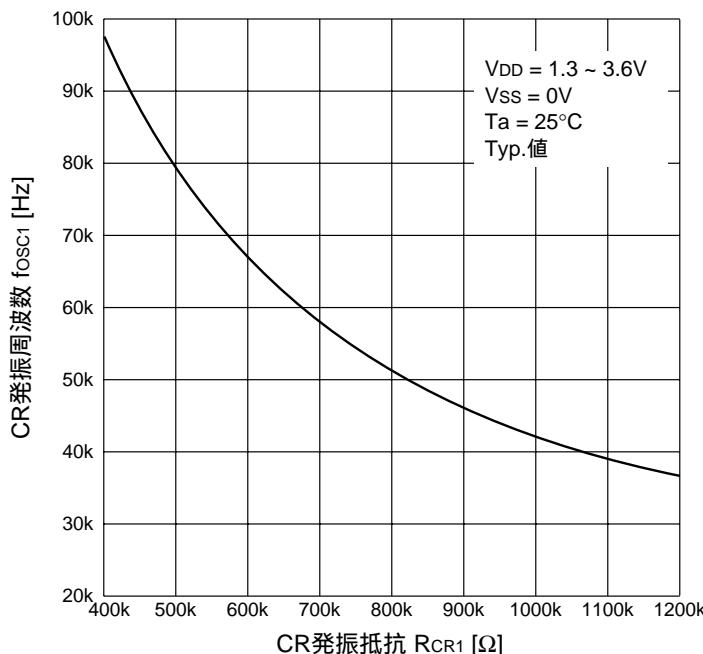

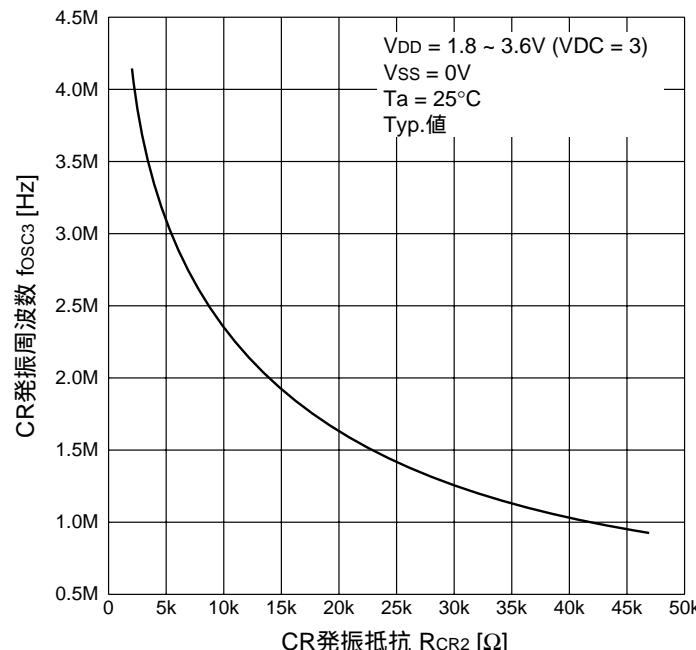

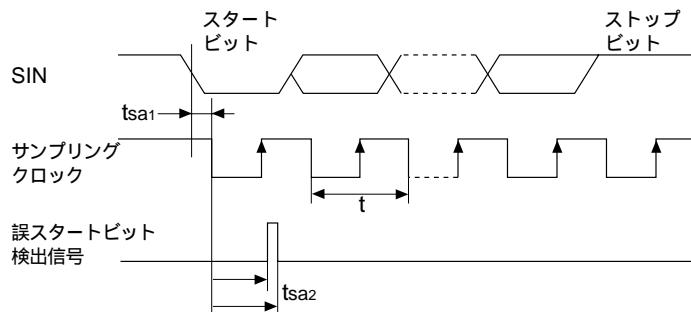

|       | R      |        |       |       | PER     | 0       |                                                                                                                                                                                                    |                                                                                                                                       |                                                                                                                                          |