CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

# S1C6P366

テクニカルマニュアル

S1C6P366 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

MS-DOS、Windows、Windows95、Windows98およびWindows NTは米国マイクロソフト社の登録商標です。

PC/AT、PS/2、PC-DOS、VGA、EGAおよびIBMは、米国International Business Machines社の登録商標です。

NEC PC-9800シリーズおよびNECは日本電気株式会社の登録商標です。

その他のブランド名または製品名は、それらの所有者の商標もしくは登録商標です。

本製品はSilicon Storage Technology, Inc.よりライセンスされたSuperFlash®テクノロジーを使用しています。

## 本版で改訂または追加された箇所

| 章 | 節/項   | 頁   | 項目                              | 内容    |

|---|-------|-----|---------------------------------|-------|

| 4 | 4.7.3 | 46  | LCD表示と駆動波形の制御<br>(1)表示のON/OFF   | 文章変更  |

|   | 4.9.5 | 73  | プログラミング上の注意事項                   | (6)追加 |

| 7 | 7.2   | 120 | 個別機能についての注意事項のまとめ<br>プログラマブルタイマ | (5)追加 |

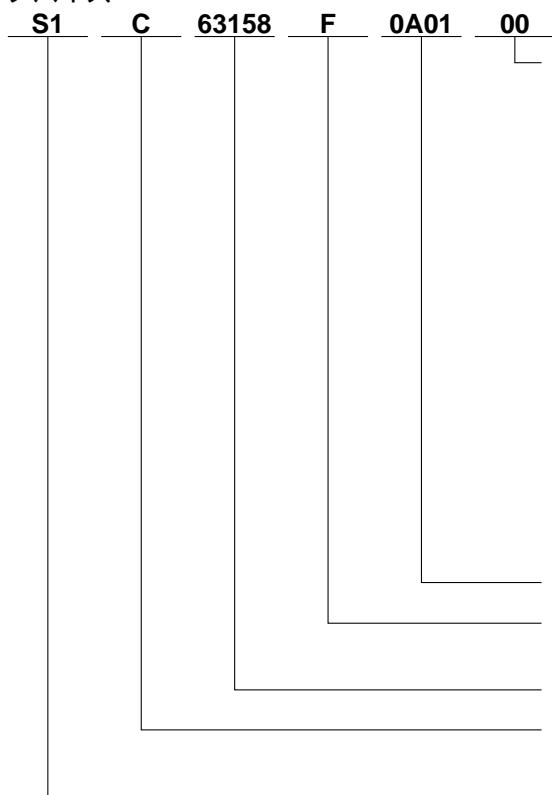

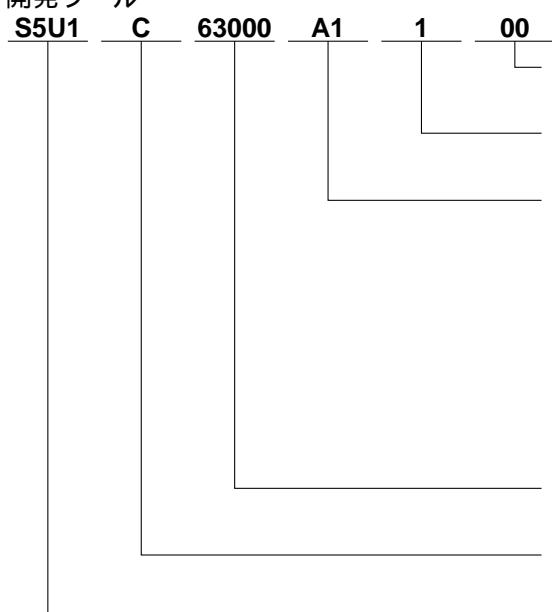

## 製品型番体系

デバイス

### 梱包仕様

- 00 : テープ&リール以外

- 0A : TCP BL 2方向

- 0B : テープ&リール BACK

- 0C : TCP BR 2方向

- 0D : TCP BT 2方向

- 0E : TCP BD 2方向

- 0F : テープ&リール FRONT

- 0G : TCP BT 4方向

- 0H : TCP BD 4方向

- 0J : TCP SL 2方向

- 0K : TCP SR 2方向

- 0L : テープ&リール LEFT

- 0M : TCP ST 2方向

- 0N : TCP SD 2方向

- 0P : TCP ST 4方向

- 0Q : TCP SD 4方向

- 0R : テープ&リール RIGHT

- 99 : 梱包仕様未定

### 仕様

[D: ベアチップ、F: QFP]

### 機種番号

#### 機種名称

[C: マイコン、デジタル製品]

#### 製品分類

[S1: 半導体]

開発ツール

### 梱包仕様

[00: 標準梱包]

### バージョン

[1: Version 1]

### ツール種類

- Hx : ICE

- Ex : EVAボード

- Px : ペリフェラルボード

- Wx: FLASHマイコン用ROMライタ

- Xx : ROMライタ周辺ボード

- Cx : Cコンパイラパッケージ

- Ax : アセンブラーパッケージ

- Dx : 機種別ユーティリティツール

- Qx : ソフトシミュレータ

### 対応機種番号

[63000: S1C63ファミリ共通]

### ツール分類

[C: マイコン用]

### 製品分類

[S5U1: 半導体用開発ツール]

## - 目 次 -

|                                                 |           |

|-------------------------------------------------|-----------|

| <b>1 概要</b>                                     | <b>1</b>  |

| 1.1 特長 .....                                    | 1         |

| 1.2 ブロック図 .....                                 | 2         |

| 1.3 端子配置図 .....                                 | 3         |

| 1.4 端子説明 .....                                  | 4         |

| 1.5 マスクオプション .....                              | 5         |

| 1.6 セグメントオプション .....                            | 5         |

| <b>2 電源系およびイニシャルリセット</b>                        | <b>6</b>  |

| 2.1 電源系 .....                                   | 6         |

| 2.1.1 発振回路用電圧<VD1> .....                        | 7         |

| 2.1.2 LCD駆動用電圧<VC1 ~ VC3> .....                 | 7         |

| 2.1.3 内部電源回路の動作モード .....                        | 7         |

| 2.2 イニシャルリセット .....                             | 8         |

| 2.2.1 リセット端子( $\overline{\text{RESET}}$ ) ..... | 8         |

| 2.2.2 イニシャルリセット時の内部レジスタ .....                   | 8         |

| 2.2.3 イニシャルリセット時の端子設定 .....                     | 9         |

| 2.3 テスト端子( $\overline{\text{TEST}}$ ) .....     | 10        |

| 2.4 Flash EEPROM専用端子 .....                      | 10        |

| <b>3 CPU, PROM, RAM</b>                         | <b>11</b> |

| 3.1 CPU .....                                   | 11        |

| 3.2 コードPROM .....                               | 11        |

| 3.3 RAM .....                                   | 11        |

| <b>4 周辺回路と動作</b>                                | <b>13</b> |

| 4.1 メモリマップ .....                                | 13        |

| 4.2 ウオッチドッグタイマ .....                            | 20        |

| 4.2.1 ウオッチドッグタイマの構成 .....                       | 20        |

| 4.2.2 割り込み機能 .....                              | 20        |

| 4.2.3 ウオッチドッグタイマのI/Oメモリ .....                   | 21        |

| 4.2.4 プログラミング上の注意事項 .....                       | 21        |

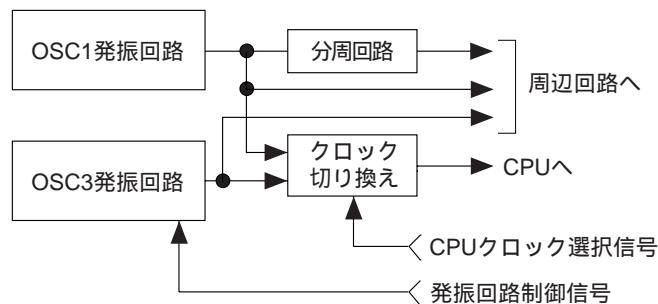

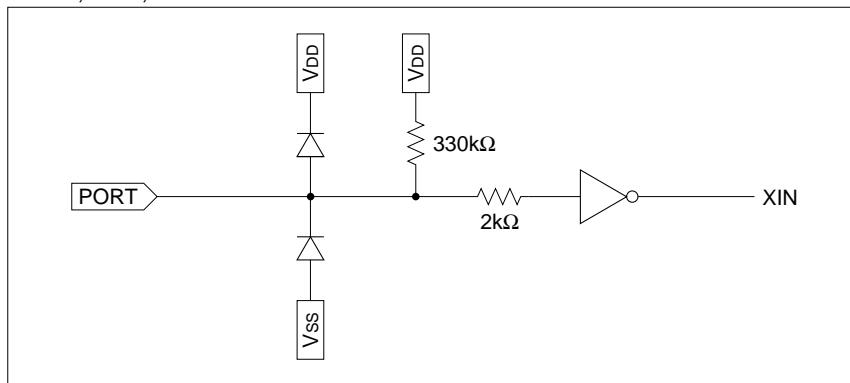

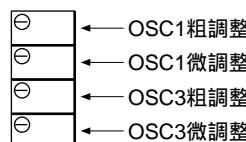

| 4.3 発振回路 .....                                  | 22        |

| 4.3.1 発振回路の構成 .....                             | 22        |

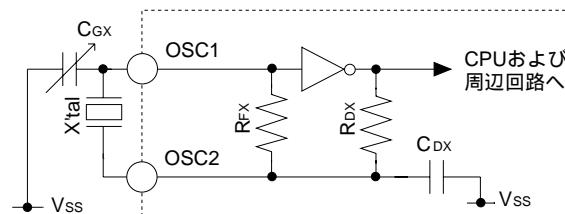

| 4.3.2 OSC1発振回路 .....                            | 22        |

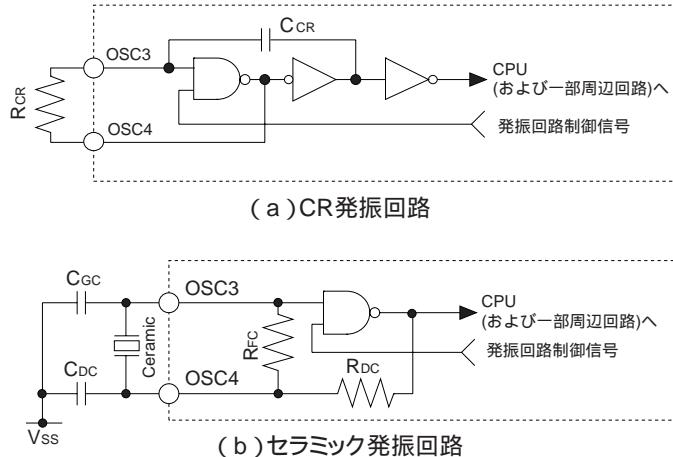

| 4.3.3 OSC3発振回路 .....                            | 23        |

| 4.3.4 動作電圧について .....                            | 24        |

| 4.3.5 動作クロックの切り換え .....                         | 24        |

| 4.3.6 クロック周波数とインストラクション実行時間 .....               | 24        |

| 4.3.7 発振回路のI/Oメモリ .....                         | 25        |

| 4.3.8 プログラミング上の注意事項 .....                       | 26        |

|         |                                                                         |    |

|---------|-------------------------------------------------------------------------|----|

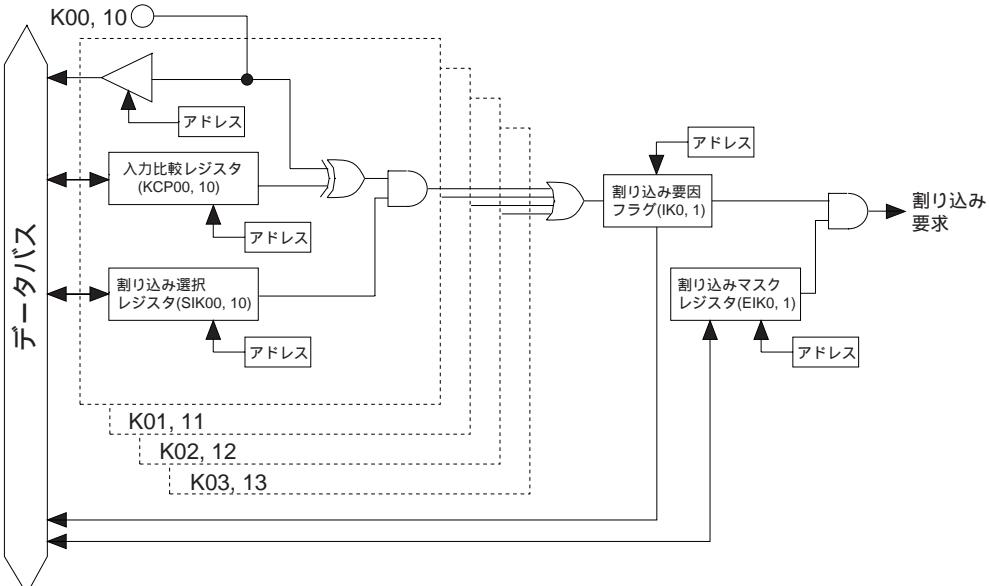

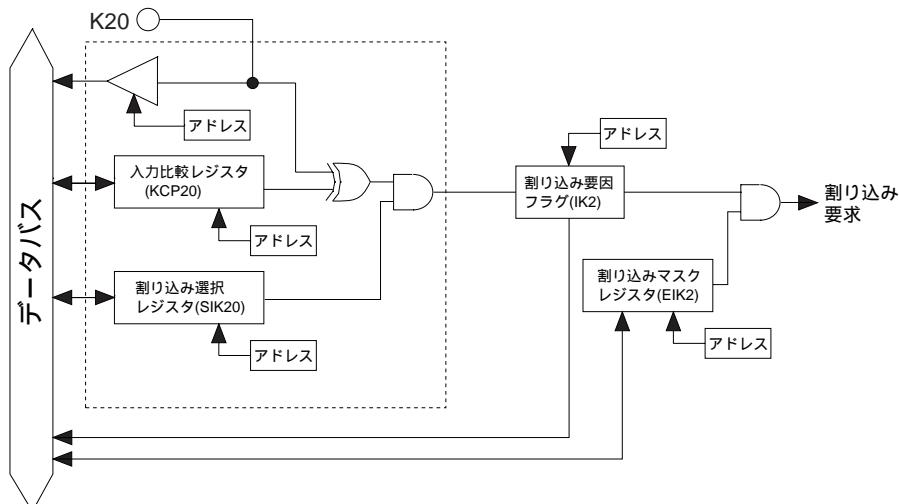

| 4.4     | 入力ポート( K00 ~ K03, K10 ~ K13, K20 ) .....                                | 27 |

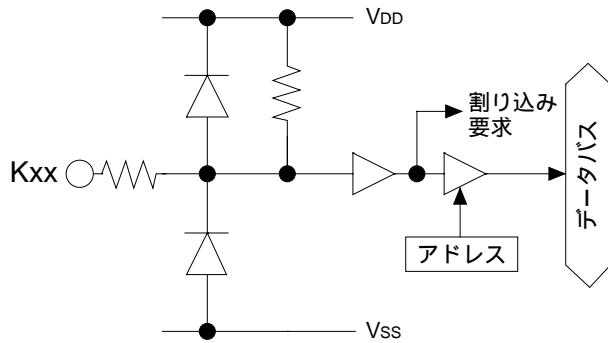

| 4.4.1   | 入力ポートの構成 .....                                                          | 27 |

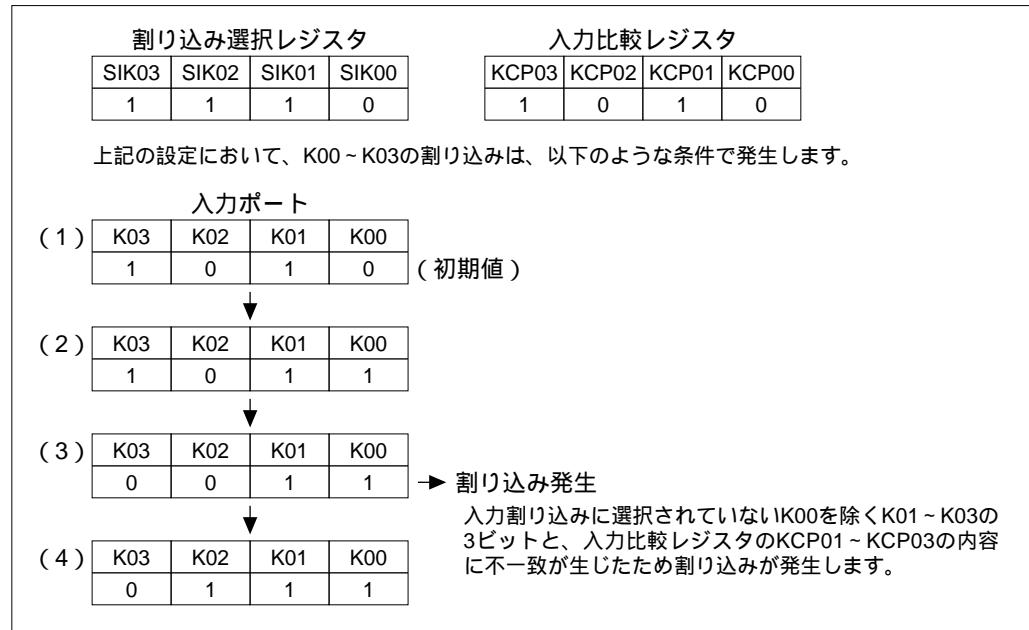

| 4.4.2   | 割り込み機能 .....                                                            | 28 |

| 4.4.3   | マスクオプション .....                                                          | 29 |

| 4.4.4   | 入力ポートのI/Oメモリ .....                                                      | 30 |

| 4.4.5   | プログラミング上の注意事項 .....                                                     | 33 |

| 4.5     | 出力ポート( R00 ~ R03, R10 ~ R13, R20 ~ R23 ) .....                          | 34 |

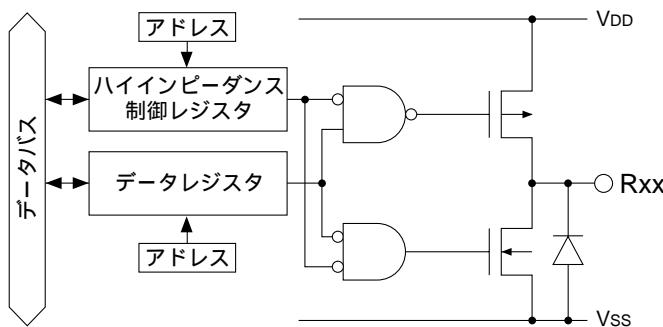

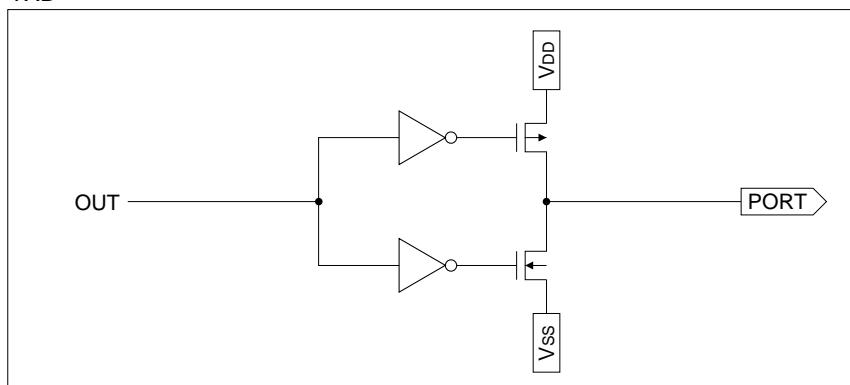

| 4.5.1   | 出力ポートの構成 .....                                                          | 34 |

| 4.5.2   | マスクオプション .....                                                          | 34 |

| 4.5.3   | ハイインピーダンス制御 .....                                                       | 35 |

| 4.5.4   | 特殊出力 .....                                                              | 35 |

| 4.5.5   | 出力ポートのI/Oメモリ .....                                                      | 37 |

| 4.5.6   | プログラミング上の注意事項 .....                                                     | 39 |

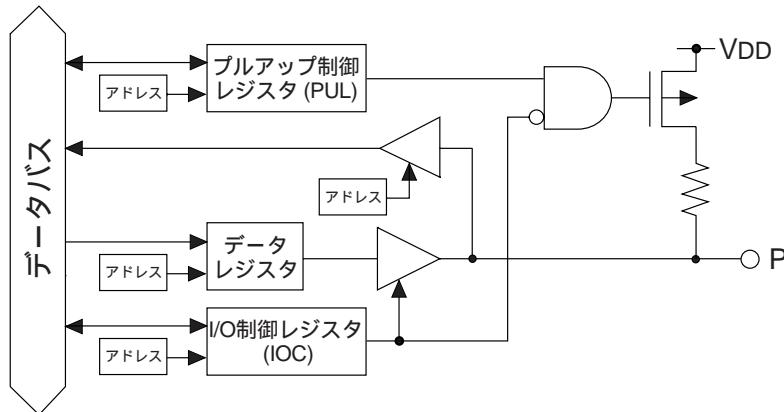

| 4.6     | 入出力兼用ポート( P00 ~ P03, P10 ~ P13, P20 ~ P23, P30 ~ P33, P40 ~ P43 ) ..... | 40 |

| 4.6.1   | 入出力兼用ポートの構成 .....                                                       | 40 |

| 4.6.2   | マスクオプション .....                                                          | 41 |

| 4.6.3   | I/O制御レジスタと入力/出力モード .....                                                | 41 |

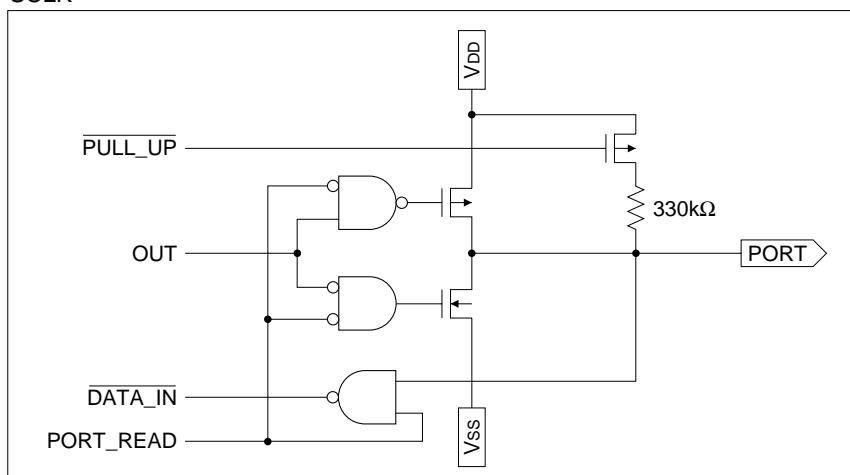

| 4.6.4   | 入力モード時のプルアップ .....                                                      | 41 |

| 4.6.5   | 入出力兼用ポートのI/Oメモリ .....                                                   | 42 |

| 4.6.6   | プログラミング上の注意事項 .....                                                     | 45 |

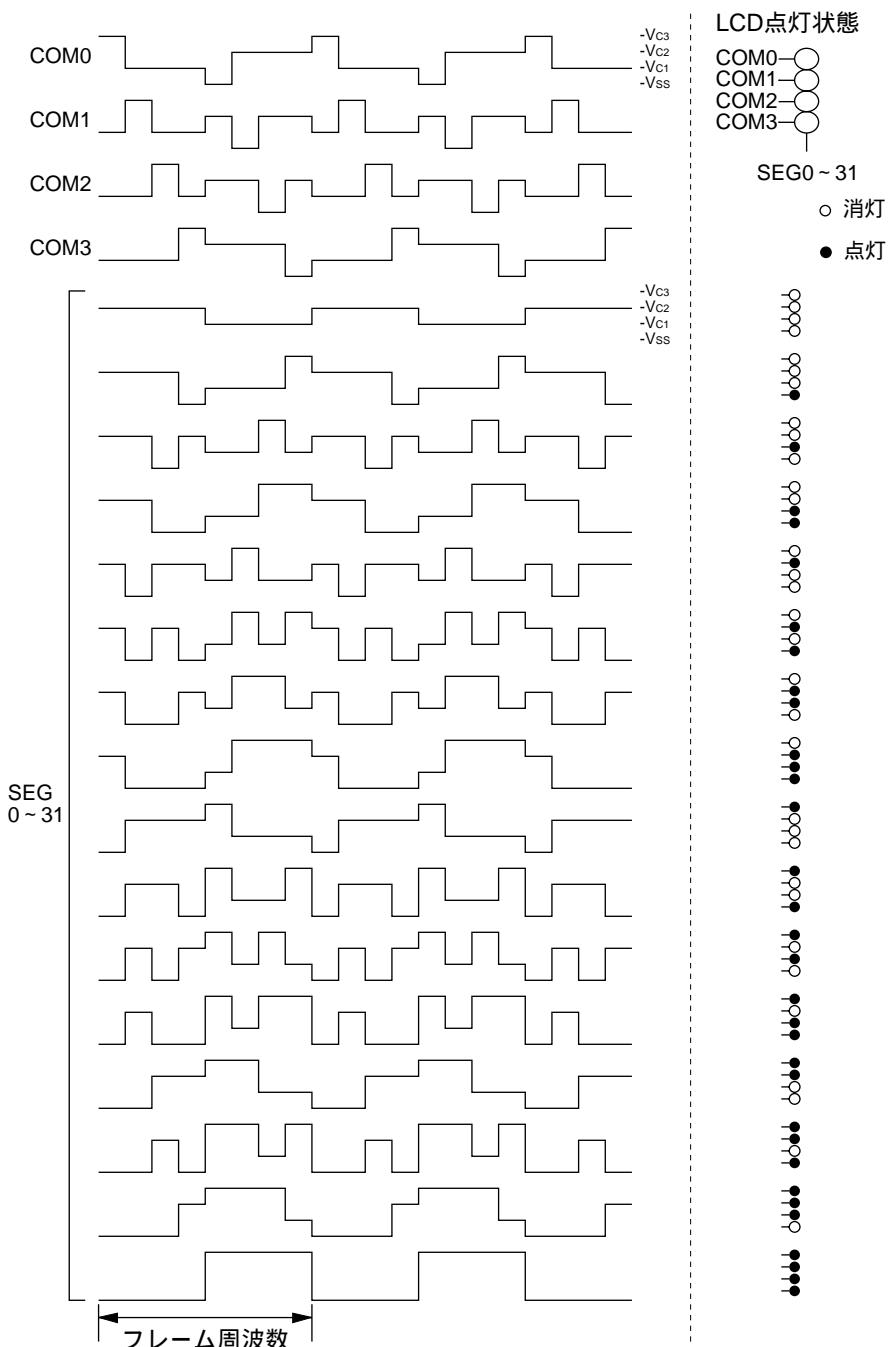

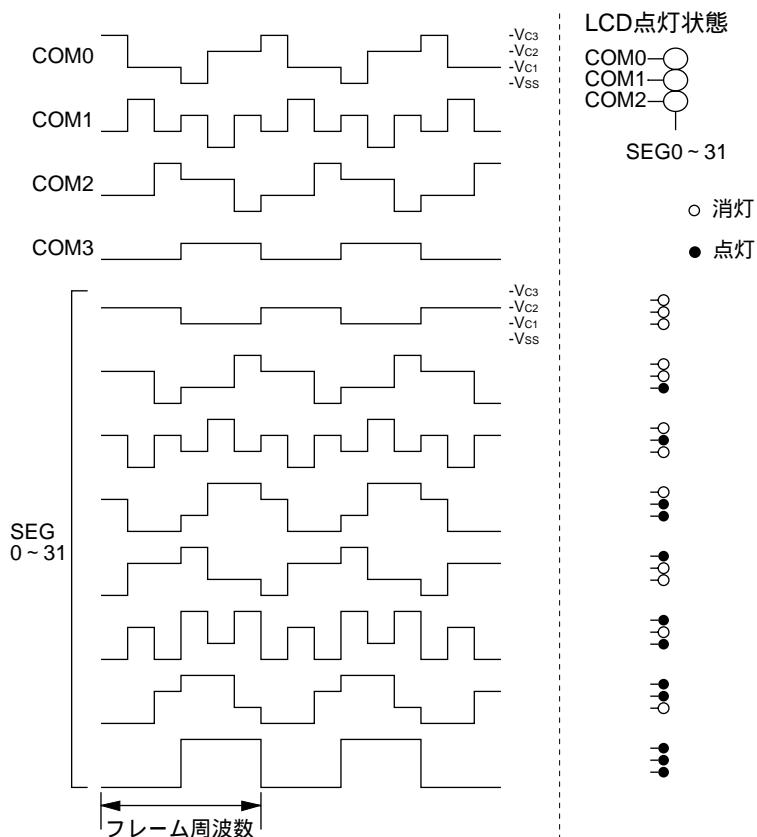

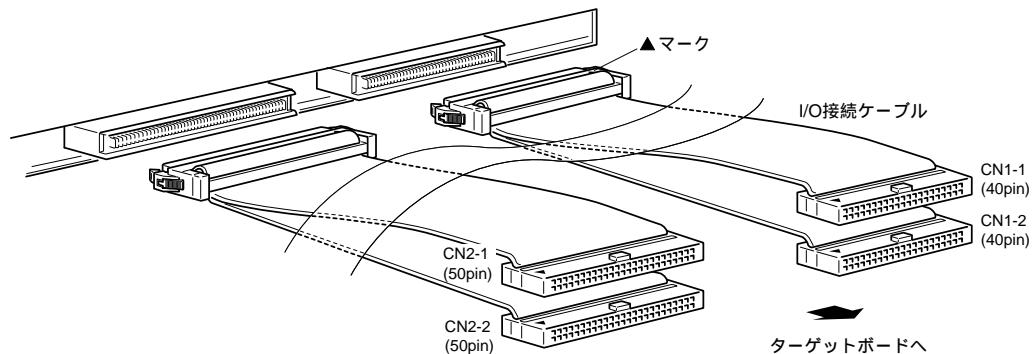

| 4.7     | LCDドライバ( COM0 ~ COM3, SEG0 ~ SEG31 ) .....                              | 46 |

| 4.7.1   | LCDドライバの構成 .....                                                        | 46 |

| 4.7.2   | LCD駆動電源 .....                                                           | 46 |

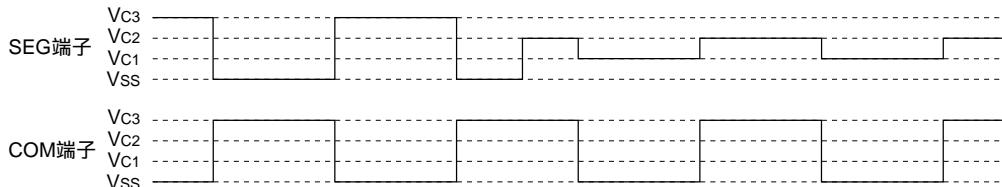

| 4.7.3   | LCD表示と駆動波形の制御 .....                                                     | 46 |

| 4.7.4   | セグメントオプション .....                                                        | 50 |

| 4.7.5   | マスクオプション .....                                                          | 51 |

| 4.7.6   | LCDドライバのI/Oメモリ .....                                                    | 52 |

| 4.7.7   | プログラミング上の注意事項 .....                                                     | 53 |

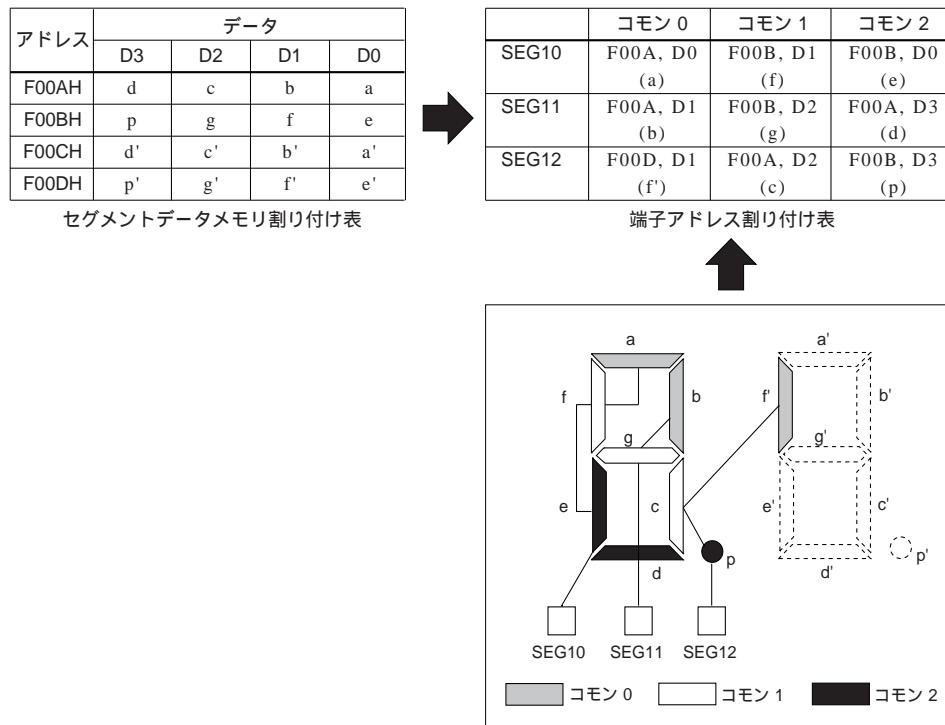

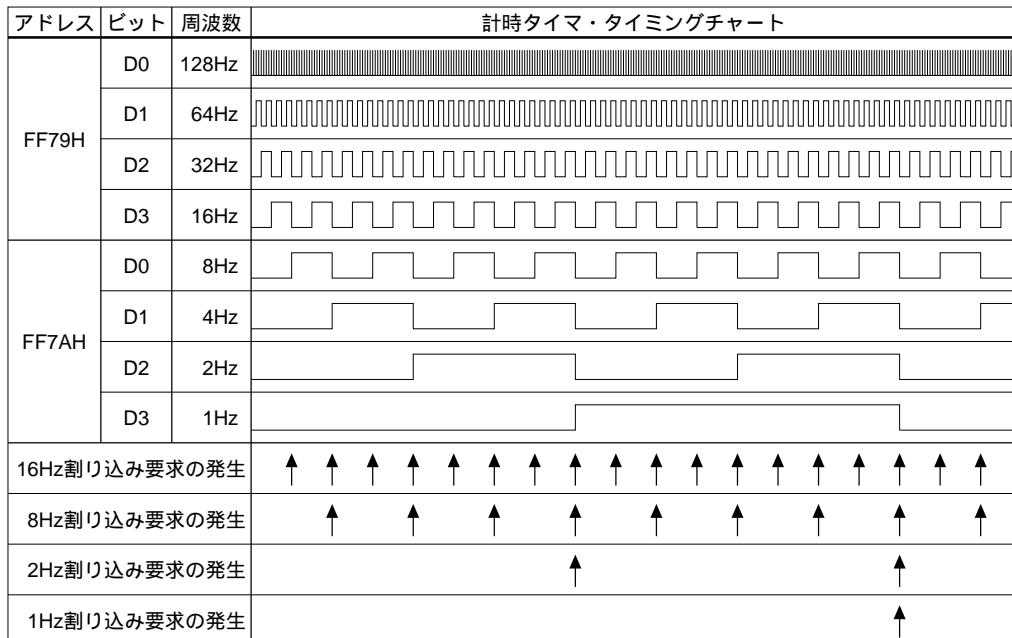

| 4.8     | 計時タイマ .....                                                             | 54 |

| 4.8.1   | 計時タイマの構成 .....                                                          | 54 |

| 4.8.2   | データの読み出しとホールド機能 .....                                                   | 54 |

| 4.8.3   | 割り込み機能 .....                                                            | 55 |

| 4.8.4   | 計時タイマのI/Oメモリ .....                                                      | 56 |

| 4.8.5   | プログラミング上の注意事項 .....                                                     | 57 |

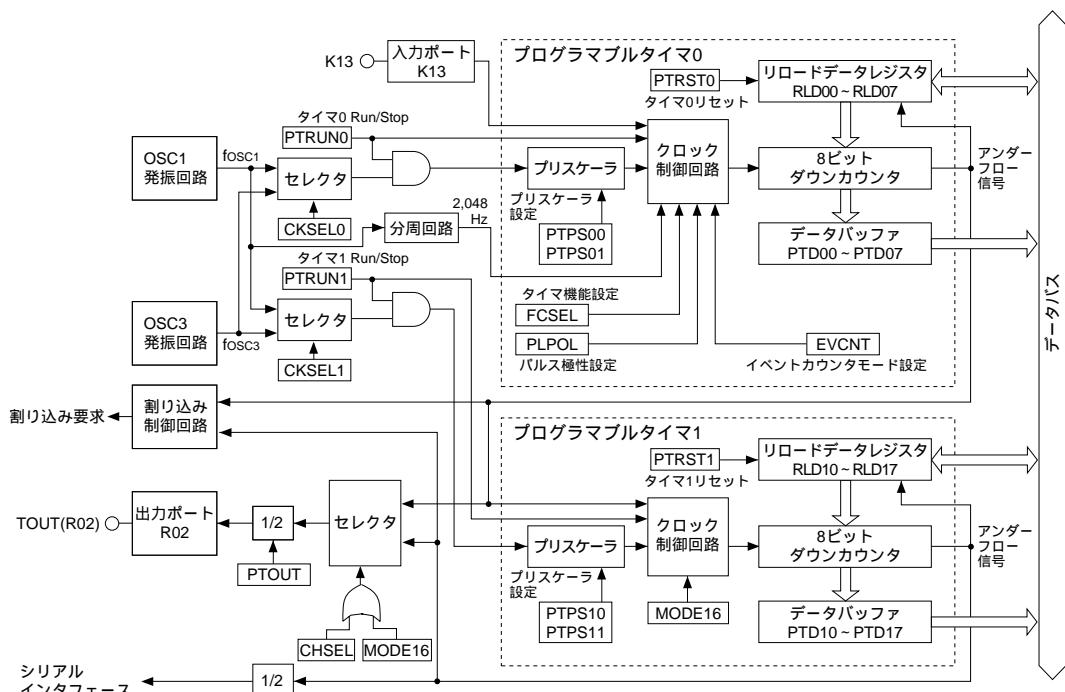

| 4.9     | プログラマブルタイマ .....                                                        | 58 |

| 4.9.1   | プログラマブルタイマの構成 .....                                                     | 58 |

| 4.9.2   | 2チャンネル×8ビットタイマ( MODE16 = "0" )の動作 .....                                 | 59 |

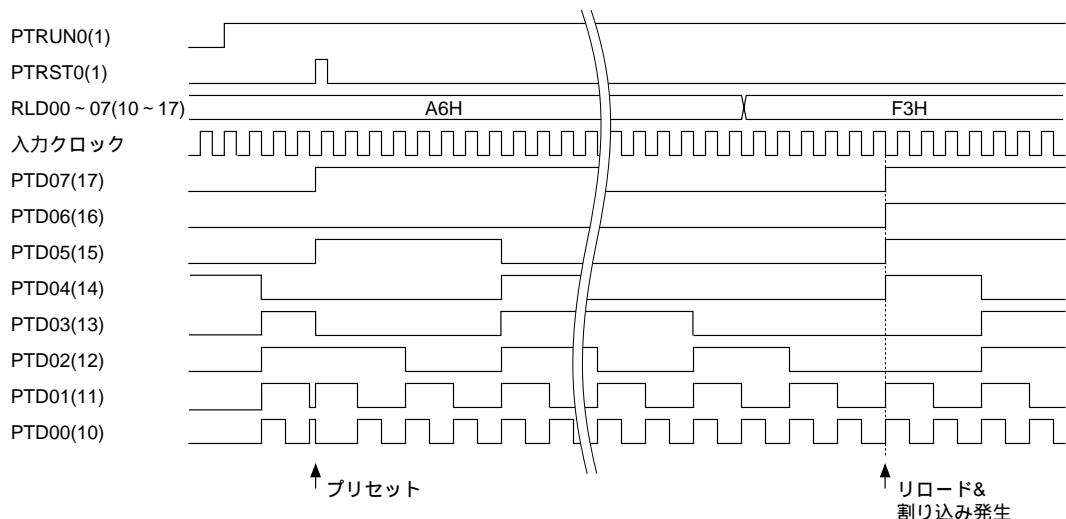

| 4.9.2.1 | カウンタ初期値の設定とダウンカウント動作 .....                                              | 59 |

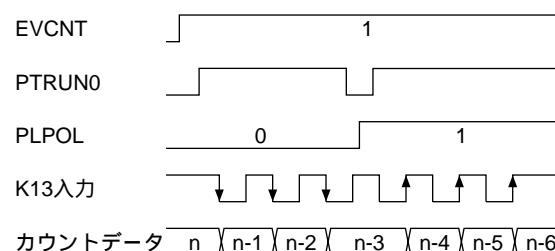

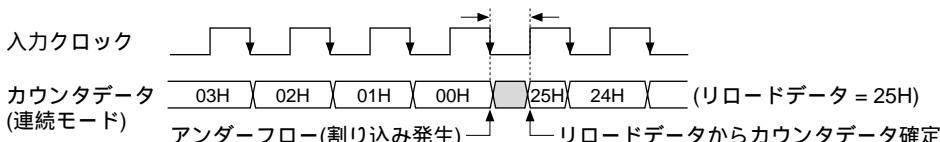

| 4.9.2.2 | カウンタモード .....                                                           | 60 |

| 4.9.2.3 | タイマモード入力クロックの設定 .....                                                   | 61 |

| 4.9.2.4 | 割り込み機能 .....                                                            | 62 |

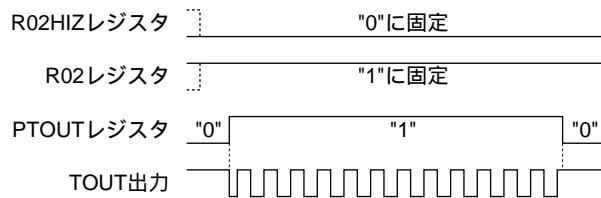

| 4.9.2.5 | TOUT出力の設定 .....                                                         | 62 |

| 4.9.2.6 | シリアルインターフェースの転送速度設定 .....                                               | 63 |

| 4.9.3   | 1チャンネル×16ビットタイマ( MODE16 = "1" )の動作 .....                                | 63 |

| 4.9.3.1 | カウンタ初期値の設定とダウンカウント動作 .....                                              | 63 |

| 4.9.3.2 | カウンタモード .....                                                           | 64 |

|                                                 |            |

|-------------------------------------------------|------------|

| 4.9.3.3 タイマモード入力クロックの設定 .....                   | 65         |

| 4.9.3.4 割り込み機能 .....                            | 66         |

| 4.9.3.5 TOUT出力の設定 .....                         | 66         |

| 4.9.3.6 シリアルインタフェースの転送速度設定 .....                | 67         |

| 4.9.4 プログラマブルタイマのI/Oメモリ .....                   | 68         |

| 4.9.5 プログラミング上の注意事項 .....                       | 73         |

| 4.10 シリアルインタフェース( SIN, SOUT, SCLK, SRDY ) ..... | 74         |

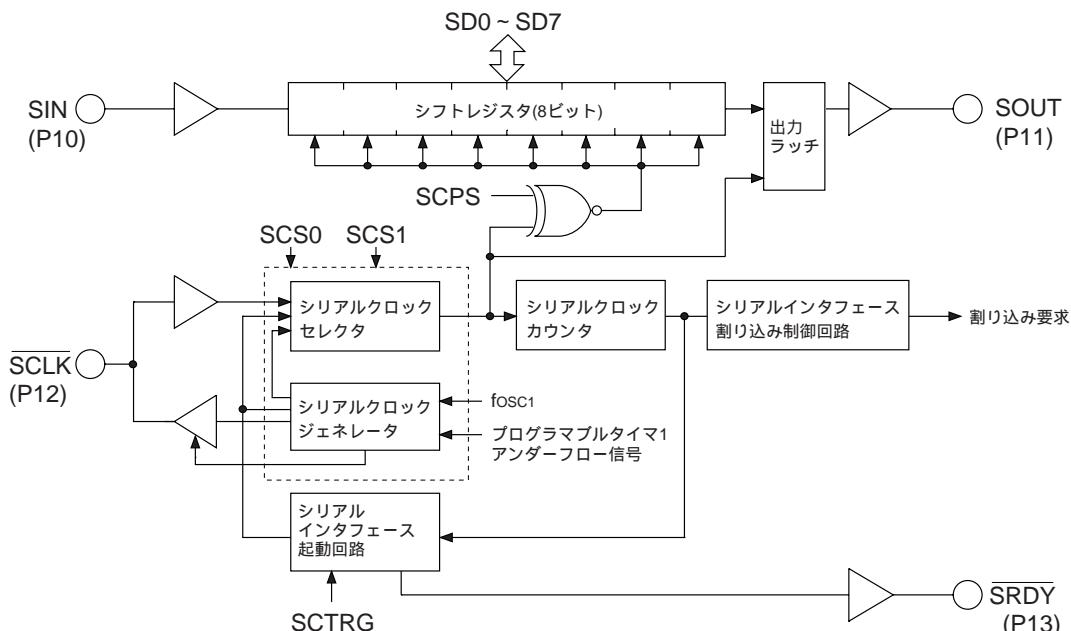

| 4.10.1 シリアルインタフェースの構成 .....                     | 74         |

| 4.10.2 マスクオプション .....                           | 75         |

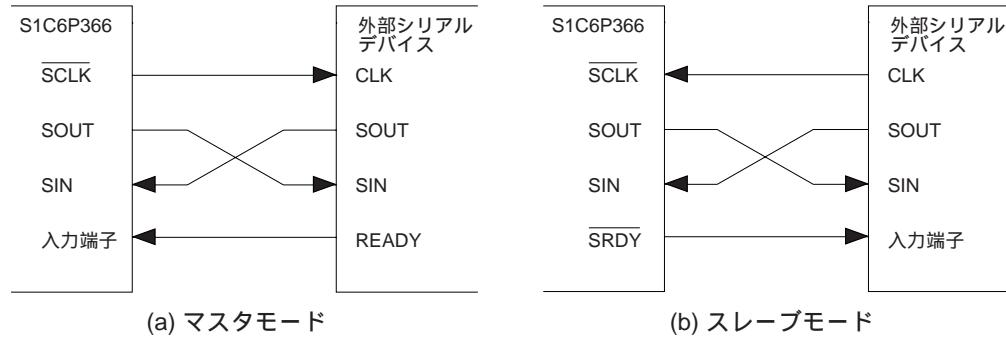

| 4.10.3 シリアルインタフェースのマスタモードとスレーブモード .....         | 75         |

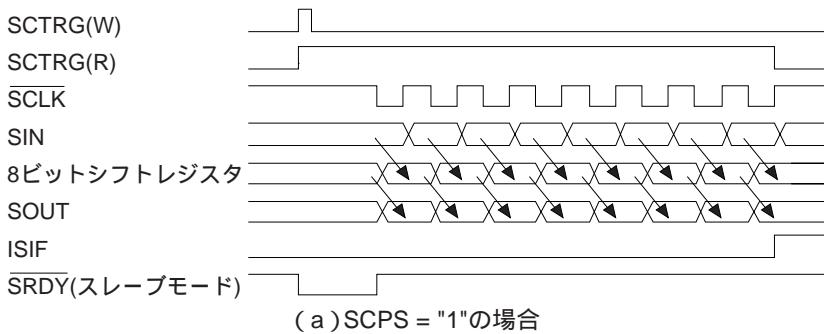

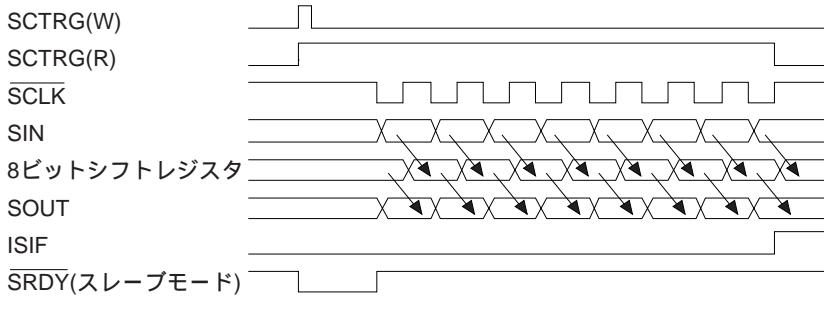

| 4.10.4 データの入出力と割り込み .....                       | 76         |

| 4.10.5 シリアルインタフェースのI/Oメモリ .....                 | 78         |

| 4.10.6 プログラミング上の注意事項 .....                      | 81         |

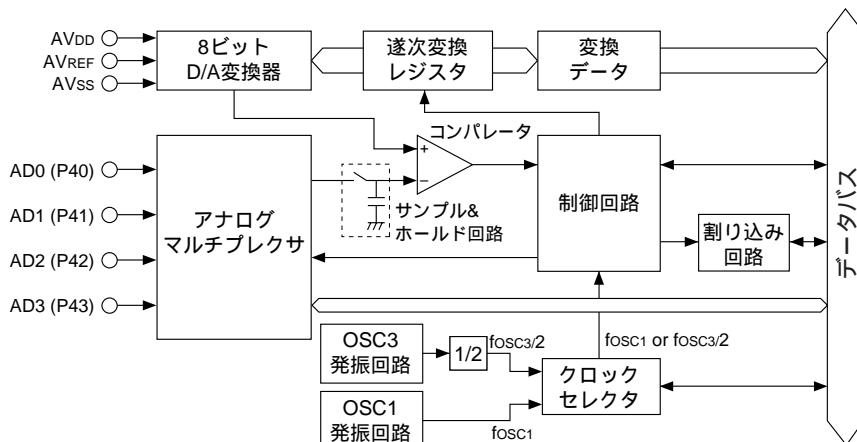

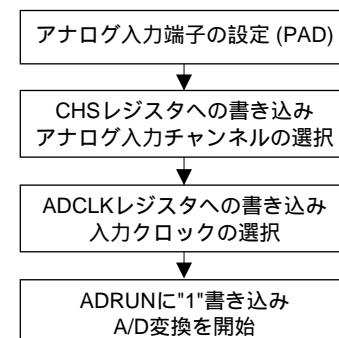

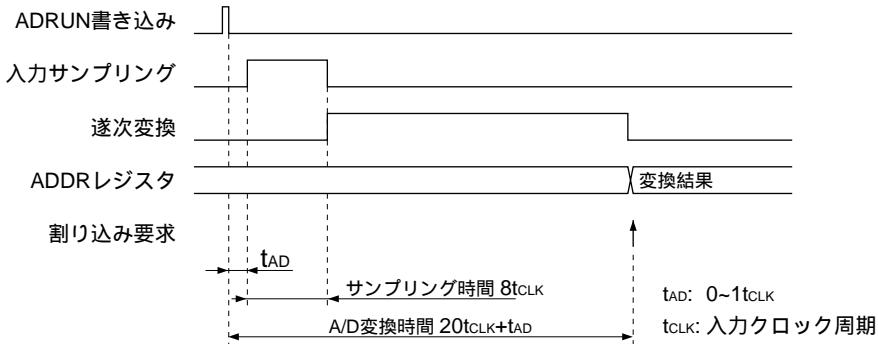

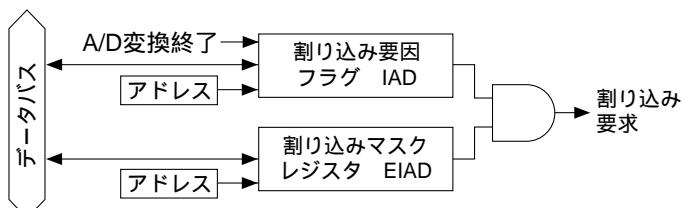

| 4.11 A/D変換器 .....                               | 82         |

| 4.11.1 A/D変換器の特徴と構成 .....                       | 82         |

| 4.11.2 A/D変換器の端子構成 .....                        | 82         |

| 4.11.3 マスクオプション .....                           | 83         |

| 4.11.4 A/D変換の制御 .....                           | 83         |

| 4.11.5 割り込み機能 .....                             | 85         |

| 4.11.6 A/D変換器のI/Oメモリ .....                      | 86         |

| 4.11.7 プログラミング上の注意事項 .....                      | 88         |

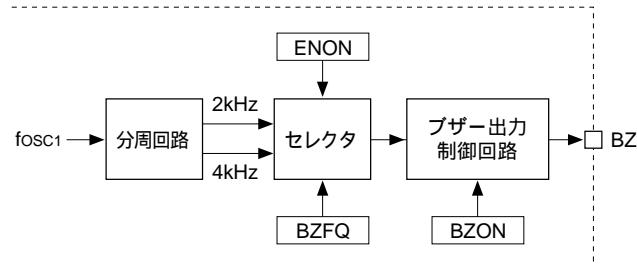

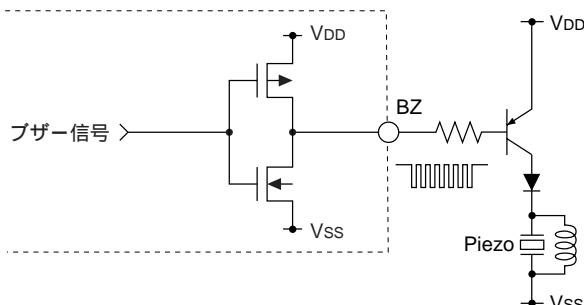

| 4.12 ブザー出力回路 .....                              | 89         |

| 4.12.1 ブザー出力回路の構成 .....                         | 89         |

| 4.12.2 マスクオプション .....                           | 89         |

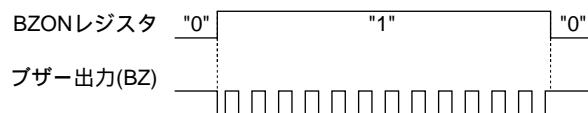

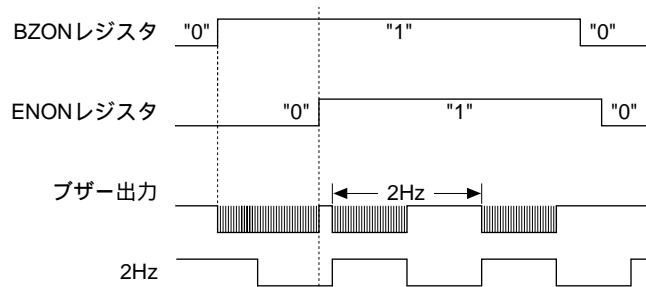

| 4.12.3 ブザー出力の制御 .....                           | 90         |

| 4.12.4 ブザー出力回路のI/Oメモリ .....                     | 91         |

| 4.12.5 プログラミング上の注意事項 .....                      | 91         |

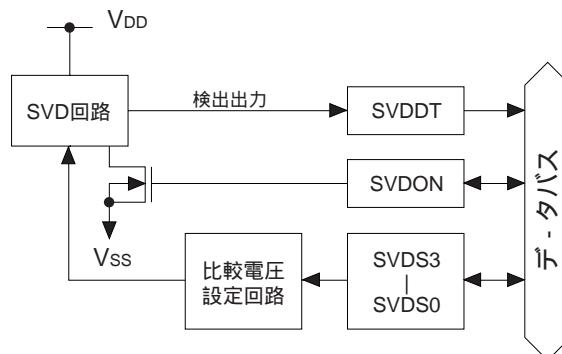

| 4.13 SVD( 電源電圧検出 )回路 .....                      | 92         |

| 4.13.1 SVD回路の構成 .....                           | 92         |

| 4.13.2 SVD動作 .....                              | 92         |

| 4.13.3 SVD回路のI/Oメモリ .....                       | 93         |

| 4.13.4 プログラミング上の注意事項 .....                      | 93         |

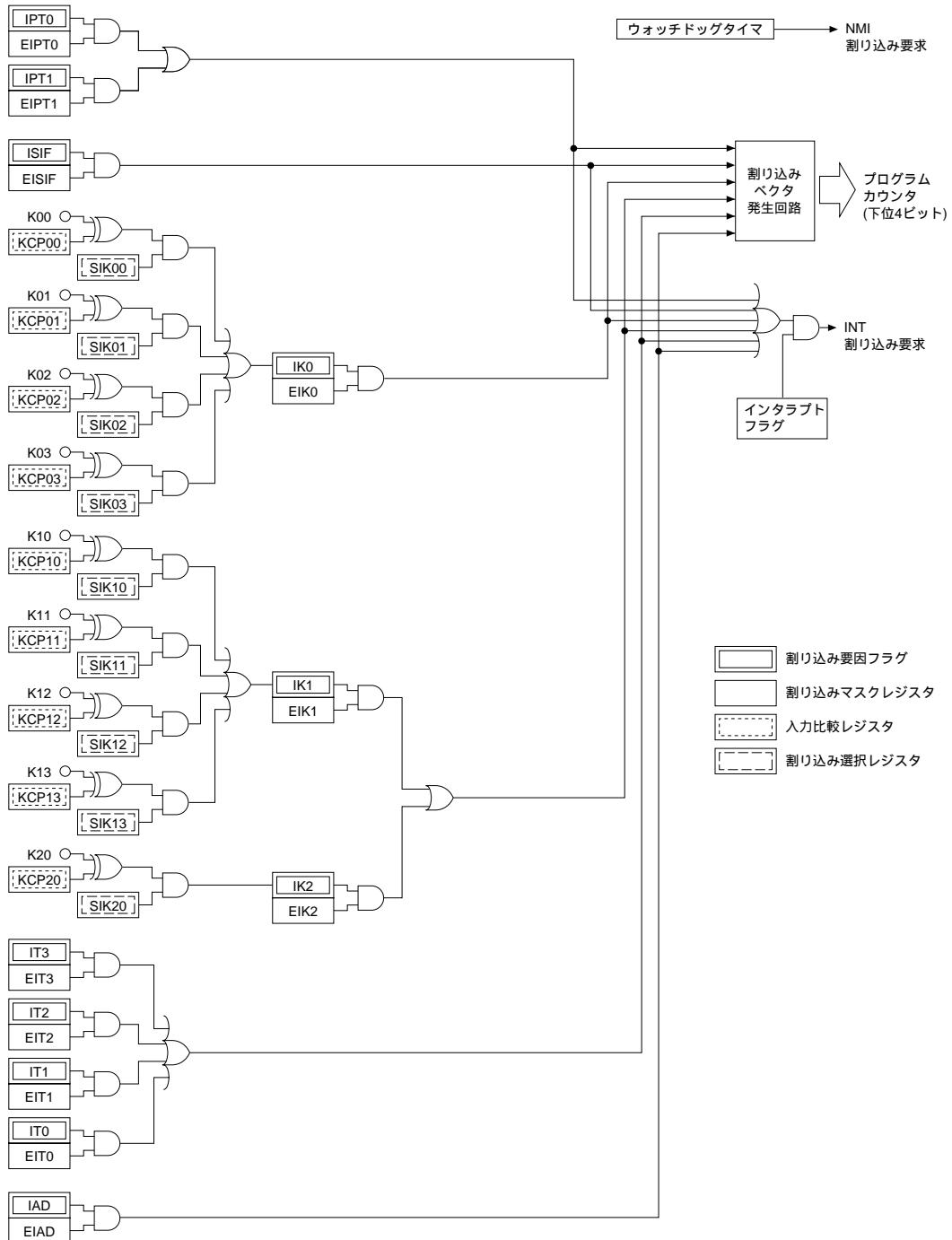

| 4.14 割り込みとHALT .....                            | 94         |

| 4.14.1 割り込みの要因 .....                            | 96         |

| 4.14.2 割り込みの個別マスク .....                         | 97         |

| 4.14.3 割り込みベクタ .....                            | 97         |

| 4.14.4 割り込みのI/Oメモリ .....                        | 98         |

| 4.14.5 プログラミング上の注意事項 .....                      | 100        |

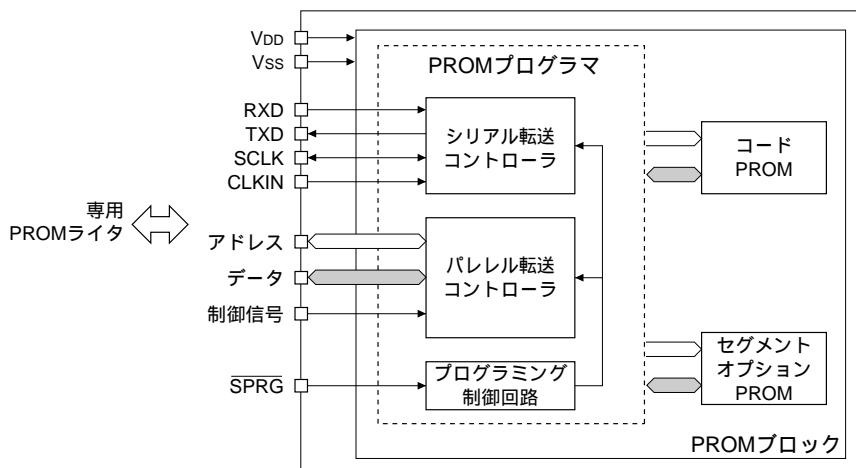

| <b>5 PROMプログラマと動作モード .....</b>                  | <b>101</b> |

| 5.1 PROMプログラマの構成 .....                          | 101        |

| 5.2 動作モード .....                                 | 103        |

| 5.2.1 通常動作モード .....                             | 103        |

| 5.2.2 シリアルプログラミングモード .....                      | 103        |

| 5.2.3 パラレルプログラミングモード .....                      | 104        |

|                       |     |

|-----------------------|-----|

| 6 マスクROM版との相違点        | 105 |

| 6.1 S1C63358との相違点     | 105 |

| 6.1.1 パッケージと端子構成      | 105 |

| 6.1.2 マスクオプション        | 106 |

| 6.1.3 電源              | 107 |

| 6.1.4 イニシャルリセット       | 109 |

| 6.1.5 PROM, RAM       | 109 |

| 6.1.6 I/Oメモリ          | 109 |

| 6.1.7 発振回路            | 109 |

| 6.1.8 SVD回路           | 110 |

| 6.2 S1C63158との相違点     | 111 |

| 6.2.1 パッケージと端子構成      | 111 |

| 6.2.2 マスクオプション        | 113 |

| 6.2.3 電源              | 114 |

| 6.2.4 イニシャルリセット       | 115 |

| 6.2.5 PROM, RAM       | 116 |

| 6.2.6 I/Oメモリ          | 116 |

| 6.2.7 発振回路            | 116 |

| 6.2.8 SVD回路           | 116 |

| 7 注意事項のまとめ            | 117 |

| 7.1 低消費電流化のための注意事項    | 117 |

| 7.2 個別機能についての注意事項のまとめ | 118 |

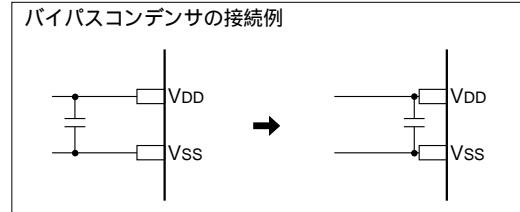

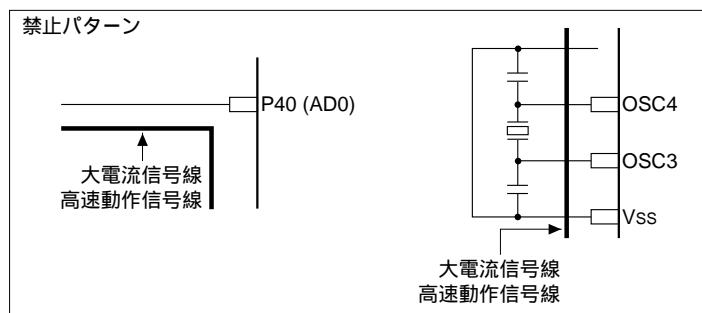

| 7.3 実装上の注意事項          | 122 |

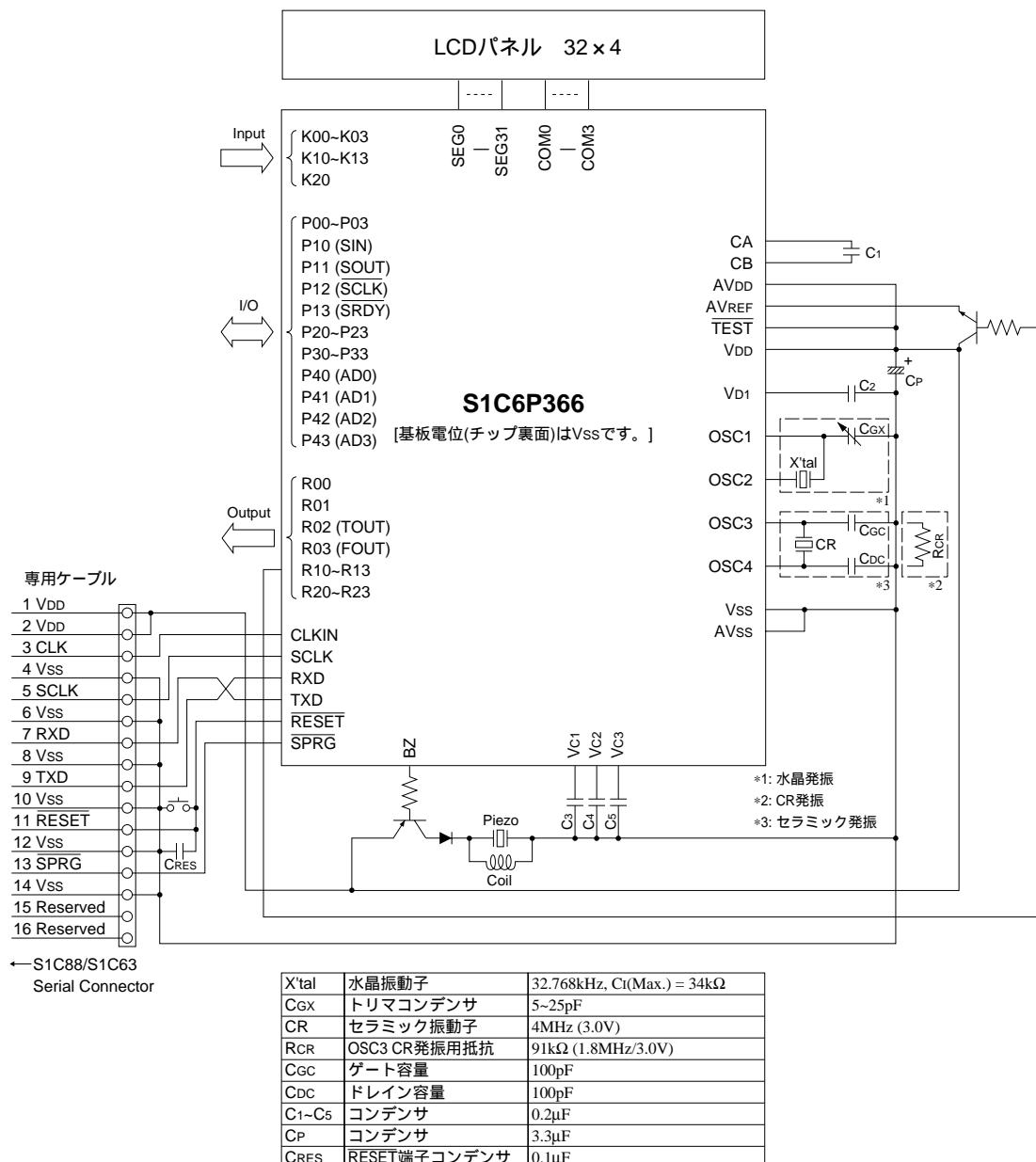

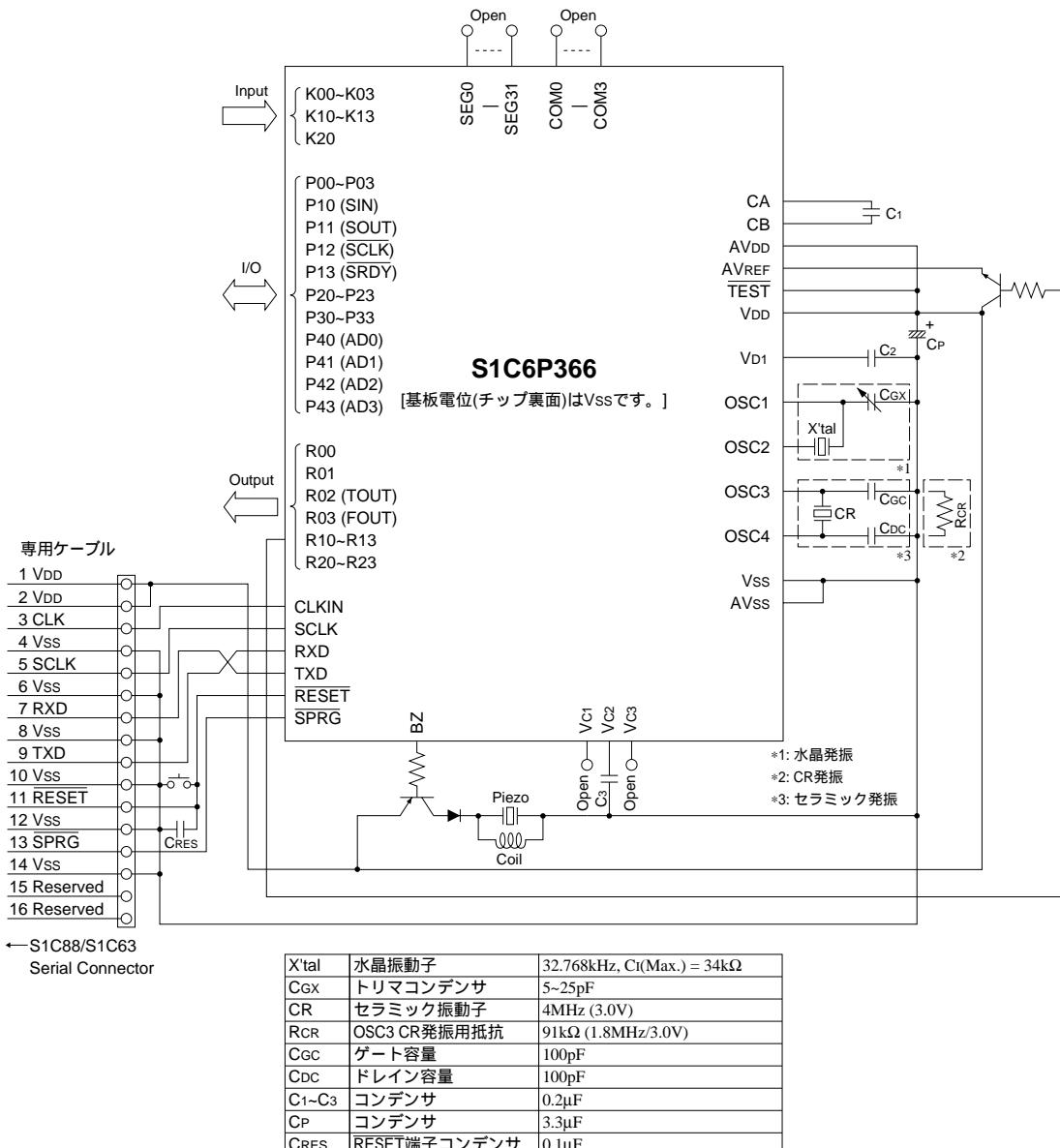

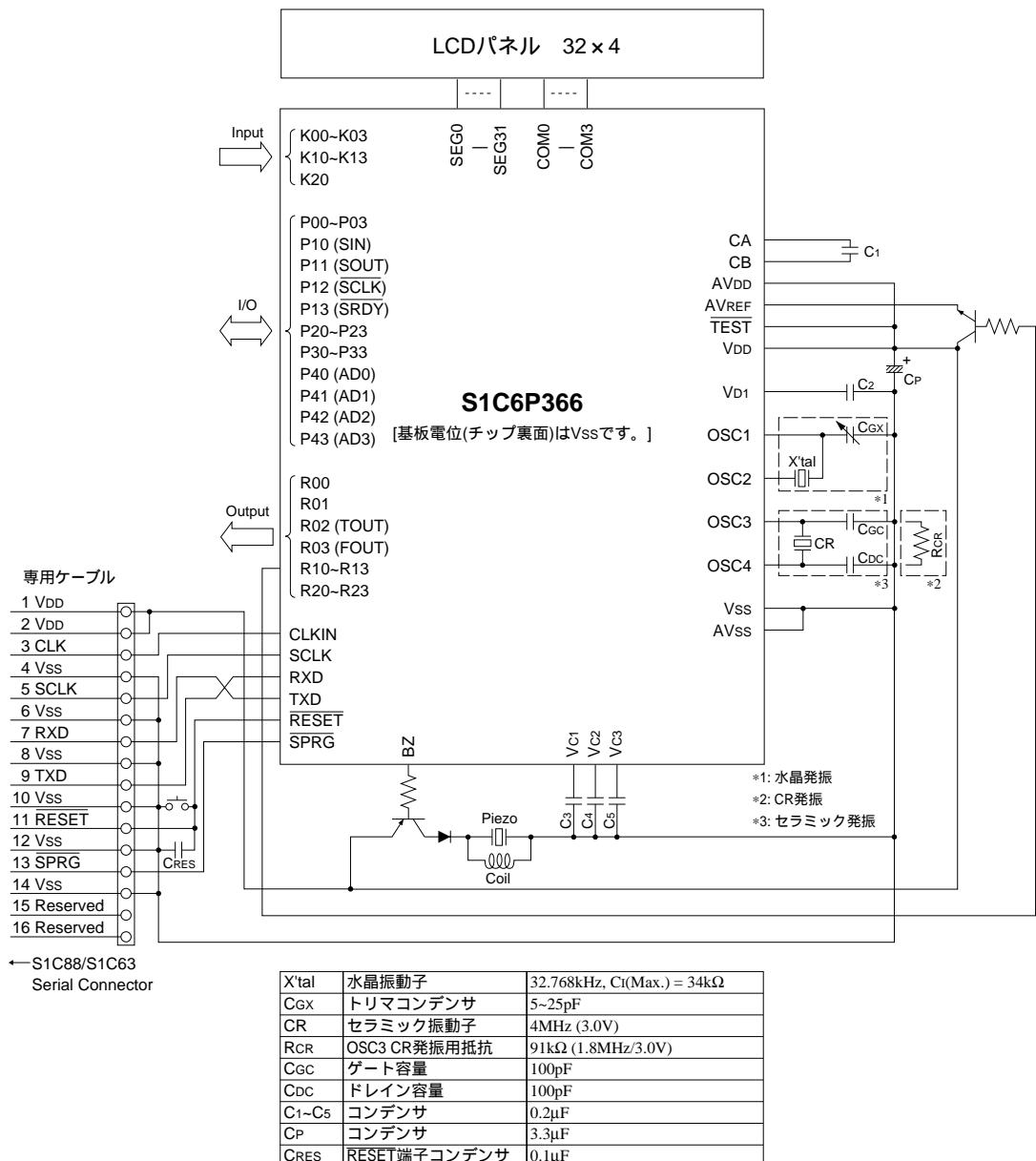

| 8 基本外部結線図             | 124 |

| 9 電気的特性               | 128 |

| 9.1 絶対最大定格            | 128 |

| 9.2 推奨動作条件            | 128 |

| 9.3 DC特性              | 129 |

| 9.4 アナログ回路特性・消費電流     | 130 |

| 9.5 発振特性              | 131 |

| 9.6 シリアルインタフェースAC特性   | 132 |

| 9.7 タイミングチャート         | 133 |

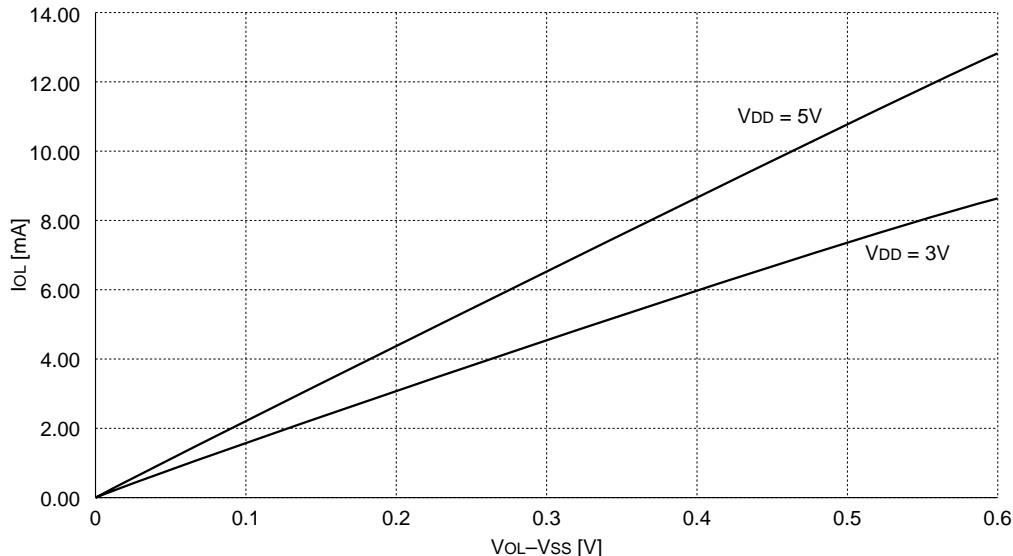

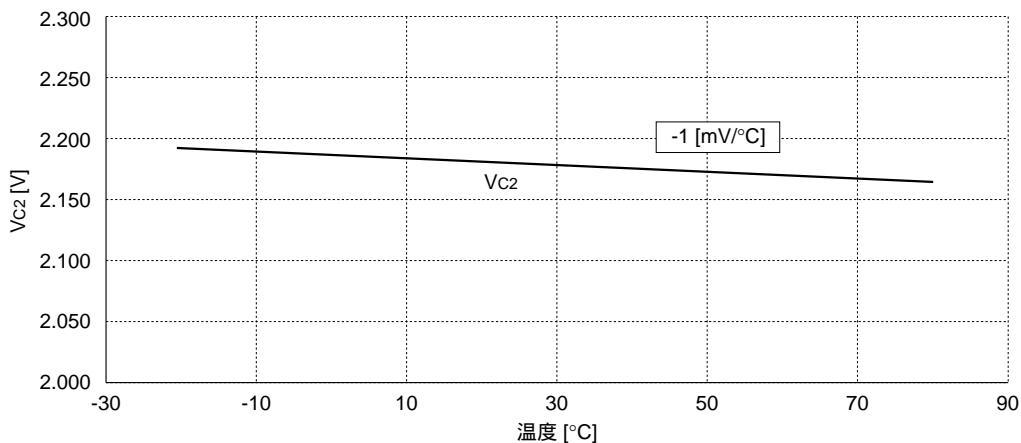

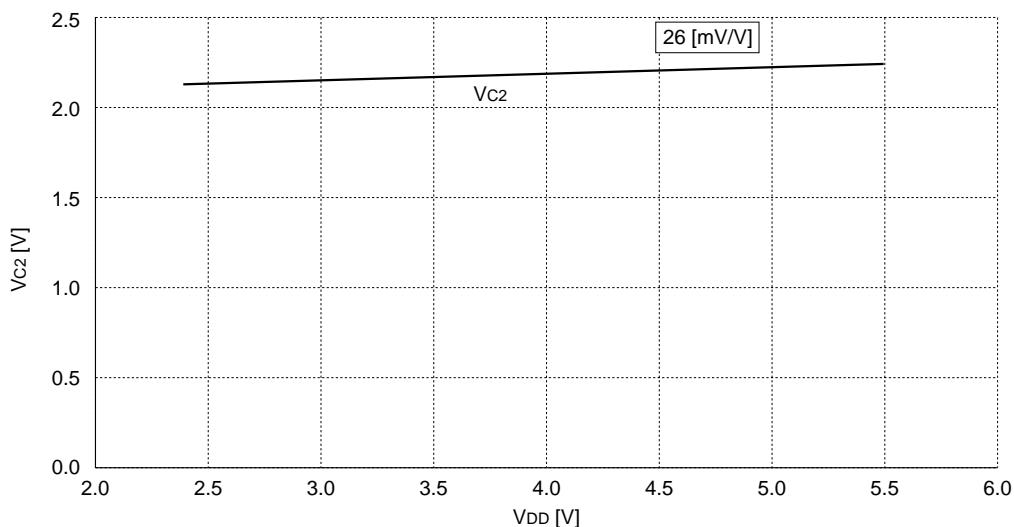

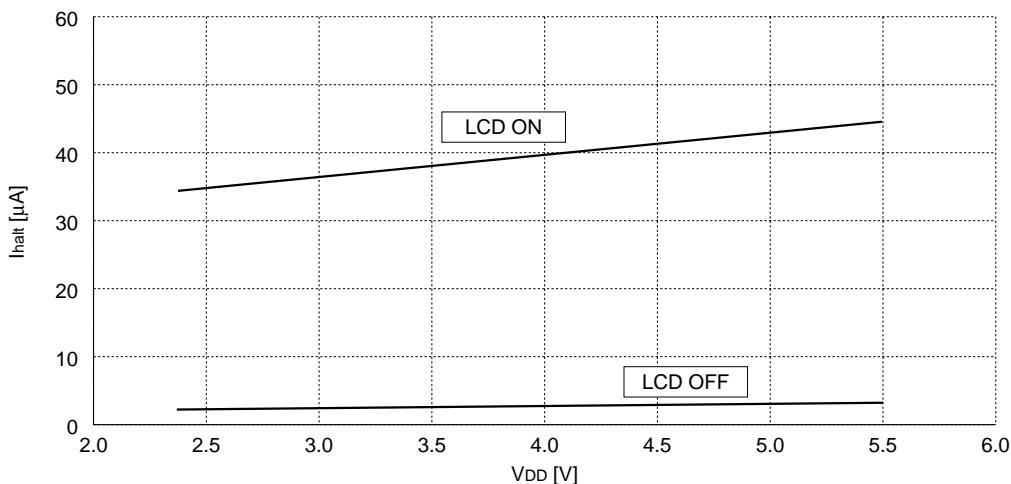

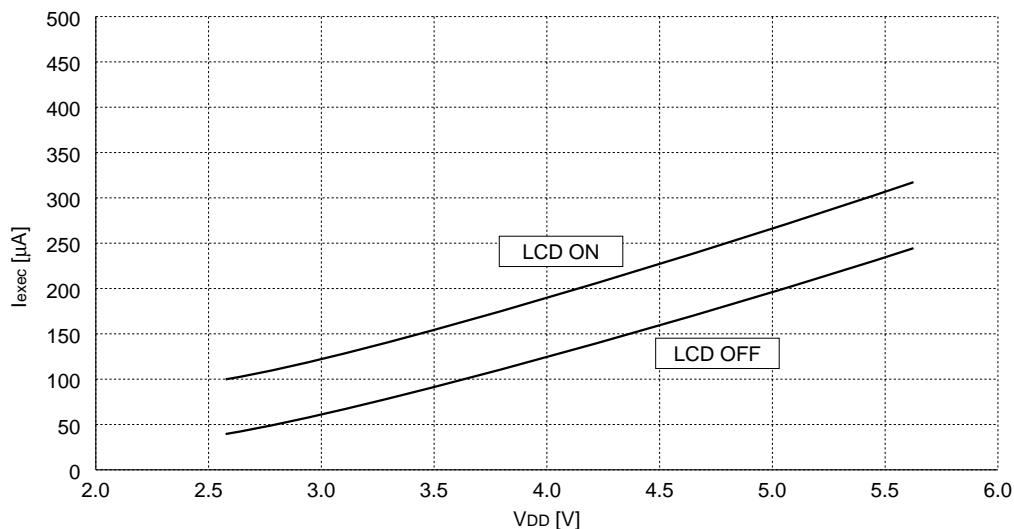

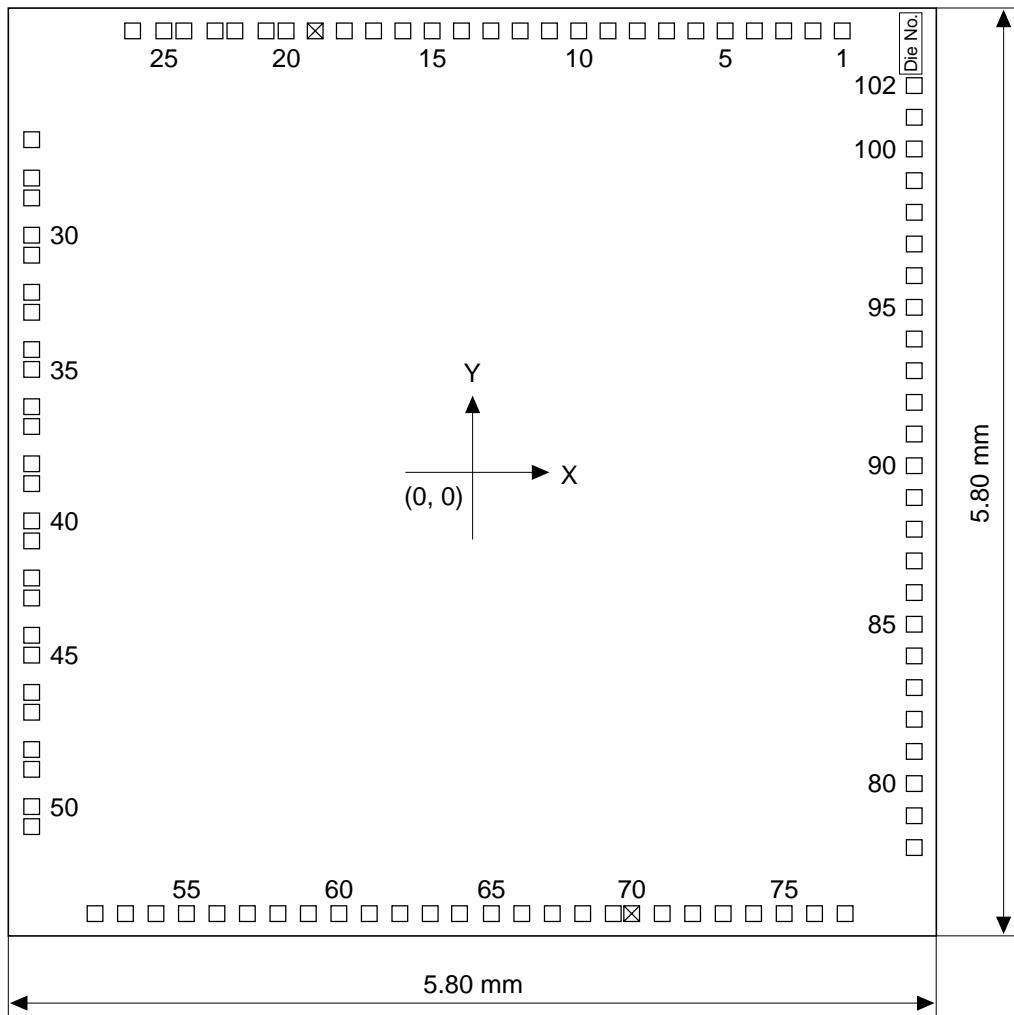

| 9.8 特性グラフ(参考値)        | 134 |

| 10 パッケージ              | 138 |

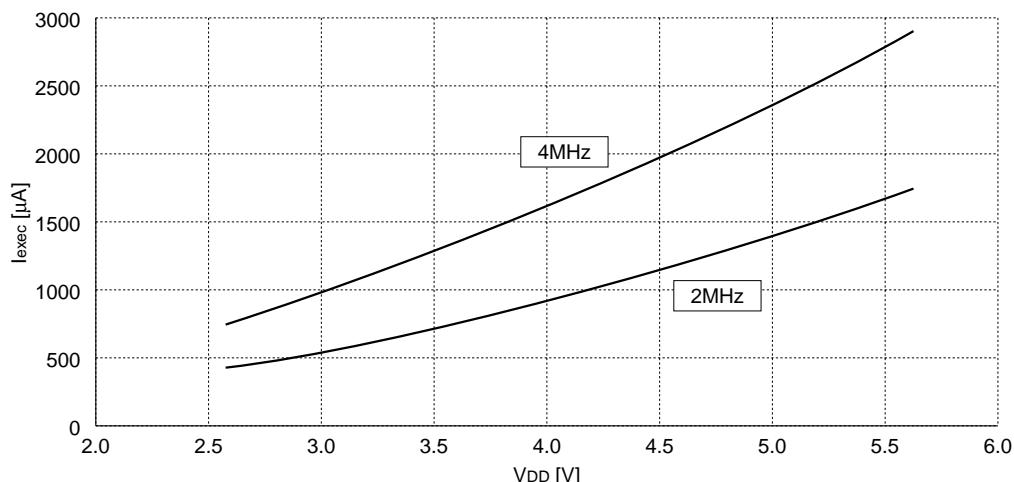

| 10.1 プラスチックパッケージ      | 138 |

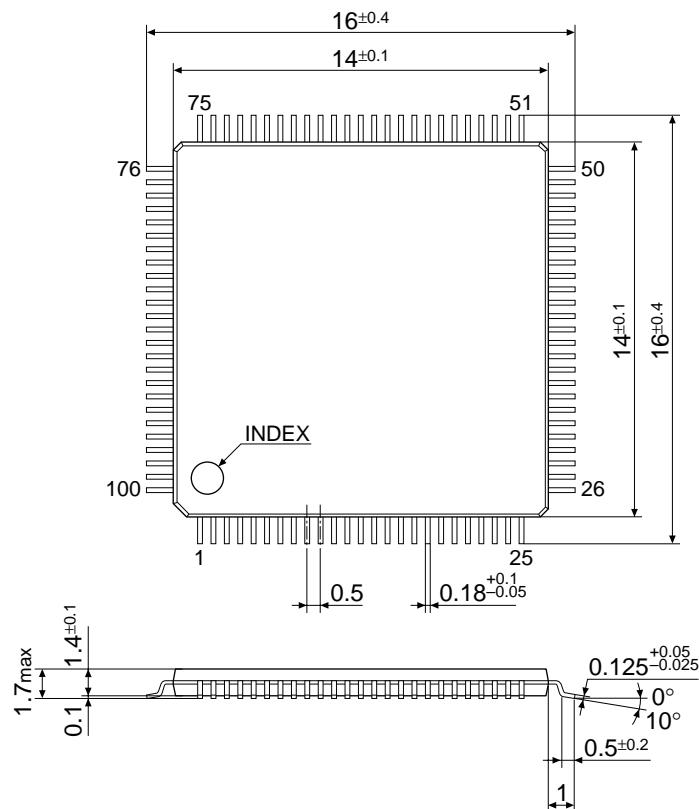

| 11 パッド配置              | 139 |

| 11.1 パッド配置図           | 139 |

| 11.2 パッド座標            | 140 |

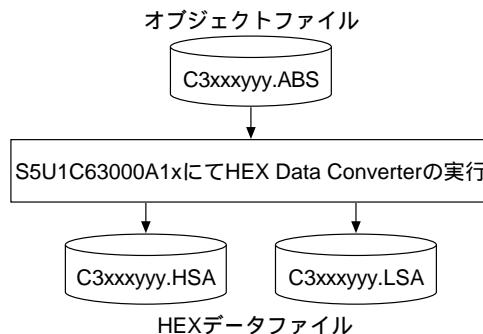

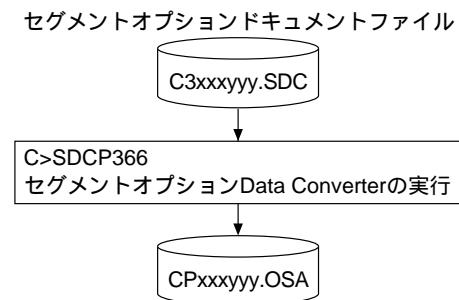

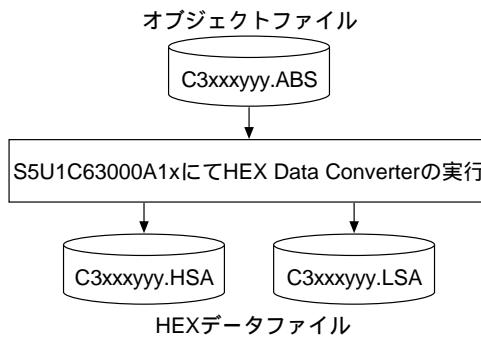

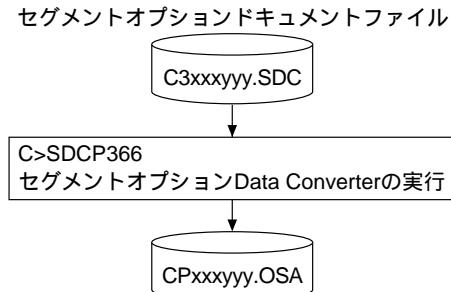

## Appendix A PROMプログラミング 141

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| A.1 書き込みツールの概要 .....                                              | 141 |

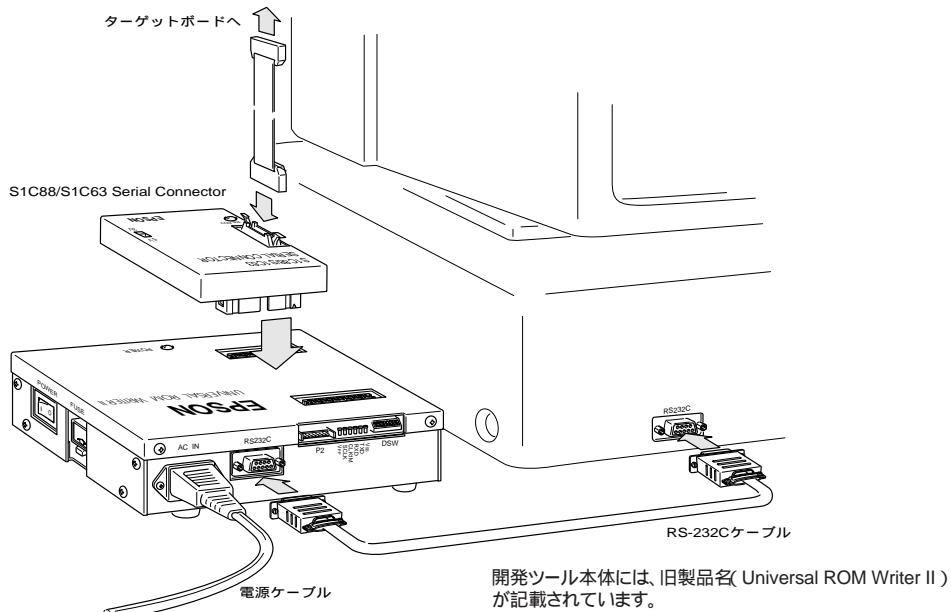

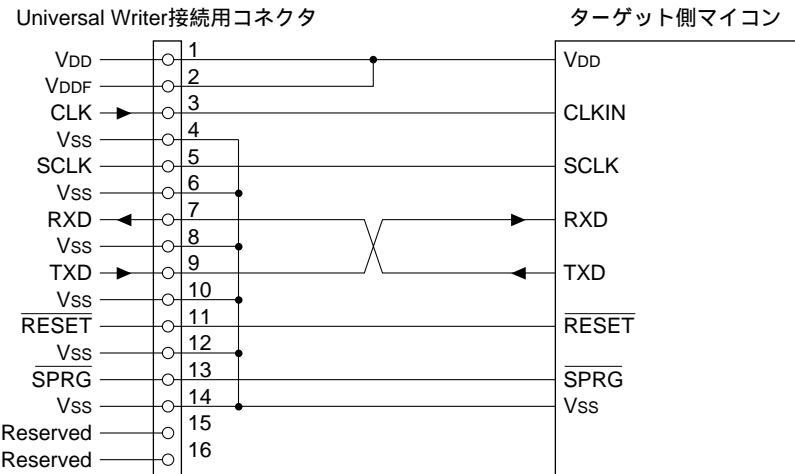

| A.2 シリアルプログラミング( S1C88/S1C63 Serial Connector ).....              | 142 |

| A.2.1 シリアルプログラミングシステム環境( S1C88/S1C63 Serial Connector ) .....     | 142 |

| A.2.2 シリアルプログラミングシステムの接続と設定( S1C88/S1C63 Serial Connector ) ..... | 144 |

| A.2.3 シリアルプログラミング手順( S1C88/S1C63 Serial Connector ) .....         | 145 |

| A.2.4 シリアルプログラミング結線図( S1C88/S1C63 Serial Connector ) .....        | 147 |

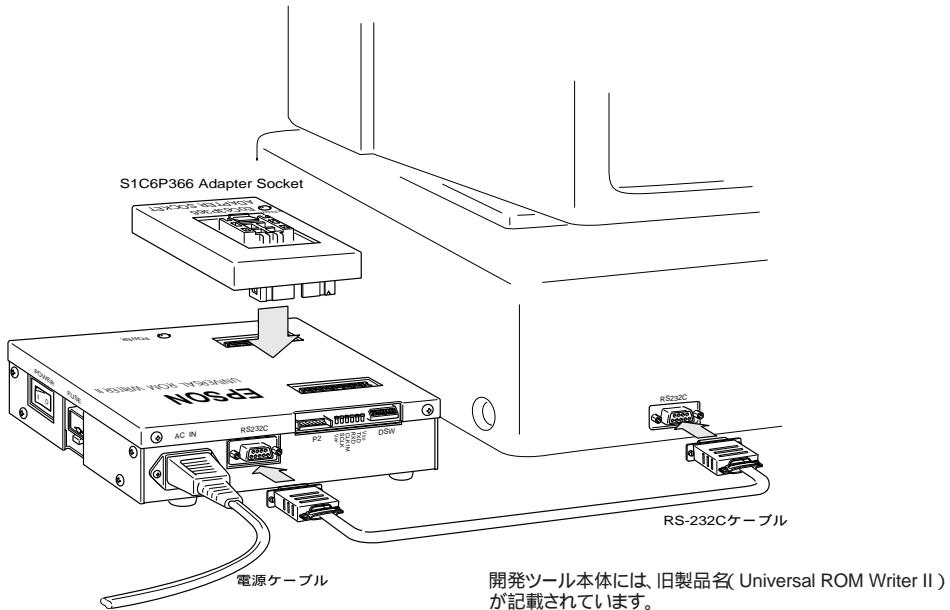

| A.3 パラレルプログラミング .....                                             | 149 |

| A.3.1 パラレルプログラミングシステム環境 .....                                     | 149 |

| A.3.2 パラレルプログラミングシステムの接続と設定 .....                                 | 151 |

| A.3.3 パラレルプログラミング手順 .....                                         | 152 |

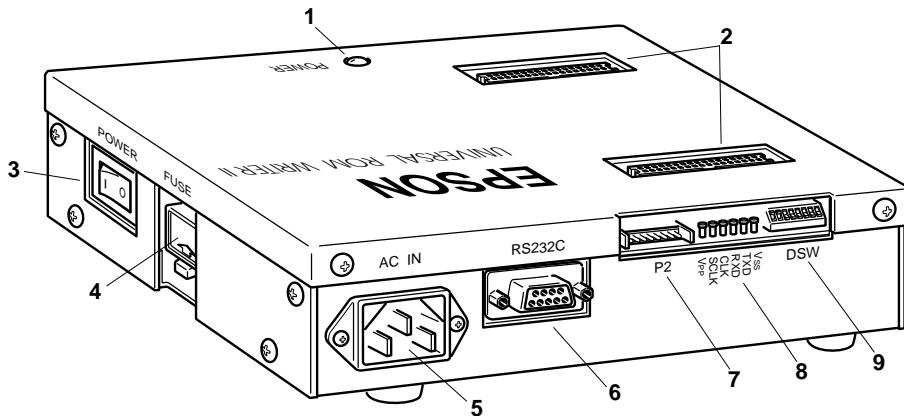

| A.4 Universal ROM Writer I( S5U1C88000W1 )仕様 .....                | 155 |

| A.4.1 Universal ROM Writer II仕様概要 .....                           | 155 |

| A.4.2 Universal ROM Writer IIコマンドの詳細説明 .....                      | 156 |

| A.4.3 PROMライタコマンド一覧表 .....                                        | 164 |

| A.4.4 Universal ROM Writer IIエラーメッセージ .....                       | 165 |

| A.5 Flash EEPROMプログラミング上の注意事項 .....                               | 166 |

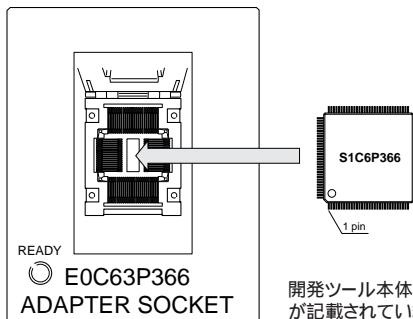

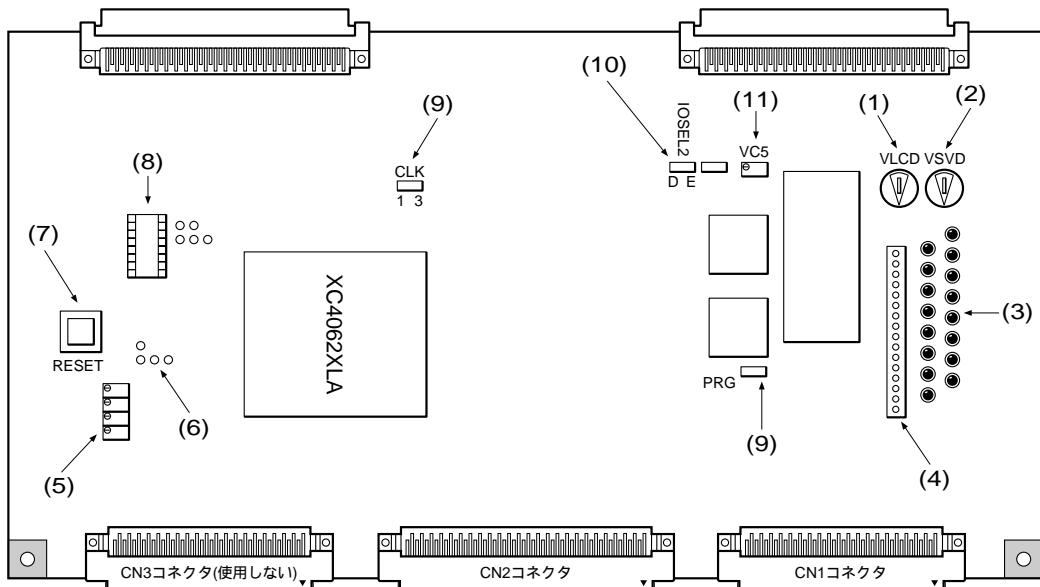

## Appendix B S5U1C63000P Manual

### ( Peripheral Circuit Board for S1C63158/358/P366 ) 167

|                         |     |

|-------------------------|-----|

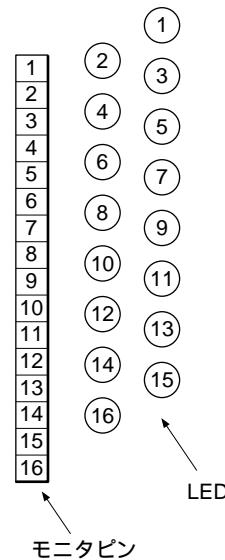

| B.1 各部の名称と機能 .....      | 167 |

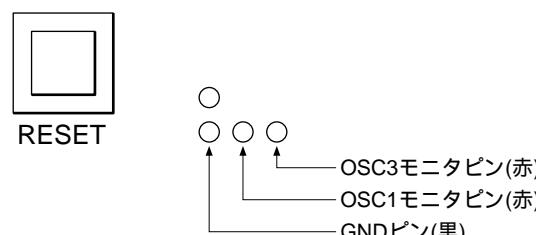

| B.2 ターゲットシステムとの接続 ..... | 170 |

| B.3 使用上の注意 .....        | 172 |

| B.3.1 操作上の注意事項 .....    | 172 |

| B.3.2 実ICとの相違点 .....    | 172 |

# 1 概要

---

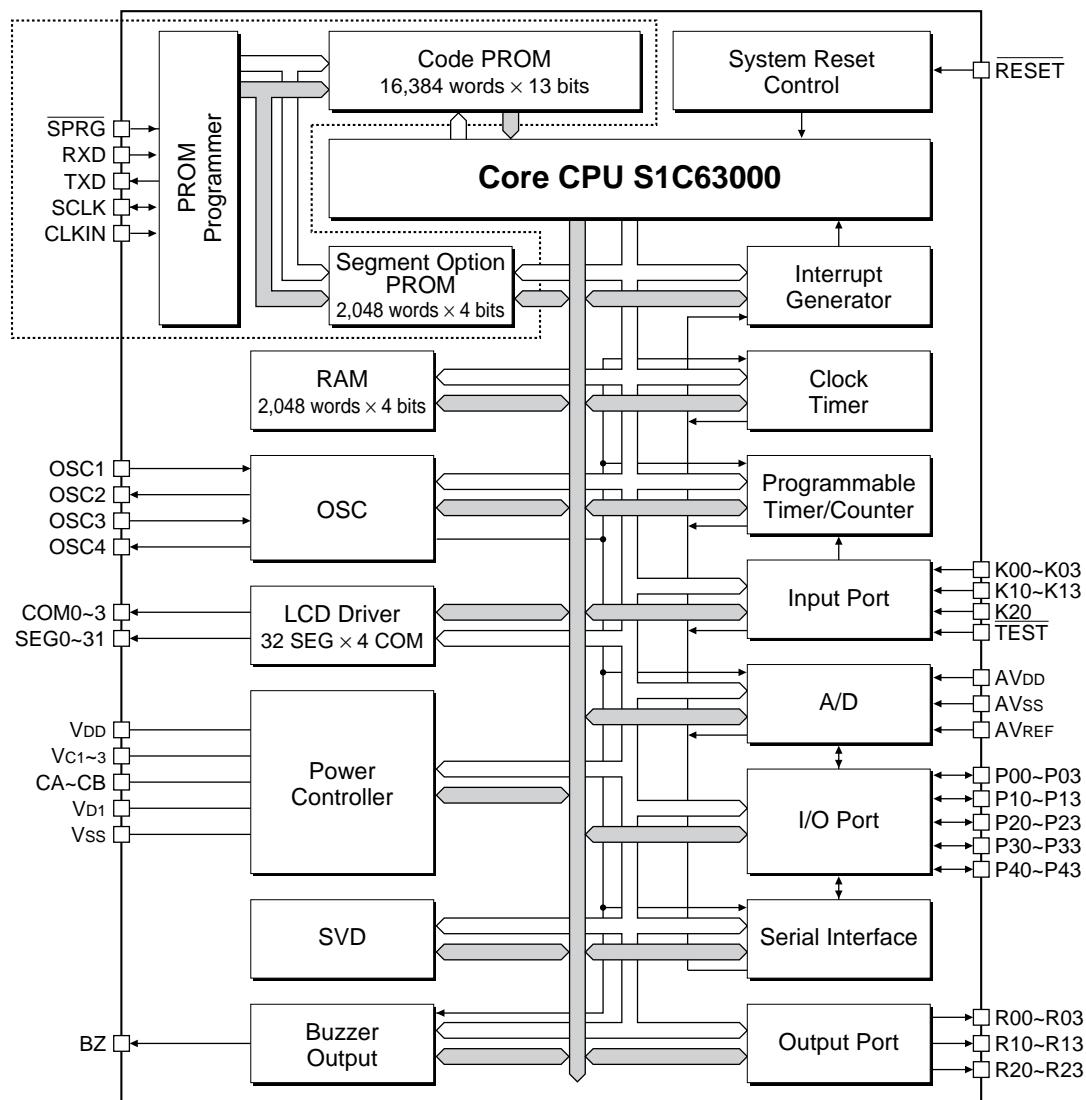

S1C6P366は4ビットCPU S1C63000を中心に、書き換え可能なPROM、RAM、シリアルインターフェース、ウォッチドッグタイマ、プログラマブルタイマ、タイムベースカウンタ(1系統)、SVD回路、最大32セグメント×4コモンのLCD駆動回路、A/D変換器、A/D変換器を使用して入力キーを識別可能な特殊入力ポート等を内蔵したマイクロコンピュータです。S1C63358およびS1C63158に対して上位互換性を持つ大容量のPROM(16K×13ビット)、RAM(2K×4ビット)を内蔵しており、プログラム開発等に使用することができます。

## 1.1 特長

|               |                                                                                                                                           |                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| OSC1発振回路      | 32.768kHz (Typ.)                                                                                                                          | 水晶発振回路                             |

| OSC3発振回路      | 1.8MHz (Typ.)                                                                                                                             | CR発振回路または4MHz (Max.) セラミック発振回路(*1) |

| インストラクションセット  | 基本命令 46種類 (全命令数 411種類)                                                                                                                    | アドレッシングモード 8種類                     |

| インストラクション実行時間 | 32.768kHz動作時: 61μsec (Min.)                                                                                                               |                                    |

|               | 4MHz動作時: 0.5μsec (Min.)                                                                                                                   |                                    |

| PROM容量        | コードPROM: 16,384ワード×13ビット                                                                                                                  |                                    |

|               | セグメントオプションPROM: 2,048ワード×4ビット                                                                                                             |                                    |

|               | プログラミング方式: パラレルおよびシリアル方式<br>(専用PROMライタを使用)                                                                                                |                                    |

|               | 書き換え回数: 100回                                                                                                                              |                                    |

| RAM容量         | データメモリ: 2,048ワード×4ビット                                                                                                                     |                                    |

|               | 表示メモリ: 32ワード×4ビット                                                                                                                         |                                    |

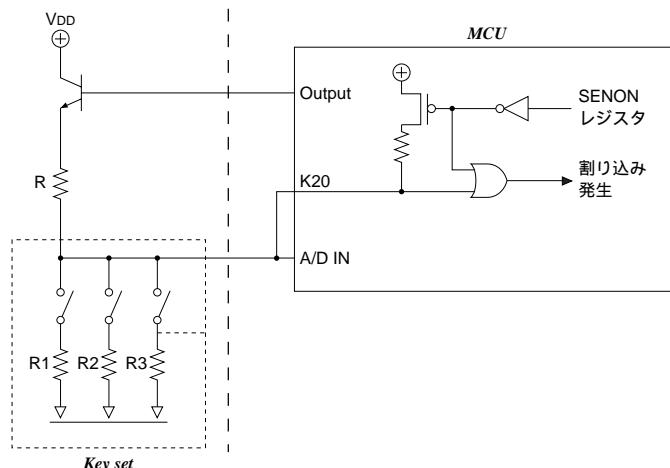

| 入力ポート         | 9ビット 8ビット (ブルアップ抵抗付き)<br>1ビット (A/D変換によるキーポジション検出割り込みを発生)                                                                                  |                                    |

| 出力ポート         | 12ビット (2ビットを特殊出力に切り替え可能*2)                                                                                                                |                                    |

| 入出力兼用ポート      | 20ビット (4ビットをシリアル入出力に切り替え可能*2)<br>(4ビットをA/D変換器入力に切り替え可能*2)                                                                                 |                                    |

| シリアルインターフェース  | 1ポート (クロック同期式8ビット)                                                                                                                        |                                    |

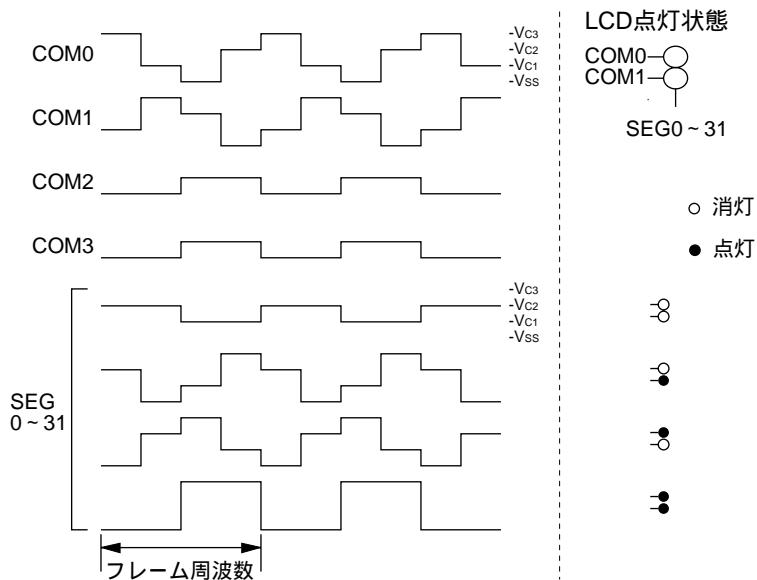

| LCDドライバ       | 32セグメント×4、3または2コモン(*2)                                                                                                                    | 1/3バイアス駆動                          |

| タイムベースカウンタ    | 1系統 (計時タイマ)                                                                                                                               |                                    |

| プログラマブルタイマ    | 内蔵 2チャンネル×8ビットまたは1チャンネル×16ビット(*2)<br>イベントカウンタ機能付き                                                                                         |                                    |

| ウォッチドッグタイマ    | 内蔵                                                                                                                                        |                                    |

| A/D変換器        | 分解能 8ビット<br>最大誤差: ±3LSB A/Dクロック: OSC1、OSC3 (2.7V ~ 5.5V)                                                                                  |                                    |

| ブザー出力         | ブザー周波数: 2kHzまたは4kHz (*2)                                                                                                                  | 2Hzインターバル出力(*2)                    |

| 電源電圧検出(SVD)回路 | 2値プログラマブル(2.7V、2.8V)                                                                                                                      |                                    |

| 外部割り込み        | 入力ポート割り込み<br>キー検出割り込み                                                                                                                     | 2系統<br>1系統                         |

| 内部割り込み        | 計時タイマ割り込み<br>プログラマブルタイマ割り込み<br>シリアルインターフェース割り込み<br>A/D変換器割り込み                                                                             | 4系統<br>2系統<br>1系統<br>1系統           |

| 電源電圧          | 2.7V ~ 5.5V                                                                                                                               |                                    |

| 動作温度範囲        | -20°C ~ 70°C                                                                                                                              |                                    |

| 消費電流(Typ.)    | シングルクロック: HALT時(32kHz) 3.0V(液晶電源OFF) 2.5μA<br>3.0V(液晶電源ON) 37μA<br>動作時(32kHz) 3.0V(液晶電源ON) 120μA<br>ツインクロック: 動作時(4MHz) 3.0V(液晶電源ON) 800μA |                                    |

| 出荷形態          | QFP15-100pin(プラスチック) またはチップ                                                                                                               |                                    |

\*1: マスクオプションにより選択

\*2: ソフトウェアにより選択

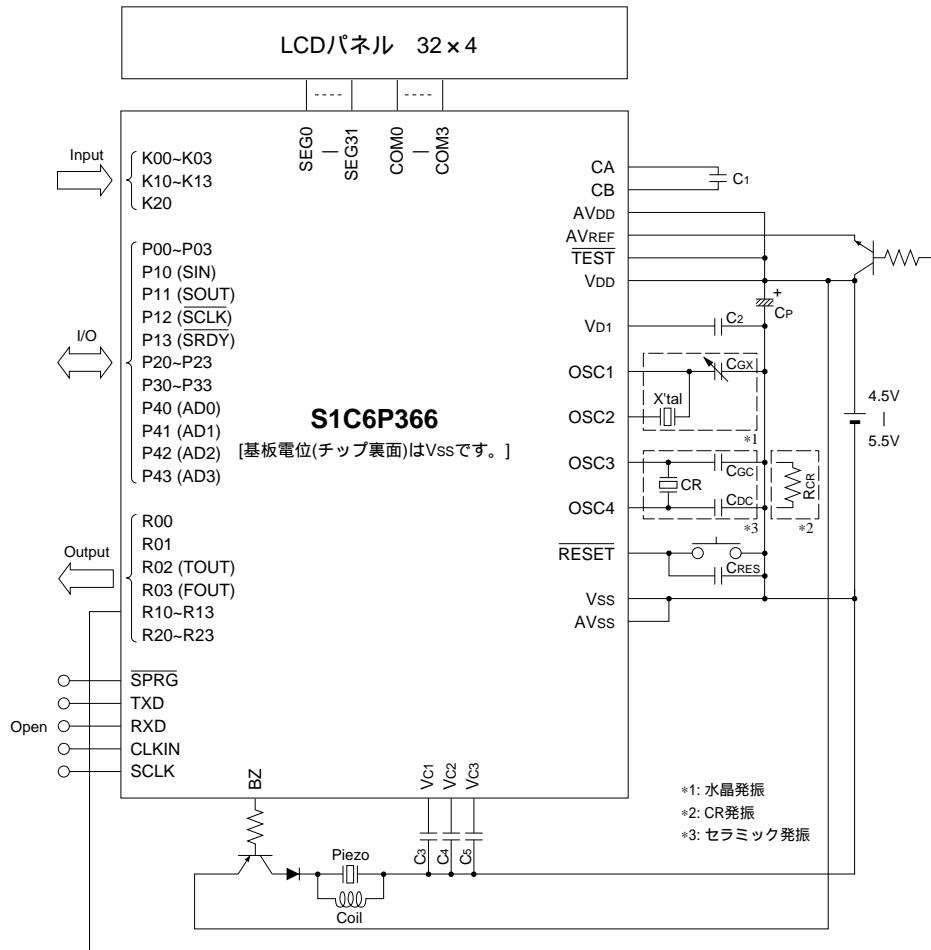

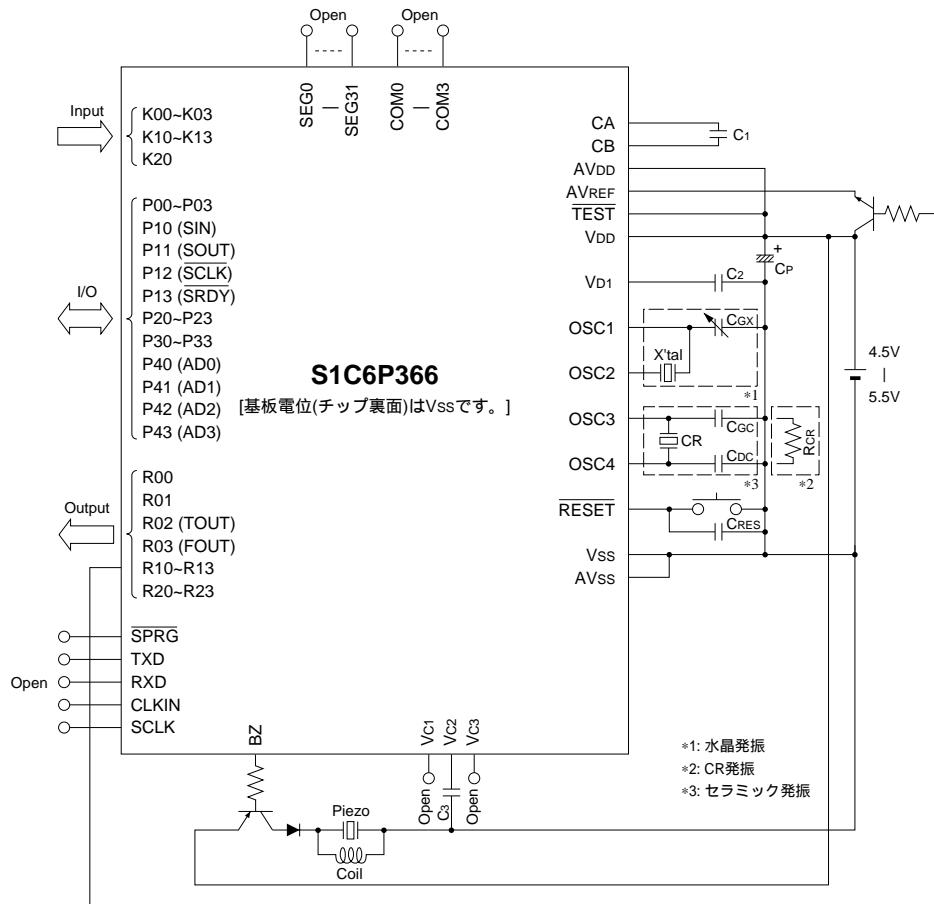

## 1.2 ブロック図

図1.2.1 ブロック図

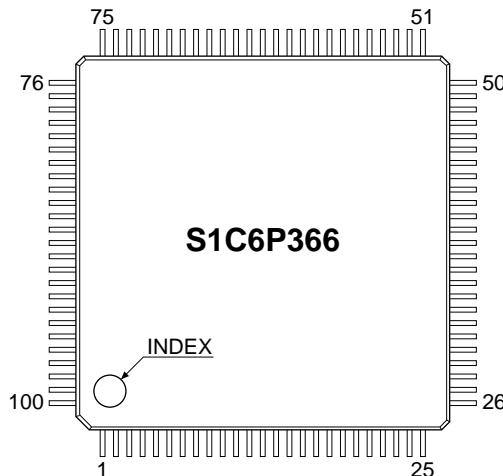

### 1.3 端子配置図

QFP15-100pin

| No. | 端子名      |          |

|-----|----------|----------|-----|----------|----------|-----|----------|----------|-----|----------|----------|

|     | S1C6P366 | S1C63358 |

| 1   | SEG7     | SEG7     | 26  | CLKIN    | N.C.     | 51  | SCLK     | N.C.     | 76  | R13      | R13      |

| 2   | SEG8     | SEG8     | 27  | SPRG     | N.C.     | 52  | P43      | P43      | 77  | R12      | R12      |

| 3   | SEG9     | SEG9     | 28  | COM0     | COM0     | 53  | P42      | P42      | 78  | R11      | R11      |

| 4   | SEG10    | SEG10    | 29  | COM1     | COM1     | 54  | P41      | P41      | 79  | R10      | R10      |

| 5   | SEG11    | SEG11    | 30  | COM2     | COM2     | 55  | P40      | P40      | 80  | R03      | R03      |

| 6   | SEG12    | SEG12    | 31  | COM3     | COM3     | 56  | P33      | P33      | 81  | R02      | R02      |

| 7   | SEG13    | SEG13    | 32  | CB       | CB       | 57  | P32      | P32      | 82  | R01      | R01      |

| 8   | SEG14    | SEG14    | 33  | CA       | CA       | 58  | P31      | P31      | 83  | R00      | R00      |

| 9   | SEG15    | SEG15    | 34  | Vc3      | Vc3      | 59  | P30      | P30      | 84  | BZ       | BZ       |

| 10  | SEG16    | SEG16    | 35  | Vc2      | Vc2      | 60  | P23      | P23      | 85  | K00      | K00      |

| 11  | SEG17    | SEG17    | 36  | Vc1      | Vc1      | 61  | P22      | P22      | 86  | K01      | K01      |

| 12  | SEG18    | SEG18    | 37  | Vss      | Vss      | 62  | P21      | P21      | 87  | K02      | K02      |

| 13  | SEG19    | SEG19    | 38  | OSC1     | OSC1     | 63  | P20      | P20      | 88  | K03      | K03      |

| 14  | SEG20    | SEG20    | 39  | OSC2     | OSC2     | 64  | P13      | P13      | 89  | K10      | K10      |

| 15  | SEG21    | SEG21    | 40  | Vd1      | Vd1      | 65  | P12      | P12      | 90  | K11      | K11      |

| 16  | SEG22    | SEG22    | 41  | OSC3     | OSC3     | 66  | P11      | P11      | 91  | K12      | K12      |

| 17  | SEG23    | SEG23    | 42  | OSC4     | OSC4     | 67  | P10      | P10      | 92  | K13      | K13      |

| 18  | SEG24    | SEG24    | 43  | Vdd      | Vdd      | 68  | P03      | P03      | 93  | K20      | K20      |

| 19  | SEG25    | SEG25    | 44  | RESET    | RESET    | 69  | P02      | P02      | 94  | SEG0     | SEG0     |

| 20  | SEG26    | SEG26    | 45  | TEST     | TEST     | 70  | P01      | P01      | 95  | SEG1     | SEG1     |

| 21  | SEG27    | SEG27    | 46  | AVREF    | AVREF    | 71  | P00      | P00      | 96  | SEG2     | SEG2     |

| 22  | SEG28    | SEG28    | 47  | AVDD     | AVDD     | 72  | R23      | R23      | 97  | SEG3     | SEG3     |

| 23  | SEG29    | SEG29    | 48  | AVSS     | AVSS     | 73  | R22      | R22      | 98  | SEG4     | SEG4     |

| 24  | SEG30    | SEG30    | 49  | RXD      | N.C.     | 74  | R21      | R21      | 99  | SEG5     | SEG5     |

| 25  | SEG31    | SEG31    | 50  | TXD      | N.C.     | 75  | R20      | R20      | 100 | SEG6     | SEG6     |

N.C. : No Connection

図1.3.1 端子配置図

## 1.4 端子説明

表1.4.1 端子説明

| 端子名        | 端子No.        | 入出力 | 機能                                     |

|------------|--------------|-----|----------------------------------------|

| VDD        | 43           | -   | 電源(+)端子                                |

| Vss        | 37           | -   | 電源(-)端子                                |

| VD1        | 40           | -   | 発振系定電圧出力端子                             |

| VC1~VC3    | 36~34        | -   | LCD系電源端子 1/3バイアス                       |

| CA, CB     | 33, 32       | -   | LCD系昇降圧コンデンサ接続端子                       |

| OSC1       | 38           | I   | 水晶発振入力端子                               |

| OSC2       | 39           | O   | 水晶発振出力端子                               |

| OSC3       | 41           | I   | セラミックまたはCR発振入力端子(マスクオプション選択)           |

| OSC4       | 42           | O   | セラミックまたはCR発振出力端子(マスクオプション選択)           |

| K00~K03    | 85~88        | I   | 入力端子                                   |

| K10~K13    | 89~92        | I   | 入力端子                                   |

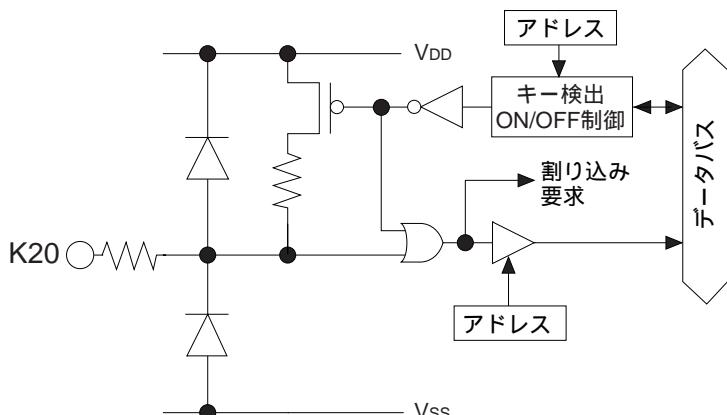

| K20        | 93           | I   | 入力端子(キーポジション検出割り込みポート)                 |

| P00~P03    | 71~68        | I/O | 入出力端子                                  |

| P10~P13    | 67~64        | I/O | 入出力端子(シリアルI/F入出力にソフト切り換え)              |

| P20~P23    | 63~60        | I/O | 入出力端子                                  |

| P30~P33    | 59~56        | I/O | 入出力端子                                  |

| P40~P43    | 55~52        | I/O | 入出力端子(A/D変換器入力として使用可能)                 |

| R00        | 83           | O   | 出力端子                                   |

| R01        | 82           | O   | 出力端子                                   |

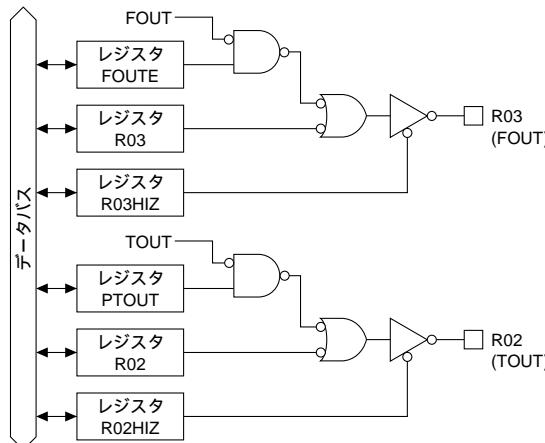

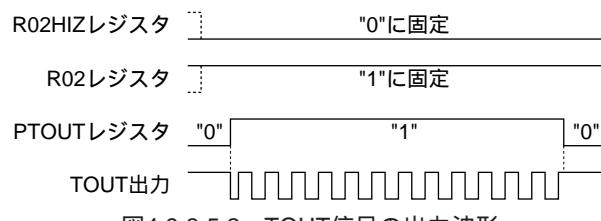

| R02        | 81           | O   | 出力端子(TOUT信号出力にソフト切り換え)                 |

| R03        | 80           | O   | 出力端子(FOUT信号出力にソフト切り換え)                 |

| R10~R13    | 79~76        | O   | 出力端子                                   |

| R20~R23    | 75~72        | O   | 出力端子                                   |

| COM0~COM3  | 28~31        | O   | LCDコモン出力端子(1/4, 1/3, 1/2デューティをソフト切り換え) |

| SEG0~SEG31 | 94~100, 1~25 | O   | LCDセグメント出力端子                           |

| AVDD       | 47           | -   | アナログ回路系電源(+)端子                         |

| AVss       | 48           | -   | アナログ回路系電源(-)端子                         |

| AVREF      | 46           | -   | アナログ回路系基準電圧端子                          |

| BZ         | 84           | O   | ブザー出力端子                                |

| RESET      | 44           | I   | イニシャルリセット入力端子                          |

| TEST       | 45           | I   | テスト用入力端子                               |

| RXD *1     | 49           | I   | Flashプログラミング用シリアルインターフェース・データ入力端子      |

| TXD *1     | 50           | O   | Flashプログラミング用シリアルインターフェース・データ出力端子      |

| SCLK *1    | 51           | I/O | Flashプログラミング用シリアルインターフェース・クロック入出力端子    |

| CLKIN *1   | 26           | I   | Flashプログラミング用クロック入力端子                  |

| SPRG *1    | 27           | I   | Flashプログラミング用制御端子                      |

\*1 S1C63358の場合N.C.

Flashプログラミング用の端子については"5 PROMプログラマと動作モード"を参照してください。

## 1.5 マスクオプション

S1C6P366には以下に示すマスクオプションが設定されています。

## S1C6P366のマスクオプション

### (1) OSC3発振回路

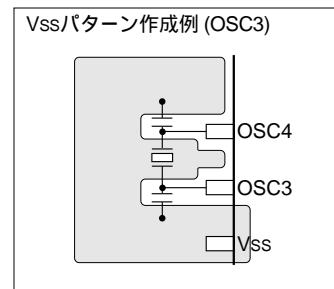

OSC3発振回路としてCR発振回路またはセラミック発振回路が選択できます。詳細については“4.3.3 OSC3発振回路”を参照してください。

S1C63358/63158に用意されているその他のマスクオプションは、以下のように固定され選択することはできません。

- ・ OSC1発振回路 ..... 水晶発振

- ・ キー同時入力リセット ..... 使用しない

- ・ キー同時入力リセット時間検定 ..... 使用しない

- ・ 入力ポートプルアップ抵抗 ..... あり

- ・ 出力ポート出力仕様 ..... コンプリメンタリ

- ・ 入出力兼用ポート出力仕様 ..... コンプリメンタリ

- ・ 入出力兼用ポートプルアップ抵抗 P1x, P2x, P3x ..... あり

P4x ..... なし

- ・ LCD駆動バイアス ..... 1/3バイアス

- ・ シリアルインターフェース入出力仕様 ..... 負極性

- ・ ブザー出力仕様 ..... 負極性

## 1.6 セグメントオプション

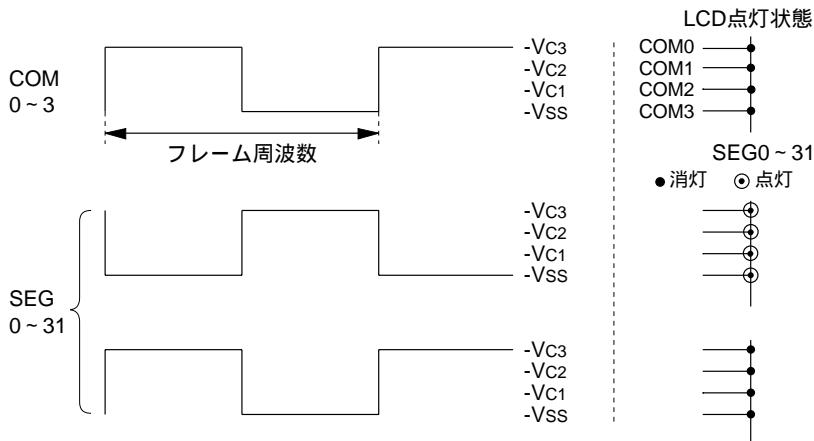

#### (1) LCDセグメントの割り付け

LCD表示メモリはデータメモリ空間上のアドレスF000H～F01FHの領域から最大128ビットまで選択できます。LCDドライバはセグメントデコーダを内蔵しており、表示メモリ領域の任意のアドレス(F000H～F01FH)データビット(D0～D3)を任意のセグメントに割り付けることができます。

この選択にはS1C63358の開発ソフトウェアツールとして用意されているセグメントオプションジェネレータSOG63358を使用します。

詳細については"4.7.4 ヤグメントオプション"を参照してください。

#### (2) LCDセグメントの出力仕様

DC出力として使用するSEG端子の設定が行えます。

詳細については"4.7.4 セグメントオプション"を参照してください。

### (3) セグメントオプションデータ

LCDセグメントオプションについてはS5U1C6P366Y1パッケージに推奨オプションデータが添付されています。LCDセグメントオプションを変更する場合はお客様の責任において書き換えを行ってください。

## 2 電源系およびイニシャルリセット

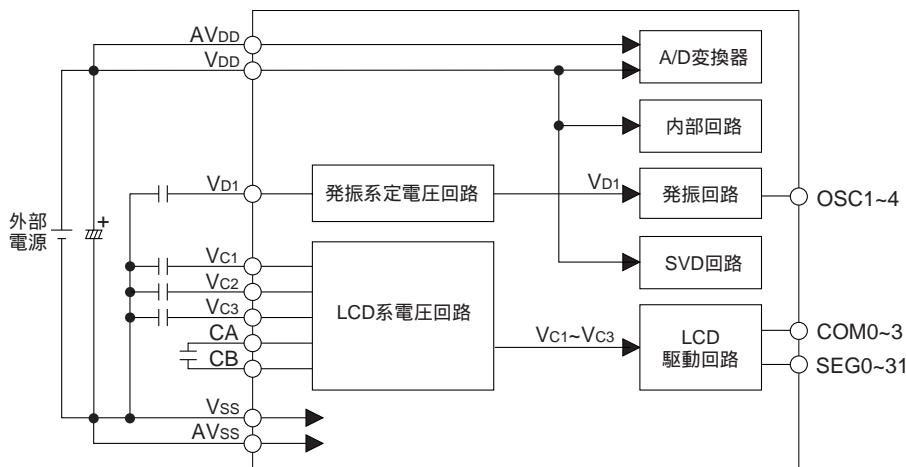

### 2.1 電源系

S1C6P366の動作電源電圧は次のとおりです。

2.7V ~ 5.5V

S1C6P366は上記範囲の単一電源をVDD/AVDD - Vss/AVss間に与えることにより動作し、内部に必要な電圧を、内蔵された以下の電源回路によりIC自身で発生します。

| 回路系      | 電源回路                                                 | 出力電圧                                |

|----------|------------------------------------------------------|-------------------------------------|

| 発振回路     | 発振系定電圧回路                                             | V <sub>D1</sub>                     |

| 内部ロジック回路 | 電源電圧(V <sub>DD</sub> )                               | V <sub>DD</sub>                     |

| LCD駆動回路  | LCD系電圧回路                                             | V <sub>C1</sub> ~ V <sub>C3</sub>   |

| 発振系定電圧回路 | 電源電圧(V <sub>DD</sub> )                               | V <sub>DD</sub>                     |

| LCD系電圧回路 | 電源電圧(V <sub>DD</sub> )                               | V <sub>DD</sub>                     |

| A/D変換器   | アナログ電源電圧(AV <sub>DD</sub> )および電源電圧(V <sub>DD</sub> ) | AV <sub>DD</sub> およびV <sub>DD</sub> |

- 注:

- 内部電源回路の出力電圧による外付け負荷の駆動は禁止します。

- S1C6P366は内部LCD系電圧回路 1/3バイアス を使用します。

- 電圧値、駆動能力については"9 電気的特性"を参照してください。

図2.1.1 電源系の構成

### 2.1.1 発振回路用電圧<VD1>

VD1は発振回路用の電圧で、発振を安定させるため発振系定電圧回路で発生しています。

S1C63358/S1C63158では、発振回路の仕様および動作周波数に対応させるため、定電圧回路で発生するVD1の出力電圧を切り換える必要がありますが、S1C6P366ではVD1出力電圧が1レベルのみの設定となっています。このため、S1C6P366では、ソフトウェアによりVD1出力電圧の設定を変更しても、実際のVD1出力には影響を与えません。ただし、S1C6P366をS1C63358/S1C63158の開発ツールとして使用する場合は、それぞれのICに合わせVD1の制御ルーチンを組み込んでおくことが必要です。

詳細については、"6 マスクROM版との相違点"を参照してください。

### 2.1.2 LCD駆動用電圧<VC1～VC3>

VC1～VC3はLCD駆動用の電圧で、表示品質を安定させるためLCD系電圧回路で発生しています。

S1C6P366の動作下限電圧は2.7Vであるため、VC2基準でLCD駆動電圧を内部発生し、その電圧を昇圧または降圧して他の2電位を発生します( VC1 = 1/2·VC2, VC3 = 3/2·VC2 )。

VC1～VC3の電圧値については"9 電気的特性"を参照してください。

### 2.1.3 内部電源回路の動作モード

S1C6P366の発振系定電圧回路およびA/D変換器の電源回路は、VDDを電源電圧とする通常モードで動作します。

S1C63358/S1C63158には、低電圧動作を保証するための昇圧モード( VC2モード )が設けられており、使用的電源電圧によっては動作モードの切り換えが必要です。S1C6P366は電源電圧が2.7V以上のため、この切り換えは不要で、制御レジスタの設定は動作モードに影響を与えません。ただし、S1C6P366をS1C63358/S1C63158の開発ツールとして使用する場合は、それぞれのICに合わせ動作モードの制御ルーチンを組み込んでおくことが必要です。

詳細については、"6 マスクROM版との相違点"を参照してください。

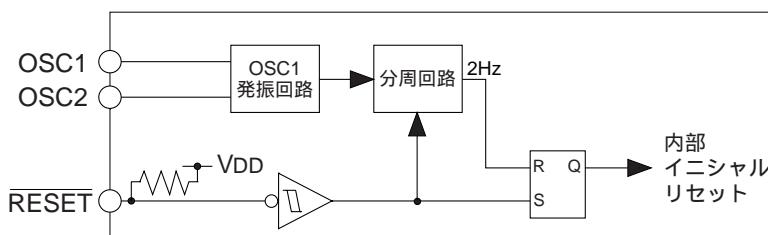

## 2.2 イニシャルリセット

S1C6P366は回路を初期化するためにイニシャルリセットを必要とします。S1C6P366のイニシャルリセット要因はリセット( RESET )端子による外部イニシャルリセットのみです。

電源投入時は必ずこのリセット機能を使用し、確実に初期化する必要があります。電源投入のみでは回路が正しく初期化される保証はありません。

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

### 2.2.1 リセット端子( RESET )

外部よりリセット端子をLOWレベル( V<sub>SS</sub> )にすることによりイニシャルリセットが行えます。

その後、リセット端子をHIGHレベル( V<sub>DD</sub> )にすることによりイニシャルリセットは解除され、CPUが動作を開始します。

リセット入力信号はRSラッチにより保持され、内部イニシャルリセット信号となります。RSラッチはOSC1クロックを分周した2Hz信号( HIGH )で解除されるようになっています。したがって、通常動作時はリセット端子がHIGHレベルになった後、内部イニシャルリセットが解除されるまで、最大250msec( fosc1=32.768kHz時 )の時間を要します。

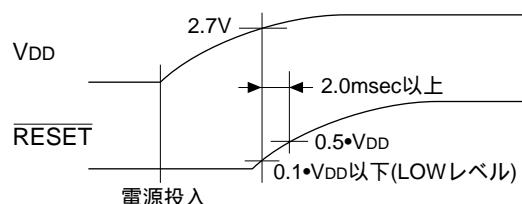

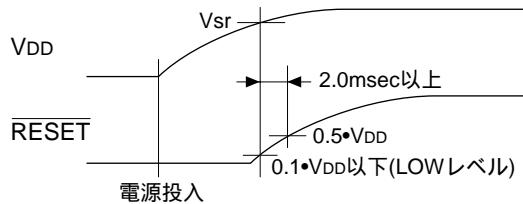

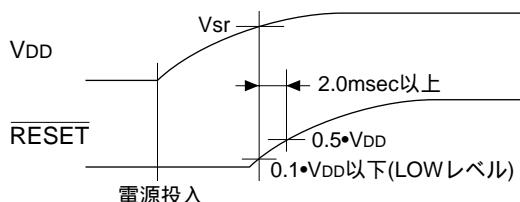

確実にイニシャルリセットを行うために、リセット入力は最低0.1msec以上、LOWレベルを保ってください。ただし、電源投入時については図2.2.1.1に示すタイミングでリセット端子をLOWレベルにしてください。

図2.2.1.1 電源投入時のイニシャルリセット

電源電圧が2.7V以上になるまで、リセット端子は0.1•V<sub>DD</sub>以下( LOWレベル )とします。

その後2.0msec以上、0.5•V<sub>DD</sub>以下のレベルを保持します。

また、S1C6P366ではリセット端子からのLOW入力信号によりIC内部の一部アナログ回路を初期化します。このとき、バイアス電流として十数μAの電流をIC内部で消費します。

### 2.2.2 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは表2.2.2.1のように初期化されます。

イニシャルリセットによって初期化されないレジスタ、フラグは必要に応じてプログラムで初期化する必要があります。

特にスタックポインタSP1およびSP2は必ずペアで設定してください。イニシャルリセット後は、SP1、SP2両方のスタックポインタがソフトウェアにより設定されるまでNMIを含むすべての割り込みがマスクされます。

EXTレジスタにデータを書き込むとEフラグがセットされ、次の命令が拡張アドレスシングモードで実行されます。そこに拡張アドレスシングが禁止されている命令を使用した場合、動作が保証されません。したがって、EXTレジスタの初期化のみを目的としたデータ書き込みは行わないでください。

拡張アドレスシングと使用可能な命令については"S1C63000コアCPUマニュアル"を参照してください。

表2.2.2.1 初期設定値

| CPUコア       |     |      |       | 周辺回路     |      |     |

|-------------|-----|------|-------|----------|------|-----|

| 名 称         | 記号  | ビット長 | 設定値   | 名 称      | ビット長 | 設定値 |

| データレジスタA    | A   | 4    | 不定    | RAM      | 4    | 不定  |

| データレジスタB    | B   | 4    | 不定    | 表示メモリ    | 4    | 不定  |

| 拡張レジスタEXT   | EXT | 8    | 不定    | その他の周辺回路 | -    | *   |

| インデックスレジスタX | X   | 16   | 不定    |          |      |     |

| インデックスレジスタY | Y   | 16   | 不定    |          |      |     |

| プログラムカウンタ   | PC  | 16   | 0110H |          |      |     |

| スタックポインタSP1 | SP1 | 8    | 不定    |          |      |     |

| スタックポインタSP2 | SP2 | 8    | 不定    |          |      |     |

| ゼロフラグ       | Z   | 1    | 不定    |          |      |     |

| キャリーフラグ     | C   | 1    | 不定    |          |      |     |

| インタラプトフラグ   | I   | 1    | 0     |          |      |     |

| 拡張フラグ       | E   | 1    | 0     |          |      |     |

| キューレジスタ     | Q   | 16   | 不定    |          |      |     |

\* "4.1 メモリマップ"参照

### 2.2.3 イニシャルリセット時の端子設定

S1C6P366の出力ポートR端子、入出力兼用ポートP端子は特殊出力端子やシリアルインターフェースの入出力端子およびA/D変換器の入力端子と兼用されており、それらの機能をソフトウェアで選択するようになっています。イニシャルリセット時、各端子はすべてが汎用出力ポート端子、汎用入出力兼用ポート端子として設定されますので、アプリケーションの初期化ルーチンでシステムに合った設定を行ってください。また、システム設計の際には、出力端子の初期状態にも注意してください。

表2.2.3.1に兼用端子設定の一覧を示します。

表2.2.3.1 兼用端子設定一覧

| 端子名     | イニシャルリセット時の<br>端子状態  | 特殊出力使用時 |      | シリアルI/F使用時 |         | A/D変換器<br>使用時 |

|---------|----------------------|---------|------|------------|---------|---------------|

|         |                      | TOUT    | FOUT | Master     | Slave   |               |

| R00     | R00 ( HIGH出力 )       |         |      |            |         |               |

| R01     | R01 ( HIGH出力 )       |         |      |            |         |               |

| R02     | R02 ( HIGH出力 )       | TOUT    |      |            |         |               |

| R03     | R03 ( HIGH出力 )       |         | FOUT |            |         |               |

| R10~R13 | R10~R13 ( HIGH出力 )   |         |      |            |         |               |

| R20~R23 | R20~R23 ( HIGH出力 )   |         |      |            |         |               |

| P00~P03 | P00~P03 ( 入力&ブルアップ ) |         |      |            |         |               |

| P10     | P10 ( 入力&ブルアップ )     |         |      | SIN(I)     | SIN(I)  |               |

| P11     | P11 ( 入力&ブルアップ )     |         |      | SOUT(O)    | SOUT(O) |               |

| P12     | P12 ( 入力&ブルアップ )     |         |      | SCLK(O)    | SCLK(I) |               |

| P13     | P13 ( 入力&ブルアップ )     |         |      |            | SRDY(O) |               |

| P20~P23 | P20~P23 ( 入力&ブルアップ ) |         |      |            |         |               |

| P30~P33 | P30~P33 ( 入力&ブルアップ ) |         |      |            |         |               |

| P40     | P40 ( 入力&ハイインピーダンス ) |         |      |            |         | AD0(I)        |

| P41     | P41 ( 入力&ハイインピーダンス ) |         |      |            |         | AD1(I)        |

| P42     | P42 ( 入力&ハイインピーダンス ) |         |      |            |         | AD2(I)        |

| P43     | P43 ( 入力&ハイインピーダンス ) |         |      |            |         | AD3(I)        |

機能の設定方法については各周辺回路の説明を参照してください。

### 2.3 テスト端子(TEST)

ICの出荷検査時に使用する端子です。通常動作時はTESTをVDDに接続してください。

### 2.4 Flash EEPROM専用端子

S1C6P366は、Flash EEPROMへの書き込みおよび出荷検査用に以下の専用端子を持っています。

- SPRG: Flash EEPROMプログラミング用制御端子

- SCLK: Flash EEPROMシリアルプログラミング用クロック入出力端子

- RXD: Flash EEPROMシリアルプログラミング用データ入力端子

- TXD: Flash EEPROMシリアルプログラミング用データ出力端子

- CLKIN: Flash EEPROM書き込み制御用クロック入力端子

上記Flash EEPROM専用端子の処理は動作モードにより異なります。詳細については、"5 PROMプログラマと動作モード"を参照してください。

## 3 CPU, PROM, RAM

### 3.1 CPU

S1C6P366はCPU部分に4ビットコアCPU S1C63000を使用しています。

S1C63000については"S1C63000コアCPUマニュアル"を参照してください。

注: S1C6P366においては、SLEEP動作を想定していないため、SLP命令は使用できません。

### 3.2 コードPROM

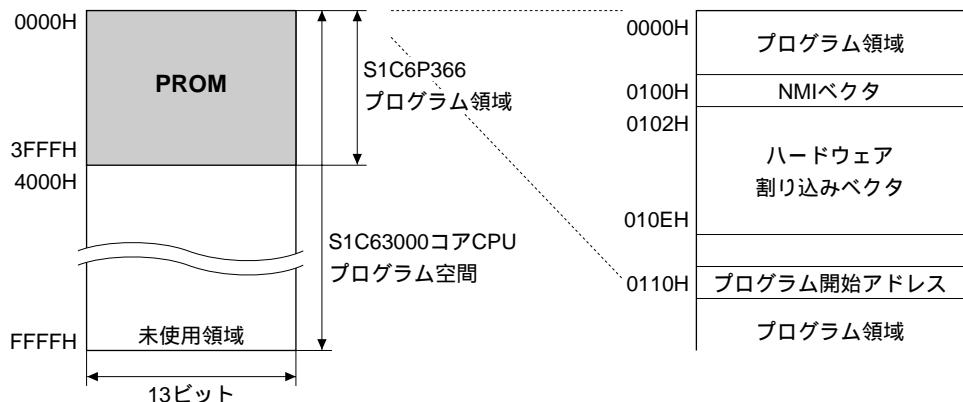

内蔵コードPROMはプログラム格納用のPROMで、16,384ステップ×13ビットの容量があります。コアCPUのプログラム領域は0000H～FFFFHステップまでリニアにアクセス可能ですが、S1C6P366では、このうち0000H～3FFFHステップがプログラム領域となります。イニシャルリセット後のプログラム開始番地が0110Hステップ、ノンマスク割り込み(NMI)ベクタが0100H、ハードウェア割り込みベクタが0102H～010EHステップに割り当てられています。

図3.2.1 コードPROMの構成

### 3.3 RAM

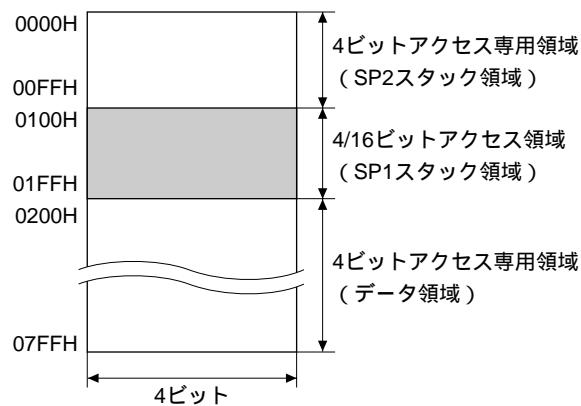

RAMは種々のデータを格納するデータメモリで、2,048ワード×4ビットの容量があります。

RAM領域は、データメモリマップ上のアドレス0000H～07FFHに割り当てられています。

この中でアドレス0100H～01FFHが4ビット/16ビットデータアクセスが可能な領域、その他の領域は4ビットデータアクセスのみ可能な領域となっています。

プログラミングの際には以下の点に注意してください。

(1)データメモリの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データ領域とスタック領域が重ならないように注意してください。

(2)S1C63000コアCPUは、4ビットデータ用スタックポインタ(SP2)および16ビットデータ用スタックポインタ(SP1)によりスタック処理を行います。SP1によるスタック処理では16ビットデータアクセスが行われますので、このスタック領域の設定は4ビット/16ビットアクセスが可能な領域内(0100H～01FFH)で行ってください。スタックポインタは、SP1が0000H～03FFH、SP2が0000H～00FFHの範囲でサイクリックに動作します。このため、SP1はS1C6P366の4ビット/16ビットアクセス領域を外れた00FFH以下の領域にも設定される可能性がありますので注意してください。SP1によるスタック操作以外のメモリアクセスは4ビットデータアクセスとなります。

また、イニシャルリセット時は、スタックポインタSP1、SP2の両方がソフトウェアで設定されるまでNMIを含むすべての割り込みがマスクされます。また、SP1、SP2を設定後どちらか一方を再設定すると、もう一方が再設定されるまでNMIを含む割り込みは再びマスクされます。したがって、SP1およびSP2の設定は必ずペアで行ってください。

(3) サブルーチンコールでは16ビットデータ用スタック(SP1)を4ワード(PCの退避)消費します。

割り込みでは16ビットデータ用スタックエリアを4ワード(PCの退避)4ビットデータ用スタックエリアを1ワード(Fレジスタの退避)消費します。

図3.3.1 データRAMの構成

## 4 周辺回路と動作

S1C6P366の周辺回路( タイマ、A/D、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

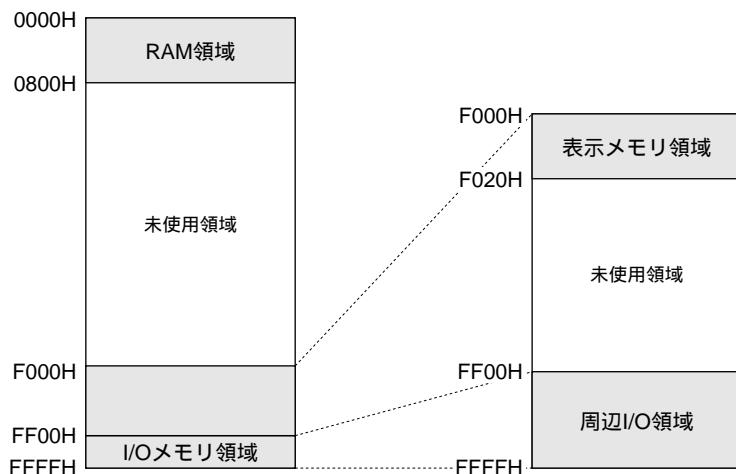

### 4.1 メモリマップ

S1C6P366のデータメモリは2,048ワードのRAM、32ワードの表示メモリ、76ワードの周辺I/Oメモリ領域で構成されます。

図4.1.1にS1C6P366の全体のメモリマップ、表4.1.1( a )~( f )に周辺回路( I/O空間 )のメモリマップを示します。

図4.1.1 メモリマップ

注：メモリマップの未使用領域にはメモリが実装されていません。また、周辺I/O領域にも非実装領域、未使用（アクセス禁止）領域が存在します。これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

周辺I/O領域については表4.1.1( a )~( f )に示すI/Oメモリマップを参照してください。

表4.1.1(a) I/Oメモリマップ(FF00H~FF28H)

| アドレス  | レジスタ   |       |       |       | 注釈                               |                          |                                      |                                                                                                                                   |

|-------|--------|-------|-------|-------|----------------------------------|--------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | D3     | D2    | D1    | D0    | Name                             | Init *1                  | 1                                    | 0                                                                                                                                 |

| FF00H | CLKCHG | OSCC  | 0     | VDC   | CLKCHG<br>OSCC<br>0 *3<br>VDC    | 0<br>0<br>-*2<br>0       | OSC3<br>On<br>(OSC3)                 | OSC1<br>Off<br>(OSC1)                                                                                                             |

|       | R/W    |       | R     | R/W   |                                  |                          |                                      | CPUクロック切り換え<br>OSC3発振On/Off<br>未使用<br>(動作電圧切り換え)                                                                                  |

| FF01H | VADSEL | VDSEL | 0     | DBON  | VADSEL<br>VDSEL<br>0 *3<br>DBON  | 0<br>0<br>-*2<br>0       | (Vc2)<br>(Vc2)<br>(On)               | (VDD)<br>(VDD)<br>(Off)                                                                                                           |

|       | R/W    |       | R     | R/W   |                                  |                          |                                      | (A/D変換器用電源選択)<br>(発振系定電圧回路用電源選択)<br>未使用<br>(昇圧回路On/Off)                                                                           |

| FF04H | SVDS3  | SVDS2 | SVDS1 | SVDS0 | SVDS3<br>SVDS2<br>SVDS1<br>SVDS0 | 0<br>0<br>0<br>0         |                                      | SVD比較電圧設定<br>[SVDS3~0] 0 1 2 3 4 5 6 7<br>電圧(V) - - - - - - - -<br>[SVDS3~0] 8 9 10 11 12 13 14 15<br>電圧(V) - - - - - - 2.70 2.80 |

|       | R/W    |       |       |       |                                  |                          |                                      |                                                                                                                                   |

| FF05H | 0      | 0     | SVDDT | SVDON | 0 *3<br>0 *3<br>SVDDT<br>SVDON   | -*2<br>-*2<br>0<br>0     | Low<br>Normal<br>On                  | 未使用<br>未使用<br>SVD検出データ<br>SVD回路On/Off                                                                                             |

|       | R      |       | R/W   |       |                                  |                          |                                      |                                                                                                                                   |

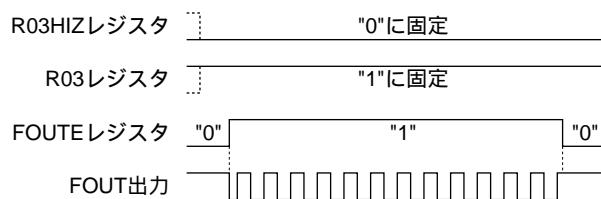

| FF06H | FOUTE  | 0     | FOFQ1 | FOFQ0 | FOUTE<br>0 *3<br>FOFQ1<br>FOFQ0  | 0<br>-*2<br>0<br>0       | Enable                               | Disable                                                                                                                           |

|       | R/W    | R     | R/W   |       |                                  |                          |                                      | FOUT出力イネーブル<br>未使用<br>[FOUT [FOFQ1, 0] 0 1 2 3<br>周波数選択 周波数 fosc1/64 fosc1/8 fosc1 fosc3                                          |

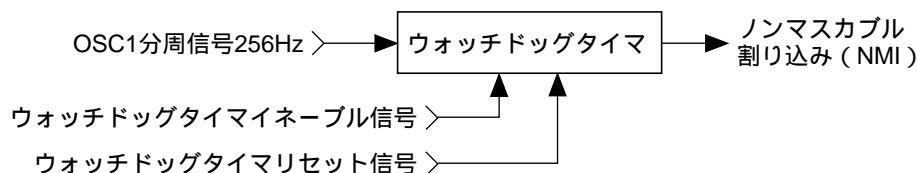

| FF07H | 0      | 0     | WDEN  | WDRST | 0 *3<br>0 *3<br>WDEN<br>WDRST *3 | -*2<br>-*2<br>1<br>Reset | Enable<br>Disable<br>Reset           | 未使用<br>未使用<br>ウォッチドッグタイマイネーブル<br>ウォッチドッグタイマリセット(書き込み時)                                                                            |

|       | R      |       | R/W   | W     |                                  |                          |                                      |                                                                                                                                   |

| FF20H | SIK03  | SIK02 | SIK01 | SIK00 | SIK03<br>SIK02<br>SIK01<br>SIK00 | 0<br>0<br>0<br>0         | Enable<br>Enable<br>Enable<br>Enable | Disable<br>Disable<br>Disable<br>Disable                                                                                          |

|       | R/W    |       |       |       |                                  |                          |                                      | K00~K03割り込み選択レジスタ                                                                                                                 |

| FF21H | K03    | K02   | K01   | K00   | K03<br>K02<br>K01<br>K00         | -*2<br>-*2<br>-*2<br>-*2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low                                                                                                          |

|       | R      |       |       |       |                                  |                          |                                      | K00~K03入力ポートデータ                                                                                                                   |

| FF22H | KCP03  | KCP02 | KCP01 | KCP00 | KCP03<br>KCP02<br>KCP01<br>KCP00 | 1<br>1<br>1<br>1         | ↓<br>↓<br>↓<br>↓                     | ↑<br>↑<br>↑<br>↑                                                                                                                  |

|       | R/W    |       |       |       |                                  |                          |                                      | K00~K03入力比較レジスタ                                                                                                                   |

| FF24H | SIK13  | SIK12 | SIK11 | SIK10 | SIK13<br>SIK12<br>SIK11<br>SIK10 | 0<br>0<br>0<br>0         | Enable<br>Enable<br>Enable<br>Enable | Disable<br>Disable<br>Disable<br>Disable                                                                                          |

|       | R/W    |       |       |       |                                  |                          |                                      | K10~K13割り込み選択レジスタ                                                                                                                 |

| FF25H | K13    | K12   | K11   | K10   | K13<br>K12<br>K11<br>K10         | -*2<br>-*2<br>-*2<br>-*2 | High<br>High<br>High<br>High         | Low<br>Low<br>Low<br>Low                                                                                                          |

|       | R      |       |       |       |                                  |                          |                                      | K10~K13入力ポートデータ                                                                                                                   |

| FF26H | KCP13  | KCP12 | KCP11 | KCP10 | KCP13<br>KCP12<br>KCP11<br>KCP10 | 1<br>1<br>1<br>1         | ↓<br>↓<br>↓<br>↓                     | ↑<br>↑<br>↑<br>↑                                                                                                                  |

|       | R/W    |       |       |       |                                  |                          |                                      | K10~K13入力比較レジスタ                                                                                                                   |

| FF28H | 0      | 0     | 0     | SIK20 | 0 *3<br>0 *3<br>0 *3<br>SIK20    | -*2<br>-*2<br>-*2<br>0   | Enable<br>Disable                    | 未使用<br>未使用<br>未使用<br>K20割り込み選択レジスタ                                                                                                |

|       | R      |       | R/W   |       |                                  |                          |                                      |                                                                                                                                   |

## [ 注釈 ]

\*1 イニシャルリセット時の初期値

\*2 回路上設定されない

\*3 読み出し時は常時"0"

表4.1.1(b) I/Oメモリマップ( FF29H ~ FF44H )

| アドレス  | レジスタ   |        |        |        | Name   | Init *1 | 1      | 0      | 注釈                                  |  |

|-------|--------|--------|--------|--------|--------|---------|--------|--------|-------------------------------------|--|

|       | D3     | D2     | D1     | D0     |        |         |        |        |                                     |  |

| FF29H | 0      | 0      | 0      | K20    | 0 *3   | - *2    | High   | Low    | 未使用                                 |  |

|       | R      |        |        | K20    | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 1      | -       |        |        | K20入力ポートデータ                         |  |

| FF2AH | 0      | 0      | 0      | KCP20  | 0 *3   | - *2    | -      | -      | 未使用                                 |  |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | KCP20  | 1       |        |        | K20入力比較レジスタ                         |  |

| FF2BH | 0      | 0      | 0      | SENON  | 0 *3   | - *2    | On     | Off    | 未使用                                 |  |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | SENON  | 1       |        |        | キー検出On/Off制御                        |  |

| FF30H | R03HIZ | R02HIZ | R01HIZ | R00HIZ | R03HIZ | 0       | High-Z | Output | R03出力ハイインピーダンス制御( FOUTE=0 )         |  |

|       | R/W    |        |        | R/W    | R02HIZ | 0       | High-Z | Output | FOUT出力ハイインピーダンス制御( FOUTE=1 )        |  |

|       | R/W    |        |        |        | R01HIZ | 0       | High-Z | Output | R02出力ハイインピーダンス制御( PTOUT=0 )         |  |

|       | R/W    |        |        |        | R00HIZ | 0       | High-Z | Output | TOUT出力ハイインピーダンス制御( PTOUT=1 )        |  |

| FF31H | R03    | R02    | R01    | R00    | R03    | 1       | High   | Low    | R03出力ポートデータ( FOUTE=0 ) FOUT出力時は1に固定 |  |

|       | R/W    |        |        | R/W    | R02    | 1       | High   | Low    | R02出力ポートデータ( PTOUT=0 ) TOUT出力時は1に固定 |  |

|       | R/W    |        |        |        | R01    | 1       | High   | Low    | R01出力ポートデータ                         |  |

|       | R/W    |        |        |        | R00    | 1       | High   | Low    | R00出力ポートデータ                         |  |

| FF32H | 0      | 0      | 0      | R1HIZ  | 0 *3   | - *2    | High-Z | Output | 未使用                                 |  |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | R1HIZ  | 0       | High-Z | Output | R1出力ハイインピーダンス制御                     |  |

| FF33H | R13    | R12    | R11    | R10    | R13    | 1       | High   | Low    | R10 ~ R13出力ポートデータ                   |  |

|       | R/W    |        |        | R/W    | R12    | 1       | High   | Low    |                                     |  |

|       | R/W    |        |        |        | R11    | 1       | High   | Low    |                                     |  |

|       | R/W    |        |        |        | R10    | 1       | High   | Low    |                                     |  |

| FF34H | 0      | 0      | 0      | R2HIZ  | 0 *3   | - *2    | High-Z | Output | 未使用                                 |  |

|       | R      |        |        | R/W    | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | 0 *3   | - *2    |        |        | 未使用                                 |  |

|       | R/W    |        |        |        | R2HIZ  | 0       | High-Z | Output | R2出力ハイインピーダンス制御                     |  |

| FF35H | R23    | R22    | R21    | R20    | R23    | 1       | High   | Low    | R20 ~ R23出力ポートデータ                   |  |

|       | R/W    |        |        | R/W    | R22    | 1       | High   | Low    |                                     |  |

|       | R/W    |        |        |        | R21    | 1       | High   | Low    |                                     |  |

|       | R/W    |        |        |        | R20    | 1       | High   | Low    |                                     |  |

| FF40H | IOC03  | IOC02  | IOC01  | IOC00  | IOC03  | 0       | Output | Input  | P00 ~ P03 I/O制御レジスタ                 |  |

|       | R/W    |        |        | R/W    | IOC02  | 0       | Output | Input  |                                     |  |

|       | R/W    |        |        |        | IOC01  | 0       | Output | Input  |                                     |  |

|       | R/W    |        |        |        | IOC00  | 0       | Output | Input  |                                     |  |

| FF41H | PUL03  | PUL02  | PUL01  | PUL00  | PUL03  | 1       | On     | Off    | P00 ~ P03 ブルアップ制御レジスタ               |  |

|       | R/W    |        |        | R/W    | PUL02  | 1       | On     | Off    |                                     |  |

|       | R/W    |        |        |        | PUL01  | 1       | On     | Off    |                                     |  |

|       | R/W    |        |        |        | PUL00  | 1       | On     | Off    |                                     |  |

| FF42H | P03    | P02    | P01    | P00    | P03    | - *2    | High   | Low    | P00 ~ P03入出力兼用ポートデータ                |  |

|       | R/W    |        |        | R/W    | P02    | - *2    | High   | Low    |                                     |  |

|       | R/W    |        |        |        | P01    | - *2    | High   | Low    |                                     |  |

|       | R/W    |        |        |        | P00    | - *2    | High   | Low    |                                     |  |

| FF44H | IOC13  | IOC12  | IOC11  | IOC10  | IOC13  | 0       | Output | Input  | P13 I/O制御レジスタ                       |  |

|       | R/W    |        |        | R/W    | IOC12  | 0       | Output | Input  | SIF(スレーブ)選択時、汎用レジスタとして機能            |  |

|       | R/W    |        |        |        | IOC11  | 0       | Output | Input  | P12 I/O制御レジスタ( ESIF=0 )             |  |

|       | R/W    |        |        |        | IOC10  | 0       | Output | Input  | SIF選択時、汎用レジスタとして機能                  |  |

表4.1.1(c) I/Oメモリマップ( FF45H ~ FF51H )

| アドレス  | レジスタ  |       |       |       | Name  | Init *1 | 1      | 0     | 注 釈                                                                               |

|-------|-------|-------|-------|-------|-------|---------|--------|-------|-----------------------------------------------------------------------------------|

|       | D3    | D2    | D1    | D0    |       |         |        |       |                                                                                   |

| FF45H | PUL13 | PUL12 | PUL11 | PUL10 | PUL13 | 1       | On     | Off   | P13ブルアップ制御レジスタ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                                        |

|       |       |       |       |       | PUL12 | 1       | On     | Off   | P12ブルアップ制御レジスタ( ESIF=0 )<br>SIF(マスター)選択時、汎用レジスタとして機能                              |

|       |       |       |       |       | PUL11 | 1       | On     | Off   | SIF(スレーブ)選択時、SCLK(1)ブルアップ制御レジスタ<br>P11ブルアップ制御レジスタ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能 |

|       |       |       |       |       | PUL10 | 1       | On     | Off   | P10ブルアップ制御レジスタ( ESIF=0 )<br>SIF選択時、SINブルアップ制御レジスタ                                 |

| FF46H | P13   | P12   | P11   | P10   | P13   | - *2    | High   | Low   | P13入出力兼用ポートデータ<br>SIF(スレーブ)選択時、汎用レジスタとして機能                                        |

|       |       |       |       |       | P12   | - *2    | High   | Low   | P12入出力兼用ポートデータ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能                                    |

|       |       |       |       |       | P11   | - *2    | High   | Low   | P11入出力兼用ポートデータ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能                                    |

|       |       |       |       |       | P10   | - *2    | High   | Low   | P10入出力兼用ポートデータ( ESIF=0 )<br>SIF選択時、汎用レジスタとして機能                                    |

| FF48H | IOC23 | IOC22 | IOC21 | IOC20 | IOC23 | 0       | Output | Input | P20～P23 I/O制御レジスタ                                                                 |

|       |       |       |       |       | IOC22 | 0       | Output | Input |                                                                                   |

| FF49H | PUL23 | PUL22 | PUL21 | PUL20 | IOC21 | 0       | Output | Input | P20～P23ブルアップ制御レジスタ                                                                |

|       |       |       |       |       | IOC20 | 0       | Output | Input |                                                                                   |

|       |       |       |       |       | PUL23 | 1       | On     | Off   |                                                                                   |

|       |       |       |       |       | PUL22 | 1       | On     | Off   |                                                                                   |

| FF4AH | P23   | P22   | P21   | P20   | PUL21 | 1       | On     | Off   | P20～P23入出力兼用ポートデータ                                                                |

|       |       |       |       |       | PUL20 | 1       | On     | Off   |                                                                                   |

|       |       |       |       |       | P23   | - *2    | High   | Low   |                                                                                   |

|       |       |       |       |       | P22   | - *2    | High   | Low   |                                                                                   |

| FF4CH | IOC33 | IOC32 | IOC31 | IOC30 | P21   | - *2    | High   | Low   | P30～P33 I/O制御レジスタ                                                                 |

|       |       |       |       |       | P20   | - *2    | High   | Low   |                                                                                   |

| FF4DH | PUL33 | PUL32 | PUL31 | PUL30 | IOC33 | 0       | Output | Input | P30～P33ブルアップ制御レジスタ                                                                |

|       |       |       |       |       | IOC32 | 0       | Output | Input |                                                                                   |

|       |       |       |       |       | IOC31 | 0       | Output | Input |                                                                                   |

|       |       |       |       |       | IOC30 | 0       | Output | Input |                                                                                   |

| FF4EH | P33   | P32   | P31   | P30   | PUL33 | 1       | On     | Off   | P30～P33入出力兼用ポートデータ                                                                |

|       |       |       |       |       | PUL32 | 1       | On     | Off   |                                                                                   |

|       |       |       |       |       | PUL31 | 1       | On     | Off   |                                                                                   |

|       |       |       |       |       | PUL30 | 1       | On     | Off   |                                                                                   |

| FF50H | IOC43 | IOC42 | IOC41 | IOC40 | P33   | - *2    | High   | Low   | P30～P33入出力兼用ポートデータ                                                                |

|       |       |       |       |       | P32   | - *2    | High   | Low   |                                                                                   |

|       |       |       |       |       | P31   | - *2    | High   | Low   |                                                                                   |

|       |       |       |       |       | P30   | - *2    | High   | Low   |                                                                                   |

| FF51H | PUL43 | PUL42 | PUL41 | PUL40 | IOC43 | 0       | Output | Input | 汎用レジスタ                                                                            |

|       |       |       |       |       | IOC42 | 0       | Output | Input |                                                                                   |

|       |       |       |       |       | IOC41 | 0       | Output | Input |                                                                                   |

|       |       |       |       |       | IOC40 | 0       | Output | Input |                                                                                   |

表4.1.1(d) I/Oメモリマップ( FF52H ~ FFC1H )

| アドレス  | レジスタ   |        |        |        | Name                | Init *1 | 1         | 0         | 注 釈                                             |

|-------|--------|--------|--------|--------|---------------------|---------|-----------|-----------|-------------------------------------------------|

|       | D3     | D2     | D1     | D0     |                     |         |           |           |                                                 |

| FF52H | P43    | P42    | P41    | P40    | P43                 | - *2    | High      | Low       | P43入出力兼用ポートデータ(PAD3=0)<br>A/Dイネーブル時、汎用レジスタとして機能 |

|       |        |        |        |        | P42                 | - *2    | High      | Low       | P42入出力兼用ポートデータ(PAD2=0)<br>A/Dイネーブル時、汎用レジスタとして機能 |

|       |        |        |        |        | P41                 | - *2    | High      | Low       | P41入出力兼用ポートデータ(PAD1=0)<br>A/Dイネーブル時、汎用レジスタとして機能 |

|       |        |        |        |        | P40                 | - *2    | High      | Low       | P40入出力兼用ポートデータ(PAD0=0)<br>A/Dイネーブル時、汎用レジスタとして機能 |

| FF60H | R/W    |        |        |        | LDUTY1              | 0       |           |           | LCD駆動デューティ [LDUTY1, 0] 0 1 2, 3                 |

|       | LDUTY1 | LDUTY0 | VCCHG  | LPWR   | LDUTY0              | 0       |           |           | 切り替え                                            |

|       |        |        |        |        | VCCHG               | 0       |           |           | 汎用レジスタ(予約レジスタ)                                  |

|       |        |        |        |        | LPWR                | 0       | On        | Off       | LCD電源On/Off                                     |

| FF61H | 0      | ALOFF  | ALON   | STCD   | 0 *3                | - *2    | All Off   | Normal    | 未使用                                             |

|       |        |        |        |        | Aloff               | 1       | All On    | Normal    | LCD全消灯制御                                        |

|       | R      | R/W    |        |        | ALON                | 0       | Static    | Normal    | LCD全点灯制御                                        |

|       |        |        |        |        | STCD                | 0       | Dynamic   | Dynamic   | コモン出力信号制御                                       |

| FF64H | 0      | ENON   | BZFQ   | BZON   | 0 *3                | - *2    | On        | Off       | 未使用                                             |

|       |        |        |        |        | ENON                | 0       | 2kHz      | 4kHz      | 2HzインターバルOn/Off制御                               |

|       | R      | R/W    |        |        | BZFQ                | 0       | On        | Off       | ブザー周波数選択                                        |

|       |        |        |        |        | BZON                | 0       |           |           | ブザー出力On/Off制御                                   |

| FF70H | 0      | ESOUT  | SCTRG  | ESIF   | 0 *3                | - *2    | Enable    | Disable   | 未使用                                             |

|       |        |        |        |        | ESOUT               | 0       | Trigger   | Invalid   | SOUT制御                                          |

|       | R      | R/W    |        |        | SCTRG               | 0       | Run       | Stop      | シリアルI/Fクロックトリガ(書き込み時)                           |

|       |        |        |        |        | ESIF                | 0       | I/O       |           | シリアルI/Fクロックステータス(読み出し時)                         |

| FF71H | R/W    |        |        |        | SDP                 | 0       | MSB first | LSB first | シリアルI/Fデータ入出力順列                                 |

|       | SDP    | SCPS   | SCS1   | SCS0   | SCPS                | 0       | ↑         | ↑         | シリアルI/Fクロックフェーズ選択 [SCS1, 0] 0 1                 |

|       |        |        |        |        | SCS1                | 0       |           |           | シリアルI/F [SCS1, 0] 2 3                           |

|       |        |        |        |        | SCS0                | 0       |           |           | クロックモード選択 クロック OSC1/2 OSC1                      |

| FF72H | SD3    | SD2    | SD1    | SD0    | SD3                 | - *2    | High      | Low       | MSB                                             |

|       |        |        |        |        | SD2                 | - *2    | High      | Low       | シリアルI/F送受信データ(下位4ビット)                           |

|       | R/W    |        |        |        | SD1                 | - *2    | High      | Low       |                                                 |

|       |        |        |        |        | SD0                 | - *2    | High      | Low       | LSB                                             |

| FF73H | SD7    | SD6    | SD5    | SD4    | SD7                 | - *2    | High      | Low       | MSB                                             |

|       |        |        |        |        | SD6                 | - *2    | High      | Low       | シリアルI/F送受信データ(上位4ビット)                           |

|       | R/W    |        |        |        | SD5                 | - *2    | High      | Low       |                                                 |

|       |        |        |        |        | SD4                 | - *2    | High      | Low       | LSB                                             |

| FF78H | 0      | 0      | TMRST  | TMRUN  | 0 *3                | - *2    |           |           | 未使用                                             |

|       |        |        |        |        | 0 *3                | - *2    |           |           | 未使用                                             |

|       | R/W    |        |        |        | TMRST <sup>*3</sup> | Reset   | Reset     | Run       | 計時タイマリセット(書き込み時)                                |

|       |        |        |        |        | TMRUN               | 0       |           |           | 計時タイマRun/Stop                                   |

| FF79H | TM3    | TM2    | TM1    | TM0    | TM3                 | 0       |           |           | 計時タイマデータ(16Hz)                                  |

|       |        |        |        |        | TM2                 | 0       |           |           | 計時タイマデータ(32Hz)                                  |

|       | R      |        |        |        | TM1                 | 0       |           |           | 計時タイマデータ(64Hz)                                  |

|       |        |        |        |        | TM0                 | 0       |           |           | 計時タイマデータ(128Hz)                                 |

| FF7AH | TM7    | TM6    | TM5    | TM4    | TM7                 | 0       |           |           | 計時タイマデータ(1Hz)                                   |

|       |        |        |        |        | TM6                 | 0       |           |           | 計時タイマデータ(2Hz)                                   |

|       | R      |        |        |        | TM5                 | 0       |           |           | 計時タイマデータ(4Hz)                                   |

|       |        |        |        |        | TM4                 | 0       |           |           | 計時タイマデータ(8Hz)                                   |

| FFC0H | MODE16 | EVCNT  | FCSEL  | PLPOL  | MODEL16             | 0       | 16bit × 1 | 8bit × 2  | タイマモード選択(8ビット×2または16ビット×1)                      |

|       |        |        |        |        | EVCNT               | 0       | Event ct. | Timer     | タイマ0カウンタモード選択                                   |

|       | R/W    |        |        |        | FCSEL               | 0       | With NR   | No NR     | タイマ0機能選択(イベントカウンタモード時)                          |

|       |        |        |        |        | PLPOL               | 0       | ↑         | ↓         | タイマ0パルス極性選択(イベントカウンタモード時)                       |

| FFC1H | CHSEL  | PTOUT  | CKSEL1 | CKSEL0 | CHSEL               | 0       | Timer1    | Timer0    | TOUT出力チャンネル選択                                   |

|       |        |        |        |        | PTOUT               | 0       | On        | Off       | TOUT出力制御                                        |

|       | R/W    |        |        |        | CKSEL1              | 0       | OSC3      | OSC1      | プリスケーラ1原振クロック選択                                 |

|       |        |        |        |        | CKSEL0              | 0       | OSC3      | OSC1      | プリスケーラ0原振クロック選択                                 |

表4.1.1(e) I/Oメモリマップ(FFC2H ~ FFD3H)

| アドレス  | レジスタ   |        |        |        | Name   | Init *1 | 1      | 0       | 注釈                                                                                             |  |  |  |  |  |

|-------|--------|--------|--------|--------|--------|---------|--------|---------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | D3     | D2     | D1     | D0     |        |         |        |         |                                                                                                |  |  |  |  |  |

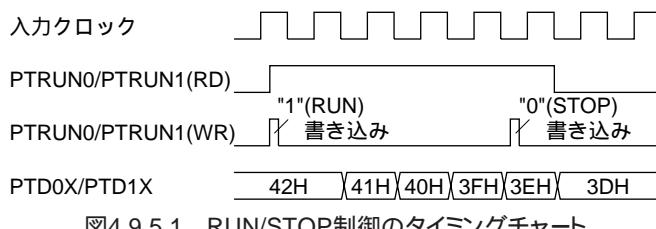

| FFC2H | PTPS01 | PTPS00 | PTRST0 | PTRUN0 | PTPS01 | 0       |        |         | プリスケーラ0 [PTPS01, 00] 0 1 2 3<br>分周比選択 分周比 1/1 1/4 1/32 1/256<br>PTRST0*3<br>PTRUN0             |  |  |  |  |  |

|       | R/W    |        | W      | R/W    | PTPS00 | 0       | Reset  | Invalid | タマリセット(リロード)<br>タマ0 Run/Stop                                                                   |  |  |  |  |  |

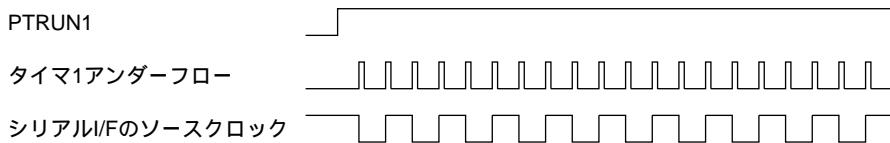

|       | PTPS11 | PTPS10 | PTRST1 | PTRUN1 | PTPS11 | 0       |        |         | プリスケーラ1 [PTPS11, 10] 0 1 2 3<br>分周比選択 分周比 1/1 1/4 1/32 1/256<br>PTRST1*3<br>PTRUN1             |  |  |  |  |  |

|       | R/W    |        | W      | R/W    | PTPS10 | 0       | Reset  | Invalid | タマリセット(リロード)<br>タマ1 Run/Stop                                                                   |  |  |  |  |  |

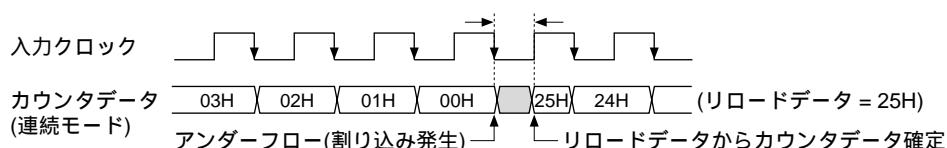

| FFC4H | RLD03  | RLD02  | RLD01  | RLD00  | RLD03  | 0       |        |         | MSB<br>プログラマブルタマ0リロードデータ(下位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | R/W    |        |        |        | RLD02  | 0       |        |         | MSB<br>プログラマブルタマ0リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | RLD07  | RLD06  | RLD05  | RLD04  | RLD07  | 0       |        |         | MSB<br>プログラマブルタマ0リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | R/W    |        |        |        | RLD06  | 0       |        |         | MSB<br>プログラマブルタマ1リロードデータ(下位4ビット)<br>LSB                                                        |  |  |  |  |  |

| FFC5H | RLD13  | RLD12  | RLD11  | RLD10  | RLD13  | 0       |        |         | MSB<br>プログラマブルタマ1リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | R/W    |        |        |        | RLD12  | 0       |        |         | MSB<br>プログラマブルタマ1リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | RLD17  | RLD16  | RLD15  | RLD14  | RLD17  | 0       |        |         | MSB<br>プログラマブルタマ1リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

|       | R/W    |        |        |        | RLD16  | 0       |        |         | MSB<br>プログラマブルタマ1リロードデータ(上位4ビット)<br>LSB                                                        |  |  |  |  |  |

| FFC6H | PTD03  | PTD02  | PTD01  | PTD00  | PTD03  | 0       |        |         | MSB<br>プログラマブルタマ0データ(下位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | R      |        |        |        | PTD02  | 0       |        |         | MSB<br>プログラマブルタマ0データ(下位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | PTD07  | PTD06  | PTD05  | PTD04  | PTD06  | 0       |        |         | MSB<br>プログラマブルタマ0データ(上位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | R      |        |        |        | PTD05  | 0       |        |         | MSB<br>プログラマブルタマ1データ(下位4ビット)<br>LSB                                                            |  |  |  |  |  |

| FFCAH | PTD13  | PTD12  | PTD11  | PTD10  | PTD13  | 0       |        |         | MSB<br>プログラマブルタマ1データ(上位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | R      |        |        |        | PTD12  | 0       |        |         | MSB<br>プログラマブルタマ1データ(上位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | PTD17  | PTD16  | PTD15  | PTD14  | PTD17  | 0       |        |         | MSB<br>プログラマブルタマ1データ(上位4ビット)<br>LSB                                                            |  |  |  |  |  |

|       | R      |        |        |        | PTD16  | 0       |        |         | MSB<br>プログラマブルタマ1データ(上位4ビット)<br>LSB                                                            |  |  |  |  |  |

| FFCBH | ADRUN  | ADCLK  | CHS1   | CHS0   | ADRUN  | 0       | Start  | Invalid | A/D変換器Run/Off制御<br>A/D変換器入力選択<br>A/D変換器入力 [CHS1, 0] 0 1 2 3<br>チャンネル選択 入力チャンネル P40 P41 P42 P43 |  |  |  |  |  |

|       | R/W    |        |        |        | ADCLK  | 0       | OSC3   | OSC1    | A/D変換器入力選択<br>A/D変換器入力 [CHS1, 0] 0 1 2 3<br>チャンネル選択 入力チャンネル P40 P41 P42 P43                    |  |  |  |  |  |

|       | PAD3   | PAD2   | PAD1   | PAD0   | PAD3   | 0       | Enable | Disable | P43入力チャンネル制御<br>P42入力チャンネル制御<br>P41入力チャンネル制御<br>P40入力チャンネル制御                                   |  |  |  |  |  |

|       | R/W    |        |        |        | PAD2   | 0       | Enable | Disable | P43入力チャンネル制御<br>P42入力チャンネル制御<br>P41入力チャンネル制御<br>P40入力チャンネル制御                                   |  |  |  |  |  |

| FFD2H | ADDR3  | ADDR2  | ADDR1  | ADDR0  | ADDR3  | -*2     |        |         | A/D変換データ( D0 ~ D3 )                                                                            |  |  |  |  |  |

|       | R      |        |        |        | ADDR2  | -*2     |        |         | A/D変換データ( D0 ~ D3 )                                                                            |  |  |  |  |  |

|       | ADDR1  | ADDR0  |        |        | ADDR1  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

|       | R      |        |        |        | ADDR0  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

| FFD3H | ADDR7  | ADDR6  | ADDR5  | ADDR4  | ADDR7  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

|       | R      |        |        |        | ADDR6  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

|       | ADDR5  | ADDR4  |        |        | ADDR5  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

|       | R      |        |        |        | ADDR4  | -*2     |        |         | A/D変換データ( D4 ~ D7 )                                                                            |  |  |  |  |  |

表4.1.1(f) I/Oメモリマップ( FFE2H ~ FFF7H )

| アドレス  | レジスタ |      |       |       | Name | Init *1 | 1      | 0    | 注釈                         |

|-------|------|------|-------|-------|------|---------|--------|------|----------------------------|

|       | D3   | D2   | D1    | D0    |      |         |        |      |                            |

| FFE2H | 0    | 0    | EIPT1 | EIPT0 | 0 *3 | - *2    | Enable | Mask | 未使用                        |

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 未使用                        |

| FFE3H | 0    | 0    | 0     | EISIF | 0 *3 | - *2    | Enable | Mask | 割り込みマスクレジスタ( プログラマブルタイマ1 ) |

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 割り込みマスクレジスタ( プログラマブルタイマ0 ) |

| FFE4H | 0    | 0    | 0     | EIK0  | 0 *3 | - *2    | Enable | Mask | 未使用                        |

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 未使用                        |

| FFE5H | 0    | 0    | EIK2  | EIK1  | 0 *3 | - *2    | Enable | Mask | 未使用                        |

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 未使用                        |

| FFE6H | EIT3 | EIT2 | EIT1  | EIT0  | EIT3 | 0       | Enable | Mask | 割り込みマスクレジスタ( 計時タイマ1Hz )    |

|       | R    | R    | R/W   |       | EIT2 | 0       | Enable | Mask | 割り込みマスクレジスタ( 計時タイマ2Hz )    |

| FFE7H | 0    | 0    | 0     | EIAD  | 0 *3 | - *2    | Enable | Mask | 割り込みマスクレジスタ( 計時タイマ8Hz )    |

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 割り込みマスクレジスタ( 計時タイマ16Hz )   |

| FFF2H | 0    | 0    | IPT1  | IPT0  | 0 *3 | - *2    | (R)    | (R)  | 未使用                        |

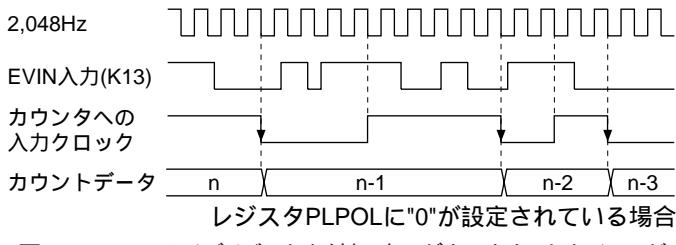

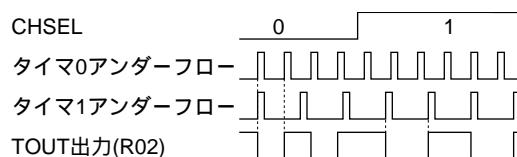

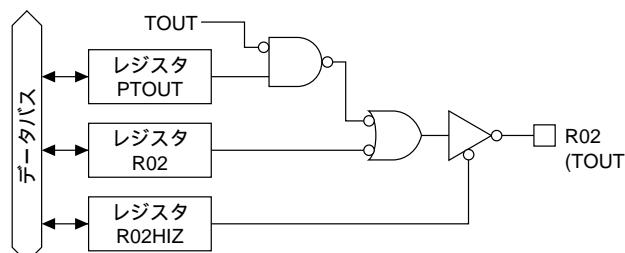

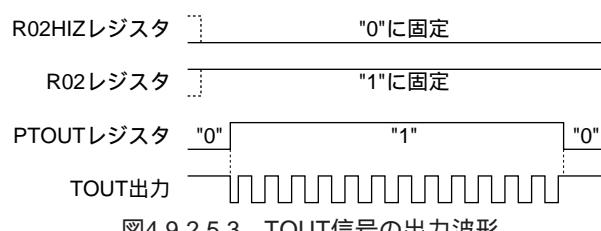

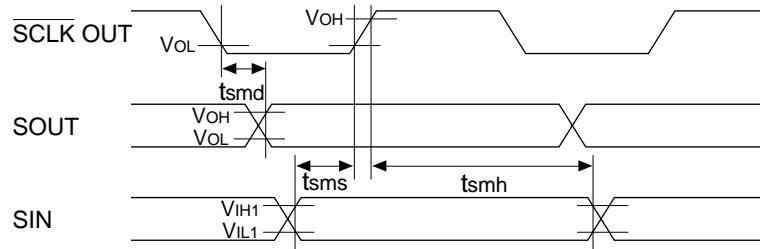

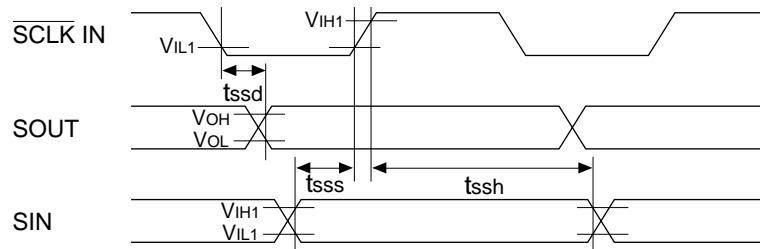

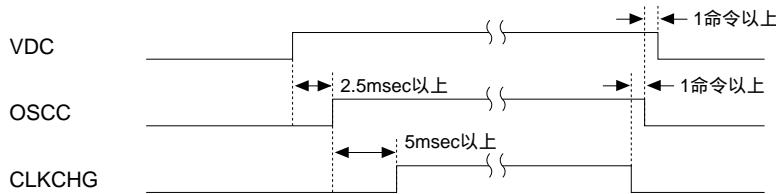

|       | R    | R    | R/W   |       | 0 *3 | - *2    |        |      | 未使用                        |