CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

**S1C60N08/60R08**

テクニカルマニュアル

S1C60N08 Technical Hardware/S1C60R08 Technical Hardware

本資料のご使用につきましては、次の点にご留意願います。

---

1. 本資料の内容については、予告なく変更することがあります。

2. 本資料の一部、または全部を弊社に無断で転載、または、複製など他の目的に使用することは堅くお断りします。

3. 本資料に掲載される応用回路、プログラム、使用方法等はあくまでも参考情報であり、これらに起因する第三者の権利(工業所有権を含む)侵害あるいは損害の発生に対し、弊社は如何なる保証を行うものではありません。また、本資料によって第三者または弊社の工業所有権の実施権の許諾を行うものではありません。

4. 特性表の数値の大小は、数直線上の大小関係で表しています。

5. 本資料に掲載されている製品のうち、「外国為替および外国貿易法」に定める戦略物資に該当するものについては、輸出する場合、同法に基づく輸出許可が必要です。

6. 本資料に掲載されている製品は、一般民生用です。生命維持装置その他、きわめて高い信頼性が要求される用途を前提としていません。よって、弊社は本(当該)製品をこれらの用途に用いた場合の如何なる責任についても負いかねます。

# **S1C60N08/S1C60R08 Technical Manual**

本書はセイコーエプソンオリジナル4ビットマイクロコンピュータS1C60N08およびS1C60R08( S1C60N08用ROMエミュレータモデル )のハードウェア仕様を個別に解説します。

## **I. S1C60N08 Technical Hardware**

ここでは、S1C60N08の機能、回路の構成、制御方法を解説します。

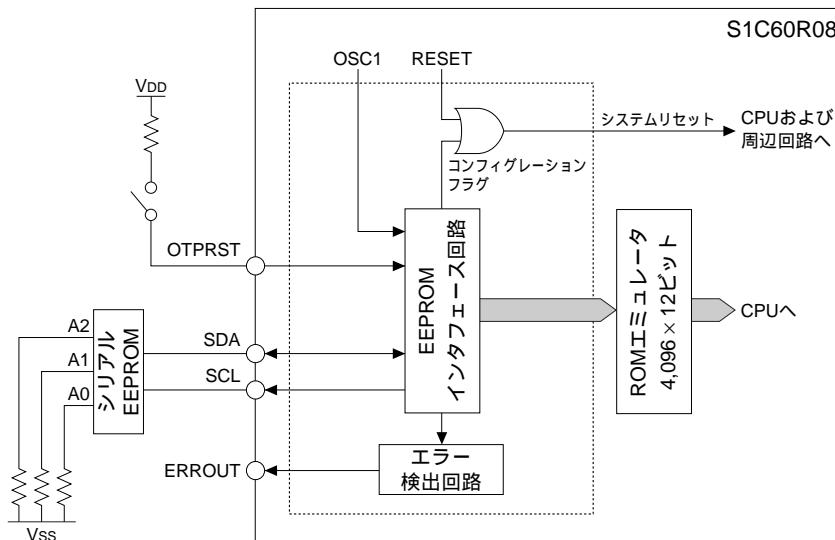

## **II. S1C60R08 Technical Hardware**

ここでは、S1C60N08と同様の機能を除いたS1C60R08のハードウェア仕様を解説します。

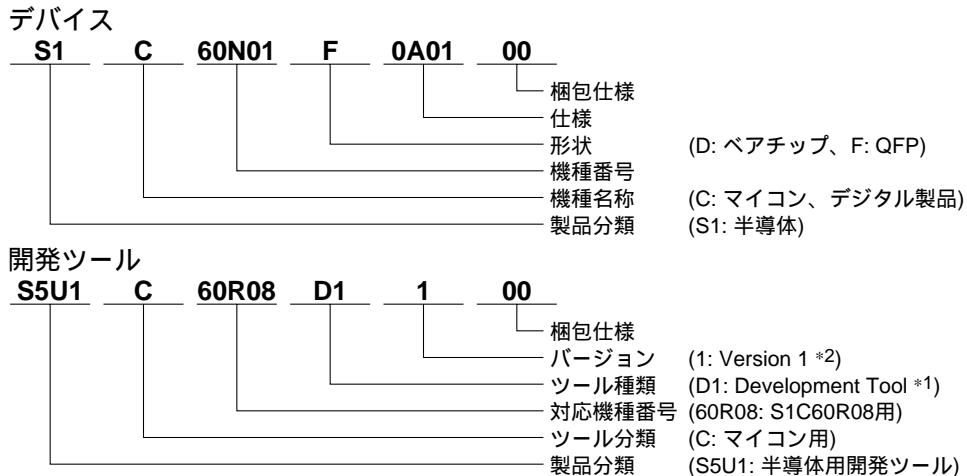

## 製品型番変更のご案内

2001年4月1日より、弊社半導体製品の製品型番が以下のとおり変更となりますので、4月1日以降のご発注につきましては変更後の製品型番にてお願い申し上げます。

なお、製品型番の詳細仕様につきましては、弊社営業担当にお問い合わせください。

## 製品型番体系

\*1: ツールの種類は、新旧型番対応表を参照してください。(マニュアル類には一桁で記載されているものもあります。)

\*2: マニュアル類には、実際のバージョンは記載されておりません。

## 新旧型番対応表

### S1C60ファミリ

| 旧型番      | 新型番      |

|----------|----------|

| E0C6001  | S1C60N01 |

| E0C6002  | S1C60N02 |

| E0C6003  | S1C60N03 |

| E0C6004  | S1C60N04 |

| E0C6005  | S1C60N05 |

| E0C6006  | S1C60N06 |

| E0C6007  | S1C60N07 |

| E0C6008  | S1C60N08 |

| E0C6009  | S1C60N09 |

| E0C6011  | S1C60N11 |

| E0C6013  | S1C60N13 |

| E0C6014  | S1C60140 |

| E0C60R08 | S1C60R08 |

### S1C62ファミリ

| 旧型番     | 新型番      |

|---------|----------|

| E0C621A | S1C621A0 |

| E0C6215 | S1C62150 |

| E0C621C | S1C621C0 |

| E0C6S27 | S1C6S2N7 |

| E0C6S37 | S1C6S3N7 |

| E0C623A | S1C6N3A0 |

| E0C623E | S1C6N3E0 |

| E0C6S32 | S1C6S3N2 |

| E0C6233 | S1C62N33 |

| E0C6235 | S1C62N35 |

| E0C623B | S1C6N3B0 |

| E0C6244 | S1C62440 |

| E0C624A | S1C624A0 |

| E0C6S46 | S1C6S460 |

| 旧型番     | 新型番      |

|---------|----------|

| E0C6247 | S1C62470 |

| E0C6248 | S1C62480 |

| E0C6S48 | S1C6S480 |

| E0C624C | S1C624C0 |

| E0C6251 | S1C62N51 |

| E0C6256 | S1C62560 |

| E0C6292 | S1C62920 |

| E0C6262 | S1C62N62 |

| E0C6266 | S1C62660 |

| E0C6274 | S1C62740 |

| E0C6281 | S1C62N81 |

| E0C6282 | S1C62N82 |

| E0C62M2 | S1C62M20 |

| E0C62T3 | S1C62T30 |

## 開発ツール新旧型番対応表

### S1C60/62ファミリ関係の開発ツール

| 旧型番      | 新型番         | 旧型番      | 新型番          | 旧型番      | 新型番          |

|----------|-------------|----------|--------------|----------|--------------|

| ASM62    | S5U1C62000A | DEV6262  | S5U1C62620D  | EVA623B  | S5U1C623B0E  |

| DEV6001  | S5U1C60N01D | DEV6266  | S5U1C62660D  | EVA623E  | S5U1C623E0E  |

| DEV6002  | S5U1C60N02D | DEV6274  | S5U1C62740D  | EVA6247  | S5U1C62470E  |

| DEV6003  | S5U1C60N03D | DEV6292  | S5U1C62920D  | EVA6248  | S5U1C62480E  |

| DEV6004  | S5U1C60N04D | DEV62M2  | S5U1C62M20D  | EVA6251R | S5U1C62N51E1 |

| DEV6005  | S5U1C60N05D | DEV6233  | S5U1C62N33D  | EVA6256  | S5U1C62N56E  |

| DEV6006  | S5U1C60N06D | DEV6235  | S5U1C62N35D  | EVA6262  | S5U1C62620E  |

| DEV6007  | S5U1C60N07D | DEV6251  | S5U1C62N51D  | EVA6266  | S5U1C62660E  |

| DEV6008  | S5U1C60N08D | DEV6256  | S5U1C62560D  | EVA6274  | S5U1C62740E  |

| DEV6009  | S5U1C60N09D | DEV6281  | S5U1C62N81D  | EVA6281  | S5U1C62N81E  |

| DEV6011  | S5U1C60N11D | DEV6282  | S5U1C62N82D  | EVA6282  | S5U1C62N82E  |

| DEV60R08 | S5U1C60R08D | DEV6S27  | S5U1C6S2N7D  | EVA62M1  | S5U1C62M10E  |

| DEV621A  | S5U1C621A0D | DEV6S32  | S5U1C6S3N2D  | EVA62T3  | S5U1C62T30E  |

| DEV621C  | S5U1C621C0D | DEV6S37  | S5U1C6S3N7D  | EVA6S27  | S5U1C6S2N7E  |

| DEV623B  | S5U1C623B0D | EVA6008  | S5U1C60N08E  | EVA6S32R | S5U1C6S3N2E2 |

| DEV6244  | S5U1C62440D | EVA6011  | S5U1C60N11E  | ICE62R   | S5U1C62000H  |

| DEV624A  | S5U1C624A0D | EVA621AR | S5U1C621A0E2 | KIT6003  | S5U1C60N03K  |

| DEV624C  | S5U1C624C0D | EVA621C  | S5U1C621C0E  | KIT6004  | S5U1C60N04K  |

| DEV6248  | S5U1C62480D | EVA6237  | S5U1C62N37E  | KIT6007  | S5U1C60N07K  |

| DEV6247  | S5U1C62470D | EVA623A  | S5U1C623A0E  |          |              |

## **I. S1C60N08 Technical Hardware**

## - 目 次 -

|       |                                    |      |

|-------|------------------------------------|------|

| 1     | 概要                                 | I-1  |

| 1.1   | 機種構成                               | I-1  |

| 1.2   | 特長                                 | I-1  |

| 1.3   | ブロック図                              | I-2  |

| 1.4   | 端子配置図                              | I-3  |

| 1.5   | 端子説明                               | I-4  |

| 1.6   | S1C60N08オプションリスト                   | I-4  |

| 2     | 電源系 および イニシャルリセット                  | I-7  |

| 2.1   | 電源系                                | I-7  |

| 2.2   | イニシャルリセット                          | I-9  |

| 2.2.1 | パワーオンリセット回路                        | I-9  |

| 2.2.2 | リセット端子( RESET )                    | I-9  |

| 2.2.3 | 入力ポート( K00 ~ K03 )の同時HIGH入力        | I-9  |

| 2.2.4 | ウォッチドッグタイム                         | I-10 |

| 2.2.5 | イニシャルリセット時の内部レジスタ                  | I-10 |

| 2.3   | テスト端子( TEST )                      | I-10 |

| 3     | CPU, ROM, RAM                      | I-11 |

| 3.1   | CPU                                | I-11 |

| 3.2   | ROM                                | I-11 |

| 3.3   | RAM                                | I-11 |

| 4     | 周辺回路と動作                            | I-12 |

| 4.1   | メモリマップ                             | I-12 |

| 4.2   | ウォッチドッグタイムのリセット                    | I-16 |

| 4.2.1 | ウォッチドッグタイムの構成                      | I-16 |

| 4.2.2 | マスクオプション                           | I-16 |

| 4.2.3 | ウォッチドッグタイムの制御方法                    | I-16 |

| 4.2.4 | プログラミング上の注意事項                      | I-16 |

| 4.3   | 発振回路とプリスケーラ                        | I-17 |

| 4.3.1 | 発振回路とプリスケーラの構成                     | I-17 |

| 4.3.2 | OSC1発振回路                           | I-17 |

| 4.3.3 | OSC3発振回路                           | I-18 |

| 4.3.4 | 発振回路とプリスケーラの制御方法                   | I-19 |

| 4.3.5 | プログラミング上の注意事項                      | I-20 |

| 4.4   | 入力ポート( K00 ~ K03, K10, K20 ~ K23 ) | I-21 |

| 4.4.1 | 入力ポートの構成                           | I-21 |

| 4.4.2 | 入力比較レジスタと割り込み機能                    | I-21 |

| 4.4.3 | マスクオプション                           | I-24 |

| 4.4.4 | 入力ポートの制御方法                         | I-24 |

| 4.4.5 | プログラミング上の注意事項                      | I-26 |

|        |                                      |      |

|--------|--------------------------------------|------|

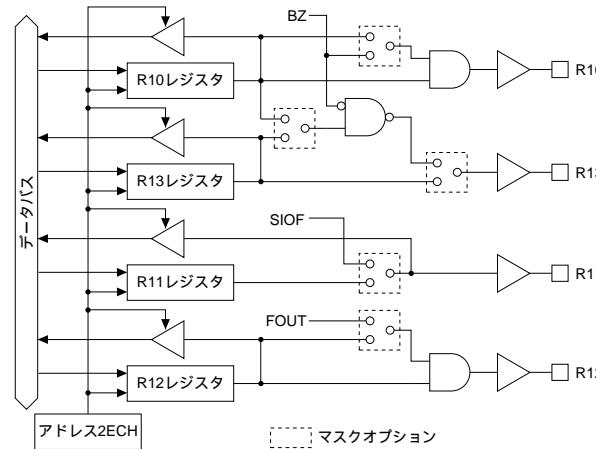

| 4.5    | 出力ポート( R00 ~ R03, R10 ~ R13 )        | I-27 |

| 4.5.1  | 出力ポートの構成                             | I-27 |

| 4.5.2  | マスクオプション                             | I-27 |

| 4.5.3  | 出力ポートの制御方法                           | I-29 |

| 4.5.4  | プログラミング上の注意事項                        | I-30 |

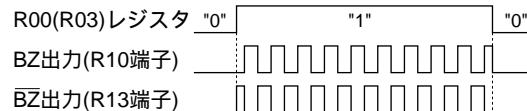

| 4.6    | 入出力兼用ポート( P00 ~ P03, P10 ~ P13 )     | I-31 |

| 4.6.1  | 入出力兼用ポートの構成                          | I-31 |

| 4.6.2  | I/O制御レジスタと入力/出力モード                   | I-31 |

| 4.6.3  | マスクオプション                             | I-31 |

| 4.6.4  | 入出力兼用ポートの制御方法                        | I-32 |

| 4.6.5  | プログラミング上の注意事項                        | I-33 |

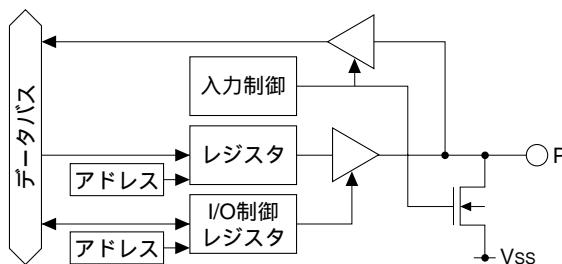

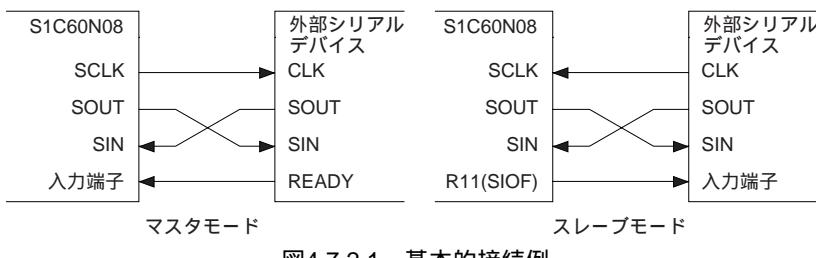

| 4.7    | シリアルインターフェース( SIN, SOUT, SCLK )      | I-34 |

| 4.7.1  | シリアルインターフェースの構成                      | I-34 |

| 4.7.2  | シリアルインターフェースのマスタモードとスレーブモード          | I-34 |

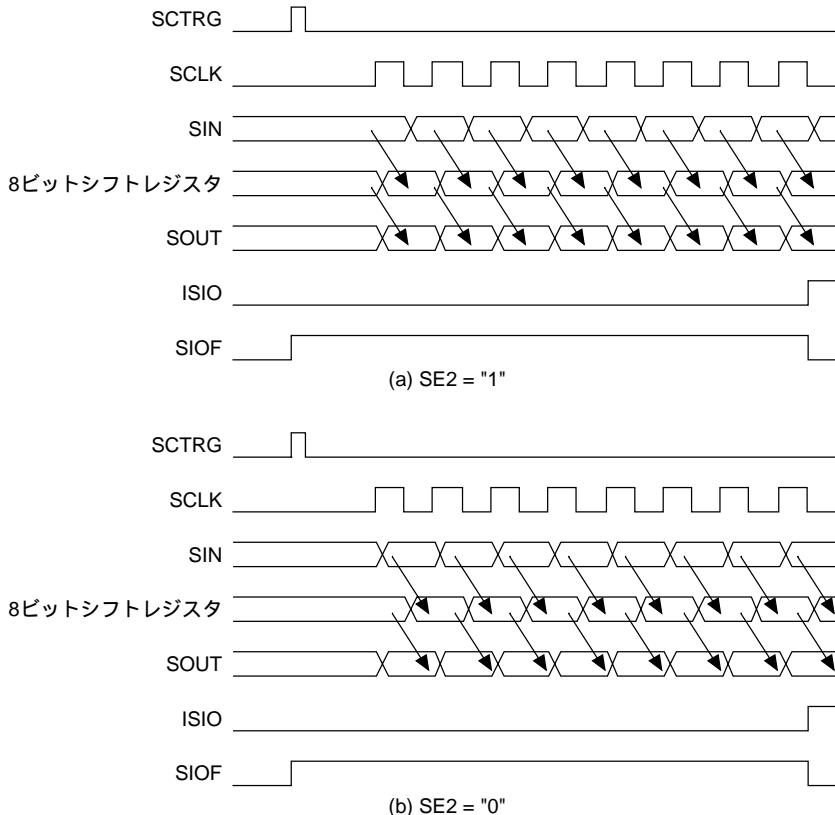

| 4.7.3  | データの入出力と割り込み                         | I-35 |

| 4.7.4  | マスクオプション                             | I-37 |

| 4.7.5  | シリアルインターフェースの制御方法                    | I-38 |

| 4.7.6  | プログラミング上の注意事項                        | I-40 |

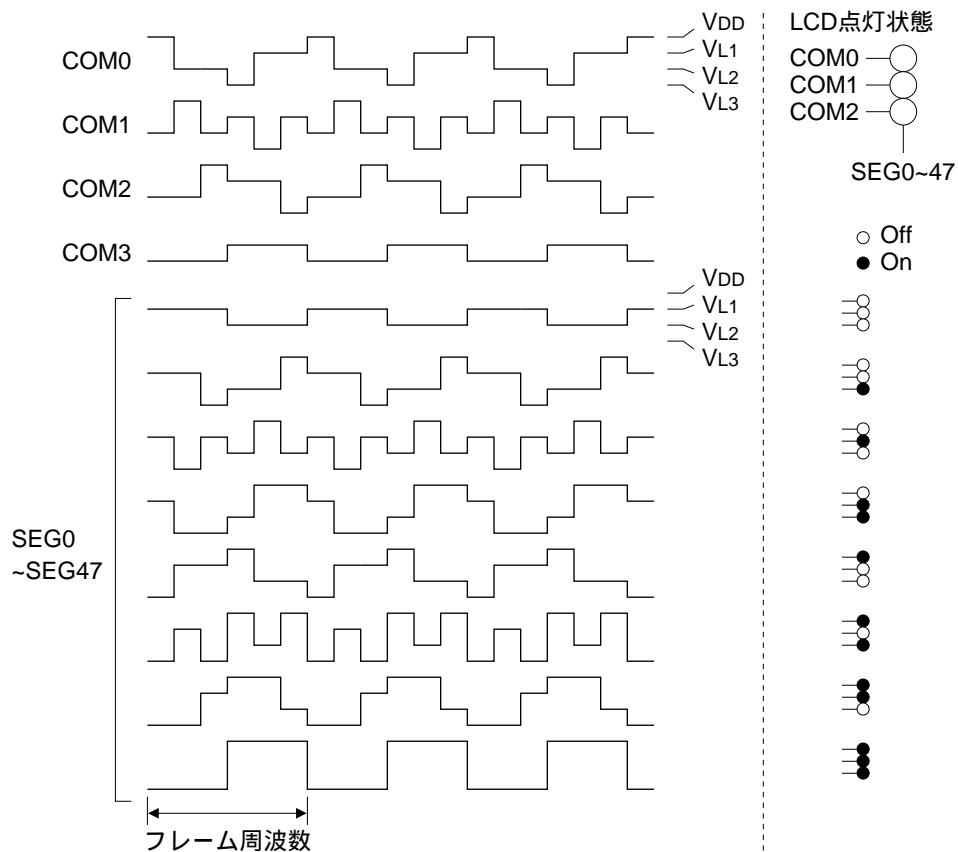

| 4.8    | LCDドライバ( COM0 ~ COM3, SEG0 ~ SEG47 ) | I-41 |

| 4.8.1  | LCDドライバの構成                           | I-41 |

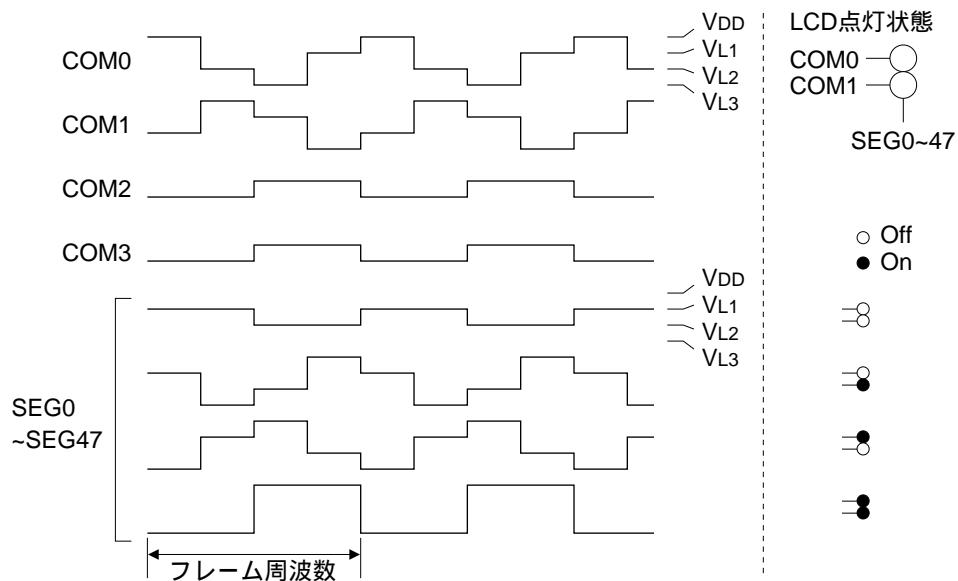

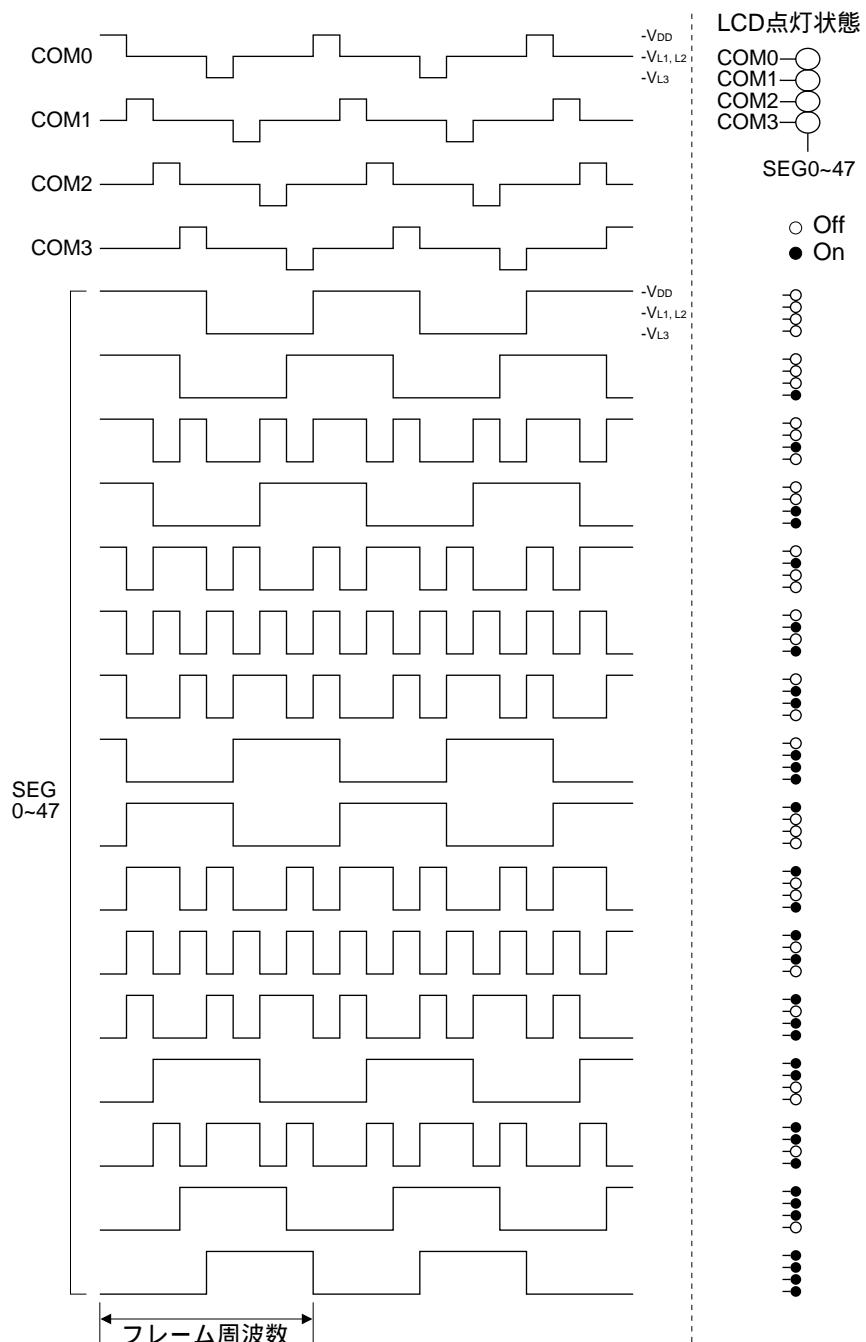

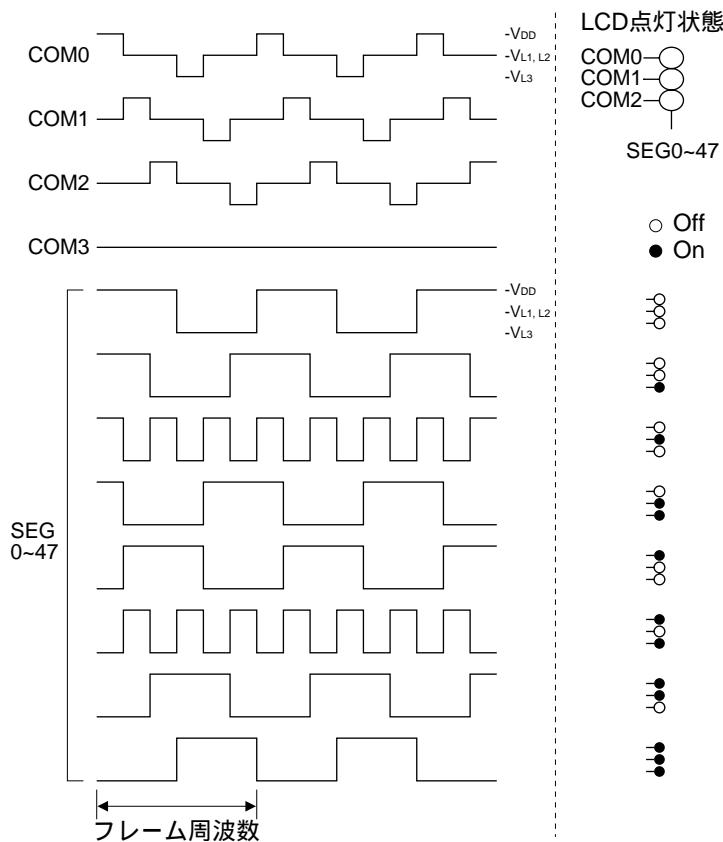

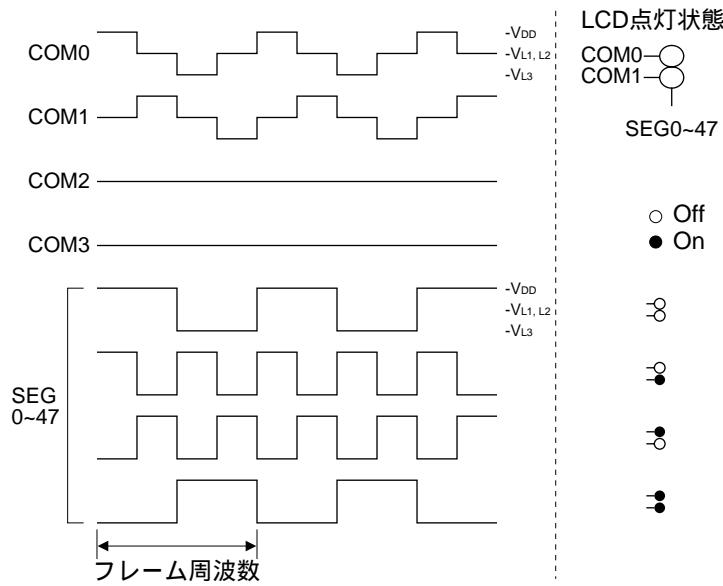

| 4.8.2  | ダイナミック/スタティック駆動切り換え                  | I-46 |

| 4.8.3  | マスクオプション( セグメント割り付け )                | I-47 |

| 4.8.4  | LCDドライバの制御方法                         | I-48 |

| 4.8.5  | プログラミング上の注意事項                        | I-49 |

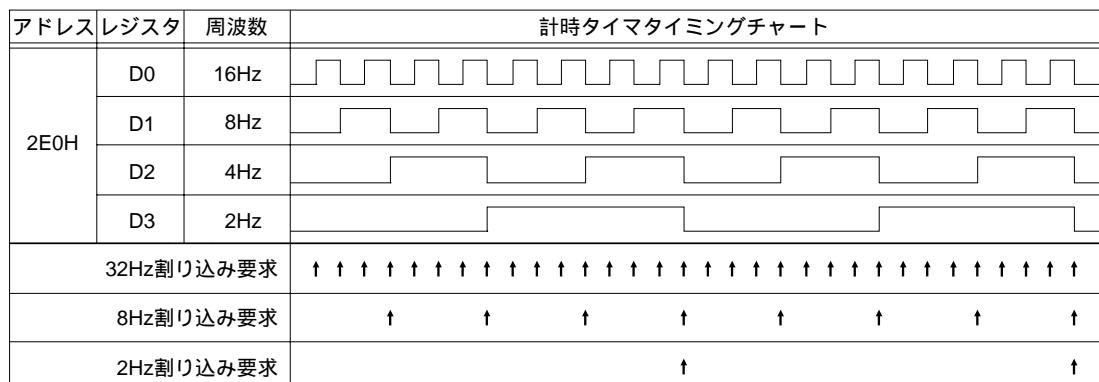

| 4.9    | 計時タイマ                                | I-50 |

| 4.9.1  | 計時タイマの構成                             | I-50 |

| 4.9.2  | 割り込み機能                               | I-50 |

| 4.9.3  | 計時タイマの制御方法                           | I-51 |

| 4.9.4  | プログラミング上の注意事項                        | I-52 |

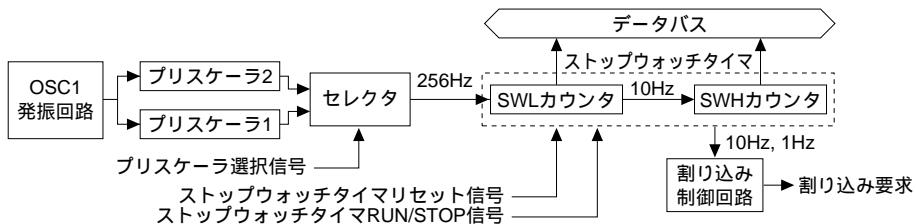

| 4.10   | ストップウォッチタイマ                          | I-53 |

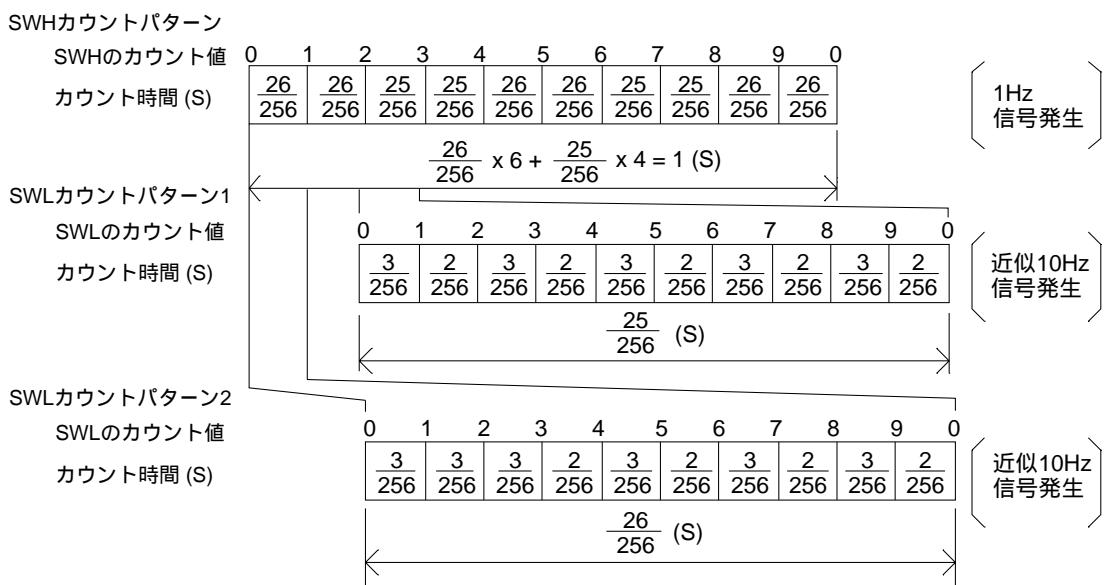

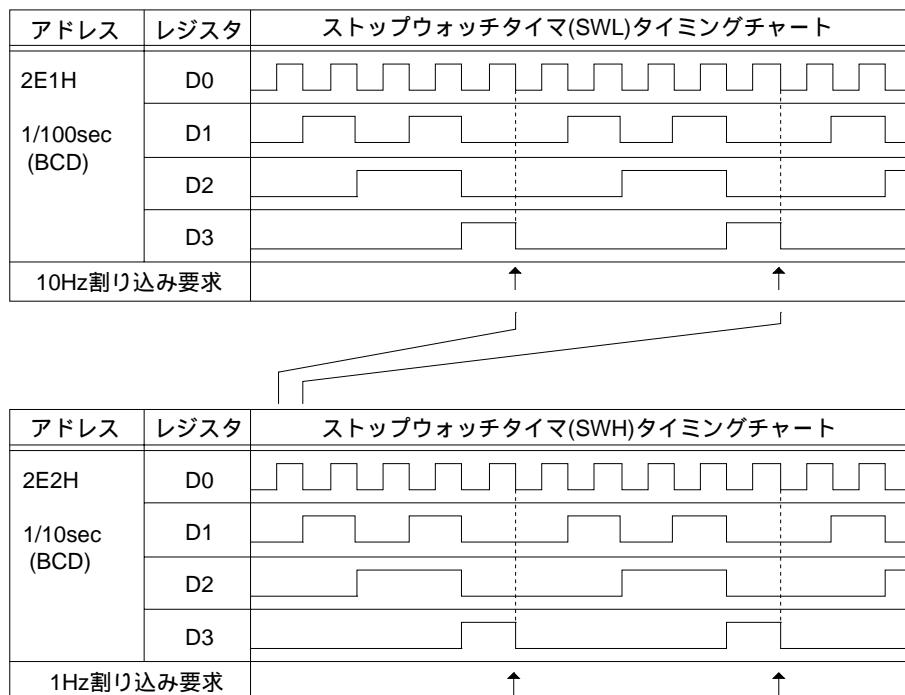

| 4.10.1 | ストップウォッチタイマの構成                       | I-53 |

| 4.10.2 | カウントアップパターン                          | I-53 |

| 4.10.3 | 割り込み機能                               | I-54 |

| 4.10.4 | ストップウォッチタイマの制御方法                     | I-55 |

| 4.10.5 | プログラミング上の注意事項                        | I-56 |

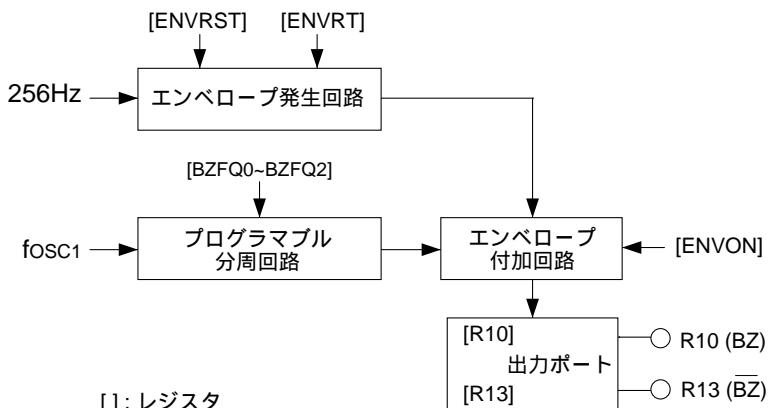

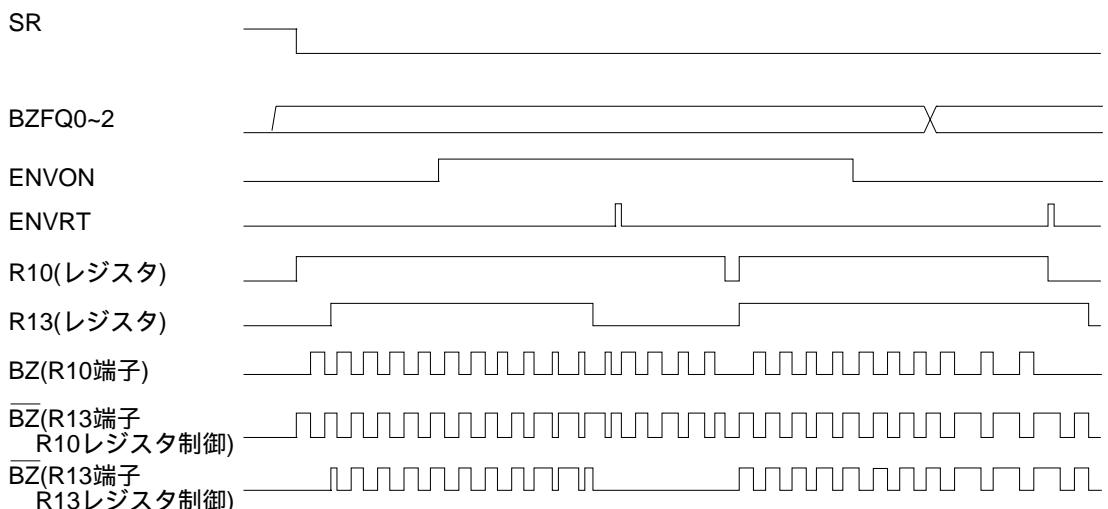

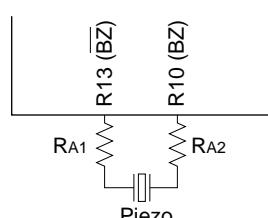

| 4.11   | サウンドジェネレータ                           | I-57 |

| 4.11.1 | サウンドジェネレータの構成                        | I-57 |

| 4.11.2 | 周波数設定                                | I-58 |

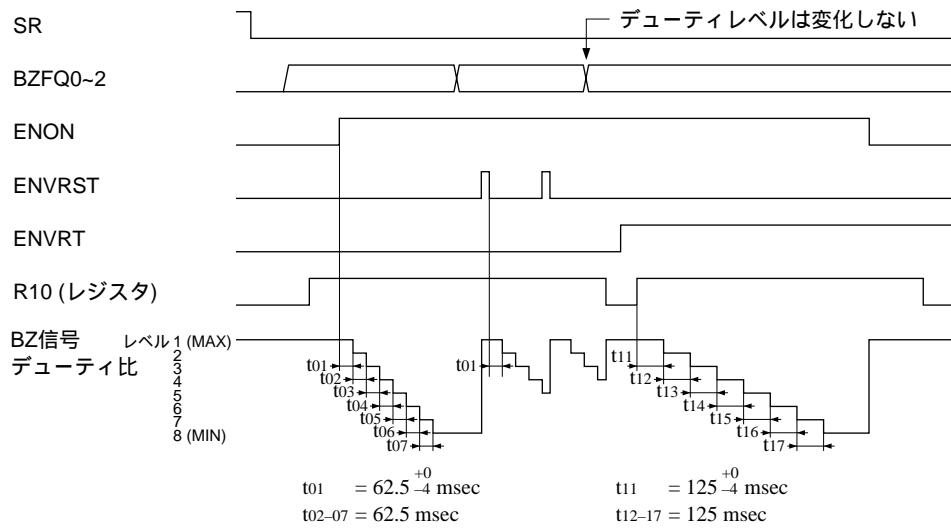

| 4.11.3 | デジタルエンベロープ                           | I-58 |

| 4.11.4 | マスクオプション                             | I-59 |

| 4.11.5 | サウンドジェネレータの制御方法                      | I-60 |

| 4.11.6 | プログラミング上の注意事項                        | I-61 |

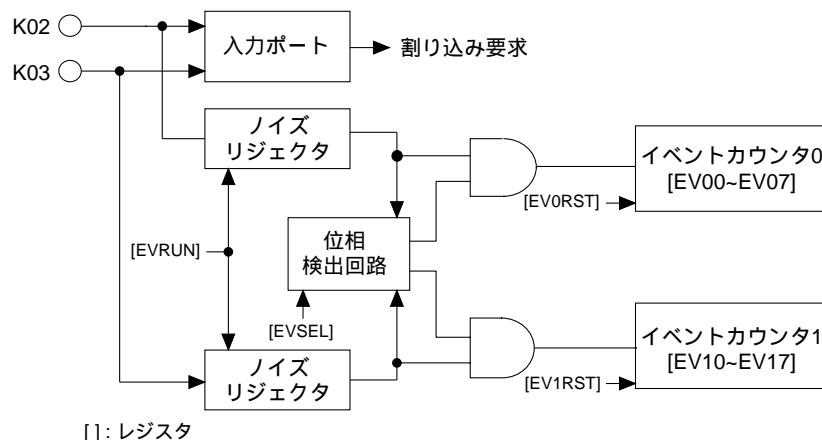

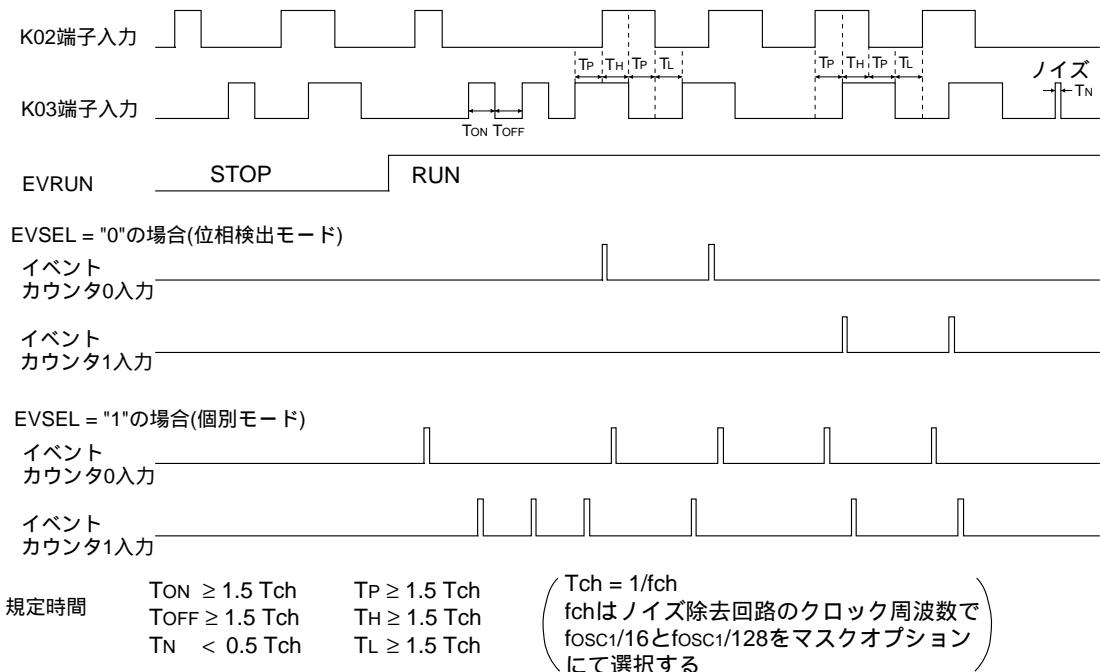

| 4.12   | イベントカウンタ                             | I-62 |

| 4.12.1 | イベントカウンタの構成                          | I-62 |

| 4.12.2 | カウントモードの切り換え                         | I-62 |

| 4.12.3 | マスクオプション                             | I-63 |

| 4.12.4 | イベントカウンタの制御方法                        | I-64 |

| 4.12.5 | プログラミング上の注意事項                        | I-65 |

|        |                      |       |

|--------|----------------------|-------|

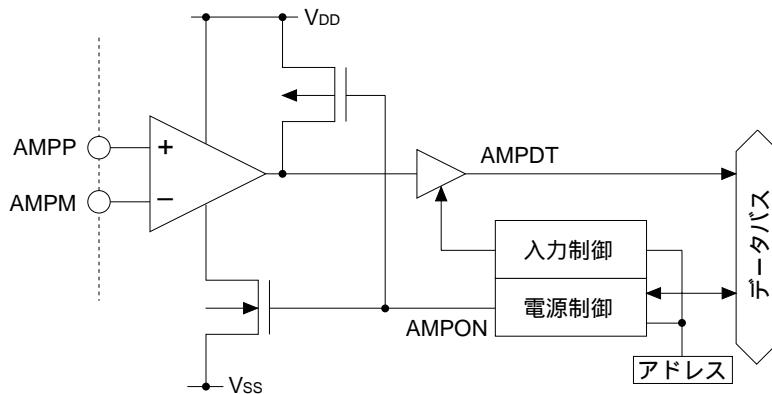

| 4.13   | アナログコンパレータ           | I-66  |

| 4.13.1 | アナログコンパレータの構成        | I-66  |

| 4.13.2 | アナログコンパレータの動作        | I-66  |

| 4.13.3 | アナログコンパレータの制御方法      | I-67  |

| 4.13.4 | プログラミング上の注意事項        | I-67  |

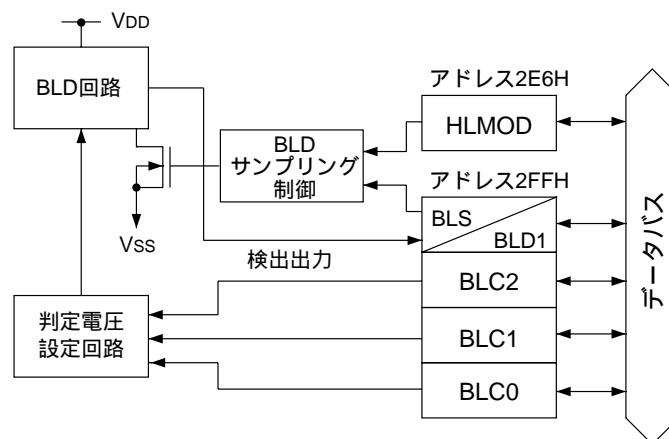

| 4.14   | 電池寿命検出(BLD)回路        | I-68  |

| 4.14.1 | BLD(電池寿命検出)回路の構成     | I-68  |

| 4.14.2 | 判定電圧のプログラマブル選択       | I-68  |

| 4.14.3 | BLD回路の検出タイミング        | I-69  |

| 4.14.4 | BLD回路の制御方法           | I-70  |

| 4.14.5 | プログラミング上の注意事項        | I-71  |

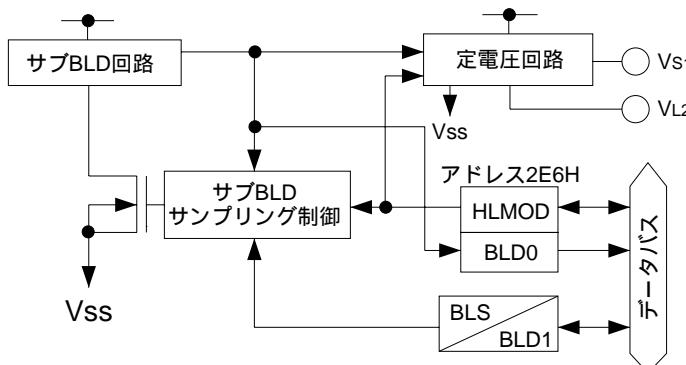

| 4.15   | 重負荷保護機能とサブBLD回路      | I-72  |

| 4.15.1 | 重負荷保護機能の構成と動作        | I-72  |

| 4.15.2 | サブBLD回路の動作           | I-73  |

| 4.15.3 | 重負荷保護機能とサブBLD回路の制御方法 | I-73  |

| 4.15.4 | プログラミング上の注意事項        | I-75  |

| 4.16   | 割り込みとHALT            | I-76  |

| 4.16.1 | 割り込みの要因              | I-78  |

| 4.16.2 | 割り込みの個別マスクと要因フラグ     | I-78  |

| 4.16.3 | 割り込みベクタ              | I-79  |

| 4.16.4 | 割り込みとHALTの制御方法       | I-80  |

| 4.16.5 | プログラミング上の注意事項        | I-81  |

| 5      | 注意事項のまとめ             | I-82  |

| 5.1    | 低消費電流化のための注意事項       | I-82  |

| 5.2    | 個別機能についての注意事項のまとめ    | I-83  |

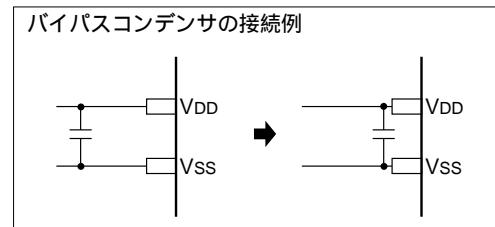

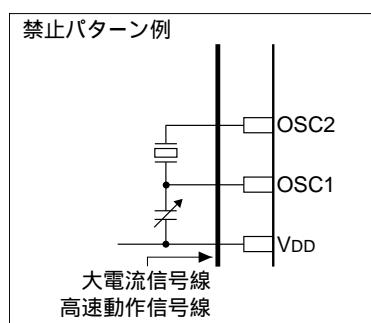

| 5.3    | 実装上の注意事項             | I-88  |

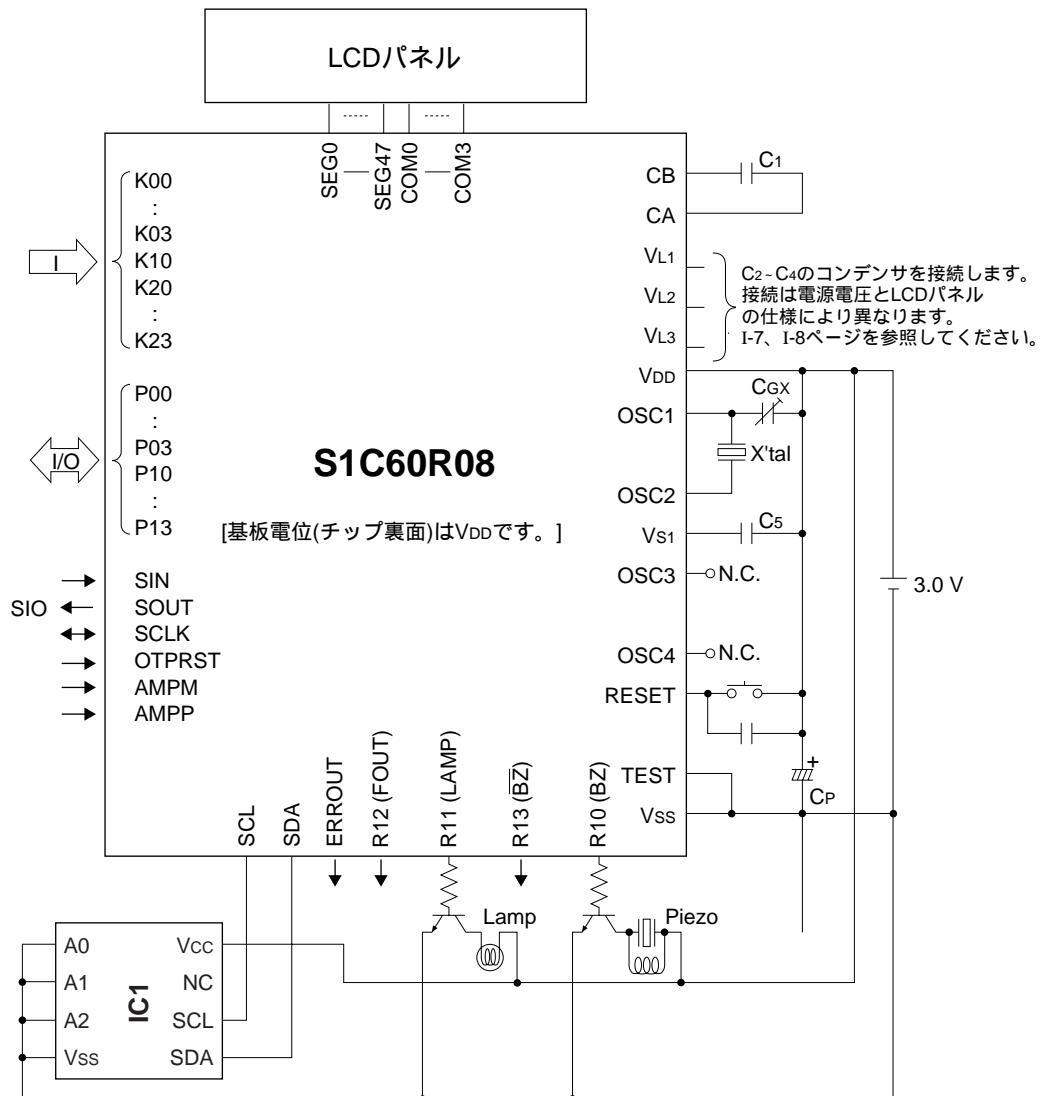

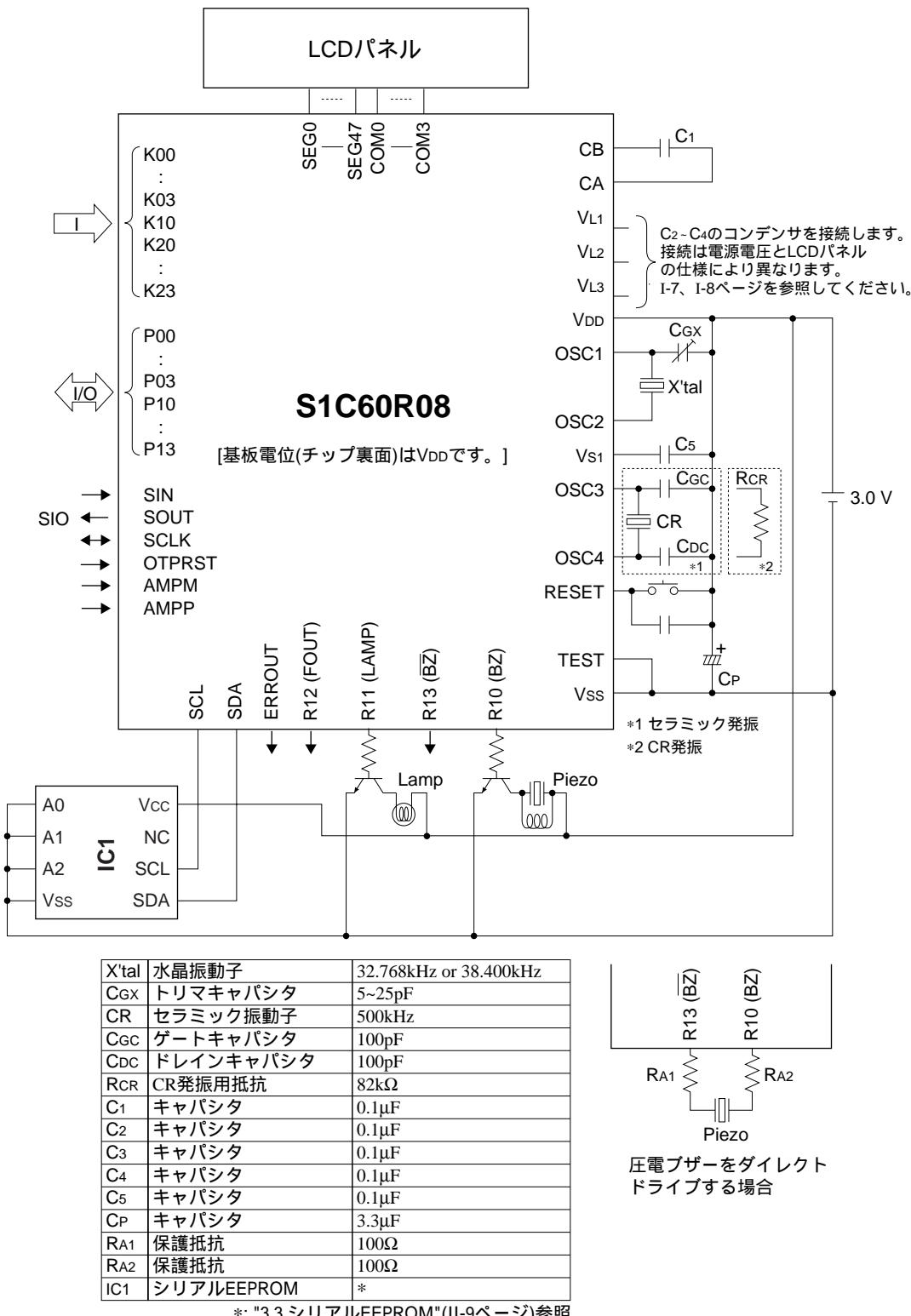

| 6      | 基本外部結線図              | I-90  |

| 7      | 電気的特性                | I-92  |

| 7.1    | 絶対最大定格               | I-92  |

| 7.2    | 推奨動作条件               | I-92  |

| 7.3    | DC特性                 | I-93  |

| 7.4    | アナログ回路特性・消費電流        | I-94  |

| 7.5    | 発振特性                 | I-97  |

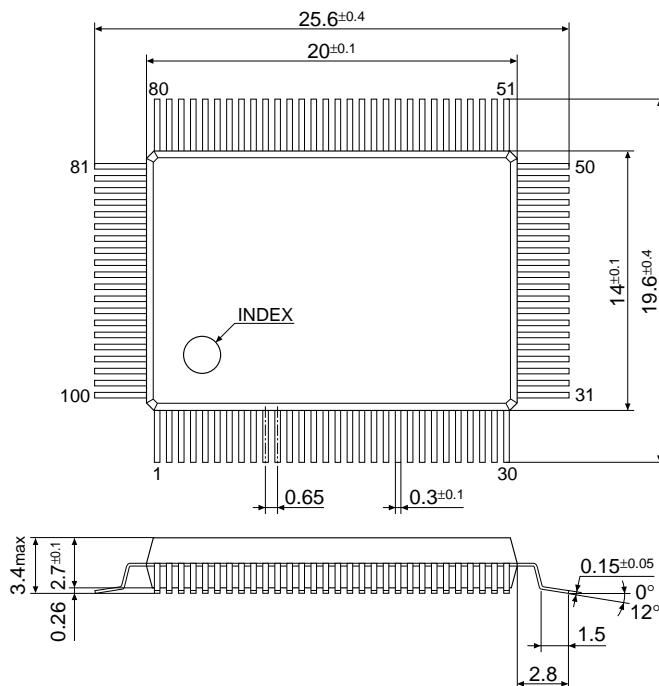

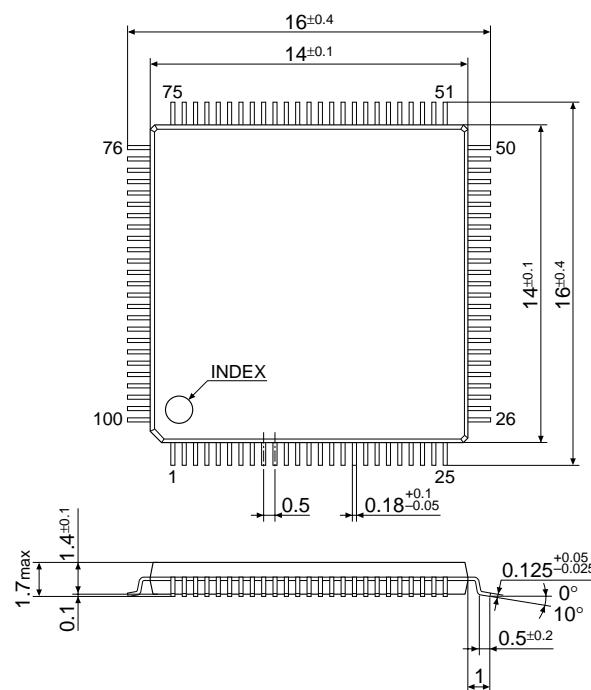

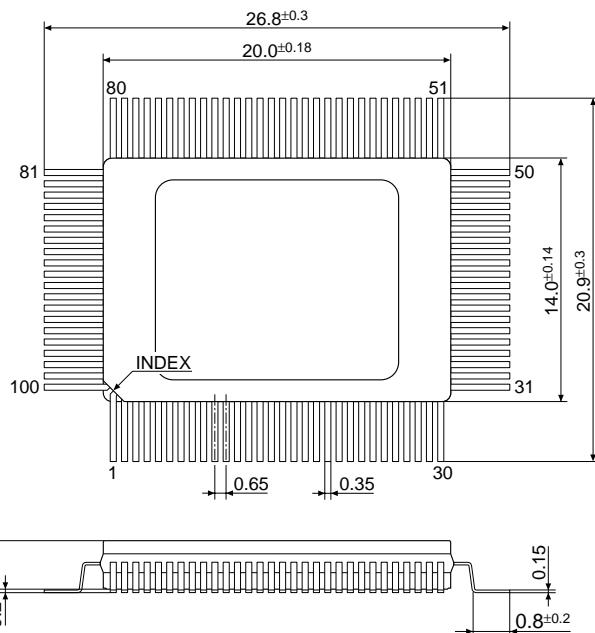

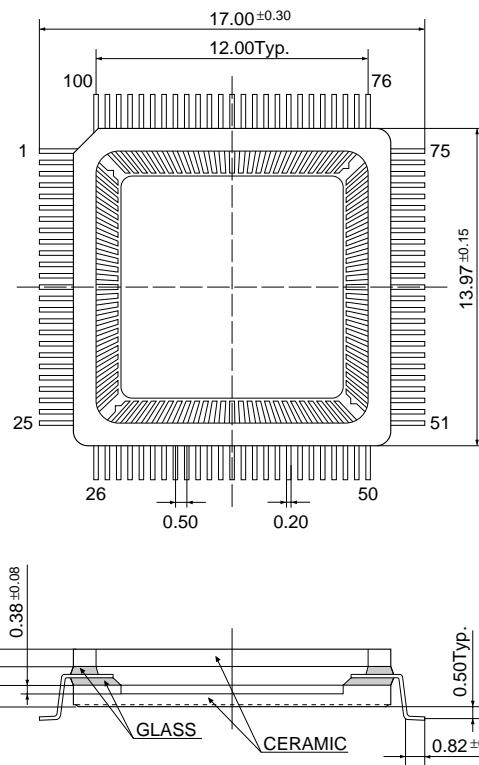

| 8      | パッケージ                | I-98  |

| 8.1    | プラスチックパッケージ          | I-98  |

| 8.2    | テストサンプル用セラミックパッケージ   | I-99  |

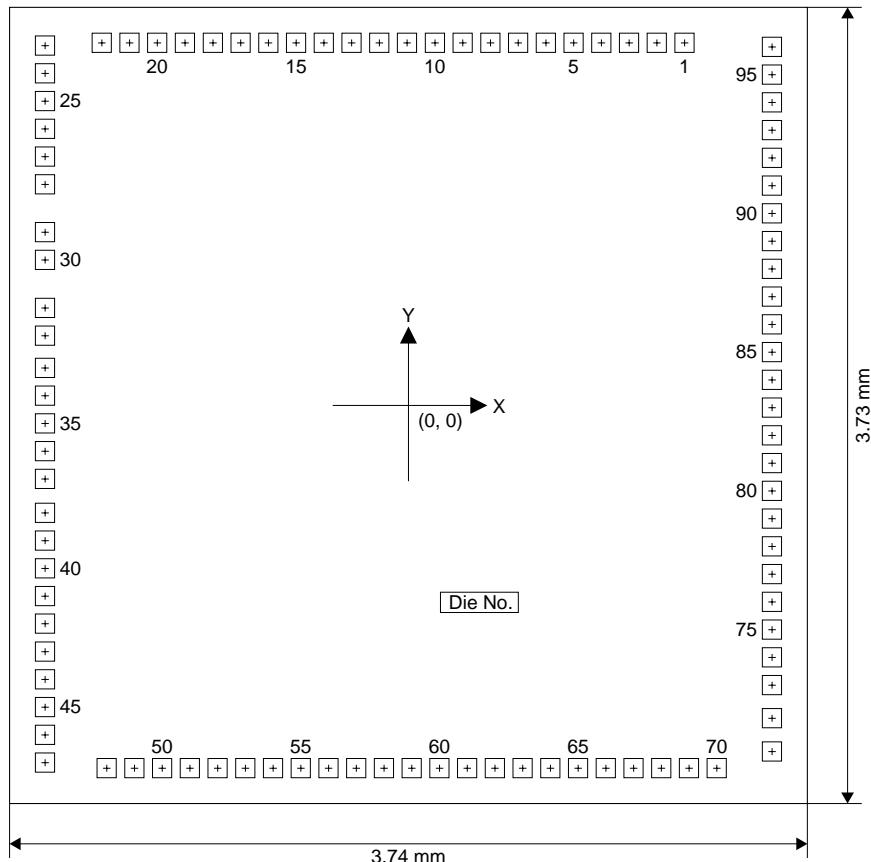

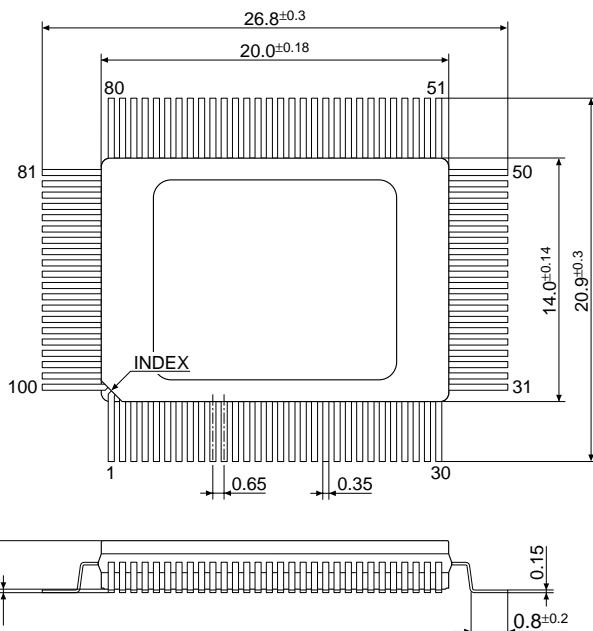

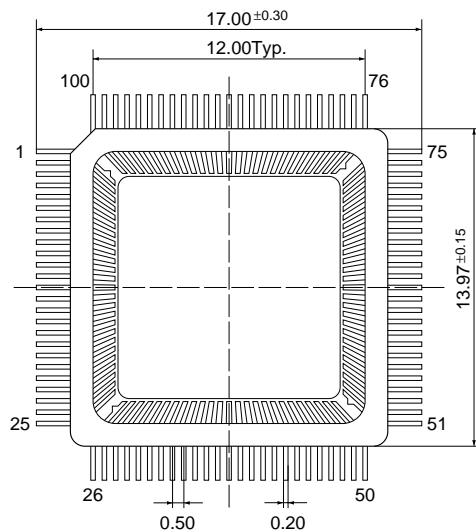

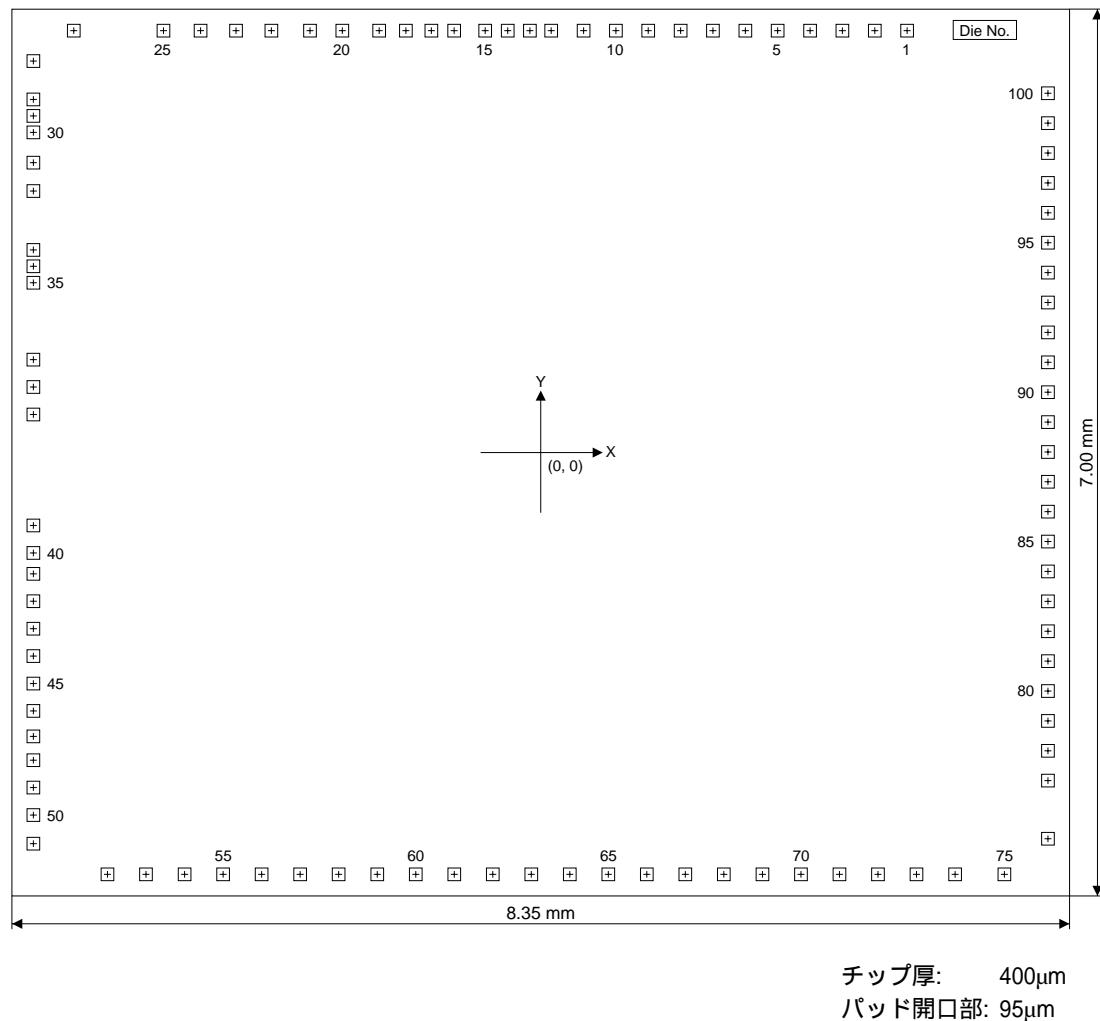

| 9      | パッド配置                | I-100 |

| 9.1    | パッド配置図               | I-100 |

| 9.2    | パッド座標                | I-101 |

# 1 概要

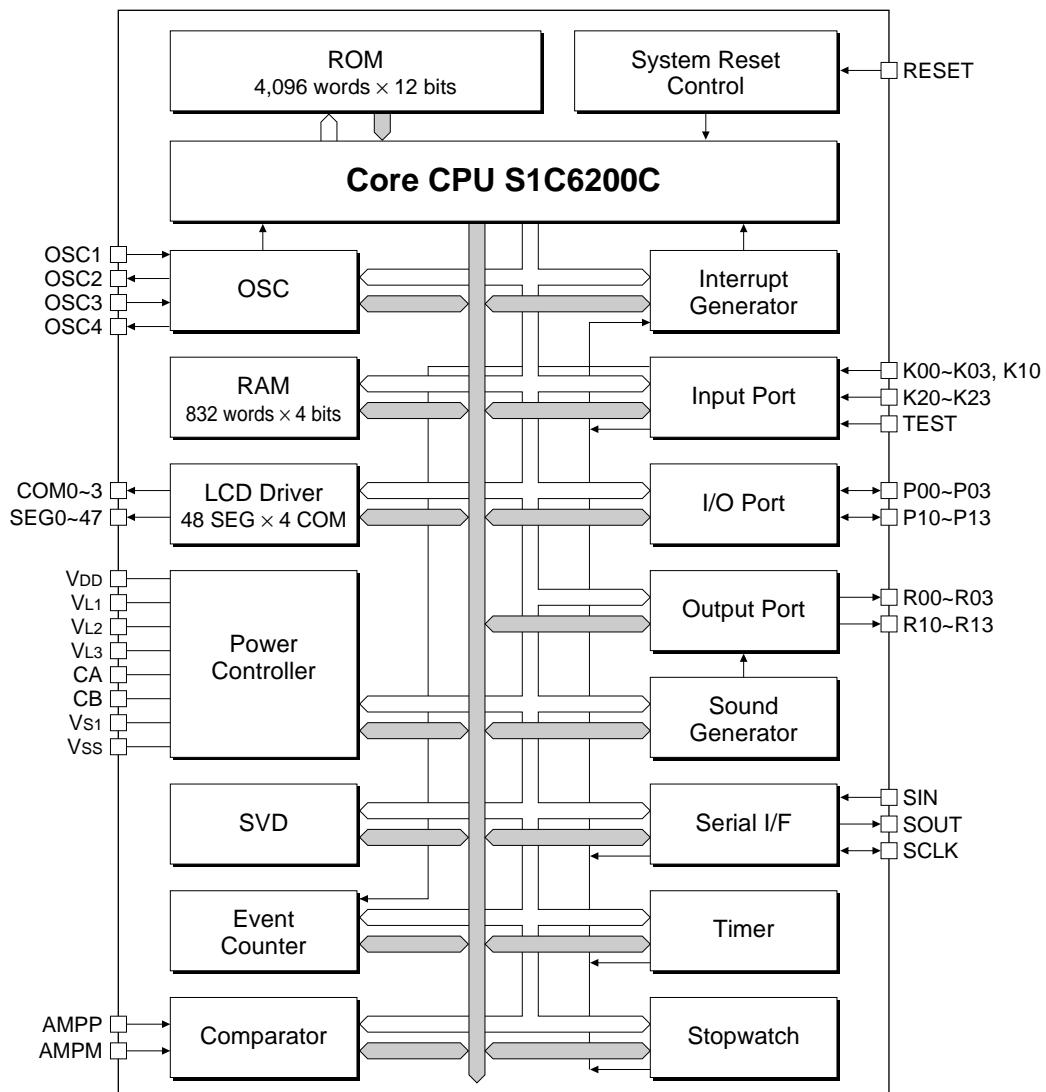

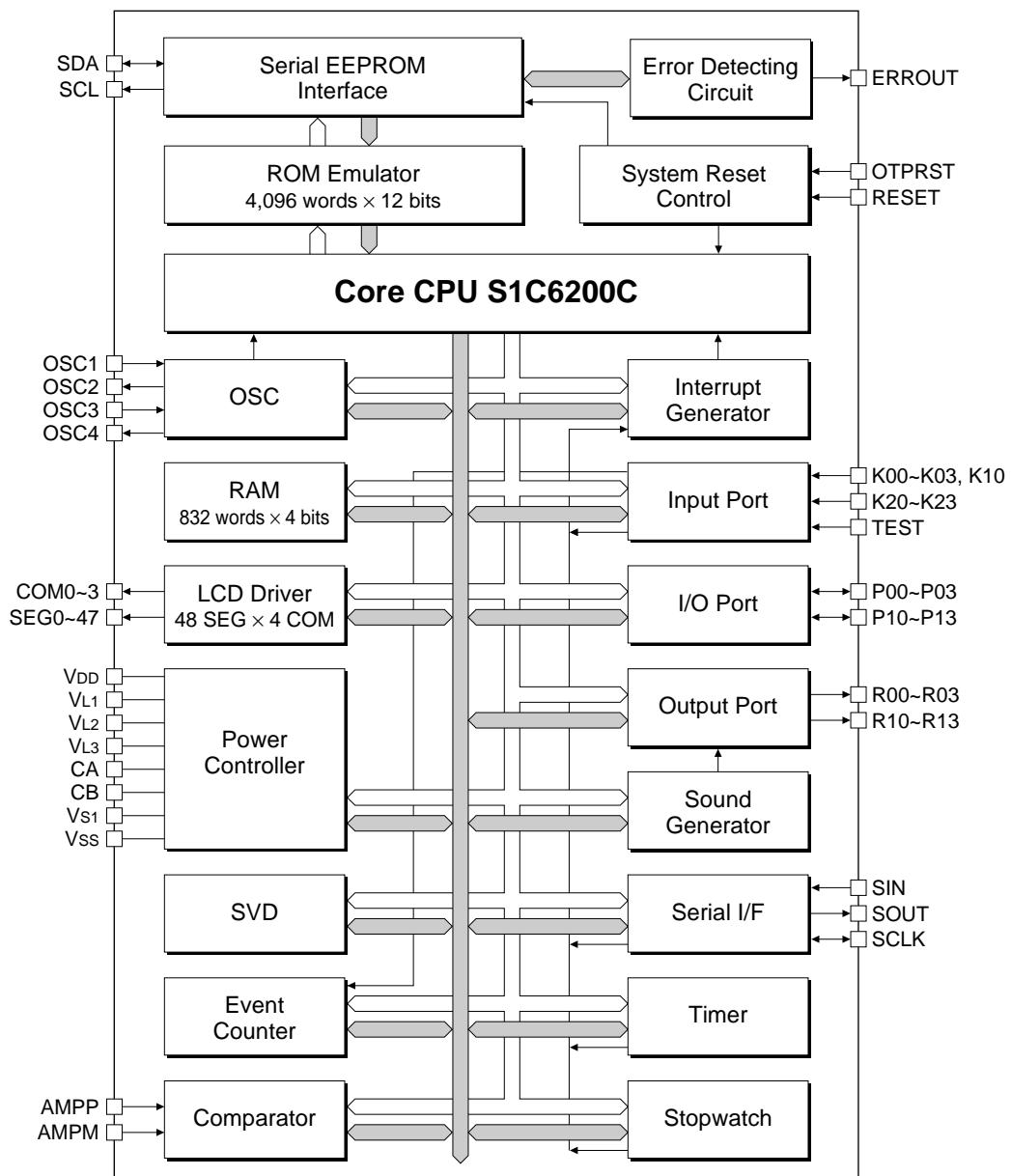

S1C60N08シリーズは4ビットコアCPU S1C6200Cを中心にして、ワンチップ上にROM(4,096ワード×12ビット)、RAM(832ワード×4ビット)、LCDドライバ、シリアルインターフェース、ダイアル入力機能付イベントカウンタ、ウォッチドッグタイマ、2系統のタイムベースカウンタ等を内蔵したマイクロコンピュータです。低電圧動作、低消費電力であるため、特に電池駆動を必要とする各種のシステムへの応用に最適です。

## 1.1 機種構成

S1C60N08シリーズは使用する電源電圧と発振回路により、以下の機種構成となります。

表1.1.1 機種構成

| 機種     | S1C60N08             | S1C60A08                | S1C60L08             |

|--------|----------------------|-------------------------|----------------------|

| 電源電圧   | 3.0V                 | 3.0V                    | 1.5V                 |

| 発振回路   | OSC1のみ<br>(シングルクロック) | OSC1, OSC3<br>(ツインクロック) | OSC1のみ<br>(シングルクロック) |

| 評価用ツール | S1C60R08             | —                       | —                    |

## 1.2 特長

表1.2.1 特長

| 機種                                      | S1C60N08/S1C60R08                                                                      | S1C60L08             | S1C60A08/S1C60R08                              |

|-----------------------------------------|----------------------------------------------------------------------------------------|----------------------|------------------------------------------------|

| OSC1発振回路                                | 水晶発振回路 32.768kHz (Typ.)/38.400kHz (Typ.)                                               | —                    | —                                              |

| OSC3発振回路                                | —                                                                                      | —                    | CRまたはセラミック発振回路(マスクオプションにて選択)<br>500 kHz (Typ.) |

| 命令セット                                   | 108種類                                                                                  | —                    | —                                              |

| 命令実行時間<br>(命令により異なる)<br>(CLK: CPU動作周波数) | 153μsec, 214μsec, 366μsec (CLK=32.768kHz)<br>130μsec, 182μsec, 313μsec (CLK=38.400kHz) | —                    | 10μsec, 14μsec, 24μsec<br>(CLK=500kHz)         |

| ROM容量                                   | 4,096ワード×12ビット                                                                         | —                    | —                                              |

| RAM容量                                   | 832ワード×4ビット                                                                            | —                    | —                                              |

| 入力ポート                                   | 9ビット(マスクオプションにてプルダウン抵抗の付加が可能)                                                          | —                    | —                                              |

| 出力ポート                                   | 8ビット(マスクオプションにてBZ, BZ̄, FOUT, SIOF出力が可能)                                               | —                    | —                                              |

| 入出力兼用ポート                                | 8ビット(入力データ読み込み時にプルダウン)                                                                 | —                    | —                                              |

| シリアルインターフェース                            | 1ポート(8ビットクロック同期式)                                                                      | —                    | —                                              |

| LCDドライバ                                 | 48セグメント×4, 3または2コモン(マスクオプションにて選択)<br>V-3V 1/4, 1/3または1/2デューティ(定電圧回路/昇圧回路を内蔵)           | —                    | —                                              |

| タイムベースカウンタ                              | 2系統(タイマおよびストップウォッチ)                                                                    | —                    | —                                              |

| ウォッチドッグタイマ                              | 内蔵(マスクオプションで未使用も可)                                                                     | —                    | —                                              |

| イベントカウンタ                                | 8ビット2入力(ダイアル入力判定型または独立型)                                                               | —                    | —                                              |

| サウンドジェネレータ                              | 8音(8周波数)プログラマブル                                                                        | —                    | —                                              |

| アナログコンバータ                               | デジタルエンベロープ機能(マスクオプションで未使用も可)                                                           | —                    | —                                              |

| 電源電圧検出回路 (BLD)                          | 反転入力×1, 非反転入力×1                                                                        | 2系統(8値プログラマブルおよび固定値) | 2.4V, 2.2~2.55V                                |

| 外部割り込み                                  | —                                                                                      | 2.4V, 1.05~1.4V      | 2.4V, 2.2~2.55V                                |

| 内部割り込み                                  | —                                                                                      | —                    | —                                              |

| 電源電圧                                    | 3.0V(1.8~3.5V)                                                                         | 1.5V(0.9~1.7V)       | 3.0V(2.2~3.5V)                                 |

| 消費電流<br>(Typ.値)                         | CLK=32.768kHz<br>(HALT時)<br>CLK=32.768kHz<br>(実行時)<br>CLK=500kHz<br>(実行時)              | 1.0μA<br>2.2μA<br>—  | 1.1μA<br>3.0μA<br>50μA                         |

| 出荷形態                                    | QFP5-100pin, QFP15-100pinまたはチップ                                                        | —                    | —                                              |

## 1.3 ブロック図

図1.3.1 ブロック図

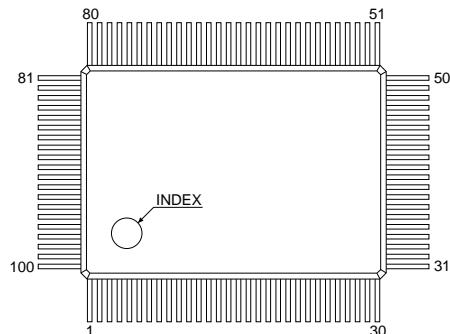

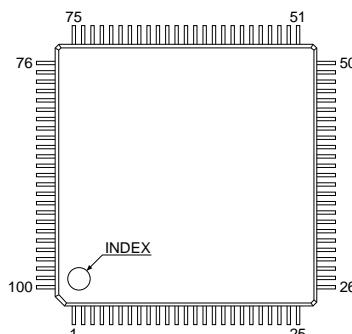

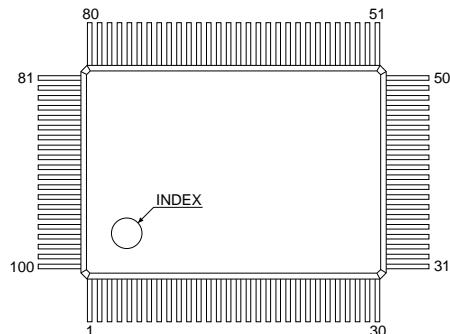

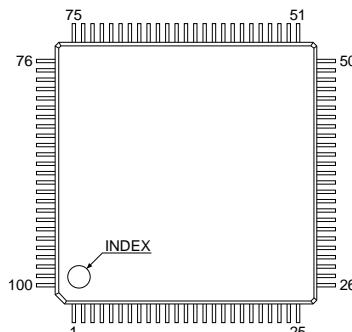

## 1.4 端子配置図

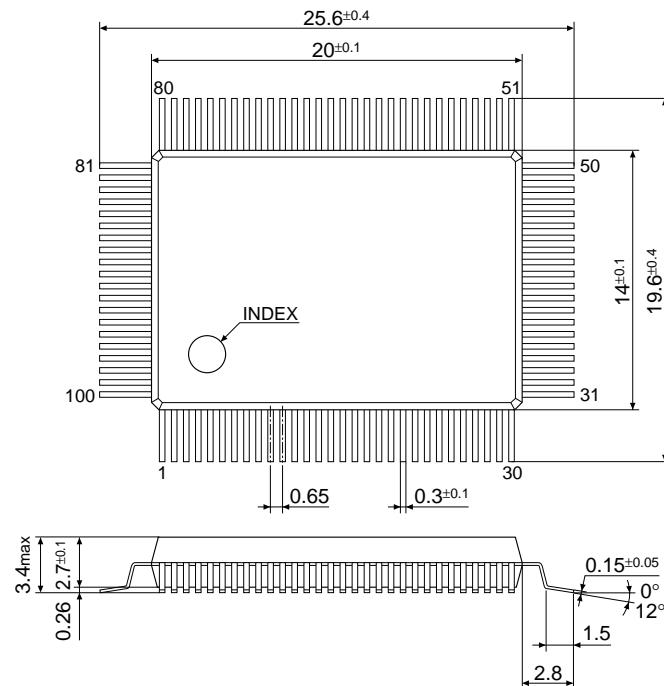

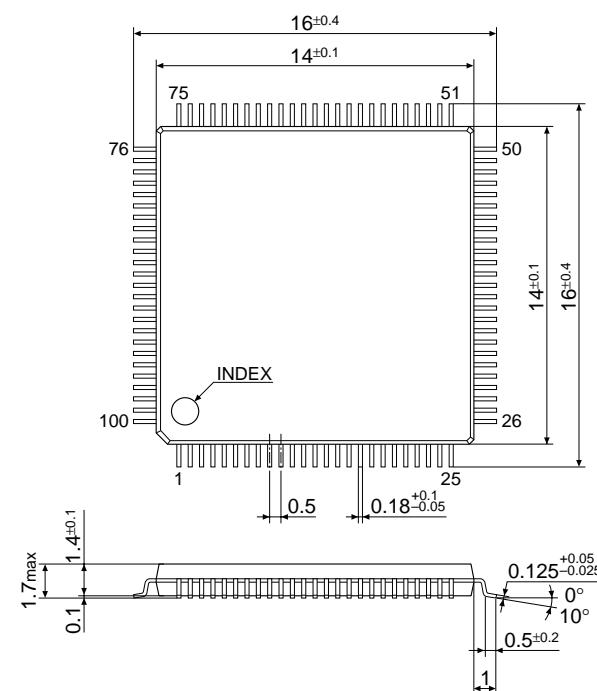

QFP5-100pin

| No. | 端子名   | No. | 端子名   | No. | 端子名  | No. | 端子名   |

|-----|-------|-----|-------|-----|------|-----|-------|

| 1   | COM1  | 26  | SEG24 | 51  | SEG0 | 76  | P10   |

| 2   | COM0  | 27  | TEST  | 52  | AMPP | 77  | R03   |

| 3   | SEG47 | 28  | SEG23 | 53  | AMPM | 78  | R02   |

| 4   | SEG46 | 29  | SEG22 | 54  | K23  | 79  | R01   |

| 5   | SEG45 | 30  | SEG21 | 55  | K22  | 80  | R00   |

| 6   | SEG44 | 31  | SEG20 | 56  | K21  | 81  | R12   |

| 7   | SEG43 | 32  | SEG19 | 57  | K20  | 82  | R11   |

| 8   | SEG42 | 33  | SEG18 | 58  | K10  | 83  | R10   |

| 9   | SEG41 | 34  | SEG17 | 59  | K03  | 84  | R13   |

| 10  | SEG40 | 35  | SEG16 | 60  | K02  | 85  | VSS   |

| 11  | SEG39 | 36  | SEG15 | 61  | K01  | 86  | RESET |

| 12  | SEG38 | 37  | SEG14 | 62  | K00  | 87  | OSC4  |

| 13  | SEG37 | 38  | SEG13 | 63  | SIN  | 88  | OSC3  |

| 14  | SEG36 | 39  | SEG12 | 64  | SOUT | 89  | VSS1  |

| 15  | SEG35 | 40  | SEG11 | 65  | N.C. | 90  | OSC2  |

| 16  | SEG34 | 41  | SEG10 | 66  | SCLK | 91  | OSC1  |

| 17  | SEG33 | 42  | SEG9  | 67  | P03  | 92  | VDD   |

| 18  | SEG32 | 43  | SEG8  | 68  | P02  | 93  | VL3   |

| 19  | SEG31 | 44  | SEG7  | 69  | P01  | 94  | VL2   |

| 20  | SEG30 | 45  | SEG6  | 70  | P00  | 95  | VL1   |

| 21  | SEG29 | 46  | SEG5  | 71  | N.C. | 96  | CA    |

| 22  | SEG28 | 47  | SEG4  | 72  | N.C. | 97  | CB    |

| 23  | SEG27 | 48  | SEG3  | 73  | P13  | 98  | N.C.  |

| 24  | SEG26 | 49  | SEG2  | 74  | P12  | 99  | COM3  |

| 25  | SEG25 | 50  | SEG1  | 75  | P11  | 100 | COM2  |

N.C. = No connection

QFP15-100pin

| No. | 端子名   | No. | 端子名   | No. | 端子名  | No. | 端子名   |

|-----|-------|-----|-------|-----|------|-----|-------|

| 1   | SEG47 | 26  | SEG23 | 51  | AMPP | 76  | R02   |

| 2   | SEG46 | 27  | SEG22 | 52  | AMPM | 77  | R01   |

| 3   | SEG45 | 28  | SEG21 | 53  | K23  | 78  | R00   |

| 4   | SEG44 | 29  | SEG20 | 54  | K22  | 79  | R12   |

| 5   | SEG43 | 30  | SEG19 | 55  | K21  | 80  | R11   |

| 6   | SEG42 | 31  | SEG18 | 56  | K20  | 81  | R10   |

| 7   | SEG41 | 32  | SEG17 | 57  | K10  | 82  | R13   |

| 8   | SEG40 | 33  | SEG16 | 58  | K03  | 83  | VSS   |

| 9   | SEG39 | 34  | SEG15 | 59  | K02  | 84  | RESET |

| 10  | SEG38 | 35  | SEG14 | 60  | K01  | 85  | OSC4  |

| 11  | SEG37 | 36  | SEG13 | 61  | K00  | 86  | OSC3  |

| 12  | SEG36 | 37  | SEG12 | 62  | SIN  | 87  | VSS1  |

| 13  | SEG35 | 38  | N.C.  | 63  | SOUT | 88  | OSC2  |

| 14  | SEG34 | 39  | SEG11 | 64  | N.C. | 89  | OSC1  |

| 15  | SEG33 | 40  | SEG10 | 65  | SCLK | 90  | VDD   |

| 16  | SEG32 | 41  | SEG9  | 66  | N.C. | 91  | VL3   |

| 17  | SEG31 | 42  | SEG8  | 67  | P03  | 92  | VL2   |

| 18  | SEG30 | 43  | SEG7  | 68  | P02  | 93  | VL1   |

| 19  | SEG29 | 44  | SEG6  | 69  | P01  | 94  | CA    |

| 20  | SEG28 | 45  | SEG5  | 70  | P00  | 95  | CB    |

| 21  | SEG27 | 46  | SEG4  | 71  | P13  | 96  | N.C.  |

| 22  | SEG26 | 47  | SEG3  | 72  | P12  | 97  | COM3  |

| 23  | SEG25 | 48  | SEG2  | 73  | P11  | 98  | COM2  |

| 24  | SEG24 | 49  | SEG1  | 74  | P10  | 99  | COM1  |

| 25  | TEST  | 50  | SEG0  | 75  | R03  | 100 | COM0  |

N.C. = No connection

図1.4.1 端子配置図

## 1.5 端子説明

表1.5.1 端子説明

| 端子名             | 端子No.                      |                       | I/O | 機能                                                     |

|-----------------|----------------------------|-----------------------|-----|--------------------------------------------------------|

|                 | QFP5-100                   | QFP15-100             |     |                                                        |

| VDD             | 92                         | 90                    | (I) | 電源端子(+)                                                |

| VSS             | 85                         | 83                    | (I) | 電源端子(-)                                                |

| V <sub>S1</sub> | 89                         | 87                    | —   | 発振および内部ロジック系動作電圧出力端子                                   |

| V <sub>L1</sub> | 95                         | 93                    | —   | LCD駆動電圧出力端子(約-1.05Vまたは1/2·V <sub>L2</sub> )            |

| V <sub>L2</sub> | 94                         | 92                    | —   | LCD駆動電圧出力端子(2·V <sub>L1</sub> または約-2.10V)              |

| V <sub>L3</sub> | 93                         | 91                    | —   | LCD駆動電圧出力端子(3·V <sub>L1</sub> または3/2·V <sub>L2</sub> ) |

| CA, CB          | 96, 97                     | 94, 95                | —   | 昇圧コンデンサ接続端子                                            |

| OSC1            | 91                         | 89                    | I   | 水晶発振入力端子                                               |

| OSC2            | 90                         | 88                    | O   | 水晶発振出力端子                                               |

| OSC3            | 88                         | 86                    | I   | CRまたはセラミック発振入力端子 *(S1C60N08/60L08はN.C.)                |

| OSC4            | 87                         | 85                    | O   | CRまたはセラミック発振出力端子 *(S1C60N08/60L08はN.C.)                |

| K00~K03         | 62~59                      | 61~58                 | I   | 入力ポート端子                                                |

| K10             | 58                         | 57                    | I   | 入力ポート端子                                                |

| K20~K23         | 57~54                      | 56~53                 | I   | 入力ポート端子                                                |

| P00~P03         | 70~67                      | 70~67                 | I/O | 入出力兼用ポート端子                                             |

| P10~P13         | 76~73                      | 74~71                 | I/O | 入出力兼用ポート端子                                             |

| R00~R03         | 80~77                      | 78~75                 | O   | 出力ポート端子                                                |

| R10             | 83                         | 81                    | O   | 出力ポート端子またはBZ出力端子 *                                     |

| R13             | 84                         | 82                    | O   | 出力ポート端子またはBZ出力端子 *                                     |

| R11             | 82                         | 80                    | O   | 出力ポート端子またはSIOF出力端子 *                                   |

| R12             | 81                         | 79                    | O   | 出力ポート端子またはFOUT出力端子 *                                   |

| SIN             | 63                         | 62                    | I   | シリアルインターフェースデータ入力端子                                    |

| SOUT            | 64                         | 63                    | O   | シリアルインターフェースデータ出力端子                                    |

| SCLK            | 66                         | 65                    | I/O | シリアルインターフェースクロック入出力端子                                  |

| AMPP            | 52                         | 51                    | I   | アナログコンパレータ非反転入力端子                                      |

| AMPM            | 53                         | 52                    | I   | アナログコンパレータ反転入力端子                                       |

| SEG0~47         | 51~28, 26~3<br>37~26, 24~1 | 50~39,<br>37~26, 24~1 | O   | LCDセグメント出力端子<br>またはDC出力端子 *                            |

| COM0~3          | 2, 1, 100, 99              | 100~97                | O   | LCDコモン出力端子(1/2, 1/3または1/4デューティを選択可能 *)                 |

| RESET           | 86                         | 84                    | I   | イニシャルリセット入力端子                                          |

| TEST            | 27                         | 25                    | I   | テスト用入力端子                                               |

\* マスクオプションにて選択

## 1.6 S1C60N08オプションリスト

S1C60N08には以下のファンクションオプションが設定されています。各周辺回路説明を参考にしてシステムに合った内容を選択してください。なお、使用しないポートについてもオプション設定が必要です。

### 1 機種 ... DEVICE TYPE

- 機種 ..... 1. S1C60N08 (NORMAL TYPE)

2. S1C60L08 (LOW POWER TYPE)

3. S1C60A08 (TWIN CLOCK TYPE)

- Evaluation board用

OSC1クロック ..... 1. 32kHz 2. 38kHz

### 2 OSC3発振回路 ... OSC3 SYSTEM CLOCK (S1C60A08選択時)

- 1. CR発振回路 2. セラミック発振回路

- [3] キー同時押しリセット ... MULTIPLE KEY ENTRY RESET**

- ・組み合わせ ..... 1. 使用しない

2. 使用する K00, K01

3. 使用する K00, K01, K02

4. 使用する K00, K01, K02, K03

- ・時間検定 ..... 1. 使用する ..... 2. 使用しない

- [4] ウォッチドッグタイマ ... WATCHDOG TIMER**

- 1. 使用する ..... 2. 使用しない

- [5] 入力割り込み ノイズリジェクト ... INPUT INTERRUPT NOISE REJECTOR**

- ・K00～K03 ..... 1. 使用する ..... 2. 使用しない

・K10 ..... 1. 使用する ..... 2. 使用しない

・K20～K23 ..... 1. 使用する ..... 2. 使用しない

- [6] 入力ポート プルダウン抵抗 ... INPUT PORT PULL DOWN RESISTOR**

- ・K00 ..... 1. あり ..... 2. なし

・K01 ..... 1. あり ..... 2. なし

・K02 ..... 1. あり ..... 2. なし

・K03 ..... 1. あり ..... 2. なし

・K10 ..... 1. あり ..... 2. なし

・K20 ..... 1. あり ..... 2. なし

・K21 ..... 1. あり ..... 2. なし

・K22 ..... 1. あり ..... 2. なし

・K23 ..... 1. あり ..... 2. なし

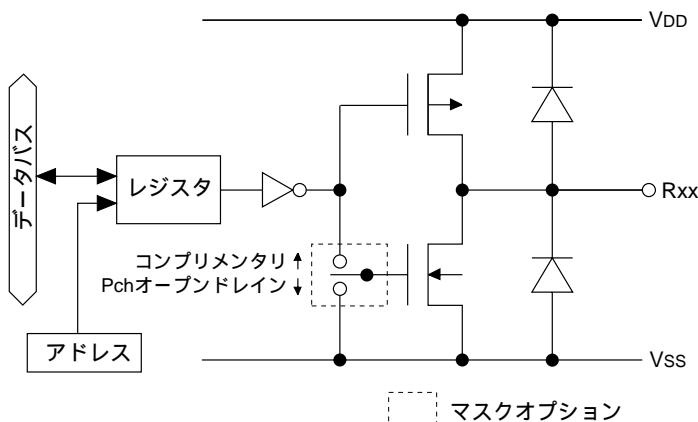

- [7] 出力ポート 出力仕様 ... OUTPUT PORT OUTPUT SPECIFICATION (R00～R03)**

- ・R00 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・R01 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・R02 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・R03 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

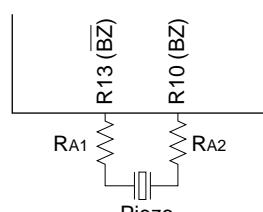

- [8] R10 端子仕様 ... R10 SPECIFICATION**

- ・出力仕様 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・出力形式 ..... 1. DC出力 ..... 2. ブザー出力

- [9] R11 端子仕様 ... R11 SPECIFICATION**

- ・出力仕様 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・出力形式 ..... 1. DC出力 ..... 2. SIOフラグ

- [10] R12 端子仕様 ... R12 SPECIFICATION**

- ・出力仕様 ..... 1. コンプリメンタリ ..... 2. Pchオーブンドレイン

・出力形式 ..... 1. DC出力

2. FOUT 32768 or 38400 [Hz]

3. FOUT 16384 or 19200 [Hz]

4. FOUT 8192 or 9600 [Hz]

5. FOUT 4096 or 4800 [Hz]

6. FOUT 2048 or 2400 [Hz]

7. FOUT 1024 or 1200 [Hz]

8. FOUT 512 or 600 [Hz]

9. FOUT 256 or 300 [Hz]

- [11] R13 端子仕様 . . . R13 SPECIFICATION**

- ・出力仕様 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・出力形式 ..... 1. DC出力

- 2. ブザー反転出力(R13ポートによる制御)

- 3. ブザー反転出力(R10ポートによる制御)

- [12] 入出力兼用ポート 出力仕様 . . . I/O PORT SPECIFICATION**

- ・P00 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P01 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P02 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P03 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P10 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P11 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P12 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・P13 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- [13] SINプルダウン抵抗 . . . SIN PULL DOWN RESISTOR**

- 1. あり 2. なし

- [14] SOUT出力仕様 . . . SOUT SPECIFICATION**

- 1. コンプリメンタリ 2. Pchオーブンドレイン

- [15] SCLK端子仕様 . . . SCLK SPECIFICATION**

- ・プルダウン抵抗 ..... 1. あり 2. なし

- ・出力仕様 ..... 1. コンプリメンタリ 2. Pchオーブンドレイン

- ・論理 ..... 1. 正 2. 負

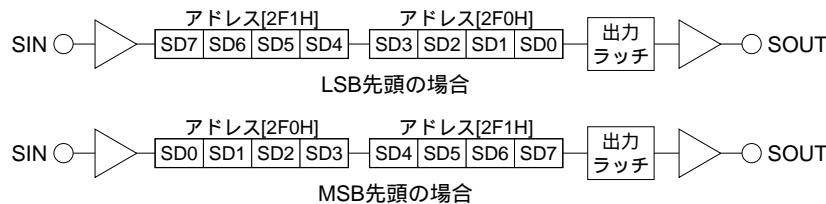

- [16] SIOデータ順列 . . . SIO DATA PERMUTATION**

- 1. MSB先頭 2. LSB先頭

- [17] イベントカウンタ ノイズリジェクト . . . EVENT COUNTER NOISE REJECTOR**

- 1. 2048 or 2400 [Hz] 2. 256 or 300 [Hz]

- [18] LCD仕様 . . . LCD SPECIFICATION**

- ・バイアス選択

- S1C60N08 ..... 1. 1/3バイアス, 定電圧回路を使用, 3V LCD

- 2. 1/3バイアス, 定電圧回路を使用しない, 3V LCD

- 3. 1/2バイアス, 定電圧回路を使用しない, 3V LCD

- 4. 1/3バイアス, 定電圧回路を使用しない, 4.5V LCD

- S1C60L08 ..... 1. 1/3バイアス, 定電圧回路を使用, 3V LCD

- 2. 1/2バイアス, 定電圧回路を使用しない, 3V LCD

- 3. 1/3バイアス, 定電圧回路を使用しない, 4.5V LCD

- S1C60A08 ..... 1. 1/3バイアス, 定電圧回路を使用, 3V LCD

- 2. 1/3バイアス, 定電圧回路を使用しない, 3V LCD

- 3. 1/2バイアス, 定電圧回路を使用しない, 3V LCD

- 4. 1/3バイアス, 定電圧回路を使用しない, 4.5V LCD

- ・デューティ ..... 1. 1/4デューティ

- 2. 1/3デューティ

- 3. 1/2デューティ

- [19] セグメントメモリアドレス . . . SEGMENT MEMORY ADDRESS**

- 1. 0ページ (040~06F) 2. 2ページ (240~26F)

## 2 電源系 および イニシャルリセット

### 2.1 電源系

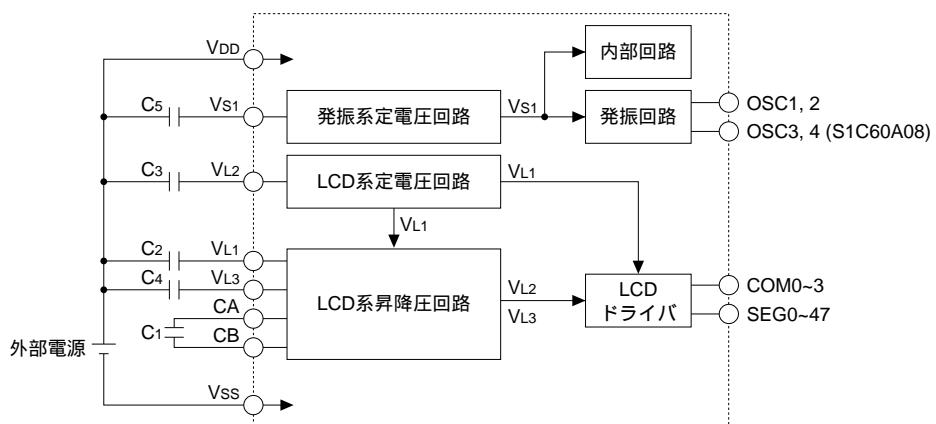

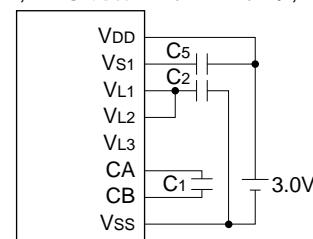

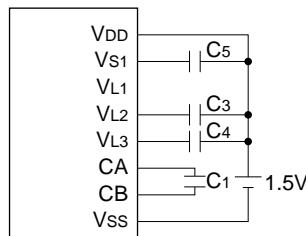

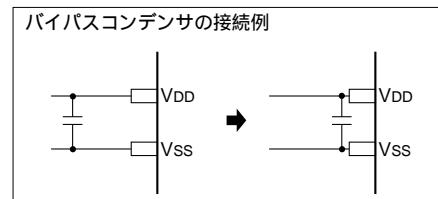

S1C60N08シリーズは外部より単一電源(\*1)をVDD～VSS間に与えることにより、内部で必要な電圧を定電圧回路(発振系<Vs1>、LCD系<VL1またはVL2>)および昇降圧回路( LCD系<VL2とVL3またはVL1とVL3>)により発生します。

\*1 電源電圧：S1C60N08/60A08 … 3V、S1C60L08 … 1.5V

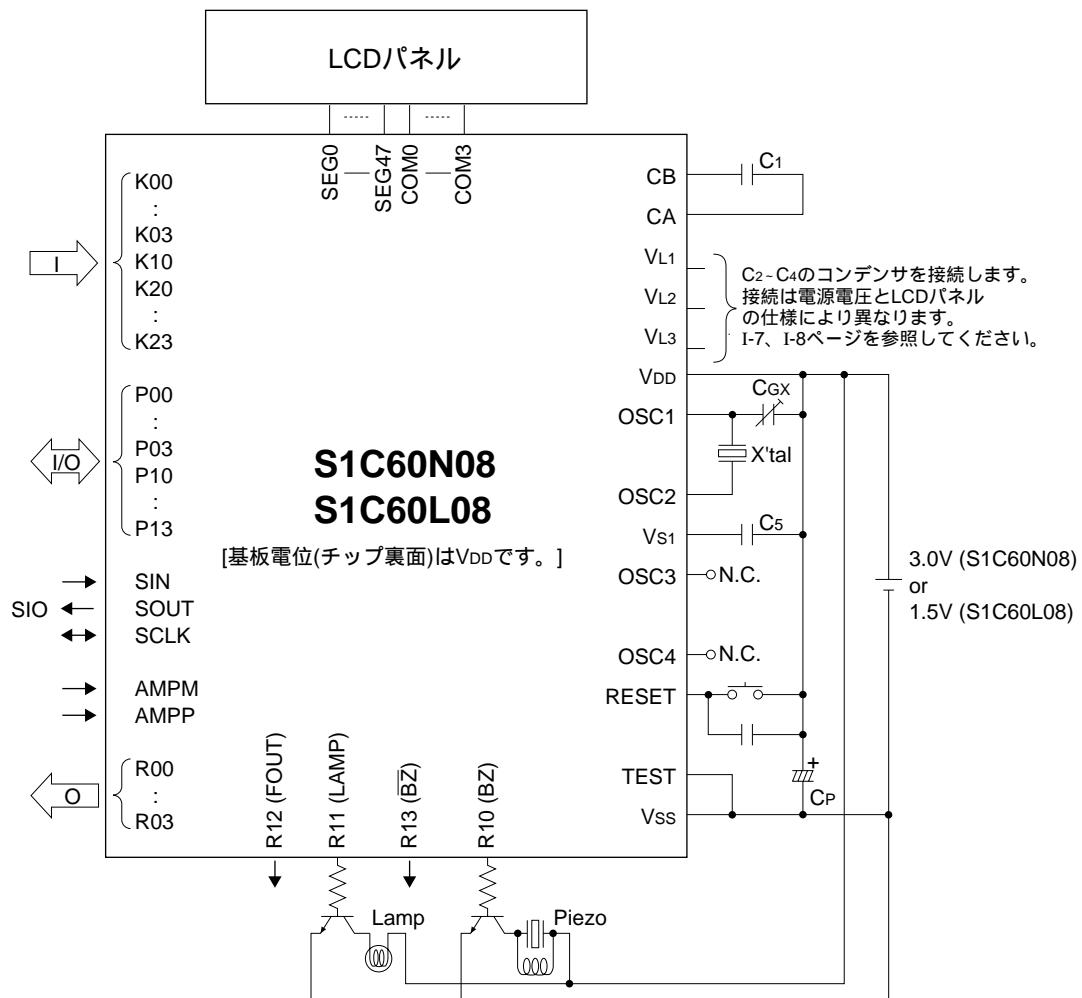

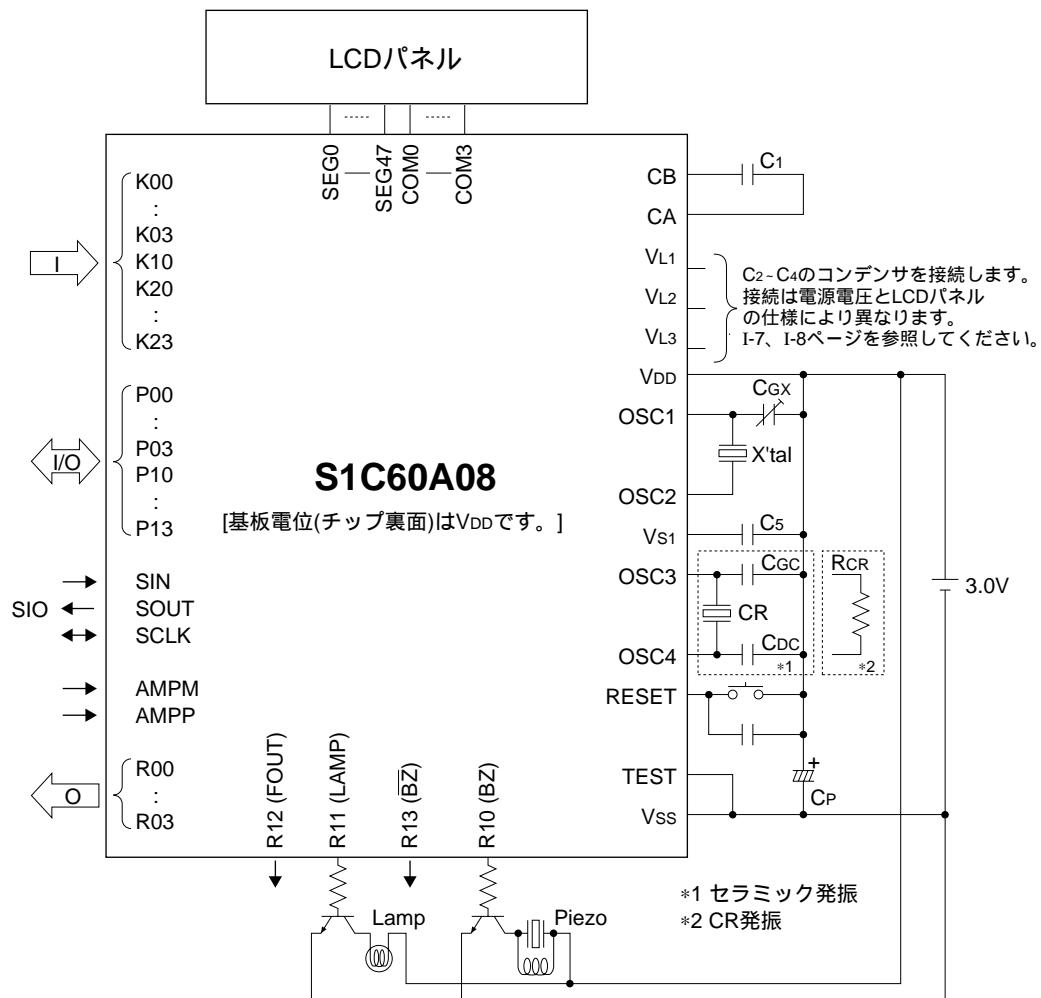

図2.1.1にS1C60N08、図2.1.2にS1C60A08/60L08の電源系の構成を示します。

内部回路の動作電圧<Vs1>は、発振系定電圧回路が発生します。

S1C60N08のLCD駆動電圧は、<VL2>をLCD系定電圧回路で、<VL1>と<VL3>を昇降圧回路で発生します。S1C60A08とS1C60L08は<VL1>をLCD系定電圧回路で、<VL2>と<VL3>を昇降圧回路で発生します。

- 注：

- 定電圧回路および昇降圧回路の出力電圧による外付け負荷の駆動は禁止します。

- 電圧値については"7 電気的特性"を参照してください。

図2.1.1 S1C60N08電源系の構成

図2.1.2 S1C60A08/60L08電源系の構成

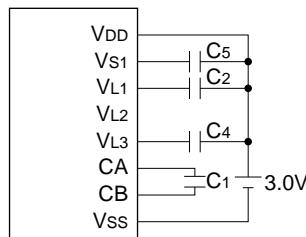

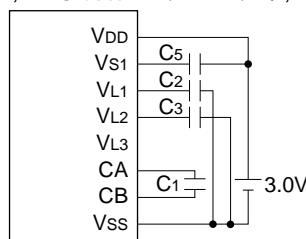

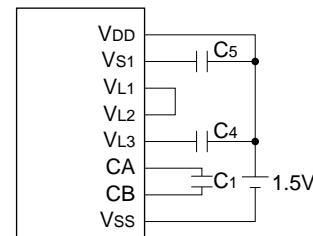

マスクオプションによりLCD系定電圧回路を使用しない構成にすることもできます。この場合、LCD系定電圧回路用のコンデンサが不要となりますので、外付け素子を削減できます。ただし、LCD系定電圧回路を使用しない場合には、使用する場合に比べて電源電圧変動(低下)時のLCDの表示品質が劣化します。

図2.1.3にLCD系定電圧回路を使用しない場合の外付け部品の構成を示します。

#### 4.5V LCDパネル

1/4, 1/3または1/2デューティ, 1/3バイアス

注: IC内部でVL2とVssが短絡されます。

#### 3V LCDパネル

1/4, 1/3または1/2デューティ, 1/3バイアス

#### 3V LCDパネル

1/4, 1/3または1/2デューティ, 1/2バイアス

注: IC内部でVL3とVssが短絡されます。

#### 4.5V LCDパネル

1/4, 1/3または1/2デューティ, 1/3バイアス

#### 3V LCDパネル

1/4, 1/3または1/2デューティ, 1/2バイアス

注: IC内部でVL1とVssが短絡されます。

### 図2.1.3 LCD系定電圧回路を使用しない場合の外付け部品の構成

注: すべての機種において、セグメント端子の一部あるいは全部をマスクオプションでDC出力に設定した場合、LCD系定電圧回路を使用することはできません。逆に、LCD系定電圧回路を使用する場合は、セグメント端子のDC出力は禁止されます。

表2.1.1 LCD系定電圧回路とセグメント端子によるDC出力

| LCD系定電圧回路 | SEG端子のDC出力 |

|-----------|------------|

| 使用する      | 不可         |

| 使用しない     | 可          |

## 2.2 イニシャルリセット

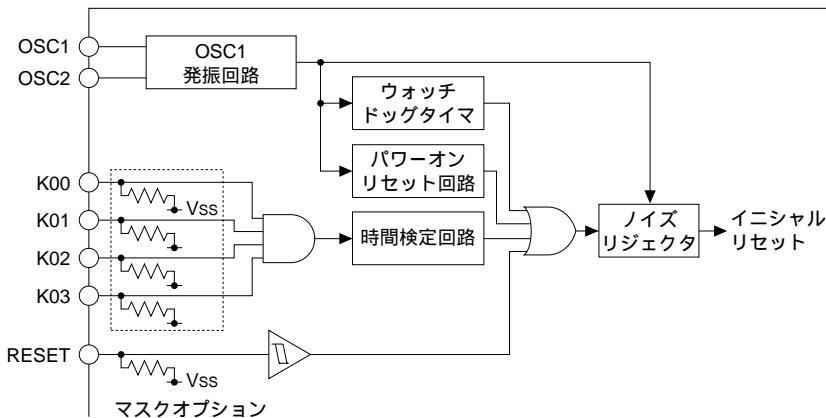

S1C60N08シリーズは回路を初期化するためにイニシャルリセットを必要とします。イニシャルリセット要因としては以下の4種類があります。

- (1)パワーオンリセット回路によるイニシャルリセット

- (2)RESET端子による外部イニシャルリセット

- (3)K00～K03端子の同時HIGHレベル入力による外部イニシャルリセット

- (4)ウォッチドッグタイマによるイニシャルリセット

図2.2.1にイニシャルリセット回路の構成を示します。

図2.2.1 イニシャルリセット回路の構成

### 2.2.1 パワーオンリセット回路

パワーオンリセット回路は、電源投入時に発振回路が発振を開始するまでイニシャルリセット信号を出力します。

注: パワーオンリセット回路は、不安定または低い電源電圧では正常に動作しない場合があります。イニシャルリセットには以下の2つの方法を推奨します。

### 2.2.2 リセット端子( RESET )

外部よりリセット端子をHIGHレベルにすることによりイニシャルリセットが行えます。イニシャルリセット回路はノイズリジェクト回路を内蔵しているため、5ms(発振周波数fosc1=32kHzの場合)以上HIGHレベルを保ってください。リセット端子がLOWレベルになると、CPUが動作を開始します。

### 2.2.3 入力ポート( K00～K03 )の同時HIGH入力

マスクオプションで選択された入力ポート( K00～K03 )に、外部から同時にHIGH入力を与えることによりイニシャルリセットが行えます。イニシャルリセット回路はノイズリジェクトを内蔵しているため、5ms(発振周波数fosc1=32kHzの場合)以上、指定入力ポート端子をHIGHレベルに保ってください。表2.2.3.1にマスクオプションで選択できる入力ポート( K00～K03 )の組合せを示します。

表2.2.3.1 入力ポートの組合せ

| 選択肢 | 組み合わせ           |

|-----|-----------------|

| A   | 使用しない           |

| B   | K00*K01         |

| C   | K00*K01*K02     |

| D   | K00*K01*K02*K03 |

たとえば、マスクオプションでDの"K00\*K01\*K02\*K03"を選択した場合、K00～K03の4ポートの入力が同時にHIGHレベルになったときにイニシャルリセットを行います。

また、同時HIGH入力の入力時間を検定し規定時間(1～2sec)以上の入力があったとき、イニシャルリセットを行う時間検定回路をマスクオプションで選択できます。

なお、この機能を使用する場合、通常動作時に指定ポートが同時にHIGHレベルにならないように注意してください。

#### 2.2.4 ウオッチドッグタイマ

ウォッチドッグタイマはCPUが何らかの原因で暴走した場合、その暴走を検出しイニシャルリセット信号を出力します。詳細は"4.2 ウォッチドッグタイマのリセット"を参照してください。

#### 2.2.5 イニシャルリセット時の内部レジスタ

イニシャルリセットによりCPUは以下のように初期化されます。

表2.2.5.1 初期設定値

| CPUコア         |     |      |       |

|---------------|-----|------|-------|

| 名 称           | 記号  | ビット長 | 初期設定値 |

| プログラムカウンタステップ | PCS | 8    | 00H   |

| プログラムカウンタページ  | PCP | 4    | 1H    |

| ニューページポインタ    | NPP | 4    | 1H    |

| スタックポインタ      | SP  | 8    | 不定    |

| インデックスレジスタX   | X   | 10   | 不定    |

| インデックスレジスタY   | Y   | 10   | 不定    |

| レジスタポインタ      | RP  | 4    | 不定    |

| 汎用レジスタA       | A   | 4    | 不定    |

| 汎用レジスタB       | B   | 4    | 不定    |

| インターラプトフラグ    | I   | 1    | 0     |

| デシマルフラグ       | D   | 1    | 0     |

| ゼロフラグ         | Z   | 1    | 不定    |

| キャリーフラグ       | C   | 1    | 不定    |

| 周辺回路     |      |       |

|----------|------|-------|

| 名 称      | ビット長 | 初期設定値 |

| RAM      | 4    | 不定    |

| 表示メモリ    | 4    | 不定    |

| その他の周辺回路 | 4    | *     |

\* "4.1 メモリマップ"参照

#### 2.3 テスト端子( TEST )

ICの出荷検査時に使用する端子です。通常動作時は必ずVssに接続してください。

## 3 CPU, ROM, RAM

### 3.1 CPU

S1C60N08シリーズはCPU部分に4ビットコアCPU S1C6200Cを使用しているため、レジスタ構成、命令等は他のS1C6200/6200A/6200B/6200Cを使用したファミリプロセッサとほぼ同様です。

コアCPUの詳細については"S1C6200/6200A Core CPU Manual"を参照してください。

なお、S1C60N08シリーズにおいては、以下の点に注意してください。

- (1) SLEEP動作を想定していないため、SLP命令は使用できません。

- (2) ROM容量は4,096ワードのためバンクビットの必要がなく、PCB、NBPは使用していません。

- (3) RAMは4ページまでの設定となっているため、アドレス指定を行うインデックスレジスタのページ部分( XP、YP )は下位2ビットのみ有効となります(上位2ビットは無視されます)。

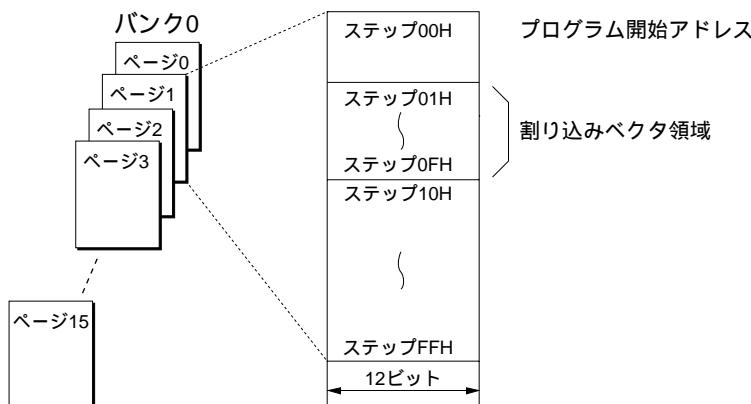

### 3.2 ROM

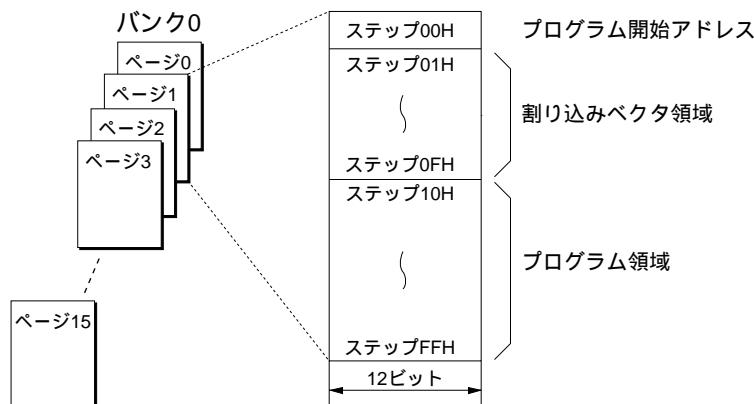

内蔵ROMはプログラム格納用のマスクROMで、4,096ステップ×12ビットの容量があります。プログラム領域は1(0～15)ページ×25(00H～FFH)ステップとなっており、イニシャルリセット後のプログラム開始番地が1ページ00Hステップに、割り込みベクタが1ページ01H～0FHステップに割り当てられています。

図3.2.1 ROMの構成

### 3.3 RAM

RAMは種々のデータを格納するデータメモリで、832ワード×4ビットの容量があります。プログラミングの際には以下の点に注意してください。

- (1) データメモリの一部をサブルーチンコールやレジスタ退避時のスタック領域としても使用しますので、データエリアとスタックエリアが重ならないように注意してください。

- (2) サブルーチンコール、割り込み等ではスタックエリアを3ワード消費します。

- (3) データメモリのアドレス000H～00FHはレジスタポインタ( RP )でアドレッシングされるメモリレジスタ領域です。

## 4 周辺回路と動作

S1C60N08シリーズの周辺回路( タイマ、I/O等 )はメモリマップドI/O方式で、CPUとインターフェースされています。このため、メモリマップ上のI/Oメモリをメモリ操作命令でアクセスすることにより、すべての周辺回路を制御することができます。

以下に、各周辺回路の動作について詳細に説明します。

### 4.1 メモリマップ

S1C60N08シリーズのデータメモリは865ワード( 表示メモリを2ページに配置した場合、913ワード )のアドレス空間を持っており、そのうち48ワードが表示メモリ、33ワードがI/Oメモリとして割り付けられています。

図4.1.1にS1C60N08シリーズの全体のメモリマップ、表4.1.1( a )~( c )に周辺回路( I/O空間 )のメモリマップを示します。

| Address<br>Page            | Low<br>High | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | A  | B  | C  | D  | E  | F  |

|----------------------------|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0                          | 0           | M0 | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 | M9 | MA | MB | MC | MD | ME | MF |

|                            | 1           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 2           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 3           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 4           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 5           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 6           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 7           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 8           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 9           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | A           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | B           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | C           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | D           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | E           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | F           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 1                          | 0           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 1           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 2           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 3           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 4           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 5           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 6           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 7           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 8           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | 9           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | A           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | B           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | C           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | D           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | E           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                            | F           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| RAM (256ワード × 4ビット)<br>R/W |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| RAM (64ワード × 4ビット)<br>R/W  |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 未使用領域                      |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| I/Oメモリ(表4.1.1参照)           |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| RAM (256ワード × 4ビット)<br>R/W |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| RAM (256ビット × 4ビット)<br>R/W |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

図4.1.1 メモリマップ

| Address<br>Page                           | Low<br>High | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

|-------------------------------------------|-------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 or 2                                    | 4           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                           | 5           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                           | 6           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 表示メモリ(48ワード × 4ビット)<br>0ページ: R/W, 2ページ: W |             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

図4.1.2 表示メモリマップ

- 注:

- 表示メモリは領域全体を0ページ( 040H ~ 06FH )か2ページ( 240H ~ 26FH )のどちらに配置するかマスクオプションで選択できます。

- 0ページ( 040H ~ 06FH )を選択すると表示メモリはRAM領域内に割り付けられ、読み出し/書き込みが可能となります。

- 2ページ( 240H ~ 26FH )を選択すると、表示メモリは書き込み専用となります。

- メモリマップ中の未使用領域、およびこの章で示されていないメモリ領域にはメモリが実装されていません。このため、これらの領域をアクセスするようなプログラムを作成した場合は、正常な動作を保証することはできません。

表4.1.1(a) I/Oメモリマップ(2D0H, 2E0H ~ 2ECH)

| アドレス | レジスタ  |       |         |         | Name                | Init *1 | 1          | 0       | コメント                        |

|------|-------|-------|---------|---------|---------------------|---------|------------|---------|-----------------------------|

|      | D3    | D2    | D1      | D0      |                     |         |            |         |                             |

| 2D0H | 0     | 0     | 0       | LOF     | 0 *3                | - *2    | -          | -       | 未使用                         |

|      |       |       |         |         | 0 *3                | - *2    | -          | -       | 未使用                         |

|      | R     |       | R/W     |         | 0 *3                | - *2    | -          | -       | 未使用                         |

|      |       |       |         |         | LOF                 | 1       | Normal     | All off | LCD全消灯制御                    |

| 2E0H | TM3   | TM2   | TM1     | TM0     | TM3                 | 0       |            |         | 計時タイマデータ(2Hz)               |

|      |       |       |         |         | TM2                 | 0       |            |         | 計時タイマデータ(4Hz)               |

|      | R     |       | R/W     |         | TM1                 | 0       |            |         | 計時タイマデータ(8Hz)               |

|      |       |       |         |         | TM0                 | 0       |            |         | 計時タイマデータ(16Hz)              |

| 2E1H | SWL3  | SWL2  | SWL1    | SWL0    | SWL3                | 0       |            |         | MSB                         |

|      |       |       |         |         | SWL2                | 0       |            |         | ストップウォッチタイマ1/100secデータ(BCD) |

|      | R     |       | R/W     |         | SWL1                | 0       |            |         | LSB                         |

|      |       |       |         |         | SWL0                | 0       |            |         |                             |

| 2E2H | SWH3  | SWH2  | SWH1    | SWH0    | SWH3                | 0       |            |         | MSB                         |

|      |       |       |         |         | SWH2                | 0       |            |         | ストップウォッチタイマ1/10 secデータ(BCD) |

|      | R     |       | R/W     |         | SWH1                | 0       |            |         | LSB                         |

|      |       |       |         |         | SWH0                | 0       |            |         |                             |

| 2E3H | K03   | K02   | K01     | K00     | K03                 | - *2    | High       | Low     | 入力ポートデータ(K00~K03)           |

|      |       |       |         |         | K02                 | - *2    | High       | Low     |                             |

|      | R     |       | R/W     |         | K01                 | - *2    | High       | Low     |                             |

|      |       |       |         |         | K00                 | - *2    | High       | Low     |                             |

| 2E4H | KCP03 | KCP02 | KCP01   | KCP00   | KCP03               | 0       | ↓          | ↑       | 入力比較レジスタ(K00~K03)           |

|      |       |       |         |         | KCP02               | 0       | ↓          | ↑       |                             |

|      | R/W   |       | R/W     |         | KCP01               | 0       | ↓          | ↑       |                             |

|      |       |       |         |         | KCP00               | 0       | ↓          | ↑       |                             |

| 2E5H | EIK03 | EIK02 | EIK01   | EIK00   | EIK03               | 0       | Enable     | Mask    | 割り込みマスクレジスタ(K00~K03)        |

|      |       |       |         |         | EIK02               | 0       | Enable     | Mask    |                             |

|      | R/W   |       | R/W     |         | EIK01               | 0       | Enable     | Mask    |                             |

|      |       |       |         |         | EIK00               | 0       | Enable     | Mask    |                             |

| 2E6H | HLMOD | BLD0  | EISWIT1 | EISWIT0 | HLMOD               | 0       | Heavy load | Normal  | 重負荷保護モードレジスタ                |

|      |       |       |         |         | BLD0                | 0       | Low        | Normal  | サブBLD判定データ                  |

|      | R/W   |       | R/W     |         | EISWIT1             | 0       | Enable     | Mask    | 割り込みマスクレジスタ(ストップウォッチ1Hz)    |

|      |       |       |         |         | EISWIT0             | 0       | Enable     | Mask    | 割り込みマスクレジスタ(ストップウォッチ10Hz)   |

| 2E7H | SCTRG | EIK10 | KCP10   | K10     | SCTRG <sup>=3</sup> | -       | Trigger    | -       | シリアルI/Fクロックトリガ              |

|      |       |       |         |         | EIK10               | 0       | Enable     | Mask    | 割り込みマスクレジスタ(K10)            |

|      | R/W   |       | R       |         | KCP10               | 0       | ↓          | ↑       | 入力比較レジスタ(K10)               |

|      |       |       |         |         | K10                 | - *2    | High       | Low     | 入力ポートデータ(K10)               |

| 2E8H | CSDC  | ETI2  | ETI8    | ETI32   | CSDC                | 0       | Static     | Dynamic | LCD駆動切り換え                   |

|      |       |       |         |         | ETI2                | 0       | Enable     | Mask    | 割り込みマスクレジスタ(計時タイマ2Hz)       |

|      | R/W   |       | R/W     |         | ETI8                | 0       | Enable     | Mask    | 割り込みマスクレジスタ(計時タイマ8Hz)       |

|      |       |       |         |         | ETI32               | 0       | Enable     | Mask    | 割り込みマスクレジスタ(計時タイマ32Hz)      |

| 2E9H | 0     | TI2   | TI8     | TI32    | 0 *3                | - *2    | -          | -       | 未使用                         |

|      |       |       |         |         | TI2 *4              | 0       | Yes        | No      | 割り込み要因フラグ(計時タイマ2Hz)         |

|      | R     |       | R/W     |         | TI8 *4              | 0       | Yes        | No      | 割り込み要因フラグ(計時タイマ8Hz)         |

|      |       |       |         |         | TI32 *4             | 0       | Yes        | No      | 割り込み要因フラグ(計時タイマ32Hz)        |

| 2EAH | IK1   | IK0   | SWIT1   | SWIT0   | IK1 *4              | 0       | Yes        | No      | 割り込み要因フラグ(K10)              |

|      |       |       |         |         | IK0 *4              | 0       | Yes        | No      | 割り込み要因フラグ(K00~K03)          |

|      | R     |       | R/W     |         | SWIT1 *4            | 0       | Yes        | No      | 割り込み要因フラグ(ストップウォッチ1Hz)      |

|      |       |       |         |         | SWIT0 *4            | 0       | Yes        | No      | 割り込み要因フラグ(ストップウォッチ10Hz)     |

| 2EBH | R03   | R02   | R01     | R00     | R03                 | 0       | High       | Low     | 出力ポート(R03)                  |

|      |       |       |         |         | R02                 | 0       | High       | Low     | 出力ポート(R02)                  |

|      | R/W   |       | R/W     |         | R01                 | 0       | High       | Low     | 出力ポート(R01)                  |

|      |       |       |         |         | R00                 | 0       | High       | Low     | 出力ポート(R00)                  |

| 2ECH | R13   | R12   | R11     | R10     | R13                 | 0       | High/On    | Low/Off | 出力ポート(R13)/BZ出力制御           |

|      |       |       | SI0F    |         | R12                 | 0       | High/On    | Low/Off | 出力ポート(R12)/FOUT出力制御         |

|      | R/W   |       | R/W     |         | R11                 | 0       | High       | Low     | 出力ポート(R11, LAMP)            |

|      |       |       | R       |         | SI0F                | 0       | Run        | Stop    | 出力ポート(SI0F)                 |

|      |       |       |         |         | R10                 | 0       | High/On    | Low/Off | 出力ポート(R10)/BZ出力制御           |

\*1 イニシャルリセット時の初期値

\*3 読み出し時は常時"0"

\*5 不定

\*2 回路上設定されない

\*4 読み出し直後、リセット(0)

表4.1.1( b ) I/Oメモリマップ( 2EDH ~ 2FAH )

| アドレス | レジスタ  |       |       |        | Name     | Init *1 | 1       | 0       | コメント                                                                                                                                     |

|------|-------|-------|-------|--------|----------|---------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------|

|      | D3    | D2    | D1    | D0     |          |         |         |         |                                                                                                                                          |

| 2EDH | P03   | P02   | P01   | P00    | P03      | - *2    | High    | Low     | 入出力兼用ポートデータ(P00~P03)<br>イニシャルリセット時、出力ラッチはリセット                                                                                            |

|      |       |       |       |        | P02      | - *2    | High    | Low     |                                                                                                                                          |

|      |       |       |       |        | P01      | - *2    | High    | Low     |                                                                                                                                          |

|      |       |       |       |        | P00      | - *2    | High    | Low     |                                                                                                                                          |

| 2EEH | R/W   |       |       |        | TMRST*3  | Reset   | Reset   | -       | 計時タイマリセット                                                                                                                                |

|      | TMRST | SWRUN | SWRST | IOCO   | SWRUN    | 0       | Run     | Stop    | ストップウォッチタイマRun/Stop                                                                                                                      |

|      | W     | R/W   | W     | R/W    | SWRST*3  | Reset   | Reset   | -       | ストップウォッチタイマリセット                                                                                                                          |

|      |       |       |       |        | IOCO     | 0       | Output  | Input   | I/O制御レジスタ0(P00~P03)                                                                                                                      |

| 2EFH | WDRST | WD2   | WD1   | WD0    | WDRST*3  | Reset   | Reset   | -       | ウォッチドッグタイマリセット                                                                                                                           |

|      |       |       |       |        | WD2      | 0       |         |         | タイマデータ(ウォッチドッグタイマ) 1/4Hz                                                                                                                 |

|      |       |       |       |        | WD1      | 0       |         |         | タイマデータ(ウォッチドッグタイマ) 1/2Hz                                                                                                                 |

|      | W     | R     |       |        | WD0      | 0       |         |         | タイマデータ(ウォッチドッグタイマ) 1Hz                                                                                                                   |

| 2F0H | SD3   | SD2   | SD1   | SD0    | SD3      | × *5    |         |         | シリアルI/Fデータレジスタ(下位4ビット)                                                                                                                   |

|      |       |       |       |        | SD2      | × *5    |         |         |                                                                                                                                          |

|      |       |       |       |        | SD1      | × *5    |         |         |                                                                                                                                          |

|      |       |       |       |        | SD0      | × *5    |         |         |                                                                                                                                          |

| 2F1H | SD7   | SD6   | SD5   | SD4    | SD7      | × *5    |         |         | シリアルI/Fデータレジスタ(上位4ビット)                                                                                                                   |

|      |       |       |       |        | SD6      | × *5    |         |         |                                                                                                                                          |

|      |       |       |       |        | SD5      | × *5    |         |         |                                                                                                                                          |

|      |       |       |       |        | SD4      | × *5    |         |         |                                                                                                                                          |

| 2F2H | SCS1  | SCS0  | SE2   | EISIO  | SCS1     | 1       |         |         | SIFクロック [SCS1,0] 0 1 2 3<br>モード選択 クロック CLK CLK/2 CLK/4 スレーブ<br>シリアルI/Fクロックエッジ選択<br>割り込みマスクレジスタ(シリアルI/F)                                  |

|      |       |       |       |        | SCS0     | 1       |         |         |                                                                                                                                          |

|      |       |       |       |        | SE2      | 0       | ↑       | Mask    |                                                                                                                                          |

|      |       |       |       |        | EISIO    | 0       | Enable  |         |                                                                                                                                          |

| 2F3H | 0     | 0     | IK2   | ISIO   | 0 *3     | - *2    | -       | -       | 未使用                                                                                                                                      |

|      |       |       |       |        | 0 *3     | - *2    | -       | -       | 未使用                                                                                                                                      |

|      |       |       |       |        | IK2 *4   | 0       | Yes     | No      | 割り込み要因フラグ(K20~K23)                                                                                                                       |

|      |       |       |       |        | ISIO *4  | 0       | Yes     | No      | 割り込み要因フラグ(シリアルI/F)                                                                                                                       |

| 2F4H | K23   | K22   | K21   | K20    | K23      | - *2    | High    | Low     | 入力ポートデータ(K20~K23)                                                                                                                        |

|      |       |       |       |        | K22      | - *2    | High    | Low     |                                                                                                                                          |

|      |       |       |       |        | K21      | - *2    | High    | Low     |                                                                                                                                          |

|      |       |       |       |        | K20      | - *2    | High    | Low     |                                                                                                                                          |

| 2F5H | EIK23 | EIK22 | EIK21 | EIK20  | EIK23    | 0       | Enable  | Mask    | 割り込みマスクレジスタ(K20~K23)                                                                                                                     |

|      |       |       |       |        | EIK22    | 0       | Enable  | Mask    |                                                                                                                                          |

|      |       |       |       |        | EIK21    | 0       | Enable  | Mask    |                                                                                                                                          |

|      |       |       |       |        | EIK20    | 0       | Enable  | Mask    |                                                                                                                                          |

| 2F6H | BZFQ2 | BZFQ1 | BZFQ0 | ENVRST | BZFQ2    | 0       |         |         | ブザー [BZFQ2~0] 0 1 2 3<br>周波数 fosc/8 fosc/10 fosc/12 fosc/14<br>選択 [BZFQ2~0] 4 5 6 7<br>周波数 fosc/16 fosc/20 fosc/24 fosc/28<br>エンベロープリセット |

|      |       |       |       |        | BZFQ1    | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | BZFQ0    | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | ENVRST*3 | Reset   | Reset   | -       |                                                                                                                                          |

| 2F7H | ENVON | ENVRT | AMPDT | AMPON  | ENVON    | 0       | On      | Off     | エンベロープOn/Off                                                                                                                             |

|      |       |       |       |        | ENVRT    | 0       | 1.0 sec | 0.5 sec | エンベロープ減衰時間                                                                                                                               |

|      |       |       |       |        | AMPDT    | 1       | + > -   | + < -   | アナログコンバレータデータ                                                                                                                            |

|      |       |       |       |        | AMPON    | 0       | On      | Off     | アナログコンバレータOn/Off                                                                                                                         |

| 2F8H | EV03  | EV02  | EV01  | EV00   | EV03     | 0       |         |         | イベントカウンタ0(下位4ビット)                                                                                                                        |

|      |       |       |       |        | EV02     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV01     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV00     | 0       |         |         |                                                                                                                                          |

| 2F9H | EV07  | EV06  | EV05  | EV04   | EV07     | 0       |         |         | イベントカウンタ0(上位4ビット)                                                                                                                        |

|      |       |       |       |        | EV06     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV05     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV04     | 0       |         |         |                                                                                                                                          |

| 2FAH | EV13  | EV12  | EV11  | EV10   | EV13     | 0       |         |         | イベントカウンタ1(下位4ビット)                                                                                                                        |

|      |       |       |       |        | EV12     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV11     | 0       |         |         |                                                                                                                                          |

|      |       |       |       |        | EV10     | 0       |         |         |                                                                                                                                          |

\*1 イニシャルリセット時の初期値

\*3 読み出し時は常時"0"

\*5 不定

\*2 回路上設定されない

\*4 読み出し直後、リセット(0)

表4.1.1(c) I/Oメモリマップ(2FBH ~ 2FFH)

| アドレス | レジスタ     |        |        |        | Name     | Init *1 | 1        | 0      | コメント                                                                                                                                           |

|------|----------|--------|--------|--------|----------|---------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

|      | D3       | D2     | D1     | D0     |          |         |          |        |                                                                                                                                                |

| 2FBH | EV17     | EV16   | EV15   | EV14   | EV17     | 0       |          |        | イベントカウンタ1(上位4ビット)                                                                                                                              |

|      |          |        |        |        | EV16     | 0       |          |        |                                                                                                                                                |

|      | R        |        |        |        | EV15     | 0       |          |        |                                                                                                                                                |

|      | EV14     |        |        |        | EV14     | 0       |          |        |                                                                                                                                                |

| 2FCH | EVSEL    | ENRUN  | EV1RST | EV0RST | EVSEL    | 0       | Separate | Phase  | イベントカウンタモード選択                                                                                                                                  |

|      |          |        |        |        | EVRUN    | 0       | Run      | Stop   | イベントカウンタRun/Stop                                                                                                                               |

|      | EV1RST*3 |        |        |        | EV1RST*3 | Reset   | Reset    | -      | イベントカウンタリセット                                                                                                                                   |

|      | EV0RST*3 |        |        |        | EV0RST*3 | Reset   | Reset    | -      | イベントカウンタリセット                                                                                                                                   |

| 2FDH | P13      | P12    | P11    | P10    | P13      | - *2    | High     | Low    | 入出力兼用ポートデータ(P10~P13)<br>イニシャルリセット時、出力ラッチはリセット                                                                                                  |

|      |          |        |        |        | P12      | - *2    | High     | Low    |                                                                                                                                                |

|      | R/W      |        |        |        | P11      | - *2    | High     | Low    |                                                                                                                                                |

|      | P10      |        |        |        | P10      | - *2    | High     | Low    |                                                                                                                                                |

| 2FEH | PRSM     | CLKCHG | OSCC   | IOC1   | PRSM     | 0       | 38 kHz   | 32 kHz | OSC1ブリスケーラ選択                                                                                                                                   |

|      |          |        |        |        | CLKCHG   | 0       | OSC3     | OSC1   | CPUクロック切り換え                                                                                                                                    |

|      | R/W      |        |        |        | OSCC     | 0       | On       | Off    | OSC3発振On/Off                                                                                                                                   |

|      | IOC1     |        |        |        | IOC1     | 0       | Output   | Input  | I/O制御レジスタ(P10~P13)                                                                                                                             |

| 2FFH | BLS      | BLC2   | BLC1   | BLC0   | BLS      | 0       | On       | Off    | BLD On/Off                                                                                                                                     |

|      | BLD1     |        |        |        | BLD1     | 0       | Low      | Normal | BLD判定データ                                                                                                                                       |

|      |          |        |        |        | BLC2     | x *5    |          |        | 判定電圧設定レジスタ                                                                                                                                     |

|      |          | R/W    |        |        | BLC1     | x *5    |          |        | [BLC2~0] 0 1 2 3 4 5 6 7<br>S1C60N08/60A08 2.20 2.25 2.30 2.35 2.40 2.45 2.50 2.55 (V)<br>S1C60L08 1.05 1.10 1.15 1.20 1.25 1.30 1.35 1.40 (V) |

|      |          |        |        |        | BLC0     | x *5    |          |        |                                                                                                                                                |

\*1 イニシャルリセット時の初期値

\*3 読み出し時は常時"0"

\*5 不定

\*2 回路上設定されない

\*4 読み出し直後、リセット(0)

## 4.2 ウオッヂドッグタイマのリセット

### 4.2.1 ウオッヂドッグタイマの構成

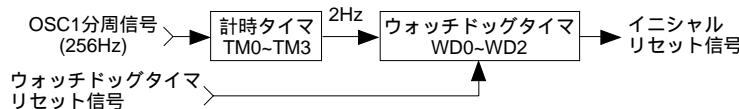

S1C60N08シリーズはOSC1( 計時タイマ2Hz信号 )を原振とするウォッヂドッグタイマを内蔵しています。ウォッヂドッグタイマはソフトウェアにより周期的にリセットする必要があります。3~4秒以上リセットが行われない場合、CPUに対して自動的にイニシャルリセット信号を出力します。

図4.2.1.1にウォッヂドッグタイマのブロック図を示します。

図4.2.1.1 ウオッヂドッグタイマのブロック図

ウォッヂドッグタイマは3ビットのバイナリカウンタ(WD0~WD2)で構成され、最上位桁のオーバーフローによってイニシャルリセット信号を内部的に発生します。

プログラムのメインルーチン上でウォッヂドッグタイマのリセット処理をすることにより、メインルーチンのウォッヂドッグタイマ処理を通らないようなプログラムの暴走を検出することができます。通常はこのルーチンをタイマ割り込みルーチンのように、定期的に処理される箇所に組み込みます。なお、ウォッヂドッグタイマはHALT時も動作しており、HALT状態を3~4秒間続けるとイニシャルリセットからの再起動となります。

### 4.2.2 マスクオプション

ウォッヂドッグタイマを使用するかしないかは、マスクオプションにより選択することができます。"使用しない"を選択した場合、ウォッヂドッグタイマをリセットする必要はありません。

### 4.2.3 ウオッヂドッグタイマの制御方法

表4.2.3.1にウォッヂドッグタイマの制御ビットを示します。

表4.2.3.1 ウオッヂドッグタイマの制御ビット

| アドレス | レジスタ  |     |     |     | Name    | Init *1 | 1     | 0 | コメント                     |

|------|-------|-----|-----|-----|---------|---------|-------|---|--------------------------|

|      | D3    | D2  | D1  | D0  |         |         |       |   |                          |

| 2EFH | WDRST | WD2 | WD1 | WD0 | WDRST*3 | Reset   | Reset | - | ウォッヂドッグタイマリセット           |

|      |       |     |     |     | WD2     | 0       |       |   | タイムデータ(ウォッヂドッグタイマ) 1/4Hz |

|      | W     | R   |     |     | WD1     | 0       |       |   | タイムデータ(ウォッヂドッグタイマ) 1/2Hz |

|      |       |     |     |     | WD0     | 0       |       |   | タイムデータ(ウォッヂドッグタイマ) 1Hz   |

\*1 イニシャルリセット時の初期値

\*3 読み出し時は常時"0"

\*5 不定

\*2 回路上設定されない

\*4 読み出し直後、リセット(0)

WDRST: ウオッヂドッグタイマリセット (2EFH・D3)

ウォッヂドッグタイマをリセットするビットです。

"1"書き込み: ウオッヂドッグタイマリセット

"0"書き込み: ノーオペレーション

読み出し: 常時"0"

WDRSTに"1"を書き込むことによりウォッヂドッグタイマはリセットされ、その直後リスタートします。"0"の書き込みはノーオペレーションとなります。

このビットは書き込み専用のため、読み出し時は常時"0"となります。

### 4.2.4 プログラミング上の注意事項

ウォッヂドッグタイマを使用する場合、3秒周期以内にソフトウェアでウォッヂドッグタイマをリセットする必要があります。この場合、タイムデータ(WD0~WD2)は計時用途に使用することはできません。

### 4.3 発振回路とプリスケーラ

#### 4.3.1 発振回路とプリスケーラの構成

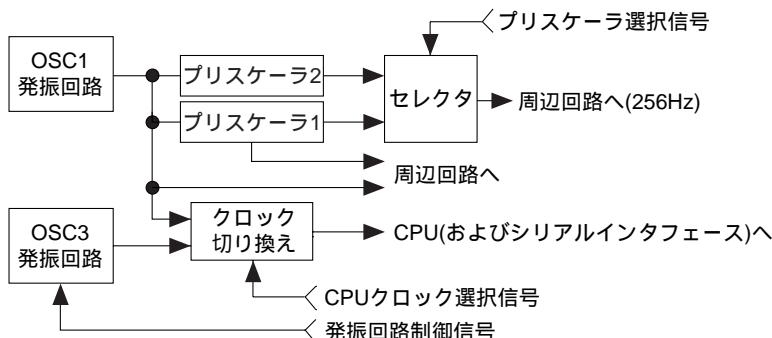

S1C60N08/60L08は1系統の発振回路( OSC1 )、S1C60A08は2系統の発振回路( OSC1とOSC3 )を内蔵しています。このうちOSC1は水晶発振回路で、CPUおよび周辺回路に動作クロックを供給します。OSC3はCRまたはセラミック発振回路で、S1C60A08において高速動作が要求される処理が必要な場合に、CPUの動作クロックをOSC1からOSC3に切り換えて使用します。

図4.3.1.1に発振系のブロック図を示します。

図4.3.1.1 発振系のブロック図

図4.3.1.1に示すとおり、OSC1発振回路には2系統のプリスケーラ(分周段)が接続されています。プリスケーラ1は32.768kHz用、プリスケーラ2は38.4kHz用の分周段です。使用する水晶振動子に合わせてソフトウェアによって選択します。この選択により、計時タイマ、ストップウォッチタイマ等を動作させる基本信号(256Hz)が得られます。

またS1C60A08においては、CPUの動作クロックをOSC1とするか、OSC3とするかをソフトウェアで選択できます。

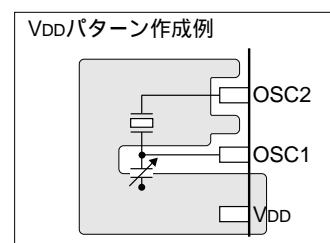

### 4.3.2 OSC1発振回路

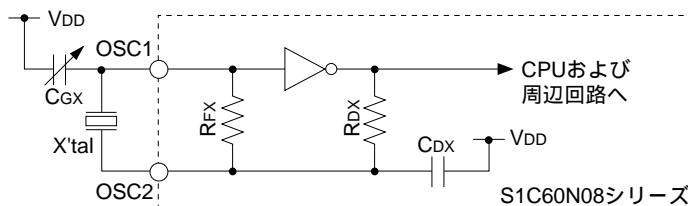

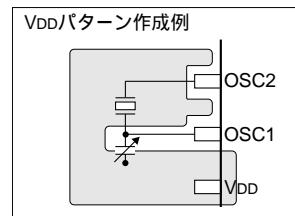

S1C60N08シリーズは水晶発振回路( OSC1発振回路 )を内蔵しています。OSC1発振回路は外付け素子として、水晶振動子( Typ. 32.768kHz )とトリマコンデンサ( 5 ~ 25pF )を接続することにより、CPUおよび周辺回路の動作クロックを発生します。

図4.3.2.1にOSC1発振回路のブロック図を示します。

図4.3.2.1 OSC1発振回路

図4.3.2.1に示すとおり、OSC1端子とOSC2端子間に水晶振動子(X'tal)を、OSC1端子とVDD間にトリマコンデンサ(C<sub>GX</sub>)をそれぞれ接続することにより、容易に水晶発振回路を構成することができます。また、水晶振動子は32.768kHzのほかに38.4kHzの振動子を接続することができます。

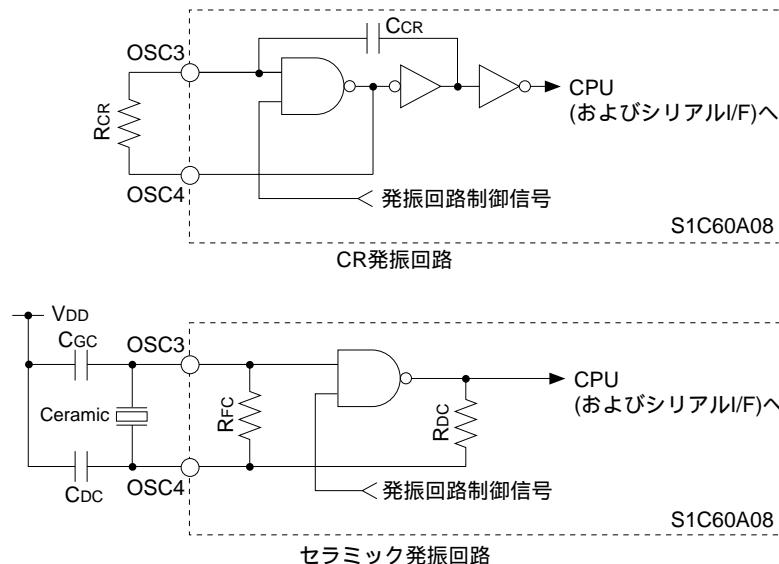

### 4.3.3 OSC3発振回路

S1C60N08シリーズ中、ツインクロック仕様のS1C60A08はCPUのサブクロックとしてCRまたはセラミック発振回路(OSC3発振回路)をマスクオプションで選択できます。発振回路そのものは内蔵されているため、CR発振選択時は外付素子として抵抗が、セラミック発振選択時はセラミック振動子とコンデンサ2個(ゲート容量とドレイン容量)が必要となります。

図4.3.3.1にOSC3発振回路のブロック図を示します。

図4.3.3.1 OSC3発振回路

図4.3.3.1に示すとおり、CR発振を選択した場合はOSC3端子とOSC4端子間に抵抗(  $R_{CR}$  )を接続するだけでCR発振回路を構成できます。 $R_{CR}$ に82k $\Omega$ を使用した場合、発振周波数は約410kHzになります。

セラミック発振を選択した場合はOSC3端子とOSC4端子間にセラミック振動子( Typ. 500kHz )を、同OSC3、OSC4端子とVDD間にコンデンサを2個(  $C_{GC}$ 、 $C_{DC}$  )それぞれ接続することでセラミック発振回路を構成できます。 $C_{GC}$ 、 $C_{DC}$ は共に100pF程度のものを接続してください。

このOSC3発振回路は消費電流を低減するために、使用しないときはソフトウェアによって発振を停止させることができます。

S1C60N08/60L08( シングルクロック仕様 )では、OSC3・OSC4をN.C( 非接続 )としてください。

#### 4.3.4 発振回路とプリスケーラの制御方法

表4.3.4.1に発振回路とプリスケーラの制御ビットを示します。

表4.3.4.1 発振回路とプリスケーラの制御ビット

| アドレス | レジスタ |        |      |      | Name   | Init *1 | コメント   |                     |

|------|------|--------|------|------|--------|---------|--------|---------------------|

|      | D3   | D2     | D1   | D0   |        |         | 1      | 0                   |

| 2FEH | PRSM | CLKCHG | OSCC | IOC1 | PRSM   | 0       | 38 kHz | 32 kHz OSC1プリスケーラ選択 |

|      |      |        |      |      | CLKCHG | 0       | OSC3   | OSC1 CPUクロック切り換え    |

|      | R/W  |        | OSCC | 0    |        | On      | Off    | OSC3発振On/Off        |

|      |      |        | IOC1 | 0    |        | Output  | Input  | I/O制御レジスタ(P10~P13)  |

\*1 イニシャルリセット時の初期値

\*3 読み出し時は常時"0"

\*5 不定

\*2 回路上設定されない

\*4 読み出し直後、リセット(0)

OSCC: OSC3発振制御( 2FEH・D1 )

OSC3発振回路の発振ON/OFFを制御します。( S1C60A08のみ )

"1"書き込み : OSC3発振ON

"0"書き込み : OSC3発振OFF

読み出し : 可能

S1C60A08において、CPUを高速に動作させる必要のある場合にOSCCを"1"とし、それ以外の場合は、消費電流低減のため"0"としてください。

S1C60N08/60L08では"0"固定としてください。

イニシャルリセット時、OSCCは"0"に設定されます。

CLKCHG: CPUクロック切り換え( 2FEH・D2 )

CPUの動作クロックを選択します。( S1C60A08のみ )

"1"書き込み : OSC3クロックを選択

"0"書き込み : OSC1クロックを選択

読み出し : 可能

S1C60A08において、CPUの動作クロックをOSC3にする場合にCLKCHGを"1"、OSC1にする場合"0"を設定してください。S1C60N08/60L08ではこのレジスタの制御は無効で、設定値にかかわらず常時OSC1が選択されます。

イニシャルリセット時、CLKCHGは"0"に設定されます。

PRSM: OSC1プリスケーラ選択( 2FEH・D3 )

OSC1発振回路の水晶振動子に対応するプリスケーラを選択します。

"1"書き込み : 38.4kHz

"0"書き込み : 32.768kHz

読み出し : 可能

この選択により、計時タイマ、ストップウォッチタイマ等は正確に動作します。なお、このレジスタの設定値が、使用する水晶振動子と対応していない場合、前記周辺回路の動作周期は以下の倍率となります。

$f_{OSC1} = 32.768\text{kHz}$ , PRSM = "1":  $T' \approx 1.172T$

$f_{OSC1} = 38.4\text{kHz}$ , PRSM = "0":  $T' \approx 0.853T$

イニシャルリセット時、PRSMは"0"に設定されます。

#### 4.3.5 プログラミング上の注意事項

- ( 1 )OSC3発振回路がONしてから発振が安定するまでに、5msec以上を必要とします。したがって、CPUの動作クロックをOSC1からOSC3に切り換える際は、OSC3発振ONの後、5msec以上経過してから行ってください。また、発振安定時間は外付け発振子の特性および使用条件等により異なりますので、充分マージンをとって待ち時間を設定してください。

- ( 2 )OSC3からOSC1へのクロック切り換えと、OSC3発振OFFは別々のインストラクションで行ってください。1インストラクションで、同時に処理するとCPUの誤動作につながります。

- ( 3 )計時タイマ、ストップウォッチタイマ等を正しく動作させるためには、使用する水晶振動子に合わせてOSC1のプリスケーラを選択してください。

## 4.4 入力ポート( K00 ~ K03, K10, K20 ~ K23 )

### 4.4.1 入力ポートの構成

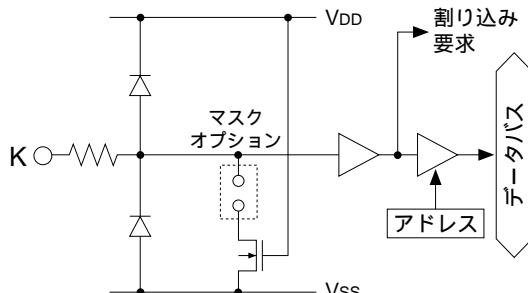

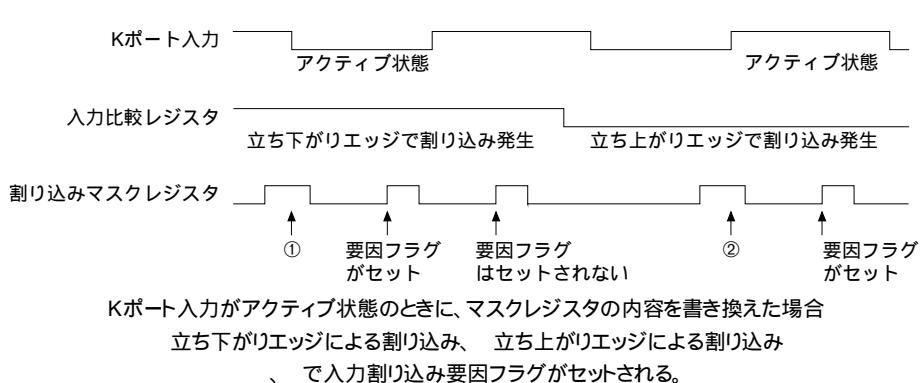

S1C60N08シリーズは9ビット(4ビット×2+1)の汎用入力ポートを内蔵しています。各入力ポート端子( K00 ~ K03, K10, K20 ~ K23 )には内蔵プルダウン抵抗が用意されており、使用するかどうかをマスクオプションで1ビットごとに選択できます。

図4.4.1.1に入力ポートの構造を示します。

図4.4.1.1 入力ポートの構造

マスクオプションで"プルダウン抵抗あり"を選択した場合、プッシュスイッチ、キーマトリクス等の入力に適当です。また、"プルダウン抵抗なし"を選択した場合、スライドスイッチ入力、他LSIとのインターフェースなどに使用できます。

また、K02、K03端子はイベントカウンタの入力端子も兼ねています(詳細は"4.12 イベントカウント"を参照してください)。

### 4.4.2 入力比較レジスタと割り込み機能

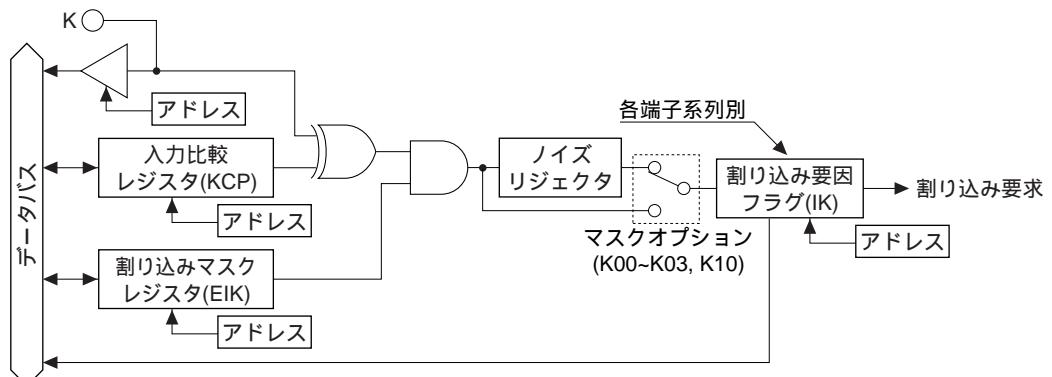

入力ポート9ビット( K00 ~ K03, K10、K20 ~ K23 )は、すべて割り込み機能を持っています。この中で、K00 ~ K03、K10の5ビットは、割り込み発生条件をソフトウェアで設定することができます。また、9ビットすべての端子について1ビットごとに、割り込みをマスクするかしないかを、同様にソフトウェアで設定することができます。

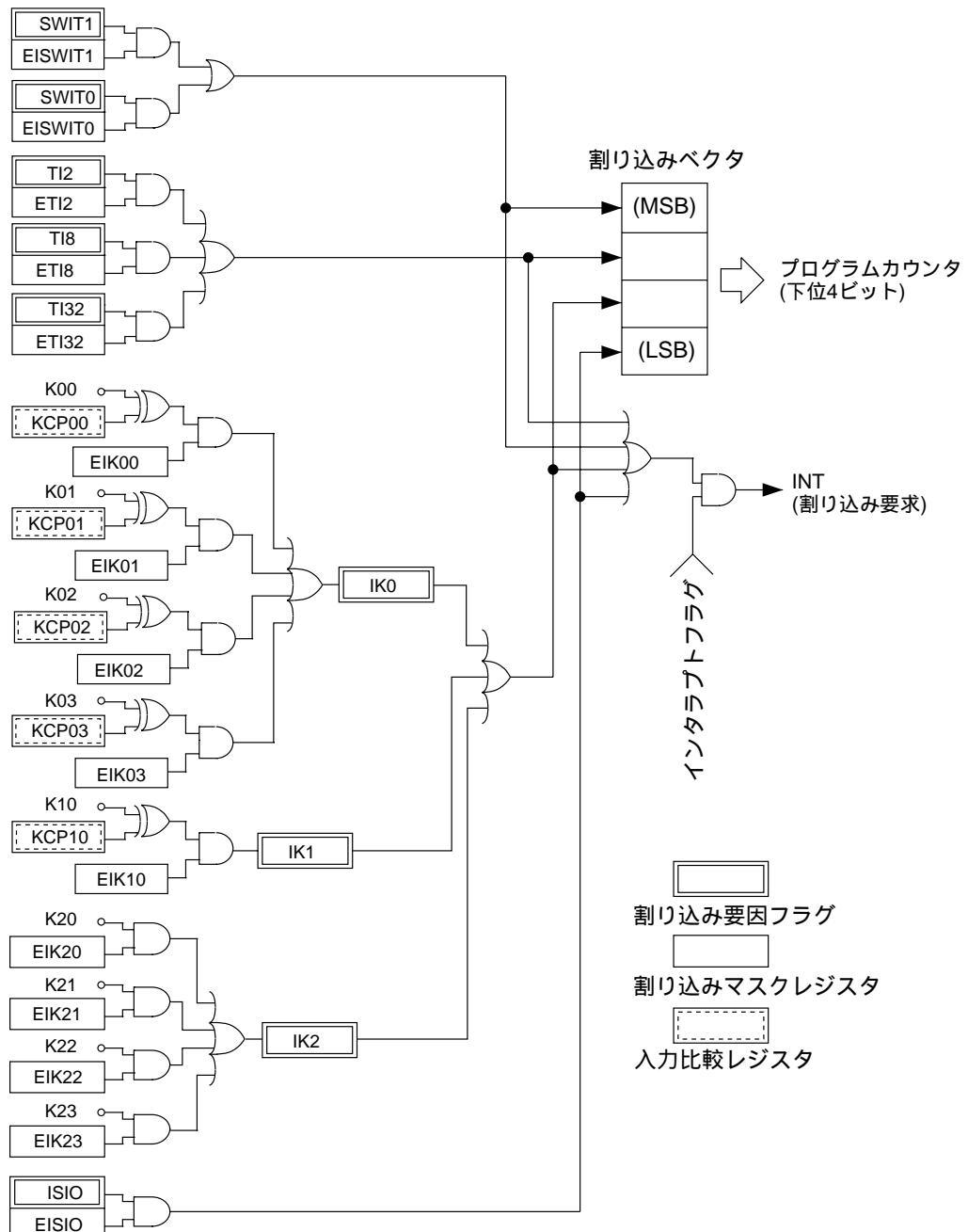

図4.4.2.1にK00 ~ K03、K10の構成図を、図4.4.2.3にK20 ~ K23の構成図をそれぞれ示します。

図4.4.2.1 入力割り込み回路構成( K00 ~ K03, K10 )

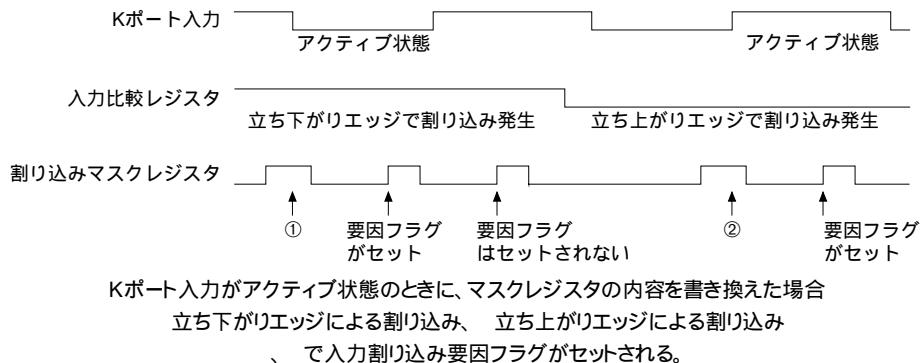

K00～K03、K10の入力割り込みタイミングは、入力比較レジスタ( KCP00～KCP03、KCP10 )の設定値により、割り込みを入力の立ち上がりエッジで発生させるか、立ち下がりエッジで発生させるかを選択することができます。

また、K00～K03、K10は割り込みマスクレジスタ( EIK00～EIK03、EIK10 )により、個別に割り込みのマスクを選択することができます。ただし、K00～K03の中で割り込みがイネーブルになっているものに対しては、入力比較レジスタとの内容が一致状態から不一致状態に変化したときに割り込みが発生します。K10については独自に同様の条件設定による割り込みが行えます。

割り込みが発生した際には、割り込み要因フラグ( IK0、IK1 )が"1"にセットされます。

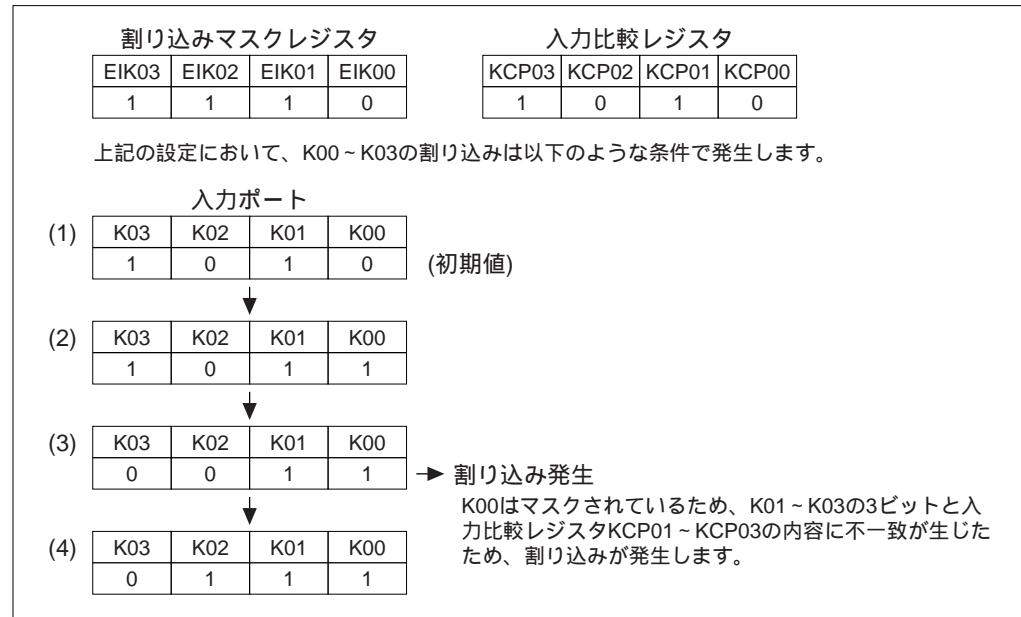

図4.4.2.2にK00～K03の割り込み発生例を示します。

図4.4.2.2 K00～K03割り込み発生例

K00は割り込みマスクレジスタ( EIK00 )によってマスクされているため、( 2 )の時点では割り込みは発生しません。次に( 3 )でK03が"0"になるため、割り込みがイネーブルになっている端子のデータと入力比較レジスタのデータとの不一致により割り込みが発生します。前述のとおり、ポートデータと入力比較レジスタの内容が一致状態から不一致状態に変化することが割り込み発生条件となるため、( 4 )のように不一致状態から、別の不一致状態に変化しても割り込みは発生しません。また、割り込みがマスクされている端子は割り込み発生条件に影響を与えません。

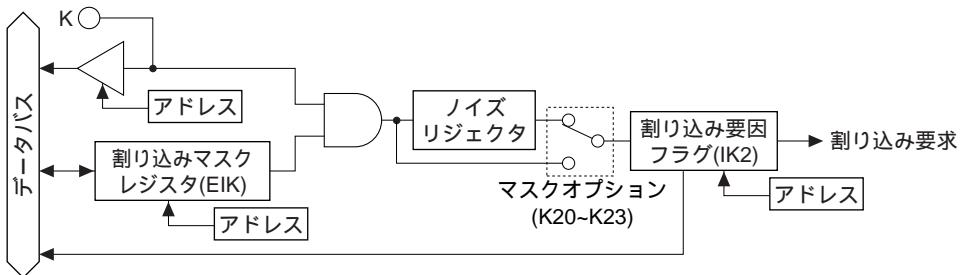

図4.4.2.3 入力割り込み回路構成( K20 ~ K23 )

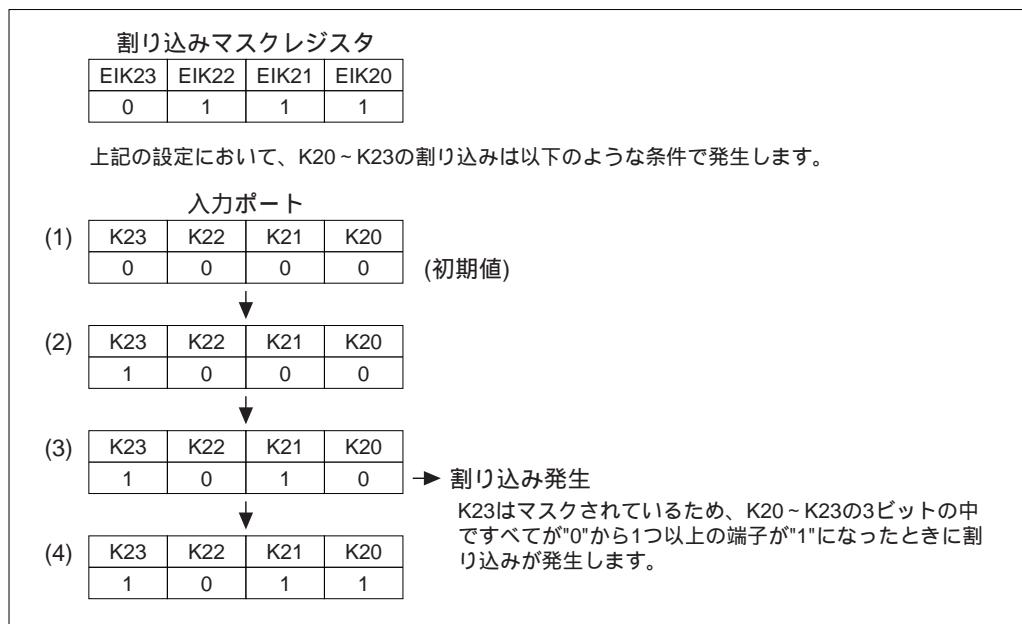

K20 ~ K23には入力比較レジスタではなく、割り込みの発生は入力の立ち上がりエッジに固定されています。割り込みのマスクは、4ビットの端子について割り込みマスクレジスタ( EIK20 ~ EIK23 )により個別に選択することができ、イネーブルになっている端子がすべて"0"の状態から1つ以上のポートが"1"の状態に変化したときに割り込みが発生します。

割り込みが発生した際には、割り込み要因フラグ( IK2 )が"1"にセットされます。

図4.4.2.4に、K20 ~ K23の割り込み発生例を示します。

図4.4.2.4 K20 ~ K23割り込み発生例

K23は割り込みマスクレジスタ( EIK23 )によってマスクされているため、( 2 )の時点では割り込みは発生しません。次に( 3 )でK21が"1"になるため、割り込みがイネーブルになっている端子がすべて"0"から1つ以上"1"に変化することにより割り込みが発生します。( 4 )においては前述の発生条件が成立しないため、割り込みは発生しません。また、割り込みがマスクされている端子は発生条件に影響を与えません。

#### 4.4.3 マスクオプション

入力ポートのマスクオプションで選択できる内容は以下のとおりです。

(1) 9ビットの入力ポート(K00~K03、K10、K20~K23)に対して、1ビットごとに内蔵プルダウン抵抗の有無を選択できます。

"プルダウン抵抗なし"を選択した場合は、入力にフローティング状態が発生しないよう注意してください。使用しない入力ポートは"プルダウン抵抗あり"を選択してください。

(2) ノイズ等による割り込みの誤発生を防ぐため、入力割り込み回路にはノイズリジェクト回路が内蔵されています。各端子系列ごとにこのノイズリジェクト回路を使用するかしないか、マスクオプションで選択することができます。

"使用する"を選択した場合、割り込み条件成立から割り込み要因フラグ(IK)が"1"にセットされるまで、最大1 msecの遅延が生じます。

#### 4.4.4 入力ポートの制御方法

表4.4.4.1に入力ポートの制御ビットを示します。

表4.4.4.1 入力ポートの制御ビット

| アドレス | レジスタ   |       |       |          | Name     | Init *1 | 1       | 0    | コメント                                                                                      |

|------|--------|-------|-------|----------|----------|---------|---------|------|-------------------------------------------------------------------------------------------|

|      | D3     | D2    | D1    | D0       |          |         |         |      |                                                                                           |

| 2E3H | K03    | K02   | K01   | K00      | K03      | - *2    | High    | Low  | 入力ポートデータ(K00~K03)                                                                         |

|      | R      |       |       | K02      | K02      | - *2    | High    | Low  |                                                                                           |

|      | R/W    |       |       | K01      | K01      | - *2    | High    | Low  |                                                                                           |

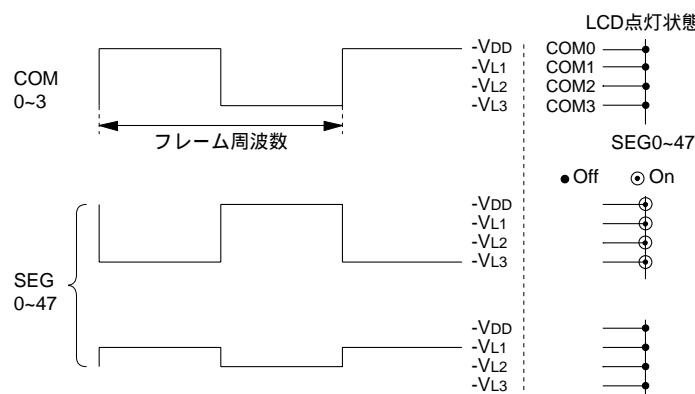

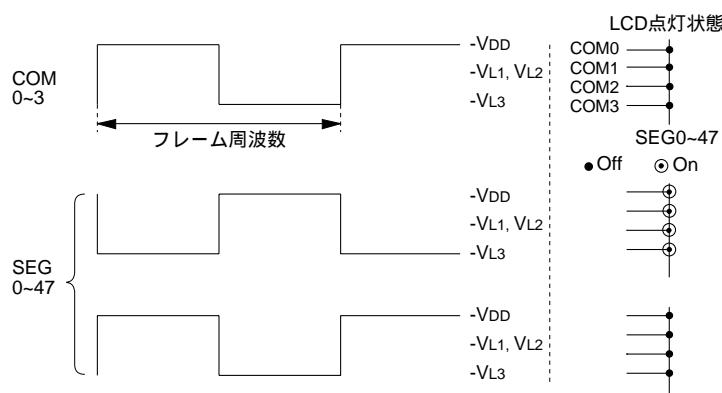

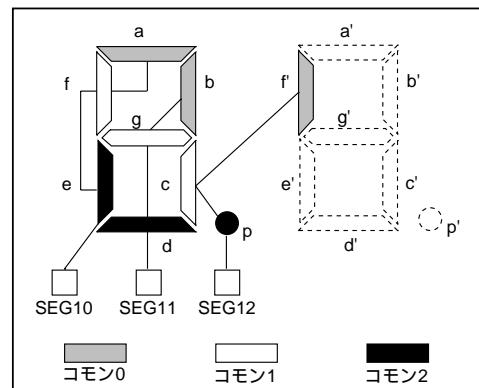

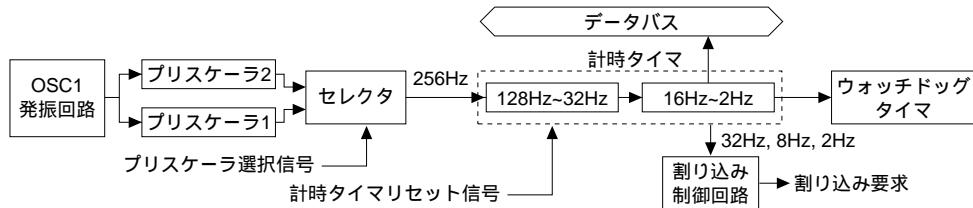

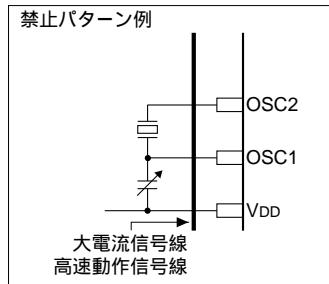

|      | R/W    |       |       | K00      | K00      | - *2    | High    | Low  |                                                                                           |